Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

957results about How to "Extended path" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

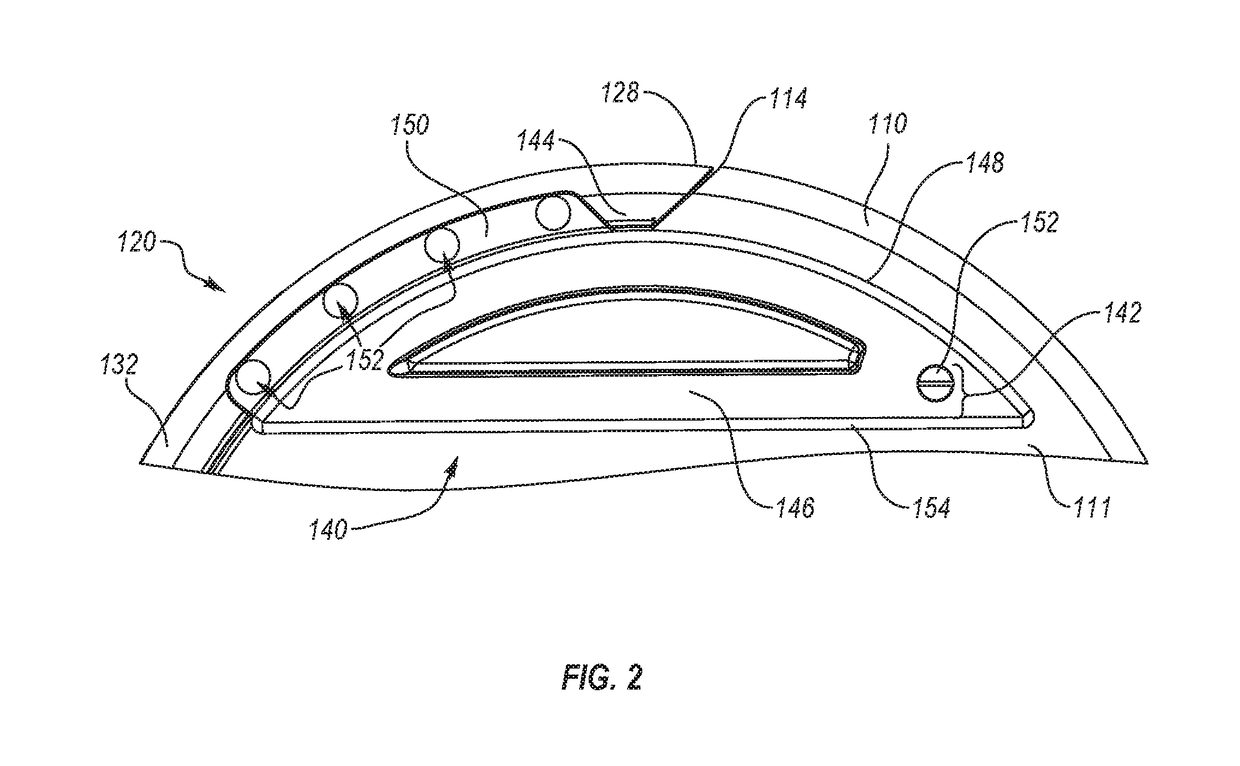

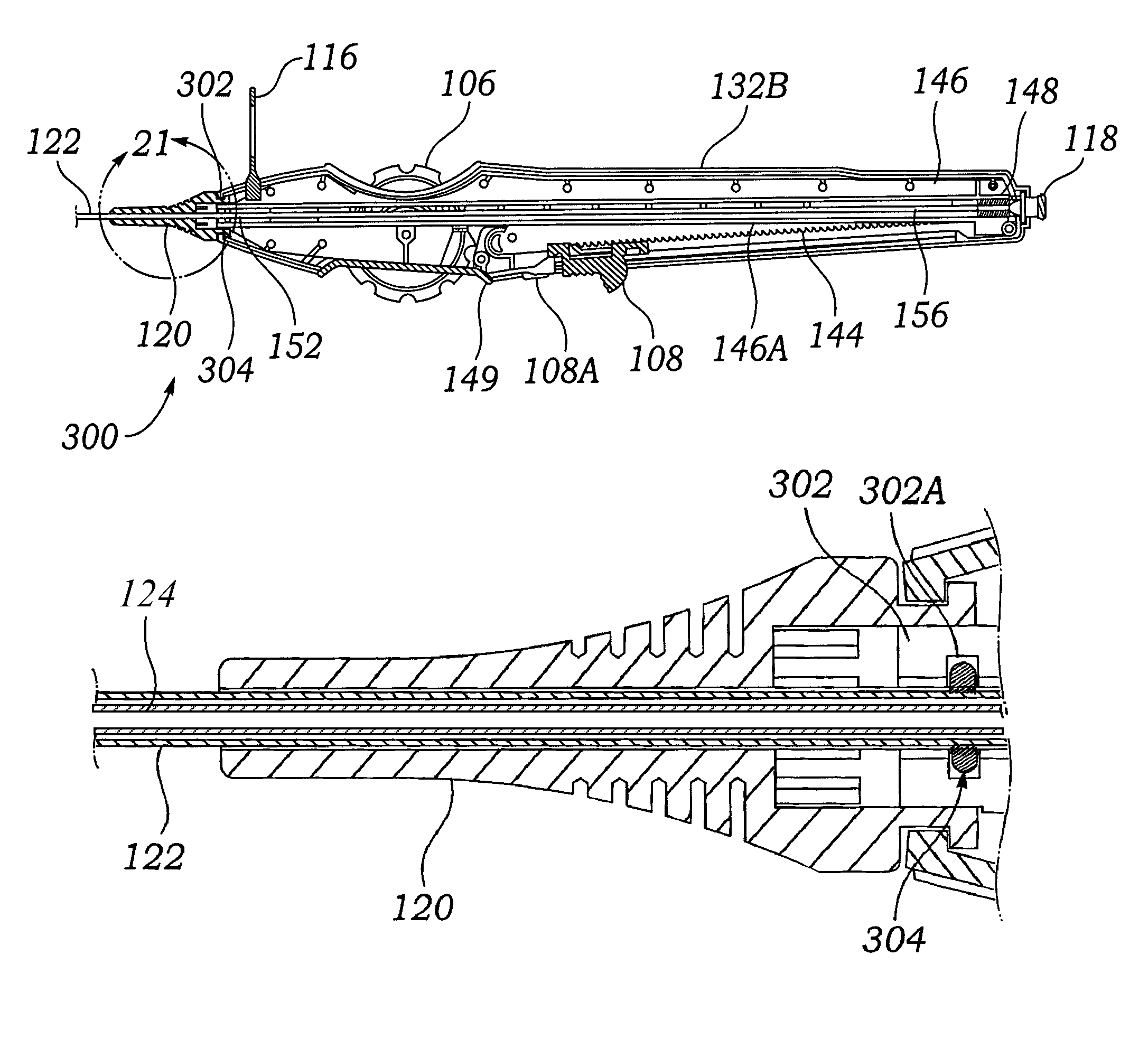

Stent Delivery System

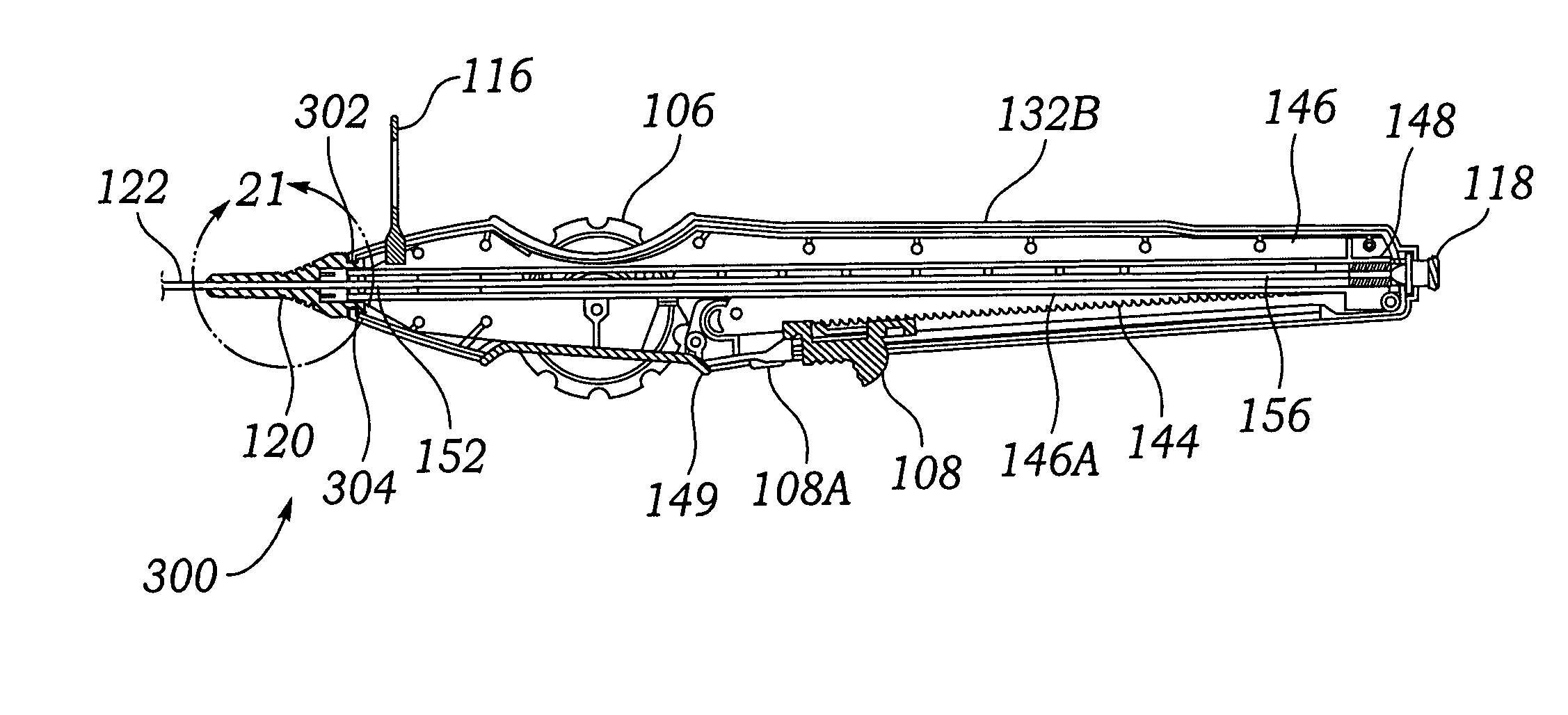

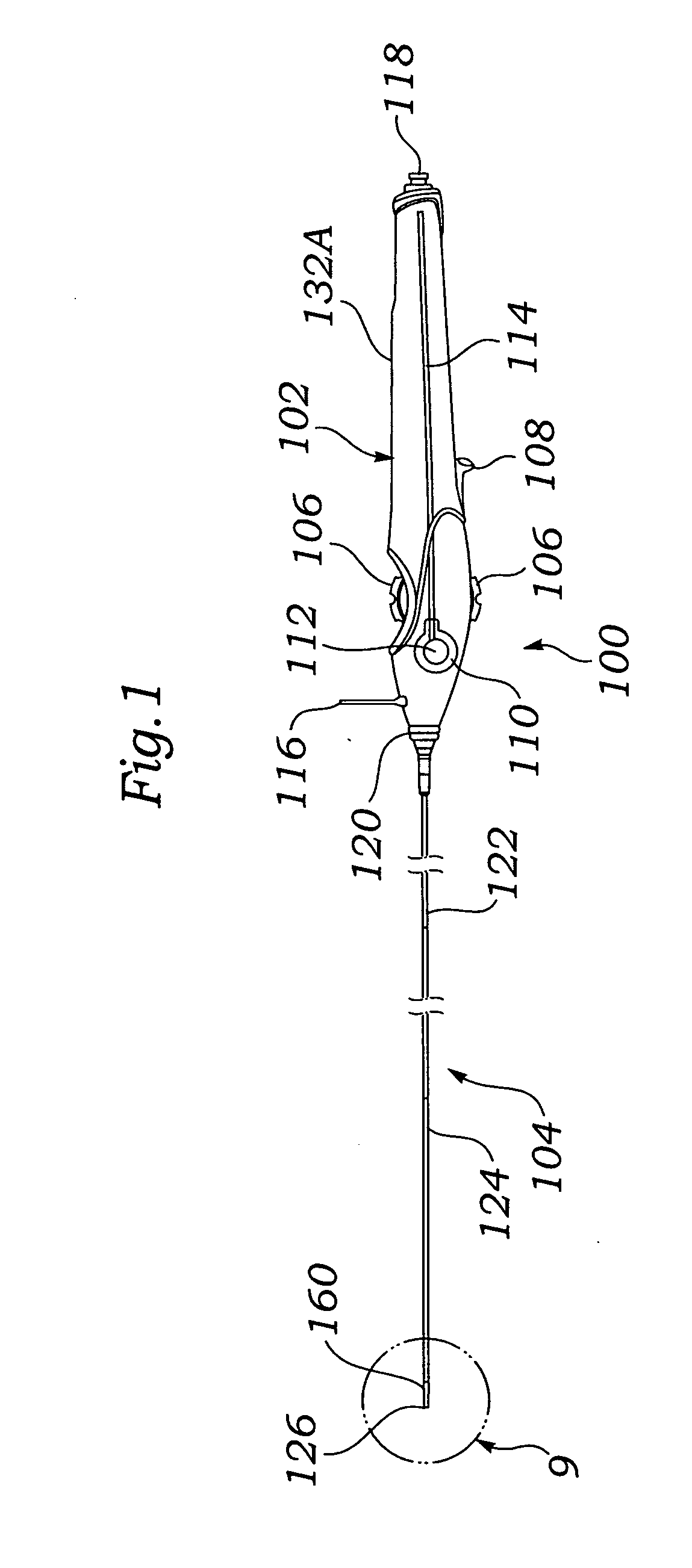

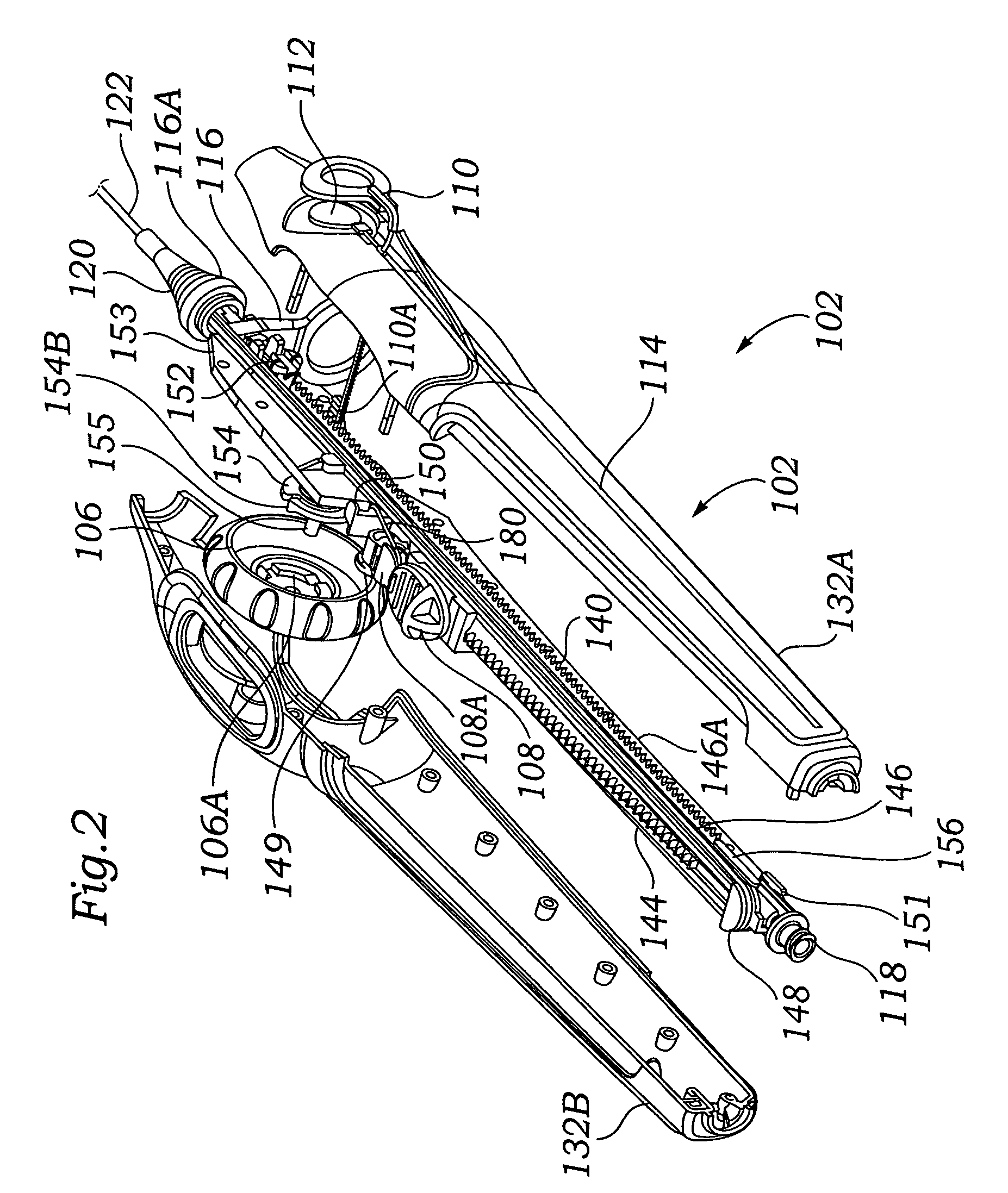

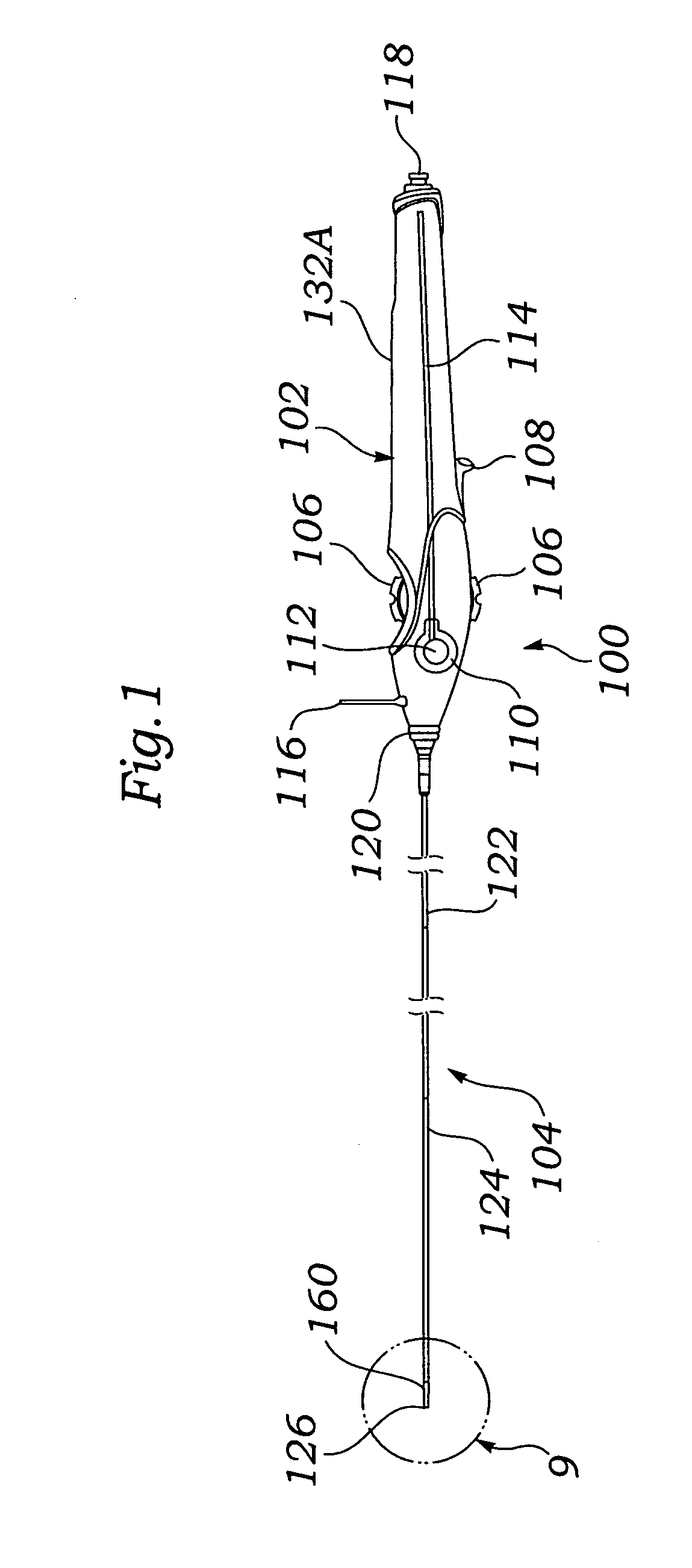

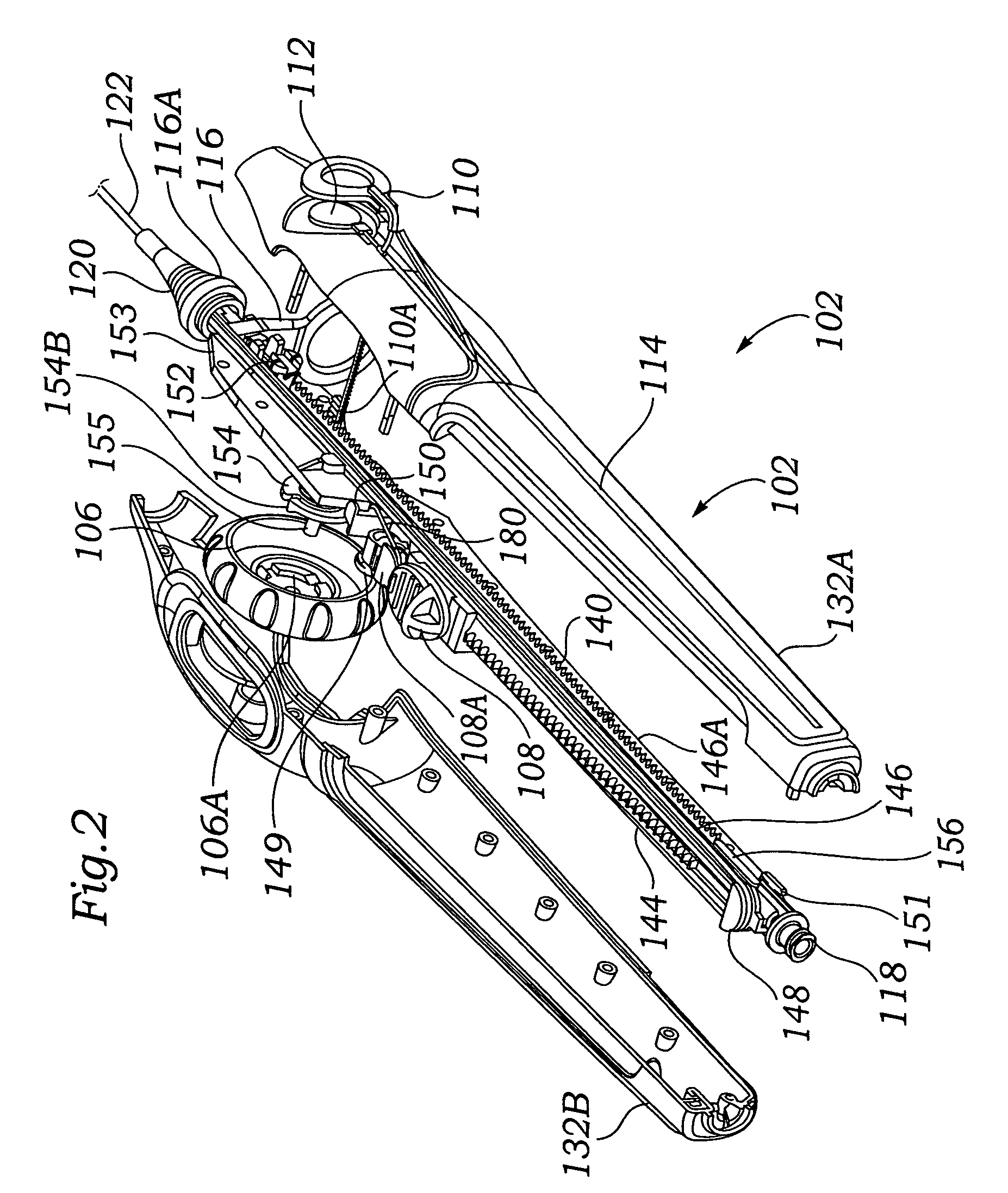

ActiveUS20070168014A1Highly controllableEasily retracts an outer jacket at different speedsStentsBlood vesselsDelivery systemStent

One preferred embodiment includes a stent delivery system including a retractable sheath and an outer stability sheath. The stability sheath freely rotates relative to the retractable sheath, relieving compression forces caused by twisting of stability sheath in when in a tortuous conformation.

Owner:CR BARD INC

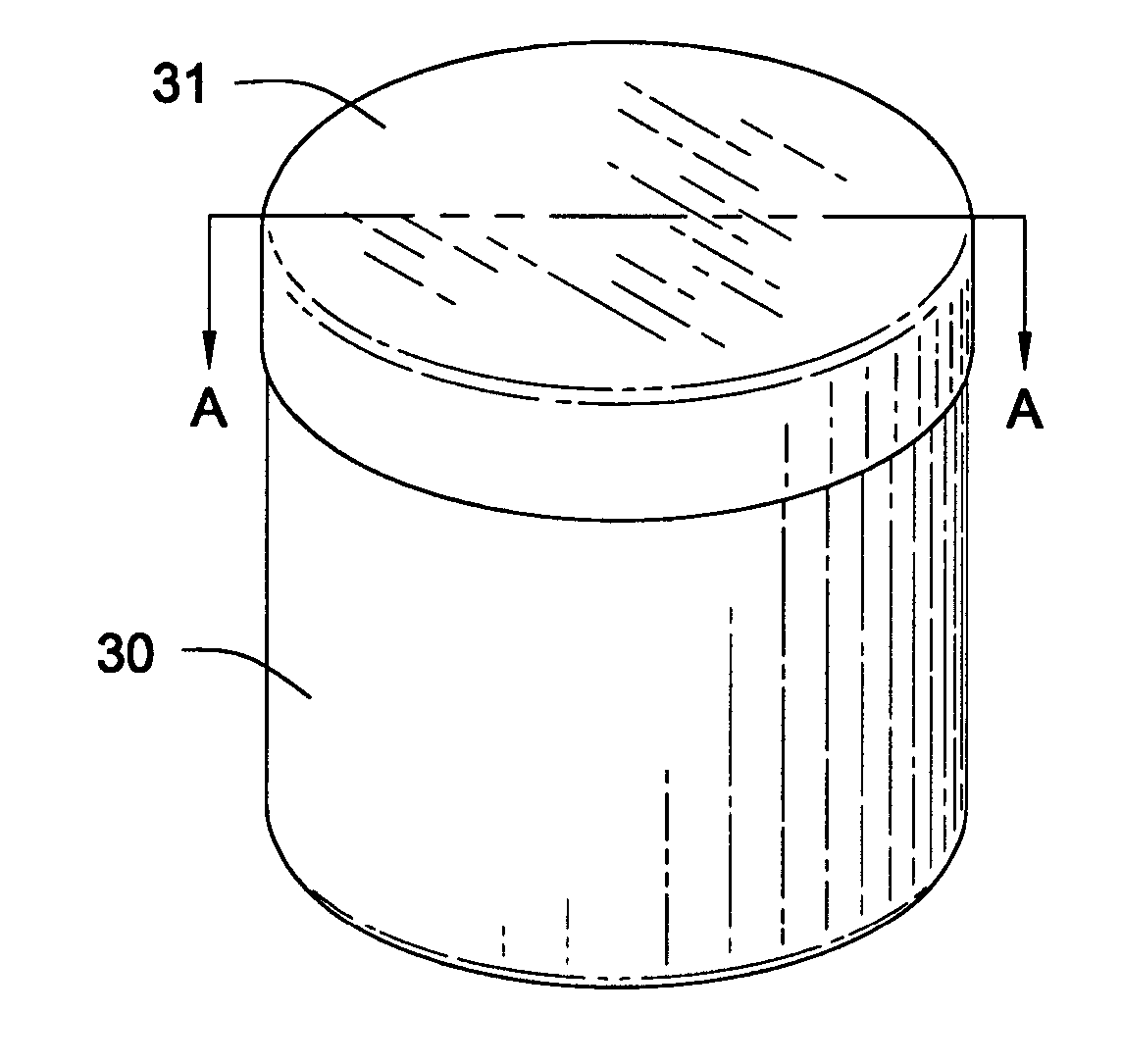

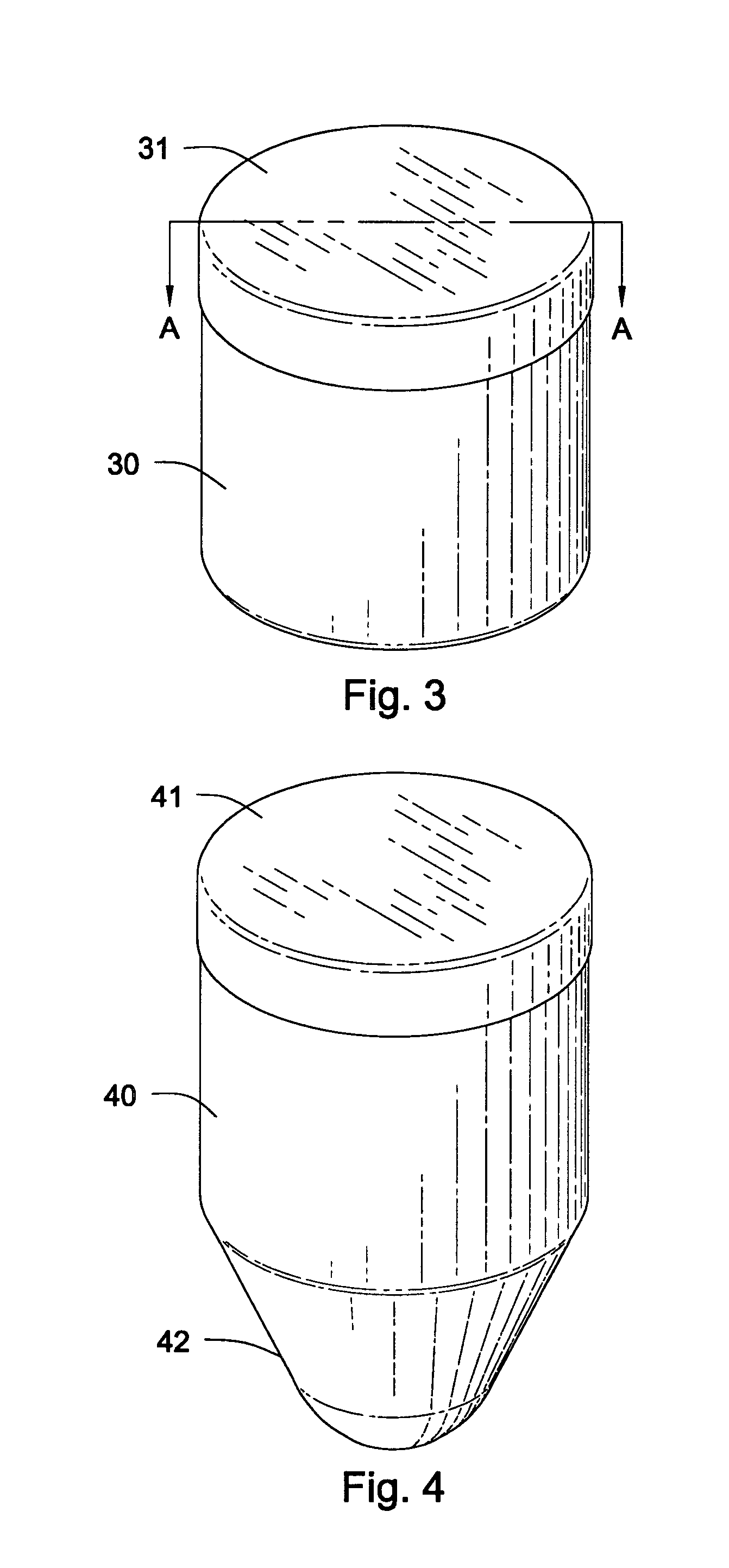

Container assembly for HPHT processing

InactiveUS20050044800A1Extended pathPigmenting treatmentPressurized chemical processHermetic sealCarbide

An assembly for High-Pressure High-Temperature (HPHT) processing comprising a can, a cap, a meltable sealant and sealant barrier, and a superhard mixture comprising superhard particles. The superhard particles may be positioned adjacent a substrate of cemented metal carbide. The can and cap contain the superhard mixture with the sealant barrier positioned within the assembly so as to be intermediate the sealant and at least a portion of the mixture, thereby preventing the sealant from coming in contact with the mixture during processing. The assembly is placed within a vacuum chamber and heated to a temperature sufficient to cleanse the assembly and then melt the sealant providing a hermetic seal for the assembly in preparation for further HPHT processing.

Owner:REEDHYCALOG UTAH LLC

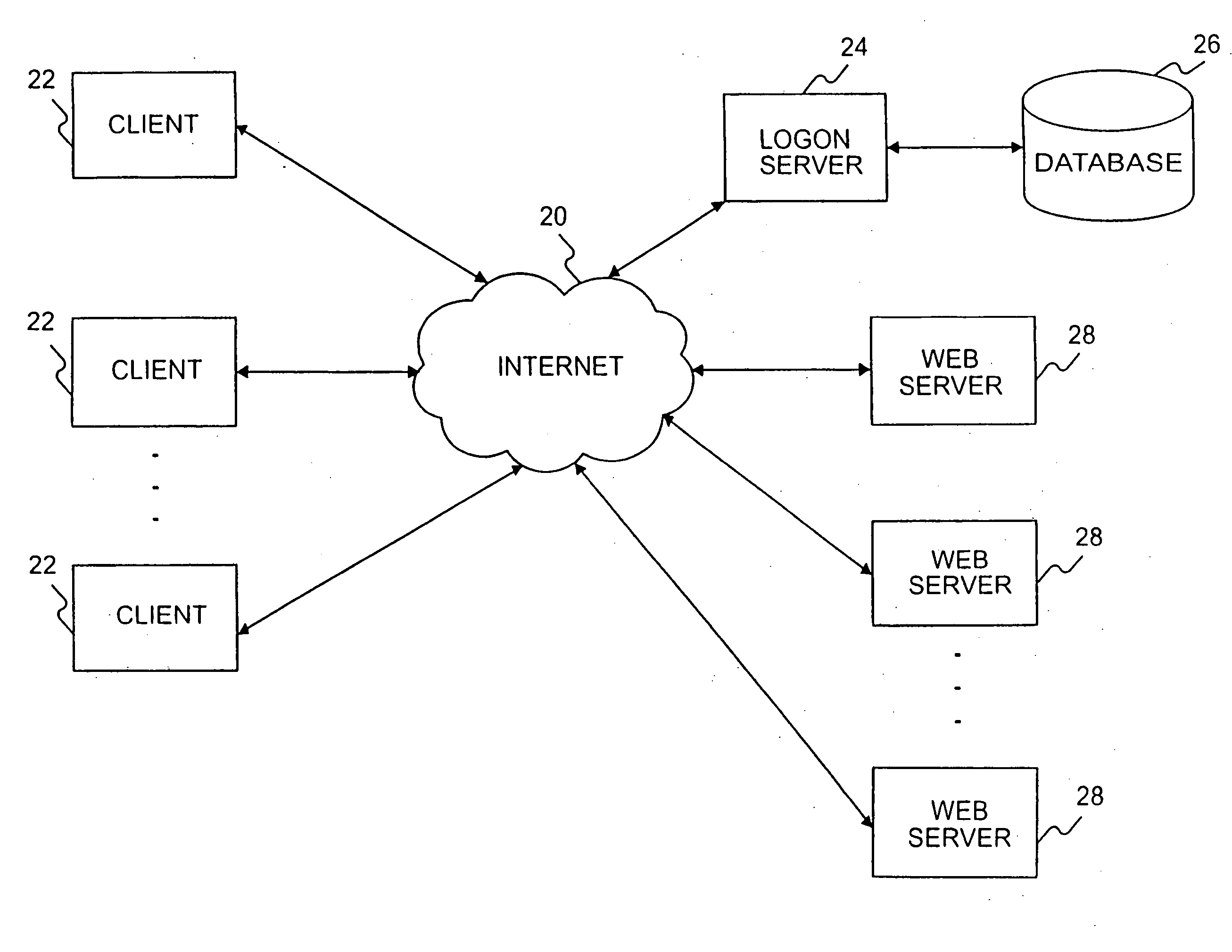

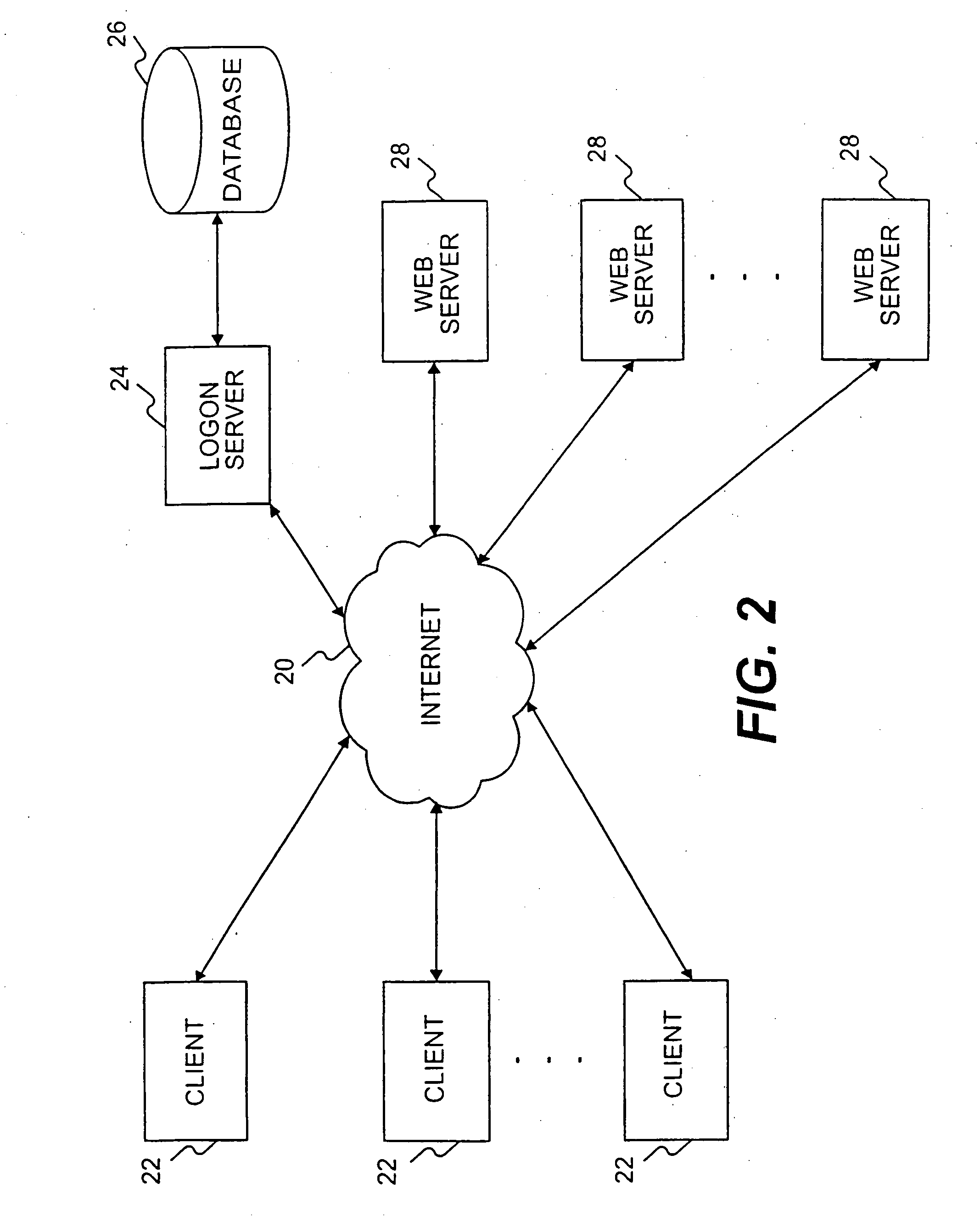

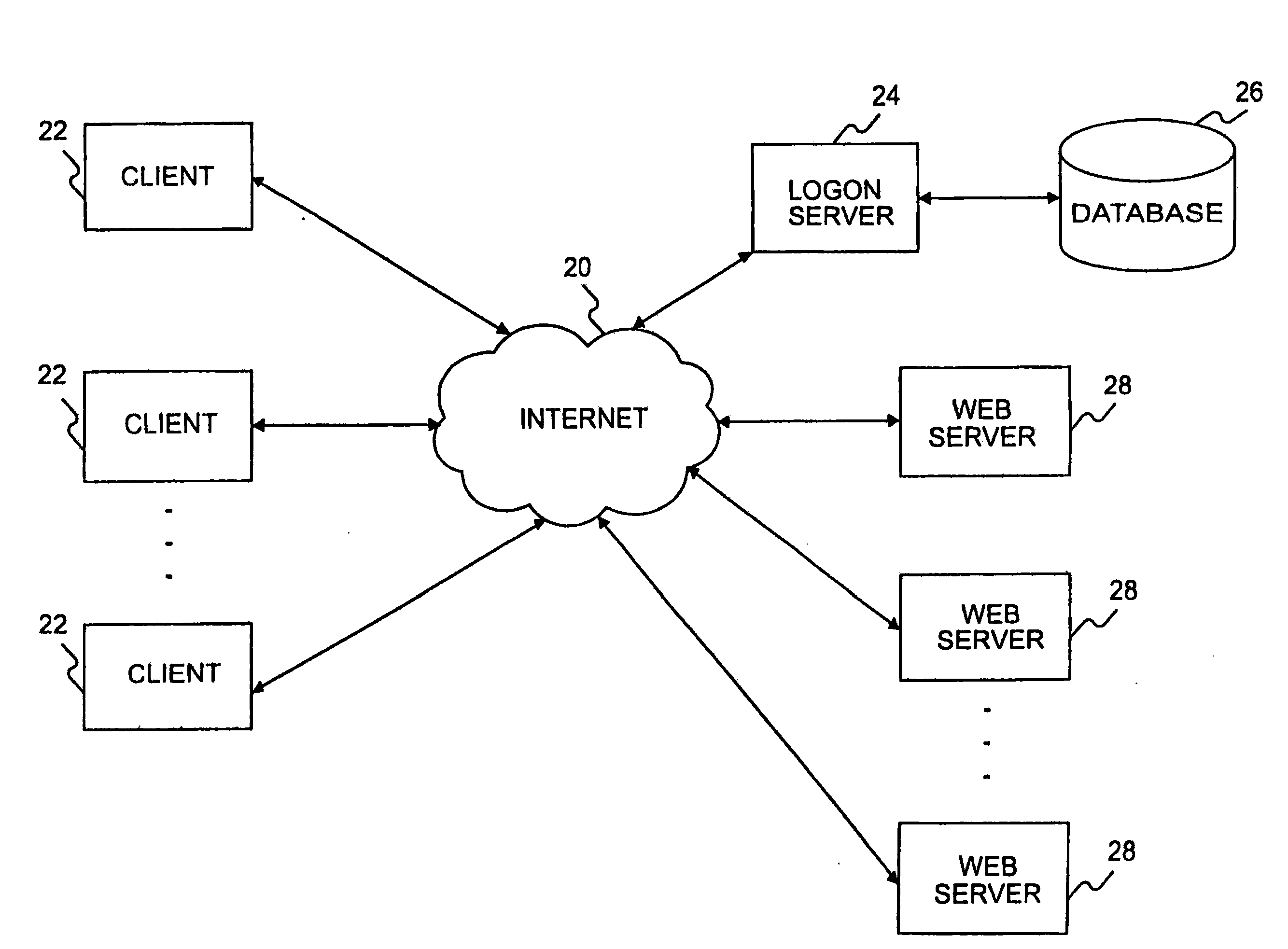

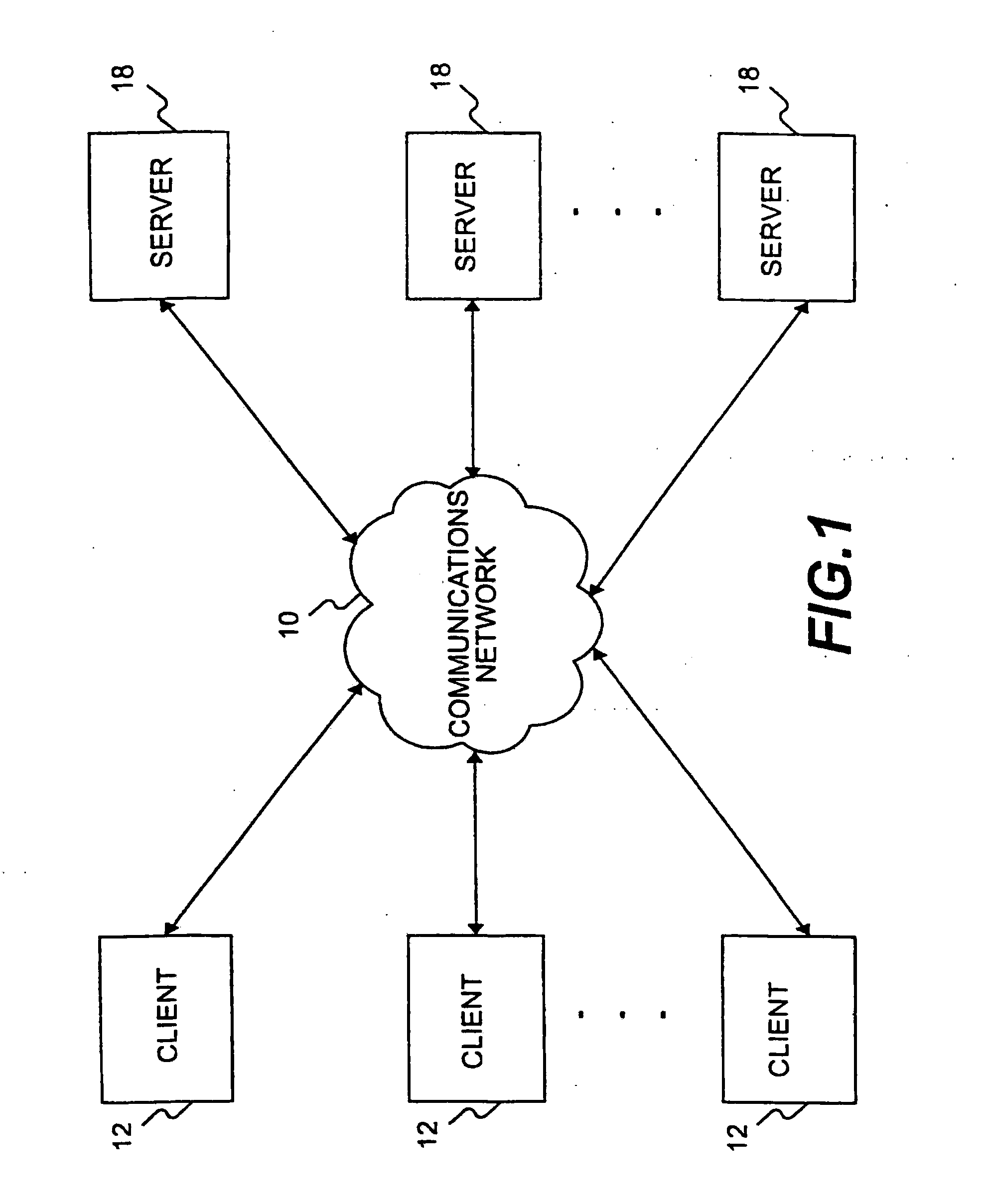

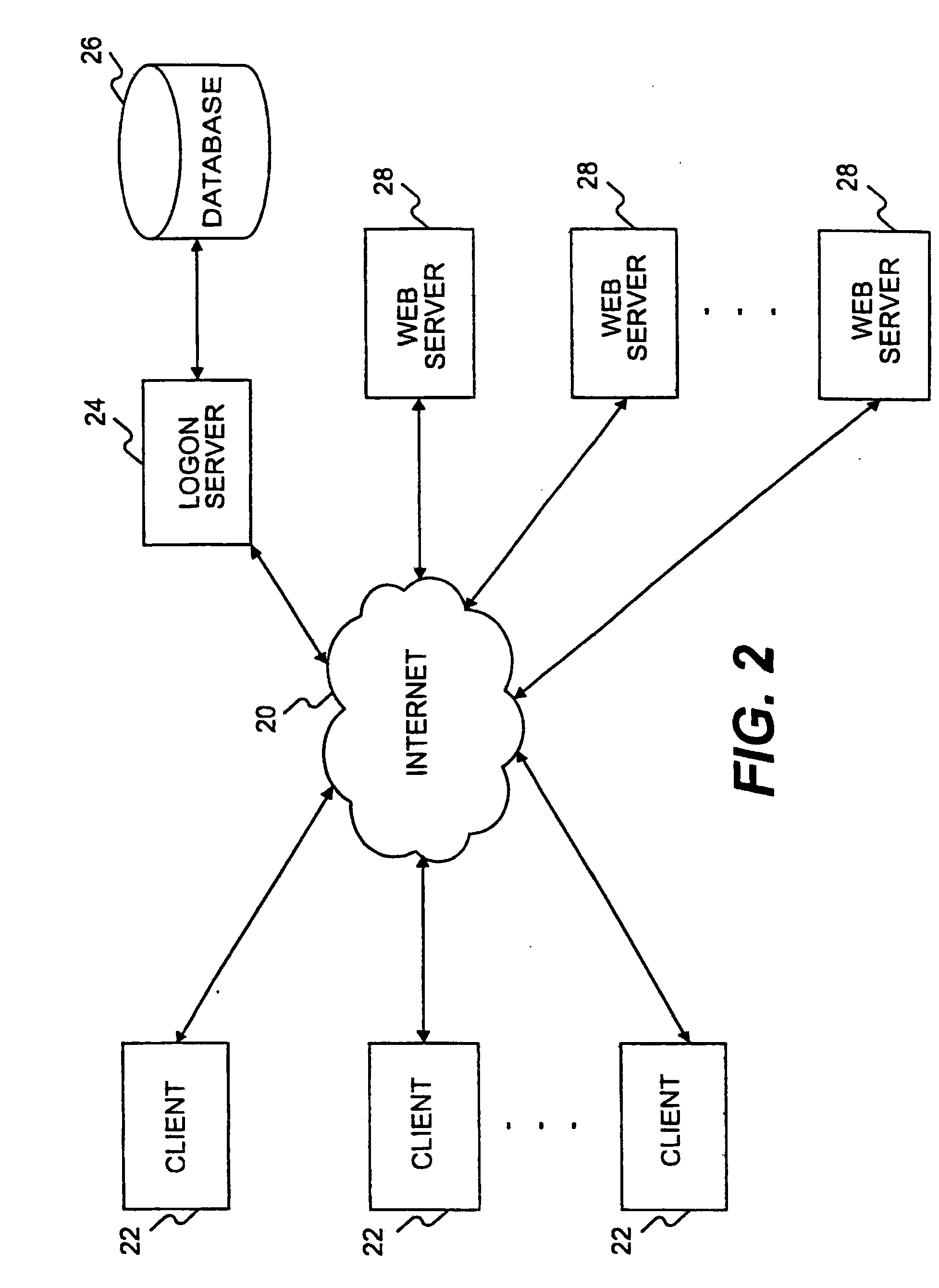

System and method for providing user authentication and identity management

InactiveUS20070277235A1Improve mobilityMore automatedUser identity/authority verificationMultiple digital computer combinationsEngineeringUser authentication

A distributed client / server system comprises a network of servers and clients, such as the Internet, in which user access to certain restricted resources is controlled by a logon procedure that identifies an authorized user to the respective administering server. The disclosed system and method includes a logon server that comprises a user authentication procedure by which a user can logon to the logon server from any client in the network and uniquely identify itself to the logon server. The logon server also includes a library of usernames and passwords for the restricted resources chosen by each user and the ability to automatically log the users on to any of the restricted resources when selected by the user through a personal catalog maintained by the logon server. The disclosed system and method also includes various other features for providing user authentication and identity management in a network environment, such as the Internet.

Owner:BARRETT PAUL D +1

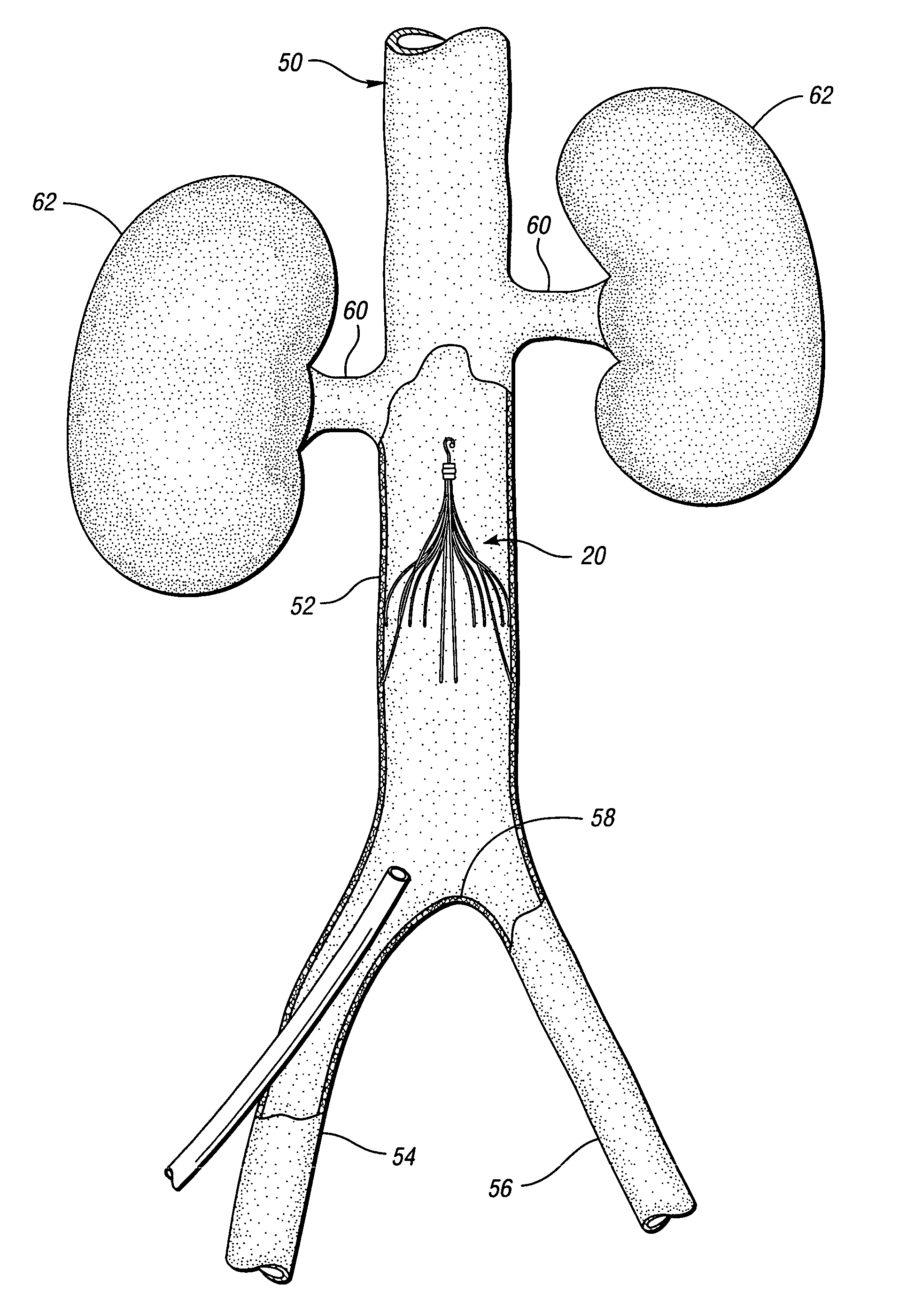

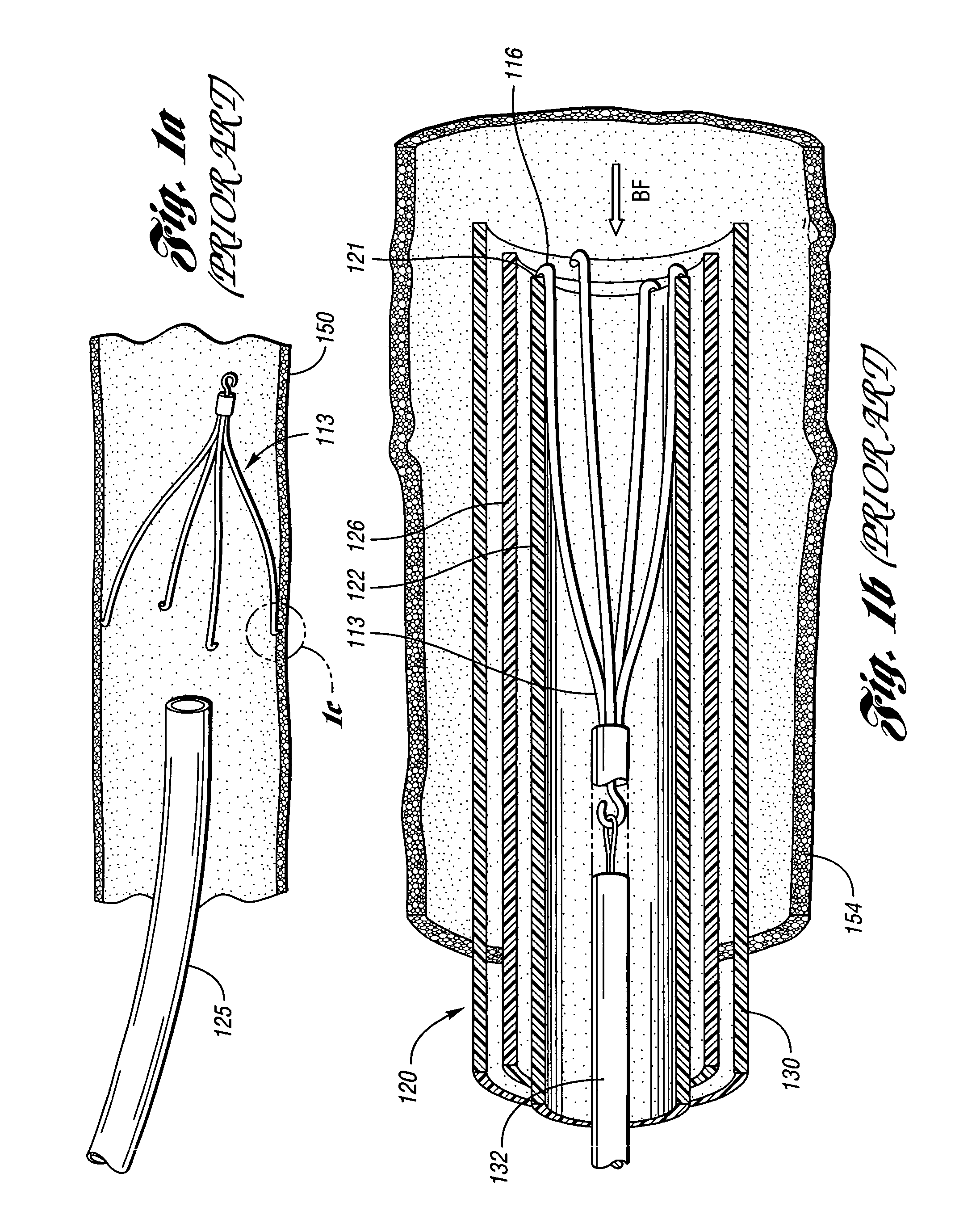

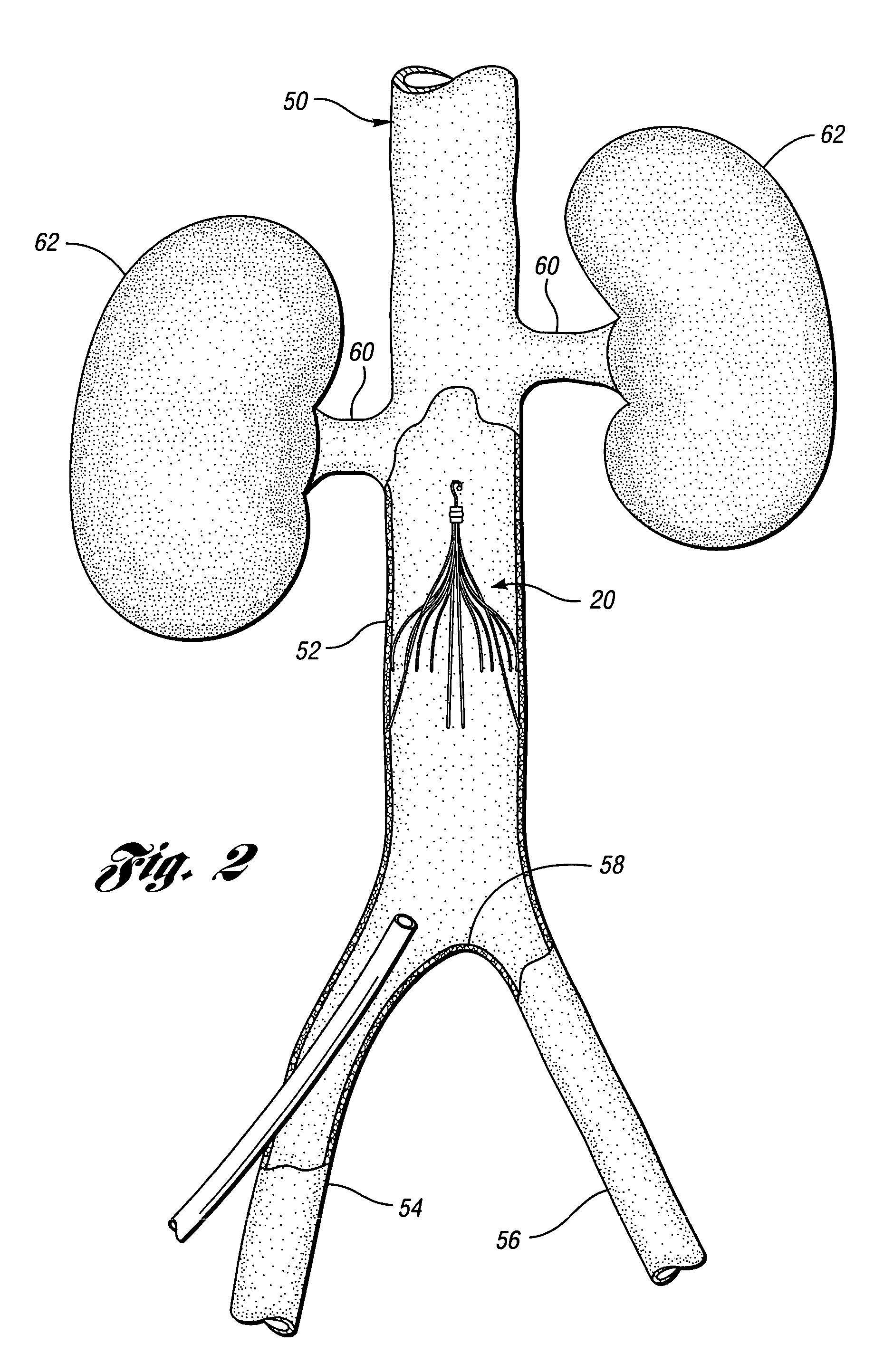

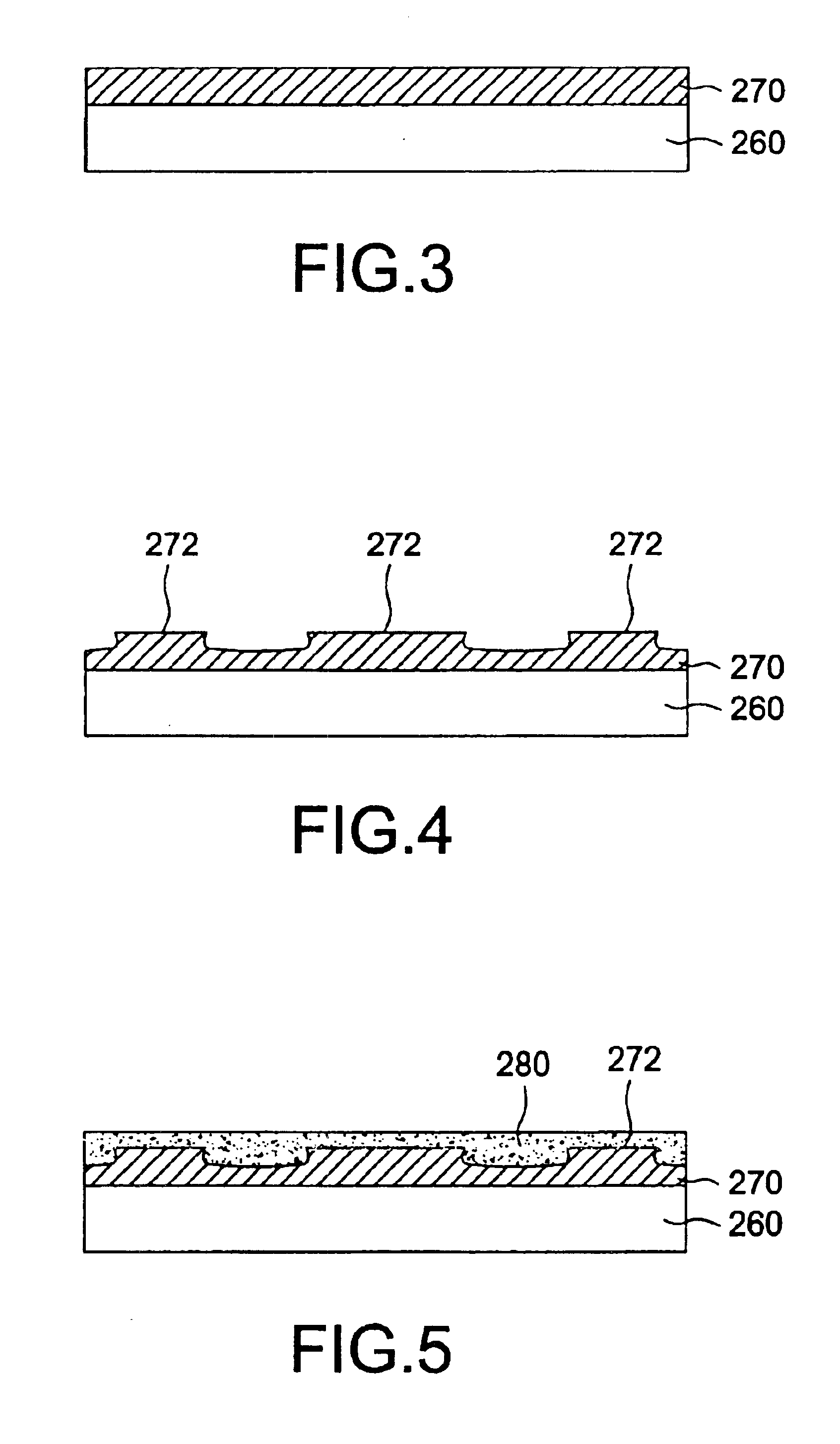

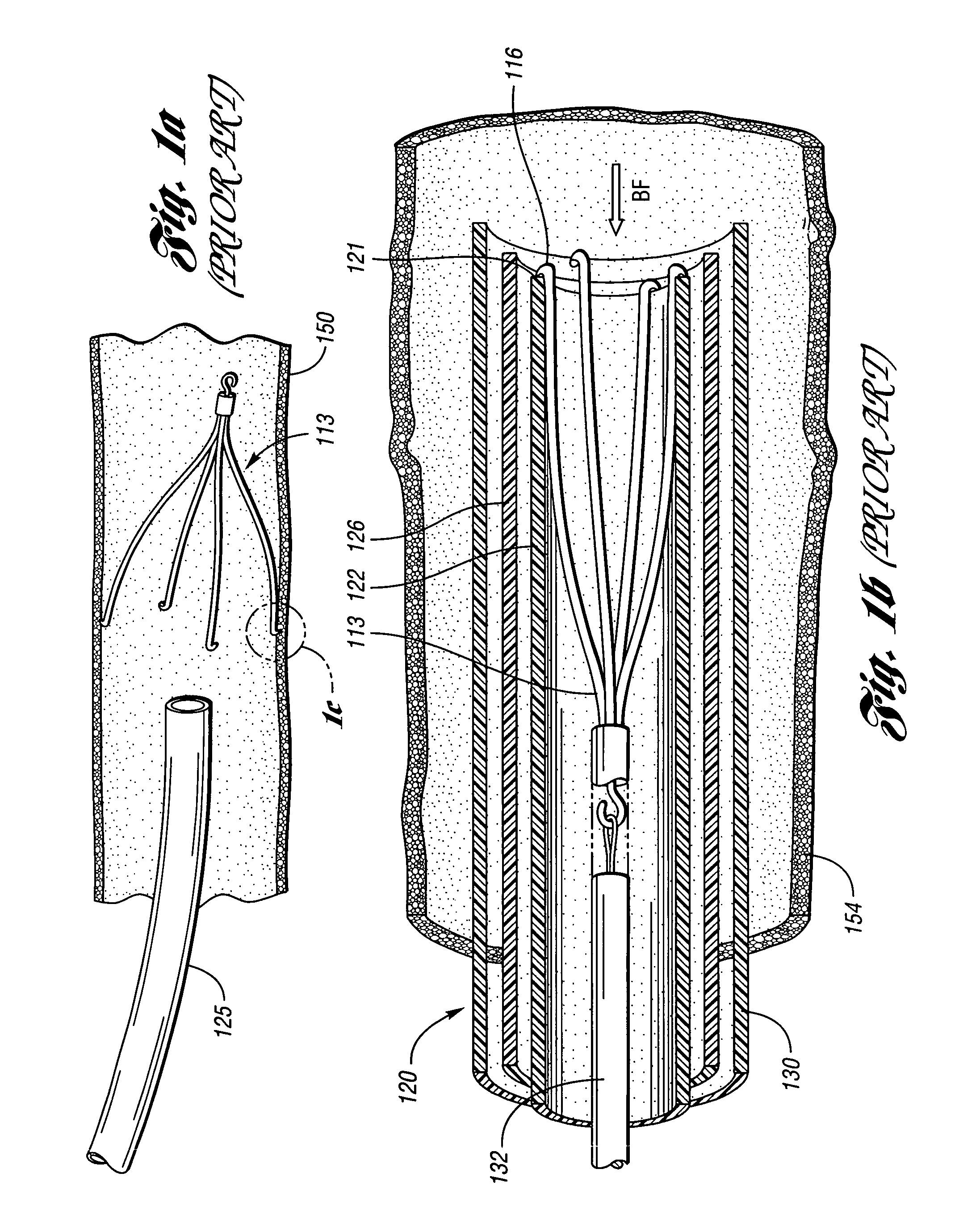

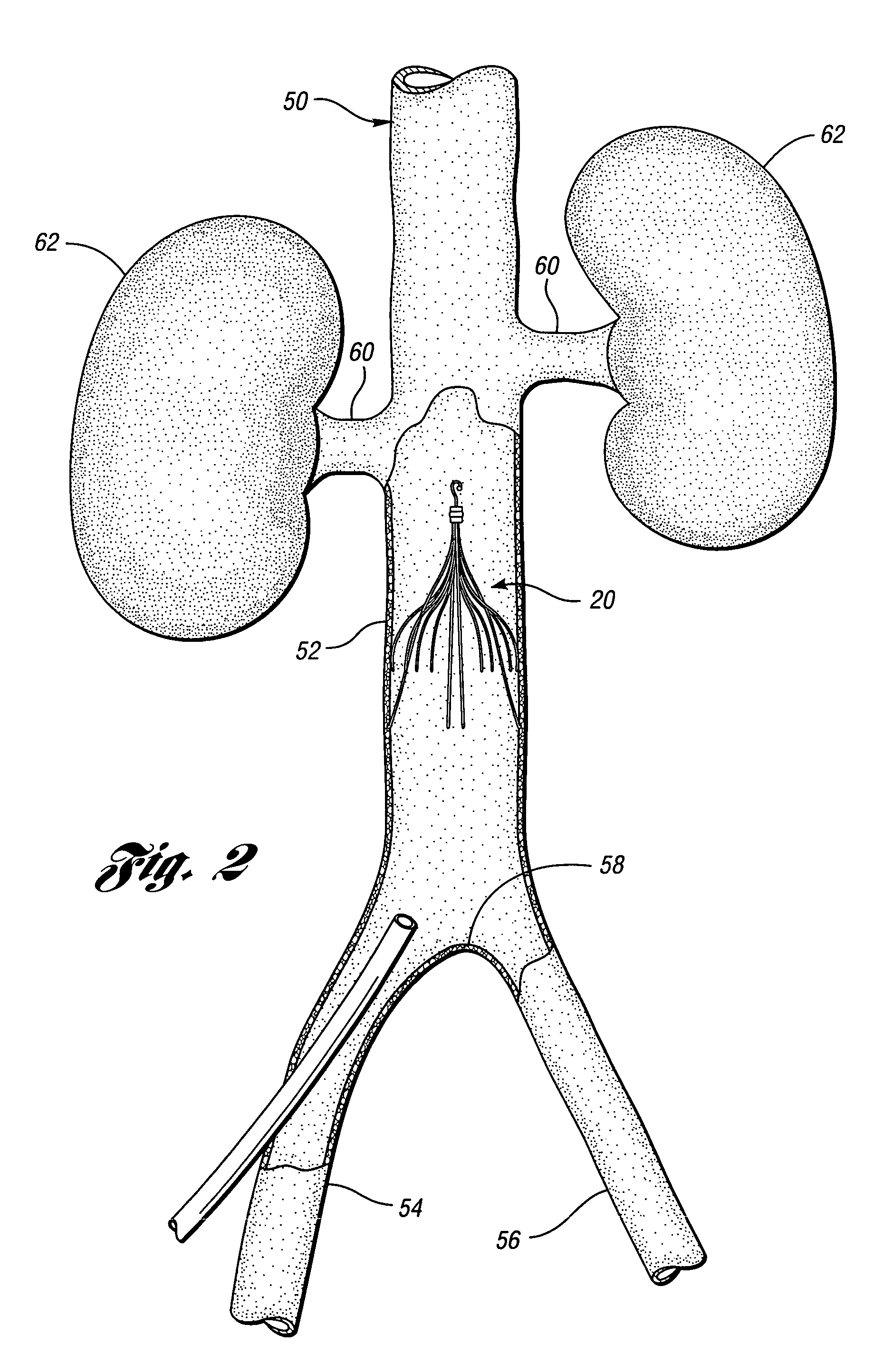

Removable vena cava filter for reduced trauma in collapsed configuration

The present invention provides a removable vena cava filter for capturing thrombi in a blood vessel. The filter comprises a plurality of primary struts having first ends attached together along a longitudinal axis. Each primary strut has an arcuate segment extending from the first end to an anchoring hook. The primary struts are configured to move between an expanded state for engaging the anchoring hooks with the blood vessel and a collapsed state for filter retrieval or delivery. Each primary strut are configured to cross another primary strut along the longitudinal axis in the collapsed state such that the arcuate segments occupy a first diameter greater than a second diameter occupied by the anchoring hooks in the collapsed state for filter retrieval or delivery.

Owner:COOK MEDICAL TECH LLC

Heat-preservation sound-proof low-density foamed concrete

The invention discloses heat-preservation sound-proof low-density foamed concrete. The heat-preservation sound-proof low-density foamed concrete is characterized by being prepared from, by weight, 40-100 parts of cement, 5-40 parts of carbide slags, 5-40 parts of active powder, 1-20 parts of foaming agents, 0.1-8 parts of foam stabilizers, 0-8 parts of water reducing agents, 0-8 parts of coagulation accelerator, 0-25 parts of waterproof agents, 0.1-5 parts of anti-cracking agents and 25-150 parts of water, and the foamed concrete is prepared from the materials through mixing, foam molding and maintenance. The heat-preservation sound-proof low-density foamed concrete has the advantages of being low in dry density, low in heat conductivity coefficient, high in strength, wide in raw material source, low in cost, simple in preparation technology, convenient to prefabricate in factories or pour on site and the like; the heat-preservation sound-proof low-density foamed concrete is suitable for building exterior wall heat-preservation engineering, roof heat-preservation engineering, floor heating heat-preservation engineering, composite heat-preservation wall engineering, backfilling engineering, retaining wall slab engineering and the like.

Owner:株洲大禹恒基新材料有限公司

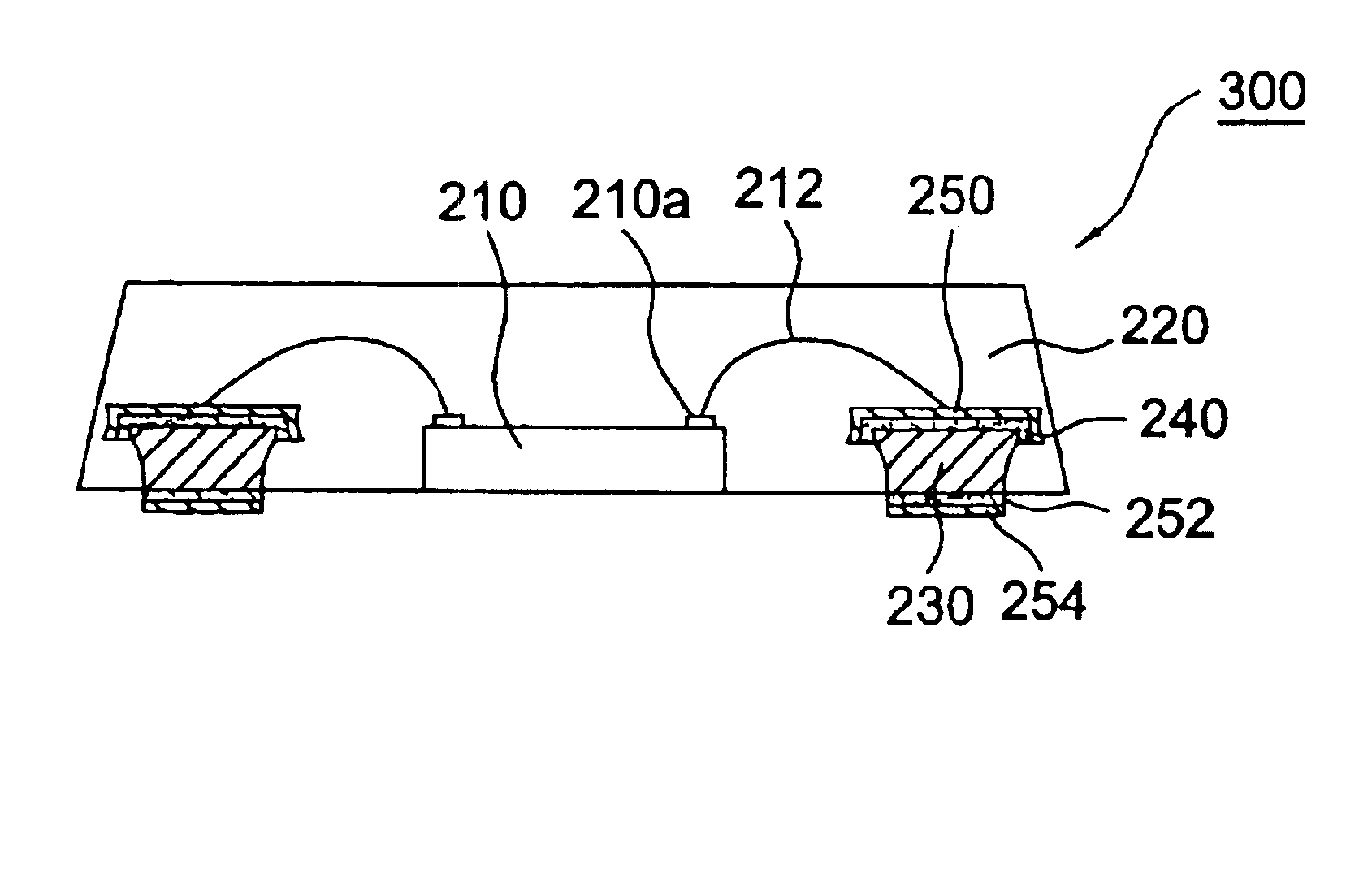

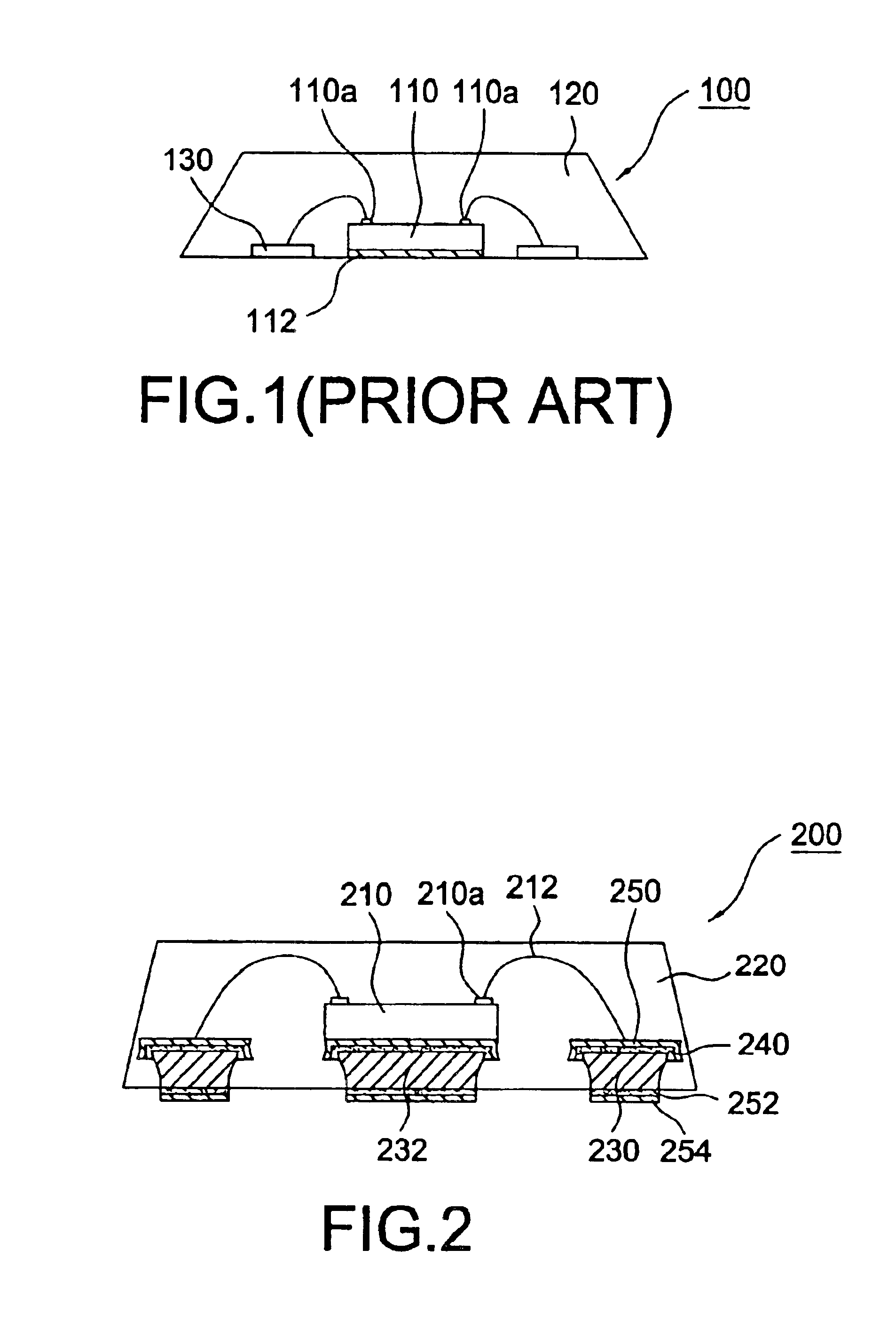

Low-pin-count chip package and manufacturing method thereof

InactiveUS6861295B2Enhancing “ locking ”Extended pathSemiconductor/solid-state device detailsSolid-state devicesMoisture diffusionEngineering

A low-pin-count chip package including a die pad for receiving a semiconductor chip and a plurality of connection pads electrically coupled to the semiconductor chip. The semiconductor chip, the die pad, and the connection pads are encapsulated in a package body such that the lower surfaces of the die pad and the connection pads are exposed through the package body. The present invention is characterized in that the die pad and the connection pads have a substantially concave profile thereby prolonging the time for moisture diffusion into the package as well as enhancing the “locking” of the die pad and the connection pads in the package body. The present invention further provides a method of producing the low-pin-count chip package described above.

Owner:ADVANCED SEMICON ENG INC

Removable vena cava filter for reduced trauma in collapsed configuration

The present invention provides a removable vena cava filter for capturing thrombi in a blood vessel. The filter comprises a plurality of primary struts having first ends attached together along a longitudinal axis. Each primary strut has an arcuate segment extending from the first end to an anchoring hook. The primary struts are configured to move between an expanded state for engaging the anchoring hooks with the blood vessel and a collapsed state for filter retrieval or delivery. Each primary strut are configured to cross another primary strut along the longitudinal axis in the collapsed state such that the arcuate segments occupy a first diameter greater than a second diameter occupied by the anchoring hooks in the collapsed state for filter retrieval or delivery.

Owner:COOK MEDICAL TECH LLC

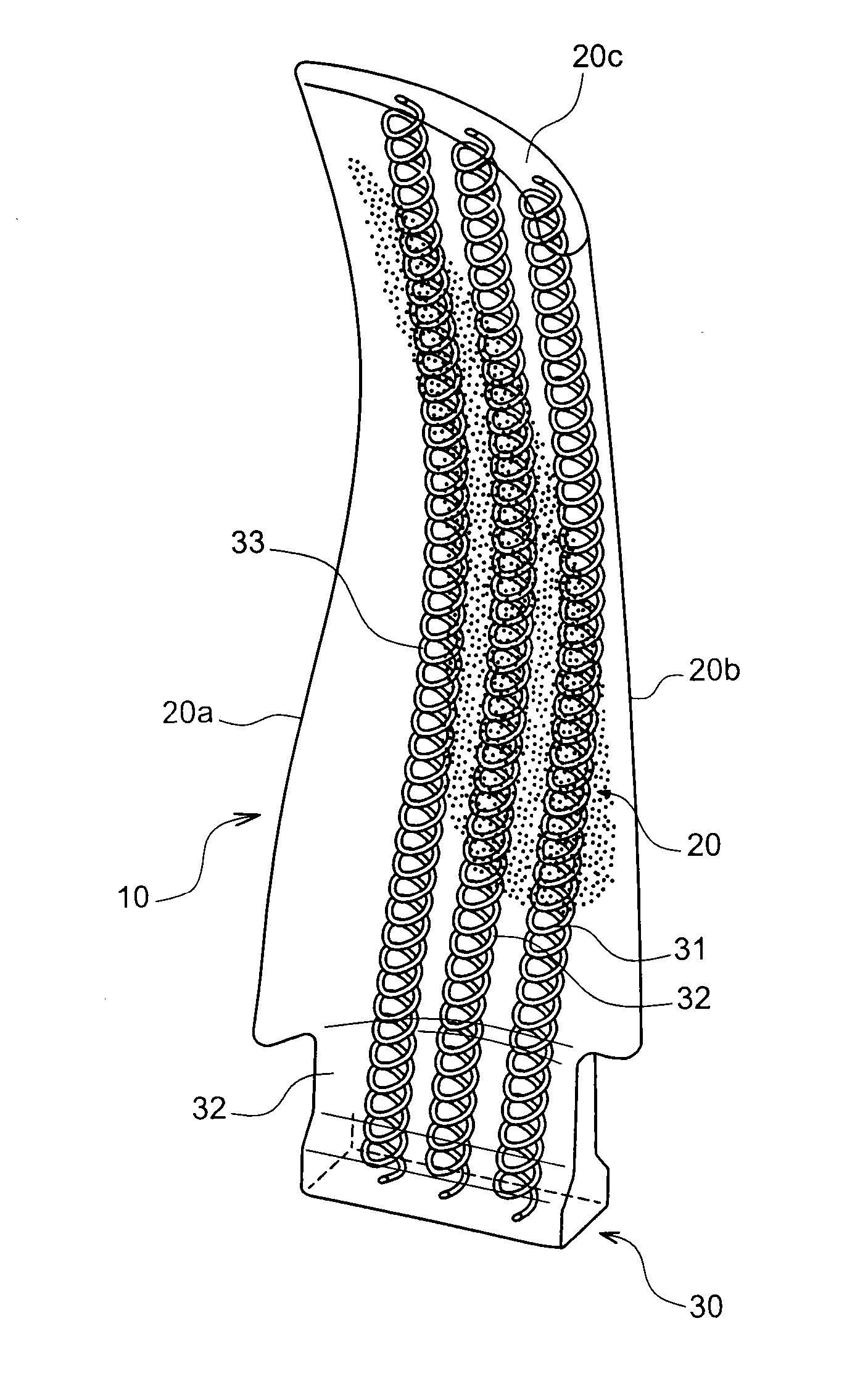

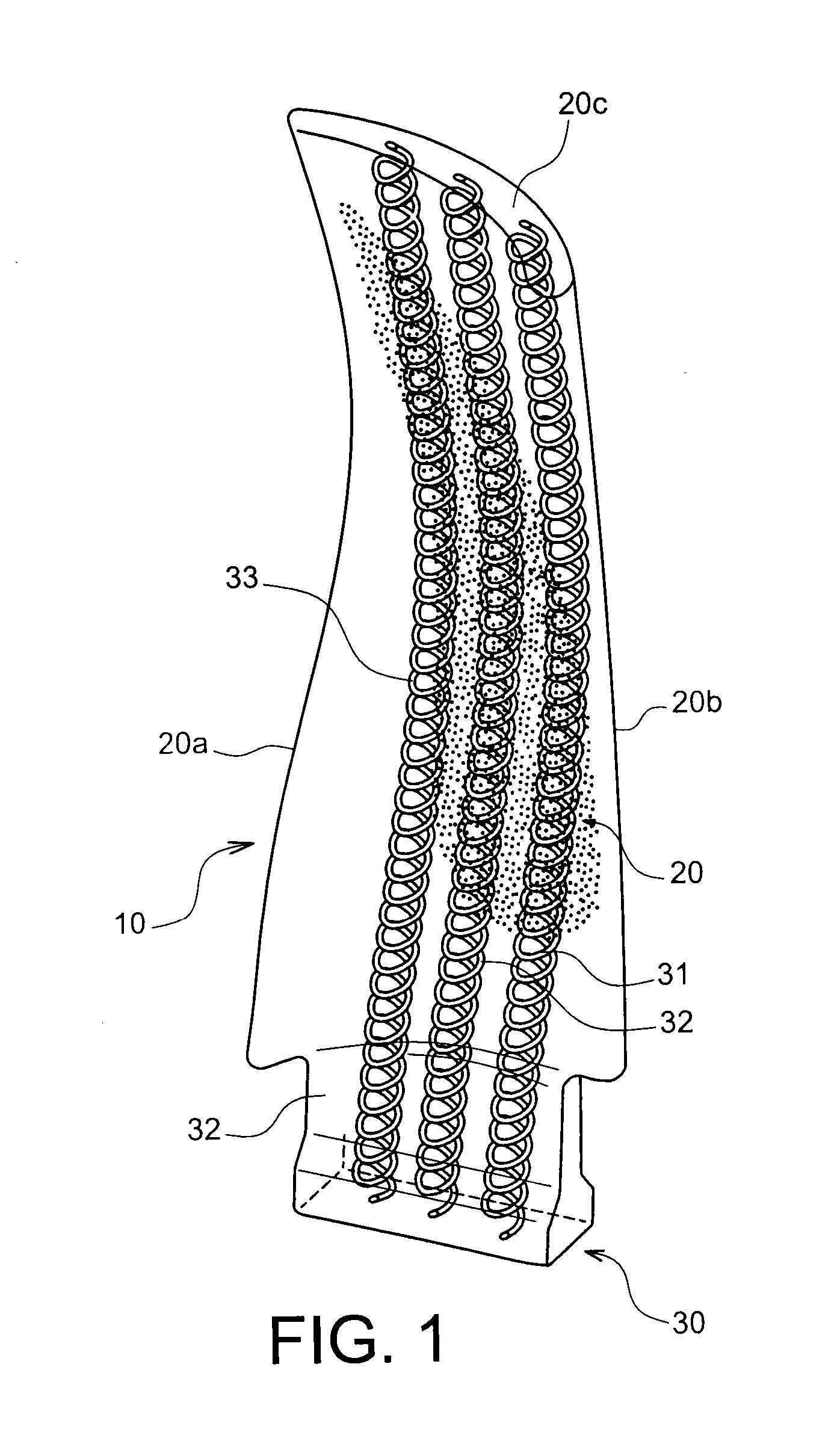

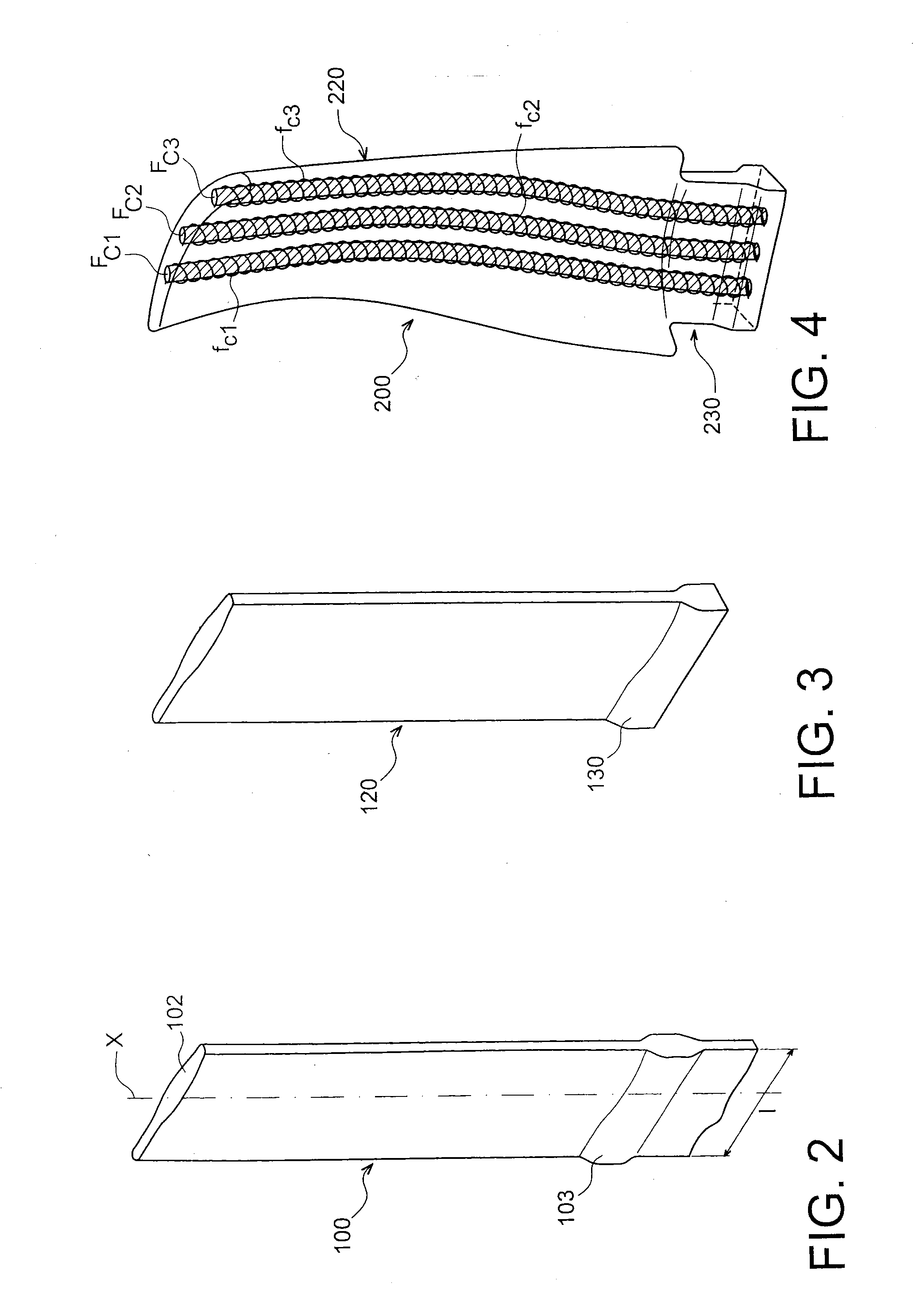

Method for manufacturing an oxide/oxide composite material turbomachine blade provided with internal channels

ActiveUS20140161626A1Improved cooling internal channelMaintain mechanical integrityPropellersEngine manufactureOxide compositeMechanical engineering

An oxide / oxide composite material turbomachine blade including a fiber reinforcement obtained by weaving a first plurality of threads and a second plurality of threads, with the threads of said first plurality of threads being arranged in successive layers and extending in the longitudinal direction of the fiber blank corresponding to the longitudinal direction of the blade is disclosed. The reinforcement is densified by a matrix, with the blade further including one or several internal channels having a coiled shape extending in the longitudinal direction of the blade.

Owner:SN DETUDE & DE CONSTR DE MOTEURS DAVIATION S N E C M A

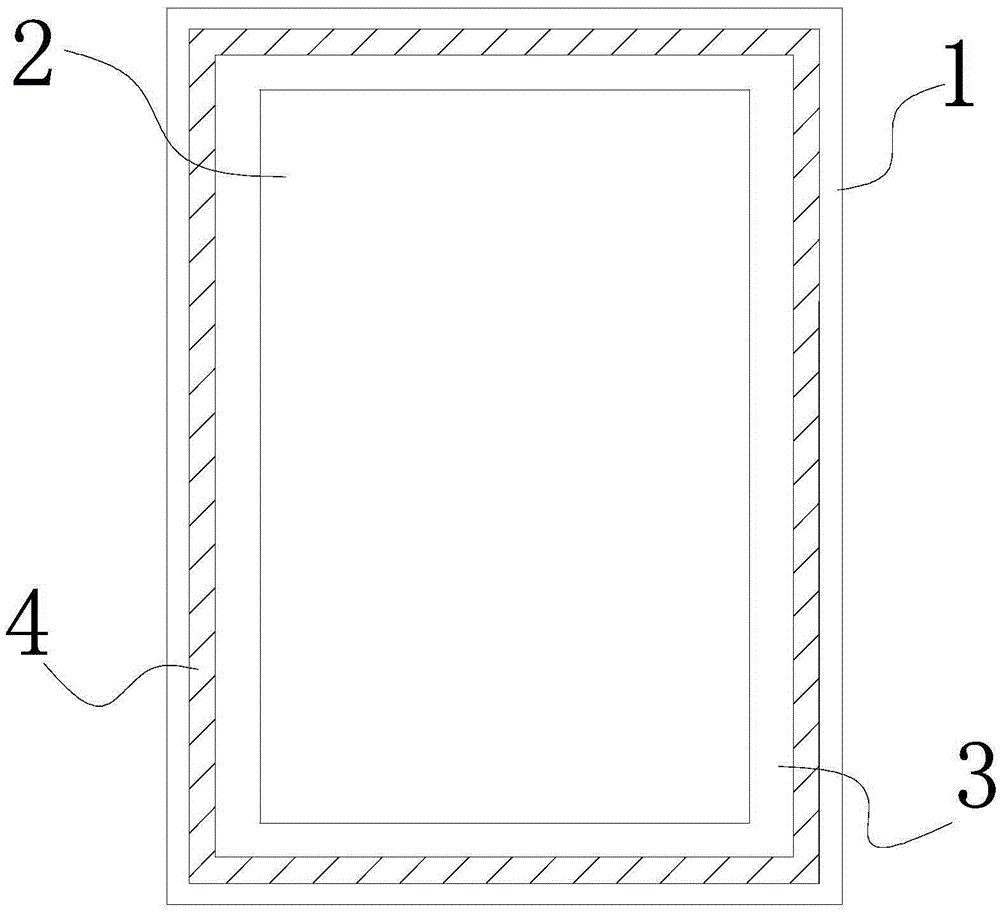

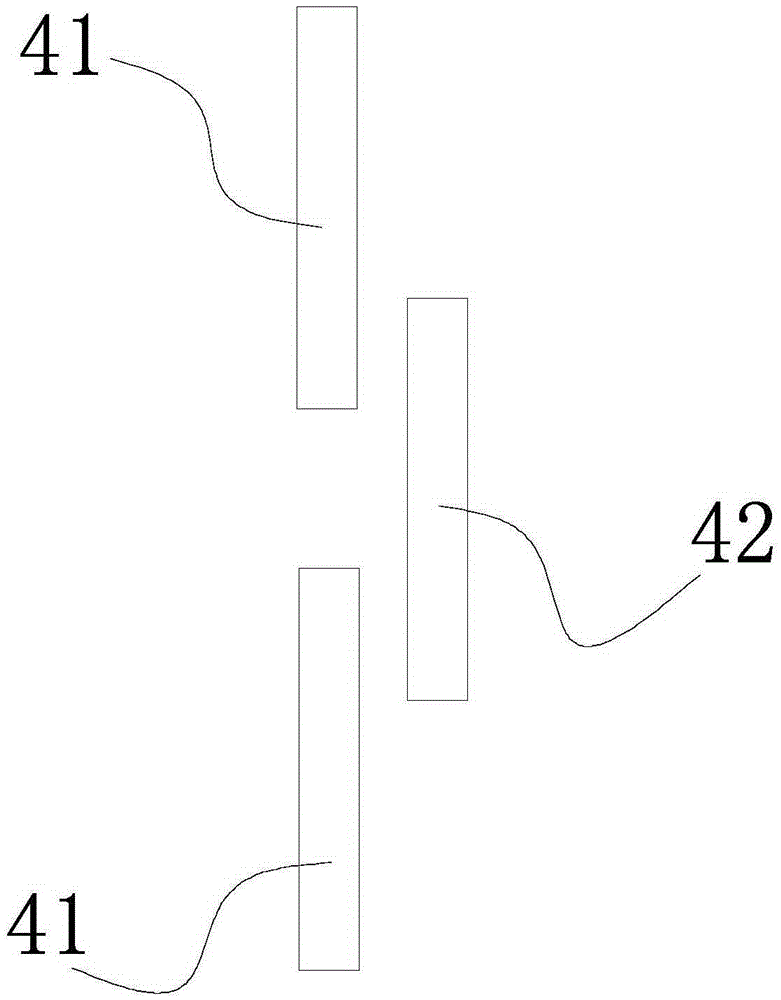

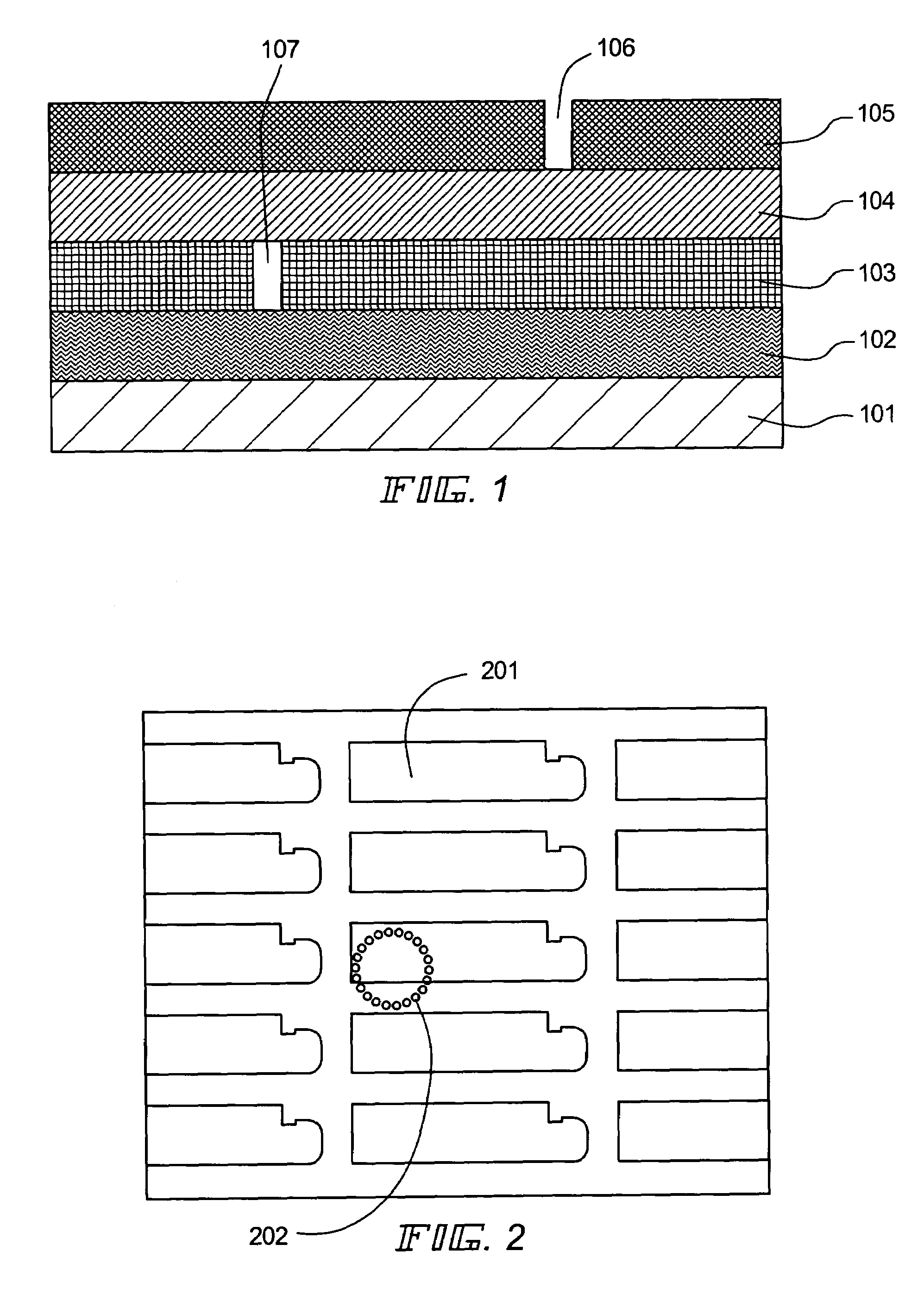

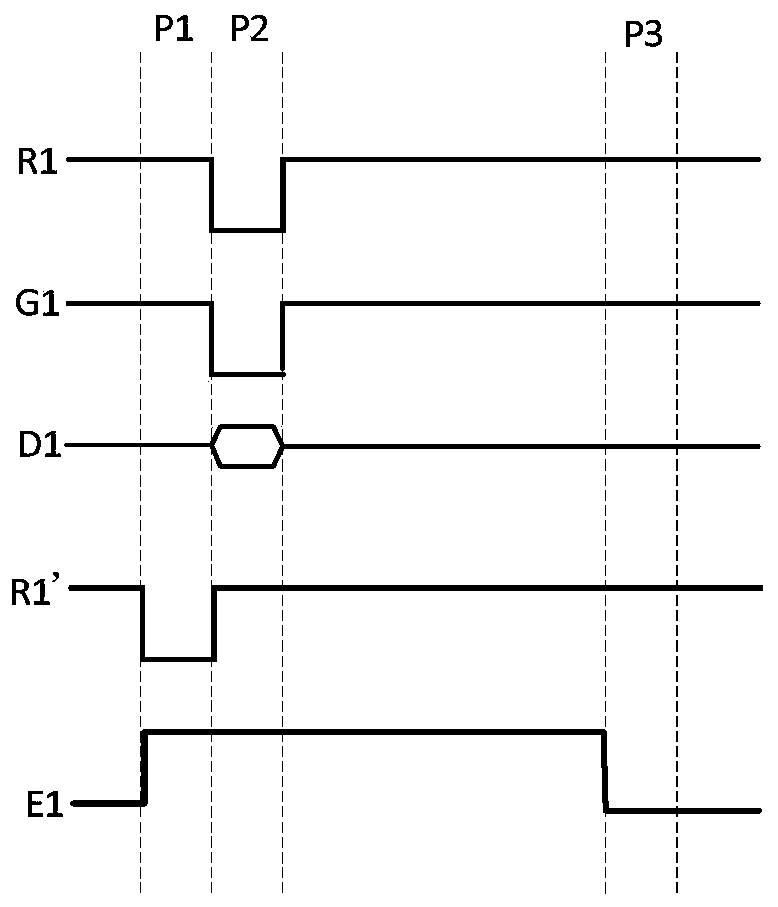

Flexible OLED display panel

ActiveCN105261712AAvoid scratchesPrevent crushingSolid-state devicesSemiconductor/solid-state device manufacturingEngineeringWater block

The invention discloses a flexible OLED display panel, which comprises a flexible substrate, an OELD device, a first encapsulation layer, a barrier layer and a second encapsulation layer, wherein the OLED device is arranged on the flexible substrate; the first encapsulation layer is arranged on the flexile substrate and covers the OLED device; the barrier layer is arranged on the flexible substrate, surrounds the periphery of the first encapsulation layer, and comprises a plurality of discontinuous barrier units; the plurality of barrier units are arranged in a chain form; and the second encapsulation layer is arranged on the flexible substrate and covers the first encapsulation material and the barrier layer. The flexible OLED display panel is capable of effectively blocking the diffusion effect of atomic deposition coating and enhancing the water blocking capacity of a thin-film encapsulation on the periphery of the flexible OLED display panel; meanwhile, the reelability of the barrier layer is increased; the development requirement of the flexible OLED display panel is relatively well met; and an important idea is also provided for development of the flexible OLED display panel.

Owner:EVERDISPLAY OPTRONICS (SHANGHAI) CO LTD

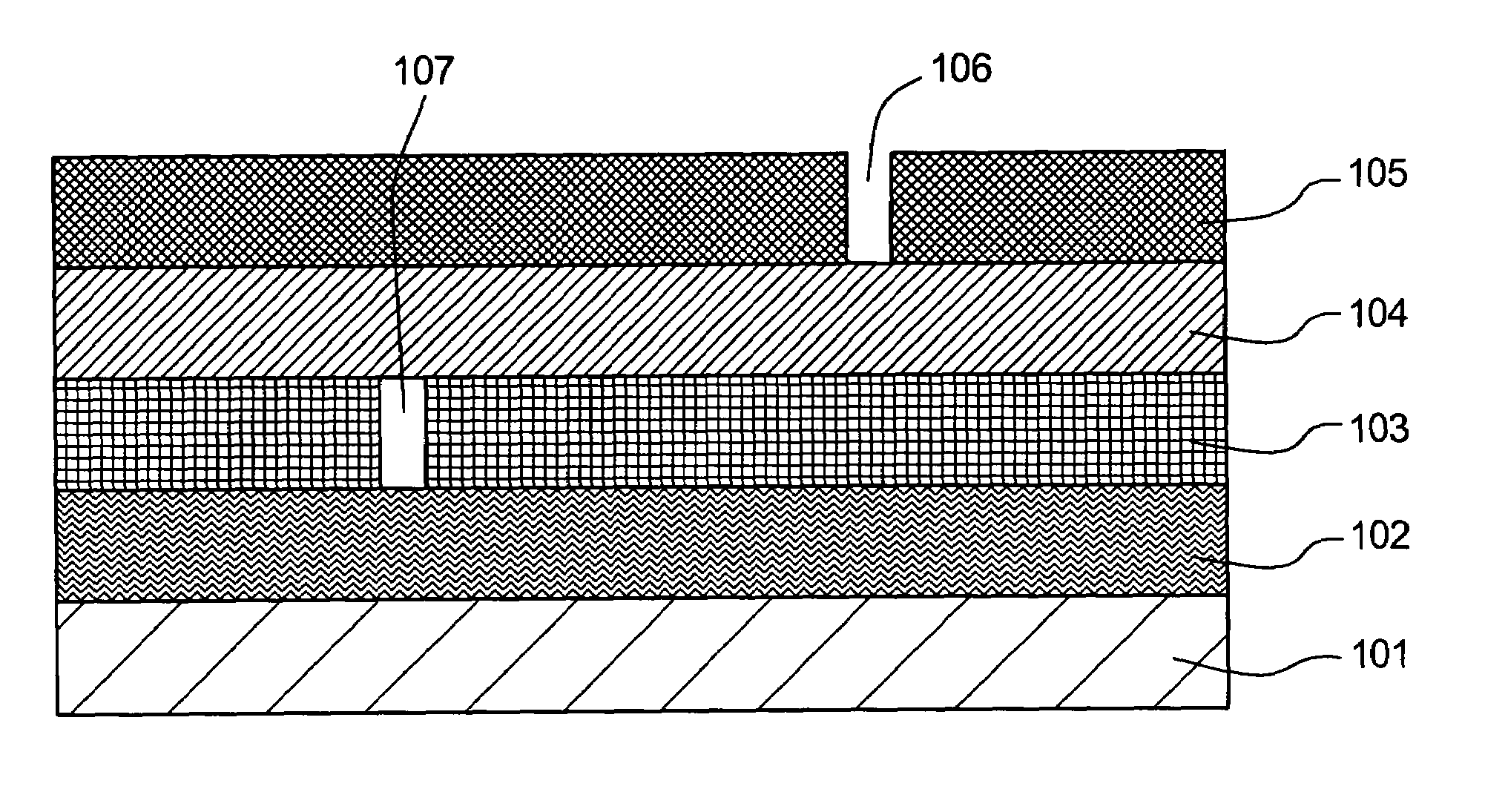

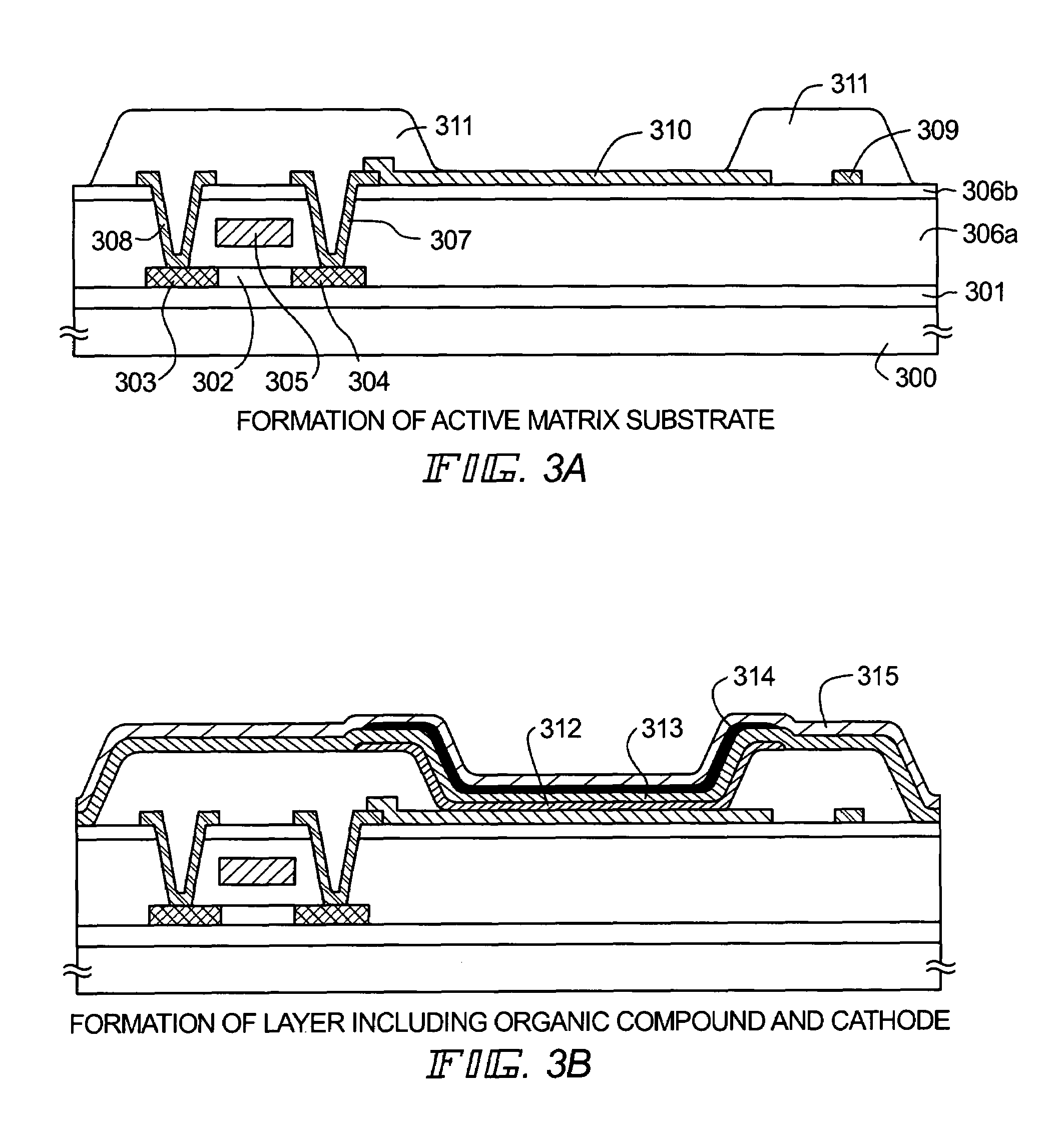

Light-emitting device having electrode formed by laminate of at least first inorganic film, organic film, and second inorganic film and method for manufacturing the same

InactiveUS7045822B2Reduce pinholesImprove reliabilityDischarge tube luminescnet screensElectroluminescent light sourcesOrganic filmDark spot

The present invention provides an organic light-emitting element where a lower electrode, an organic compound layer and an upper electrode are laminated on a substrate, wherein the upper electrode of the organic EL element is formed by a laminate of at least a conductive first inorganic film, a conductive organic film and a conductive second inorganic film, in order to suppress the occurrence of dark spot, so that the occurrence of pinholes in the upper electrode leading to dark spots is suppressed. Here, pinholes refer to holes in the upper electrode that penetrate upper electrode from the organic compound layer underneath to the atmosphere above.

Owner:SEMICON ENERGY LAB CO LTD

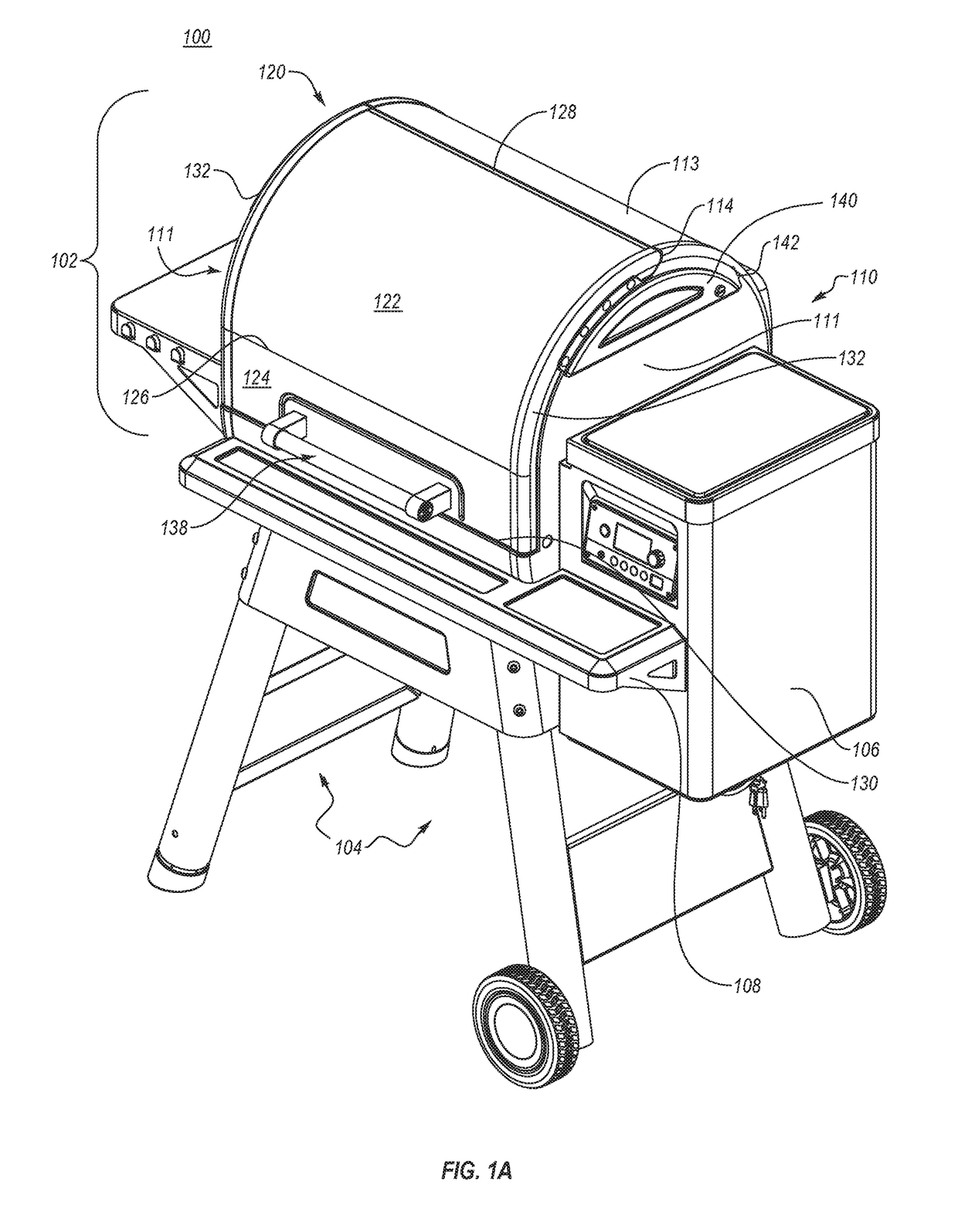

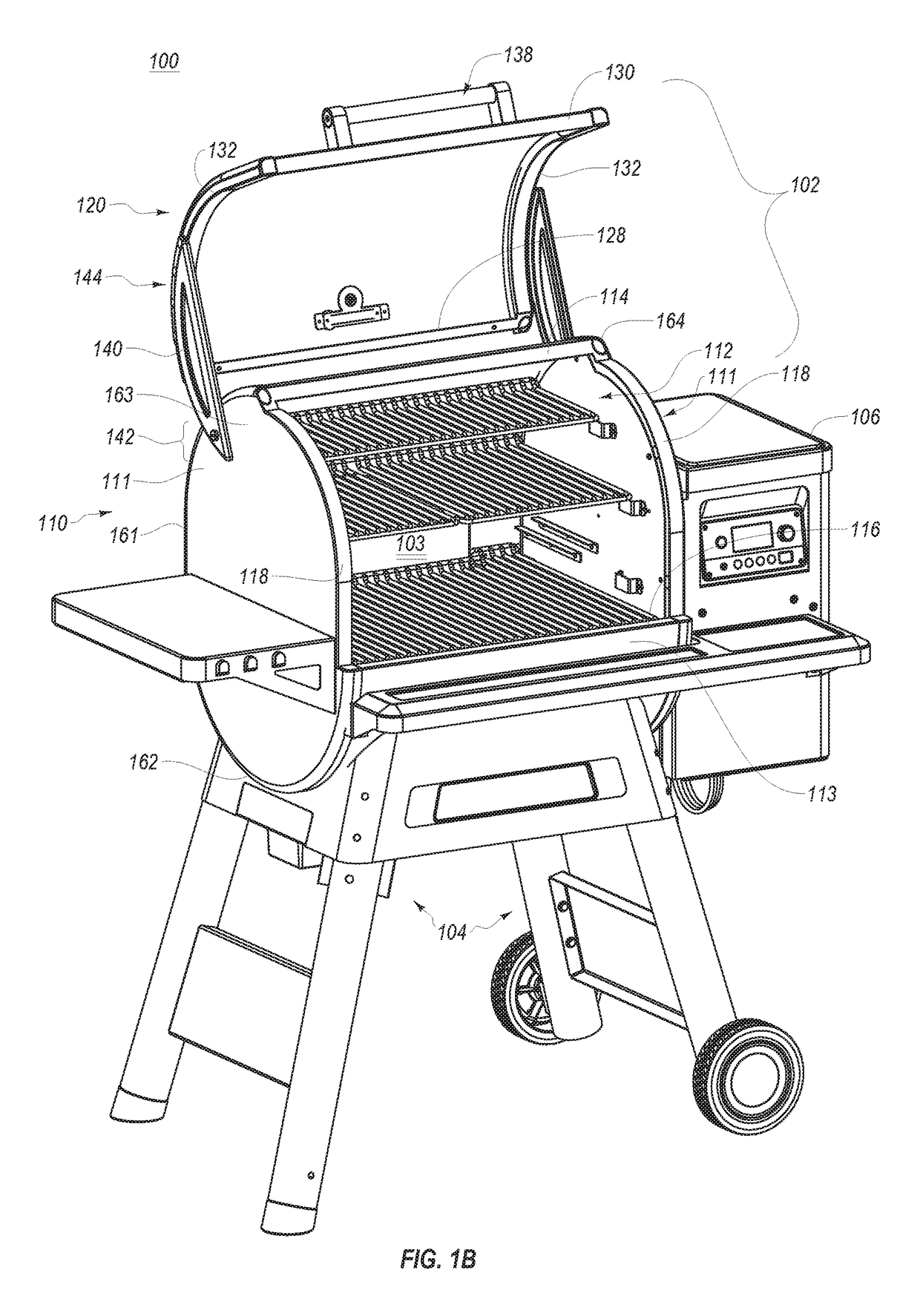

Oval-shaped grill with hinged lid

ActiveUS10213051B2Extended pathEasy to startDomestic stoves or rangesLiquid heating fuelPosterior regionEngineering

A grilling device includes an oven section having an outer wall with opposing side portions and an encircling body portion extending therebetween. The body portion has an access opening and the grilling device includes a lid that selectively covers the access opening by means of a handle attached thereto. The grilling device also includes opposing hinge elements connected to opposite sides of the lid and to the side portions of the outer wall, as opposed to the encircling body portion. In particular, the hinge elements are connected to respective rear areas of the side portions. Accordingly, the path of opening the lid has a different shape or curvature and thereby positions the handle substantially lower than if the hinge elements were connected to the body portion adjacent to the access opening. The opposing side portions have a substantially oval shape and the hinge elements have an elongated configuration.

Owner:TRAEGER PELLET GRILLS LLC

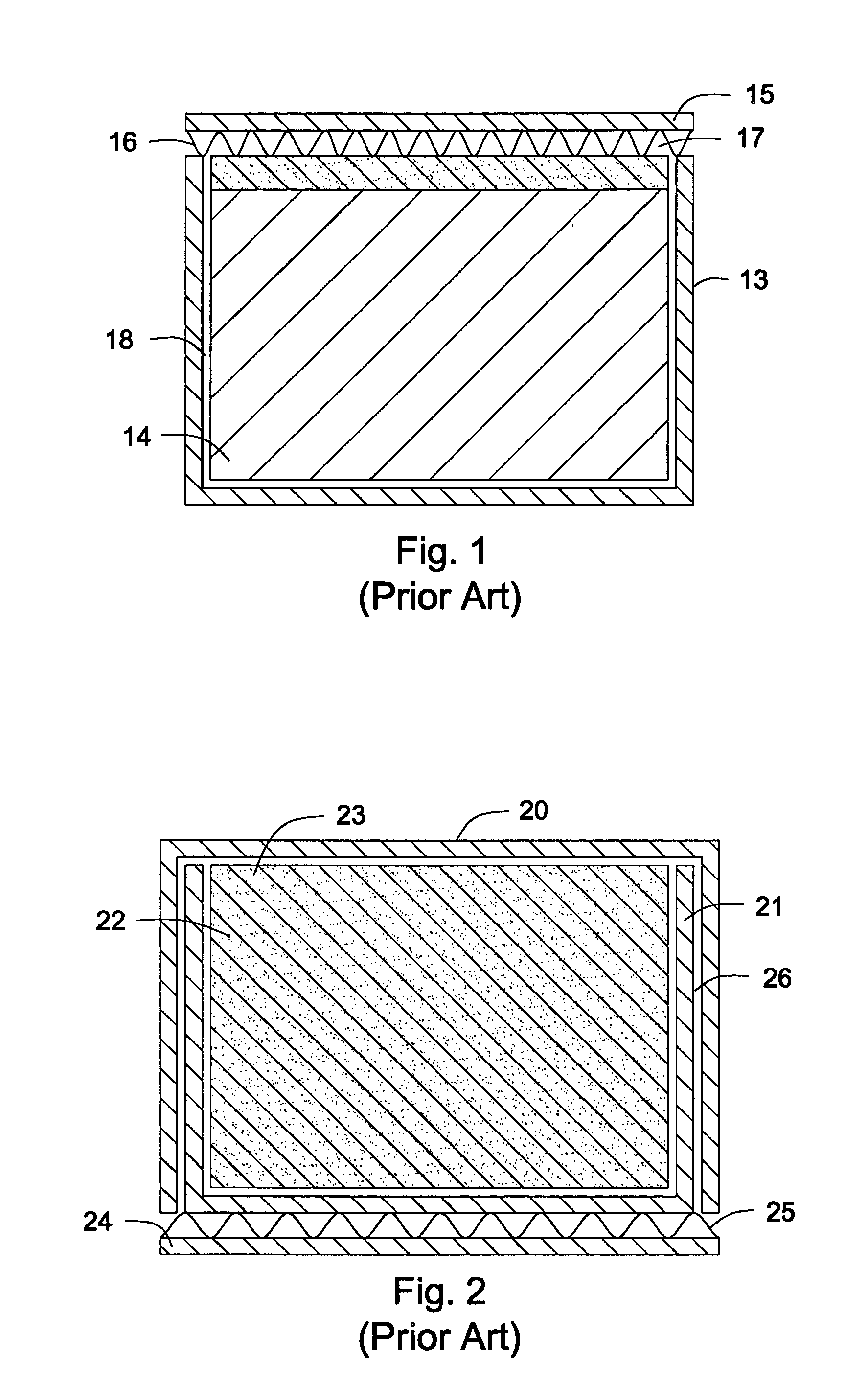

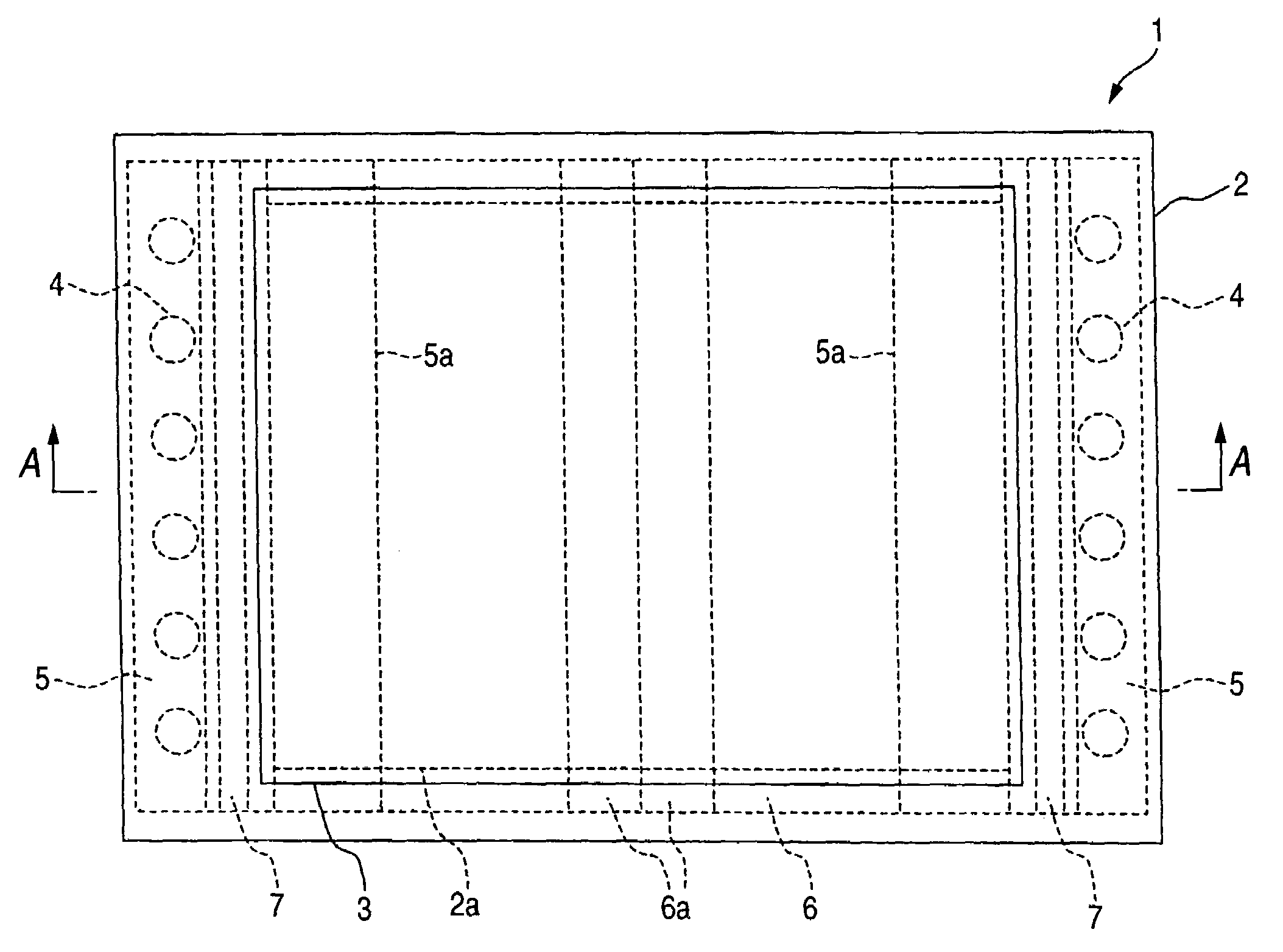

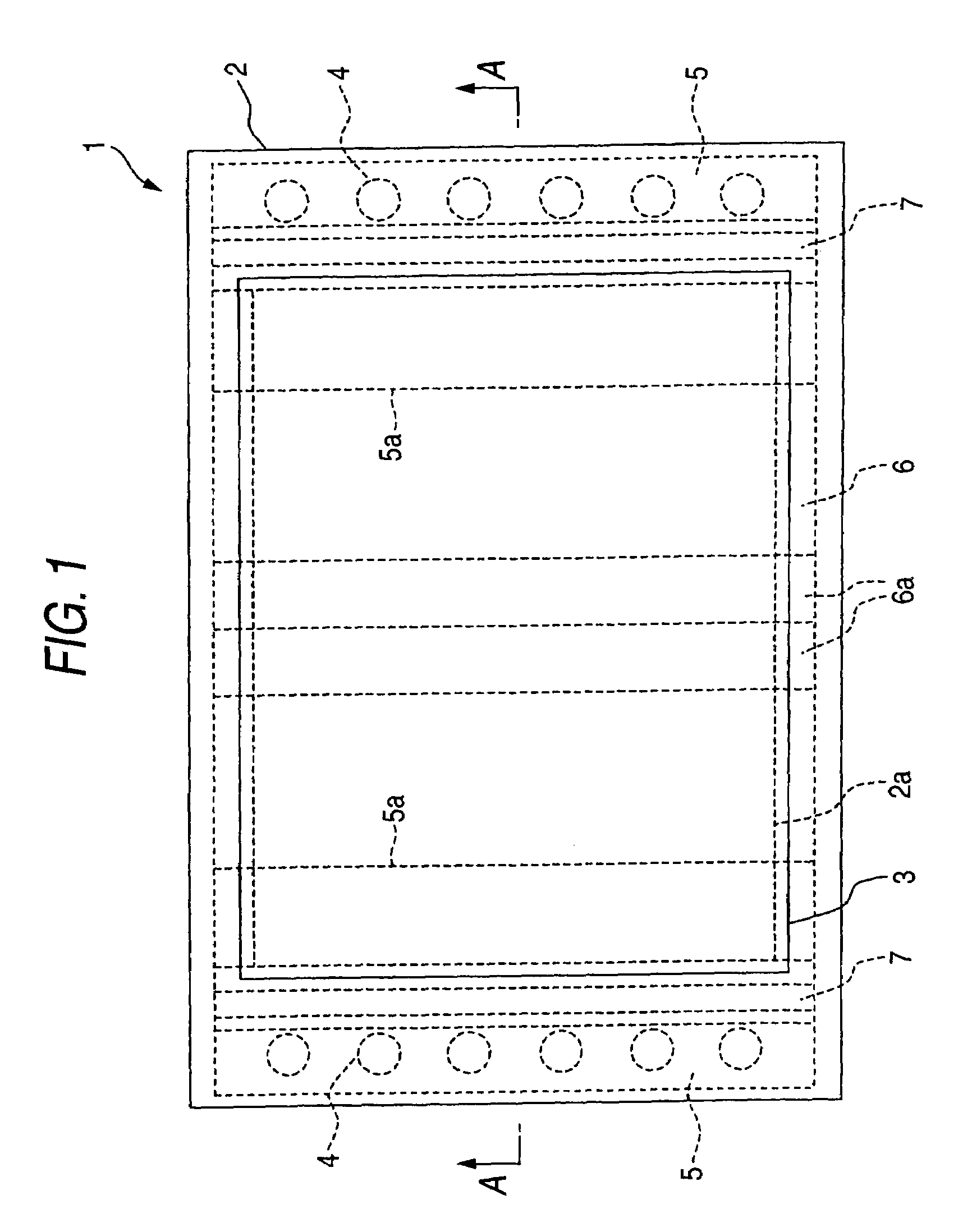

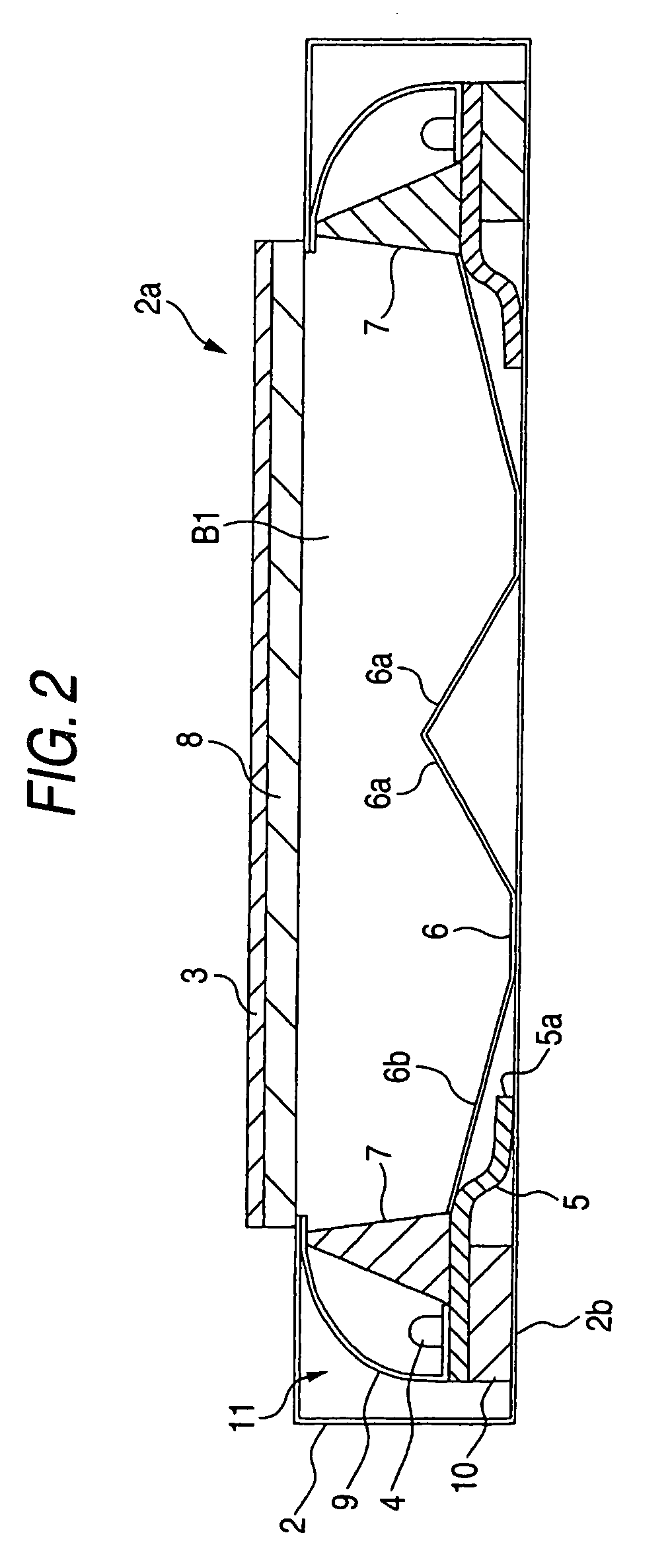

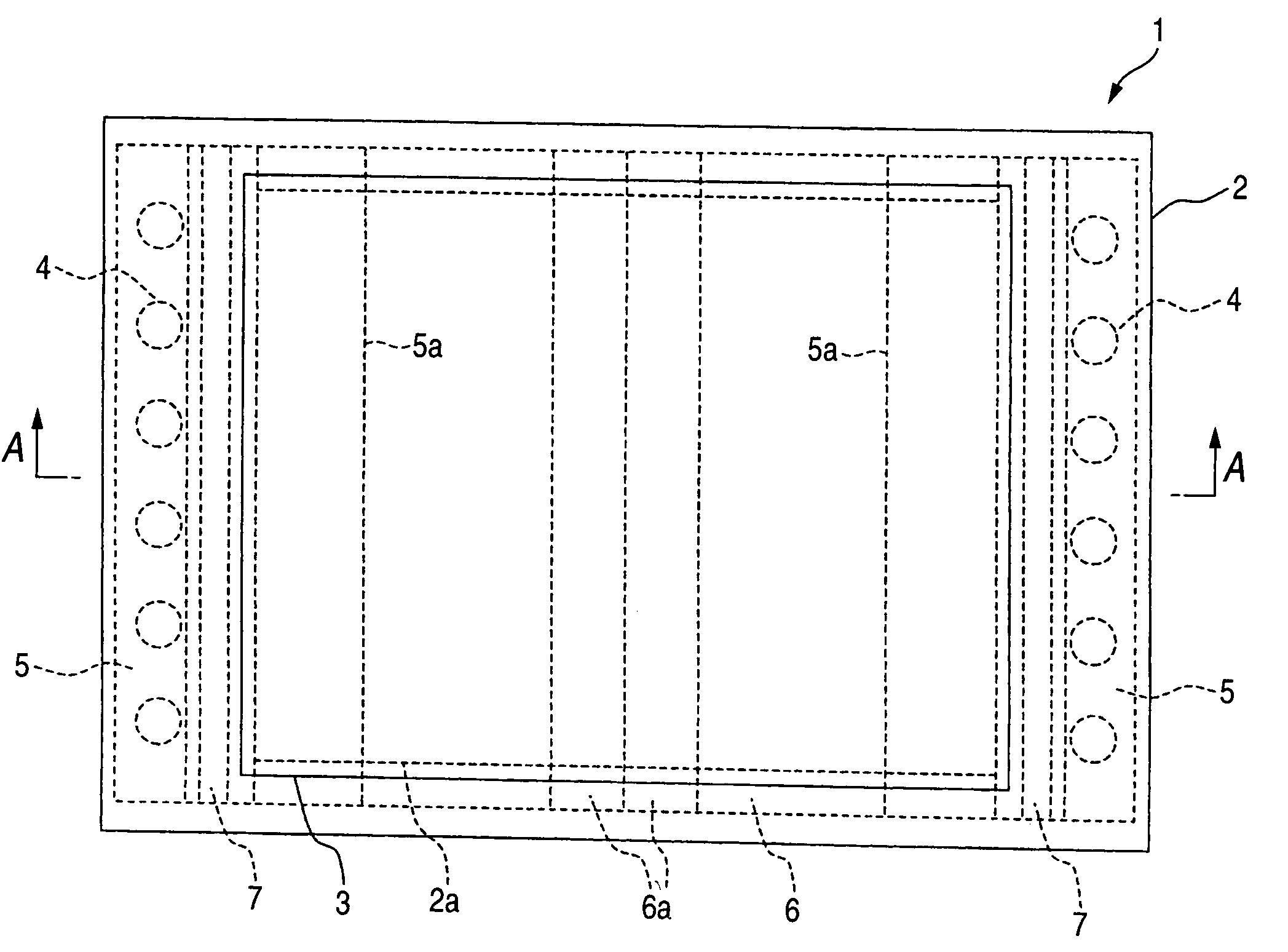

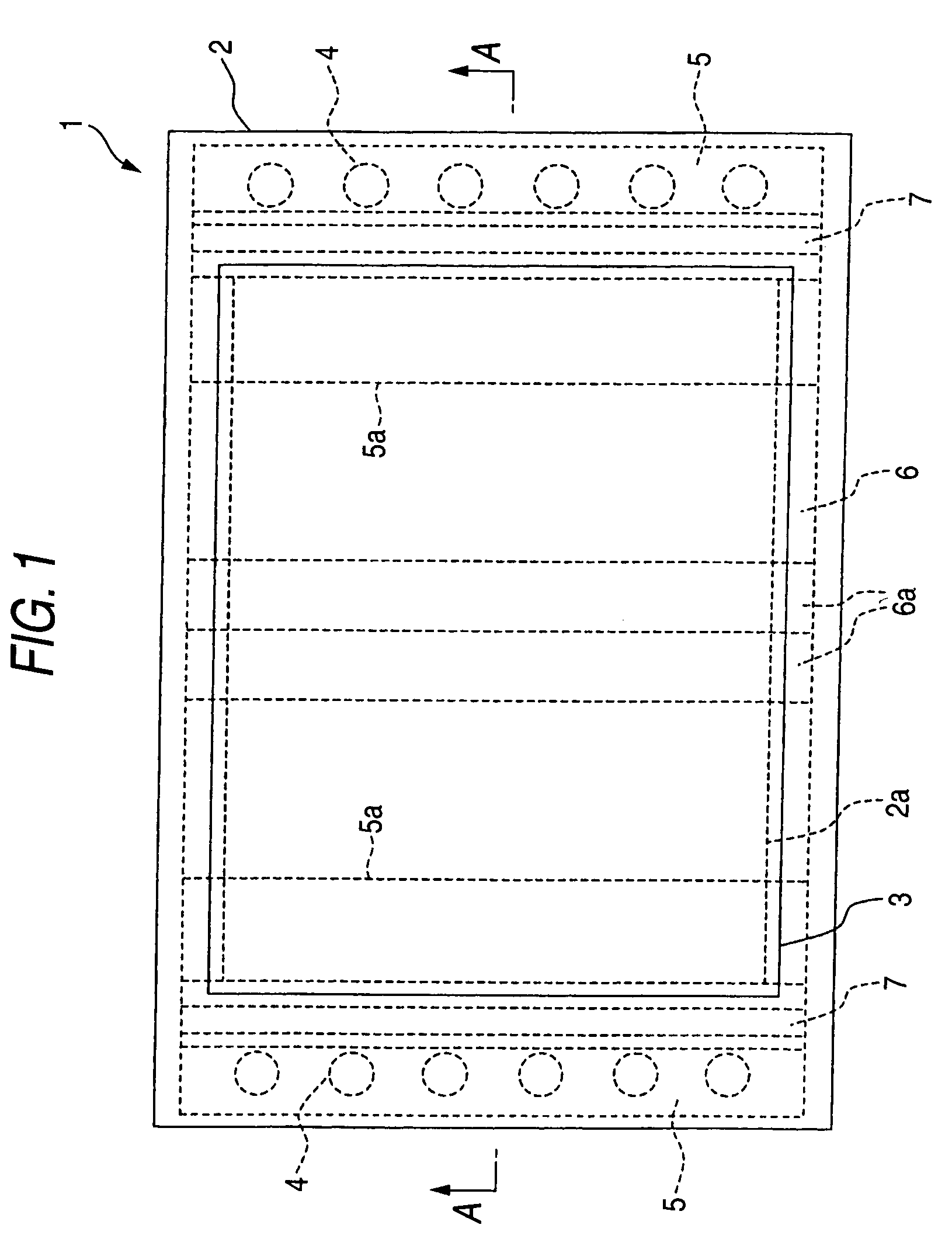

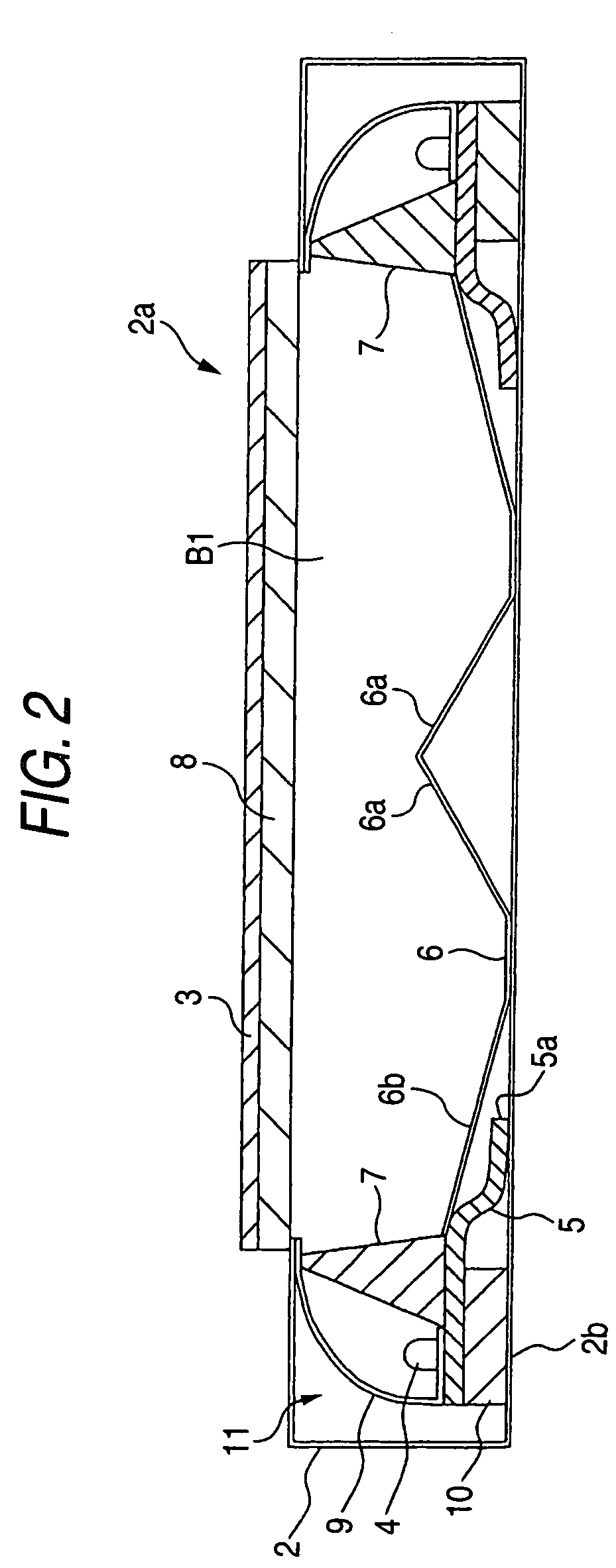

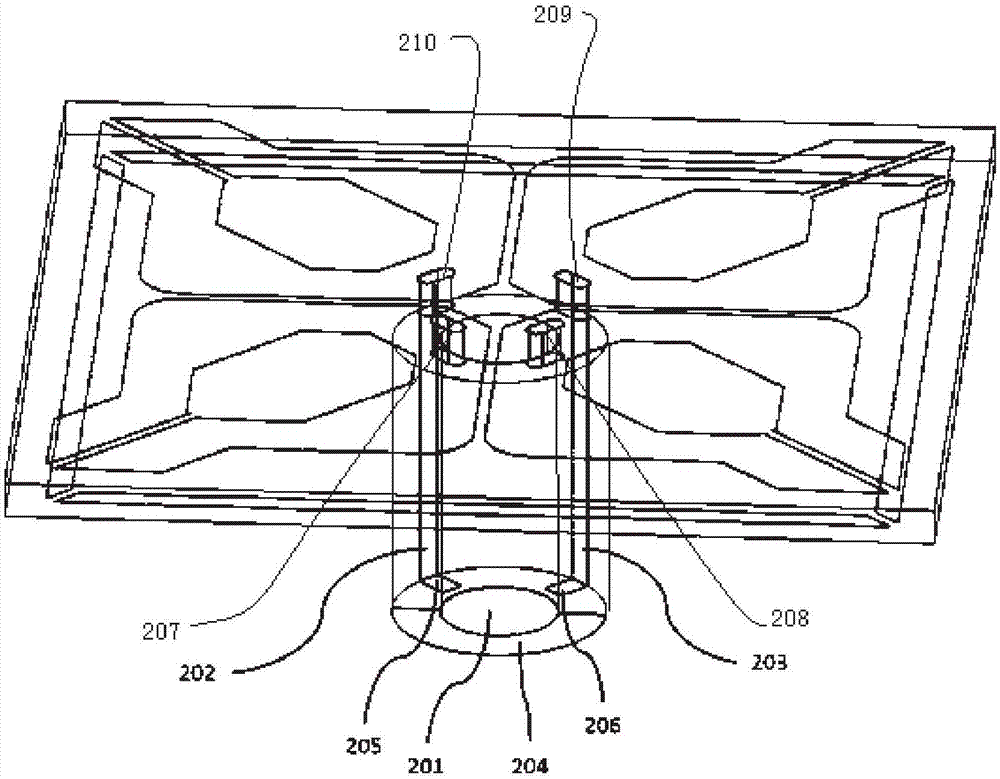

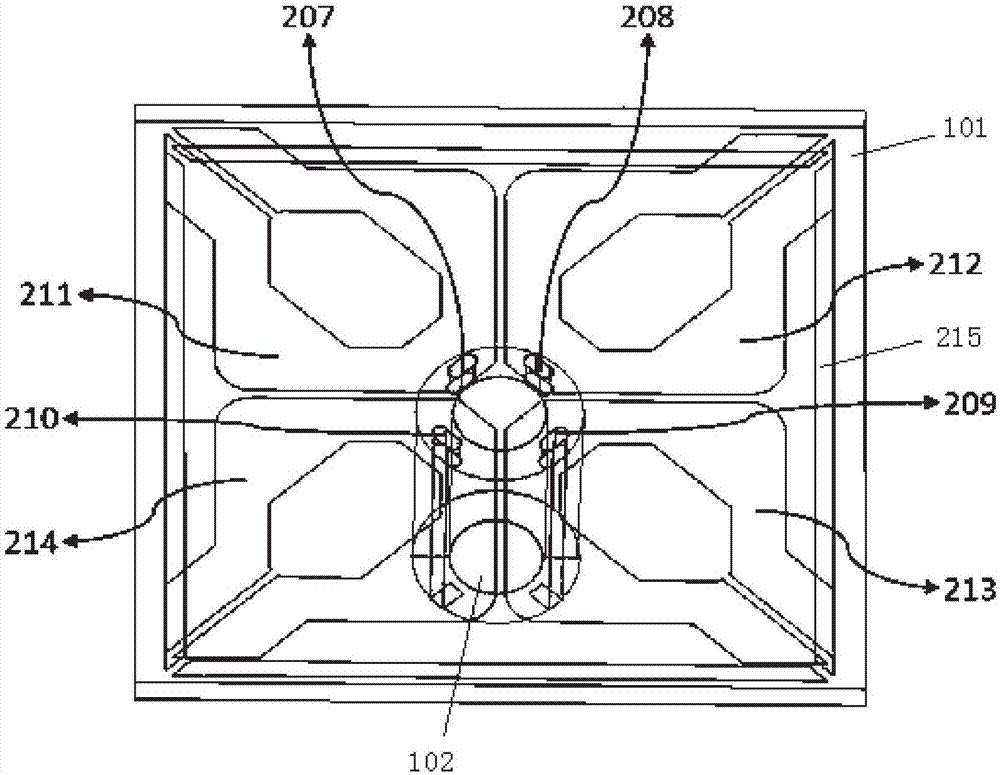

Planar light source apparatus and liquid display apparatus

InactiveUS7201488B2Downsizing and thinning apparatusConvenient lightingMechanical apparatusPoint-like light sourcePoint lightOptoelectronics

A planar light source including a diffusing plate provided at an opening portion of a cabinet, a plurality of point light sources provided along a hollow region formed on a rear face side of the diffusing plate, a reflecting plate provided at inside of a cabinet relative to the diffusing plate by interposing the hollow region therebetween and arranging an end portion thereof on a side of the point light source to be inclined to a front side, and a flexible board provided with a wiring pattern for supplying power to the respective point light sources, in which an end portion of the flexible board is constituted to be arranged at inside of the cabinet by being flexed to a back side of the end portion of the reflecting plate.

Owner:MITSUBISHI ELECTRIC CORP

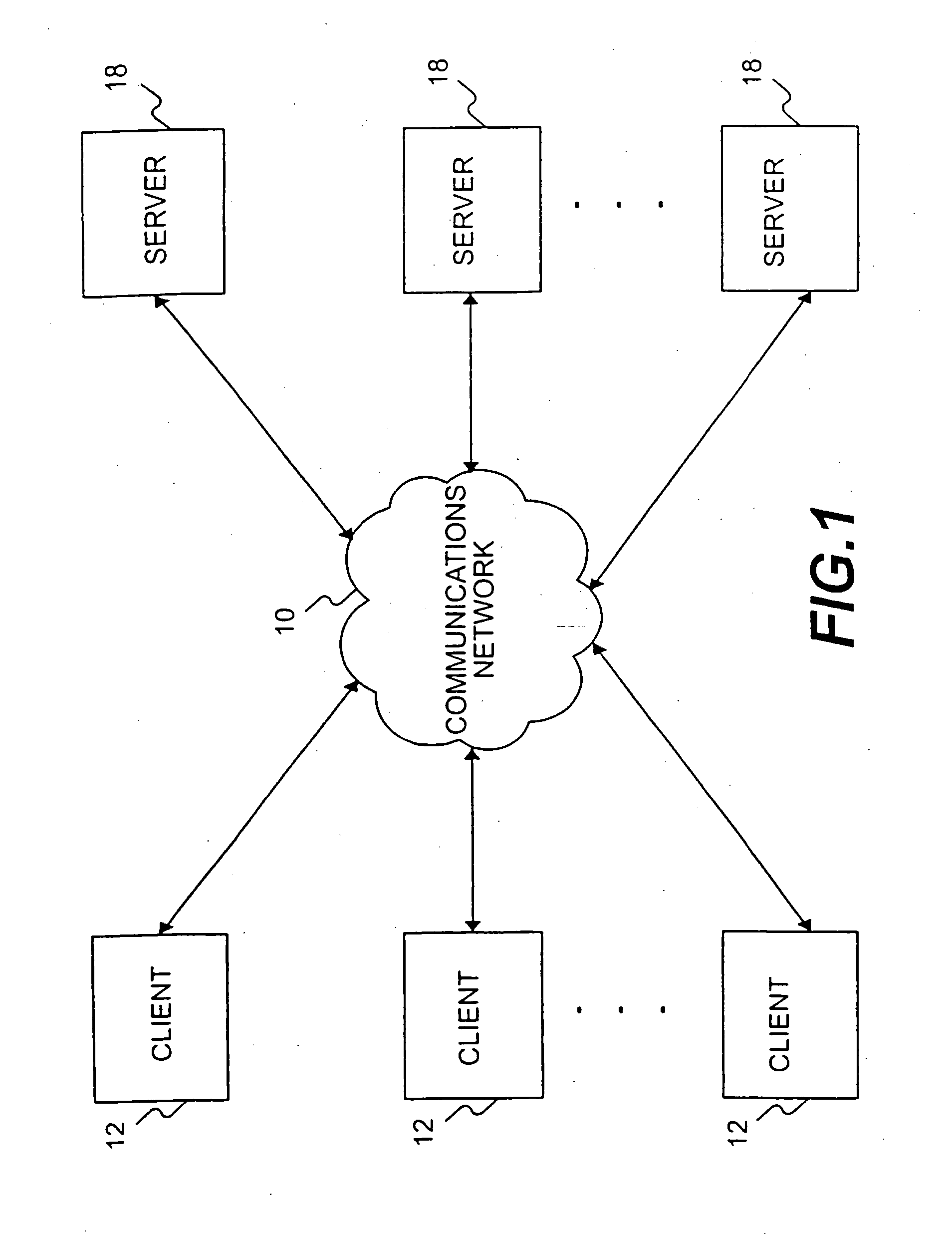

System and method for providing user authentication and identity management

InactiveUS20110138446A1Simple procedureImprove mobilityDigital data processing detailsUser identity/authority verificationPasswordInternet privacy

Owner:BARRETT PAUL D +1

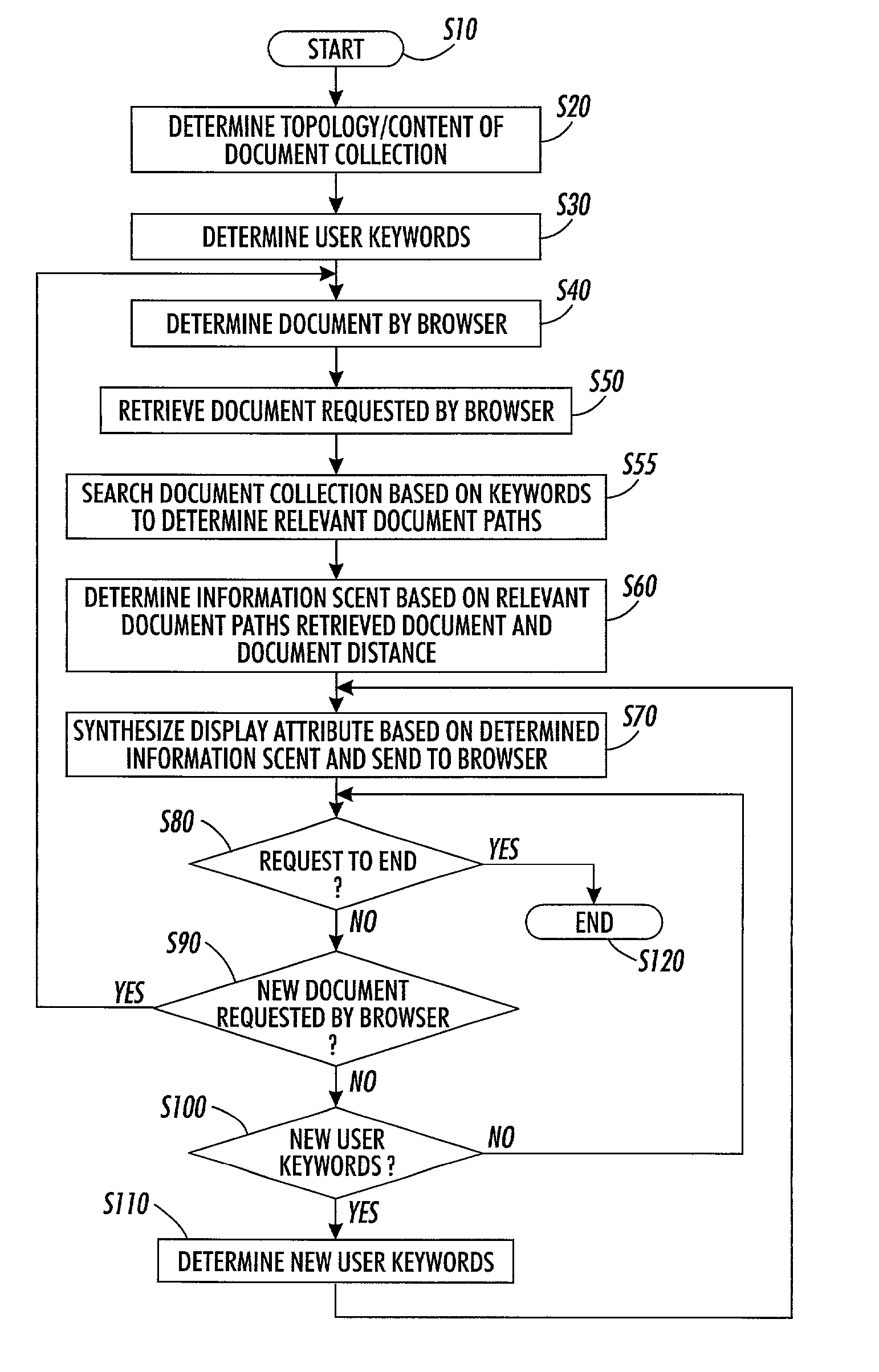

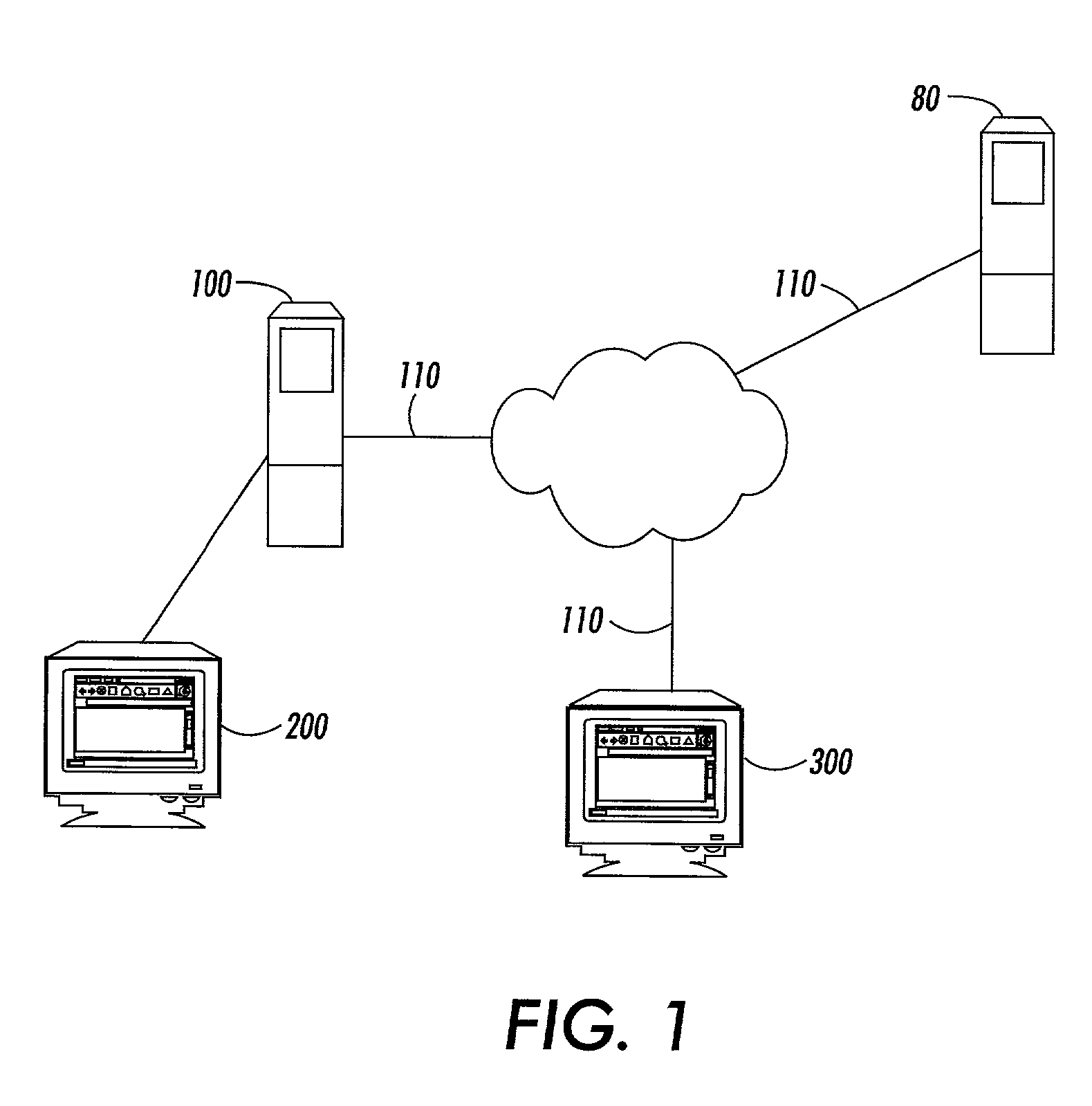

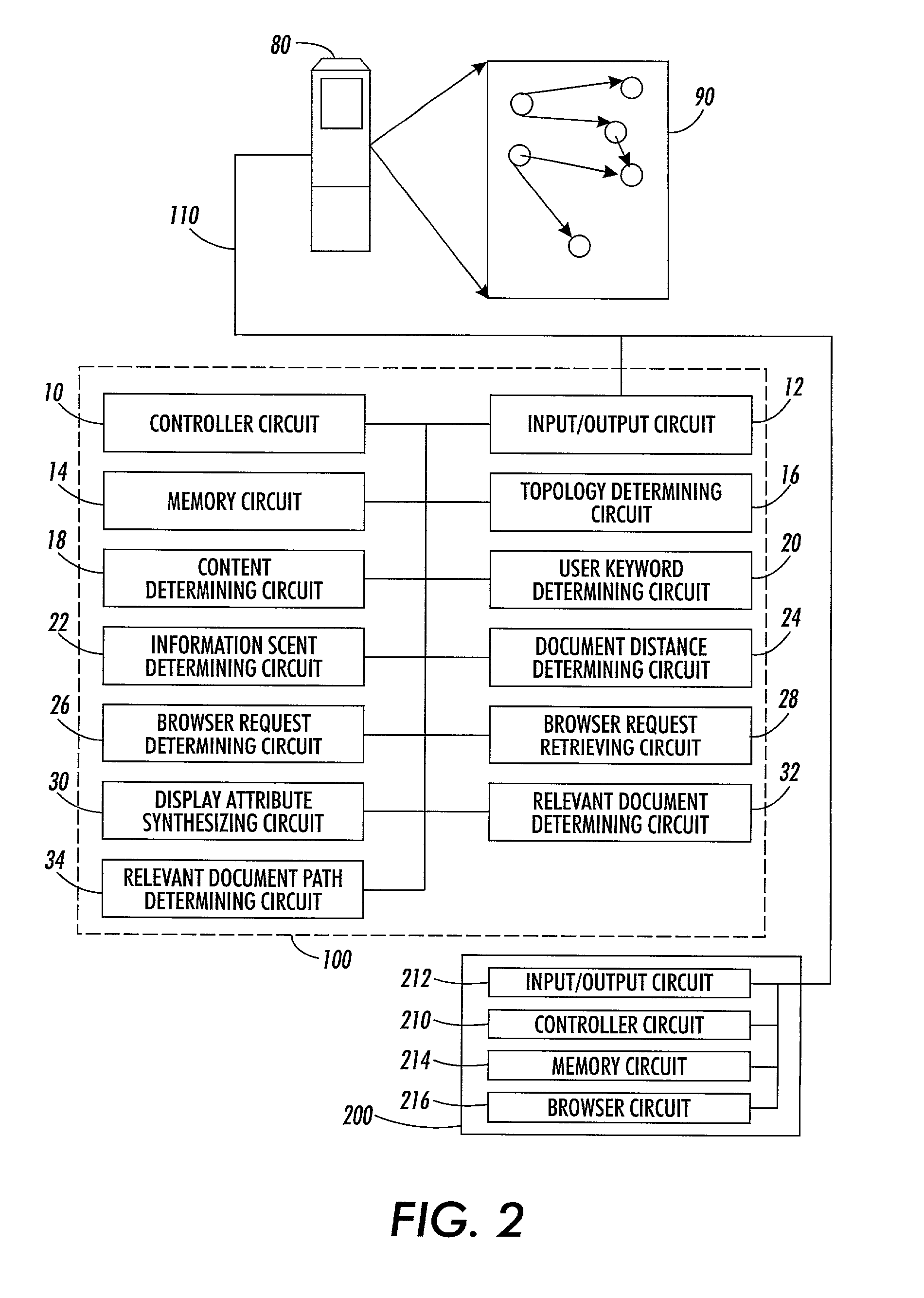

Systems and methods for combined browsing and searching in a document collection based on information scent

InactiveUS7043535B2Extended pathWeb data indexingMultiple digital computer combinationsWeb siteDocumentation procedure

Techniques are provided for combining searching and browsing into a single interface. The topology and content of a document collection or web site is determined and user information need keywords are determined. Relevant documents are identified using search techniques and the relevant document paths determined. The relevant document paths are analyzed using information scent to generate information scent values for the relevant document paths. A display attribute of the associated connection or link is then synthesized based on the information scent, the keywords and the document. The process repeats for each new document or web page.

Owner:XEROX CORP

Planar light source apparatus and liquid display apparatus

InactiveUS20050185394A1Side light can be restrained being enlargedIncrease board areaMechanical apparatusPoint-like light sourcePoint lightOptoelectronics

A planar light source including a diffusing plate provided at an opening portion of a cabinet, a plurality of point light sources provided along a hollow region formed on a rear face side of the diffusing plate, a reflecting plate provided at inside of a cabinet relative to the diffusing plate by interposing the hollow region therebetween and arranging an end portion thereof on a side of the point light source to be inclined to a front side, and a flexible board provided with a wiring pattern for supplying power to the respective point light sources, in which an end portion of the flexible board is constituted to be arranged at inside of the cabinet by being flexed to a back side of the end portion of the reflecting plate.

Owner:MITSUBISHI ELECTRIC CORP

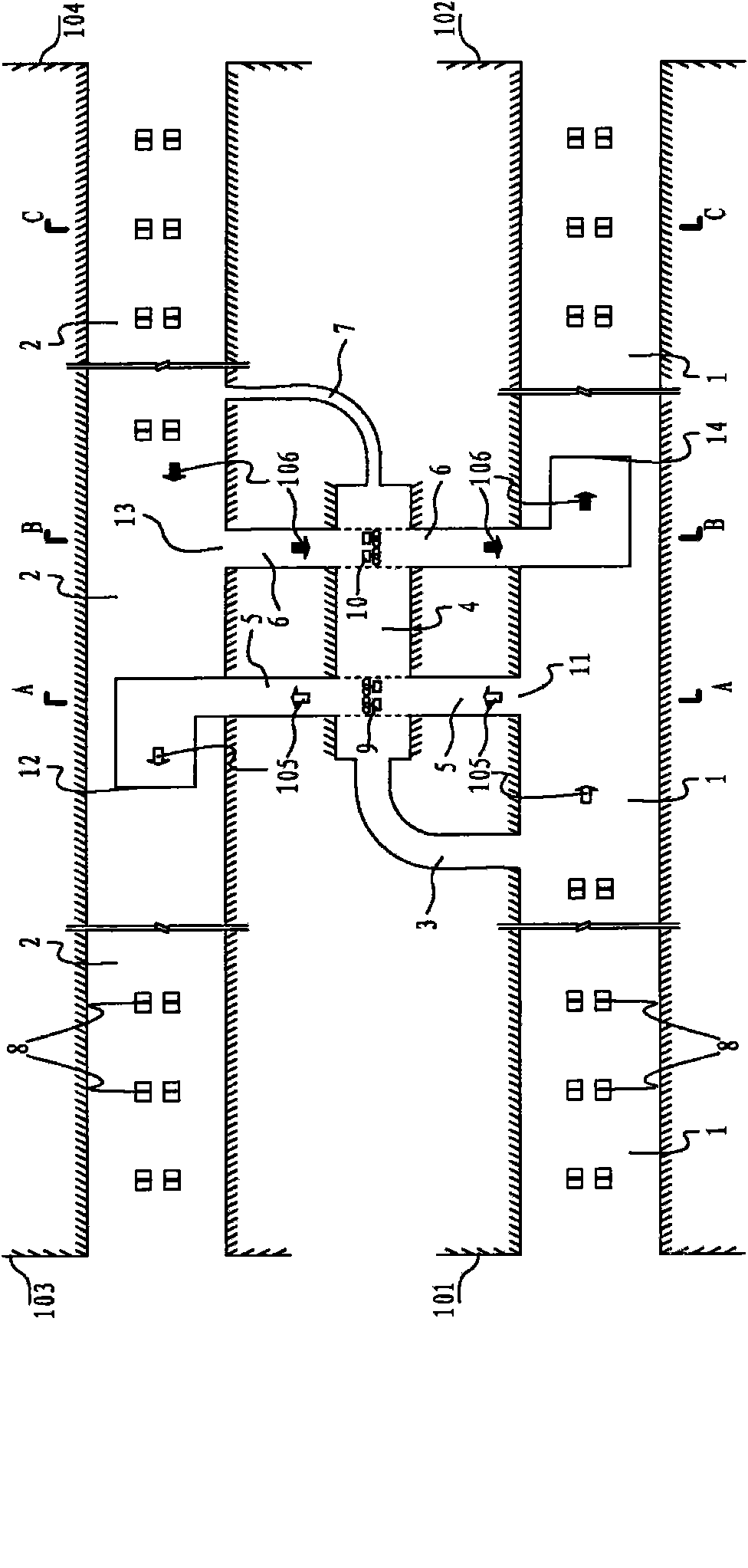

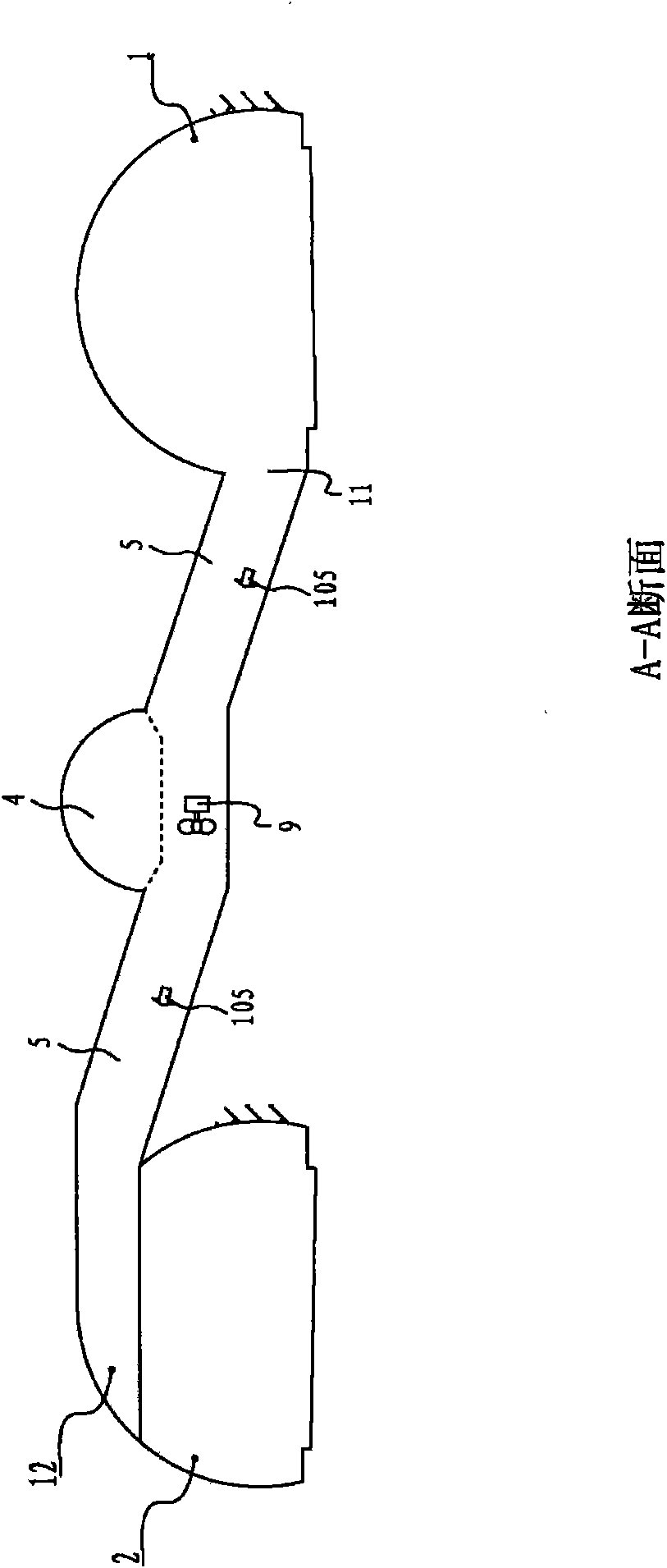

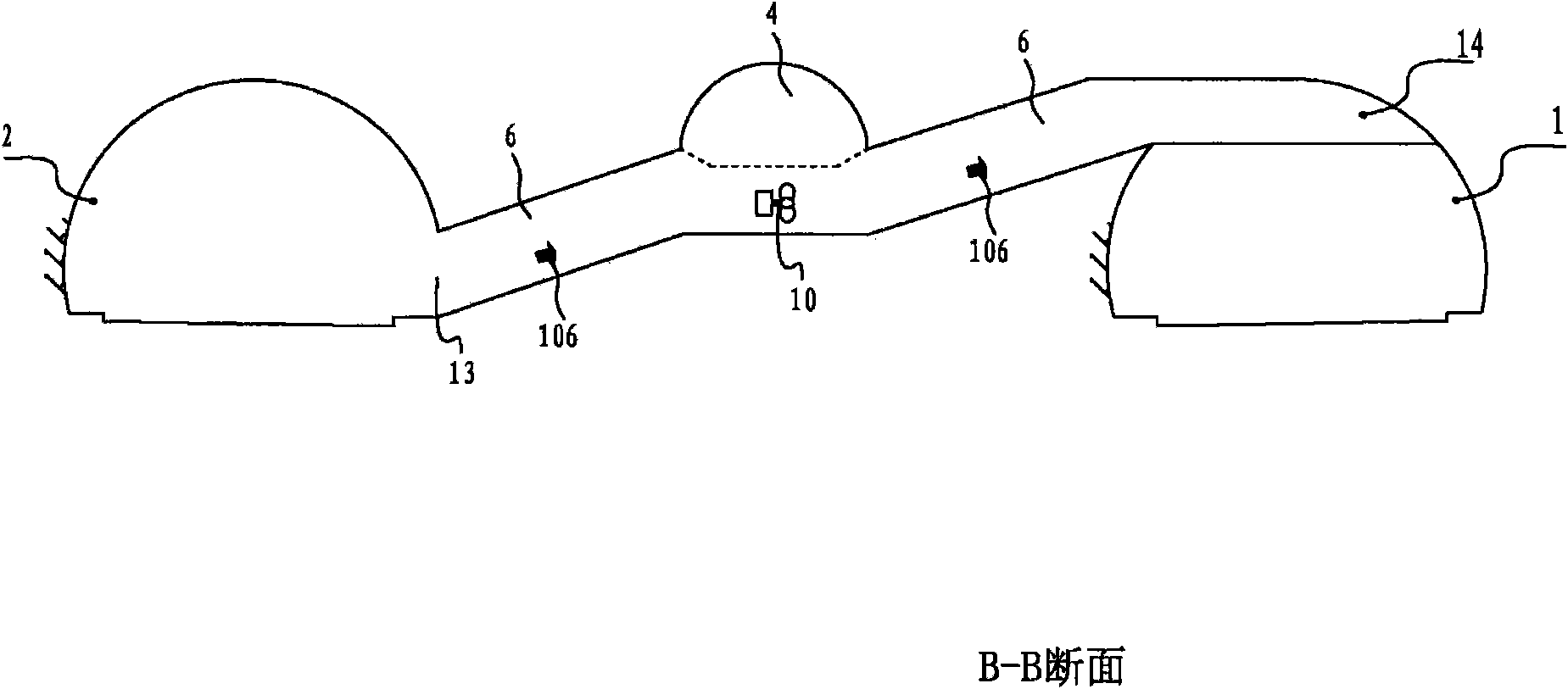

Road tunnel intercommunication type longitudinal ventilation mode

InactiveCN102400701AReduce in quantityLow costTunnel/mines ventillationDaily operationVentilation mode

The invention discloses a road tunnel intercommunication type longitudinal ventilation mode. The road tunnel intercommunication type longitudinal ventilation mode is characterized in that: an underground fan room and a connection ventilation duct are arranged at an appropriate position between two adjacent tunnels; the underground fan rooms are used for installing ventilation fans; the connection ventilation ducts are used for connecting the air flow of two tunnels; the automobile tail gas, which is generated in sections from the underground fan rooms to outlets, of pure uphill tunnels or uphill-major tunnels (uphill tunnels for short) is diluted by using cleaner air in pure downhill tunnels or downhill-major tunnels (downhill tunnels for short); and the polluted air, which is generated in sections from inlets to the underground fan rooms, of the uphill tunnels is discharged through the outlets of the downhill tunnels. By adoption of the road tunnel intercommunication type longitudinal ventilation mode, ventilation equipment can be reduced, ventilation shafts, inclined shafts or electrostatic dust removal stations are eliminated, and ventilation power consumption in daily operation is low, so that civil engineering cost and operation cost are reduced.

Owner:SHANGHAI TONGYAN CIVIL ENGINEERING TECHNOLOGY CORP LTD

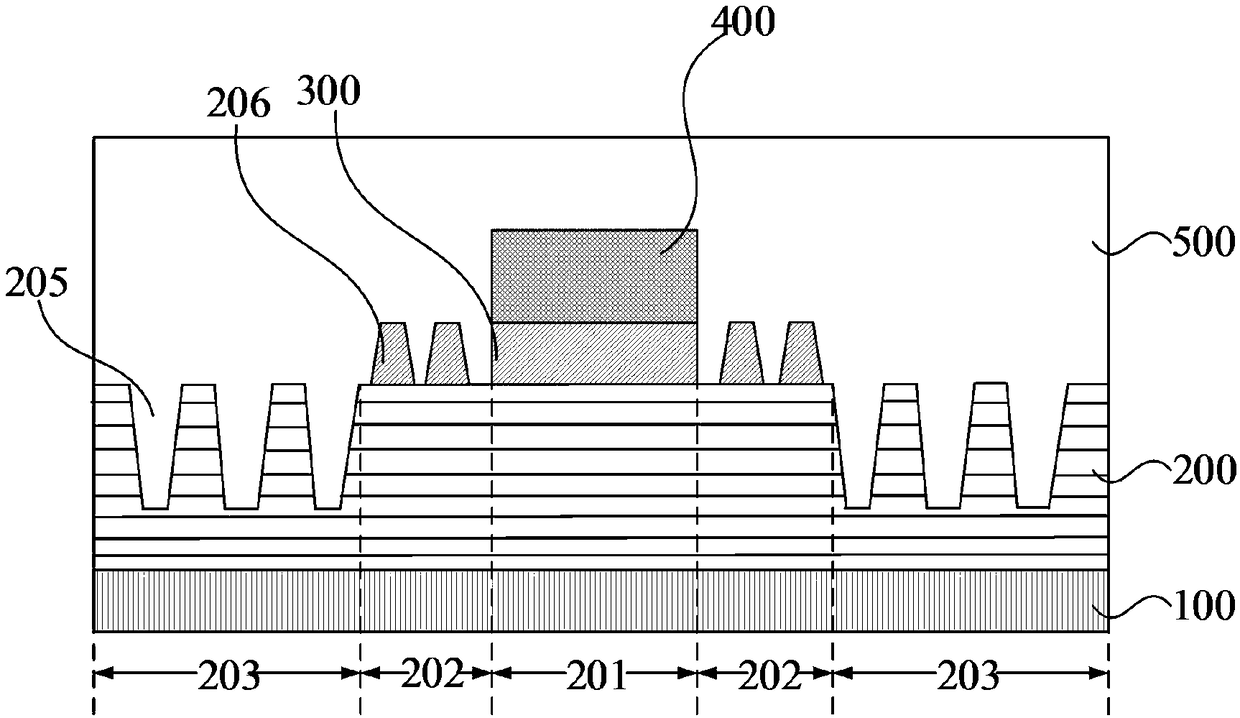

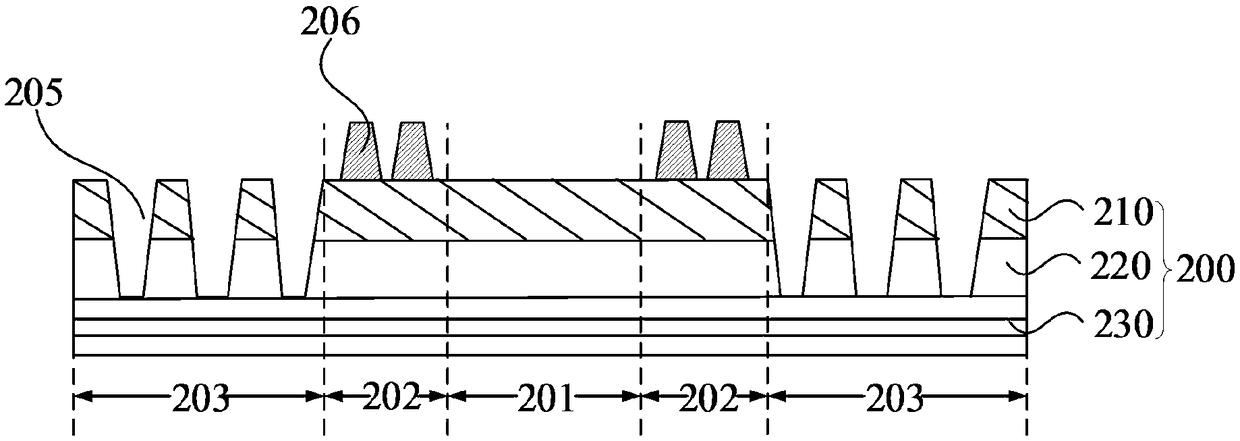

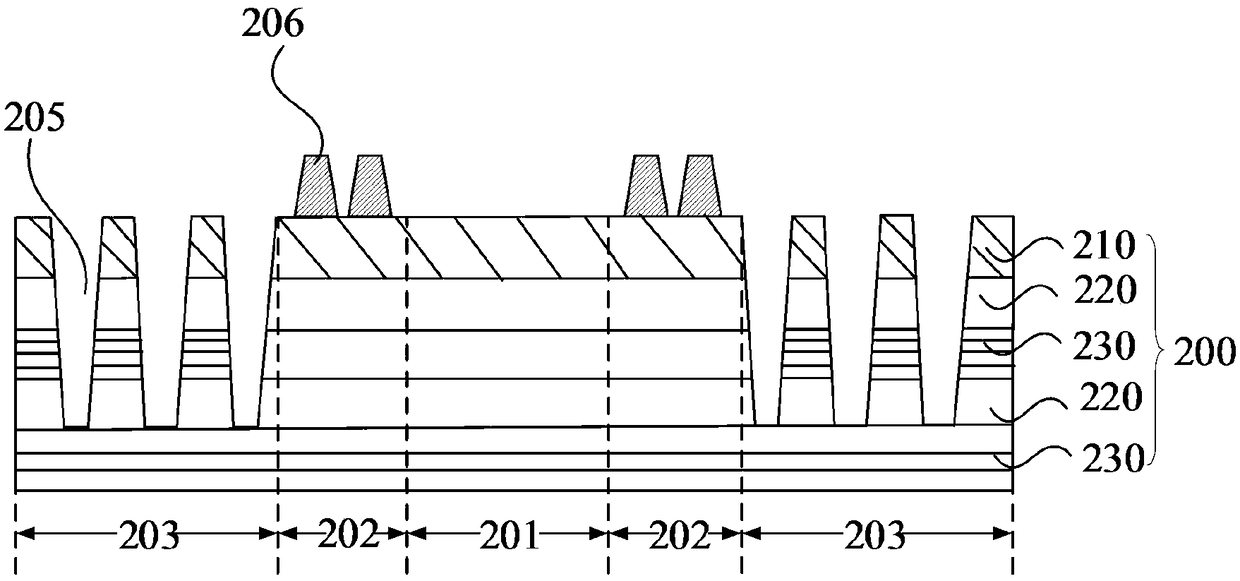

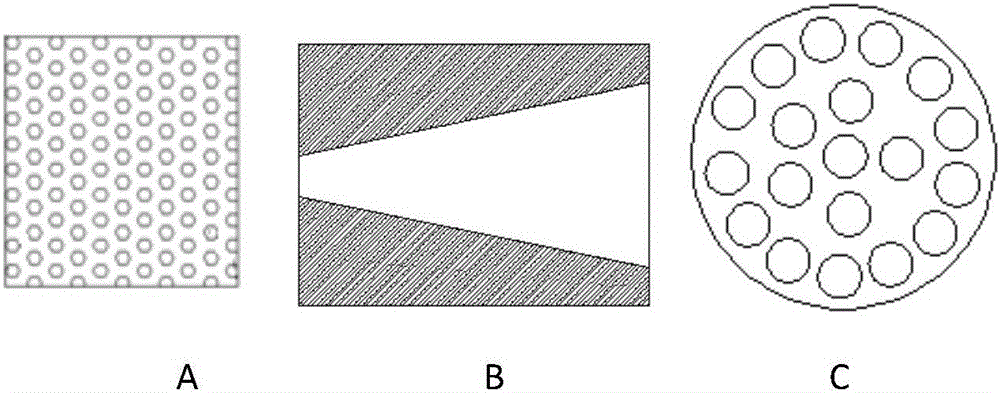

Flexible OLED display device and production method thereof

ActiveCN108281458AExtended pathProlonged intrusion pathSolid-state devicesSemiconductor/solid-state device manufacturingDisplay deviceEngineering

The invention relates to a flexible OLED (Organic Light-Emitting Diode) display device and a production method thereof. The flexible OLED display device comprises a flexible substrate, an obstructionlayer, a flattening layer, a display layer and a film packaging layer. The obstruction layer comprises a display area, first edge areas set at outer sides of the display area, and second edge areas set at the outer sides of the first edge areas. Lug bosses are set in the first edge areas. Grooves are set in the second edge areas. The flattening layer and the display layer are set on the display area. The film packaging layer covers the display area, the first edge areas and the second edge areas. The flexible OLED display device has good water and oxygen obstruction performance, and the service life of the display device can be improved.

Owner:KUNSHAN NEW FLAT PANEL DISPLAY TECH CENT +1

Vacuum insulation panel core material with high performance and low cost and manufacturing method thereof

ActiveCN102330475ALow costThe overall thickness is thinClimate change adaptationInsulation improvementGlass fiberSizing

The invention discloses a method for manufacturing a vacuum insulation panel core material with high performance and low cost. The method comprises the following steps of: pulping glass fiber cotton which is produced by a centrifuge method; diluting; screening; performing dehydration molding; performing pressure roller sizing; performing vacuum negative pressure dehydration; drying; cooling; and cutting. In the manufacturing method, the glass fiber cotton which is completely produced by the centrifuge method is used as a raw material of the vacuum insulation panel core material with high performance and low cost, the coefficient of thermal conductivity of the produced vacuum insulation panel core is between 0.003 and 0.008 W / m.k, and the coefficient of heat insulation is greatly improved;the thickness of the panel core material is between 0.5 and 30 mm, and the thickness is thinner; and the glass fiber cotton with the diameter of 3.5 to 5 mu m and the length of 5 to 20 mm has low cost and low overall manufacturing cost, and the overall cost of the vacuum insulation panel is lowered.

Owner:许立江

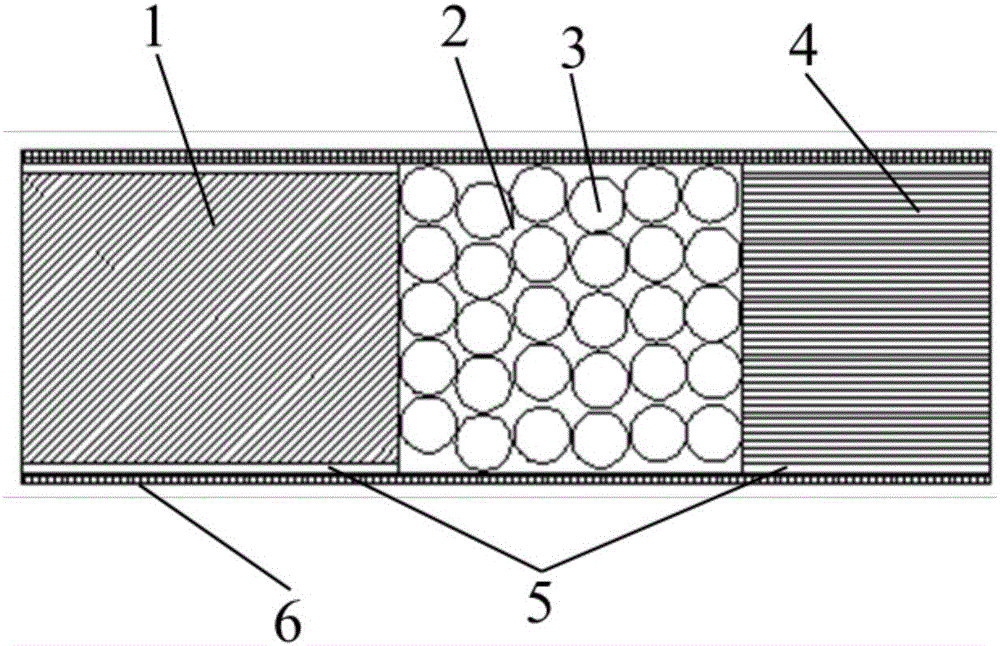

Three-component-unit compounding filter tip rod

InactiveCN105077576AReduce flue gas temperatureReduce suction resistanceTobacco smoke filtersFilling materialsSmoke

The invention provides a three-component-unit compounding filter tip rod. The three-component-unit compounding filter tip rod comprises three component units including a solid filter (1), a cavity (2) and a filter (4) which are sequentially arranged from the near lip end to the far lip end, wherein a piece of first forming paper (5) covers the outer side of the solid filter (1); a piece of first forming paper (5) covers the outer side of the filter (4); then, the three component units are compounded and formed through a piece of second forming paper (6); and the cavity (2) is filled with filling materials (3). The three-component-unit compounding filter tip rod has the effects of lowering the smoke gas temperature, increasing the smoke quantity, reducing the sucking resistance, reducing the CO content in the smoke gas and the like.

Owner:CHINA TOBACCO YUNNAN IND

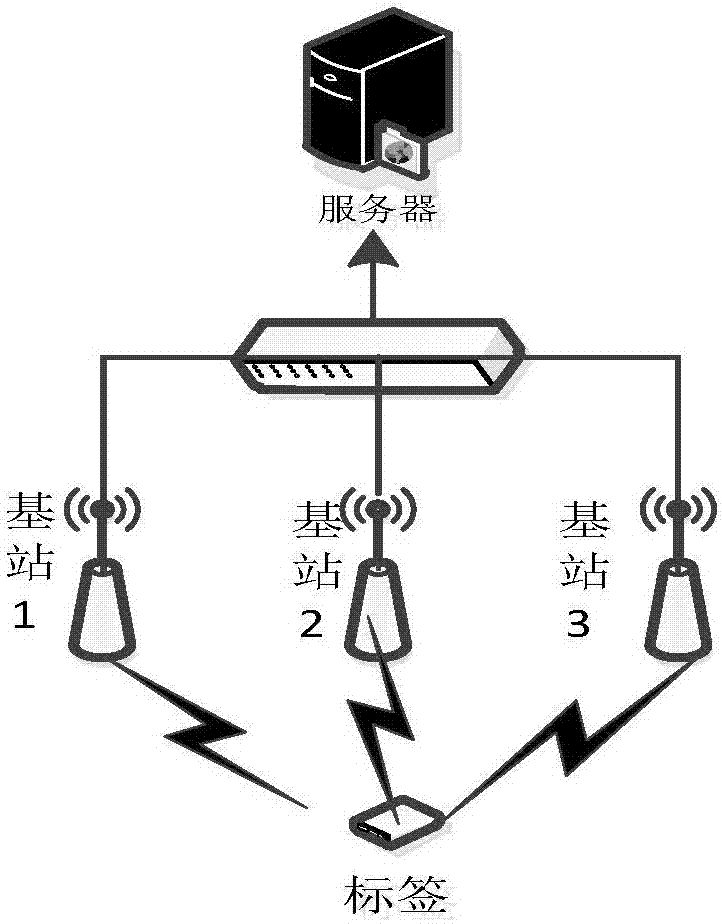

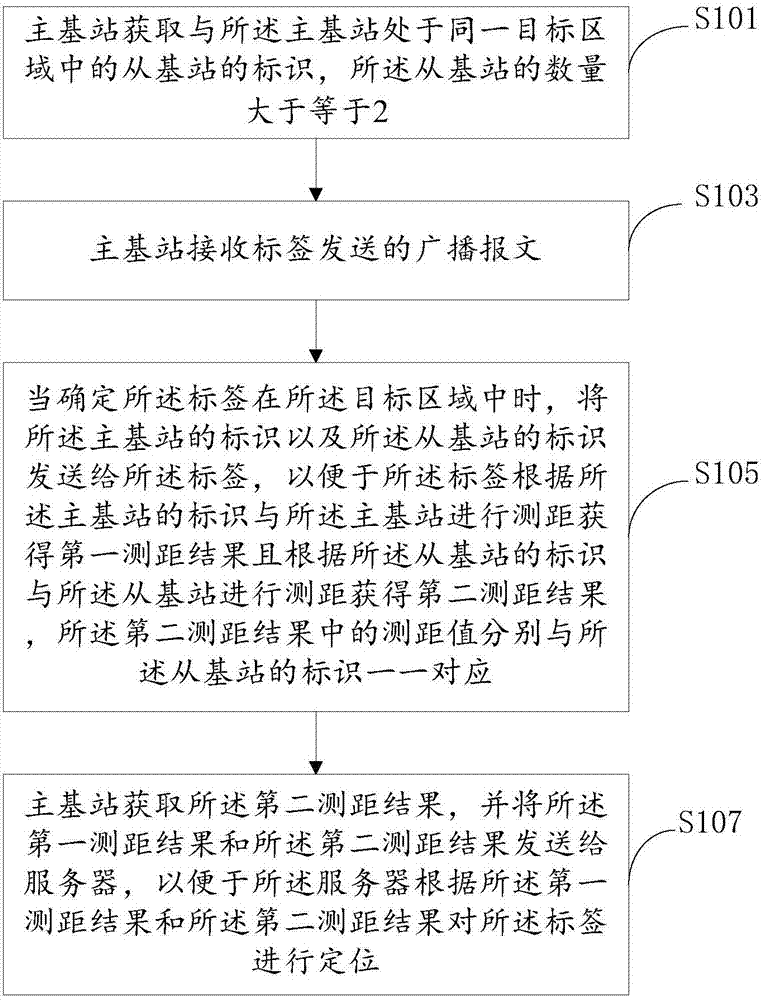

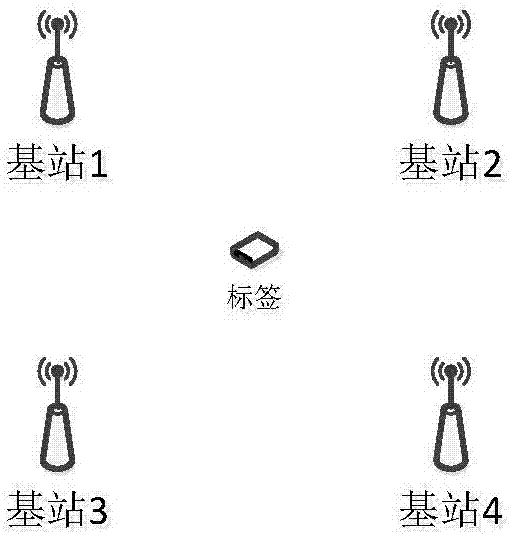

Method and master base station for positioning labels in wireless network

ActiveCN107231614AReduce construction costsFlexible layoutPower managementPosition fixationWireless mesh networkDistance measurement

The embodiment of the invention provides a method for positioning labels in a wireless network. The method comprises the following steps that the master base station obtains identifiers of slave base stations, wherein the slave base stations and the master base station are located in the same target area, and the number of the slave base stations is greater than or equal to 2; the master base station receives broadcasting messages sent by the labels and sends the identifier of the master base station and the identifiers of the slave base stations to the labels when the labels are in the target area; and the master base station obtains a second distance measurement result and sends a first distance measurement result and the first distance measurement result to a server. The embodiment of the invention also provides the master base station for positioning the labels in the wireless network. Compared with an existing UWB (Ultra Wideband) positioning scheme, the labels are allocated and managed at base station ends, so paths as short as possible are employed, the instable delay and factors are reduced to the lowest, and the positioning system is relatively reliable.

Owner:BEIJING XINWANG RUIJIE NETWORK TECH CO LTD

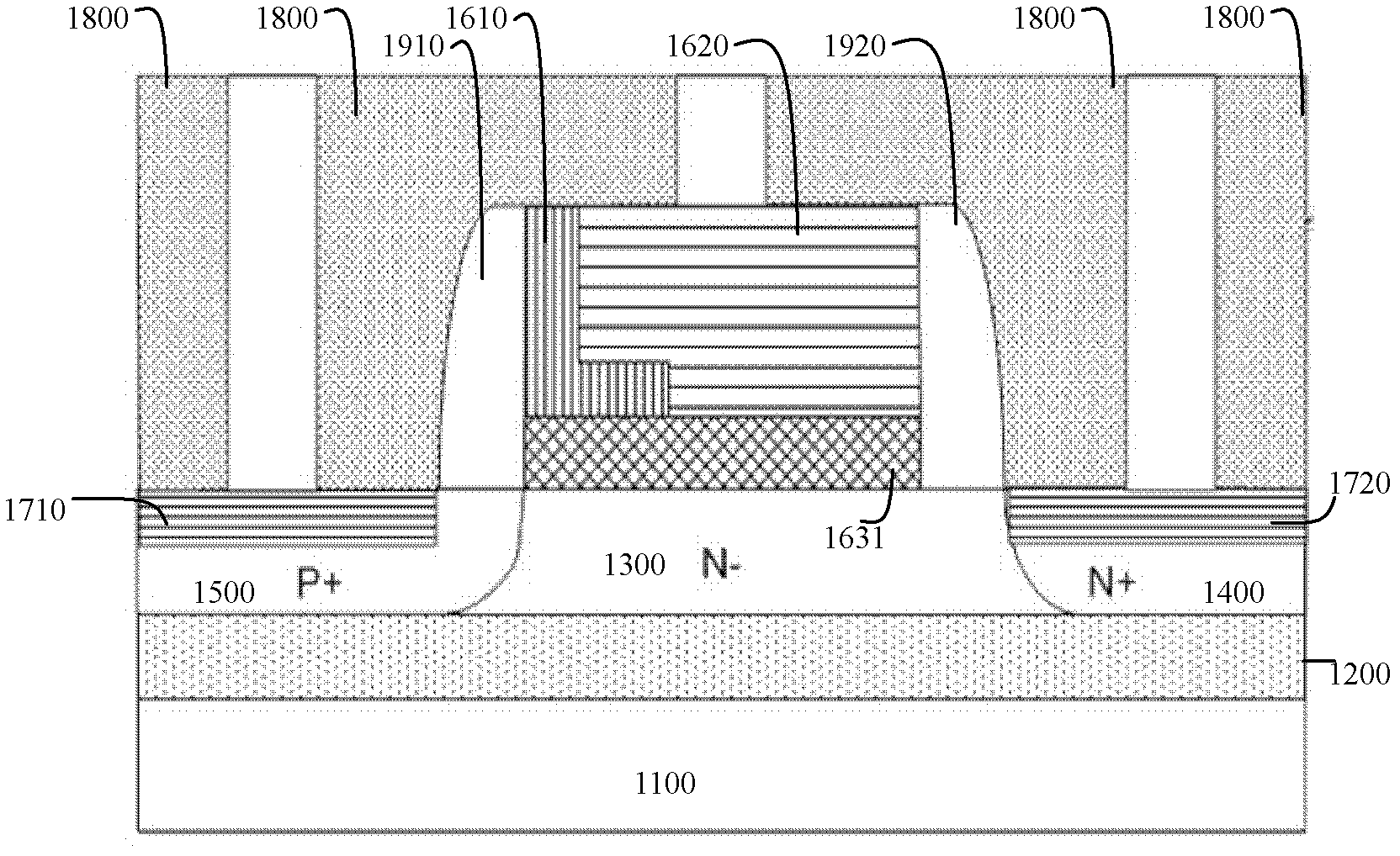

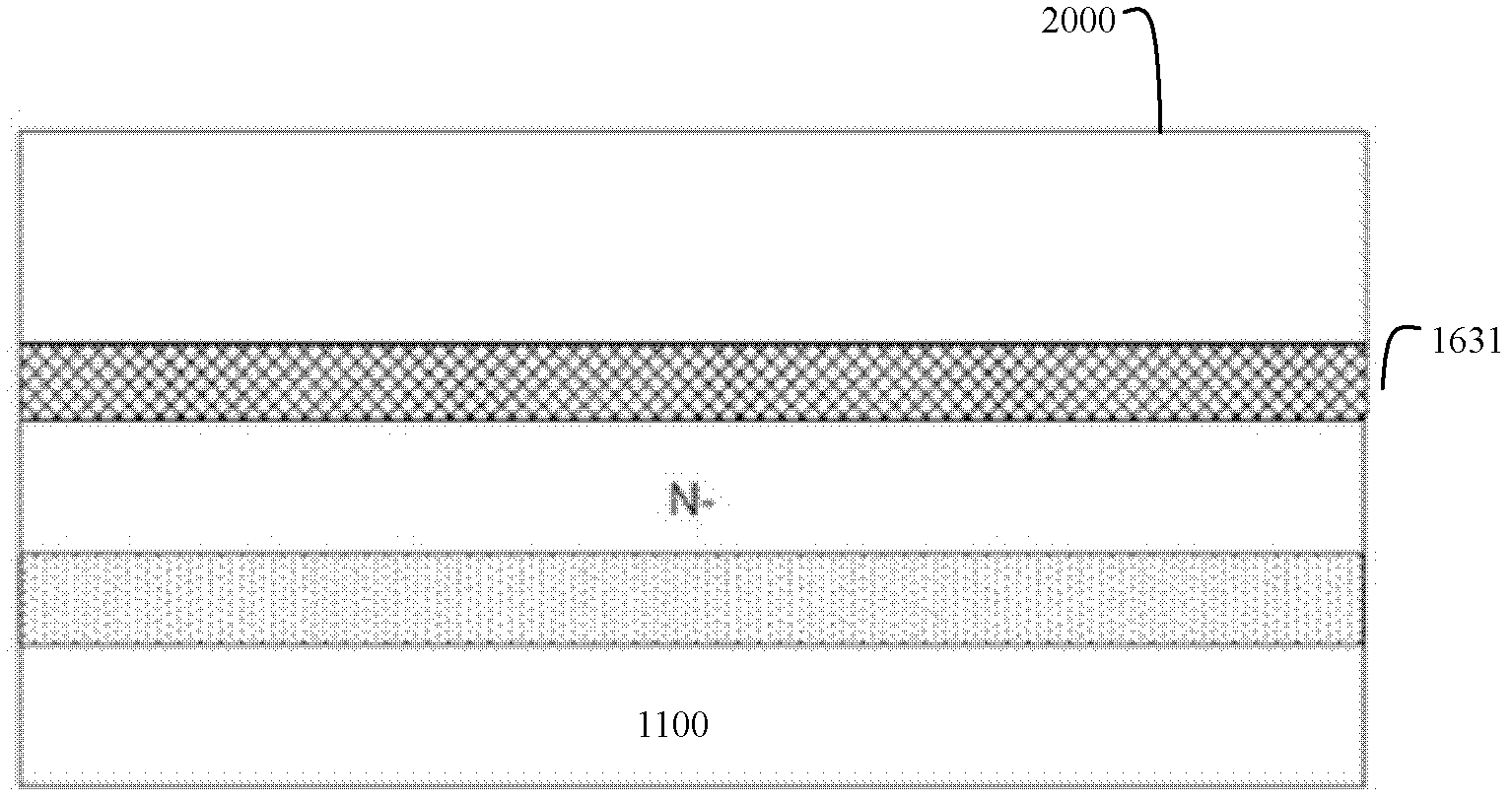

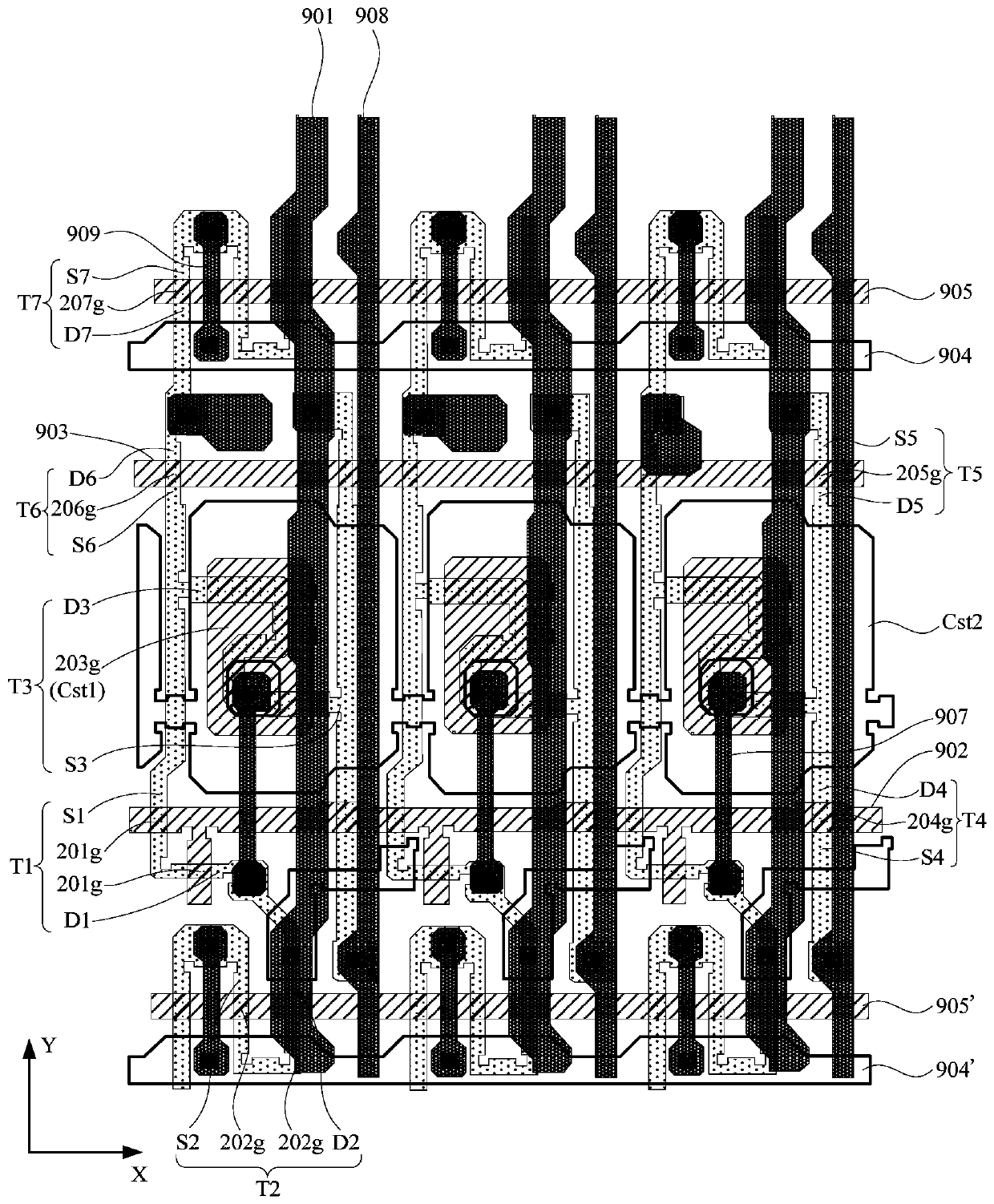

Heterogeneous gate tunneling transistor and forming method thereof

ActiveCN102629627AReduce controlReduce capacitanceSemiconductor/solid-state device manufacturingSemiconductor devicesDriving currentCapacitance

The invention provides a structure of a heterogeneous gate tunneling transistor of an under-gate process and a forming method of the heterogeneous gate tunneling transistor. The heterogeneous gate tunneling transistor comprises a substrate, a channel region, a source region, a drain region and a gate stack, wherein the channel region is formed in the substrate; the source region and the drain region are arranged on the two sides of the channel region; the doping types of the source region and the drain region are reverse; the gate stack is formed on the channel region and comprises a gate dielectric layer, a first gate electrode, a second gate electrode, a first vacuum side wall and a second vacuum side wall; the first gate electrode and the second gate electrode are formed on the gate dielectric layer and have different work functions; and the first vacuum side wall and the second vacuum side wall are formed on the two sides of the first gate electrode and the second gate electrode. Since the vacuum side wall from the gate to the drain region is introduced, the control of the gate over the drain region is weakened, and the gate-drain capacitance is reduced; a certain distance which can be accurately controlled exists between the gate stack and the drain region of a device, so that a tunneling potential barrier path is increased, and a double-pole window is expanded; and the energy band distribution of the channel region is modulated by a work function structure of the transverse heterogeneous gate, so that the sub-threshold slope of a transistor is obviously reduced, the driving current is increased and the performance of the device is enhanced.

Owner:TSINGHUA UNIV

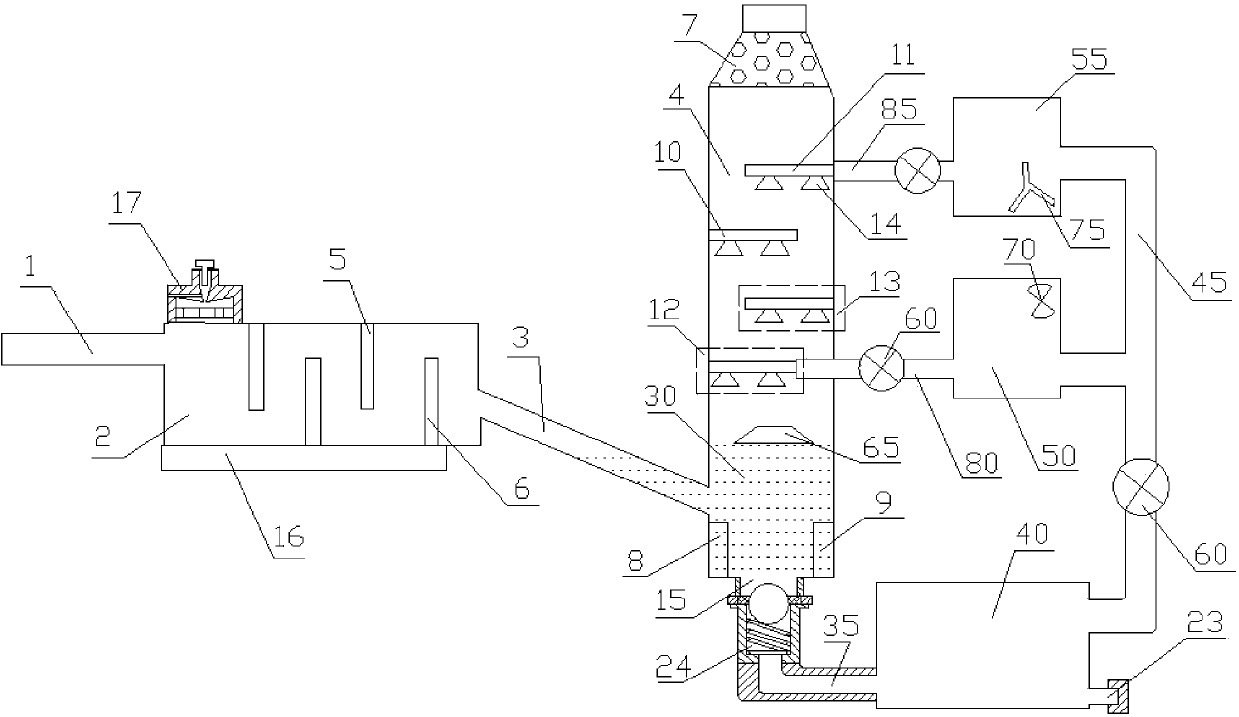

Waste gas purifying device applicable to incinerator

The invention discloses a waste gas purifying device applicable to an incinerator. The waste gas purifying device comprises an incinerator waste gas purifying device body, and a waste gas inlet pipe communicated with the exhaust port of an incinerator body, wherein the tail end of the waste gas inlet pipe is communicated with a dust catcher; an upper dust removal baffle and a lower dust removal baffle are arranged in the dust catcher; the upper dust removal baffle and the lower dust removal baffle are arranged at intervals; the tail end of the dust catcher is communicated with a waste gas exhaust pipe; the tail end of the waste gas exhaust pipe is communicated with an exhaust chimney; a left supporting plate and a right supporting plate which are longitudinally staggered are arranged on the inner side wall of the exhaust chimney; a flue gas pre-spray heat sink is arranged on the left supporting plate; a flue gas pre-spray desulfurizer is arranged on the right supporting plate; a waste gas purifying tank is formed at the bottom of the exhaust chimney; a deslagging door is arranged at the bottom of the dust catcher; a pressure release valve is arranged at the top of the dust catcher. The waste gas purifying device can filter poisonous gas, heavy metal and dust produced during the combustion of fire coal, effectively solves the problem of waste gas pollution, and avoids the risk of explosion caused by overlarge air pressure inside the device.

Owner:广州拉斯卡工程技术有限公司

Stent delivery system

ActiveUS8808346B2Highly controllableEasily retracts an outer jacket at different speedsStentsBlood vesselsDelivery systemStent

Owner:CR BARD INC

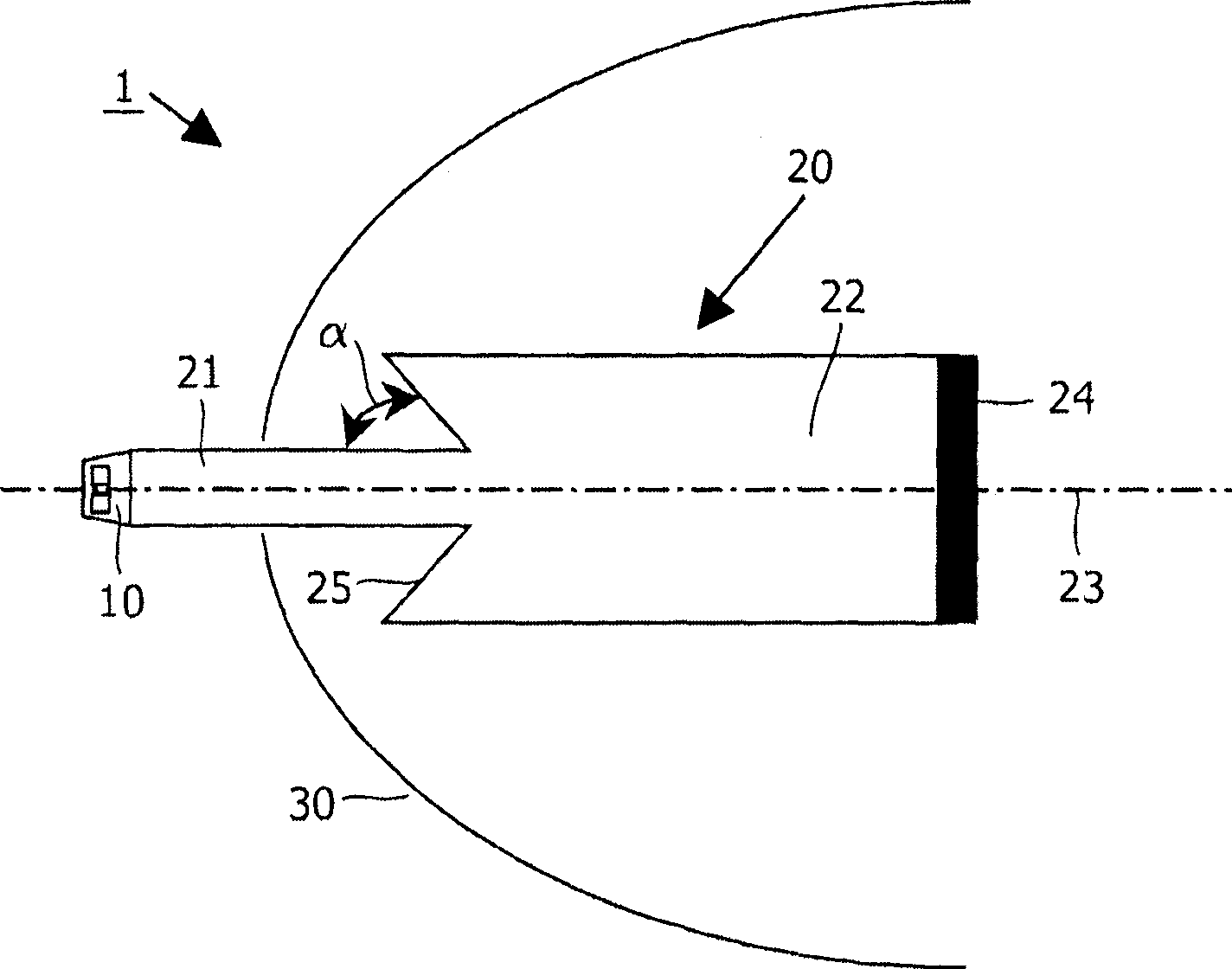

An illumination device comprising a light source and a light-guide

ActiveCN101501392AWith firmnessEconomical to useMechanical apparatusPoint-like light sourceLight equipmentLight guide

Proposed is an illumination device (1), comprising a semiconductor light source (10) for generating light, a primary optical system (20) for feeding the light to a secondary optical system (30), which is provided for radiating the light and for achieving a desired radiation pattern. The semiconductor light source may comprise LEDs and / or Laser- Diodes. The primary optical system comprises a light-guide with a mirrored end-face (24) and an out-coupling structure (25) for directing light into the secondary optical system. The mirrored end-face optically folds the light-guide, effectively extending the length over which the light is advantageously homogenized inside the light guide. Furthermore, optically folding the light-guide makes more economical use of the space inside the secondary optical system. This is especially advantageous when designing an LED based retrofit for existing form factors of halogen based illumination devices.

Owner:SIGNIFY HLDG BV

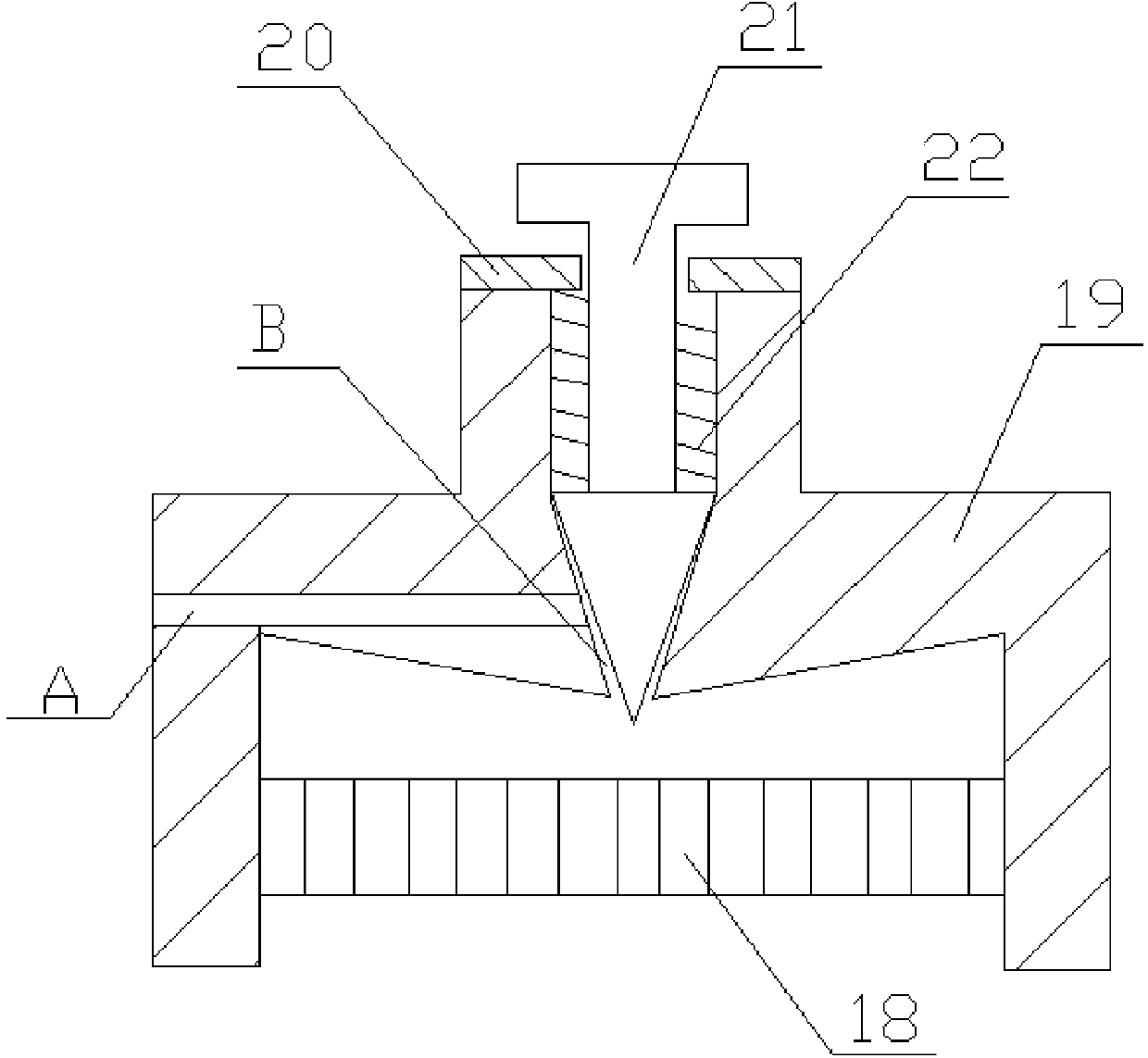

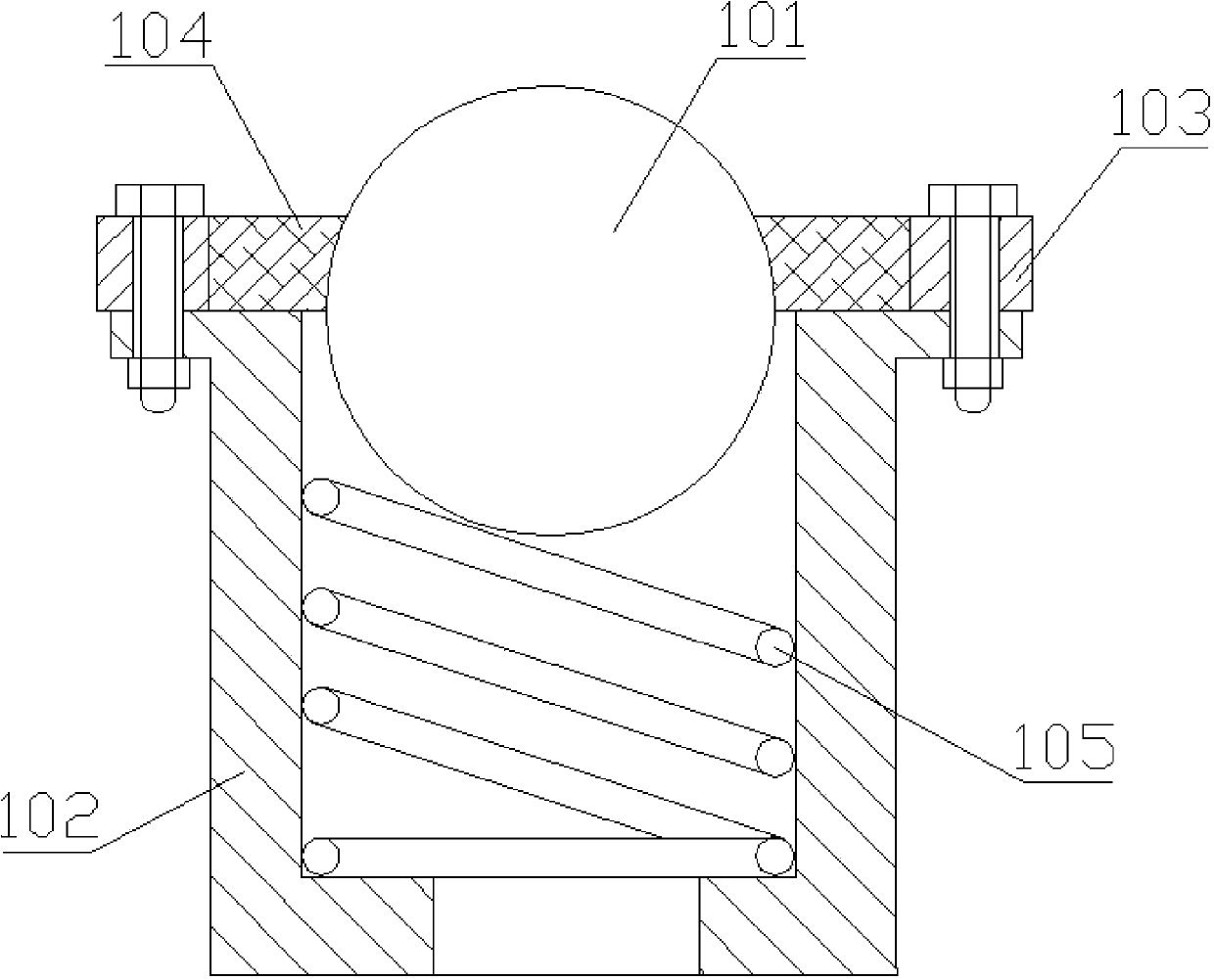

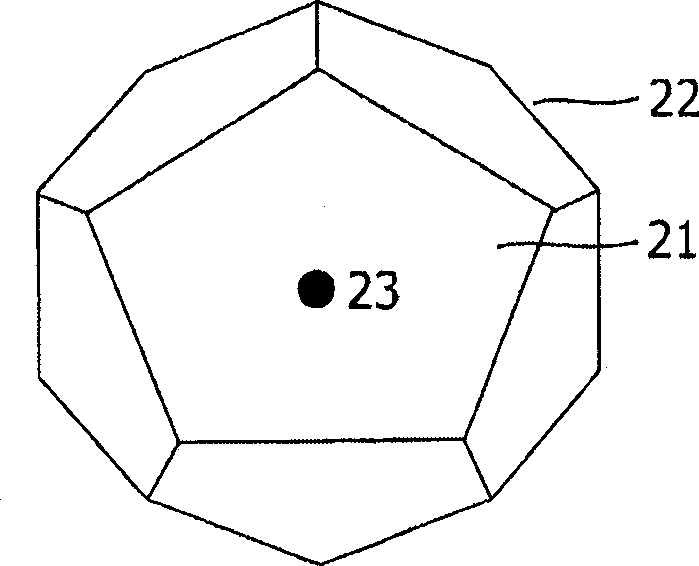

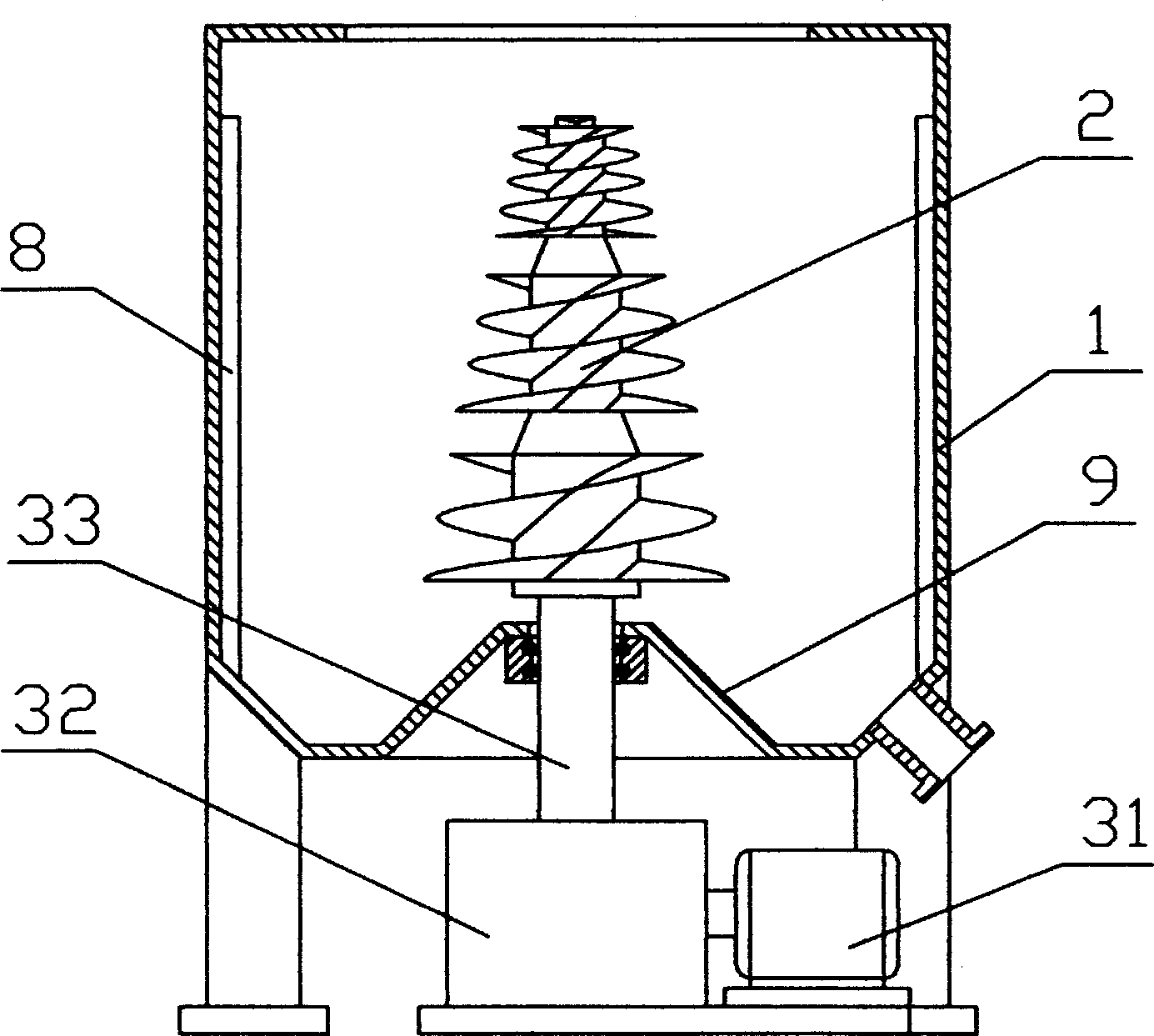

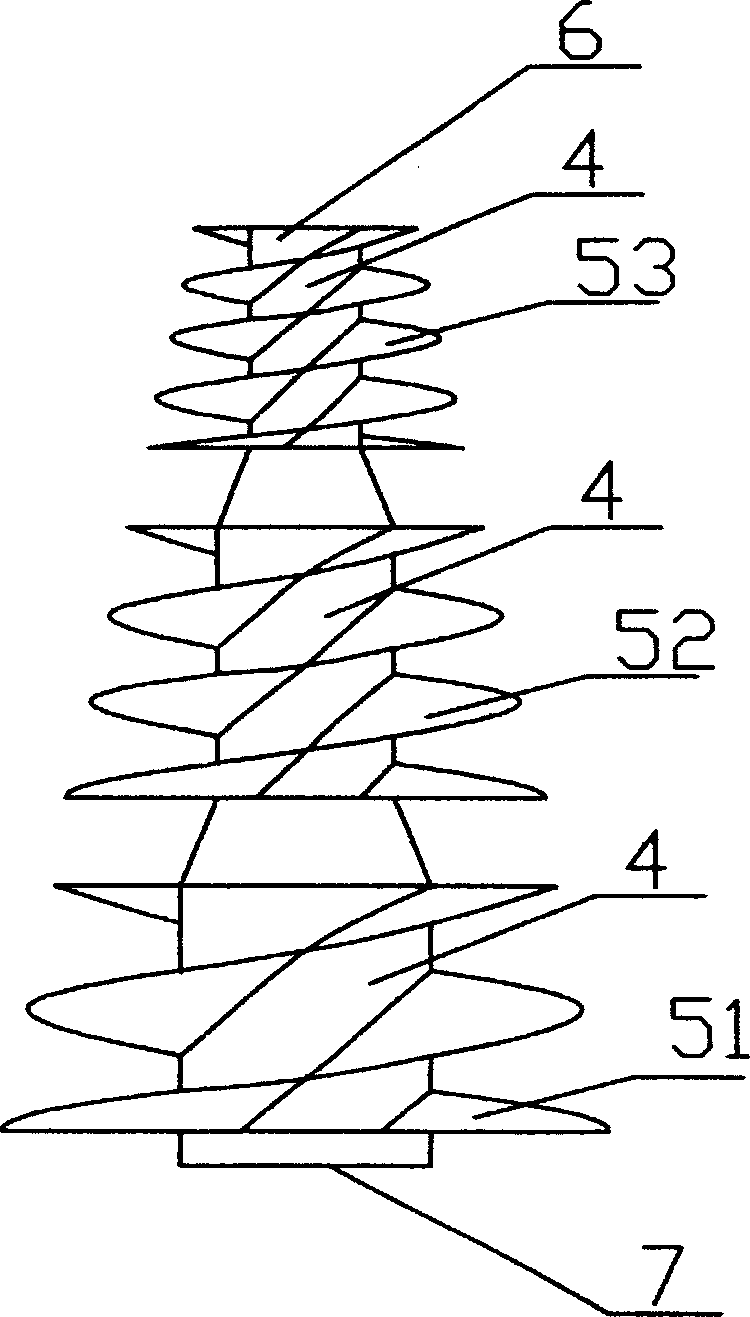

Middle high density hydraulic pulper

InactiveCN1657692AAvoid frictionReduce power consumptionPaper recyclingRaw material divisionEnergy costHigh density

The invention discloses a hydraulic pulp kneader, including the trough solid whose bottom has pulp kneader with corkscrew leaf set vertically, the driving end of pulp kneader is connected to the driving device below the trough solid, and the bottom of trough solid of the pulp kneader driving end is saddlebacked, making the leaf of pulp kneader get away from the bottom of trough solid, avoiding friction between the trough solid and pulp kneader completely, decides the route of whole vorticity circulation and local vorticity circulation formed in the trough solid is lengthed, so that the times of collision is increased and the waste paper is scattered to be the single fiber and it won't be cut off, also, all kinds of nonfiber mixture are kept wholly, it has decreased the energy cost and increased the quality of paper pulp.

Owner:李风宁

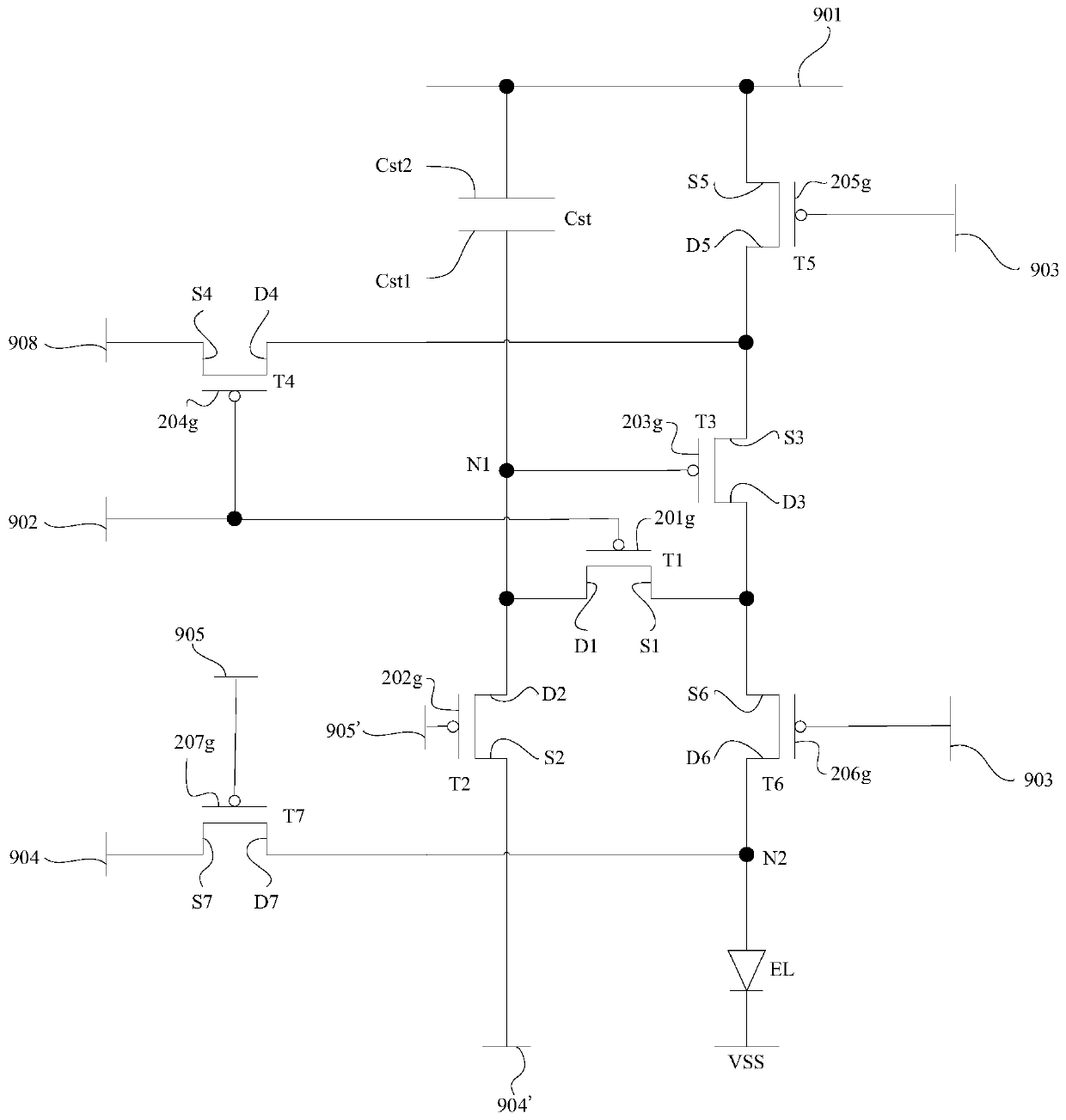

Display panel, manufacturing method thereof and display device

ActiveCN111584599AExtended Diffusion PathSlow release rateStatic indicating devicesSolid-state devicesGraphicsDisplay device

The invention provides a display panel, a manufacturing method thereof and a display device, relates to the technical field of the display, and aims to solve the problem that in the use process of a display product, water molecules in a flat layer escape and erode a light-emitting functional layer, so that the service life of the display product is shortened. The display panel comprises a substrate and a plurality of pixel units arranged on the substrate, the plurality of pixel units are distributed in an array, and each pixel unit comprises a plurality of sub-pixels; each sub-pixel comprisesa sub-pixel driving circuit, a flat layer and an anode pattern which are sequentially stacked; the anode patterns in at least part of the sub-pixels comprise middle parts and edge parts surrounding the middle parts; the surfaces, back to the substrate, of the flat layers are provided with grooves, the orthographic projections of the grooves on the substrate surrounds the orthographic projections of the middle parts on the substrate, and the orthographic projections of at least parts of the edge parts on the substrate are located in the orthographic projections of the grooves on the substrate.The display panel provided by the invention is used for displaying pictures.

Owner:BOE TECH GRP CO LTD +1

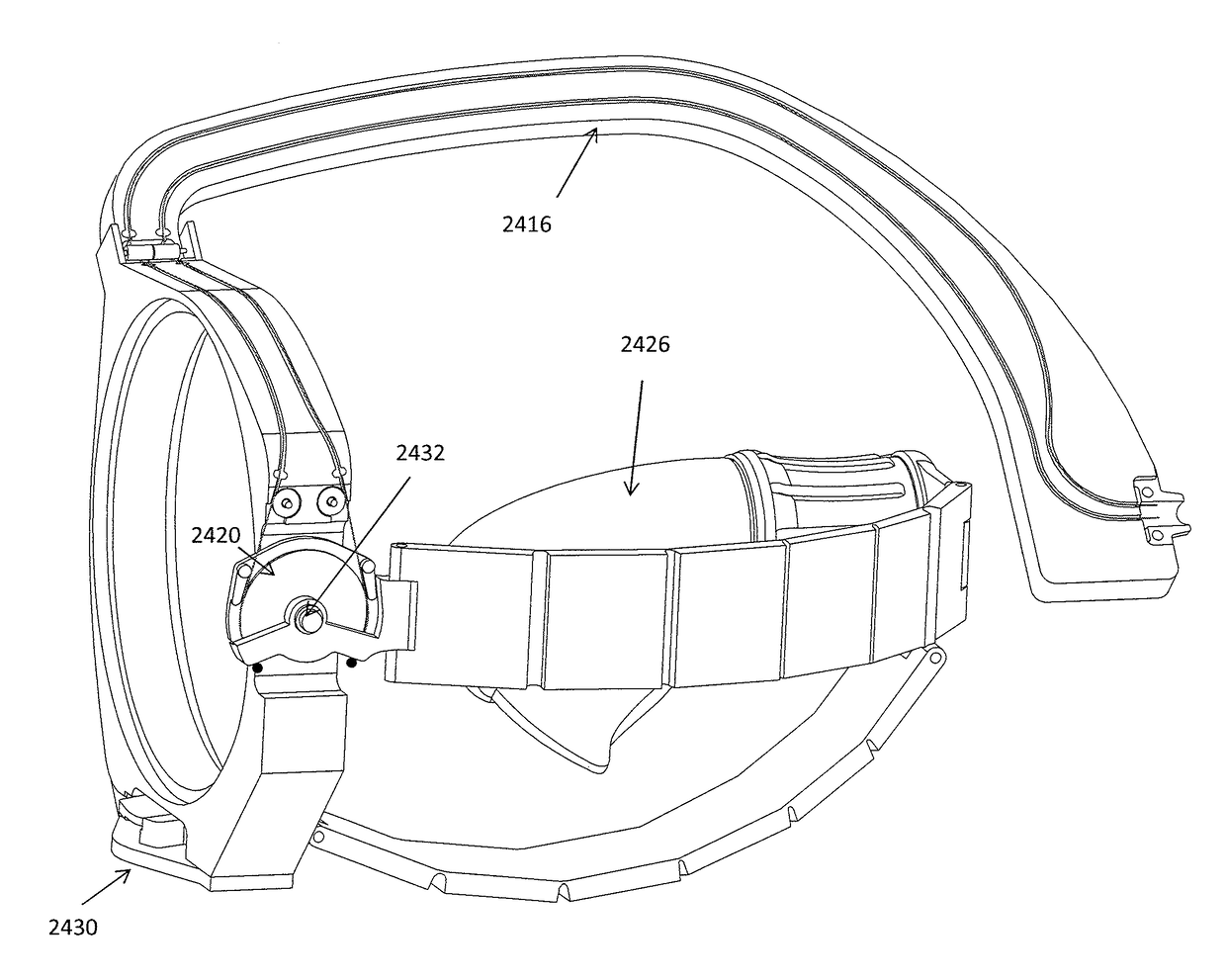

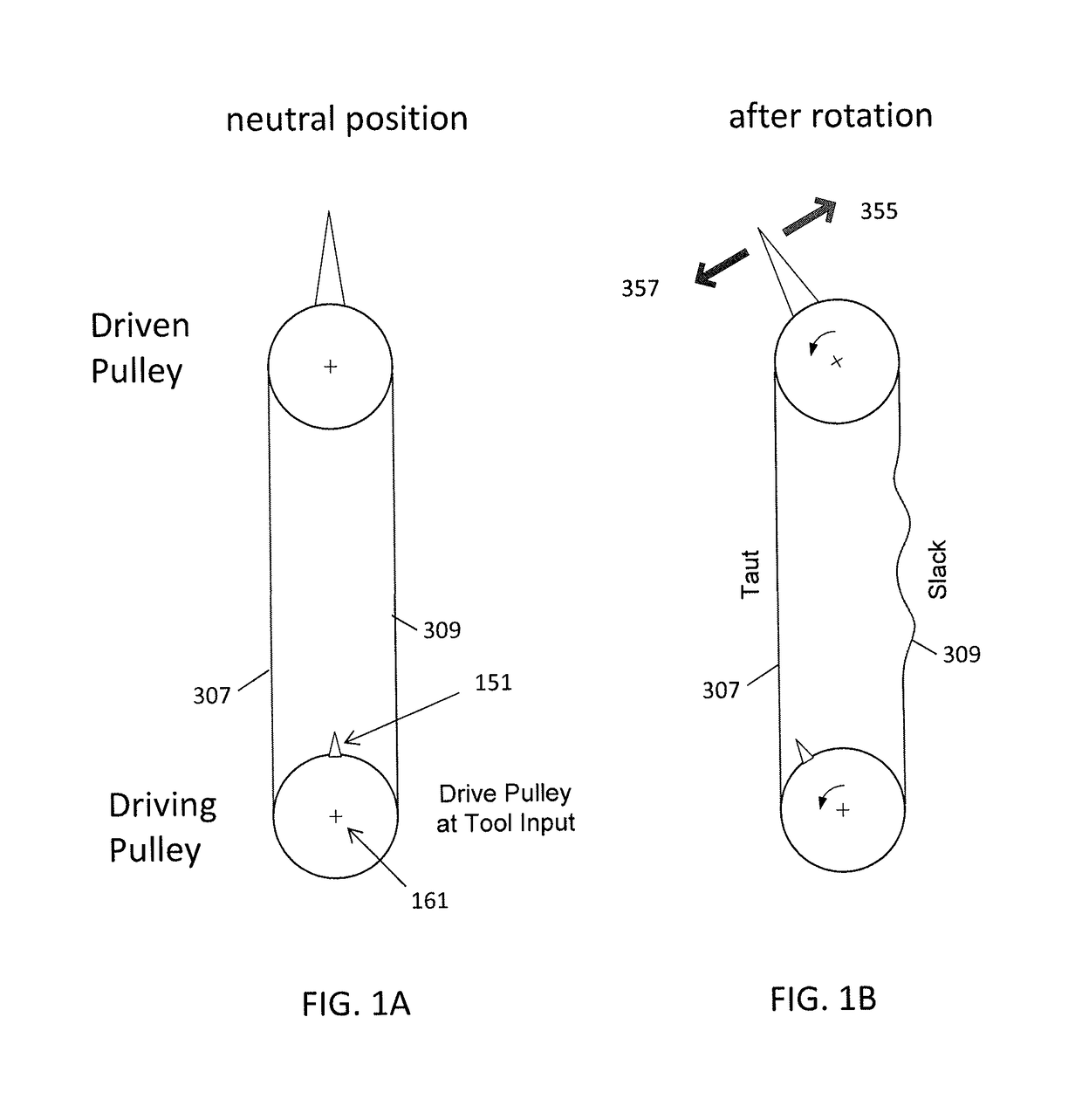

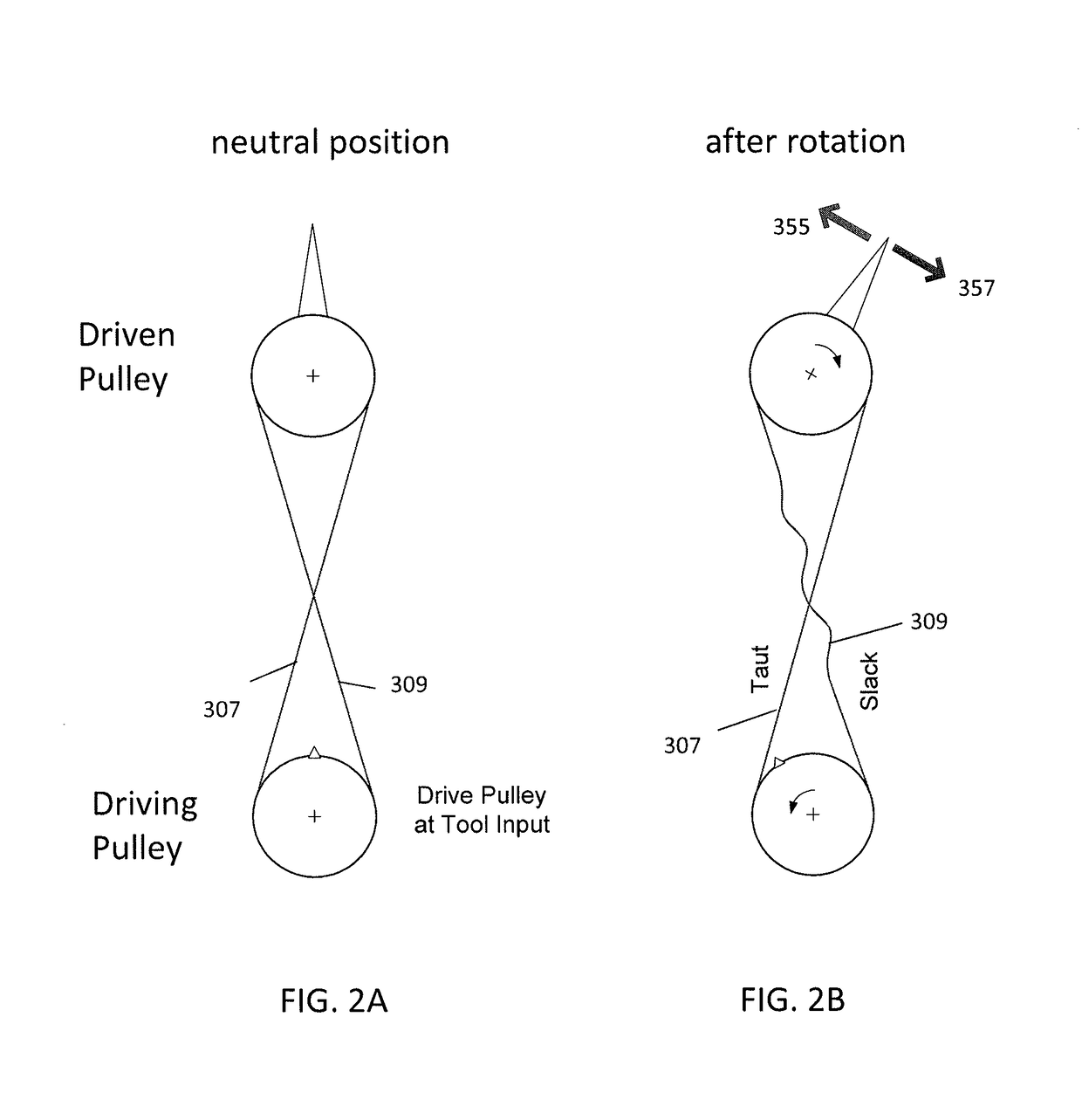

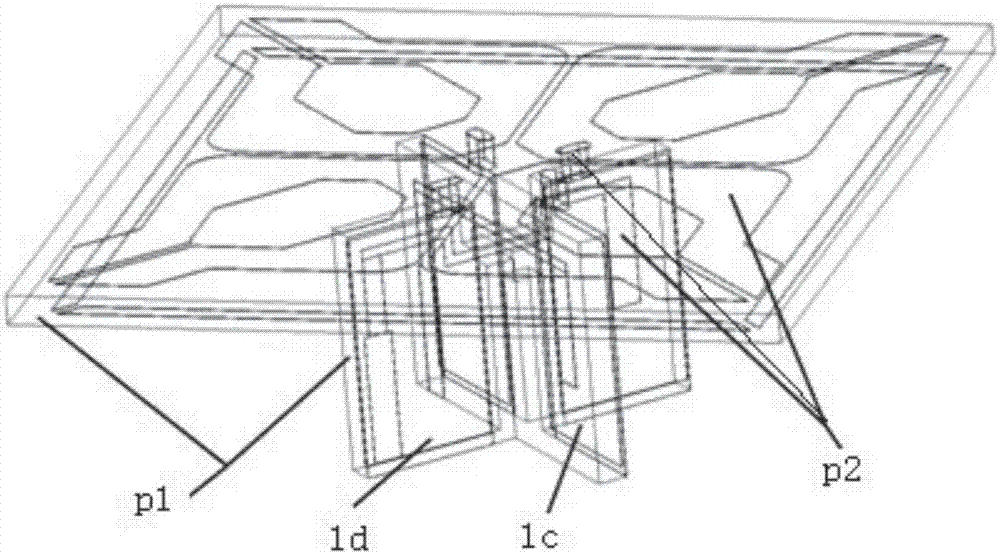

Tension management apparatus for cable-driven transmission

ActiveUS20180080533A1Reduce and eliminate slackIncrease wrap angleEndoscopesLaproscopesPath lengthEngineering

Slack-compensating pulleys, transmission systems including slack-compensating pulleys, and methods of operating these. In general, slack-compensating pulleys include a pulley body onto which a cable can wind, and one or more (e.g., two) slack take-up surfaces that rotate with the pulley body that are configured to remove slack form an outgoing length of cable by increasing the cable path length and wrap angle. In particular, described herein are minimal access tools having slack-compensating transmissions.

Owner:RGT UNIV OF MICHIGAN

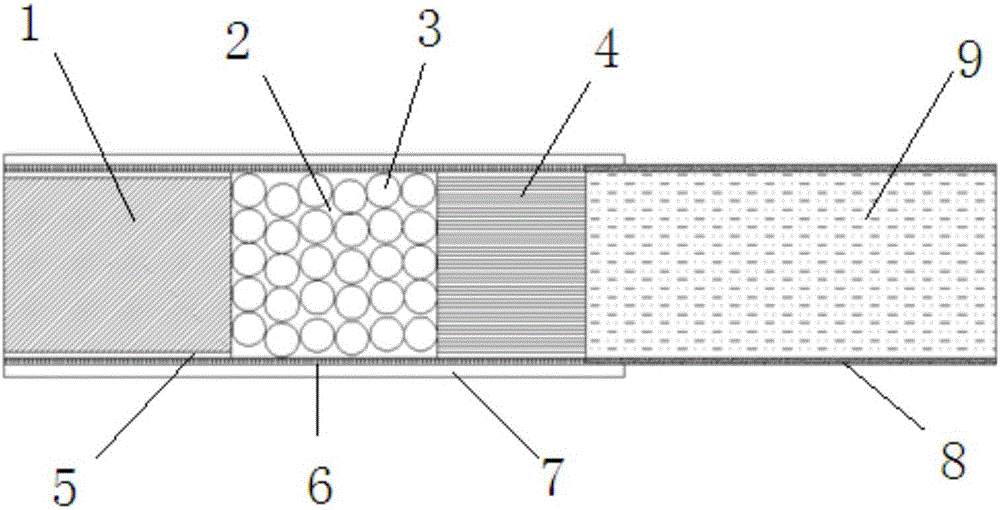

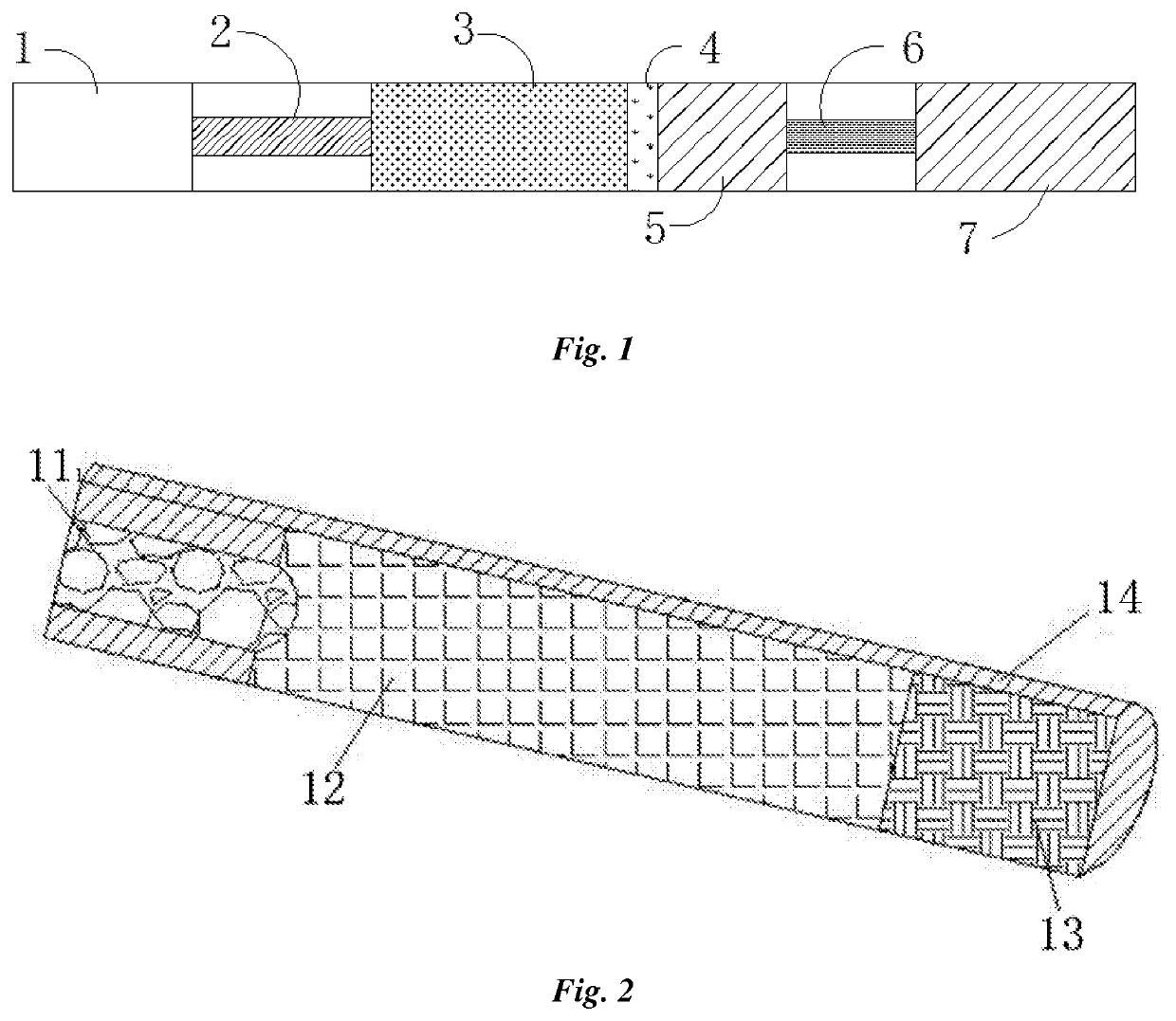

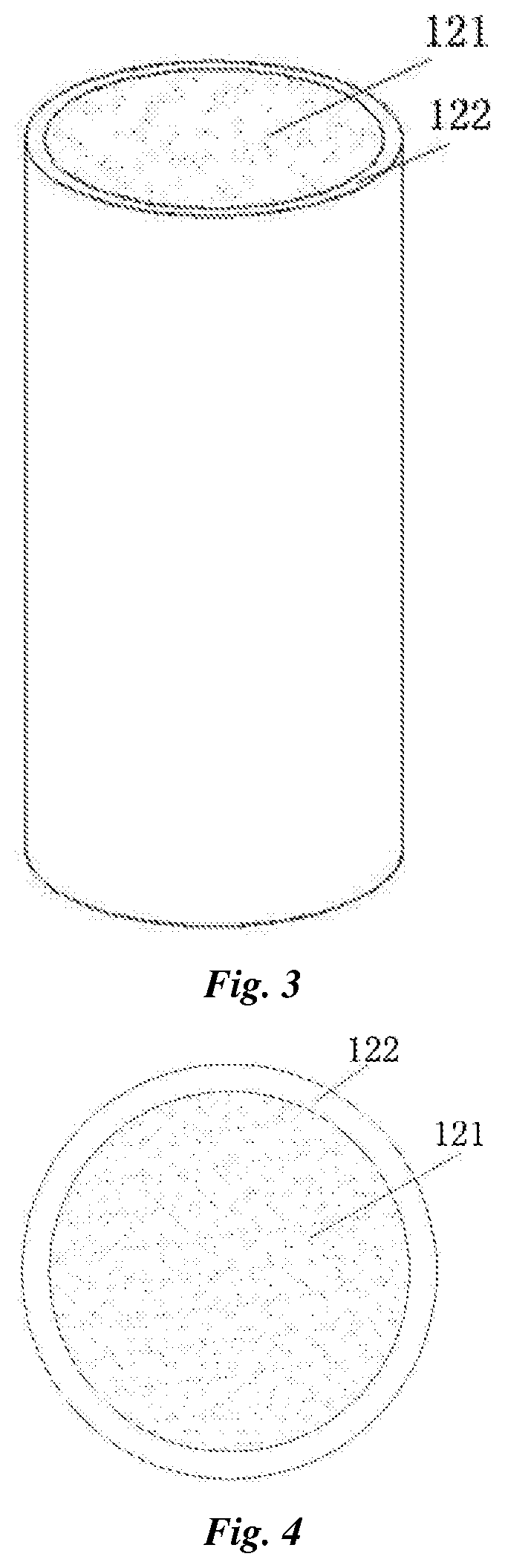

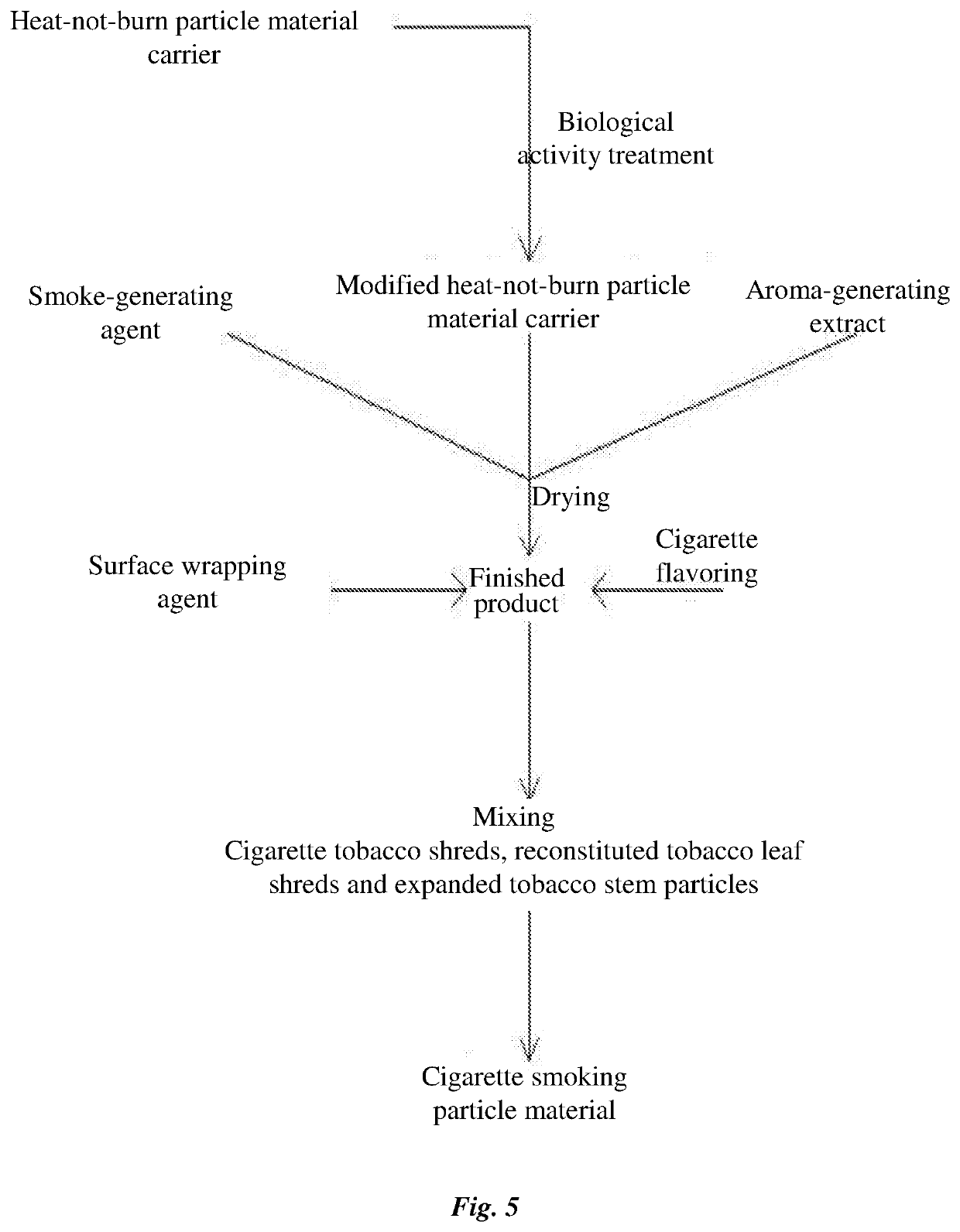

Integrally-formed Heat-not-burn Smoking Article and Manufacturing Method therefor

PendingUS20200229487A1Simple manufacturing processSimple formatAdditive manufacturing apparatusTobacco treatmentMechanical engineeringComposite material

An integrally-formed heat-not-burn smoking article and a manufacturing method therefor, wherein the smoking article comprises a lip-proximal end and a lip-distal end, and the smoking article is formed by integrally filling a piece of forming paper having a constant thickness, from the lip-distal end to the lip-proximal end, with four or more different unit sections comprising a filter unit, a gel cooling aroma-carrying unit, a hollow special particle unit, a hollow supporting unit, a cavity unit, a blocking sheet unit and a smoking unit. The manufacturing method involves corresponding integral filling, with the manner of the filling comprising positioned filling in with independent units and integral filling in with combined units. The present invention can reduce the temperature of smoke, reduce a burning, hot and spicy feeling caused by the smoke entering the oral cavity, improve the feeling of a smoking experience.

Owner:YUNNAN XIKE TECH CO LTD

Base station antenna unit and base station antenna

InactiveCN107508037AReduce weldingReduce weightAntenna supports/mountingsRadiating elements structural formsMetal stripsCoupling

The present invention provides a base station antenna unit and a base station antenna. The base station antenna unit includes an integrally formed non-metal structure and a metal pattern formed on the non-metal structure through an LDS (laser direct shaping) or LEP (laser enhanced plating) process, wherein the non-metal structure comprises at least a non-metal substrate, and the metal pattern at least comprises vibrator arms, coupling metal strips and metallized through holes, wherein the vibrator arms are formed at the front surface of the non-metal substrate, the coupling metal strips are formed at the back surface of the non-metal substrate, and the metallized through holes are formed at the connection through holes of the vibrator arms and are connected with the vibrator arms. The base station antenna unit has the advantages of light weight, high surface accuracy and high production consistency.

Owner:SHANGHAI AMPHENOL AIRWAVE COMM ELECTRONICS CO LTD

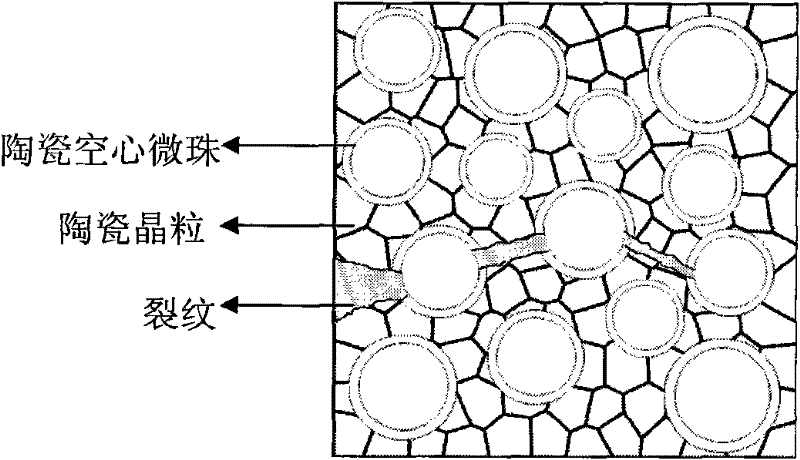

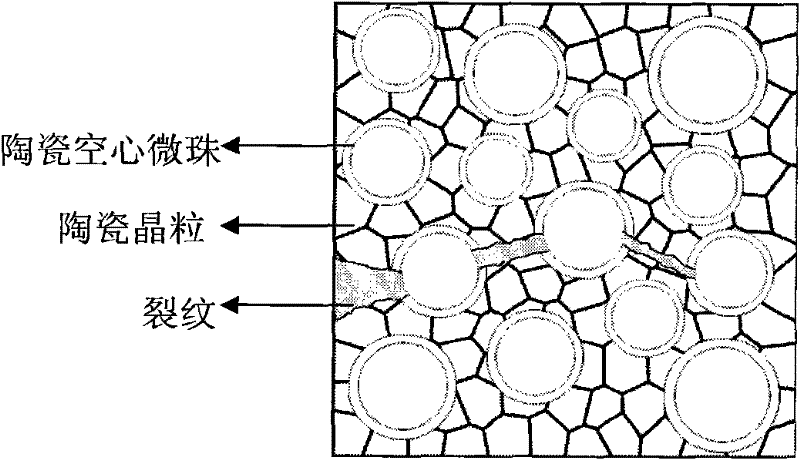

Ceramic with light weight, high strength and high toughness and preparation method thereof

The invention provides a ceramic with light weight, high strength and high toughness and a preparation method thereof. The method comprises the following steps: 1) presintering ceramic cenosphere powder to increase the strength of the ceramic cenosphere powder; 2) adding the presintered ceramic cenosphere powder in ceramic powder, adding the related additives; 3) selecting a moulding technology to mould the ceramic; 4) drying the obtained blank; and 5) sintering the dried blank. The invention provides the ceramic with light weight, high strength and high toughness and the preparation method thereof, wherein the ceramic cenosphere is a ceramic material toughened by the toughening body.

Owner:HEBEI YL BANGDA NEW MATERIALS LTD CO

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com