Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

32results about How to "Eliminate transmission delays" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Virtual interactive global exchange

InactiveUS20020128952A1More liquidityLess expenseFinanceSpecial data processing applicationsSystem usageVirtual reality

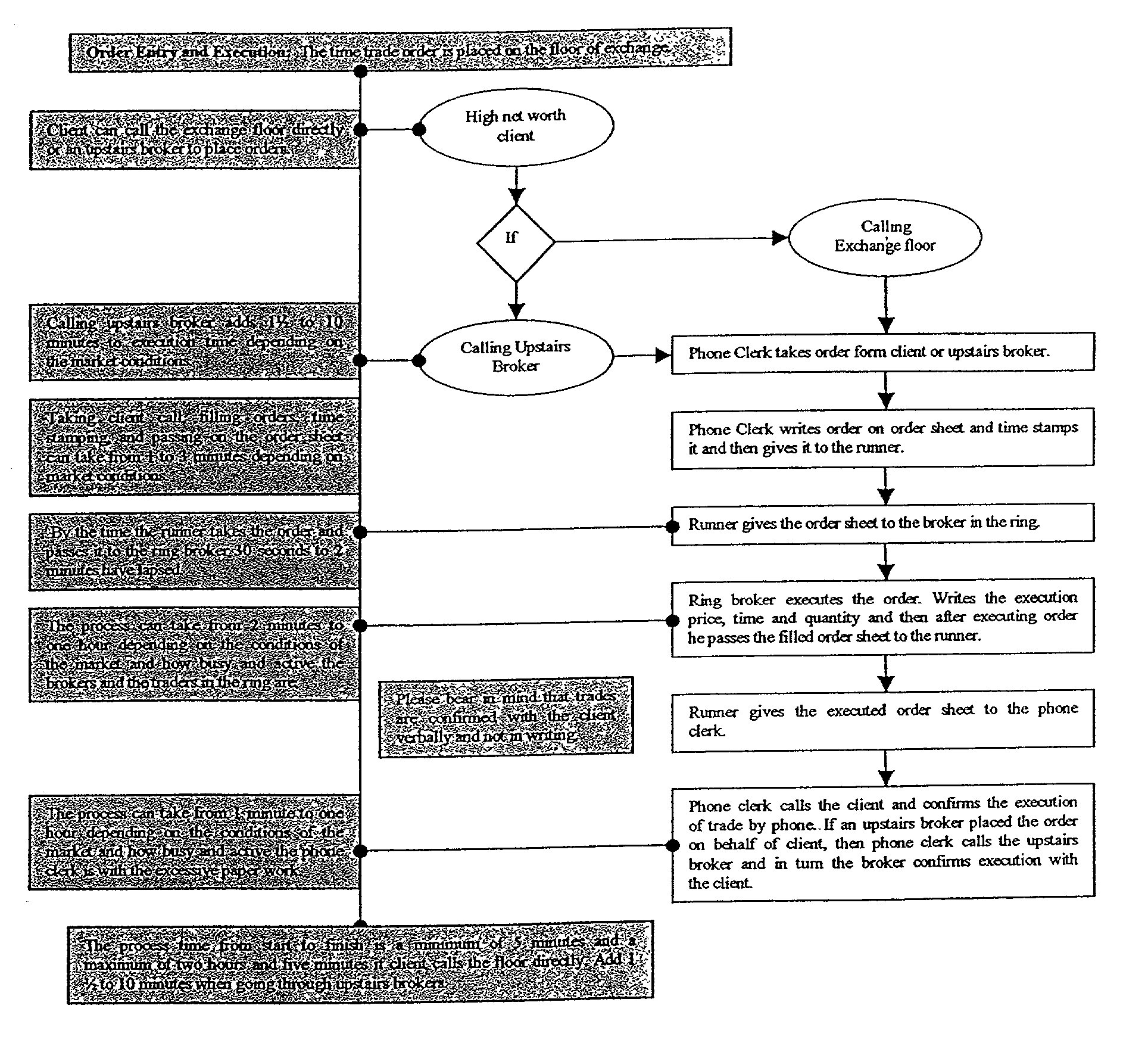

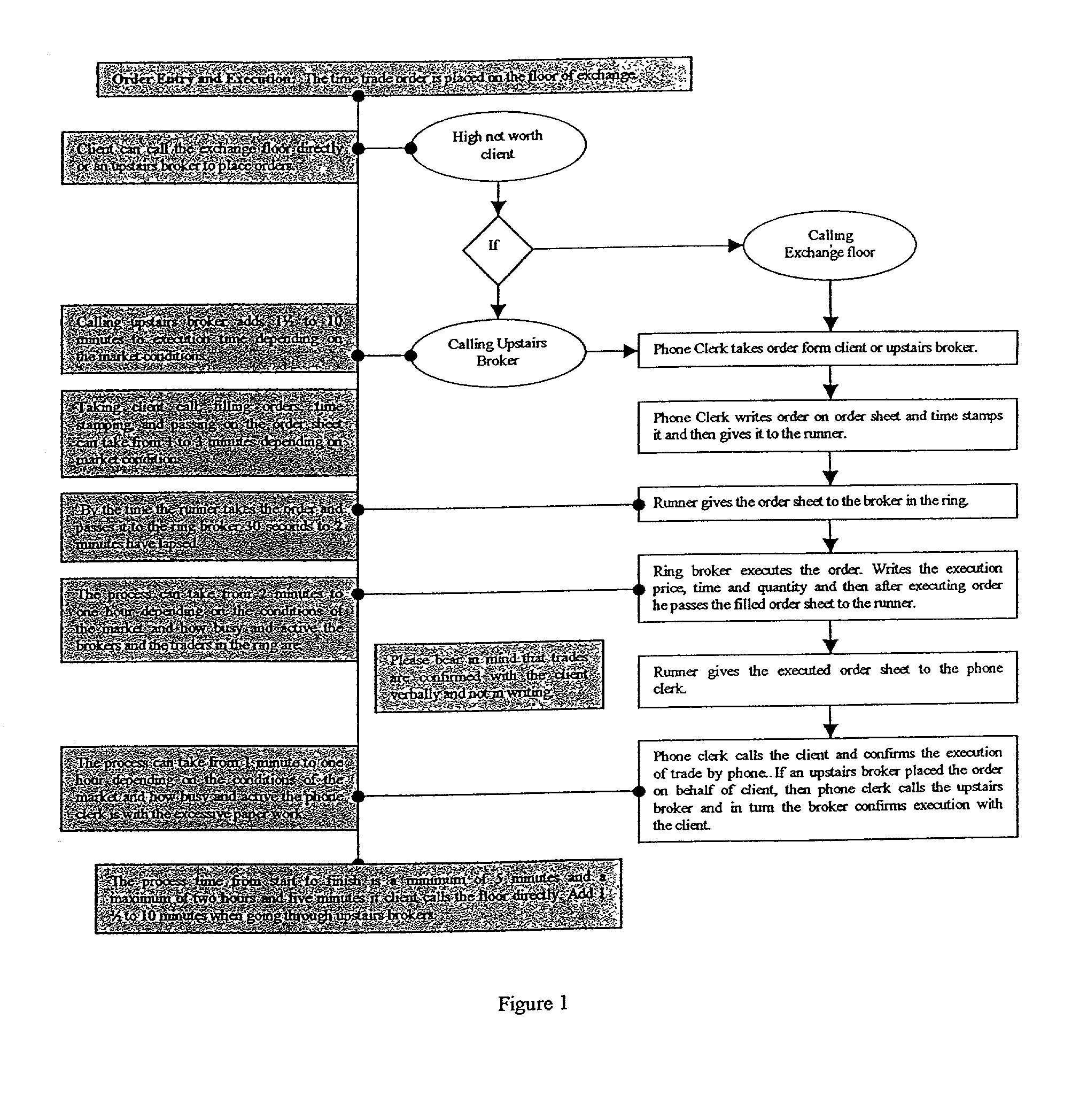

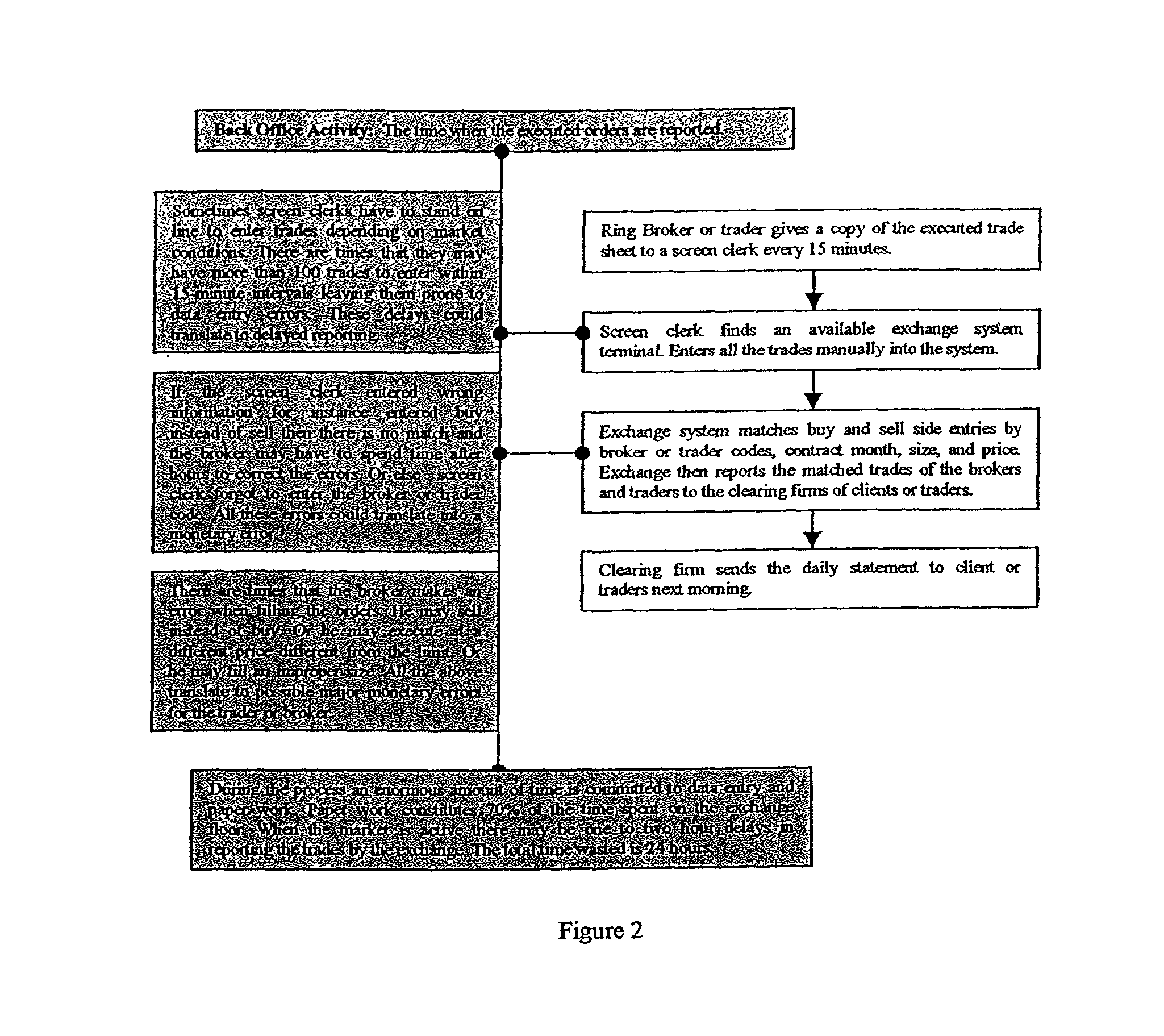

A computer based virtual reality trading system for trading financial products such as commodities and stocks uses a server based system for generating a virtual trading floor to simulate an exchange. Traders use local PC's to direct their individual avatars interactively on the virtual trading floor, using hand and voice signals similar to a non-virtual exchange. This allows an exchange to be de-coupled from its physical geographic location as traders in diverse locations can interact on the virtual trading floor. The system enables accurate tracking for audit of the trade activity and simplified trade clearing, while retaining the dynamics of a non-virtual exchange.

Owner:MELKOMIAM RAYMOND

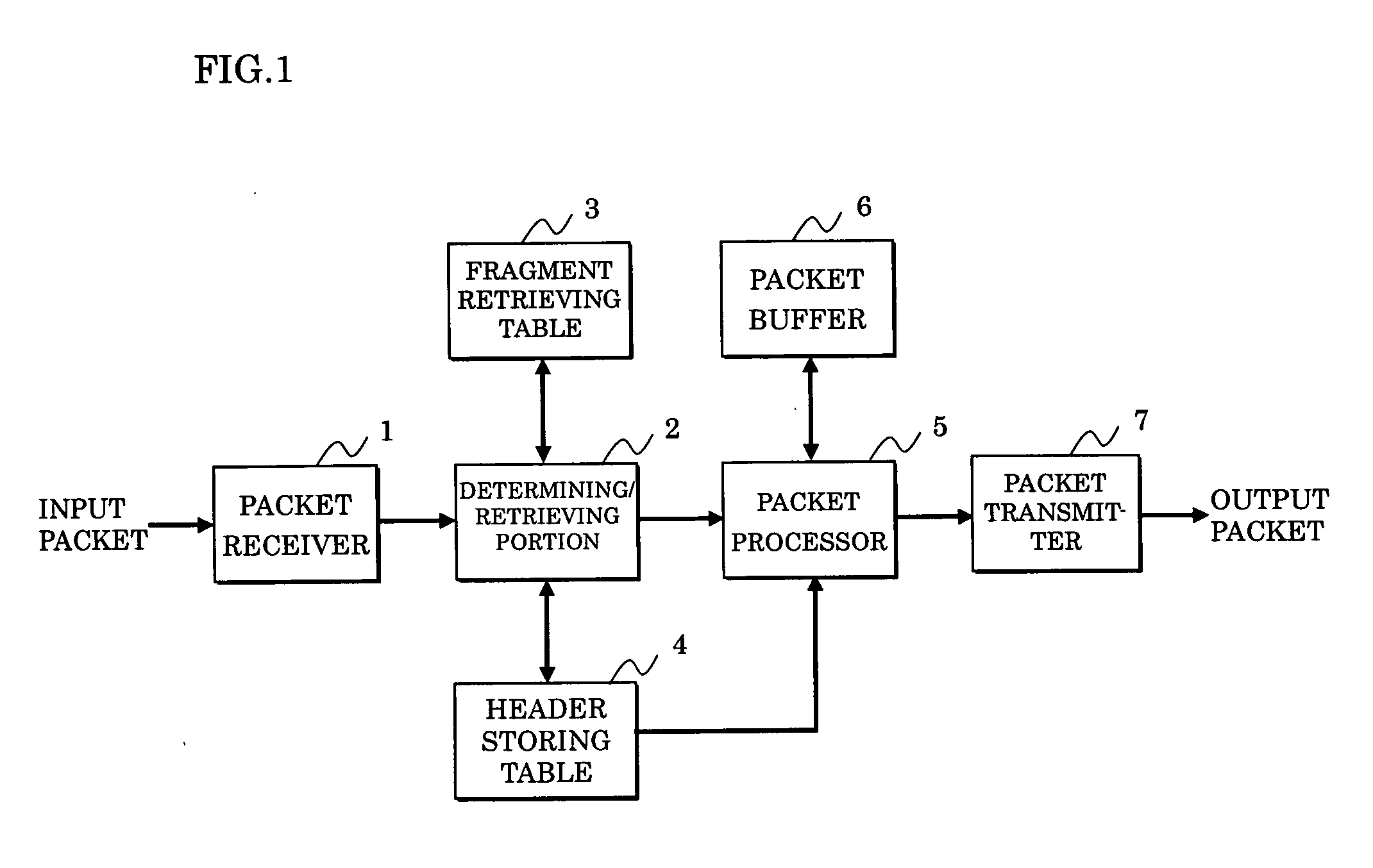

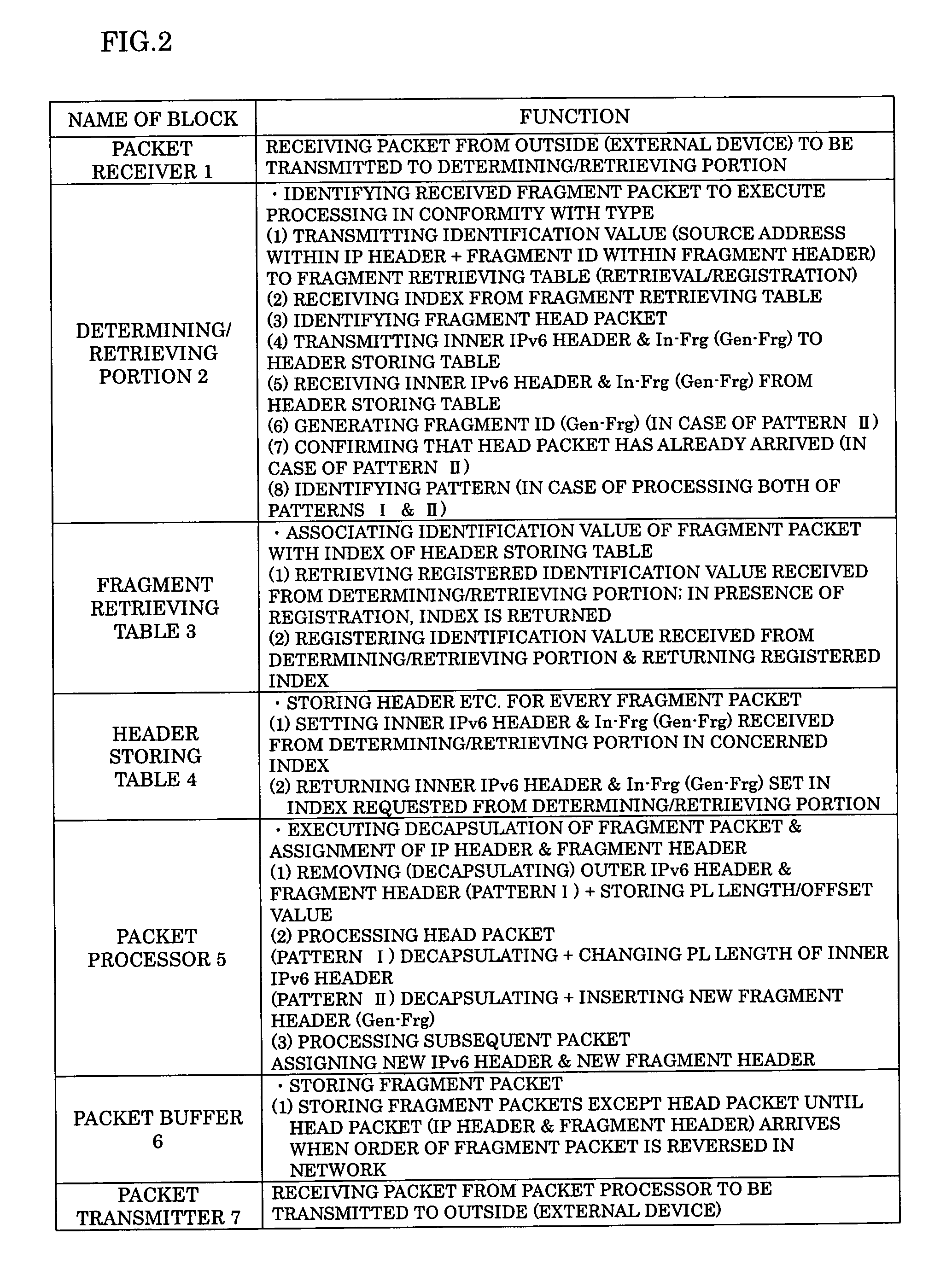

Packet transfer method and device

InactiveUS20050243834A1Reduce transmission delayEliminate transmission delaysData switching by path configurationSecuring communicationComputer hardware

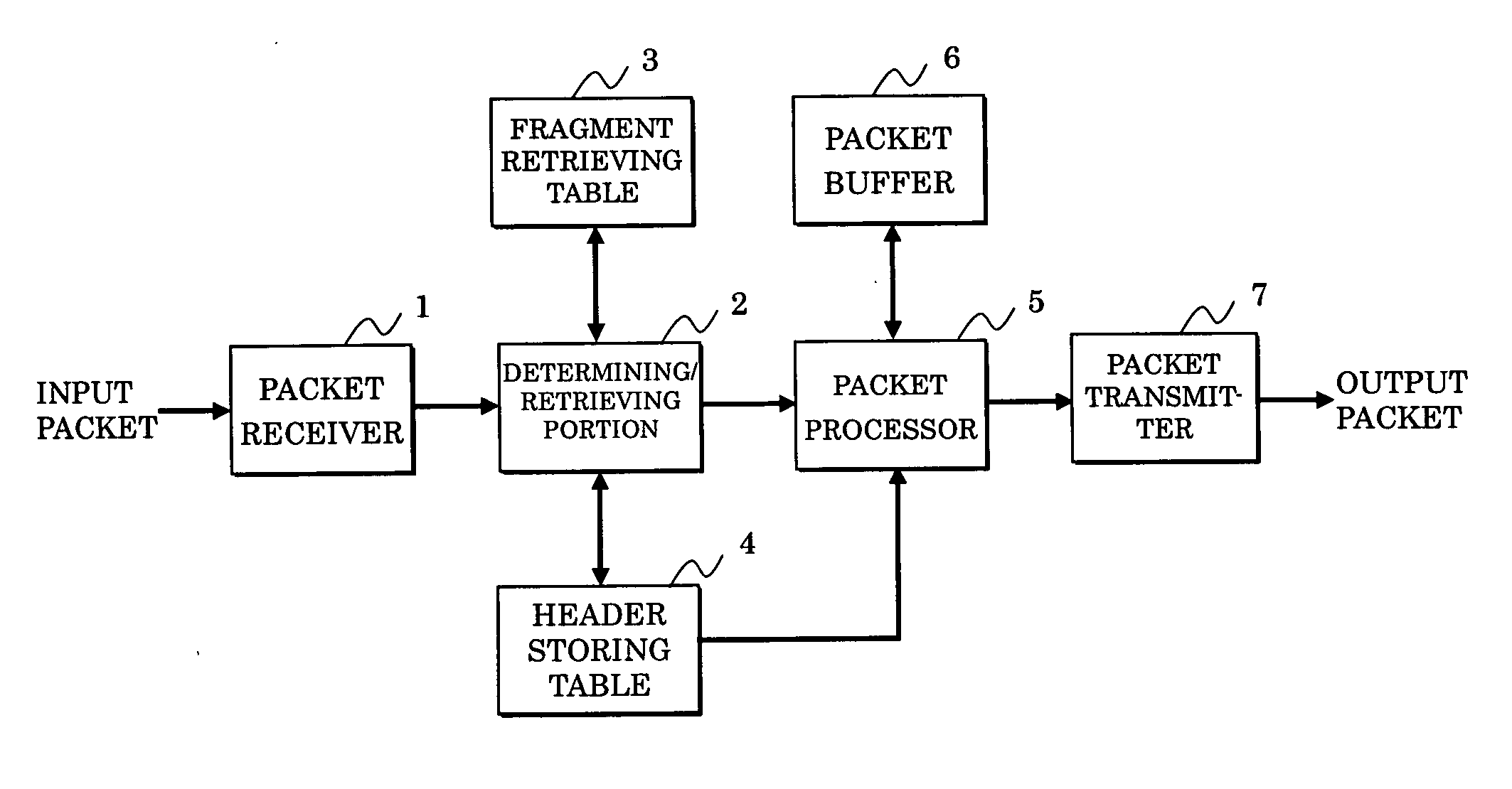

In a packet transfer method and device which can reduce a transfer delay and transfer a packet with a small-scale hardware when the packet to which fragmentation is performed after encapsulation is received, a head packet and a subsequent packet are detected from received packets to which the fragmentation is performed after the encapsulation, an inner header of the head packet detected is stored and then decapsulated, the inner header is changed in conformity with the decapsulation, the subsequent packet is further decapsulated, and the inner header of the head packet changed as mentioned above and a fragment offset value in conformity with the fragmentation are assigned to each packet to be outputted.

Owner:FUJITSU LTD

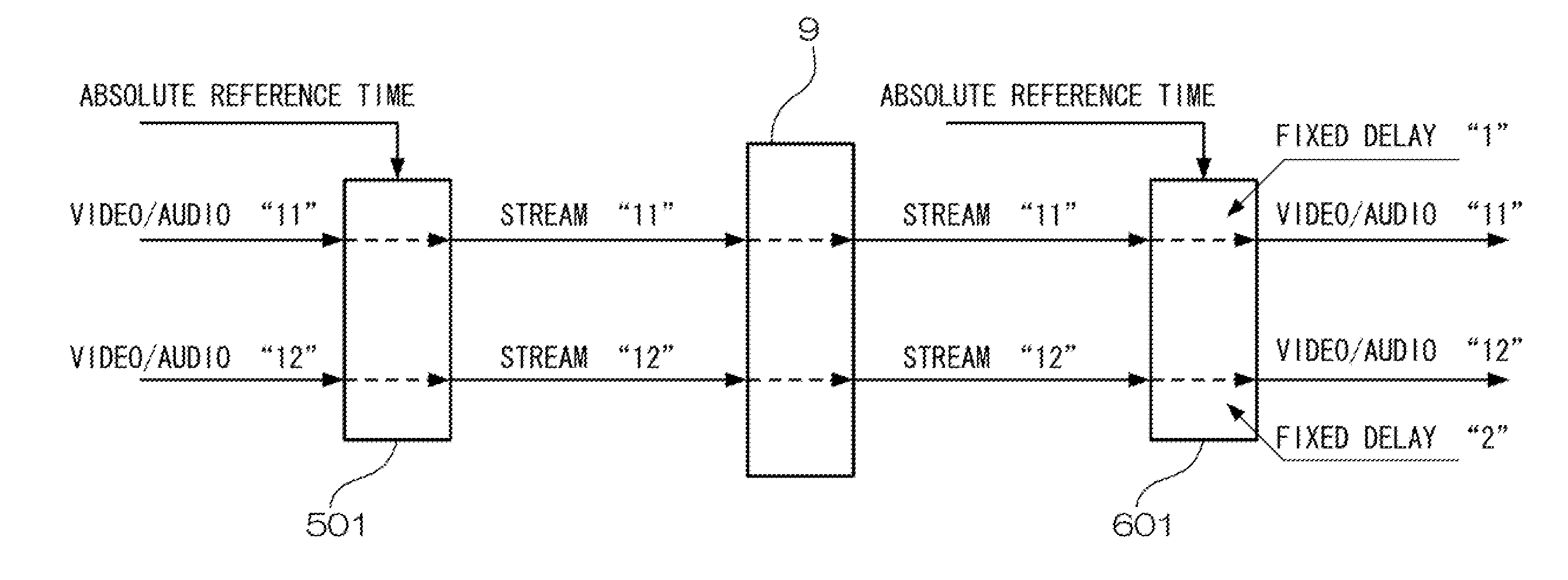

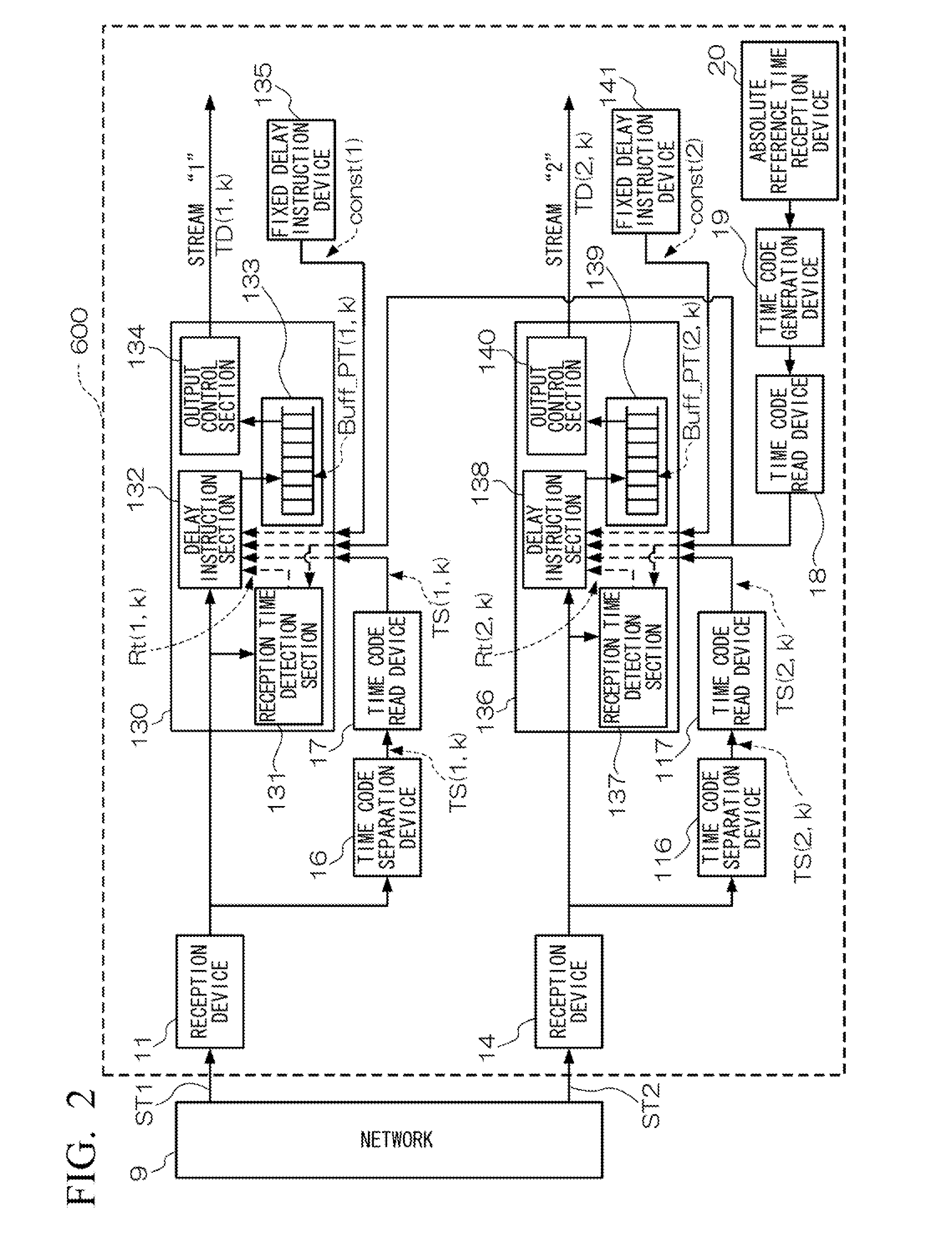

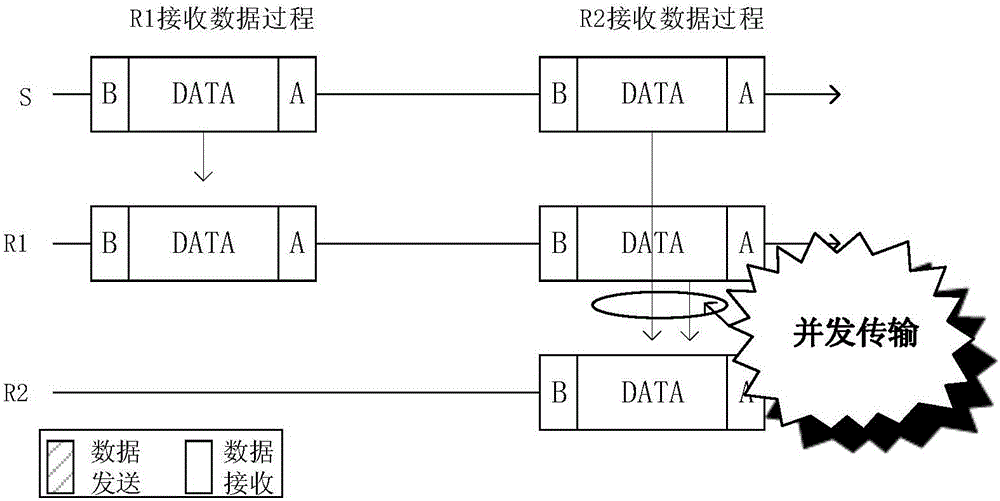

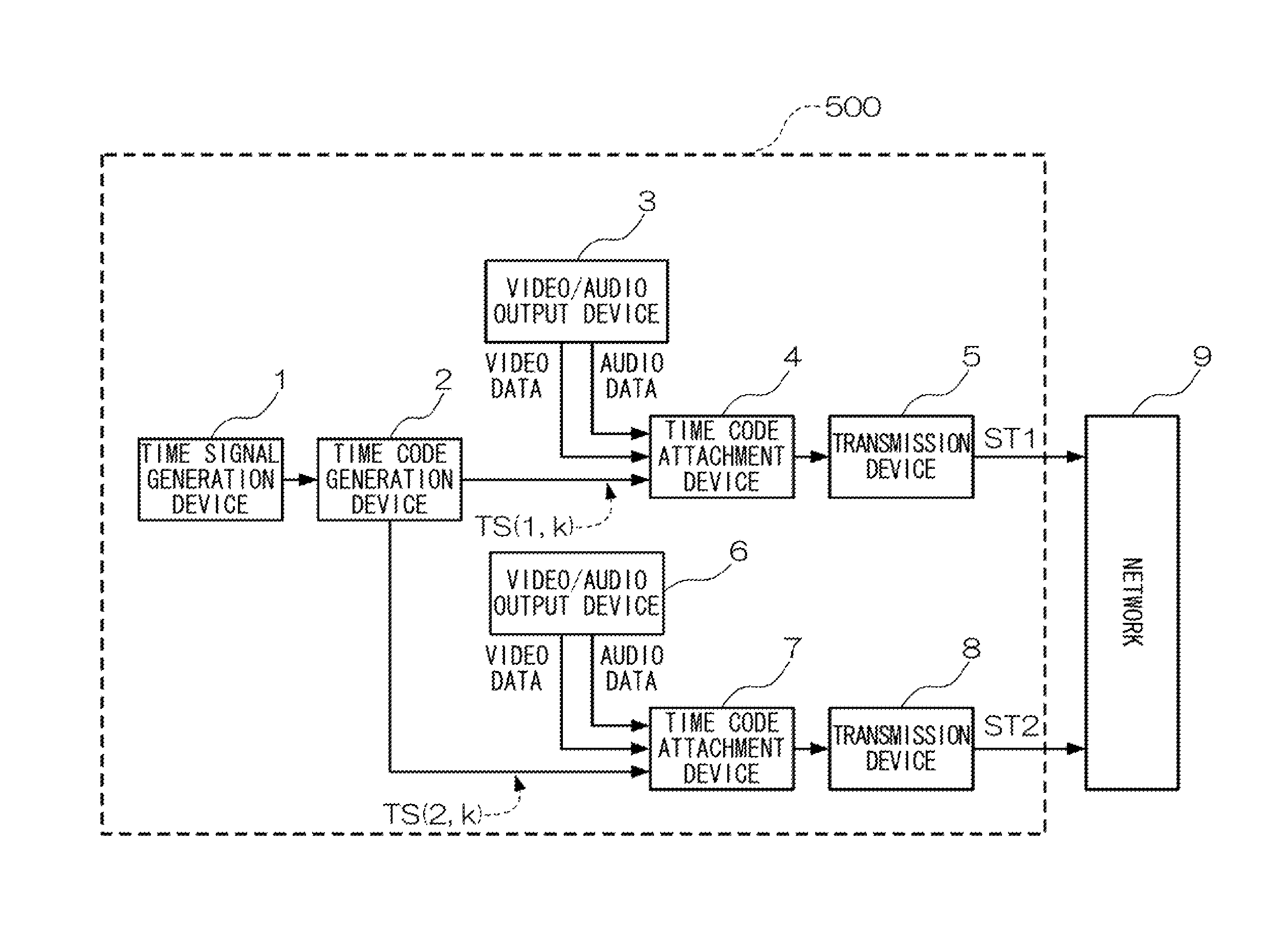

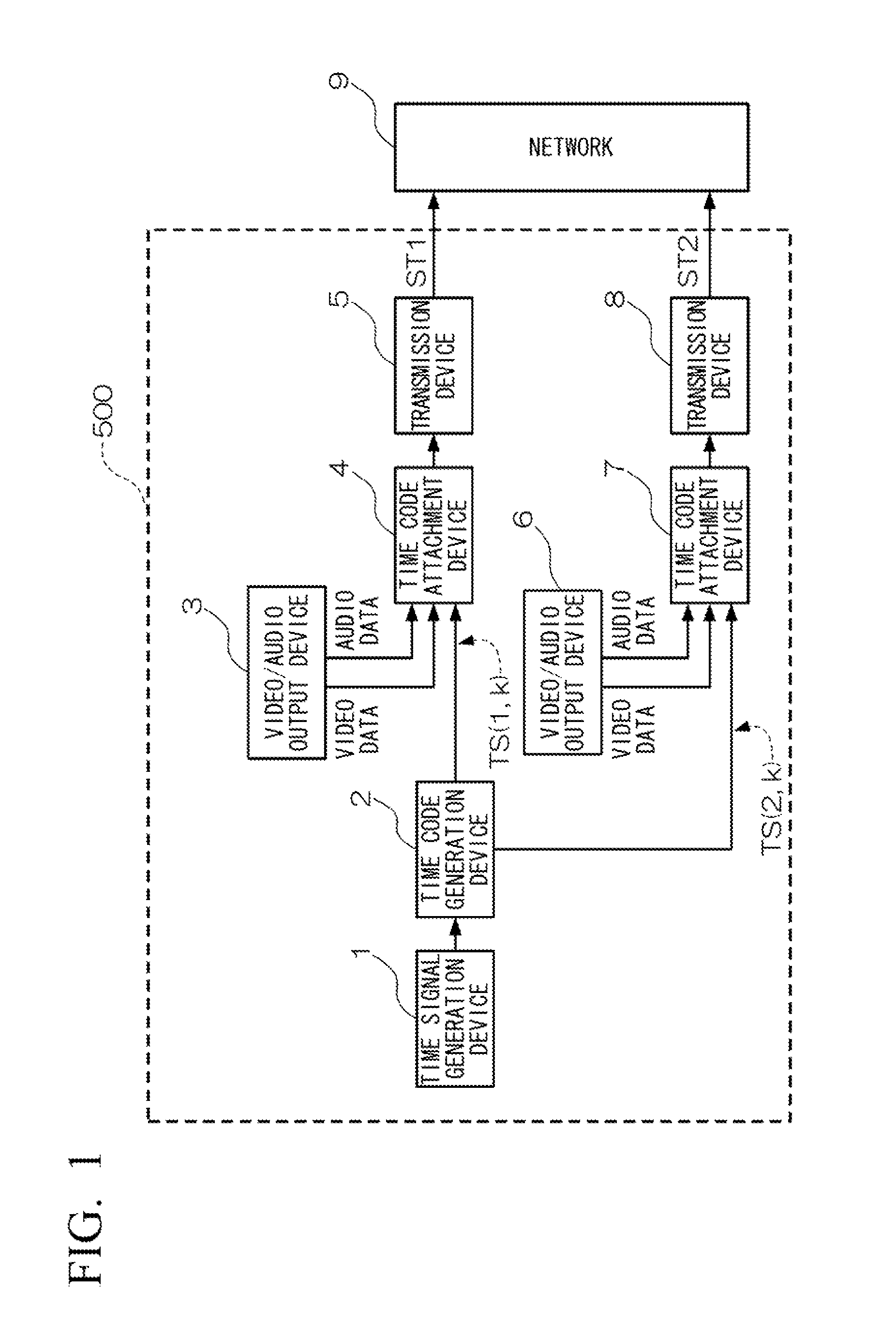

Stream signal transmission device and transmission method

InactiveUS20110291723A1Absorb fluctuation in transmission timeEliminate transmission delay fluctuationPulse modulation television signal transmissionPulse automatic controlTransmission delayControl unit

Provided is a stream signal transmission device that can eliminate transmission delay fluctuation with a fast change such as network jitter with high accuracy and synchronize a plurality of streams. The stream signal transmission device includes at least one reception unit that receives a stream signal to which a time code is attached from a network, at least one extraction unit that extracts the time code from the stream signal received by the reception unit, and at least one delay control unit that determines an output time by adding a predetermined fixed delay to a time indicated by the time code extracted by the extraction unit, and outputs the stream signal received by the reception unit after holding the stream signal up to the output time.

Owner:NEC CORP

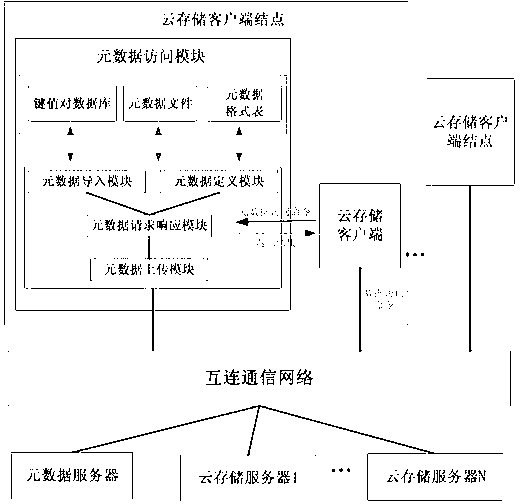

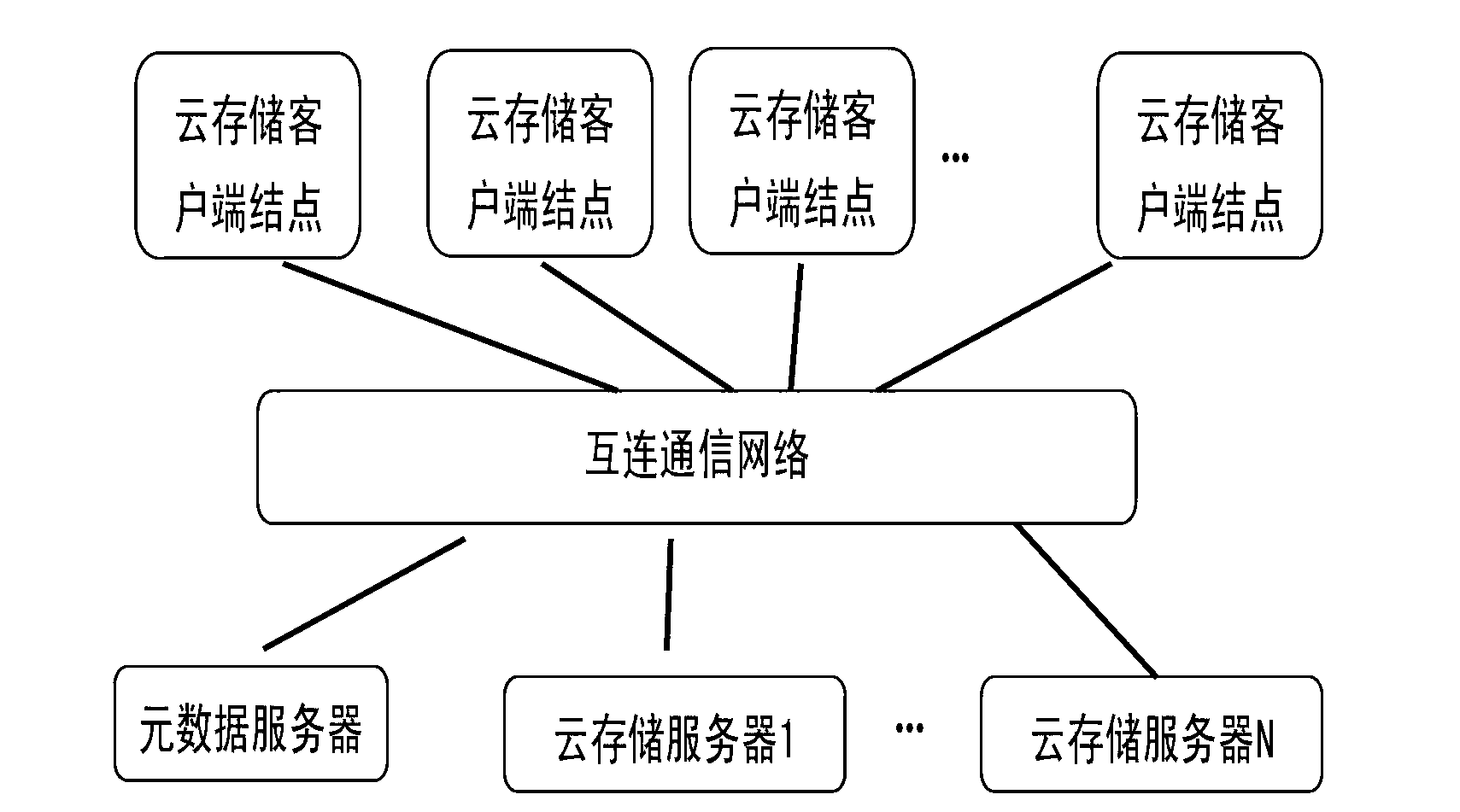

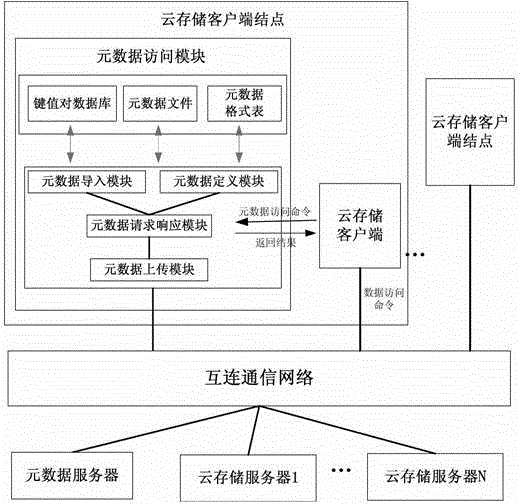

Low-latency metadata access method of cloud storage client

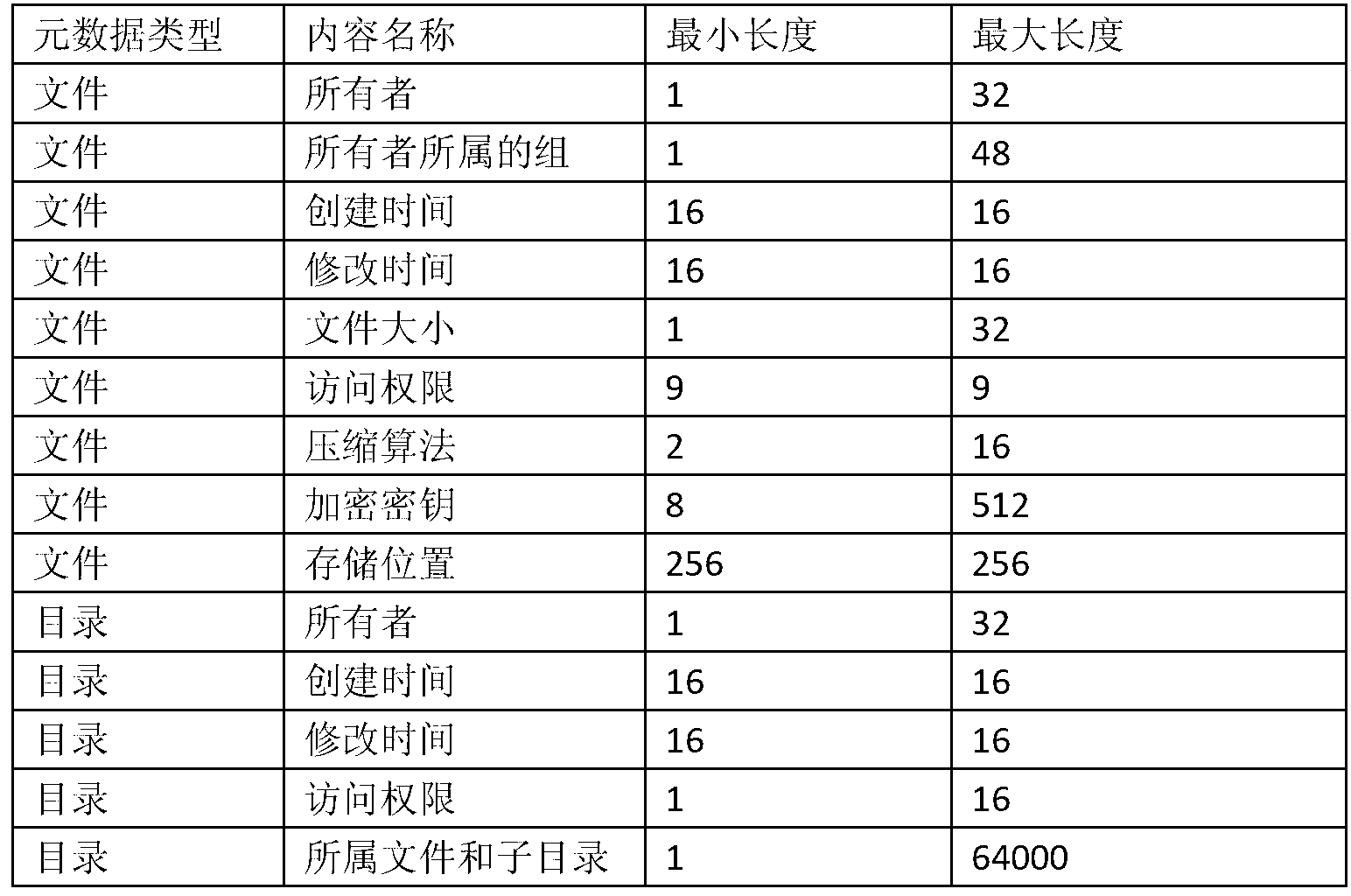

InactiveCN103023982AEliminate transmission delaysAvoid performance bottlenecksTransmissionAccess methodNetworked Transport of RTCM via Internet Protocol

The invention discloses a low-latency metadata access method of a cloud storage client, aiming to solve the problems of slow metadata access response and the like during metadata access. The technical proposal is as follows: a metadata access module composed of a metadata definition module, a metadata importing module, a metadata request response module and a metadata uploading module is mounted on the cloud storage client node; the metadata definition module determines the content and the format of the used metadata; the metadata importing module imports a metadata file into a key value pair database from the cloud storage server; the metadata request response module performs metadata operation according to a metadata access command; and the metadata uploading module uploads a local metadata file to the cloud storage server. Due to the adoption of the low-latency metadata access method provided by the invention, the network transmission latency of metadata access can be eliminated, the metadata server can be prevented from becoming performance bottleneck, the condition that the same cloud storage client node can access heteroid cloud storage systems is supported and the security of the metadata is improved.

Owner:NAT UNIV OF DEFENSE TECH

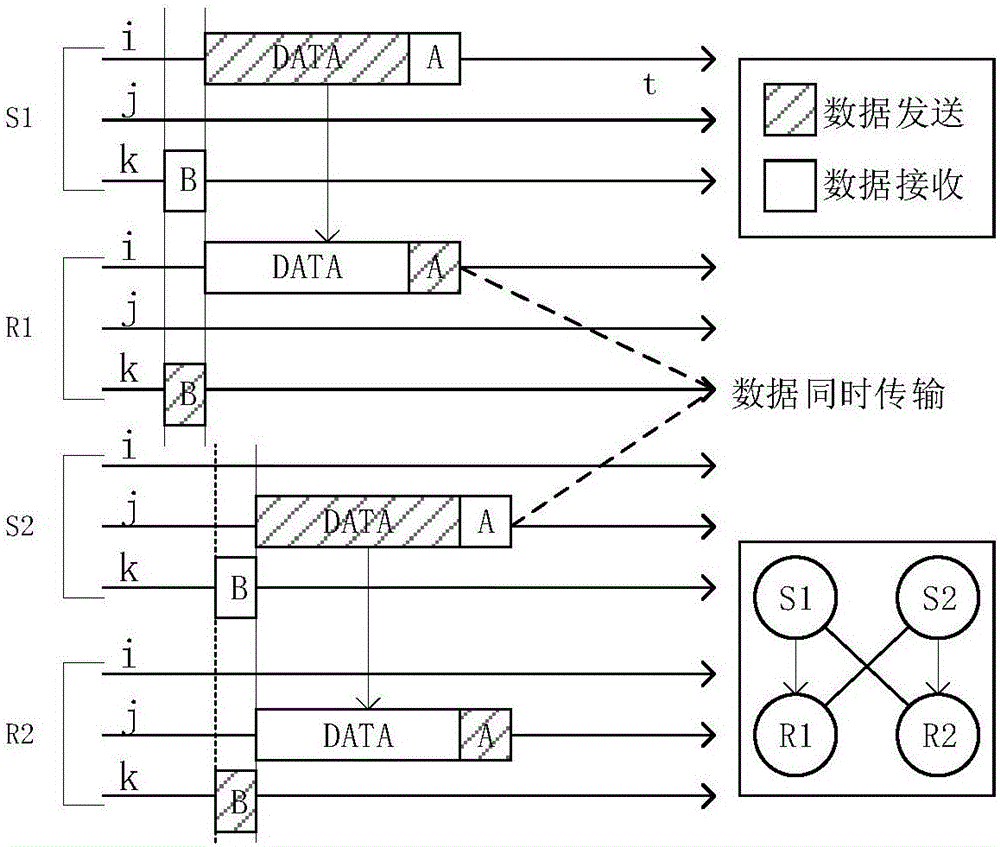

Implementation method for ACT-MAC (Asynchronous Concurrent Transmission MAC) protocol for intensive wireless sensor

InactiveCN106131800AReduce idle listening timeShort possession timePower managementNetwork traffic/resource managementTraffic capacityAsynchronous communication

The invention discloses an implementation method for an ACT-MAC (Asynchronous Concurrent Transmission MAC) protocol for an intensive wireless sensor. The method comprises the following steps of adopting an asynchronous communication mechanism which is initiated based on a receiver while utilizing a dynamic prediction awakening mechanism on a sender to reduce the idle listening time of the receiver and the sender and the occupied time of the sender about a channel in a communication process; adopting a multi-channel dynamic switching mechanism to shunt the network load to realize simultaneous transmission of data at different nodes and eliminate the transmission delay and the power consumption increase which are caused by a hidden terminal; and adopting a constructive interference technology to realize concurrent transmission of the same data packet and effectively broadcasting the data in an intensive network in a multi-hop way. The ACT-MAC protocol for the intensive wireless sensor, which is provided by the invention, is not only suitable for a burst traffic load scene but also for a low traffic load scene.

Owner:SOUTHEAST UNIV

Oscillator circuit

ActiveCN107681994AImprove stabilityEliminate the effects ofElectric pulse generatorCapacitanceVoltage reference

The invention discloses an oscillator circuit. The oscillator circuit comprises an oscillation generation circuit, a transmission delay compensation circuit and a reference voltage generation circuit;the oscillation generation circuit comprises a capacitor, a capacitor charge and discharge circuit, a current mirror circuit and a band-gap reference source; and the reference voltage generation circuit generates a high reference voltage and a low reference voltage and controls the oscillation frequency of the oscillation generation circuit through a difference of the two reference voltages. According to the oscillator circuit, the influences of offset voltages of comparators on the frequency are eliminated by means of the mode of controlling the oscillation frequency generated by the chargeand discharge capacitor through the difference of the two reference voltages; and transmission delay is eliminated by the transmission delay compensation circuit, therefore, the stability of the generated frequency can be kept, the area of a needed chip is small, and the power consumption is low.

Owner:SHENZHEN UNIV

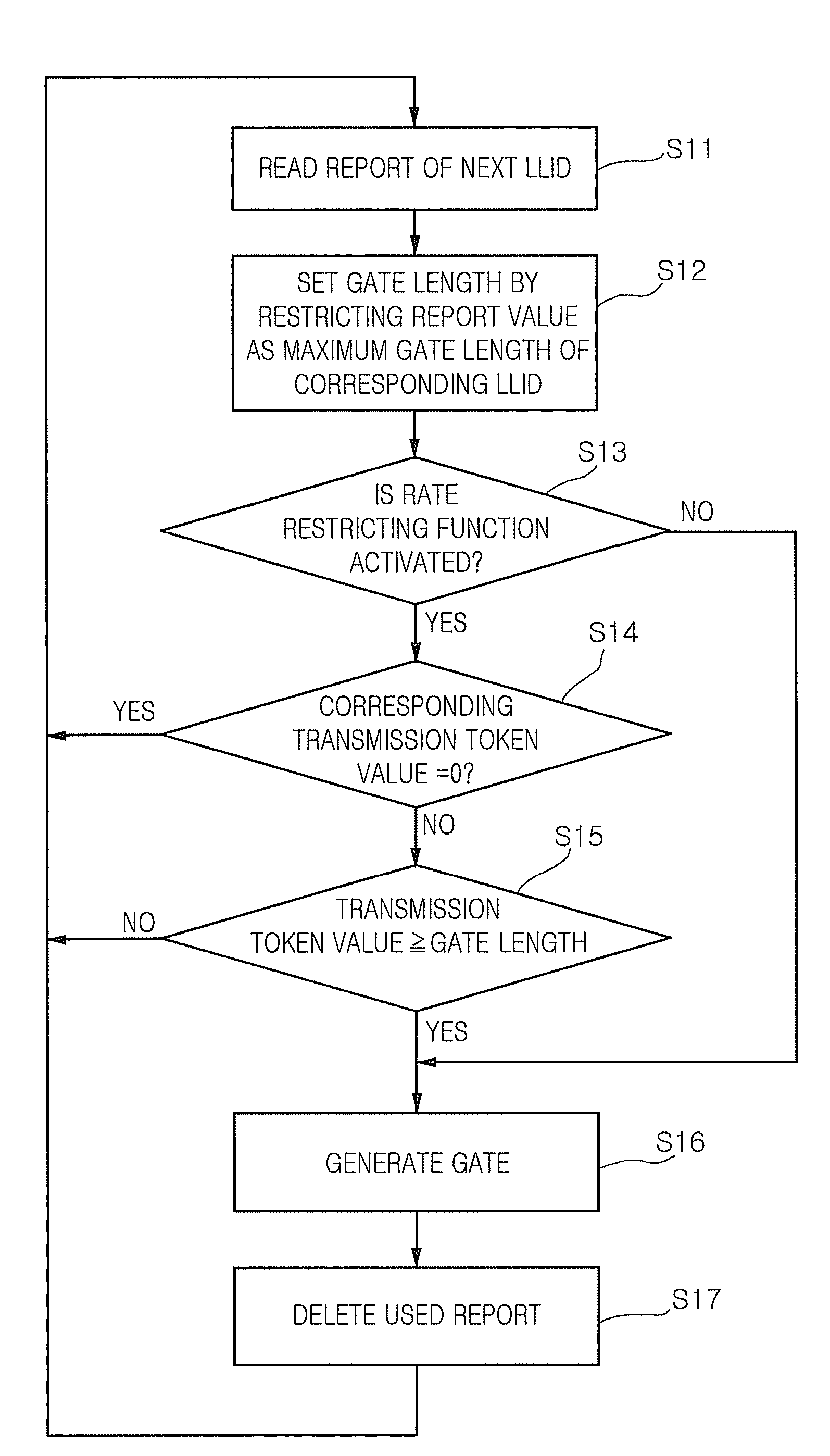

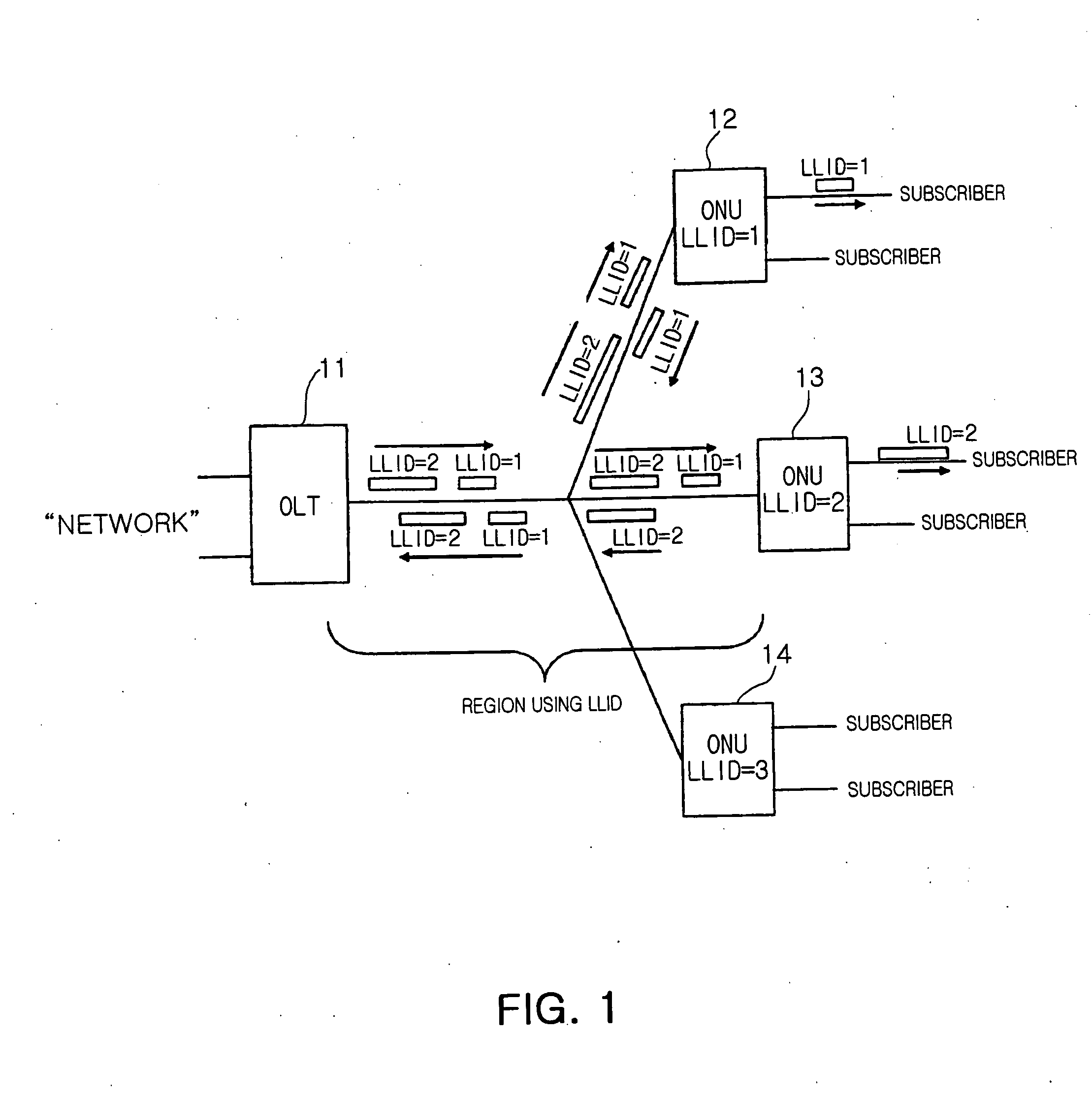

Method and apparatus for dynamically allocating bandwidth by hierarchical weight round robin

InactiveUS20080130657A1Eliminate transmission delaysImprove throughputMultiplex system selection arrangementsTime-division multiplexComputer architectureValue set

Provided are method and apparatus for dynamically allocating unlink bandwidth in Ethernet PON. In the method and apparatus, report value, which are received for each logical link identifications (LLID), is controlled to be less than a maximum gate value set for each LLID in sequence for all of LLIDs without a predetermined interval. A gate having a length corresponding to the restricted report value is generated. LLIDs are grouped into classes and processing is done class by class. For each class processing, if maximum processing time is reached or maximum total allocation is reached, the processing is switched to a lower class. Also each class processing, if any higher class has its maximum yield processing time or maximum yield allocated gate reached, the processing is switched to that higher class.

Owner:ELECTRONICS & TELECOMM RES INST

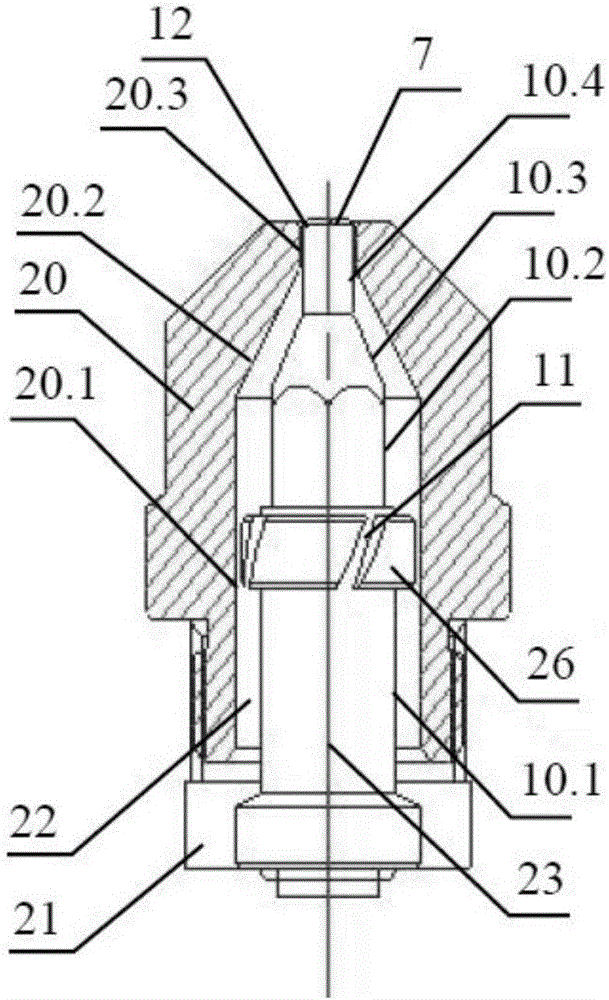

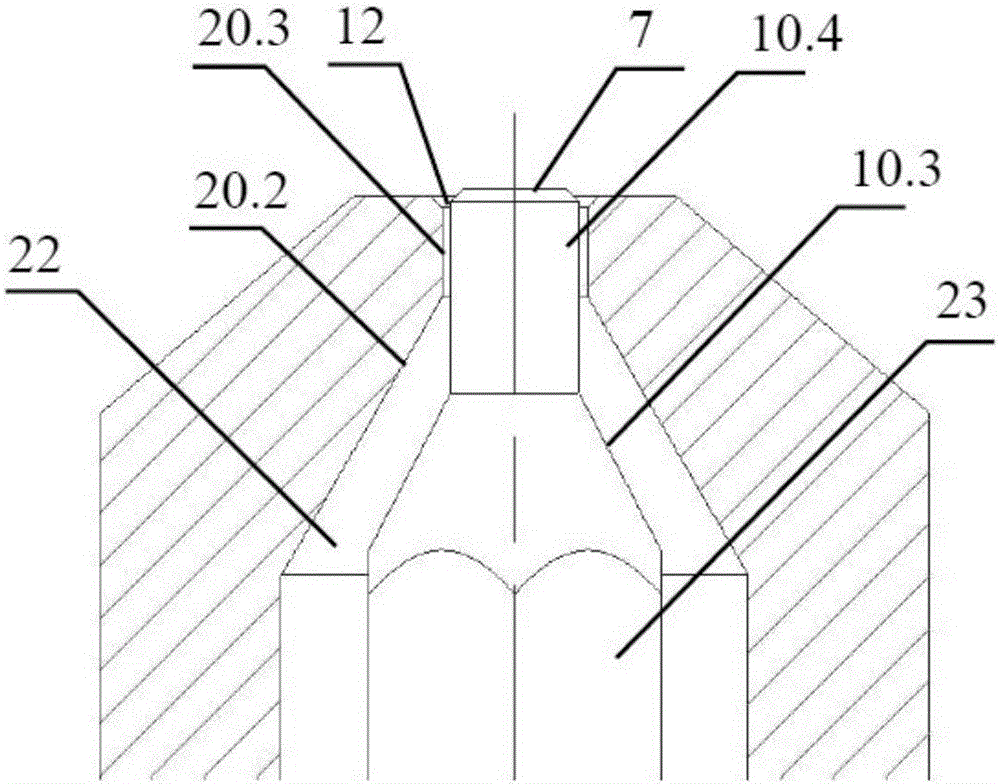

Gas jet flow type blue adding combined ejector and application thereof

InactiveCN106150612AReduce riskEliminate transmission delayExhaust apparatusSilencing apparatusEngineeringLiquid phase

Owner:WUHAN UNIV OF TECH +1

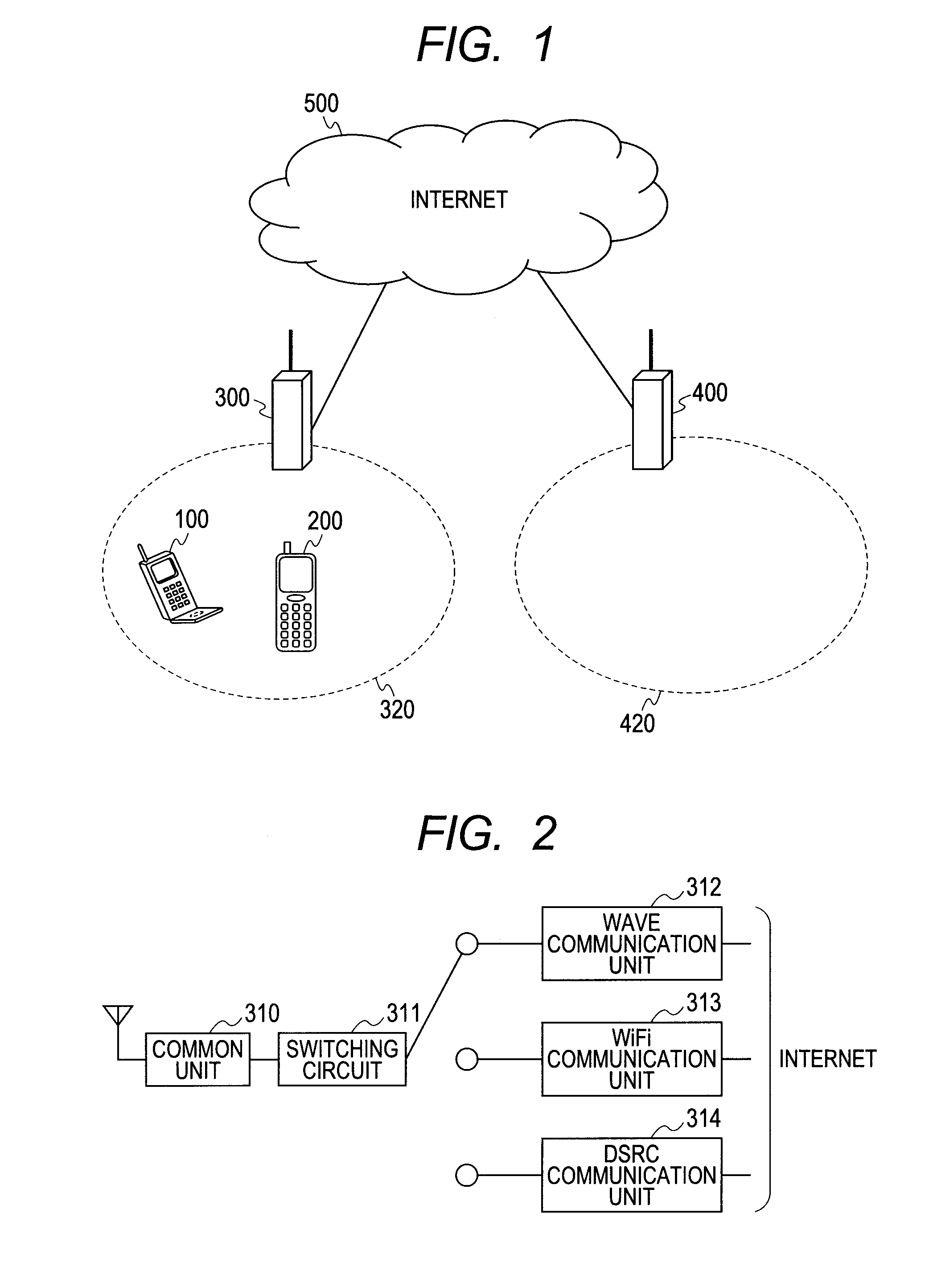

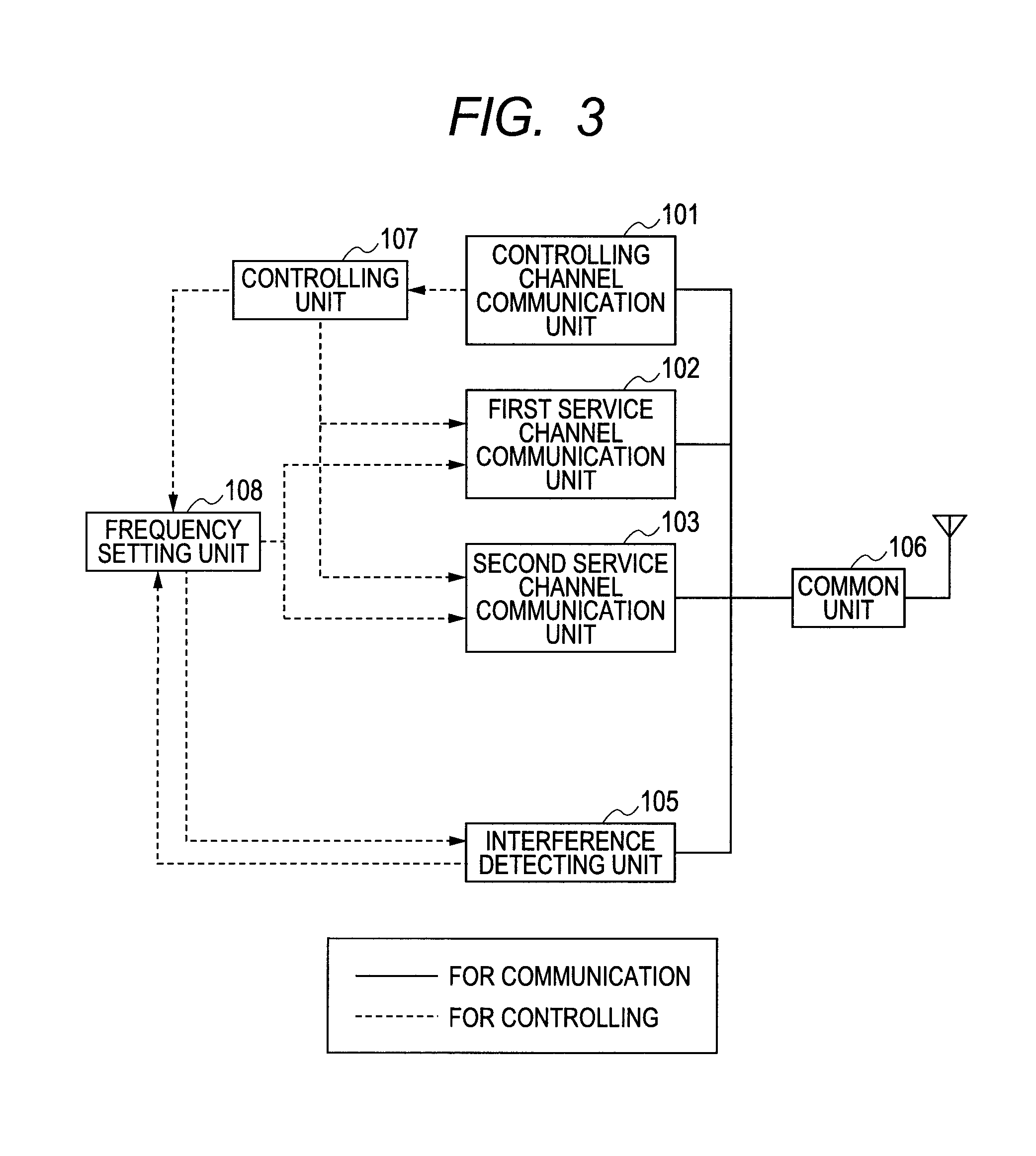

Wireless communication device and communication method of wireless communication device

InactiveUS20110021233A1Decrease usage rateEliminate delayEmergency connection handlingConnection managementTransmission delayRadio wave

An object of the present invention is to provide means for eliminating a transmission delay when transmitting emergency information for the sake of relief, security, or the like in a wireless device in conformity with the wireless LAN standard in which if radio waves transmitted from peripheral devices are detected, transmission has to be stopped. In a multimode wireless communication scheme having two or more communication schemes, priorities of the communication schemes are set. A high priority or low priority regarding to a message is described in a“message type” data field of a frame of a controlling channel output from the access point side to the terminal side. When the frame of the controlling channel is decrypted on the terminal side, the message type is confirmed, so that the type of a service channel used thereafter is confirmed and the channel is coupled.

Owner:RENESAS ELECTRONICS CORP

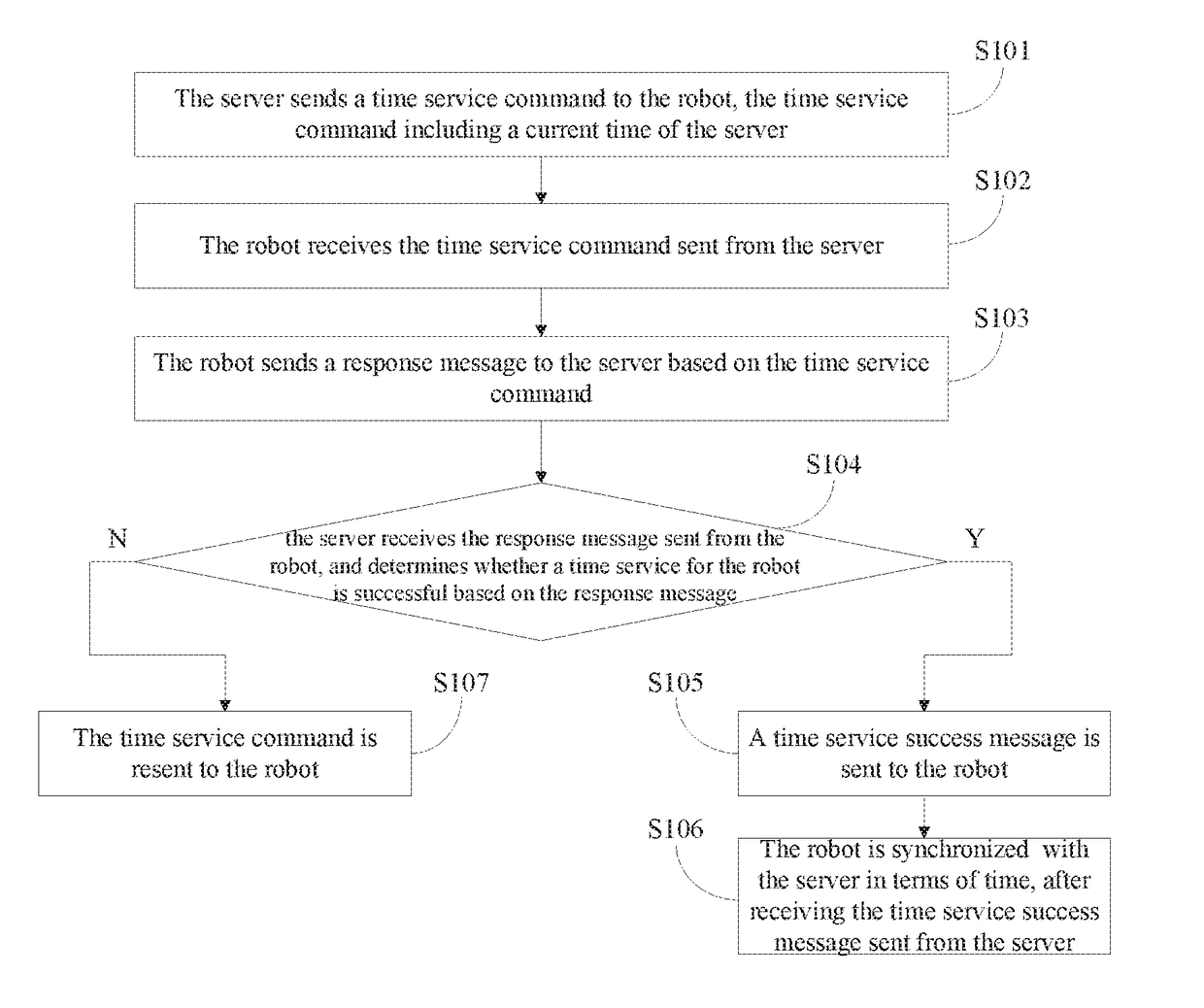

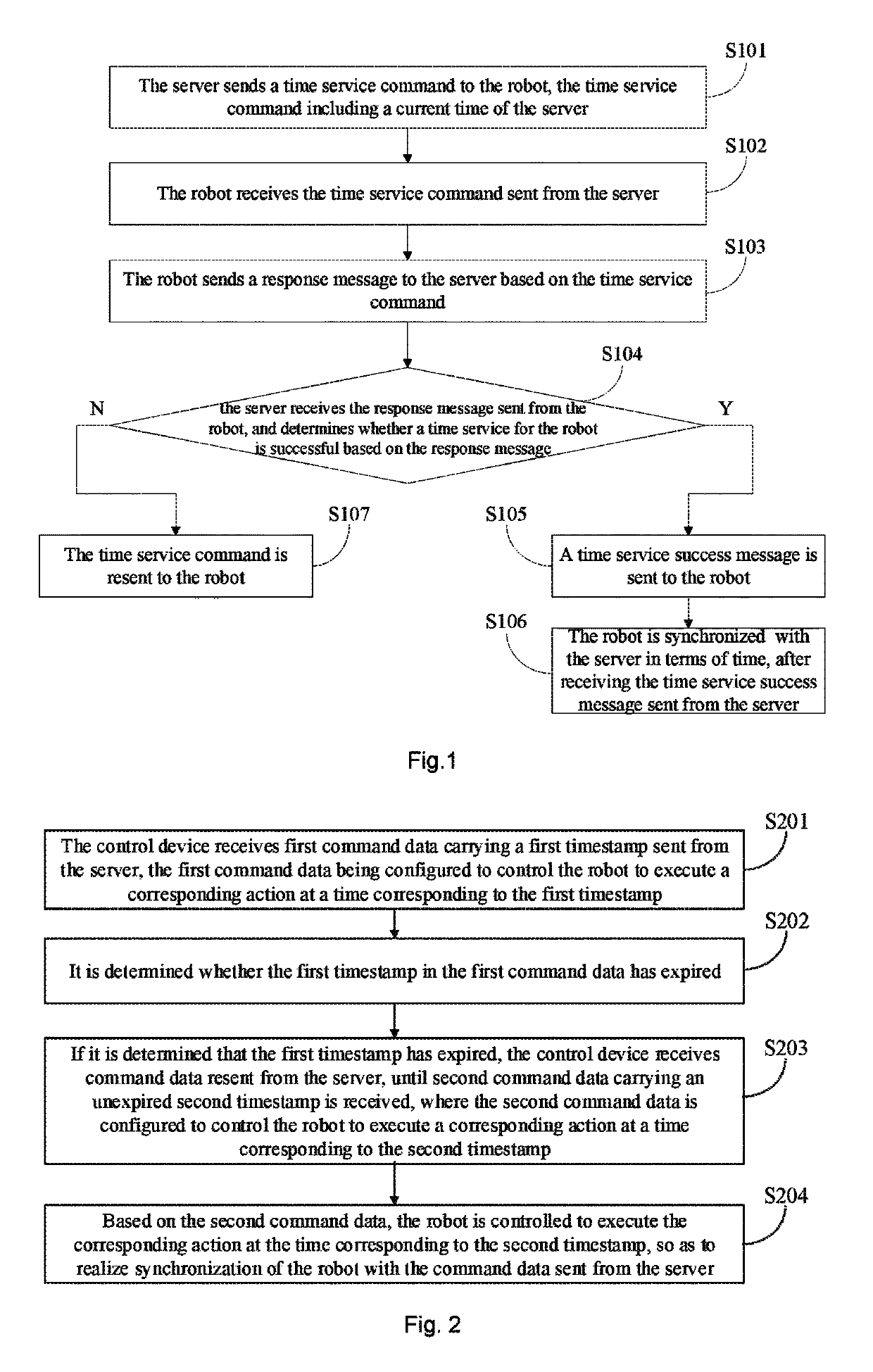

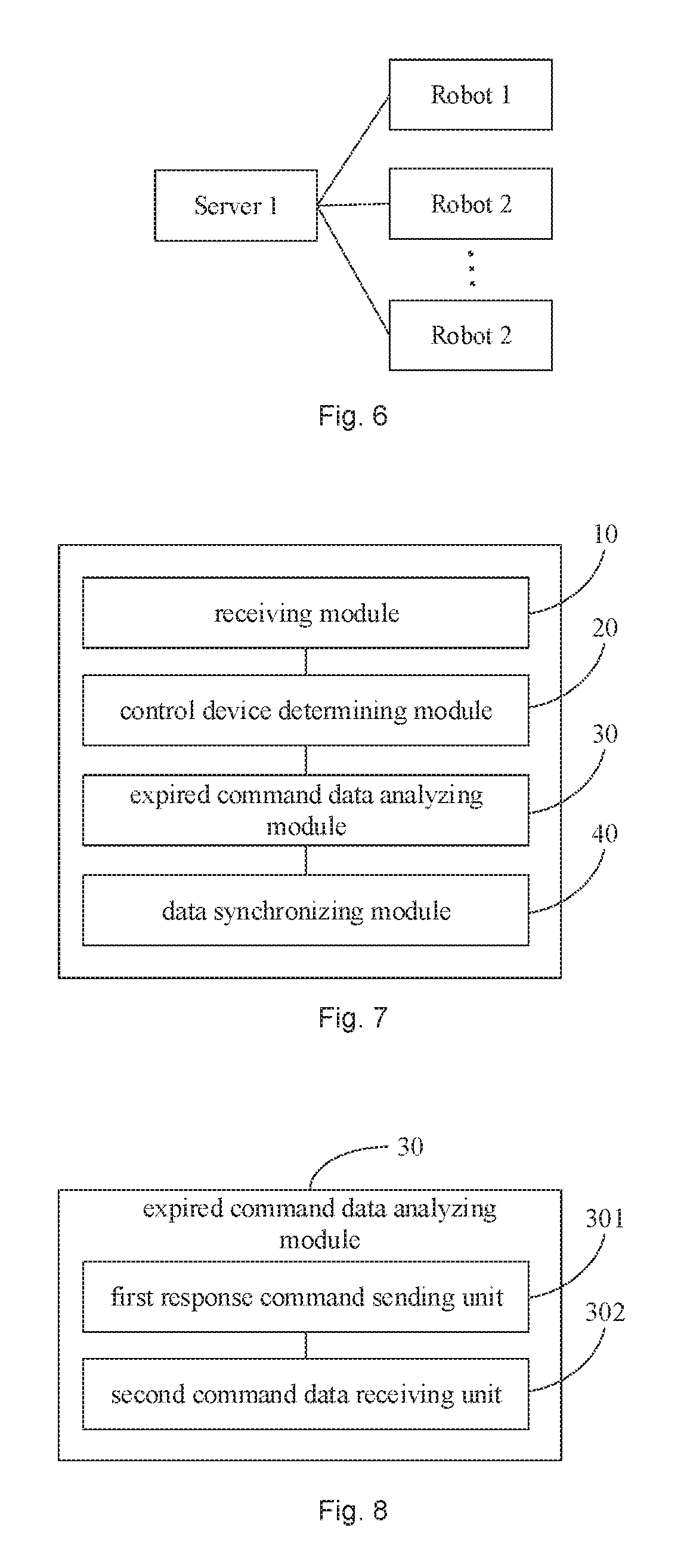

Method and system for synchronizing robot with server

ActiveUS20180302461A1Transmission delay be eliminateImprove abilityProgramme-controlled manipulatorSynchronisation arrangementTimestampCurrent time

Provided are a method and system for synchronizing a robot with a server. The service sends a time service command including a current time of the server to the robot, and the robot receives the time service command, so as to enable time synchronization of the robot with the server. A control device receives first command data carrying a first timestamp sent from the server, and then determines whether the first timestamp in the first command data has expired. If the first timestamp has expired, the control device receives command data resent from the server until second command data carrying an unexpired second timestamp is received. Finally, the control device controls the robot to execute a corresponding action at a time corresponding to the second timestamp based on the second command data, so as to realize the synchronization of the robot with the command data sent from the server.

Owner:ZHEJIANG LIBIAO ROBOT CO LTD

Safety network system

InactiveUS7103422B2Low response timeAccurately recognizeSafety arrangmentsComputer controlReliability engineeringHost machine

Owner:ORMON CORPORATION

Stream signal transmission device and transmission method

InactiveUS8874058B2Absorb fluctuation in transmission timeEliminate transmission delaysPulse modulation television signal transmissionError preventionTransmission delayControl unit

Provided is a stream signal transmission device that can eliminate transmission delay fluctuation with a fast change such as network jitter with high accuracy and synchronize a plurality of streams. The stream signal transmission device includes at least one reception unit that receives a stream signal to which a time code is attached from a network, at least one extraction unit that extracts the time code from the stream signal received by the reception unit, and at least one delay control unit that determines an output time by adding a predetermined fixed delay to a time indicated by the time code extracted by the extraction unit, and outputs the stream signal received by the reception unit after holding the stream signal up to the output time.

Owner:NEC CORP

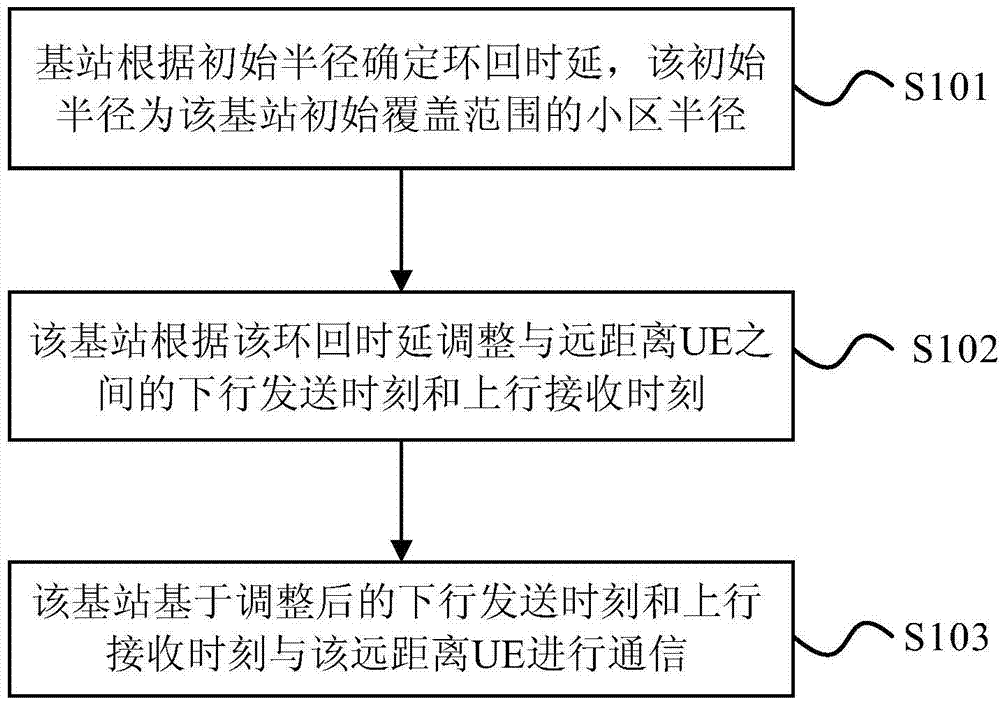

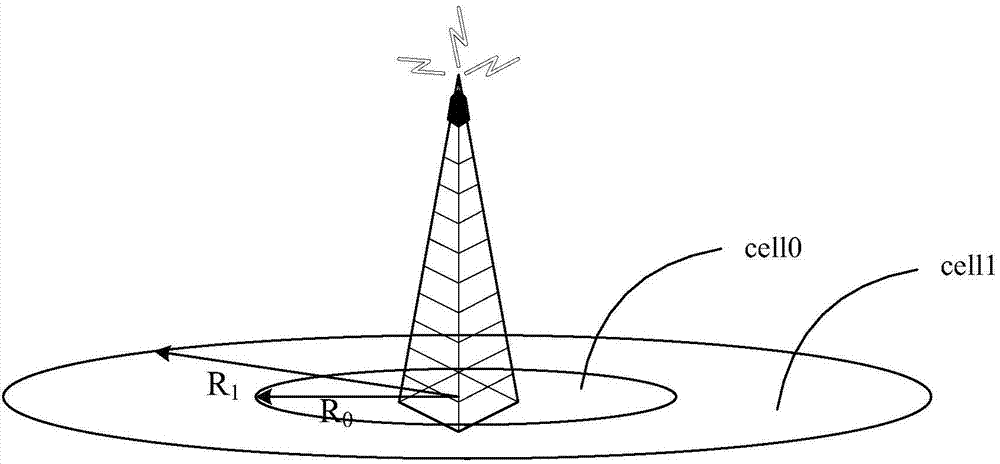

Remote coverage method and base station

ActiveCN103843383ARealization of long-distance coverageEliminate transmission delaysSynchronisation arrangementNetwork planningNetworking protocolEngineering

The present invention provides a method and a base station for remote coverage. The method for remote coverage comprises: the base station determines loopback delay according to an initial radius which is the radius of an initial coverage cell by the base station; the base station adjusts downlink transmission time and the uplink receiving time between the remote user equipment UE based on the look back delay; and the base station communicates with the remote UE based on the adjusted downlink transmission time and the uplink receiving time. The embodiment of the present invention adjusts the downlink transmission time and / or the uplink receiving time of the base station to eliminate the transmission delay caused by remote communication, and realizes remote coverage of the base station on the basis of no-changing the present networking protocol.

Owner:HUAWEI TECH CO LTD

Novel driving system and control device of servo press

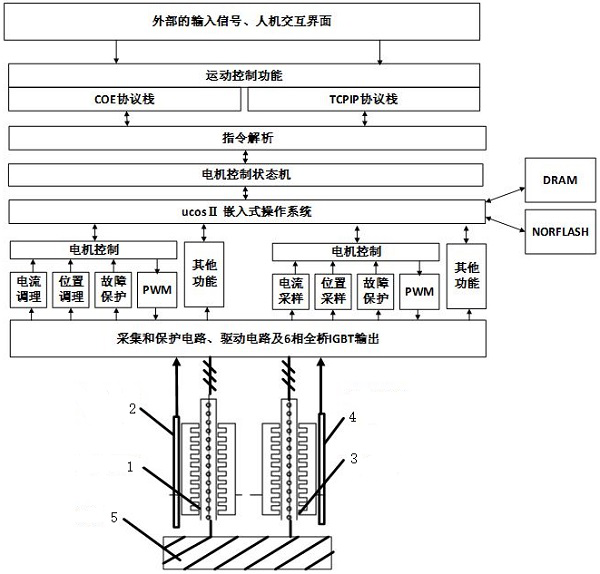

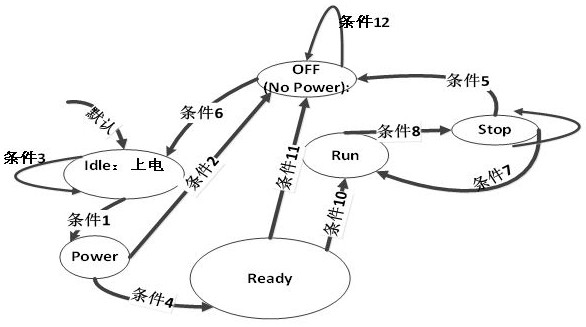

PendingCN112810226AEliminate gapsRealize synchronous independent control functionForging press drivesPressesKinematic controllerGear wheel

The invention relates to the technical field of forging machines and motor control, in particular to a novel driving system and control device of a servo press. The novel driving system and control device of the servo press comprises a servo press external input signal, a human-computer interaction interface, a motion control function module, a high-level protocol stack COE, a TCP / IP protocol stack, an instruction analysis module, a ucos II embedded operating system, a motor control state machine, a motor control module, a current signal conditioning circuit, a position signal conditioning circuit, a fault protection module, a PWM module, other functional hardware, a power driving circuit, a six-phase full-bridge IGBT module, two three-phase linear motors, position sensors of the two three-phase linear motors, sampling circuits and a sliding block, wherein the current signal conditioning circuit, the position signal conditioning circuit, the fault protection module and the PWM module belong to hardware. According to the technical scheme, a motion controller and two servo controllers are integrated, communication delay is eliminated, a gear is omitted, a gap is eliminated, and the control precision of the position of the sliding block is improved; and due to the fact that the two motors are adopted for independent control, closed-loop real-time control over left-right balance of the sliding block can be achieved.

Owner:JINING KELI PHOTOELECTRIC IND CO LTD +1

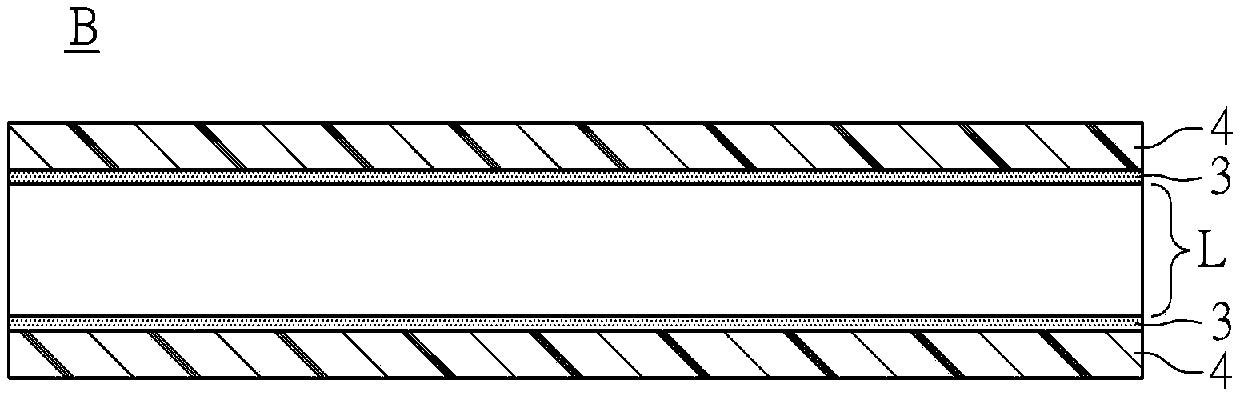

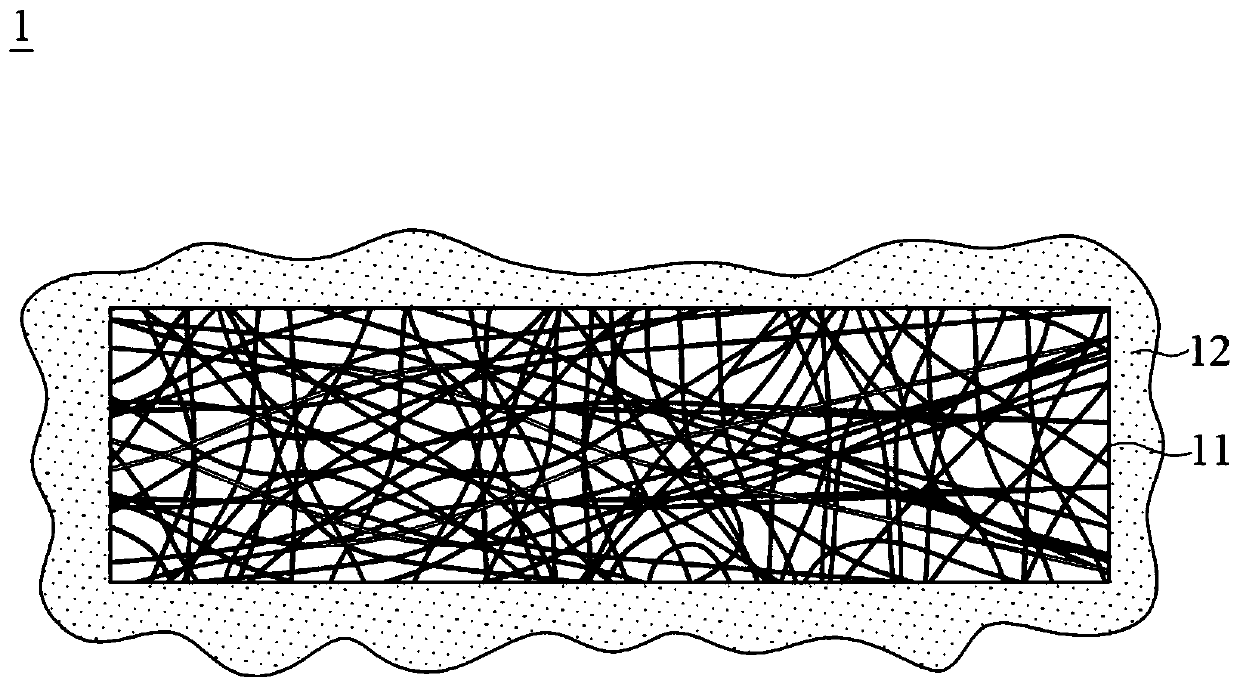

Polymer matrix composite, and prepreg and printed circuit board using the same

PendingCN109575516AEliminate transmission delaysLamination ancillary operationsDielectric materialsPolymer sciencePolymer resin

The present invention provides a polymer matrix composite, and a prepreg and a printed circuit board using the same. The polymer matrix composite includes a polymeric resin and a non-woven reinforcingmaterial having a dielectric constant of from about 1.5 to about 4.8 and a dissipation factor at 10 GHz below 0.003. The printed circuit board uses the laminate including the polymer matrix compositeas a core layer which is sandwiched between at least two outer layers. The disclosed polymer matrix composite, the laminate including the polymer matrix composite, the prepreg using the polymer matrix composite and the printed circuit board using the polymer matrix composite can effectively reduce transmission delay and weaving effects through adopting the specific non-woven reinforcing material.

Owner:ITEQ CORP

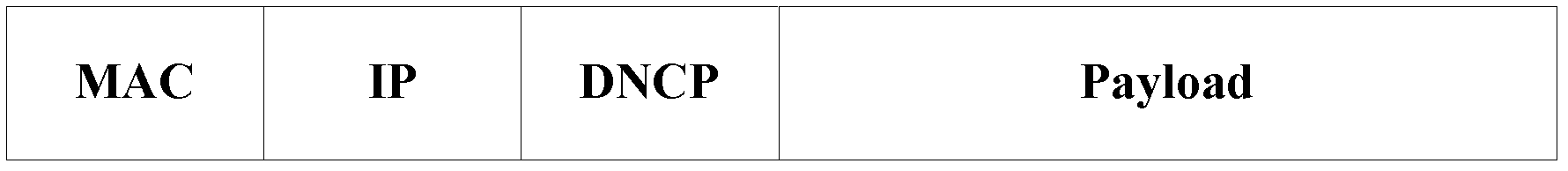

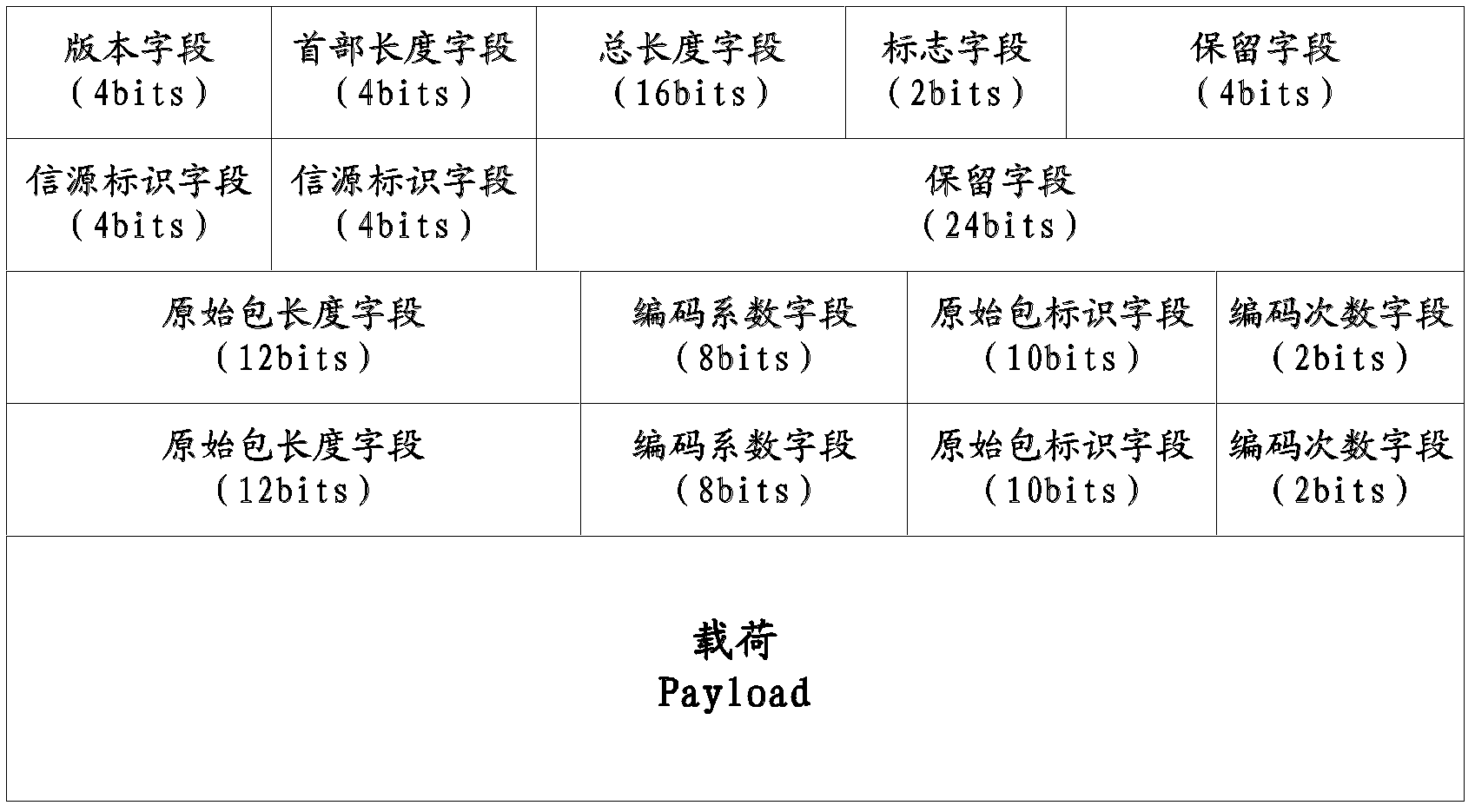

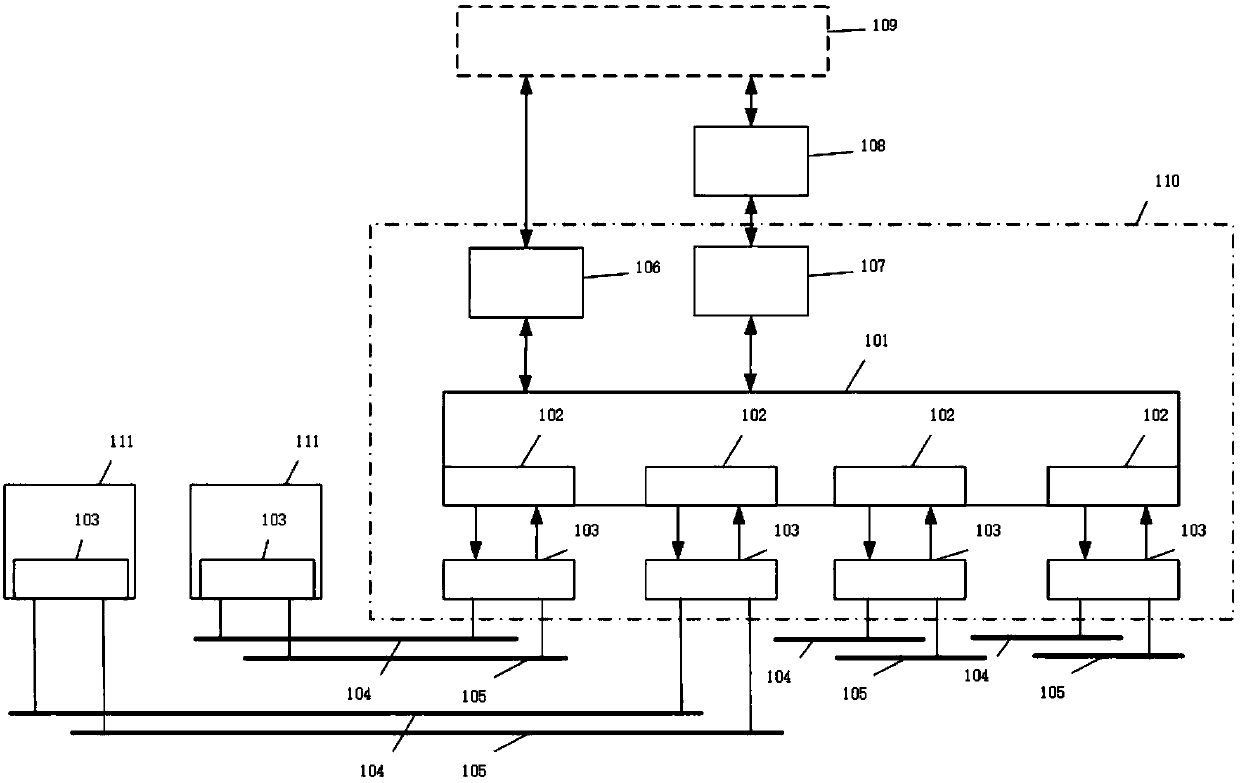

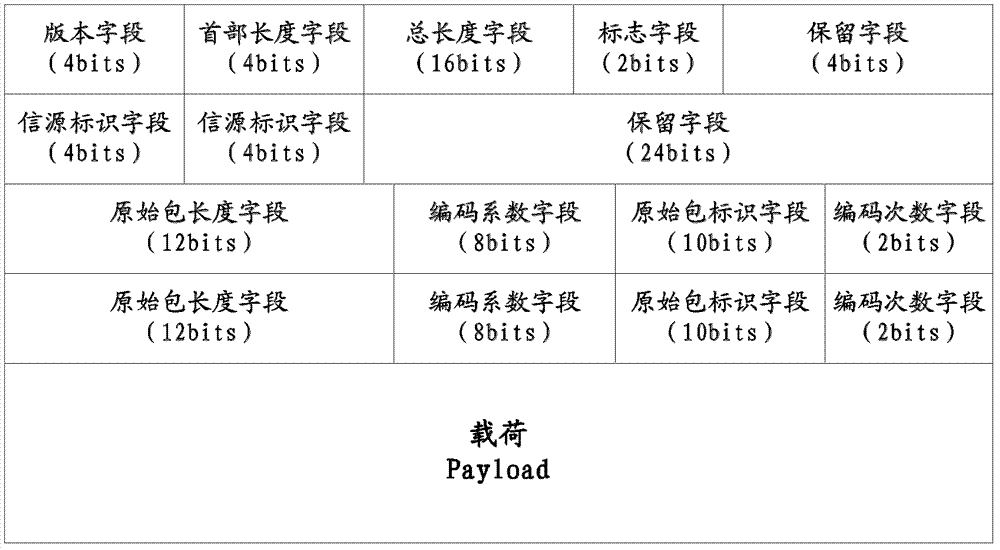

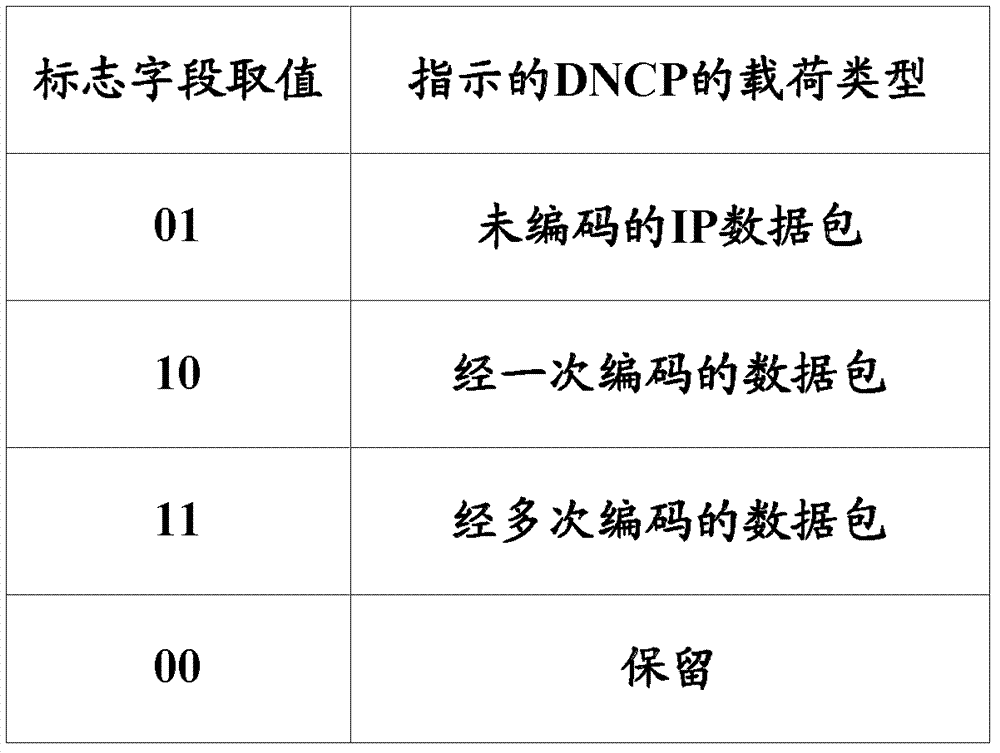

Coding and decoding method, related devices and related communication system

ActiveCN102916761AImprove throughputImprove versatilityForward error control useData switching networksComputer hardwareDecoding methods

An embodiment of the invention discloses a coding and decoding method, related devices and a related communication system. The scheme includes that coding and decoding between two information sources are supported by a DNCP (dynamic host configuration protocol), a coding device performs random linear coding for two IP (internet protocol) data packets with the arrival interval shorter than a set duration and identical target addresses, and accordingly influence of the problem of mismatching of transmission delays, sending rates and the like in an actual network is advantageously eliminated to a certain degree; DNCP packet headers of DNCP data packets carry two information source identities, two IP data packet identities and coding coefficient and vector information related to coding coefficients and vectors, accordingly, a foundation is laid for the coding device to continue repeated coding or a decoding device to quickly decode, and the universality of network coding in the actual network is improved advantageously; and as the coding and decoding method, the related devices and the communication system are implemented on the basis of a network coding technology, network resources can be sufficiently utilized, the throughput rate of the network is obviously increased, and high transmission efficiency is achieved.

Owner:HONOR DEVICE CO LTD

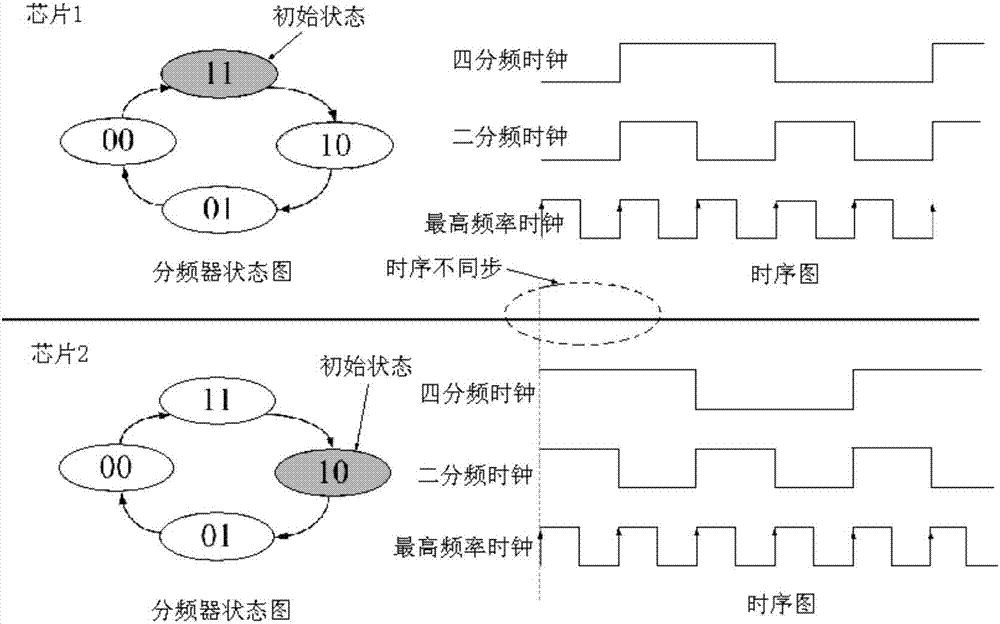

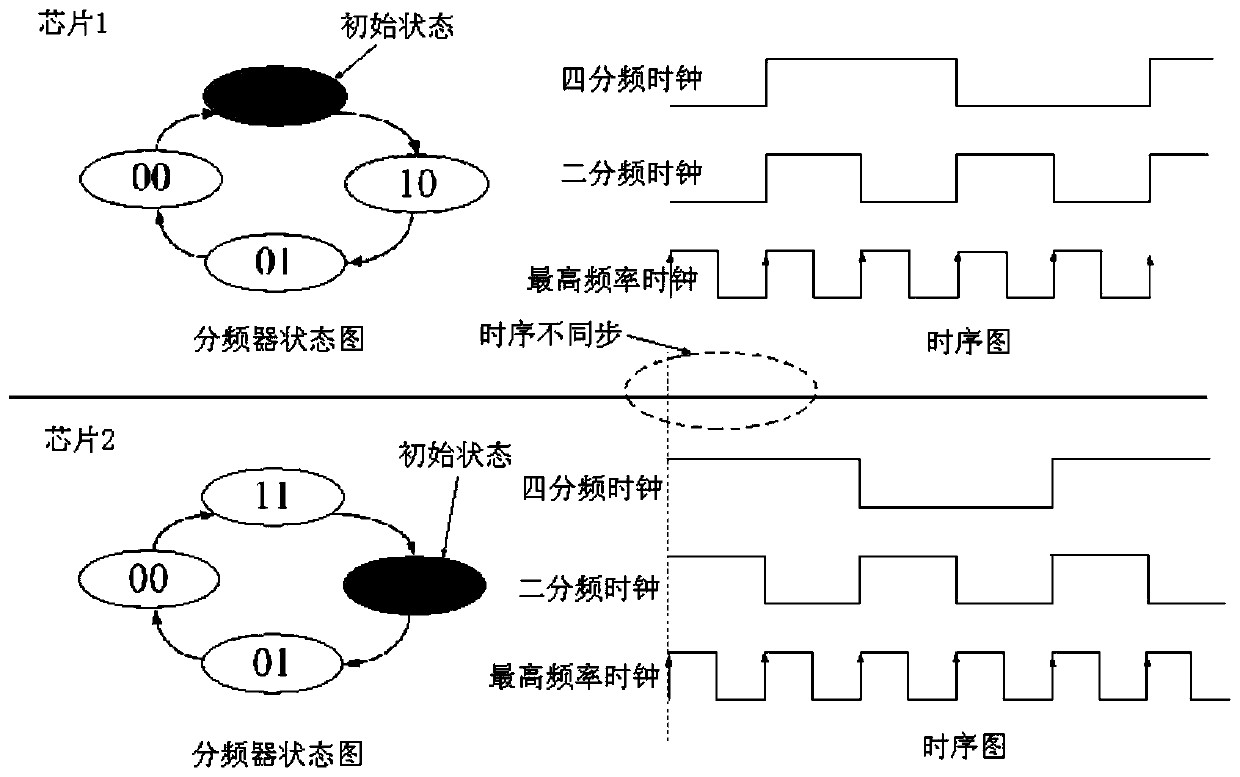

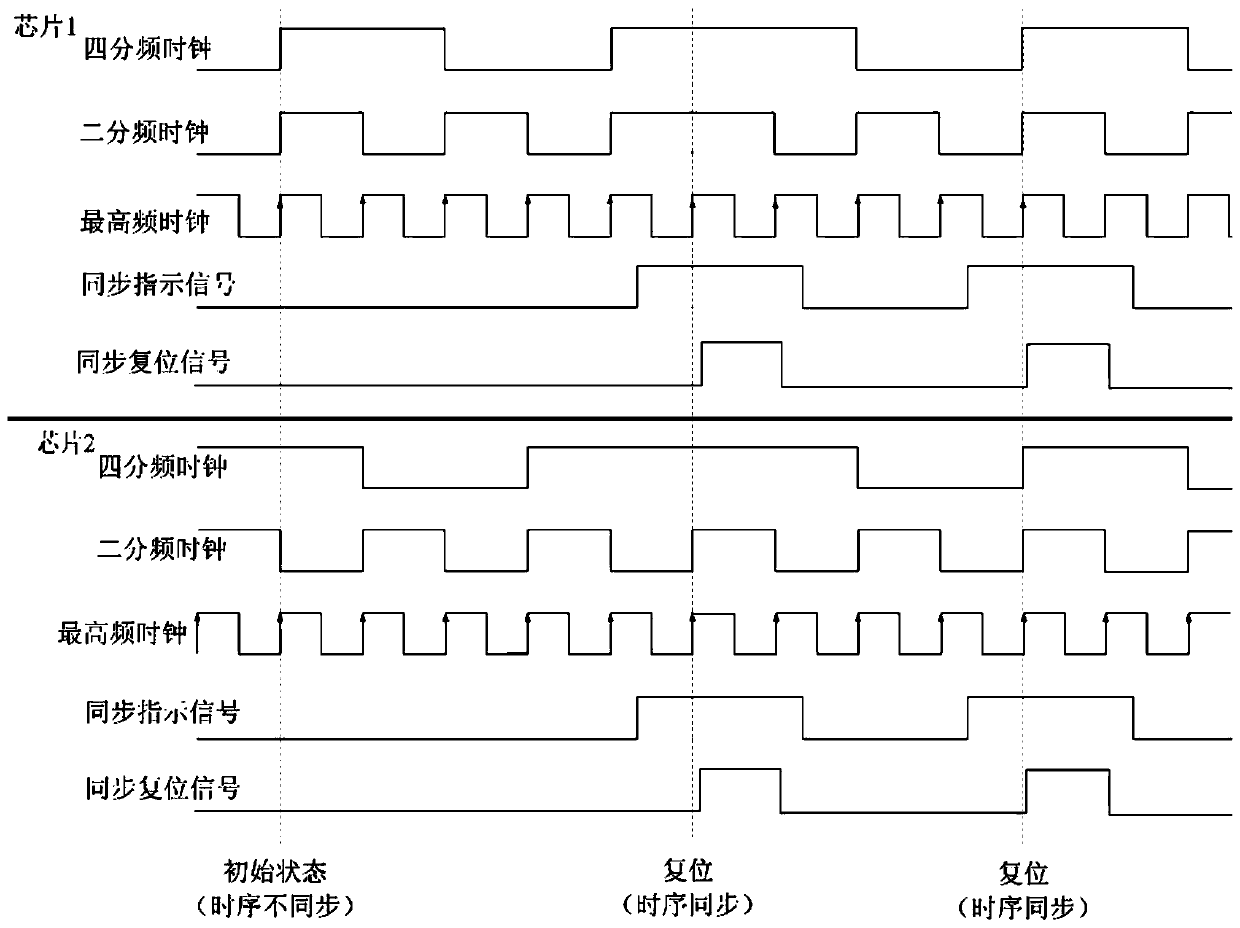

Multichip synchronization structure based on time-digital converter circuit

ActiveCN106970679AReduce loadEliminate transmission delaysGenerating/distributing signalsDigital converterSignal source

The invention discloses a multichip synchronization structure based on a time-digital converter circuit. The multichip synchronization structure comprises N circuit chips provided with built-in time-digital converters and time sequence regulation modules. Each chip contains a synchronization indicating signal receiving end, a synchronization indicating signal output end, one time-digital converter and one time sequence regulation module, wherein the synchronization indicating signal receiving end is used for receiving a synchronization indicating signal input into the chip externally; the synchronization indicating signal output end is used for outputting a synchronization indicating signal subjected to time sequence resampling through a trigger in the chip, wherein the sampling frequency of the trigger is completely aligned with a time sequence of a maximum frequency clock; the time-digital converter is used for quantizing time sequence delays of two input signals into digital values, wherein the input signal IN1 is the synchronization indicating signal input into the chip externally, and the input signal IN2 is the synchronization indicating signal subjected to time sequence resampling through the trigger in the chip; and the time sequence regulation module is used for regulating output delays of the synchronization indicating signals according to the input digital values. By the adoption of a daisy chain structure, the load on a synchronization indicating signal source is relieved.

Owner:NO 24 RES INST OF CETC

Method and system for synchronizing robot with server

ActiveUS10341413B2Eliminate transmission delaysGuaranteed to workProgramme-controlled manipulatorSynchronisation arrangementTimestampTime synchronization

Provided are a method and system for synchronizing a robot with a server. The service sends a time service command including a current time of the server to the robot, and the robot receives the time service command, so as to enable time synchronization of the robot with the server. A control device receives first command data carrying a first timestamp sent from the server, and then determines whether the first timestamp in the first command data has expired. If the first timestamp has expired, the control device receives command data resent from the server until second command data carrying an unexpired second timestamp is received. Finally, the control device controls the robot to execute a corresponding action at a time corresponding to the second timestamp based on the second command data, so as to realize the synchronization of the robot with the command data sent from the server.

Owner:ZHEJIANG LIBIAO ROBOT CO LTD

CAN FD bus automatic control system and method based on hardware logic

InactiveCN110557309AReasonable designClear structureShort range communication serviceBus networksAutomatic controlTransmission delay

The invention discloses a CAN FD bus automatic control system and method based on hardware logic. The CAN FD bus automatic control system comprises an upper PC and a lower computer hardware circuit. The lower computer hardware circuit comprises a microcontroller, a Bluetooth module, a USB3.1 module and a CAN FD transceiver; the lower computer hardware circuit is wirelessly connected to the PC through a USB3.1 cable or Bluetooth, and the lower computer hardware circuit is connected and communicated with the controlled node through a CAN FD bus CANH and a CAN FD bus CANL at the same time; the microcontroller is connected with at least four CAN FD controllers; a TX pin and an RX pin of each CAN FD controller are respectively connected with a TX pin and an RX pin of the CAN FD transceiver; theCANH of the CAN FD transceiver is connected to the CAN FD bus CANH, and the CANL of the CAN FD transceiver is connected to the CAN FD bus CANL. According to the invention, the non-real-time performance of the upper computer and the influence caused by transmission delay are eliminated, the control precision is improved, and the cost of the control system is reduced.

Owner:上海千顾汽车科技有限公司

Coding and decoding method, related devices and related communication system

ActiveCN102916761BImprove throughputImprove versatilityForward error control useData switching networksDecoding methodsComputer architecture

Disclosed in the embodiment of the present invention are a method for coding thereof related device and communication system. In the embodiment of the present invention, DNCP(DNCP: Doublesource Network Coding Protocol) is provided for supporting coding and decoding between two signal sources, wherein, the coding device performs random linear coding to two IP packages whose arrival interval are smaller than the setting duration and the destination addresses are same, through this ,it is useful for partly eliminating the influence of mismatch of transmitting rate and transfer delay in the actual network; at the same time, the header of DNCP package carries two source IDs, two IP package IDs and coding coefficient vector information which is related to the coding coefficient vector, which lays the foundation for the coding device continuously to code multi times or for the decoding device to decode rapidly, and benefits improving the generality of network coding in the actual network; and as the present invention is carried out based on network coding technology, therefore it can make full use of network resource and increase the network throughout rate obviously and achieve higher transmission efficiency.

Owner:HONOR DEVICE CO LTD

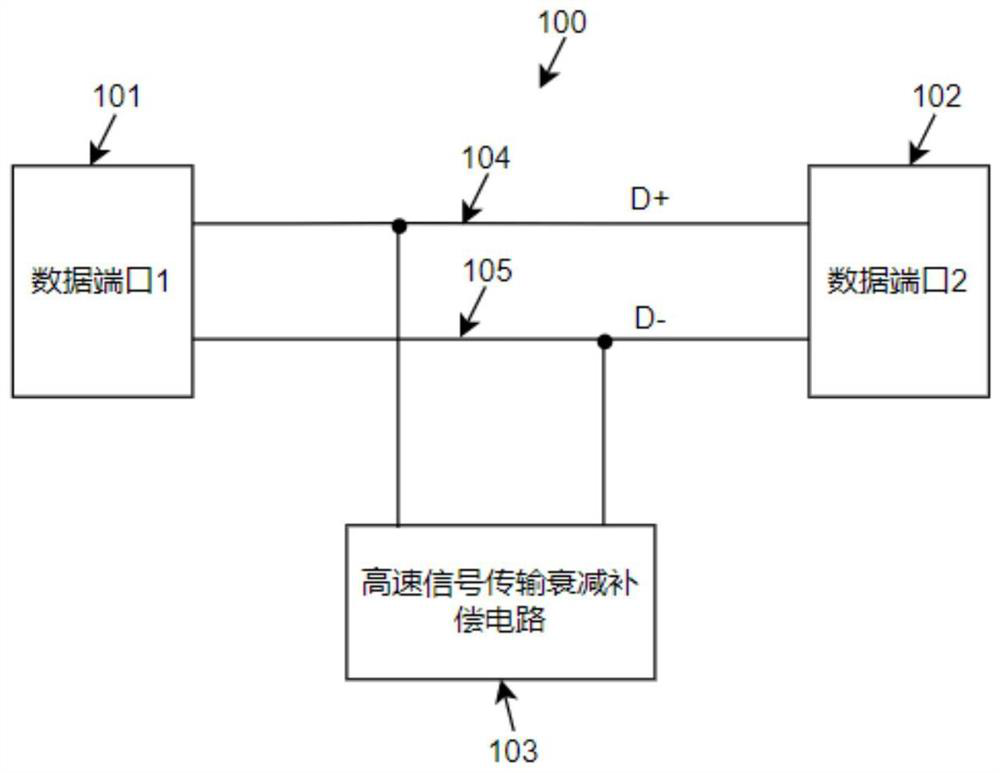

Signal transmission loss compensation circuit, integrated circuit and transmission system

ActiveCN113590515AEliminate transmission delaysReduce Design ComplexityTransmitter/receiver shaping networksElectric digital data processingSoftware engineeringTransmission loss

A signal transmission loss compensation circuit is connected with a digital signal transmission line in parallel and used for carrying out loss compensation on digital signals transmitted through the transmission line. The compensation circuit comprises a direct current level compensating circuit and an edge port adjusting circuit. And the edge port adjusting circuit is connected with the digital signal transmission line and is used for adjusting a digital signal edge port and adjusting a data conversion rate. And the direct current level compensation circuit is connected with the digital signal line port and the output end of the edge port adjustment circuit, and is used for increasing the direct current level value of the digital signal when the level is high.

Owner:上海锐星微电子科技有限公司

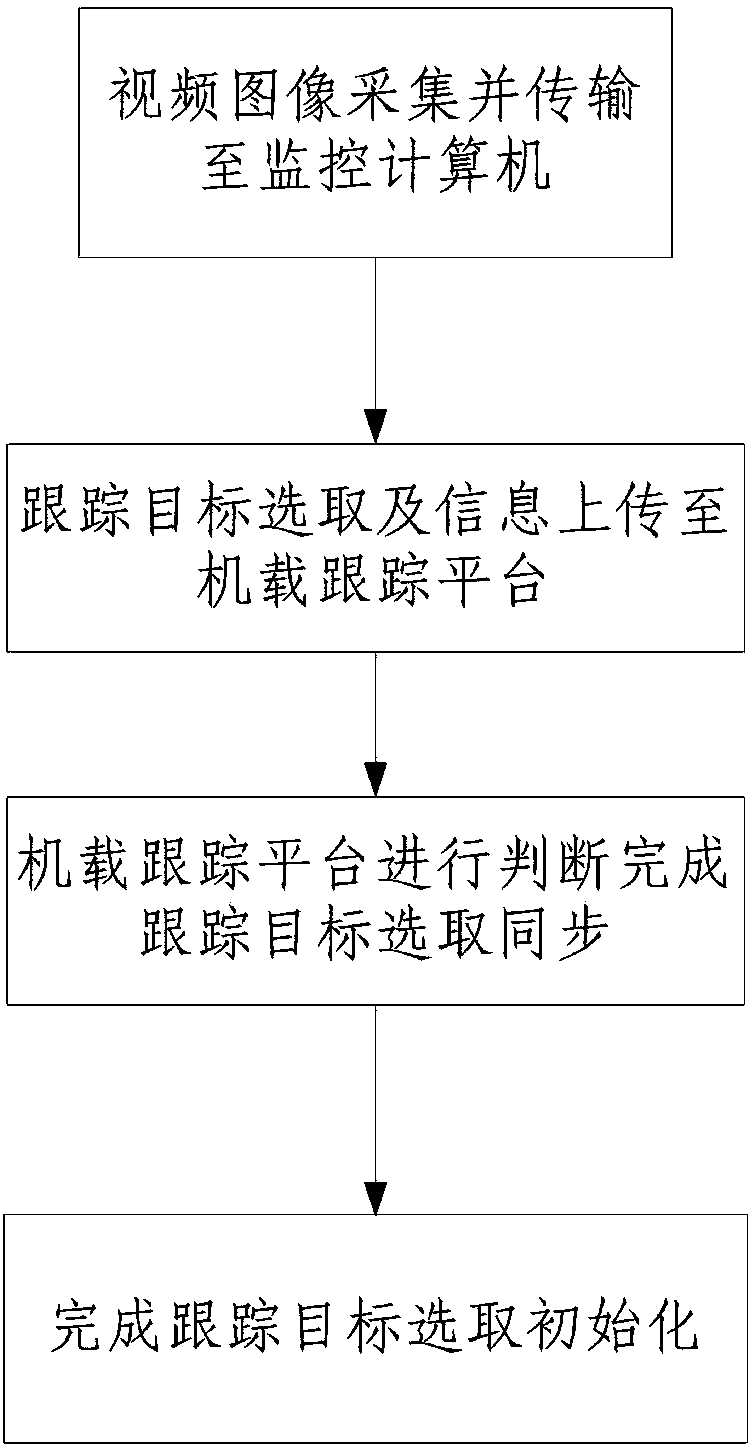

A tracking target selection synchronization method for patrol drones

InactiveCN107426289BSimple structureReasonable designImage enhancementTelevision system detailsHuman–machine interfaceWireless transmission

The invention discloses a tracking target selection synchronization device and method for a cruise unmanned aerial vehicle. The device includes an airborne tracking platform and a monitoring terminal. The airborne tracking platform includes a main controller, an image wireless sending module, a first data communication module and the first image cache module, the input terminal of the main controller is connected with a video acquisition module, and the monitoring terminal includes a monitoring computer, a man-machine interface operation module, an image wireless receiving module, a second data communication module and a second image Buffering module; the method includes the following steps: one, video image collection and transmission to the monitoring computer; two, tracking target selection and information upload to the airborne tracking platform; three, the airborne tracking platform judges and completes the tracking target selection synchronization, and completes the tracking Target selection initialization. The invention has a reasonable design, can accurately obtain the initial tracking target selected by the monitoring terminal of the ground station, and realizes the synchronization of the tracking target selection of the patrol drone and the monitoring terminal.

Owner:ROCKET FORCE UNIV OF ENG

Wireless communication device and communication method of wireless communication device

InactiveUS8249637B2Prevent disturbance of image qualityIncrease in sizeEmergency connection handlingConnection managementData fieldMessage type

An object of the present invention is to provide means for eliminating a transmission delay when transmitting emergency information for the sake of relief, security, or the like in a wireless device in conformity with the wireless LAN standard in which if radio waves transmitted from peripheral devices are detected, transmission has to be stopped. In a multimode wireless communication scheme having two or more communication schemes, priorities of the communication schemes are set. A high priority or low priority regarding to a message is described in a “message type” data field of a frame of a controlling channel output from the access point side to the terminal side. When the frame of the controlling channel is decrypted on the terminal side, the message type is confirmed, so that the type of a service channel used thereafter is confirmed and the channel is coupled.

Owner:RENESAS ELECTRONICS CORP

A video overlay device and method

ActiveCN107454348BEliminate transmission delaysAccurate overlay in real timeTelevision system detailsColor television detailsComputer hardwareVideo overlay

The invention relates to a video overlay device and method. The video overlay device includes a first dynamic video signal storage module for storing a dynamic video signal and transmitting the dynamic video signal to a storage control module; the storage control module for controlling the real-time storage of the dynamic video signal and transmitting the dynamic video signal to a second dynamic video signal storage module; the second dynamic video signal storage module for storing the dynamic video signal and transmitting the dynamic video signal to a video overlay module; a local video signal storage module for storing a local video signal and transmitting the local video signal to a video overlay module; the video overlay module for overlaying the dynamic video signal and the local video signal and transmitting the overlaid video signal to a display module; and the display module for receiving the overlaid video signal transmitted by the video overlay module and displaying the overlaid video signal.

Owner:深圳市亿威尔信息技术股份有限公司

Prepreg, laminated board and printed wiring board

InactiveCN110724366AOptimum Glass Transition TemperatureEliminate transmission delaysDielectric materialsSynthetic resin layered productsPolymer scienceDielectric loss

The invention discloses a prepreg, a laminated board and a printed circuit board. The prepreg includes a halogen-free epoxy resin composition and a partially cured nonwoven reinforcing material impregnated therein. The nonwoven reinforcing material has a dielectric strength of 1.5-4.8 and a loss factor of below 0.003 at 10 GHz, and the halogen-free epoxy resin composition includes, by weight, (a)100 parts of a halogen-free naphthalene type epoxy resin, (b) 10-25 parts of a DOPO modifying hardener, (c) 25-45 parts of a cyanate ester resin, (d) 35-60 parts of bismaleimide, (e) 45-65 parts of anon-DOPO flame retardant and (f) 0.5-15 parts of a hardening accelerator. The prepreg effectively improves the delay effect, and has the characteristics of high glass transition temperature, low dielectric loss, high heat resistance and high storage modulus.

Owner:ITEQ WUXIELECTRONICS TECH

Low-latency metadata access method of cloud storage client

InactiveCN103023982BEliminate transmission delaysAvoid performance bottlenecksTransmissionAccess methodNetworked Transport of RTCM via Internet Protocol

The invention discloses a low-latency metadata access method of a cloud storage client, aiming to solve the problems of slow metadata access response and the like during metadata access. The technical proposal is as follows: a metadata access module composed of a metadata definition module, a metadata importing module, a metadata request response module and a metadata uploading module is mounted on the cloud storage client node; the metadata definition module determines the content and the format of the used metadata; the metadata importing module imports a metadata file into a key value pair database from the cloud storage server; the metadata request response module performs metadata operation according to a metadata access command; and the metadata uploading module uploads a local metadata file to the cloud storage server. Due to the adoption of the low-latency metadata access method provided by the invention, the network transmission latency of metadata access can be eliminated, the metadata server can be prevented from becoming performance bottleneck, the condition that the same cloud storage client node can access heteroid cloud storage systems is supported and the security of the metadata is improved.

Owner:NAT UNIV OF DEFENSE TECH

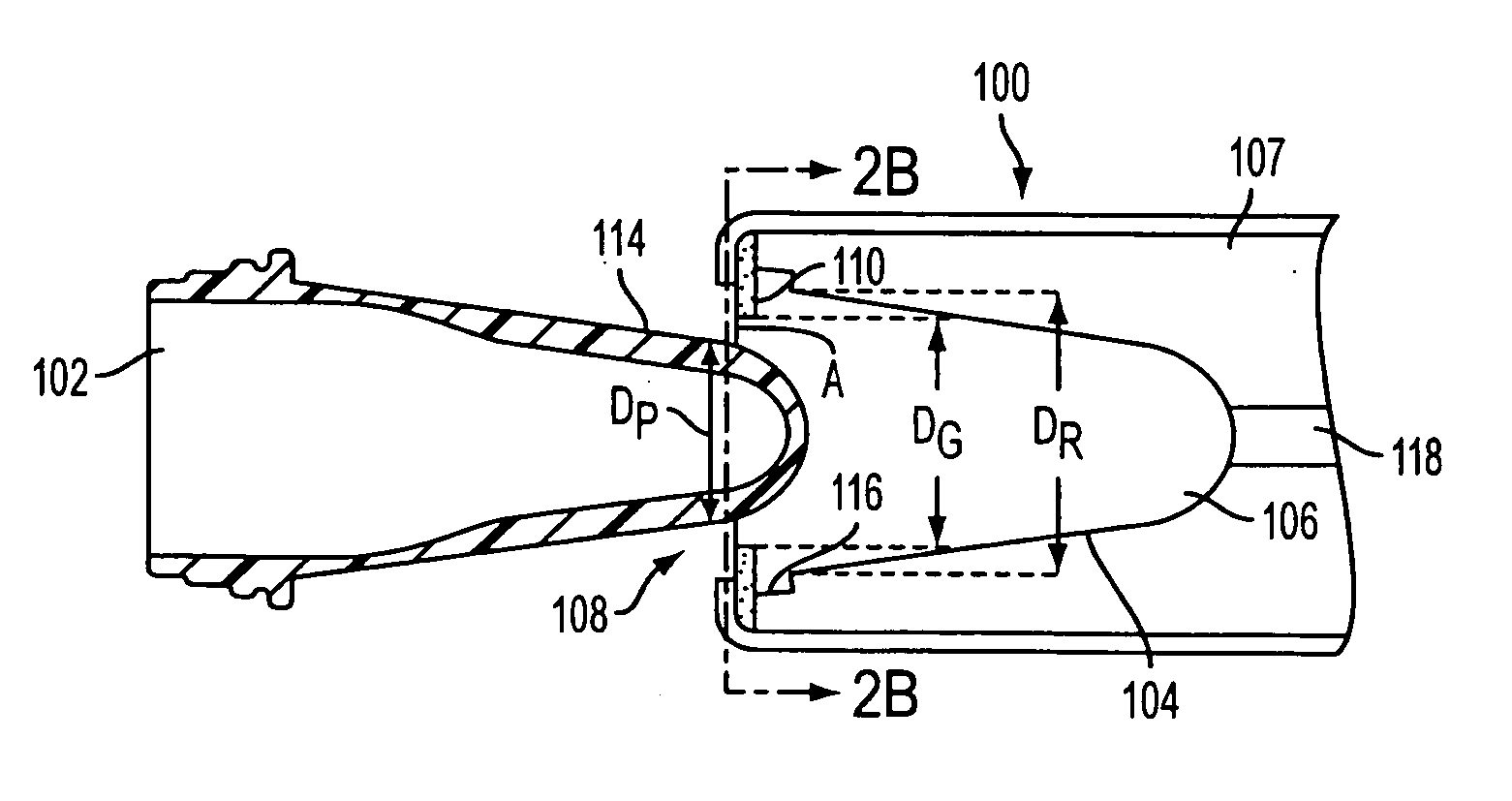

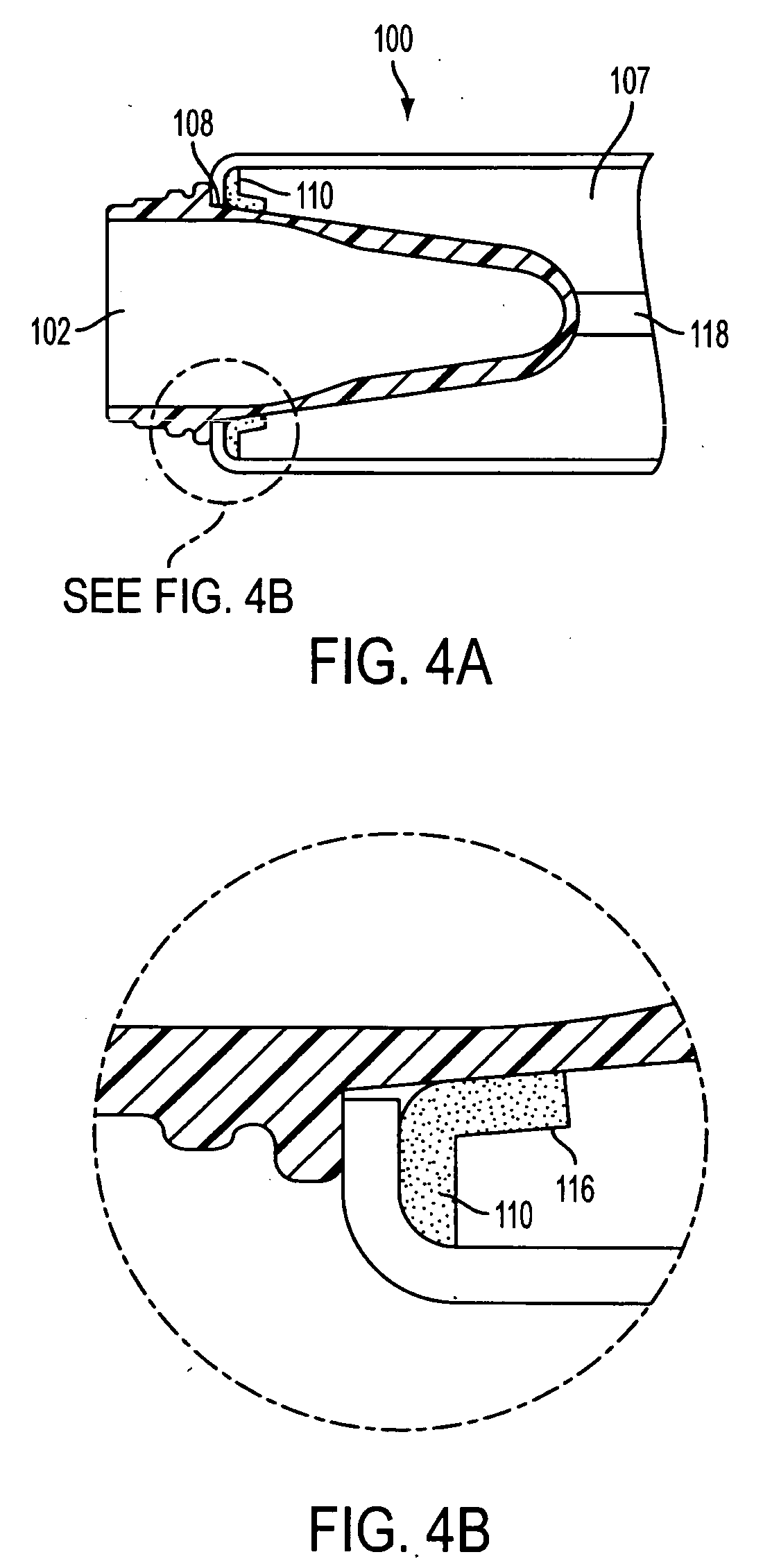

Injection perform transfer improvement

InactiveUS20060103053A1Easy to adaptGood curative effectMouldsConfectioneryEngineeringMechanical engineering

A take-off tube assembly for transferring a preform and methods of use are discussed. The assembly has walls defining a receptacle, and the receptacle has an open end with a cross sectional area. A preform guide is located along the walls of the receptacle, the preform guide having an open end with a cross sectional area smaller than the cross sectional area of the receptacle. A vacuum inlet is also be present, allowing connection of the assembly to a vacuum so that a vacuum draw can facilitate transfer of the preform to the take-off tube.

Owner:GRAHAM PACKAGING CO LP

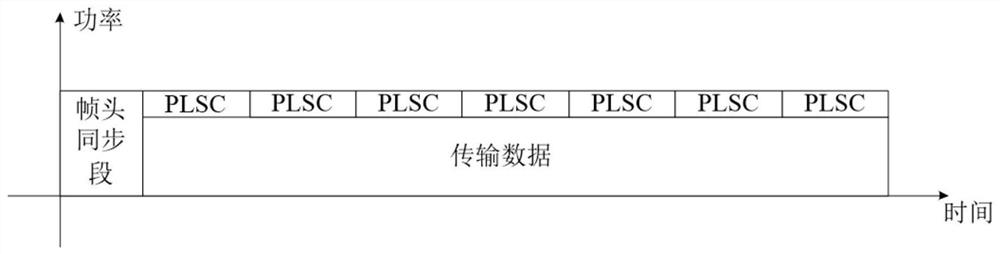

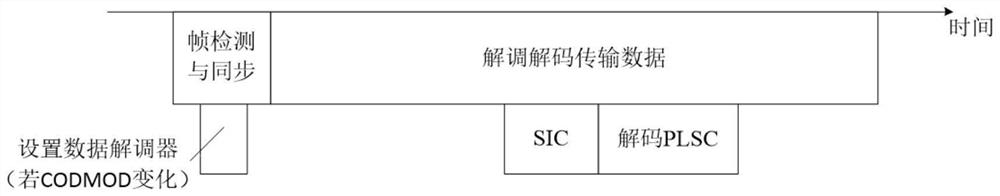

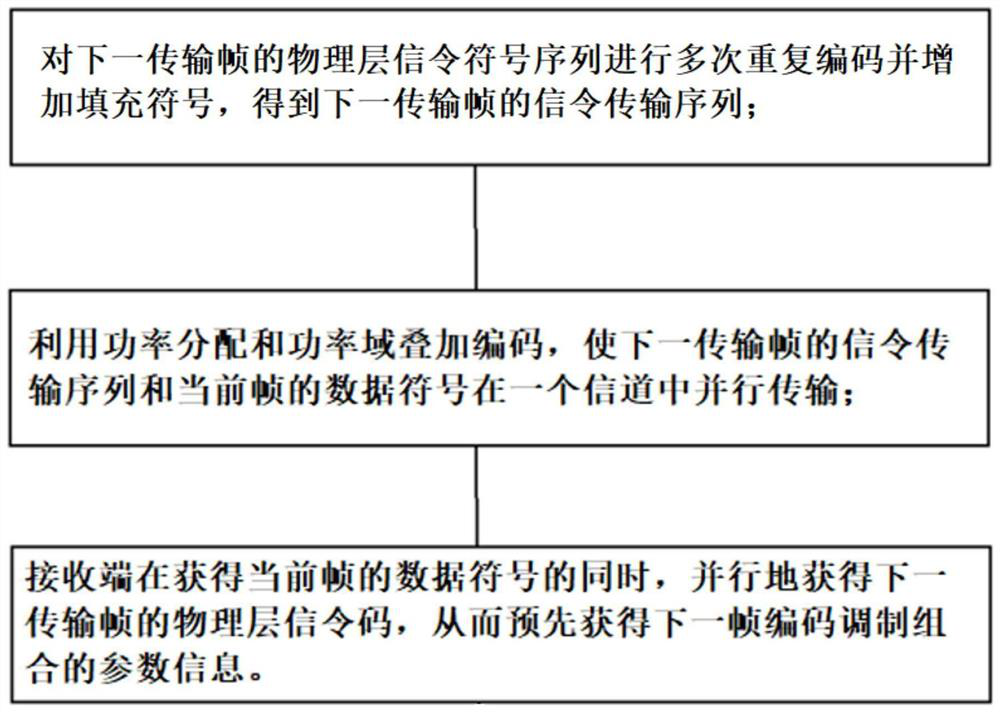

Frame signaling transmission method based on power multiplexing

PendingCN113783821AImplement parallel transferEliminate transmission delaysSynchronisation error detectionMultiple carrier systemsMultiplexingSuperposition coding

The invention belongs to the technical field of wireless data transmission and signal processing, and particularly relates to a frame signaling transmission method based on power multiplexing, which is used for a transmission system using a variable modulation coding / adaptive modulation coding system. The method comprises the following steps: carrying out specific modulation mapping on a physical layer signaling code PLSC of a transmission frame to form a physical layer signaling symbol sequence of the transmission frame, carrying out repeated coding on the physical layer signaling symbol sequence of the next transmission frame, and adding a filling symbol to obtain a signaling transmission sequence of the next transmission frame; enabling the signaling transmission sequence of the next transmission frame and the data symbol of the current frame to be transmitted in parallel in the same channel by using power distribution and power domain superposition coding; when the receiving end obtains the data symbol of the current frame, the receiving end obtains the physical layer signaling code of the next transmission frame in parallel, so that the parameter information of the coding modulation combination of the next frame is obtained in advance, the receiving end carries out corresponding configuration on a data demodulator and a decoder in time, and the continuity of receiving, demodulating and decoding is kept.

Owner:NAT SPACE SCI CENT CAS

A Multi-chip Synchronization Architecture Based on Time-to-Digital Converter Circuit

ActiveCN106970679BReduce loadEliminate transmission delaysGenerating/distributing signalsComputer moduleEngineering

The invention discloses a multichip synchronization structure based on a time-digital converter circuit. The multichip synchronization structure comprises N circuit chips provided with built-in time-digital converters and time sequence regulation modules. Each chip contains a synchronization indicating signal receiving end, a synchronization indicating signal output end, one time-digital converter and one time sequence regulation module, wherein the synchronization indicating signal receiving end is used for receiving a synchronization indicating signal input into the chip externally; the synchronization indicating signal output end is used for outputting a synchronization indicating signal subjected to time sequence resampling through a trigger in the chip, wherein the sampling frequency of the trigger is completely aligned with a time sequence of a maximum frequency clock; the time-digital converter is used for quantizing time sequence delays of two input signals into digital values, wherein the input signal IN1 is the synchronization indicating signal input into the chip externally, and the input signal IN2 is the synchronization indicating signal subjected to time sequence resampling through the trigger in the chip; and the time sequence regulation module is used for regulating output delays of the synchronization indicating signals according to the input digital values. By the adoption of a daisy chain structure, the load on a synchronization indicating signal source is relieved.

Owner:NO 24 RES INST OF CETC

Long distance coverage method and base station

ActiveCN103843383BRealization of long-distance coverageEliminate transmission delaysSynchronisation arrangementNetwork planningUser equipmentRADIUS

Owner:HUAWEI TECH CO LTD

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com