Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

56results about How to "Efficient counting" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

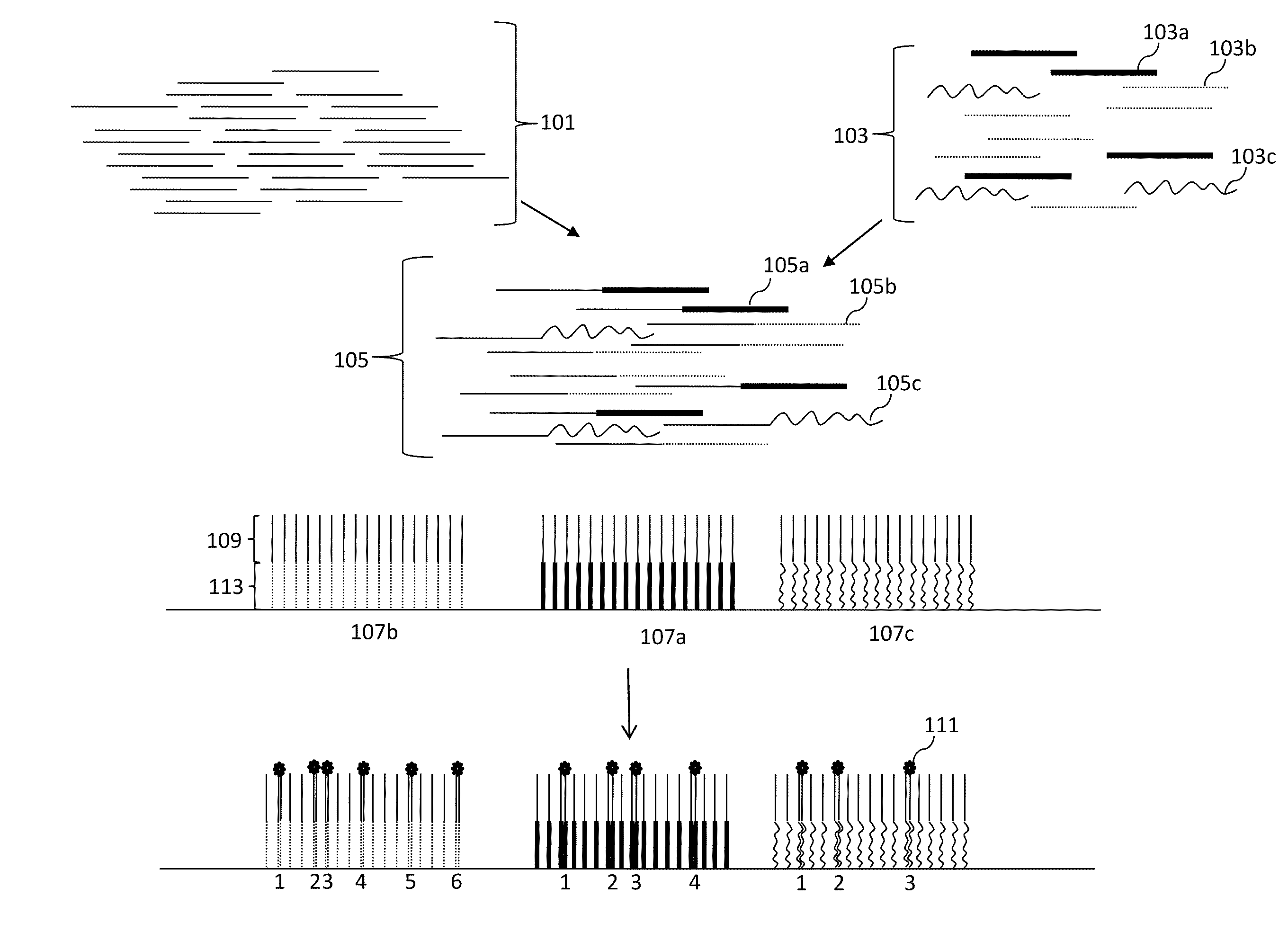

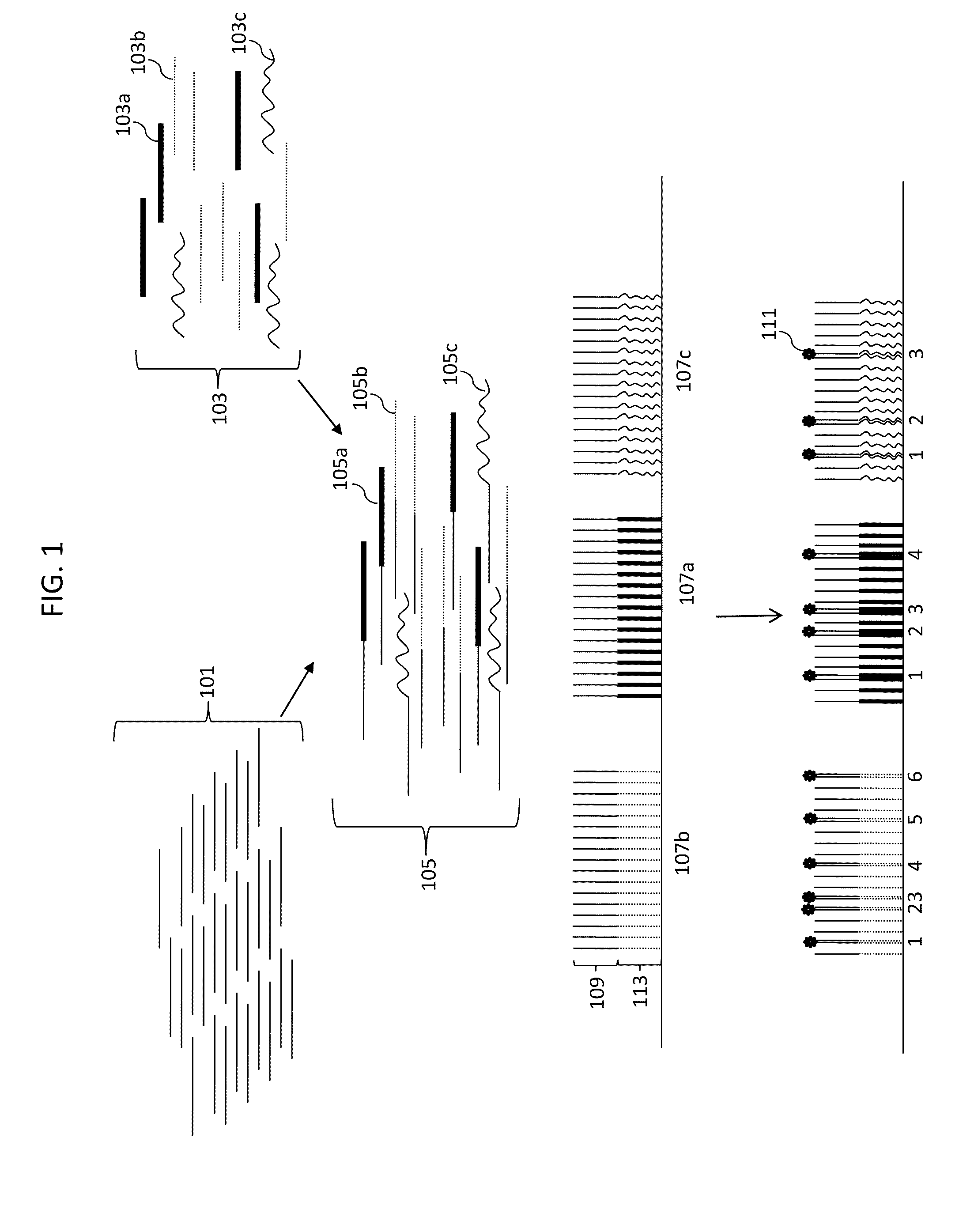

Digital Counting of Individual Molecules by Stochastic Attachment of Diverse Labels

ActiveUS20110160078A1Highly precise relative and absolute counting statisticRaise countNucleotide librariesMicrobiological testing/measurementBiologyMultiple methods

Owner:BECTON DICKINSON & CO

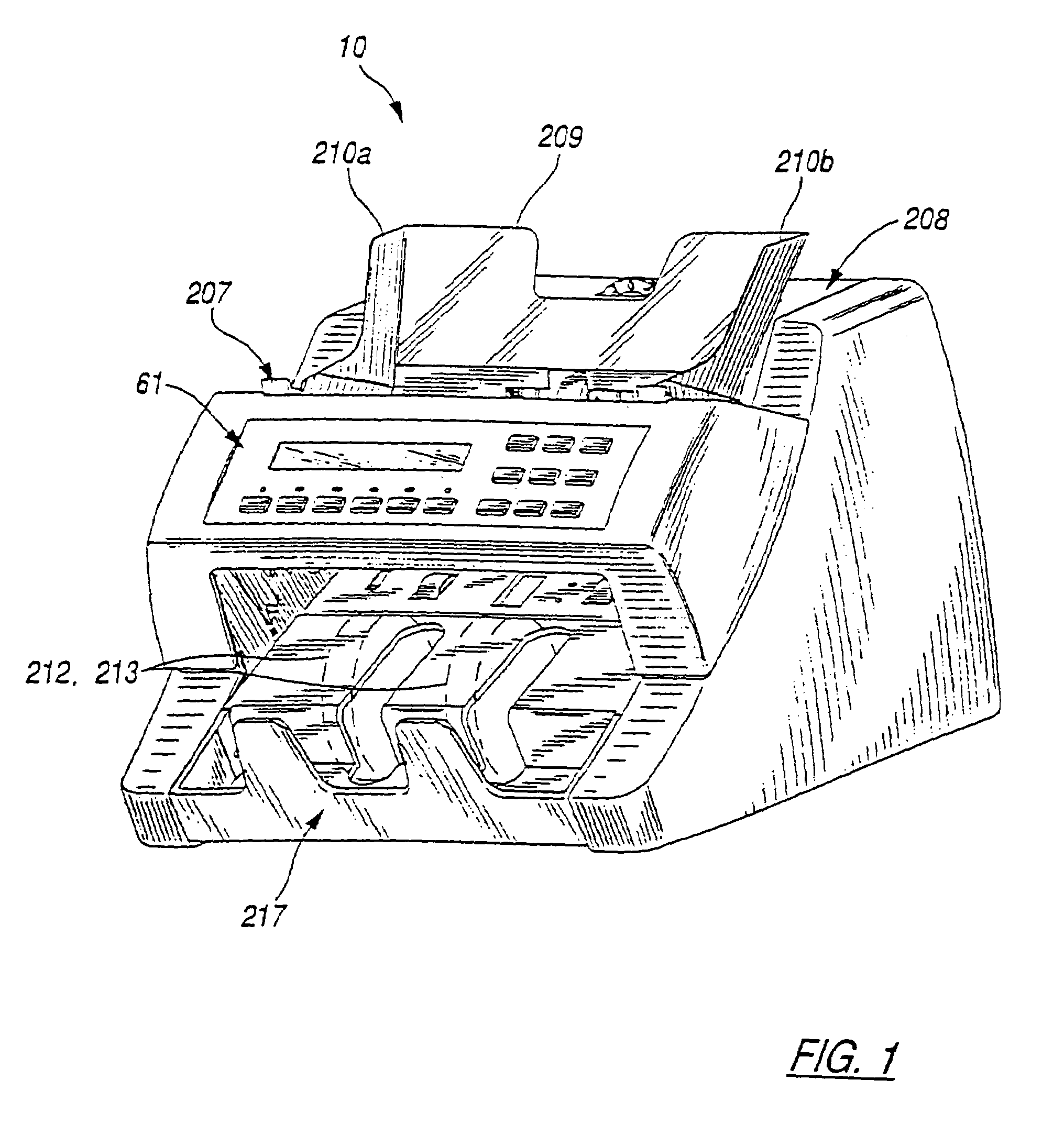

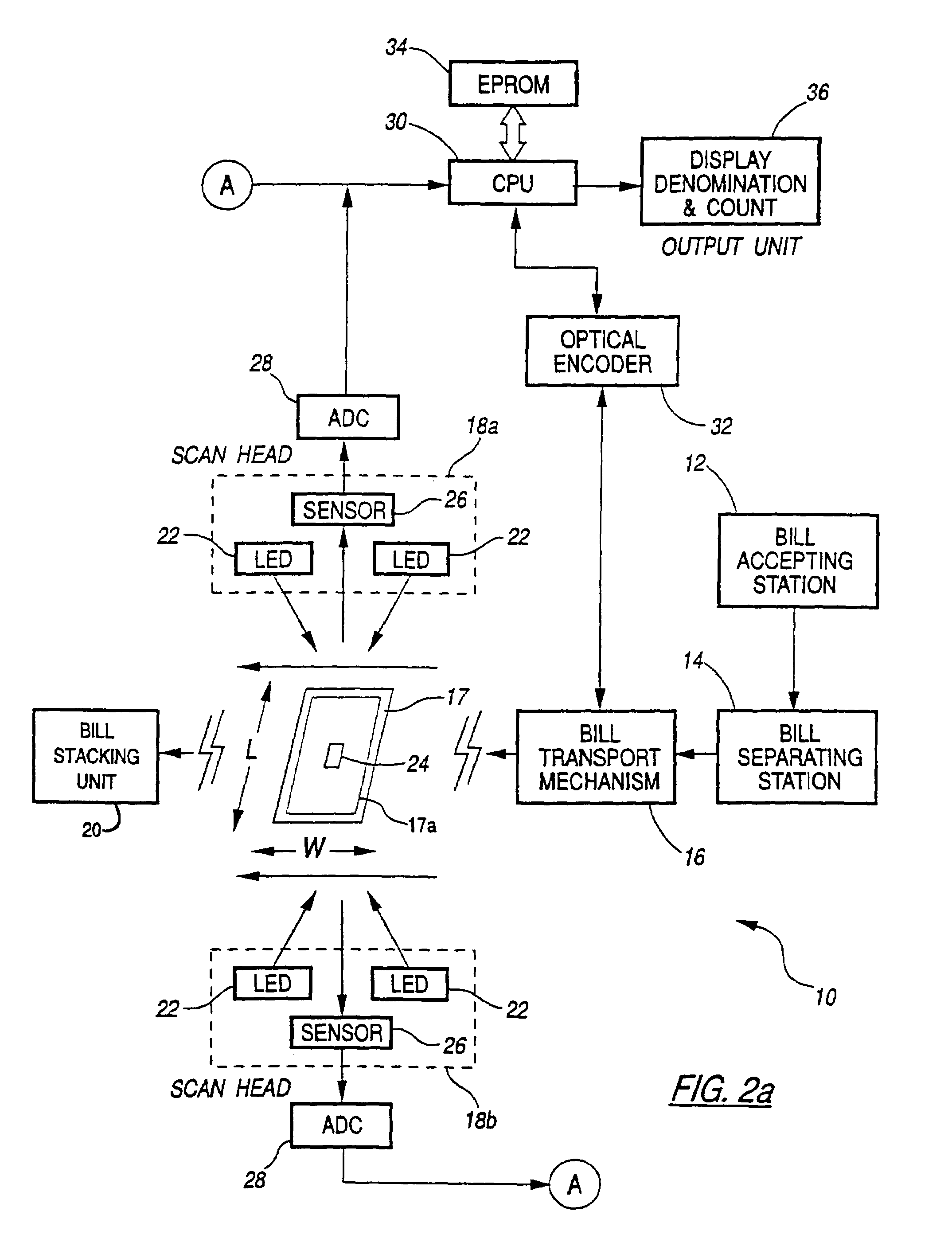

Method and apparatus for discriminating and counting documents

InactiveUS6980684B1Efficient countingEfficient discriminationCoin/currency accepting devicesCharacter and pattern recognitionEngineeringIdentification device

Owner:CUMMINS-ALLISON CORP

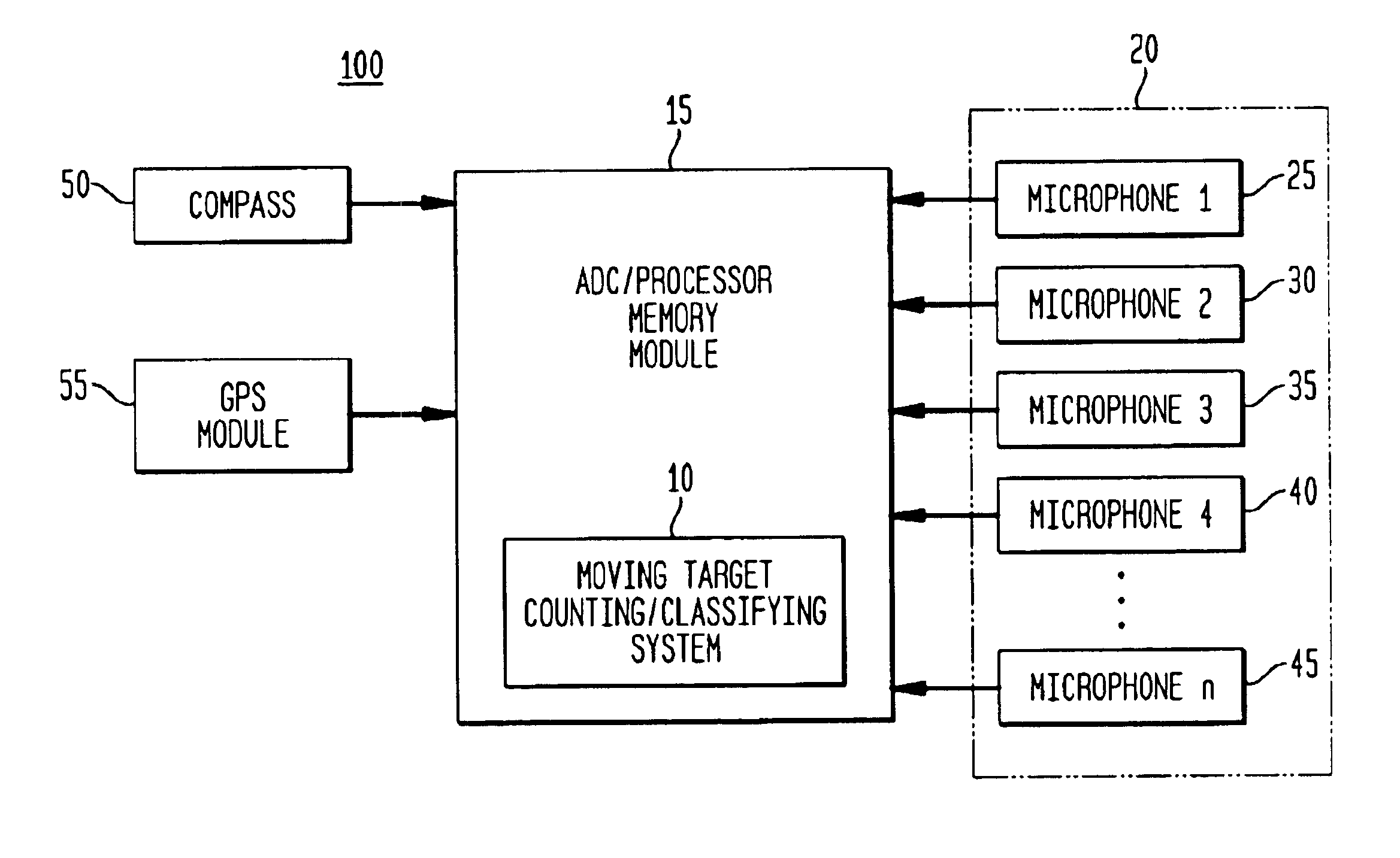

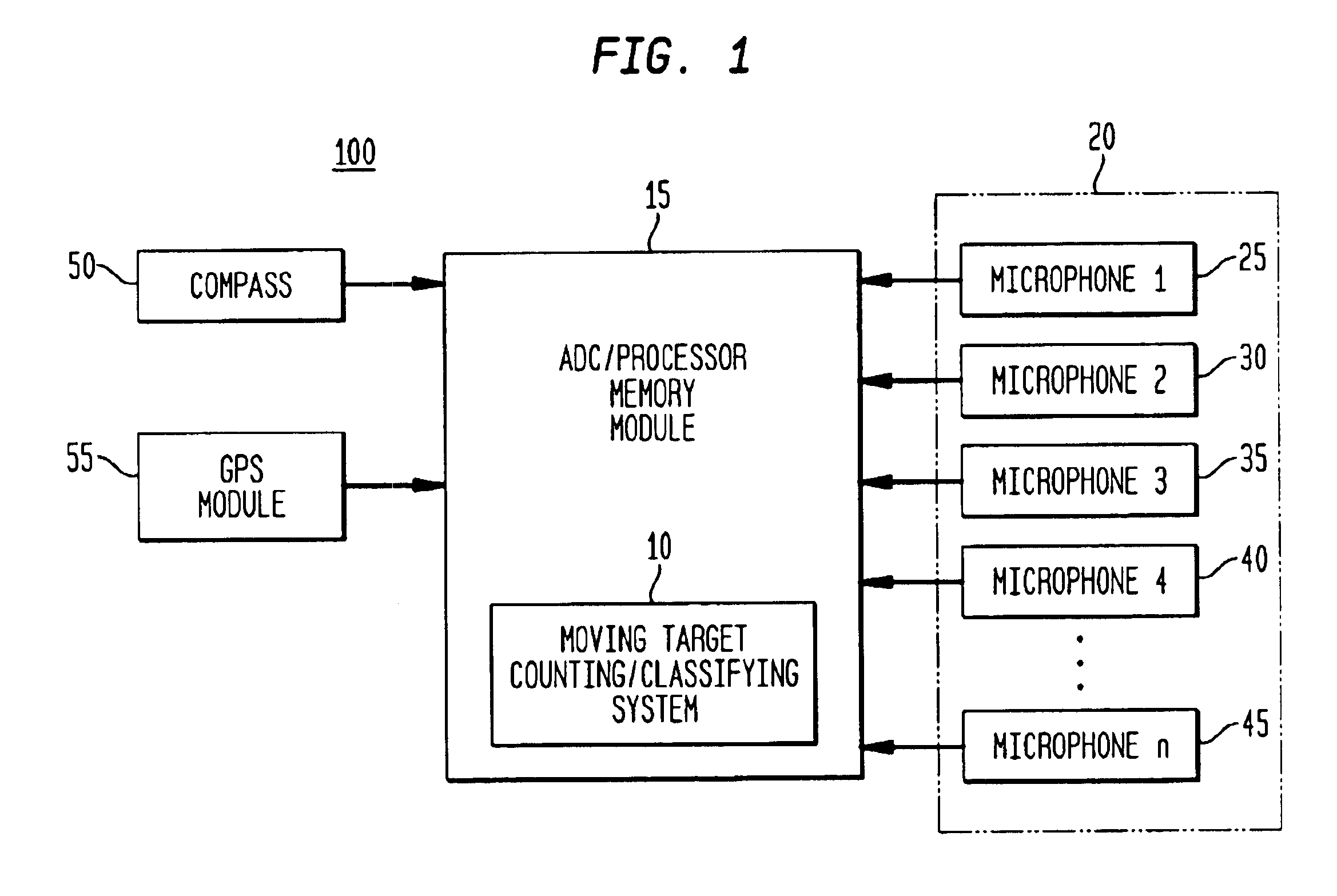

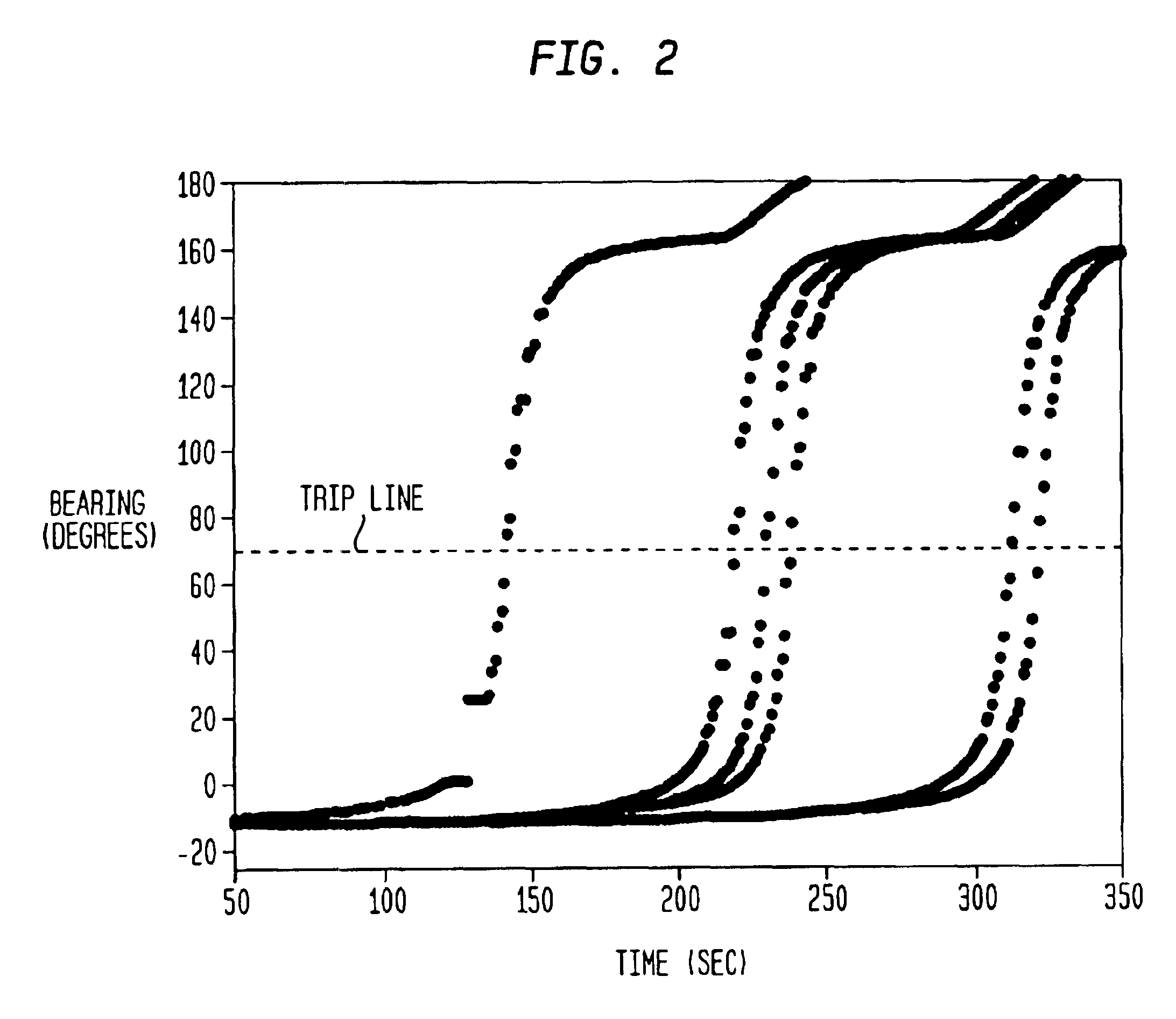

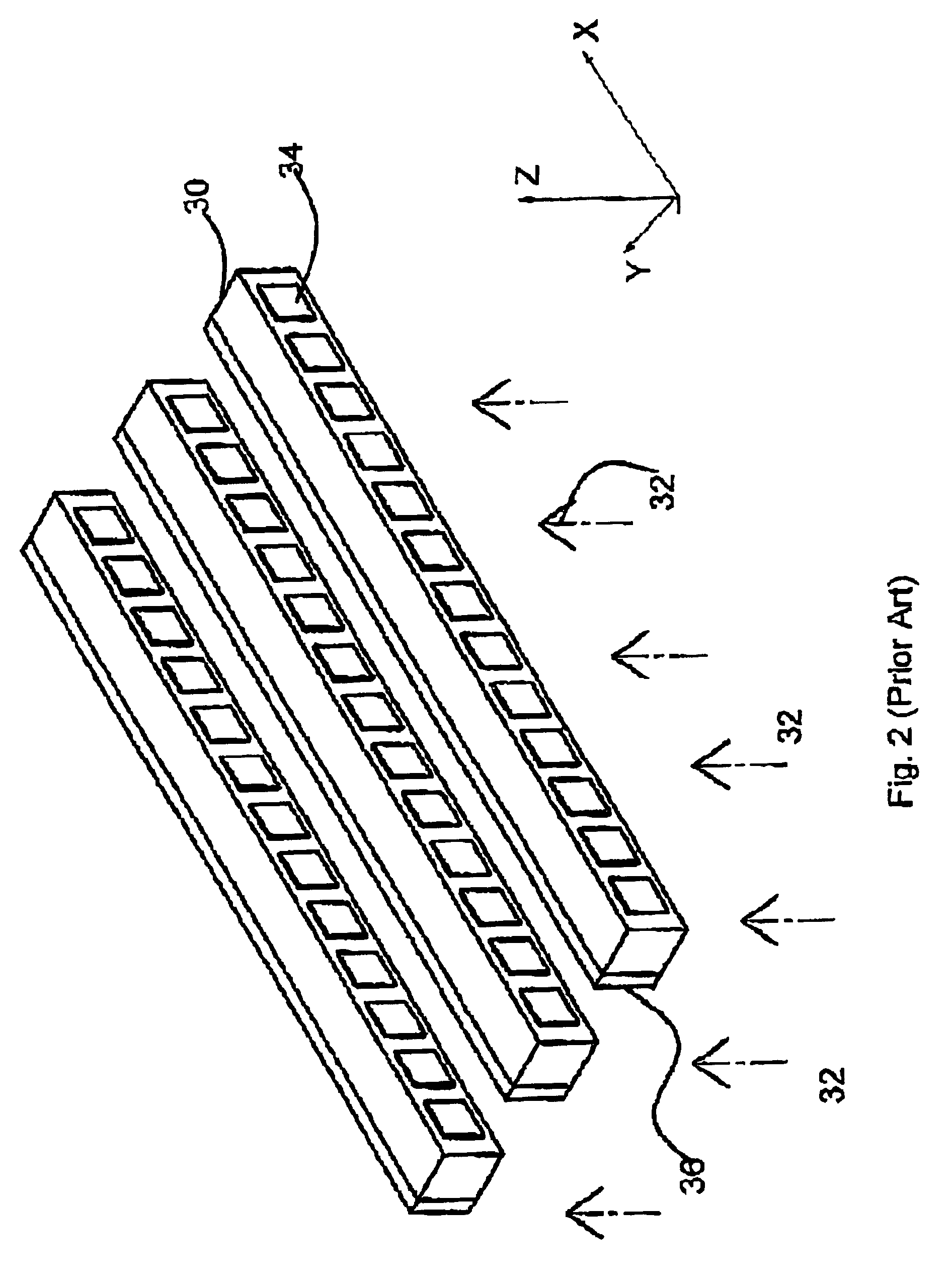

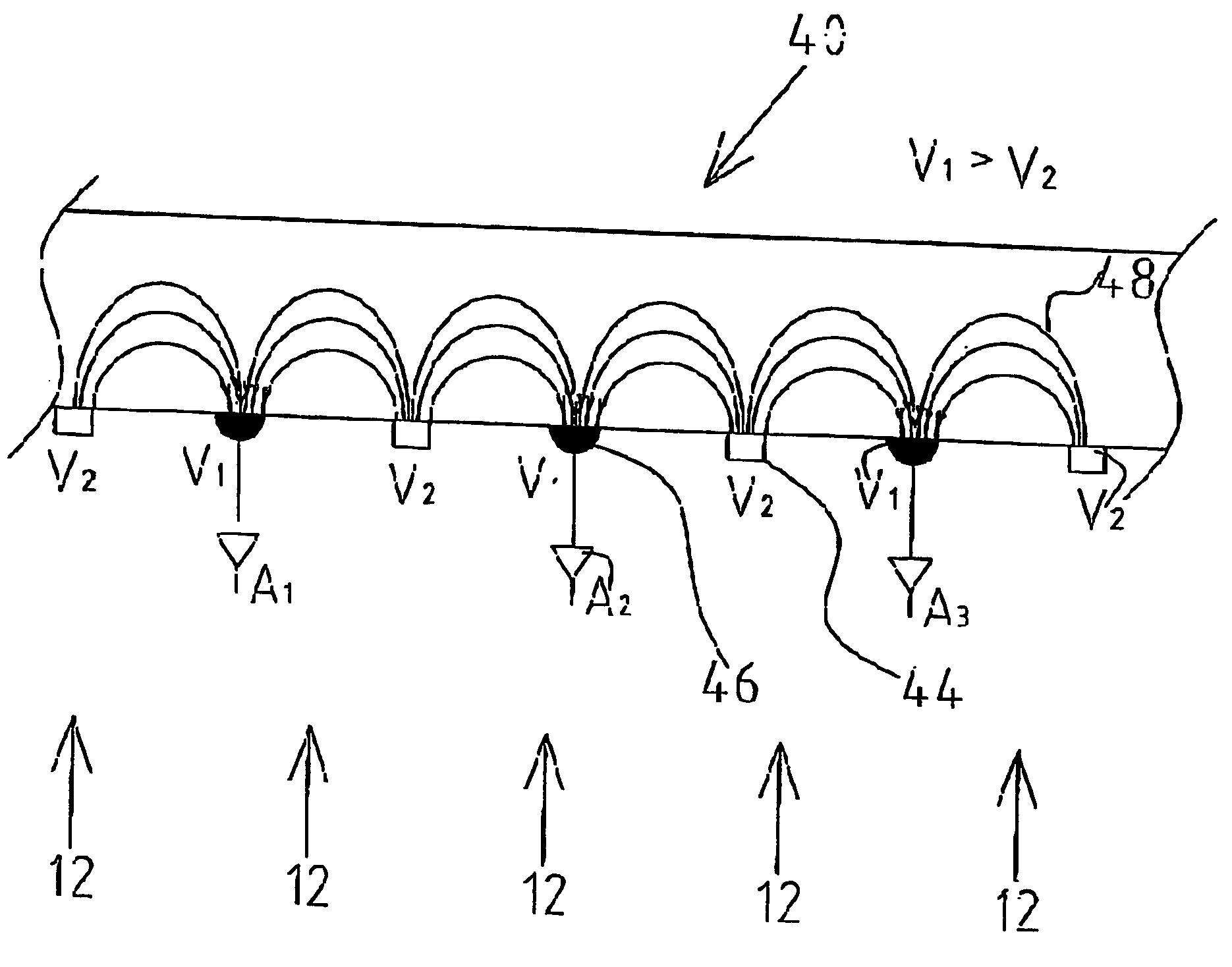

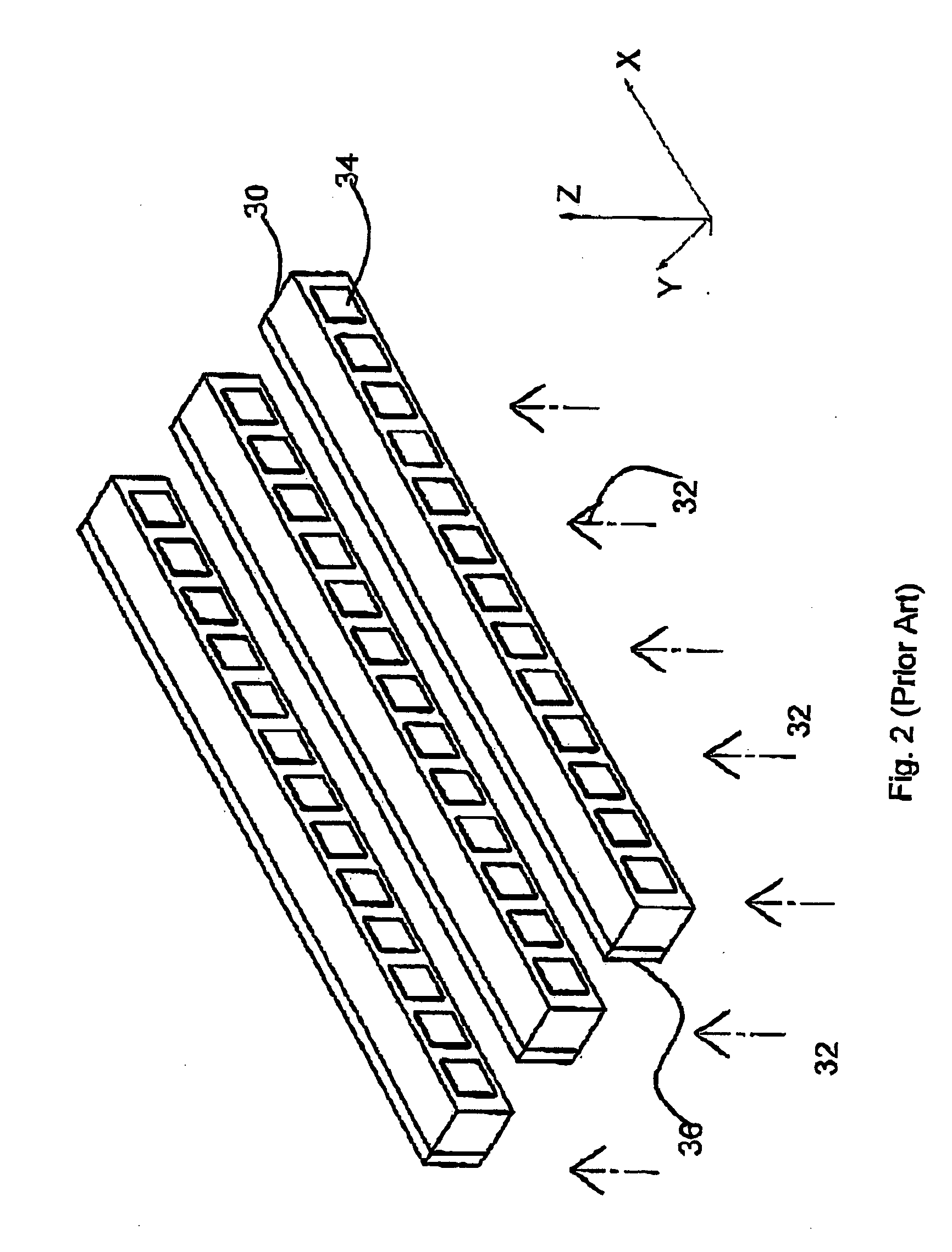

Method for detecting extended range motion and counting moving objects using an acoustics microphone array

InactiveUS6914854B1Reduce uncertaintyHighly accurate vehicle countMulti-channel direction findingUsing reradiationMotion detectorAcoustic array

An acoustic array platform comprising multiple spaced microphones and associated processing electronics / algorithms projects distinct beams in a chosen look direction across which moving objects such as vehicles pass. These moving objects are accurately detected, classified and counted at extended ranges. The acoustic microphone array employs optimized beamforming to create specially focused listening directions that function as a “motion detector” and “trip line counter”. Algorithms detect and confirm the appropriate presence of objects moving through the beams and perform other algorithmic tests to verify that the object is a valid object to be counted. The proposed approach is realized with modest sized acoustic arrays and a reasonable number of microphones by employing an adaptive beamforming algorithm that achieves enhanced directivity in a principal look direction and which significantly reduces the effects of interferers outside the precise steering direction of the “trip line”.

Owner:UNITED STATES OF AMERICA THE AS REPRESENTED BY THE SEC OF THE ARMY

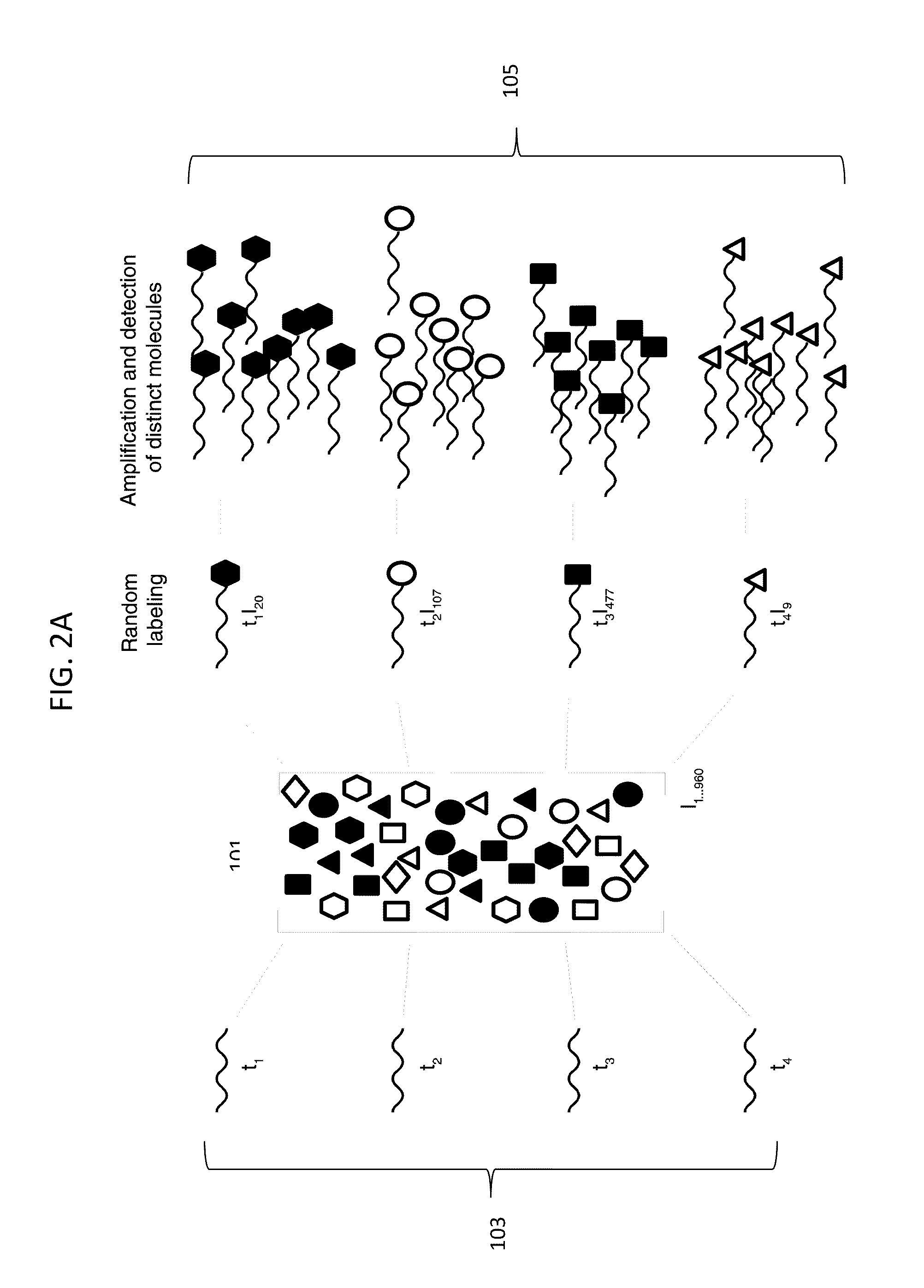

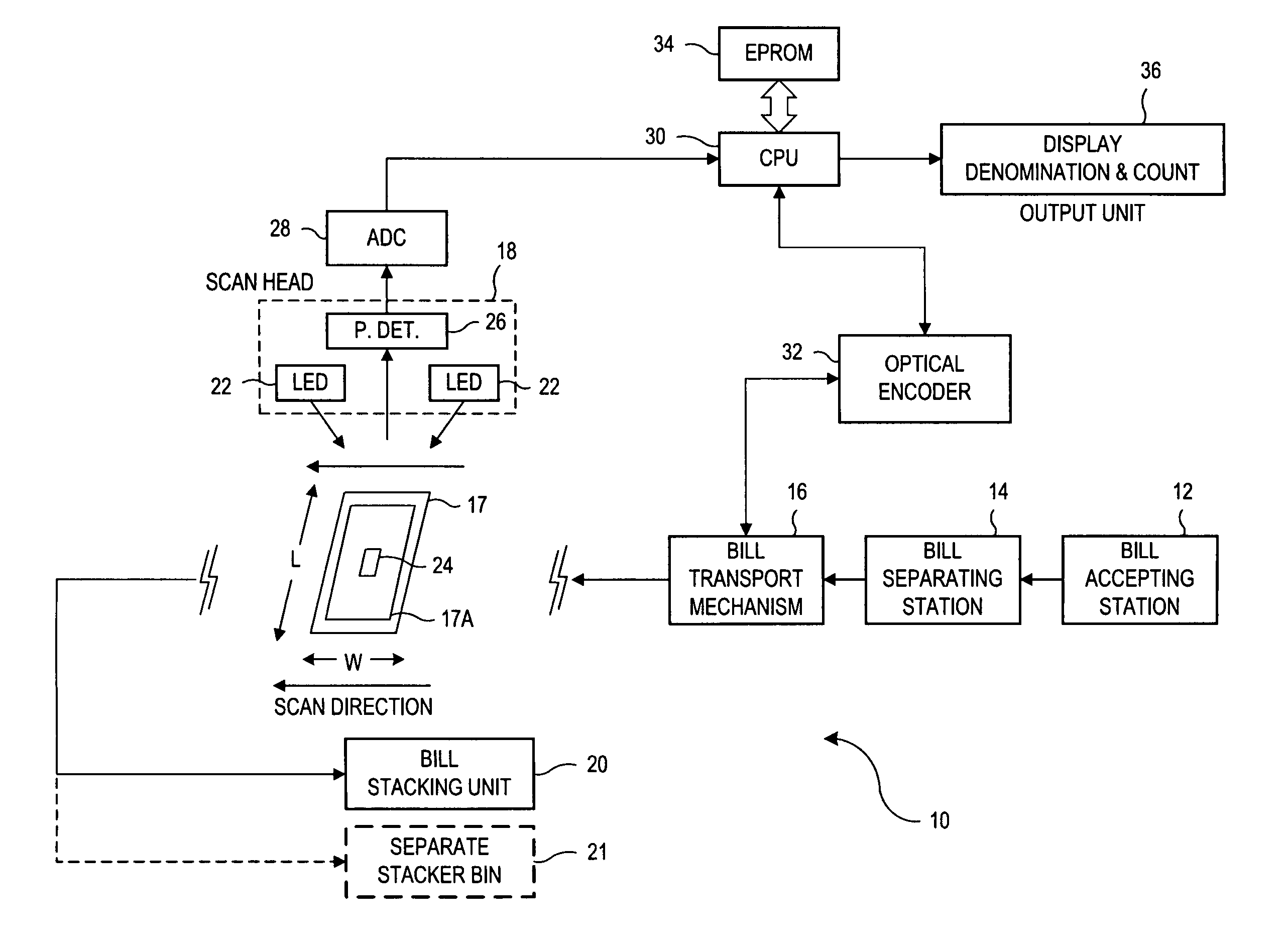

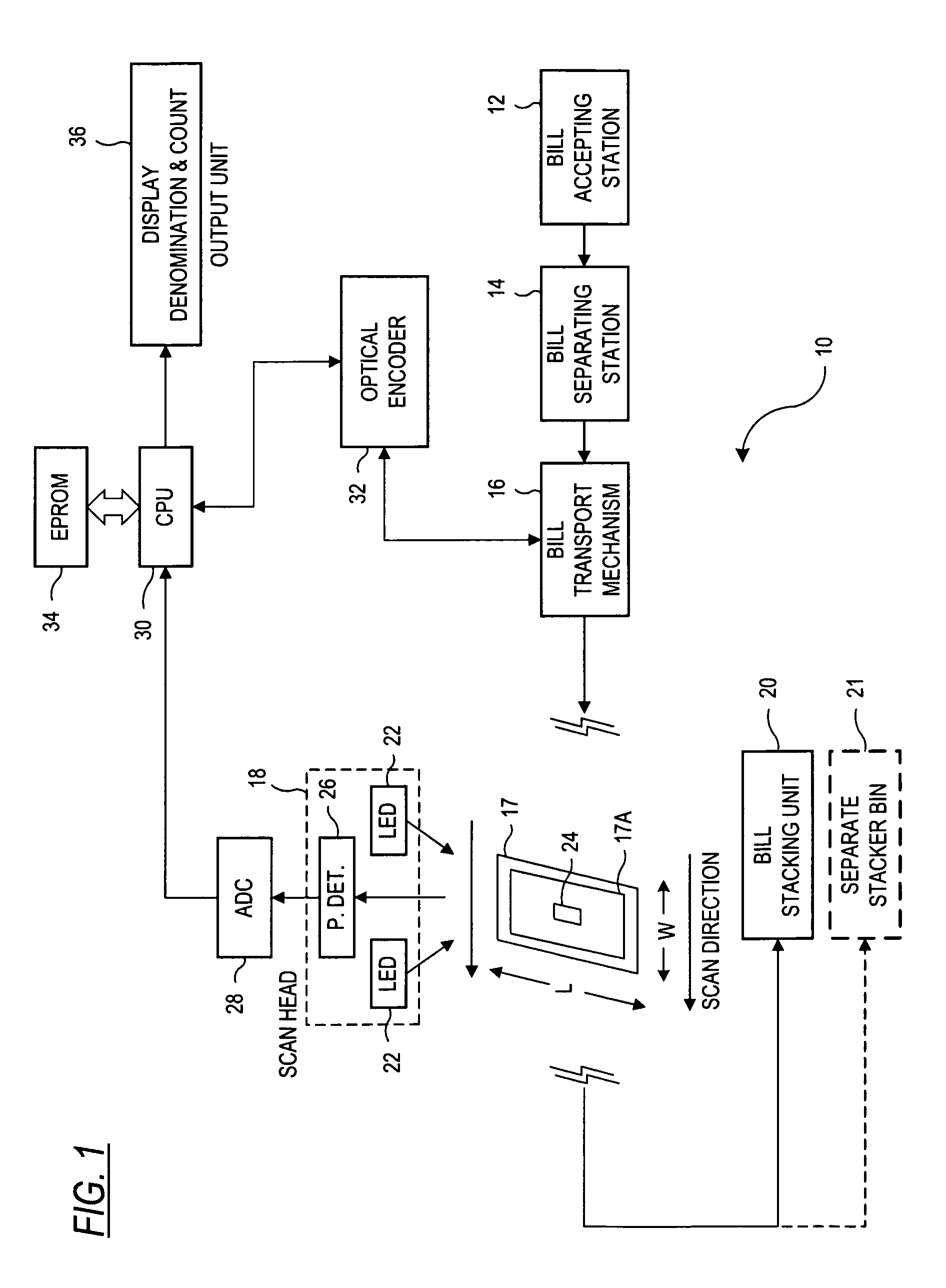

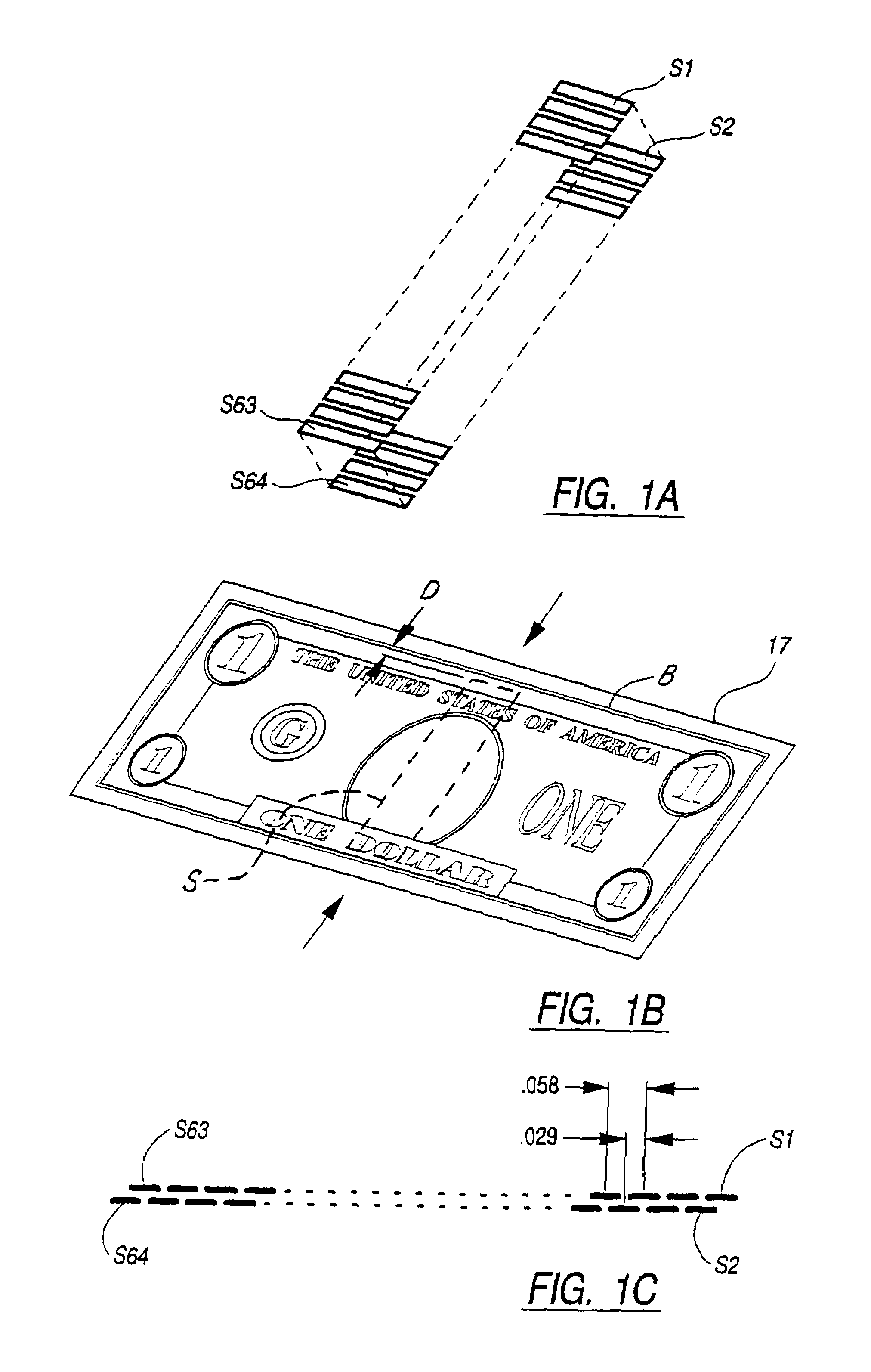

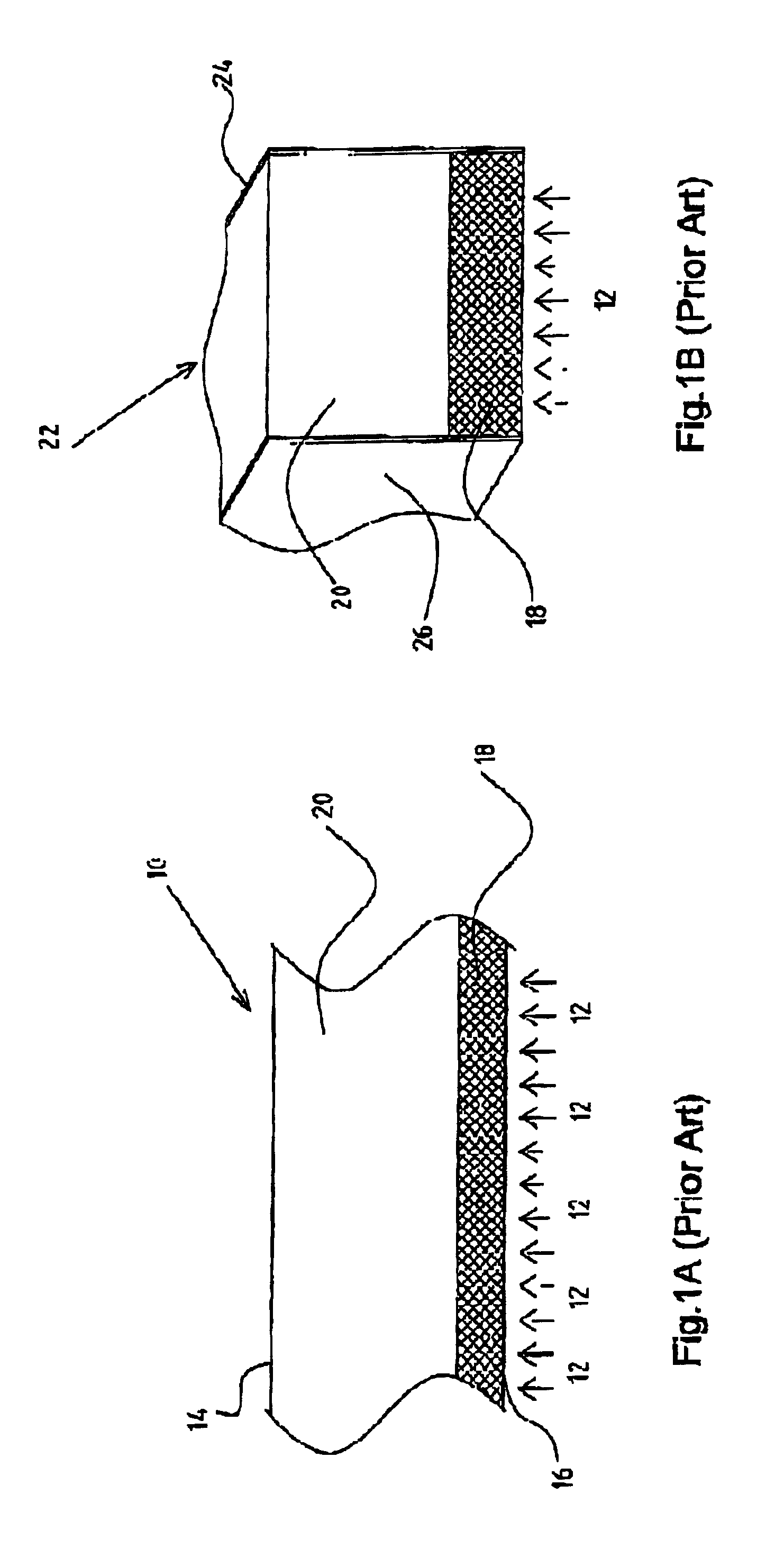

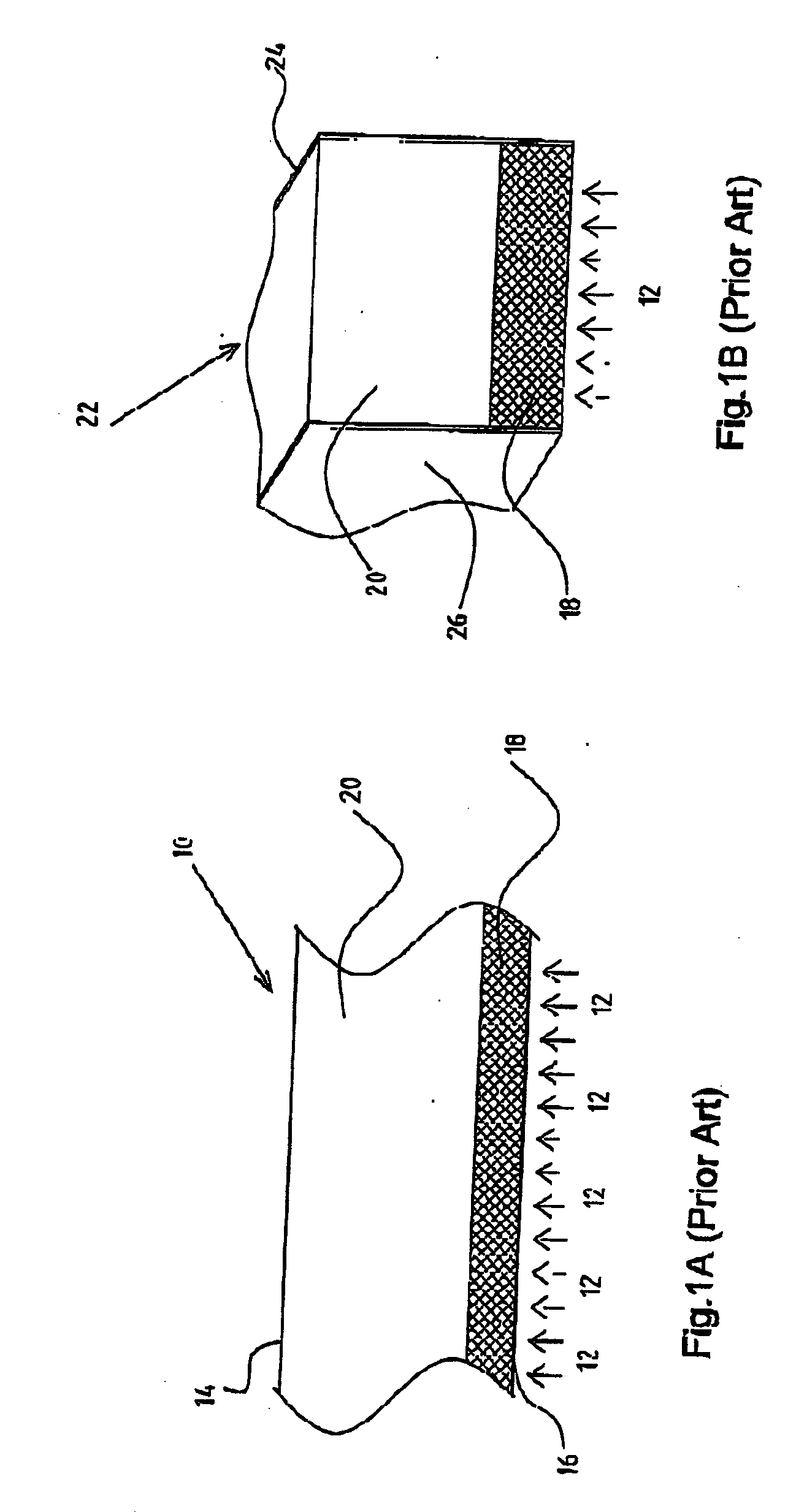

Method and apparatus for currency discrimination and counting

InactiveUS7536046B2Efficient countingEfficient discriminationComplete banking machinesImage analysisStackerBank note

A currency evaluation device for receiving a stack of U.S. currency bills and rapidly evaluating all the bills in the stack comprises an input receptacle adapted to receive a stack of U.S. currency bills of a plurality of denominations to be evaluated. According to one embodiment, a transport mechanism transports the bills, one at a time, from the input receptacle along a transport path at a rate of at least about 800 bills per minute. A denomination discriminating unit which includes a detector positioned along the transport path evaluates the bills. The device comprises a single denominated bill output receptacle positioned to receive bills whose denomination have been determined by the discriminating unit including bills of a plurality of denominations. A separate stacker bin is provided and a diverter positioned along the transport path routes bills whose denomination cannot be determined to the separate stacker bin.

Owner:CUMMINS-ALLISON CORP

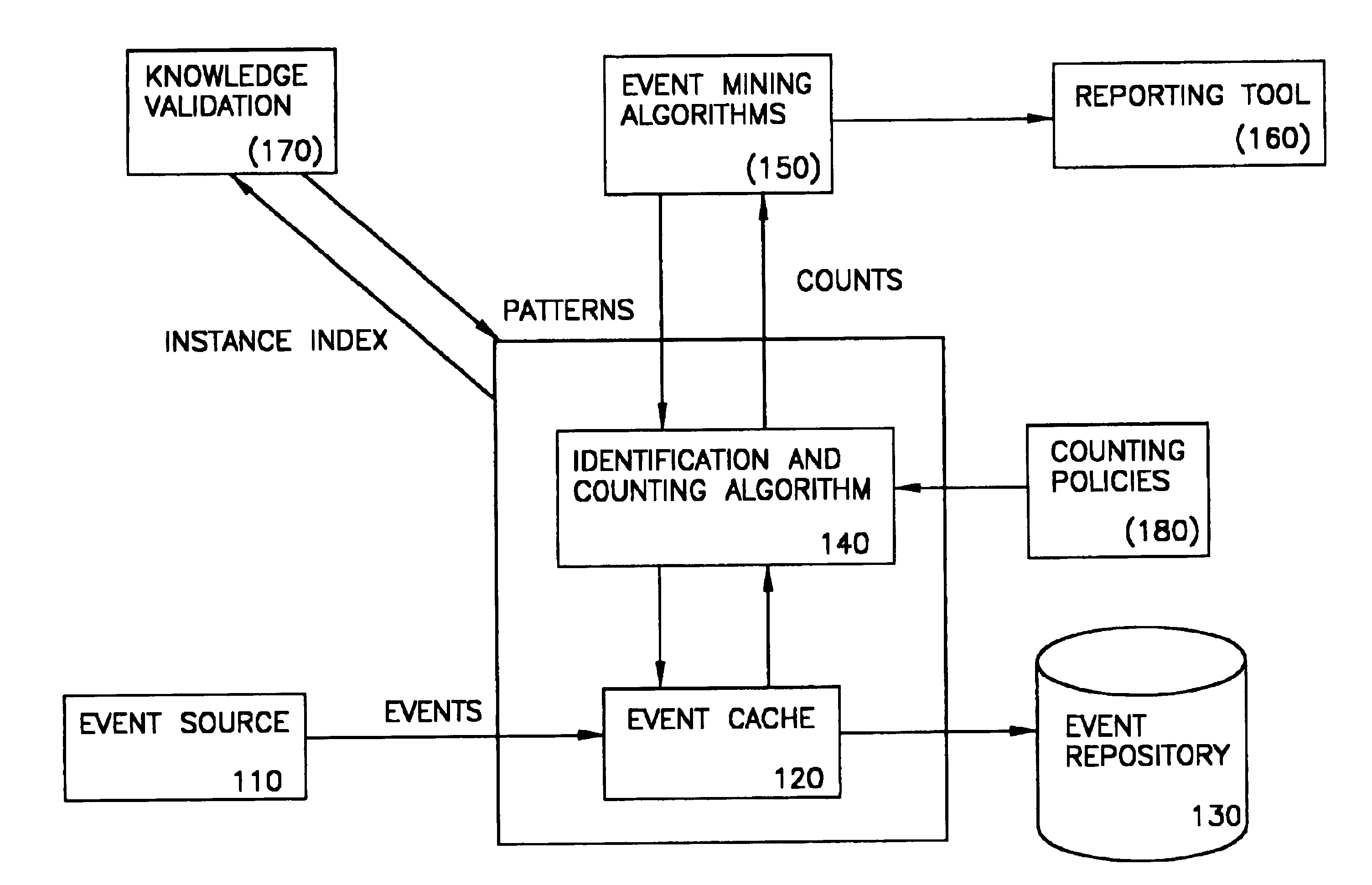

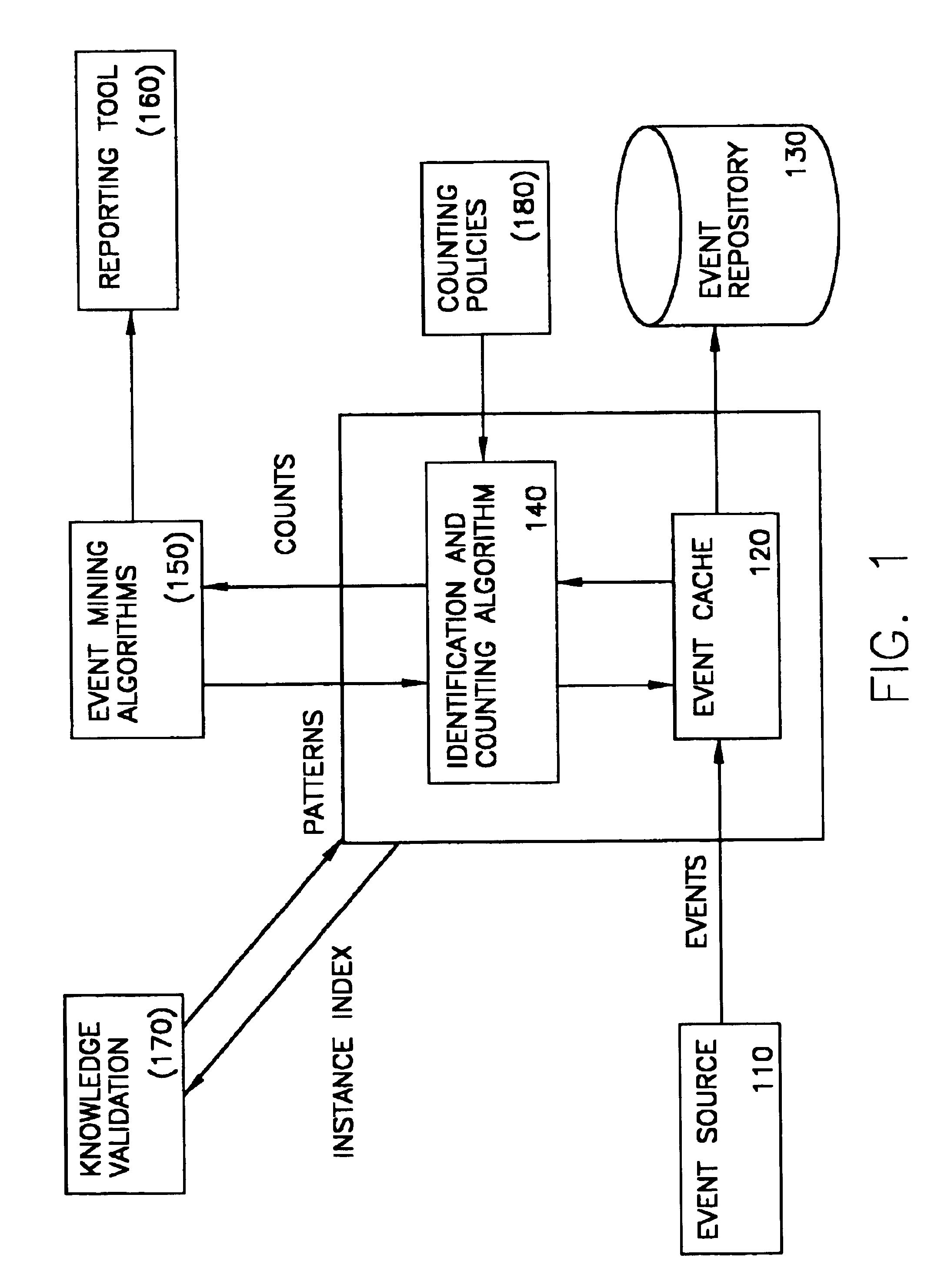

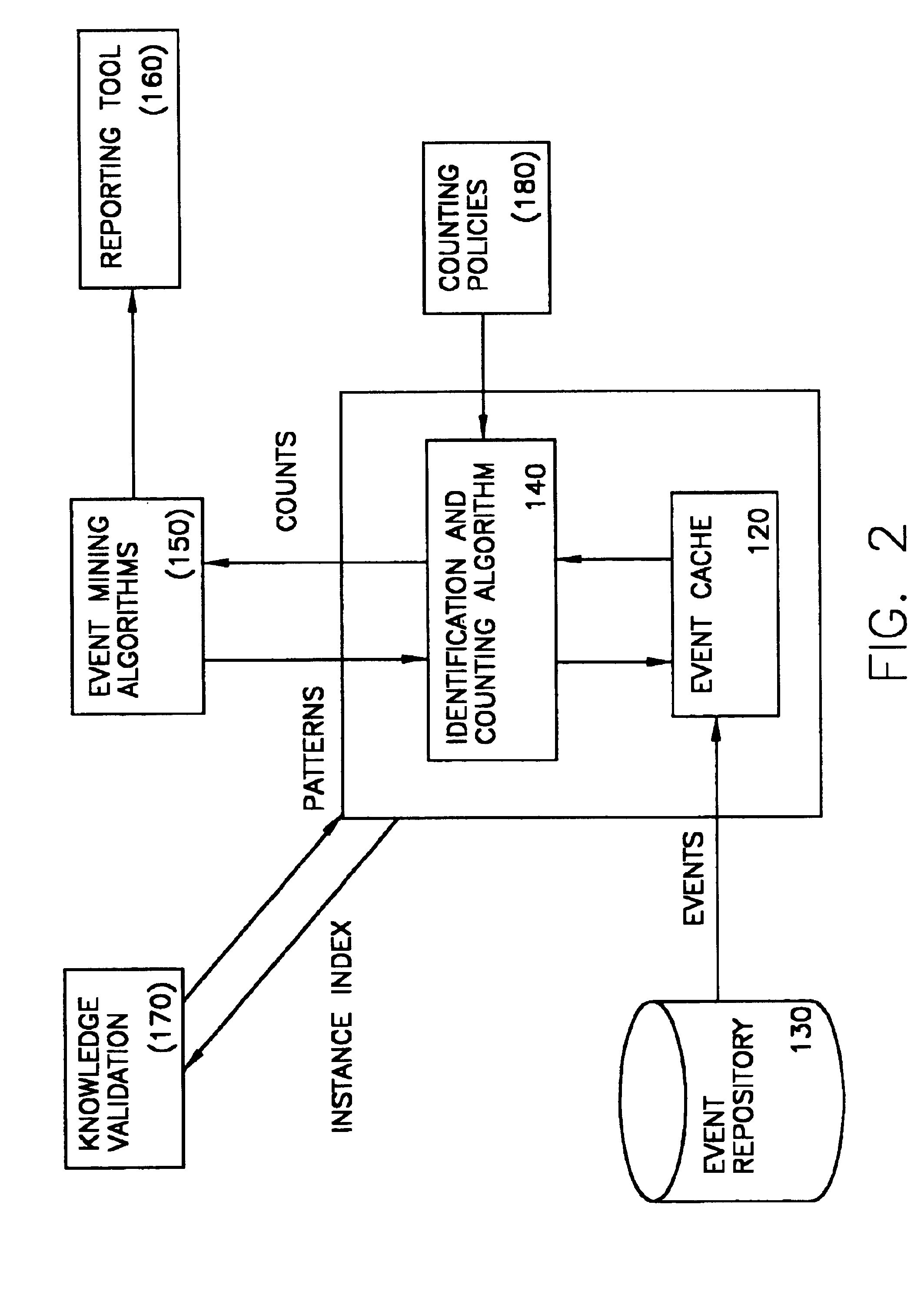

Systems and methods for identifying and counting instances of temporal patterns

InactiveUS6907426B2Accurate countImprove efficiencyData processing applicationsDigital data processing detailsComputer scienceIncremental computing

Systems and methods for instance counting and for the identification of a temporal pattern in an event sequence. The system addresses the use of “earliest-first” and “no-reuse” policies as criteria for the correctness of counting. The system also achieves higher performance than conventional methods by utilizing incremental computation.

Owner:TREND MICRO INC

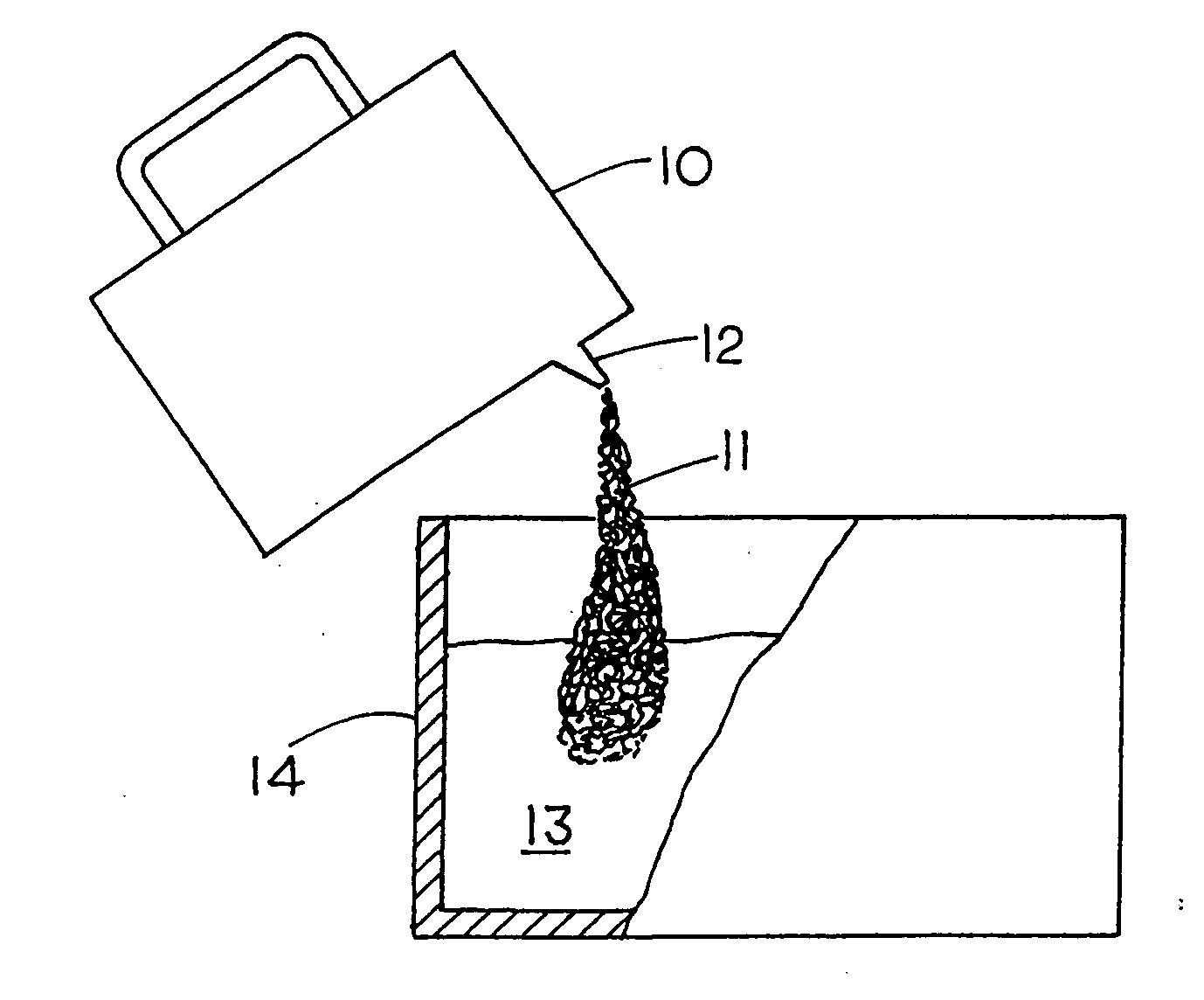

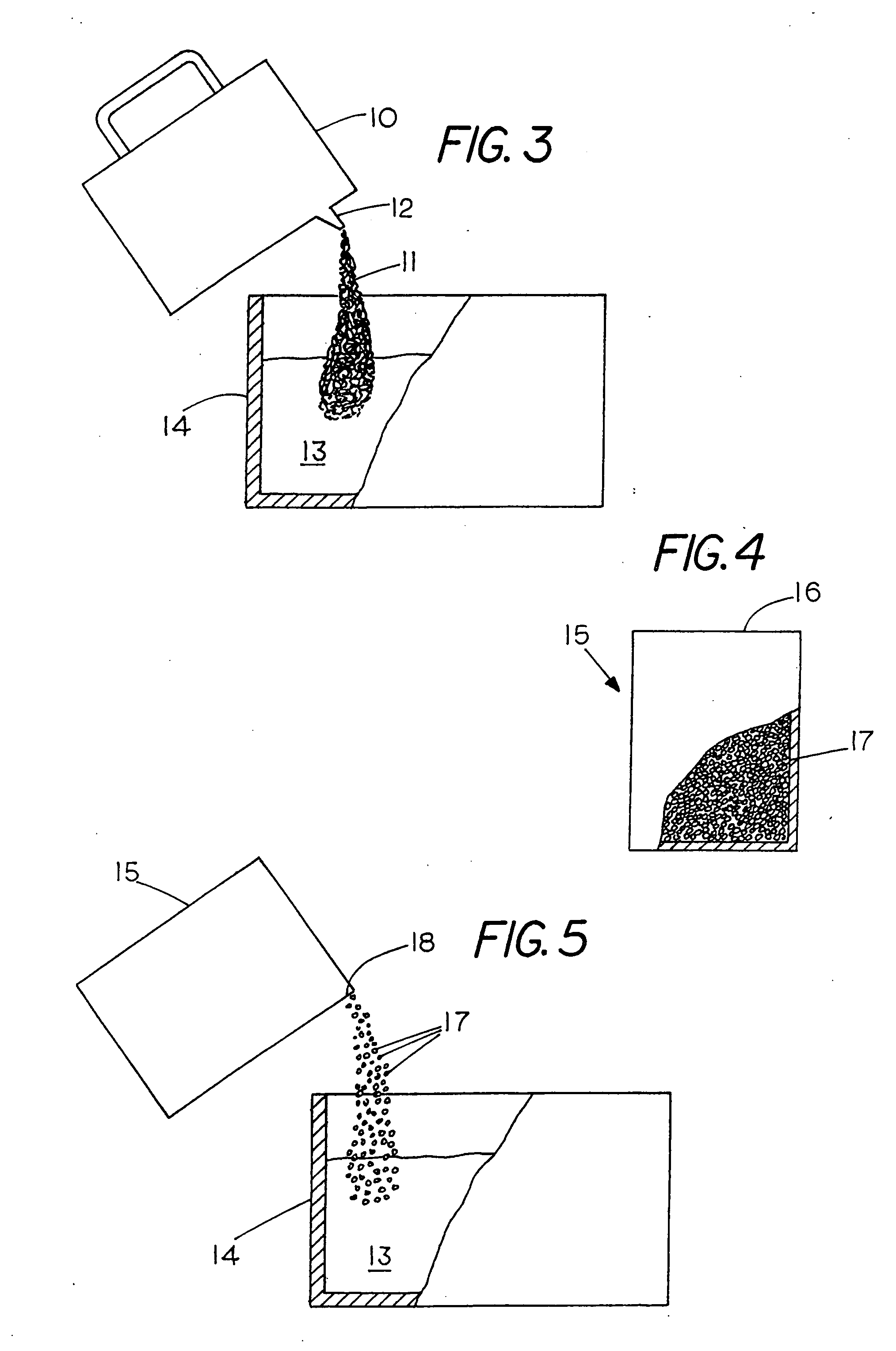

Water treatment

ActiveUS20110094972A1Improve efficiencyEfficient countingBiocidePowder deliveryNuclear chemistryMetal

A sanitizing agent for maintaining a biocidal effective bacteria count in a body of water comprising a metal ion donor for donating a metal ion and a compound containing a hydantoin ring with the combination of the compound containing the hydantoin ring with the metal ion donor enhancing the effectiveness of the sanitizing agent to enable the sanitizing agent to maintain a biocidal effective bacteria count in the body of water.

Owner:KING TECH

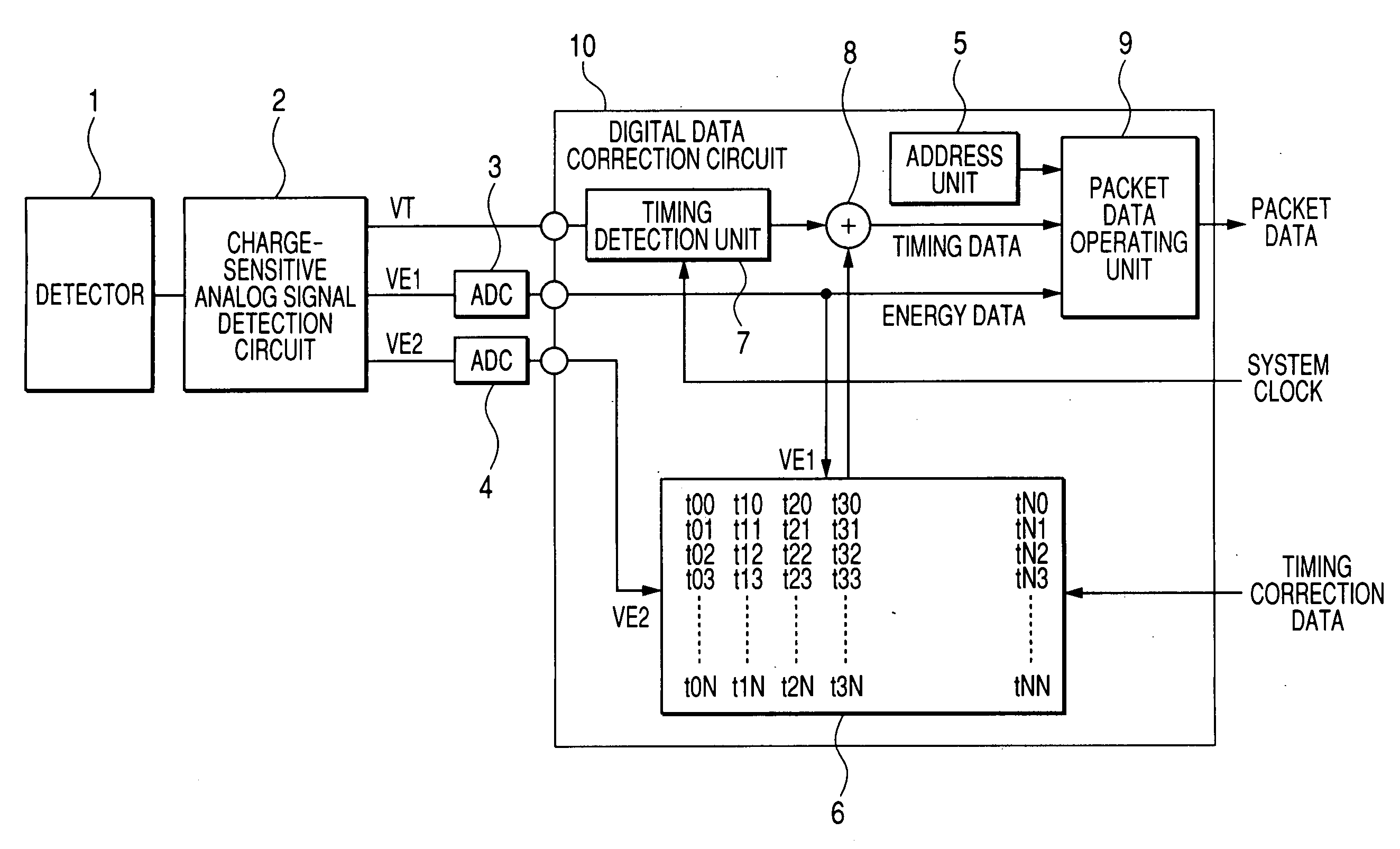

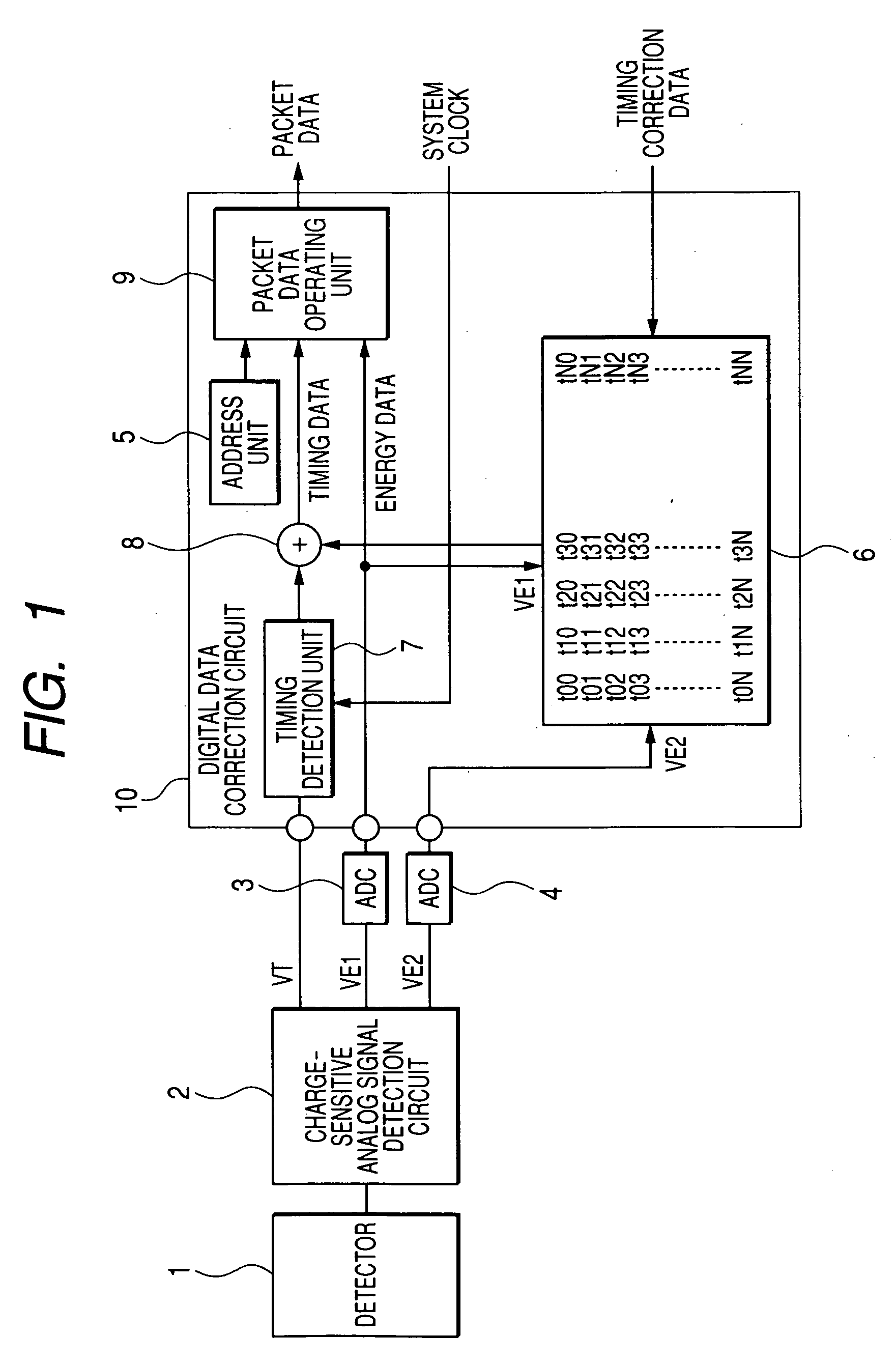

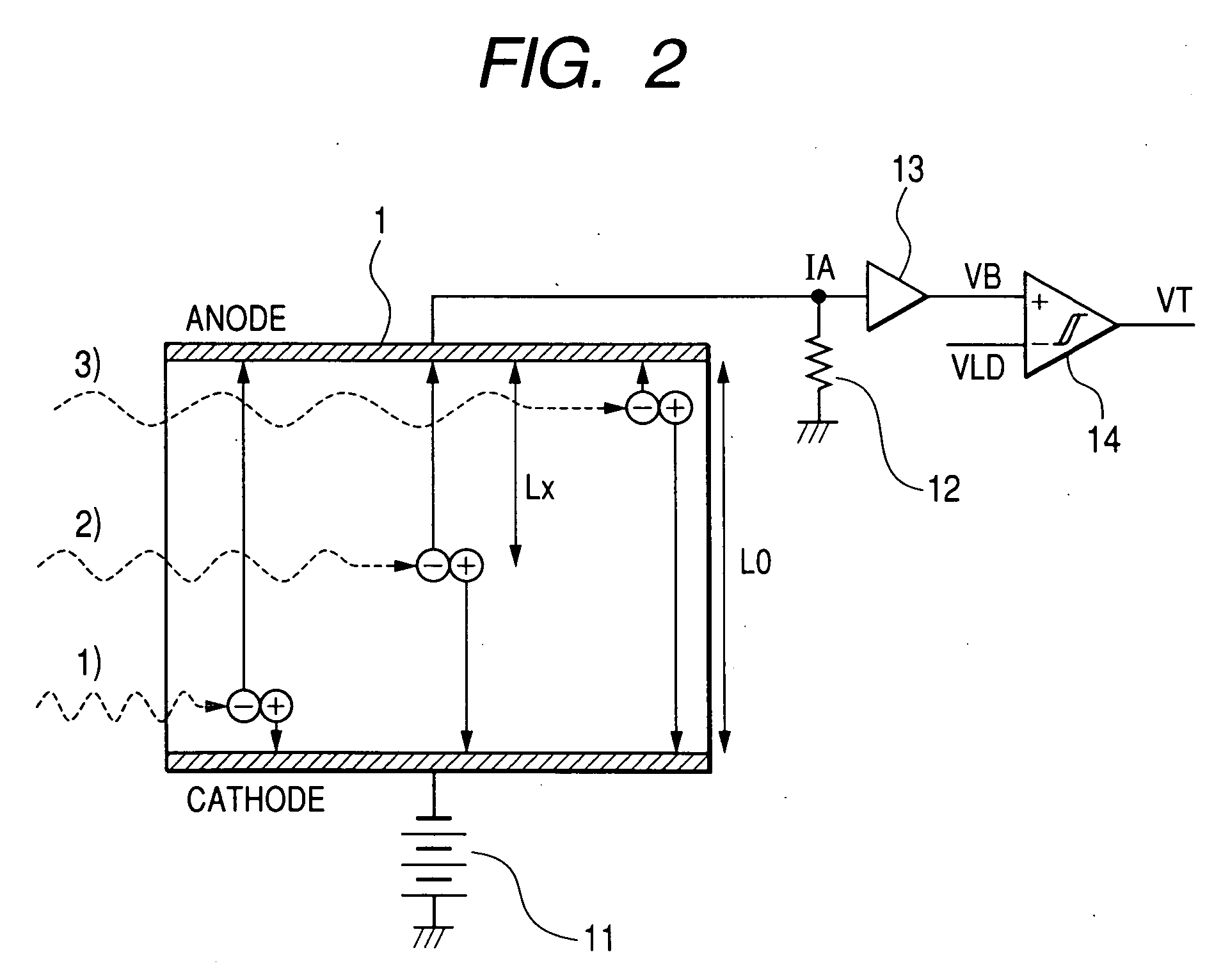

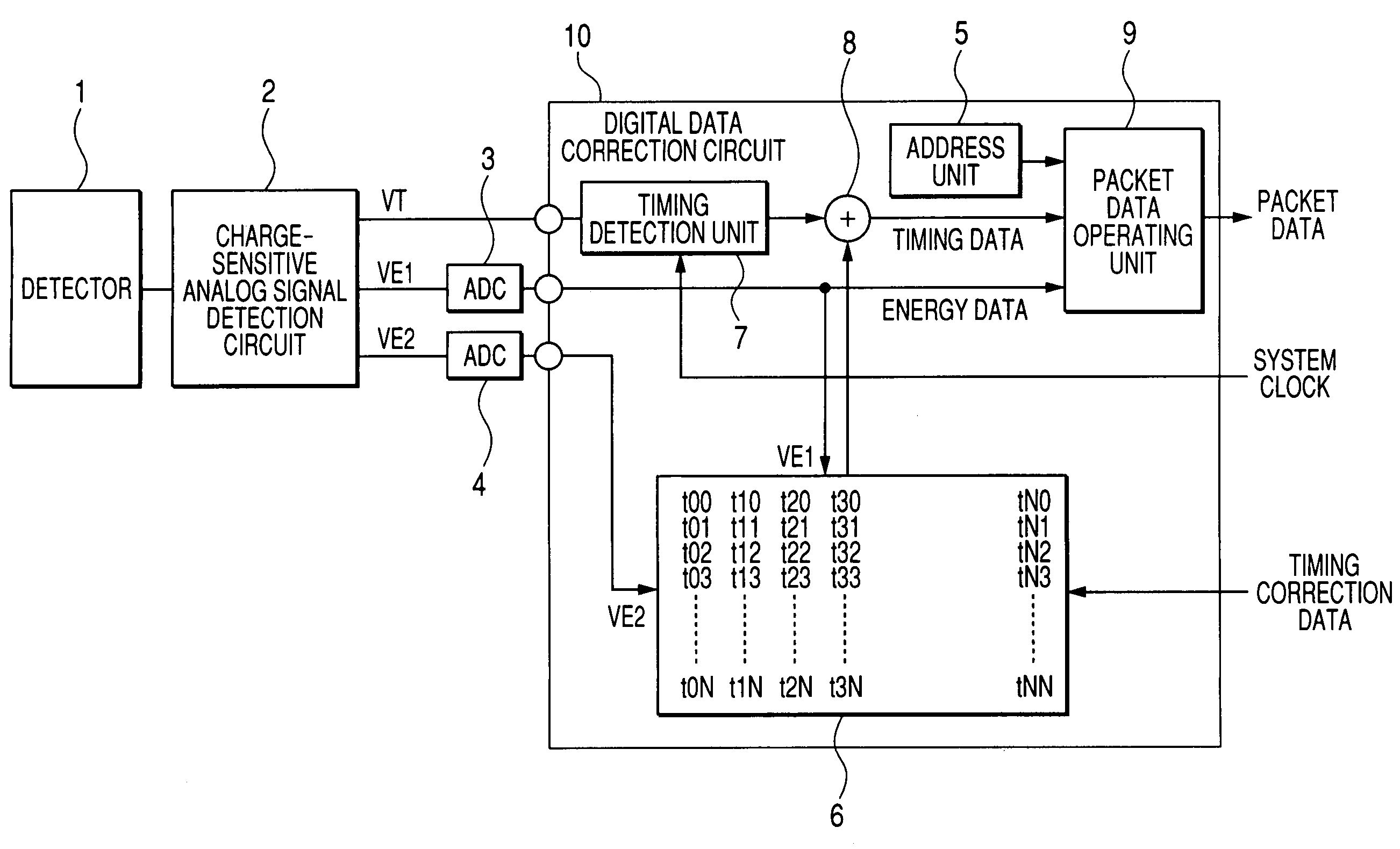

Radiation detection circuit and radiological imaging apparatus using the same

InactiveUS20070051893A1Shorten diagnostics imaging timeImprove diagnostics image contrastSolid-state devicesMaterial analysis by optical meansDiscriminatorPeak value

There is a need for high-precision detection timing in a radiological imaging apparatus using a semiconductor detector so as to decrease time variations against a noise and easily correct process variations. A radiation detection circuit includes: a semiconductor detector; charge accumulation means connected to the semiconductor detector; a circuit to discriminate timing of a signal generated from the charge accumulation means based on a specified threshold value; a shaper 1 to limit a band from the charge accumulation means using a first time constant; a shaper 2 to limit a band from the charge accumulation means using a second time constant; a circuit 1 to hold an analog peak value 1 for the shaper 1; and a circuit 2 to hold an analog peak value 2 for the shaper 2. The radiation detection circuit performs a signal process to generate timing correction data based on the analog peak values 1 and 2 and correct timing data from the timing discriminator circuit.

Owner:HITACHI LTD

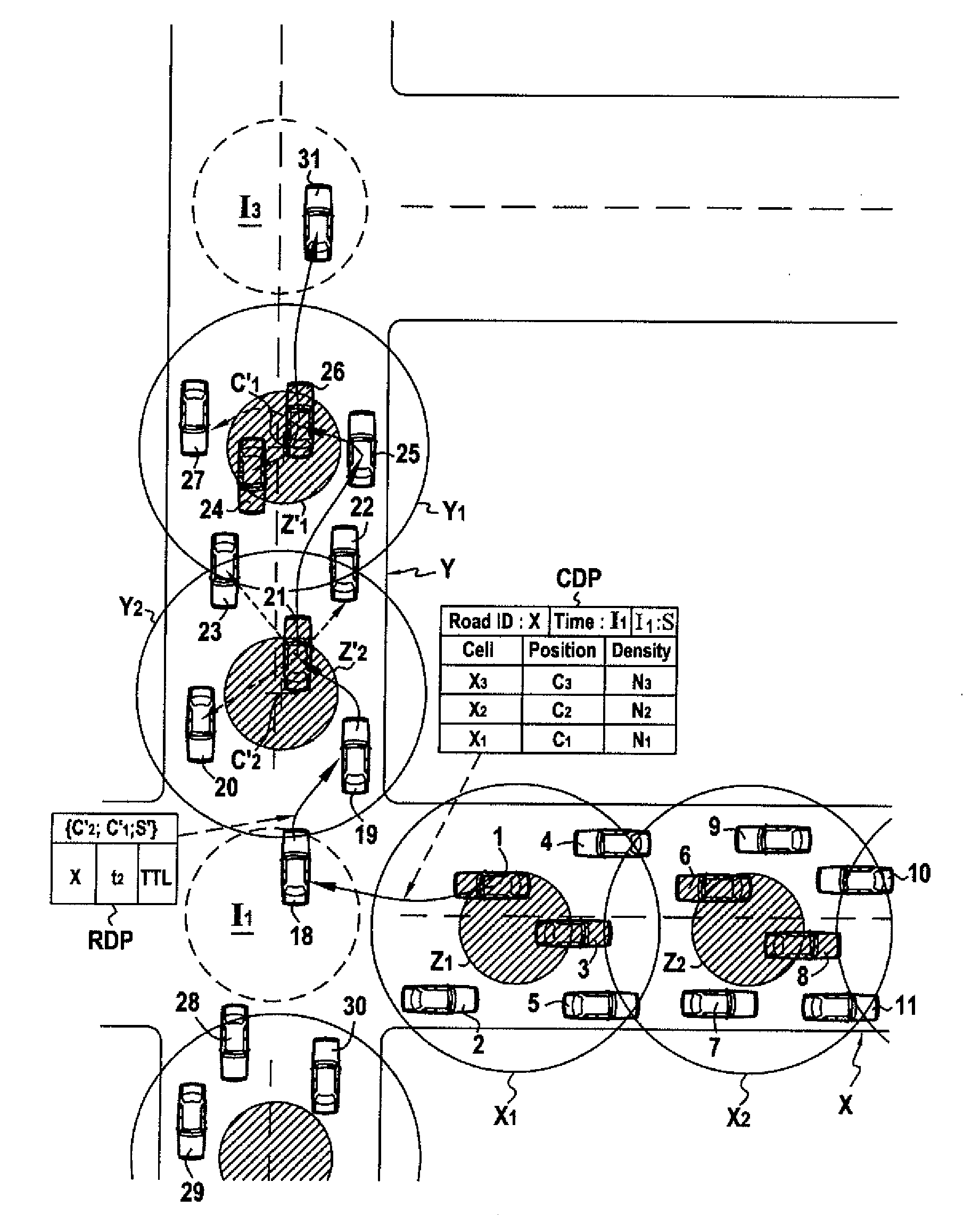

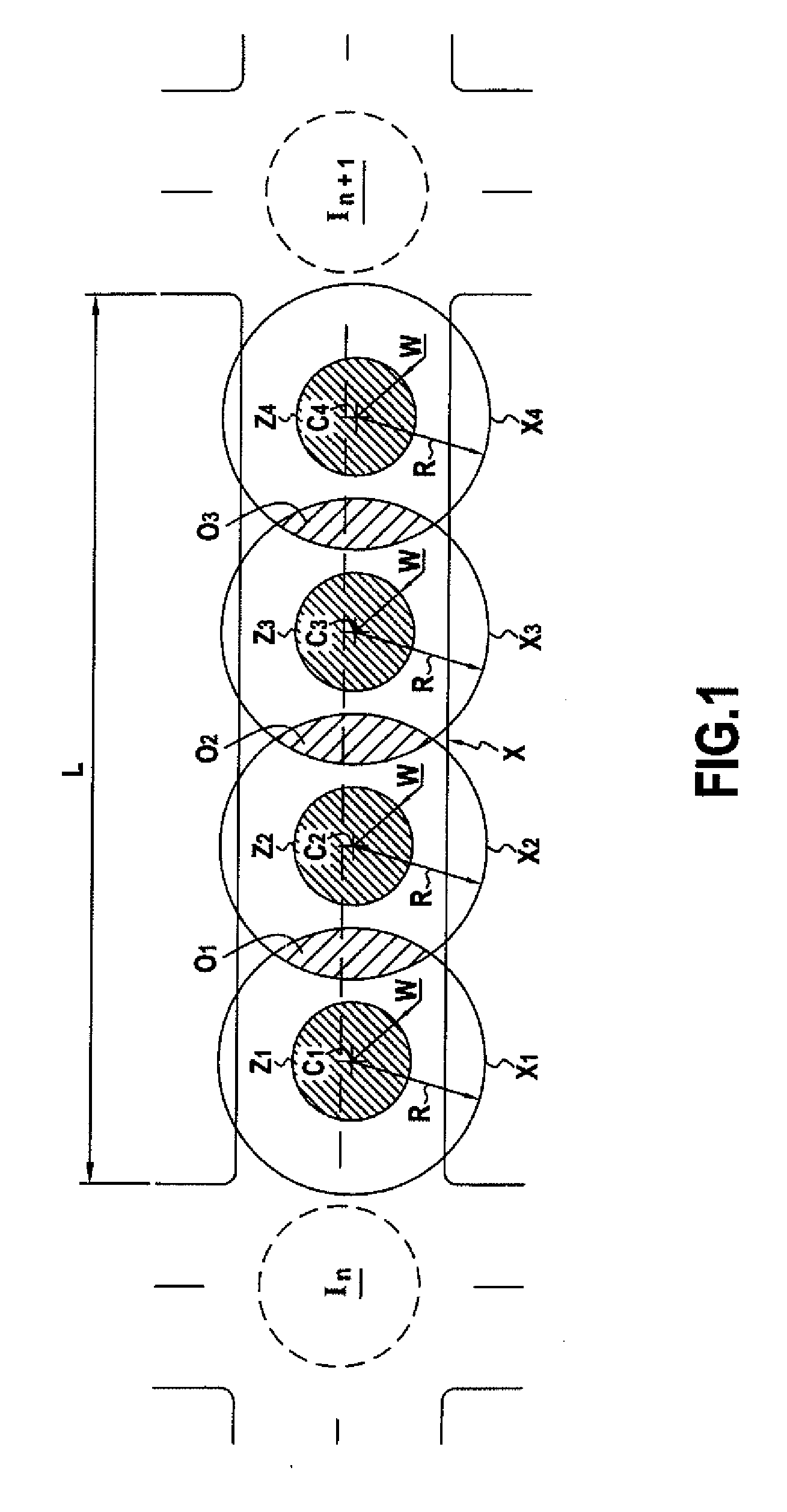

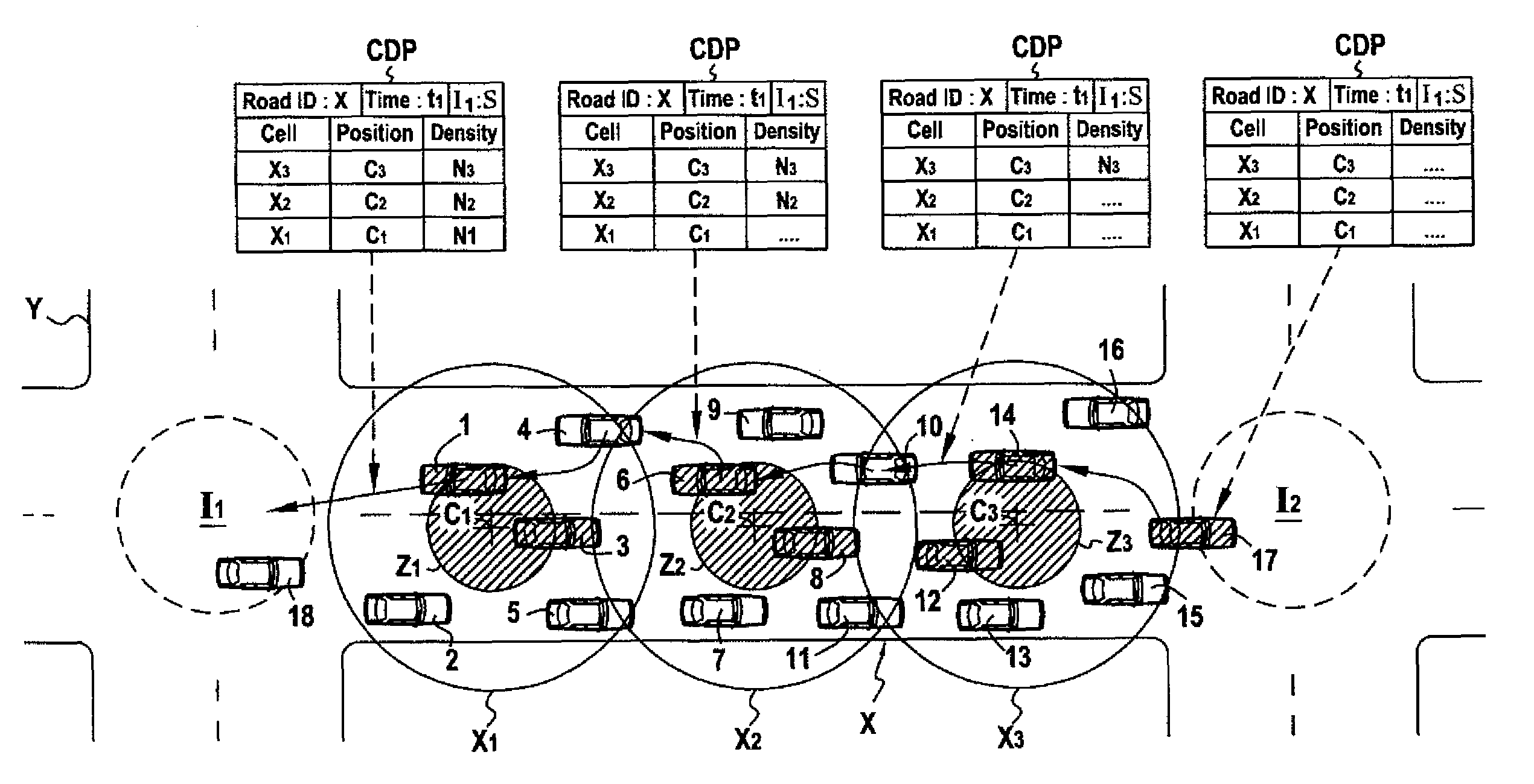

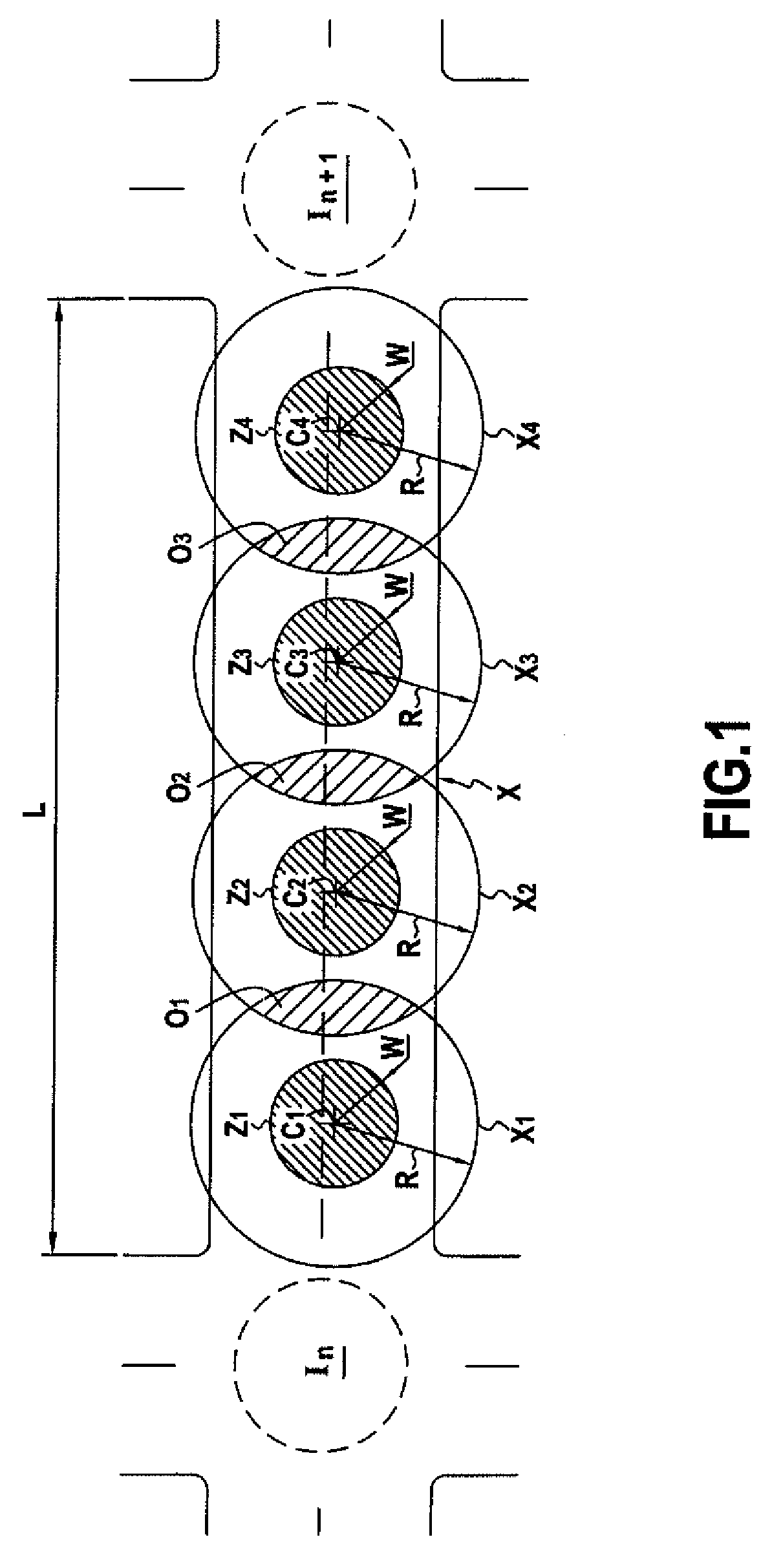

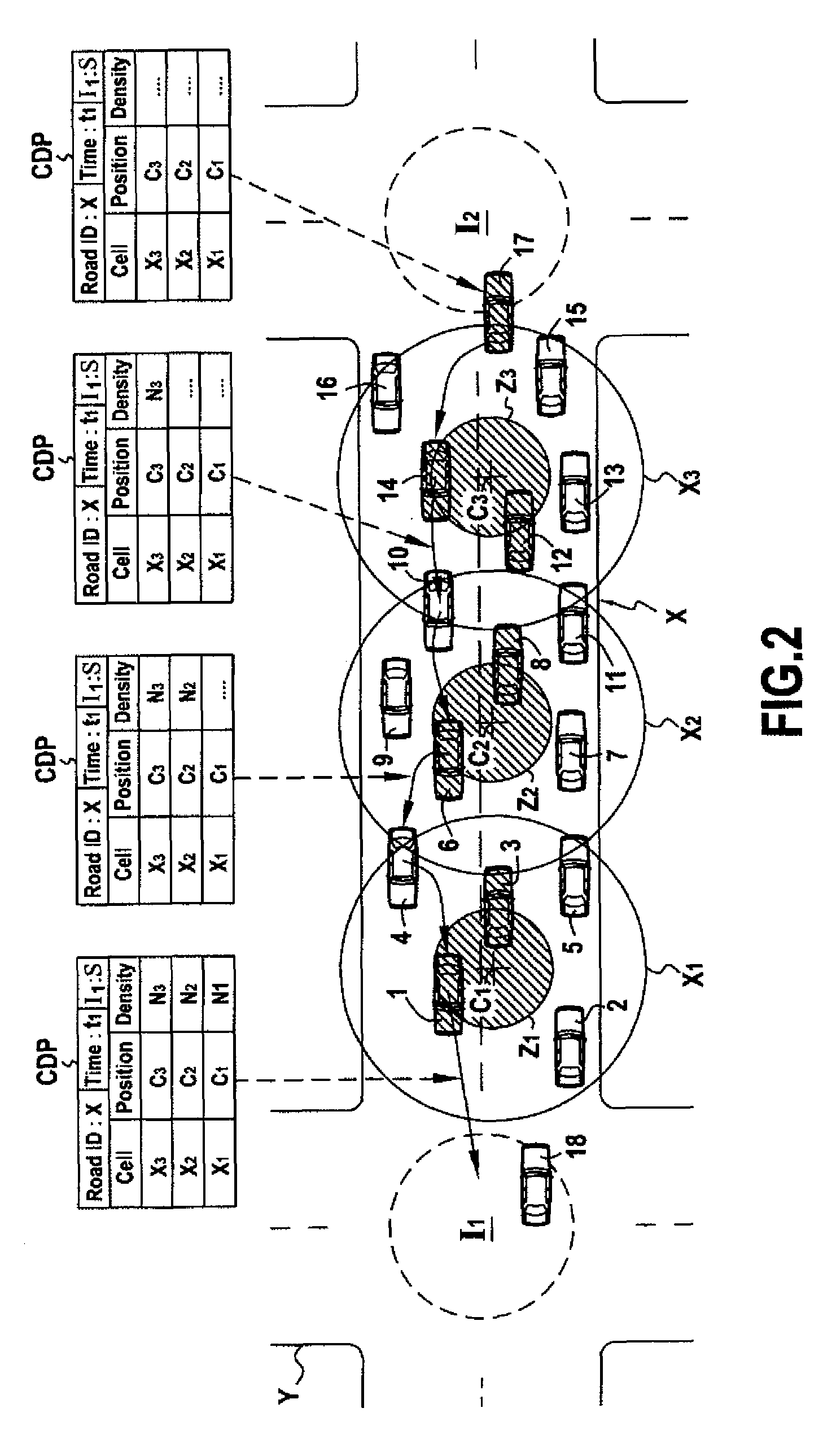

Method for Estimating and Signalling the Density of Mobile Nodes in a Road Network

ActiveUS20090323549A1Avoid OverloadingEfficient countingError preventionTransmission systemsRoad networksNetwork on

A method and an associated device for estimating the density of mobile node traffic in an ad-hoc network on the roads of a predetermined geographical network in which mobile nodes move. Each road is divided into coverage cells. For each cell, a principal mobile node located at the center of the cell counts the number of nodes in the cell, and inserts this number into a cell density packet (CDP) transmitted from cell to cell during a first stage.

Owner:FRANCE TELECOM SA

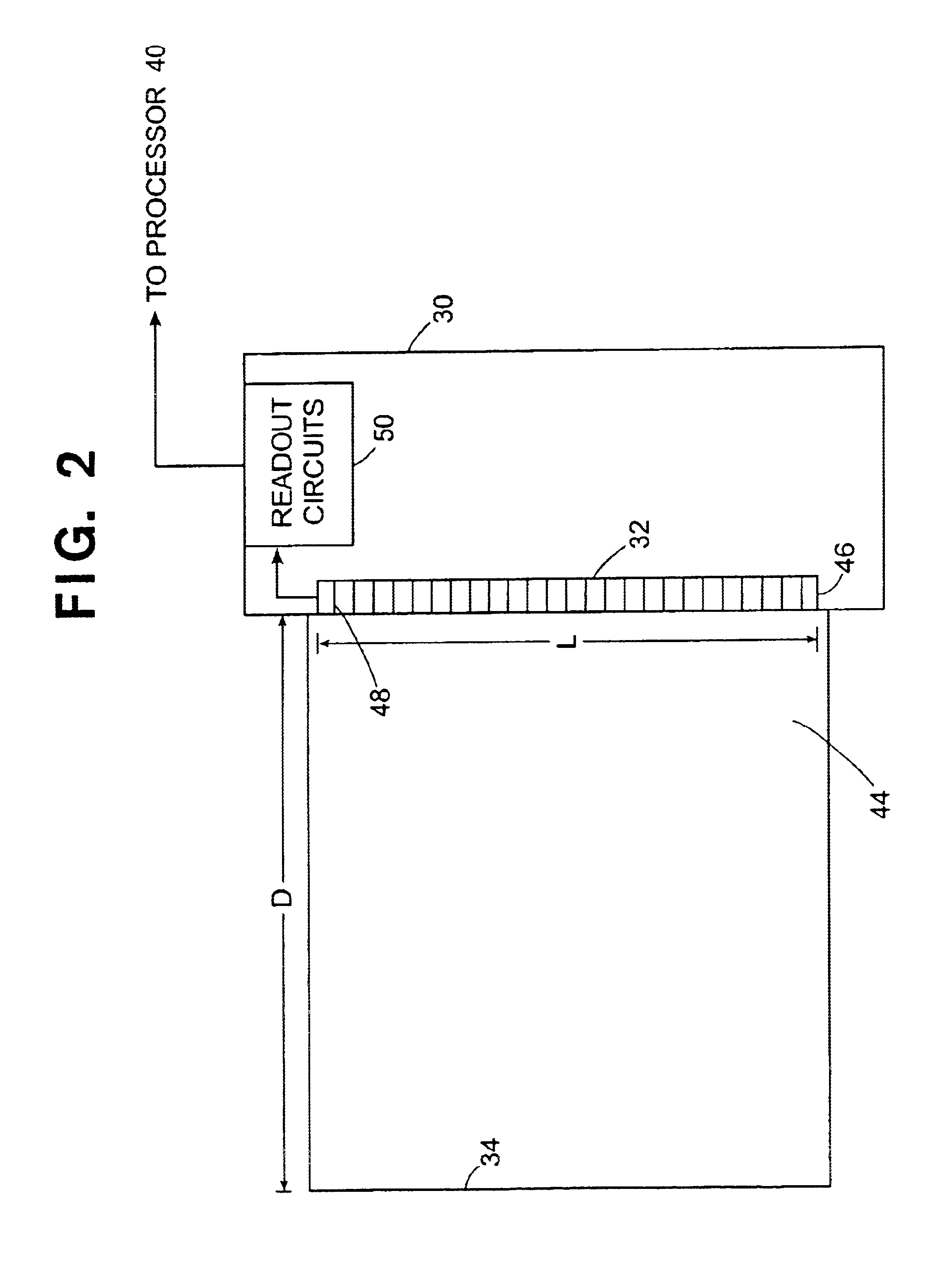

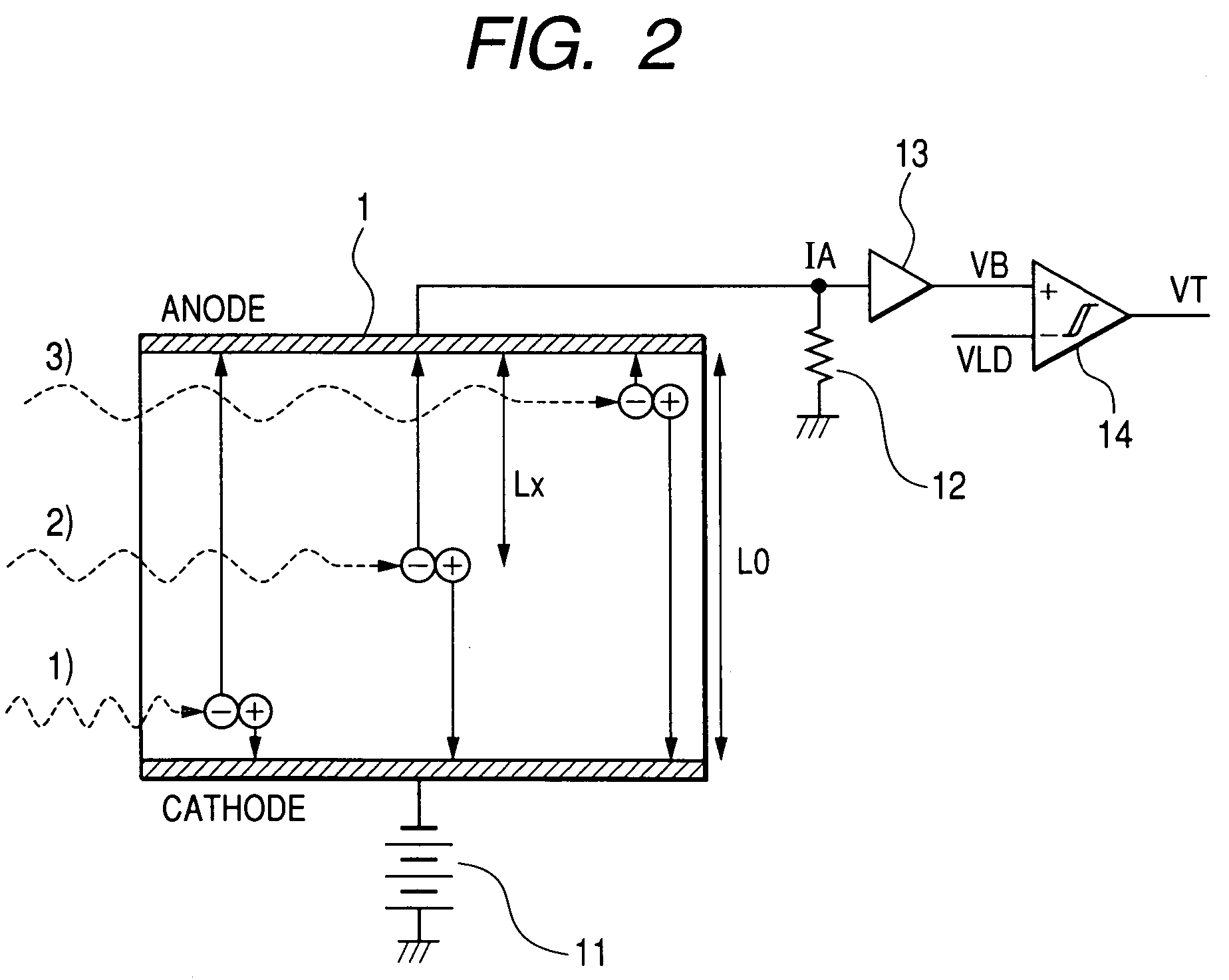

Two-dimensional radiation detector

InactiveUS6946660B2Improve efficiencyLower levelSolid-state devicesMaterial analysis by optical meansSemiconductor radiation detectorsAnode spot

A two-dimensional, pixellated, monolithic semiconductor radiation detector, in which each detector pixel is essentially a perpendicular mode detector. This is achieved by an arrangement of anode spots, one for each pixel located on the flux-exposed front surface of the detector substrate, surrounding by a cathode array preferably in the form of a network of lines, such that the field between the anodes and cathodes on this front surface has a major component in the direction parallel to the surface, and hence perpendicular to the incident photon flux. The conductivity of the substrate is high near this front surface, since this is where the highest level of absorption of photons takes place, and a significant photoconductive current is thus generated between cathodes and anodes. The conductivity is proportional to the incoming photon flux, and decays exponentially with depth into the detector. Since all of the conduction paths are in parallel to each other, the resultant conductance between each anode and its surrounding cathode is the summation of all those conductances.

Owner:GE MEDICAL SYST ISRAEL

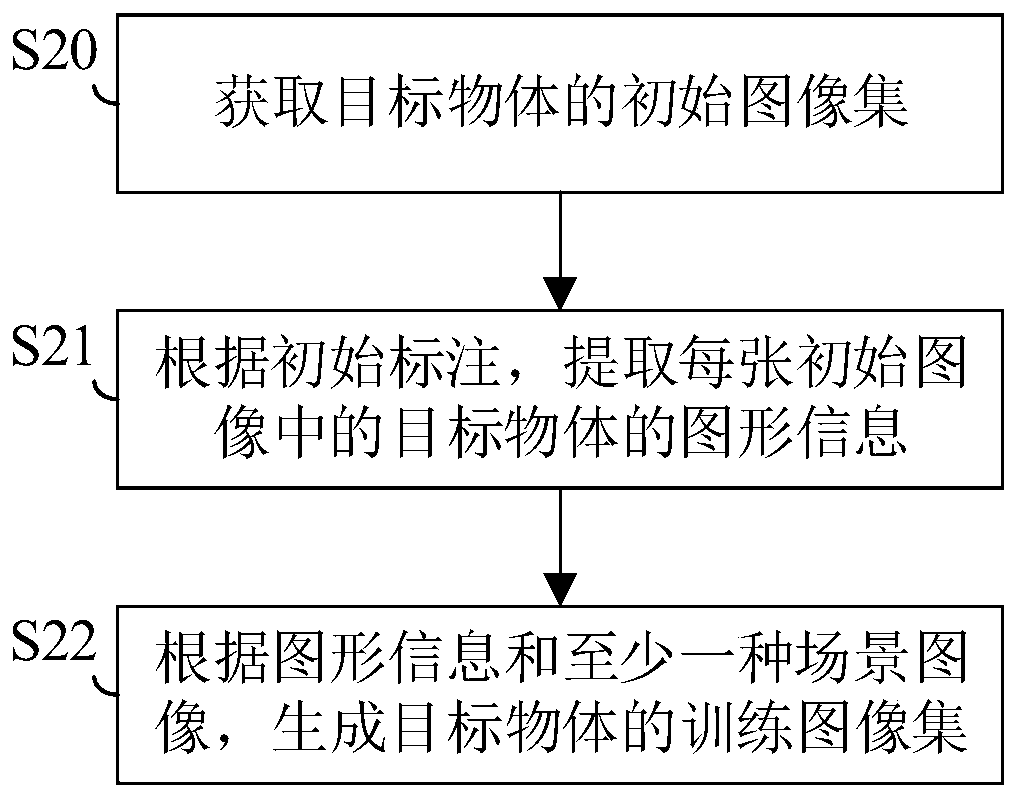

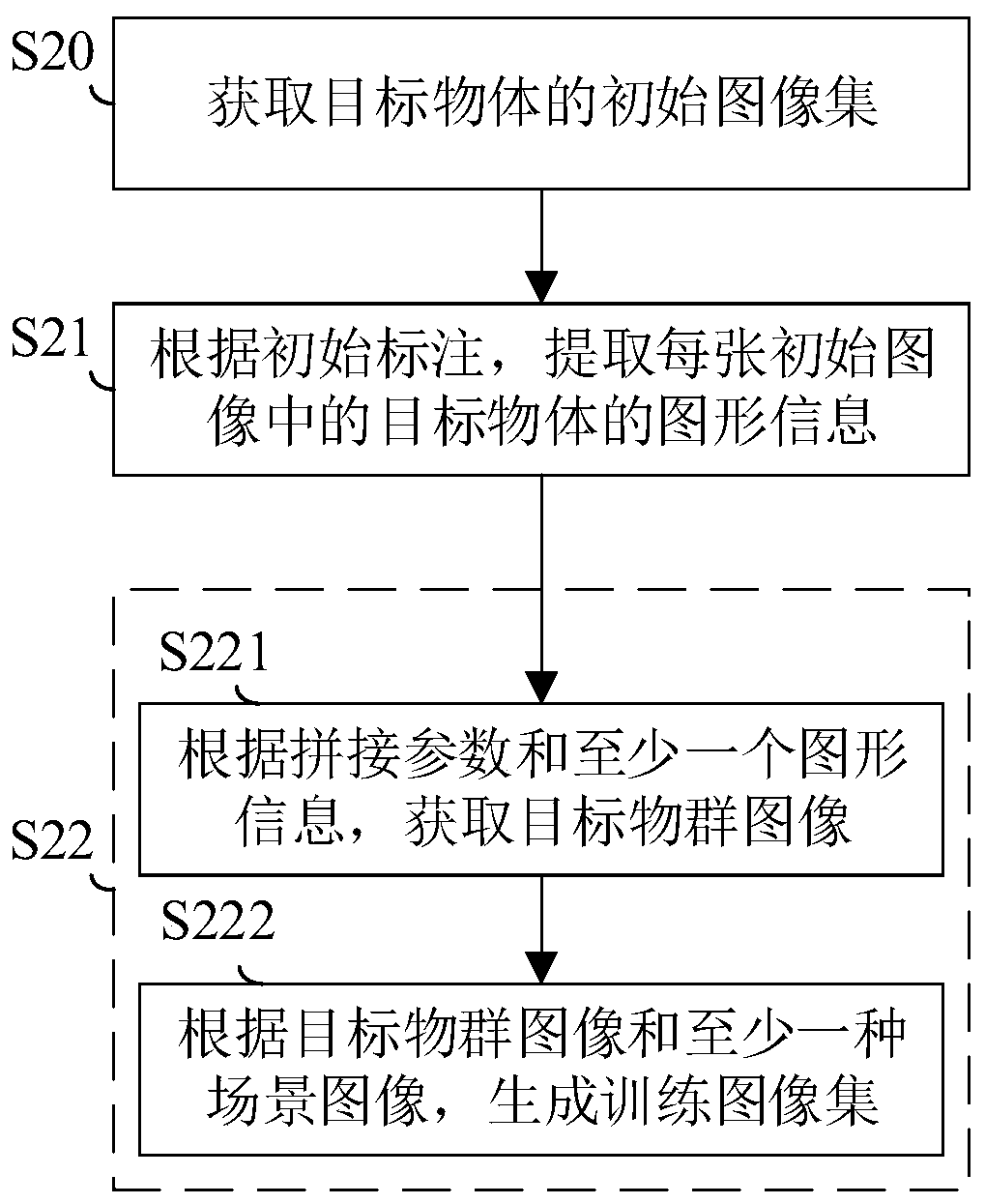

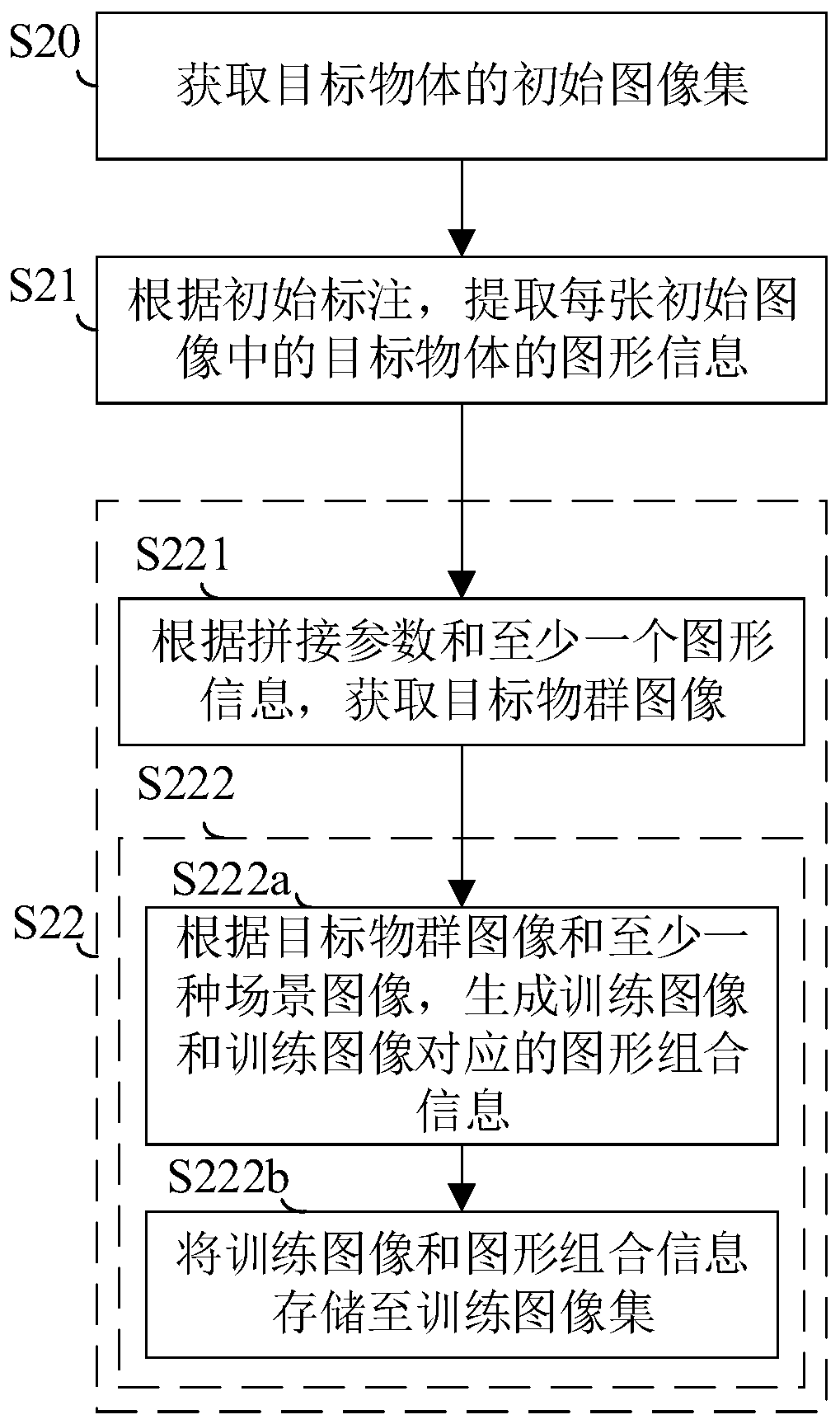

Training image acquisition method, model training method and related devices

ActiveCN110472593AReduce labeling costsImplement object countingImage enhancementImage analysisAnnotationImage acquisition

The invention provides a training image acquisition method applied to object counting, a model training method and a related device, and relates to the field of object counting. The training image acquisition method comprises the following steps: acquiring an initial image set of a target object; wherein the initial image set comprises a plurality of initial images and initial annotations corresponding to the initial images; wherein the initial annotation represents feature information of a target object in the corresponding initial image; extracting graphic information of a target object in each initial image according to the initial label; generating a training image set of the target object according to the graphic information and the at least one scene image; wherein the training imageset comprises a plurality of training images, and each training image comprises graphic information and graphic combination information of any scene image. By using the training image acquisition method provided by the invention, the marking of the training image of the target object can be realized by only needing a small amount of data marking, the marking cost of the training image is effectively reduced, and efficient object counting is realized.

Owner:重庆紫光华山智安科技有限公司

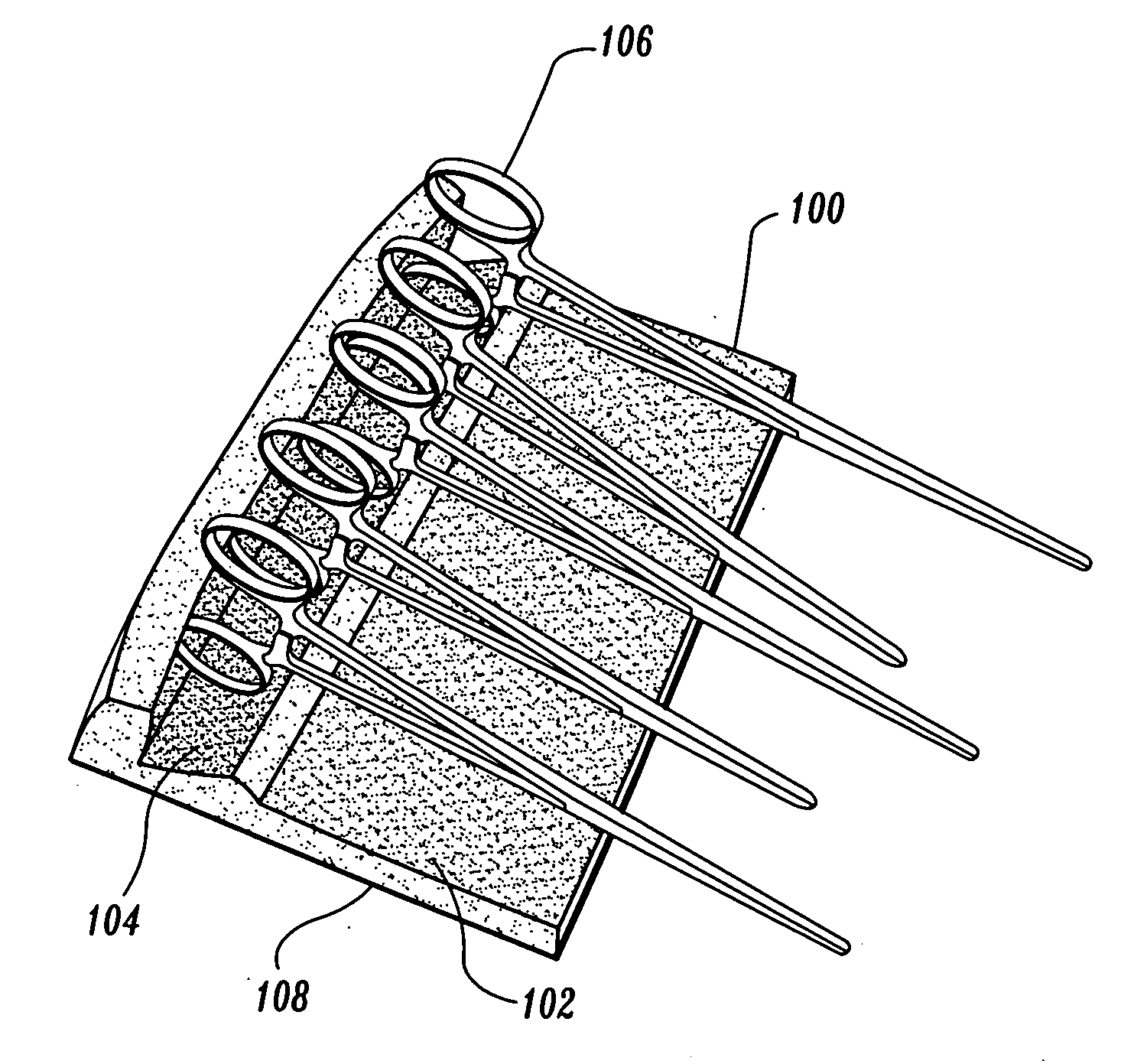

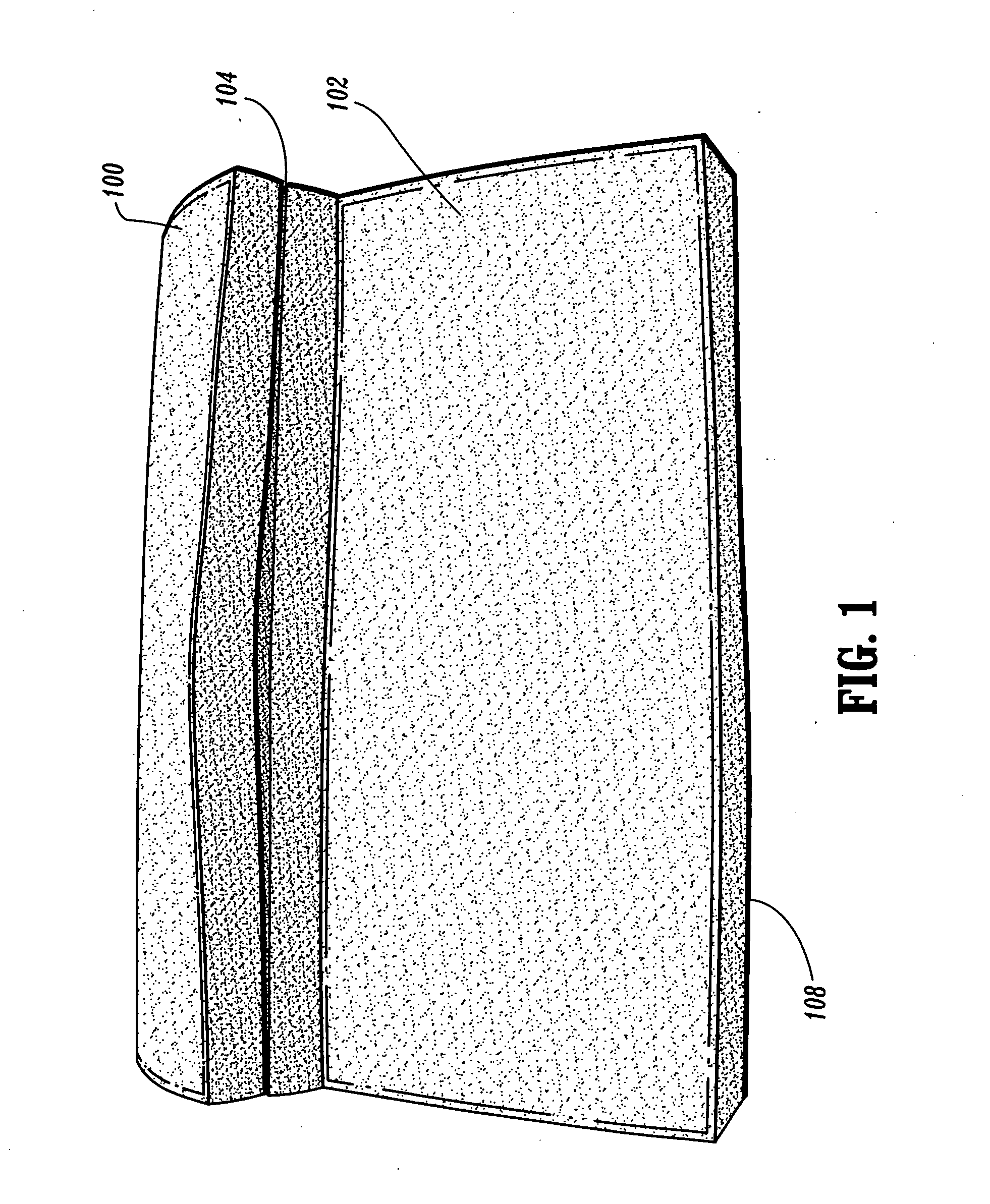

Surgical instrument organizer

InactiveUS20050061696A1Improve organizationEasy to useSurgical furnitureDispensing apparatusSurgical ManipulationEngineering

A slotted disposable foam instrument holder is provided for use in organizing surgical instruments wherein the surgical instruments are easily organized and available for efficient use during surgical operation. The inventive slotted disposable foam instrument holder provides the surgical technician with a uniform organizer that makes pre and post surgical counts accurate. The slotted nature of the organizer allows for the secure placement of surgical instruments preventing the toppling of the instruments during the surgical procedure and helps maintain the instruments in an organized and upright state.

Owner:SWANK RONALD

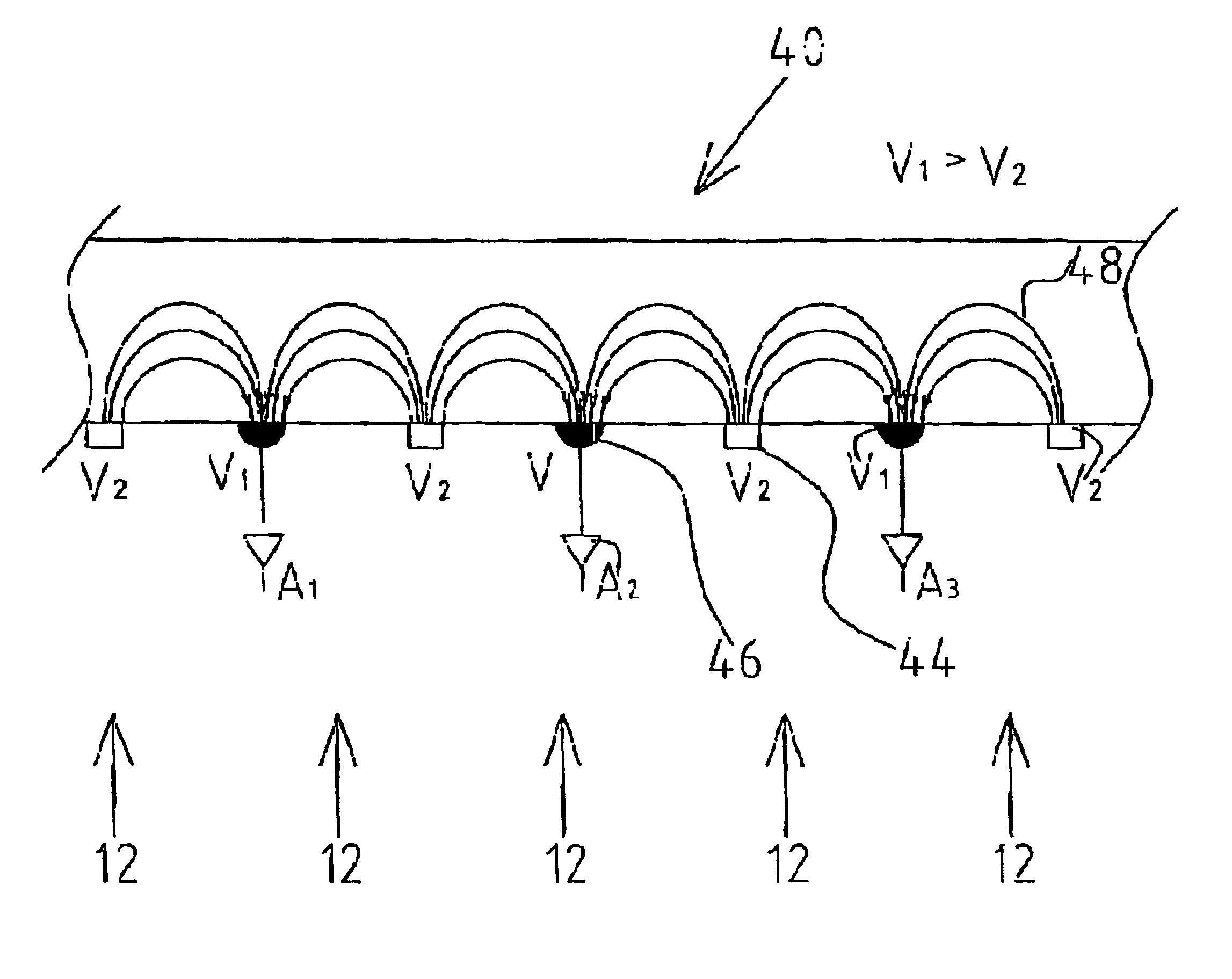

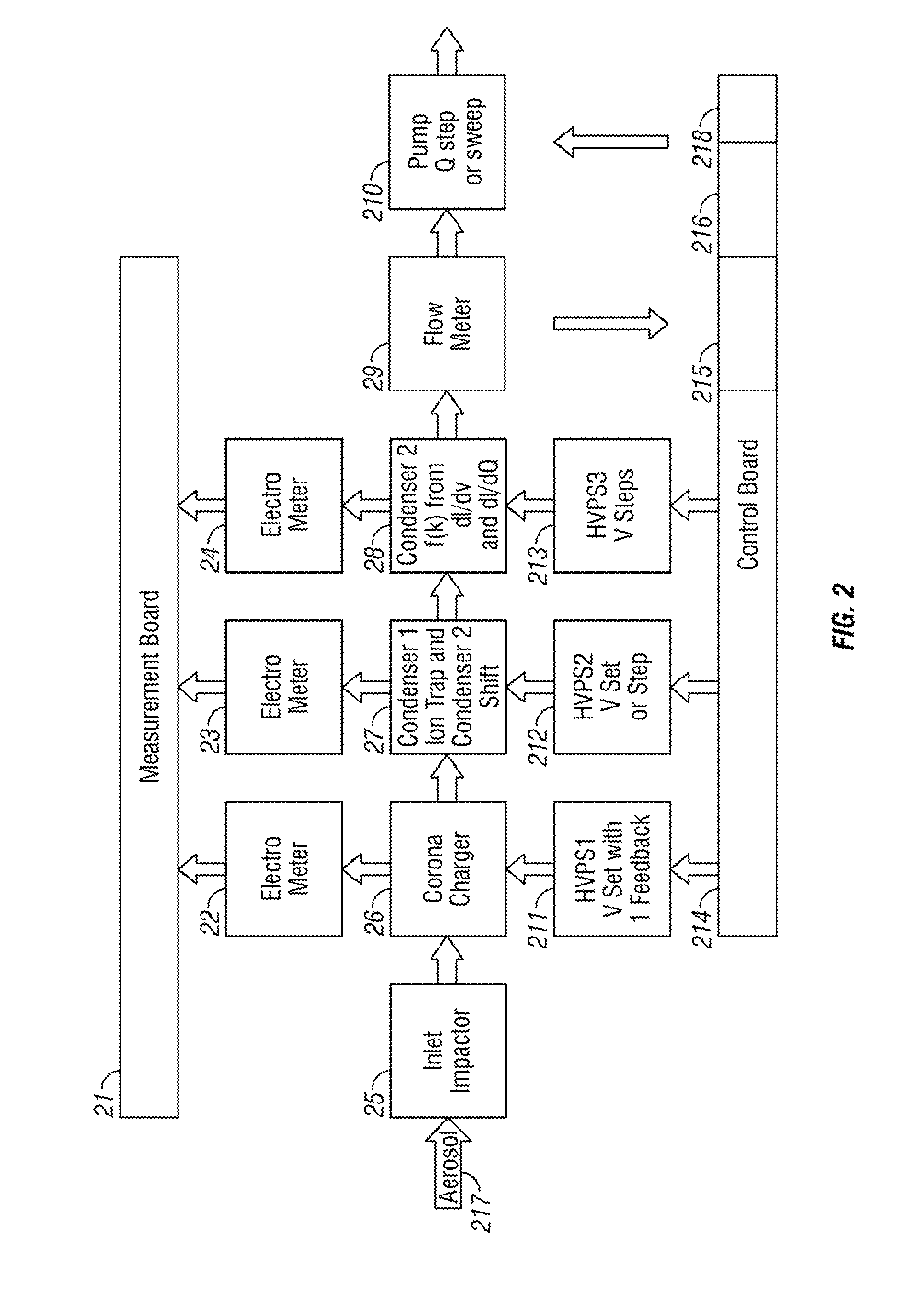

Micro-fabricated double condenser method and apparatus for the measurement of number-size distribution of airborne nano-particles

ActiveUS20110246089A1Efficient countingGuaranteed effective sizeNanoparticle analysisMaterial analysis by electric/magnetic meansNanoparticleMeasuring instrument

A micro-fabricated double condenser method and apparatus for the measurement of number-size distribution of airborne nanoparticles is provided. The invention is an instrument which can measure particle size under 100 nanometers in-situ. The present invention includes features such as a small nanoparticle airborne particulate analyzer, with a voltage-stable and feedback-controlled instrument package. The invention features also include a micro-fabricated nanoparticle charging and sorting device (NCaS). The present invention provides a portable, lightweight, and efficacious particle-sizing instrument that is able to effectively count and size nanoparticles over a wide range of operating conditions.

Owner:UNIVERSITY OF VERMONT

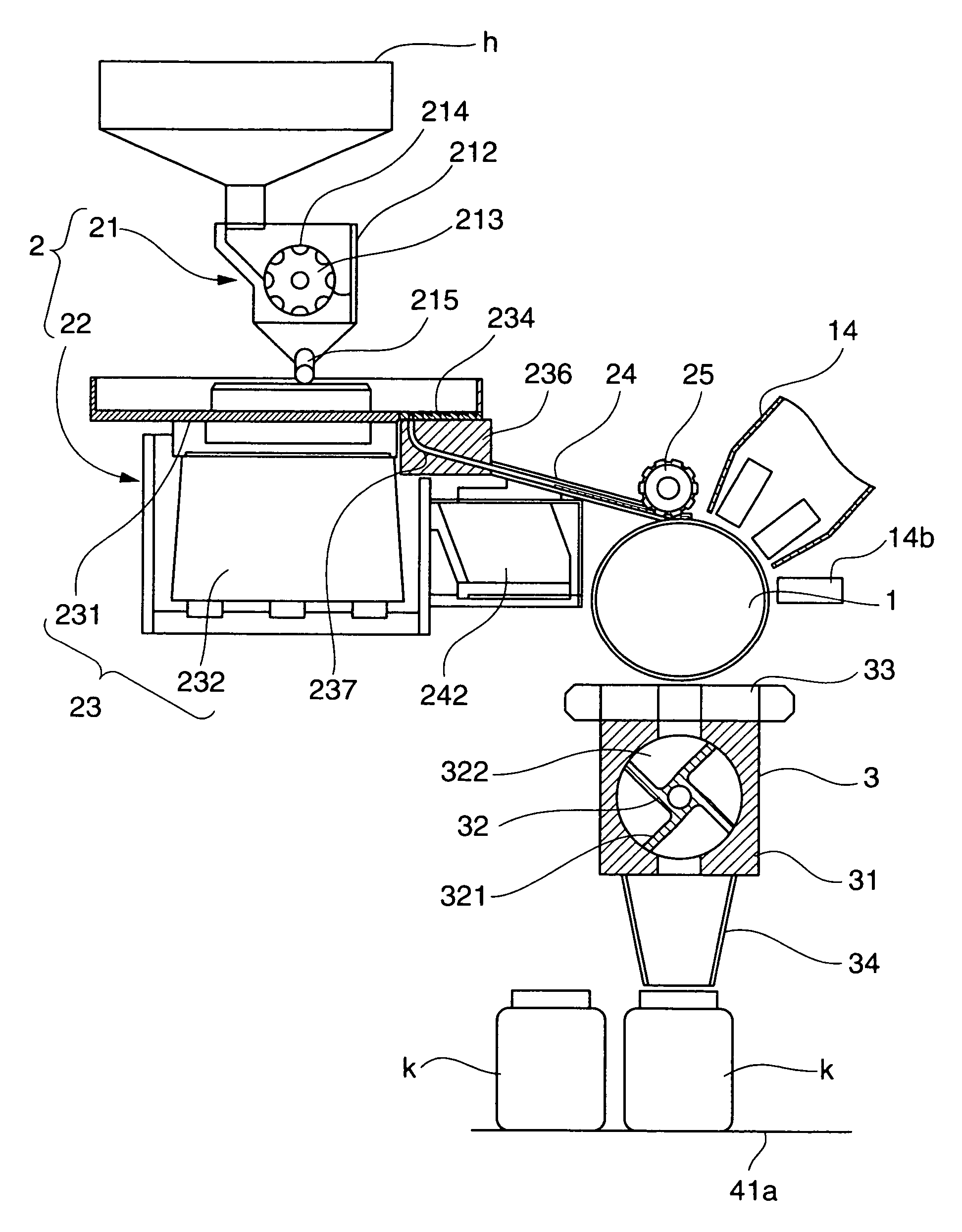

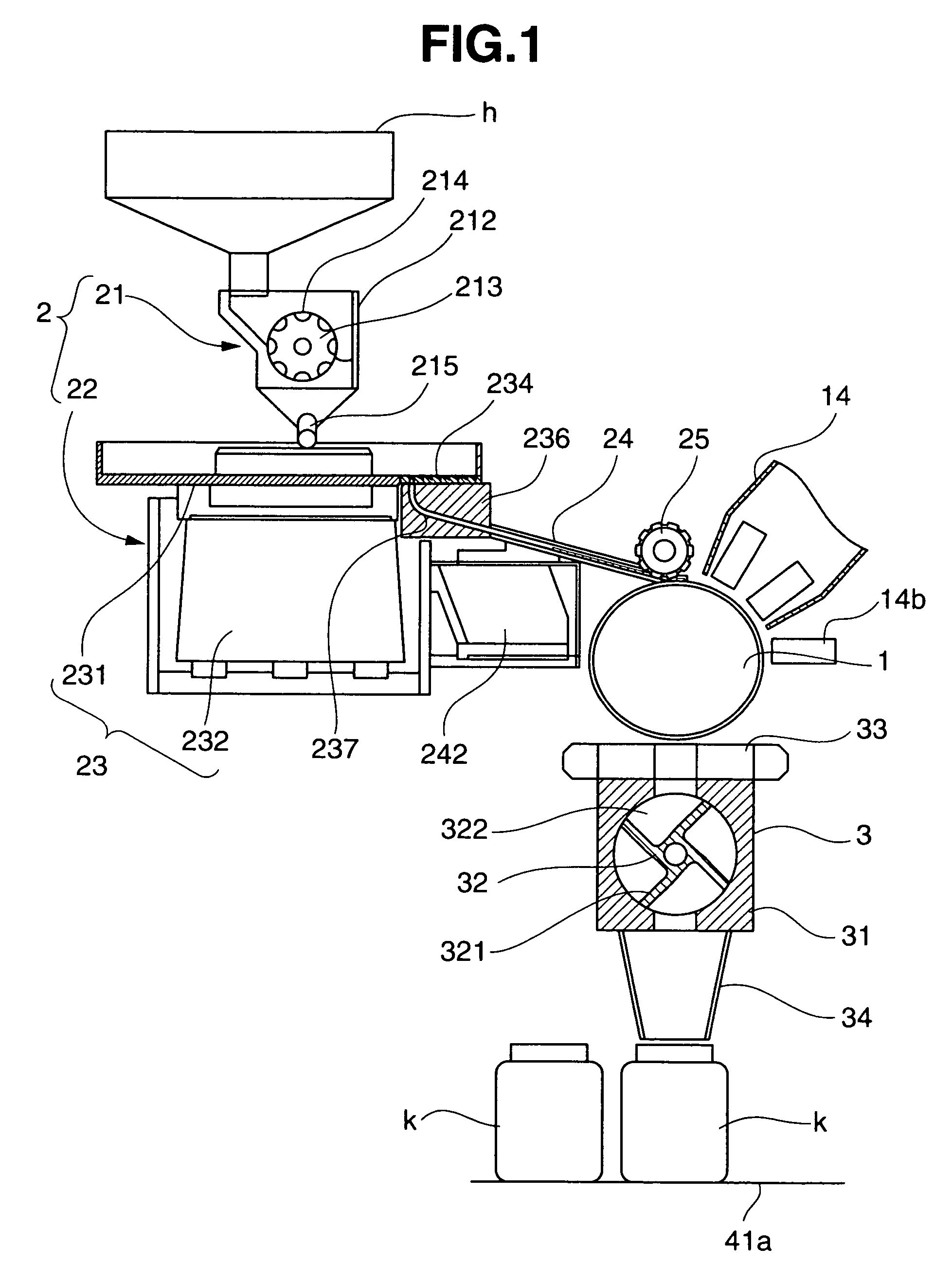

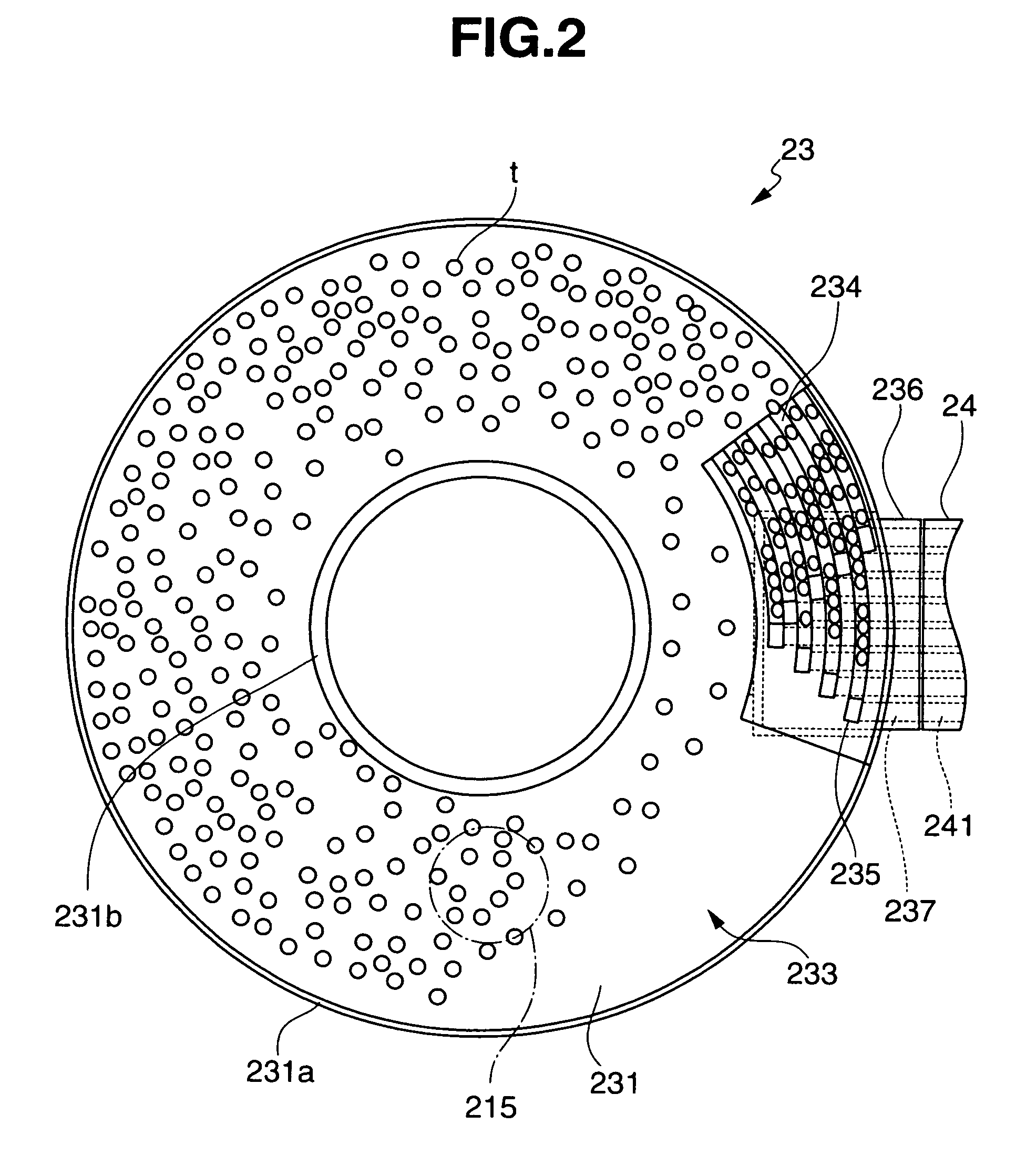

Counting and feeding device for small article

InactiveUS7004353B2Avoid problemsOptimization mechanismCoin-freed apparatus detailsCounting objects on conveyorsMechanical engineering

A counting and feeding apparatus for small article, characterized in that tablets are fed intermittently from a feeding means (2) to the outer peripheral surface of a transfer drum (1) multiple pieces at a time and suckingly held on the outer peripheral surface of the transfer drum (1), a plurality rows of tablets orderly arranged along the circumferential direction of the drum are formed on the outer peripheral surface of the transfer drum (1) and transferred, one tablet is inputted from each of the rows into a temporary reservation means at a specified transfer position, and these steps are repeated specified times, whereby the tablets can be counted for each row, and the specified quantity of tablets can be reserved in the temporary reservation means and then fed to containers or a packing mechanism section.

Owner:SHIONOGI QUALICAPS

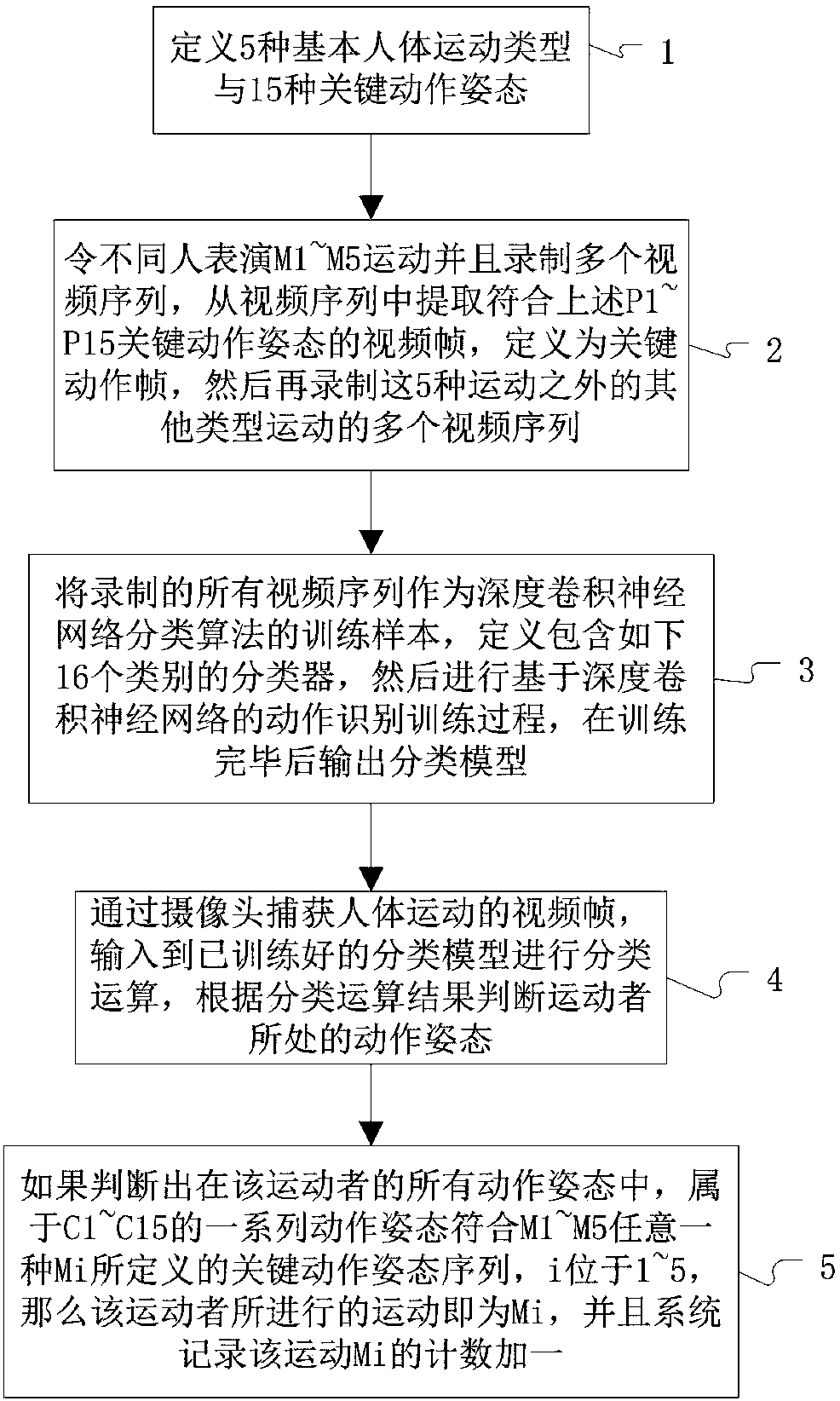

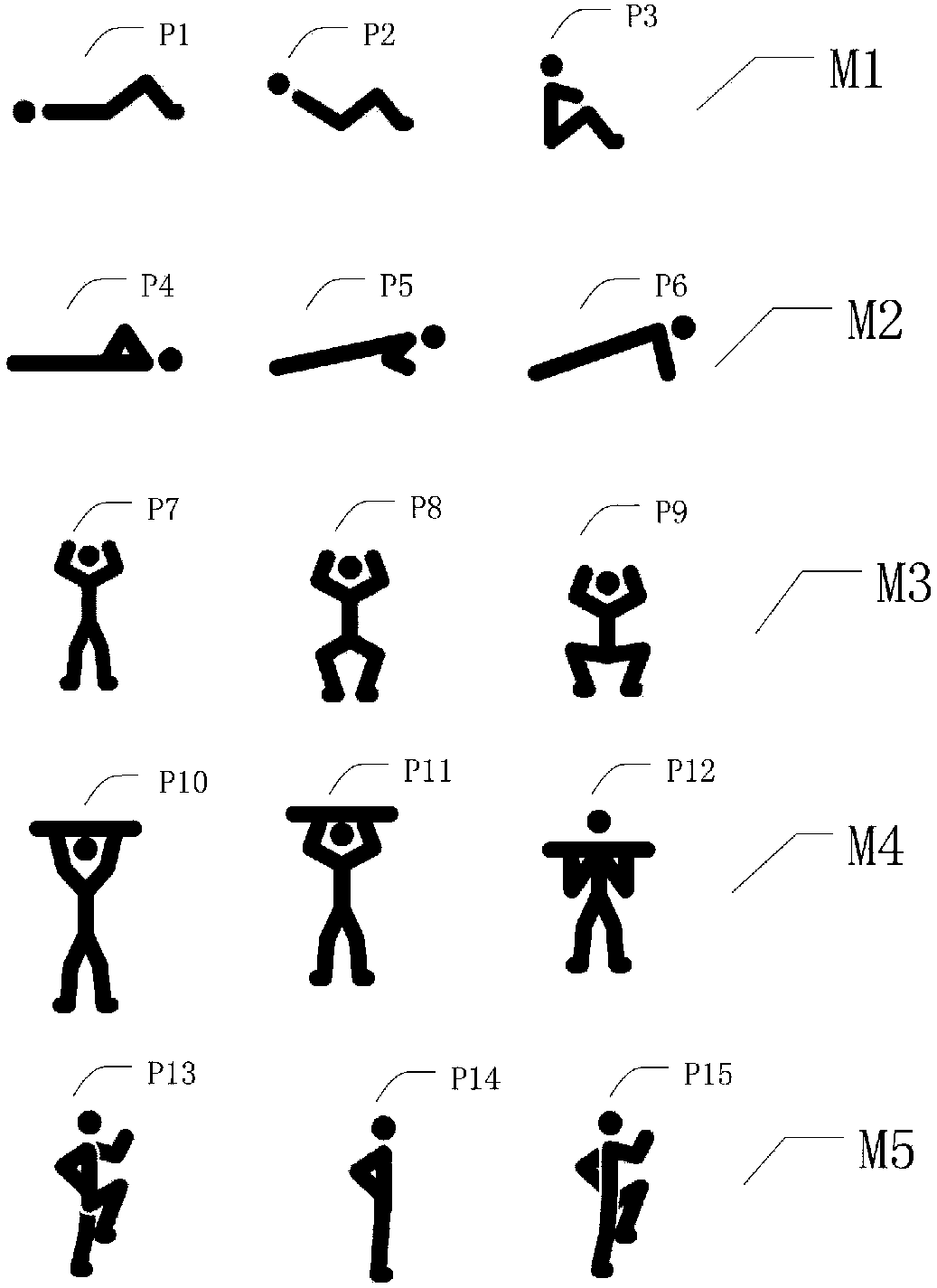

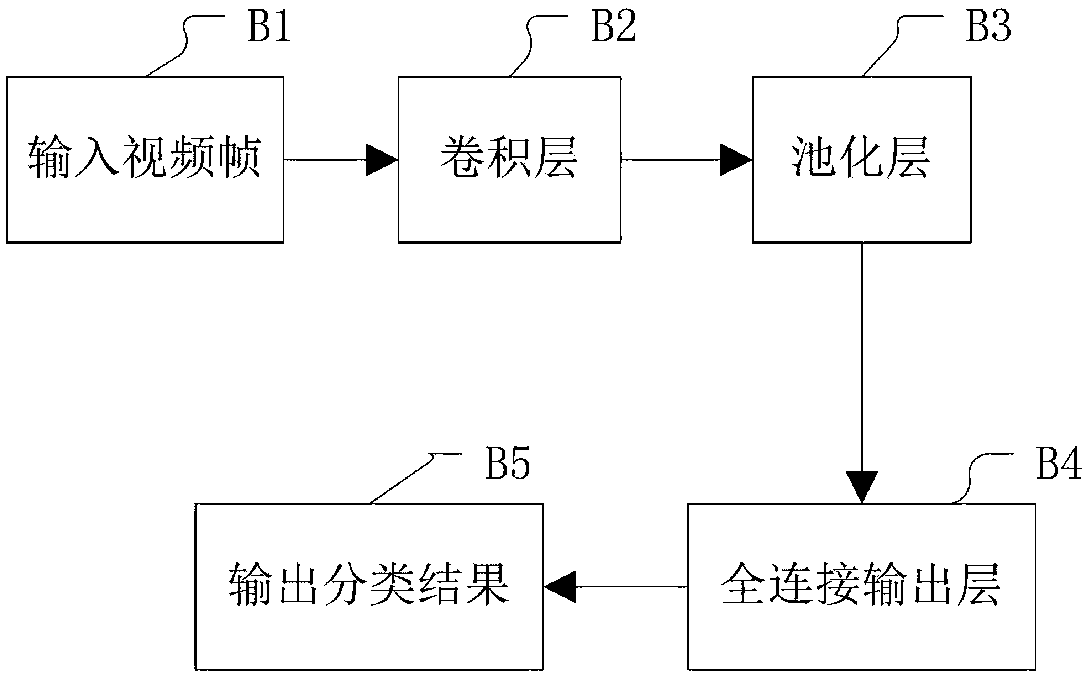

Human motion counting method based on deep convolutional neural network

InactiveCN110163038AFocus on fitnessEfficient countingCharacter and pattern recognitionNeural architecturesDistractionVideo sequence

The invention discloses a human motion counting method based on a deep convolutional neural network. The method comprises the following steps: defining five basic human motion types and three key motion posture sequences of each motion type; enabling different people to perform five motions and recording video sequences of the five motions and other types of motions, taking the video sequences astraining samples, combining the training samples with 16 types of classifiers, performing an action recognition training process based on a deep convolutional neural network, and outputting a classification model after training is completed; capturing a video frame of human motion through a camera; inputting the data into a trained classification model for classification operation; judging the action posture of the exerciser and the type of the performed exercise according to the classification operation result, and adding one to the belonging exercise count. Five kinds of motion can be automatically and efficiently identified and counted, an exerciser can do body-building motion without distractions, the identification process of a motion video is calibrated in a standard mode, and nonstandard motion counting is eliminated.

Owner:NANJING SILICON INTELLIGENCE TECH CO LTD

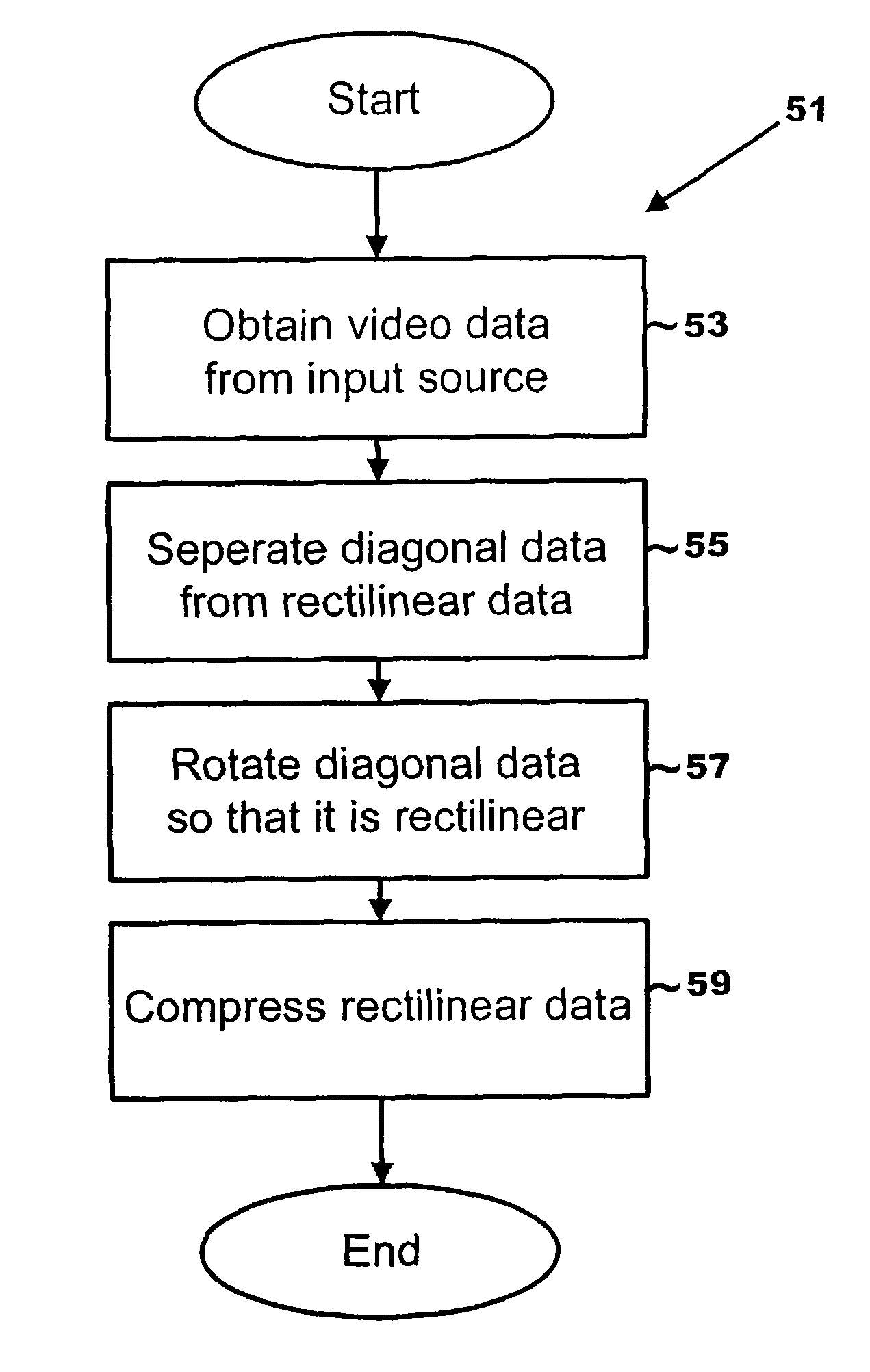

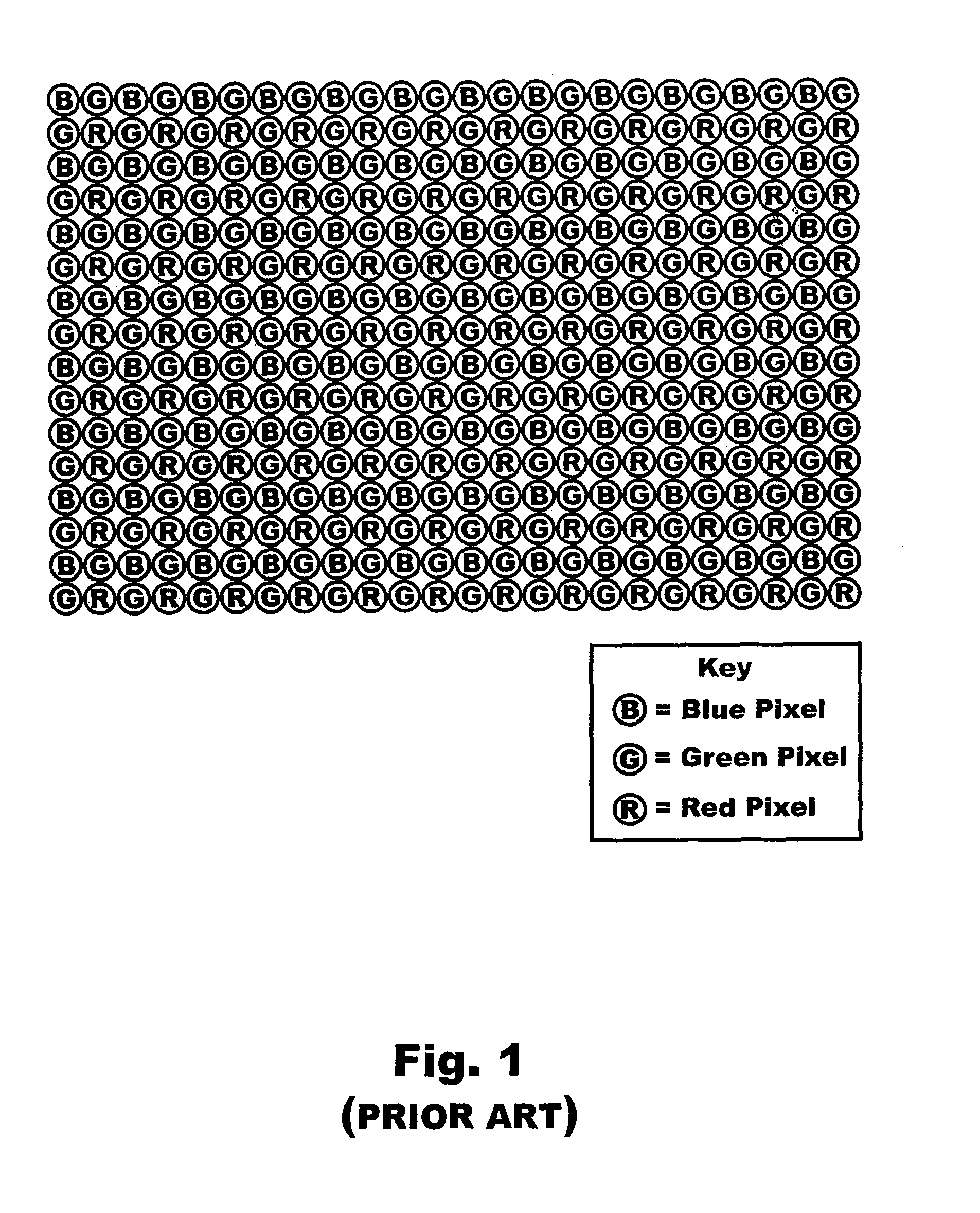

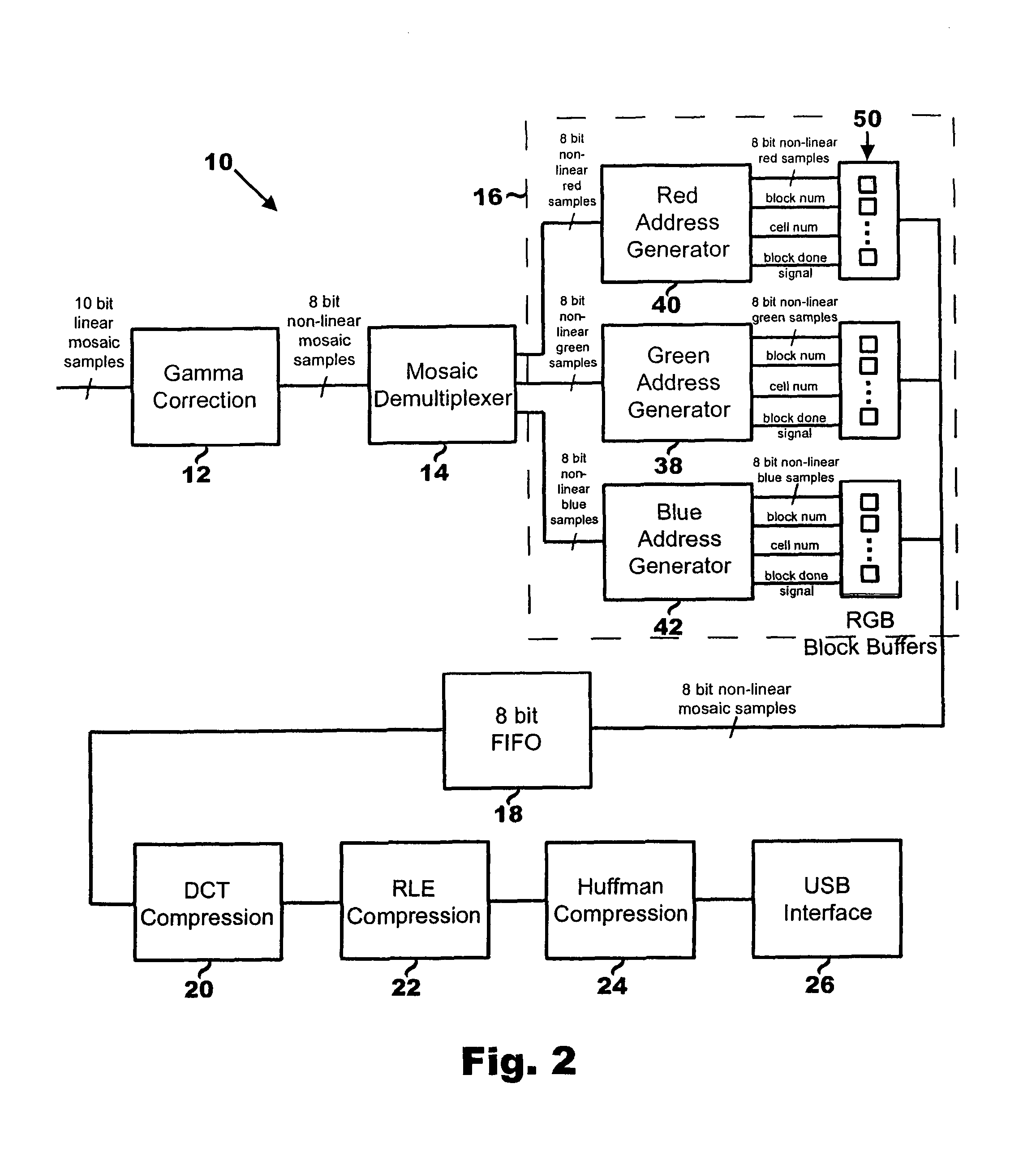

Method and apparatus for video data compression

InactiveUS8179971B1Efficient countingColor television with pulse code modulationColor television with bandwidth reductionData compressionComputer graphics (images)

A method for diagonal processing of video data includes separating diagonally arranged data from rectilinearly arranged data in a video stream, rotating the diagonally arranged data to a rectilinear position; and compressing the rotated diagonally arranged data by a rectilinear compression algorithm. Alternatively stated, the method includes recognizing diagonally arranged data in a video stream, processing the diagonally arranged data into rectilinear data, and compressing the rectilinear data by a rectilinear compression algorithm. An apparatus for diagonal processing of video data includes a demultiplexer receptive to a video stream and developing a plurality of separated color planes, at least one of which is a rectilinear color plane and at least one of which is a rotated color plane, a number of address generators associated with the plurality of color planes, wherein an address generator associated with the rotated color plane is operative to rotate the rotated color plane to a rectilinear position; and a data compressor receptive to the address generators and operative to compress the plurality of color planes with a rectilinear compression algorithm.

Owner:DBEZ FIRENZE LLC

Method for estimating and signalling the density of mobile nodes in a road network

ActiveUS8208382B2Efficient countingReliable estimateError preventionFrequency-division multiplex detailsNetwork onRoad networks

A method and an associated device for estimating the density of mobile node traffic in an ad-hoc network on the roads of a predetermined geographical network in which mobile nodes move. Each road is divided into coverage cells. For each cell, a principal mobile node located at the center of the cell counts the number of nodes in the cell, and inserts this number into a cell density packet (CDP) transmitted from cell to cell during a first stage.

Owner:FRANCE TELECOM SA

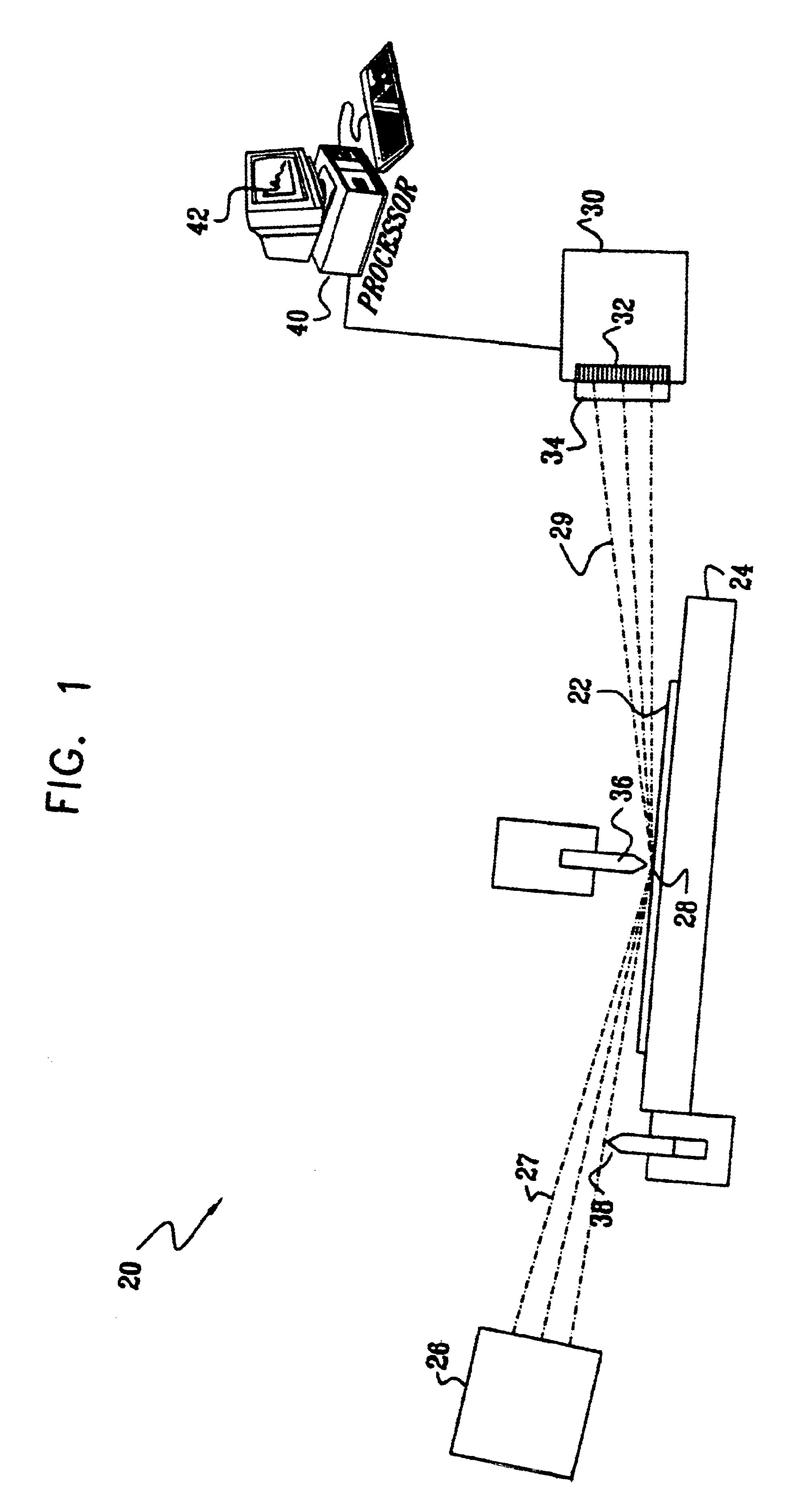

XRR detector readout processing

InactiveUS6895071B2Improve spatial resolutionImprove dynamic rangeX-ray spectral distribution measurementHandling using diaphragms/collimetersFluenceReflectometry

Reflectometry apparatus includes a radiation source, adapted to irradiate a sample with radiation over a range of angles relative to a surface of the sample, and a detector assembly, positioned to receive the radiation reflected from the sample over the range of angles and to generate a signal responsive thereto. A shutter is adjustably positionable to intercept the radiation, the shutter having a blocking position, in which it blocks the radiation in a lower portion of the range of angles, thereby allowing the reflected radiation to reach the array substantially only in a higher portion of the range, and a clear position, in which the radiation in the lower portion of the range reaches the array substantially without blockage.

Owner:BRUKER TECH LTD

Two-dimensional radiation detector

InactiveUS20050242292A1Improve efficiencyLower levelElectric discharge tubesPhotometrySemiconductor radiation detectorsAnode spot

A two-dimensional, pixellated, monolithic semiconductor radiation detector, in which each detector pixel is essentially a perpendicular mode detector. This is achieved by an arrangement of anode spots, one for each pixel located on the flux-exposed front surface of the detector substrate, surrounding by a cathode array preferably in the form of a network of lines, such that the field between the anodes and cathodes on this front surface has a major component in the direction parallel to the surface, and hence perpendicular to the incident photon flux. The conductivity of the substrate is high near this front surface, since this is where the highest level of absorption of photons takes place, and a significant photoconductive current is thus generated between cathodes and anodes. The conductivity is proportional to the incoming photon flux, and decays exponentially with depth into the detector. Since all of the conduction paths are in parallel to each other, the resultant conductance between each anode and its surrounding cathode is the summation of all those conductances.

Owner:ORBOTECH LTD

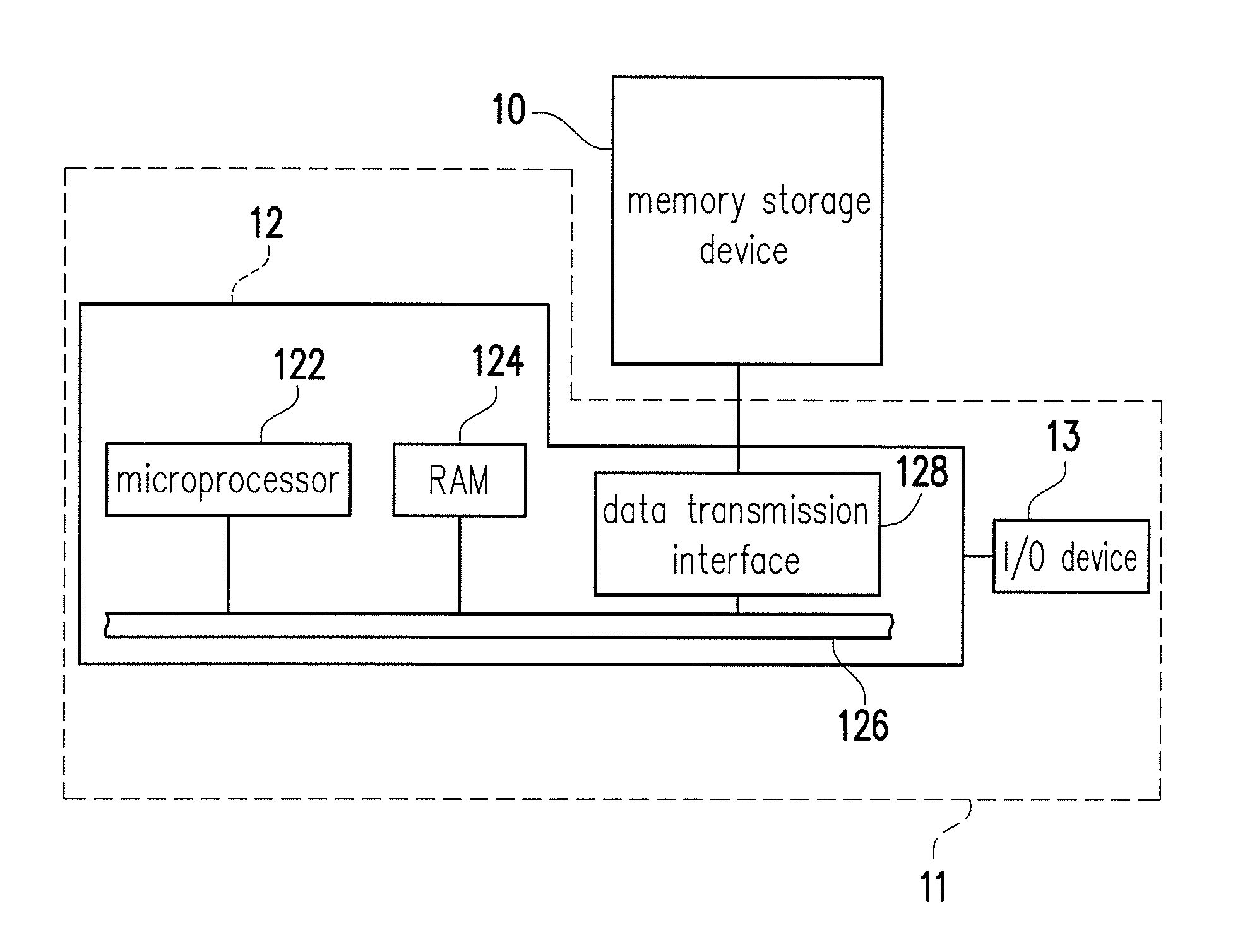

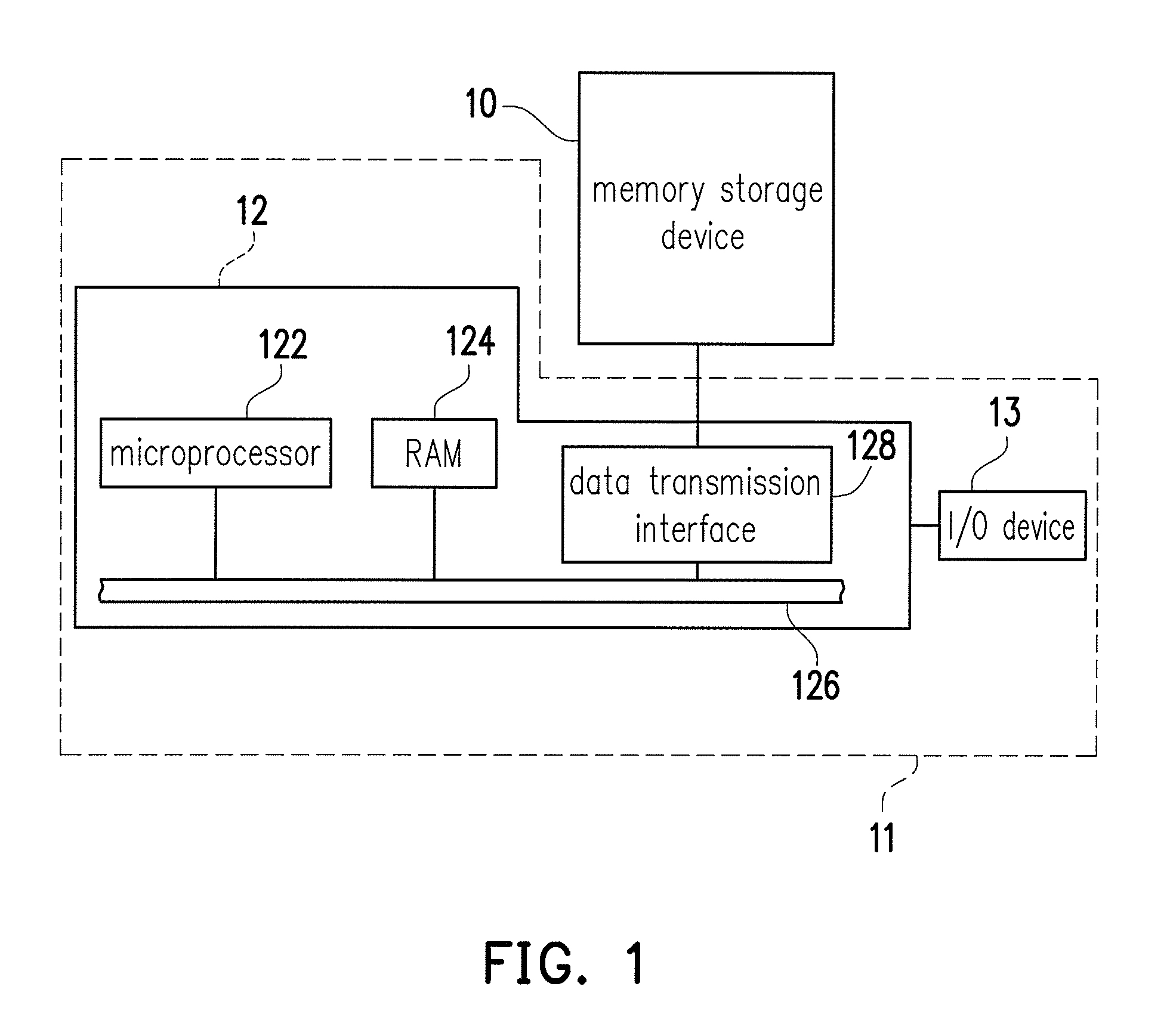

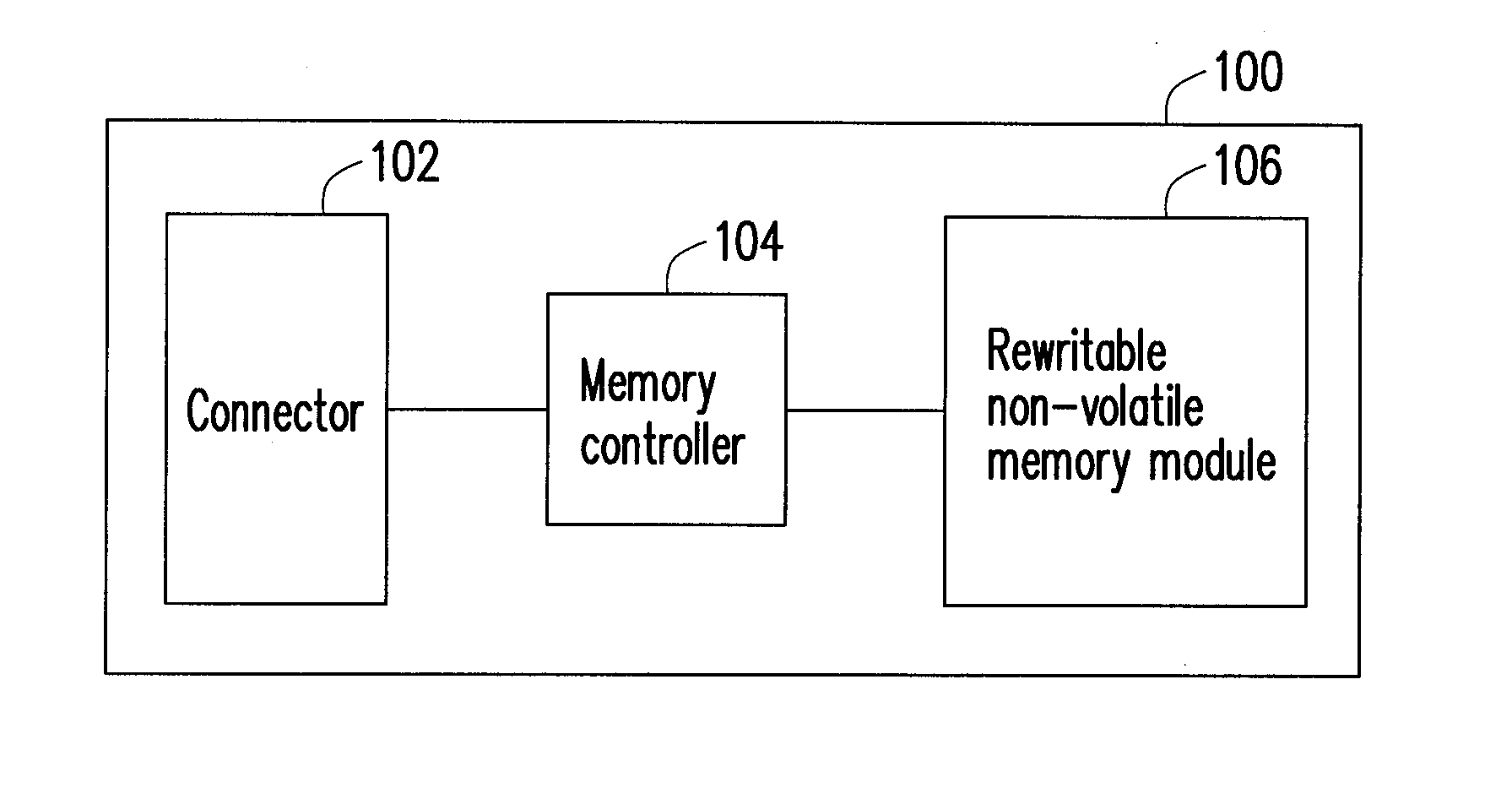

Wear leveling method, memory storage device and memory control circuit unit

ActiveUS20170010961A1Prolonged life timeEffectively keeping wear levelMemory architecture accessing/allocationMemory adressing/allocation/relocationTimestampVolatile memory

A wear leveling method for a rewritable non-volatile memory module is provided. The method includes: recording a timestamp for each of physical erasing units storing valid data according to a programming sequence of the physical erasing units storing valid data among the physical erasing units, and recording an erase count for each of physical erasing units. The method also includes: selecting a first physical erasing unit from the physical erasing units storing valid data according to the timestamps, selecting a second physical erasing unit from physical erasing units not storing valid data among the physical erasing units according to the erase counts, and writing valid data of the first physical erasing unit into the second physical erasing unit, and marking the first physical erasing unit as a physical erasing unit not storing valid data.

Owner:PHISON ELECTRONICS

Radiation detection circuit and radiological imaging apparatus using the same

InactiveUS7528375B2Miniaturizing physical shapeReduce rateSolid-state devicesMaterial analysis by optical meansDiscriminatorRC time constant

There is a need for high-precision detection timing in a radiological imaging apparatus using a semiconductor detector so as to decrease time variations against a noise and easily correct process variations. A radiation detection circuit includes: a semiconductor detector; charge accumulation means connected to the semiconductor detector; a circuit to discriminate timing of a signal generated from the charge accumulation means based on a specified threshold value; a shaper 1 to limit a band from the charge accumulation means using a first time constant; a shaper 2 to limit a band from the charge accumulation means using a second time constant; a circuit 1 to hold an analog peak value 1 for the shaper 1; and a circuit 2 to hold an analog peak value 2 for the shaper 2. The radiation detection circuit performs a signal process to generate timing correction data based on the analog peak values 1 and 2 and correct timing data from the timing discriminator circuit.

Owner:HITACHI LTD

Storage unit management method, memory controller and memory storage device using the same

ActiveUS20130304965A1Avoid unevennessExtended service lifeMemory architecture accessing/allocationMemory systemsLogic cellMemory controller

A storage unit management method for managing a plurality of physical units in a rewritable non-volatile memory module is provided, wherein the physical units are at least grouped into a data area and a spare area. The method includes configuring a plurality of logical units for mapping to the physical units belonging to the data area, and determining whether the rewritable non-volatile memory module contains cold data. The method further includes performing a first wear-leveling procedure on the physical units if it is determined that the rewritable non-volatile memory module does not contain any cold data, and performing a second wear-leveling procedure on the physical units if it is determined that the rewritable non-volatile memory module contains the cold data.

Owner:PHISON ELECTRONICS

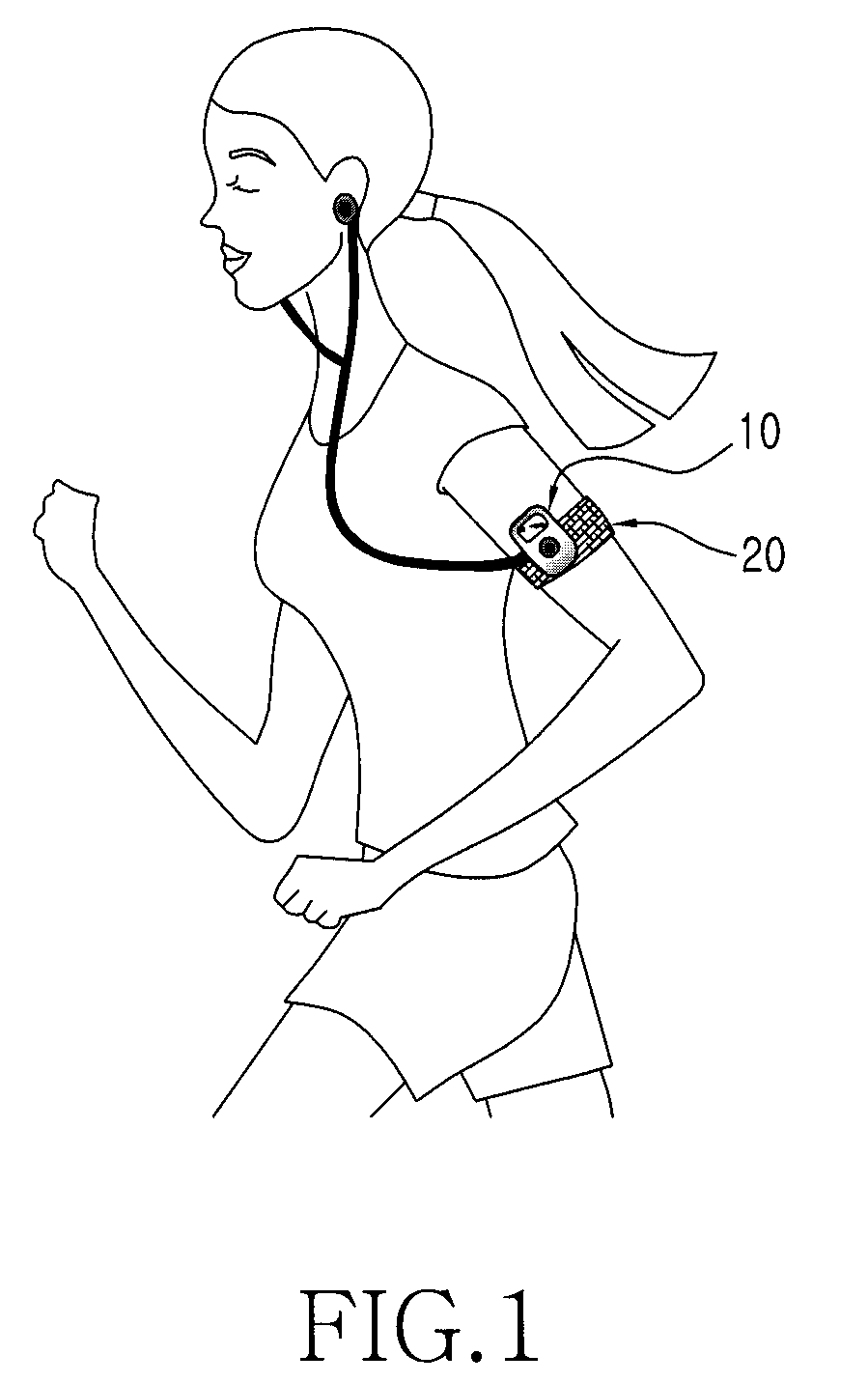

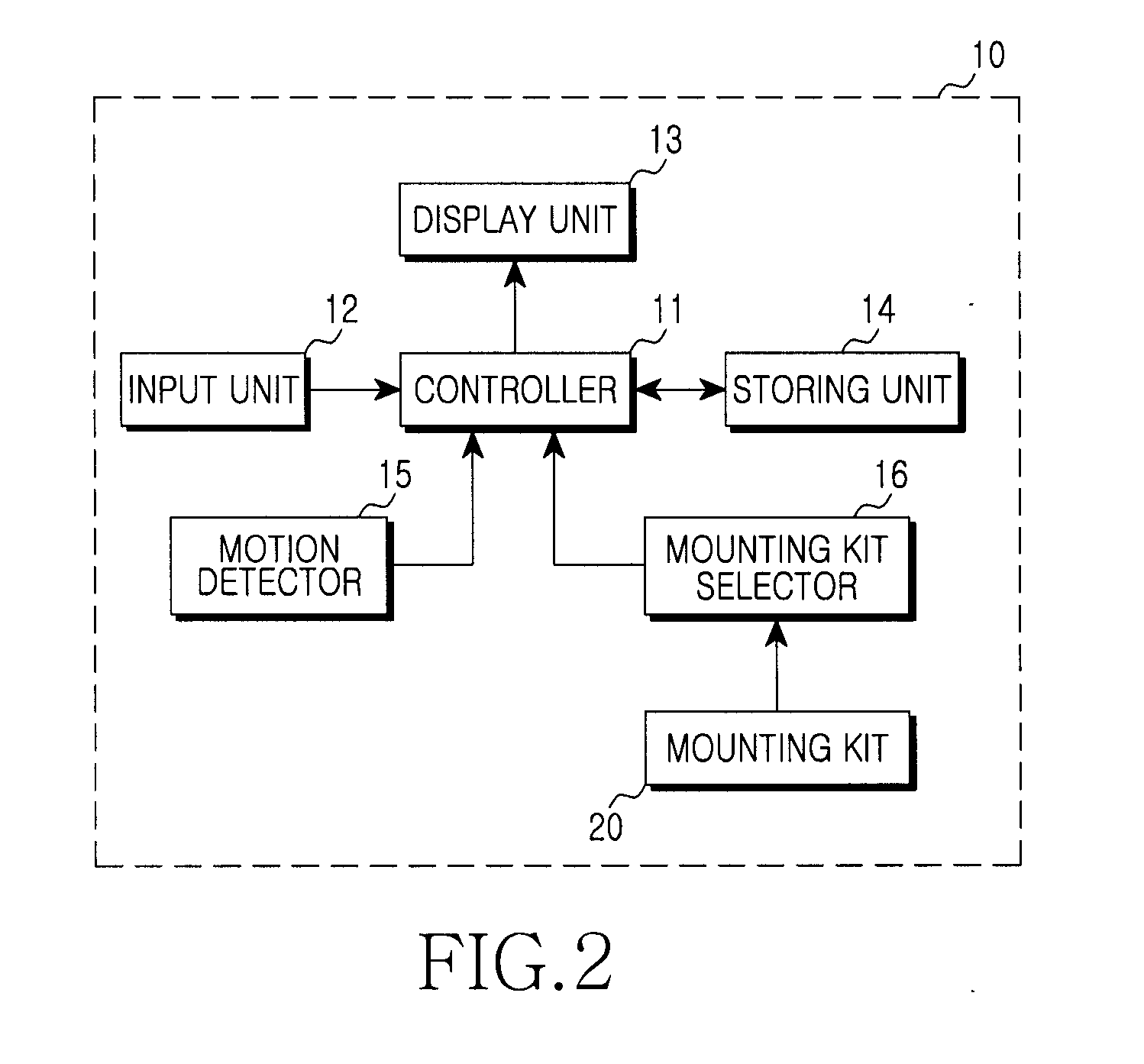

Assembly and the operating method for exercise amount measuring

InactiveUS20100234181A1Efficient countingEffective motionGymnastic exercisingDistance measurementMeasurement deviceEngineering

An assembly for measuring an exercise amount corresponding to a user's motion is provided. The assembly includes mounting kits and a unit for measuring an exercise amount. The unit is selectively fixed to one of the mounting kits that are placed on designated body portions of the user to measure an exercise amount corresponding to a motion of the user by applying an algorithm corresponding to the selected mounting kit. The assembly makes accurate measurement of an exercise amount possible by detecting various mounting locations of the unit mounted on a user and automatically applies an algorithm optimized for different locations.

Owner:SAMSUNG ELECTRONICS CO LTD

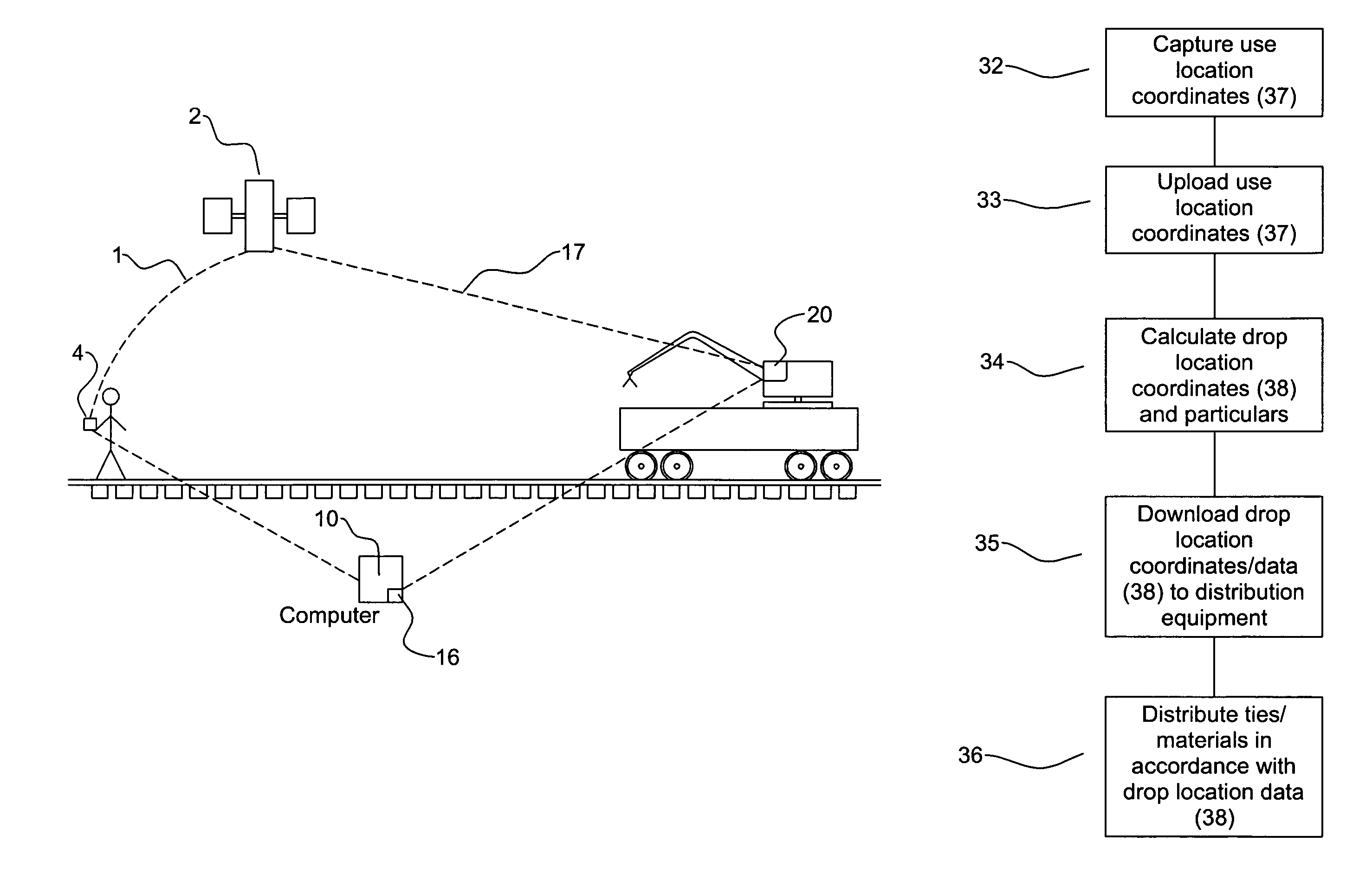

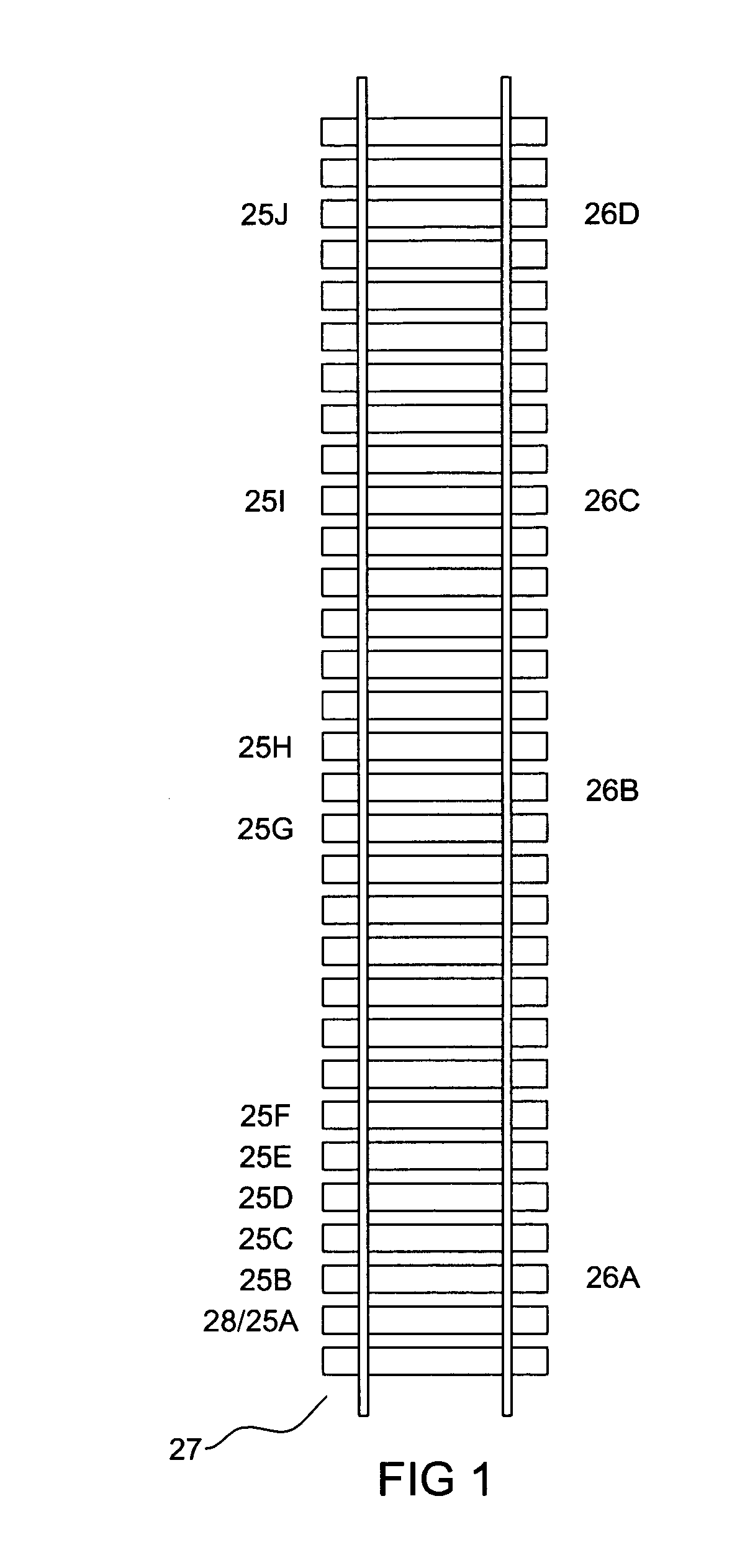

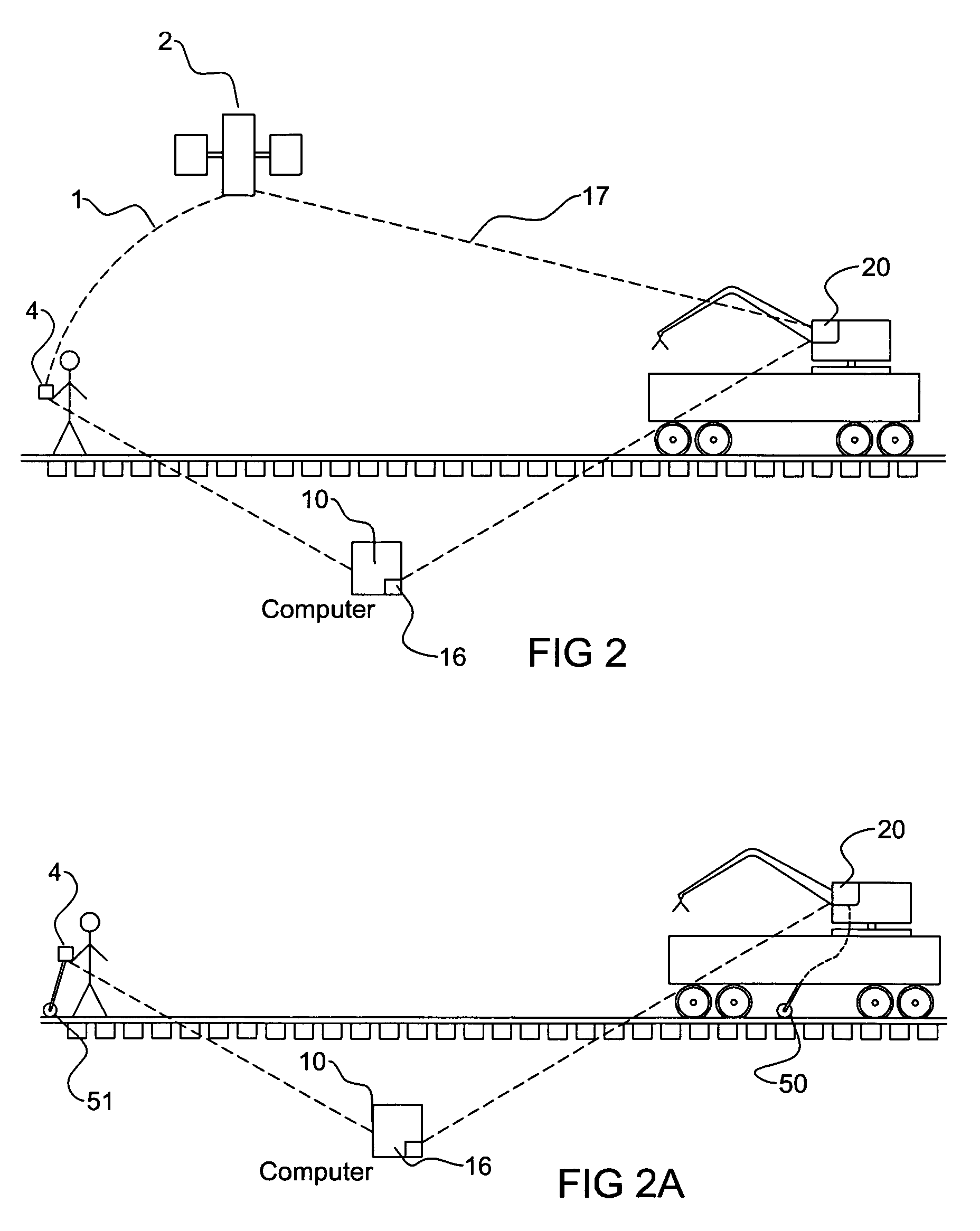

Method and apparatus for adaptive coordinated distribution of materials in railway maintenance and other applications

ActiveUS7162327B1Minimal costOptimize locationDigital data processing detailsPosition fixationData acquisitionEngineering

A method of distributing railroad ties or other materials in variable quantities at randomly spaced intervals. GPS coordinates are recorded for individual use locations where ties or materials are required. From the coordinates of these use locations, drop locations are selected at which materials can be conveniently dropped for subsequent use or installation. Capture of the use location coordinates is done by separate equipment from the distribution equipment, so that the data capture and distribution crews can work at their own efficiencies. The apparatus can be built into new railroad equipment or the like, or can also be manufactured in such a fashion as it can be retrofit. Computer software for the optimization and location of the drop locations is also disclosed.

Owner:BRANDT ROAD RAIL CORP

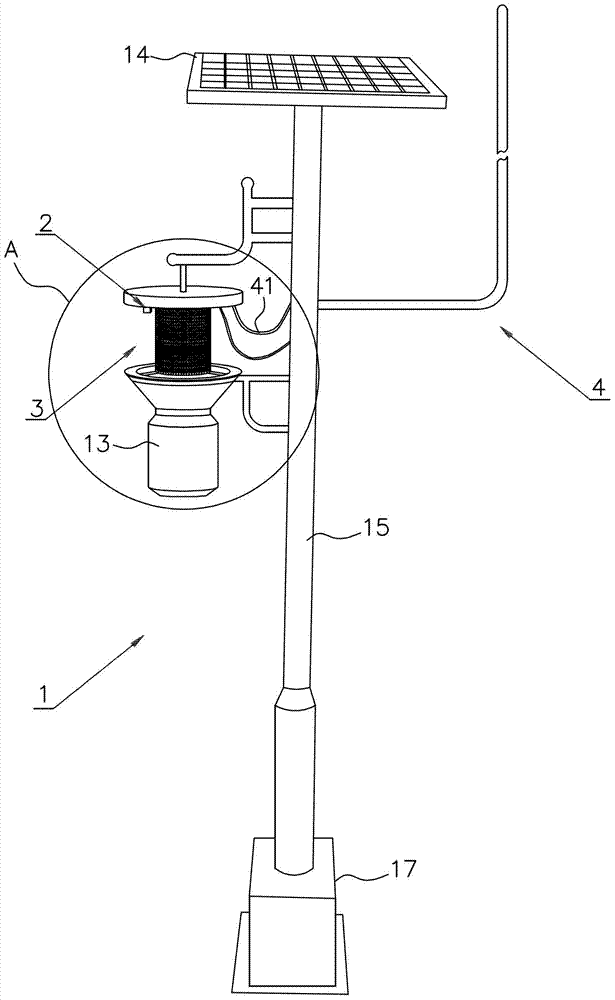

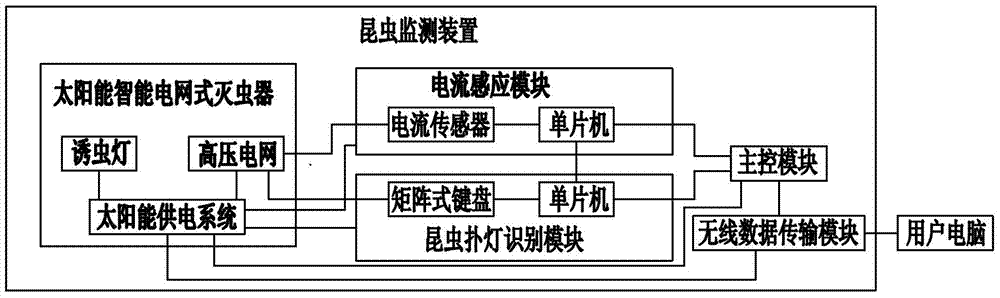

Insect monitoring device

ActiveCN103478101AAvoid any chance factors affecting the countEfficient countingCounting mechanisms/objectsInsect catchers and killersPower flowPaleontology

The invention discloses an insect monitoring device which comprises an electric-net-type insect killer, a current sensing module, an insect lamp-swooping recognition module and a main control module. The electric-net-type insect killer comprises a trapping light source and an electric net arranged around the trapping light source and is used for trapping and killing insects, the current sensing module is used for monitoring original-side current changes of the electric net, the insect lamp-swooping recognition module comprises a matrix-type keyboard arranged on the outer side of the electric net and is used for counting lamp-swooping insects, and the main control module is used for receiving signals output by the current sensing module and the insect lamp-swooping recognition module and counting the total number of the lamp-swooping insects. The insect monitoring device can complete counting at the moment when the insects swoop a lamp, so that any accidental factors which may affect counting are effectively avoided.

Owner:ZHEJIANG UNIV

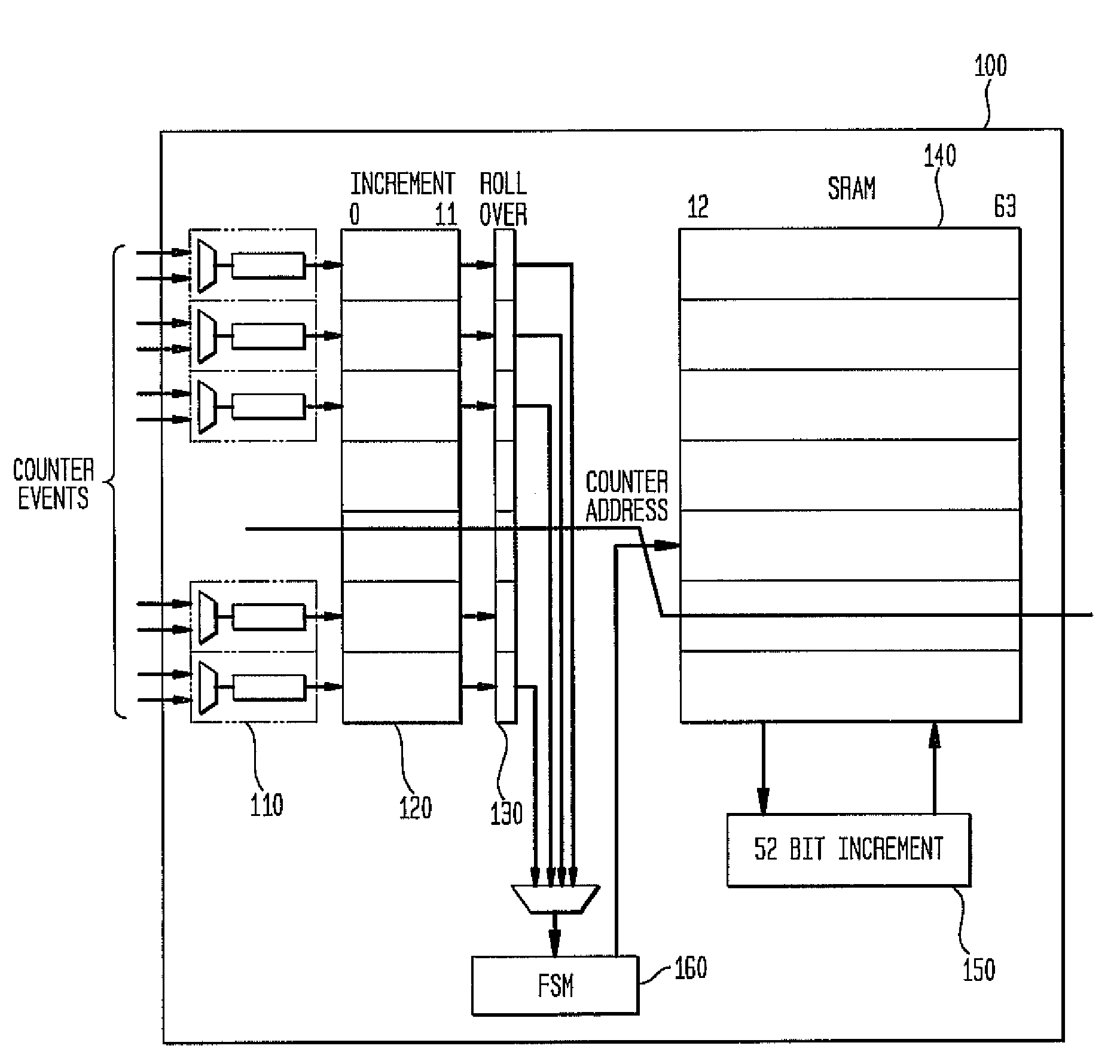

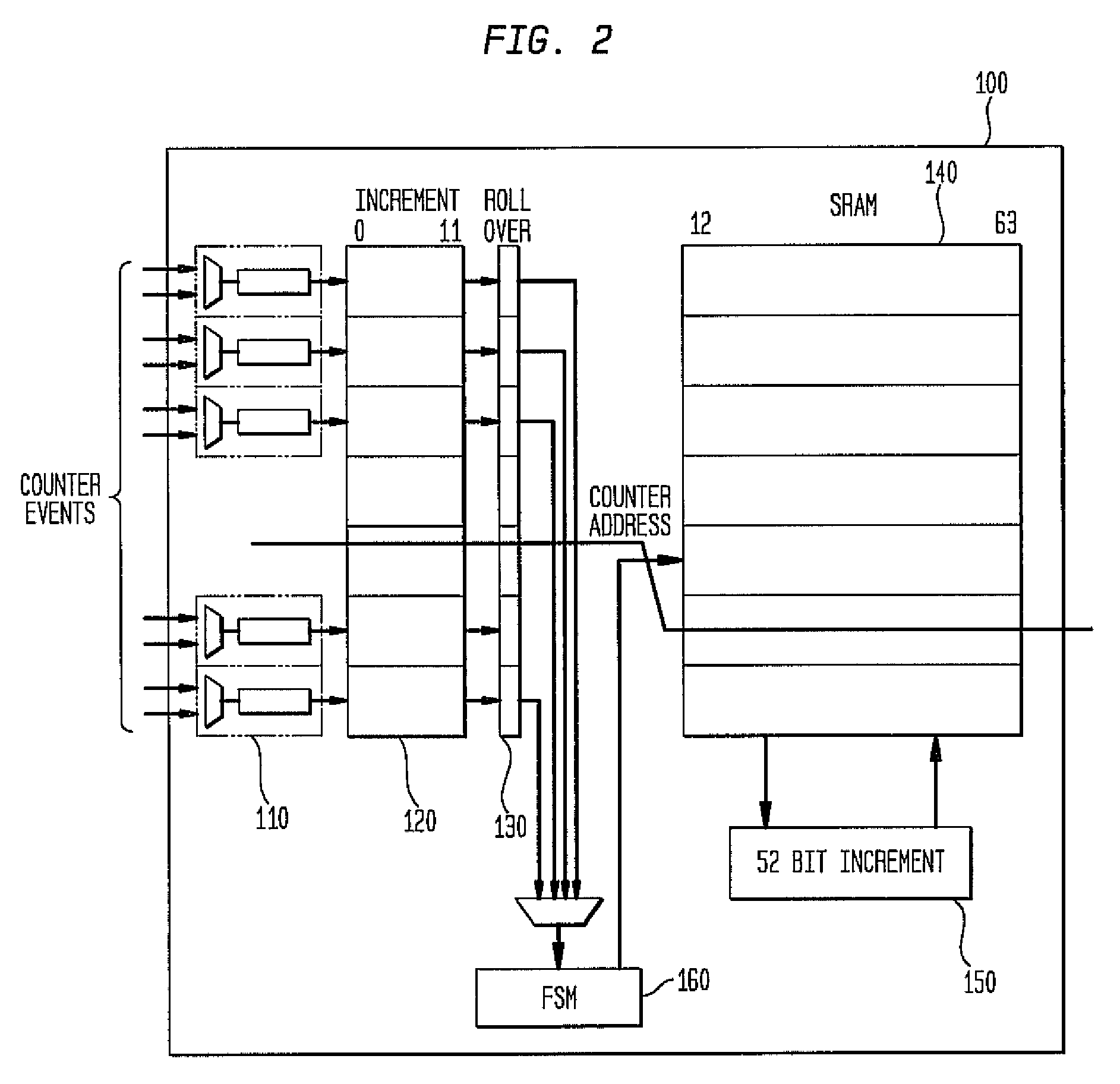

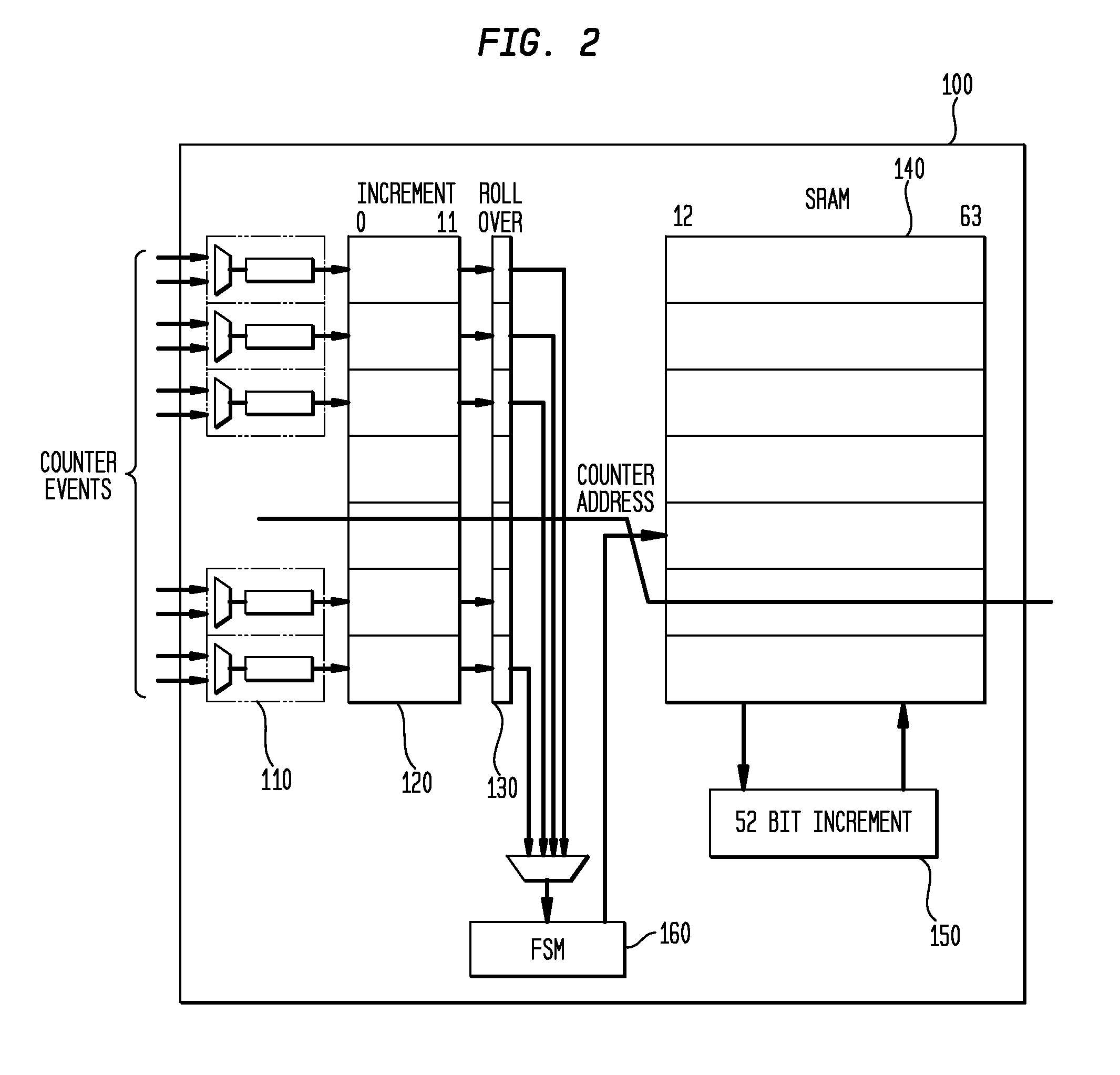

Low latency counter event indication

InactiveUS7426253B2Reduce area requirementsReduce the required powerCounting chain synchronous pulse countersElectric unknown time interval measurementLatency (engineering)Device Monitor

Owner:GLOBALFOUNDRIES INC

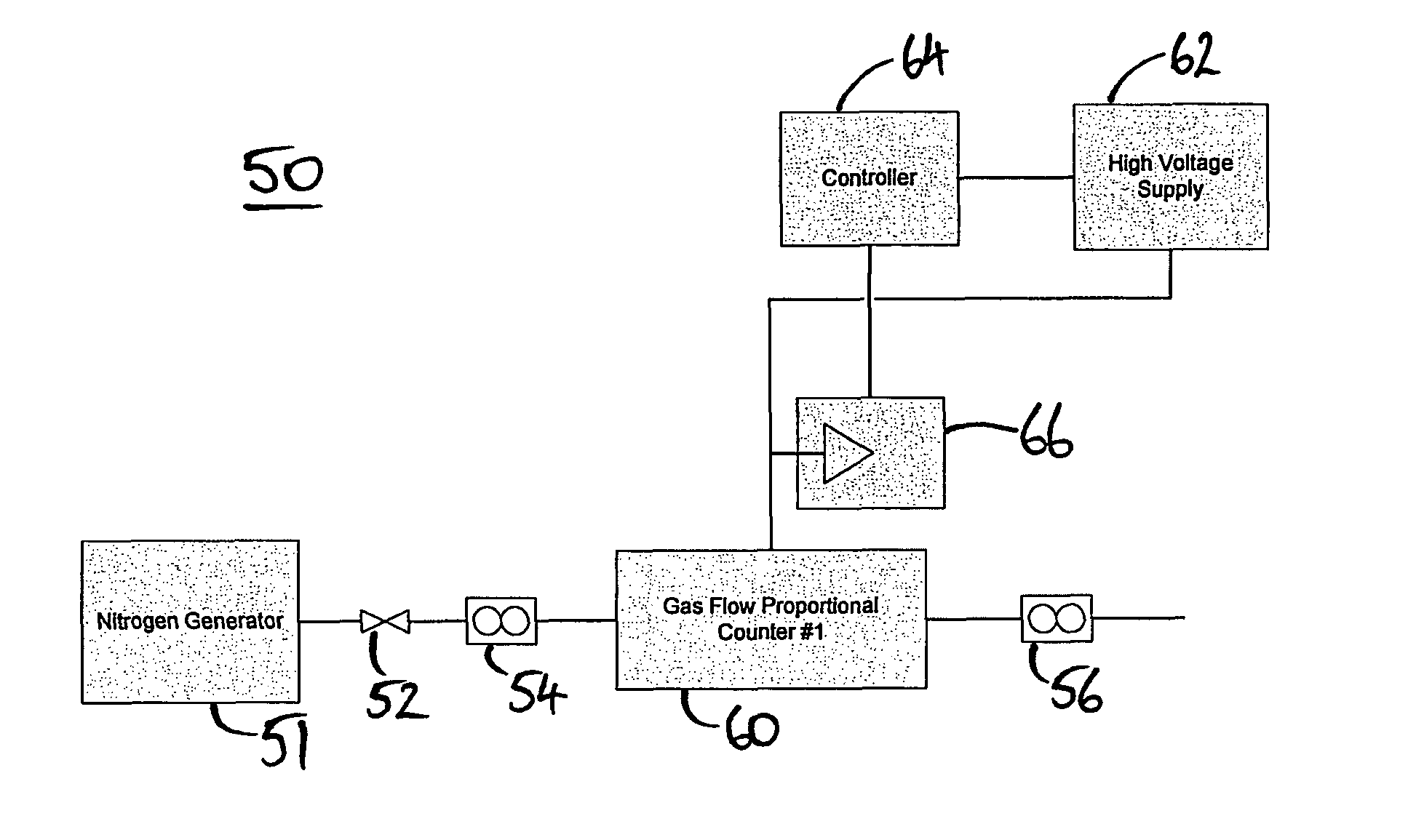

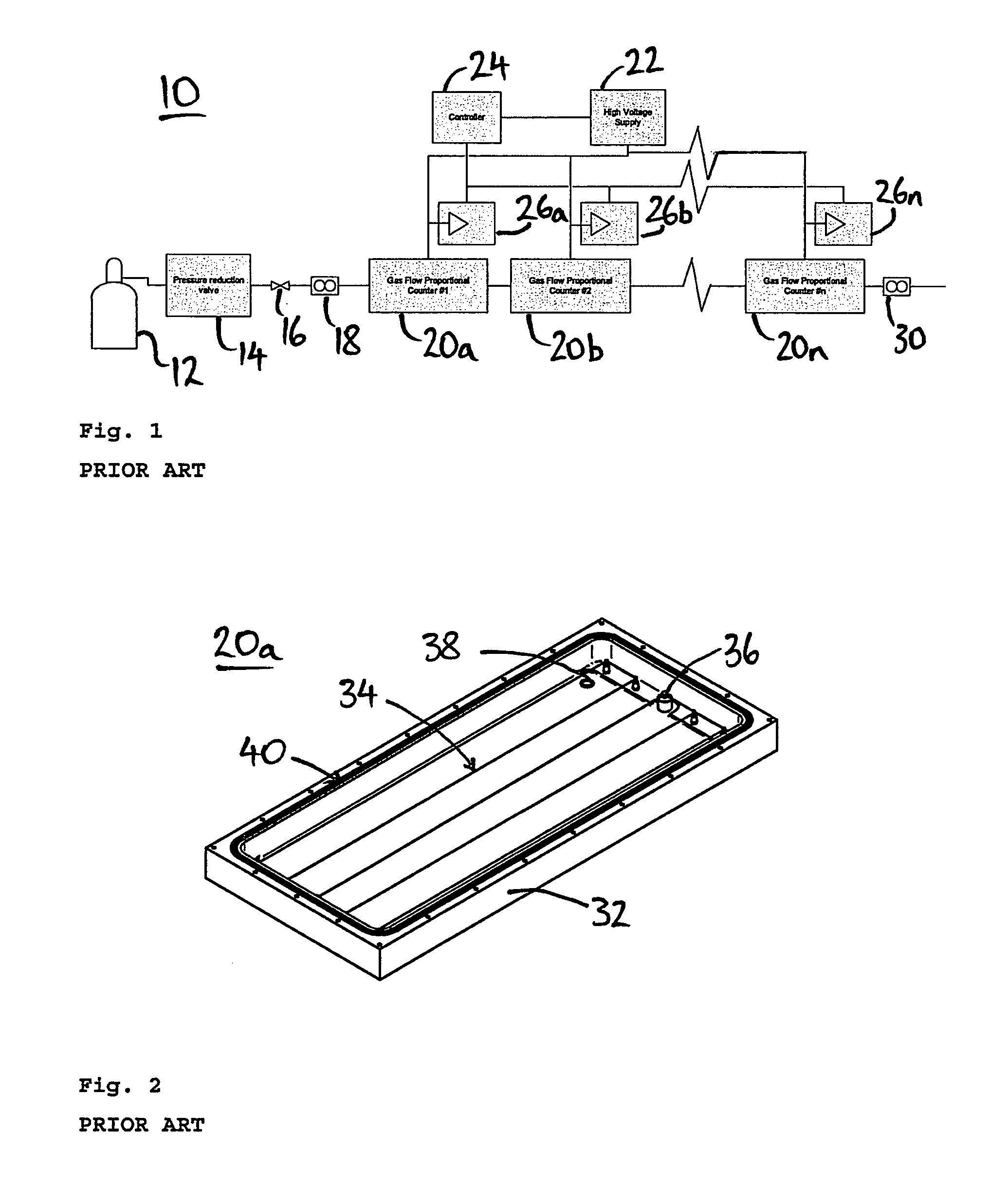

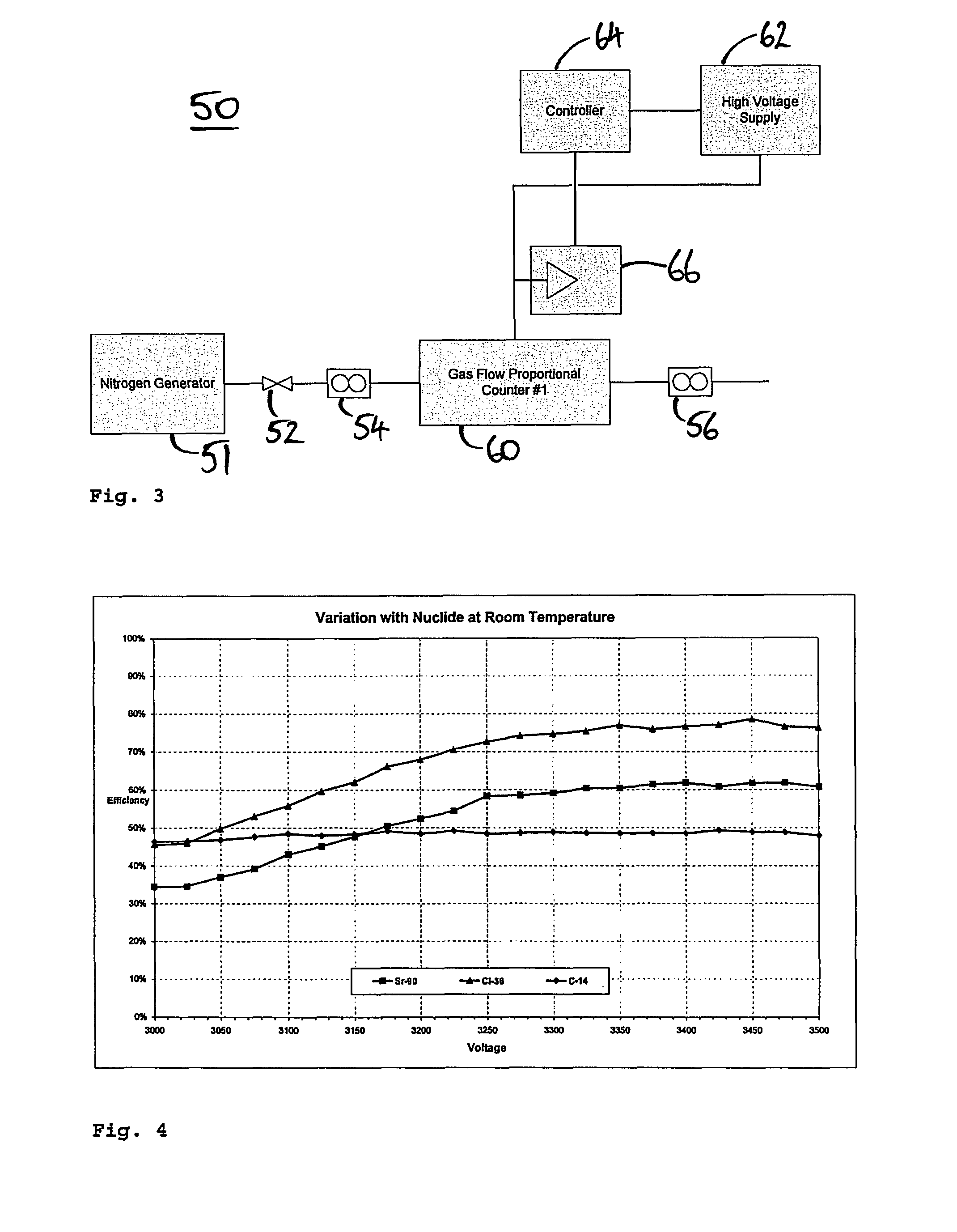

Beta radiation monitor and method

ActiveUS8680476B2Reduce sensitivityReduce usageElectric discharge tubesMaterial analysis by optical meansNitrogen generatorElectrical resistance and conductance

A beta radiation monitor (70,90), comprising a gas flow proportional detector (60) for detecting beta radiation emitted by a beta emitter external to the detector; a fill gas supply (51) configured to supply a fill gas to the detector, wherein the fill gas comprises nitrogen; a temperature sensor (72) for measuring temperature; and a controller (64) in communication with the temperature sensor for adjusting an operational parameter of the monitor in accordance with the measured temperature. The operational parameter may comprise a voltage applied across the fill gas, which may be thermistor controlled, or a beta radiation detection threshold of the detector. The fill gas is supplied by a nitrogen generator. The gas flow proportional detector may be a large-area detector.

Owner:THERMO ELECTRONICS LTD

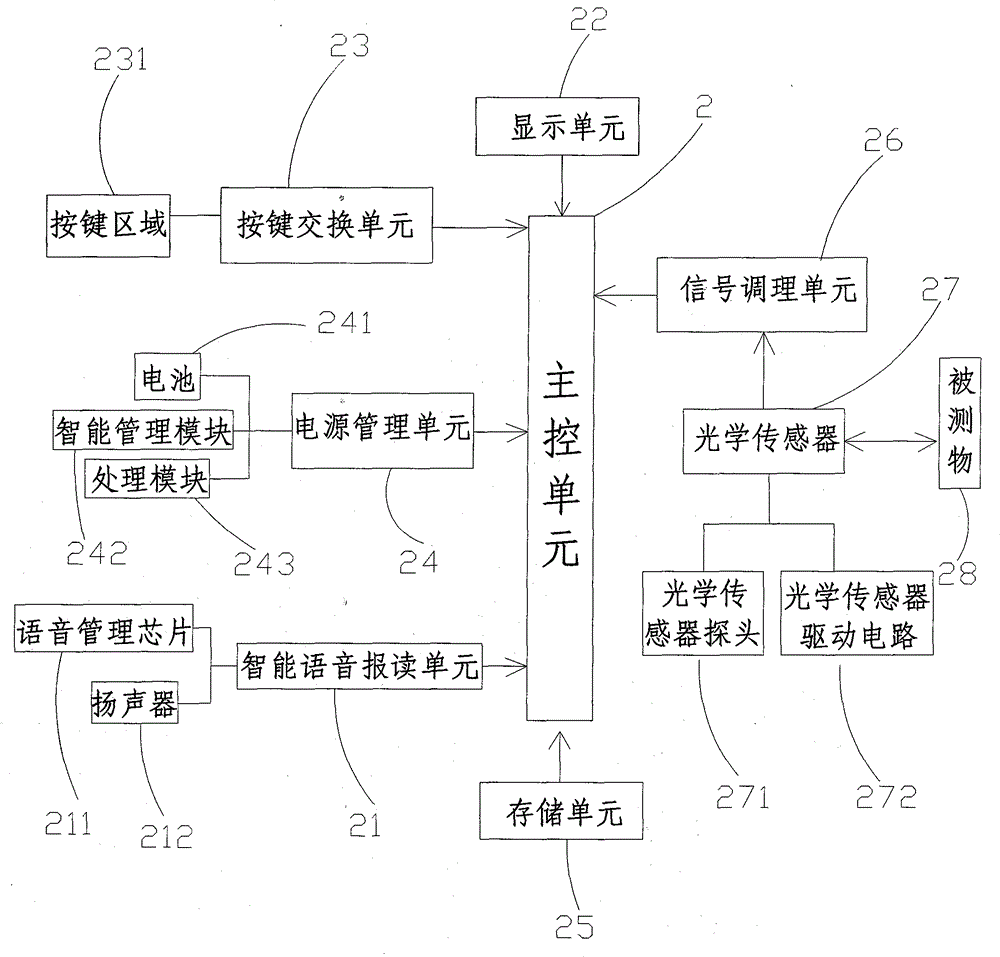

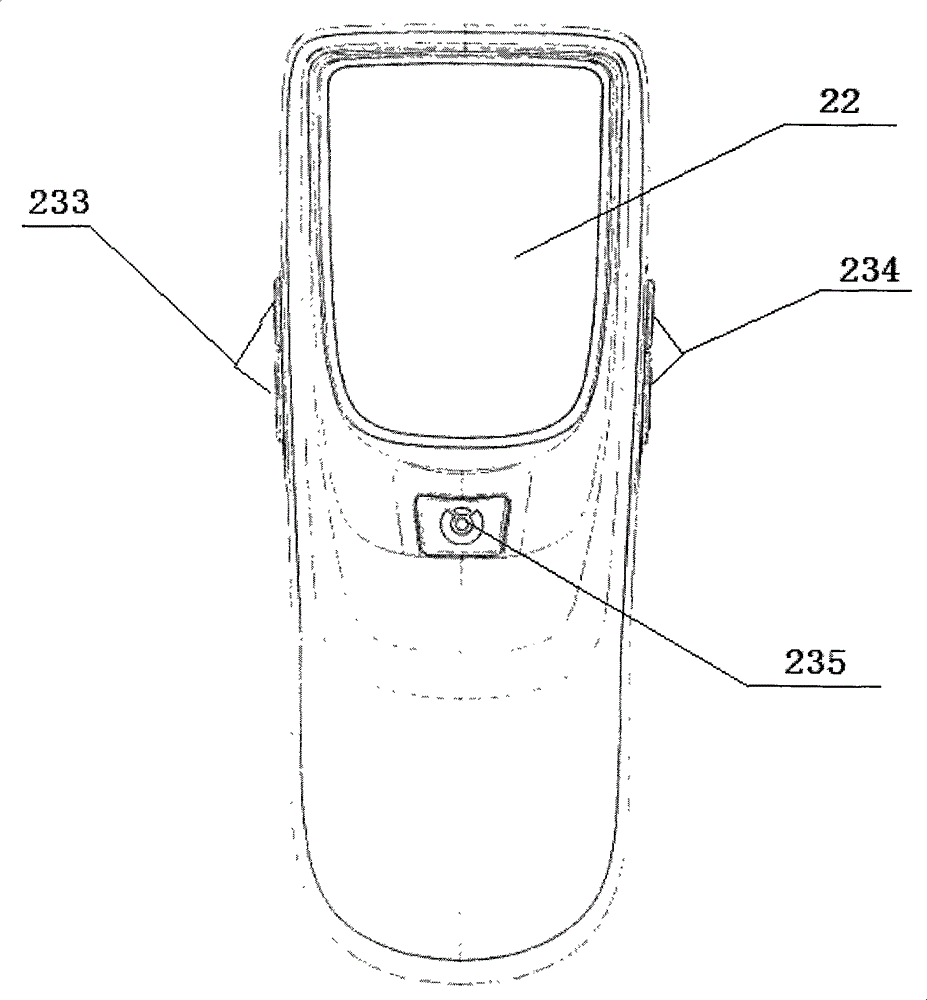

Intelligent handheld multifunctional card counting device

InactiveCN104050502AAccurate statisticsImprove user experienceCounting objects on conveyorsLoudspeakerMultiple function

The invention relates to an intelligent multifunctional handheld card counting device which comprises a master control unit arranged in a casing, wherein an intelligent voice reading unit, a display unit, a key exchange unit and a power supply management unit are connected onto the master control unit. The intelligent handheld multifunctional card counting device further comprises an optical sensor connected with the master control unit through a signal conditioning unit. The intelligent voice reading unit comprises a voice management chip and a loudspeaker connected with the master control unit through the voice management chip. The intelligent multifunctional handheld card counting device is based on the VCSEL technology and utilizes the novel VCSEL sensor, and therefore, adaptability to dimensions, colors and location places of detected objects is improved. Furthermore, the intelligent multifunctional handheld card counting device has an intelligent reading function, the number of cards can be read by two languages, a colorful display screen is adopted, and therefore, the intelligent multifunctional handheld card counting device can count cards efficiently and accurately in a wider industry field.

Owner:北京天华恒信智能科技有限公司

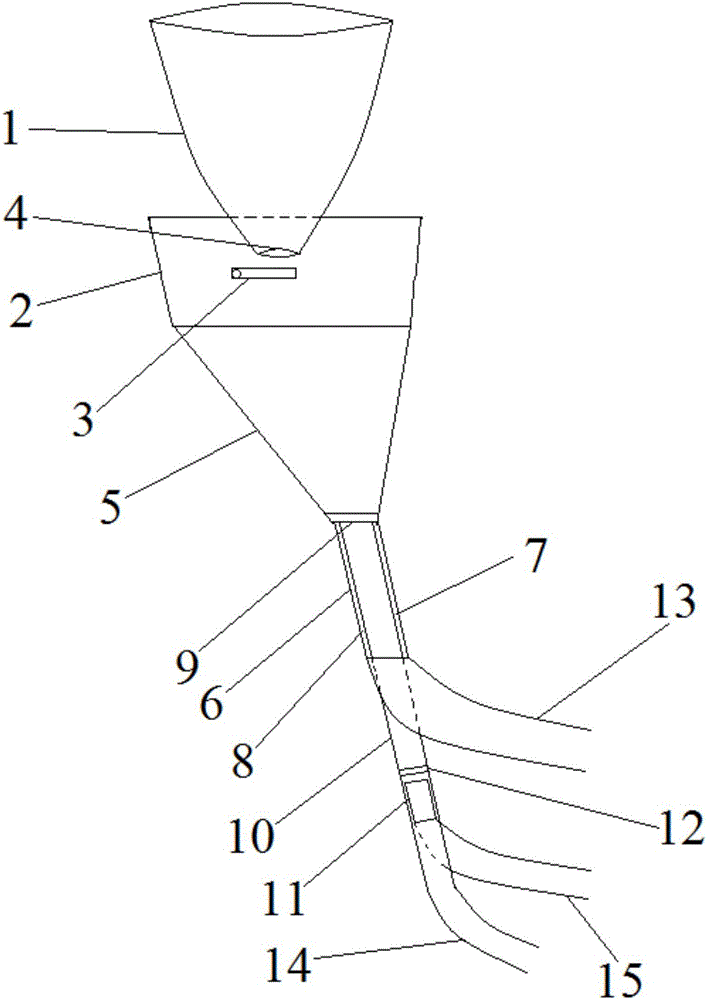

Simple coin sorting and counting device

InactiveCN106447888AEasy to separateEfficient separationCoin/paper handlersCounter deviceEngineering

The invention relates to a simple coin sorting and counting device. The simple coin sorting and counting device comprises a funnel coin conveying unit, a slide coin sorting unit which is connected with the funnel coin conveying unit and a coin counting unit which is connected with the slide coin sorting unit. The funnel coin conveying unit comprises a funnel, a platform arranged at the bottom of the funnel, and a transfer arm arranged on the platform. The slide coin sorting unit consists of a first slide coin sorting mechanism and a second slide coin sorting mechanism. The coin counting unit is connected to the first slide coin sorting mechanism and the second slide coin sorting mechanism, respectively. The coin is transported from the bottom of the funnel to the platform and then transported by the transfer arm to the slide coin sorting unit. Thereafter, the coins of different diameters are separated by the first slide coin sorting mechanism and the second slide coin sorting mechanism successively and counted by the coin counting unit. Compared with the prior art, the present device integrates coin separation and counting. The coin sorting and counting device sorts coins according to the principle that various types of coins have different diameters with good separation effect, accurate counting and greatly reduces the cost and difficulty of sorting and counting of coin.

Owner:SHANGHAI UNIVERSITY OF ELECTRIC POWER

Method and apparatus for updating wide storage array over a narrow bus

InactiveUS20080126634A1Eliminate needReduce area requirementsEnergy efficient ICTEnergy efficient computingArray data structureArray element

A method and apparatus for transferring wide data (e.g., n bits) from a narrow bus (m bits, where m<n) for updating a wide data storage array. The apparatus includes: a staging latch accommodating m bits, e.g., 32 bits; control circuitry for depositing the m bits of data from a data bus port into the staging latch addressed using a specific register address; and control circuitry adapted to merging the m bit data contained in the staging latch with m bit data from a data bus port, to generate the n bit wide data, for example, 64 bits, that is written atomically to a storage array specified by an address corresponding to a storage array location. Thus, writing a first set of bits to the staging latch is performed by providing, as a target address of a write (store) operation, the mapped address of the staging latch, and then providing a subsequent set of bits (the remaining bits) together with an array element target specification (encoded as a plurality of the bits of the address specified in the write transaction), in a subsequent write transaction (store).

Owner:IBM CORP

System and method to generate a transaction count using filtering

ActiveUS20160275420A1Efficiently stored in databaseEfficient countingDigital data information retrievalError detection/correctionData setOriginal data

The present disclosure relates to a system and method of generating a transaction count using filtering. Transaction data is collected for a set of transactions from an original data set. The collected transaction data is narrowed into a transaction data set by identifying a specific range of the data to be extracted. This transaction data set is filtered against one or more criteria. The transactions included in the transaction data set are then arranged into data packs in a format enabling efficient count generation. The count generation determines how many transactions meet the applied criteria. The data may then be efficiently stored in a database for later retrieval.

Owner:CA TECH INC

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com