Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

33results about How to "Control profile" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

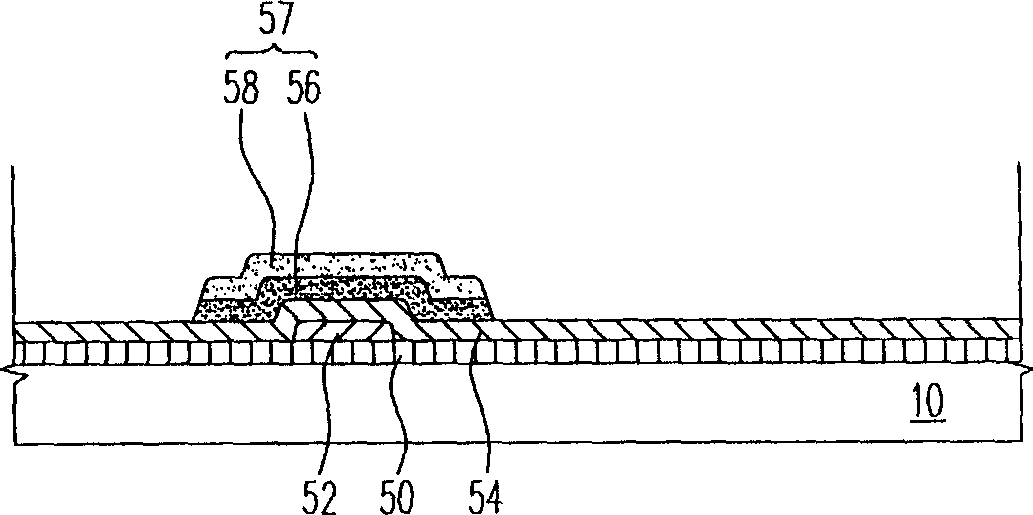

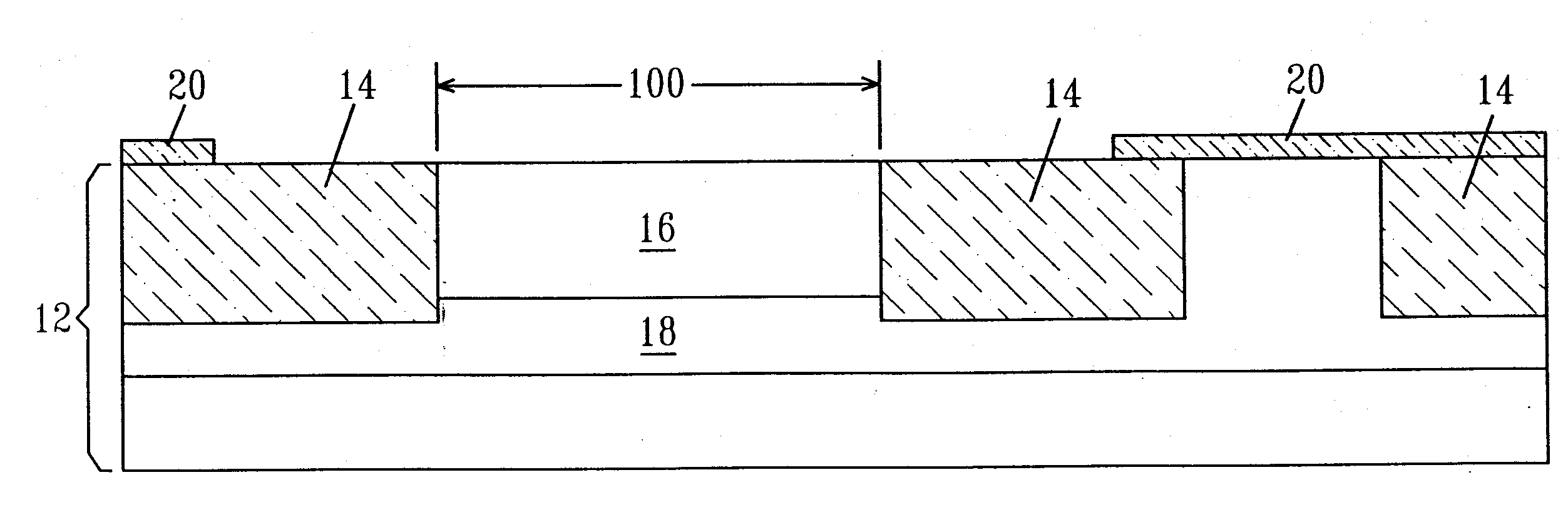

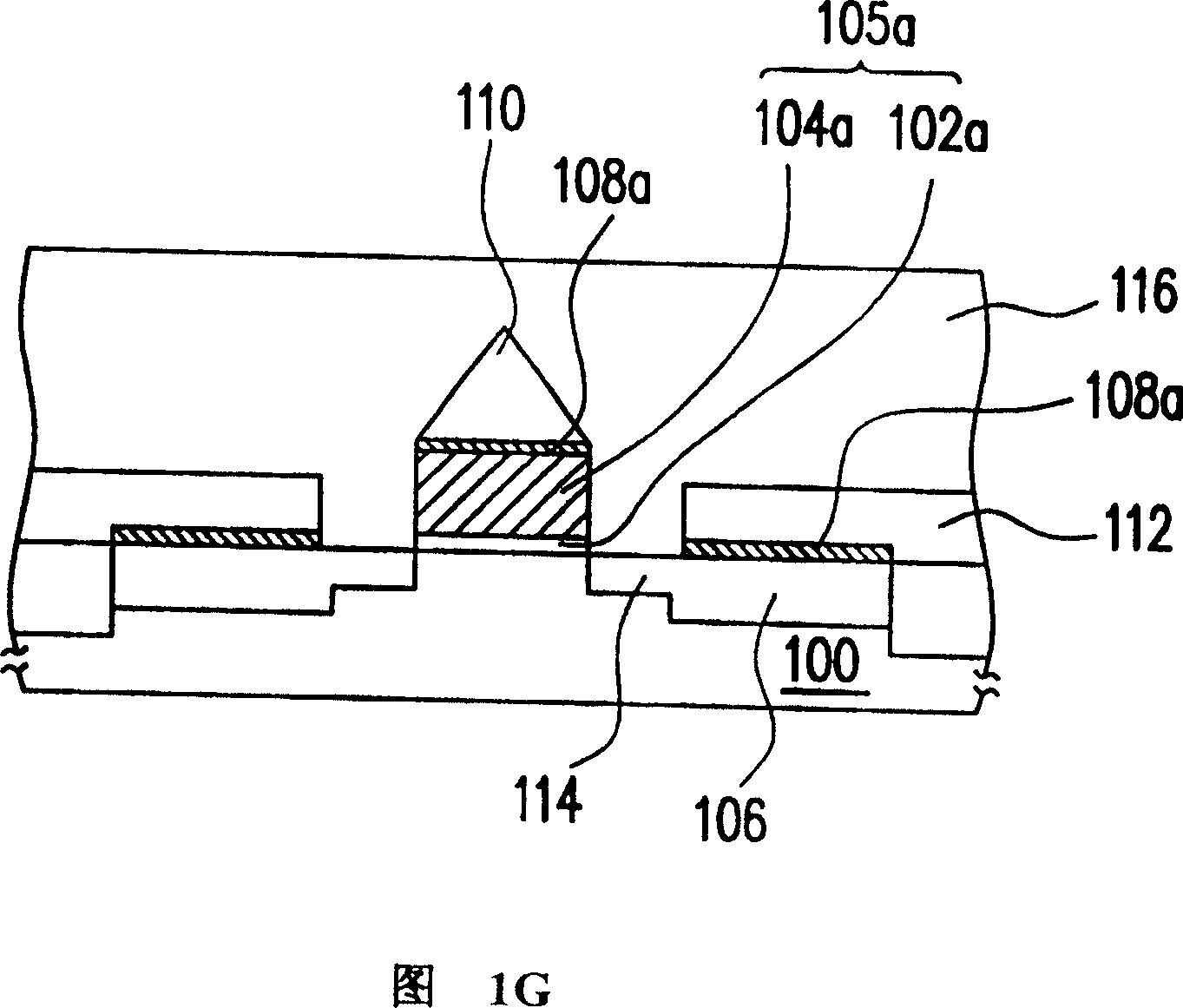

Method for making picture element structure

InactiveCN1828871AControl depthControl profileSemiconductor/solid-state device manufacturingNon-linear opticsPhotoresistPhotolithography

The present invention discloses a dot structure manufacturing method. It contains providing a substrate formed with a scanning wiring, a data wiring and an active element, wherein active element and scanning wiring and data wiring being electrically connected, forming dielectric layer substrate, forming patterning photoresist layer on dielectric layer, wherein patterning photoresist layer having a first pass through hole and plurality of first cave, first pass through hole exposing partial dielectric layer, using patterning photoresist layer as shade to remove partial dielectric layer for forming patterning dielectric layer, wherein patterning dielectric layer having a second pass through hole and plurality of second cave, and second pass through hole exposing partial active element, then removing patterning photoresist layer, forming reflecting layer on patterning dielectric layer, wherein reflecting layer covering second cave and reflecting layer connected with active element. Said invented second cave depth and outline can be comparatively controlled, said reflecting layer unease to generate broke up phenomena.

Owner:AU OPTRONICS CORP

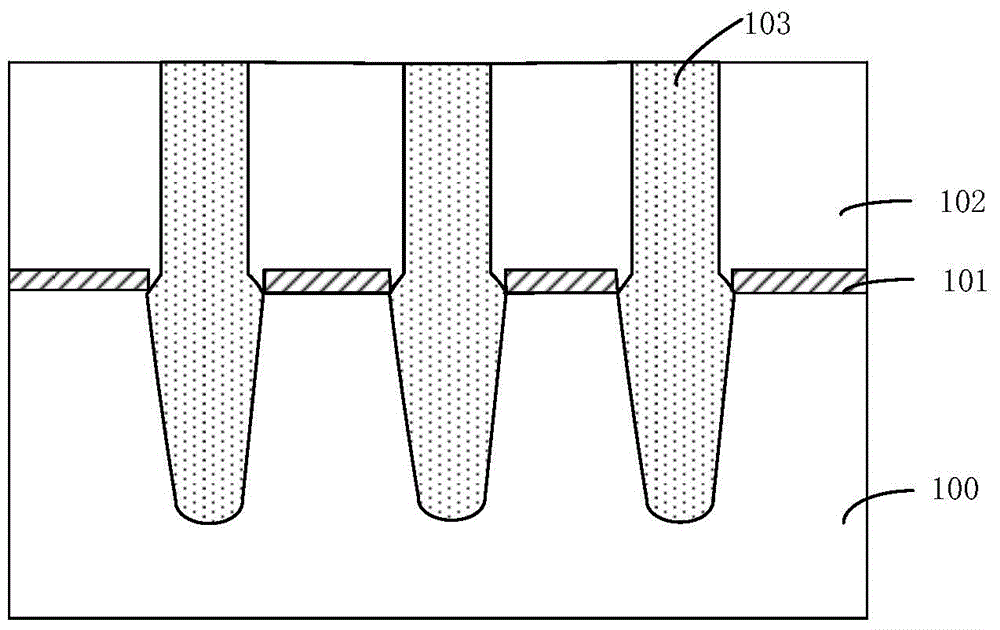

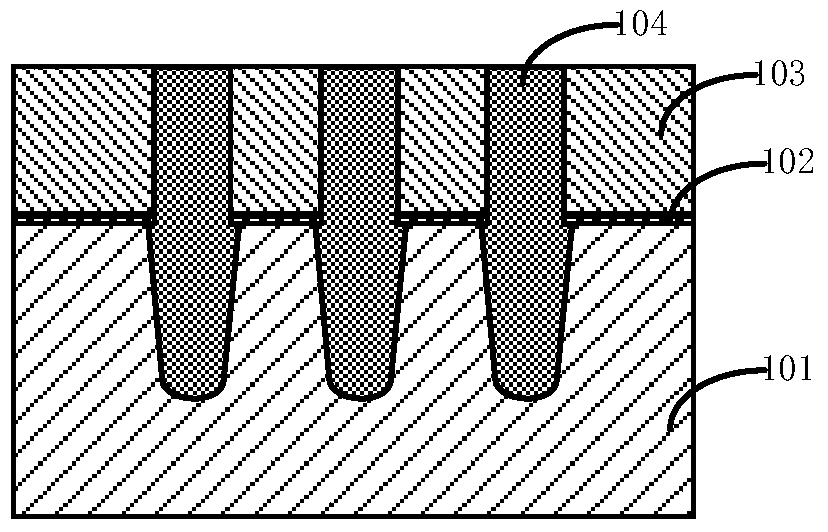

Method for manufacturing groove and its method for manufacturing image sensor

ActiveCN101183658AControl profileReduce depthSemiconductor/solid-state device manufacturingRadiation controlled devicesElectrical conductorEngineering

The invention relates to a groove-forming method in a laminated medium layer, which comprises: a first medium layer is formed on a semiconductor base; a first opening is formed on the first medium layer; a first sacrificial layer is filled in the first opening; at least a second medium layer is formed on the first medium layer, and a second opening is formed on the second medium layer; the second opening is positioned above the first opening, and the depth of the second opening is same with the thickness of the second medium layer; the second sacrificial layer is filled in the second opening; the first sacrificial layer and the second sacrificial layer are removed. The invention has an advantage of capability of forming a better groove contour.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

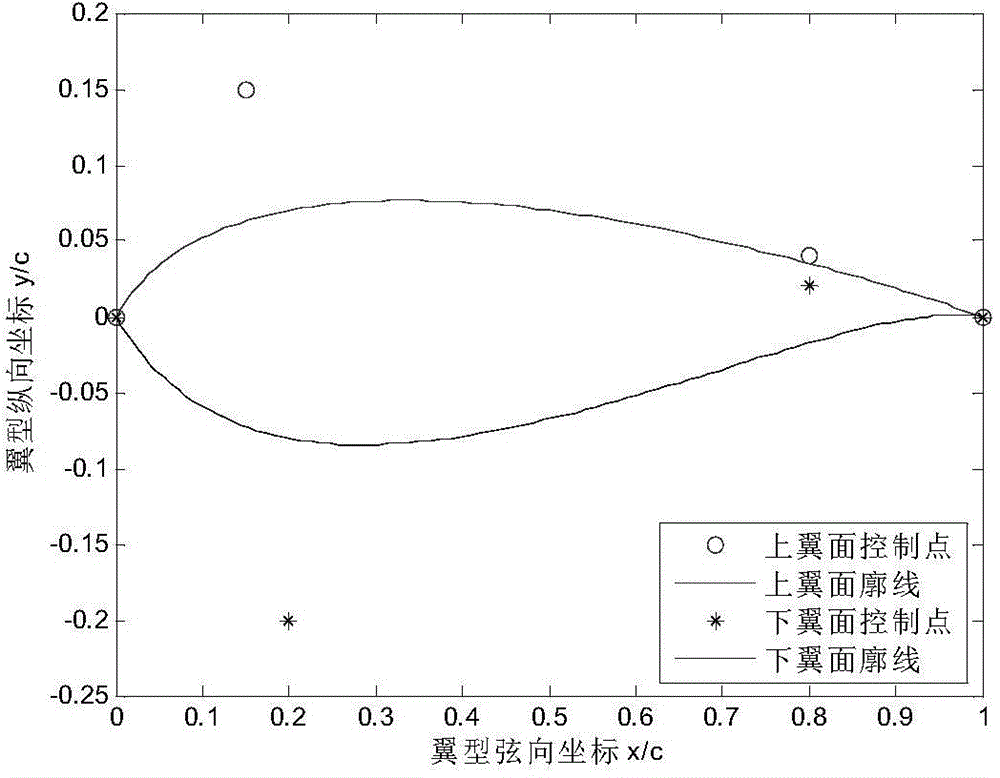

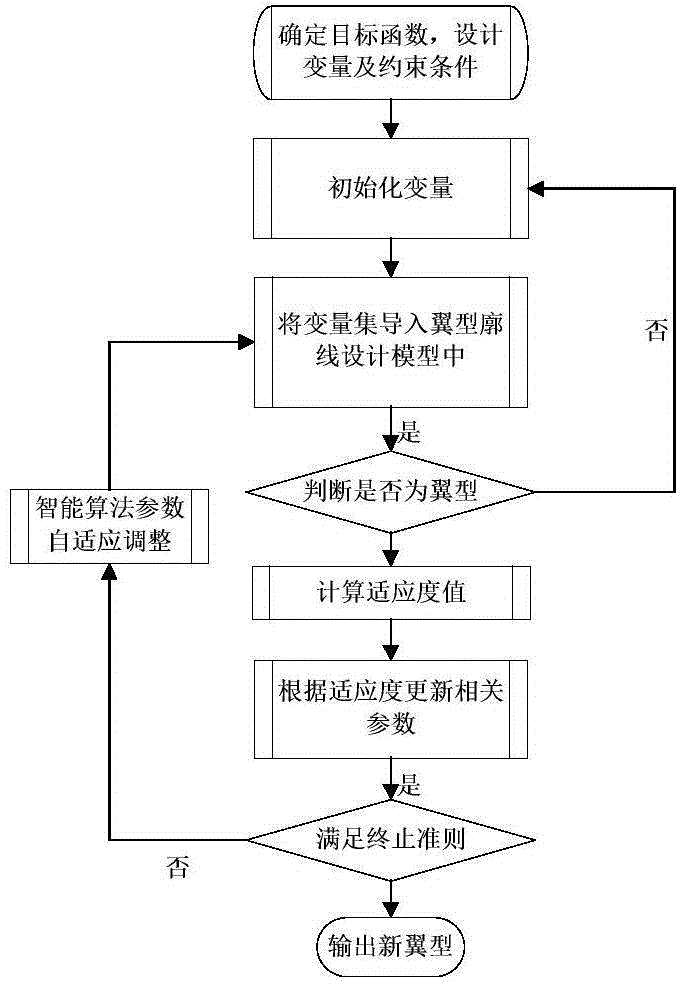

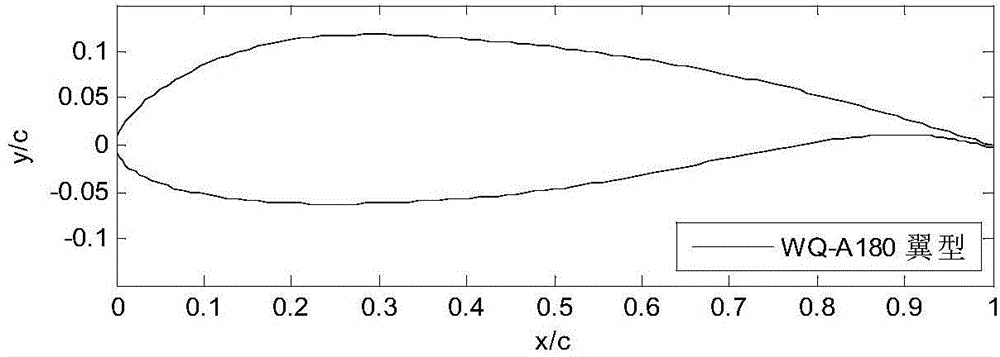

Method for designing wind turbine airfoil by using Bessel function curve

InactiveCN104863799AControl profileImprove design efficiencyWind motor componentsTurbine bladeEconomic benefits

The invention discloses a method for designing a wind turbine airfoil by using a Bessel function curve. According to the method, the third-order Bessel function is adopted and can represent a section of curve through four control points only, and in addition, the starting point and the end point are fixed, so that only two control points are required to be changed for a section of the curve; each of an upper wing surface and a lower wing surface of the airfoil is represented by a section of curve, the starting points and the end points of the upper wing surface and the lower wing surface respectively coincide, and then the staring points and the end points are in smooth connection. According to the invention, the airfoil profile can be controlled more conveniently and effectively by using several points in space, so that optimization design time of the airfoil is shortened, and airfoil design efficiency is improved; the designed airfoil has an extremely high lift coefficient, so that chord length of a blade is reduced, and the material required by the blade is reduced; a higher lift-drag ratio is realized, so that the wind-power utilization coefficient is increased; the method can be popularized to design of wind turbine airfoils of different thicknesses, plane airfoils, turbine blade profiles and other complex curves and has a high social value and a good economic benefit.

Owner:HUBEI UNIV OF TECH

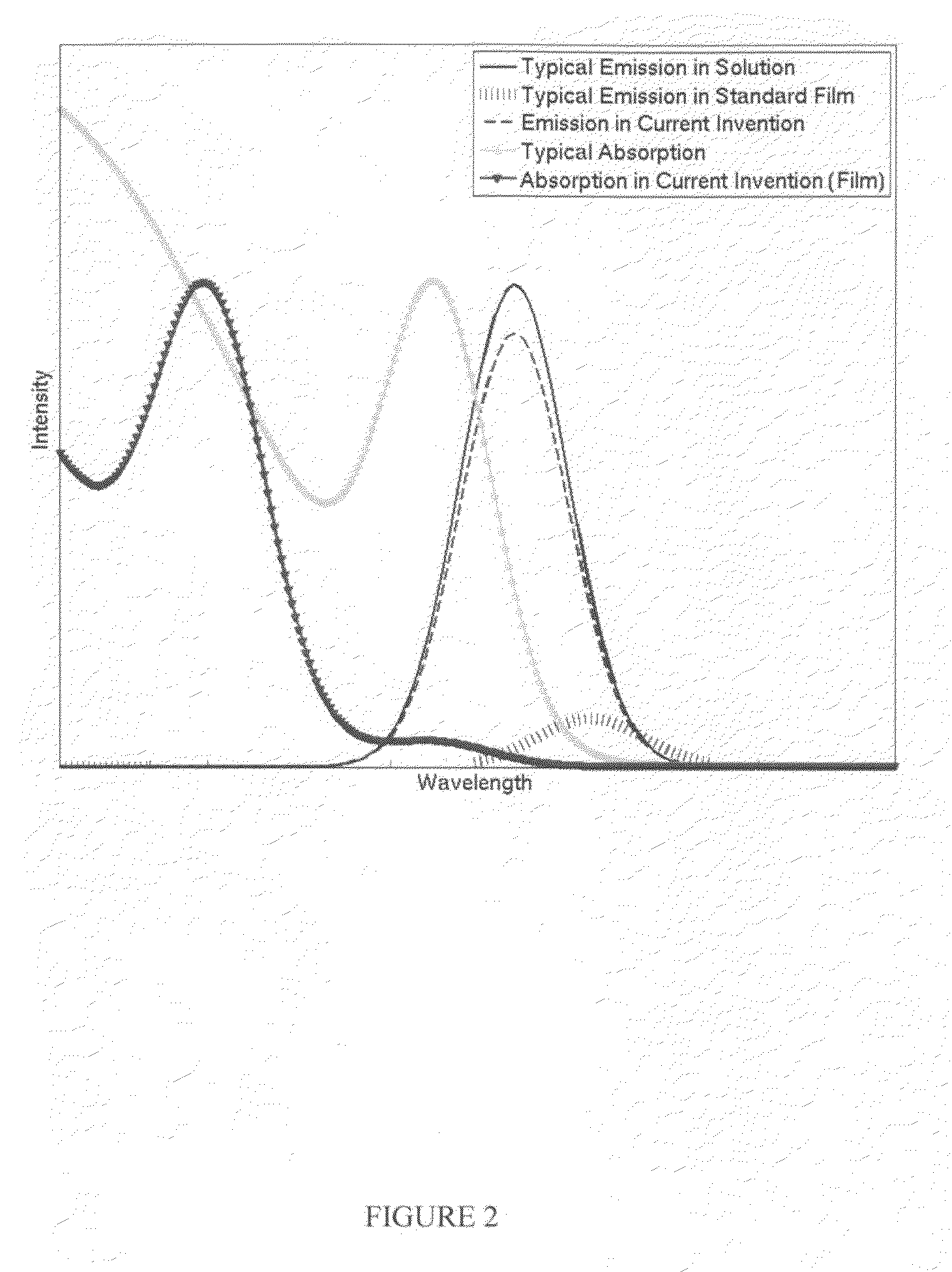

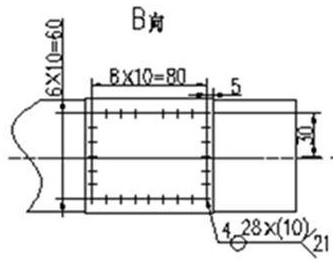

Mixed semiconductor nanocrystal compositions

InactiveUS20100013376A1Minimize “bad” energy transferReduce reabsorptionMaterial nanotechnologyDischarge tube luminescnet screensPeak valueColloid

Composition comprising one or more energy donors and one or more energy acceptors, wherein energy is transferred from the energy donor to the energy acceptor and wherein: the energy acceptor is a colloidal nanocrystal having a lower band gap energy than the energy donor; the energy donor and the energy acceptor are separated by a distance of 40 nm or less; wherein the average peak absorption energy of the acceptor is at least 20 meV greater than the average peak emission energy of the energy donor; and wherein the ratio of the number of energy donors to the number of energy acceptors is from about 2:1 to about 1000:1.

Owner:LOS ALAMOS NATIONAL SECURITY

Profile tolerance compensation method of S-shaped ball-end milling cutter

ActiveCN106774153AControl profileImprove processing qualityProgramme controlComputer controlCompensation pointEngineering

The invention provides a profile tolerance compensation method of an S-shaped ball-end milling cutter. The profile tolerance compensation method comprises the following steps: selecting a plurality of points needing profile tolerance compensation according to a profile graph of the S-shaped ball-end milling cutter and determining coordinates of the compensation points; selecting a proper interpolation or fitting method to approach the compensation points to obtain a radius transition curve; obtaining a radius corrected value of each grinding point according to the radius transition curve; moving a grinding wheel along a relief angle tangent plane normal direction of the grinding point according to the radius corrected value. The method provided by the invention can be used for effectively controlling the profile tolerance of a ball end and the machining quality of a ball-end S-shaped edge is improved.

Owner:KEDE NUMERICAL CONTROL CO LTD

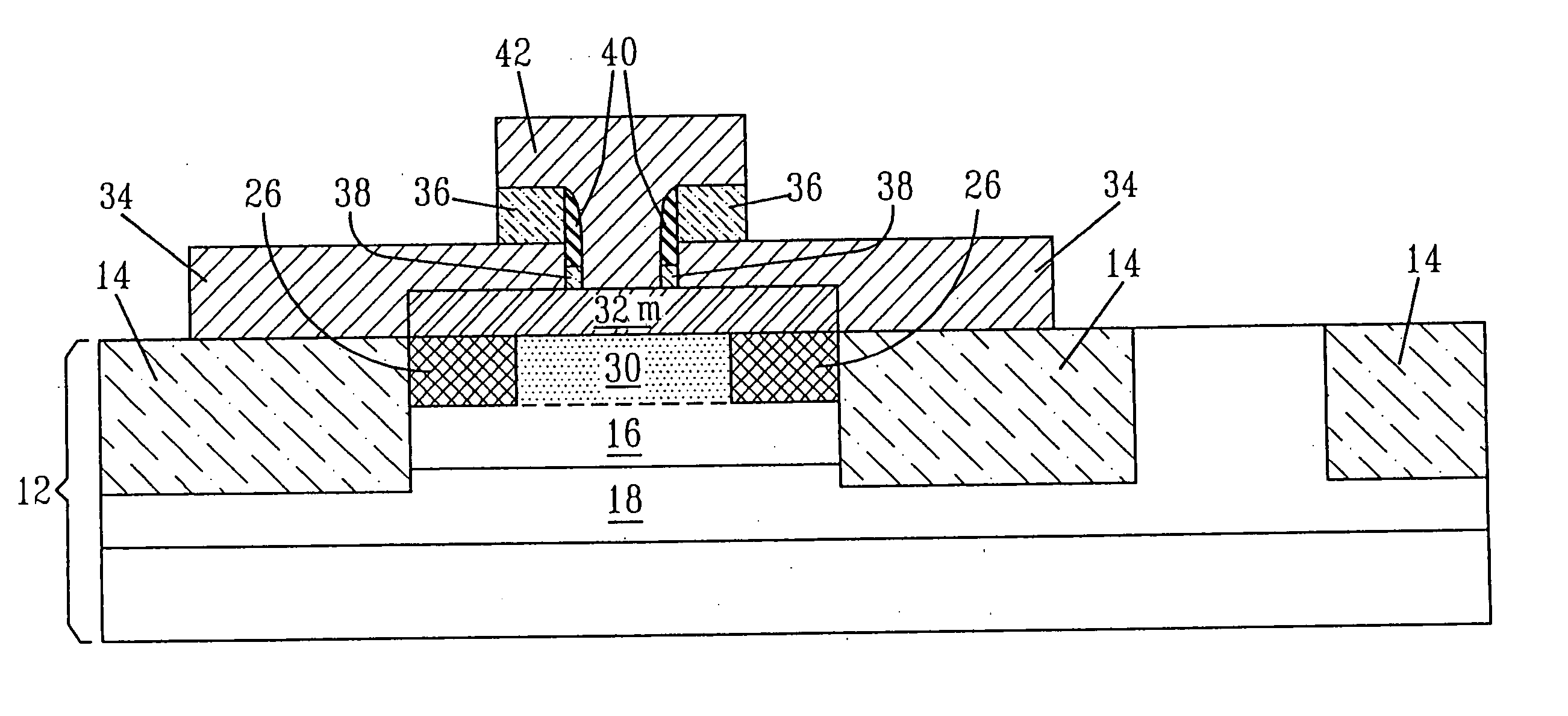

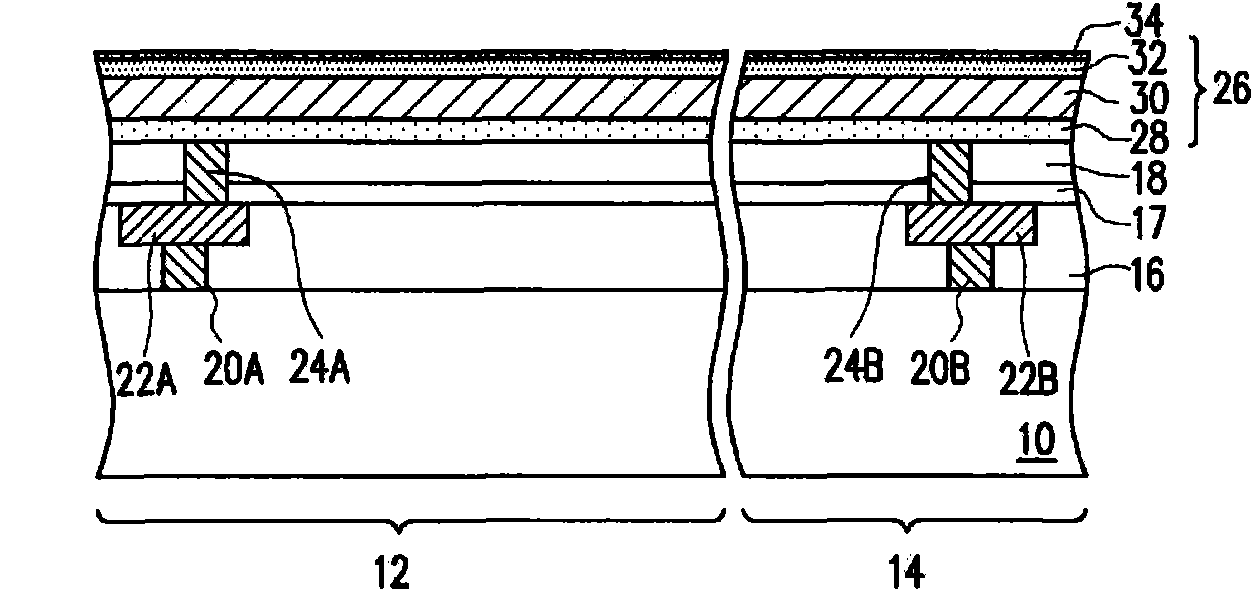

BIPOLAR TRANSISTOR WITH COLLECTOR HAVING AN EPITAXIAL Si:C REGION

InactiveUS20060154476A1Lower parasitic CCBReduce perimeter componentSolid-state devicesSemiconductor/solid-state device manufacturingHeterojunctionIon implantation

A structure and method where C is incorporated into the collector region of a heterojunction bipolar device by a method which does not include C ion implantation are provided. In the present invention, C is incorporated into the collector by epitaxy in a perimeter trench etched into the collector region to better control the carbon profile and location. The trench is formed by etching the collector region using the trench isolation regions and a patterned layer over the center part of the collector as masks. Then, Si:C is grown using selective epitaxy inside the trench to form a Si:C region with sharp and well-defined edges. The depth, width and C content can be optimized to control and tailor the collector implant diffusion and to reduce the perimeter component of parasitic CCB.

Owner:IBM CORP

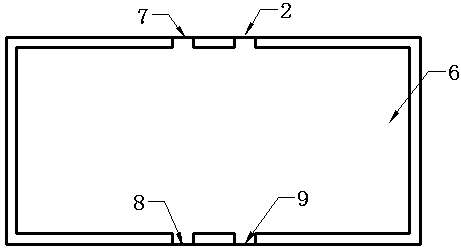

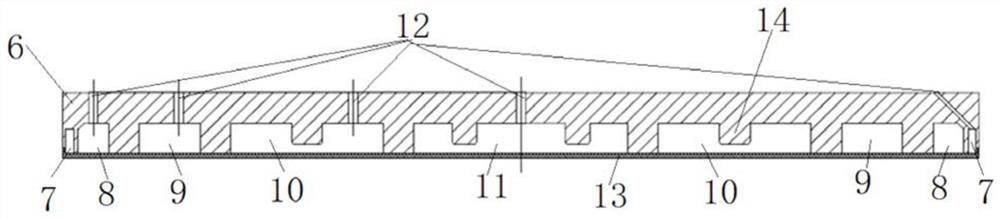

Bearing head and polishing device with same

ActiveCN111251177AConvenient air pressure controlSimple structureLapping machinesGrinding feed controlPhysicsEngineering

The invention relates to the technical field of semiconductor manufacturing process polishing, in particular to a bearing head and a polishing device with the same. The bearing head comprises a body made of a non-flexible material, wherein a plurality of concave cavities are formed in the end, close to a wafer to be polished, of the body, and a vent hole connected with an air source is formed in each concave cavity; and a flexible film is fixedly connected to the end and is suitable for making contact with the wafer to be polished. According to the bearing head, the body is made of the non-flexible material, so that a plurality of concave cavities are conveniently formed in the body; the vent holes connected with the air source are formed in the concave cavities, so that the air pressure of each concave cavity is conveniently controlled; due to the fact that the flexible film is fixedly connected to the end part, close to the wafer to be polished, of the body and is in contact with thewafer to be polished, the compactness between the flexible film and the wafer to be polished is guaranteed; and due to the fact that independent control over all the cavities is guaranteed by directly forming the cavities in the body made of the non-flexible material to be matched with the flexible film without independently arranging sealing mechanisms among all the cavities, and therefore the structure and the process manufacturing of the bearing head simpler.

Owner:北京晶亦精微科技股份有限公司

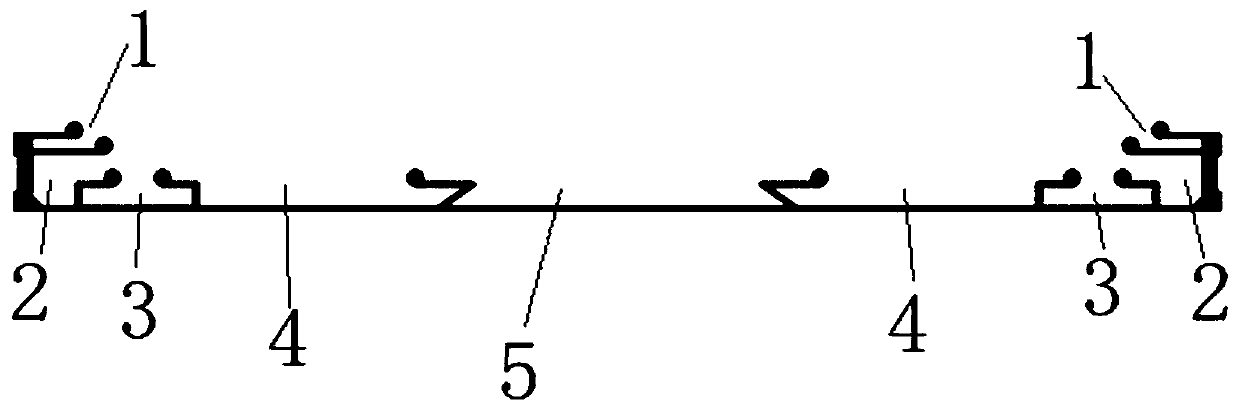

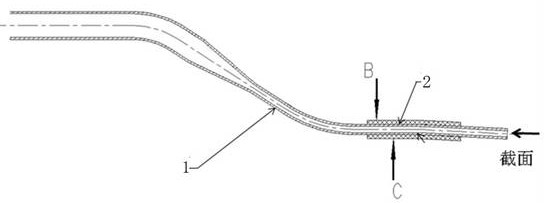

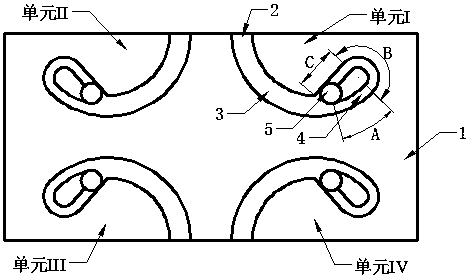

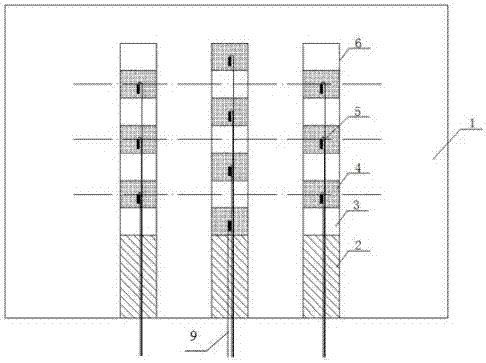

Drivage peripheral hole homoenergetic blasting method

The invention discloses a drivage peripheral hole homoenergetic blasting method. Peripheral holes (6) are dug on a roadway contour line of a surrounding rock (1) at the end part of a roadway; explosives (4) and cushioning materials (3) are alternatively arranged in each peripheral hole (6) from inside to outside; the explosives (4) in the adjacent peripheral holes (6) are distributed in a shape of a Chinese character pin; detonators (5) are arranged in sections along the explosives (4); nonel tubes (9) of the detonators (5) are led out of the holes along the hole walls of the peripheral holes (6); hole orifices of the peripheral holes (6) are plugged by stemming (2); then detonation is carried out according to a designed detonation network connecting line. According to the method disclosed by the invention, the explosives (4) and the cushioning materials (3) are distributed symmetrically, so that energy is more uniformly distributed, an energy utilization rate of the explosives is improved, a contour of a roadway section is well controlled, the back break phenomenon is avoided, and roadway supporting cost is reduced; meanwhile, the uniformly distributed explosive energy can enable a fragment size for blasting to be uniform, obviously improve a blasting effect and improve shovel-loading efficiency after blasting.

Owner:SINOSTEEL MAANSHAN INST OF MINING RES +1

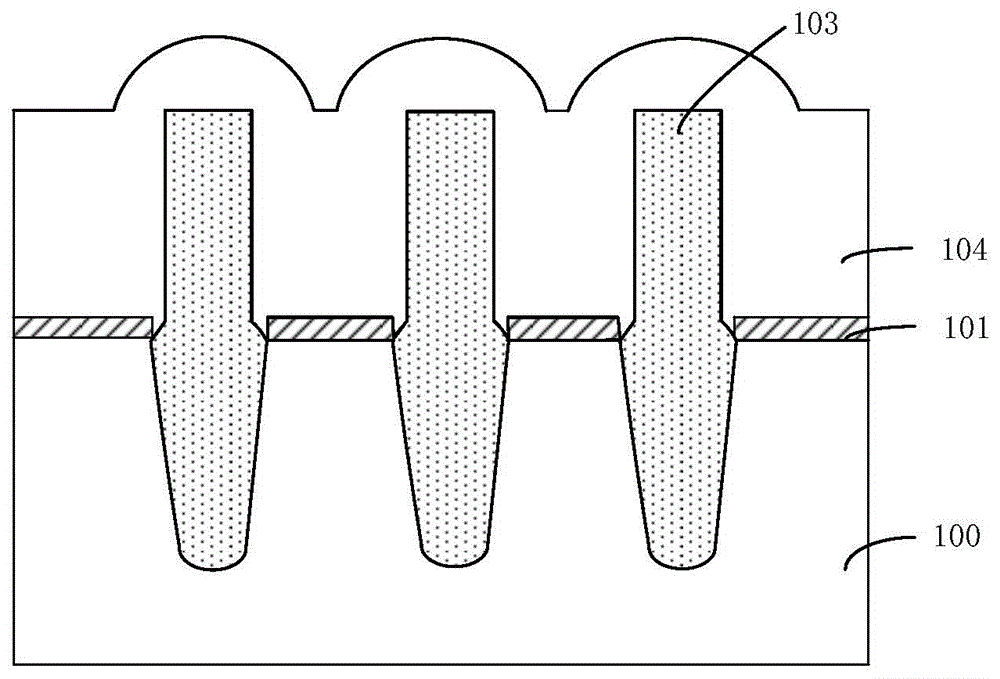

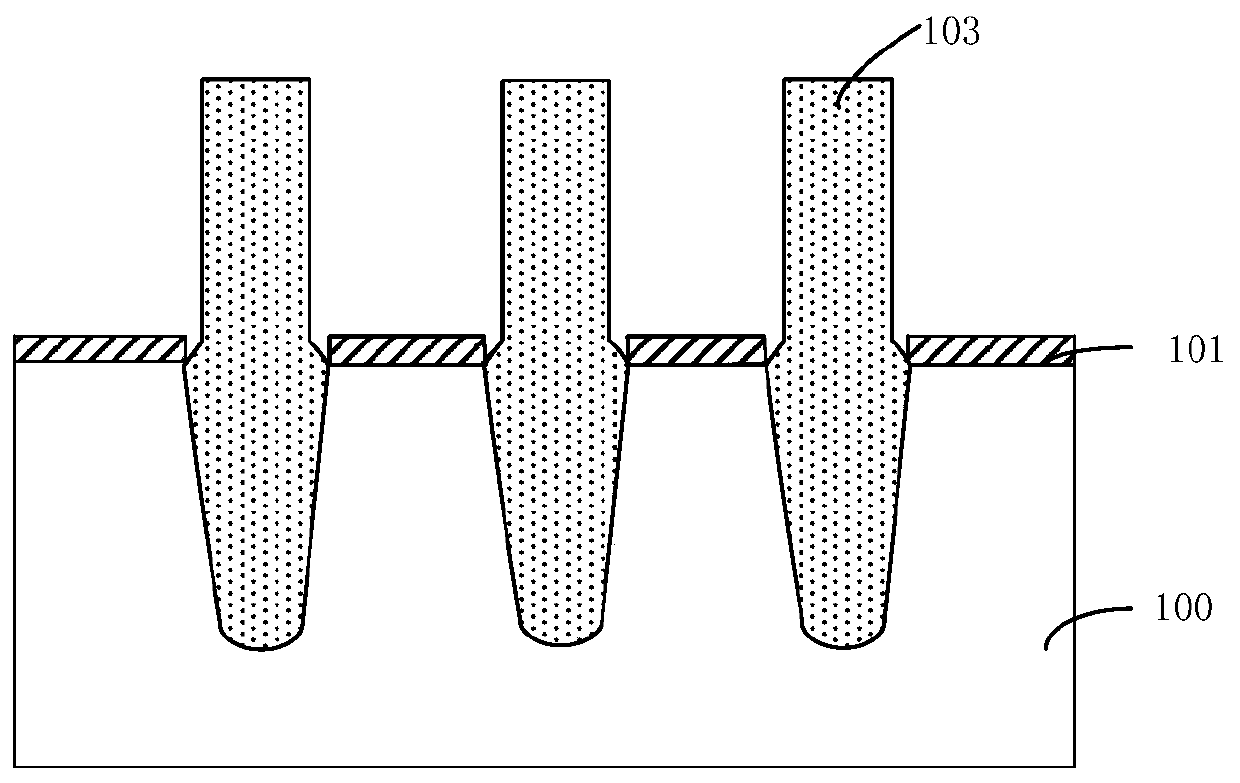

Semiconductor device and manufacturing method thereof and electronic device

ActiveCN105448921AControl profileImprove the coupling rateSolid-state devicesSemiconductor/solid-state device manufacturingPower semiconductor deviceProcess window

The invention discloses a semiconductor device and a manufacturing method thereof and an electronic device. The method comprises the following steps: forming a first hard mask layer, a second hard mask layer, a sacrificial layer and a third hard mask layer on a semiconductor substrate in sequence; carrying out etching process to form shallow trenches; filling isolation material layers in the shallow trenches; carrying out back etching to remove the sacrificial layer; removing the second hard mask layer; removing the first hard mask layer; forming a tunneling oxide layer on the exposed semiconductor substrate; forming a floating gate material layer on the semiconductor substrate; and carrying out planarization process. The manufacturing method provides a good process window for the formation of a shallow trench isolation structure oxide layer and floating gate polycrystalline silicon; contour of a floating gate is controlled well; and the physical contour of the floating gate helps to improve coupling efficiency of the device.

Owner:SEMICON MFG INT (SHANGHAI) CORP

Semiconductor device and manufacturing method thereof, and electronic device

ActiveCN105336590AImprove device couplingGood breakdown voltageSolid-state devicesSemiconductor/solid-state device manufacturingOxidePolycrystalline silicon

The invention discloses a semiconductor device and a manufacturing method thereof, and an electronic device. The method comprises the following steps: forming a hard mask layer on a semiconductor substrate; etching the hard mask layer and the semiconductor substrate so as to form a shallow trench; filling an isolation material layer in the shallow trench; removing the hard mask layer; forming a tunneling oxide layer on the exposed semiconductor substrate; forming a first floating gate material layer on the semiconductor substrate; executing a planarization technology; forming a second floating gate material layer whose width is greater than that of the first floating gate material layer on the first floating gate material layer by use of an epitaxial growth technology; and successively forming a dielectric layer and a control gate material layer on the semiconductor substrate. According to the manufacturing method provided by the invention, a good technical window is provided for forming a shallow trench isolation structure oxide layer and floating gate polysilicon.

Owner:SEMICON MFG INT (SHANGHAI) CORP

Color-based writing trace extraction method, system and device under complex background

ActiveCN110532980AImprove connectivityEfficient extractionDigital ink recognitionCharacter recognitionImaging qualityChange color

The invention belongs to the technical field of target extraction, particularly relates to a color-based writing trace extraction method, system and device under a complex background, and aims to solve the problems that an existing extraction method is incomplete in writing trace extraction and high in image quality requirement, and writing traces with changed colors cannot be extracted under a complex environment. The method comprises the steps of converting a to-be-detected image containing a to-be-detected writing trace into an HSV color space, selecting seed points based on the HSV color space, and dynamically obtaining pixel points on an edge image from the seed points to serve as newly-added to-be-traversed points; and based on the seed points and newly added points to be traversed,obtaining a pixel set of writing traces to be detected through image refinement. According to the method, the connectivity of the correction trace can be enhanced, and the correction trace can be effectively extracted in a complex scene; meanwhile, the conditions of newly-added points to be traversed are strictly set, the outline of the writing trace can be effectively controlled, excessive noiseis prevented from being introduced, and subsequent processing is facilitated.

Owner:BEIJING YUNJIANG TECH CO LTD

Embedded flash memory, manufacturing method therefor, and electronic device

InactiveCN105845631AAvoid holesImprove coupling performanceSolid-state devicesSemiconductor/solid-state device manufacturingOxideHigh pressure

The present invention relates to an embedded flash memory, a preparation method thereof, and an electronic device. The method includes step S1: providing a substrate, and a high-voltage oxide layer and a tunneling oxide layer are respectively formed on different regions of the substrate; step S2: Depositing a floating gate material layer and a mask layer on the high voltage oxide layer and the tunnel oxide layer, and forming a shallow trench extending into the substrate in the floating gate material layer and the mask layer trench isolation oxide; step S3: remove the mask layer to expose a part of the height of the shallow trench isolation oxide; step S:4: etch back the exposed shallow trench isolation oxide to reduce the exposed The critical dimension of the shallow trench isolation oxide; step S5: depositing the floating gate material layer to the top of the shallow trench isolation oxide again, and step S6 etching the floating gate material layer and the shallow trench isolation Oxide; step S7 : removing the portion of the shallow trench isolation oxide where the critical dimension is reduced, so as to form a T-shaped floating gate.

Owner:SEMICON MFG INT (SHANGHAI) CORP

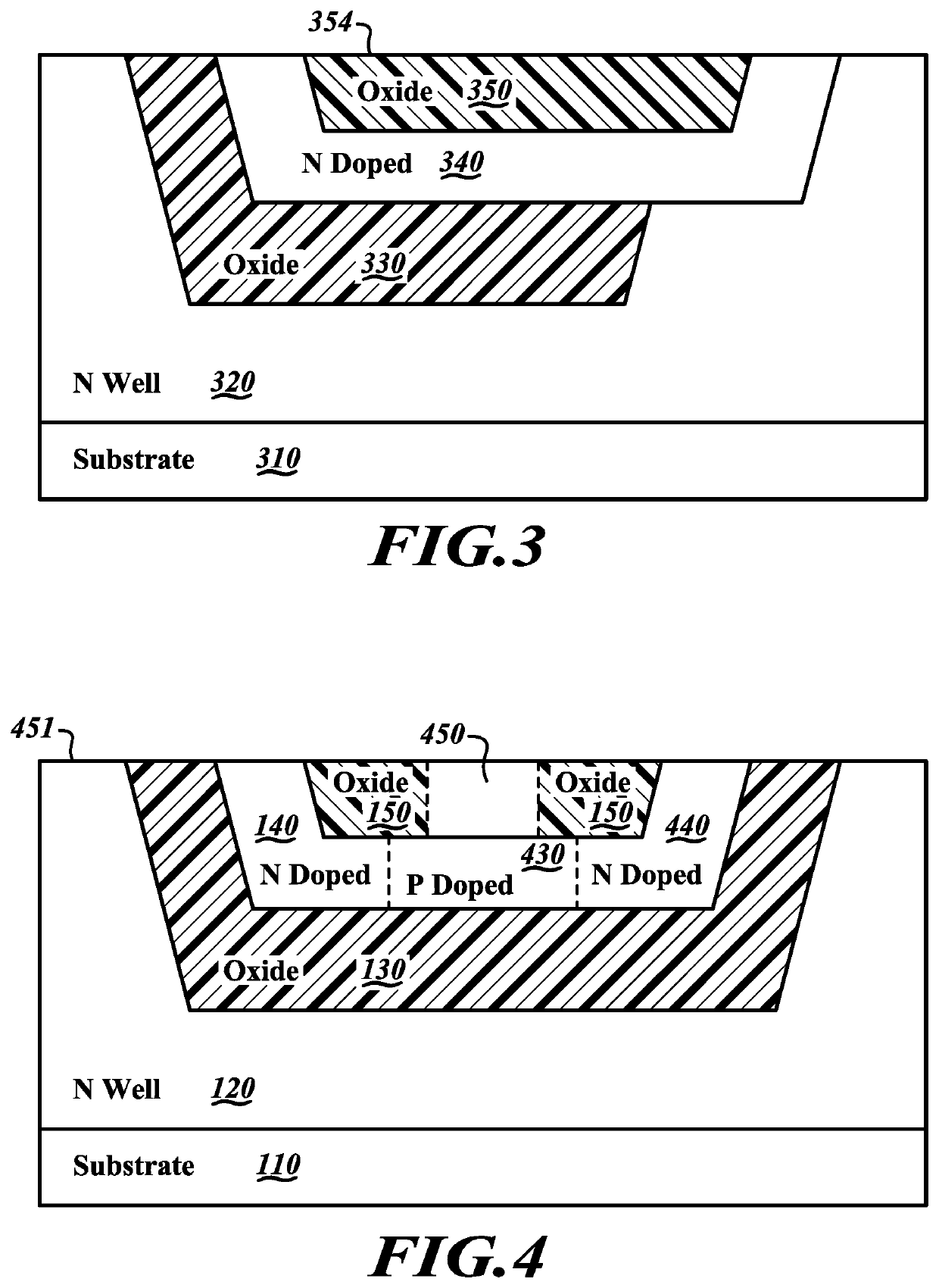

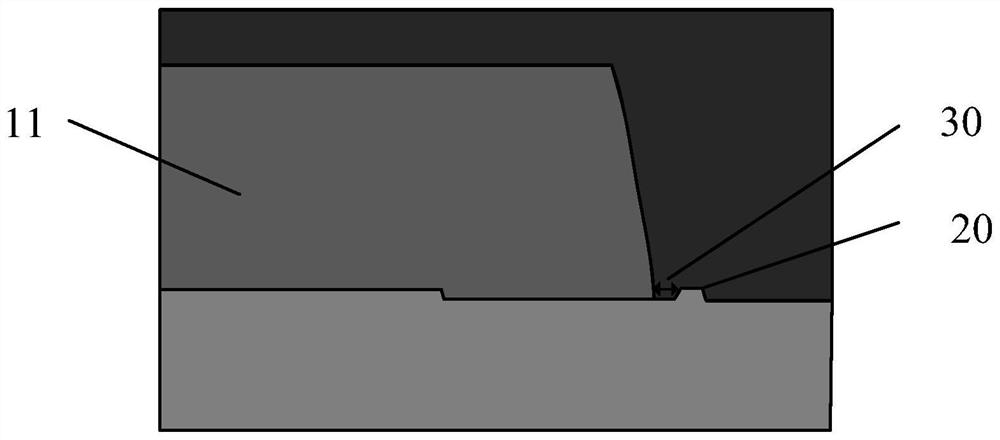

Semiconductor structure with partially embedded insulation region

ActiveUS10796942B2Control profileControl shapeSemiconductor/solid-state device manufacturingSemiconductor devicesSemiconductor structurePhysical chemistry

Owner:STMICROELECTRONICS SRL

Bipolar transistor with collector having an epitaxial Si:C region

InactiveUS20060289852A1The location is limitedControl profileSemiconductor/solid-state device manufacturingSemiconductor devicesHeterojunctionIon implantation

A structure and method where C is incorporated into the collector region of a heterojunction bipolar device by a method which does not include C ion implantation are provided. In the present invention, C is incorporated into the collector by epitaxy in a perimeter trench etched into the collector region to better control the carbon profile and location. The trench is formed by etching the collector region using the trench isolation regions and a patterned layer over the center part of the collector as masks. Then, Si:C is grown using selective epitaxy inside the trench to form a Si:C region with sharp and well-defined edges. The depth, width and C content can be optimized to control and tailor the collector implant diffusion and to reduce the perimeter component of parasitic CCB.

Owner:INT BUSINESS MASCH CORP

Preparation method of bulk silicon-based longitudinal stack-type silicon nanowire field effect transistor (SiNWFET)

ActiveCN102623322BEfficient releaseNo self-heating effectSemiconductor/solid-state device manufacturingSemiconductor devicesSilicon nanowiresHeating effect

The invention discloses a method for preparing a vertically stacked SiNWFET based on bulk silicon, comprising: providing an integrated silicon substrate, on which SiGe layers and Si layers are alternately grown; Photolithography and etching to form a fin-shaped active region, and the remaining SiGe layer and Si layer are used as source and drain regions; the SiGe layer in the fin-shaped active region is removed by selective etching to form silicon nanowires, the Silicon nanowires are stacked vertically; a gate oxide layer is formed on the silicon nanowires, bulk silicon substrate, and source and drain regions; a gate is formed on the bulk silicon substrate between the source and drain regions; An isolation dielectric layer is formed between the drain region and the gate. The invention is based on bulk silicon and has no self-heating effect; adopts a conventional gate oxide layer; and is a rear isolation layer process without side wall process; the active area and the upper surface of the gate are on the same horizontal plane, which is beneficial to the subsequent contact hole process. The silicon nanowires are vertically stacked, which is beneficial to increase the integration degree of the device and the current driving capability of the device.

Owner:SHANGHAI HUALI MICROELECTRONICS CORP

A method and structure for welding bushings on flat tubes

ActiveCN110814496BControl profileGuaranteed not to deformResistance welding apparatusMetal sheetCantilever

The invention discloses a method for welding a bushing on a flat tube, comprising: 1. Inserting a skid into the flat tube; 2. Fitting and welding the middle section of the U-shaped bushing to one surface of the flat tube; 3. 1. Bend the two cantilevers of the bushing to fit the other side of the flat tube. 4. Place a high-conductivity metal sheet on the outside of the bushing on the welded surface, and connect the metal sheet to the flat tube with a metal wire ; Five, the unwelded surface of the welded flat tube. With this method, the surface of the conduit can be controlled to ensure that the conduit is not deformed during the welding process; the distribution position of the solder joints can be freely selected to ensure the accuracy of the number and position of the solder joints.

Owner:CHINA HANGFA GUIZHOU LIYANG AVIATION POWER CO LTD

Mixed semiconductor nanocrystal compositions

InactiveUS7888855B2Minimize “bad” energy transferReduce reabsorptionMaterial nanotechnologyDischarge tube luminescnet screensColloidPeak value

Owner:LOS ALAMOS NATIONAL SECURITY

Method for fabricating a mosfet and reducing line width of gate structure

InactiveCN1312747CReduce line widthLine widthTransistorSemiconductor/solid-state device manufacturingMOSFETLine width

A method for fabricating a MOSFET is provided. The method comprises: providing a substrate, the substrate having a gate structure; forming a drain region and a source region in the substrate, the drain region and the source region being on two sides of the gate structure respectively; forming a metal suicide layer on the surface of the gate structure, the drain region, and the source region; forming a patterned block on the metal silicide layer above the gate structure, and forming a first dielectric layer above the substrate except the gate strcutre, the patterned block being formed above the center of the gate structure and the metal silicide layer above the gate structure beside two sides of the patterned block being exposed; removing a portion of the metal silicide layer and a portion of the gate structure by using the patterned block as a mask; and forming a drain extension region and a source extension region in the substrate, beside two sides of the remaining gate structure.

Owner:MACRONIX INT CO LTD

An embedded flash memory, preparation method thereof, and electronic device

ActiveCN105575968BAvoid it happening againIncreased process windowSolid-state devicesSemiconductor devicesPhysical chemistryEngineering

The invention relates to an embedded flash memory, a preparation method thereof, and an electronic device. The method includes providing a substrate, in which an active area isolated by a shallow trench isolation oxide is formed, and the top of the shallow trench isolation oxide is formed. Higher than the surface of the substrate; deposit a floating gate material layer to cover the active area and the shallow trench isolation oxide; planarize the floating gate material layer to expose the surface of the shallow trench isolation oxide; etch back The floating gate material layer is used to reduce the thickness of the floating gate material layer to expose a portion of the shallow trench isolation oxide; the exposed shallow trench isolation oxide is etched back to reduce the exposed shallow trench isolation oxide. critical dimensions of the shallow trench isolation oxide; redeposit the floating gate material layer to the top of the shallow trench isolation oxide to surround the shallow trench isolation oxide, planarize the floating gate material layer; remove the shallow trench isolation oxide The trench isolates portions of the oxide with reduced critical dimensions to form a T-shaped floating gate over the active area.

Owner:SEMICON MFG INT (SHANGHAI) CORP

A kind of semiconductor device and its manufacturing method and electronic device

ActiveCN105448921BControl profileImprove the coupling rateSolid-state devicesSemiconductor devicesDevice materialSemiconductor

Owner:SEMICON MFG INT (SHANGHAI) CORP

An automatic water control valve for horizontal wells

ActiveCN107288579BEasy to installNot affected by temperature and pressureWell/borehole valve arrangementsSealing/packingOil phaseOil water

Owner:SOUTHWEST PETROLEUM UNIV

A kind of semiconductor device and its manufacturing method and electronic device

ActiveCN105448836BControl profileImprove the coupling rateSolid-state devicesSemiconductor devicesDevice materialEngineering

The invention discloses a semiconductor device, a manufacturing method thereof and an electronic device. A hard mask layer is formed on a semiconductor substrate; the hard mask layer and the semiconductor substrate are etched; and in the shallow trench Filling the isolation material layer; removing the hard mask layer to expose the semiconductor substrate; forming a tunnel oxide layer on the exposed semiconductor substrate; forming a first floating gate material layer on the semiconductor substrate ; Forming a sacrificial layer on the semiconductor substrate; removing the first floating gate material layer that is not covered with the sacrificial layer; removing the sacrificial layer; using an epitaxial growth process on the first floating gate material layer A second layer of floating gate material is formed. The manufacturing method according to the present invention provides a good process window for the formation of the shallow trench isolation structure oxide layer and floating gate polysilicon; the outline of the floating gate is well controlled; the physical outline of the floating gate has It is beneficial to improve the device coupling rate.

Owner:SEMICON MFG INT (SHANGHAI) CORP

Carrier head and polishing device with same

The invention relates to the technical field of semiconductor manufacturing process polishing, in particular to a carrier head and a polishing device having the same. The carrier head includes: a body made of non-flexible material, the end of the body close to the wafer to be polished is provided with a plurality of concave cavities, and each concave cavity is provided with a ventilation hole connected with the air source; the flexible film is fixedly connected to the end, suitable for in contact with the wafer to be polished. By setting the body to be made of inflexible material, it is convenient to open a plurality of concave cavities on the body, and a ventilation hole connected to the air source is arranged on the concave cavity, so that the air pressure control of each concave cavity is more convenient. The end of the polished wafer is fixedly connected to the flexible film, and the flexible film is used to contact the wafer to be polished to ensure the fit between the flexible film and the wafer to be polished. The non-flexible material body is used to directly open a concave cavity in the form of a flexible film to ensure the independent control of each cavity, so that the structure and process of the bearing head are relatively simple.

Owner:BEIJING SEMICORE PRECISION MICROELECTRONICS EQUIP CO LTD

Semiconductor Strucure with Partially Embedded Insulation Region

ActiveUS20200058540A1Simple designAchieve isolationSemiconductor/solid-state device manufacturingSemiconductor devicesSemiconductor structureEngineering

A technique to make silicon oxide regions from porous silicon and related semiconductor structures are disclosed. The porous silicon is made in situ by anodizing P doped silicon regions. Thus, the shape and profile of the oxide regions may be controlled by controlling the shape and profile of the P doped silicon regions.

Owner:STMICROELECTRONICS SRL

A Method for Uniform Energy Blasting of Peripheral Holes in Roadway Excavation

The invention discloses a drivage peripheral hole homoenergetic blasting method. Peripheral holes (6) are dug on a roadway contour line of a surrounding rock (1) at the end part of a roadway; explosives (4) and cushioning materials (3) are alternatively arranged in each peripheral hole (6) from inside to outside; the explosives (4) in the adjacent peripheral holes (6) are distributed in a shape of a Chinese character pin; detonators (5) are arranged in sections along the explosives (4); nonel tubes (9) of the detonators (5) are led out of the holes along the hole walls of the peripheral holes (6); hole orifices of the peripheral holes (6) are plugged by stemming (2); then detonation is carried out according to a designed detonation network connecting line. According to the method disclosed by the invention, the explosives (4) and the cushioning materials (3) are distributed symmetrically, so that energy is more uniformly distributed, an energy utilization rate of the explosives is improved, a contour of a roadway section is well controlled, the back break phenomenon is avoided, and roadway supporting cost is reduced; meanwhile, the uniformly distributed explosive energy can enable a fragment size for blasting to be uniform, obviously improve a blasting effect and improve shovel-loading efficiency after blasting.

Owner:SINOSTEEL MAANSHAN INST OF MINING RES +1

A kind of semiconductor device and its manufacturing method and electronic device

ActiveCN105336590BControl profileImprove the coupling rateSolid-state devicesSemiconductor/solid-state device manufacturingDielectric layerSemiconductor

The invention discloses a semiconductor device, a manufacturing method thereof and an electronic device. A hard mask layer is formed on a semiconductor substrate; the hard mask layer and the semiconductor substrate are etched to form a shallow trench; Filling the shallow trench with a layer of isolation material; removing the hard mask layer; forming a tunnel oxide layer on the exposed semiconductor substrate; forming a first floating gate material on the semiconductor substrate layer; perform a planarization process; use an epitaxial growth process to form a second floating gate material layer with a width greater than that of the first floating gate material layer on the first floating gate material layer; in the semiconductor A dielectric layer and a control gate material layer are formed on the substrate in sequence. The fabrication method according to the present invention provides a good process window for the formation of the shallow trench isolation structure oxide layer and floating gate polysilicon.

Owner:SEMICON MFG INT (SHANGHAI) CORP

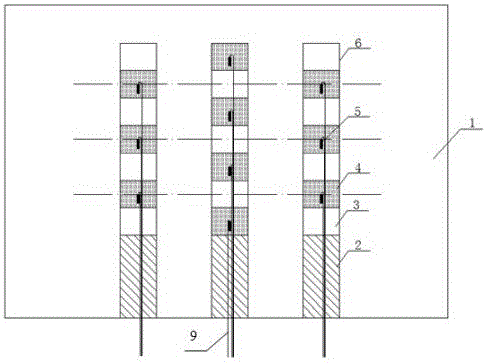

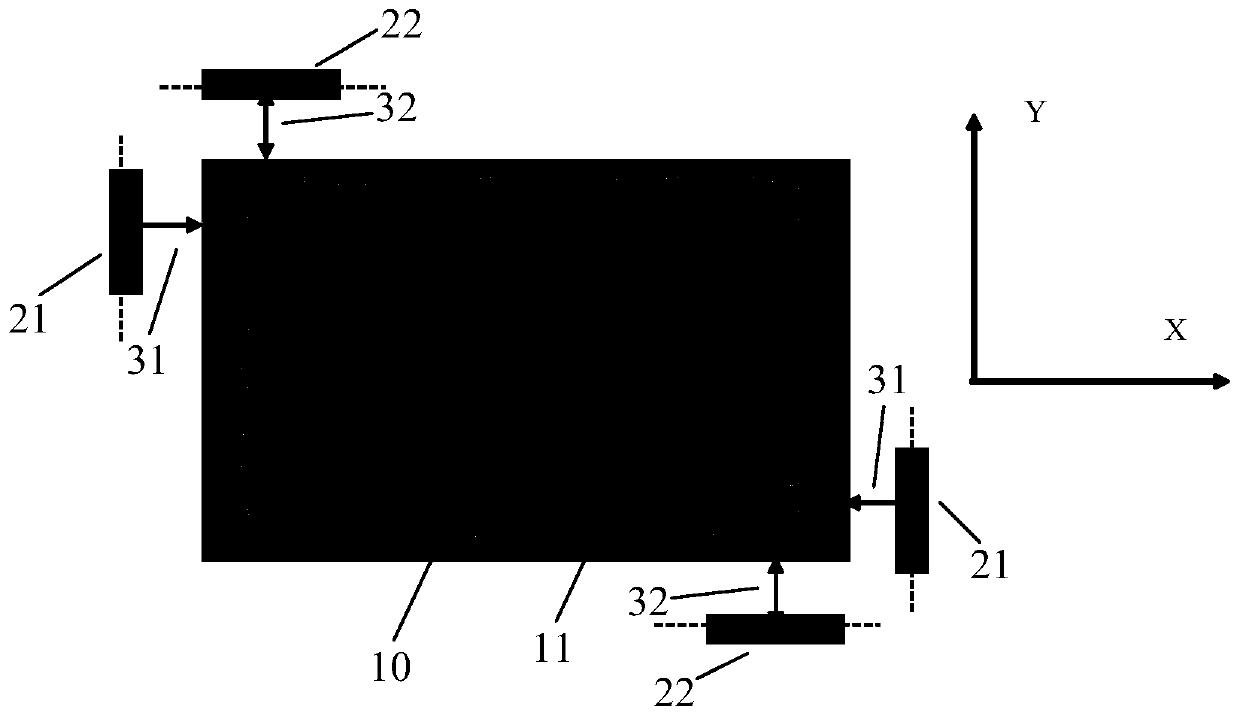

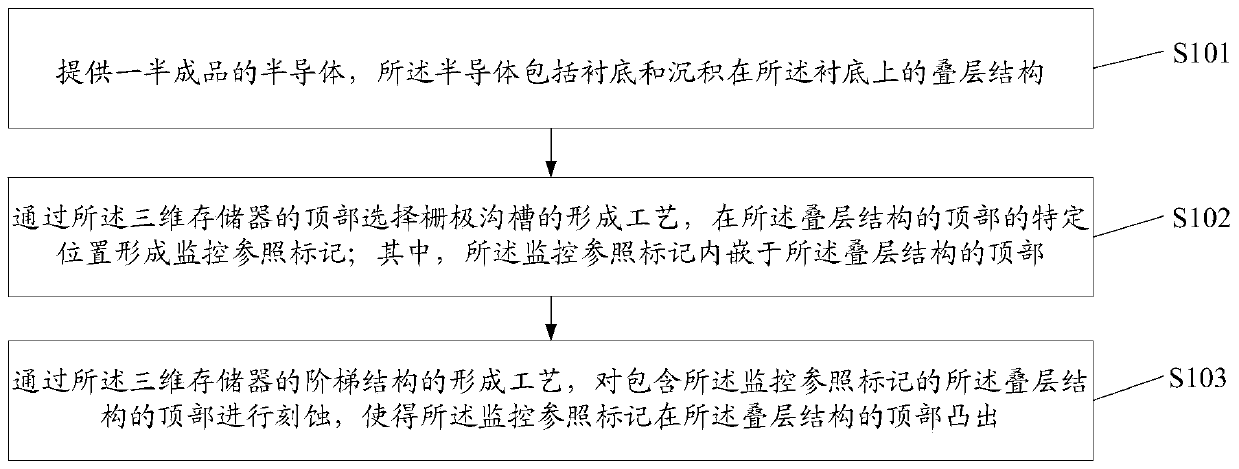

A method for forming a monitoring reference mark, a monitoring reference mark, and a three-dimensional memory

ActiveCN111584461BMonitor critical dimensionsSmall sizeSemiconductor/solid-state device detailsSolid-state devicesMechanical engineeringSemiconductor

The embodiment of the present application discloses a method for forming a monitoring reference mark, a monitoring reference mark, and a three-dimensional memory, wherein the method is applied to the formation process of a three-dimensional memory, including: providing a semi-finished semiconductor, the semiconductor including a substrate and a deposition A stacked structure on the substrate; through the formation process of the top selection gate trench of the three-dimensional memory, a monitoring reference mark is formed at a specific position on the top of the stacked structure; wherein, the monitoring reference mark Embedded in the top of the stacked structure; through the formation process of the ladder structure of the three-dimensional memory, the top of the stacked structure including the monitoring reference mark is etched, so that the monitoring reference mark is on the The top of the laminated structure protrudes.

Owner:YANGTZE MEMORY TECH CO LTD

Monitoring reference mark forming method, monitoring reference mark and three-dimensional memory

ActiveCN111584461AMonitor critical dimensionsSmall sizeSemiconductor/solid-state device detailsSolid-state devicesMechanical engineeringSemiconductor

The embodiment of the invention discloses a monitoring reference mark forming method, a monitoring reference mark and a three-dimensional memory, and the method is applied to a forming process of thethree-dimensional memory and comprises the steps: providing a semi-finished semiconductor which comprises a substrate and a laminated structure deposited on the substrate; forming a monitoring reference mark at a specific position of the top of the laminated structure through a forming process of a top selection gate trench of the three-dimensional memory, wherein the monitoring reference mark isembedded in the top of the laminated structure; and etching the top of the laminated structure containing the monitoring reference mark through a forming process of the stepped structure of the three-dimensional memory, so that the monitoring reference mark protrudes out of the top of the laminated structure.

Owner:YANGTZE MEMORY TECH CO LTD

Manufacturing method of semiconductor element

ActiveCN101964304BImprove the performance of stress migrationReduce sidewall protrusionsSemiconductor/solid-state device manufacturingSemiconductor devicesCopperPhotoresist

The invention relates to a manufacturing method of a semiconductor element, which comprises the following steps of: firstly, forming a lower electrode material layer containing aluminum and copper on a substrate; secondly, forming an insulating material layer and an upper electrode material layer on the surface of the lower electrode material layer in sequence; thirdly, forming a patterned photoresist layer on the upper electrode material layer, and patterning the upper electrode material layer by using the photoresist layer as a mask to form a patterned upper electrode material layer; fourthly, ashing and removing the patterned photoresist layer by using a plasma, and fusing the patterned lower electrode material layer; and finally, patterning the insulating material layer and the lower electrode material layer to form a patterned insulating layer and a lower patterned electrode layer.

Owner:UNITED MICROELECTRONICS CORP

Method and structure for welding bushing on flat pipe

ActiveCN110814496AGuaranteed accuracyProfile can be controlledResistance welding apparatusMetal sheetPipe

The invention discloses a method for welding a bushing on a flat pipe. The method comprises the following steps: firstly, inserting a cushion wood into the flat pipe; secondly, bonding and welding themiddle section of the U-shaped bushing and one surface of the flat pipe; thirdly, bending two cantilever arms of the bushing to be attached to the other surface of the flat pipe; fourthly, padding ametal sheet with high conductivity outside the welded surface of the bushing, and connecting the metal sheet with the flat pipe by using a metal wire; and fifthly, welding the unwelded surface of theflat pipe. By adopting the method, the profile of the guide pipe can be controlled, and it is ensured that the guide pipe is not deformed in the welding process; and the distribution positions of welding spots can be freely selected, and the quantity and the position accuracy of the welding spots are guaranteed.

Owner:CHINA HANGFA GUIZHOU LIYANG AVIATION POWER CO LTD

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com