Manufacturing method of semiconductor element

A manufacturing method and semiconductor technology, applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve problems such as large resistance displacement distribution, capacitor bridging, short circuit, etc., to reduce sidewall protrusions, avoid bridging, and control The effect of silhouette

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

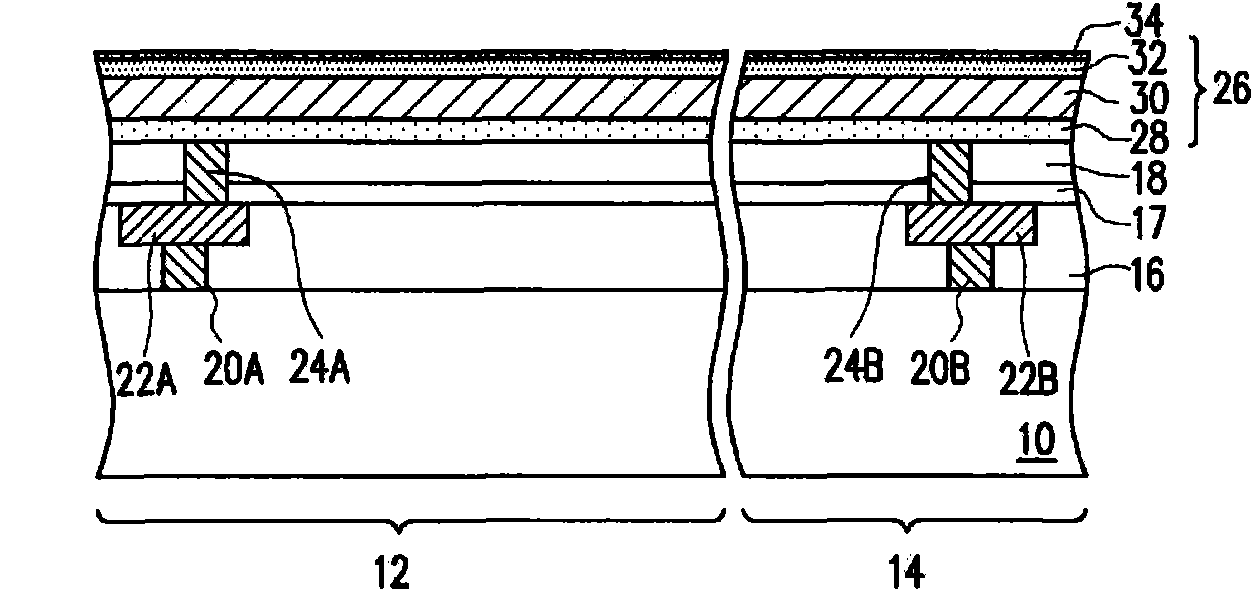

[0038] Figures 1A to 1G It is a schematic cross-sectional view of a process flow of a method for manufacturing a semiconductor device according to an embodiment of the present invention.

[0039] Please refer to Figure 1A As shown, the substrate 10 includes a first circuit area 12 and a second circuit area 14 . The first circuit area 12 is, for example, a core circuit area; the second circuit area 14 is, for example, a logic circuit area. A dielectric layer 16 and a dielectric layer 18 have been formed on the first circuit area 12 and the second circuit area 14 of the substrate 10 . The dielectric layer 16 on the first circuit area 12 has a via plug 20A and a wire 22A; the dielectric layer 18 on the first circuit area 12 has a via plug 24A in it. The dielectric layer 16 on the second circuit area 14 has a via plug 20B and a wire 22B; the dielectric layer 18 on the second circuit area 14 has a via plug 24B in it. Transistors, other dielectric layers, via plugs, metal wires...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com