Method for fabricating a mosfet and reducing line width of gate structure

A technology of oxide semiconductors and manufacturing methods, which is applied in semiconductor/solid-state device manufacturing, transistors, semiconductor devices, etc., and can solve problems such as reduced process margins, difficulty in forming correct line widths, and inability to form metal silicide layers well , to achieve the effect of easy control, lower thermal budget and wide process margin

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

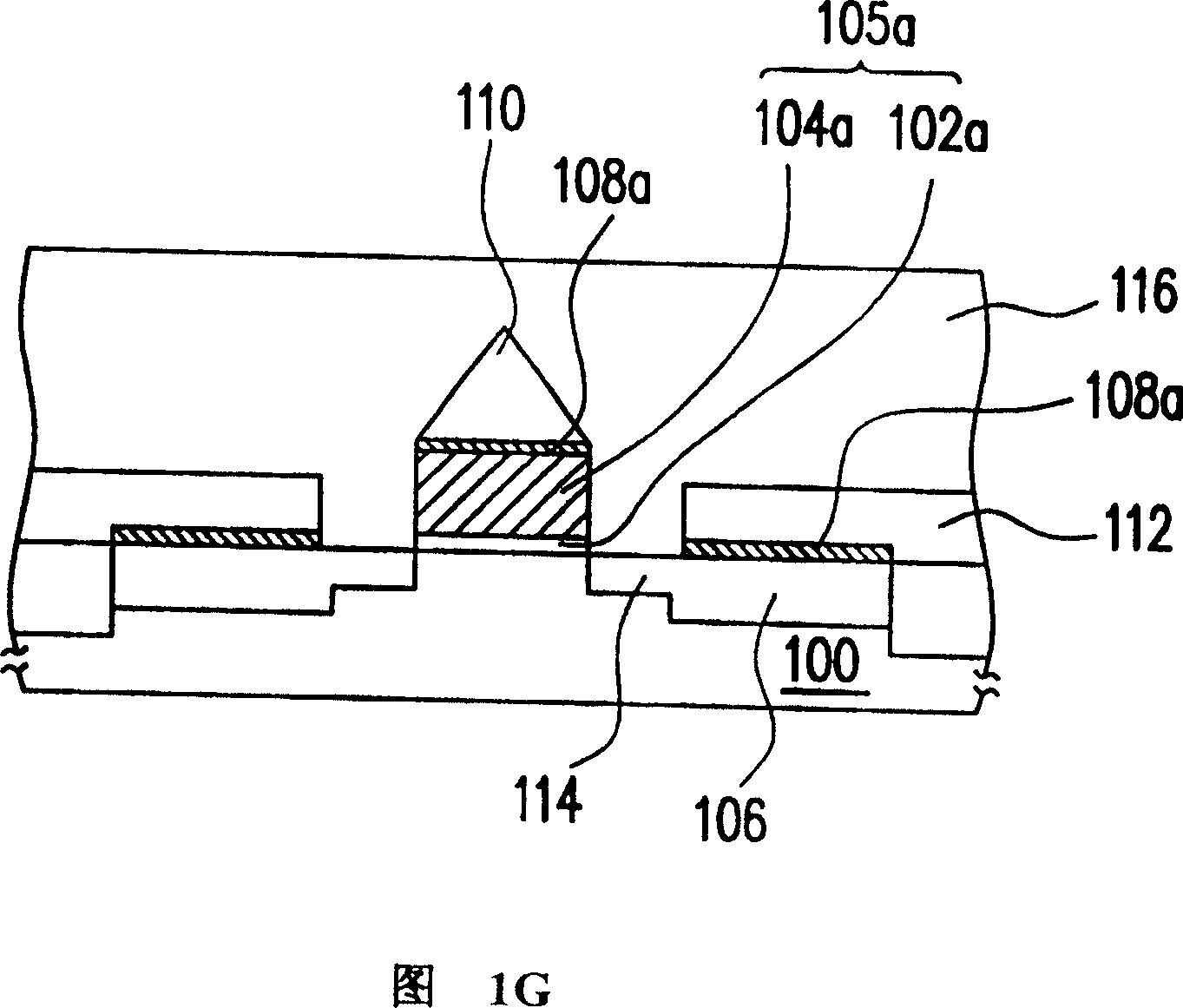

[0028] 1A to 1G are schematic cross-sectional flow diagrams illustrating a method for manufacturing a metal oxide semiconductor transistor according to a preferred embodiment of the present invention.

[0029] First, referring to FIG. 1A , a substrate 100 on which a gate structure 105 has been formed is provided, wherein the gate structure 105 is formed by sequentially stacking a gate dielectric layer 102 and a conductor layer 104. The material of the substrate 100 is, for example, The material of the silicon substrate and the gate dielectric layer 102 is, for example, silicon oxide; (not shown), and then pattern the dielectric material layer and the conductive material layer to form.

[0030] Next, referring to FIG. 1B , source / drain regions 106 are formed in the substrate 100 on both sides of the gate structure 105 by, for example, using the gate structure 105 as a mask to perform an ion implantation process on the substrate 100. , to form source / drain regions 106 in the su...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com