Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

56 results about "Effective density" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

The effective density of states comes from the fundamental definition of the free carrier density in a solid. which depends on the density of states N(E). The density of states (DOS) is determined by the electron structure of the solid.

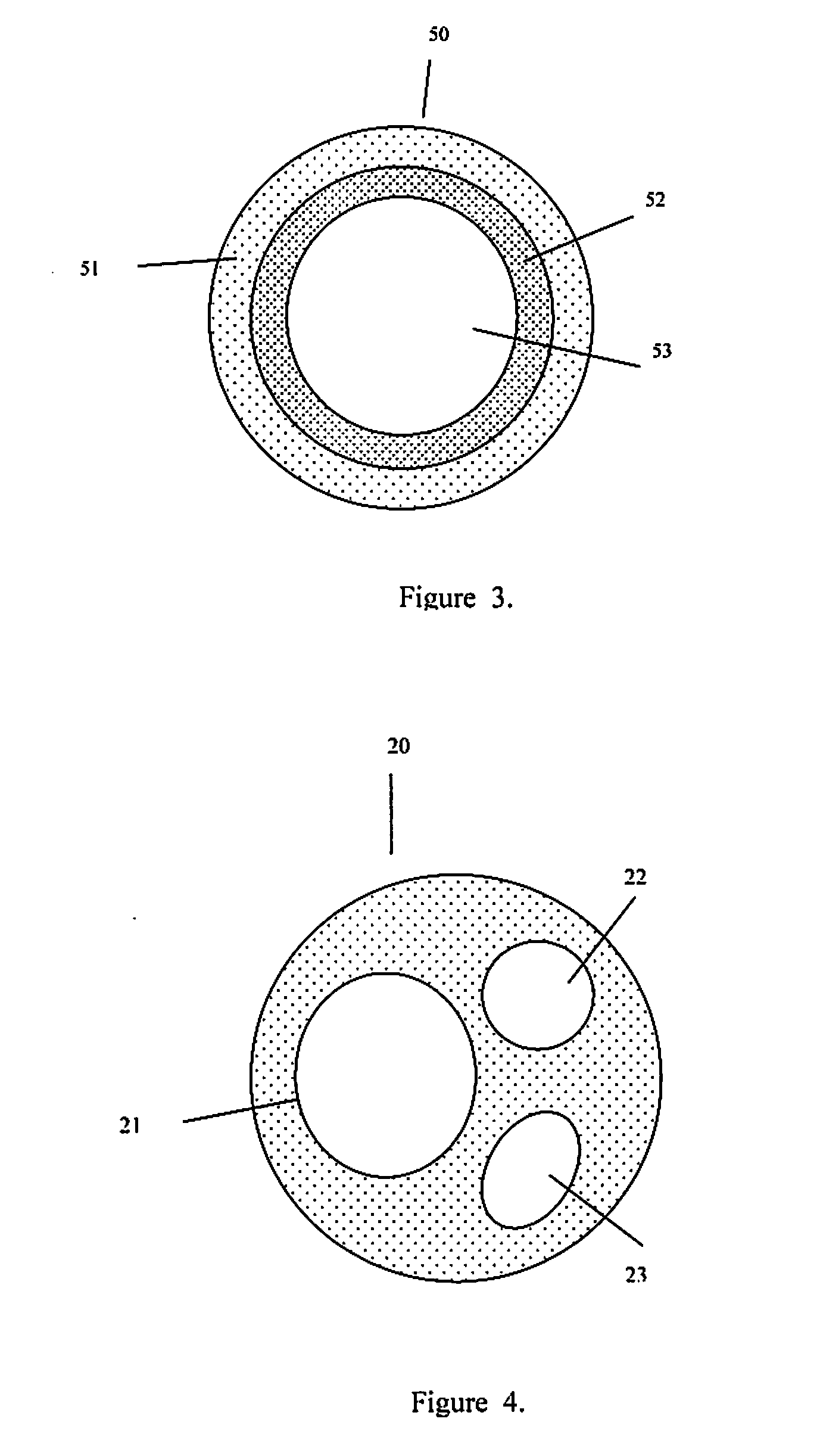

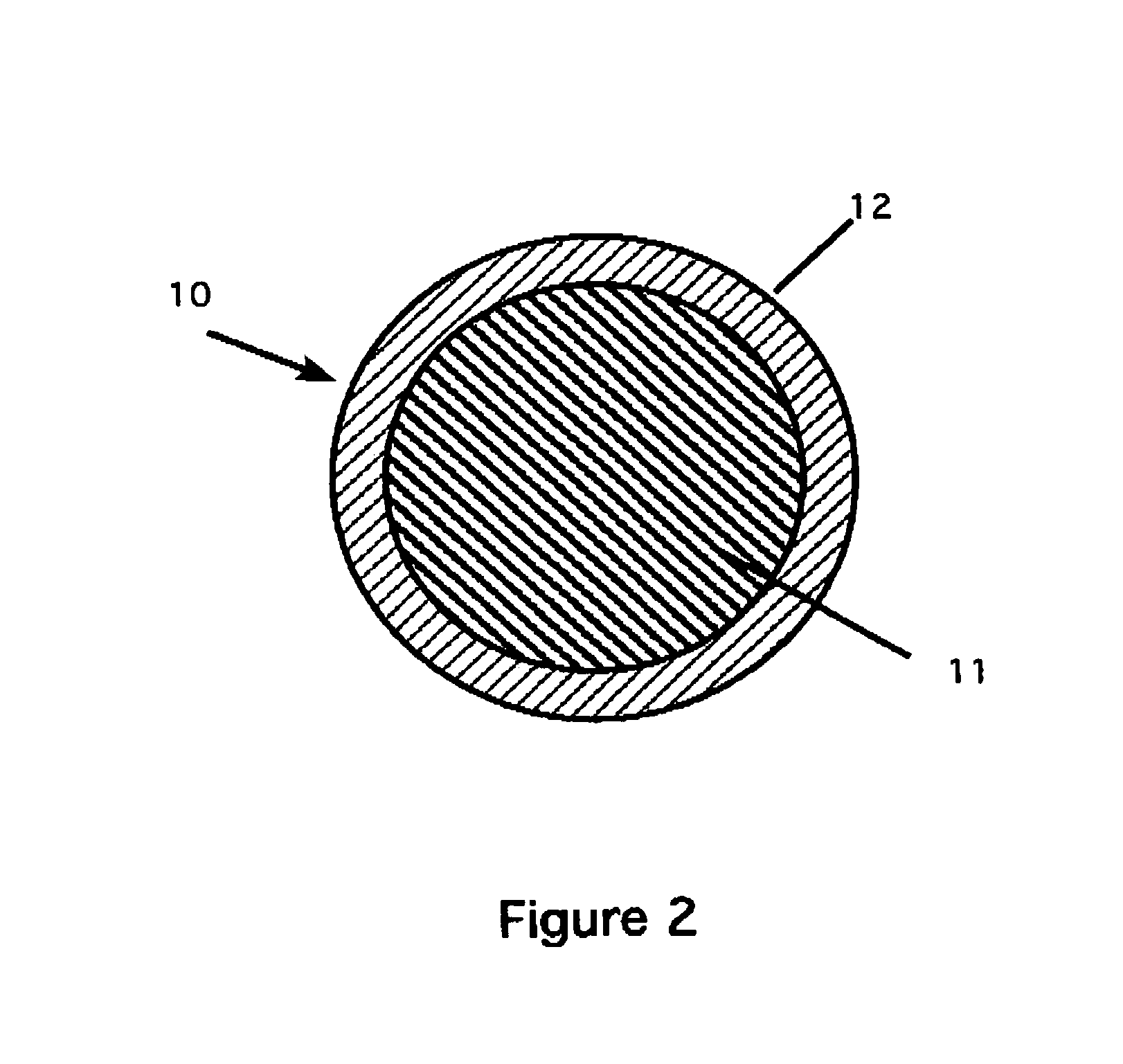

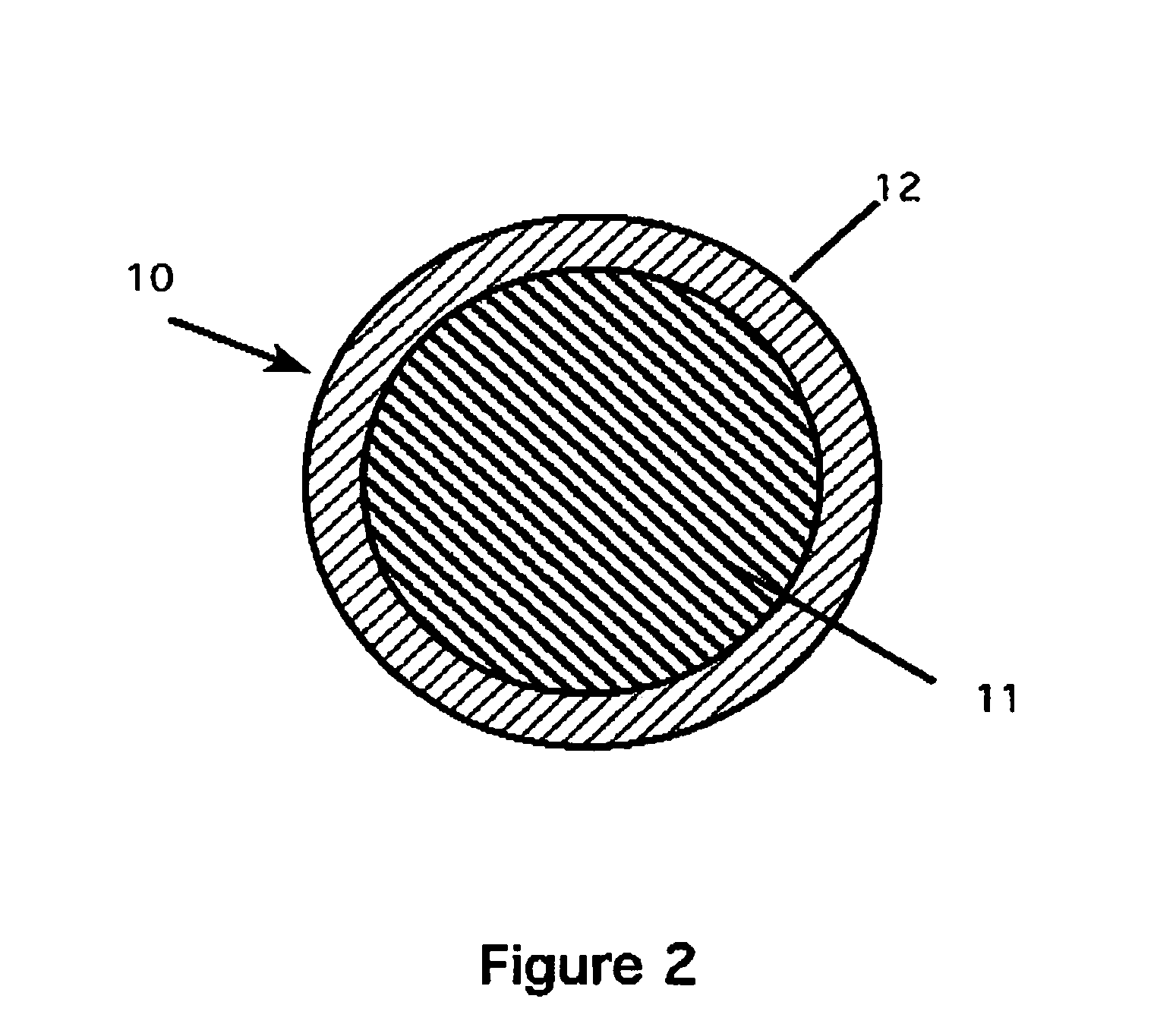

Injectable hollow tissue filler

The present invention comprises a plurality of injectable hollow particulate fillers suspended in a biocompatible fluid carrier to significantly improve the clumping resistance and injectability of the composition. The hollow particulate fillers have a lower effective density and are able to suspend in the carrier without precipitation. The loss of skin volume as a result of aging, diseases, weight loss, and injury can lead to uneven skin surface (e.g. wrinkle, etc.). The uneven skin can be repaired by injecting appropriate amount of hollow fillers underneath the skin. Some cases of urinary incontinence occur when the resistance to urine flow has decreased excessively. Continence is restored by injecting the present invention to the urethra tissue to increase resistance to urine outflow. Similarly, the present invention allows for the control of gastric fluid reflux by submucosal injections of the fillers to the esophageal-gastric and gastric-pyloric junction. For patients with vesicoureteral reflux, it can be treated by injection of the present invention into patients' ureteral tissue. This invention can also be used to repair defective or inadequately functioning muscles of the anal sphincter by administering an effective amount of injectable hollow fillers into the defect or anal sinuses.

Owner:CHU JACK FA DE

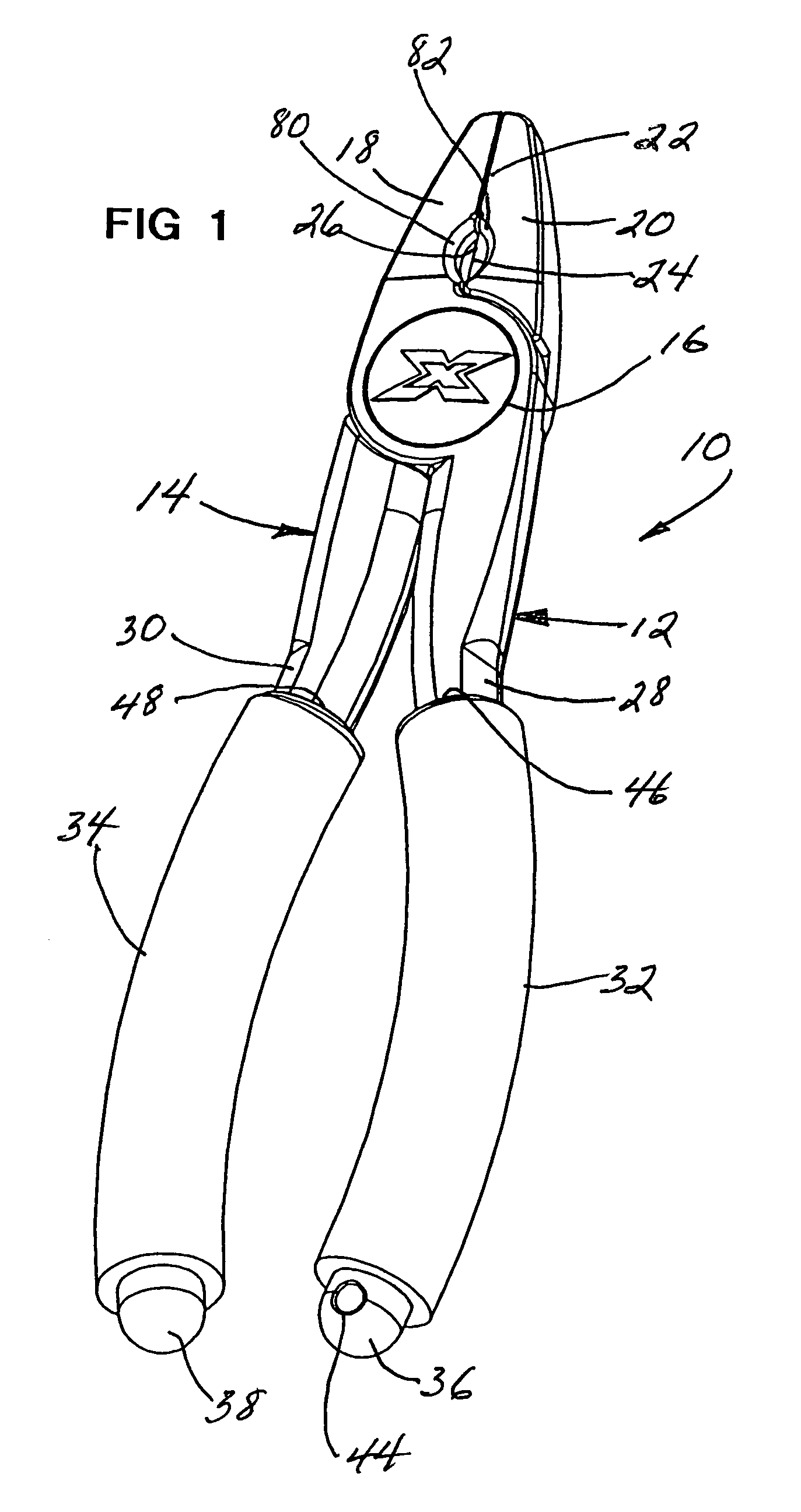

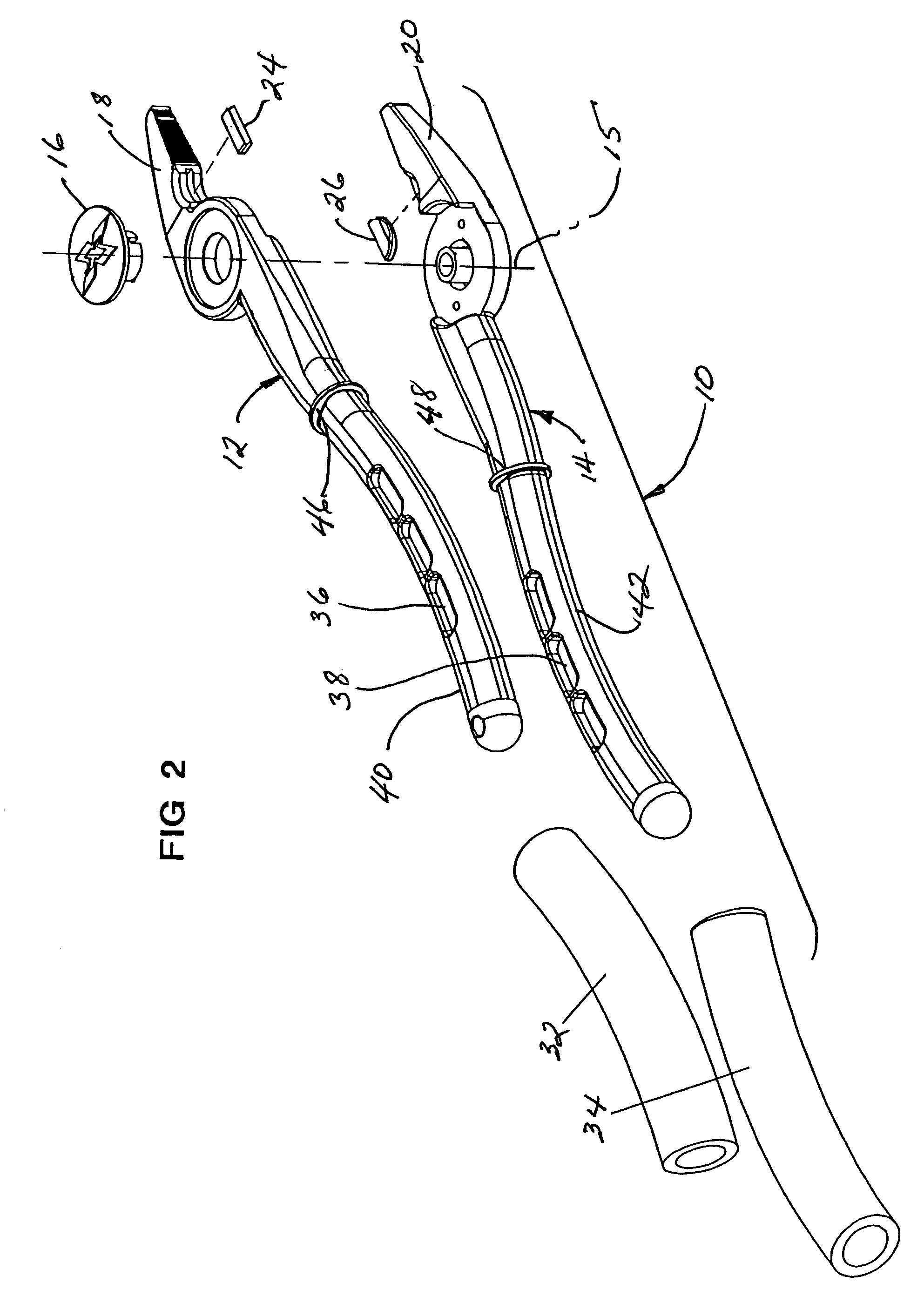

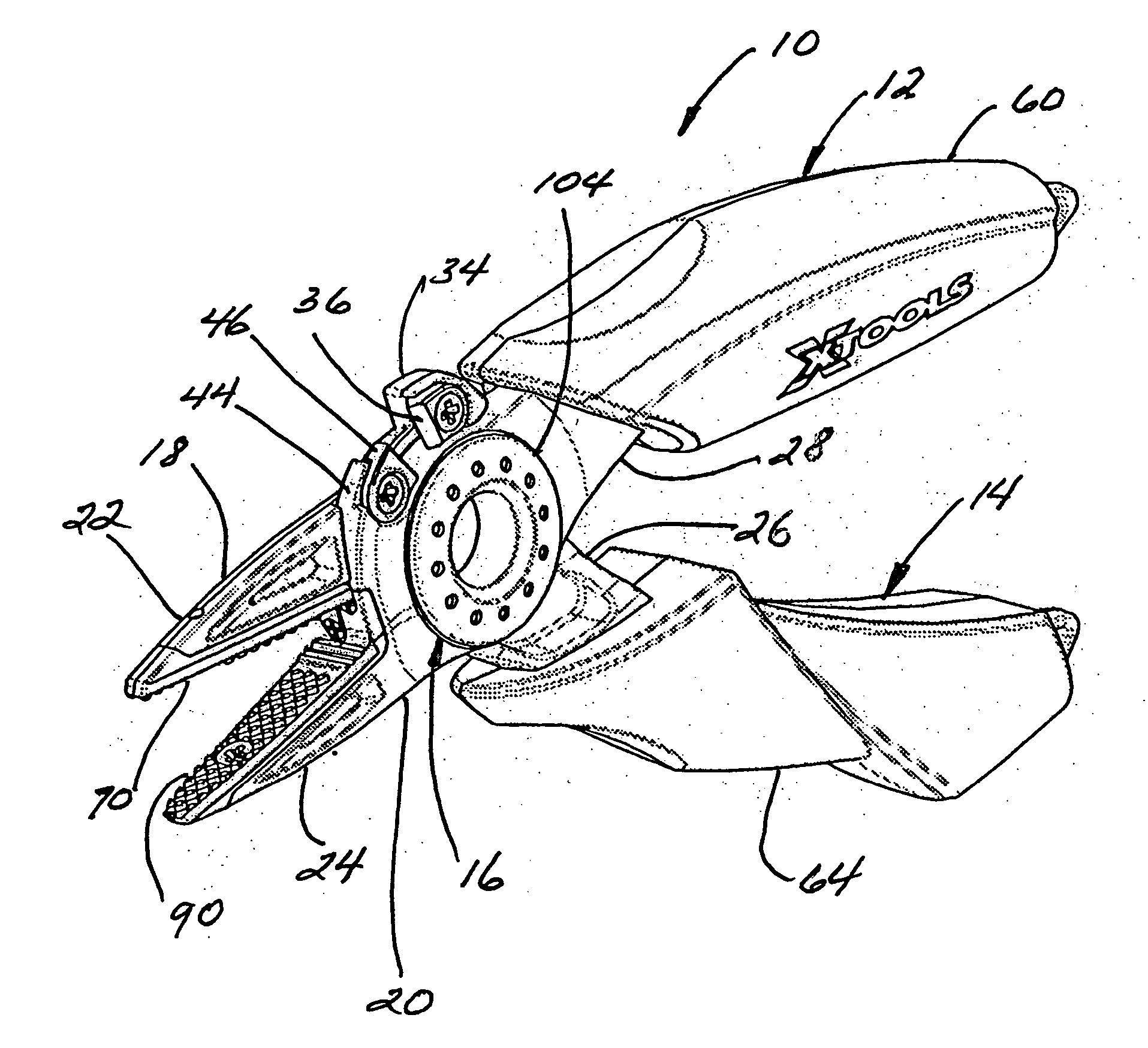

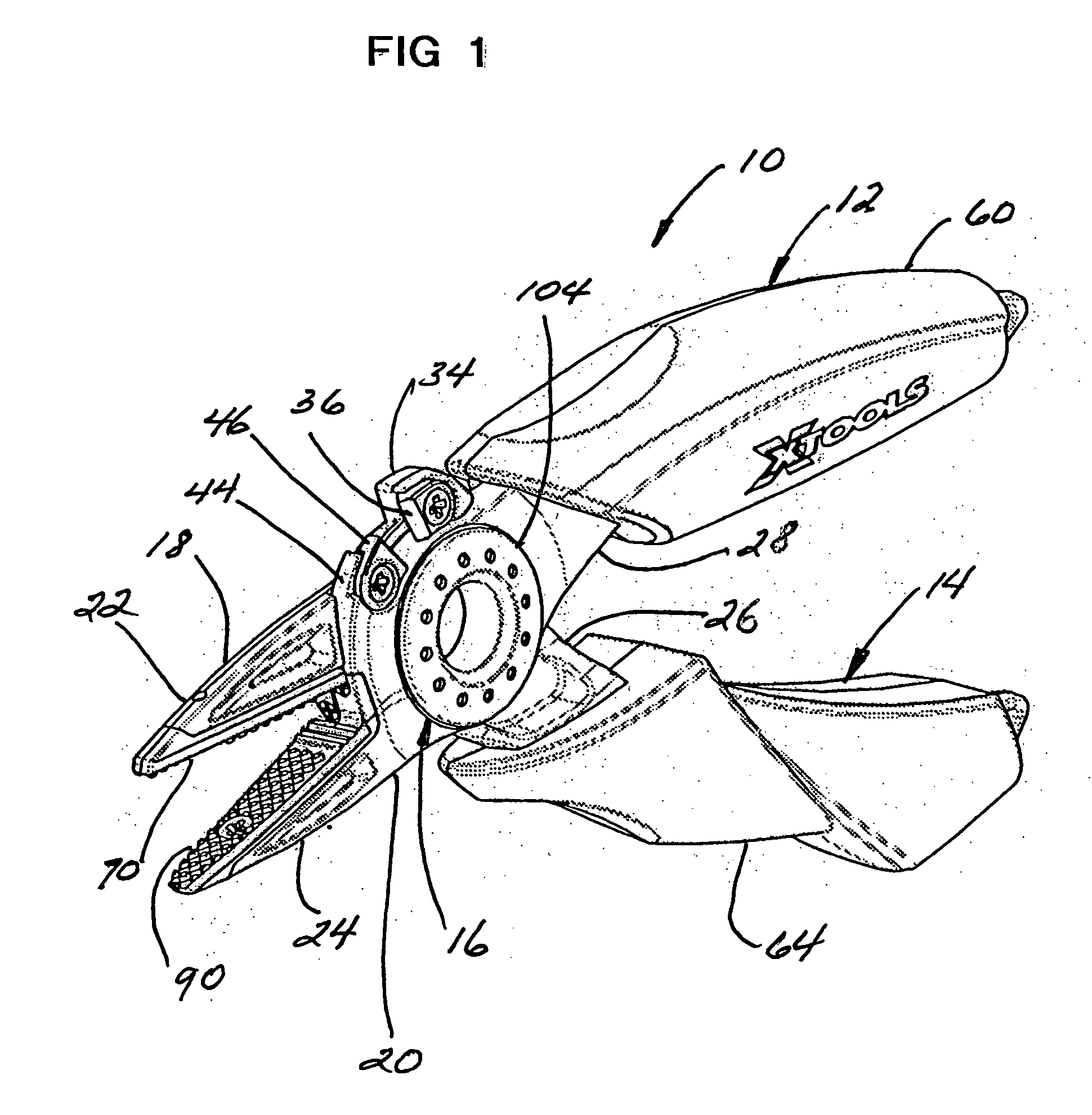

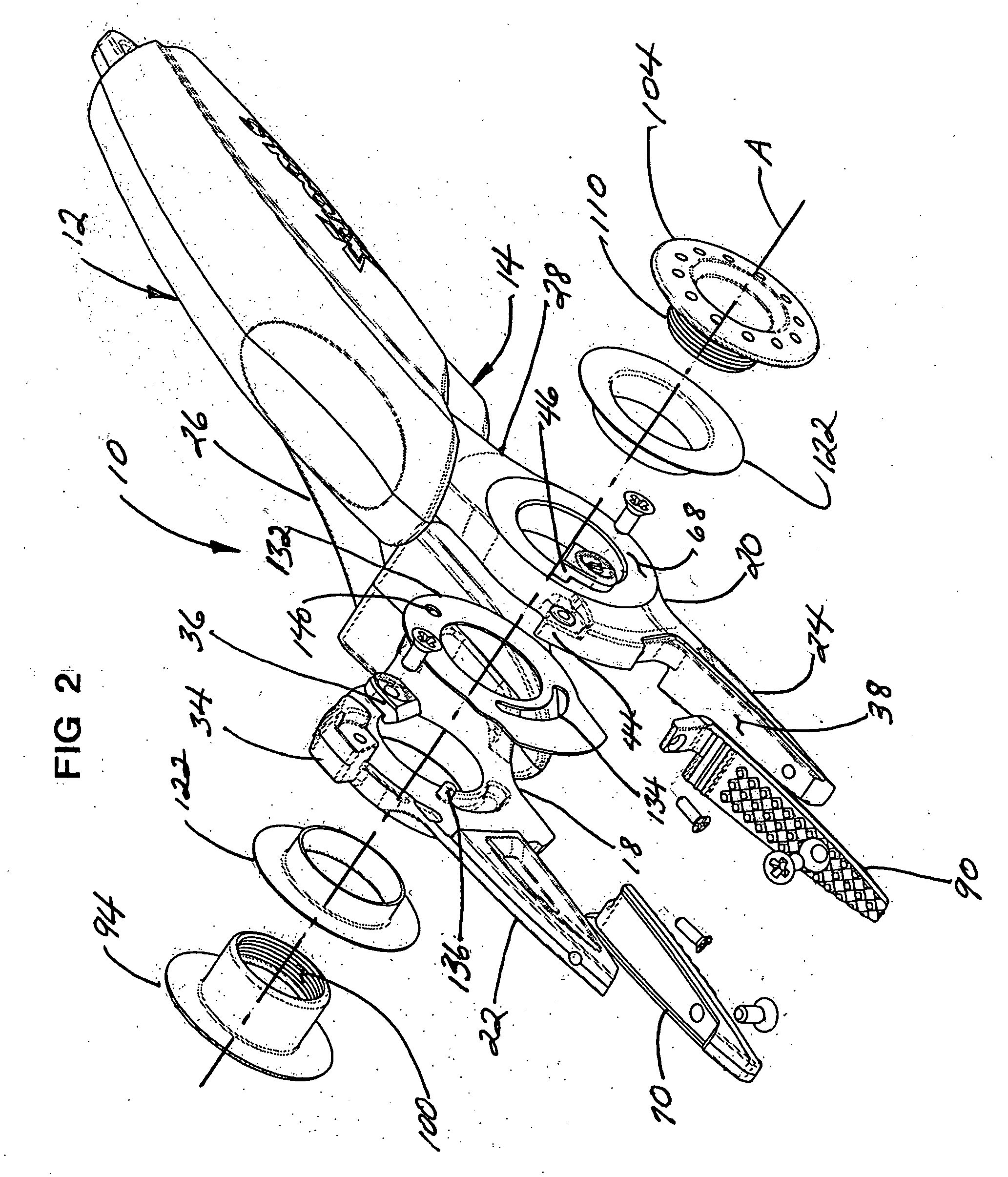

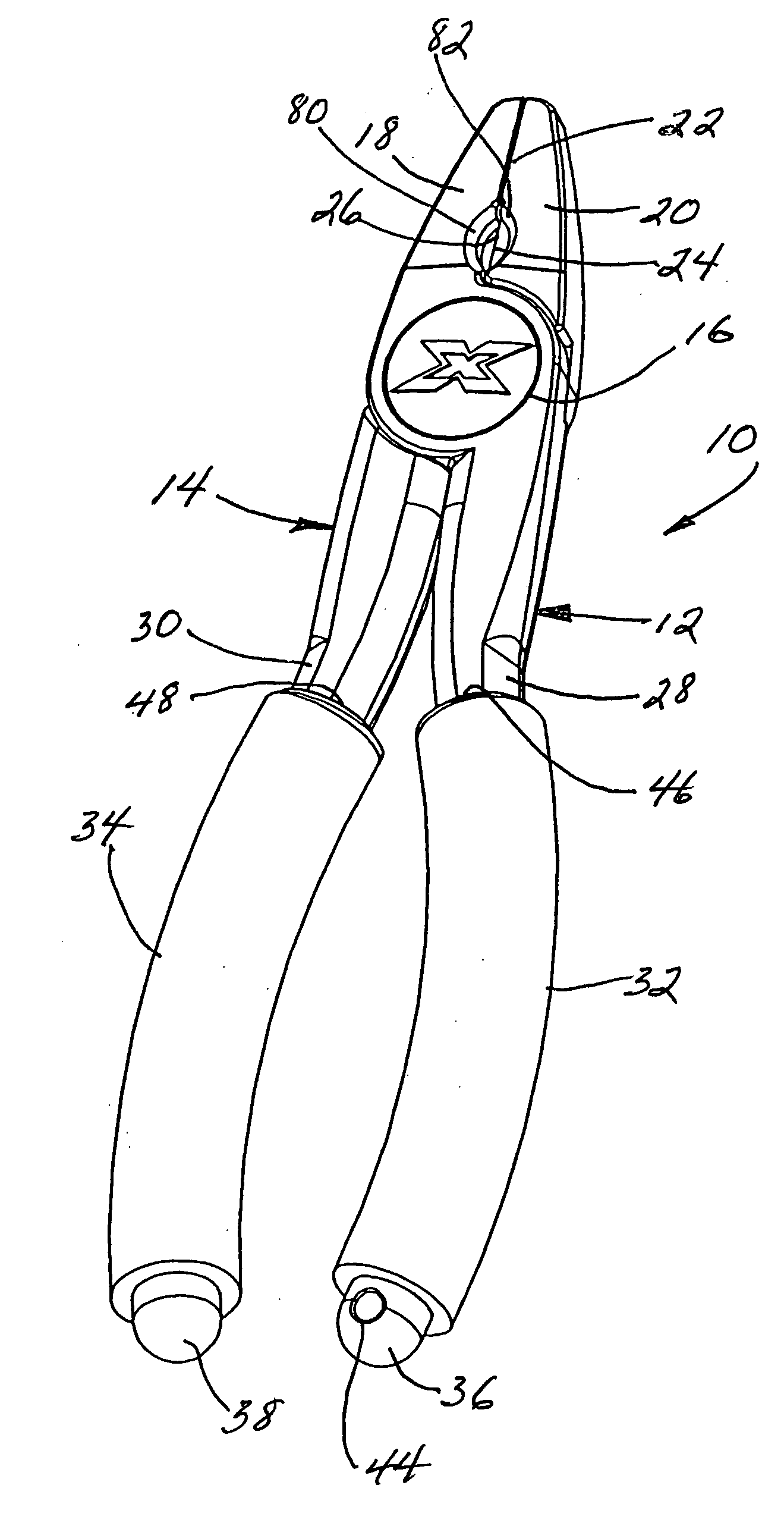

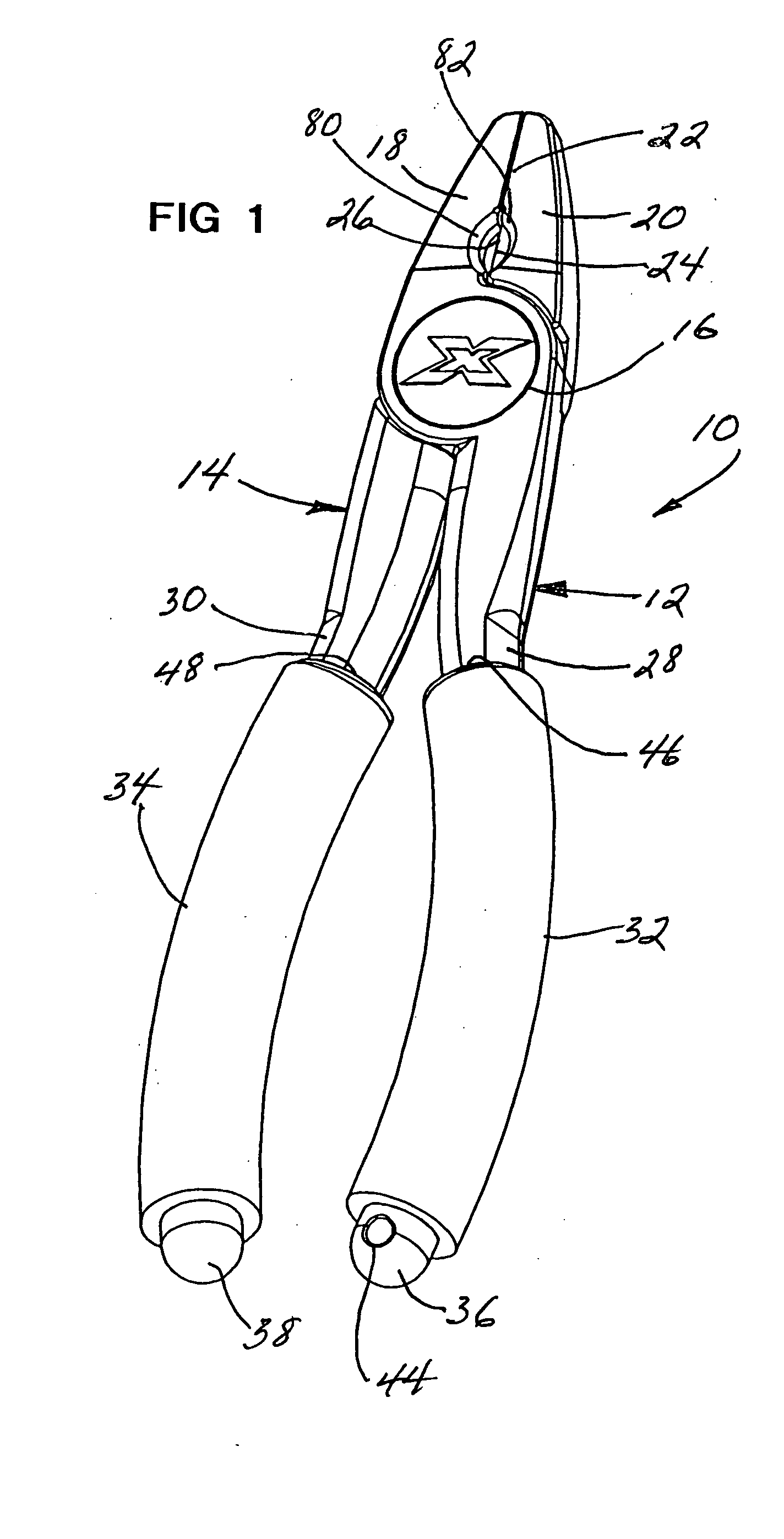

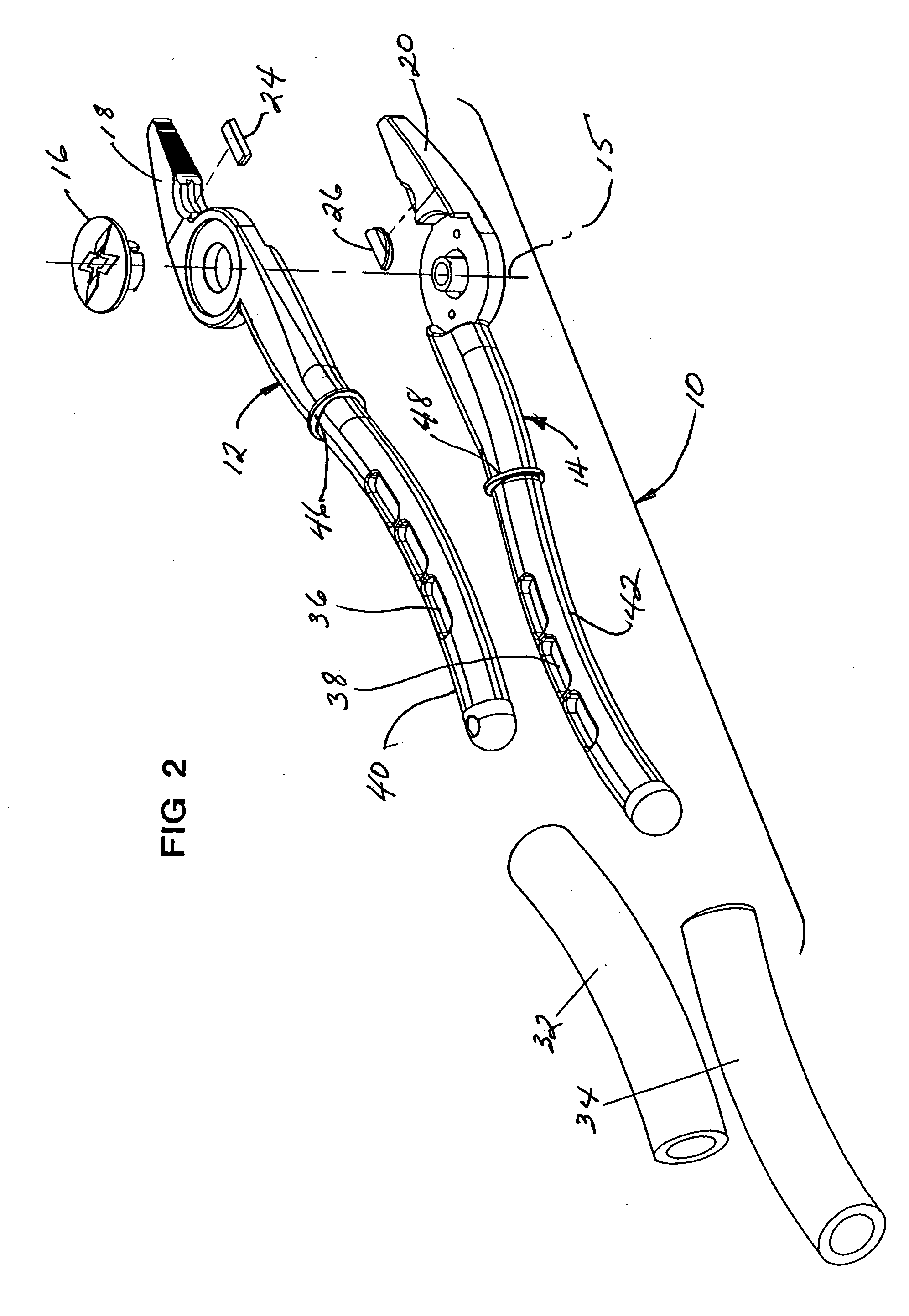

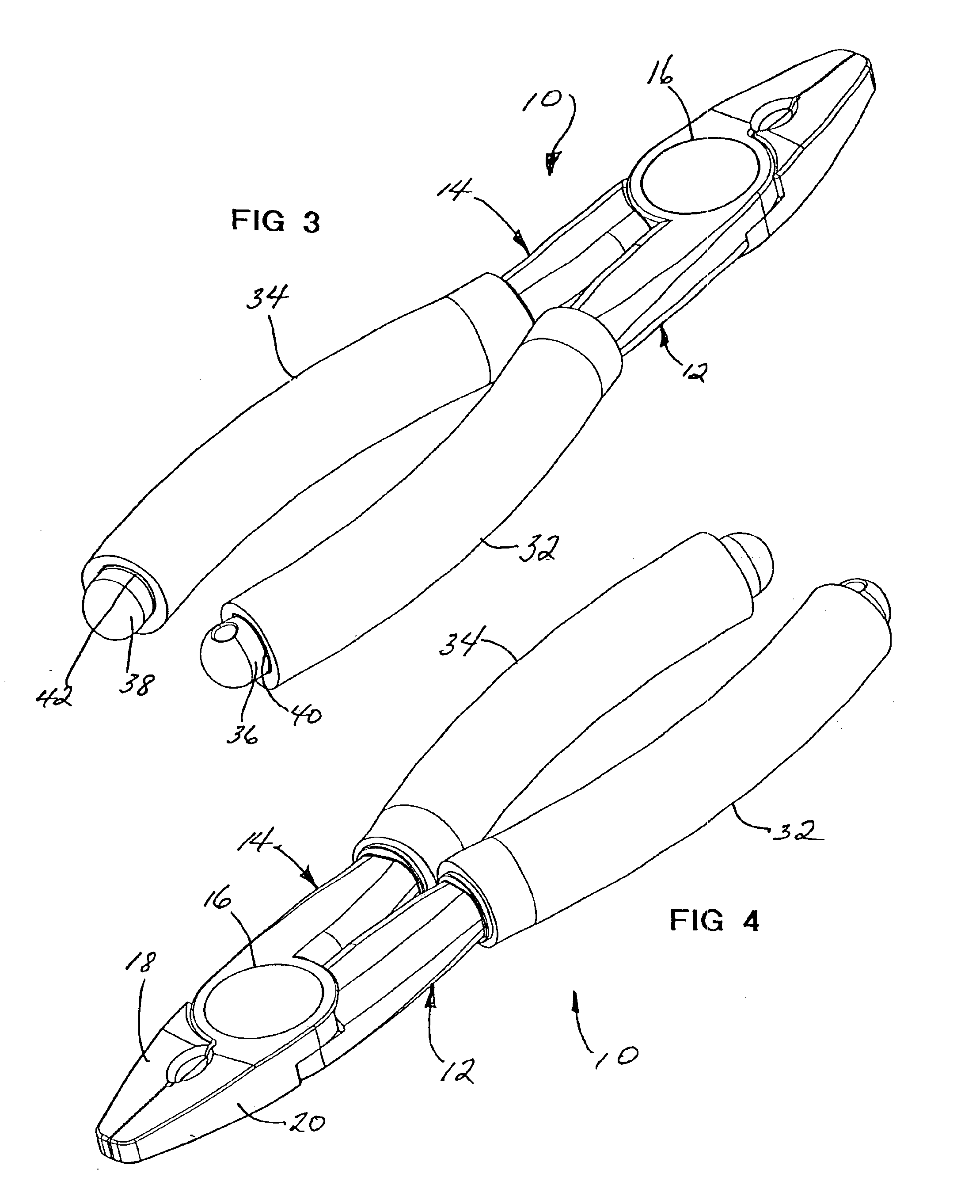

Non-metallic hand pliers with wire cutter

InactiveUS6966244B2Efficient arrangementReduce arrangementPliersMetal working apparatusEffective densityWire cutting

A pair of preferably substantially buoyant-in-water hand pliers comprising a pair of non-metallic lever members each having a handle portion and a jaw portion and formed of material preferably having a density greater than water. The lever members are pivotally connected together at common central portions between the jaw and handle portions. Each handle portion preferably has one or more outwardly opening cavities formed into a side surface of the handle portions. An elongated tubular sheath preferably formed of material buoyant in water covers and sealingly encloses the cavities whereby the effective density of the pliers is less than that of water. An effective, durable, non-corrosive wire cutting arrangement is also provided, the components uniquely configured and supported in the non-metallic jaw portions.

Owner:SHAKESPEARE CO

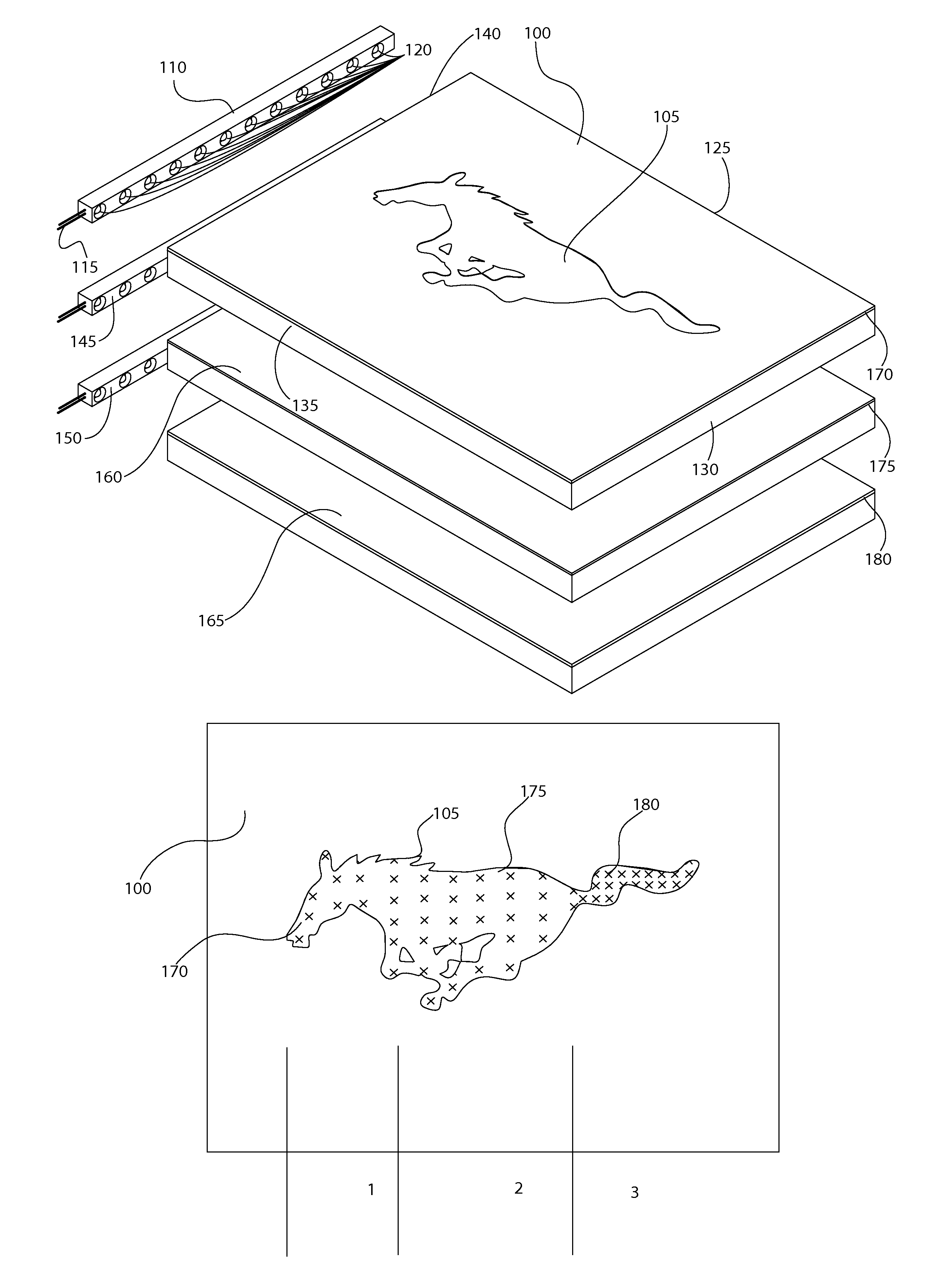

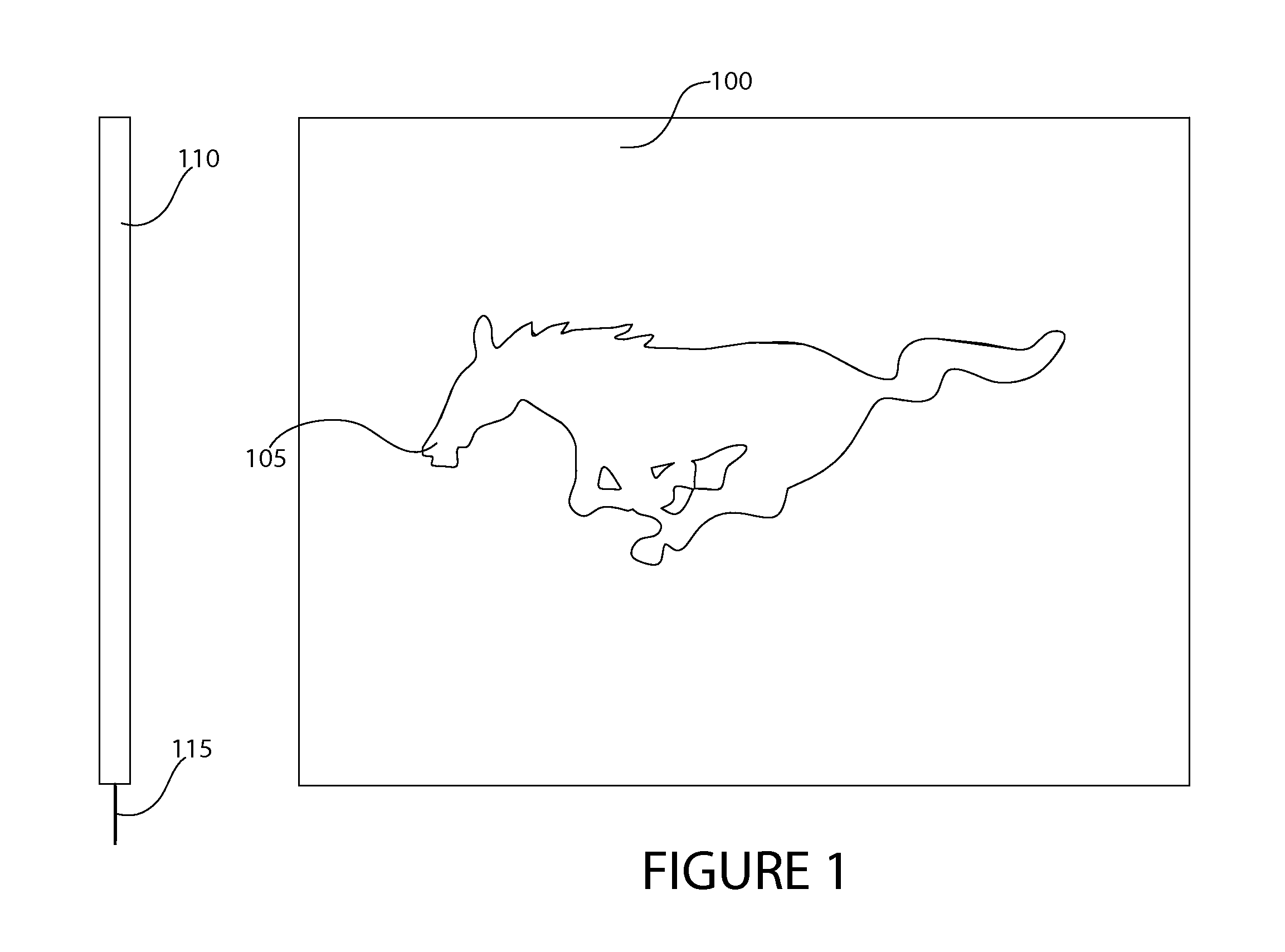

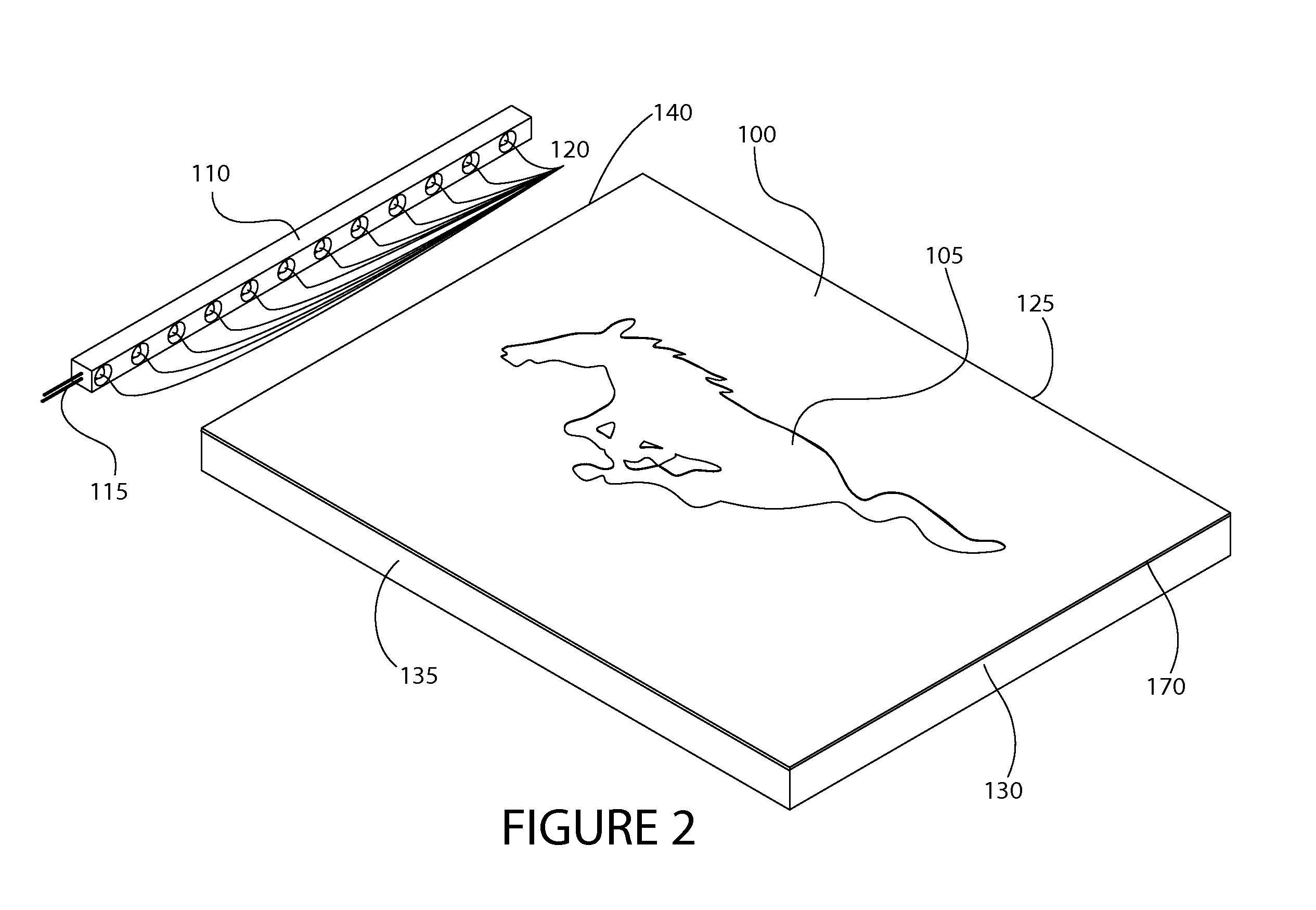

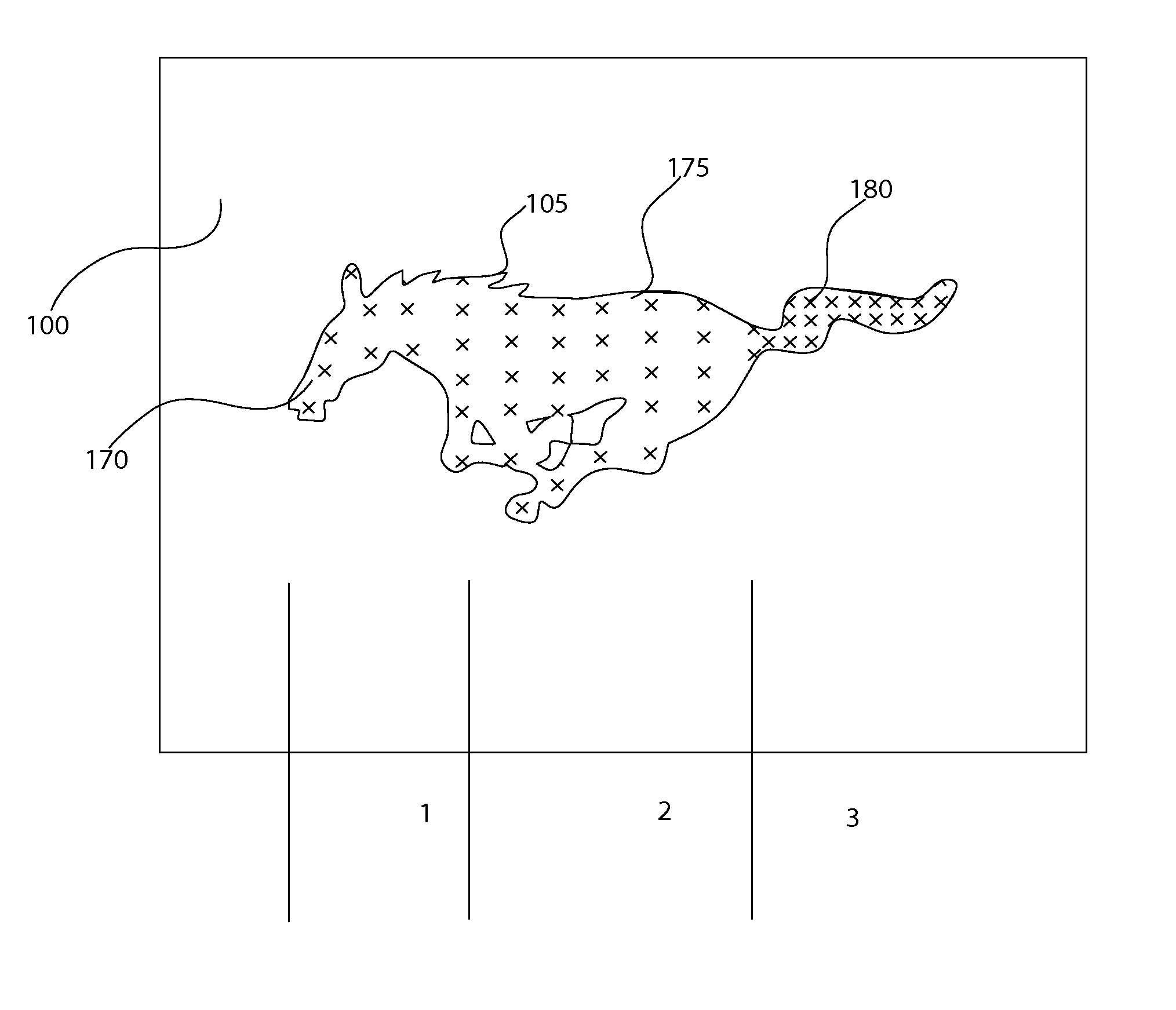

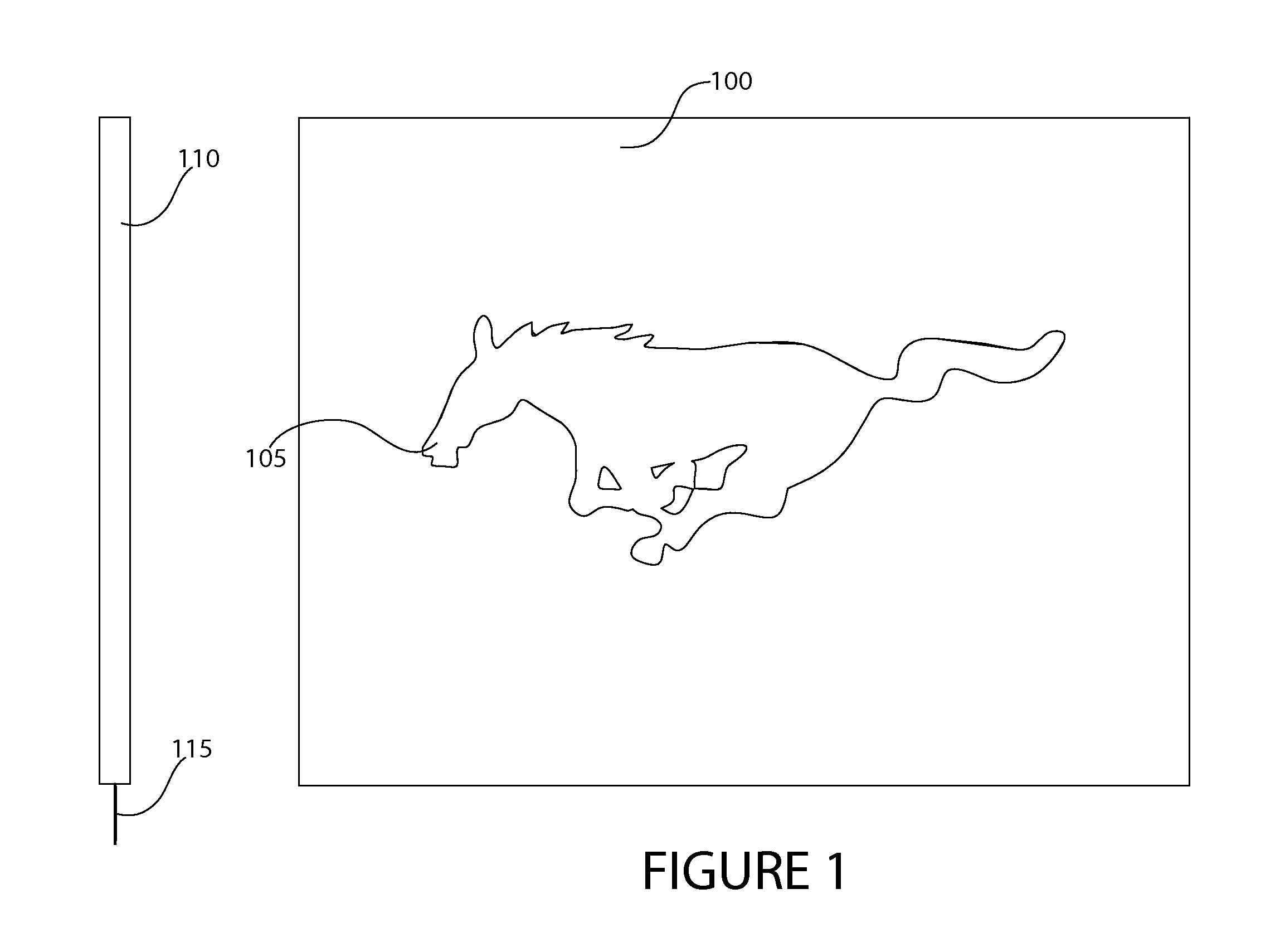

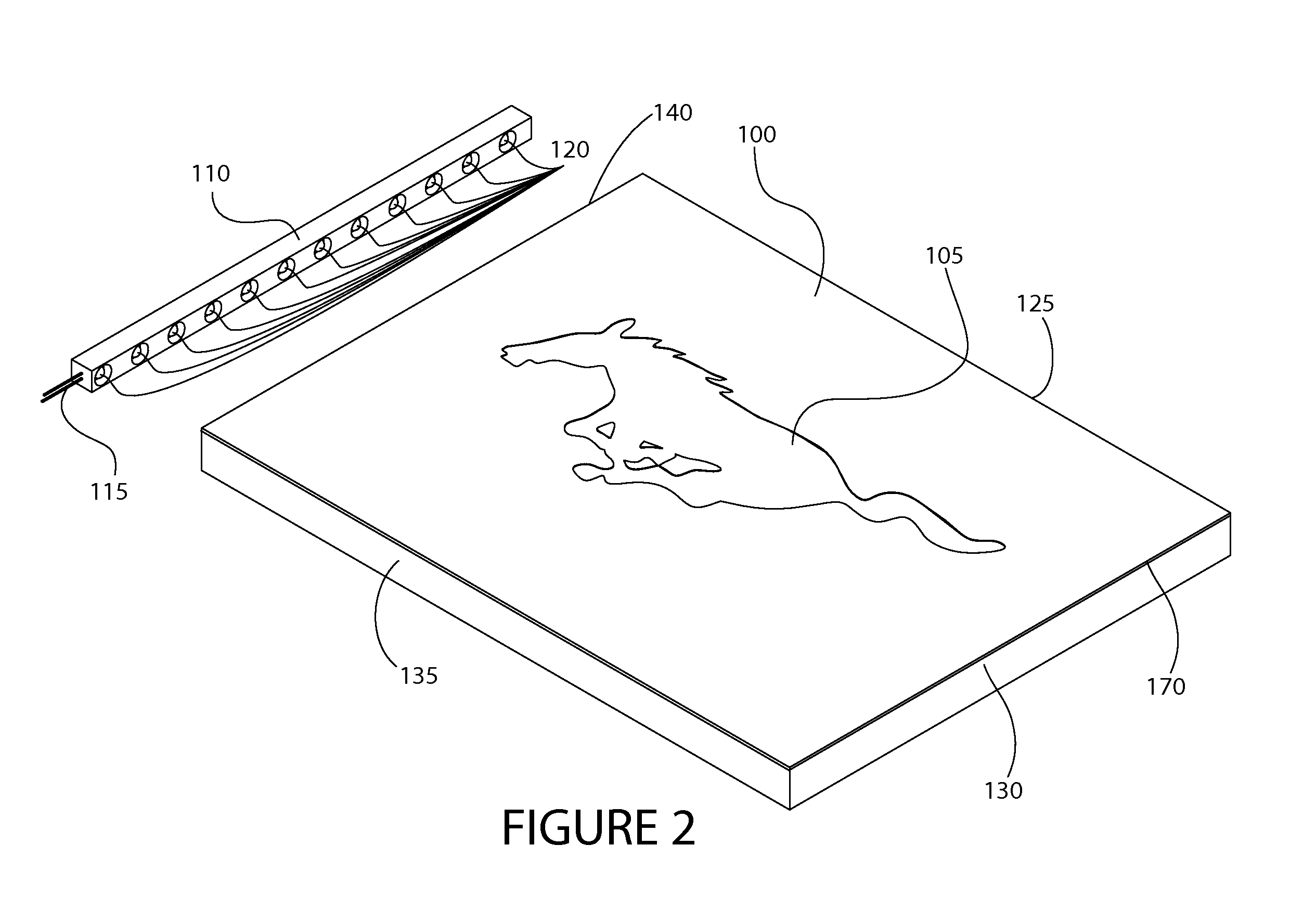

Optimized distribution of light extraction from an edge lit light source

InactiveUS7762704B2Reliable methodUniform lightPlanar/plate-like light guidesCoupling light guidesEffective densityPixel density

An edge-lit panel features extractor patterns that produce uniform illumination. The effective density of extractor pattern pixels is adjusted to achieve uniform illumination. A method of adjusting the effective pixel density of extractor pattern pixels to achieve uniform illumination entails adjusting areas of darkness of a grayscale image, then producing a binary image by dithering the grayscale image, and applying an extractor pattern corresponding to the binary image to a surface of the panel. The extractor pixels correspond to pixels of the binary image derived from a dithered grayscale image, with the darkness of the grayscale image increasing with distance from the light source. Effective pixel density is increased to compensate for attenuated output in dim areas. By adjusting gray shading darkness of a grayscale image, pixel density can be adjusted to achieve uniform light emission. The extractor pixels may be applied using a radiation curable ink, which can be used in high speed inkjet printers that can achieve production speeds. The resulting print is waterproof, embossed and vibrant.

Owner:BRYTER TECH

Optimized distribution of light extraction from an edge lit light source

InactiveUS20100124074A1Reliable methodUniform lightPlanar/plate-like light guidesCoupling light guidesPixel densityEffective density

An edge-lit panel features extractor patterns that produce uniform illumination. The effective density of extractor pattern pixels is adjusted to achieve uniform illumination. A method of adjusting the effective pixel density of extractor pattern pixels to achieve uniform illumination entails adjusting areas of darkness of a grayscale image, then producing a binary image by dithering the grayscale image, and applying an extractor pattern corresponding to the binary image to a surface of the panel. The extractor pixels correspond to pixels of the binary image derived from a dithered grayscale image, with the darkness of the grayscale image increasing with distance from the light source. Effective pixel density is increased to compensate for attenuated output in dim areas. By adjusting gray shading darkness of a grayscale image, pixel density can be adjusted to achieve uniform light emission. The extractor pixels may be applied using a radiation curable ink, which can be used in high speed inkjet printers that can achieve production speeds. The resulting print is waterproof, embossed and vibrant.

Owner:BRYTER TECH

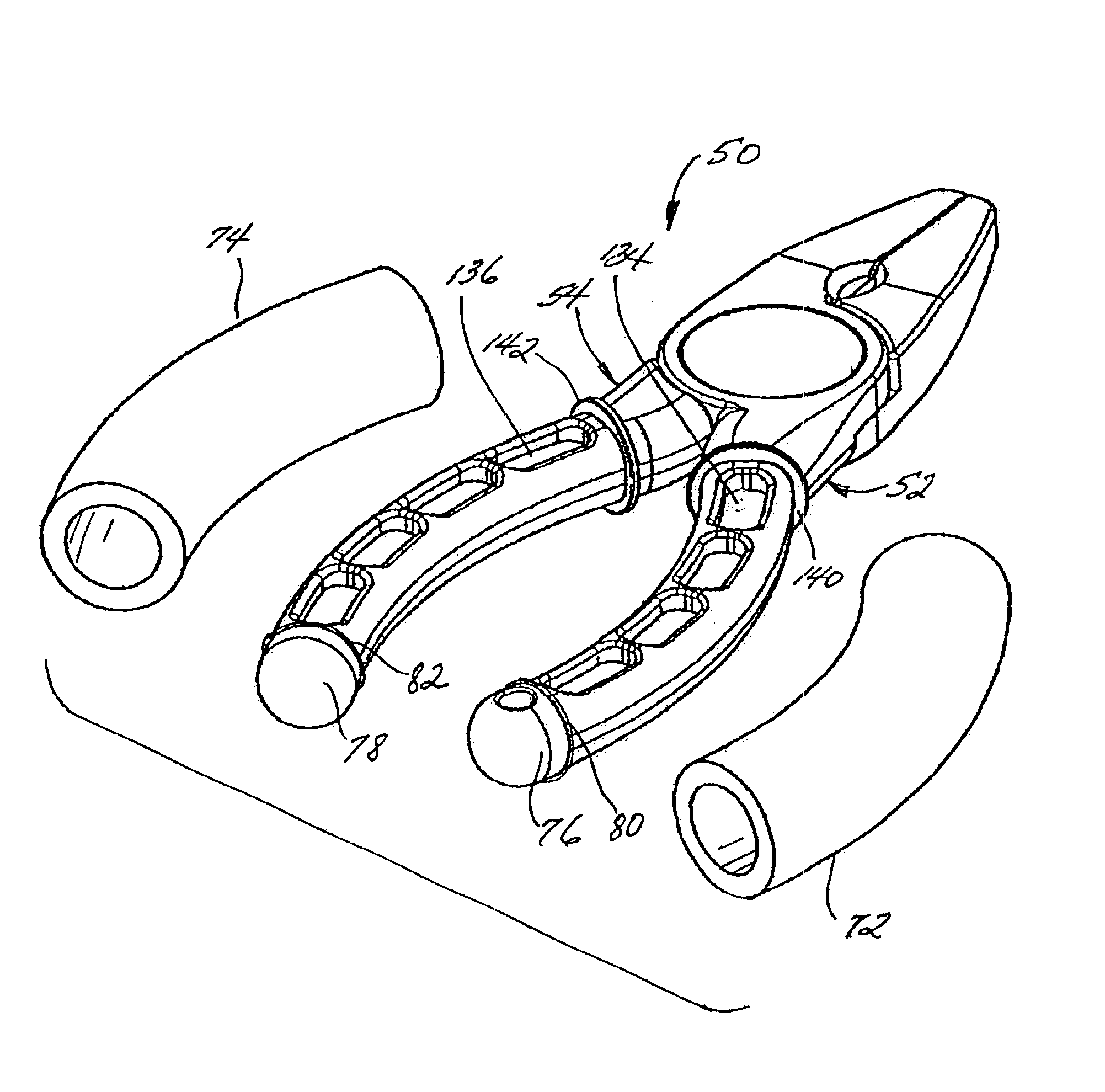

Buoyant metal composite pliers

A pair of composite material substantially buoyant-in-water hand pliers including a pair of elongated metallic lever members each having a handle portion and a jaw portion and formed of higher rigidity metallic material having a density greater than water. The lever members are pivotally connected together at common central portions between the jaw and handle portions. Each handle portion is substantially encapsulated by an elongated molded-in-place contoured grip formed of material buoyant in water wherein the effective density of the pliers is in very close proximity to that of water. Uniquely configured jaw inserts are also provided.

Owner:SHAKESPEARE CO

Injectable hollow tissue filler

InactiveUS20110091564A1Equally distributedLow densityPowder deliverySkin implantsParticulatesEffective density

The present invention comprises a plurality of injectable hollow particulate fillers suspended in a biocompatible fluid carrier to significantly improve the clumping resistance and injectability of the composition. The hollow particulate fillers have a lower effective density and are able to suspend in the carrier without precipitation. The loss of skin volume as a result of aging, diseases, weight loss, and injury can lead to uneven skin surface (e.g. wrinkle, etc.). The uneven skin can be repaired by injecting appropriate amount of hollow fillers underneath the skin. Some cases of urinary incontinence occur when the resistance to urine flow has decreased excessively. Continence is restored by injecting the present invention to the urethra tissue to increase resistance to urine outflow. Similarly, the present invention allows for the control of gastric fluid reflux by submucosal injections of the fillers to the esophageal-gastric and gastric-pyloric junction. For patients with vesicoureteral reflux, it can be treated by injection of the present invention into patients' ureteral tissue. This invention can also be used to repair defective or inadequately functioning muscles of the anal sphincter by administering an effective amount of injectable hollow fillers into the defect or anal sinuses.

Owner:CHU JACK FA DE

Non-metallic hand pliers with wire cutter

InactiveUS20050097998A1Efficient arrangementBuoyant in waterPliersMetal working apparatusEffective densityWire cutting

A pair of preferably substantially buoyant-in-water hand pliers comprising a pair of non-metallic lever members each having a handle portion and a jaw portion and formed of material preferably having a density greater than water. The lever members are pivotally connected together at common central portions between the jaw and handle portions. Each handle portion preferably has one or more outwardly opening cavities formed into a side surface of the handle portions. An elongated tubular sheath preferably formed of material buoyant in water covers and sealingly encloses the cavities whereby the effective density of the pliers to less than that of water. An effective, durable, non-corrosive wire cutting arrangement is also provided, the components uniquely configured and supported in the non-metallic jaw portions.

Owner:SHAKESPEARE CO

Buoyant hand tool

InactiveUS6877405B2Buoyancy in waterAchieves buoyancyPliersMulti-purpose toolsEffective densityConductive materials

A non-conductive substantially buoyant-in-water hand tool comprising an elongated handle portion formed of non-corrosive, non-conductive material having a density greater than water and an elongated working tool connected to and extending axially from a proximal end of said handle portion. The handle portion has one or more outwardly opening cavities formed into a side surface of the handle portion. An elongated tubular sheath formed of material buoyant in water covers and sealingly encloses and forms one or more airtight cavities whereby the effective density of the hand tool is less than that of water.

Owner:SHAKESPEARE ALL STAR ACQUISITION LLC

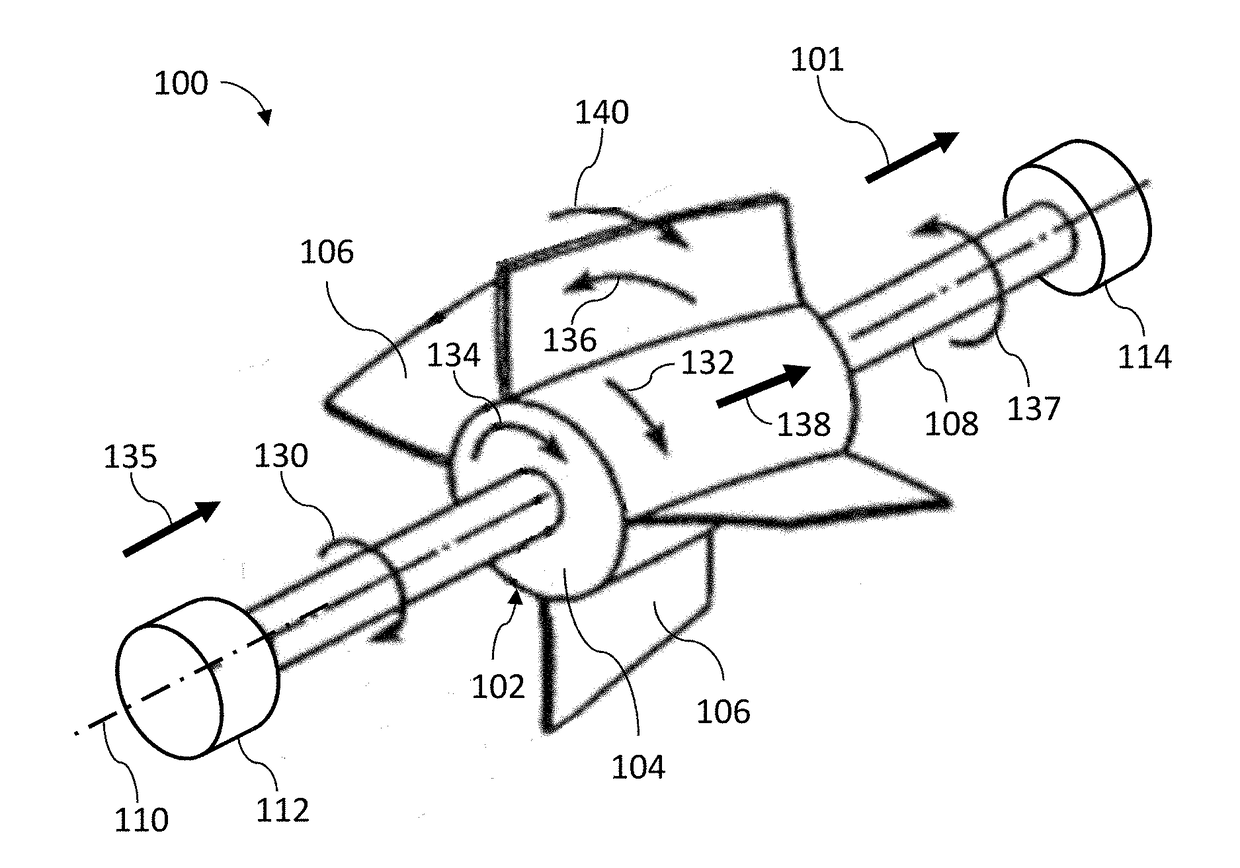

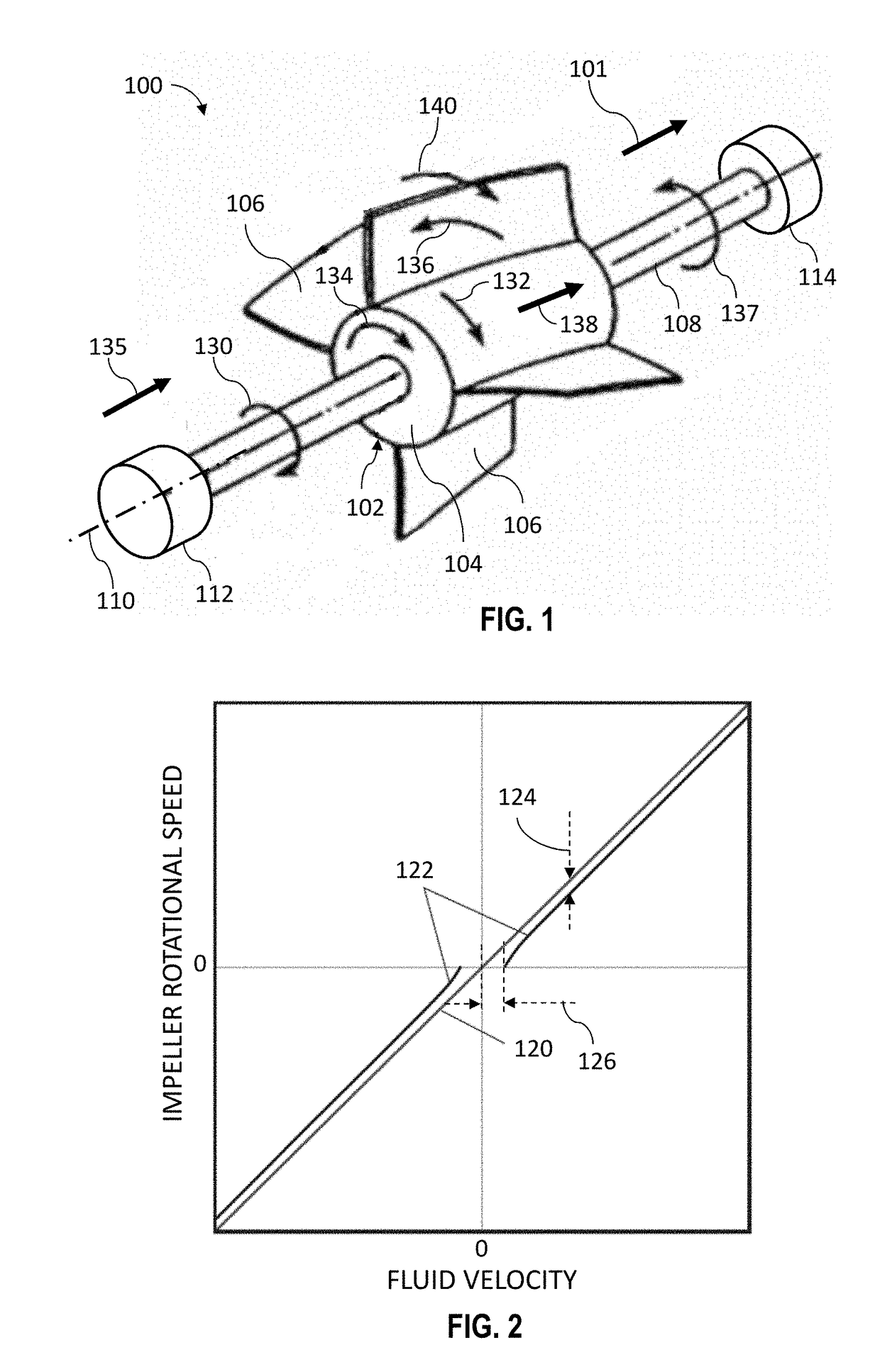

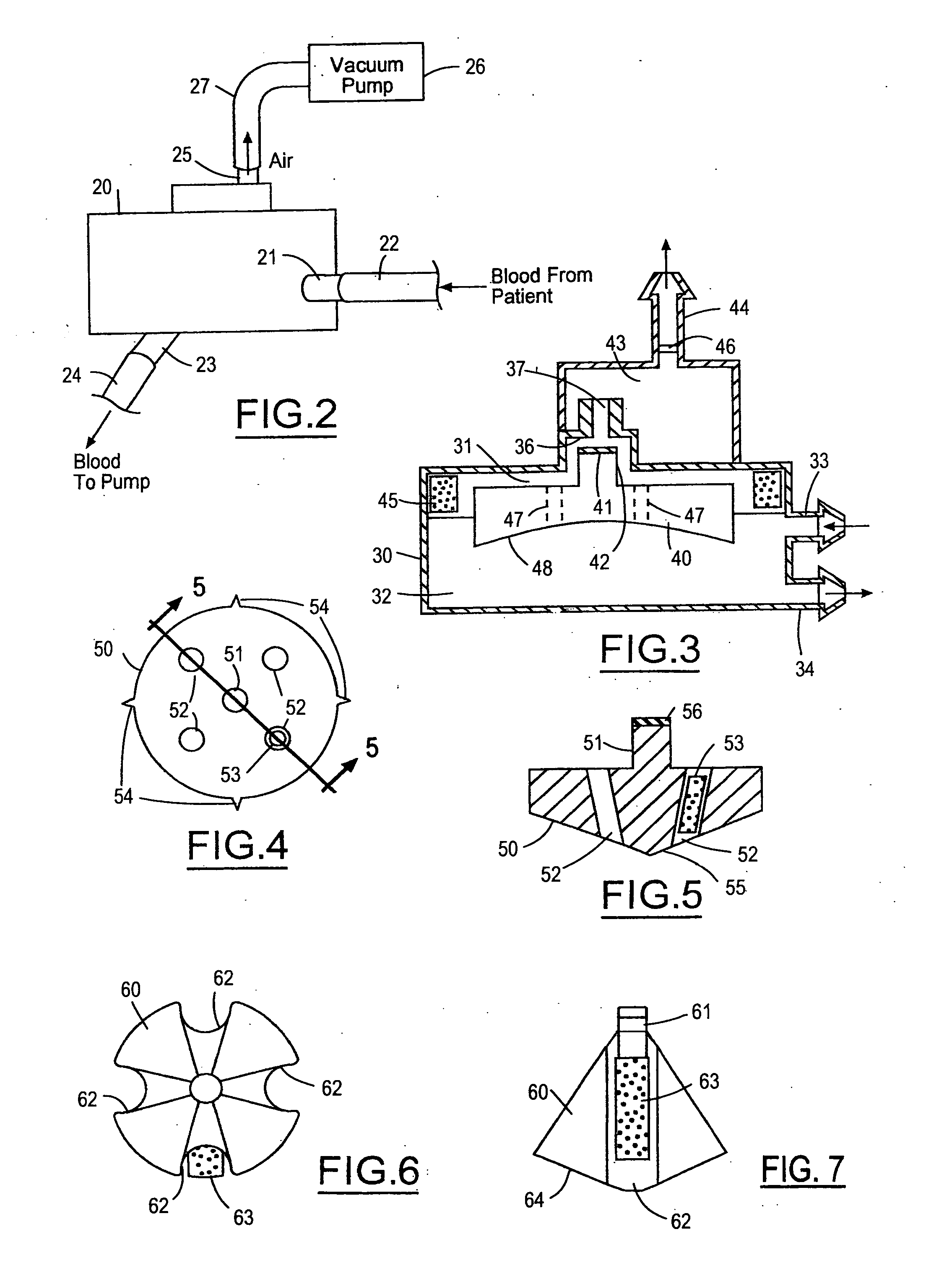

Downhole Fluid Property Measurement

InactiveUS20170227388A1Flow propertiesVolume/mass flow by mechanical effectsImpellerEffective density

An apparatus having an impeller for measuring a property of a fluid in a wellbore, wherein an effective density of the impeller is substantially not greater than a density of the fluid. The apparatus is operable within a fluid flowing in a wellbore that extends into a subterranean formation, thereby measuring a property of the flowing fluid.

Owner:SCHLUMBERGER TECH CORP

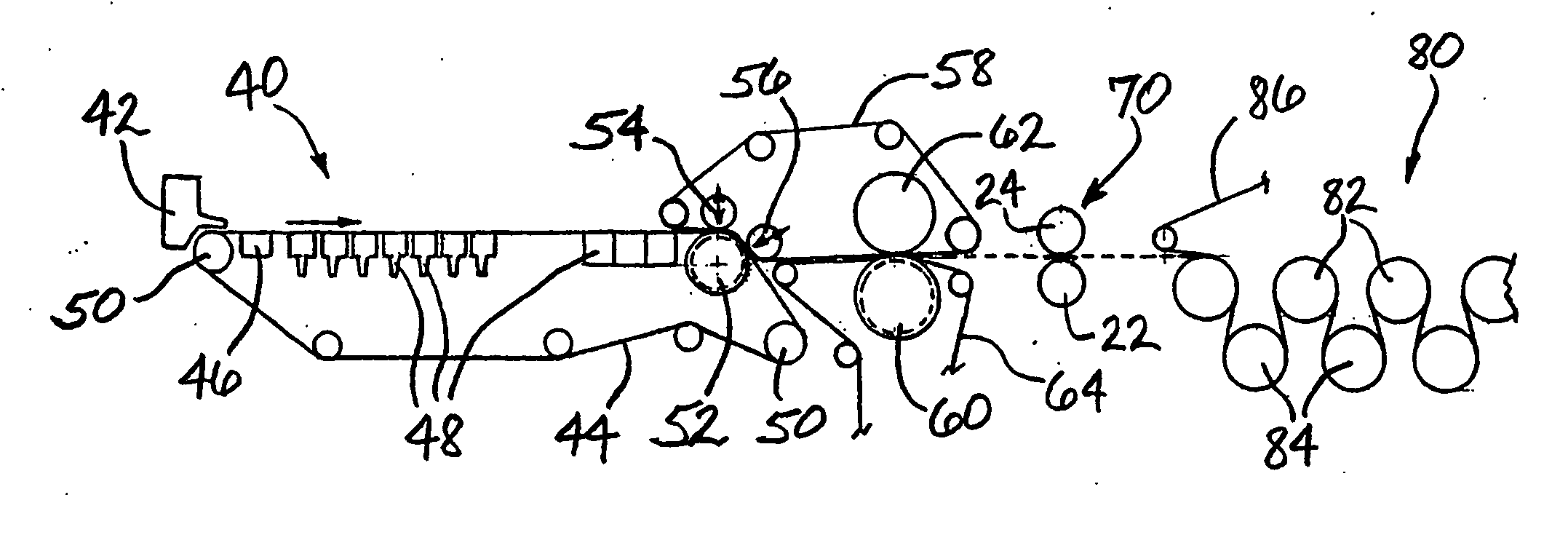

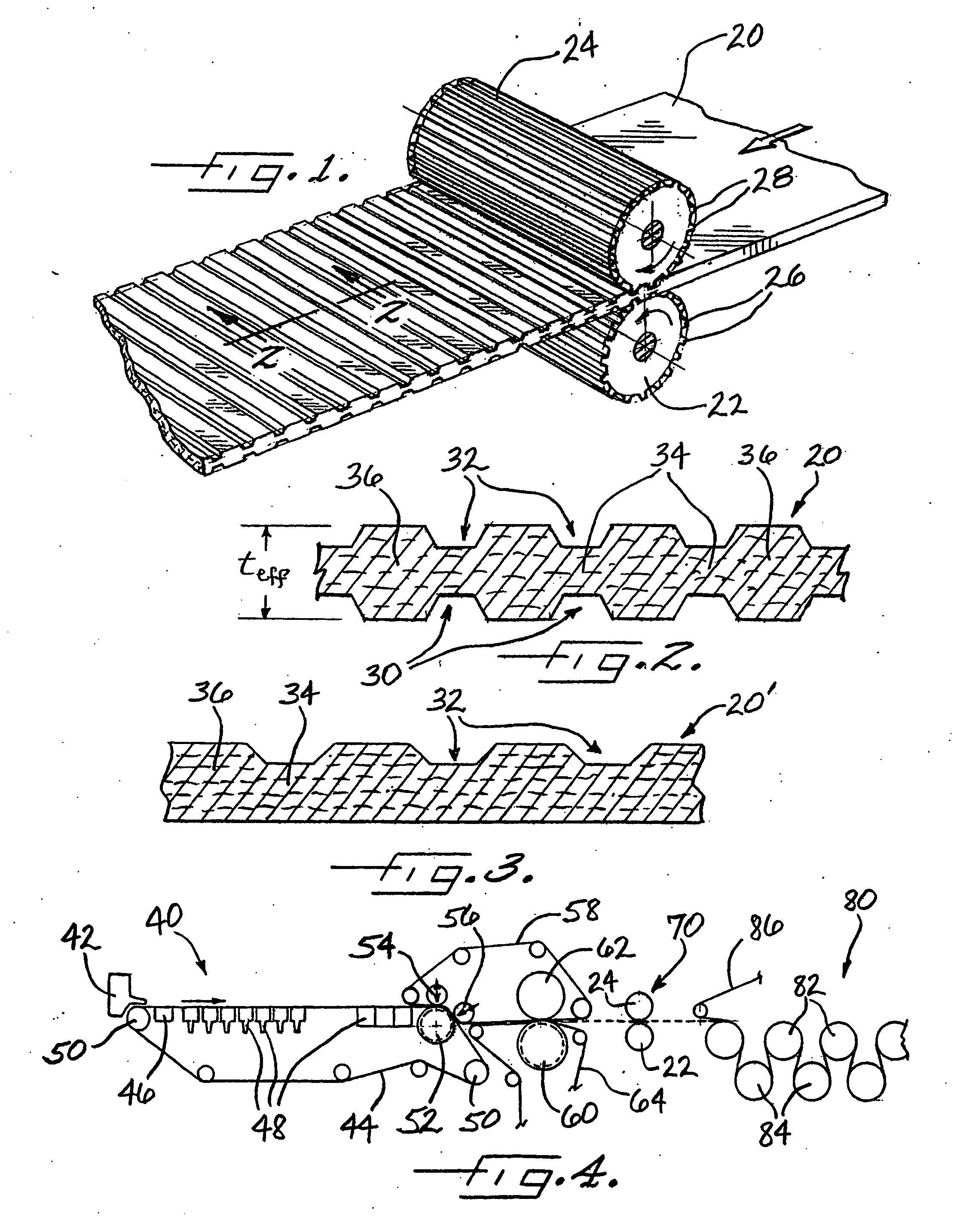

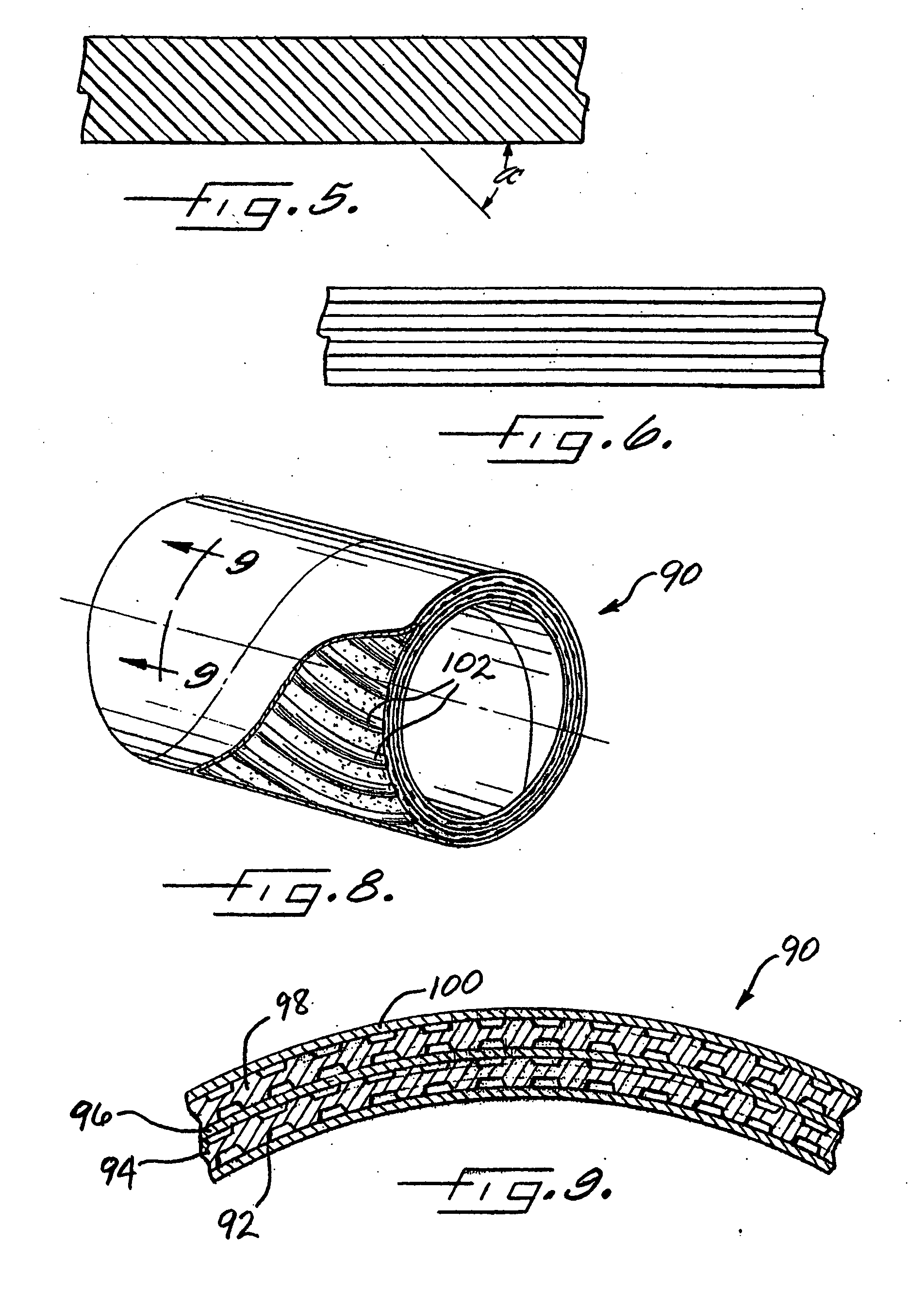

Paperboard with discrete densified regions, process for making same, and laminate incorporating same

InactiveUS20070131368A1Improve mechanical propertiesReduce thicknessNon-fibrous pulp additionNatural cellulose pulp/paperEffective densityPaperboard

Paperboard is densified in selected discrete regions spaced apart along the board such that the effective caliper of the board (defined between the surfaces of the board in the areas outside the densified regions) remains essentially unchanged compared to an equivalent board that is not selectively densified. Thus, the effective density of the board also remains unchanged. The densified regions impart mechanical properties to the paperboard. The shapes, sizes, depths, and arrangement of the densified regions can be selected to impart increased strength in certain directions. For example, the ratio of the machine direction (MD) to cross-machine direction (CD) compressive strength can be manipulated through selective densification in accordance with the invention. The paperboard is useful in laminate structures and other uses.

Owner:SONOCO DEV INC

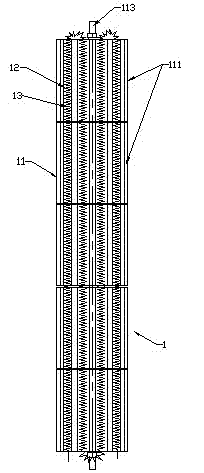

Electric heating element and pipeline electric heater

InactiveCN102811514AHigh densityIncrease heating powerPipe heating/coolingHeating element shapesElectrical resistance and conductanceHigh density

The invention relates to an electric heating device and particularly relates to an electric heating element for heating gas flowing in a pipeline and a pipeline electric heater adopting the electric heating element. The electric heating element comprises a cylindrical base body which is manufactured by a fireproof material; vertical mounting grooves are uniformly distributed on the outer cylindrical face of the base body; a spiral resistance wire is placed in each mounting groove in a reciprocated manner; and extraction electrodes are arranged at the two ends of each resistance wire. According to the electric heating element disclosed by the invention, the resistance wires are highly-densely distributed on the vertical mounting grooves on the outer cylindrical face of the base body; the structure is compact and the occupied space is small; and the effective density and the heating power of the heating elements of the pipeline electric heater are effectively improved.

Owner:ZHENJIANG WSK ELECTRICAL APPLIANCES

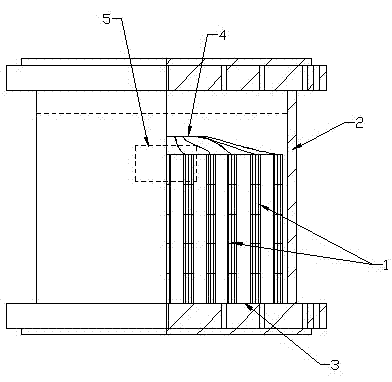

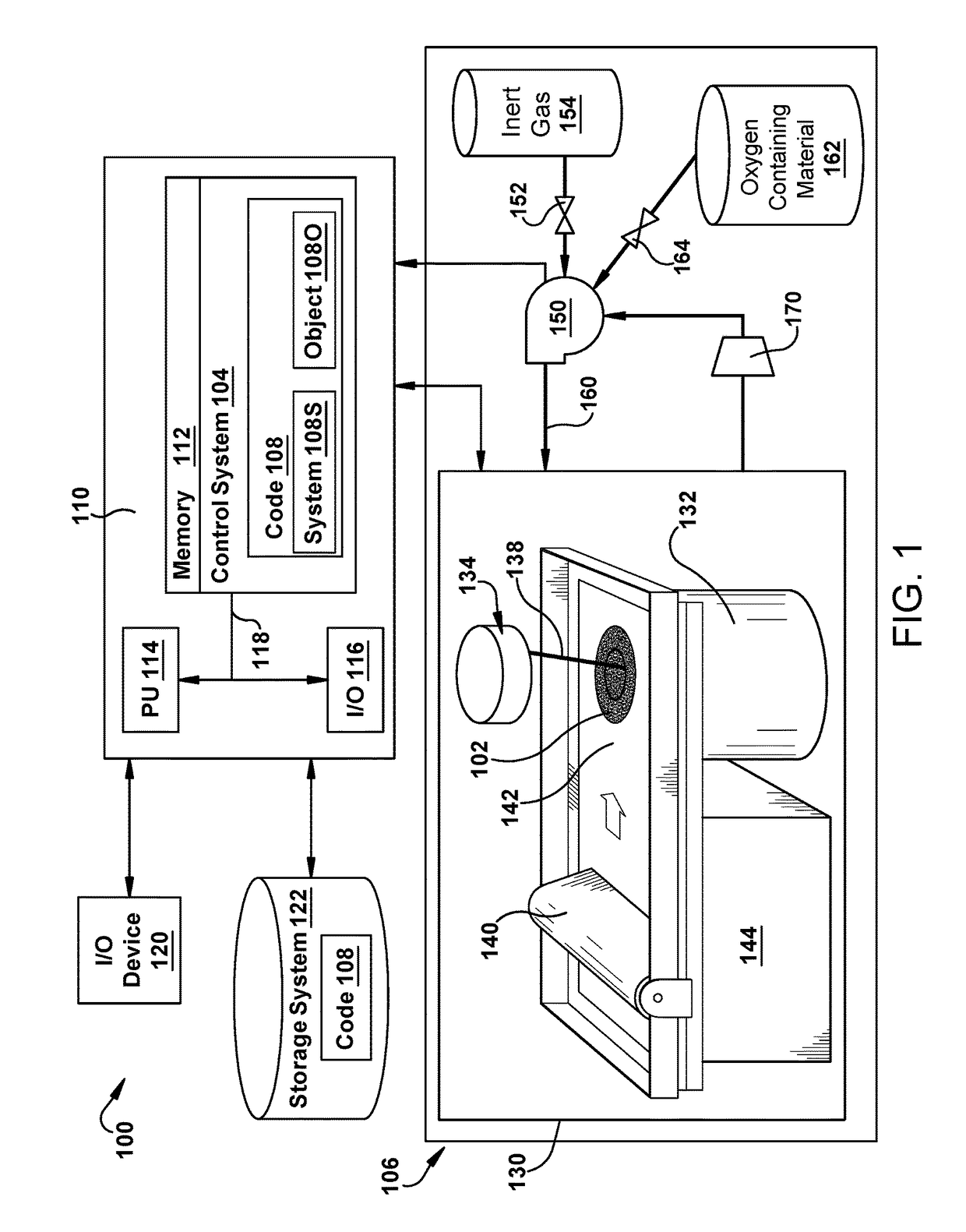

Metal additive manufacturing using gas mixture including oxygen

ActiveUS20170182594A1Additive manufacturing apparatusIncreasing energy efficiencyPorosityEffective density

A metal powder additive manufacturing system and method are disclosed that use increased trace amounts of oxygen to improve physical attributes of an object. The system may include: a processing chamber; a metal powder bed within the processing chamber; a melting element configured to sequentially melt layers of metal powder on the metal powder bed to generate an object; and a control system configured to control a flow of a gas mixture within the processing chamber from a source of inert gas and a source of an oxygen containing material, the gas mixture including the inert gas and oxygen from the oxygen containing material. The method may result in an object having a surface porosity of no greater than approximately 0.1%, and an effective density of greater than approximately 99.9%.

Owner:GENERAL ELECTRIC CO

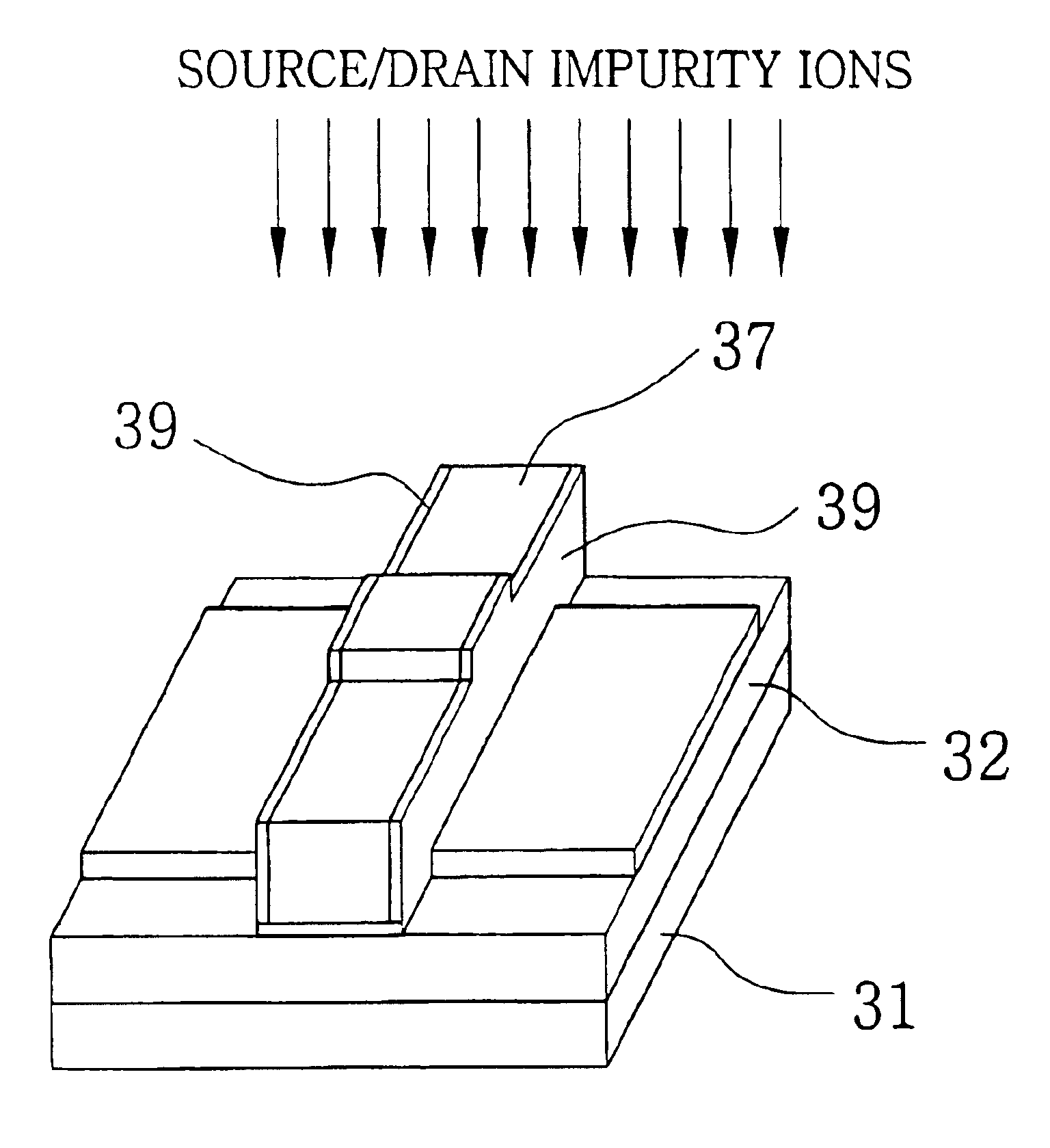

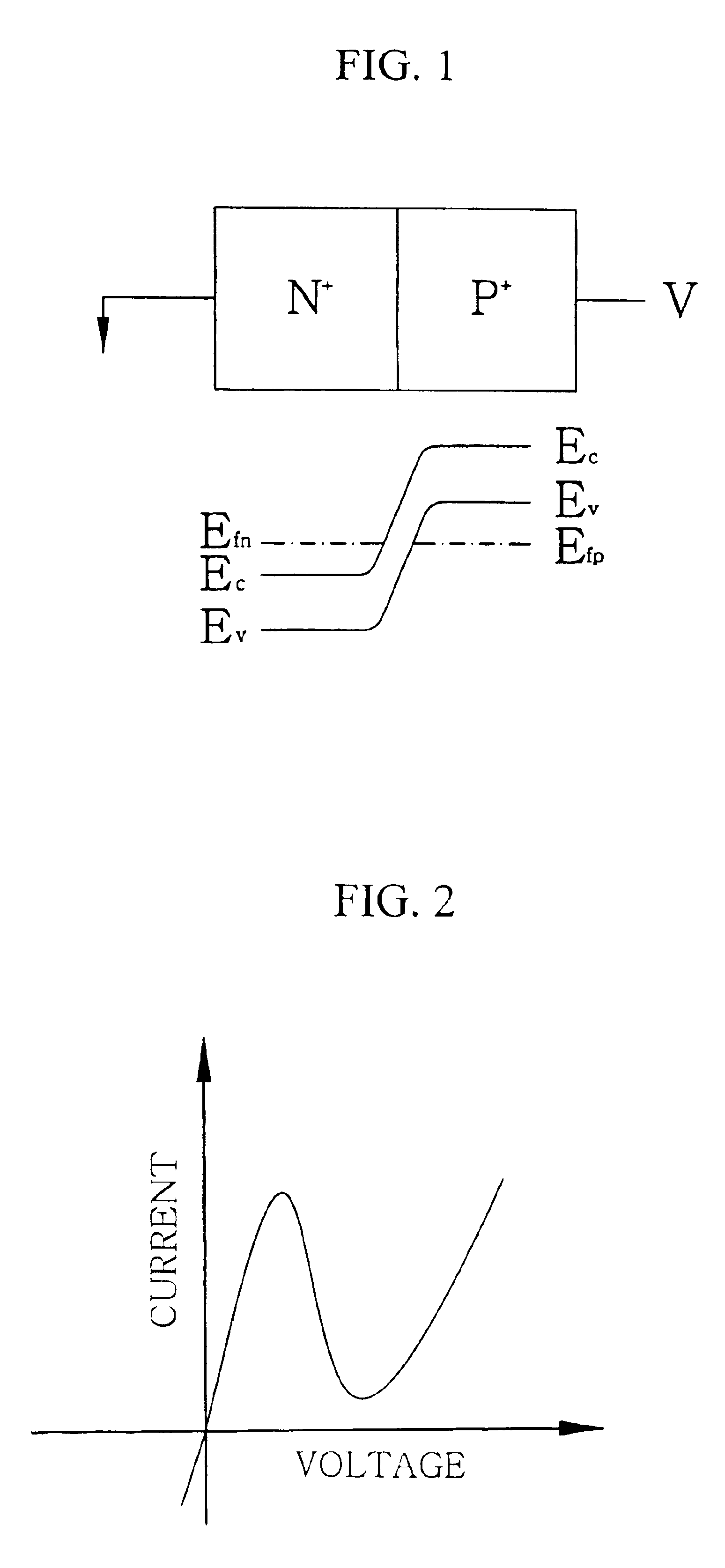

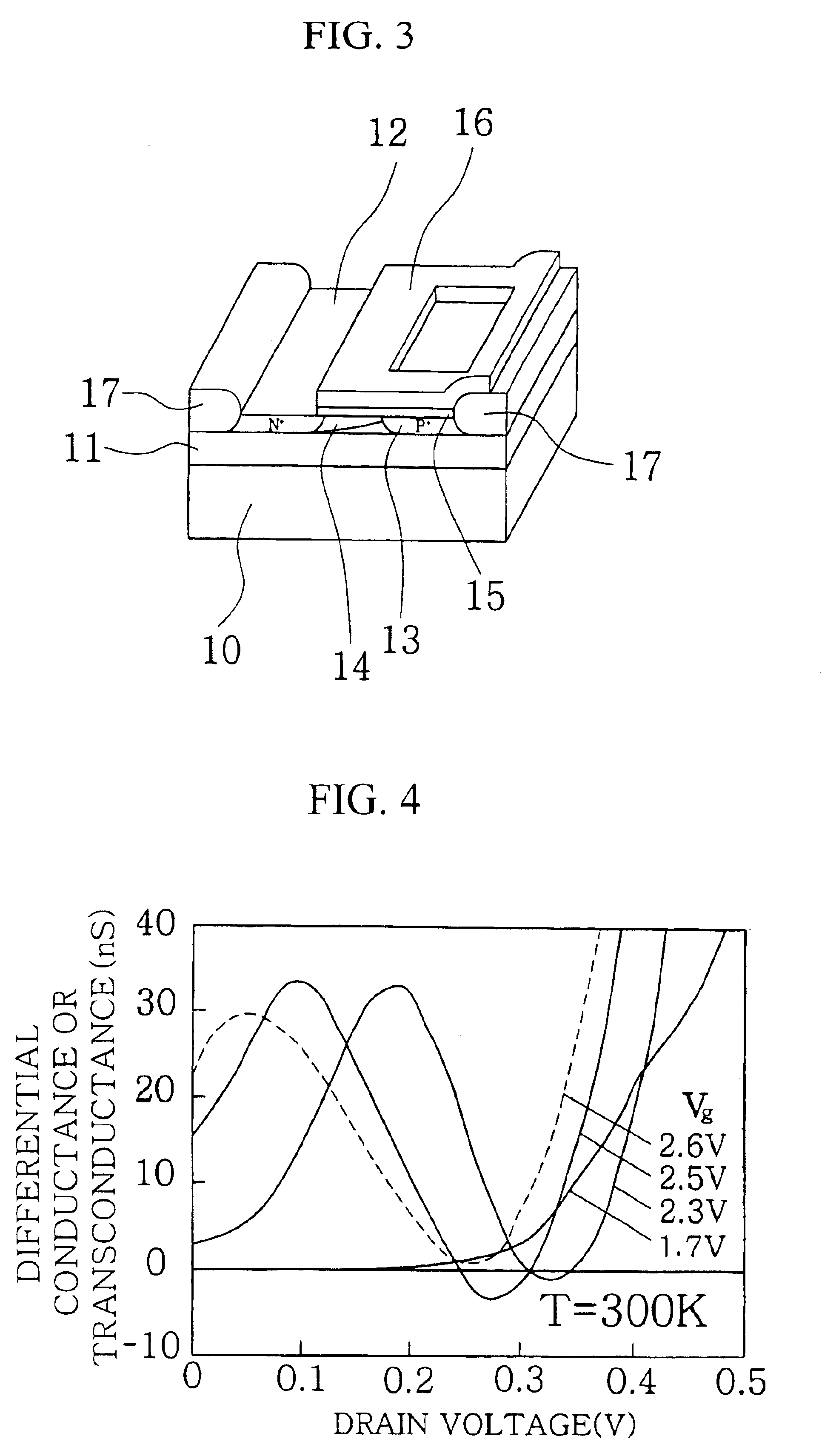

Method for fabricating semiconductor device with negative differential conductance or transconductance

The present invention relates to a method for fabricating semiconductor device with negative differential conductance or transconductance. According to the present invention, a fabrication process thereof can be simplified by using an SOI (Silicon-On-Insulator) substrate, and a tunneling device exhibiting the negative differential conductance or transconductance at room temperature can be implemented by using P+-N+ junction barriers as tunneling barriers and implanting impurity ions into a channel region so that their density is higher than the effective density of states where electrons or holes can exist thereon. Since the semiconductor device with the negative differential conductance or transconductance can be also be implemented even at room temperature, there is an advantage in that the present invention can be applied to an SRAM or a logic device using a device which can be turned on / off in response to a specific voltage.Further, according to the fabrication method of the present invention. miniaturization of the device can be easily made, and the reproducibility and the mass productivity of the process can be enhanced. Simultaneously, the gate, the source / drain and the channel regions are formed by the self-aligned process. Thus, there is another advantage in that a gate pitch can also be reduced.In addition, there is a further advantage in that the semiconductor device fabricated according to the present invention has the characteristic of a single electron transistor by using the channel region as the quantum dot and the two P+-N+ junctions as the tunneling barriers.

Owner:SEOUL NAT UNIV R&DB FOUND

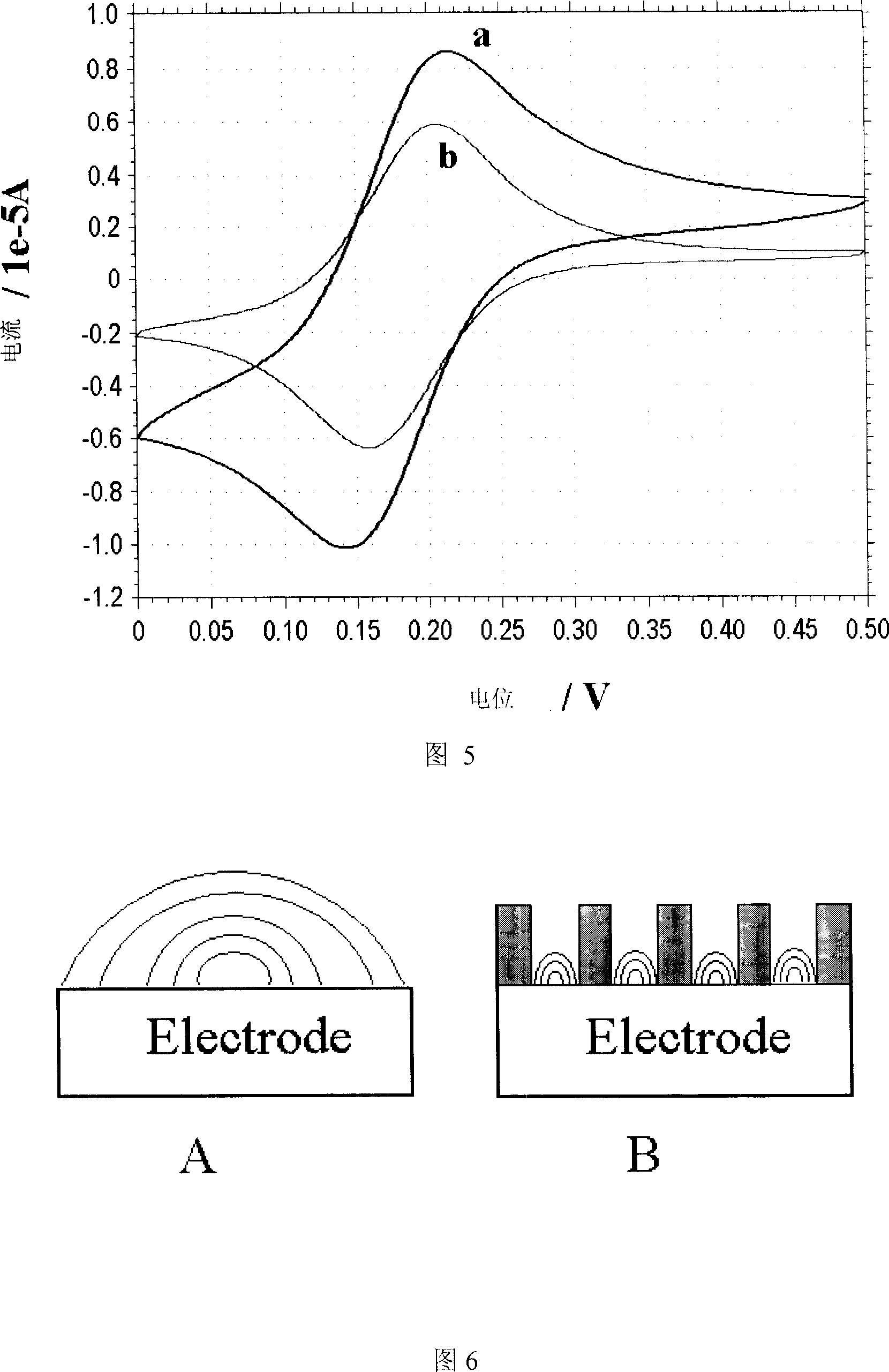

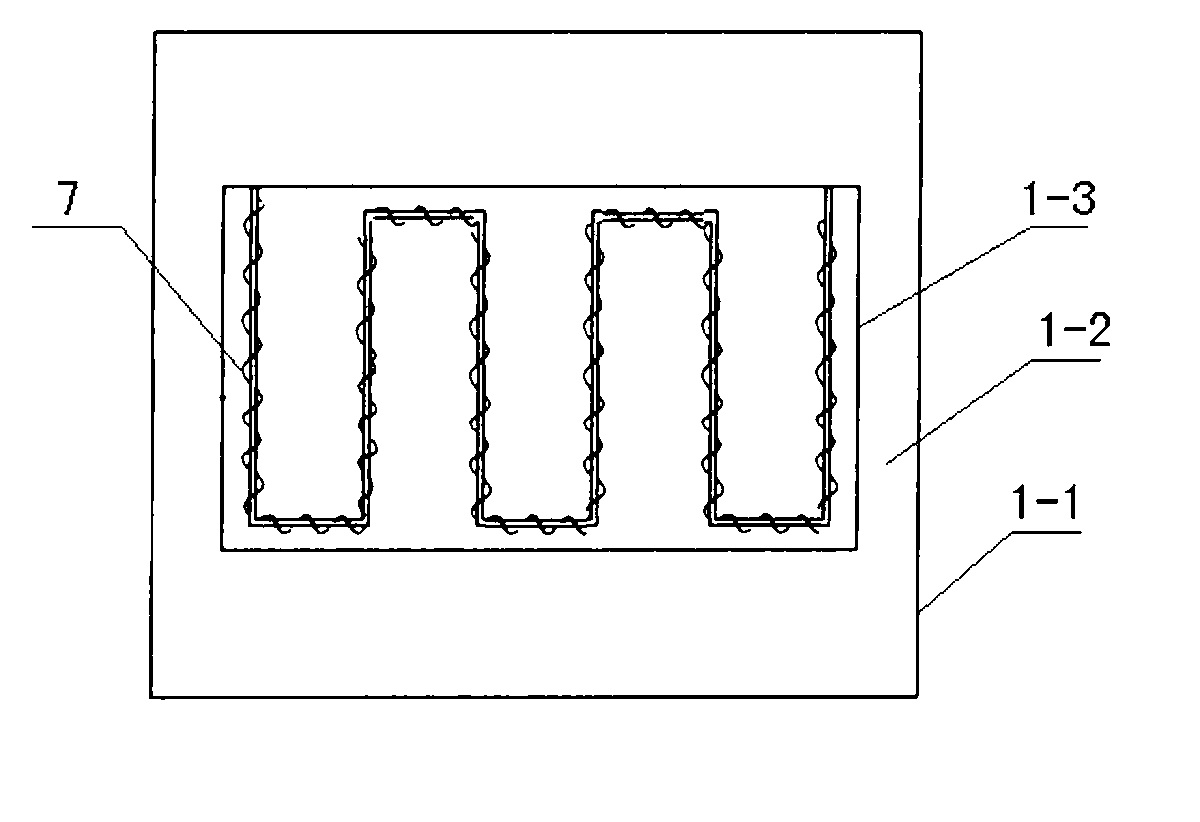

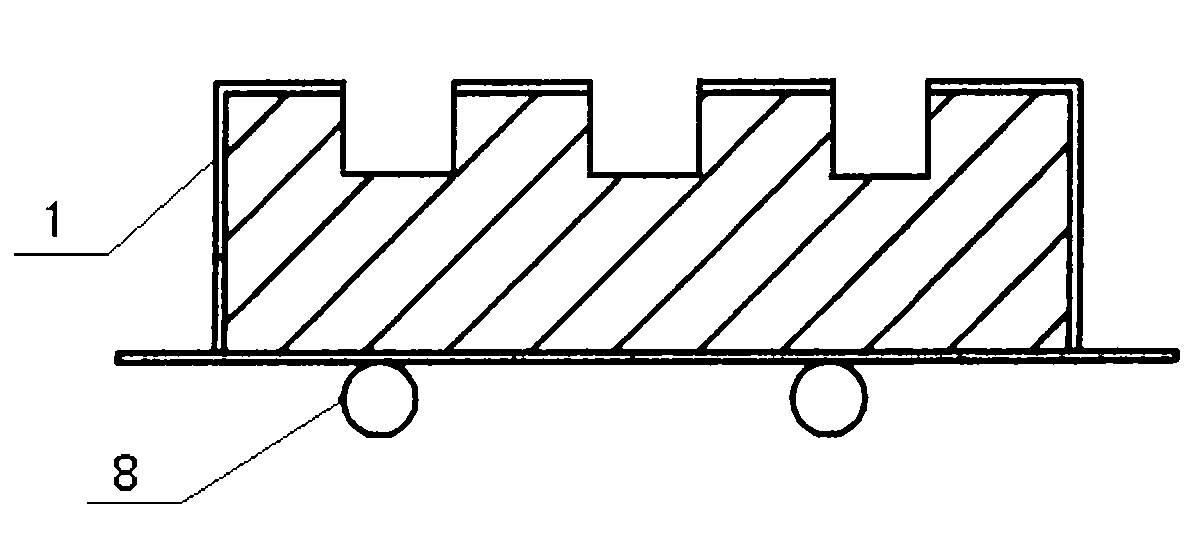

Electrochemical method for detecting anodic oxidation aluminium formwork effective hole density

InactiveCN1987419ASimple methodImprove reliabilityPermeability/surface area analysisMaterial electrochemical variablesPlatinumEffective density

The invention especially related to electrochemical method for measuring effective density of hole in anodic aluminum oxide (AAO) template. Usual three-electrode system and potentiostat are adopted in the method. Working electrode is dish electrode of metal platinum (or gold, glassy carbon), and there is electrode of AAO template. Ferricyanide is as solution. Na2SO4 or KCl is as electrolyte. Using diffusibility of ferricyanide on surface of working electrode, the method measures effective density of hole in AAO template by using electrochemical voltmeter-ammeter method. Features are: simple method and good reliability.

Owner:FUDAN UNIV

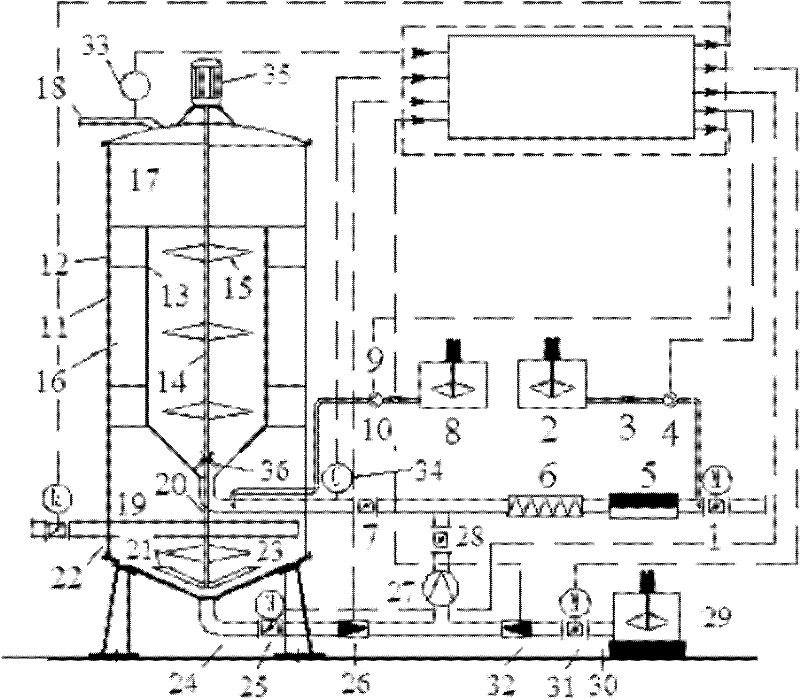

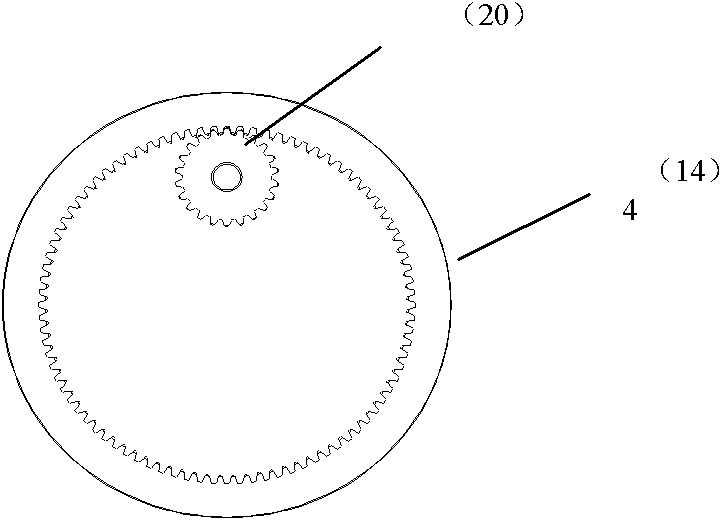

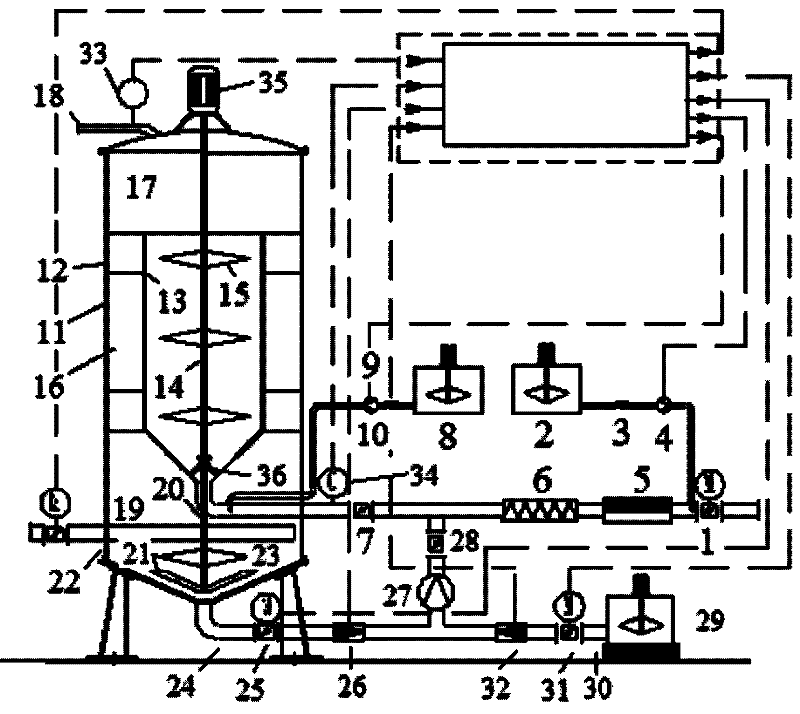

Micro-sand synergism and caked flocculation integrated water quality purification device

ActiveCN102531123AAchieve recyclingIncrease concentrationWater/sewage treatment by flocculation/precipitationEffective densityTurbidity

Owner:XI'AN UNIVERSITY OF ARCHITECTURE AND TECHNOLOGY

Medicine for curing cardiovascular disease and its preparation method

InactiveCN1927329ASimple production processGood curative effectCardiovascular disorderPlant ingredientsEffective densityThree vessels

The invention relates to a drug used to treat heart blood vessel disease, and relative production. Wherein, said drug is formed by the alcohol extractives of chavicol and leek, and relative auxiliary materials; and the extraction method of them comprises adding alcohol water solution into chavicol and leek, to be heated, refluxed and extracted; combining the extractive solutions, recycling and concentrating alcohol until the volume percentage of alcohol is lower than 5%; diluting with water, adding porous adsorption resin, washing out foreign material with water, and washing with alcohol water solution, collecting the alcohol elution, concentrating and recycling the alcohol to obtains said alcohol extractives. Compared with present traditional medicine, the invention has high effective density, reduce the oral amount, and remove the inactive component.

Owner:TIANJIN UNIV

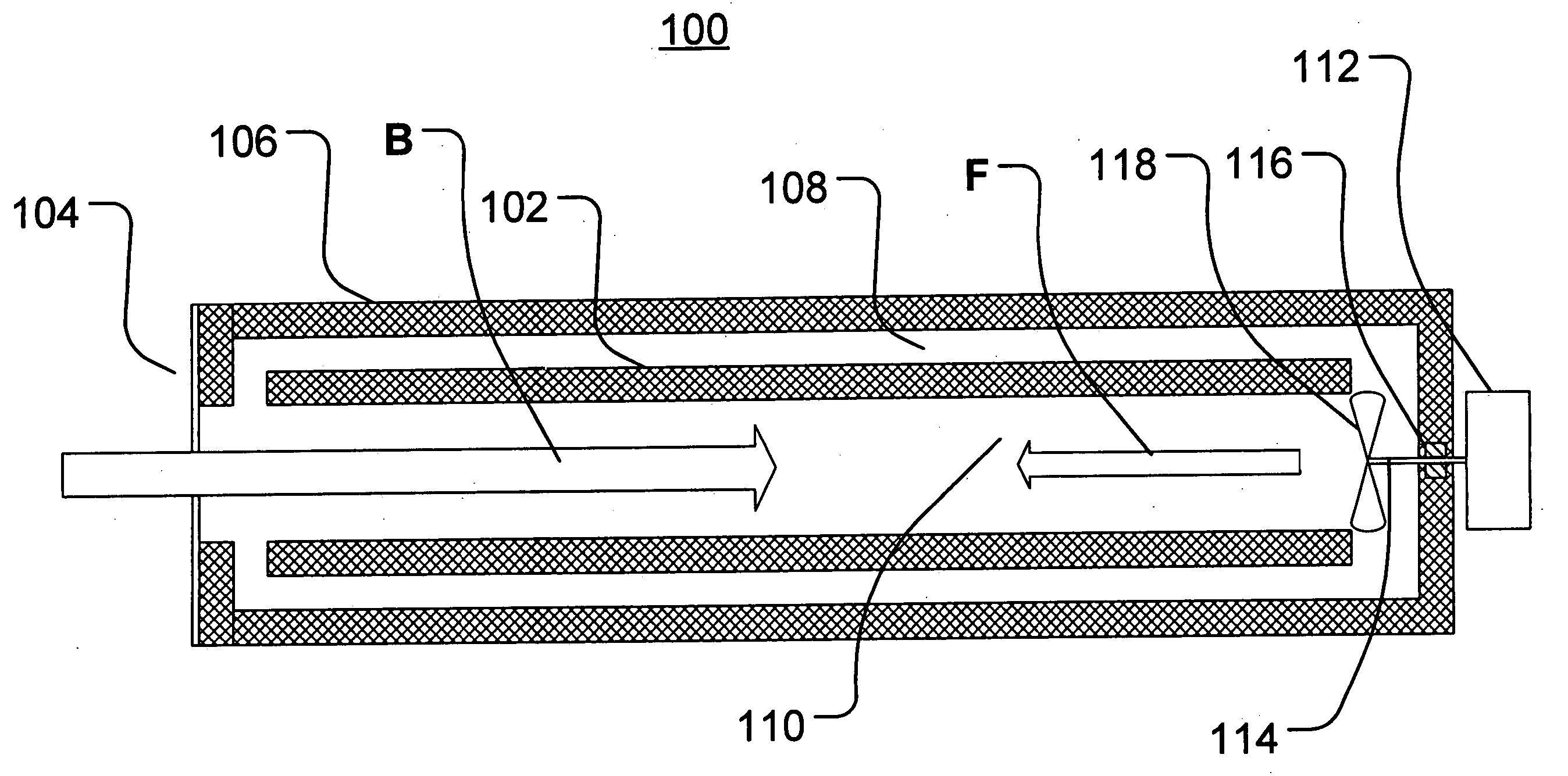

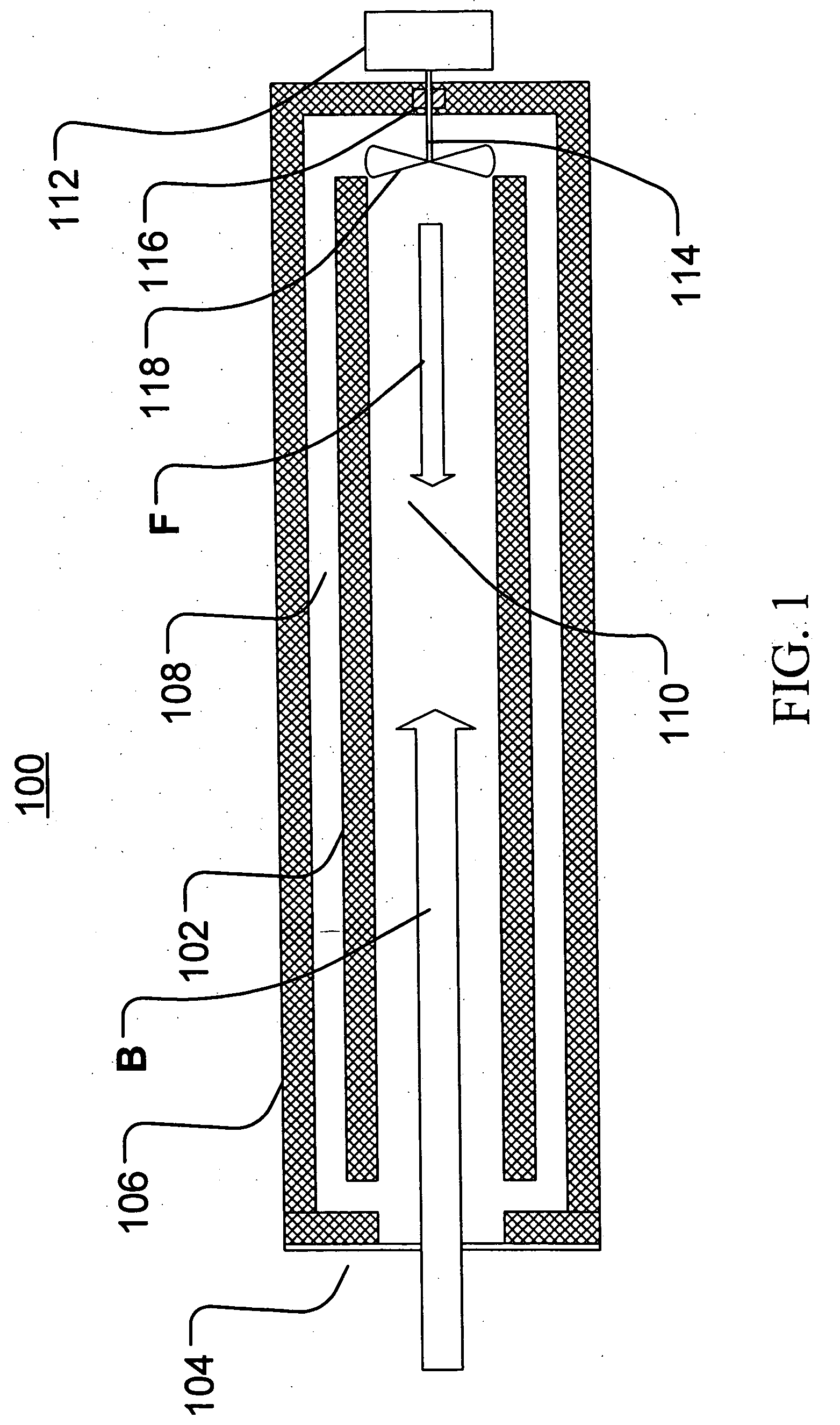

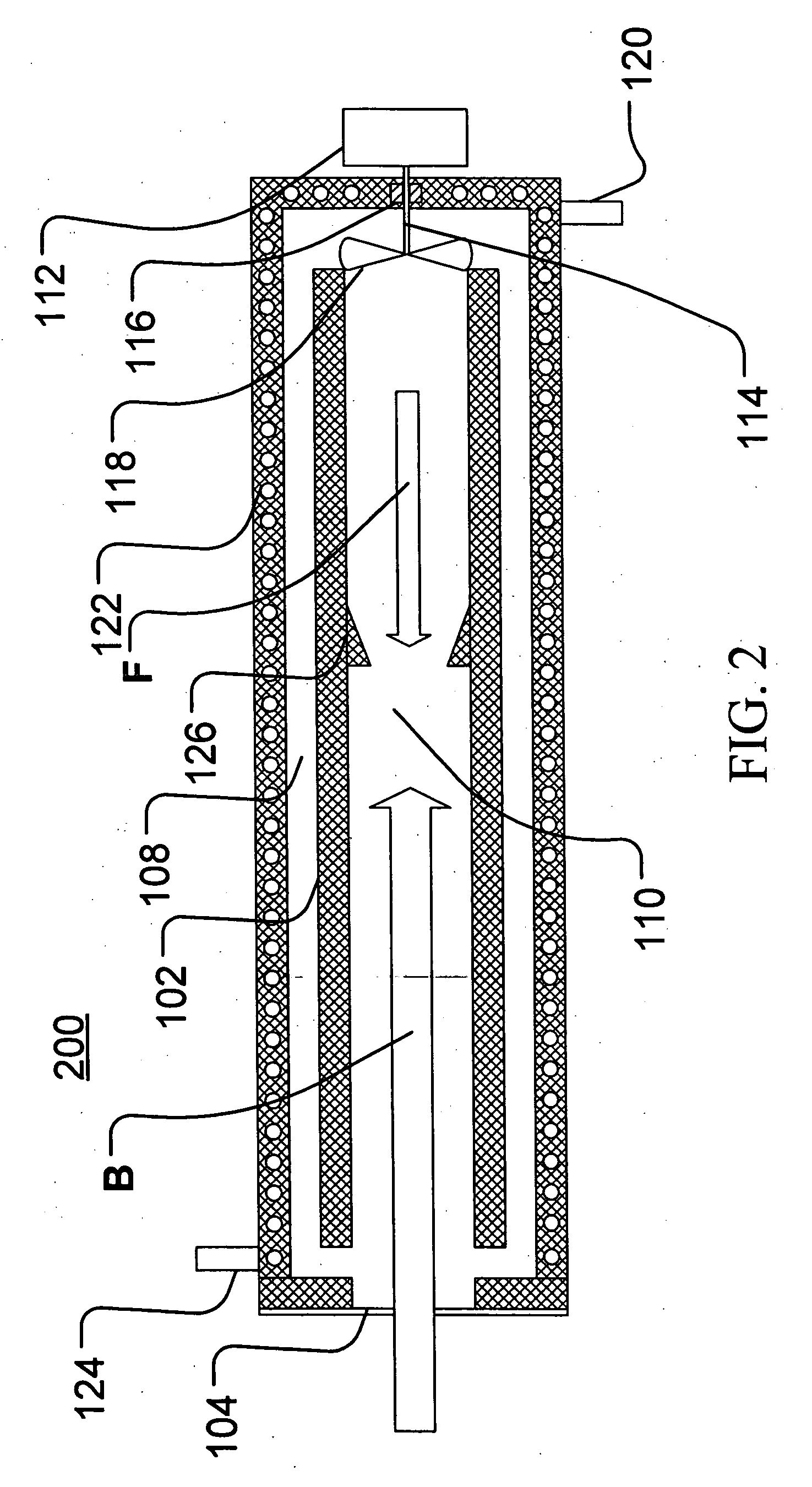

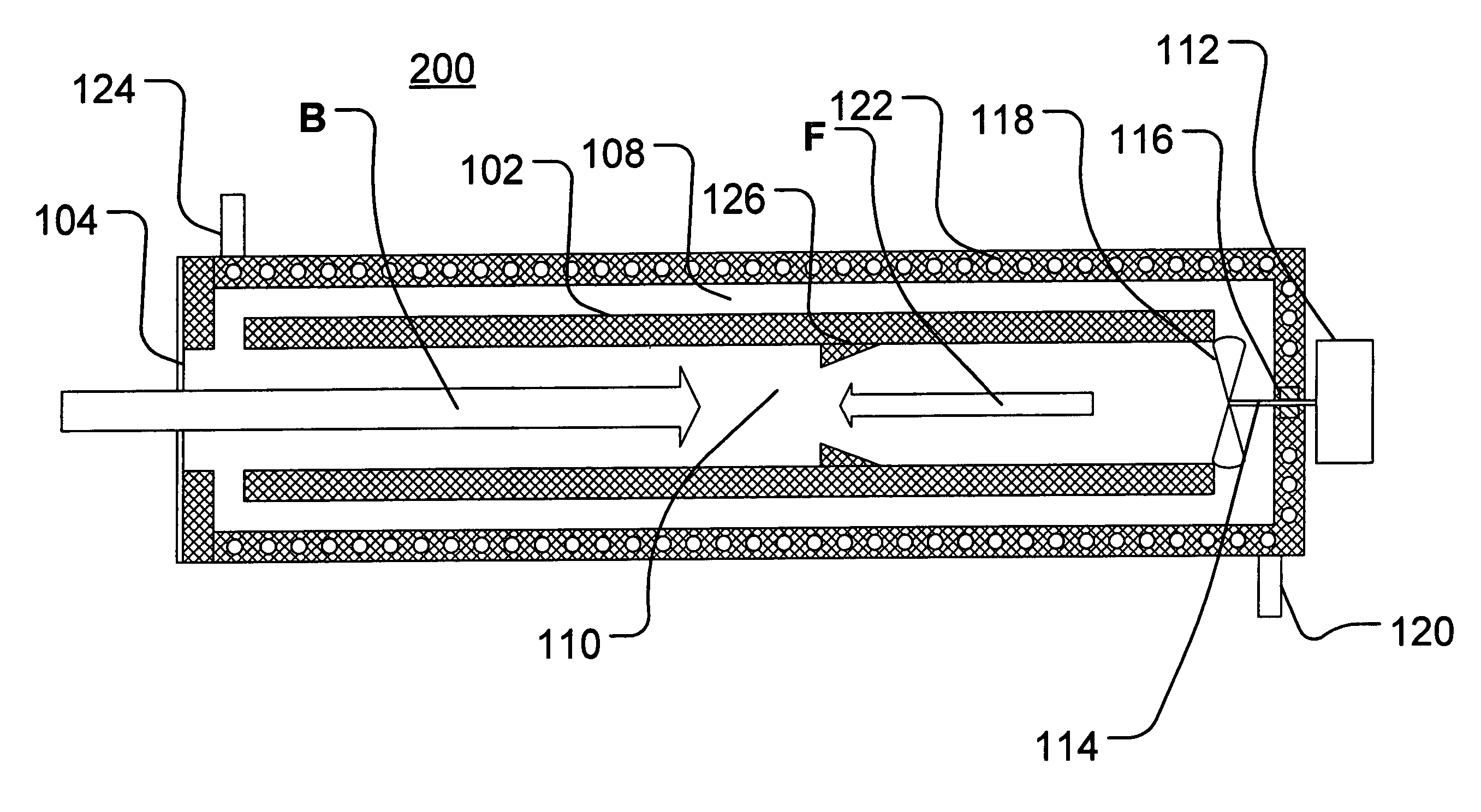

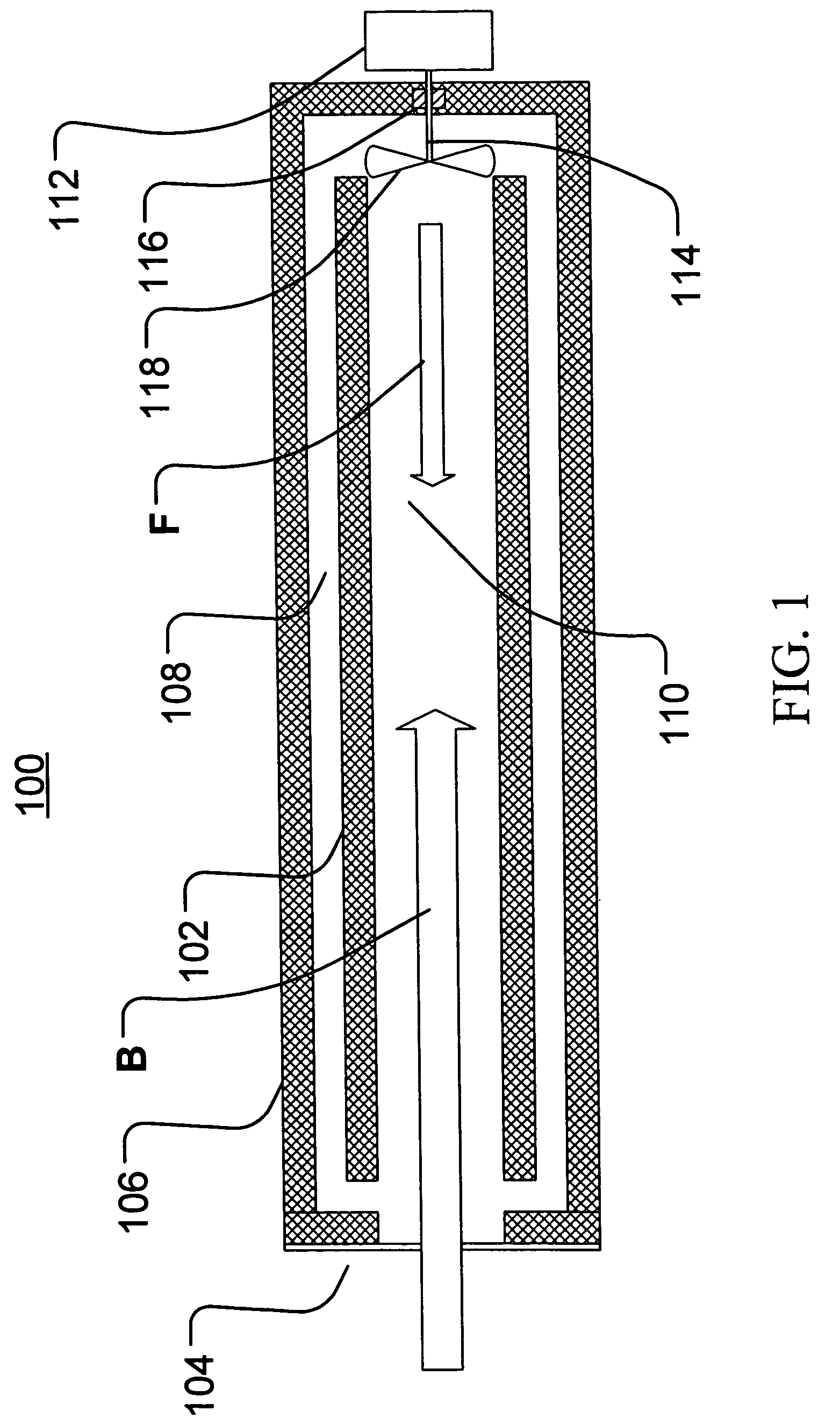

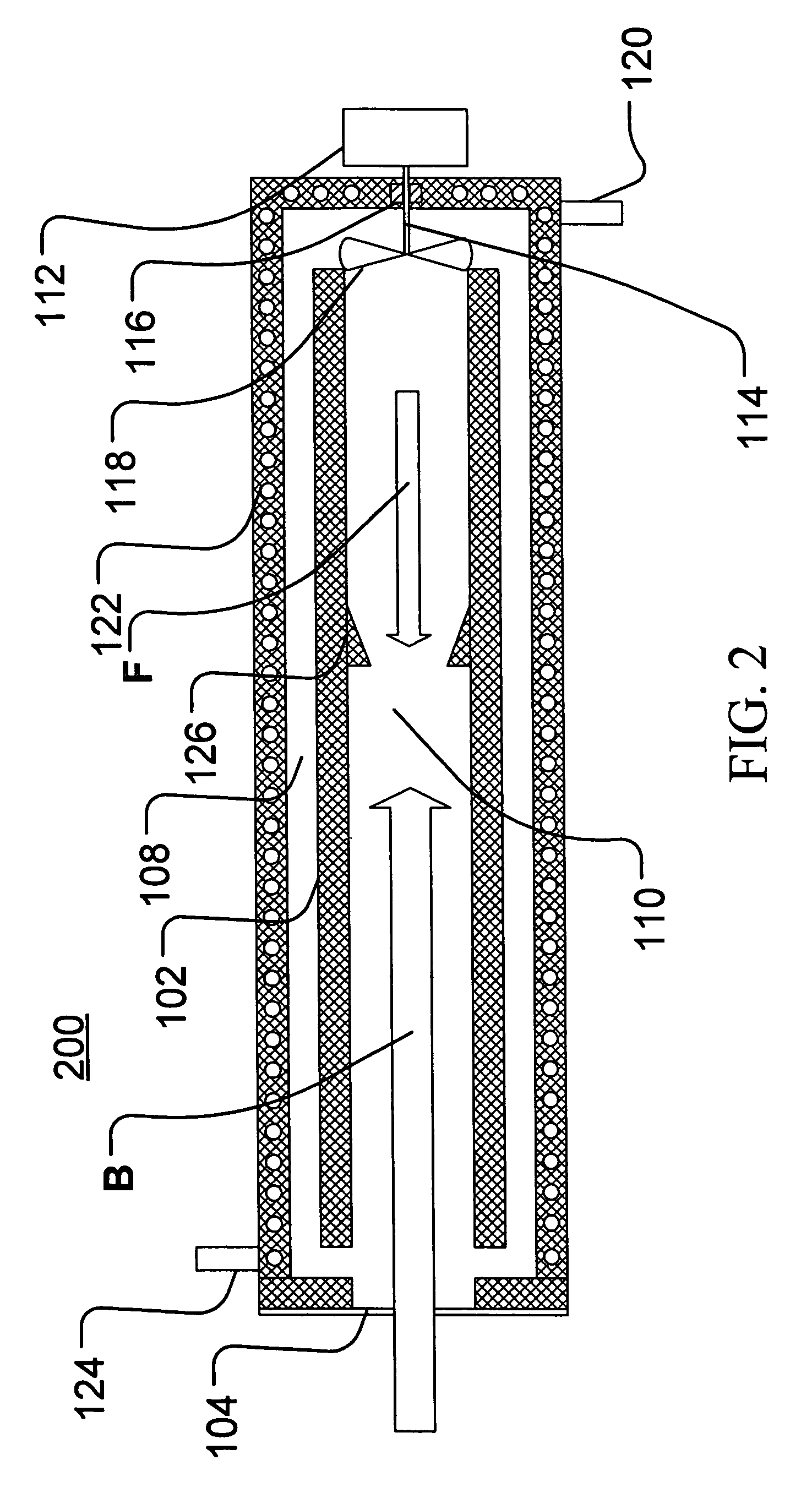

Forced convection target assembly

InactiveUS20060050832A1Effective density increaseIncrease productionParticle separator tubesRadiation/particle handlingEffective densityNatural convection

Provided is a modified target assembly in which the target fluid is moved within the target assembly in a manner that increases the effective density of the target fluid within the beam path, thereby increasing beam yield utilizing forced convection. The target may also include optional structures, such as nozzles, diverters and deflectors for guiding and / or accelerating the flow of the target fluid. The target assembly directs the target fluid along an inner sleeve in a direction opposite the direction of the beam current to produce a counter current flow and may also direct the flow of the target fluid away from the inner surface of the inner sleeve and toward a central region in the target cavity. This countercurrent flow suppresses natural convection that tends to reduce the density of the target fluid in the beam path and tends to increase the heat transfer from the target.

Owner:ADVANCED APPLIED PHYSICS SOLUTIONS

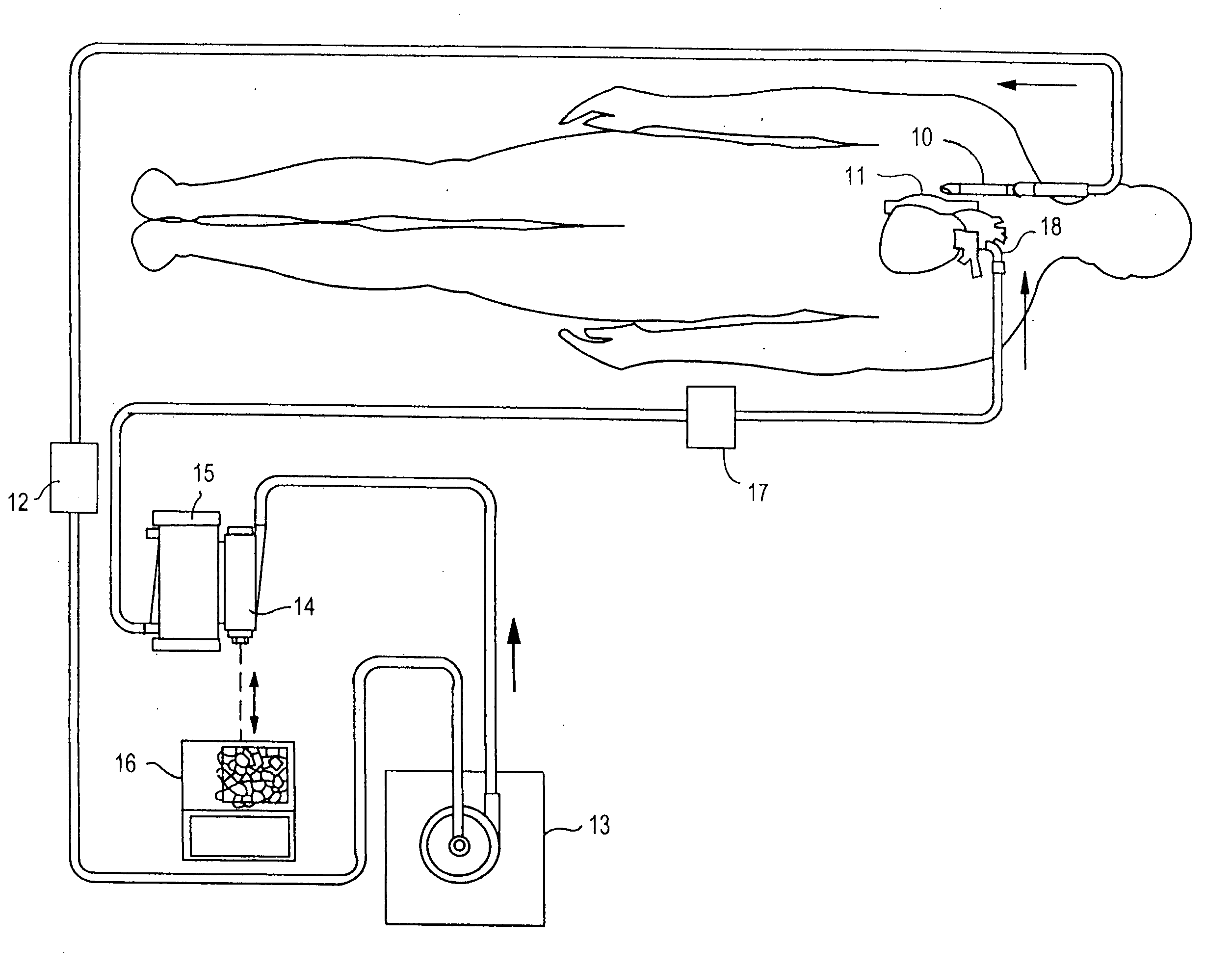

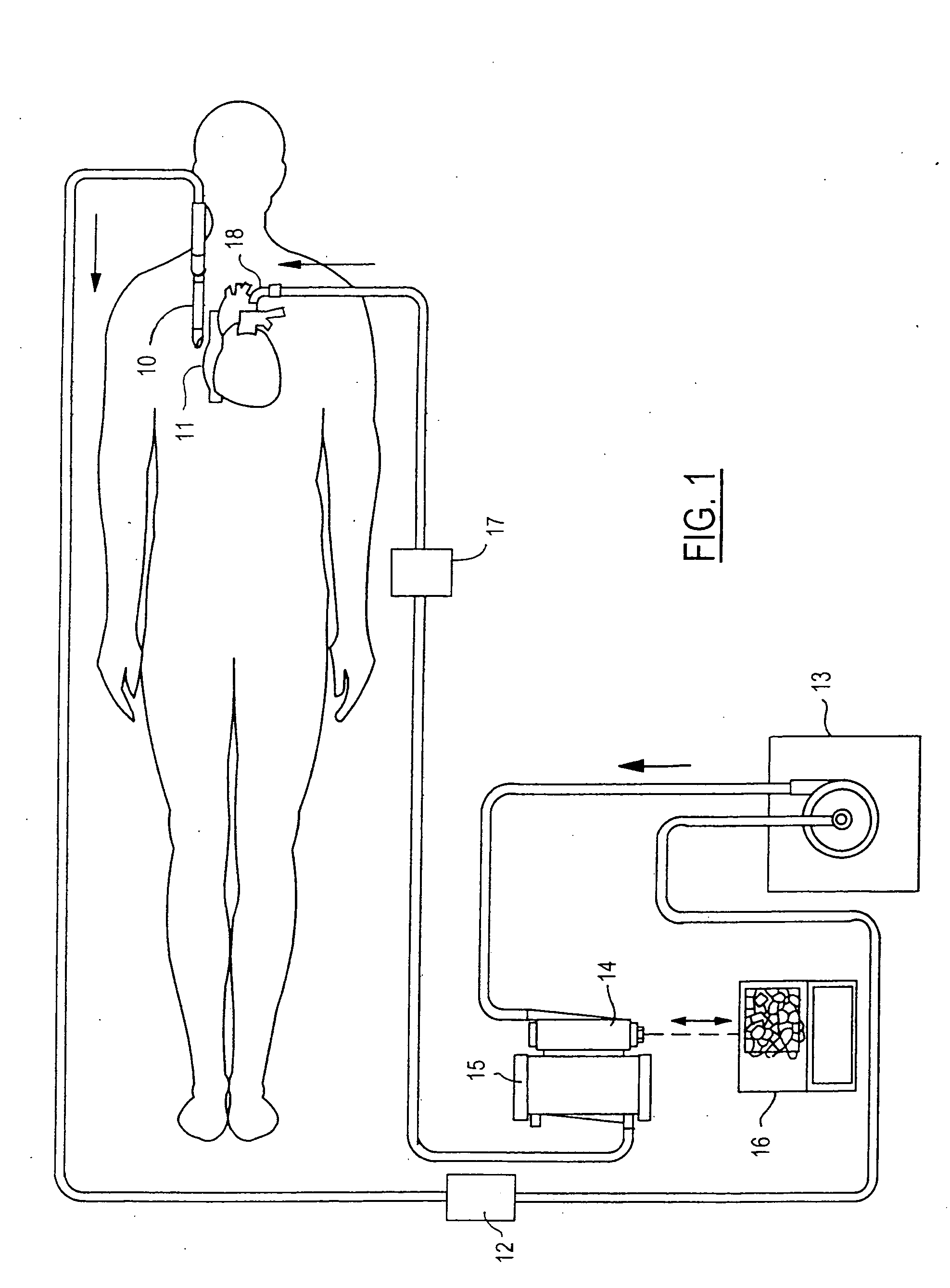

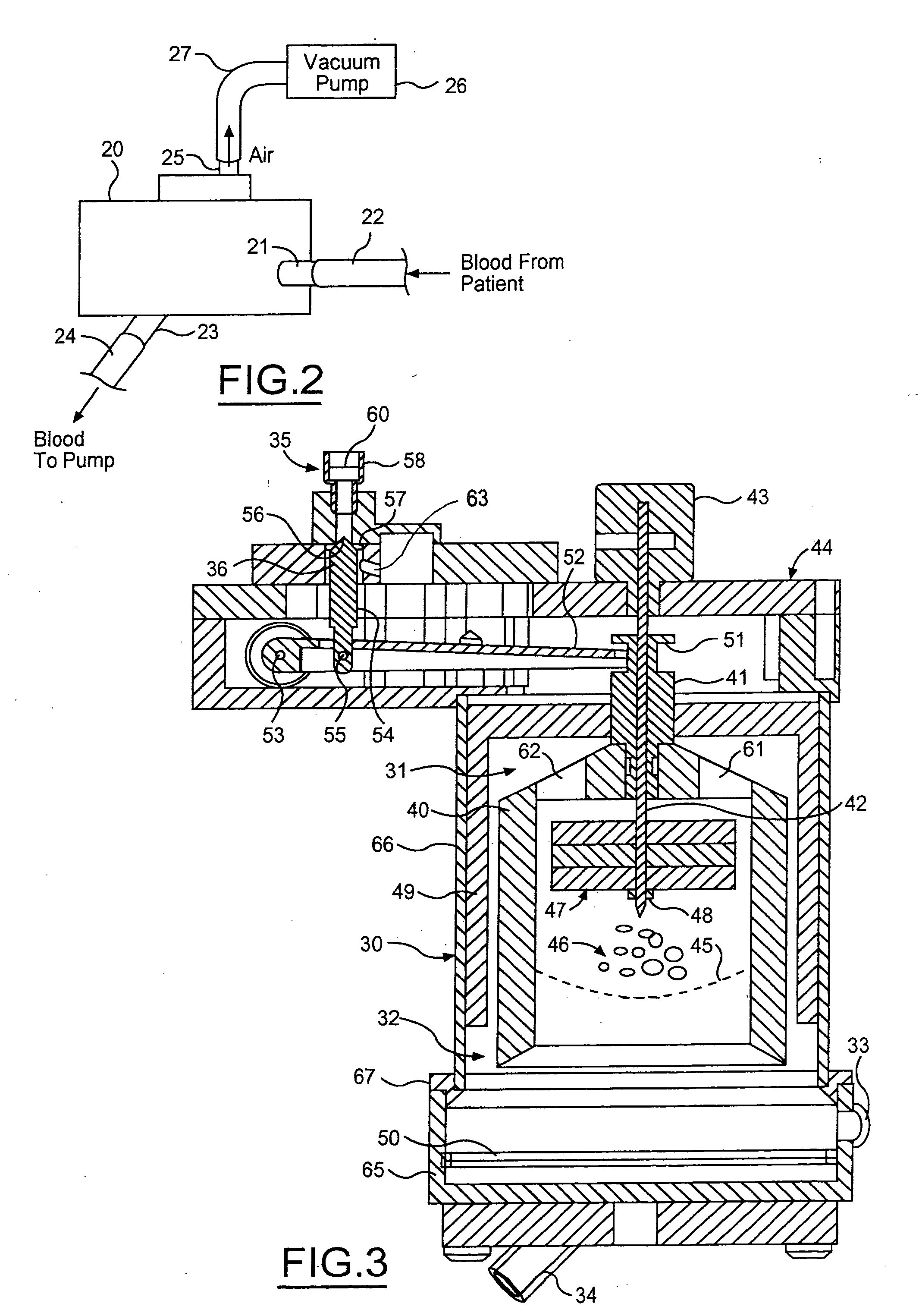

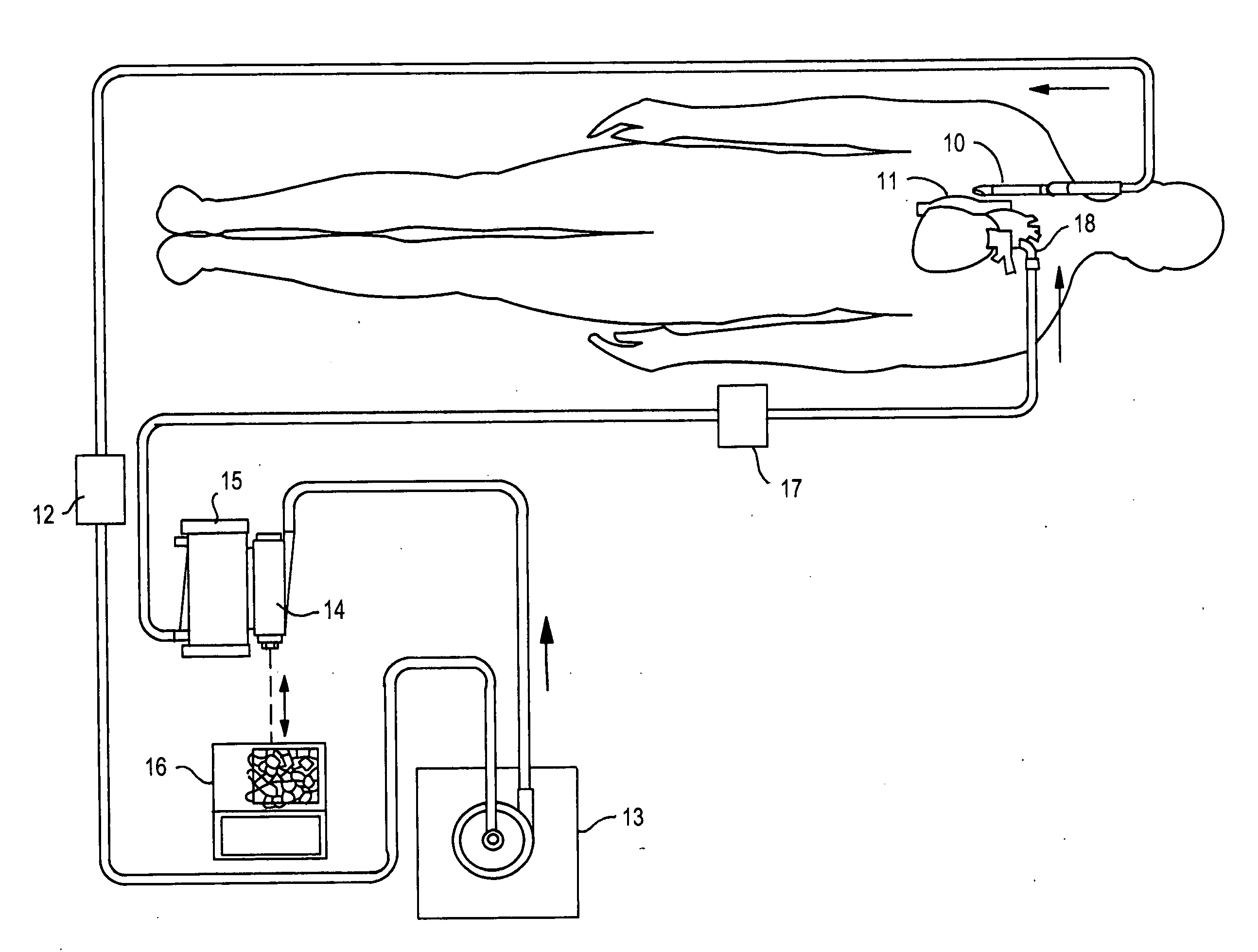

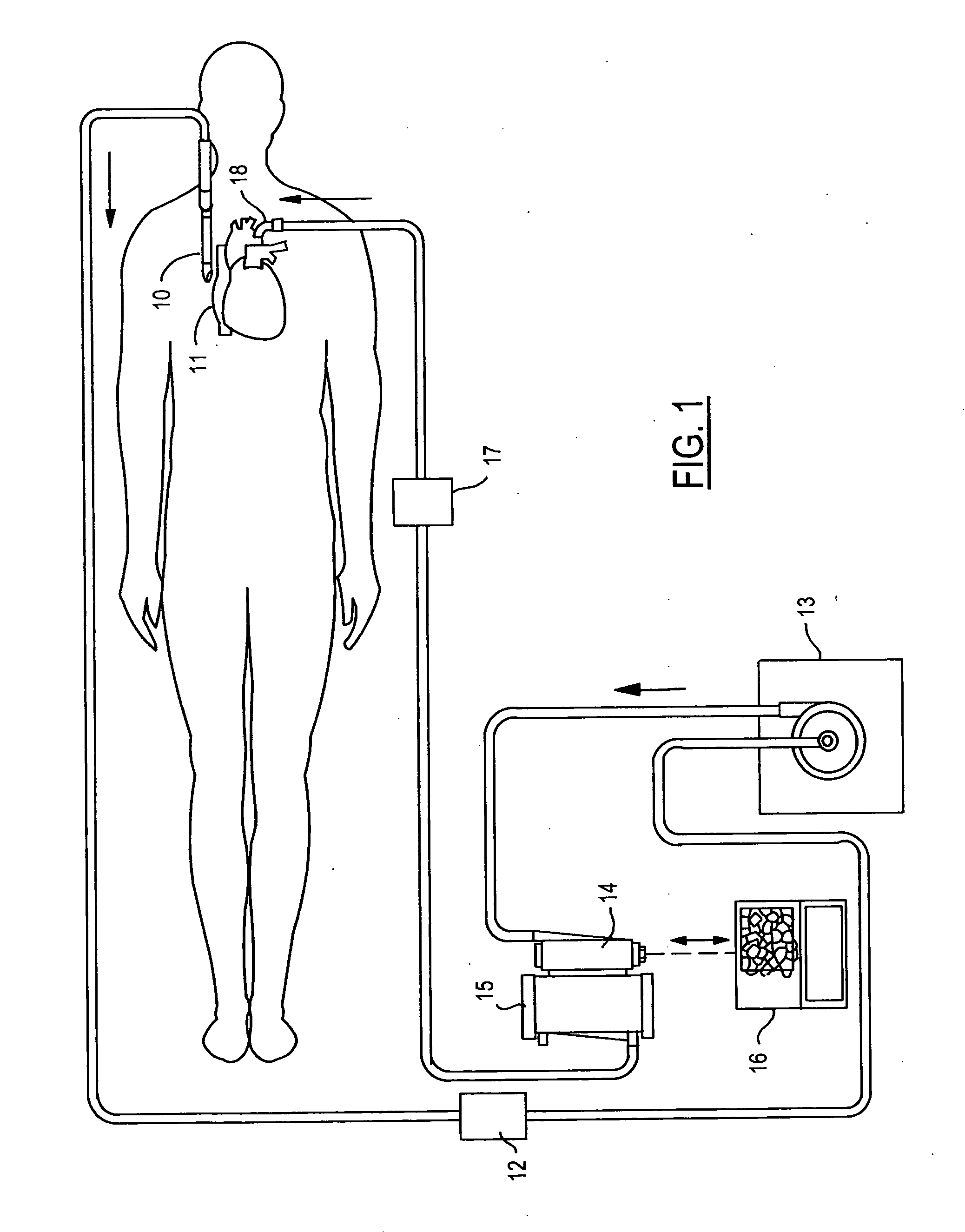

Float-driven lever arm for blood perfusion air removal device

InactiveUS20060041215A1Low prime volumeEfficient air removalHaemofiltrationMedical devicesEffective densityBlood flow

An air removal device removes air from blood flowing in a perfusion system. A chamber is provided having a blood flow region at a lower end thereof and having an air collection region at an upper end thereof. The chamber further has an inlet, a blood outlet, and an air outlet vertically higher than the inlet. There is a vertical guide structure in the air collection region. A float is disposed for vertical movement following the vertical guide structure, wherein the float has an effective density less than the density of blood. A lever arm having a first end follows vertical movement of the float and has a second end pivotally mounted at a pivot point that is stationary with respect to the vertical guide structure. A valve is coupled to the air outlet and to an intermediate point of the lever arm for closing the air outlet when the float is at its vertically highest position.

Owner:TERUMO CARDIOVASCULAR SYST CORP

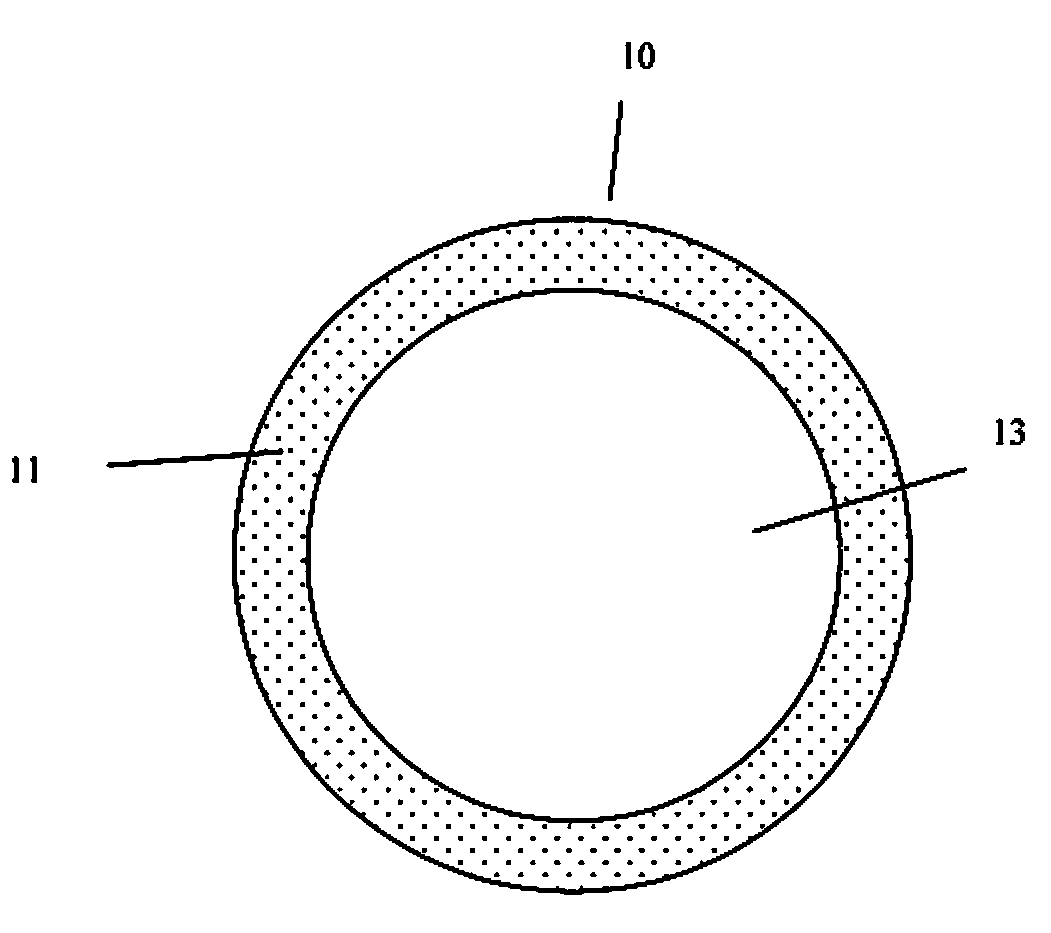

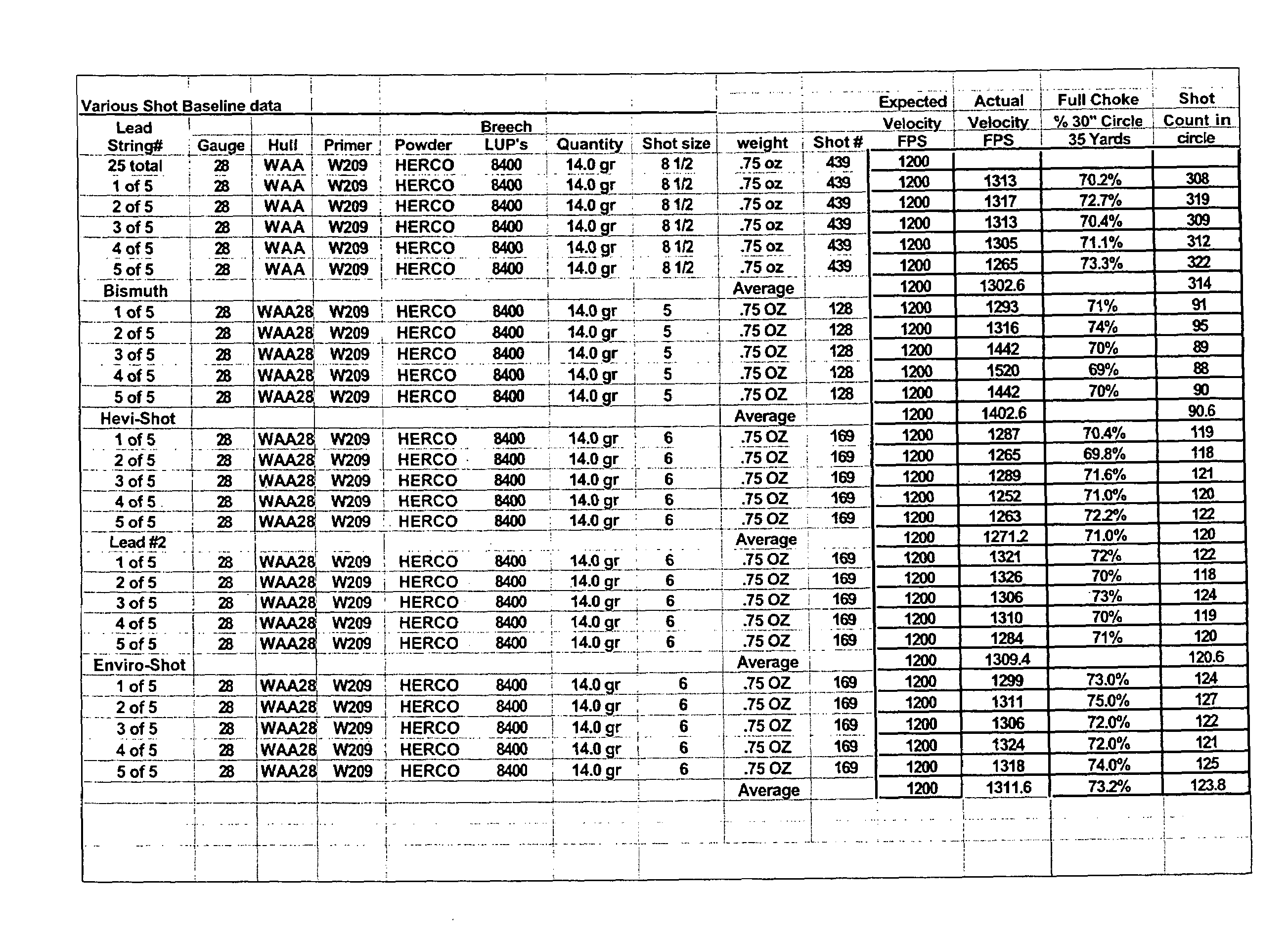

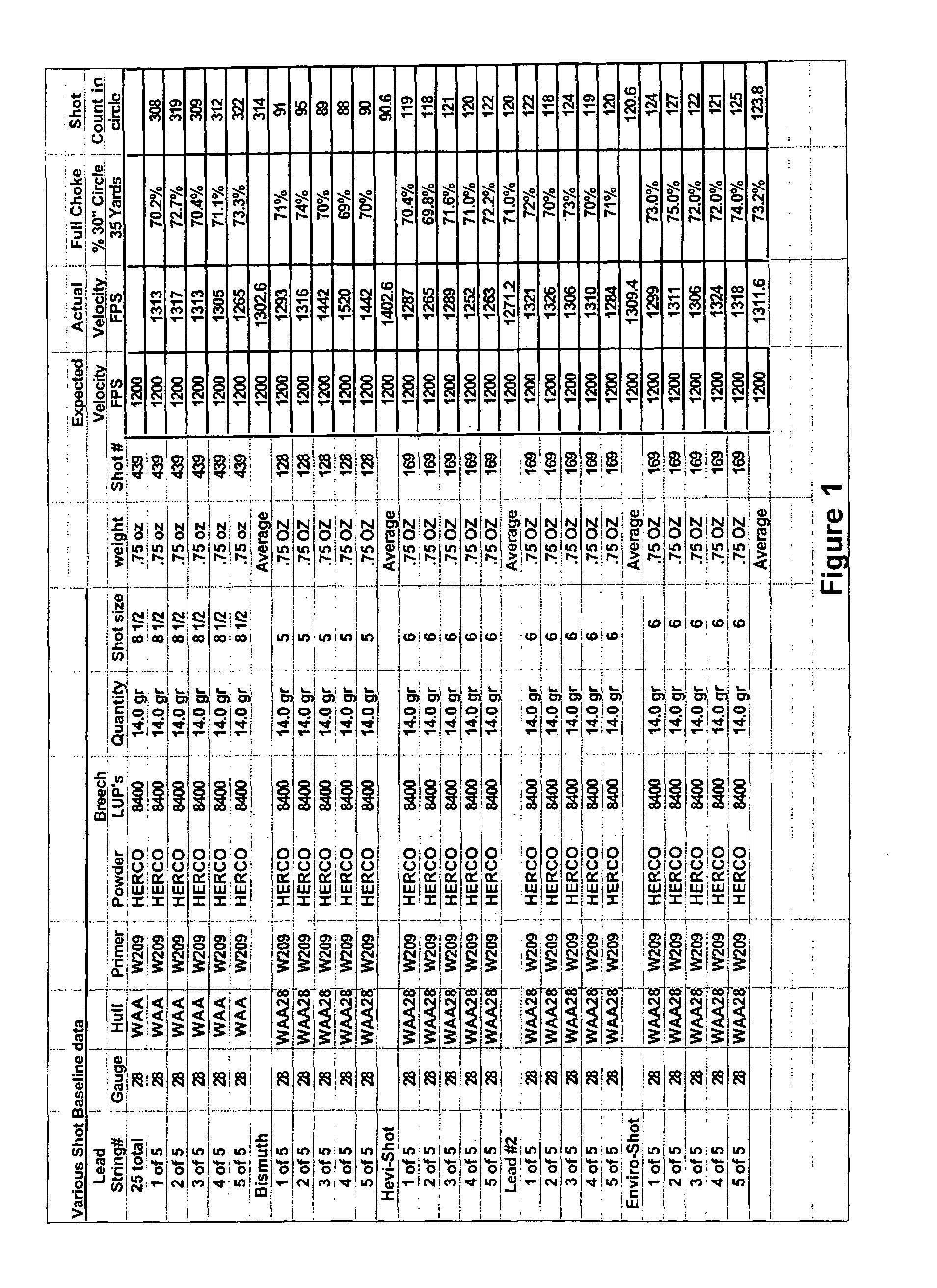

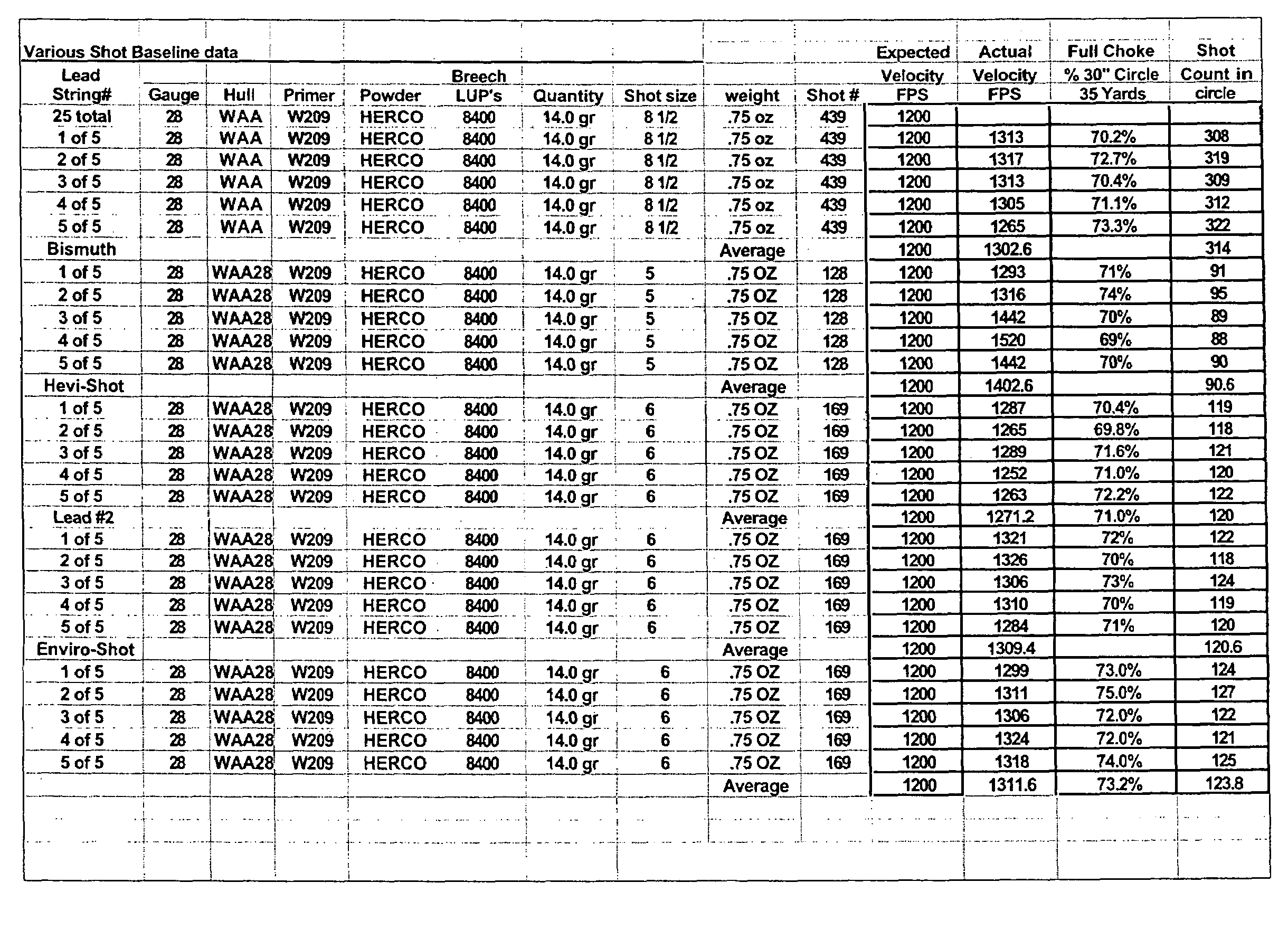

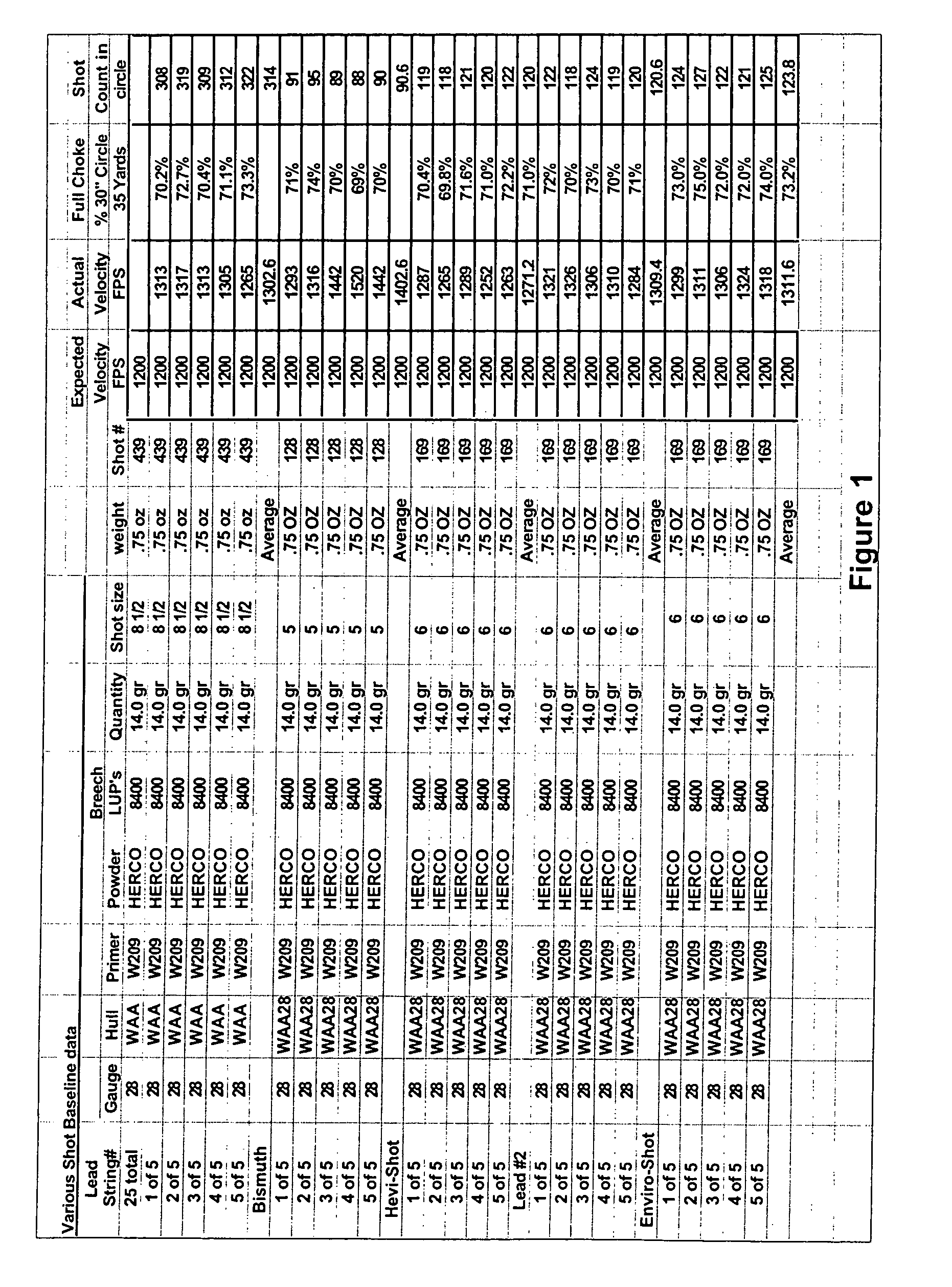

Method of making an environmentally safe substitute for lead shot

InactiveUS7013786B1Improve energy transferAmmunition projectilesShotgun ammunitionEnergy transferEffective density

A shot pellet that, has an inner core of a material such tungsten carbide, that is coated with a layer of bismuth. This coating is molecularly bonded to the tungsten carbide and is not an alloy. The unique properties of the shot pellet allow its density to be tailored. Under this process, the effective density of the pellet can be made to be identical to lead for direct replacement in current lead loading formulations. Additionally, the density can be made to be lower than lead for shotguns requiring low barrel pressures, or higher than lead for enhanced energy transfer while maintaining the other advantages of the instant invention.

Owner:ALLEN JAMES ROBERT +1

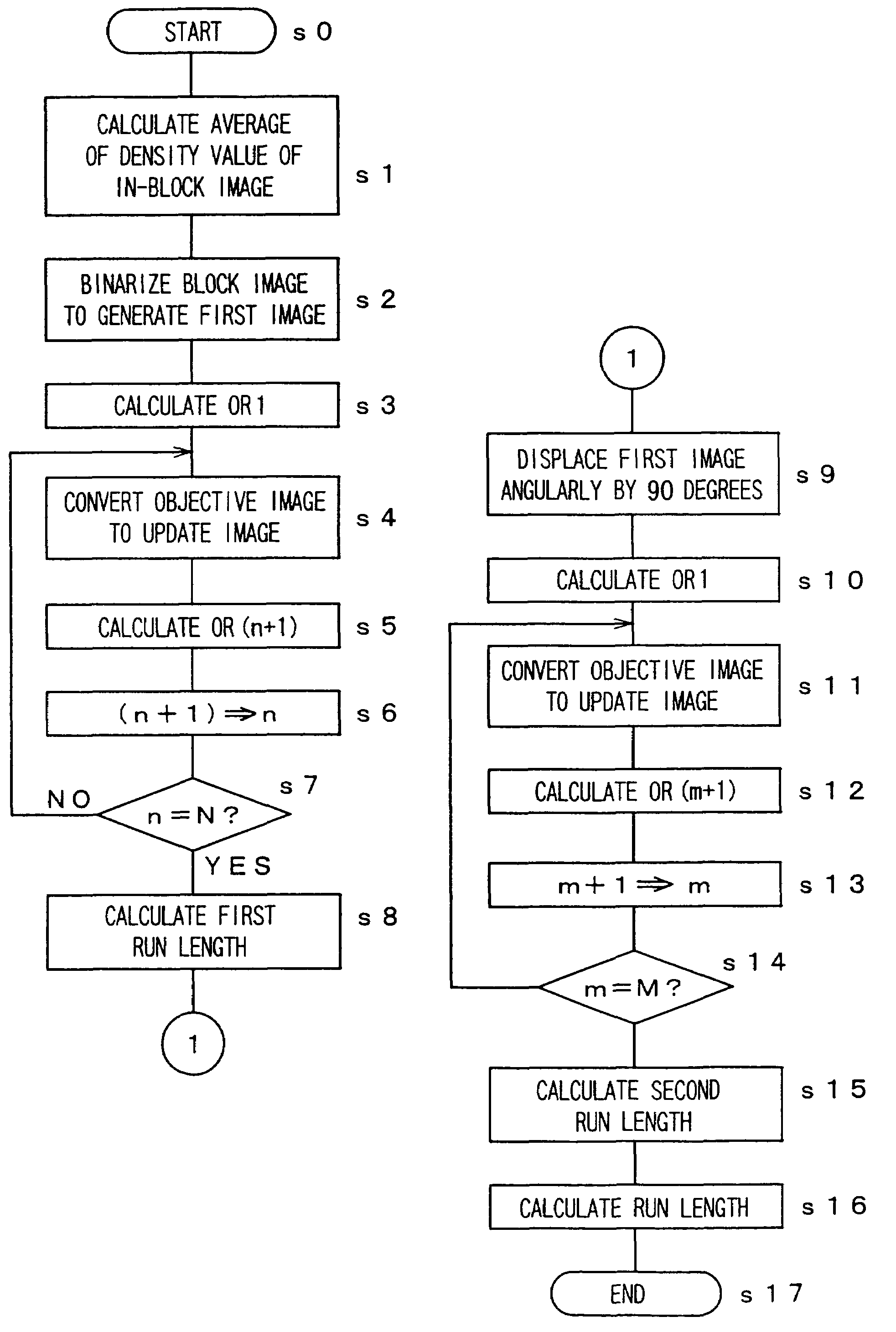

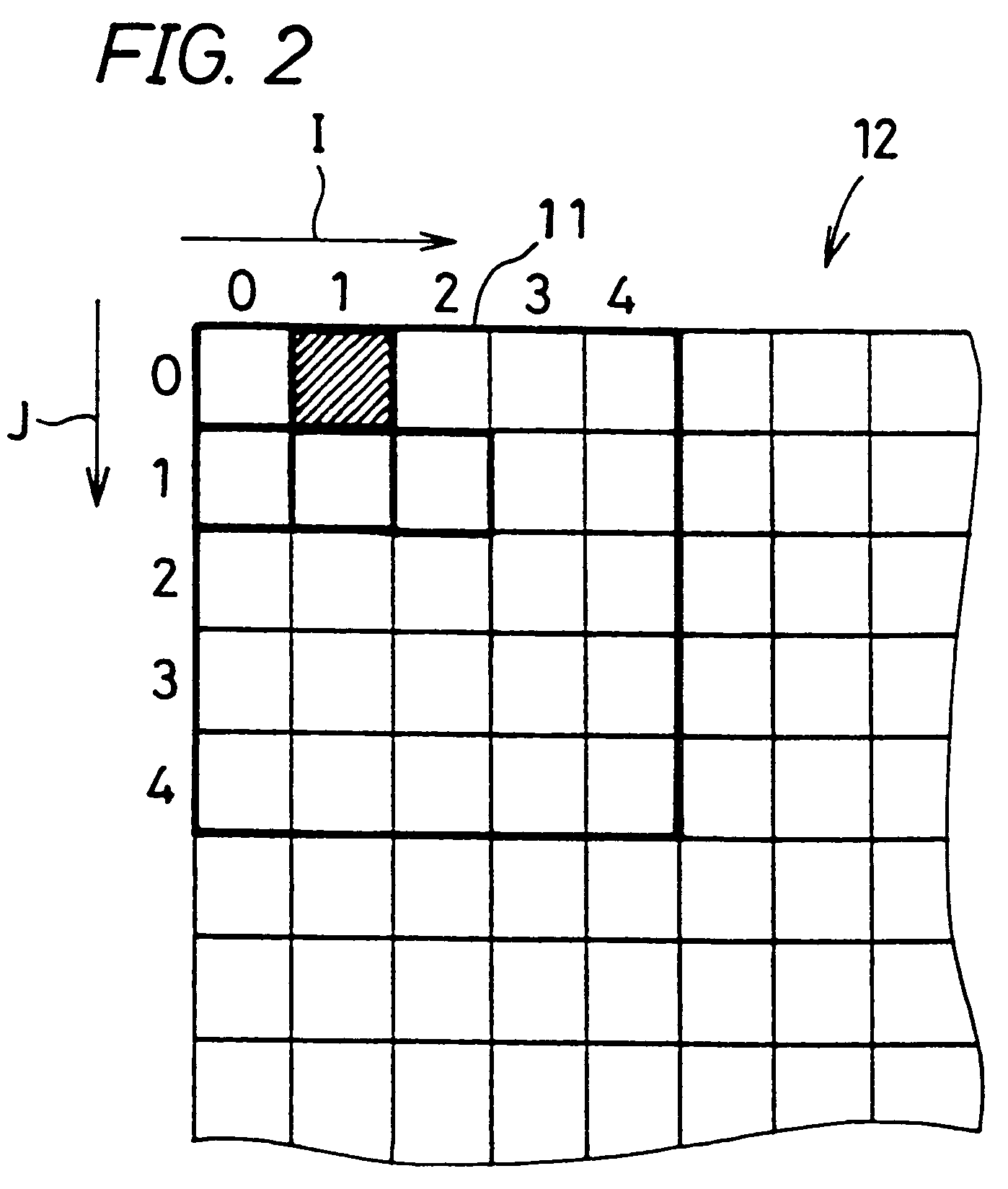

Image processing method and image processing apparatus, program and recording medium, and image forming apparatus

ActiveUS7295344B2Reduce circuit sizeReduce problem sizeImage enhancementDigitally marking record carriersImaging processingEffective density

A parameter representing whether an effective density pixel exists in an objective image is calculated. As to each interest pixel in the objective image having one pixel neighboring a downstream side in a first direction, the interest pixel is defined as an effective density pixel when a first condition and a second condition is an effective density pixel are satisfied, and in other case, the interest pixel is defined as an ineffective density pixel. The objective image is converted to an update image on one-line reduced lines in the first direction. A parameter representing whether an effective density pixel exists in the update image is calculated. The conversion and the calculation are repeated about the update image as the objective image. When the objective image converts one line in the first direction, the number of continuous pixels of the effective density pixels spatially continuing is calculated based on each parameter.

Owner:SHARP KK

Method of making an environmentally safe substitute for lead shot

InactiveUS7073425B1Improve energy transferAmmunition projectilesShotgun ammunitionEnergy transferEffective density

A shot pellet that, has an inner core of a material such tungsten carbide, that is coated with a layer of bismuth. This coating is molecularly bonded to the tungsten carbide and is not an alloy. The unique properties of the shot pellet allow its density to be tailored. Under this process, the effective density of the pellet can be made to be identical to lead for direct replacement in current lead loading formulations. Additionally, the density can be made to be lower than lead for shotguns requiring low barrel pressures, or higher than lead for enhanced energy transfer while maintaining the other advantages of the instant invention.

Owner:ALLEN JAMES ROBERT +1

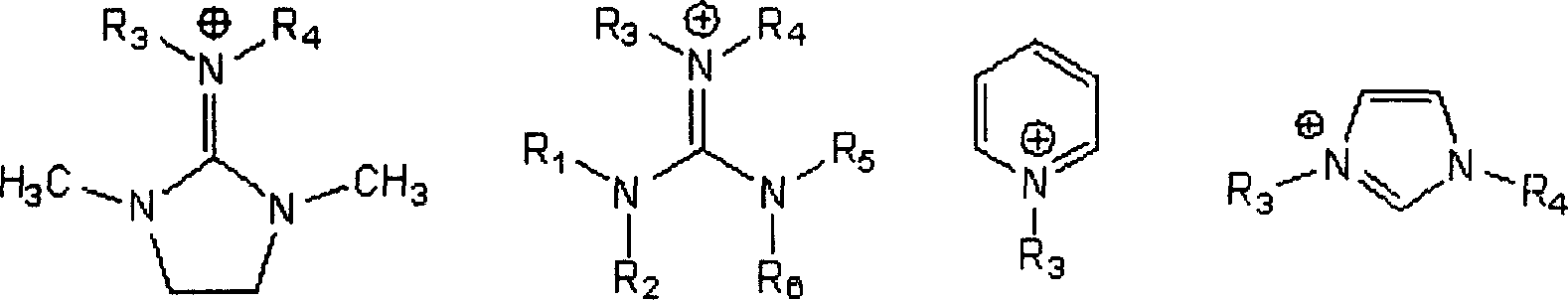

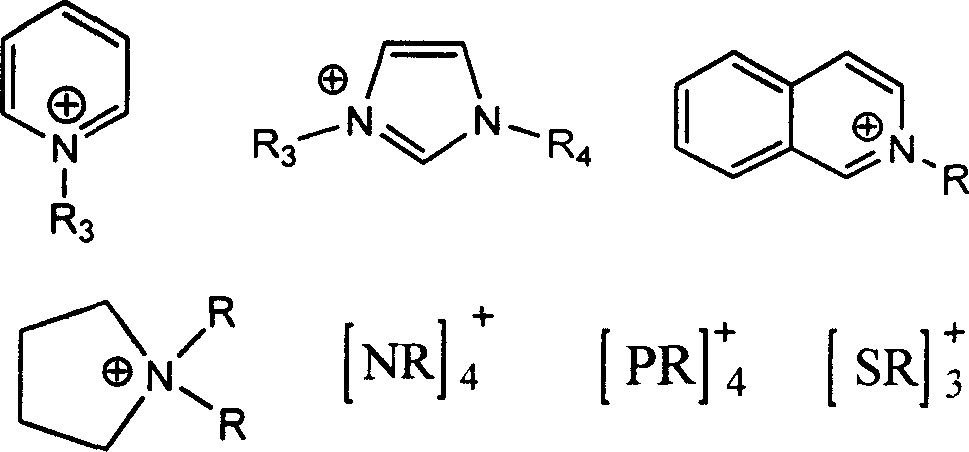

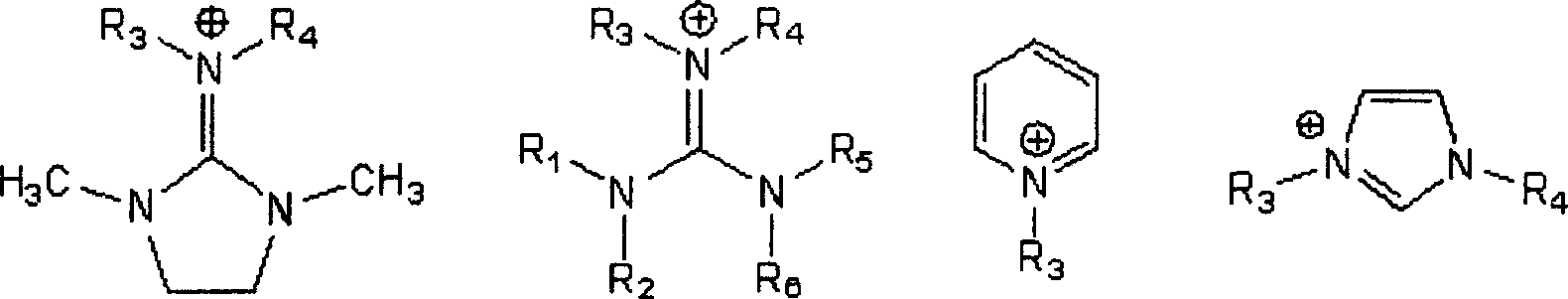

Synthesis and uses of serial ion liquid as candidate drug with anticancer activity

InactiveCN1970543AEnhanced inhibitory effectReduce inhibitionOrganic active ingredientsOrganic chemistryEffective densityStructural formula

The invention discloses an artificial synthetic new-typed anti-cancer drug with a series of ion liquid structure, whose structural formula is displayed in the formula (I), wherein R1,R2, R3,R4,R5,R6,X are defined as instruction; the compound inhibits tumour cell strongly such as Hela299,B16,SMMC-7721 and so on in the external anticancer activity test with effective density less than 10 mug / ml.

Owner:CHANGCHUN INST OF APPLIED CHEMISTRY - CHINESE ACAD OF SCI

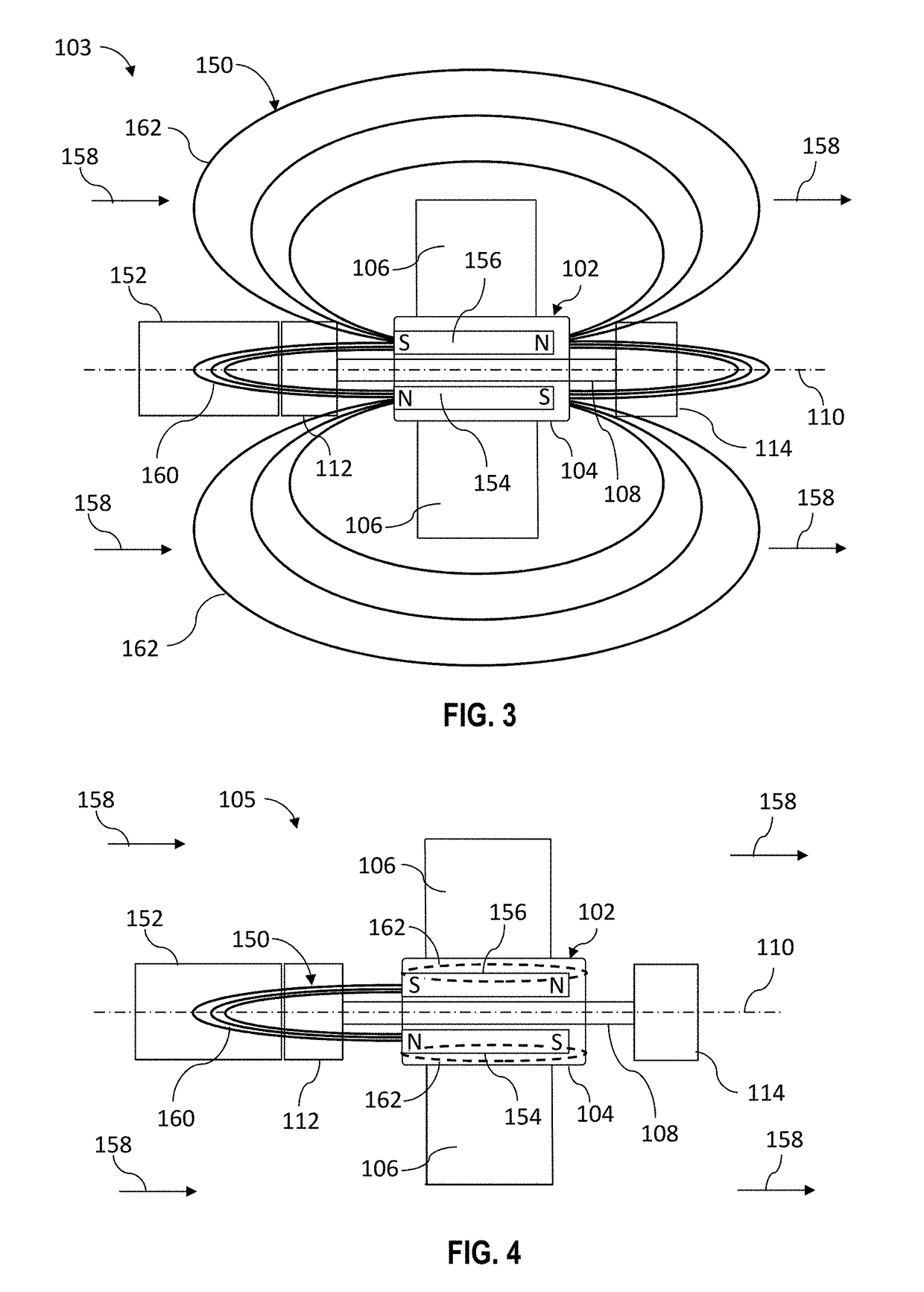

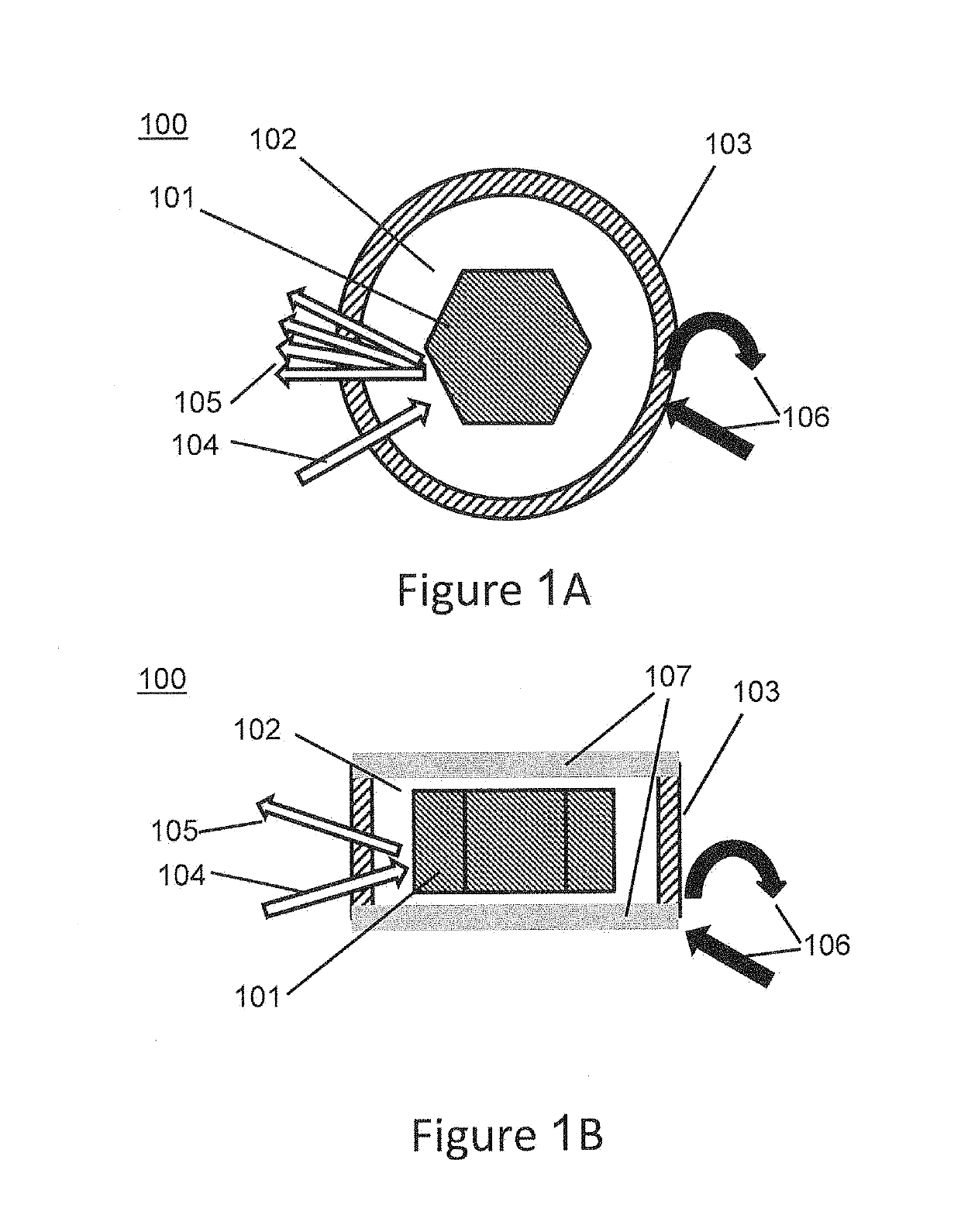

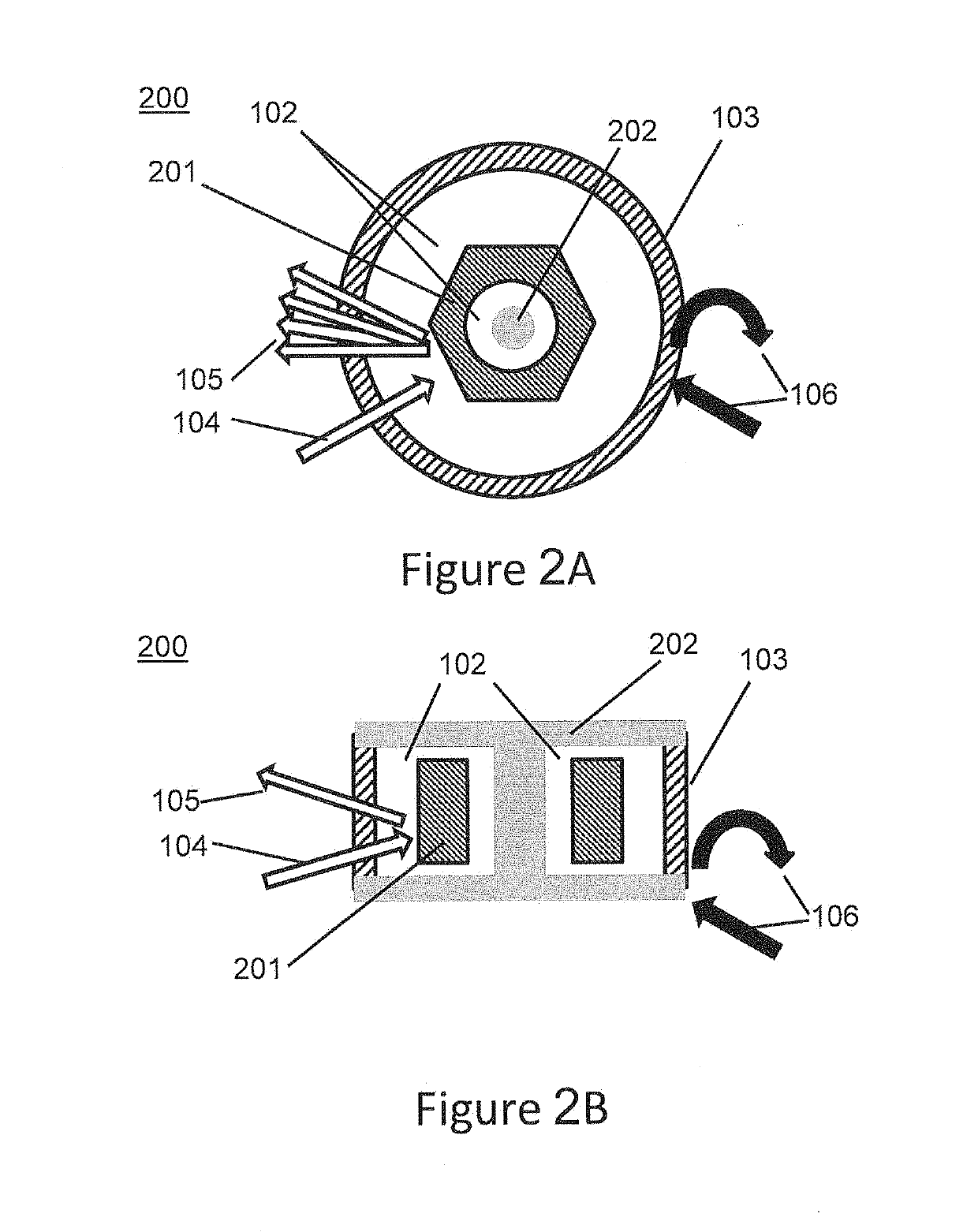

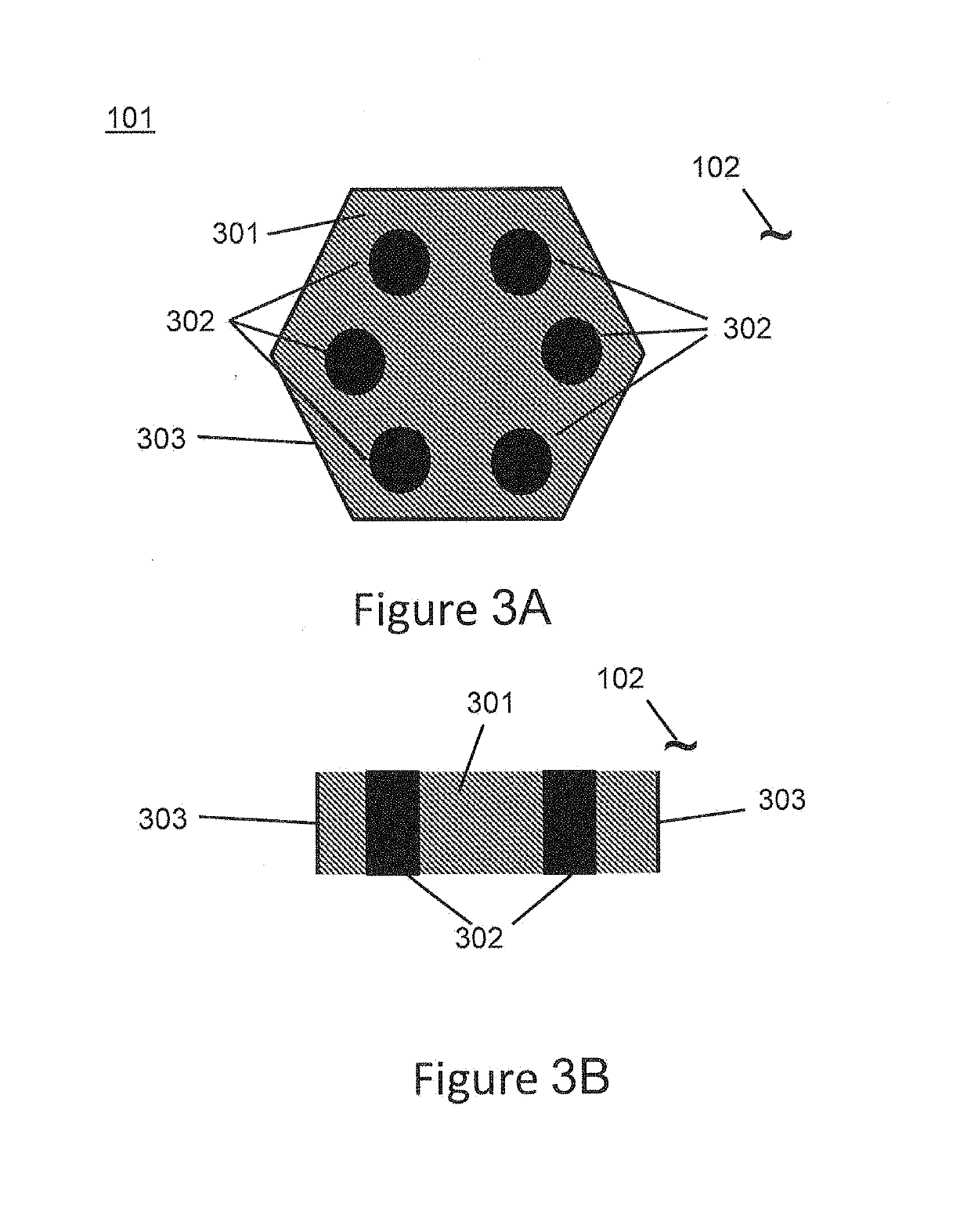

Optical beam steering devices having polygonal reflectors therein

An optical beam steering device includes an at least partially optically transparent container having a polygonal reflector therein that is at least partially surrounded within the container by an optically transparent liquid. The polygonal reflector may be configured to have a center of mass, which is equivalent to its geometric center. In addition, the polygonal reflector may be configured so that a difference between an effective density of the polygonal reflector and a density of the optically transparent liquid is preferably less than about 2.1 grams per cubic centimeter. More preferably, the polygonal reflector and the optically transparent liquid may be collectively configured to be neutrally buoyant relative to each other within the container.

Owner:MIRADA TECH INC

Air removal device with float valve for blood perfusion system

InactiveUS20050261618A1Low prime volumeEfficient air removalOther blood circulation devicesMedical devicesEffective densityEngineering

An input blood supply within a blood perfusion system is pumped through a chamber. A centrifugal flow of the input blood supply is formed in a bottom region of the chamber to cause air to migrate toward an axial center of the chamber. A float is buoyantly suspended on the centrifugal flow wherein the float is disposed for vertical movement in the chamber, and wherein the float has an effective density less than the density of the blood. When a volume of air present within the chamber is less than a predetermined volume, then the float closes a valve at an air outlet from the chamber. When a volume of air present within the chamber is greater than the predetermined volume, then the float opens the valve to remove air from the chamber.

Owner:TERUMO KK

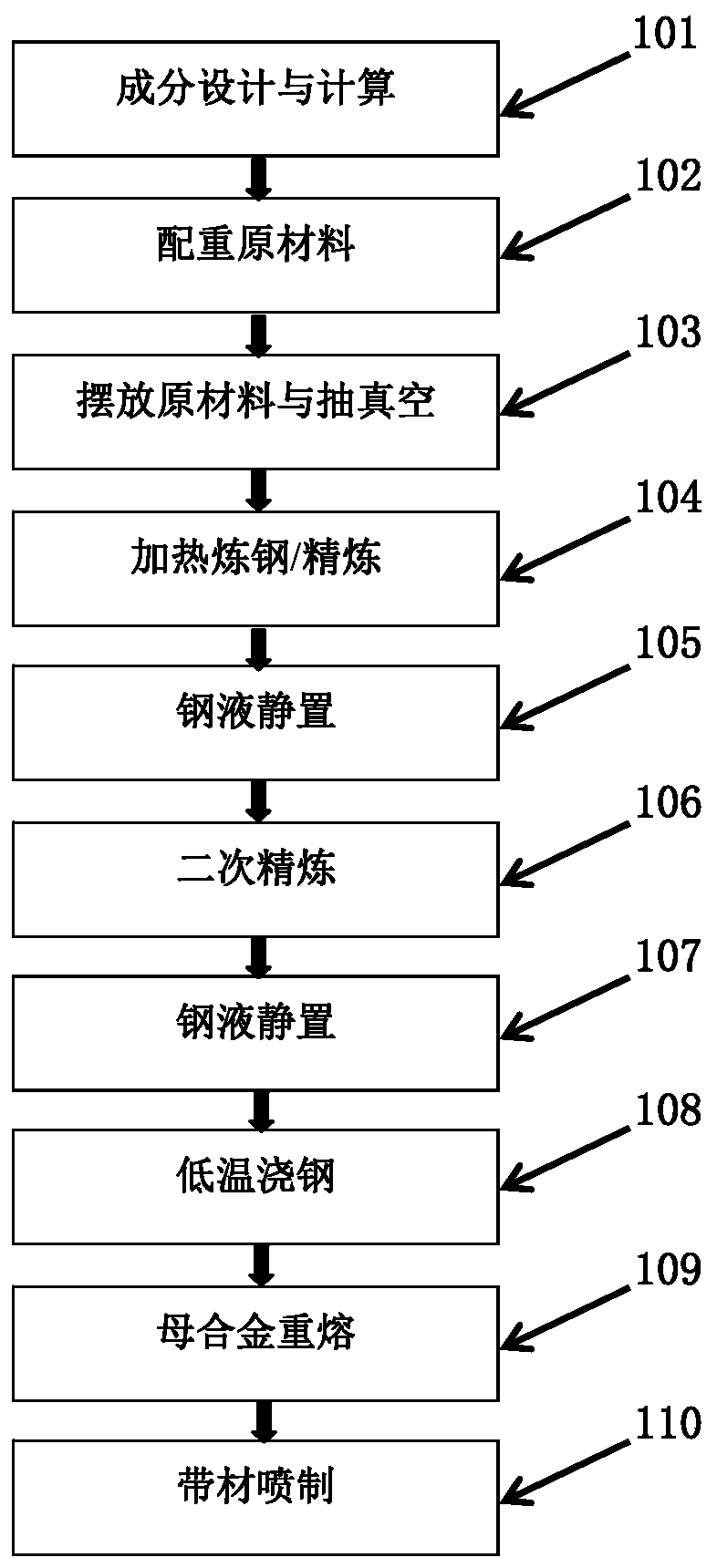

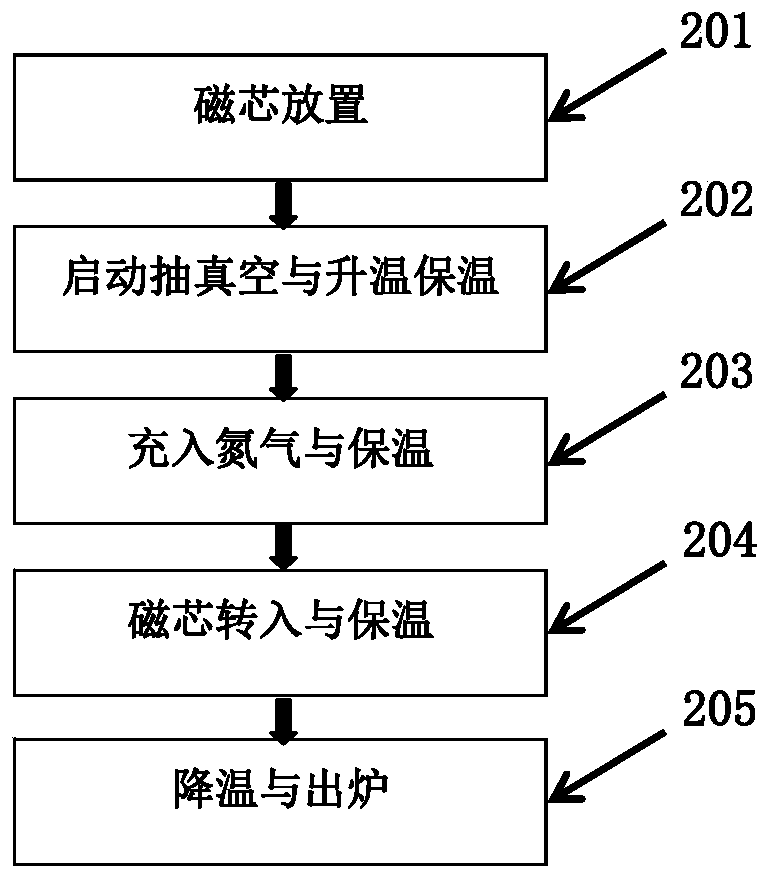

Iron-based spheroidized micro-nano magnetic powder core and preparation method thereof

InactiveCN110571009ALow costRapid regulationMagnetic materialsMagnetic core manufactureMicro nanoEffective density

The invention discloses an iron-based spheroidized micro-nano magnetic powder core and a preparation method thereof. The iron-based spheroidized micro-nano magnetic powder core is prepared from the following raw material components in percentage by weight: 83.2 to 84.8 wt% of iron, 8.3 to 8.9 wt% of silicon, 1.55 to 1.95 wt% of boron, 3.9 to 4.1 wt% of niobium, 0.9 to 1.1 wt% of molybdenum, 0.13 to 0.17 wt% of nickel and 0.95 to 1.05 wt% of copper. The corresponding preparation method comprises the following steps of: 1) preparing a quenched strip, 2) strip heat treatment, 3) ball-milling to prepare magnetic powder, 4) carrying out plasma spheroidizing treatment, and 5) integrally molding and pressing the spheroidized magnetic powder into a magnetic powder core. The iron-based micro-nano magnetic powder subjected to plasma spheroidizing treatment is mostly of a spherical structure, copper wire breakage in the pressing process cannot be caused, the pressing tonnage (65 T is increased to100 T) of the integrally-formed magnetic powder core can be improved, the effective density is increased by about 5 to 10%, and the comprehensive magnetic performance parameters are remarkably improved; the surface layer is formed by secondary remelting, metallurgical strength and plasticity are achieved, and secondary embrittlement in the pressing process of the integrally-formed magnetic powdercore can be effectively reduced.

Owner:广东咏旺新材料科技有限公司

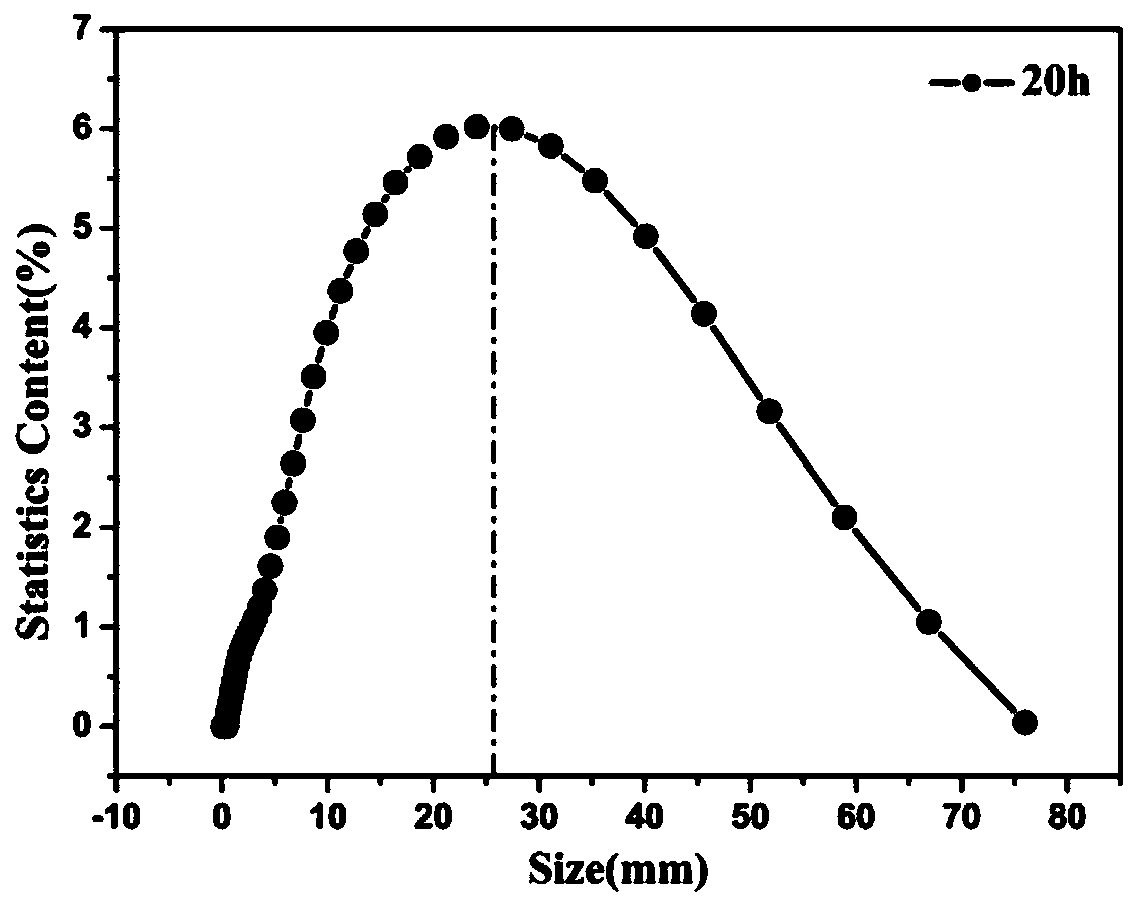

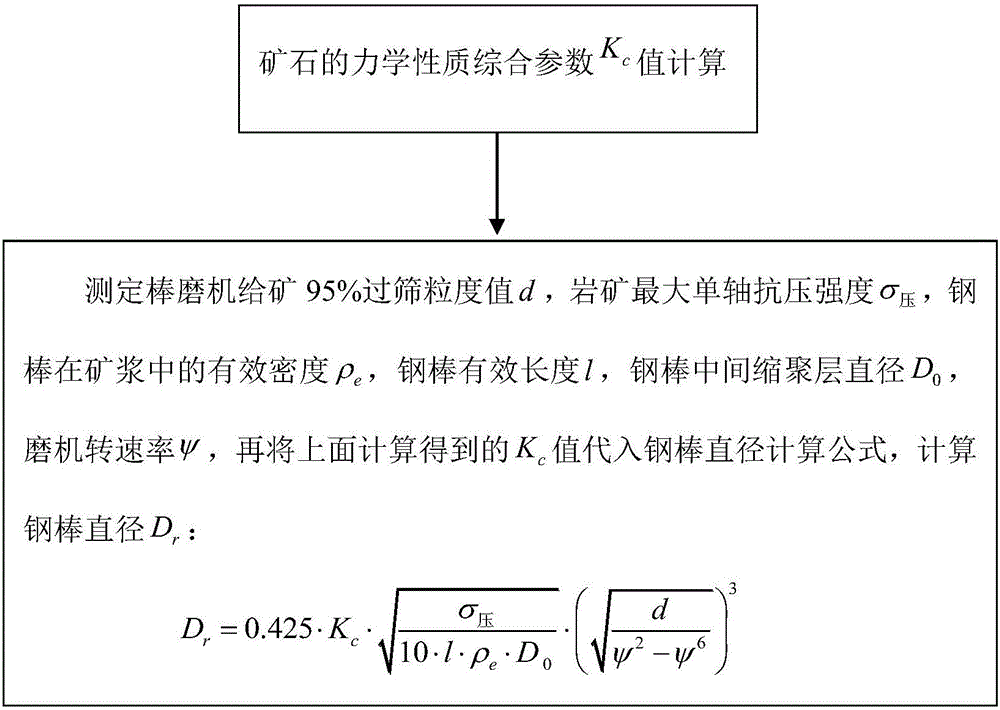

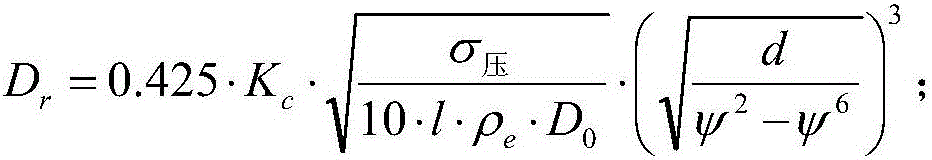

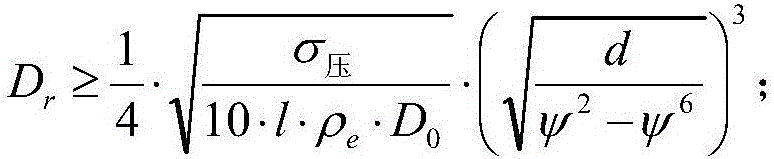

Method for accurately selecting diameters of steel rods of rod mills

ActiveCN106650035AReduced compressive strengthUniversalDesign optimisation/simulationGrain treatmentsEffective densityEffective length

The invention relates to a method for accurately selecting diameters of steel rods of rod mills, and belongs to the field of ore grinding in ore dressing. The method comprises the following steps of: firstly calculating a mechanical property comprehensive parameter Kc according to secant Poisson ratio of ores; substituting a measured rod mill 95%-feeding screening particle size value d, a rock ore maximum uniaxial compressive strength <sigma>, an effective density <rho>e of a steel rod in ore pulp, an effective length l of the steel rod, a middle poly-condensation layer diameter D0 of the steel rod and a rotation rate <gamma> of a mill into a steel rod diameter calculation formula, so as to calculate an accurately determined steel rod diameter Dr; and finally carrying out ore grinding comparison experiment on the calculated Dr diameter and the other steel rods with different sizes under same conditions, so as to verify the accuracy of Dr via optimum ore grinding effect. According to the method provided by the invention, dozens of factors such as compressive strength and tenacity of the ore, the rotation rate of the mill, a filling ratio, an ore grinding concentration and the like are considered, so that the universality and pertinence are stronger, and a feasible method is provided for accurately selecting the diameters of the steel rods of the rod mills.

Owner:KUNMING UNIV OF SCI & TECH

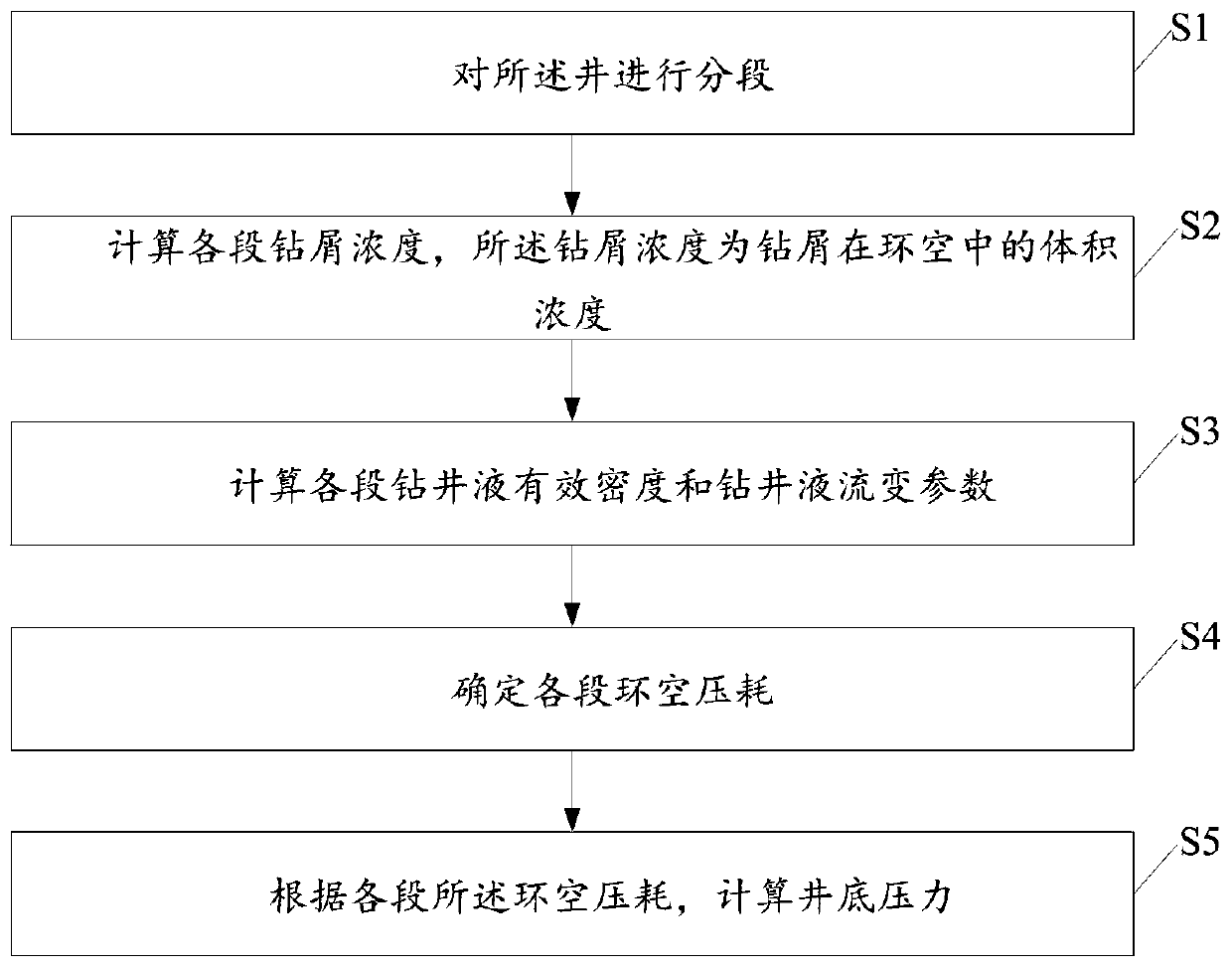

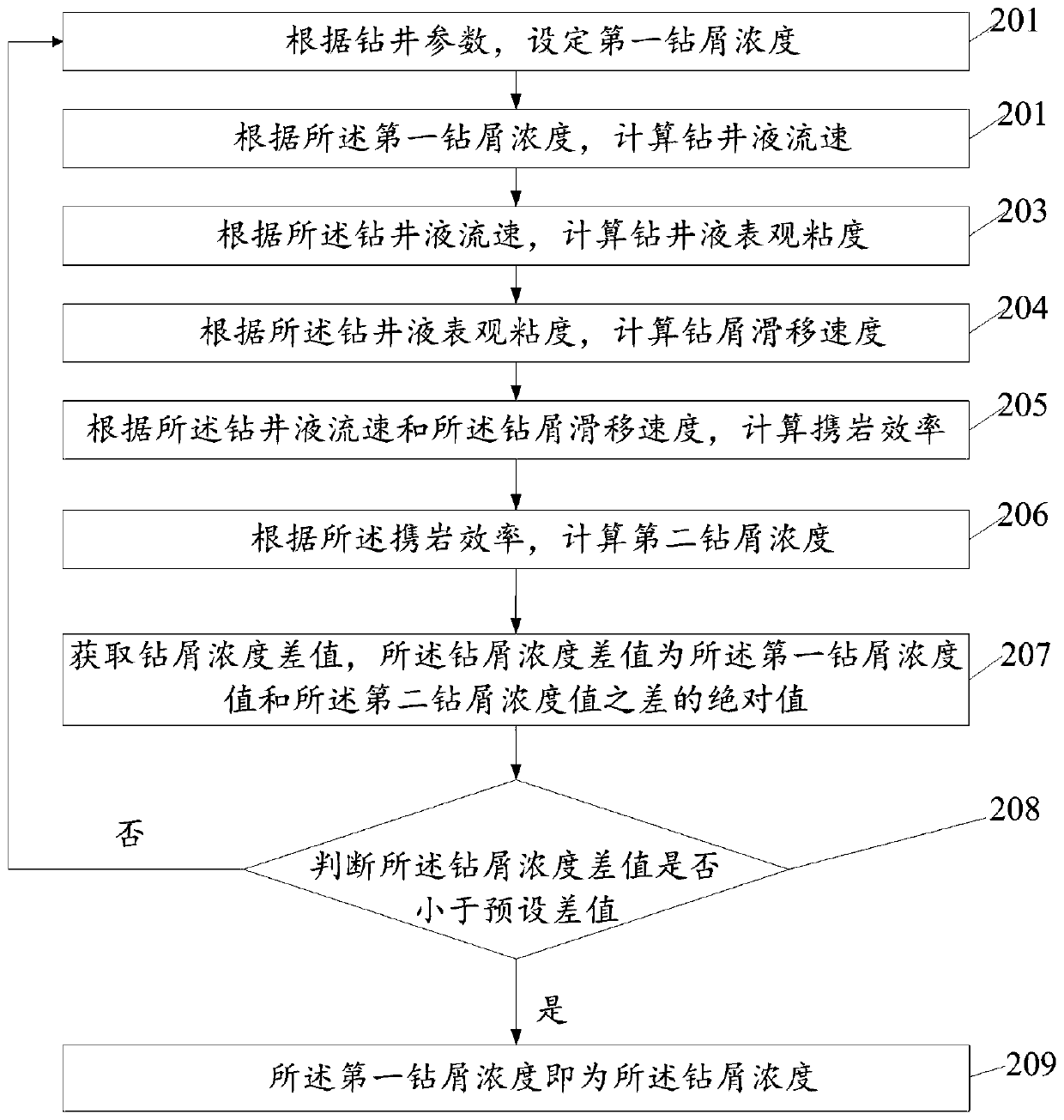

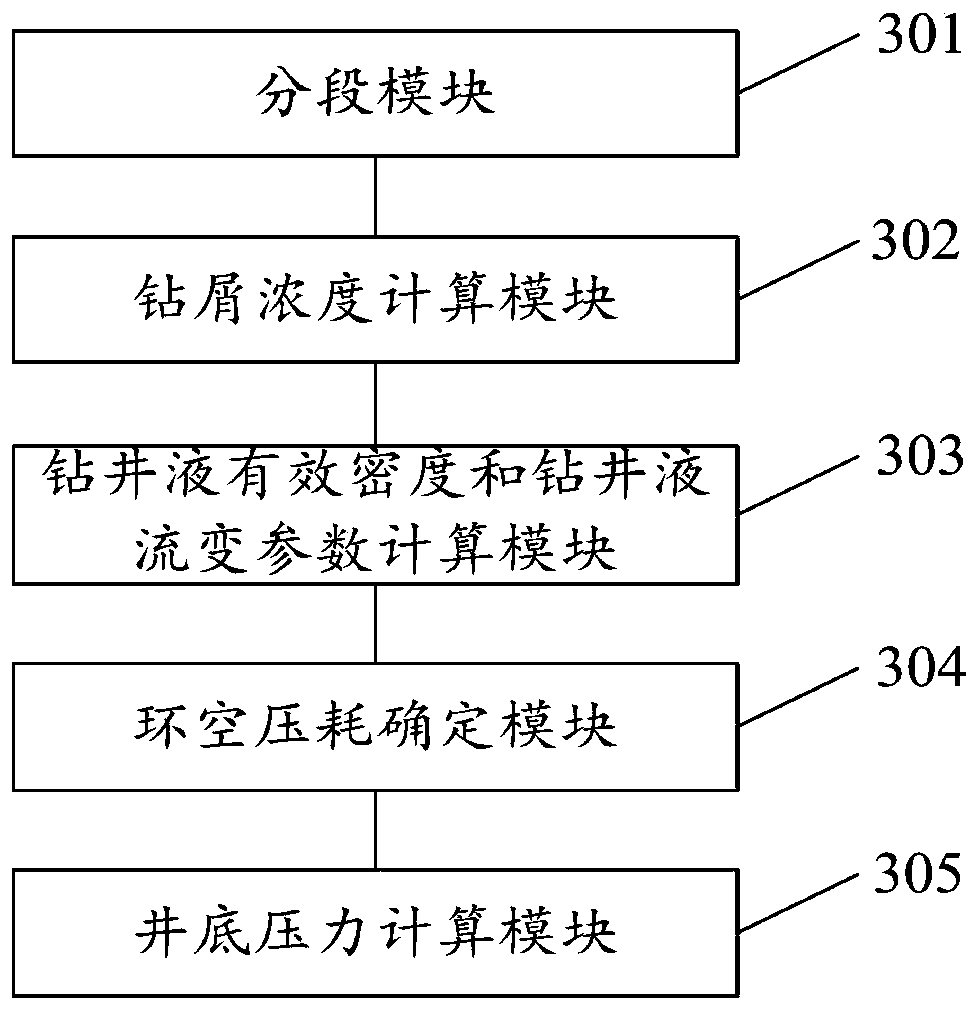

Method and system for predicting shaft bottom pressure

The invention discloses a method and system for predicting the shaft bottom pressure. The method comprises the steps: a shaft is sectioned; the drilling cutting concentration of all sections is calculated, and the drilling cutting concentration is the volume concentration of drilling cuttings in annuluses; the effective density and rheological parameters of drilling fluid of all the sections are calculated; annulus pressure losses of all the sections are determined; and according to the annulus pressure losses of all the sections, the shaft bottom pressure is calculated. By considering influences of the drilling cuttings on the rheological property of the drilling fluid, the predicting accuracy rate of the shaft bottom pressure can be increased, and thus the predicted shaft bottom pressureis closer to the real shaft bottom pressure.

Owner:SOUTHWEST PETROLEUM UNIV

Novel low-detonation velocity explosive suitable for titanium material compounding, and preparation method thereof

InactiveCN105384588AMeet the needs of the development of domestic chemical industry and other industriesDensity adjustmentNon-explosive/non-thermic compositionsEffective densityEmulsion explosive

The invention discloses a novel low-detonation velocity explosive suitable for titanium material compounding, and a preparation method thereof. The method comprises the following steps: taking 40 parts by weight of a rock powdery emulsion explosive with the bulk density of 0.58-0.62g.cm<-3>, the detonation velocity of 3500-3700m / s, the brisance of 15-17mm, the gap distance of 9-11cm and the work capacity of 360 / ml, taking 45 parts of sands with the bulk density of 1.40g.cm<-3> and the particle size of 300 meshes, putting above taken materials in a medicine mixer, stirring the materials for 3-5min, taking 7 parts of bran with the bulk density of 0.50g.cm<-3> and the particle size of 300 meshes, putting the taken bran in the medicine mixer, stirring the obtained mixture for 20min until fullness and uniformity, and detecting the density and the detonation velocity of the above obtained product. The sands are used to reduce the detonation velocity, and the bran is used as a density adjusting agent to adjust the density of the obtained mixed explosive; and the effective density of the rock powdery emulsion explosive is reduced through synergism of the sands and the bran, and the novel low-detonation velocity explosive prepared through mixing above materials in proportion can improve the production efficiency, and solves the problem of lack-of-fit of large-area titanium-steel composite plates.

Owner:安徽宝泰特种材料有限公司

Forced convection target assembly

InactiveUS8249211B2Effective density increaseIncrease productionParticle separator tubesDomestic cooling apparatusEffective densityPower flow

Provided is a modified target assembly in which the target fluid is moved within the target assembly in a manner that increases the effective density of the target fluid within the beam path, thereby increasing beam yield utilizing forced convection. The target may also include optional structures, such as nozzles, diverters and deflectors for guiding and / or accelerating the flow of the target fluid. The target assembly directs the target fluid along an inner sleeve in a direction opposite the direction of the beam current to produce a counter current flow and may also direct the flow of the target fluid away from the inner surface of the inner sleeve and toward a central region in the target cavity. This countercurrent flow suppresses natural convection that tends to reduce the density of the target fluid in the beam path and tends to increase the heat transfer from the target.

Owner:ADVANCED APPLIED PHYSICS SOLUTIONS

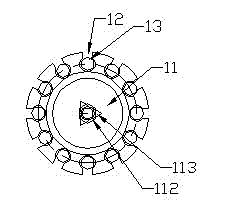

Electrical kiln used for firing cadmium red glaze porcelain with three-meter height

ActiveCN102706133ALower temperature riseImprove product qualityElectric heating for furnacesVertical furnacesEffective densityHearth

The invention relates to an electrical kiln used for firing a cadmium red glaze porcelain with three-meter height. The electrical kiln comprises a furnace body and a base, wherein the furnace body is internally provided with a hearth, a furnace shell is arranged outside of the furnace body, a first insulating layer is arranged between the furnace shell and the hearth, and the inner side of the first insulating layer is provided with a first temperature-resistant layer; the base comprises a base shell, a second insulating layer and a second temperature-resistant layer, wherein the second insulating layer is arranged between the base shell and the second temperature-resistant layer, and the hearth is internally provided with first heating resistance wires; the base is provided with second heating resistance wires, the first heating resistance wires are arranged on the middle part and the lower part in the hearth, and the first heating resistance wires count 50%-75% of the whole hearth space; and a spacing between every two wires of the first heating resistance wire is 10-25 centimeters, and a spacing between every two wires of the second heating resistance wires is 10-30 centimeters. The electrical kiln provided by the invention has the advantages that the structure is simple and compact, the distributing wire density is relatively large, the configuration is reasonable, the power effective density is reasonable, the heat uniformity is good, the service life is long, and the application rang is wide.

Owner:长沙大红陶瓷发展有限责任公司

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com