Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

48 results about "Diffusion transistor" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

A diffused junction transistor is a transistor formed by diffusing dopants into a semiconductor substrate. The diffusion process was developed later than the alloy junction and grown junction processes for making BJTs.

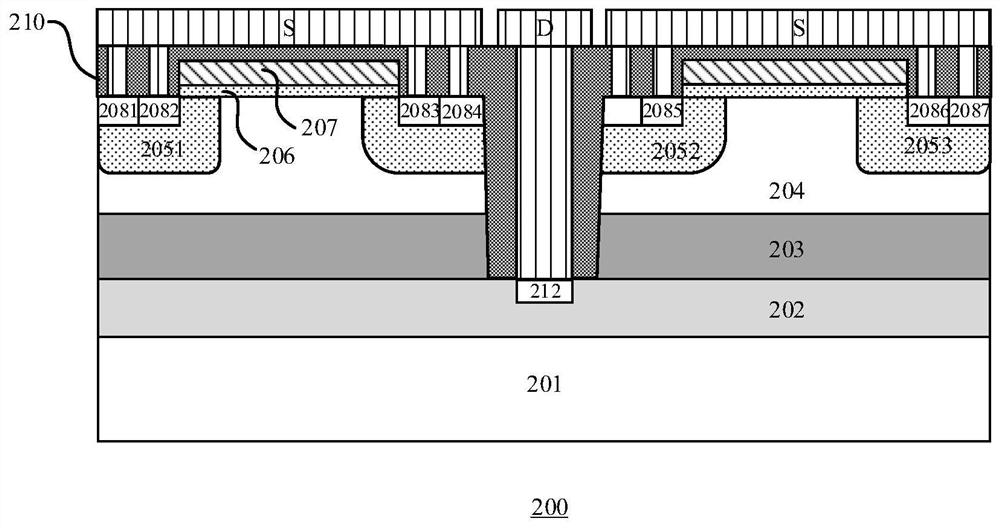

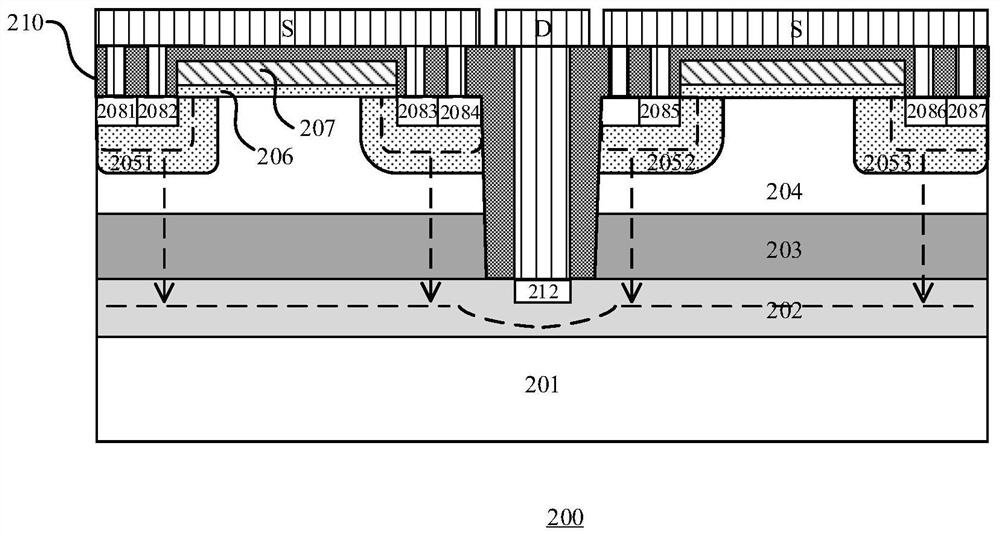

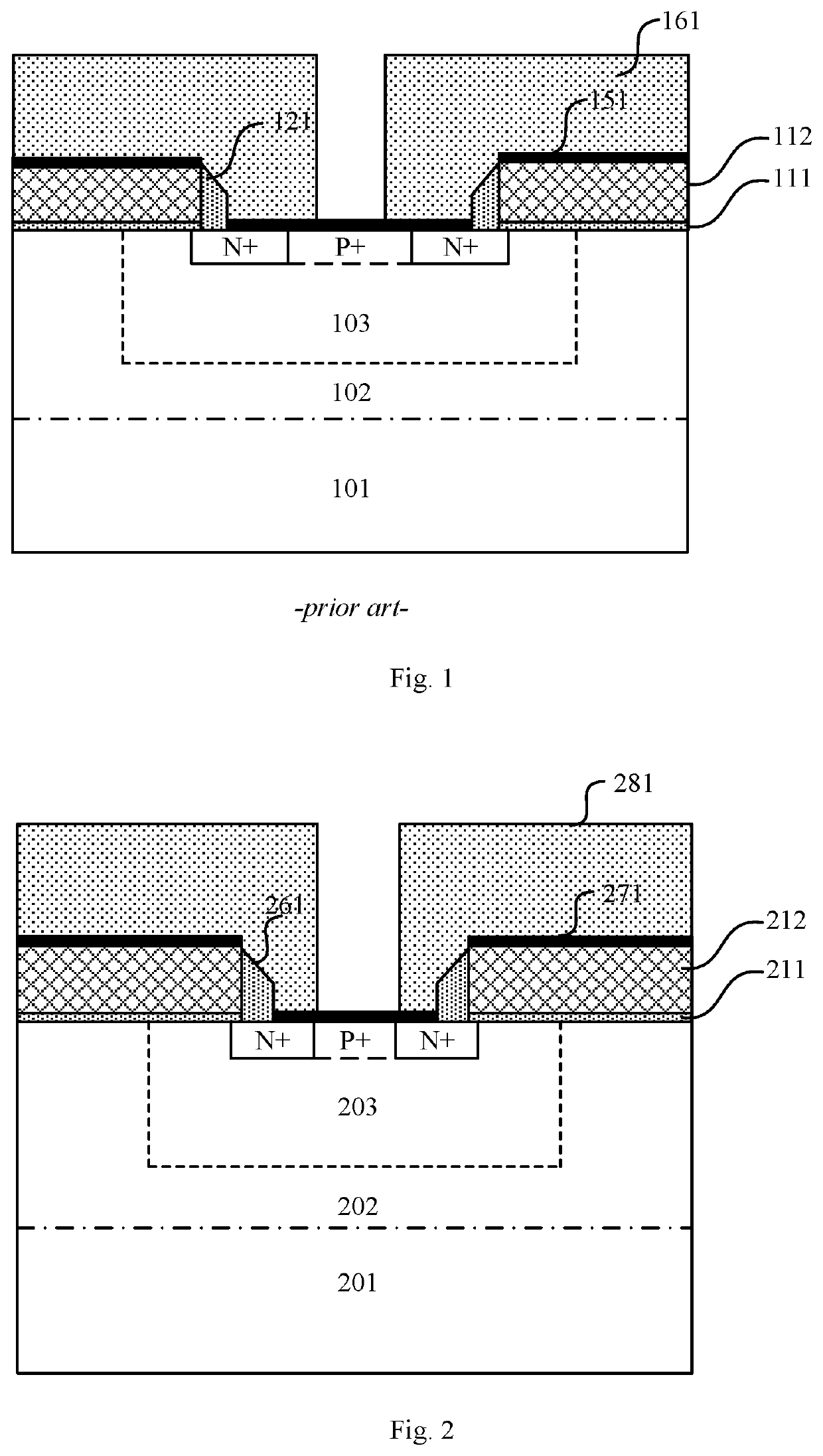

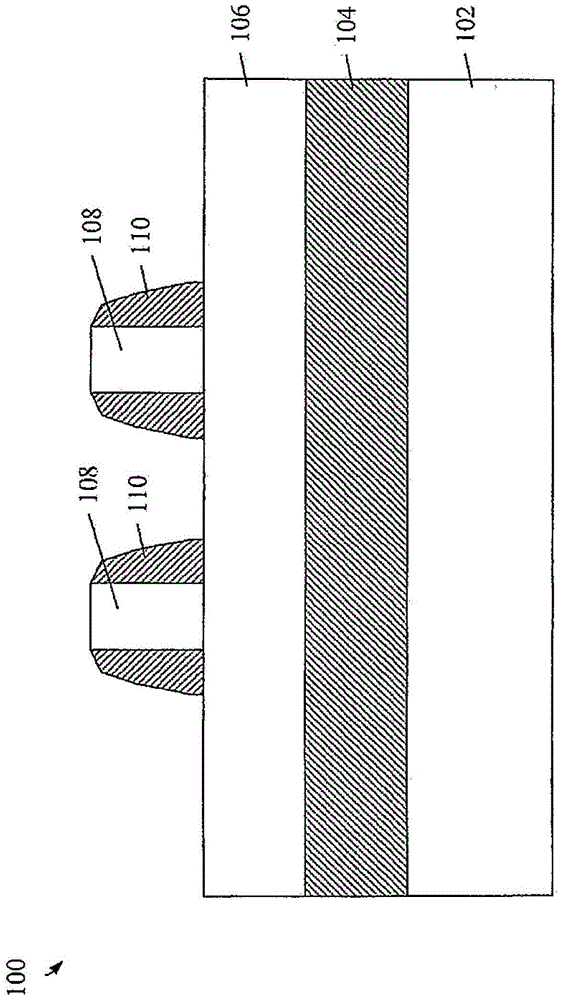

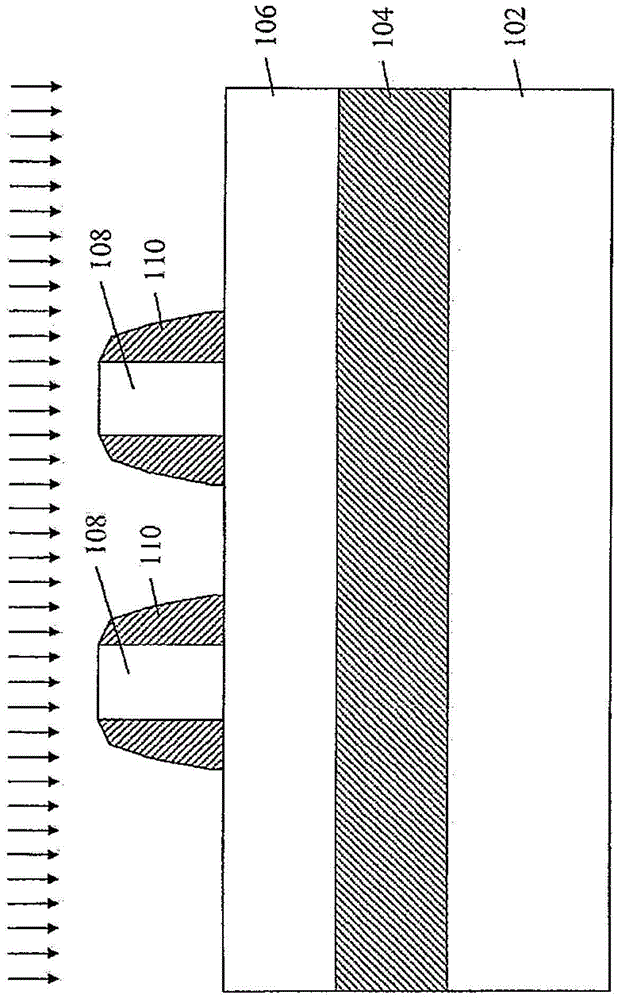

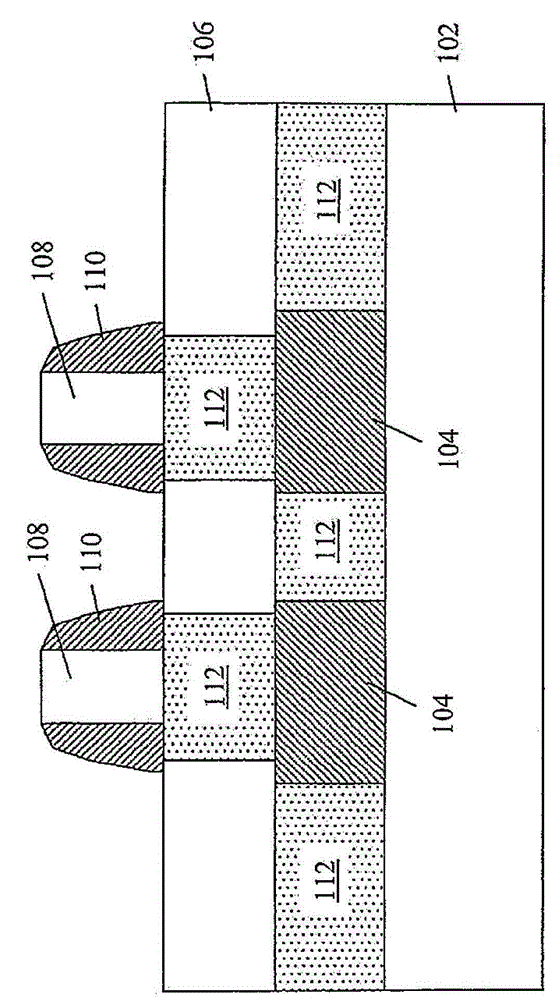

Double diffused MOS transistor and method for manufacturing same

InactiveUS6773995B2Increase currentReduce resistanceTransistorSolid-state devicesDevice materialIsolation layer

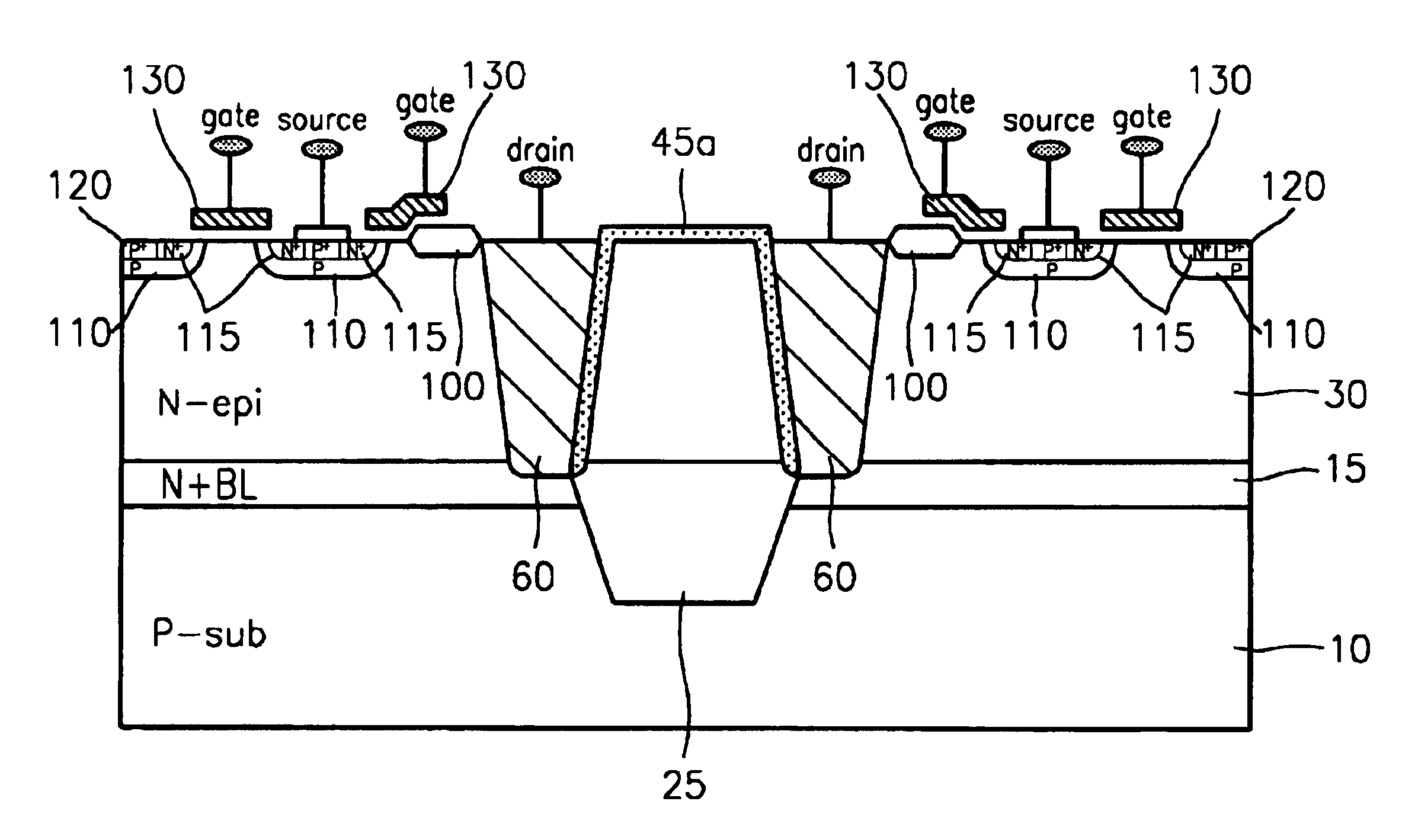

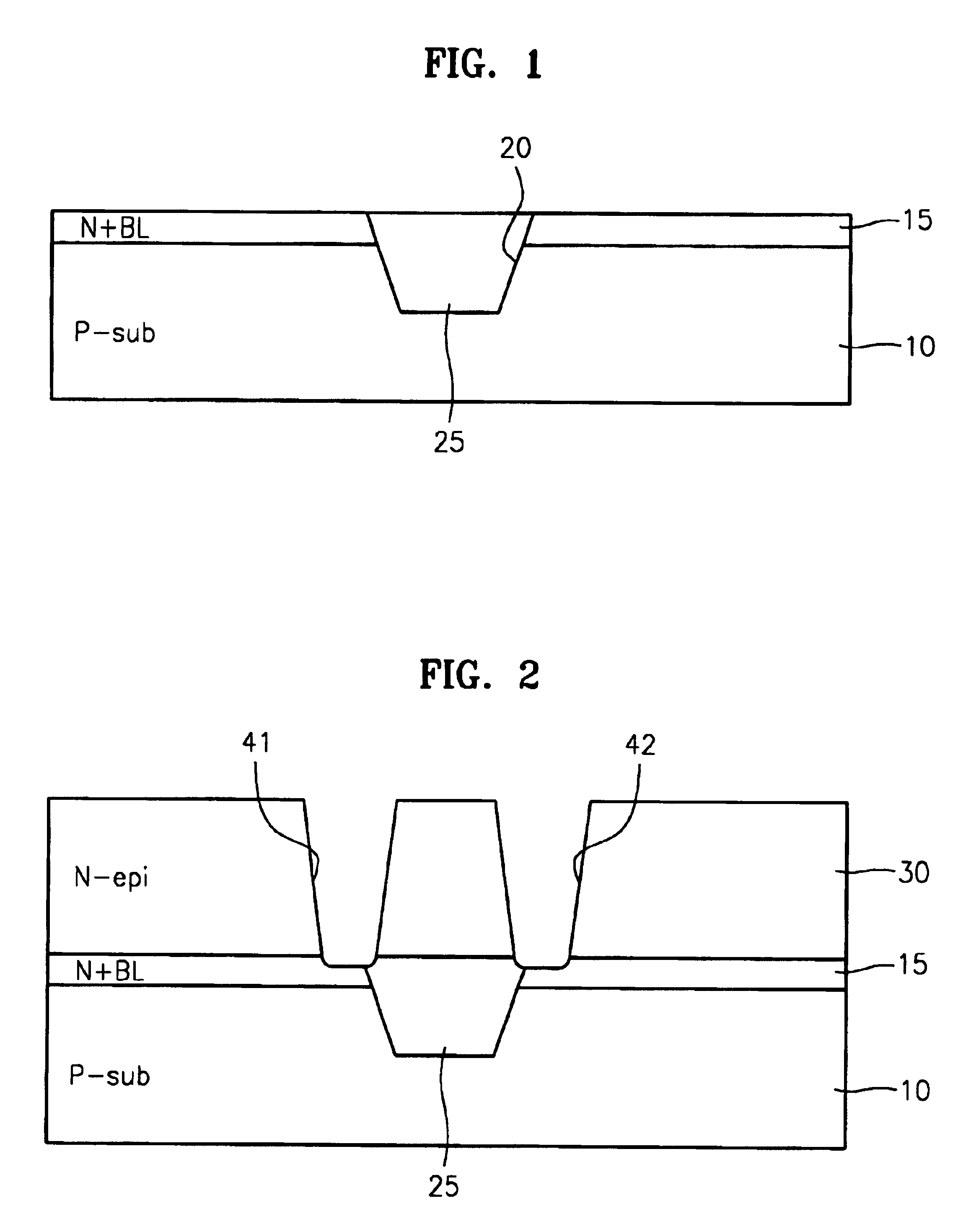

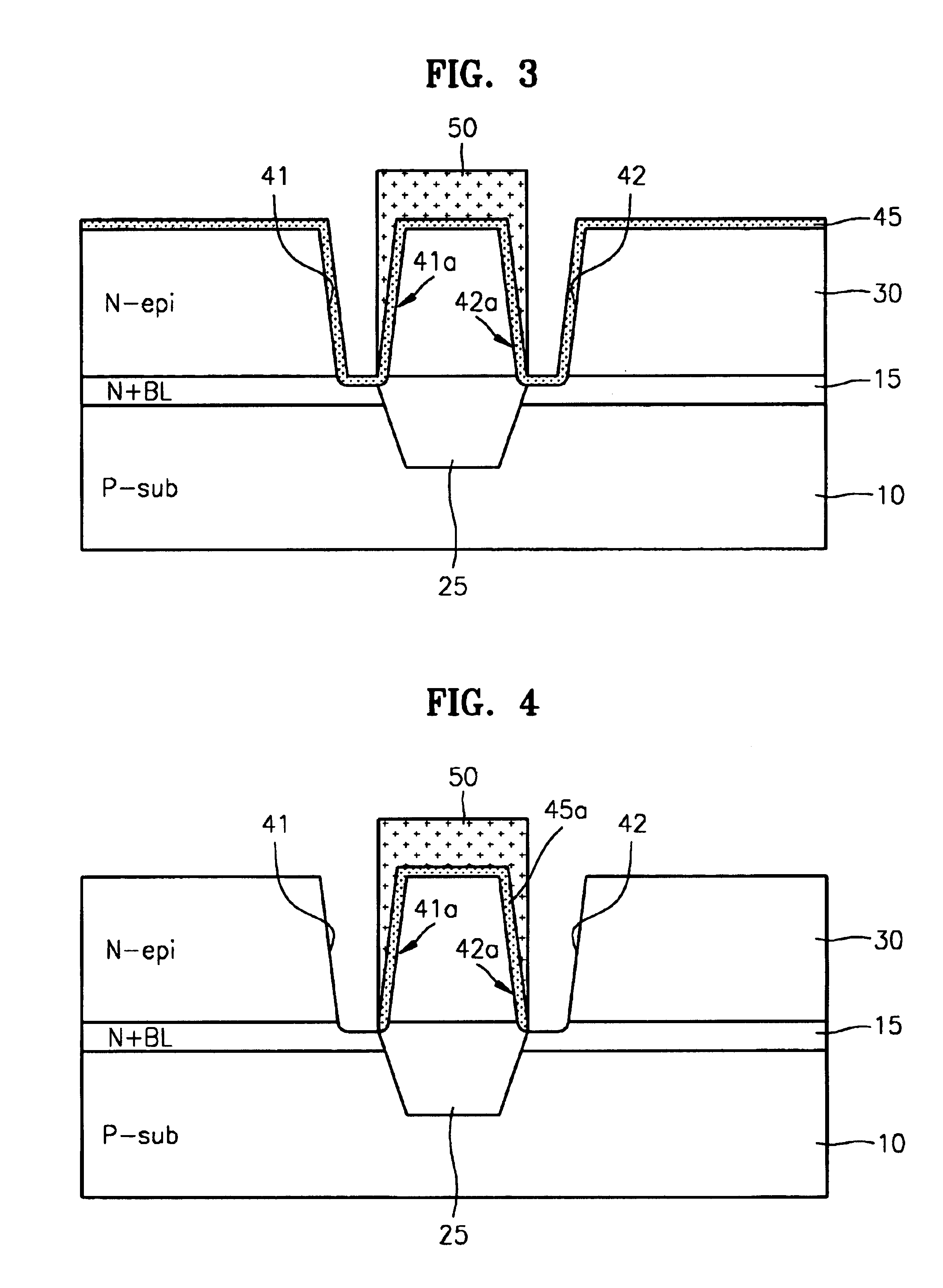

A method of manufacturing a semiconductor device, such as a double-diffused metal oxide semiconductor (DMOS) transistor, where a first layer may be formed on a semiconductor substrate, with isolation trenches formed in the first layer and semiconductor substrate, and with the trenches being filled with an isolation layer. A second layer may be formed on the first layer and semiconductor substrate, and a plurality of drain trenches may be formed therein. A pair of plug-type drains may be formed in the trenches, to be separated from the isolation layer by a dielectric spacer. Gates and source areas may be formed on a resultant structure containing the plug-type drains. Accordingly, current may be increased with a reduction in drain-source on resistance, and an area of the isolation layer can be reduced, as compared to an existing isolation layer, potentially resulting in a reduction in chip area.

Owner:SAMSUNG ELECTRONICS CO LTD

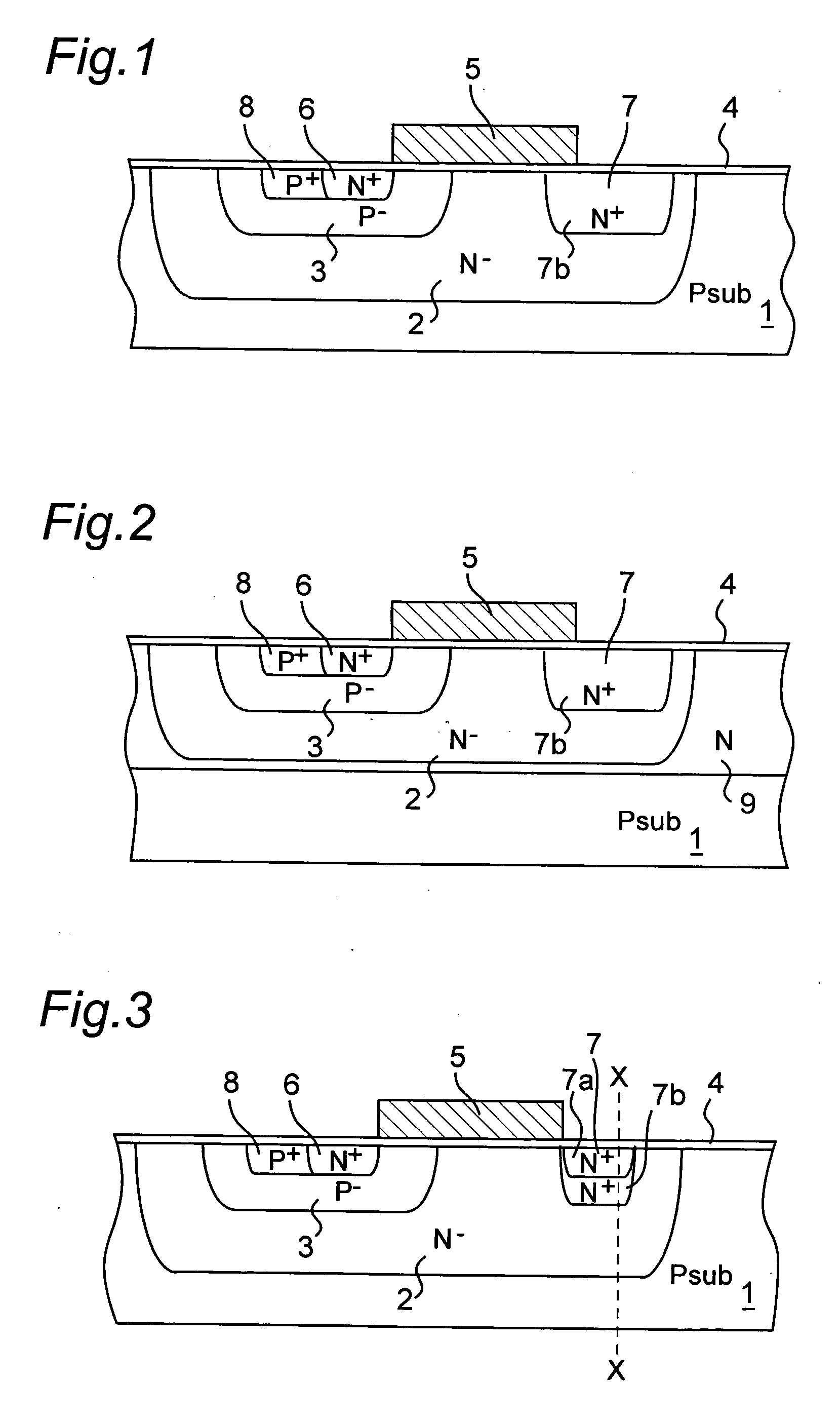

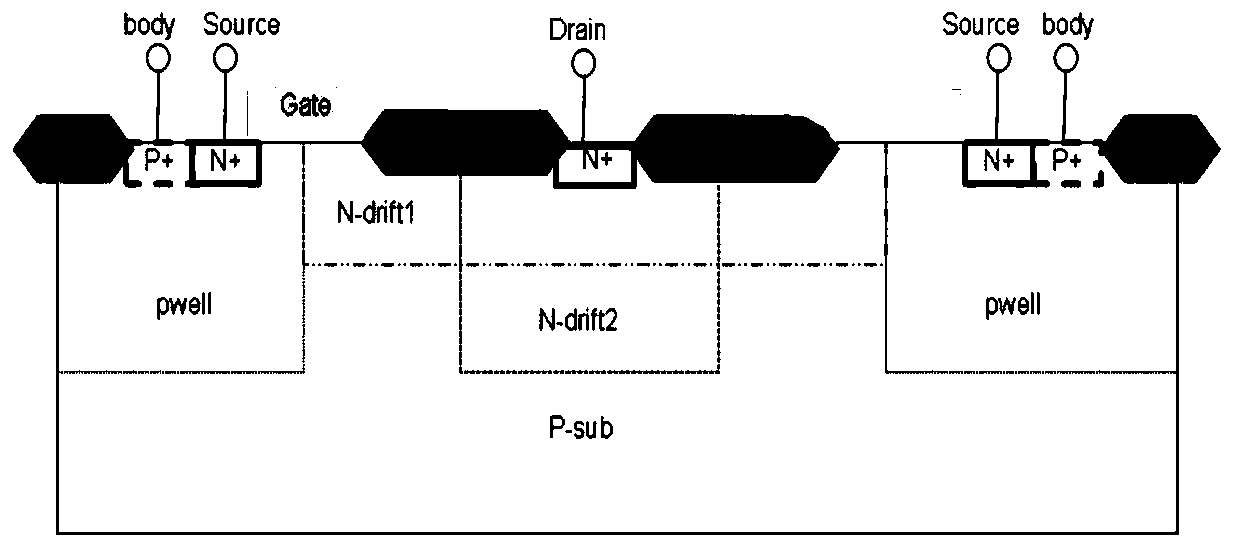

Lateral double-diffused MOS transistor and manufacturing method therefor

InactiveUS20060157781A1Improve breakdown voltageLower on-resistanceTransistorAnalogue/digital conversionPeak valueSemiconductor

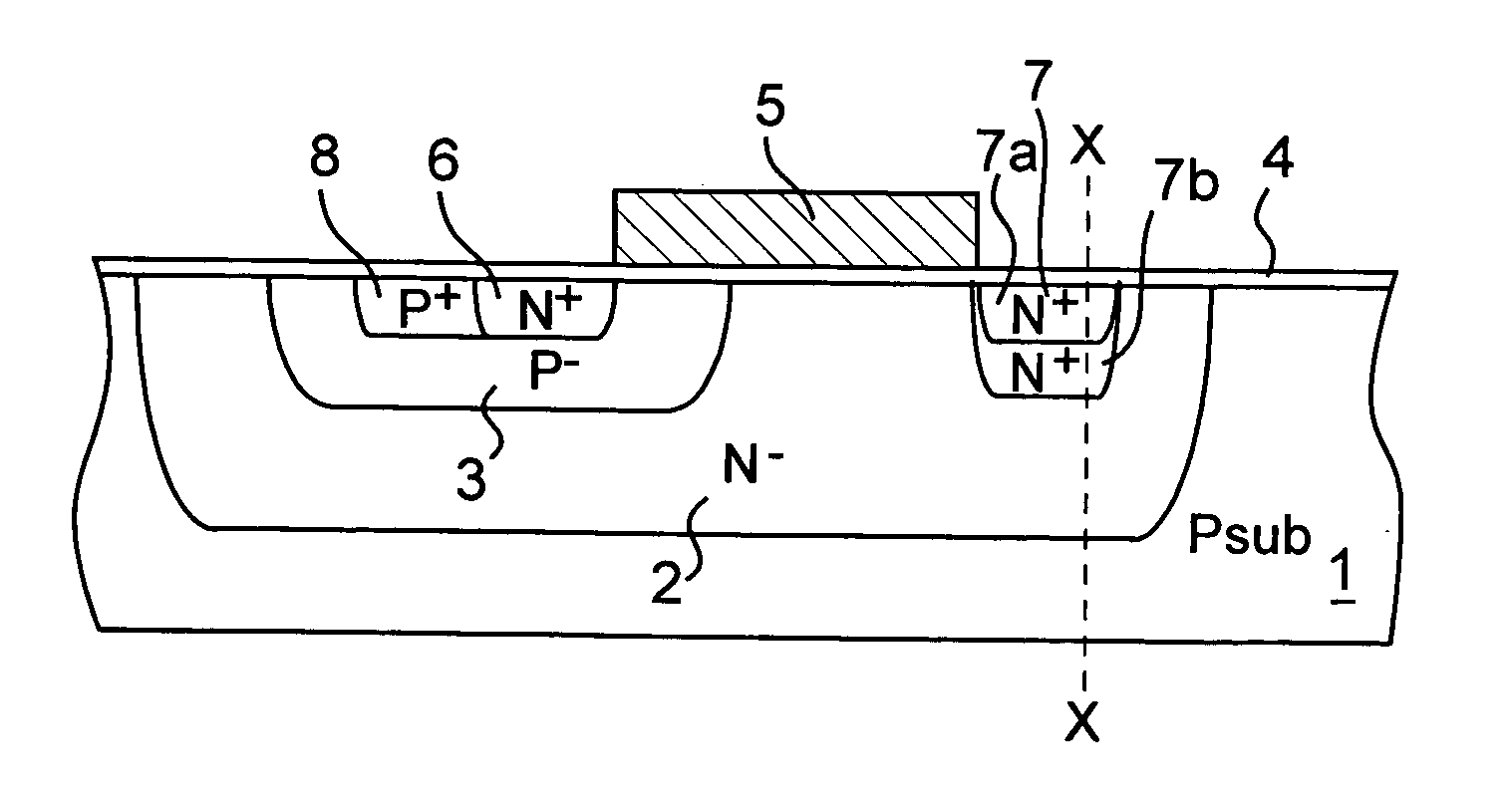

The lateral double-diffused MOS transistor includes a drift region of a first conductive type provided on a semiconductor substrate of a second conductive type, and a body diffusion region of the second conductive type formed on the surface within the drift region. The MOS transistor includes a gate electrode formed in such a position as it covers from part of the body diffusion region to part of the drift region located outside the diffusion region via an insulating film. The MOS transistor further includes a source diffusion region of the first conductive type and a drain diffusion region of the first conductive type formed on top of the body diffusion region and top of the drift region, respectively, both of which correspond to both sides of the gate electrode. The drain diffusion region includes a deep diffusion portion which has a 1 / 1000 or more concentration of a peak concentration of the source diffusion region and which is positioned deeper than the source diffusion region.

Owner:SHARP KK

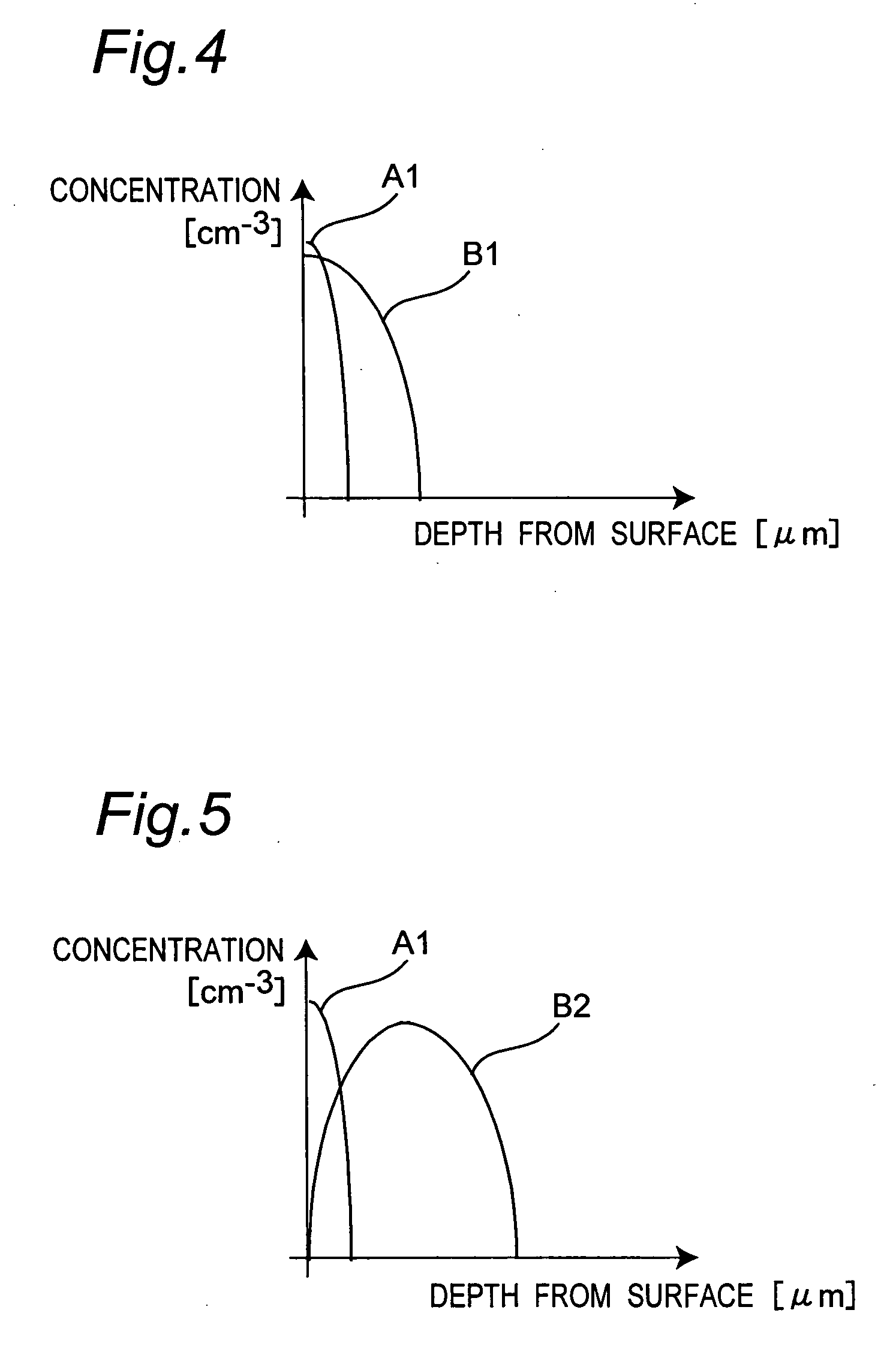

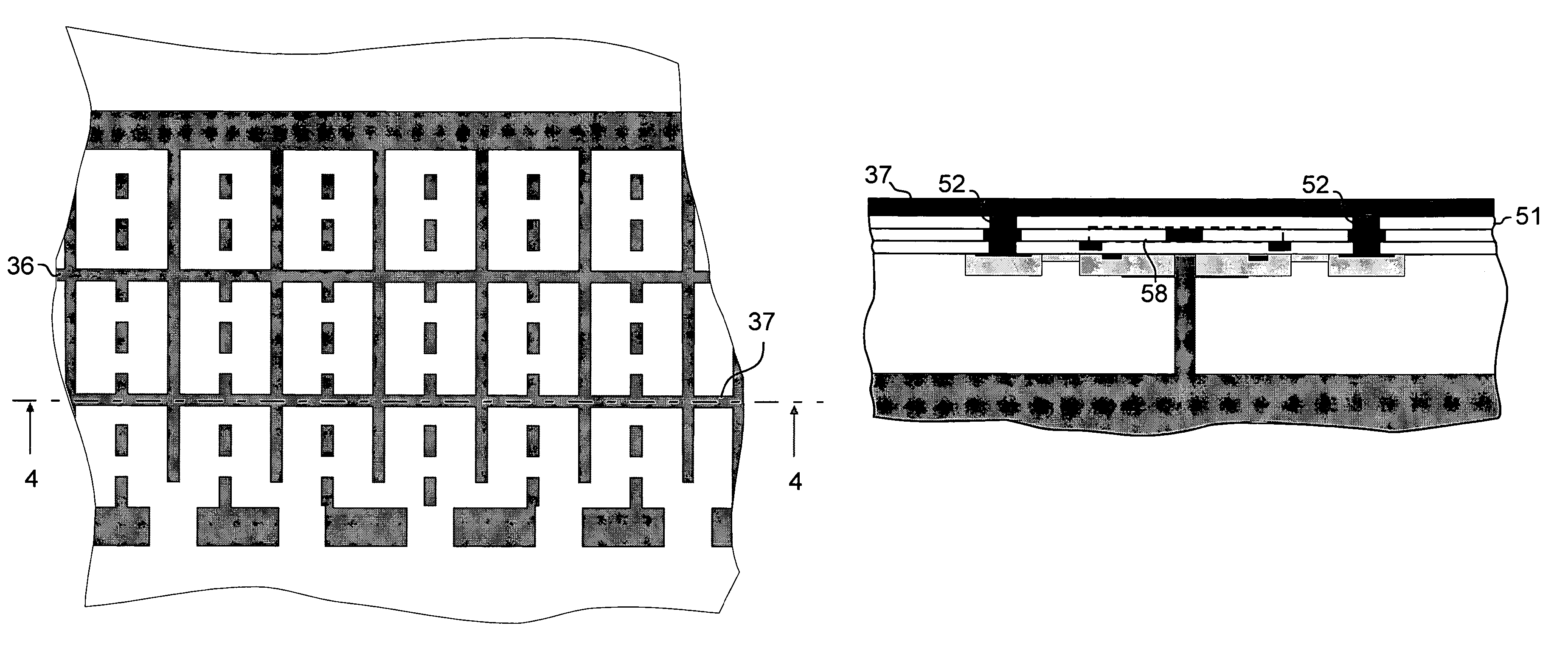

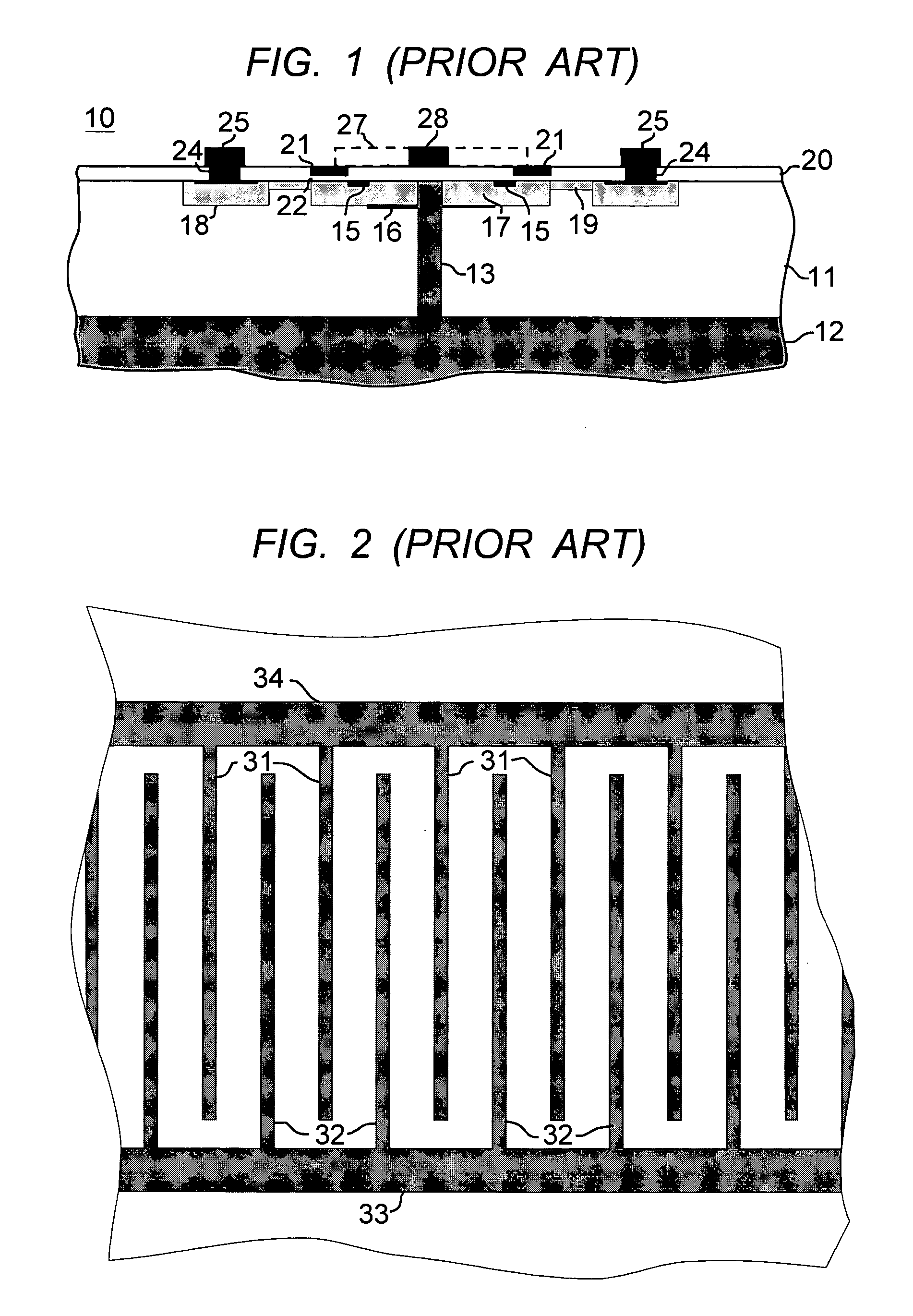

Lateral double diffused MOS transistors

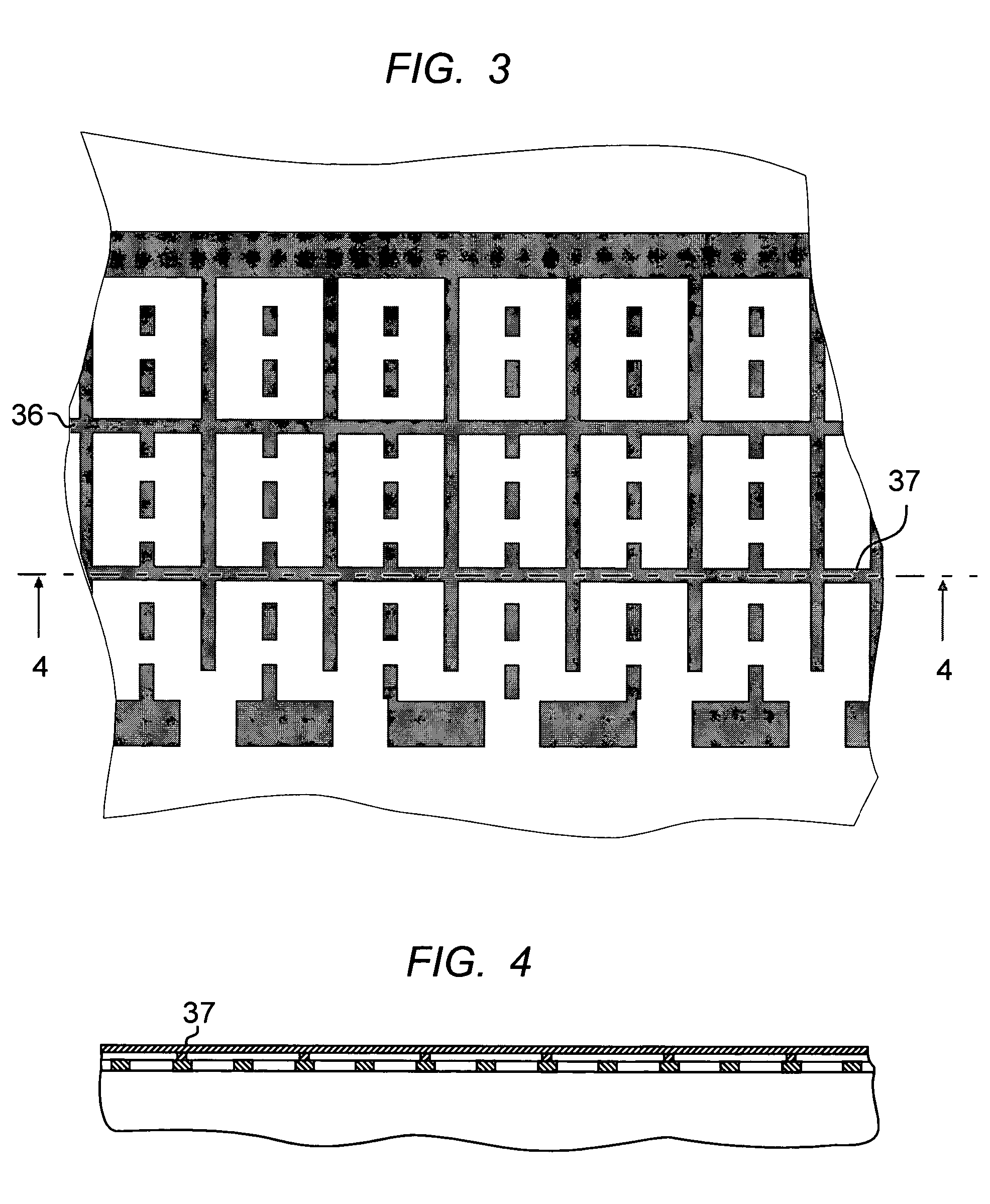

InactiveUS20060091480A1Simple mechanical structureIncreases likelihood of mechanical failureTransistorSemiconductor/solid-state device detailsCross connectionMechanical integrity

The specification describes an improved mechanical electrode structure for MOS transistor devices with elongated runners. It recognizes that shrinking the geometry increases the likelihood of mechanical failure of comb electrode geometries. The mechanical integrity of a comb electrode is improved by interconnecting the electrode fingers in a cross-connected grid. In one embodiment, the transistor device is interconnected with gate fingers on a lower metaliization level, typically the first level metal, with the drain interconnected at a higher metal level. That allows the drain fingers to be cross-connected with a vertical separation between drain and gate comb electrodes. The cross-connect members may be further stabilized by adding beam extensions to the cross-connect members. The beam extensions may be anchored in an interlevel dielectric layer for additional support.

Owner:BELL SEMICON LLC

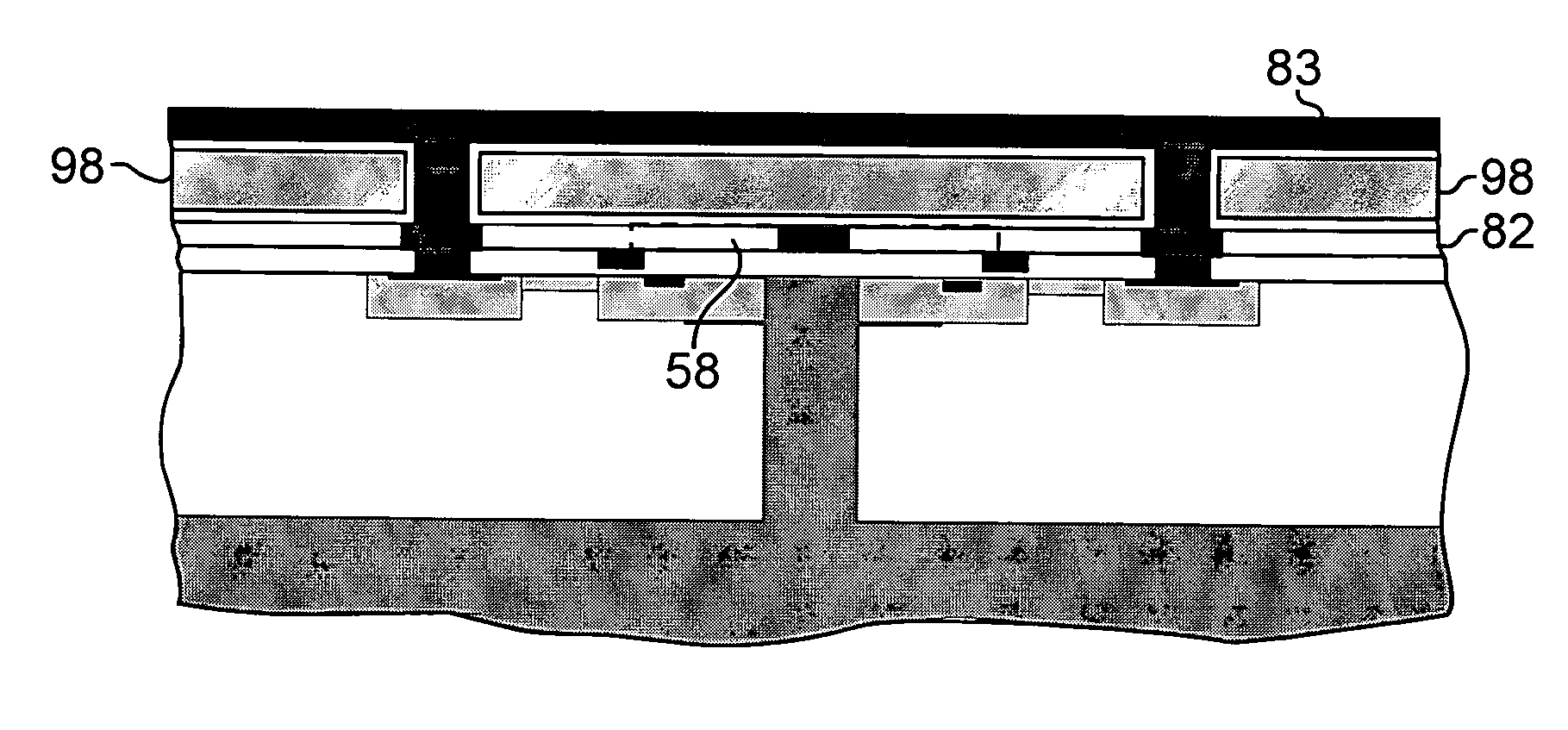

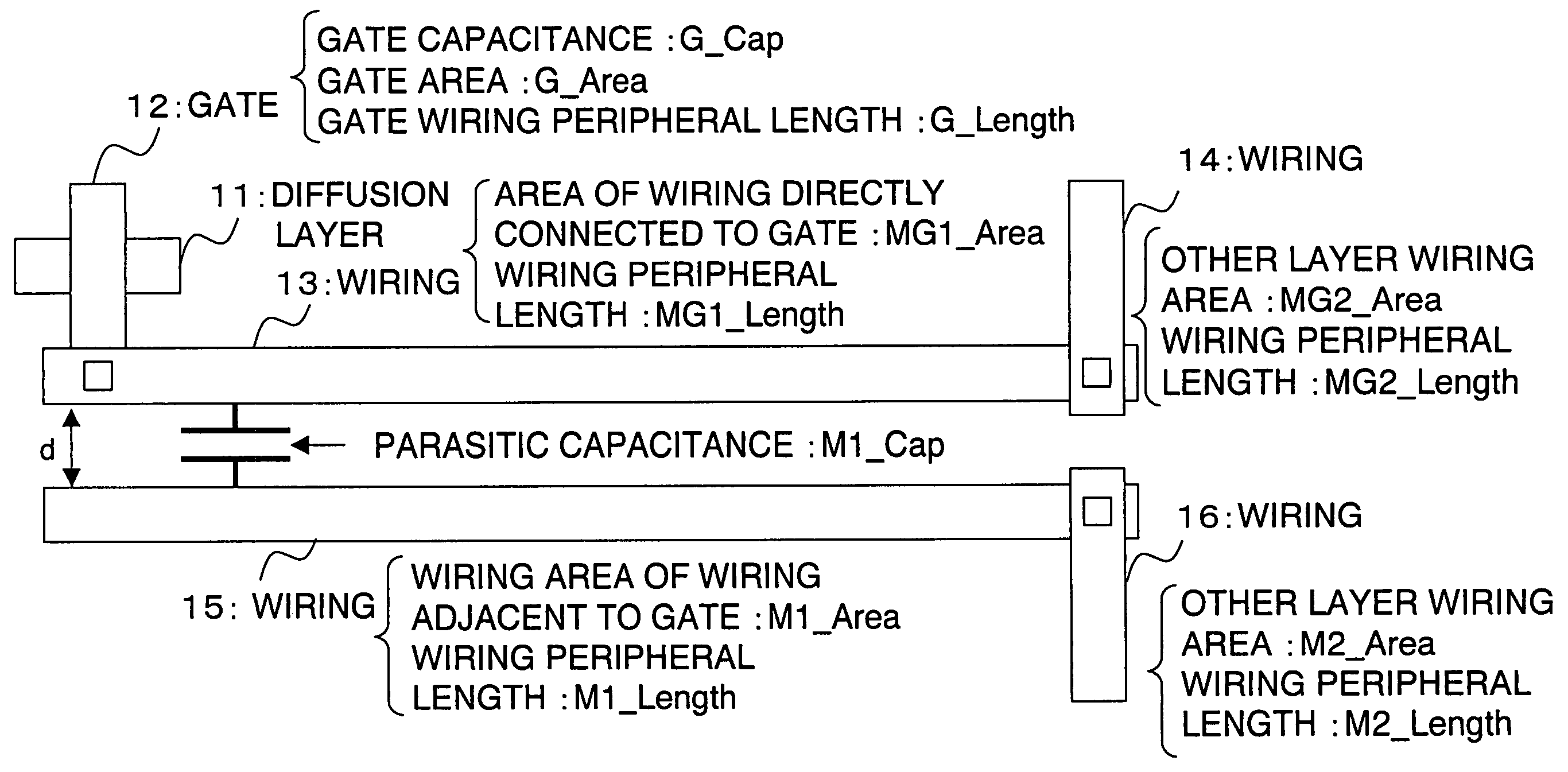

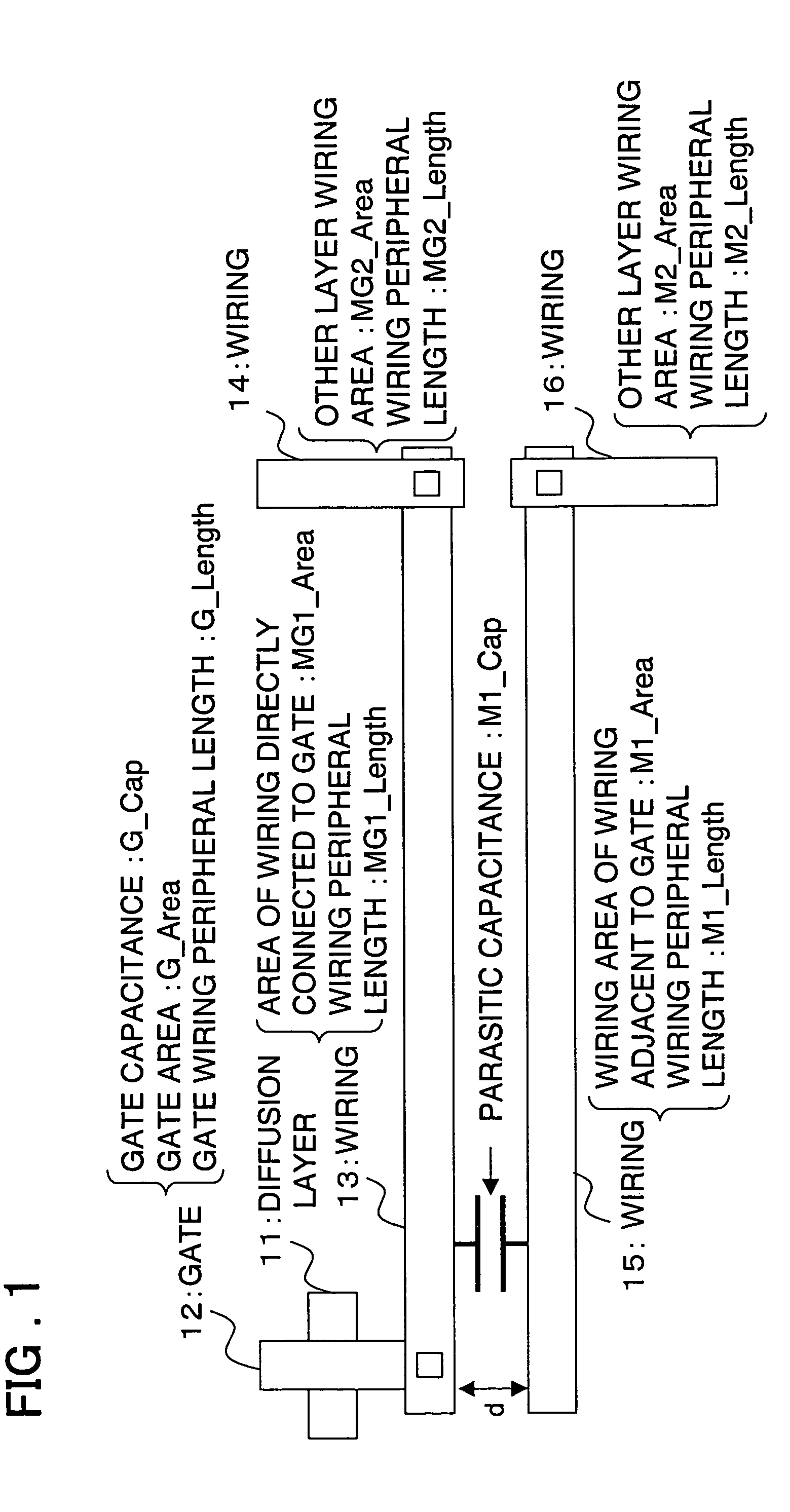

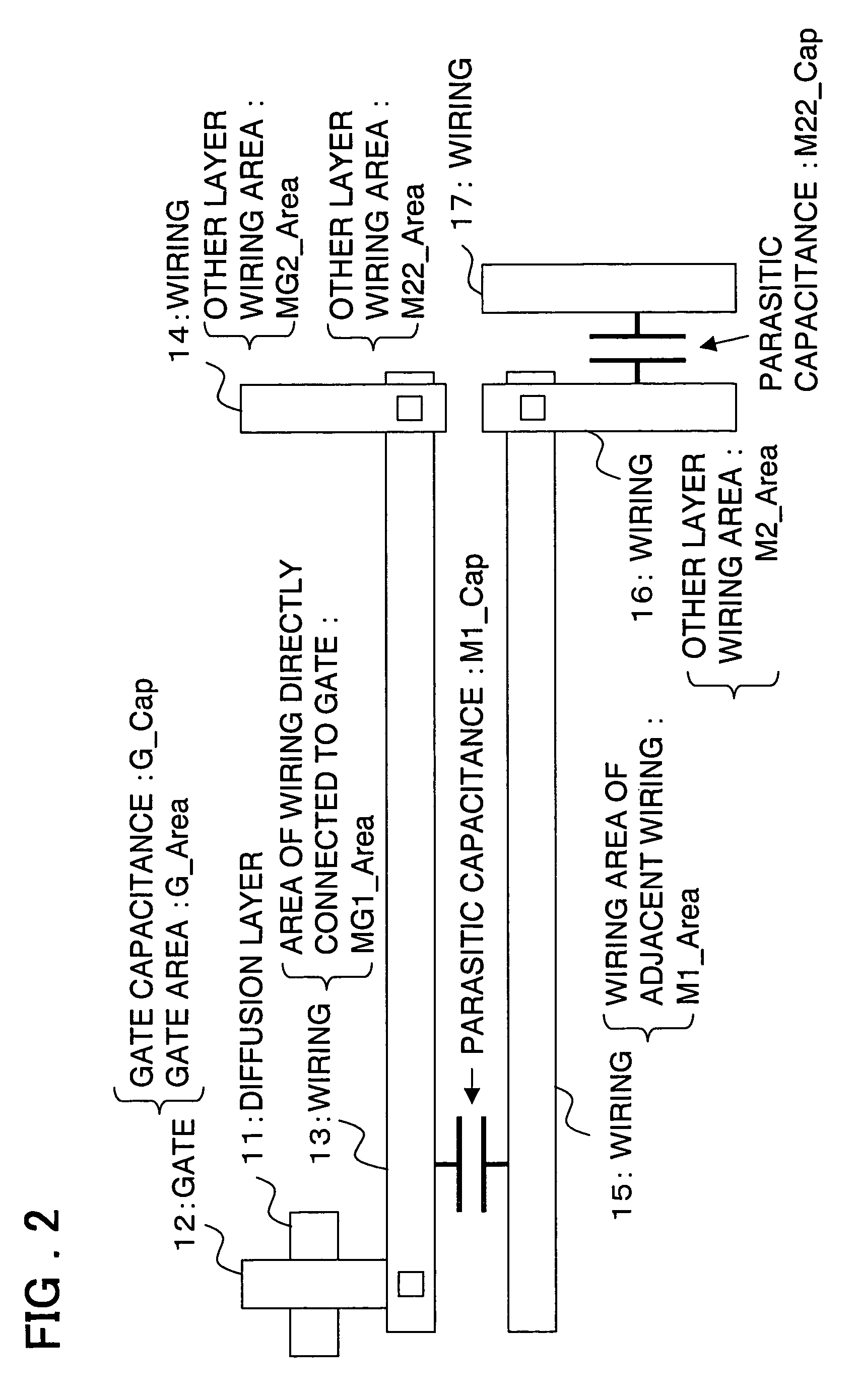

Semiconductor integrated device for preventing breakdown and degradation of a gate oxide film caused by charge-up in manufacturing steps thereof, design method thereof, designing apparatus method thereof, and maunfacturing apparatus thereof

InactiveUS7523419B2Semiconductor/solid-state device detailsSolid-state devicesParasitic capacitanceEngineering

Semiconductor integrated circuit that prevents breakdown and degradation of a gate oxide film caused by charge-up in manufacturing steps thereof is provided. The circuit includes a gate 12 provided insulated from a transistor diffusion layer 11, wirings 13 and 14 connected to the gate 12, a wiring 15 parallel to and adjacent to the wiring 13, and a wiring 16 connected to the wiring 15. The gate area of the gate 12 is indicated by G_Area, and the gate capacitance of the gate 12 is indicated by G_Cap. The areas of the wirings 13, 14, 15, and 16 are indicated by MG1_Area, MG2_Area, M1_Area, and M2_Area, respectively, and a parasitic capacitance between the wirings 13 and 15 is indicated by M1_Cap. An antenna ratio R1 calculated from the areas is given by an equation R1={(MG1_Area+MG2_Area)+alpha(M1_Area+M2_Area)} / G_Area. alpha is a parameter determined by a function of the G_Cap and the M1_Cap. Layout of the wirings is performed so that a relation R1<L1 (which is a specified value that causes damage to a gate oxide film).

Owner:RENESAS ELECTRONICS CORP

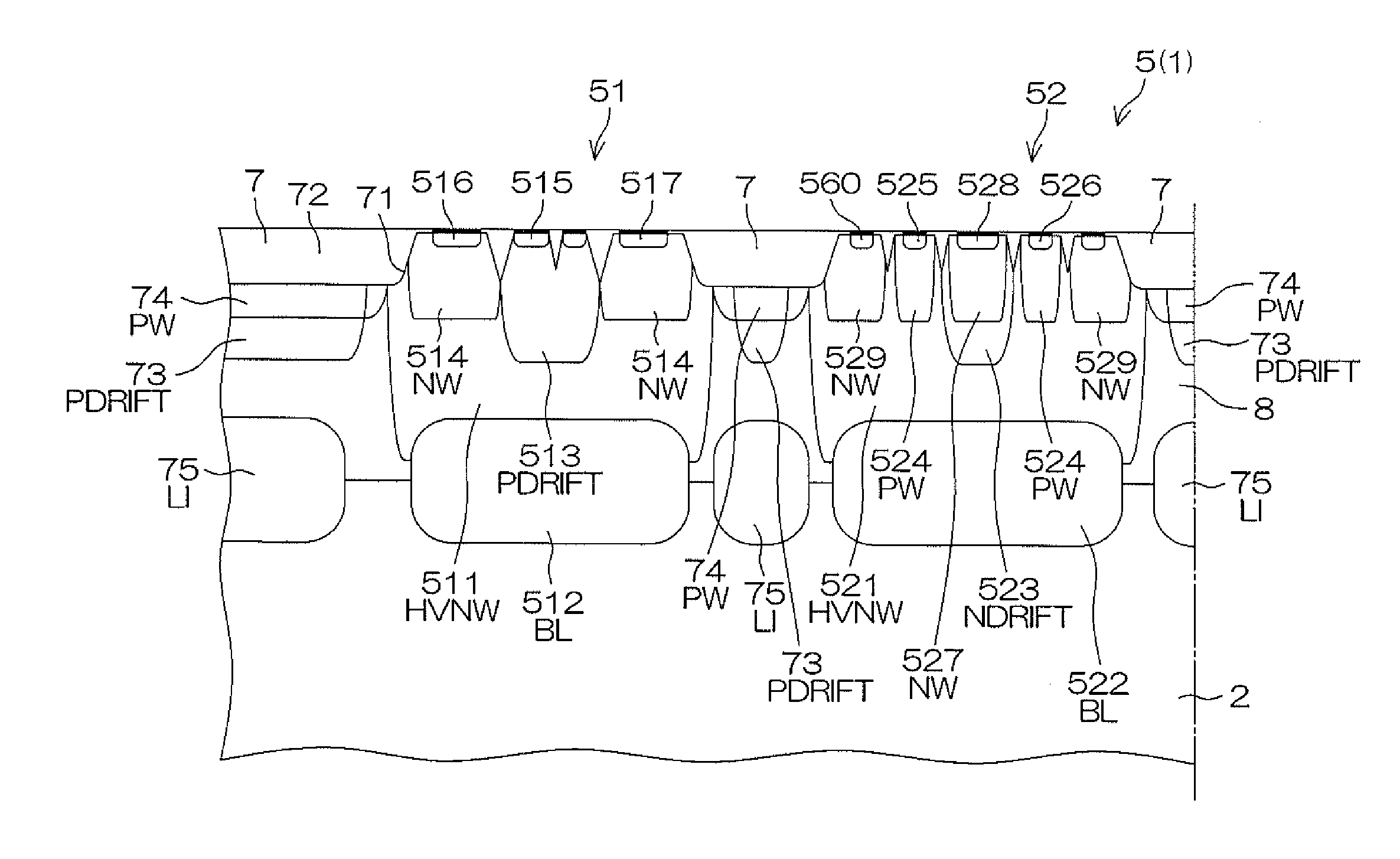

N-channel double diffusion mos transistor, and semiconductor composite device

ActiveUS20140210002A1Improve switching characteristicsTransistorSolid-state devicesPhysical chemistryDiffusion transistor

The n-channel double diffusion MOS transistor includes a p-type semiconductor substrate, a p-type epitaxial layer, and an n-type buried layer provided in a boundary between the p-type semiconductor substrate and the p-type epitaxial layer. In a p-type body layer provided in a surface portion of the p-type epitaxial layer, an n-type source layer is provided to define a double diffusion structure together with the p-type body layer. An n-type drift layer is provided in a surface portion of the p-type epitaxial layer in spaced relation from the p-type body layer. An n-type drain layer is provided in a surface portion of the p-type epitaxial layer in contact with the n-type drift layer. A p-type buried layer having a lower impurity concentration than the n-type buried layer is buried in the p-type epitaxial layer between the n-type drift layer and the n-type buried layer in contact with an upper surface of the n-type buried layer.

Owner:ROHM CO LTD

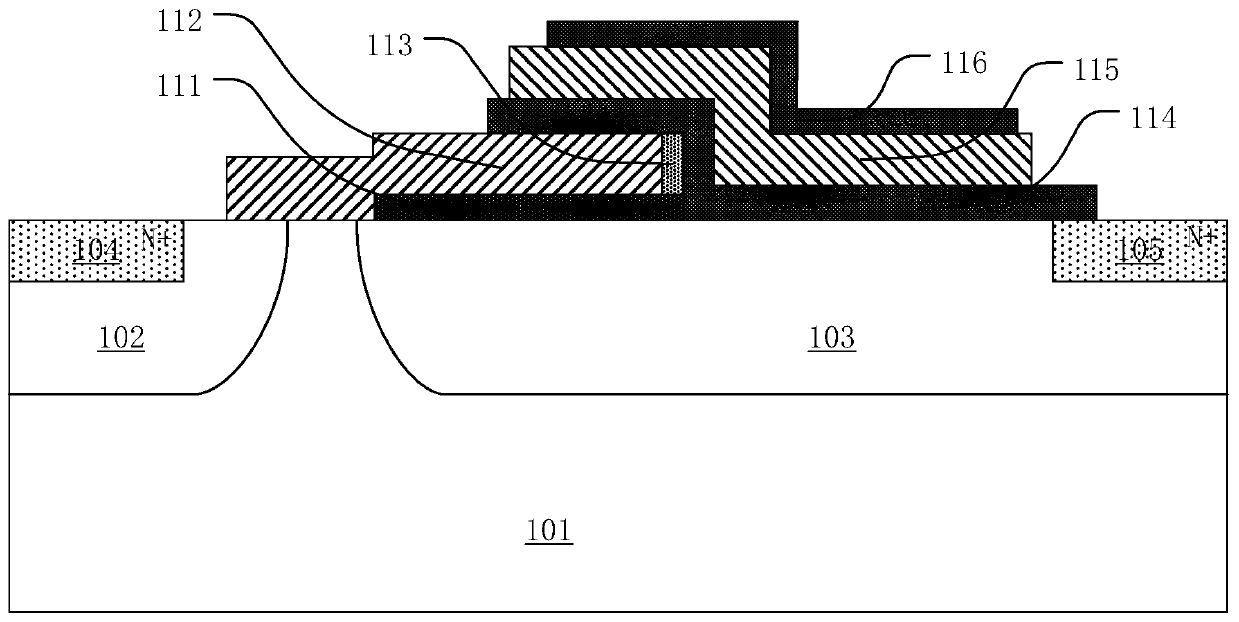

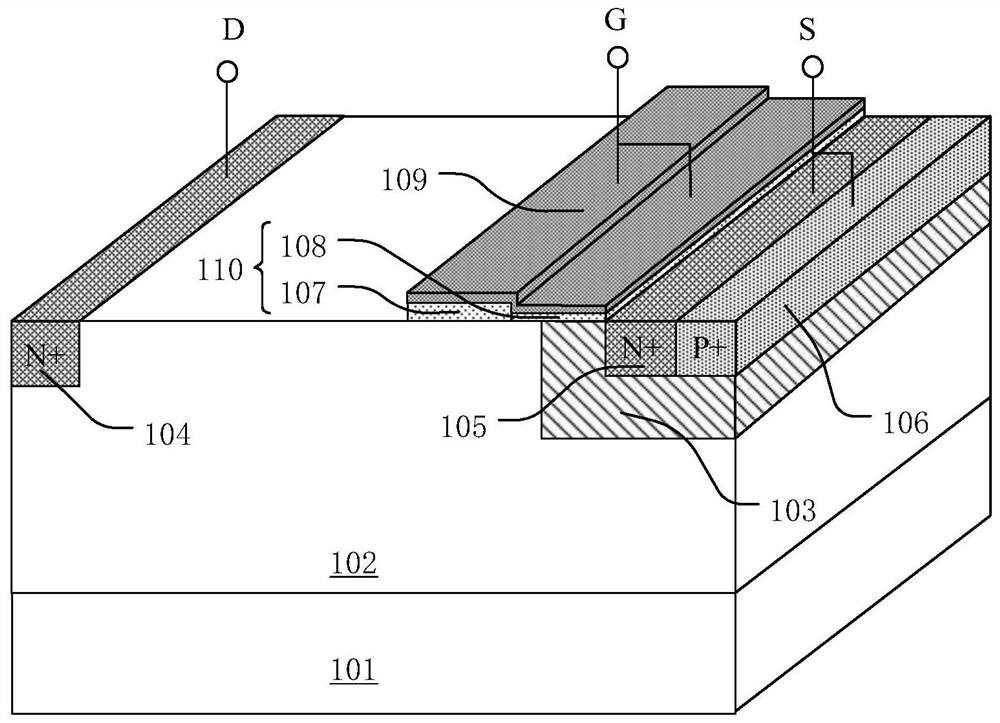

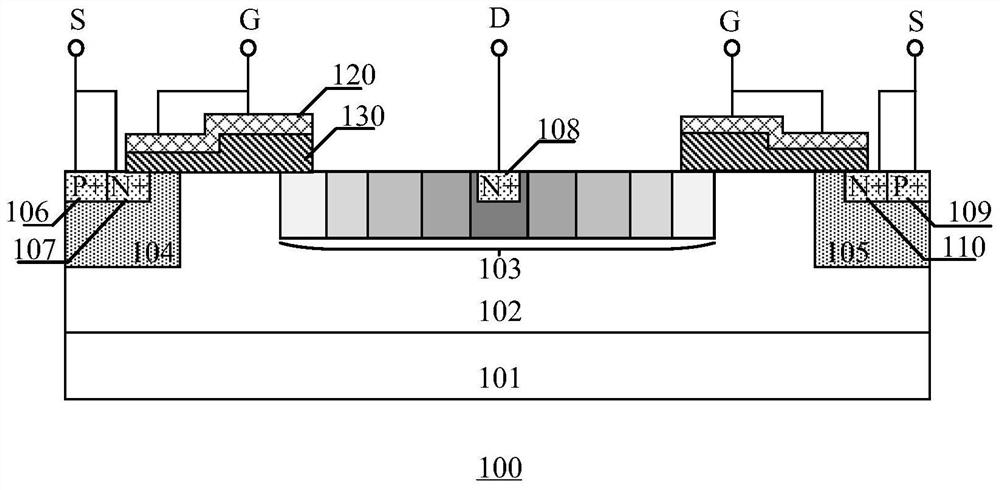

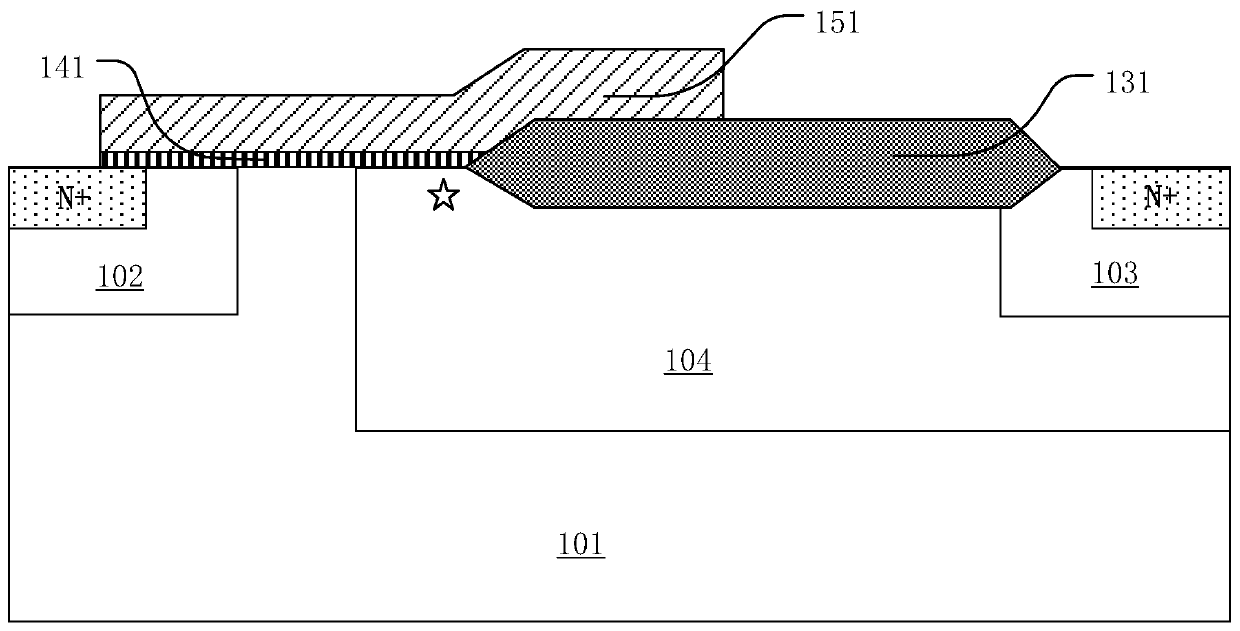

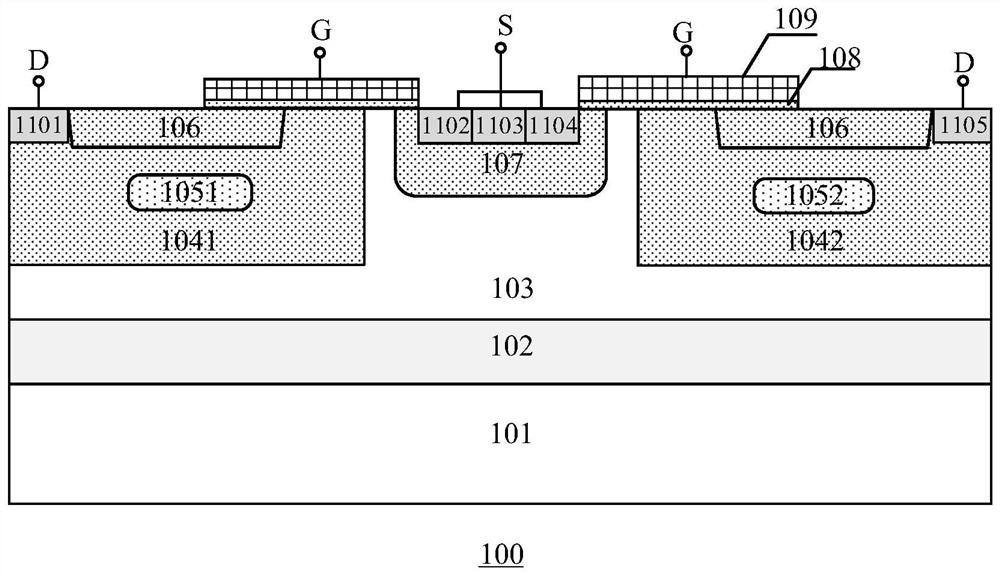

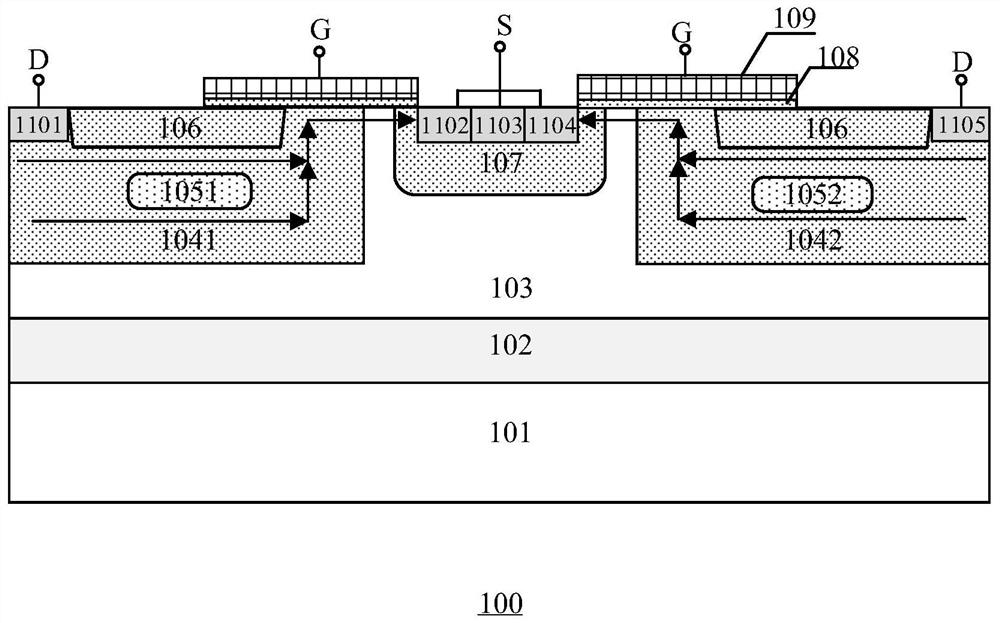

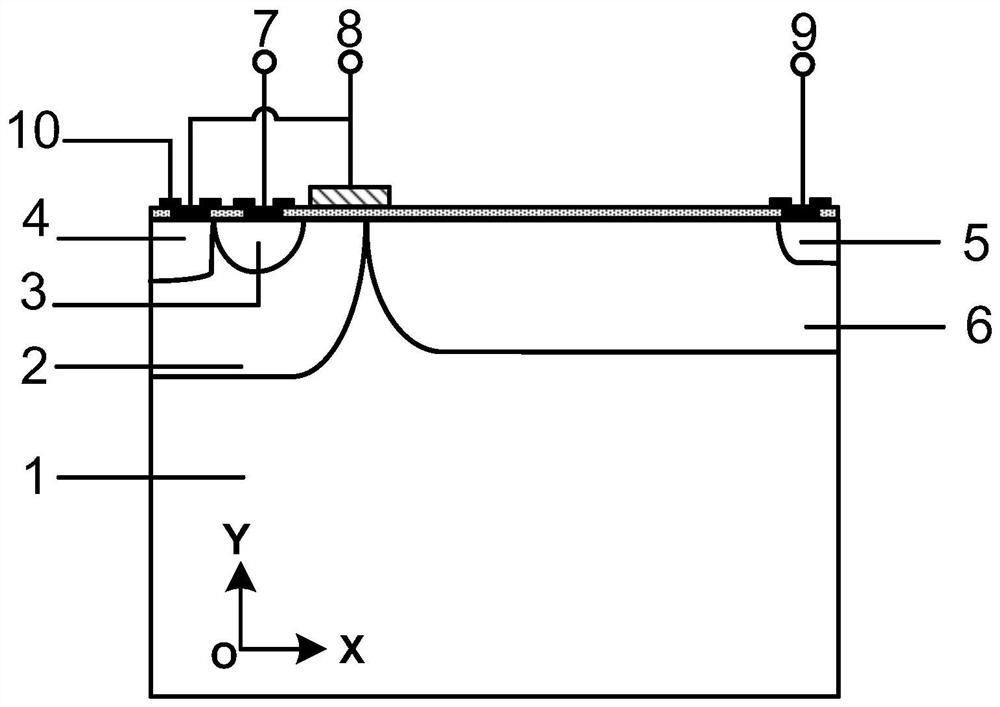

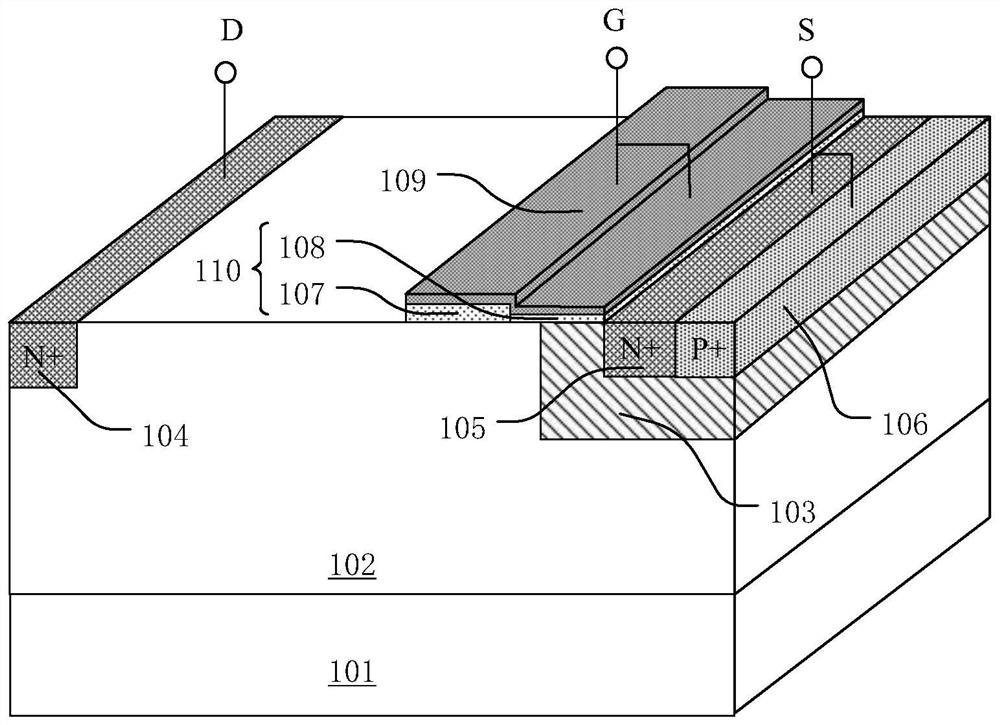

Lateral double-diffused transistor and manufacturing method thereof

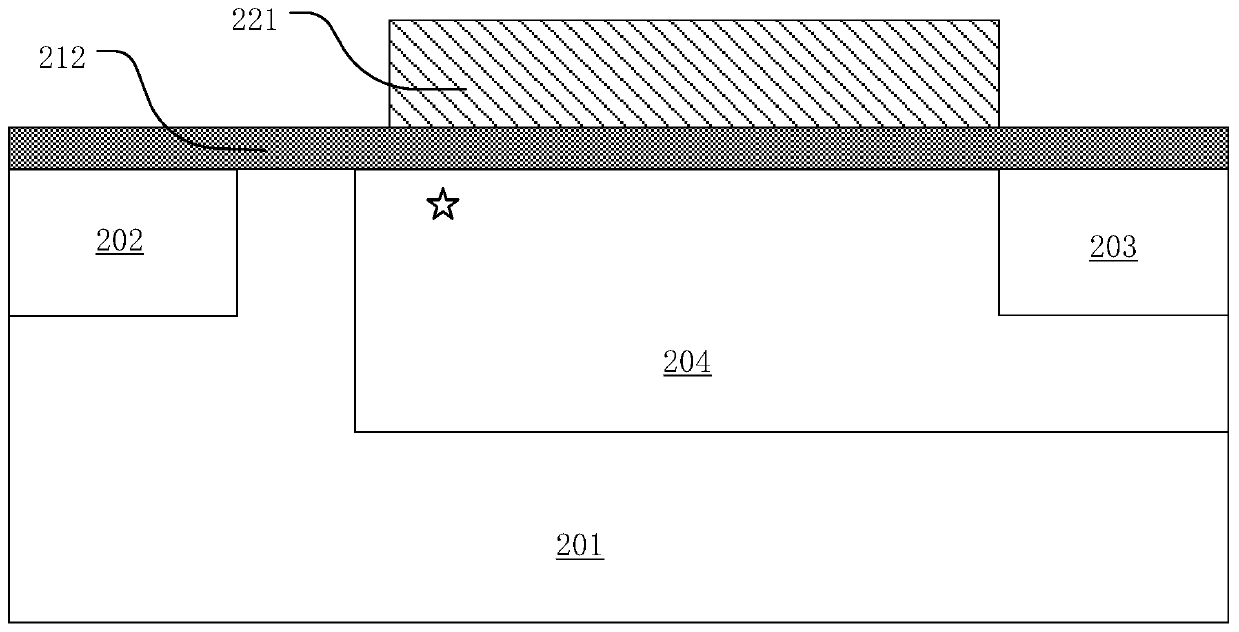

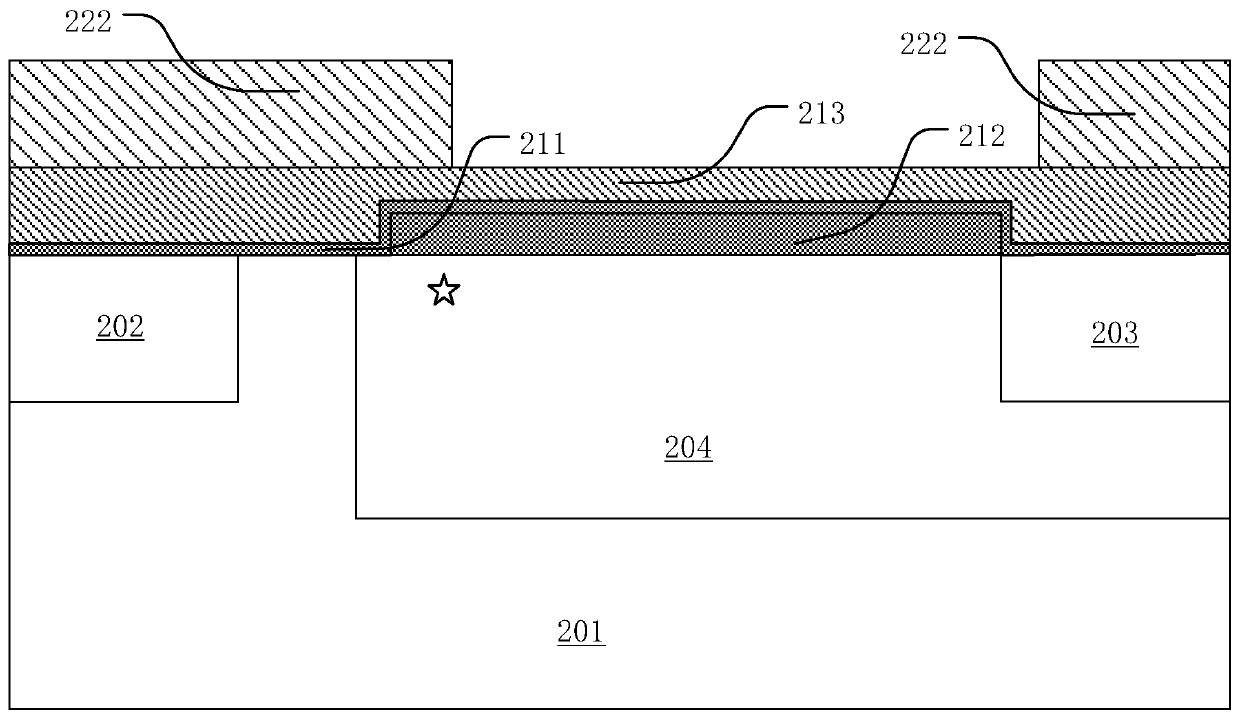

PendingCN111092123AImprove breakdown voltageLower on-resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesEngineeringDielectric layer

The invention discloses a lateral double-diffused transistor and a manufacturing method thereof. The lateral double-diffused transistor comprises a substrate, a well region and a drift region which are located at the top of the substrate, a source region and a drain region which are located in the well region and the drift region respectively, a first dielectric layer located on a surface of the drift region, a first field plate which is located on a surface of the drift region and covers a part of a surface of the first dielectric layer, a second dielectric layer which partially covers the surface of the first field plate and is stacked on a part of the surface of the first dielectric layer, and a second field plate positioned on a surface of the second dielectric layer, wherein the second field plate comprises at least one contact channel. The lateral double-diffusion transistor is advantaged in that a contact channel is used as the second field plate, so the manufacturing process isreduced, a distance between the second field plate and the silicon substrate is increased, a breakdown voltage of the transistor is increased, and the-powered-on resistance is reduced.

Owner:JOULWATT TECH INC LTD

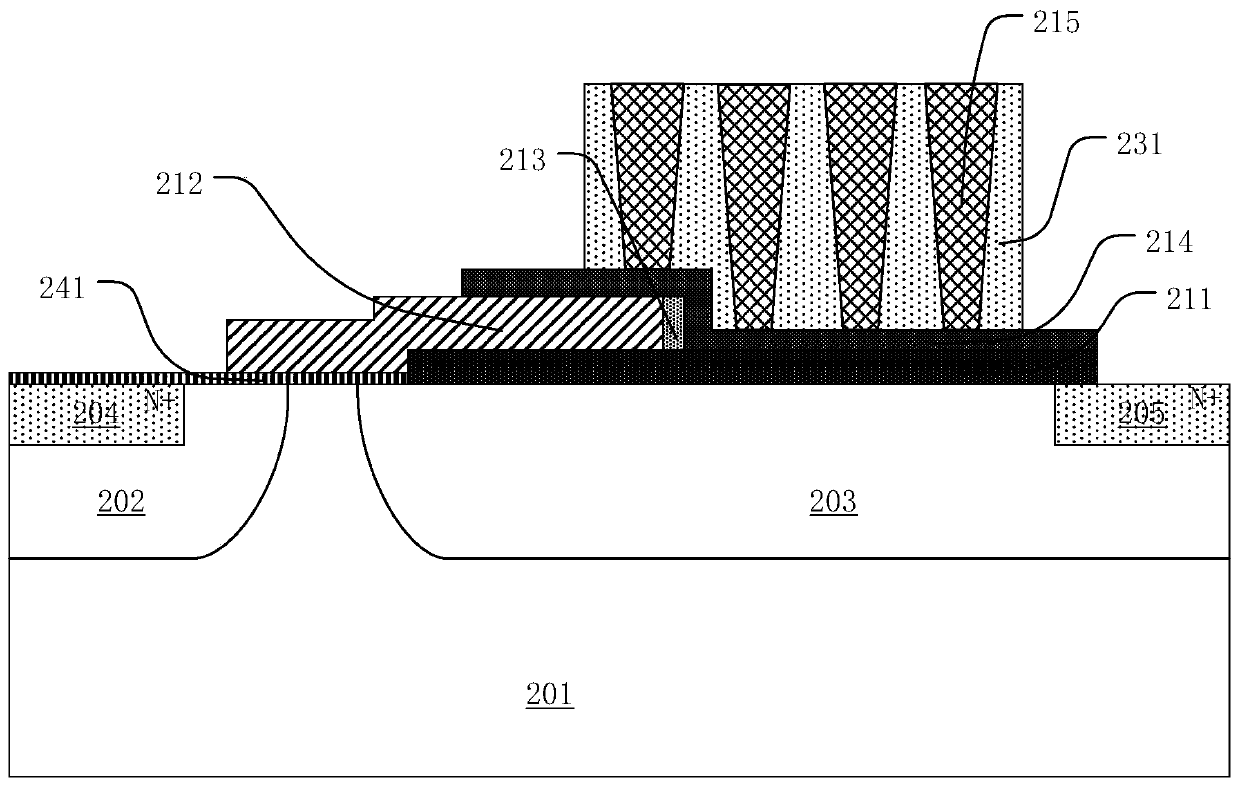

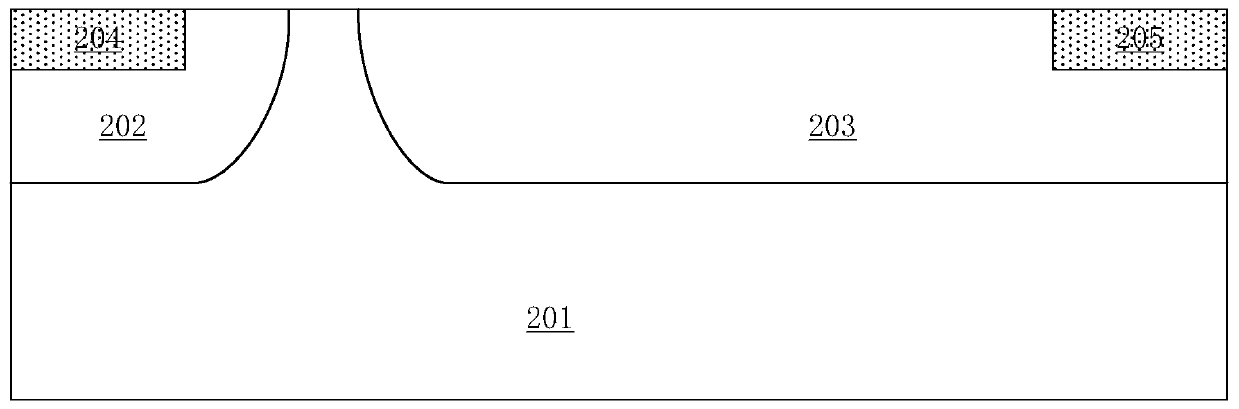

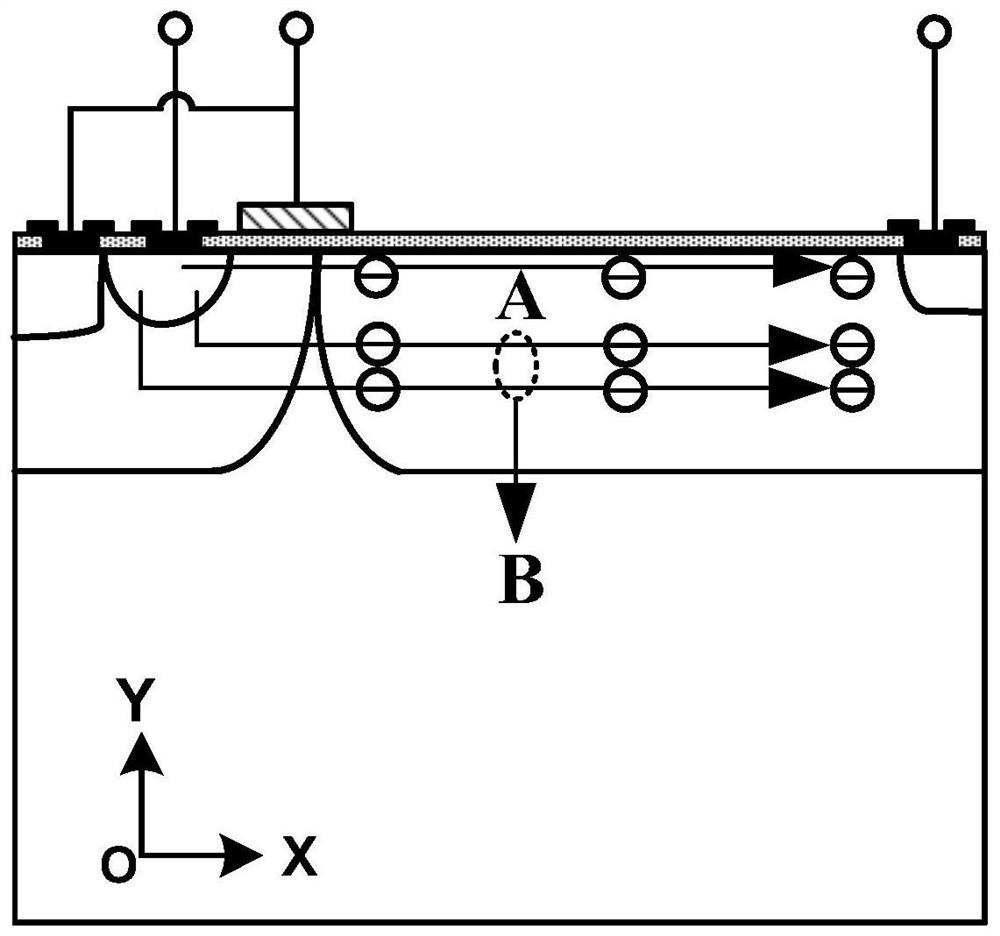

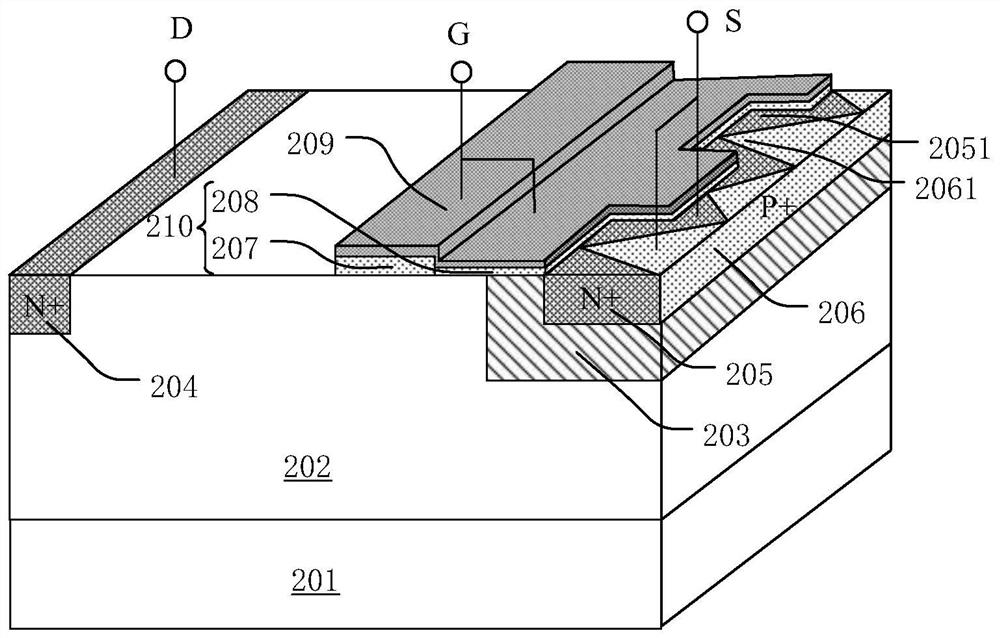

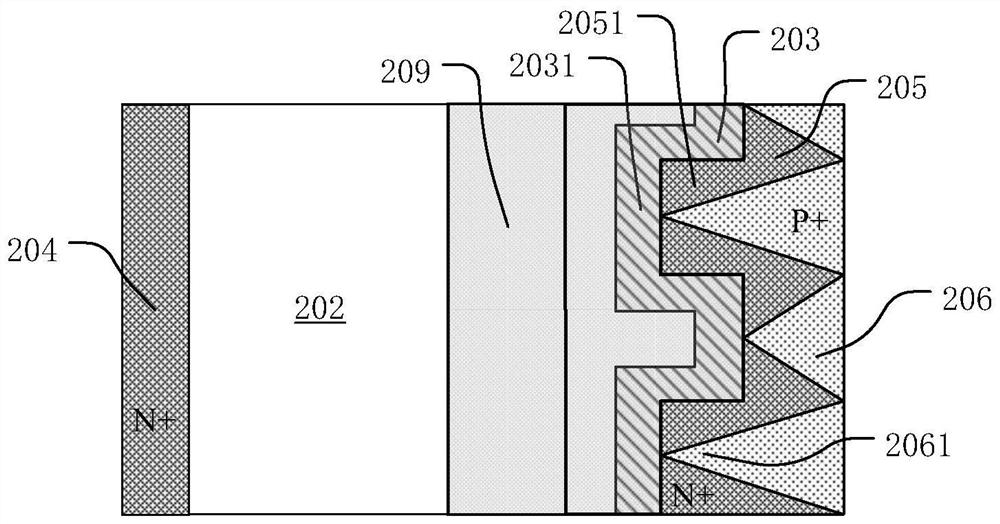

Lateral double-diffused transistor and manufacturing method thereof

ActiveCN111710723AIncrease channel densityLower channel resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesElectrical resistance and conductanceChannel density

The invention discloses a lateral double-diffused transistor and a manufacturing method thereof. The lateral double-diffused transistor comprises: a substrate; a drift region located at the top of thesubstrate; a drain region and a body region respectively positioned on two opposite sides of the top of the drift region; a source region and a body contact region positioned in the body region and adjacent to each other; and a dielectric layer and a field plate layer sequentially stacked on the surface of the drift region, wherein the body region partially extends towards the direction of the drain region to form at least one body region extending region, the body region extending region and the drift region adjacent to the body region extending region are distributed in an interdigitated manner, at least one groove is formed in the side, away from the drain region, of the top of the body region, the source region and the body contact region are located on the side, provided with the groove, in the body region, and the source region is located at the top of the body region and located above the body contact region. Due to the existence of the interdigitated body region and the body contact region of the lateral double-diffused transistor, the channel density of the device is increased, and the leading-out area of the body contact region is increased, so that the on resistance andthe body region resistance are reduced, and parasitic NPN mis-opening is effectively prevented.

Owner:JOULWATT TECH INC LTD

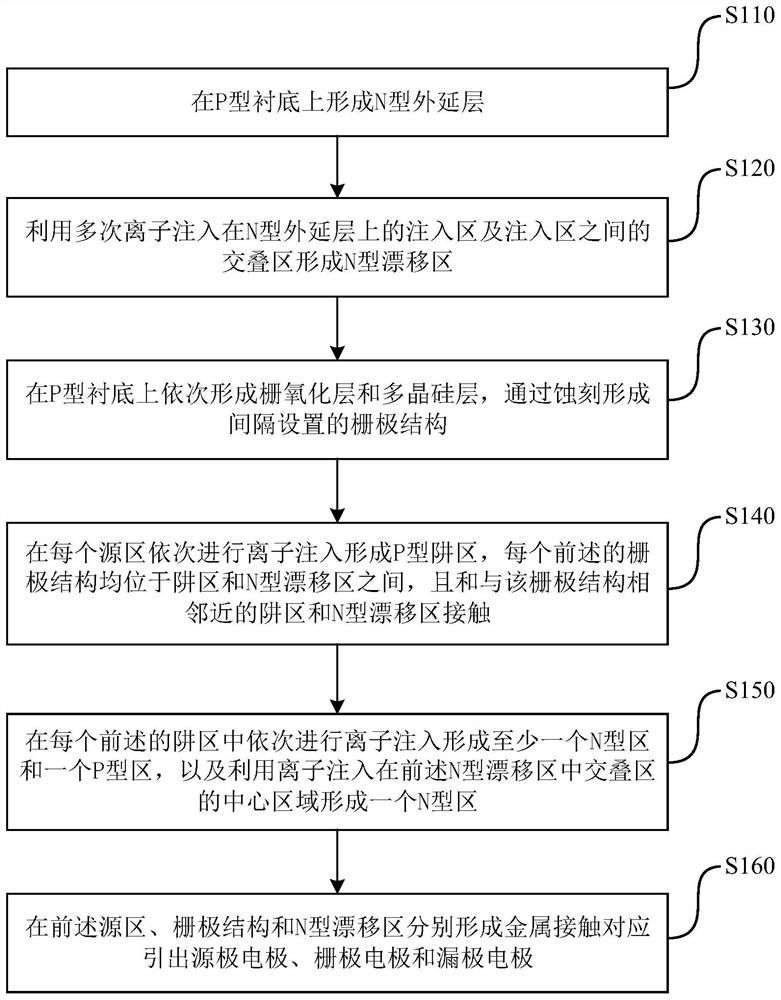

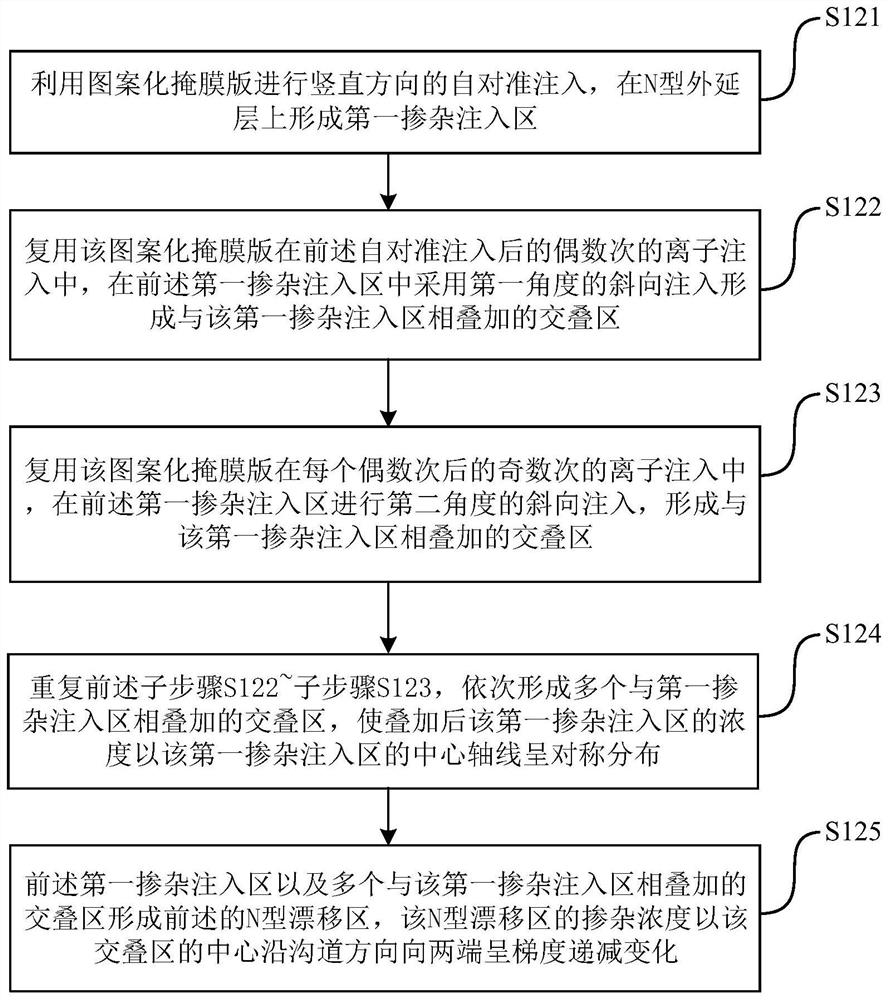

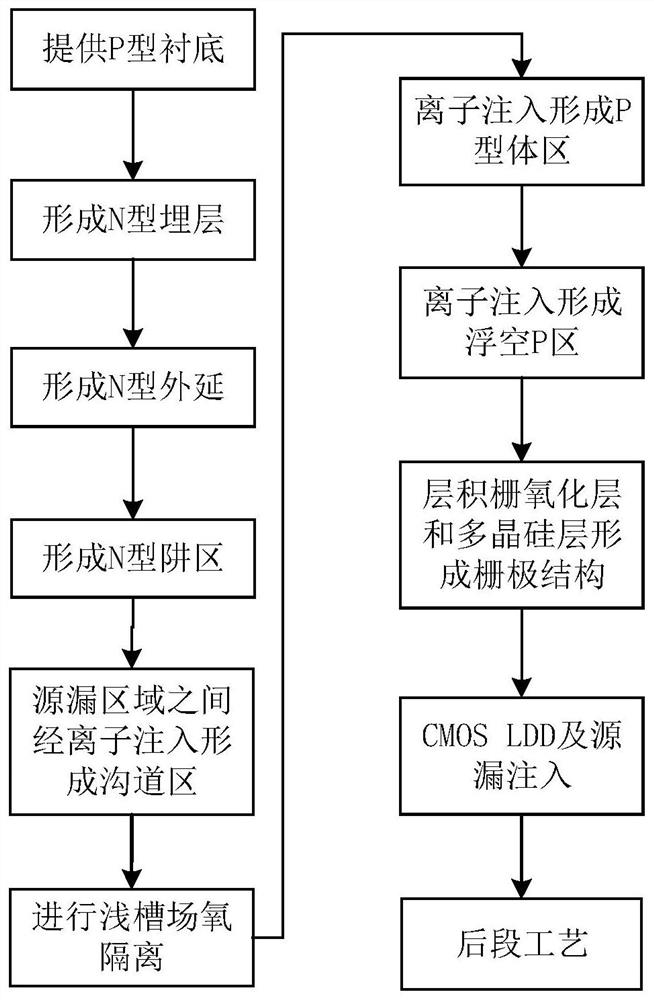

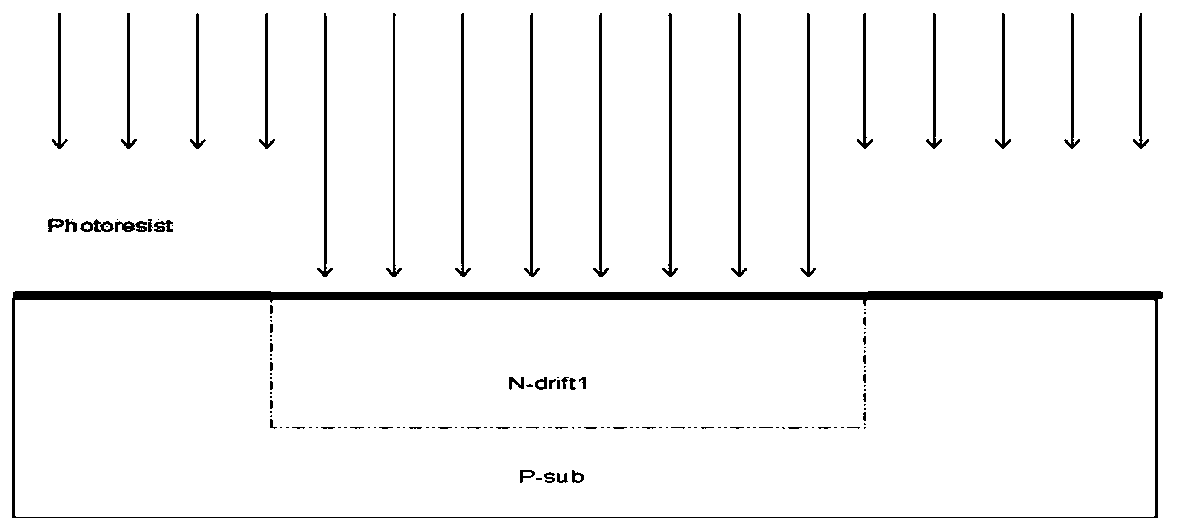

Manufacturing method of lateral double-diffused transistor

ActiveCN111987166AImprove electric field distributionImprove breakdown voltageSemiconductor/solid-state device manufacturingSemiconductor devicesImpurity dopingDiffusion transistor

The invention relates to the technical field of semiconductor power devices. The invention provides a manufacturing method of a lateral double-diffusion transistor. A drift region of a first doping type is formed in injection regions on a substrate and an overlapping region between the injection regions by utilizing multiple times of ion implantation (oblique angle implantation); and the doping concentration of the drift region is distributed in a gradient decreasing (linear variable doping concentration) manner from the center of the overlapping region to the two ends along the channel direction, so that a formed device is of a bilaterally symmetrical structure by taking the central axis of the drift region as the center. The breakdown voltage of the device is improved; enough impurity doping concentration is ensured; therefore, the device has relatively small on-resistance; the performance of the formed device is improved; according to the manufacturing method, the phenomenon that aspecially-made mask with a specific window design is used for forming the linear variable doping drift region in the prior art is avoided, the manufacturing cost is saved, and the linear distributionof the doping concentration of the drift region can be controlled by controlling the ion implantation frequency and angle through the process, so that the applicability of the manufacturing method isimproved.

Owner:JOULWATT TECH INC LTD

Manufacturing method of lateral double-diffused transistor

ActiveCN110957370AImprove breakdown voltageIncrease the lengthSemiconductor/solid-state device manufacturingSemiconductor devicesEngineeringNitride

The present invention discloses a manufacturing method of a lateral double-diffused transistor. The method comprises the steps that a liner oxide layer and a first hard mask are sequentially depositedon the surface of a substrate, and a P-type well region and an N-type well region which are separated from each other are formed on the substrate; an N-type drift region is formed in the substrate through the opening of the first hard mask, the N-type drift region is spaced apart from the P-type well region and adjacent to the N-type well region; a second hard mask is deposited on the surfaces ofthe first hard mask and the liner oxide layer; and a field oxide layer is formed over the N-type drift region via the opening of the second hard mask. According to the manufacturing method, the opening is formed by etching the first hard mask; a drift region is formed via openings, the mask is saved, and the second hard mask is deposited above the first hard mask, so that the thickness of the nitride layer above the drift region is smaller than that of the nitride layer in other regions, the length of the beak is increased, the electric field of the silicon substrate below a beak region is reduced, and the breakdown voltage of the transistor is effectively improved while the process cost is saved.

Owner:JOULWATT TECH INC LTD

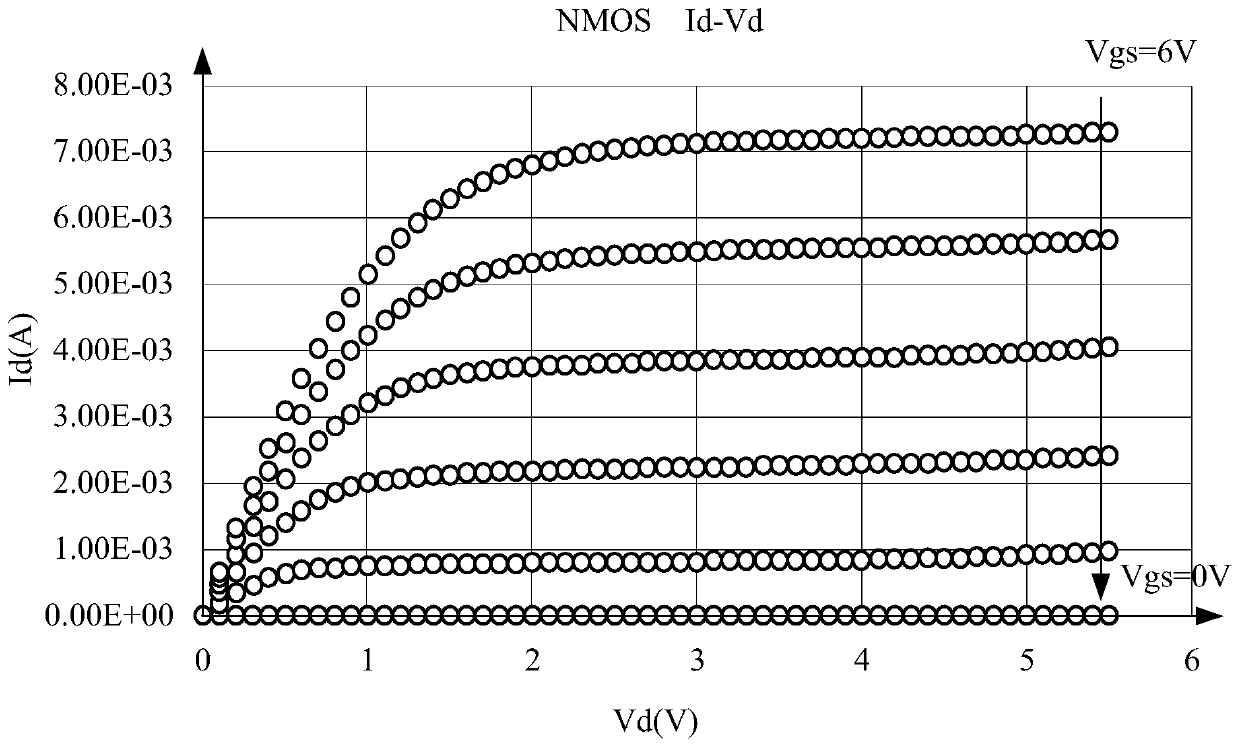

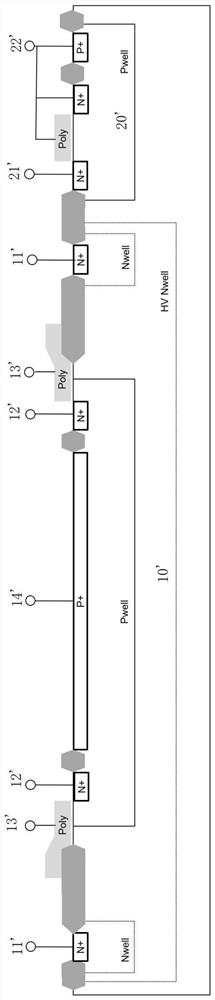

Circuit model of lateral double-diffused transistor and modeling method thereof

ActiveCN111368490AShorten the design cycleOvercoming the inability to accurately characterize the characteristics of LDMOSCAD circuit designLDMOSElectrical resistance and conductance

The invention discloses a circuit model of a lateral double-diffused transistor and a modeling method thereof. The circuit model comprises a standard BSIM4 model; a drift region equivalent resistor, wherein the drift region equivalent resistor comprises a plurality of resistance correction term coefficients and is used for correcting the resistance of the drift region, and the circuit model is used for representing the change characteristics of the saturation threshold voltage and the drain current of the lateral double-diffusion transistor. The LDMOS circuit model and the modeling method of the LDMOS circuit model are based on a BSIM4 model. Custom-made drift region equivalent resistance is added; the quasi-saturation effect in the LDMOS can be accurately represented; according to the circuit model, the convergence, compatibility and high simulation speed of the BSIM4 model are utilized, various characteristics of the LDMOS can be accurately represented, the circuit design period is shortened, and the problem that the BSIM model cannot accurately represent the characteristics of the LDMOS is solved.

Owner:JOULWATT TECH INC LTD

Manufacturing method of lateral double-diffused transistor

ActiveCN111048420AImprove breakdown voltageReduce electric fieldSemiconductor/solid-state device manufacturingSemiconductor devicesDiffusion transistorHard mask

The invention relates to a manufacturing method of a lateral double-diffused transistor. The manufacturing method comprises the following steps that: a first liner oxide layer is formed on the surfaceof a substrate, and a P-type well region and an N-type well region which are separated from each other are formed on the substrate; an N-type drift region is formed in the substrate through the opening of a first hard mask, wherein the N-type drift region is spaced apart from the P-type well region and adjacent to the N-type well region; a second liner oxide layer is formed on the N-type drift region and the N-type well region via the opening of the first hard mask, wherein the second liner oxide layer has a thickness greater than that of the first liner oxide layer; and a field oxide layer is formed on the N-type drift region via the opening of a second hard mask, wherein the second hard mask blocks a portion of the second liner oxide, wherein the portion of the second liner oxide is adjacent to the P-type well region. According to the manufacturing method, the drift region and the second liner oxide layer are formed through the opening of the first hard mask, so that the thickness of the edge of the beak region of the field oxide layer is increased, and therefore, the electric field of the substrate below the beak region is reduced, and the breakdown voltage of the transistor iseffectively improved while process cost is saved.

Owner:JOULWATT TECH INC LTD

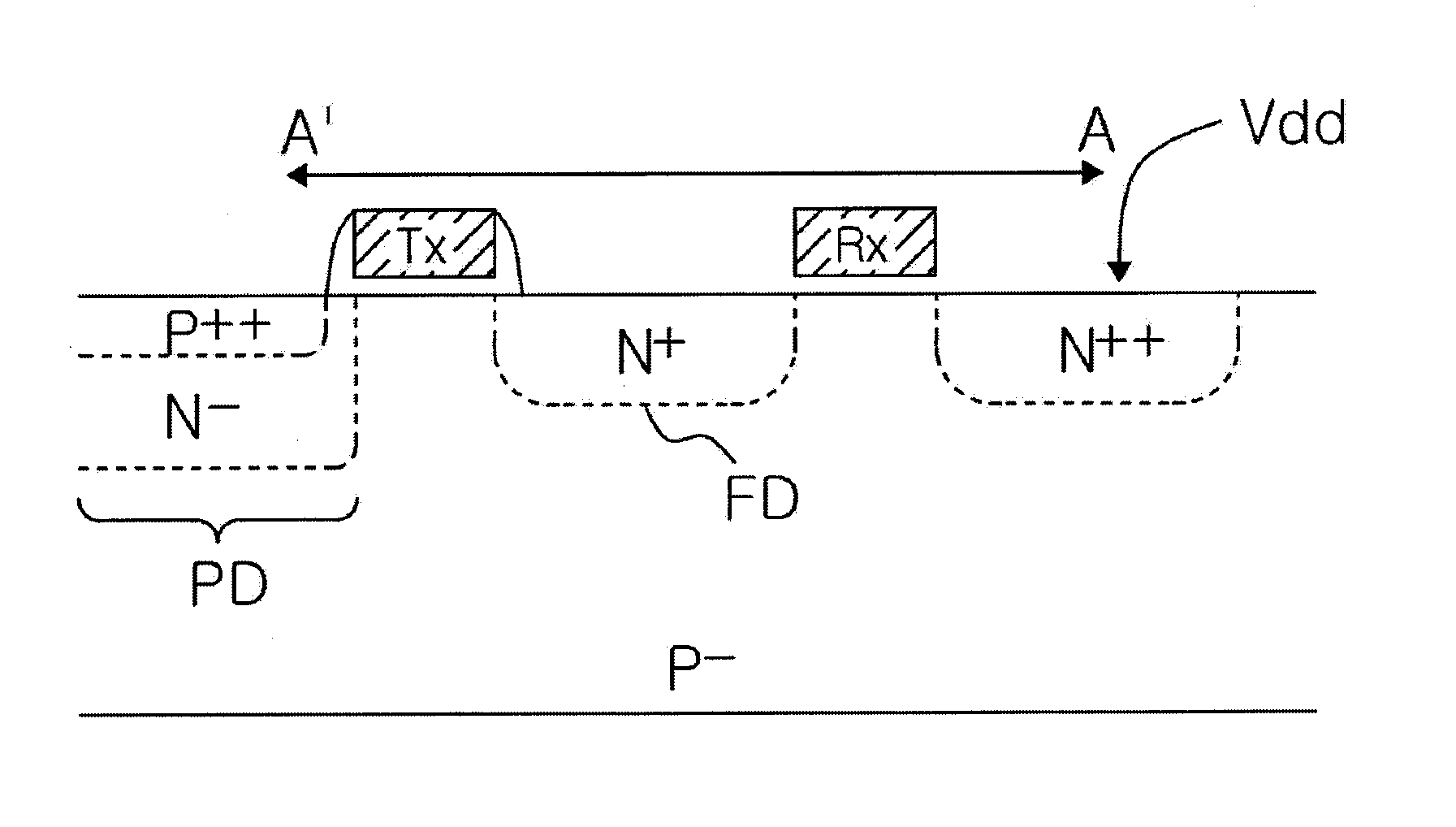

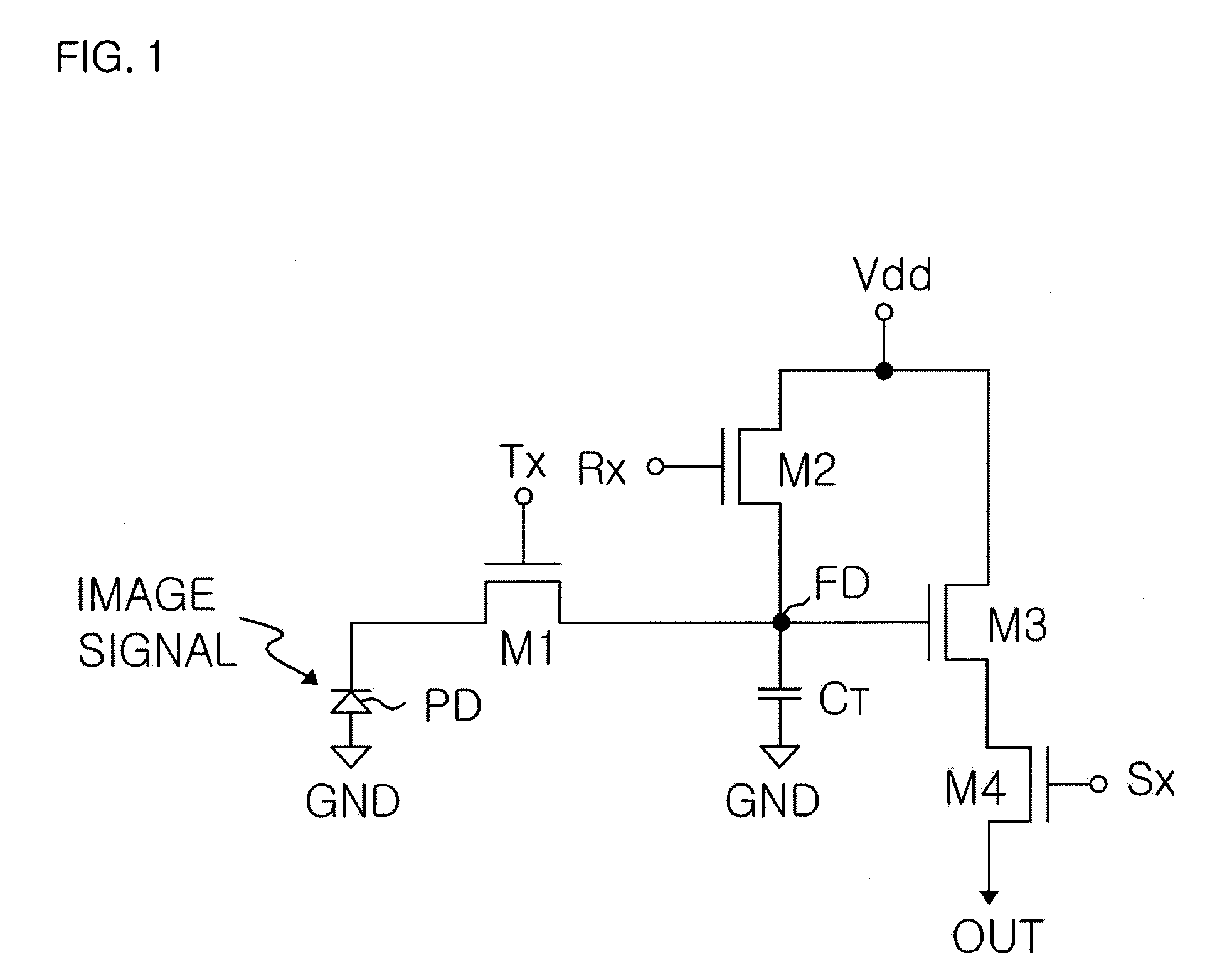

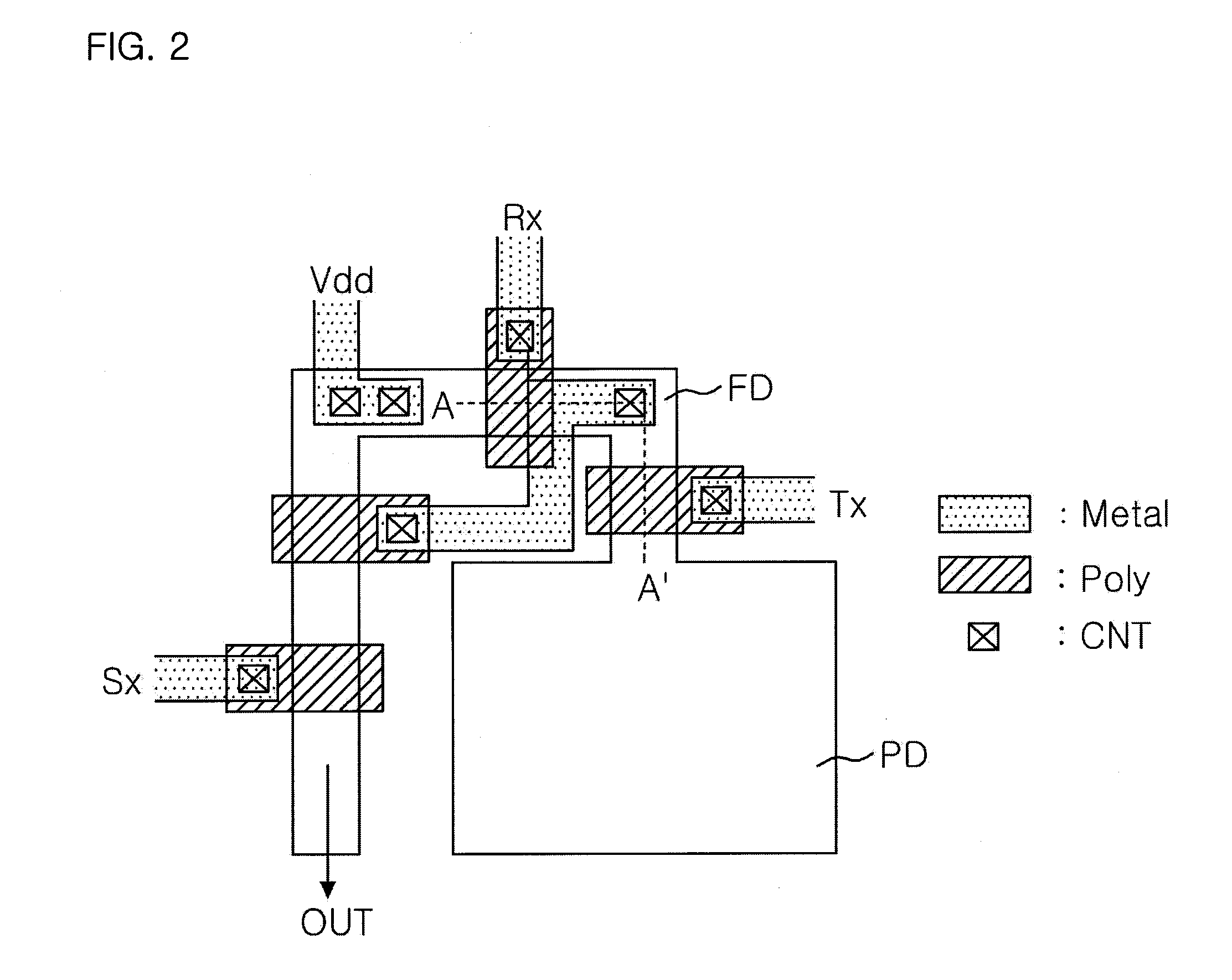

Unit pixel improving image sensitivity and dynamic range

InactiveUS20100200895A1Improving low illumination conditionImprove dynamic rangeSolid-state devicesSemiconductor/solid-state device manufacturingIlluminanceEngineering

Provided are a unit pixel for improving sensitivity in low illumination conditions and a method of manufacturing the unit pixel. The unit pixel includes: a photodiode generating image charges corresponding to an image signal; a transfer transistor transferring the image charges to a floating diffusion area; and a reset transistor having a terminal connected to the floating diffusion area and the other terminal applied with a power supply, wherein concentration of impurity ions implanted into the floating diffusion area is lower than concentration of impurity ions implanted into a diffusion area of the reset transistor applied with the power supply.

Owner:SILICONFILE TECH INC

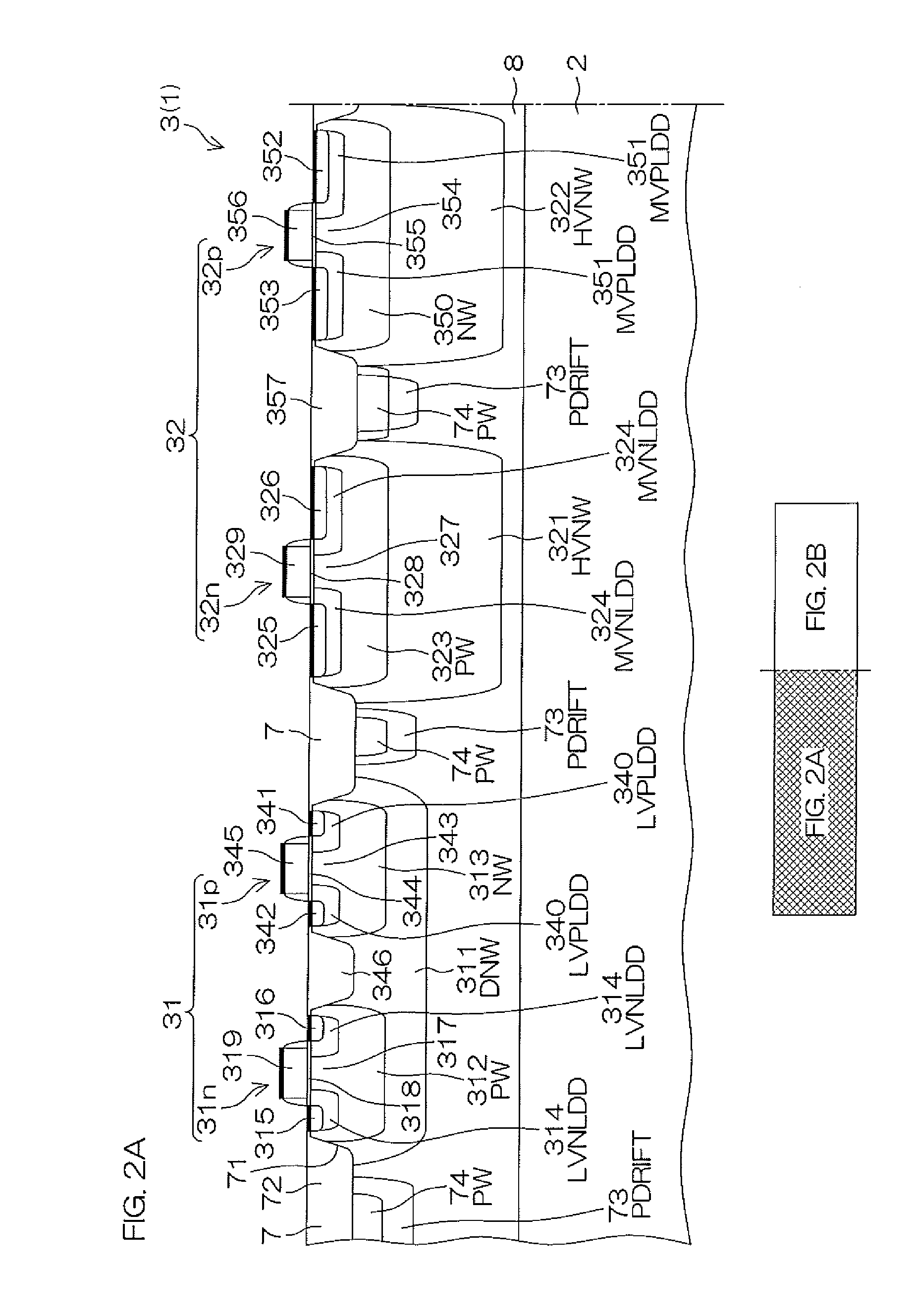

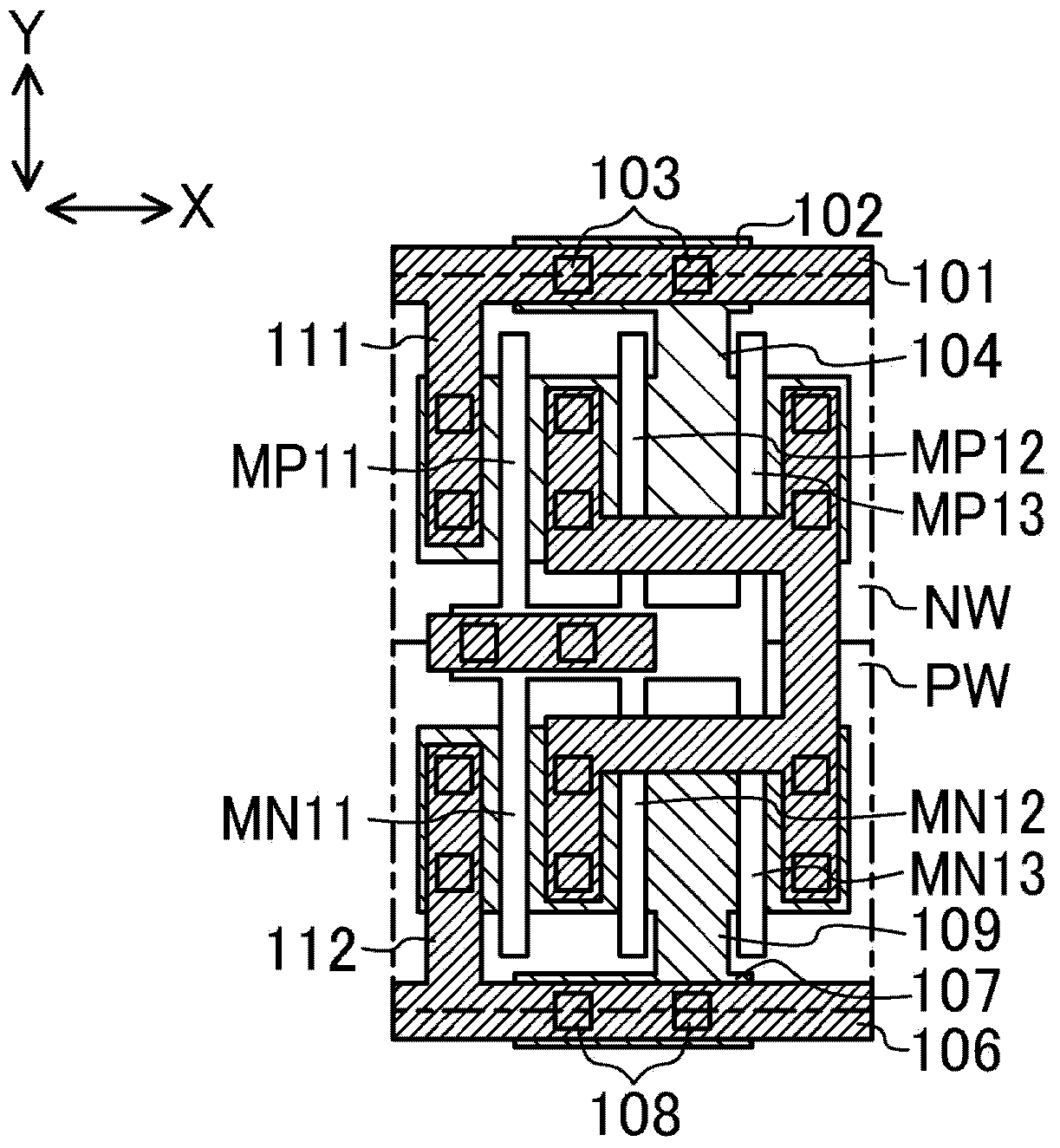

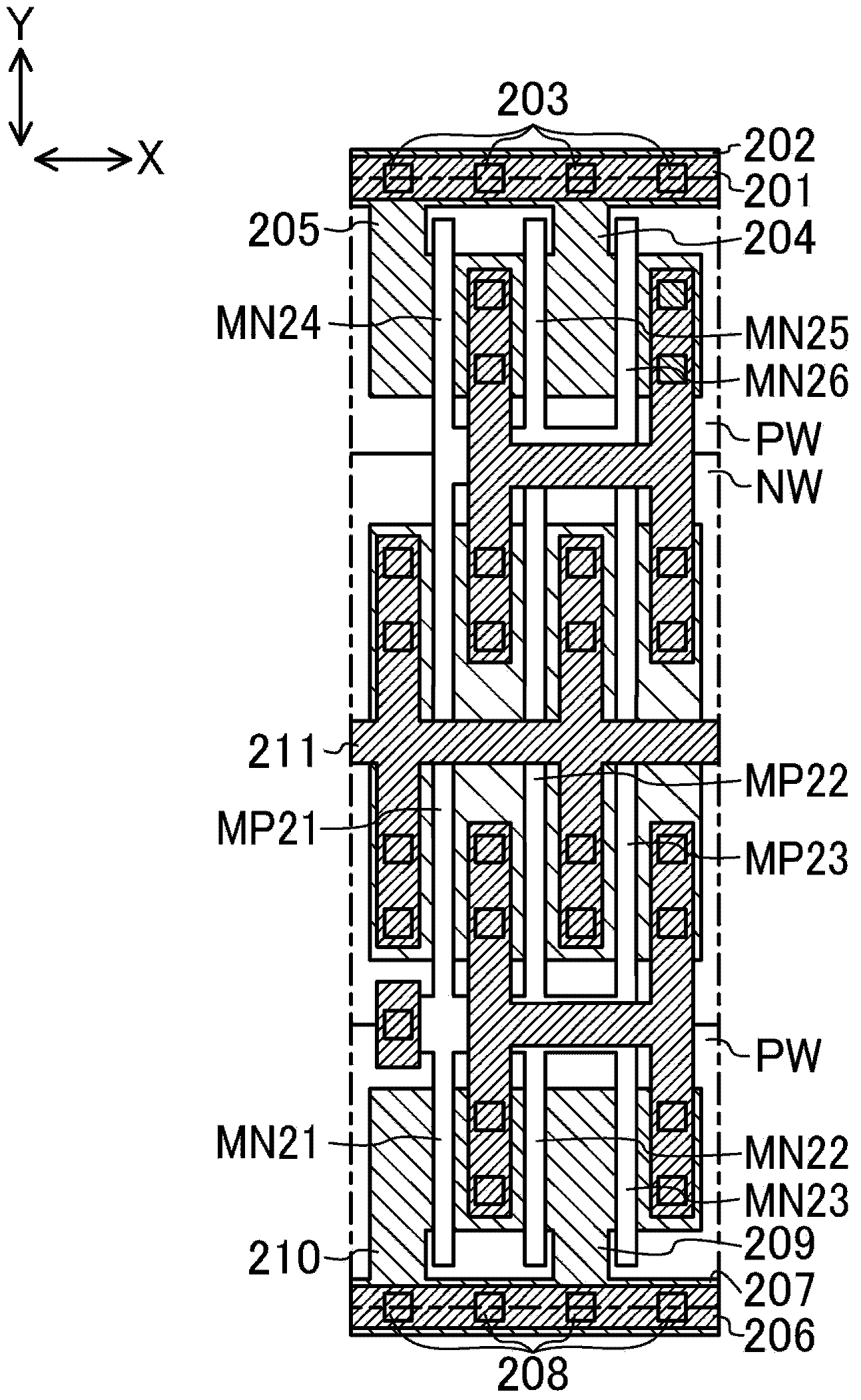

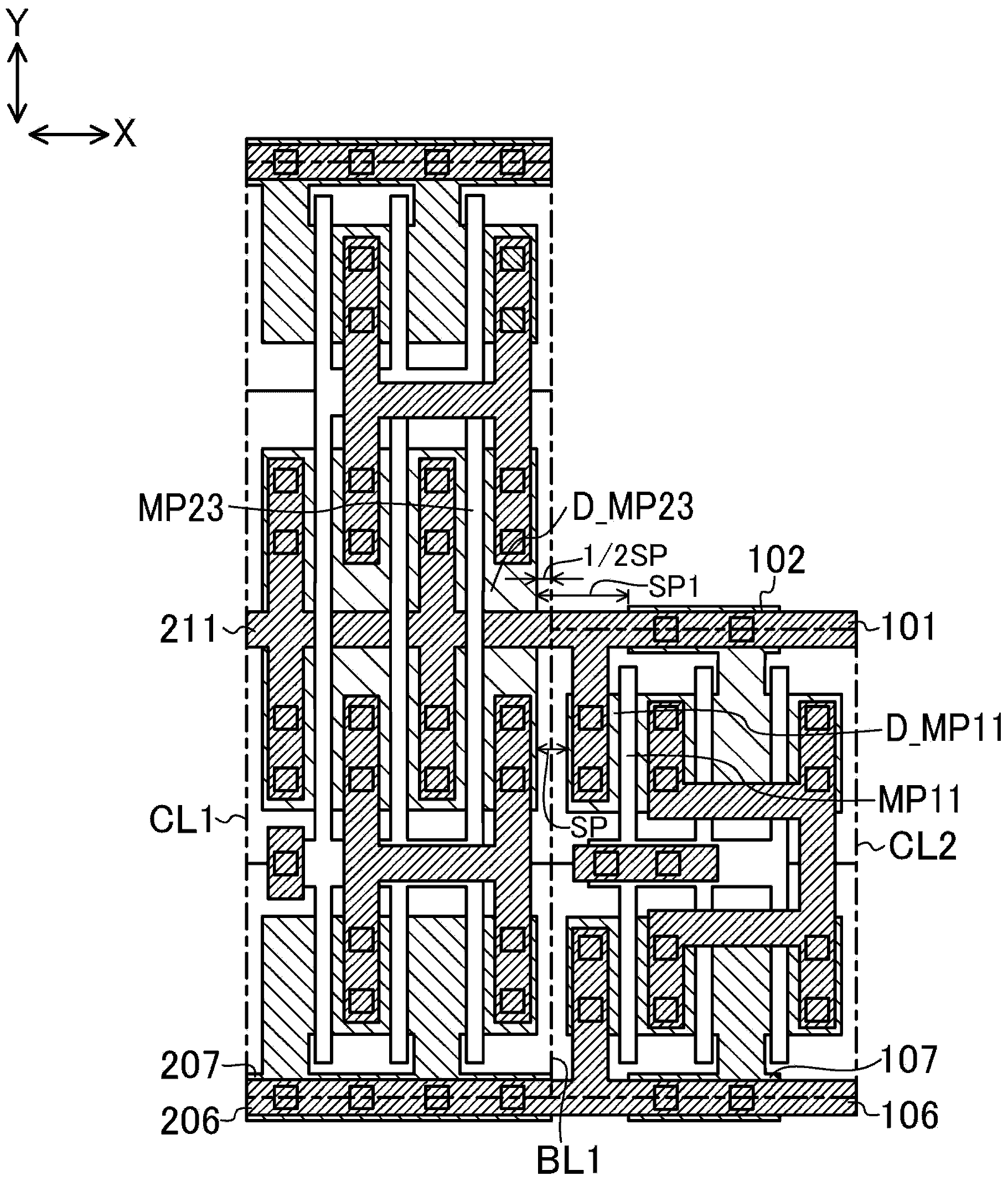

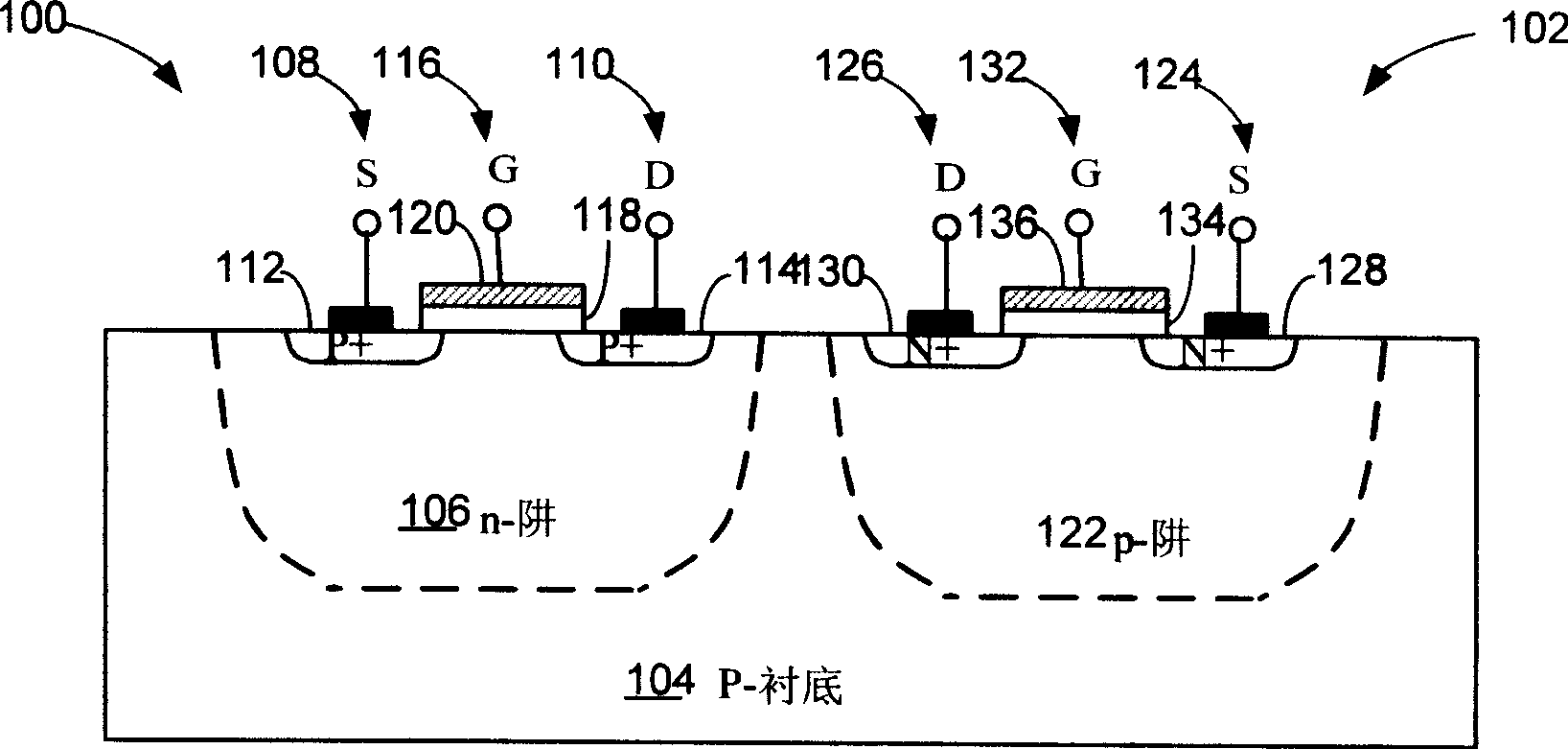

Semiconductor integrated circuit device

InactiveCN103890929AImprove driving abilitySolid-state devicesSemiconductor/solid-state device manufacturingMetal interconnectImpurity diffusion

A first cell having a cell height N times as large as a reference cell height (N is an integer equal to or more than 2) is adjoined by a second cell in the cell width direction. A diffusion interconnect made of an impurity diffusion region is formed under a metal interconnect for power supply in the second cell. The first cell includes a transistor diffusion region formed, opposed to the diffusion interconnect, so as to stride across a region extended in the cell with direction of the metal interconnect. The diffusion interconnect is placed apart from the cell boundary in the cell width direction.

Owner:SOCIONEXT INC

Lateral double diffused MOS transistors

InactiveUS7573097B2Simple mechanical structureIncreases likelihood of mechanical failureTransistorSemiconductor/solid-state device detailsCross connectionMechanical integrity

Owner:BELL SEMICON LLC

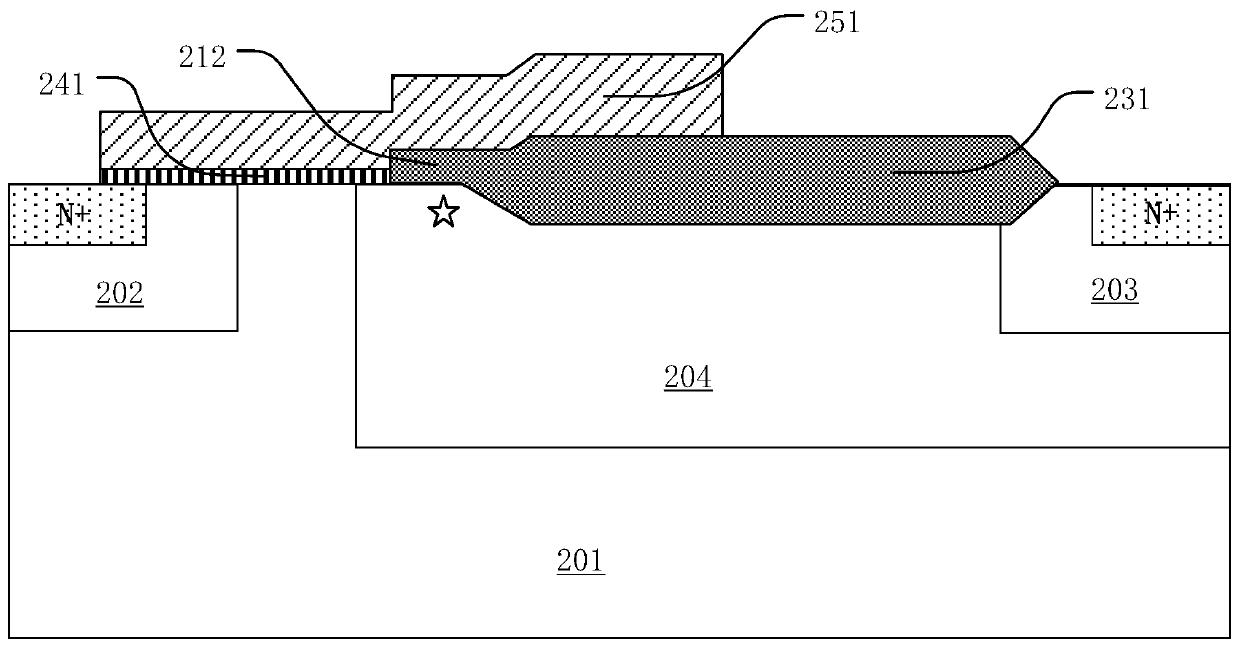

Laterally diffused transistor and manufacturing method thereof

PendingCN112002759AEnhanced leadImprove the protective effectSemiconductor/solid-state device manufacturingSemiconductor devicesEngineering physicsBody region

The invention discloses a lateral double-diffused transistor and a manufacturing method thereof. The lateral double-diffused transistor comprises a substrate, a drift region, a drain region, a body region, a source region, a body contact region and a gate structure, wherein the drift region is positioned on the upper surface of the substrate; the drain region is positioned at one end of the upperpart of the drift region; the body region is positioned at the other end; the source region and the body contact region are positioned at the upper part of the body region and are sequentially arranged from inside to outside; and the gate structure is located on the upper surface of the body region and extends to at least one part of the upper surface of the drift region, and the body contact region is arranged in the body region in a manner that the bottom is deeper than the bottom of the source region, so that the self-protection capability of the lateral diffusion transistor is enhanced.

Owner:JOULWATT TECH INC LTD

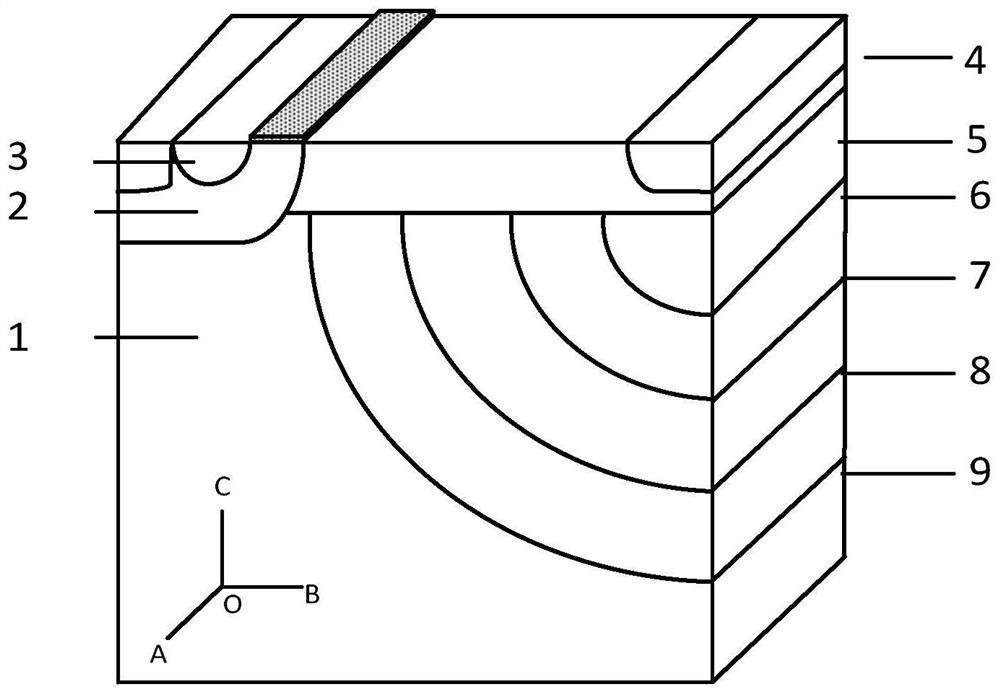

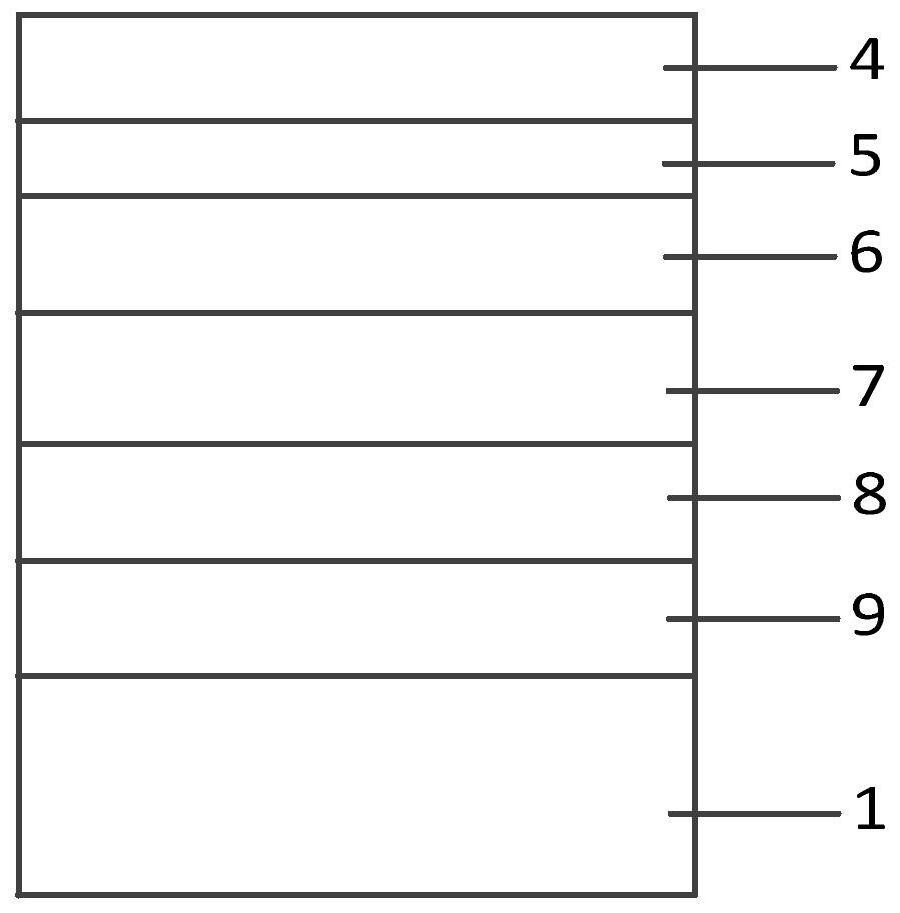

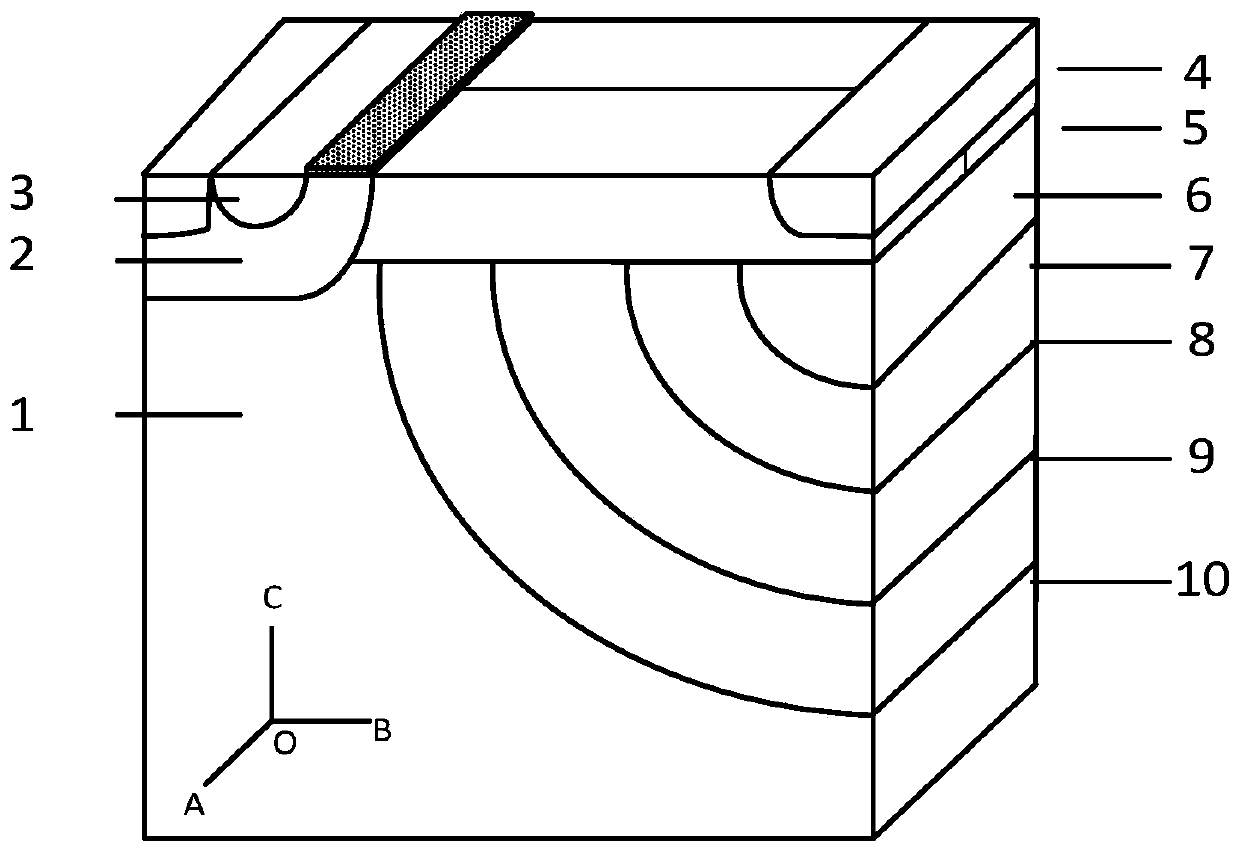

Lateral double-diffused transistor and manufacturing method thereof

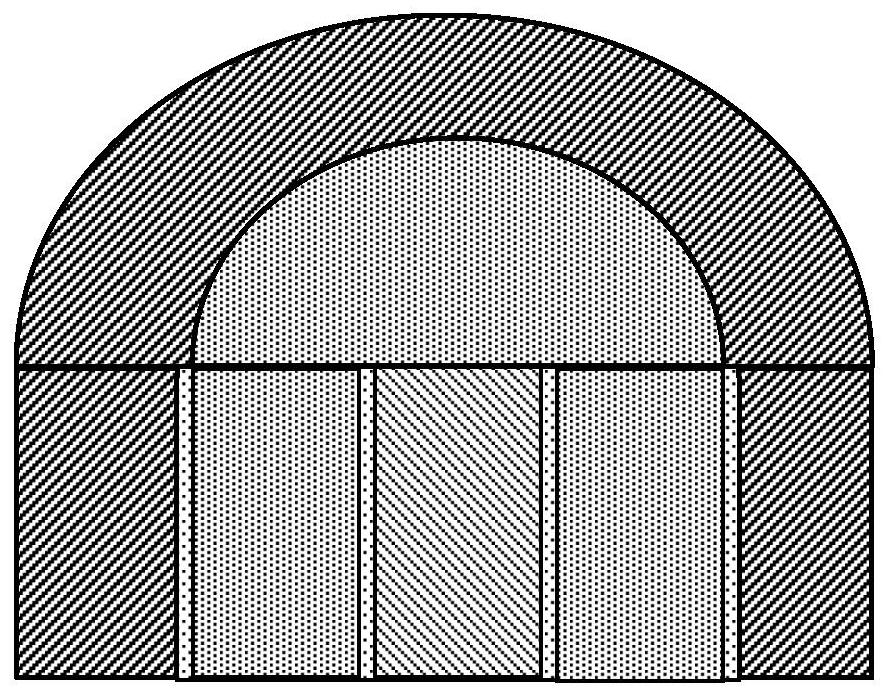

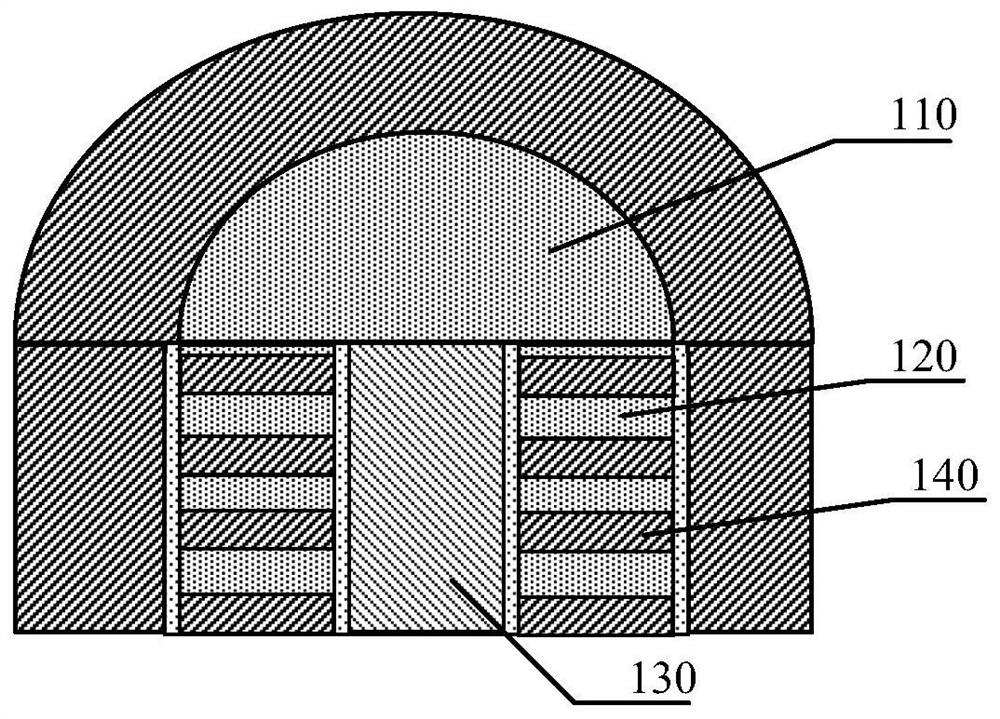

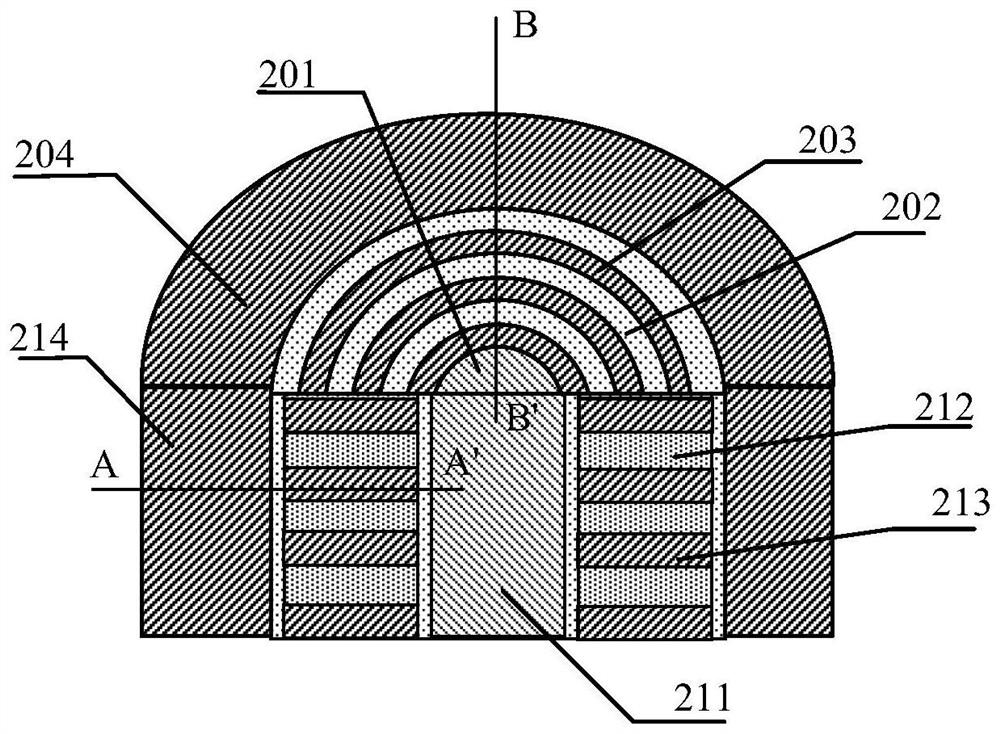

ActiveCN111710720AImprove breakdown voltageImprove effective utilizationSemiconductor/solid-state device manufacturingSemiconductor devicesDiffusion transistorSemiconductor

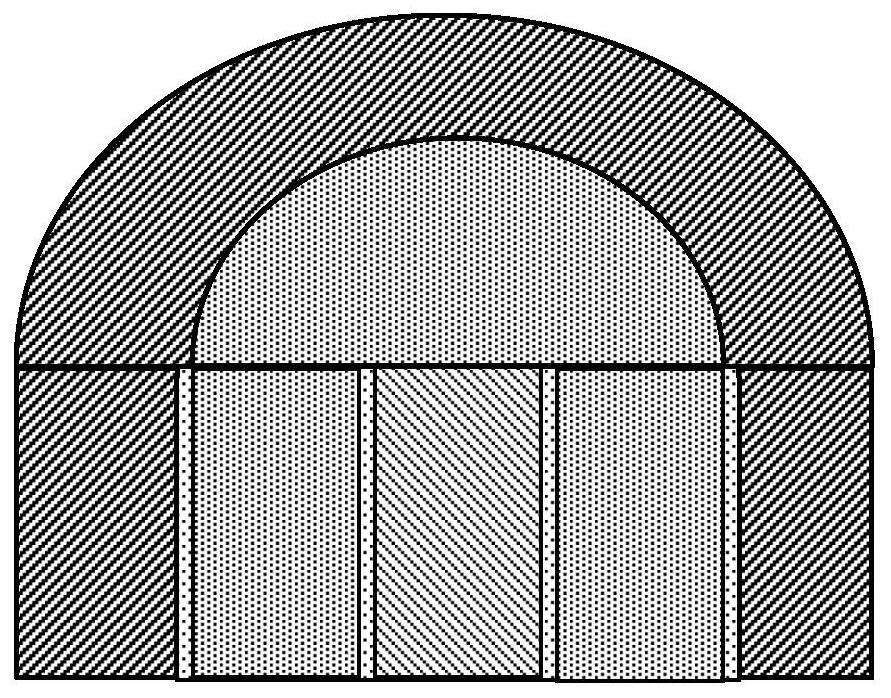

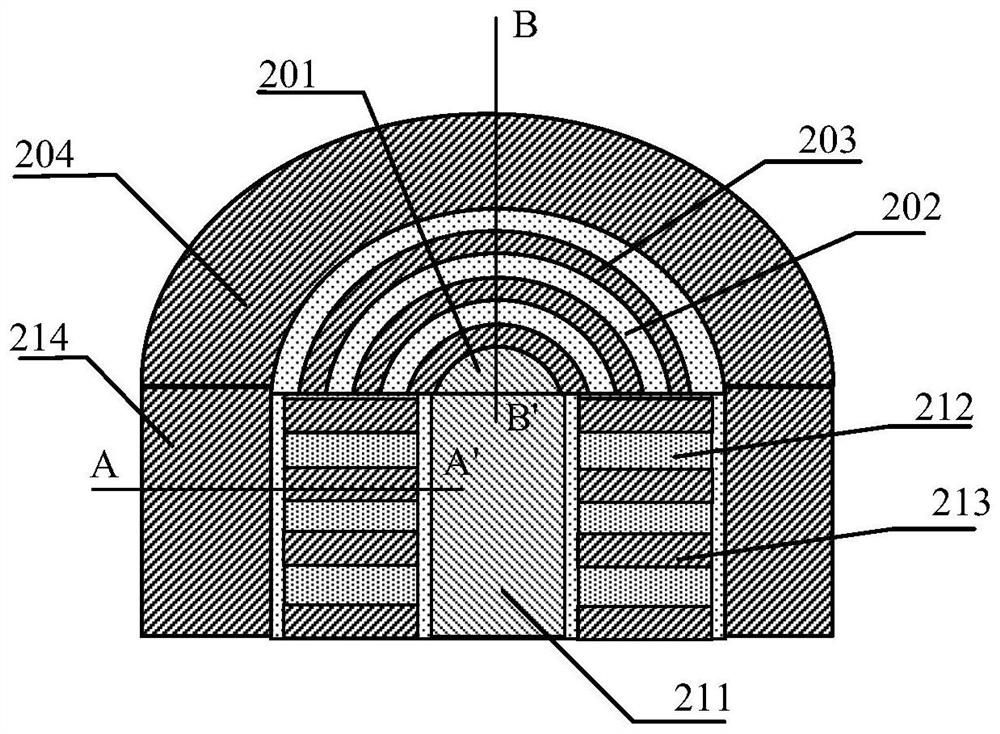

The invention relates to the technical field of semiconductors, and provides a lateral double-diffused transistor and a manufacturing method thereof. The lateral double-diffusion transistor comprisesa straight channel part and a bent channel part, wherein the straight channel part comprises a straight channel drain end, a straight channel drift region, a straight channel source gate and a substrate, the straight channel source gate and the substrate are arranged on the two sides of the straight channel drain end, the straight channel drift region is arranged among the straight channel drain end, the straight channel source gate and the substrate, the bent channel part comprises a bent channel drain end, a bent channel source gate, a substrate, a bent channel drift region positioned amongthe bent channel drain end, the bent channel source gate and the substrate, and a plurality of bent channel doping strips, the bent channel drift region, the bent channel source gate and the substrateare of a semi-circular ring structure concentric with the bent channel drain end and are sequentially arranged on the periphery of the bent channel drain end, the bent channel doping strips are arranged in the bent channel drift region at intervals, and the extending direction of the center line of at least one bent channel doping strip coincides with the radius of the semi-circular ring structure of the bent channel part. According to the invention, charge balance can be realized to improve the breakdown voltage, and the source-drain on-resistance is effectively reduced.

Owner:JOULWATT TECH INC LTD

Lateral double-diffused mosfet (LDMOS) transistor and a method of fabricating the same

Owner:VOLTERRA SEMICONDUCTOR

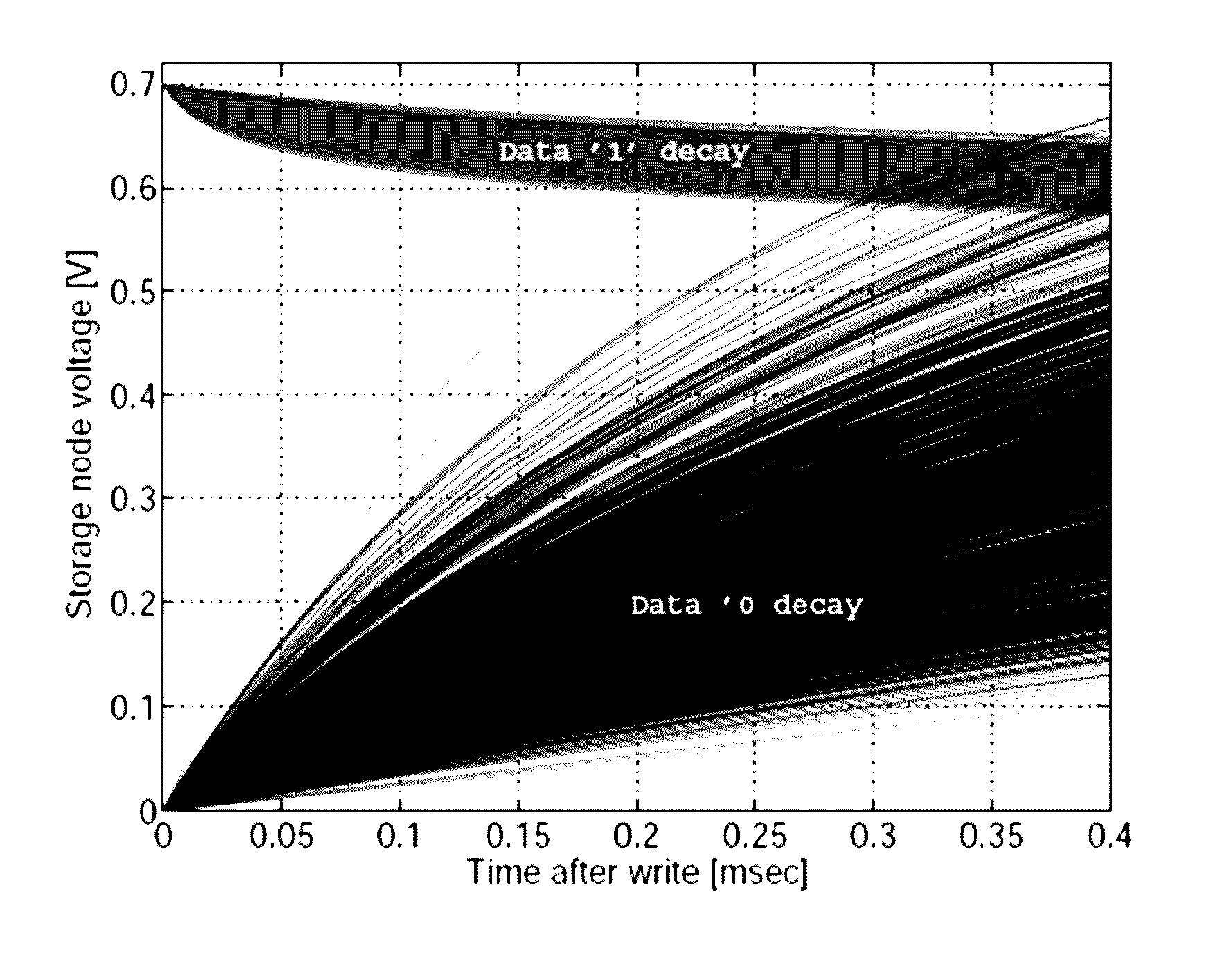

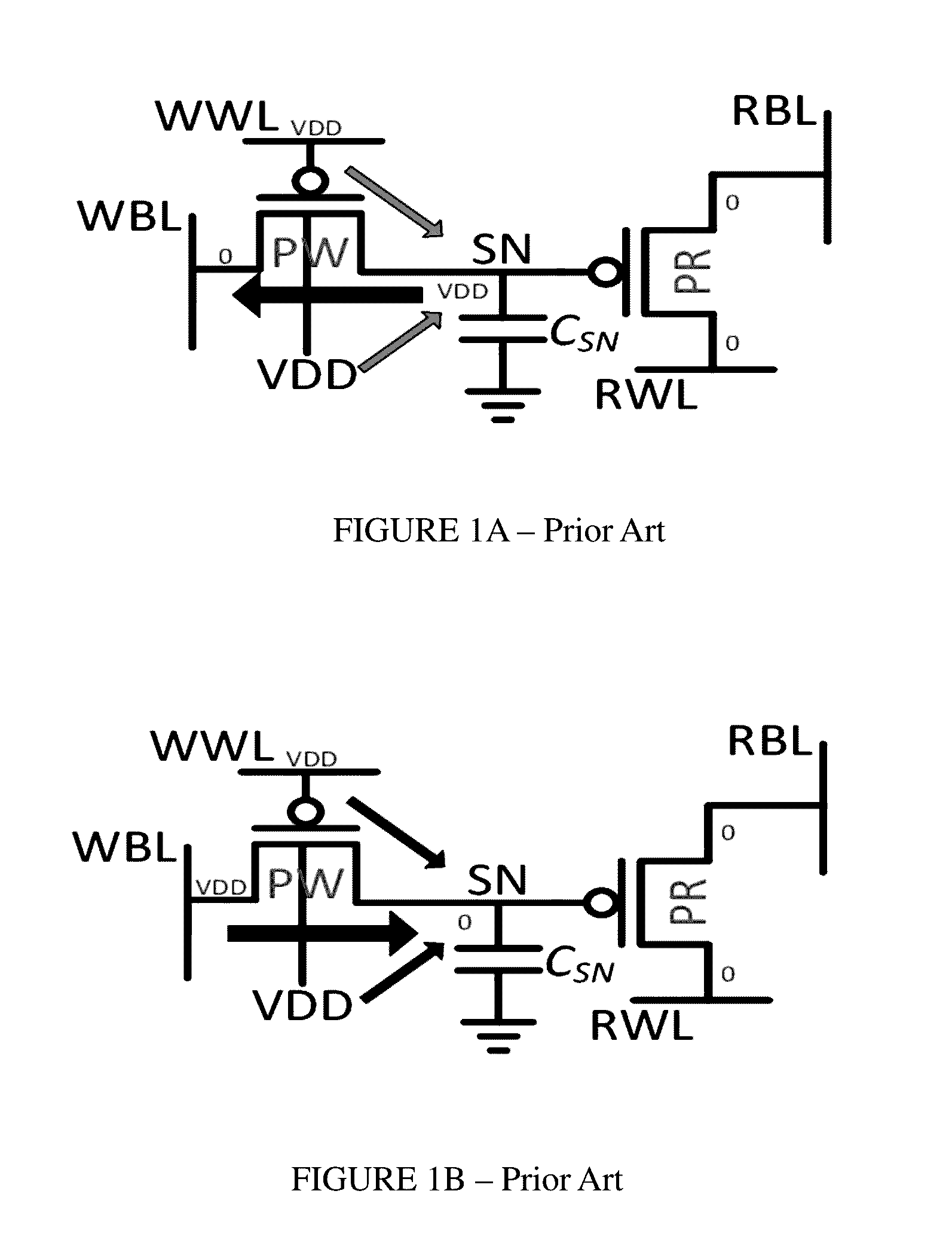

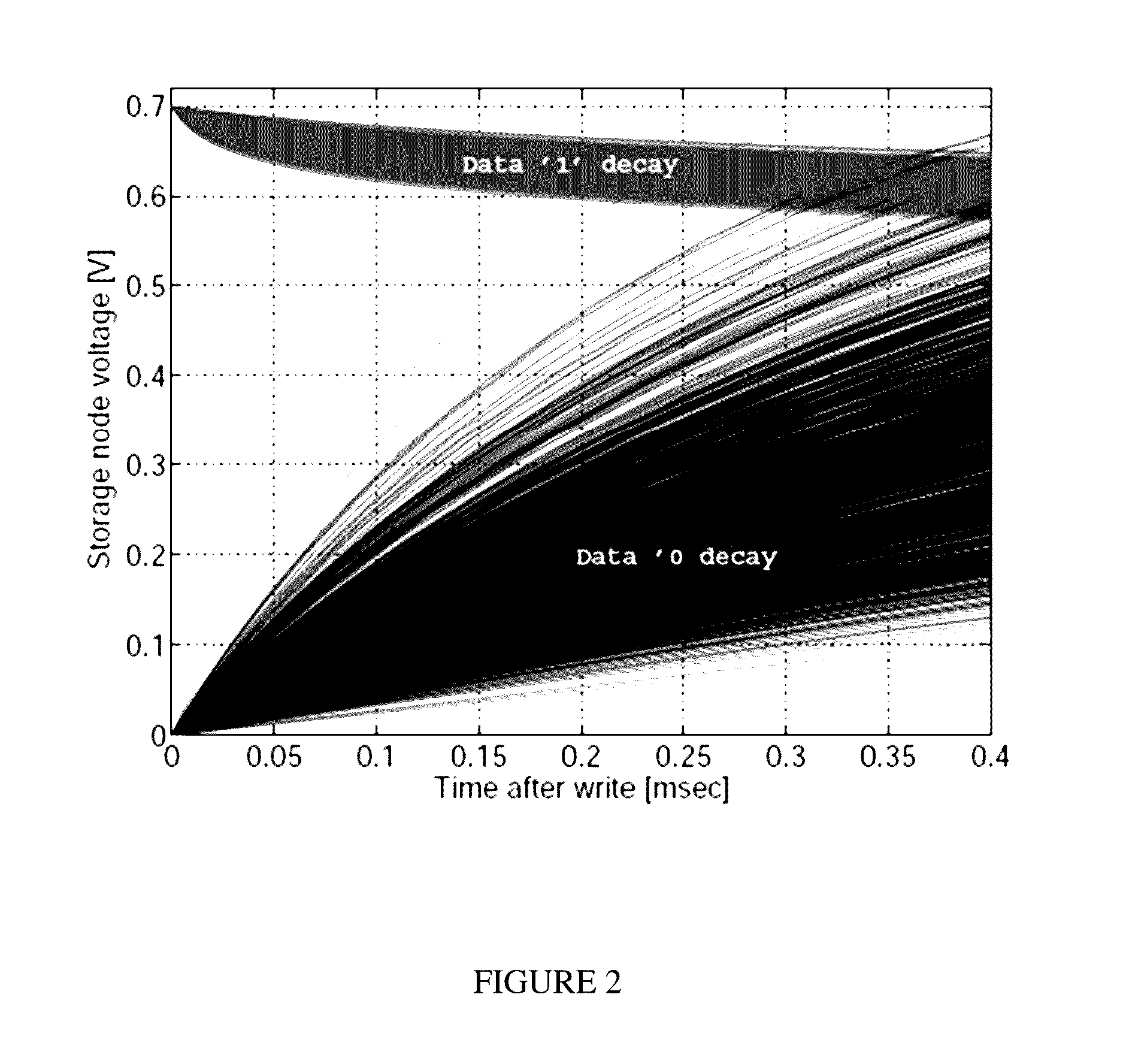

Transistor gain cell with feedback

A gain cell includes a write bit line input, a read bit line output, a write trigger input and a read trigger input. The gain cell also includes a write transistor, retention element and read transistor. Each of the transistors includes a respective first diffusion connection, gate connection and second diffusion connection. The write transistor first diffusion connection is connected to the write bit line input and the write transistor gate connection is connected to the write trigger input. The read transistor first diffusion connection being connected to the read bit line output and the second diffusion connection is connected to the read trigger input. The retention element buffers between write transistor and the read transistor during data retention. The retention element also connects or disconnects a write transistor diffusion connection to / from a constant voltage in accordance with a retained data level at the read transistor gate connection.

Owner:BAR ILAN UNIV

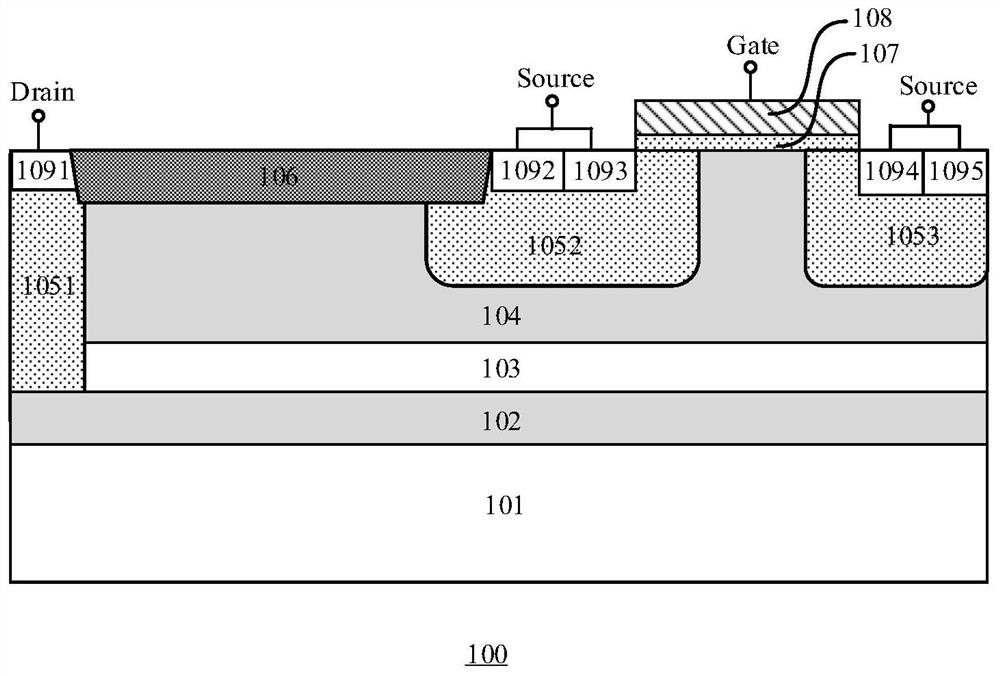

Lateral double-diffused transistor and manufacturing method thereof

ActiveCN112599599ALower resistanceImprove pressure resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesContact formationIsolation layer

The invention relates to the technical field of semiconductors, and provides a lateral double-diffused transistor and a manufacturing method thereof. The formed lateral double-diffused transistor comprises: a buried layer, a first epitaxial layer and a second epitaxial layer which are sequentially formed on a substrate, and a plurality of isolation layers transversely arranged between the first epitaxial layer and the second epitaxial layer at intervals; a first drift region located in the second epitaxial layer, high-voltage well regions located on the two sides of the first drift region, anda plurality of floating doped regions transversely distributed in the first drift region at intervals; a plurality of grooves formed in the upper surface of the second epitaxial layer at intervals; and a plurality of body regions transversely distributed between two adjacent grooves on the second epitaxial layer at intervals, wherein each body region is in contact with isolation layers corresponding to the upper position and the lower position through the floating doped regions with the same doping type to form a body region with a super junction structure. According to the invention, the effects of enhancing body region depletion and RESURF can be realized in the device so as to obtain higher withstand voltage and lower on resistance, and the current capability of the device can be enhanced.

Owner:JOULWATT TECH INC LTD

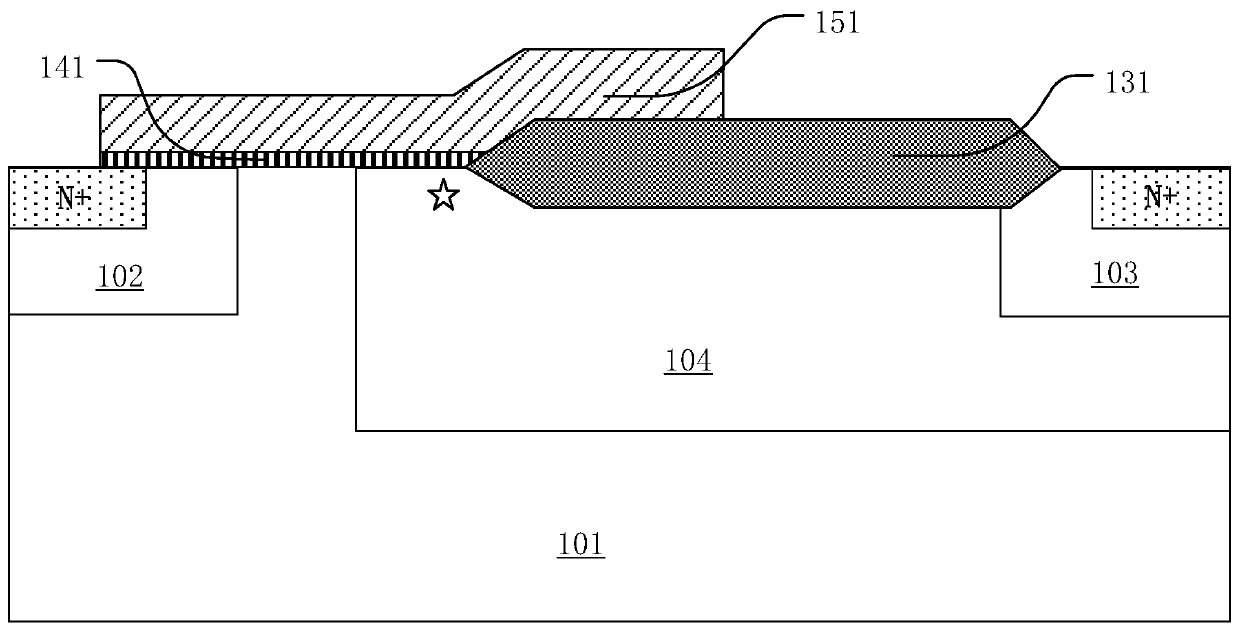

Lateral double-diffused transistor and manufacturing method of drift region of lateral double-diffused transistor

ActiveCN110729194AReduce processReduce manufacturing costFinal product manufactureSemiconductor/solid-state device manufacturingAnisotropic etchingDielectric layer

The invention discloses a manufacturing method of the drift region of a lateral double-diffused transistor. According to the method, an adhesive layer and a mask layer are designed; with the adhesivelayer coating a final dielectric layer adopted as a barrier, anisotropic etching is performed on a second dielectric layer, or second dielectric layer and a third dielectric layer, so that the middleregion of the drift region is opened, primary drift region injection is performed; with the adhesive layer or the third dielectric layer adopted as a barrier, isotropic etching is performed on the second dielectric layer, the adhesive layer or the adhesive layer and the third dielectric layer is / or removed, secondary drift region injection is performed with the second dielectric layer adopted as abarrier; between the two times of drift region injection, only one-time photoetching is needed, so that a linear gradient drift region can be formed. With the manufacturing method adopted, technological process and manufacturing cost are reduced, and requirements for higher turn-off breakdown voltage and lower conduction impedance can be met.

Owner:JOULWATT TECH INC LTD

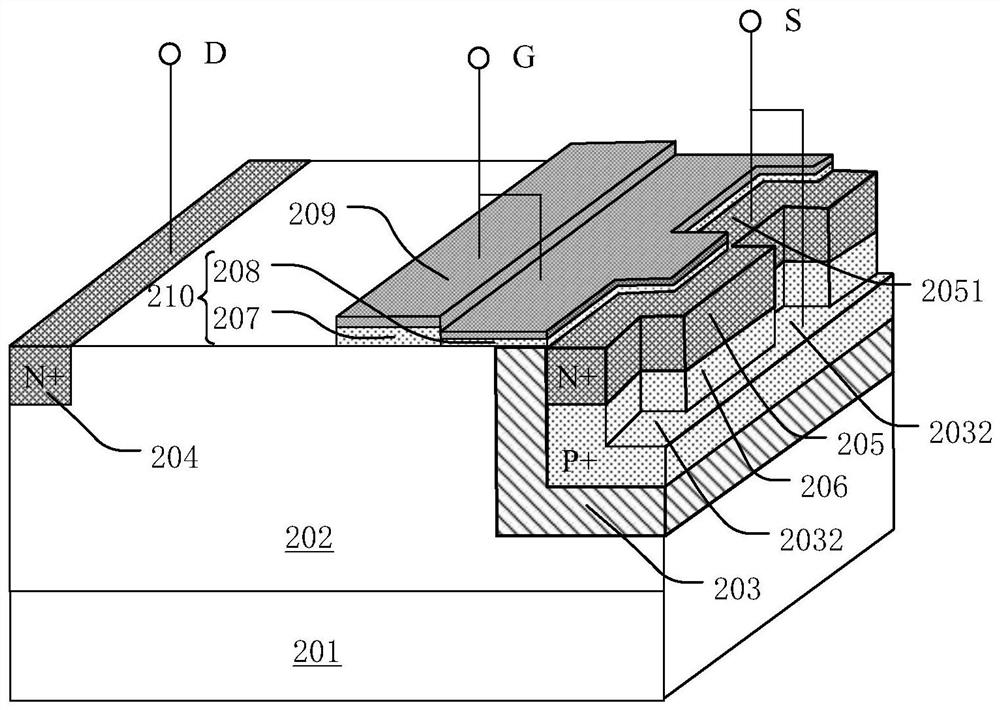

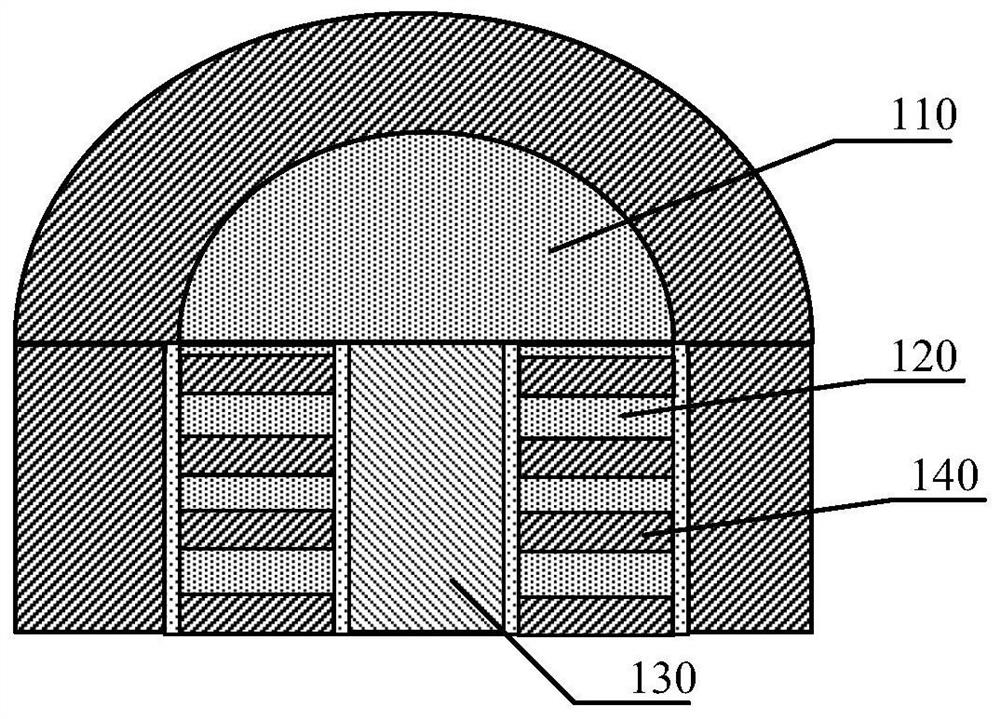

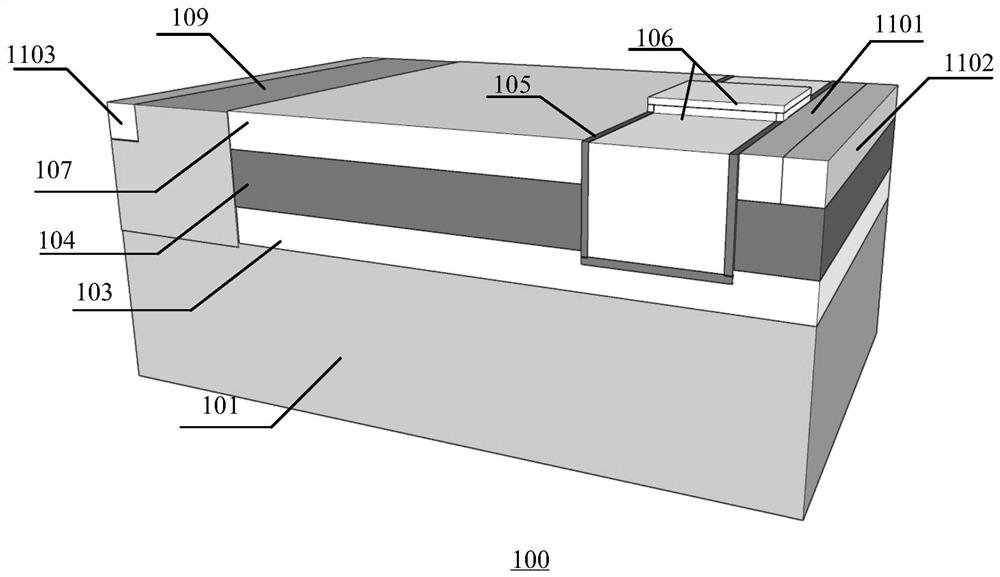

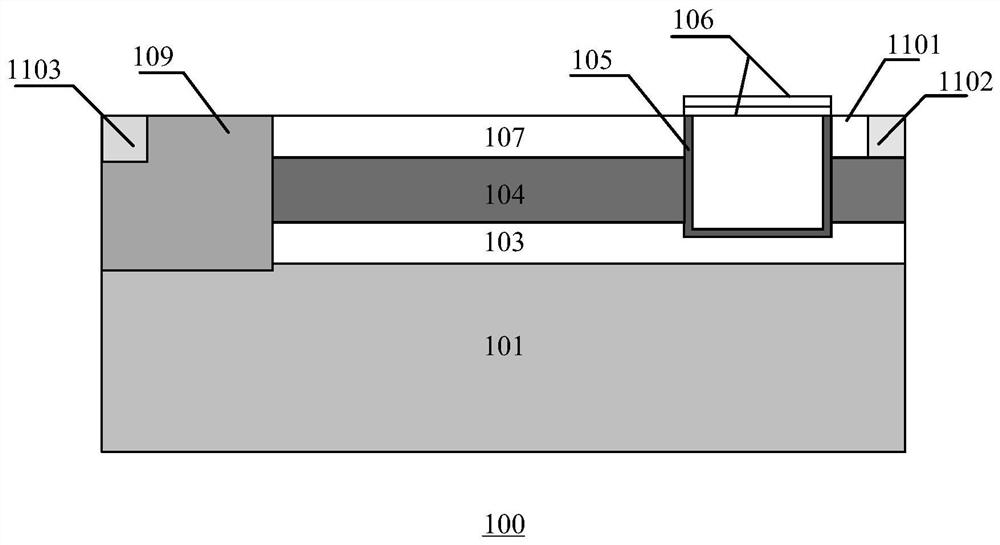

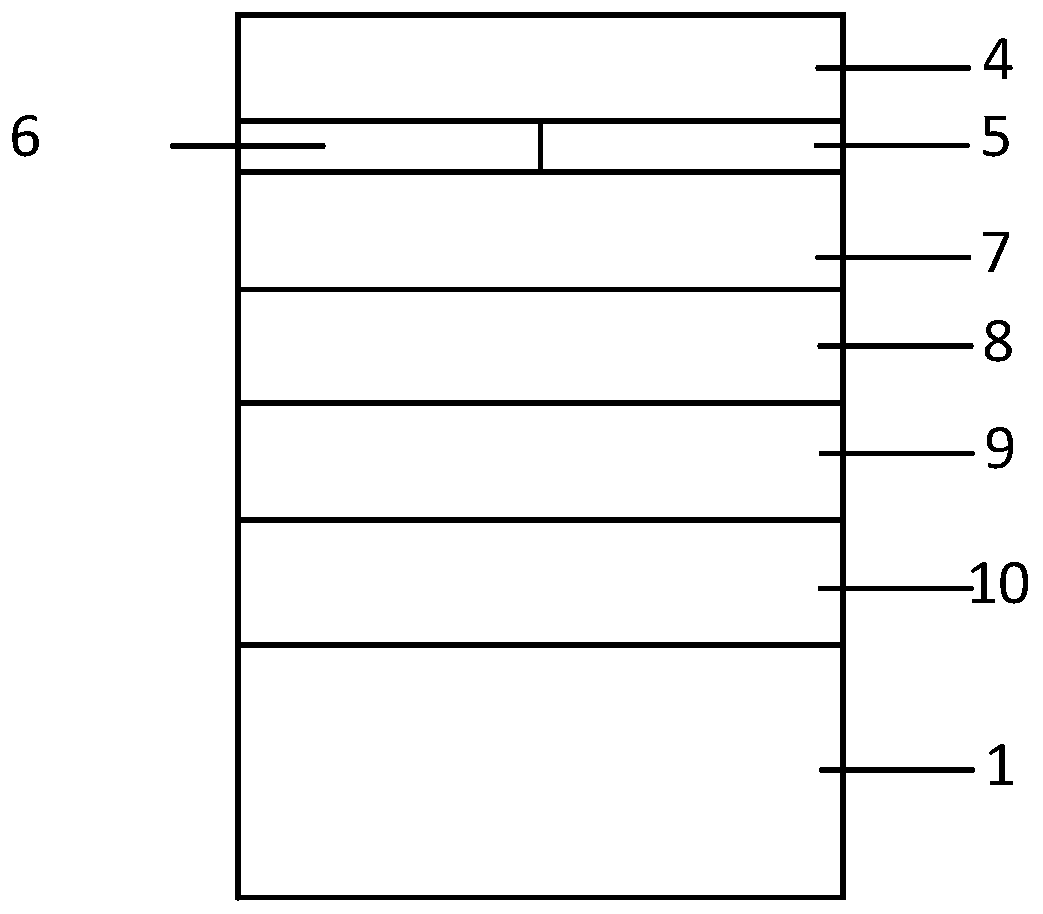

Vertical double-diffused transistor and manufacturing method thereof

PendingCN112599600AReduce widthImprove integration densitySemiconductor/solid-state device manufacturingSemiconductor devicesBody regionDiffusion transistor

The invention relates to the technical field of semiconductors, and provides a vertical double-diffused transistor and a manufacturing method thereof. A formed VDMOS device is of an axial symmetry structure with the central axis of a first trench as the axis of symmetry; the VDMOS device forms metal contact in a drain region through the first trench penetrating to the upper surface of a first buried layer so as to lead out a drain electrode; and the led-out drain electrode is positioned on the top surface, far away from the substrate, of the high-voltage VDMOS device. Therefore, the VDMOS device can be integrated in a BCD process, driving capability with low on resistance and high current is realized, the drain electrode does not need to be led out from the bottom of a device structure, and the integration density of the device is improved. Meanwhile, at least two buried layer structures in longitudinal gradient distribution are used for replacing a drift region to form a PN junction with a body region, and the PN junction is close to a parallel plane junction by utilizing a drain electrode communicating to an injection region in the first buried layer when the device is reverselybroken down, so the withstand voltage of the VDMOS device is effectively improved.

Owner:JOULWATT TECH INC LTD

Lateral double diffused transistor and method of making the same

ActiveCN111710720BImprove breakdown voltageImprove effective utilizationSemiconductor/solid-state device manufacturingSemiconductor devicesEngineeringCondensed matter physics

The invention relates to the technical field of semiconductors, and provides a lateral double-diffused transistor and a manufacturing method thereof. The lateral double-diffused transistor includes a straight part and a curved part, and the straight part includes a straight drain end, a straight drift region, a straight source gate and a substrate. , the straight source gate and the substrate are arranged on both sides of the straight drain end, the straight drift region is arranged between the straight drain end, the straight source gate and the substrate; the curved part includes the curved drain end, the curved source gate and the lining The bottom and the curved drift region located between the curved drain end and the curved source gate and the substrate, and a plurality of curved doping strips, wherein the curved drift region, the curved source gate and the substrate are connected to the curved source gate and the substrate. The concentric semi-circular ring structure of the channel drain end is arranged on the periphery of the curved channel drain end in turn, a plurality of curved doping strips are arranged in the curved drift region at intervals, and the extension direction of the center line of at least one curved doping strip is the same as that of the curved channel. The radii of the semicircular structures of the track parts are coincident. Thereby, charge balance can be achieved to improve the breakdown voltage and effectively reduce the source-drain on-resistance.

Owner:JOULWATT TECH INC LTD

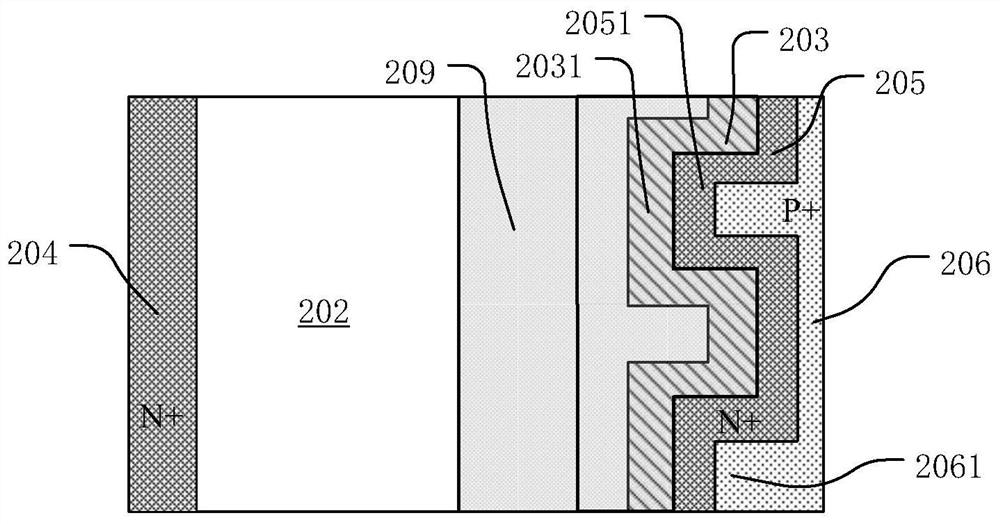

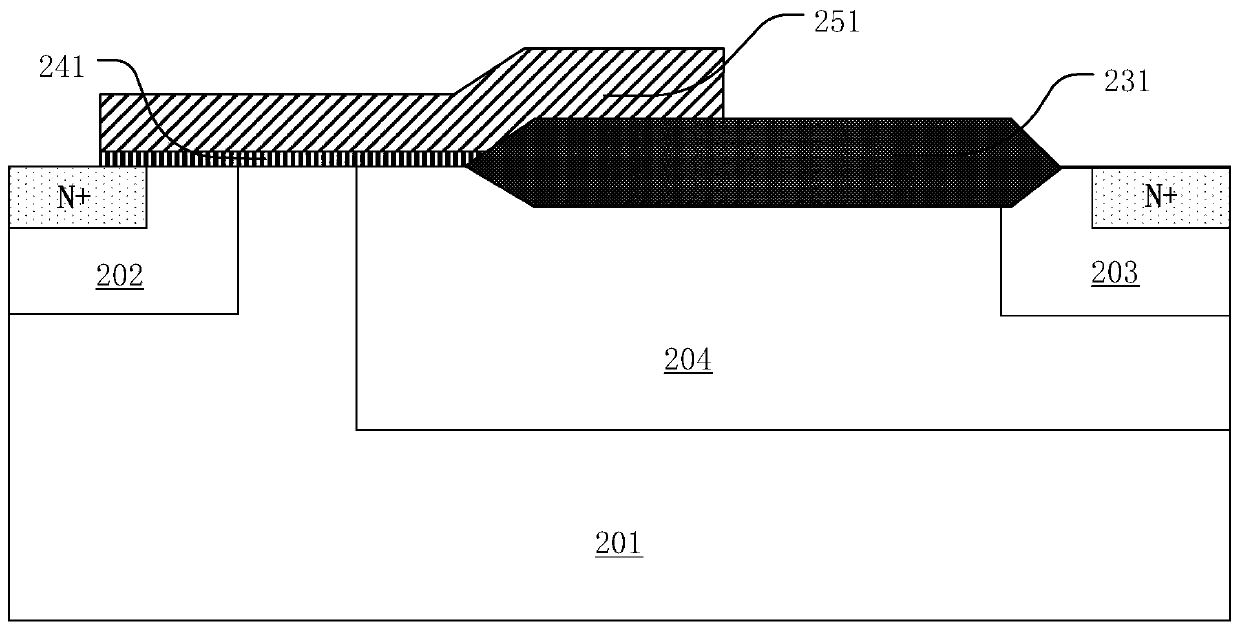

Lateral double-diffused transistor and manufacturing method thereof

PendingCN112909091AIncrease the areaImprove pressure resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesLDMOSEngineering

The invention relates to the technical field of semiconductors, and provides a lateral double-diffused transistor and a manufacturing method thereof. The LDMOS device comprises a first epitaxial layer and a second epitaxial layer which are arranged on a substrate; the two trench gate structures are arranged in the second epitaxy along the first direction and are distributed at an interval; a first drift region and a drain end region on one side of the trench gate structure on the second epitaxial layer are defined along a second direction, and a source end region on the other side of the trench gate structure is defined; a plane gate structure is arranged on the second epitaxial layer between the two trench gate structures along the first direction; a drain injection region is arranged in the drain end region; and a source injection region is arranged in the source end region; and the metal contacts on the drain injection region, the source injection region and the gate structure are respectively and correspondingly led out to a drain electrode, a source electrode and a gate electrode. Therefore, the withstand voltage of the LDMOS device can be effectively improved, and the on-resistance of the LDMOS device is reduced.

Owner:JOULWATT TECH INC LTD

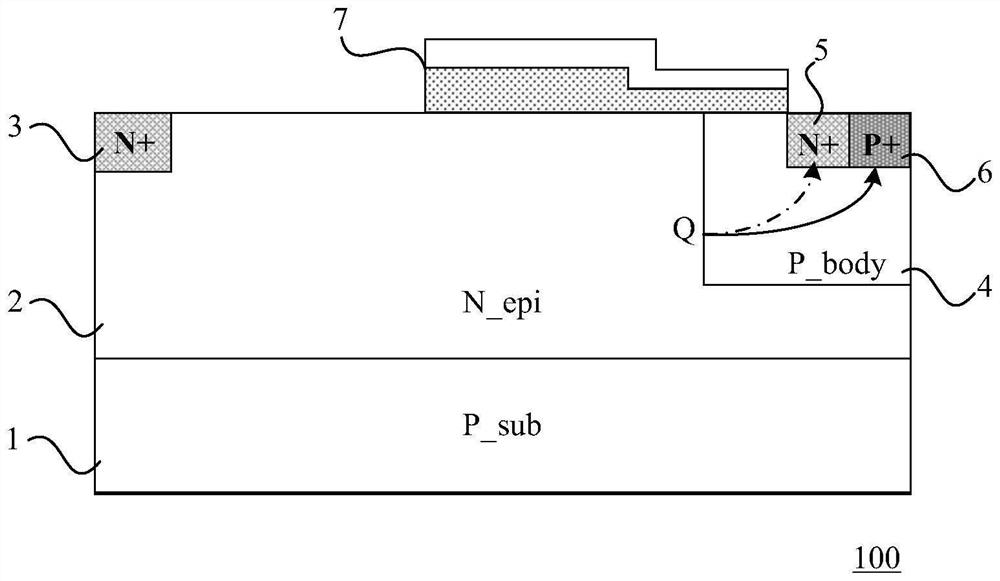

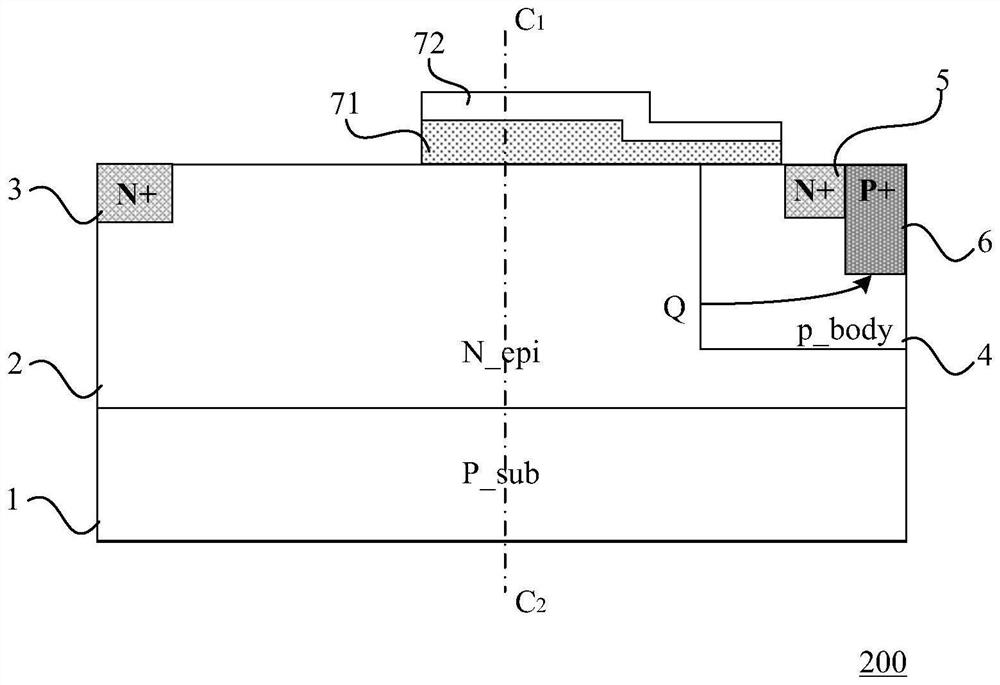

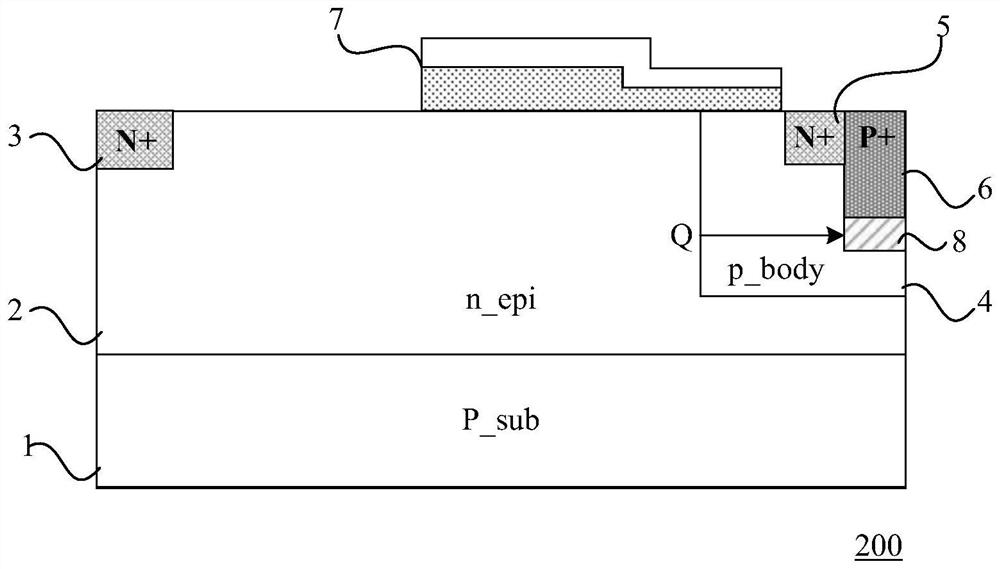

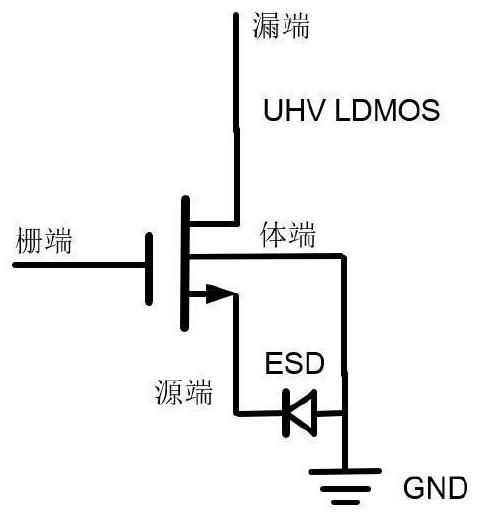

A gate-controlled bipolar-field-effect compound element semiconductor-based lateral double-diffused metal oxide semiconductor transistor

ActiveCN110212032BAvoid secondary breakdownLower breakdown voltageSemiconductor devicesSemiconductor materialsParasitic bipolar transistor

The invention discloses a gate-controlled bipolar-field effect compound element semiconductor-based lateral double-diffused metal oxide semiconductor transistor. It is isolated from the source and electrically connected to the gate to meet: when the gate is connected to the voltage, the voltage obtained by the base region makes the parasitic bipolar transistor of the device turn on, replacing the base region and the source region in the traditional elemental semiconductor lateral double-diffusion transistor Short-circuited electrode connection. Compared with the traditional device, the invention greatly increases the on-current of the device and reduces the on-resistance of the device while ensuring the same breakdown voltage of the device.

Owner:XIDIAN UNIV

A wide-bandgap semiconductor lateral double-diffused transistor with multi-ring electric field modulation substrate

ActiveCN107808902BExtended longitudinal space charge regionImprove breakdown voltageSemiconductor/solid-state device manufacturingSemiconductor devicesElectric field modulationField-effect transistor

The invention discloses a wide-bandgap semiconductor lateral double-diffusion transistor with a multi-ring electric field modulation substrate. The substrate under the drift region in this structure is a charge compensation polyring structure. The multi-ring charge compensation of the substrate can expand the vertical space charge region of the lateral double-diffused metal oxide semiconductor field effect transistor. The modulation effect simultaneously modulates the surface transverse electric field and the body longitudinal electric field, so that the surface transverse electric field and the body longitudinal electric field are simultaneously optimized. This structure not only breaks through the breakdown voltage saturation problem of the lateral double-diffused transistor due to the limited vertical withstand voltage, but also achieves the simultaneous optimization of the surface lateral electric field and the internal vertical electric field, which can greatly increase the breakdown voltage of the device.

Owner:XIDIAN UNIV

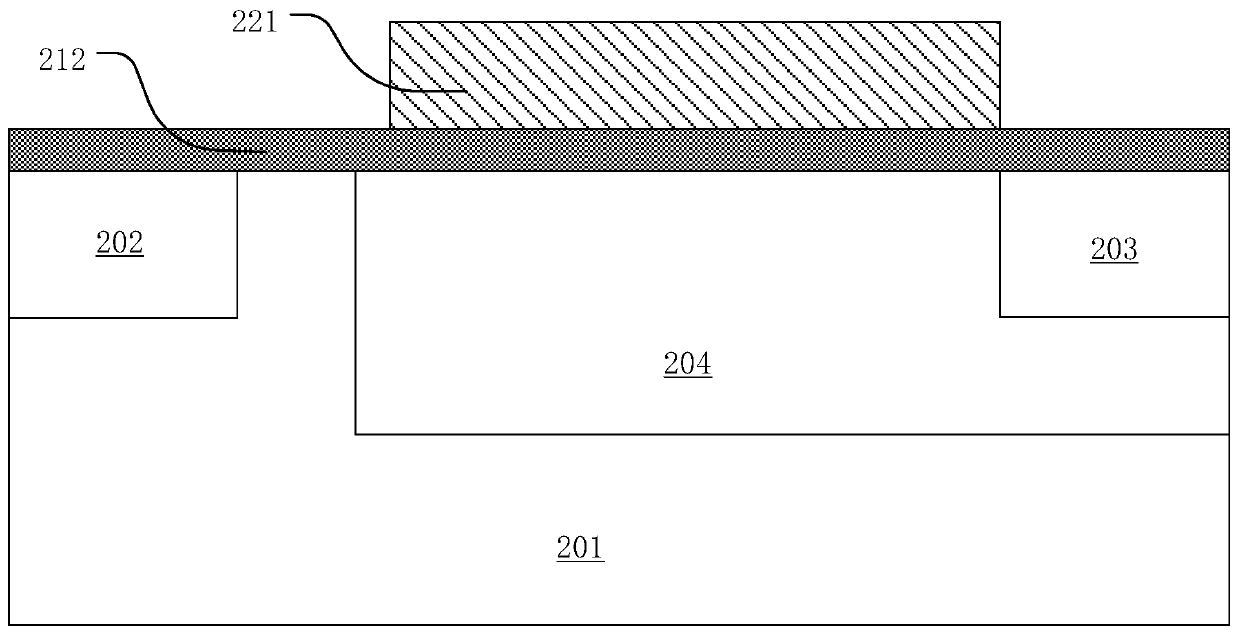

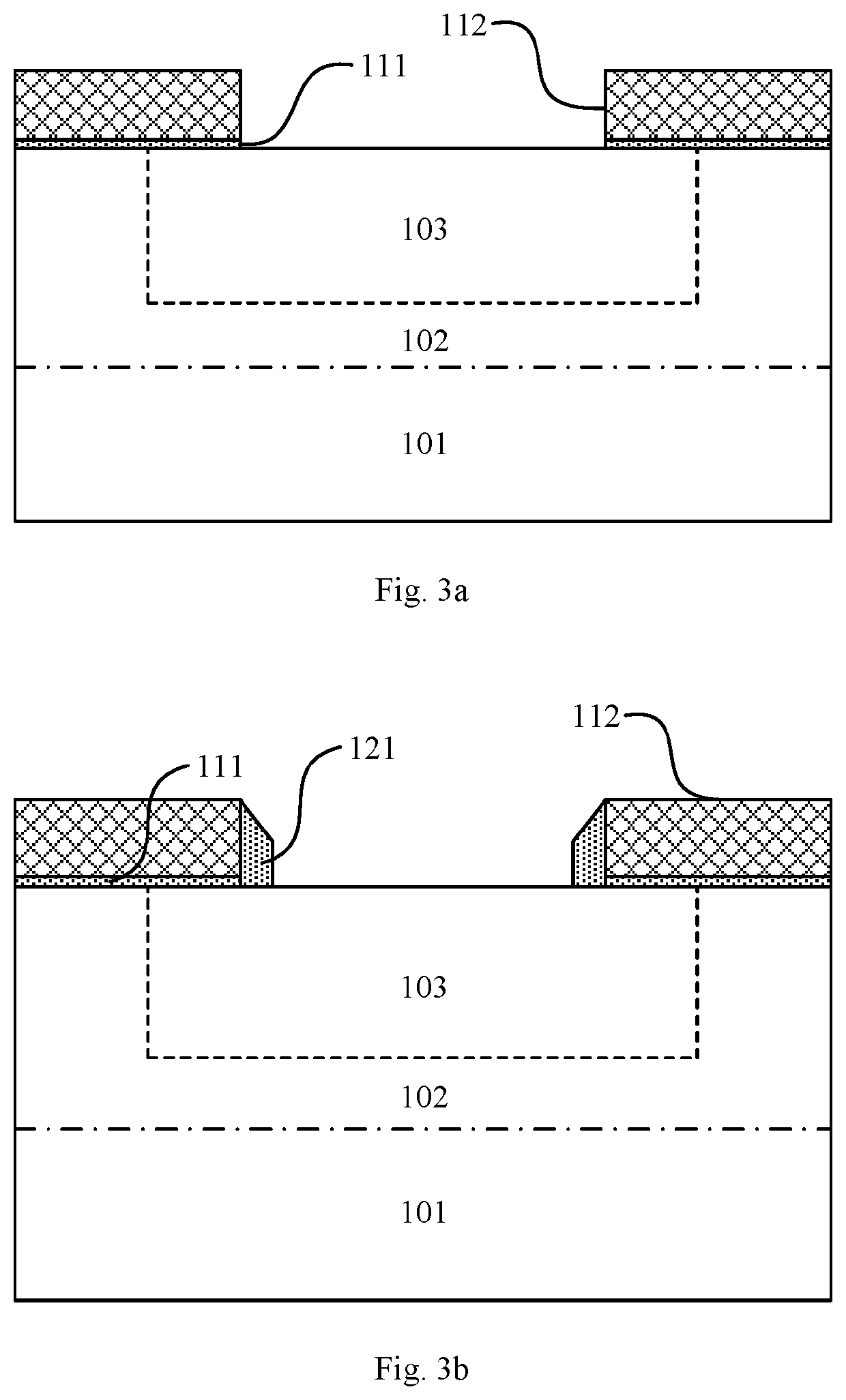

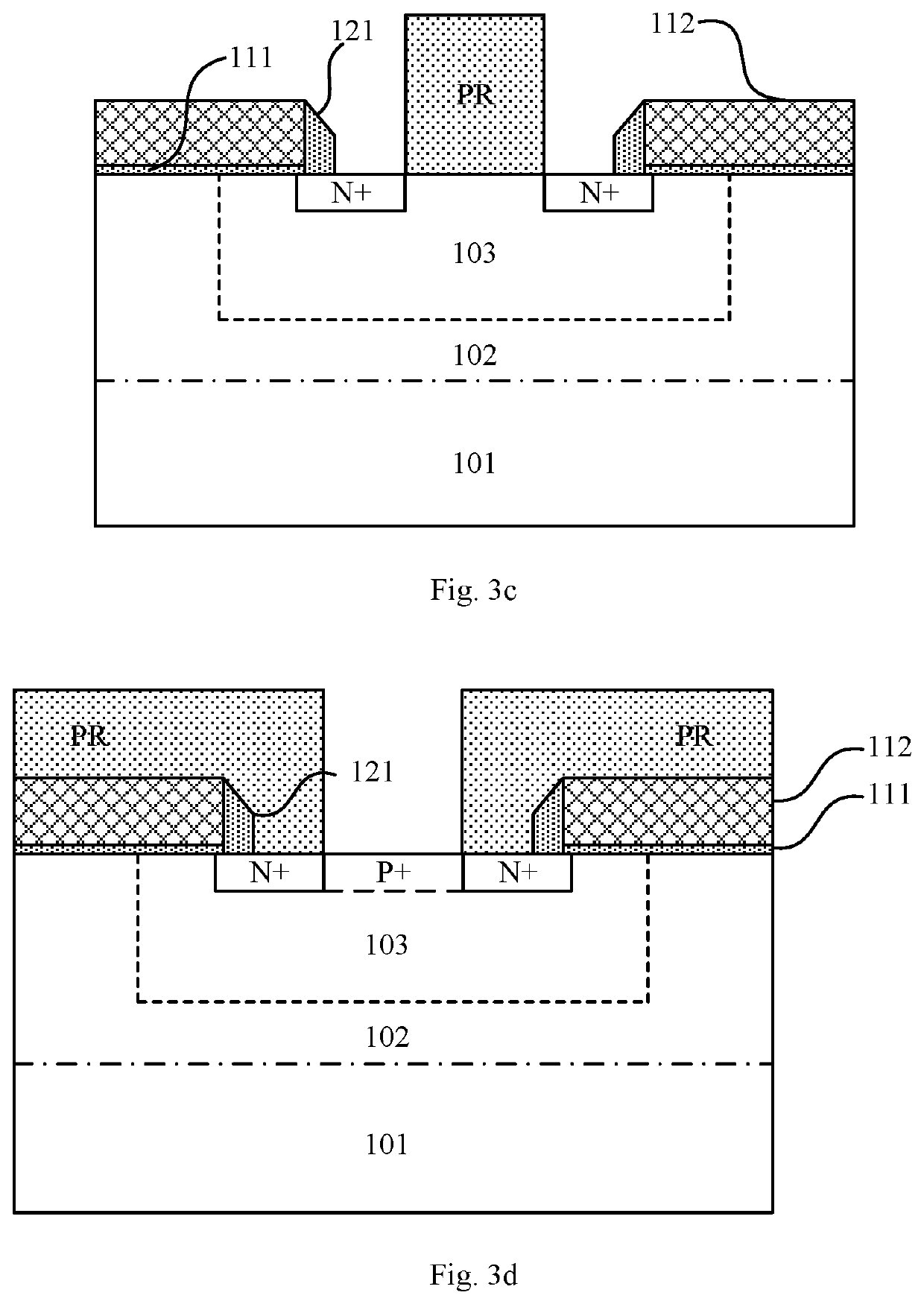

Manufacture method of lateral double-diffused transistor

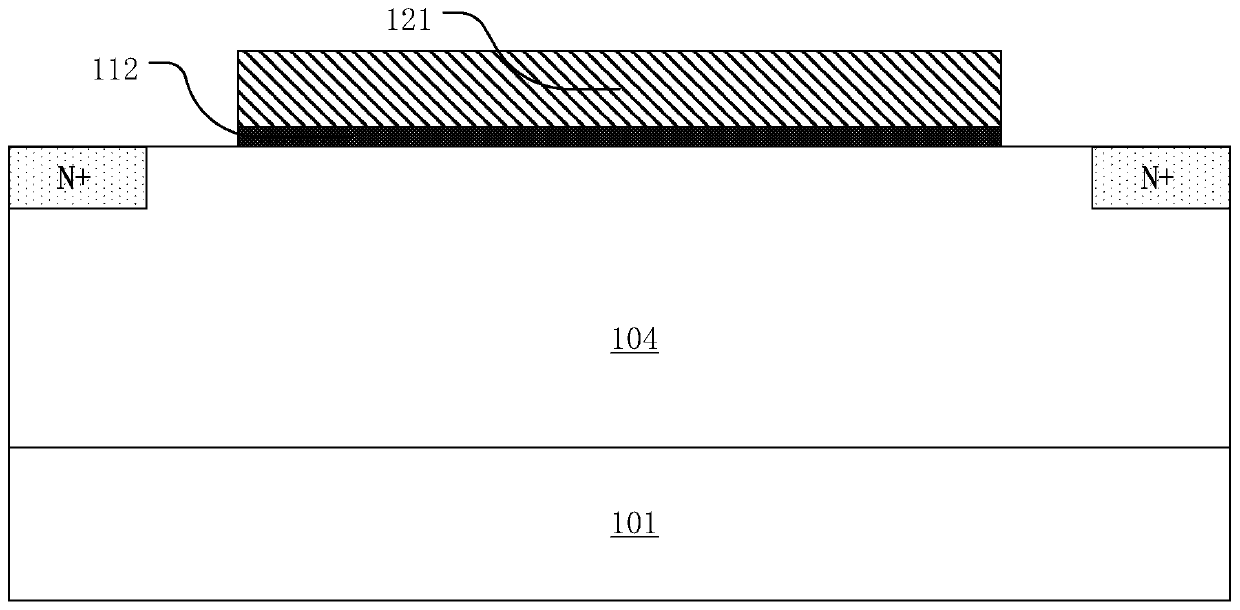

ActiveUS11495675B2More conciseSave materialSemiconductor/solid-state device manufacturingSemiconductor devicesLDMOSElectrical conductor

The present disclosure provides a manufacture method of an LDMOS. The manufacture method includes: forming a drift region in a substrate; forming a gate structure on the substrate, the gate structure defining a source region and a drain region which are separated from each other, and the gate structure including a gate oxide layer and a gate conductor layer which are successively stacked on the substrate; forming a first doped region in the source region, wherein the first doped region is surrounded by the drift region; forming a first barrier layer with a first opening on the source region and in connect with sidewall of the gate structure; forming a first implantation region in the source region through self-aligned implantation on the basis of the first opening of the first barrier layer; and forming a second implantation region and a third implantation region respectively.

Owner:JOULWATT TECH INC LTD

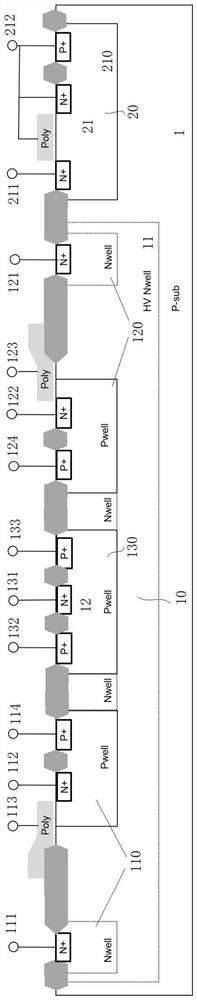

A lateral double diffused transistor

ActiveCN113345964BAvoid non-uniform openingImprove the ability to prevent ESDSolid-state devicesDiodeEngineeringCommon drain

Owner:JOULWATT TECH INC LTD

Lateral double-diffused transistor and manufacturing method thereof

ActiveCN111710722AExpand the effective lead-out areaIncrease channel densitySemiconductor/solid-state device manufacturingSemiconductor devicesChannel densityDielectric layer

The invention discloses a lateral double-diffused transistor and a manufacturing method thereof. The lateral double-diffused transistor comprises: a substrate; a drift region located at the top of thesubstrate; a drain region and a body region respectively positioned on two opposite sides of the top of the drift region; a source region and a body contact region positioned in the body region and adjacent to each other; and a dielectric layer and a field plate layer sequentially stacked on the surface of the drift region, wherein the body region partially extends towards the direction of the drain region to form at least one body region extending region, the body region extending region and the drift region adjacent to the body region extending region are distributed in an interdigitated manner, the body contact region is located on the side, away from the drain region, in the body region, and the body contact region partially extends in the direction where the drain region is located to form a body contact region extending region. According to the lateral double-diffused transistor, the interdigital body region and the sawtooth-shaped body contact region are arranged, so that the channel density of the device is increased, the on resistance is reduced, the body region resistance can be effectively reduced, and parasitic NPN false opening is prevented.

Owner:JOULWATT TECH INC LTD

An elemental semiconductor lateral superjunction double-diffused transistor with a multi-ring electric field modulating substrate

ActiveCN107681003BEliminate auxiliary exhaustion problemsExtended longitudinal space charge regionSemiconductor devicesElectric field modulationParticle physics

Owner:成都稳海半导体有限公司

Creating Anisotropic Diffused Junctions in Field Effect Transistor Devices

InactiveCN103201832BSolid-state devicesSemiconductor/solid-state device manufacturingDopantEngineering

A method for forming a transistor device comprising implanting a diffusion-inhibiting species in a semiconductor-on-insulator substrate, the semiconductor-on-insulator substrate comprising a bulk substrate, a buried insulator layer, and a semiconductor-on-insulator layer, the semiconductor-on-insulator layer having one or more gate structures formed thereon such that a diffusion inhibiting species is disposed in a portion of the semiconductor-on-insulator layer corresponding to the channel region, and in a portion of the buried insulator layer associated with the source and In the part corresponding to the drain region. Transistor dopant species are introduced in the source and drain regions. The anneal is performed to diffuse the transistor dopant species in a substantially vertical direction while substantially preventing lateral diffusion of the transistor dopant species into the channel region.

Owner:GLOBALFOUNDRIES INC

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com