Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

1761 results about "Axis of symmetry" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

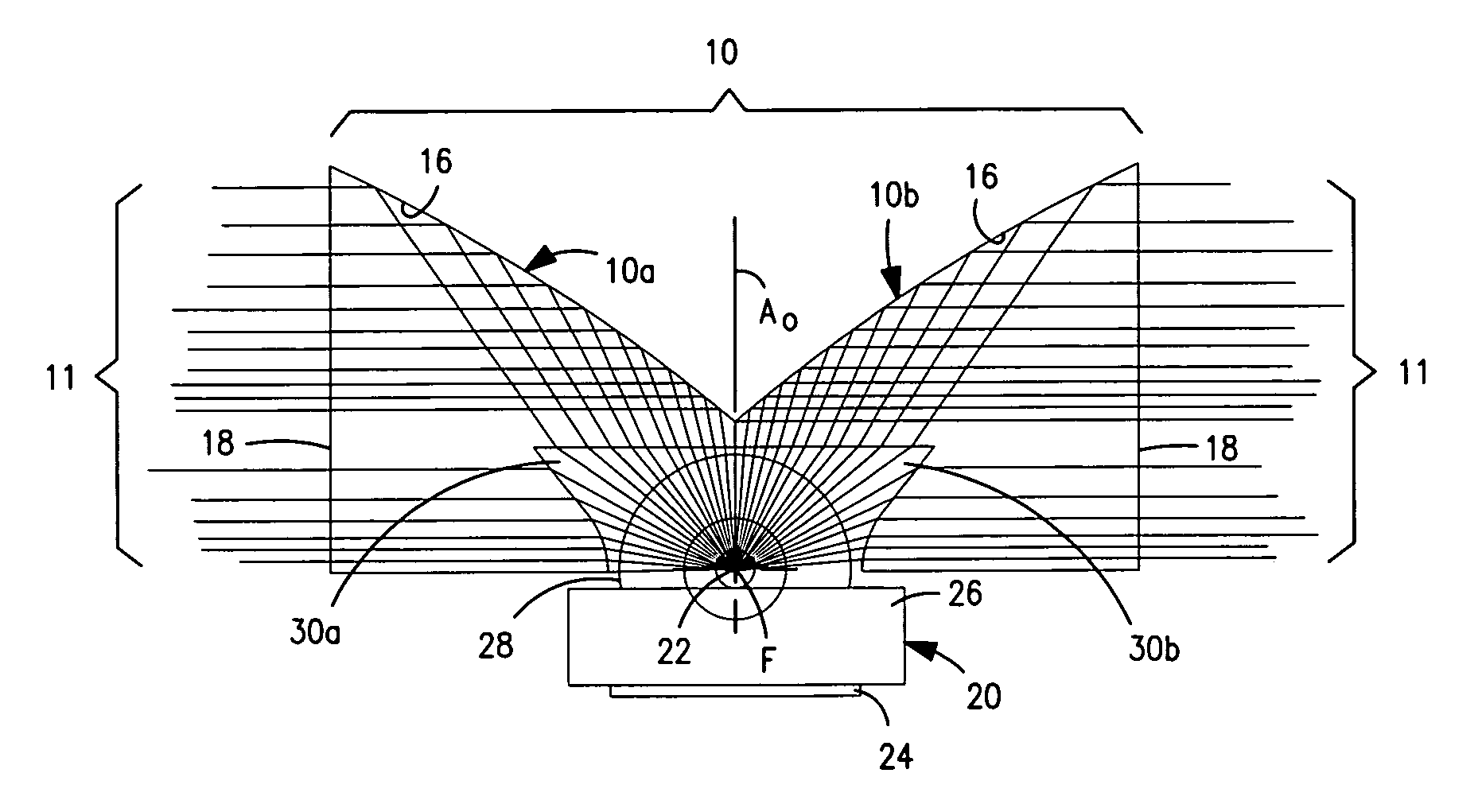

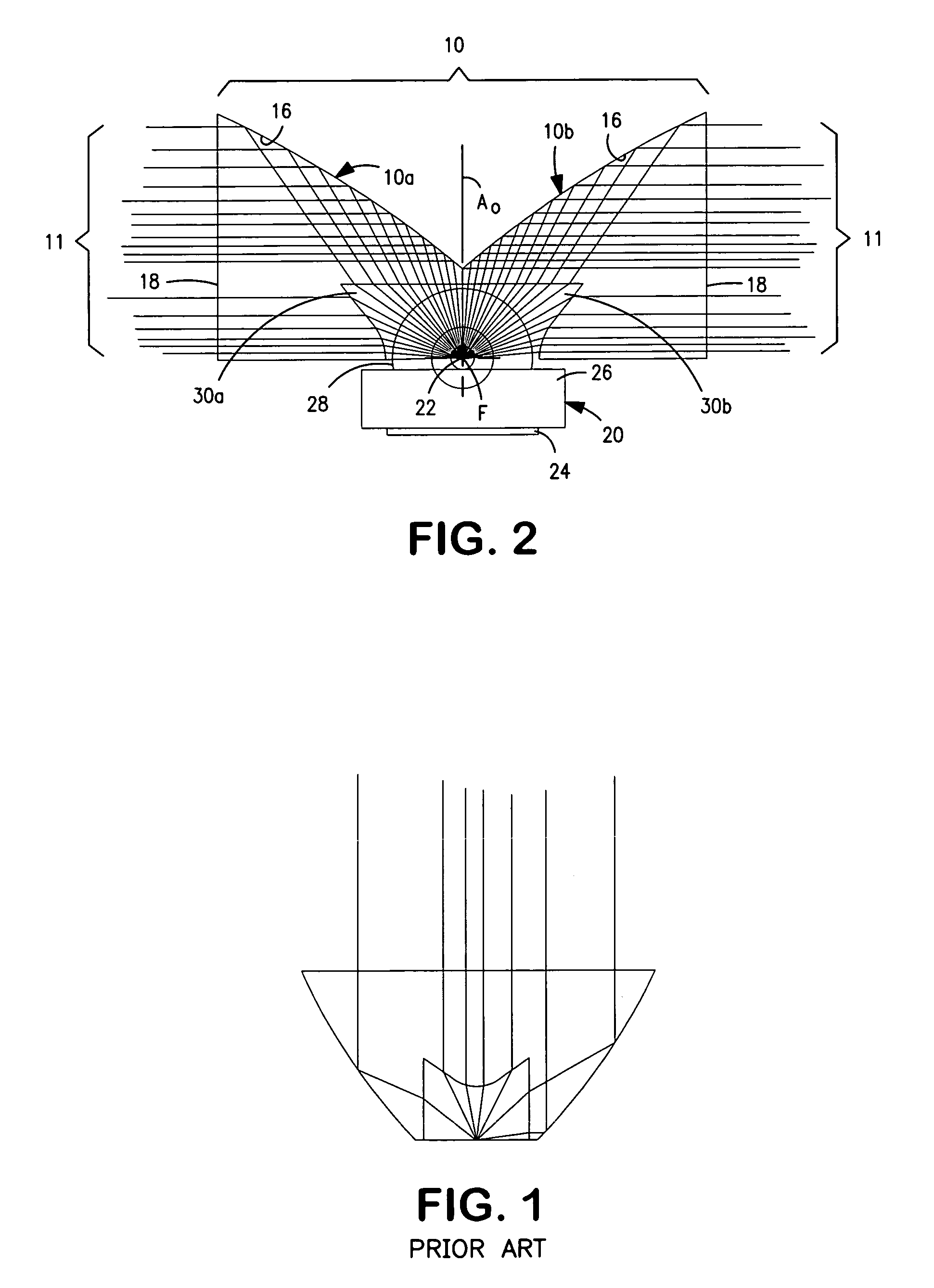

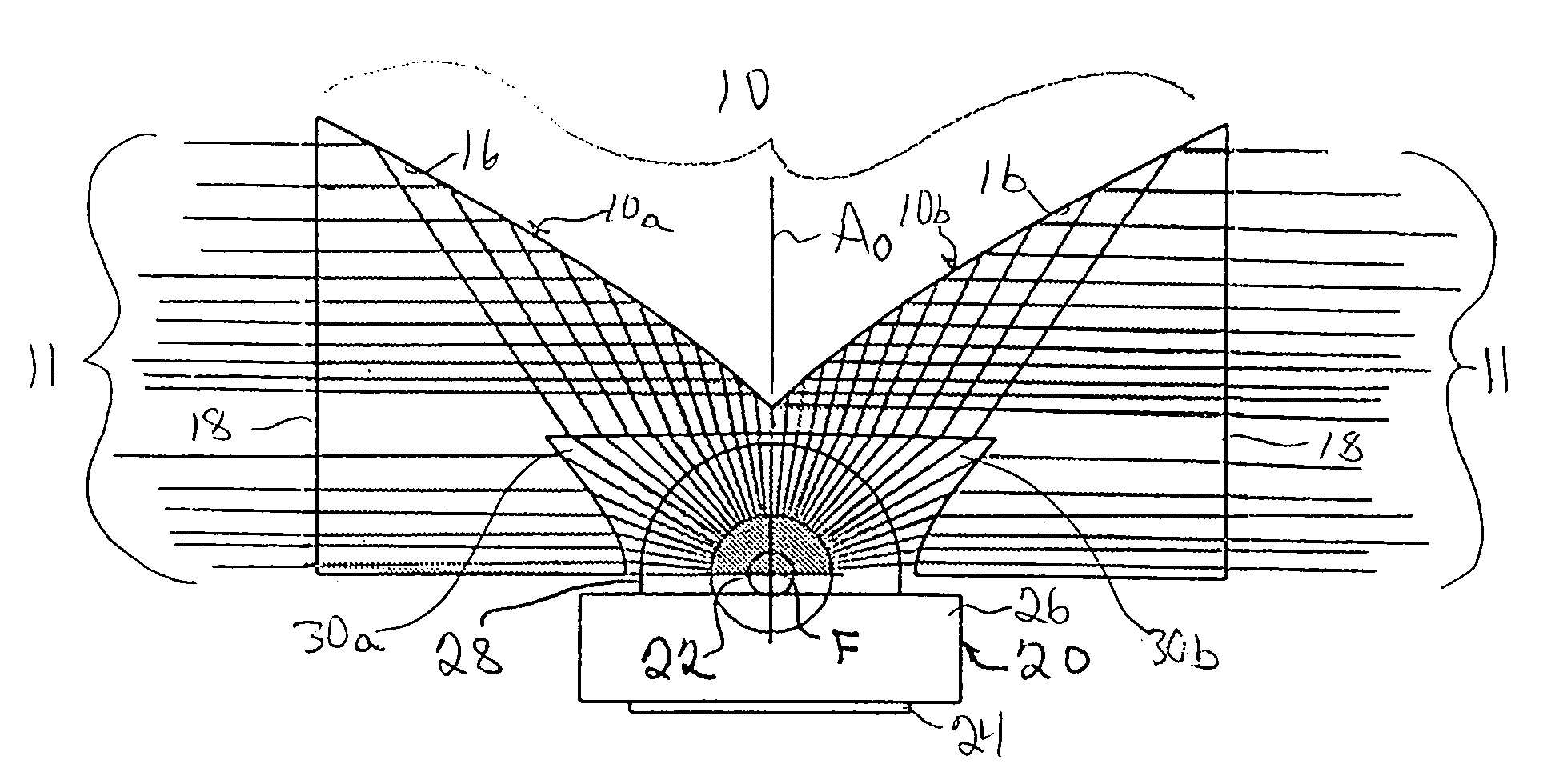

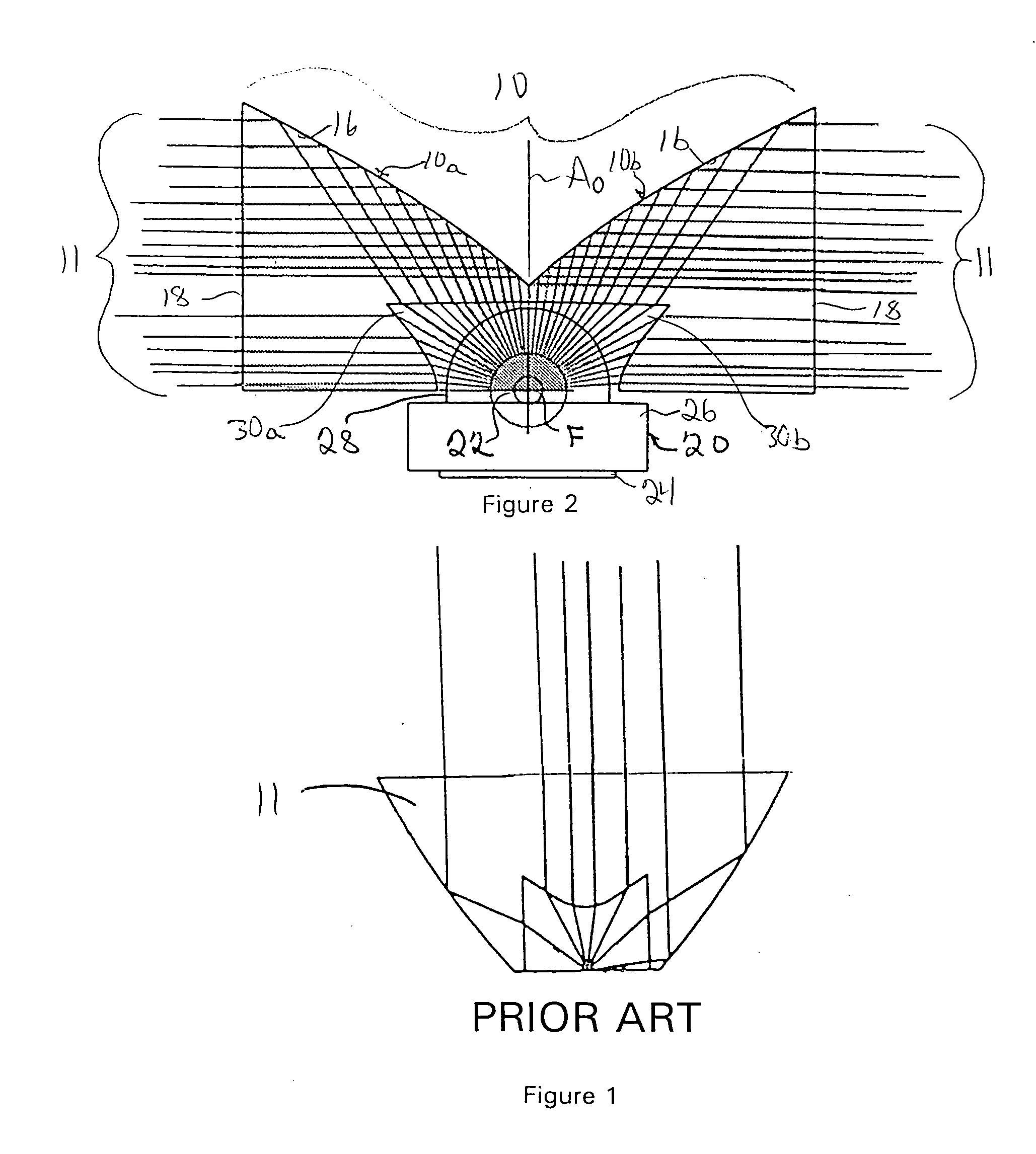

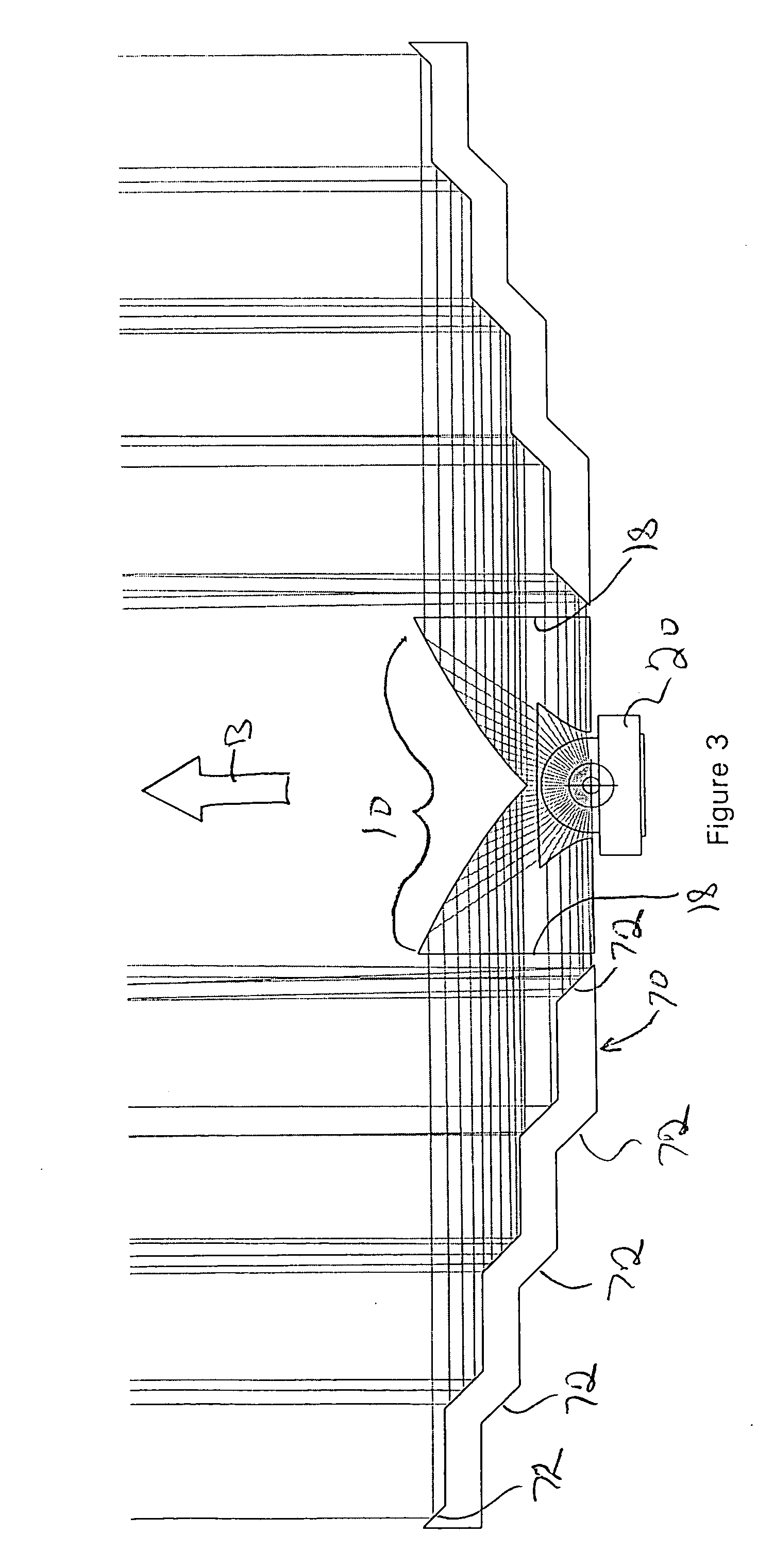

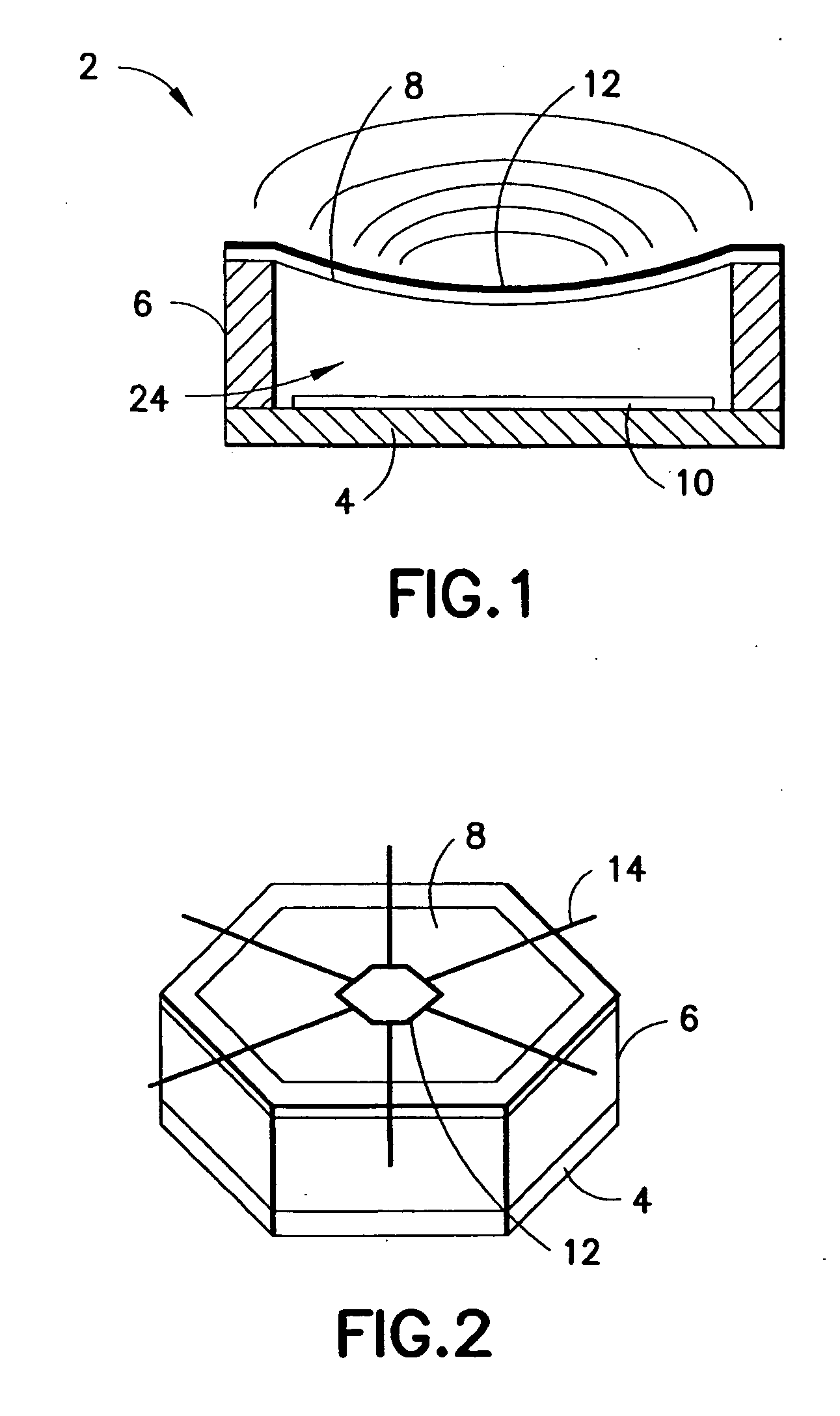

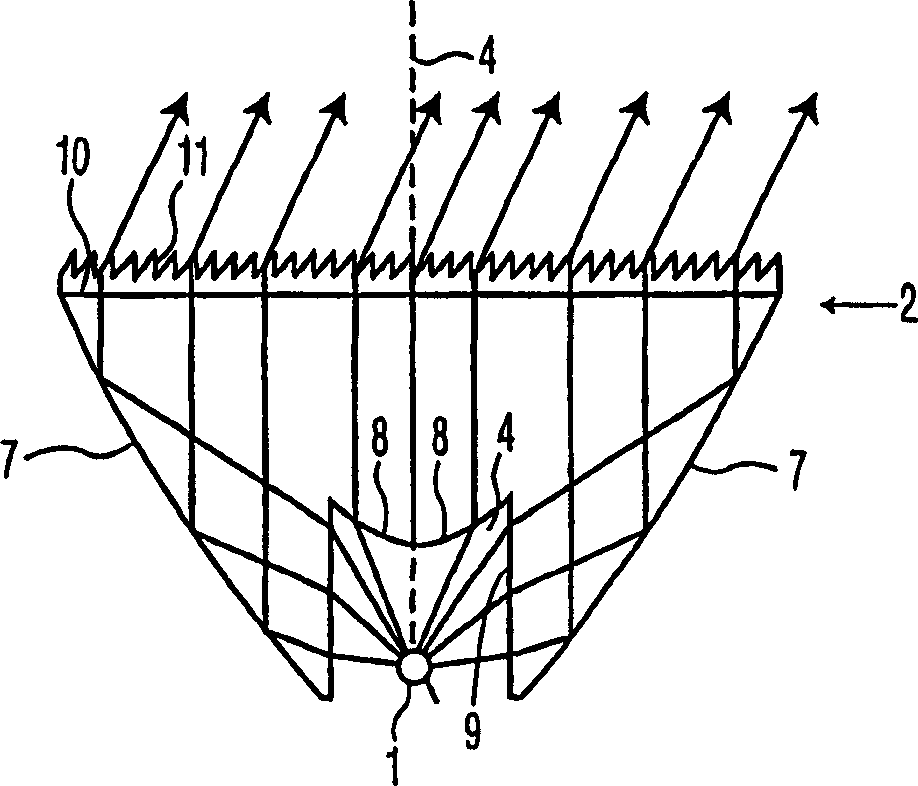

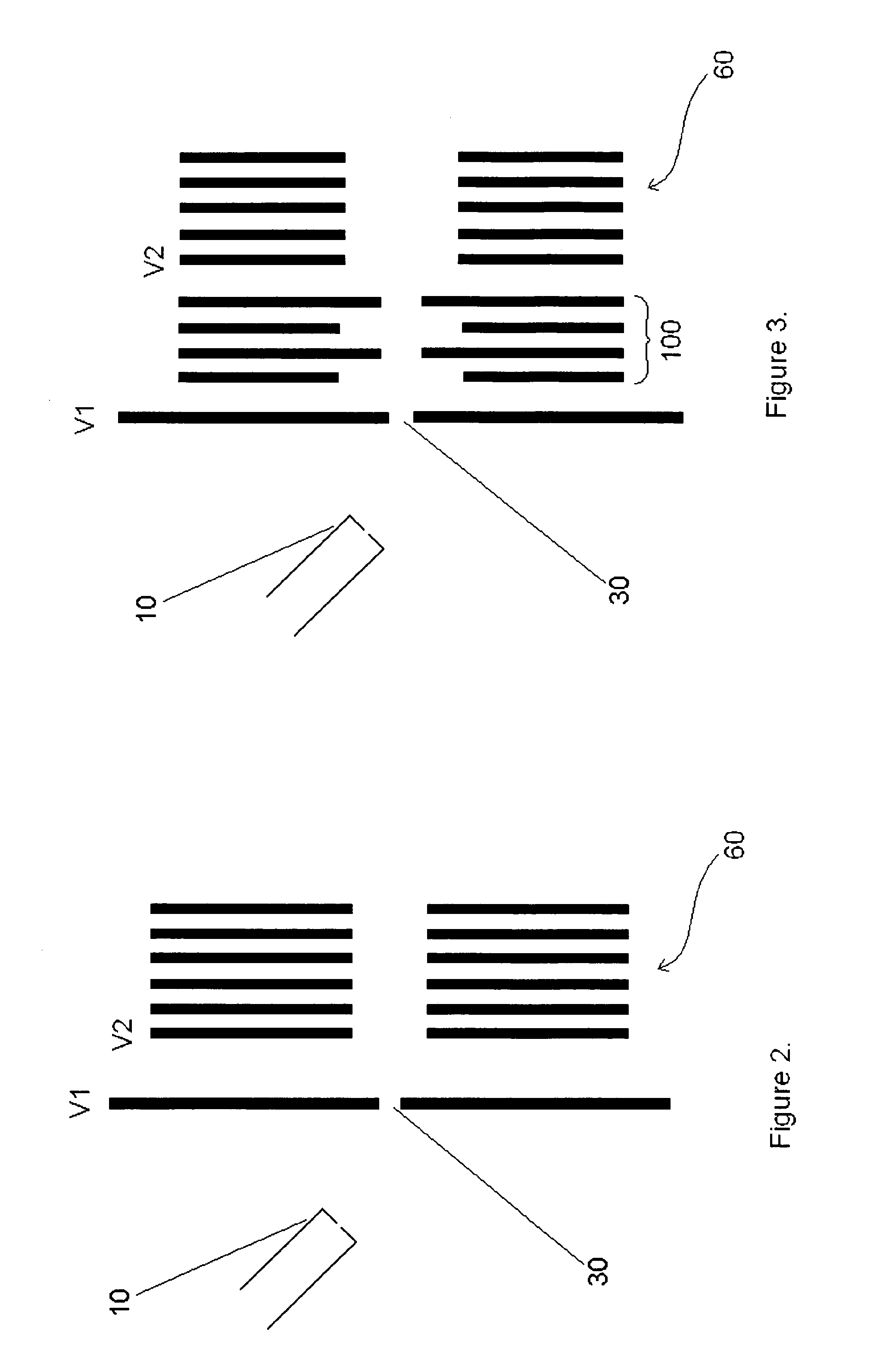

Side-emitting collimator

A side-emitting collimator employs a combination of refraction and internal reflection to organize light from a light source into oppositely directed collimated beams. A light source chamber over the light source is defined by substantially cylindrical and aspheric refracting surfaces positioned to gather light into the collimating lens. The aspheric refracting surfaces redirect a portion of the light from the light source into a direction perpendicular to the optical axis of the light source. The substantially cylindrical surfaces refract light from the light source onto an aspheric upper reflecting surface. Light incident upon the aspheric upper reflecting surface is collimated into a direction perpendicular to the optical axis of the light source. The side-emitting collimator includes mirror image collimator halves, each producing a collimated beam. The collimator halves are rotationally symmetric about a common axis of symmetry above a plane including the axis of symmetry.

Owner:WHELEN ENGINEERING COMPANY

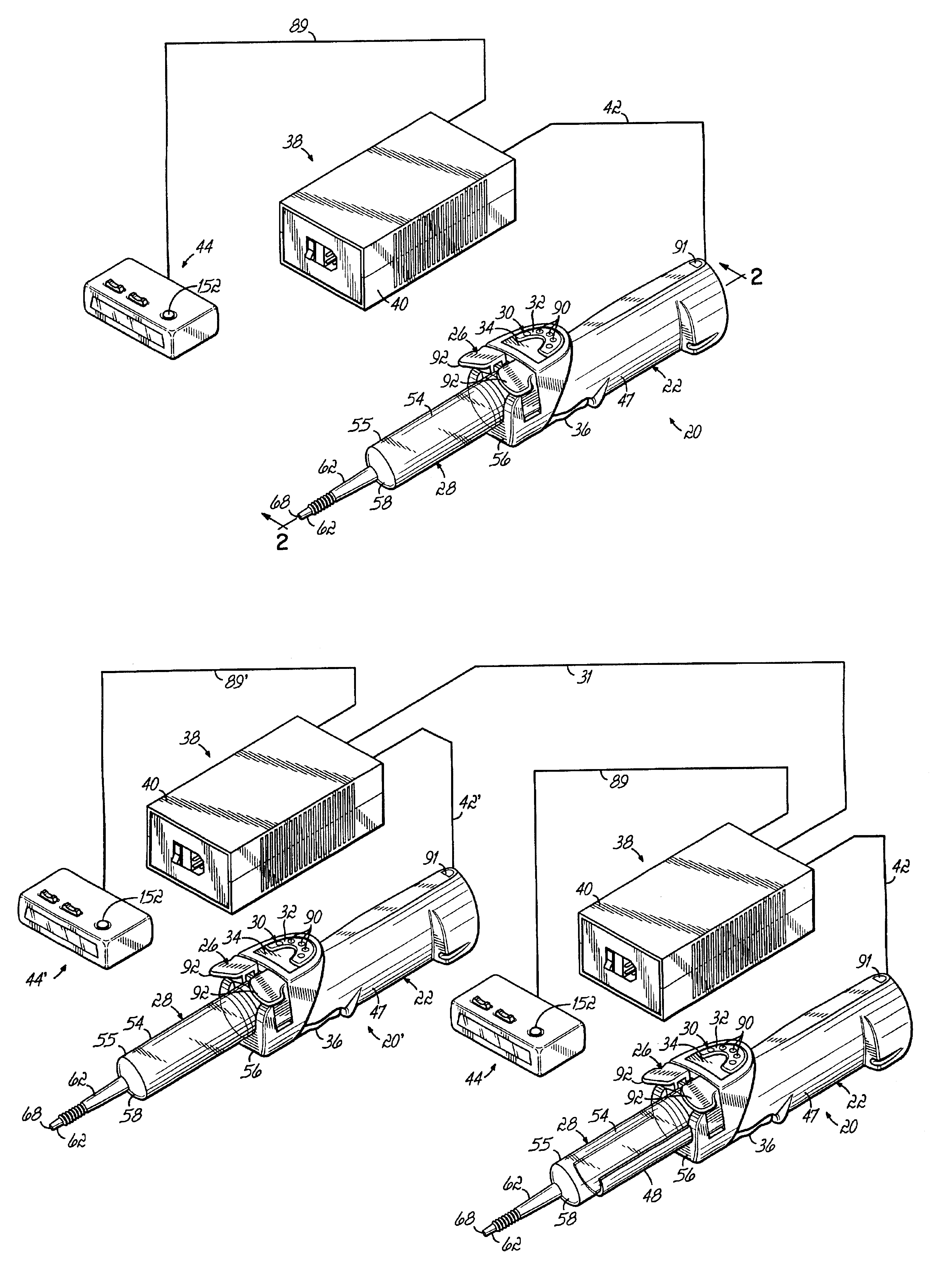

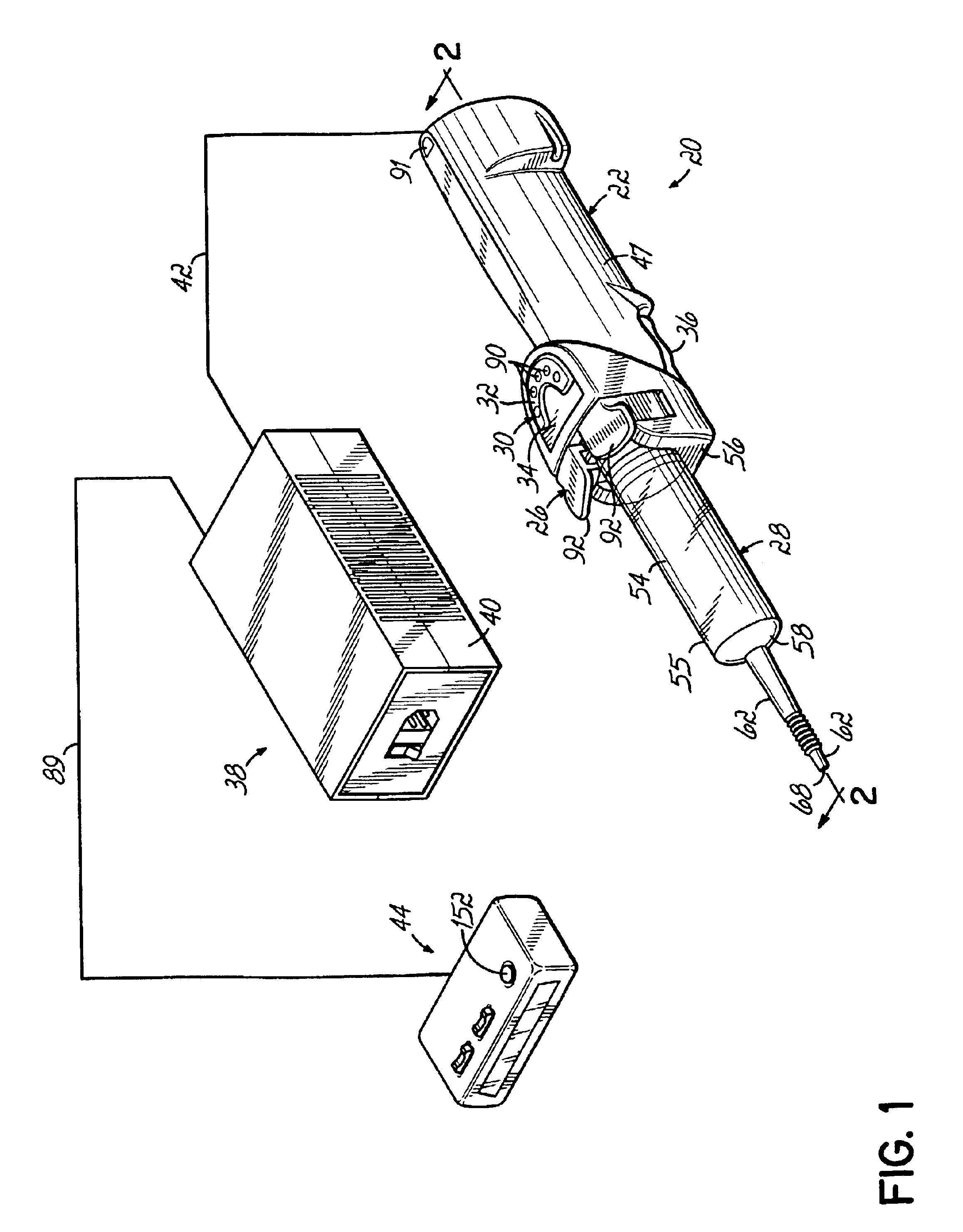

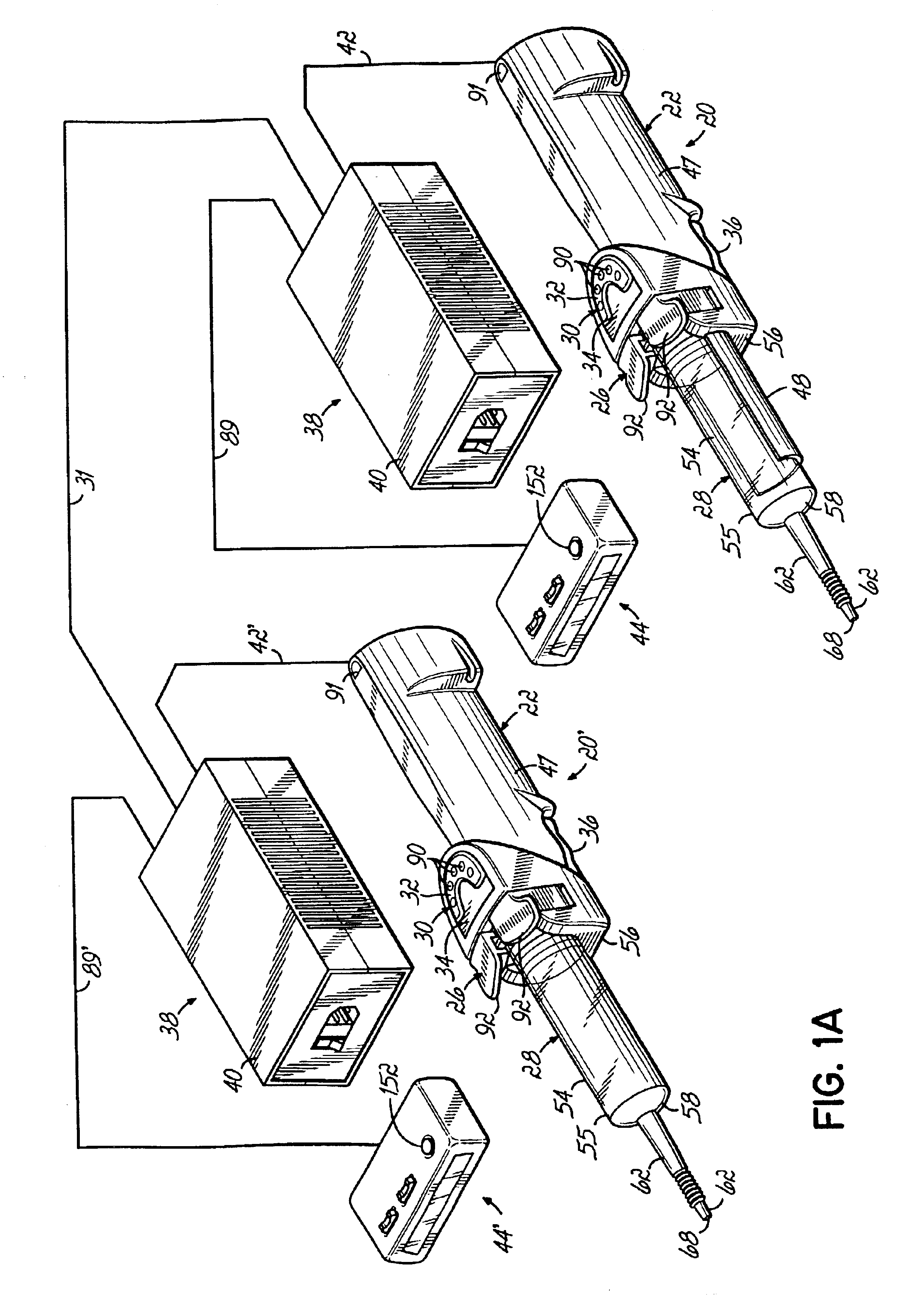

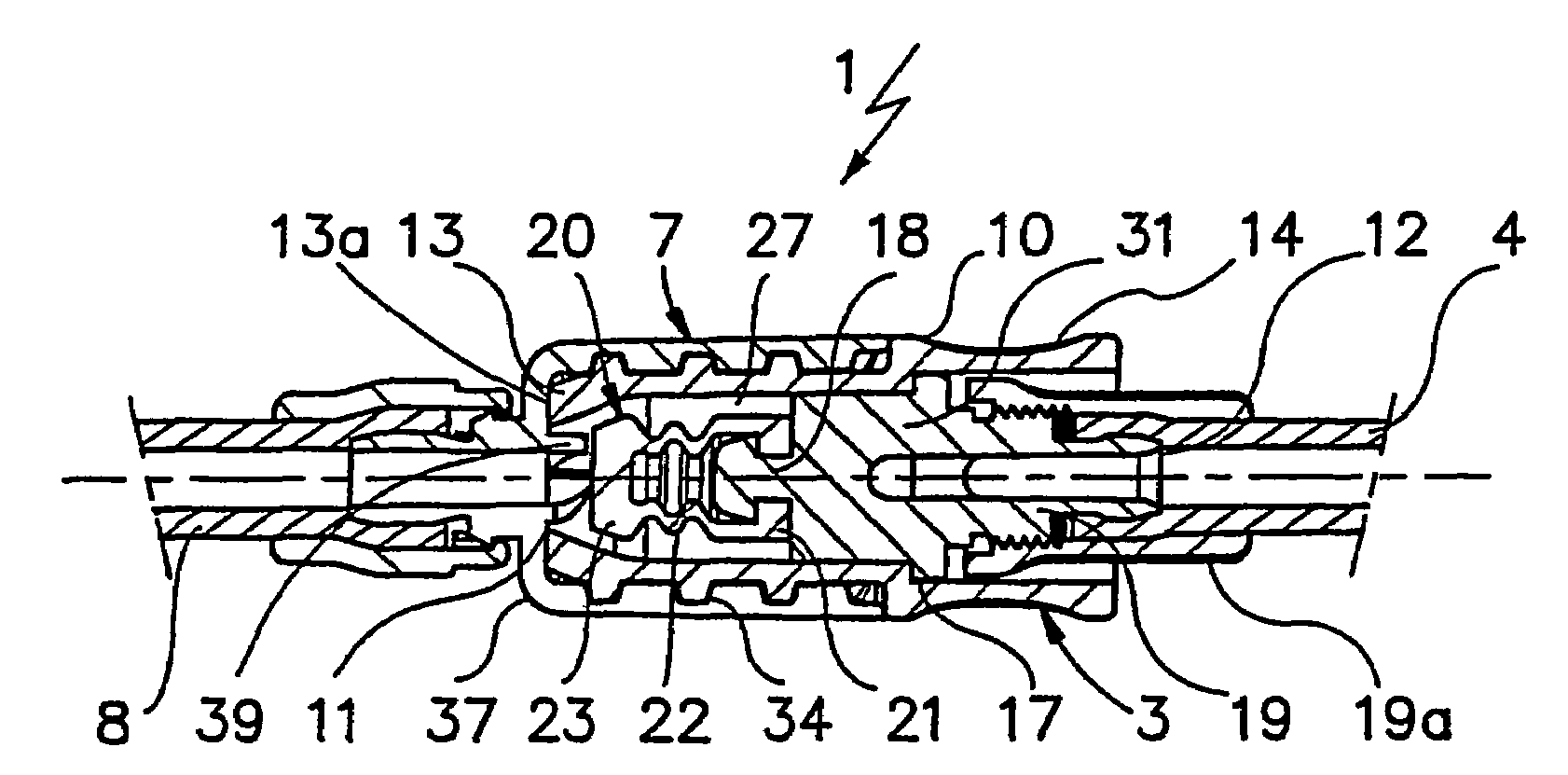

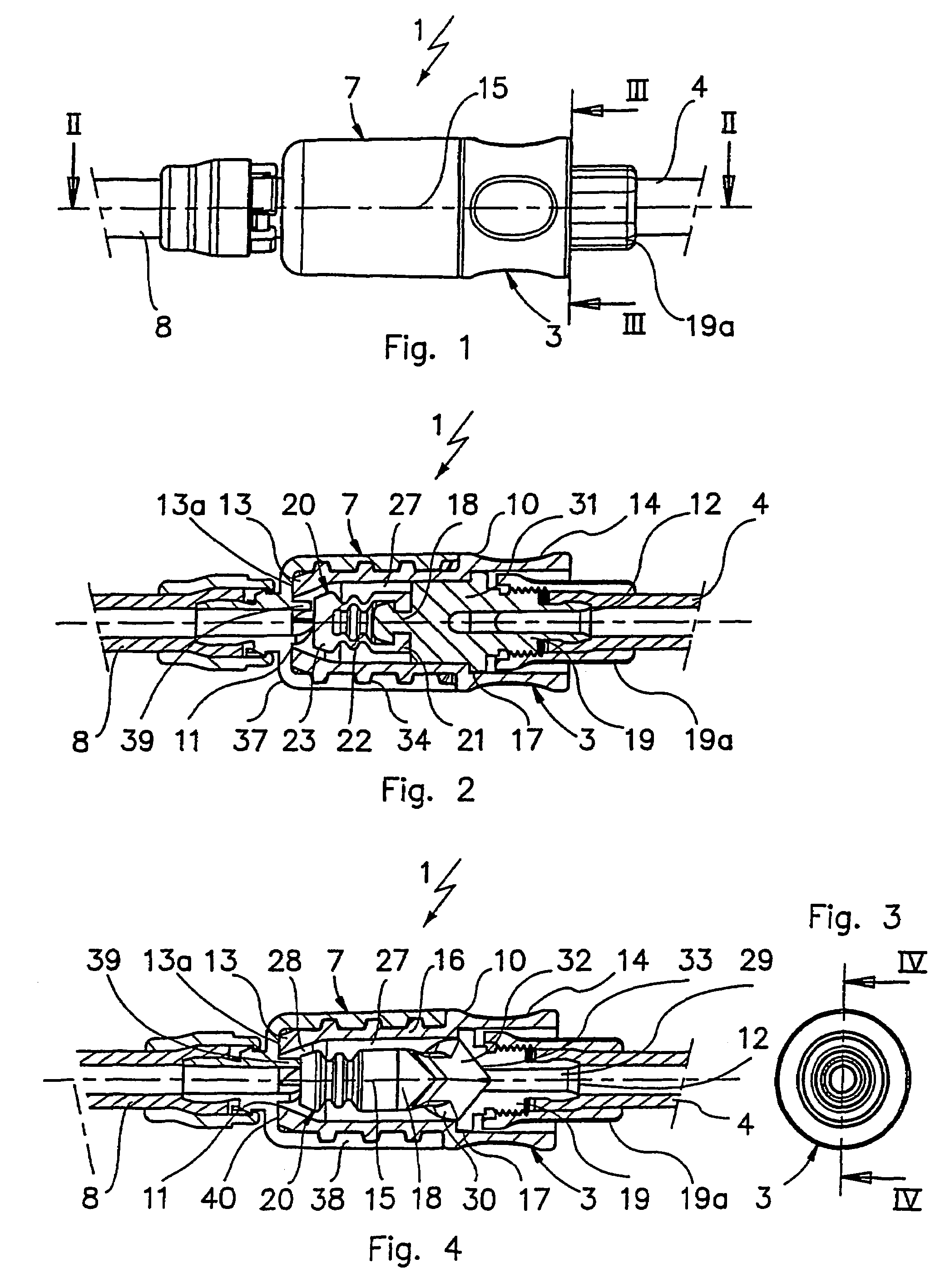

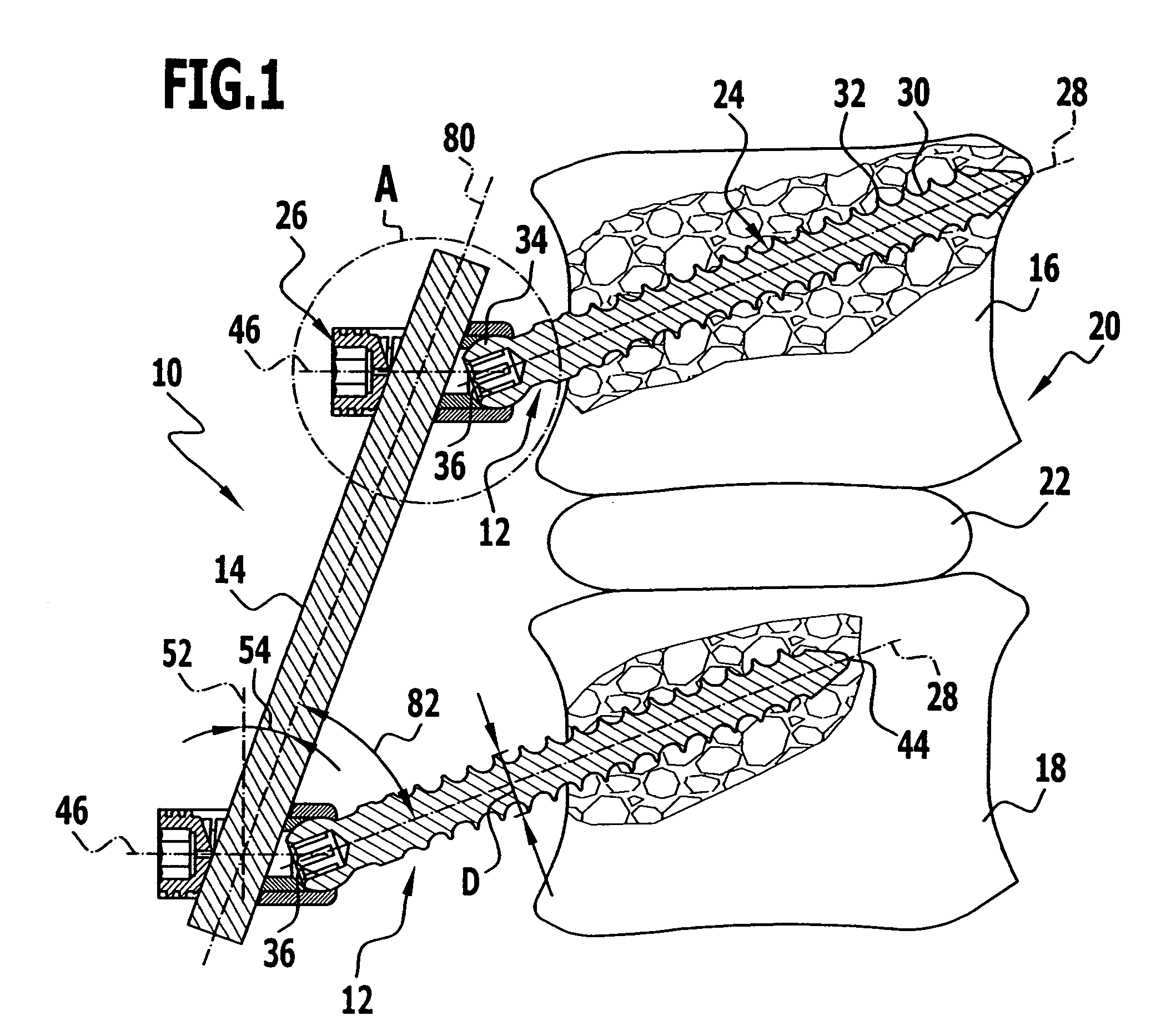

Injector

InactiveUS6929619B2Reduces and eliminates power connectionGood adhesionAutomatic syringesMedical devicesAxis of symmetryRadiographic contrast media

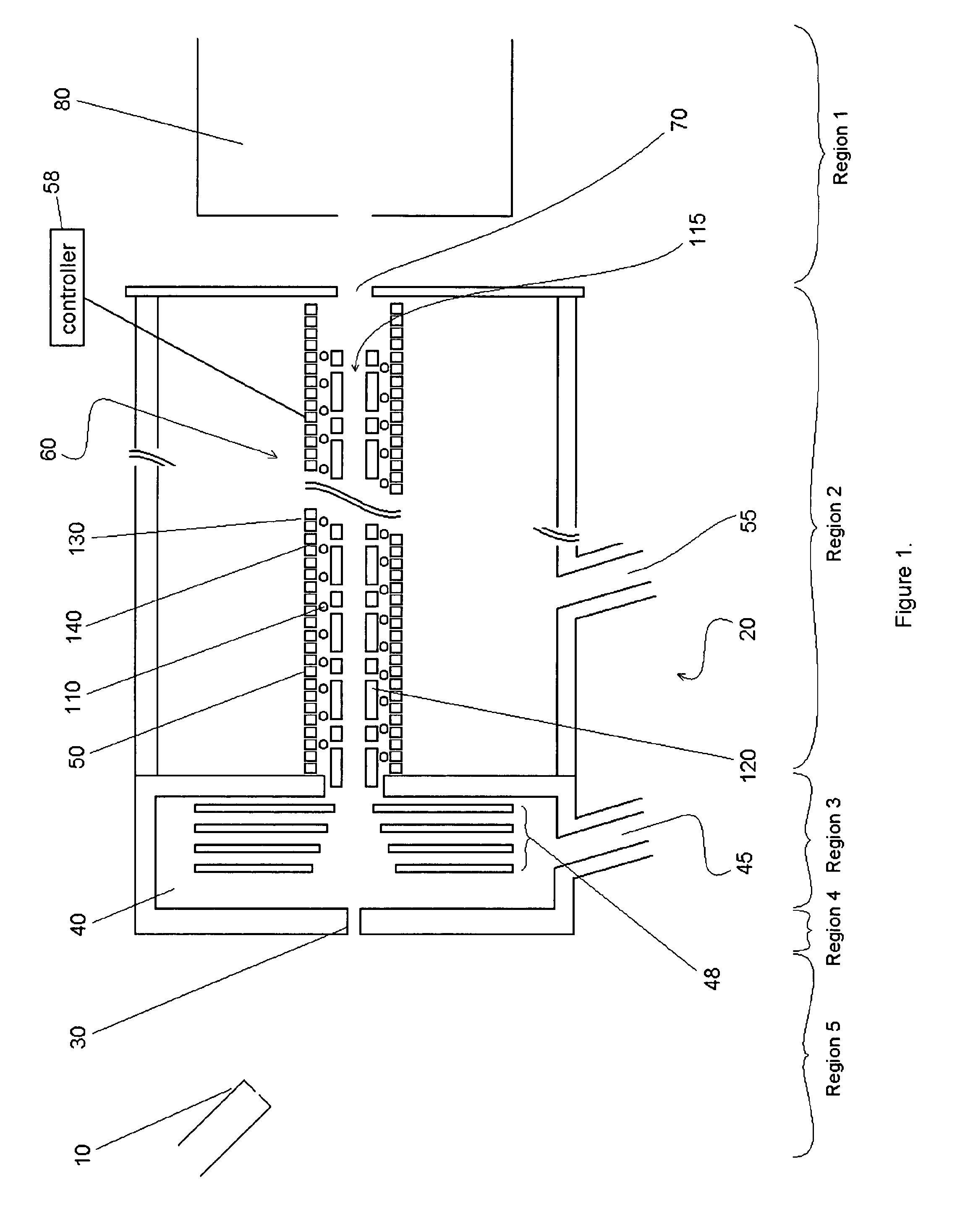

An injector 20 that may be used to deliver radiographic contrast media and / or flushing solution into a patient's vascular system for the purposes such as obtaining enhanced diagnostic x-ray images. The injector includes the following features: (1) a syringe mount 26 for attachment of a syringe 28 to the injector 20; (2) display 34 and controls 90 for volume and flow rates; (3) automatic limiting of the operating pressure of the injector 20 as determined by the selection of a flow rate; (4) a syringe cradle 48 having a warming capability; (5) a purge / retract trigger 36 for control of the injection procedure having intuitive direction (i.e., forward for injecting, reverse for filing), non-contact control transmission through the housing of an injector 20 for an improved seal integrity, a speed lock, and / or the ability to change the concentration and / or flow rate of media or other fluid during an injection procedure; (6) a switch to determine when the drive ram 46 is in a “home” position; (7) a “soft” on / off power switch separate from the injector; and (8) a structure to prevent rotation of the drive ram 46 about its axis of symmetry 76. Additionally, the injector system includes software for the control of various components.

Owner:LIEBEL FLARSHEIM CO

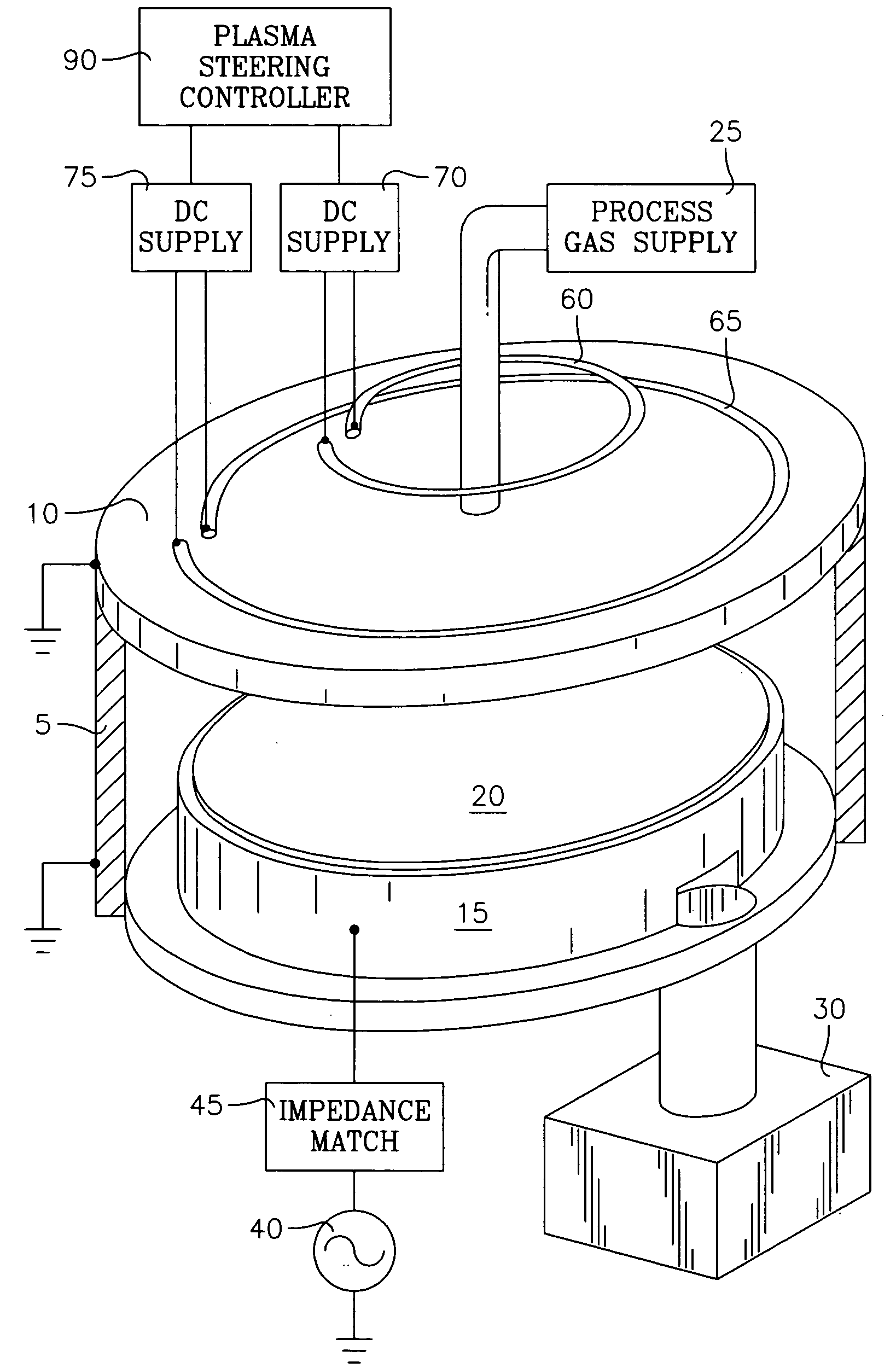

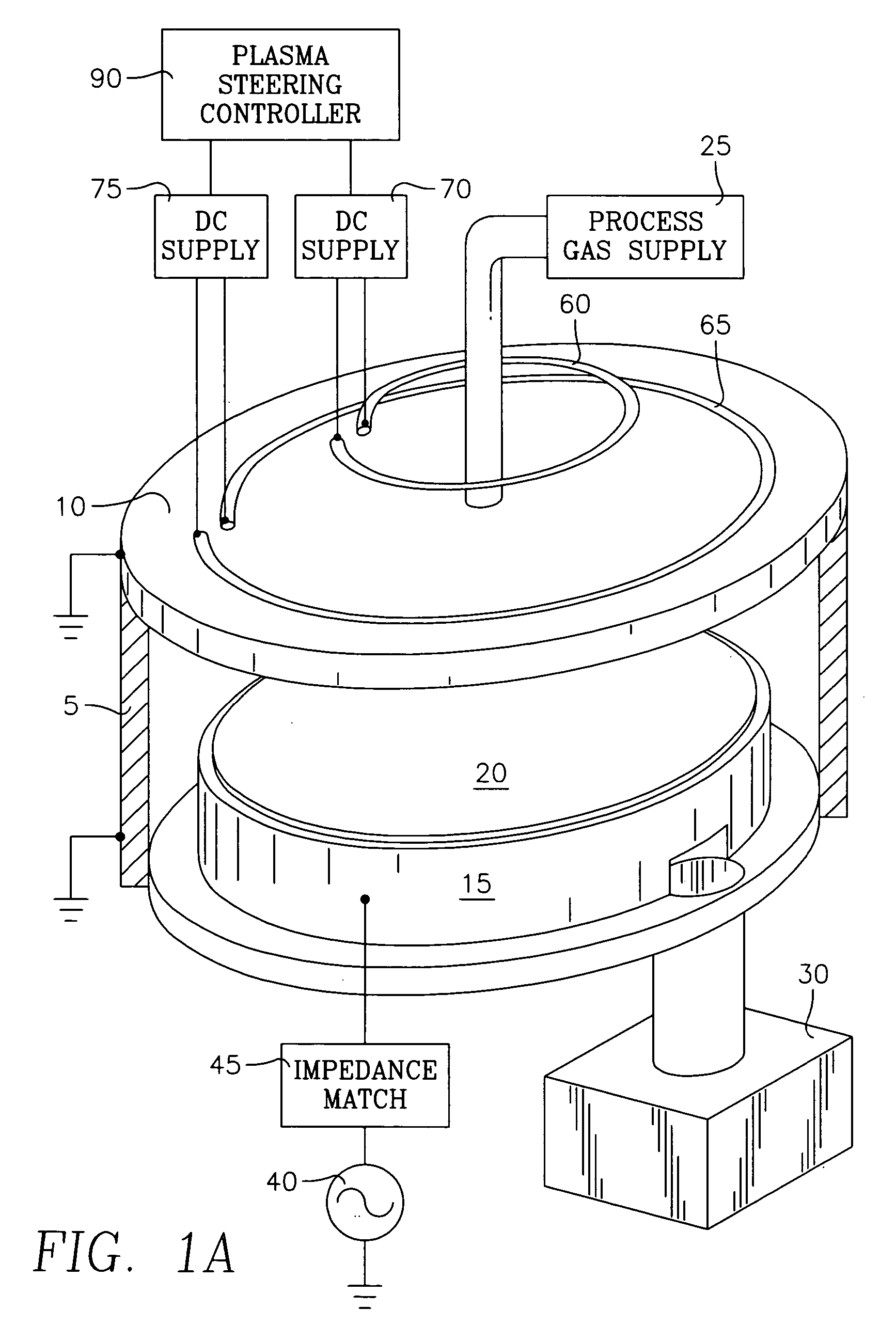

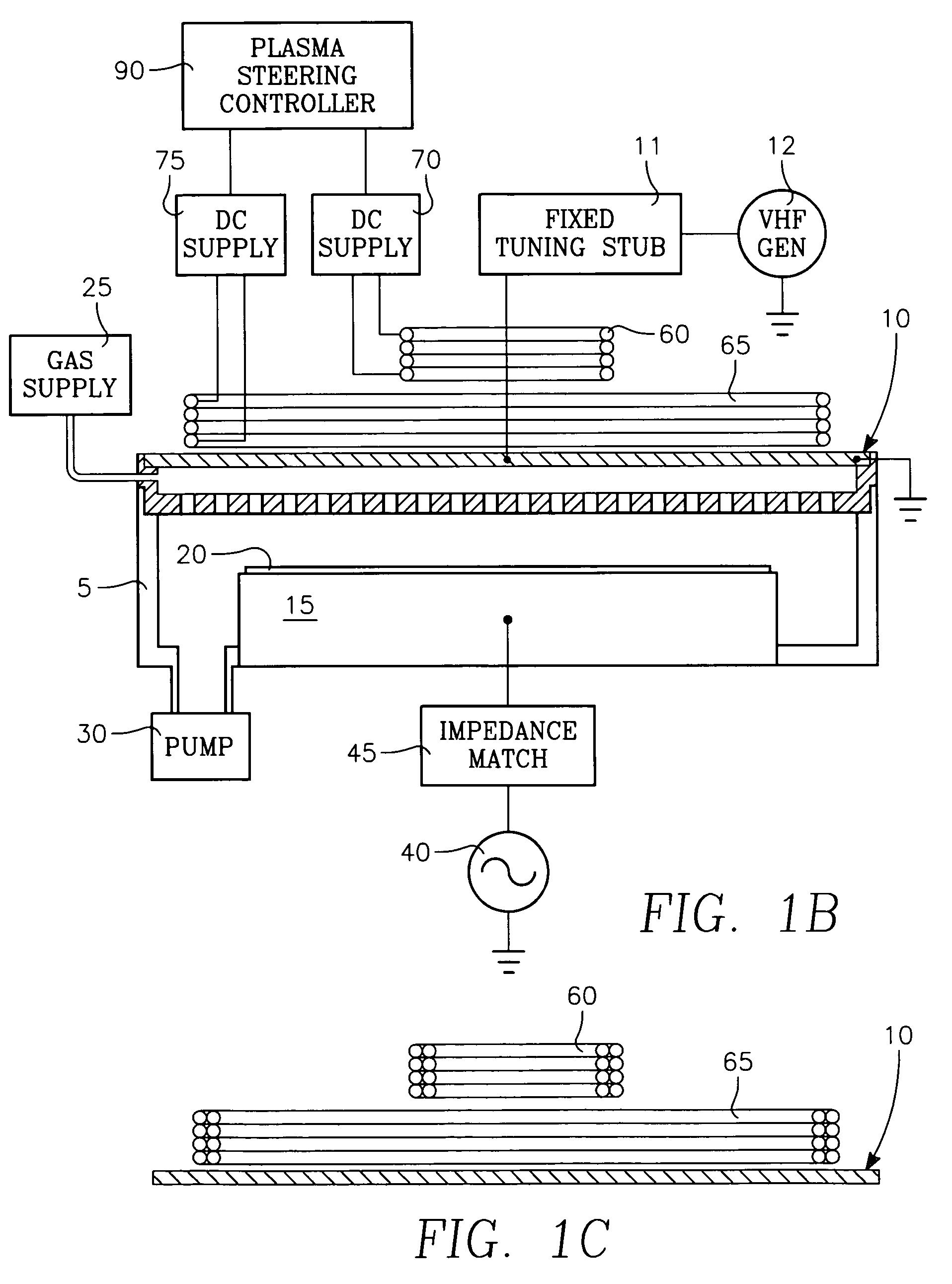

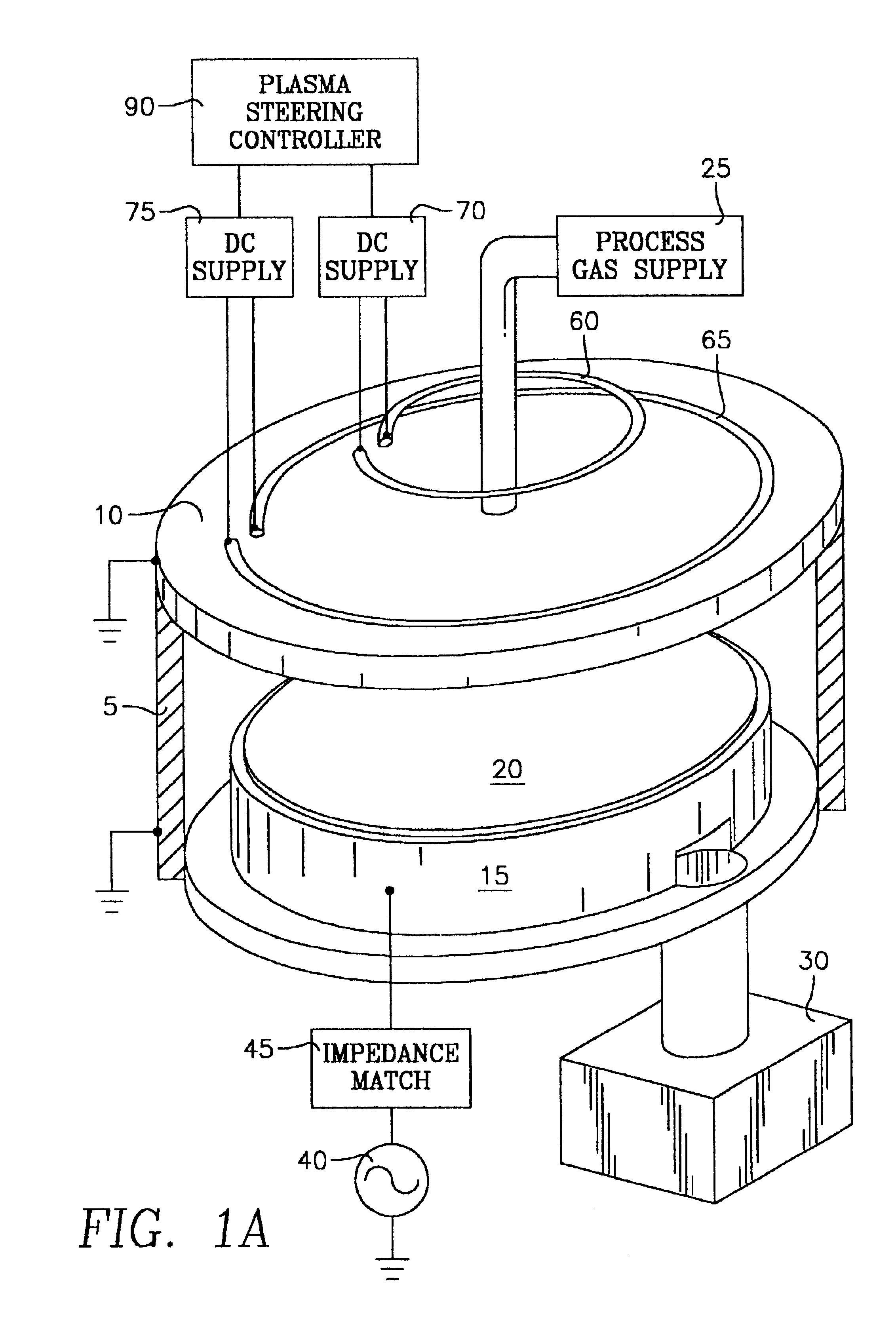

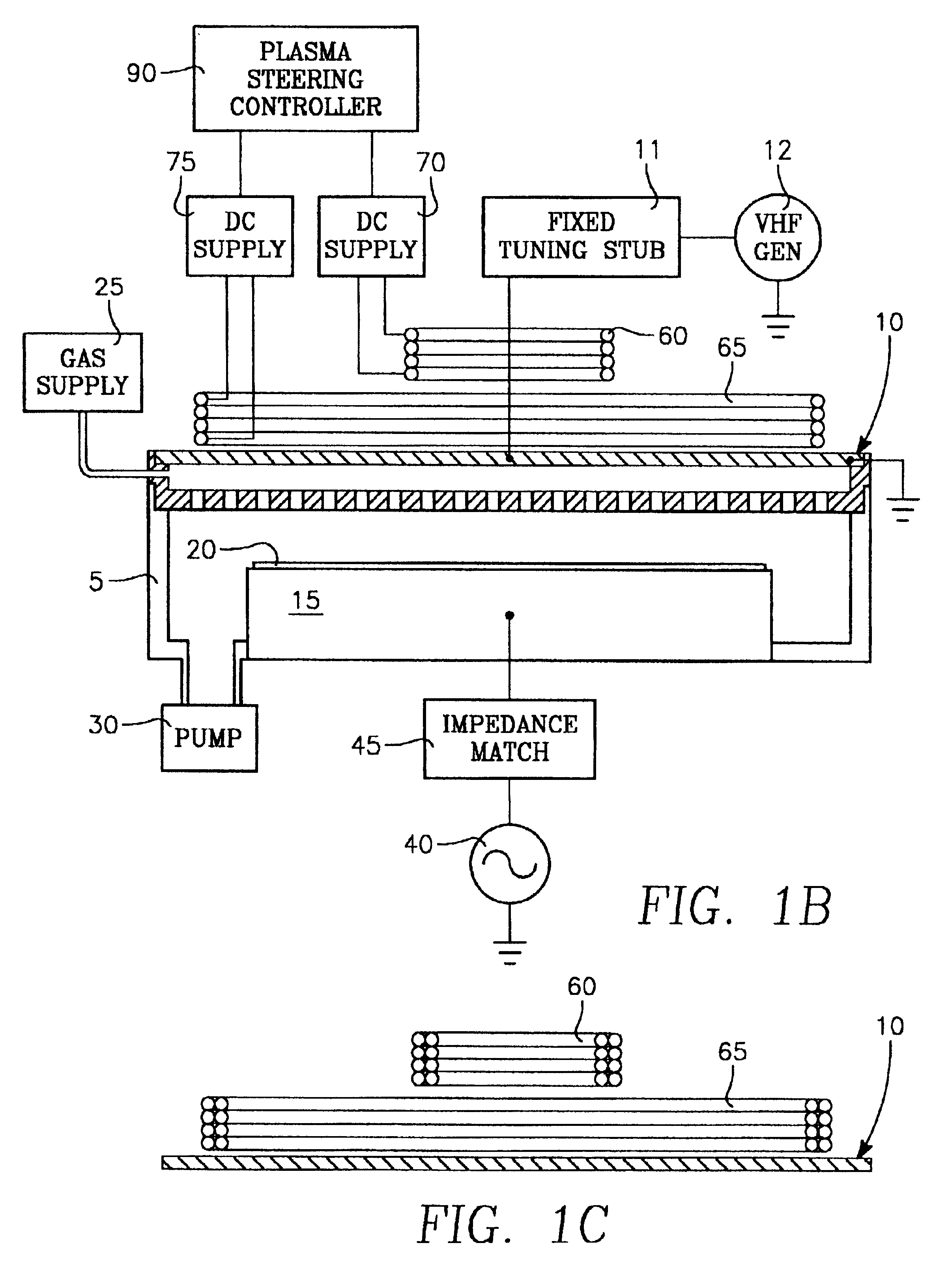

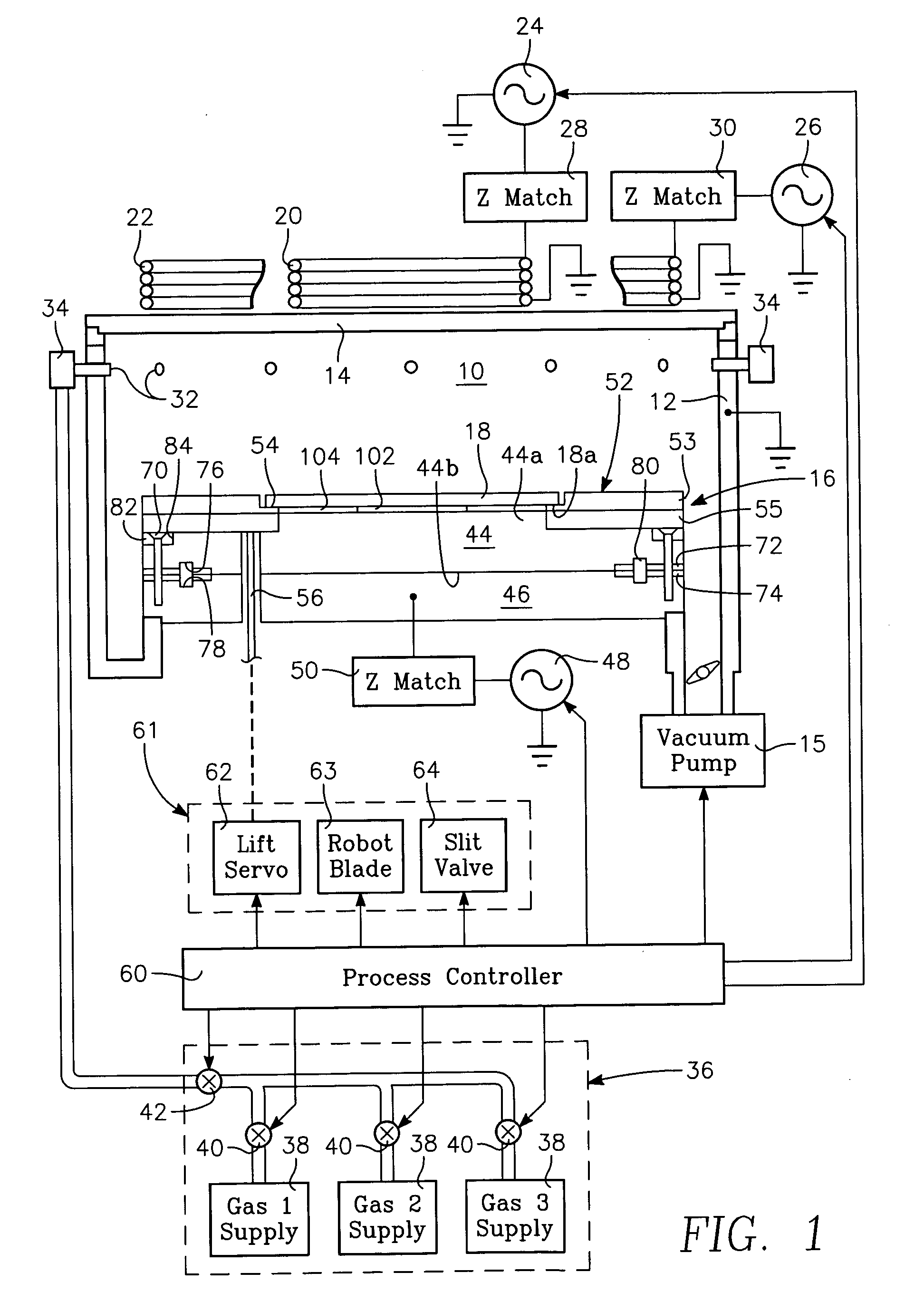

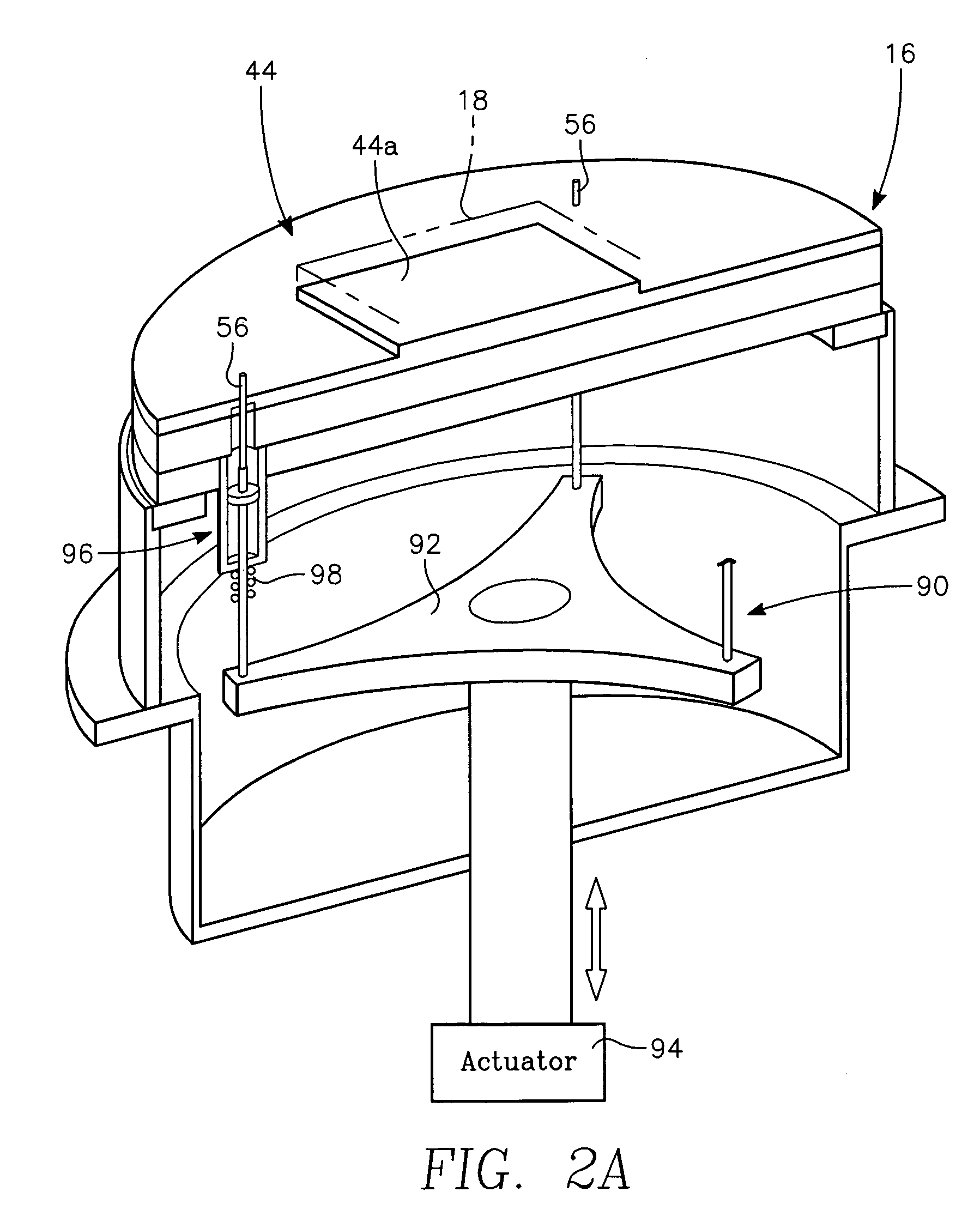

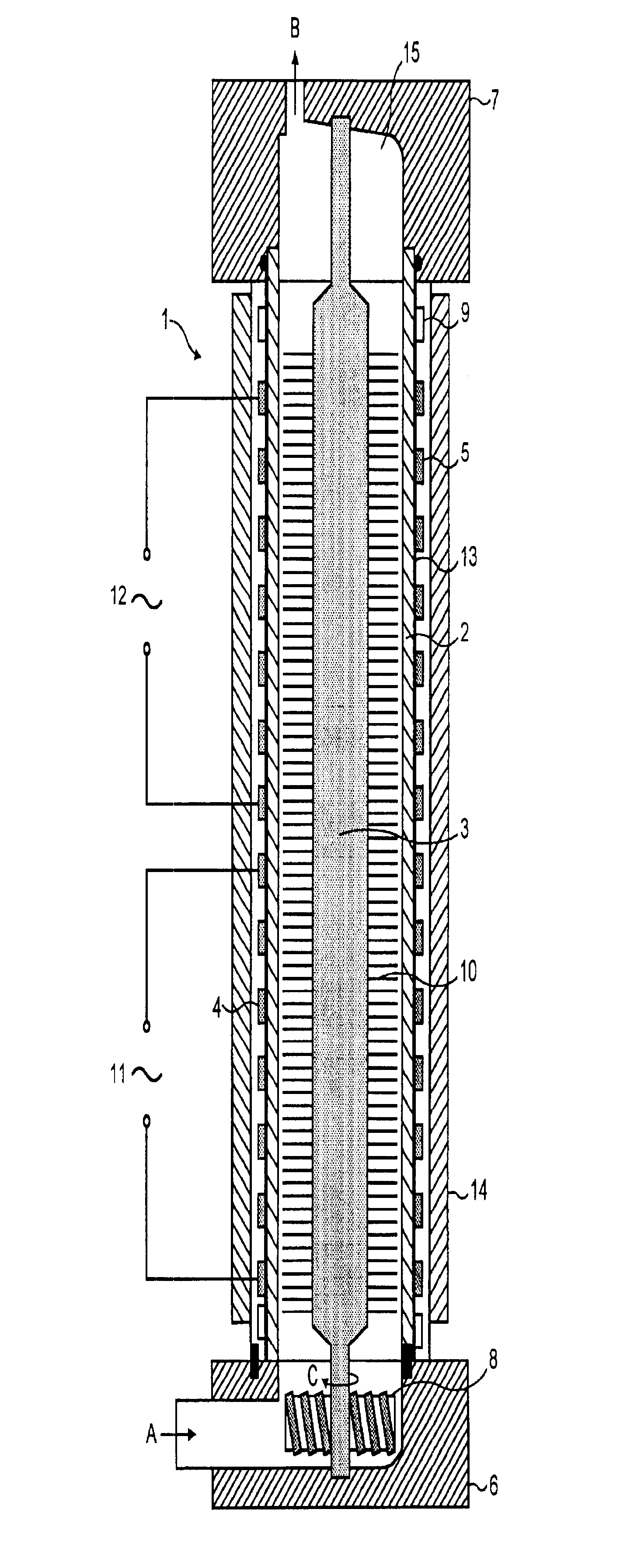

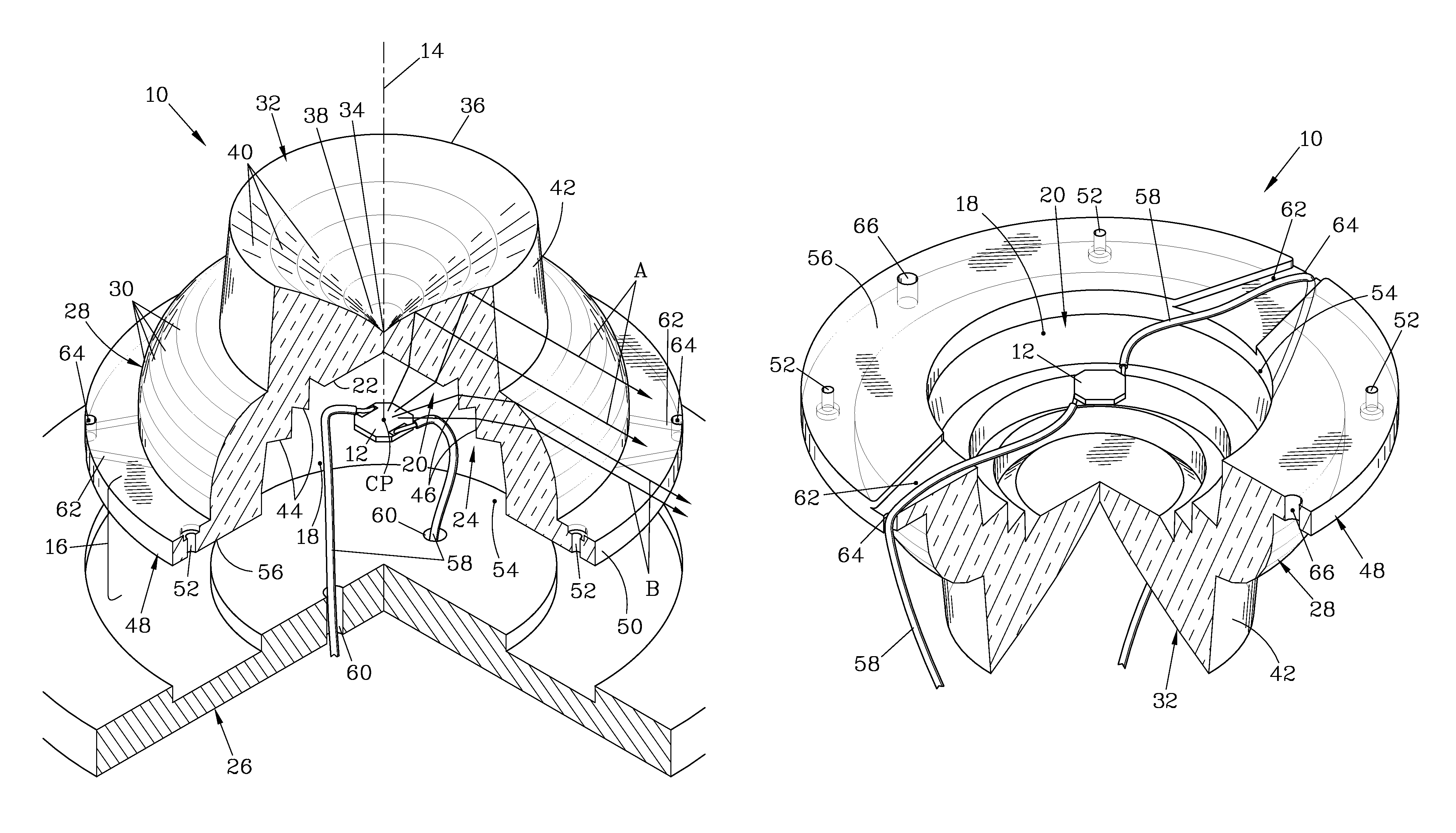

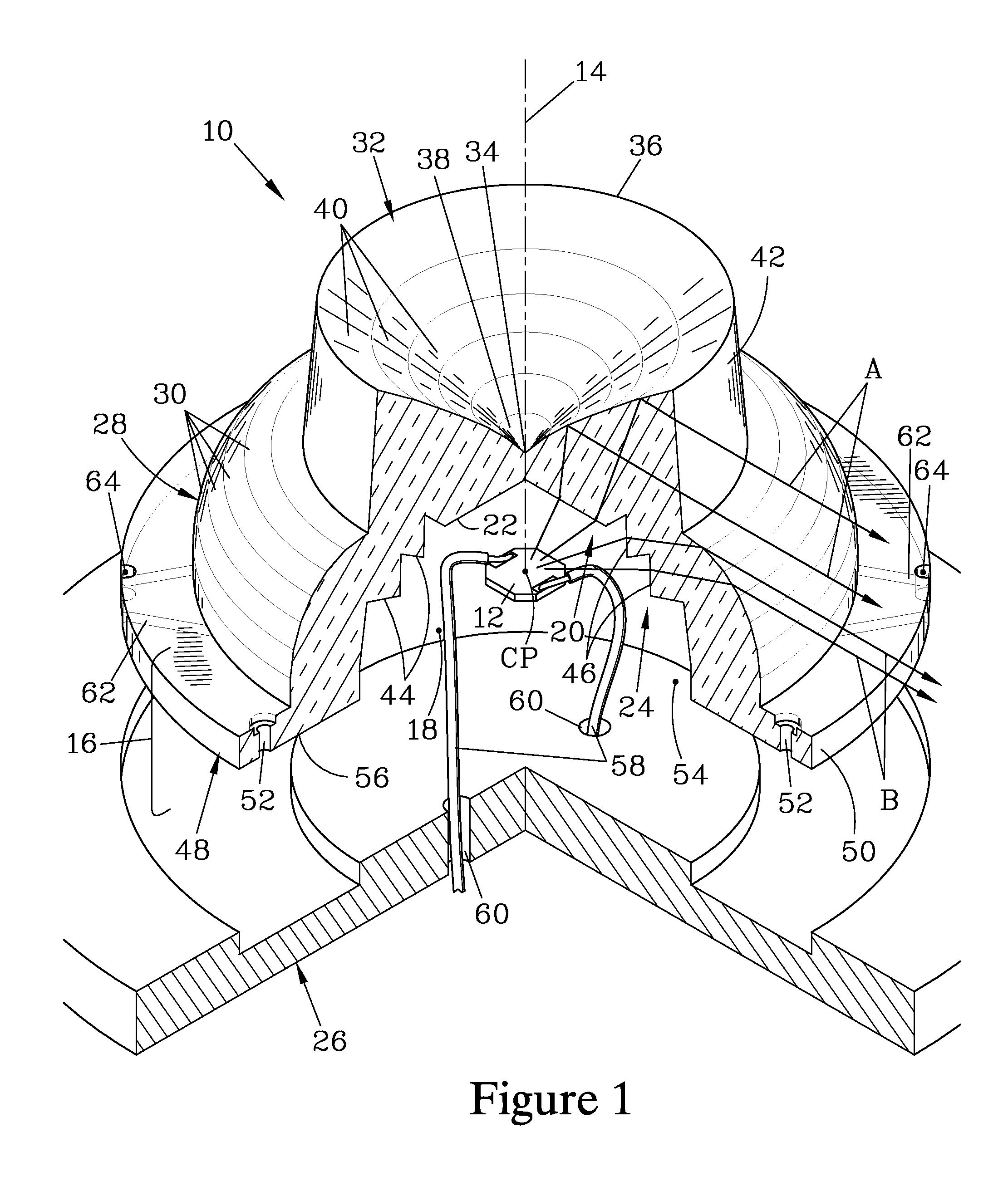

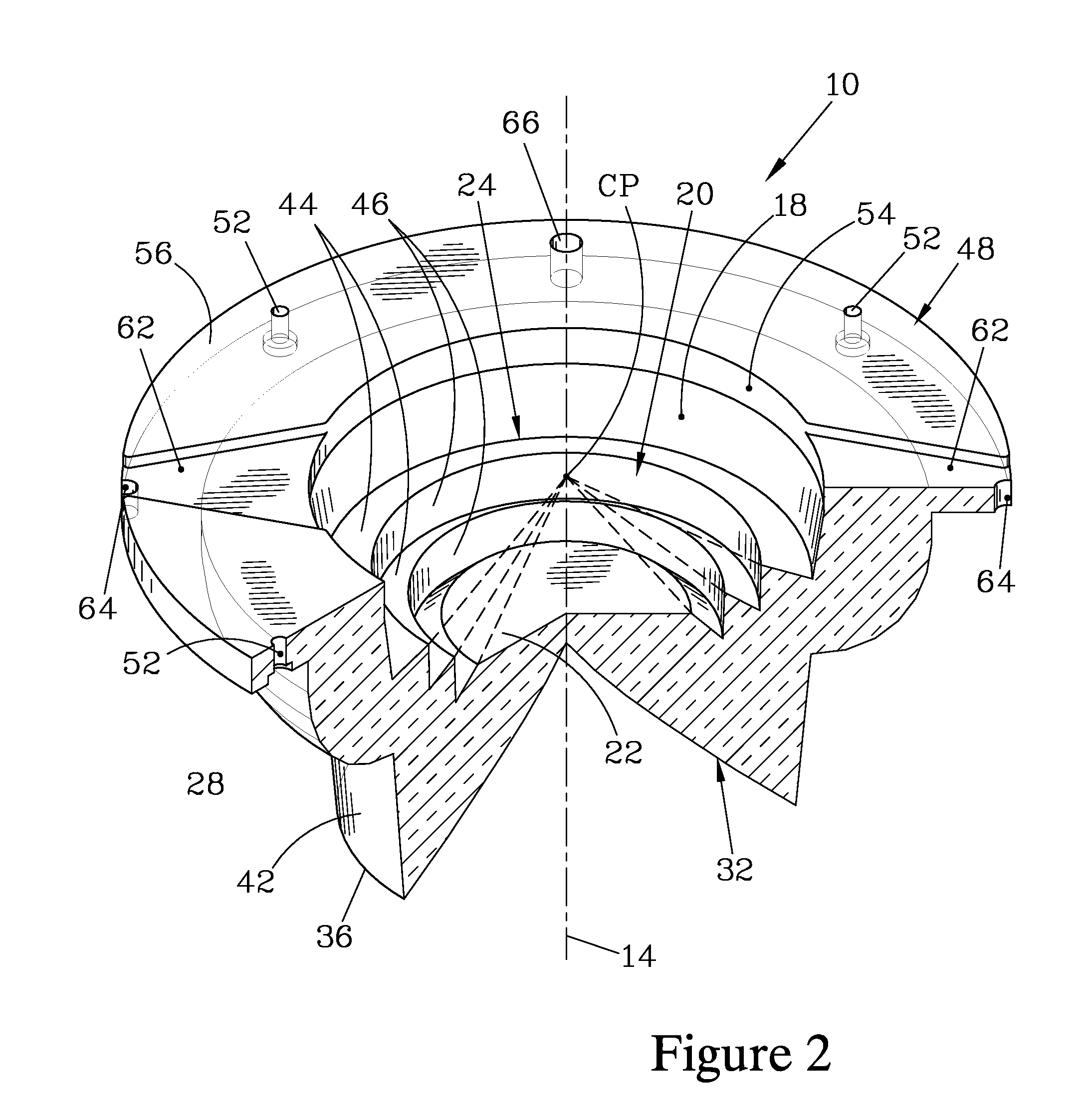

Capacitively coupled plasma reactor with magnetic plasma control

InactiveUS20050001556A1Plasma uniformity can be improvedImprove uniformityElectric discharge tubesElectric arc lampsCapacitanceAxis of symmetry

A plasma reactor includes a vacuum enclosure including a side wall and a ceiling defining a vacuum chamber, and a workpiece support within the chamber and facing the ceiling for supporting a planar workpiece, the workpiece support and the ceiling together defining a processing region between the workpiece support and the ceiling. Process gas inlets furnish a process gas into the chamber. A plasma source power electrode is connected to an RF power generator for capacitively coupling plasma source power into the chamber for maintaining a plasma within the chamber. The reactor further includes at least a first overhead solenoidal electromagnet adjacent the ceiling, the overhead solenoidal electromagnet, the ceiling, the side wall and the workpiece support being located along a common axis of symmetry. A current source is connected to the first solenoidal electromagnet and furnishes a first electric current in the first solenoidal electromagnet whereby to generate within the chamber a magnetic field which is a function of the first electric current, the first electric current having a value such that the magnetic field increases uniformity of plasma ion density radial distribution about the axis of symmetry near a surface of the workpiece support.

Owner:APPLIED MATERIALS INC

Capacitively coupled plasma reactor with magnetic plasma control

InactiveUS6853141B2Plasma uniformity can be improvedImprove uniformityElectric arc lampsSemiconductor/solid-state device manufacturingCapacitanceAxis of symmetry

A plasma reactor includes a vacuum enclosure including a side wall and a ceiling defining a vacuum chamber, and a workpiece support within the chamber and facing the ceiling for supporting a planar workpiece, the workpiece support and the ceiling together defining a processing region between the workpiece support and the ceiling. Process gas inlets furnish a process gas into the chamber. A plasma source power electrode is connected to an RF power generator for capacitively coupling plasma source power into the chamber for maintaining a plasma within the chamber. The reactor further includes at least a first overhead solenoidal electromagnet adjacent the ceiling, the overhead solenoidal electromagnet, the ceiling, the sidewall and the workpiece support being located along a common axis of symmetry. A current source is connected to the first solenoidal electromagnet and furnishes a first electric current in the first solenoidal electromagnet whereby to generate within the chamber a magnetic field which is a function of the first electric current, the first electric current having a value such that the magnetic field increases uniformity of plasma ion density radial distribution about the axis of symmetry near a surface of the workpiece support.

Owner:APPLIED MATERIALS INC

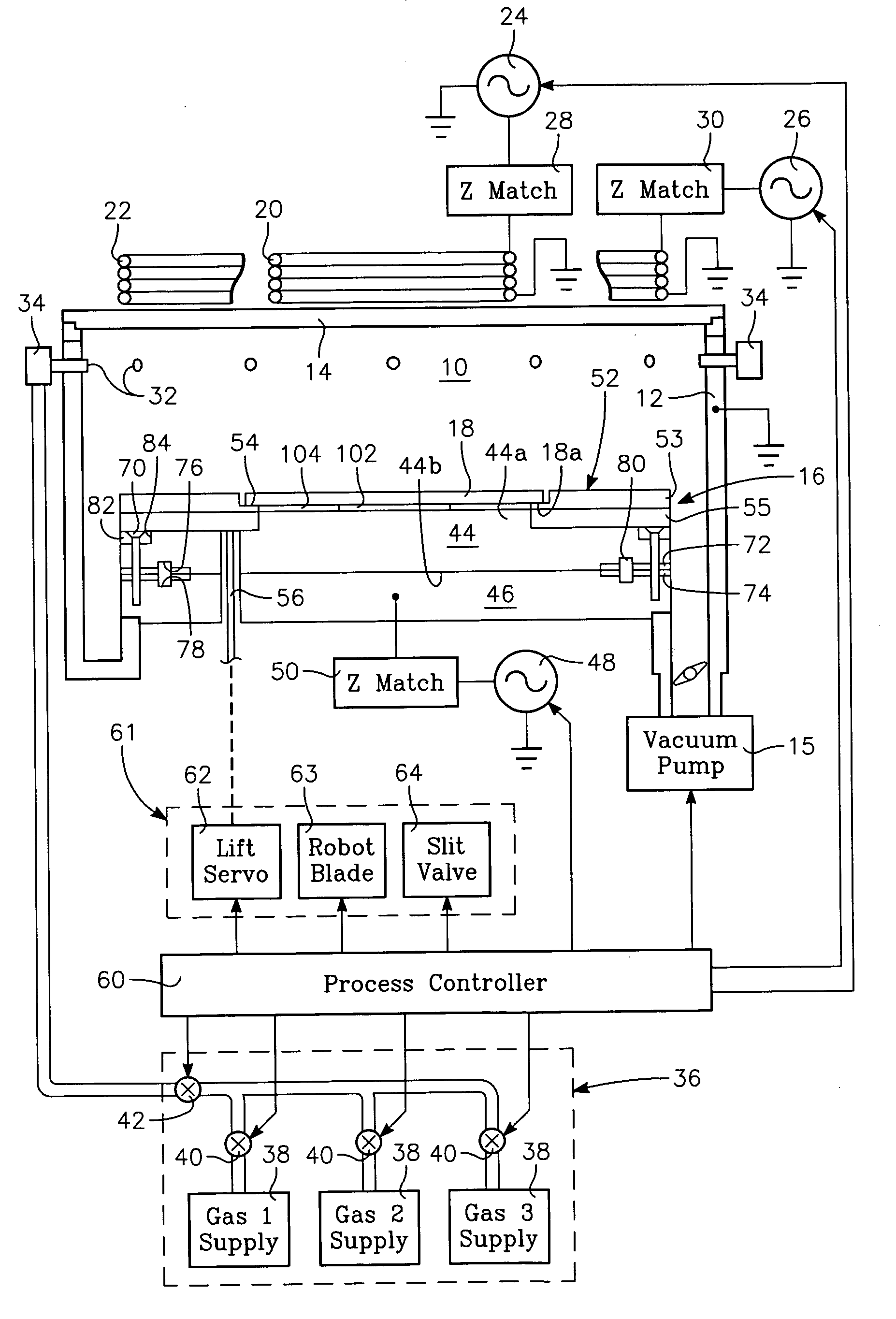

Mask etch plasma reactor with cathode providing a uniform distribution of etch rate

ActiveUS20080100222A1Reduce RF non-uniformitiesImprove uniformityElectric discharge tubesElectric arc lampsAxis of symmetryEngineering

A plasma reactor for etching a workpiece such as a rectangular or square mask, includes a vacuum chamber having a ceiling and a sidewall and a workpiece support pedestal within the chamber including a cathode having a surface for supporting a workpiece, the surface comprising plural respective zones, the respective zones of the surface being formed of respective materials of different electrical characteristics. The zones can be arranged concentrically relative to an axis of symmetry of the wafer support pedestal.

Owner:APPLIED MATERIALS INC

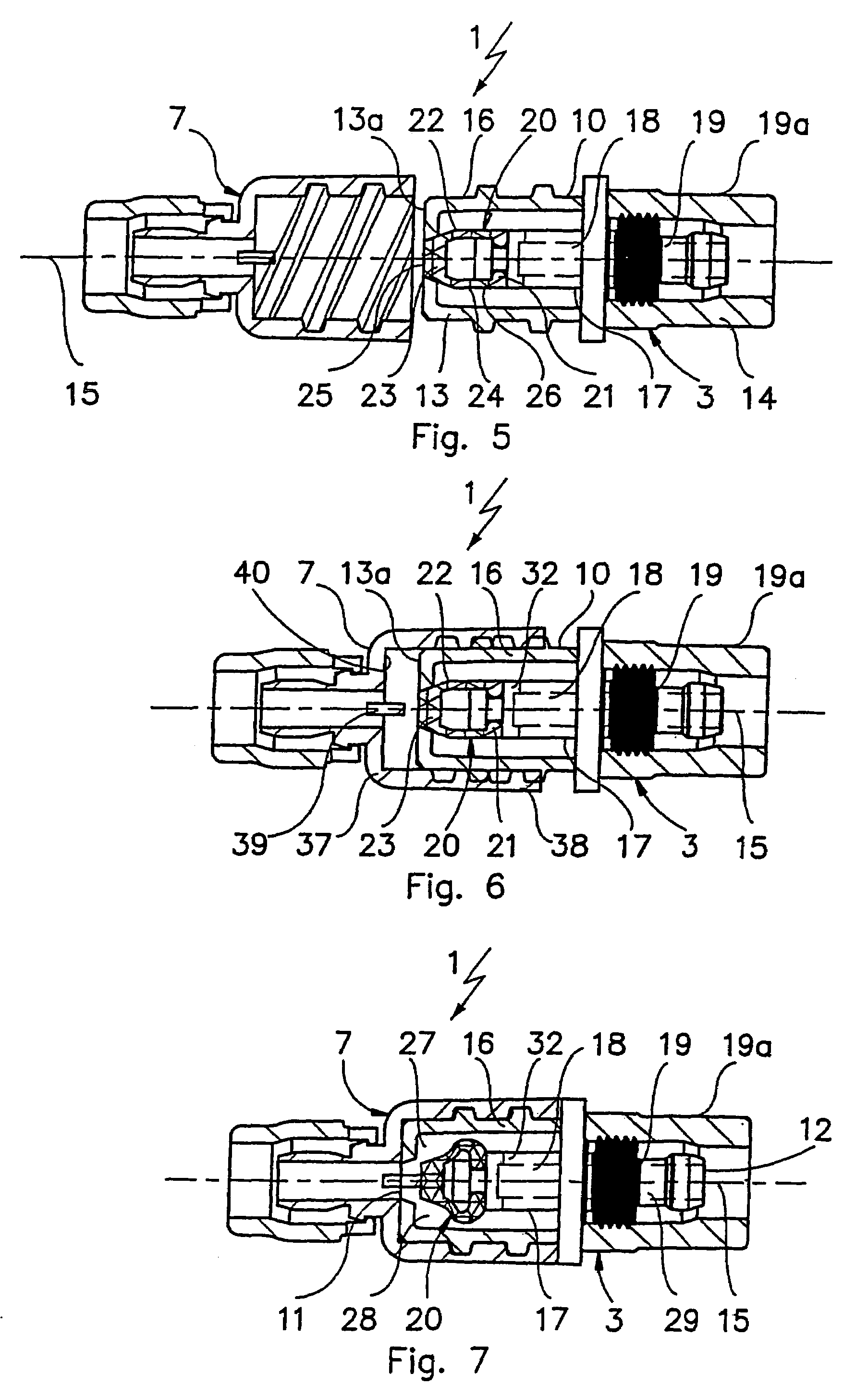

Connection element and connecting device for tubes

InactiveUS7306197B2Reduce total pressure lossLittle encouragementValve arrangementsInfusion devicesPeritoneal dialysisAxis of symmetry

Owner:GAMBRO LUNDIA AB

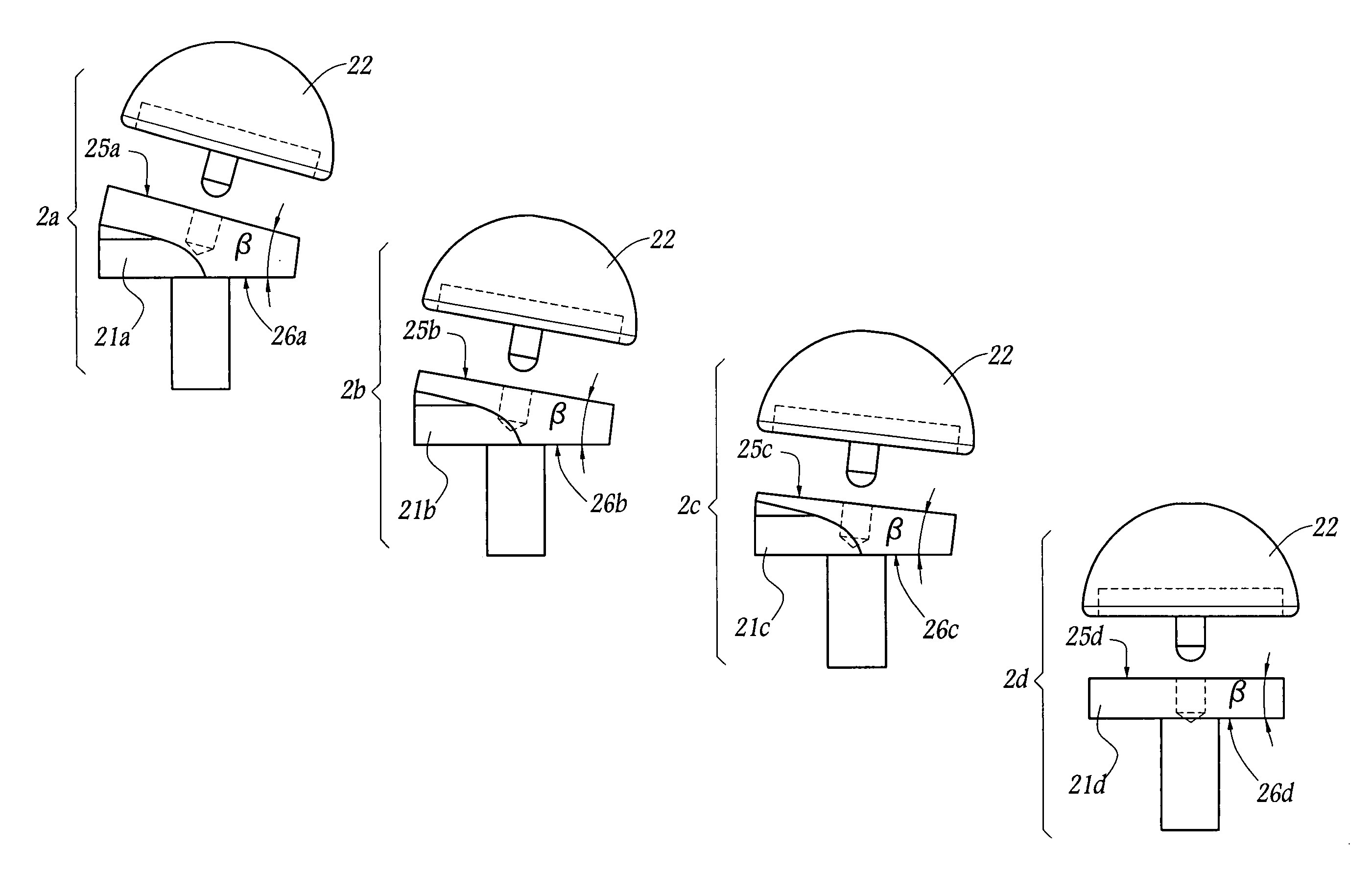

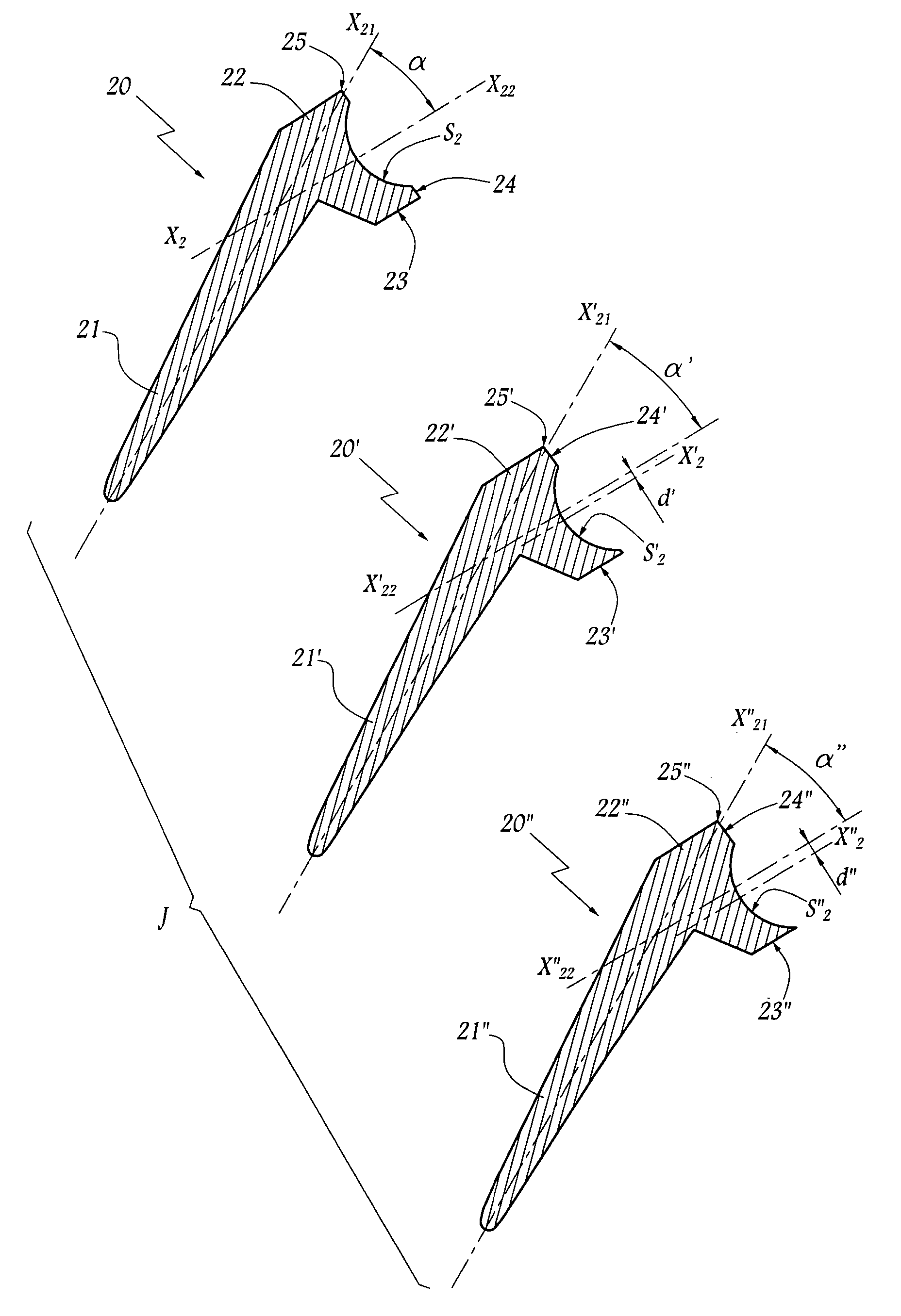

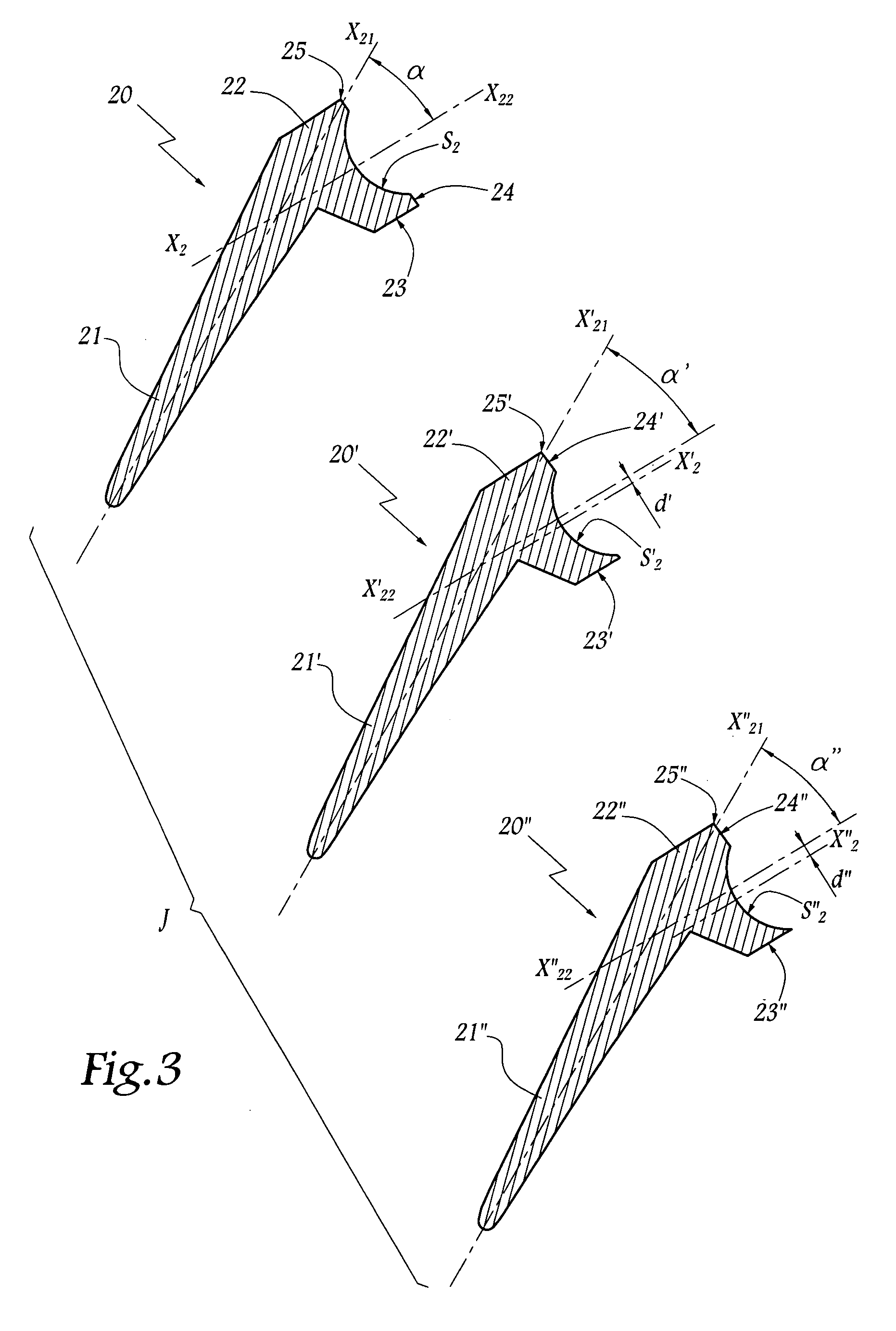

Glenoidal component, set of such components and shoulder prosthesis incorporating such a glenoidal component

ActiveUS20050278030A1Precise positioningJoint implantsShoulder jointsSpinal columnArticular surfaces

This glenoidal component for a shoulder prosthesis comprises a base which may be immobilized on the glenoid cavity of a shoulder, and an element provided to be mounted on this base and forming a convex surface of articulation centred on an axis of symmetry. This axis of symmetry is non perpendicular to a rear face of the base intended to abut against the glenoid cavity, this making it possible to compensate a defect in parallelism between the resectioned surface of the glenoid cavity and the axis of the patient's spinal column. A surgeon can select the component most adapted to the orientation of the resectioned surface from a set of components in which the axes of symmetry of the components are oriented differently with respect to their rear faces.

Owner:TORNIER SA SAINT ISMIER

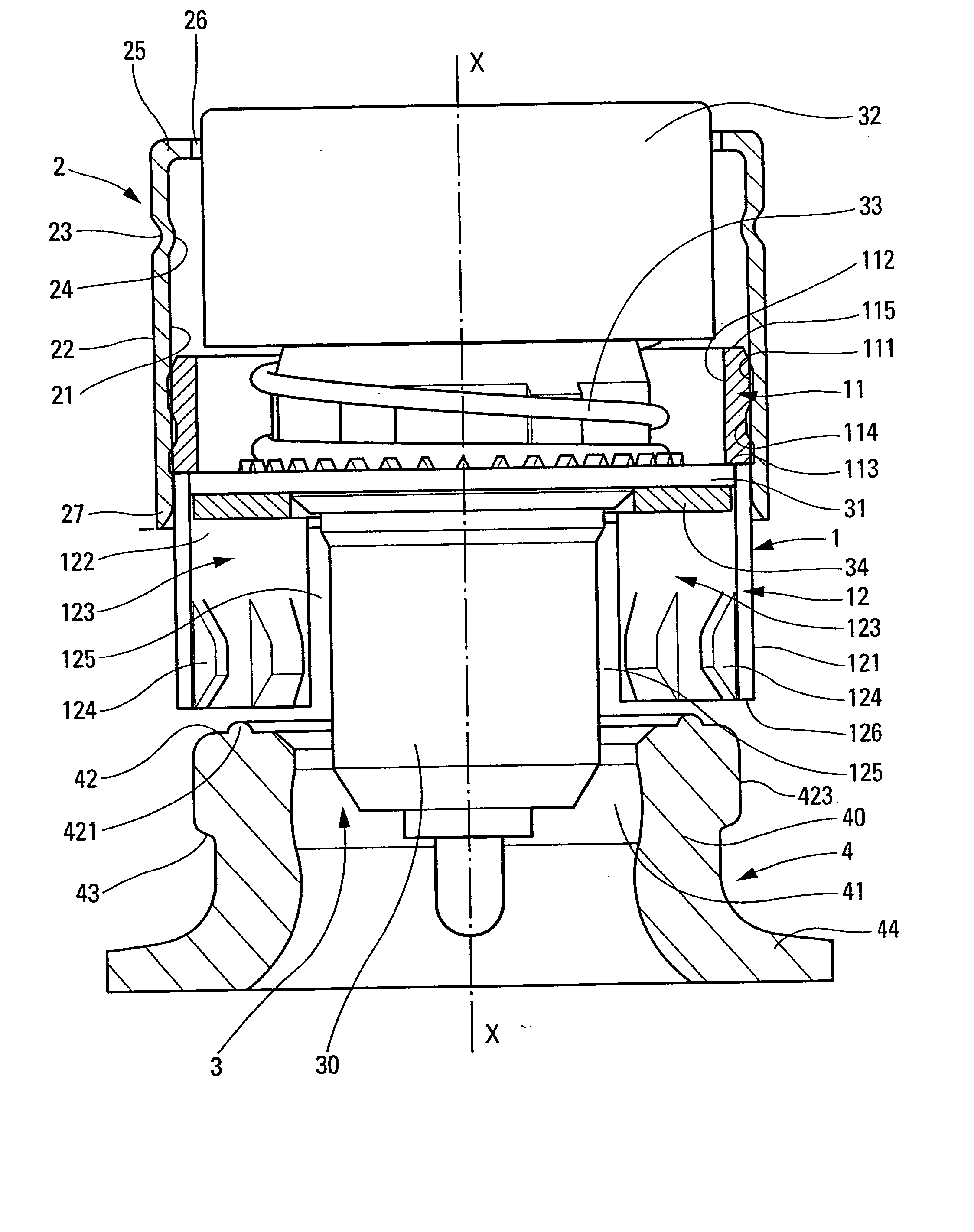

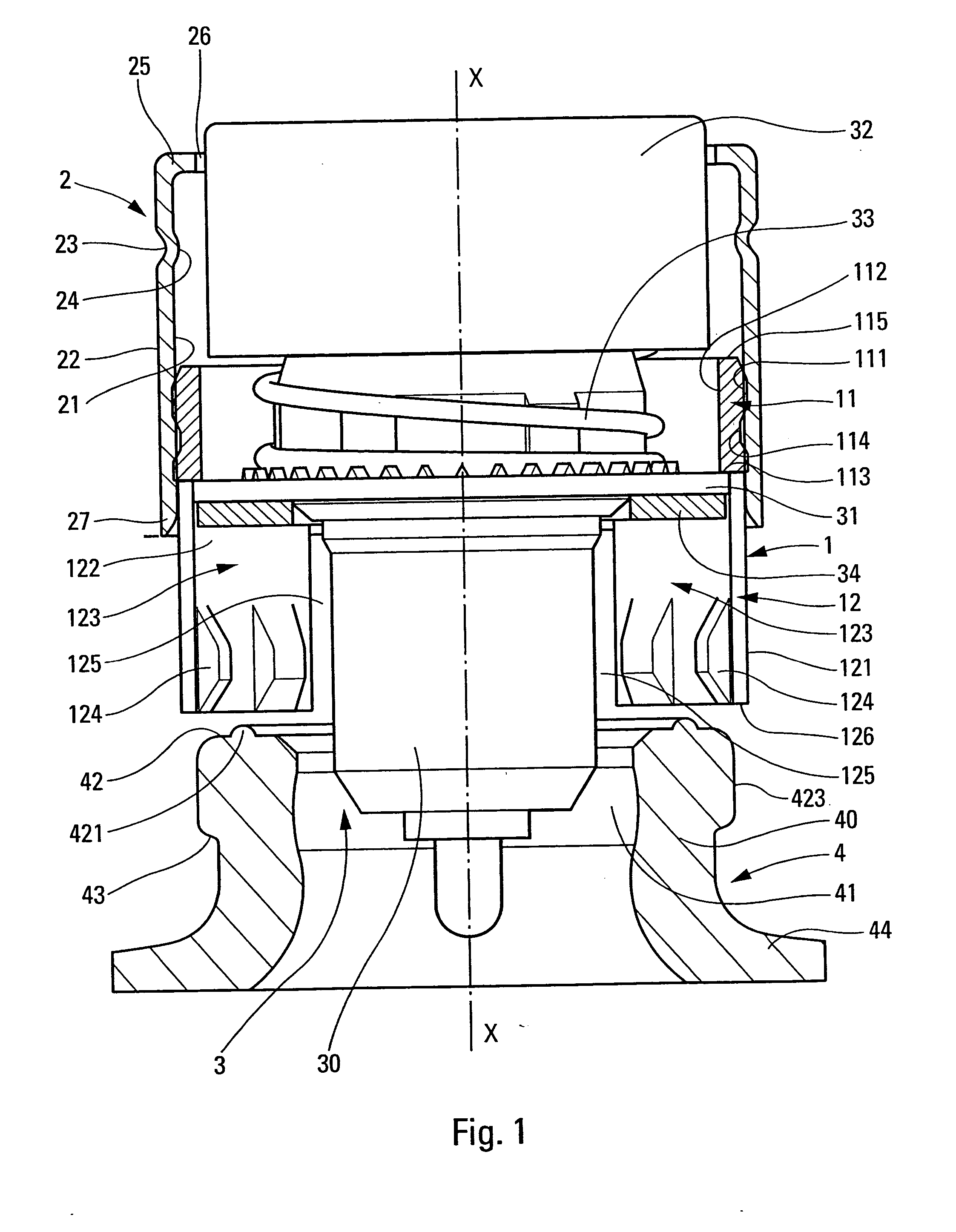

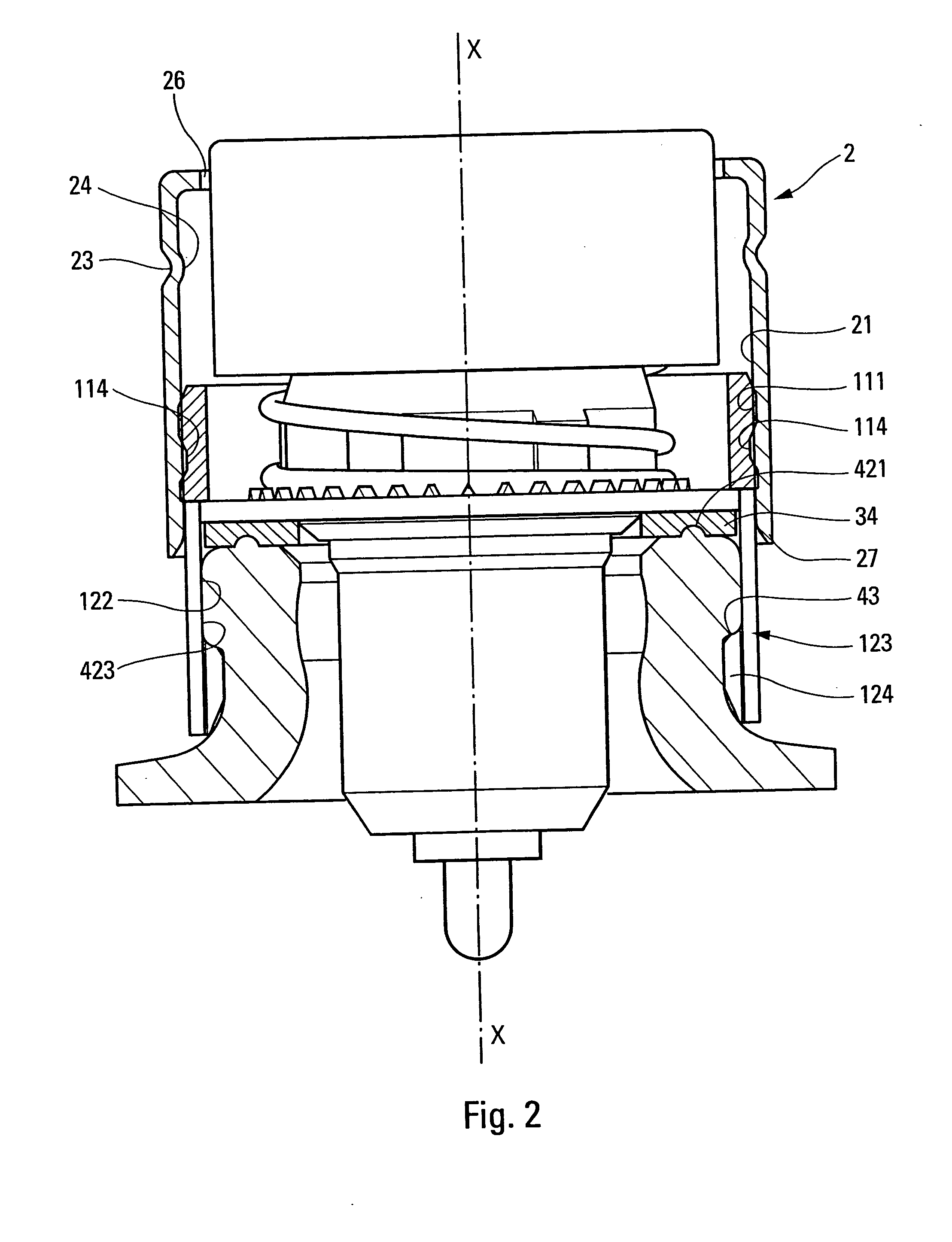

Fixing device and a fitting method for fixing a dispenser member to a reservoir opening

A fixing device for fixing a dispenser member (3) to an opening (41) in a fluid reservoir (4), said device having an axis of symmetry (X) and comprising a fixing ring (1) provided with means (113) for receiving the dispenser member (3) and with means (12) for fixing to the opening in the reservoir, said ring having a peripheral outside wall (111, 121), and a band (2) mounted on the ring so as to lock the ring on the reservoir opening, said band having an inside wall (21) designed to come into contact with the outside wall of the ring, said fixing device being characterized in that the outside wall of the ring is provided with at least one recess (114) and the inside wall (21) of the band is provided with at least one projecting profile (24) serving to come into engagement in the recess in the ring.

Owner:VALOIS SA

Side-emitting collimator

ActiveUS20050286251A1Effective lightingLighting support devicesPoint-like light sourceAxis of symmetryOptical axis

A side-emitting collimator employs a combination of refraction and internal reflection to organize light from a light source into oppositely directed collimated beams. A light source chamber over the light source is defined by substantially cylindrical and aspheric refracting surfaces positioned to gather light into the collimating lens. The aspheric refracting surfaces redirect a portion of the light from the light source into a direction perpendicular to the optical axis of the light source. The substantially cylindrical surfaces refract light from the light source onto an aspheric upper reflecting surface. Light incident upon the aspheric upper reflecting surface is collimated into a direction perpendicular to the optical axis of the light source. The side-emitting collimator includes mirror image collimator halves, each producing a collimated beam. The collimator halves are rotationally symmetric about a common axis of symmetry above a plane including the axis of symmetry.

Owner:WHELEN ENGINEERING COMPANY

Process to design and fabricate a custom-fit implant

InactiveUS8706285B2High precisionImprove accuracyProgramme controlImage enhancementAxis of symmetryCustom made implant

A process for designing and fabricating a custom-fit implant, comprising: a) processing medical image data of a patient's pathologically defective or anatomically deformed area having a symmetrical part to construct a three-dimensional (3D) digital model; b) forming a mirror image of the left or right side of the three-dimensional (3D) digital model based on its axis of symmetry depending on which side the pathologically defective or anatomically deformed area is; c) overlying the mirror image on the original image to form a composite image with a non-overlapping area wherein the implant will be fitted; d) generating a digital implant by cutting off the non-overlapping area of the mirror image; e) designing mounting points between the digital implant and the pathologically defective or anatomically deformed area where the implant is mounted thereon; f) building a positive and a negative mold based on the digital implant to fabricate a custom-fit implant.

Owner:UNIVERSITI MALAYA

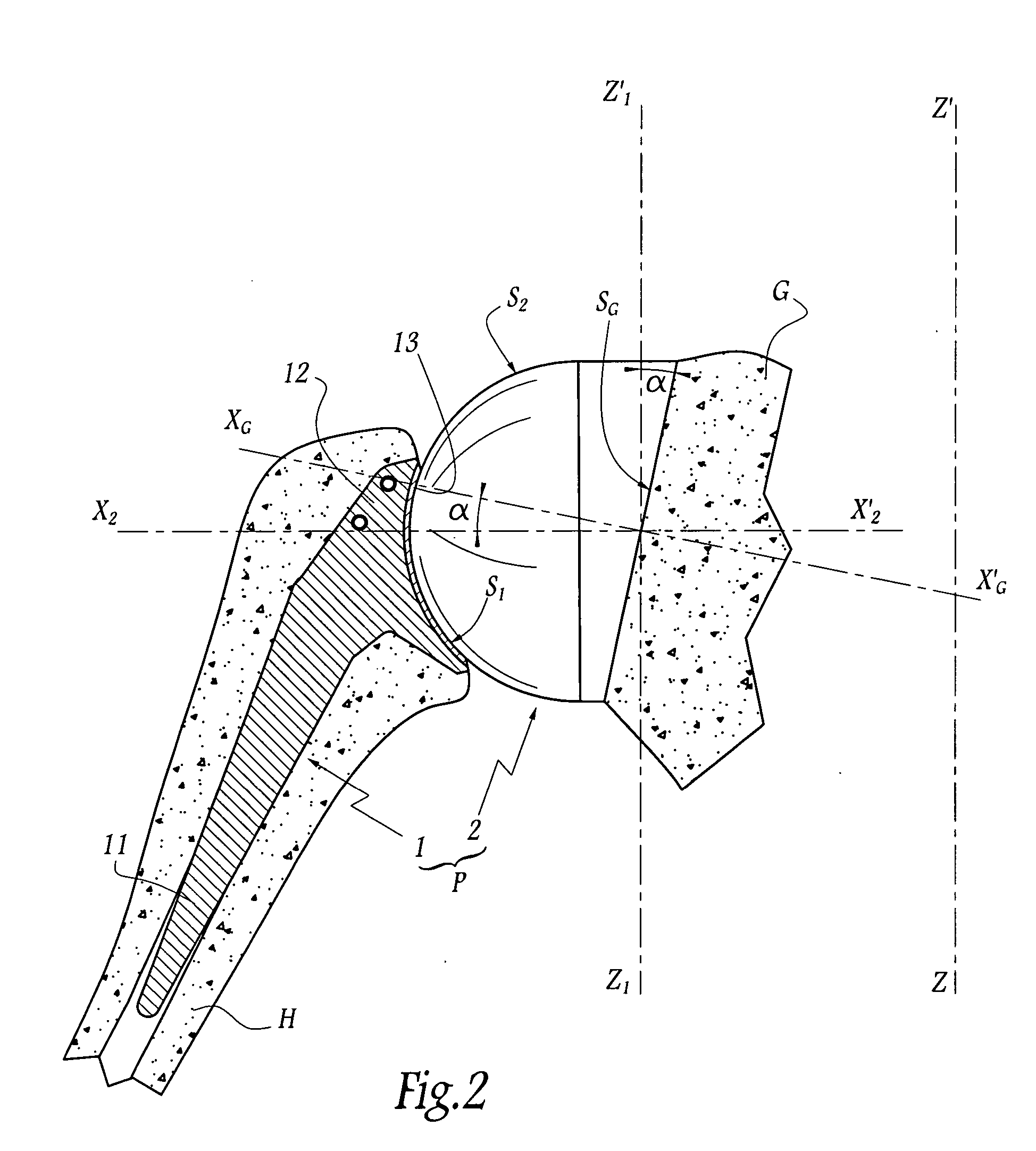

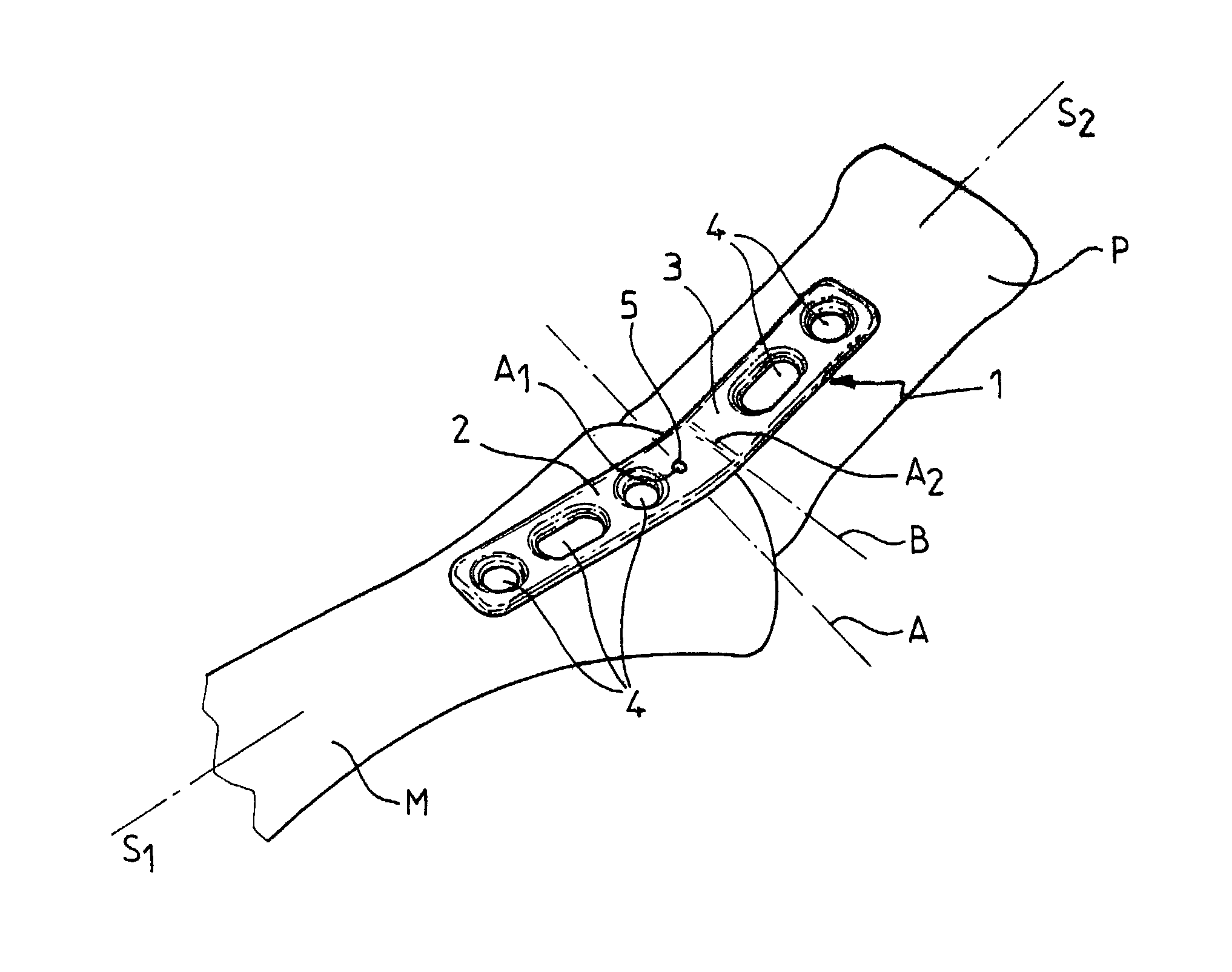

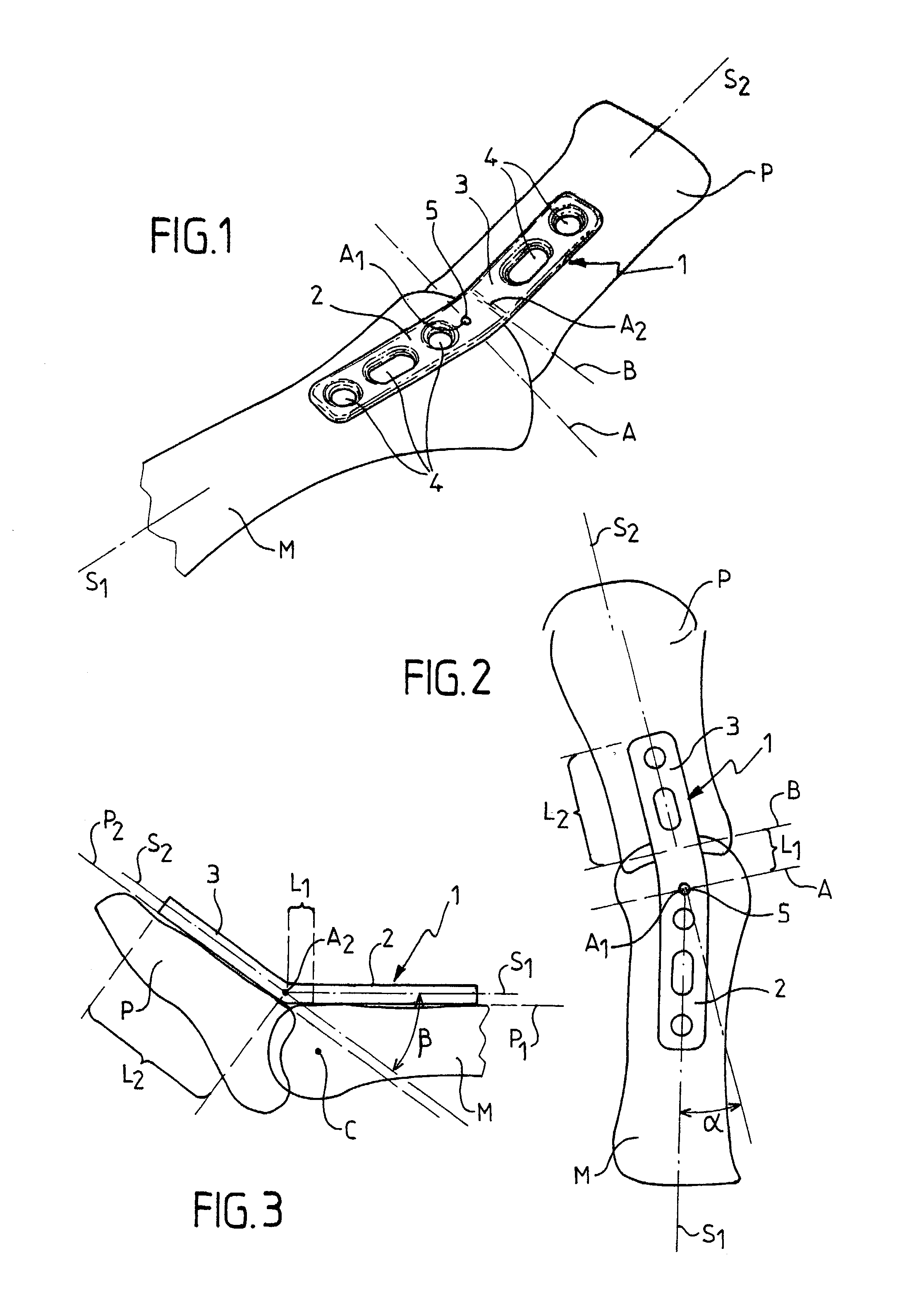

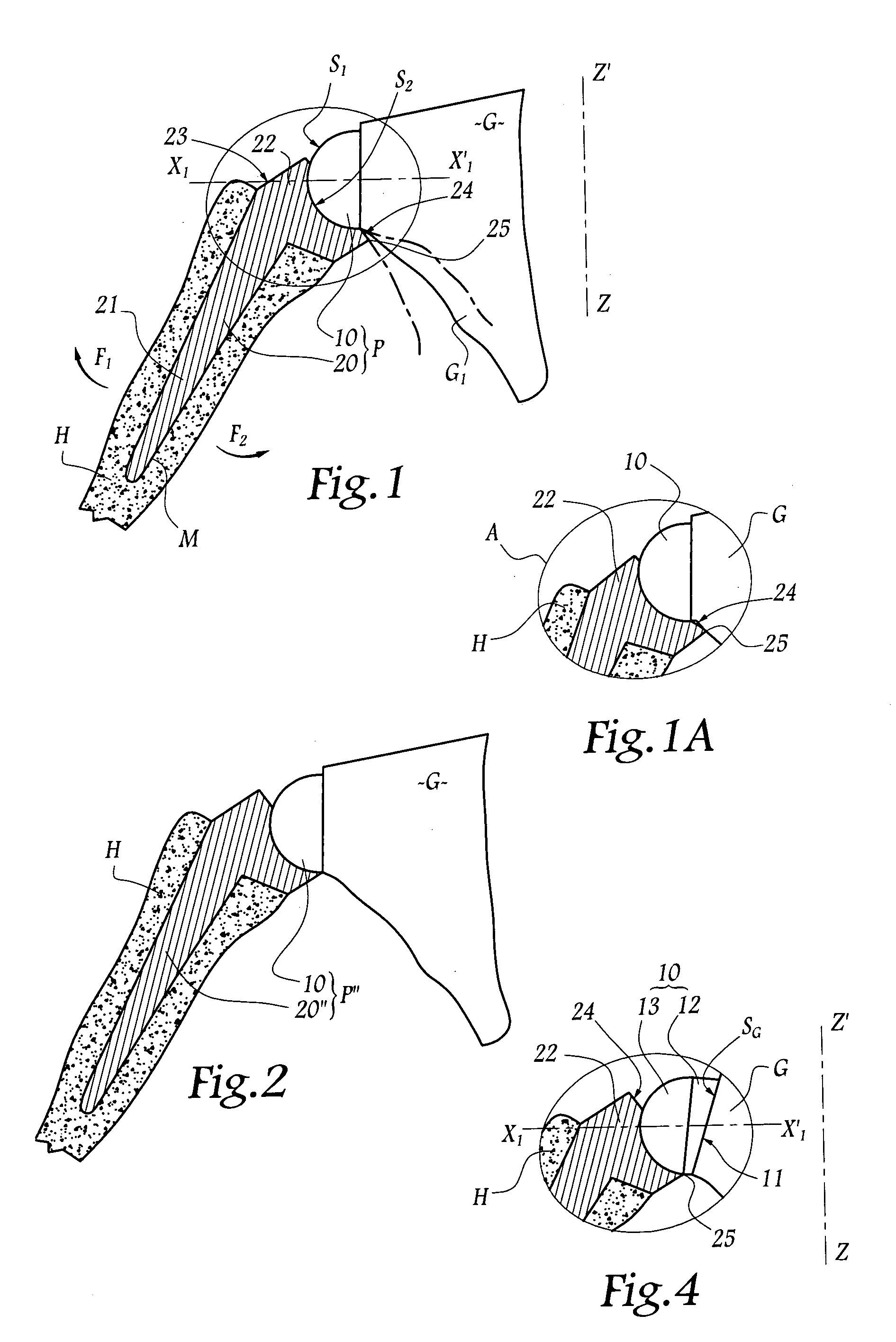

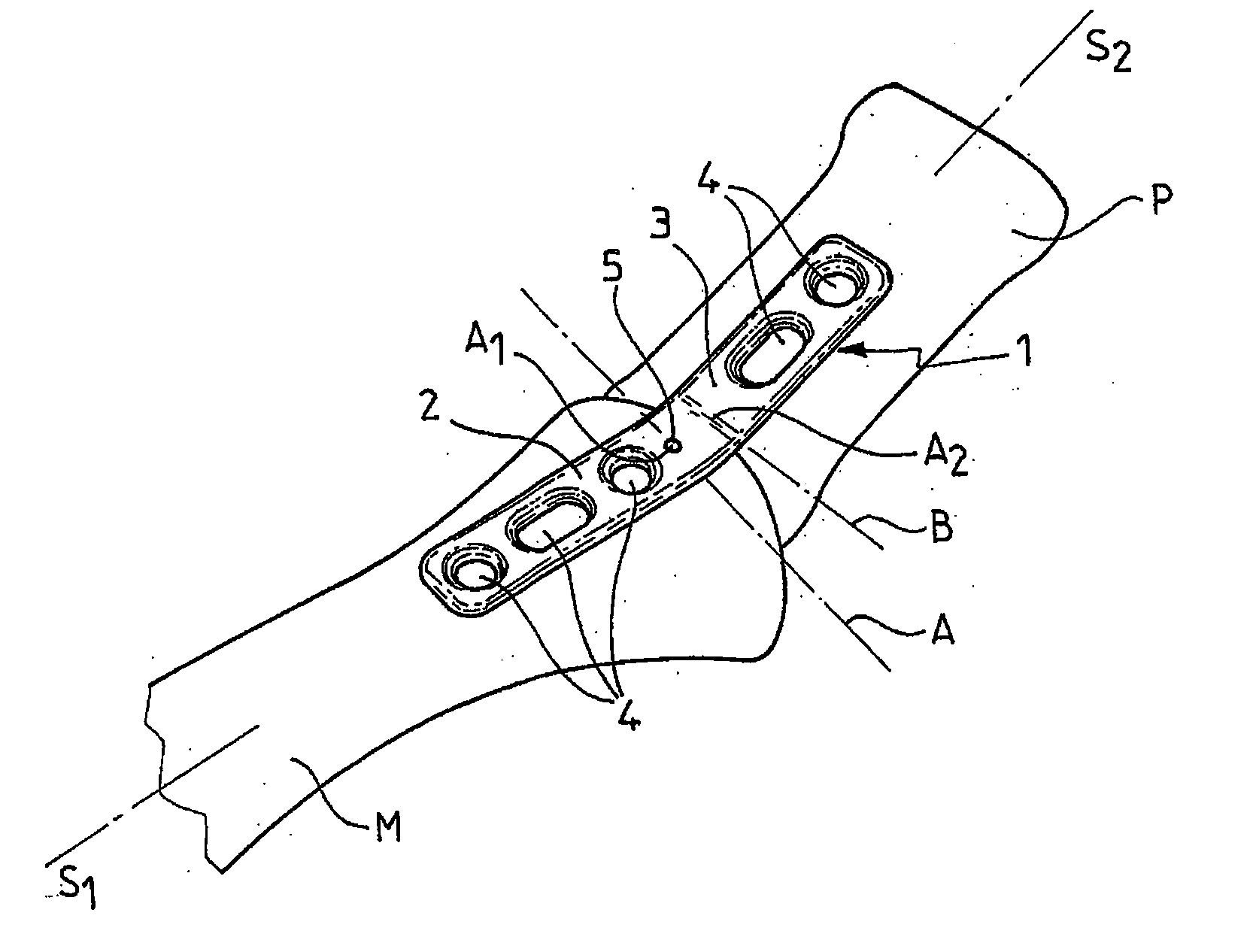

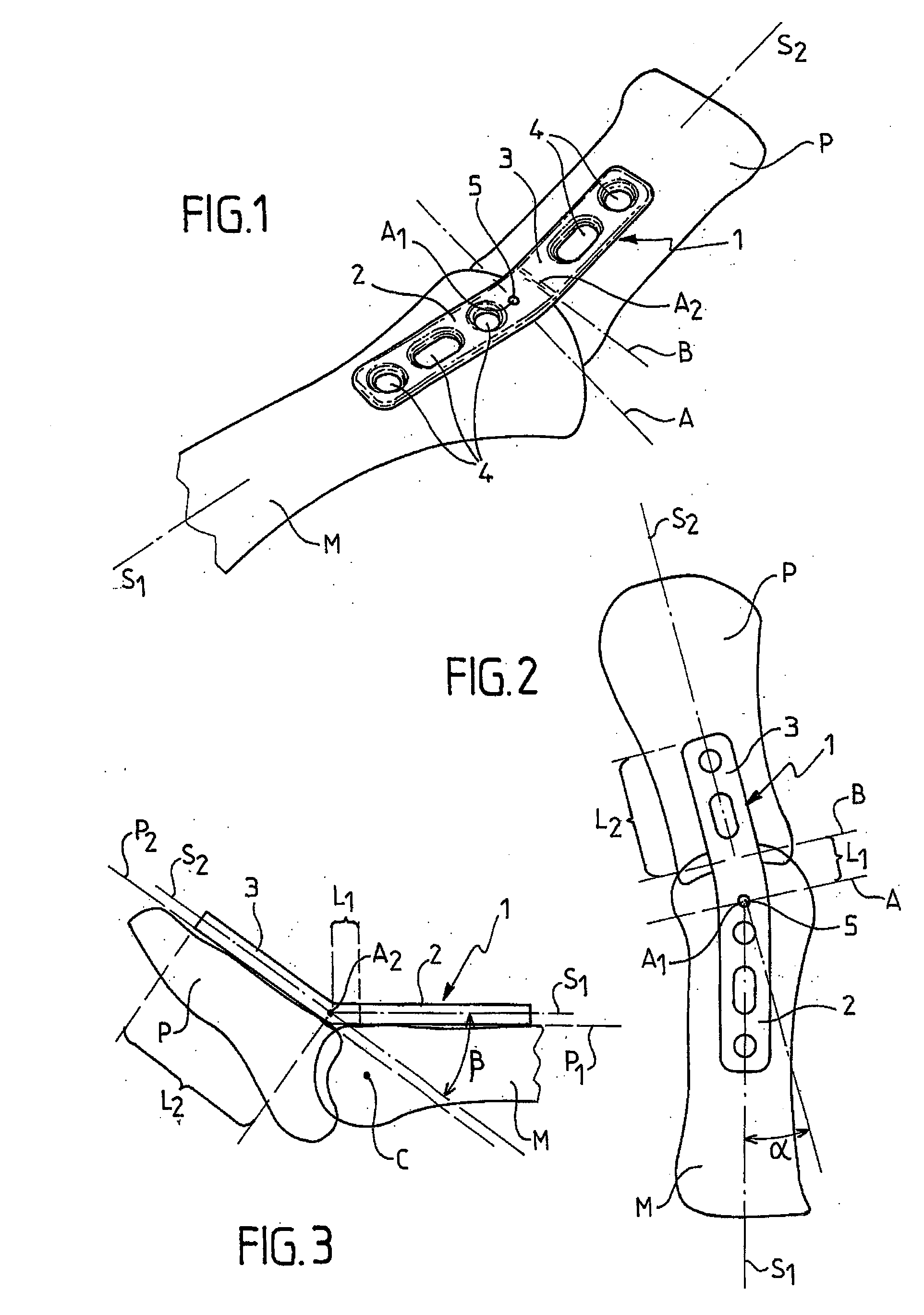

Plate for fixing the bones of a joint, in particular a metatarso-phalangeal joint

InactiveUS20030060827A1Improve accuracyEasy to placeJoint implantsBone platesJoint arthrodesisVertical plane

The invention relates to a plate for fixing the bones of a joint, in particular of a metatarso-phalanageal joint, for the purpose of performing arthrodesis, wherein: the plate comprises two sections, respectively a proximal section and a distal section, each section having a respective longitudinal axis of symmetry S1, S2 such that the projection onto a horizontal plane of tie axis of symmetry S2 of the distal section presents an angle of inclination relative to the projection of the axis of symmetry S1 of the proximal portion, the projections intersecting at a point A; and the projection onto a vertical plane of the axis of symmetry S2 presents an angle of inclination relative to the projection of the axis of symmetry S1, their intersection taking place at a point A2 which is distinct from the point A1

Owner:SMITH & NEPHEW INC

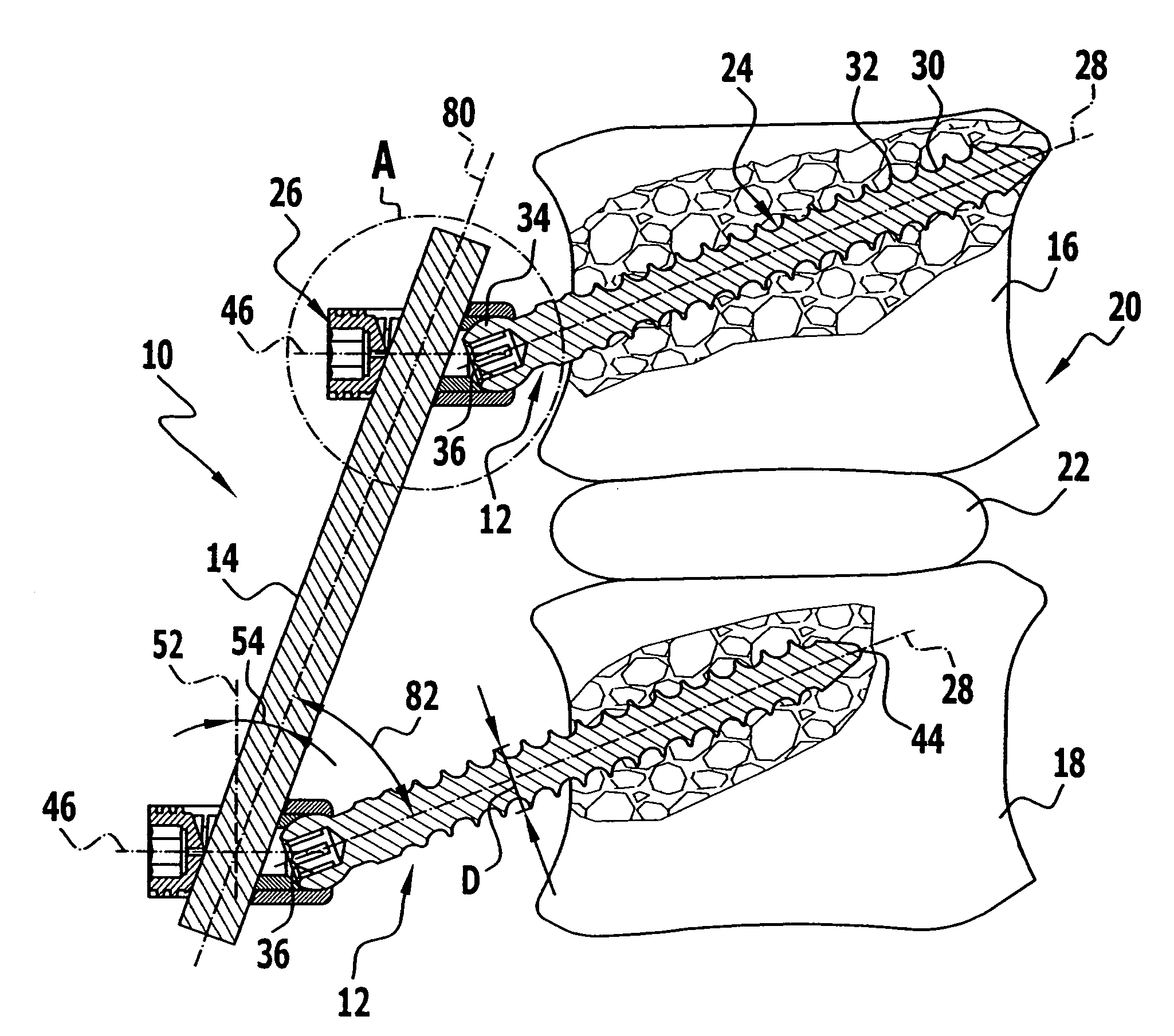

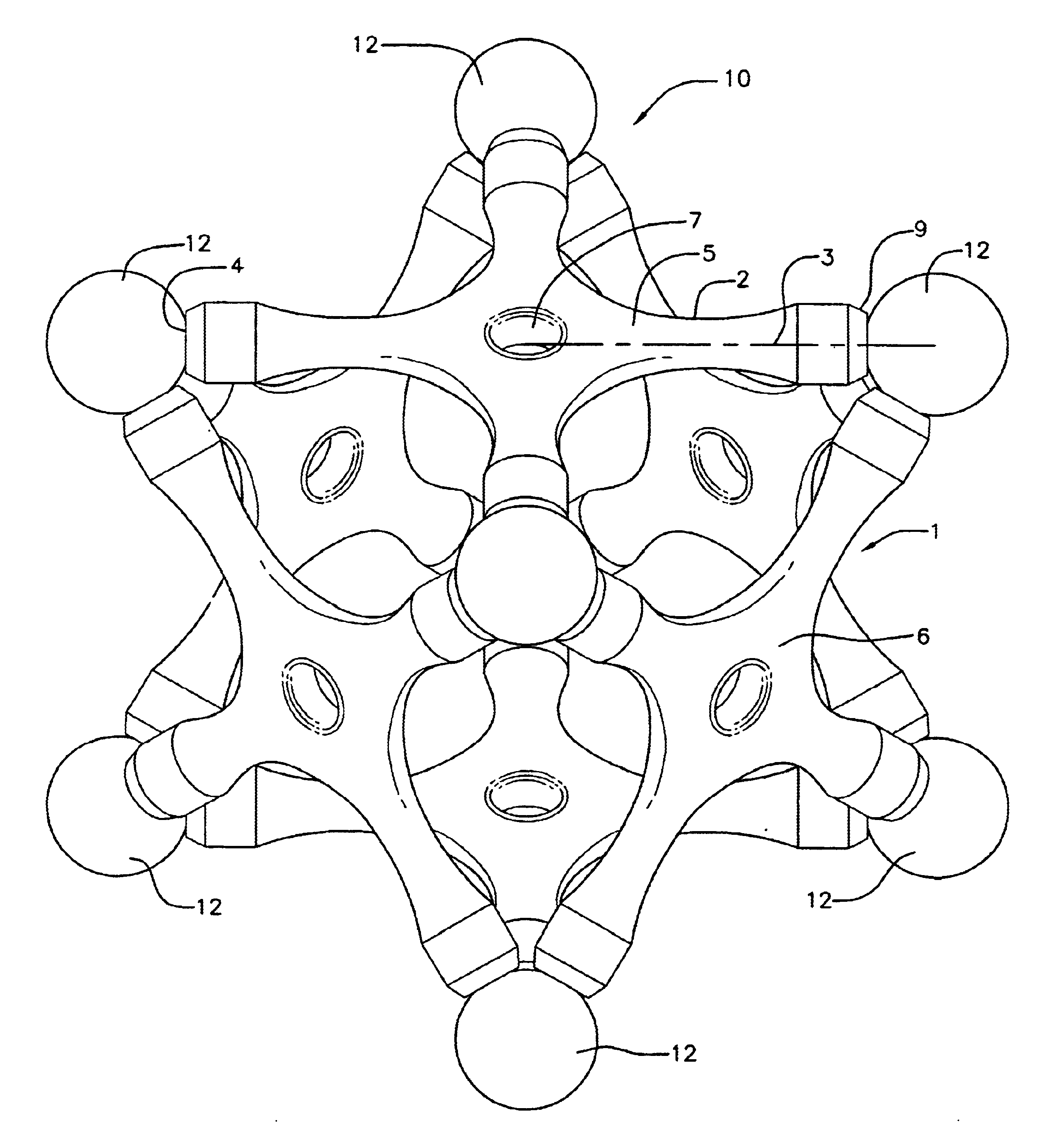

Implant system and fastening element for an implant system

InactiveUS20060195098A1Easy to optimizeStable supportSuture equipmentsInternal osteosythesisAxis of symmetryEngineering

The present invention relates to a fastening element for an implant system, which comprises at least two fastening elements fixable to bone parts or the like and at least one connecting element fixable to the at least two fastening elements, wherein the fastening element comprises a fastening part with a fastening portion at the distal end as well as a receiving part connected to the fastening part, wherein the receiving part comprises a connecting-element receiver for receiving the connecting element as well as a fixing element for fixing the fastening element in the connecting-element receiver, wherein the connecting-element receiver is designed asymmetrically in relation to an axis of symmetry or longitudinal axis of the fixing element.

Owner:AESCULAP AG

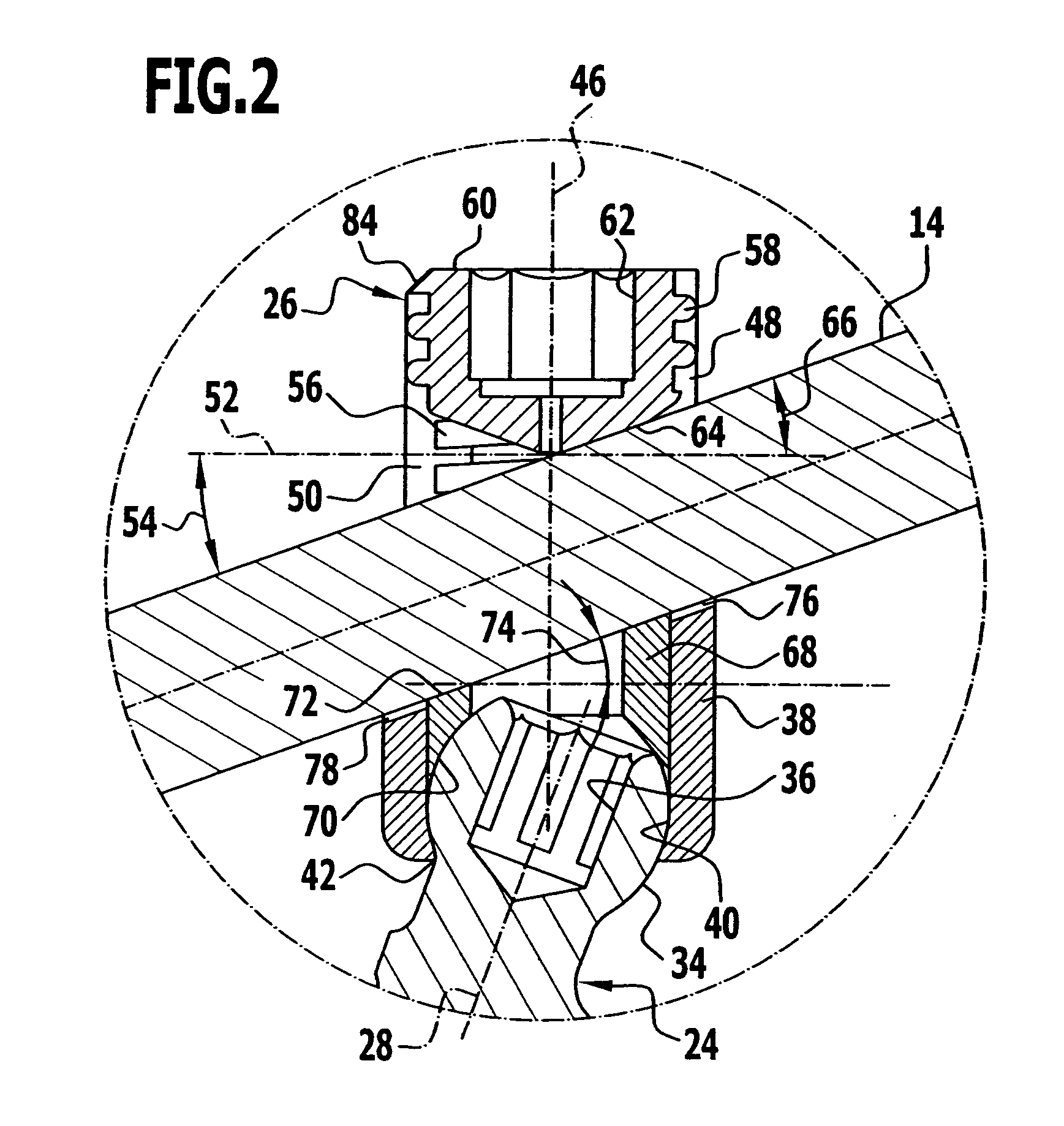

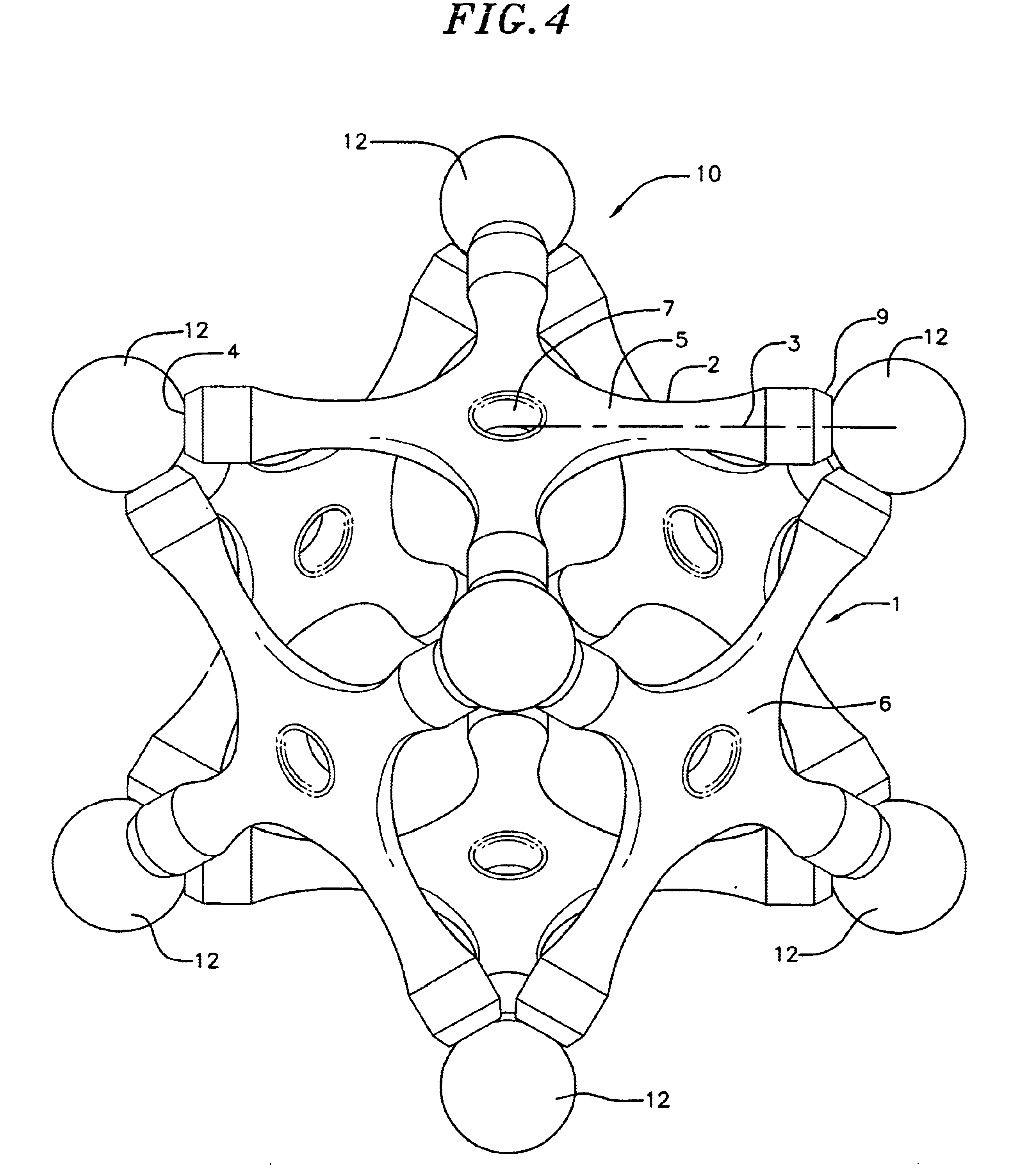

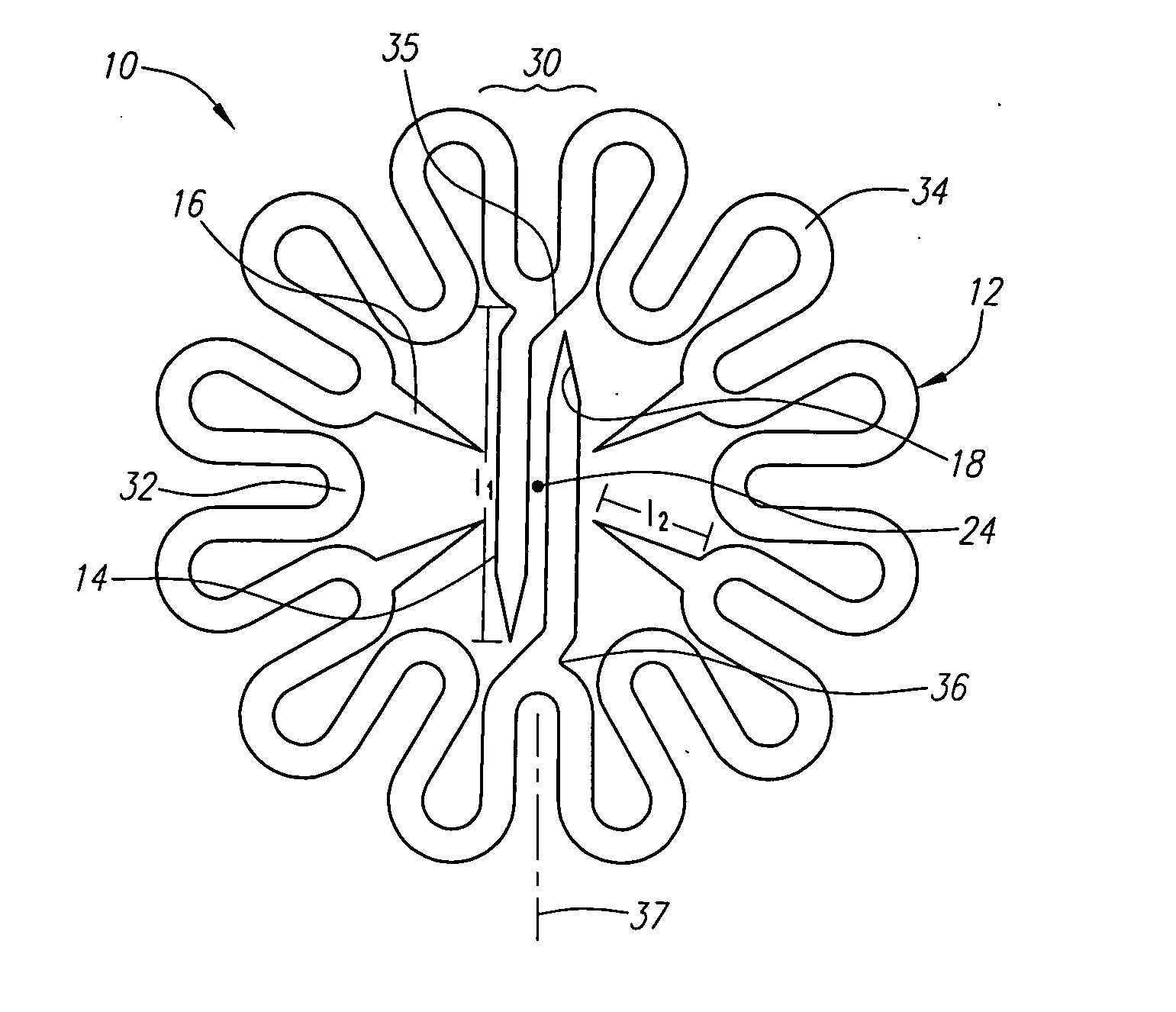

Magnetic construction toy

The invention relates to an improved geometric construction toy for building geometrical sculptures and consists of a multiplicity of magnetizable bodies and a multiplicity of construction members. The construction members have a plurality of connecting arms that have a first cantilevered end and a second portion that is integral with a hub portion and a permanent magnet in the first end for magnetically coupling with a magnetizable body. The hub portion has a geometrical center and the connecting arms have an axis of symmetry that passes through the geometrical center where the axes of symmetry are in the same plane and where the peripheral surface of a connecting arm intermediate the first end and second portion is symmetrical to the axis of symmetry in planes orthogonal to the axis.

Owner:BALANCHI STEVE H

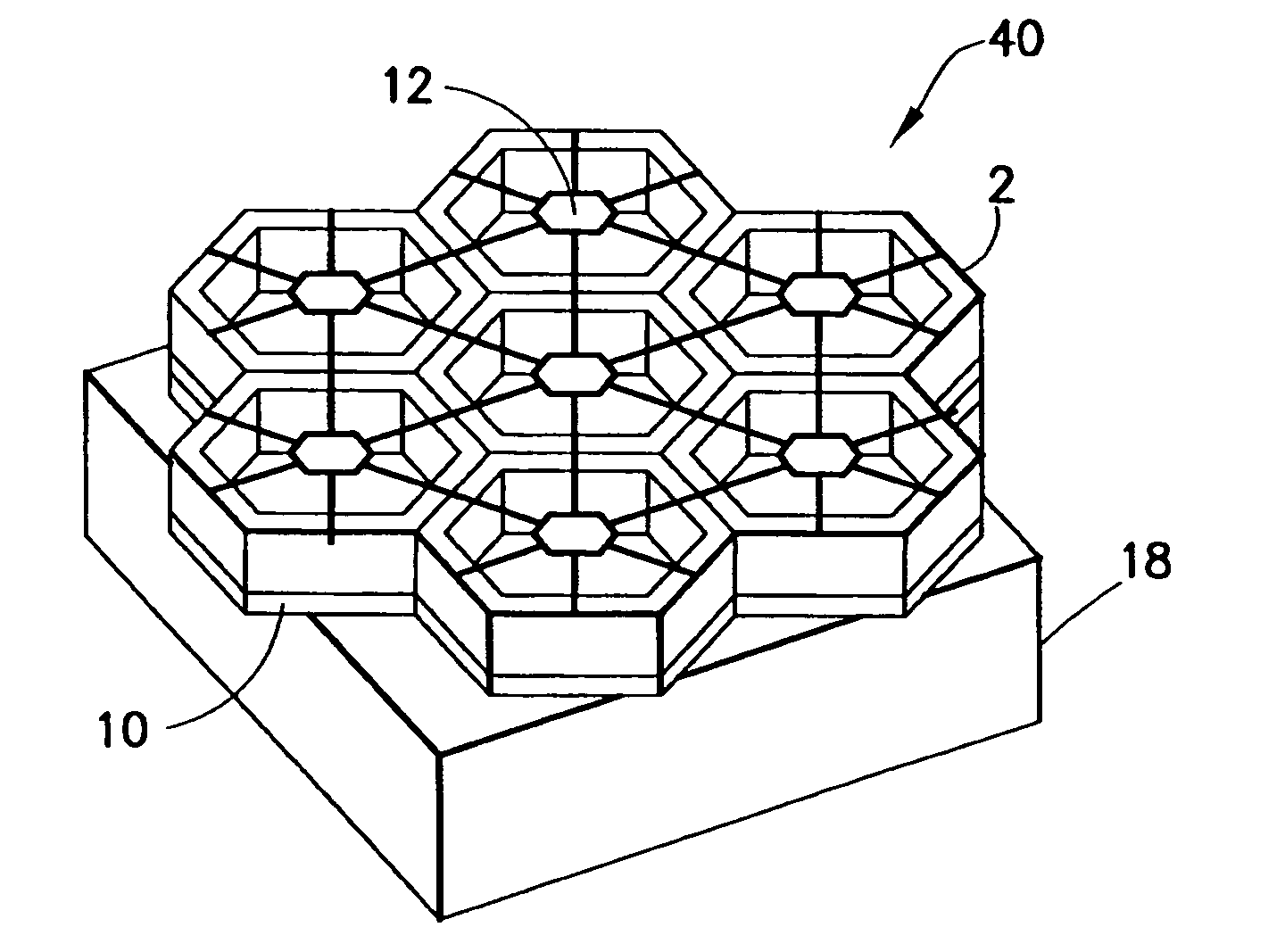

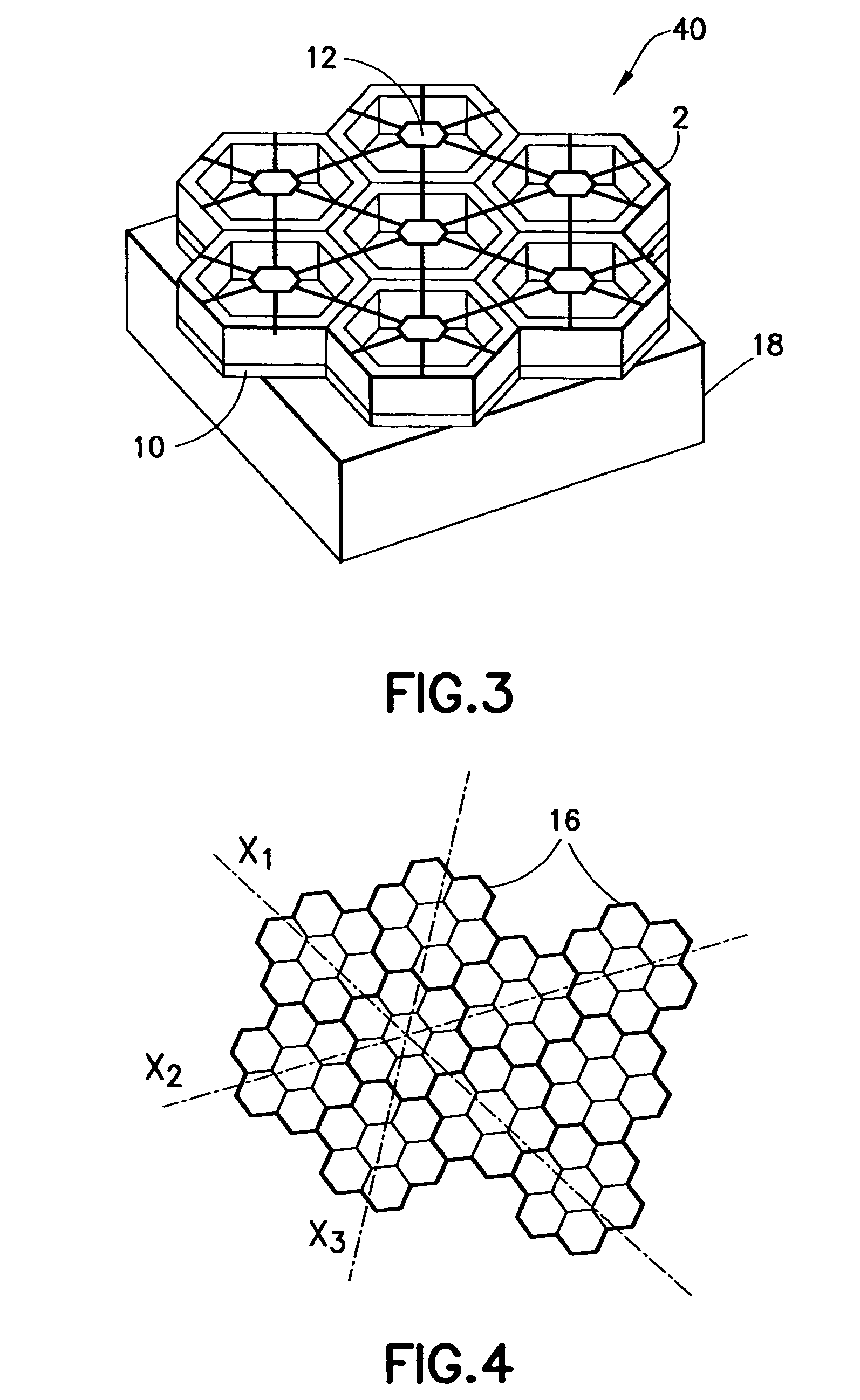

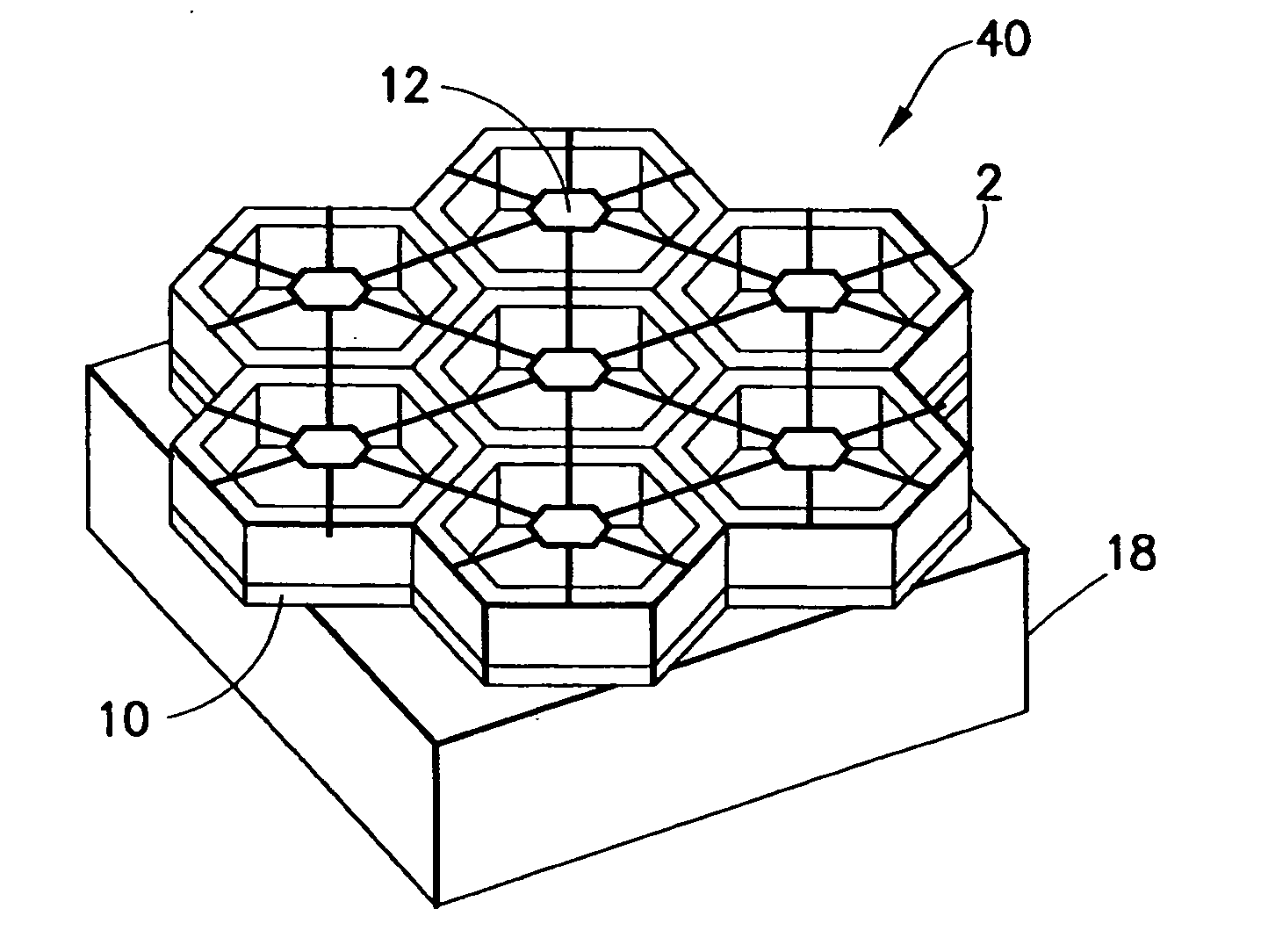

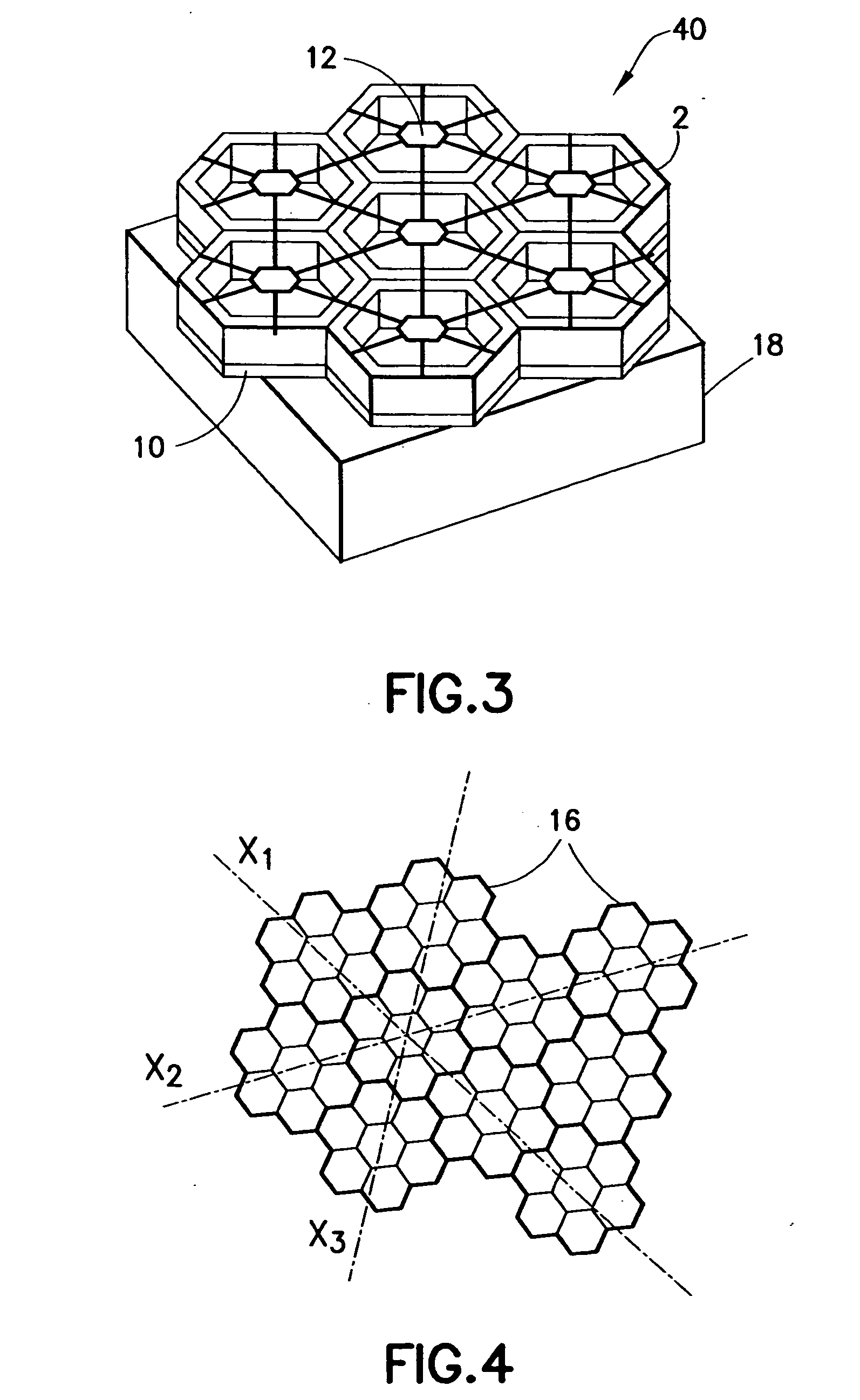

Alignment method for fabrication of integrated ultrasonic transducer array

InactiveUS7052464B2Ultrasonic/sonic/infrasonic diagnosticsDecorative surface effectsCMOSAxis of symmetry

An integrated circuit is fabricated by micromachining a hexagonal array of cMUT elements on top of a substrate comprising a hexagonal array of CMOS cells. Each cMUT element overlies a respective CMOS cell in one-to-one correspondence. During layout of the mask for micromachining the cMUT layer, either the hexagonal pattern or the alignment key is rotated until an axis of symmetry of the hexagonal pattern is aligned with an axis of the alignment key. Later, when the mask is superimposed on the CMOS substrate, the alignment key on the mask is aligned with an alignment key on the substrate. This ensures that the cMUT elements formed by optical lithography will be matched to the CMOS cells.

Owner:GENERAL ELECTRIC CO

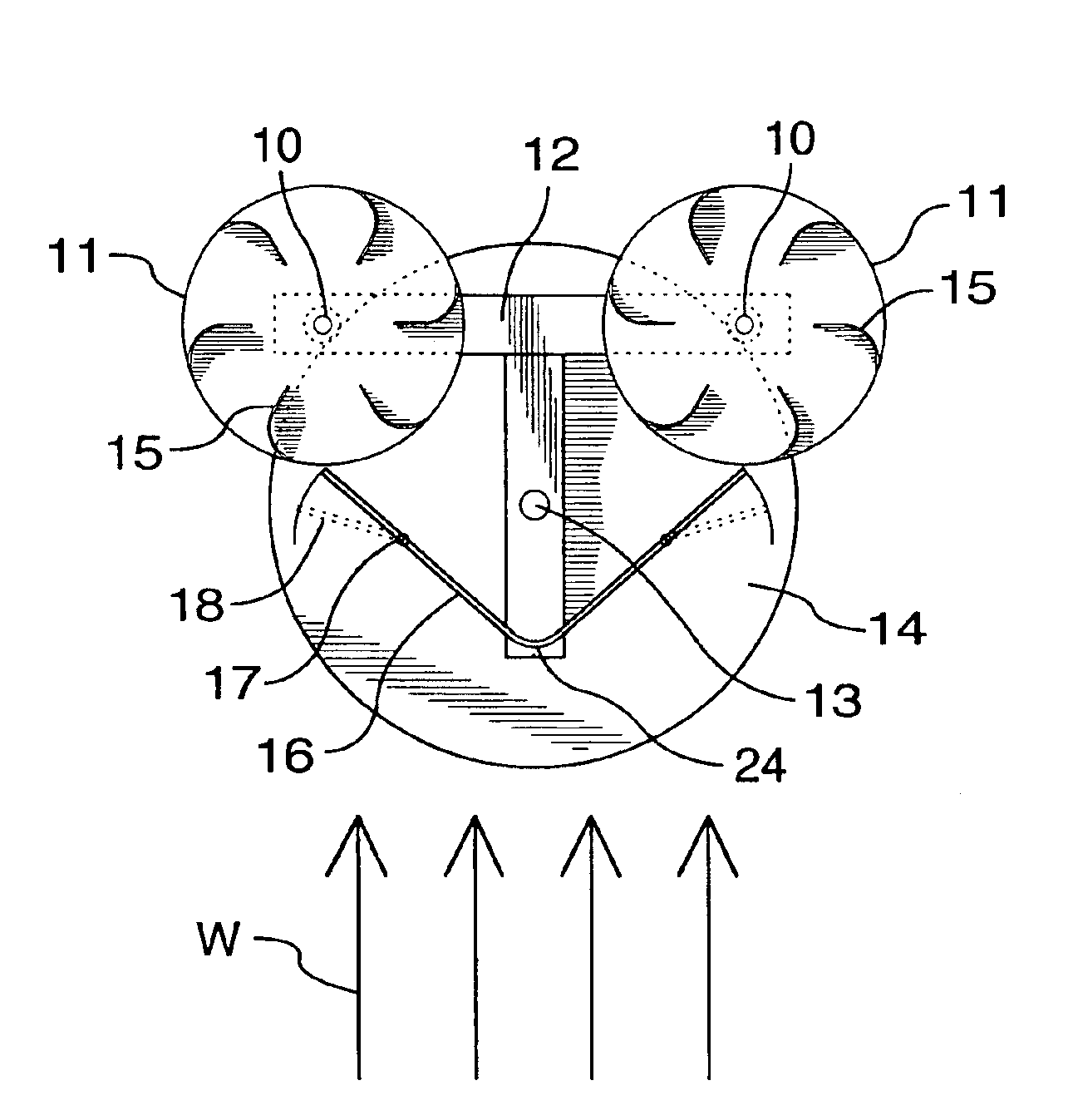

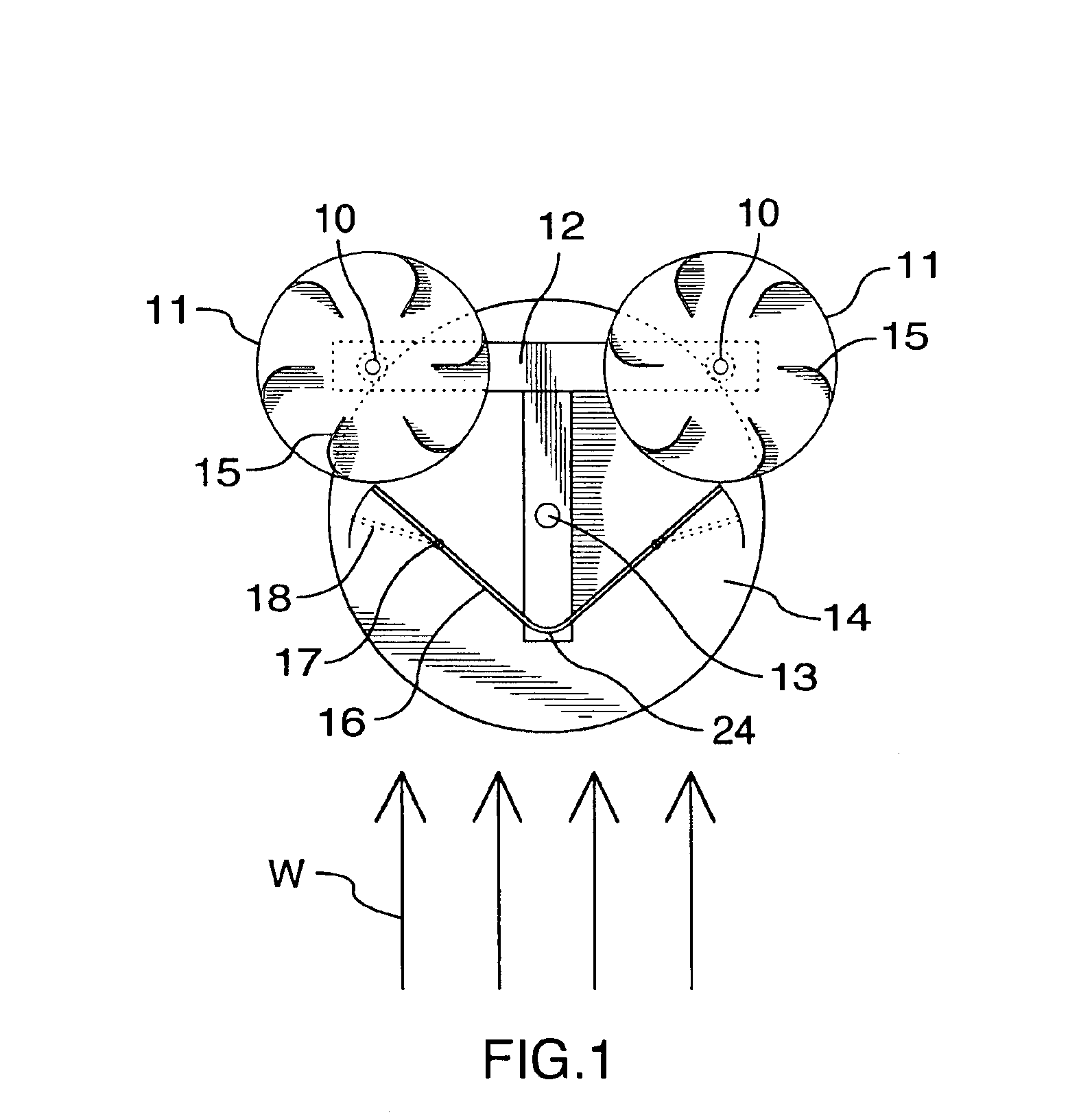

Vertical axis wind turbine

InactiveUS6942454B2Improve efficiencyPropellersWind motor controlAxis of symmetryVertical axis wind turbine

The vertical axis wind turbine has two counter-rotating rotors mounted on first and second spaced apart vertical axes. Each rotor has a plurality of rotor blades extending generally inwardly from an outer circumference, the vertical axes being mounted on a support structure which is in turn rotatable on a third vertical axis on a platform. The third axis is spaced from a point midway between the first and second axes in a direction at 90 degrees to and forward from a line between the first and second axes. The vertical axis wind turbine further has a guide vane mounted on the support structure, having a vertex forward of the third vertical axis in the direction at 90 degrees from a line between the first and second axes. The guide vane has left and right symmetrical vane portions extending towards the rotors so as to direct airflow from wind primarily towards portions of the rotors outboard of the first and second axes. The guide vane also tends to keep the vertical axis wind turbine oriented with the guide vane's axis of symmetry pointing forwardly into the wind. Movable deflector flaps pivotally mounted adjacent opposite ends of the vane portions can deflect air at least partially away from the rotors. The structure of the wind turbine can support an unrelated structure such as a restaurant.

Owner:OHLMANN HANS ARMIN

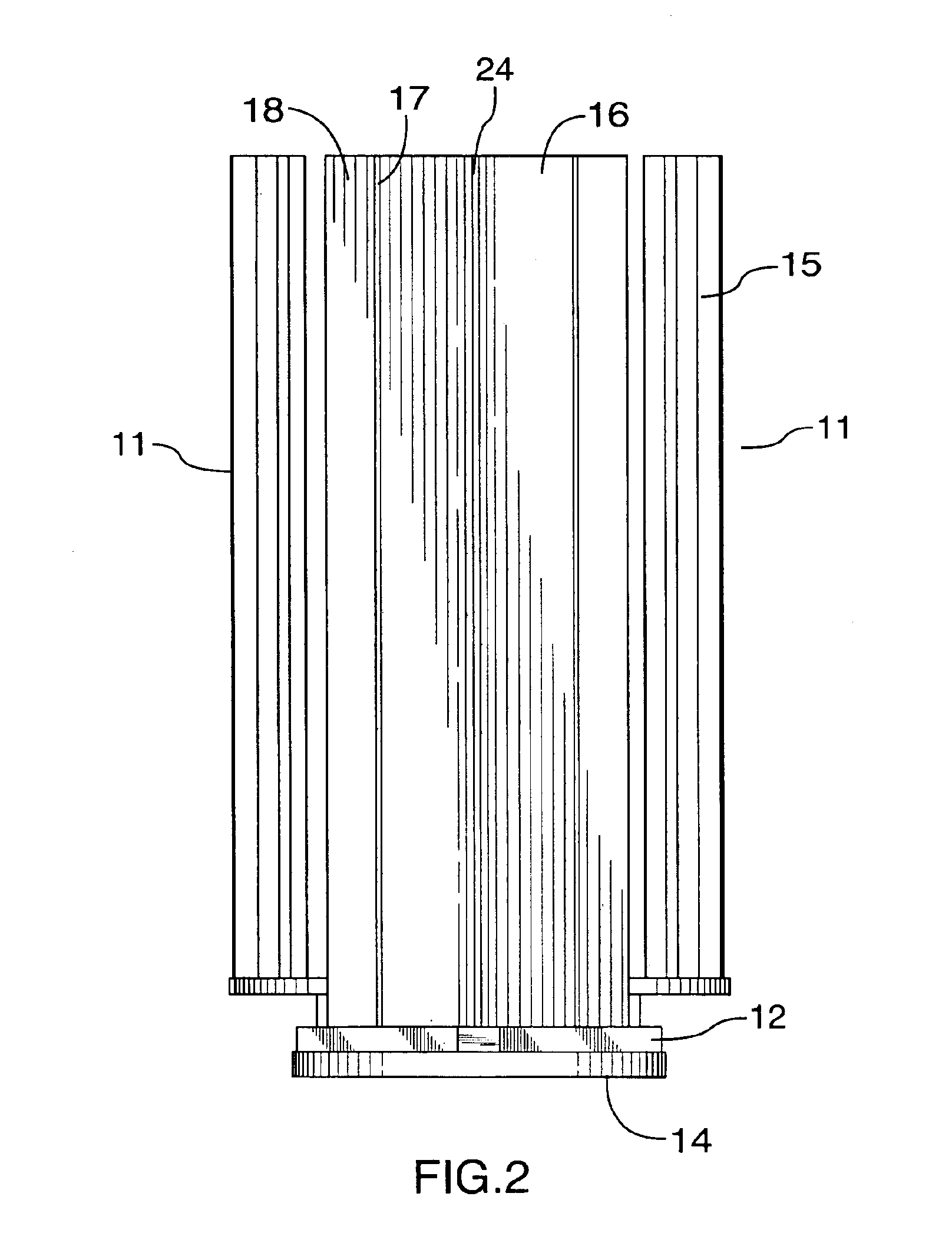

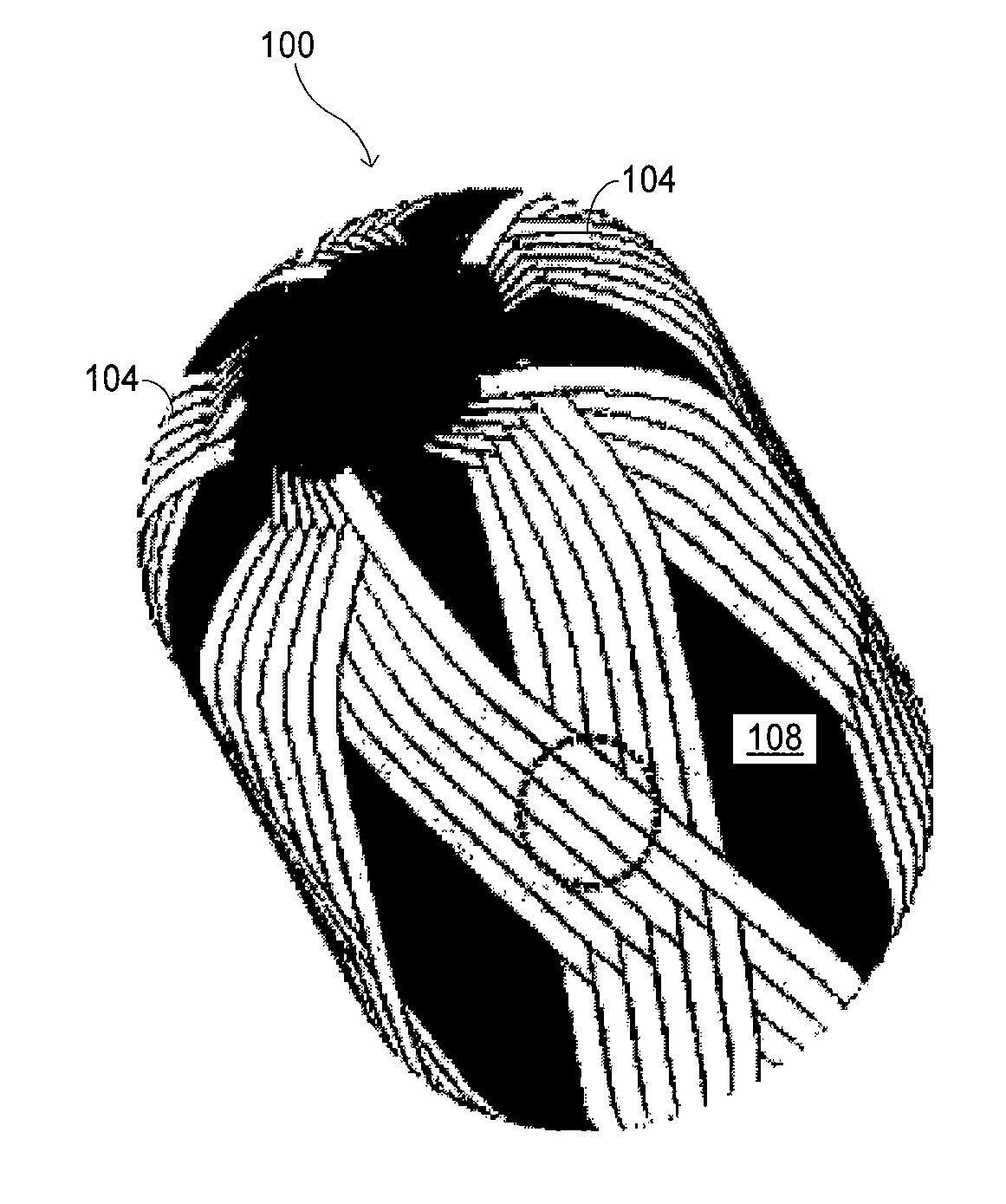

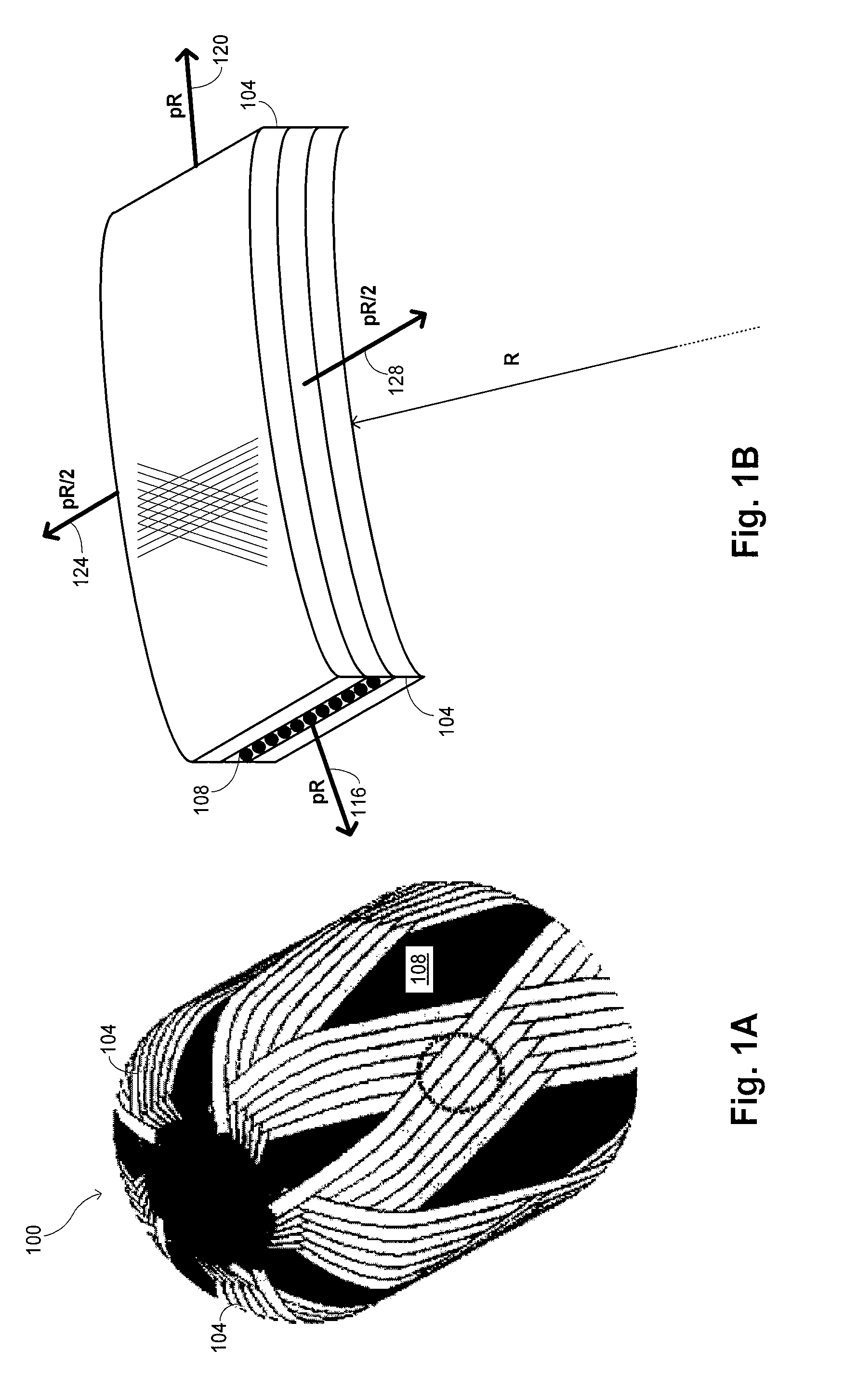

Damage and leakage barrier in all-composite pressure vessels and storage tanks

ActiveUS20090314785A1Superior barrier against leakageStrengthAdhesive processesGas handling applicationsFiberAxis of symmetry

A linerless tank structure has a body that defines an enclosed interior volume. The body has a cylindrical section having an axis of symmetry and a dome section coupled with the cylindrical section. The construction of the pressure vessel includes multiple fiber plies. At least one of the fiber plies is a helical ply having fibers traversing the dome helically about the axis of symmetry. At least a second of the fiber plies is a braided or woven ply.

Owner:COMPOSITE TECH DEV

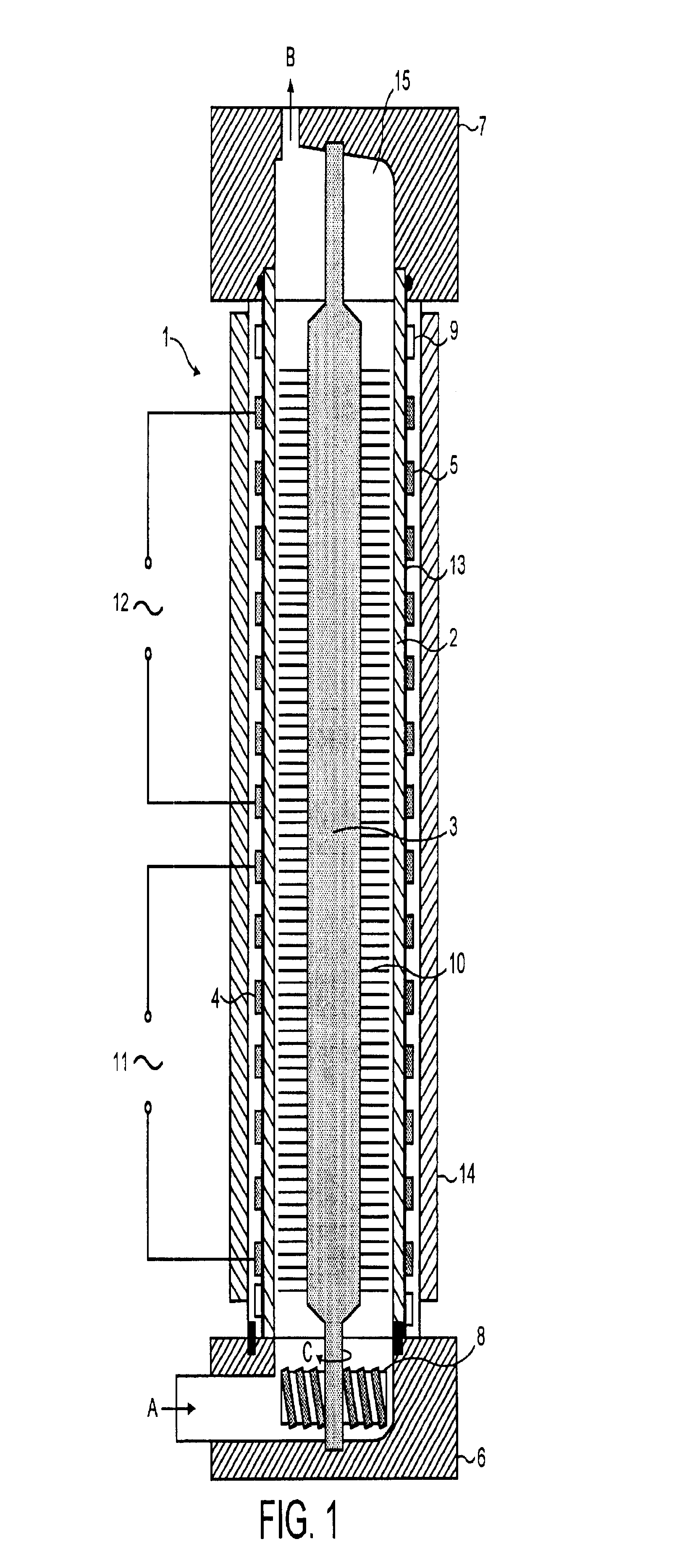

Process and module for heating liquid

InactiveUS6459854B1Accurate temperature rangeImprove heat transfer performanceImmersion heating arrangementsLiquid transferring devicesAxis of symmetryEngineering

A liquid heating module for use in a hot beverage machine, a beverage forming system that includes the module, and a process for heating liquid for forming beverages. The liquid heating module includes a hollow metal tube, a cylindrical insert which is disposed inside the hollow tube along its entire length and substantially along its axis of symmetry, at least one electrical resistor on a first outer part of the tube for preheating liquid flowing through the tube, and at least one additional electrical resistor on a second outer part of the tube for temperature adjustment of the liquid flowing through the tube.

Owner:NESTEC SA

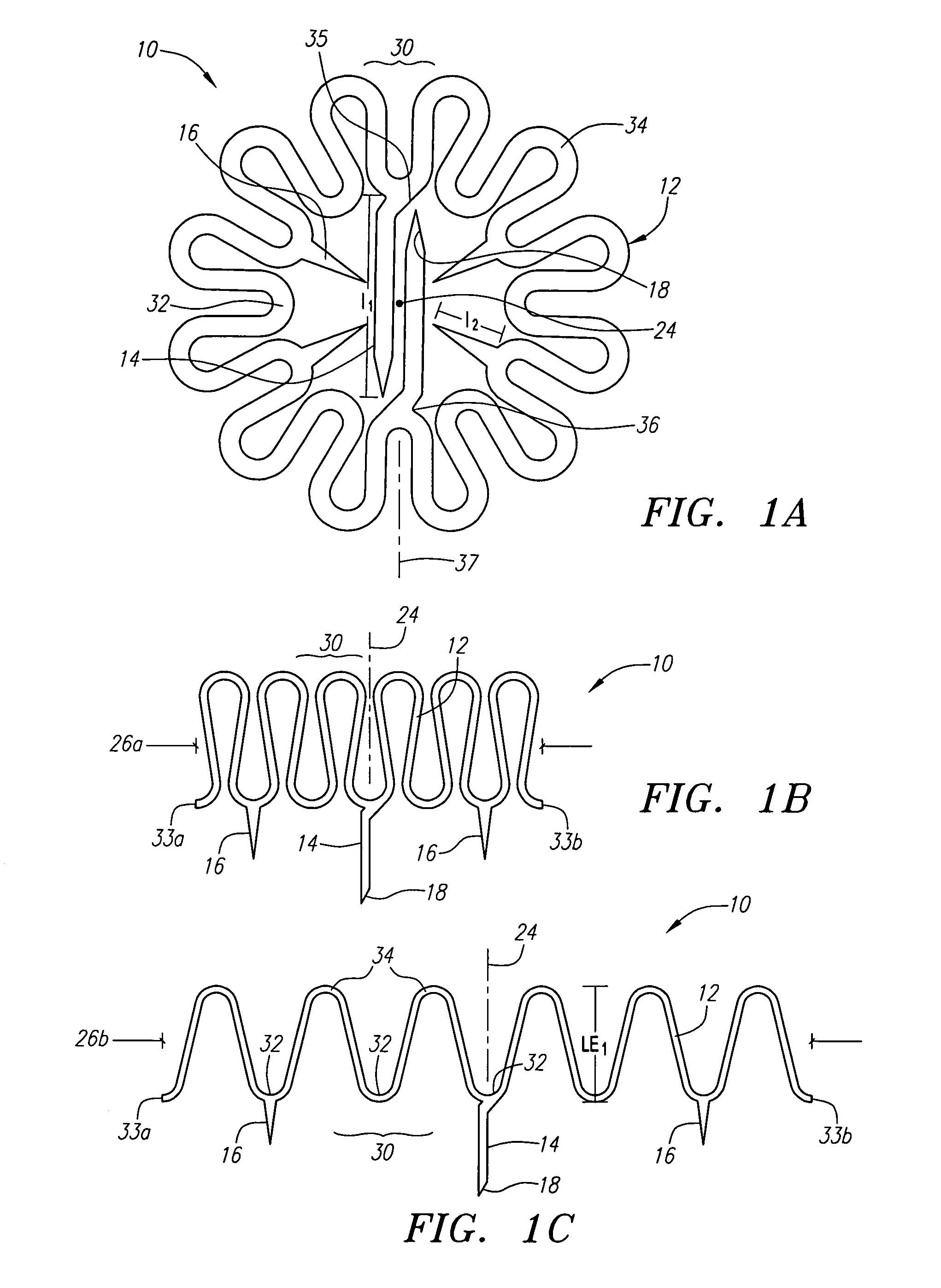

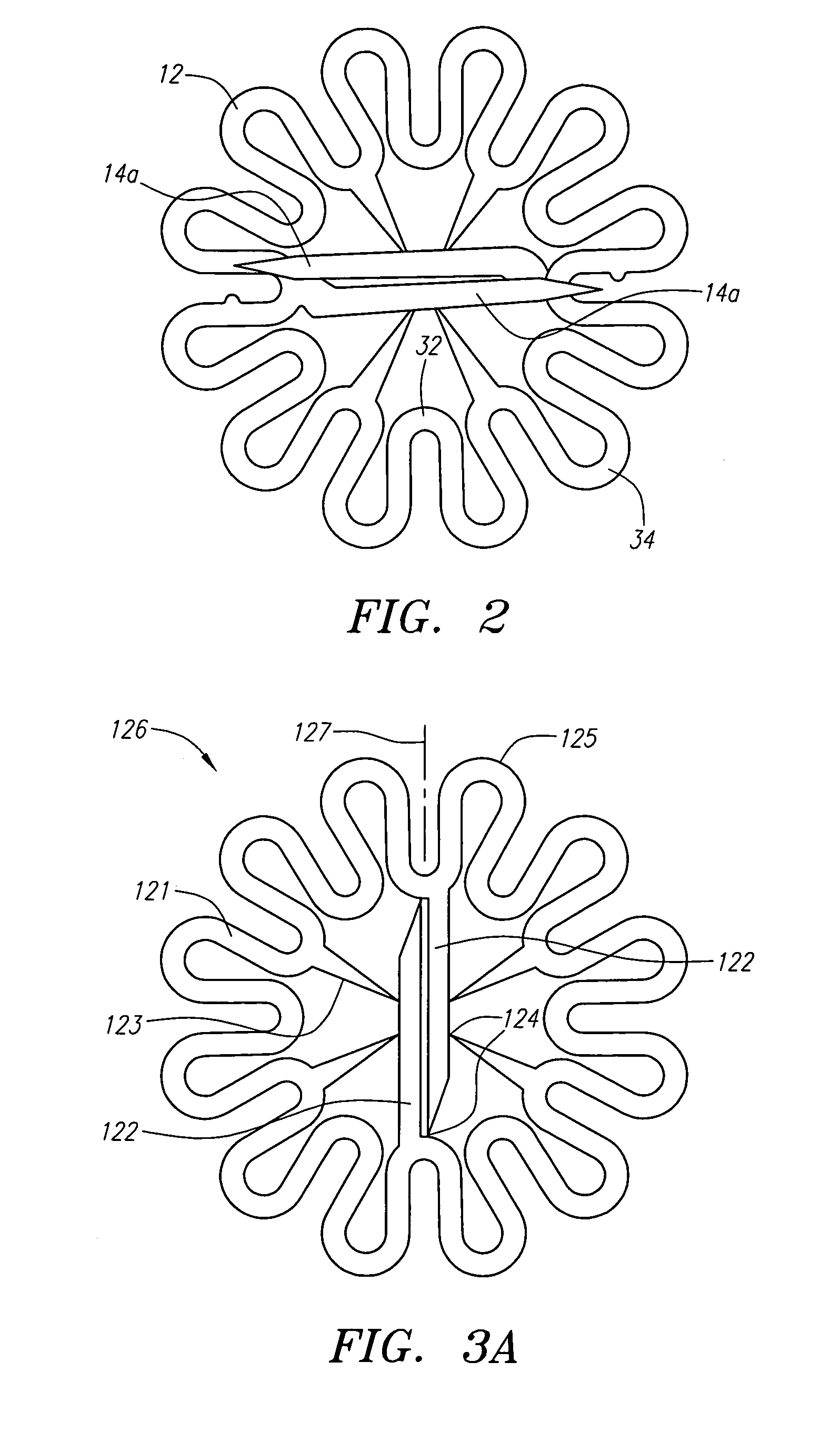

Closure device

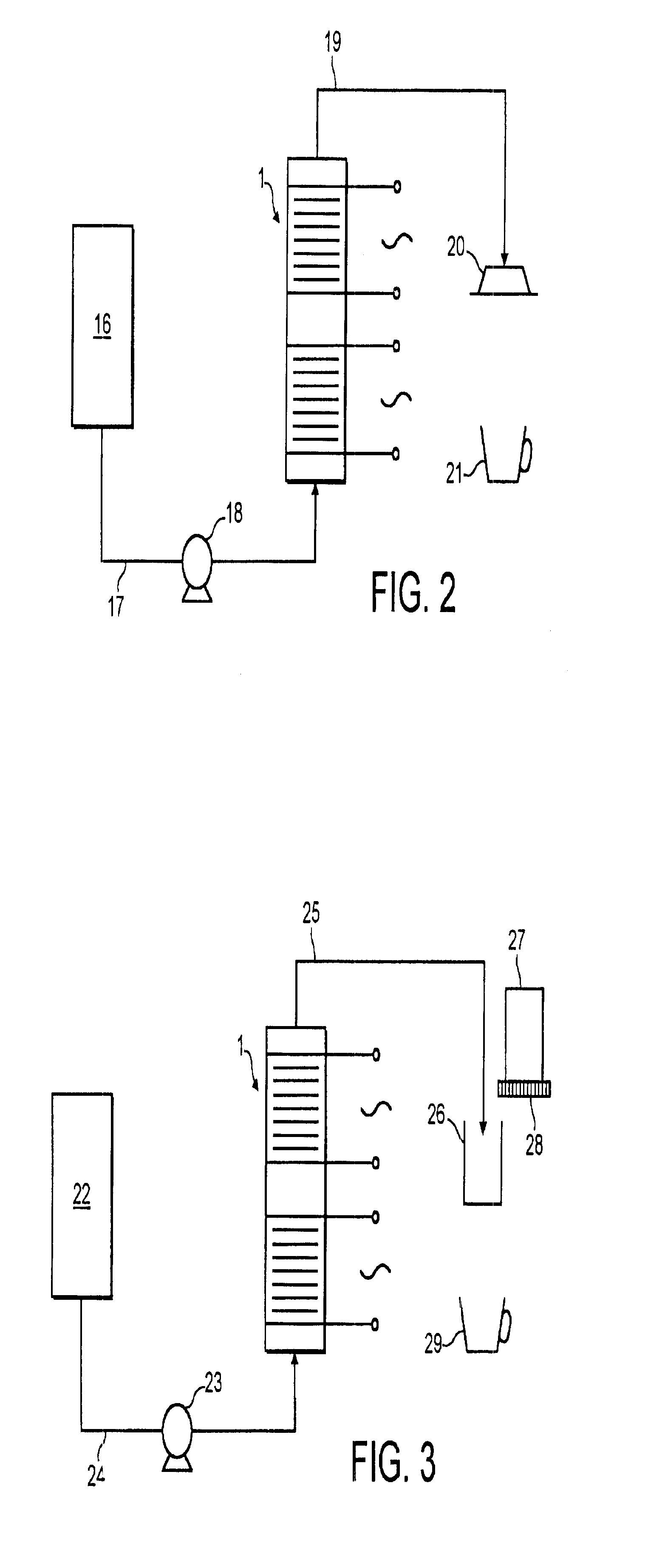

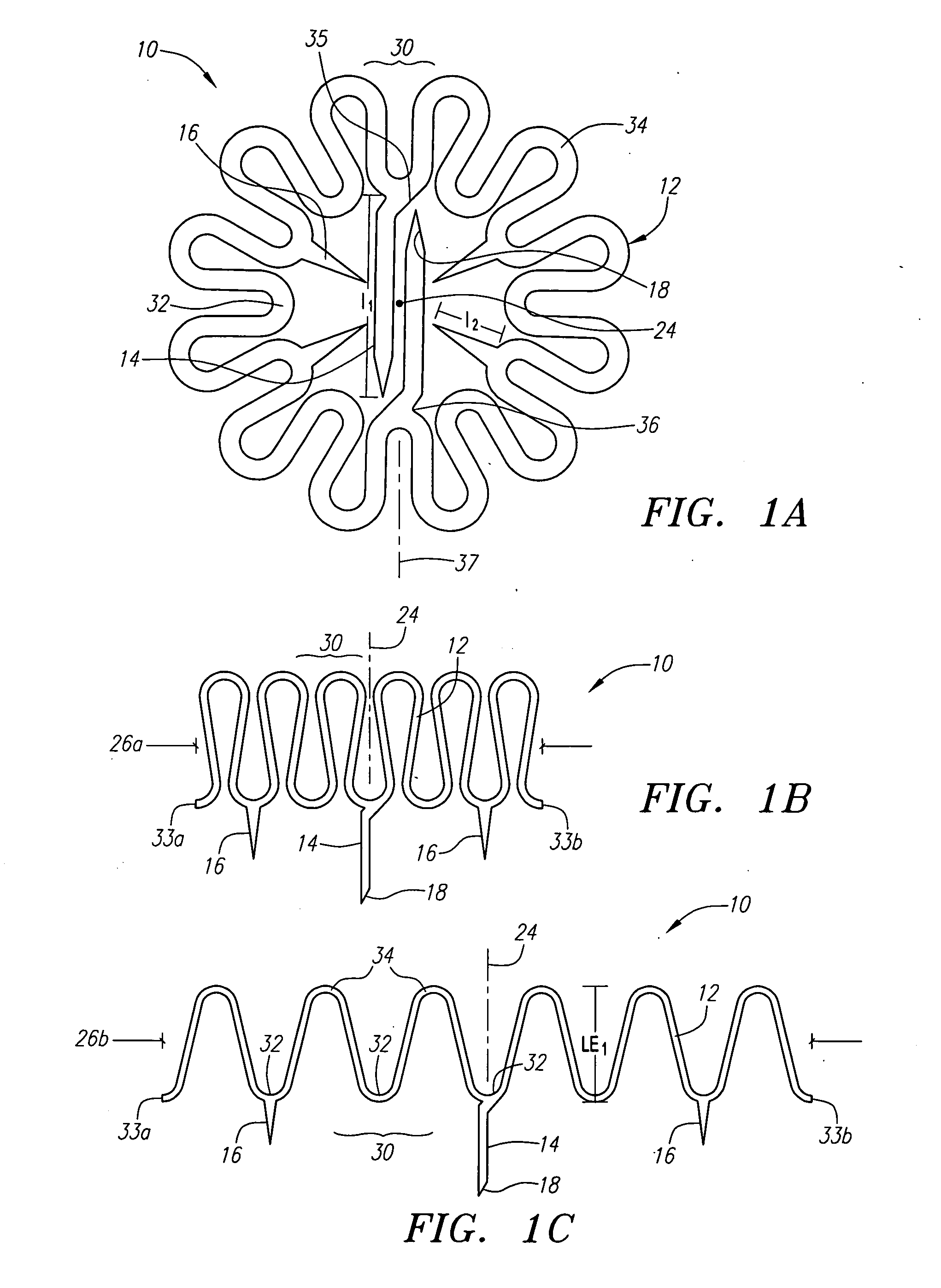

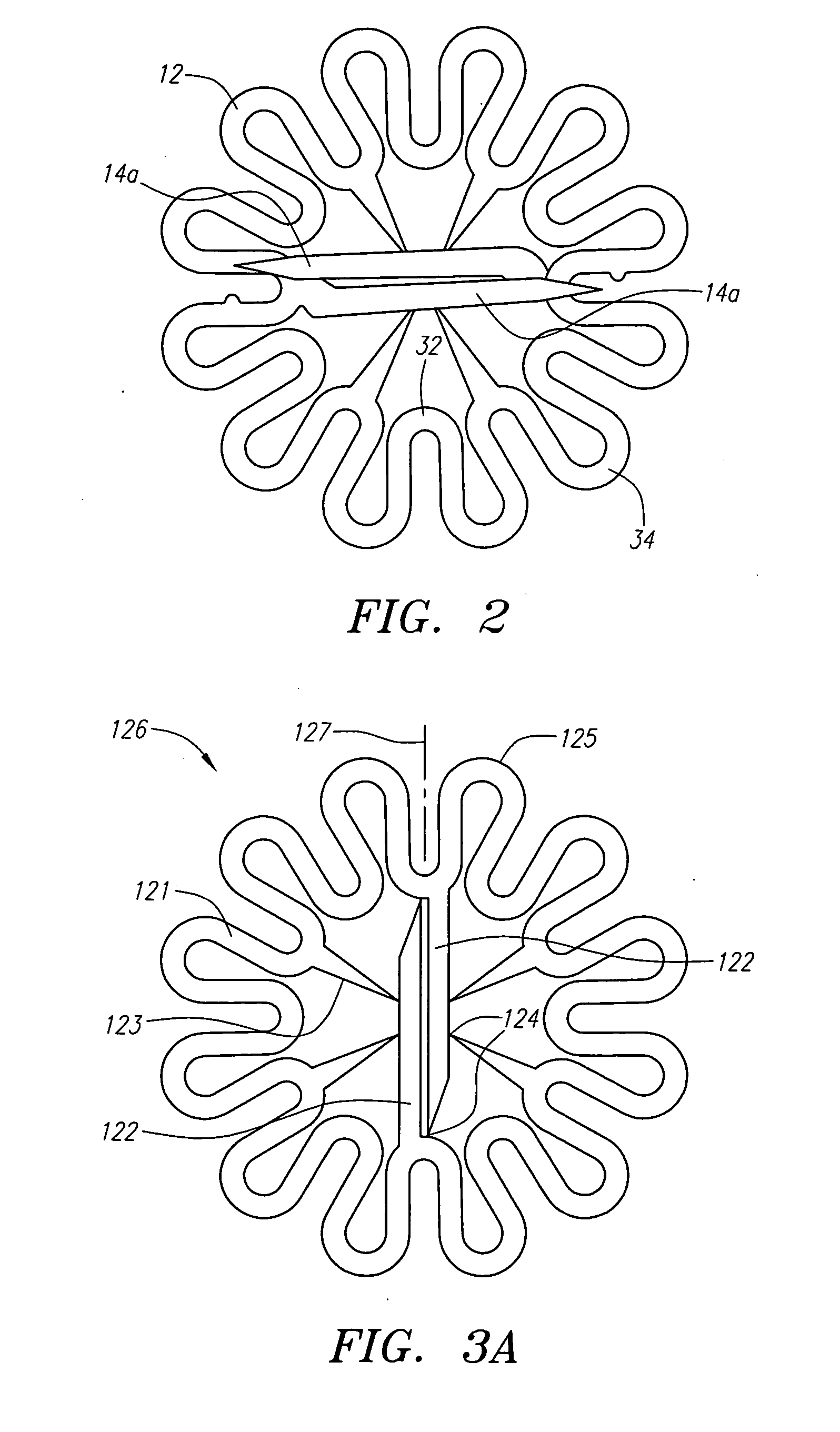

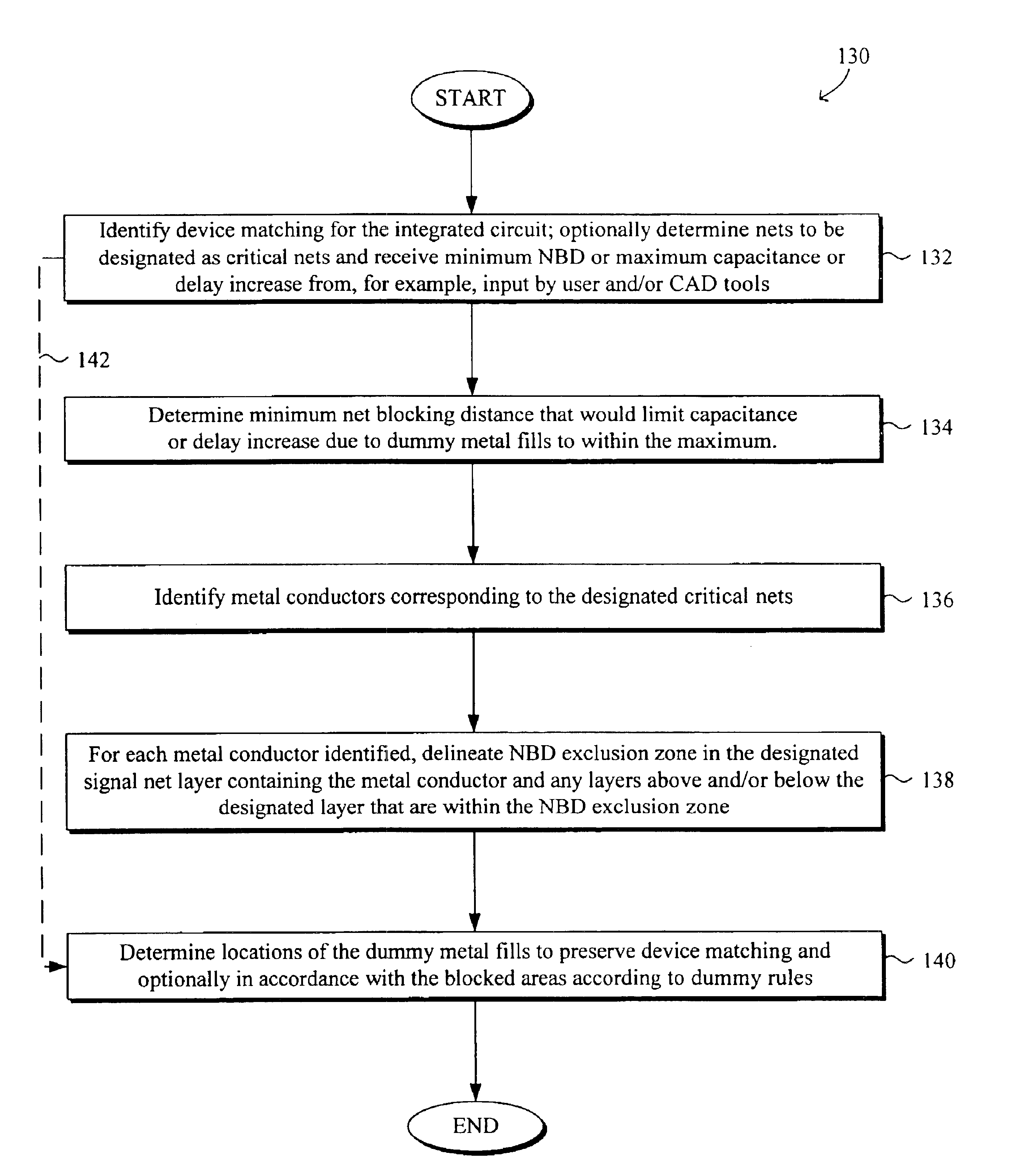

InactiveUS20060135989A1Improve performance consistencyTrend downDiagnostic markersStaplesLinear regionAxis of symmetry

A clip for engaging tissue includes a generally annular-shaped body defining a plane and disposed about a central axis extending normal to the plane. The body includes alternating inner and outer curved regions, defining a zigzag pattern about a periphery of the clip. The body is biased towards a planar configuration lying in the plane and deflectable towards a transverse configuration extending out of the plane. Tines extend from the inner curved regions, the tines being oriented towards the central axis in the planar configuration, and parallel to the central axis in the transverse configuration. The tines include primary tines and secondary tines that are shorter than the primary tines. The primary tines may be disposed on opposing inner curved regions and oriented towards one another. The primary tines are configured such that they are offset from the axes of symmetry of the curved regions from which they extend and are connected to the curved regions by curved or linear regions or are connected directly to the curved regions. The primary tines may overlap the body and may be of different lengths.

Owner:INTEGRATED VASCULAR SYST

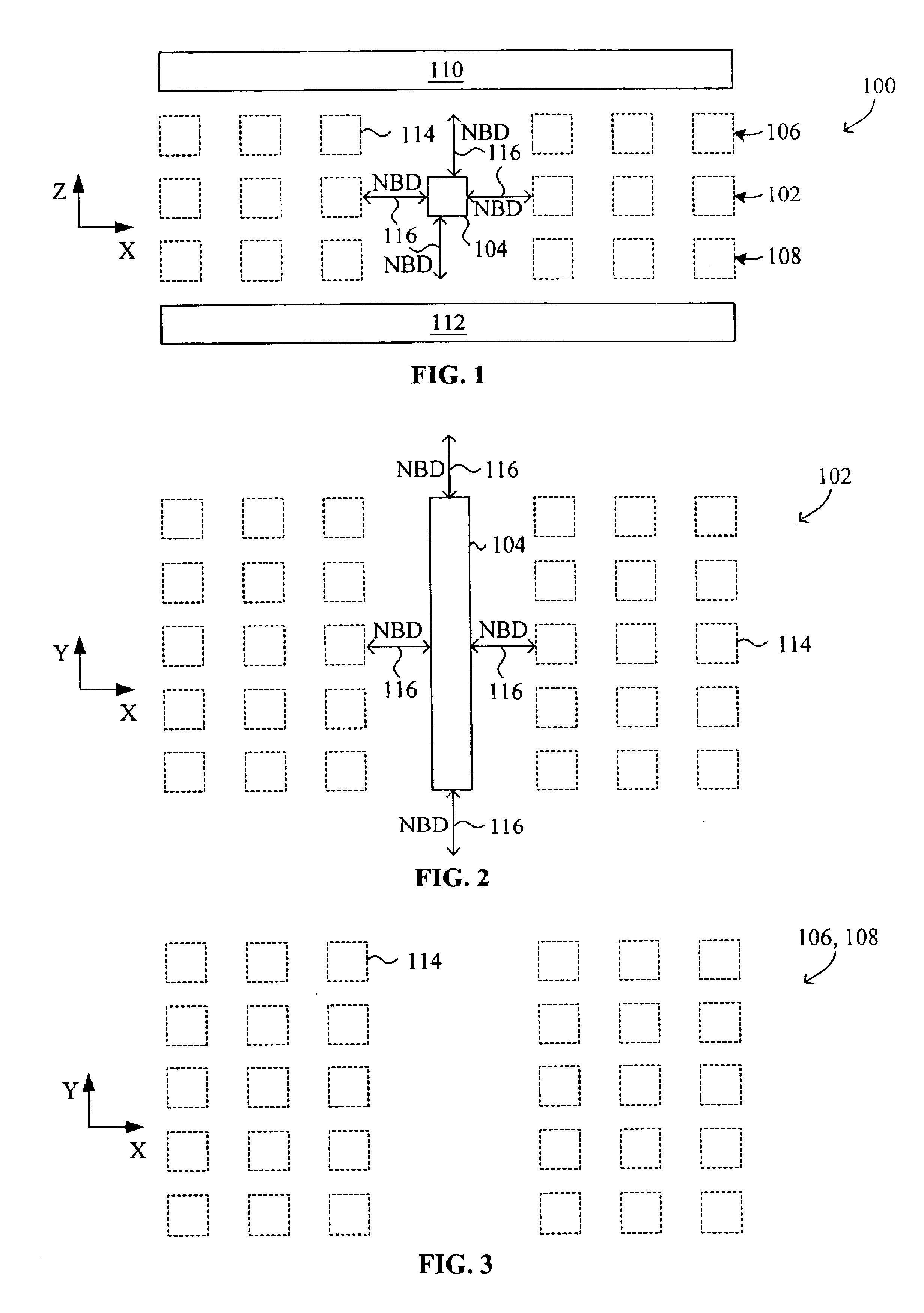

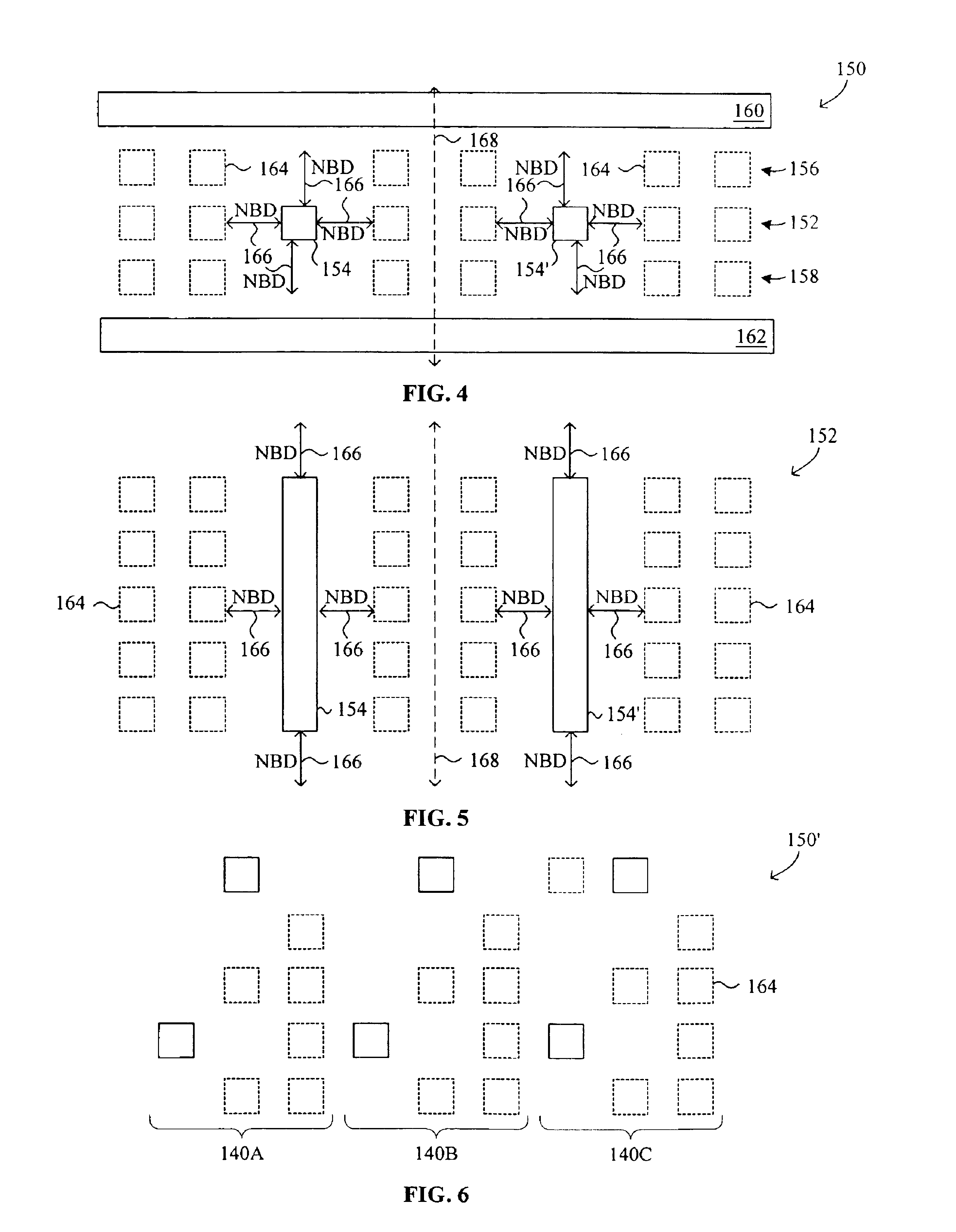

System and method for placement of dummy metal fills while preserving device matching and/or limiting capacitance increase

InactiveUS6904581B1CAD circuit designSoftware simulation/interpretation/emulationCapacitanceElectrical conductor

Systems and methods for placement of dummy metal fills while preventing disturbance of device matching and optionally limiting capacitance increase are disclosed. A computer-automated method for locating dummy fills in an integrated circuit fabrication process generally comprises receiving an input layout of the integrated circuit and specification of device matching for the integrated circuit and locating the dummy fills in the integrated circuit according to dummy rules while preserving device matching. Locating the dummy fills may include locating the dummy fills along the at least one axis of symmetry where device matching is along an axis of symmetry and locating the dummy fills so as to preserve matching of the repeated elements where device matching is repeated matched elements. The method may also include designating at least one net of the integrated circuit as a critical net, the critical nets being only a subset of all nets of the integrated circuit, identifying metal conductors corresponding to each designated critical net from the layout file, and delineating a net blocking exclusion zone extending a distance of a minimum net blocking distance (NBD) from the metal conductor for each metal conductor identified, wherein the step of locating locates the dummy fills outside of the net blocking exclusion zone.

Owner:MAGMA DESIGN AUTOMATION

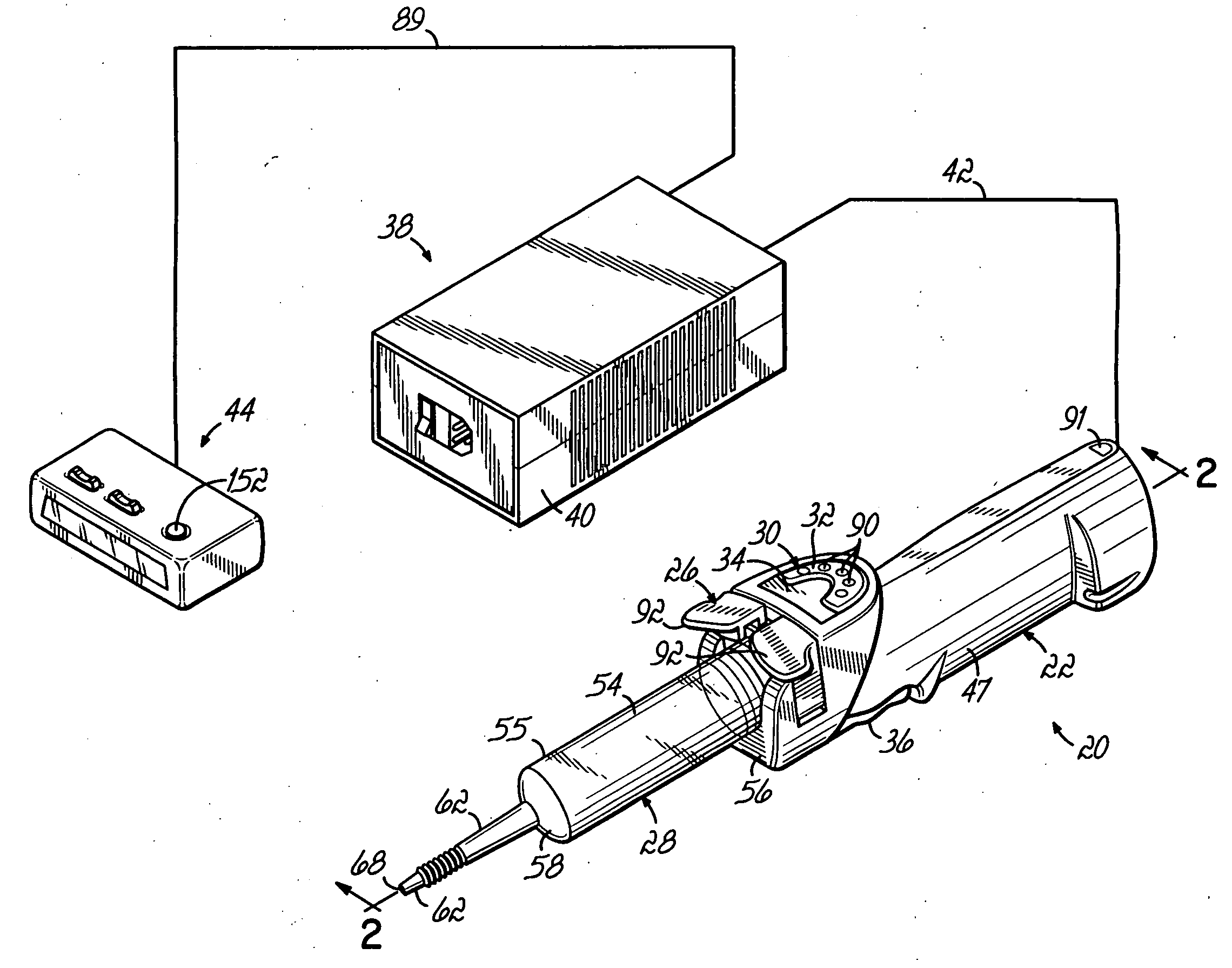

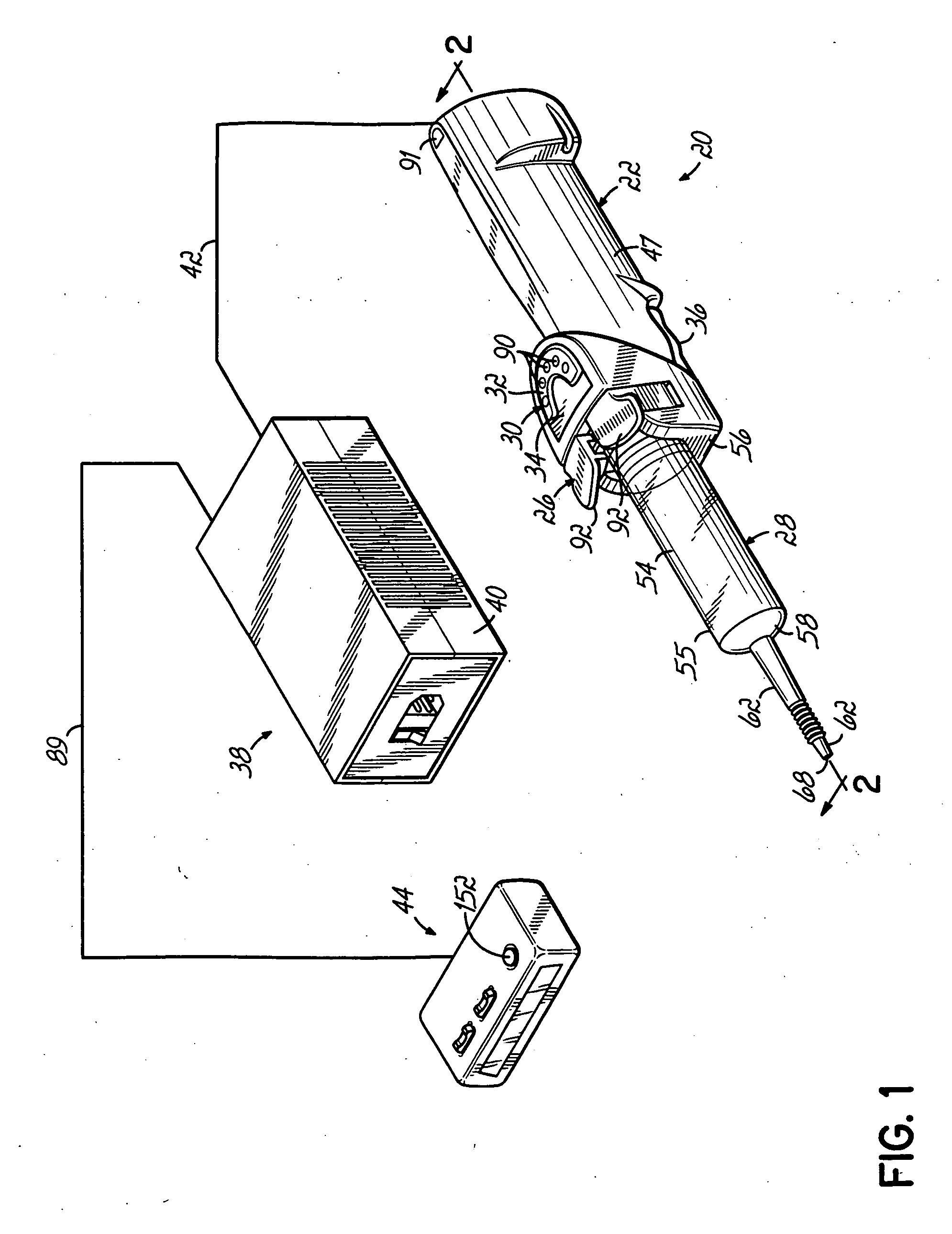

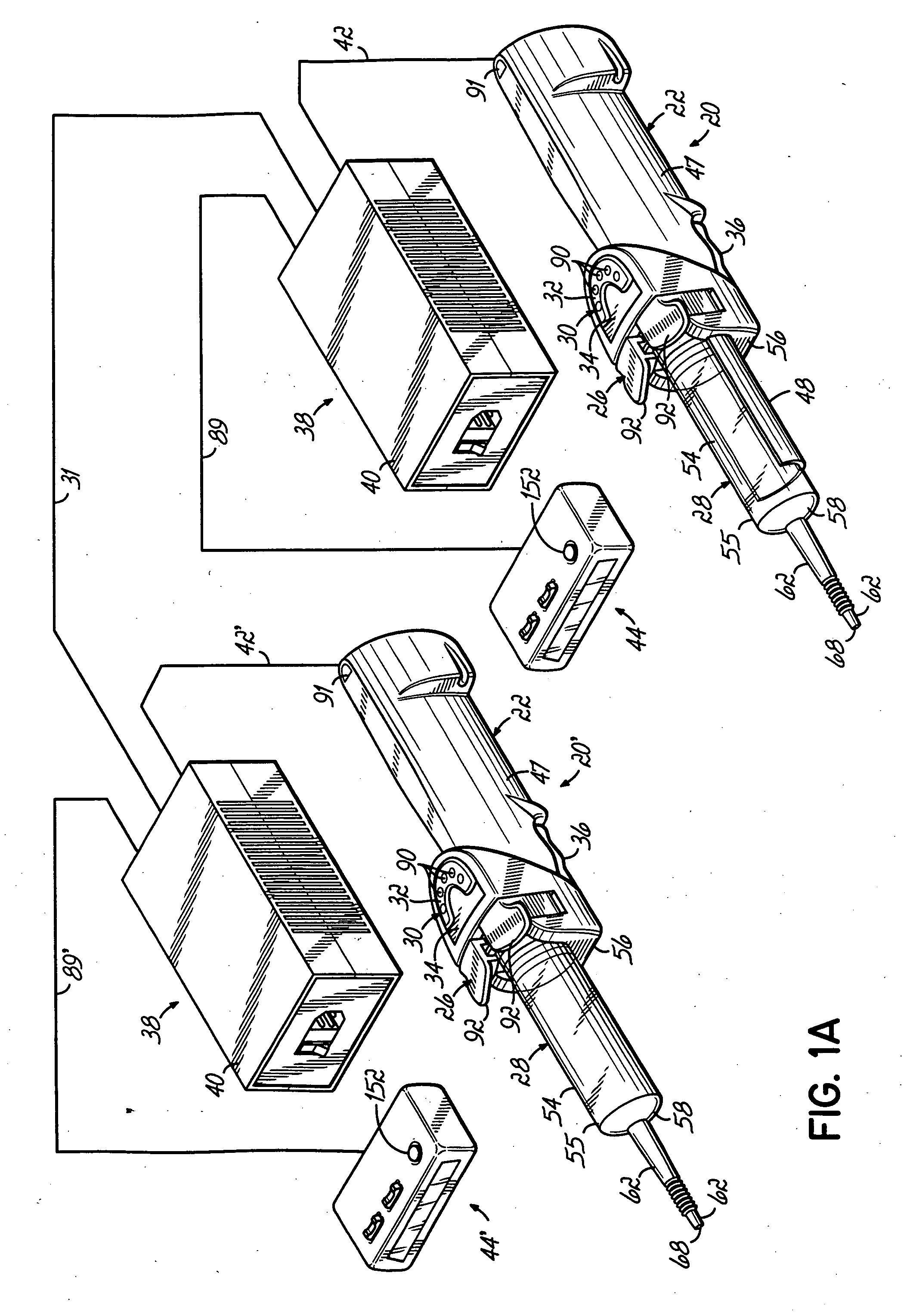

Injector

InactiveUS20050038390A1Reduces and eliminates power connectionGood adhesionAutomatic syringesMedical devicesAxis of symmetryRadiographic contrast media

An injector 20 that may be used to deliver radiographic contrast media and / or flushing solution into a patient's vascular system for the purposes such as obtaining enhanced diagnostic x-ray images. The injector includes the following features: (1) a syringe mount 26 for attachment of a syringe 28 to the injector 20; (2) display 34 and controls 90 for volume and flow rates; (3) automatic limiting of the operating pressure of the injector 20 as determined by the selection of a flow rate; (4) a syringe cradle 48 having a warming capability; (5) a purge / retract trigger 36 for control of the injection procedure having intuitive direction (i.e., forward for injecting, reverse for filing), non-contact control transmission through the housing of an injector 20 for an improved seal integrity, a speed lock, and / or the ability to change the concentration and / or flow rate of media or other fluid during an injection procedure; (6) a switch to determine when the drive ram 46 is in a “home” position; (7) a “soft” on / off power switch separate from the injector; and (8) a structure to prevent rotation of the drive ram 46 about its axis of symmetry 76. Additionally, the injector system includes software for the control of various components.

Owner:LIEBEL FLARSHEIM CO

Set of humeral components for total shoulder prosthesis

ActiveUS20050278031A1Easy to adaptMinimizes partJoint implantsShoulder jointsAxis of symmetryMedicine

In this set of humeral components for a total shoulder prosthesis, each component is formed by an anchoring stem and a metaphyseal part which defines a concave surface of articulation globally in the form of a portion of sphere. The offset between the axis of symmetry of this surface and the central axis of the metaphyseal part of the different components is variable. This makes it possible to limit or to avoid, by a reasoned choice of the humeral component used, an interference with the pillar of the scapula during the movement of adduction.

Owner:TORNIER SA SAINT ISMIER

Side-emitting lens for LED lamp

ActiveUS7703950B2Improve evenlyLighting applicationsPoint-like light sourceAxis of symmetryOptoelectronics

Owner:C R CONTROL SYST

Closure device

InactiveUS7806904B2Improve deformationStress minimizationDiagnostic markersStaplesLinear regionAxis of symmetry

A clip for engaging tissue includes a generally annular-shaped body defining a plane and disposed about a central axis extending normal to the plane. The body includes alternating inner and outer curved regions, defining a zigzag pattern about a periphery of the clip. The body is biased towards a planar configuration lying in the plane and deflectable towards a transverse configuration extending out of the plane. Tines extend from the inner curved regions, the tines being oriented towards the central axis in the planar configuration, and parallel to the central axis in the transverse configuration. The tines include primary tines and secondary tines that are shorter than the primary tines. The primary tines may be disposed on opposing inner curved regions and oriented towards one another. The primary tines are configured such that they are offset from the axes of symmetry of the curved regions from which they extend and are connected to the curved regions by curved or linear regions or are connected directly to the curved regions. The primary tines may overlap the body and may be of different lengths.

Owner:INTEGRATED VASCULAR SYST

Alignment method for fabrication of integrated ultrasonic transducer array

InactiveUS20050148132A1Ultrasonic/sonic/infrasonic diagnosticsDecorative surface effectsCMOSAxis of symmetry

An integrated circuit is fabricated by micromachining a hexagonal array of cMUT elements on top of a substrate comprising a hexagonal array of CMOS cells. Each cMUT element overlies a respective CMOS cell in one-to-one correspondence. During layout of the mask for micromachining the cMUT layer, either the hexagonal pattern or the alignment key is rotated until an axis of symmetry of the hexagonal pattern is aligned with an axis of the alignment key. Later, when the mask is superimposed on the CMOS substrate, the alignment key on the mask is aligned with an alignment key on the substrate. This ensures that the cMUT elements formed by optical lithography will be matched to the CMOS cells.

Owner:GENERAL ELECTRIC CO

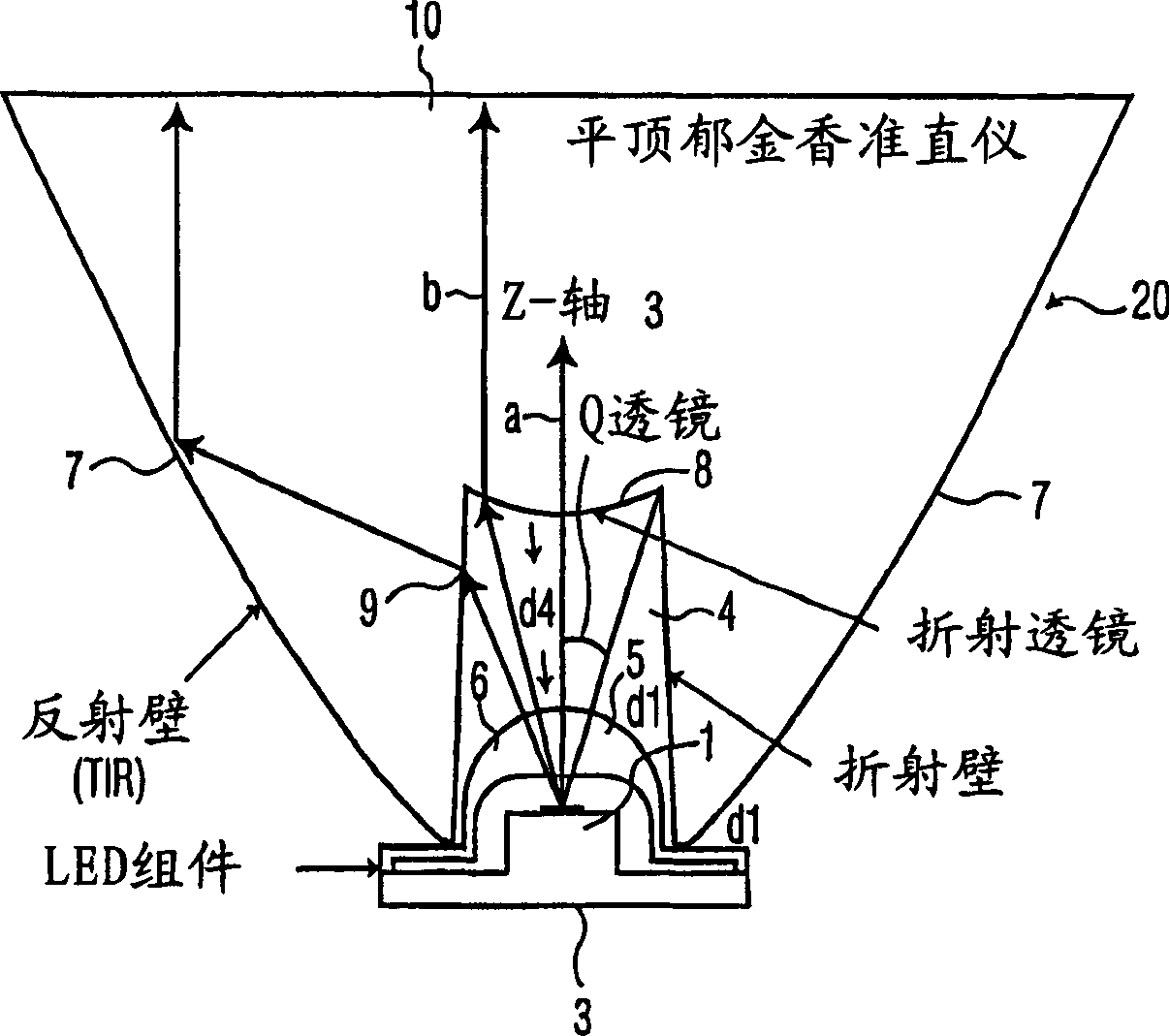

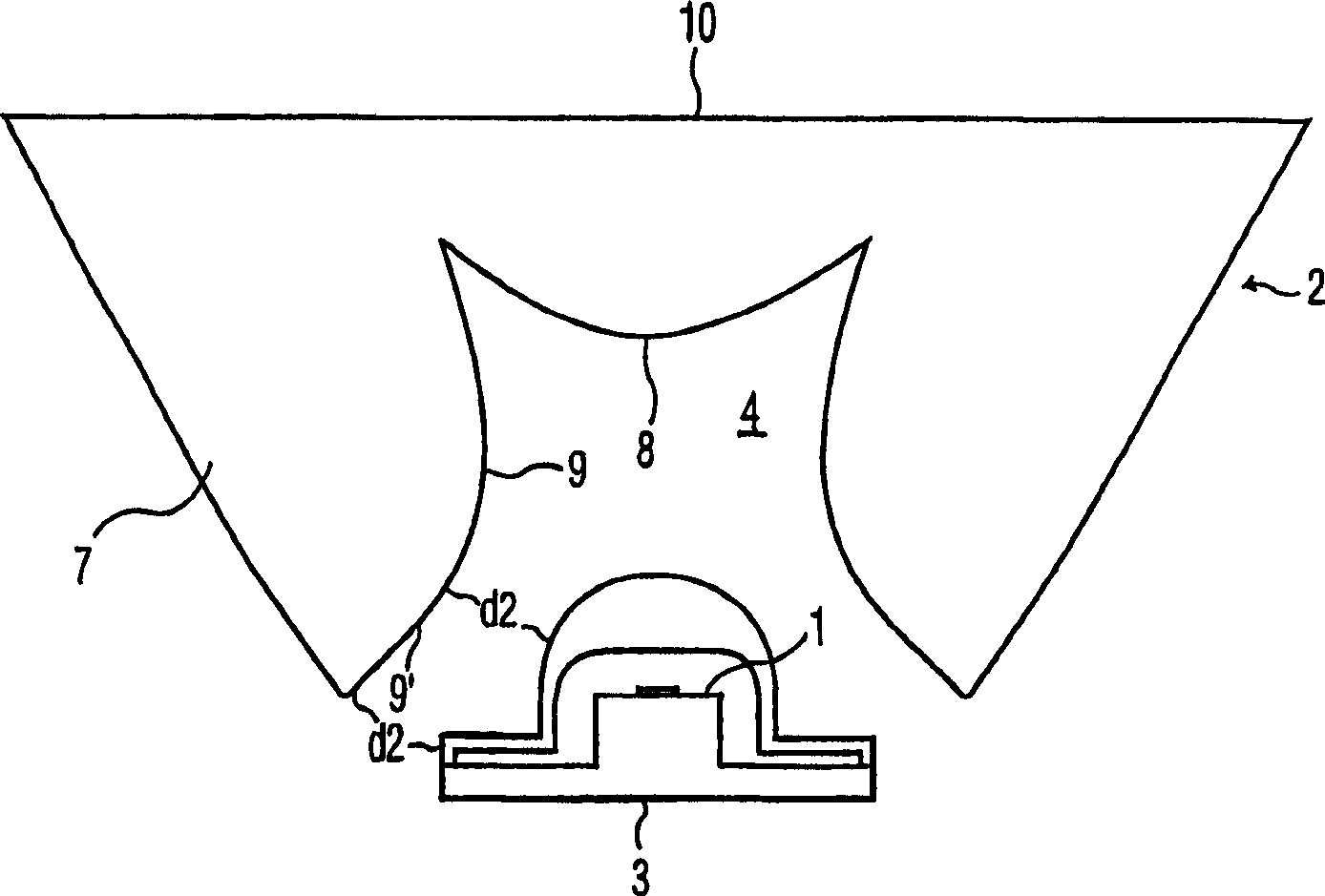

LED module

An LED module that includes an LED (light-emitting diode) (1) and a rotationally symmetrical, bowl-shaped collimator lens (2) is provided. The collimator lens has an inner refractive wall (9), an outer reflective wall (7), a first surface (8) having an entrance aperture (3) with a recess (4) in which the LED is situated and which collimator lens is also provided with a second surface (10) from which light generated by the LED emerges, the normal to the surface extending substantially parallel to the axis of symmetry of the lens, and the LED module also includes one or more of the following structures : (1) a conic wall portion of the recess (4) of the inner refractive wall (9) at the entrance aperture (3) that includes a curved portion (9'), and an outer reflective wall (7) so configured in accordance with the structure of the inner refractive wall (9) to achieve substantial collimation of a source of light (1) at the entrance aperture; and / or (2) a first surface (8) of the lens (2) that is recessed away from the LED source (1); and / or (3) two surfaces (8), (11) of said refractive wall (9) between which the refractive function of said refractive wall (9) is divided. The LED module offers an improvement in the performance of the Flat top Tulip Collimator known in terms of reduced size, beam divergence, beam uniformity, and to some degree efficiency. Moreover, it allows a wider variety of choices in optimizing various performance characteristics, and this in turn allows more flexibility in the structure design.

Owner:SIGNIFY HLDG BV

Plate for fixing the bones of a joint, in particular a metatarso-phalangeal joint

InactiveUS20080091197A1Improve accuracyEasy to placeJoint implantsBone platesAxis of symmetryVertical plane

A plate for fixing the bones of a joint, in particular of a metatarso-phalangeal joint, for the purpose of performing arthodesis. The plate comprises two sections, respectively a proximal section and a distal section, each section having a respective longitudinal axis of symmetry S1, S2 such that the projection onto a horizontal plane of the axis of symmetry S2 of the distal section presents an angle of inclination relative to the projection of the axis of symmetry S1 of the proximal portion, the projections inserting at a point A. The projection onto a vertical plane of the axis of symmetry S2 presents an angle of inclination relative to the projection of the axis of symmetry S1, their intersection taking place at a point A2 which is distinct from the point A1.

Owner:NEWDEAL

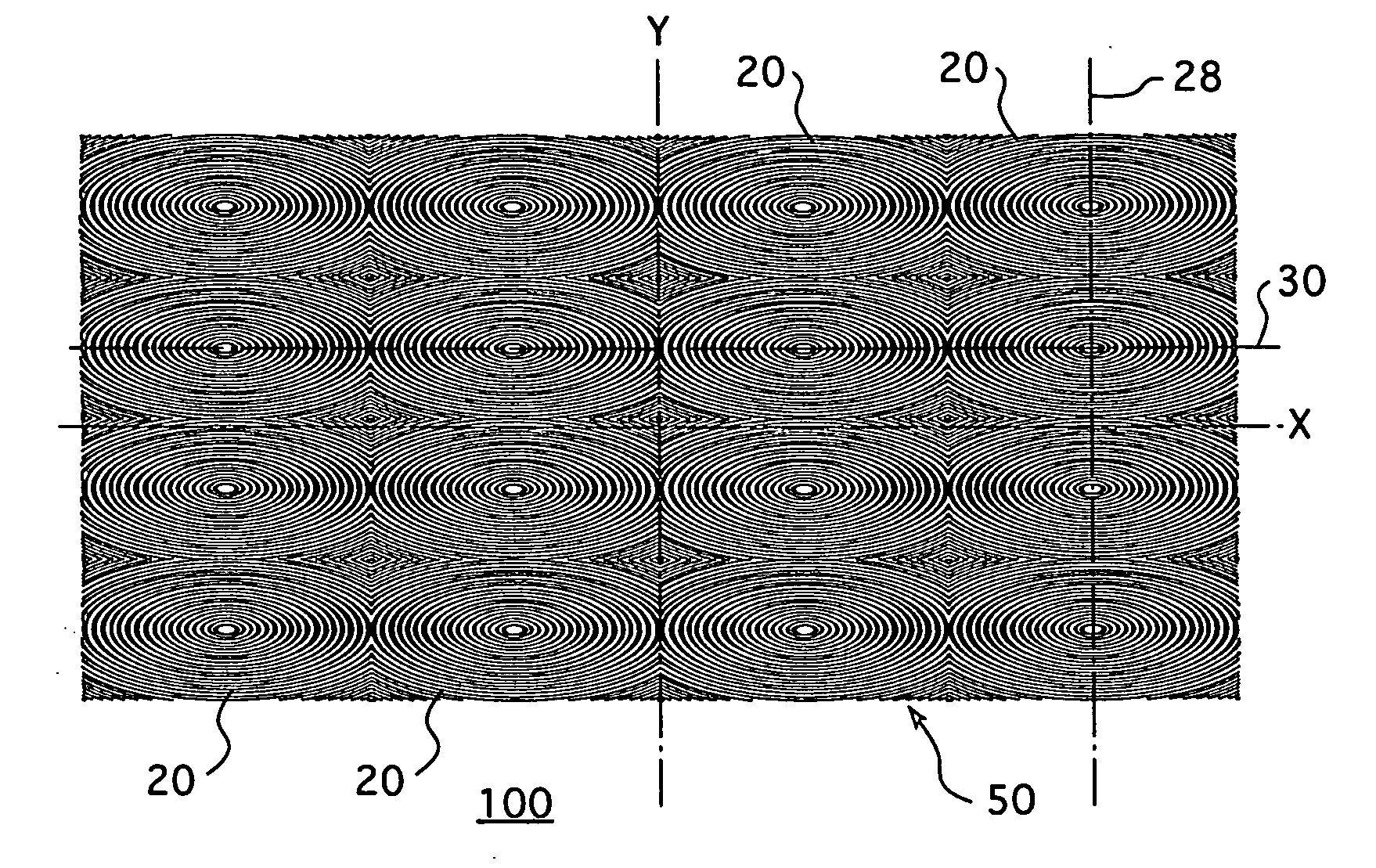

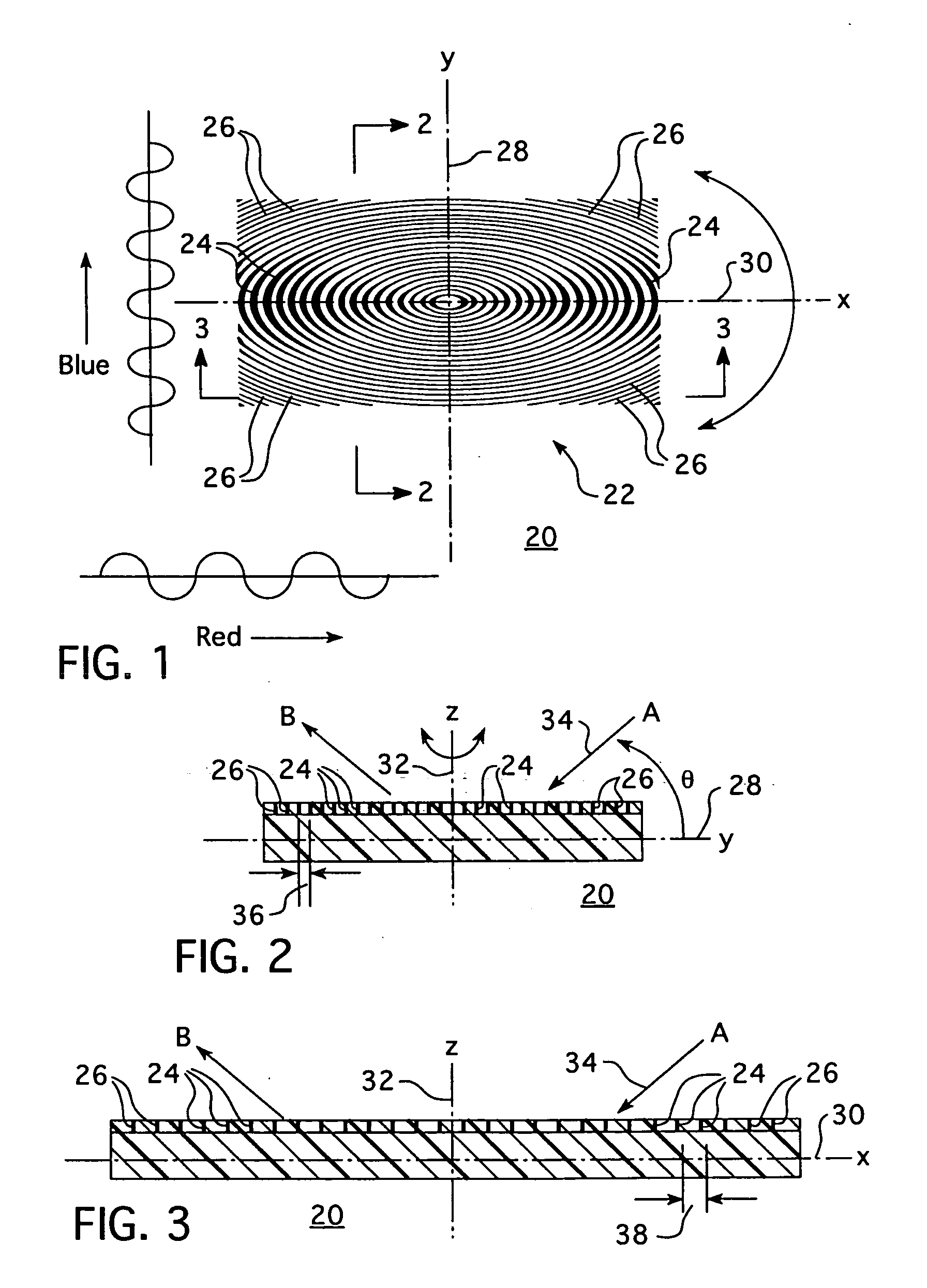

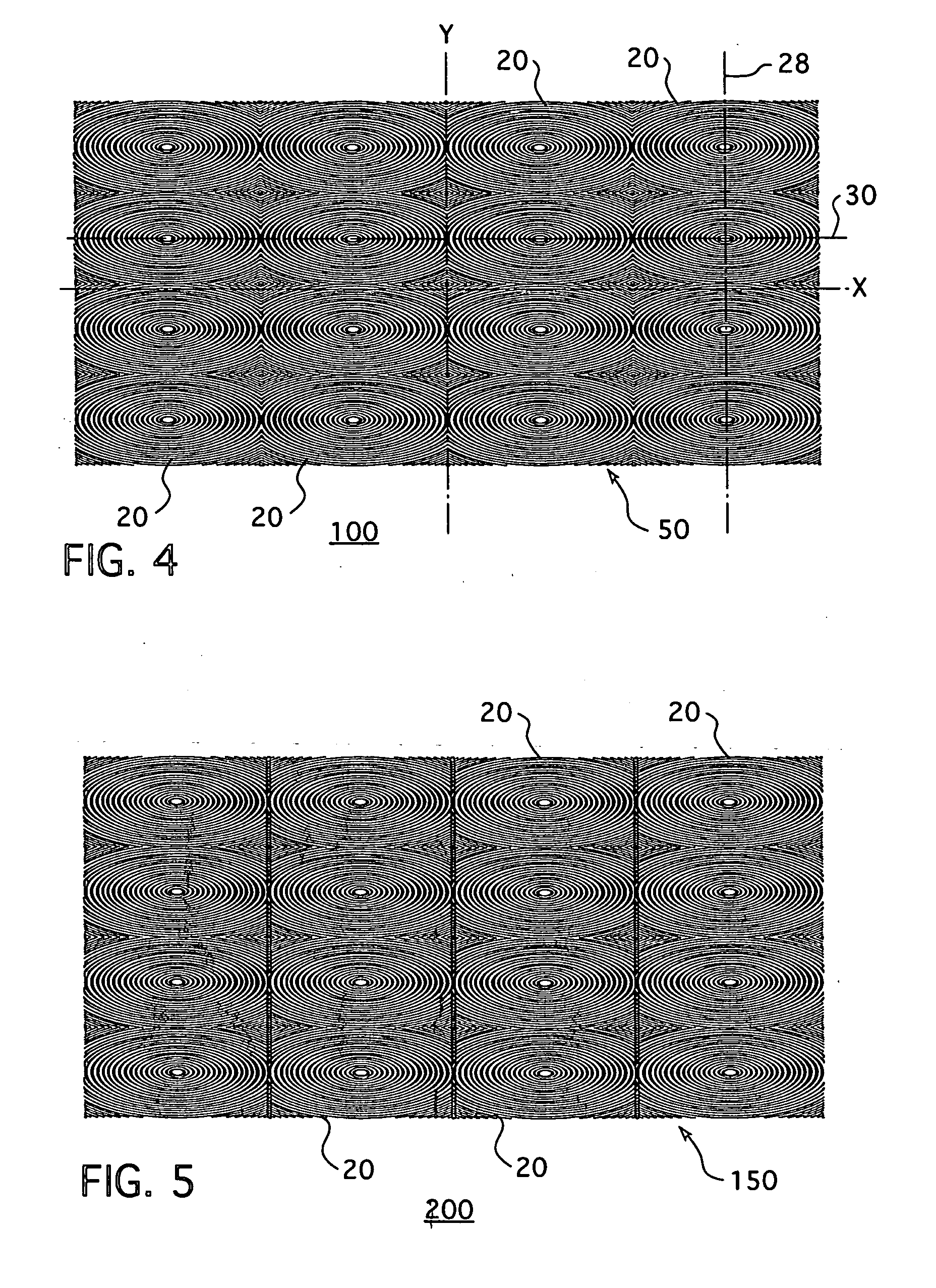

Diffraction-based optical grating structure and method of creating the same

InactiveUS20060018021A1Novel propertyEasy and economical to fabricateAcutation objectsDiffraction gratingsEngineeringAxis of symmetry

Optical elements include an optical grating structure which exhibits novel pleochroic properties when rotated or viewed from changing observation locations. The optical grating structure is formed from a plurality of selectively arranged grating elements which are preferably, but not necessarily, formed from a plurality of lines or grooves having a closed-loop shape. The preferred closed-loop lines and grooves are disposed one inside another and preferably include at least one common axis of symmetry. A two-dimensional array of such elements is arranged to define an optically variable device. A method of creating elements, arrays and optically variable devices and articles employing the same are also disclosed.

Owner:OPSEC SECURITY GROUP

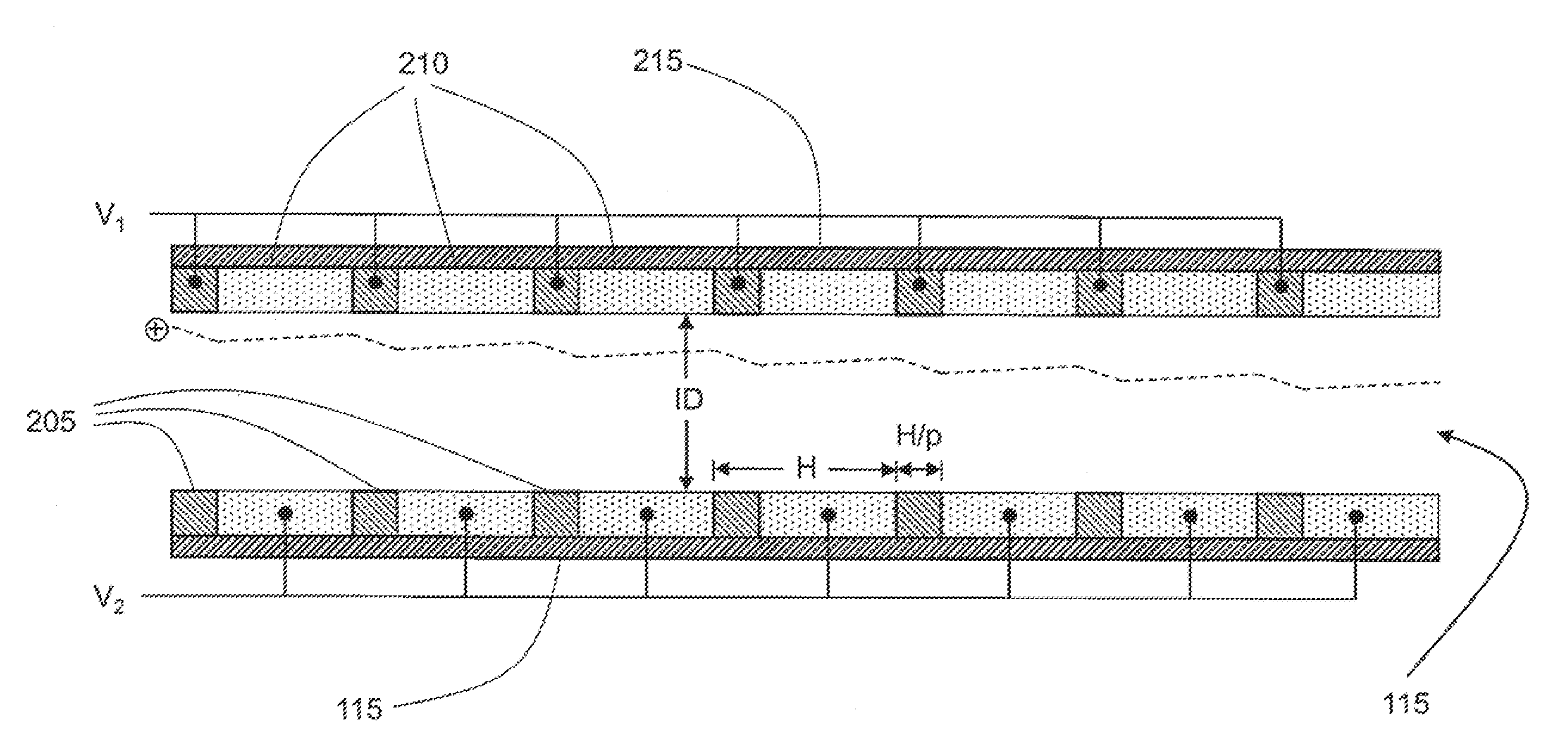

Ion transfer tube with spatially alternating DC fields

An ion transfer arrangement for transporting ions between higher and lower pressure regions of a mass spectrometer includes an electrode assembly (120) with a first plurality of ring electrodes (205) arranged in alternating relation with a second plurality of ring electrodes (210). The first plurality of ring electrodes (205) are narrower than the second plurality of ring electrodes (210) in a longitudinal direction, but the first plurality of ring electrodes have a relatively high magnitude voltage of a first polarity applied to them whereas the second plurality of ring electrodes (210) have a relatively lower magnitude voltage applied to them, of opposing polarity to that applied to the first set of ring electrodes (205). In this manner, ions passing through the ion transfer arrangement experience spatially alternating asymmetric electric fields that tend to focus ions away from the inner surface of the channel wall and towards the channel plane or axis of symmetry.

Owner:THERMO FISHER SCI BREMEN

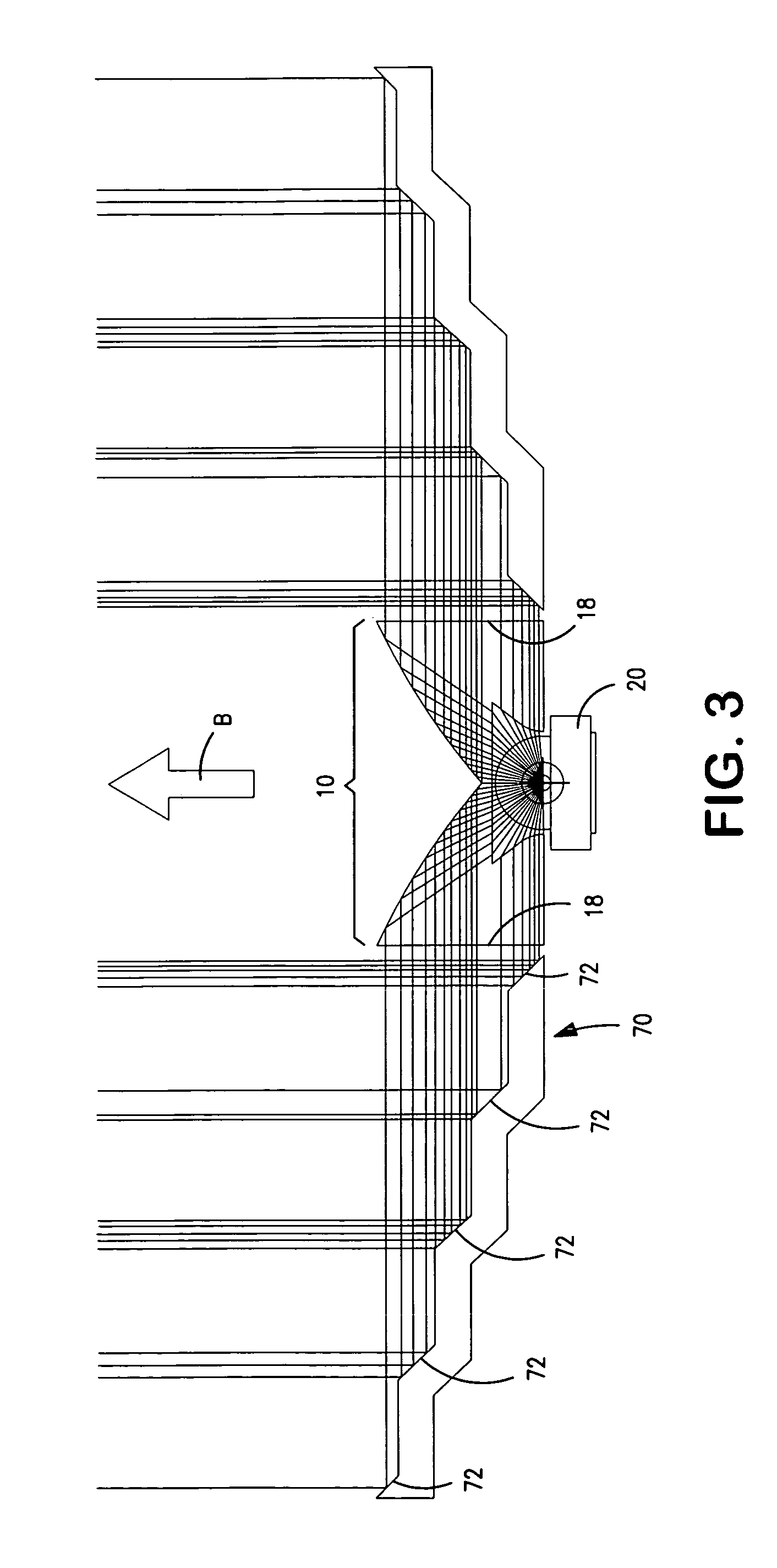

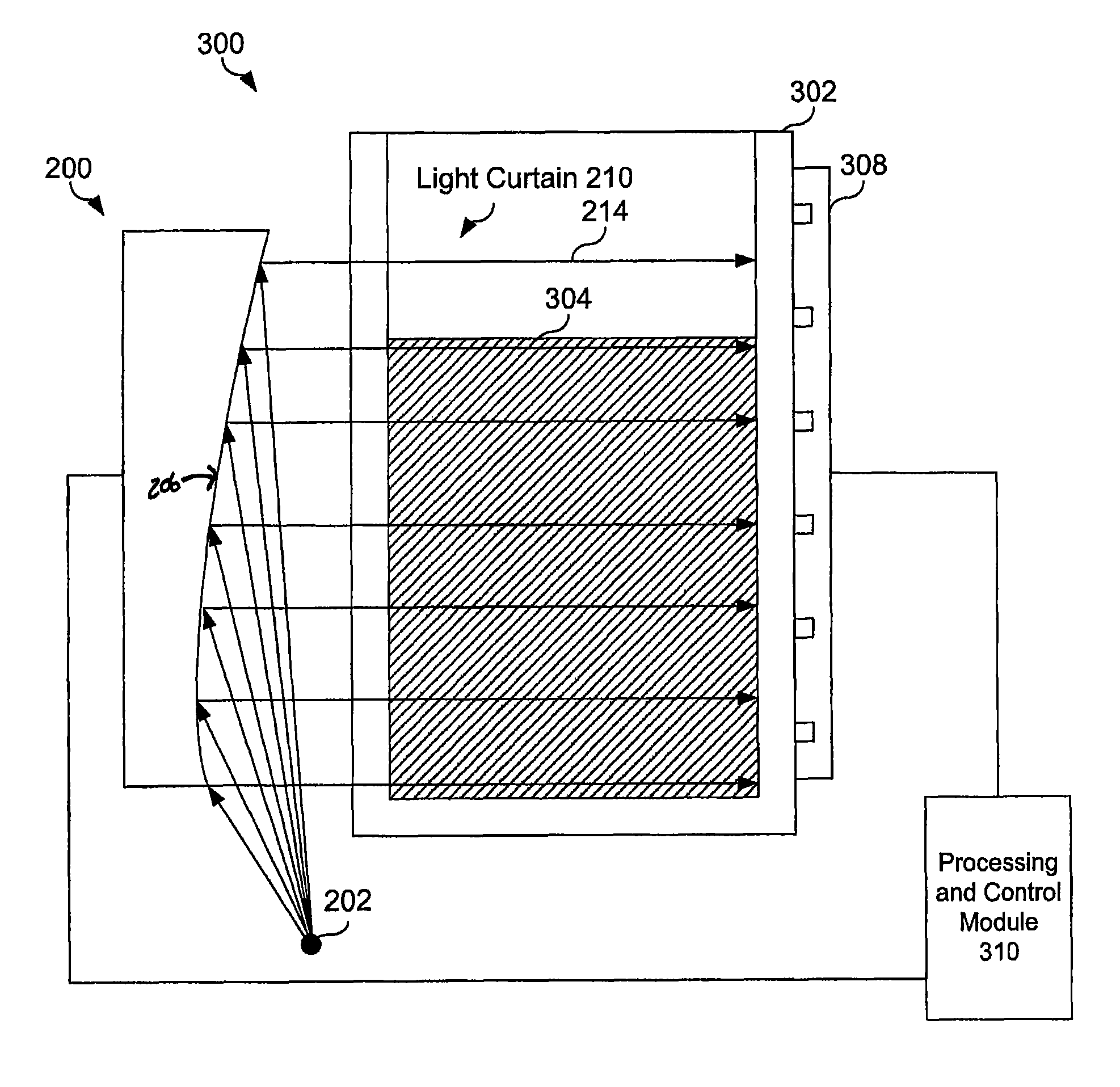

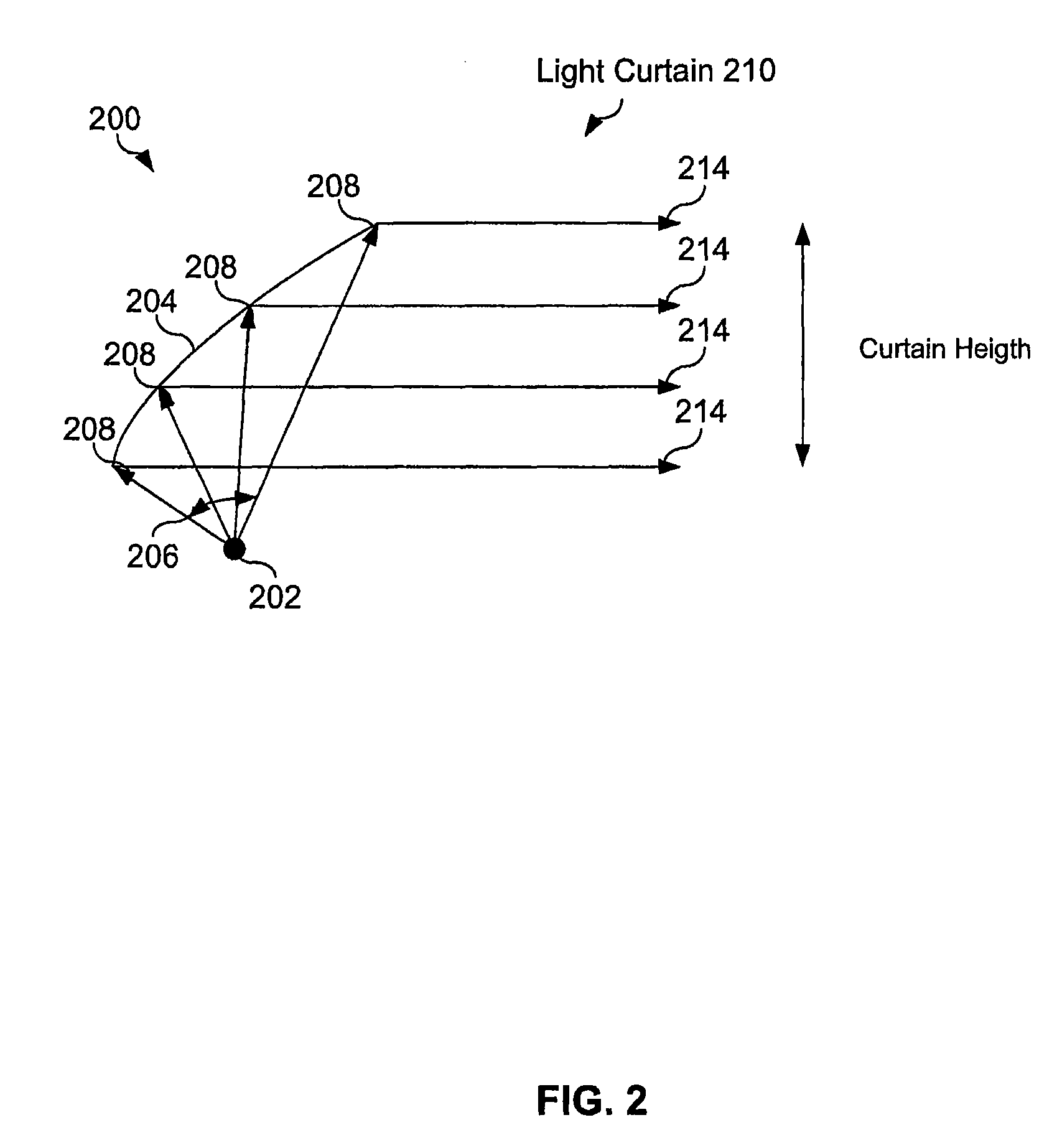

Single light source uniform parallel light curtain

ActiveUS7872746B2Prevents physical contaminationEye surgeryWithdrawing sample devicesSensor arrayAxis of symmetry

A continuous high resolution fluid level monitoring system is provided by embodiments of the present invention. This continuous high resolution fluid level monitoring system includes a unique fluid level sensor having a point light source, parabolic reflector, sensor array, and detection, processing and control system. The point light source illumines a parabolic reflector wherein the point light source is located at the focus of the parabolic reflector. The parabolic reflector reflects light from the point light source to produce a parallel light curtain. This parallel light curtain is parallel to an axis of symmetry of the parabolic reflector. The parallel light curtain illumines a chamber such as a chamber in an ophthalmic surgical device used to contain surgical fluid. The sensor array coupled to the chamber detects the parallel light curtain illuminating the chamber. The sensor array provides an output to a detection / processing / control system in order to determine the fluid level within the chamber. This optical method of determining the surgical fluid levels may be advantageous in that it prevents physical contamination of the surgical fluids.

Owner:ALCON INC

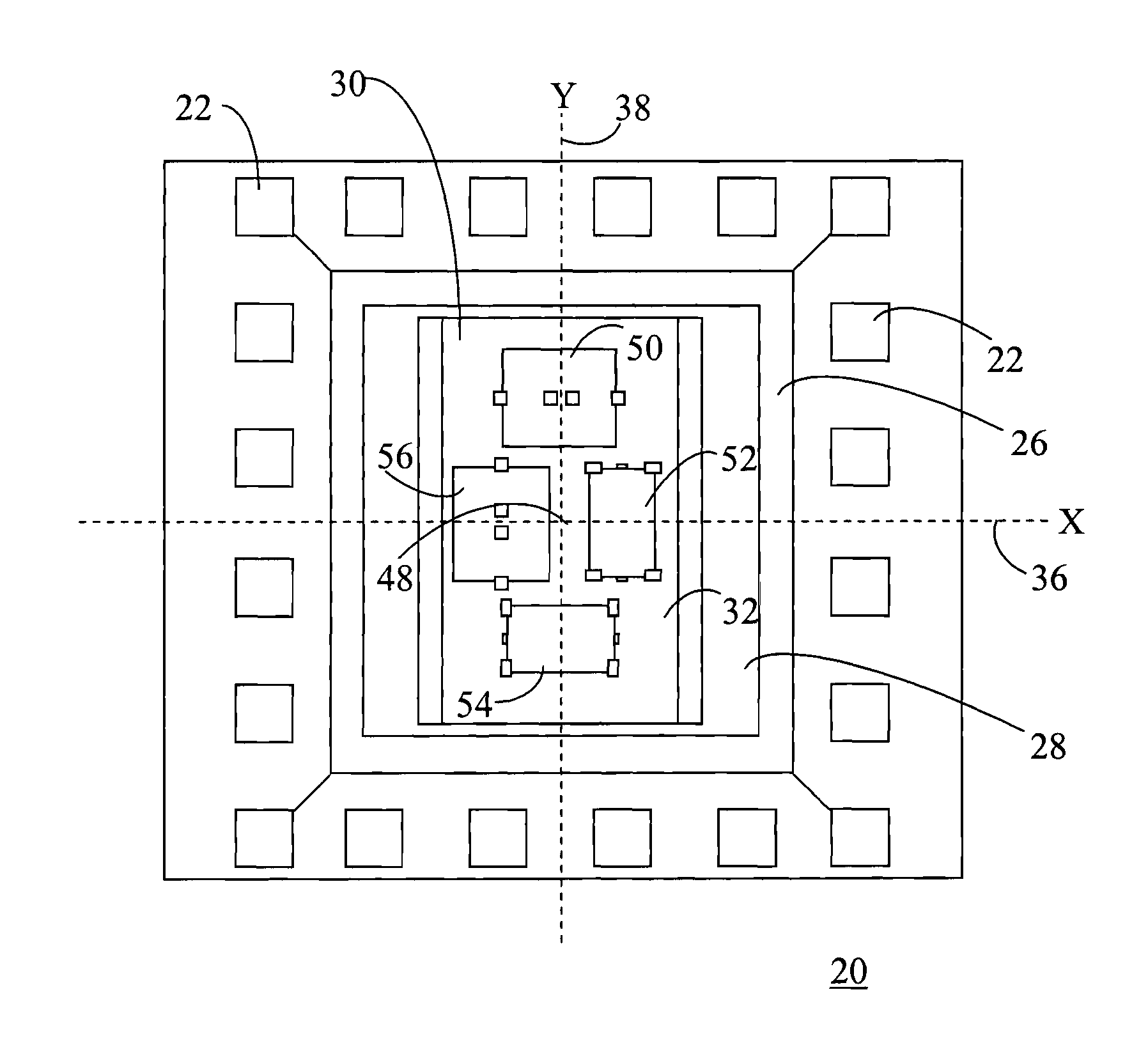

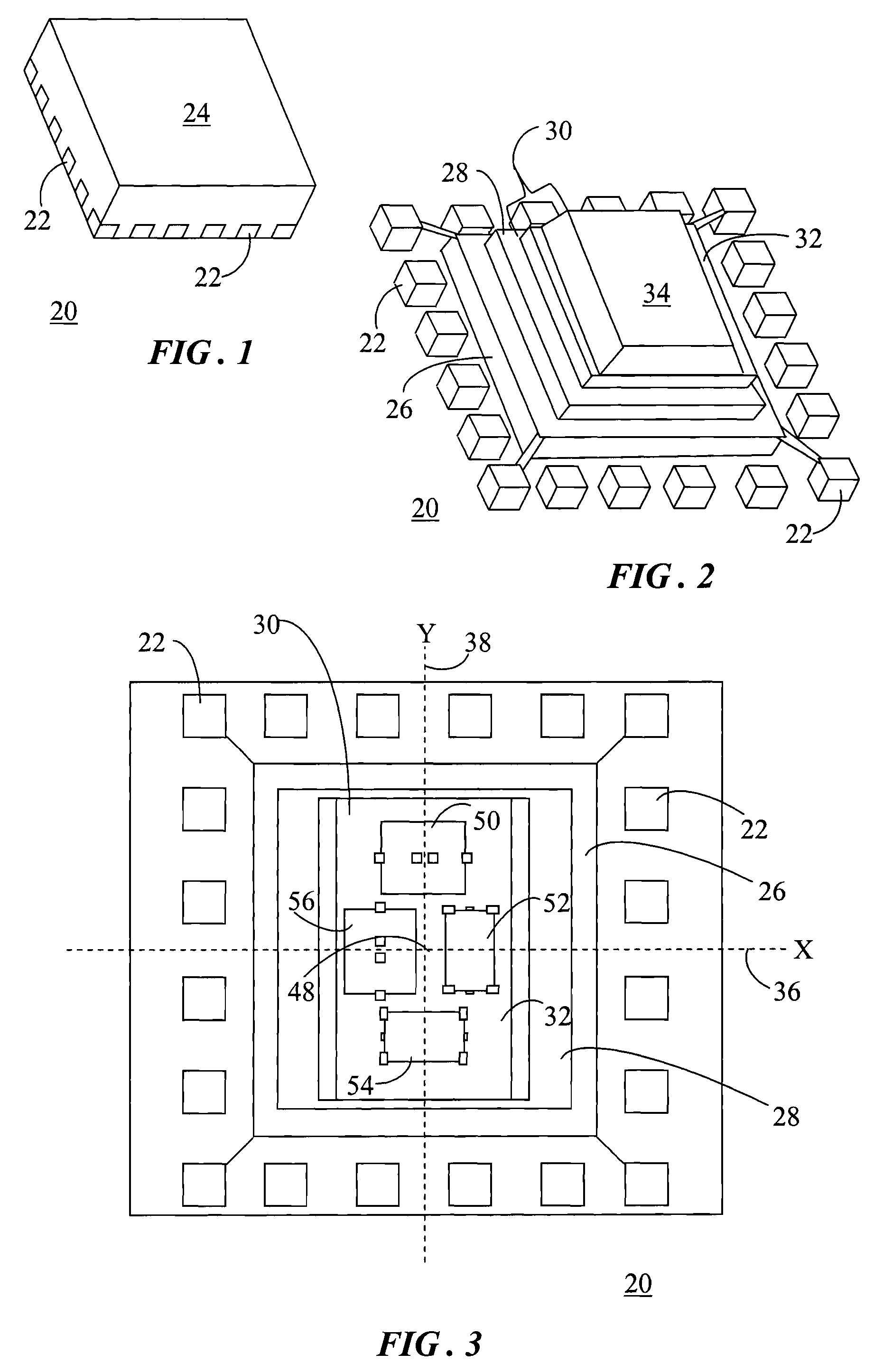

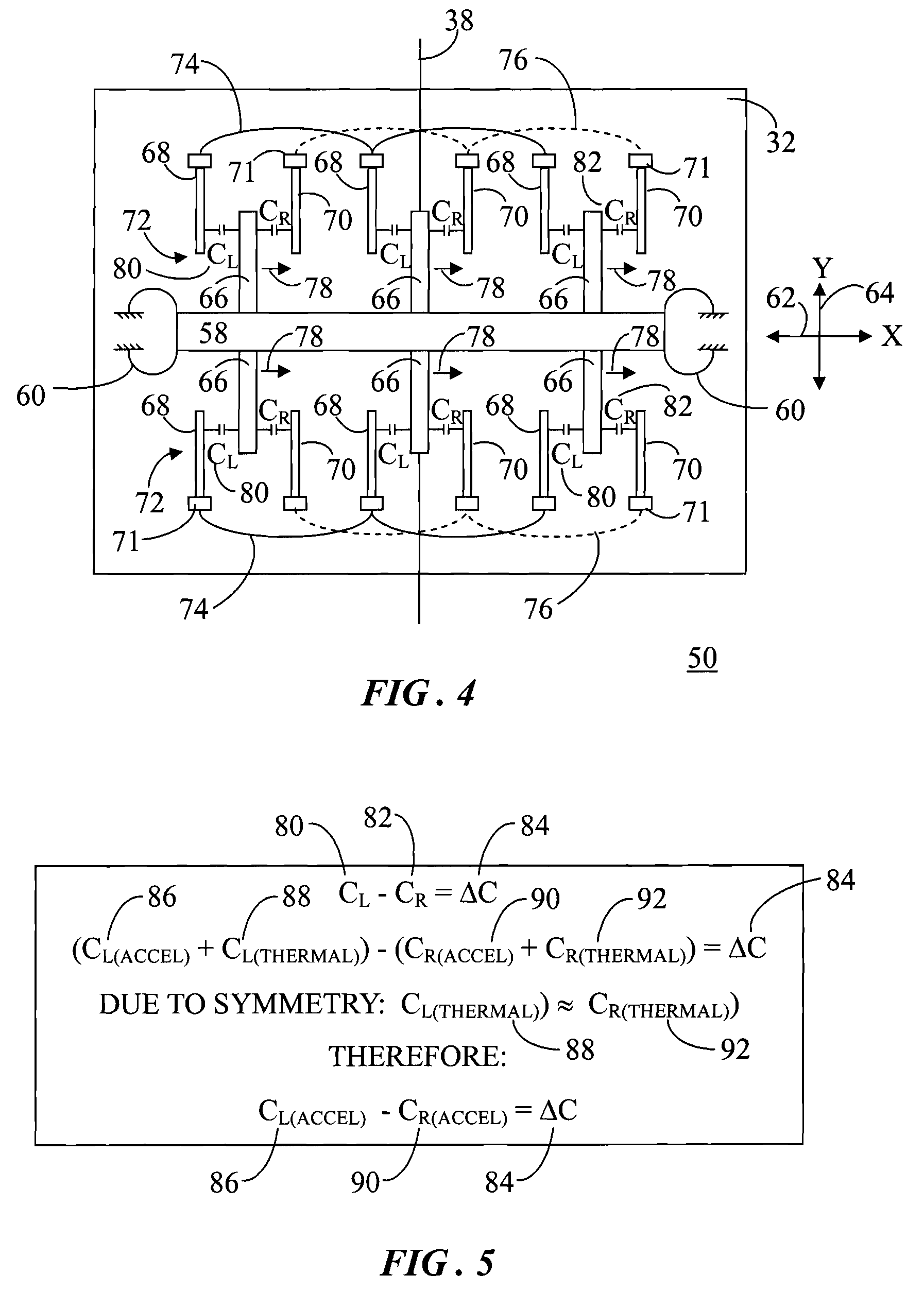

Multiple axis transducer with multiple sensing range capability

InactiveUS7779689B2Acceleration measurement using interia forcesManufacture of electrical instrumentsAxis of symmetryTransducer

A transducer package 20 includes a substrate 32 having a first axis of symmetry 36 and a second axis of symmetry 38 arranged orthogonal to the first axis of symmetry 36. At least a first sensor 50 and a second sensor 52 each of which are symmetrically arranged on the substrate 32 relative to one of the first and second axes of symmetry 36 and 38.The first and second sensors 50 and 52 are adapted to detect movement parallel to the other of the first and second axes of symmetry 36 and 38. The first sensor 50 is adapted to detect movement over a first sensing range and the second sensor 52 is adapted to detect movement over a second sensing range, the second sensing range differing from the first sensing range.

Owner:NORTH STAR INNOVATIONS

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com