Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

93results about How to "Negligible effect" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

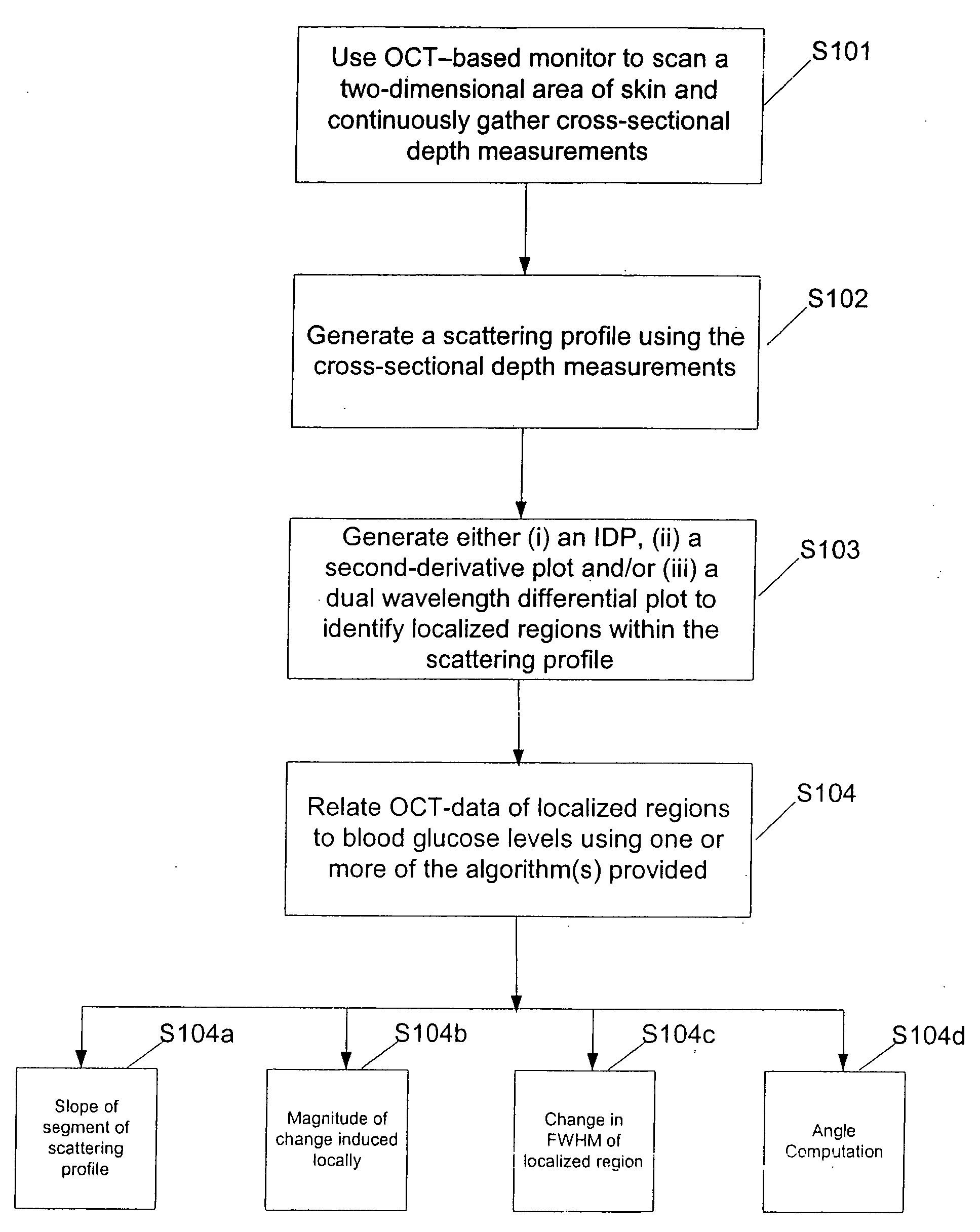

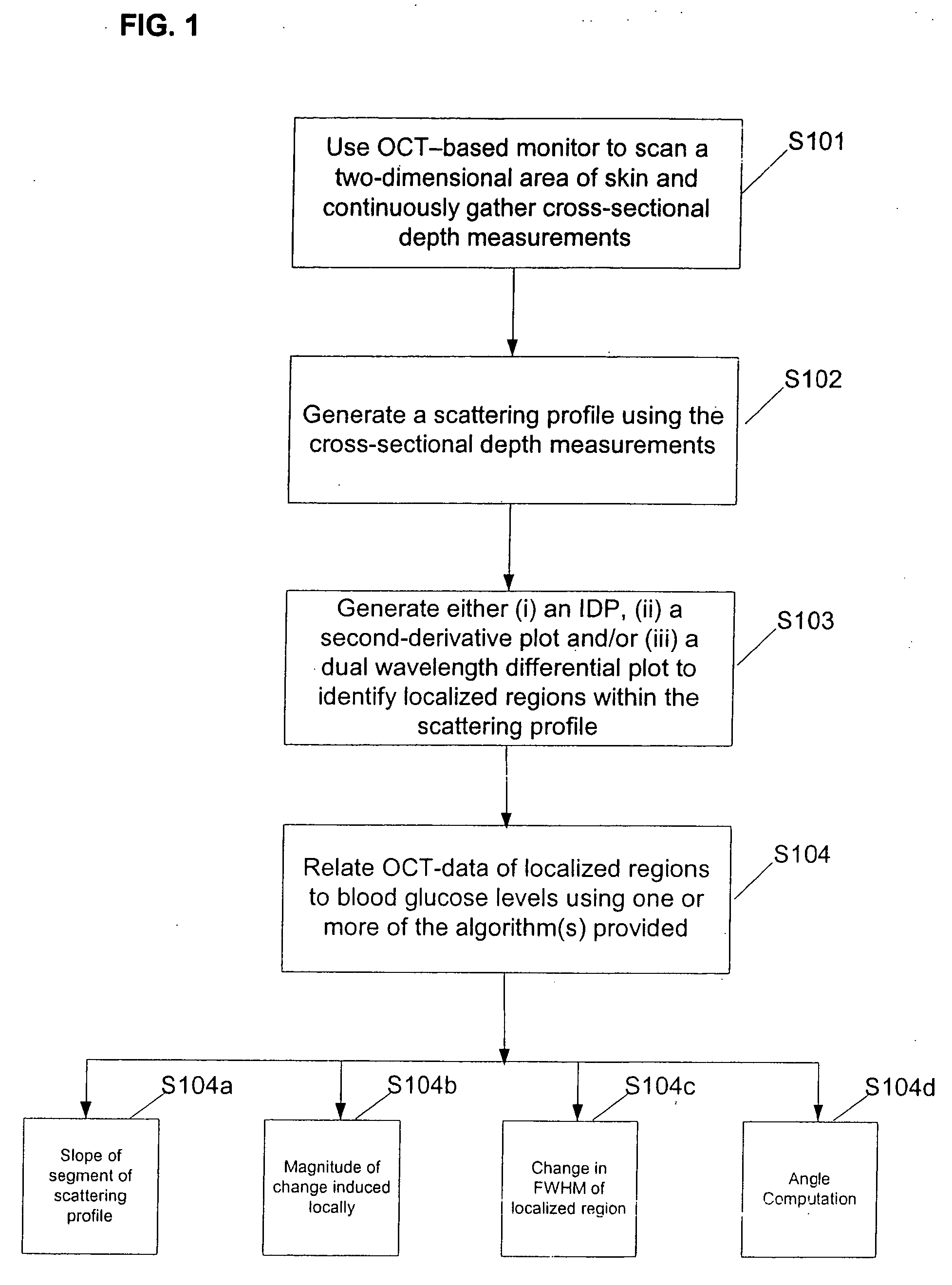

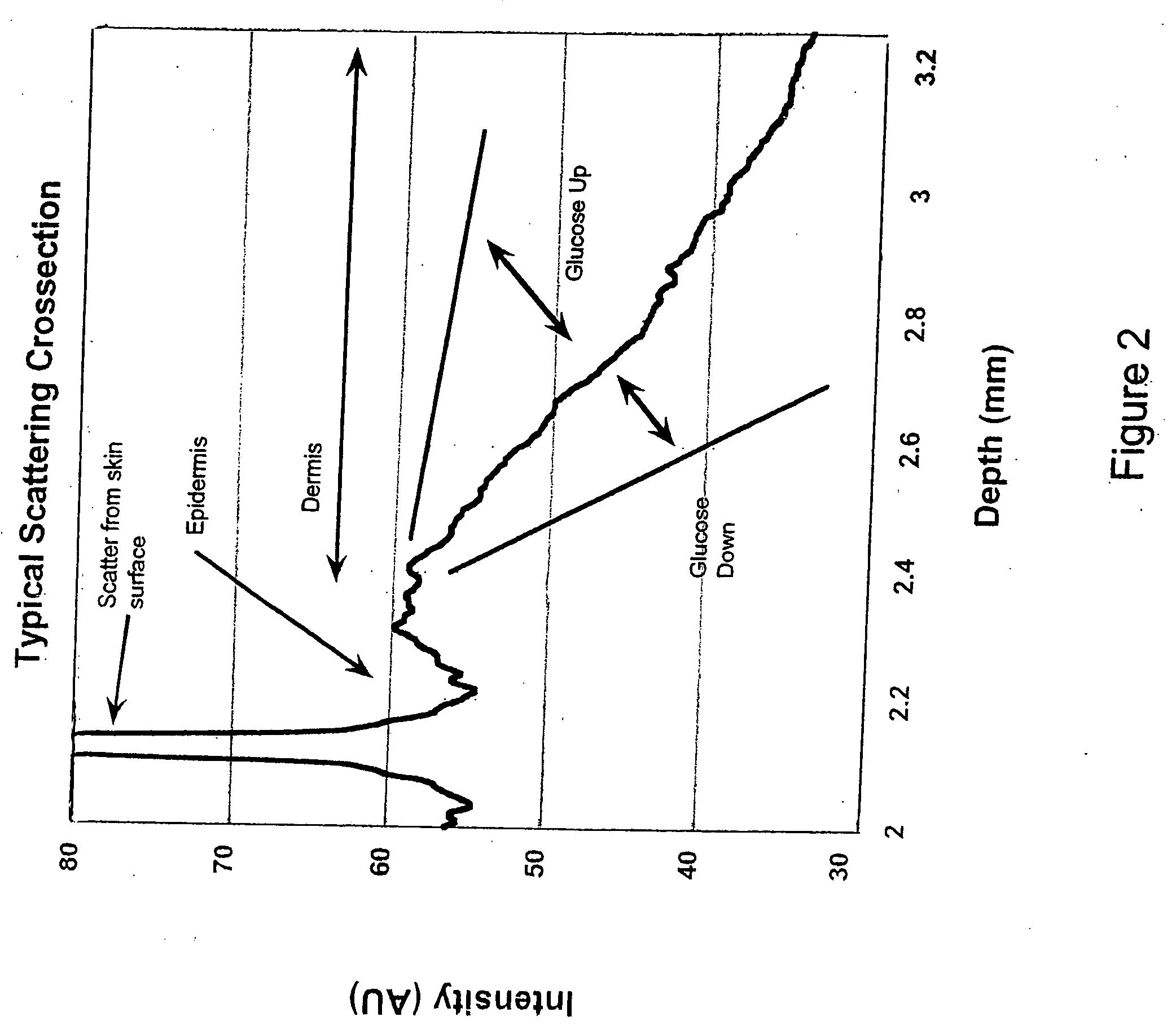

Methods for noninvasively measuring analyte levels in a subject

ActiveUS8036727B2Non-invasively measureNegligible effectDiagnostic recording/measuringSensorsAnalyteGlucose polymers

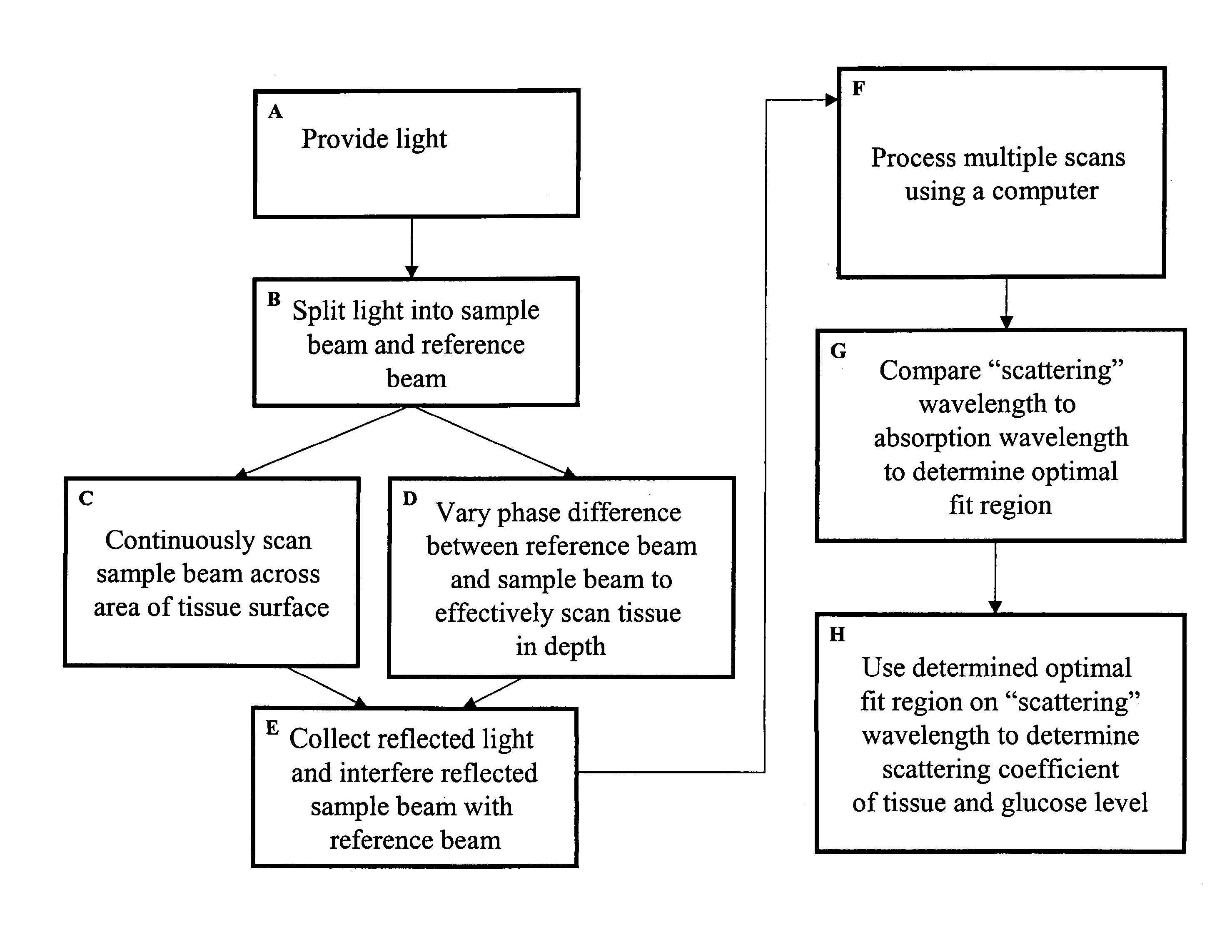

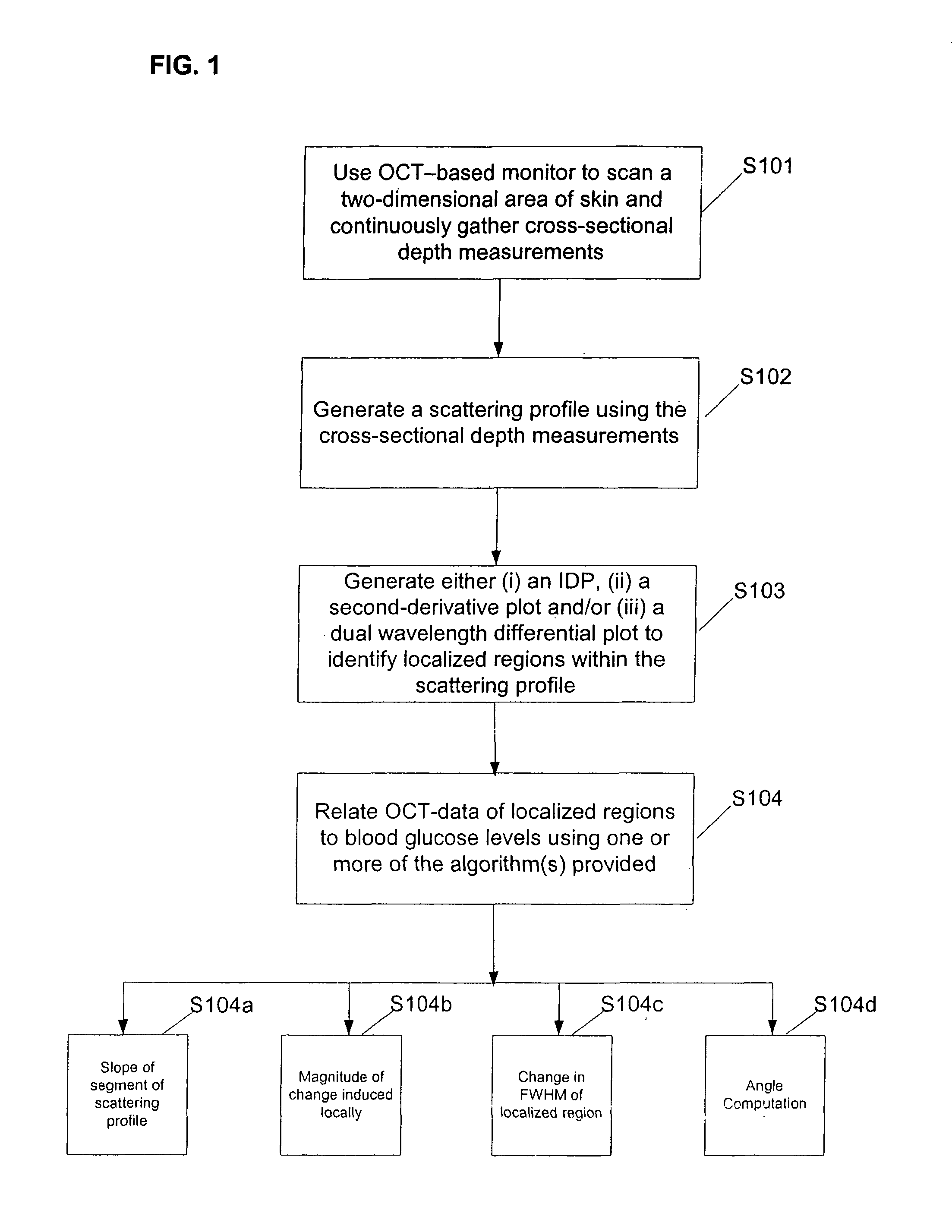

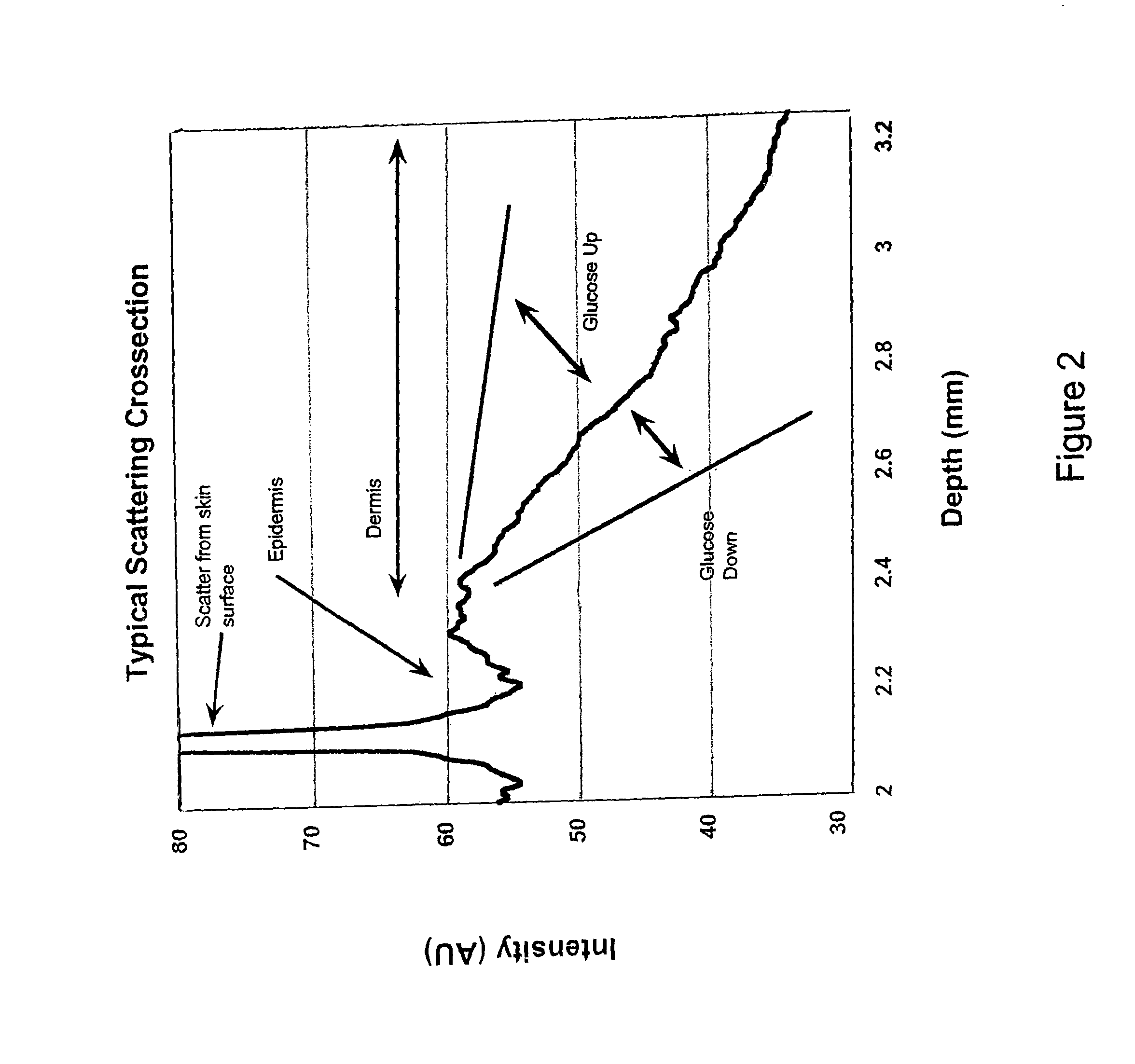

A method for noninvasively measuring analytes such as blood glucose levels includes using a non-imaging OCT-based system to scan a two-dimensional area of biological tissue and gather data continuously during the scanning. Structures within the tissue where measured-analyte-induced changes to the OCT data dominate over changes induced by other analytes are identified by focusing on highly localized regions of the data curve produced from the OCT scan which correspond to discontinuities in the OCT data curve. The data from these localized regions then can be related to measured analyte levels.

Owner:MASIMO CORP

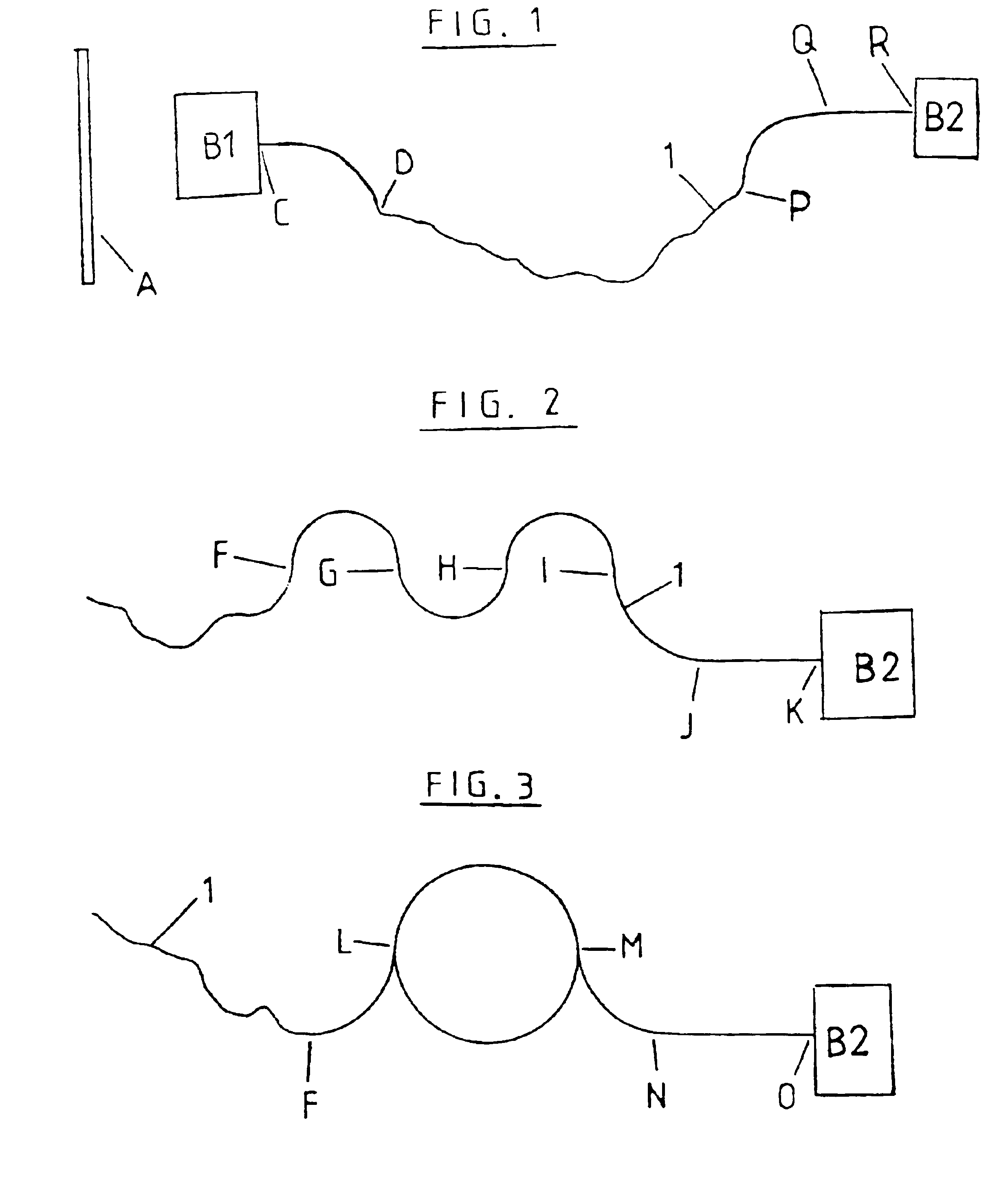

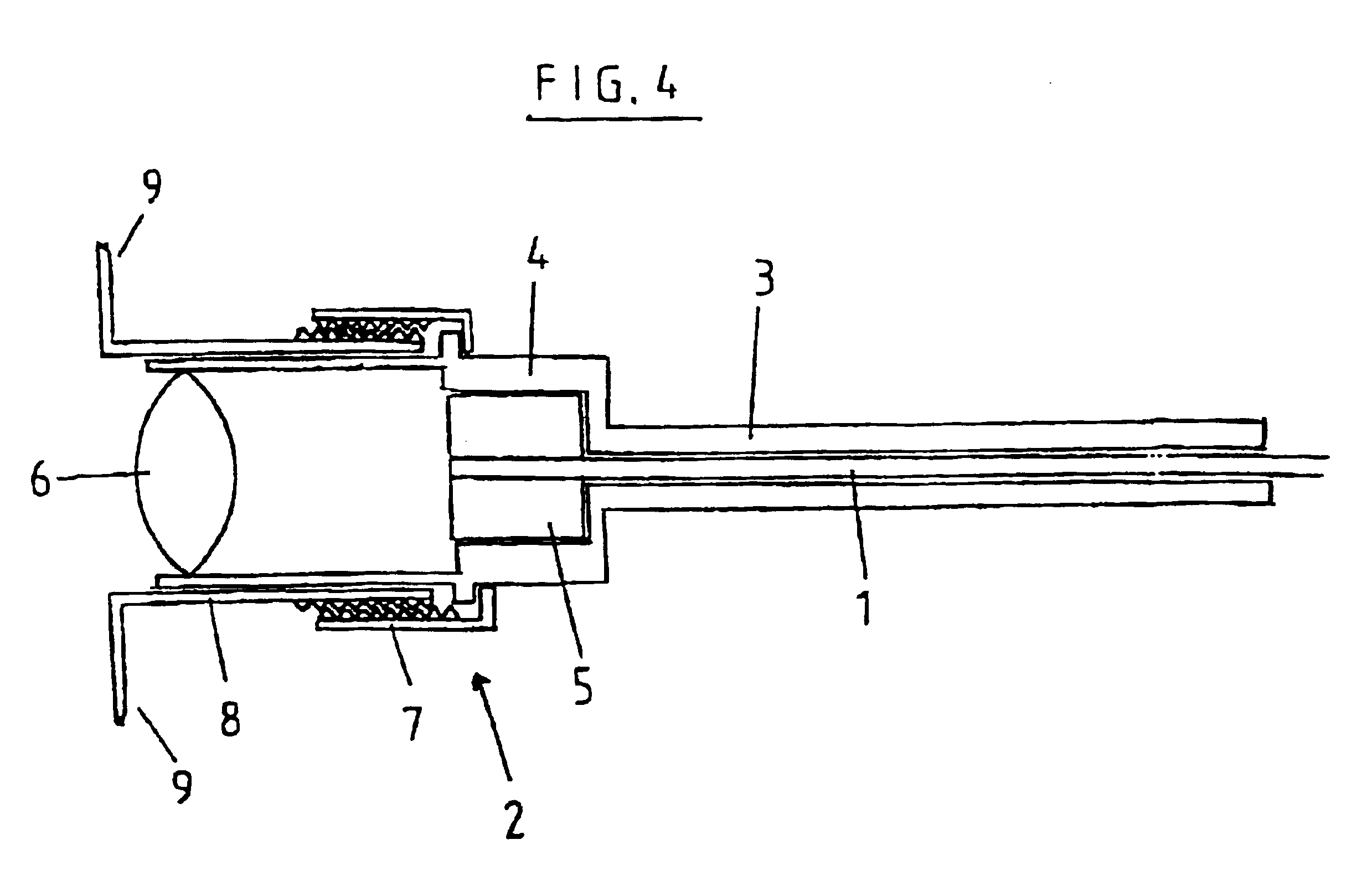

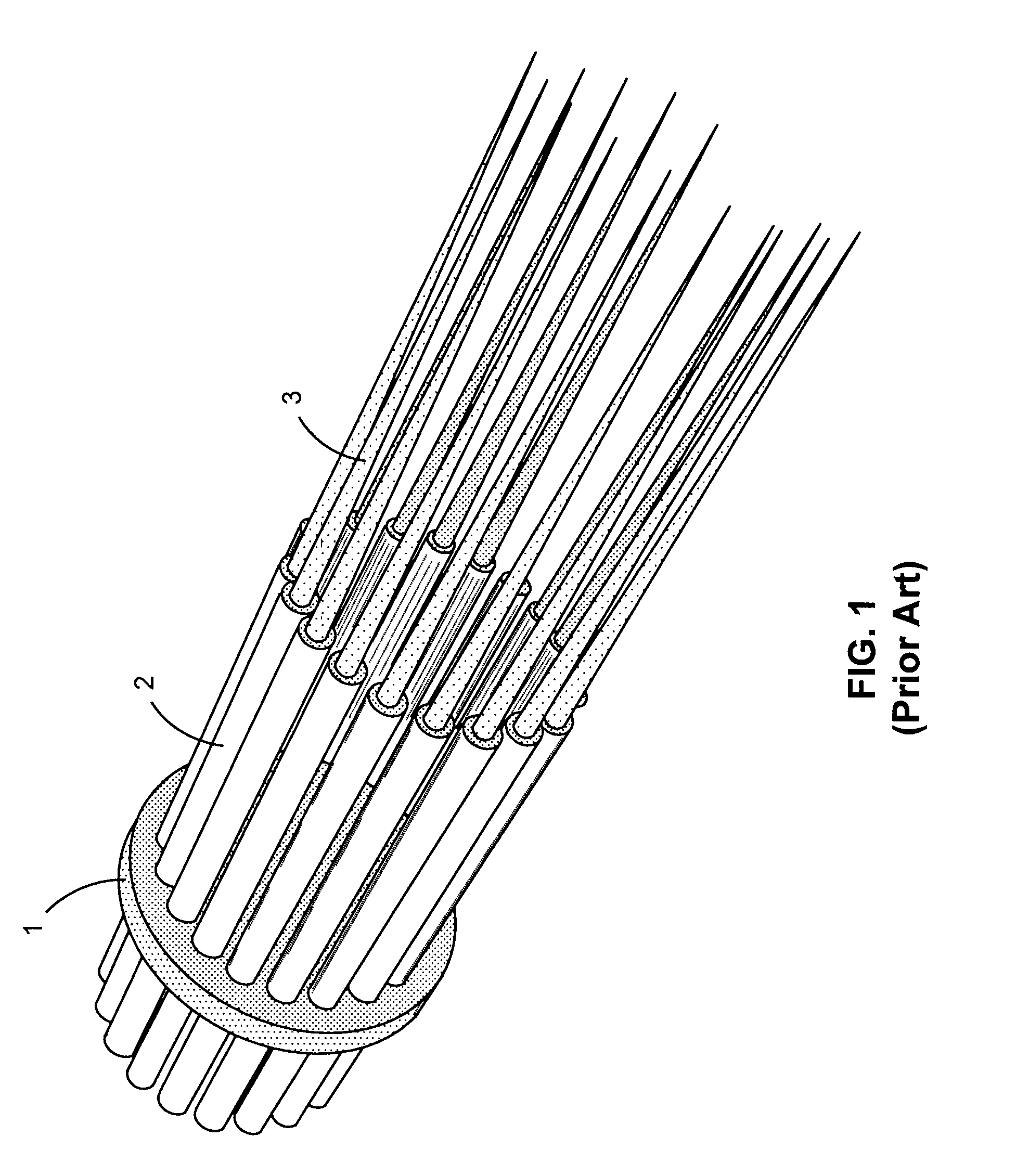

Device and method for transmitting light over an optical fiber

InactiveUS6947635B2Suppress changeEasily measureCoupling light guidesOptical waveguide light guideOptical measurementsMode mixing

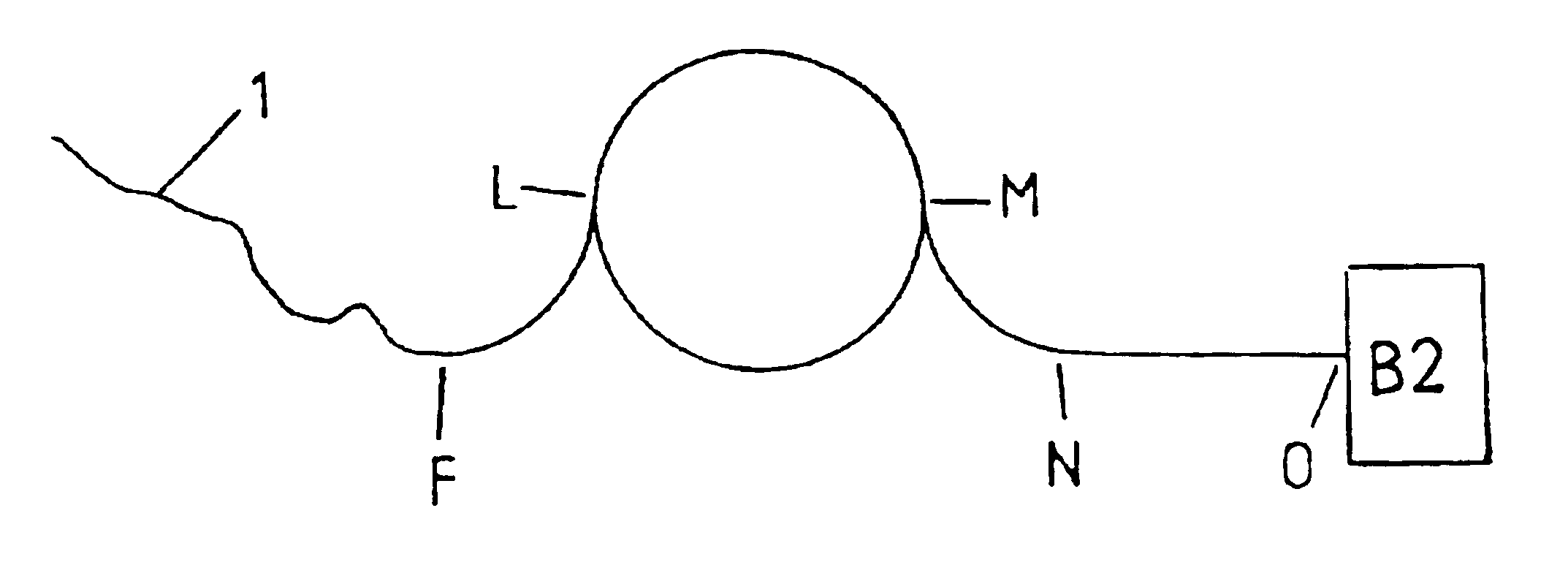

The invention relates to a method and device for transmitting light over a fat fiber (1) between optical components (B1; B2) of an optical measuring device, which are provided at a launching end (C) and at an extraction end (R; K; O) of the fat fiber (1). Said measuring device comprises a guiding means for the curved rigid guidance of a first partial section (PQ; FGHI; IJ; FL; LM; MN) of the fat fiber (1). If the radius of curvature of the curved guidance falls below a first limit, the light beam profile of the fat fiber (1) is homogenized by a mode mixing. In order to diminish the effect on the transmitted light caused by a permitted change in position of the fat fiber (1), a stiffening means, which is rigidly connected to the guiding means, is provided for rigidly guiding a second partial section (QR; JK; NO) of the fat fiber (1). Said second partial section connects to the first partial section (PQ; FGH; IJ; FL; LM; MN) and extends essentially up to the optical component (B2) located at the extraction end (R; K; O), whereby the entire length of the first and second partial section is at least provided with a length that renders the extraction end (R; K; O) of the fat fiber (1) mechanically stable.

Owner:INSTR SYST

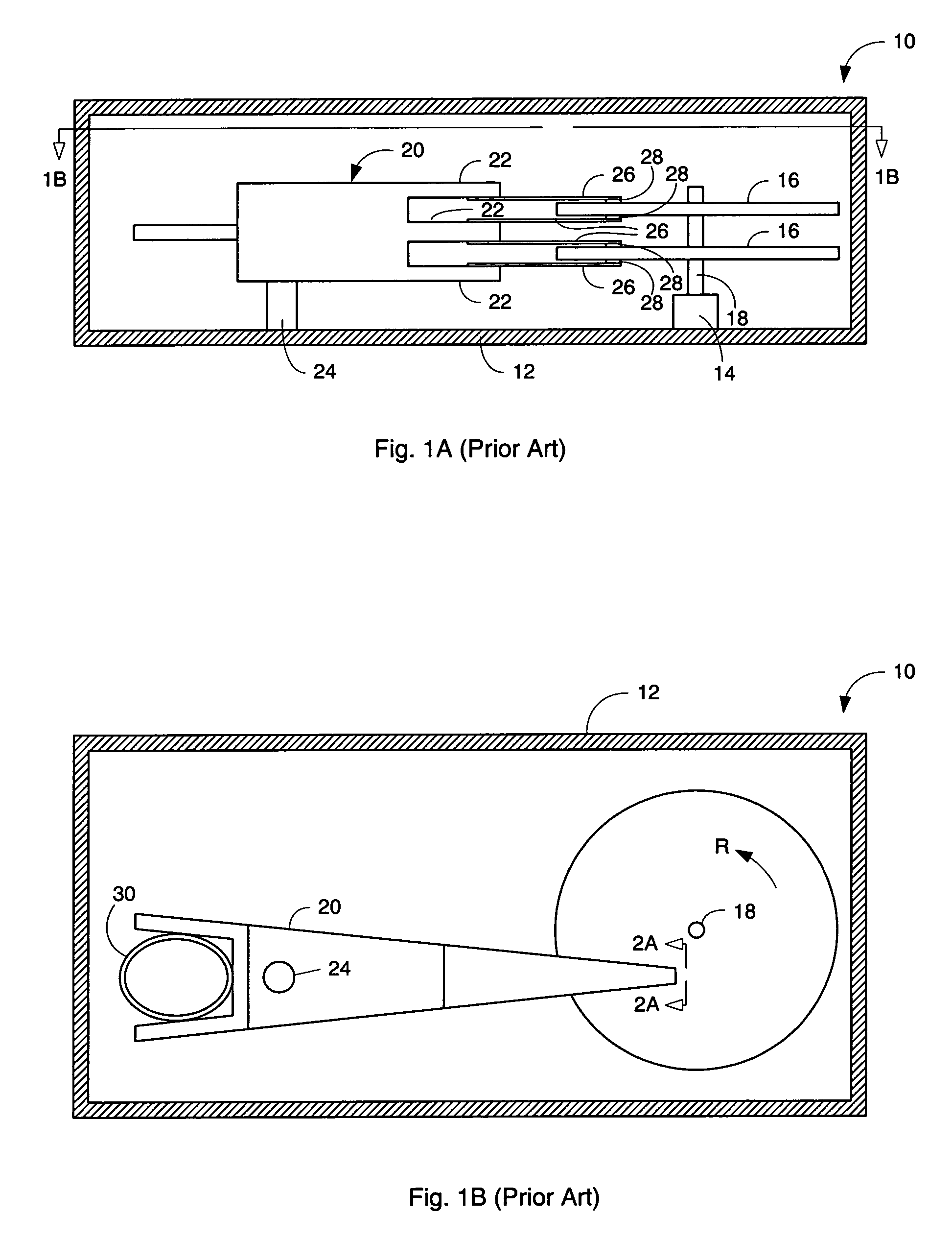

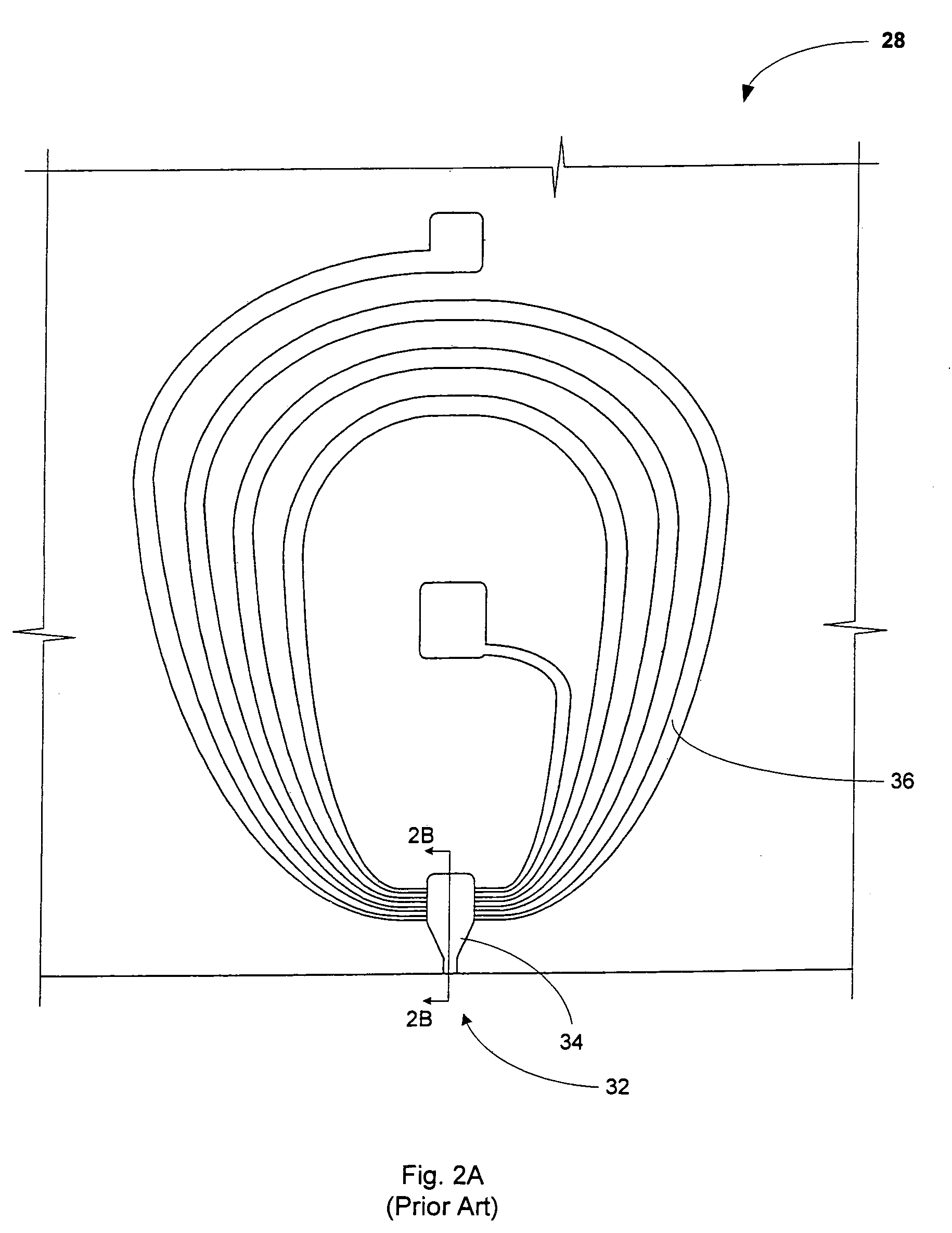

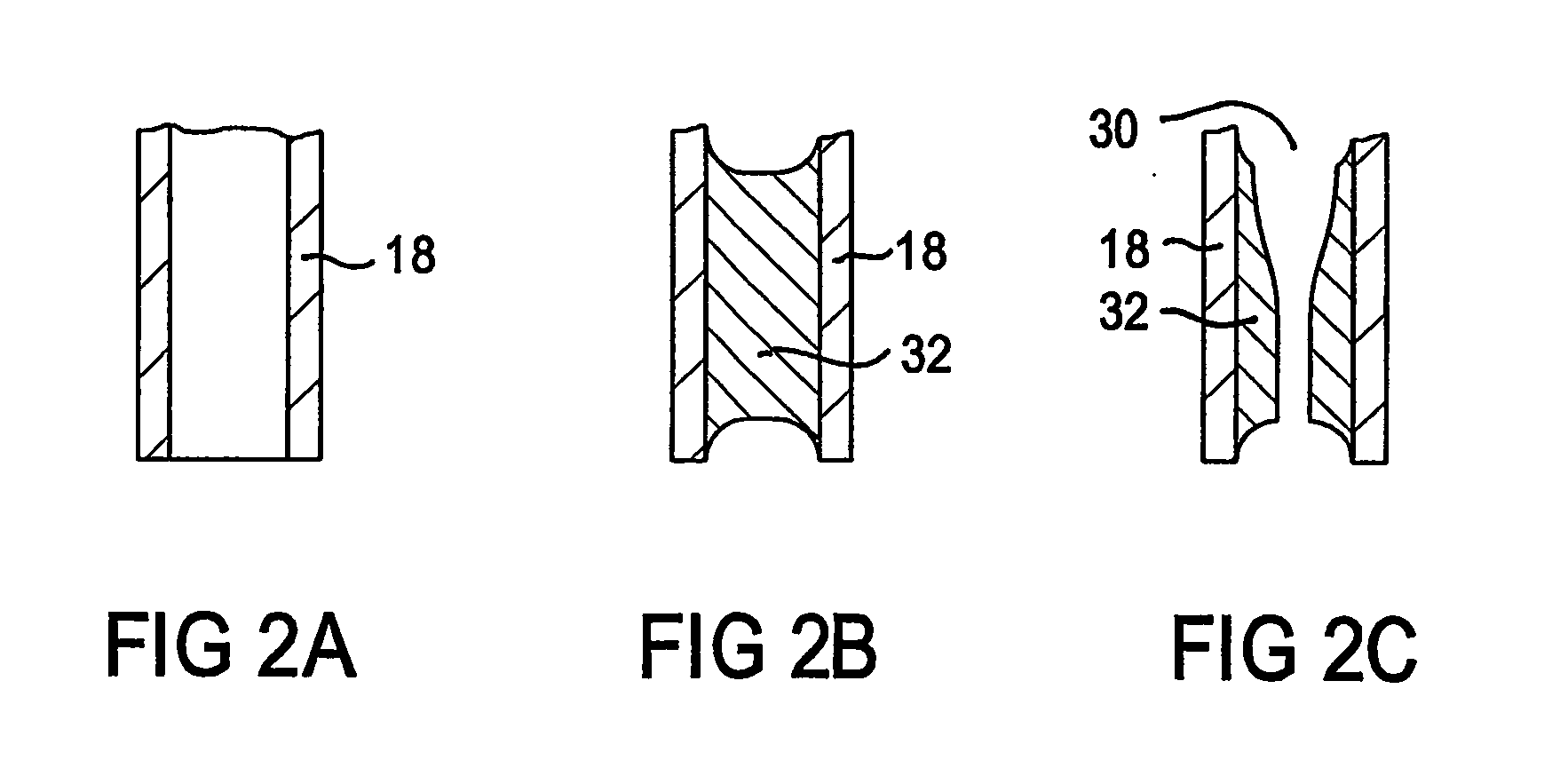

Inductive write head having high magnetic moment poles and low magnetic moment thin layer in the back gap, and methods for making

InactiveUS6989962B1Avoid corrosionNegligible effectHeads using thin filmsRecord information storageMagnetic polesThin layer

The present invention provides a write element for use in magnetic data recording system such as a computer disk drive. The write head utilizes the advantageous properties of high magnetic moments while overcoming the corrosion problems engendered by such materials. The write element includes a magnetic yoke constructed of first and second magnetic poles joined to one another at a back gap. While the majority of the poles are constructed of a high magnetic moment material a layer of relatively low magnetic moment material is provided on the first pole at the back gap portion of the first pole. The relatively low magnetic moment material prevents corrosion of the first pole during subsequent manufacturing of the write head. An electrically conductive coil passes through the magnetic yoke and is insulated there from. By passing an electrical current through the electrical coil, a magnetic flux is generated in the yoke. This magnetic flux then generates a magnetic fringing field in at a write gap of the yoke. The fringing field imparts magnetic data onto a recording medium passing thereby.

Owner:WESTERN DIGITAL TECH INC

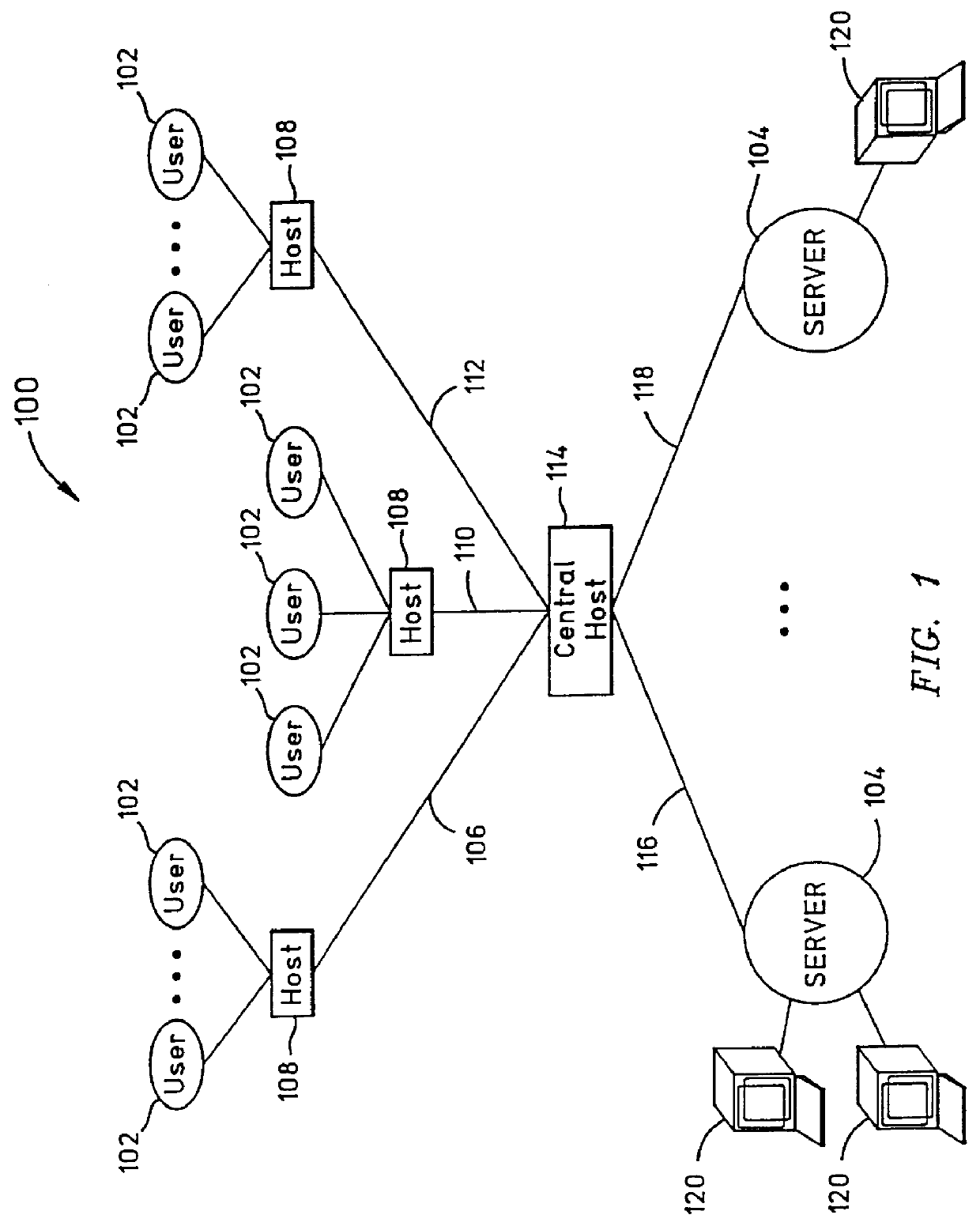

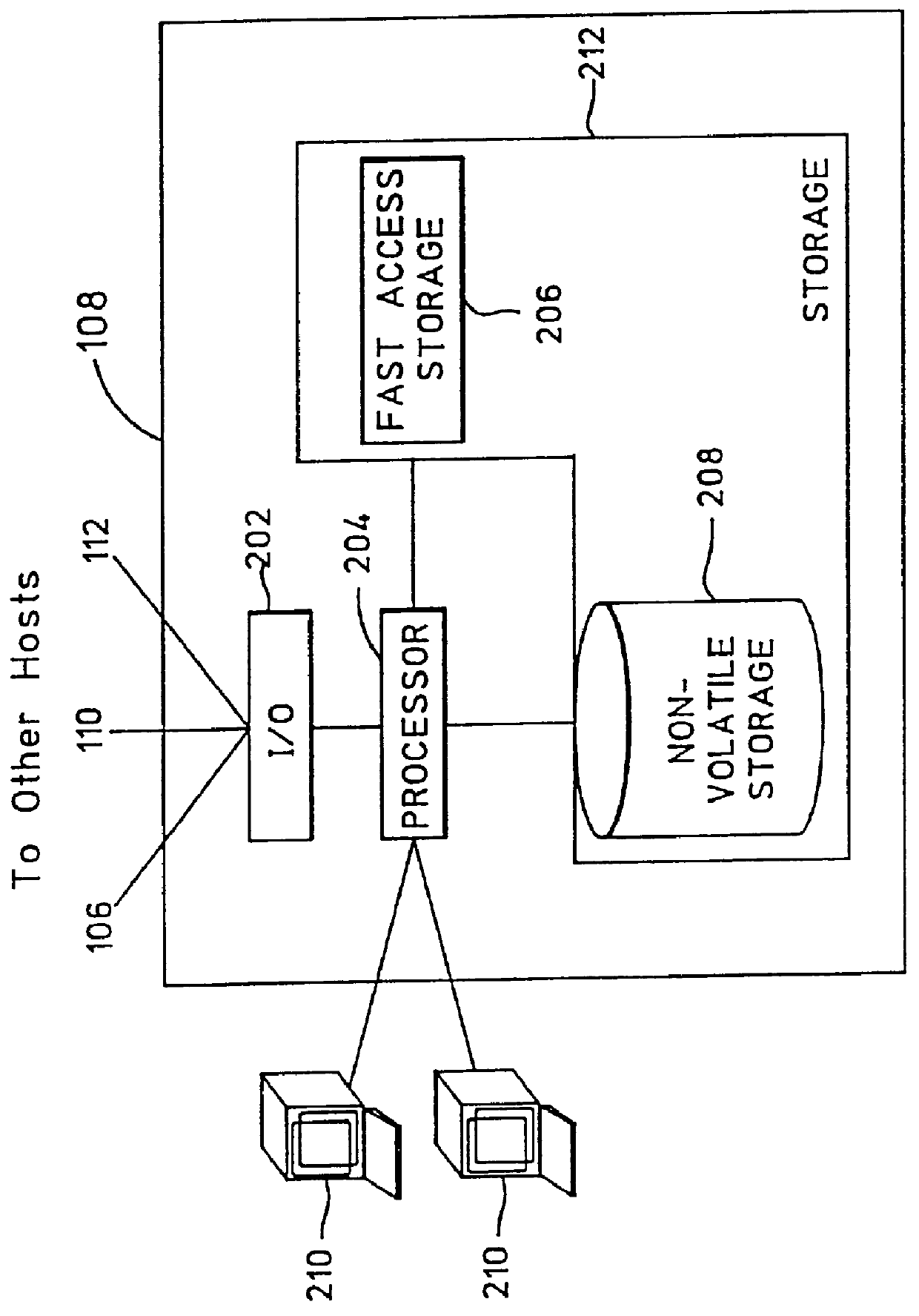

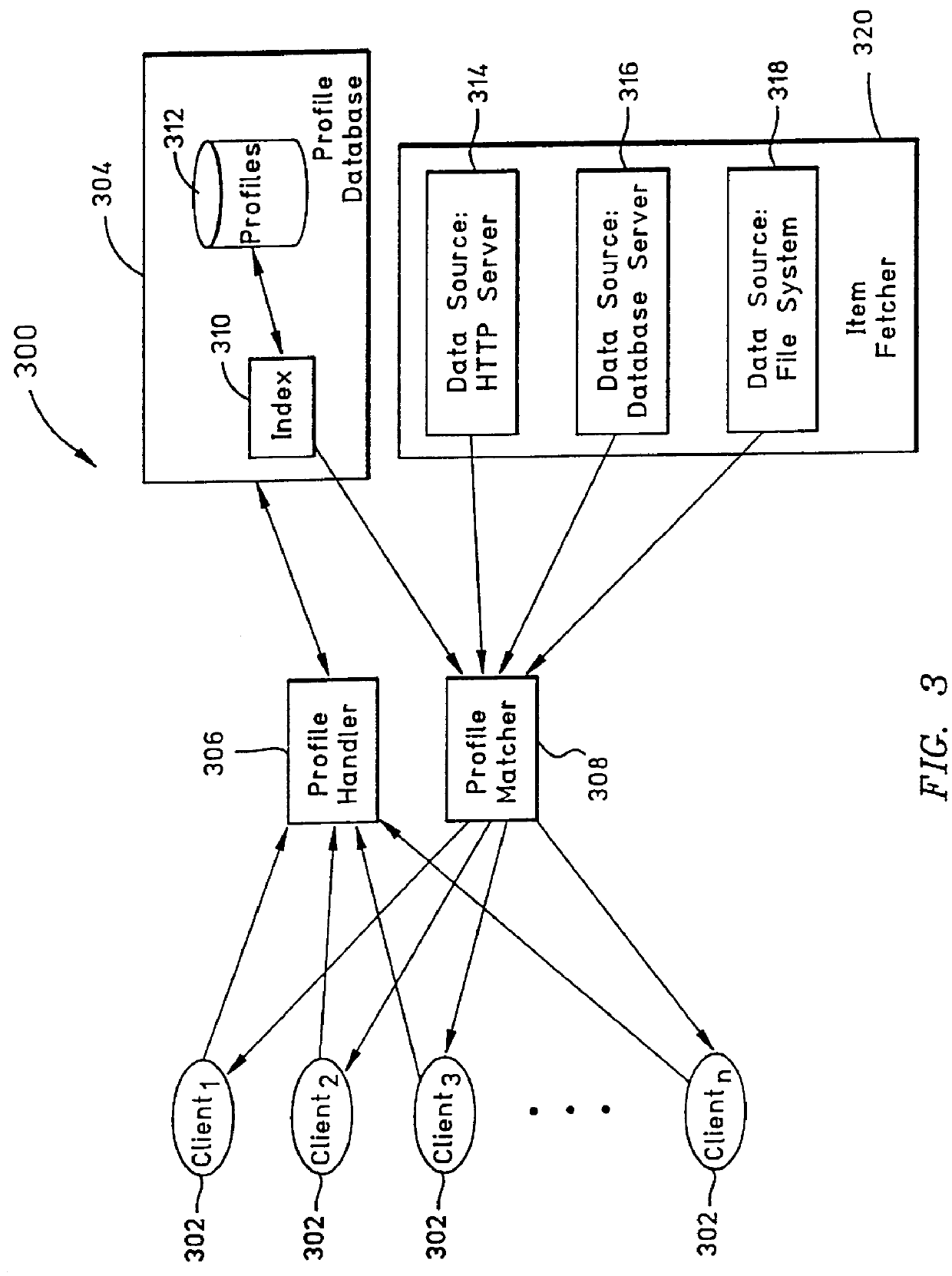

Method and apparatus for efficient profile matching in a large scale webcasting system

InactiveUS6108645AImprove performanceNear-optimal performanceData processing applicationsDigital data information retrievalDocument preparationUser profile

A method and apparatus for efficiently matching a large collection of user profiles against a large volume of data in a webcasting system. The method removes redundant patterns in user profiles and information content to improve matching performance based on a Boolean-based query language. Users can select desired information content by choosing a set of predicates to assert the properties for each cyberspace document desired. Boolean operators of AND, OR and NOT connect predicates together on the information items that will be pushed to them. The method includes dynamic cost / credit adjustment based profile indexing and matching.

Owner:IBM CORP

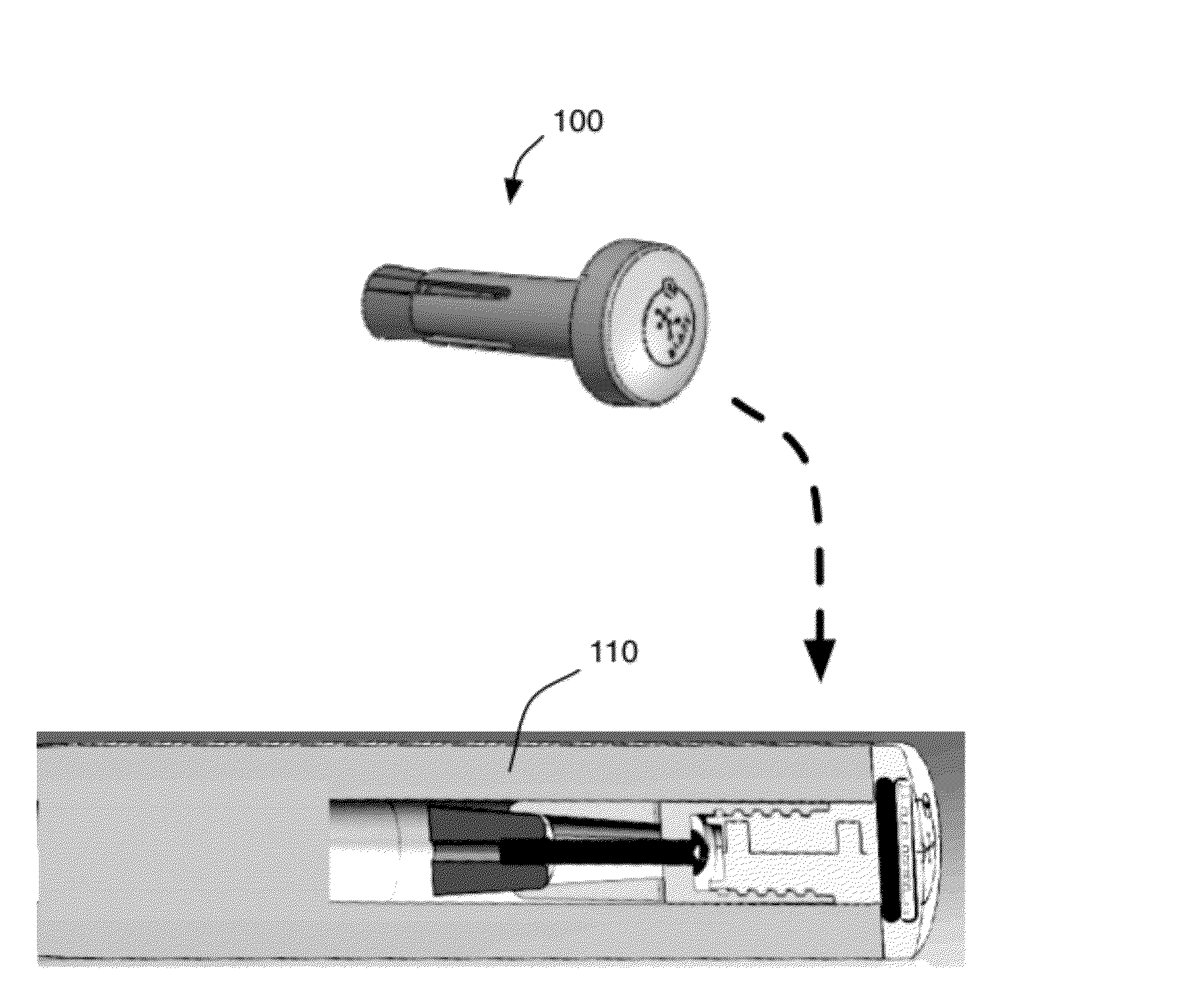

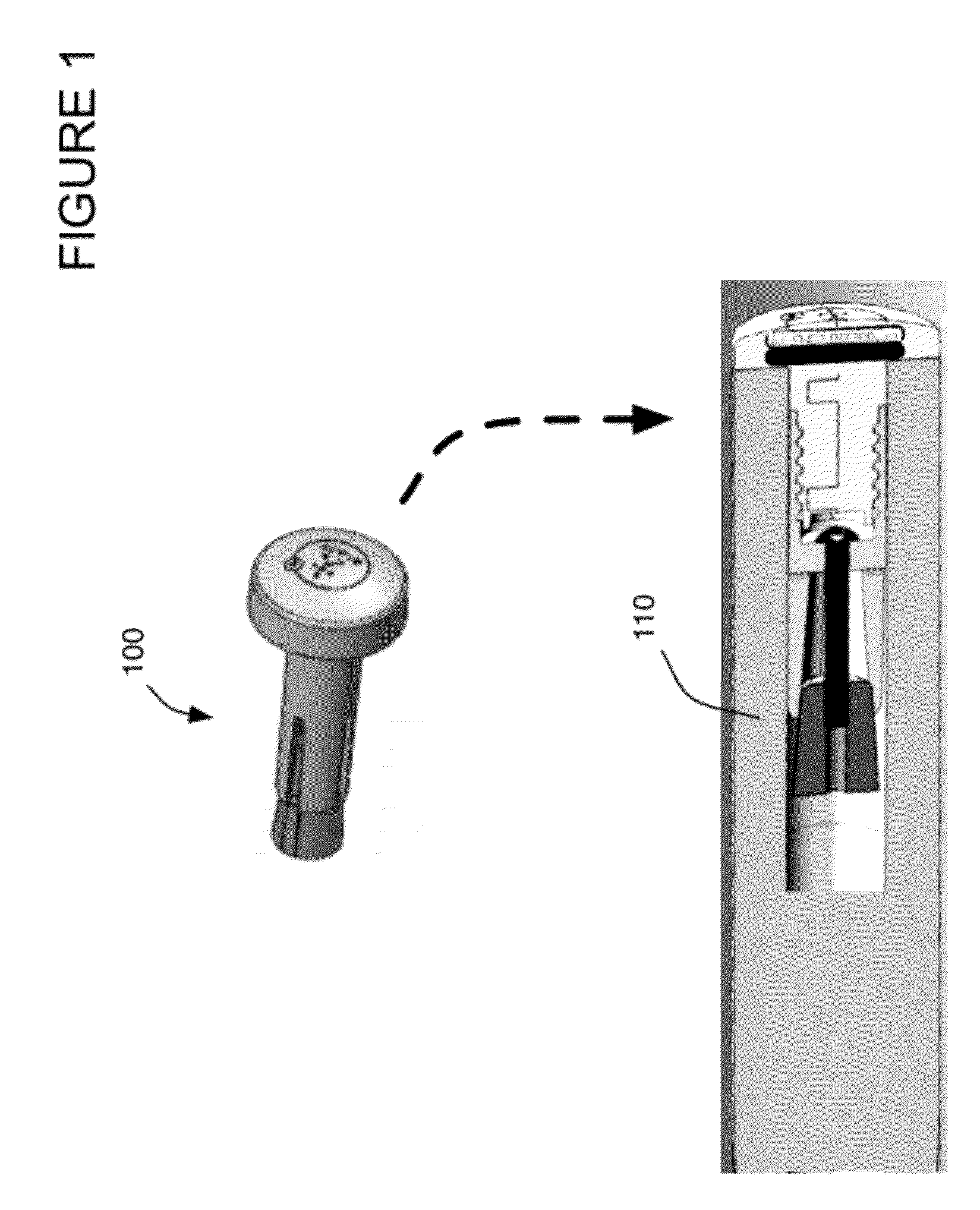

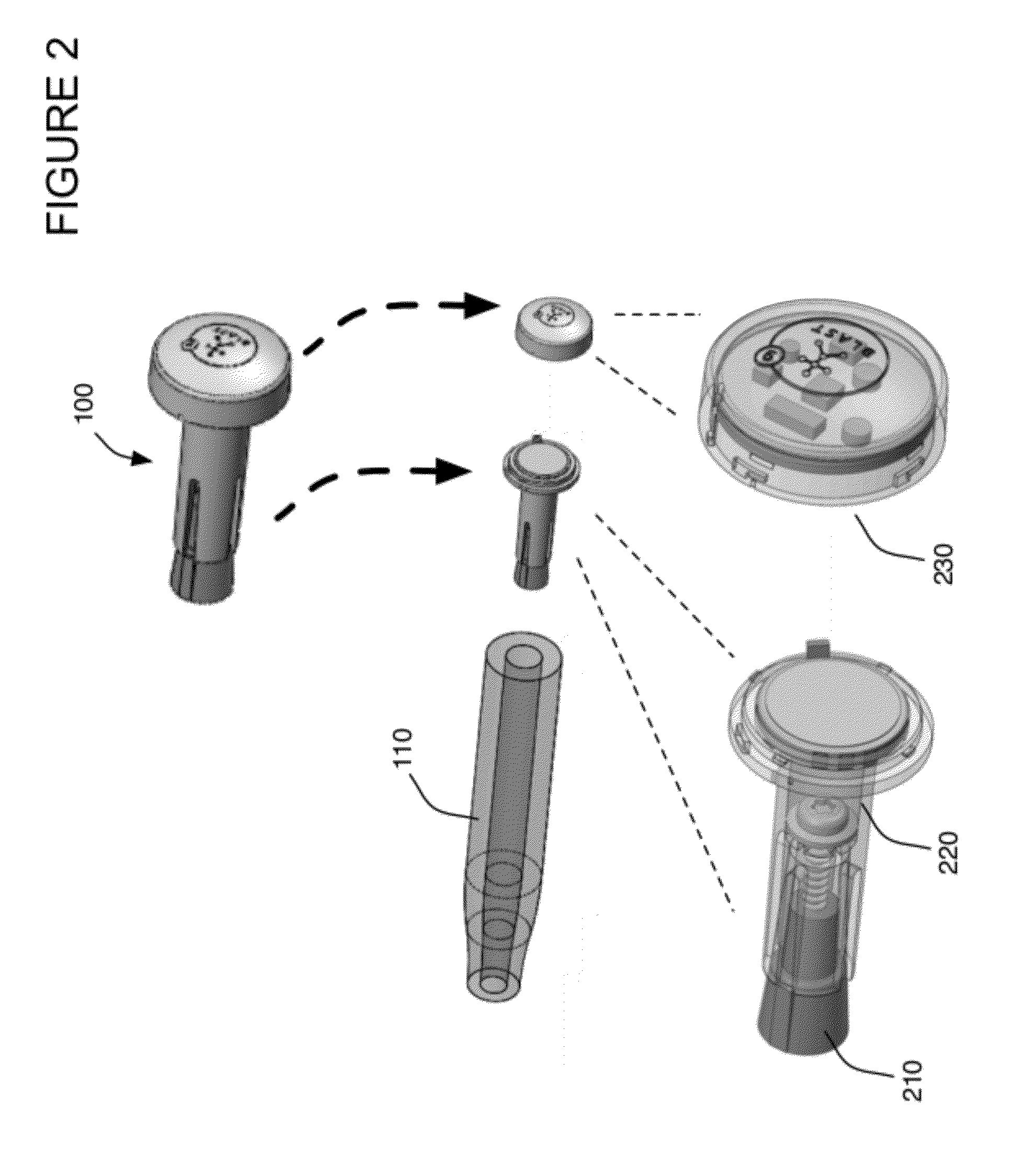

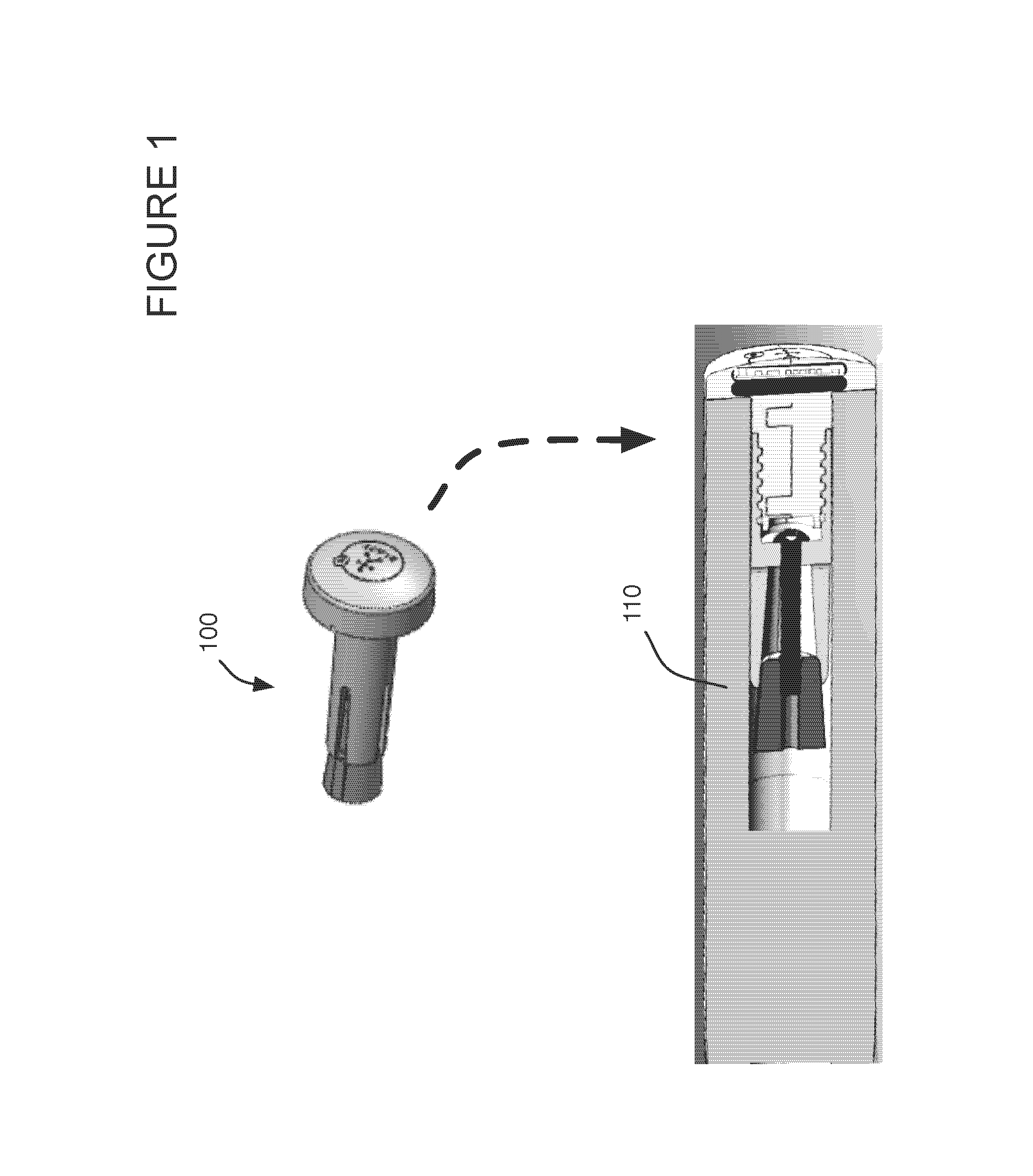

Motion capture element mount

ActiveUS20120120572A1Avoid lostReduce weightCandle holdersLighting support devicesEngineeringGolf Ball

Enablescoupling or retrofitting a golf club with active motion capture electronics that are battery powered, passive or active shot count components, for example a passive RFID, and / or a visual marker on the cap for use with visual motion capture cameras. Does not require modifying the golf club. Electronics package and battery can be easily removed and replaced, without any tools. May utilize a weight that is removed when inserting the electronic package, wherein the weight element may have the same weight as an electronics package, for no net change or minimal change in club weight. May be implemented with a shaft enclosure and expander that may be coupled with a screw aligned along an axis parallel to the axis of the golf club shaft. May utilize non-permanently and / or friction coupling between the mount and golf club shaft. Cap may include a visual marker and / or logo.

Owner:NEWLIGHT CAPITAL LLC

Methods for noninvasively measuring analyte levels in a subject

ActiveUS20060276696A1Non-invasively measureNegligible effectDiagnostic recording/measuringSensorsAnalyteGlucose polymers

A method for noninvasively measuring analytes such as blood glucose levels includes using a non-imaging OCT-based system to scan a two-dimensional area of biological tissue and gather data continuously during the scanning. Structures within the tissue where measured-analyte-induced changes to the OCT data dominate over changes induced by other analytes are identified by focusing on highly localized regions of the data curve produced from the OCT scan which correspond to discontinuities in the OCT data curve. The data from these localized regions then can be related to measured analyte levels.

Owner:MASIMO CORP

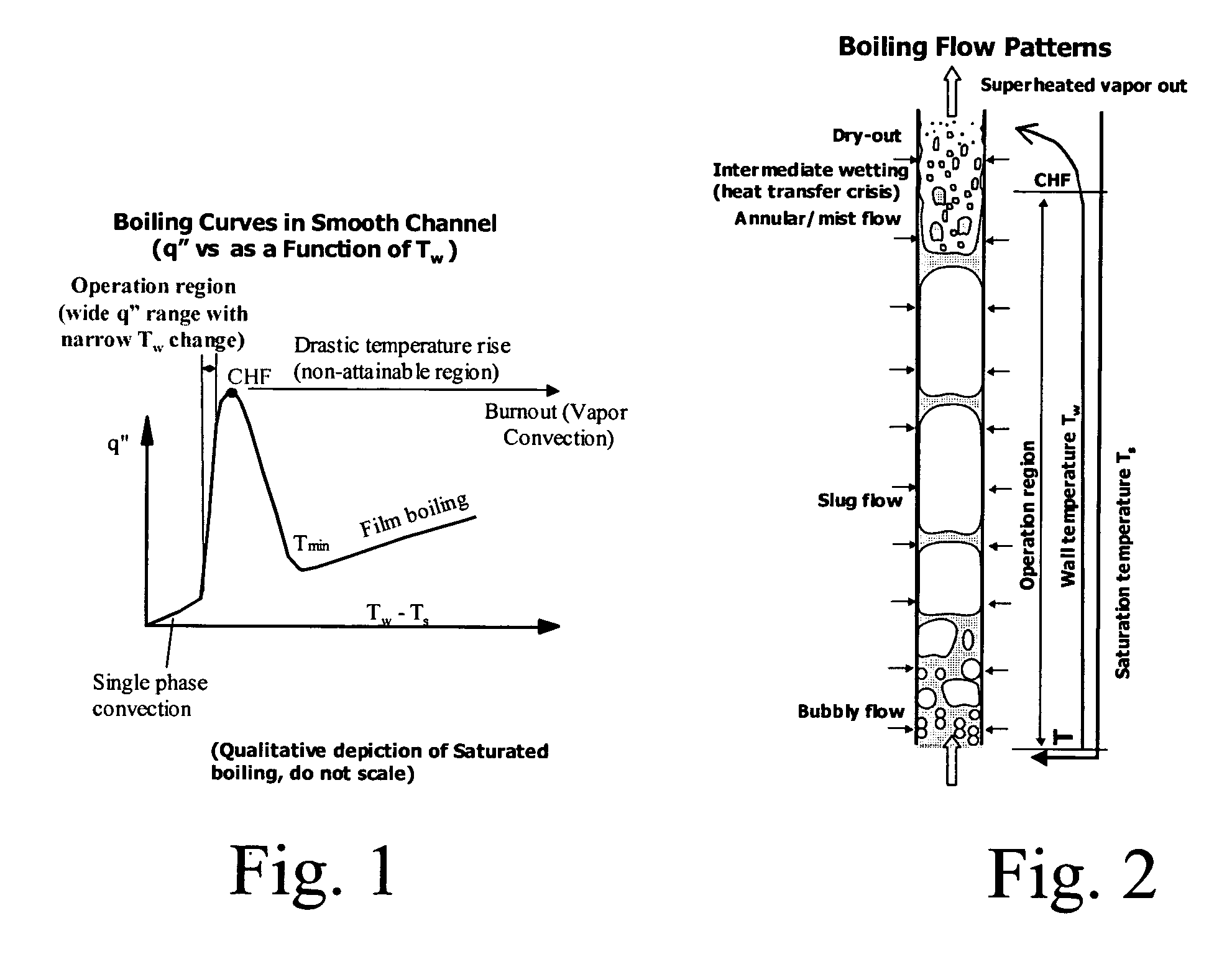

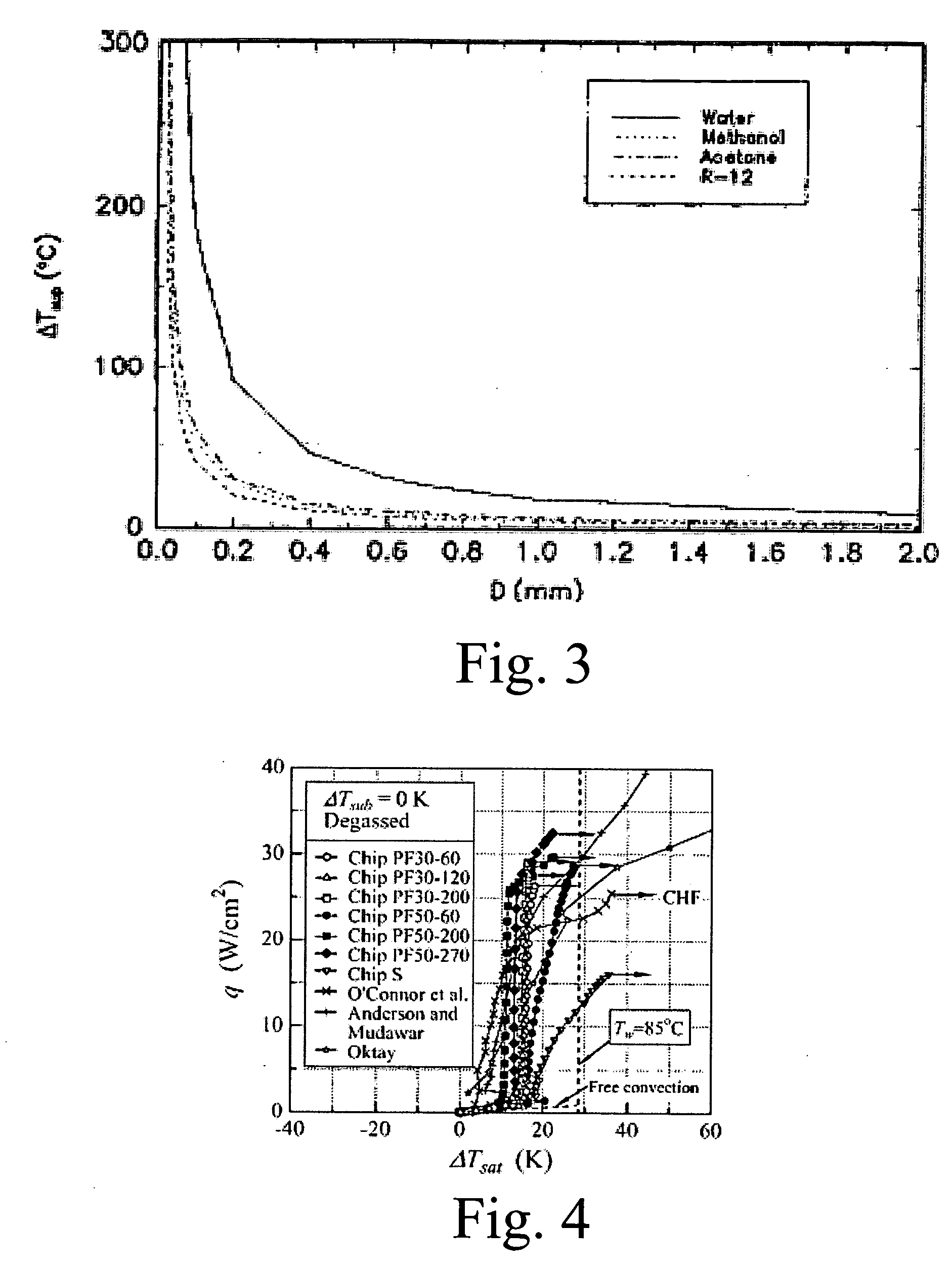

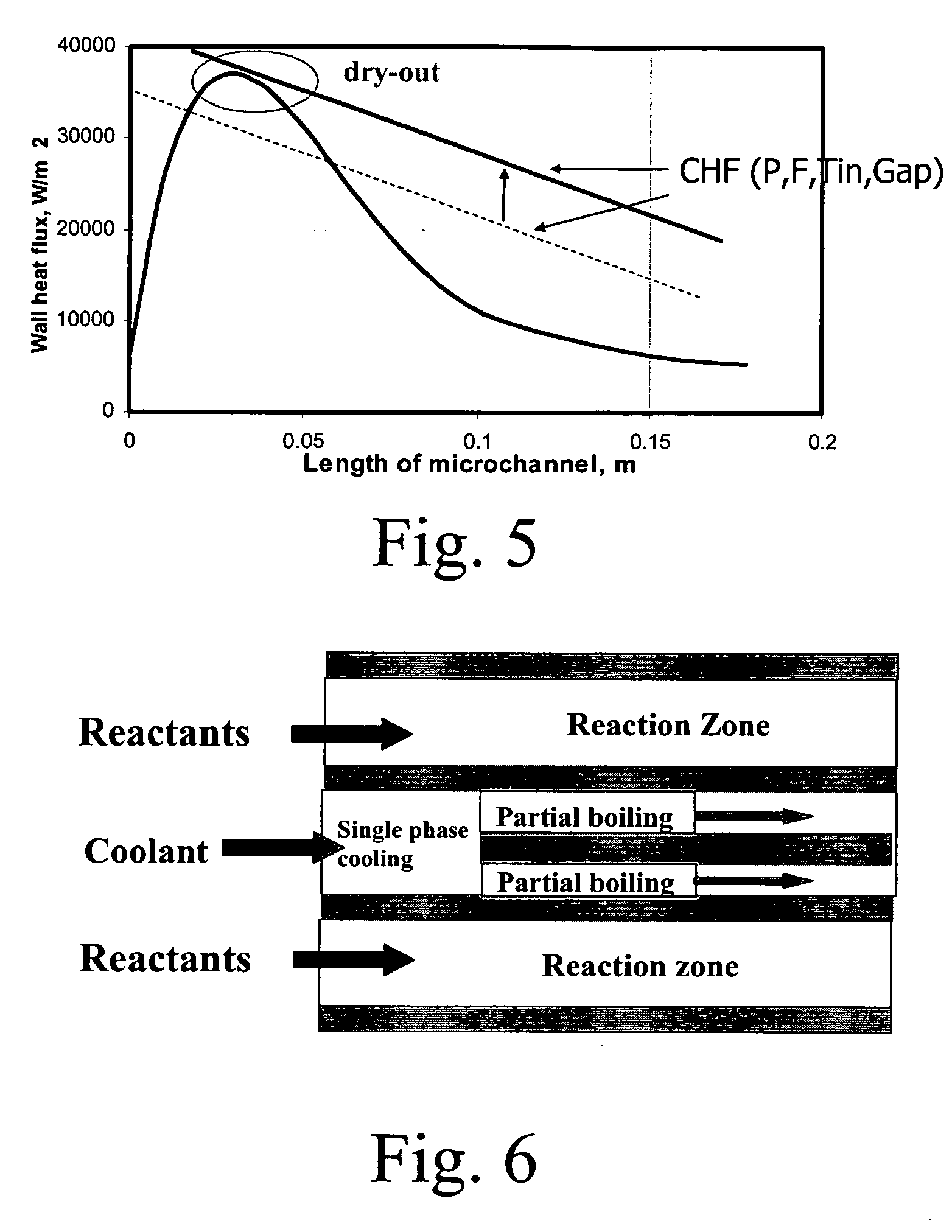

Partial boiling in mini and micro-channels

ActiveUS20060142401A1Less bubbleHigh densityOrganic compounds purification/separation/stabilisationOrganic compound preparationExothermic processChemistry

The invention provides methods, apparatus and systems in which there is partial boiling of a liquid in a mini-channel or microchannel. The partial boiling removes heat from an exothermic process.

Owner:VELOCYS CORPORATION

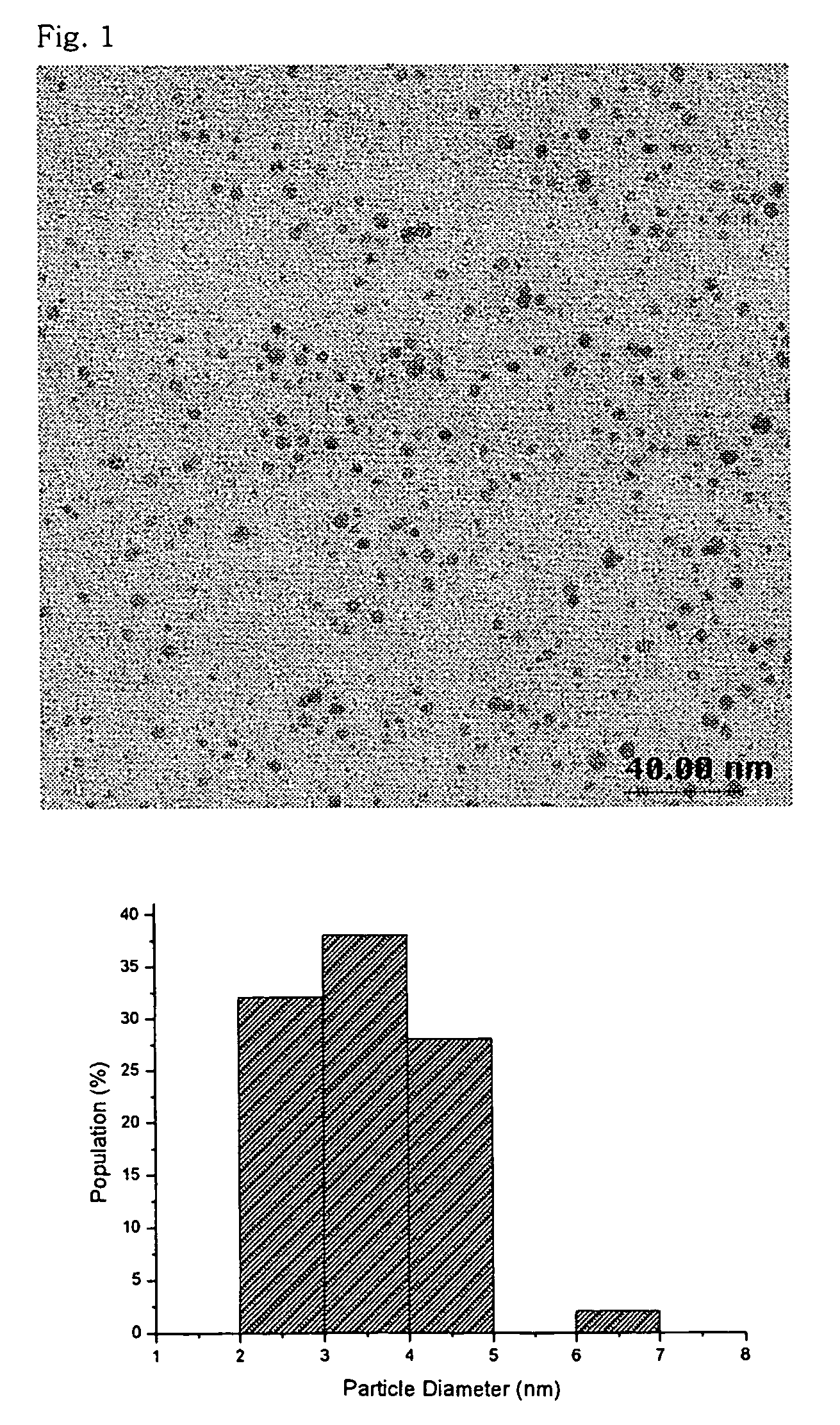

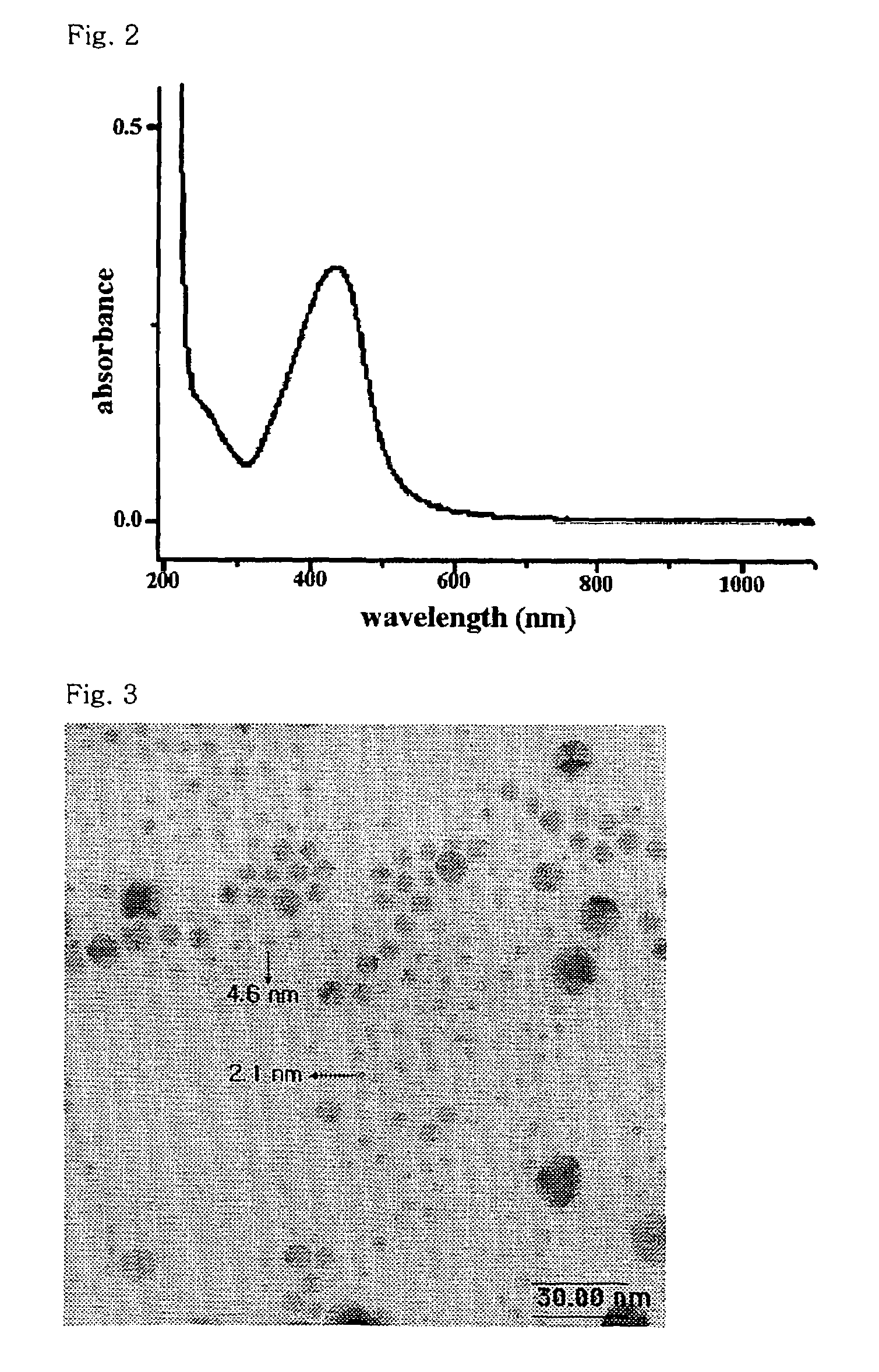

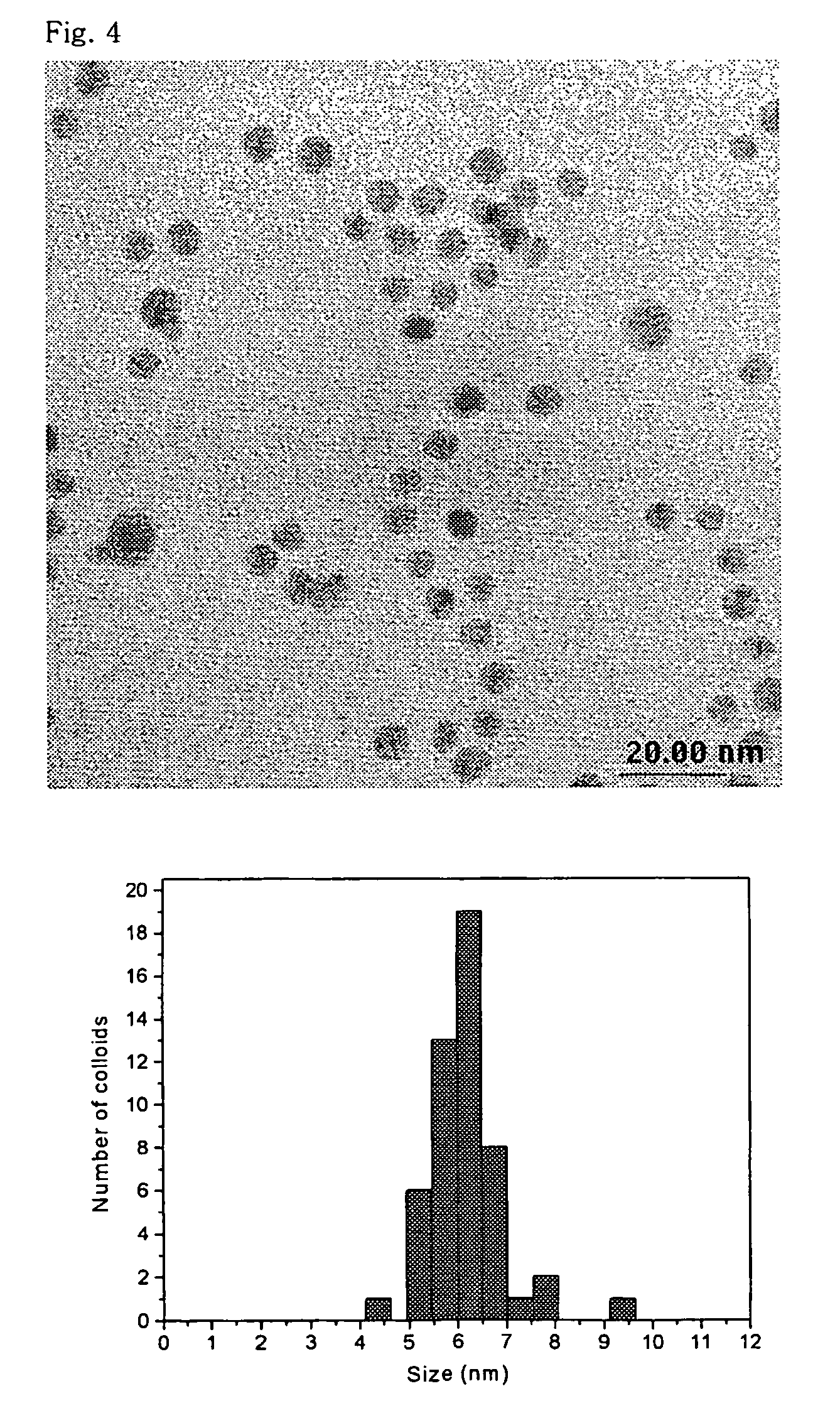

Colloid solution of metal nanoparticles, metal-polymer nanocomposites and methods for preparation thereof

InactiveUS7348365B2Easy to controlGood effectOther chemical processesTransportation and packagingStabilizer for polymersNanometre

A metal nanoparticle colloid solution, metal-polymer nanocomposites, and methods for preparing the same are provided. The metal nanoparticle colloid solution and the metal-polymer nanocomposites can be prepared with a variety of polymeric stabilizers and have uniform particle diameter and shape. The metal nanoparticle colloid solution and the metal-polymer nanocomposites have wide applications, for example, as an antibacterial agent, a sterilizer, a conductive adhesiv, conductive ink or an electromagnetic wave shielder for an image display.

Owner:POSTECH ACAD IND FOUND +1

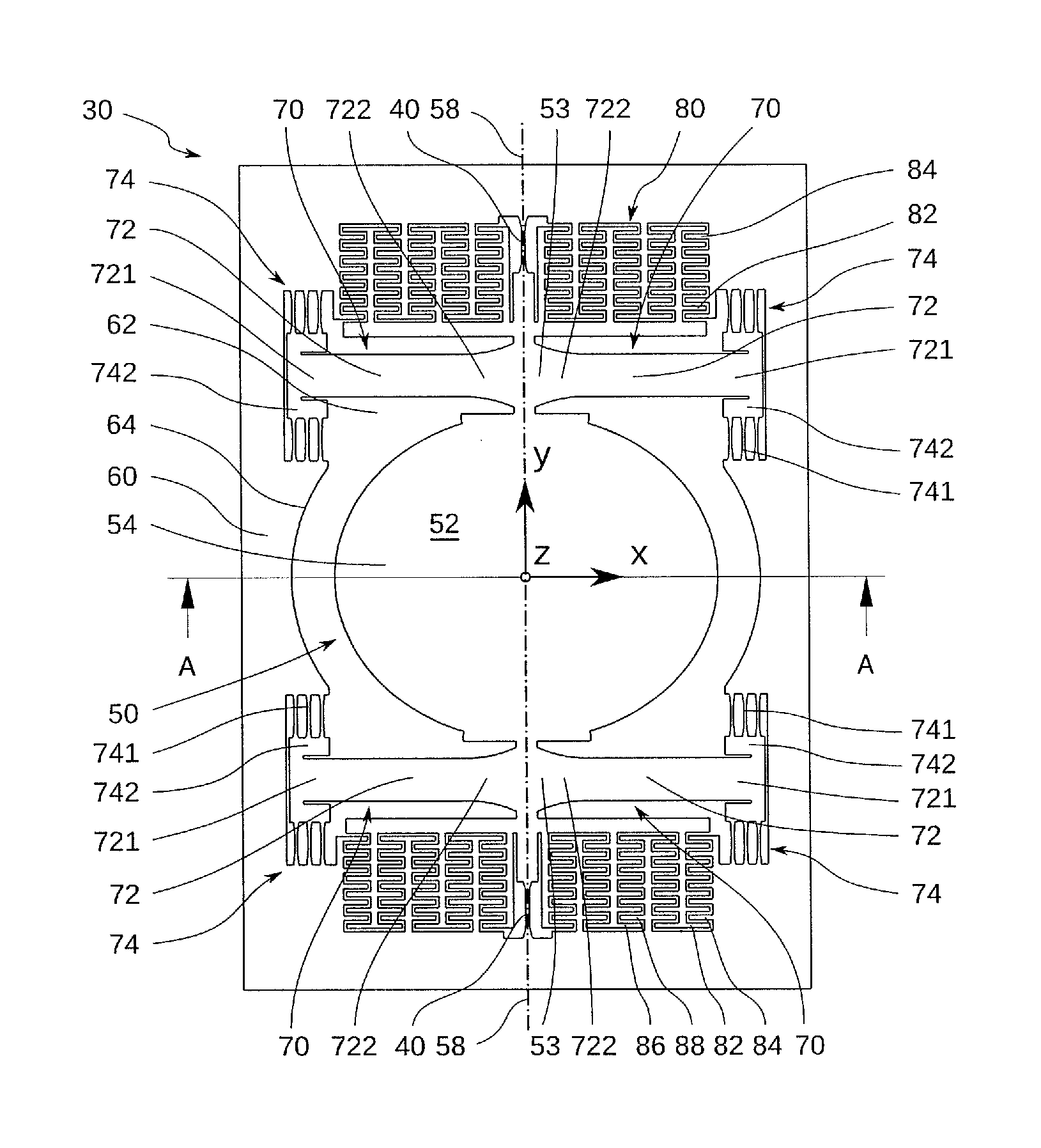

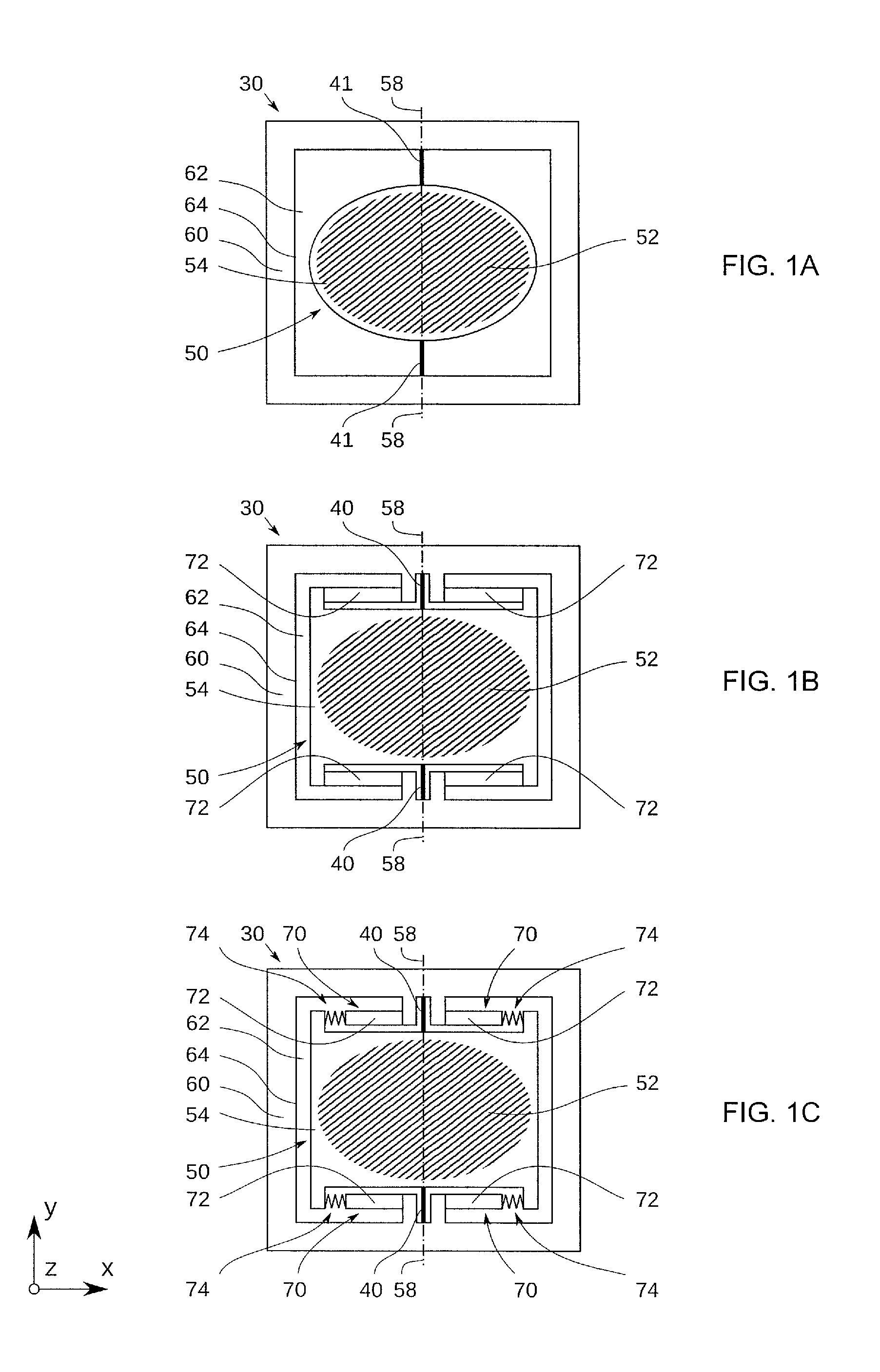

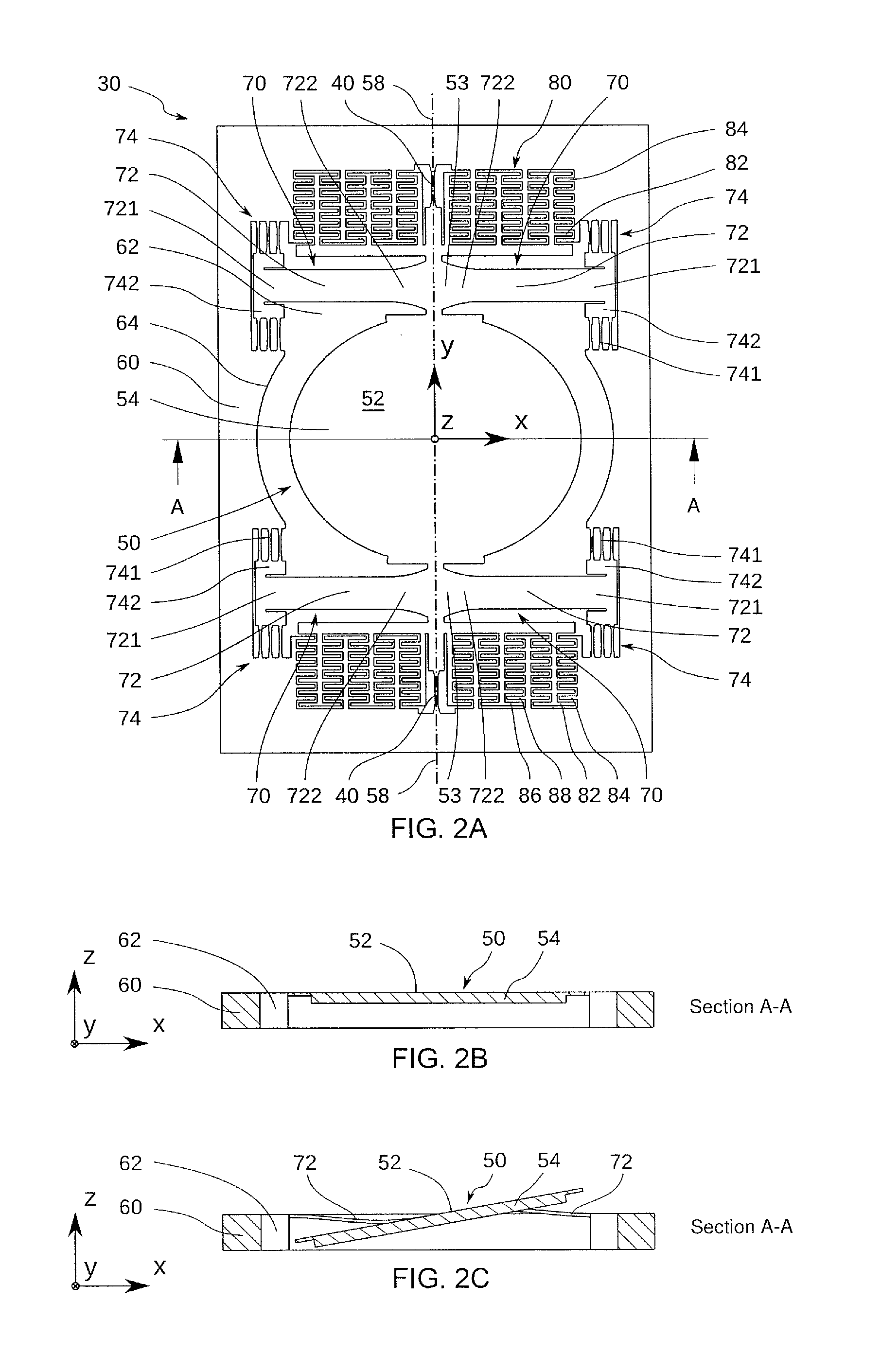

MEMS scanning micromirror

ActiveUS20140300942A1Negligible effectIncrease the tensile stressFlexible microstructural devicesOptical elementsEngineeringCantilever

A MEMS micromirror (30) is presented including a frame (60) with a mirror body (50) arranged therein. The mirror body (50) is rotatable around a rotation axis (58) extending in a plane (x-y) defined by the frame (60). The MEMS micromirror (30) further includes at least one cantilever beam assembly (70) having a longitudinal direction and extending within said plane. The MEMS micromirror (30) also includes vertical support beams (40) connected between the mirror body (50) and the frame (60) along the rotation axis (58). The at least one cantilever beam assembly (70) has a cantilever beam (72) with a first and a second end (721, 722) and a relief means (74) at the first end (721) allowing for a translation of the cantilever beam (72) at its first end (721) in said longitudinal direction. The first end (721) is coupled via the relief means (74) to the frame (60) and the second end (722) is fixed to the mirror body (50). The cantilever beam (72) has a thickness, perpendicular to a plane of the frame (60), that is smaller than its width, in the plane of the frame (60).

Owner:INNOLUCE

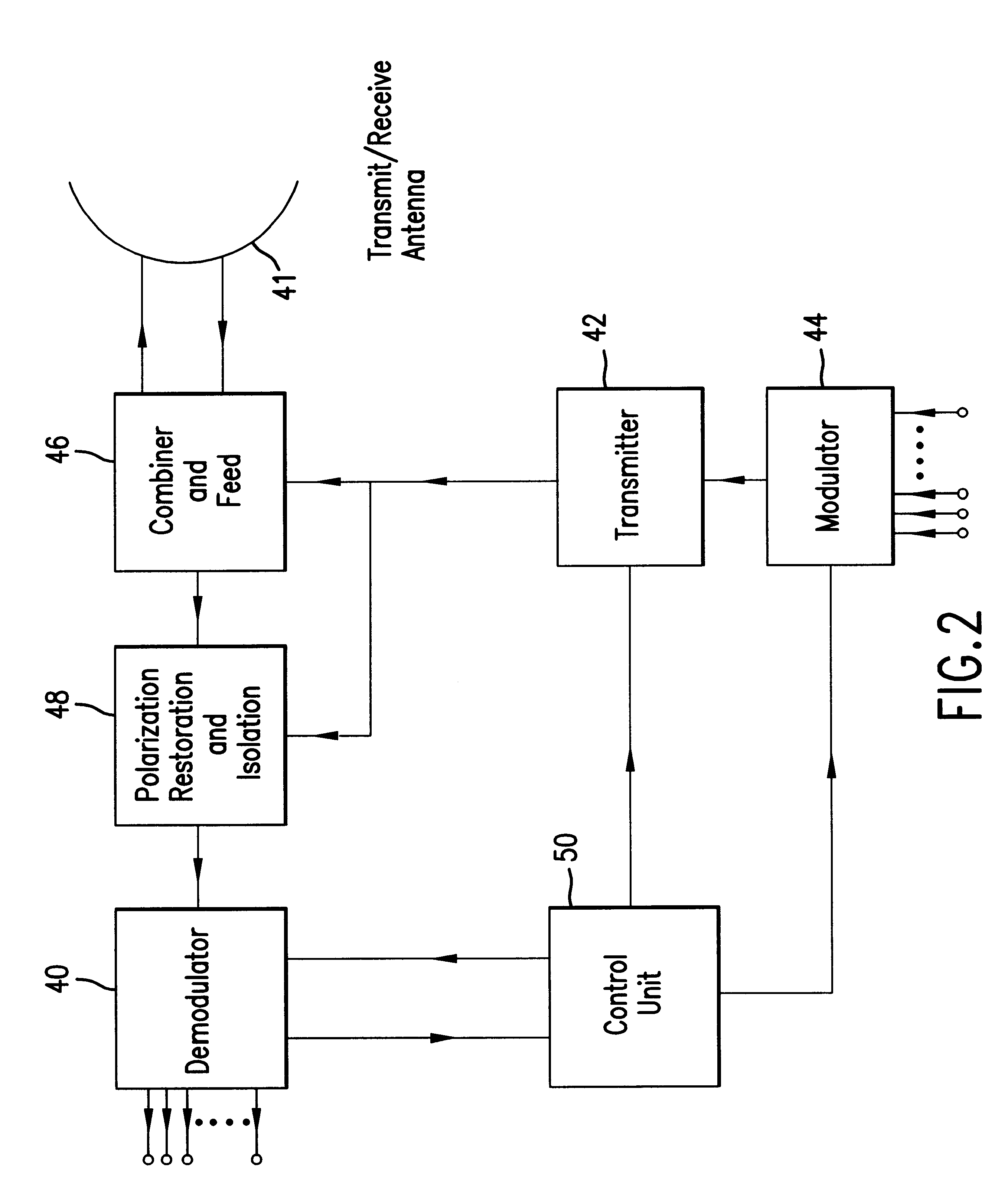

Multi-function interactive communications system with circularly/elliptically polarized signal transmission and reception

InactiveUS6233435B1Increase channel capacityNegligible effectPolarisation/directional diversityRadio/inductive link selection arrangementsPolarization diversityTransceiver

A communications system that uses electromagnetic waves. The communications system preferably operates in the millimeter-wave frequencies, and provides relatively high signal restoration and isolation. The communications system can use polarization diversity to increase the capacity of a channel. Isolation and restoration features in the transceivers eliminate or reduce the effects of precipitation and / or reflection and diffraction from objects, and thus is well-suited for an urban environment.The transceiver will select the proper antenna and signal path for optimal information throughput as the conditions in the propagation medium of the network vary.

Owner:TELECOMM EQUIP

Clock data recovery loop with separate proportional path

InactiveUS7580497B2Improve stabilityLittle effectReceiver initialisationModulated-carrier systemsPhase detectorLoop filter

A clock data recovery loop that can be used over a wide range of data rates and maintain second-order behavior includes a nonlinear (e.g., Bang-Bang) phase detector, a charge pump, an RC loop filter, and signal generator (e.g., a voltage controlled oscillator (VCO)). At low data rates, the loop may be operated with the charge pump and loop filter with stable second-order behavior, with the resistor R of the loop filter serving as a proportional path. A separate proportional path is also provided that provides phase detector output directly to a control input of the VCO, while the resistor R of the loop filter is also bypassed. As increasing data rates give rise to third-order effects, the separate proportional path may be activated to maintain second-order behavior.

Owner:ALTERA CORP

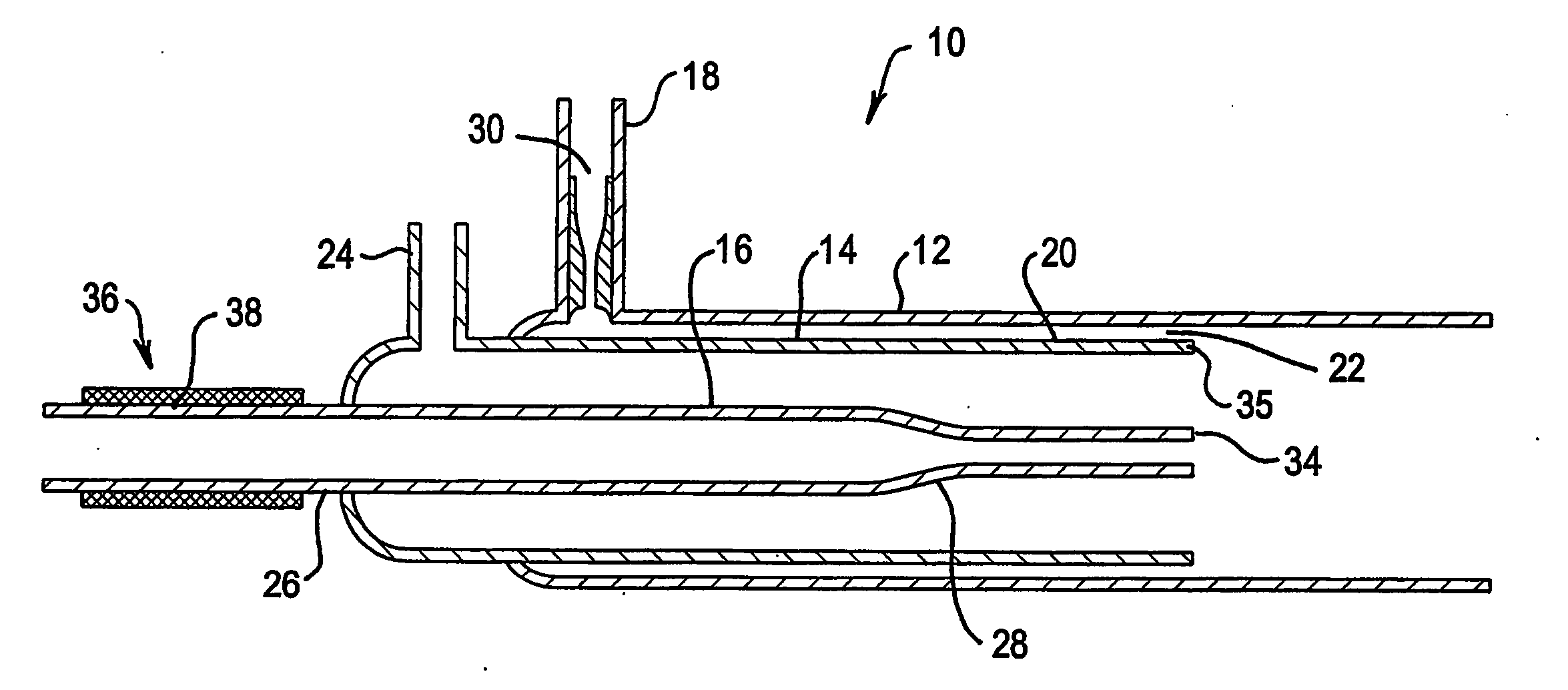

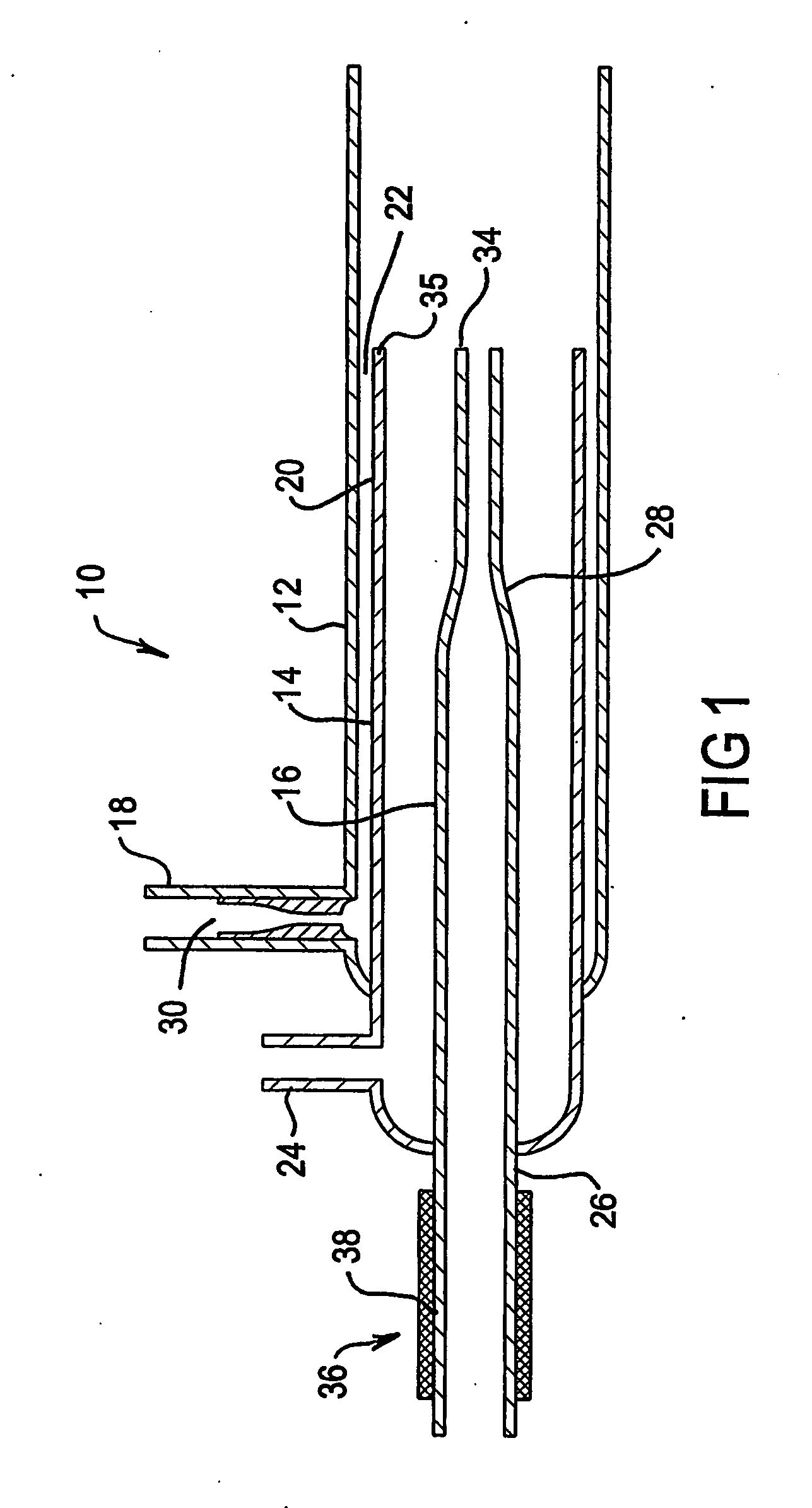

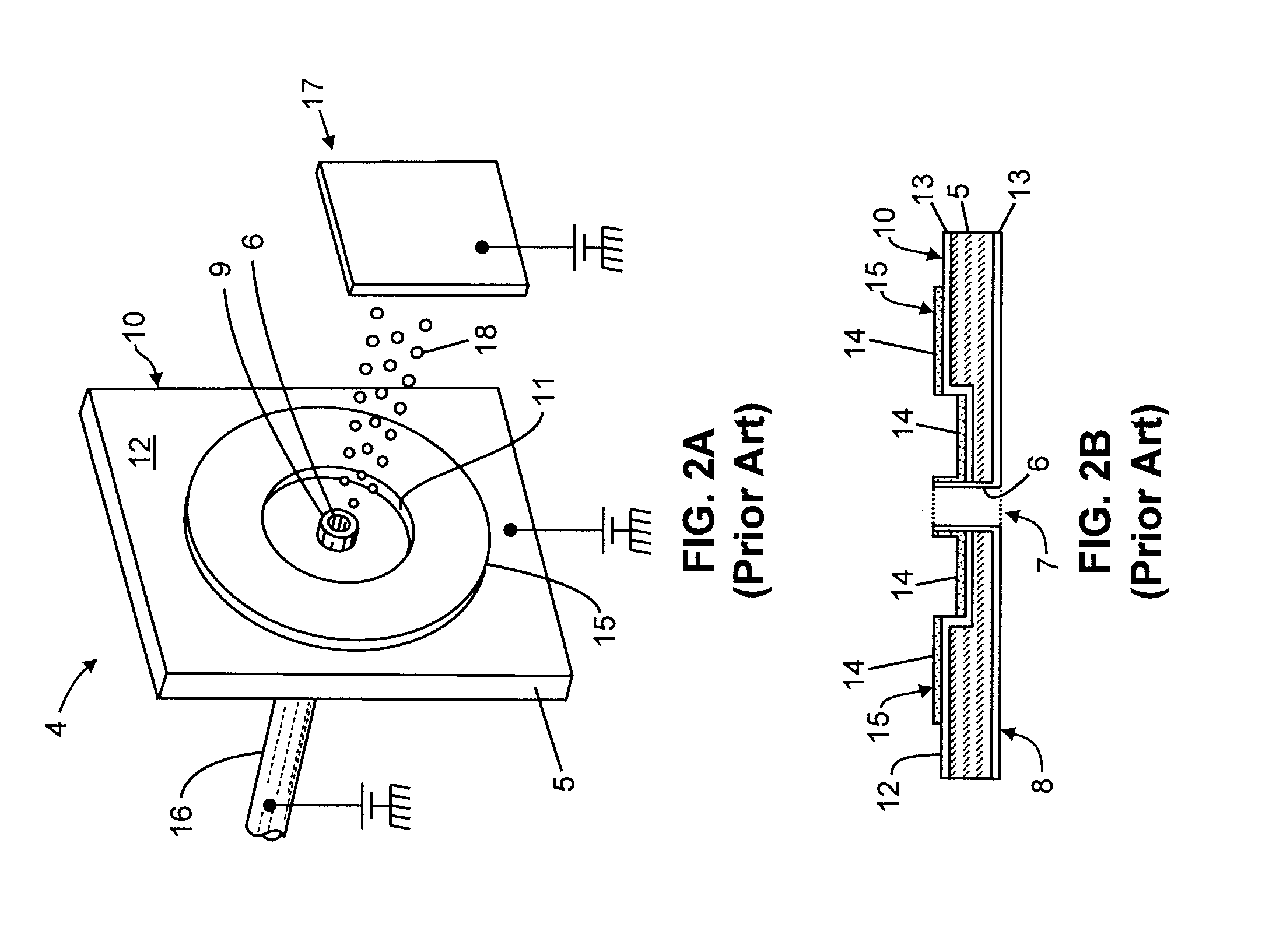

Plasma torch for microwave induced plasmas

InactiveUS20050242070A1Avoid rapid degradationReduce sensitivityMaterial analysis using microwave meansArc welding apparatusMicrowaveEngineering

A Plasma torch (10) for microwave induced plasma spectrochemical analysis of a sample includes a nozzle (30) in an inlet (18) for the main plasma gas flow between outer tube (12) and intermediate tube (14) of the torch (10). The nozzle (30) increases the gas flow velocity in the sheathing gas layer for the plasma which is provided by the gas flow from the annular gap (22) between the tubes (12 and 14). The increased velocity of the gas in the sheathing gas layer “stiffens” that layer and thus better confines the microwave induced plasma (such better confinement not being necessary for an ICP torch). Thus the torch is of improved durability for a microwave induced plasma compared to an ICP torch. The sample injection (inner) tube (16) may have a reduced diameter outlet at its end (34) which is substantially level with the end (35) of intermediate tube (14) to improve injection of a sample into the microwave induced plasma. The inlet end (26) of the sample injection tube (16) may include a heater (36) to assist in preventing blockages in tube (16) near its outlet end.

Owner:VARIAN AUSTRALIA PTY LTD

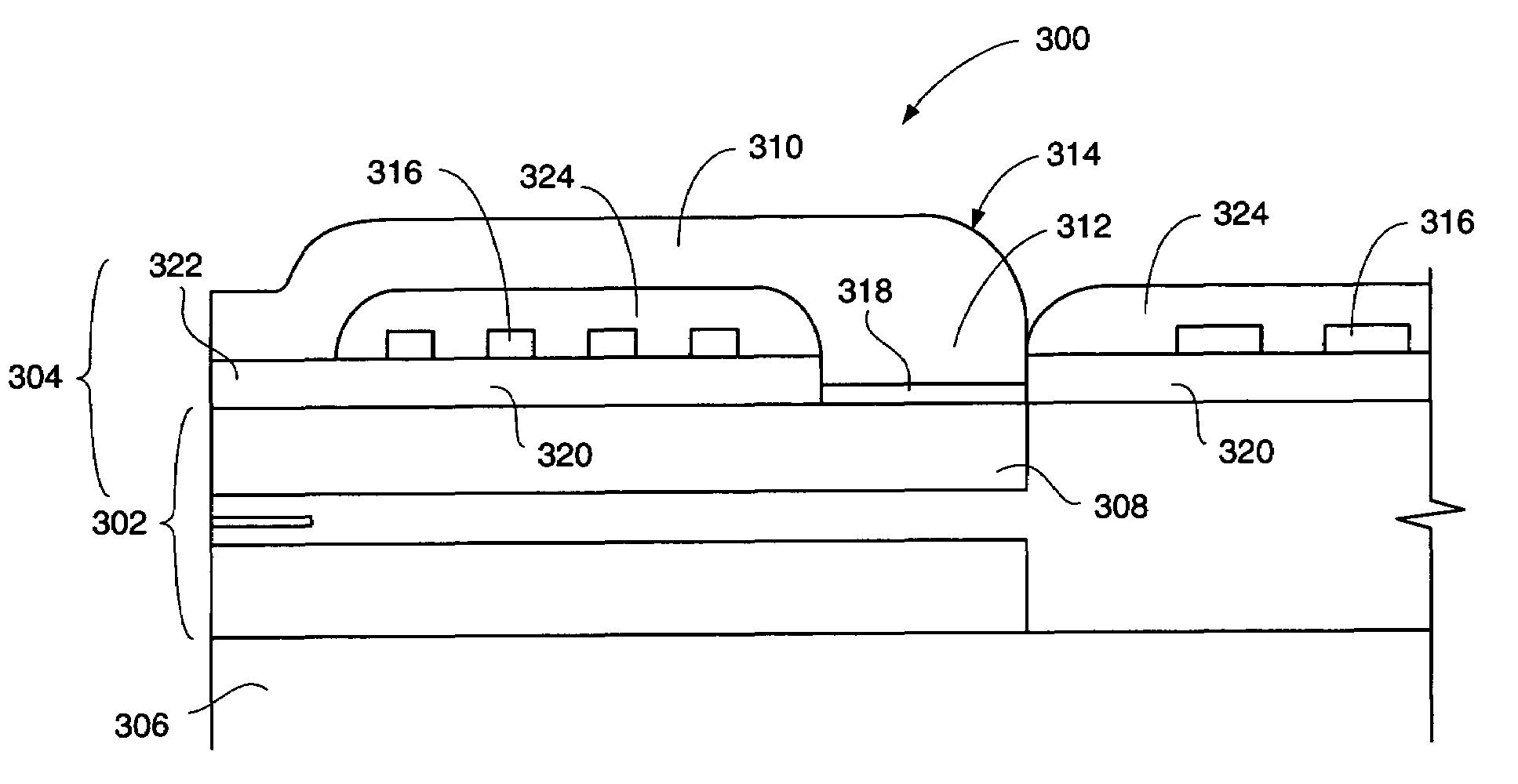

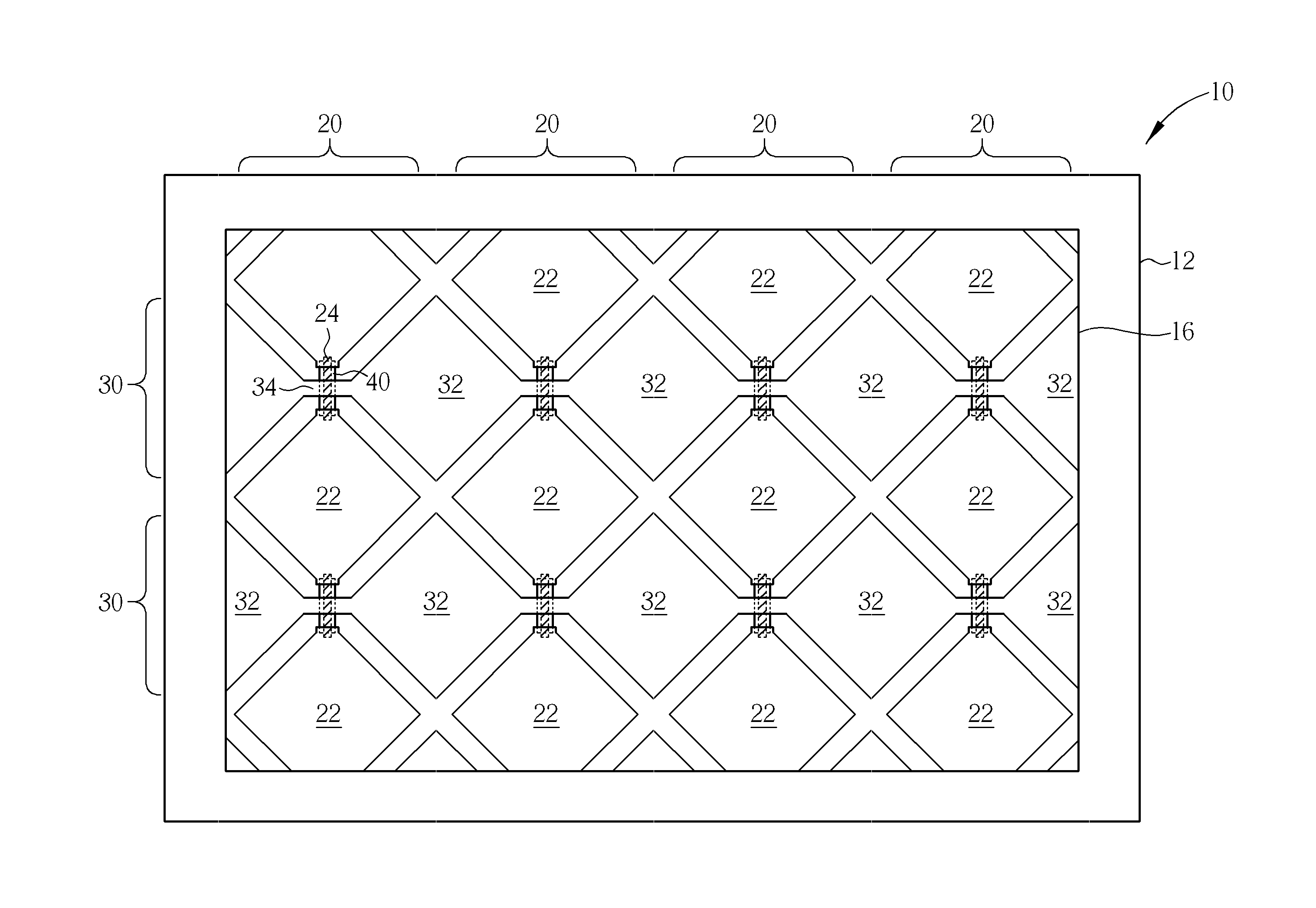

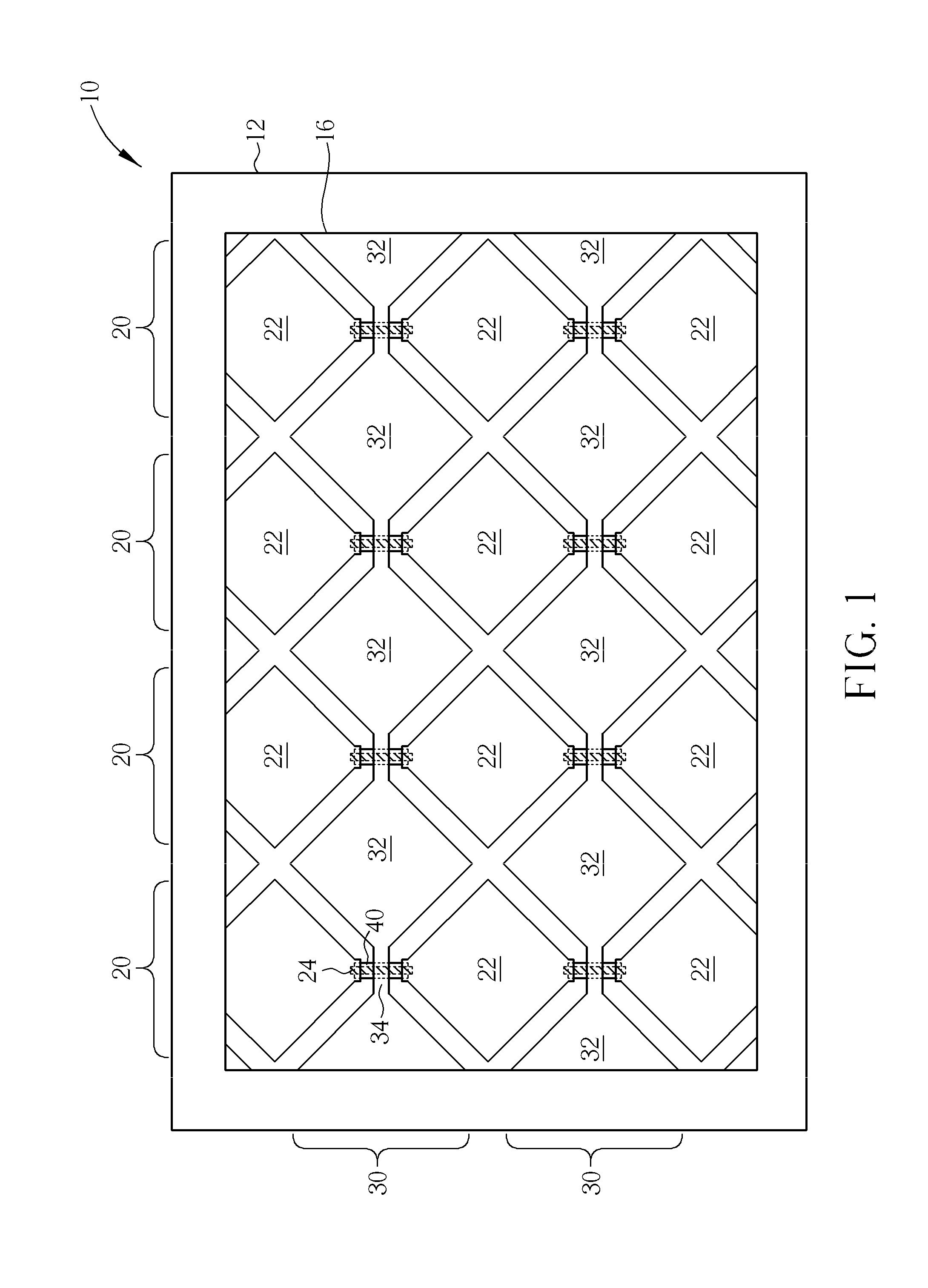

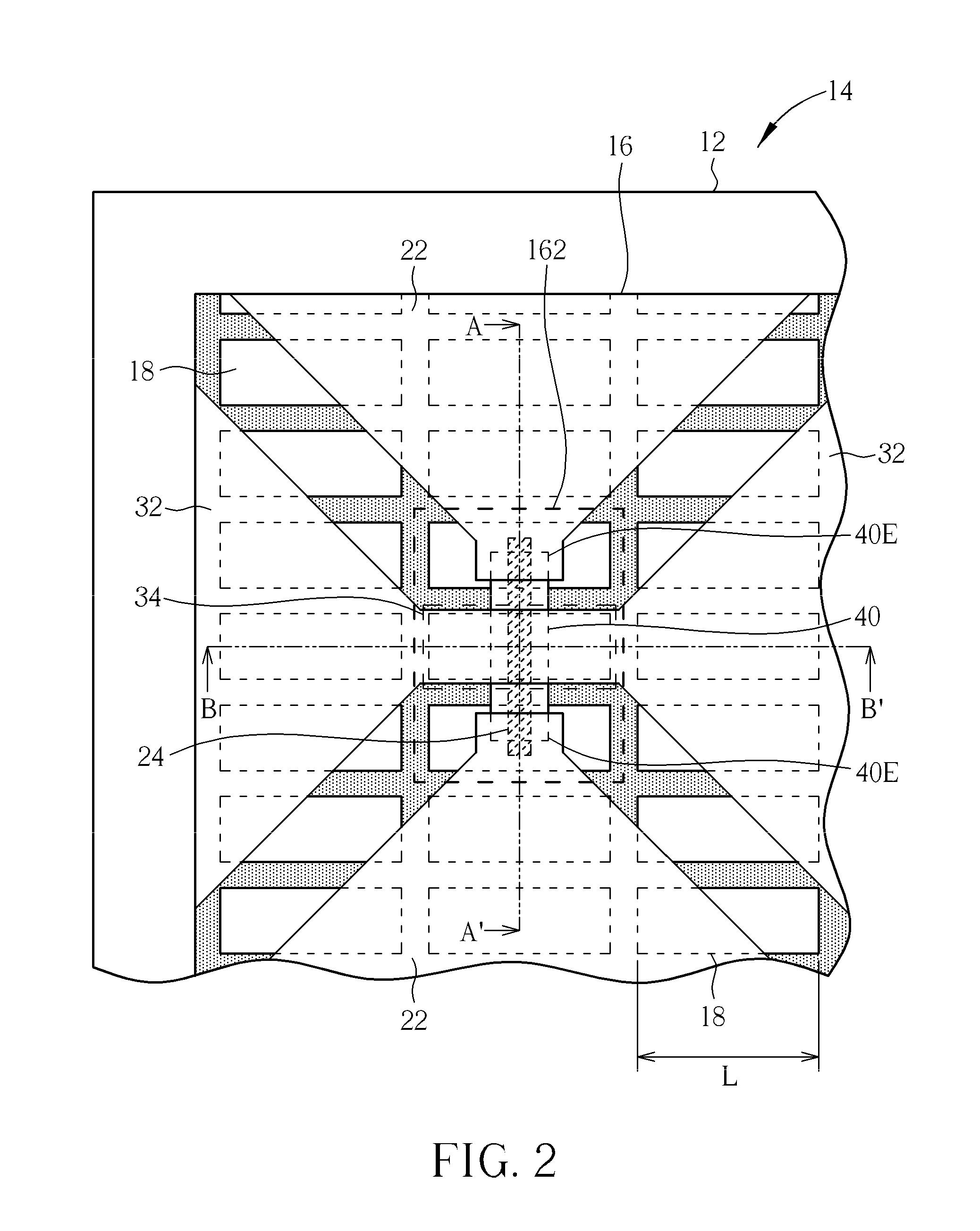

Touch display panel and touch sensing unit thereof

ActiveUS20110096018A1Negligible effectImprove touch sensitivityInput/output processes for data processingMicrometerLine width

A touch display panel includes a display panel and a touch sensing unit. The touch sensing unit includes first sensing series, and second sensing series. Each of the first sensing series includes a plurality of first transparent sensing pads disposed along a first direction, and a plurality of non-transparent bridge lines disposed along the first direction. Each of the non-transparent bridge lines is disposed between two adjacent first transparent sensing pads, overlapping with two adjacent first transparent sensing pads, and electrically connected to two adjacent first transparent sensing pads. The line width of each non-transparent bridge line is substantially between 0.5 micrometers and 10 micrometers, and the reduction of aperture ratio in a pixel region of the touch display panel caused by the non-transparent bridge lines is substantially between 0.1% and 5%.

Owner:AU OPTRONICS CORP

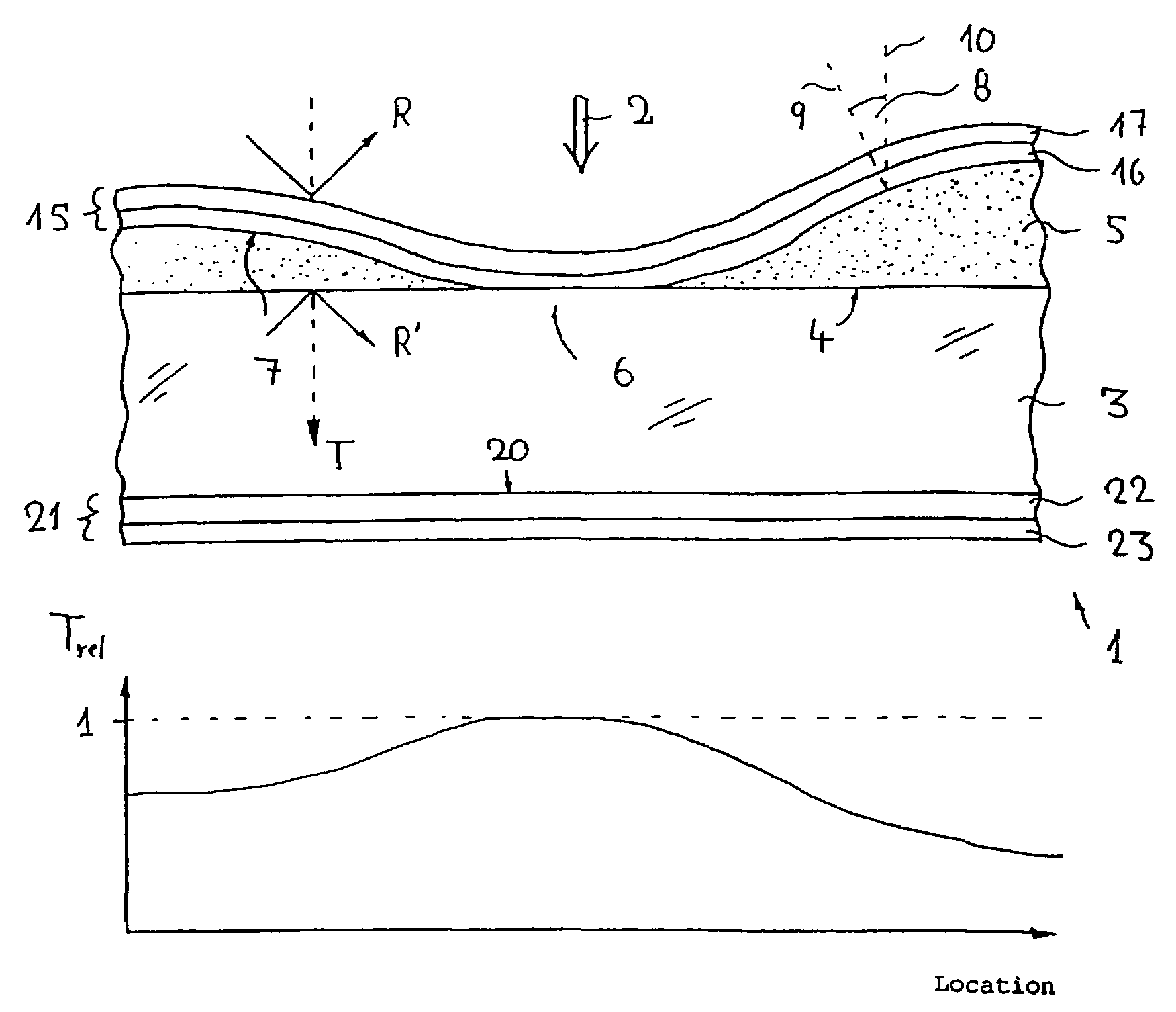

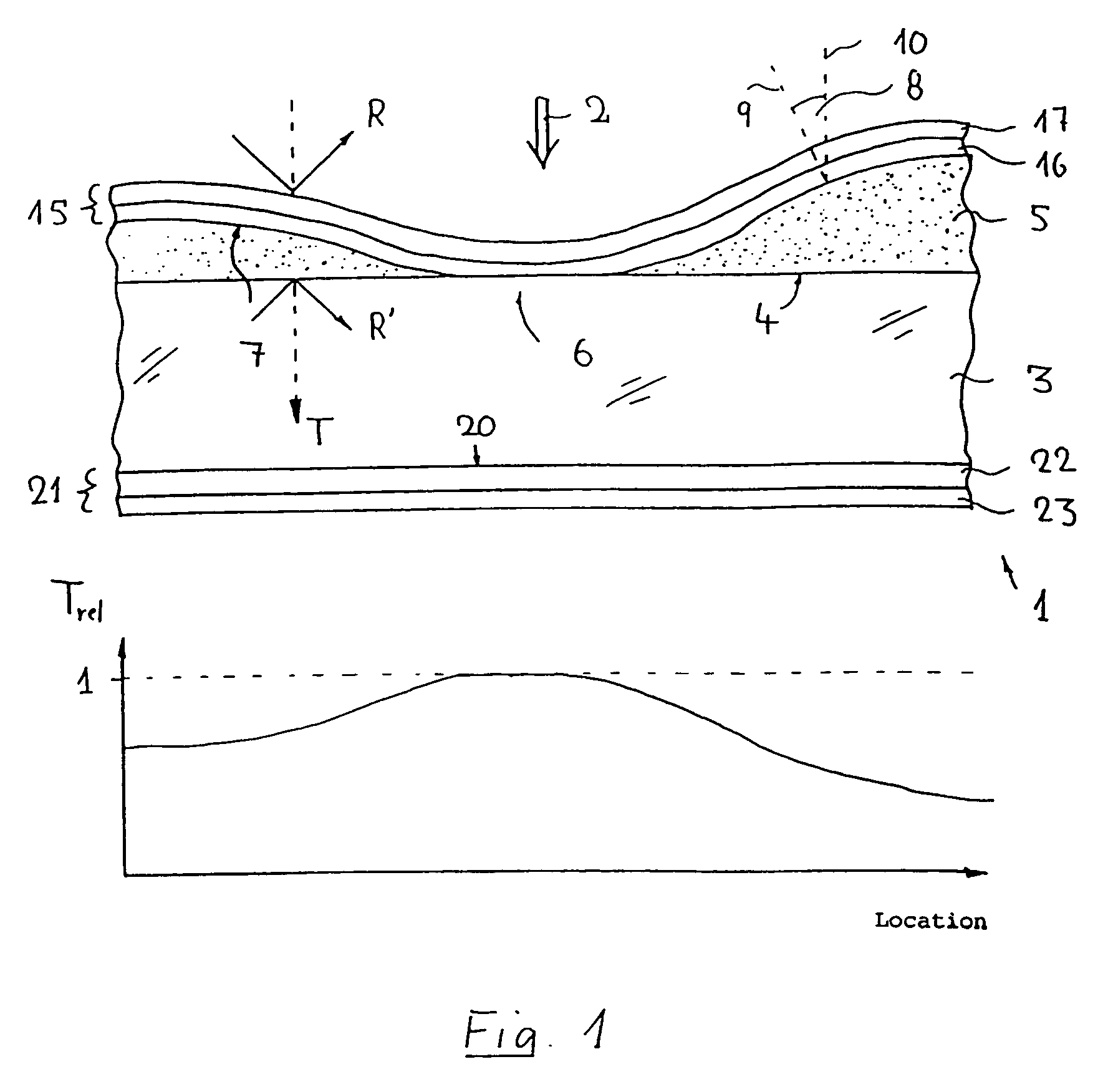

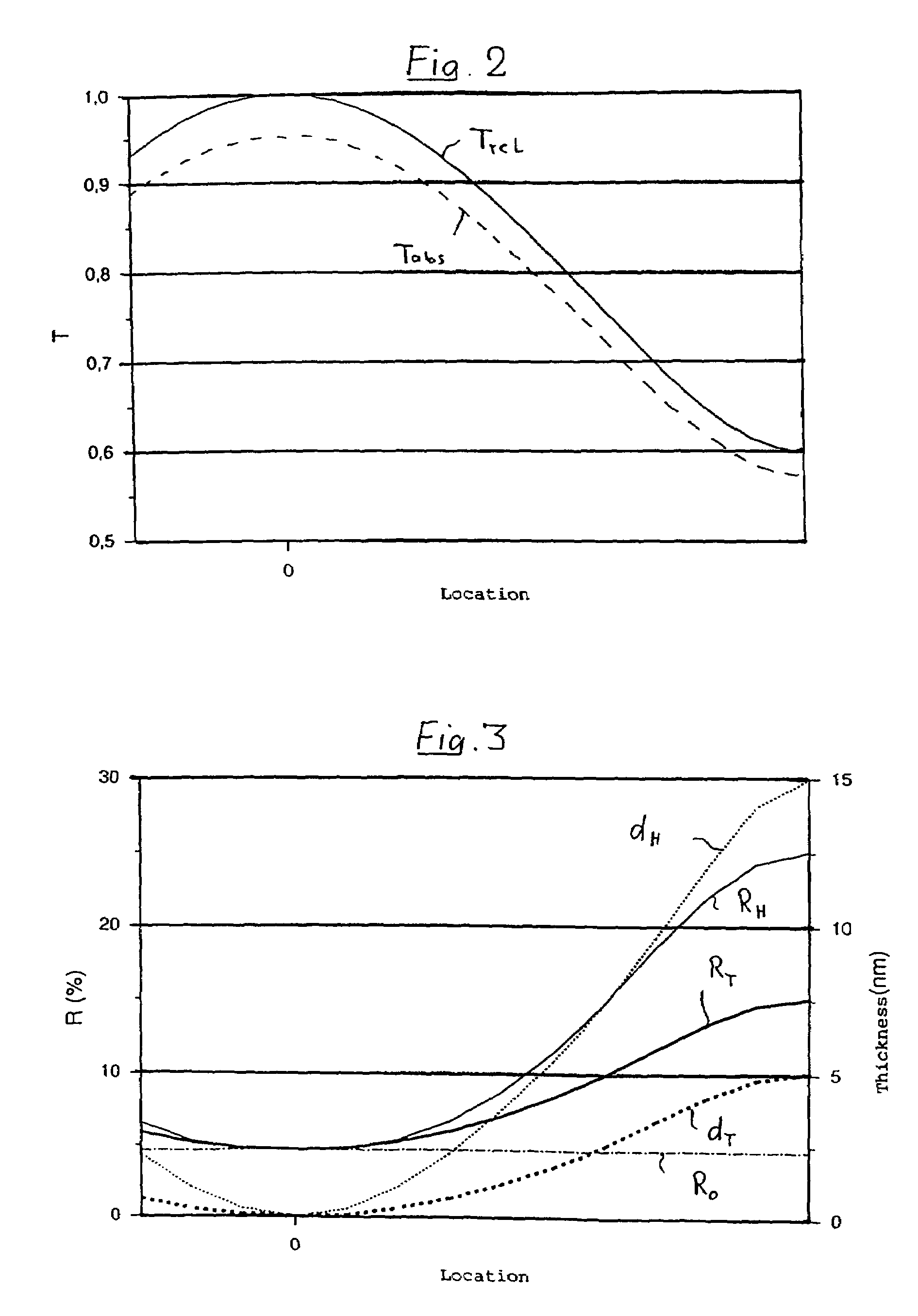

Attenuating filter for ultraviolet light

InactiveUS7196842B2Simple and inexpensive to fabricateVariation of the transmittance of the filter coatingMirrorsOptical filtersSpectral transmittanceUltraviolet lights

Owner:CARL ZEISS SMT GMBH

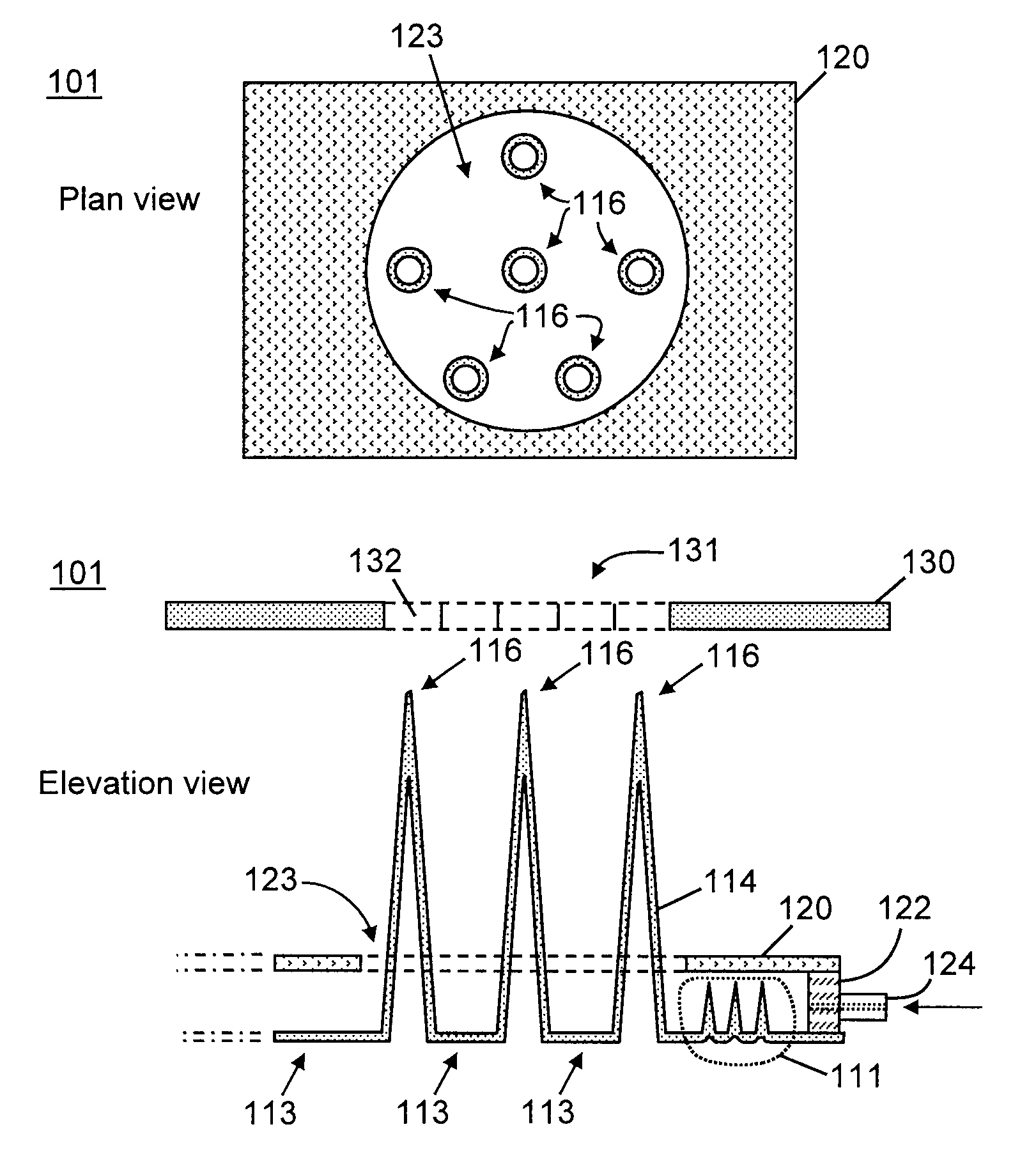

Multi-needle multi-parallel nanospray ionization source for mass spectrometry

ActiveUS8207496B2Low densityNegligible effectValve arrangementsWater/sewage treatment by irradiationMass analyzerVoltage source

Owner:THERMO FINNIGAN

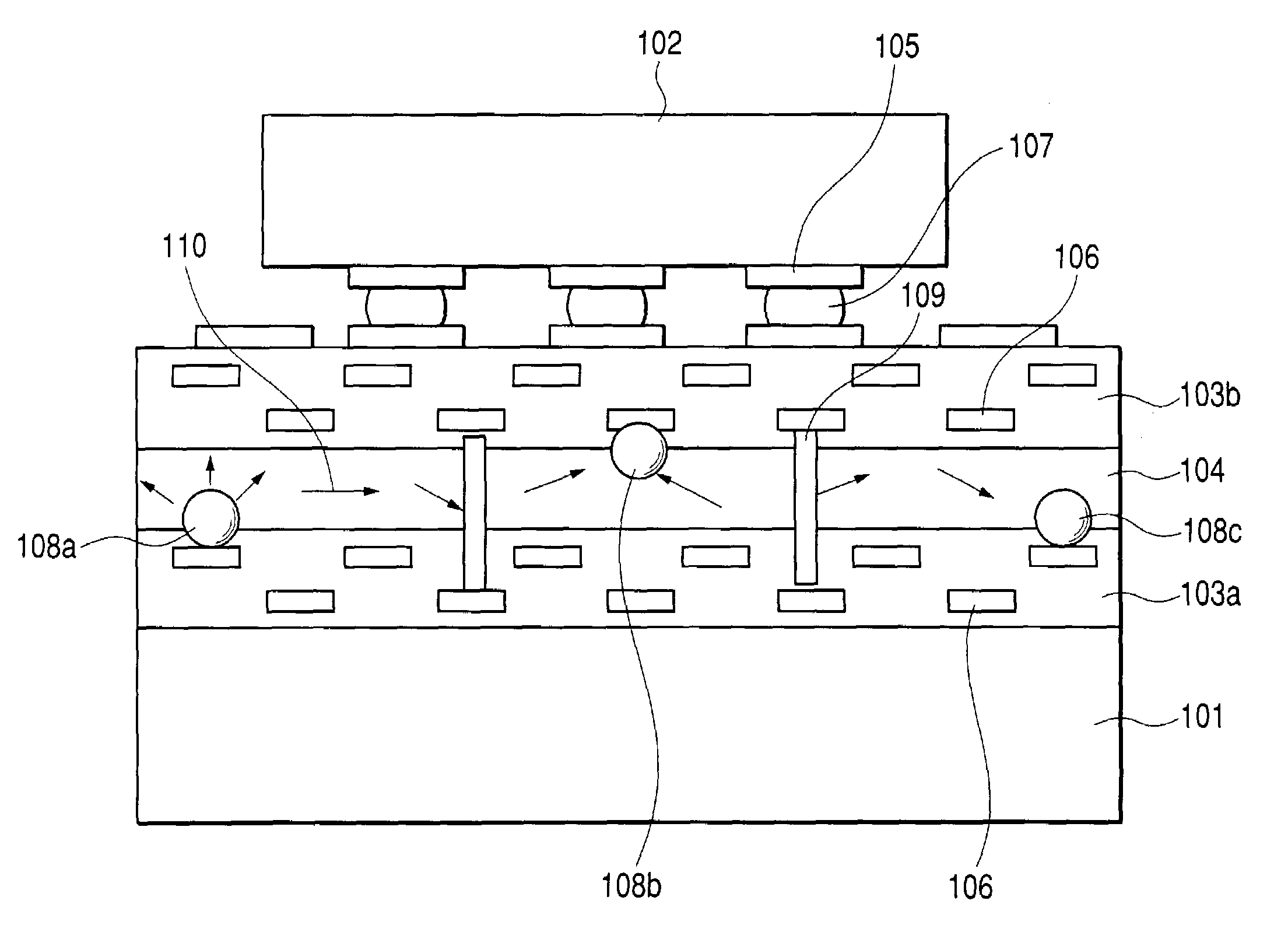

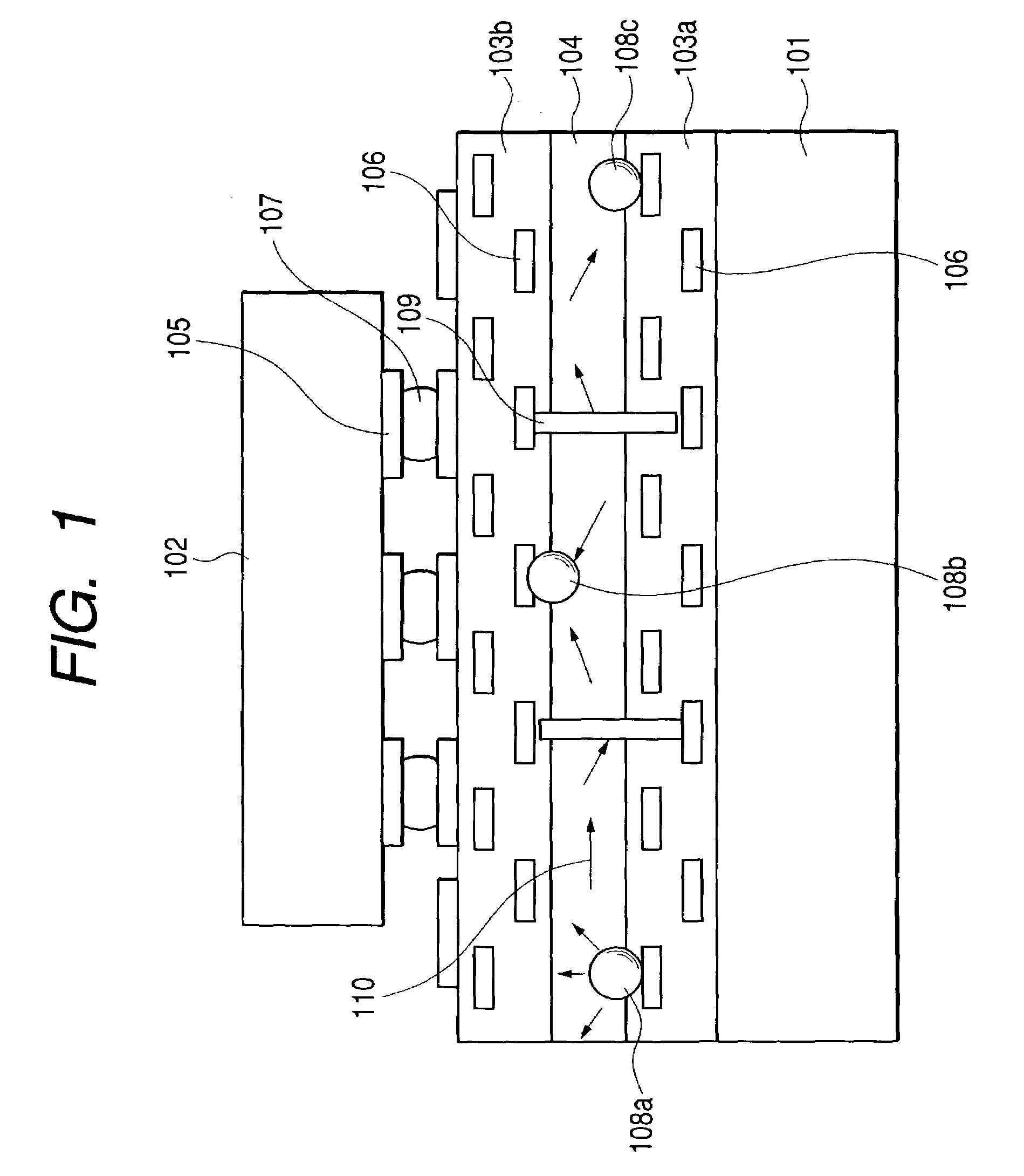

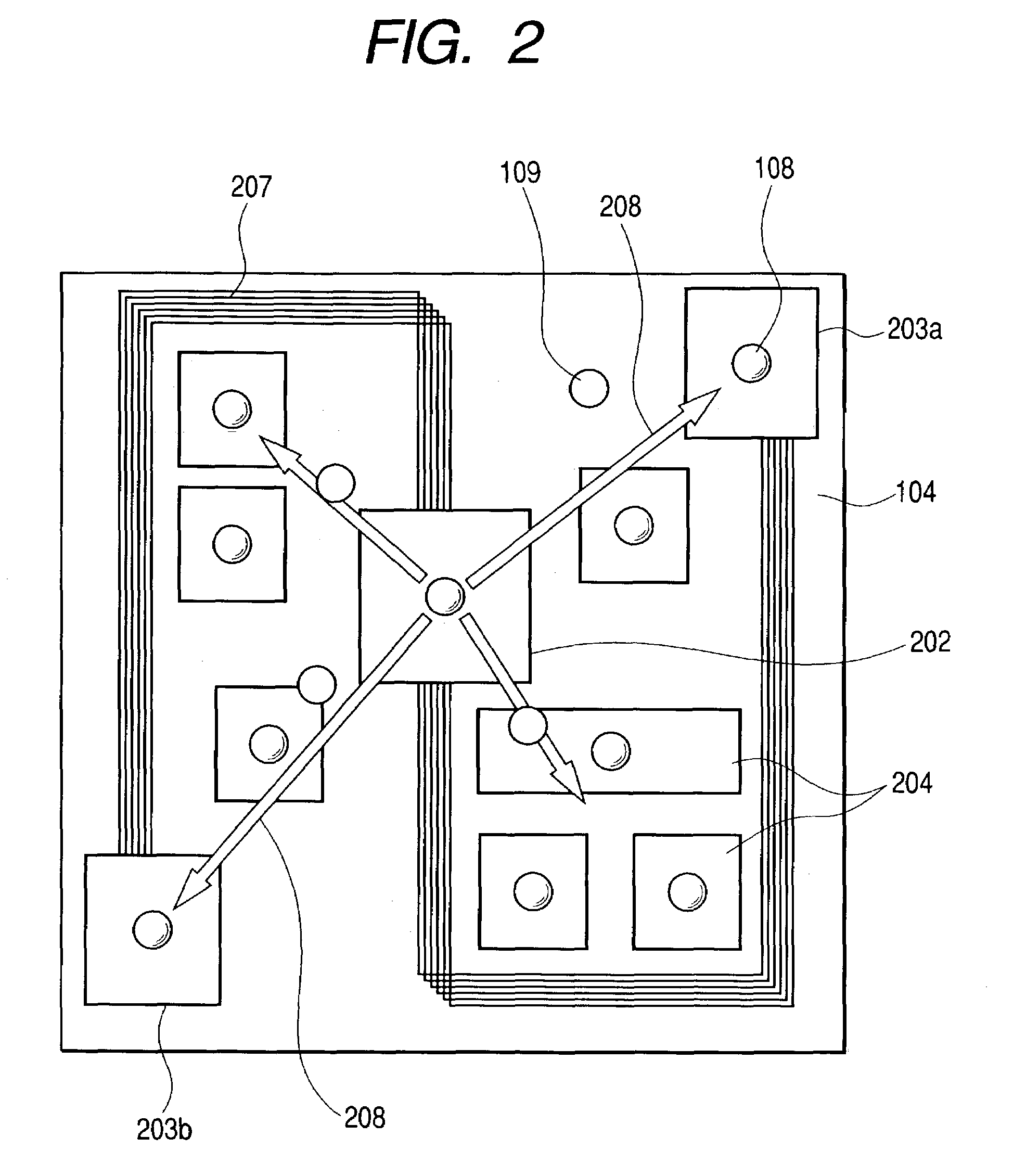

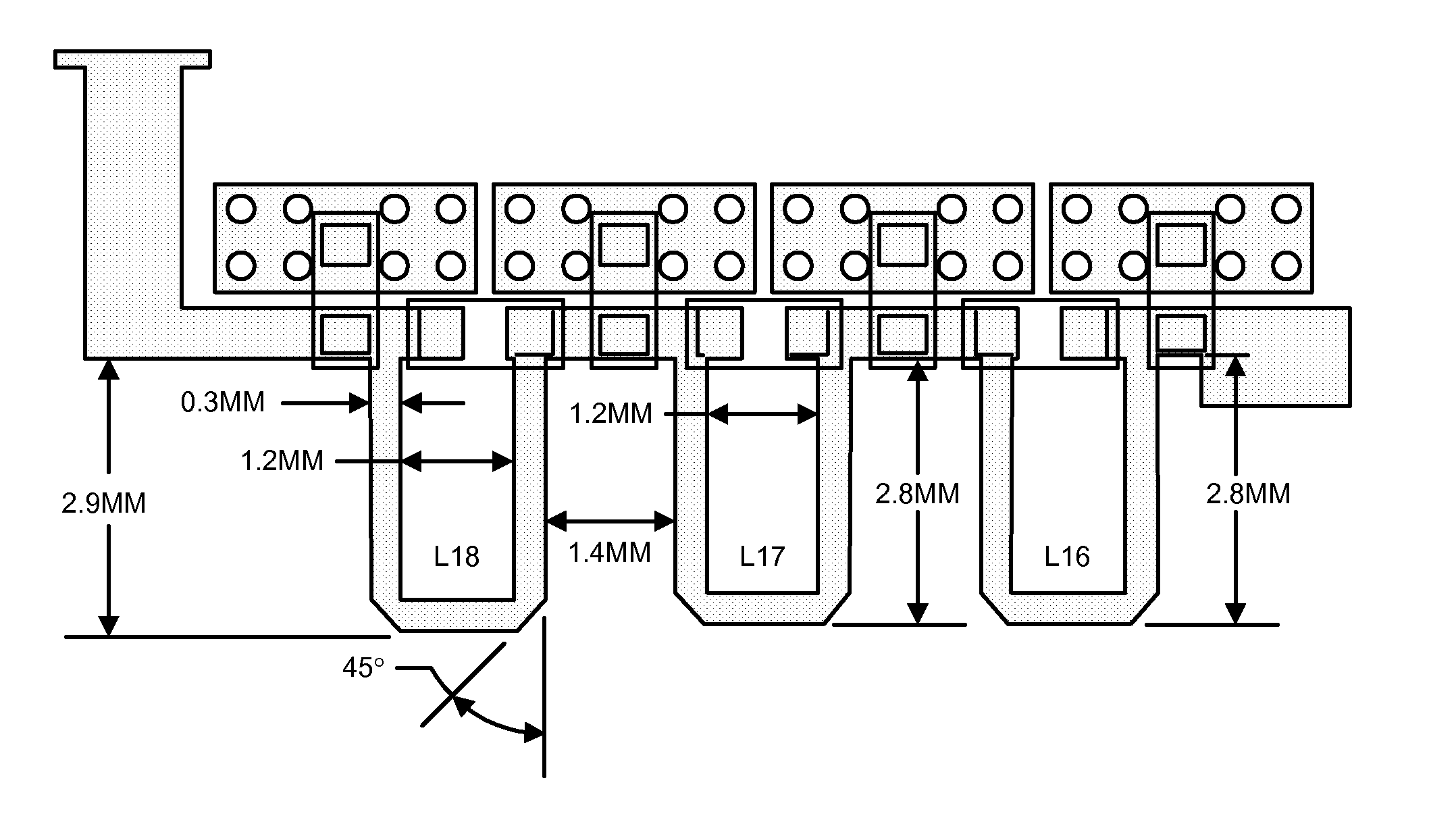

Electronic circuit board

InactiveUS6977820B2Increase wiring sizeNegligible effectCircuit optical detailsCoupling light guidesEngineeringWaveguide

An electronic circuit board having an optical wiring layer sandwiched between two electrical wiring layers. The optical wiring layer is structured to be a two-dimensional optical waveguide. An E / O device and an O / E device are provided in the optical wiring layer or at an interface between the optical wiring layer and the electrical wiring layer. A via piercing the optical wiring layer connects the two electrical wiring layers. It is possible to efficiently input and output light to and from an optical wiring layer.

Owner:CANON KK

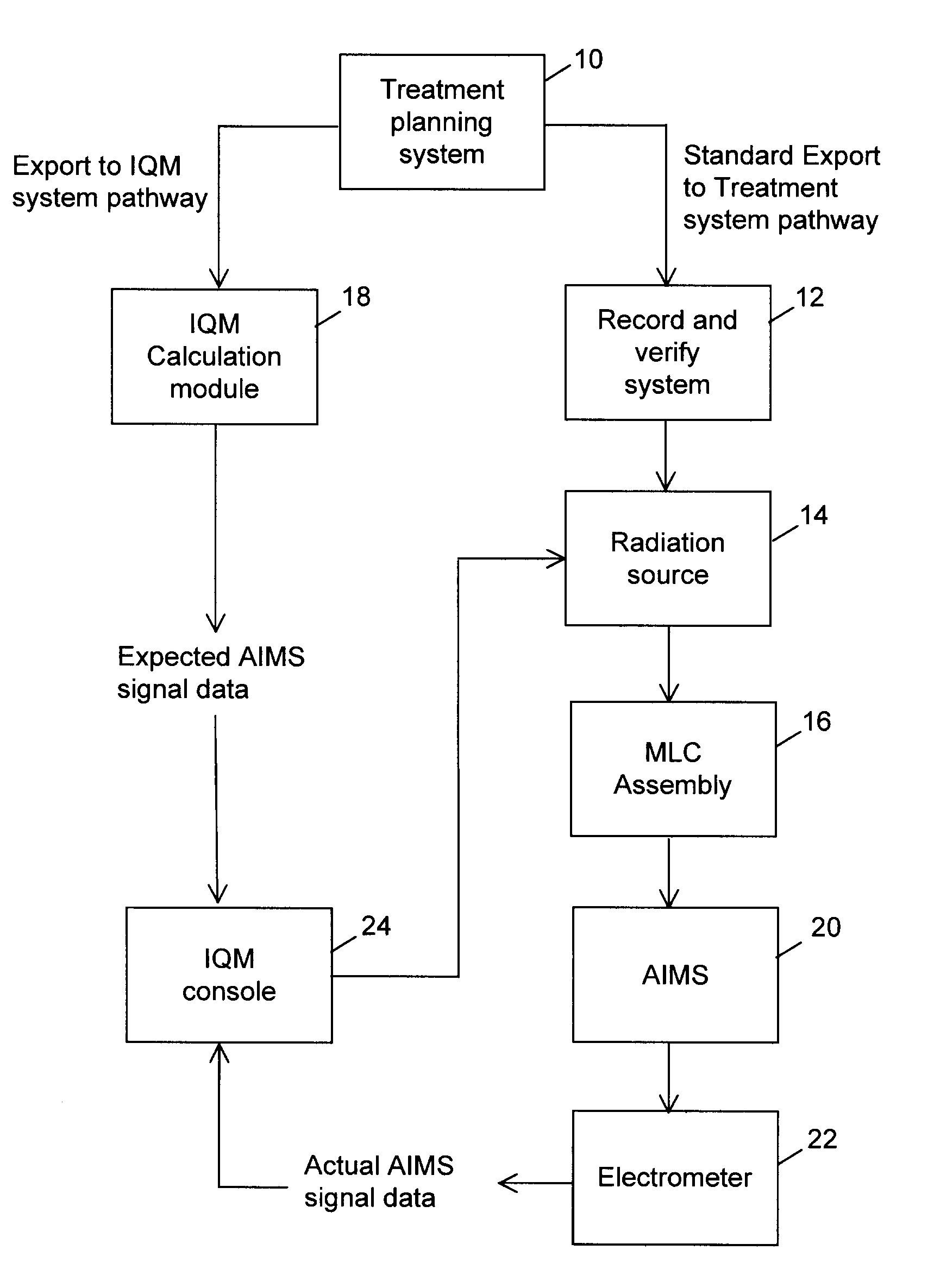

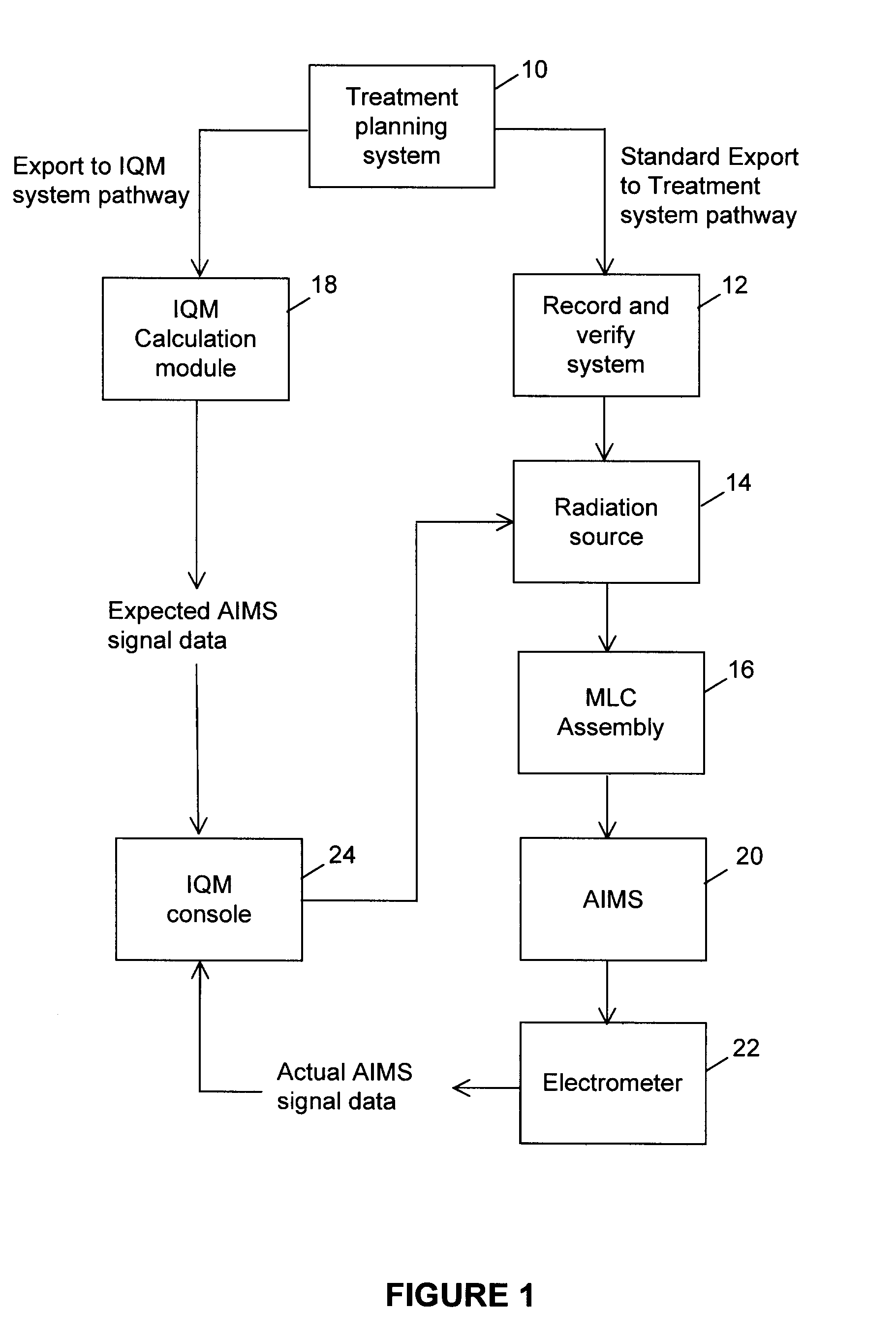

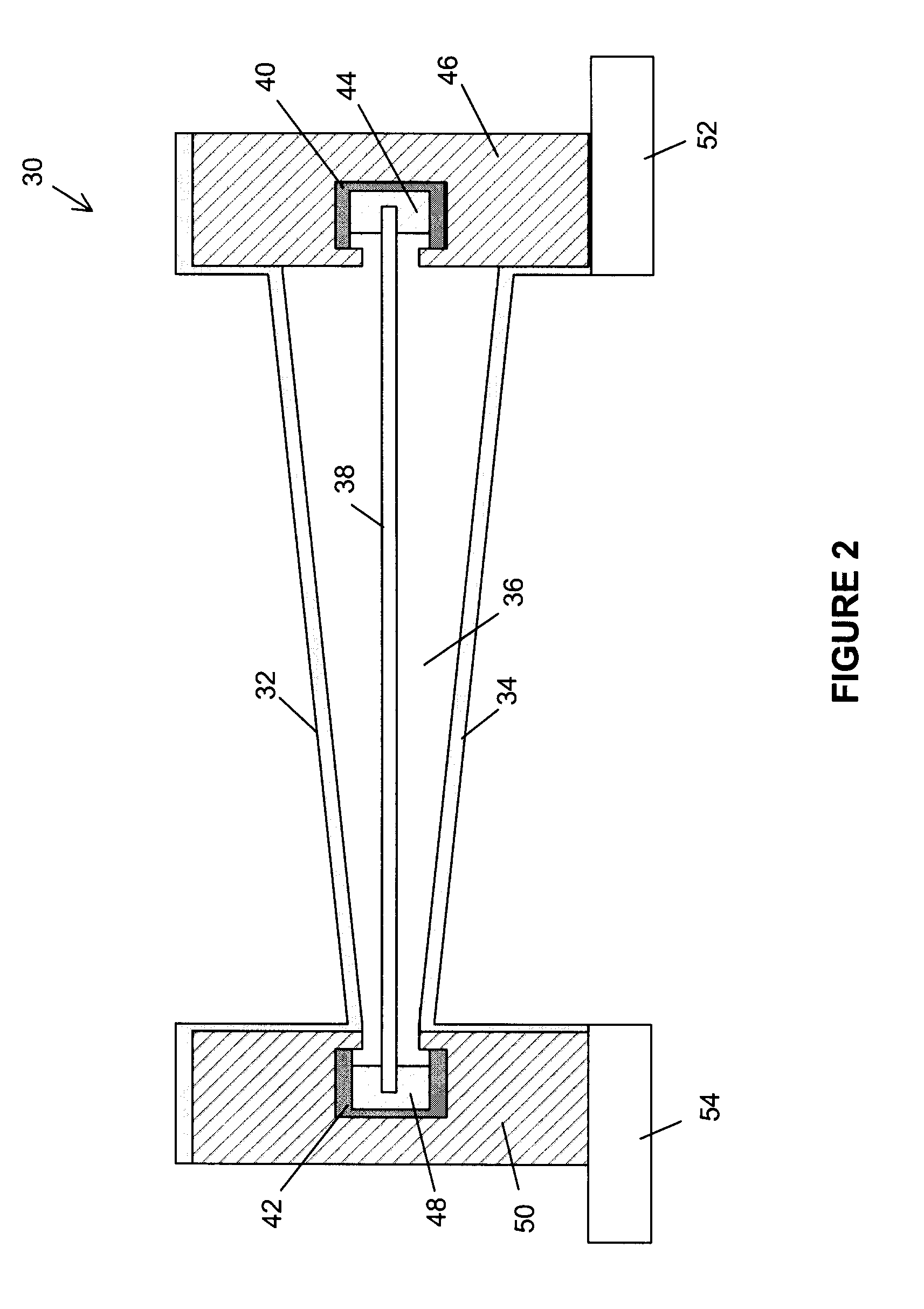

Apparatus and methods for real-time verification of radiation therapy

ActiveUS20100012829A1Negligible effectReduce leakage current effectElectric discharge tubesMaterial analysis by optical meansReal time validationTreatment system

Various embodiments are described herein for an area integrated fluence monitoring sensor that can be used to measure a radiation dose. The sensor comprises at least one Gradient Ion Chamber (GIC) comprising an ion chamber having a volume gradient across a length or width thereof, a gas or liquid located within the ion chamber and an electrode to detect ions generated within the gas or liquid when the at least one GIC is subjected to an ionizing radiation beam. Various embodiments are also described herein for an Integral Quality Monitoring system and associated method that can be used to measure and monitor the quality of radiation doses provided by a radiation treatment system.

Owner:UNIV HEALTH NETWORK

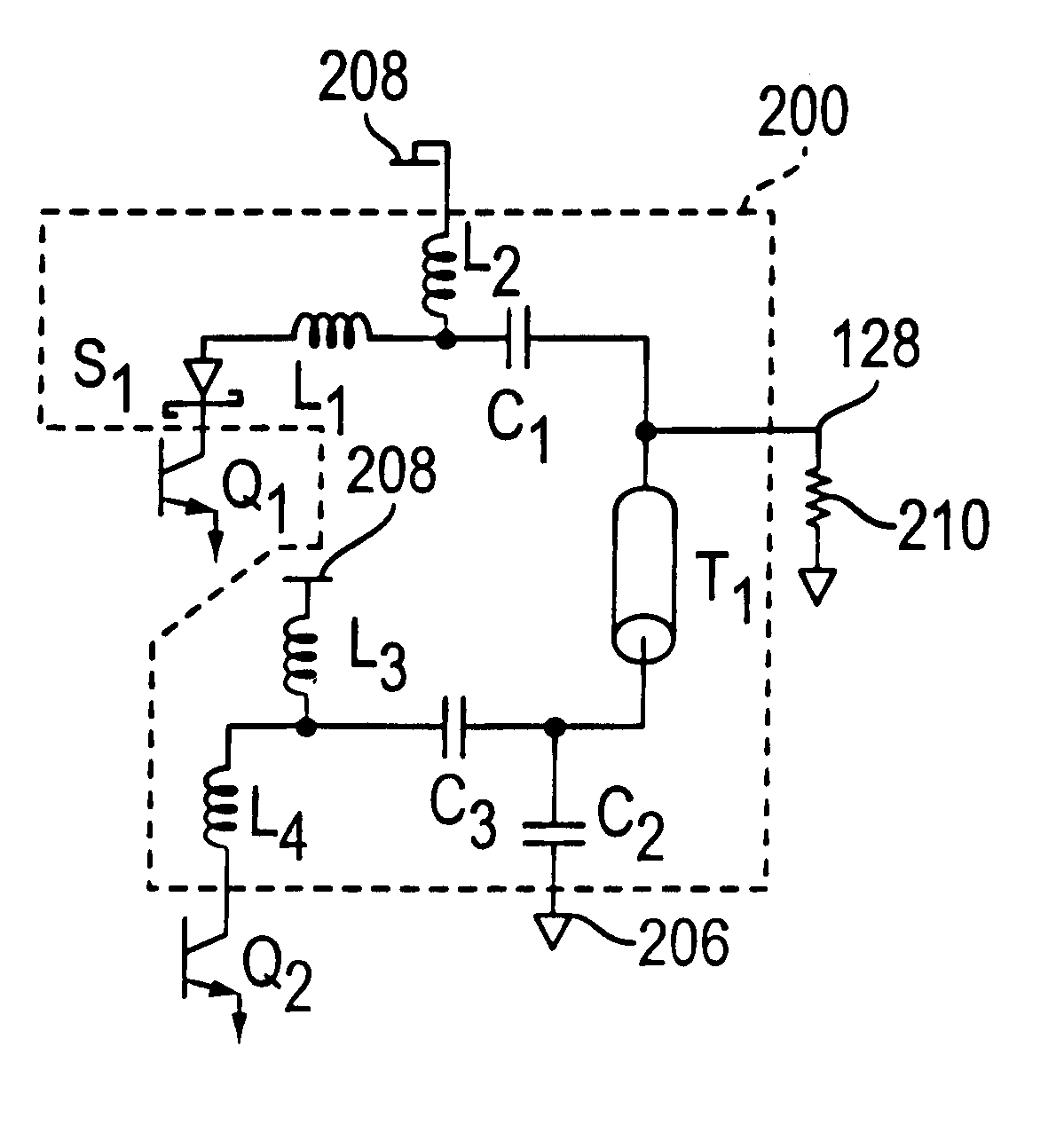

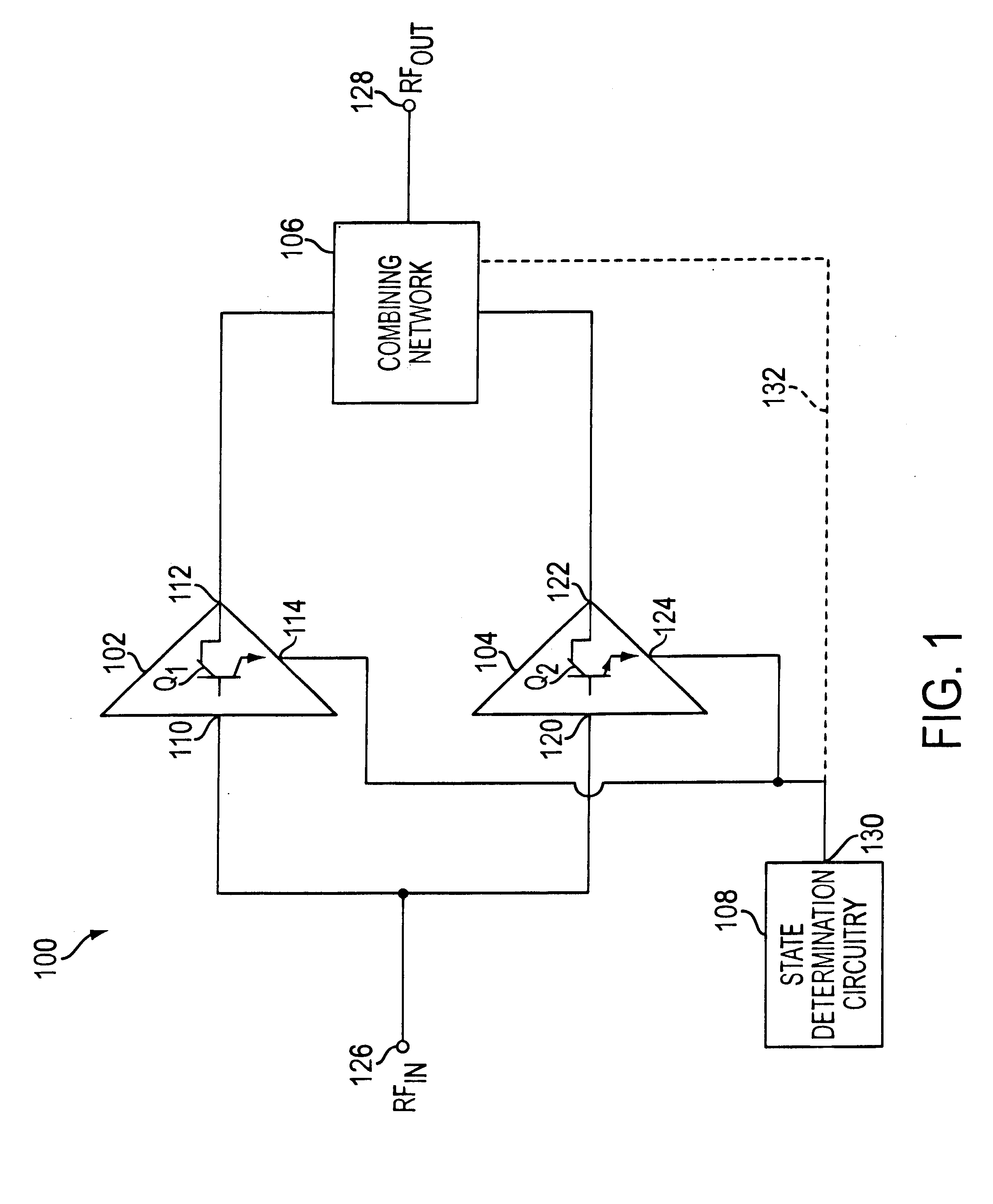

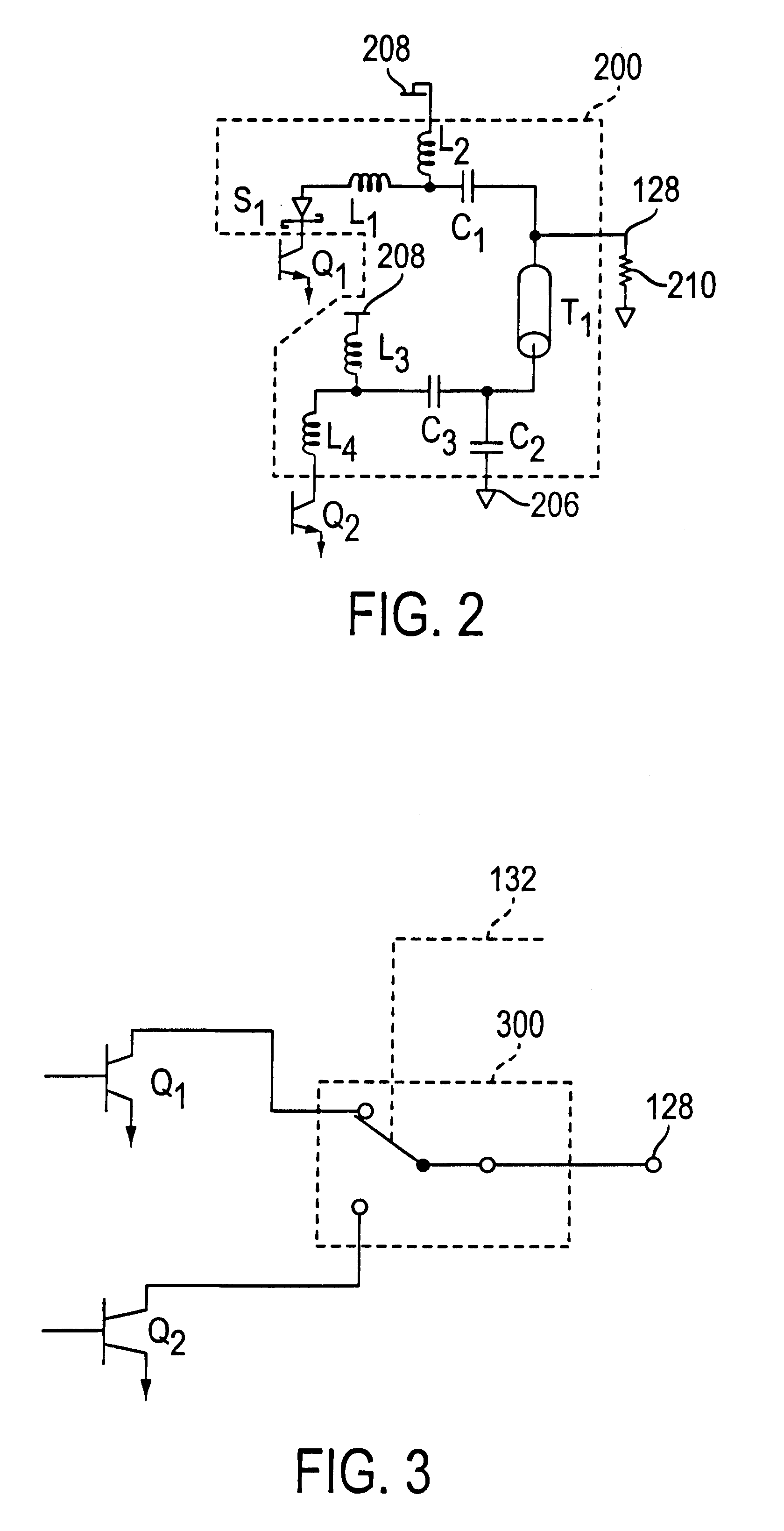

Switchable path power amplifier with combining network

InactiveUS6359514B1Negligible effectGated amplifiersPower amplifiersPower efficientAudio power amplifier

The present invention teaches a power amplifier having two output power devices and a mechanism for switching the output path between these two power devices. The first output power device is designed for power efficient signal amplification at the power amplifier's highest output power level. The second output power device is designed for power efficient signal amplification at the output power level that the power amplifier is most likely to operate. By switching between the two power devices according to the output power level, a high level of power efficiency can be achieved across a broad range of operating states of the power amplifier.

Owner:MAXIM INTEGRATED PROD INC

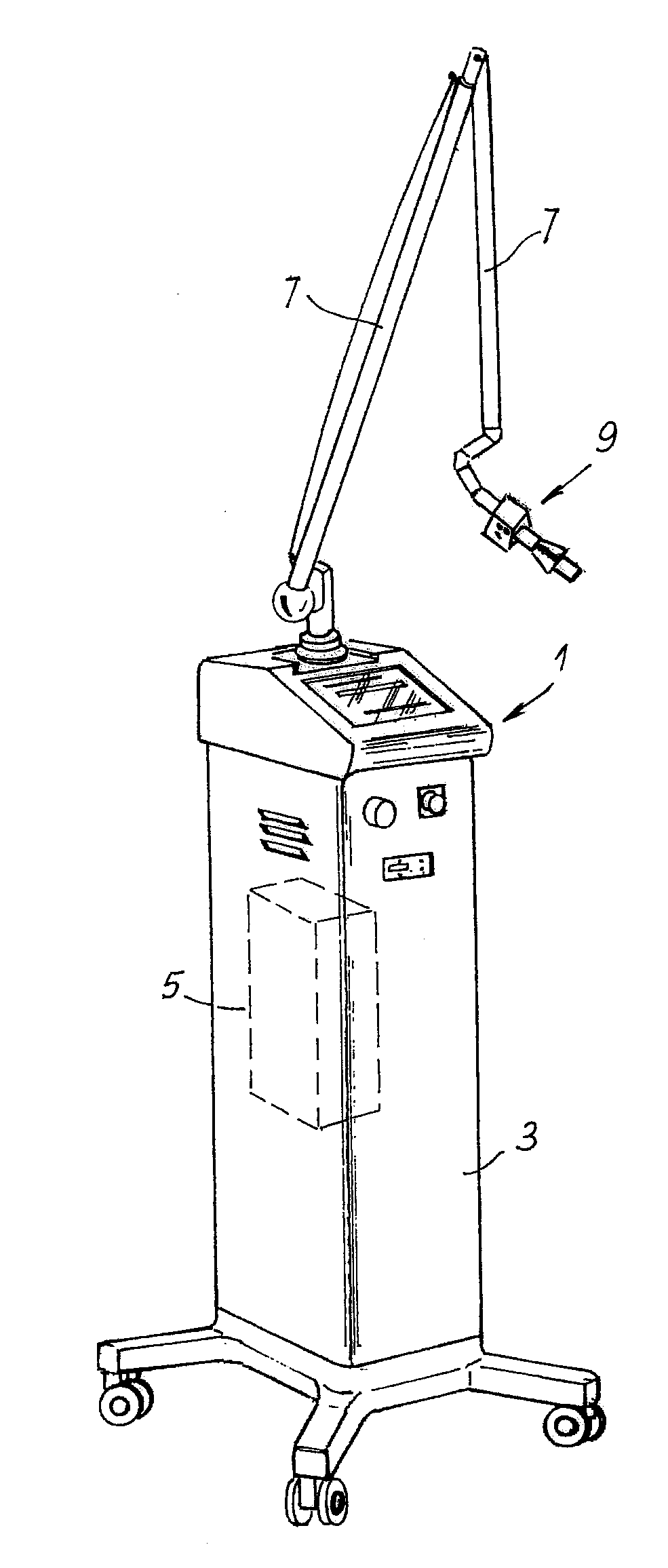

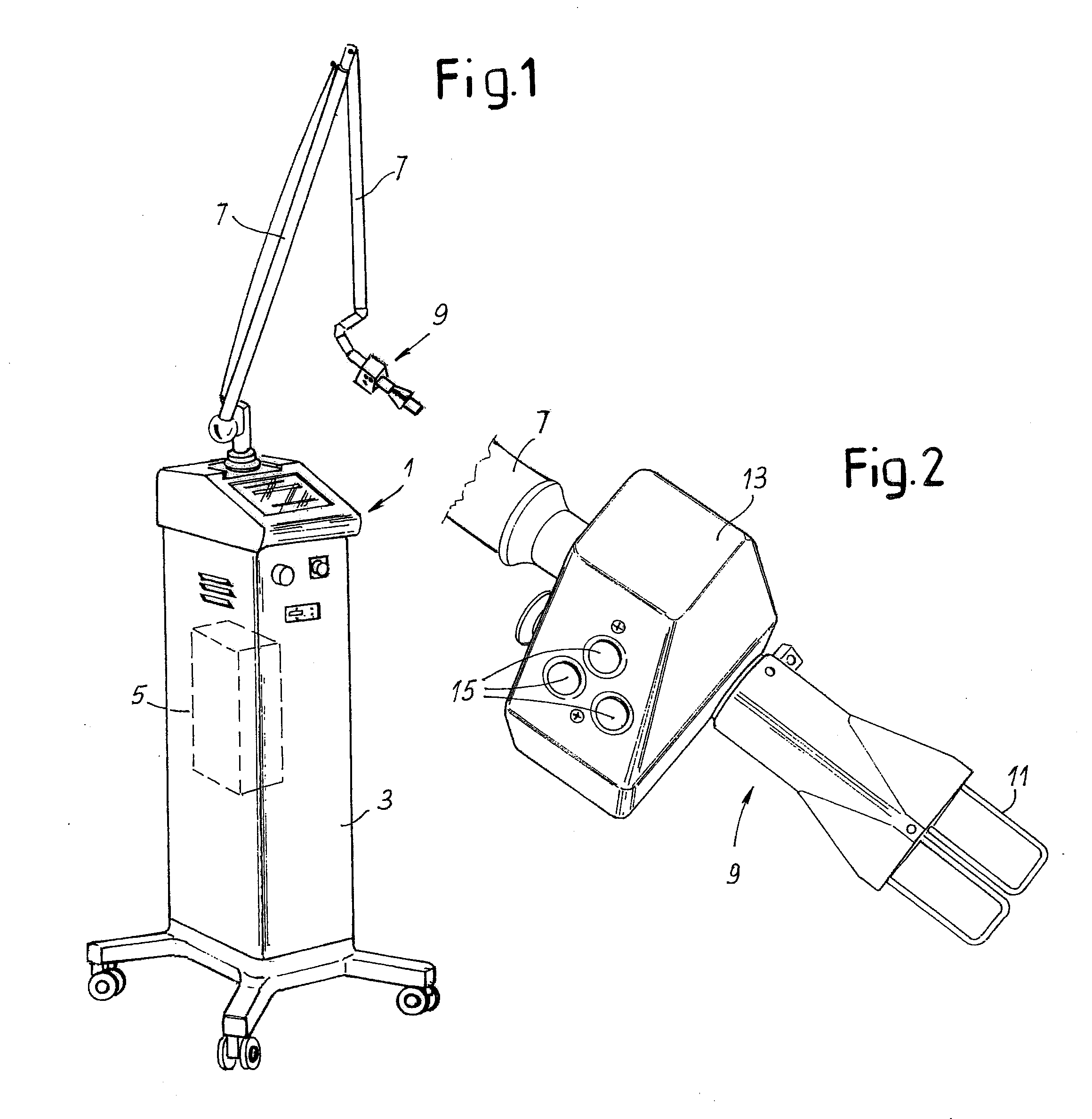

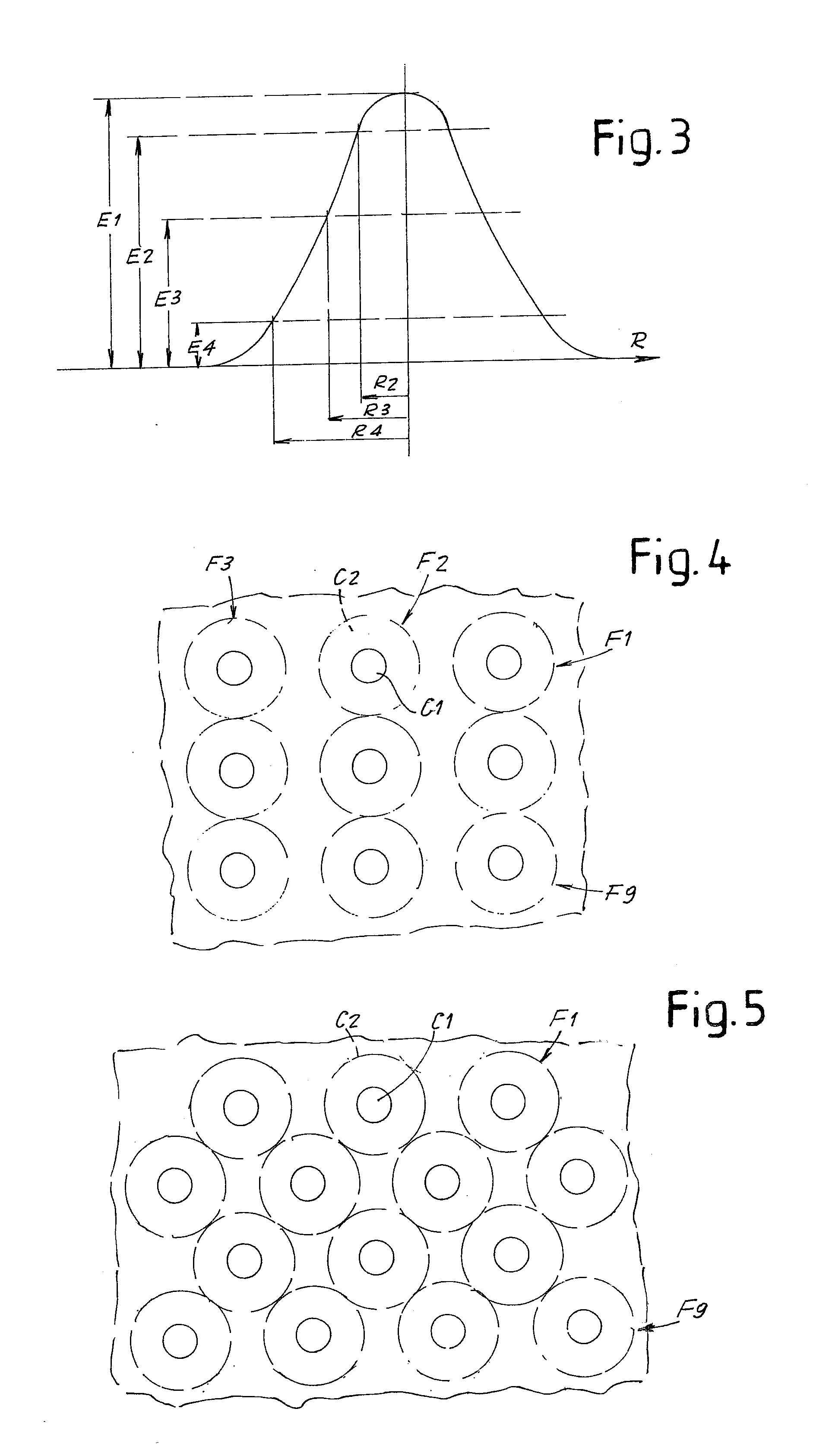

Device and method for treating the epidermis

InactiveUS20120330288A1Efficient heatingBig advantageSurgical instrument detailsOptoelectronicsLaser source

Owner:EL EN SPA

Motion capture element mount

Enables coupling or retrofitting a golf club with active motion capture electronics that are battery powered, passive or active shot count components, for example a passive RFID, and / or a visual marker on the cap for use with visual motion capture cameras. Does not require modifying the golf club. Electronics package and battery can be easily removed and replaced, for example without any tools. May utilize a weight that is removed when inserting the electronic package in the mount, wherein the weight element may have the same weight as an electronics package, for no net change or minimal change in club weight. May be implemented with a shaft enclosure and expander that may be coupled with a screw aligned along an axis parallel to the axis of the golf club shaft. May utilize non-permanently and / or friction coupling between the mount and golf club shaft. Cap may include a visual marker and / or logo.

Owner:NEWLIGHT CAPITAL LLC

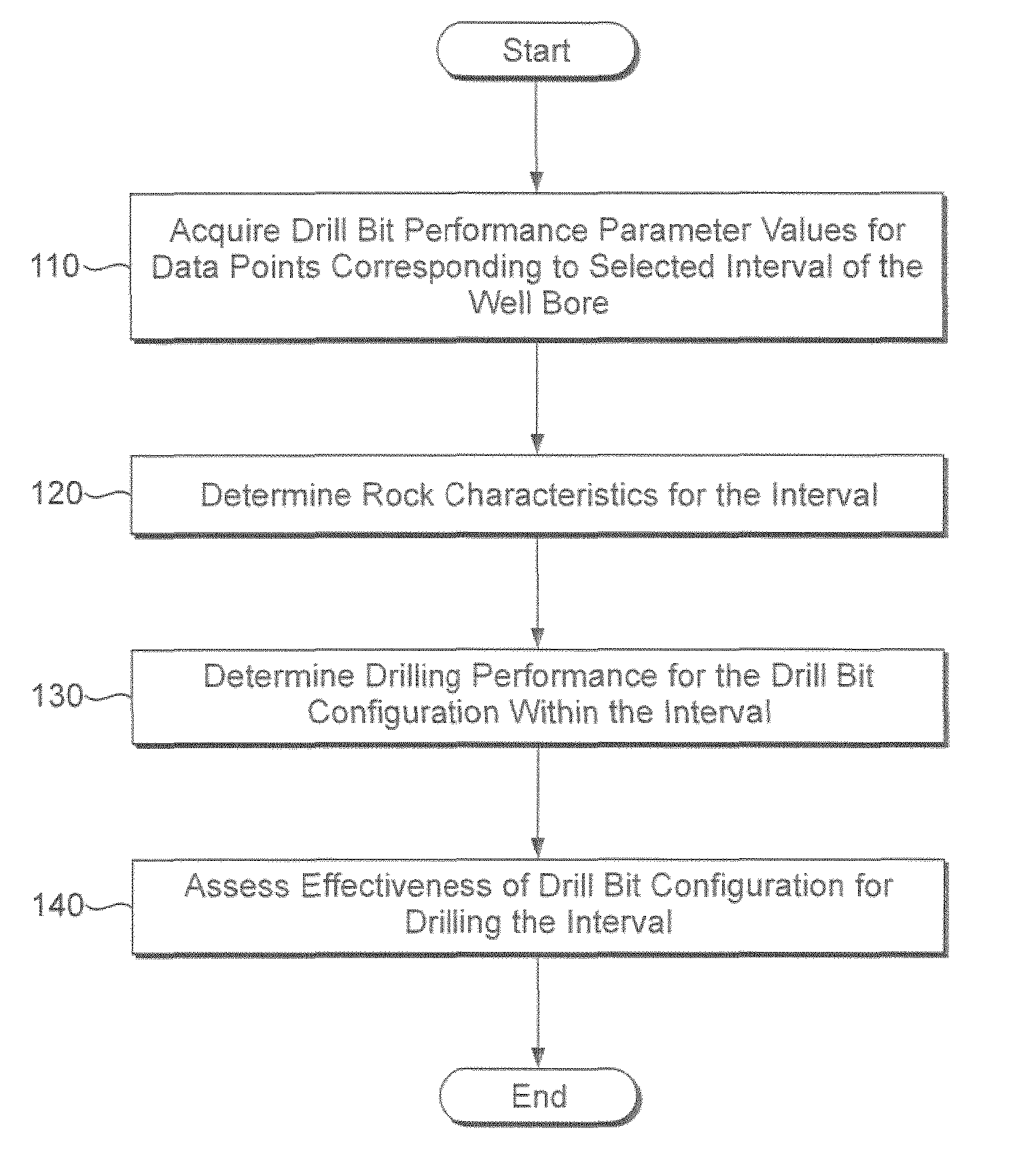

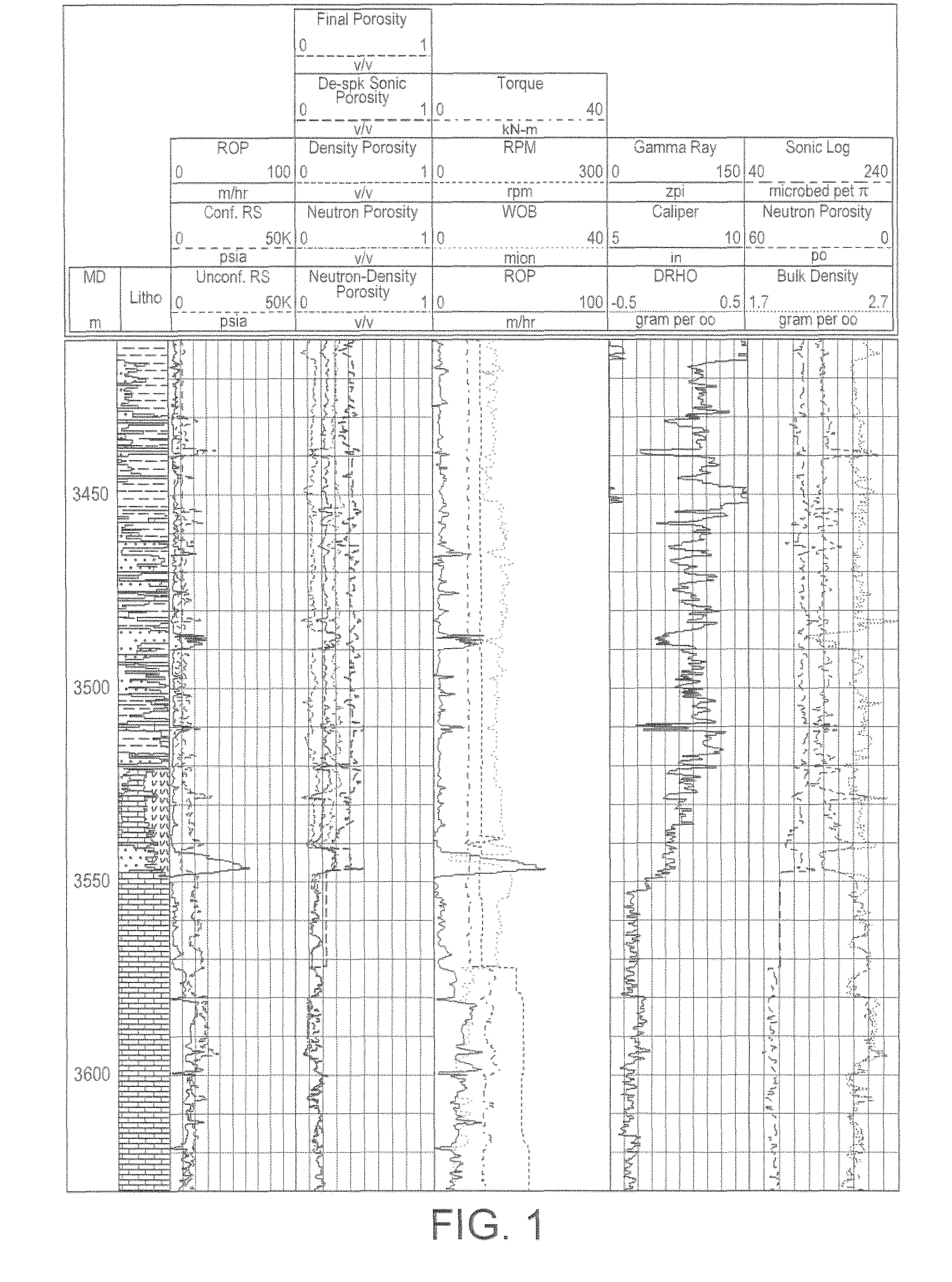

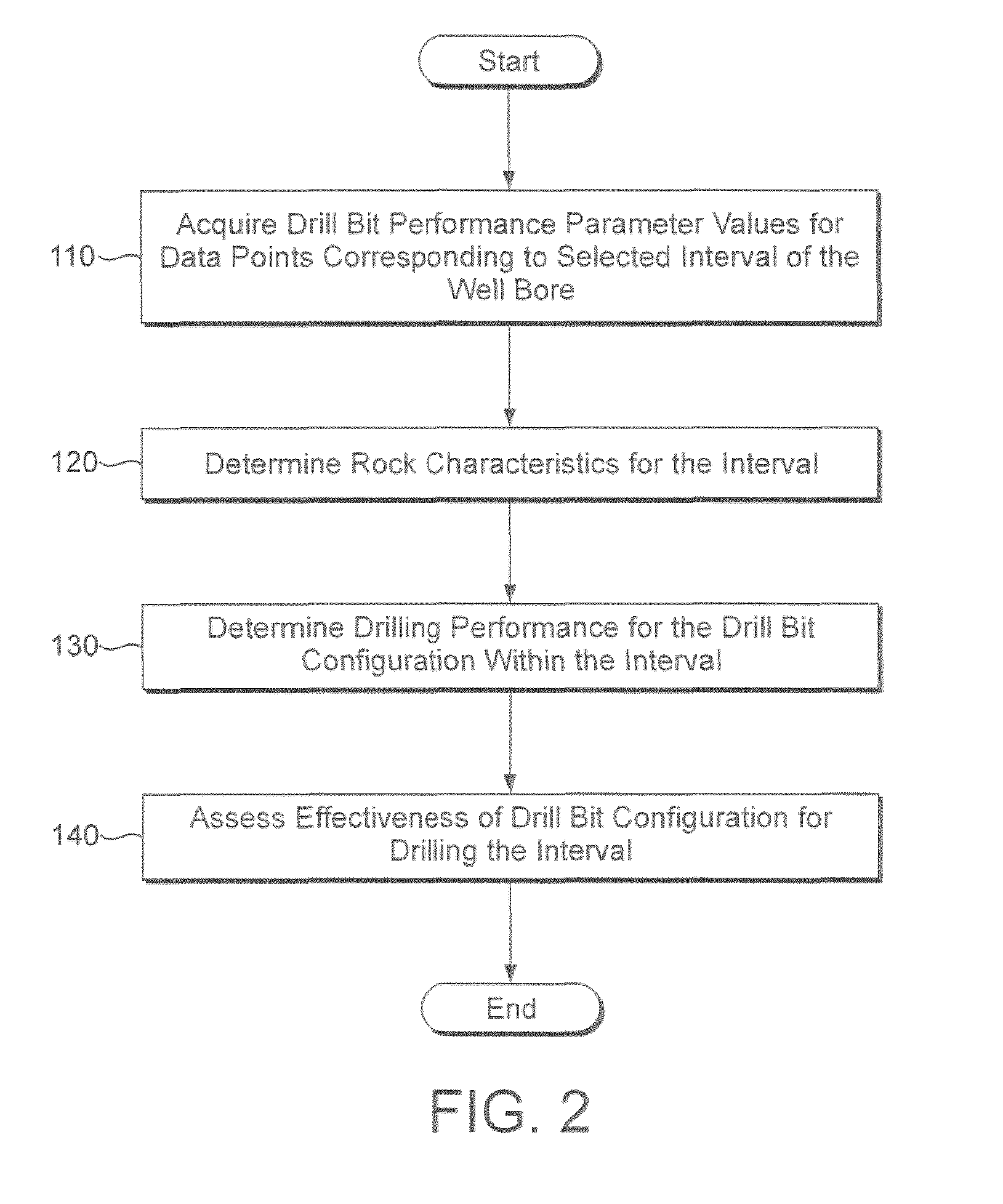

Method for assessing the performance of a drill bit configuration, and for comparing the performance of different drill bit configurations for drilling similar rock formations

ActiveUS20140318866A1Effective performance valueNegligible effectSurveyDrill bitsWell drillingMultiple point

There is disclosed herein a method for assessing the drilling performance of a drill bit configuration used to drill at least a portion of a wellbore in a formation, comprising: determining a value of at least one drill bit performance parameter at points along the wellbore, at least including at multiple points along an interval constituting at least part of the portion drilled using the drill bit configuration; determining rock characteristics for the interval; determining the drilling performance for said drill bit configuration in the interval based on the values for the drill bit performance parameter; and assessing the effectiveness of the drill bit configuration for drilling the interval based on the determined drilling performance and the determined rock characteristics. Also disclosed are related methods for comparing the performance of at least two different drill bit configurations; of designing a drill bit configuration for drilling at least part of a wellbore; for selecting a drill bit design for drilling at least part of a wellbore; and of well planning for drilling wells in a well field.

Owner:HALLIBURTON ENERGY SERVICES INC

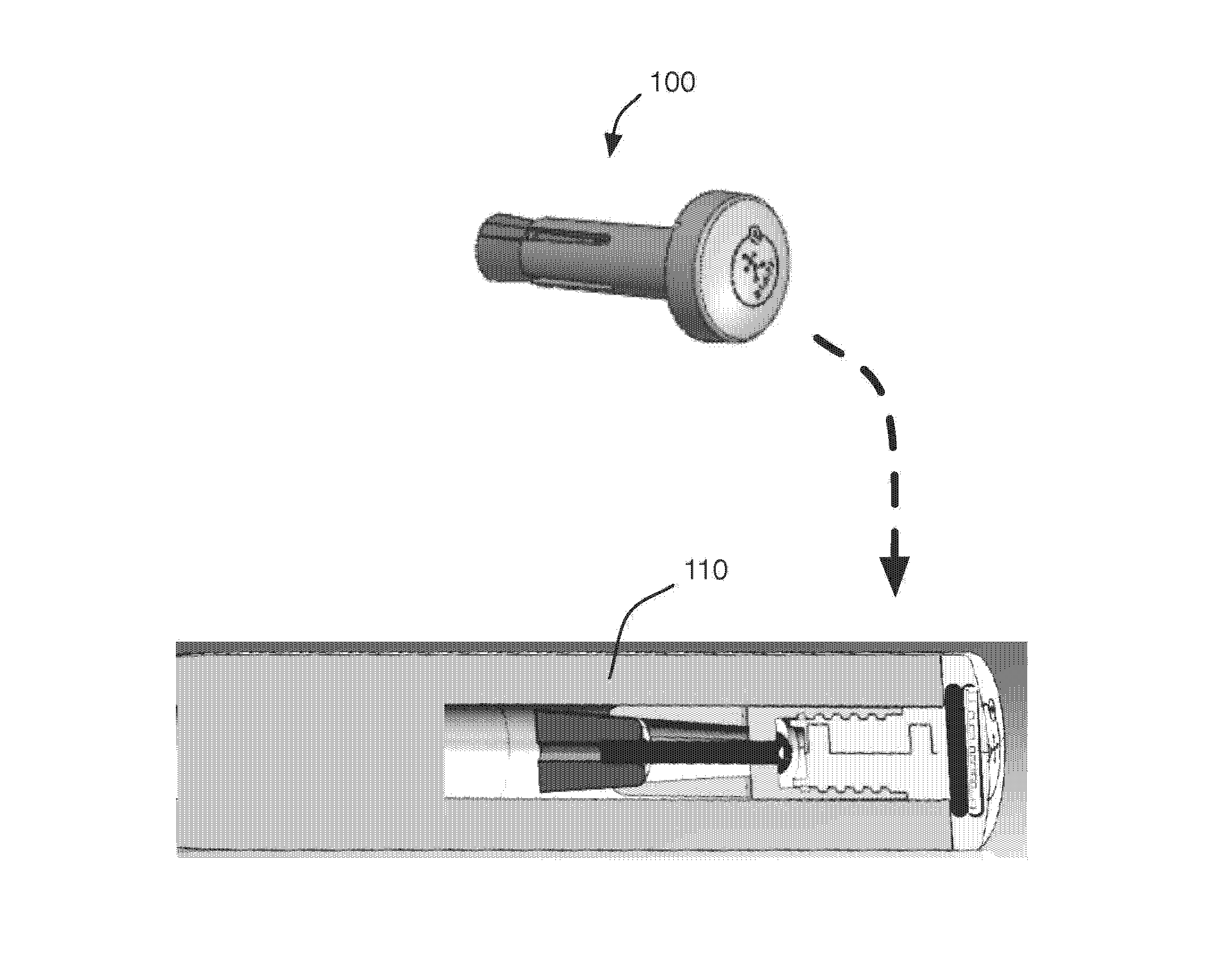

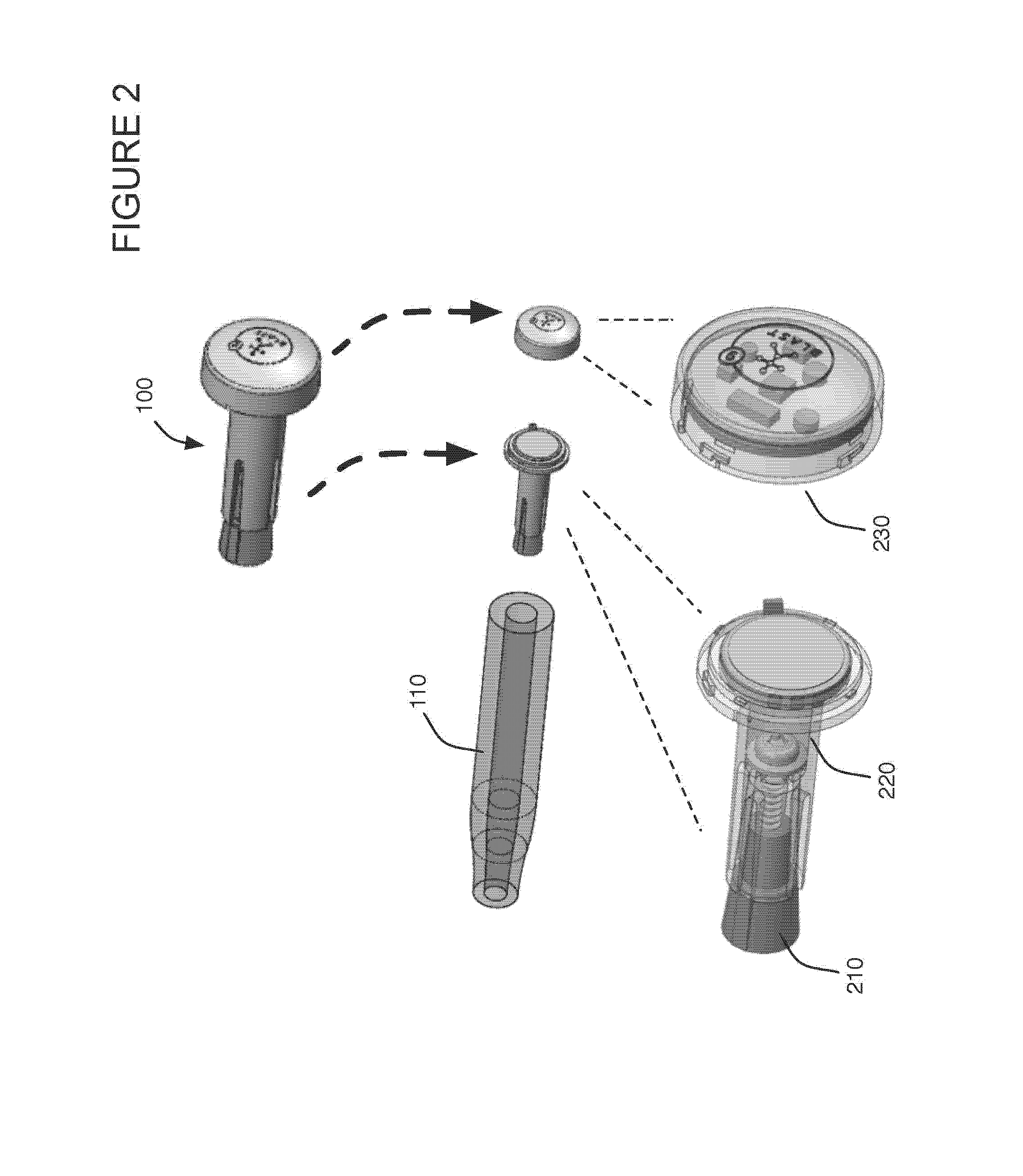

Handle integrated motion capture element mount

ActiveUS8613676B2Extend battery lifeElectrical contact is lostCandle holdersLighting support devicesEngineeringMotion capture

Handle integrated motion capture element mount that enables coupling or retrofitting a golf club with active motion capture electronics that are battery powered, passive or active shot count components, for example a passive RFID, and / or a visual marker on the cap for use with visual motion capture cameras. Does not require modifying the golf club. Electronics package and battery can be easily removed and replaced, for example without any tools. May utilize a weight that is removed when inserting the electronic package in the mount, wherein the weight element may have the same weight as an electronics package, for no net change or minimal change in club weight. May be implemented with a handle without electronics for future upgrading. May utilize non-permanently and / or friction coupling between the mount and equipment.

Owner:NEWLIGHT CAPITAL LLC

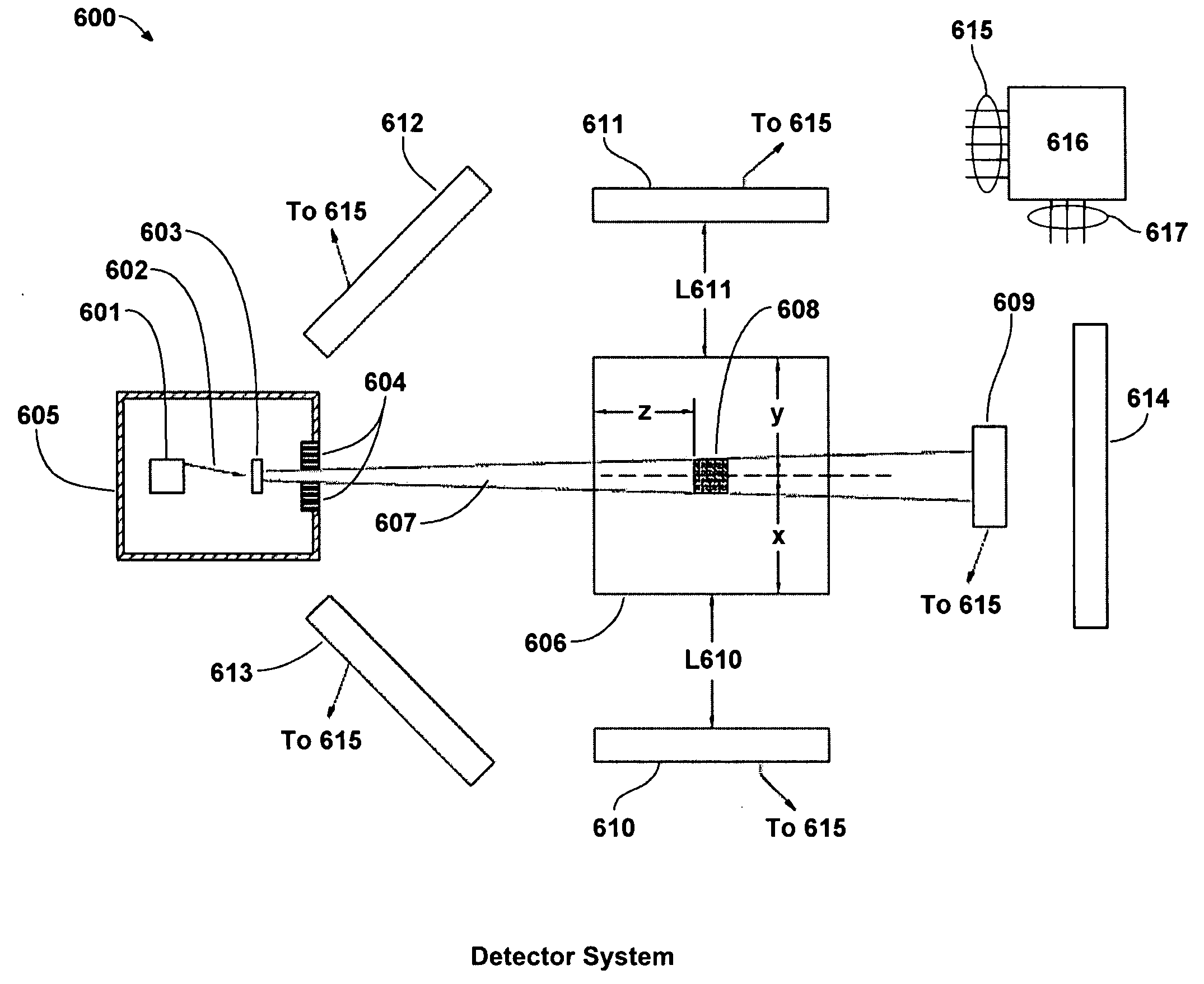

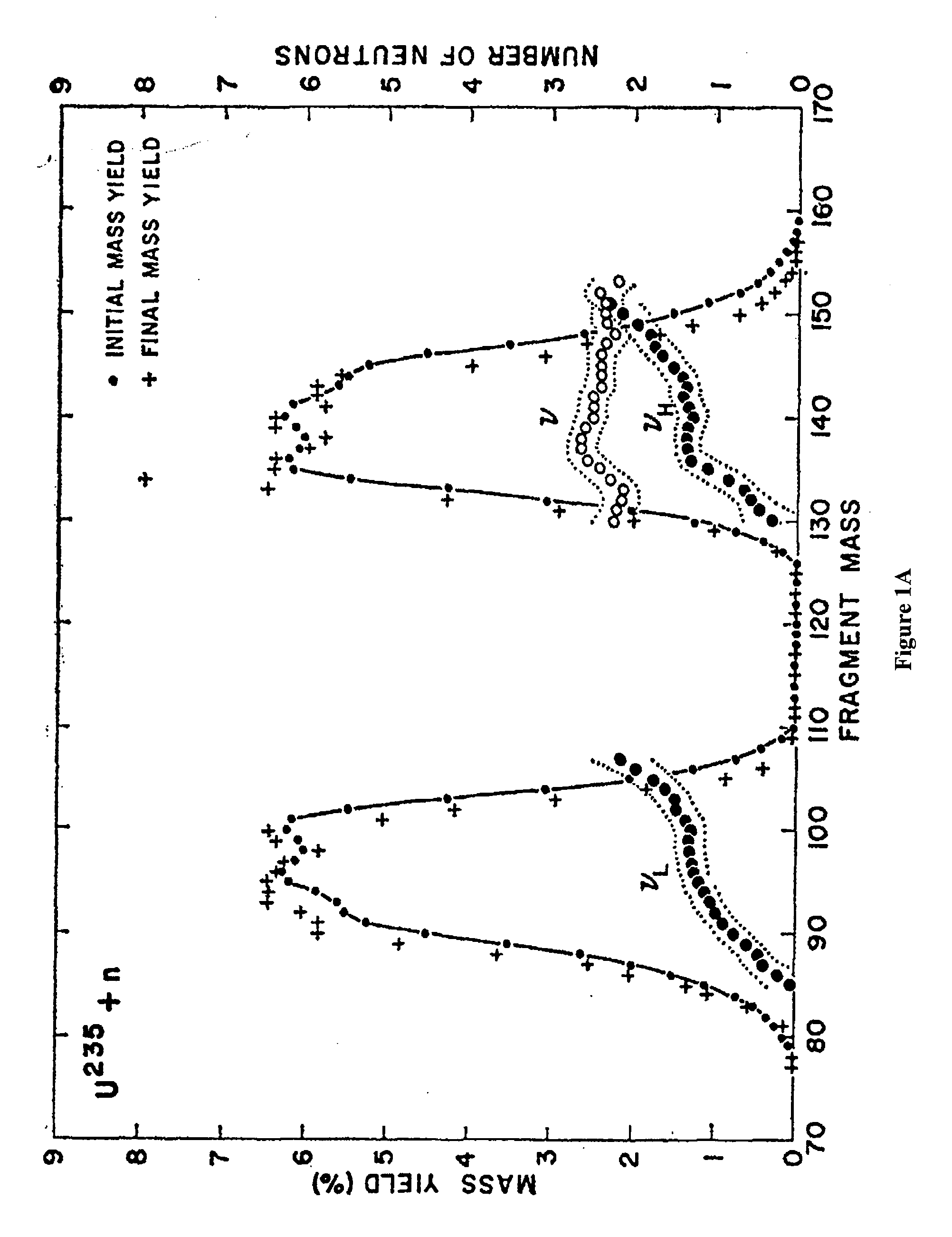

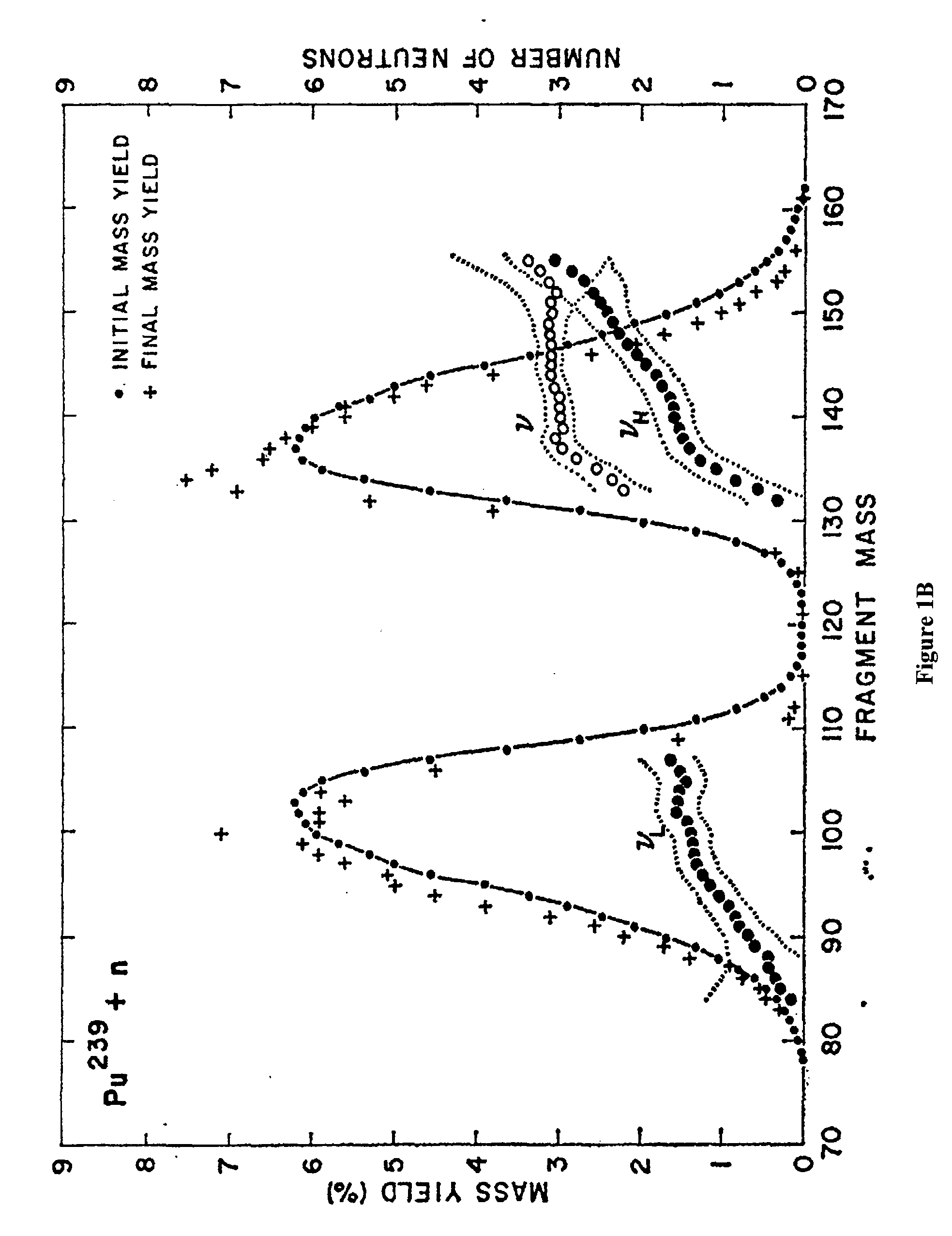

Non-intrusive method to identify presence of nuclear materials using energetic prompt neutrons from photon-induced fission

InactiveUS20090074128A1Improve detection rateSolve the high false positive rateConversion outside reactor/acceleratorsNeutron radiation measurementBeam energySmall fragment

Methods and systems for non-intrusively detecting the existence of fissile materials in a container via the measurement of energetic prompt neutrons are disclosed. The methods and systems use the unique nature of the prompt neutron energy spectrum from photo-fission arising from the emission of neutrons from almost fully accelerated fragments to unambiguously identify fissile material. The angular distribution of the prompt neutrons from photo-fission and the energy distribution correlated to neutron angle relative to the photon beam are used to distinguish odd-even from even-even nuclei undergoing photo-fission. The independence of the neutron yield curve (yield as a function of electron beam energy or photon energy) on neutron energy also is also used to distinguish photo-fission from other processes such as (γ, n). Different beam geometries are used to detect localized samples of fissile material and also fissile materials dispersed as small fragments or thin sheets over broad regions. These signals from photo-fission are unique and allow the detection of any material in the actinide region of the nuclear periodic table.

Owner:PASSPORT SYSTEMS INC

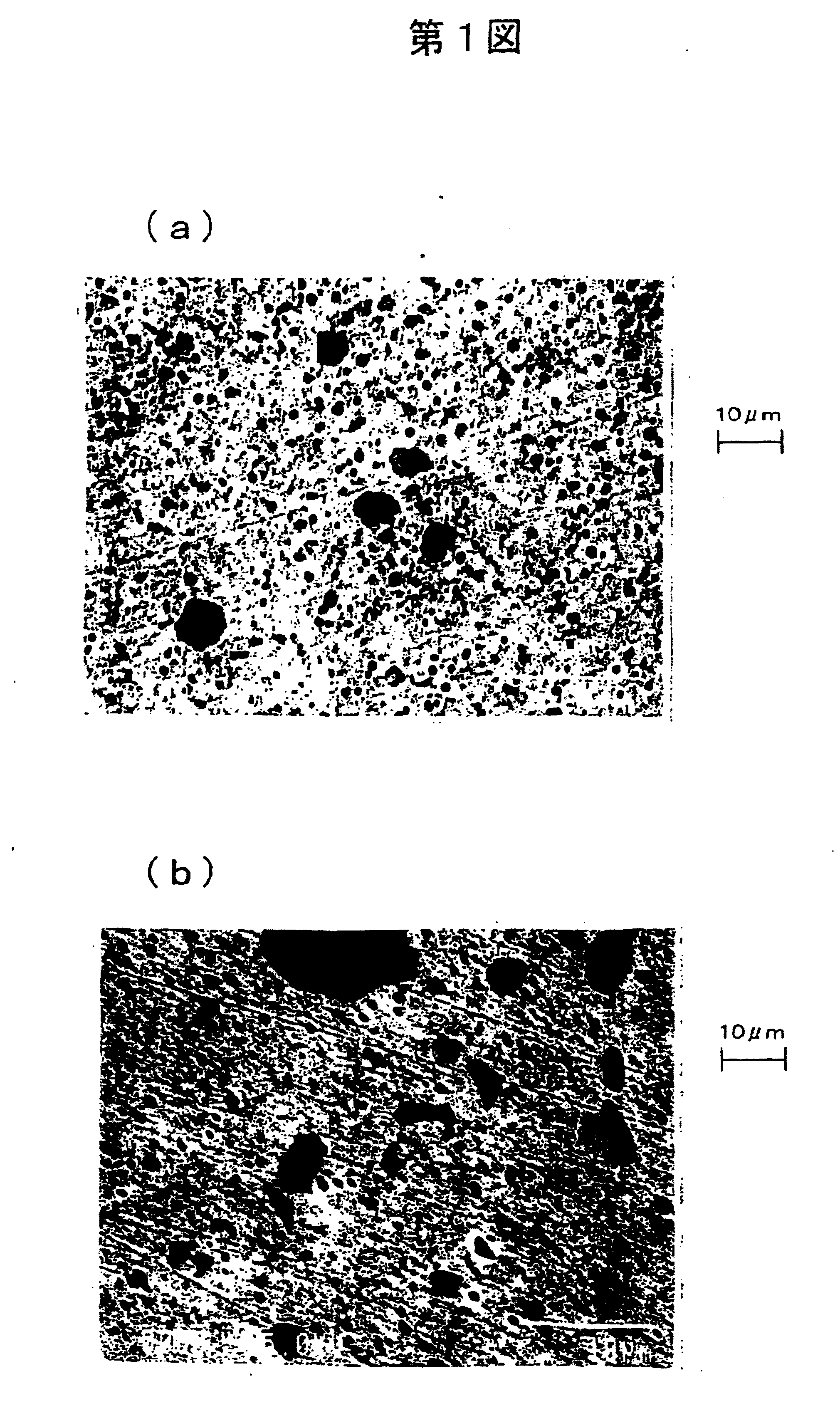

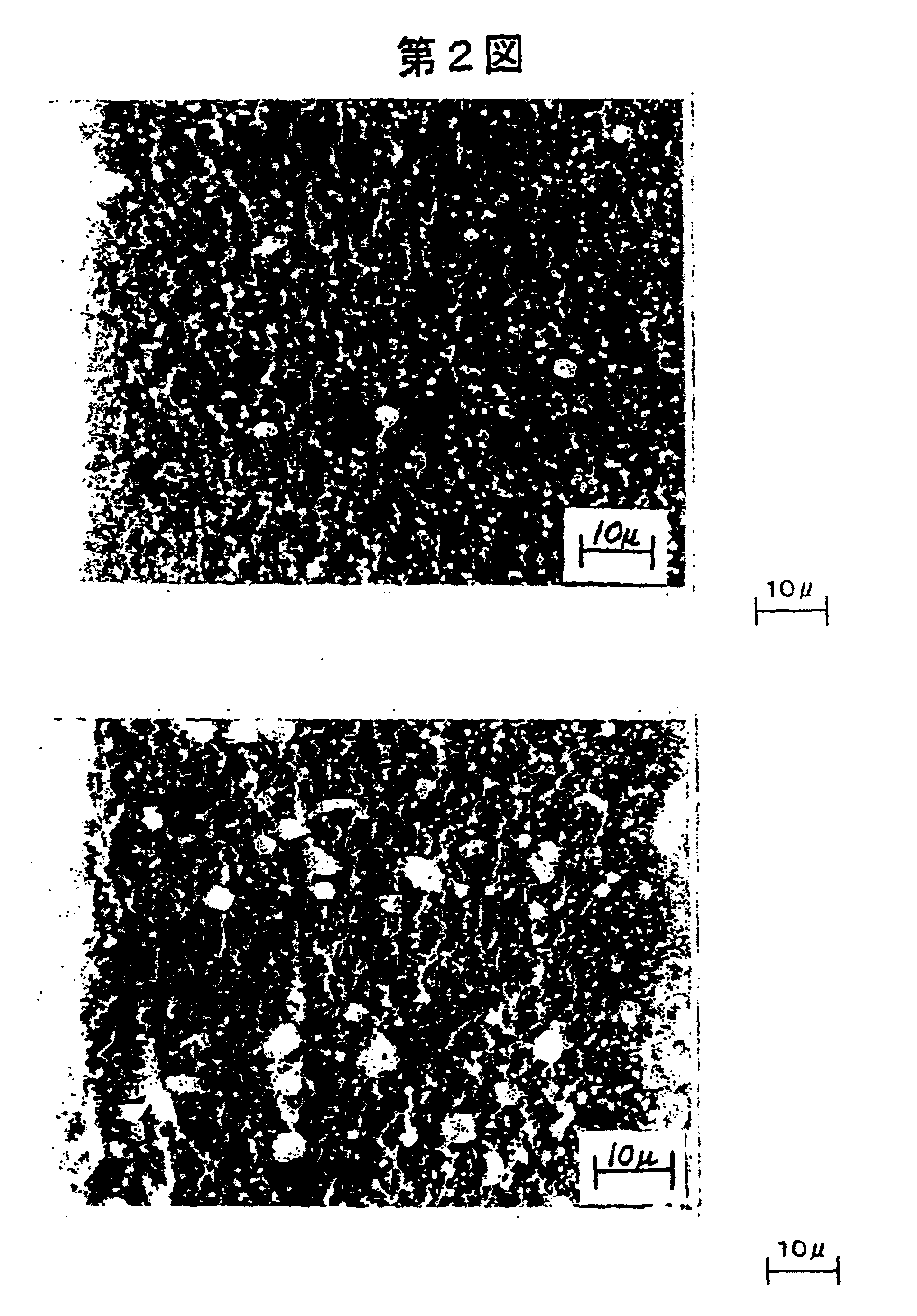

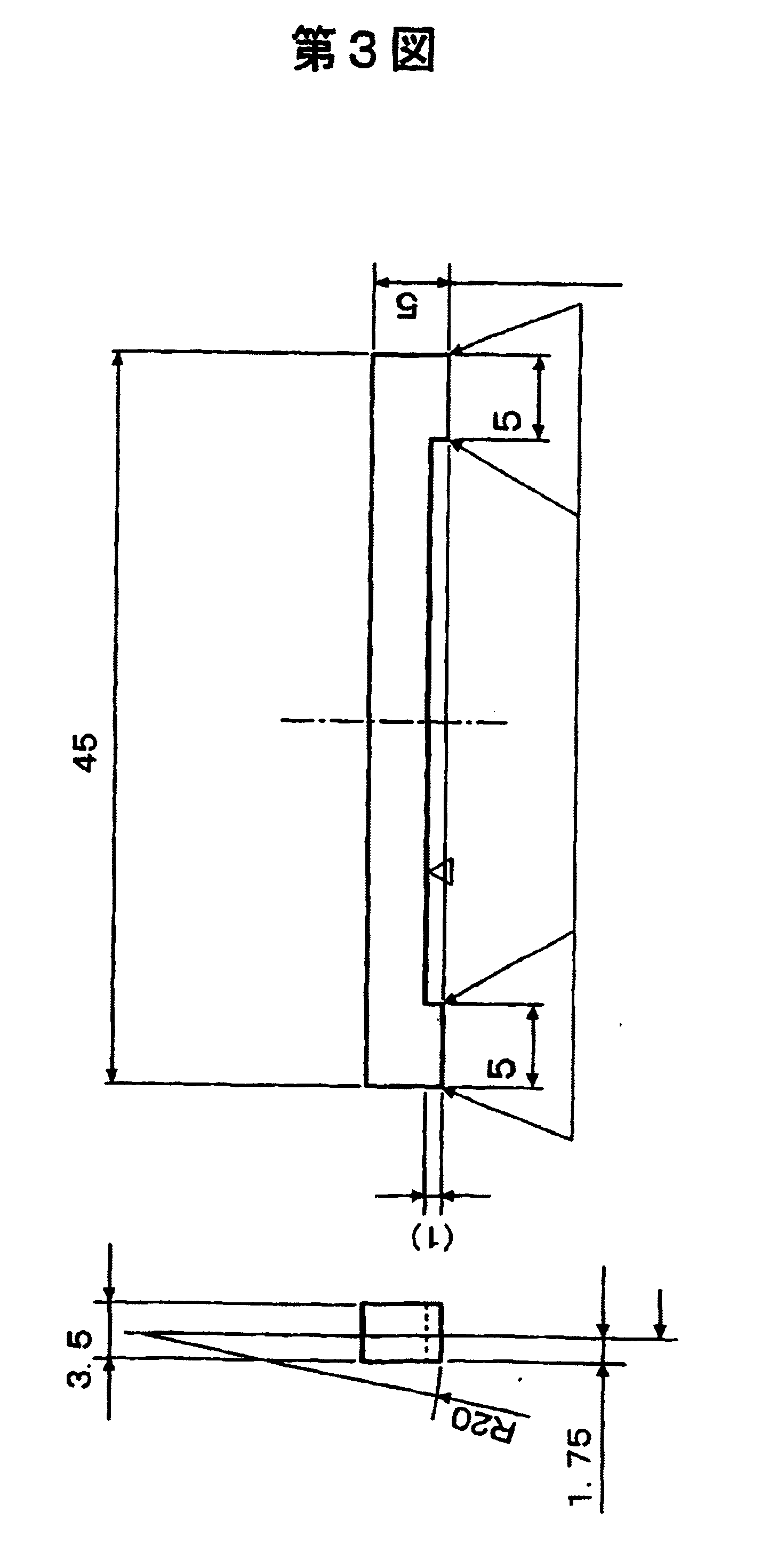

Piston ring excellent in resistance to scuffing, cracking and fatigue and method for producing the same, and combination of piston ring and cylinder block

InactiveUS20040040631A1Easy to wearEnhances scuffing resistancePiston ringsSolid state diffusion coatingCrack resistanceLongest Diameter

A piston ring having improved scuffing resistance, cracking resistance and fatigue resistance, consists of a high-chromium martensitic stainless steel and a sliding nitriding layer formed on the surface of said steel. The stainless steel consists of C: 0.3 to 1.0%; Cr: 14.0 to 21.0%, N: 0.05 to 0.50%, at least one of Mo, V, W and Nb: 0.03 to 3.0% in total, Si: 0.1 to 1.0%, Mn 0.1 to 1.0%, P: 0.05% or less, S: 0.05% or less, the balance being Fe and unavoidable impurities. The sliding nitriding layer comprises on its surface hard particles mainly consisting of nitrides in a range of from 0.2 to 2.0 mum of average particle size, 7 mum or less of the longest diameter, and from 5 to 30% in area ratio.

Owner:RIKEN CO LTD +1

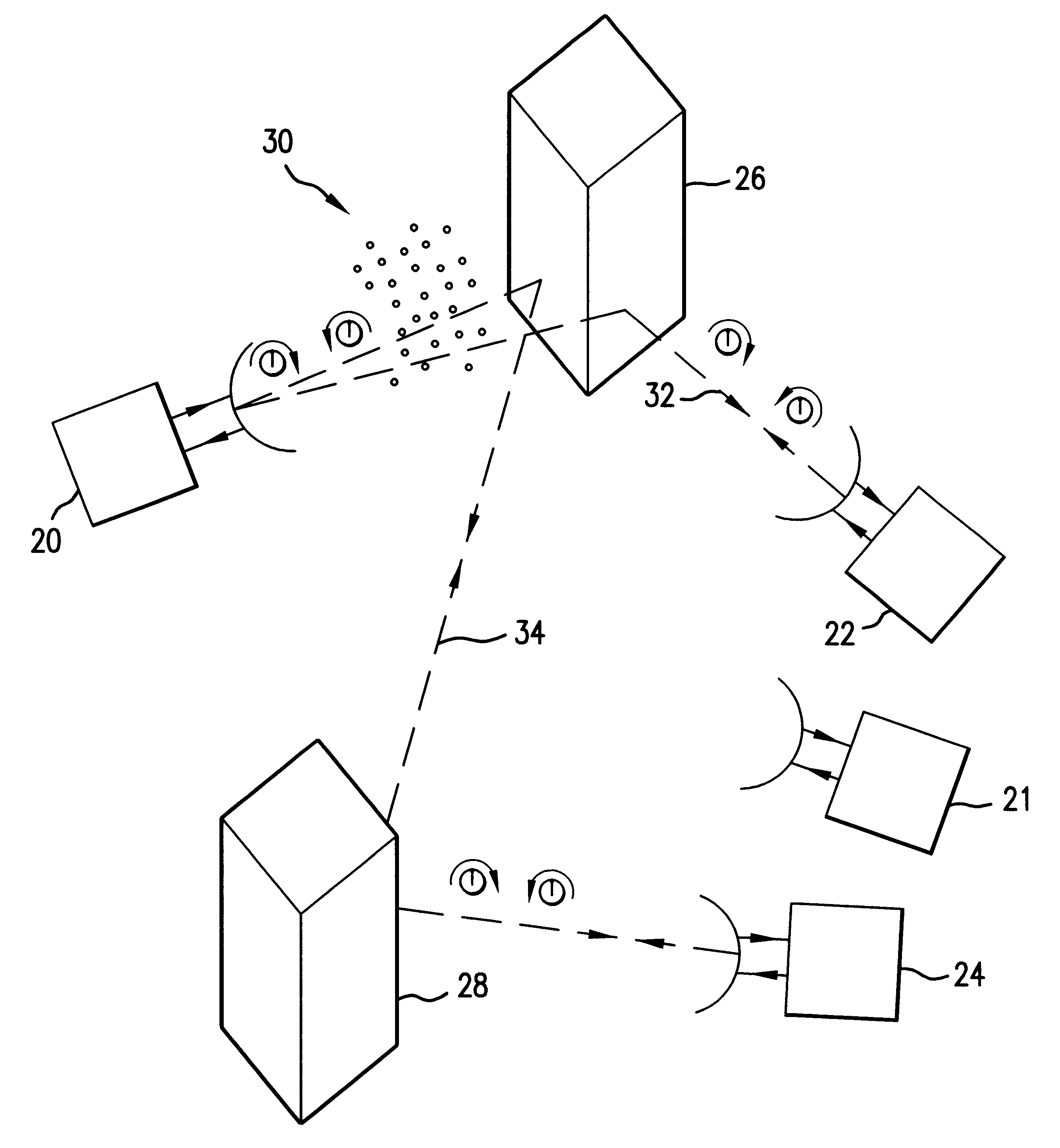

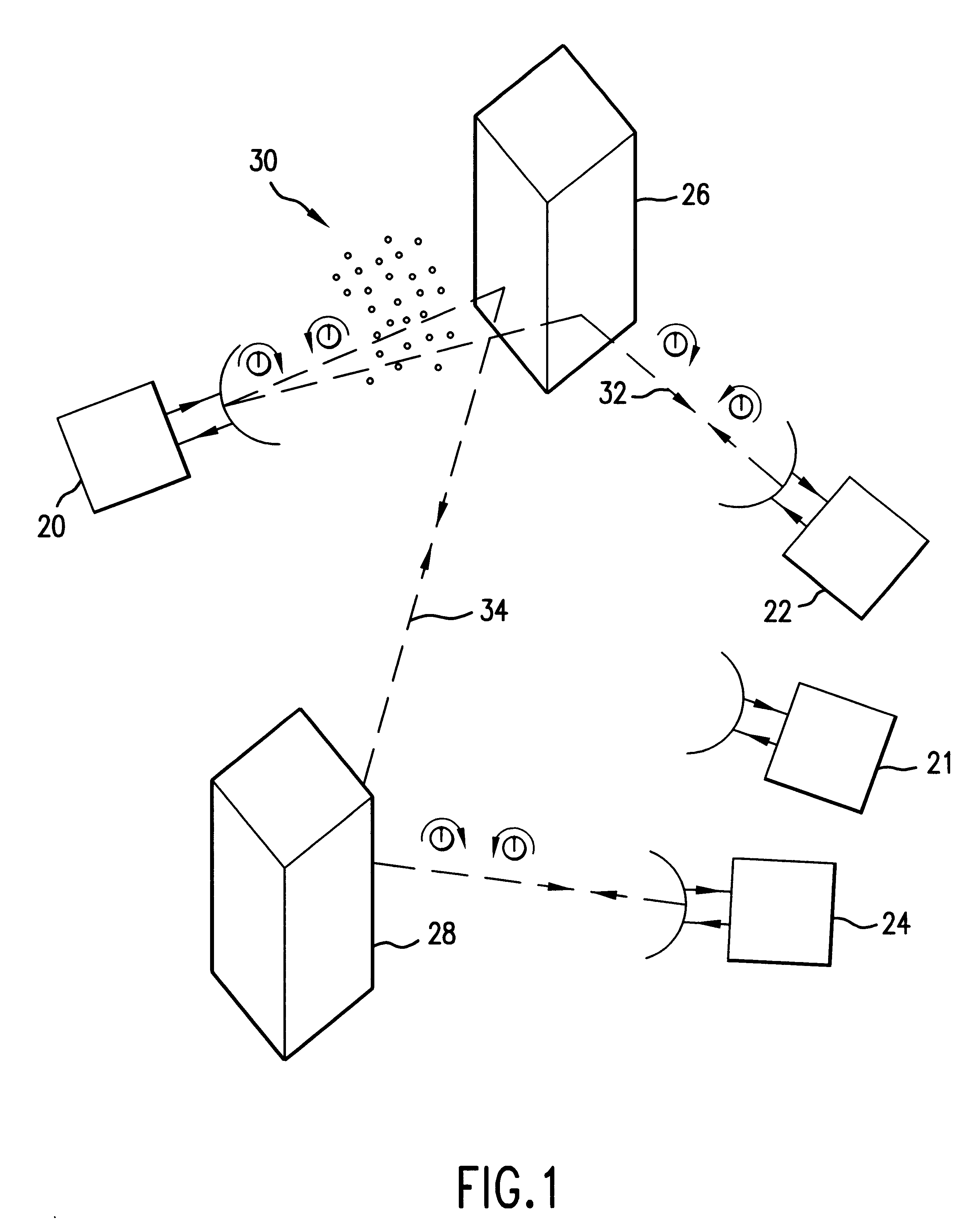

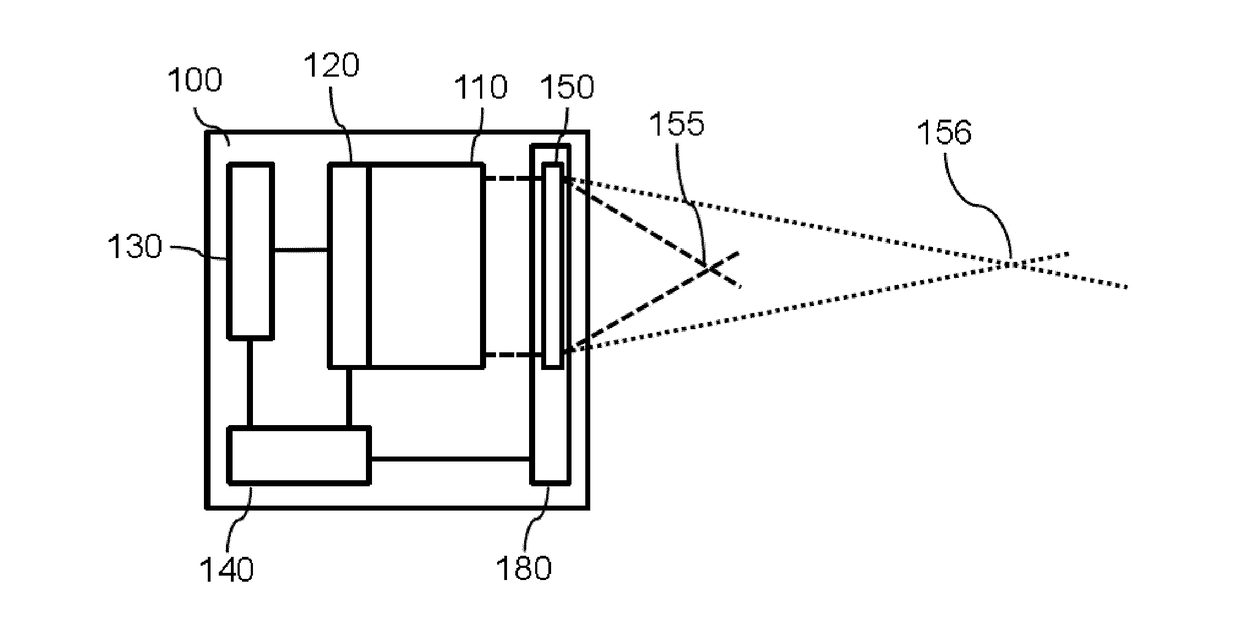

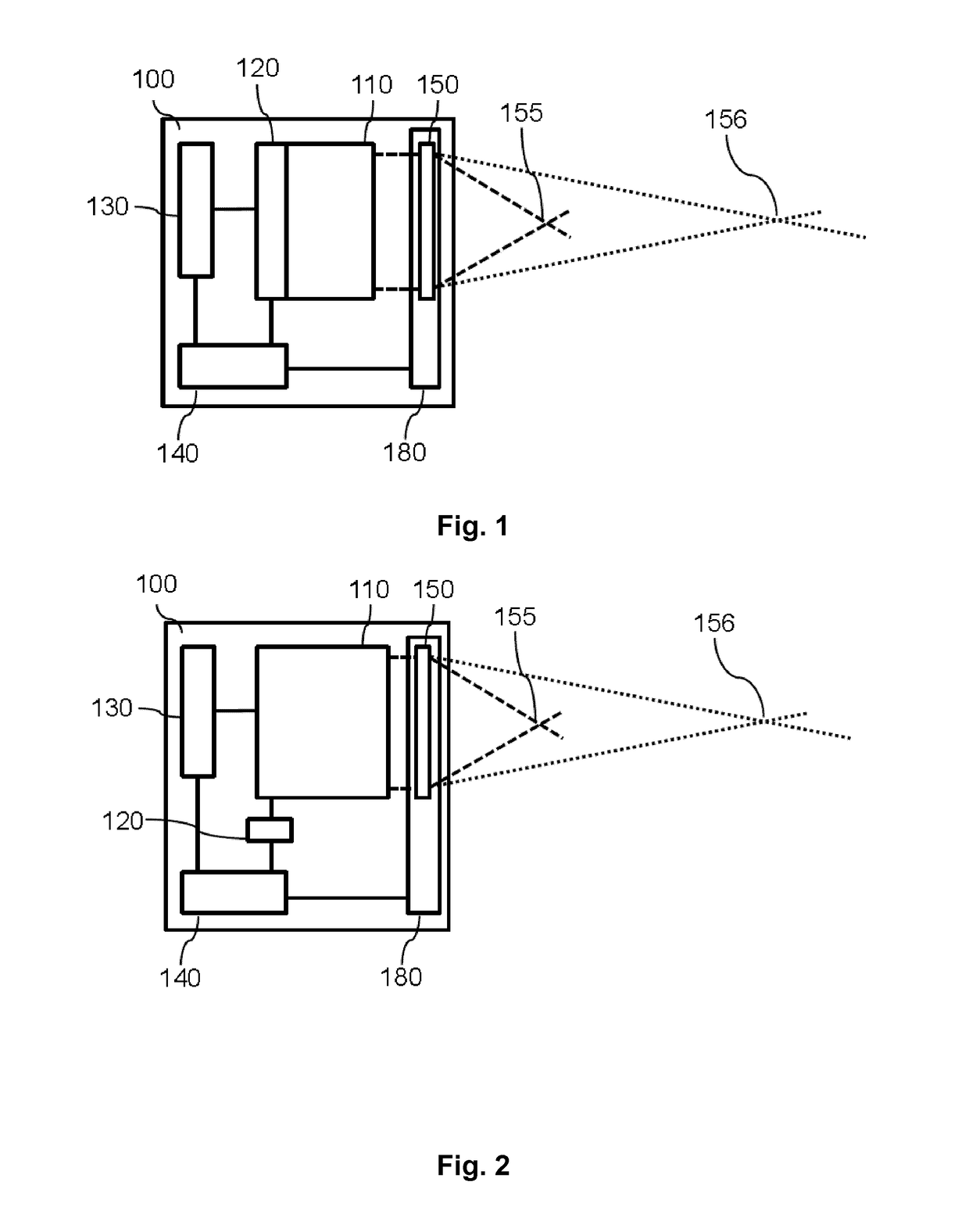

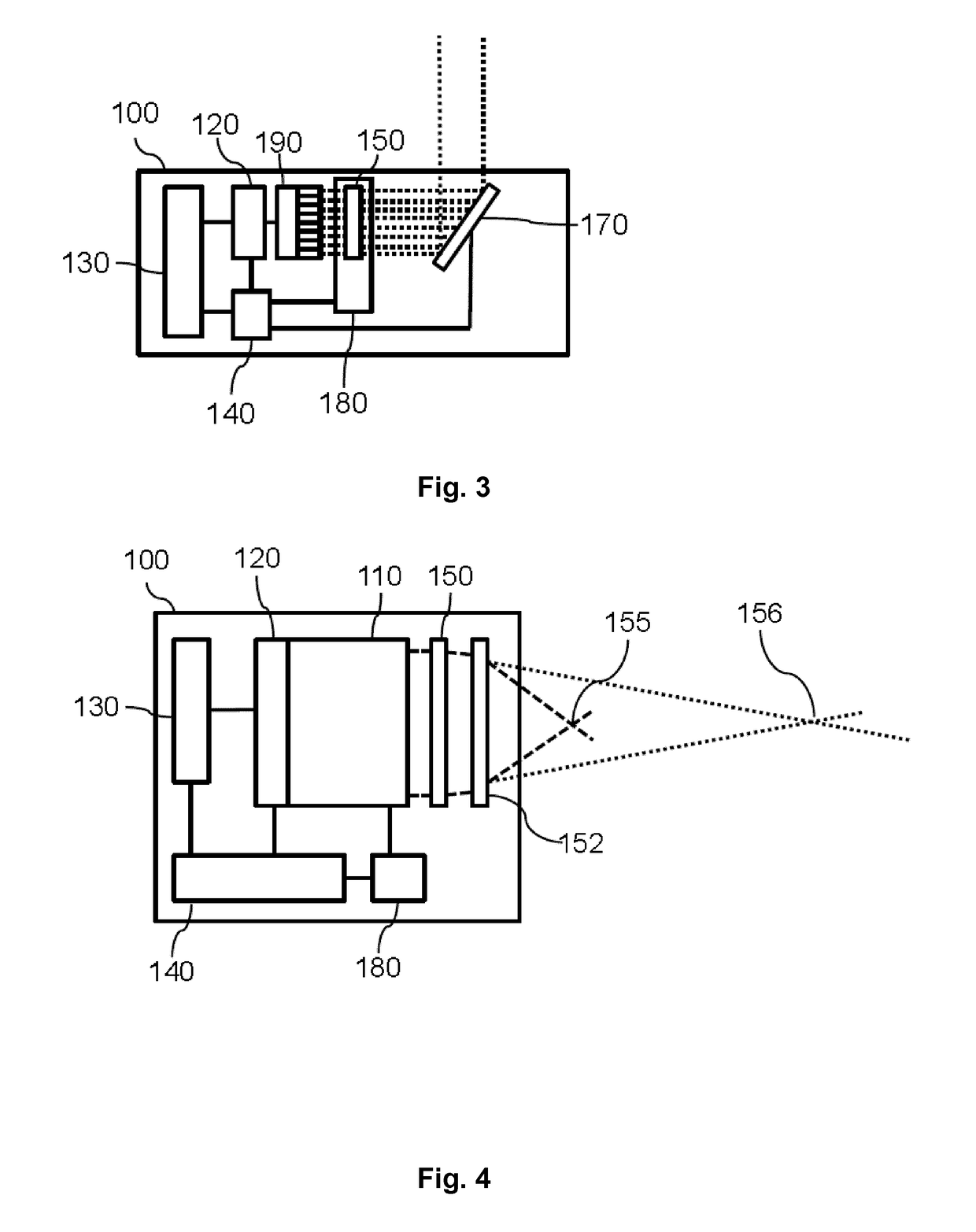

Laser sensor for multi parameter detection

ActiveUS20180224368A1Negligible effectParticle size analysisUsing optical meansLaser sensorLaser beams

The invention describes a laser sensor module (100) which is adapted to detect or determine at least two different physical parameters by means of self-mixing interference by focusing a laser beam to different positions. Such a laser sensor module (100) may be used as an integrated sensor module, for example, in mobile devices (250). The laser sensor module (100) may be used as an input device and in addition as a sensor for detecting physical parameters in an environment of the mobile communication device (250). One physical parameter in the environment of the mobile communication device (250) may, for example, be the concentration of particles in the air (air pollution, smog . . . ). The invention further describes a related method and computer program product.

Owner:TRUMPF PHOTONIC COMPONENTS GMBH

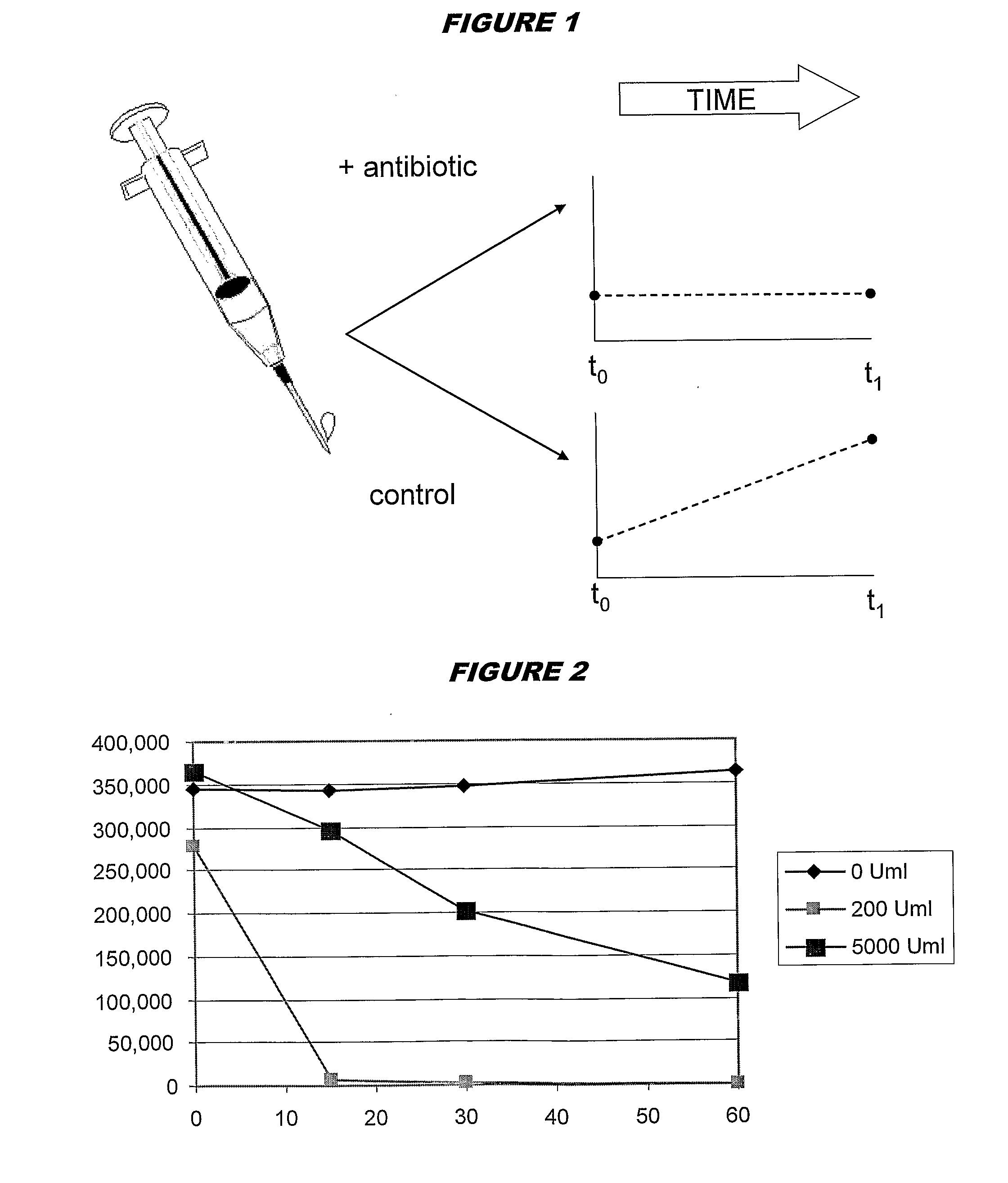

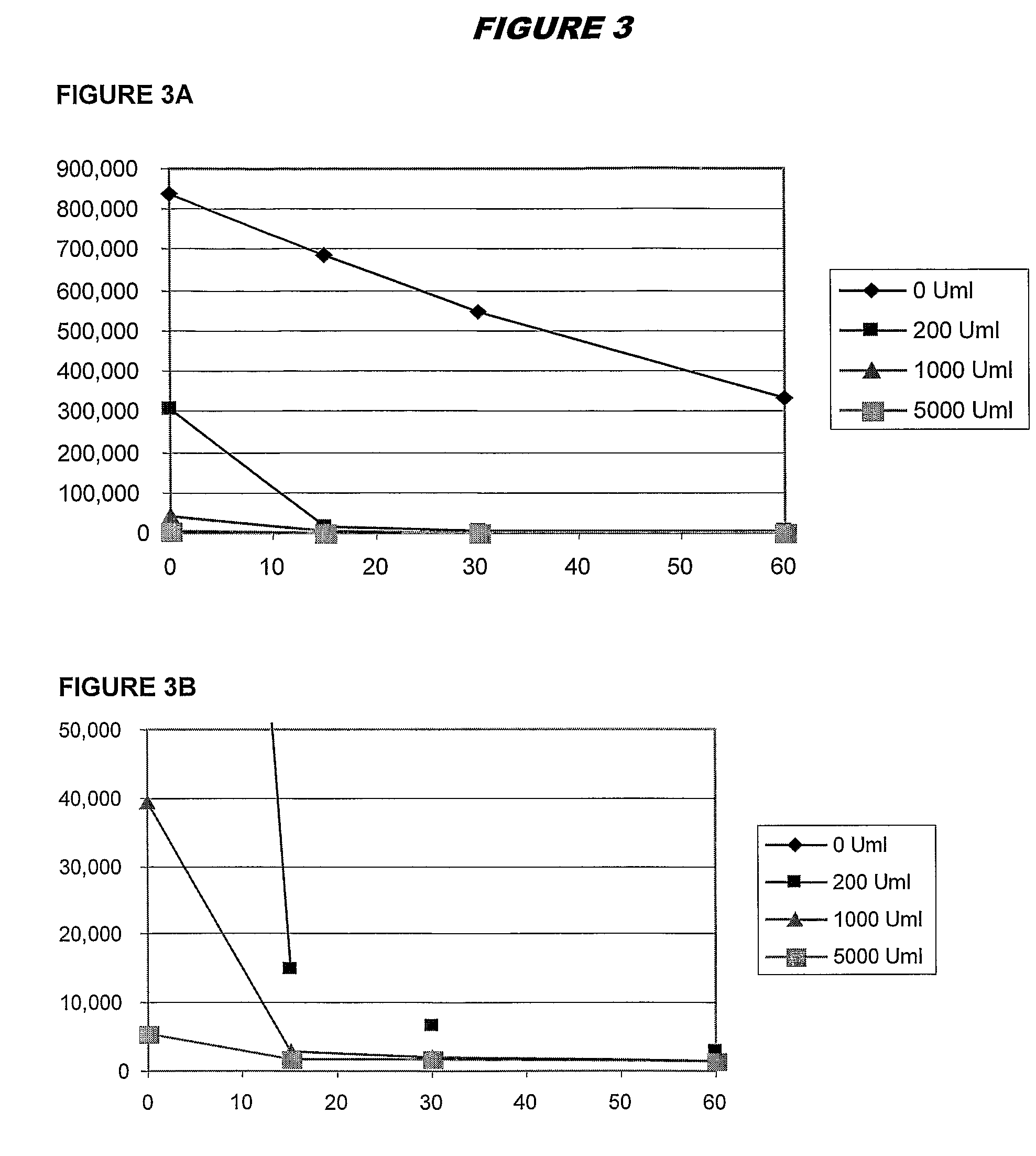

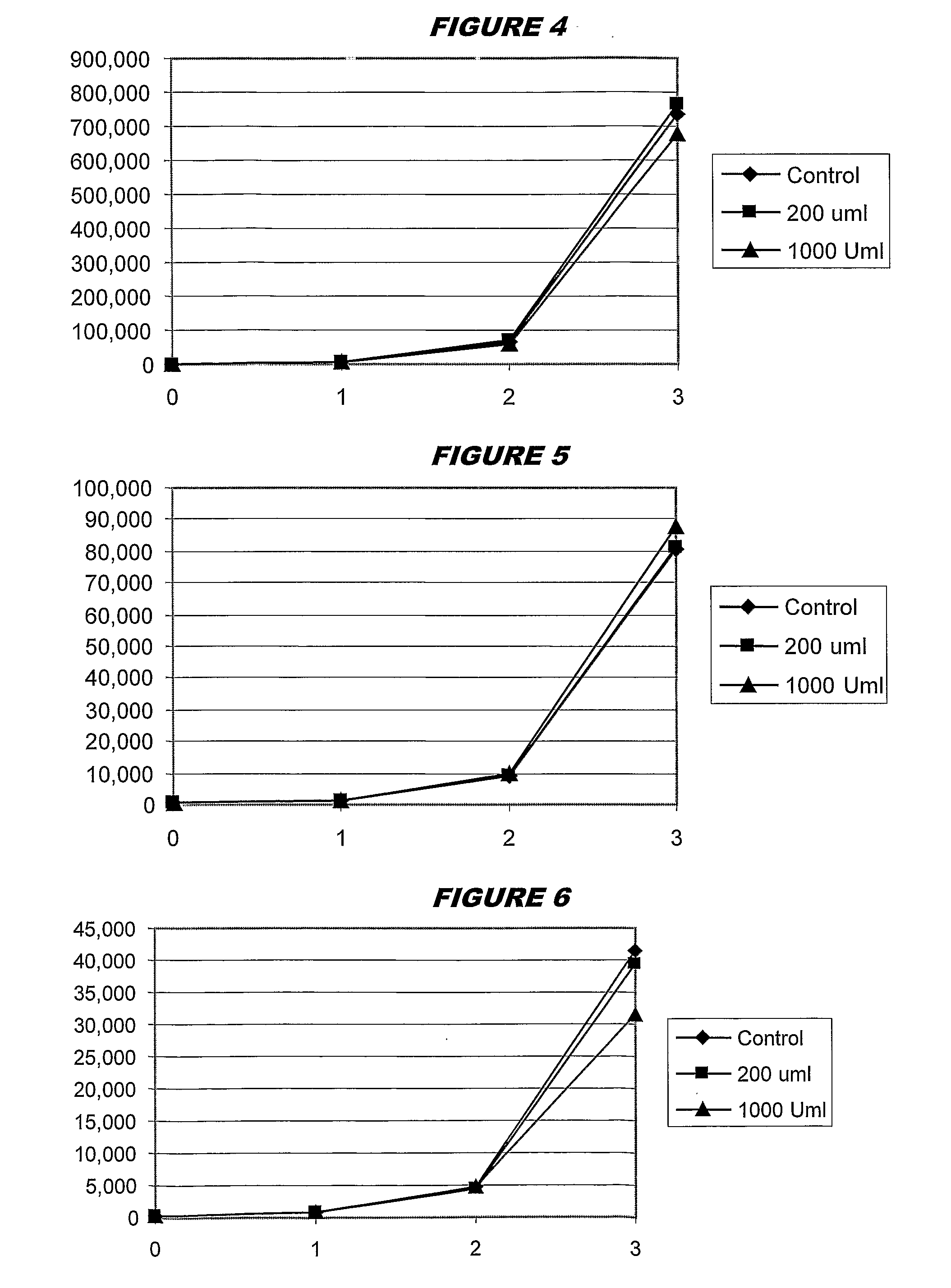

Distinguishing cells in a sample by inactivating extracellular enzyme before releasing intracellular enzyme

ActiveUS20090275063A1Easy to useInactivationMicrobiological testing/measurementBiological material analysisExtracellularAdenylate kinase activity

A method for detecting the absence or presence of cells of interest in a liquid sample, wherein: (a) the sample: (i) comprises an extracellular medium containing an enzyme with a measurable activity; and (ii) is suspected of containing cells of interest that contain an enzyme with said measurable activity; and (b) the method comprises the steps of: (i) treating the liquid sample with a reagent that inactivates said measurable activity in the extracellular medium, but does not inactivate the measurable activity in said cells of interest; (ii) lysing the cells of interest to release the intracellular enzyme; and (iii) measuring said measurable activity. Thus the intracellular enzyme can be measured without interference from the extracellular enzyme. The invention is particularly useful for treatment of bacterially-infected blood using a detection assay based on adenylate kinase activity.

Owner:3M INNOVATIVE PROPERTIES CO

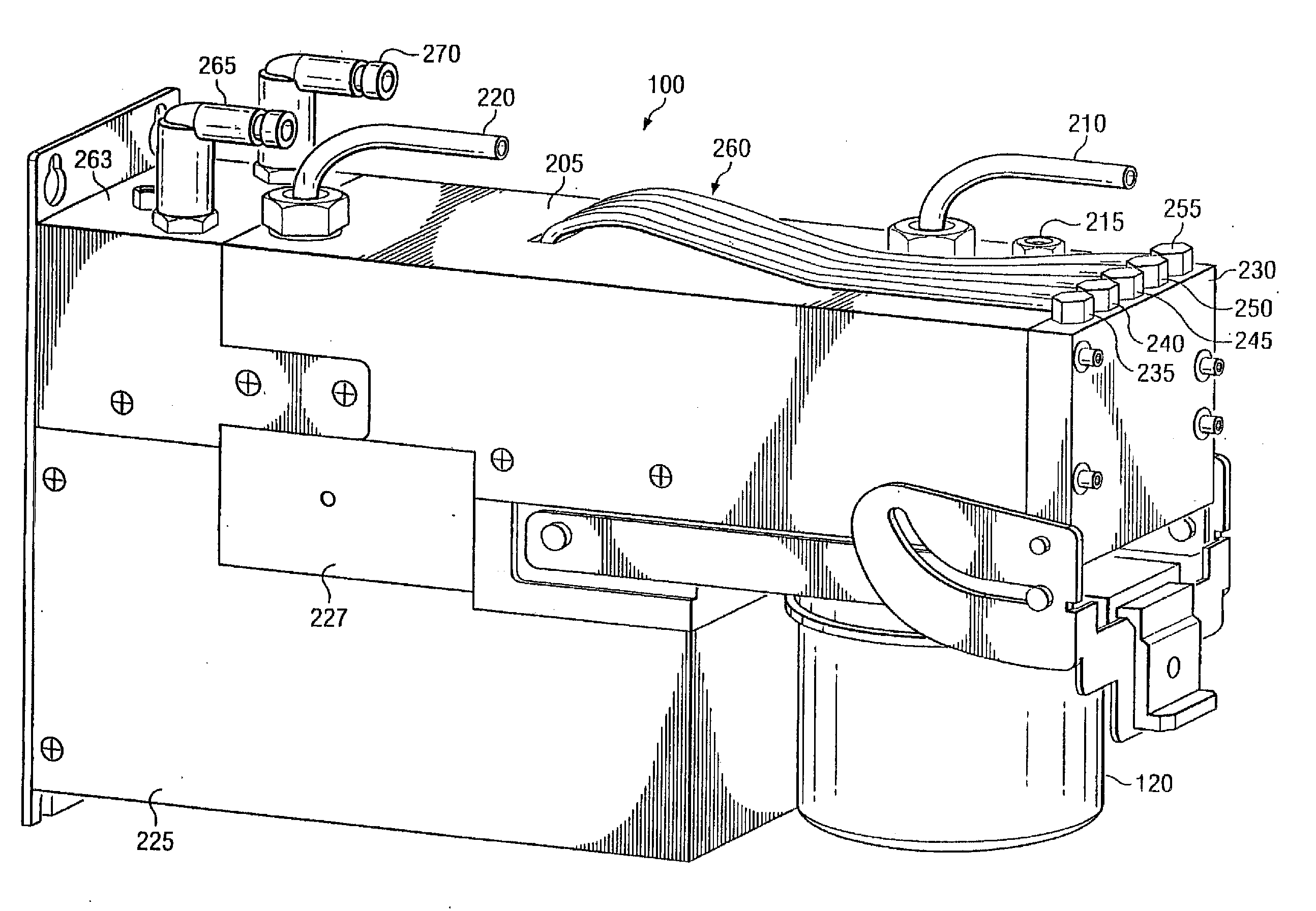

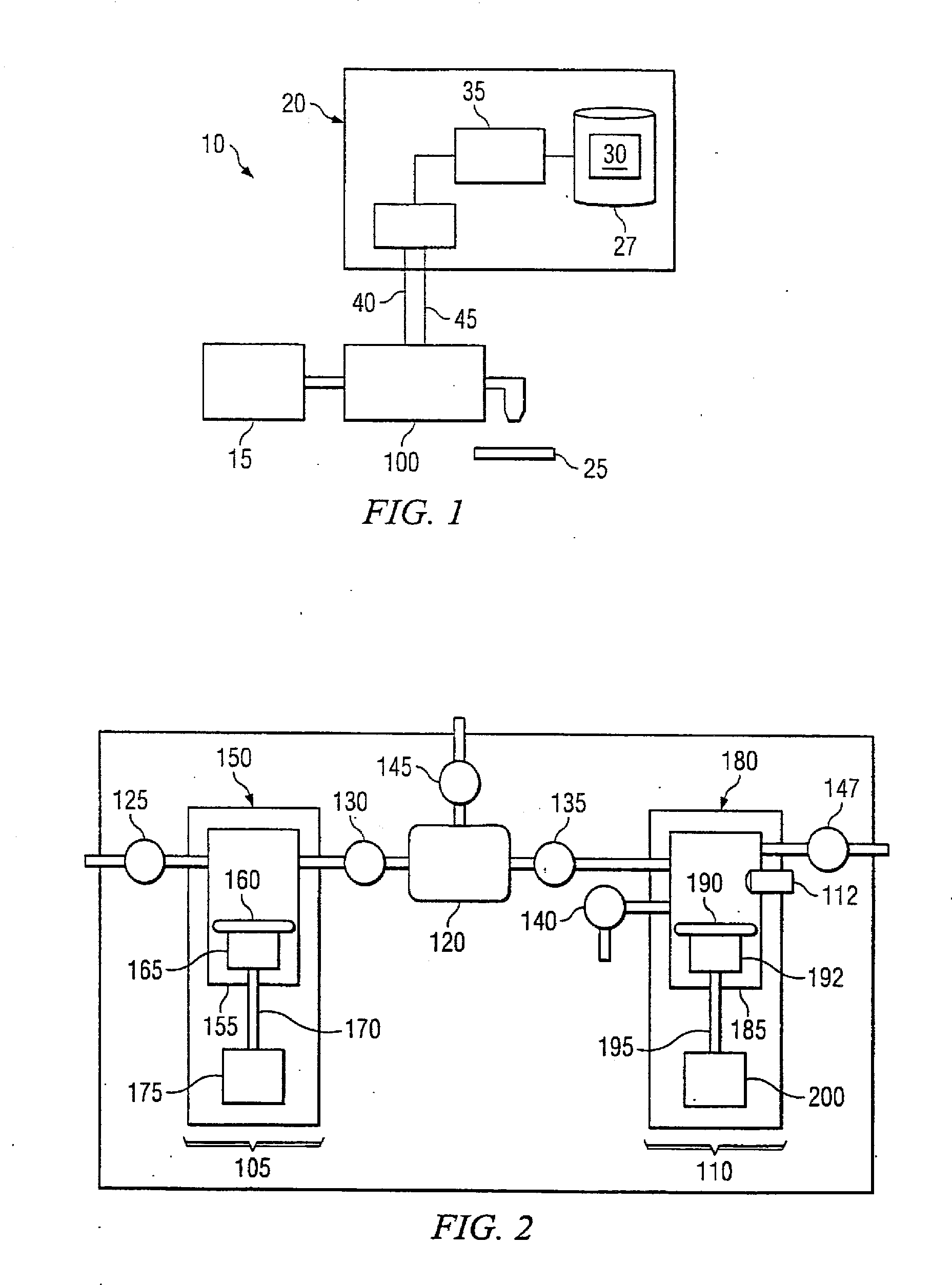

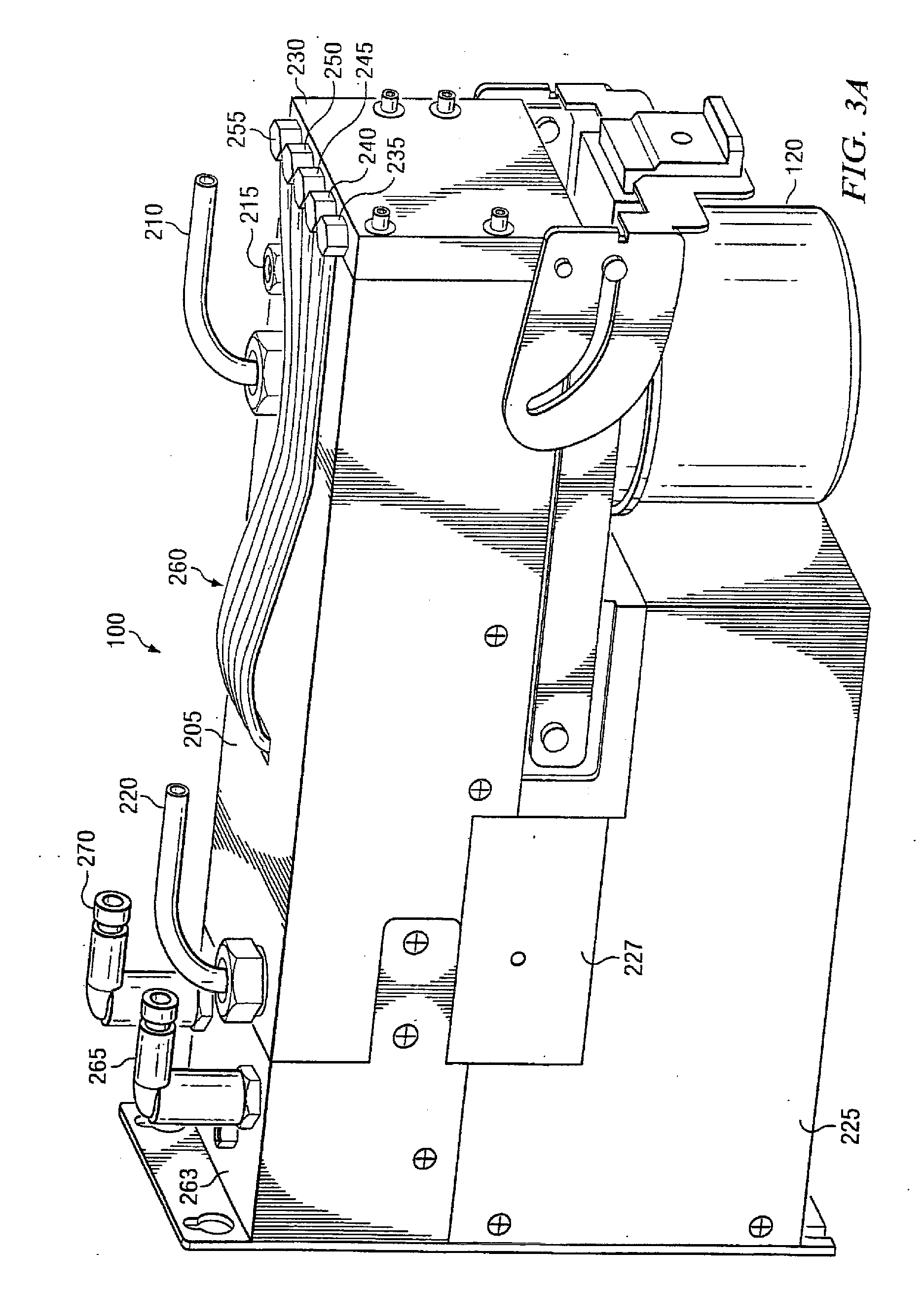

System and Method for Correcting for Pressure Variations Using a Motor

InactiveUS20120091165A1Accurate pressureEliminates and reduces disadvantagePower operated devicesFlexible member pumpsEngineeringMechanical engineering

Systems and methods for compensating for pressure increase which may occur in various enclosed spaces of a pumping apparatus are disclosed. Embodiments of the present invention may compensate for pressure increases in chambers of a pumping apparatus by moving a pumping means of the pumping apparatus to adjust the volume of the chamber to compensate for a pressure increase in the chamber. More specifically, in one embodiment, to account for unwanted pressure increases to the fluid in a dispense chamber the dispense motor may be reversed to back out piston to compensate for any pressure increase in the dispense chamber.

Owner:ENTEGRIS INC

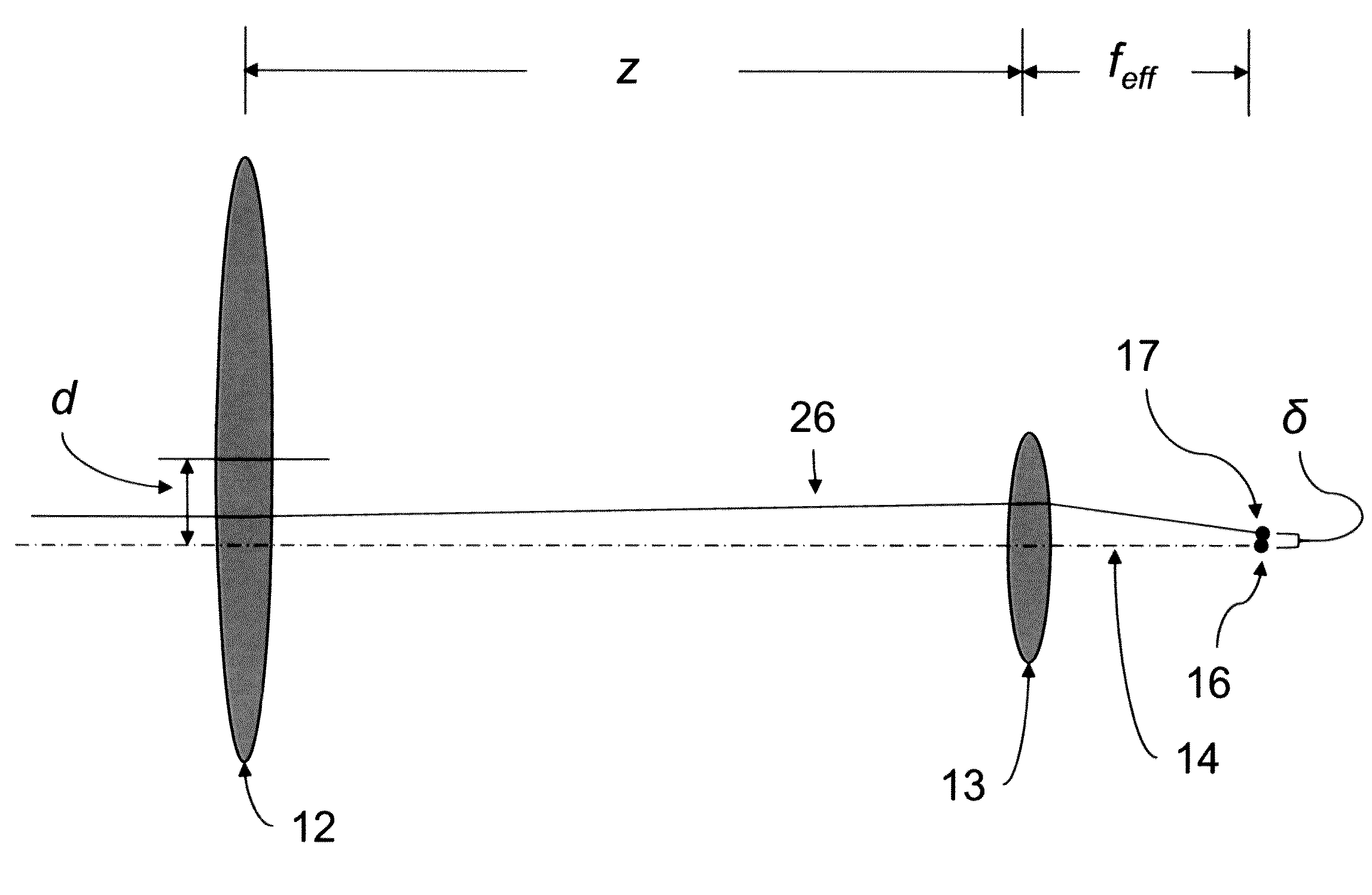

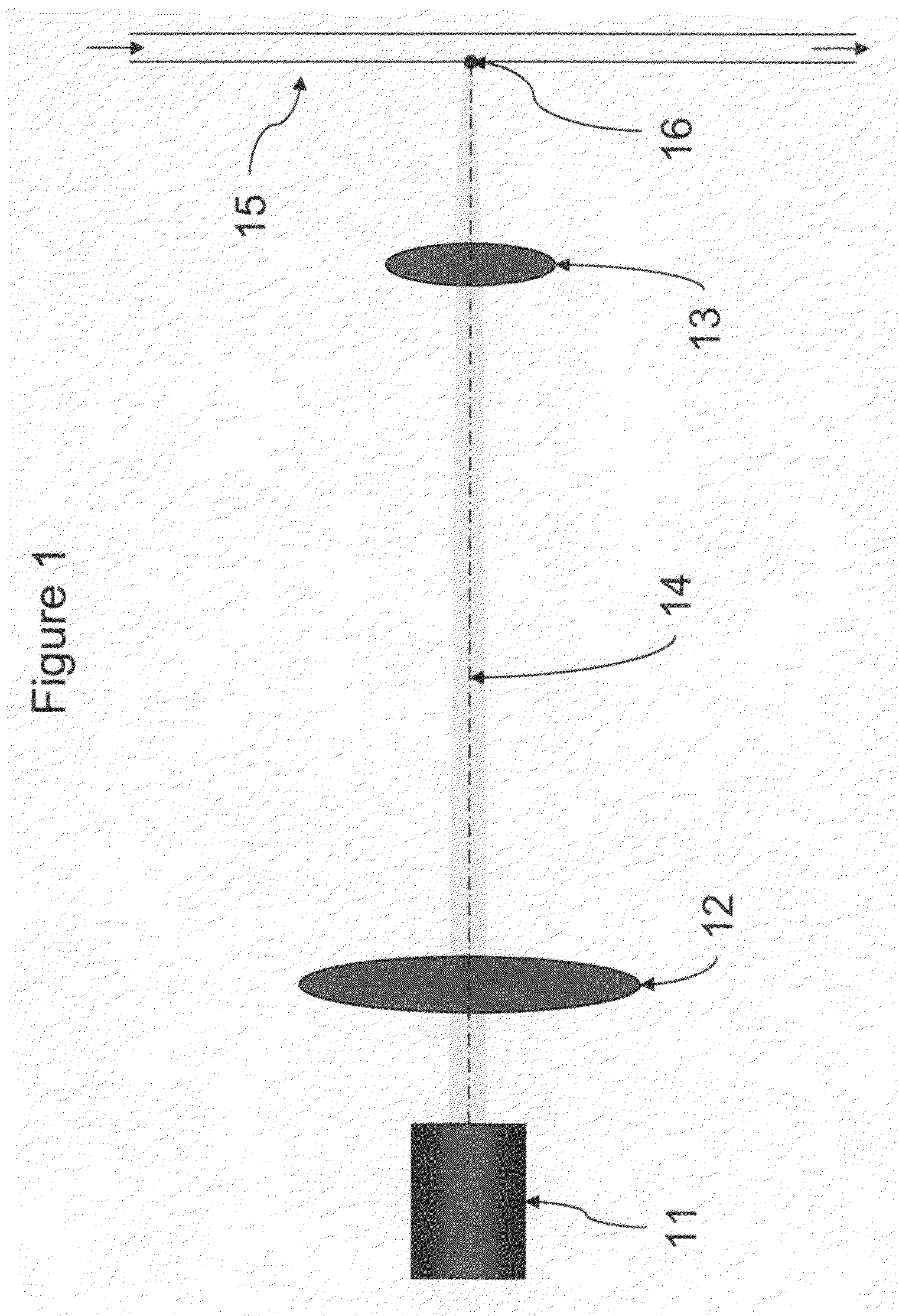

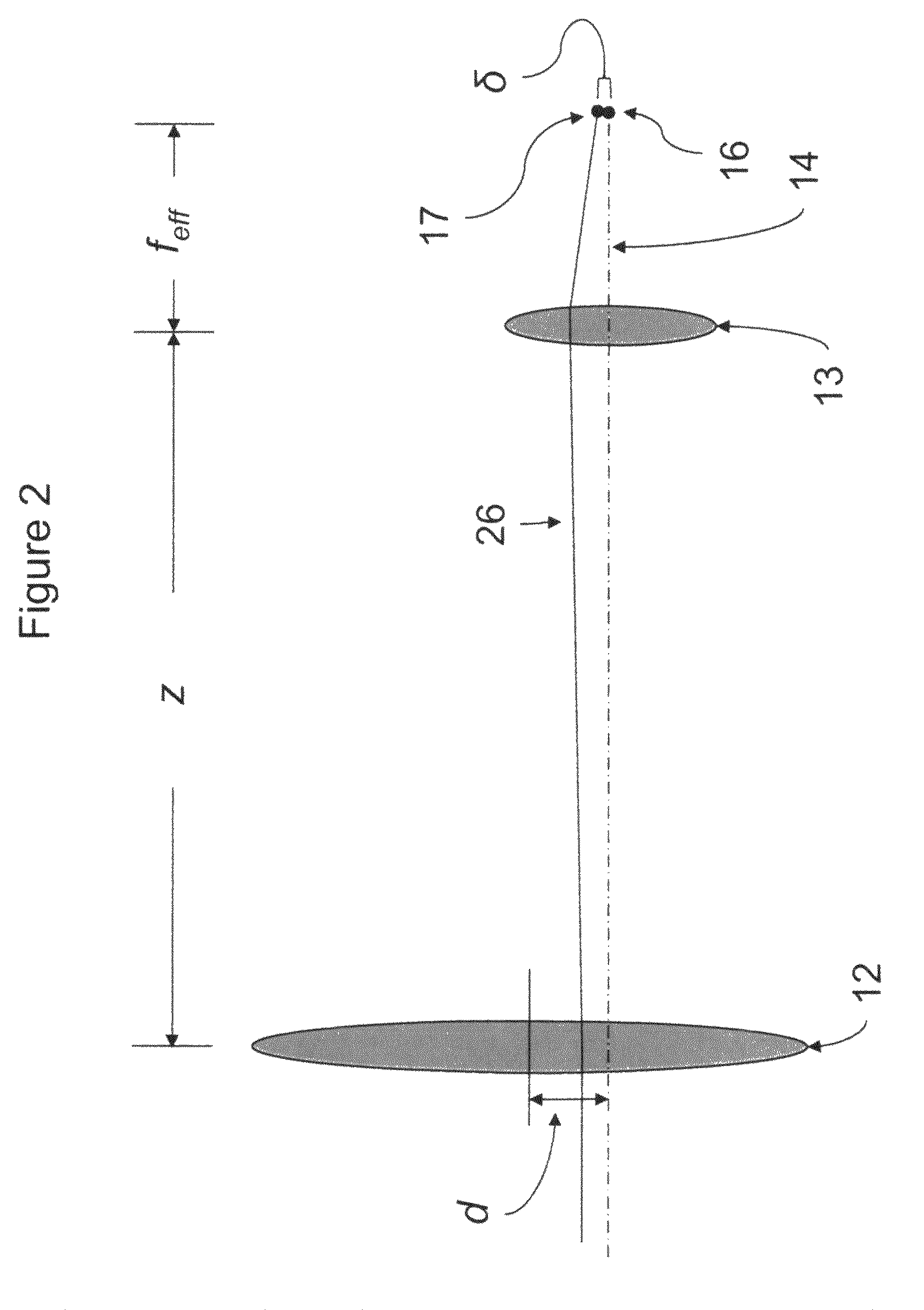

Beam-adjusting optics

ActiveUS7787197B2Precise positioningReduce sensitivityMaterial analysis by optical meansMountingsBeam sourceLight beam

The present invention provides an optical analyzer having illumination optics that include a light source, such as a laser or other source, adapted to emit a collimated, or approximately collimated, light beam, a focusing lens that focuses the beam onto a focus spot within a detection region, and beam-adjusting optics positioned in the light path between the light beam source and the focusing lens, which allow for precise positioning of the focus spot within the detection region. The beam-adjusting optics of the present invention comprise at least one movable focusing lens, mounted in a positioning device that allows repositioning of the lens in a plane perpendicular to the light path.

Owner:BECTON DICKINSON & CO

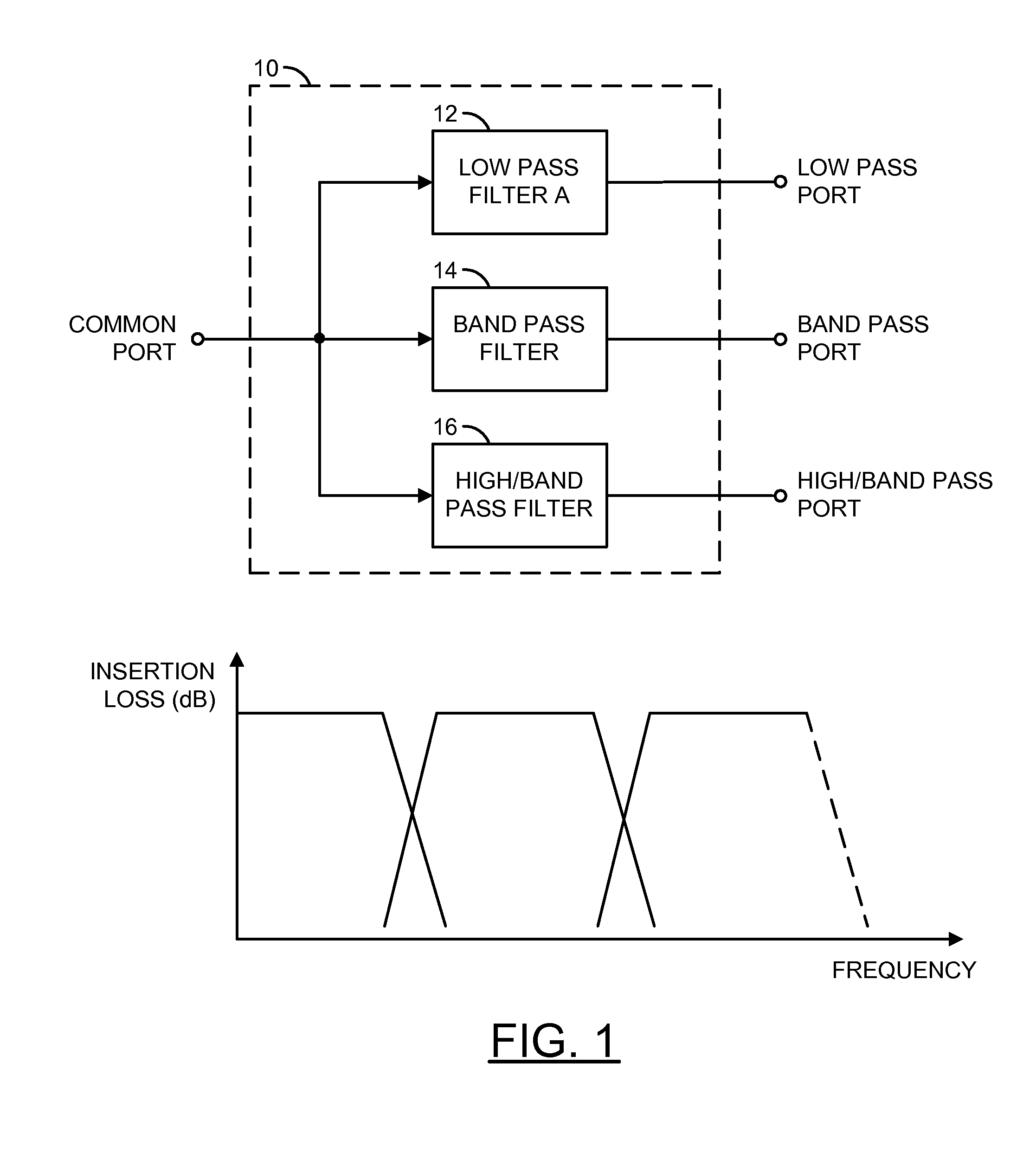

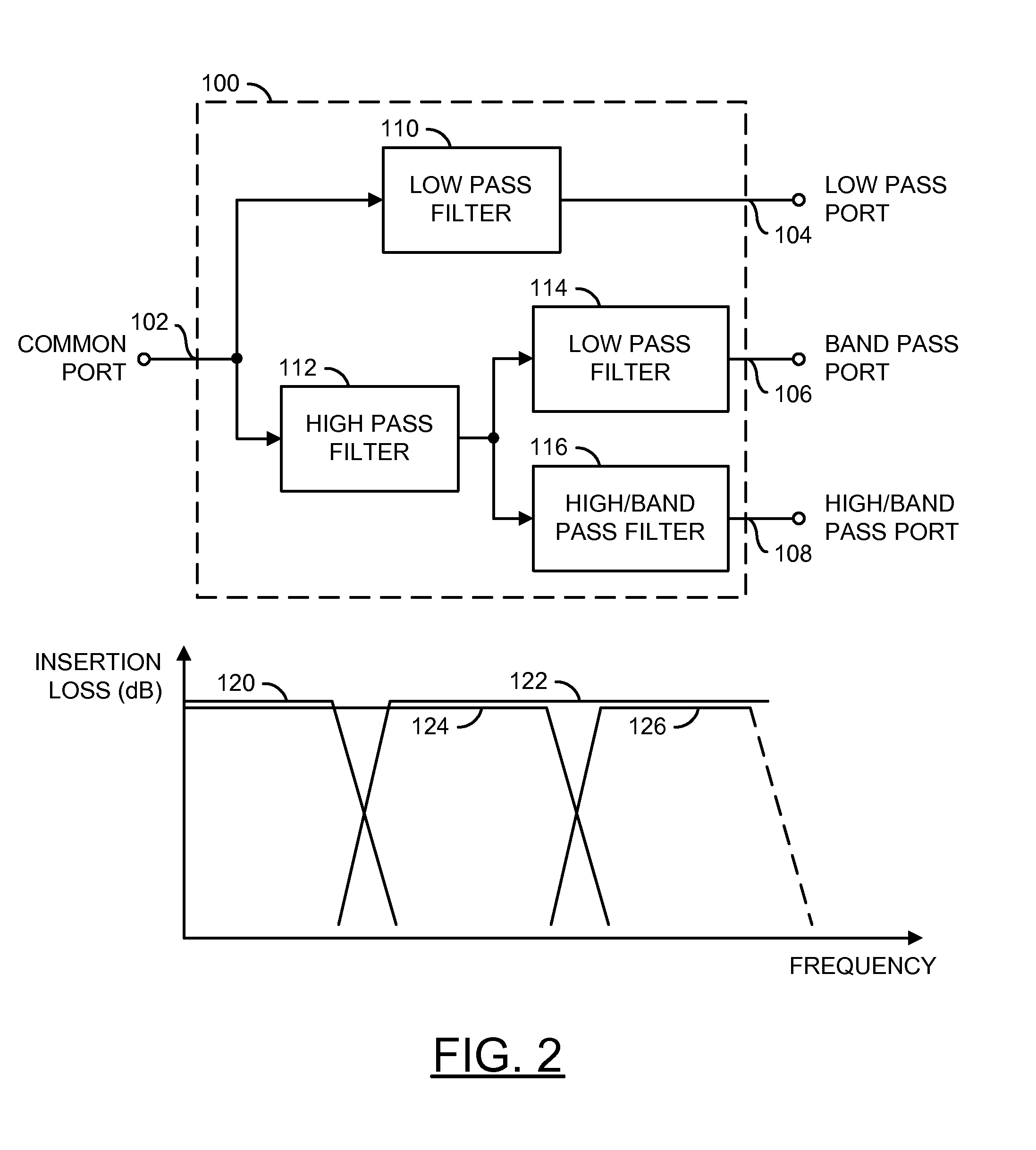

Triplexer topology

InactiveUS8736399B2High impedanceNegligible effectMultiple-port networksCoupling devicesEngineeringAll-pass filter

An apparatus comprising a first filter, a second filter, a third filter, and a fourth filter. The first filter may comprise a low pass filter having a first bandwidth and configured to present a first output signal in response to an input signal received at an input port of the apparatus. The second filter may comprise a high pass filter having a second bandwidth and configured to present a second output signal in response to the input signal received at the input port of the apparatus. The third filter may comprise a low pass filter having a third bandwidth and configured to present a third output signal in response to the second output signal. The fourth filter may comprise a high pass filter having a fourth bandwidth and configured to present a fourth output signal in response to the second output signal.

Owner:MACOM TECH SOLUTIONS HLDG INC

Motion capture element mount

Enables coupling or retrofitting a golf club with active motion capture electronics that are battery powered, passive or active shot count components, for example a passive RFID, and / or a visual marker on the cap for use with visual motion capture cameras. Does not require modifying the golf club. Electronics package and battery can be easily removed and replaced, without any tools. May utilize a weight that is removed when inserting the electronic package, wherein the weight element may have the same weight as an electronics package, for no net change or minimal change in club weight. May be implemented with a shaft enclosure and expander that may be coupled with a screw aligned along an axis parallel to the axis of the golf club shaft. May utilize non-permanently and / or friction coupling between the mount and golf club shaft. Cap may include a visual marker and / or logo.

Owner:NEWLIGHT CAPITAL LLC

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com