Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

38results about How to "High electric field" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

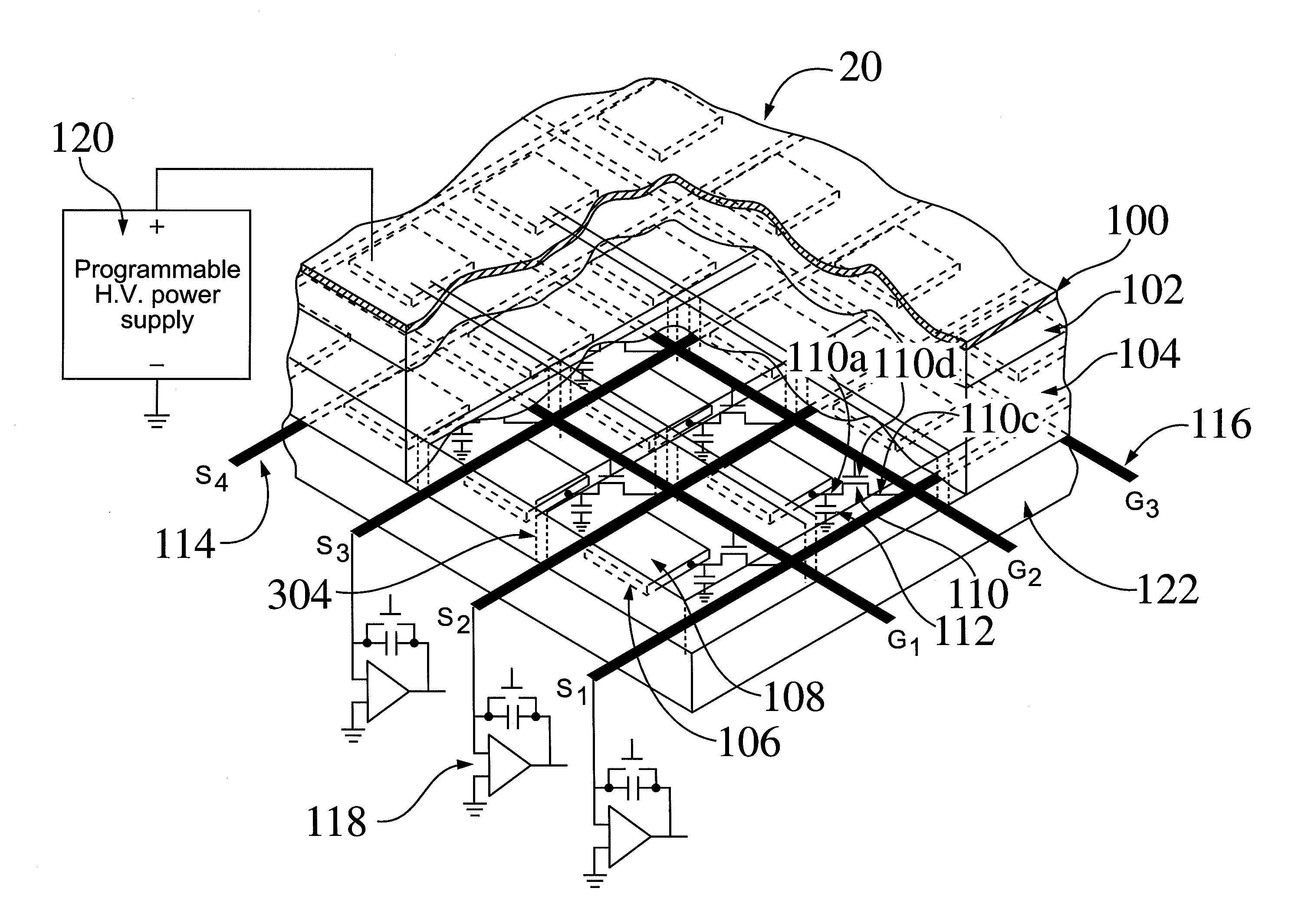

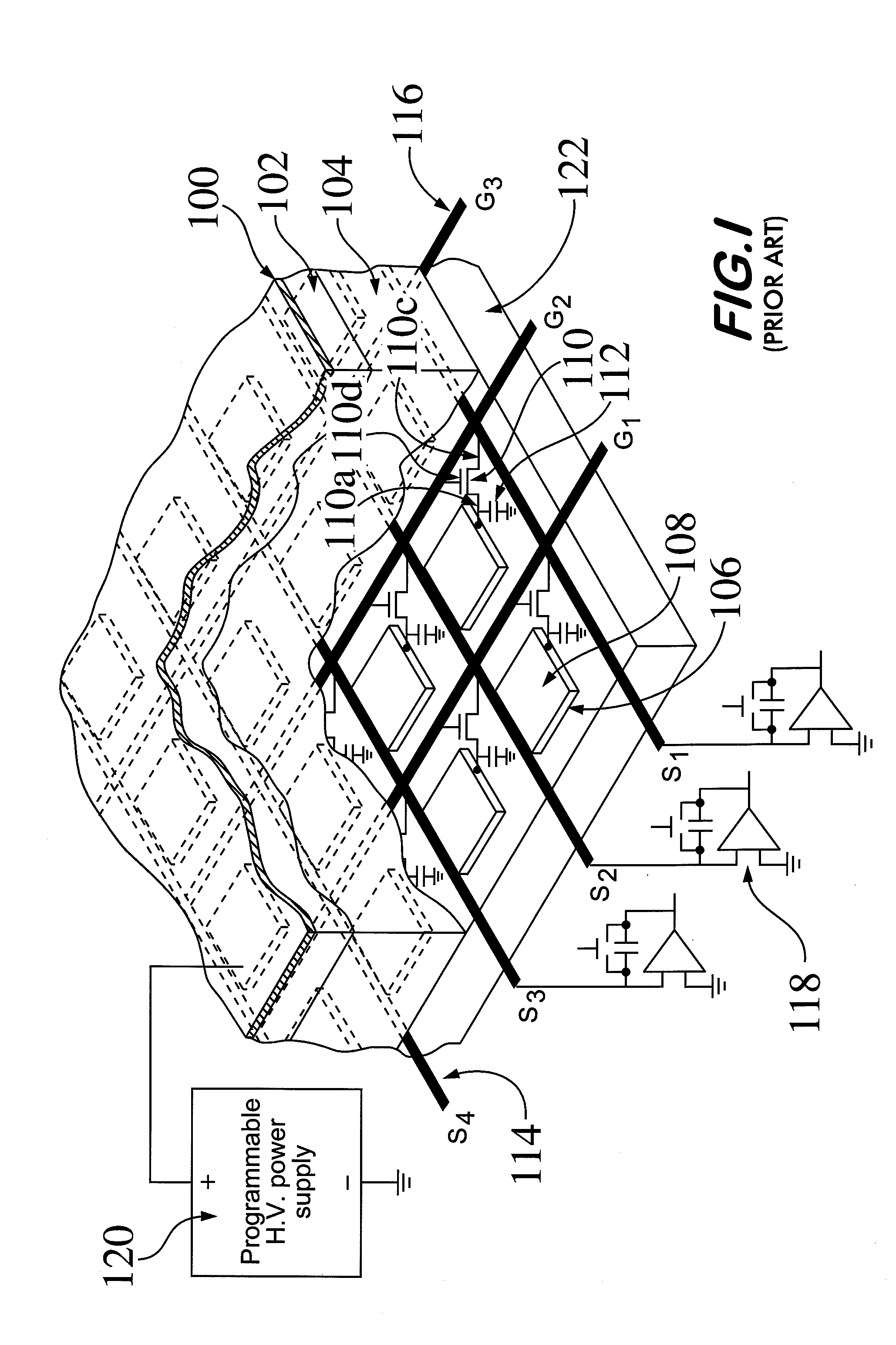

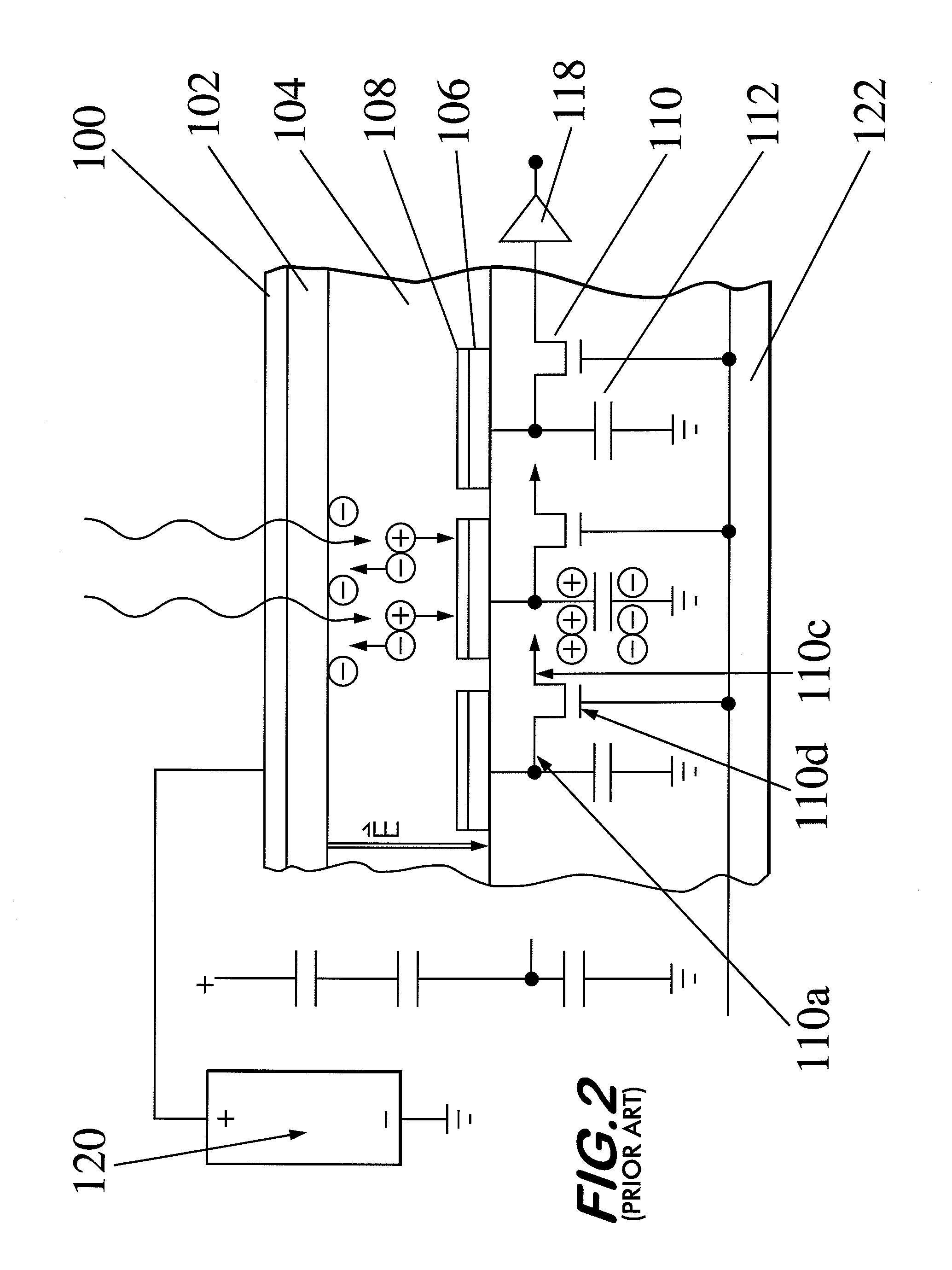

Flat panel X-ray imager with a grid structure

ActiveUS7256402B1High conductivityExtend useful lifeSolid-state devicesMaterial analysis by optical meansPolymerThermal expansion

A flat panel X-ray imager using an amorphous selenium detector which uses a polymer grid structure within the X-ray conversion layer to form an interface between the X-ray conversion layer and the pixel electrodes. The grid structure provides an additional physical barrier between pixel electrodes that reduces electrical bridging due to crystallization of the amorphous selenium due to temperature increases while also reducing the delamination temperature by providing a good anchor to the selenium, as well as a “cushion” for thermal expansion or contraction of the pixel electrodes. The grid can further include one or more grid electrodes for effecting avalanche-gain within the X-ray conversion layer while minimizing dark current entry into the selenium layer from the pixel electrode.

Owner:VIEWORKS +1

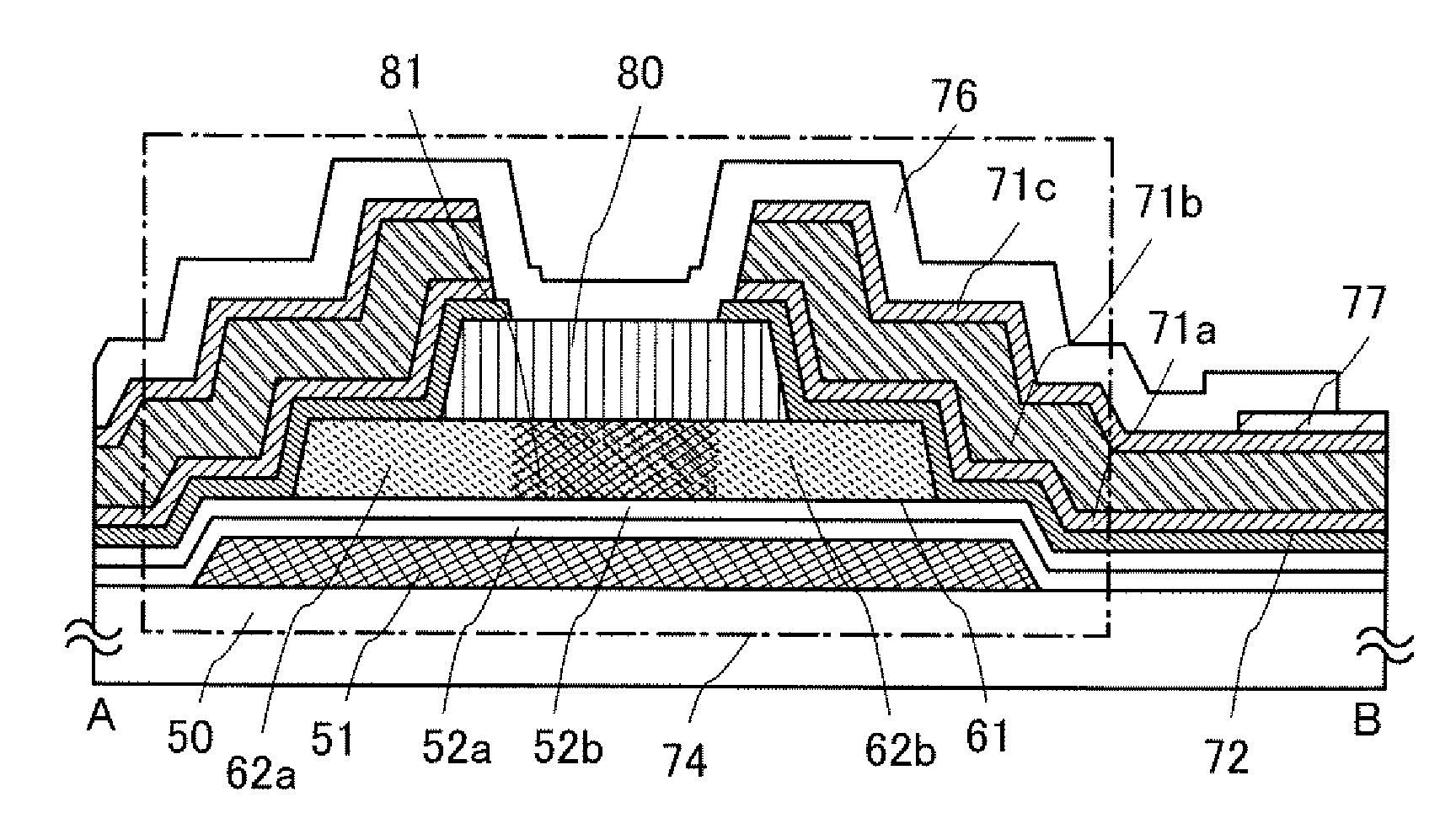

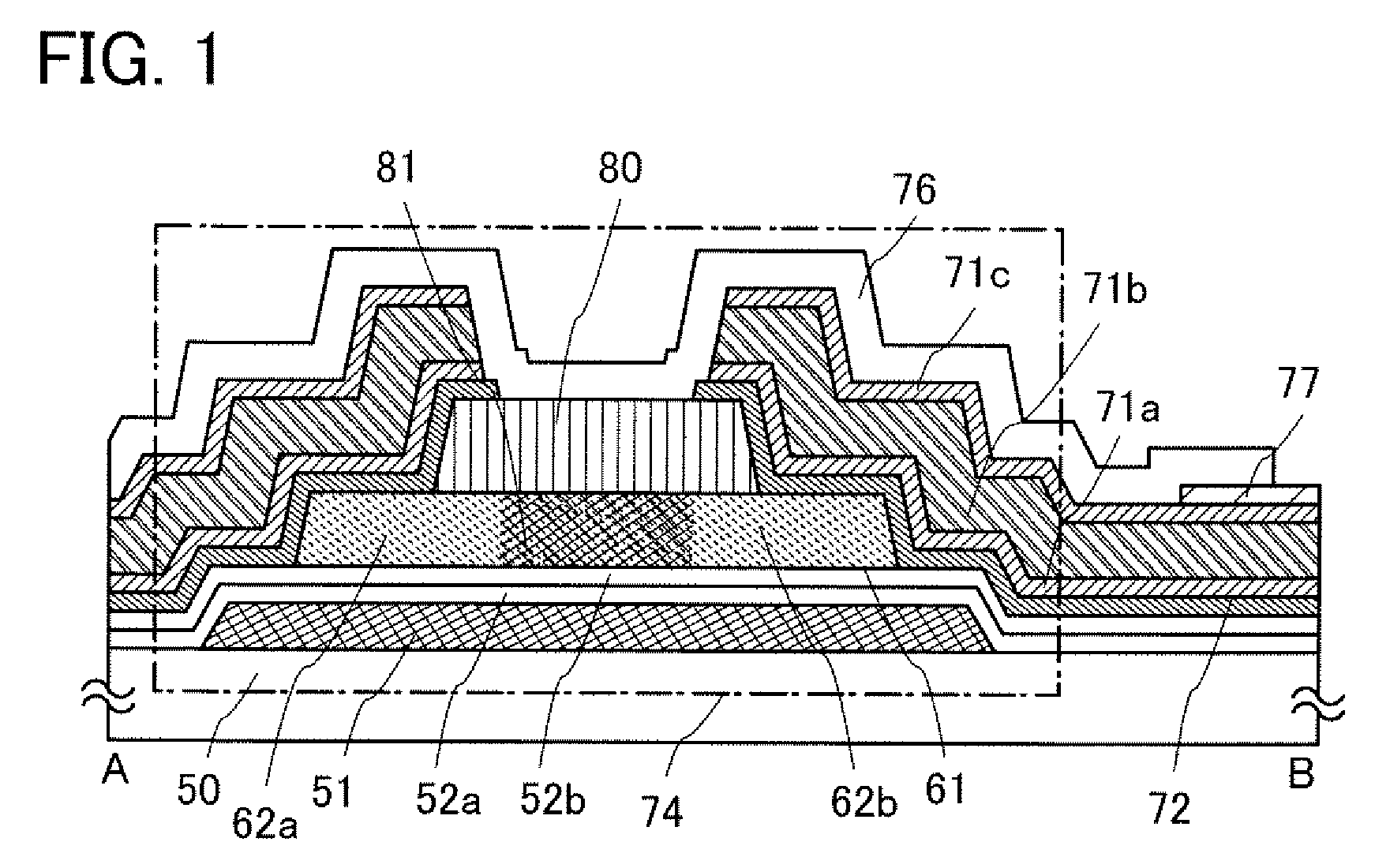

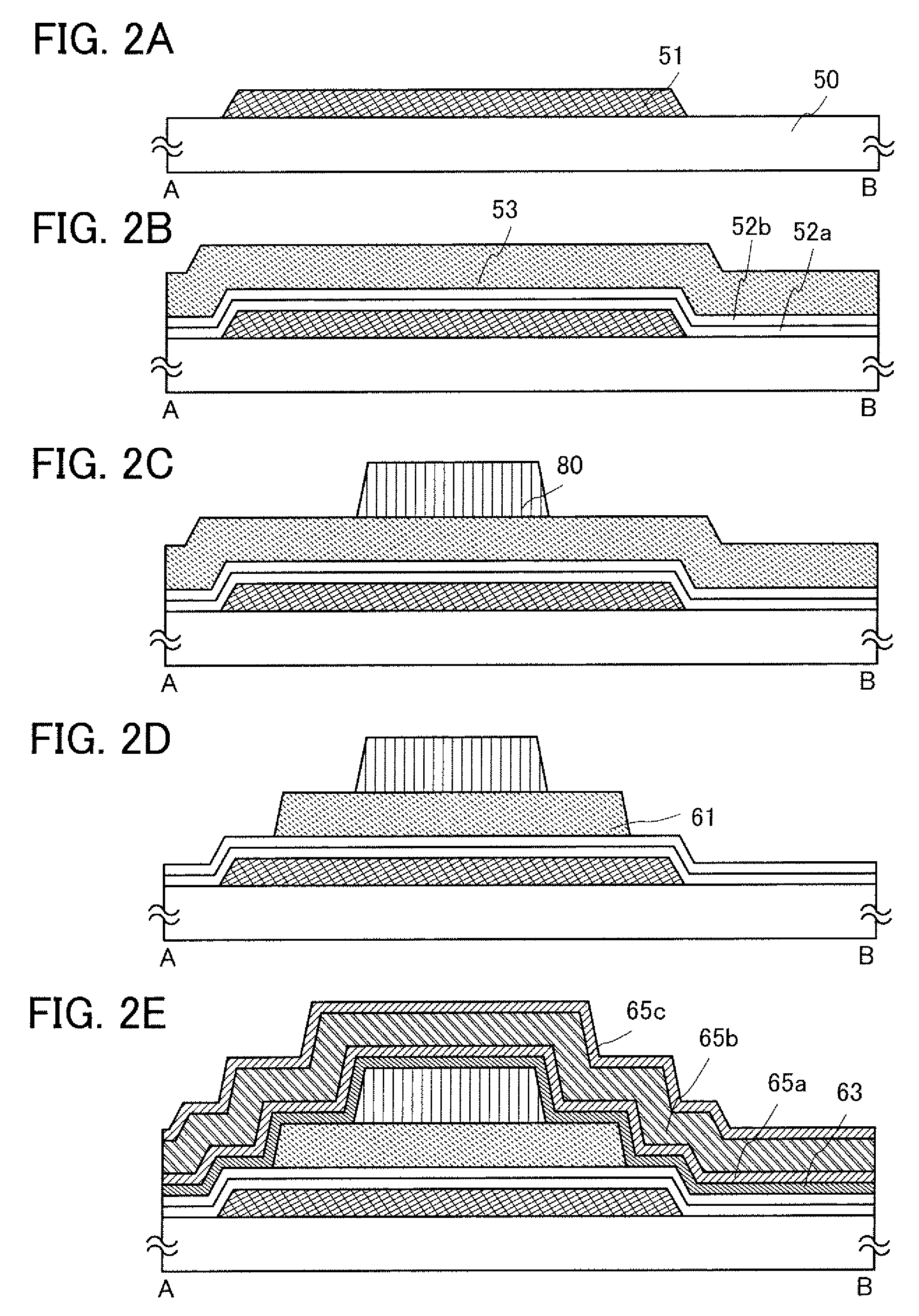

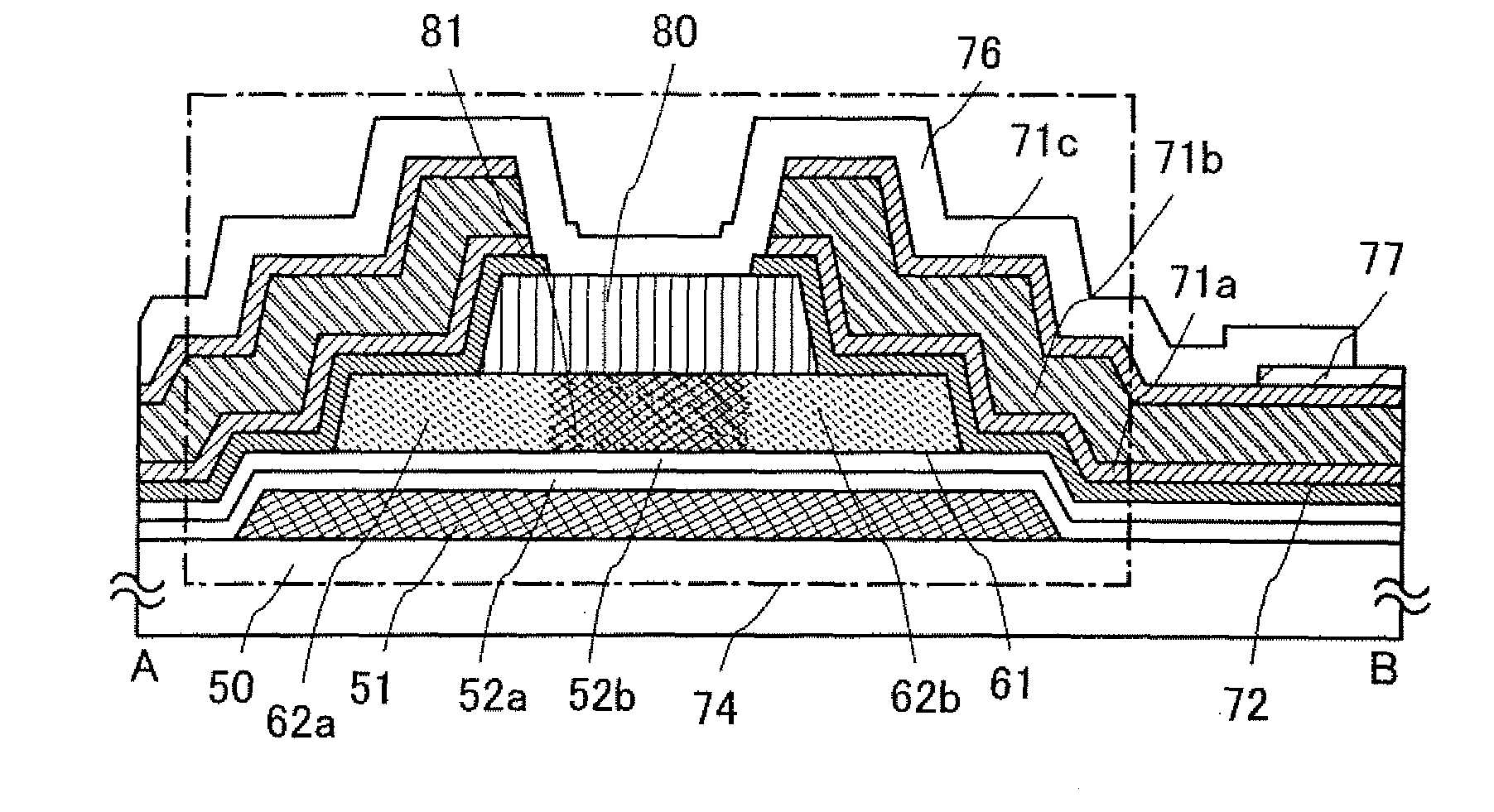

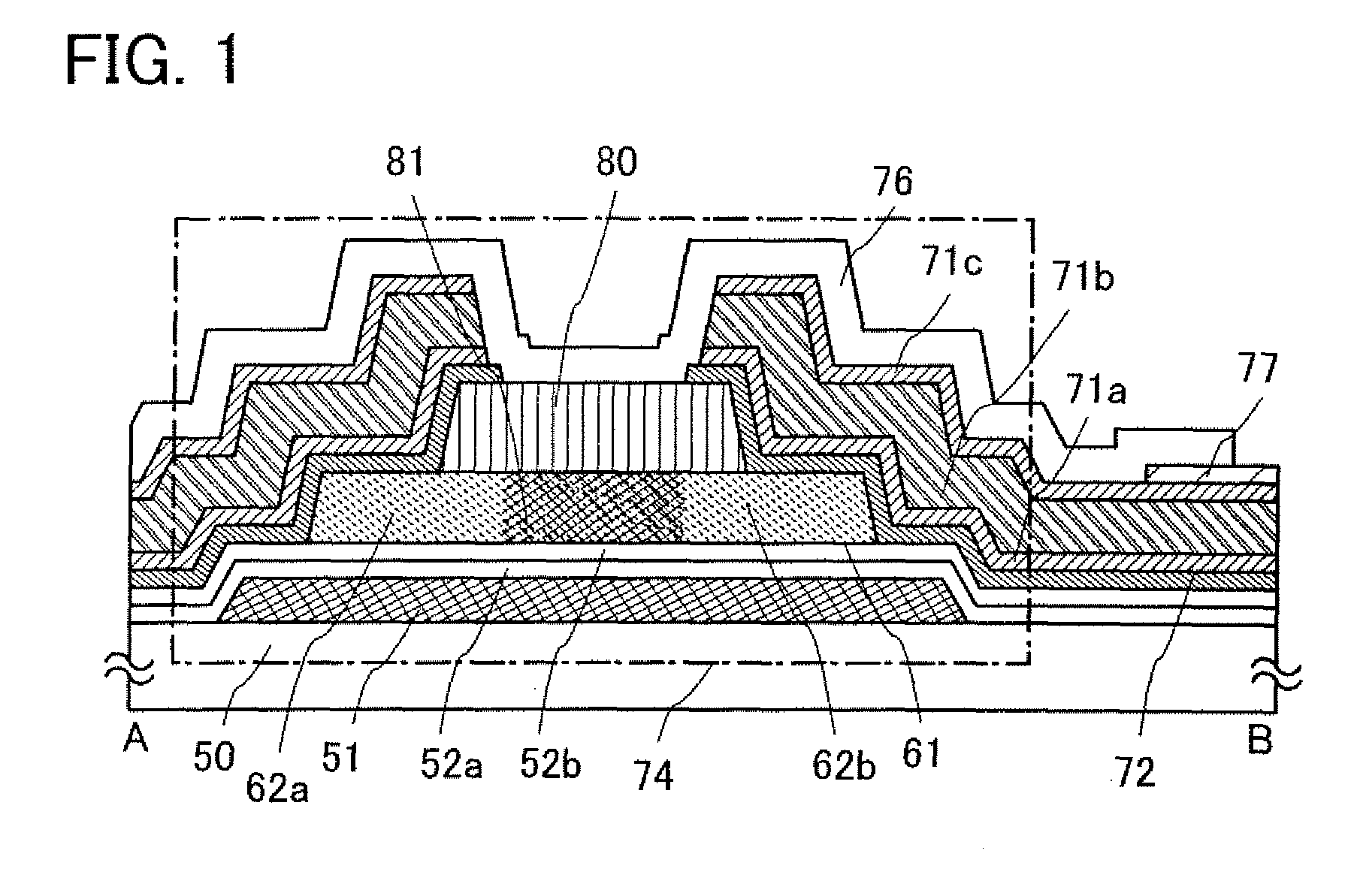

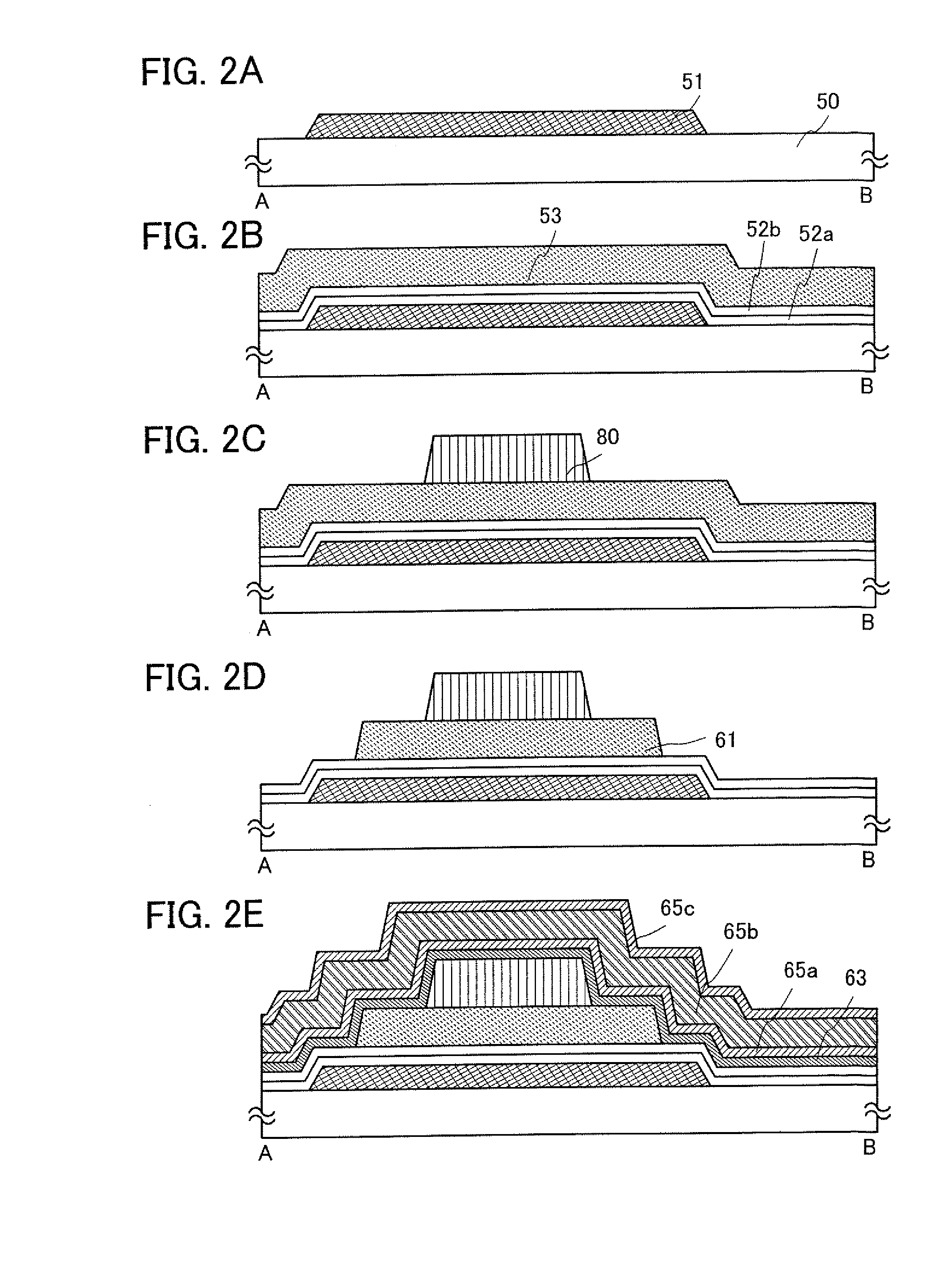

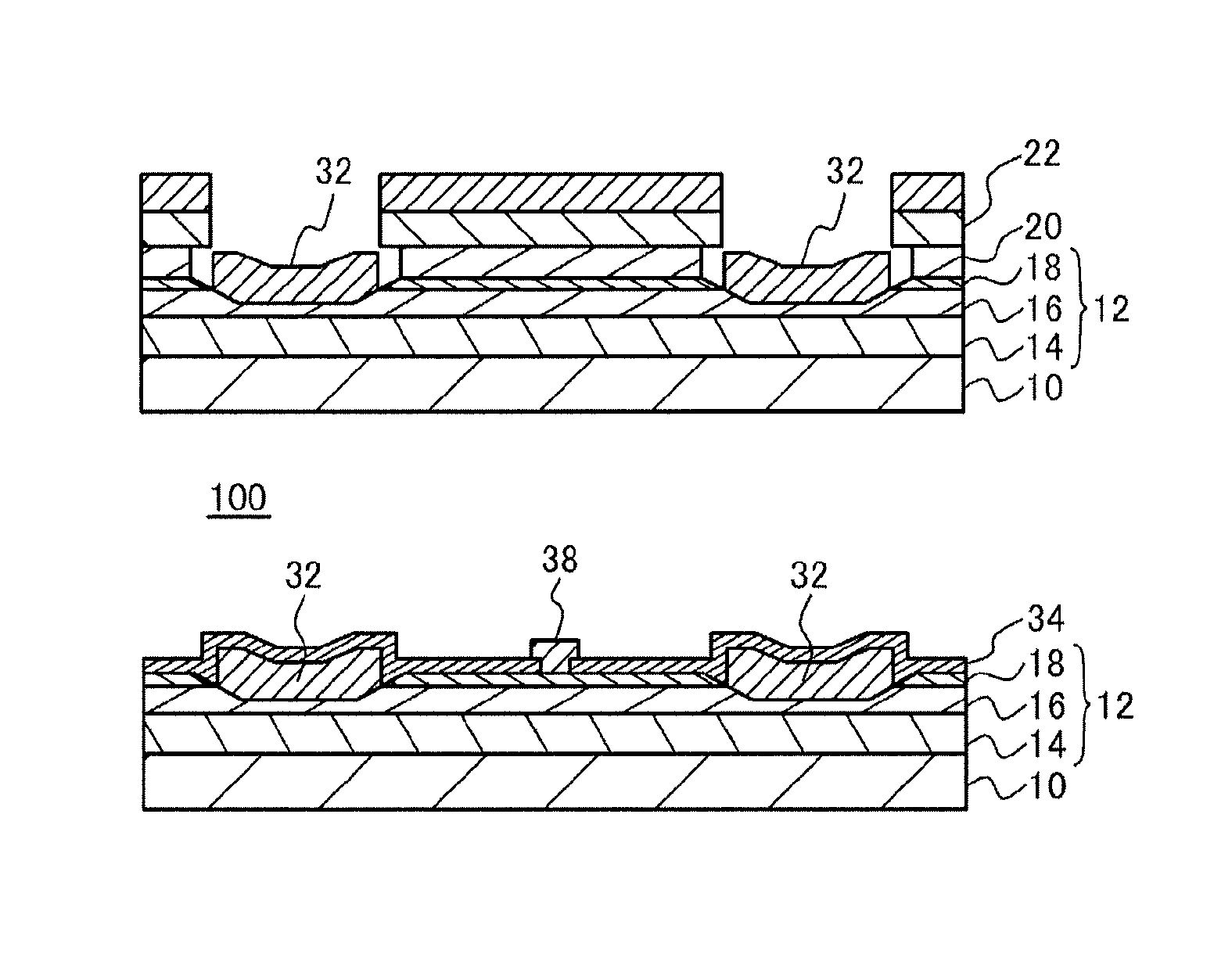

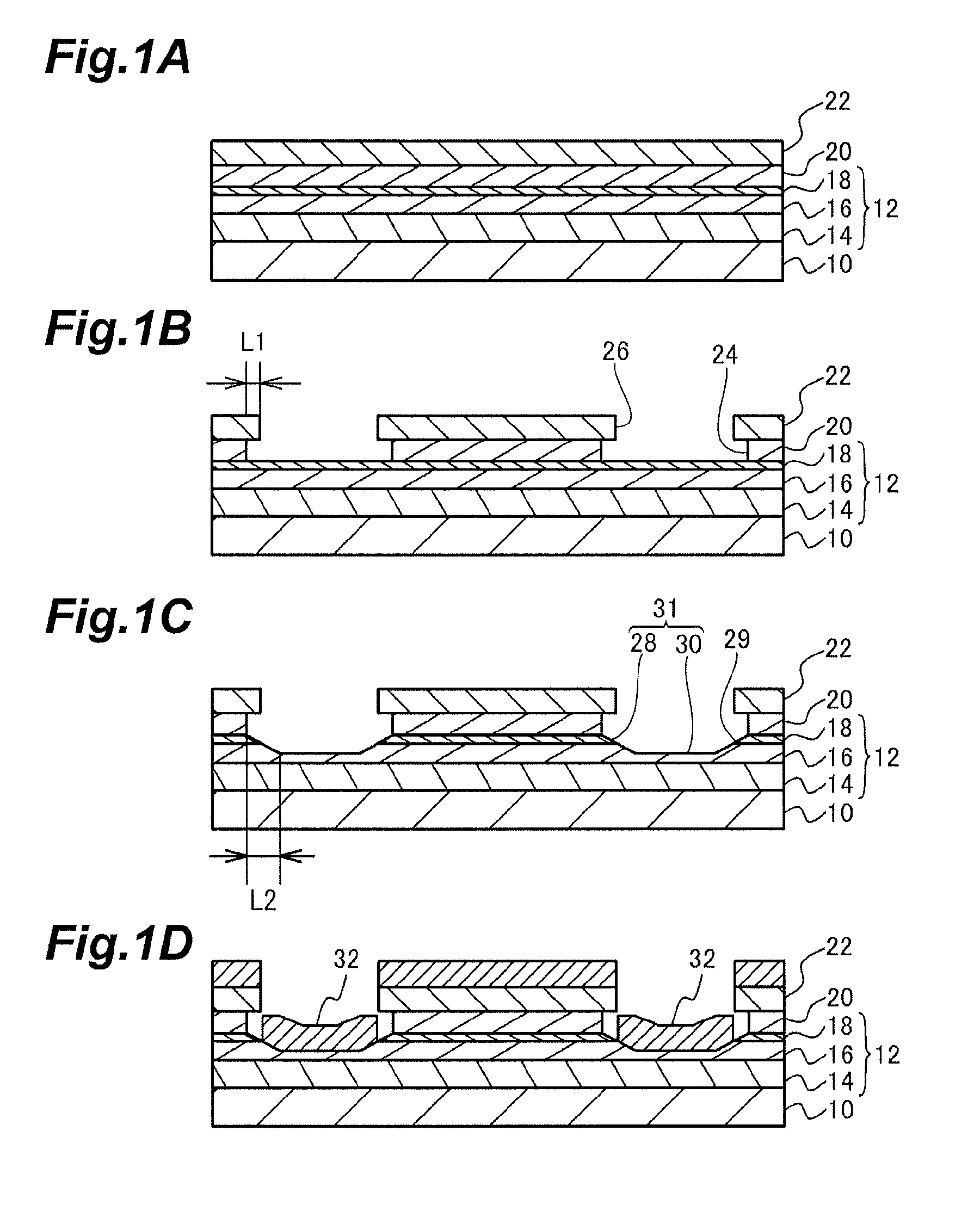

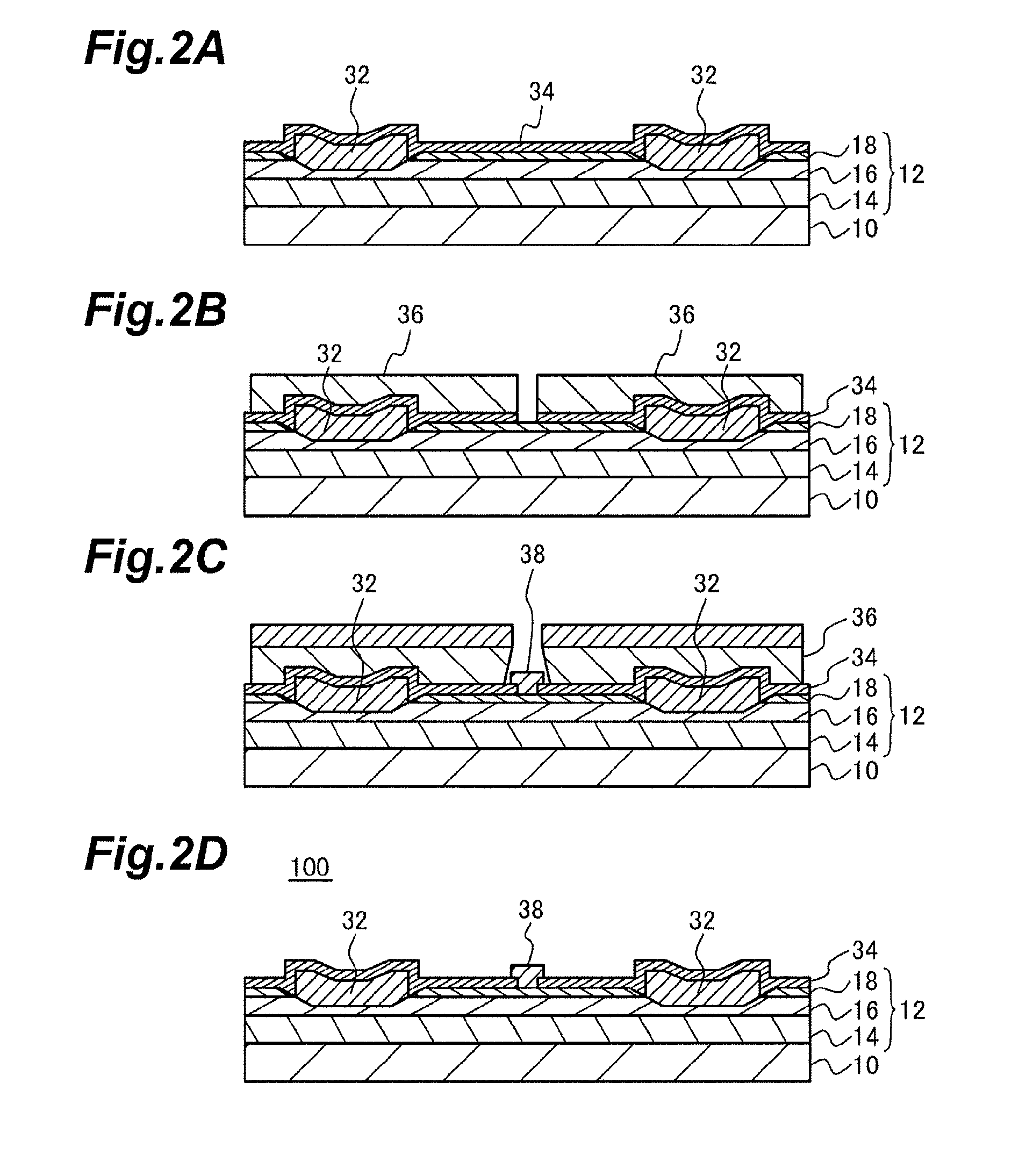

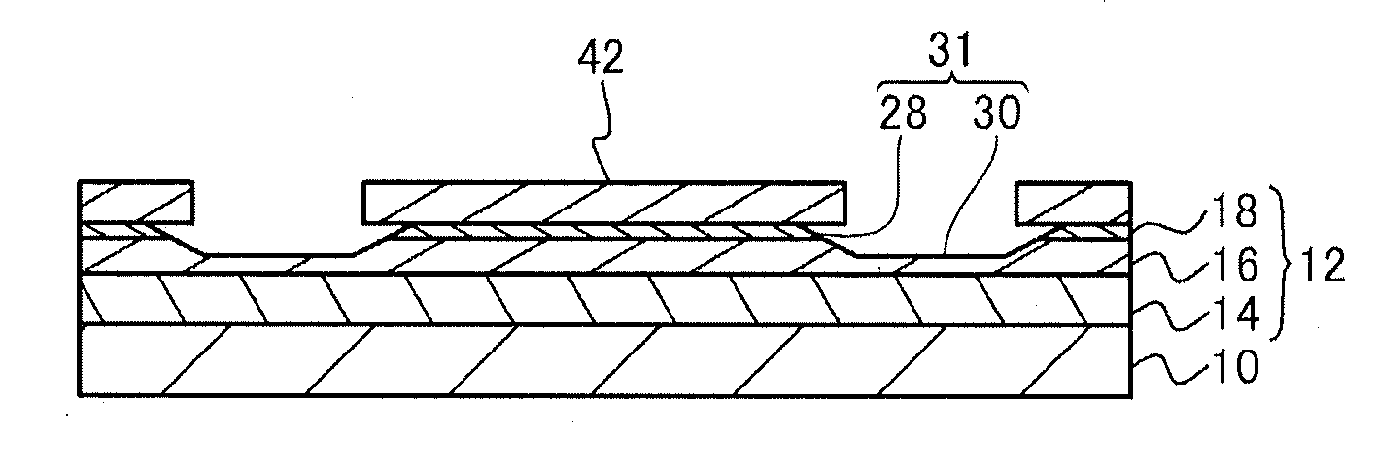

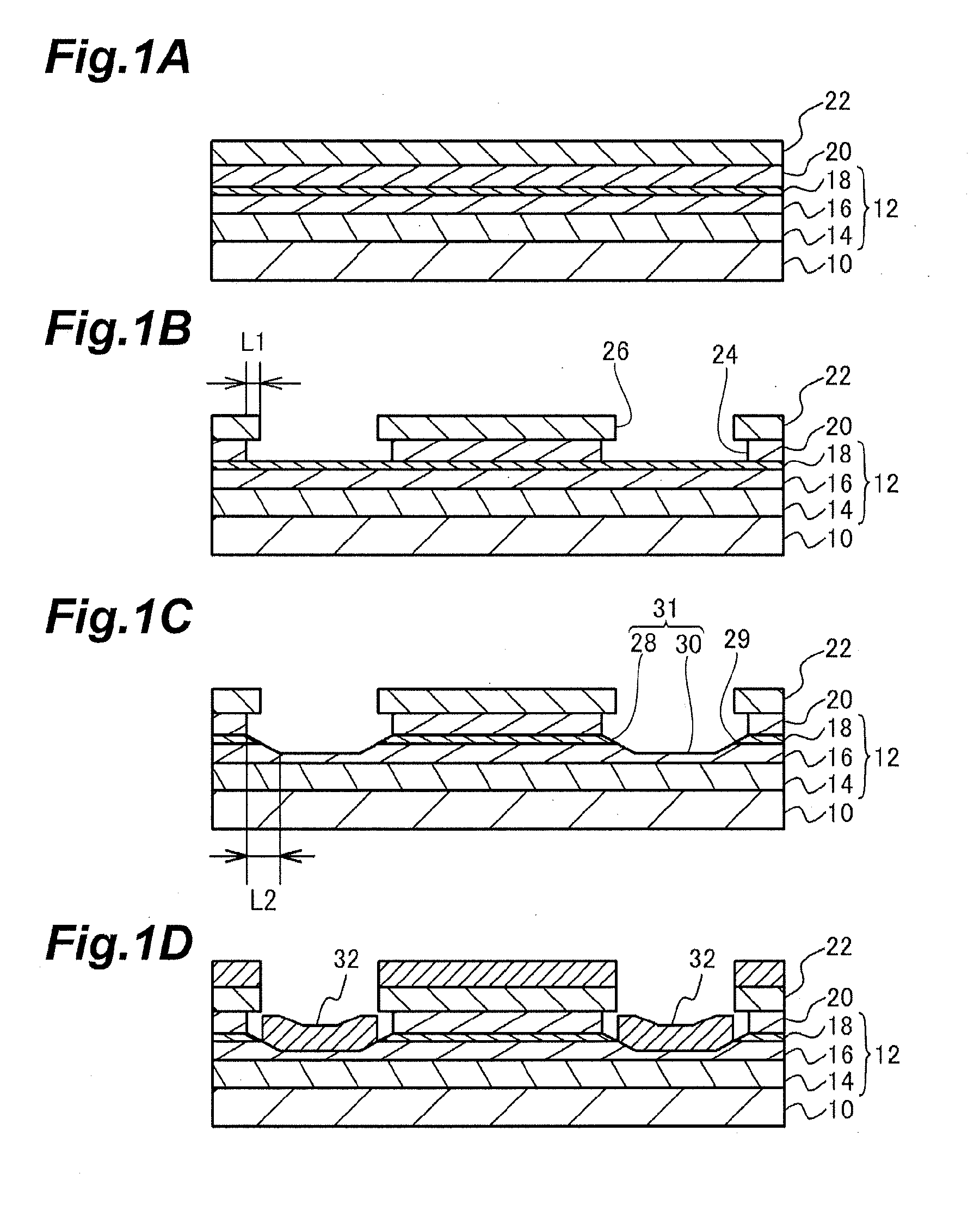

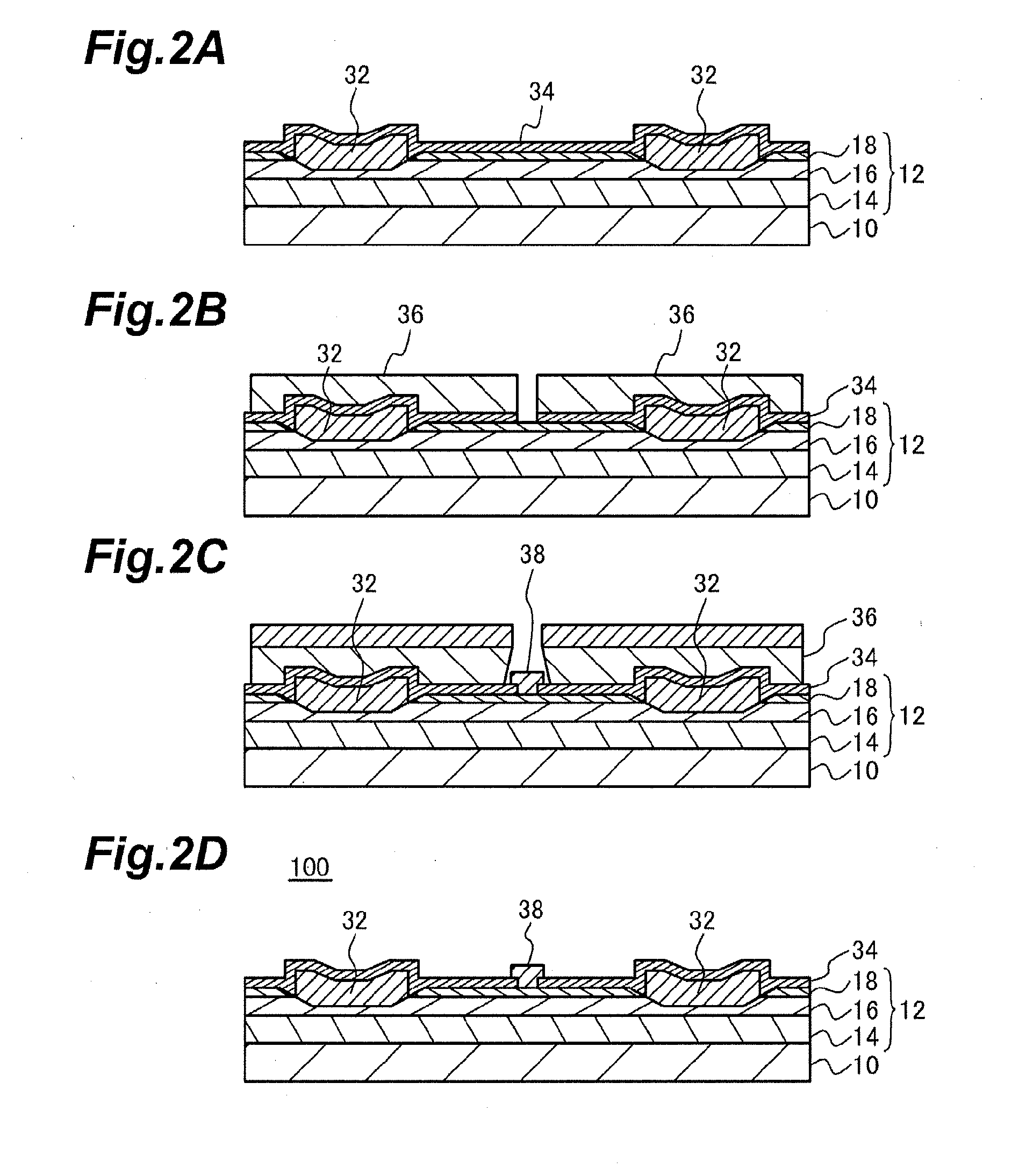

Display device and manufacturing method thereof

InactiveUS7791075B2Improve featuresImprove reliabilitySolid-state devicesSemiconductor/solid-state device manufacturingDisplay deviceEngineering

A display device including a thin film transistor with high electric characteristics and high reliability, and a method for manufacturing the display device in high yield are proposed. In a display device including a channel stop thin film transistor with an inverted-staggered structure, the channel stop thin film transistor with the inverted-staggered structure includes a microcrystalline semiconductor film including a channel formation region. An impurity region including an impurity element imparting one conductivity type is formed as selected in a region in the channel formation region of the microcrystalline semiconductor film which does not overlap with a source electrode or a drain electrode. In the channel formation region, a non-doped region, to which the impurity element imparting one conductivity type is not added, is formed between the impurity region, which is a doped region to which the impurity element is added, and the source region or the drain region.

Owner:SEMICON ENERGY LAB CO LTD

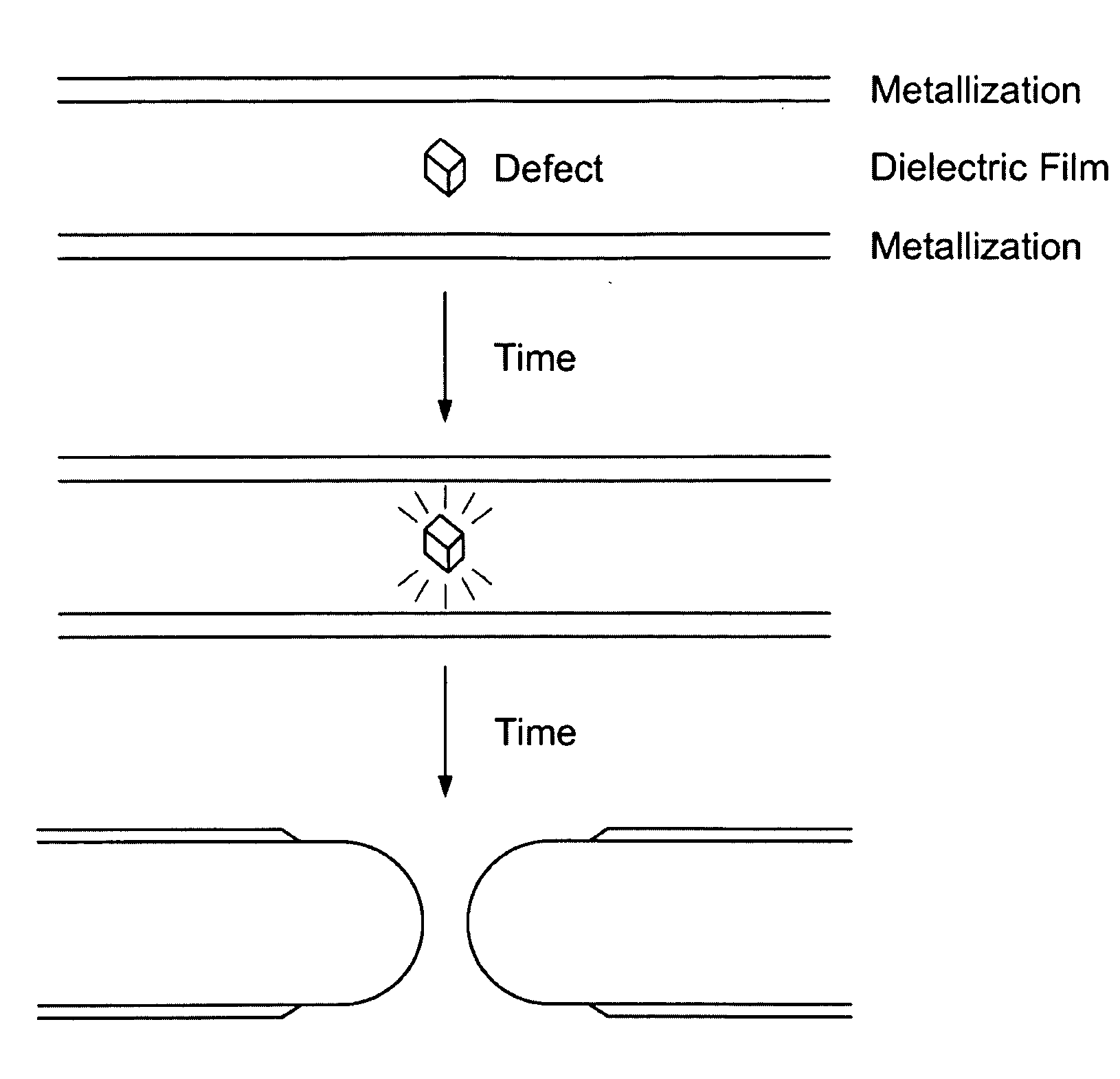

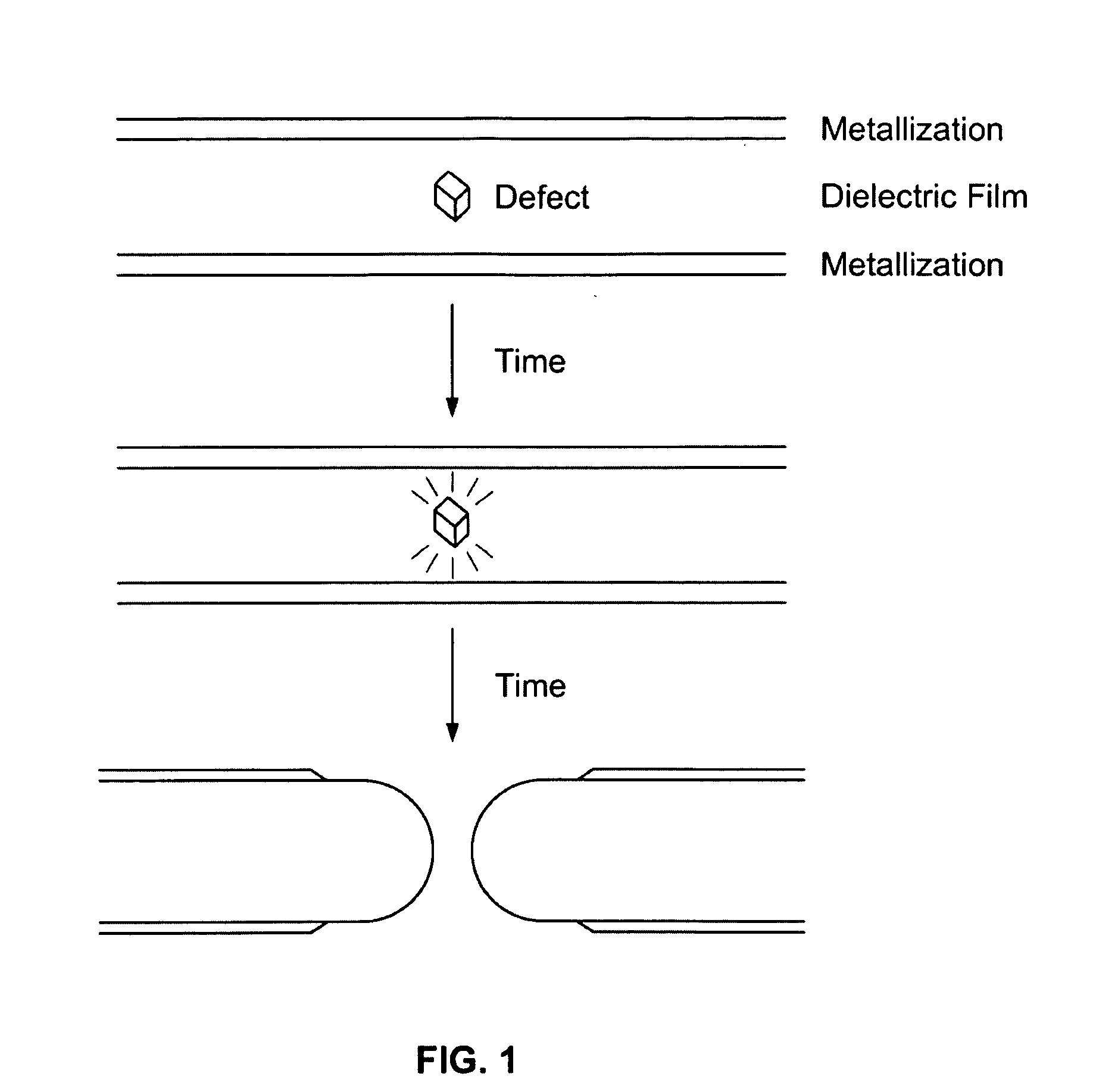

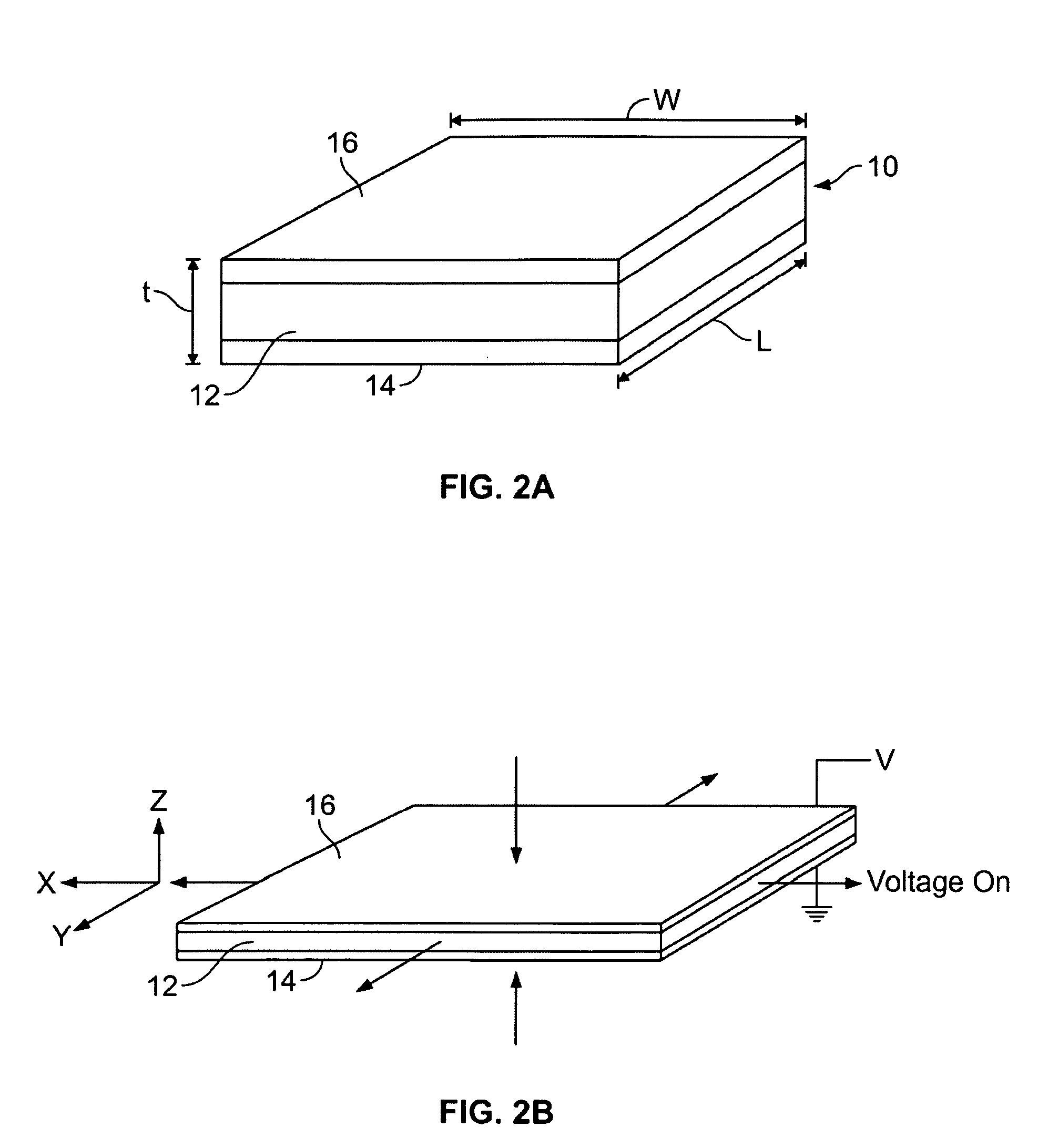

Fault-tolerant materials and methods of fabricating the same

ActiveUS20080180875A1Optimize fault toleranceHigh performance featuresPiezoelectric/electrostrictive device manufacture/assemblyFixed capacitor electrodesSelf-healingElectroactive materials

Compliant / stretchable electroactive materials which exhibit self-healing / clearing properties are disclosed.

Owner:COVESTRO DEUTSCHLAND AG

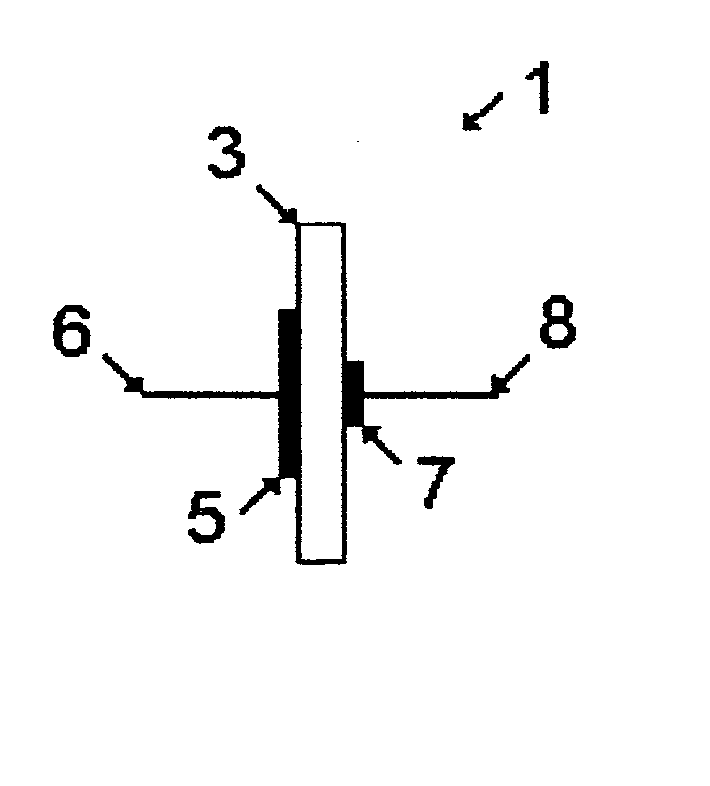

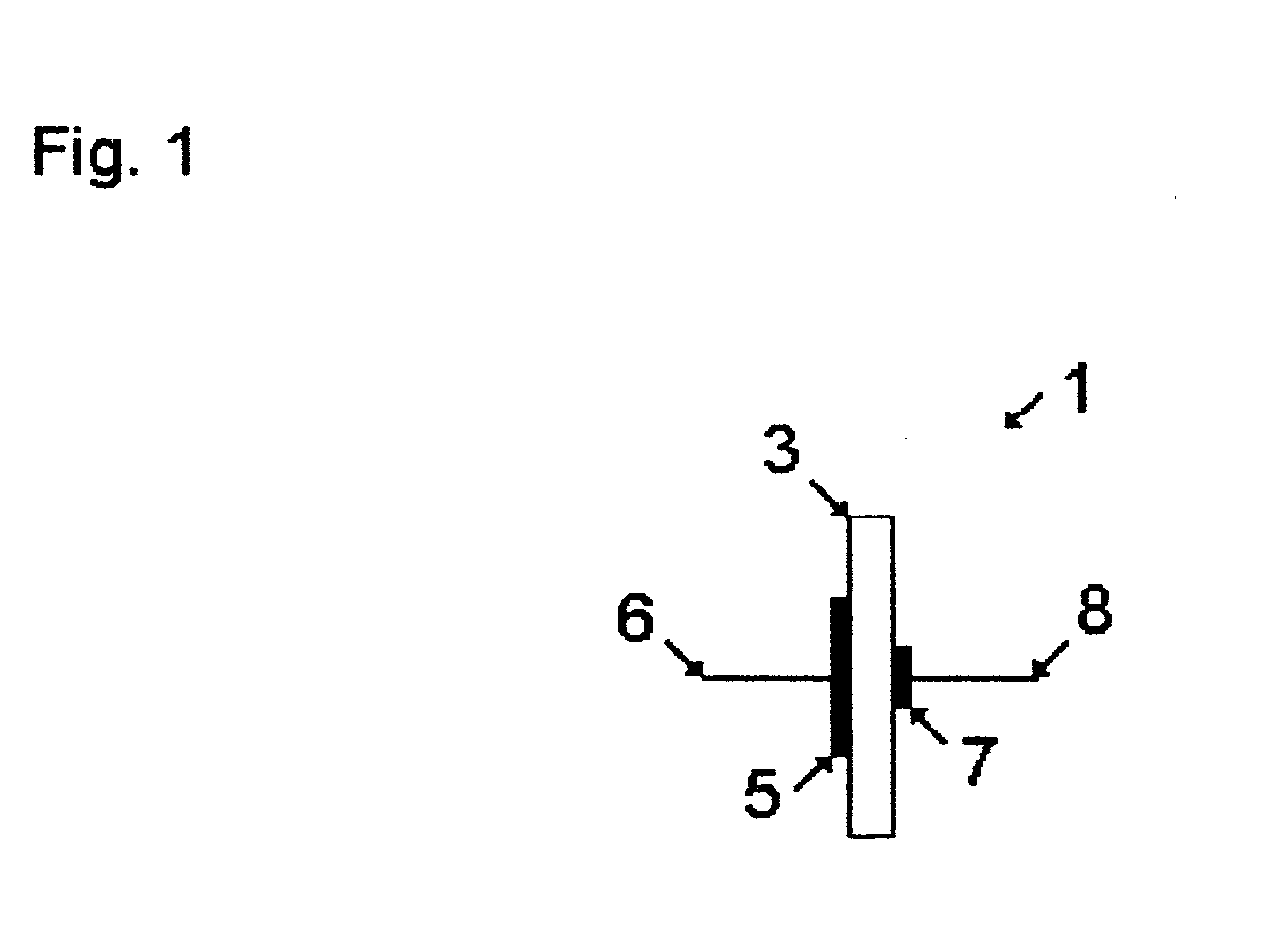

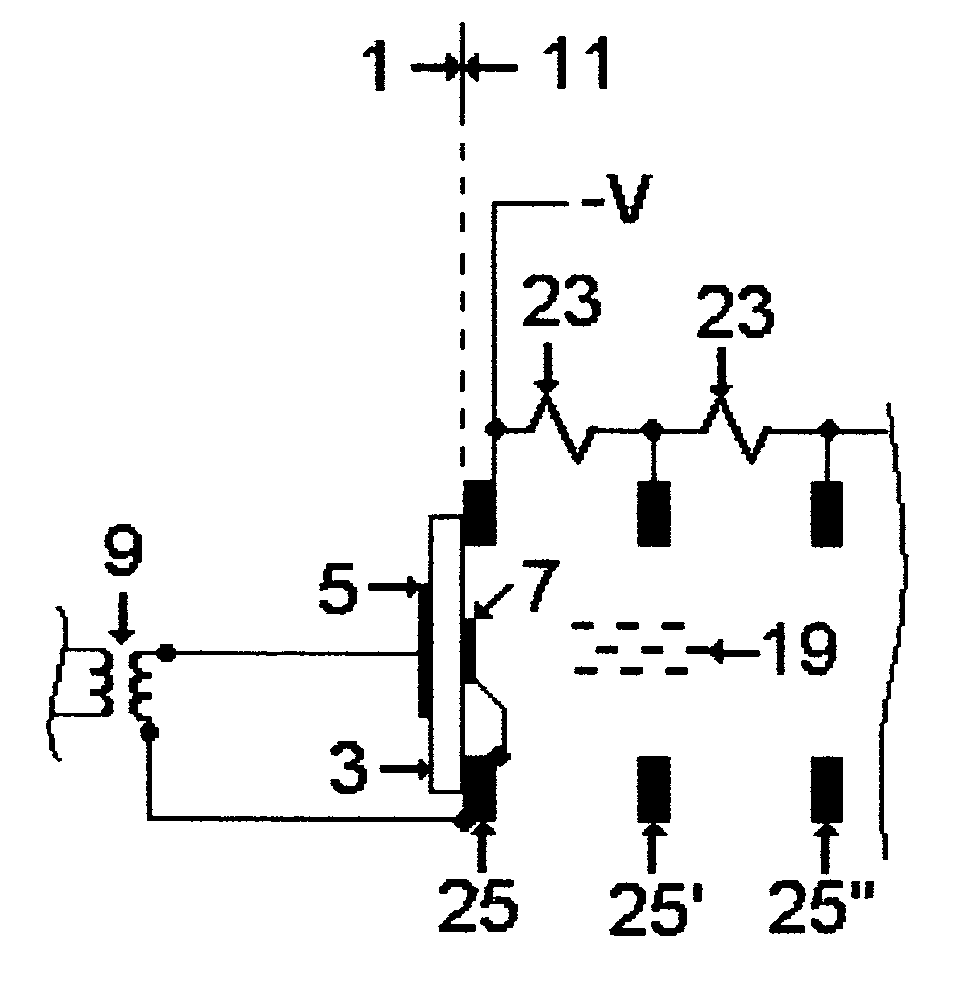

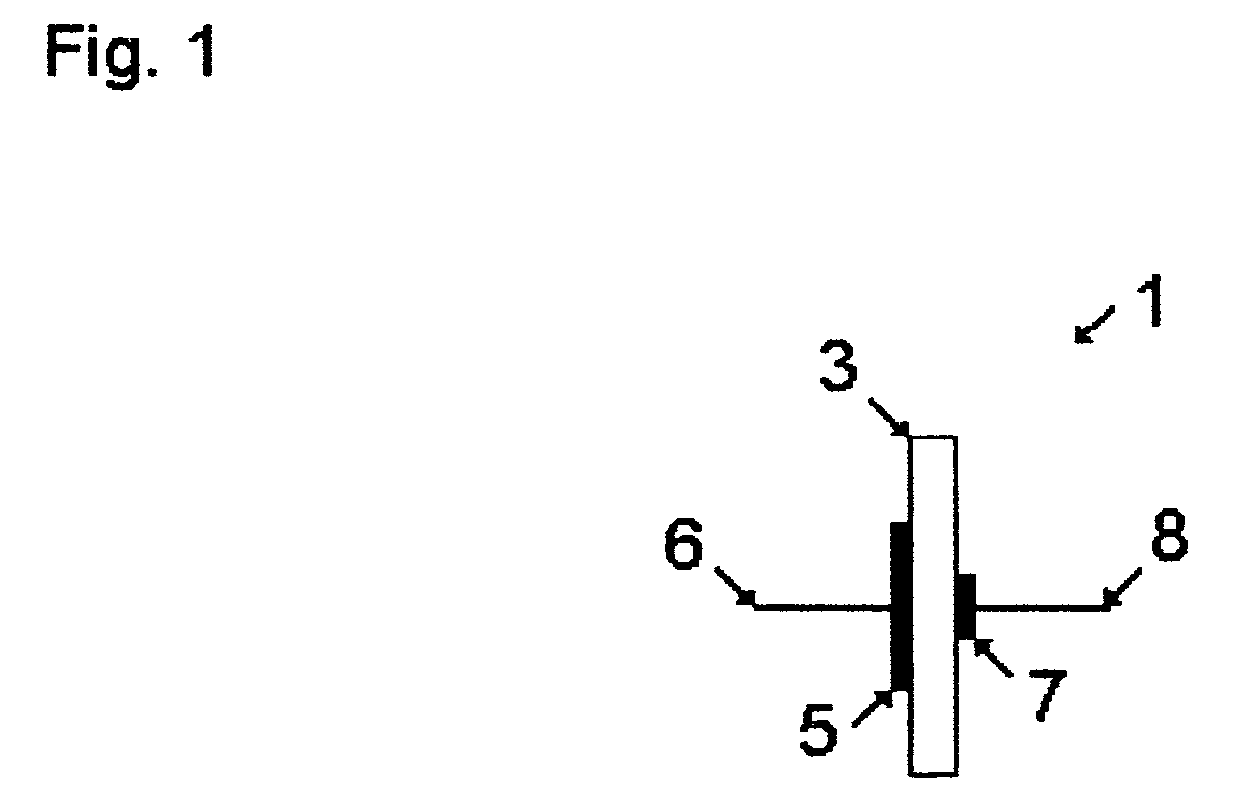

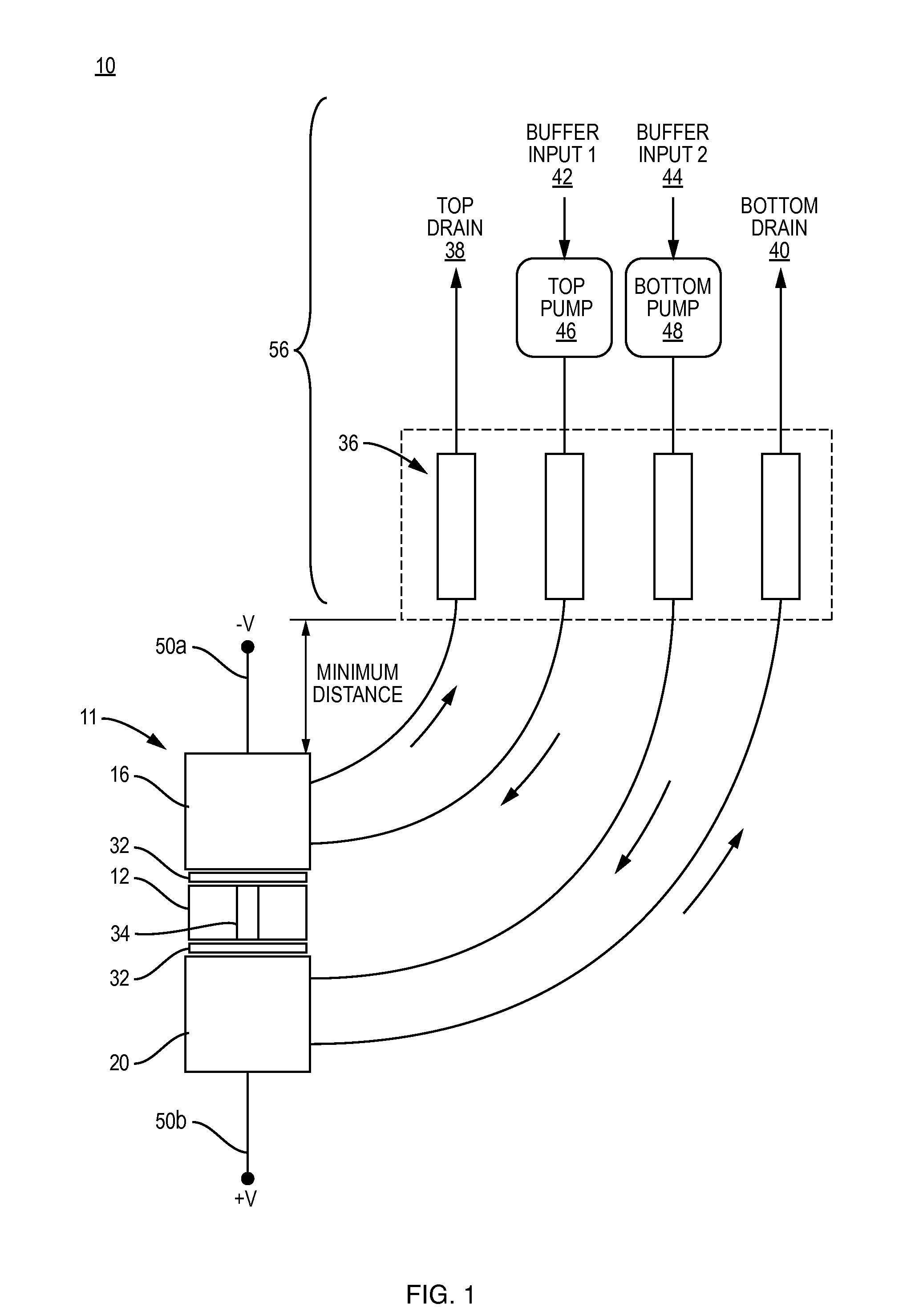

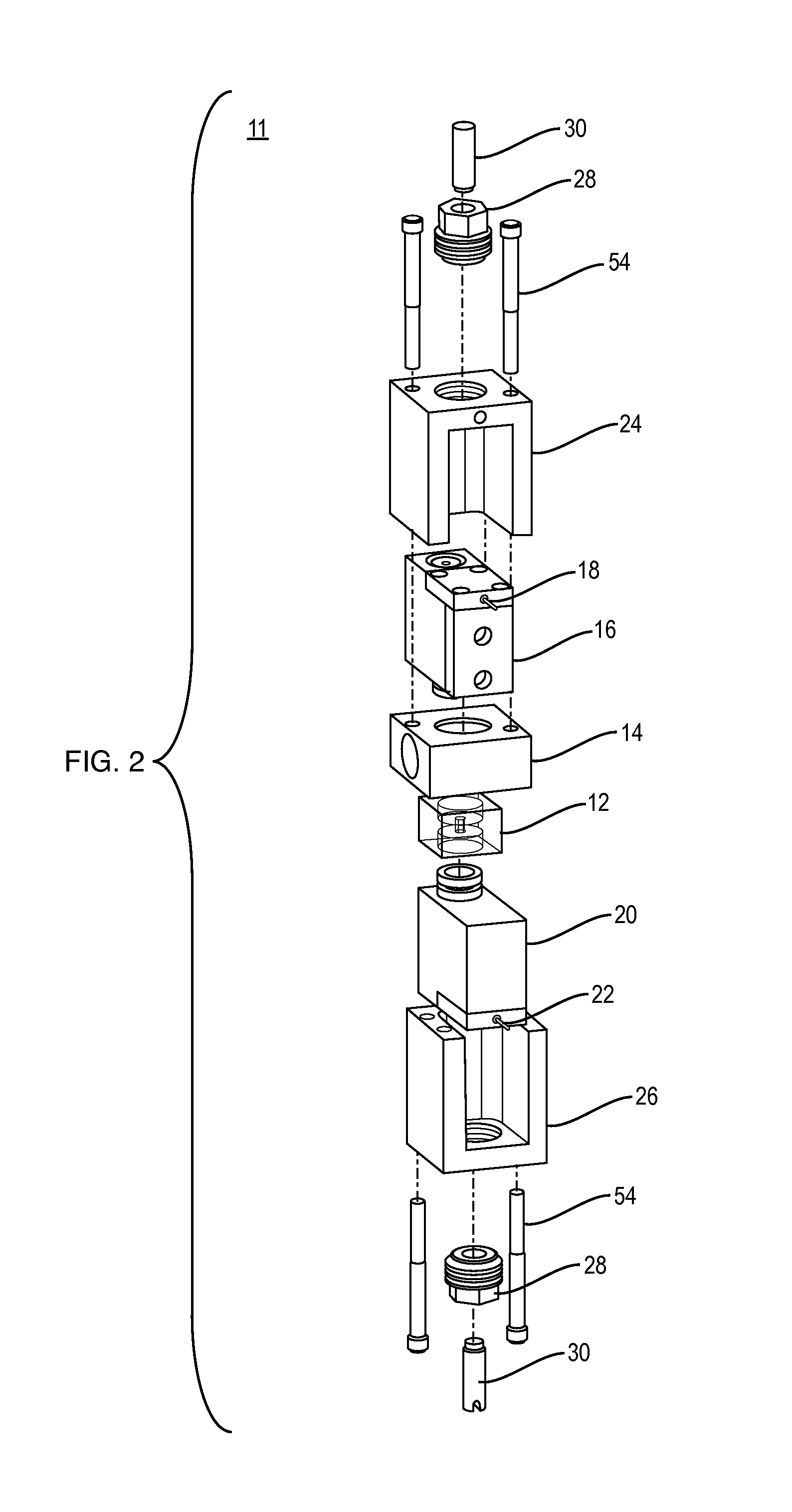

Coupled ionization apparatus and methods

ActiveUS20060284102A1High electric fieldElectric arc lampsMaterial analysis by optical meansIonizationRadio frequency

Apparatus for generating ions in a gaseous medium, the apparatus including two electrodes separated by a dielectric material and a means for generating radio frequency pulses. The electrodes are of dissimilar size and are attached to opposite sides of the dielectric material. The smaller electrode shape and circumference is configured to control the quantity of plasma that is produced. Method of generating ions in a gaseous medium having the step of applying a radio frequency voltage between two electrodes separated by a dielectric material so as to generate a plasma ion source. Locating the plasma ion source in a confined area to yield NO3-ions. Locating the plasma ion source in an open configuration to yield predominantly CO3-ions with minor amounts of O2- and O3-ions.

Owner:INTERLINK ELECTRONICS

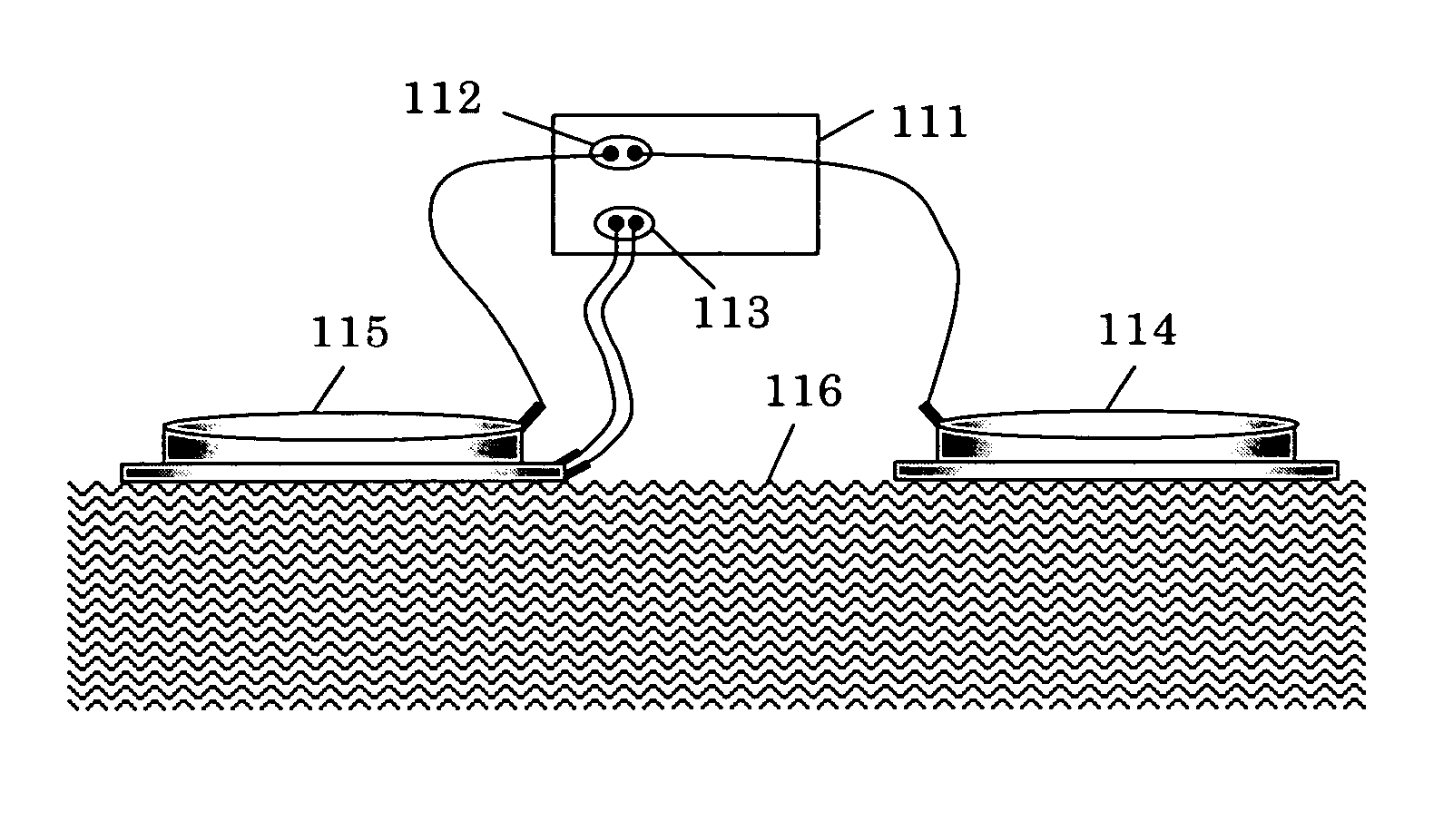

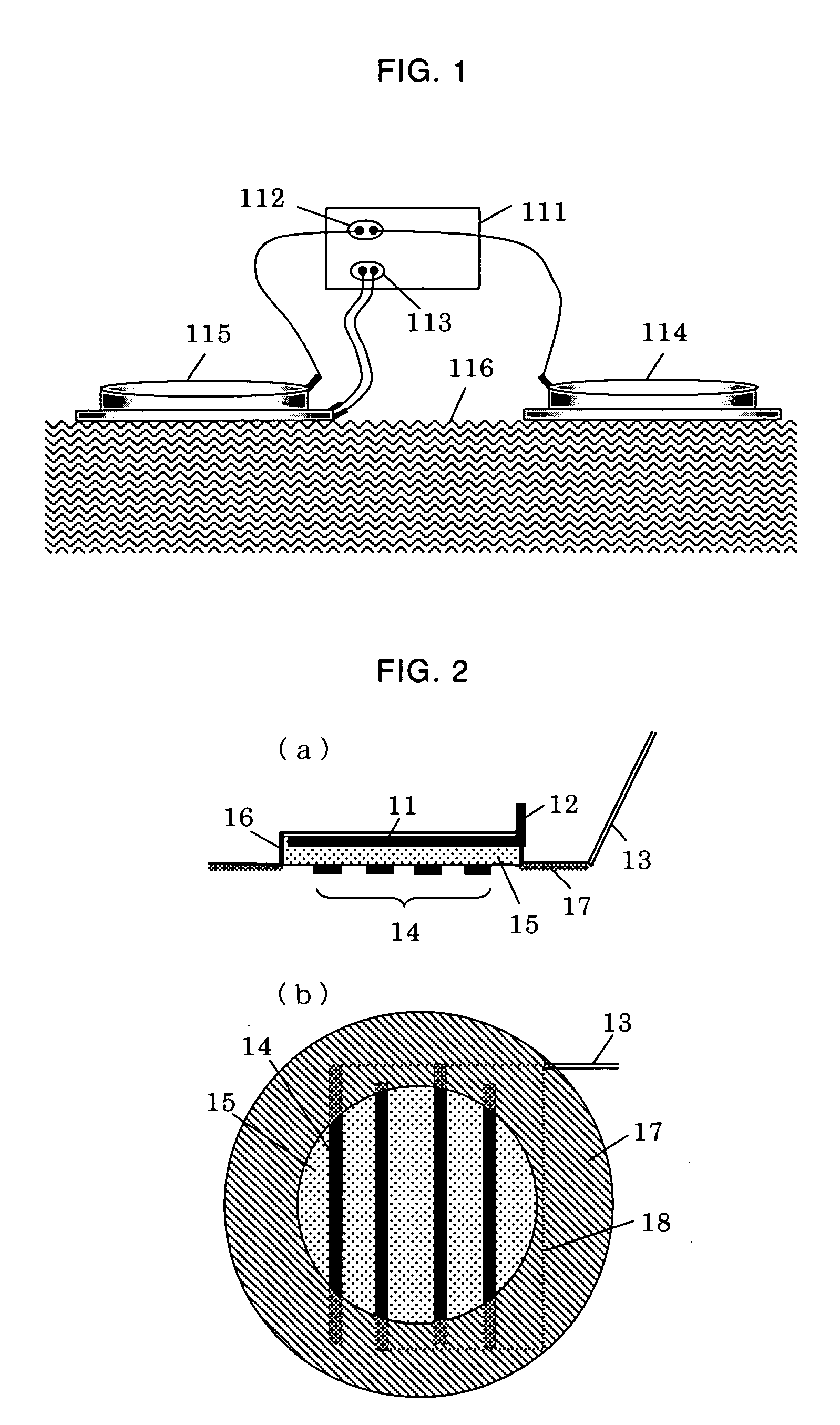

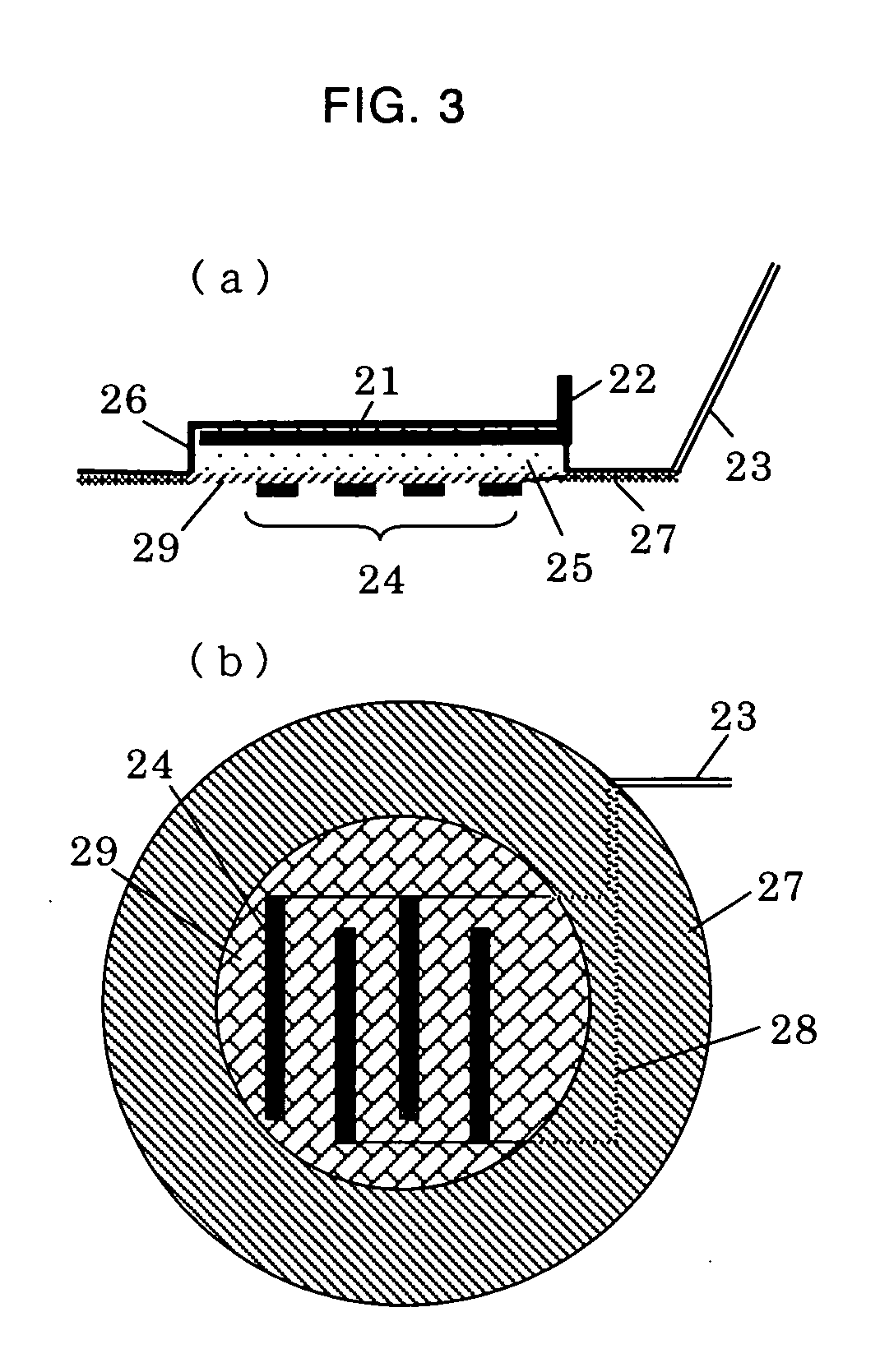

Insulin administration apparatus

InactiveUS20050169976A1High electric fieldGood absorption rateElectrotherapyPeptide/protein ingredientsStructural formulaElectroporation

The present invention provides an insulin-administering device enabling the effective administration of insulin via a percutaneous or submucous administration route. The present device is used to percutaneously or transmucosally administer an insulin lispro represented by the structural formula indicated below, or a pharmaceutically acceptable salt thereof, using iontophoresis and electroporation.

Owner:HISAMITSU PHARM CO INC

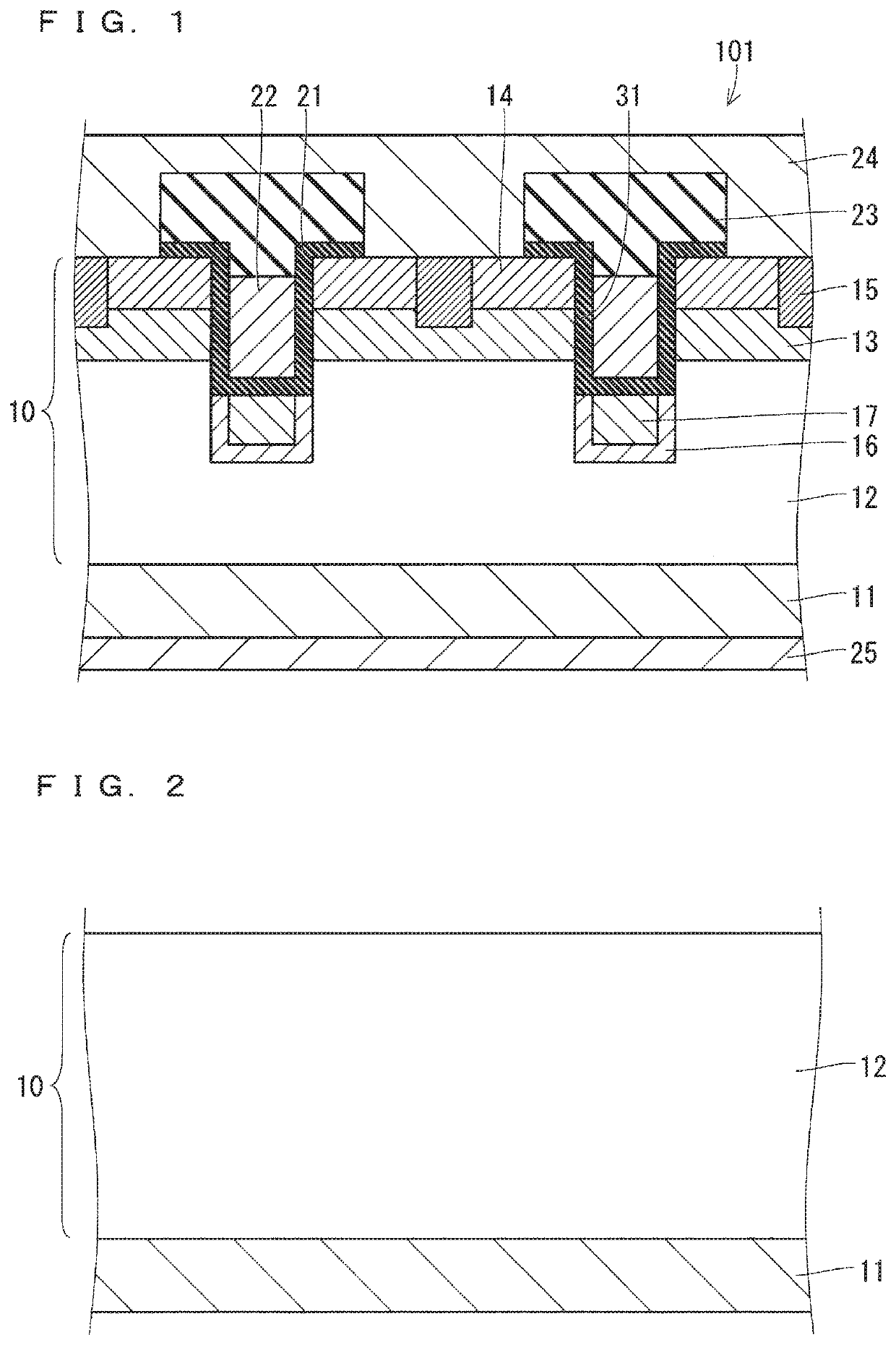

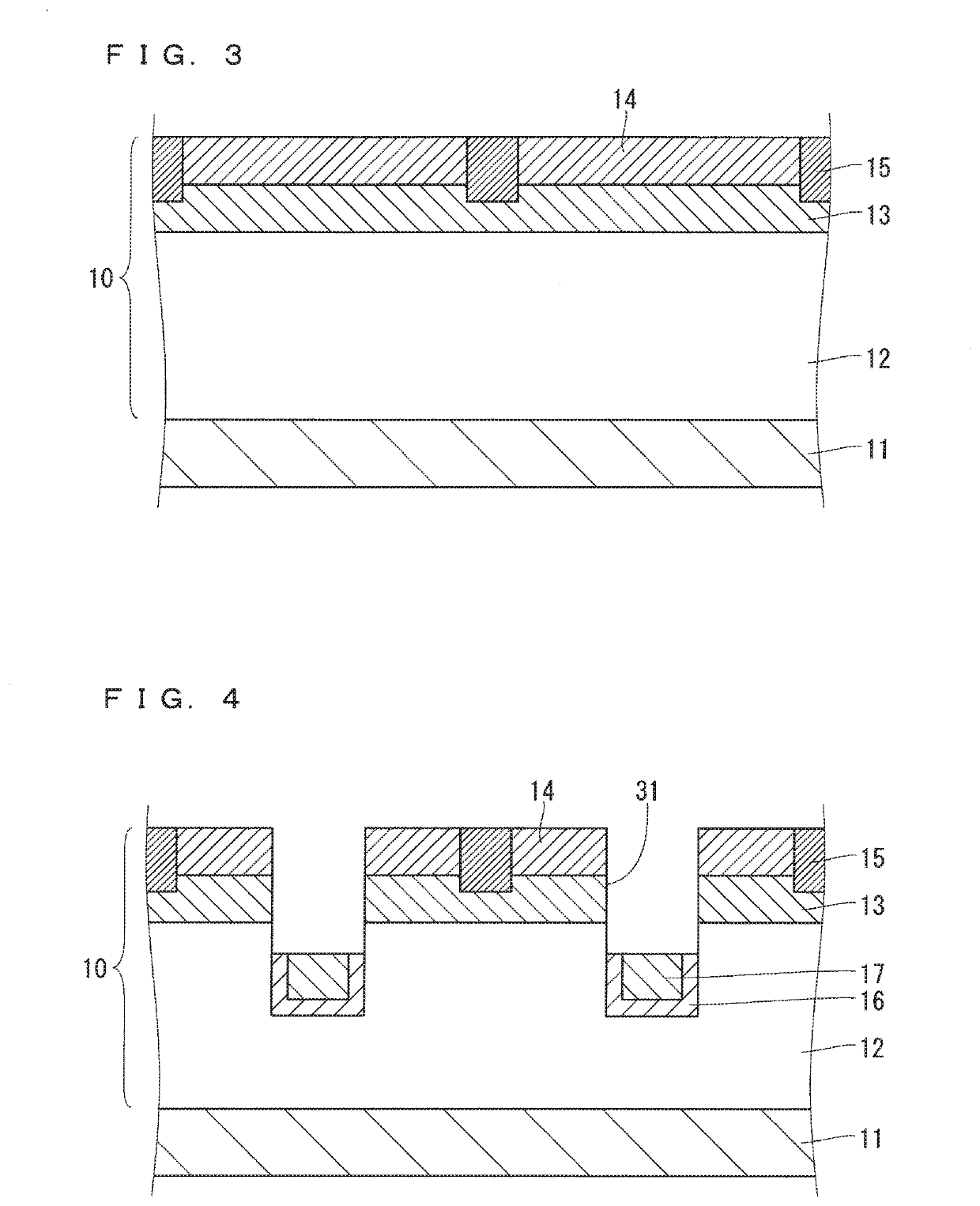

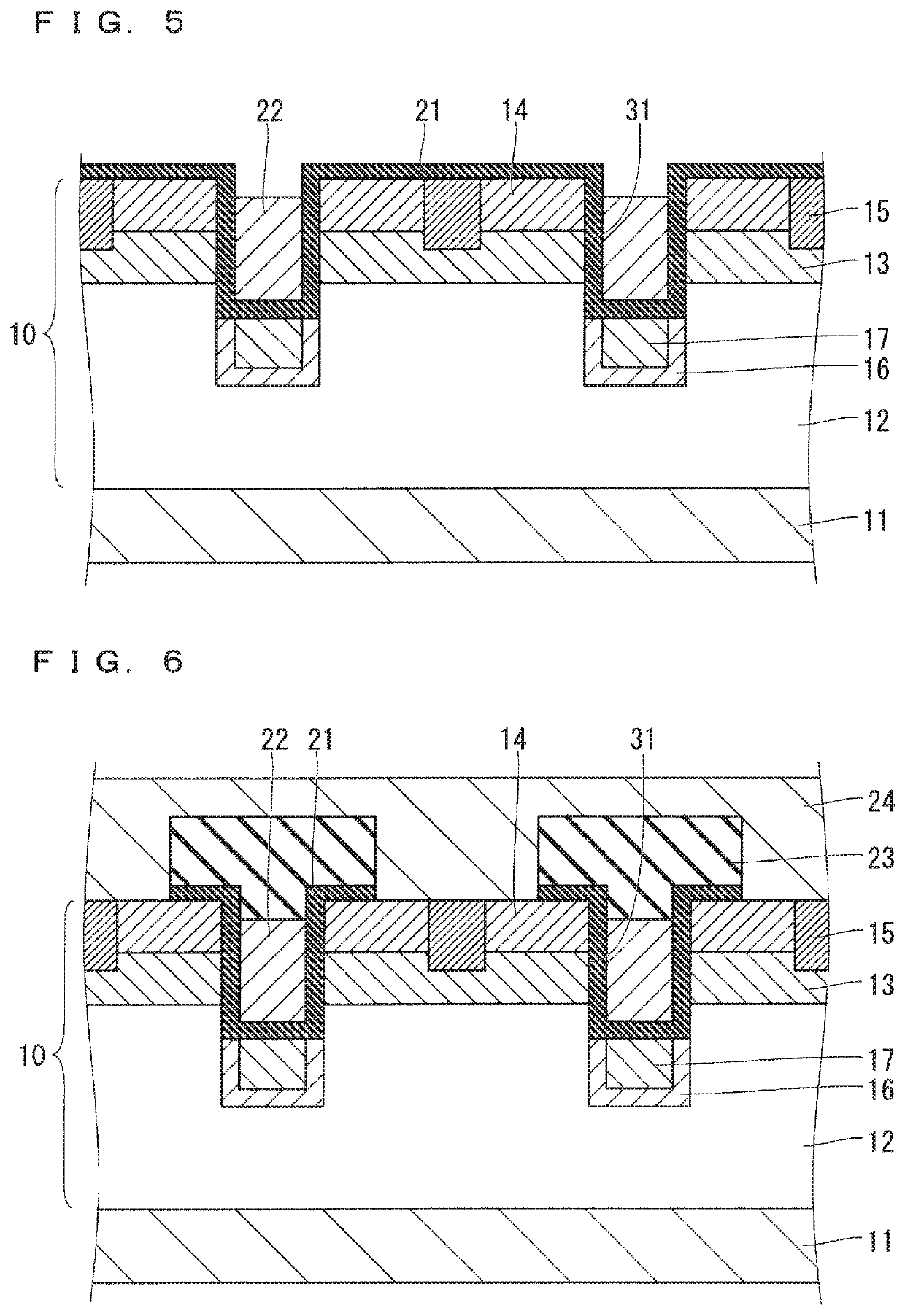

Display device and manufacturing method thereof

InactiveUS20100304515A1Improve featuresImprove reliabilitySemiconductor/solid-state device manufacturingSemiconductor devicesDisplay deviceNon doped

A display device including a thin film transistor with high electric characteristics and high reliability, and a method for manufacturing the display device in high yield are proposed. In a display device including a channel stop thin film transistor with an inverted-staggered structure, the channel stop thin film transistor with the inverted-staggered structure includes a microcrystalline semiconductor film including a channel formation region. An impurity region including an impurity element imparting one conductivity type is formed as selected in a region in the channel formation region of the microcrystalline semiconductor film which does not overlap with a source electrode or a drain electrode. In the channel formation region, a non-doped region, to which the impurity element imparting one conductivity type is not added, is formed between the impurity region, which is a doped region to which the impurity element is added, and the source region or the drain region.

Owner:SEMICON ENERGY LAB CO LTD

Coupled ionization apparatus and methods

ActiveUS7157721B1High electric fieldTime-of-flight spectrometersElectric arc lampsIonizationRadio frequency

Apparatus for generating ions in a gaseous medium, the apparatus including two electrodes separated by a dielectric material and a means for generating radio frequency pulses. The electrodes are of dissimilar size and are attached to opposite sides of the dielectric material. The smaller electrode shape and circumference is configured to control the quantity of plasma that is produced. Method of generating ions in a gaseous medium having the step of applying a radio frequency voltage between two electrodes separated by a dielectric material so as to generate a plasma ion source. Locating the plasma ion source in a confined area to yield NO3-ions. Locating the plasma ion source in an open configuration to yield predominantly CO3-ions with minor amounts of O2- and O3-ions.

Owner:INTERLINK ELECTRONICS

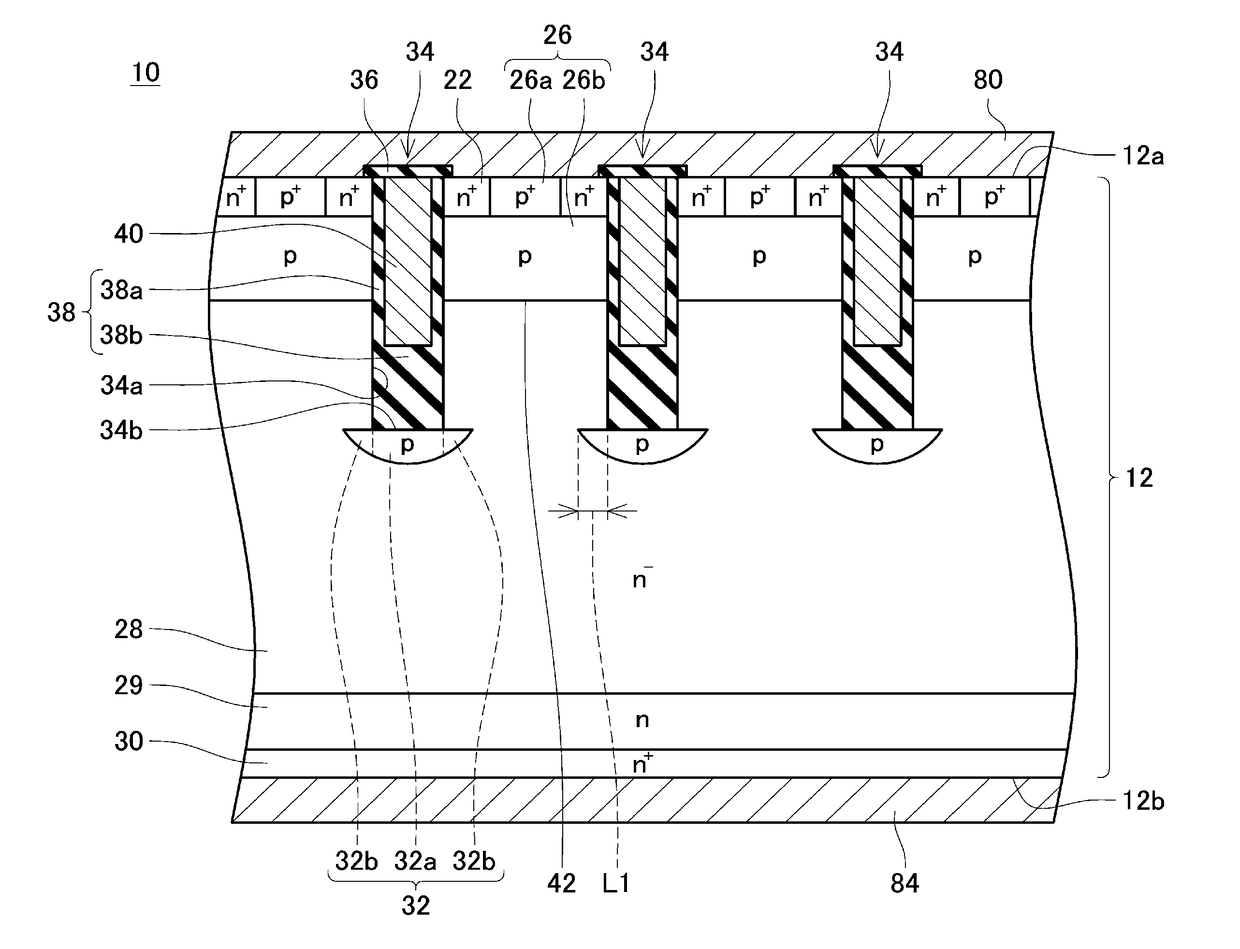

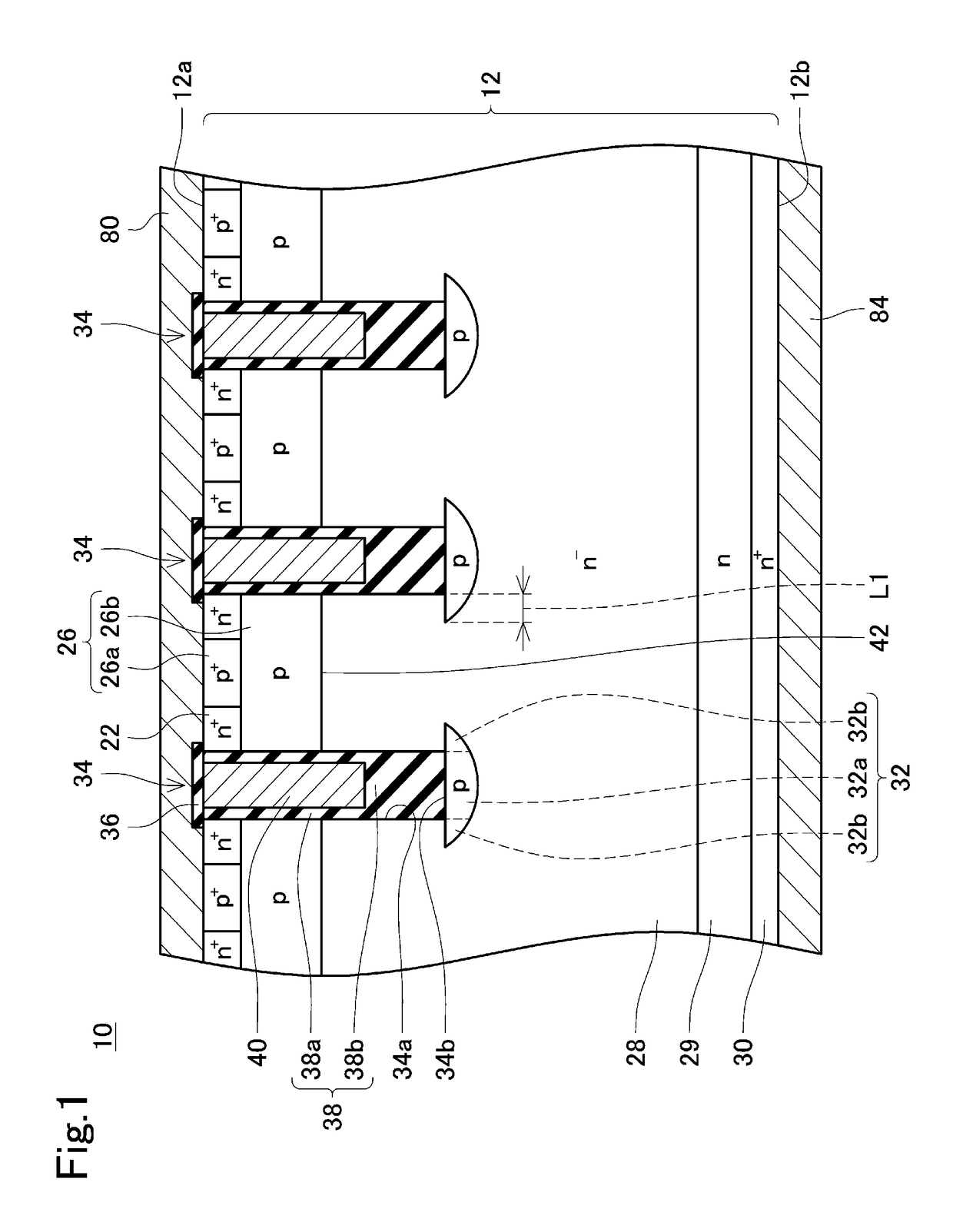

Silicon carbide semiconductor device, power converter, and method of manufacturing silicon carbide semiconductor device

InactiveUS20190348524A1Reduce generationHigh electric fieldTransistorSemiconductor/solid-state device manufacturingSemiconductorCondensed matter physics

A drift layer has a first conductivity type and is provided on a silicon carbide substrate. A well region has a second conductivity type and is provided on the drift layer. A source region has the first conductivity type and is provided on the well region. A gate trench has an inner surface with a bottom located at a deeper position than the well region and a lateral part continuous with the bottom. An electric field relaxation region has the second conductivity type and has at least a part located below the bottom of the gate trench. A surge relaxation region has the first conductivity type, contacts at least a part of the bottom of the gate trench, and is separated from the drift layer by the electric field relaxation region.

Owner:MITSUBISHI ELECTRIC CORP

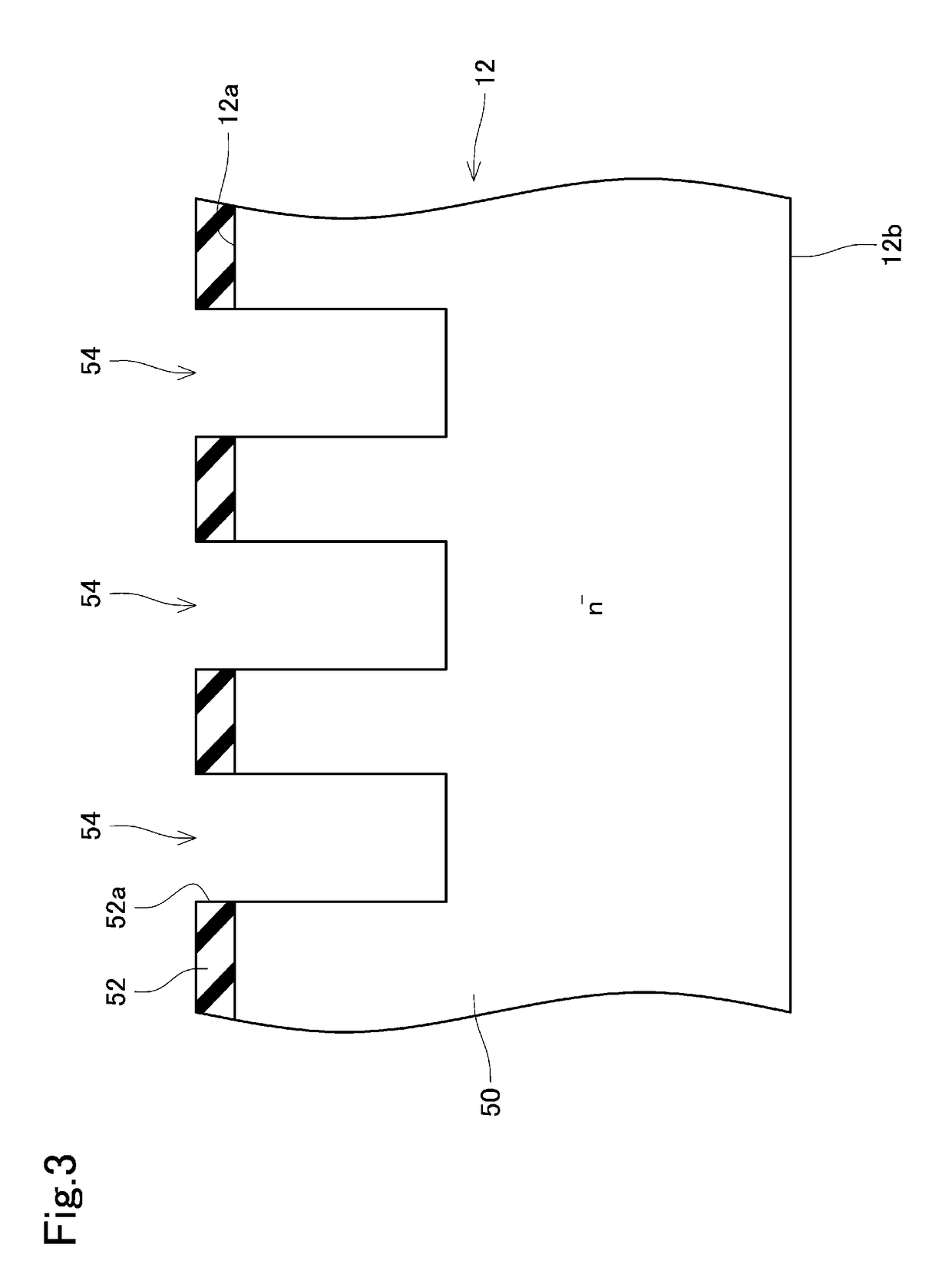

Insulated gate switching device and method for manufacturing the same

ActiveUS20180175149A1Wider widthProtruding amount of the implanted region of the p-type impurities (Semiconductor/solid-state device manufacturingSemiconductor devicesEngineeringBody region

A method for manufacturing an insulated gate switching device is provided. The method includes: forming a first trench in a surface of a first SiC semiconductor layer; implanting p-type impurities into a bottom surface of the first trench; depositing a second SiC semiconductor layer on an inner surface of the first trench to form a second trench; and forming a gate insulating layer, a gate electrode, a first region and a body region so that the gate insulating layer covers an inner surface of the second trench, the gate electrode is located in the second trench, the first region is of n-type and in contact with the gate insulating layer, the body region is of p-type, separated from the implanted region, and in contact with the gate insulating layer under the first region.

Owner:TOYOTA JIDOSHA KK +1

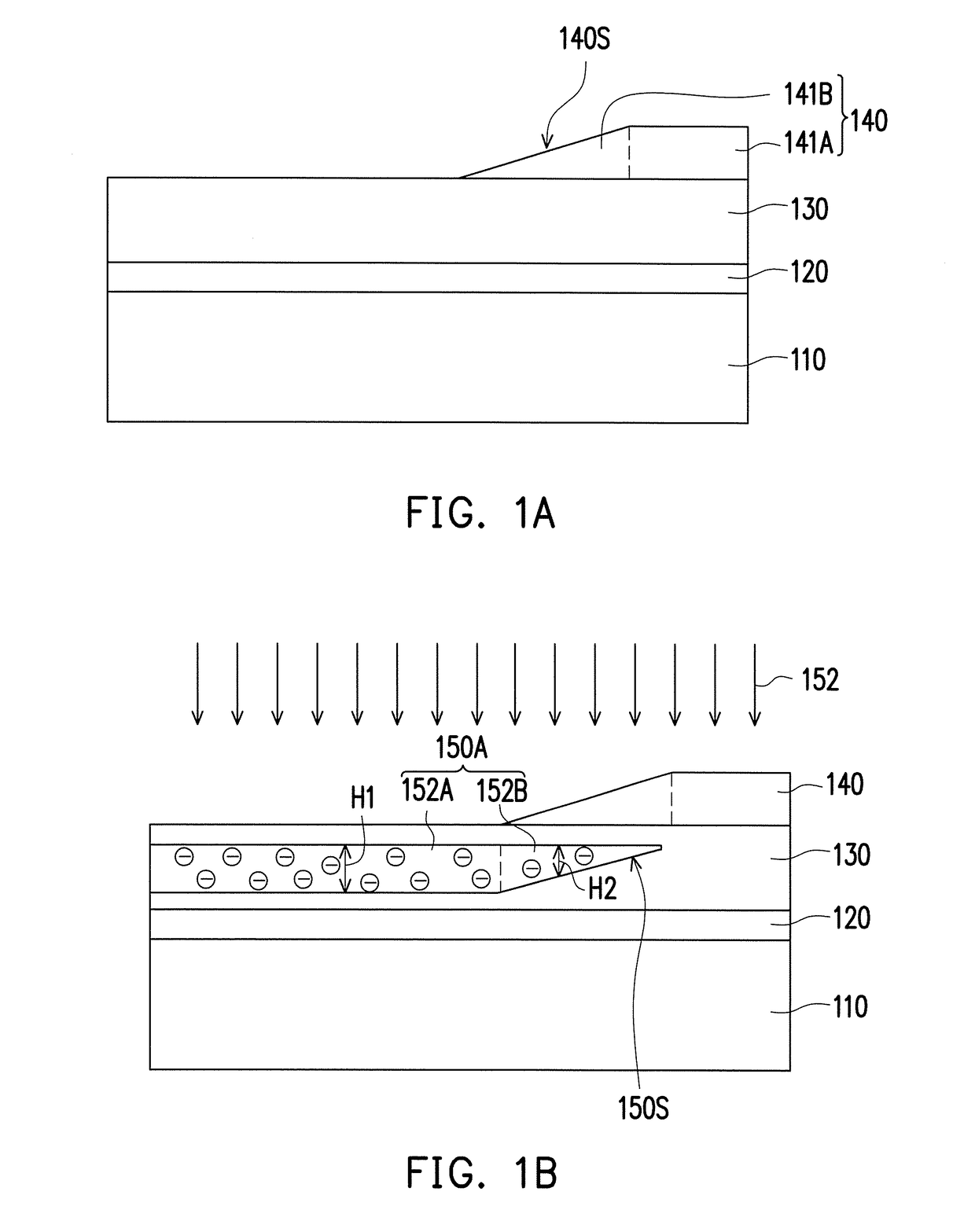

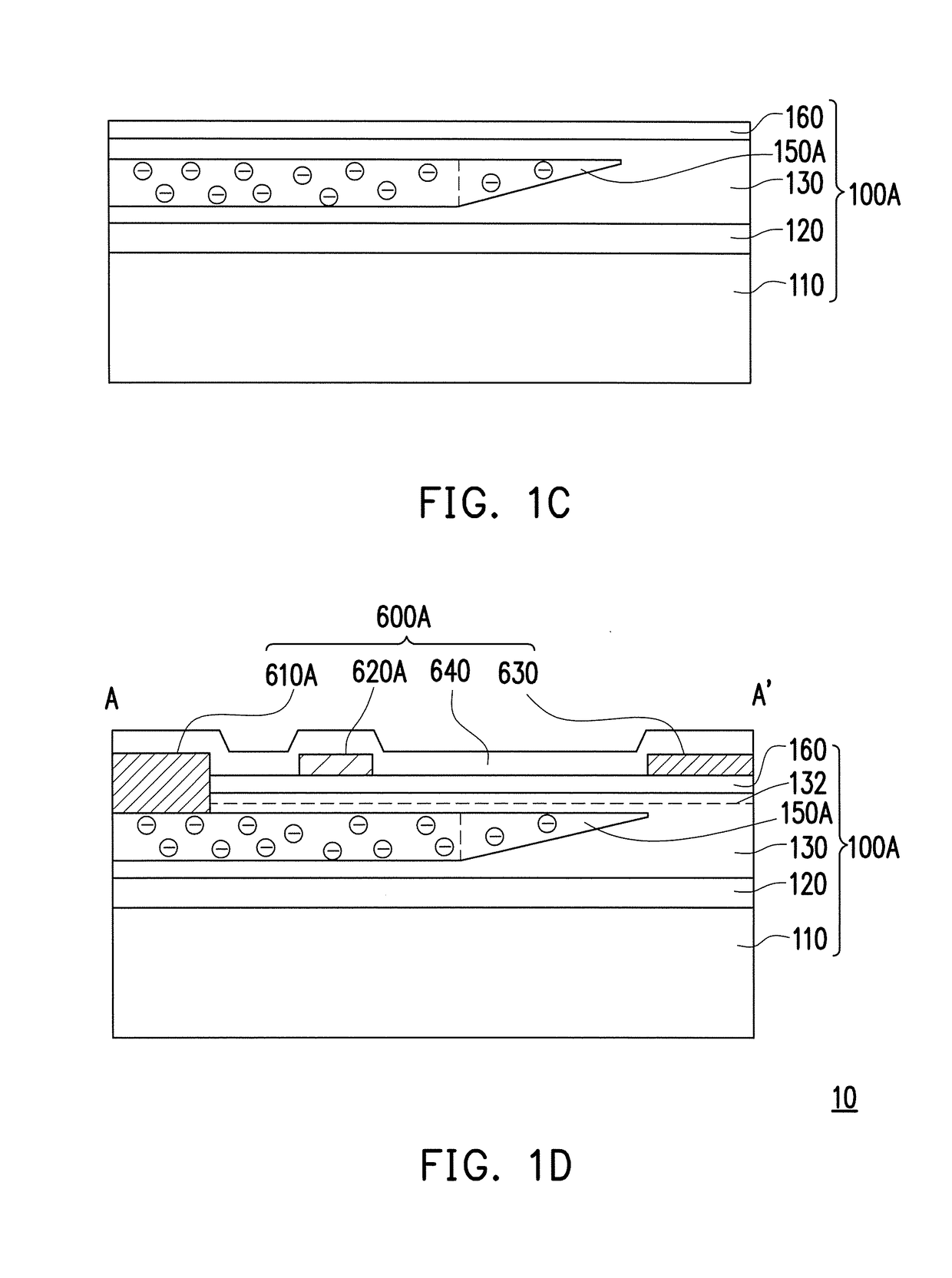

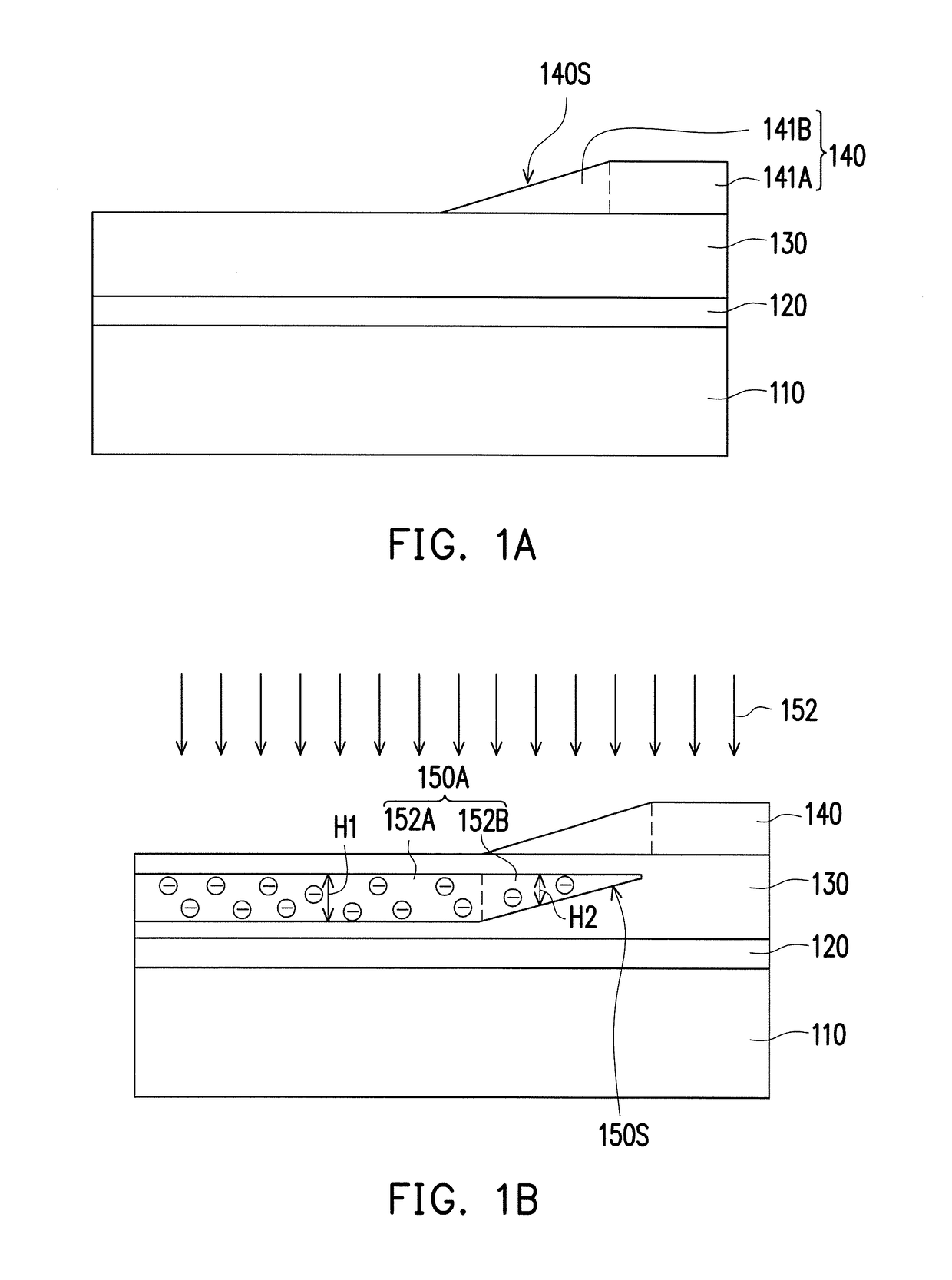

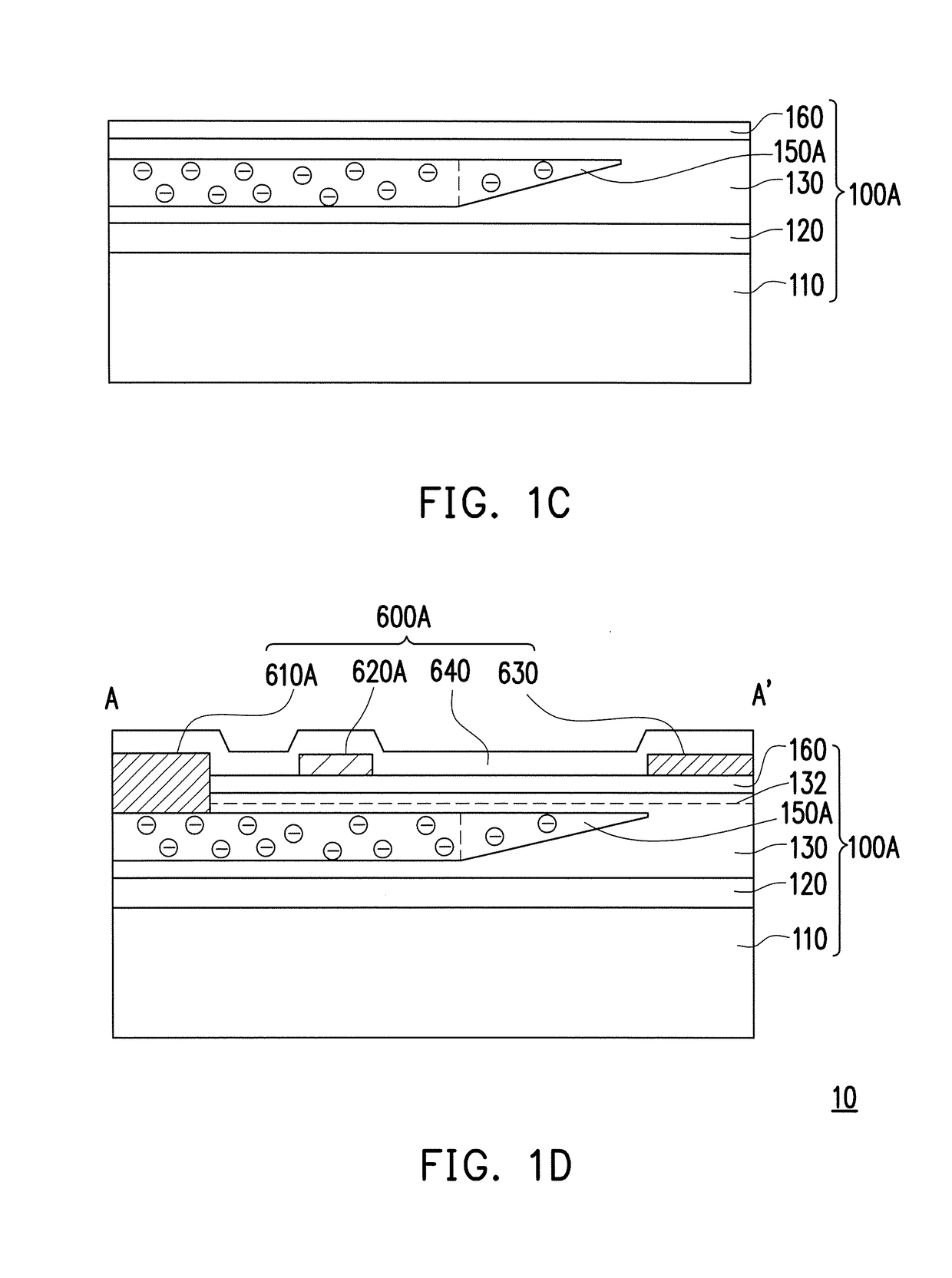

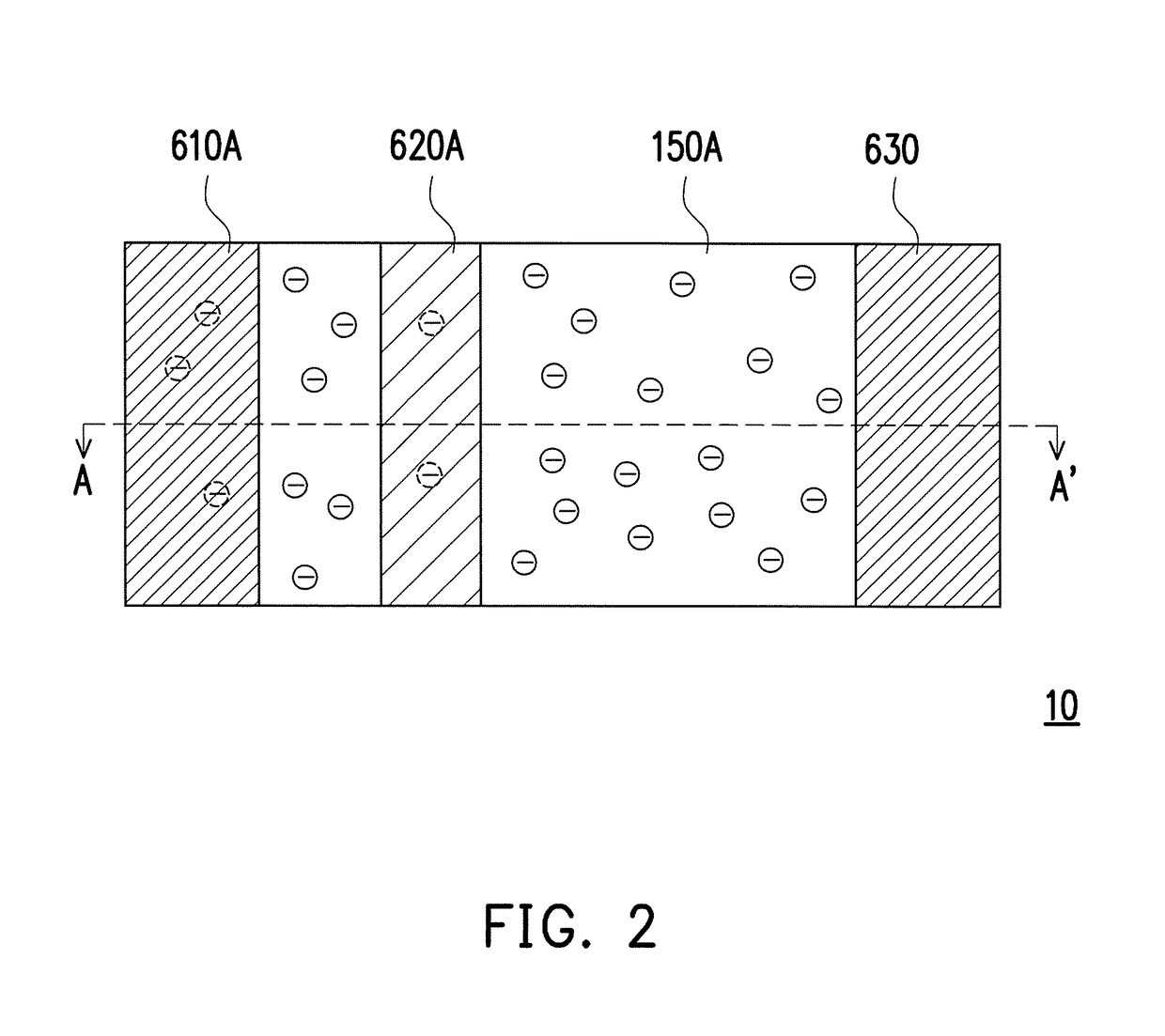

Semiconductor substrate and semiconductor device

ActiveUS20180175186A1Effective dispersionReduce parasitic capacitanceSemiconductor/solid-state device manufacturingSemiconductor devicesSemiconductorElectron

A semiconductor substrate and a semiconductor device are disclosed. The semiconductor substrate includes a base layer, a buffer layer disposed on the base layer, a channel layer disposed on the buffer layer, a barrier layer disposed on the channel layer, and a buried field plate region embedded in the channel layer. In an embodiment, the channel layer includes a two-dimensional electron gas (2DEG), and the buried field plate region is located below the two-dimensional electron gas.

Owner:NUVOTON

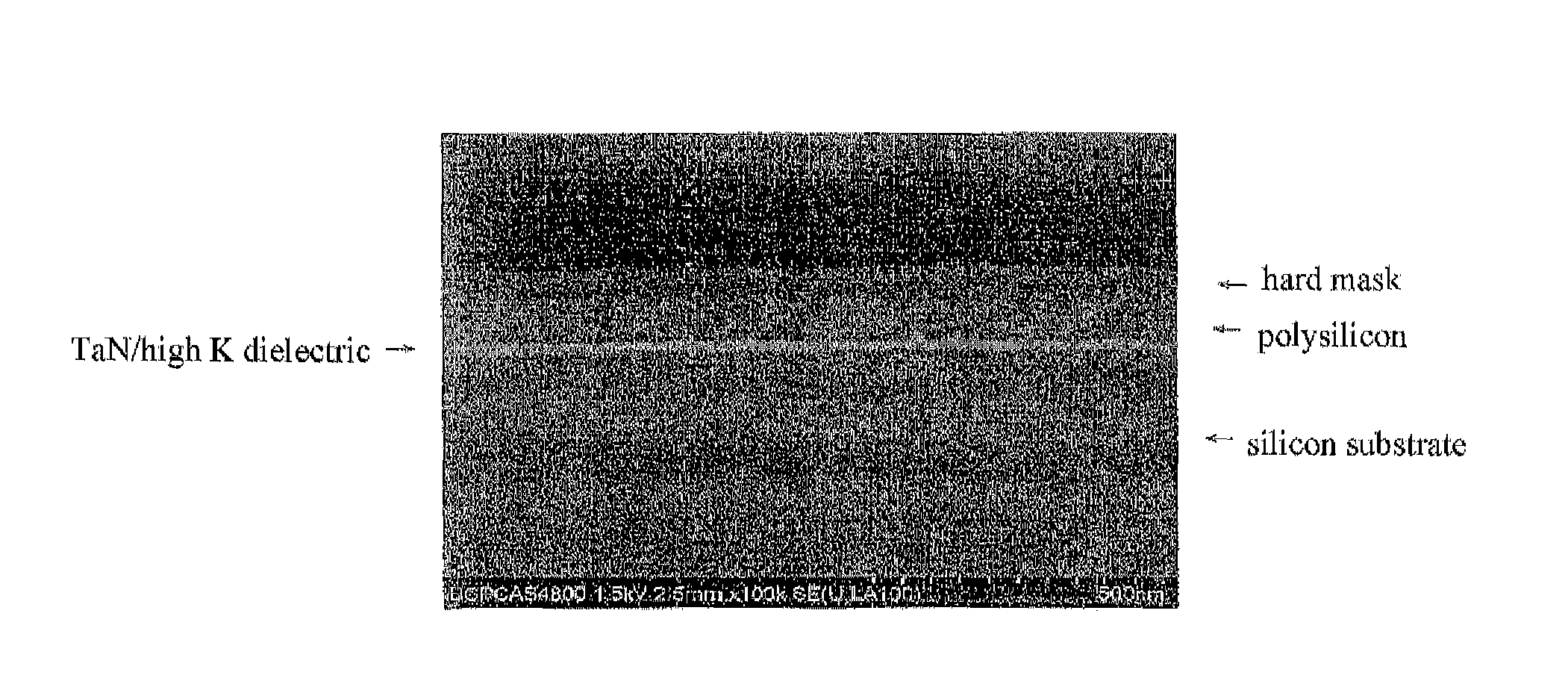

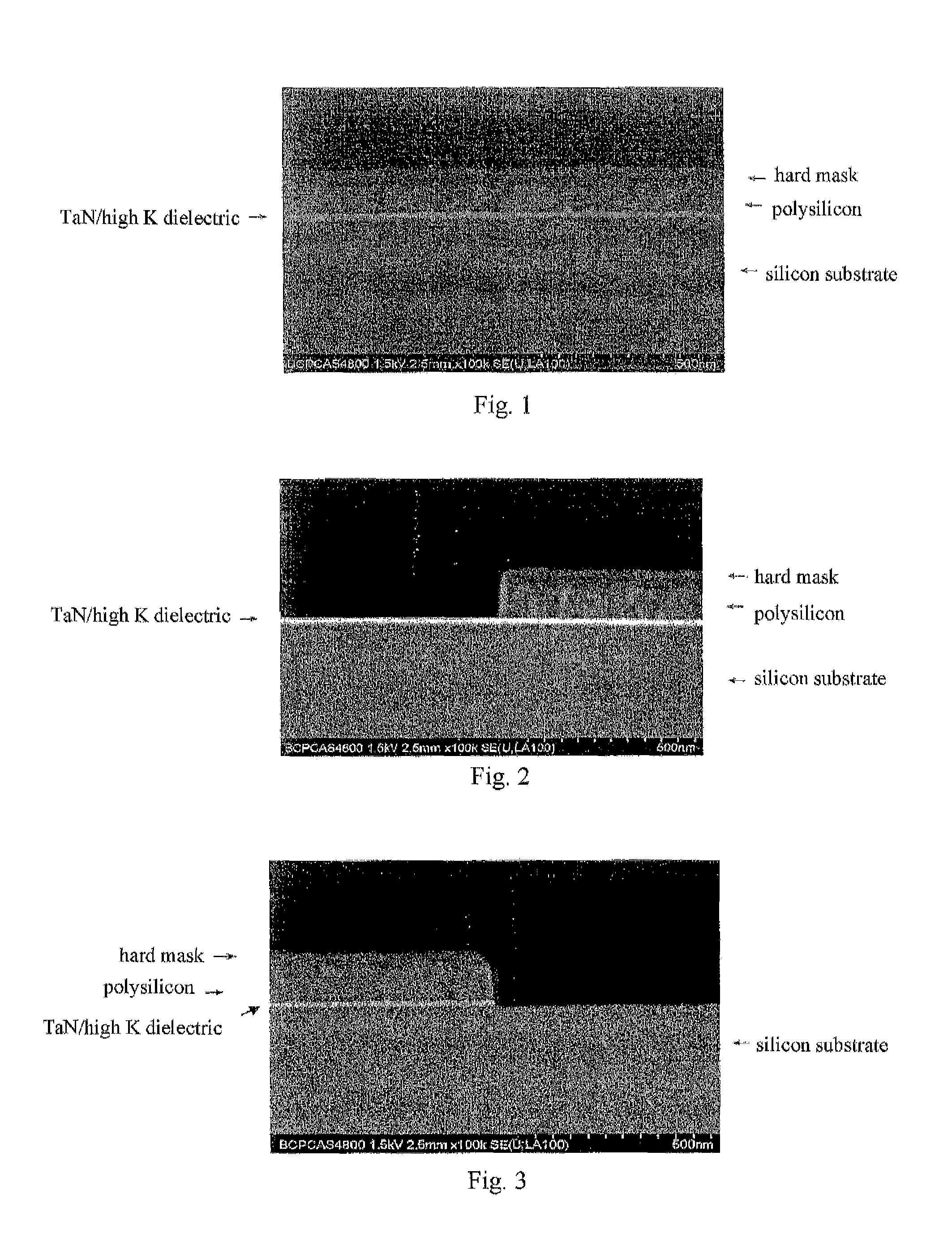

Method for manufacturing a metal gate electrode/high k dielectric gate stack

ActiveUS20110256704A1Steep etching profileImprove etch selectivitySemiconductor/solid-state device manufacturingSemiconductor devicesDielectricGate stack

A method of manufacturing a metal gate / high K dielectric gate stack includes the steps of: forming an interfacial layer of SiON or SiO2 on a silicon substrate; depositing a high K dielectric film on the interfacial layer; performing a rapid thermal anneal of the high K dielectric film; depositing a TaN metal gate electrode film on the high K dielectric film; depositing a polysilicon gate layer on the TaN metal gate electrode film, and then depositing a hard mask layer; patterning a photoresist mask, and performing an anisotropic etching of the hard mask layer; removing the photoresist mask, and etching the polysilicon by reactive ion etching with the hard mask as masking layer using a mixed gas of Cl2 / HBr; and etching the TaN metal gate electrode / high K dielectric gate stack by reactive ion etching with the hard mask as masking layer using BCl3-based etchant gas.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

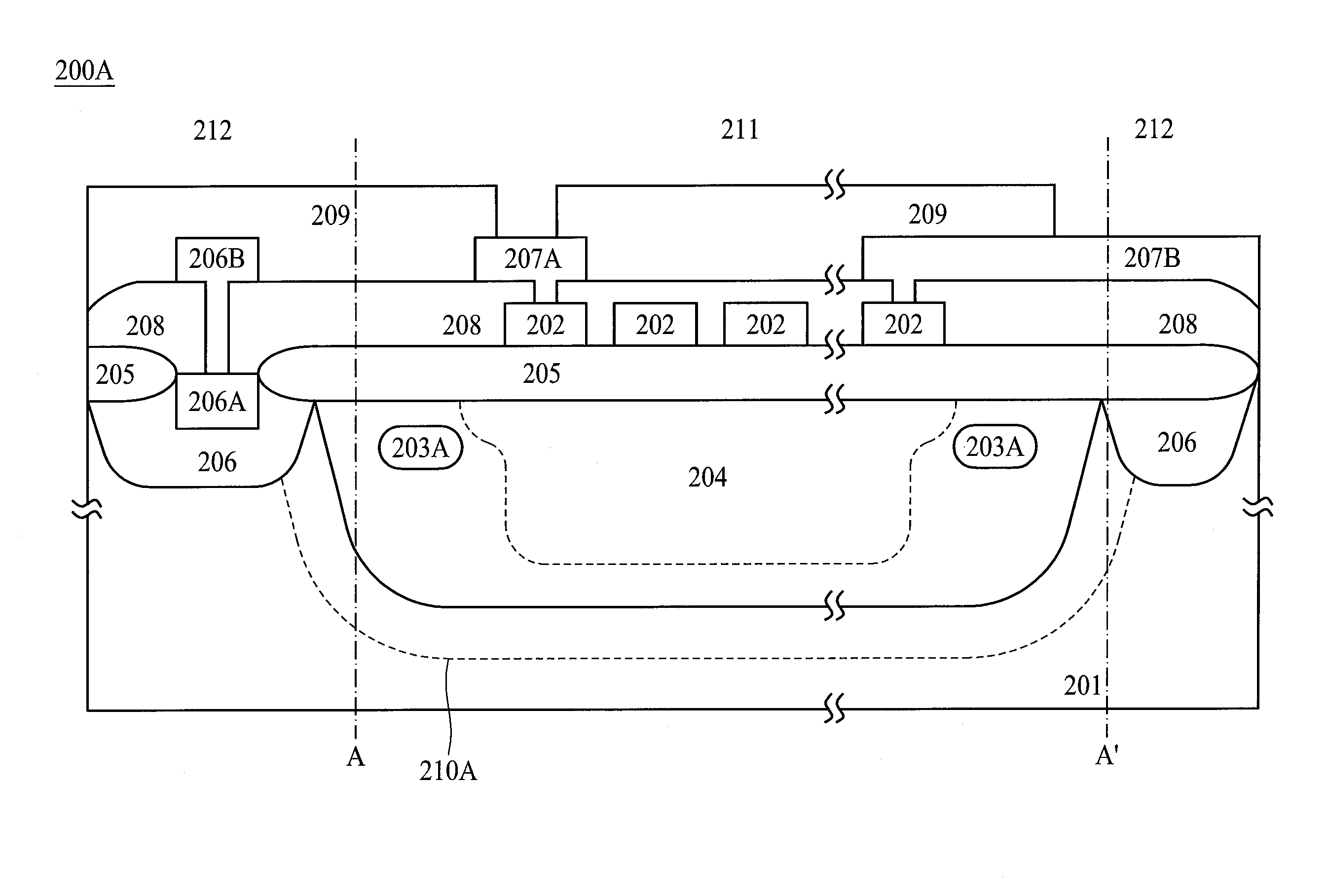

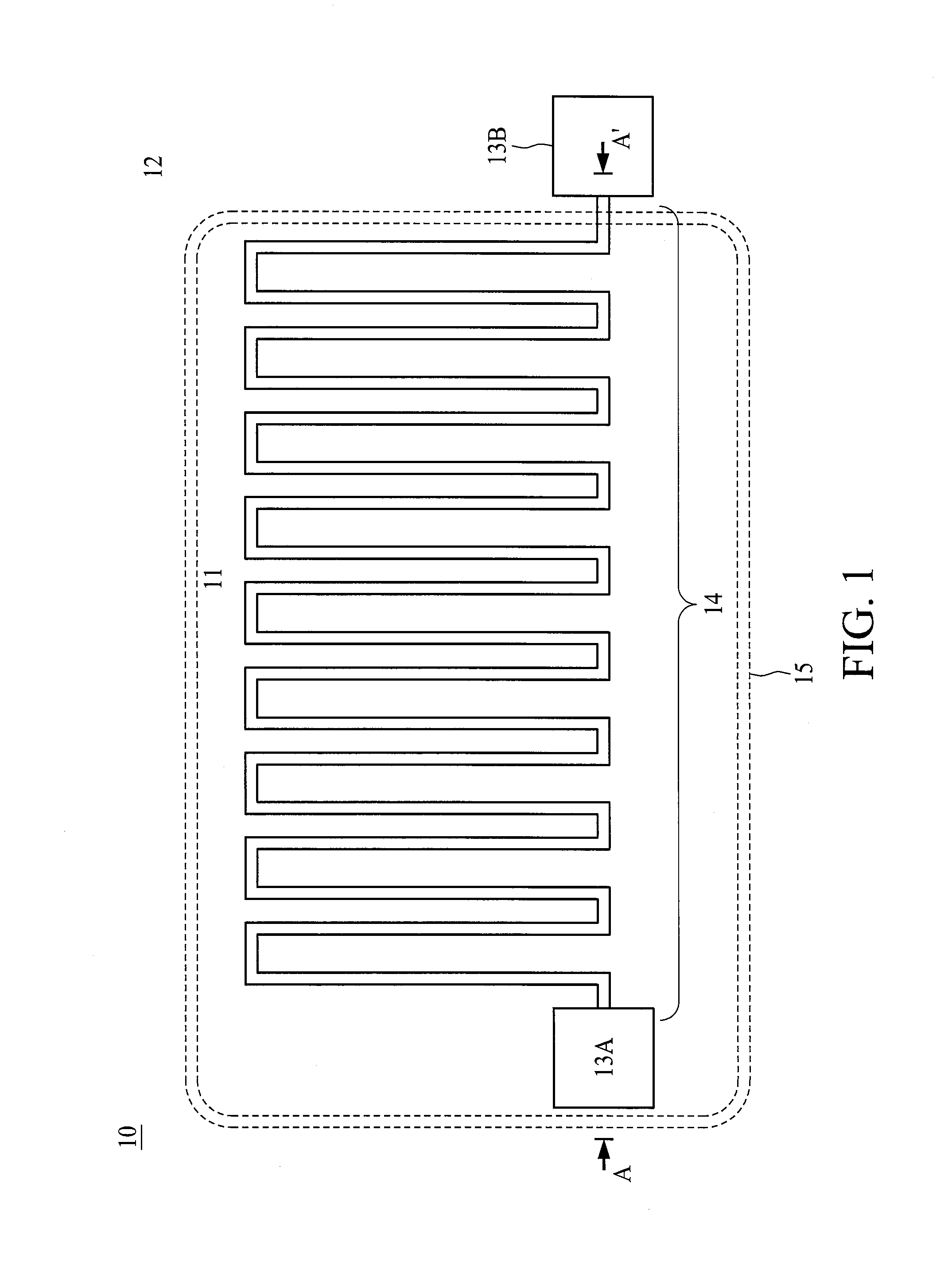

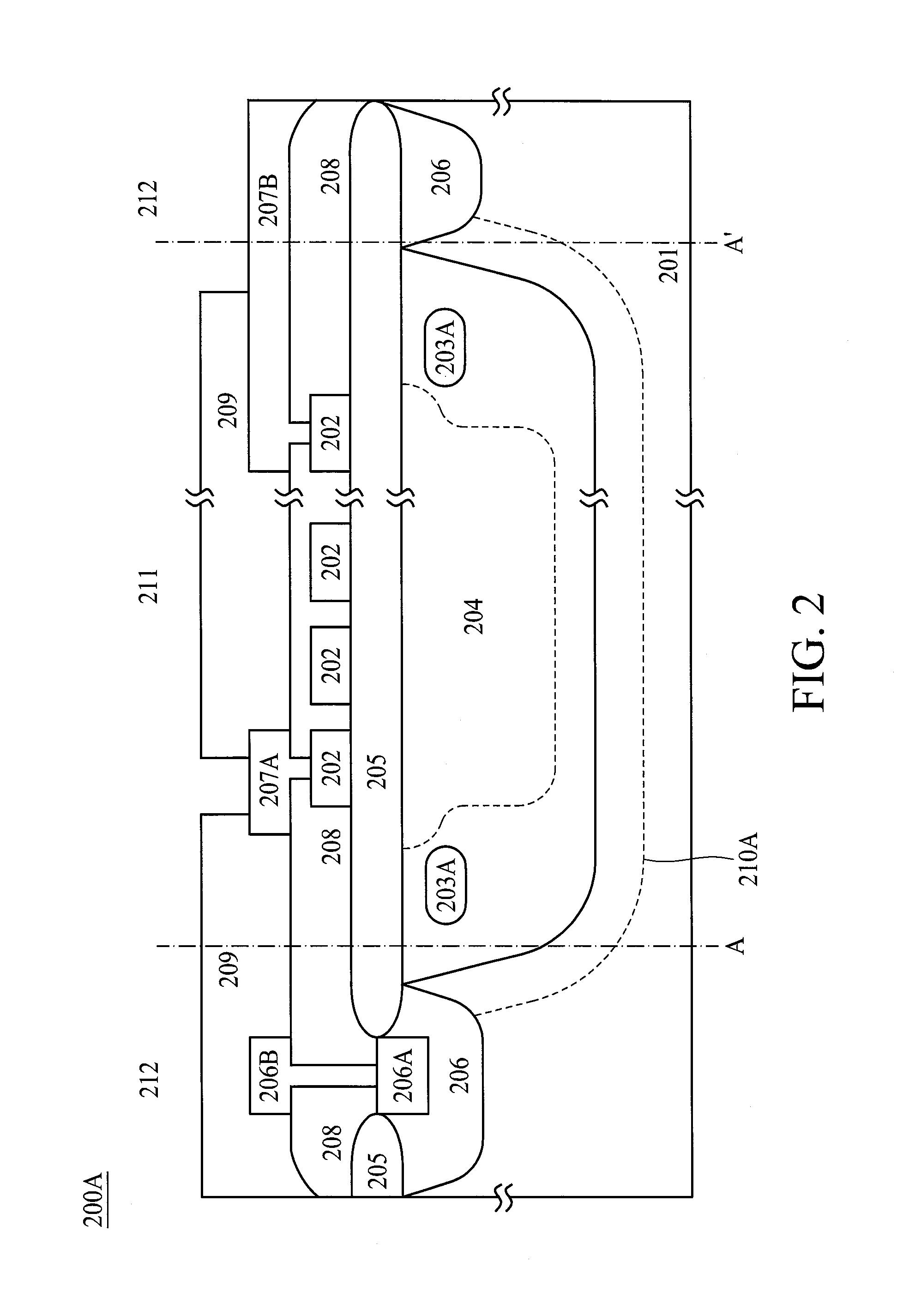

Semiconductor structure and method of manufacturing the same

ActiveUS20140266409A1Improve breakdown voltageIncrease depletion widthTransistorSolid-state devicesSemiconductor structureLow voltage

A semiconductor structure with a high voltage area and a low voltage area includes a substrate of a first conductivity type accommodating the high voltage area and the low voltage area. A resistor is on the substrate, connecting the high voltage area and the low voltage area, and the resistor resides substantially in the high voltage area. The structure further includes a first doped region of the first conductivity type in the substrate between the high voltage area and the low voltage area, and a second doped region of a second conductivity type between the substrate and the first doped region. Moreover, an insulating layer is formed between the resistor and the first doped region.

Owner:MACRONIX INT CO LTD

Avalanche Photodetector with Single Mesa Shape

A photodetector is provided. The photodetector is an avalanche photodiode of indium aluminum arsenide (InAlAs). An epitaxial-layers structure with n-side down is used. The strongest electric field of a multiplication layer (M-layer) is coated in inner bottom layers to avoid surface breakdown. An intrinsic layer is thickened; only one absorption layer is used; and a DBR layer is added below an n-type ohmic contact layer. A graded bandgap layer is etched to form a single mesa shape. Through the single mesa shape, all layers are far below breakdown except the M-layer has a particularly high electric field for restraining the electric field. Thus, the present invention changes holes into electrons through p-type-doping the absorption layer; because electrons run fast, carriers is made run fast; and junction capacitance is reduced with surface area increased by depletion layer thickened. Consequently, fast response speed is obtained while sensitivity is effectively improved.

Owner:NAT CENT UNIV

Method for manufacturing a metal gate electrode/high K dielectric gate stack

ActiveUS8258063B2Improve etch selectivityReduce manufacturing costSemiconductor/solid-state device manufacturingSemiconductor devicesDielectricGate stack

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

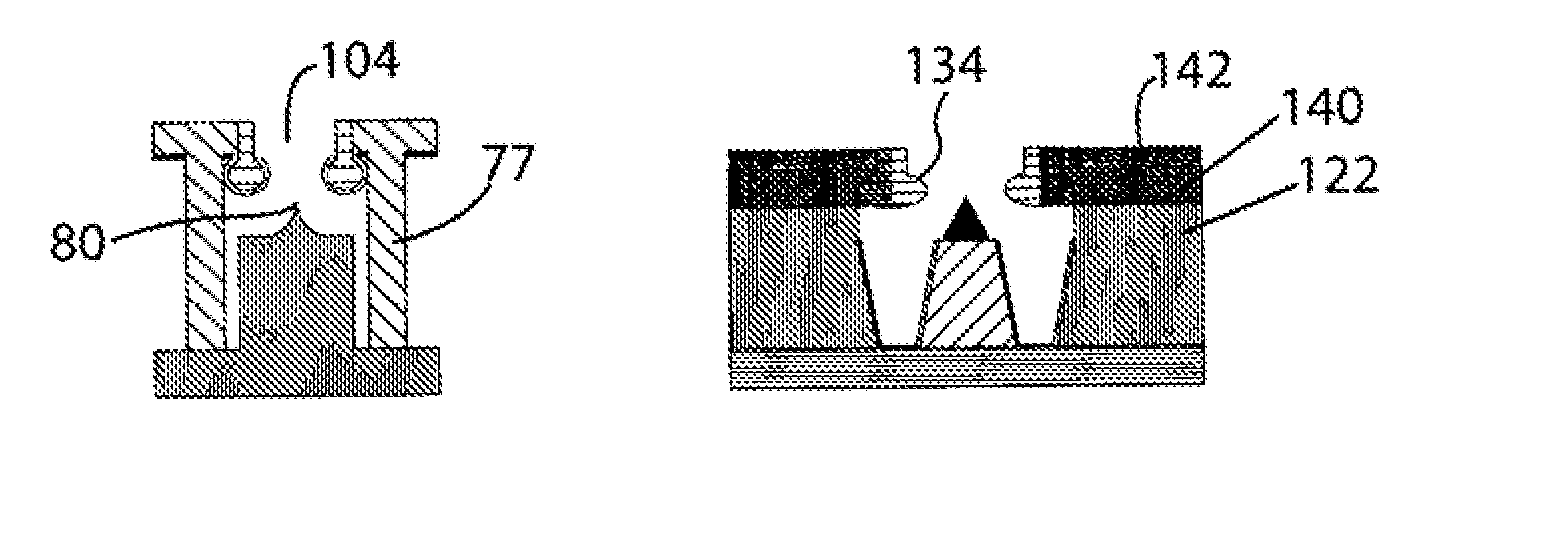

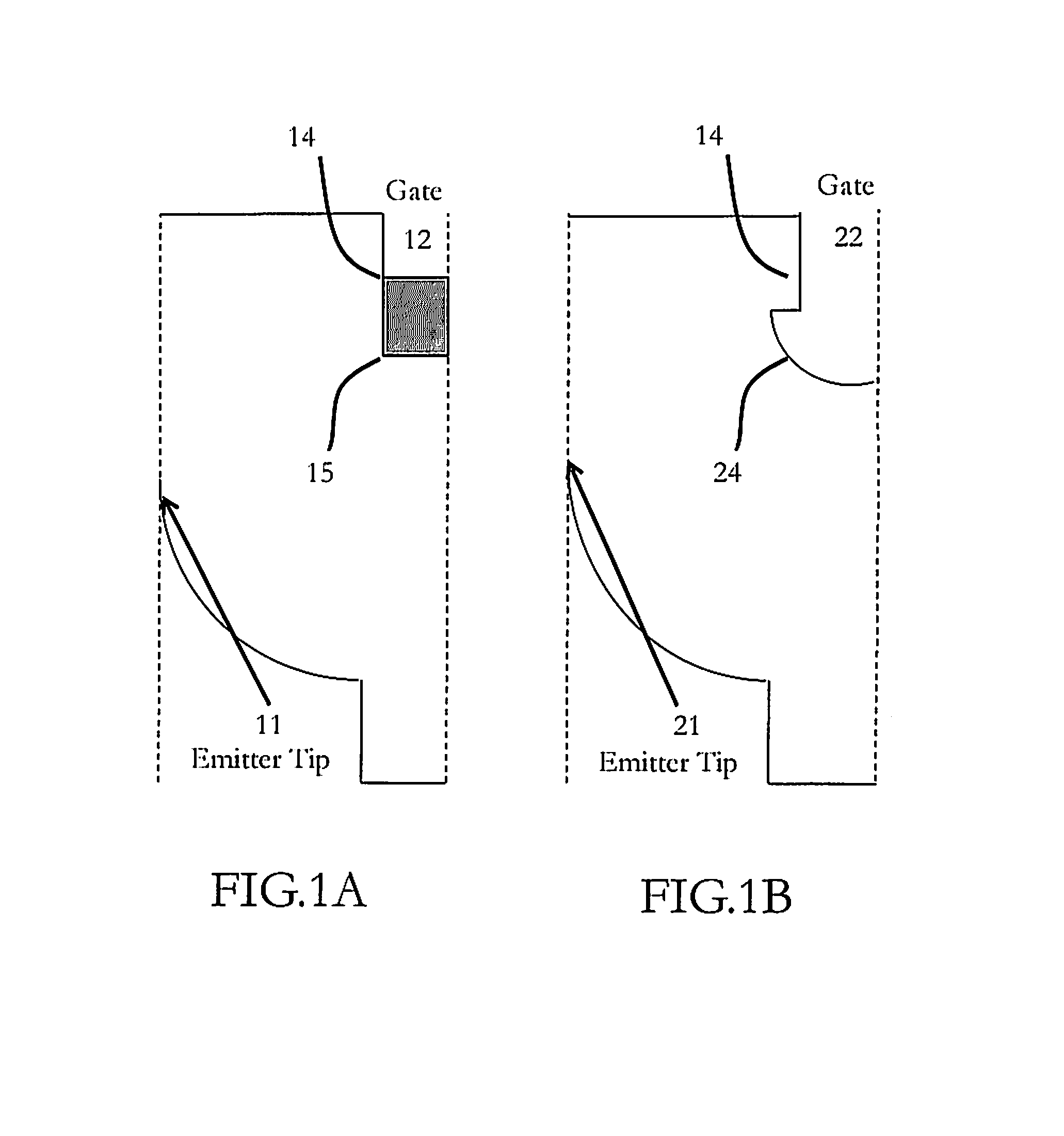

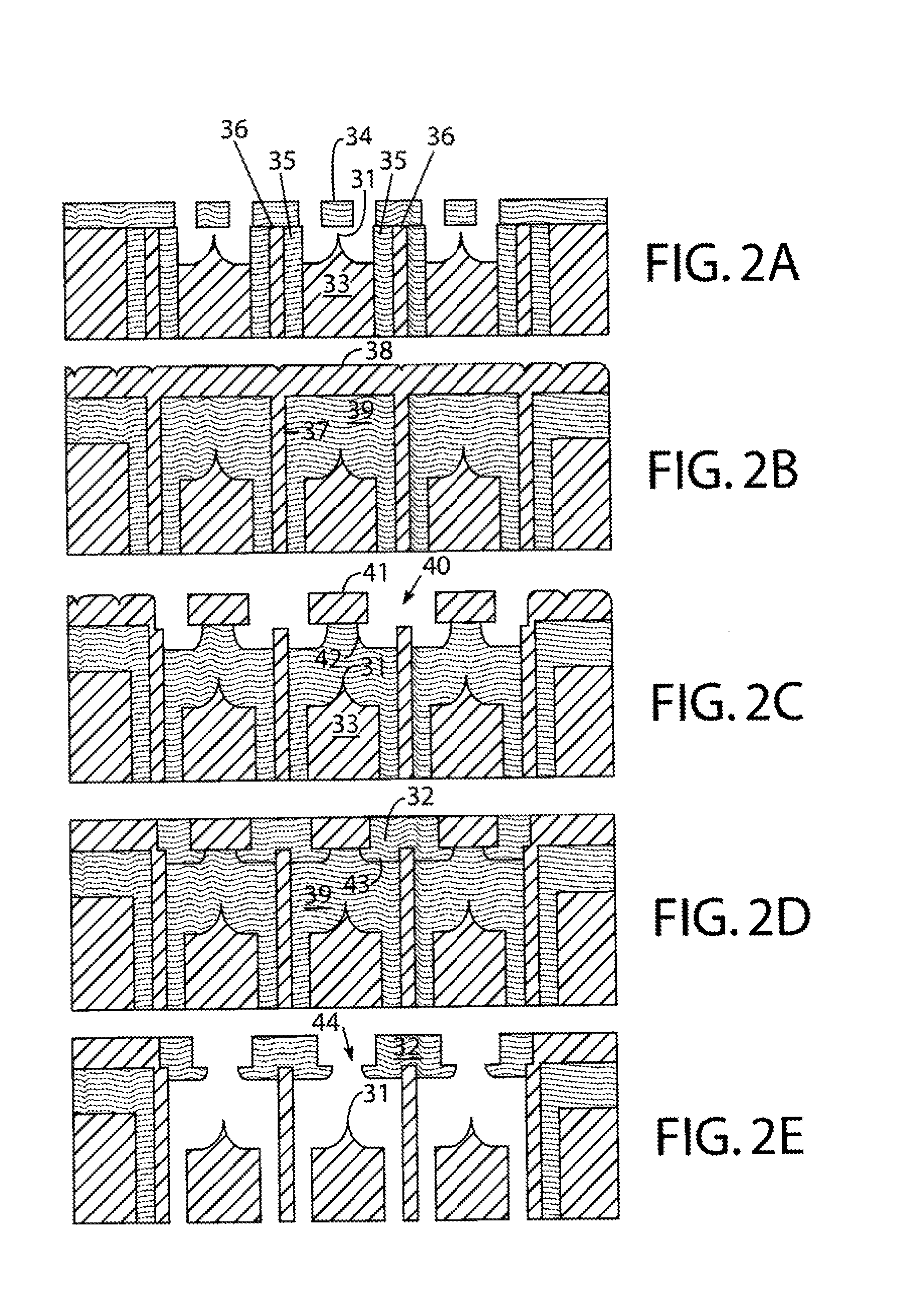

Integrated field emission array for ion desorption

ActiveUS8536564B1Minimize electric field concentratorsMaximized ratioSemiconductor/solid-state device manufacturingDischarge tube ion gunsDesorptionDielectric layer

An integrated field emission array for ion desorption includes an electrically conductive substrate; a dielectric layer lying over the electrically conductive substrate comprising a plurality of laterally separated cavities extending through the dielectric layer; a like plurality of conically-shaped emitter tips on posts, each emitter tip / post disposed concentrically within a laterally separated cavity and electrically contacting the substrate; and a gate electrode structure lying over the dielectric layer, including a like plurality of circular gate apertures, each gate aperture disposed concentrically above an emitter tip / post to provide a like plurality of annular gate electrodes and wherein the lower edge of each annular gate electrode proximate the like emitter tip / post is rounded. Also disclosed herein are methods for fabricating an integrated field emission array.

Owner:NAT TECH & ENG SOLUTIONS OF SANDIA LLC

X-ray Tube Anode Arrangement

ActiveUS20160203939A1Improve reliabilityHigh power operationX-ray tube anode coolingX-ray tube electrodesAlloyMaterials science

A method of manufacturing an X-ray tube component, includes diffusion bonding or brazing an anode of rhodium, molybdenum or tungsten to a heat spreader of molybdenum, tungsten, or a composite of molybdenum and / or tungsten. Suitable joint materials for diffusion bonding include gold; suitable joint materials for brazing include an alloy of silver and copper, an alloy of silver, copper and palladium, an alloy of gold and copper or an alloy of gold, copper and nickel. The resulting tube component delivers reliable behaviours and the joint can withstand high temperatures, high temperature gradients, fast temperature changes, extremely high radiation and extremely high electric field, while maintaining good high vacuum properties.

Owner:PANALYTICAL BV

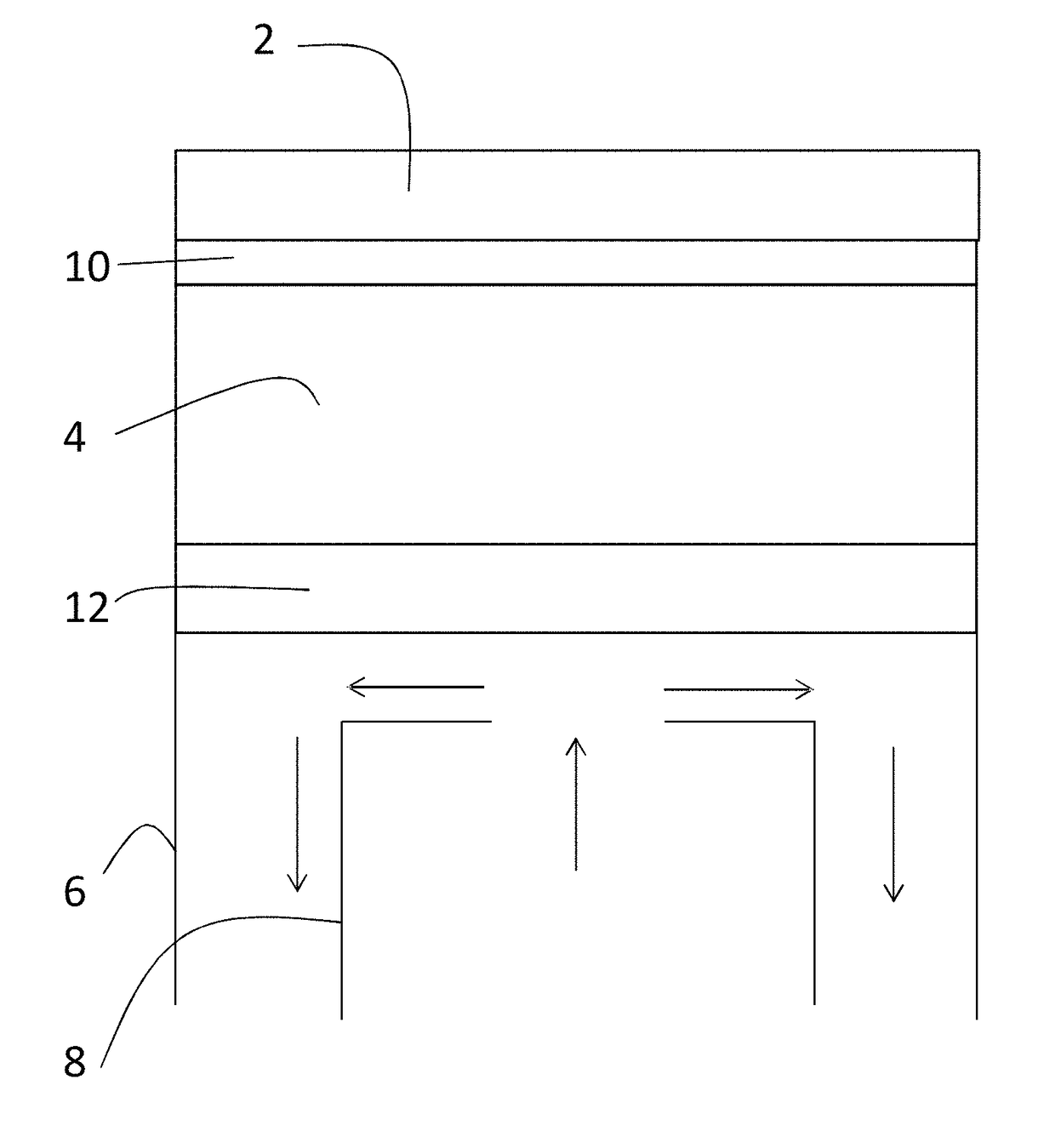

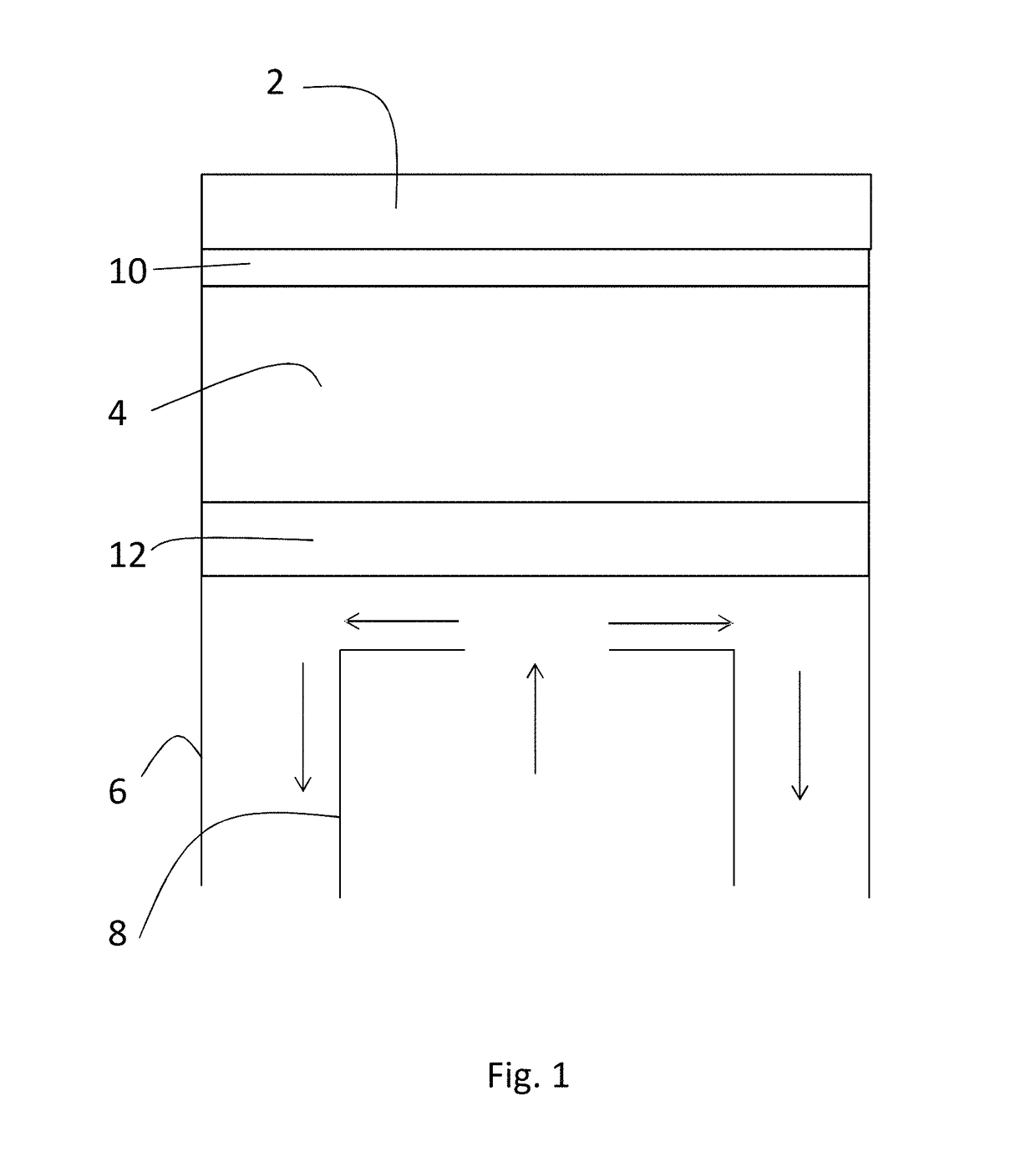

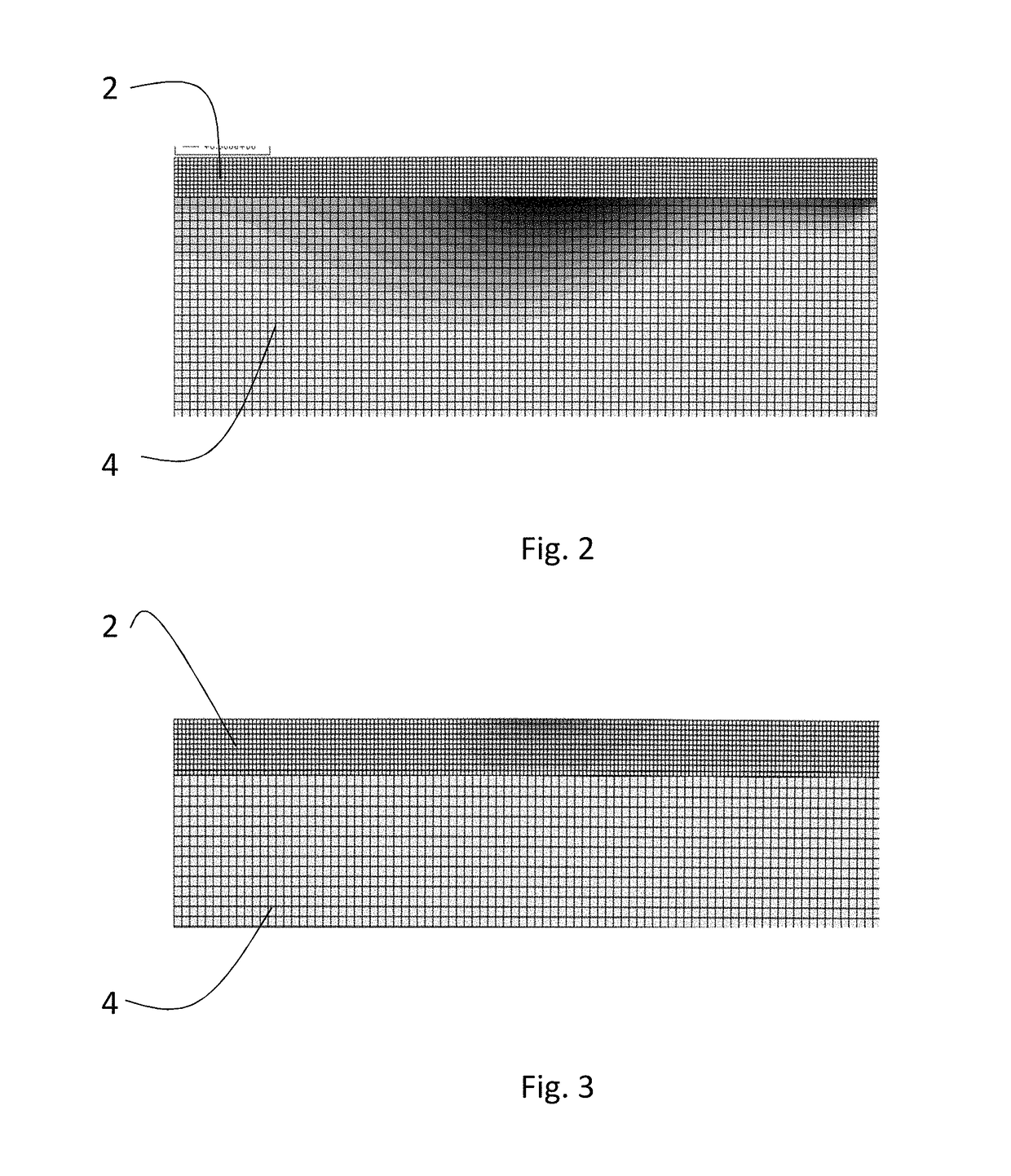

Membrane confined electrophoresis

InactiveUS20130175175A1High electric fieldHigh detectionCellsFatty/oily/floating substances removal devicesIonQuartz

A membrane confined electrophoresis cuvette assembly is used to measure the effective charge and electrophoretic mobility of macromolecules in solution. The cuvette assembly features a sample including macro-ions or macromolecules of undetermined type and quantity that is held in suspension in a quartz cuvette sealed at either end by membranes. An electrical current is passed through the cuvette which establishes an electric field along the length of the cuvette assembly. The electric field forces charged macroions to move through the cuvette. The cuvette is bathed in collimated UV light while an absorbance profile measures the ion concentration distribution along the cuvette. The membrane confined electrophoresis provides two complimentary modes of sample analysis: steady state electrophoresis and real-time electrophoretic mobility. The cuvette assembly can be used with a software program that features experiment design control, and complete data analysis of the experiment(s).

Owner:SPIN ANALYTICAL

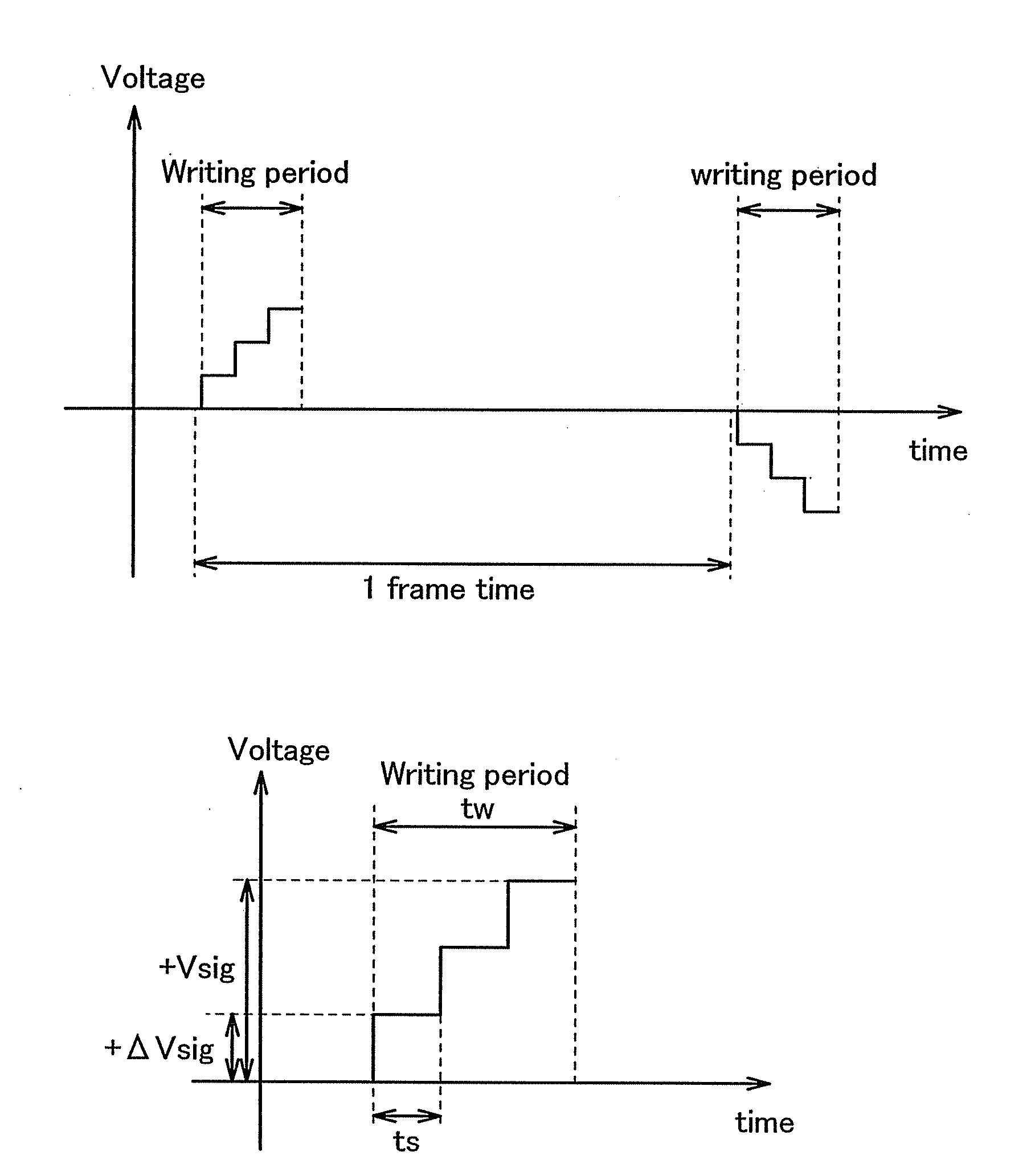

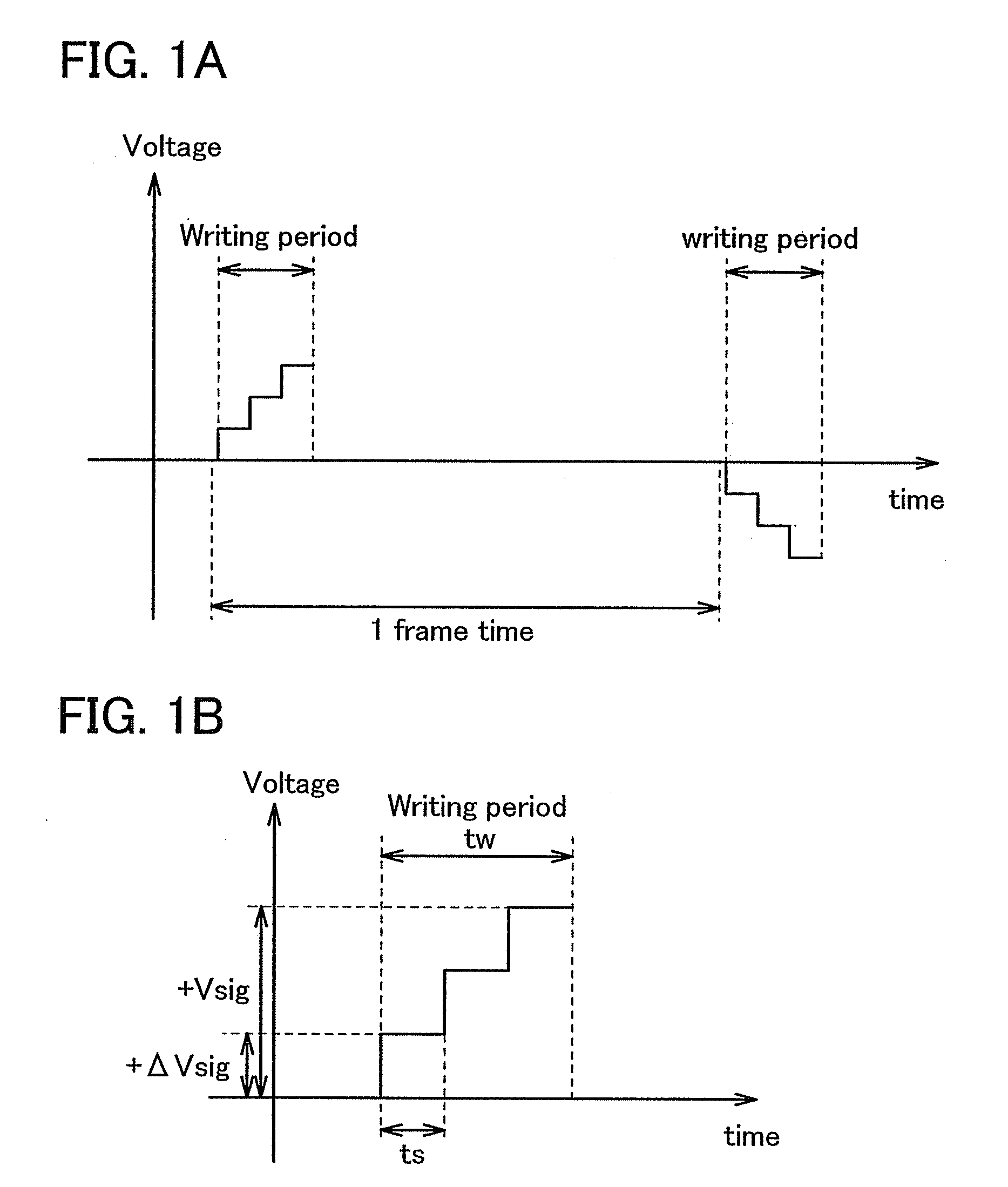

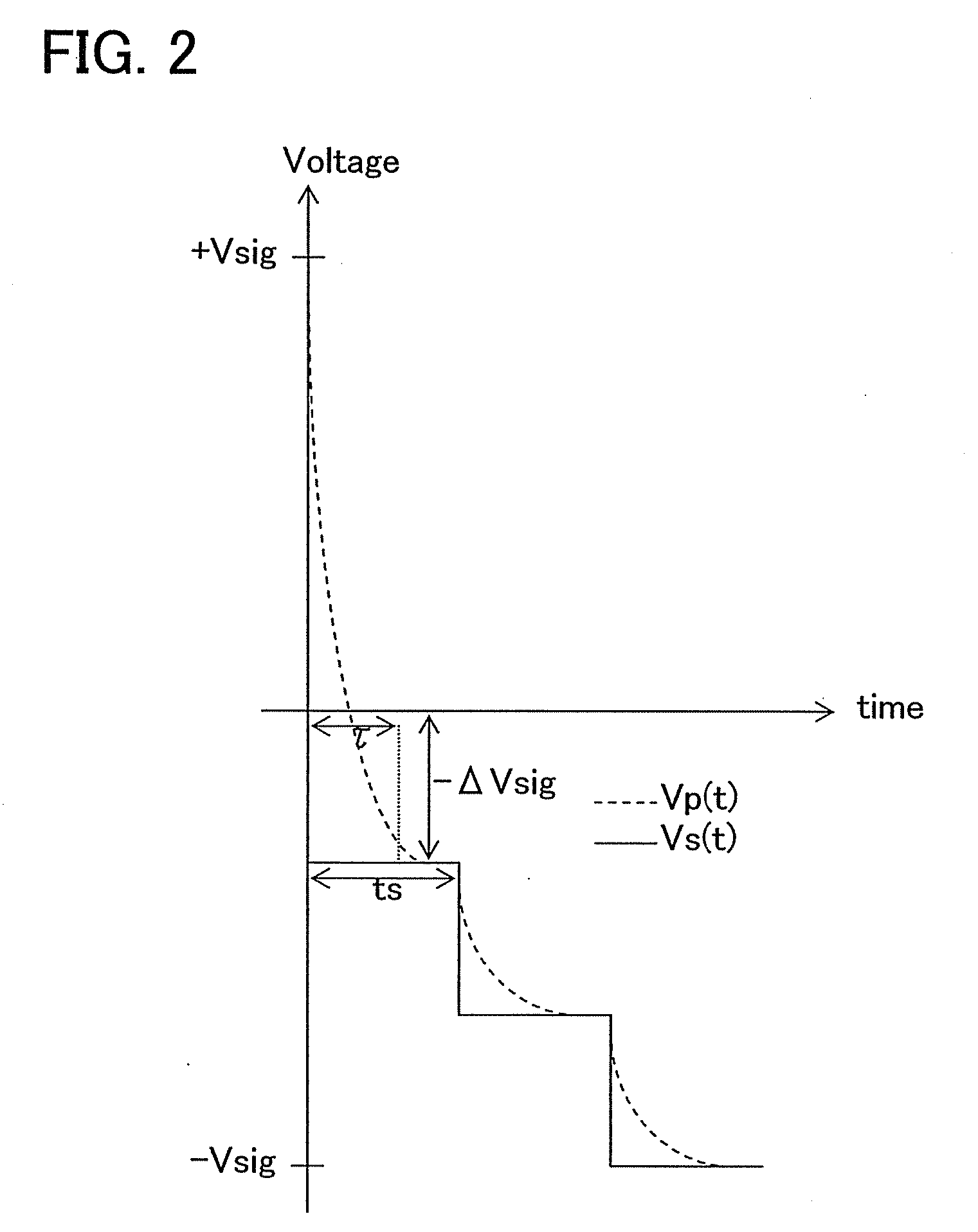

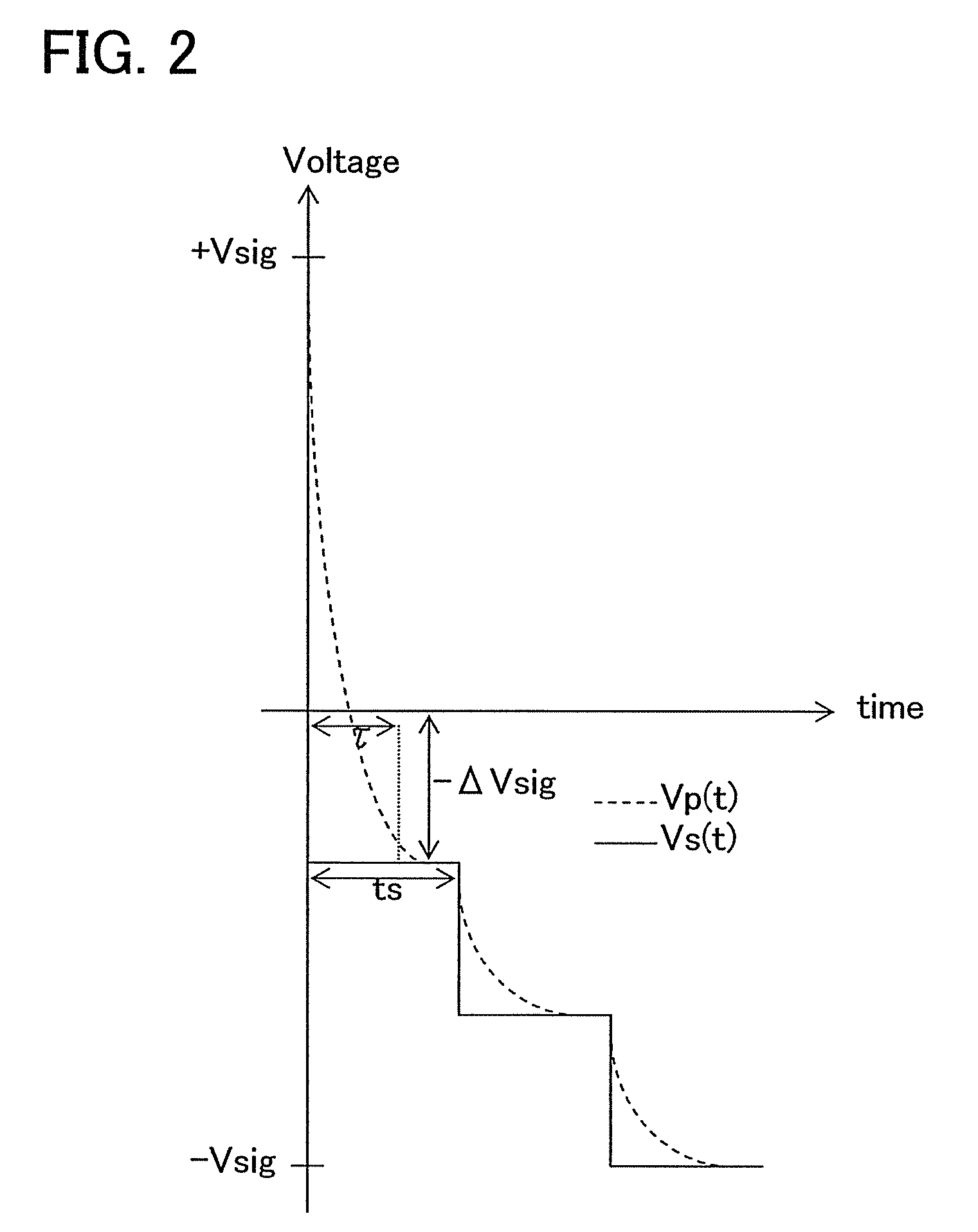

Display Device, and Driving Method of Display Device

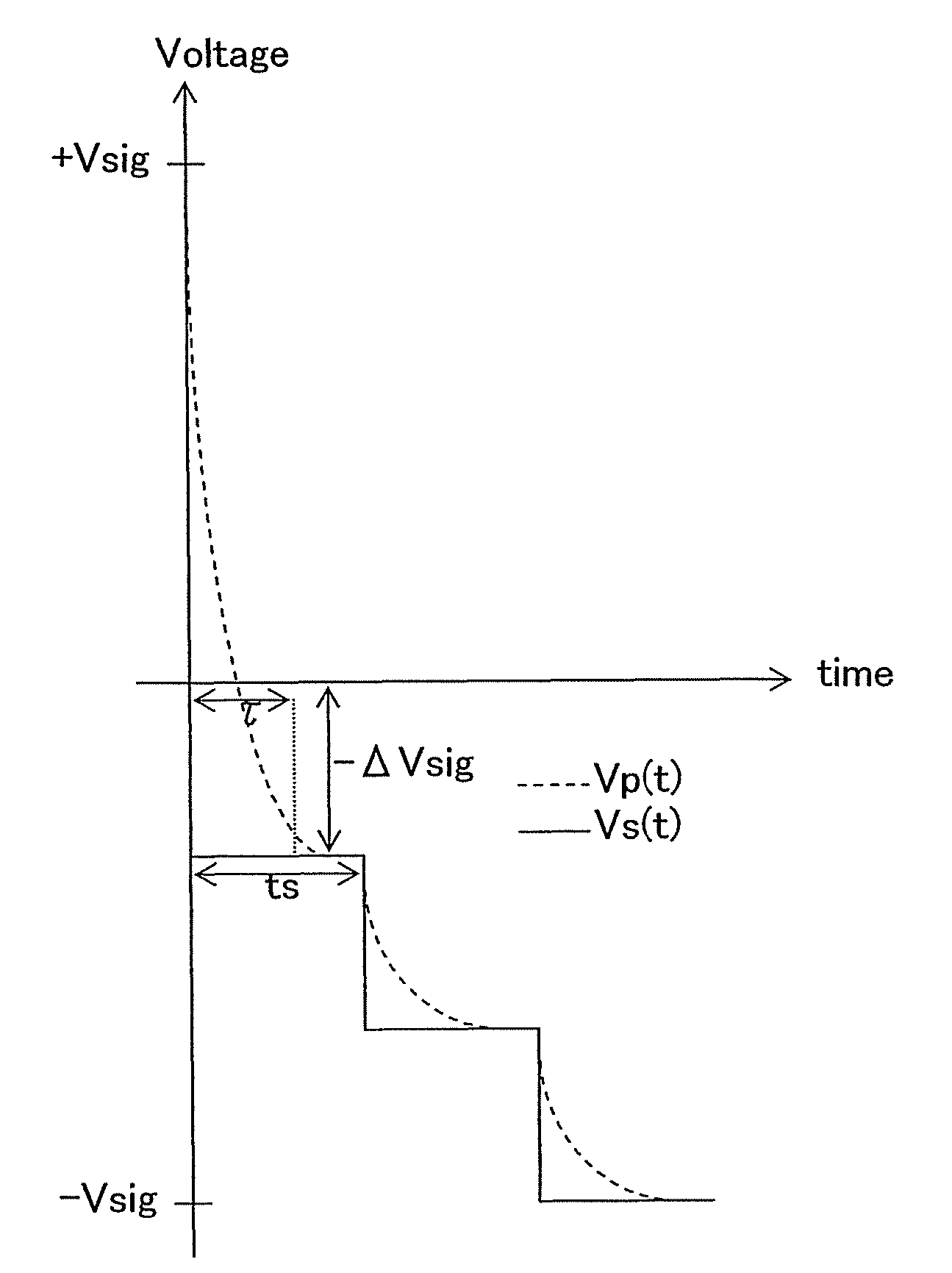

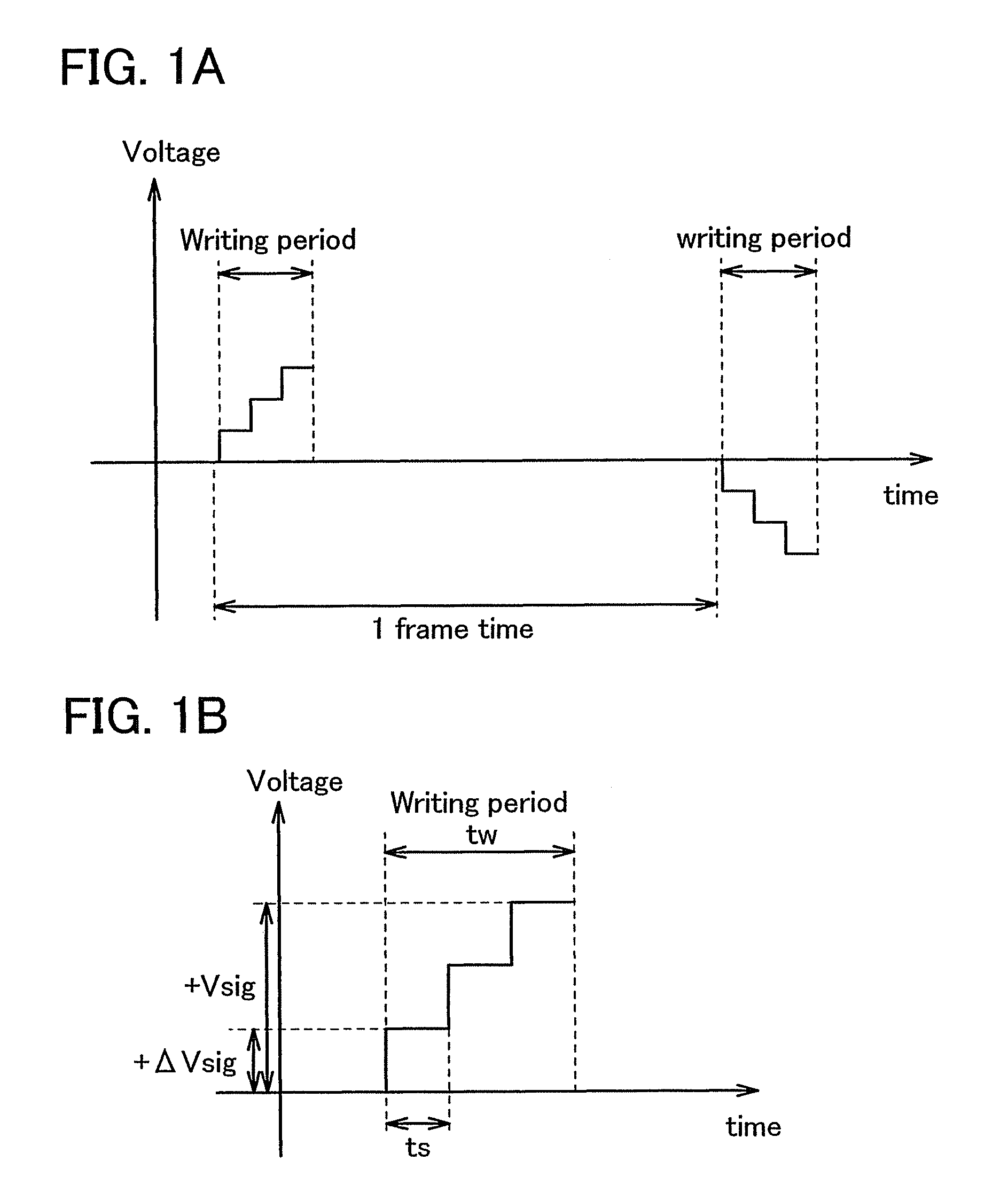

InactiveUS20080231622A1Reliable switchingImprove display reliabilityCathode-ray tube indicatorsNon-linear opticsDisplay deviceCapacitor

It is an object to provide a high reliable display device which can suppress the generation of high electric field near the drain of the transistor used as a switching element and a driving method thereof. A relaxation time when charge is stored in the display element of the pixel and other capacitors connected to the display element in parallel is focused on, and the voltage applied between the source and the drain of the transistor in the writing period is suppressed by changing the video signal applied to the signal line step by step and finally setting it at the desired level.

Owner:SEMICON ENERGY LAB CO LTD

Semiconductor device and method of manufacturing the same

ActiveUS9306030B2Suppress failureHigh electric fieldSemiconductor devicesEngineeringElectrode Contact

A semiconductor device includes a semiconductor layer formed on a substrate, an electrode contact window that includes a recess formed on a surface of the semiconductor layer, an inner wall having a slope, and a source electrode, a drain electrode, and a gate electrode formed on the semiconductor layer, in which the drain electrode is in contact with the slope of the inner wall.

Owner:SUMITOMO ELECTRIC DEVICE INNOVATIONS

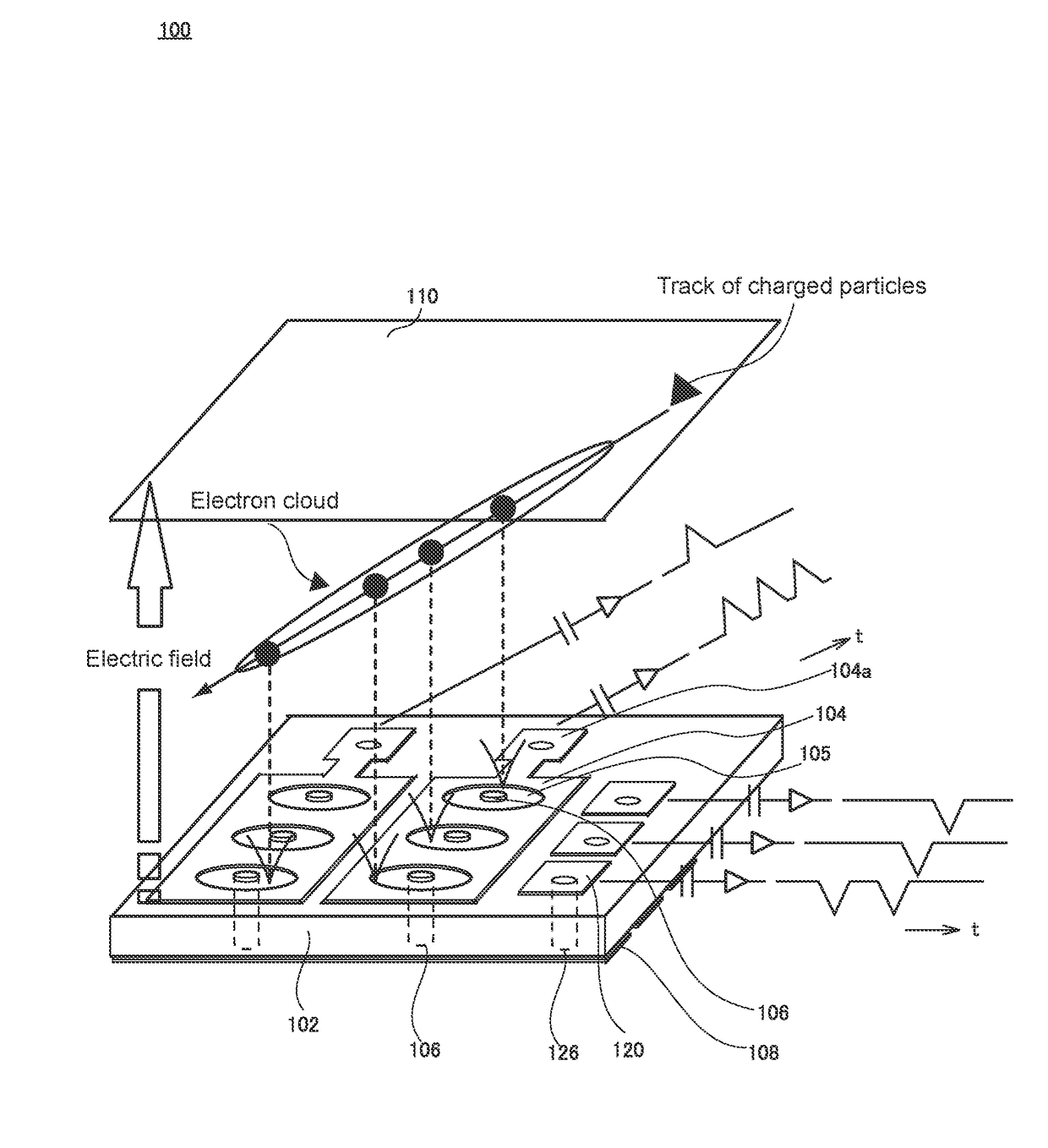

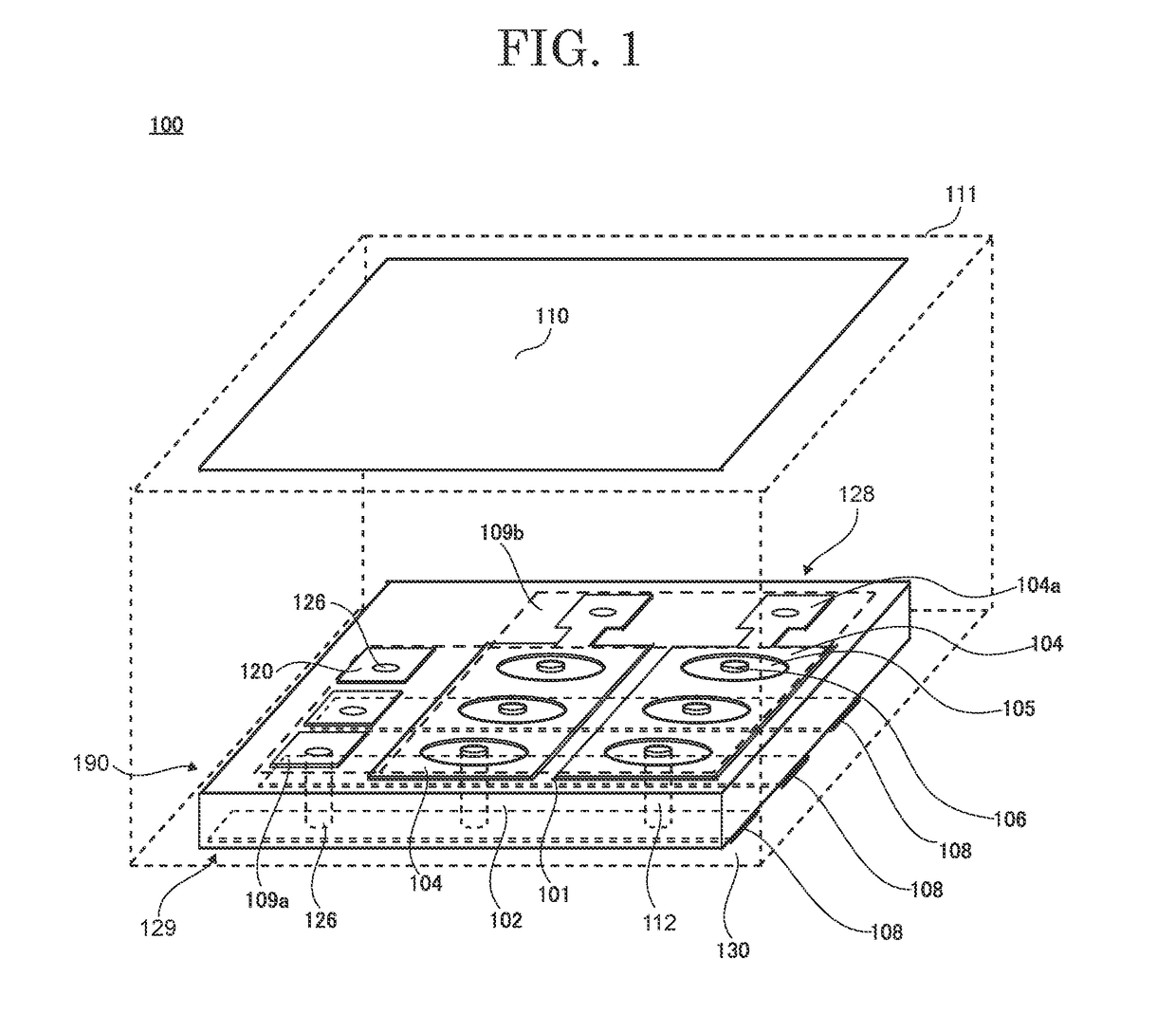

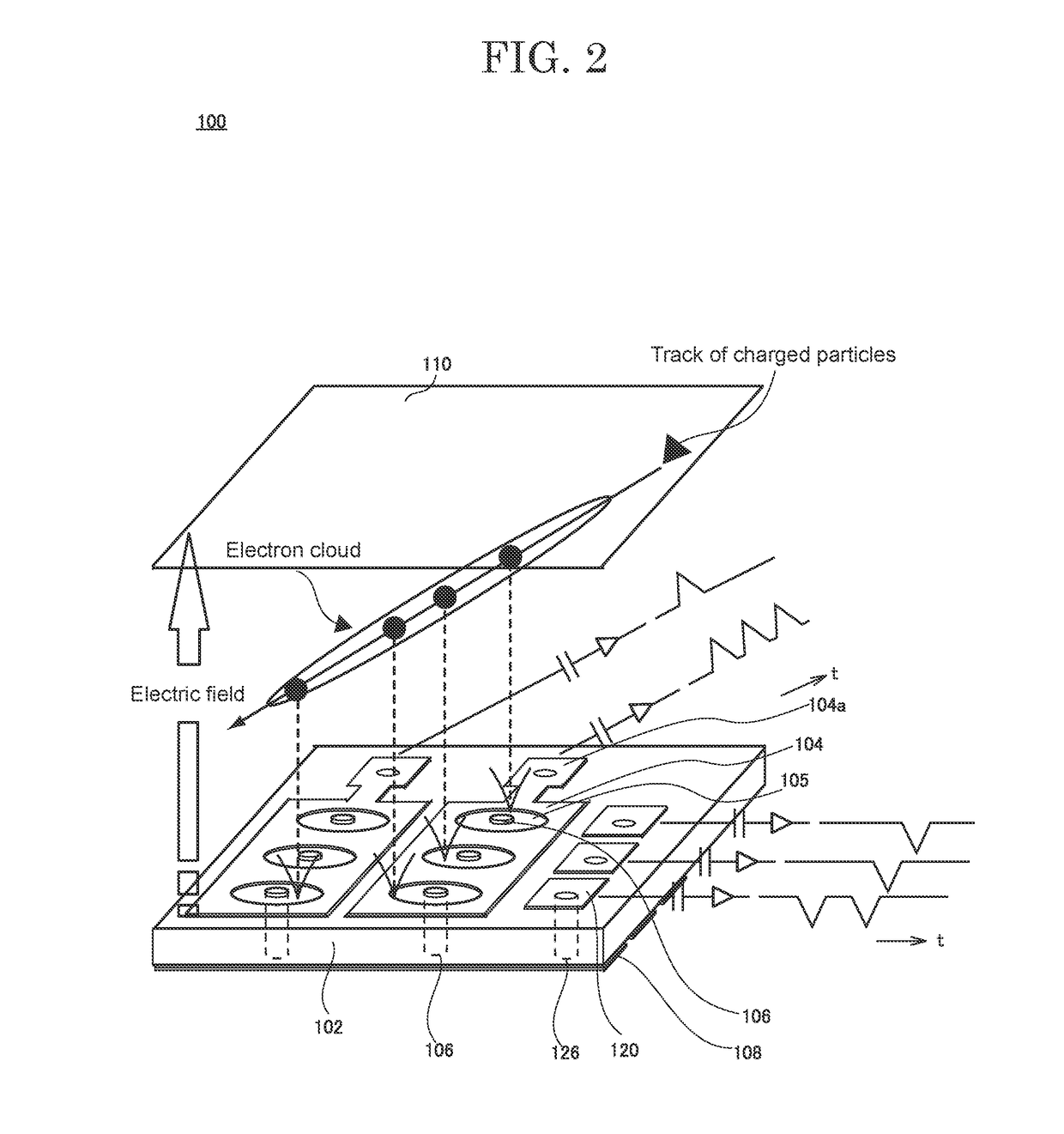

Detection element

ActiveUS20180246226A1High electric fieldIncrease signal strengthElectric discharge tubesX/gamma/cosmic radiation measurmentPhysicsHigh signal intensity

A detection element can obtain a high-resolution radiation image having a high signal intensity and a high S / N ratio. A detection element including a substrate having a through hole, an insulating layer arranged inside of the through hole, a through electrode arranged further to the inner side of the through hole than the insulating layer, a resin layer having insulating properties and having an opening portion exposing the through electrode, a first electrode arranged above the through electrode and the resin layer, the first electrode being connected to the through electrode through the opening portion, and a second electrode arranged above the resin layer, the second electrode being separated from the first electrode.

Owner:DAI NIPPON PRINTING CO LTD

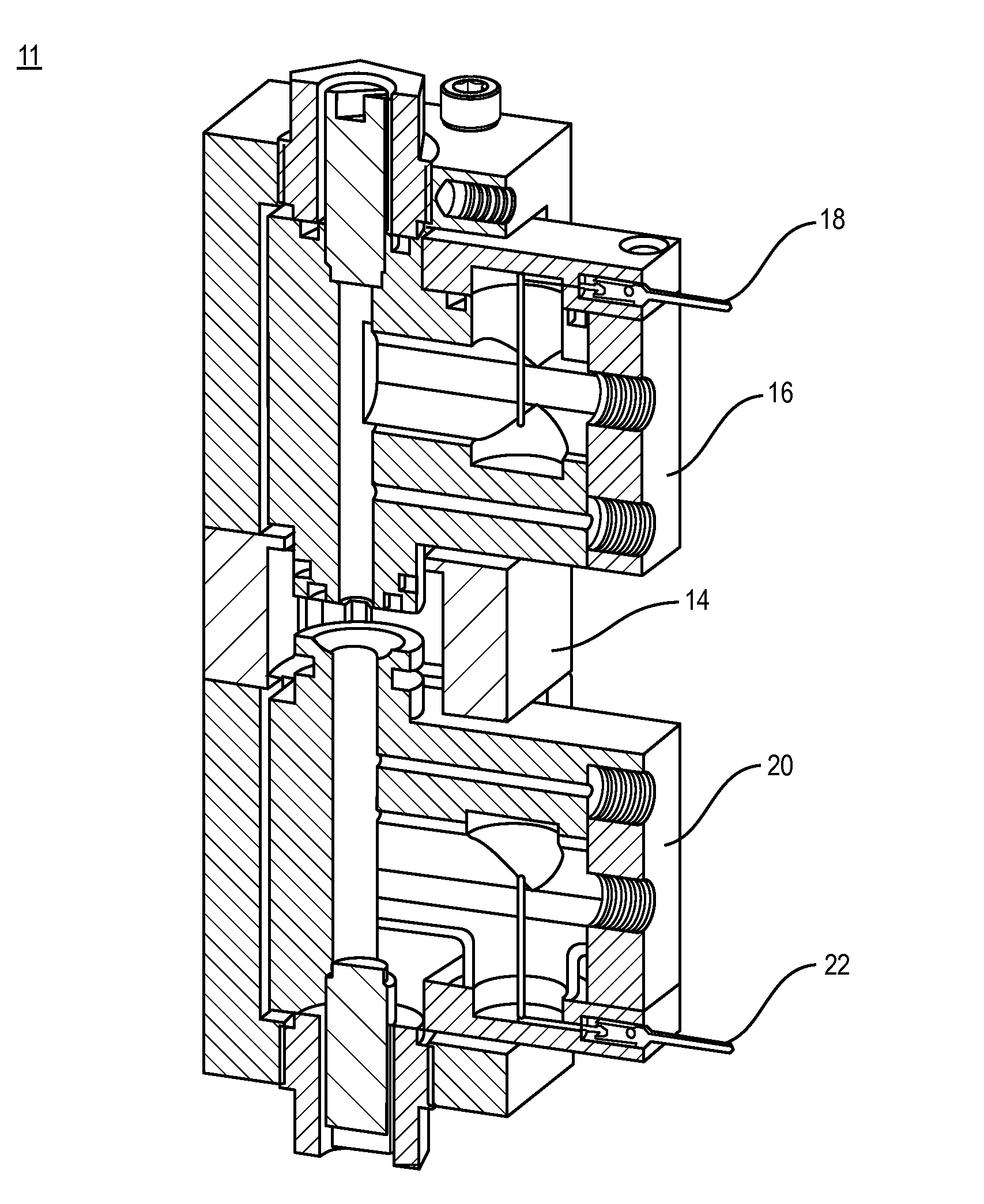

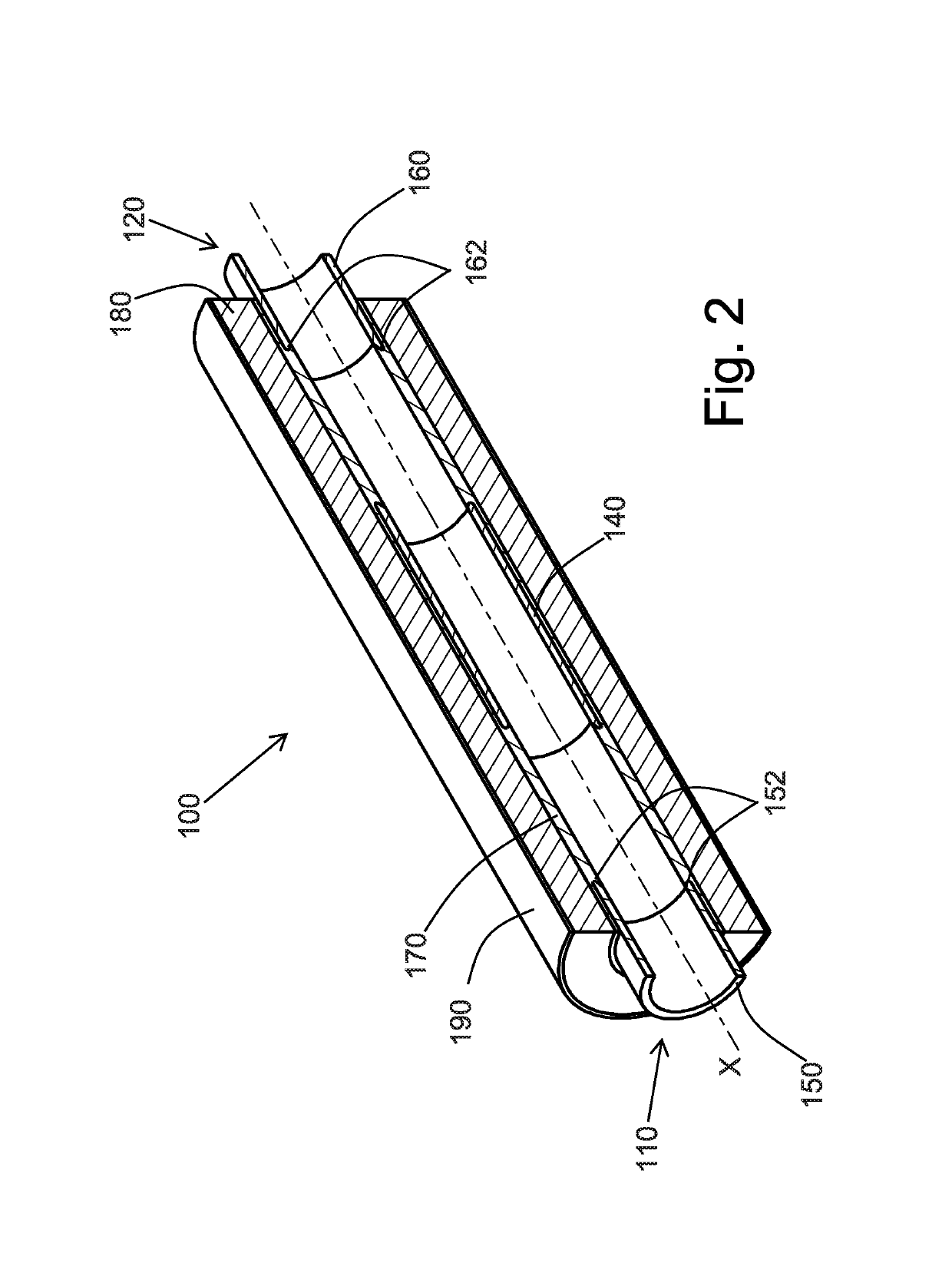

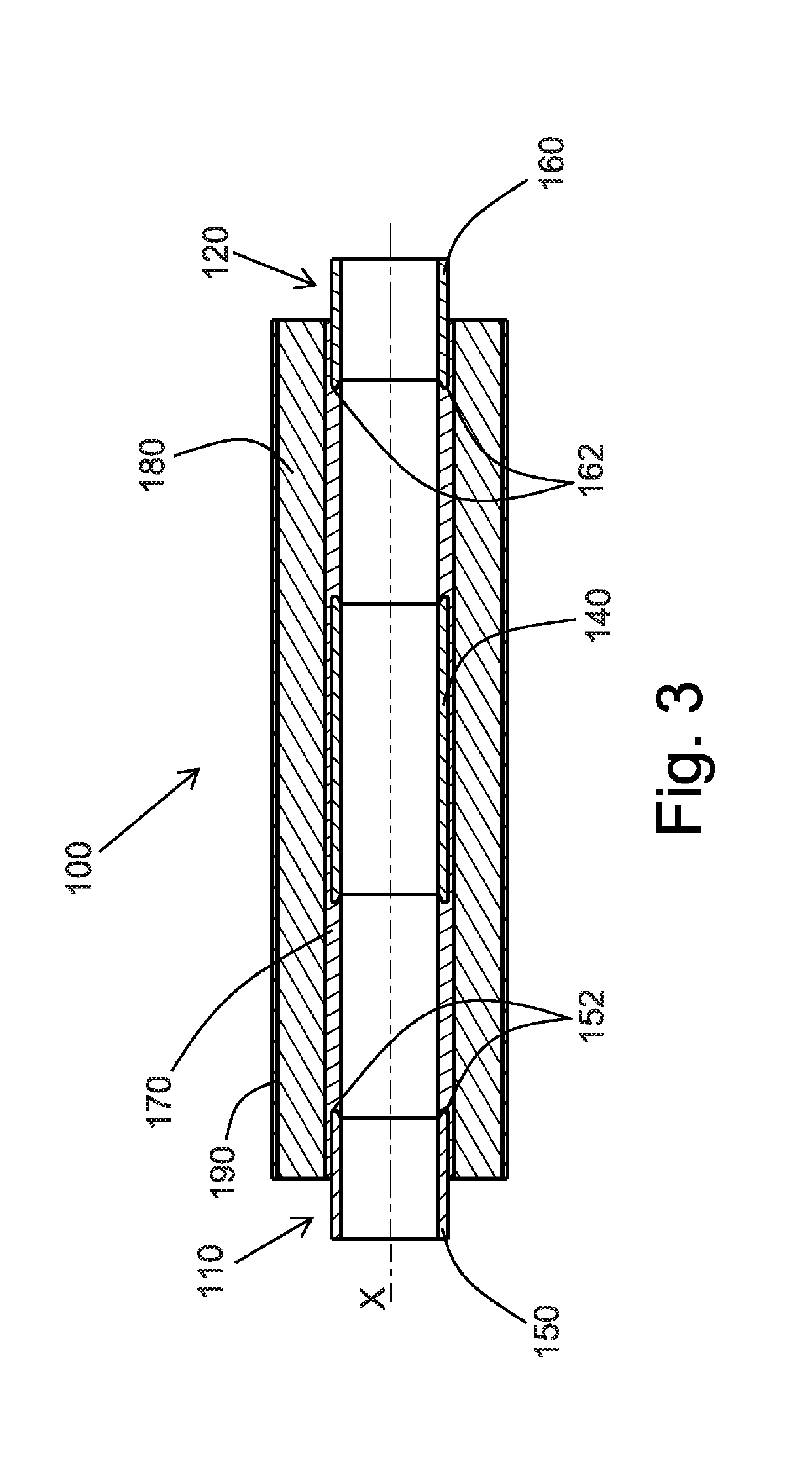

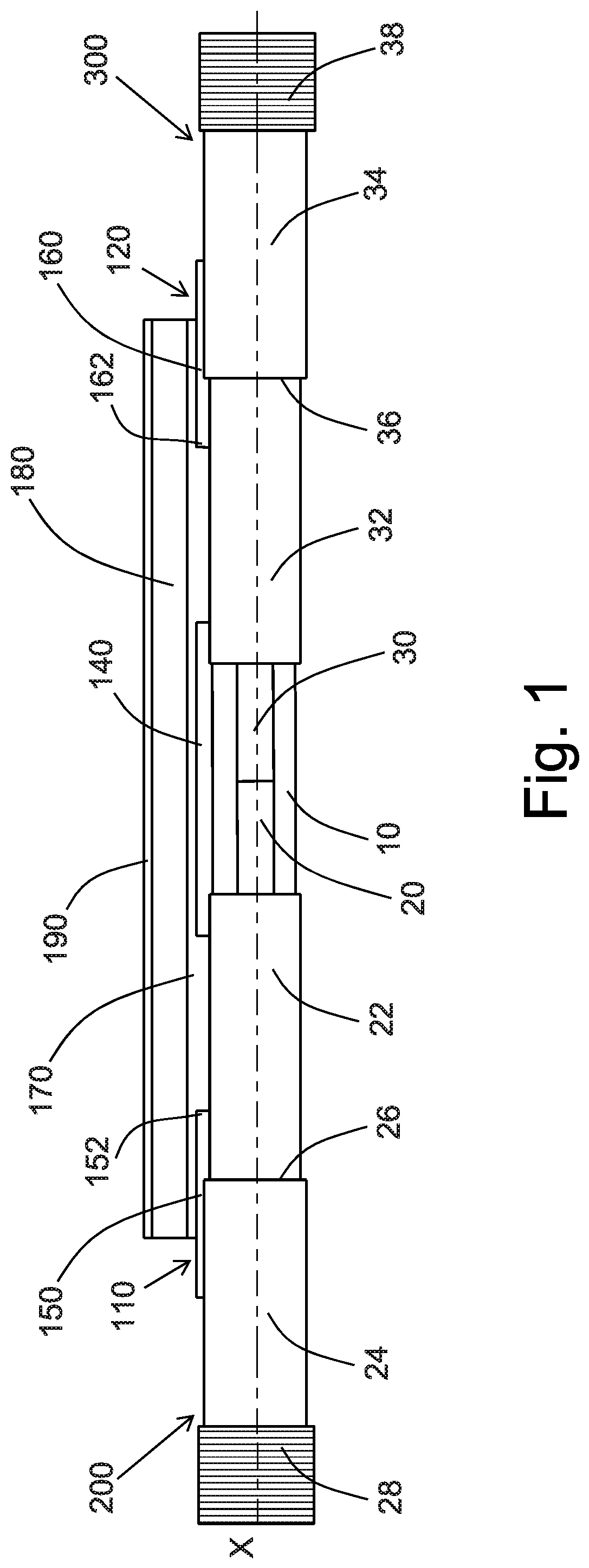

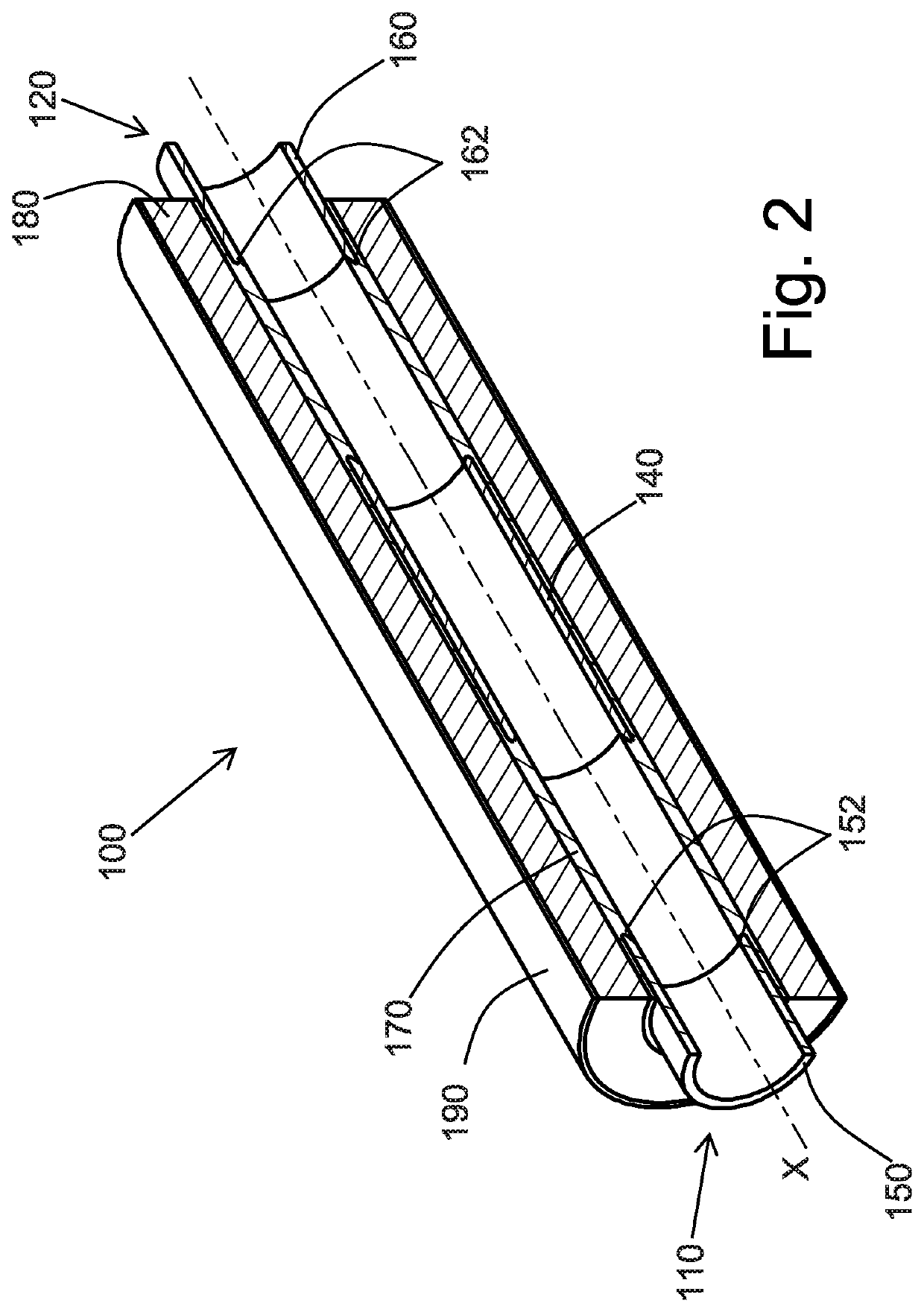

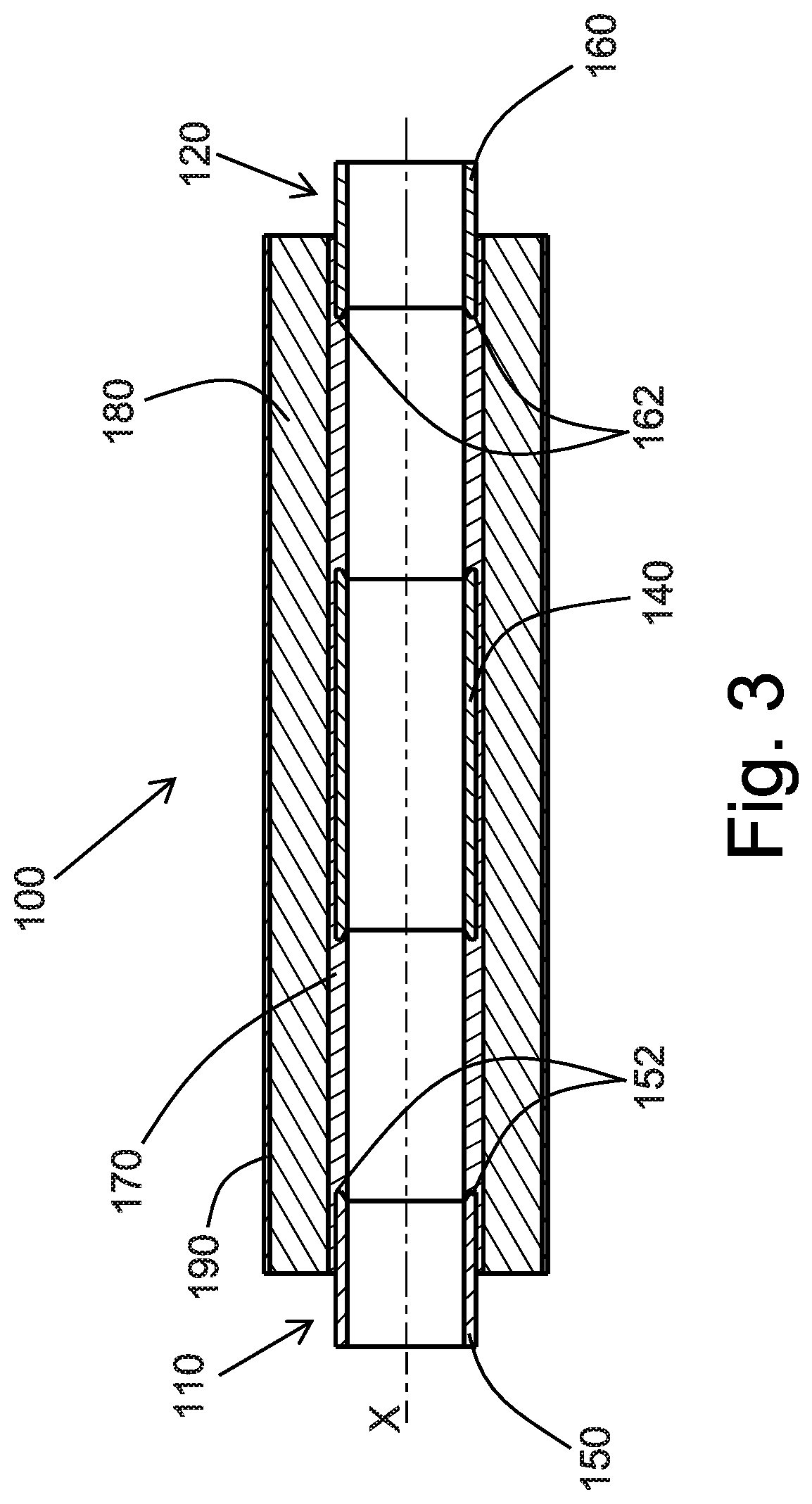

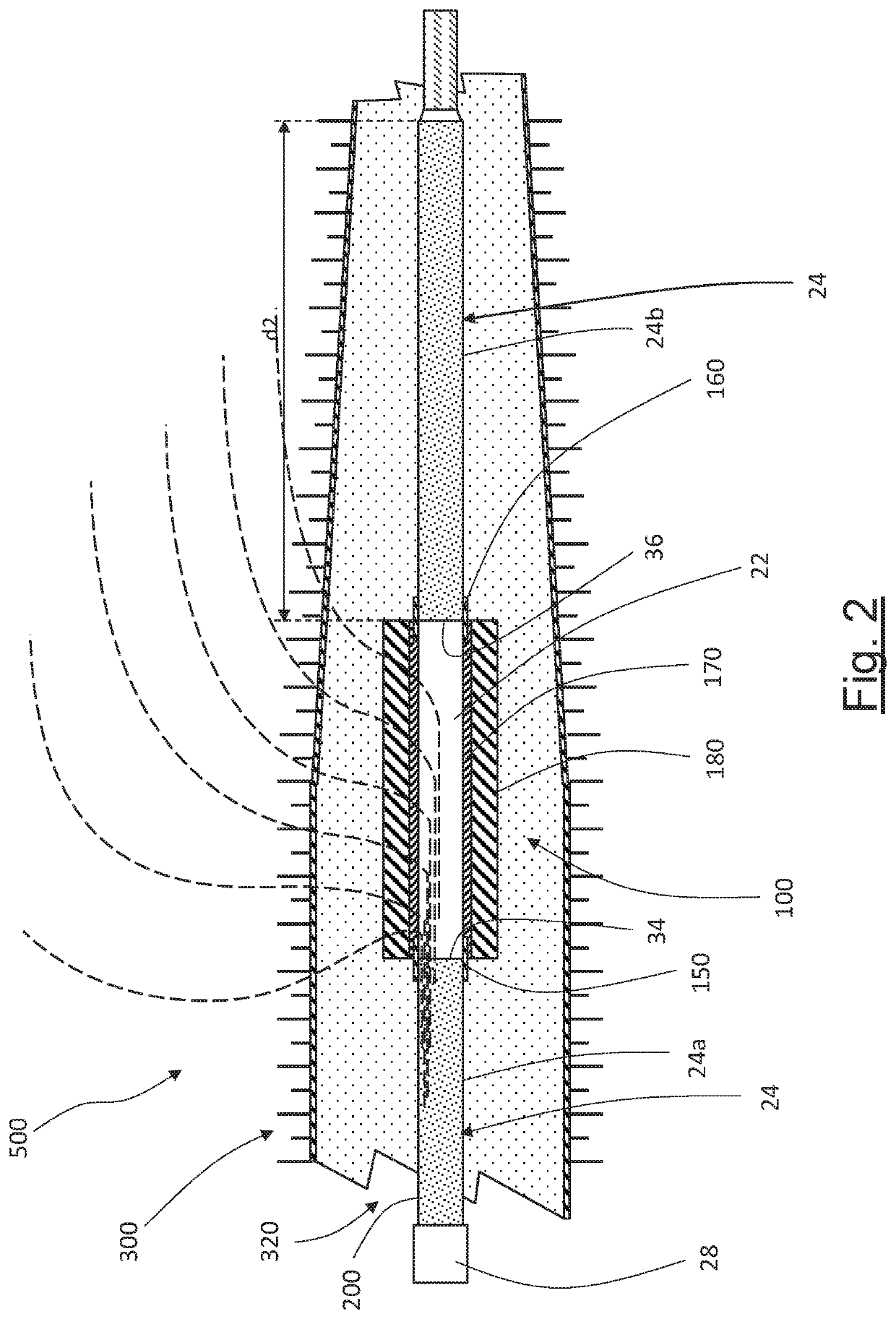

Joint for high voltage direct current cables

ActiveUS20190237958A1Reduce riskPrevents undesired charge accumulationCable fittingsElectricityHigh-voltage direct current

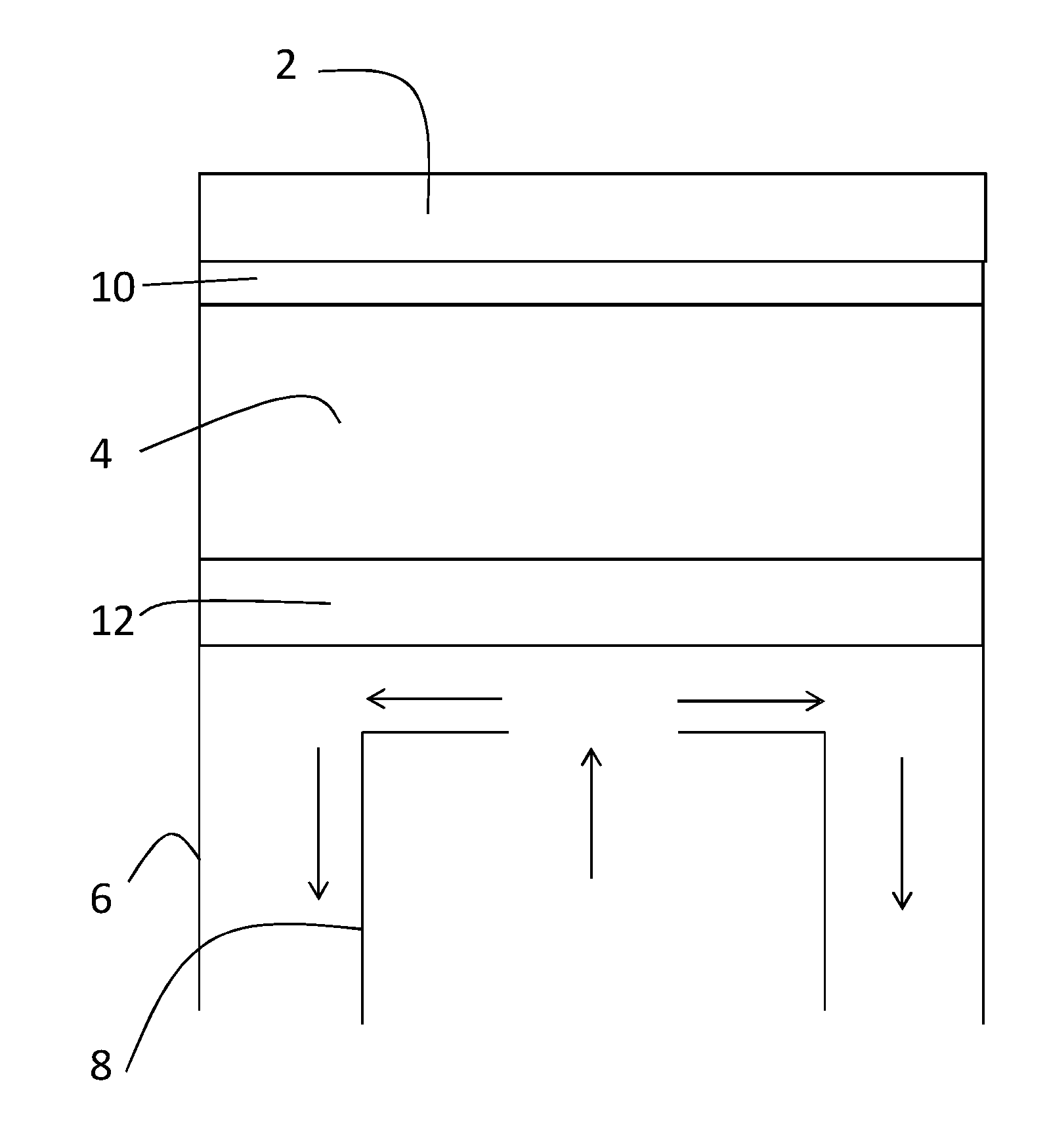

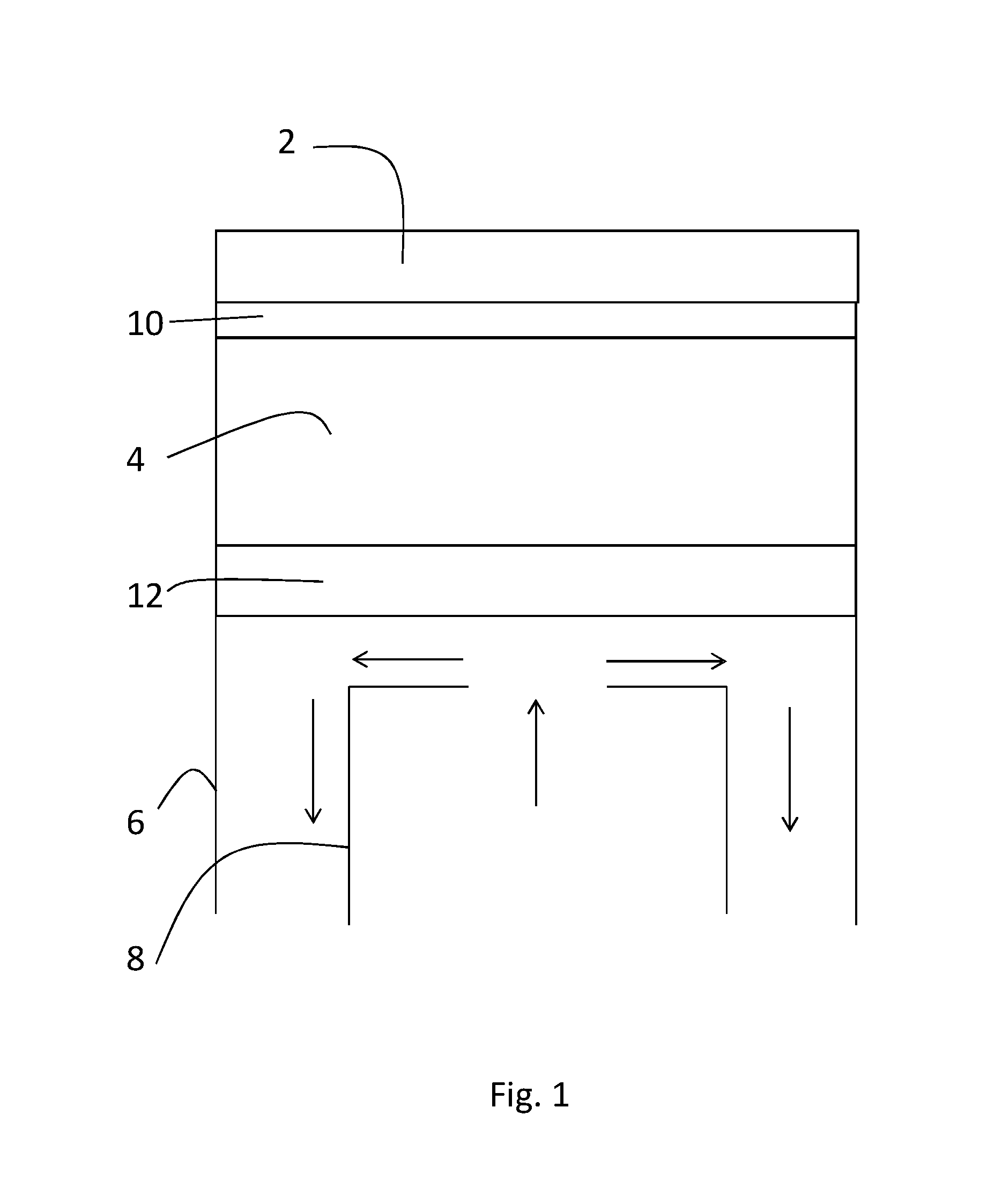

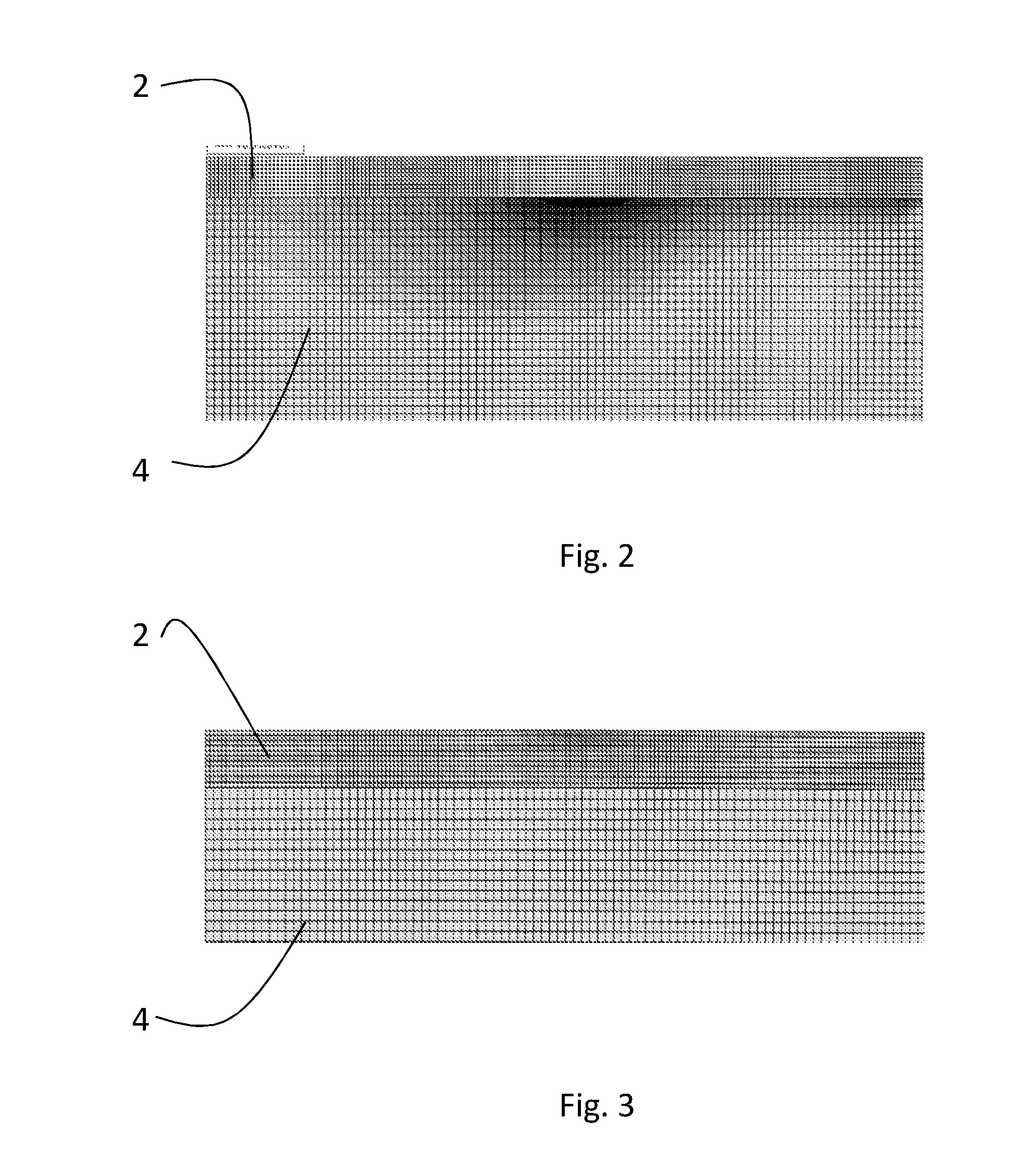

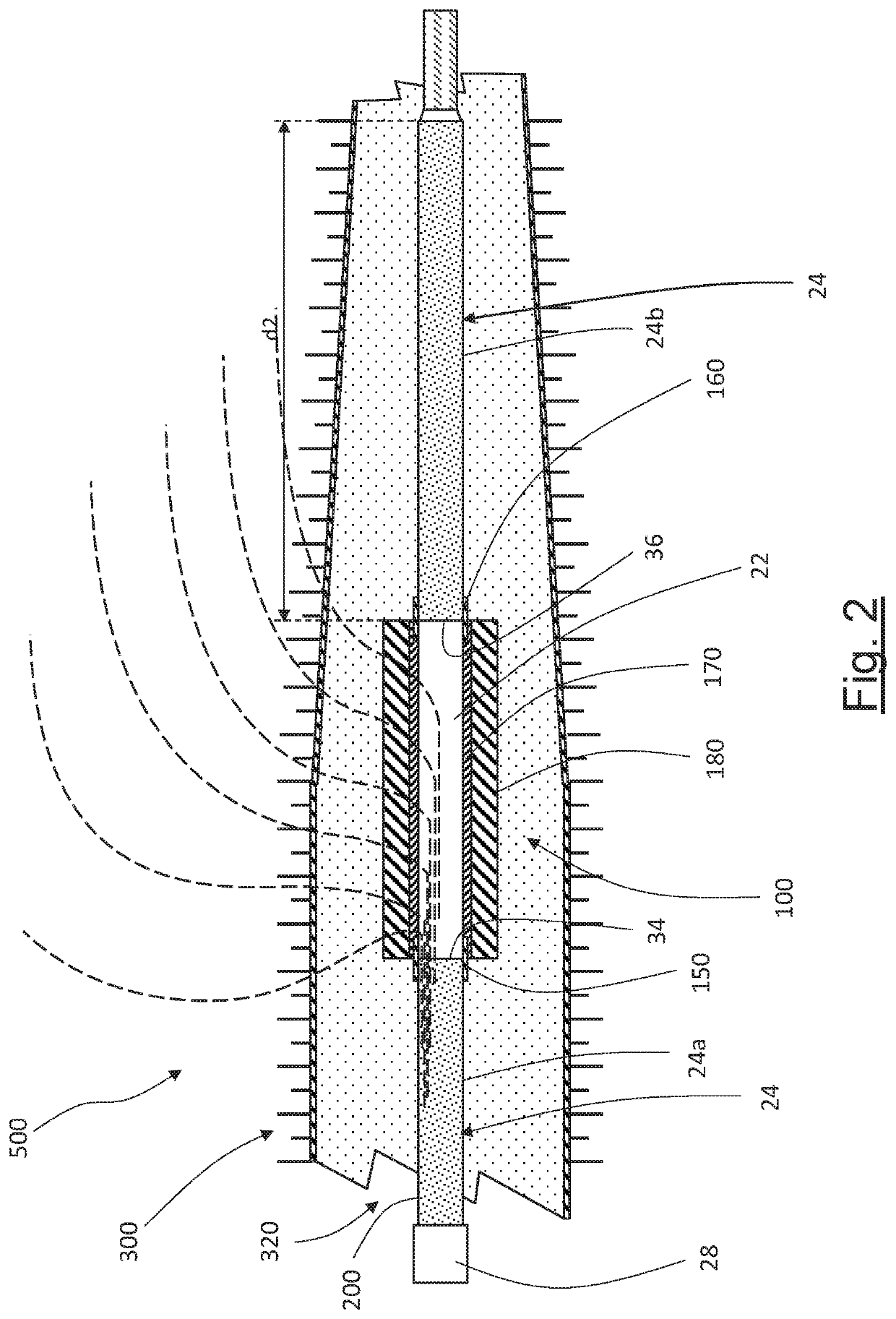

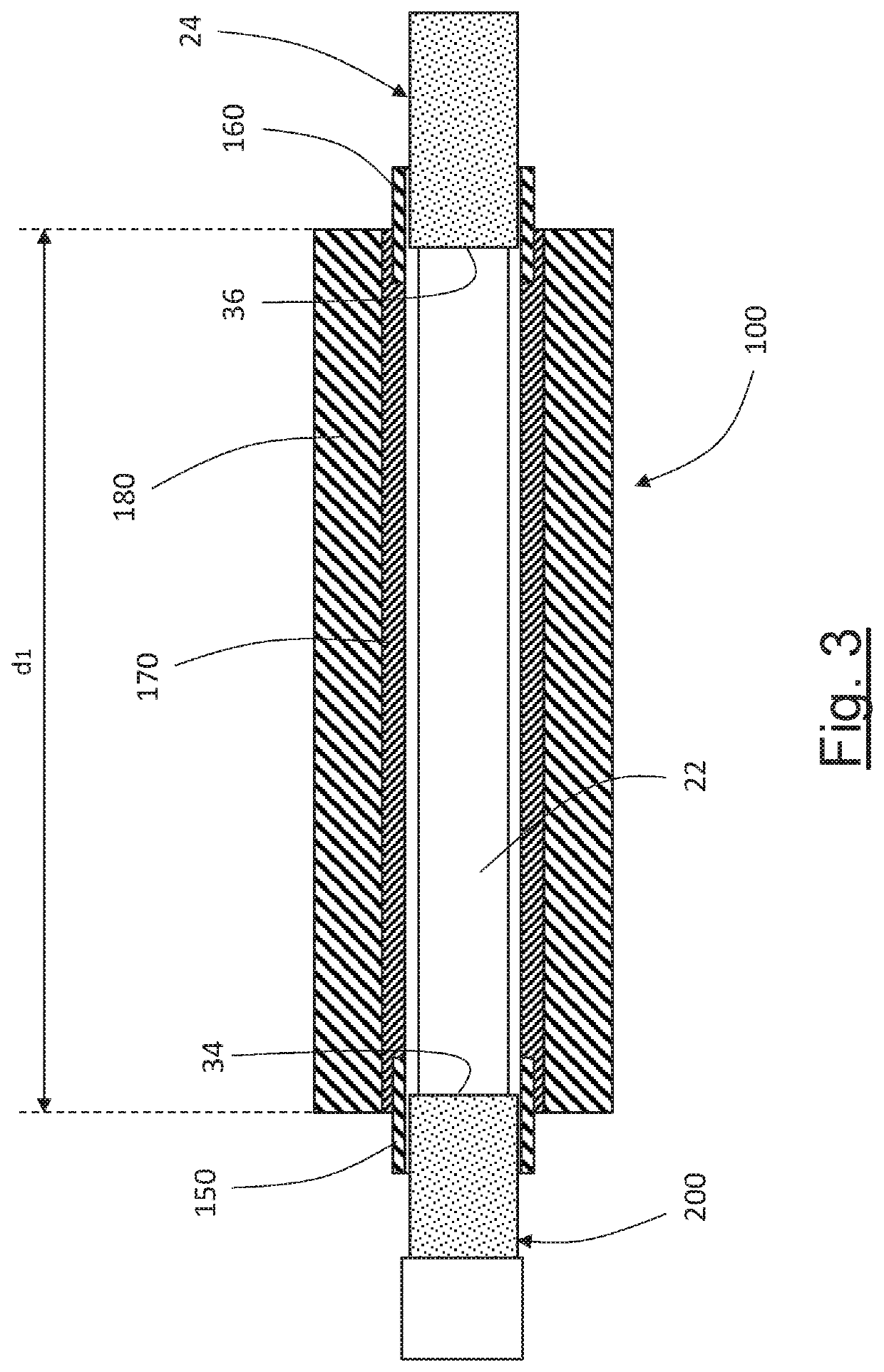

The present invention relates to a joint (100) for high voltage direct current cables (200, 300) extending 5 along a longitudinal axis (X) between two opposite end portions (110, 120), the joint (100) comprising: —a central semiconducting electrode (140); —two semiconducting deflectors (150, 160); —a field grading layer (170) longitudinally extending 10 between each one of the deflectors (150, 160) and the central electrode (140) and in electric contact therewith; —a joint insulating layer (180) surrounding the central electrode (140), the two deflectors (150, 160) 15 and the field grading layer (170); and —a joint outer semiconductive layer (190) surrounding and in direct contact with the insulating layer (180).

Owner:PRYSMIAN SPA

Semiconductor device and method of manufacturing the same

ActiveUS20140306233A1Suppress failureImprove apparatus characteristicSemiconductor/solid-state device manufacturingSemiconductor devicesEngineeringElectrode Contact

A semiconductor device includes a semiconductor layer formed on a substrate, an electrode contact window that includes a recess formed on a surface of the semiconductor layer, an inner wall having a slope, and a source electrode, a drain electrode, and a gate electrode formed on the semiconductor layer, in which the drain electrode is in contact with the slope of the inner wall.

Owner:SUMITOMO ELECTRIC DEVICE INNOVATIONS

X-ray tube anode arrangement

ActiveUS9911569B2Improve cooling effectImprove reliabilityX-ray tube anode coolingX-ray tube electrodesAlloyElectric field

A method of manufacturing an X-ray tube component, includes diffusion bonding or brazing an anode of rhodium, molybdenum or tungsten to a heat spreader of molybdenum, tungsten, or a composite of molybdenum and / or tungsten. Suitable joint materials for diffusion bonding include gold; suitable joint materials for brazing include an alloy of silver and copper, an alloy of silver, copper and palladium, an alloy of gold and copper or an alloy of gold, copper and nickel. The resulting tube component delivers reliable behaviors and the joint can withstand high temperatures, high temperature gradients, fast temperature changes, extremely high radiation and extremely high electric field, while maintaining good high vacuum properties.

Owner:PANALYTICAL BV

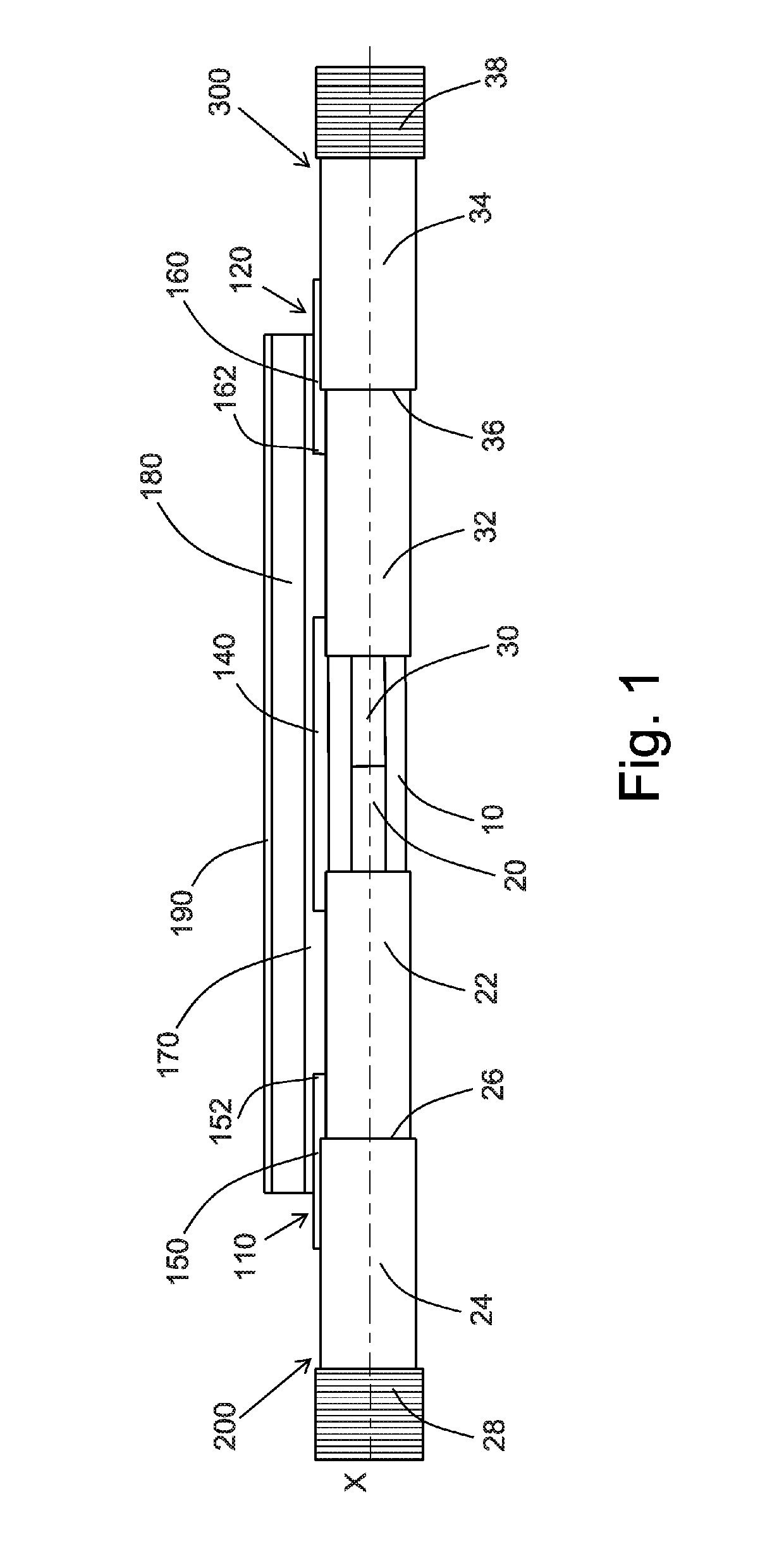

Joint for high voltage direct current cables

ActiveUS10903639B2Reduce riskPrevents undesired charge accumulationCable fittingsHigh-voltage direct currentElectric cables

A joint for high voltage direct current cables extending along a longitudinal axis between two opposite end portions, the joint including: —a central semiconducting electrode; —two semiconducting deflectors; —a field grading layer longitudinally extending between each one of the deflectors and the central electrode and in electric contact therewith; —a joint insulating layer surrounding the central electrode, the two deflectors and the field grading layer; and —a joint outer semiconductive layer surrounding and in direct contact with the insulating layer.

Owner:PRYSMIAN SPA

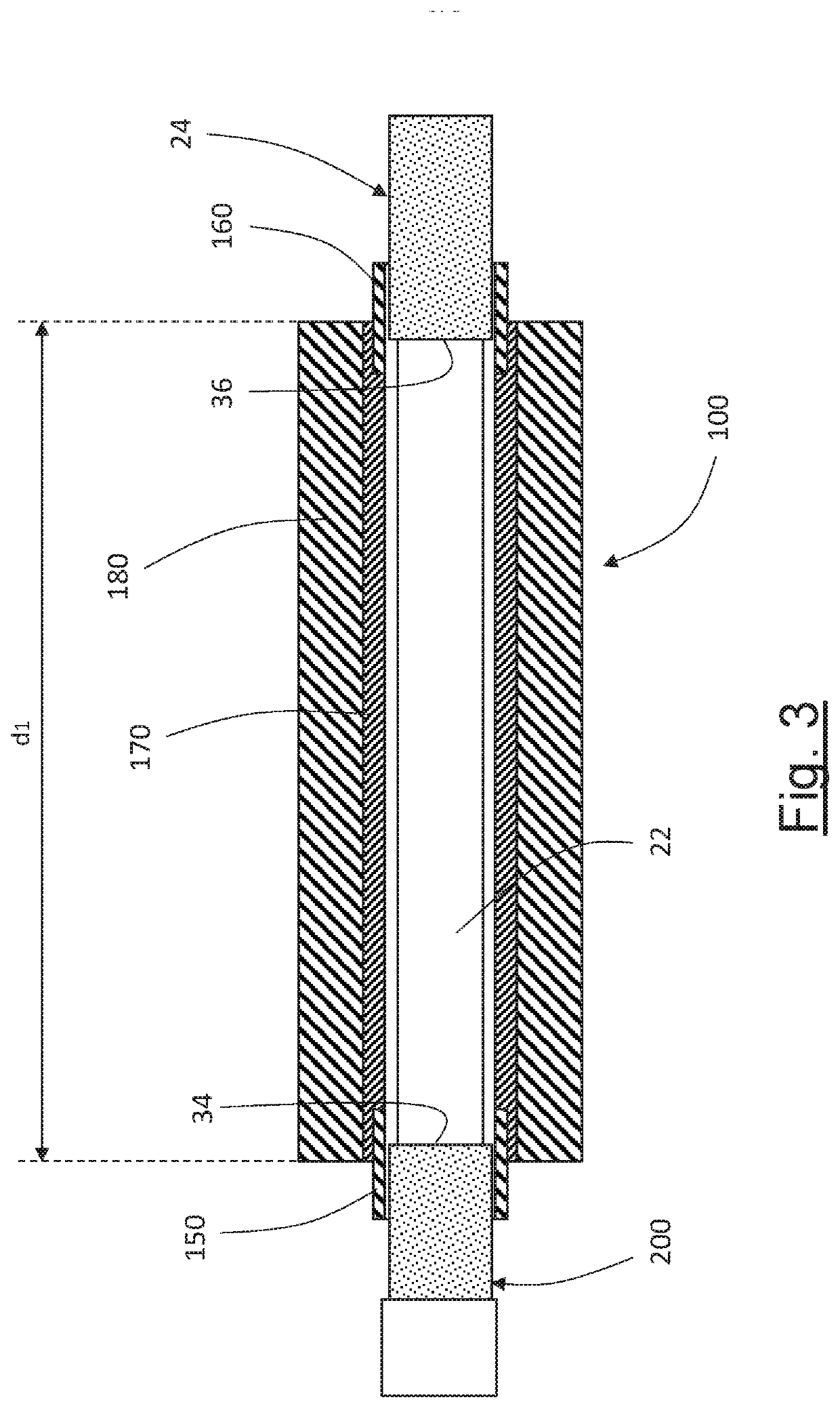

Cable termination system, termination assembly and method for installing such a termination assembly

ActiveUS11056873B2Reduce riskPrevent undesired charge accumulationCable fittingsApparatus for removing/armouring cablesSemiconductor electrodePower cable

The present invention relates to a cable termination system comprising: —a power cable sequentially comprising a first length of exposed outer semiconductive layer, a length of exposed insulating layer and a length of exposed electric conductor, —an electric field control element adapted to be arranged around a portion of said power cable, said electric field control element comprising: —first and second longitudinally spaced semiconducting electrodes; —a field grading layer longitudinally extending between the first and second semiconducting electrodes and in electric contact therewith; —an insulating layer surrounding the semiconducting electrodes and the field grading layer, —wherein the first semiconducting electrode is positioned across a first boundary between the first length of exposed outer semiconductive layer and the length of exposed insulating layer, —wherein said second semiconducting electrode (160) is electrically connected with said length of exposed electric conductor (20), —a tubular insulating body adapted to house said power cable and said electric field control element.

Owner:PRYSMIAN SPA

Display device, and driving method of display device

InactiveUS8199141B2Simple structureAvoid changeCathode-ray tube indicatorsNon-linear opticsDisplay deviceEngineering

It is an object to provide a high reliable display device which can suppress the generation of high electric field near the drain of the transistor used as a switching element and a driving method thereof. A relaxation time when charge is stored in the display element of the pixel and other capacitors connected to the display element in parallel is focused on, and the voltage applied between the source and the drain of the transistor in the writing period is suppressed by changing the video signal applied to the signal line step by step and finally setting it at the desired level.

Owner:SEMICON ENERGY LAB CO LTD

Cable termination system, termination assembly and method for installing such a termination assembly

ActiveUS20200169074A1Prevents undesired charge accumulationHigh electric fieldCable fittingsApparatus for removing/armouring cablesSemiconductor electrodePower cable

The present invention relates to a cable termination system comprising: —a power cable sequentially comprising a first length of exposed outer semiconductive layer, a length of exposed insulating layer and a length of exposed electric conductor, —an electric field control element adapted to be arranged around a portion of said power cable, said electric field control element comprising: —first and second longitudinally spaced semiconducting electrodes; —a field grading layer longitudinally extending between the first and second semiconducting electrodes and in electric contact therewith; —an insulating layer surrounding the semiconducting electrodes and the field grading layer, —wherein the first semiconducting electrode is positioned across a first boundary between the first length of exposed outer semiconductive layer and the length of exposed insulating layer, —wherein said second semiconducting electrode (160) is electrically connected with said length of exposed electric conductor (20), —a tubular insulating body adapted to house said power cable and said electric field control element.

Owner:PRYSMIAN SPA

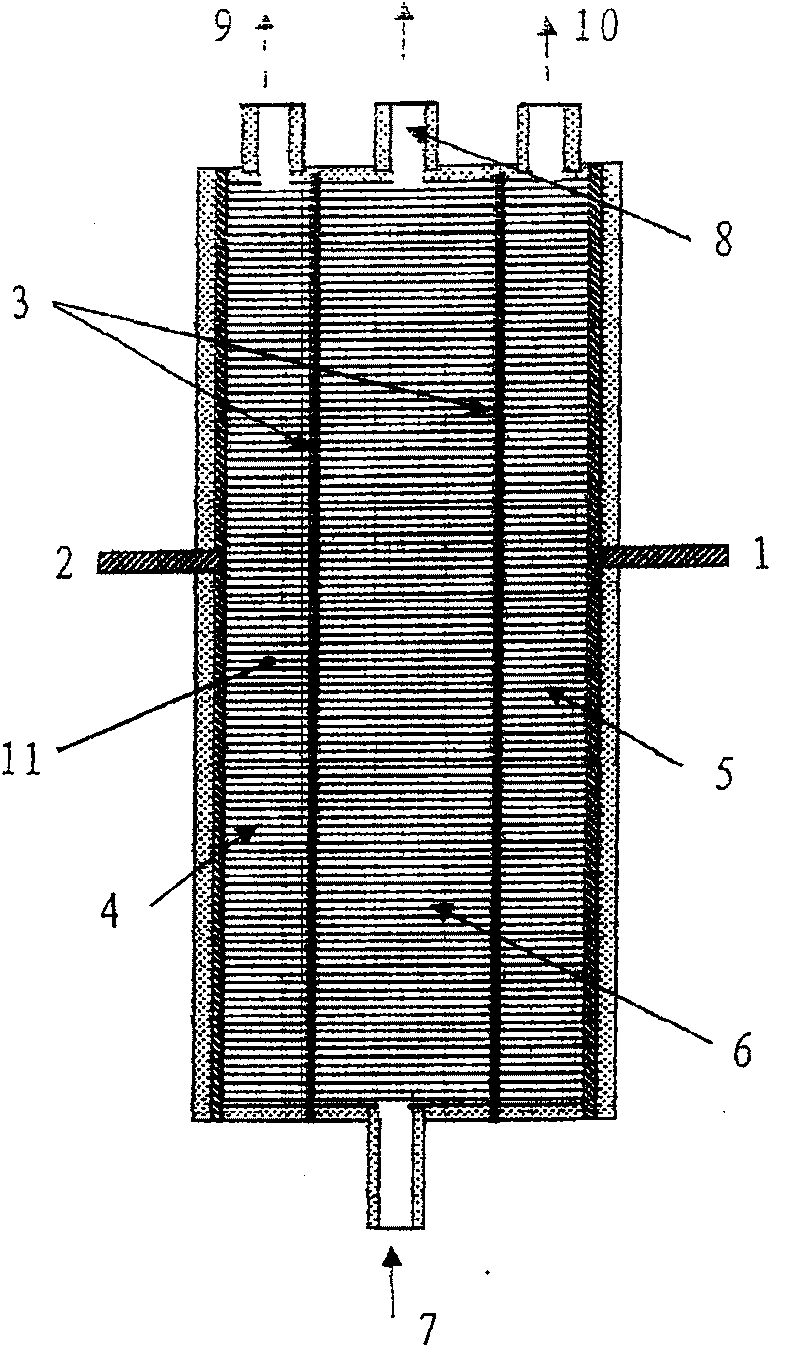

High-voltage electrodialysis water purifier

InactiveCN101239746BIncrease profitReduce weightDispersed particle separationElectrodialysisElectrical field strengthWater source

The present invention provides a high voltage electrodialysis water purifier, belonging to water processing field, the barrier of the present electrodialysis unit is made of multiple ionic membrane, and the present electrodialysis unit changes frequently, has a lower purification efficiency, not suitable for purification of groundwater with high hardness, and has a high cost, the invnetion is made of acrylic braided fabric, neutral semipermeable membrane or pylome foam plastic plate etc, a supporter is made of insulating material, voltage between anode and cathode is 100-200V, electrical field strength is 5-100V / cm, the invention has effect of high purification efficiency, simple technology, large or small purifying scale, suitable for water purification having higher pollution degree, and lower operating cost.

Owner:北京索能技术有限公司

Semiconductor substrate and semiconductor device

ActiveUS10217855B2Effective dispersionIncrease capacitanceSemiconductor/solid-state device manufacturingSemiconductor devicesSemiconductorElectron

A semiconductor substrate and a semiconductor device are disclosed. The semiconductor substrate includes a base layer, a buffer layer disposed on the base layer, a channel layer disposed on the buffer layer, a barrier layer disposed on the channel layer, and a buried field plate region embedded in the channel layer. In an embodiment, the channel layer includes a two-dimensional electron gas (2DEG), and the buried field plate region is located below the two-dimensional electron gas.

Owner:NUVOTON

Insulated gate switching device and method for manufacturing the same

ActiveUS10153345B2Protruding amount of the implanted region of the p-type impurities (Easy to relaxSemiconductor/solid-state device manufacturingSemiconductor devicesBody regionImpurity

A method for manufacturing an insulated gate switching device is provided. The method includes: forming a first trench in a surface of a first SiC semiconductor layer; implanting p-type impurities into a bottom surface of the first trench; depositing a second SiC semiconductor layer on an inner surface of the first trench to form a second trench; and forming a gate insulating layer, a gate electrode, a first region and a body region so that the gate insulating layer covers an inner surface of the second trench, the gate electrode is located in the second trench, the first region is of n-type and in contact with the gate insulating layer, the body region is of p-type, separated from the implanted region, and in contact with the gate insulating layer under the first region.

Owner:TOYOTA JIDOSHA KK +1

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com