Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

37results about How to "Avoid plasma damage" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

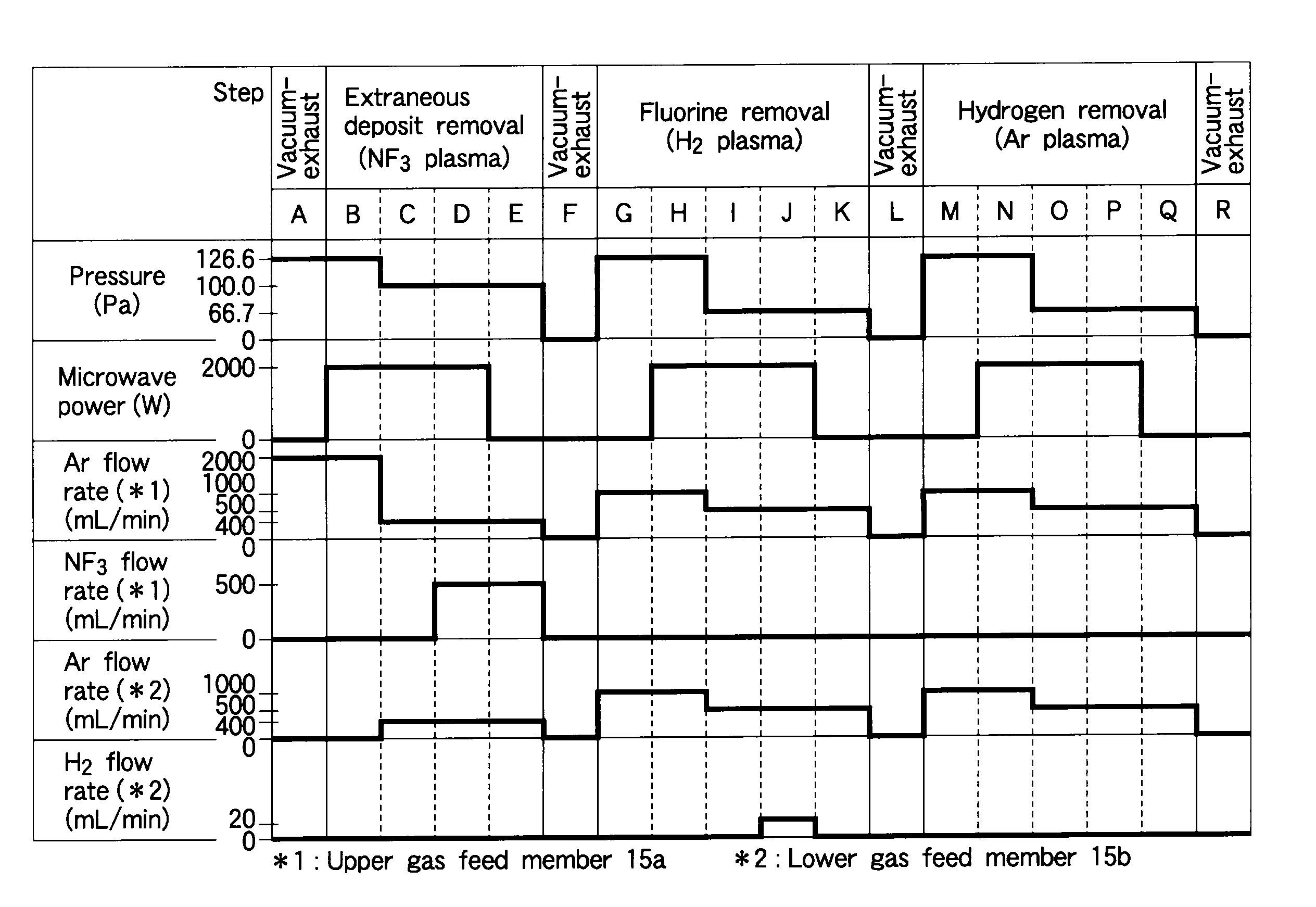

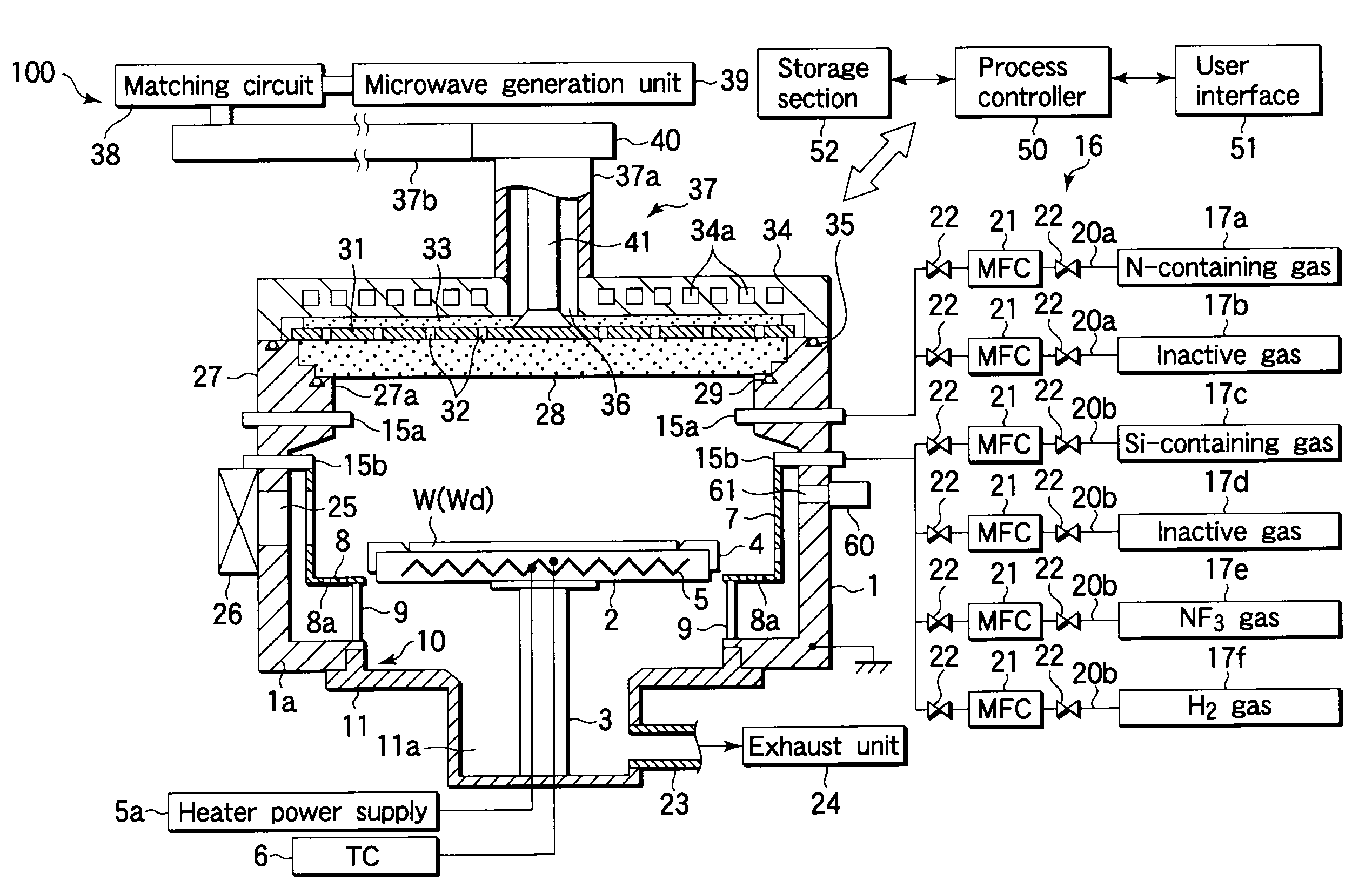

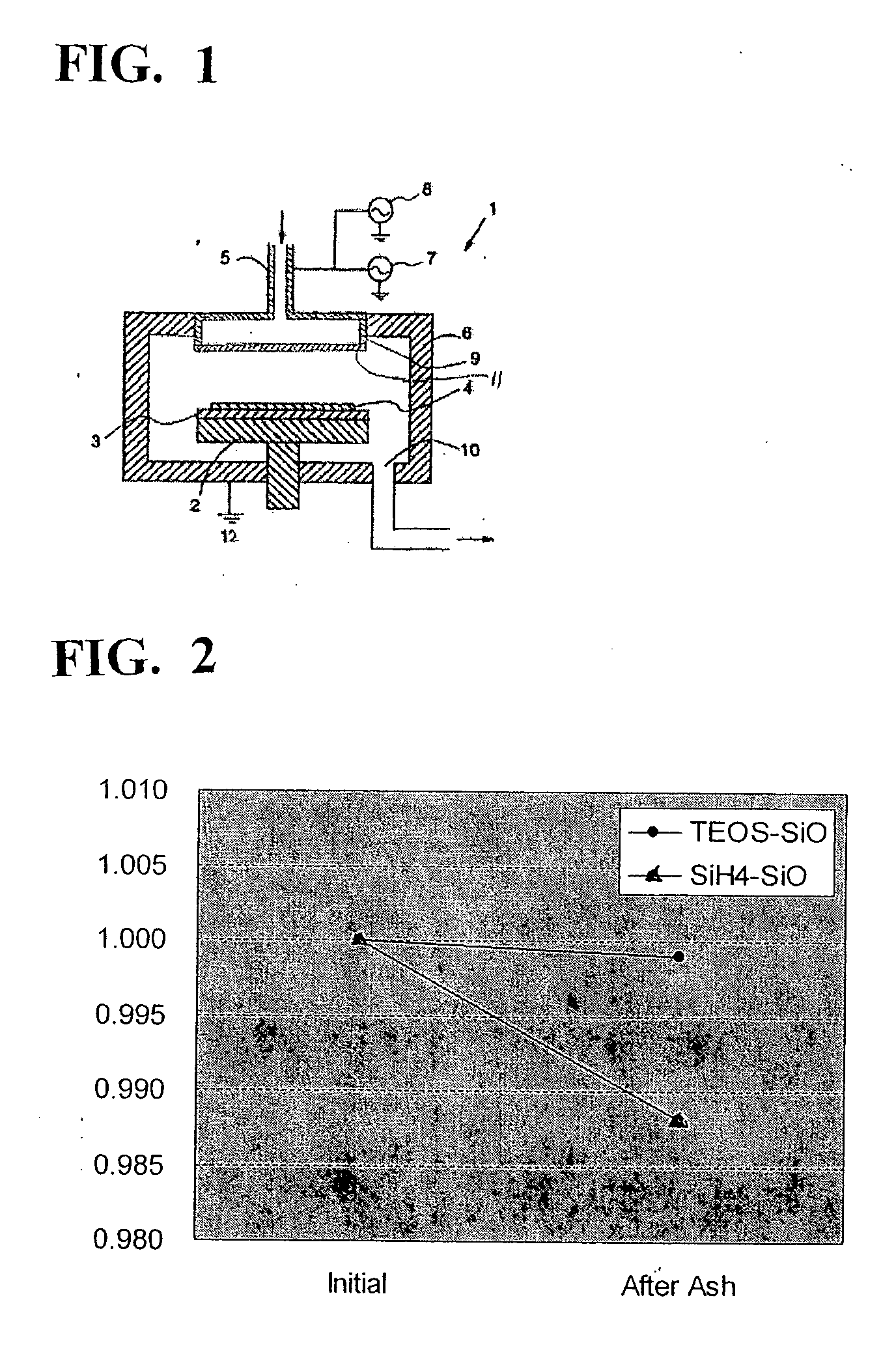

Plasma cleaning method and plasma CVD method

ActiveUS8366953B2Reliably decrease residual fluorineImprove throughputElectric discharge tubesVacuum gauge using ionisation effectsHydrogenNoble gas

A plasma cleaning method is performed in a plasma CVD apparatus for depositing a silicon nitride film on a surface of a target substrate, and includes a stage (S1) of supplying a cleaning gas containing NF3 gas into a process container, thereby removing extraneous deposits formed on portions inside the process container; a stage (S2) of supplying a gas containing hydrogen gas into the process container and generating plasma thereof, thereby removing residual fluorine inside the process container; and a stage (S3) of supplying a gas containing a rare gas into the process container and generating plasma thereof, thereby removing residual hydrogen inside the process container.

Owner:TOKYO ELECTRON LTD

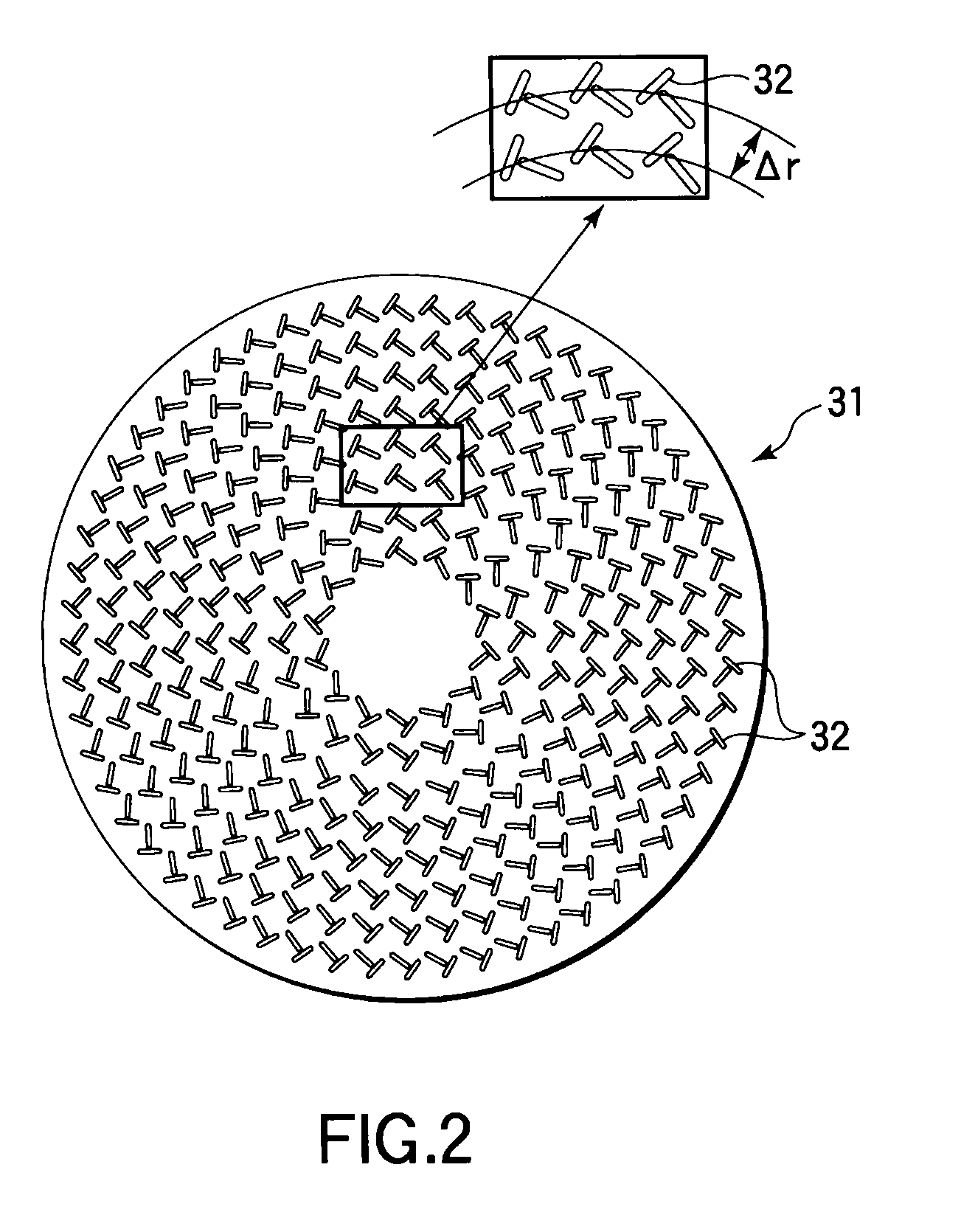

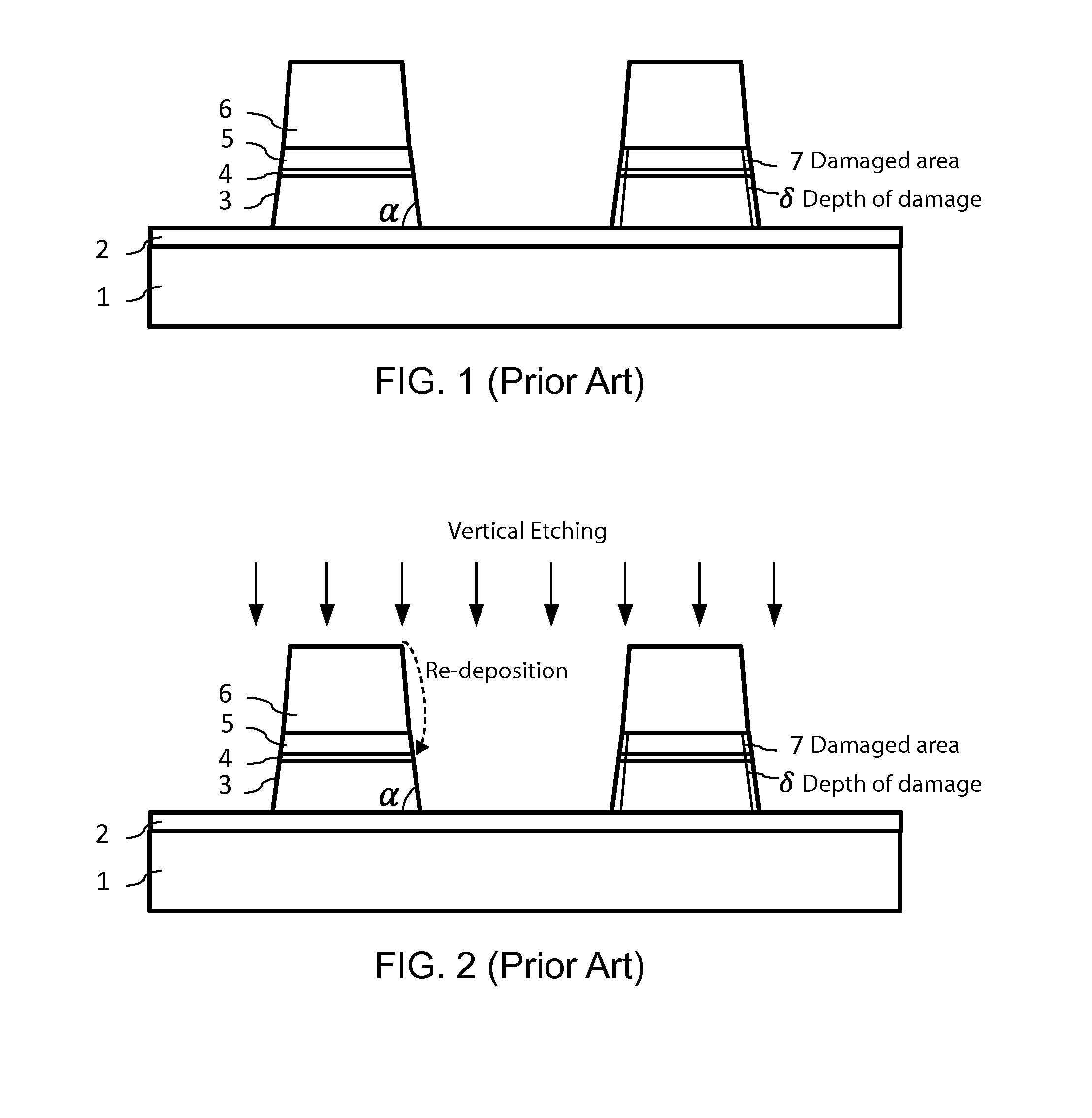

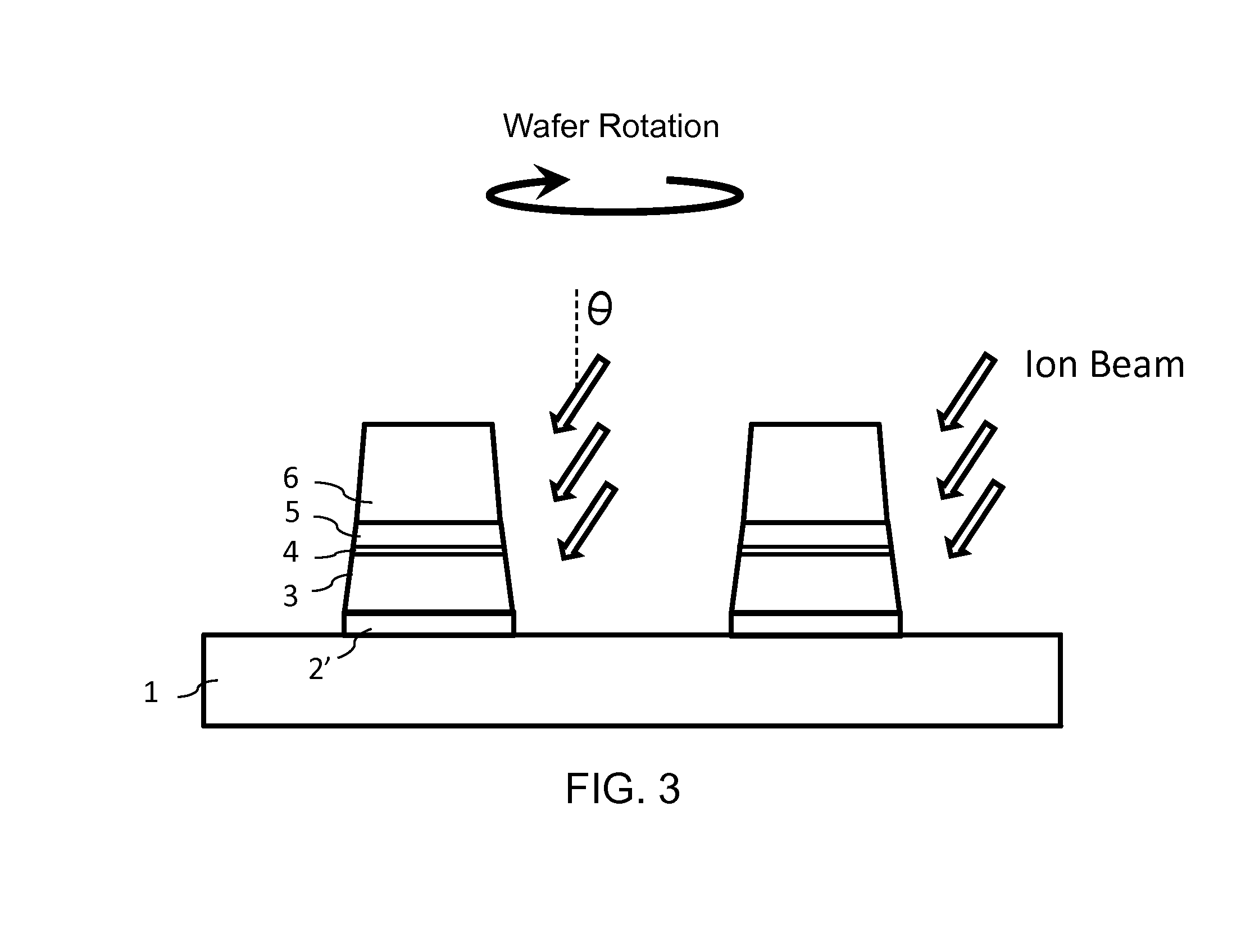

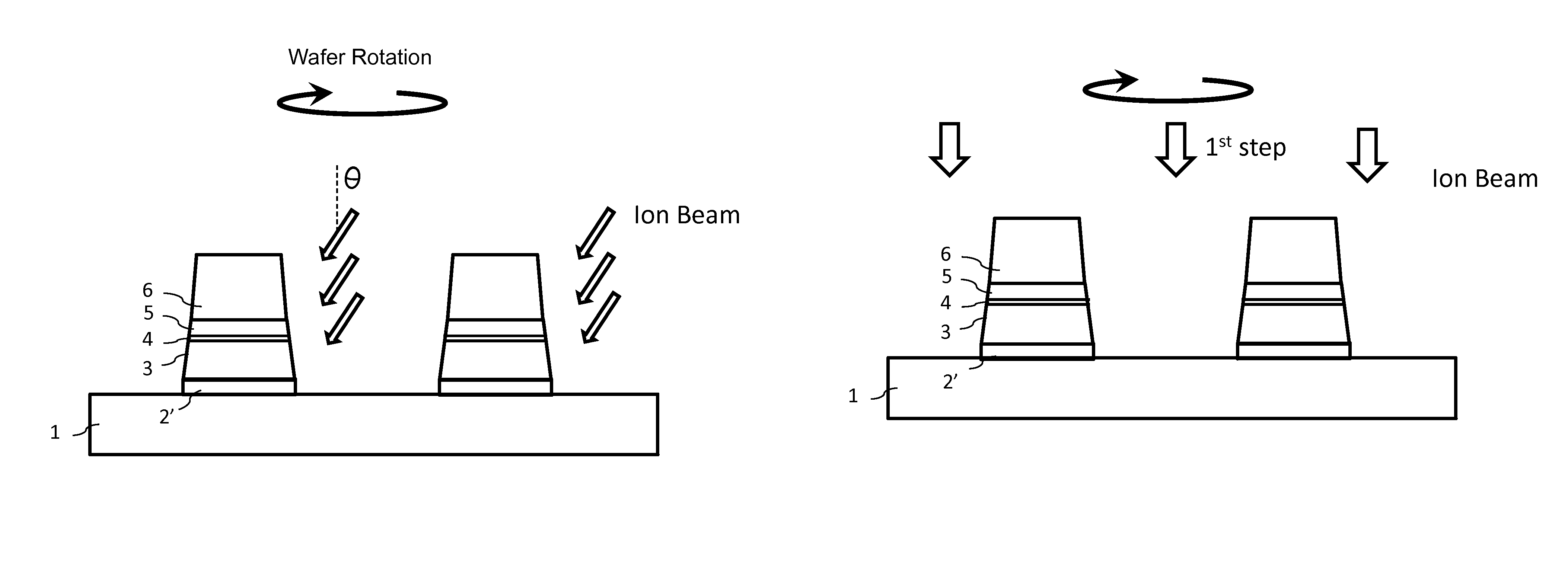

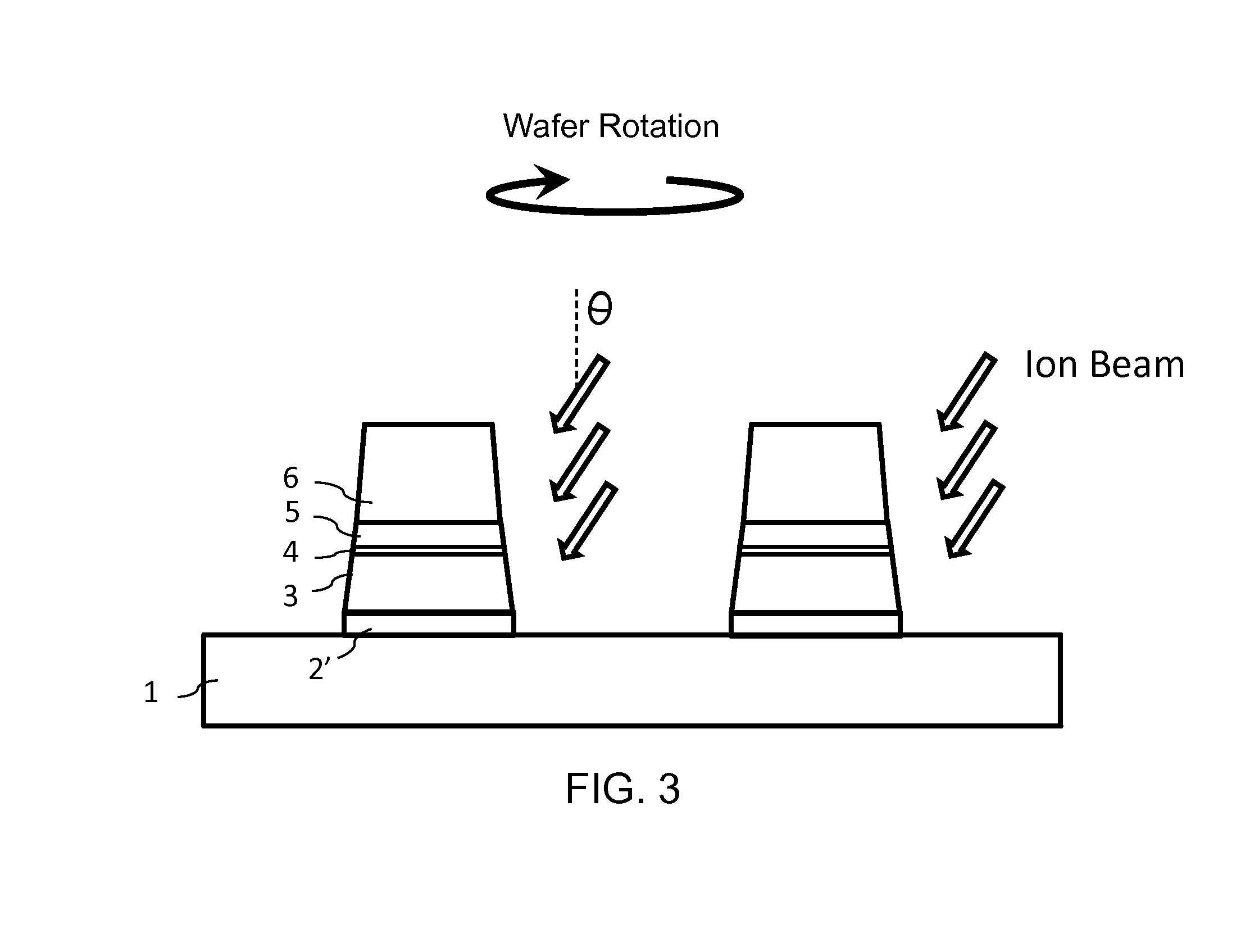

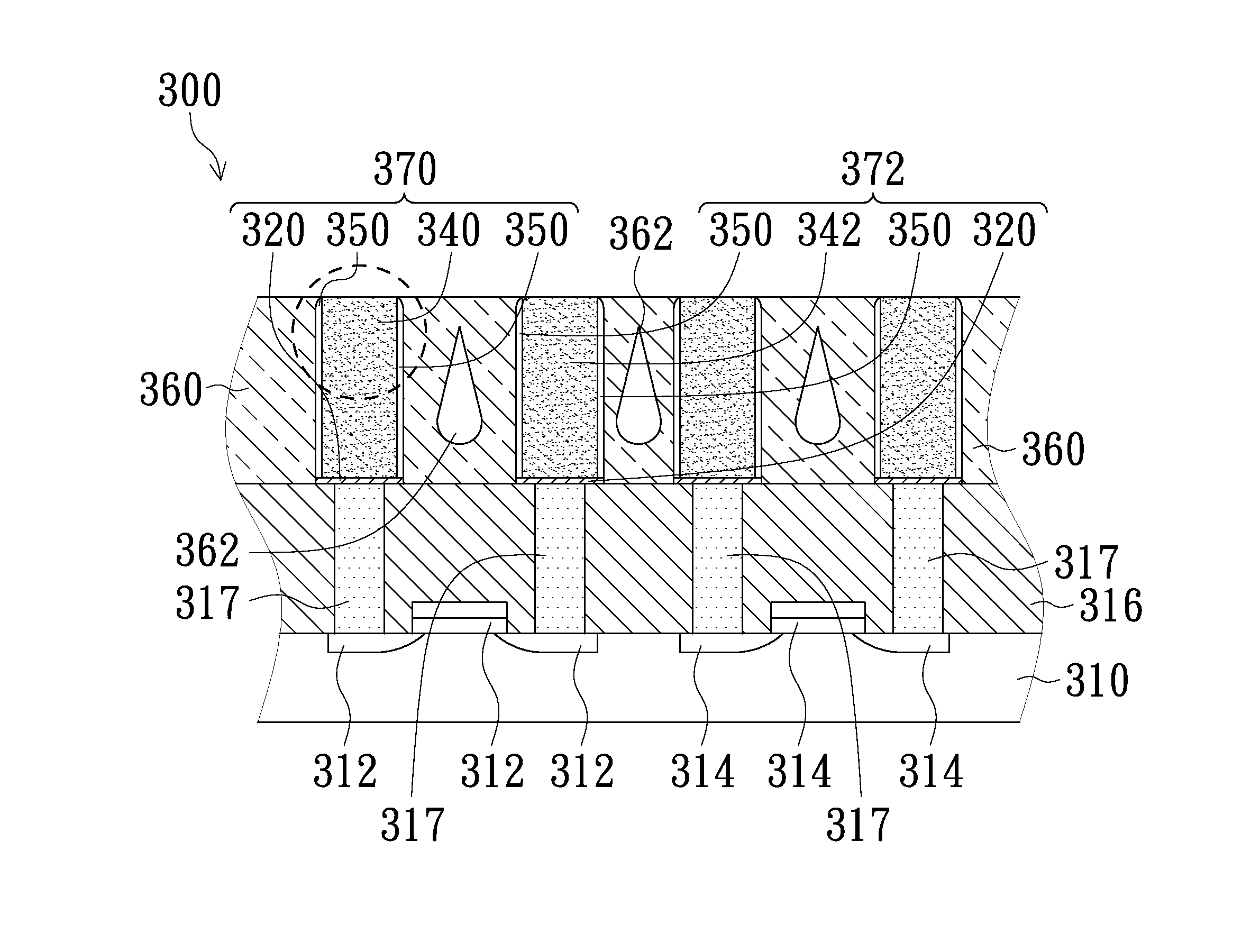

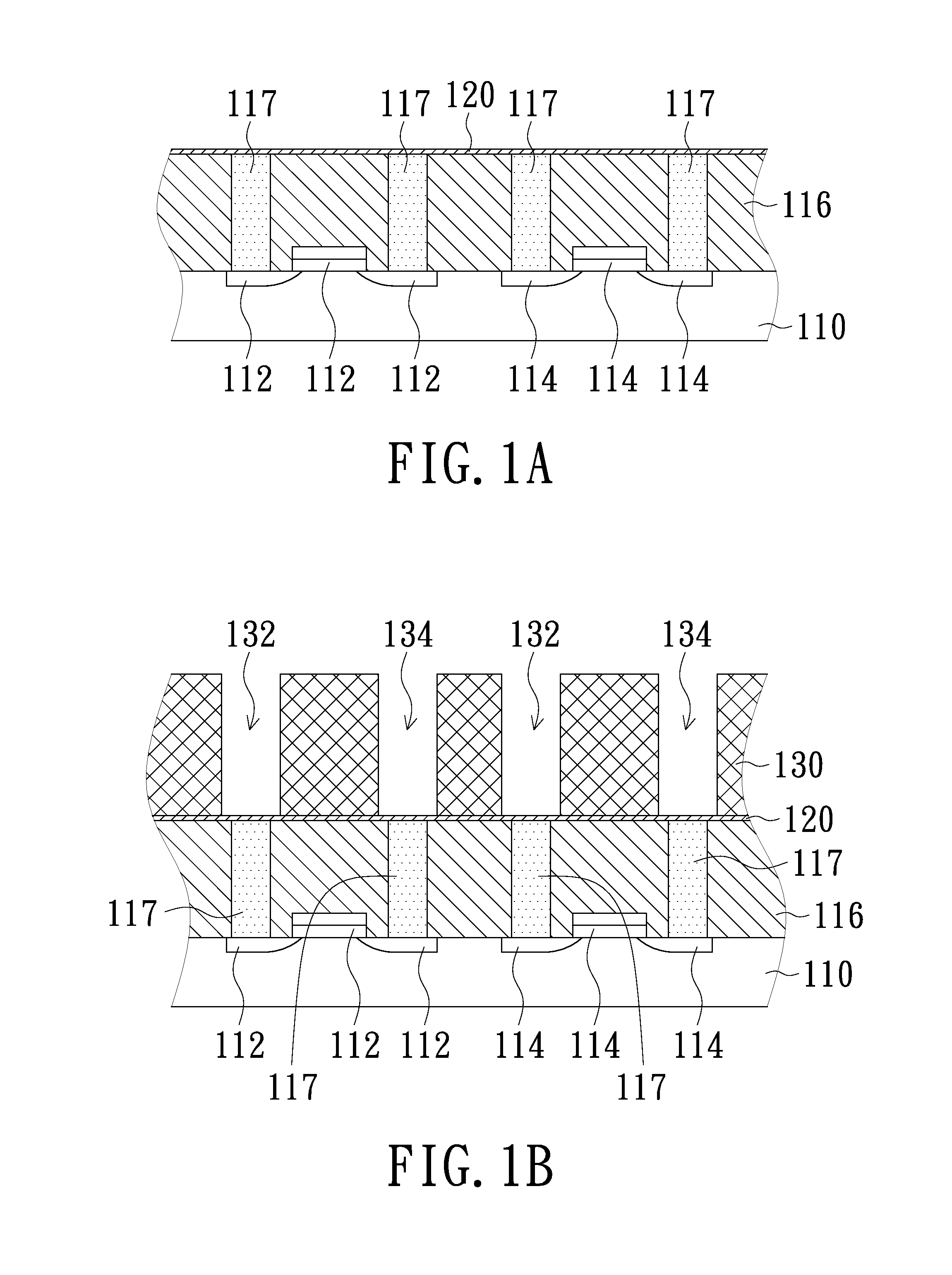

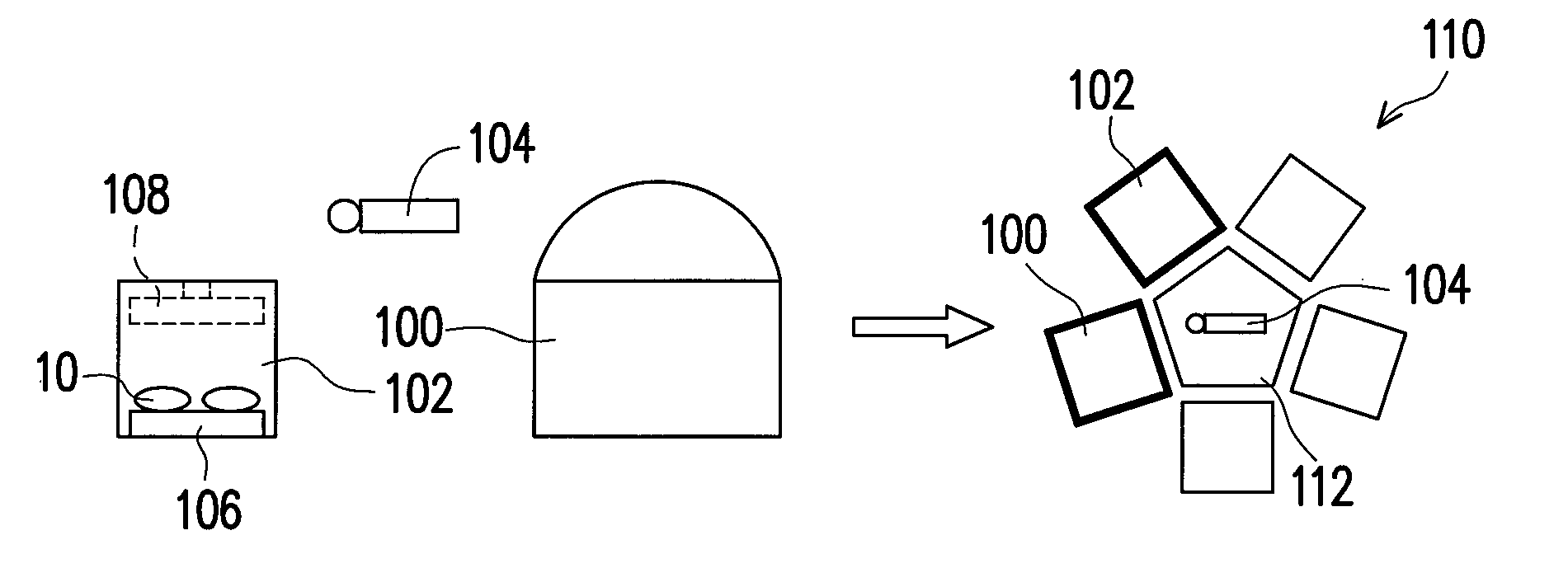

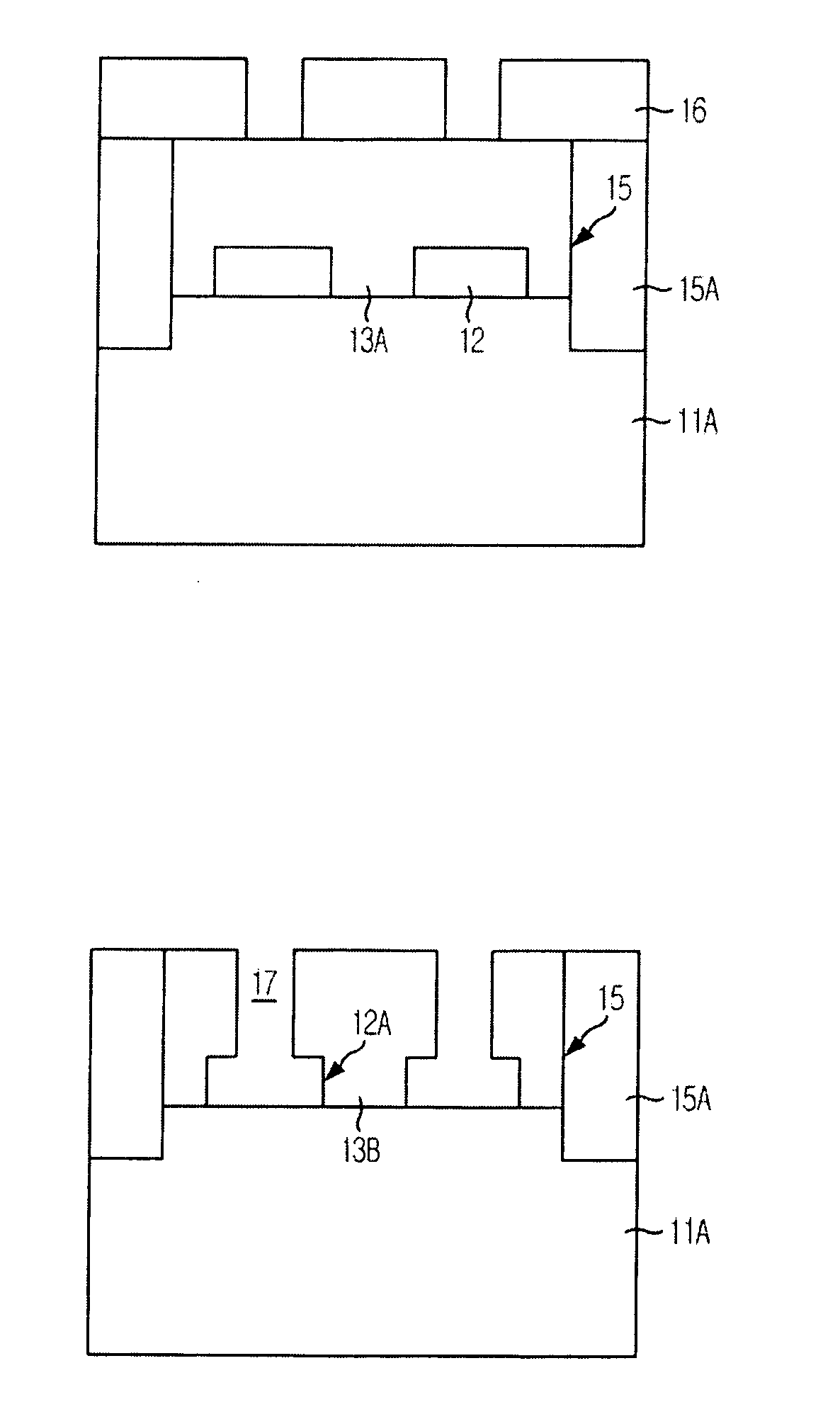

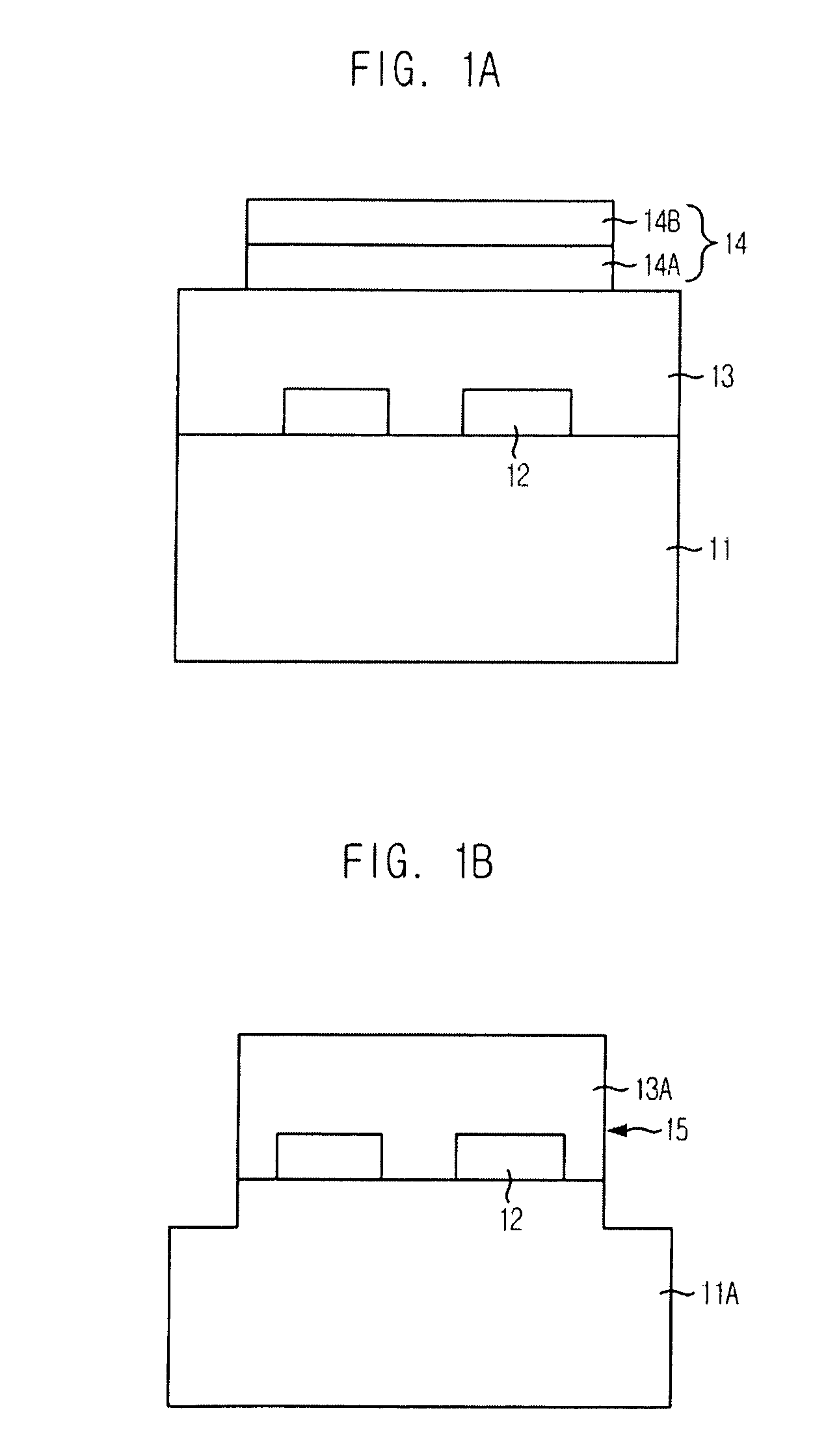

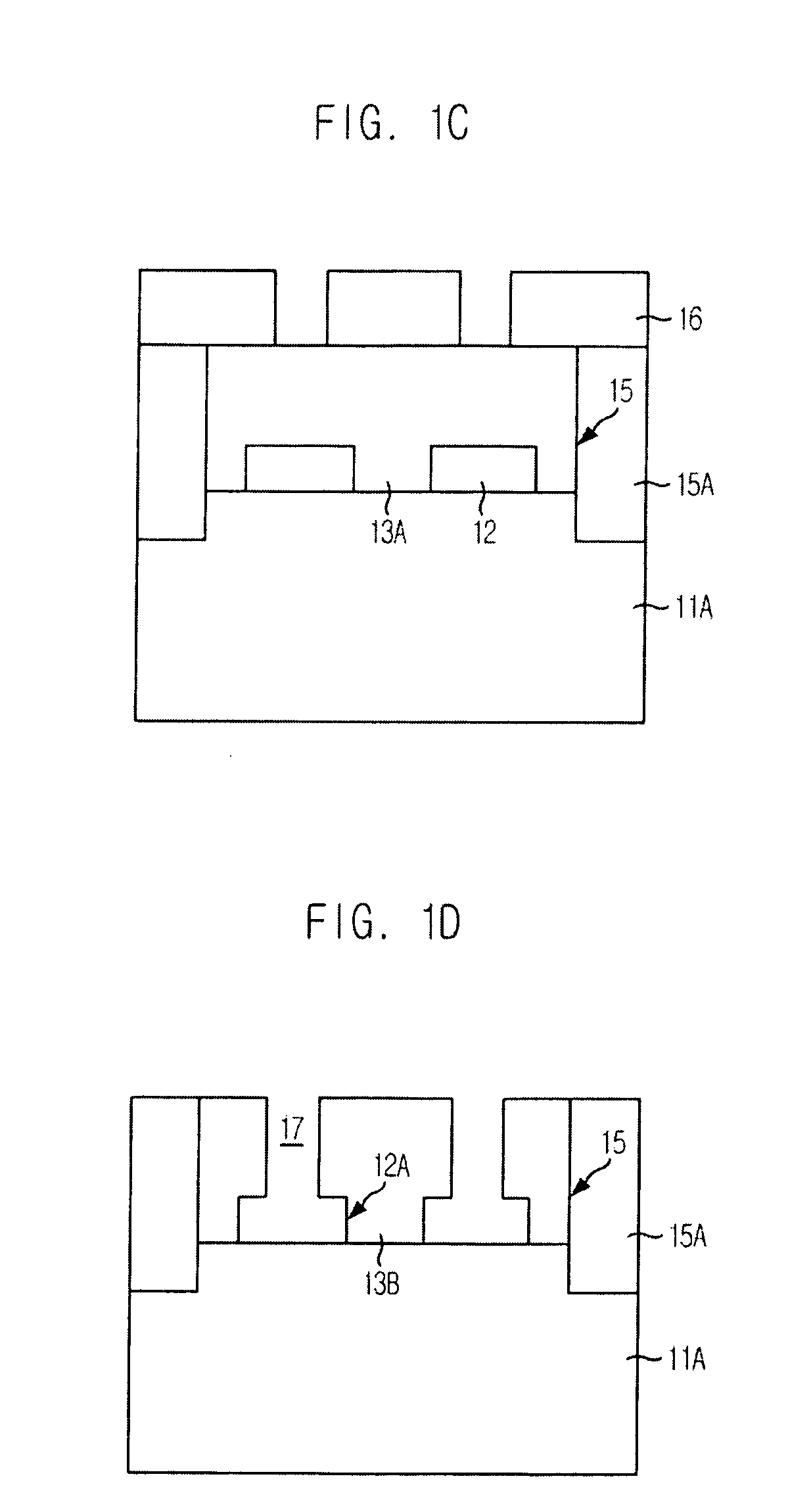

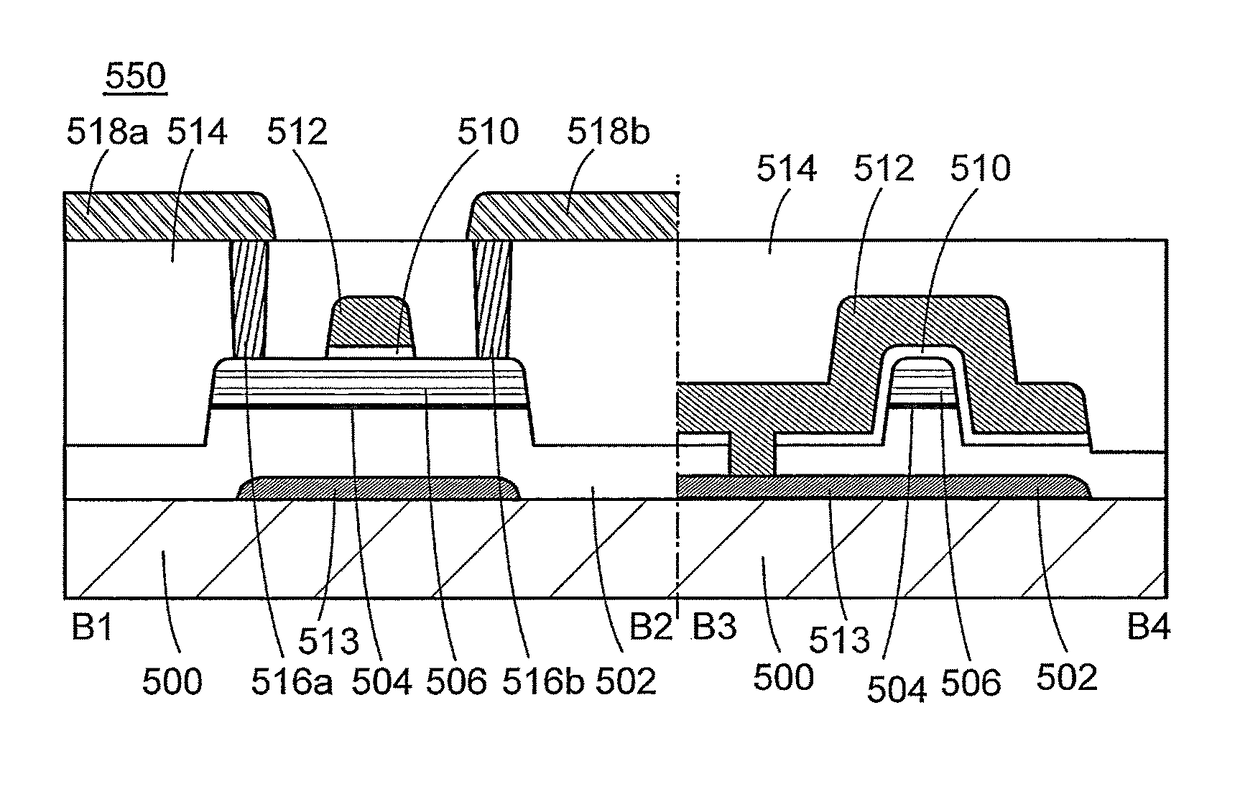

Mtj stack and bottom electrode patterning process with ion beam etching using a single mask

ActiveUS20140170776A1High selectivityAvoid damageSemiconductor/solid-state device manufacturingGalvano-magnetic device manufacture/treatmentEngineeringInductively coupled plasma

Fabrication methods using Ion Beam Etching (IBE) for MRAM cell memory elements are described. In embodiments of the invention the top electrode and MTJ main body are etched with one mask using reactive etching such as RIE or magnetized inductively coupled plasma (MICP) for improved selectivity, then the bottom electrode is etched using IBE as specified in various alternative embodiments which include selection of incident angles, wafer rotational rate profiles and optional passivation layer deposited prior to the IBE. The IBE according to the invention etches the bottom electrode without the need for an additional mask by using the layer stack created by the first etching phase as the mask. This makes the bottom electrode self-aligned to MTJ. The IBE also achieves MTJ sidewall cleaning without the need for an additional step.

Owner:AVALANCHE TECH

MTJ stack and bottom electrode patterning process with ion beam etching using a single mask

ActiveUS9166154B2Avoid damageAvoid plasma damageGalvano-magnetic device manufacture/treatmentSemiconductor devicesInductively coupled plasmaRotational rate

Fabrication methods using Ion Beam Etching (IBE) for MRAM cell memory elements are described. In embodiments of the invention the top electrode and MTJ main body are etched with one mask using reactive etching such as RIE or magnetized inductively coupled plasma (MICP) for improved selectivity, then the bottom electrode is etched using IBE as specified in various alternative embodiments which include selection of incident angles, wafer rotational rate profiles and optional passivation layer deposited prior to the IBE. The IBE according to the invention etches the bottom electrode without the need for an additional mask by using the layer stack created by the first etching phase as the mask. This makes the bottom electrode self-aligned to MTJ. The IBE also achieves MTJ sidewall cleaning without the need for an additional step.

Owner:AVALANCHE TECH

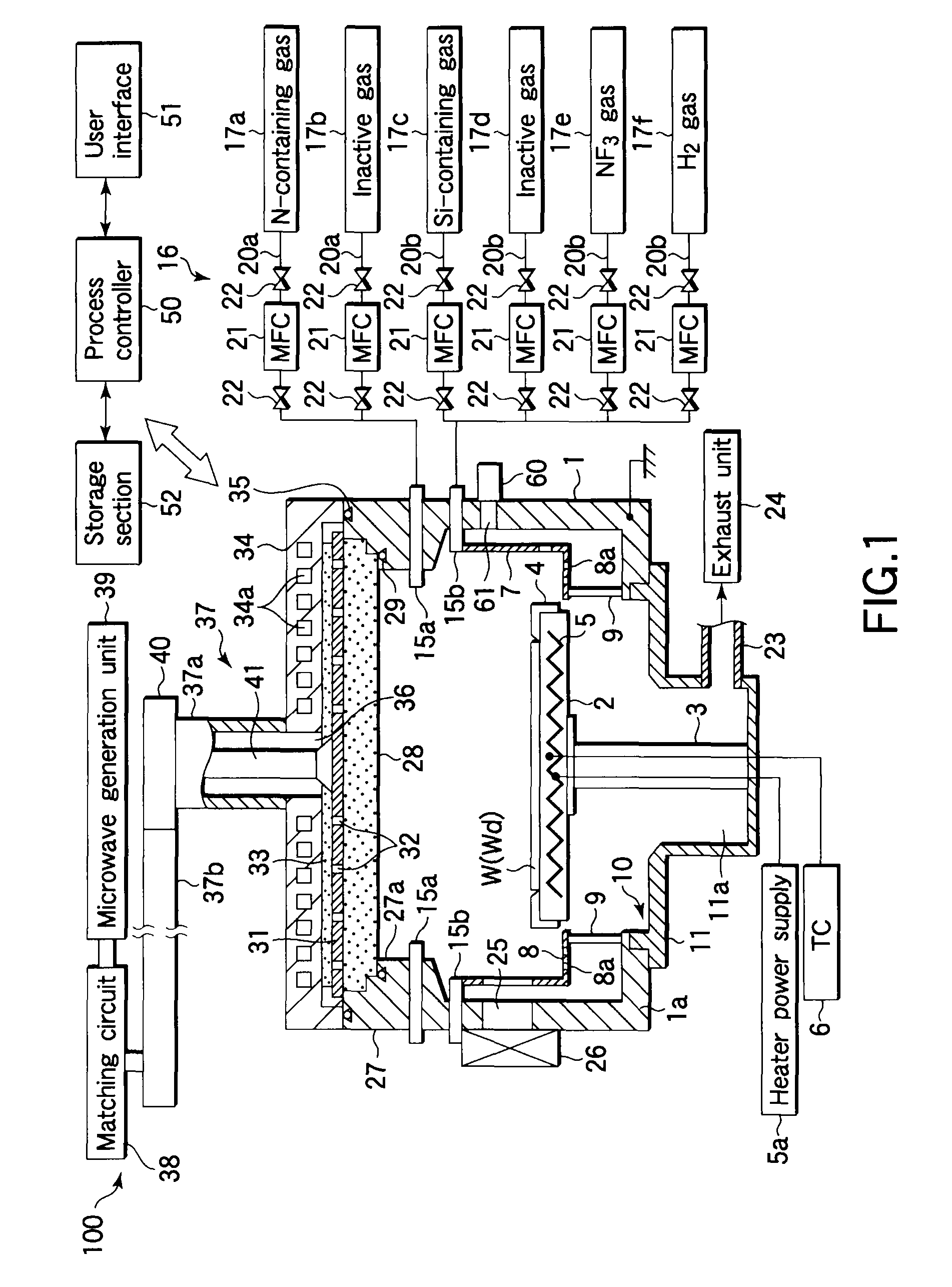

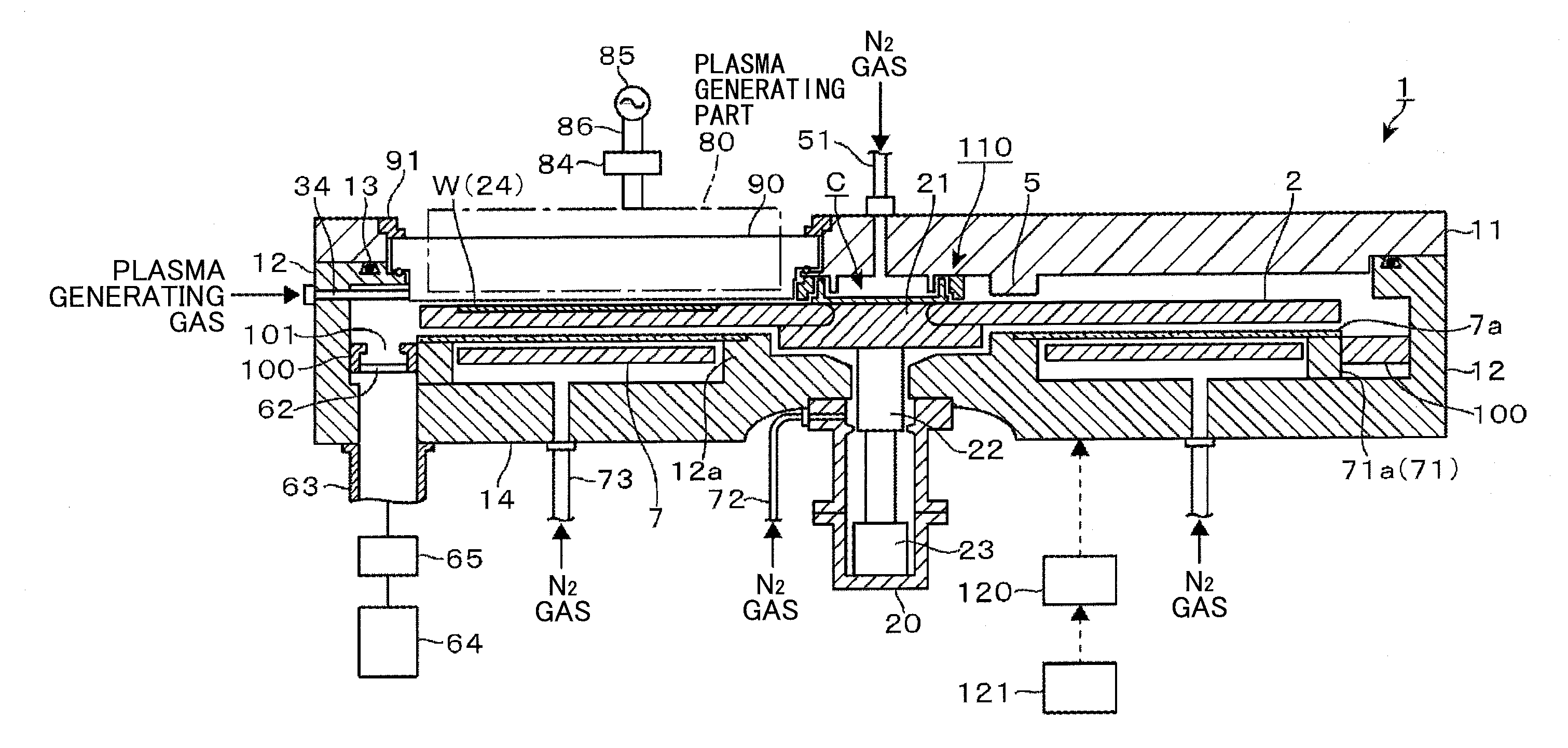

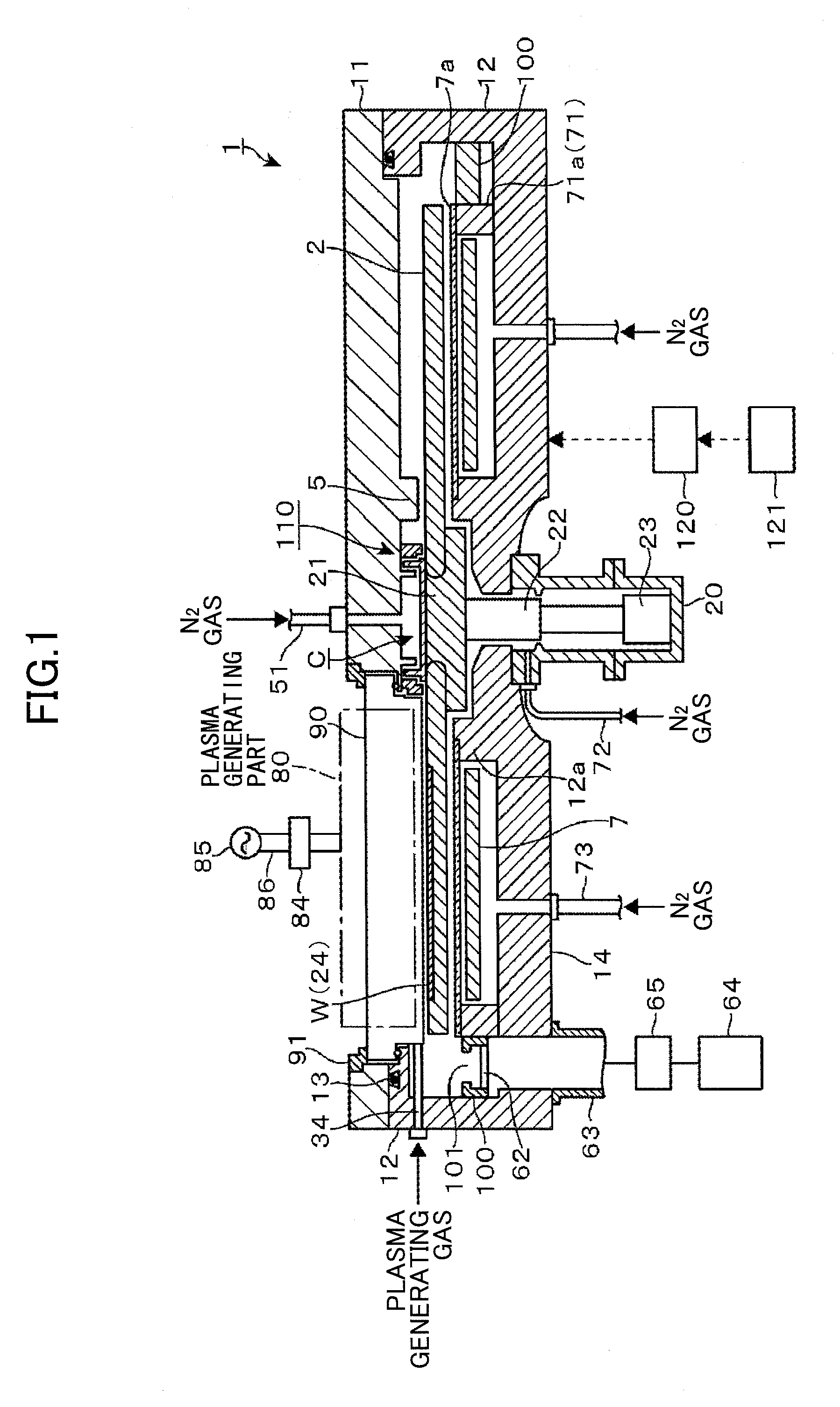

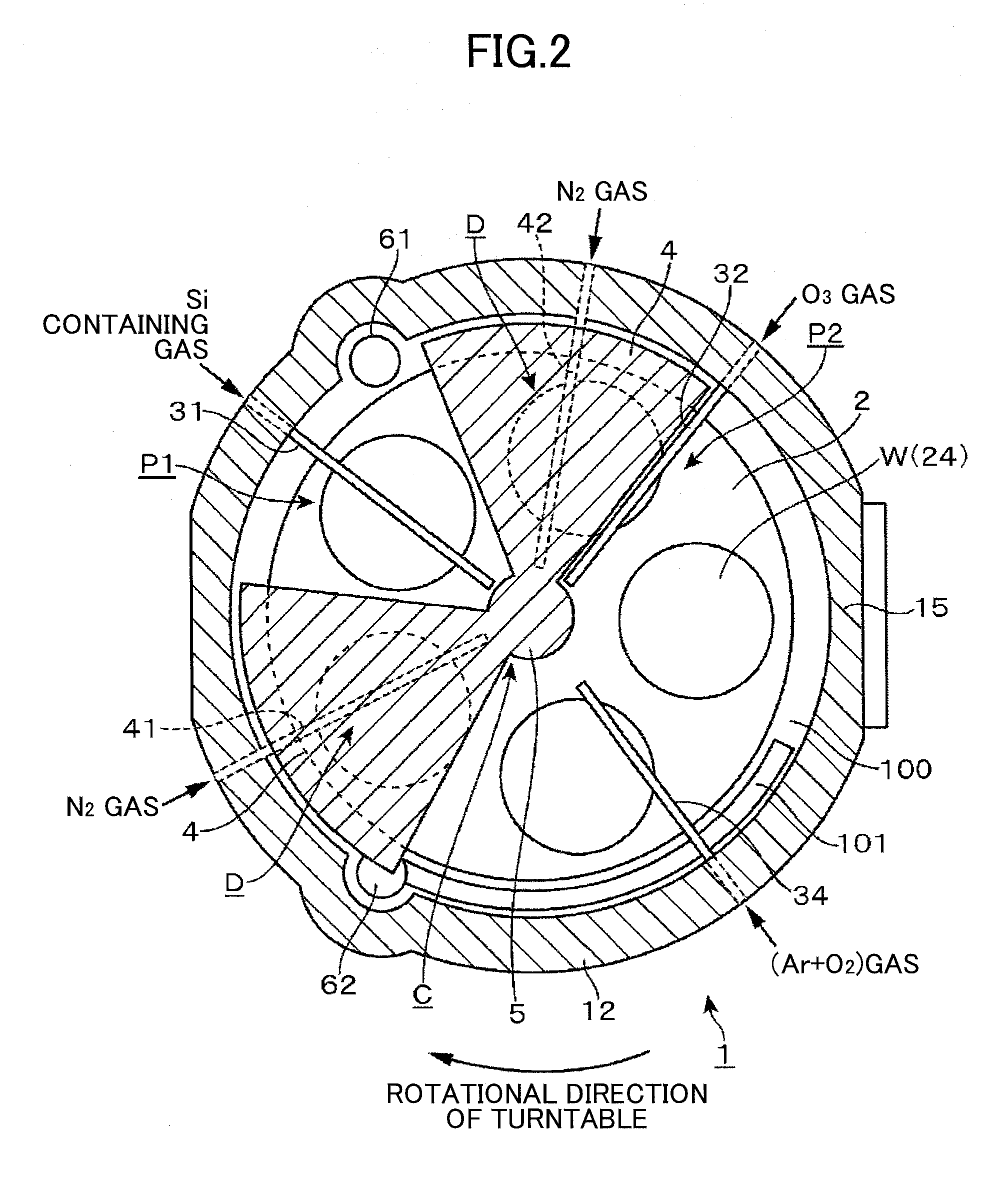

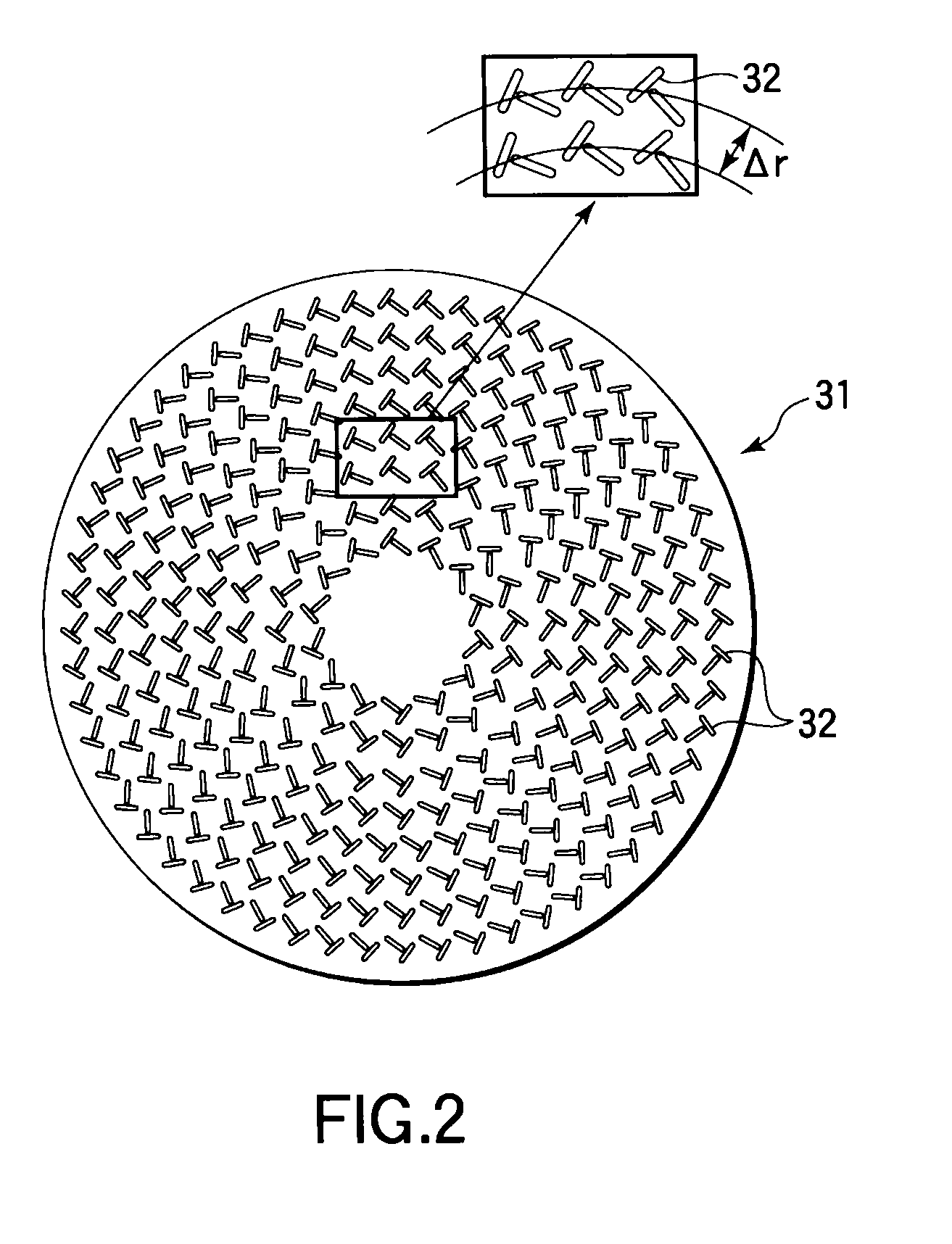

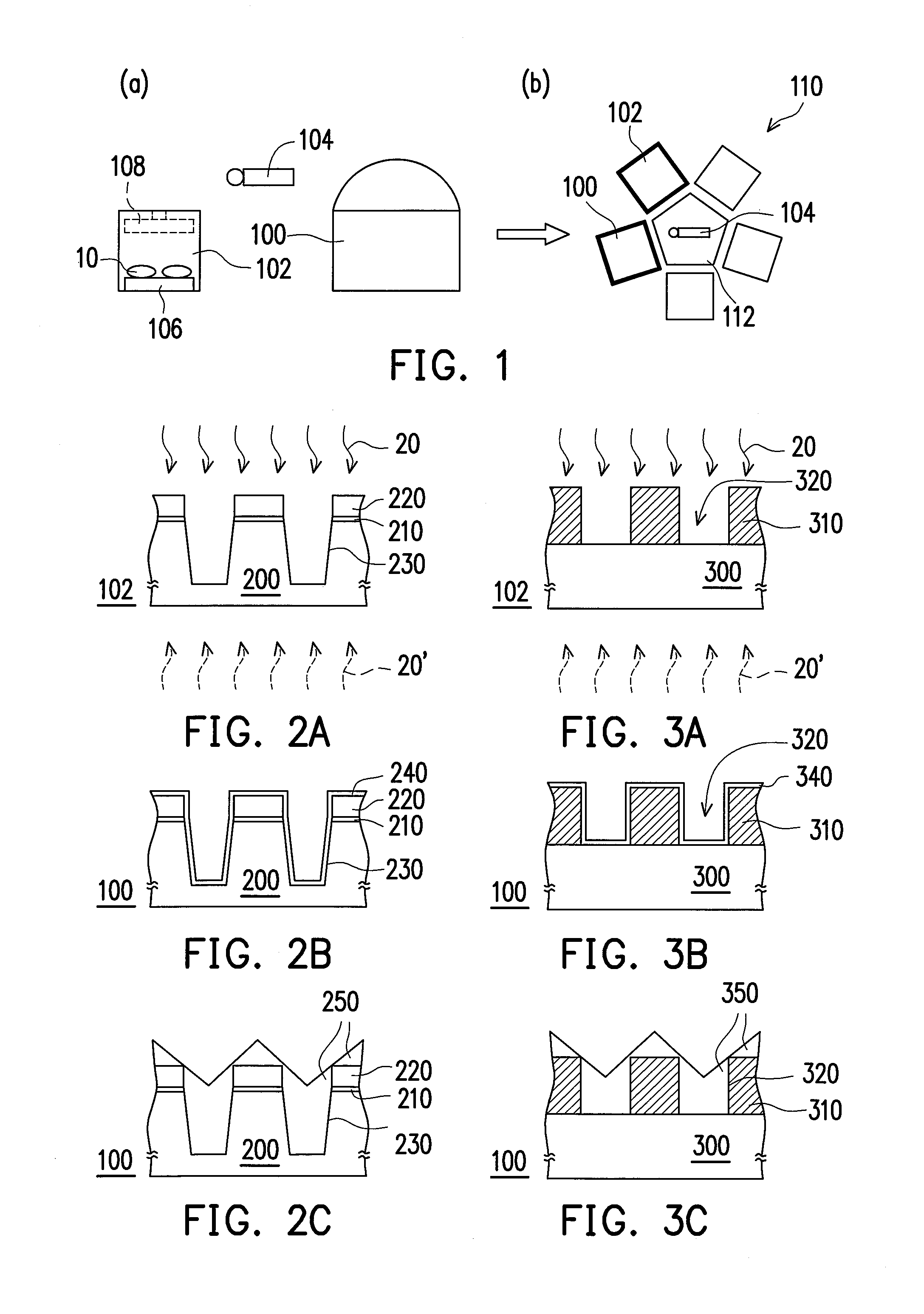

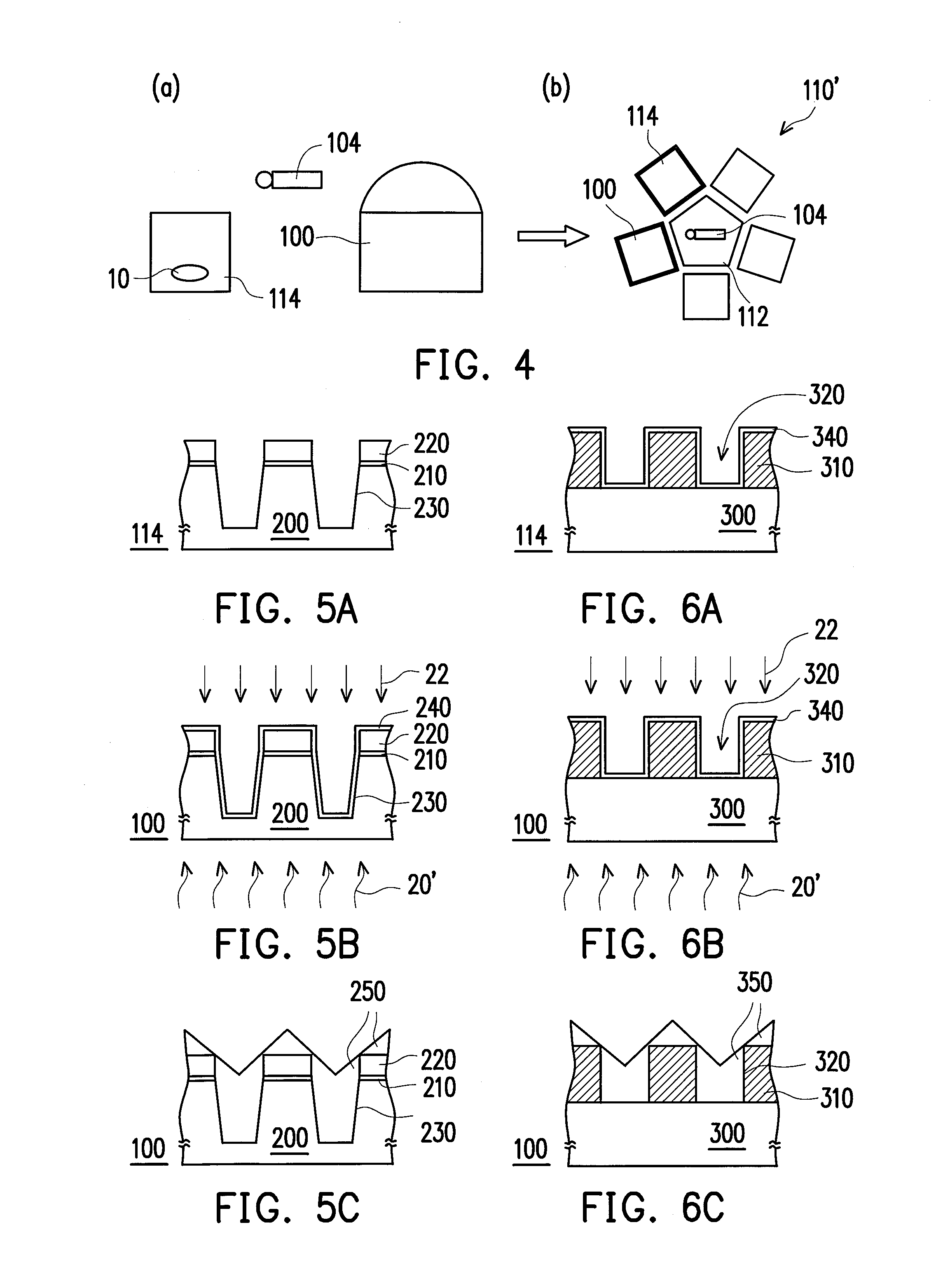

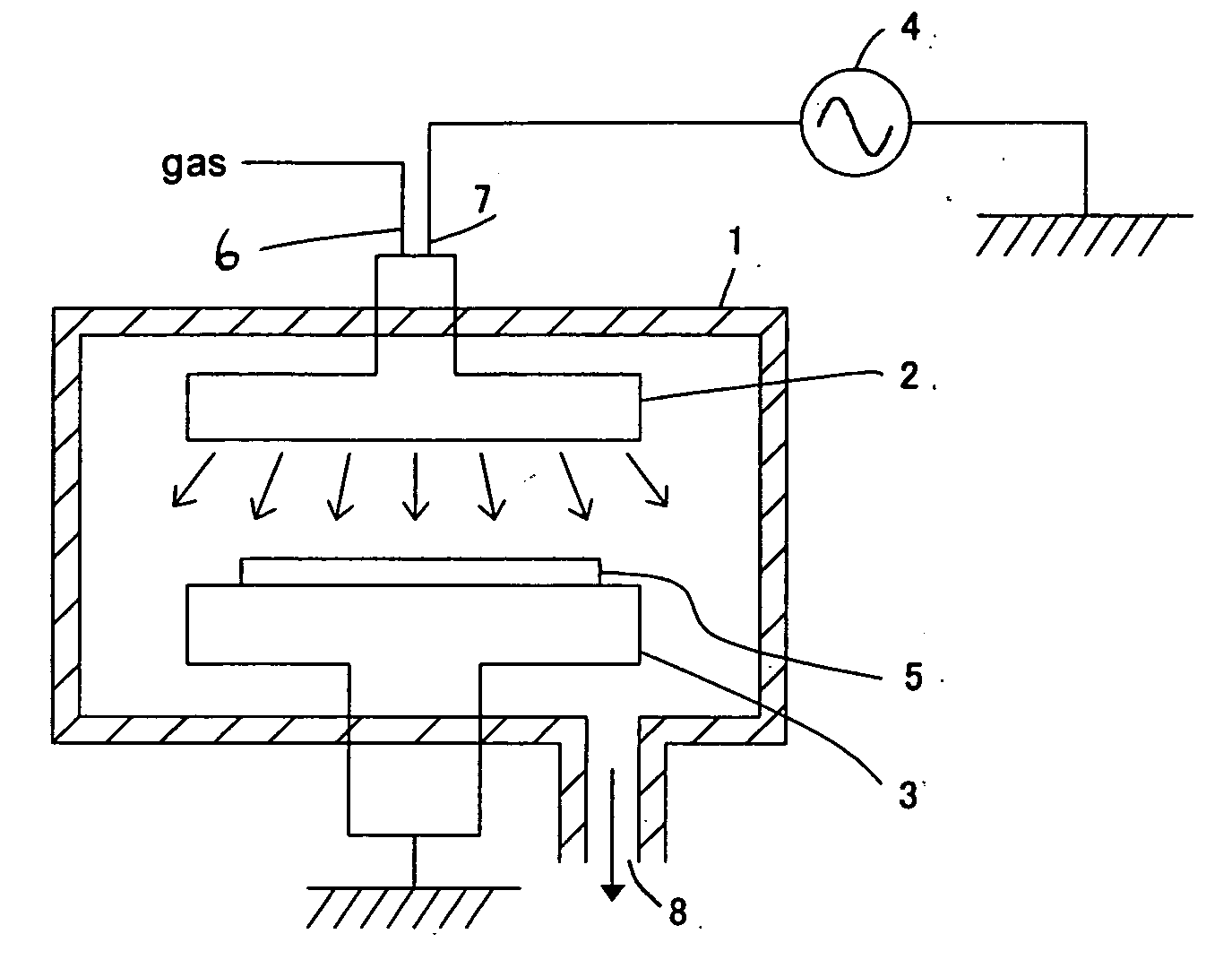

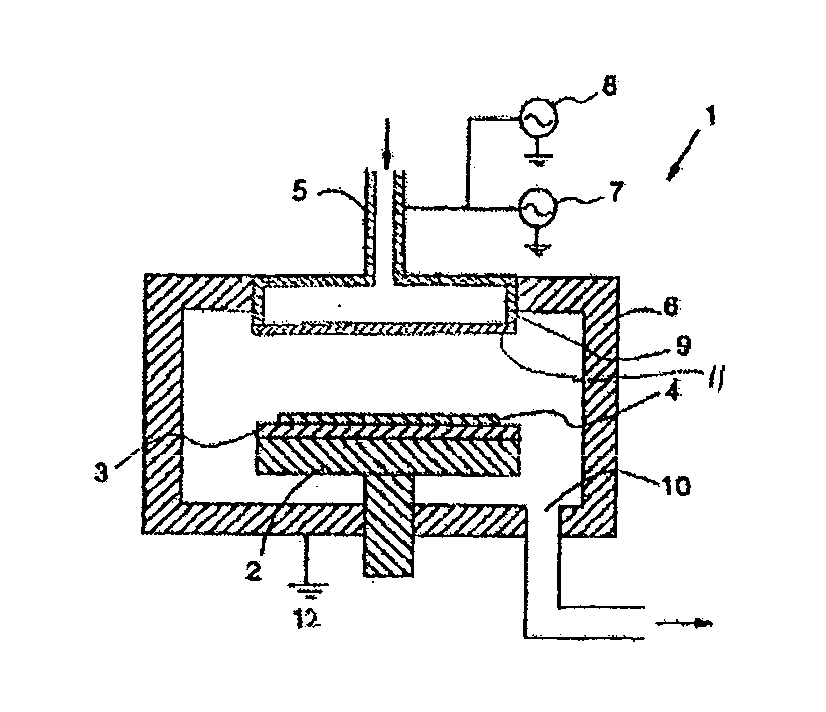

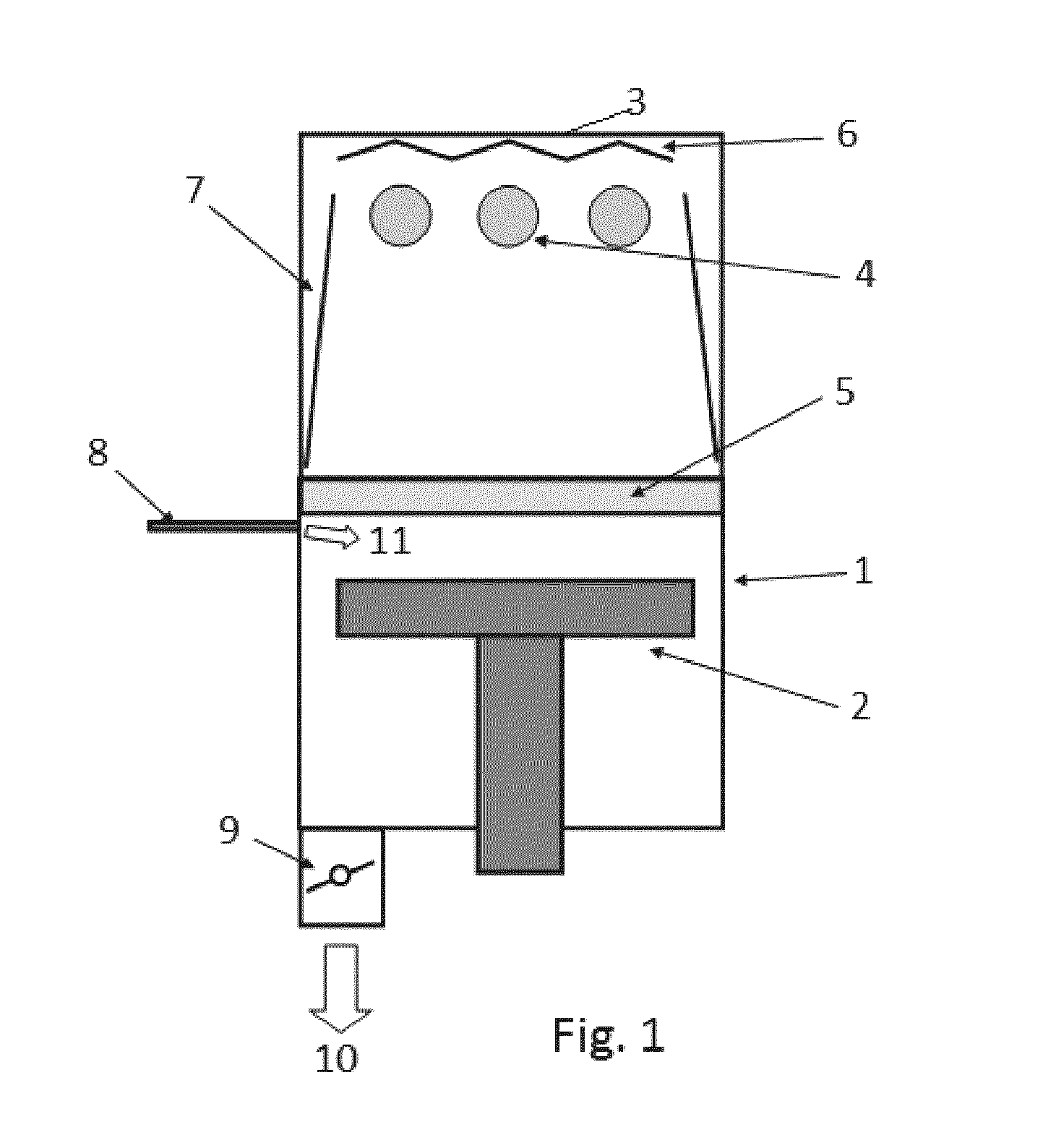

Film deposition apparatus, substrate processing apparatus, and plasma generating device

InactiveUS20130047923A1Avoid plasma damageElectric discharge tubesSemiconductor/solid-state device manufacturingElectromagnetic fieldVacuum chamber

A disclosed film deposition apparatus which forms a film on a substrate inside a vacuum chamber including a turntable having a substrate mounting area, includes an antenna facing the substrate mounting area for converting the plasma generating gas to plasma, a Faraday shield intervening between the antenna and the substrate to prevent an electric field of an electromagnetic field from passing therethrough, the Faraday shield including slits arranged on the conductive plate parallel to the antenna, the slits being opened on the conductive plate in perpendicular to a direction of arranging the slits to enable a magnetic field to reach the substrate, a window opened in an area of the conductive plate surrounded by the slits, an inner conductive path between the slits and the window and grounded, and an outer conductive path on a side opposite to the window relative to the slits and surrounds the slits.

Owner:TOKYO ELECTRON LTD

Plasma cleaning method and plasma CVD method

ActiveUS20090308840A1Reliably decrease residual fluorineImprove throughputElectric discharge tubesVacuum gauge using ionisation effectsHydrogenNoble gas

A plasma cleaning method is performed in a plasma CVD apparatus for depositing a silicon nitride film on a surface of a target substrate, and includes a stage (S1) of supplying a cleaning gas containing NF3 gas into a process container, thereby removing extraneous deposits formed on portions inside the process container; a stage (S2) of supplying a gas containing hydrogen gas into the process container and generating plasma thereof, thereby removing residual fluorine inside the process container; and a stage (S3) of supplying a gas containing a rare gas into the process container and generating plasma thereof, thereby removing residual hydrogen inside the process container.

Owner:TOKYO ELECTRON LTD

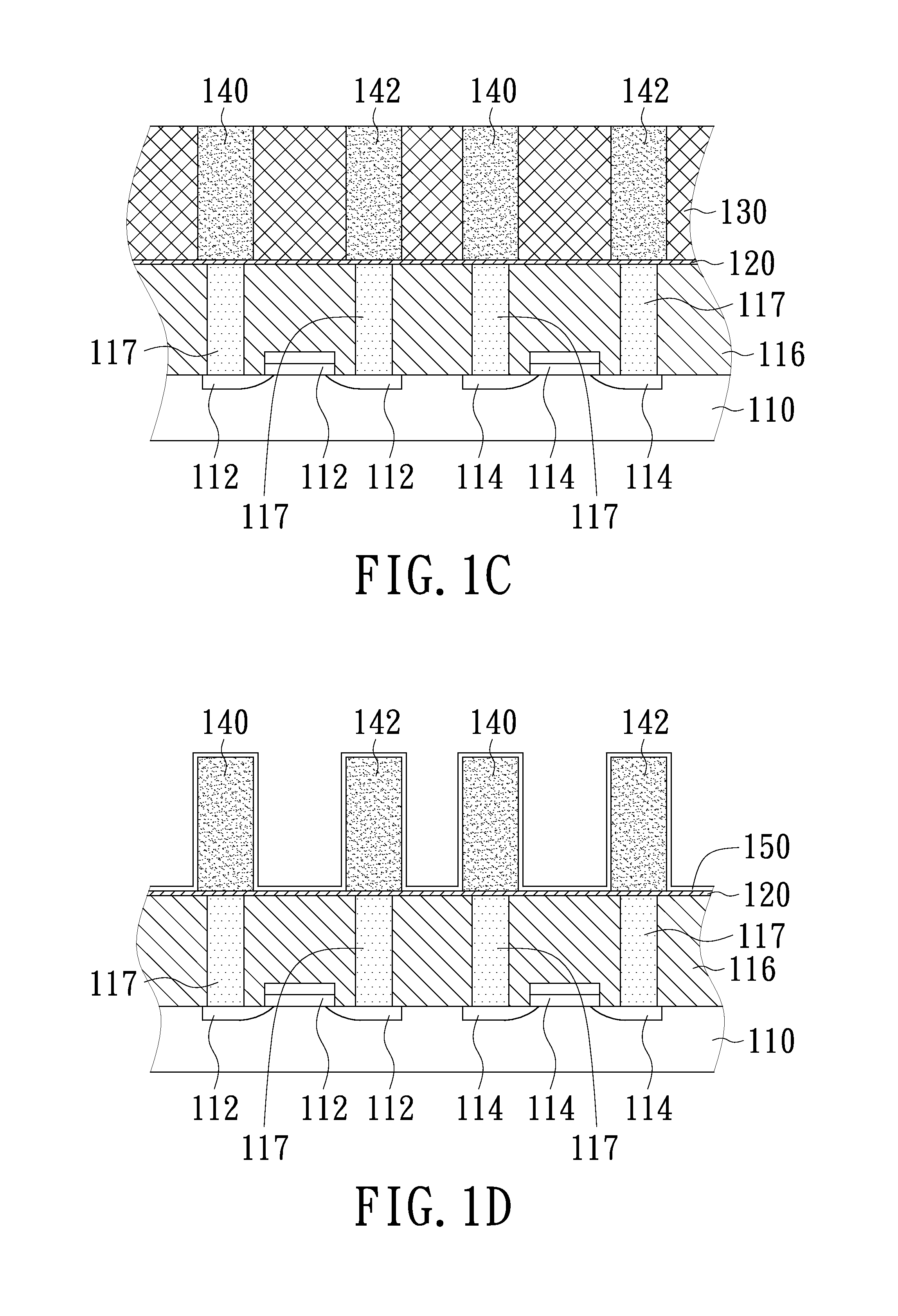

Manufacturing method for metal line

InactiveUS20140073128A1Reduce parasitic capacitanceImprove electrical performanceSemiconductor/solid-state device detailsSolid-state devicesDevice materialMetallic materials

A method for manufacturing metal lines in a semiconductor device is provided. The method includes steps of: providing a substrate; forming a first barrier layer on the substrate; forming a sacrificial layer on the first barrier layer; forming an opening penetrating through the sacrificial layer to expose a portion of the first barrier layer; depositing a metal material on the exposed first barrier layer to form a metal line in the opening; removing the sacrificial layer and forming a second barrier layer over the resulting structure; etching the second barrier layer and the first barrier layer while remaining a barrier spacer on a sidewall of the metal line; and forming an insulating layer on the substrate and the barrier spacer. A semiconductor device having the metal lines produced by the method is also provided.

Owner:NAT APPLIED RES LAB

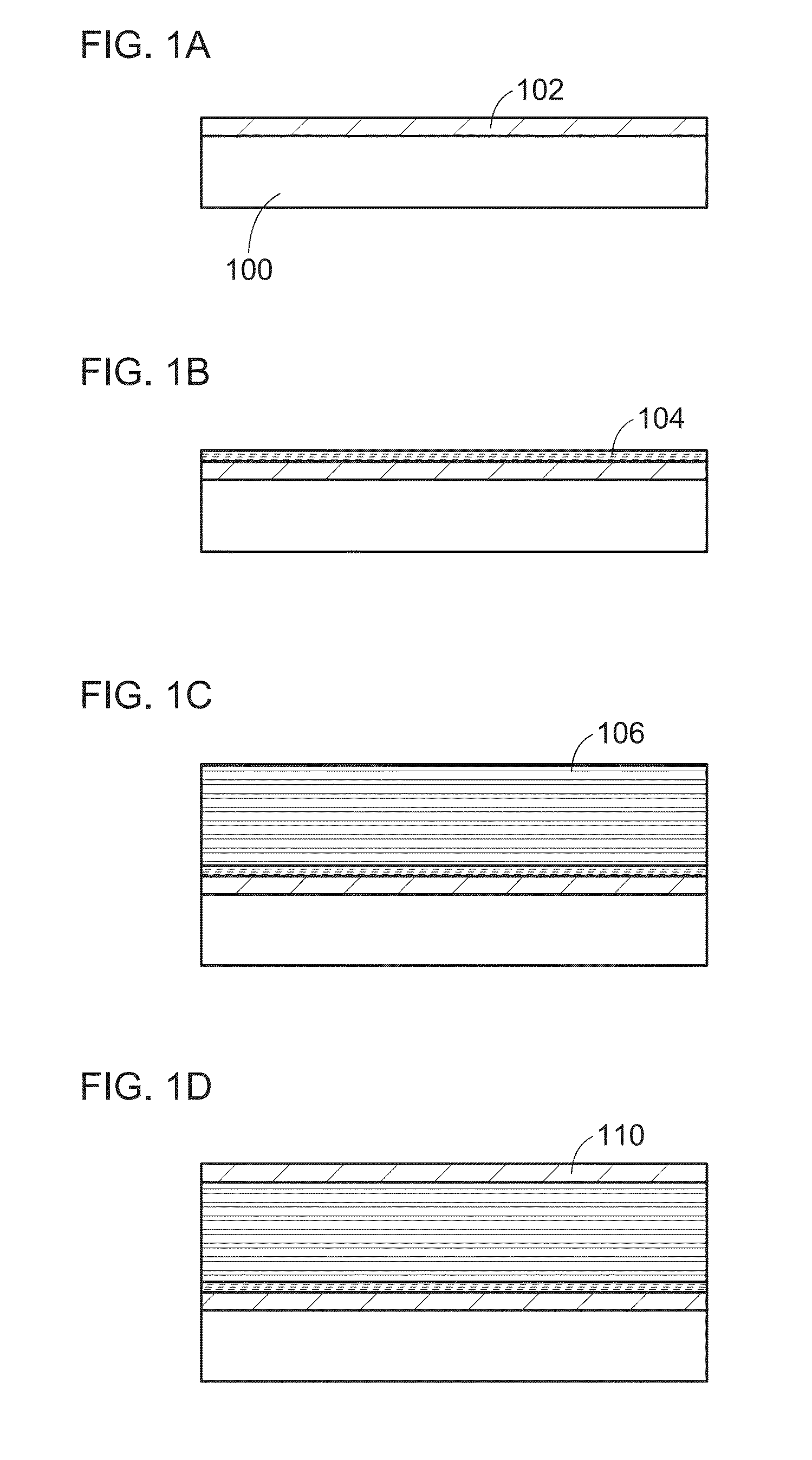

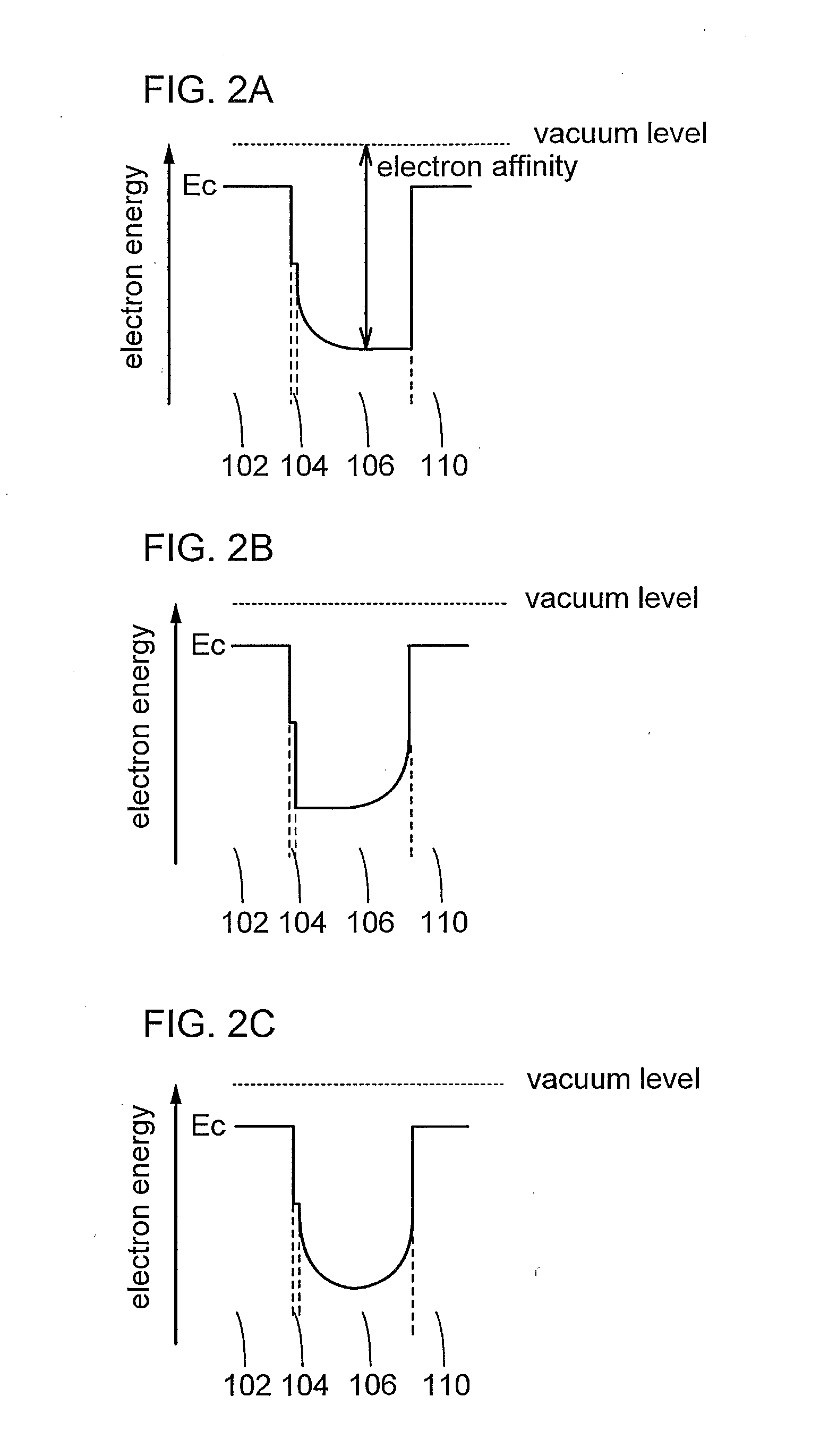

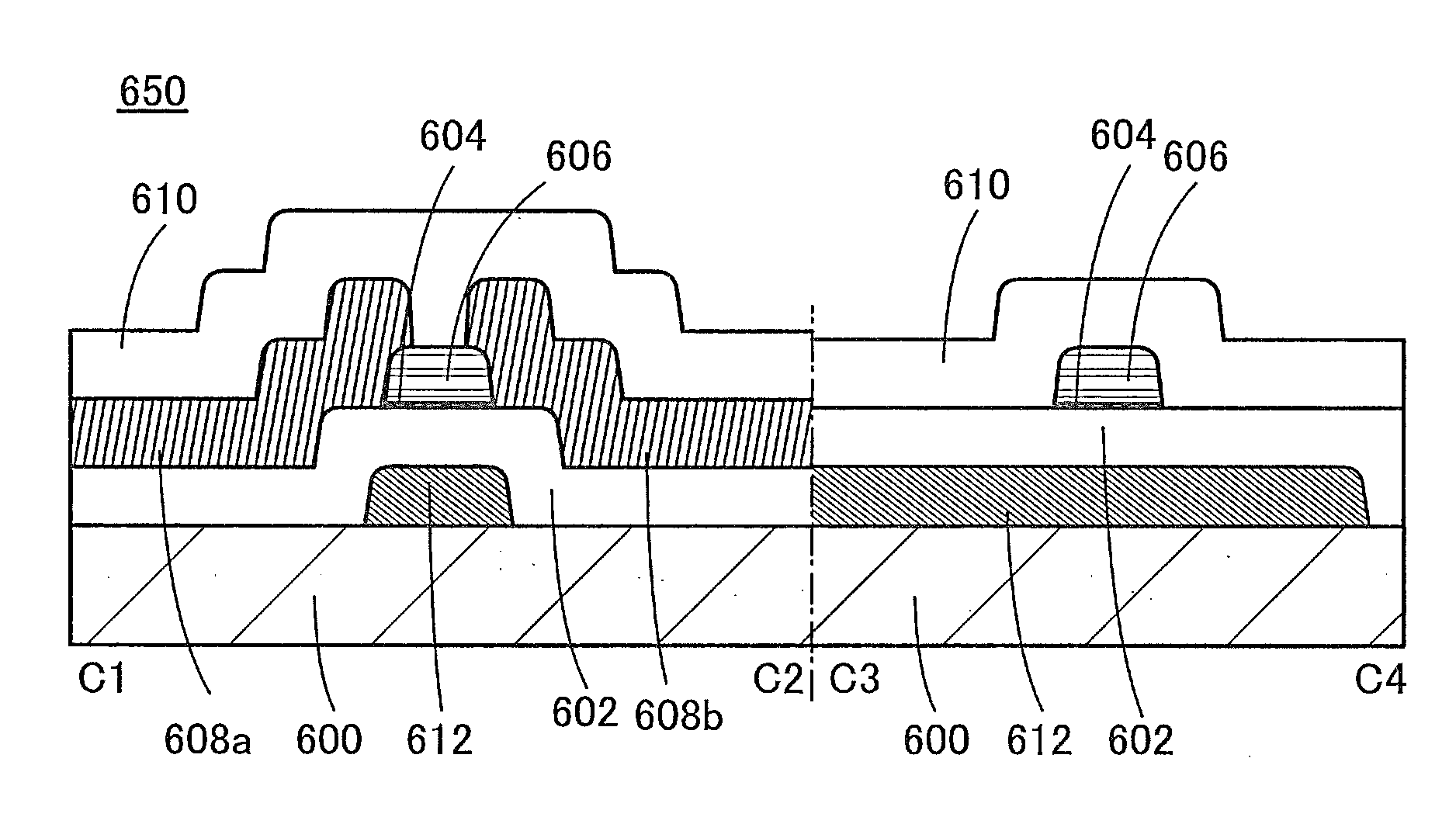

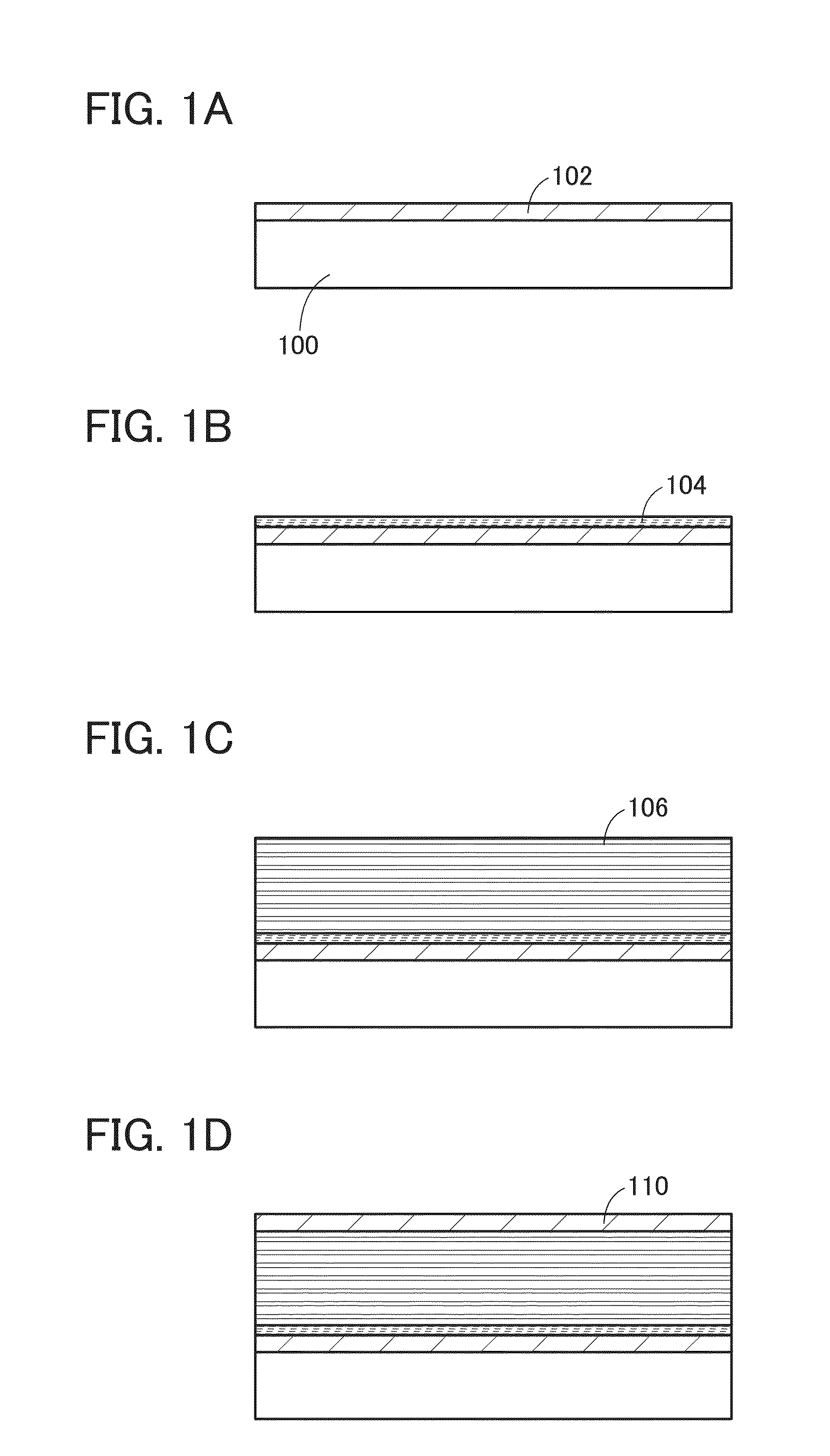

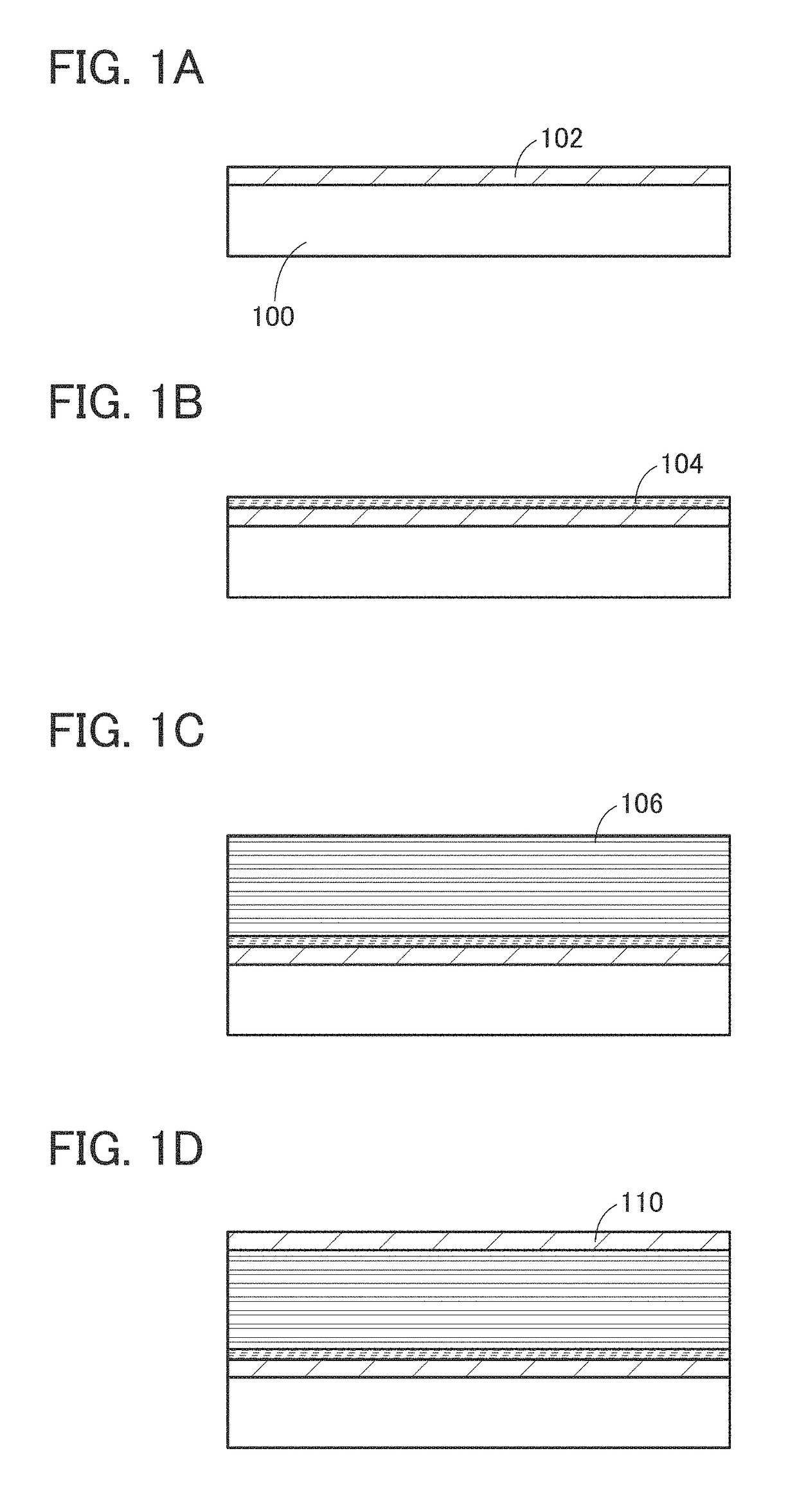

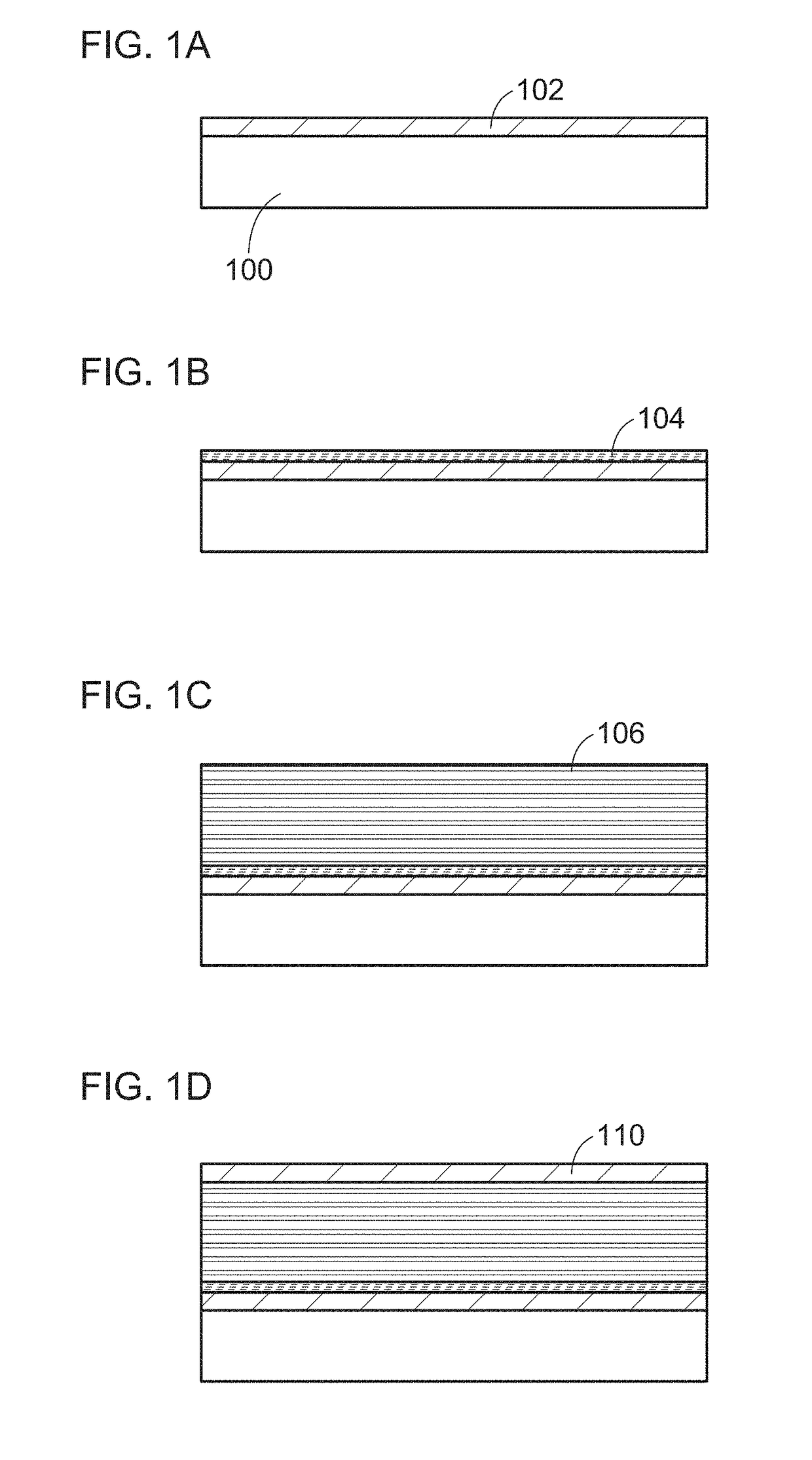

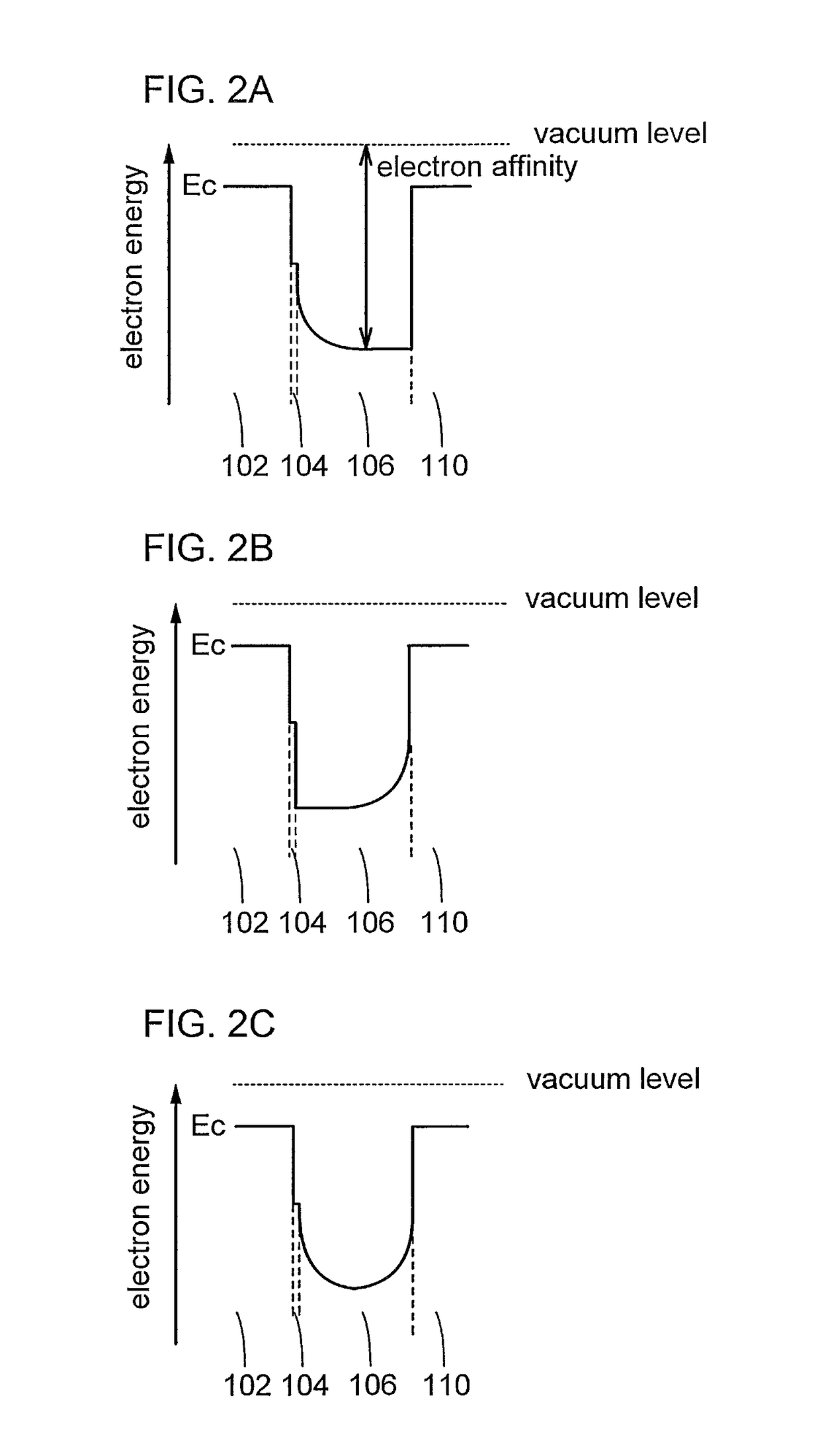

Method for manufacturing semiconductor device

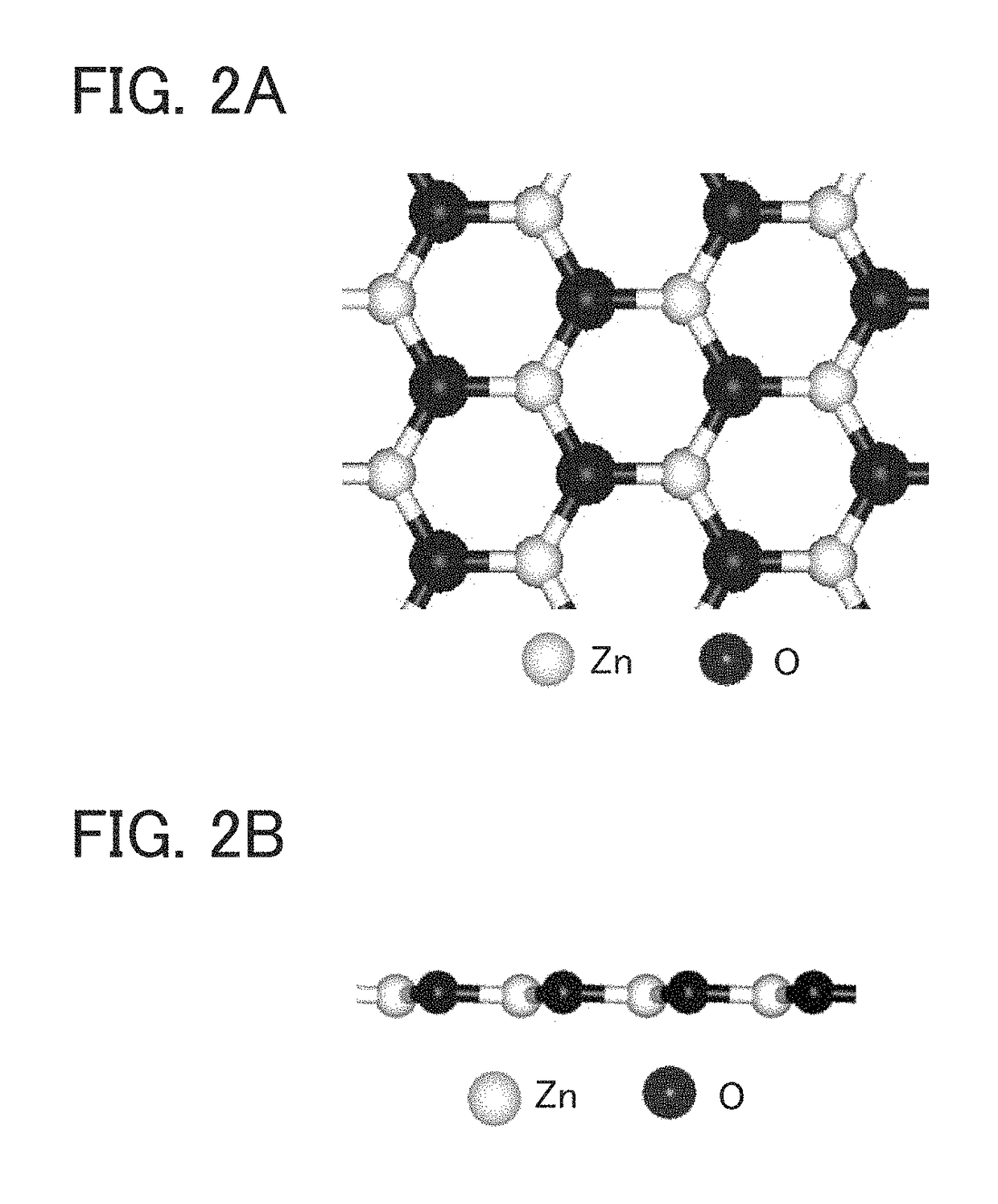

InactiveUS20150079728A1Reduce numberImprove reliabilitySemiconductor/solid-state device manufacturingSemiconductor devicesPhysicsOxide semiconductor

Provided are an oxide semiconductor layer in which the number of defects is reduced and a highly reliable semiconductor device including the oxide semiconductor. A first oxide semiconductor layer having a crystal part is formed over a substrate by a sputtering method. A second oxide semiconductor layer is formed by a thermal chemical vapor deposition method over the first oxide semiconductor layer. The second oxide semiconductor layer is formed by epitaxial growth using the first oxide semiconductor layer as a seed crystal. A channel is formed in the second oxide semiconductor layer.

Owner:SEMICON ENERGY LAB CO LTD

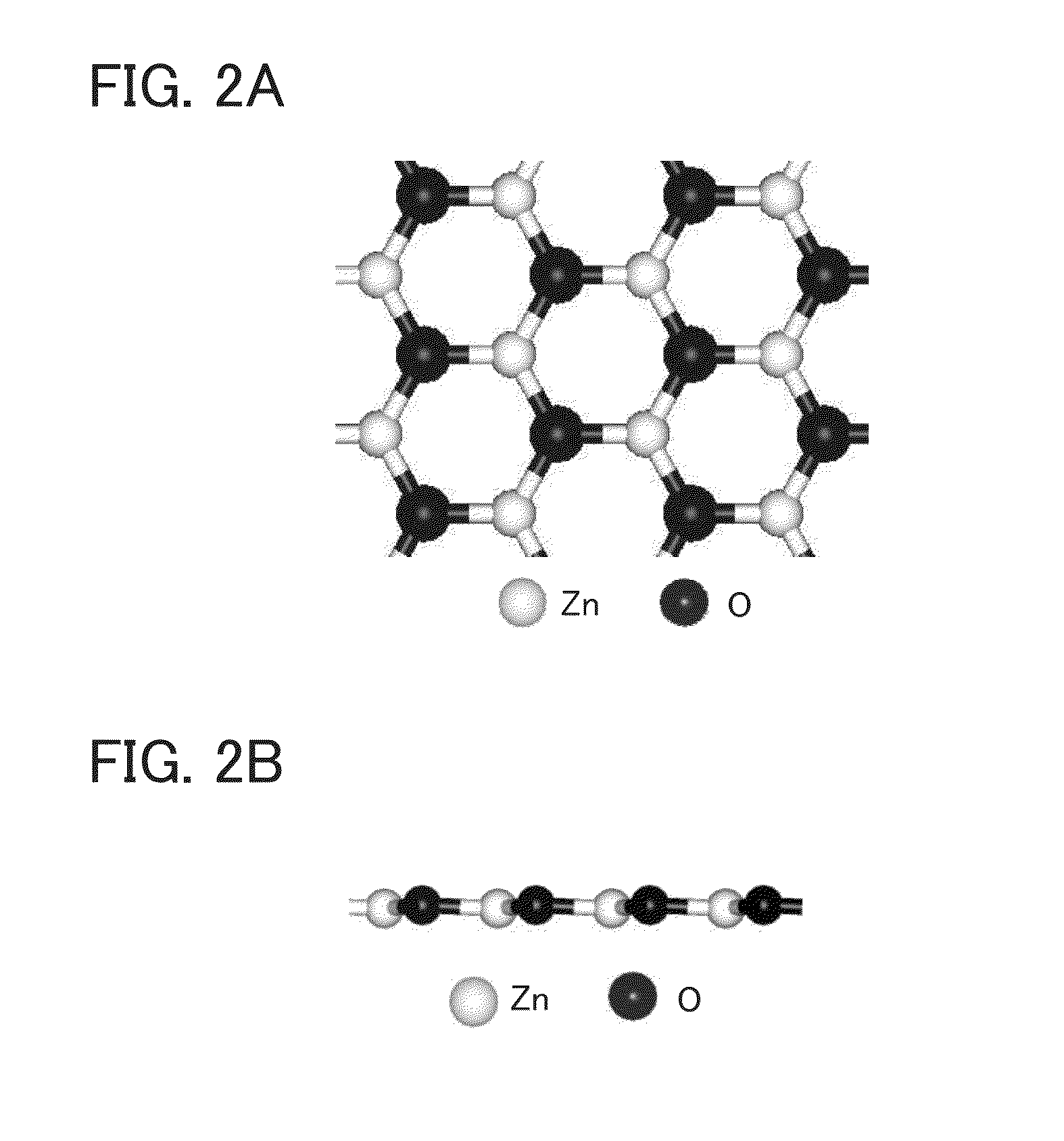

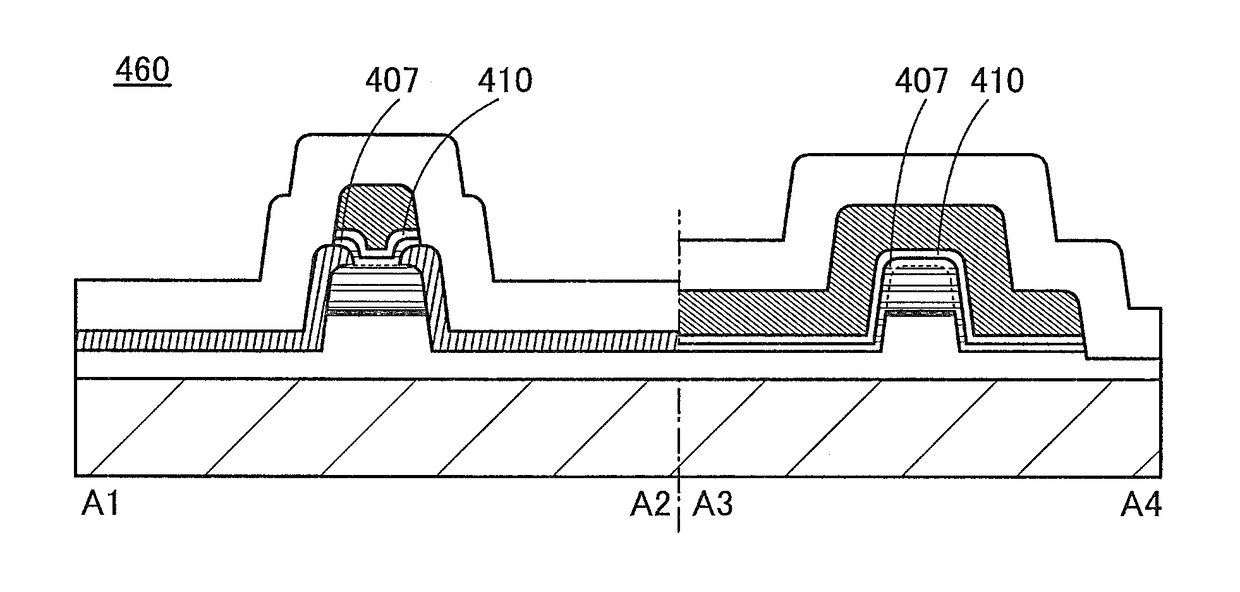

Method of manufacturing semiconductor device

InactiveUS20150079729A1Improve reliabilityReduce in quantityTransistorSemiconductor/solid-state device manufacturingGas phaseThermal chemical vapor deposition

Provided are an oxide semiconductor layer in which the number of defects is reduced and a highly reliable semiconductor device including the oxide semiconductor. A first oxide semiconductor layer containing a single metal element as a constituent element is formed over a substrate by a thermal chemical vapor deposition method. A second oxide semiconductor layer containing two or more metal elements as constituent elements is formed successively after the first oxide semiconductor layer is formed. The second oxide semiconductor layer is formed by epitaxial growth using the first oxide semiconductor layer as a seed crystal. A channel is formed in the second oxide semiconductor layer.

Owner:SEMICON ENERGY LAB CO LTD

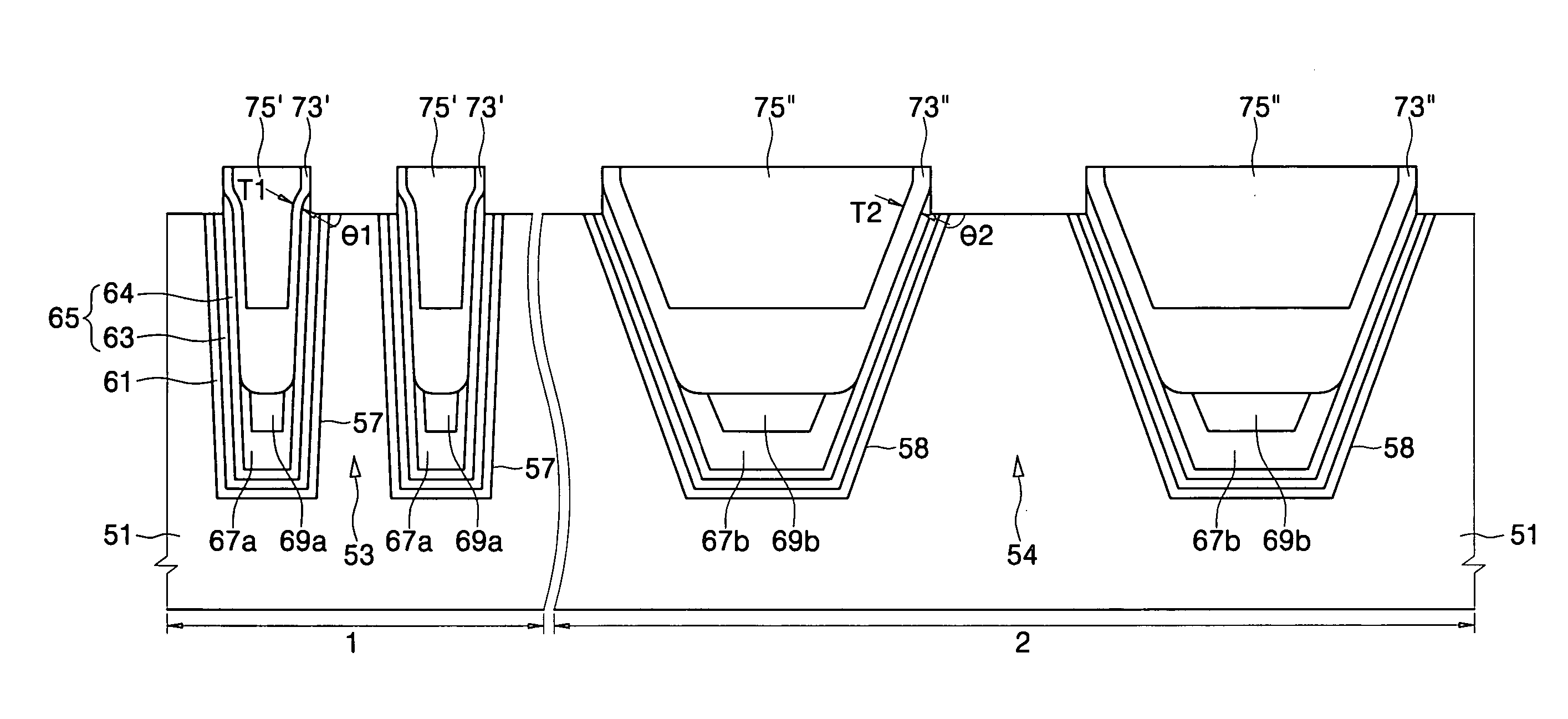

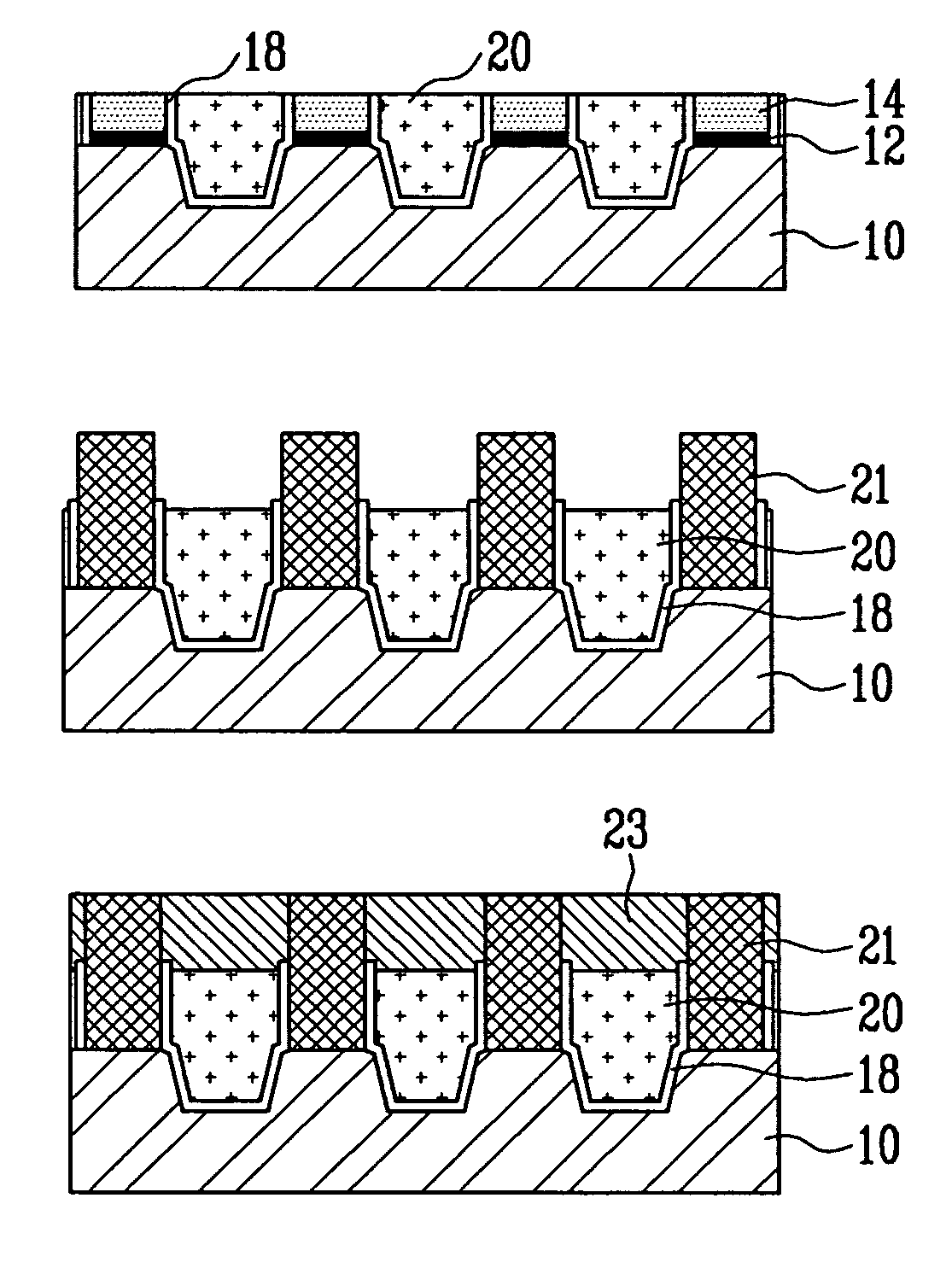

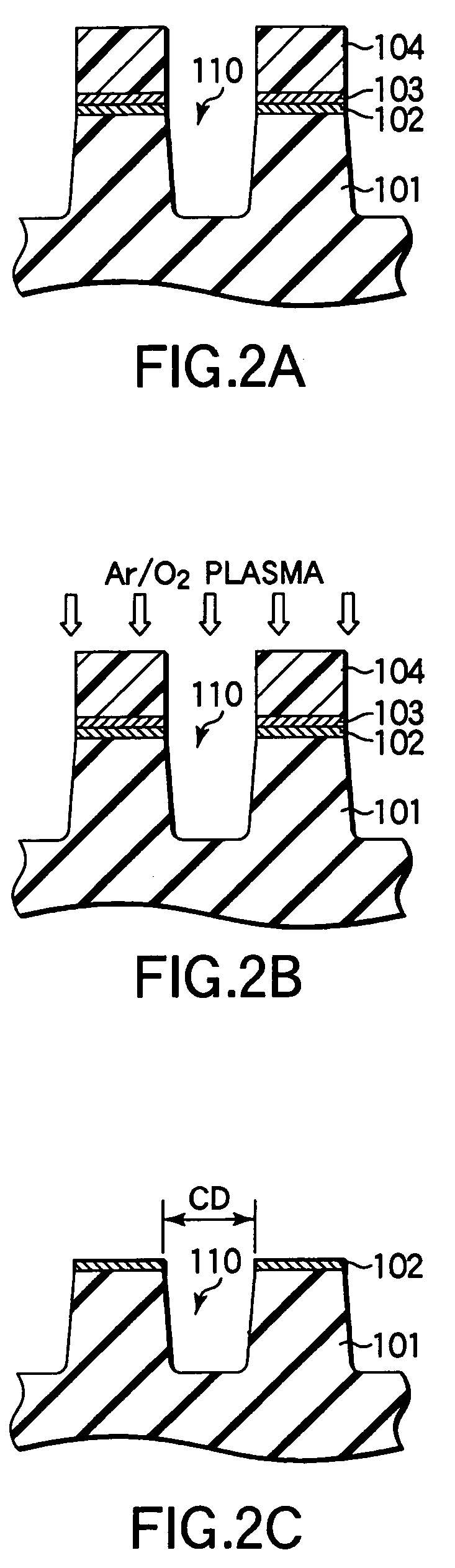

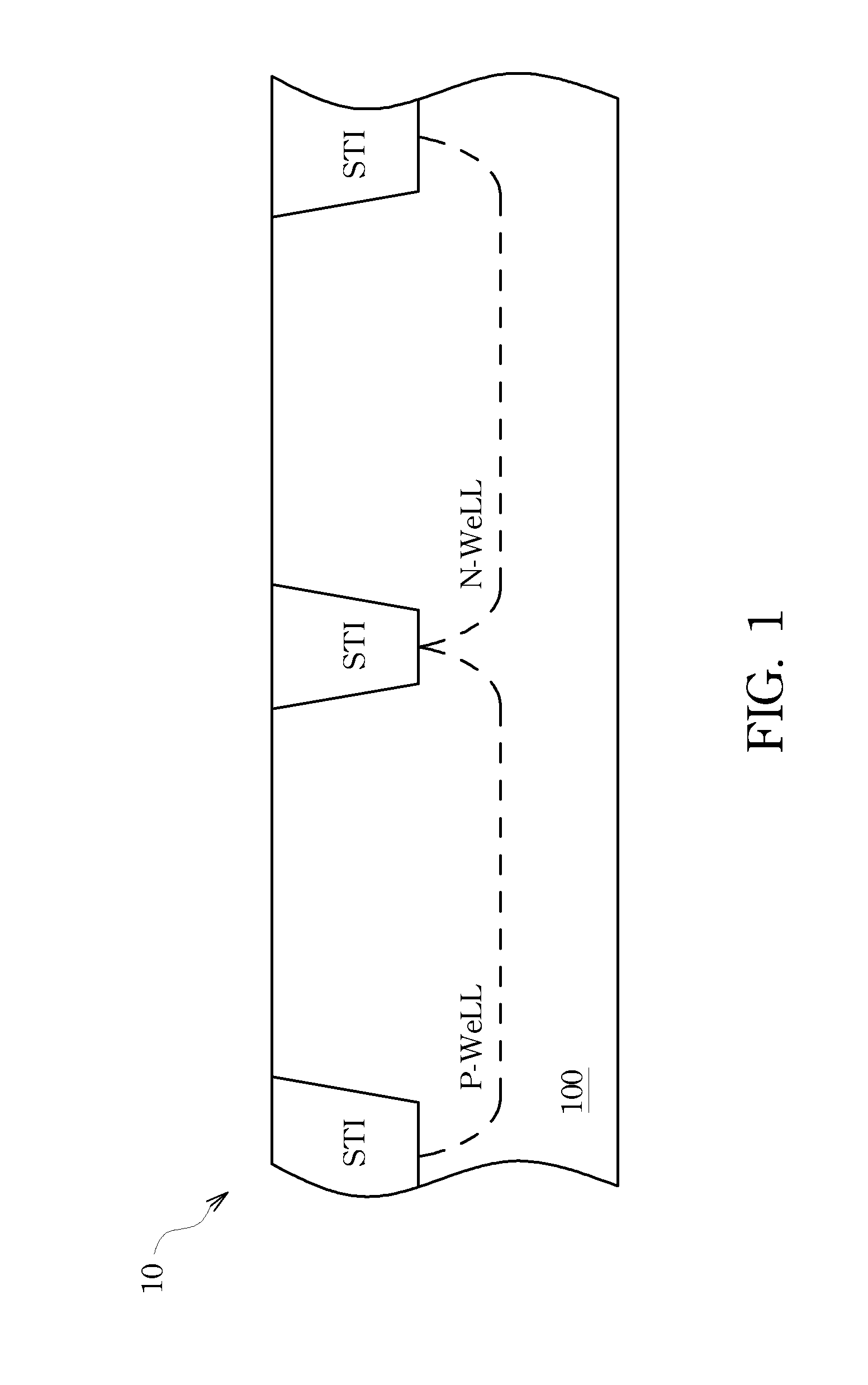

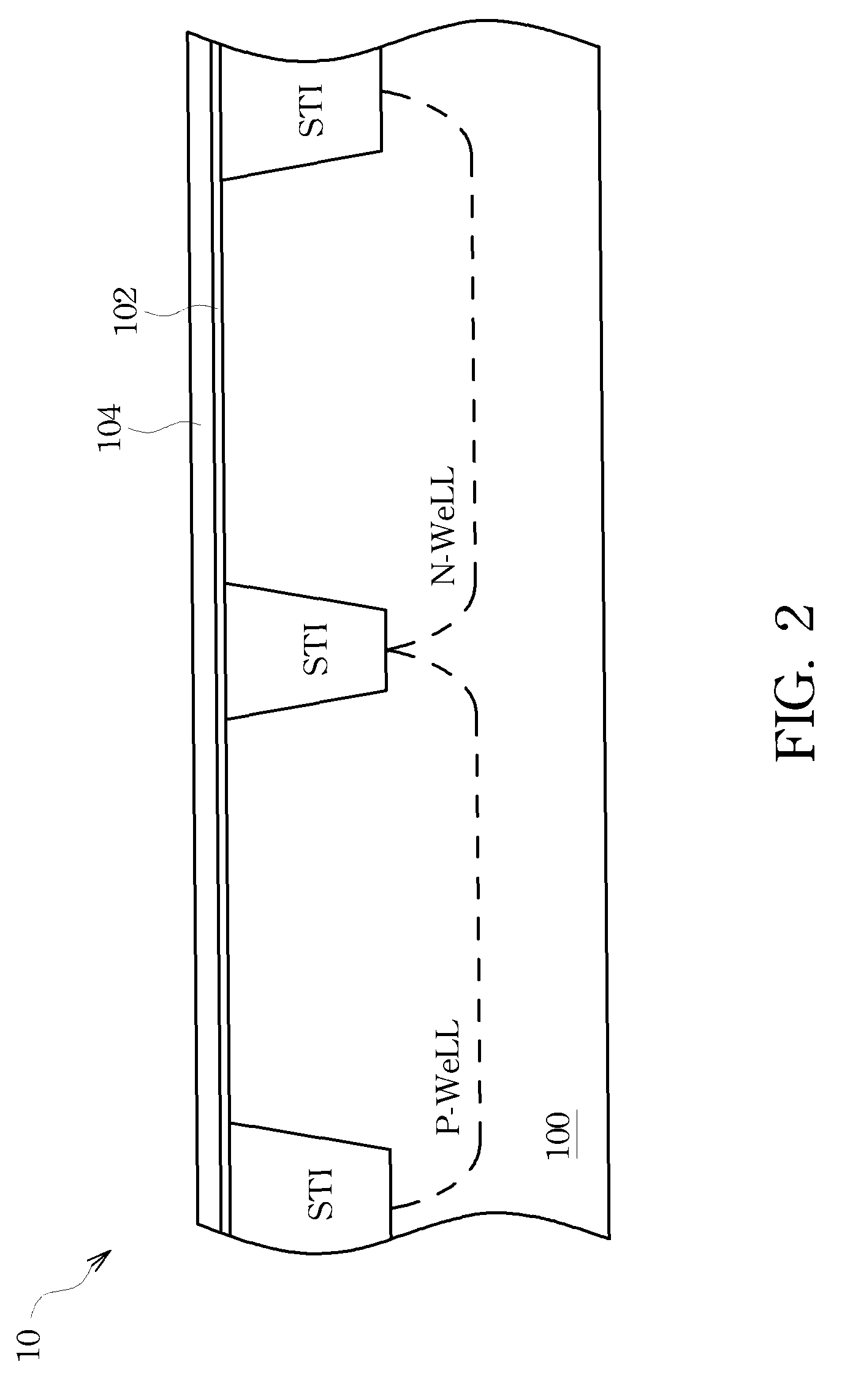

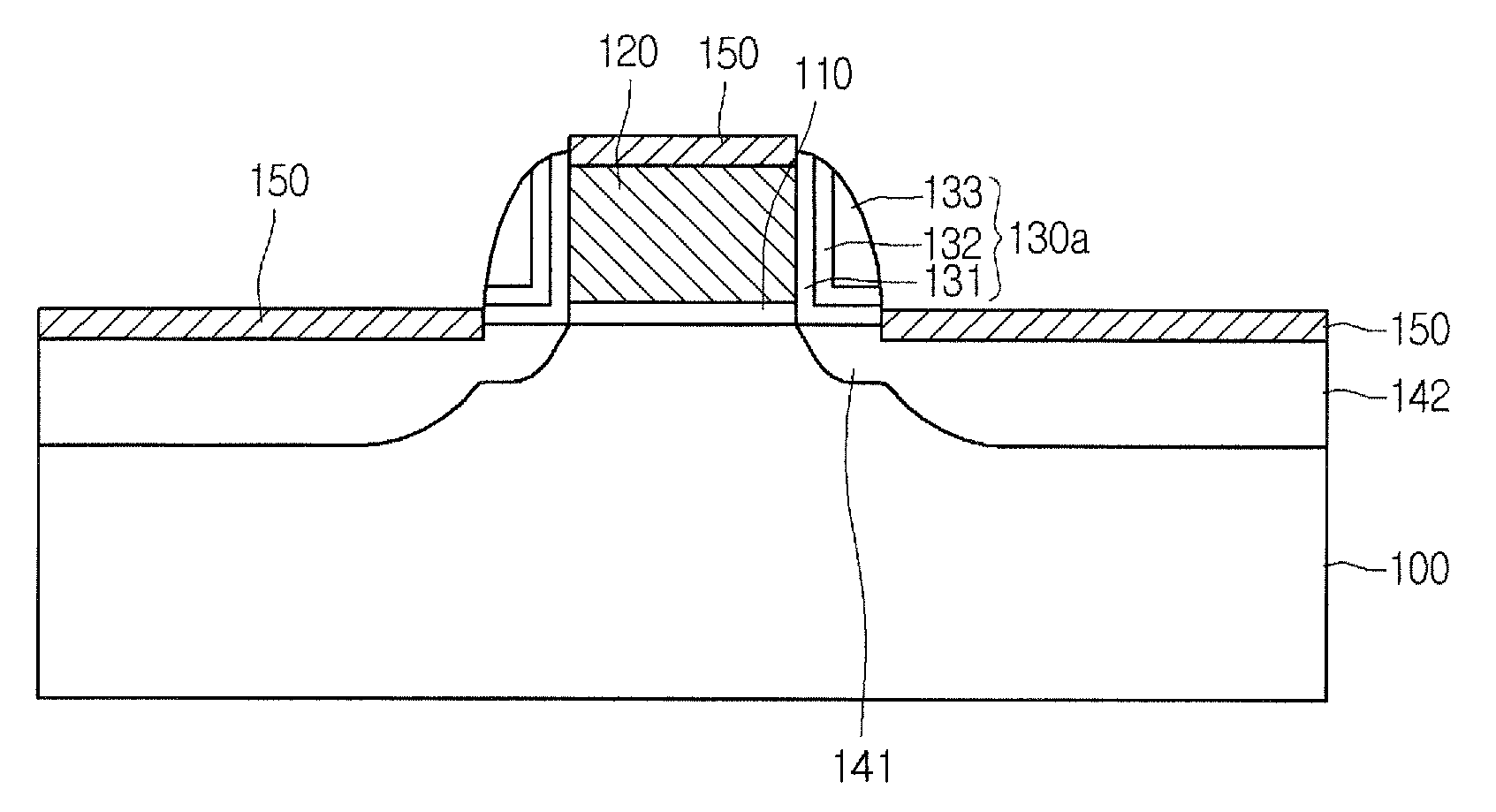

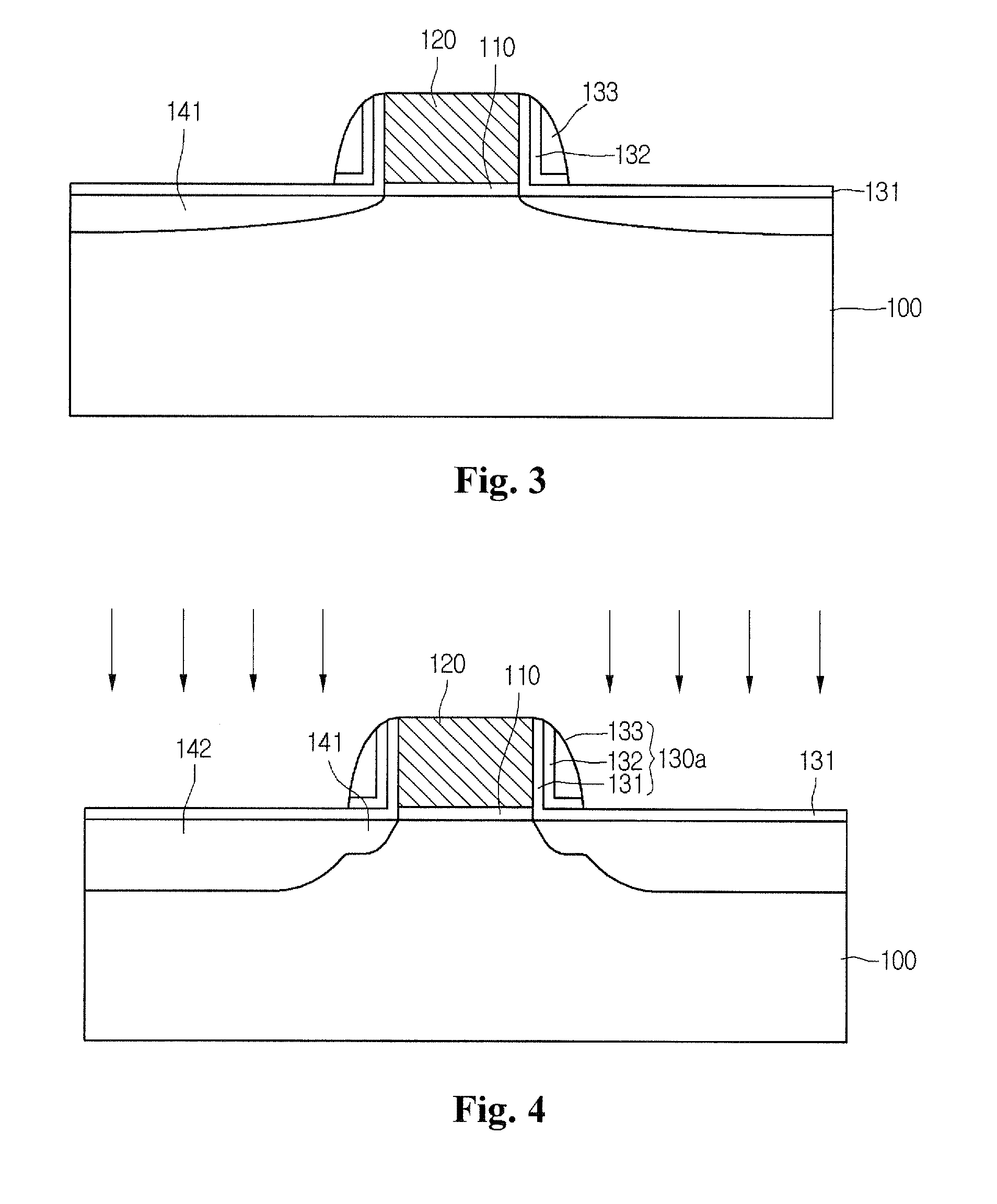

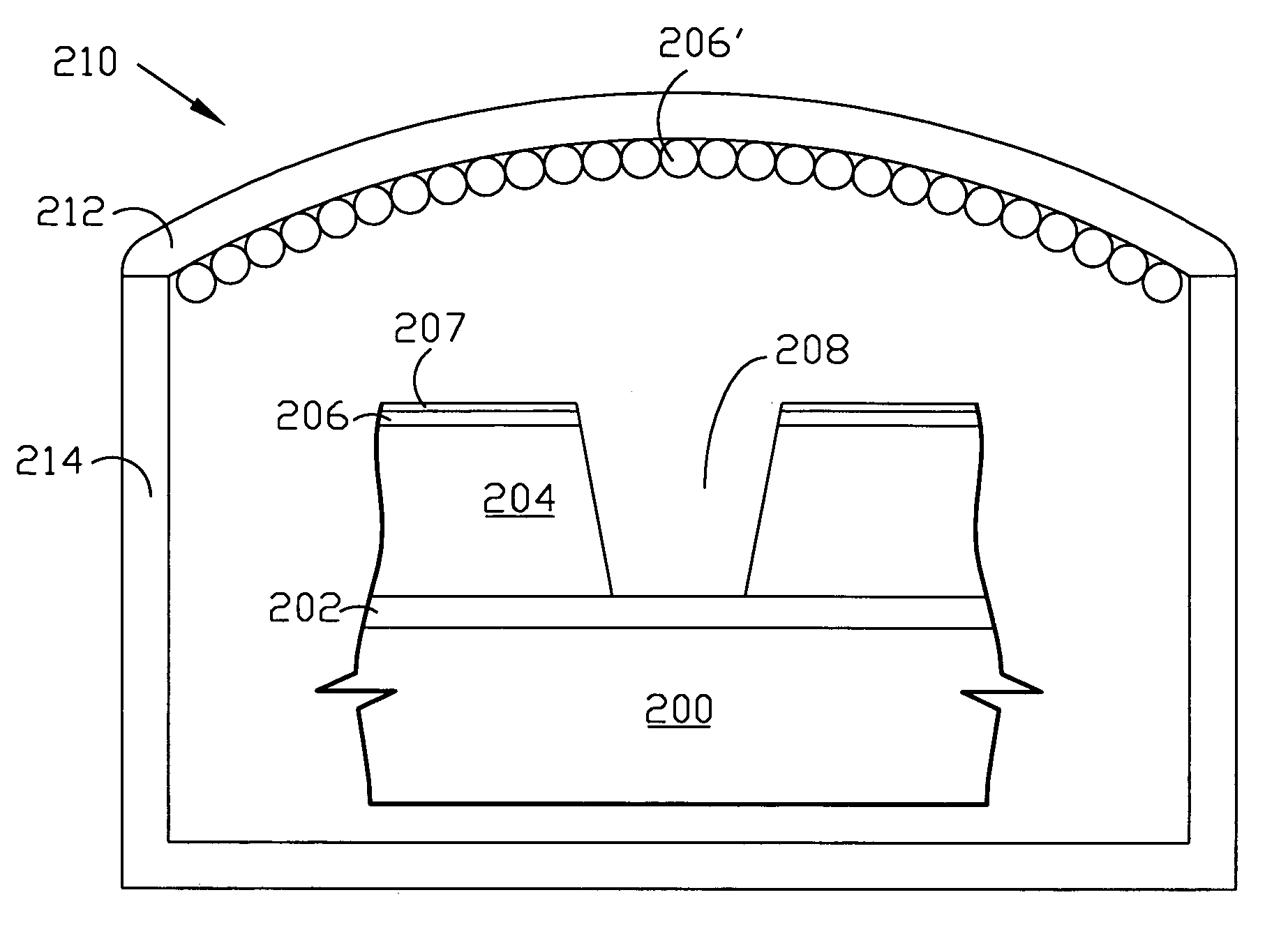

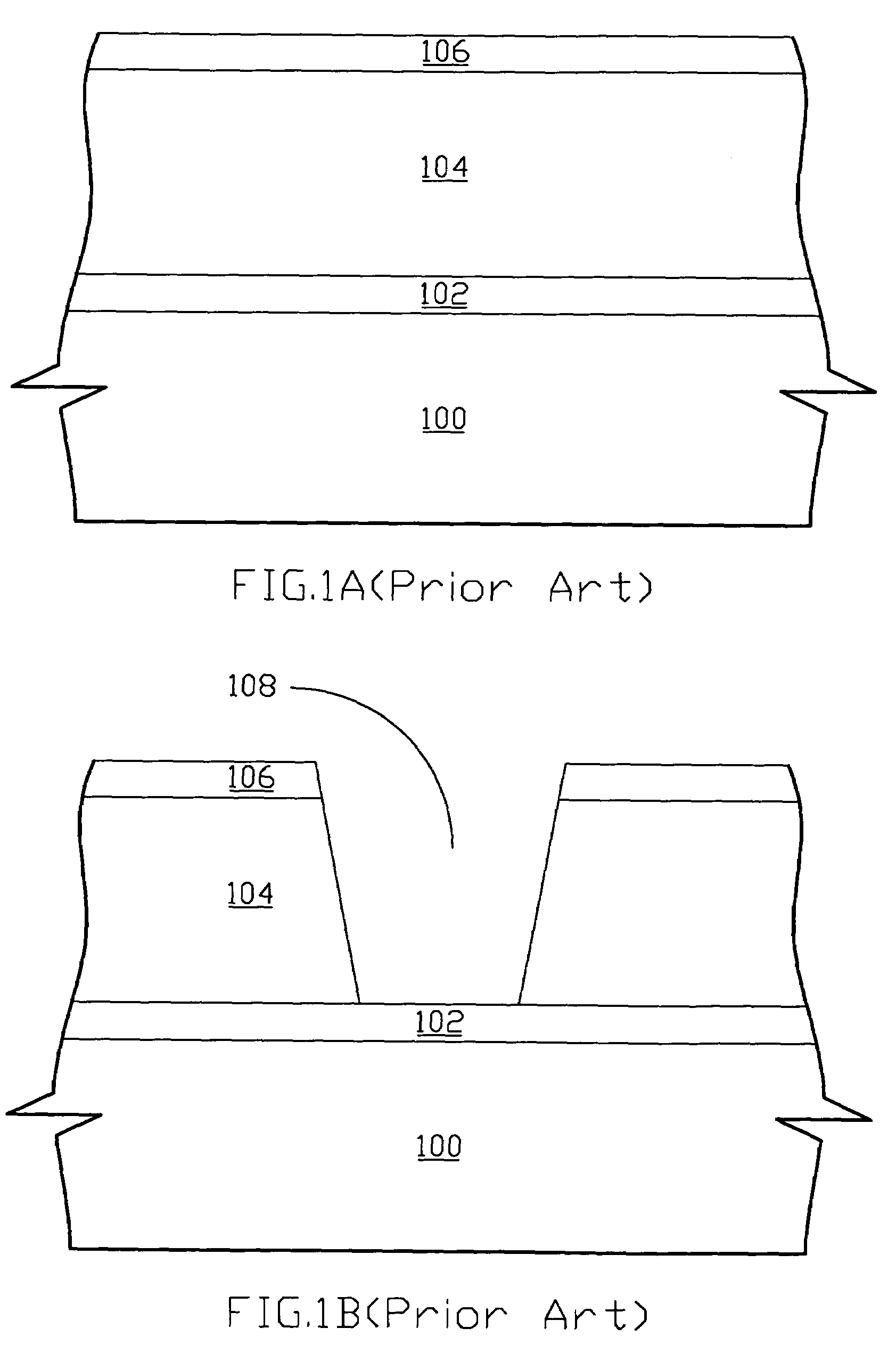

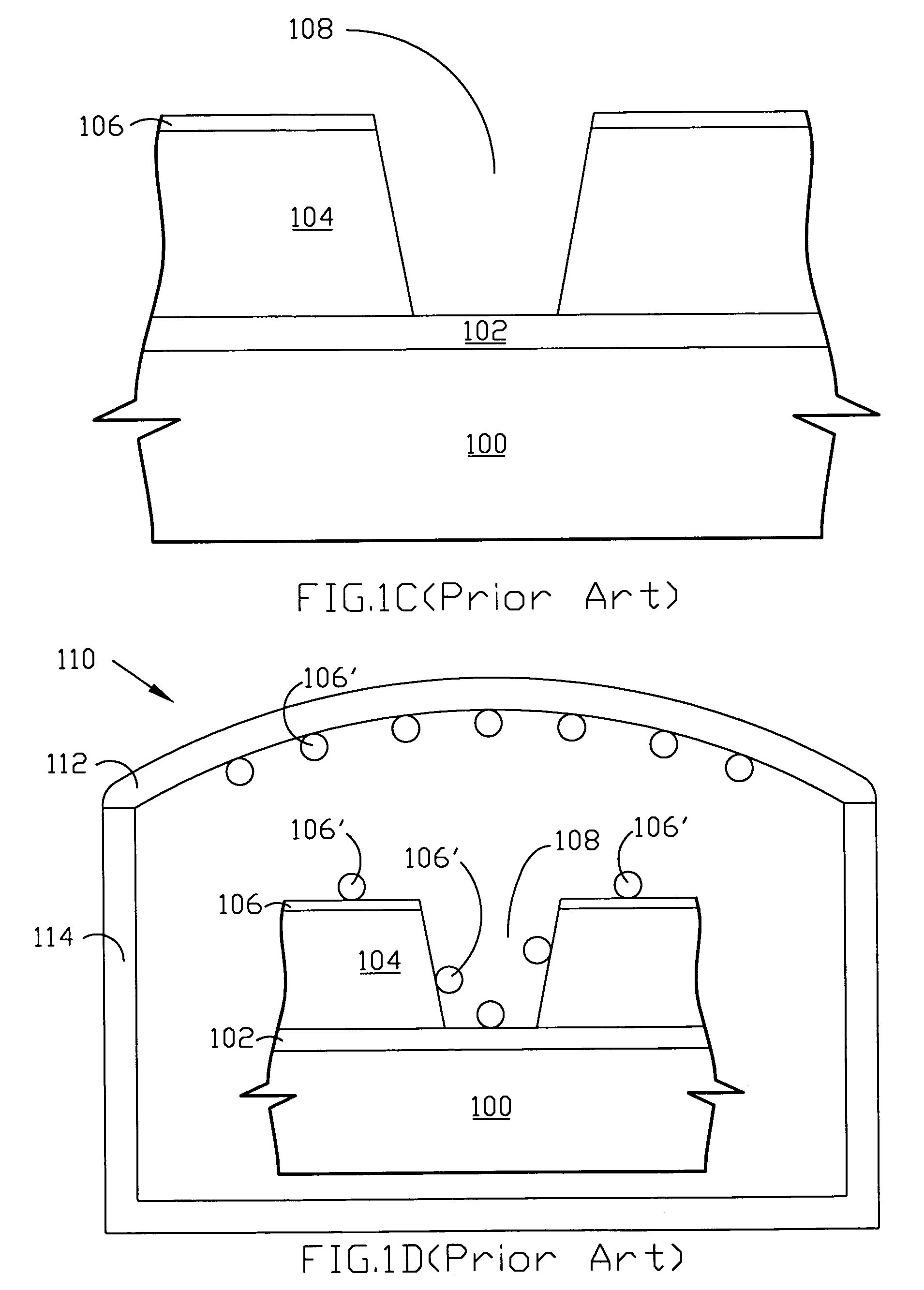

Semiconductor devices including trench isolation structures and methods of forming the same

InactiveUS20070059898A1Avoid plasma damageHigh bias powerElectric discharge tubesSemiconductor/solid-state device detailsHigh densityDevice material

Trench isolation methods include forming a first trench and a second trench, having a larger width than the first trench, in a semiconductor substrate. A lower isolation layer is formed having a first thickness on an upper sidewall of the first trench and a second thickness on an upper sidewall of the second trench using a first high density plasma deposition process, the second thickness being greater than the first thickness. An upper isolation layer is formed on the semiconductor substrate including the lower isolation layer using a second high density plasma deposition process, different from the first high density plasma deposition process. The first and second high density plasma deposition processes may be chemical vapor deposition processes. Semiconductor devices including a trench isolation structure are also provided.

Owner:SAMSUNG ELECTRONICS CO LTD

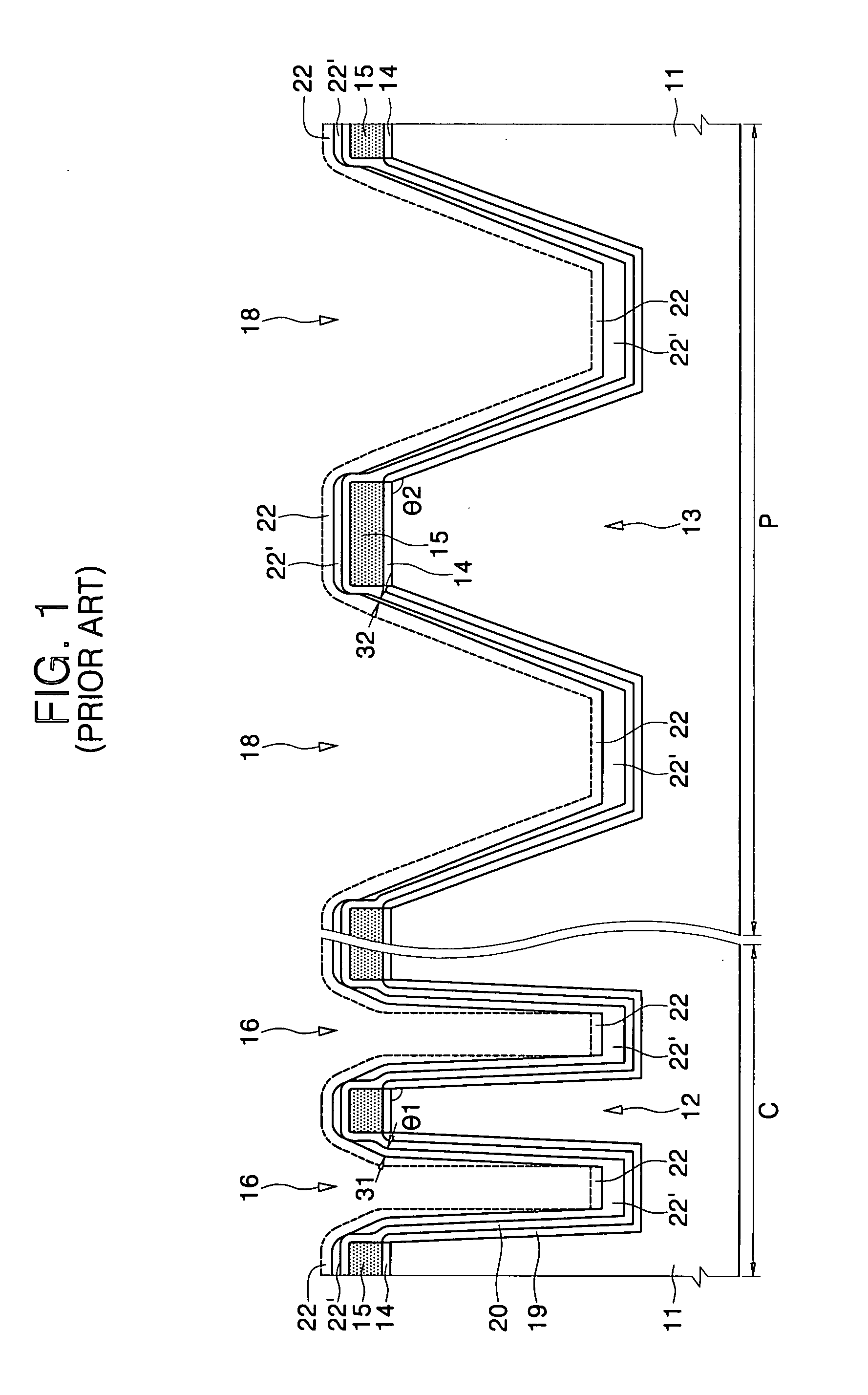

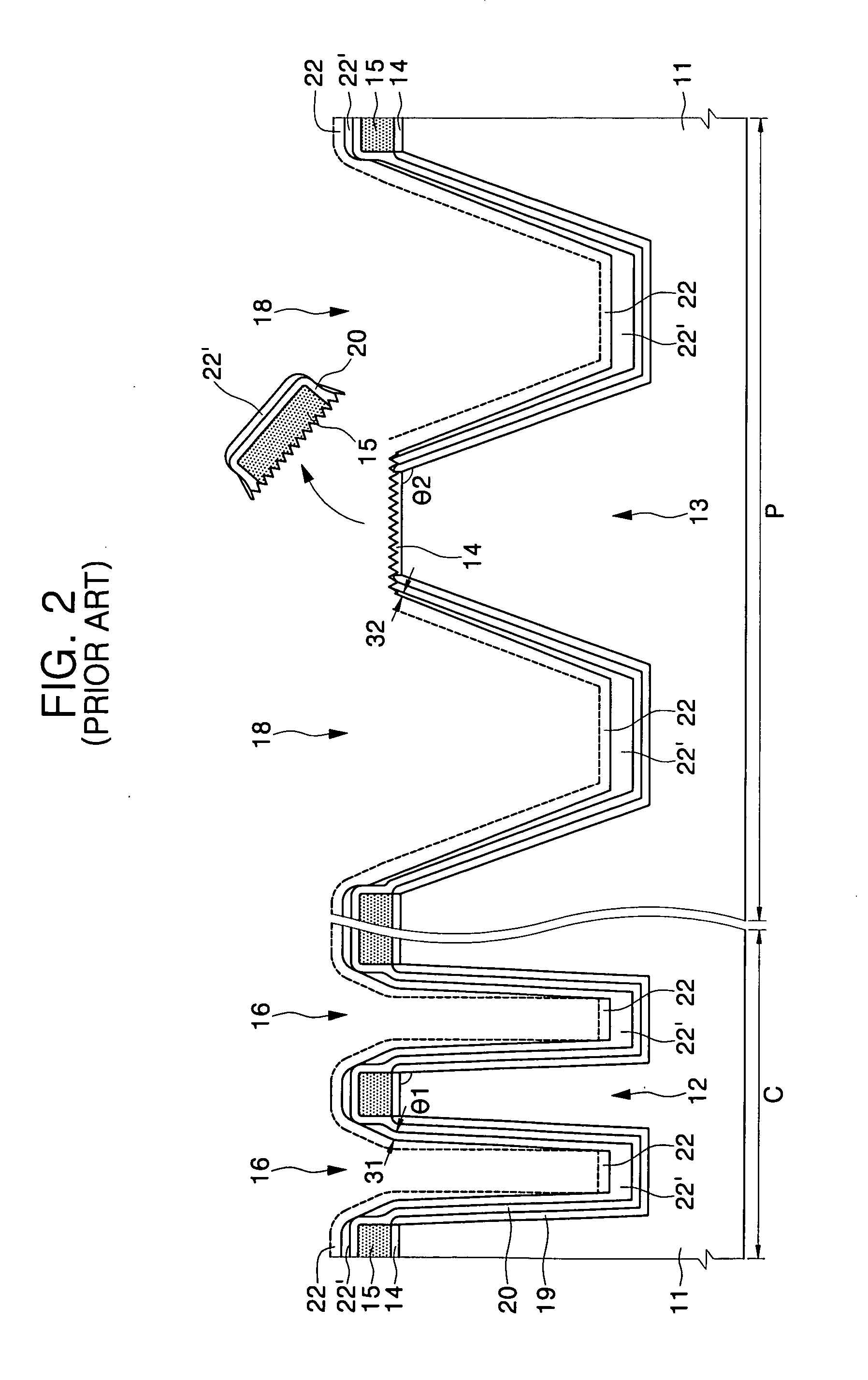

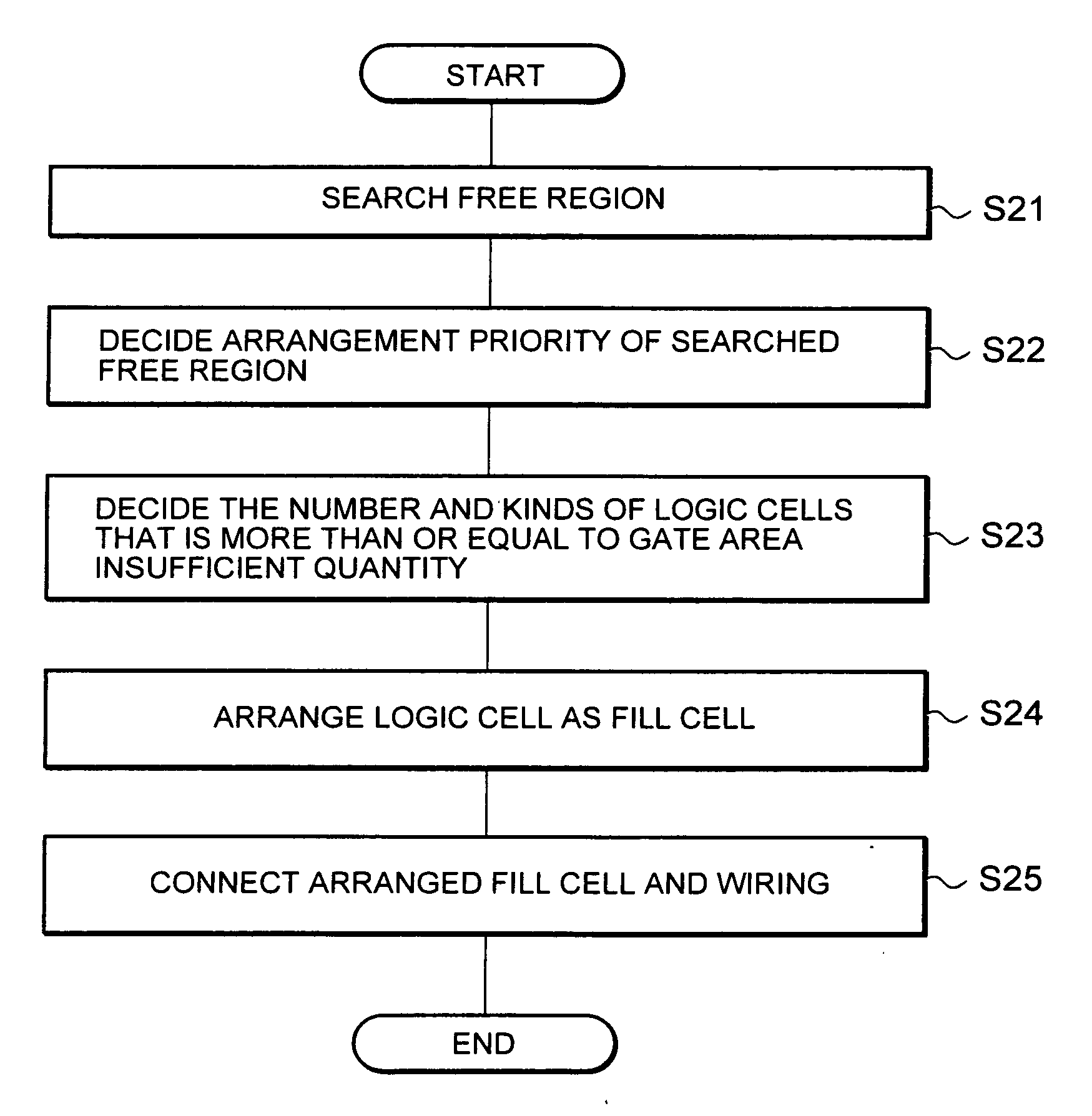

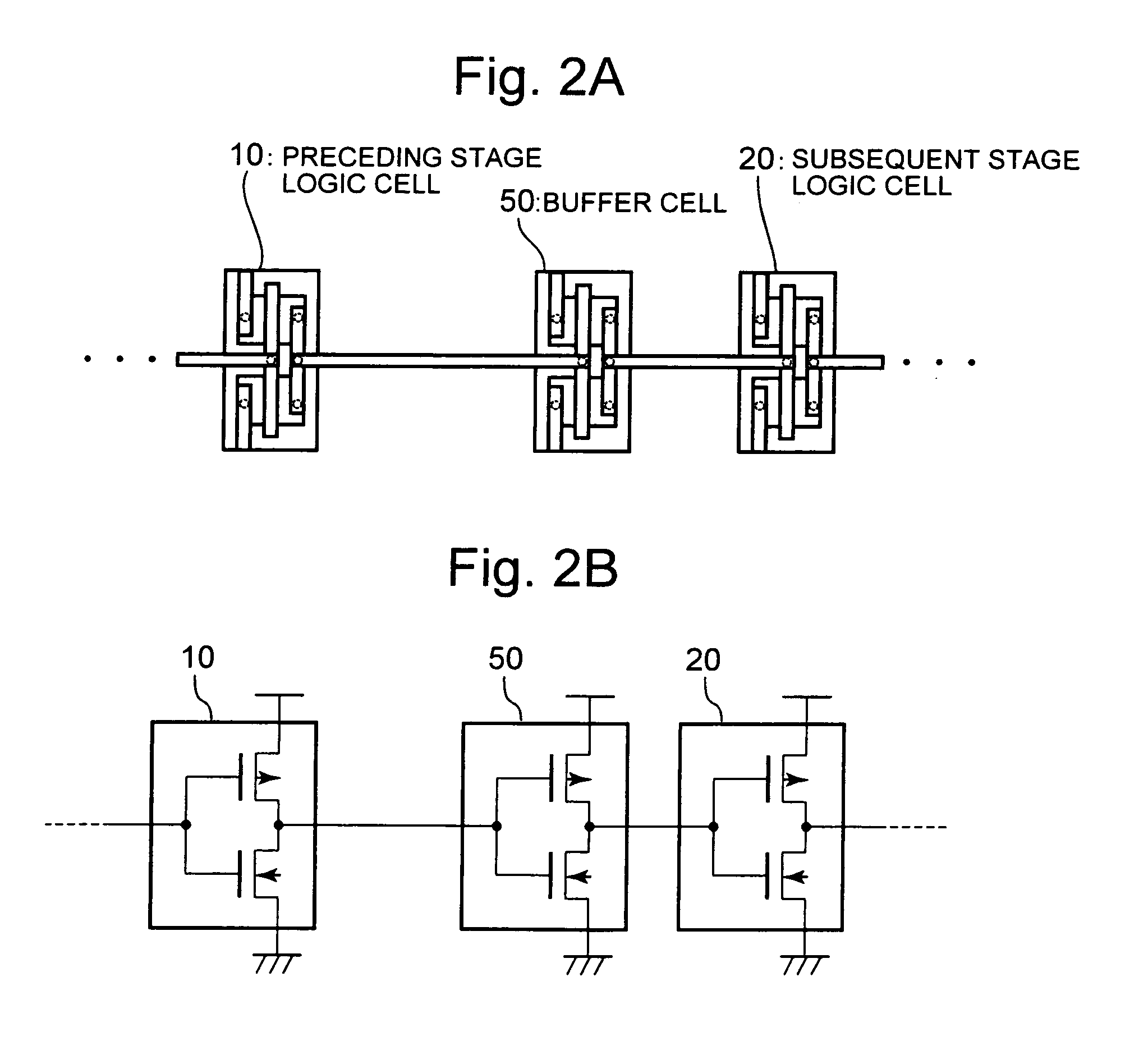

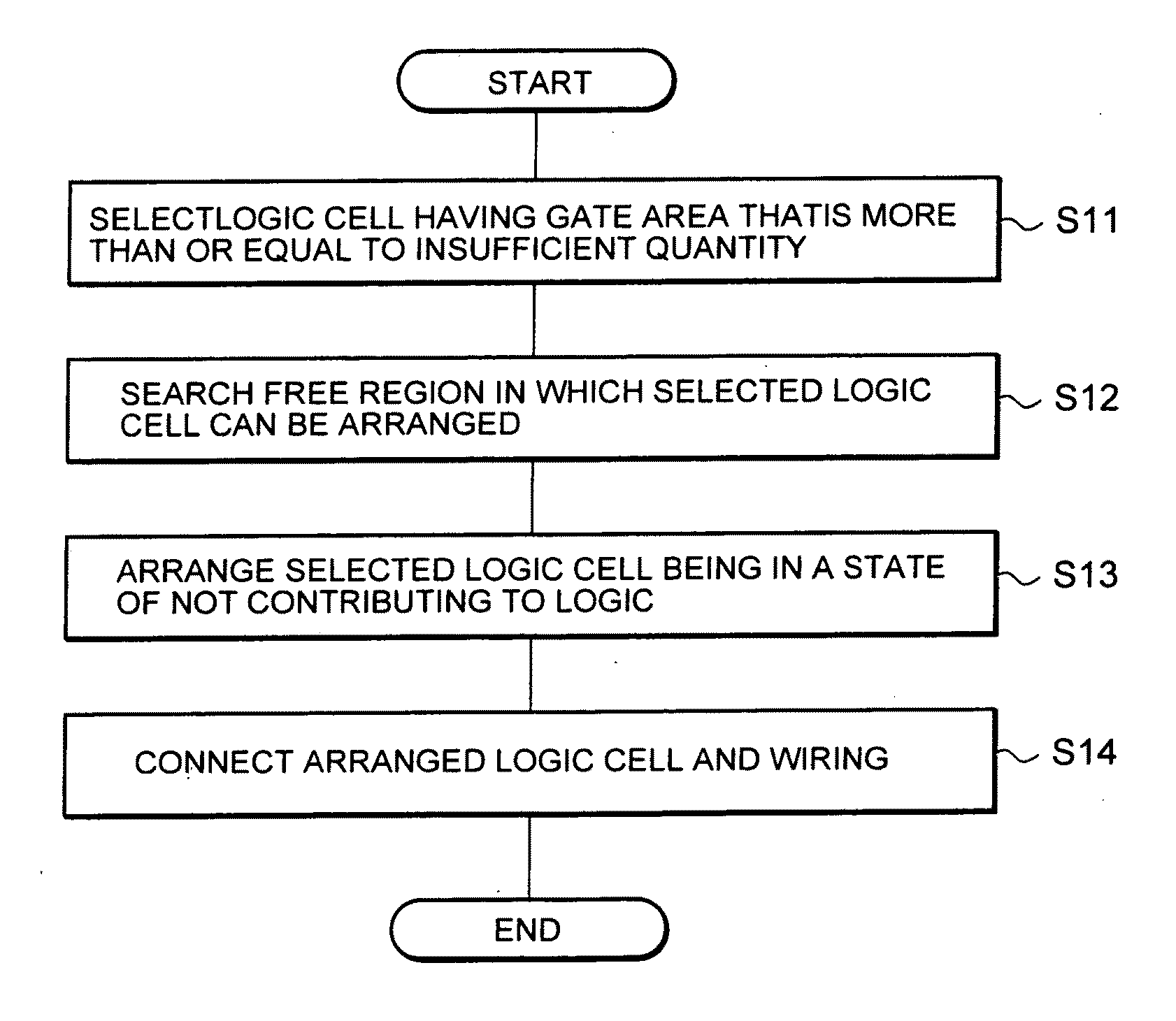

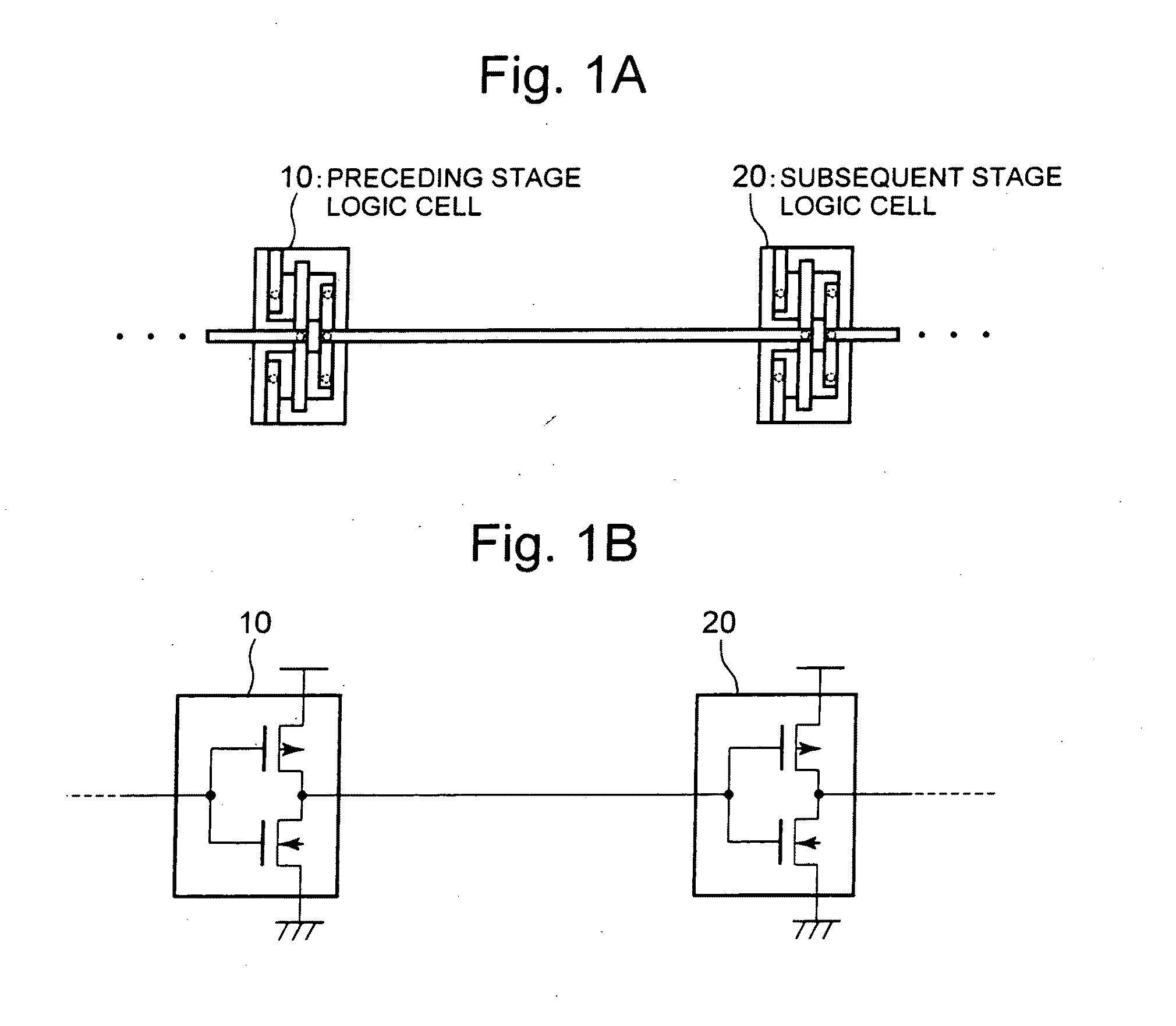

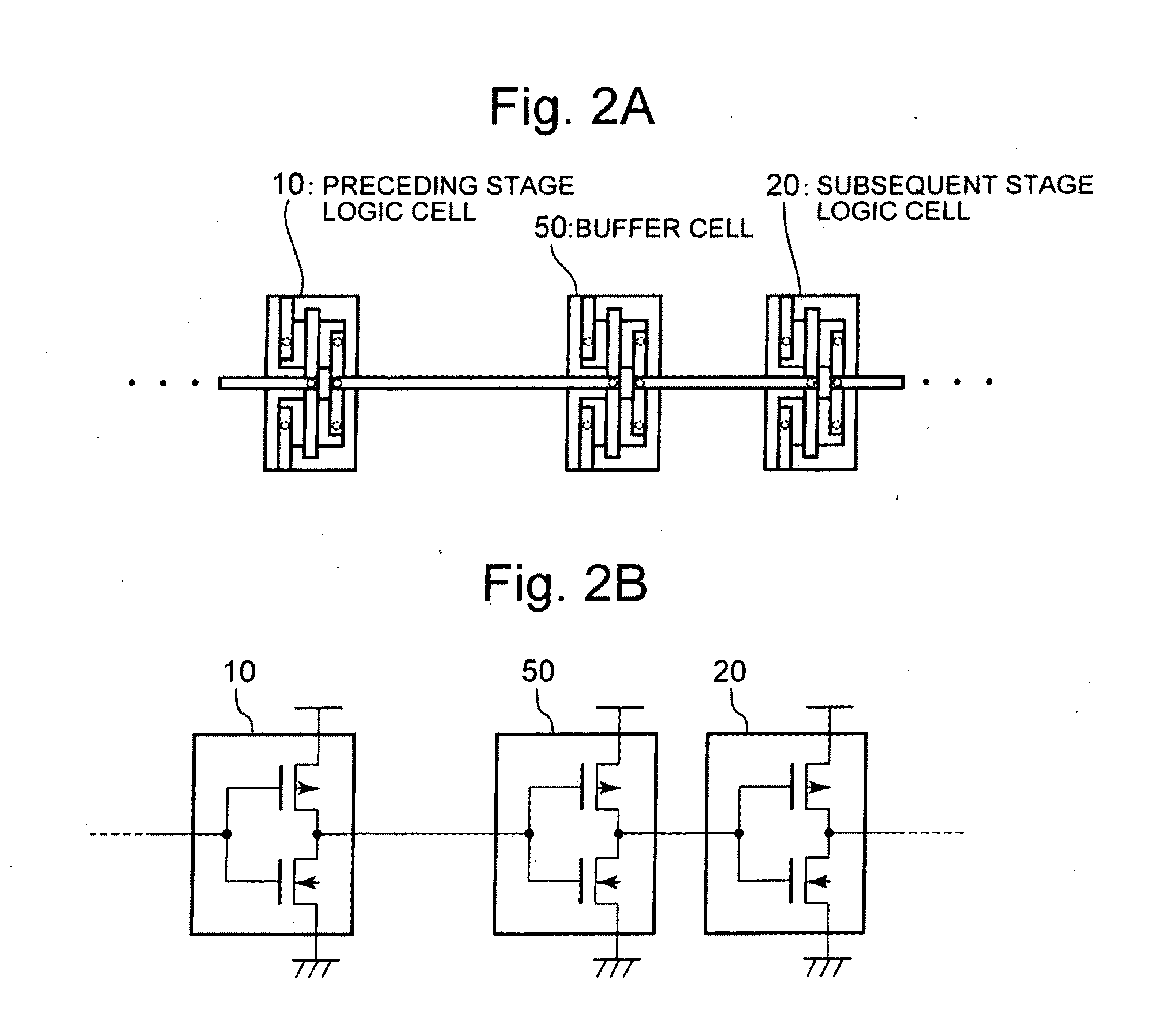

Method for designing semiconductor integrated circuit which includes metallic wiring connected to gate electrode and satisfies antenna criterion

InactiveUS20100001403A1Improve antenna ratioPlasma damage of be lightenSemiconductor/solid-state device detailsSolid-state devicesIntegrated circuitSemiconductor

A method of designing a semiconductor integrated circuit, includes verifying an antenna ratio of a metallic wiring connected to a first gate electrode and the first gate electrode, based on a layout information, and computing a gate area that should be added to avoid a plasma damage to the first gate electrode, based on the verifying. The method further includes modifying a layout of the semiconductor integrated circuit, based on the computing, by arranging a logic cell having a second gate electrode having the gate area or more and is in a state where the logic cell makes no contribution to a logic operation of the semiconductor integrated circuit, in a free region of the layout, and connecting the second gate electrode to the metallic wiring.

Owner:RENESAS ELECTRONICS CORP

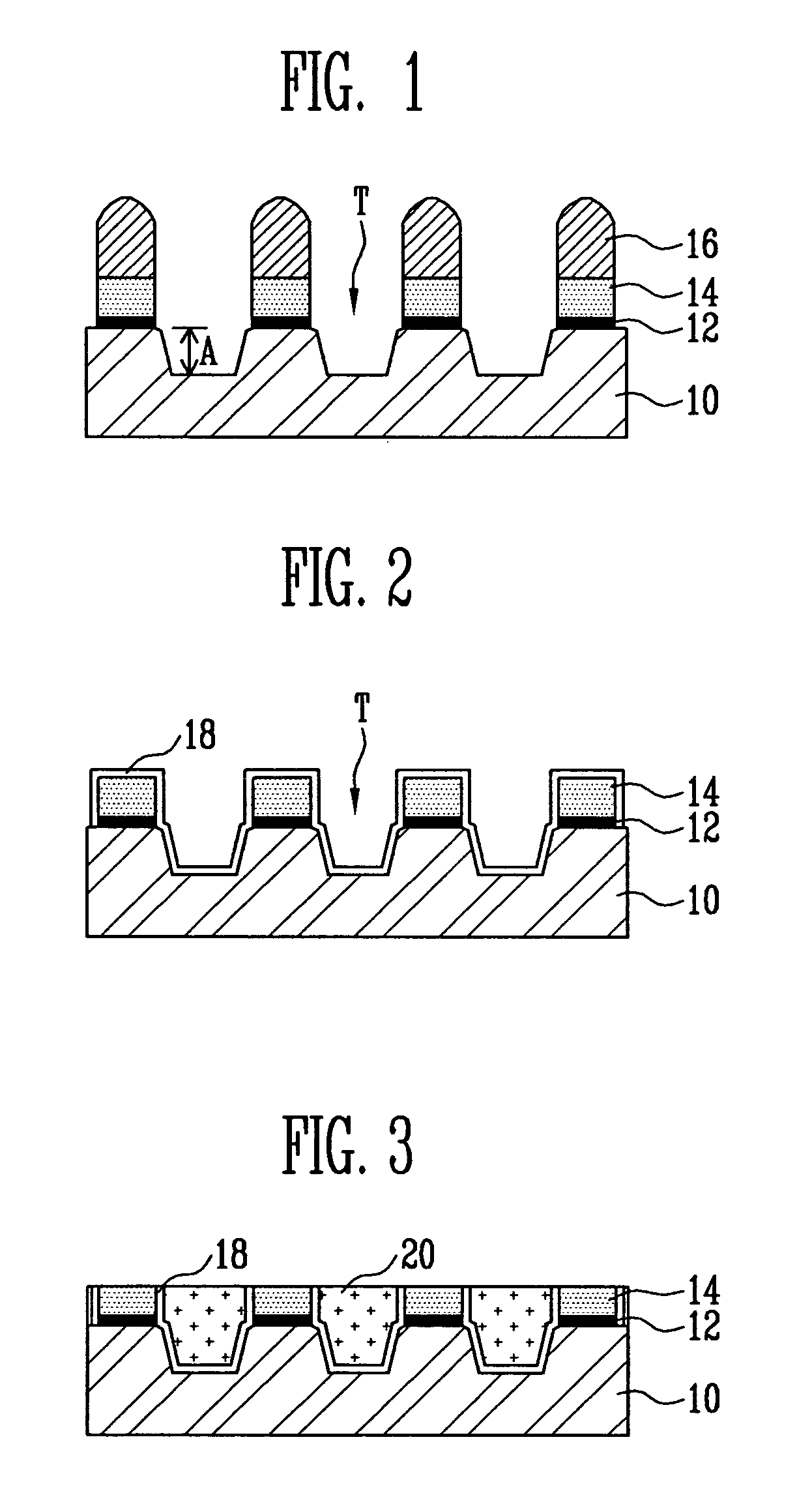

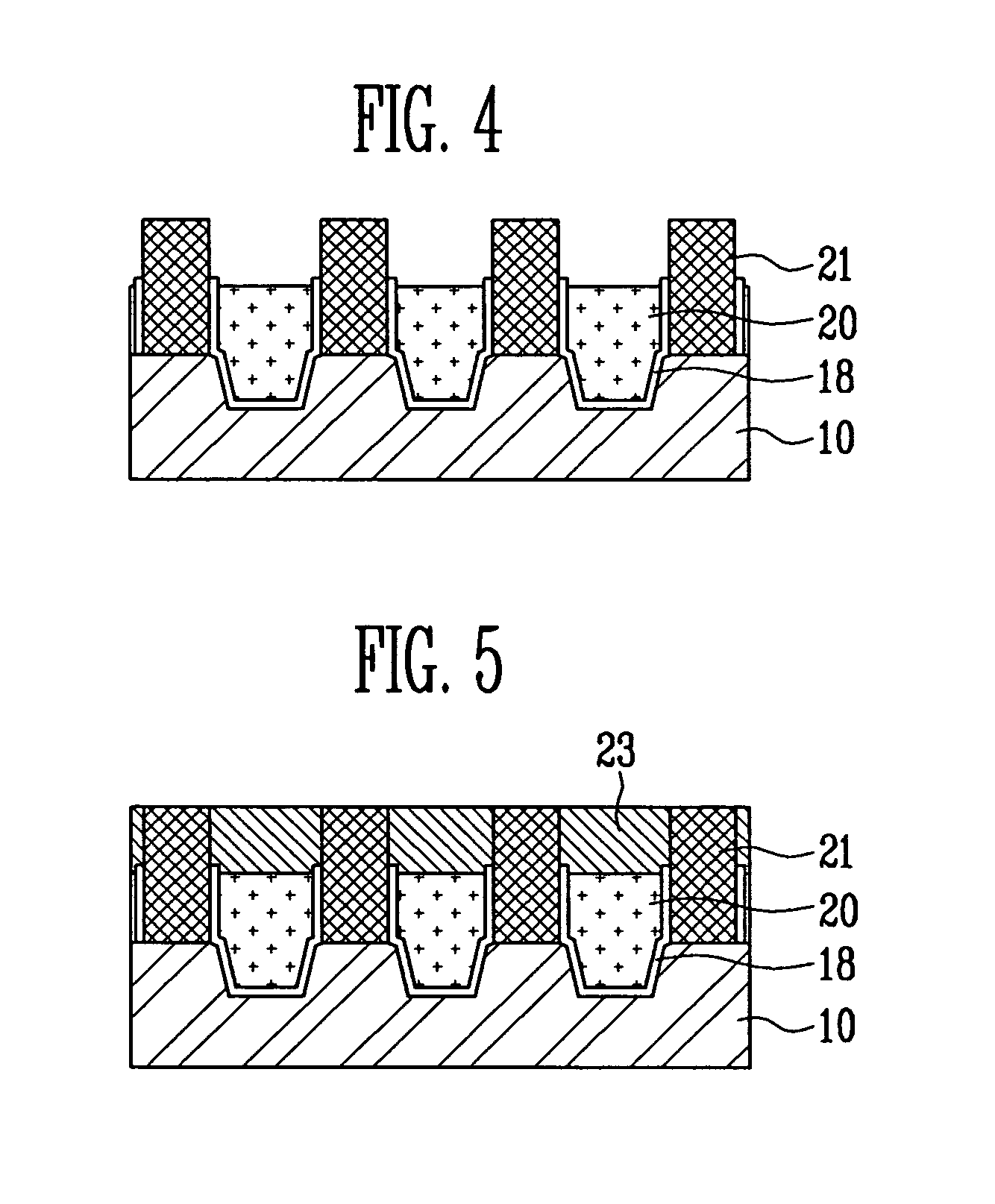

Method of forming isolation film in semiconductor device

InactiveUS7018905B1Prevent be damageAvoid plasma damageSemiconductor/solid-state device manufacturingOxideEngineering

The present invention relates to a method of forming an isolation film of a semiconductor device. According to the present invention, the method includes the steps of forming a pad film on a semiconductor substrate, and patterning the pad film of a predetermined region and a predetermined depth of the semiconductor substrate to form trenches, forming sidewall oxide films on sidewalls of the trenches thereby defining a non-active region and an active region, forming a first oxide film for trench burial on the entire surface including the sidewall oxide films, and then performing a polishing process until the pad film is exposed, thus forming a first isolation film, removing the pad film to expose the semiconductor substrate in the active region, forming a silicon layer, which has a height higher than that of the first isolation film, on the exposed semiconductor substrate in the active region, and forming a second oxide film for trench burial on the entire surface, and then performing a polishing process until the silicon layer is exposed, thus forming a second isolation film, whereby an isolation film in which the first isolation film and the second isolation film are stacked is formed.

Owner:SK HYNIX INC

Hdp-cvd process, filling-in process utilizing hdp-cvd, and hdp-cvd system

ActiveUS20100041245A1Improve material qualityQuality improvementSemiconductor/solid-state device manufacturingChemical vapor deposition coatingRoom temperatureProcess engineering

An HDP-CVD process is described, including a deposition step conducted in an HDP-CVD chamber and a pre-heating step that is performed outside of the HDP-CVD chamber before the deposition step and pre-heats a wafer to a temperature higher than room temperature and required in the HDP-CVD process deposition step.

Owner:MACRONIX INT CO LTD

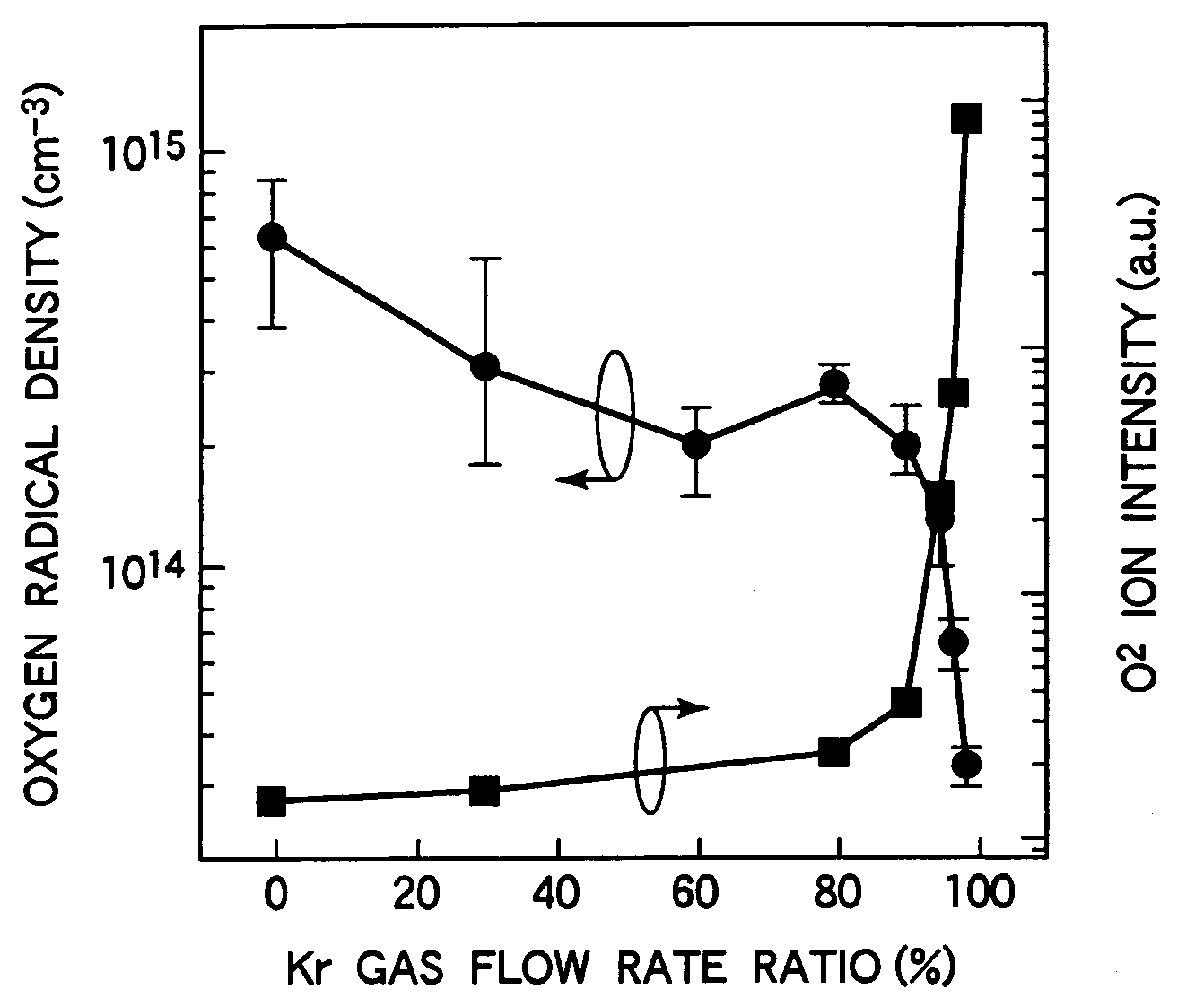

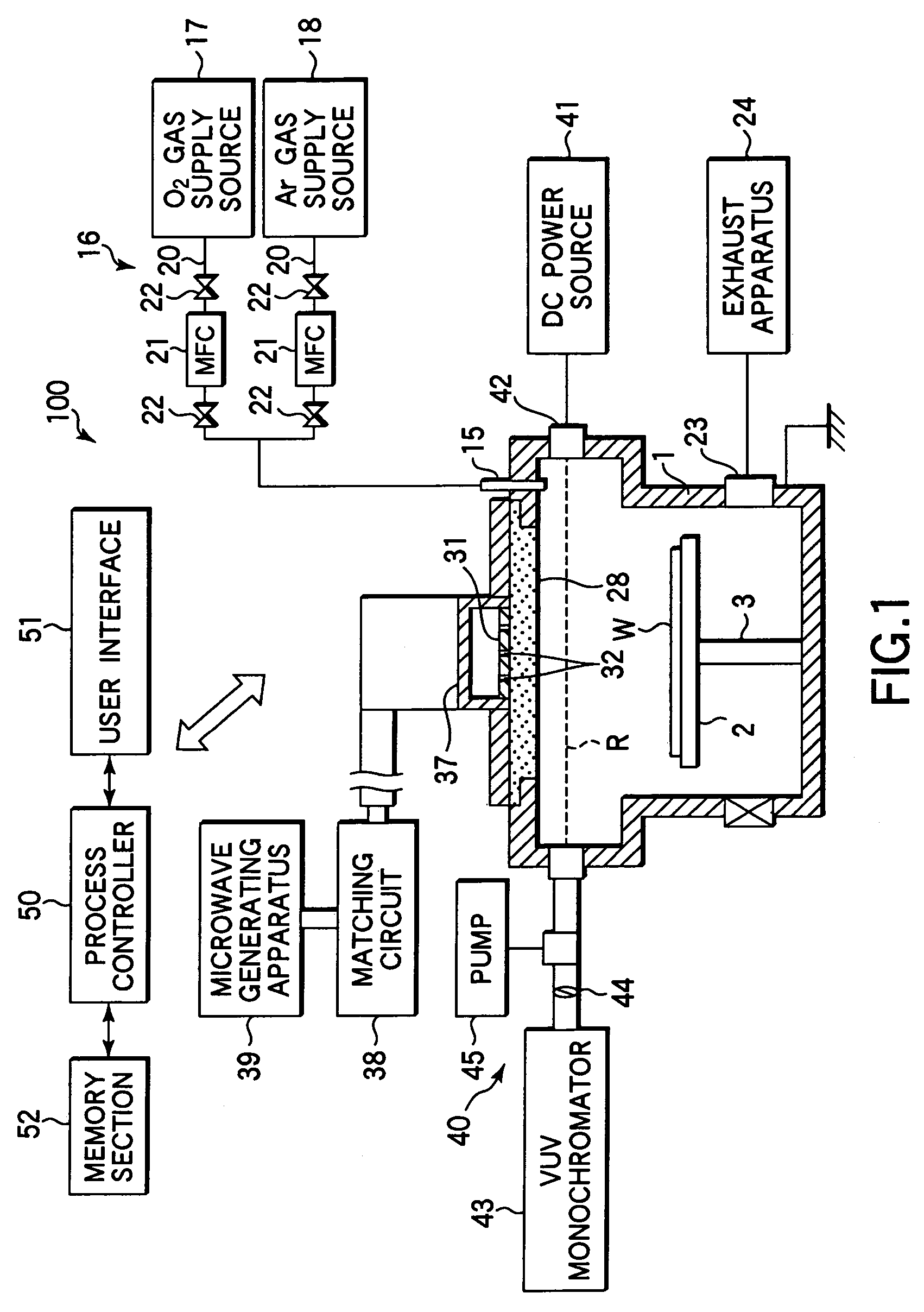

Plasma processing method and plasma processing apparatus

InactiveUS7393460B2Avoid plasma damageEfficient removalElectric discharge tubesDecorative surface effectsIon densityOxygen

The plasma processing method comprises the step of removing an organic material film forming an upper layer relative to a patterned SiOCH series film by the processing with a plasma of a process gas containing an O2 gas, wherein the plasma has an O2+ ion density not lower than 1×1011 cm−3 and an oxygen radical density not higher than 1×1014 cm−3.

Owner:TOKYO ELECTRON LTD

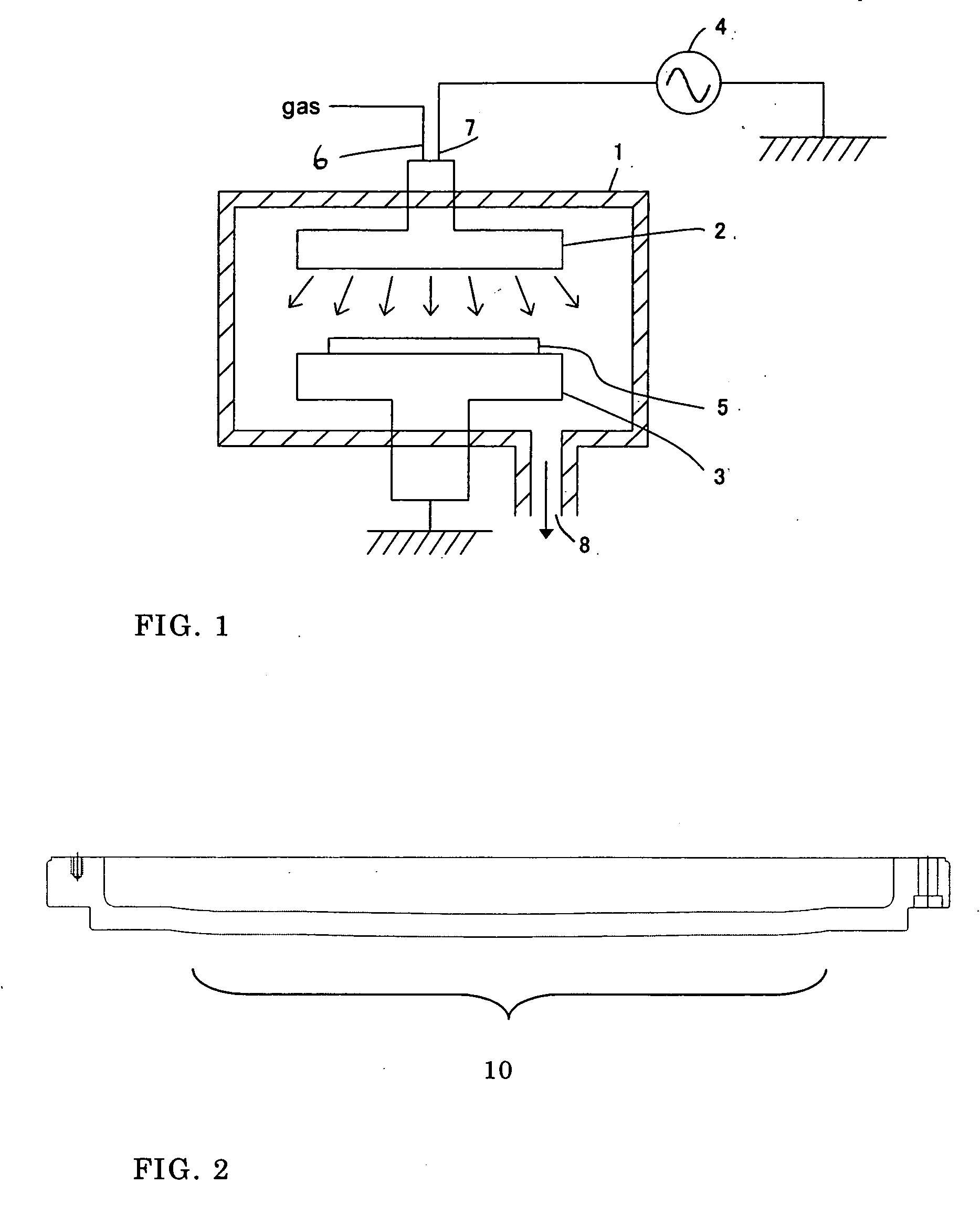

Method of stabilizing film quality of low-dielectric constant film

ActiveUS20060216433A1Reduced strengthLow dielectric constantElectric discharge tubesSemiconductor/solid-state device manufacturingGas passingEngineering

A method of forming a film having a low dielectric constant, comprises the steps of: placing a substrate between an upper electrode and a lower electrode inside a reaction chamber, introducing a silicon-containing hydrocarbon compound source gas, an additive gas, and an inert gas into a space between the upper and lower electrodes by controlling a gas flow ratio, generating a plasma by applying RF power to the space between the upper and lower electrodes in a state in which an interval between the upper electrode and the substrate is narrower in the vicinity of a center of the substrate than that in the vicinity of its periphery, and forming a film having a low dielectric constant on the substrate at a deposition rate of less than approx. 790 nm / min by controlling a flow rate of the process gas.

Owner:ASM JAPAN

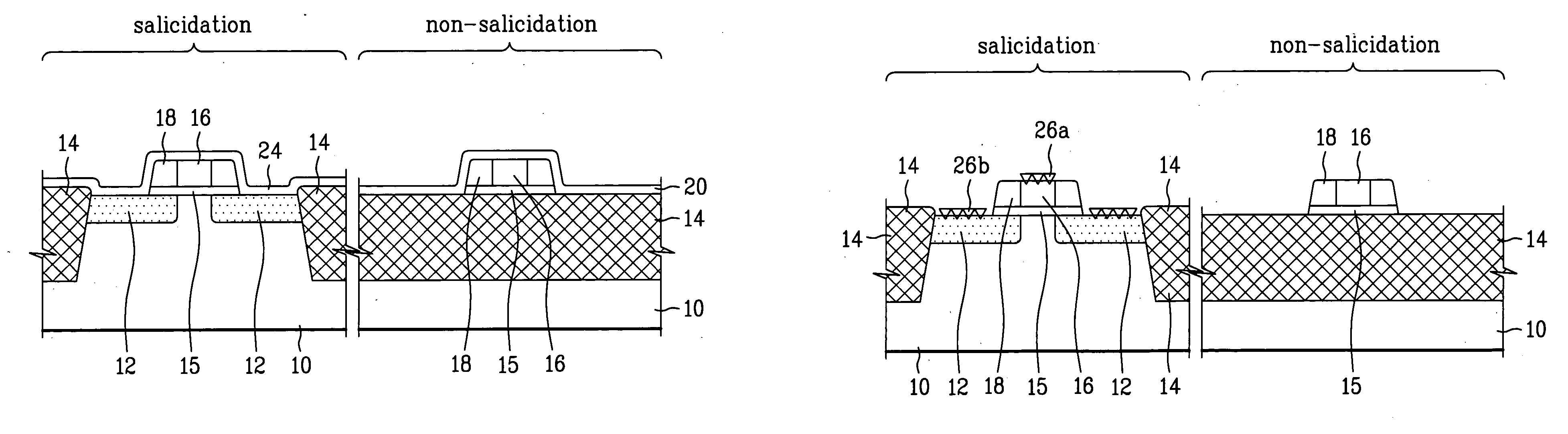

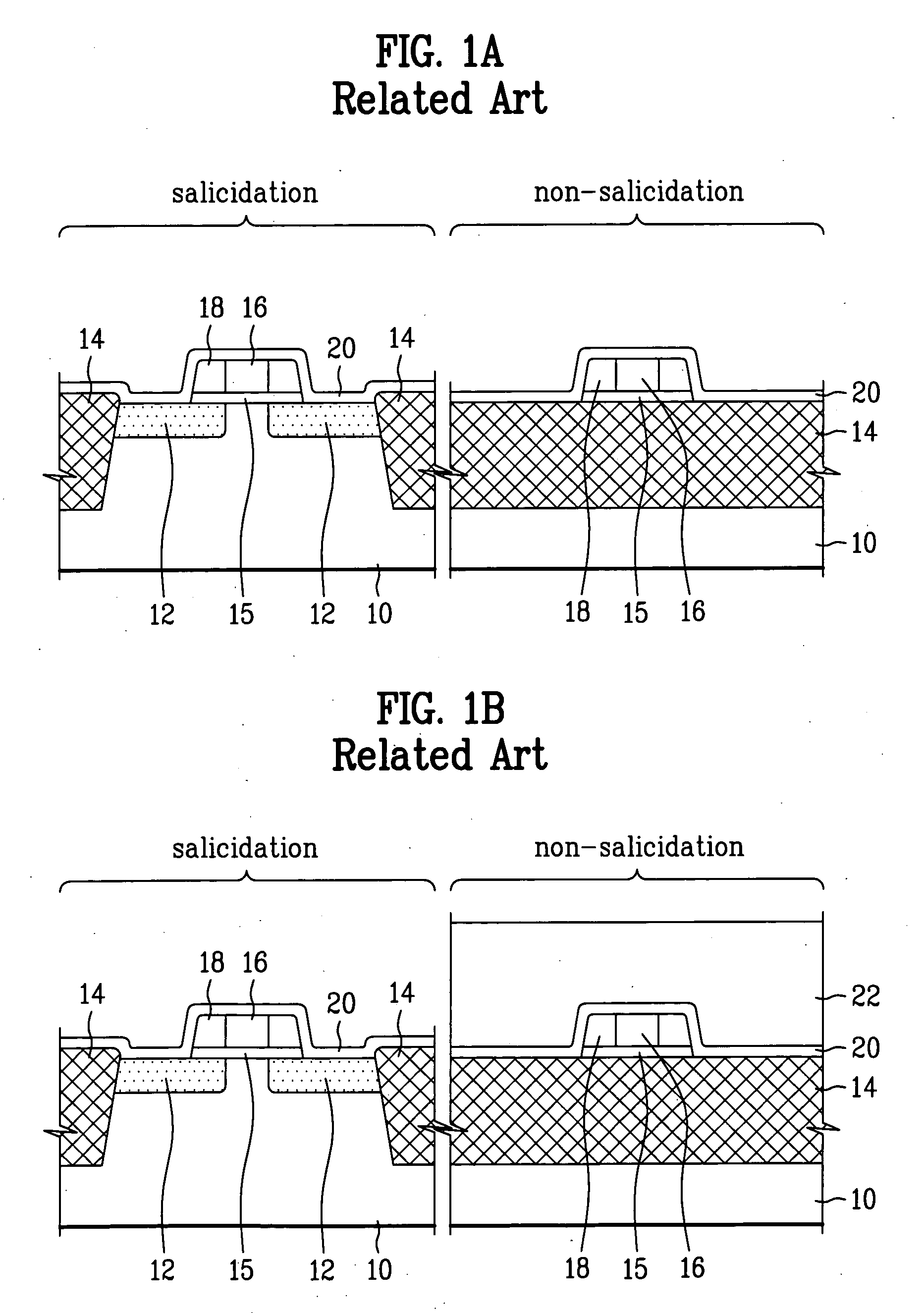

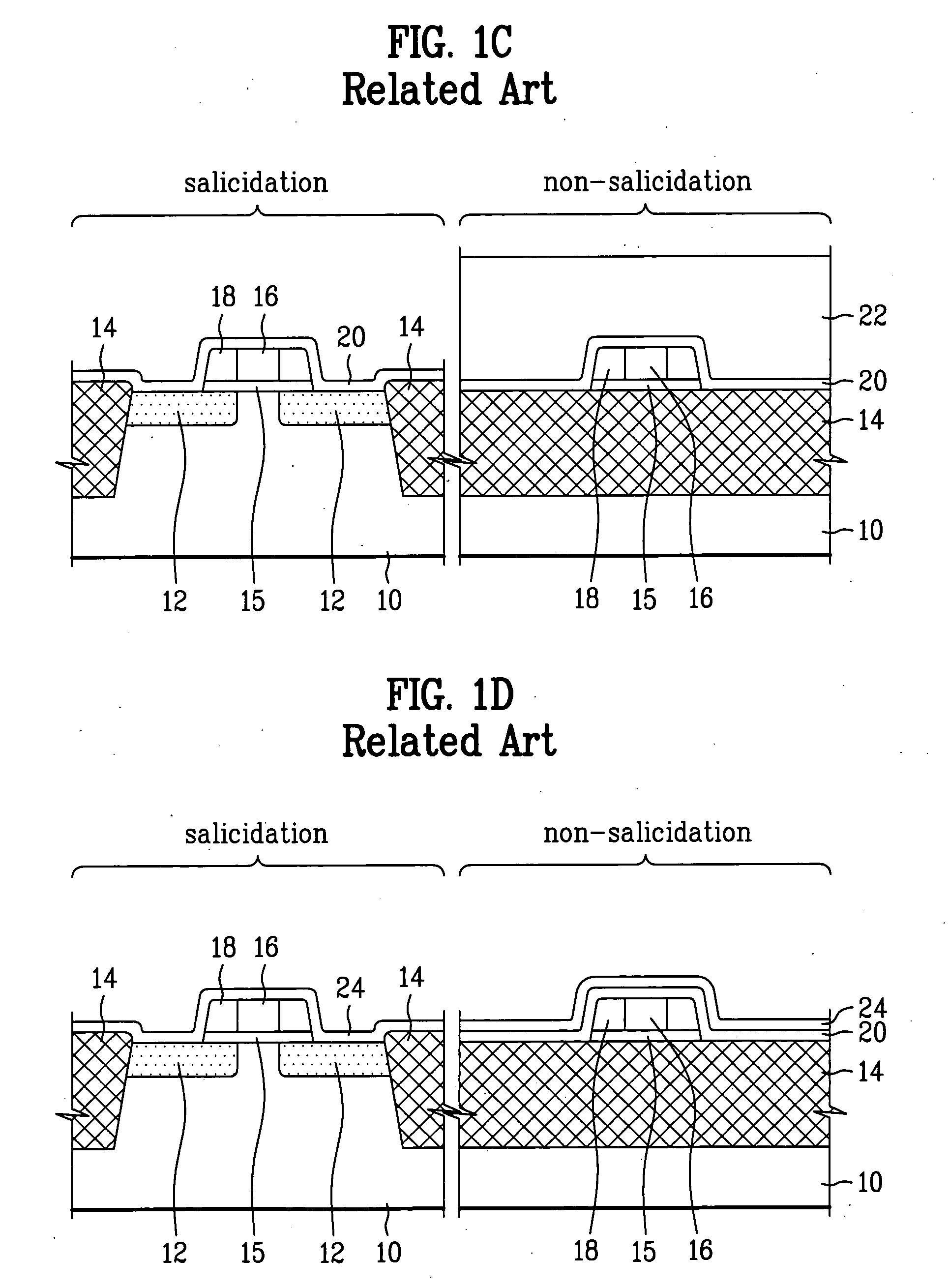

Method for forming salicide layer in semiconductor device

InactiveUS20060148228A1Easy to manufactureReduce processing stepsSemiconductor/solid-state device manufacturingSemiconductor devicesSalicideDevice material

A method for forming a silicide layer in a semiconductor device selectively forms a self-aligned layer of silicide in a salicidation area only, without having to use a salicide blocking material such as an oxide or a nitride. The method includes steps of defining a salicidation area and a non-salicidation area on a substrate; depositing a salicide forming metal on the substrate after forming a gate electrode and a source-drain diffusion region; forming a photoresist pattern on the salicidation area; removing the salicide forming metal from the non-salicidation area; removing the photoresist pattern; and annealing the salicide forming metal.

Owner:DONGBU ELECTRONICS CO LTD

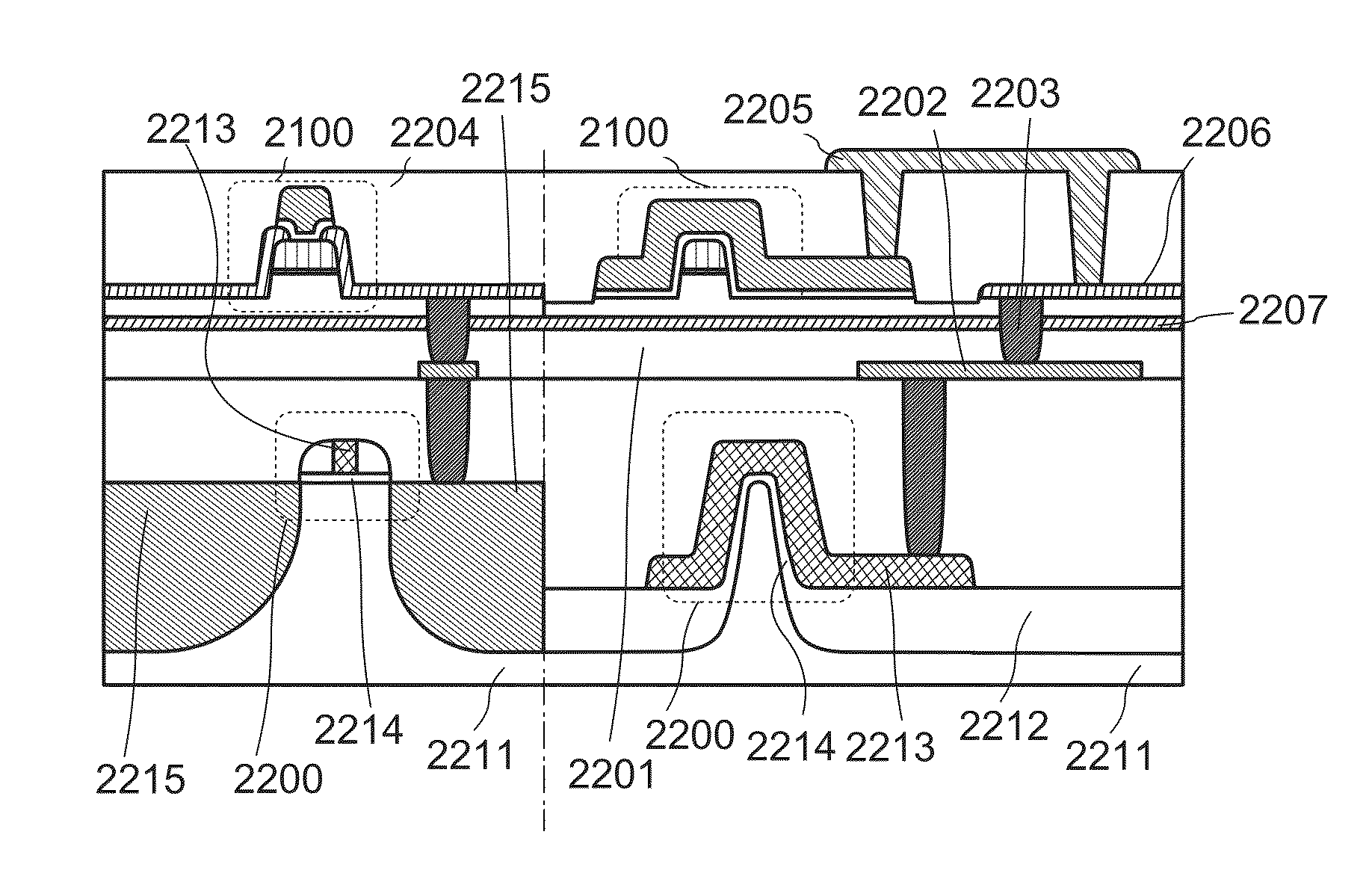

Method for fabricating semiconductor device with bulb-shaped recess gate

InactiveUS20070148980A1Avoid plasma damageDecorative surface effectsSemiconductor/solid-state device manufacturingDevice materialSilicon

A method for fabricating a semiconductor device with a bulb-shaped recess gate pattern is provided. The method includes forming a plurality of oxide layers over a substrate; forming a silicon layer to cover the oxide layers; forming a mask over the silicon layer; etching the silicon layer using the mask as an etch mask to form a plurality of first recesses to expose the oxide layers; etching the oxide layers to form a plurality of second recesses; and forming a plurality of gate patterns at least partially buried into the first recesses and the second recesses.

Owner:SK HYNIX INC

Method of forming organosilicon oxide film and multilayer resist structure

ActiveUS20070141273A1Excellent ashing resistanceImprove productivityElectric discharge tubesSemiconductor/solid-state device manufacturingResistSusceptor

A method of forming an organosilicon oxide film by plasma CVD includes: (i) adjusting a temperature of a susceptor on which a substrate is placed to lower than 300° C.; (ii) introducing at least tetraethylorthosilicate (TEOS) and oxygen into a reactor in which the susceptor is disposed; (iii) applying high-frequency RF power and low-frequency RF power; and (iv) thereby depositing an organosilicon oxide film on the substrate.

Owner:ASM JAPAN

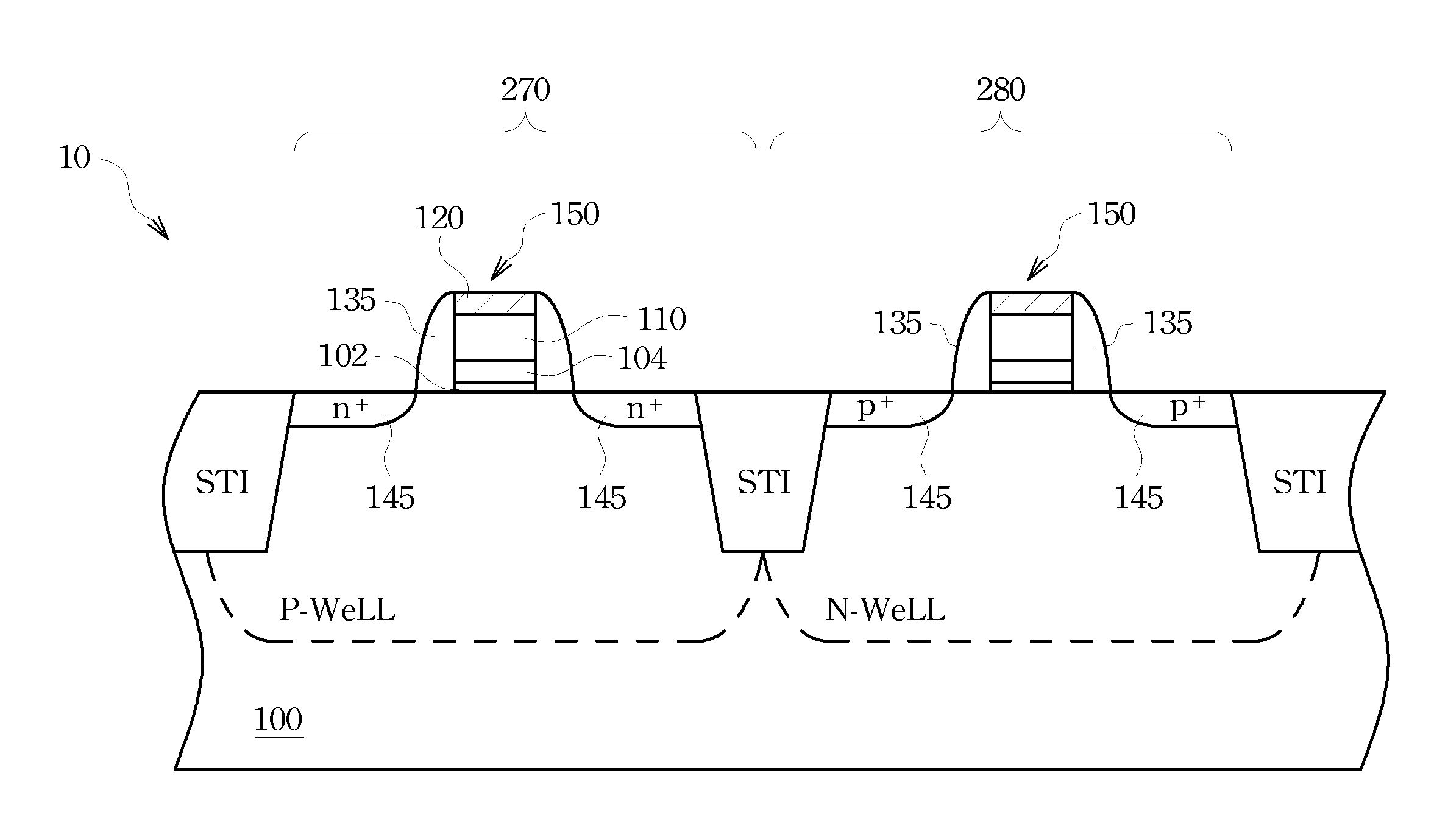

MOSFETs having stacked metal gate electrodes and method

InactiveUS8138076B2Low oxygenAvoid layeringSemiconductor/solid-state device manufacturingSemiconductor devicesInterfacial oxideMOSFET

Owner:TAIWAN SEMICON MFG CO LTD

Semiconductor structure and method of forming same

ActiveCN109309088AImprove performanceImprove reliabilityTransistorSolid-state devicesGate dielectricSemiconductor structure

The invention provides a semiconductor structure and a method of forming the same. The method comprises the steps of providing a substrate comprising a core region and a peripheral region; forming a dummy gate structure on the substrate, the dummy gate structure including a gate oxide layer and a dummy gate electrode layer on the gate oxide layer; forming an interlayer dielectric layer on the exposed substrate of the dummy gate structure, the interlayer dielectric layer exposing the top of the dummy gate structure; removing the dummy gate structure of the core region, and forming a first opening exposing the substrate in the interlayer dielectric layer of the core region; forming a sacrificial layer on the exposed substrate of the first opening; after the sacrificial layer is formed, removing the dummy gate electrode layer of the peripheral region, and forming a second opening in the interlayer dielectric layer of the peripheral region; removing the sacrificial layer; and forming a high-k gate dielectric layer on the gate oxide layer in the bottom and the sidewall of the first opening, sidewall of a second opening and a gate oxide layer in the second opening. Through the technicalscheme of the present invention, the quality and thickness uniformity of the gate oxide layer in the peripheral region are improved, and the process of removing the dummy gate electrode layer in the peripheral region prevents causing loss or damage to the substrate of the core region.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

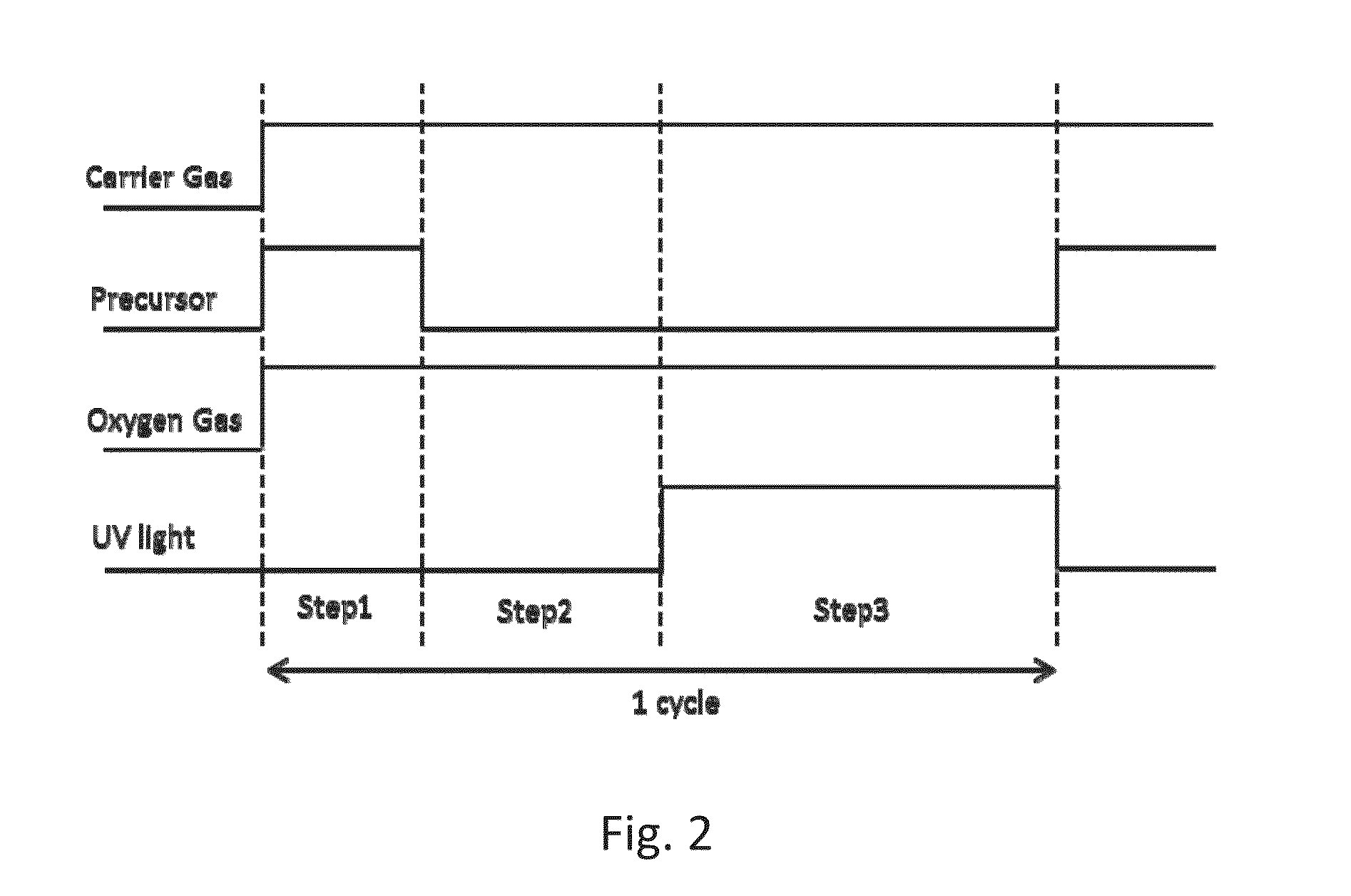

Method For Restoring Porous Surface Of Dielectric Layer By UV Light-Assisted ALD

ActiveUS20150064932A1Good step coverageAvoid plasma damageSemiconductor/solid-state device manufacturingChemical vapor deposition coatingChemical adsorptionDielectric layer

A method for restoring a porous surface of a dielectric layer formed on a substrate, includes: (i) providing in a reaction space a substrate on which a dielectric layer having a porous surface with terminal hydroxyl groups is formed as an outer layer; (ii) supplying gas of a Si—N compound containing a Si—N bond to the reaction space to chemisorb the Si—N compound onto the surface with the terminal hydroxyl groups; (iii) irradiating the Si—N compound-chemisorbed surface with a pulse of UV light in an oxidizing atmosphere to oxidize the surface and provide terminal hydroxyl groups to the surface; and (iv) repeating steps (ii) through (iii) to form a film on the porous surface of the dielectric layer for restoration.

Owner:ASM IP HLDG BV

Method of manufacturing semiconductor device

InactiveUS9716003B2Improve reliabilityImprove featuresTransistorSemiconductor/solid-state device manufacturingGas phaseThermal chemical vapor deposition

Provided are an oxide semiconductor layer in which the number of defects is reduced and a highly reliable semiconductor device including the oxide semiconductor. A first oxide semiconductor layer containing a single metal element as a constituent element is formed over a substrate by a thermal chemical vapor deposition method. A second oxide semiconductor layer containing two or more metal elements as constituent elements is formed successively after the first oxide semiconductor layer is formed. The second oxide semiconductor layer is formed by epitaxial growth using the first oxide semiconductor layer as a seed crystal. A channel is formed in the second oxide semiconductor layer.

Owner:SEMICON ENERGY LAB CO LTD

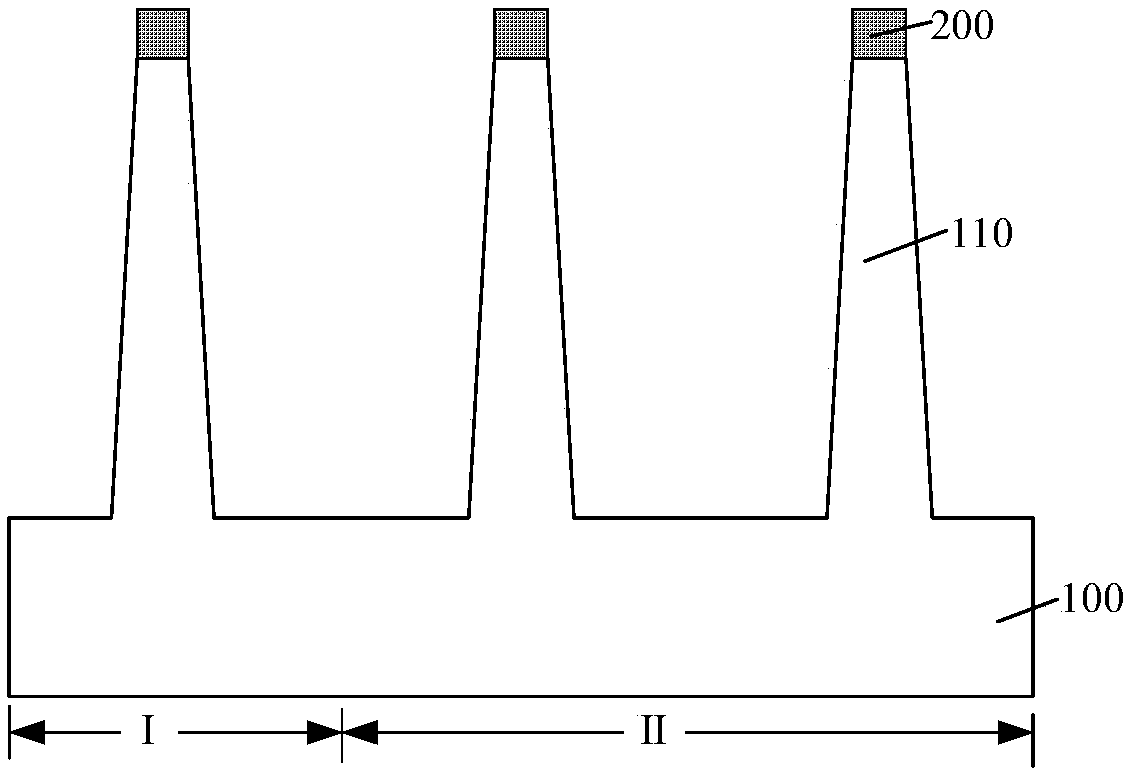

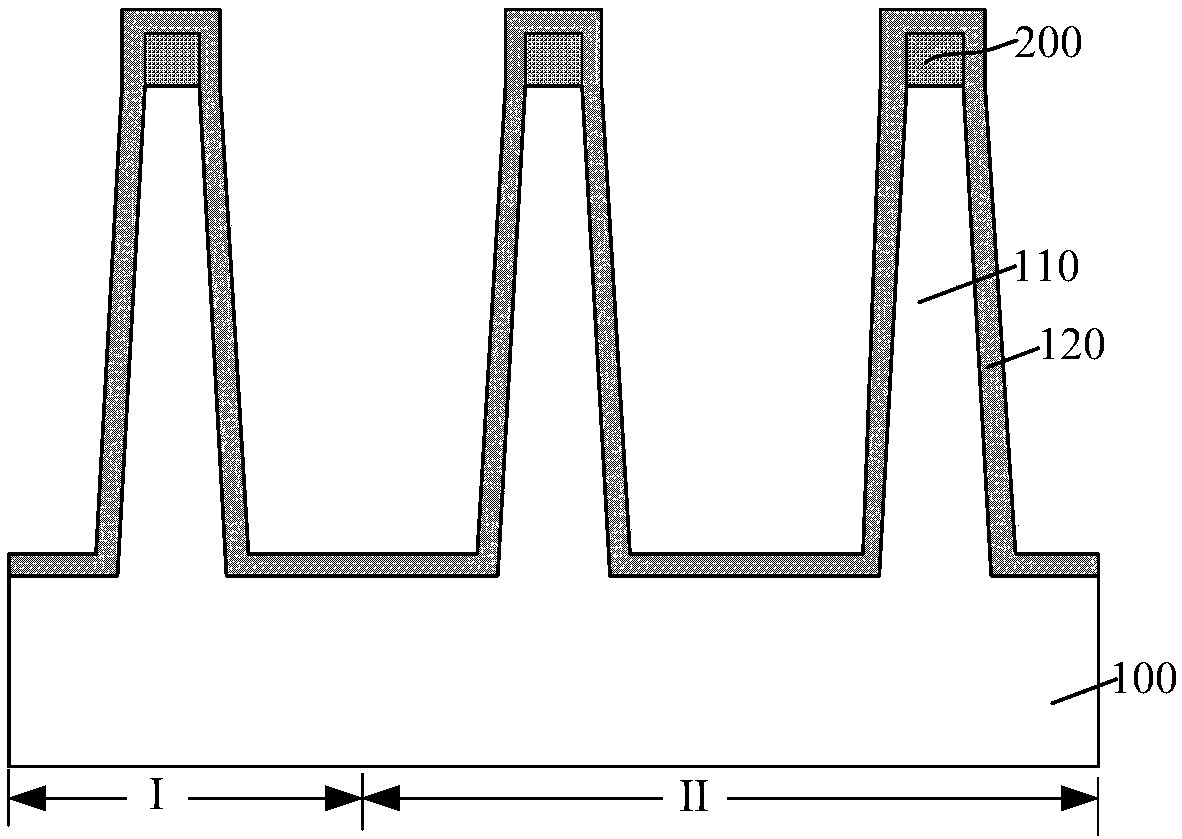

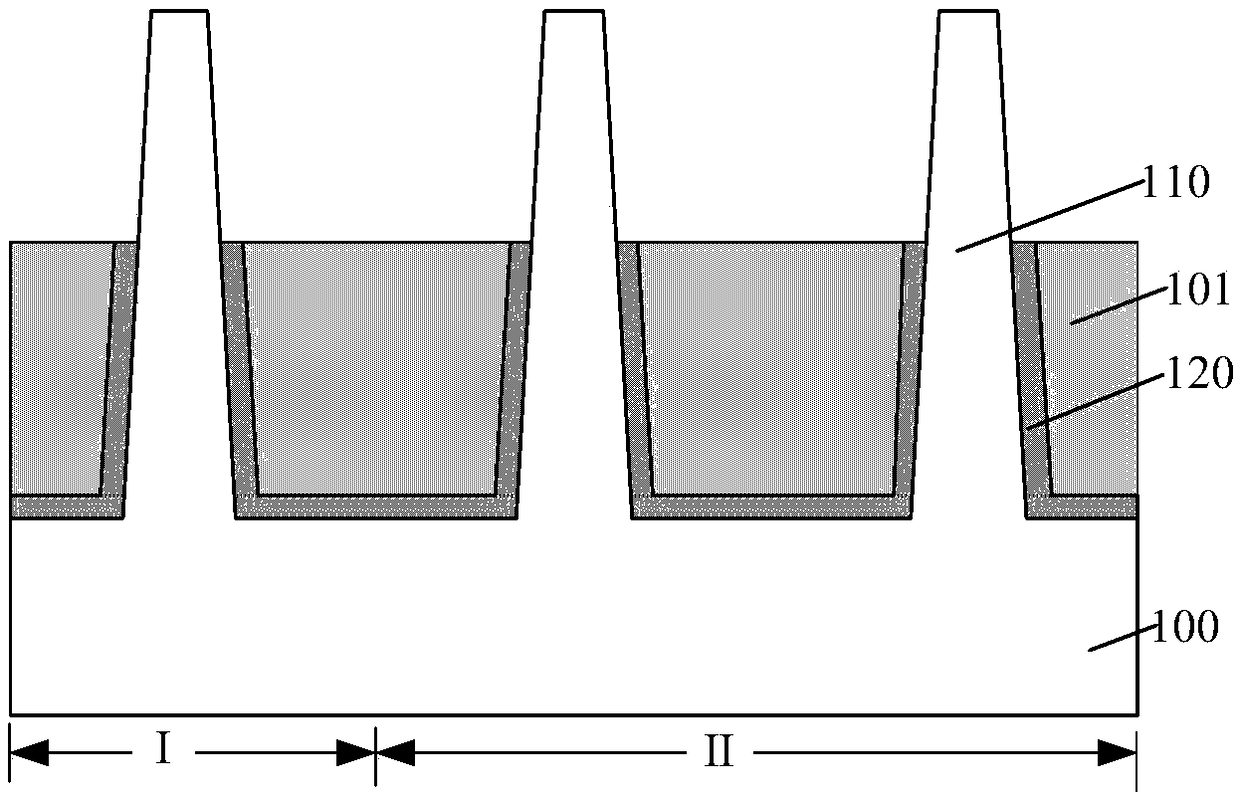

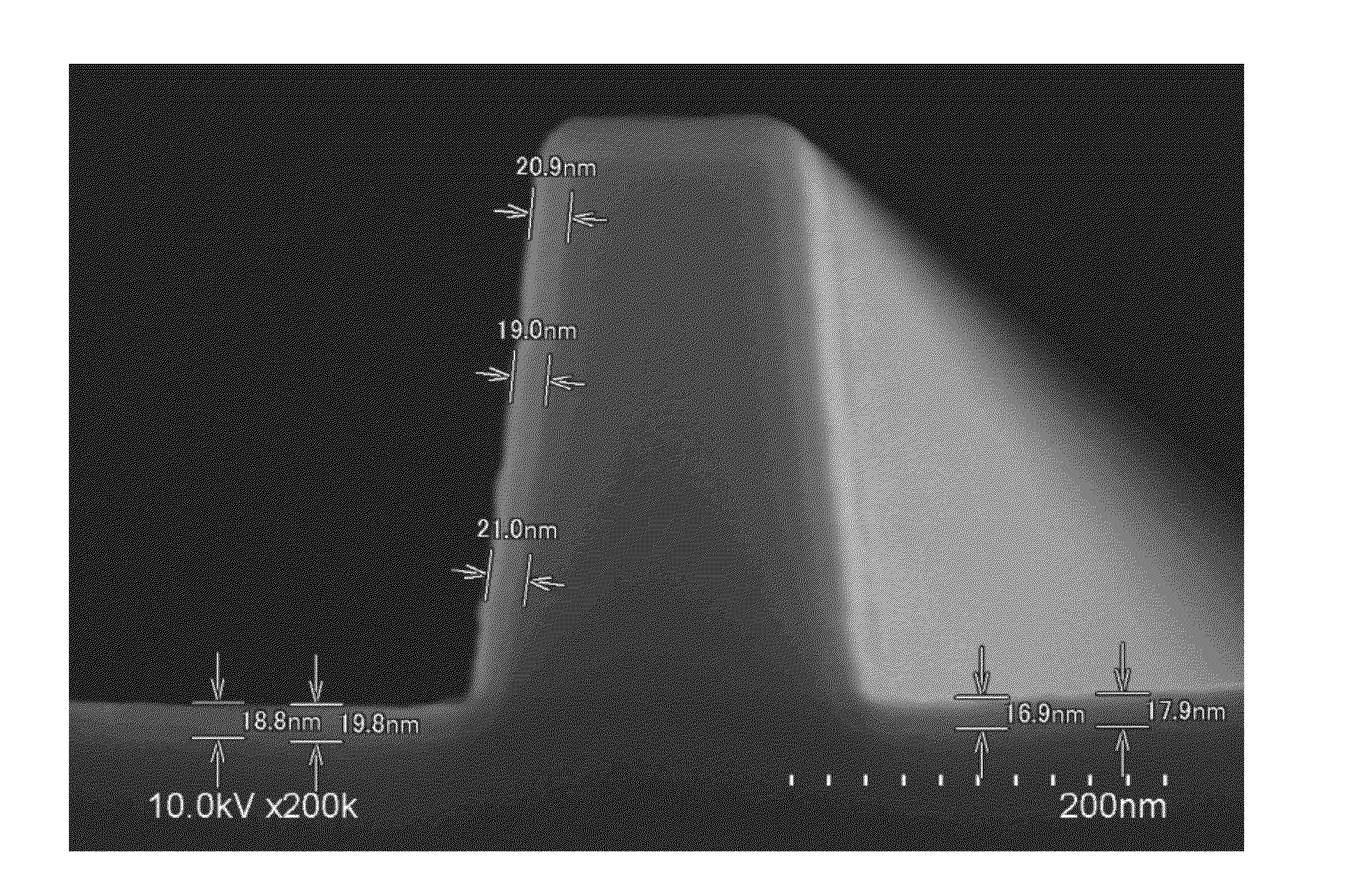

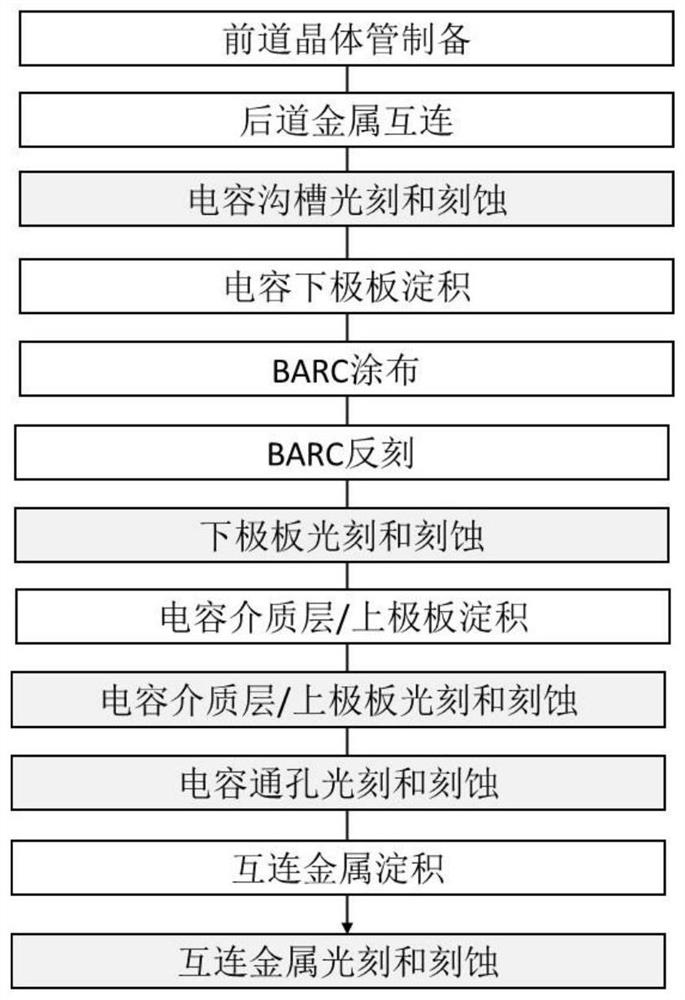

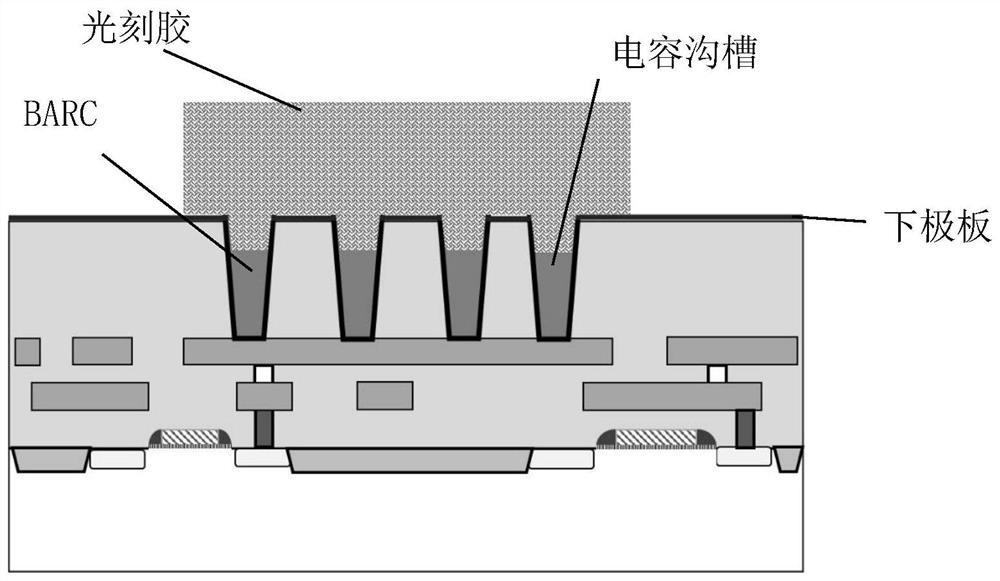

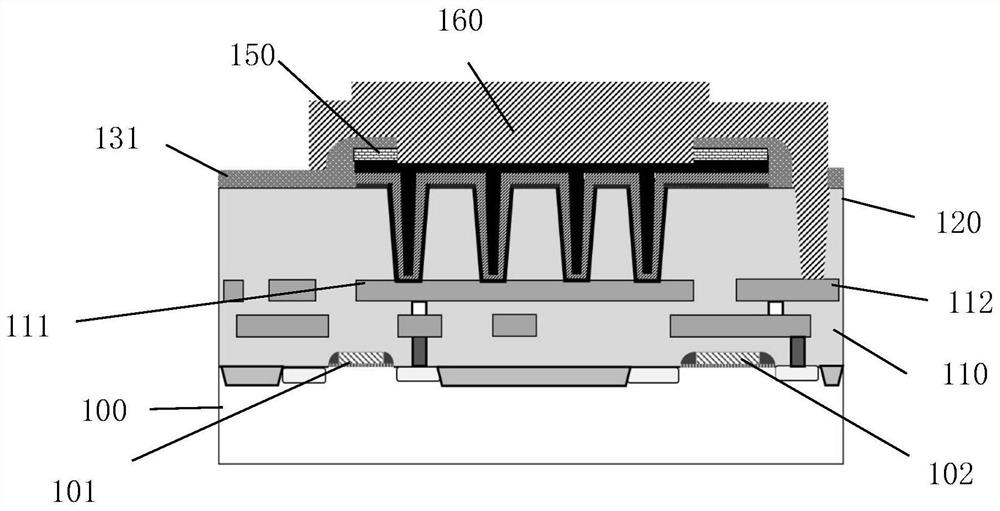

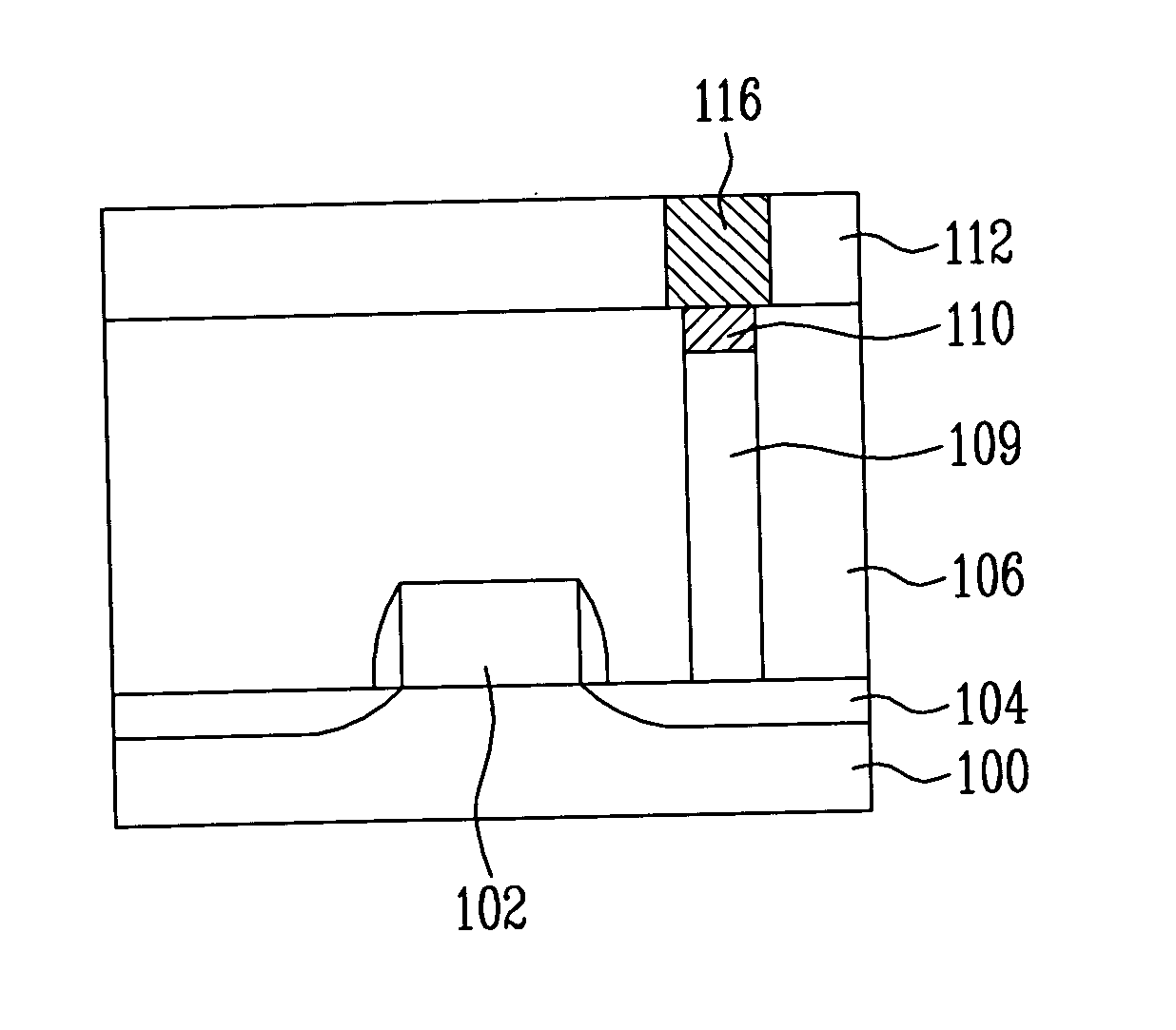

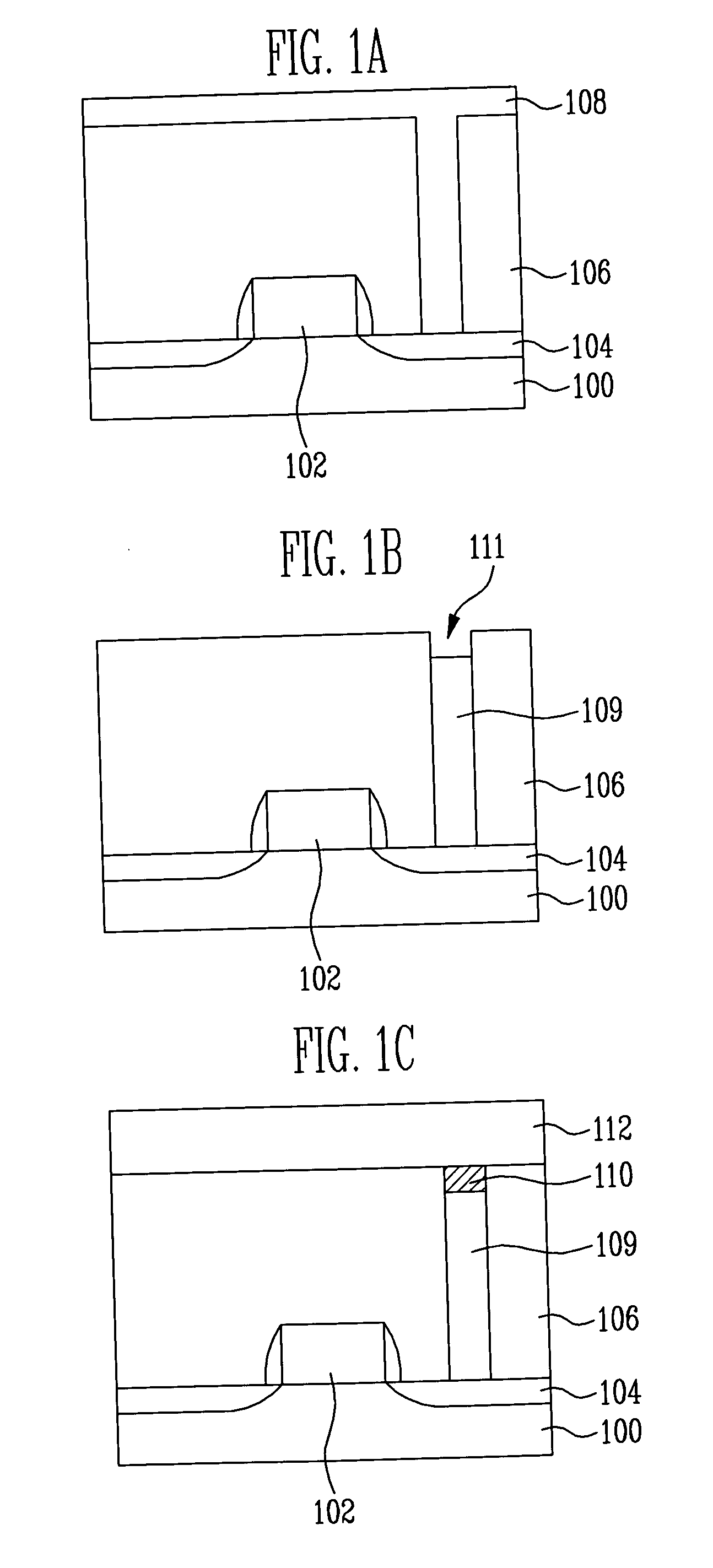

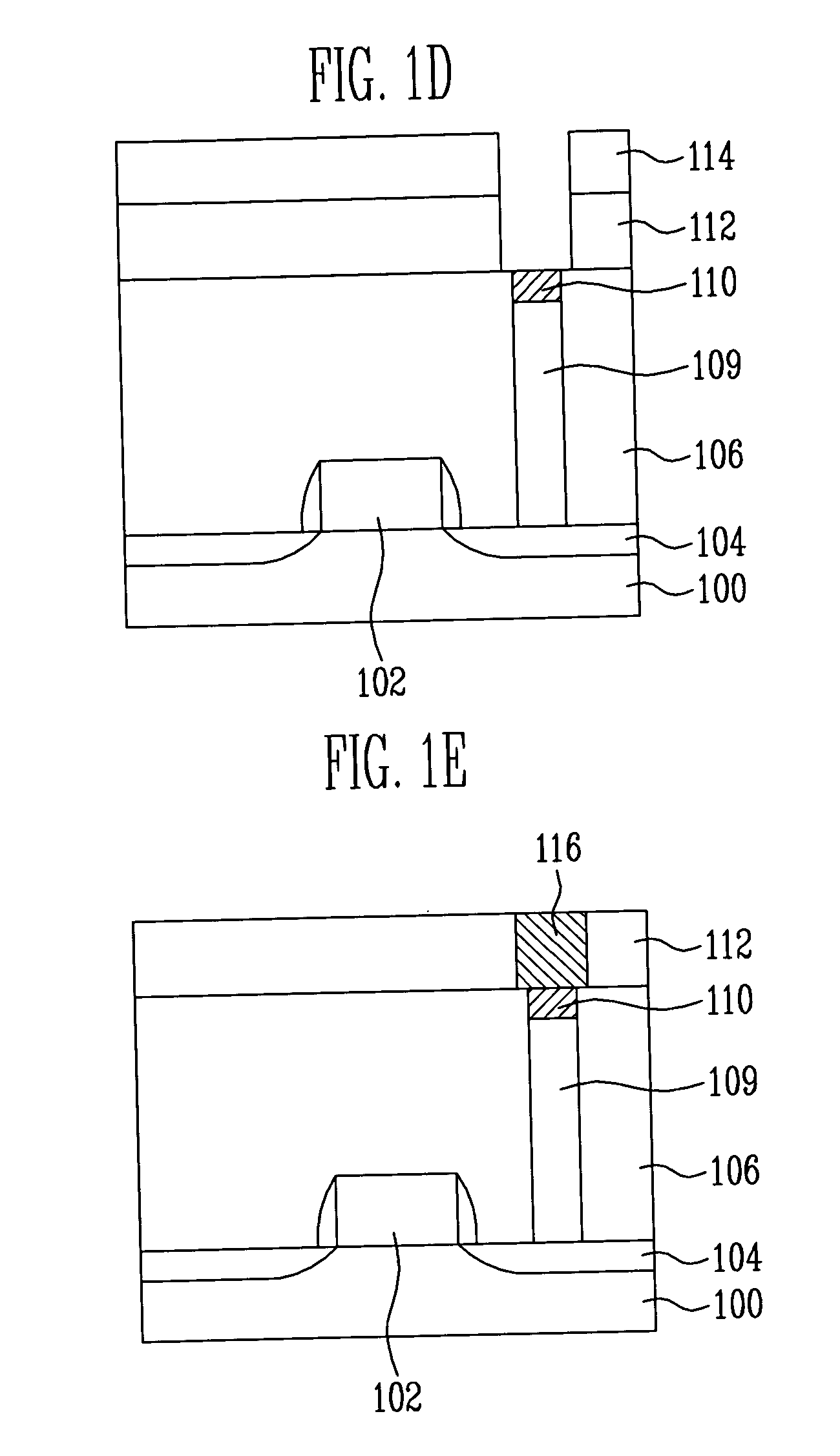

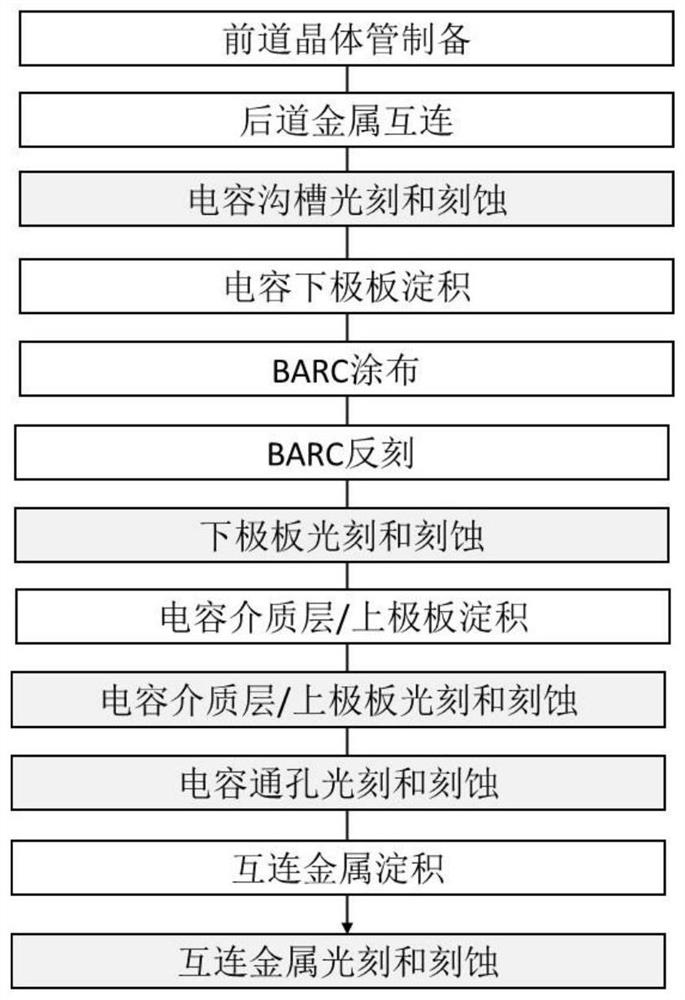

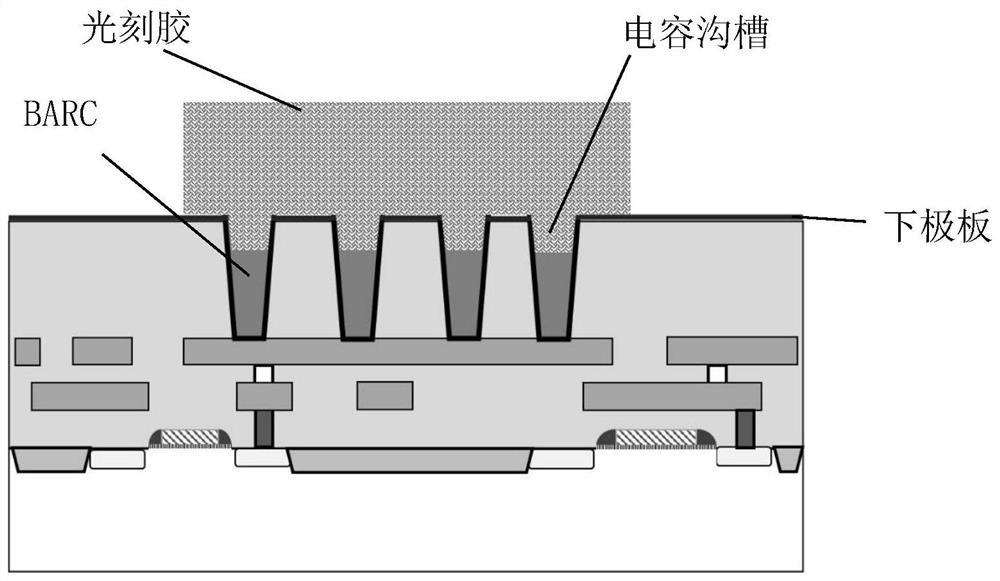

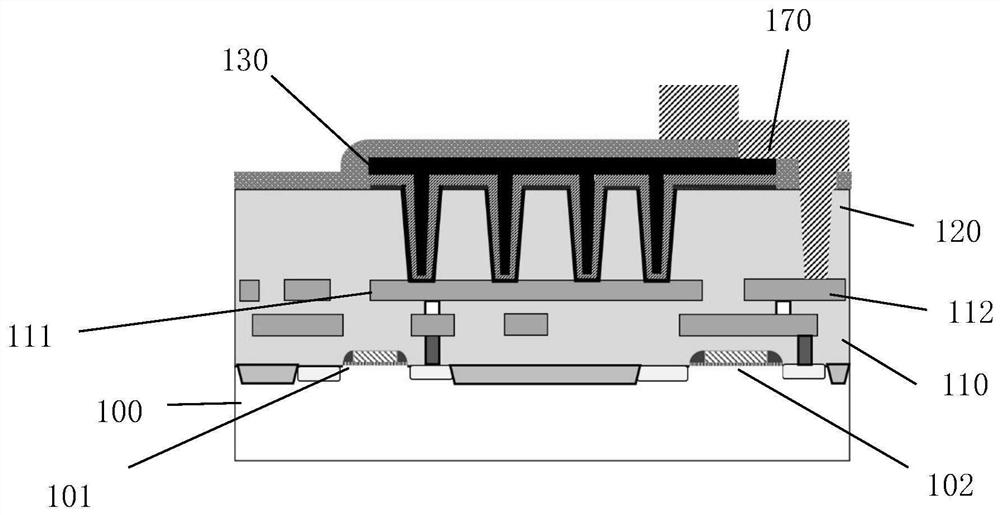

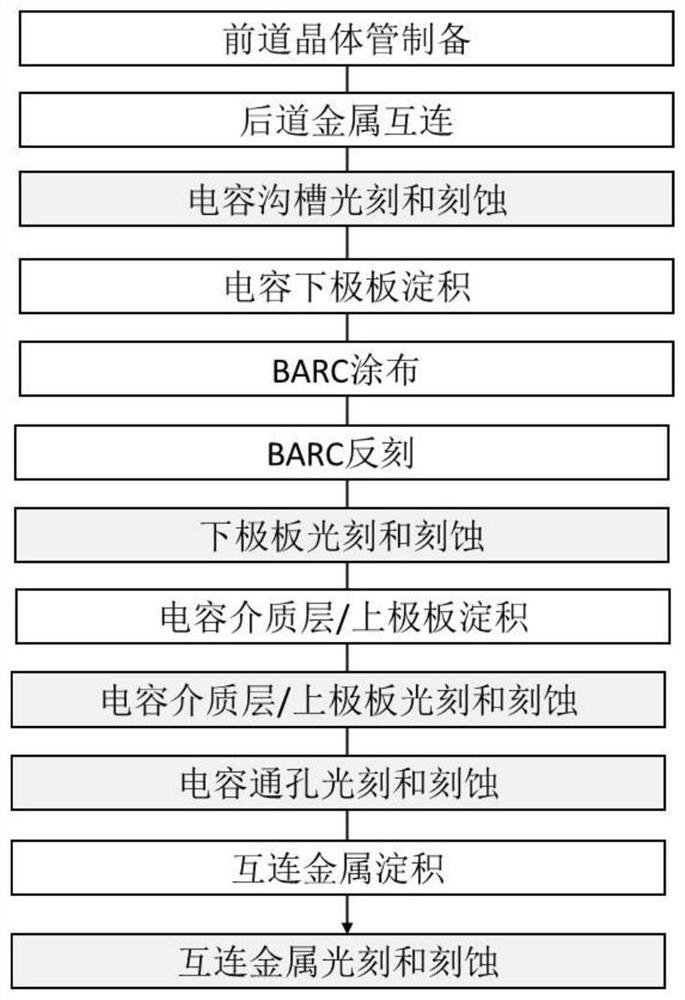

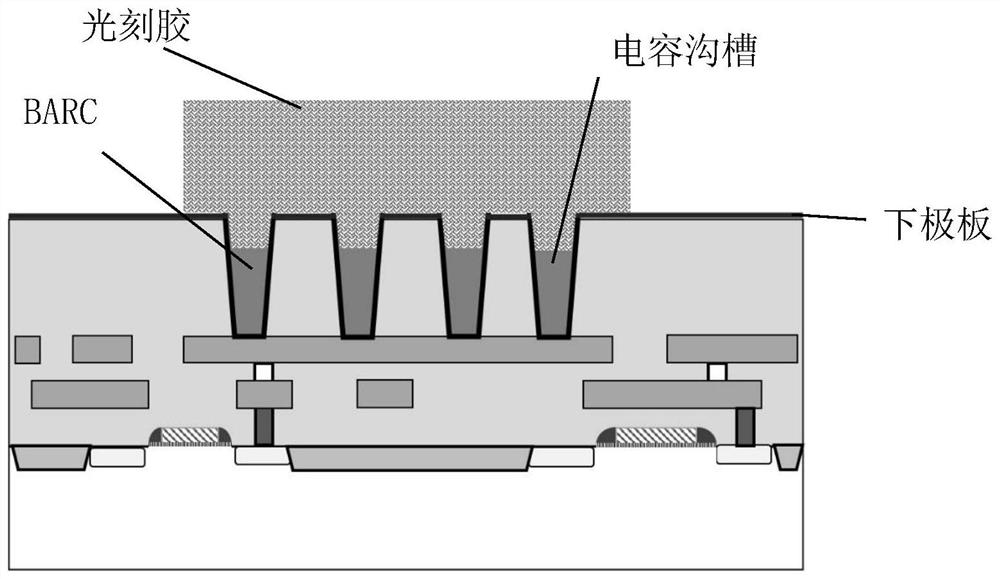

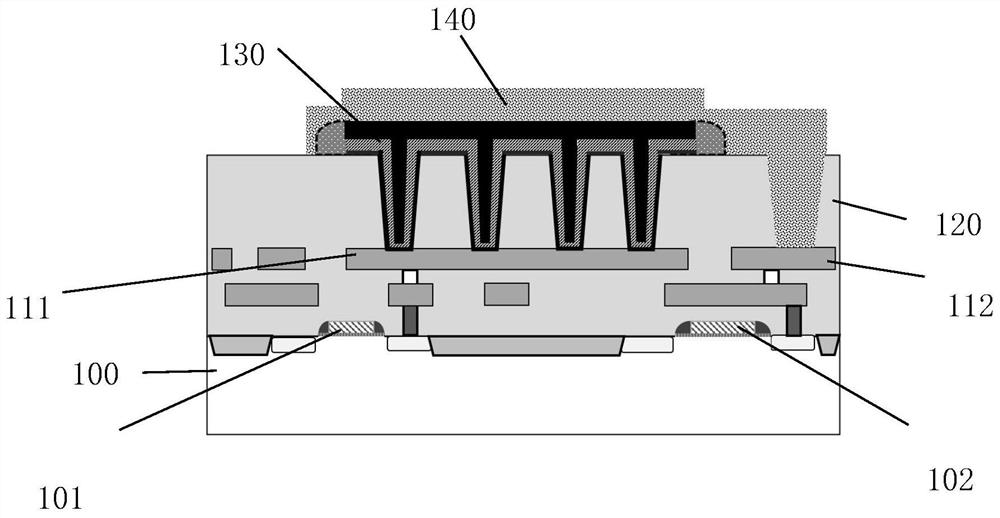

Trench type capacitor device and preparation method

InactiveCN112614833AAvoid plasma damageAvoid residueSolid-state devicesSemiconductor/solid-state device manufacturingCapacitanceMetal interconnect

The invention provides a preparation method of a trench type capacitor device. A trench capacitor region located on a first metal interconnection layer comprises a plurality of first trenches and capacitor structures which are located on a first dielectric layer and fill the first trenches, and the first trenches penetrate through the first dielectric layer and end at the first metal interconnection layer; a second trench penetrates through the first dielectric layer and ends at a second metal interconnection layer; an electrode interconnection layer is positioned on the capacitor structures; the capacitor structures are provided with openings; a second dielectric layer located on an upper electrode layer, and the openings penetrate through the second dielectric layer and end at the upper electrode layer; and the electrode interconnection layer is located on the second dielectric layer, fills the openings and the second trench, and is electrically connected with the upper electrode layer and the second metal interconnection layer. According to the invention, additional BARC filling and reverse etching are not needed, and independent photoetching and etching on the lower electrode layer are not needed either, so that the method has significant meaning.

Owner:上海微阱电子科技有限公司

Method for manufacturing semiconductor device

InactiveUS20090162984A1Improve featuresGood imaging propertiesTransistorSolid-state devicesCMOSNitride

Disclosed are methods for manufacturing a semiconductor device. One method includes the steps of forming a gate electrode on a semiconductor substrate, sequentially forming a first oxide layer, a nitride layer and a second oxide layer on the semiconductor substrate including the gate electrode, dry-etching the second oxide layer, wet-etching the nitride layer, and forming source and drain regions at sides of the gate electrode by implanting ions into the semiconductor substrate on which the first oxide layer is formed. According to the method, in the process of forming a gate spacer in the semiconductor device, an oxide layer of the gate spacer remains on the source and drain regions, and then an ion implantation process is performed, so that plasma damage and current leakage can be inhibited from occurring in the source and drain regions. Thus, device characteristics of a CMOS image sensor can be improved.

Owner:DONGBU HITEK CO LTD

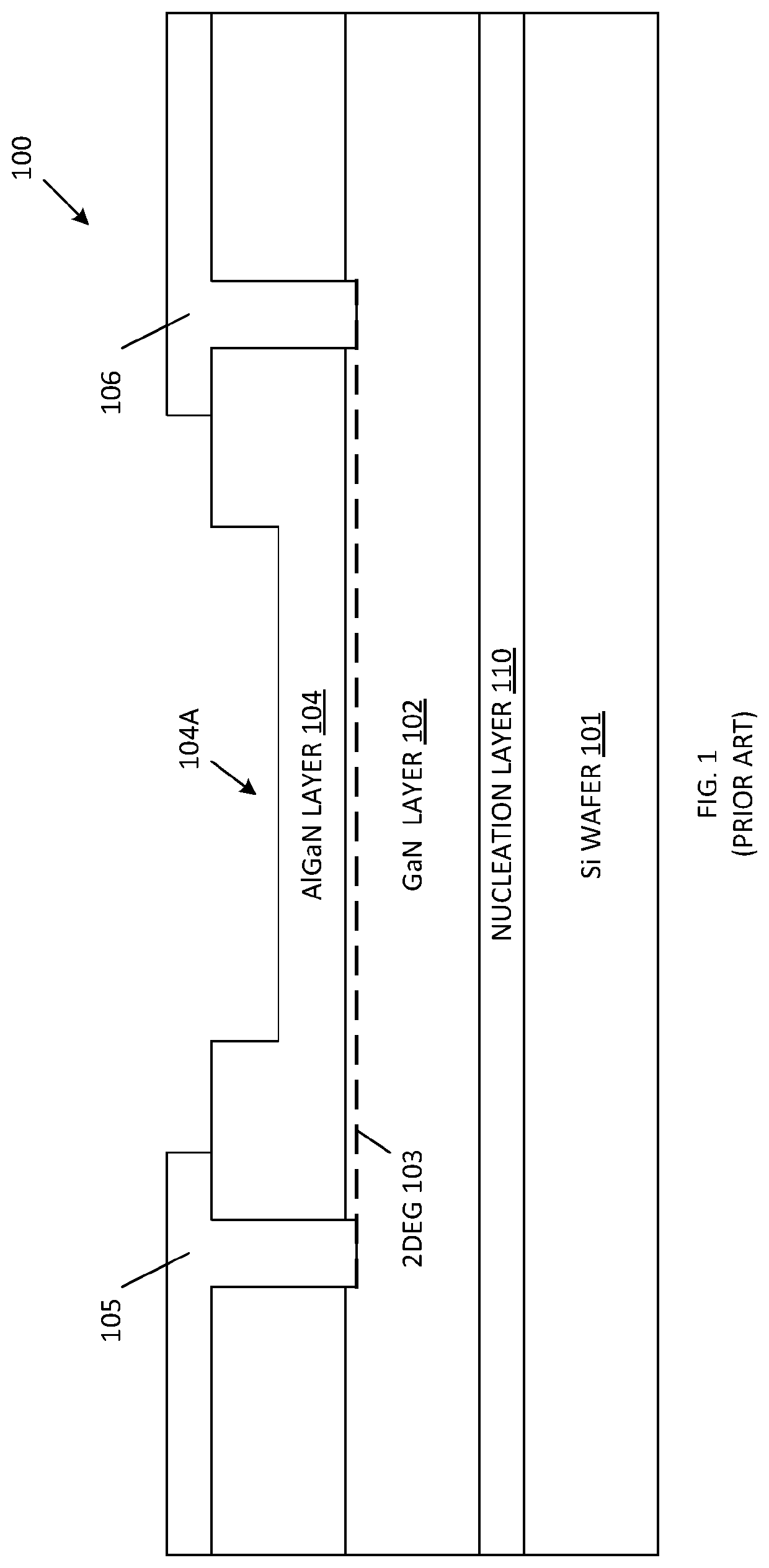

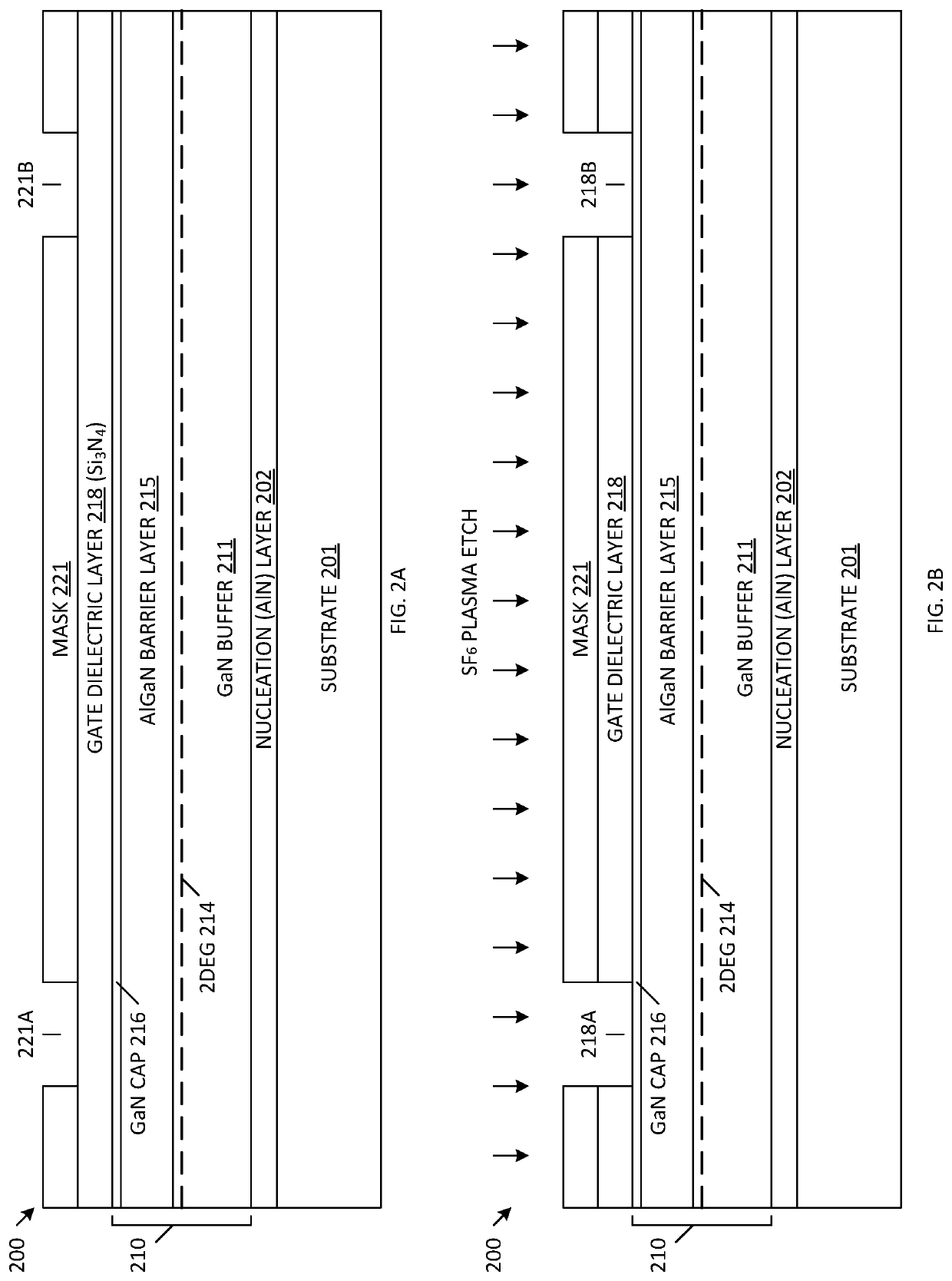

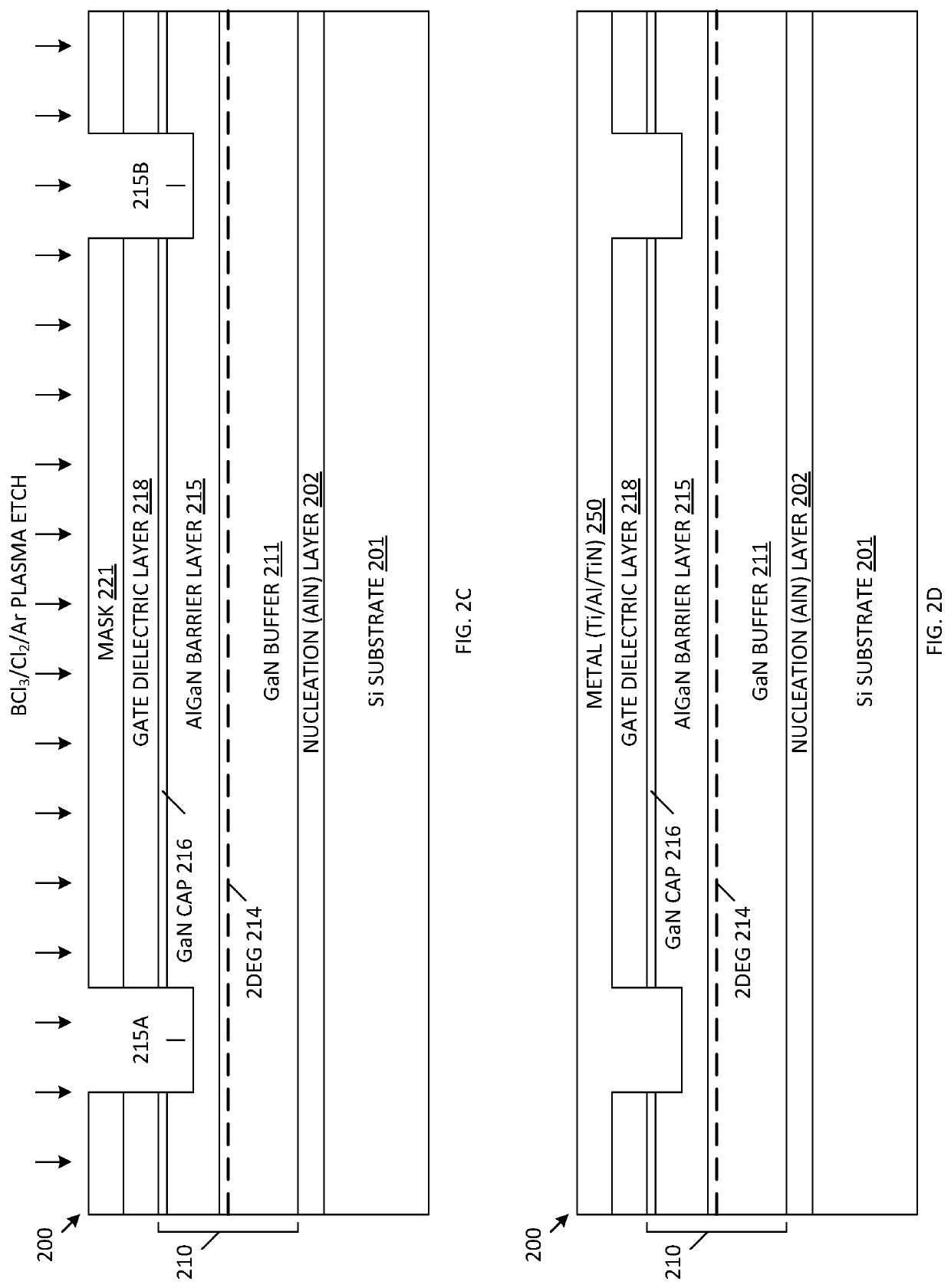

Method of forming a GaN sensor having a controlled and stable threshold voltage

ActiveUS11195933B2Easy to controlIncrease distanceMaterial analysis by electric/magnetic meansSemiconductor/solid-state device manufacturingHeterojunctionGate dielectric

A method fabricating a GaN based sensor including: forming a gate dielectric layer over a GaN hetero-structure including a GaN layer formed over a substrate and a first barrier layer formed over the GaN layer; forming a first mask over the gate dielectric layer; etching the gate dielectric layer and the first barrier layer through the first mask, thereby forming source and drain contact openings; removing the first mask; forming a metal layer over the gate dielectric layer, wherein the metal layer extends into the source and drain contact openings; forming a second mask over the metal layer; etching the metal layer, the gate dielectric layer and the GaN heterostructure through the second mask, wherein a region of the GaN heterostructure is exposed; and thermally activating the metal layer in the source and drain contact openings. The gate dielectric may exhibit a sloped profile, and dielectric spacers may be formed.

Owner:TOWER SEMICONDUCTOR

Method for manufacturing semiconductor device

InactiveUS9805952B2Improve reliabilityImprove featuresTransistorSemiconductor/solid-state device manufacturingThermal chemical vapor depositionGas phase

Provided are an oxide semiconductor layer in which the number of defects is reduced and a highly reliable semiconductor device including the oxide semiconductor. A first oxide semiconductor layer having a crystal part is formed over a substrate by a sputtering method. A second oxide semiconductor layer is formed by a thermal chemical vapor deposition method over the first oxide semiconductor layer. The second oxide semiconductor layer is formed by epitaxial growth using the first oxide semiconductor layer as a seed crystal. A channel is formed in the second oxide semiconductor layer.

Owner:SEMICON ENERGY LAB CO LTD

Method of forming bit line of semiconductor device

InactiveUS20070010089A1Reduce resistanceIncrease resistanceSolid-state devicesSemiconductor/solid-state device manufacturingBit lineSemiconductor

A method of forming a semiconductor device includes forming a contact hole in a first interlayer insulating layer that is provided on a semiconductor substrate. The contact hole has a sidewall defined by the first interlayer insulating layer. A first conductive layer is provided within the contact hole. The first conductive layer directly contacts the first interlayer insulating layer that defines the sidewall of the contact hole. The first conductive layer is etched to define a recess within the contact hole, the recess being provided directly above the first conductive layer. An interface metal layer is provided within the recess. A second interlayer insulating layer is formed on the interface metal layer. The second interlayer insulating layer is etched to expose the interface metal layer. A second conductive layer is deposited on the exposed interface metal layer to form a bit line.

Owner:SK HYNIX INC

Trench type capacitor device and preparation method

InactiveCN112635440AAvoid residueAvoid plasma damageSemiconductor/solid-state device detailsSolid-state devicesCapacitanceMetal interconnect

The invention provides a preparation method of a trench type capacitor device, a trench capacitor region comprises: a plurality of trenches and a capacitor structure, wherein the trenches penetrate through a first dielectric layer and end at a first metal interconnection layer, and the capacitor structure is located on the first dielectric layer and fills the trenches; a second dielectric layer with a first opening, a second opening penetrating through the second dielectric layer and the first dielectric layer and ending at a second metal interconnection layer, and an electrode interconnection layer filling the first opening and the second opening. The side wall of the side, close to the second opening, of the first opening is overlapped with an extension line of the side wall of the side of the second opening, so that the depth of the second opening is further increased, the opening size of the second opening is reduced, the capacitance value per unit area is effectively increased, and a high-performance trench type capacitor device is formed, thus having significant significance.

Owner:上海微阱电子科技有限公司

Method for manufacturing a complementary metal-oxide semiconductor sensor

ActiveUS7115438B2Prevent fallingIncrease productionSemiconductor/solid-state device manufacturingChemical vapor deposition coatingPresent methodElectrical conductor

A method for manufacturing a complementary metal-oxide semiconductor sensor is provided. The present method provides a semiconductor structure including a plurality of conductors thereon. An inter-metal dielectric layer is formed on the conductors. A silicon nitride film is applied on the inter-metal dielectric layer. An oxide layer is formed on the silicon nitride film. The oxide layer, the silicon nitride film and the inter-metal dielectric are etched to expose portions of the conductors. The oxide layer and the exposed conductors are cleaned in a cleaning step later.

Owner:UNITED MICROELECTRONICS CORP

Groove type capacitor device and preparation method

InactiveCN112510012AAvoid plasma damageAvoid residueSemiconductor/solid-state device detailsSolid-state devicesCapacitanceMetal interconnect

The invention provides a groove type capacitor device and a preparation method. A groove capacitor structure of the groove type capacitor device is located at one side, far away from a substrate, of agroove dielectric layer, a first groove penetrating through the groove dielectric layer is filled, the groove capacitor structure is electrically connected with a first metal interconnection layer, acapacitor side wall covers the side surface of the groove capacitor structure, and an electrode interconnection layer fills a second trench penetrating through the trench dielectric layer and is electrically connected with the second metal interconnection layer. The capacitor side wall avoids the short circuit of an upper electrode layer and a lower electrode layer of the trench capacitor structure, achieves the purpose of improving the performance and reliability of a device, and has remarkable significance.

Owner:SHANGHAI INTEGRATED CIRCUIT EQUIP & MATERIALS IND INNOVATION CENT CO +2

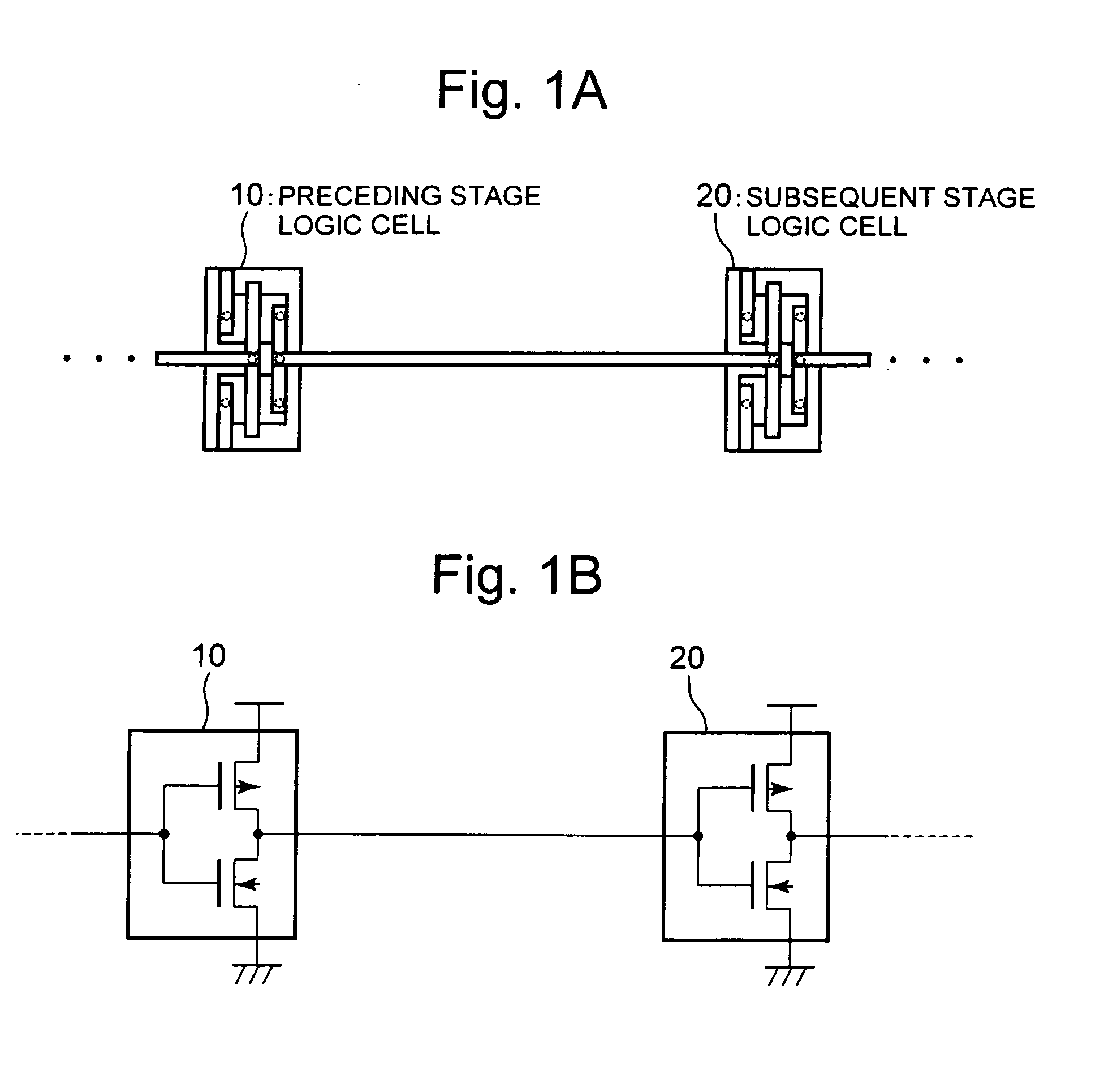

Method for designing semiconductor integrated circuit which includes metallic wiring connected to gate electrode and satisfies antenna criterion

InactiveUS20110165737A1Avoid plasma damageRaise the ratioSolid-state devicesSemiconductor/solid-state device manufacturingLogic cellSemiconductor

A method of forming a semiconductor integrated circuit, includes providing a first logic cell, a second logic cell and a metallic wiring connected to the first logic cell and a gate electrode of the second logic cell, and providing a third logic cell including a gate electrode connected to the metallic wiring, such that the third logic cell makes no contribution to a logic operation of the semiconductor integrated circuit, in order that an antenna ratio of the first gate electrode to the metallic wiring does not satisfy an antenna criterion, and an antenna ratio of the first gate electrode and the second gate electrode to the metallic wiring satisfies the antenna criterion.

Owner:RENESAS ELECTRONICS CORP

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com