Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

32results about How to "Achieve High Density Storage" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Antimony-rich high-speed phase change material for phase change memory, method for preparing antimony-rich high-speed phase change material and application of material

ActiveCN102800808ARegulated contentAchieve High Density StorageElectrical apparatusVacuum evaporation coatingPhase-change memoryHigh density

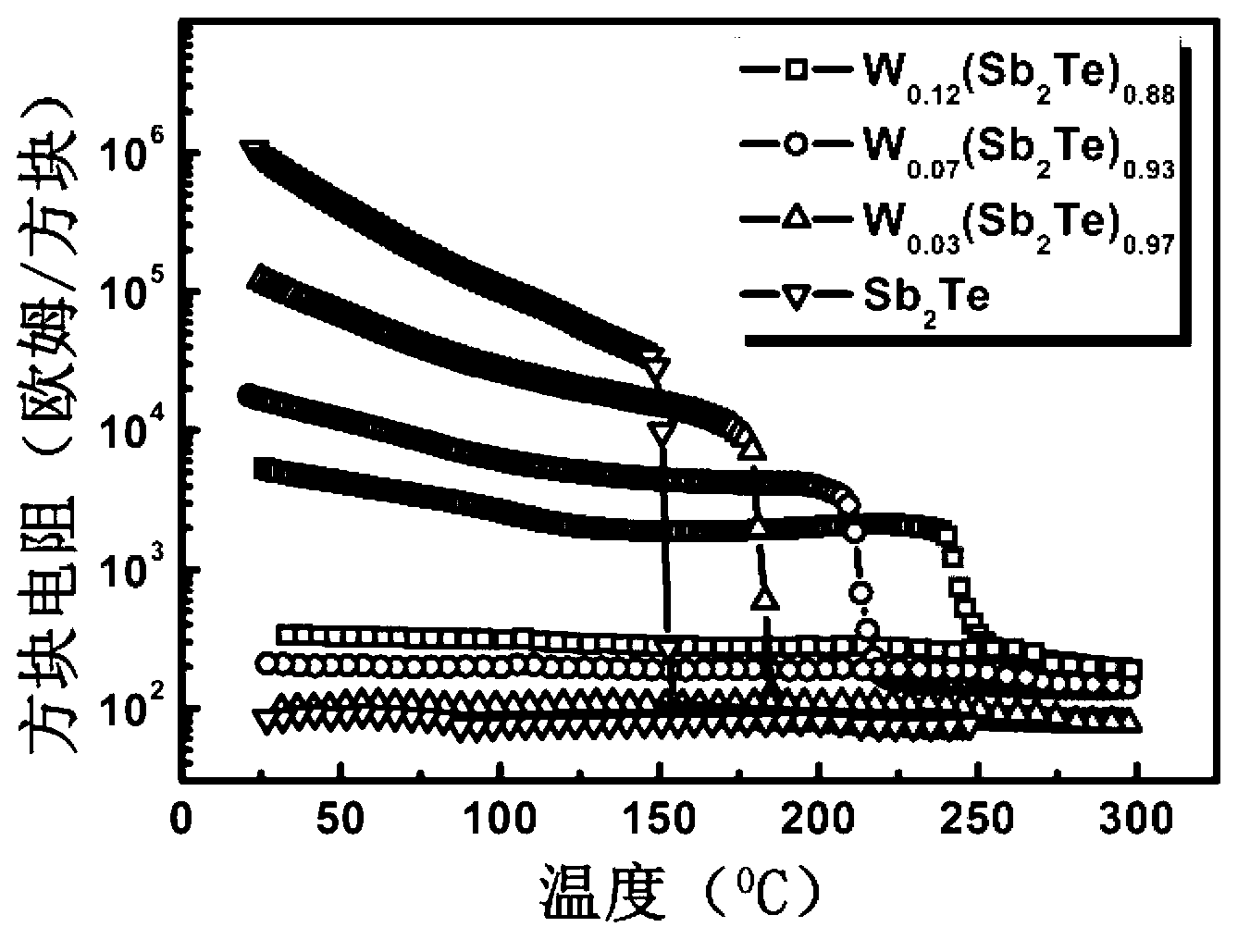

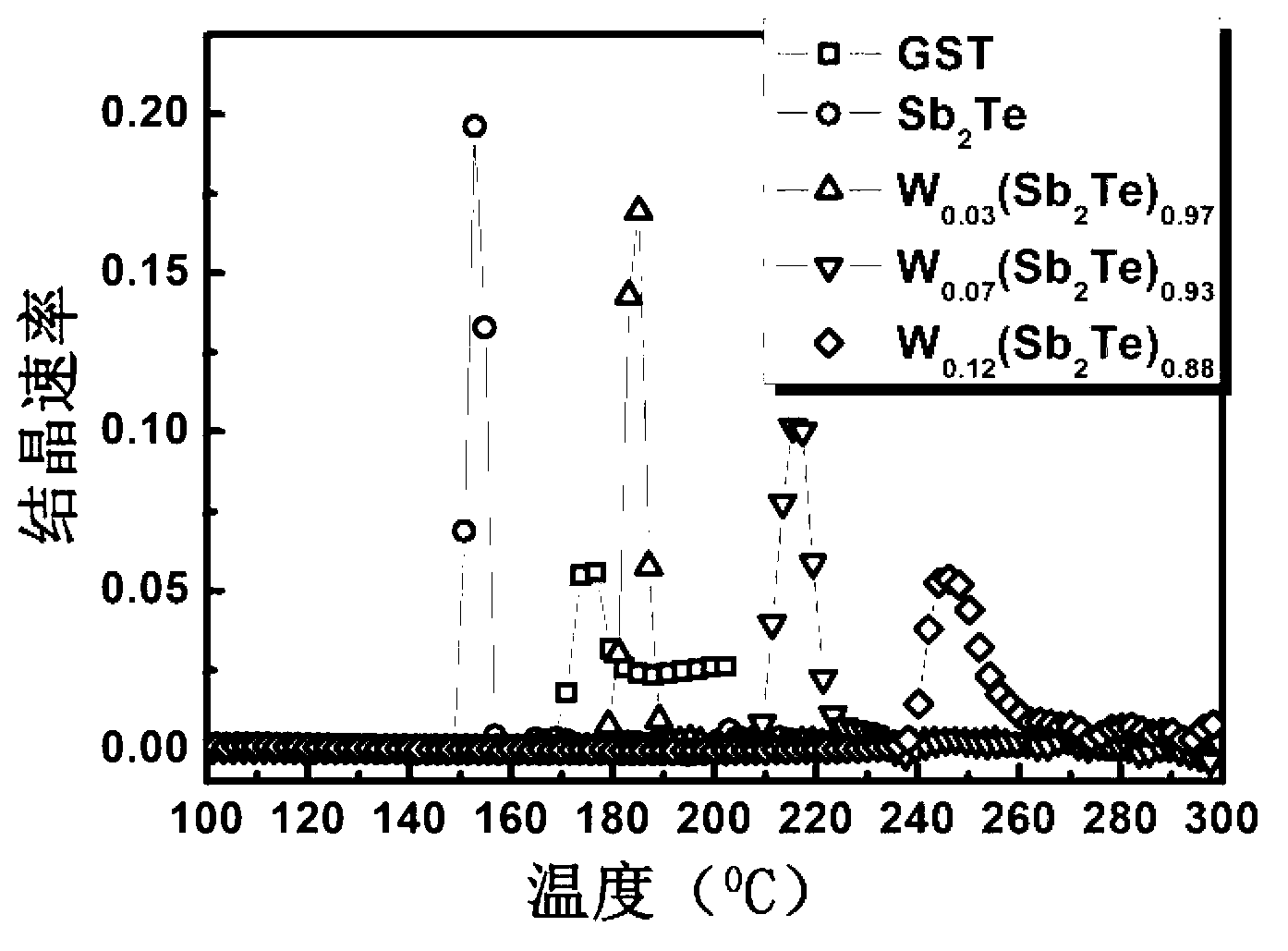

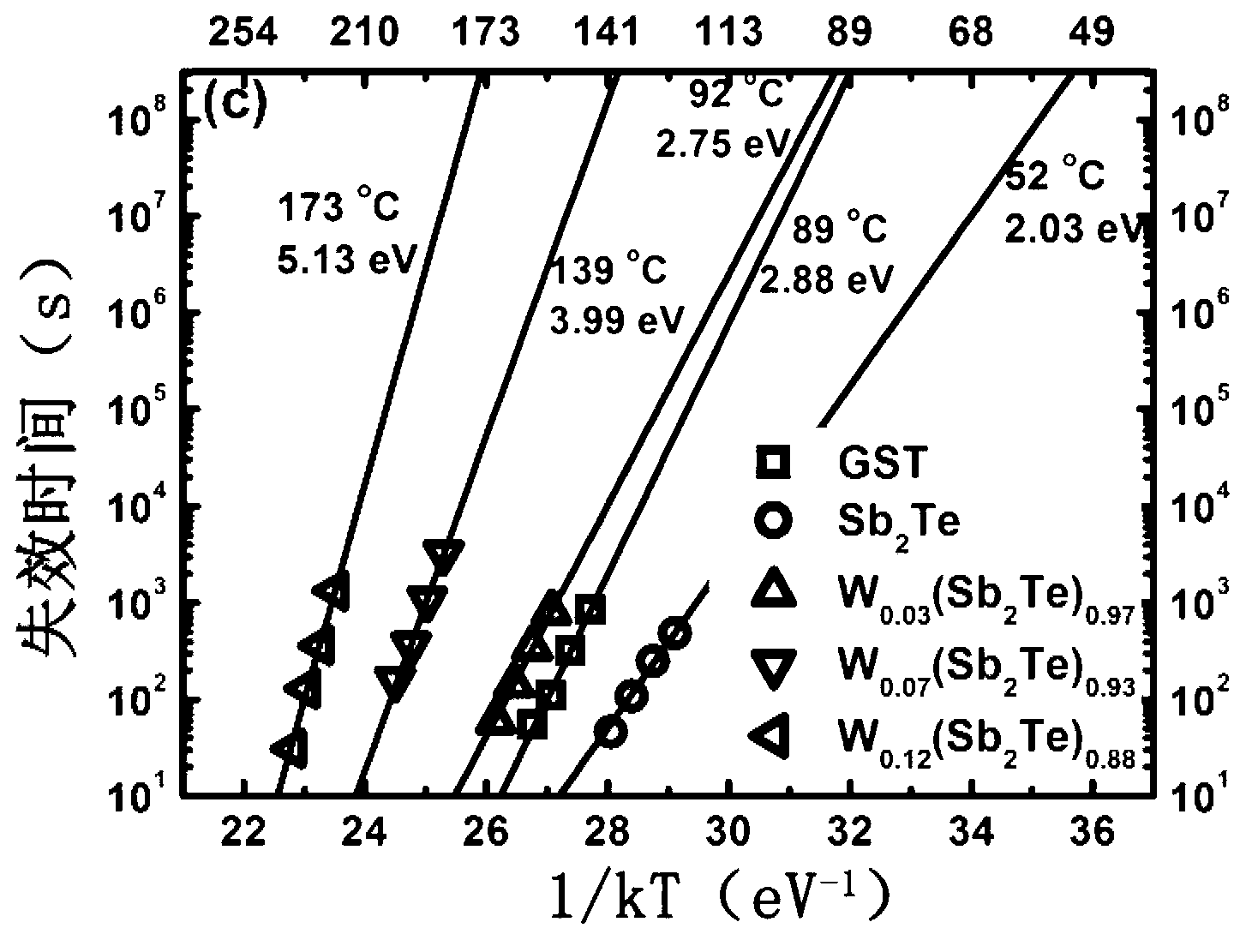

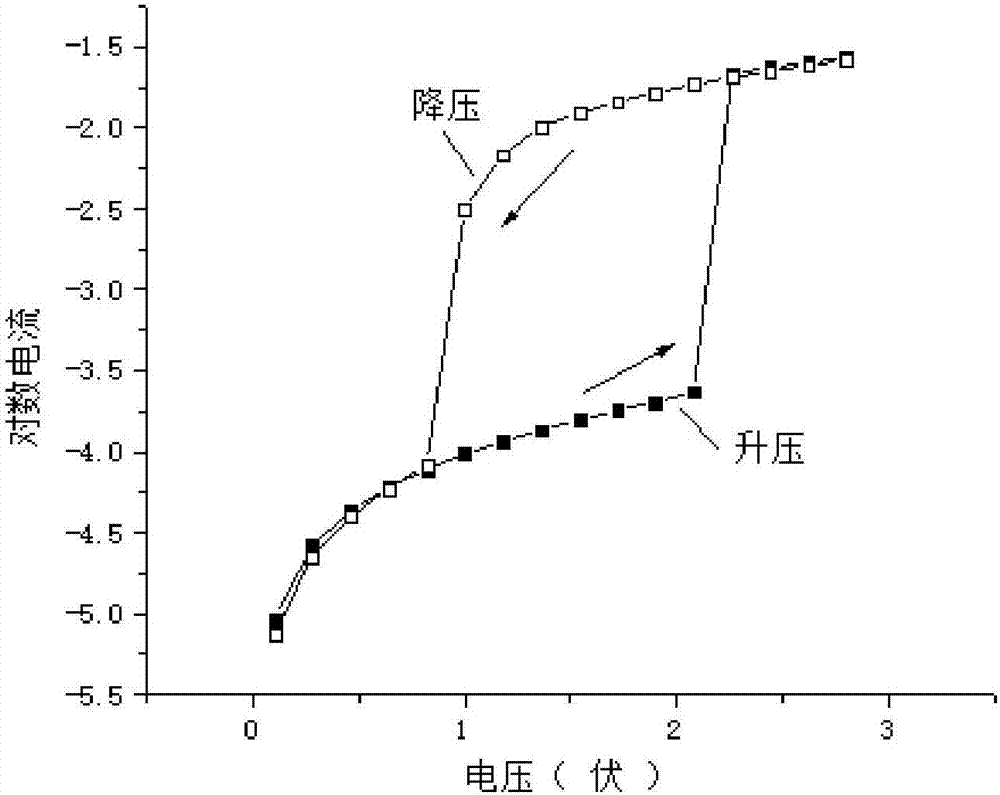

The invention relates to a phase change material doped with metallic elements in the microelectronic technical field, and in particular relates to an antimony-rich high-speed phase change material for a phase change memory, a method for preparing the antimony-rich high-speed phase change material and an application of the material. The antimony-rich high-speed phase change material for the phase change memory has a chemical formula of Ax(Sb2Te)(1 minus x), where the x is atomic percent, A is selected from W, Ti, Ta or Mn, and x is larger than zero and less than 0.5. The phase change material provided by the invention is similar to the common GeSbTe materials, and is contributed to realizing high density storage. The phase change material can be performed on reversible phase change under the action that nanosecond-level pulse is driven by external electricity. The phase change speed of a W-Sb-Te phase change material is three times that of the GeSbTe materials, and is contributed to realizing the high density storage.

Owner:SHANGHAI INST OF MICROSYSTEM & INFORMATION TECH CHINESE ACAD OF SCI

4U high-density storage server

InactiveCN103970215AAchieve High Density StorageAddressing High Cooling DemandsDigital data processing detailsComputer moduleMotherboard

The invention discloses a 4U high-density storage server, and belongs to a server. The 4U high-density storage server structurally comprises a case, a power module, a main board, a fan region and a storage device region, wherein the power module, the main board, the fan region and the storage device region are arranged in the case, four storage nodes which can be plugged in a thermal mode serve as the storage device region, the storage nodes are communicated with the main board through an expanded controller and transmission cables, and each storage node is provided with twelve 3.5-inch hard disks which can be plugged in a thermal mode. Compared with the prior art, the 4U high-density storage server can support the forty-eight 3.5-inch hard disks and allow plugging operation to be conducted in the thermal mode, and high-density storage in the 4U server is achieved.

Owner:LANGCHAO ELECTRONIC INFORMATION IND CO LTD

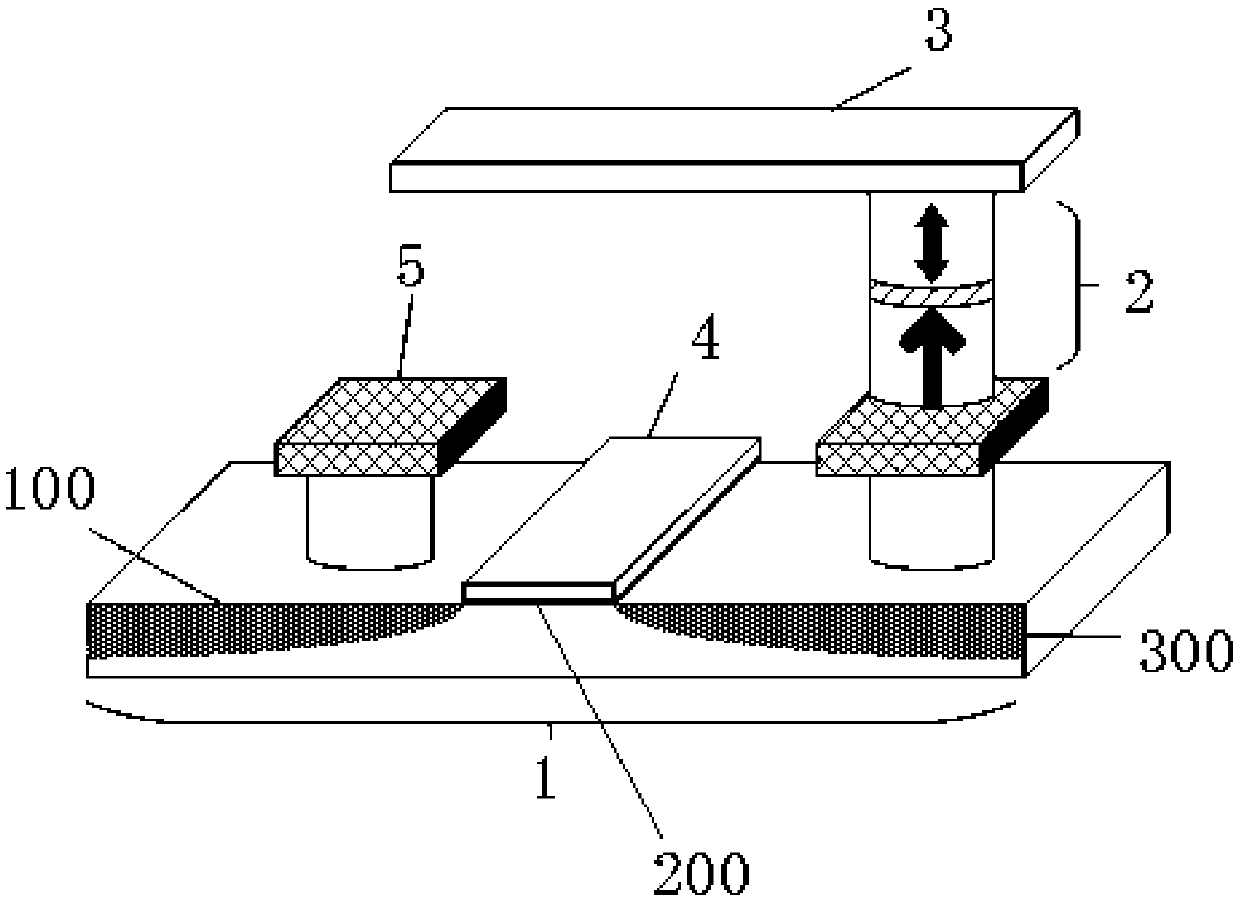

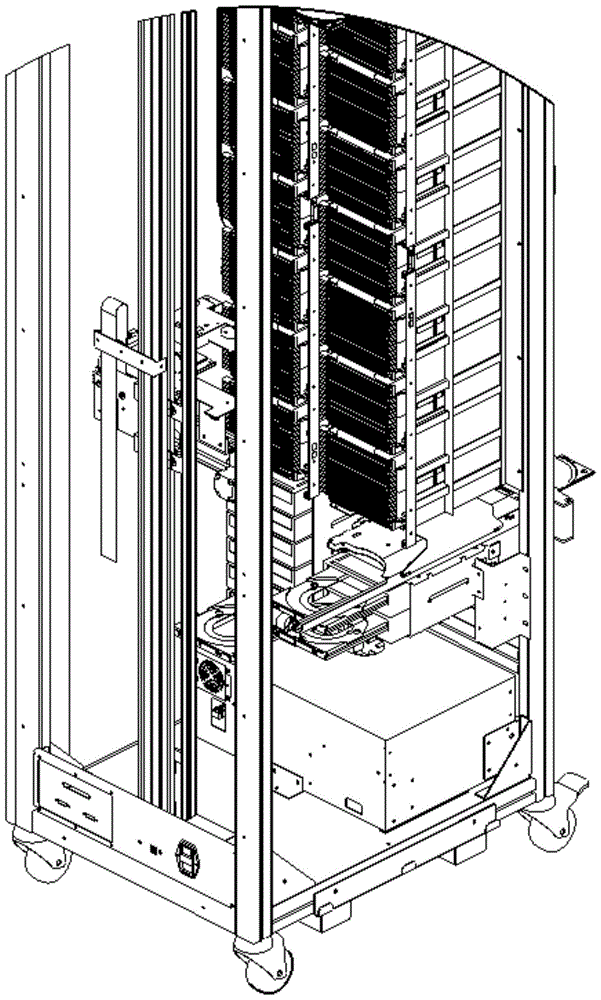

Modularized high-speed optical disc juke-box for equipment cabinet

ActiveCN104616684AImprove storage densityImprove space utilizationRecord information storageRecord carrier contruction detailsPush and pullModularity

The invention discloses a modularized high-speed optical disc juke-box for an equipment cabinet. The modularized high-speed optical disc juke-box comprises an equipment cabinet, a server module, a mechanical hand component and a pushing-pulling framework, wherein a disc bin array is arranged along one side wall of the equipment cabinet; the disc bin array comprises a plurality of stacked disc bins, and optical disc sheet boxes are arranged in the stacked disc bins; the server module is arranged above the disc bin array in the equipment cabinet, and comprises a server and an optical disc driver set connected with the server through a data line; the mechanical hand component which is arranged towards the side opening of the disc bin array is arranged in the equipment cabinet; the mechanical hand component is used for getting out a target optical disc in the selected disc bin; the pushing-pulling framework is corresponding to the disc bin array and used for pushing and pulling one or more disc bins in the disc bin array. The modularized high-speed optical disc juke-box for the equipment cabinet disclosed by the invention adopts a modularized design and mutually independent components, and is convenient to maintain; the disc bin array, the server module and the opposite mechanical hand component are stacked, so that the optical disc storage density and the integral space utilization rate of the optical disc juke-box can be increased.

Owner:SUZHOU NETZON INFORMATION STORAGE TECH

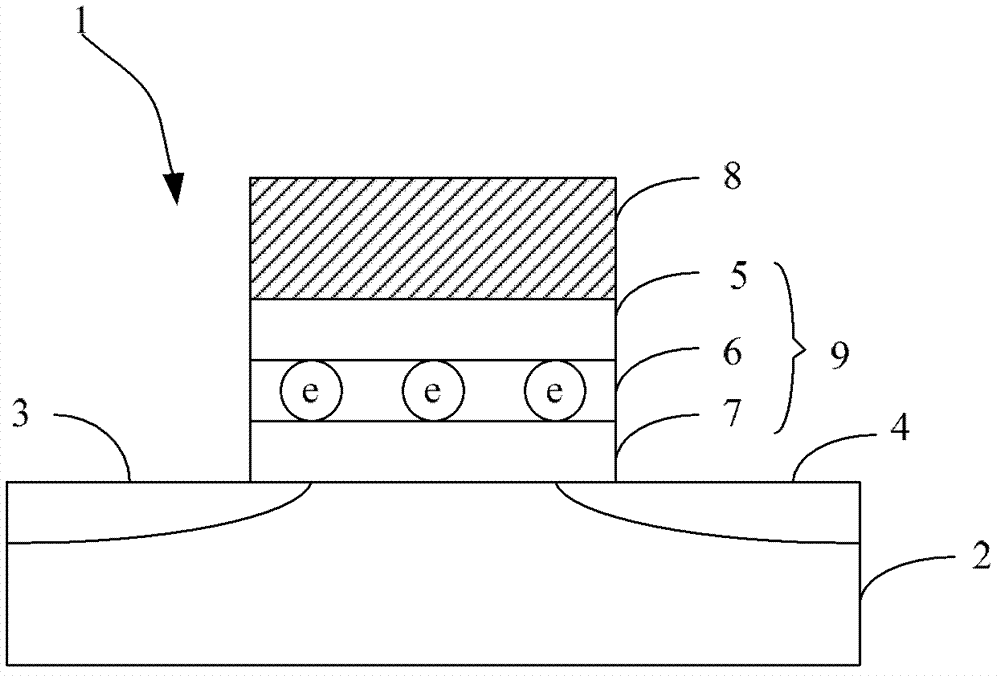

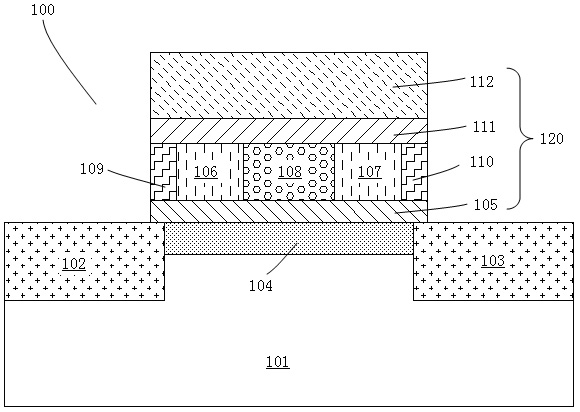

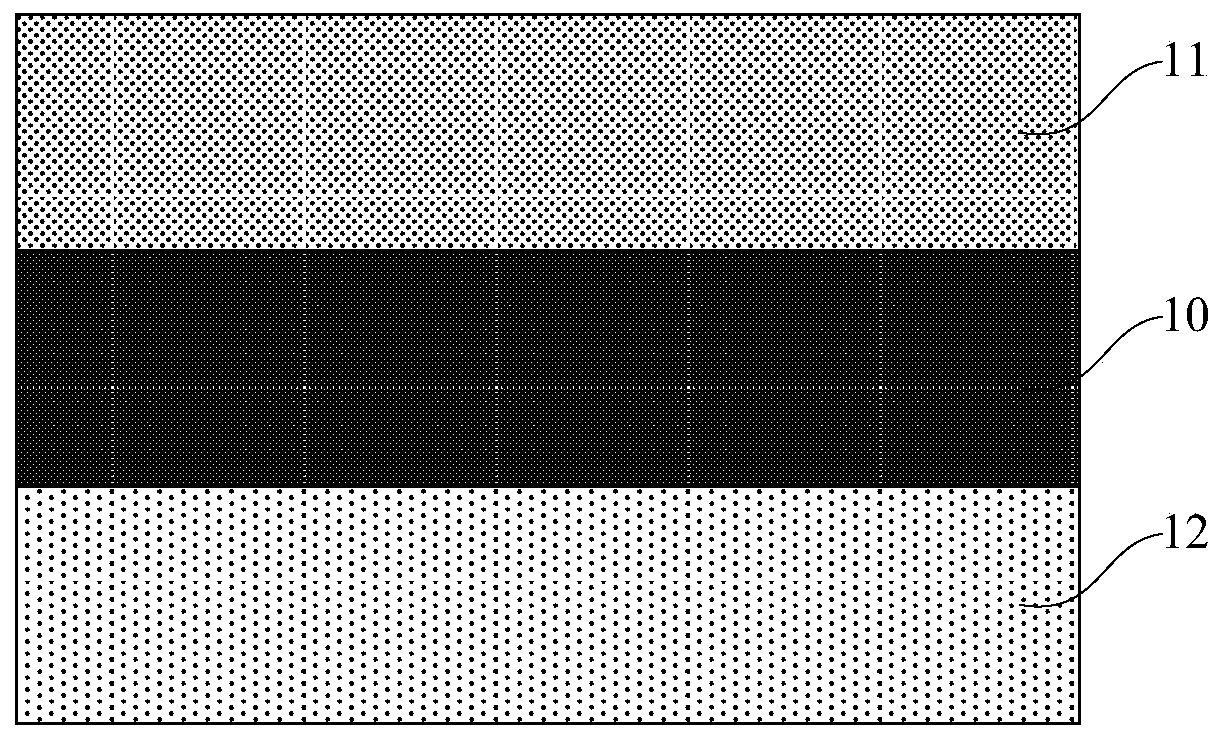

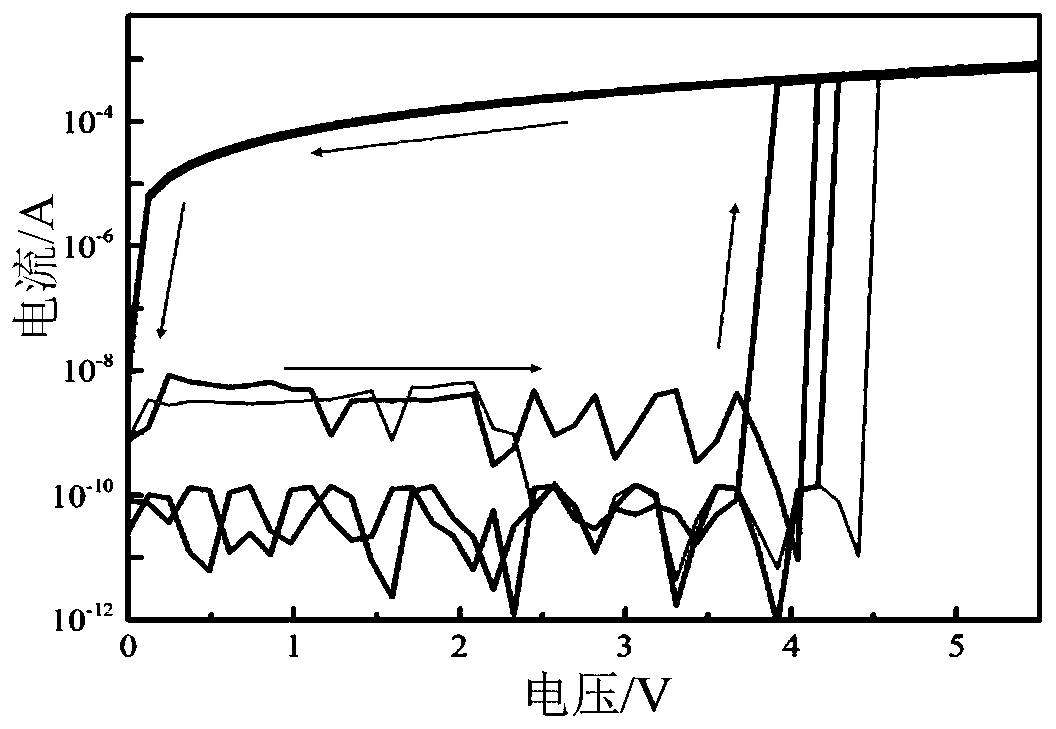

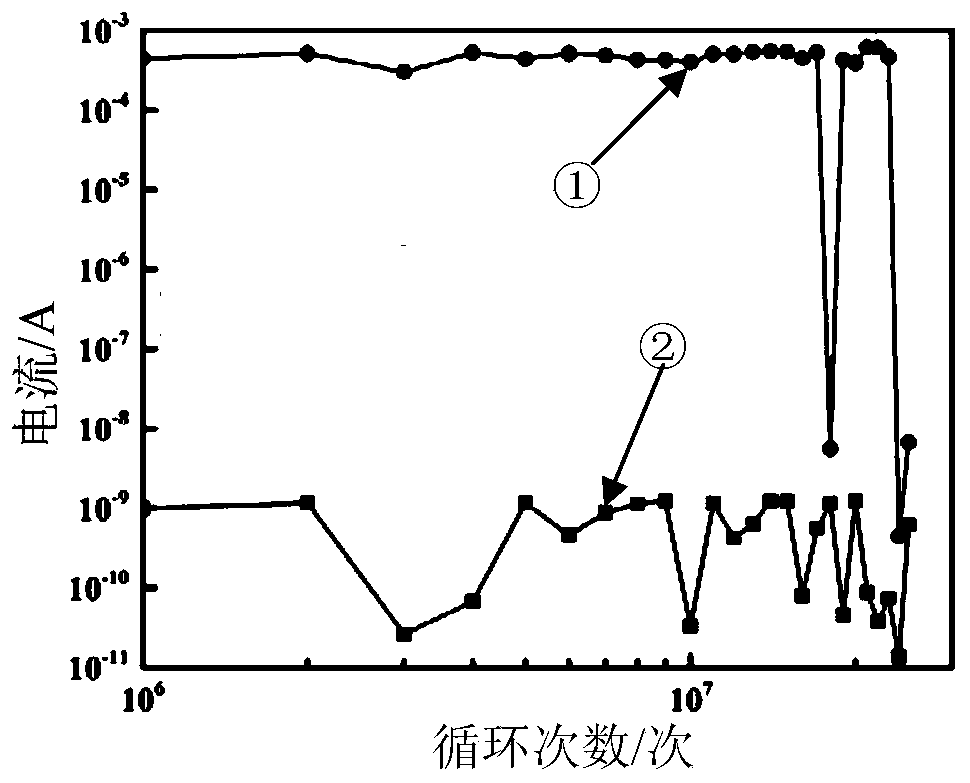

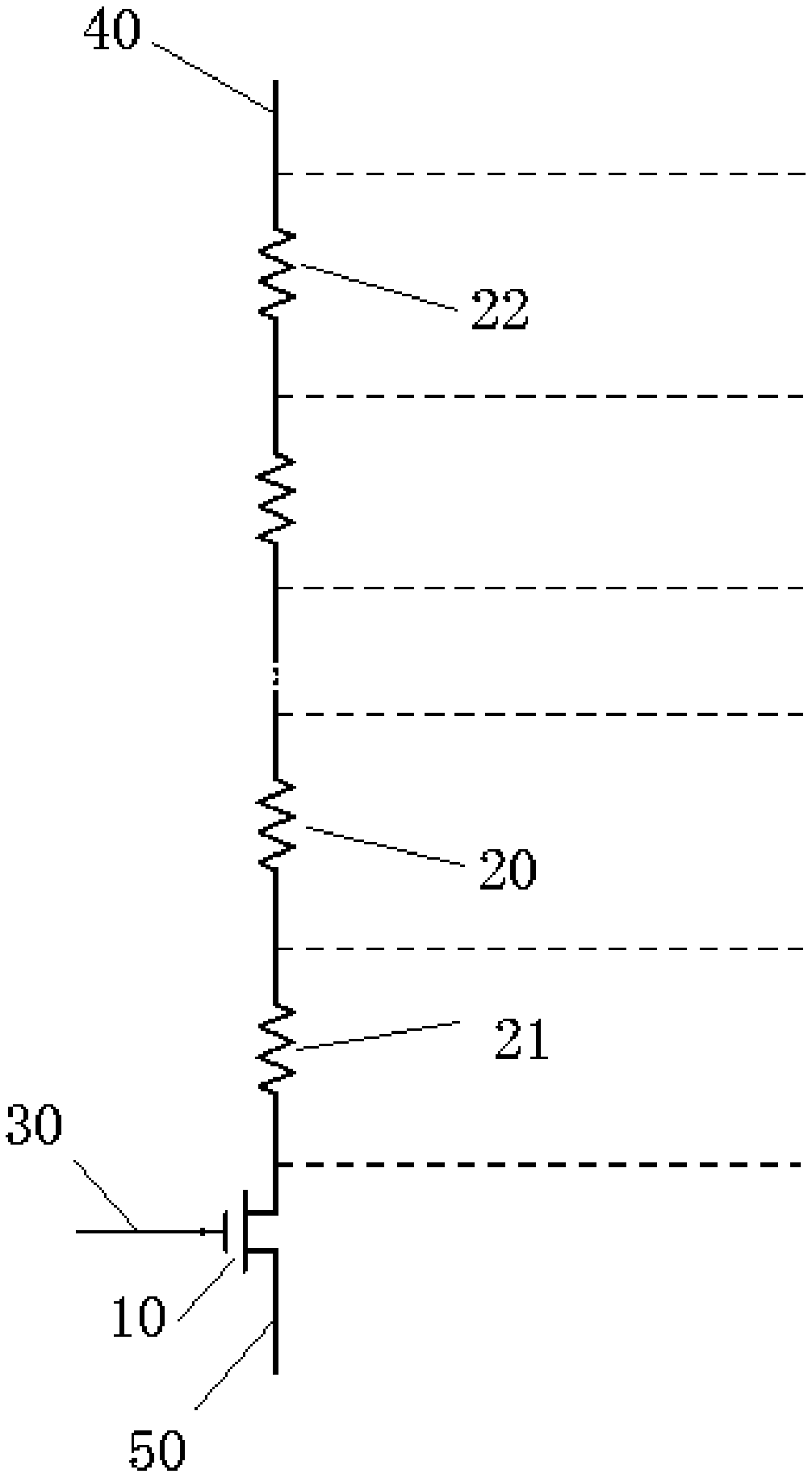

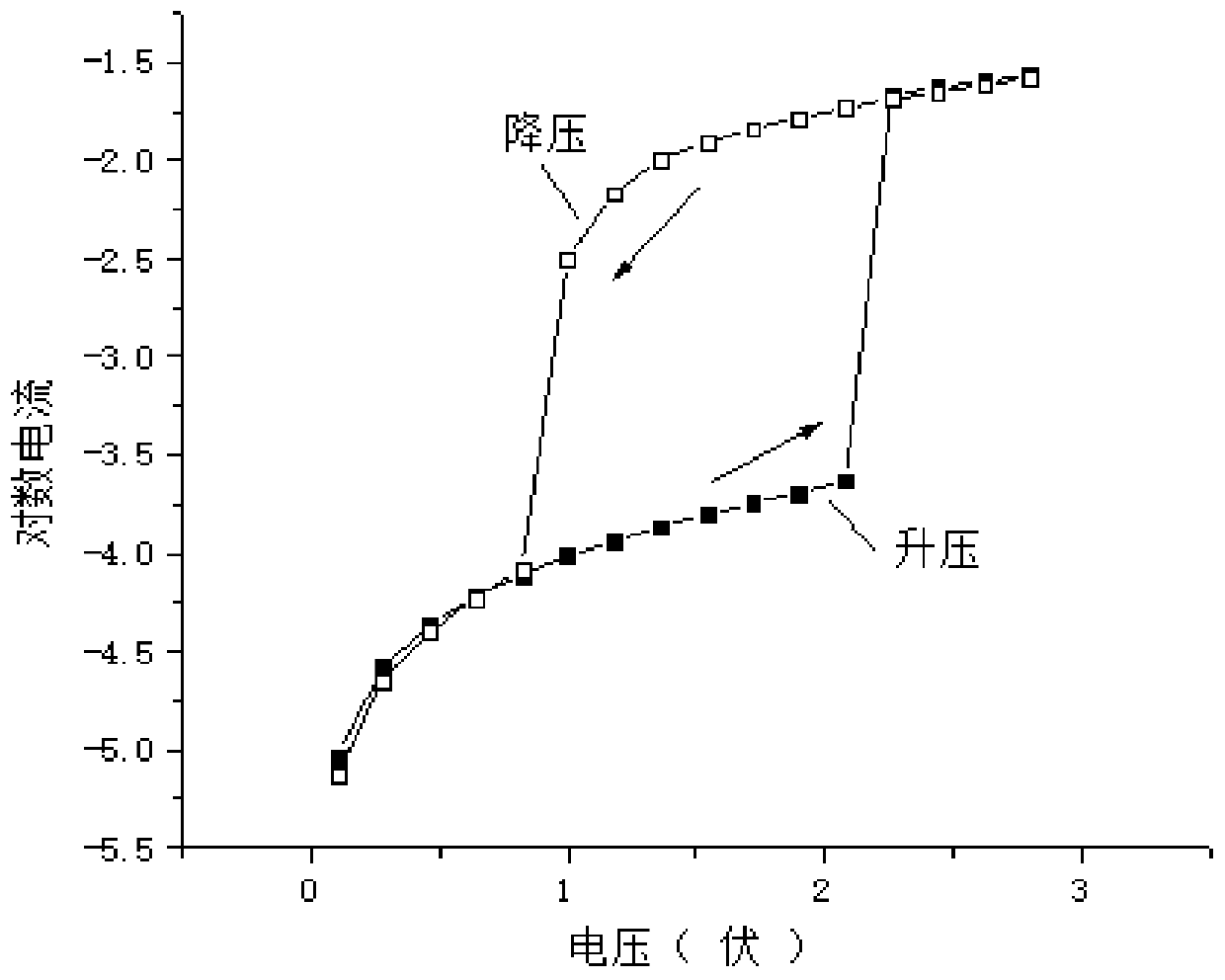

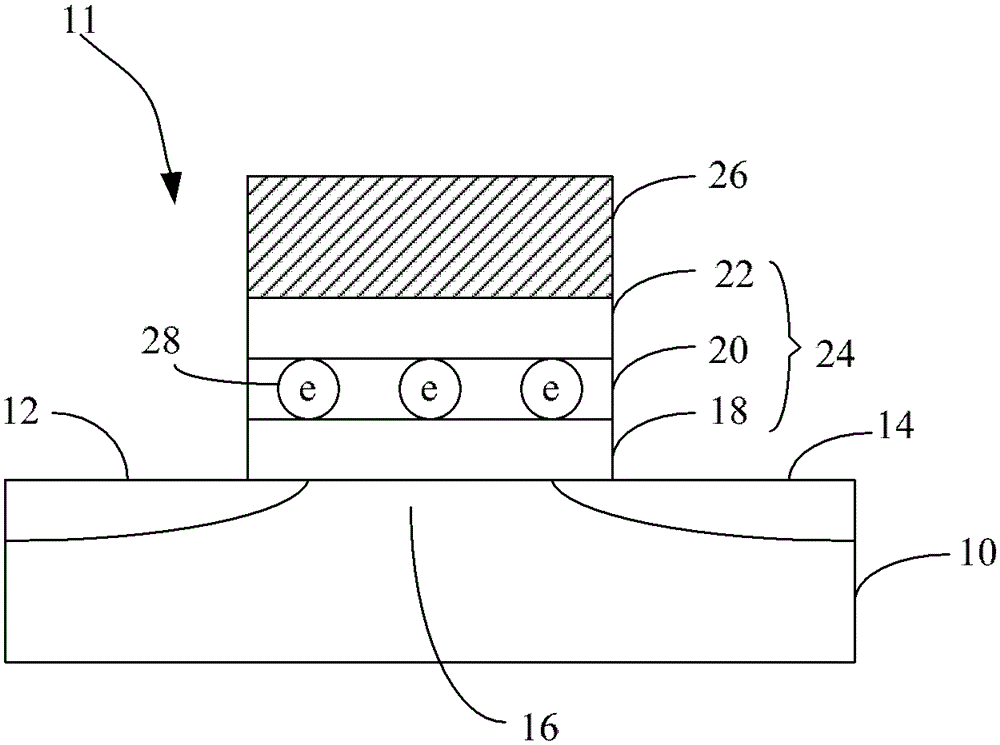

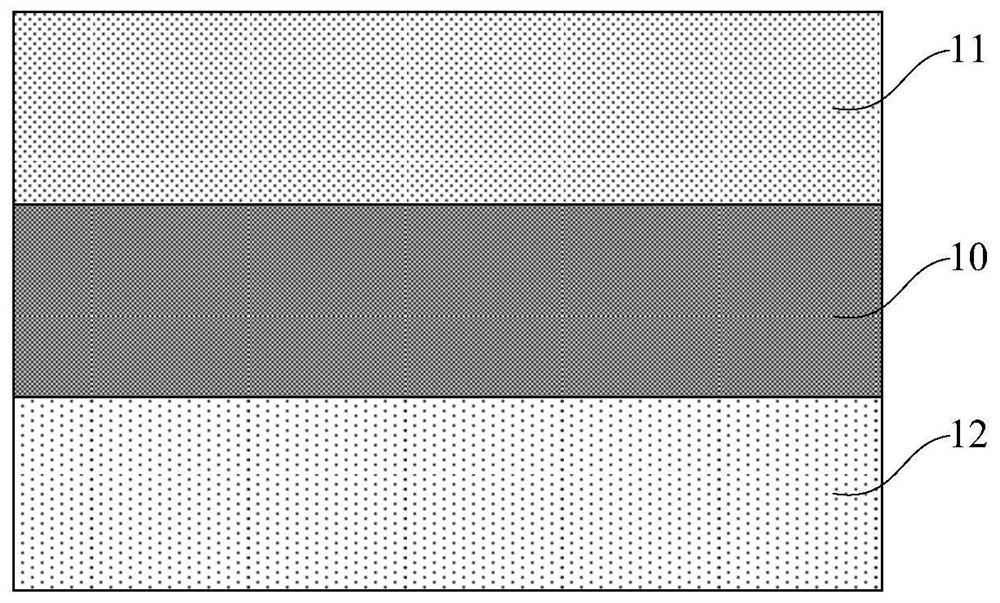

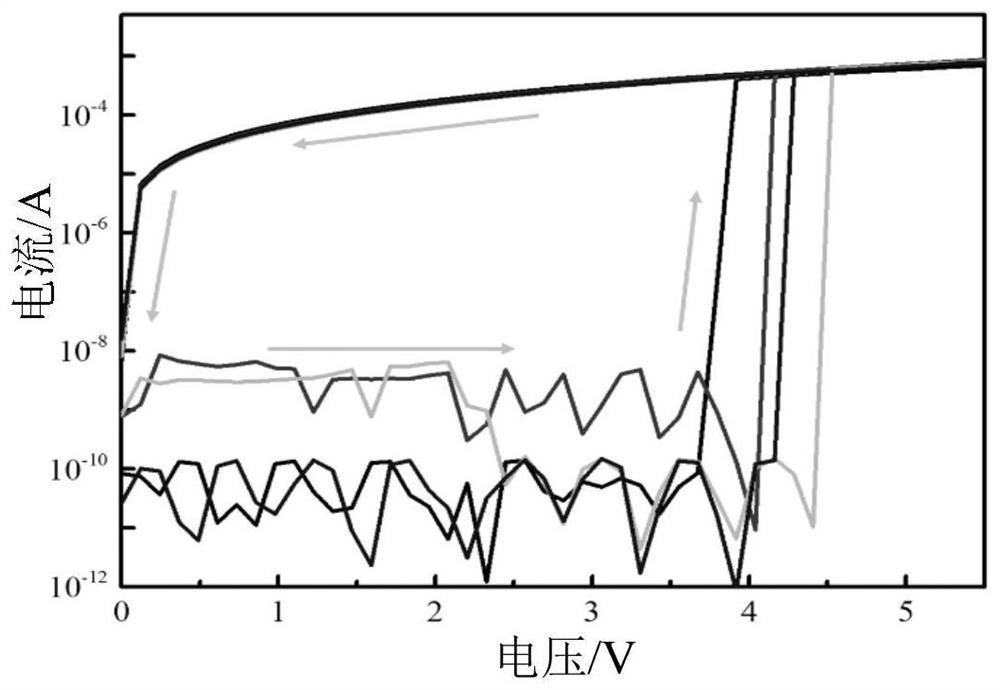

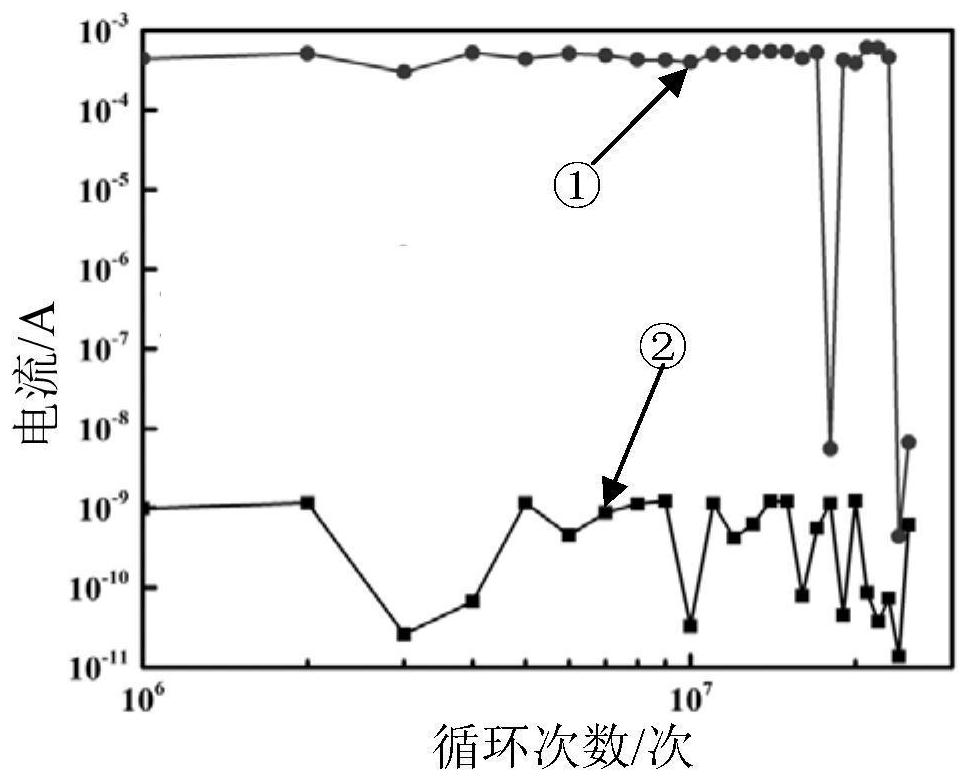

Phase change storage unit based on VOx gate tube

ActiveCN106992251AAchieve High Density StorageSimple preparation processElectrical apparatusDigital storagePhase-change memoryLow voltage

The invention discloses a phase change storage unit based on a VOx gate tube. The storage unit comprises a lower electrode layer, a VOx gating layer, a phase change function layer and an upper electrode layer. According to the invention, by use of the VOx, the gating of the phase change function layer is achieved; storage of the data is achieved on the basis of gating of the phase change function layer; by imposing voltage on the VOx, the state switching of the VOx is controlled, so an objective that the phase change storage unit is in a non-gating state during low voltage and in a gating system during high voltage can be achieved; through the switch control of the VOx, leakage current of the a phase change memory array can be effectively reduced and enough big Reset current is provided; a high-temperature technique condition is not required; preparation technique of the phase change memory is simplified; cost is reduced; and it is possible to commercialize the highly integrated phase change memory.

Owner:HUAZHONG UNIV OF SCI & TECH

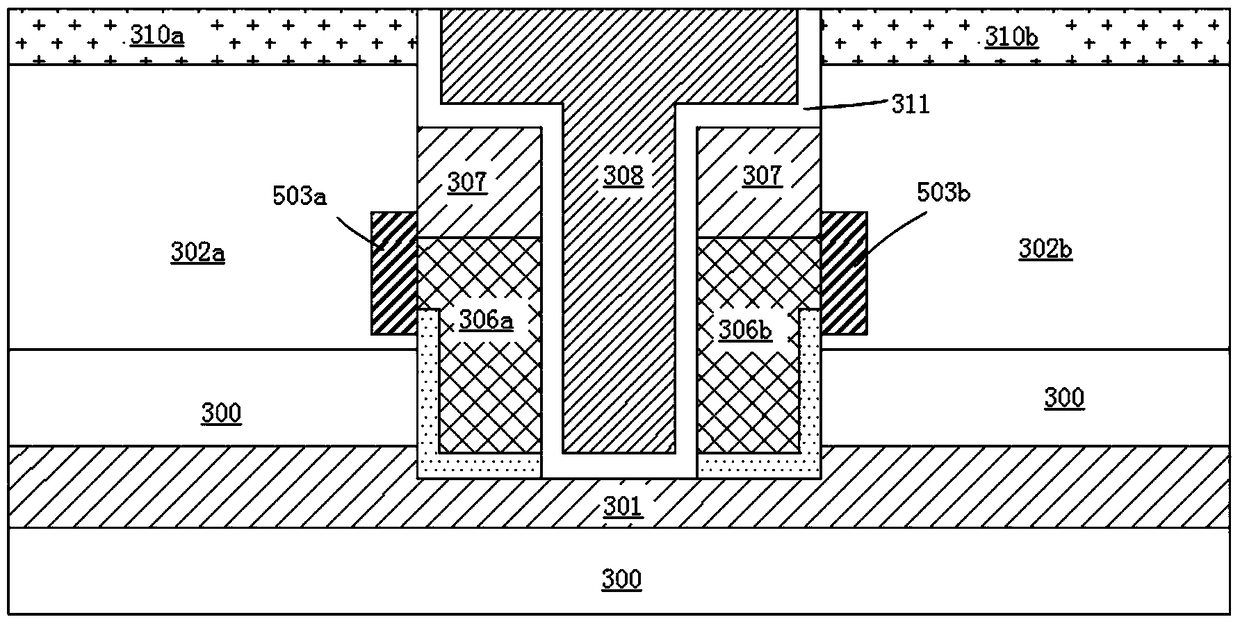

8-bit semi-conductor storage unit, manufacture method and storage unit array of 8-bit semi-conductor storage unit

ActiveCN103094283AAchieve High Density StorageSolid-state devicesSemiconductor/solid-state device manufacturingSource area8-bit

The invention provides an 8-bit semi-conductor storage unit, a manufacture method and a storage unit array of the 8-bit semi-conductor storage unit. The 8-bit semi-conductor storage unit comprises a source area, four drain areas, four grid areas, four strip-shaped semi-conductor fins and eight charge storage composite layers, wherein four drains are symmetrically arranged outside a source electrode, one strip-shaped semi-conductor fin with a channel region is arranged between each drain electrode and the source electrode, each drain electrode is arranged between each two adjacent strip-shaped semi-conductor fins, and each grid are in contact with the channel region between the semi-conductor fins at two sides of the corresponding grid through the charge storage composite layers with charge capture layers. By means of the novel structure, 8-bit storage of the storage unit is ingeniously achieved, and storage density of the storage unit is further improved.

Owner:SEMICON MFG INT (SHANGHAI) CORP

Magnetic random access memory and writing method, reading method and preparation method thereof

ActiveCN107946454AAchieve writeReduce write energy consumptionMagnetic-field-controlled resistorsDigital storageMagnetic ramAntiferromagnetic coupling

The invention discloses a magnetic random access memory (MRAM) and a writing method, a reading method and a preparation method thereof. The magnetic RAM includes a substrate layer, a ferroelectric layer, a composite anti-ferromagnetic structure, a first isolation layer and a first ferromagnetic layer that are successively stacked. The composite anti-ferromagnetic structure is the free layer of theMRAM. The first ferromagnetic layer is the fixed layer of the MRAM. The ferroelectric layer is subjected to polarization or lattice distortion under the effect of applied voltage in order to change the coupling state of the composite anti-ferromagnetic structure. The first ferromagnetic layer has a constant first magnetic moment direction. The first isolation layer is configured to control the first magnetic moment direction not to be affected by the coupling state of the composite anti-ferromagnetic structure. The MRAM achieves writing by using the transformation of ferromagnetic coupling and anti-ferromagnetic coupling of the composite anti-ferromagnetic structure under the effect of an electric field, and solves a problem that the MRAM has a large size and a low storage density becauseof a large line width during the writing achieved by the induction magnetic field or polarization current of a wire.

Owner:SOUTH UNIVERSITY OF SCIENCE AND TECHNOLOGY OF CHINA

Nano composite phase-change material and preparation method thereof

ActiveCN101521260AGood dielectricGood insulation performanceElectrical apparatusVacuum evaporation coatingDielectricPhase-change memory

The invention relates to a novel nano composite phase-change material and a preparation method thereof. The nano composite phase-change material is characterized in that a phase-change material and a ferroelectric material are compounded, and the ferroelectric material separates the phase-change material into even nano-scale areas with controllable shapes and sizes so as to limit the phase change of the phase-change material within a small area; and simultaneously, because the ferroelectric material has good dielectric and insulating properties, the ferroelectric material enhances the dielectric property and breakdown resisting capability of the composite material, inhibits the growth of phase-change material crystals, promotes the specific resistance of the material, and increases the heat capacity of the material. The novel nano composite phase-change material applied to a memory is favorable for achieving high-density storage, improves heating efficiency during programming of a phase-change memory, reduces the power consumption of the memory, improves the storage speed, and promotes data retention capability, fatigue property, radiation resistance and the like.

Owner:SHANGHAI INST OF MICROSYSTEM & INFORMATION TECH CHINESE ACAD OF SCI

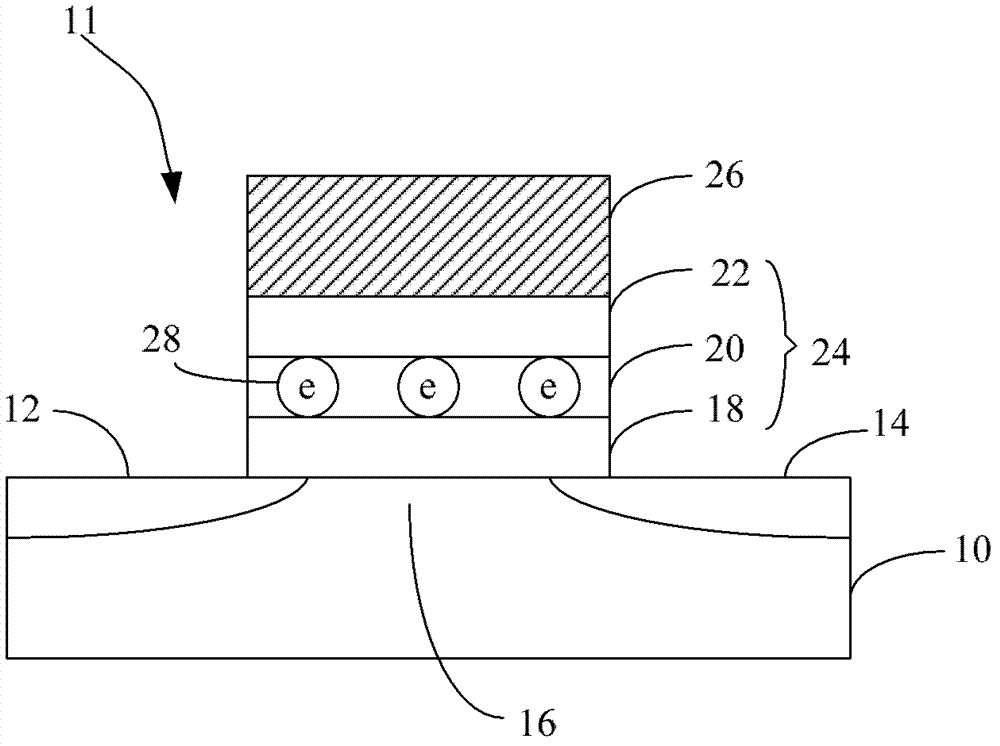

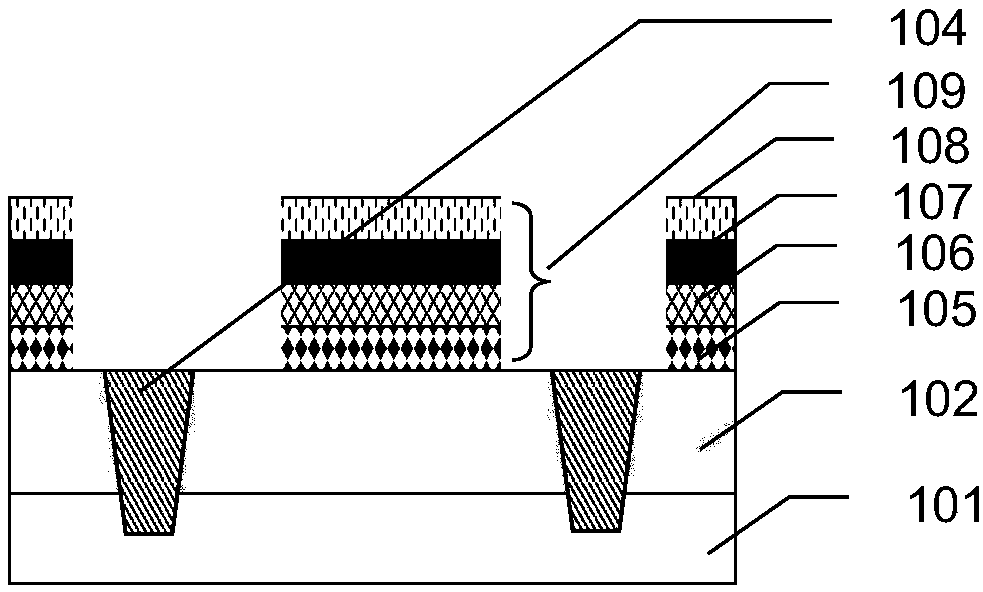

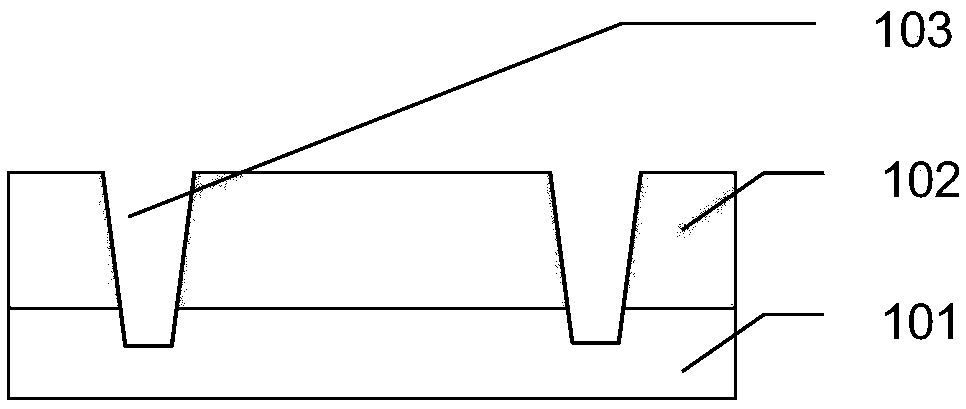

High-density phase change memory and preparation method thereof

ActiveCN109686755AReduce power consumptionReduce contact areaSolid-state devicesSemiconductor/solid-state device manufacturingManufacturing cost reductionPhase-change memory

The invention discloses a high-density phase change memory including a Schottky diode, a phase change layer and an upper electrode from bottom to top. The Schottky diode includes a semiconductor layerand a metal layer forming a Schottky barrier with the semiconductor layer. The metal layer serves as a lower electrode of the phase change layer at the same time. The semiconductor layer, the metal layer, the phase change layer and the upper electrode are of a flat layer structure stacked from bottom to top, or the semiconductor layer, the phase change layer and the upper electrode are of a planar structure arranged from bottom to top, the metal layer is connected with a planar bottom surface and a vertical sidewall, the metal layer is overlapped with the semiconductor layer below the metal layer through the bottom surface and is connected to the phase change layer above the metal layer through the sidewall, and the phase change layer is stacked on the upper electrode. The memory can effectively improve the density of phase change memory units, reduce the number of lithography, simplify the process and reduce the manufacturing cost. The invention also discloses a preparation method ofthe high-density phase change memory.

Owner:SHANGHAI INTEGRATED CIRCUIT RES & DEV CENT

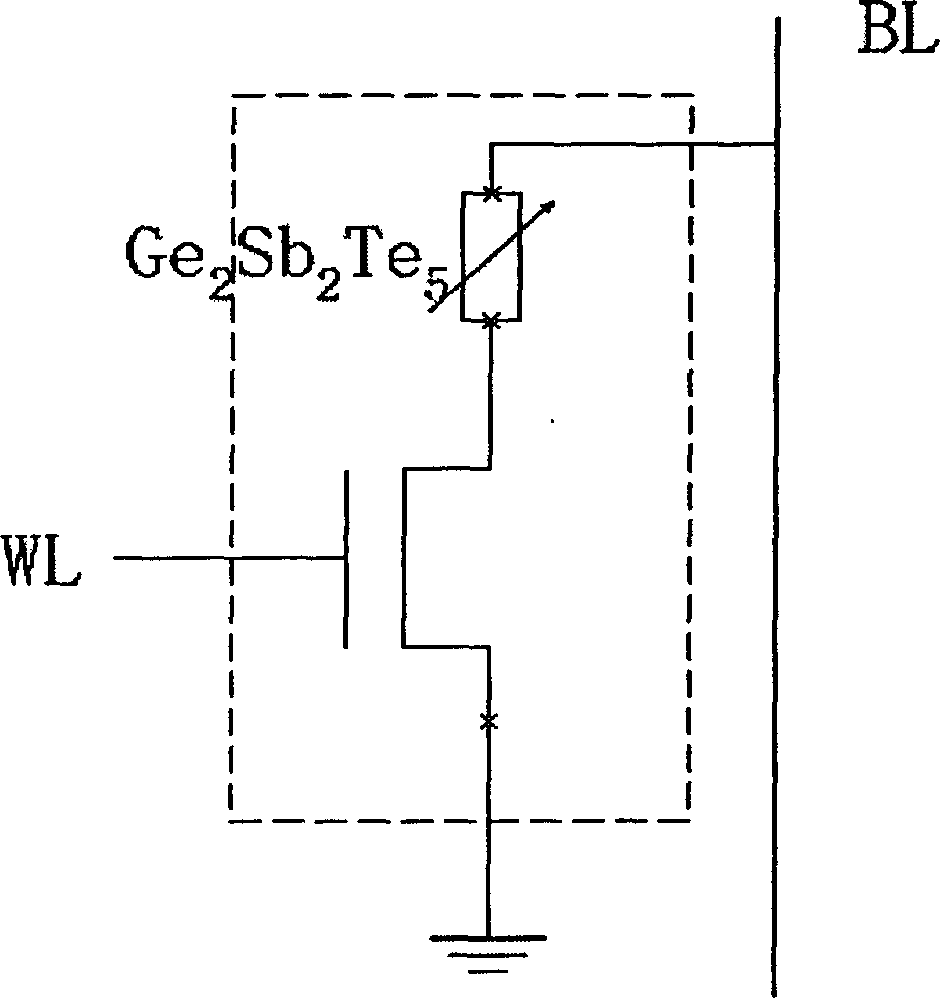

Achieving method for multi-valued phase changing storage device

InactiveCN1812124ASolve big problemsRealize multi-plant storageSemiconductor devicesSemiconductor materialsPhase-change material

This invention belongs to the field of microelectronic technology. It is a kind of method of multi-valued phase transformation memorizer. It uses semiconductor characters of phase transformation membrane material or composite material of other semiconductor material and phase transformation membrane to form semiconductor membrane transistor. It uses characters that phase transformation material can change reversibly under electricity effect to change channeling length of semiconductor membrane transistor so as to achieving storing long number in single memory cell. The membrane transistor can form spatial stereoscopic structure to increase density and do not need to occupy area of silicon substrate. Such, this invention can increase storing density greatly and solve the question of 1T1R structure phase transformation memorizer peripheral circuit occupying too large areas of silicon substrate.

Owner:FUDAN UNIV +1

Use and structure of bisazo benzene polymer as two-photon optical storage medium

InactiveCN101763868AIncrease concentrationWon't gatherRecord information storageRecord carrier materialsPolyvinyl alcoholBright spot

The invention relates to an erasable two-photon polarized multivariate, multistage and multilayer optical storage technology based on a bisazo benzene polymer. The prepared bisazo benzene polymer is used as the two-photon optical storage medium. Linearly polarized titanium: sapphire laser (wavelength: 800mm, pulse cycle: 80fs and repetition frequency: 80MHz) two photons are used to write data and a reflective confocal laser scanning microscopy is used to read the data. When the bisazo benzene polymer is used for two-photon storage, if light polarization direction is read that the light polarization direction is changed from the direction in parallel with writing light to the direction forming an angle of 45 degrees with the writing light and then to the direction perpendicular to the writing light, the data undergoes a change from 'dark spot' to 'disappearance' and then to 'bright spot'. Based on the characteristic, polarized multivariate and multistage optical storage can be realized. The written data is erasable. Data can be rewritten after being erased. A composite multilayer film which takes a bisazo benzene polymer layer as a storage layer and takes a polyvinyl alcohol (PVA) layer as a spacing layer is prepared, so multilayer storage can be realized on the basis of polarized multivariate and multistage optical storage. Thereby, a new way is provided for the realization of high-density optical storage.

Owner:UNIV OF SCI & TECH OF CHINA

Semiconductor memory with vertical structure and manufacturing method thereof

InactiveCN101901813AReduce areaAchieve High Density StorageSolid-state devicesSemiconductor/solid-state device manufacturingEngineeringVertical channel

The invention belongs to the technical field of semiconductor memories and in particular relates to a semiconductor memory with a vertical structure and a manufacturing method thereof. The memory provided by the invention is a vertical channel double-metal floating gate memory and comprises at least one substrate region, a drain region, a source region, two floating gate regions and a control grid, wherein the floating gate regions of the memory are used for storing electric charges. The invention also discloses a manufacturing method of the double-metal floating gate memory. The memory adopts a vertical channel structure and doest not occupy more chip area while increasing grid length so as to contribute to high-integration development of the chip; and a double-bit storage unit with small area is manufactured by the simplified method, so that more storage units can be manufactured on the silicon substrate with the same area and high-density storage can be realized.

Owner:FUDAN UNIV

Gating tube material, gating tube unit and memory device structure

ActiveCN111384238ALarge turn-on currentReduce leakage currentElectrical apparatusHeat stabilityEngineering

The invention provides a gating tube material, a gating tube unit and a memory device structure. The gating tube material is a compound at least comprising Ge and S, the chemical general formula of the gating tube material is (GexS<1-x>)<1-y>My, M comprises a doped material, x is greater than or equal to 0.1 and less than or equal to 0.9, and y is greater than or equal to 0 and less than or equalto 0.5. The gating tube is made of a GexS<1-x> material, and the material has the advantages of large turn-on current, small leakage current, good thermal stability, simple material, no toxicity and the like when being used for a gating tube unit. According to the gating tube material, the doped material is doped into the GexS<1-x> material, so that the threshold voltage, the turn-on current, thefatigue characteristic and other properties of the gating tube unit made of the gating material can be adjusted and optimized. The thermal stability of the gating tube unit made of the gating materialcan be improved, the leakage current of the gating tube unit made of the gating material is reduced, and the repeatability of the gating tube unit made of the gating tube material is enhanced.

Owner:SHANGHAI INST OF MICROSYSTEM & INFORMATION TECH CHINESE ACAD OF SCI

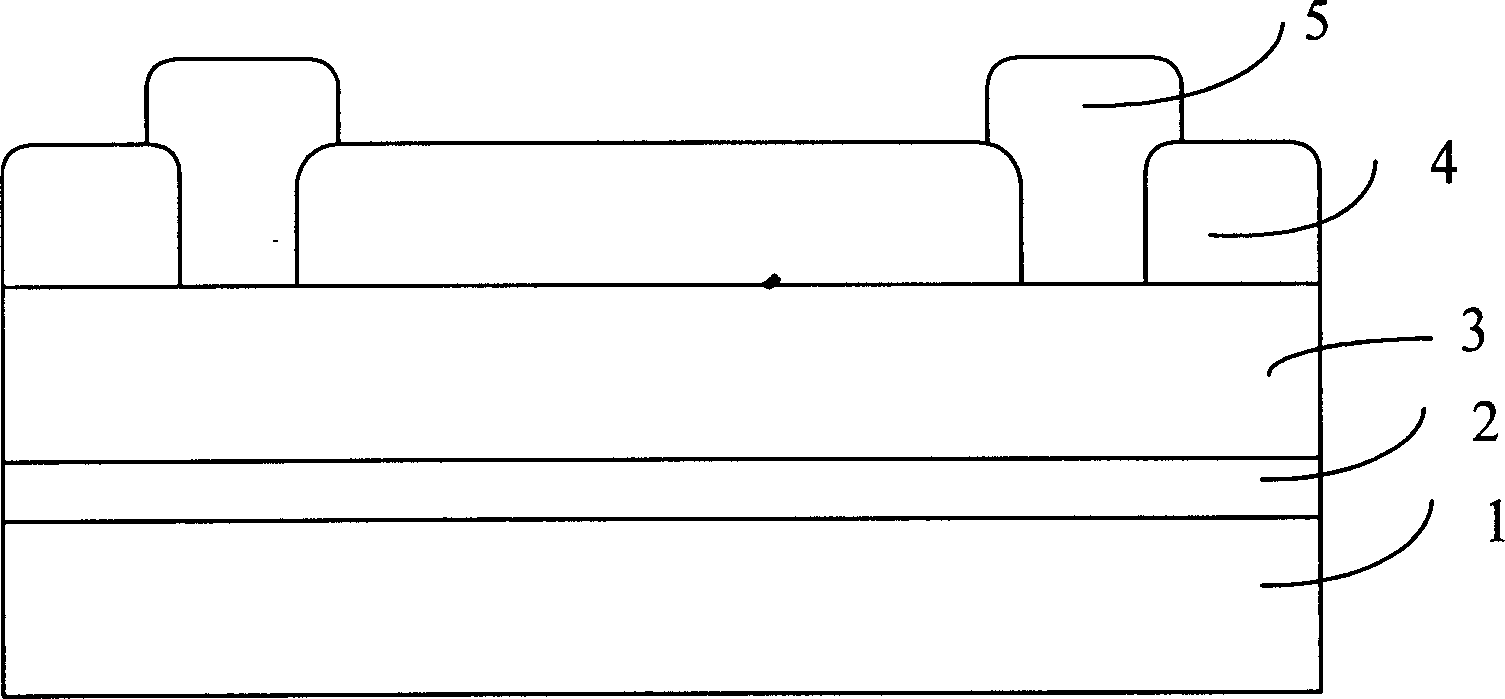

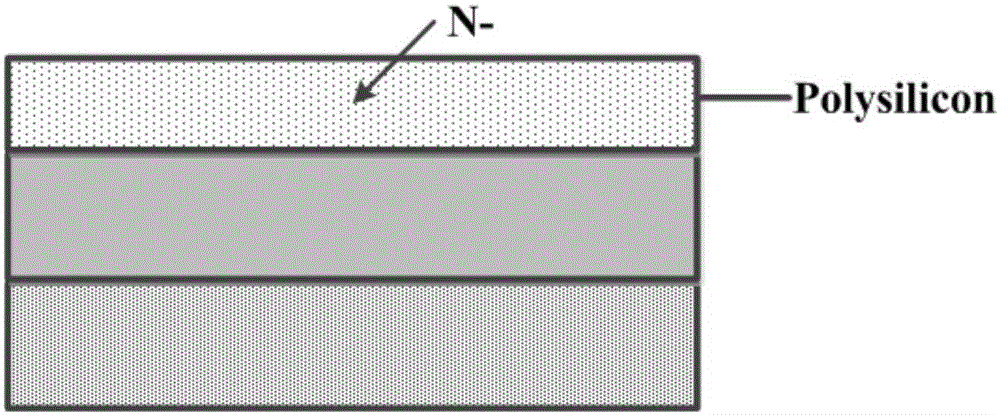

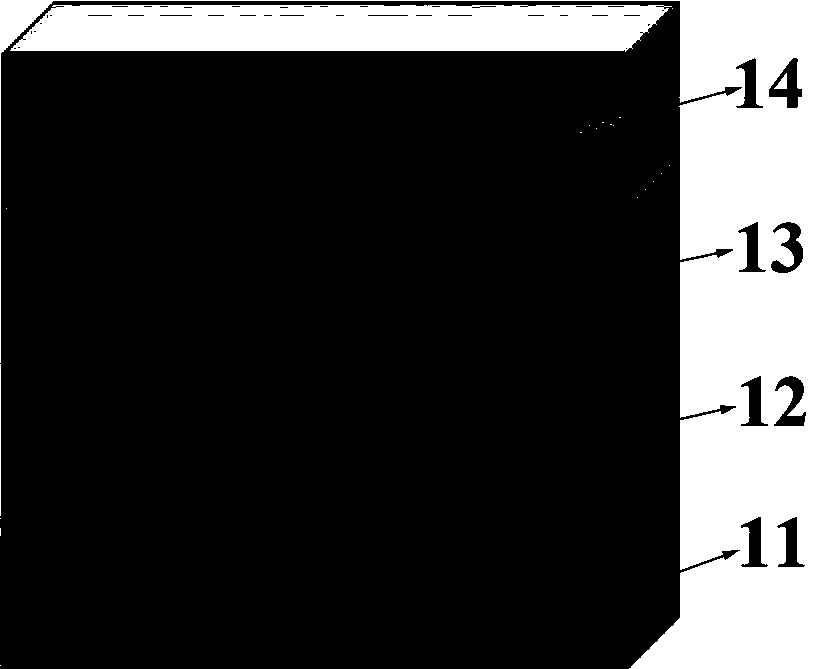

Polysilicon floating gate memorizer based on organic field effect transistor and preparation method therefor.

InactiveCN105006488AReduce manufacturing costAchieve High Density StorageTransistorSolid-state devicesOrganic field-effect transistorOrganic semiconductor

The invention discloses a polysilicon floating gate memorizer based on an organic field effect transistor and a preparation method therefor. A gate electrode employs a heavy-doping low-resistance monocrystalline silicon substrate with a thickness of 100-300nm; a gate insulation dielectric layer is formed on the surface of the silicon substrate of the gate electrode; a polysilicon floating gate is embedded between the gate insulation dielectric layer and a tunneling insulation dielectric layer and employed as a charge storage unit; the tunneling insulation dielectric layer is formed on the surface of the floating gate; an organic semiconductor material is grown on the surface of the tunneling insulation dielectric layer and forms an active layer of a device; vacuum vapor plating of metal through metal masks is carried out on the surface of the active layer, and a source electrode and a drain electrode of the device are formed. The beneficial effects are that a work voltage of a floating gate memorizer based on an organic field effect transistor is decreased, high-density storage of a device is achieved, the device maintaining performance is raised, and the device manufacturing cost is lowered.

Owner:LANZHOU UNIVERSITY

LED panel pixel correction method and apparatus

InactiveCN105491363ASolve the problem that pixel correction cannot be performed on large-size and high-density LED panelsSolve the problem of pixel correctionColor signal processing circuitsBrightness and chrominance signal processing circuitsHigh densityData set

The invention discloses an LED panel pixel correction method and apparatus. The method comprises the following steps: receiving single-frame video data, wherein the single-frame video data is one frame of data in a video to be corrected; storing the single-frame video data to a dynamic memory; reading a correction data set and the single-frame video data from the dynamic memory, wherein the dynamic memory stores the correction data set in advance, and the correction data set comprises multiple correction arrays correcting multiple pixel points on an LED panel; and correcting the single-frame video data according to the correction data set. Through the LED panel pixel correction method and apparatus, the problem of incapability of performing pixel correction on a large-size high-density LED panel in related arts is solved.

Owner:LEYARD

Memory and writing method and reading method thereof

InactiveCN110660428AAchieve High Density StorageSolve the problem of difficult to achieve high-density storageDigital storageBit lineHigh density

The invention provides a memory and a writing method and a reading method thereof. The memory comprises a plurality of memory units, each storage unit comprises an MOS tube, N MTJs connected in series, a bit line, a word line and a source line. The N MTJs are arranged on the surface of the MOS tube and are sequentially arranged in an overlapped mode in the direction away from the MOS tube. In theN MTJs, the MTJ with the smallest distance from the MOS tube is a bottom end MTJ; wherein the MTJ with the largest distance from the MOS tube is the top end MTJ, one end of the bottom end MTJ is electrically connected with one of the source electrode and the drain electrode of the MOS tube, the source line is electrically connected with the other one of the source electrode and the drain electrode, one end of the top end MTJ is electrically connected with the bit line, the grid electrode of the MOS tube is electrically connected with the word line, N >=2 and N is an integer. The storage unit of the memory can store more information under the same area, and high-density storage can be realized.

Owner:CETHIK GRP

Ferromagnetic random access memory, writing method thereof, reading method thereof and preparation method thereof

ActiveCN107946461AIncrease the on-off ratioIncrease storage windowElectrical apparatusElectrical resistance and conductanceStatic random-access memory

The invention discloses a ferromagnetic random access memory, a writing method thereof, a reading method thereof and a preparation method thereof. The iron resistance variable memory includes a substrate layer, a bottom electrode, a switch layer and a top electrode which are successively stacked. The switch layer includes a ferroelectric layer and at least one semiconductor layer disposed adjacentto the ferroelectric layer. The ferroelectric layer is polarized under the effect of an electric field and is configured to change the potential barrier of the switch layer. By adding at least one semiconductor layer to the switch layer and disposing the semiconductor layer adjacent to the ferroelectric layer, a variable barrier layer is provided so as to increase the resistance ratio of the highand low resistance states of the switch layer under the effect of the electric field, that is, the storage window of the ferromagnetic random access memory is increased. Thus, the high-density storage of the ferromagnetic random access memory is realized, and the small storage window of the ferromagnetic random access memory is solved.

Owner:SOUTH UNIVERSITY OF SCIENCE AND TECHNOLOGY OF CHINA

Polysilicon floating gate memory based on organic field effect transistor and its preparation method

InactiveCN105006488BReduce manufacturing costAchieve High Density StorageTransistorSolid-state devicesHigh densityOrganic field-effect transistor

The invention discloses a polysilicon floating gate memory based on an organic field effect transistor and a preparation method thereof. The gate electrode adopts a heavily doped low-resistance single crystal silicon substrate with a thickness of 100-300nm; the gate insulation formed on the surface of the gate electrode silicon substrate dielectric layer; a polysilicon floating gate embedded between the gate insulating dielectric layer and the tunneling insulating dielectric layer as a charge storage unit; a tunneling insulating dielectric layer formed on the surface of the floating gate; growing an organic semiconductor on the surface of the tunneling insulating dielectric layer material to form the active layer of the device; on the surface of the active layer, metal is vacuum-evaporated through a metal mask to form the source and drain of the device. The beneficial effect of the invention is to reduce the working voltage of the floating gate memory based on the organic field effect transistor, realize high-density storage of the device, improve the retention characteristic of the device, and reduce the manufacturing cost of the device.

Owner:LANZHOU UNIVERSITY

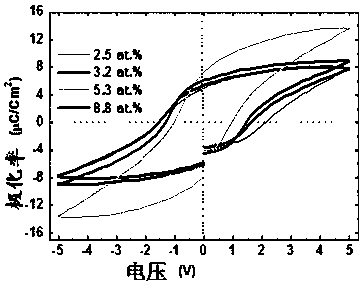

A Multi-valued Storage Unit Based on Co-control of Conductive Filament and Polarization

The invention relates to a multi-valued storage unit based on the co-control of conductive filaments and polarization. The multi-valued storage unit based on the co-control of conductive filaments and polarization consists of a bottom electrode, a ferroelectric functional layer, a semiconductor Functional layer and top electrode; the multi-value storage unit realizes the characteristics of multi-value storage through the migration of the top electrode metal atoms in the semiconductor functional layer, and the polarization reversal and oxygen vacancy concentration change of the ferroelectric functional layer, which can realize non- Destructive reading and high storage density, in addition to simple operation, low operating voltage, and compatible with Si process, can realize low voltage writing and reading, overcome the ferroelectric tunnel junction in the past using probes to write and read multiple values Storage, the use of expensive substrates, expensive electrode materials, and the limitations of incompatibility with Si technology, and the realization of multi-value storage, is conducive to the realization of industrialization.

Owner:XIANGTAN UNIV

Semiconductor memory with vertical structure and manufacturing method thereof

InactiveCN101901813BReduce areaAchieve High Density StorageSolid-state devicesSemiconductor/solid-state device manufacturingEngineeringVertical channel

The invention belongs to the technical field of semiconductor memories and in particular relates to a semiconductor memory with a vertical structure and a manufacturing method thereof. The memory provided by the invention is a vertical channel double-metal floating gate memory and comprises at least one substrate region, a drain region, a source region, two floating gate regions and a control grid, wherein the floating gate regions of the memory are used for storing electric charges. The invention also discloses a manufacturing method of the double-metal floating gate memory. The memory adopts a vertical channel structure and doest not occupy more chip area while increasing grid length so as to contribute to high-integration development of the chip; and a double-bit storage unit with small area is manufactured by the simplified method, so that more storage units can be manufactured on the silicon substrate with the same area and high-density storage can be realized.

Owner:FUDAN UNIV

Semi-floating gate memory, its manufacturing method and half-floating gate memory array

ActiveCN104637945BReduce areaIncrease gate lengthSolid-state devicesSemiconductor devicesBit lineHigh density

The invention discloses a semi-floating gate memory, which comprises at least one U-shaped groove formed in a semiconductor substrate, one buried source region formed in the semiconductor substrate at the bottom of the U-shaped groove, and two buried source regions formed in the semiconductor substrate at the bottom of the U-shaped groove. Drain regions respectively formed in the semiconductor substrate on both sides of the U-shaped groove, a control gate and two floating gates for storing charges formed in the U-shaped groove, the control gate and any one of the floating gates formed in the U-shaped groove The combination of the drain region selects one floating gate, and two gate-controlled pn junction diodes respectively formed in the semiconductor substrate on both sides of the U-shaped groove and connected to the drain region and the floating gate. A half-floating gate memory array, in which the angle between the bit line and the corresponding active area is less than 80 degrees, more half-floating gate memories can be manufactured in the same semiconductor substrate size, and high-density storage can be realized. The invention adopts a self-alignment process to manufacture the half-floating gate memory and the half-floating gate memory array, and the process is simple and easy to control.

Owner:SUZHOU ORIENTAL SEMICONDUCTOR CO LTD

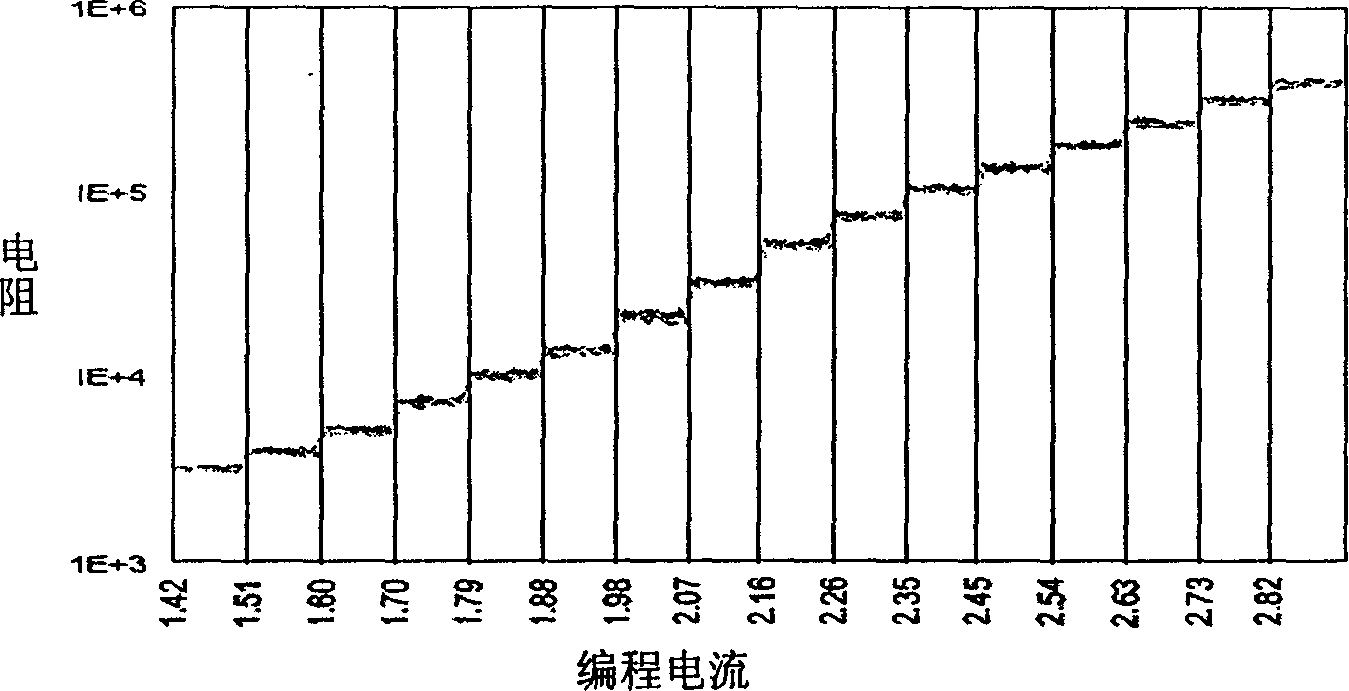

Multi-level storage reading and writing method and system for phase change memory

ActiveCN110335636BAchieve High Density StorageReduce the impact of resistance driftRead-only memoriesHigh densityResistance drift

The invention provides a multistage storage read-write method and system for a phase change memory, and the system comprises a data storage module which comprises a plurality of data units for storingdata; a reference module which comprises a plurality of reference units, wherein 2k-1 reference unit corresponds to one data unit and are used for storing a reference signal corresponding to the stored data, and k is a stored data bit; and a reading function module which reads the reference signal corresponding to a certain data unit when reading the data unit, and restores the data stored in thedata unit. According to the invention, a 2T2R structure is used as a basic unit for data storage, the influence caused by resistance drift is reduced to a certain extent through the combination of different resistances of the two phase change storage elements, and high-density storage is realized; an error detection and correction function is set, and the reliability of multi-value storage of thephase change memory is improved through error detection and correction; a reference unit is arranged, the stored data is calculated and restored through the reference unit, and high-reliability reading is achieved; meanwhile, the difficulty of error detection and correction is reduced, and the reliability is further improved.

Owner:SHANGHAI INST OF MICROSYSTEM & INFORMATION TECH CHINESE ACAD OF SCI

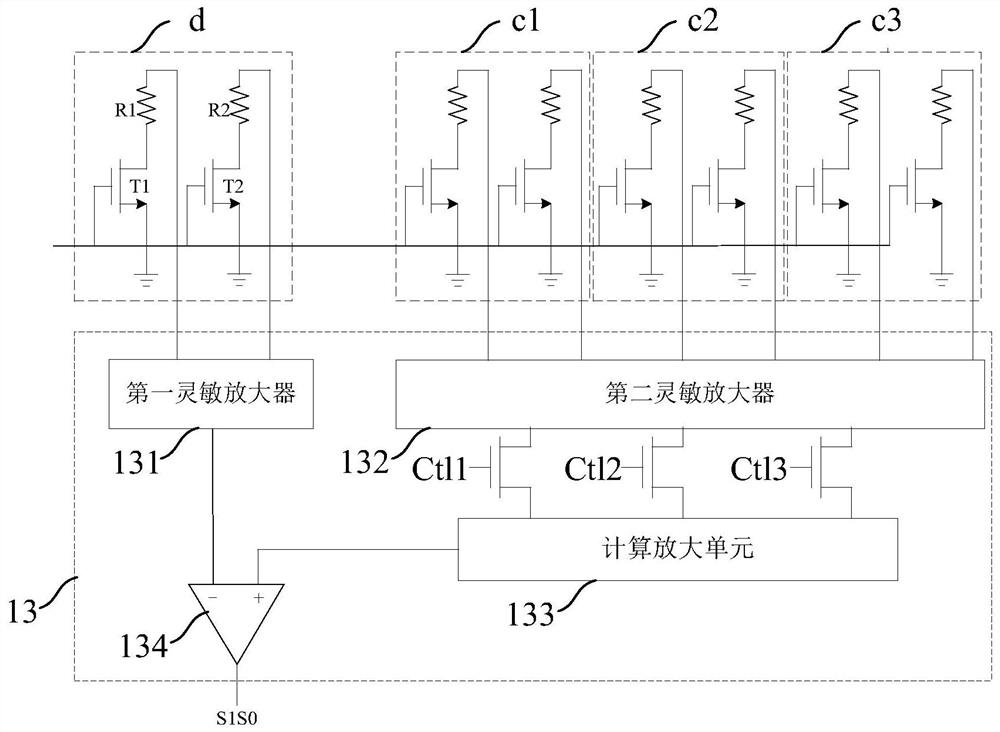

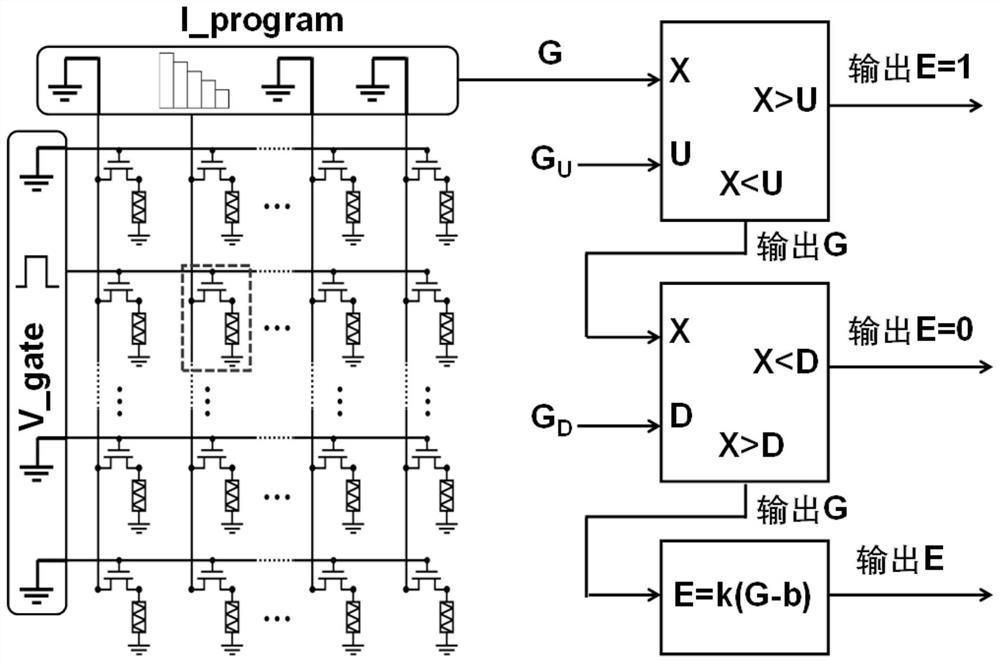

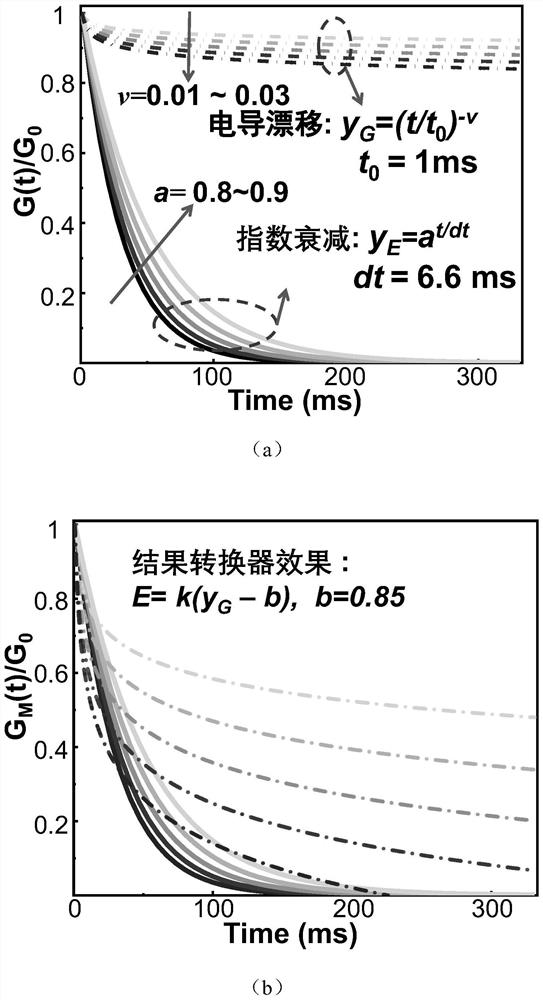

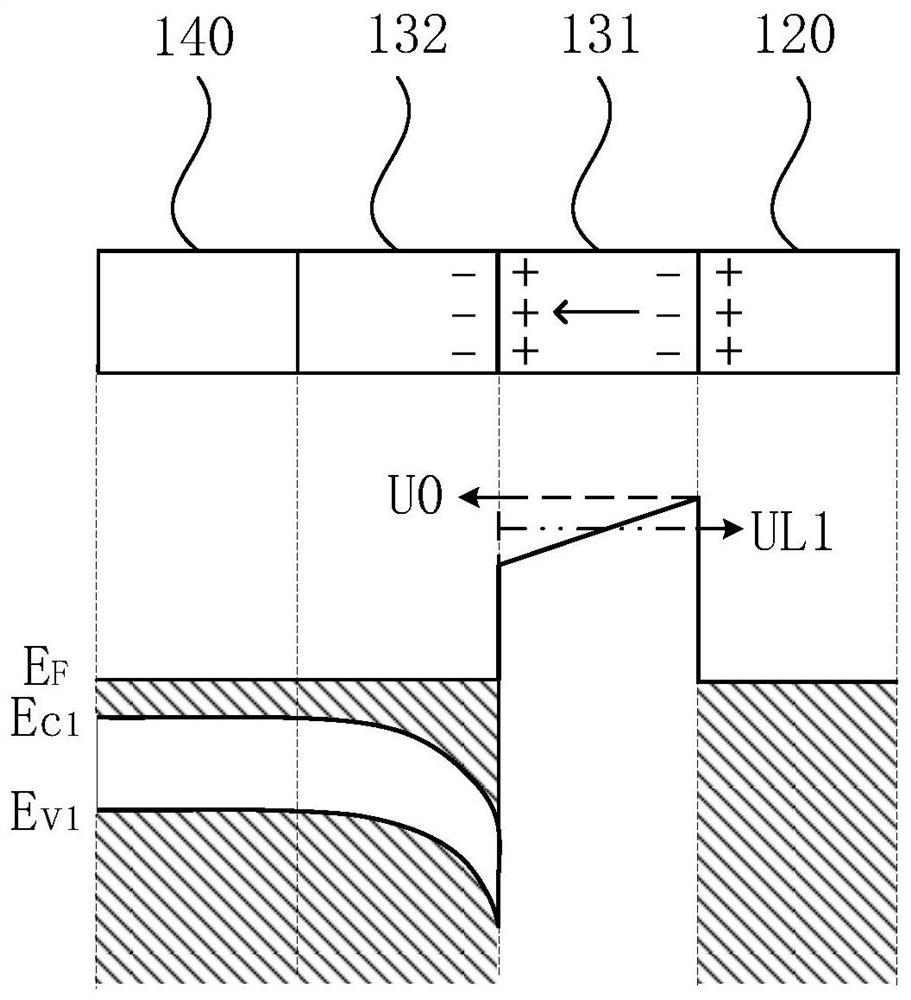

Qualification trace calculator based on phase change memory

PendingCN113867639AAdjust decay speedReduce in quantityInput/output to record carriersNeural learning methodsConvertersPhase-change memory

The invention discloses a qualification trace calculator based on a phase change memory. The qualification trace calculator comprises a phase change memory array and a result converter. The multi-valued characteristic of the phase change memory is utilized, qualification trace data is stored in the memory units in a conductive mode, and compared with a traditional binary storage mode, the number of the memory units can be effectively reduced, and high-density storage is achieved; attenuation operation along with time is spontaneously realized by utilizing the conductance drift effect of the phase change memory, other operational circuits are not needed, and the hardware overhead of operation is effectively reduced; and storage and attenuation operation of qualification trace data are carried out in the phase change memory, so that huge energy consumption caused by frequent data carrying is avoided. In addition, by adjusting parameters in the result converter, the attenuation speed of the qualification trace can be flexibly adjusted, so that the method is suitable for reinforcement learning tasks with different requirements. The limitation of a storage wall in a traditional calculation architecture can be broken through, and further development of reinforcement learning is promoted.

Owner:PEKING UNIV

A ferro-resistance variable memory and its writing method, reading method and preparation method

ActiveCN107946461BIncrease the on-off ratioIncrease storage windowElectrical apparatusElectrical resistance and conductanceHigh density

The invention discloses a ferro-resistance variable memory, a writing method, a reading method and a preparation method thereof. The ferroelectric RRAM includes a substrate layer, a bottom electrode, a switch layer and a top electrode stacked in sequence; the switch layer includes a ferroelectric layer and at least one semiconductor layer adjacent to the ferroelectric layer; the iron The electric layer is polarized under the application of an electric field for changing the potential barrier of the switch layer. In the present invention, at least one semiconductor layer is added to the switch layer, and the semiconductor layer is adjacent to the ferroelectric layer, which is equivalent to adding a variable barrier layer, which increases the resistance ratio of the high and low resistance states of the switch layer under the action of an electric field , that is, the storage window of the ferro-resistive variable memory is increased, and the high-density storage of the ferro-resistive variable memory is realized, and the problem of a small storage window of the ferro-resistive variable memory is solved.

Owner:SOUTH UNIVERSITY OF SCIENCE AND TECHNOLOGY OF CHINA

Cabinet Modular High Speed Optical Disk Library

ActiveCN104616684BImprove storage densityImprove space utilizationRecord information storageRecord carrier contruction detailsPush and pullModularity

The invention discloses a modularized high-speed optical disc juke-box for an equipment cabinet. The modularized high-speed optical disc juke-box comprises an equipment cabinet, a server module, a mechanical hand component and a pushing-pulling framework, wherein a disc bin array is arranged along one side wall of the equipment cabinet; the disc bin array comprises a plurality of stacked disc bins, and optical disc sheet boxes are arranged in the stacked disc bins; the server module is arranged above the disc bin array in the equipment cabinet, and comprises a server and an optical disc driver set connected with the server through a data line; the mechanical hand component which is arranged towards the side opening of the disc bin array is arranged in the equipment cabinet; the mechanical hand component is used for getting out a target optical disc in the selected disc bin; the pushing-pulling framework is corresponding to the disc bin array and used for pushing and pulling one or more disc bins in the disc bin array. The modularized high-speed optical disc juke-box for the equipment cabinet disclosed by the invention adopts a modularized design and mutually independent components, and is convenient to maintain; the disc bin array, the server module and the opposite mechanical hand component are stacked, so that the optical disc storage density and the integral space utilization rate of the optical disc juke-box can be increased.

Owner:SUZHOU NETZON INFORMATION STORAGE TECH

a vo-based x phase change memory cell

ActiveCN106992251BAchieve High Density StorageSimple preparation processElectrical apparatusDigital storagePhase-change memoryLow voltage

The invention discloses a VO based x The phase-change memory cell of the gating tube, including the lower electrode layer, VO x Gate layer, phase change function layer and upper electrode layer. The present invention adopts VO x To realize the gating of the phase change functional layer, data storage can be realized on the basis of the gating of the phase change functional layer. by giving to VO x Applying a voltage to control its state switching can achieve the purpose of the phase-change memory cell being in a non-gated state when the voltage is low and being in a gated state when the voltage is high. The present invention through VO x The switch control of the phase change memory can effectively reduce the leakage current of the phase change memory array and provide a sufficiently high Reset current; the invention does not require high temperature process conditions, simplifies the preparation process of the phase change memory, saves costs, and is a highly integrated phase change memory. The commercialization of memory provides the possibility.

Owner:HUAZHONG UNIV OF SCI & TECH

8-bit semiconductor storage unit, manufacturing method and storage unit array thereof

ActiveCN103094283BAchieve High Density StorageSolid-state devicesSemiconductor/solid-state device manufacturingBand shapeEngineering

Owner:SEMICON MFG INT (SHANGHAI) CORP

Gate material, gate unit and memory device structure

ActiveCN111384238BLarge turn-on currentReduce leakage currentElectrical apparatusPhysical chemistryHeat stability

The invention provides a gating tube material, a gating tube unit and a storage device structure, the gating tube material is a compound including at least Ge and S, and the general chemical formula of the gating tube material is (Ge x S 1‑x ) 1‑y m y , wherein M includes doping materials, and 0.1≤x≤0.9, 0≤y≤0.5. The gating tube material of the present invention selects Ge x S 1‑x material, when the material is used for the gating tube unit, it has the advantages of large opening current, small leakage current, good thermal stability, simple material and non-toxicity; the gating tube material of the present invention passes through Ge x S 1‑x The material is mixed with doping material, which can adjust and optimize the threshold voltage, turn-on current and fatigue characteristics of the gating tube unit made of the gating material; it can improve the thermal stability of the gating tube unit made of the gating material 1. Reduce the leakage current of the gate tube unit made of the gate material, and enhance the repeatability of the gate tube unit made of the gate material.

Owner:SHANGHAI INST OF MICROSYSTEM & INFORMATION TECH CHINESE ACAD OF SCI

Preparation method of novel ferroelectric topological domain storage unit

PendingCN111540742AImprove conductivityImprove performanceSolid-state devicesSemiconductor devicesEvaporation (deposition)Conductive atomic force microscopy

The invention discloses a preparation method of a novel ferroelectric topological domain storage unit. The preparation method comprises the following steps: S1, depositing a layer of BFO (BiFeO3) thinfilm on an STO (SrTiO3) single crystal substrate in a (001) direction by adopting a pulse laser deposition method; s2, deposting a gold plating layer on the surface of the BFO thin film through a thermal evaporation method, and preparing a ferroelectric material; s3, preparing a storage unit: scraping the surface of the gold plating layer in the S2 by adopting a conductive atomic force microscope(PFM) probe, scraping off a local gold plating layer to expose a BFO region, grounding gold at the periphery of the BFO region to serve as a gold electrode, and taking the center of the BFO region asa BFO electrode to prepare the storage unit; and S4, regulation and control of the storage unit: applying a point voltage to the BFO electrode to induce the BFO region to form a central convergence domain or a central divergence domain. Compared with the prior art, the topological domain which is convenient to regulate and control and high in stability is prepared, and high-density storage can beachieved.

Owner:SOUTH CHINA NORMAL UNIVERSITY

High density phase change memory and preparation method thereof

ActiveCN109686755BReduce power consumptionReduce contact areaSolid-state devicesSemiconductor/solid-state device manufacturingManufacturing cost reductionPhase-change memory

The invention discloses a high-density phase-change memory, comprising from bottom to top: a Schottky diode, a phase-change layer and an upper electrode, the Schottky diode comprising a semiconductor layer and a metal layer forming a Schottky potential barrier with the semiconductor layer , the metal layer serves as the lower electrode of the phase change layer at the same time; the semiconductor layer, the metal layer, the phase change layer and the upper electrode are a flat layer structure stacked from bottom to top, or, the semiconductor layer, the phase change layer and the upper electrode are self- Bottom-up planar structure, the metal layer is connected with a planar bottom surface and vertical sidewalls, the metal layer is stacked with the semiconductor layer below it through its bottom surface, and is connected to the phase change layer above it through its sidewalls , the phase change layer is stacked with the upper electrode. The invention can effectively improve the density of the phase change memory unit, reduce the number of photolithography, simplify the process and reduce the manufacturing cost. The invention also discloses a preparation method of the above-mentioned high-density phase change memory.

Owner:SHANGHAI INTEGRATED CIRCUIT RES & DEV CENT

A kind of zncuno/zncolio multiferroic magnetoelectric coupling homogeneous pn junction and its preparation method and application

ActiveCN104867987BGood lattice matchingImprove ferroelectric propertiesSemiconductor/solid-state device manufacturingSemiconductor devicesHigh densityMaterial synthesis

The invention belongs to the technical field of material synthesis, and particularly discloses a ZnCuNO / ZnCoLiO multiferroic magnetoelectric coupling homogeneous PN junction, a preparation method thereof and applications. The homogeneous PN junction comprises a ZnO buffer layer deposited on an n-Si (111) substrate base body, a p-type ZnCuNO ferromagnetic layer deposited on the ZnO buffer layer, an n-type ZnCoLiO ferroelectric layer deposited on the ZnCuNO ferromagnetic layer, a top electrode layer and a bottom electrode layer. The magnetoelectric coupling homogeneous PN junction has good lattice matching performance with Si, and has good ferroelectricity, a ferromagnetic property and a magnetoelectric coupling characteristic. The magnetoelectric coupling homogeneous PN junction has two degrees of freedom of electric charge and spinning, and control can be carried out on the two degrees of freedom through an external electric field and a magnetic field respectively, thereby being used for designing and developing a ternary or quaternary memory device, realizing high-density storage of information, and having great application prospects in the field of high-density memories.

Owner:LINGNAN NORMAL UNIV

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com