Achieving method for multi-valued phase changing storage device

A technology of phase-change memory and multi-value storage, which is applied in the field of microelectronics to achieve multi-plant storage, reduce the erasing and writing current, and solve the problem of large peripheral circuits

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

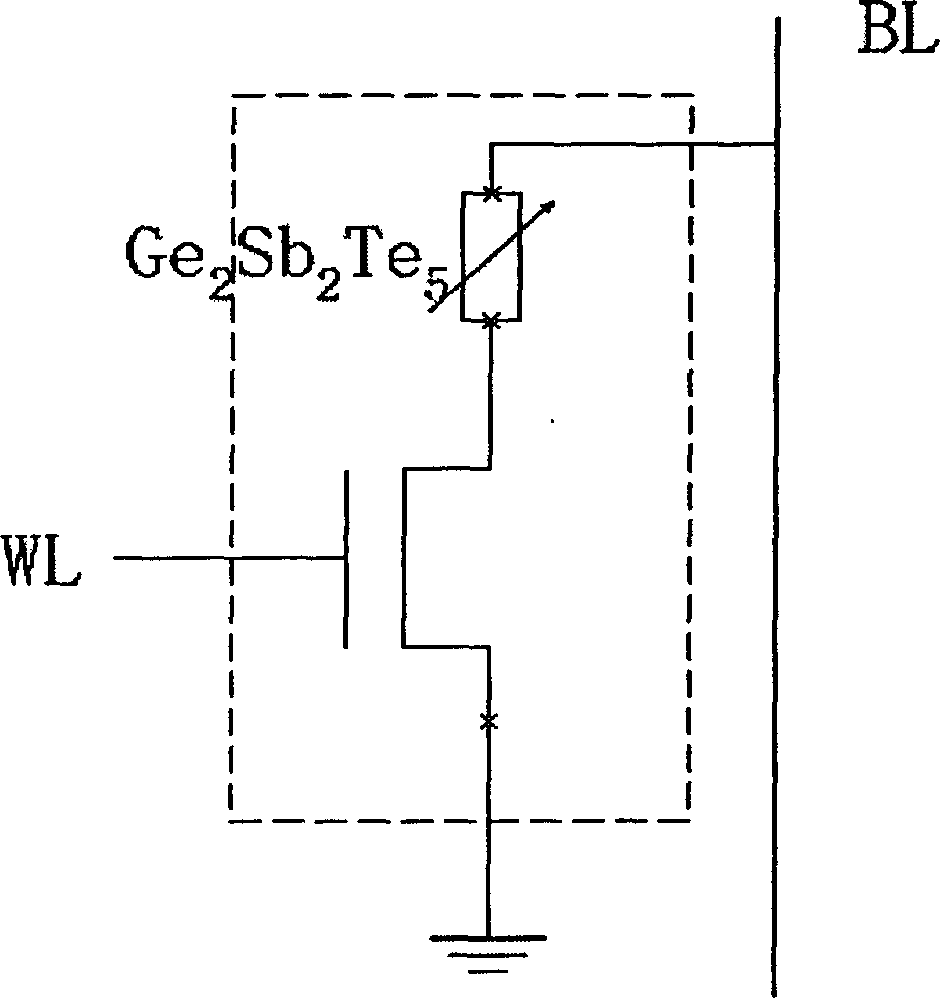

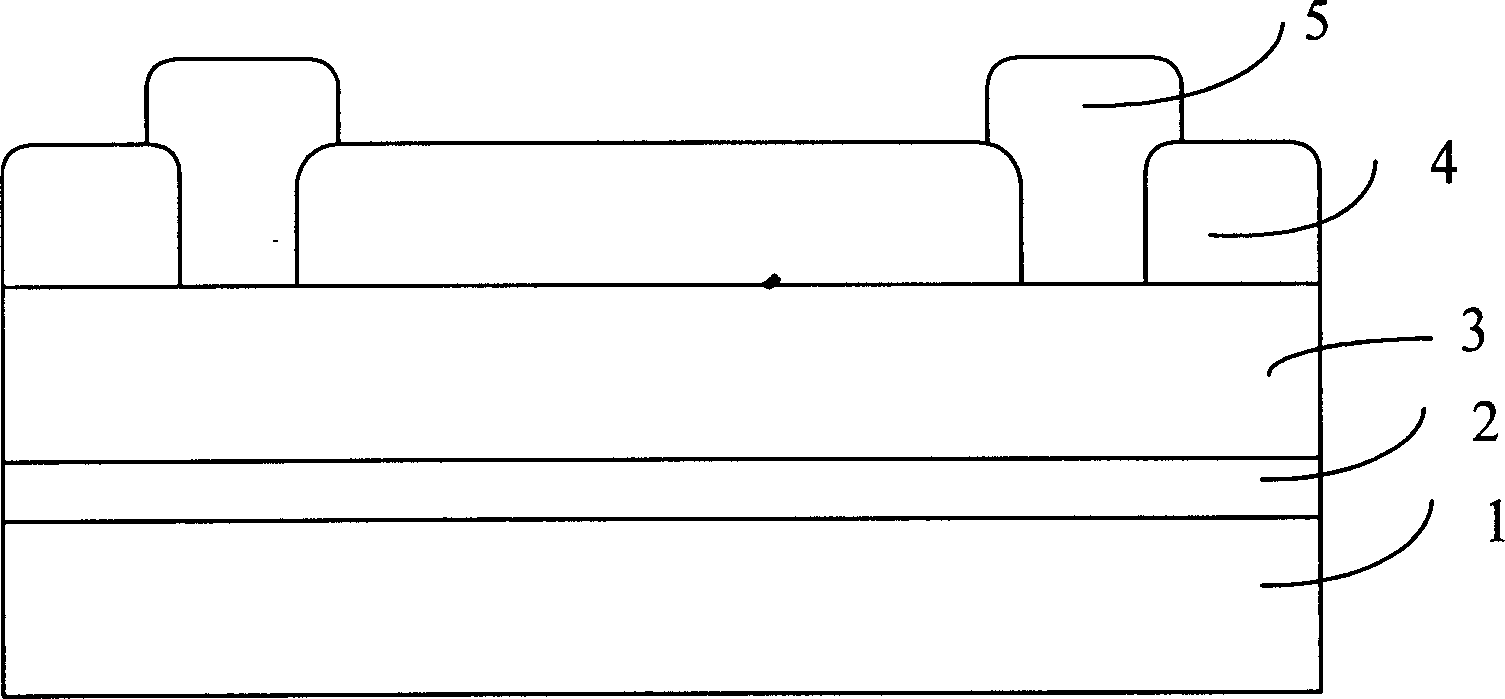

[0030] image 3 It is a structure of the present invention, wherein the gate electrode 1 is low-resistance n-type silicon, the high-resistance dielectric layer 2 is aluminum oxide (or silicon oxide, zirconium oxide, etc.), and 3 is amorphous Ge 2 Sb 2 Te 5 , The source and drain electrodes 5 are tungsten.

[0031] Figure 4 , 6 , 8 and 10 are the "read" operation process of the thin film transistor multi-value phase change memory. Figure 4 It is a schematic diagram of the “read” operation in the initial state of the thin film transistor: when a voltage higher than the threshold voltage is applied to the gate electrode 1, aluminum oxide and amorphous Ge 2 Sb 2 Te 5 The contact interface produces a carrier channel. Under the action of the source and drain electric fields, the carriers move in the channel to form a current. Obviously, the carrier channel length is the longest at this time, which is the distance between the two electrodes.

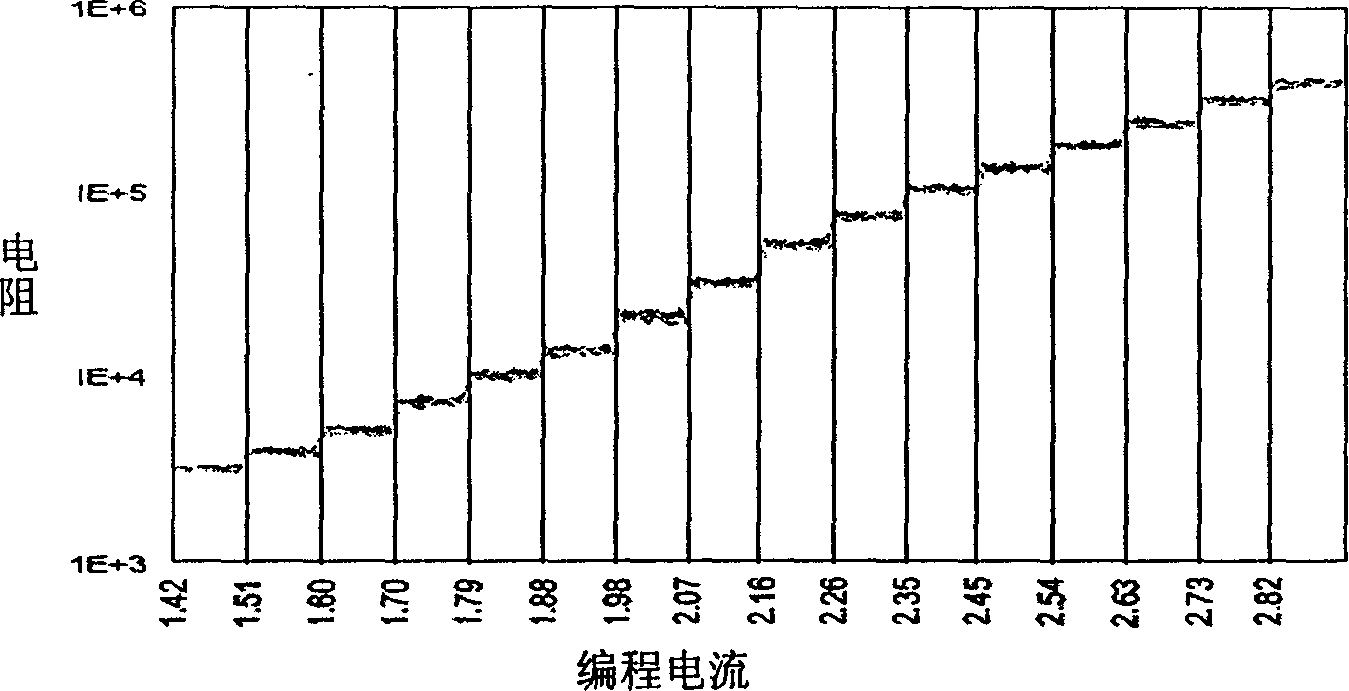

[0032] by Figure 5 , 7 And 9 write oper...

Embodiment 2

[0037] Figure 14 It is another specific implementation structure of the present invention. Among them, the gate electrode 1 is low-resistance n-type silicon, the high-resistance dielectric layer 2 is aluminum oxide (or silicon oxide, zirconium oxide, etc.), and 3 is amorphous Ge 2 Sb 2 Te 5 , The source and drain electrodes 5 are tungsten. When performing a "read" operation, a voltage higher than the threshold voltage is applied to the gate electrode 1. Aluminum oxide 2 and amorphous Ge 2 Sb 2 Te 5 A carrier channel is generated on the contact interface. Under the action of the source and drain electric field, the carrier moves in the channel to form a current, such as Figure 16 . When the “write” operation is performed, the source and drain tungsten electrodes 5 are grounded, and a programming voltage pulse is applied to the gate electrode 1. The aluminum oxide heats the Ge 2 Sb 2 Te 5 Crystallize or return it to an amorphous state to achieve non-volatile storage, seeFigure 15...

Embodiment 3

[0039] Figure 17 It is also a specific implementation structure of the present invention. Among them, the gate electrode 1 is low-resistance n-type silicon, the high-resistance dielectric layer 2 is aluminum oxide (or silicon oxide, zirconium oxide, etc.), and 3 is amorphous Ge 2 Sb 2 Te 5 , The source and drain electrodes 5 are tungsten, 7 is aluminum oxide (or silicon oxide, zirconium oxide, amorphous carbon, etc.), and 8 is a tungsten bottom electrode. When performing a "read" operation, a voltage higher than the threshold voltage is applied to the gate electrode 1. Aluminum oxide and amorphous Ge 2 Sb 2 Te 5 A carrier channel is generated on the contact interface. Under the action of the source and drain electric field, the carrier moves in the channel to form a current, such as Figure 19 . When the “write” operation is performed, the common electrode 8 is grounded, and a programming voltage pulse is applied to the source and drain electrodes 5, and the aluminum oxide 7 hea...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com