Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

69 results about "Source–measurement unit" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

The Source–measurement unit is a type of test equipment which, as the name indicates, is capable of both sourcing and measuring at the same time.

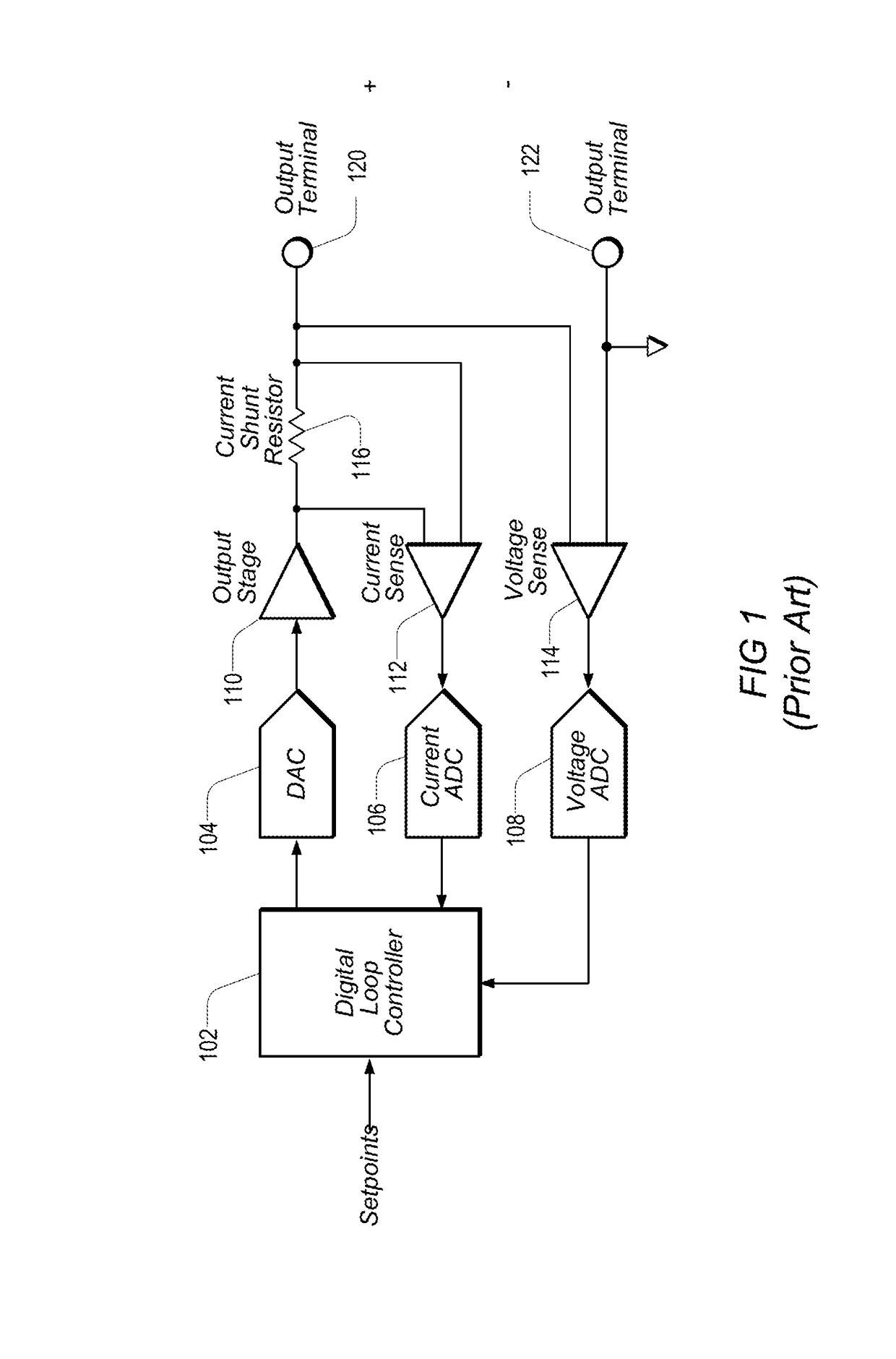

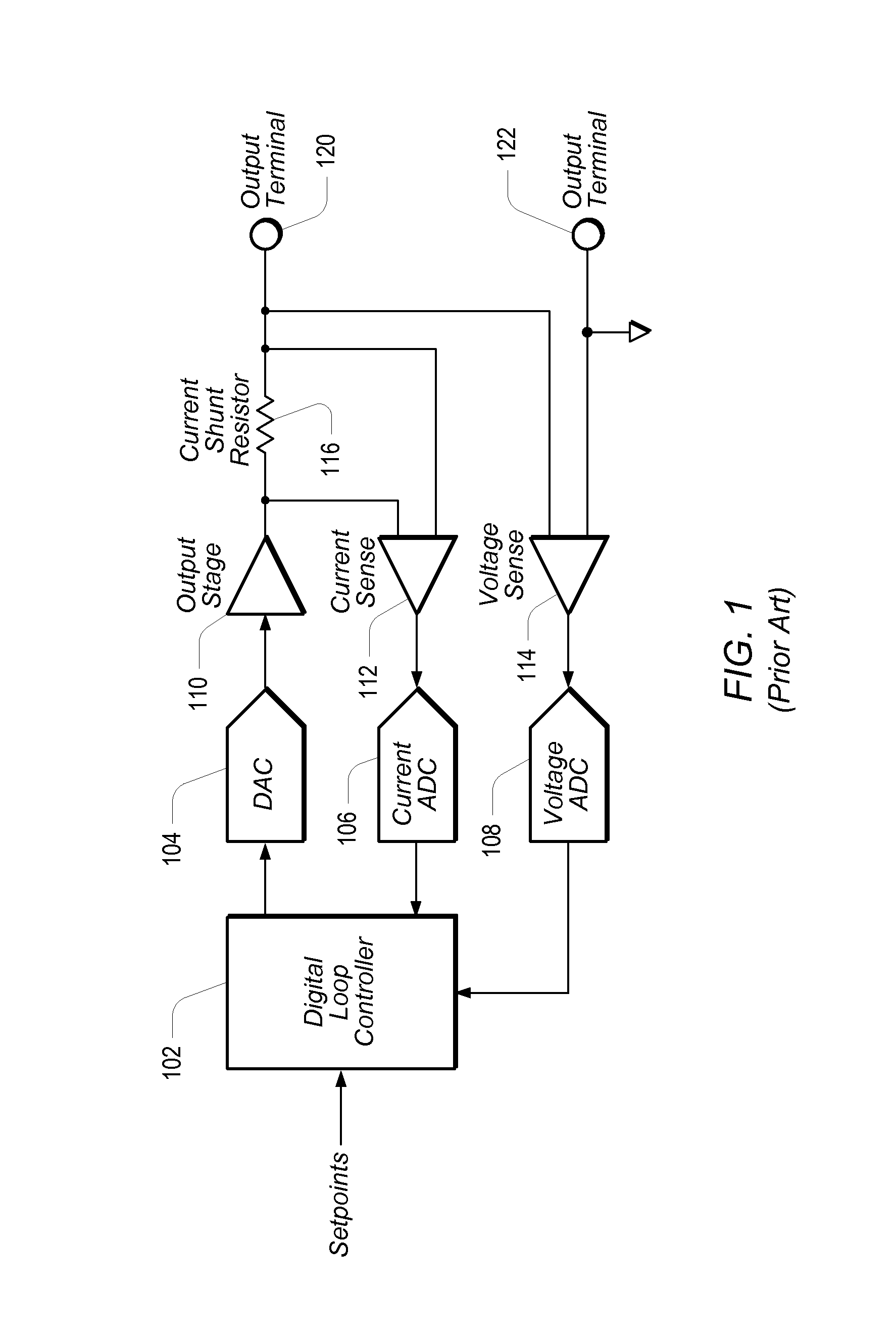

Source-Measure Unit Based on Digital Control Loop

ActiveUS20090121908A1Increase flexibilityConvenient and accurateElectric signal transmission systemsElectric devicesDigital signal processingMeasuring output

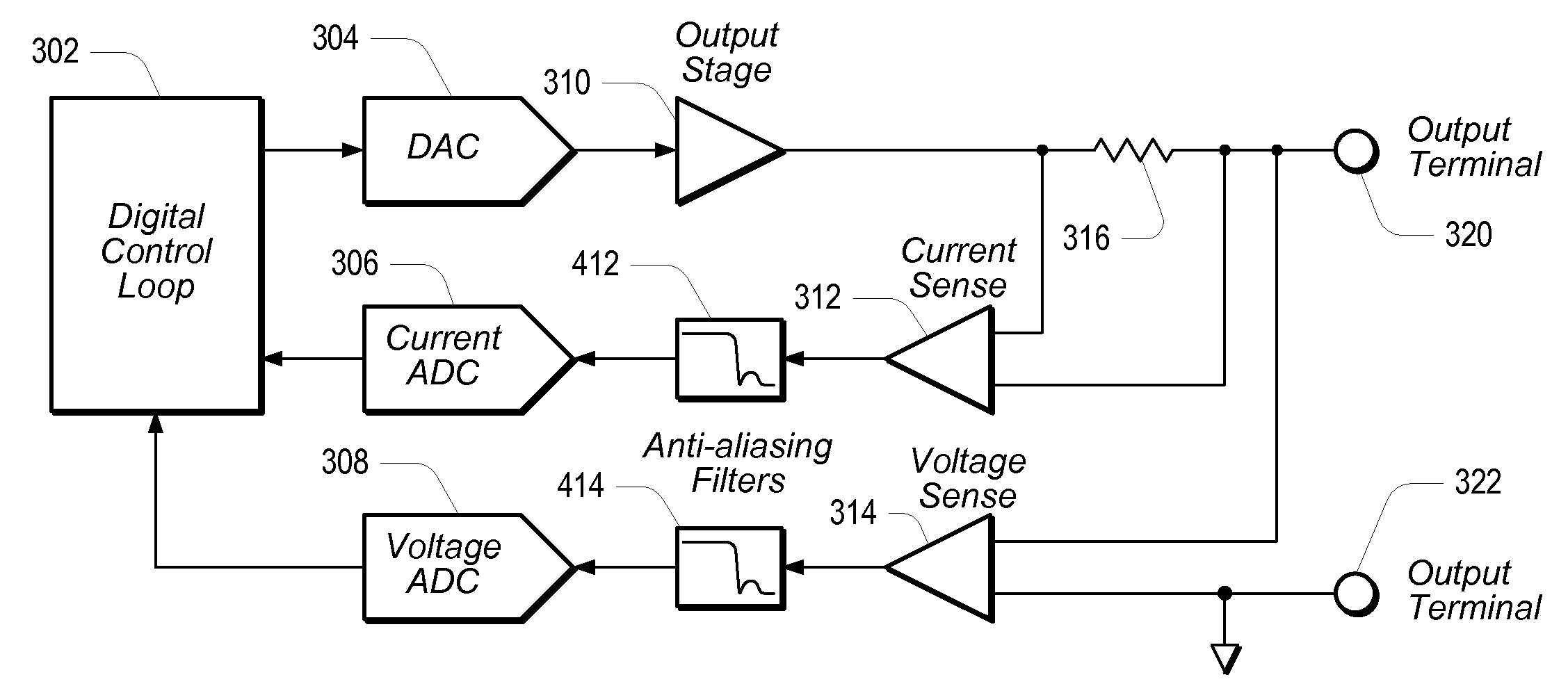

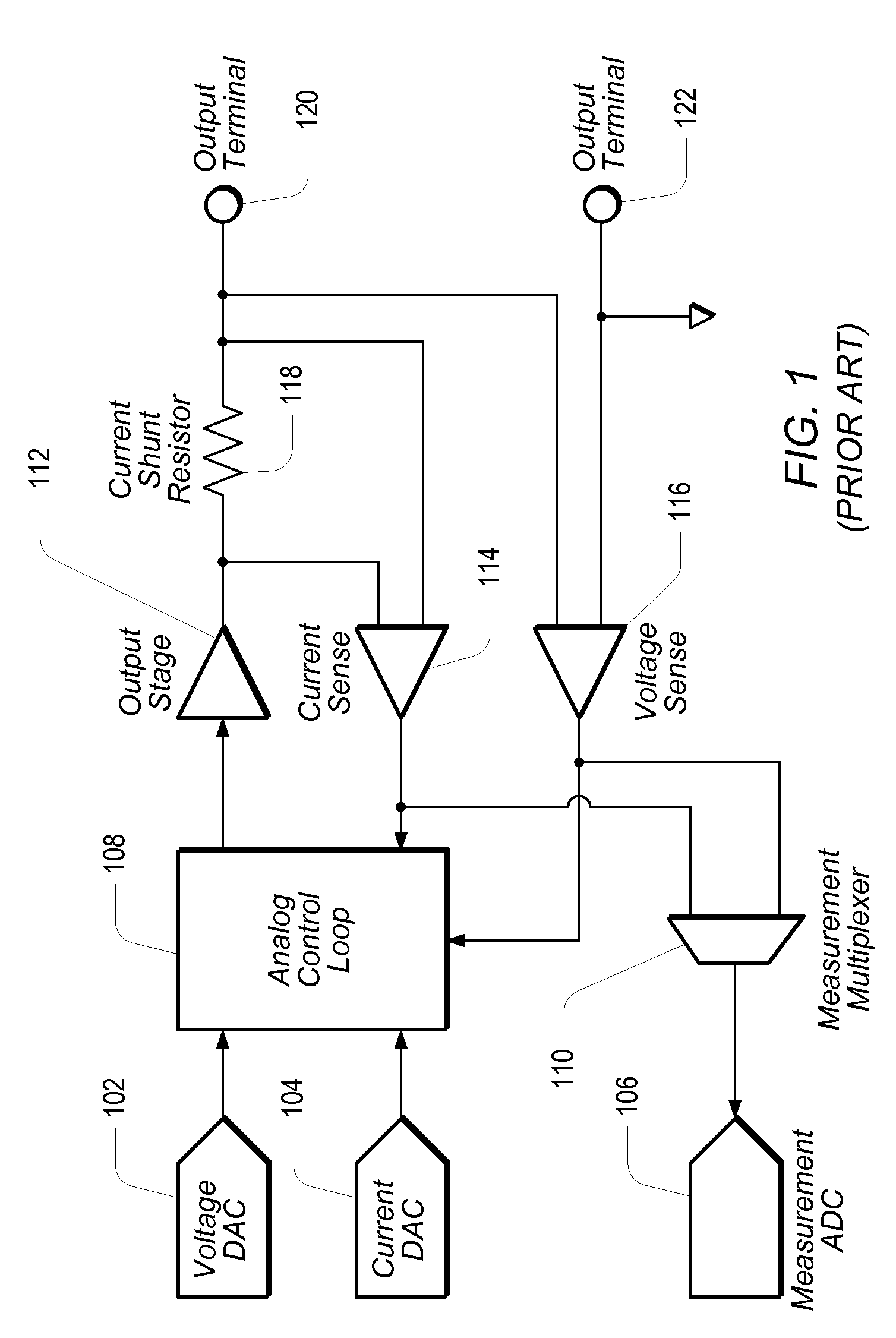

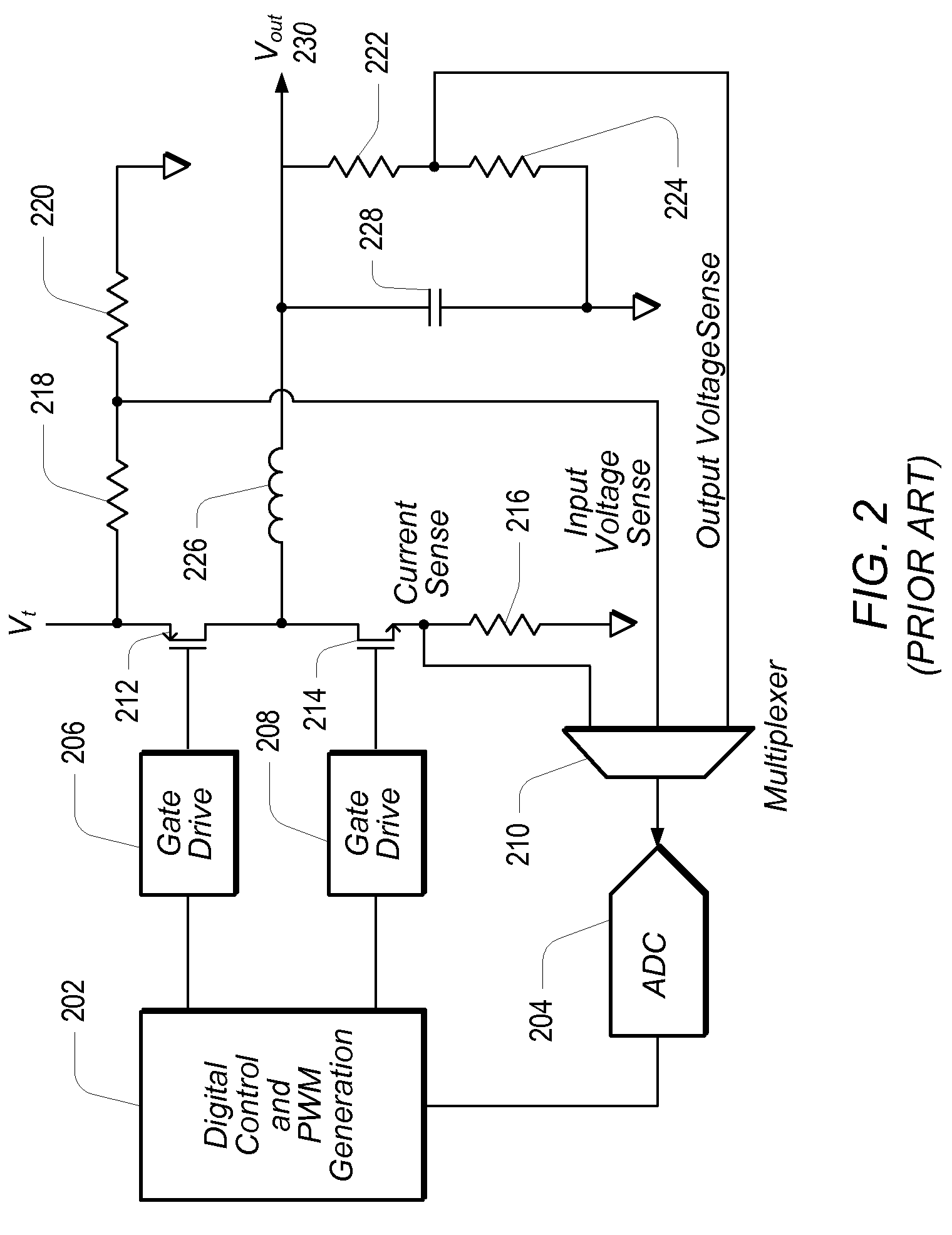

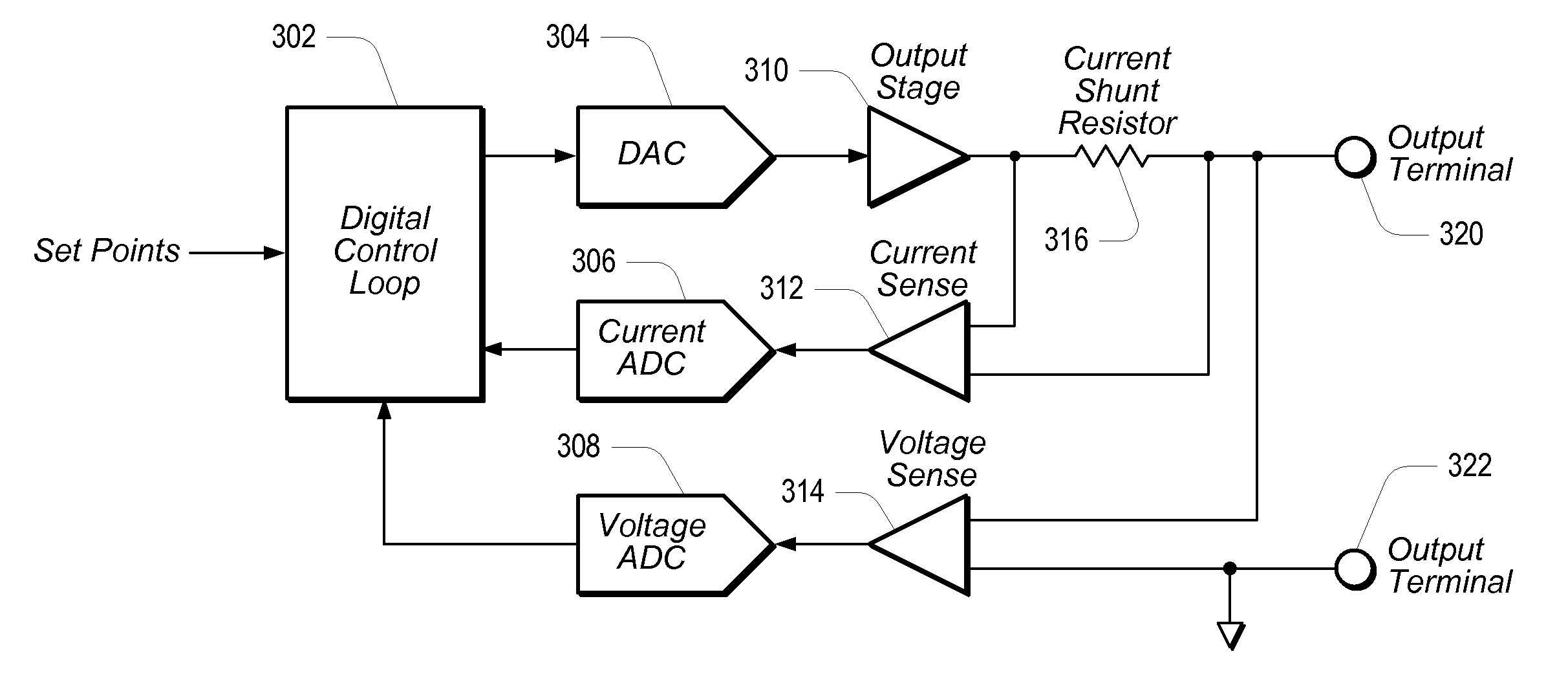

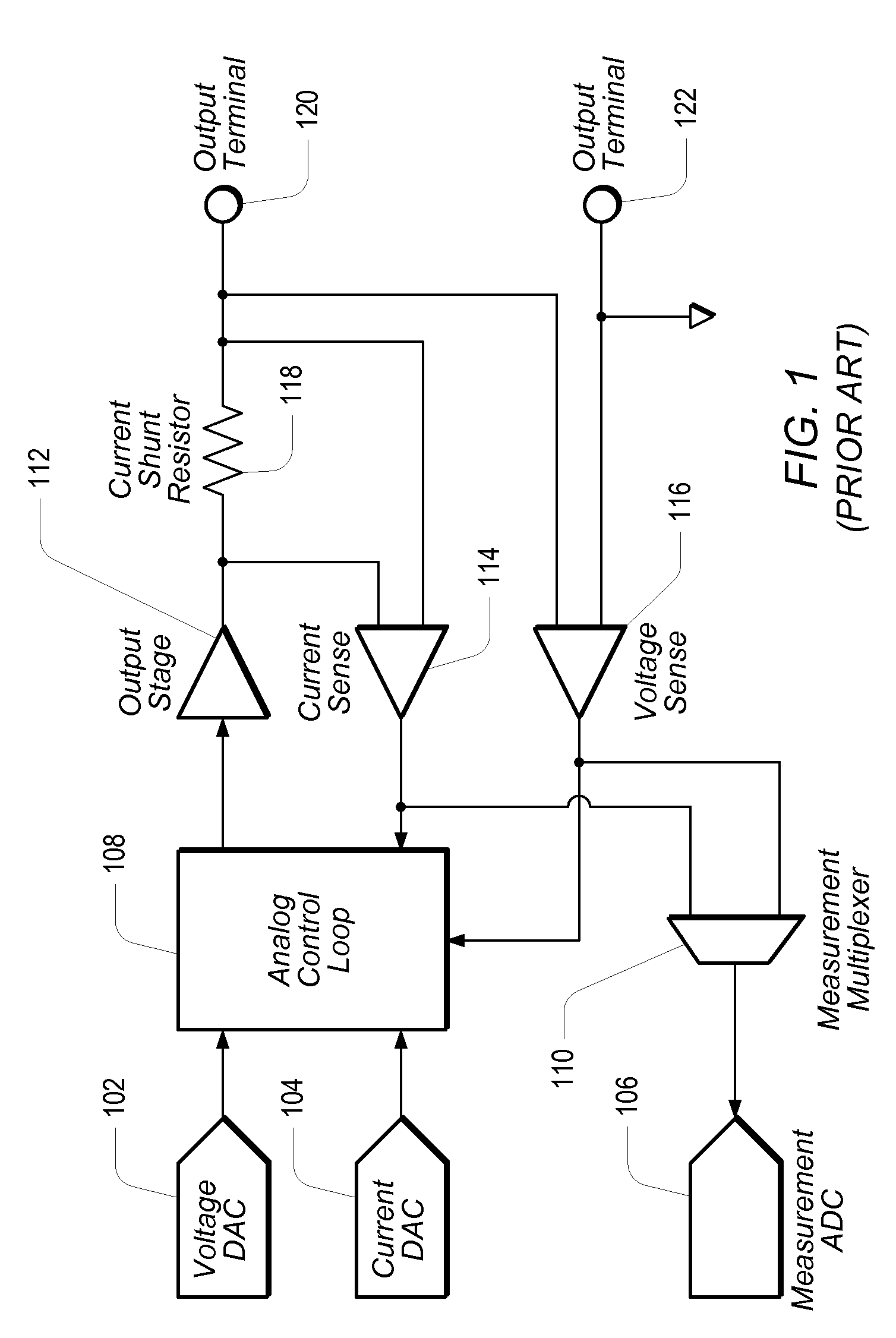

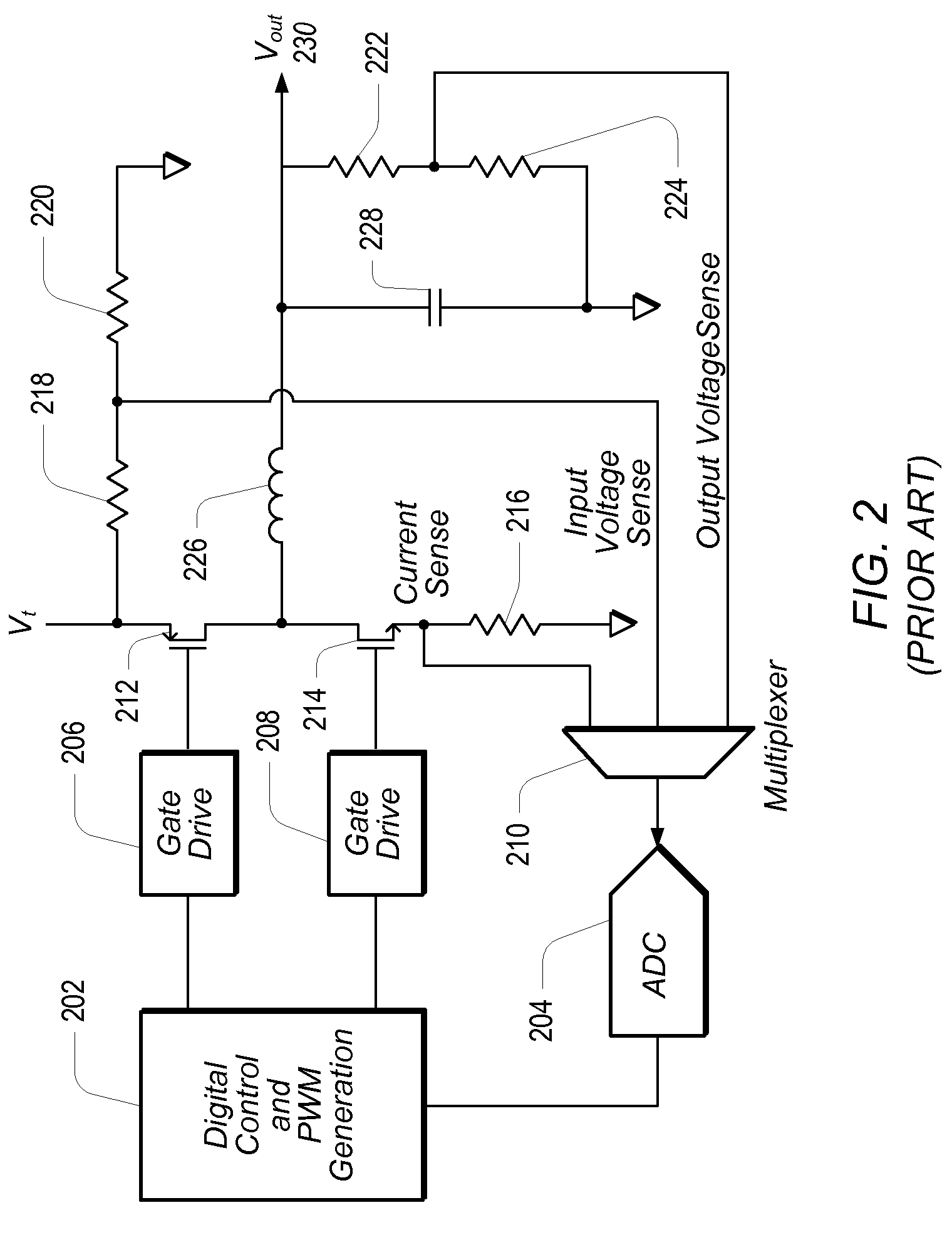

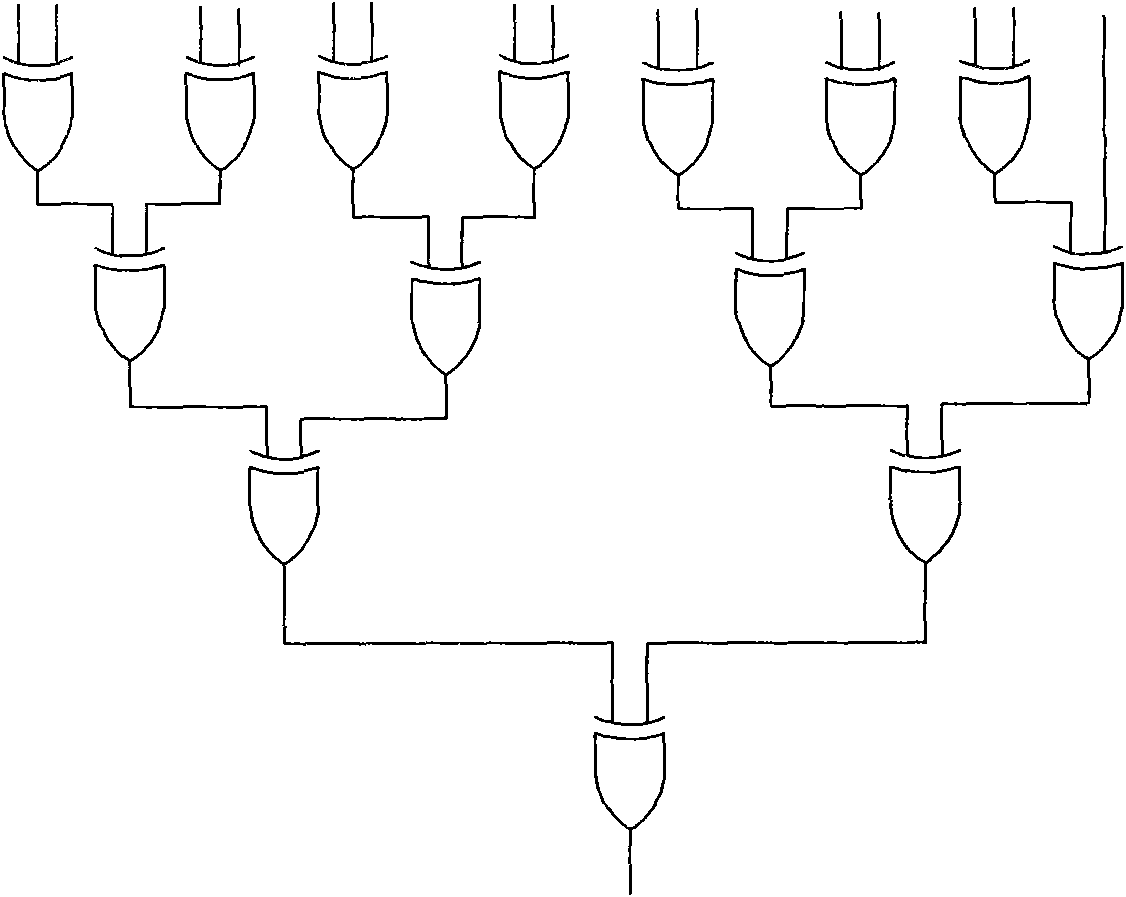

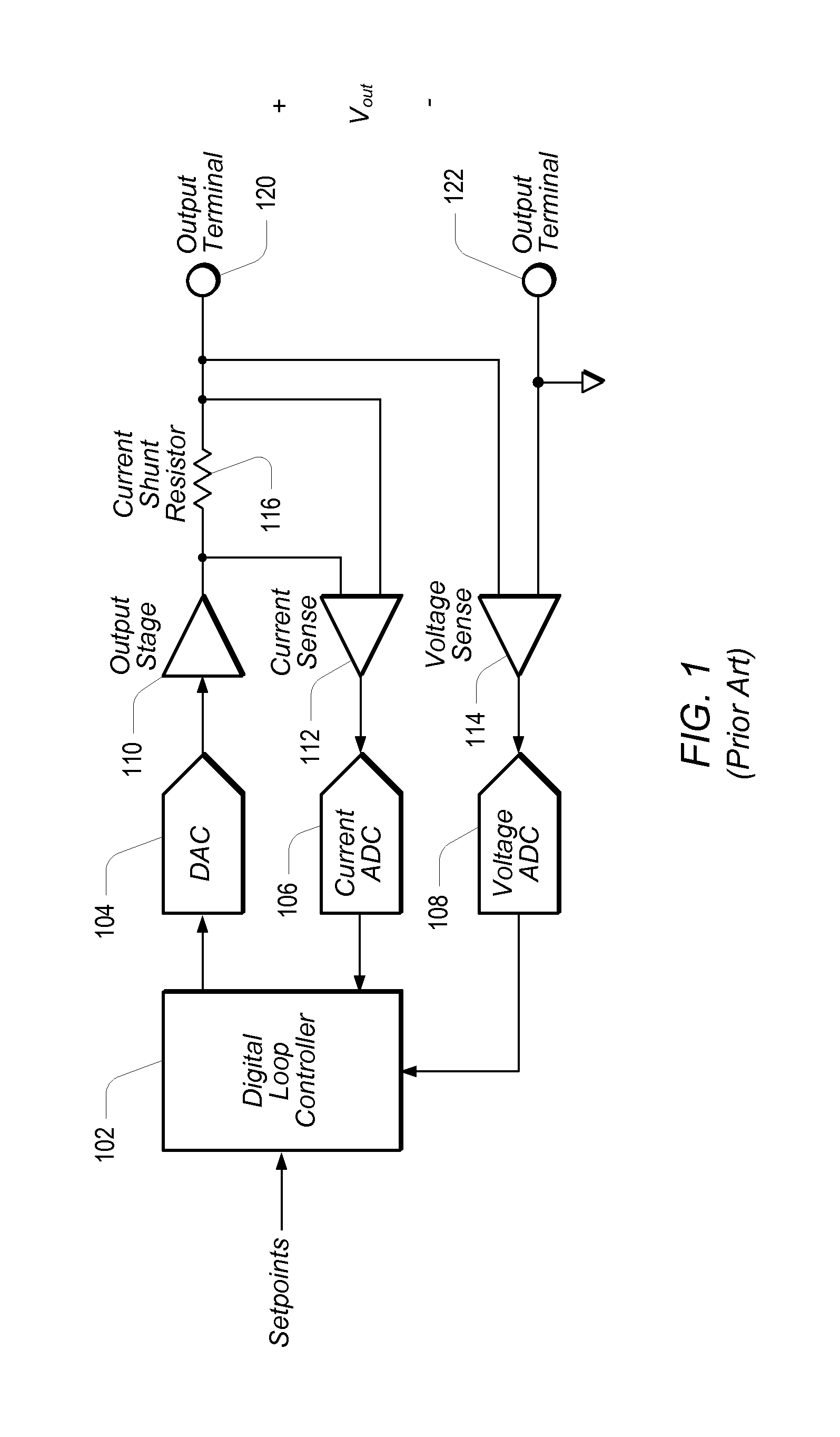

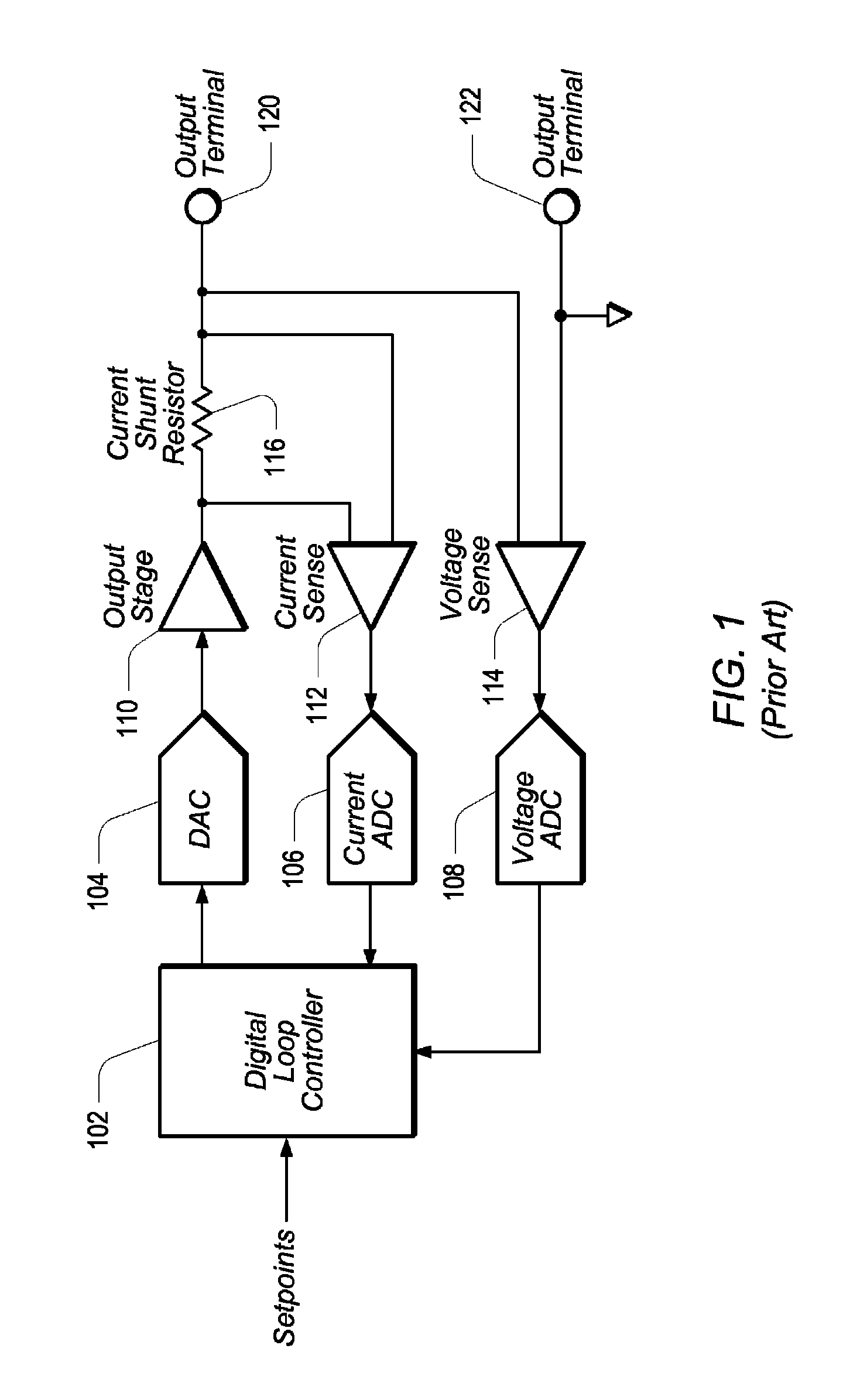

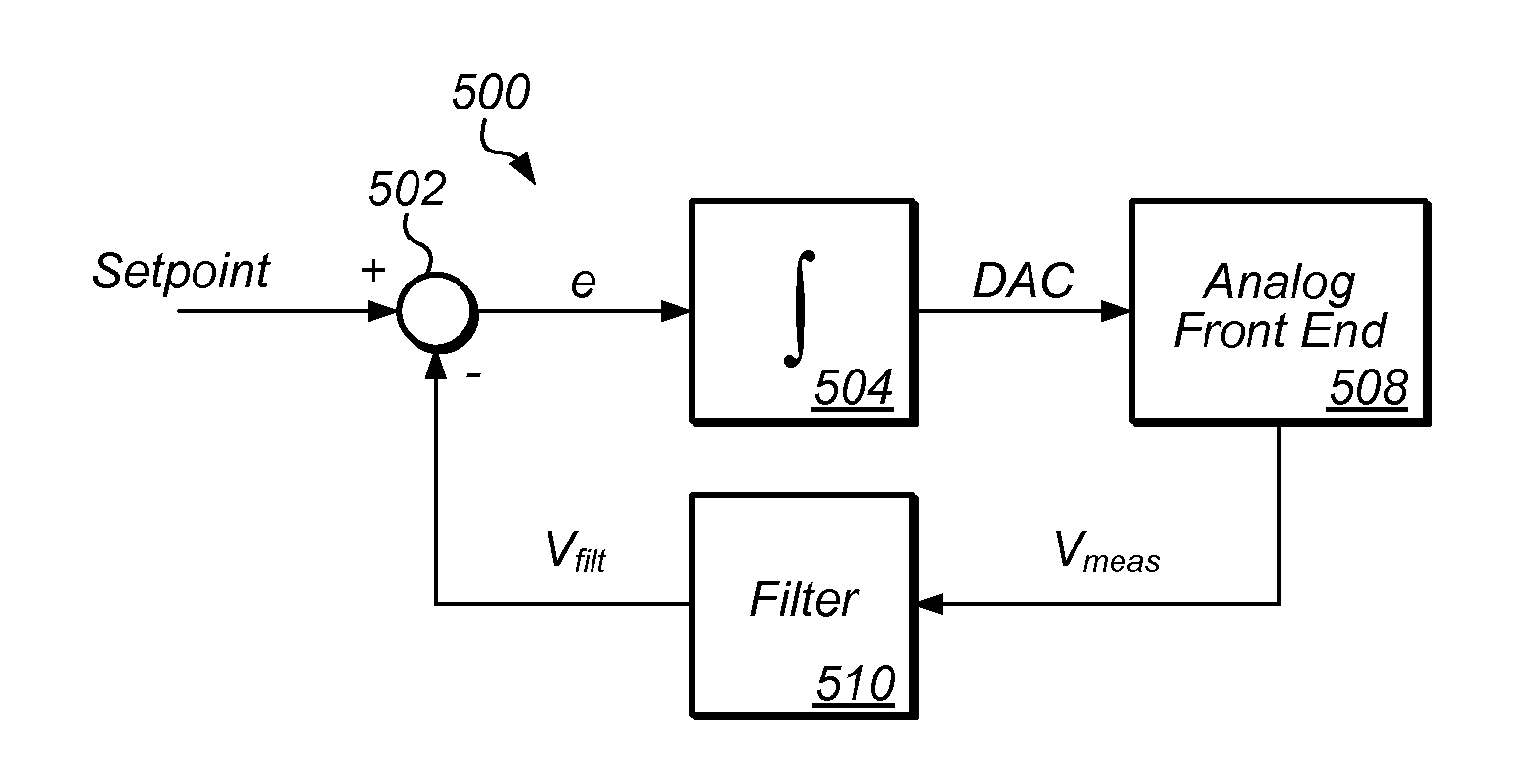

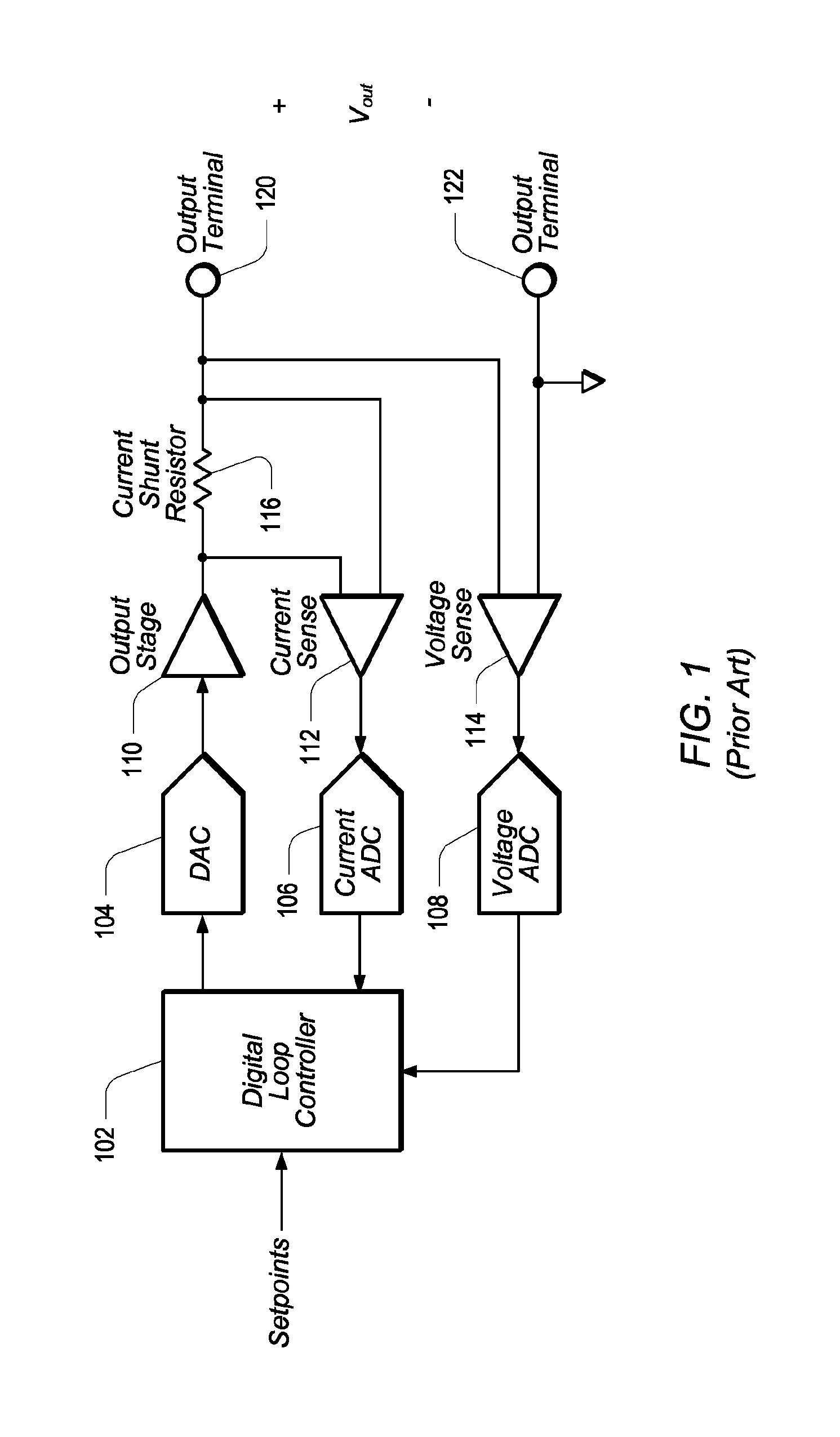

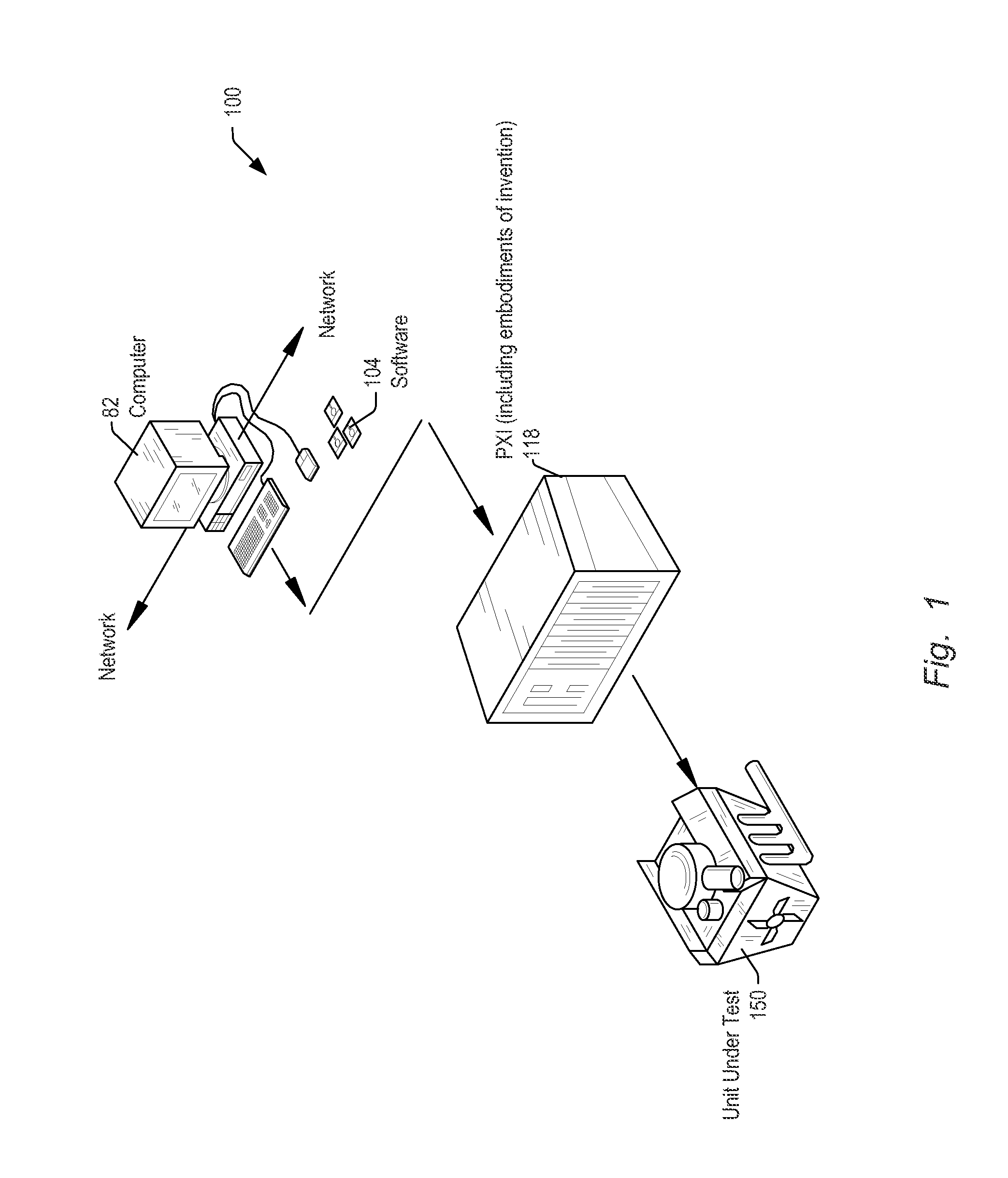

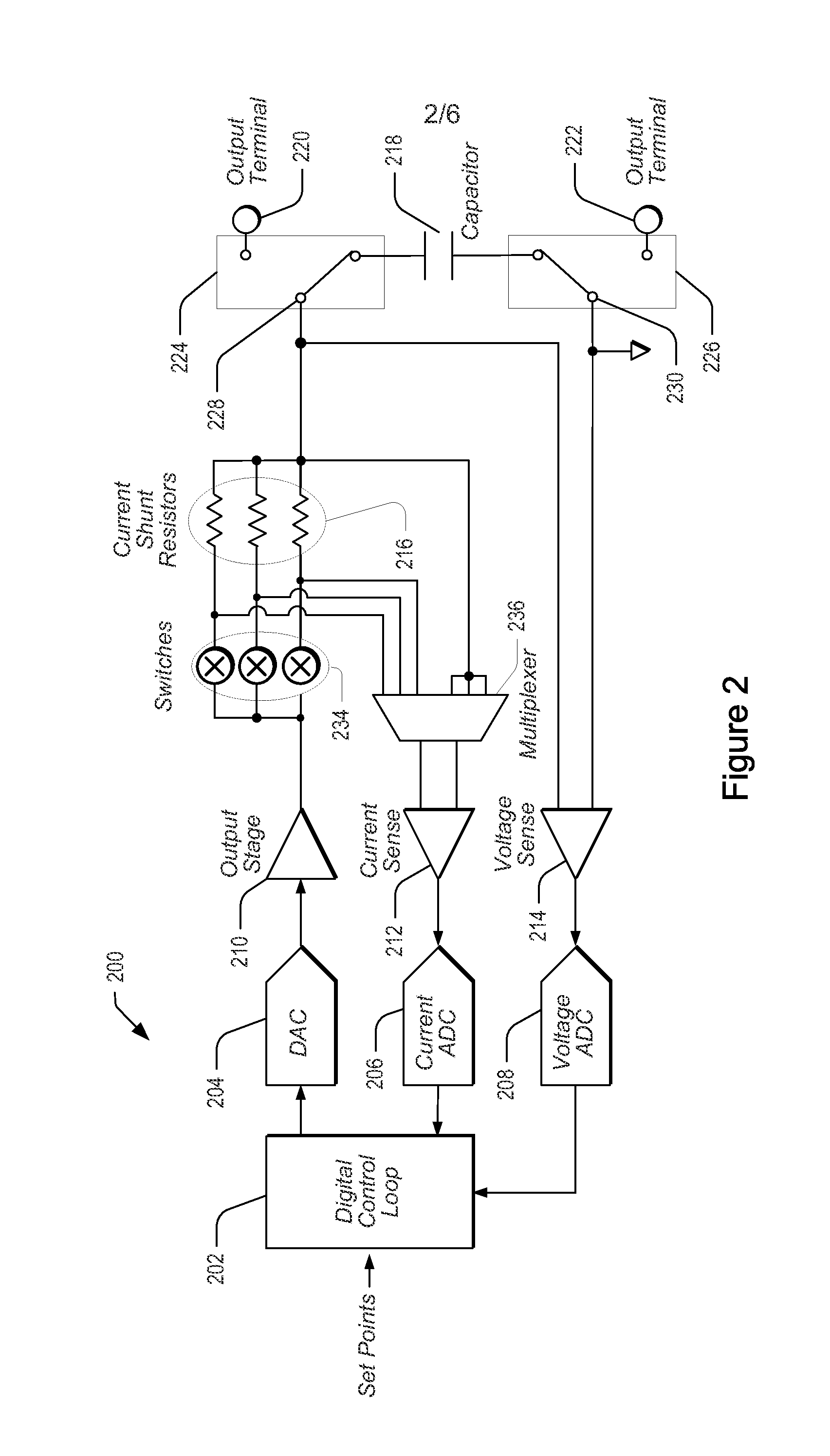

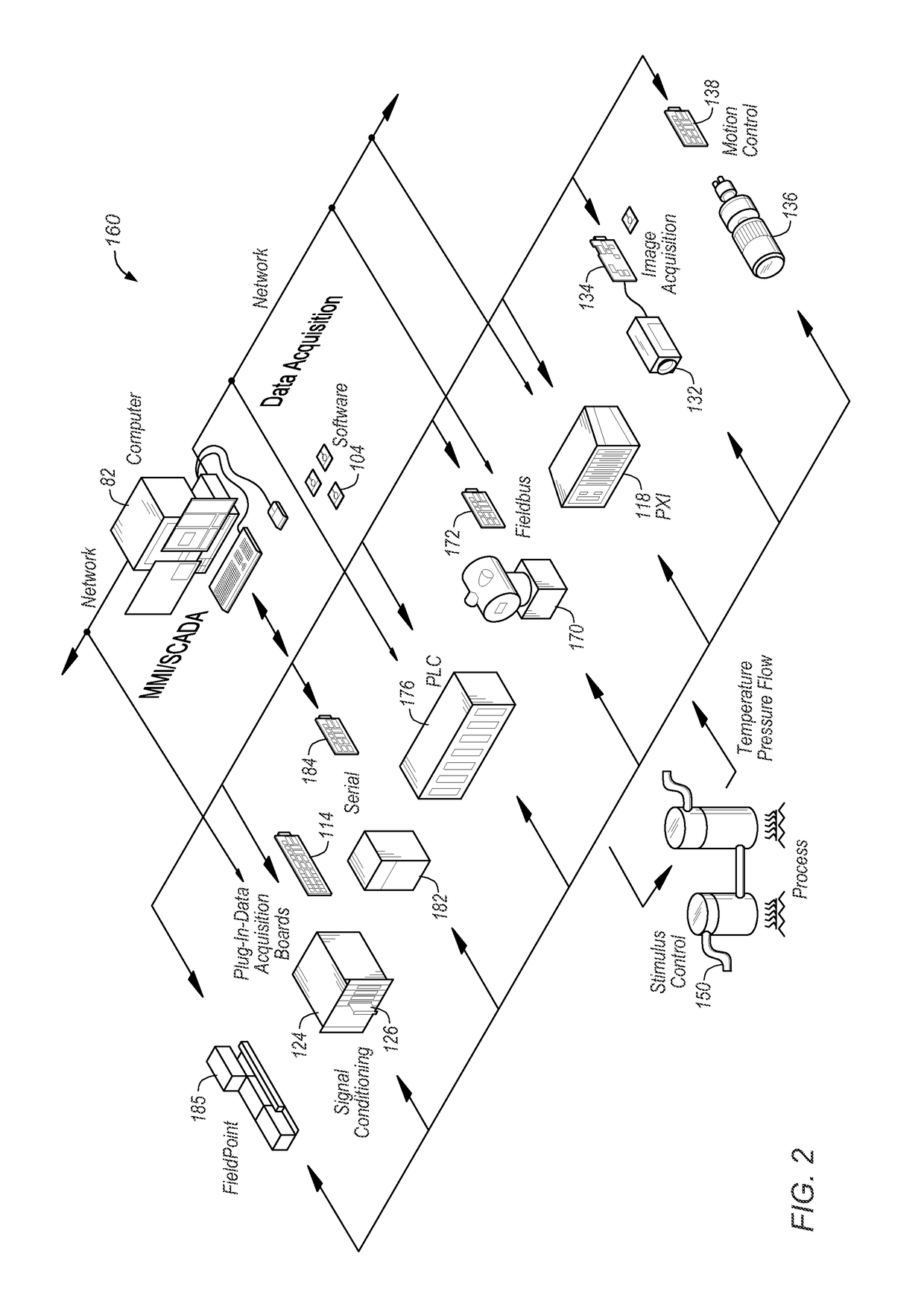

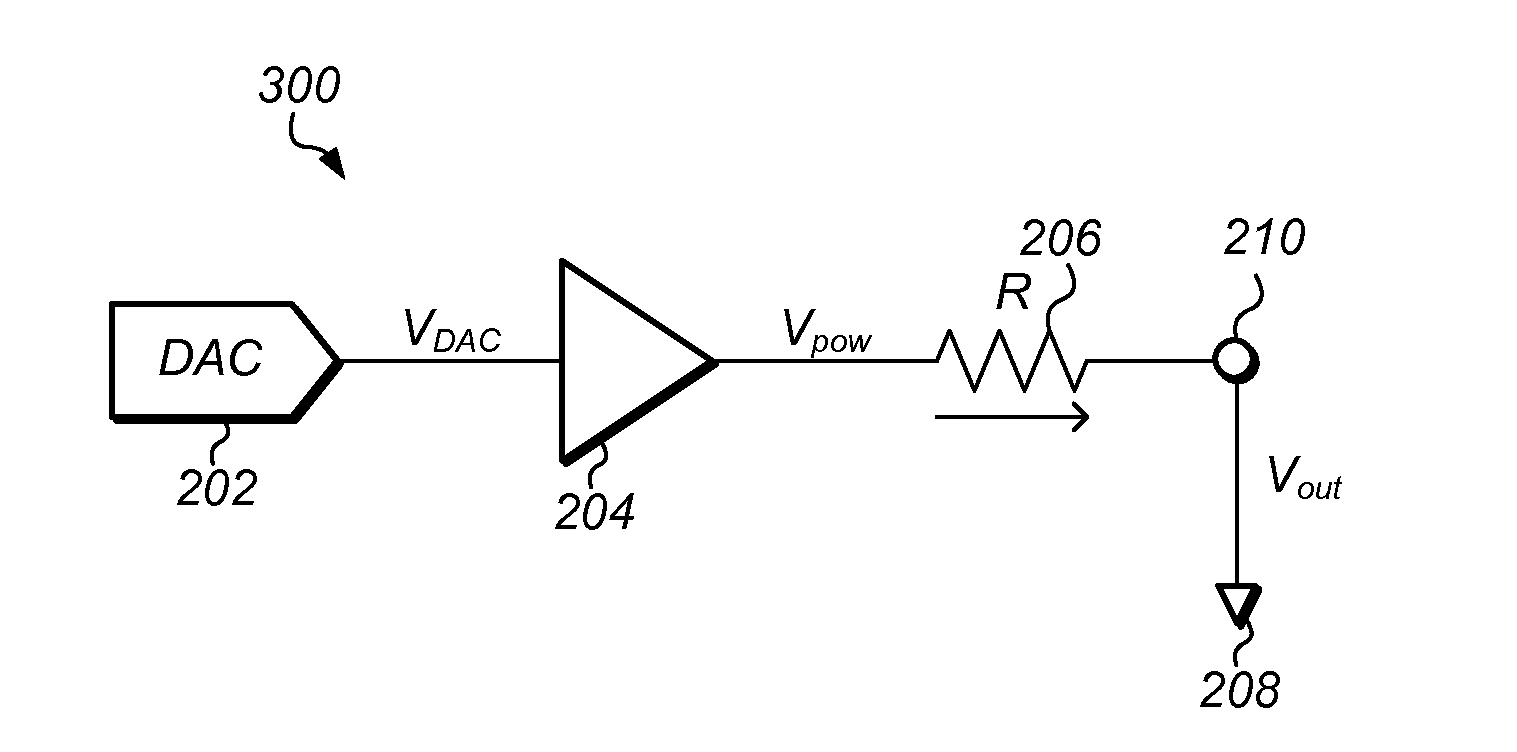

A source-measure unit (SMU) may be implemented with a control loop configured in the digital domain. The output voltage and output current may be measured with dedicated ADCs (analog-to-digital converters). The readings obtained by the ADCs may be compared to a setpoint, which may be set in an FPGA (field programmable gate array) or DSP (digital signal processing) chip. The FPGA or DSP chip may then be used to produce an output to drive a DAC (digital-to-analog converter) until the output voltage and / or output current reach the respective desired levels. The readback values may be obtained by averaging the voltage and / or current readings provided by the ADCs. The averaging may be weighted to improve noise rejection. The digital control loop provides added flexibility to the SMU and a decrease in the accuracy requirements on the DAC, while also for solving potential range-switching issues that may arise within the SMU.

Owner:NATIONAL INSTRUMENTS

Source-measure unit based on digital control loop

ActiveUS7903008B2Increase flexibilityConvenient and accurateElectric signal transmission systemsElectric devicesDigital signal processingMeasuring output

A source-measure unit (SMU) may be implemented with a control loop configured in the digital domain. The output voltage and output current may be measured with dedicated ADCs (analog-to-digital converters). The readings obtained by the ADCs may be compared to a setpoint, which may be set in an FPGA (field programmable gate array) or DSP (digital signal processing) chip. The FPGA or DSP chip may then be used to produce an output to drive a DAC (digital-to-analog converter) until the output voltage and / or output current reach the respective desired levels. The readback values may be obtained by averaging the voltage and / or current readings provided by the ADCs. The averaging may be weighted to improve noise rejection. The digital control loop provides added flexibility to the SMU and a decrease in the accuracy requirements on the DAC, while also for solving potential range-switching issues that may arise within the SMU.

Owner:NATIONAL INSTRUMENTS

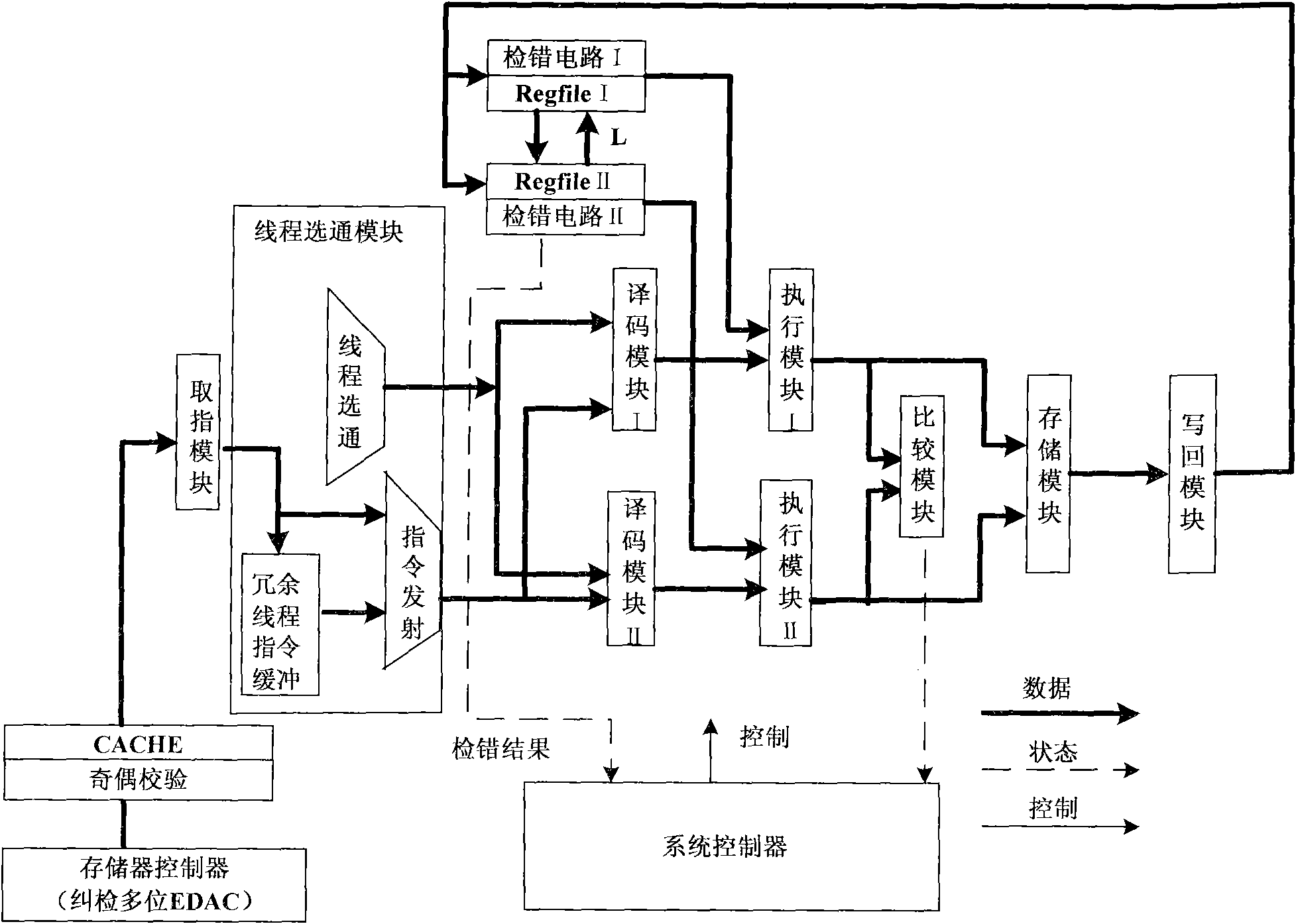

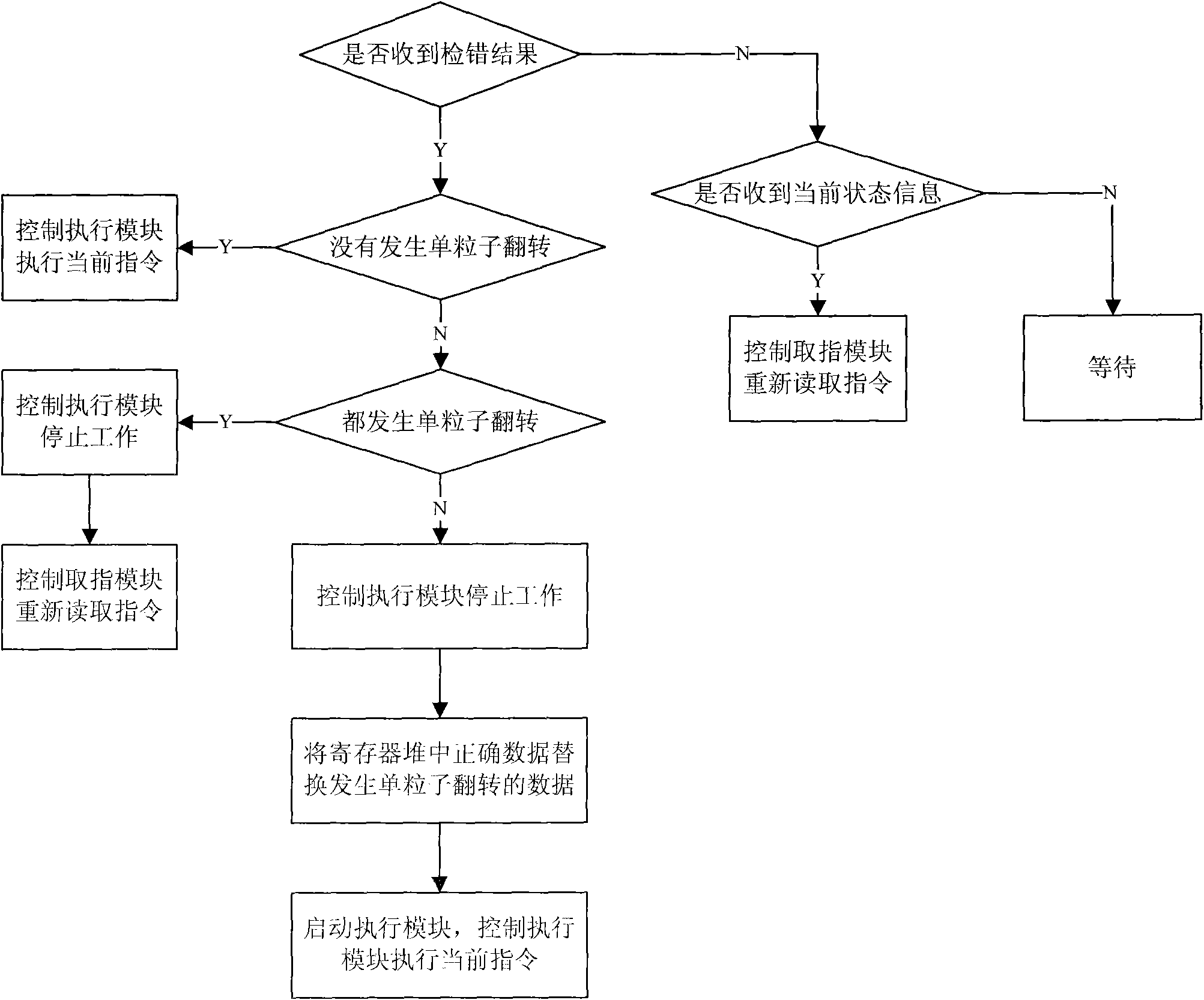

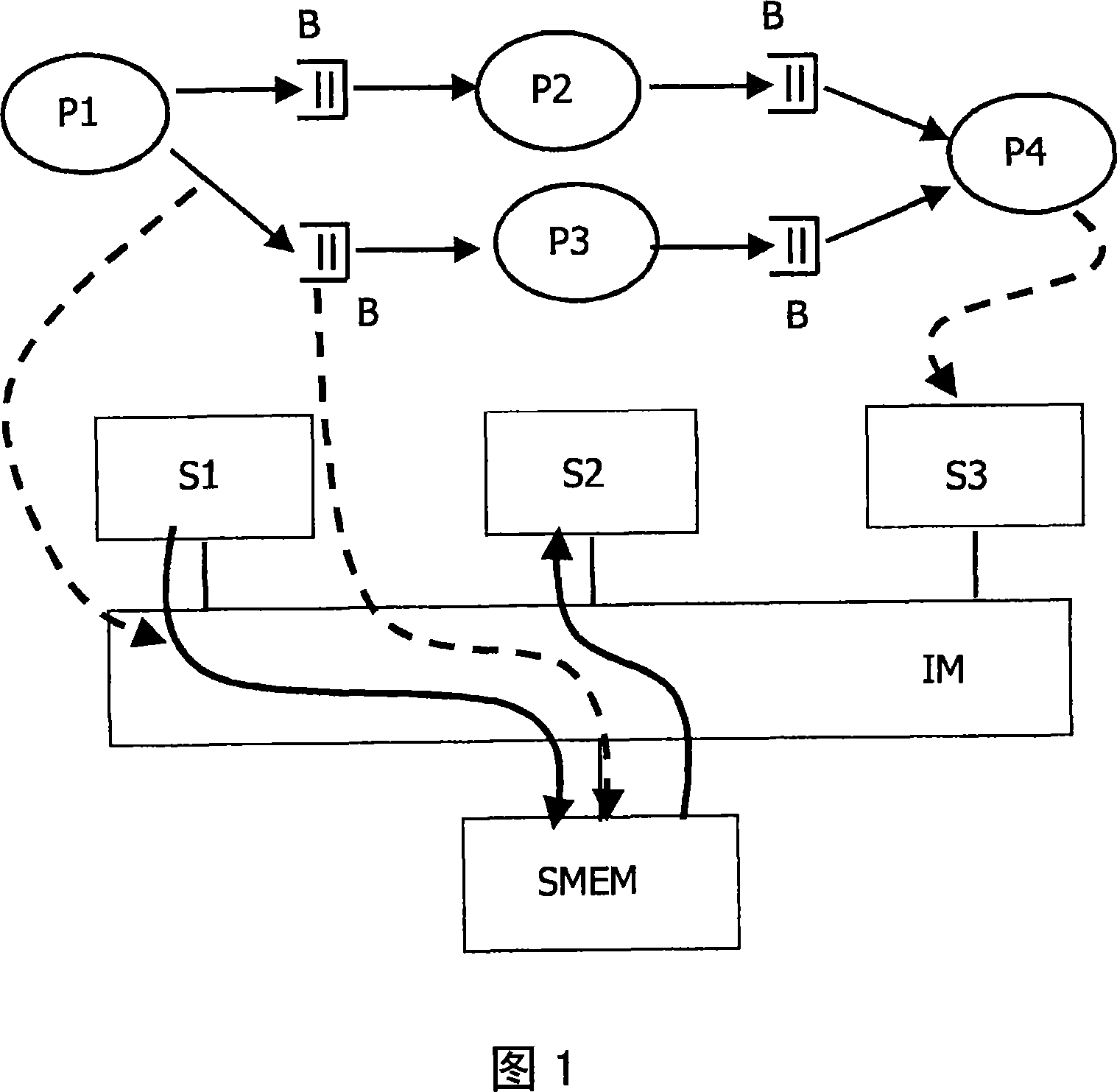

An anti-SEE system and method based on synchronizing redundant threads and coding technique

InactiveCN101551764AAvoid complex processingIndependent executionConcurrent instruction executionRedundant operation error correctionProcessor registerSingle event upset

Through the research and improvement of error-correcting codes and error-detecting codes, the anti-SEE system and method based on synchronizing redundant threads and coding technique enables this coding technique to quickly detect the SEU (single event upset) occurring in register file and meanwhile design the both-threaded mechanism of the processor into a redundant both-threaded mechanism. When the register file of a thread is found with SEU, the register data with upset error will be corrected through replacing this register file with the register file of the other redundant thread; through the comparison mechanism of synchronous execution results in the layer of redundant both-threaded instructions, the pipelined circuit is judged whether there is SET (single-event transient) error. If such error occurs, it will be quickly eliminated from the pipeline through the designed redundant thread pipeline restart mechanism. This method satisfactorily solves the two frequent and difficult problems: SMU of register file in processor and pipeline SET.

Owner:BEIJING MXTRONICS CORP +1

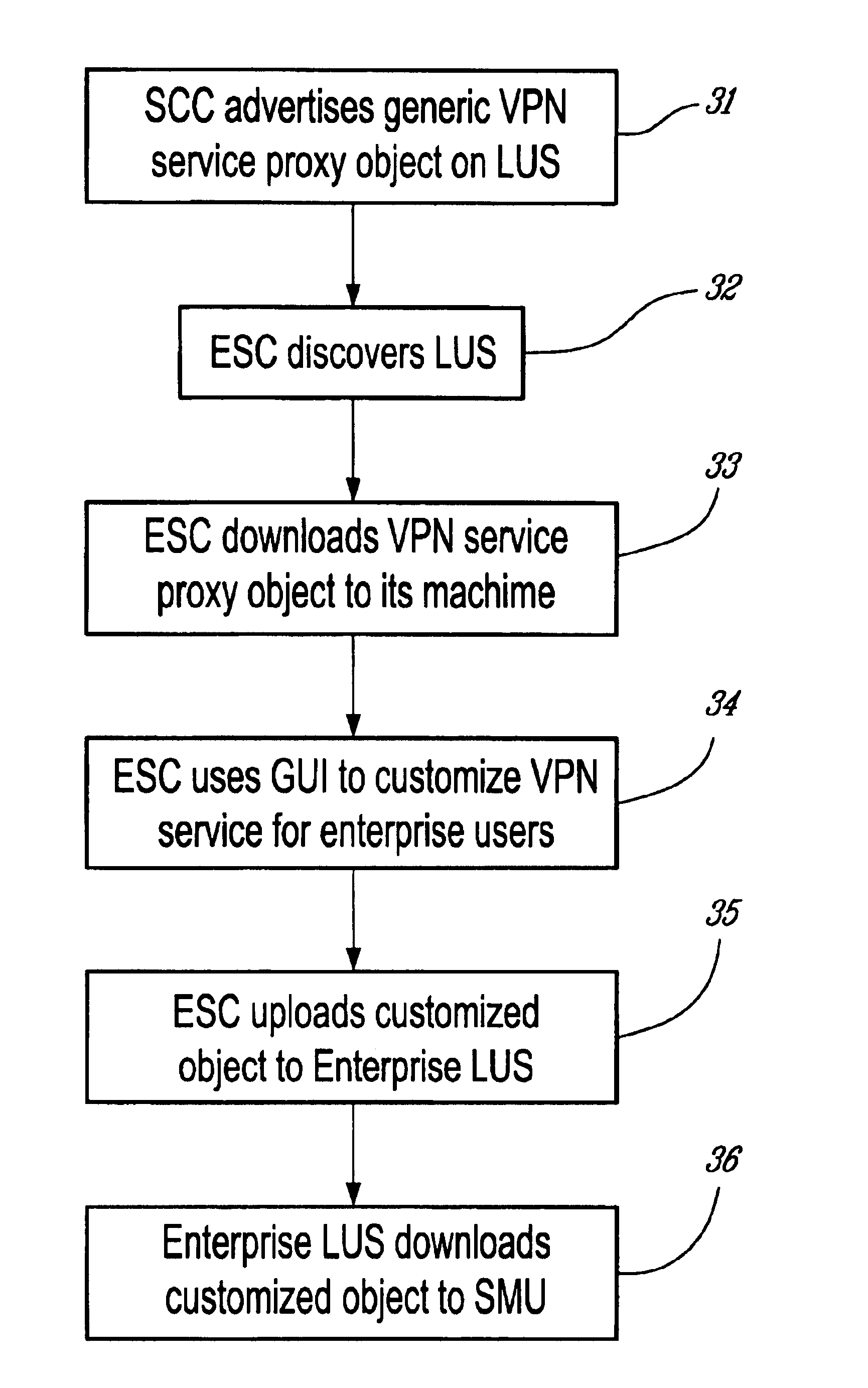

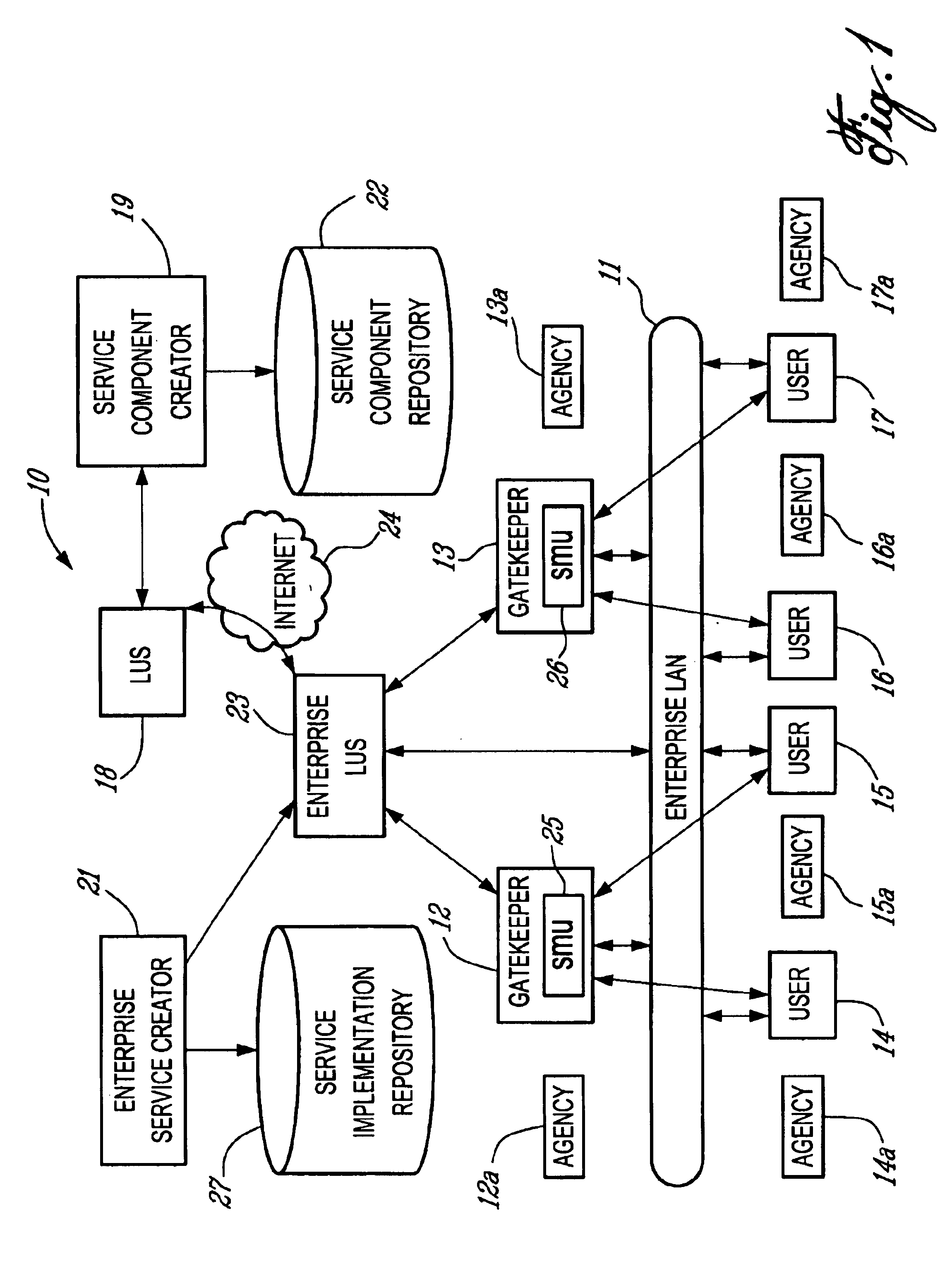

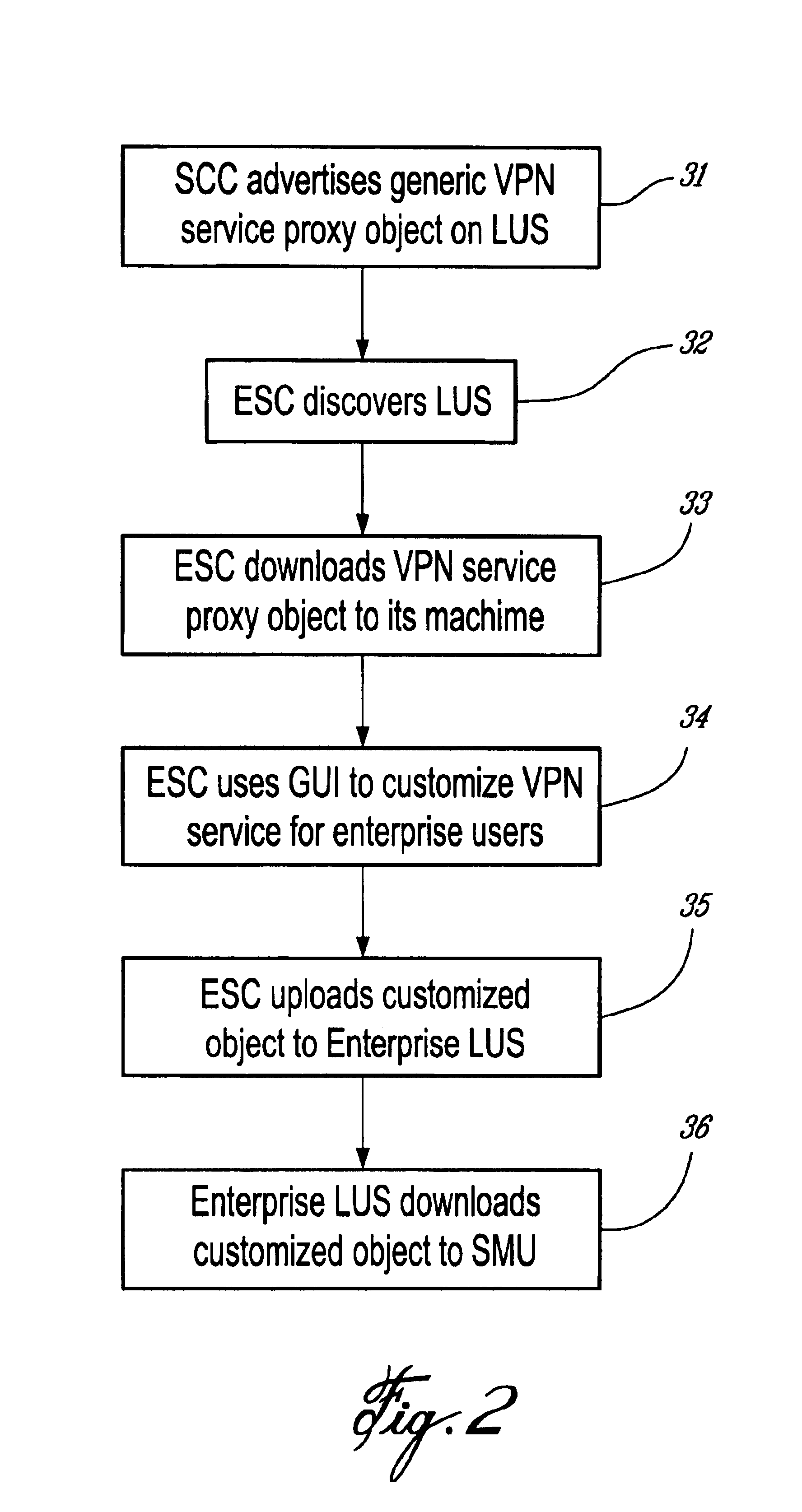

System and method of creating subscriber services in an IP-based telecommunications network

InactiveUS6711157B1Special service provision for substationDigital data information retrievalInternet ProtocolMobile agent

A system and method of creating subscriber services in an Internet Protocol (IP)-based telecommunications network. A service creation architecture includes a Service Component Creator (SCC) that creates service proxy objects, and posts them on a Lookup Service (LUS). The LUS is accessible through the Internet by Enterprise Service Creators (ESCs). The ESCs download the posted service proxy objects from the LUS, and customize the downloaded objects to create customized services for enterprise users. The ESCs upload the customized service proxy objects to an Enterprise LUS, and the, Enterprise LUS downloads the customized service proxy objects to a Service Management Unit (SMU) serving the end user. A gatekeeper serving the end users utilizes the service proxy code downloaded to the SMU to determine the location of a Service Implementation Repository (SIR) that stores actual service code for implementing the customized service. The gatekeeper then downloads the actual service code from the SIR, constructs a customized User Service Agent (USA) that includes the actual service code, and sends the customized USA to an agency (mobile agent platform) at the user's terminal.

Owner:OPTIS WIRELESS TECH LLC

Gas sensing apapratus

ActiveUS20140174154A1Reduce decreaseSamplingMaterial analysis by electric/magnetic meansEngineeringGas concentration

A method of selectively sensing the concentration of a target gas in polluted ambient air comprises the steps of: —providing a target gas sensor (220) sensitive to the target gas; —providing a first gas flow derived from the ambient air, from which first flow the target gas is substantially removed; —providing a second gas flow derived from the ambient air, substantially comprising the same target gas concentration as the ambient air; —exposing the target gas sensor to the first gas flow during a first time interval, and obtaining from the sensor a first output signal (Smf); —exposing the target gas sensor to the second gas flow during a second time interval not overlapping with the first time interval, and obtaining a second output signal (Smu); —calculating the difference (SΔ) between the first and the second output signals; calculating the concentration of the target gas from the calculated signal difference (SΔ).

Owner:KONINKLIJKE PHILIPS ELECTRONICS NV

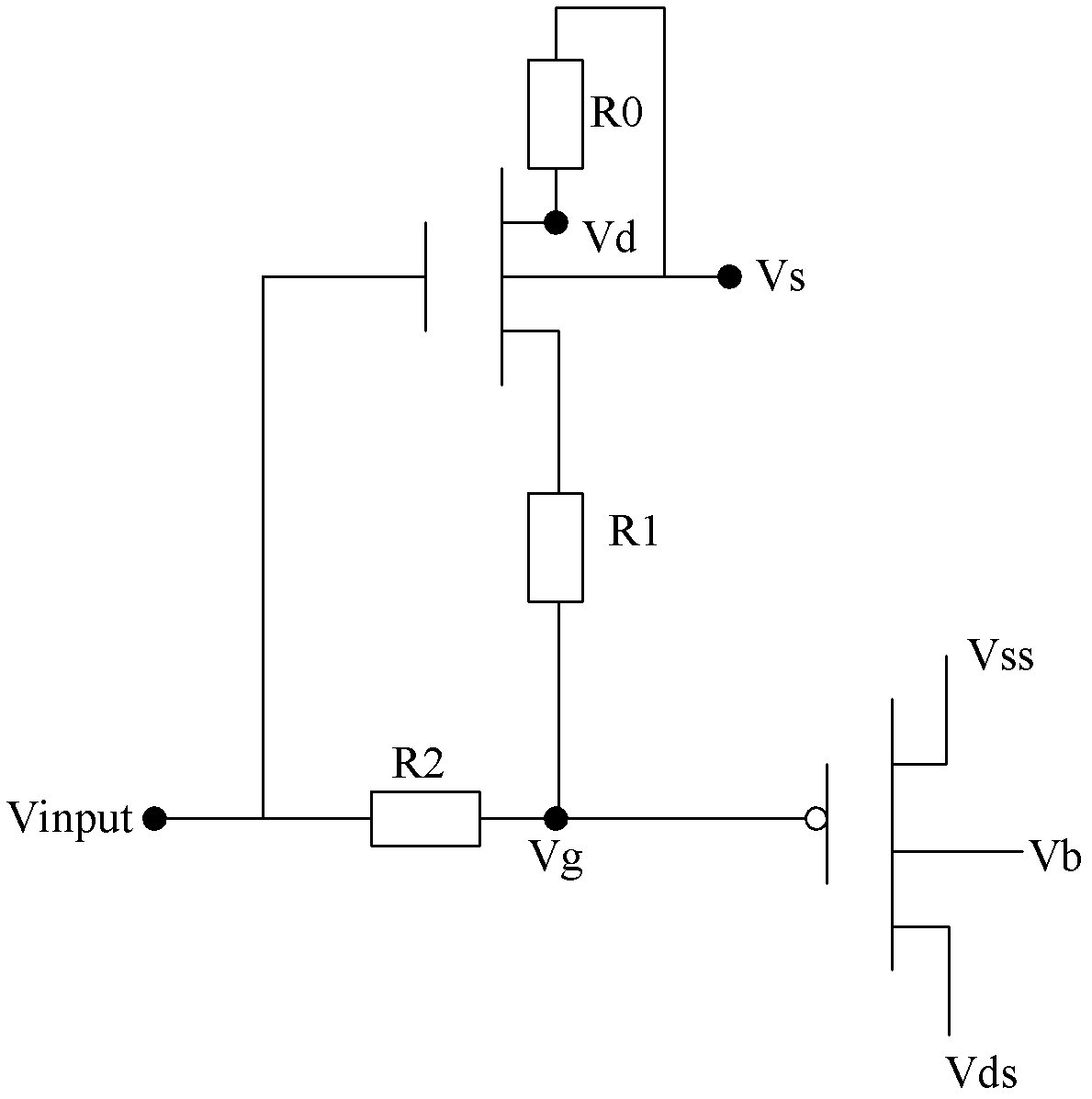

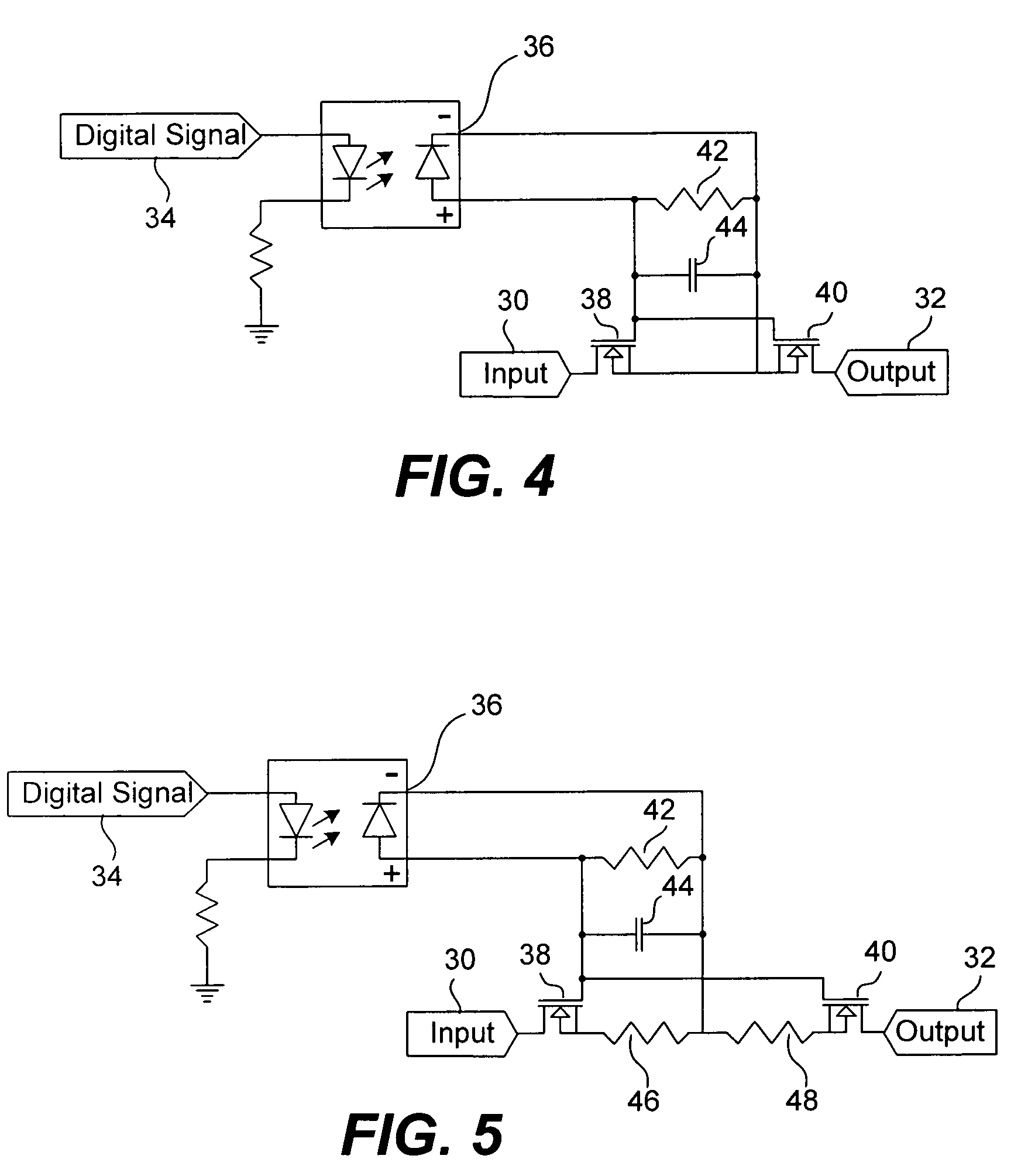

Building-out circuit and testing method for testing negative bias temperature instability

ActiveCN102866340ARestoration Effect InhibitionAccurate measurementIndividual semiconductor device testingEngineeringP channel

The invention provides a building-out circuit and a testing method for testing the negative bias temperature instability (NBTI). The building-out circuit is respectively connected with a source-measurement unit and a PMOS (P-channel Metal Oxide Semiconductor) to be measured; the building-out circuit comprises an NMOS (N-channel metal oxide semiconductor); a base electrode of the NMOS is electrically connected with a source electrode of the NMOS by a resistor R0; a drain electrode fo the NMOS is electrically connected with a grid electrode of the PMOS to be measured by a resistor R1; a grid electrode fo the NMOS is electrically connected with the grid electrode of the PMOS to be measured by a resistor R2; the potential of the base electrode of the NMOS is set into a value of less than 0V; and the voltage input end of the source-measurement unit is connected with the grid electrode of the NMOS. When an input voltage of the source-measurement unit is changed into 0V, due to the voltage division of the resistor R2, the voltage of the grid electrode of the PMOS to be measured is less than 0V, i.e. when the NBTI recovery effect occurs after the stress voltage is switched off, a partial pressure of the R2 is still applied to the grid electrode of the PMOS to be measured to inhibit the NBTI recovery effect in the PMOS, so that the measurement result is more accurate.

Owner:SEMICON MFG INT (SHANGHAI) CORP

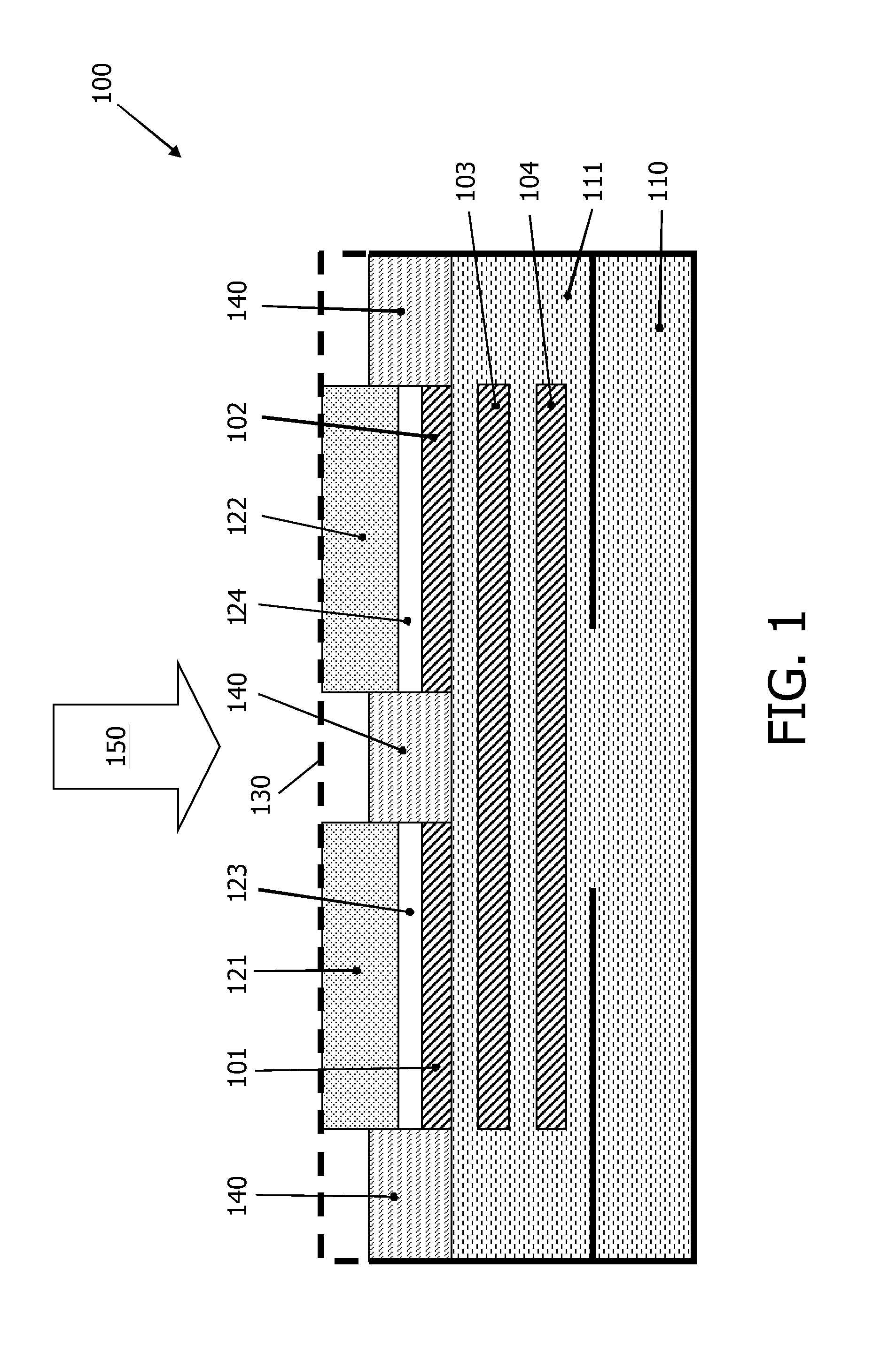

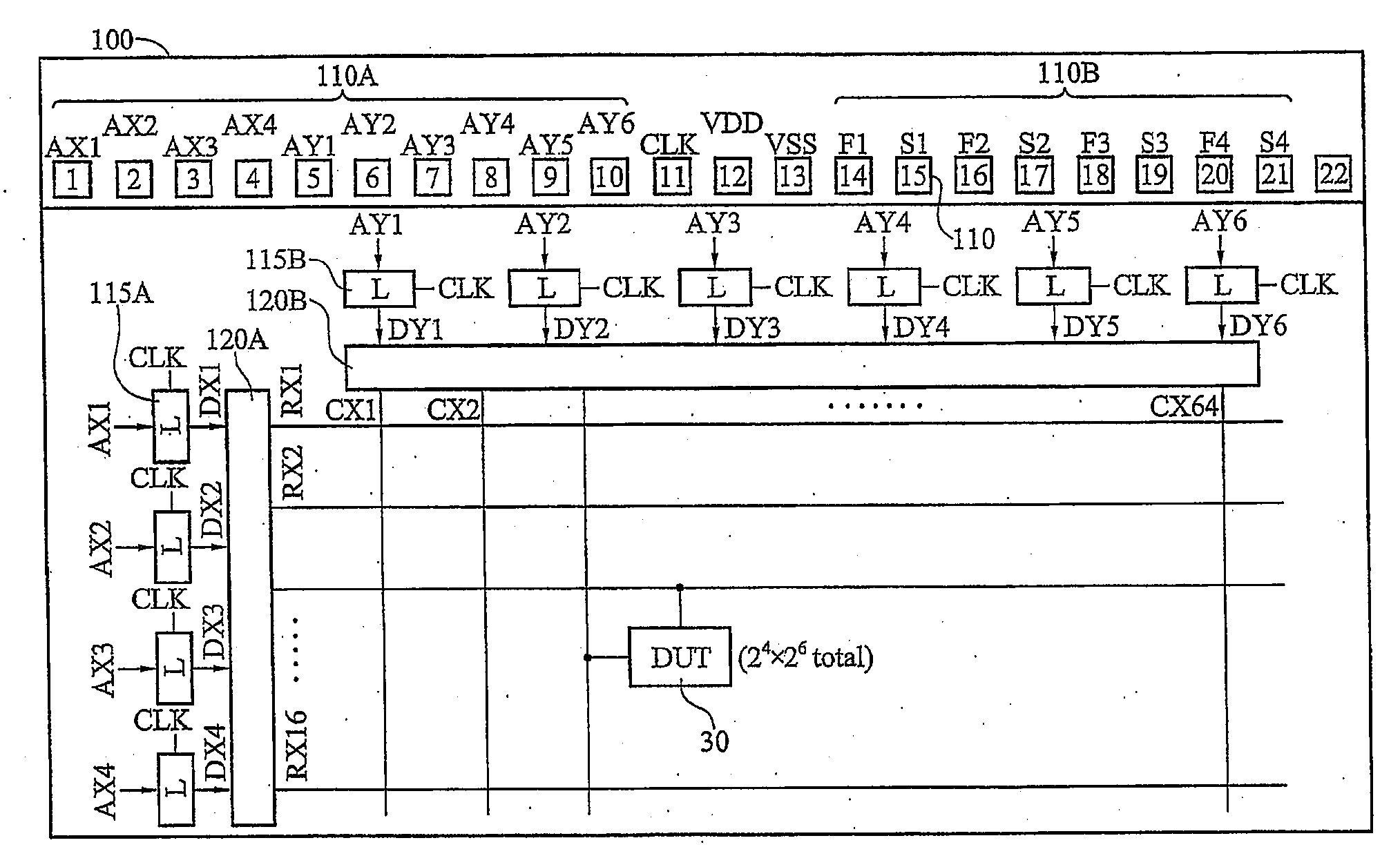

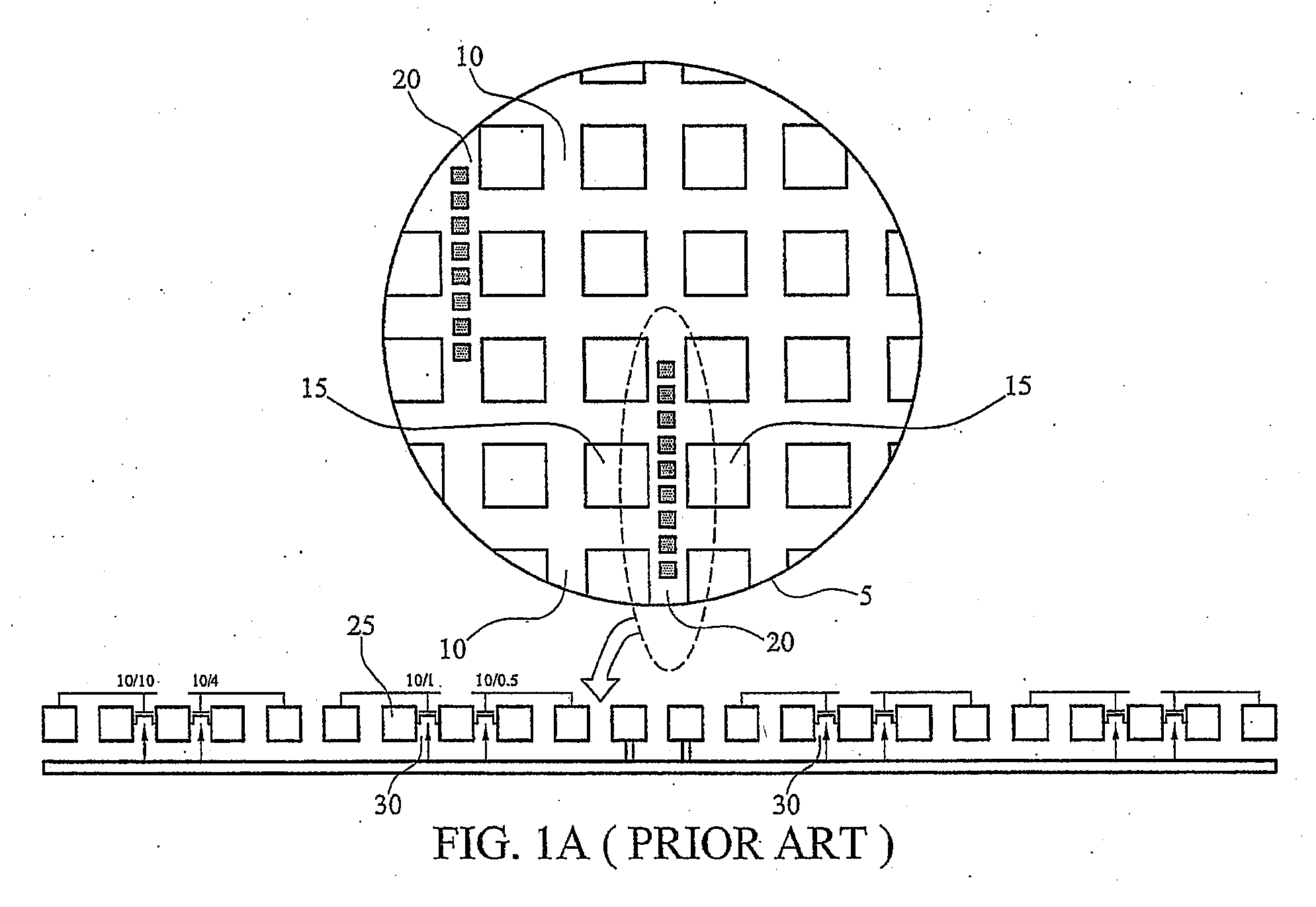

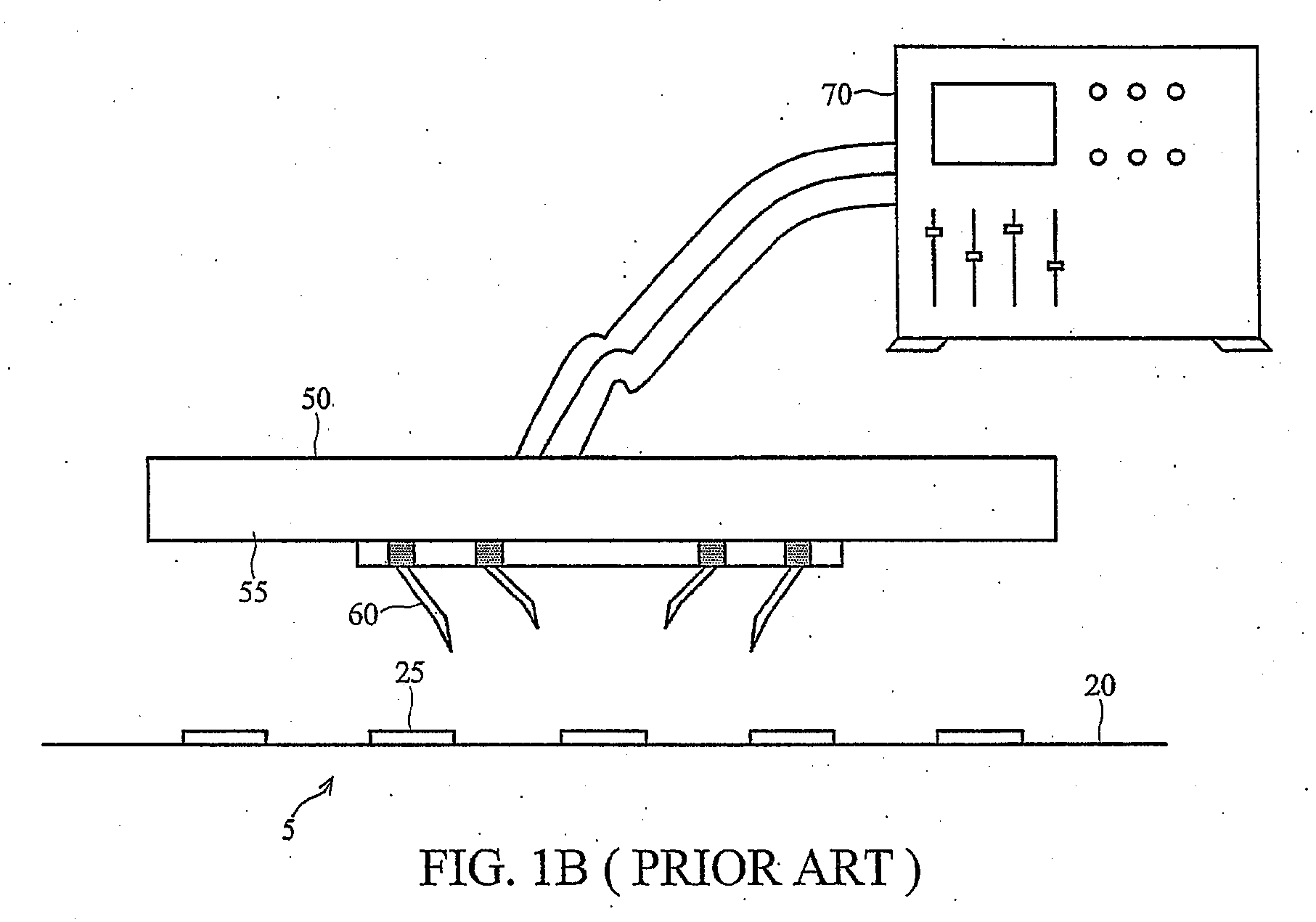

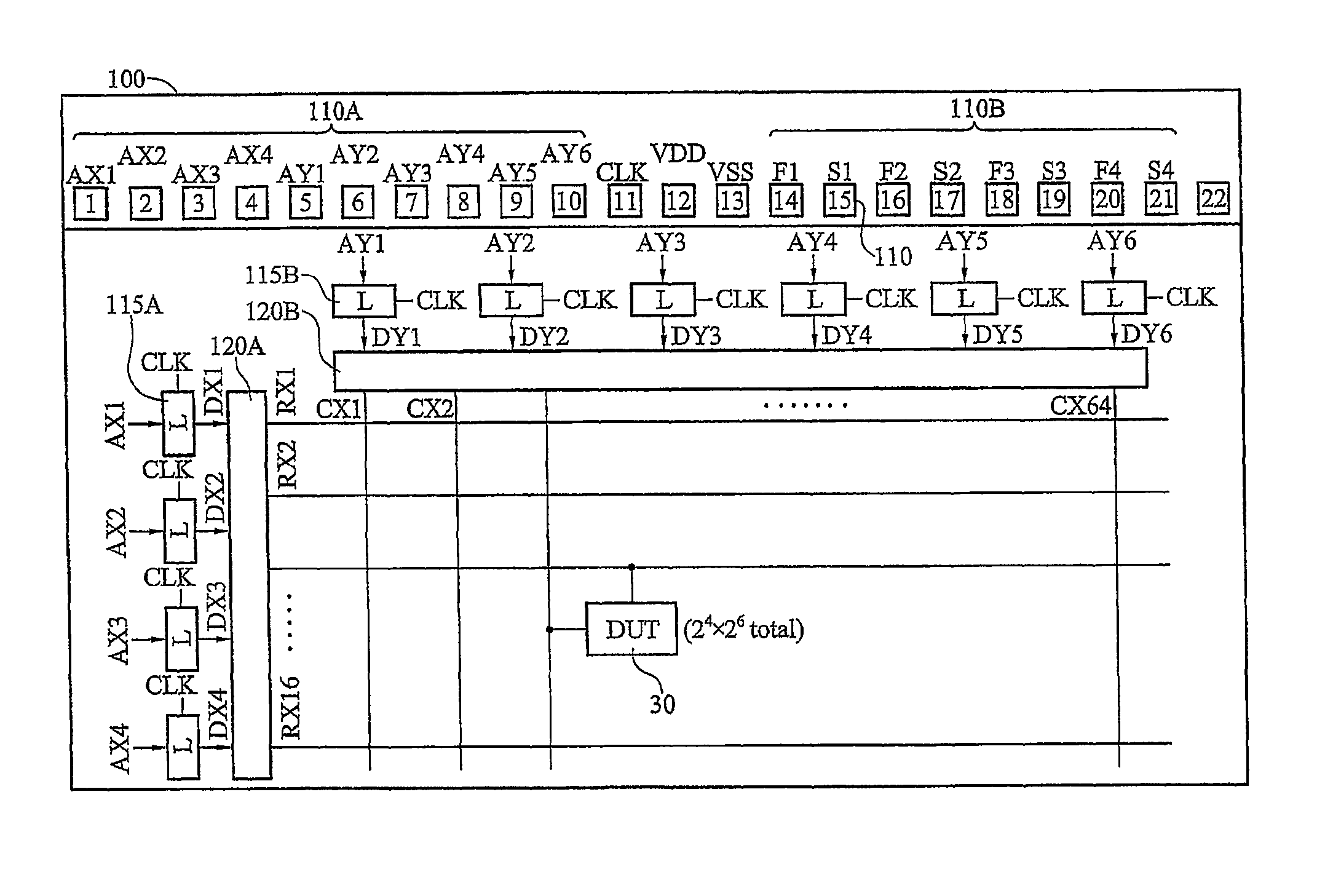

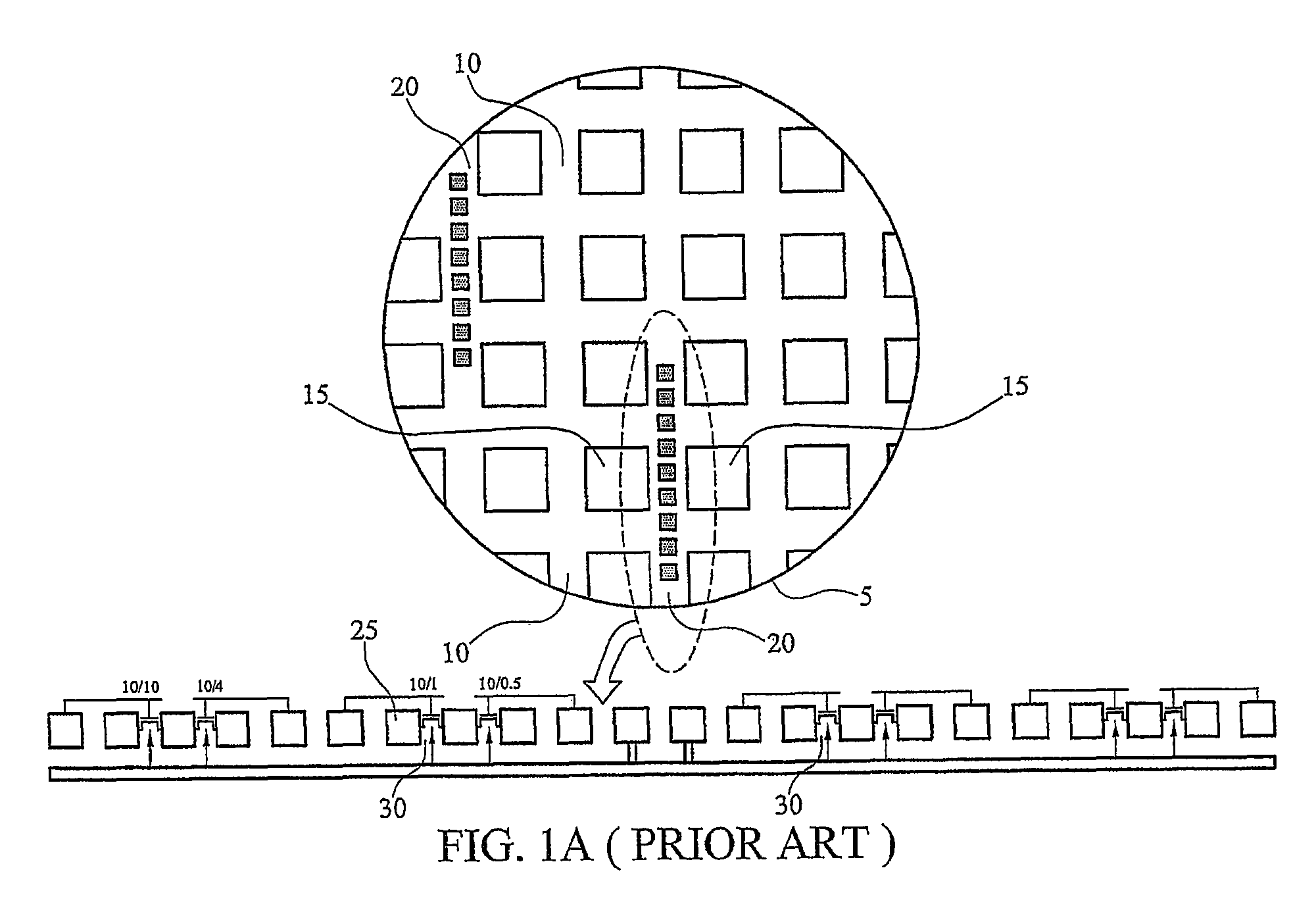

High accuracy and universal on-chip switch matrix testline

ActiveUS20080238453A1Improvement on testline space utilizationIncrease flexibilitySolid-state devicesElectrical testingFunctional testingDevice form

A testline structure made for integrated circuit tests is presented. The structure includes an array of testline pads formed in the scribe line area or integrated circuit die area on a semiconductor substrate, a plurality of test devices formed under the pads area, and a select circuit selectively connecting one of the test devices. The testline structure of this invention enables access to a large number of test devices through the same number of pads as on a conventional testline and can be employed to conduct parametric, reliability, and functional tests on the same. A source measurement unit (SMU) in a conventional integrated circuit tester is employed to sense and force predetermined test conditions on the test device terminals and conduct accurate Kelvin tests on the selected device. A method of using this testline structure is also presented.

Owner:TAIWAN SEMICON MFG CO LTD

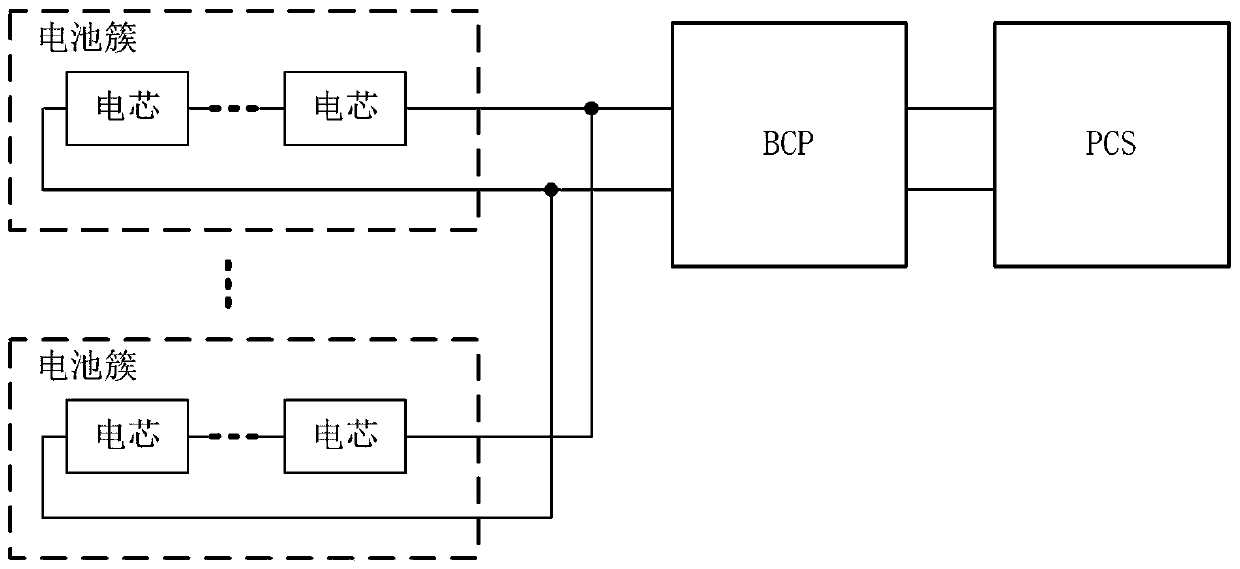

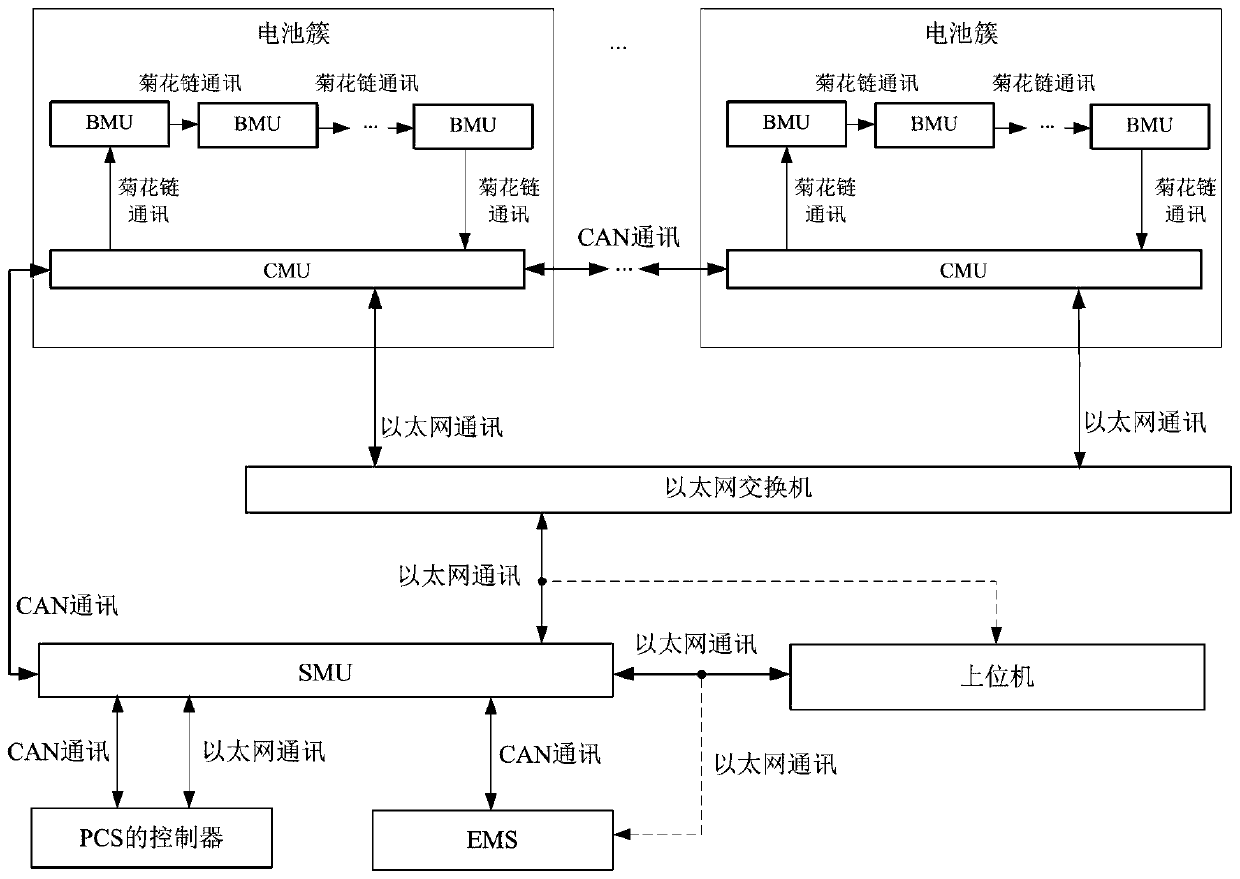

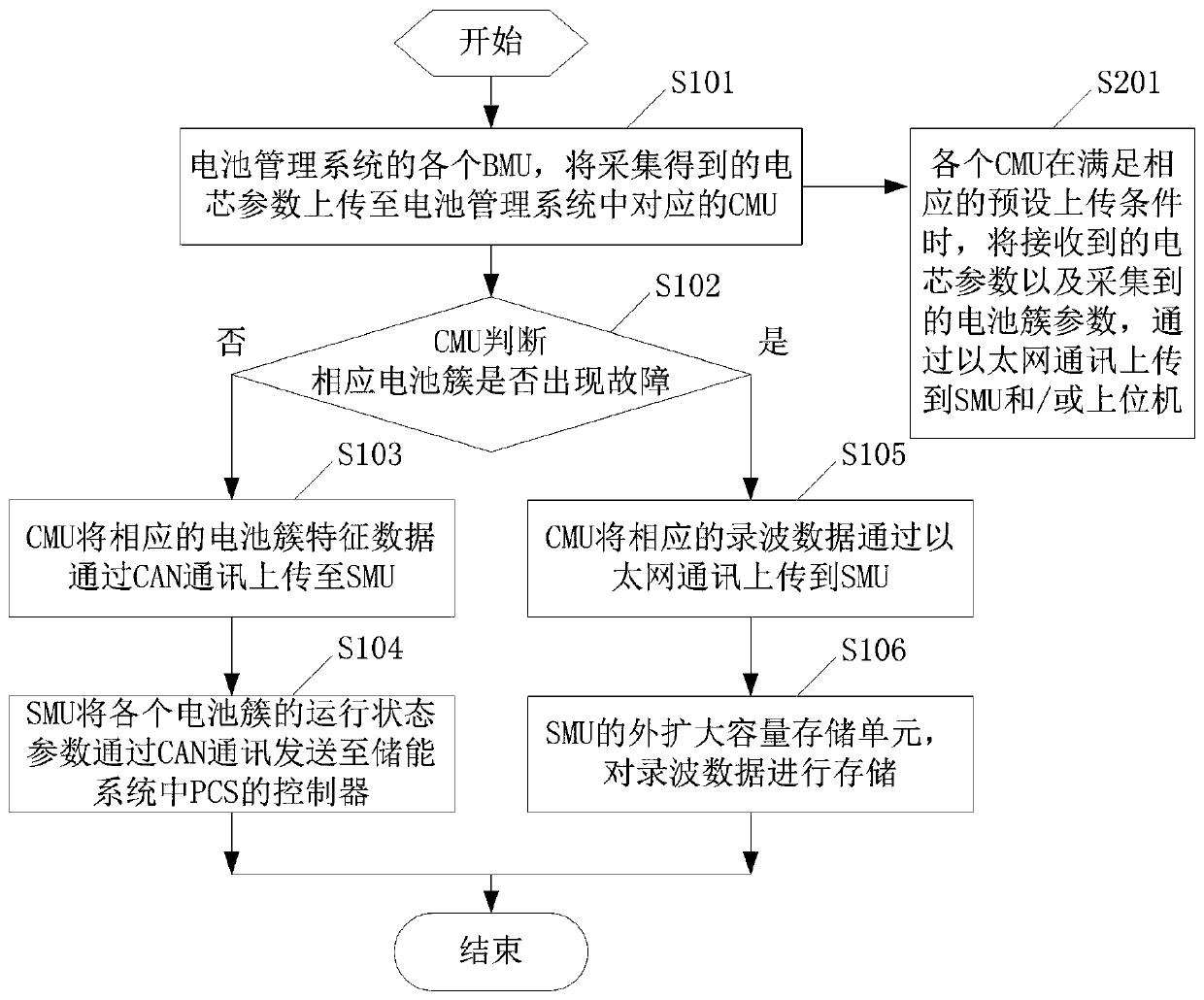

Energy storage system, battery management method and system of energy storage system

InactiveCN110588434AImprove the satisfaction of real-time interaction requirementsCells structural combinationElectric vehicle charging technologySource–measurement unitEthernet communication

The invention provides an energy storage system, a battery management method and system of the energy storage system. The core parameters collected by each BMU of the energy storage system are uploaded to the corresponding CMU, and then the corresponding CMU judges whether the corresponding battery cluster is in a failure according to the received core parameters and the collected battery clusterparameters; and if the corresponding battery cluster runs normally, the corresponding CMU uploads the corresponding battery cluster characteristic data to SMU via CAN communication, and if the batterycluster fails, the corresponding CMU uploads the corresponding record edict data to the SMU via Ethernet communication. Compared with the prior art, the real-time interaction requirement satisfactiondegree of large-capacity data in the energy storage system is improved.

Owner:SUNGROW POWER SUPPLY CO LTD

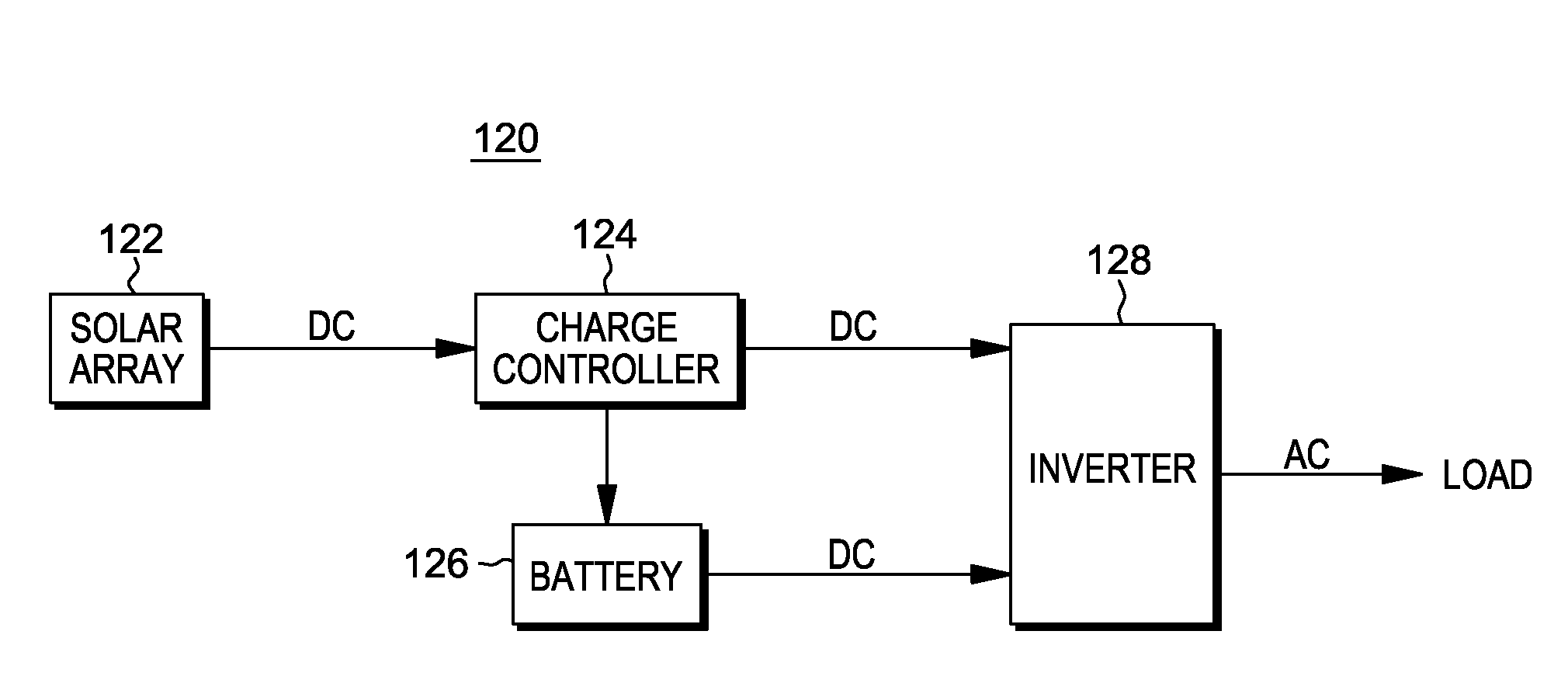

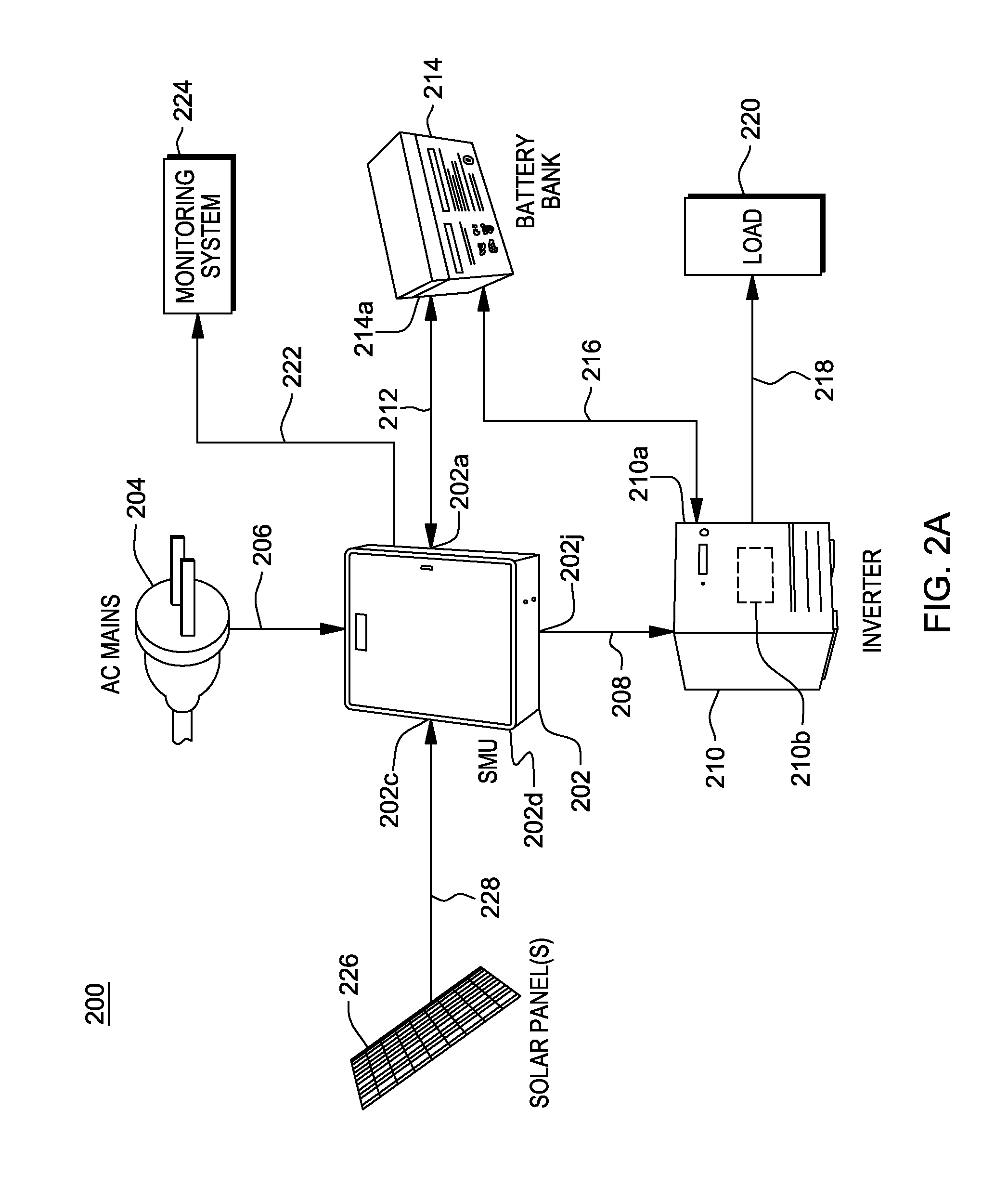

Method, system and apparatus for redirecting use of any inverter or uninterruptable power supply with improved solar power management

Method, apparatus and system for converting or redirecting use of any inverter or uninterruptable power supply (UPS) with the help of the proposed Solar Management Unit (SMU) into a standalone or off-grid solar system of equivalent capacity solar power. The SMU simplifies the system design to utilize existing investment in an inverter and other equipment and reduces solar system installation time.

Owner:NAVSEMI ENERGY

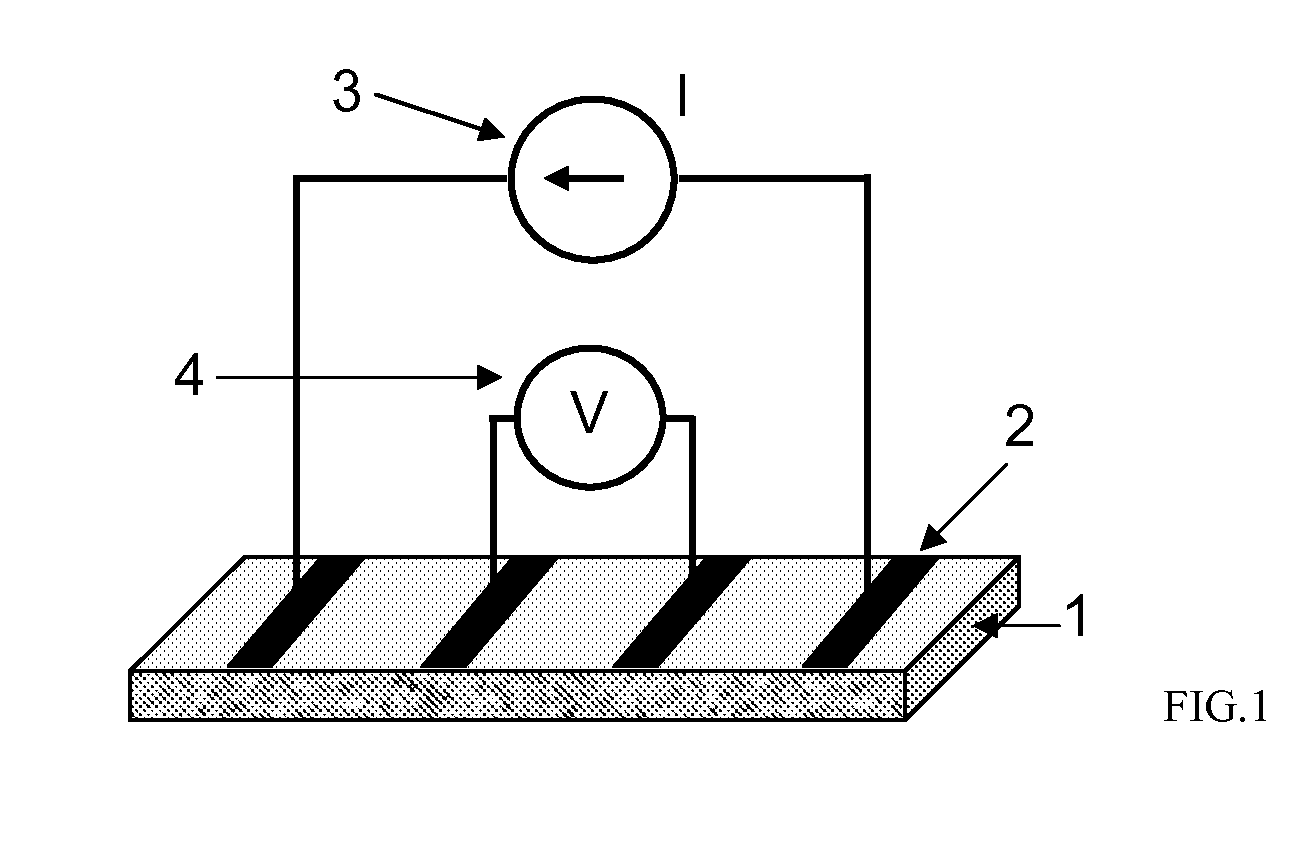

Freestanding carbon nanotube networks based temperature sensor

InactiveUS20110210415A1Reduce the possibilitySimple cuttingMaterial nanotechnologyThermometers using electric/magnetic elementsElectricityCarbon nanotube

The present invention introduces a small-size temperature sensor, which exploits a random or oriented network of un-functionalized, single or multi-walled, carbon nanotubes to monitor a wide range of temperatures. Such network is manufactured in the form of freestanding thin film with an electric conductance proven to be a monotonic function of the temperature, above 4.2 K. Said carbon nanotube film is wire-connected to a high precision source-measurement unit, which measures its electric conductance by a standard two or four-probe technique. Said temperature sensor has a low power consumption, an excellent stability and durability, a high sensitivity and a fast response; its manufacturing method is simple and robust and yields low-cost devices. Said temperature sensor, freely scalable in dimension, is suitable for local accurate measurements of rapidly and widely changing temperatures, while introducing a negligible disturb to the measurement environment.

Owner:UNIV DEGLI STUDI DI PARMA

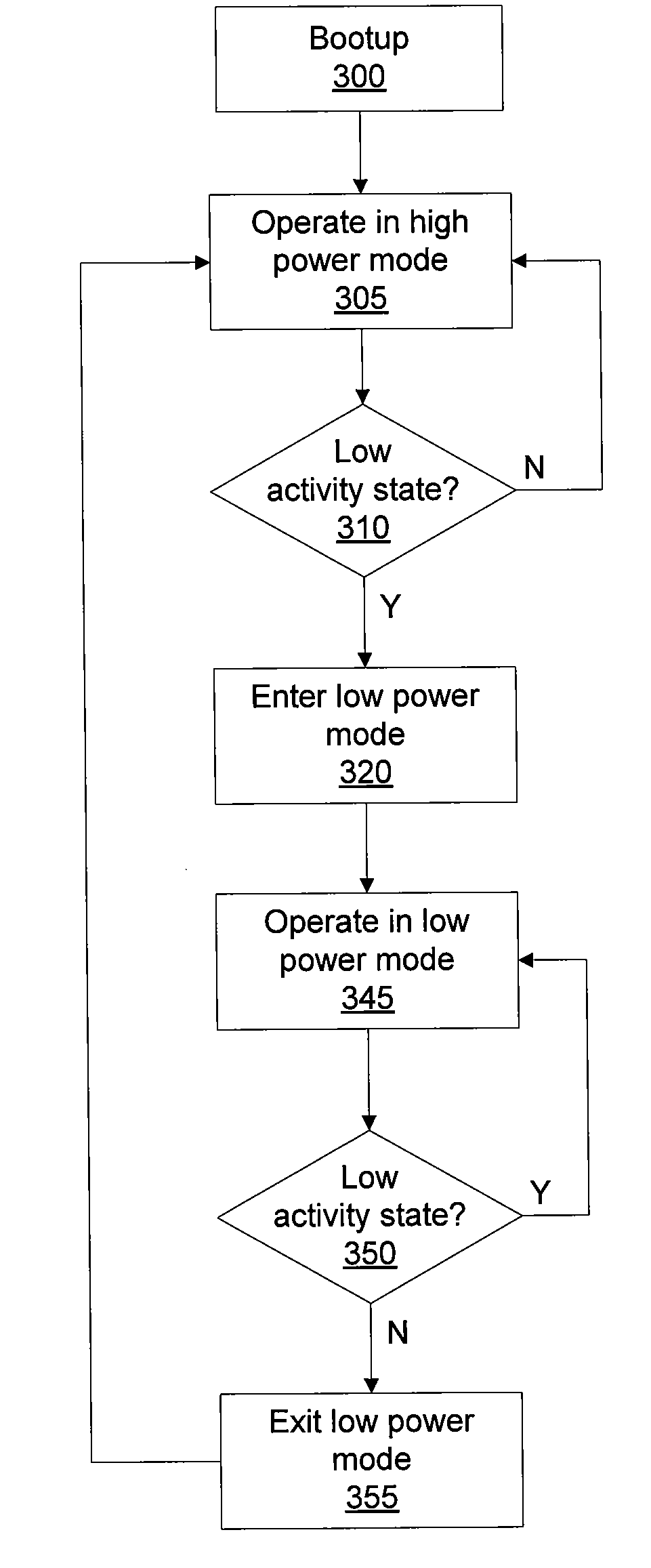

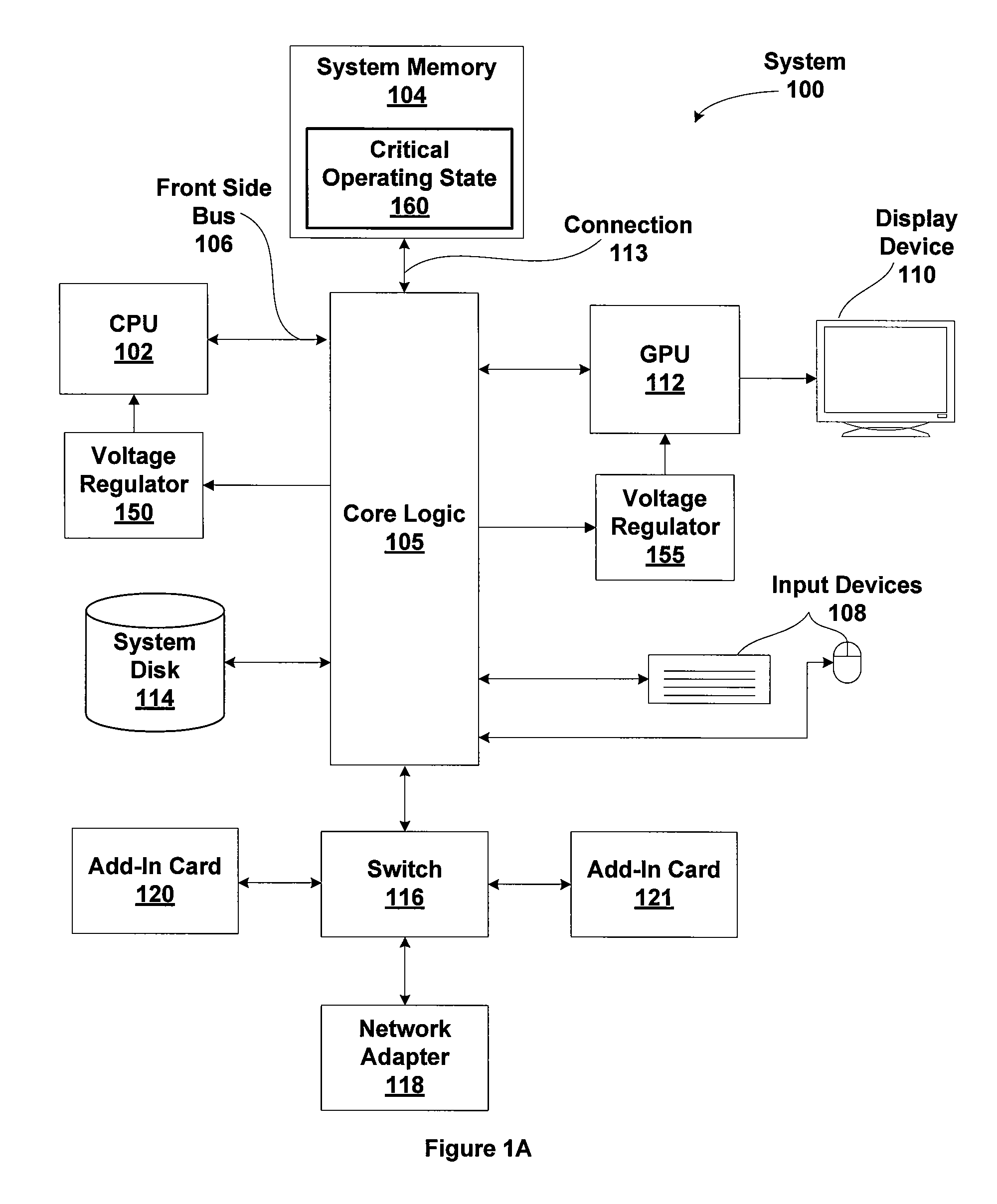

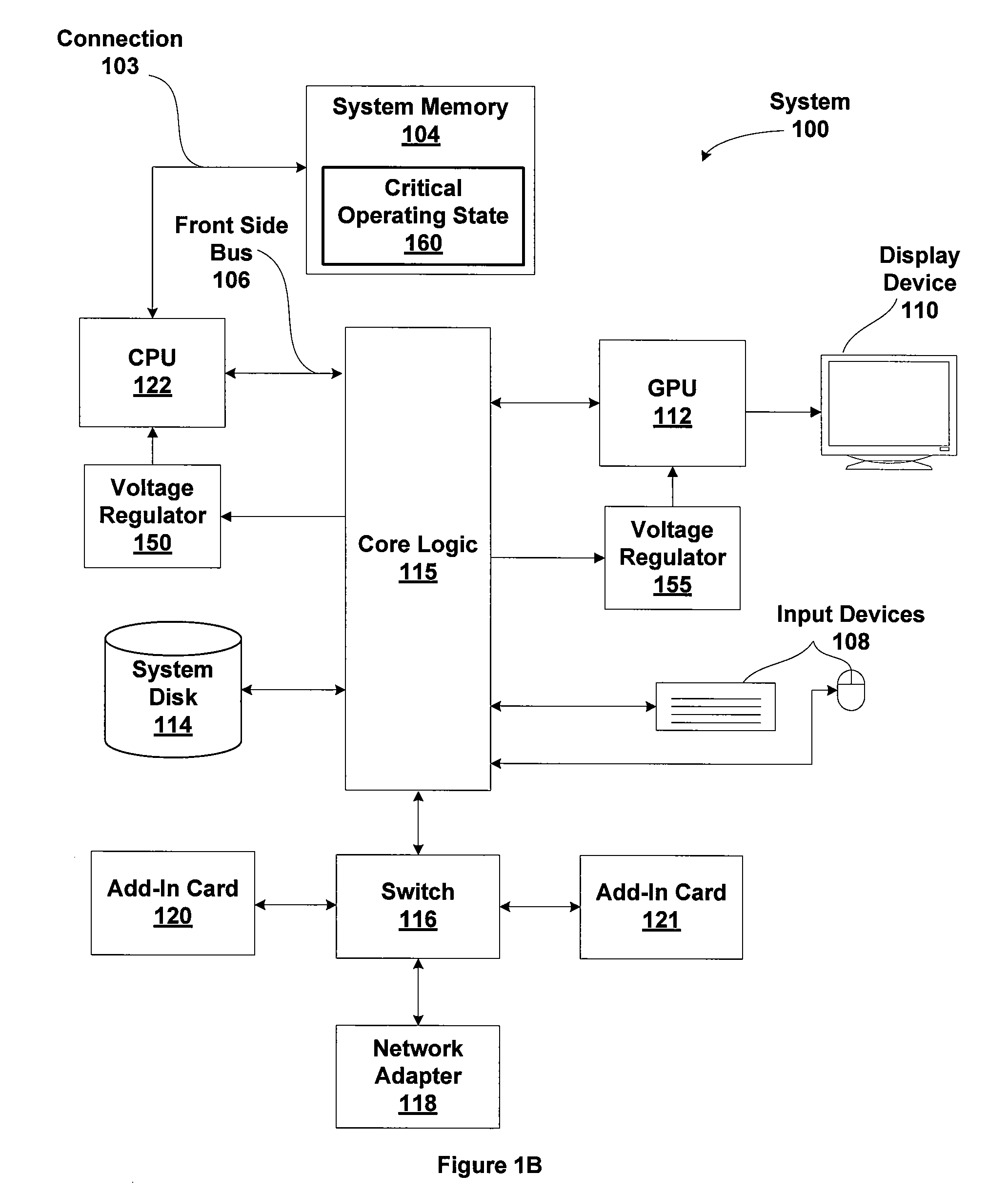

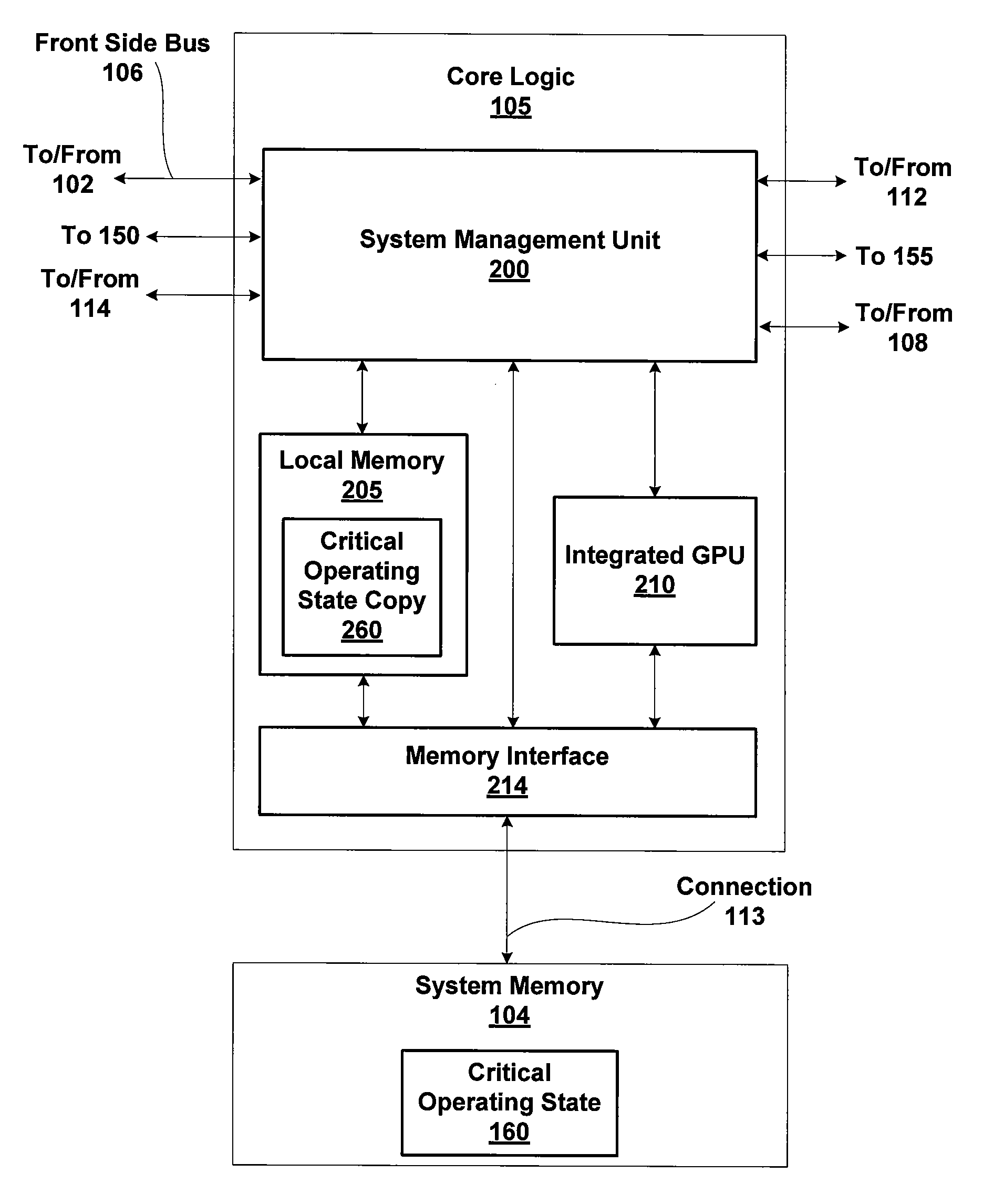

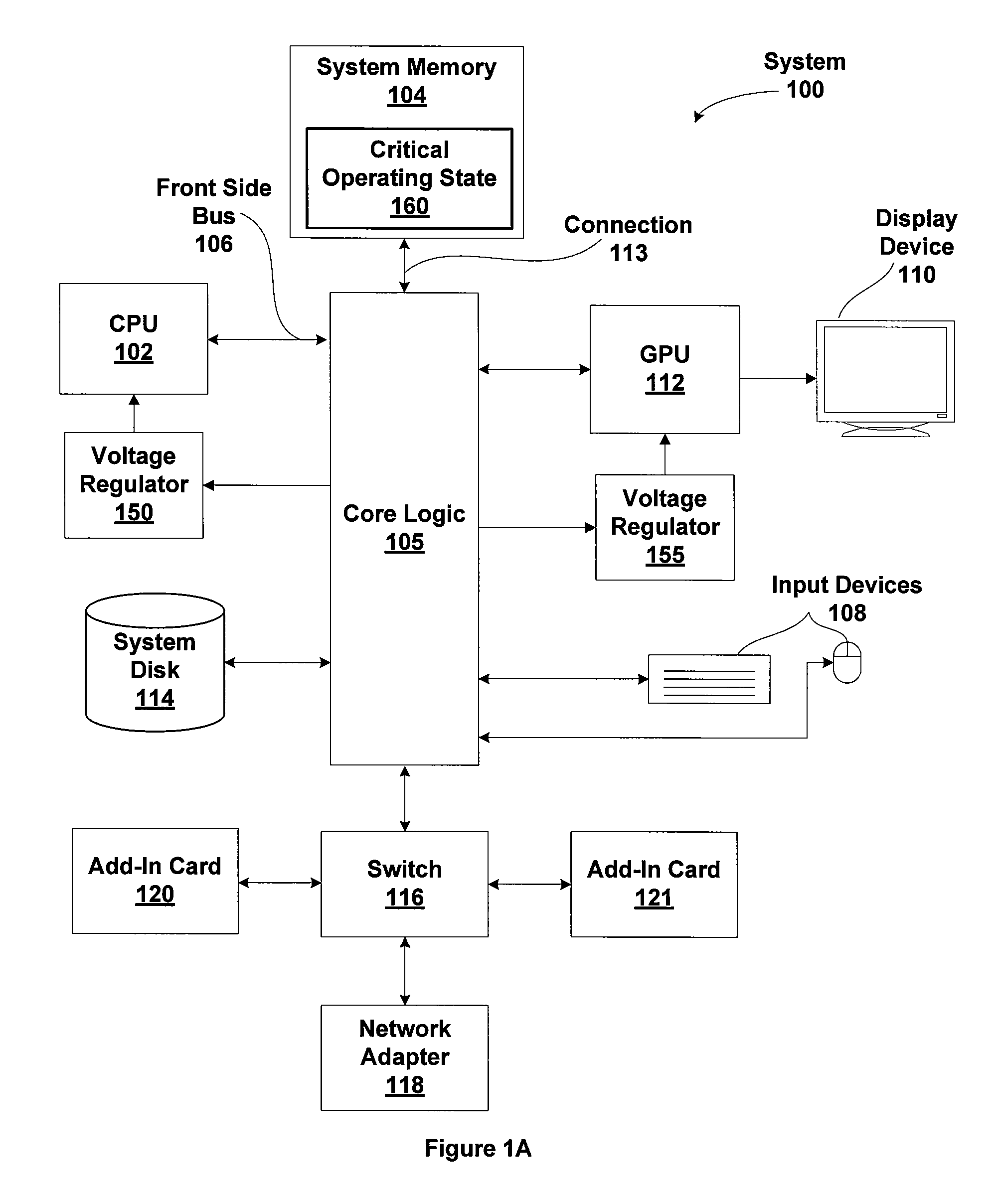

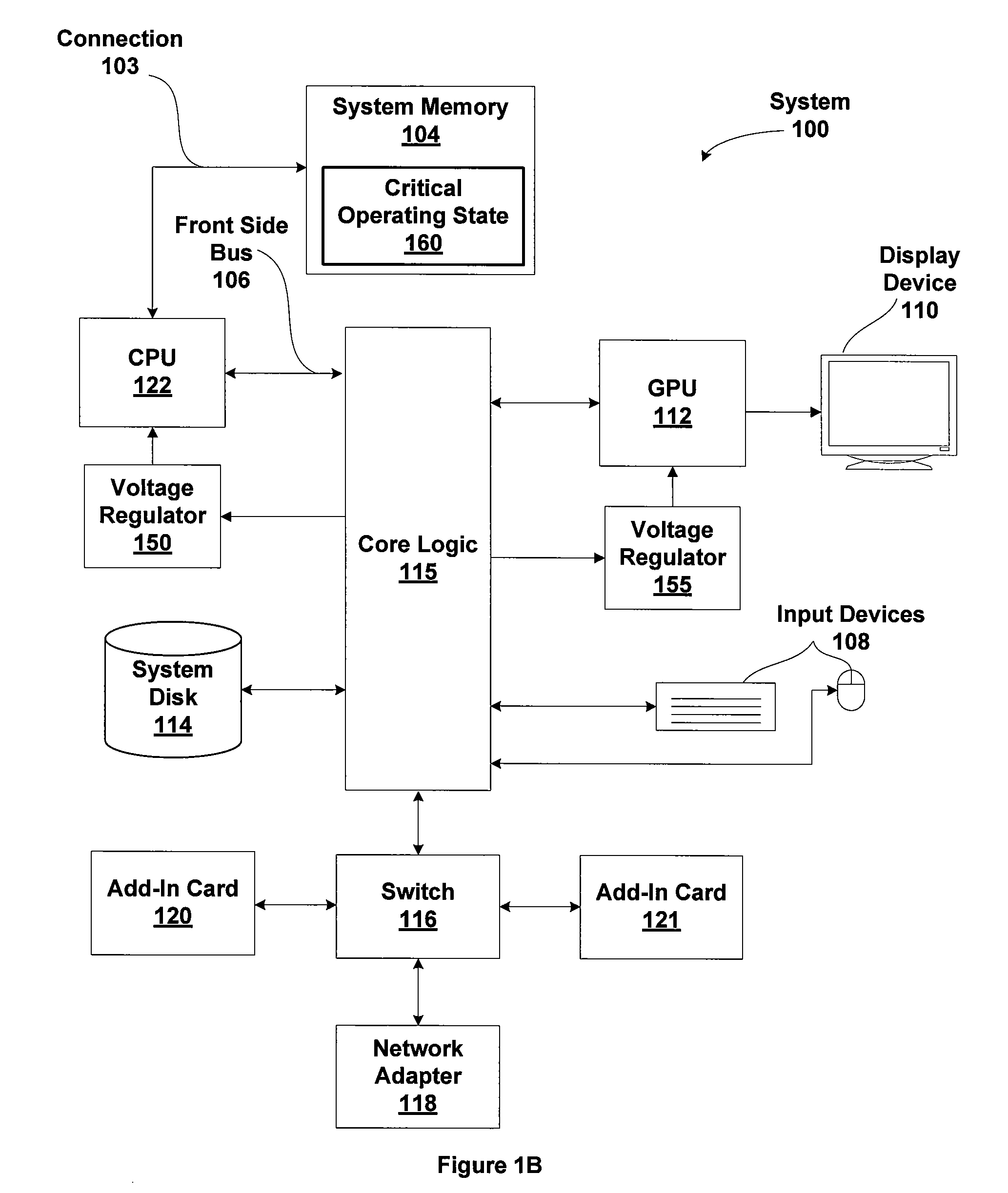

Platform-Based Idle-Time Processing

ActiveUS20100031071A1Extends CPU idle timeReduce power consumptionPower supply for data processingMemory systemsLow activityPower mode

A system and method for transitions a computing system between operating modes that have different power consumption characteristics. When a system management unit (SMU) determines that the computing system is in a low activity state, the SMU transitions the central processing unit (CPU) into a low power operating mode after the CPU stores critical operating state of the CPU in a memory. The SMU then intercepts and processes interrupts intended for the CPU, modifying a copy of the critical operating state. This effectively extends the time during which the CPU stays in lower power mode. When the SMU determines that the computing system exits a low activity state, the copy of the critical operating state is stored in the memory and the SMU transitions the CPU into a high power operating mode using the modified critical operating state.

Owner:NVIDIA CORP

Digitally Compensating for the Impact of Input Bias Current on Current Measurements

ActiveUS20170146575A1Reduce the impactEliminate the effects ofCurrent measurements onlyVoltage/current isolationEngineeringDigital control

A source-measure unit (SMU) may be implemented with digital control loops and circuitry to digitally compensate for the impact of input bias current on current measurements. One or more buffers having well-defined characteristics with respect to certain parameters which may affect the current measurements may be used in the output signal path of the SMU where a shunt voltage developed across a current sense element is measured. For example, the buffers may conduct / develop respective input bias currents that change perceptibly and predictably with temperature. By measuring the temperature and adjusting a control voltage—which is used to develop the shunt voltage—according to the temperature measurements, the impact of the input bias current[s] on the current measurement[s] may be reduced to negligible levels and / or may be eliminated. The control voltage may be adjusted by adjusting a voltage feedback value representative of the measured shunt voltage, and / or by adjusting a current setpoint used for generating the control voltage.

Owner:NATIONAL INSTRUMENTS

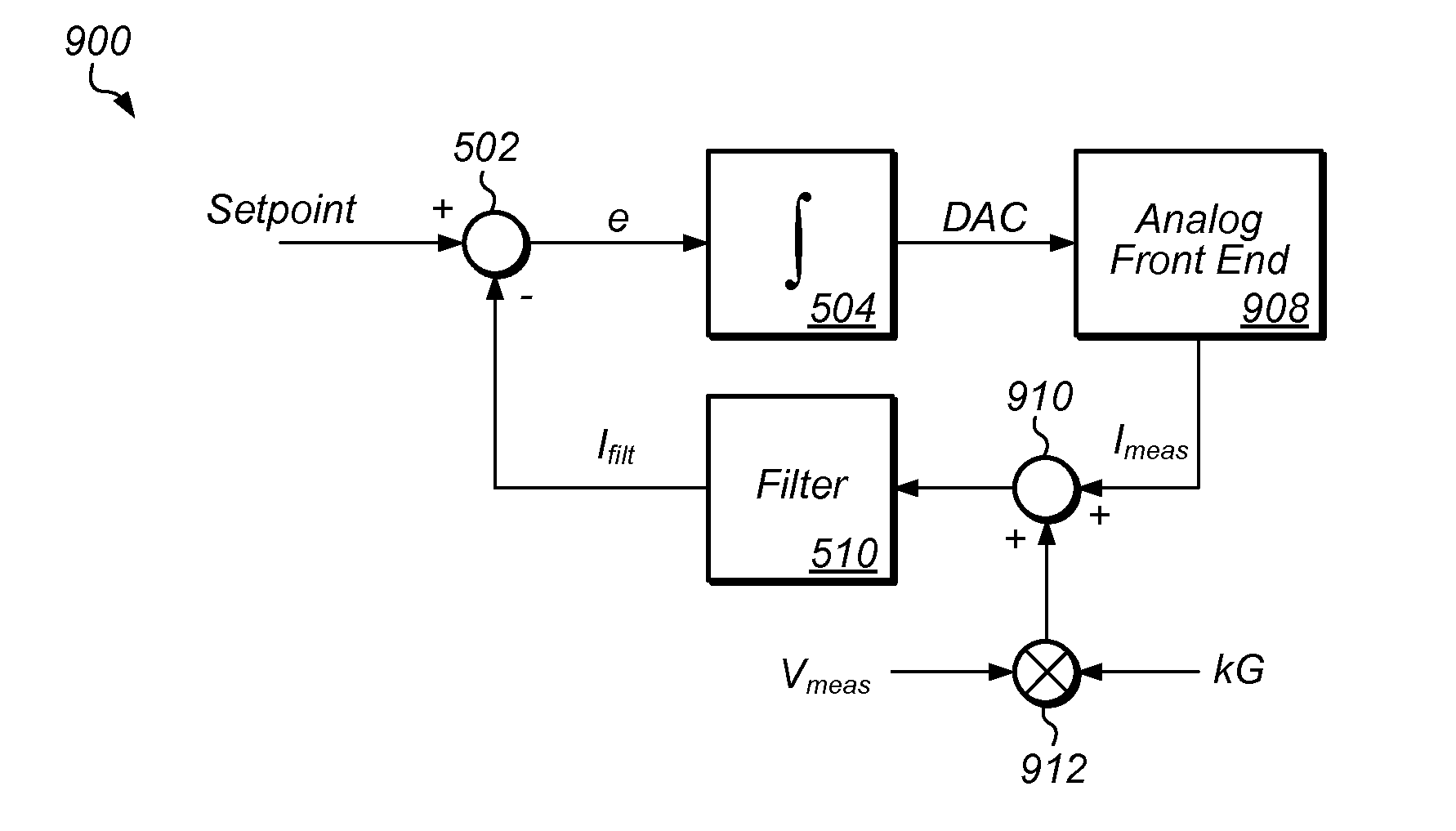

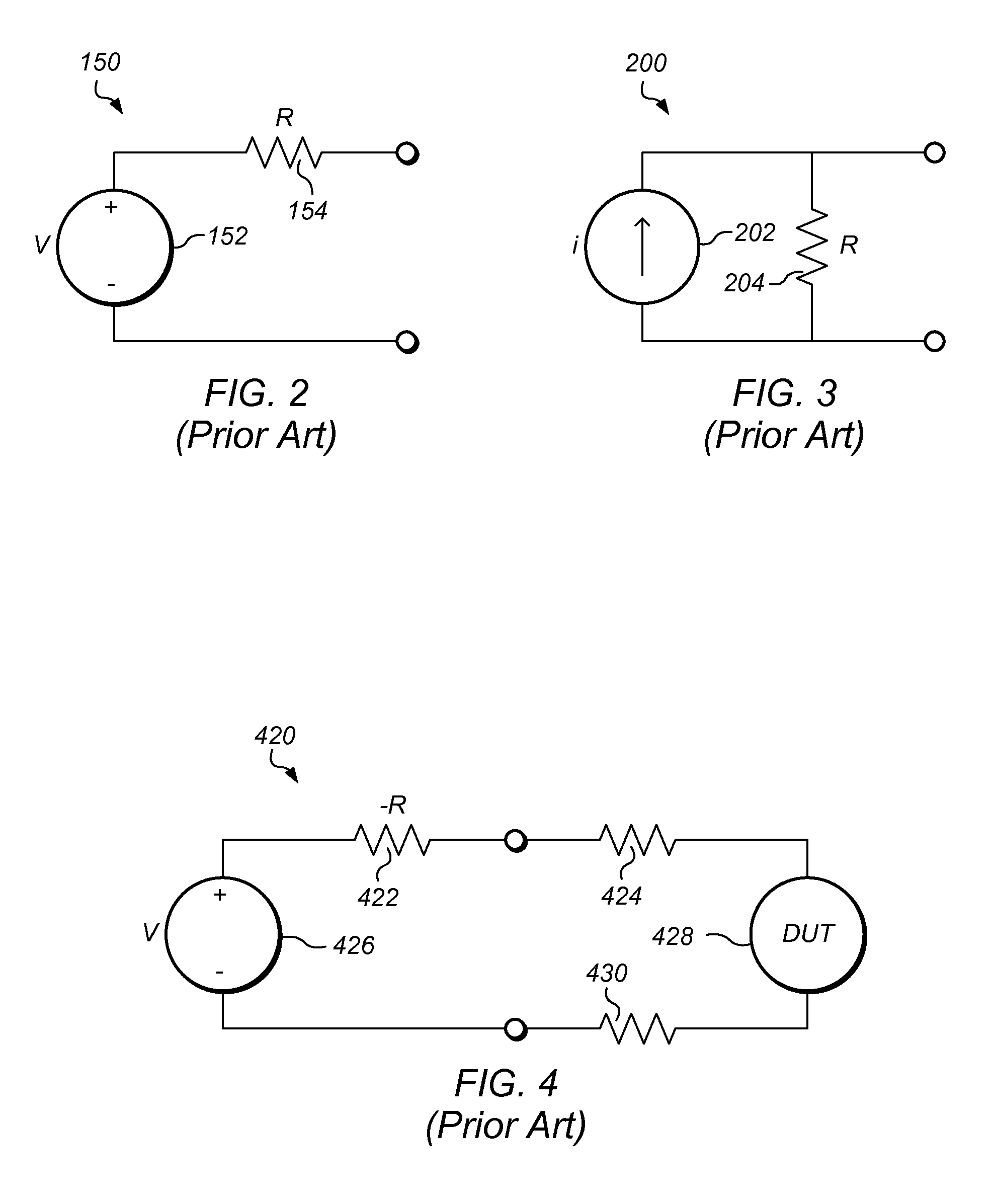

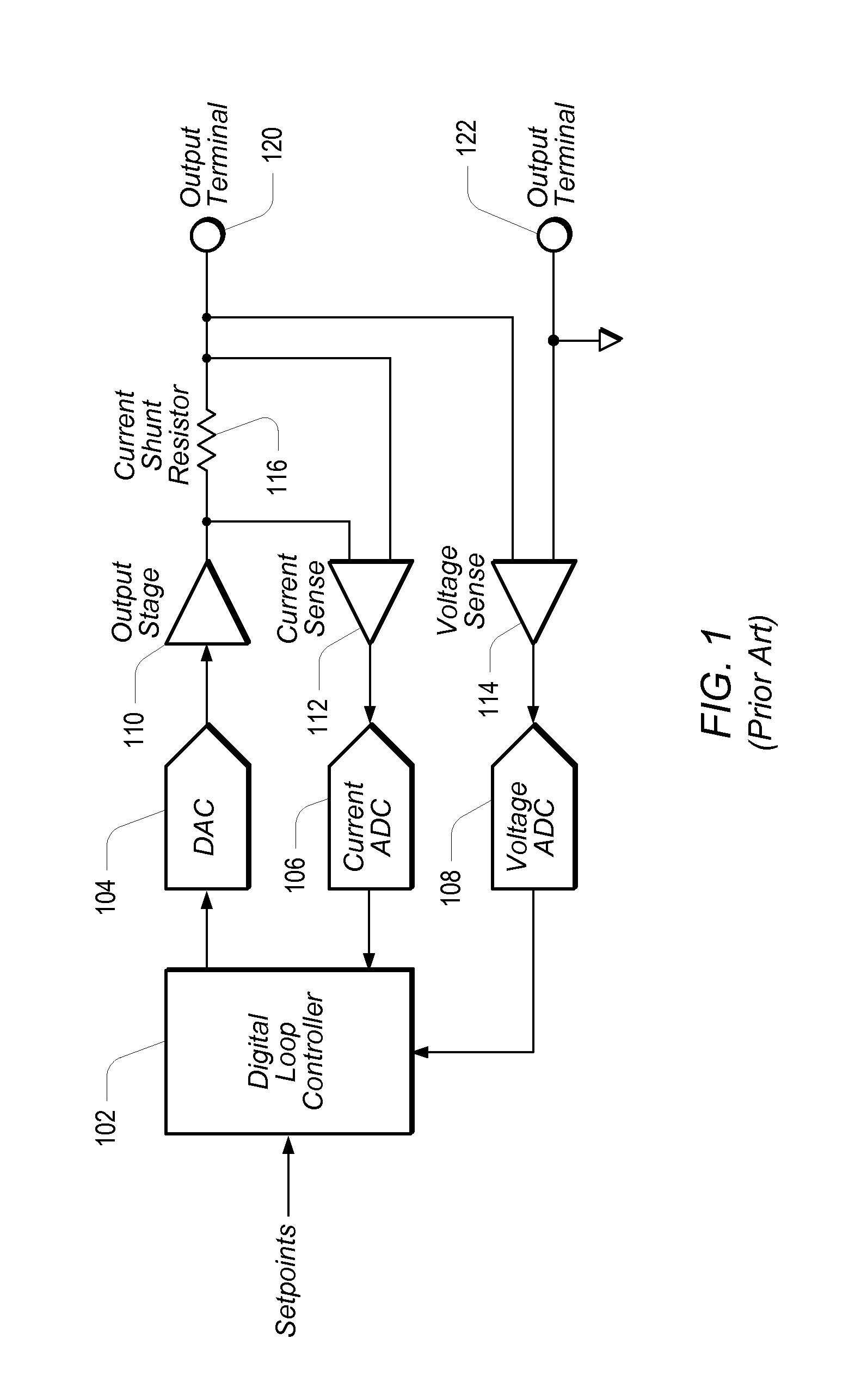

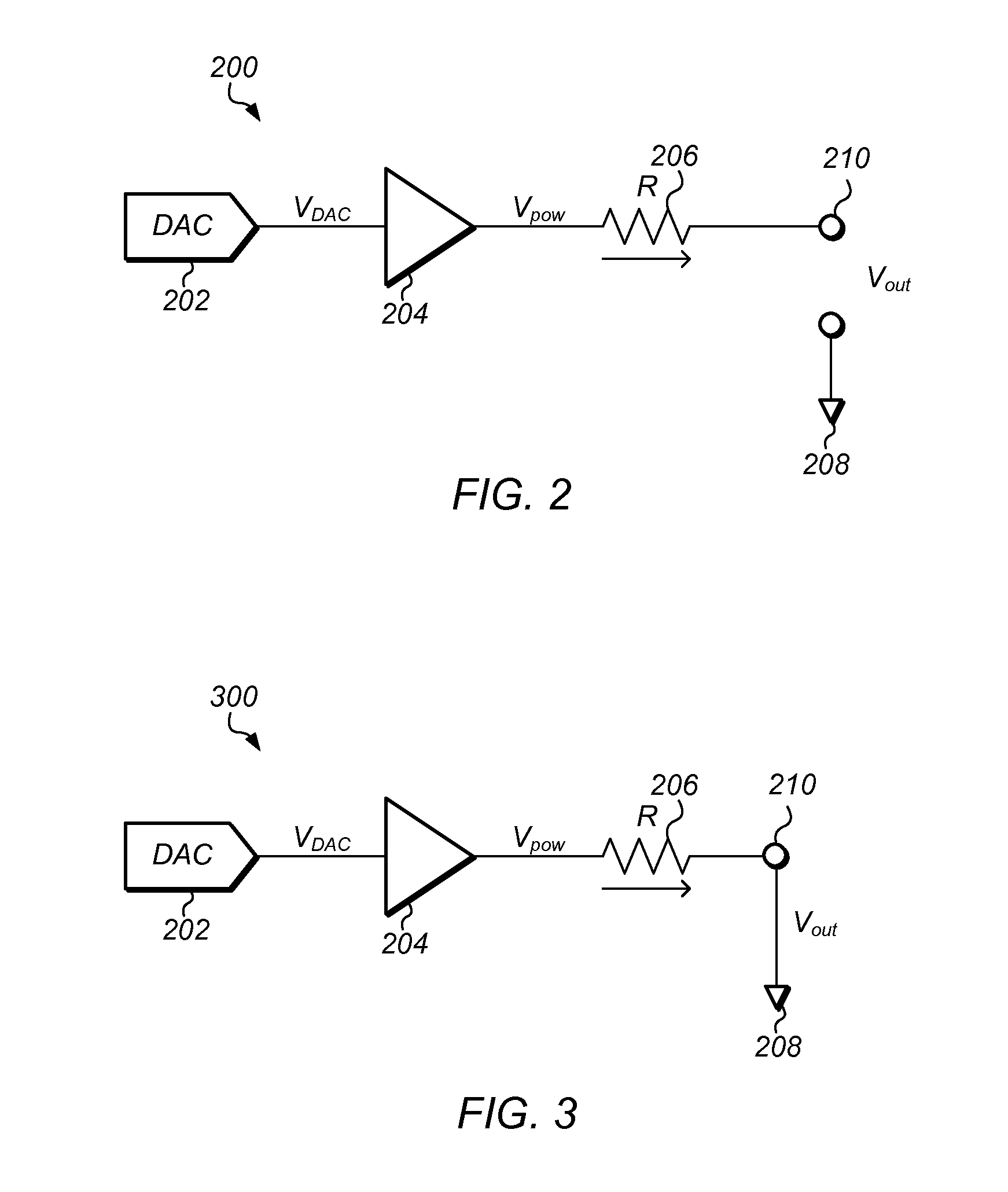

Resistance Simulation and Common Mode Rejection for Digital Source-Measure Units

ActiveUS20120306460A1Increase flexibilityConvenient and accurateAnalogue/digital conversionElectric signal transmission systemsElectrical resistance and conductanceDigital analog converter

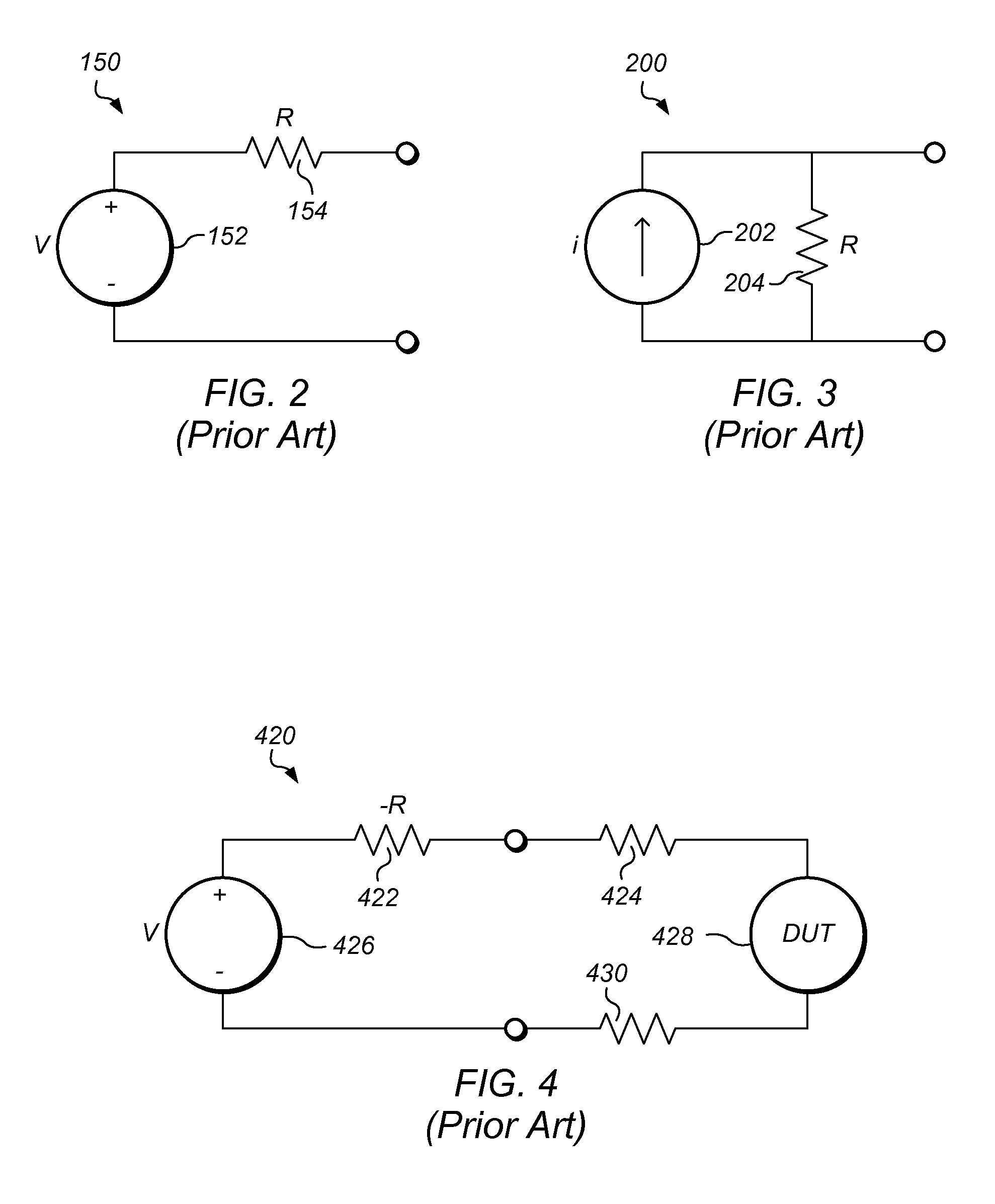

A source-measure unit (SMU) may be implemented with digital control loops. The output voltage and output current may be measured with dedicated ADCs (analog-to-digital converters), and the readings obtained by the ADCs may be compared to a setpoint in a digital loop controller, which may produce an output to drive a DAC (digital-to-analog converter) to maintain the output voltage and / or output current at a desired setpoint. The digital loop controller may also digitally implement simulated resistance with high resolution, accuracy, and range, using Thévenin and Norton power supply models. Simulated resistor values may range from 10Ω to 10Ω for output currents in the 100 mA range, with a sub-200μΩ resolution. The range may be expanded up to 100 kΩ for output currents in the 10 μA range. The Norton and Thévenin implementations may be combined, and a “pure resistance” mode may be created for simulating any desired resistance value. A variation of the general resistance-simulation technique may also be used to compensate for Common Mode Voltage effects in the current measurement path, providing tighter output and measurement specifications at a lower component cost.

Owner:NATIONAL INSTRUMENTS

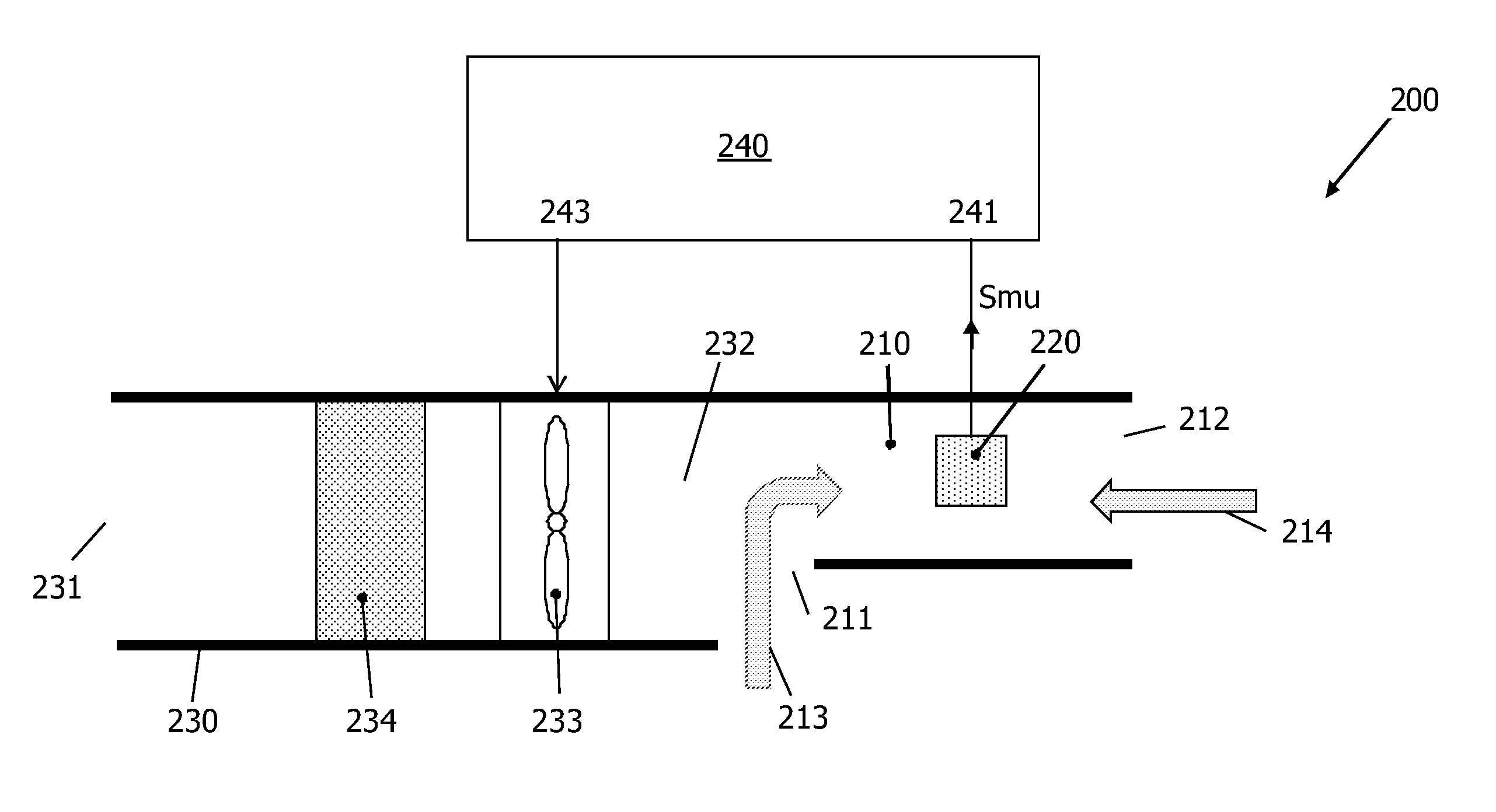

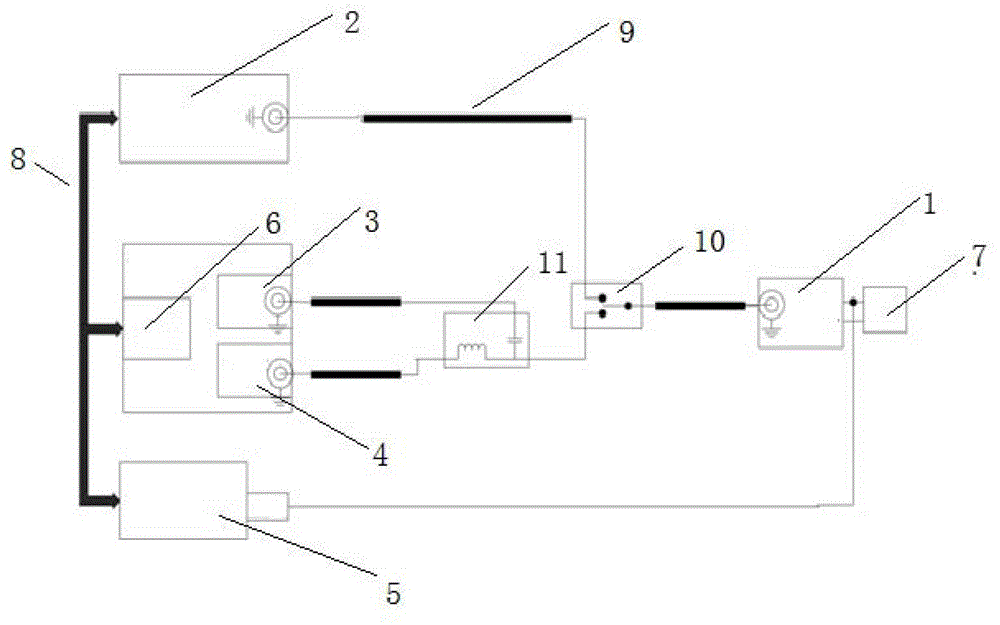

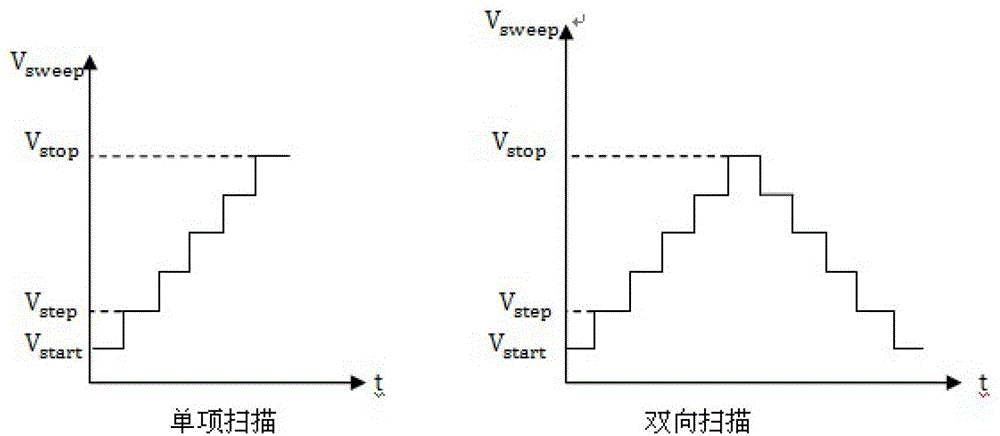

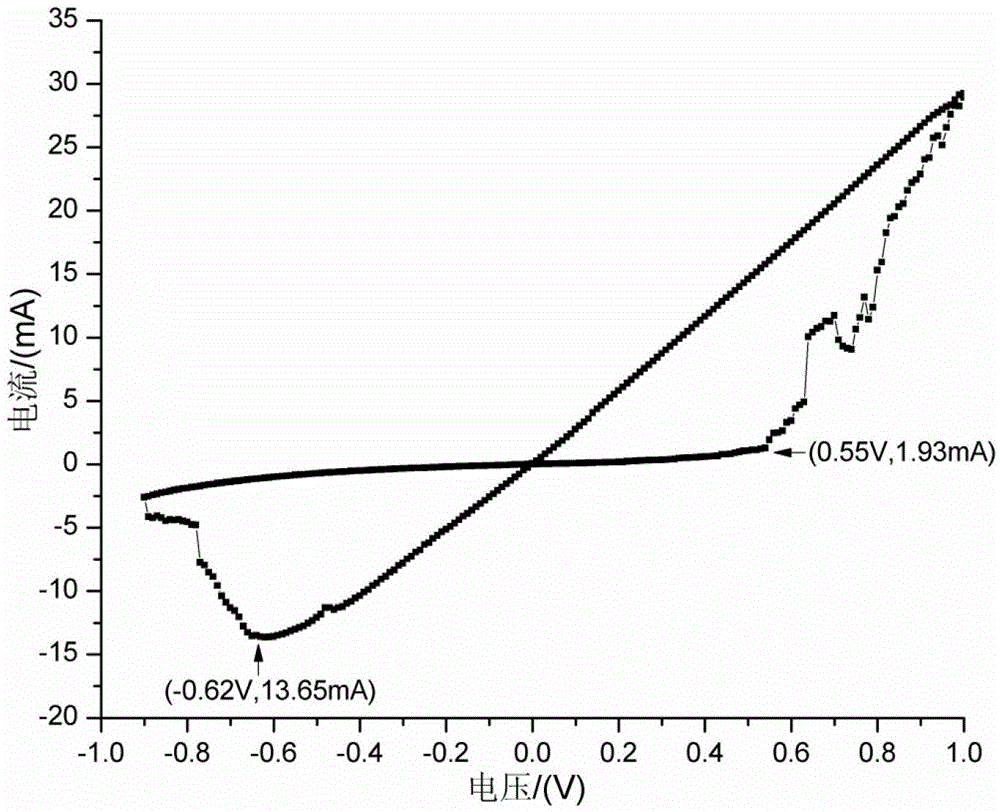

Test system and test method for electrical properties of memristor component unit

ActiveCN103063950AComprehensive Characterization TestSpecification characteristic testElectrical testingVoltage pulseAlternating current

The invention discloses a test system for electrical properties of a memristor component unit. The test system for the electrical properties of the memristor component unit comprises a probe station, a pulse generator, a pulse generation module, a source-measurement unit, an oscilloscope and a central control unit. A probe of the probe station is used for electrically contacting electrodes of a test sample so as to carry out relevant tests; the pulse generator is used for generating voltage pulse signals, and measuring corresponding resistance value states of the test sample through the source-measurement unit; the pulse generation module is used for generating alternating current signals, and processing response conditions of the test sample through the oscilloscope; and the source-measurement unit is also used for executing test instructions of direct current I-V characteristic tests and retention tests except being used for measuring alternating current characteristics. The invention further discloses a corresponding test method for the electrical properties of the memristor component unit. By means of the test system and the test method for the electrical properties of the memristor component unit, comprehensive electrical properties of a memristor can be acquired through the method which is efficient and convenient to operate, measurement accuracy and automation degree can be improved, and meanwhile, strong test expansion capability can be achieved.

Owner:HUAZHONG UNIV OF SCI & TECH

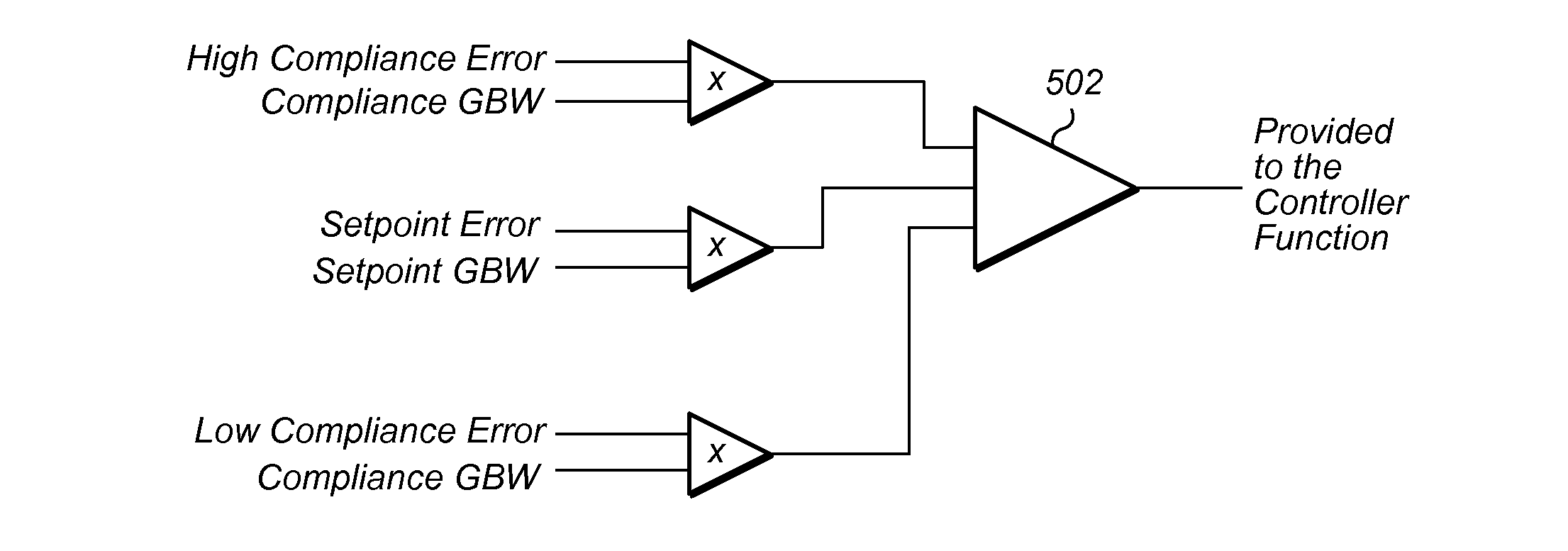

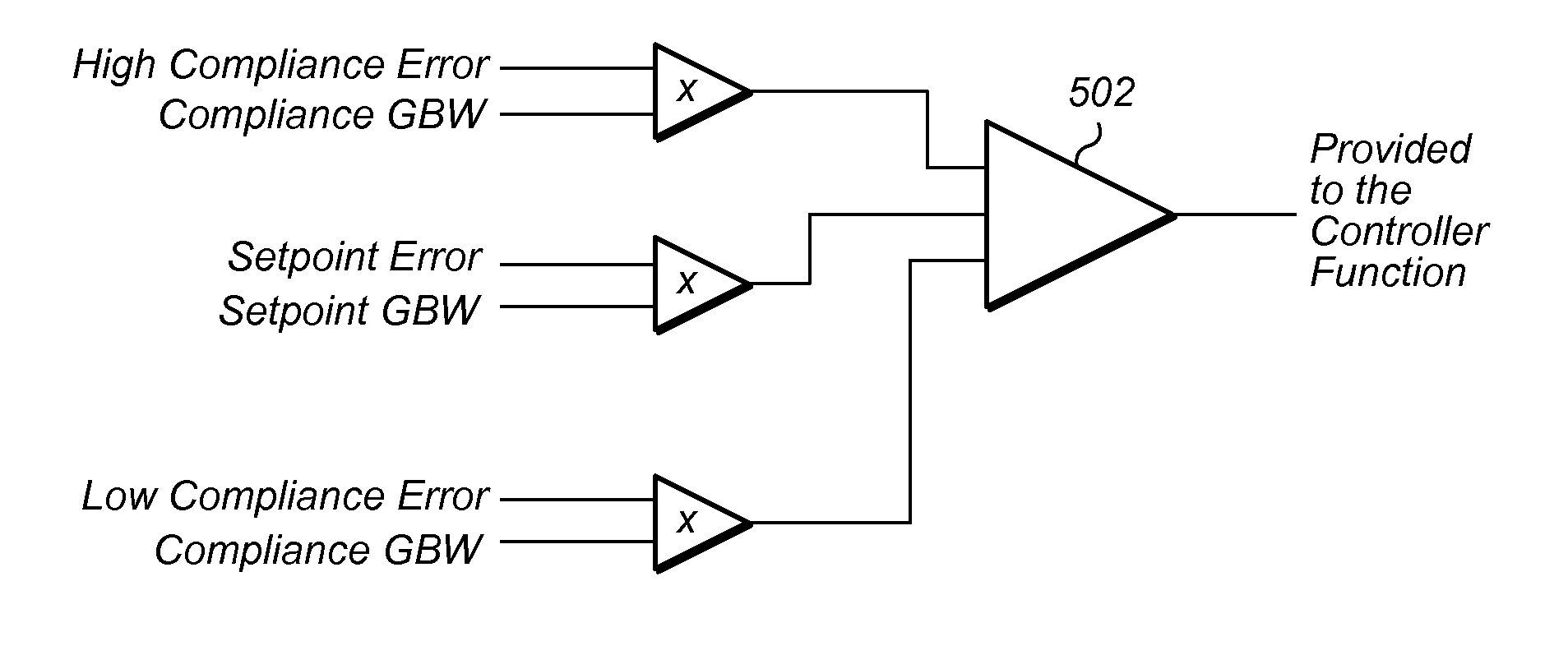

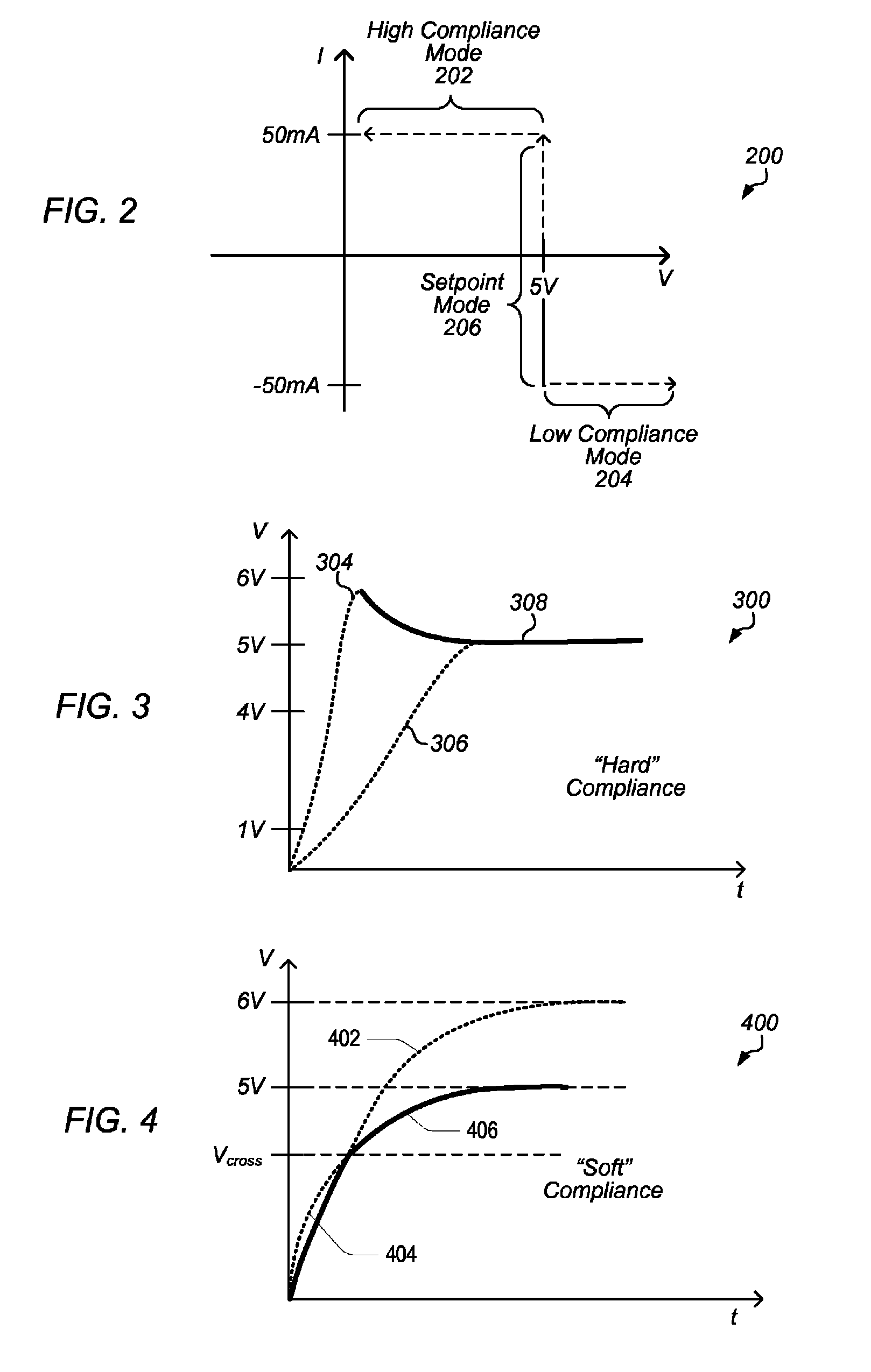

Compliance Methods for Source Measure Units Operating with Digital Control Loops

ActiveUS20120306559A1Convenient and accurateIncrease flexibilityElectric signal transmission systemsElectric devicesIntegratorMode change

A source-measure unit (SMU) may be implemented with respective digital control loops for output voltage and output current. The digital control loop associated with the output that is being regulated may be the setpoint control loop while the digital control loop associated with the other output may be the compliance control loop. The digital loop controller may switch between the setpoint control loop and the compliance control loop without generating a mode-change glitch, by maintaining a single integrator. The compliance methods may differ in how and when the decision is made to select which of the measured signals provides the error signal to the integrator. Thus, there may be no issue with integrator wind-up, which might be the case if there were two complete control loops operating continuously.

Owner:NATIONAL INSTRUMENTS

High accuracy and universal on-chip switch matrix testline

ActiveUS7782073B2Improve accuracySolid-state devicesSemiconductor devicesFunctional testingDevice form

A testline structure made for integrated circuit tests is presented. The structure includes an array of testline pads formed in the scribe line area or integrated circuit die area on a semiconductor substrate, a plurality of test devices formed under the pads area, and a select circuit selectively connecting one of the test devices. The testline structure of this invention enables access to a large number of test devices through the same number of pads as on a conventional testline and can be employed to conduct parametric, reliability, and functional tests on the same. A source measurement unit (SMU) in a conventional integrated circuit tester is employed to sense and force predetermined test conditions on the test device terminals and conduct accurate Kelvin tests on the selected device. A method of using this testline structure is also presented.

Owner:TAIWAN SEMICON MFG CO LTD

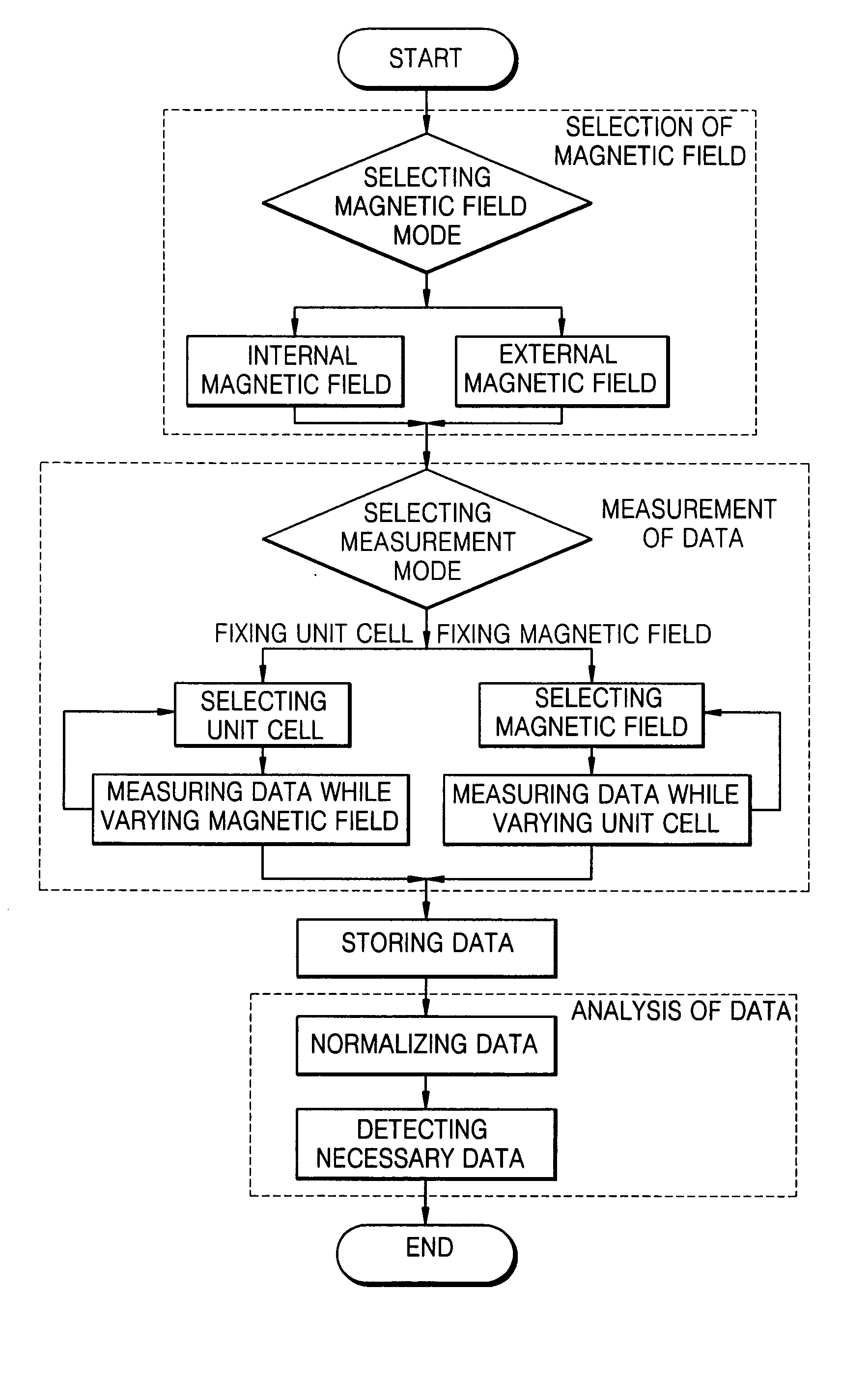

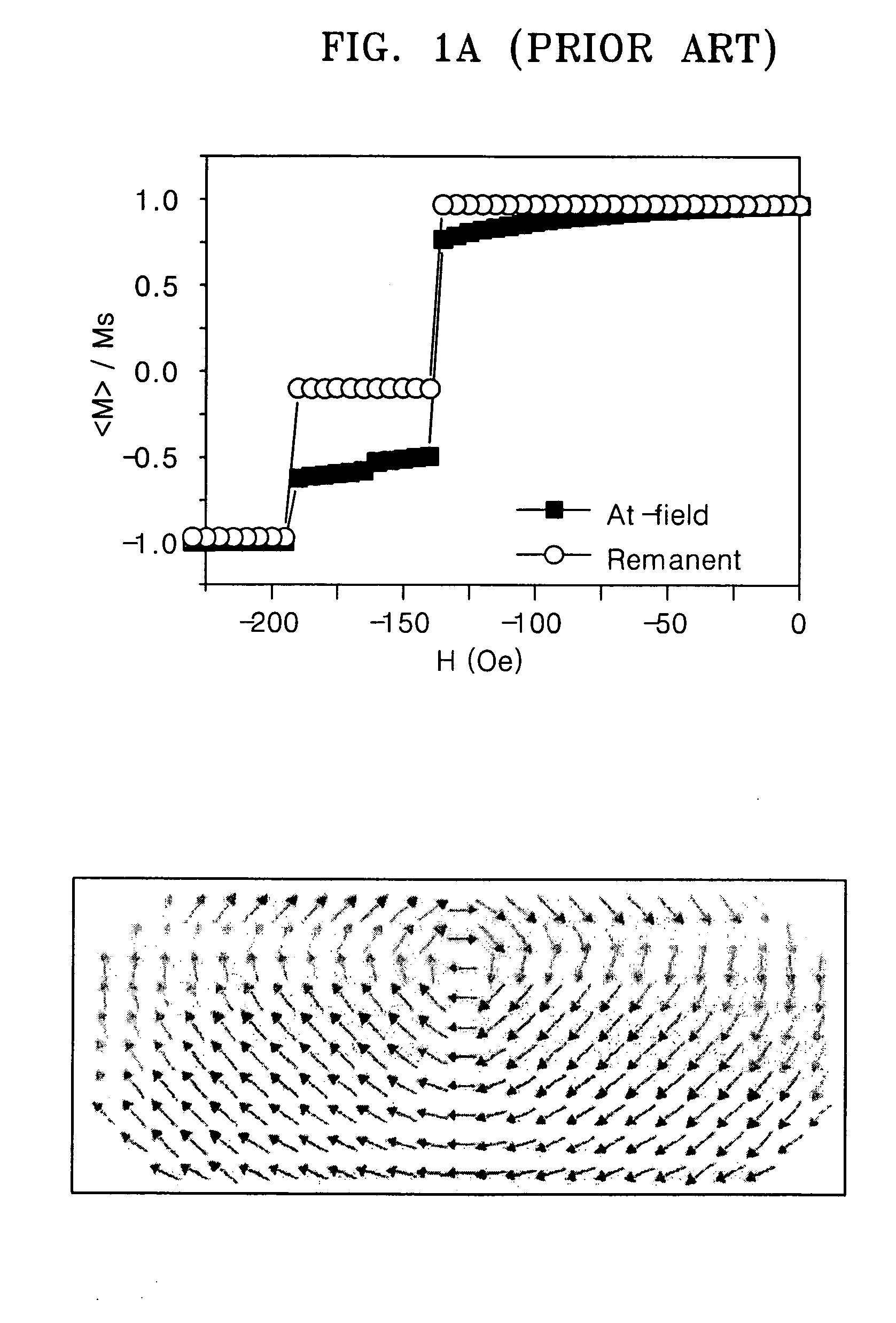

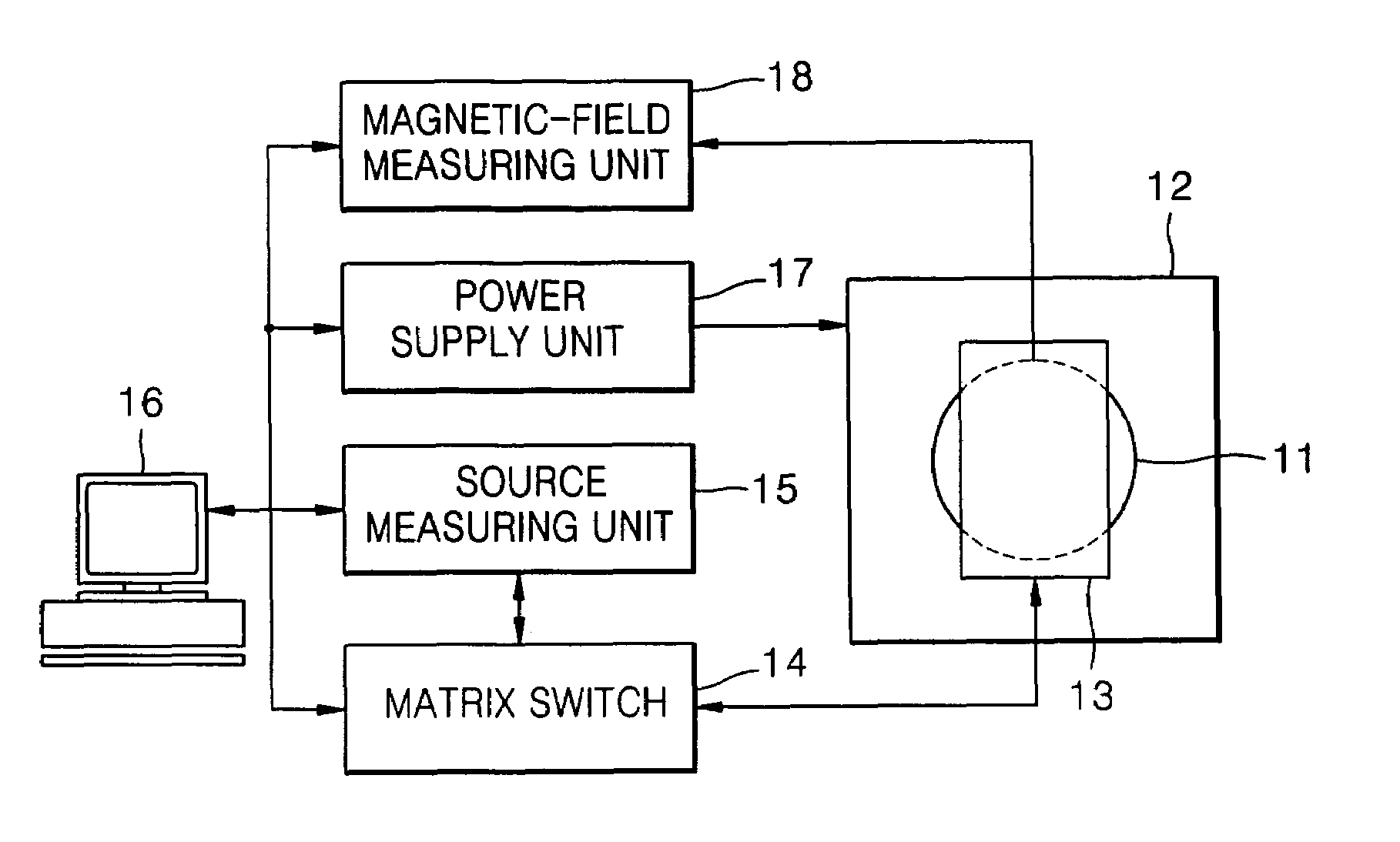

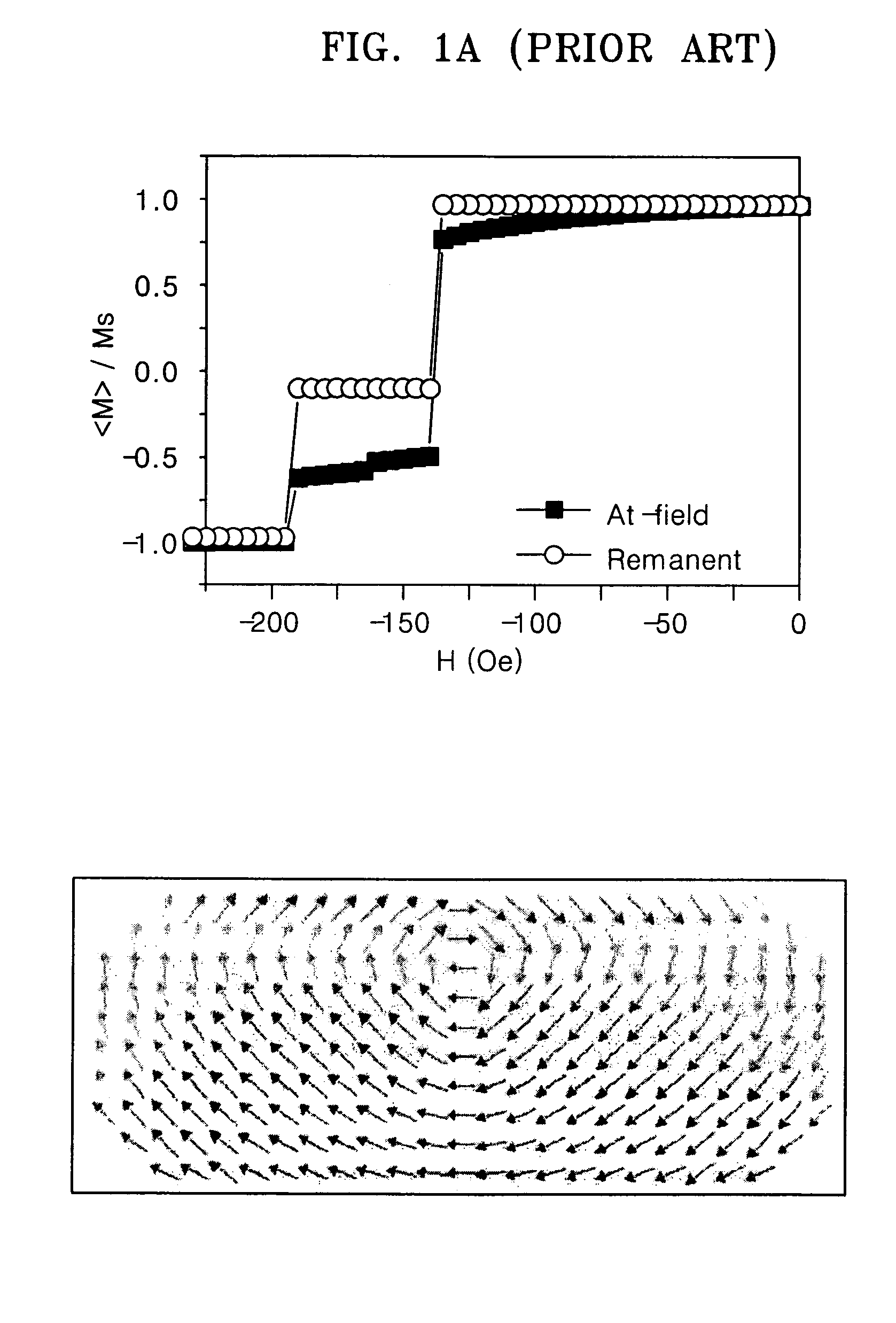

Apparatus and method of analyzing a magnetic random access memory

ActiveUS20050111253A1Quick measurementQuickly measuring characteristicError detection/correctionMagnetic-field-controlled resistorsRandom access memoryEngineering

In an apparatus for analyzing a magnetic random access memory (MRAM), and a method of analyzing an MRAM, the apparatus includes an MRAM mounting unit on which an MRAM is mounted, a magnetic field applying unit positioned around the MRAM mounting unit for applying an external magnetic field to the MRAM mounted on the MRAM mounting unit, a cell addressing unit for selecting one of a plurality of unit cells of the MRAM mounted on the MRAM mounting unit, a source measurement unit for applying an internal magnetic field to the selected unit cell of the MRAM or for measuring a resistance of the selected unit cell of the MRAM, and a computer unit for storing and for analyzing data regarding the measured resistance of the each of the plurality of unit cells of the MRAM.

Owner:SAMSUNG ELECTRONICS CO LTD

Apparatus and method of analyzing a magnetic random access memory

ActiveUS7165197B2Quick measurementSimple structureError detection/correctionMagnetic-field-controlled resistorsStatic random-access memoryRandom access memory

In an apparatus for analyzing a magnetic random access memory (MRAM), and a method of analyzing an MRAM, the apparatus includes an MRAM mounting unit on which an MRAM is mounted, a magnetic field applying unit positioned around the MRAM mounting unit for applying an external magnetic field to the MRAM mounted on the MRAM mounting unit, a cell addressing unit for selecting one of a plurality of unit cells of the MRAM mounted on the MRAM mounting unit, a source measurement unit for applying an internal magnetic field to the selected unit cell of the MRAM or for measuring a resistance of the selected unit cell of the MRAM, and a computer unit for storing and for analyzing data regarding the measured resistance of the each of the plurality of unit cells of the MRAM.

Owner:SAMSUNG ELECTRONICS CO LTD

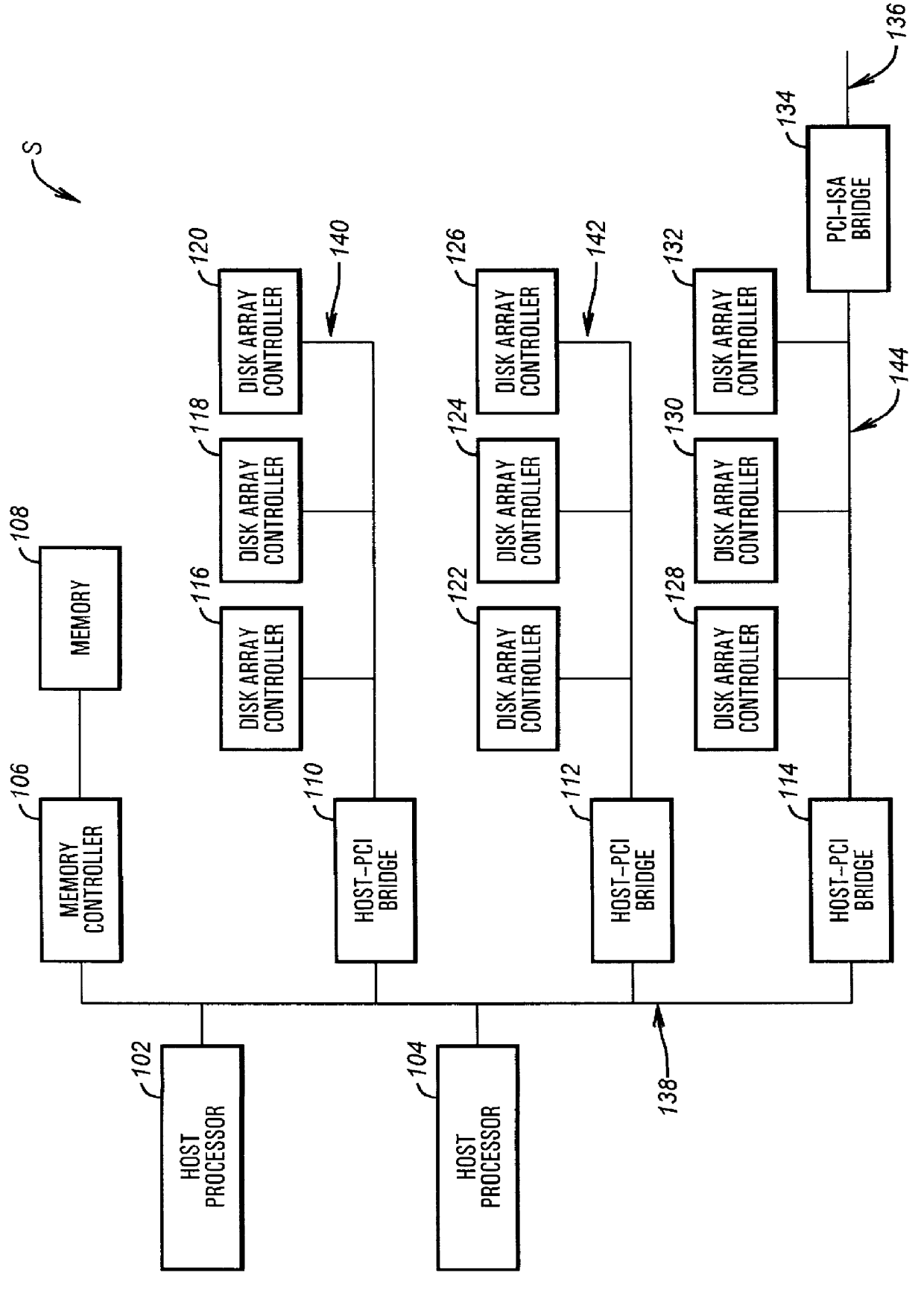

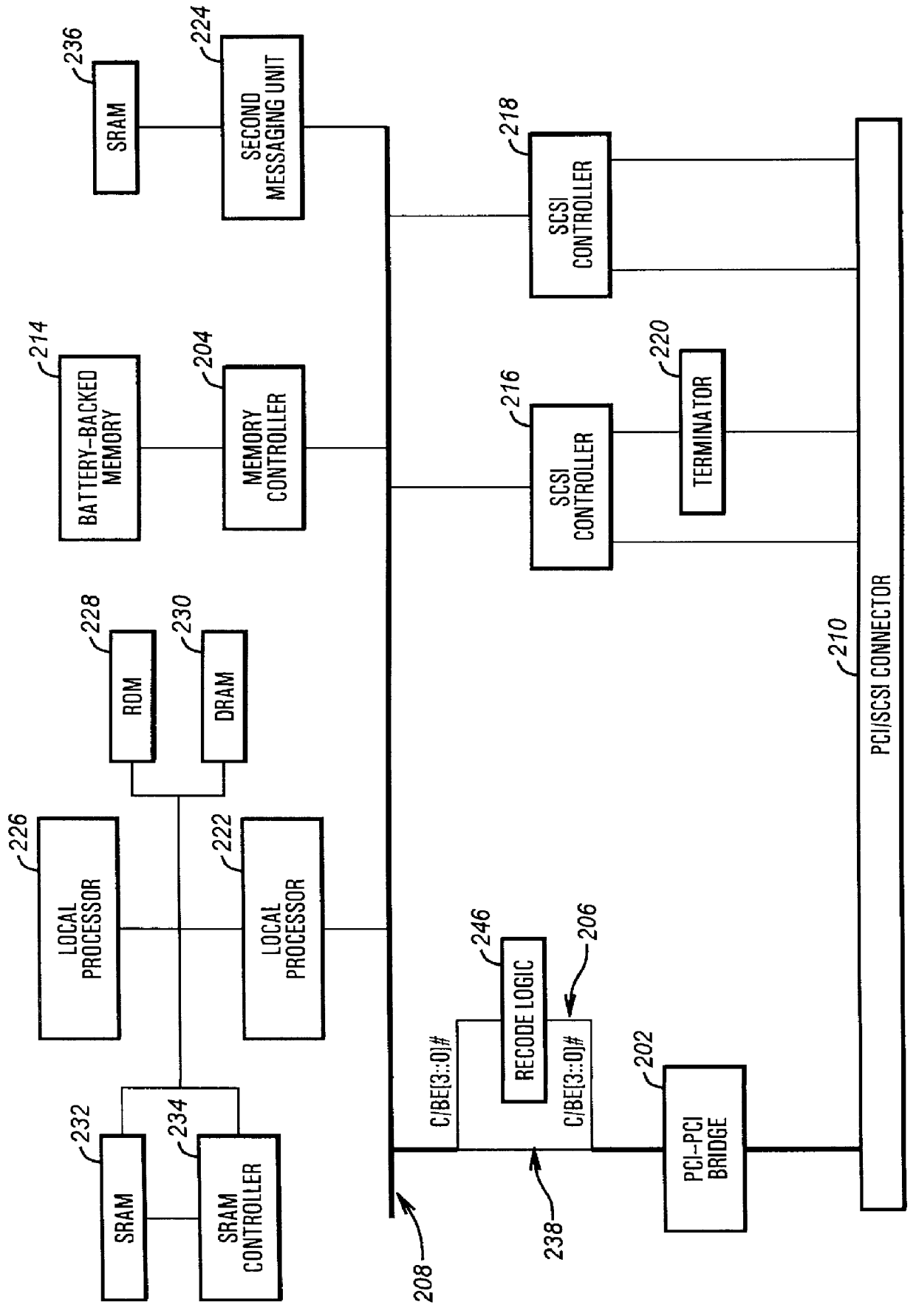

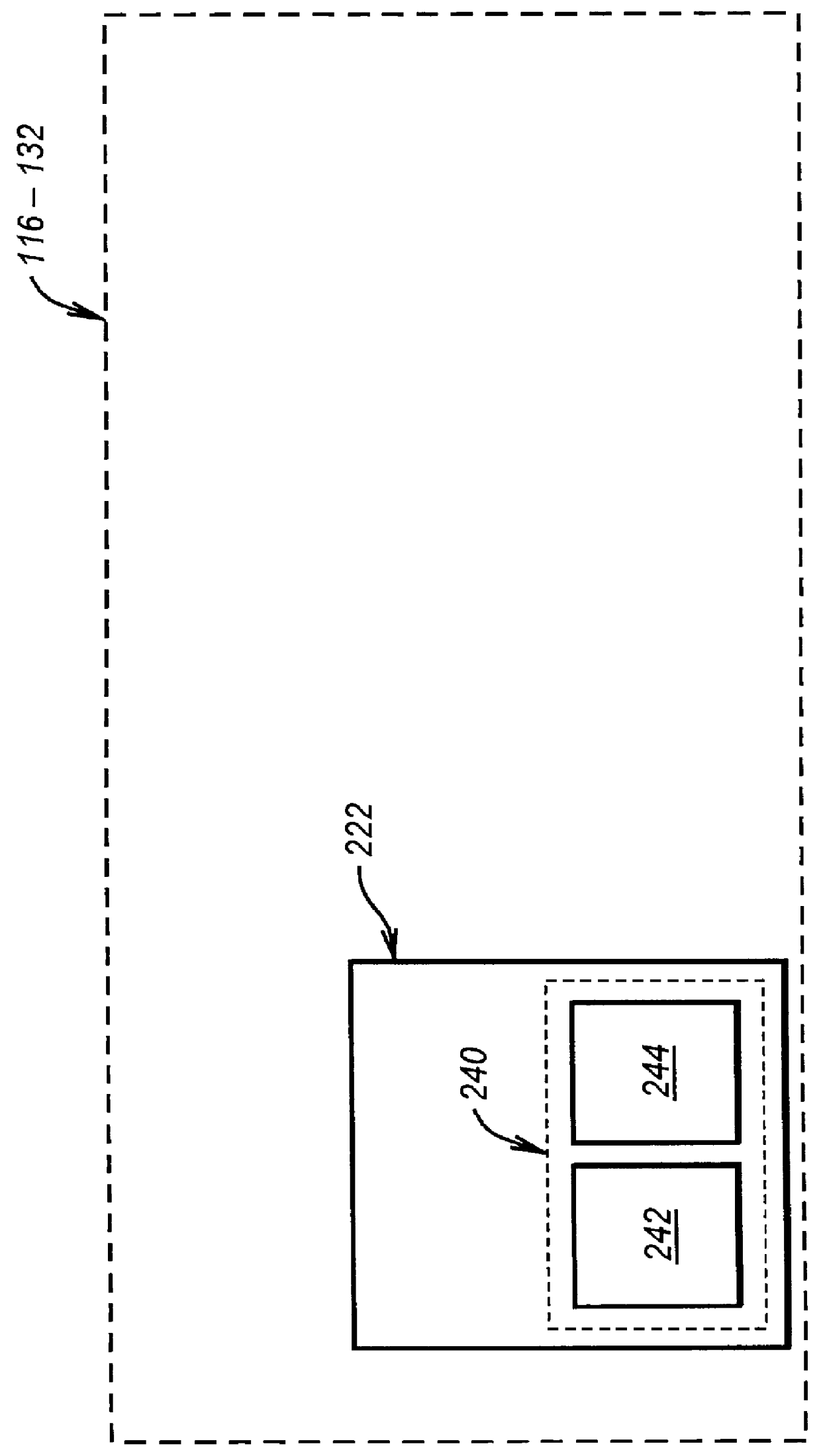

Peripheral controller comprising first messaging unit for communication with first OS driver and second messaging unit for communication with second OS driver for mass-storage peripheral

An embodiment of the present invention provides a peripheral controller for coupling a mass storage peripheral to a computer system. In a disclosed embodiment the peripheral controller is a disk array controller programmed for RAID. The peripheral controller includes a first messaging unit (FMU), a second messaging unit (SMU), and a peripheral interface which are connected by a local bus. The FMU responds to messages from a first operating system driver. The SMU responds to messages from a different second operating system driver. In one embodiment, the FMU responds to commands from the first operating system driver which is non-standard. In another embodiment, the SMU responds to commands from the second operating system driver which is compatible with the I2O standard. In the disclosed embodiment, the peripheral interface controls mass storage peripherals in response to messages sent to the FMU or the SMU.

Owner:HEWLETT-PACKARD ENTERPRISE DEV LP

Platform-based idle-time processing

ActiveUS7779191B2Reduce power consumptionProgram initiation/switchingPower supply for data processingPower modeLow activity

A system and method for transitions a computing system between operating modes that have different power consumption characteristics. When a system management unit (SMU) determines that the computing system is in a low activity state, the SMU transitions the central processing unit (CPU) into a low power operating mode after the CPU stores critical operating state of the CPU in a memory. The SMU then intercepts and processes interrupts intended for the CPU, modifying a copy of the critical operating state. This effectively extends the time during which the CPU stays in lower power mode. When the SMU determines that the computing system exits a low activity state, the copy of the critical operating state is stored in the memory and the SMU transitions the CPU into a high power operating mode using the modified critical operating state.

Owner:NVIDIA CORP

Compliance methods for source measure units operating with digital control loops

ActiveUS8456338B2Convenient and accurateNoise rejection advantagesElectric signal transmission systemsElectric devicesIntegratorMode change

Owner:NATIONAL INSTRUMENTS

Resistance simulation and common mode rejection for digital source-measure units

ActiveUS8604765B2Increase flexibilityConvenient and accurateAnalogue/digital conversionElectric signal transmission systemsElectrical resistance and conductanceDigital analog converter

A source-measure unit (SMU) may be implemented with digital control loops. The output voltage and output current may be measured with dedicated ADCs (analog-to-digital converters), and the readings obtained by the ADCs may be compared to a setpoint in a digital loop controller, which may produce an output to drive a DAC (digital-to-analog converter) to maintain the output voltage and / or output current at a desired setpoint. The digital loop controller may also digitally implement simulated resistance with high resolution, accuracy, and range, using Thévenin and Norton power supply models. Simulated resistor values may range from 10Ω to 10Ω for output currents in the 100 mA range, with a sub-200μΩ resolution. The range may be expanded up to 100 kΩ for output currents in the 10 μA range. The Norton and Thévenin implementations may be combined, and a “pure resistance” mode may be created for simulating any desired resistance value. A variation of the general resistance-simulation technique may also be used to compensate for Common Mode Voltage effects in the current measurement path, providing tighter output and measurement specifications at a lower component cost.

Owner:NATIONAL INSTRUMENTS

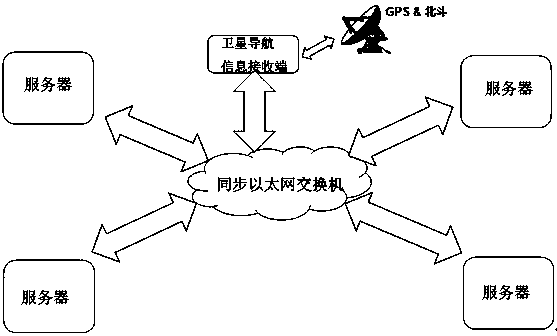

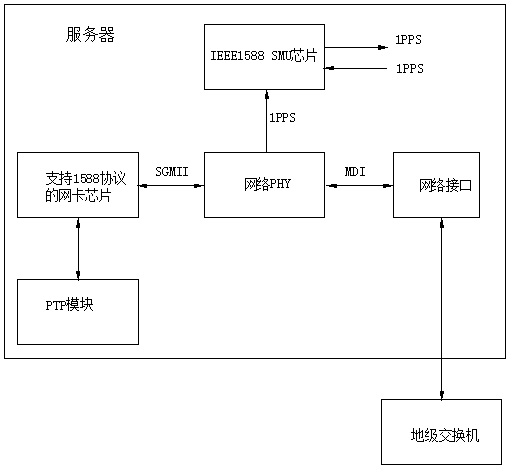

System and method of synchronizing clocks of servers based on PTP protocol

ActiveCN107947887AReduce time communication delaySolve the transaction delay application requirementsTime-division multiplexTime informationOperational system

The invention discloses a system of synchronizing clocks of servers based on a PTP protocol, and relates to a server clock synchronization technology. The servers around the world, when being startedup, starts up the local clock by default, loads a PTP module drive after entering an operating system and obtains a PTP signal transmitted from a satellite navigation information receiving end throughaccessing a synchronous Ethernet switch; the servers around the world parse the PTP signal to obtain clock and time information, provides the clock information to system hardware and synchronizes thetime information to the operating system; and the servers realize high-precision clock time synchronization of multiple servers and reduce cross-server time communication delay through integral design of a network PHY chip, an IEEE1588 SMU chip and a network card chip supporting IEEE1588 synchronization. The system of synchronizing clocks of servers based on the PTP protocol can be deployed in each key application field conveniently and improves application transaction reliability greatly; and a method of synchronizing clocks of servers based on the PTP protocol is also provided.

Owner:ZHENGZHOU YUNHAI INFORMATION TECH CO LTD

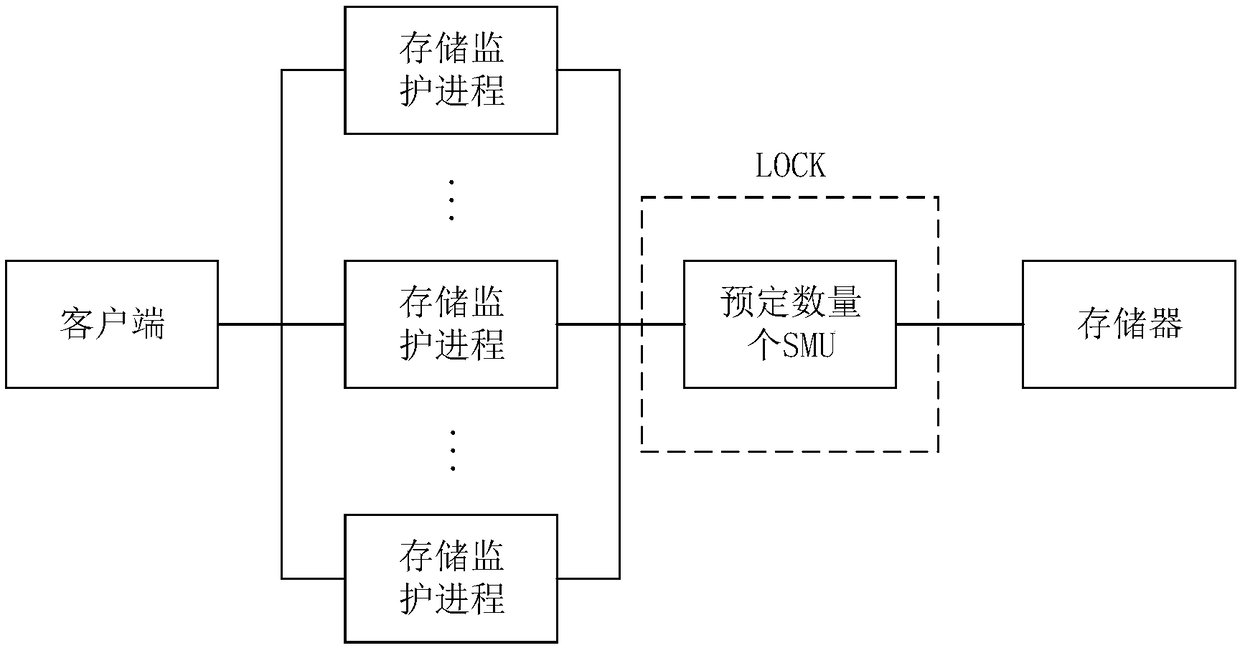

Data storage method, device and related equipment

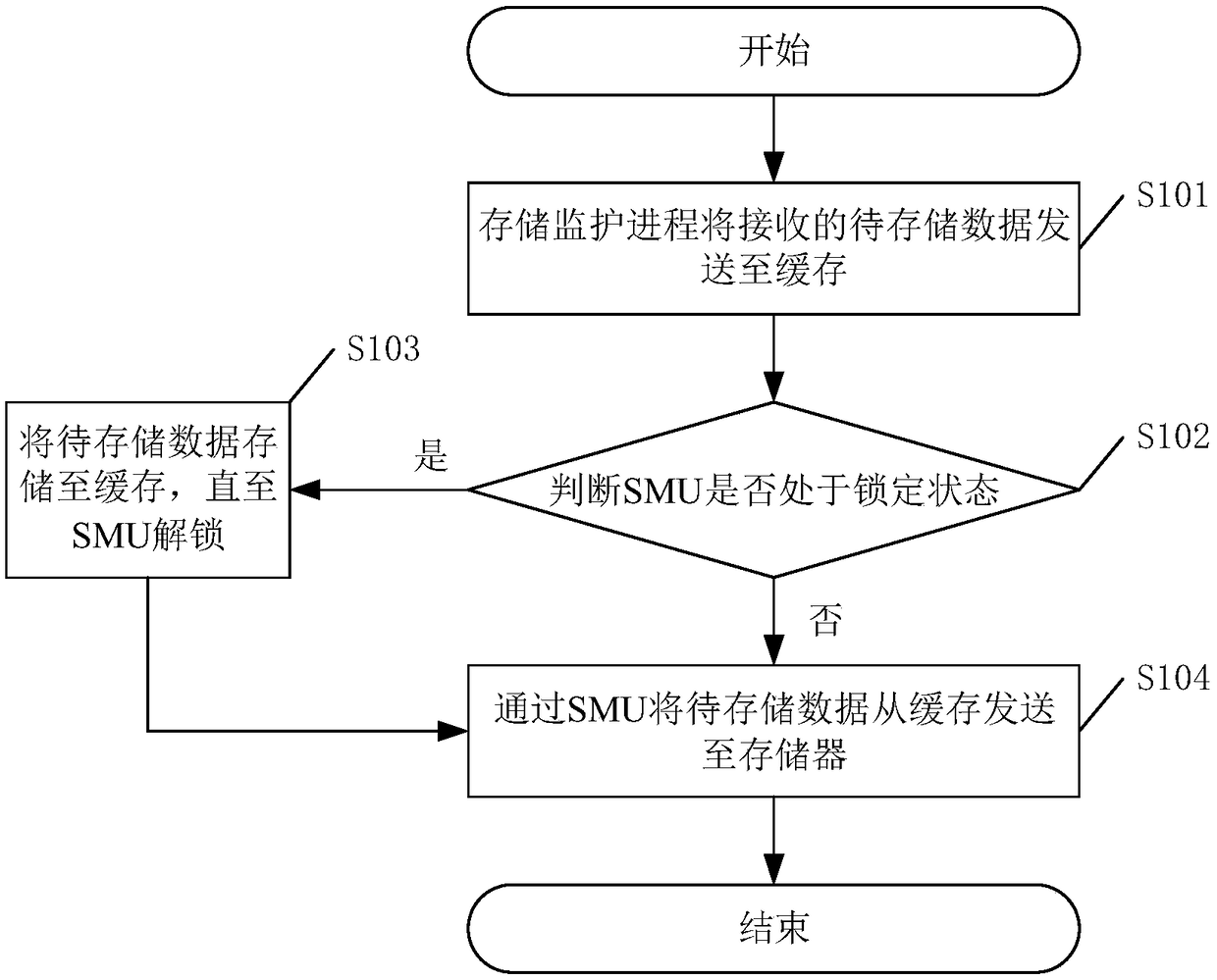

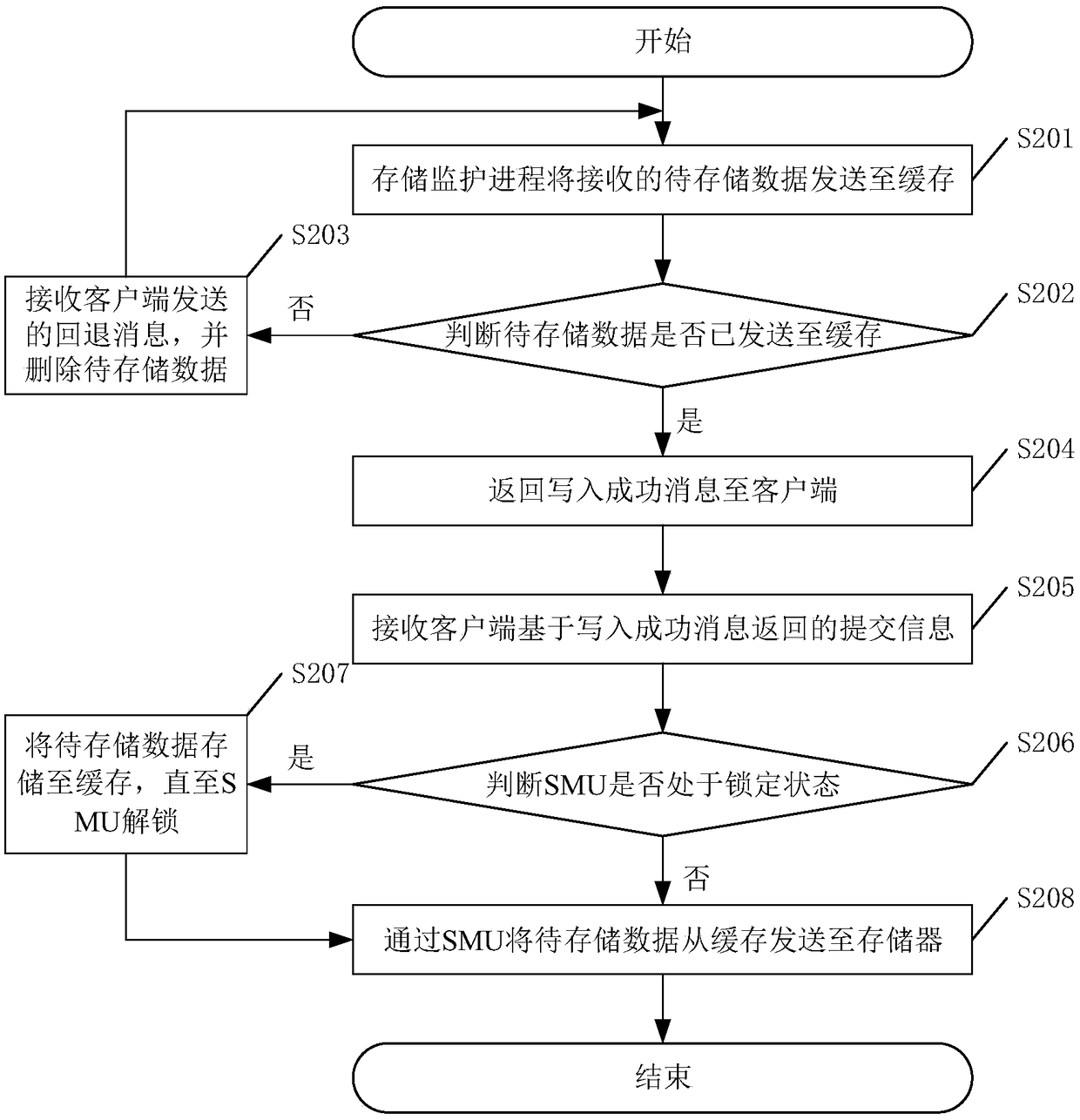

ActiveCN109240614ASolve the problem of write delayImprove write concurrencyInput/output to record carriersSource–measurement unitOperating system

The invention discloses a data storage method, which comprises the following steps: sending the received data to be stored to a buffer by a storage monitoring process; Judging whether the SMU is in alocked state; If the SMU is in the locked state, storing the data to be stored into the buffer until the SMU is unlocked; If the SMU is not in the locked state, sending the data to be stored from thebuffer to the memory through the SMU; The data storage method can effectively avoid the problems of front-end data accumulation and write delay caused by SMU locking when the system fails, improve theconcurrency of data writing, and complete the data storage with high efficiency. The present application also discloses a data storage device, a system and a computer-readable storage medium, which also have the above-mentioned beneficial effects.

Owner:ZHENGZHOU YUNHAI INFORMATION TECH CO LTD

Self-Calibration of Source-Measure Unit via Capacitor

ActiveUS20150168529A1Maximize signal to noise ratioElectronic circuit testingPower flowCurrent range

Systems and methods for calibration and operation of a source-measure unit (SMU). The system may include a functional unit and output terminals coupled to the functional unit. An excitation signal may be applied to a capacitor by the SMU. The capacitor may be included in a calibration circuit. The method may include obtaining one or more of a current calibration coefficient (CCC) or a voltage calibration coefficient (VCC). The CCC may correspond to a current-range setting and the VCC may correspond to a voltage-range setting. The CCC may be obtained from a value of a first current and a value of a second current developed in the capacitor responsive to the excitation signal. The VCC may be obtained from a value of a first voltage and a value of a second voltage developed across the capacitor responsive to the excitation signal.

Owner:NATIONAL INSTRUMENTS

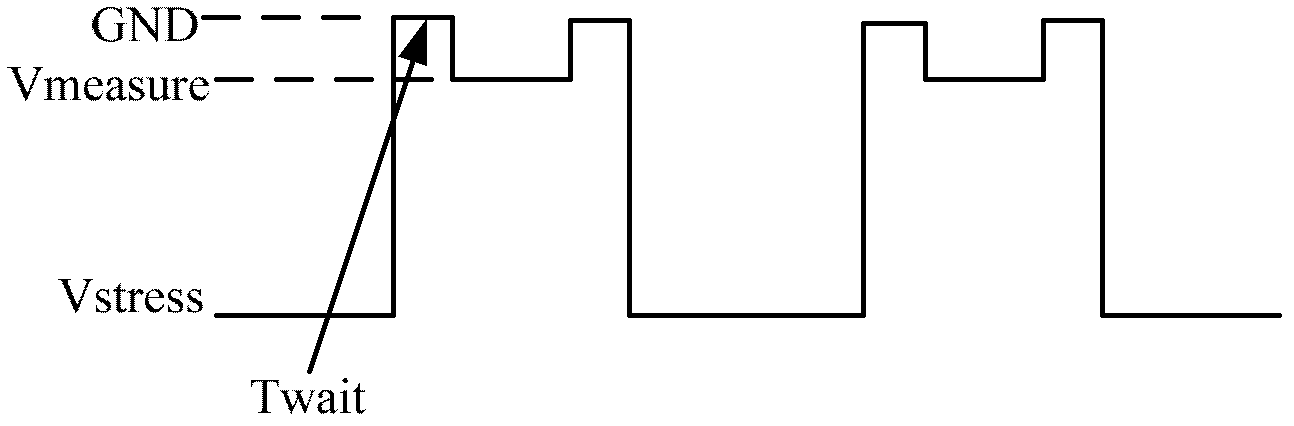

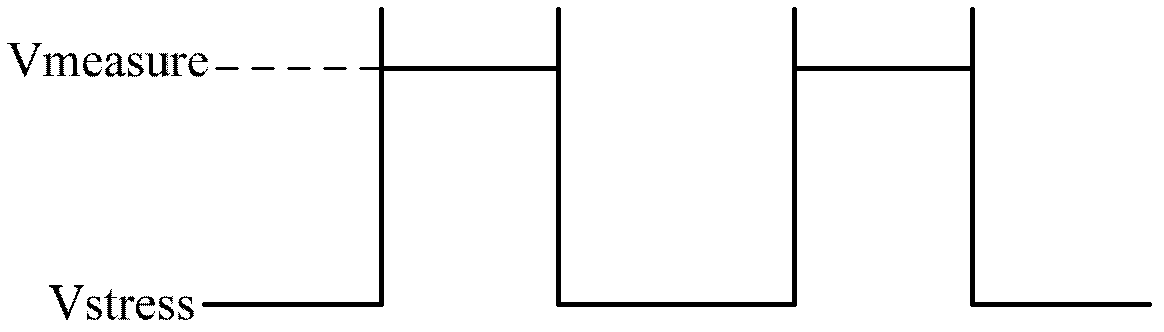

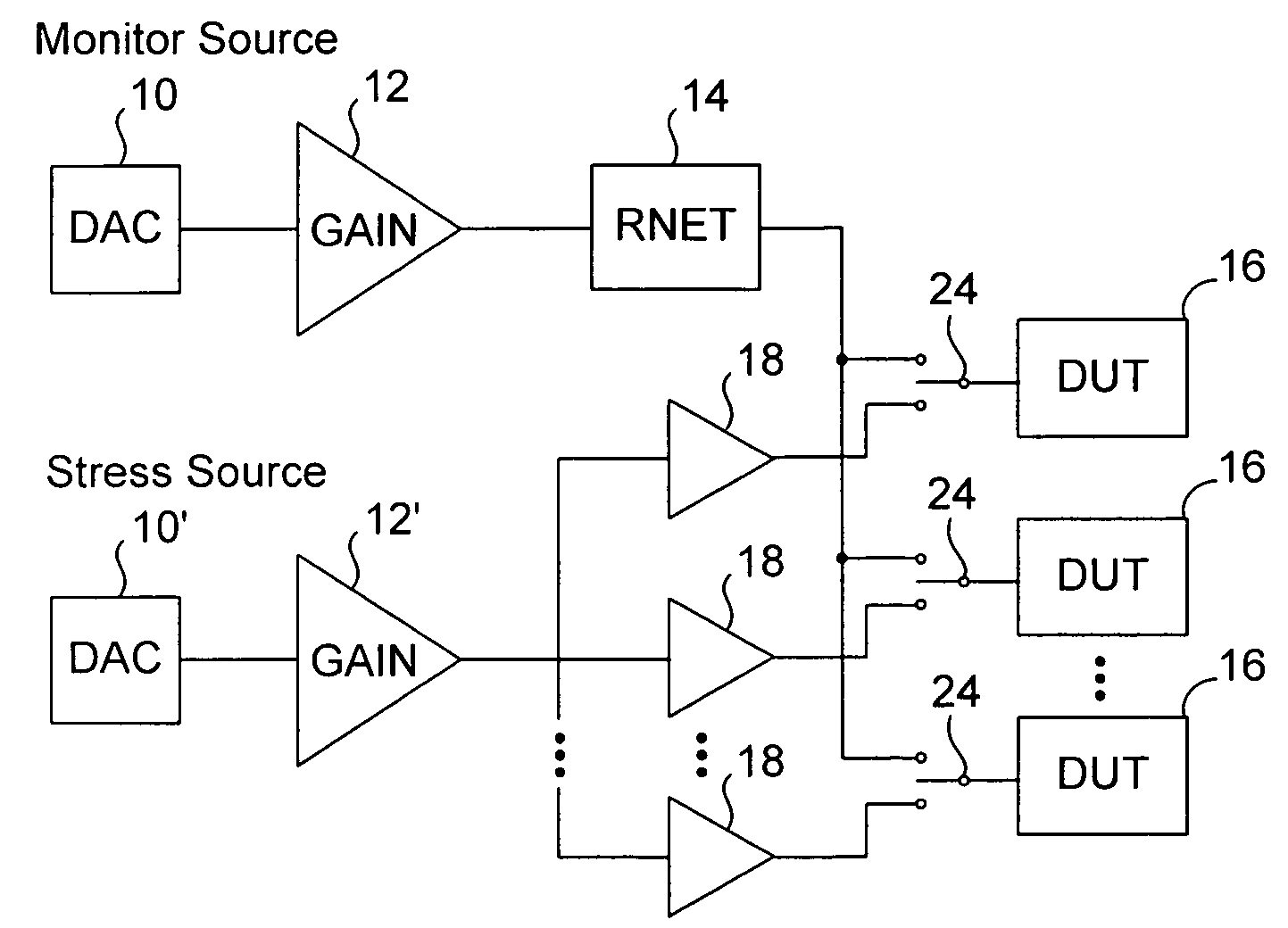

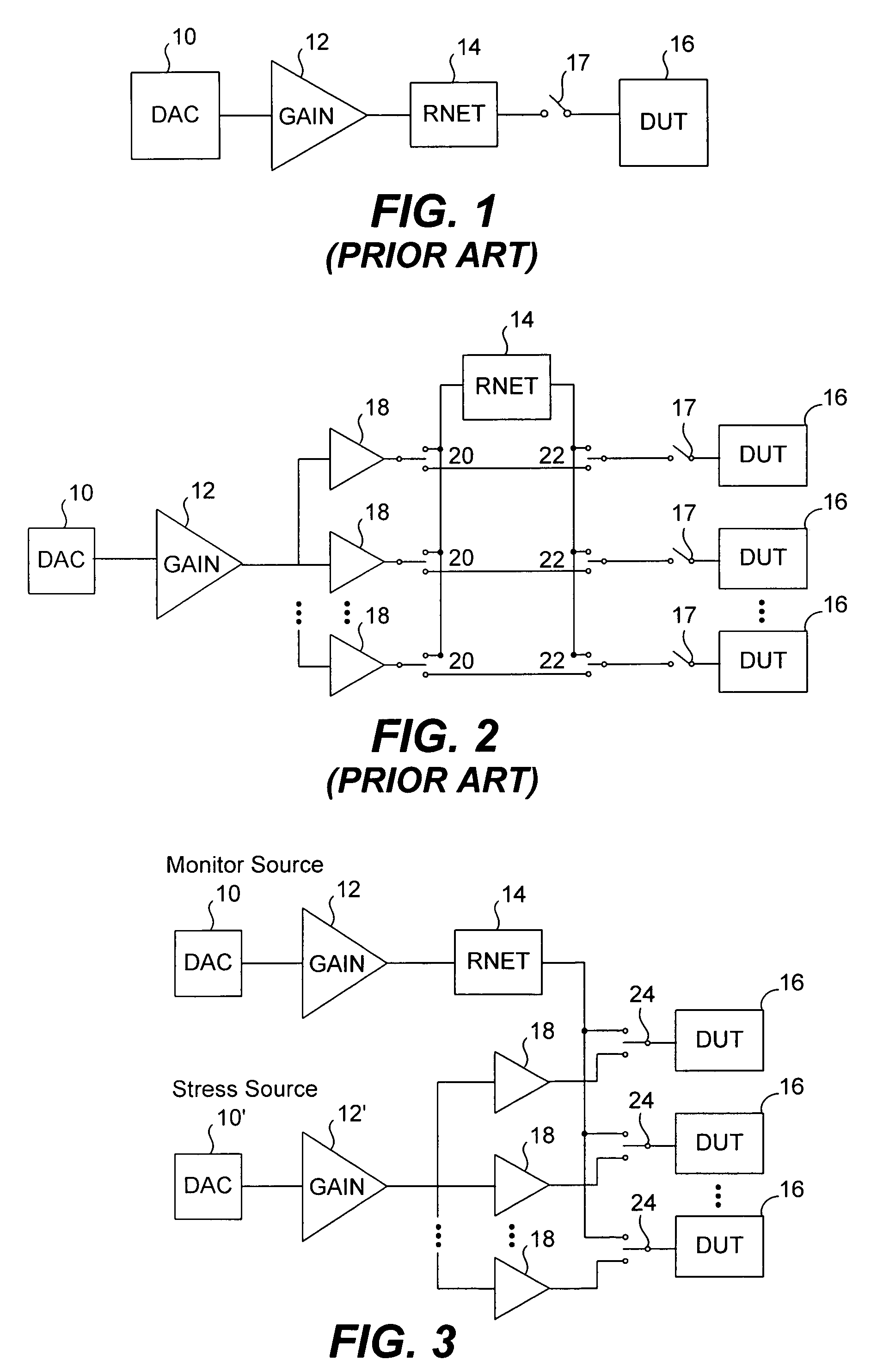

Dual channel source measurement unit for semiconductor device testing

ActiveUS7151389B2Digital circuit testingElectrical measurement instrument detailsDevice materialElectrical devices

A dual channel source measurement unit for reliability testing of electrical devices provides a voltage stress stimulus to a device under test and monitors degradation to the device under test caused by the stress simulator. The dual channel source measurement unit decouples the stress and monitor portions of the unit so that the requirements of each can be optimized. Deglitching and current clamp switches can be incorporated in the dual channel source measurement unit to prevent glitches in the switching circuitry and to limit or clamp current flow to or from the monitor and stress sources.

Owner:QUALITAU

Fully new LED (Light Emitting Diode) crystal grain detection technology

ActiveCN104808129ASave measurement timeSpeed up photoelectricity measurementsIndividual semiconductor device testingElectric propertiesSource–measurement unit

The invention discloses a detection method, and aims to provide a crystal grain detection technology which is low in production cost and can greatly shorten the measurement time of a chip. According to a fully new LED (Light Emitting Diode) crystal grain detection technology, a performance test probe is additionally arranged on a table; firstly the electrostatic discharge capacity of the chip is measured by using an ESD (Electronic Static Discharge) unit probe; the chip after the antistatic property measurement moves; in a movement process of the chip, the movement of the chip is controlled through a servo driver; the chip is placed just below an SMU (Source Measure Unit) unit probe to guarantee that the detection position of the SMU unit probe is the same as the detection position of the ESD unit probe and measure and record the electric property of the chip; when the electric property of the chip is measured by the SMU unit probe, all data of the same chip is comprehensively recorded at the same time, so the measurement time of the chip is shortened, the production cost can be greatly reduced, the positions in two measurement processes are positioned at the same position of the chip, and extra damage is not caused to the appearance of the chip.

Owner:山西高科华兴电子科技有限公司

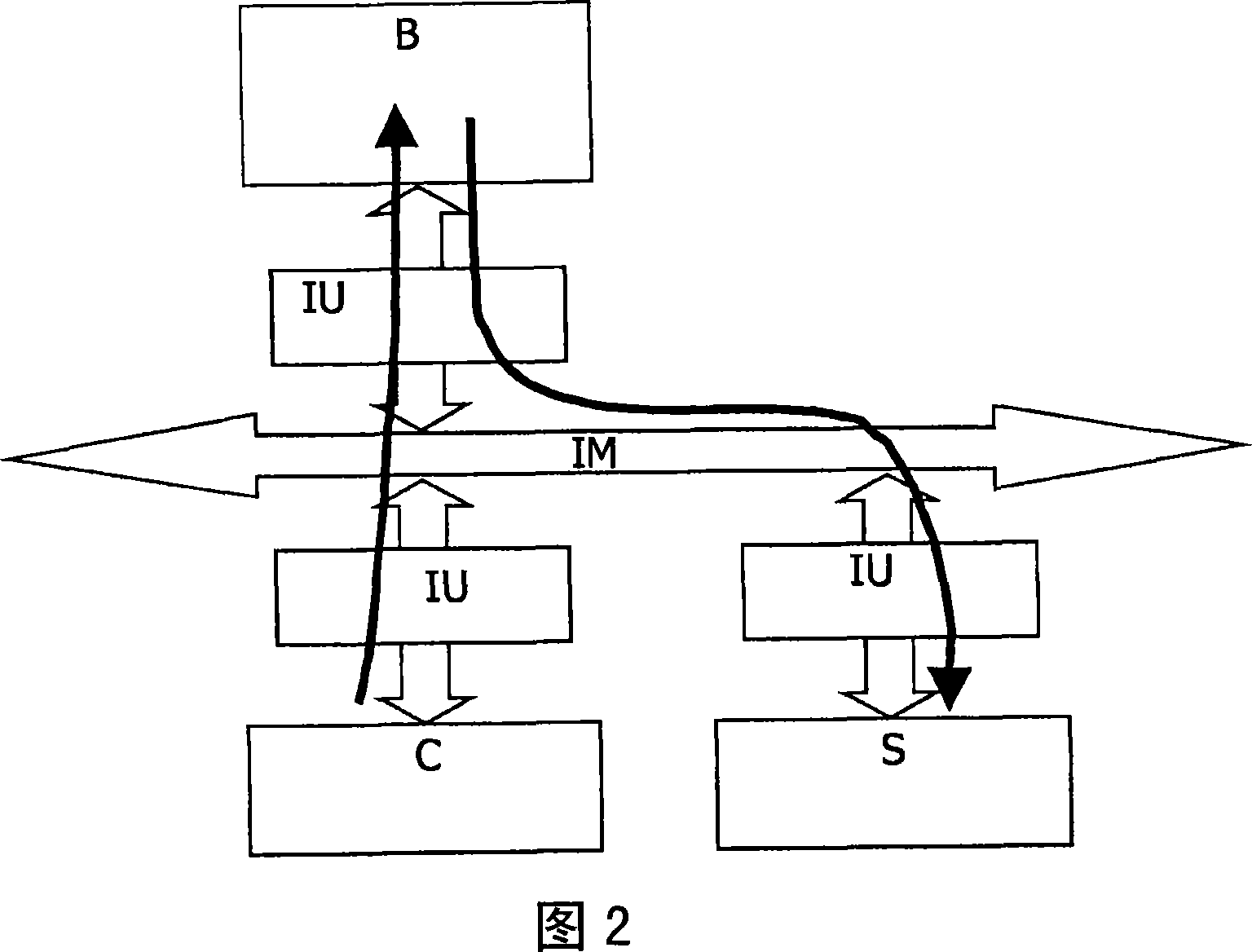

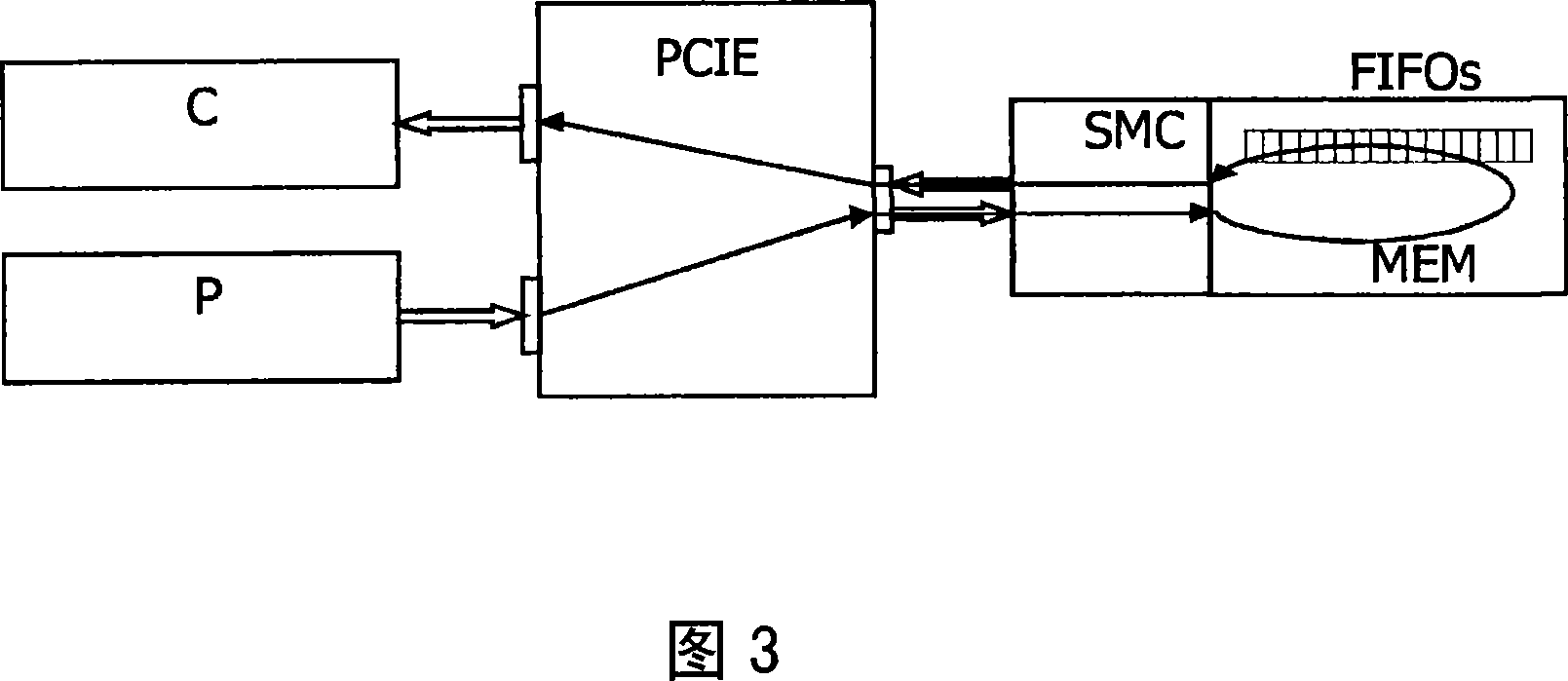

Streaming memory controller

A memory controller (SMC) is provided for coupling a memory (MEM) to a network (N). The memory controller (SMC) comprises a first interface (PI), a streaming memory unit (SMU) and a second interface (MI). The first interface (PI) is used for connecting the memory controller (SMC) to the network (N) for receiving and transmitting data streams (STl - ST4). The streaming memory unit (SMU) is coupled to the first interface (PI) for controlling data streams (STl - ST4) between the network (N) and the memory (MEM). The streaming memory unit (SMU) comprises a buffer (B) for temporarily storing at least part of the data streams (STl - ST4) and a buffer managing unit (BMU) for managing the temporarily storing of the data streams (STl - ST4) in the buffer (B). The second interlace (MI) is coupled to the streaming memory unit (SMU) for connecting the memory controller (SMC) to the memory (MEM) in order to exchange data with the memory (MEM) in bursts. The streaming memory unit (SMU) is provided to implement network services of the network (N) onto the memory (MEM).

Owner:NXP BV

Digital Approach to the Removal of AC Parasitics for Impedance Measurements

ActiveUS20170139001A1Accurate measurementCurrent measurements onlyAutomated test systemsOff the shelfFunction generator

An improved measurement system may include a source measure unit (SMU) capable of performing accurate low-level current measurements. Based on an SMU design that provides a controlled DC voltage source with precision current limiting and a controlled 0V (zero Volt) DC at the measurement terminal, an AC design may be implemented to establish the same (or very similar) conditions over a specified frequency range. Instead of controlling each digital-to-analog converter (DAC) at respective source terminals of the SMU as a respective DC output, each DAC may be controlled as a respective function generator with programmable frequency and continuously variable phase and amplitude. Off-the-shelf pipelined analog-to-digital converters (ADCs) may be used to monitor voltage, current and the voltage at the measurement terminal, and a Fourier transform may be used to obtain both the amplitude and relative phase measurements to be provided to respective control loops.

Owner:NATIONAL INSTRUMENTS

Fast Current Saturation Recovery for a Digital Source Measure Unit (SMU)

ActiveUS20120306518A1Convenient and accurateIncrease flexibilityFault location by increasing destruction at faultMarginal circuit testingDigital controlAnalog-to-digital converter

A source-measure unit (SMU) may be implemented with respective digital control loops for output voltage and output current. The output voltage and output current may be measured with dedicated ADCs (analog-to-digital converters). The readings obtained by the ADCs may be compared to a setpoint, which may be set in a digital loop controller (DLC). The DLC may be used to produce an output to drive a DAC (digital-to-analog converter) until the output voltage and / or output current and / or a function thereof reach the respective desired levels. The DLC may perform a threshold check to determine if the output current is outside a specified measurable range, and generate an override signal to drive the DAC to rapidly return the output current to the measurable range. Once the current is within the measurable range, the DAC may once again be driven according to the respective digital control loops for the output voltage and the output current.

Owner:NATIONAL INSTRUMENTS

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com