Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

92 results about "Memory process" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Cache memory background preprocessing

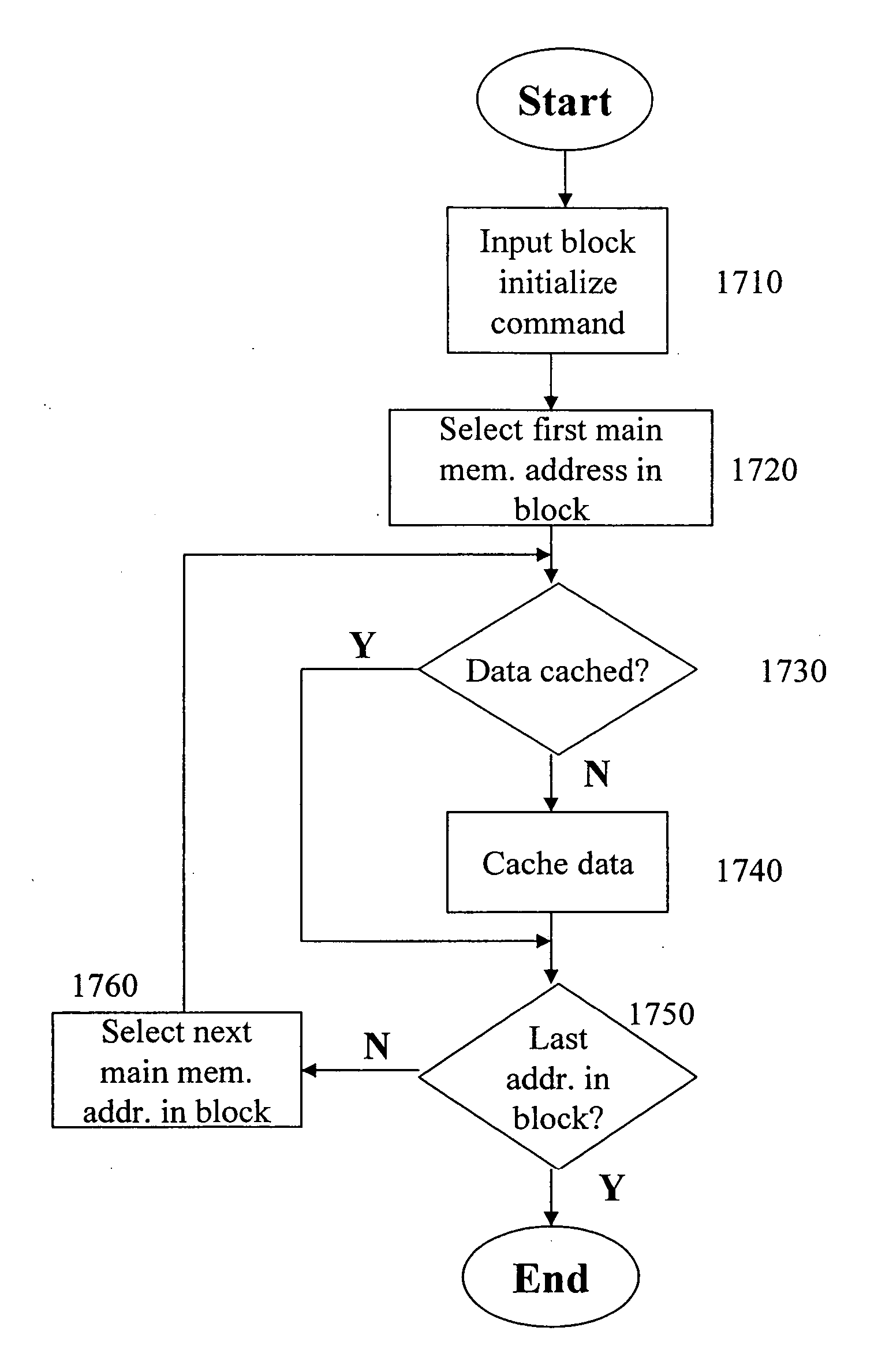

A cache memory preprocessor prepares a cache memory for use by a processor. The processor accesses a main memory via a cache memory, which serves a data cache for the main memory. The cache memory preprocessor consists of a command inputter, which receives a multiple-way cache memory processing command from the processor, and a command implementer. The command implementer performs background processing upon multiple ways of the cache memory in order to implement the cache memory processing command received by the command inputter.

Owner:ANALOG DEVICES INC

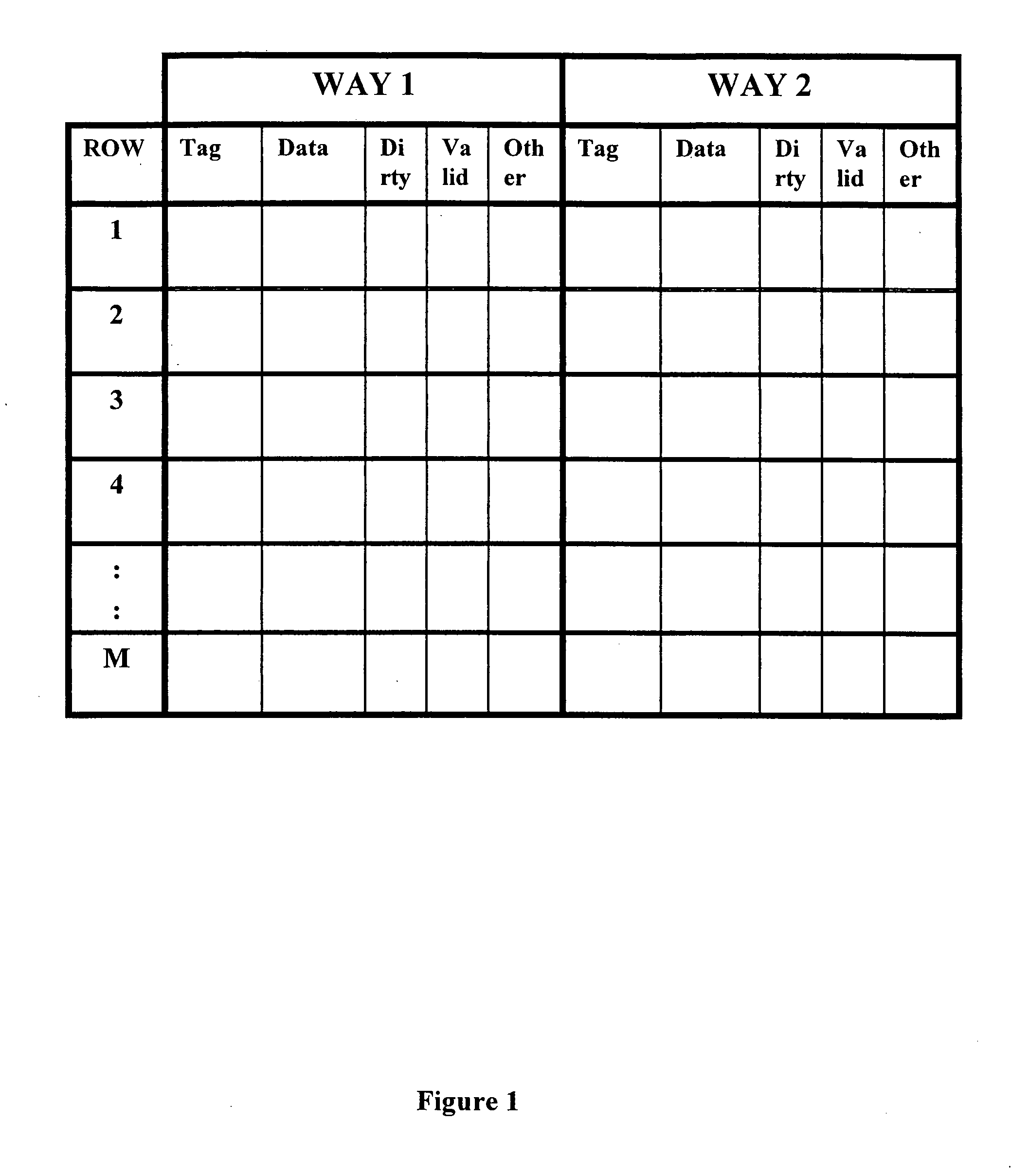

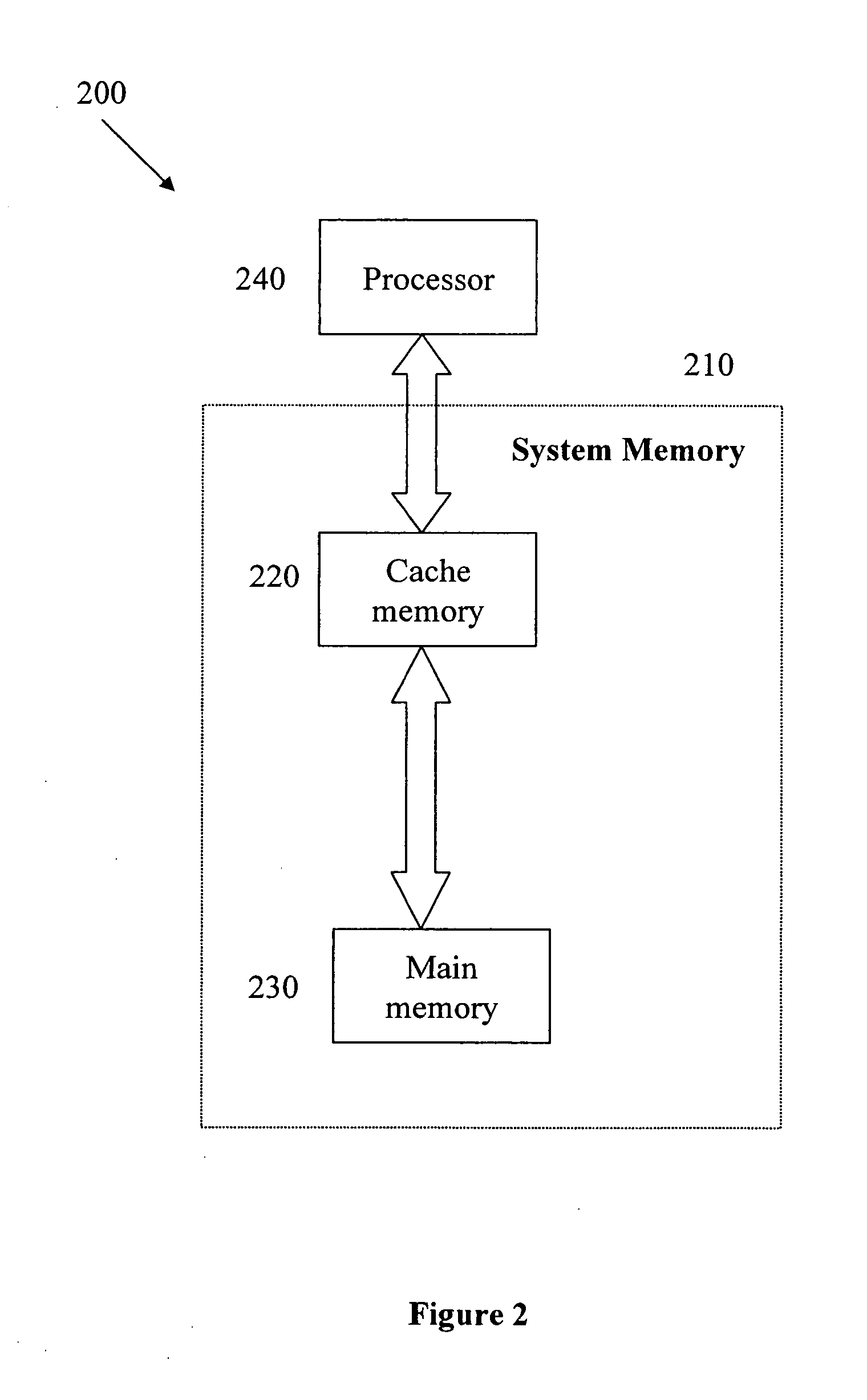

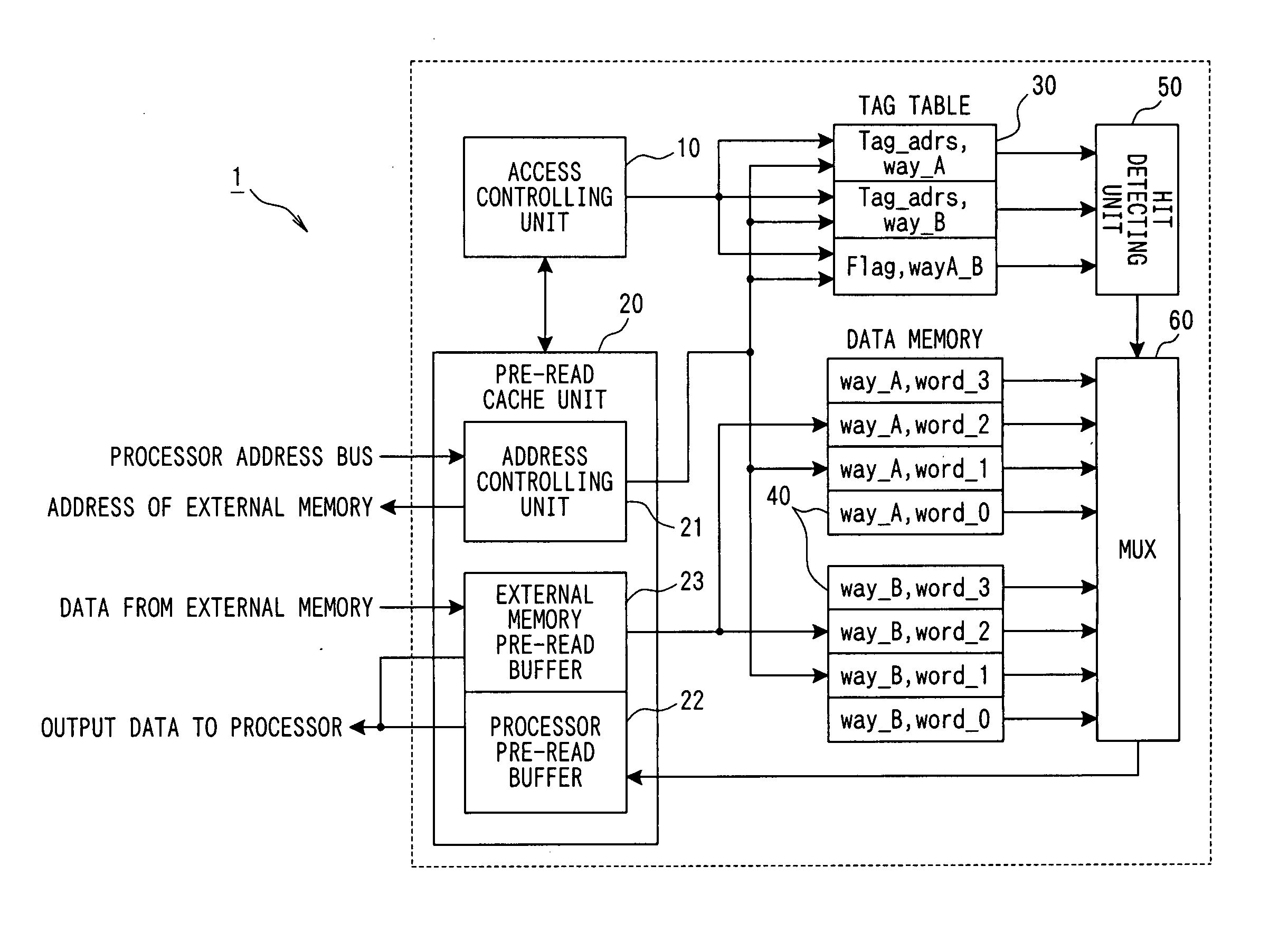

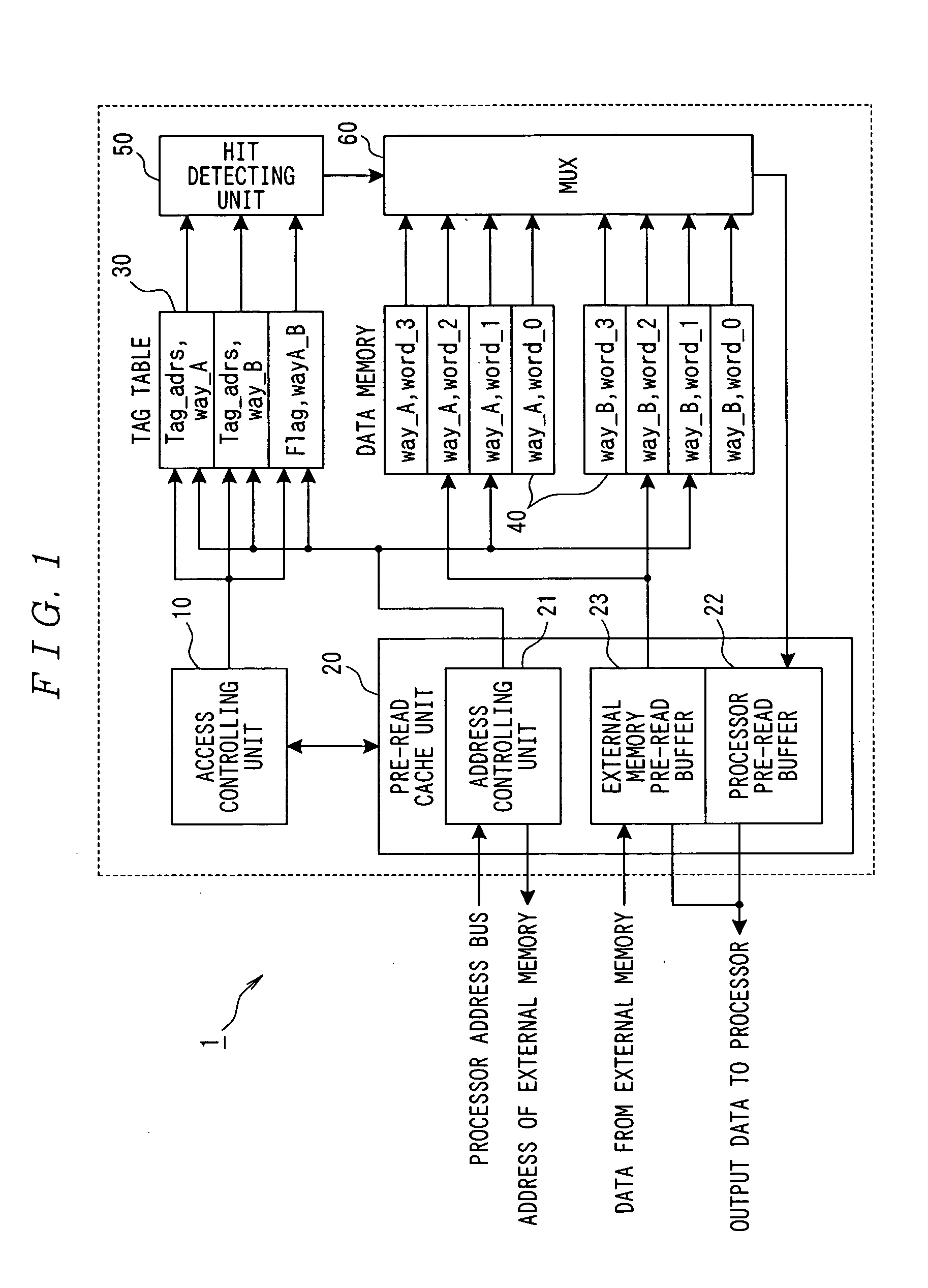

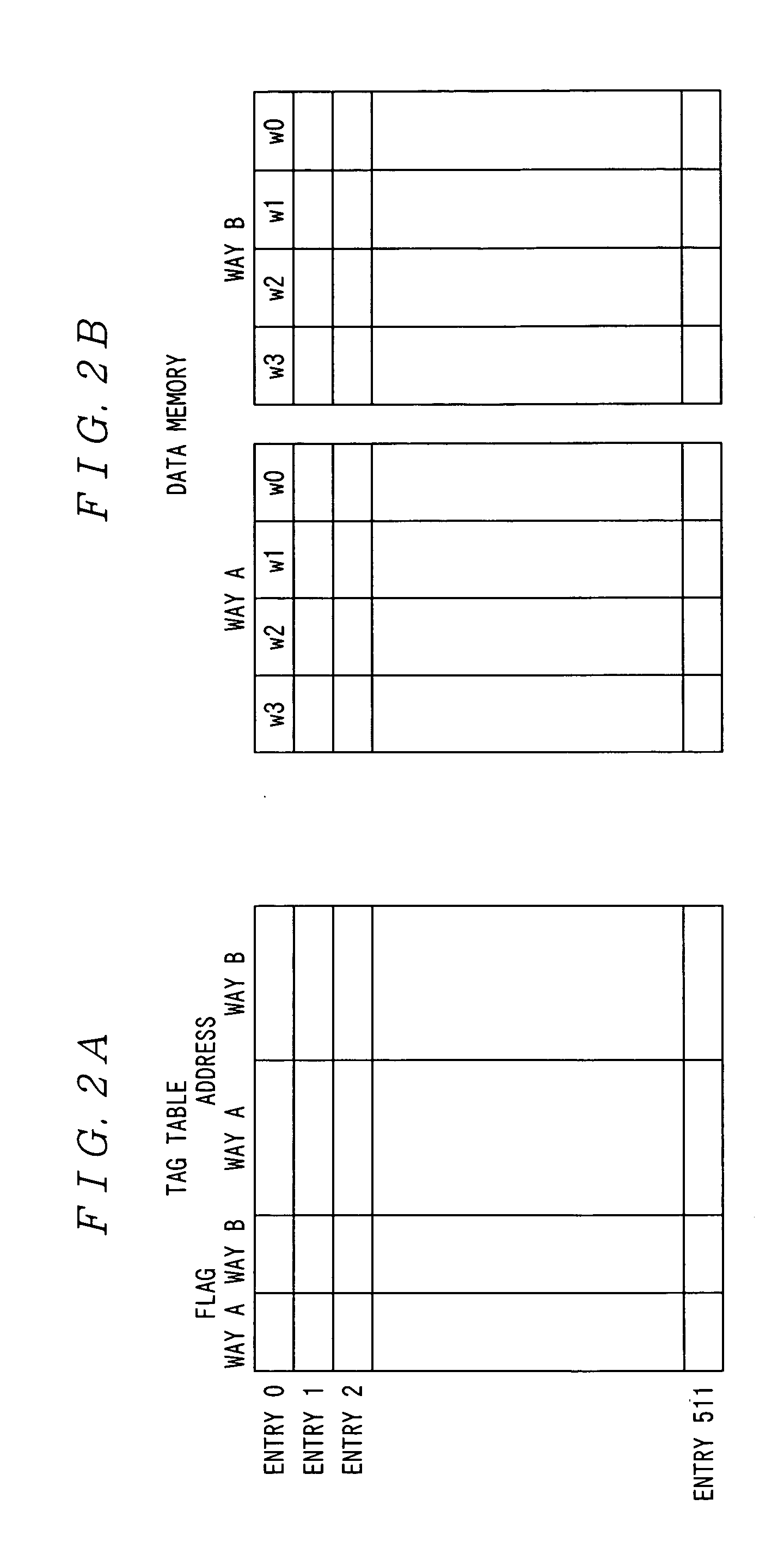

Cache memory controlling apparatus, information processing apparatus and method for control of cache memory

InactiveUS20050086435A1Avoid accessNumber of accessesEnergy efficient ICTMemory adressing/allocation/relocationInformation processingMemory process

Processing in a cache memory is made appropriate. A cache memory controlling apparatus 1 detects whether data expected to be read subsequently is cached or not while data to be read is read from a processor. If the data to be read subsequently is stored in a cache, the data is stored in a pre-read cache unit 20, and if the data to be read subsequently is not stored in the cache, the data is read from an external memory and stored in the pre-read cache unit 20. Thereafter, if an address of data actually read from the processor in a subsequent cycle matches an address of data stored in the pre-read cache unit 20, the data is outputted from the pre-read cache unit 20 to the processor.

Owner:SEIKO EPSON CORP

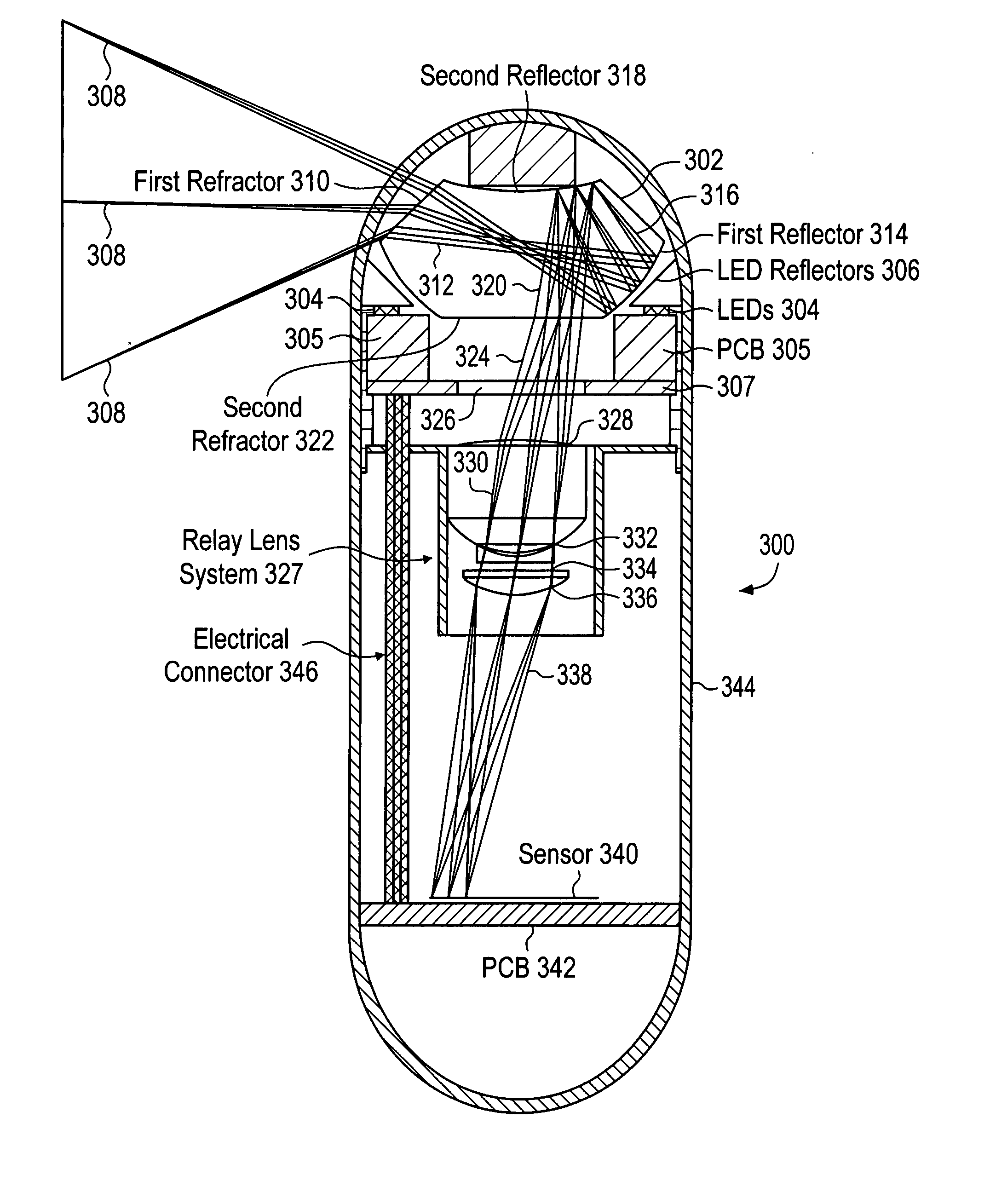

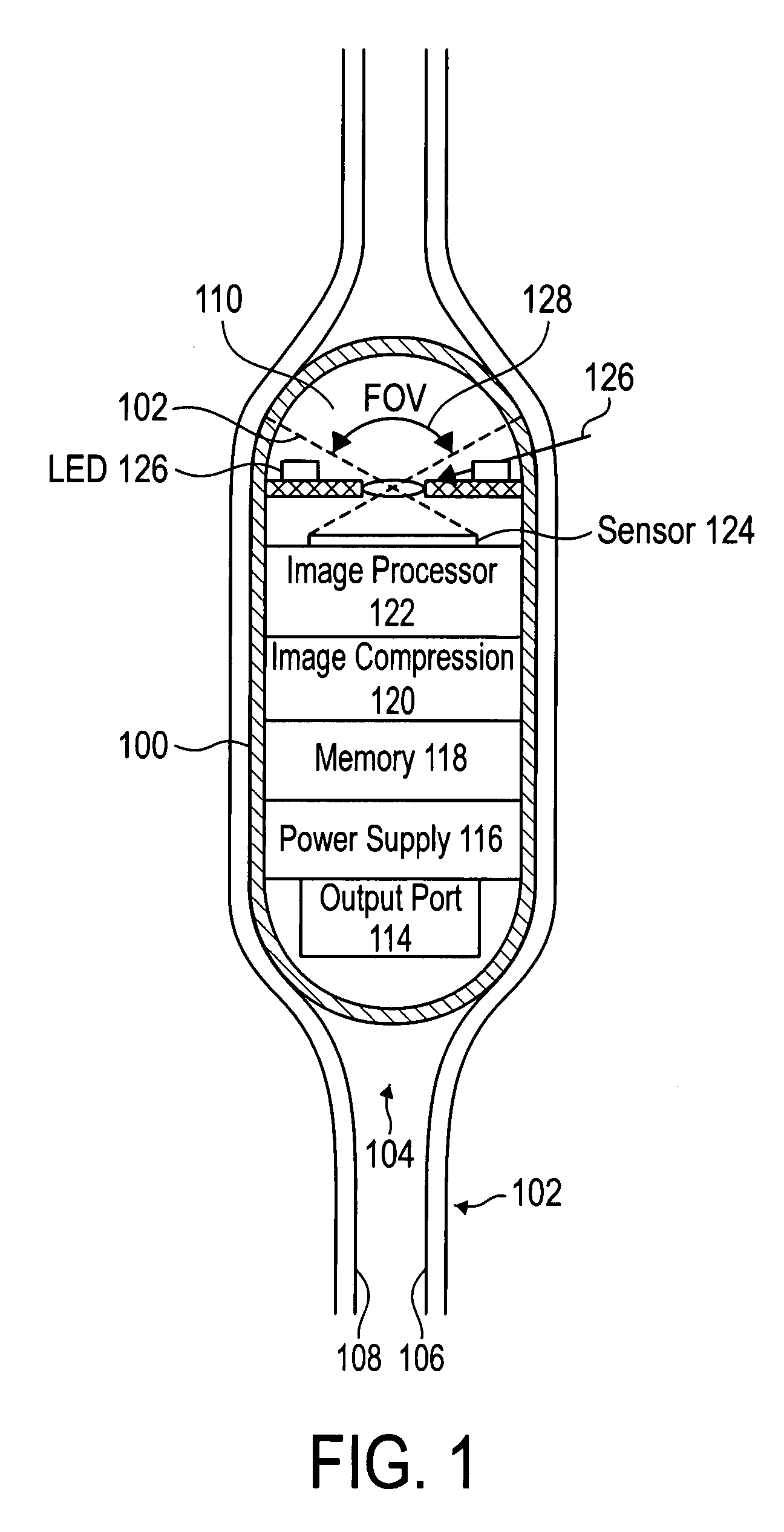

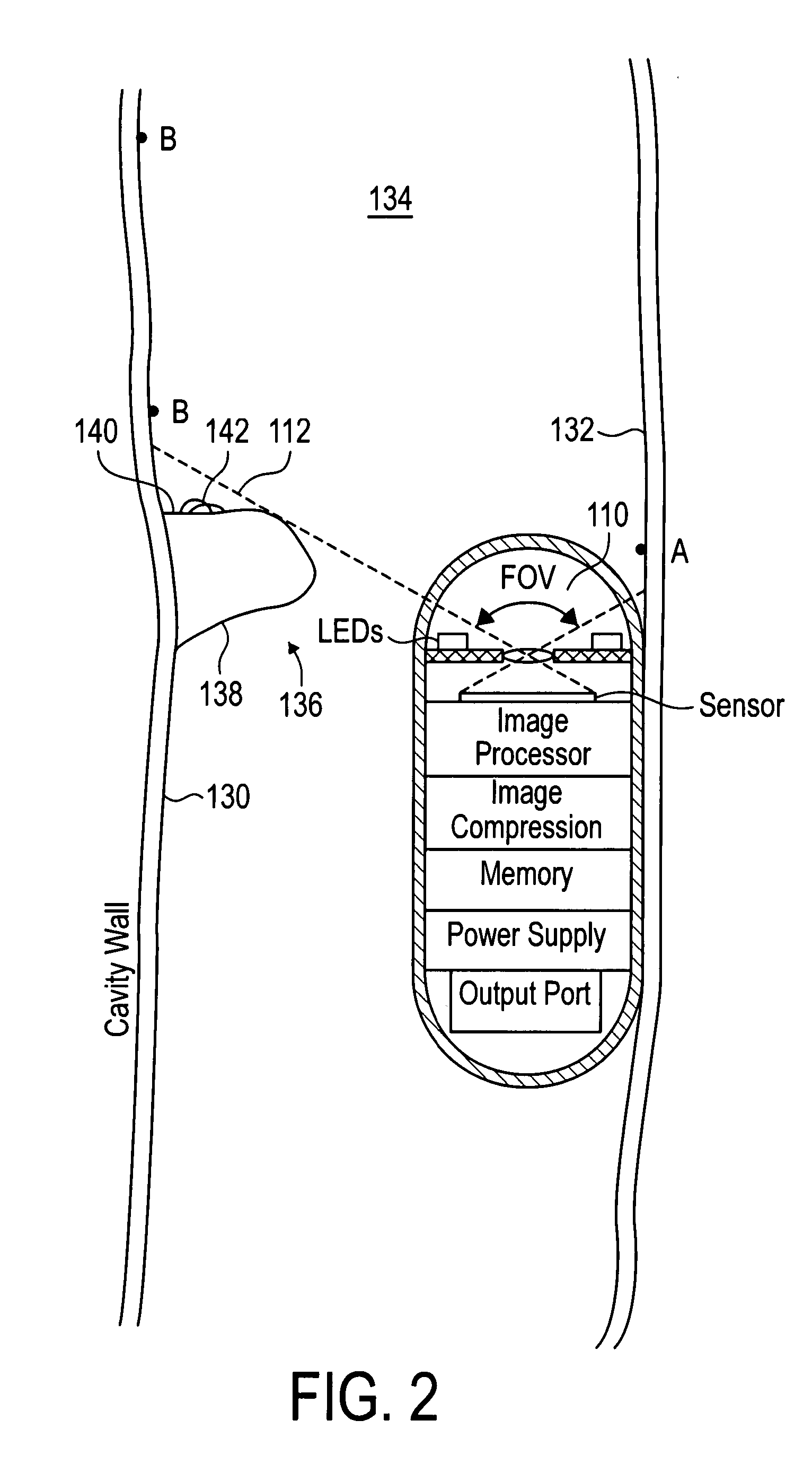

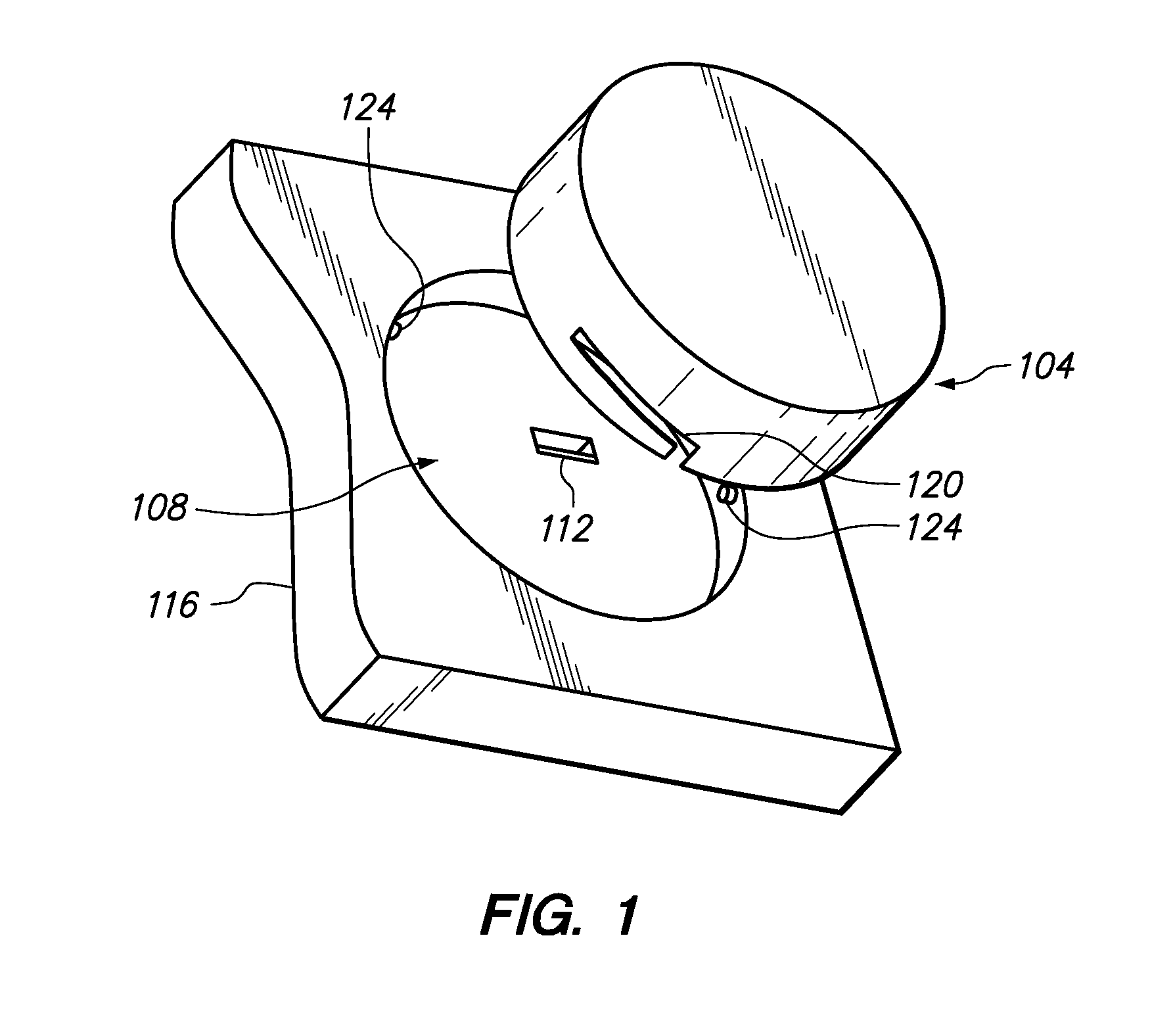

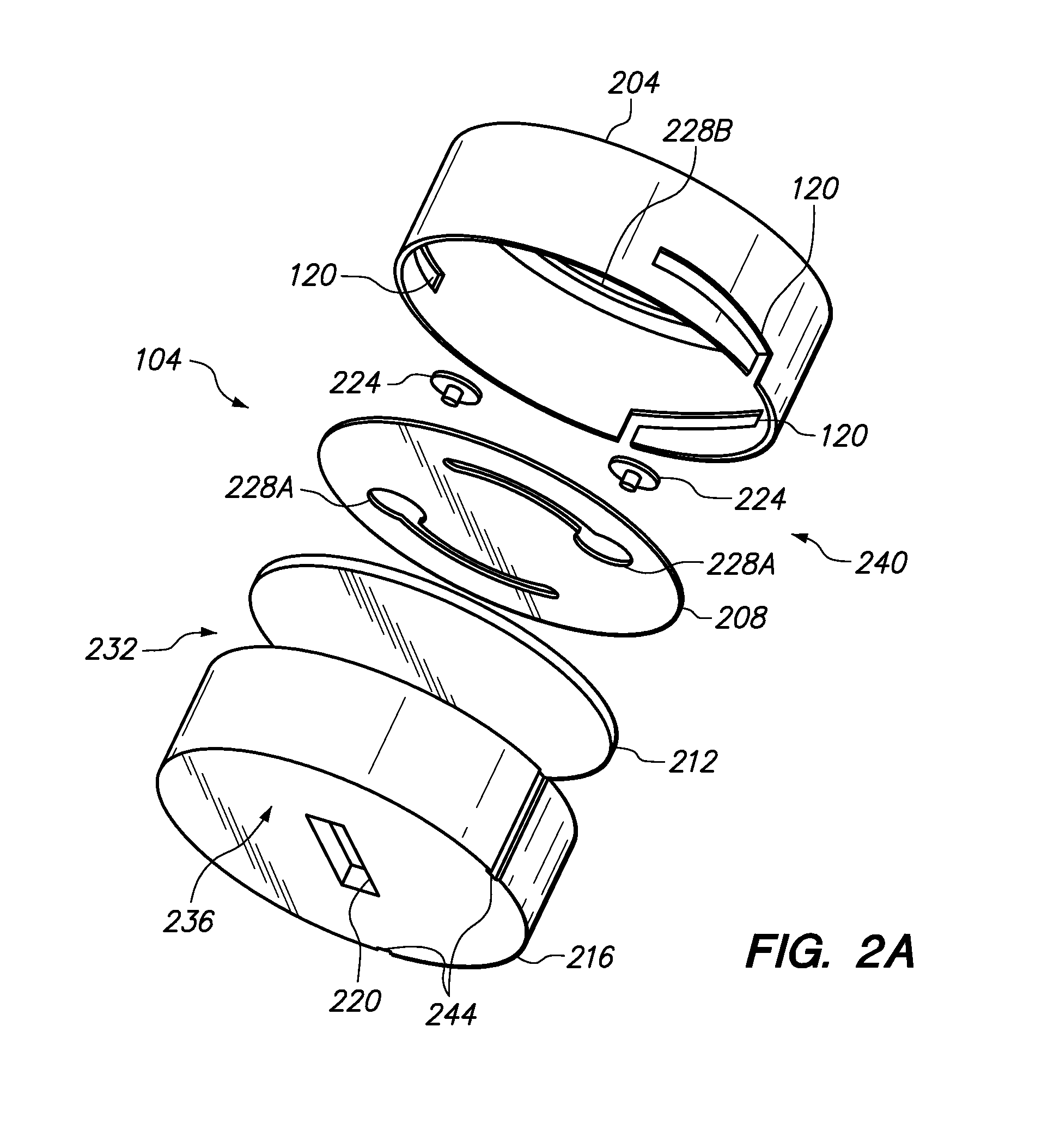

System and method for in vivo imager with stabilizer

A swallowable capsule with a camera and a memory for imaging the colon. Standard semiconductor memory (memories made of standard memories processes or processes modified from standard process by adopting comprehensible silicon planar technology process steps) is used. This is made possible by the use of an optimal type of image compression that can be performed with limited processing power and limited memory (e.g., without requiring a full size frame buffer). Also, controls on the number of images taken are used in one embodiment.

Owner:CAPSO VISION INC

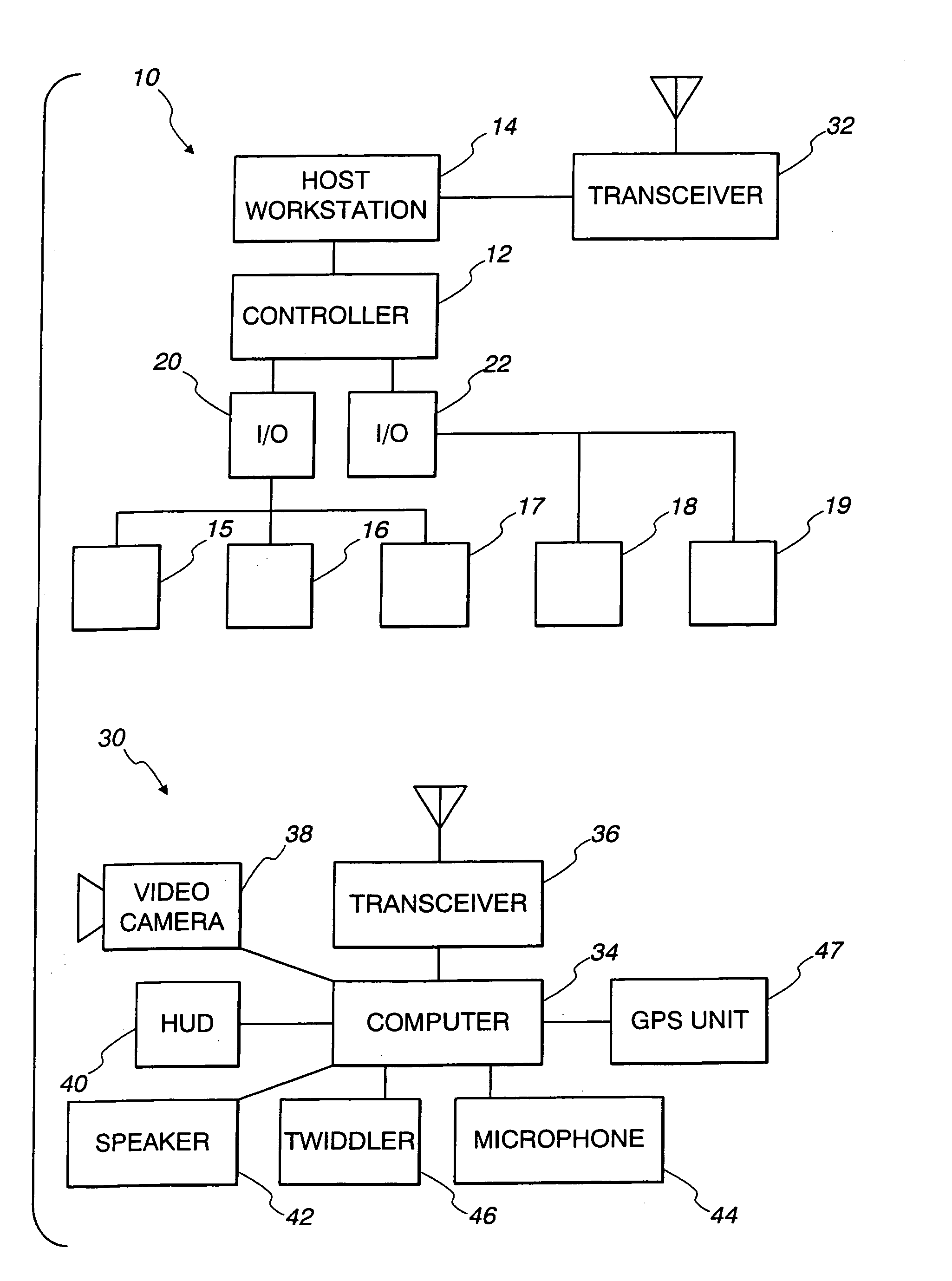

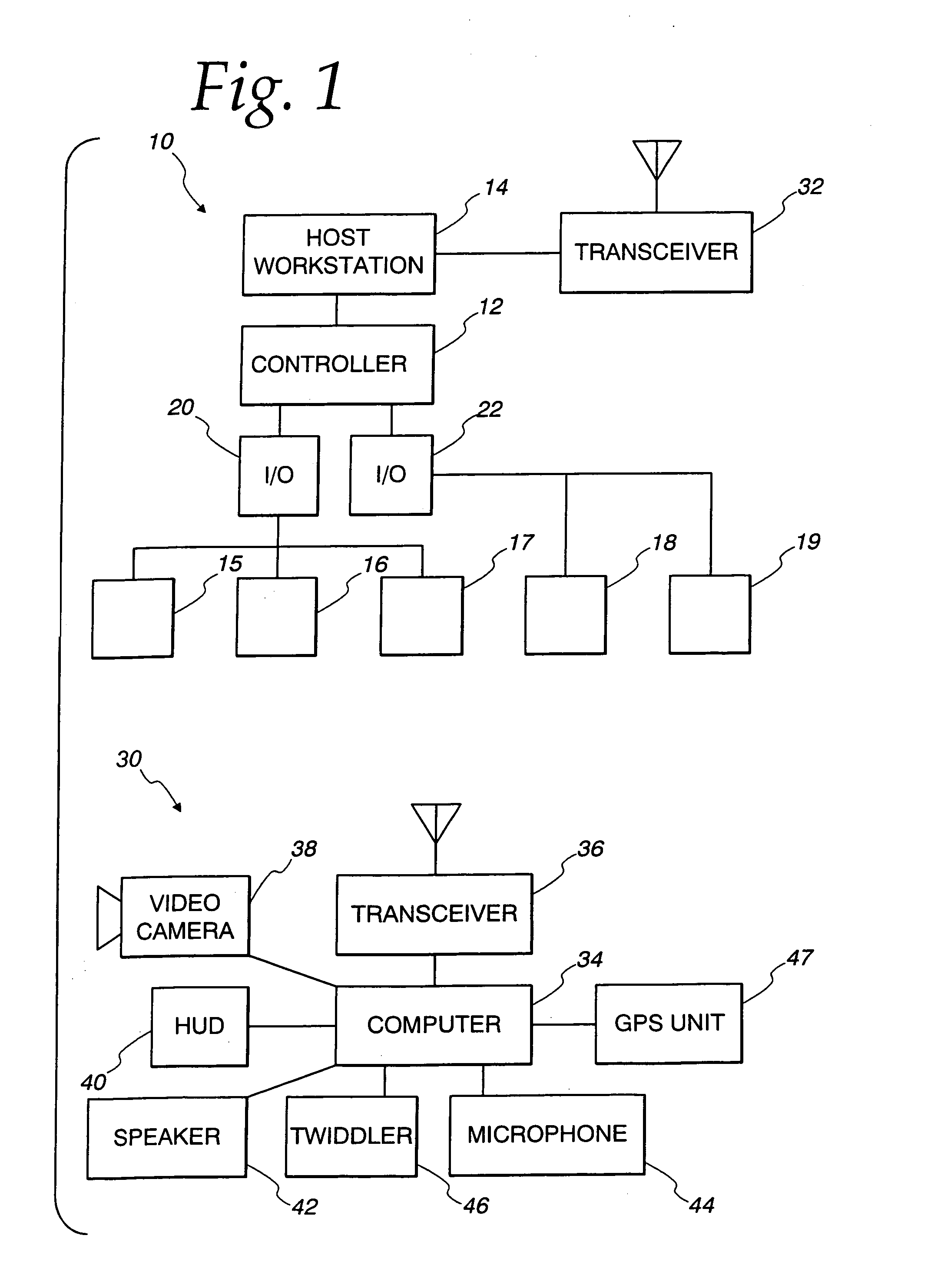

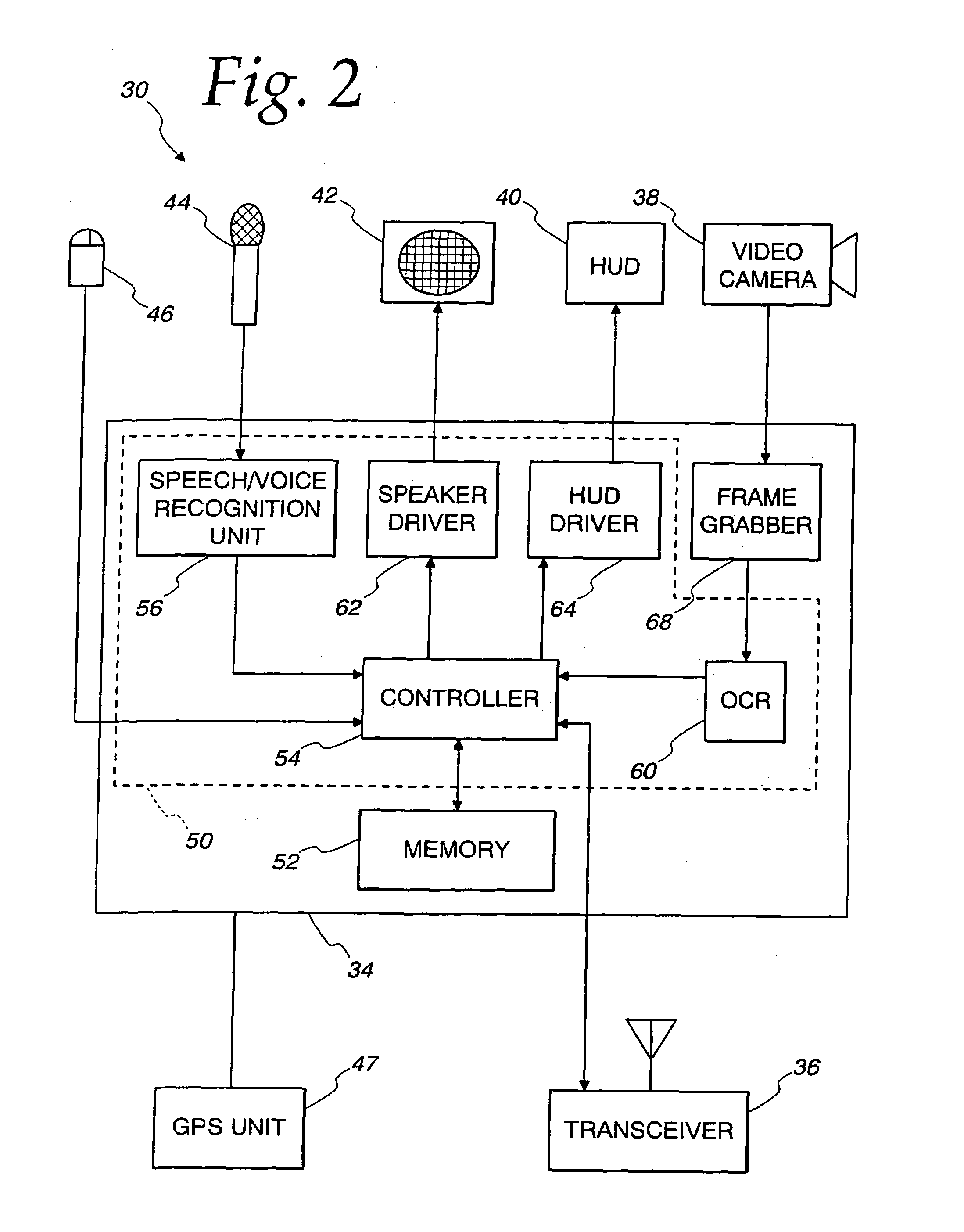

Portable computer in a process control environment

Owner:FISHER-ROSEMOUNT SYST INC

J Patrick's Ladder A Machine Learning Enhancement Tool

The invention is an add-on implementation of a stabilized association memory matrix system to an existing convolutional neural network framework. This invention emulates the intra-action and the inter-action of the cognitive processes of the (logical) left-brain and (intuitive) right-brain. The invention is a numerically stable soft-ware based implementation that (1) reduces the long training times, (2) reduces the execution time, and (3) produces intralayer and interlayer connections. The implementation of this joint processing architecture is designed to take an existing hierarchy of stepped based processes, add next to it a parallel hierarchy of associative memory processes, and then connect the two processes by another set of associative memory processes. Or, the stepped-based process may be replaced with additional associative memory processes to enhance the emulation of several bidirectional intralayer and interlayer cognitive process communication. In addition, the invention can be used as a neural network layer compression tool that takes in a multilayer perceptron, also known as a multilayer neural network, and outputs a single layer perceptron. The final construction can be visualized as two vertical rails connected with a set of horizontal rungs which motivates the name to this invention: J. Patrick's Ladder: A Machine Learning Enhancement Tool.

Owner:LARUE JAMES +1

Ceramic filter containing carbonaceous material and bonded with silica adhesive and manufacturing method thereof

The invention relates to a ceramic filter suitable for filtering metal fused mass, comprising refractory material, carbonaceous material and silica adhesive. The invention also relates to making method for the filter. The ceramic filter has the advantages of more economical making, high mechanical strength not shrinkage during sintering process, more stable performance in memory process and more safe usage.

Owner:JINAN SHENGQUAN DOUBLE SURPLUS CERAMIC FILTER

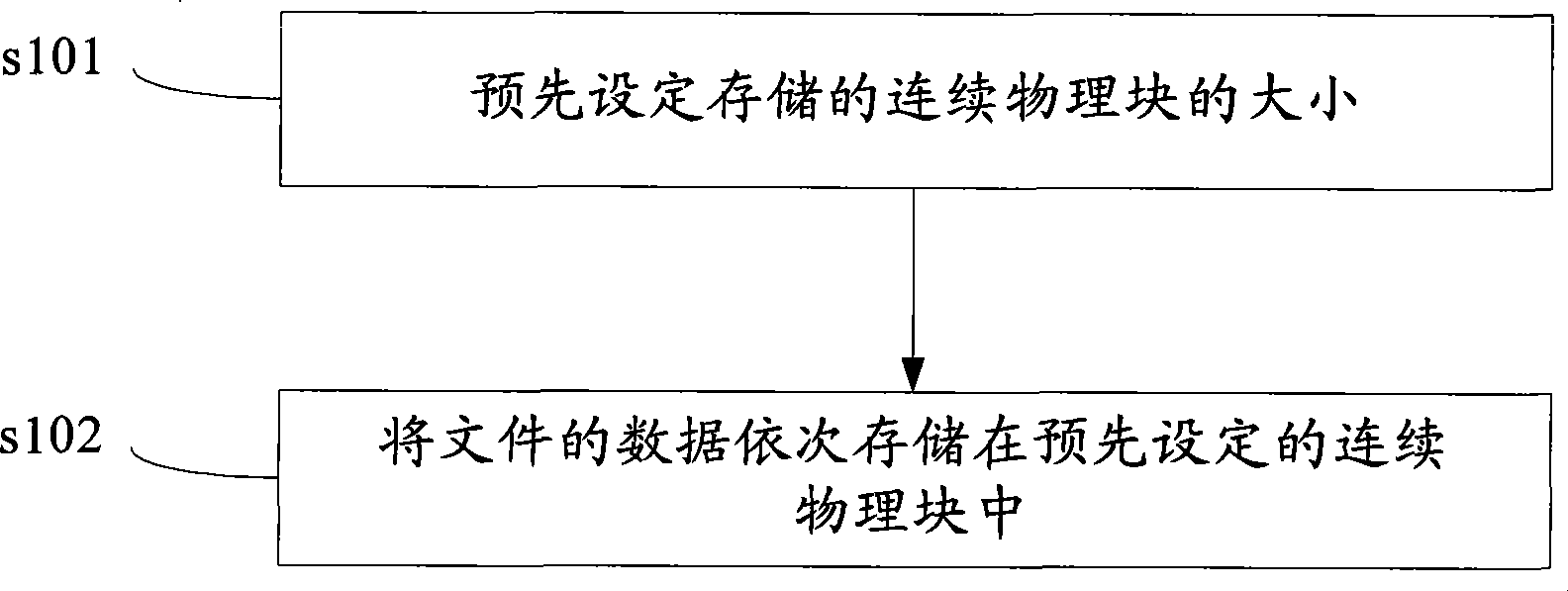

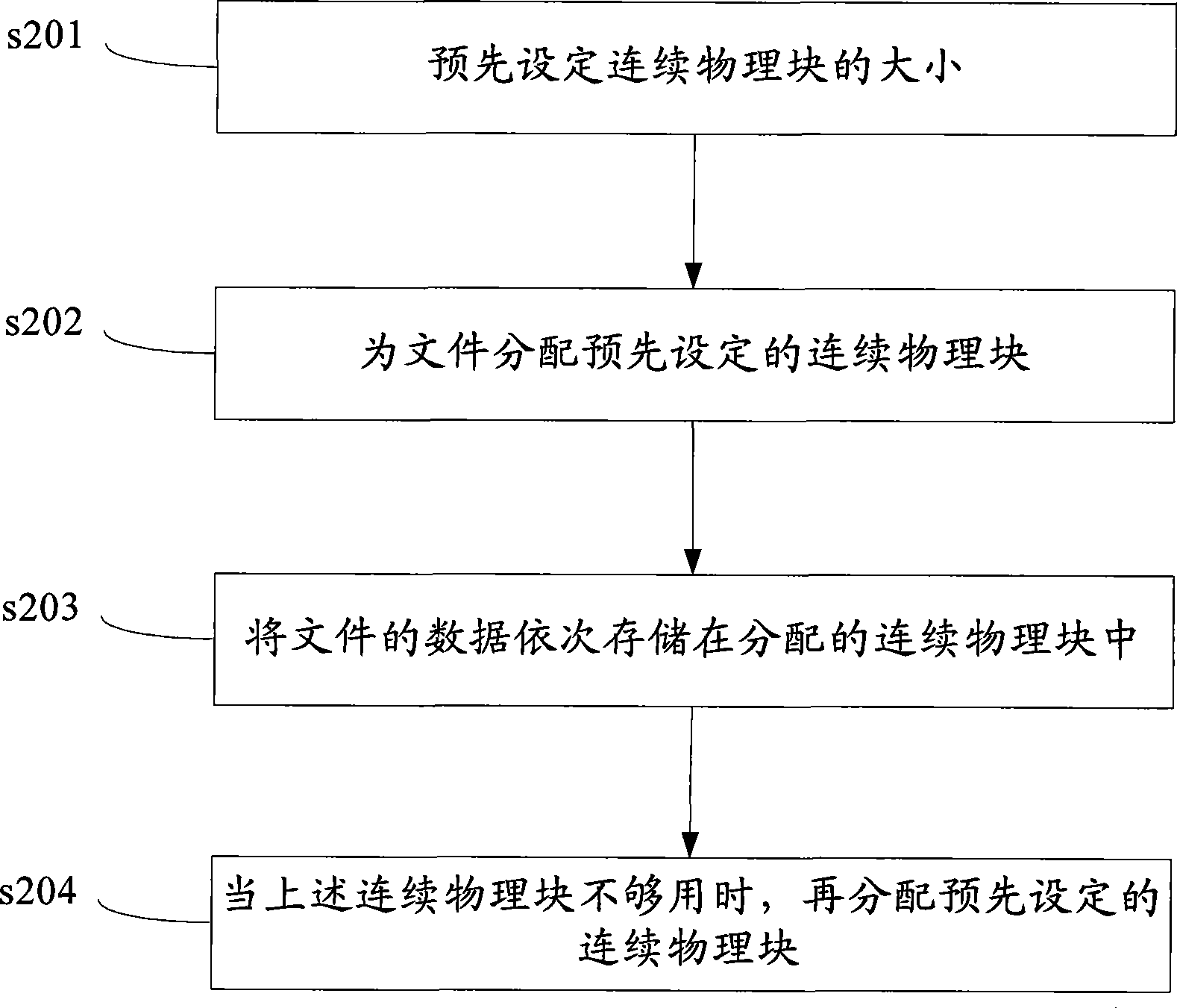

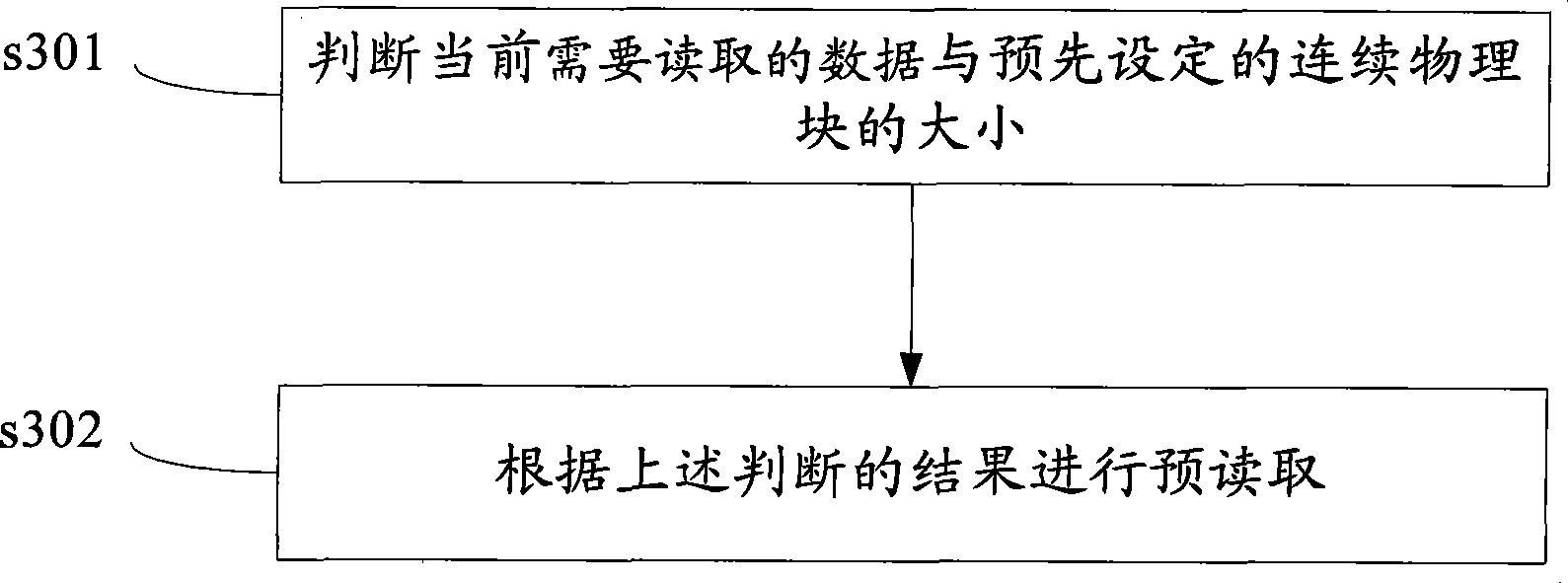

File memory method, apparatus and system

InactiveCN101382948AImprove read performanceSpecial data processing applicationsMemory processFile allocation

The embodiment of the invention discloses a file memory method, a device thereof and a system thereof. The method comprises the following steps: the size of continuous physical blocks of memory is preset; and file data are stored in the preset continuous physical blocks successively. During the file memory process in the embodiment of the invention, the continuous physical blocks are distributed to files and a continuous memory of the files is ensured in the continuous physical blocks, thus being capable of setting the pre-reading strategy of the files and improving the reading performance of a file system.

Owner:HUAWEI DIGITAL TECH (CHENGDU) CO LTD

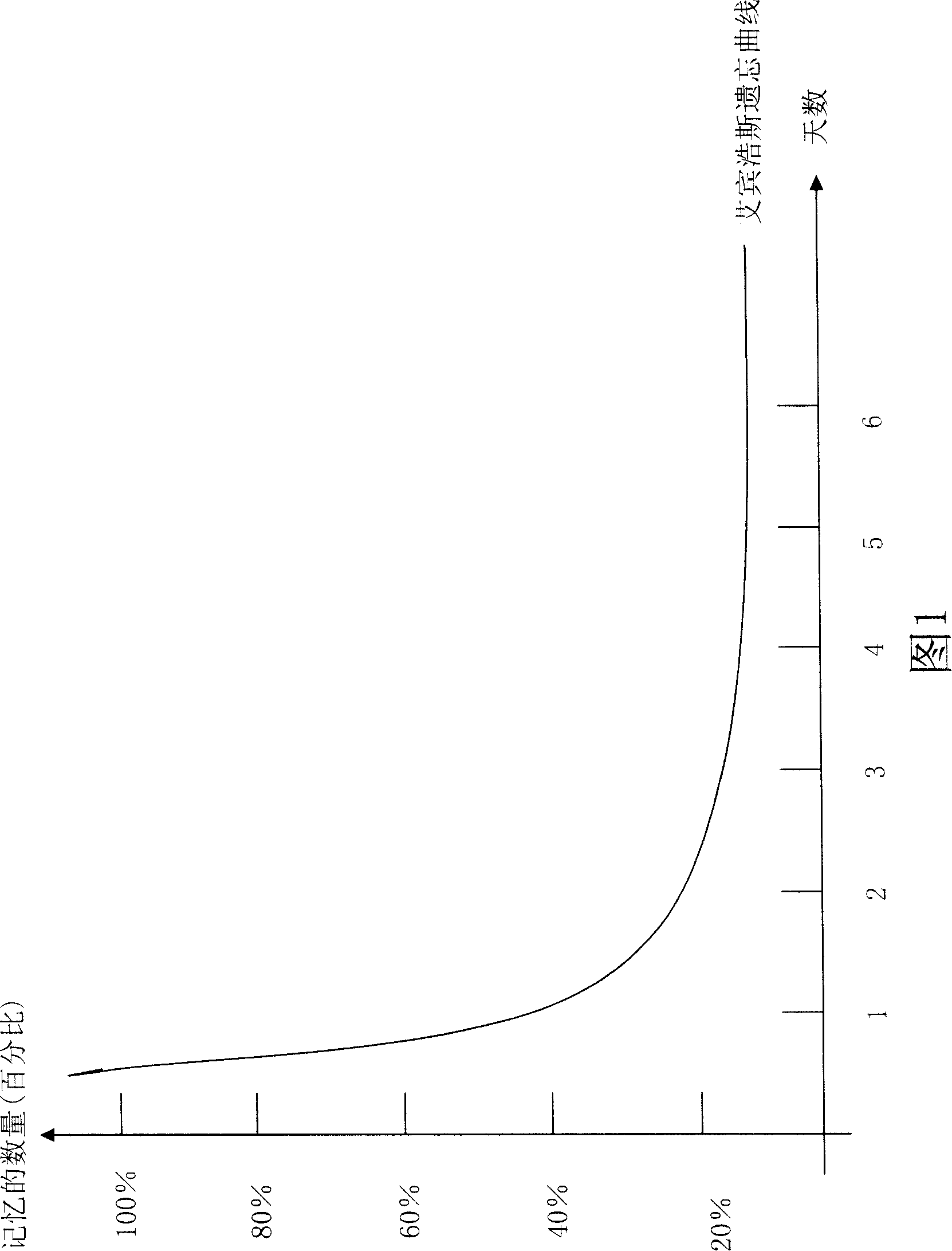

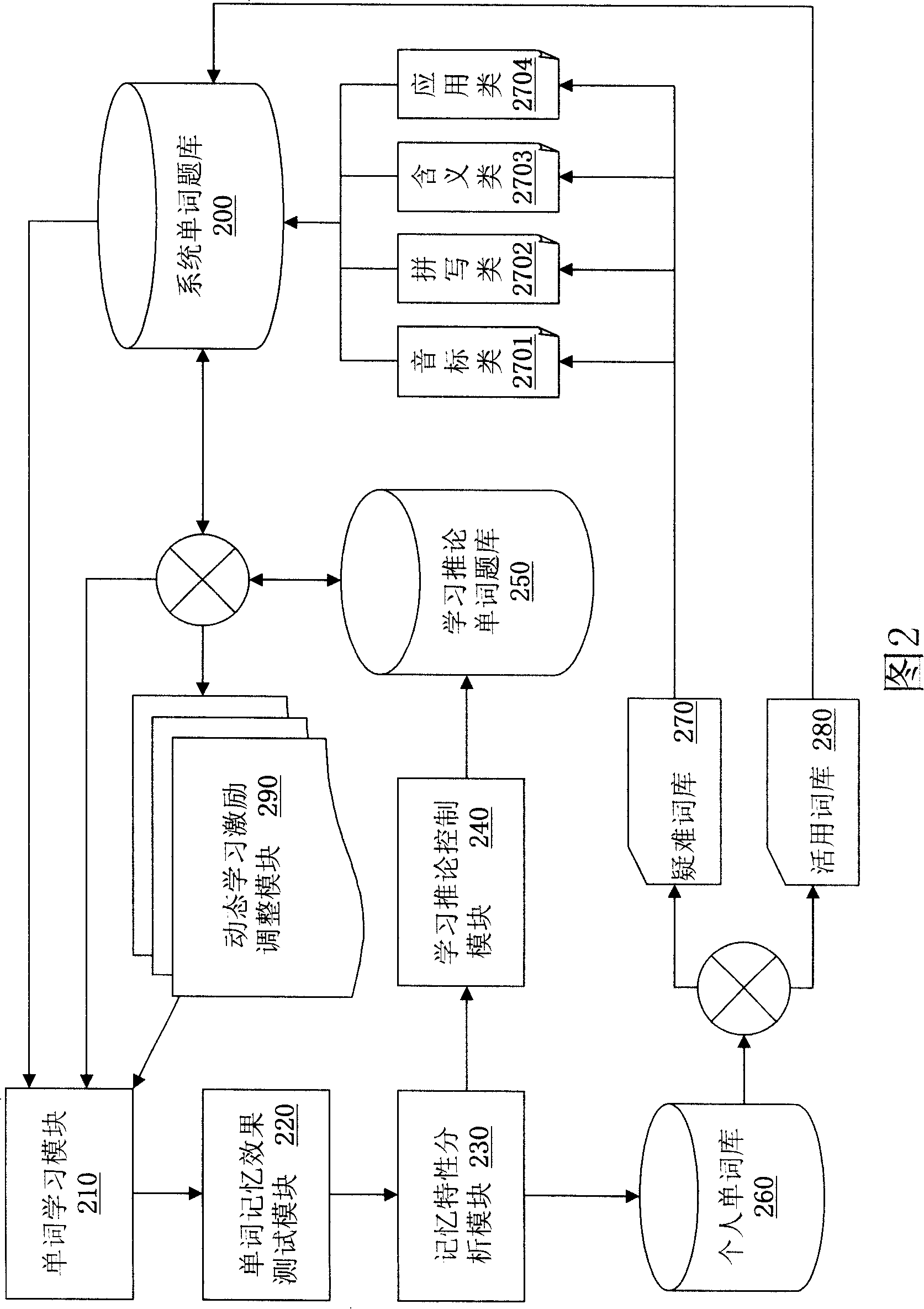

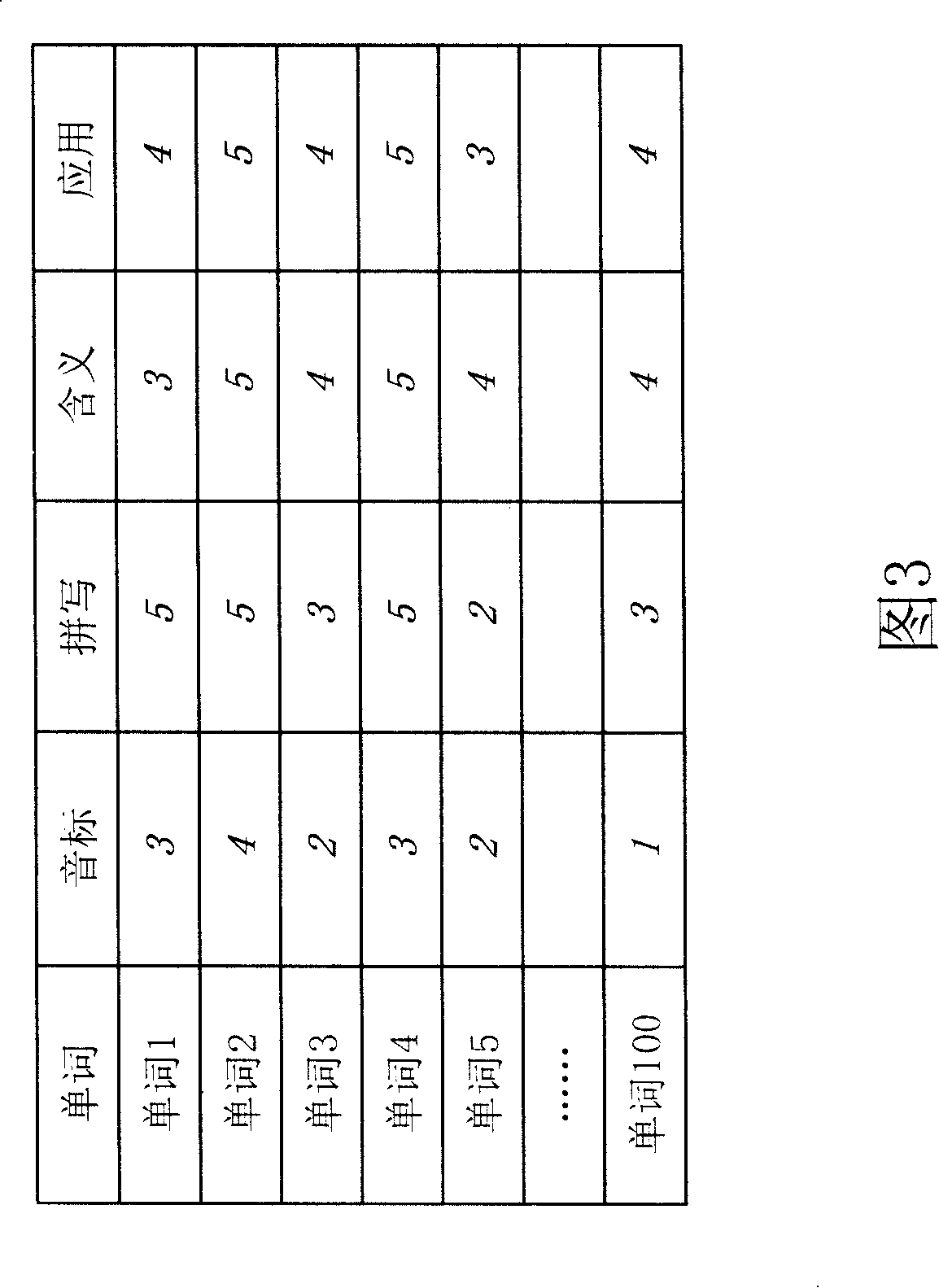

System and method for executive auxiliary learning of language word by computer

InactiveCN101201812AImprove memory efficiencyAvoid boringSpecial data processing applicationsTeaching apparatusMemory processPersonalization

The invention relates to a system that assists to study language word and is implemented by a computer and a method thereof, comprising a system word test item bank, a word studying module, a module used for testing the effect of memorizing words, an analysis module of characteristics of memory, a control module of studying inferences, a word test item bank of studying inferences, an individual word bank and a dynamic study field-controlled module; the forgetting curve and the memory defects are obtained by the statistics and analysis for the personal memory process of a learner and a individual word test item bank is customized for the individual according to the two characteristics, thus improving the efficiency of assisting to study language word.

Owner:INVENTEC CORP

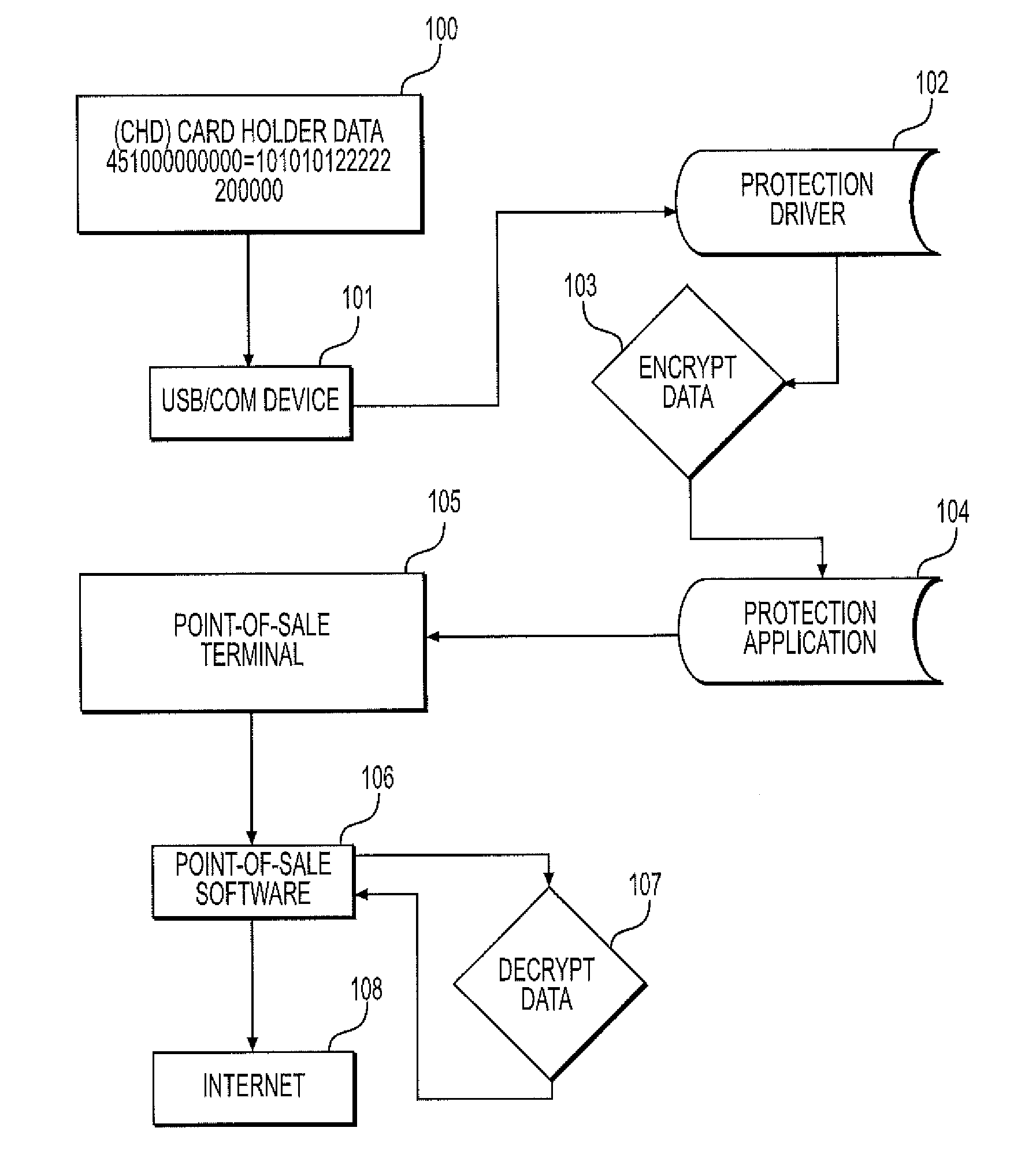

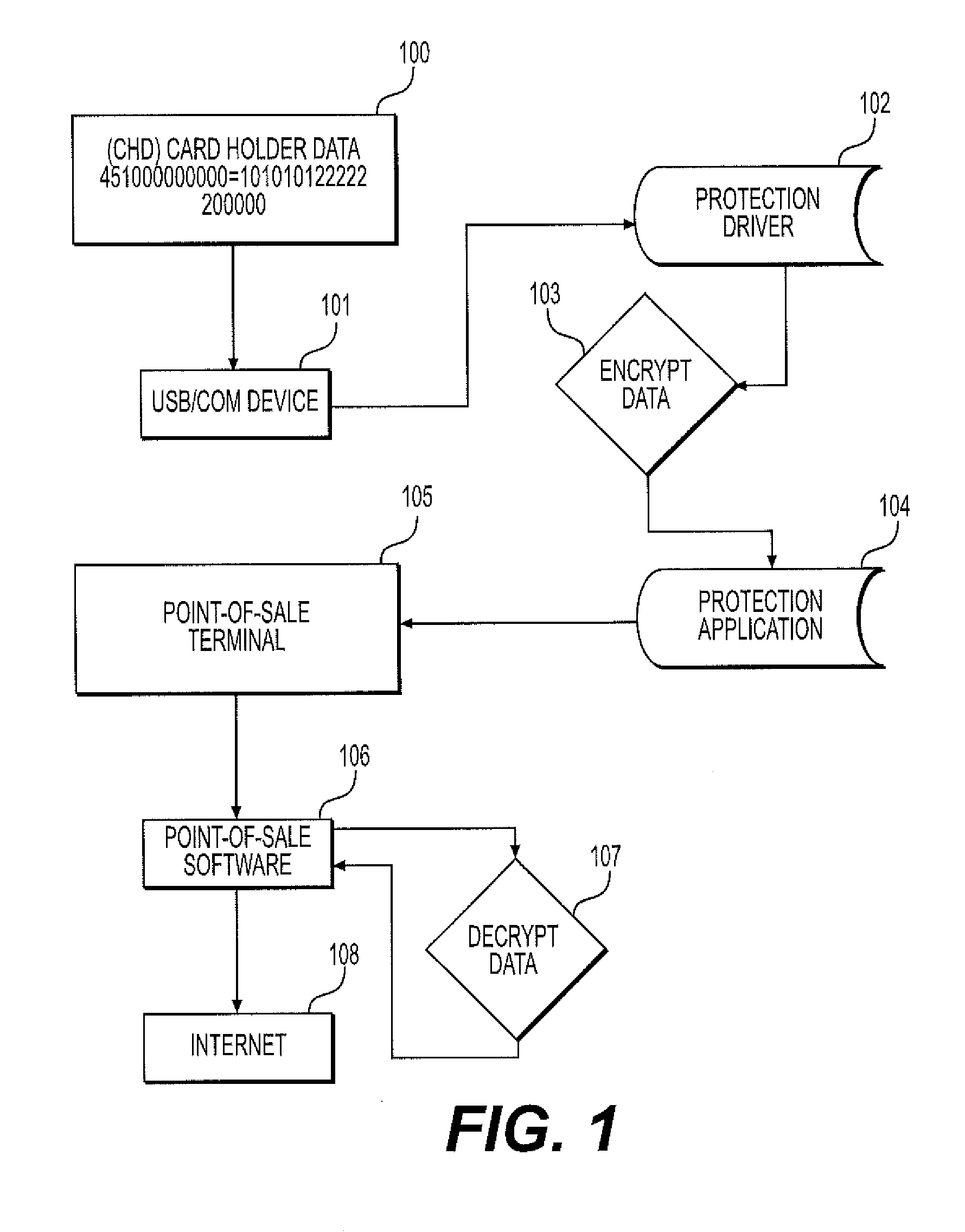

System and method for protecting against point of sale malware using memory scraping

A software, system and methodology for protecting against malware Point-of-Sale attacks that utilize, for example, memory scraping techniques. The application protects Point-of-sale hardware and its software against memory scraping malware attacks, and the loss of critical user credit card and confidential information often swiped at a terminal or stored in point of sale application databases. An embodiment of a method for blocking memory scraping attacks includes the following steps. Upon detecting a credit card swipe submission event from local hardware or comport event specific memory table events are flagged as unreadable, and immediately after allowing the data to be properly submitted, the system memory tables are cleared of data and specific memory processes are flagged as readable again. The method prevents memory scraping or point of sale malware from capturing swiped credit card data or input data, thereby protecting the user from theft of credit card data or other credentials.

Owner:TRUSTED KNIGHT CORP

Method for introducing regular file into data base

ActiveCN101059799AFlexibleWith characteristicsSpecial data processing applicationsMemory processData file

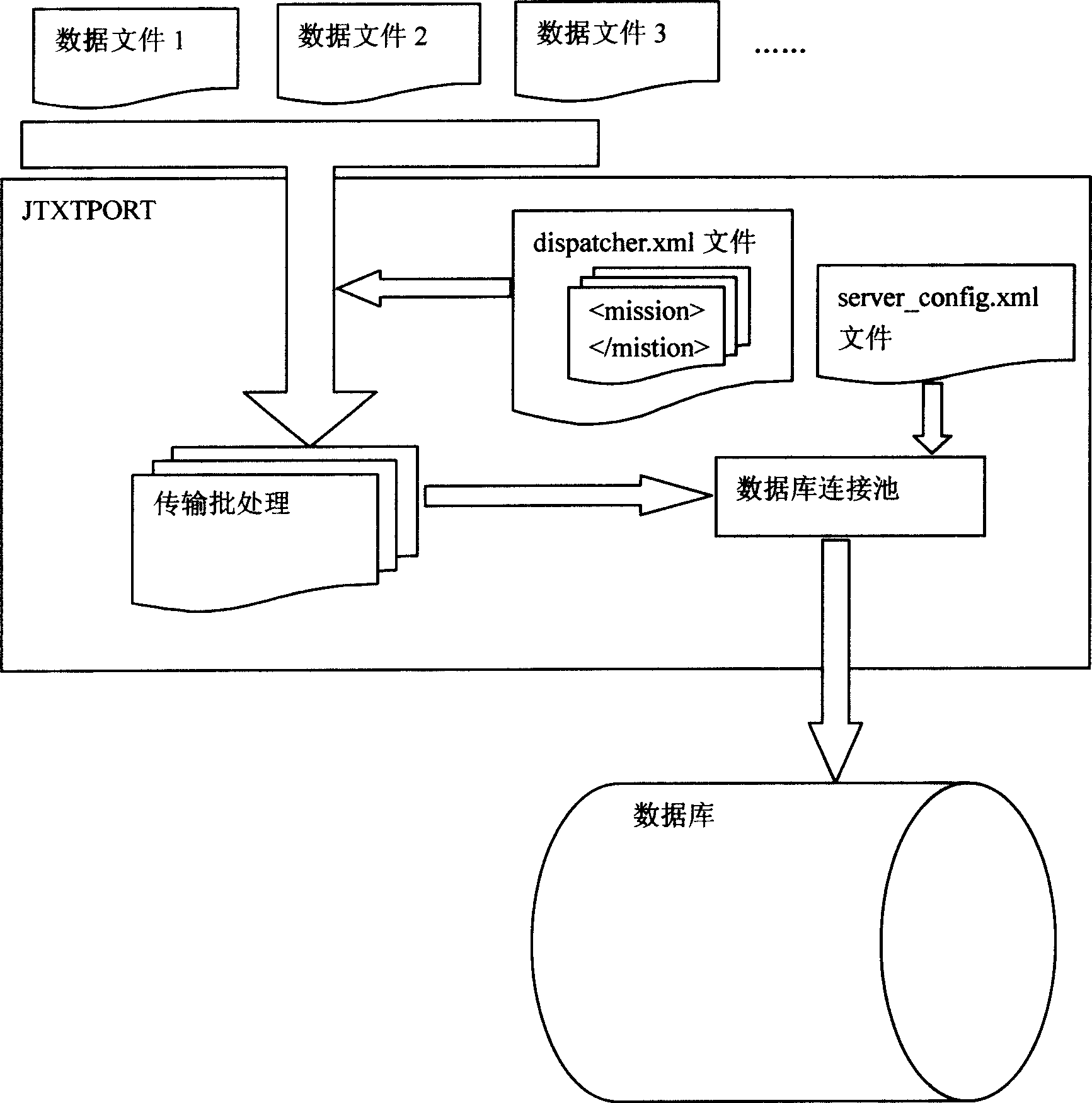

The invention discloses a method for leading regular text data into a database, comprising that 1, setting at least one data structure description, which is described based on object data list name, text document name, following distribution memory process name, data separator, and the structure leading data, 2, setting a database connecting description comprising the descriptions of database connection, text data document storage path and batch provided data record number, 3, building an application service platform, 4, transmitting the data structure description document generated in the first step and the database connecting description document generated in the second step to a special distribution path, 5, publishing the distribution path and the description document on the application service platform. The invention can analyze text and organize data to be leaded into database list, which can be applied for kinds of databases and data list structures, with strong flexibility and expansion.

Owner:SHANGHAI BAOSIGHT SOFTWARE CO LTD

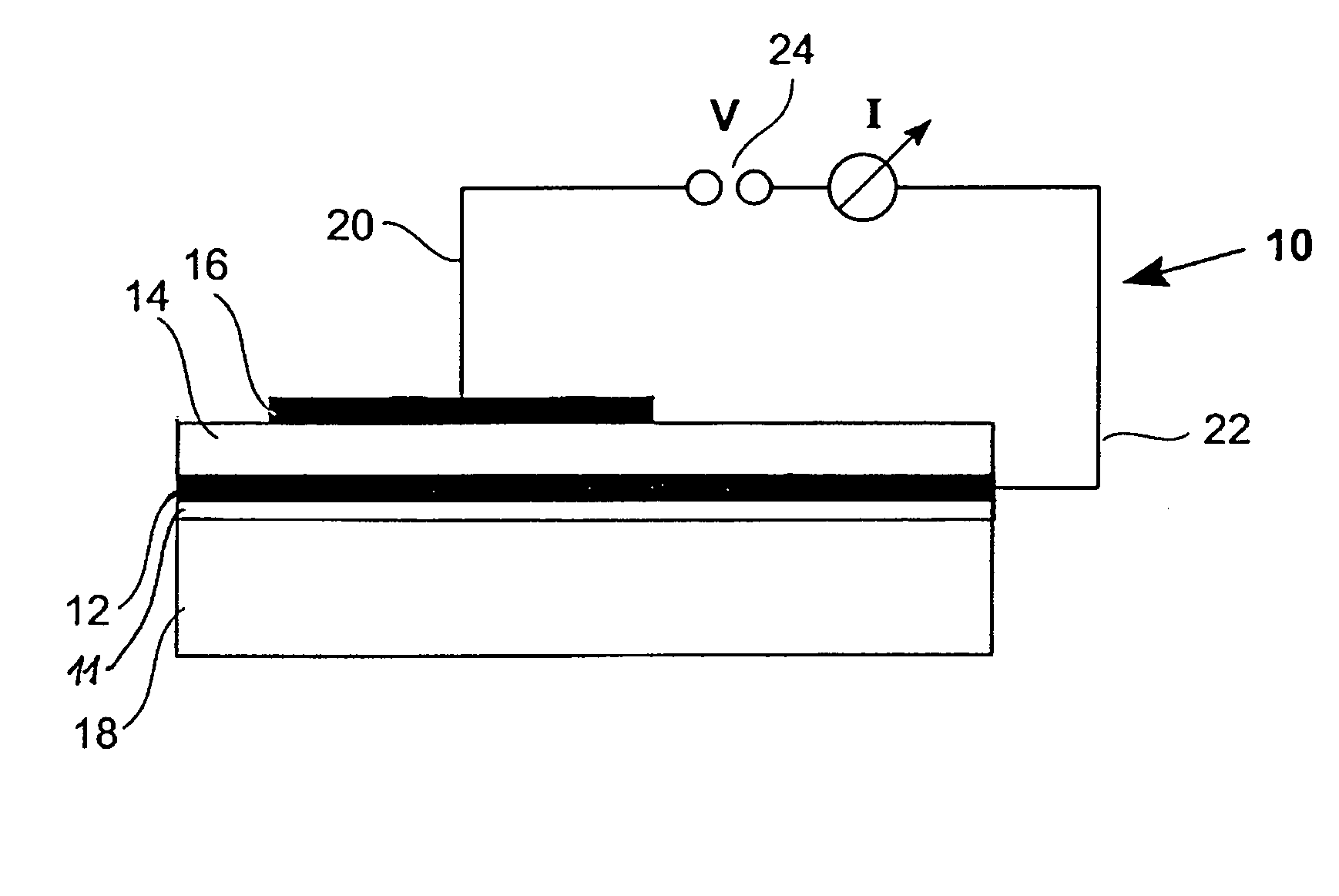

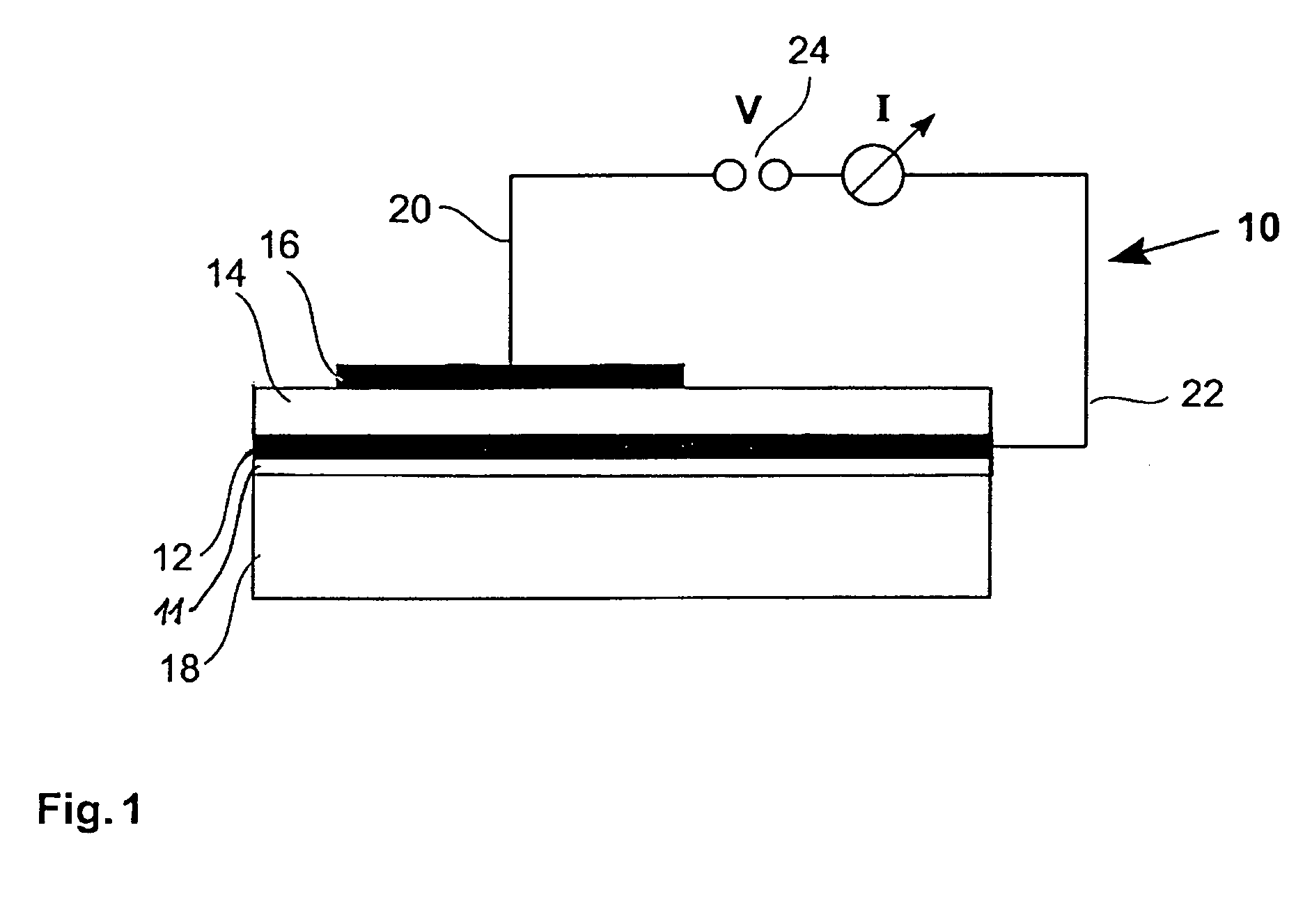

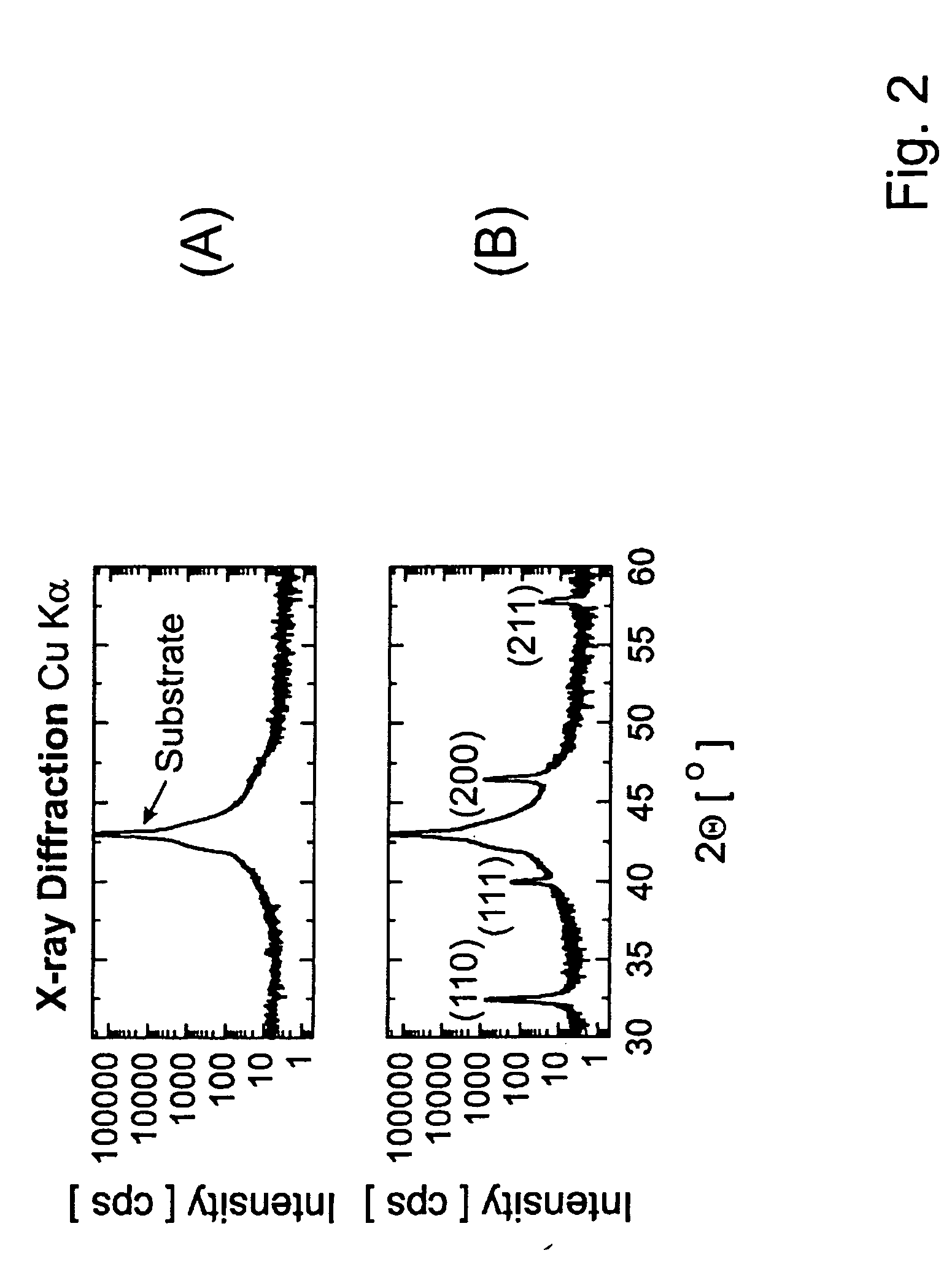

Non-volatile resistance switching memory

InactiveUS20050260839A1Cost-effective manufacturingReliable and reliableSolid-state devicesSemiconductor/solid-state device manufacturingMemory processCMOS

Processes, apparatus and systems for depositing a switching material that is switchable between conductivity states and where the states are persistent. The invention further relates to a microelectronic device or non-volatile resistance switching memory comprising the switching material for storing digital information. A process includes a step of depositing the switching material by a CMOS deposition technique at a temperature lower than 400° C.

Owner:GLOBALFOUNDRIES US INC

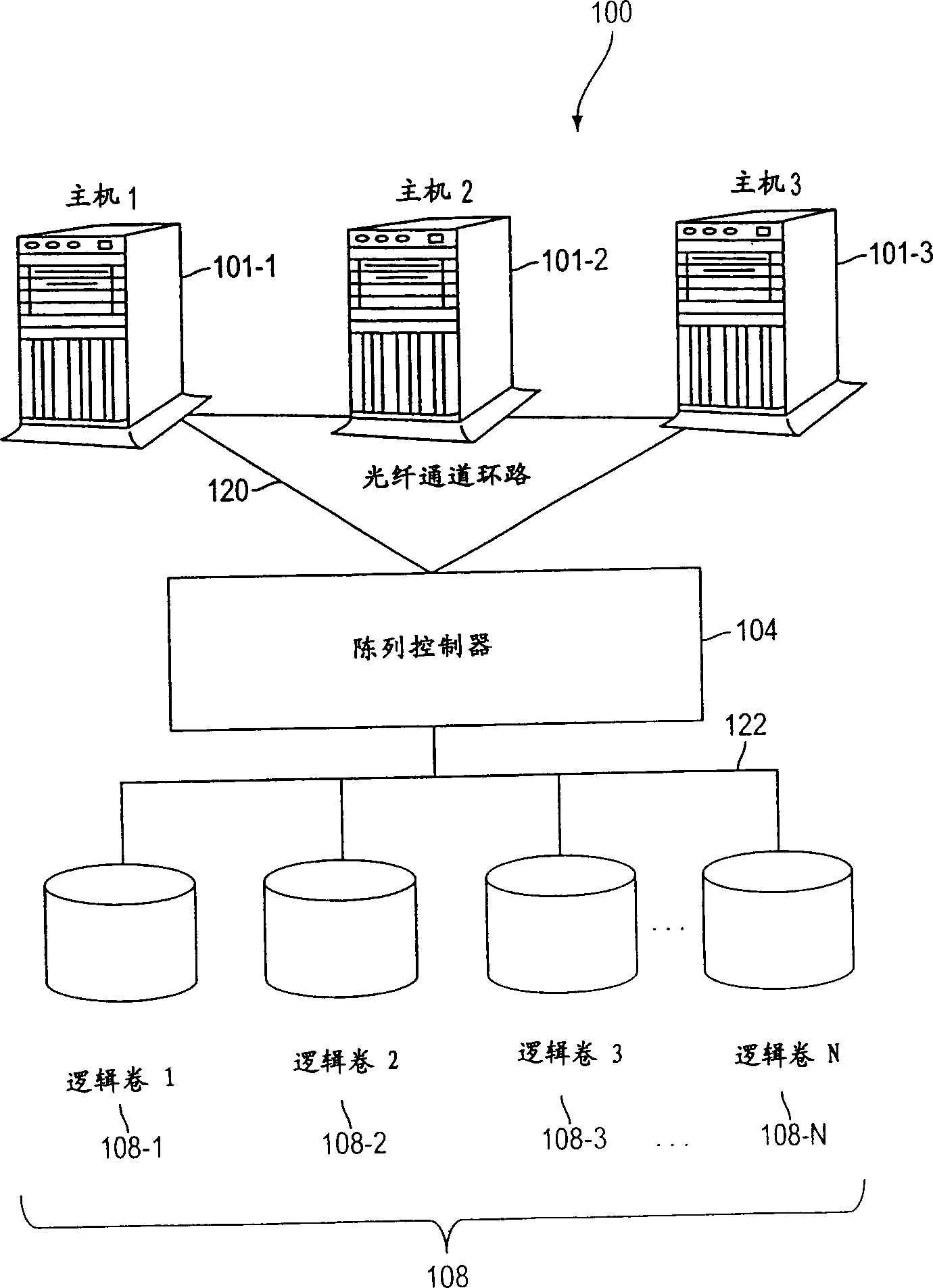

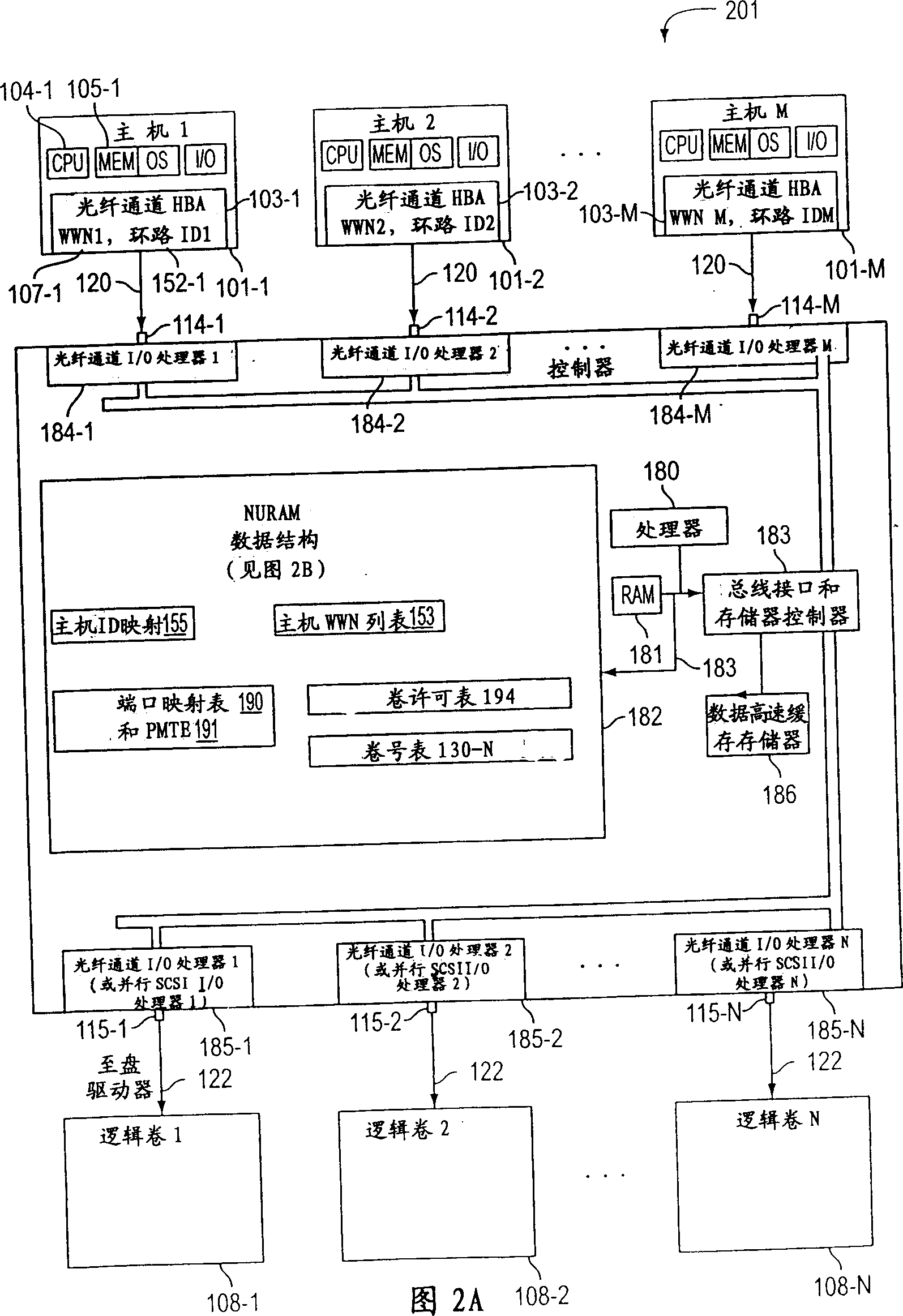

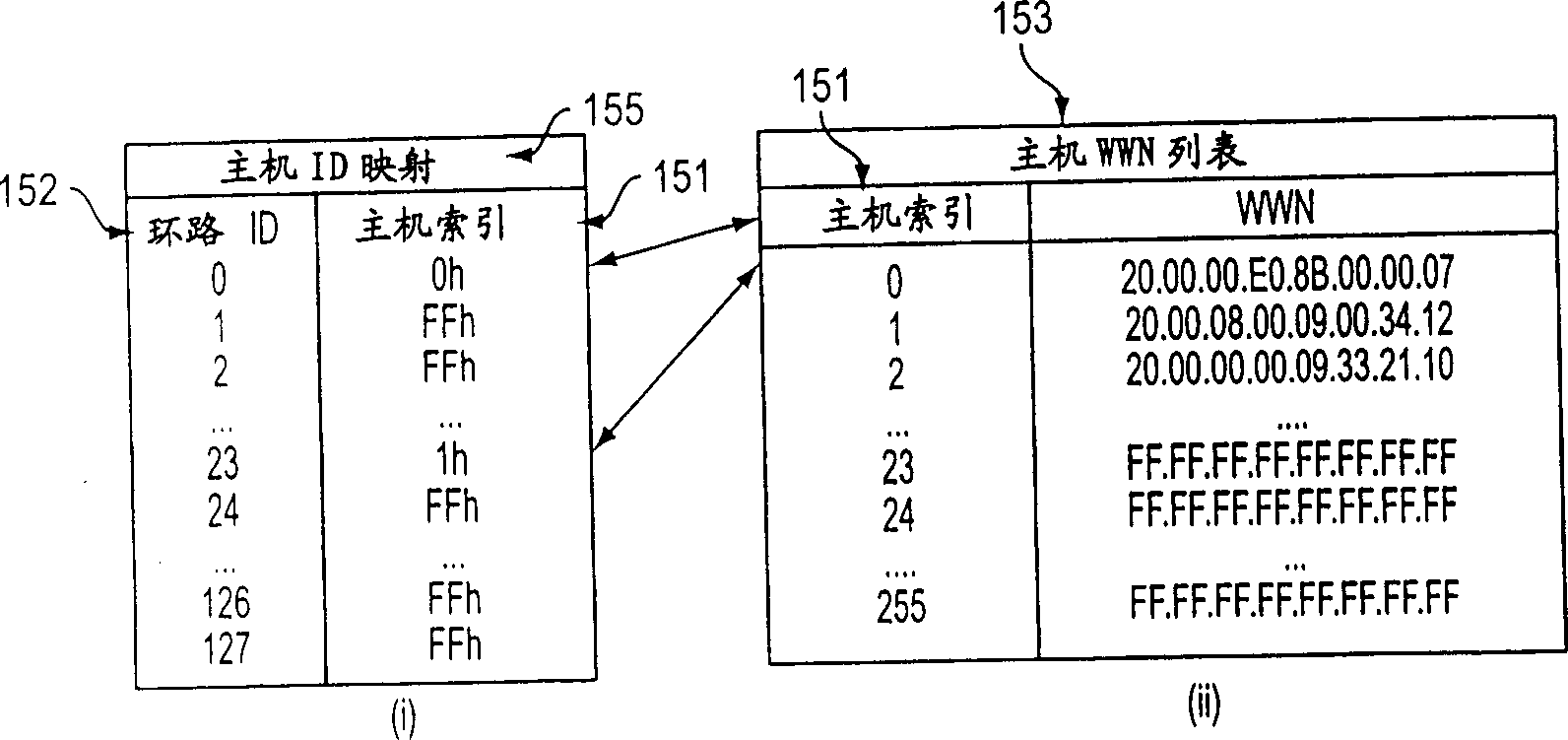

System and method for host volume mapping for shared storage volumes in multi-host computing environment

InactiveCN1373874AInput/output to record carriersUnauthorized memory use protectionMemory processUnique identifier

The present invention provides a structure and method for controlling access to shared storage devices, such as disk drive memory arrays, in computer systems and networks having multiple host computers (101). A method for controlling access to a hardware device (106) in a computer system having a plurality of computers and at least one hardware device (106) connected to the plurality of computers. The method includes the steps of: associating a locally unique identifier (130) with each of the plurality of computers; and defining in memory a data structure for identifying which of the computers are allowed based on the locally unique identifier accessing the device (190); and querying the data structure to determine whether a requesting one of the computers should be allowed access to the hardware device. In one embodiment, the process of defining the data structure in the memory includes: defining a host computer ID mapping data structure in the memory; defining a port mapping table data structure in the memory that includes a plurality of port mapping table entries; A host identifier list data structure is defined in the memory; a volume permission table data structure is defined in the memory; and a volume number table data structure is defined in the memory.

Owner:IBM CORP

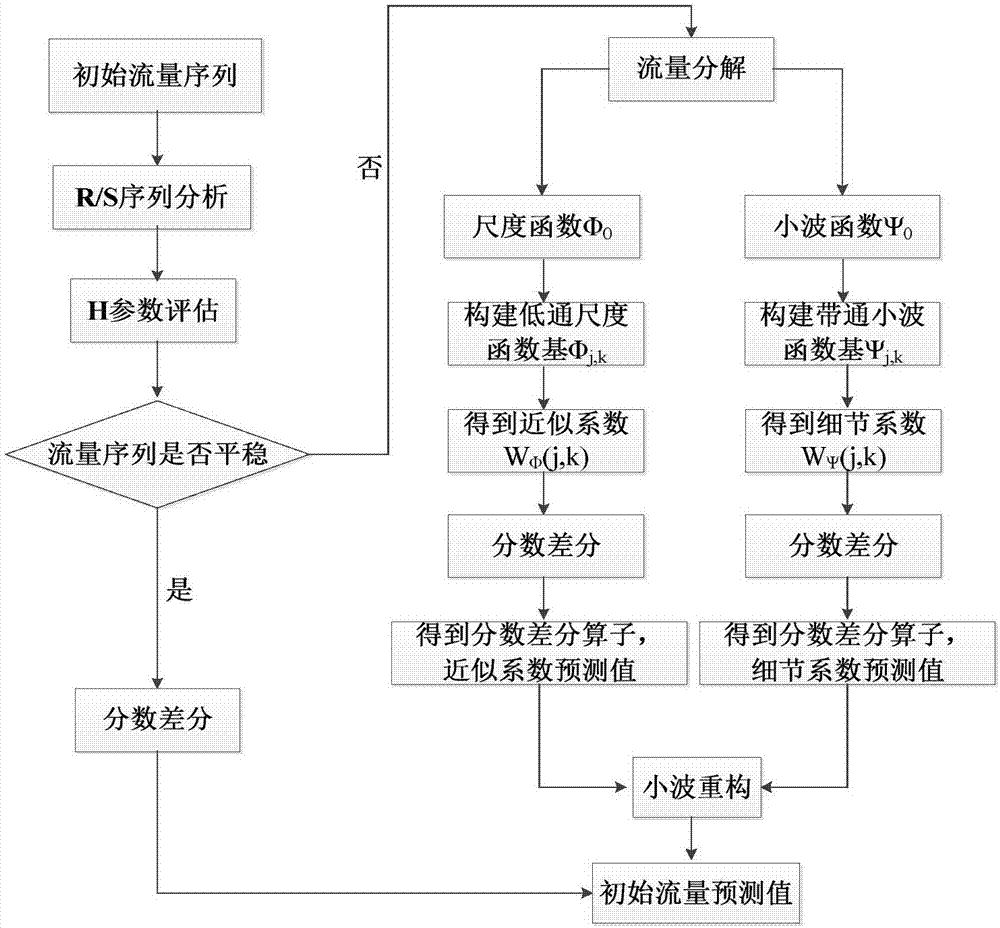

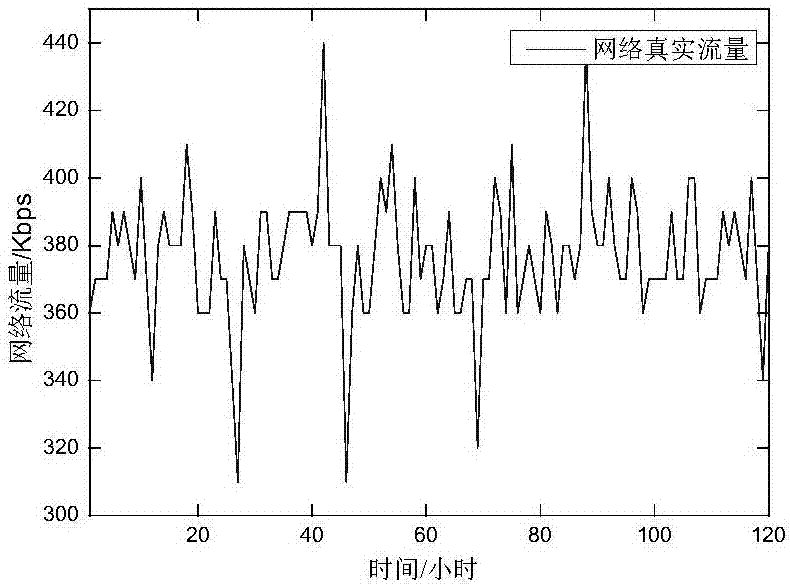

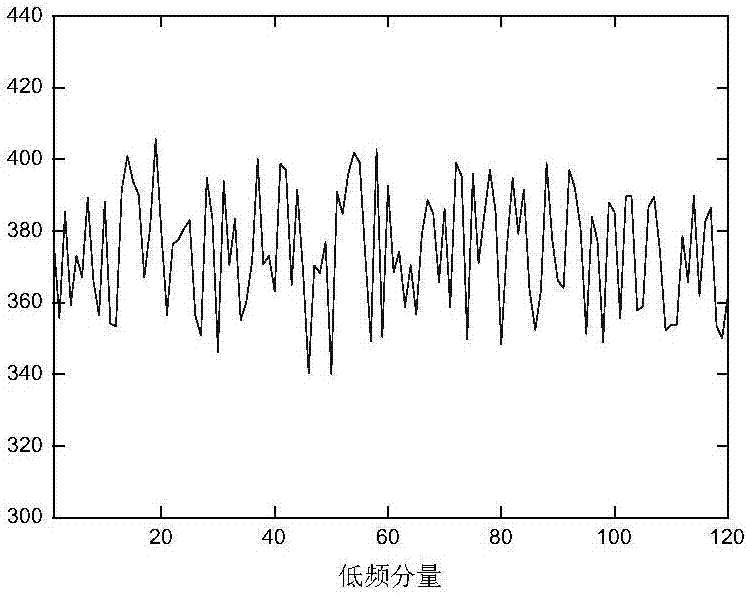

Data communication network traffic predicting method based on traffic analysis

ActiveCN107026763AHigh-precision long-term forecastingFast convergenceData switching networksTraffic capacityQuality of service

The invention provides a method which uses Hurst parameter values to represent self-similarity presented by network traffic, and analyzes statistic characteristics of the network traffic in big time scale in combination with the R / S series analysis method. Since the R / S series analysis method can better describe fractal characters and long-time memory process of the network traffic, and the FARIMA model which is used at later stage can also describe long-range dependence and short-range dependence of the network traffic, according to the invention, the method can conduct long-time prediction on the network traffic in a precise manner, has better astringency, and is very significant in terms of increasing network properties and service quality.

Owner:ZHONGSHAN POWER SUPPLY BUREAU OF GUANGDONG POWER GRID

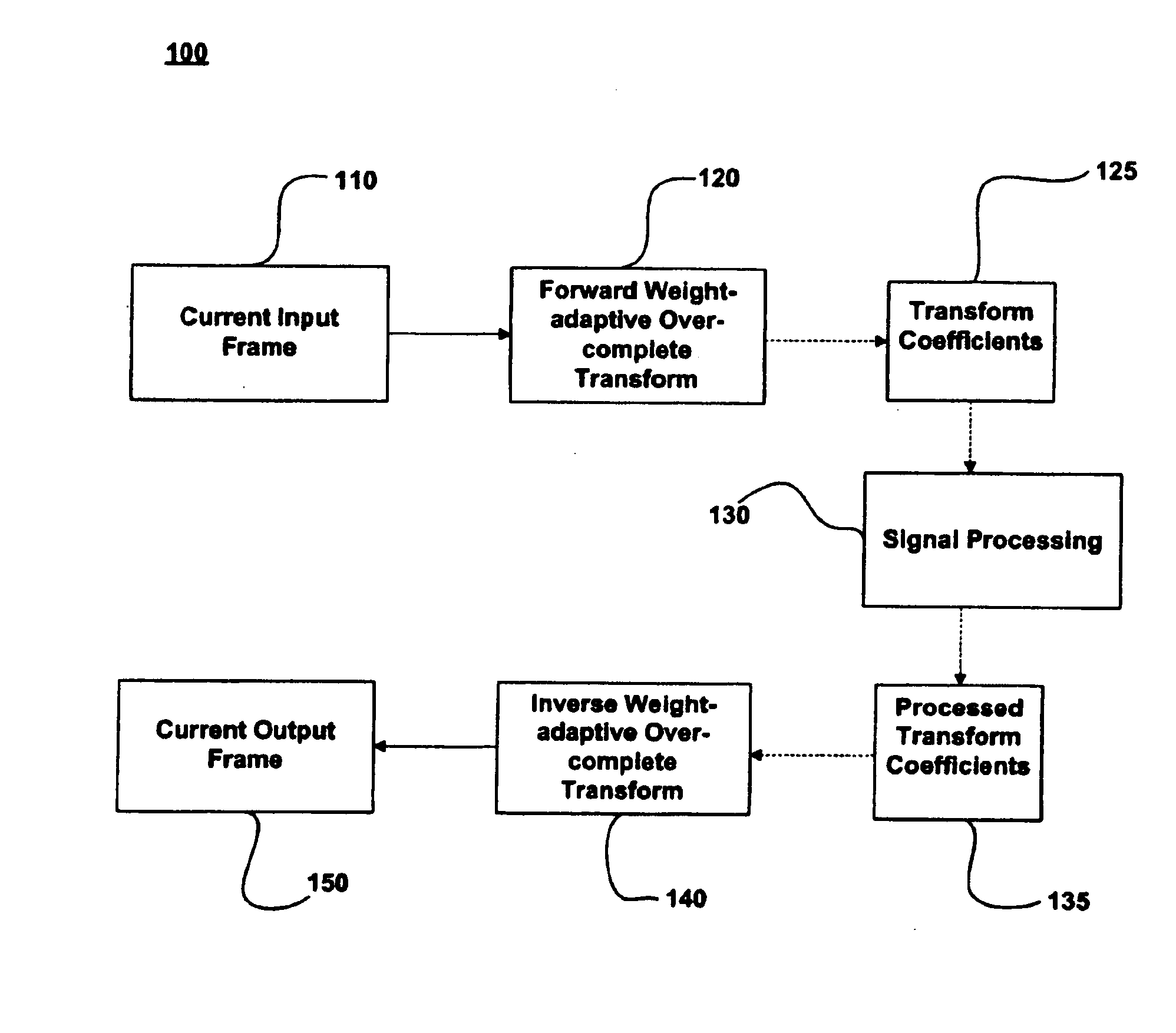

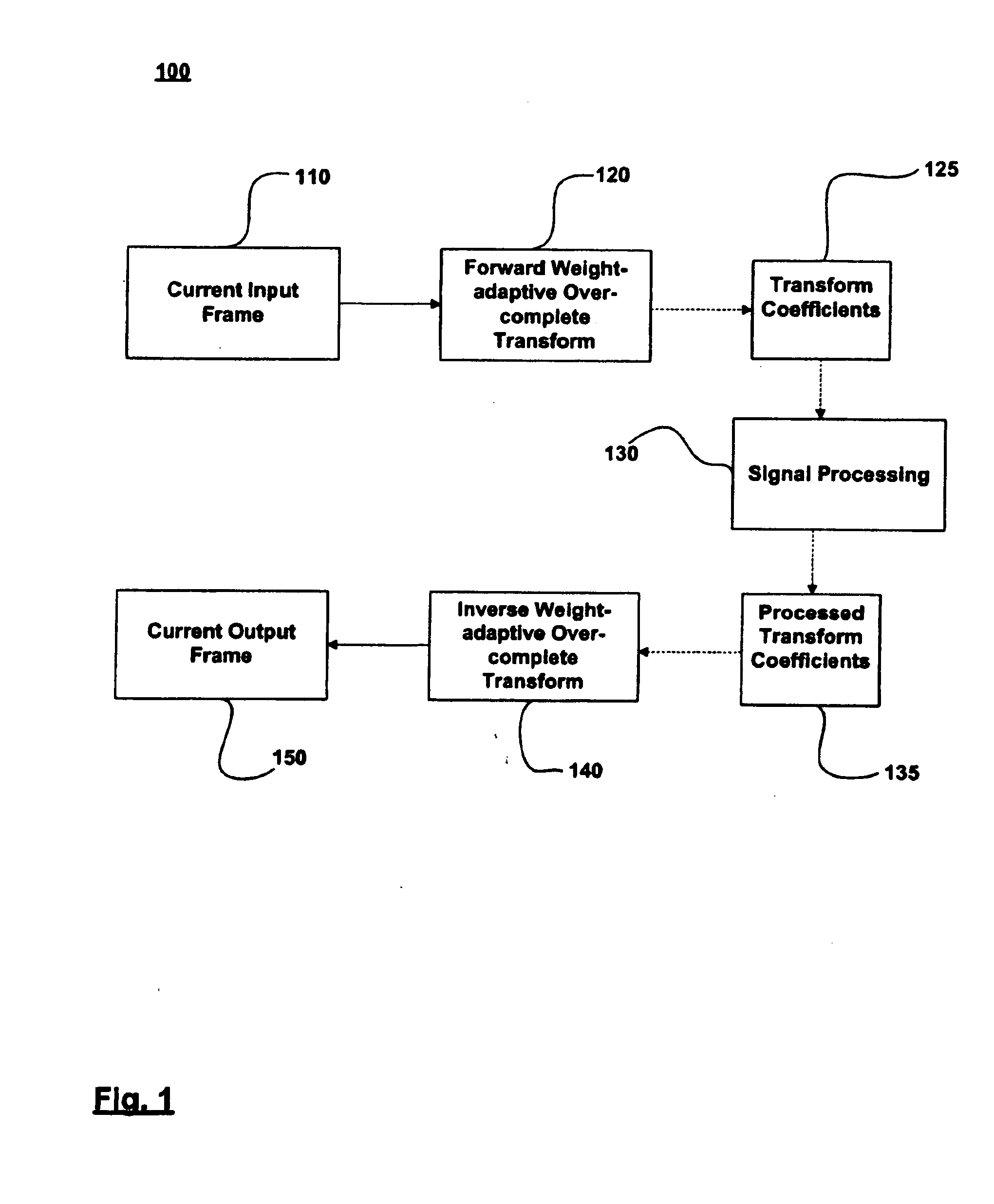

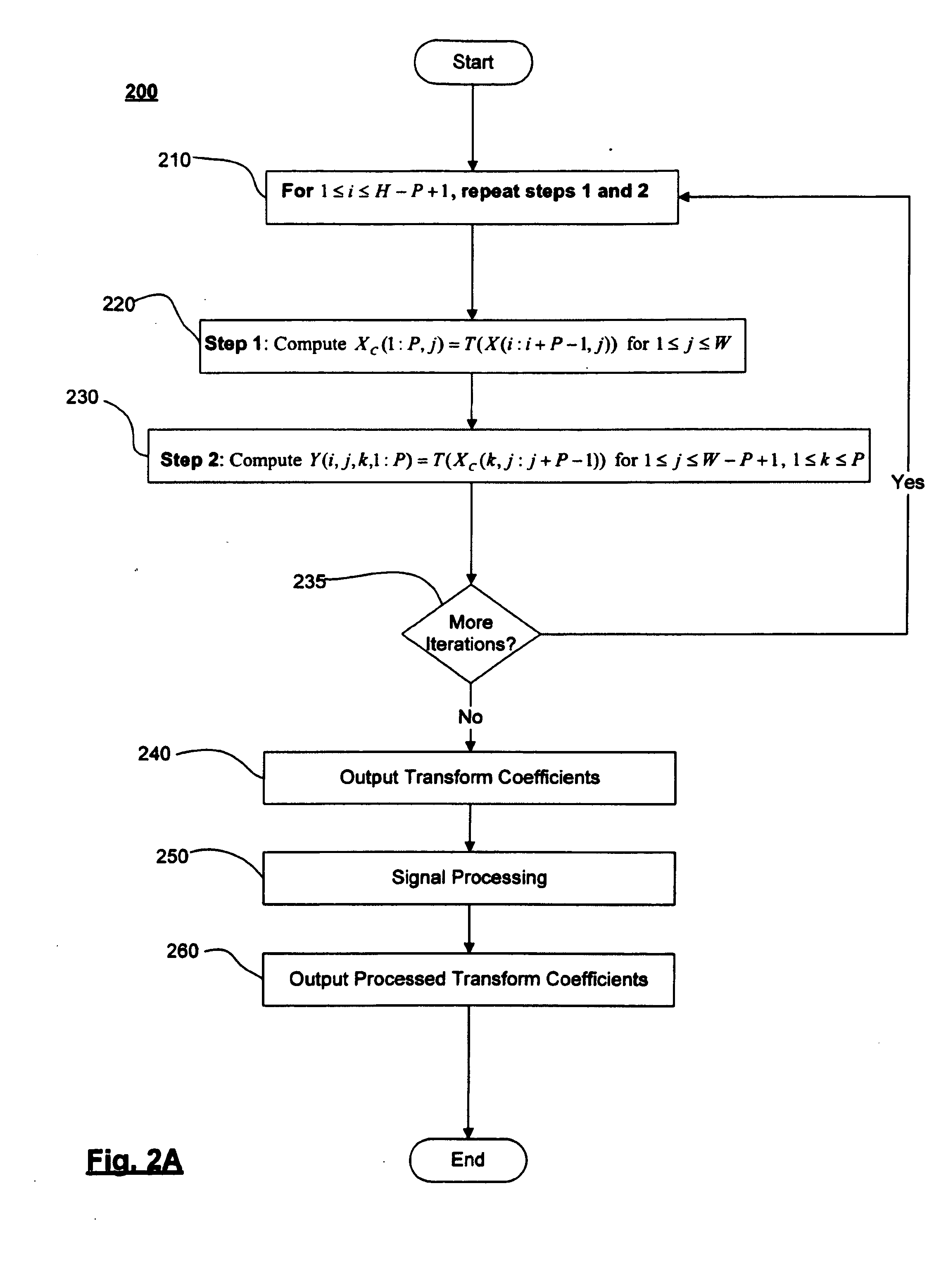

Methods for fast and memory efficient implementation of transforms

Embodiments of the present invention include a set of processes and systems for implementing a forward weight-adaptive over-complete transform of an image / video frame, an inverse weight-adaptive over-complete transform of an image / video frame, and fast and low-memory processes for performing the forward weight-adaptive over-complete transform, processing coefficients in the transform domain and performing the inverse weight-adaptive over-complete transform simultaneously.

Owner:NTT DOCOMO INC

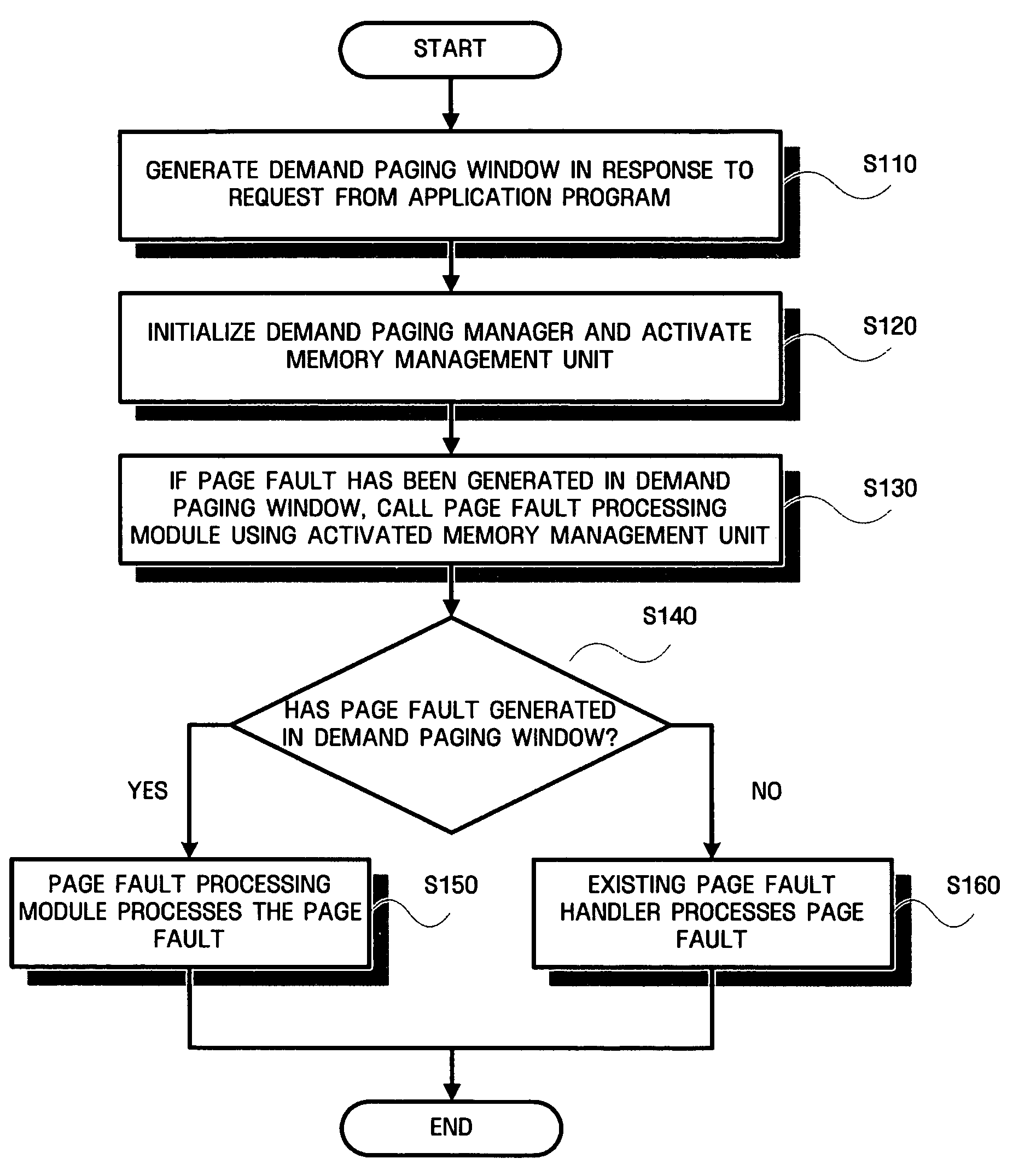

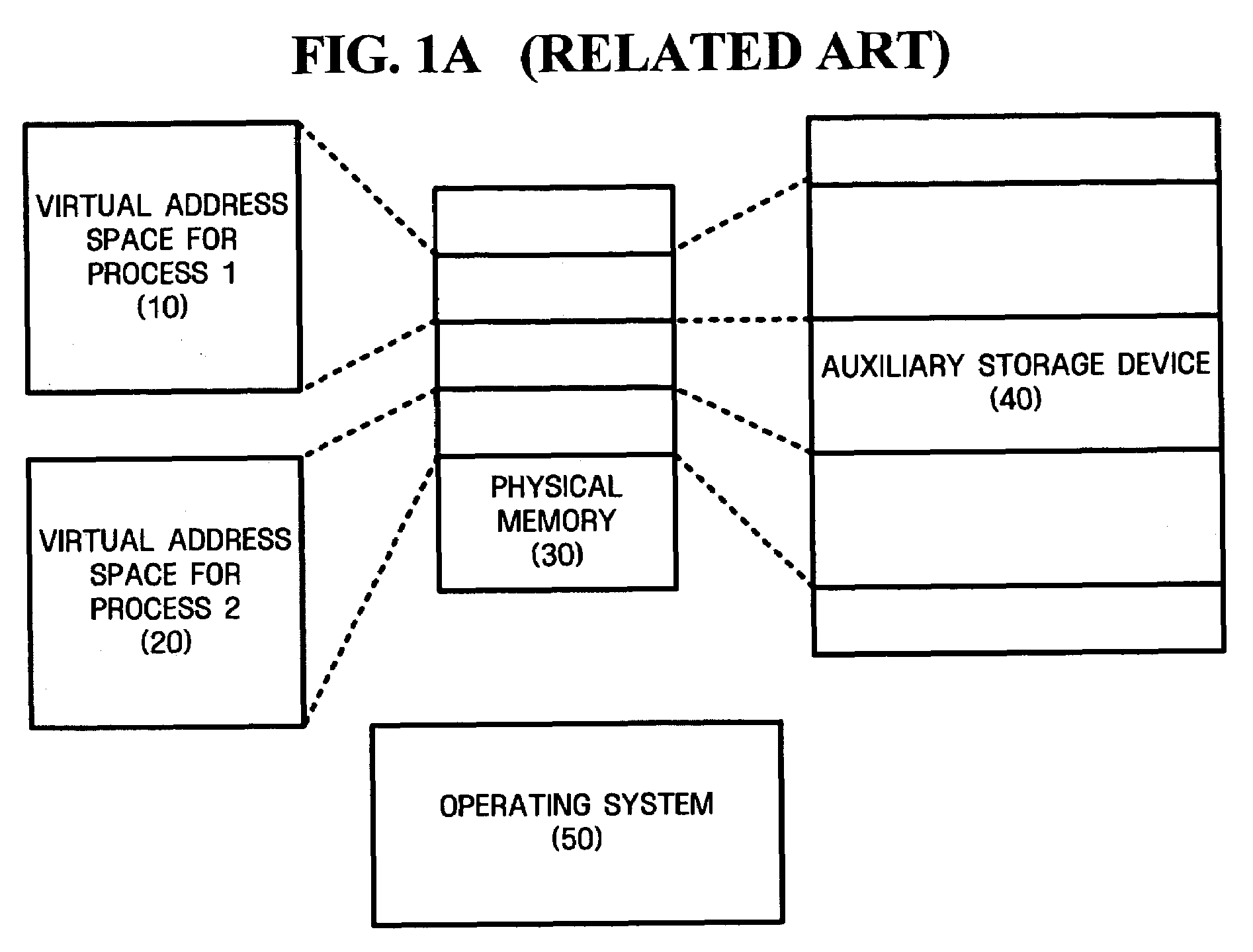

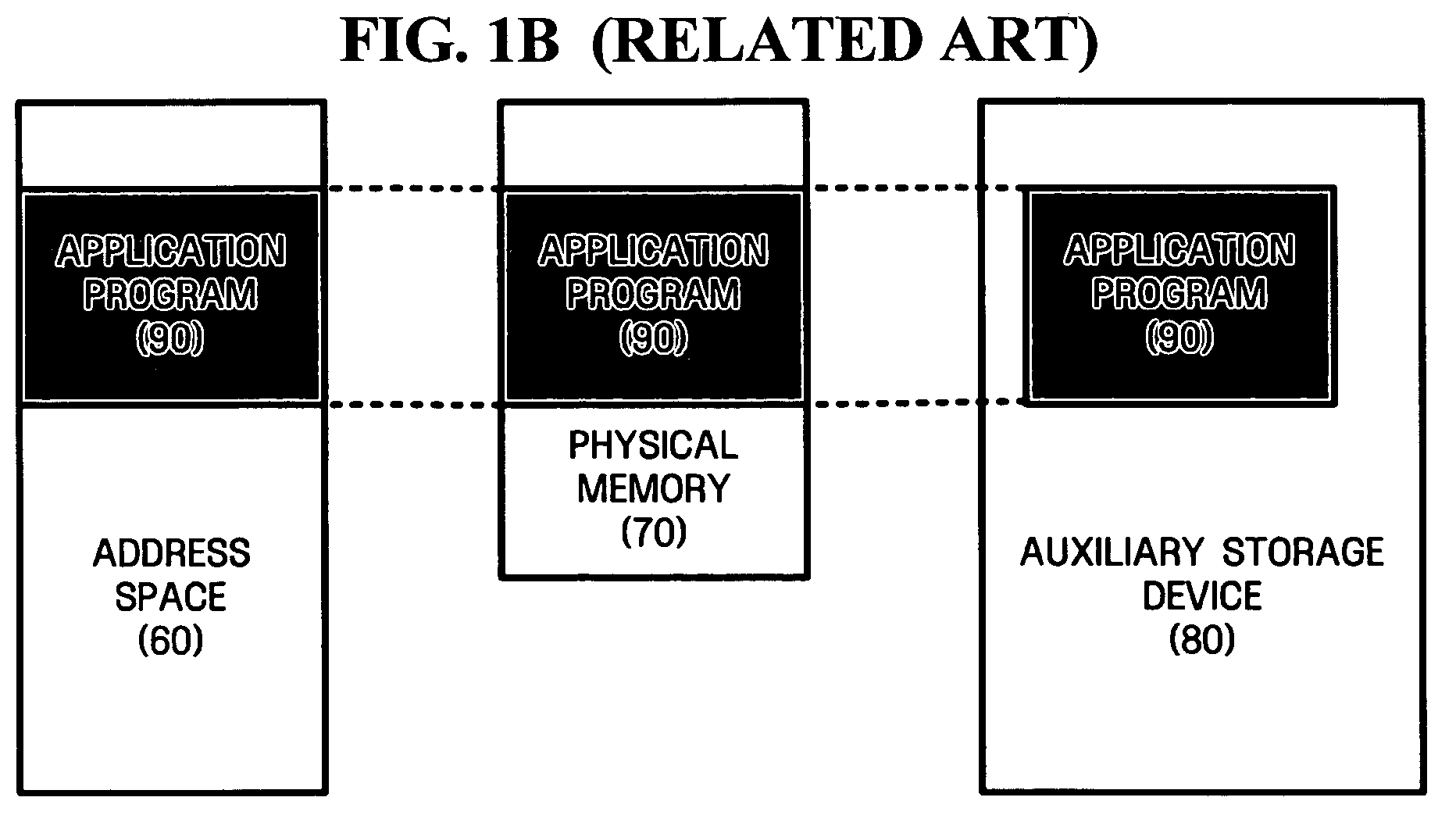

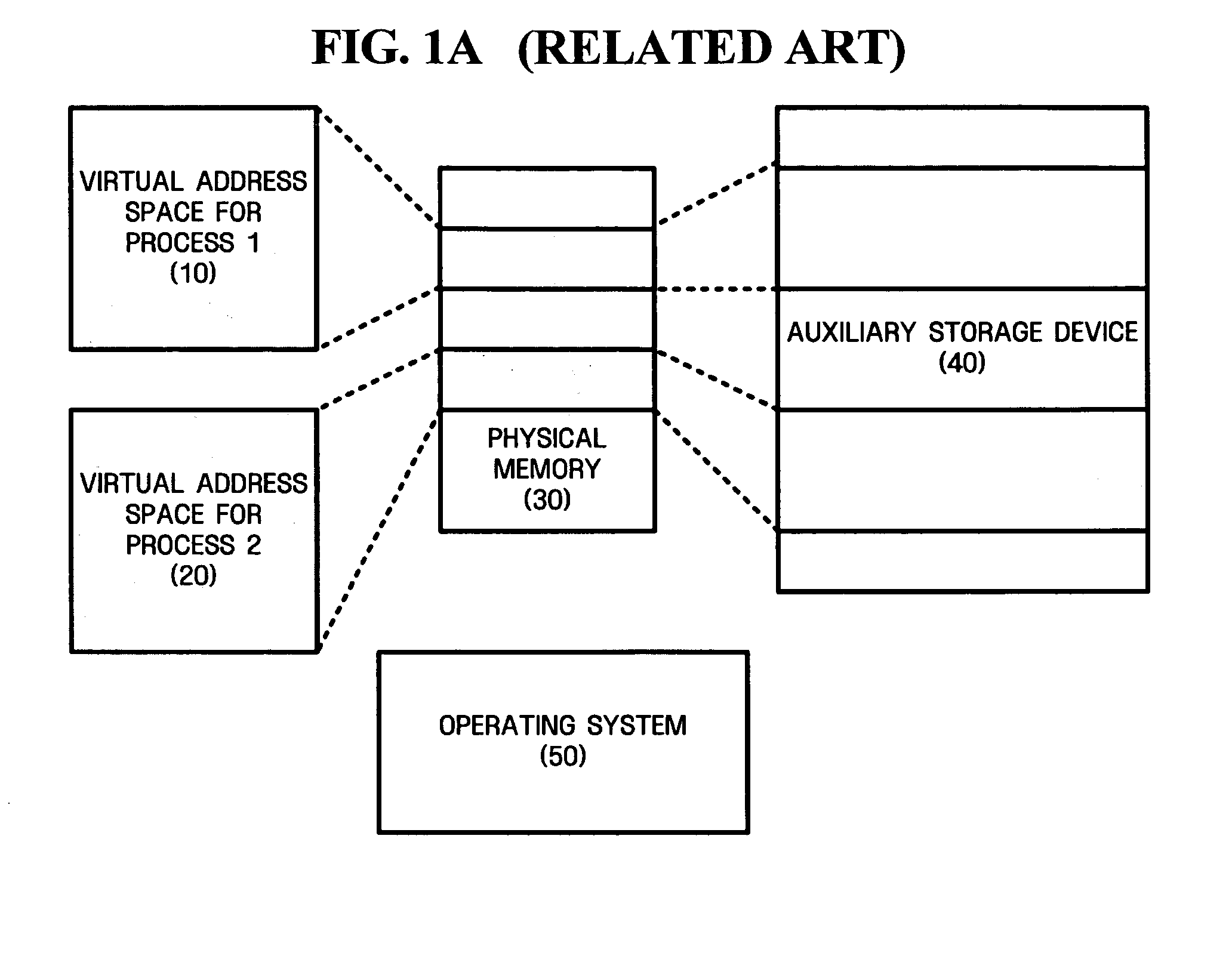

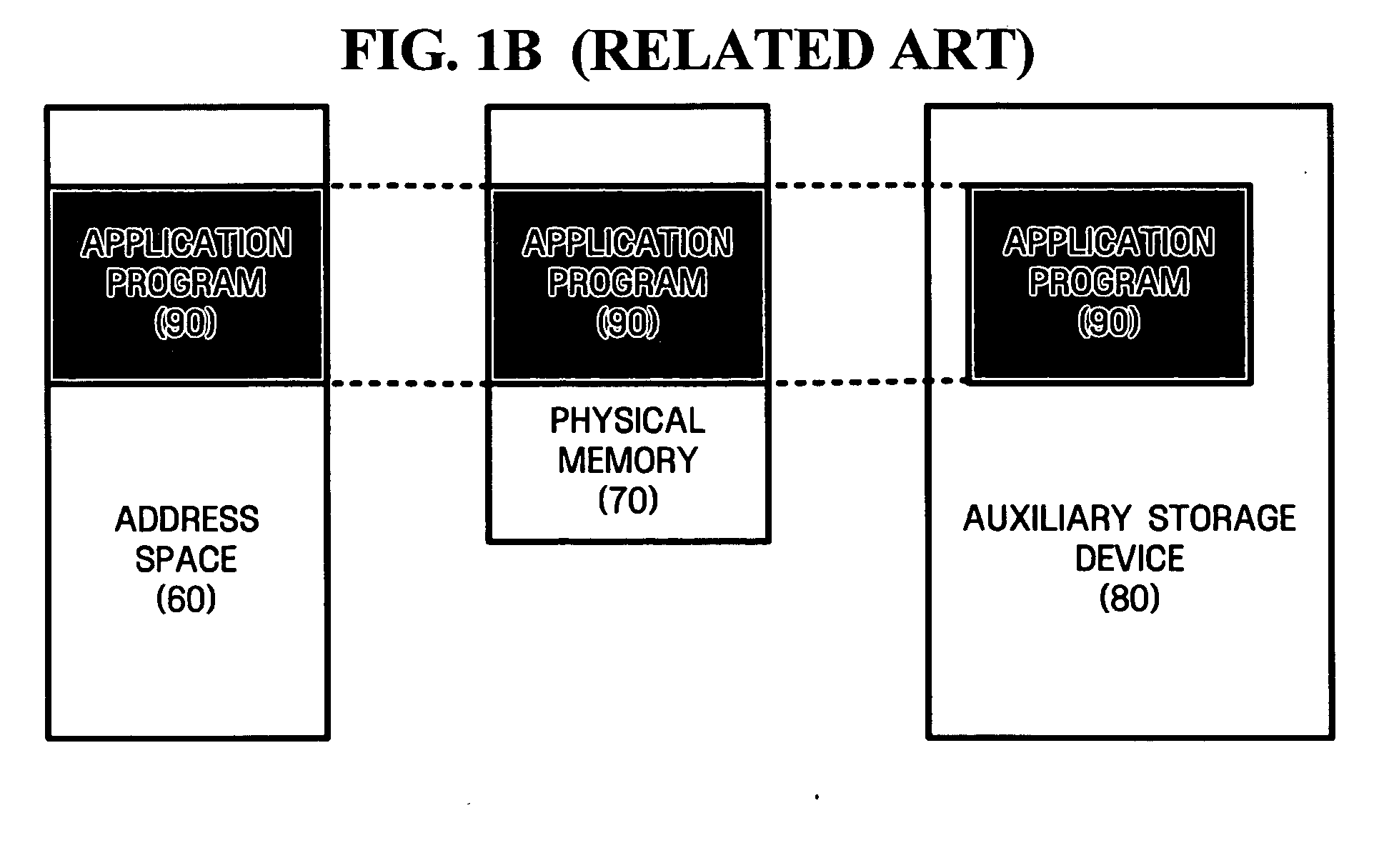

Demand paging apparatus and method for embedded system

ActiveUS7617381B2Memory adressing/allocation/relocationMicro-instruction address formationMemory processPaging

A demand paging apparatus and a method for an embedded system are provided. The demand paging apparatus includes a nonvolatile storage device, a physical memory, a demand paging window, and a demand paging manager. The nonvolatile storage device stores code and data which are handled by demand paging. The physical memory processes information about a requested page that is read from the nonvolatile storage device. The demand paging window generates a fault for the page and, thus, causes demand paging to occur. The demand paging window is part of an address space to which an application program stored in the nonvolatile storage device refers. The demand paging manager processes the page fault generated in the demand paging window.

Owner:SAMSUNG ELECTRONICS CO LTD

Demand paging apparatus and method for embedded system

ActiveUS20070150695A1Memory adressing/allocation/relocationMicro-instruction address formationMemory processPaging

A demand paging apparatus and a method for an embedded system are provided. The demand paging apparatus includes a nonvolatile storage device, a physical memory, a demand paging window, and a demand paging manager. The nonvolatile storage device stores code and data which are handled by demand paging. The physical memory processes information about a requested page that is read from the nonvolatile storage device. The demand paging window generates a fault for the page and, thus, causes demand paging to occur. The demand paging window is part of an address space to which an application program stored in the nonvolatile storage device refers. The demand paging manager processes the page fault generated in the demand paging window.

Owner:SAMSUNG ELECTRONICS CO LTD

Method for manufacturing three-dimensionally stacked resistance conversion memory

ActiveCN101834152AProcess compatibleImprove reliabilitySolid-state devicesSemiconductor/solid-state device manufacturingMemory processEtching

The invention provides a method for manufacturing a three-dimensionally stacked resistance conversion memory, which comprises the following steps of: sequentially depositing an adhesion layer and a metal layer on the surface provided with a peripheral circuit and a resistance converting storage array, and planing the surface under the assistance of chemically mechanical polishing to form a wafer 1 needing to be bonded; manufacturing a wafer 2 needed by bonding, namely, forming a PN layer on the wafer, activating the wafer, sequentially depositing an adhesion layer and a metal layer on the surface of the wafer, and planing the surface; bonding the wafer 1 and the wafer 2; and removing excessive part of the wafer 2 through subsequent processes, such as back etching, polishing or annealing and stripping process. The invention also includes the method for manufacturing the three-dimensionally stacked resistance conversion memory for manufacturing a schottky diode strobe. The method of the invention can make a process and a resistance conversion memory process compatible, has high reliability and fewer shortcomings, and is expected to be widely applied in three-dimensional stack.

Owner:SHANGHAI INST OF MICROSYSTEM & INFORMATION TECH CHINESE ACAD OF SCI

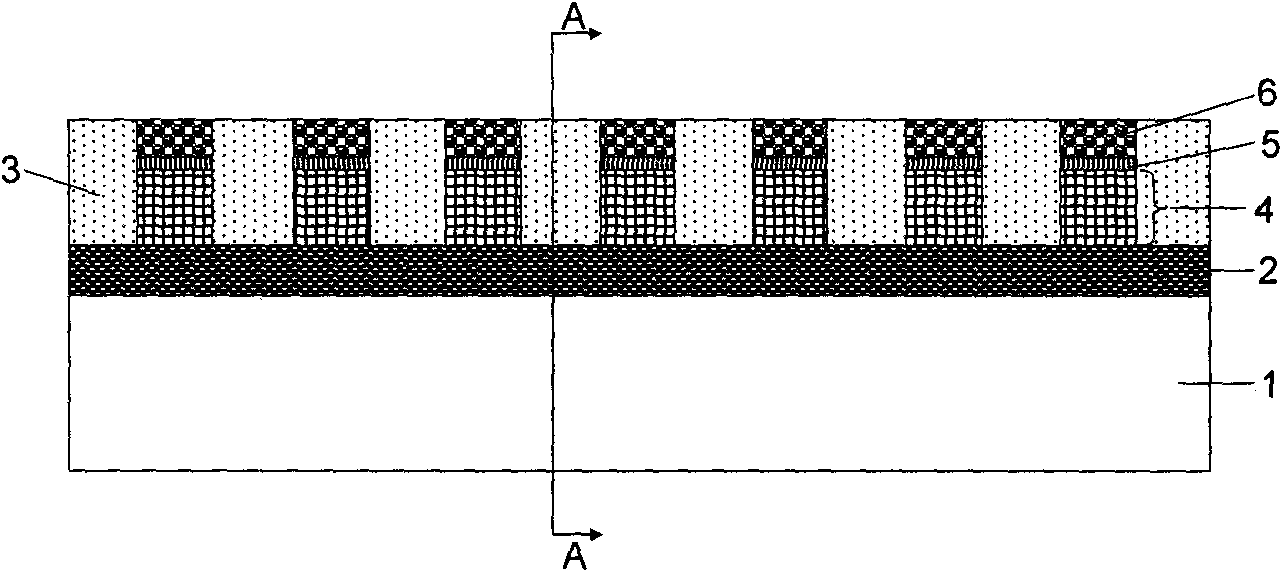

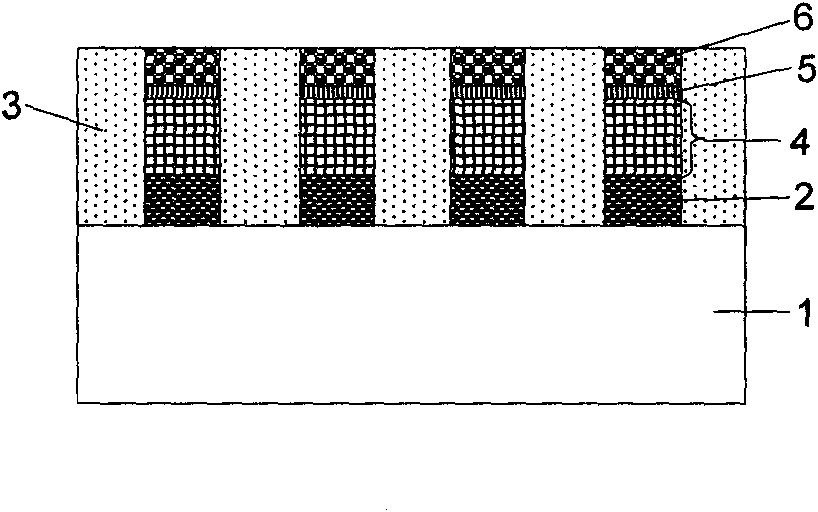

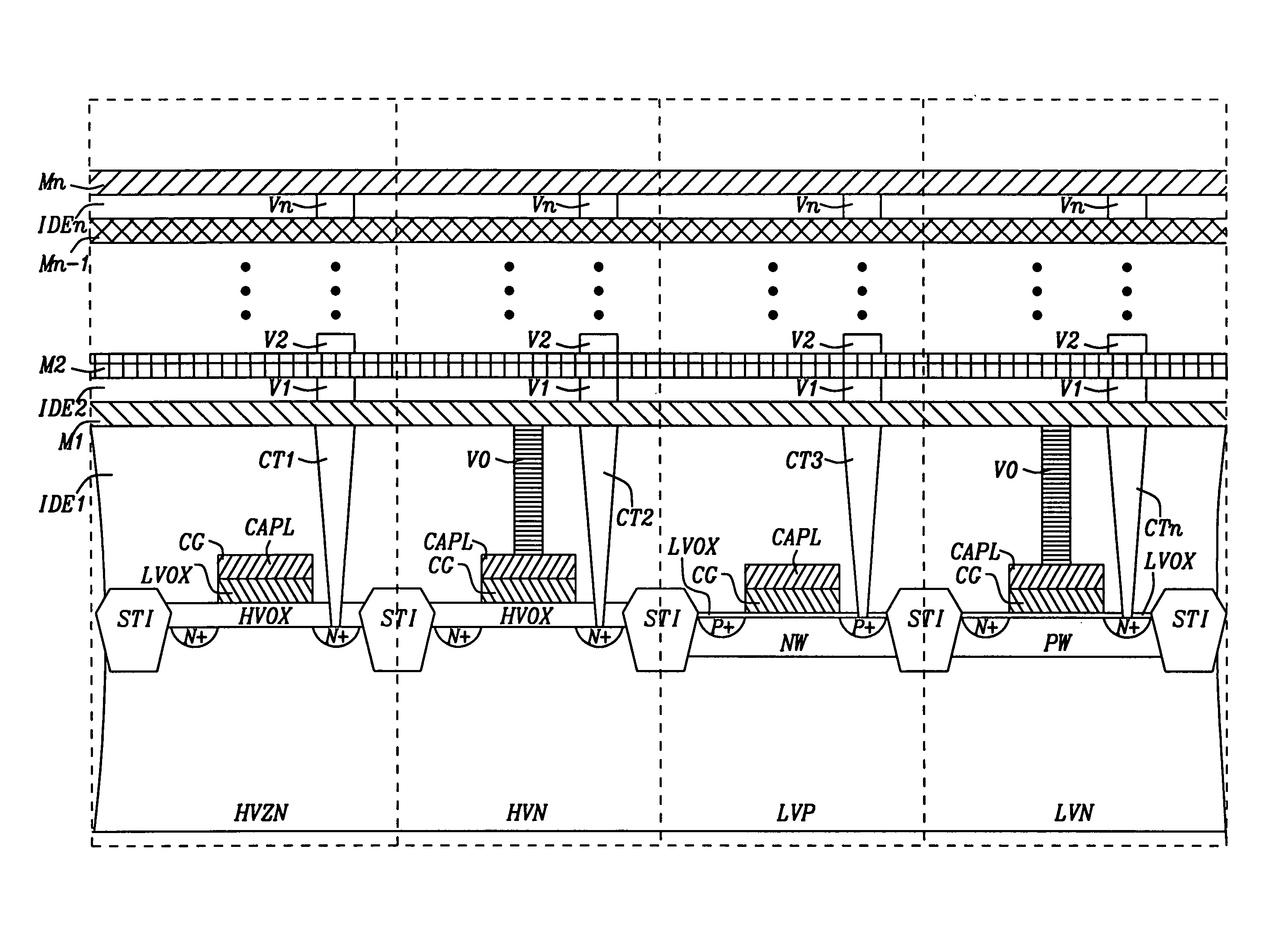

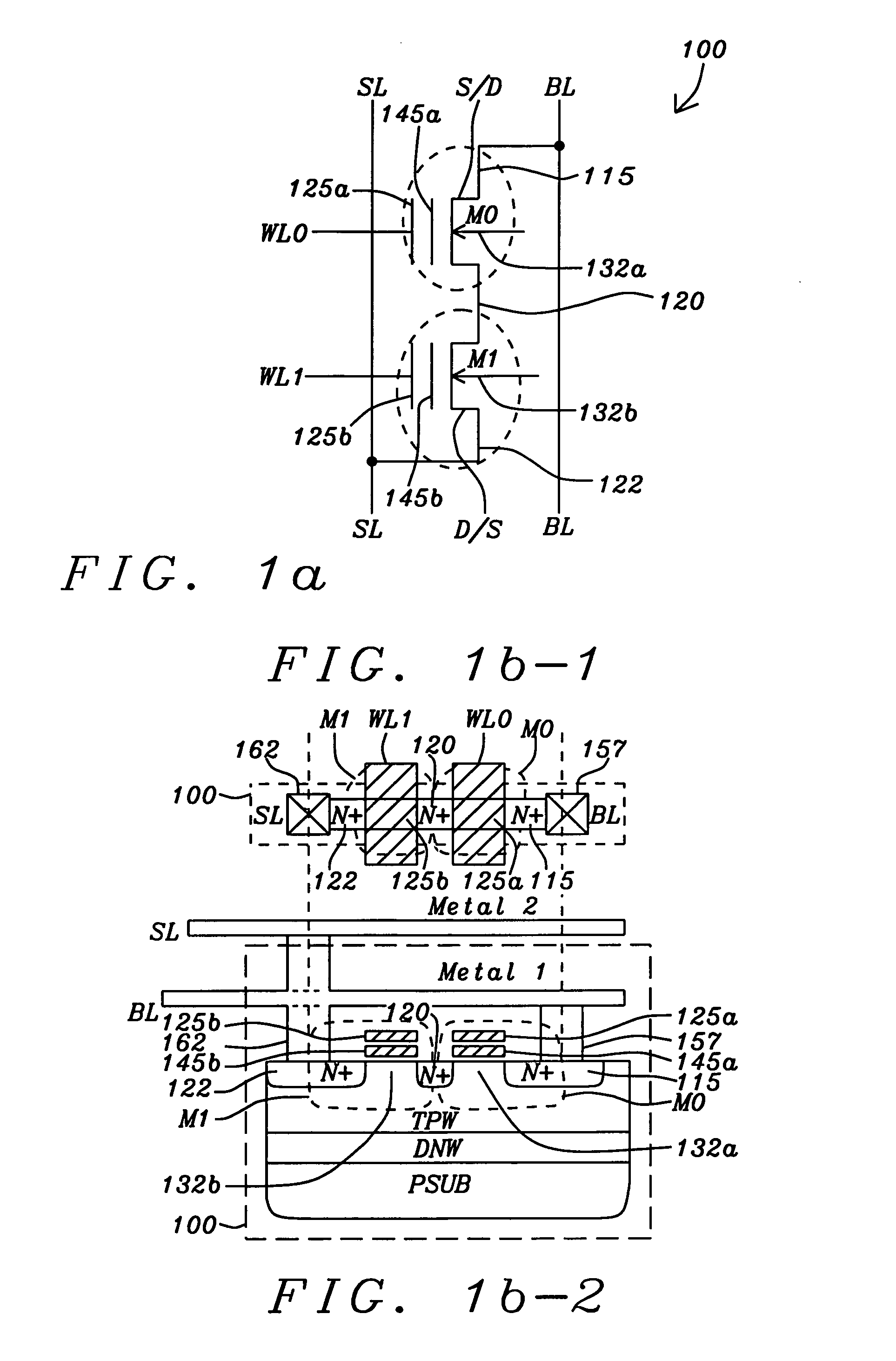

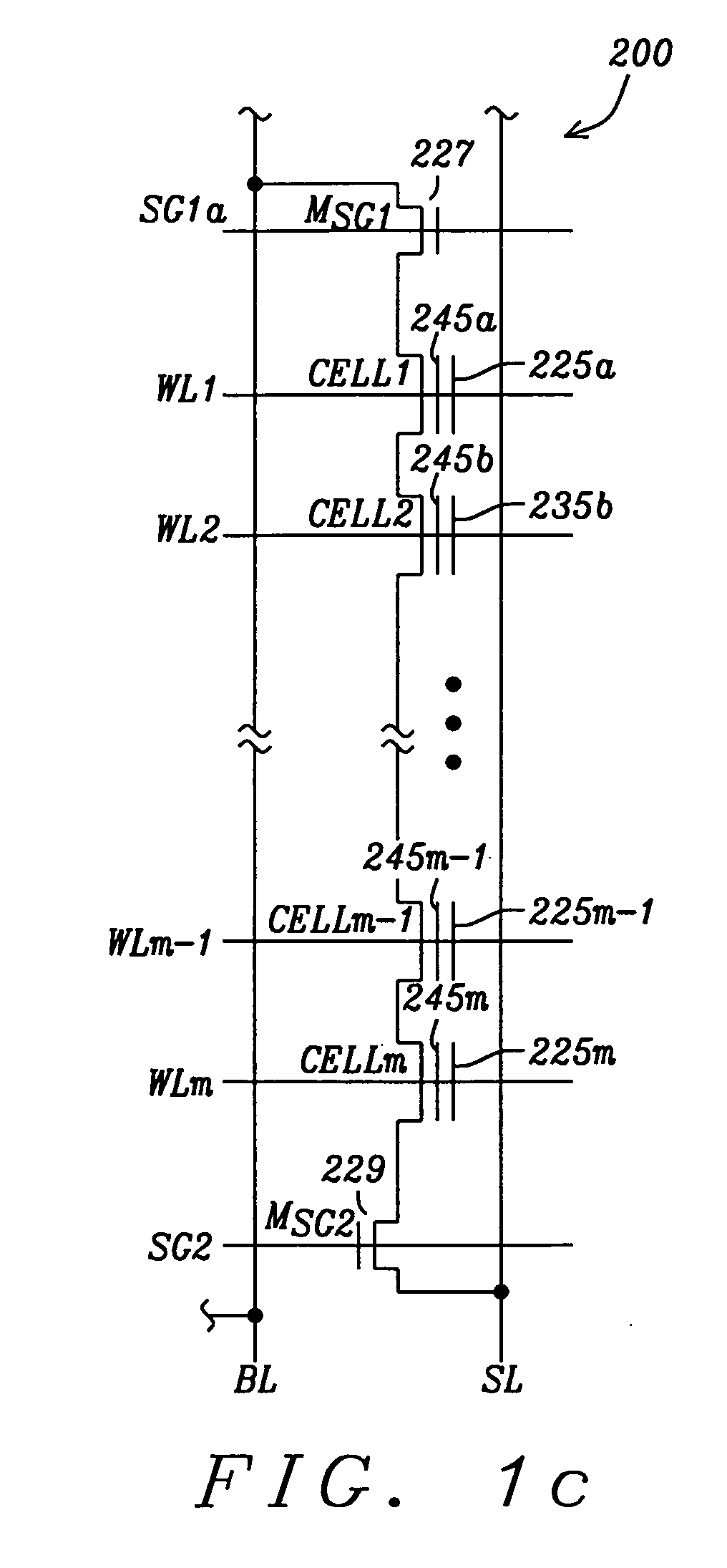

Embedded NOR flash memory process with NAND cell and true logic compatible low voltage device

InactiveUS8455923B2Avoid leakage currentImprove performanceSemiconductor/solid-state device detailsSolid-state devicesMemory processCharge retention

An integrated circuit formed of nonvolatile memory array circuits, logic circuits and linear analog circuits is formed on a substrate. The nonvolatile memory array circuits, the logic circuits and the linear analog circuits are separated by isolation regions formed of a shallow trench isolation. The nonvolatile memory array circuits are formed in a triple well structure. The nonvolatile memory array circuits are NAND-based NOR memory circuits formed of at least two floating gate transistors that are serially connected such that at least one of the floating gate transistors functions as a select gate transistor to prevent leakage current through the charge retaining transistors when the charge retaining transistors is not selected for reading. Each column of the NAND-based NOR memory circuits are associated with and connected to one bit line and one source line.

Owner:APLUS FLASH TECH

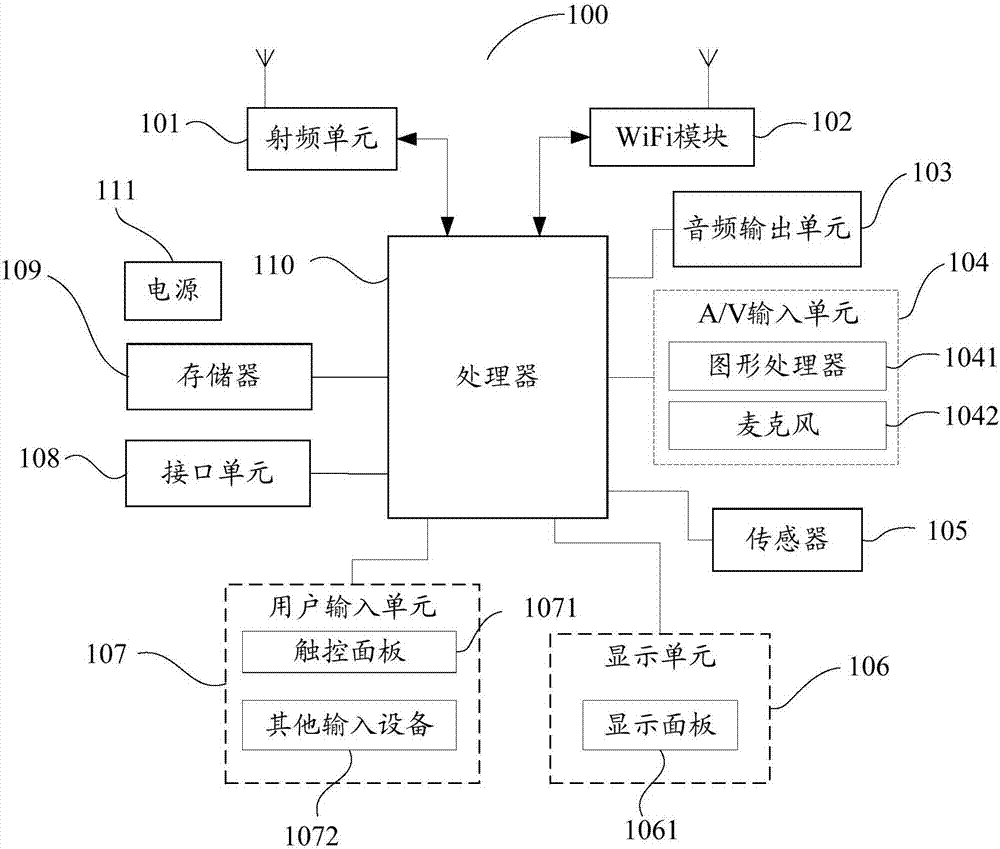

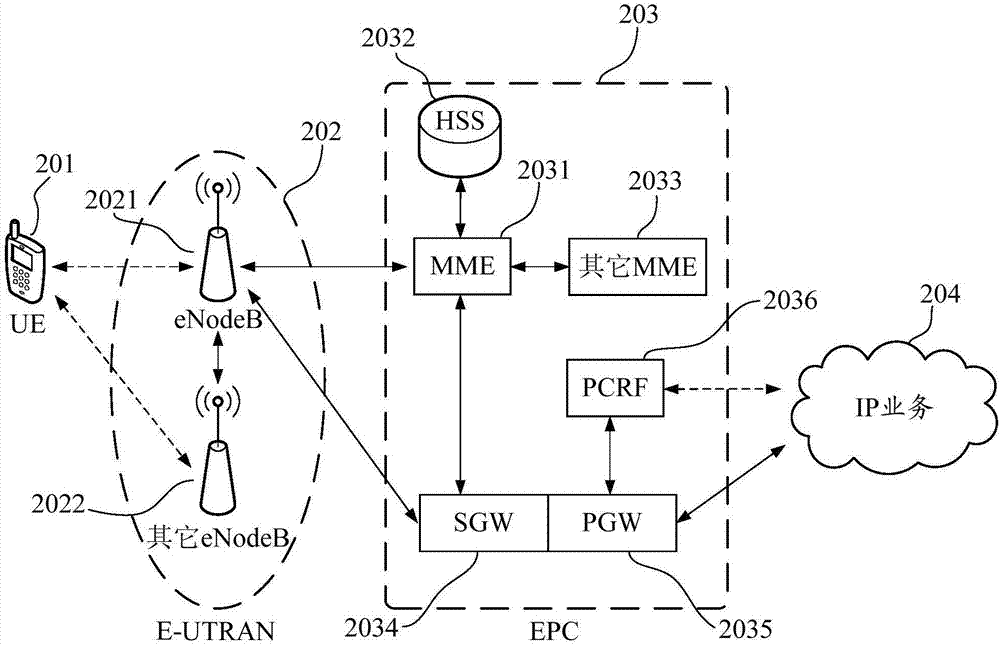

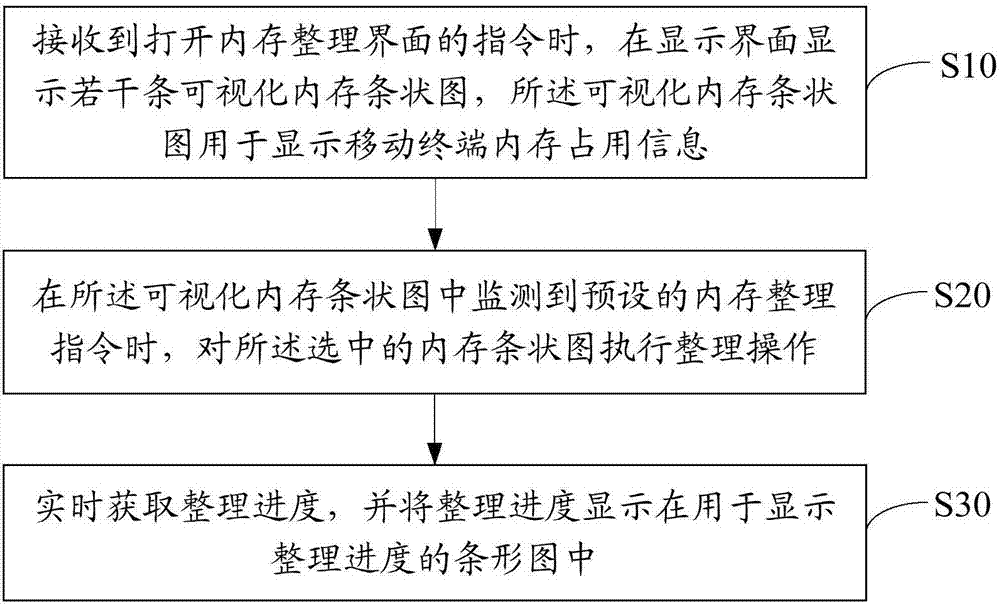

Method for organizing graphical memory, mobile terminal and readable storage medium

InactiveCN107273305ASatisfy the visual experienceResource allocationMemory adressing/allocation/relocationMemory processOperating system

The invention discloses a method for organizing a graphical memory. The method includes the following steps of when receiving an instruction for opening a memory organizing interface, displaying a plurality of visualized memory bar graphs, which are used for displaying occupying information of the memory of a mobile terminal, on a display interface, and conducting organizing operation on a selected memory bar graph when a preset memory organizing instruction is detected in the visualized memory bar graphs; acquiring an organizing schedule in real time, and displaying the organizing schedule in the bar graph which is used for showing the organizing schedule. The invention also discloses a mobile terminal and a readable storage medium. According to the method for organizing a graphical memory, the mobile terminal and the readable storage medium, visualization of a memory deletion process can be achieved, and therefore specification of memory processes can be achieved so that better visual experience can be brought to the user.

Owner:NUBIA TECHNOLOGY CO LTD

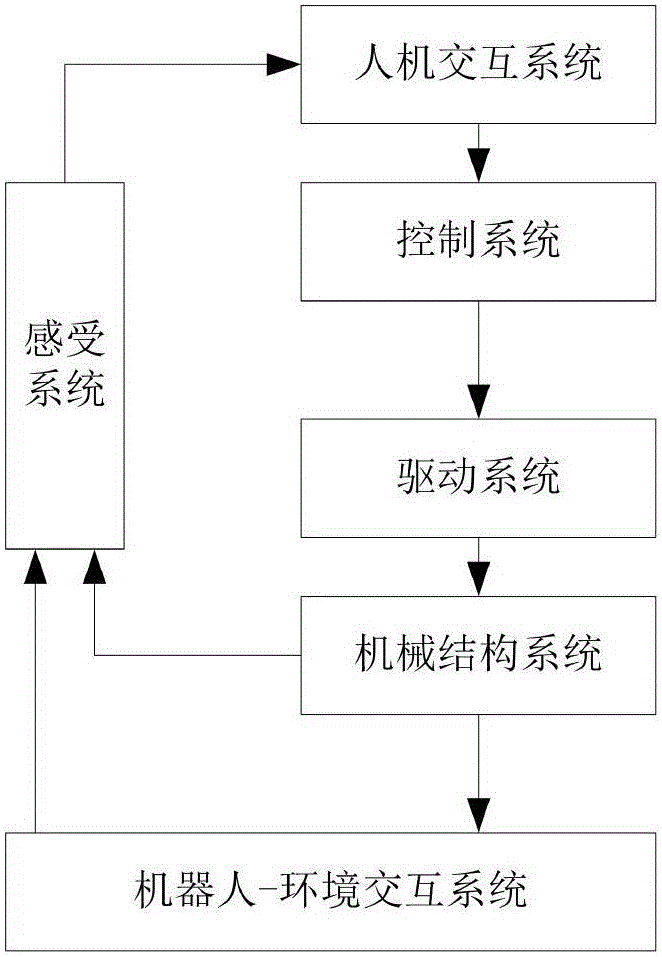

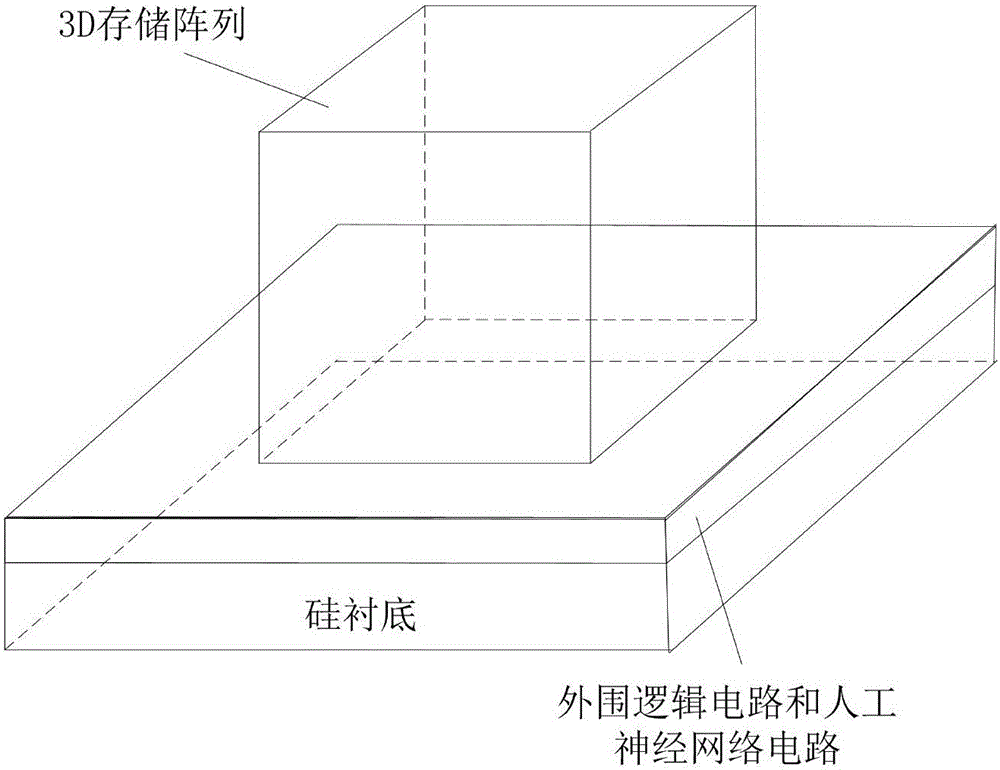

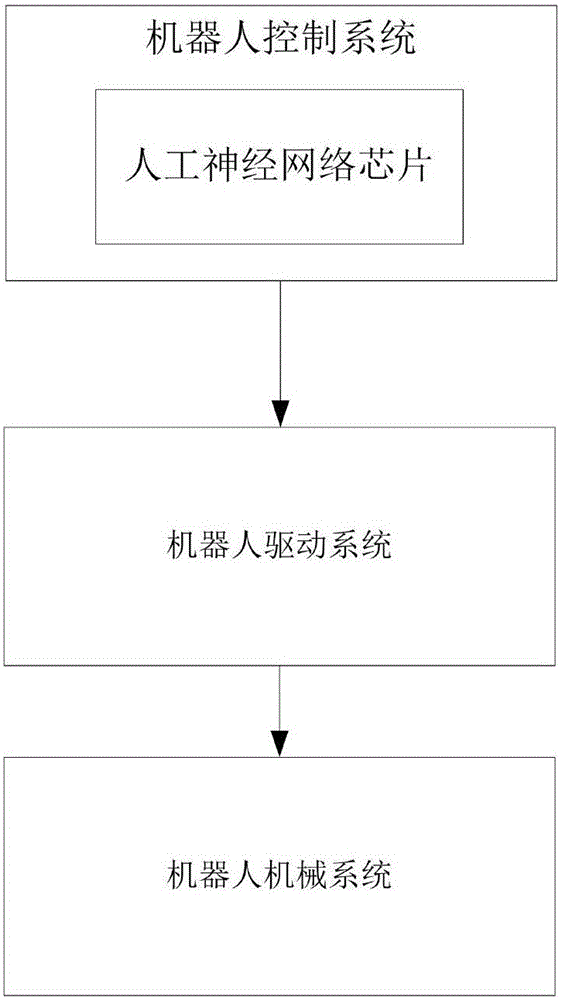

Artificial neural network chip and robot with artificial neural network chip

InactiveCN105760931AIncrease flexibilityImprove learning abilityProgramme-controlled manipulatorRead-only memoriesMemory processElectricity

The invention provides an artificial neural network chip and a robot with the artificial neural network chip. The chip comprises a silicon substrate and a 3D memory array, between which a peripheral logic circuit and an artificial neural network circuit are arranged; the chip is prepared based on 3D nonvolatile memory processes; the peripheral logic circuit of a 3D nonvolatile memory and the artificial neural network circuit are realized by employing front-end processes. The robot comprises the artificial neural network chip. The artificial neural network chip employs the 3D nonvolatile memory as a mechanism of memory, possesses an ultra-large capacity data storage capability, and can still maintain data after power failure. Accordingly, compared with traditional robots, the robot with the artificial neural network chip has the characteristics of high flexibility, strong learning capability and adjustable dynamic condition.

Owner:SHANGHAI XINCHU INTEGRATED CIRCUIT

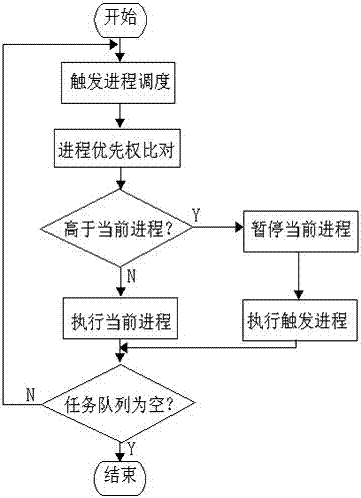

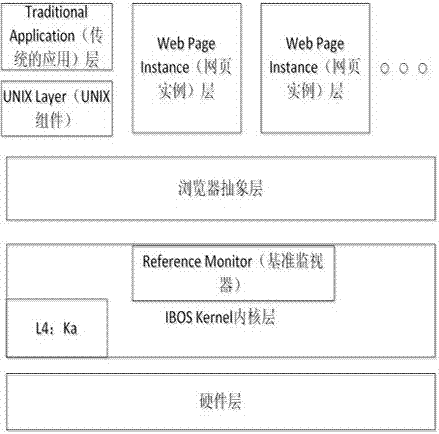

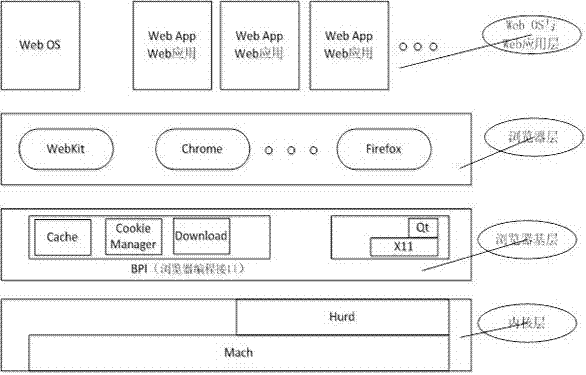

Browser operating system design method for achieving service migration of heterogenous operating system

InactiveCN107015814AFast securityImprove efficiencyInterprogram communicationSoftware designMemory processVirtual memory

The invention discloses a browser operating system design method for achieving service migration of a heterogenous operating system. A browser operating system is the operating system based on a Hurd system and comprises a process scheduling program, a memory management program, a device driving program and a file system, wherein the process scheduling program performs scheduling through a CPU according to the importance level of a process, the memory management program comprises memory process management, memory allocation and memory mapping and sharing, the memory device driving program is an interface for an operating system kernel and machine hardware, the device driving program shields details of the hardware for application programs, and the file system is responsible for file establishment, storage, reading, modification and file transfer and storage for a user and control of file access and revocation. In the memory management program, cookie management is performed, and the safety is improved. By adopting mapping between a virtual memory and a physical memory, the access and processing speed and efficiency of the browser operating system are improved.

Owner:STATE GRID JIBEI ELECTRIC POWER COMPANY +4

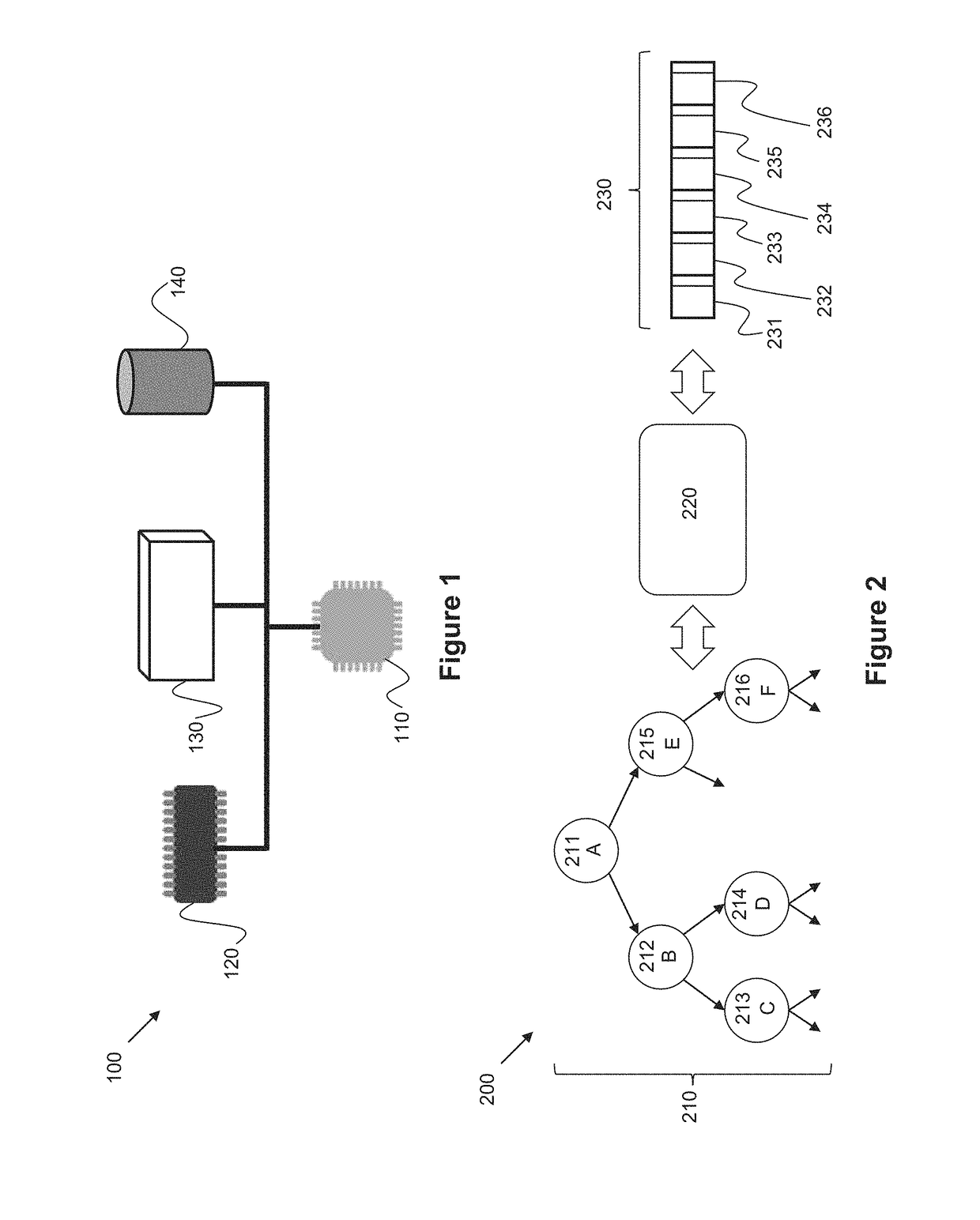

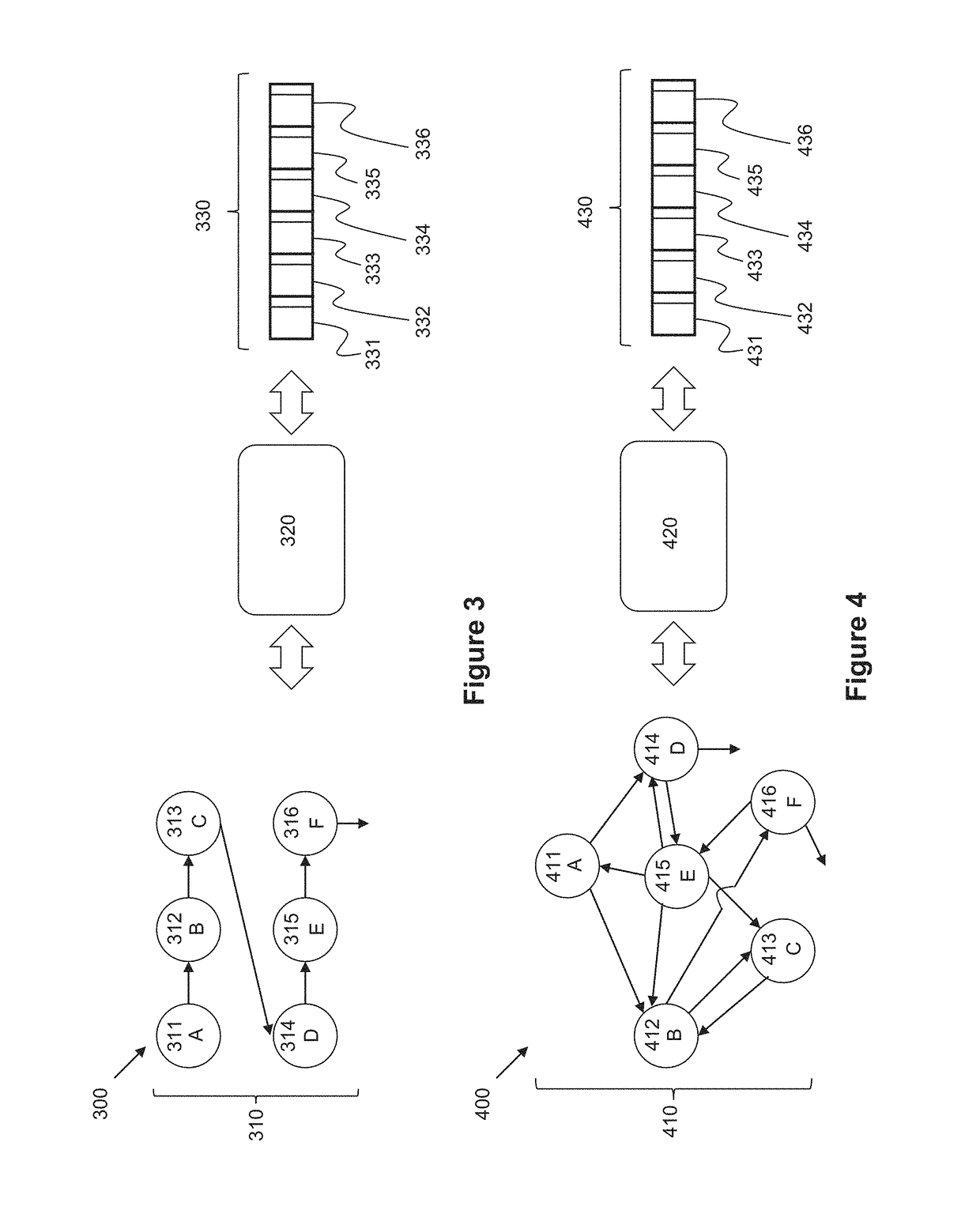

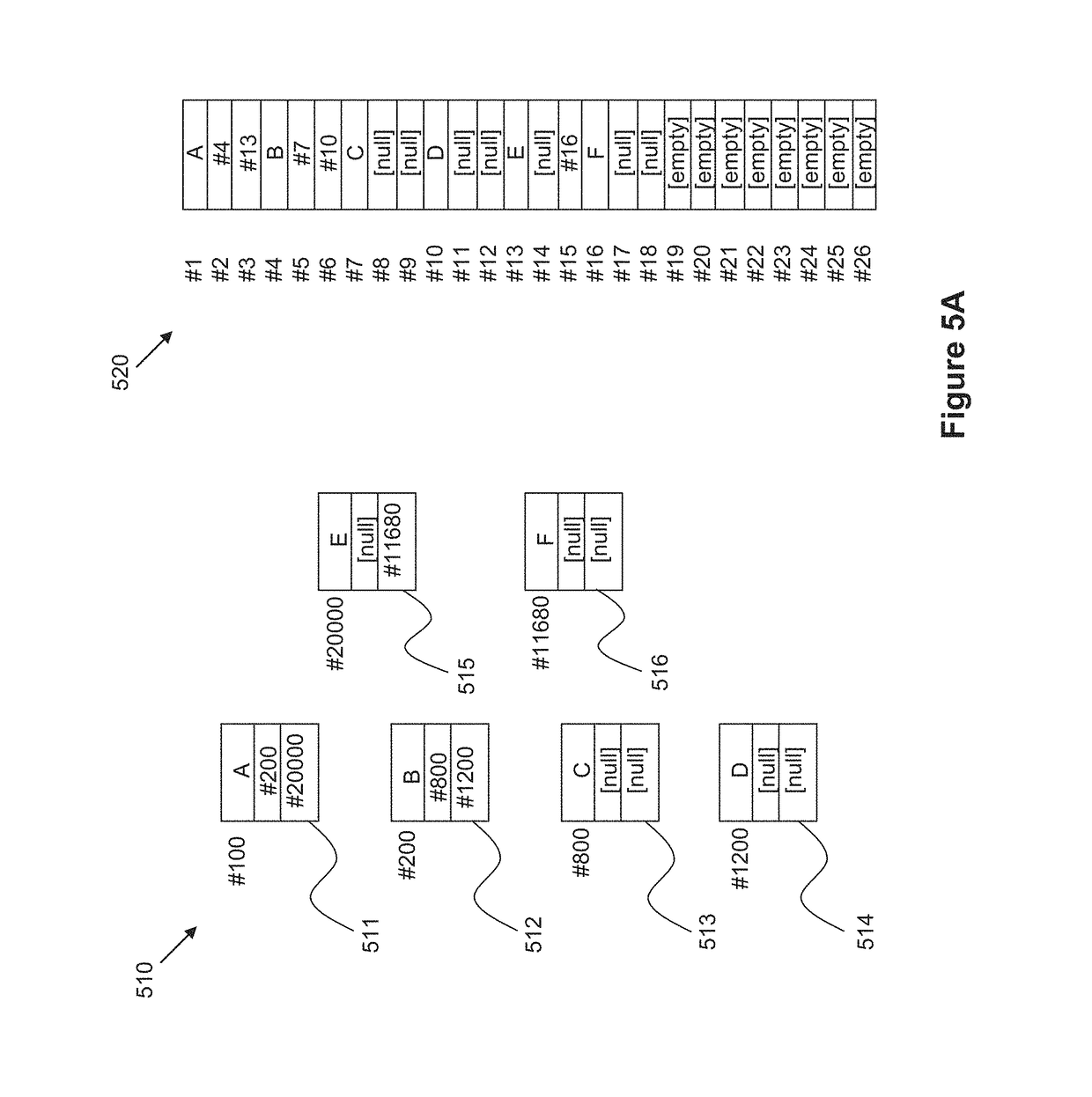

Tree structure serialization and deserialization systems and methods

ActiveUS10216627B1Fast wayMemory architecture accessing/allocationMemory adressing/allocation/relocationMemory processTheoretical computer science

An improved persistent memory process is disclosed that persists a traversable data structure by converting the traversable data structure into one or more traversable array structures that are saved on a secondary memory. The traversable array structure could be rapidly traversed and maintained, and can be used to restore one or more portions of the traversable data structure.

Owner:LEVYX LLC

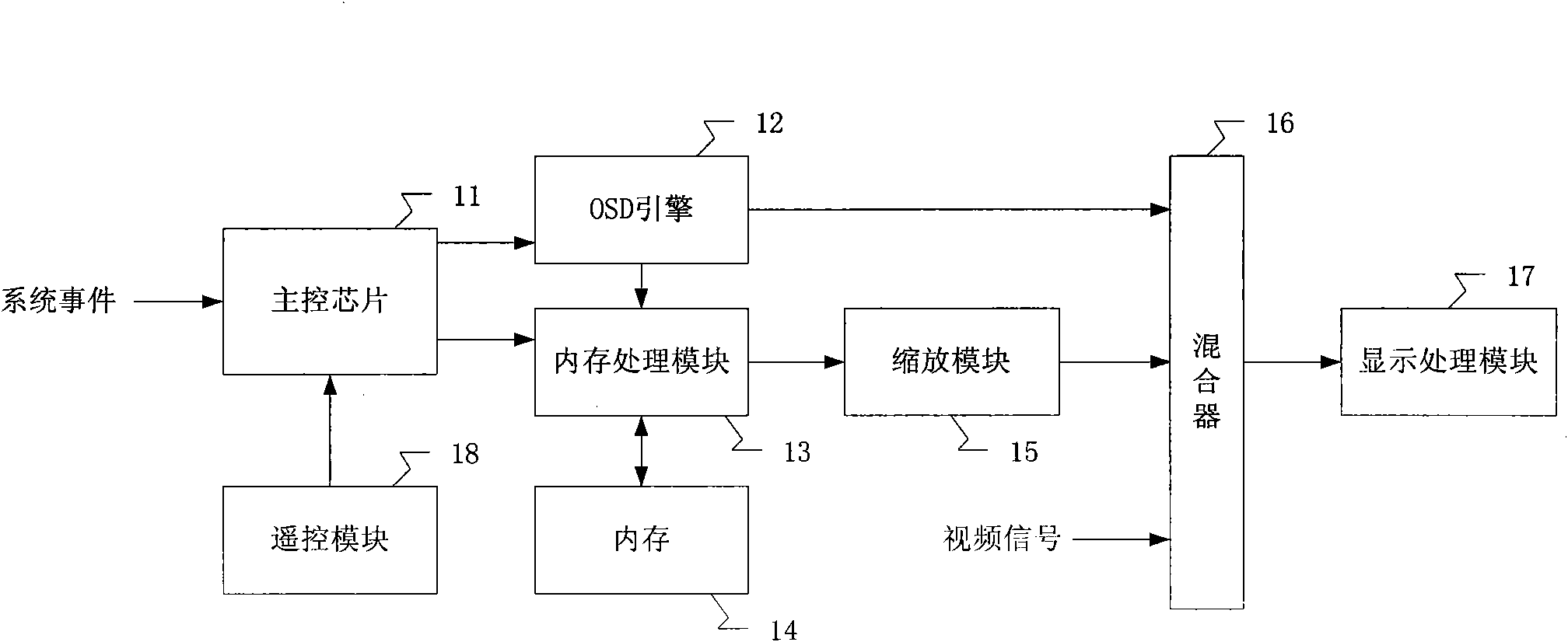

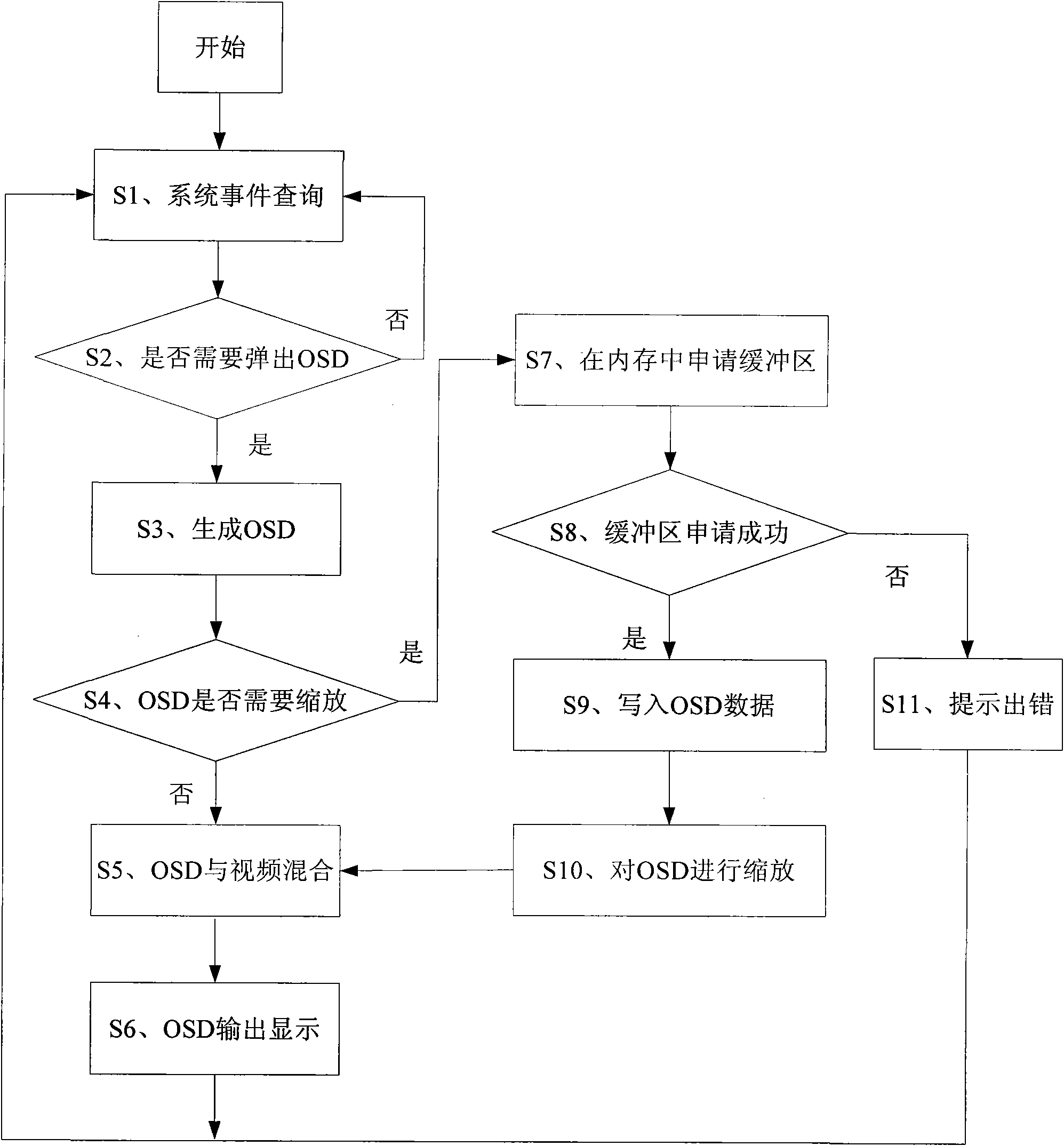

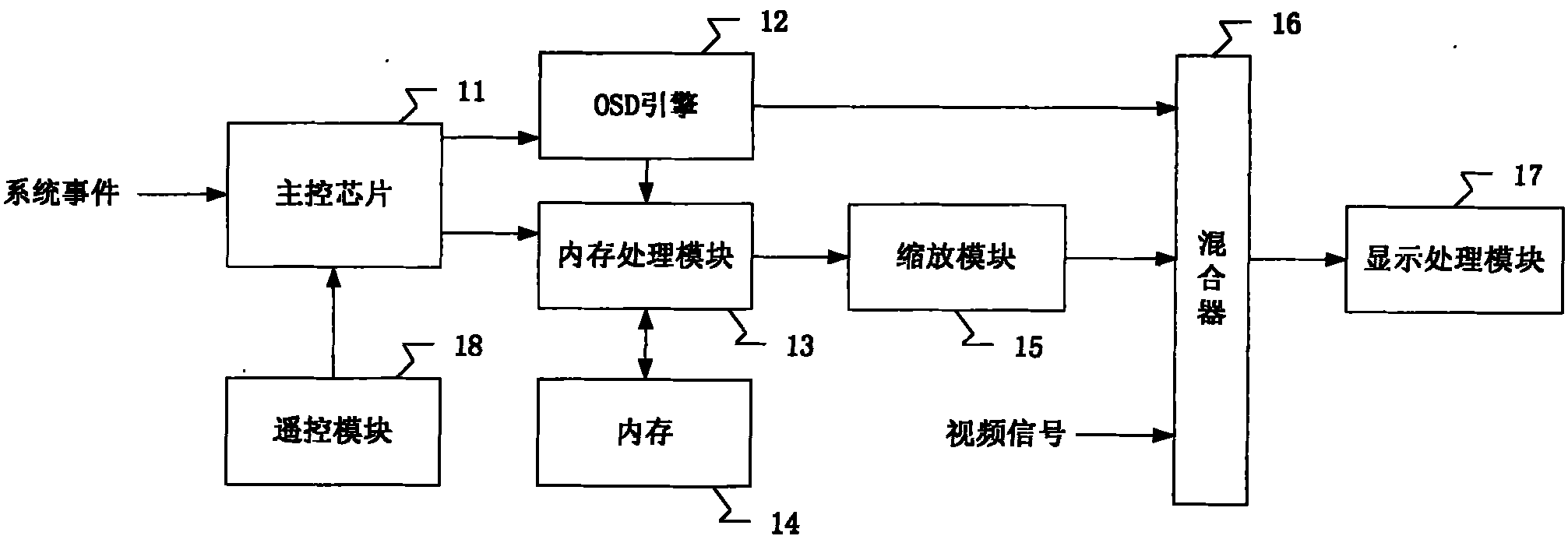

System and method for displaying on-screen menus of television

InactiveCN102404523AEfficient outputTelevision system detailsColor television detailsMemory processMemory processing

The invention provides a system for displaying on-screen menus of a television, which comprises a main control chip, an on-screen display (OSD) engine, a mixer, a display processing module, a memory processing module, a memory and a zoom module, wherein the main control chip is used for making the OSD engine generate the on-screen menus according to an OSD request, the memory processing module is used for selectively saving the on-screen menus in the memory in a picture form according to the type of a video signal, and the zoom module is used for zooming the on-screen menus in the picture form, then outputting on-screen menus to the mixer for mixing, and finally outputting the on-screen menus to the display processing module for display. According to the system and a method for displaying the on-screen menus of the television, OSD containing fill color, characters and icons is comprehensively zoomed and is favorably output without changing the size and the shape through specific conversion of a three-dimensional (3D) display screen, so that the zoom of an OSD region containing the fill color, the characters and the icons is free from the limitation of the performance of the OSD engine.

Owner:SHENZHEN TCL NEW-TECH CO LTD +1

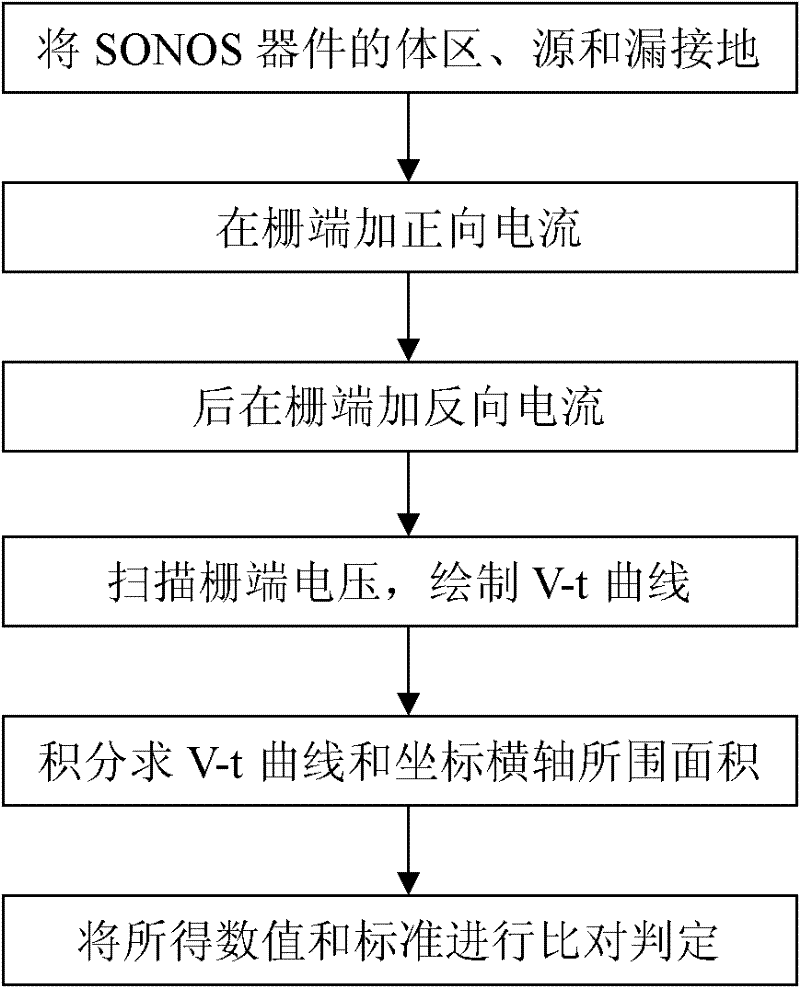

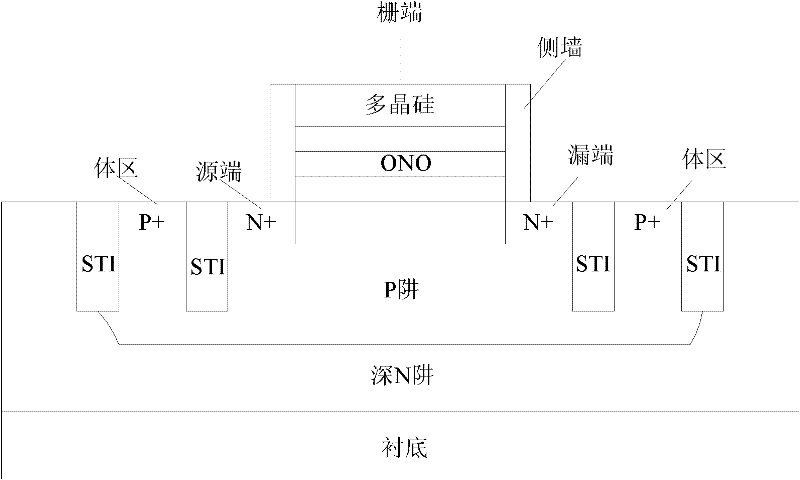

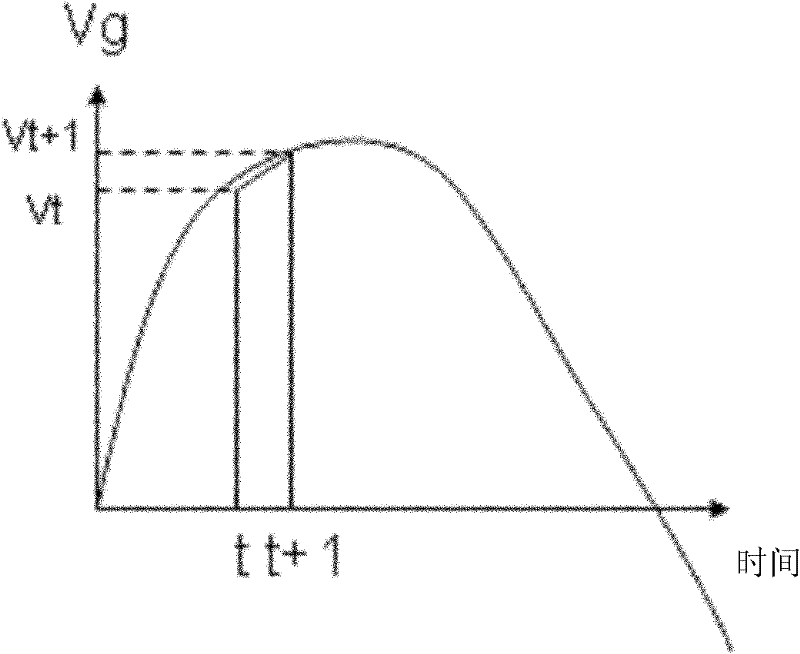

Method for on-line monitoring of quality of ONO (Oxide-Nitride-Oxide) film in SONOS (Silicon Oxide Nitride Oxide Semiconductor) memory process

ActiveCN102543214AReach monitoringReal time monitoringSemiconductor/solid-state device testing/measurementStatic storageMemory processProduction line

The invention discloses a method for on-line monitoring of the quality of an ONO (Oxide-Nitride-Oxide) film in SONOS (Silicon Oxide Nitride Oxide Semiconductor) memory process. The method comprises: 1) grounding a body region, a source port and a drain port of an SONOS memory structure; 2) supplying forward current less than 1muA to a grid port of the SONOS memory structure and lasting for 20-30 seconds; 3) successively supplying a reverse current less than 1nA to the grid port, scanning the voltage of the grid port and drawing a voltage-time curve; 4) carrying out integration to calculate out the area surrounded by the drawn voltage-time curve and the lateral axis of a coordinate; 5) comparing the numerical value obtained in step 4) with a standard numerical value so as to judge the quality of the ONO film. With the method, a device can be tested once being produced and monitored in real time, so that the result can be fed back to the production line in time, and the influence on the production line due to delayed judgment can be avoided.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

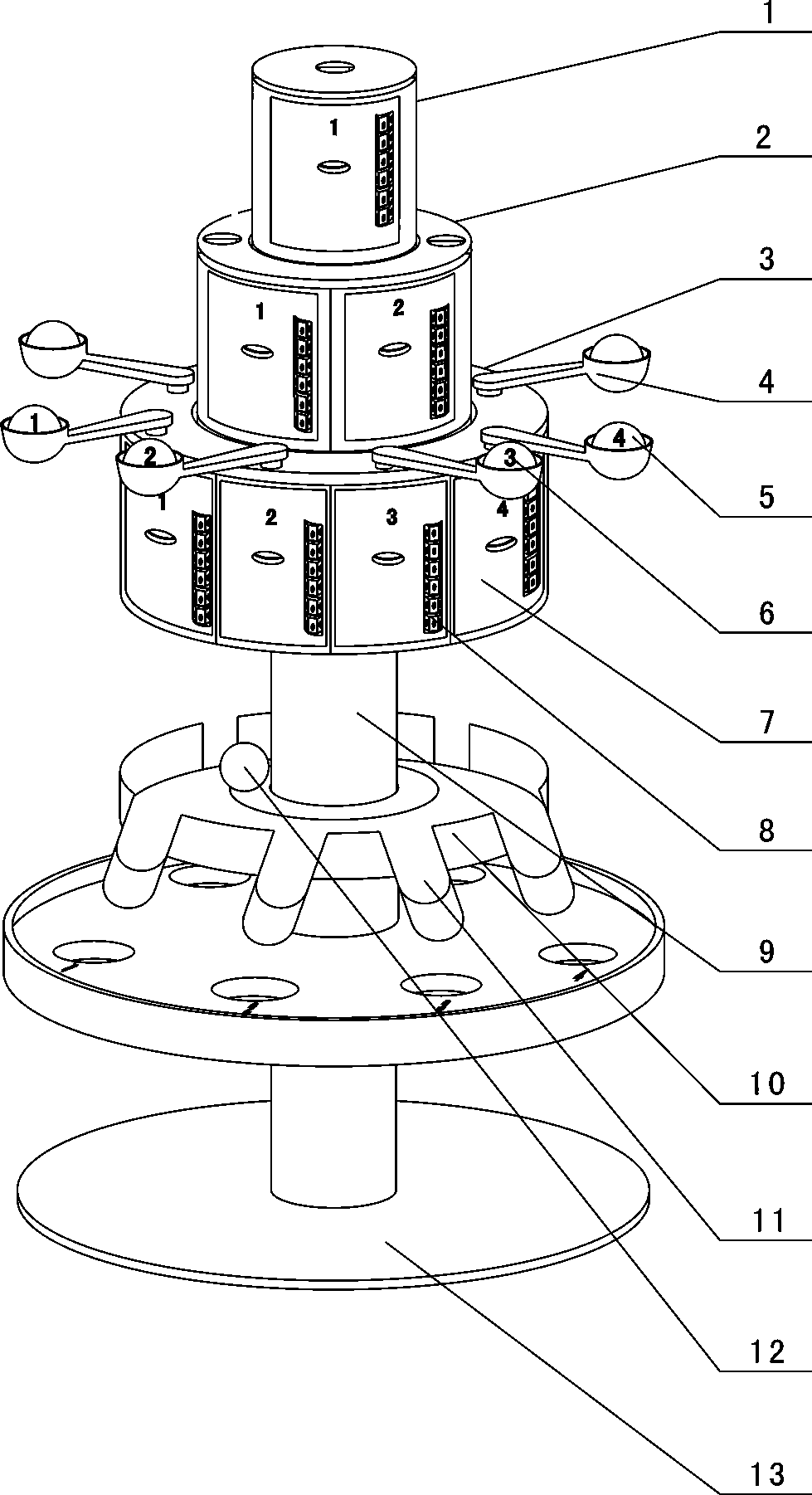

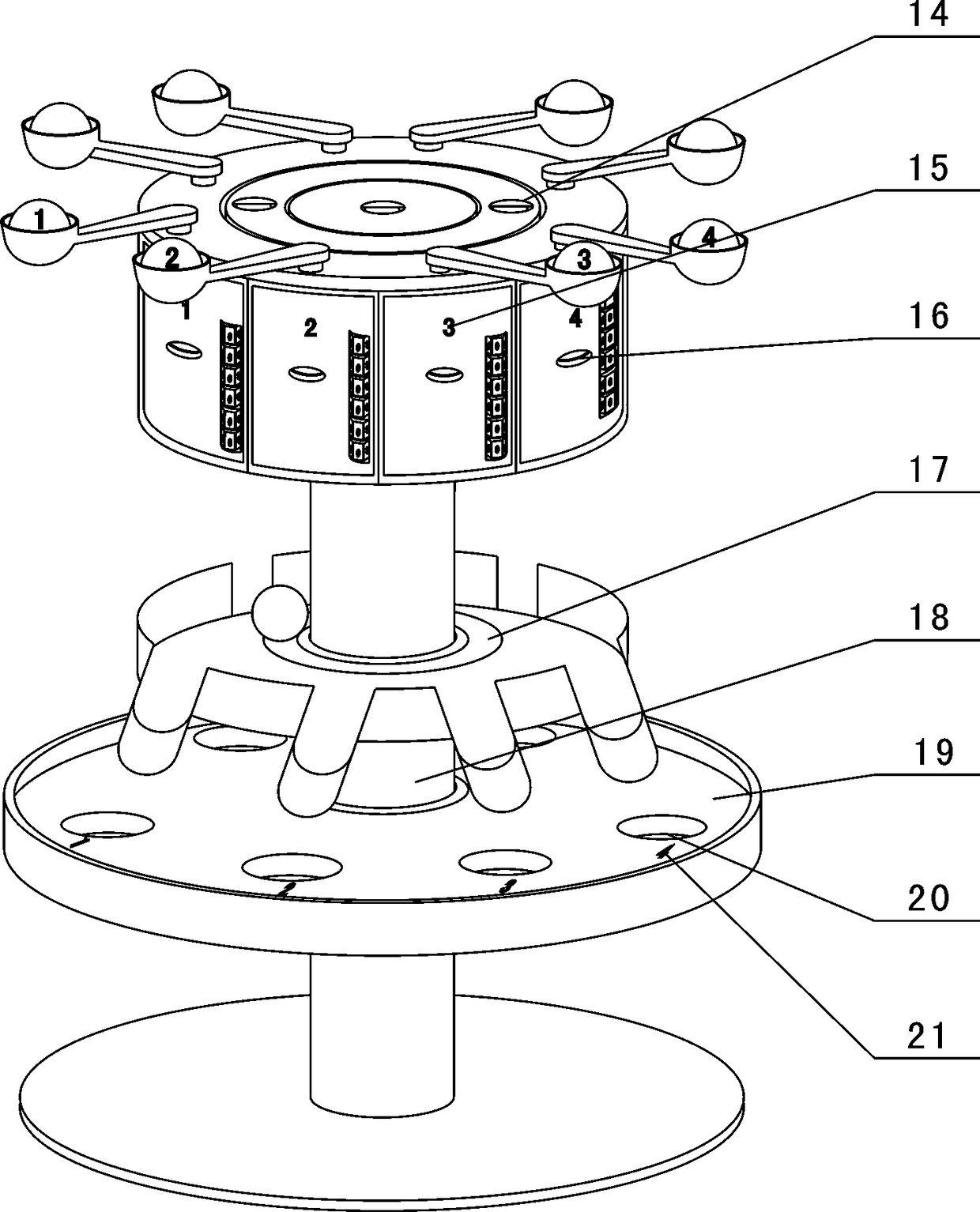

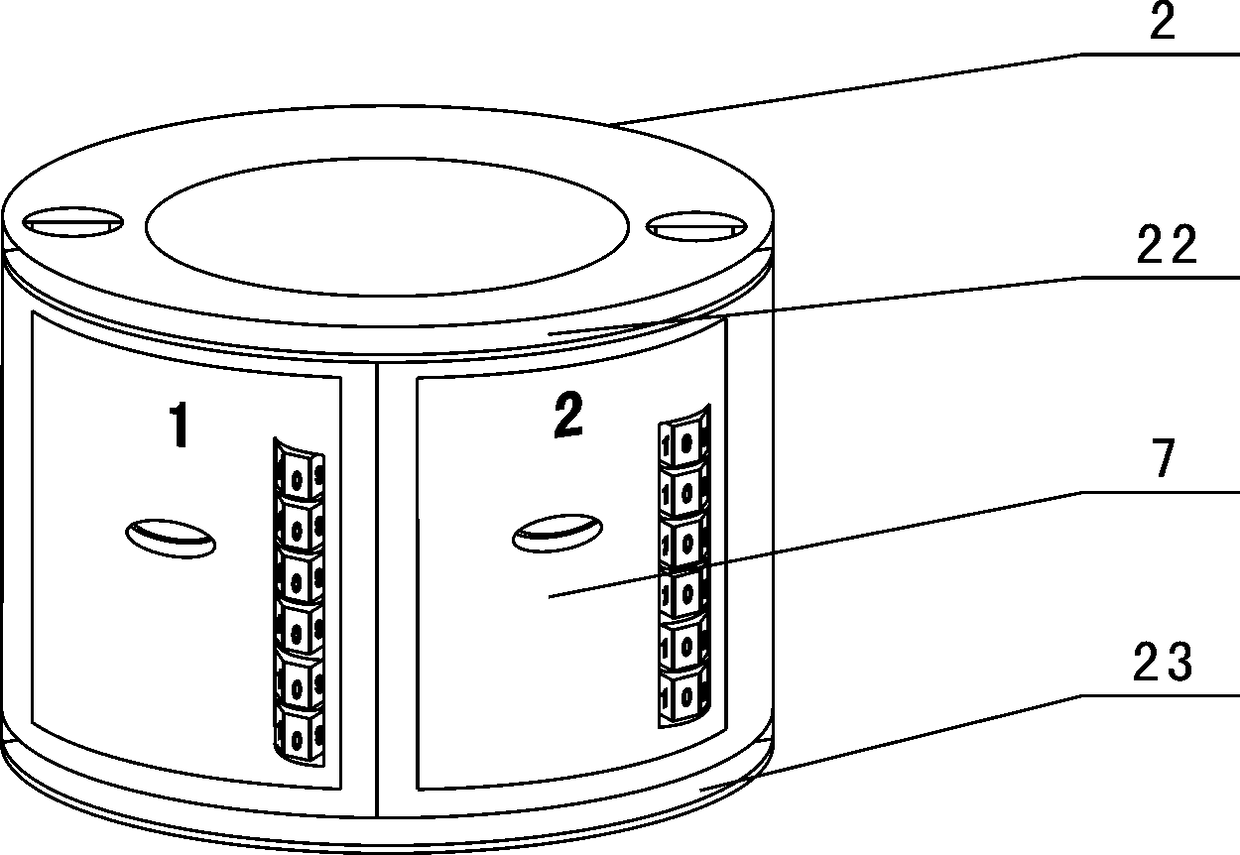

Professional learning equipment

The invention relates to professional learning equipment. A combined box body is composed of a base layer box body (3), multiple intermediate layer box bodies (2) and a top layer box body (1), the multiple intermediate layer box bodies sleeve with one another, and sizes of the intermediate layer box bodies successively decrease; the base layer box body (3) internally sleeves the multiple intermediate layer box bodies (2) and the top layer box body (1), multiple drawing boxes (7) arranged in an annular form are respectively mounted on the peripheries of the base layer box body (3), multiple intermediate layer box bodies (2) and top layer box body. The equipment solves the problems that understanding and recitation are complex in the professional learning process, so that the interest is easily lost, related knowledge cannot be memorized profoundly, and the memory confusion easily occurs in the memory process, the enjoyment of the class is enhanced, teaching through lively activities isachieved, the interactive teaching and knowledge contest organization are achieved, and the knowledge understanding and memory are strengthened in a contest.

Owner:JILIN INST OF PHYSICAL EDUCATION

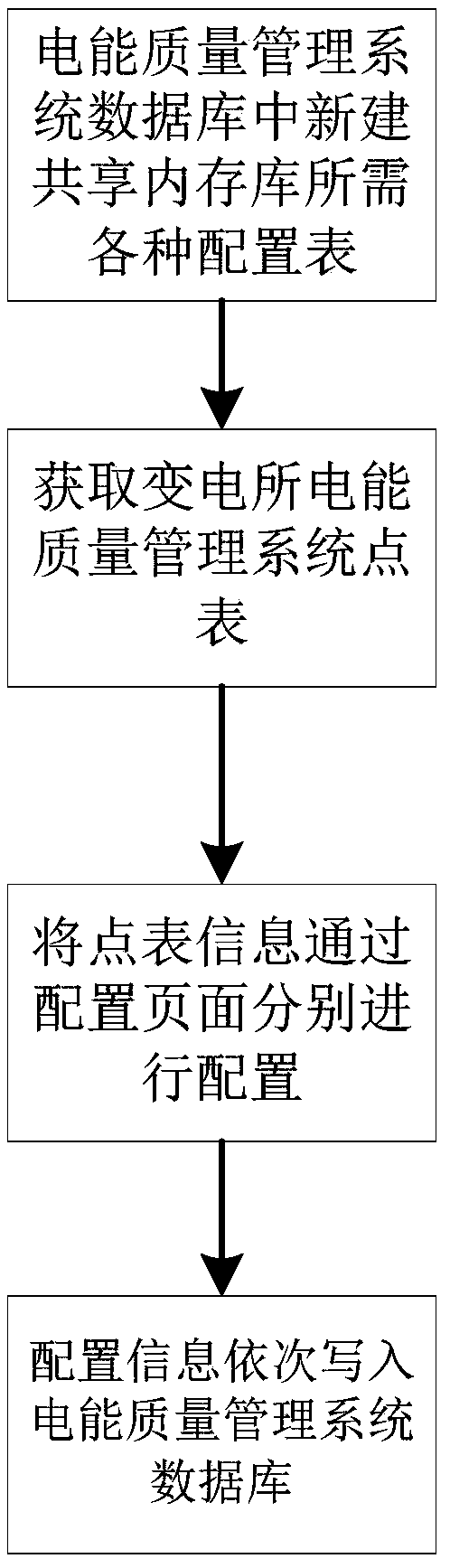

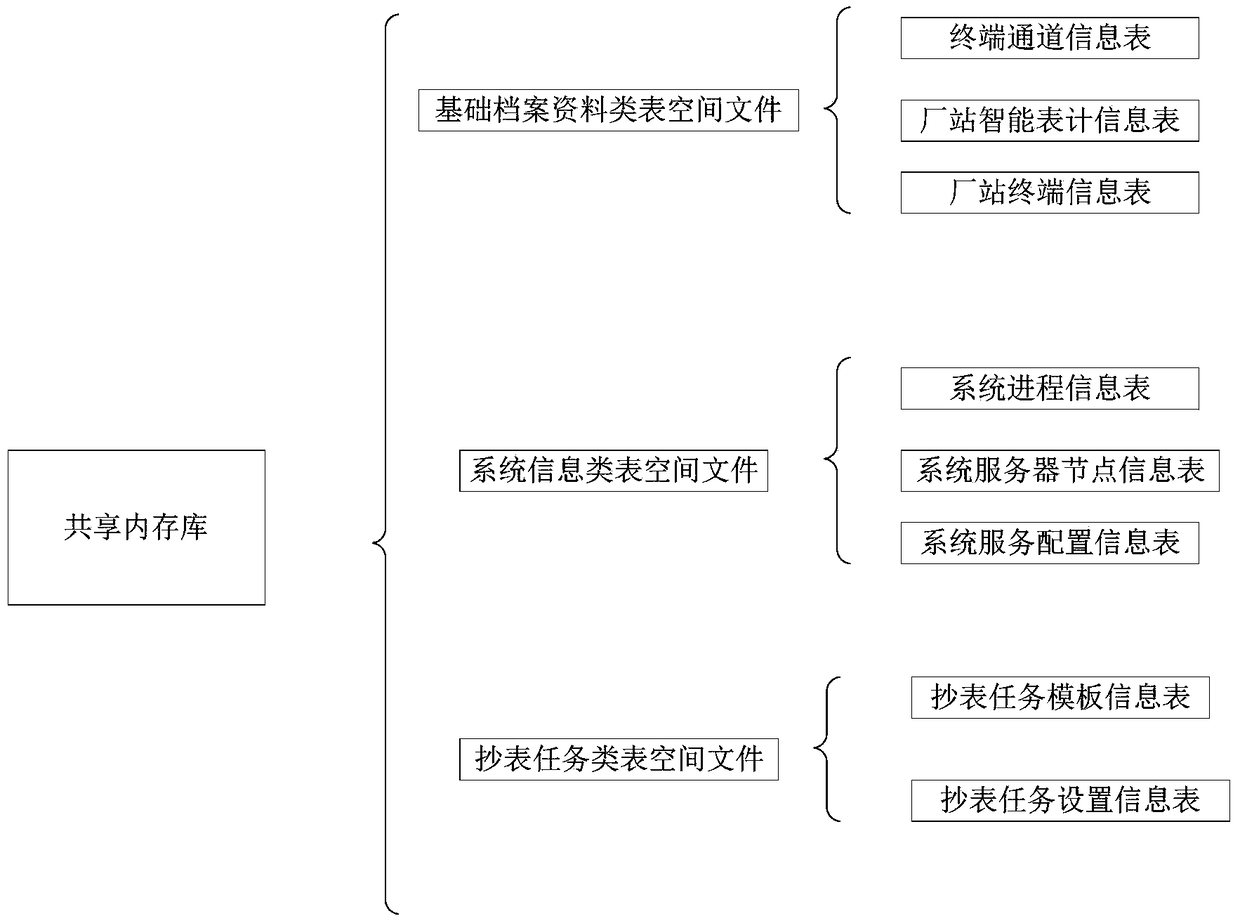

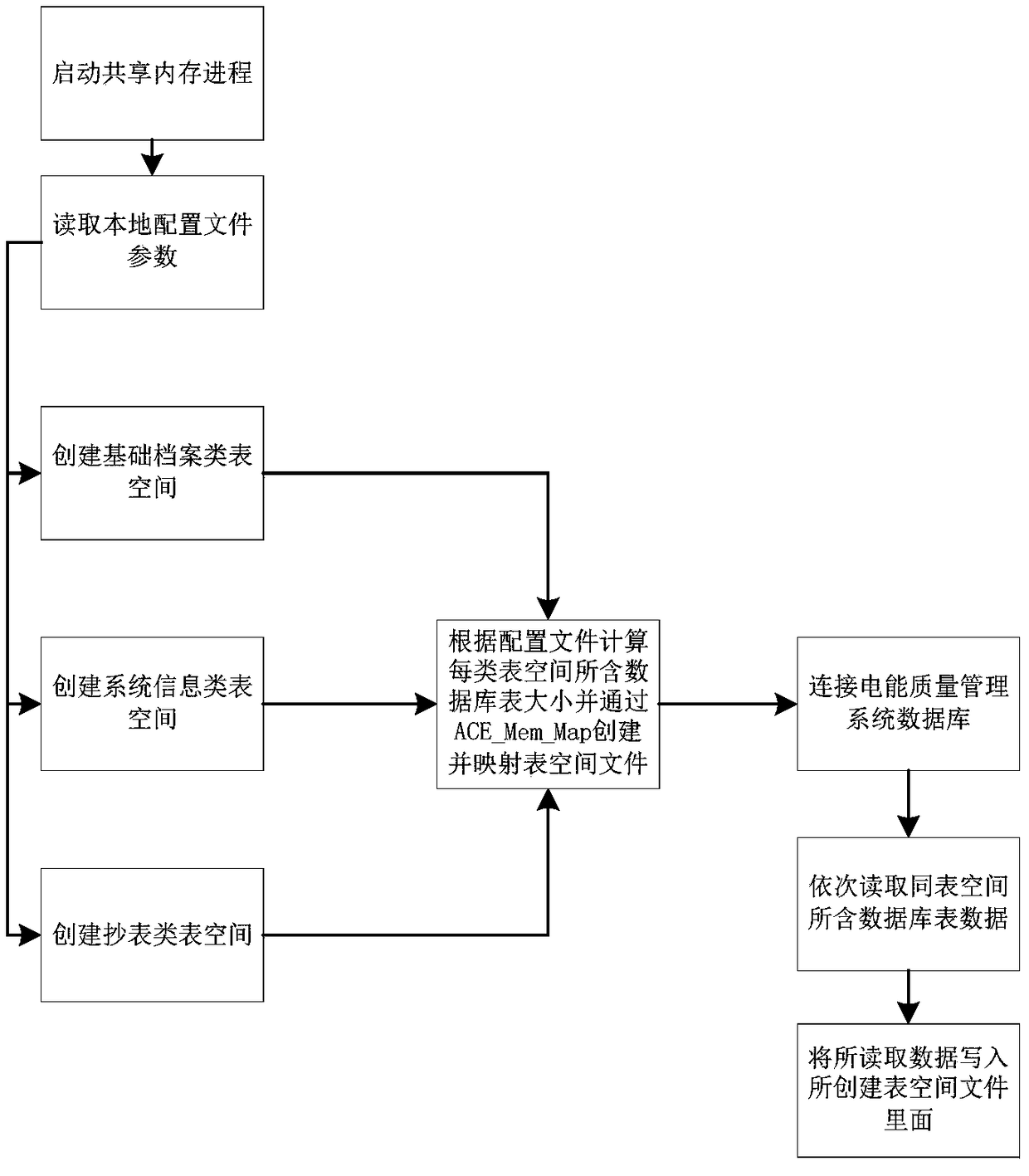

Method for implementing shared memory of power quality management system

ActiveCN109032817AAdvantages of shared memory implementationReduce reading and writing errorsInterprogram communicationSpecial data processing applicationsPower qualityMemory process

The invention provides a method for implementing the shared memory of a power quality management system, which comprises the following steps: S1, data initialization setting, completing basic configuration of each data of the power quality management system in a database; 2, creating a shared memory library; S3, creating a shared memory process to realize the memory sharing of the power quality management system. The method for realizing the shared memory of the power quality management system directly realizes the shared memory file mapping, does not need to carry out bottom setting, reducesthe read and write errors of the memory of the power quality management system, and ensures the continuous and stable operation of the shared memory of the power quality management system.

Owner:TIANJIN KEYVIA ELECTRIC CO LTD

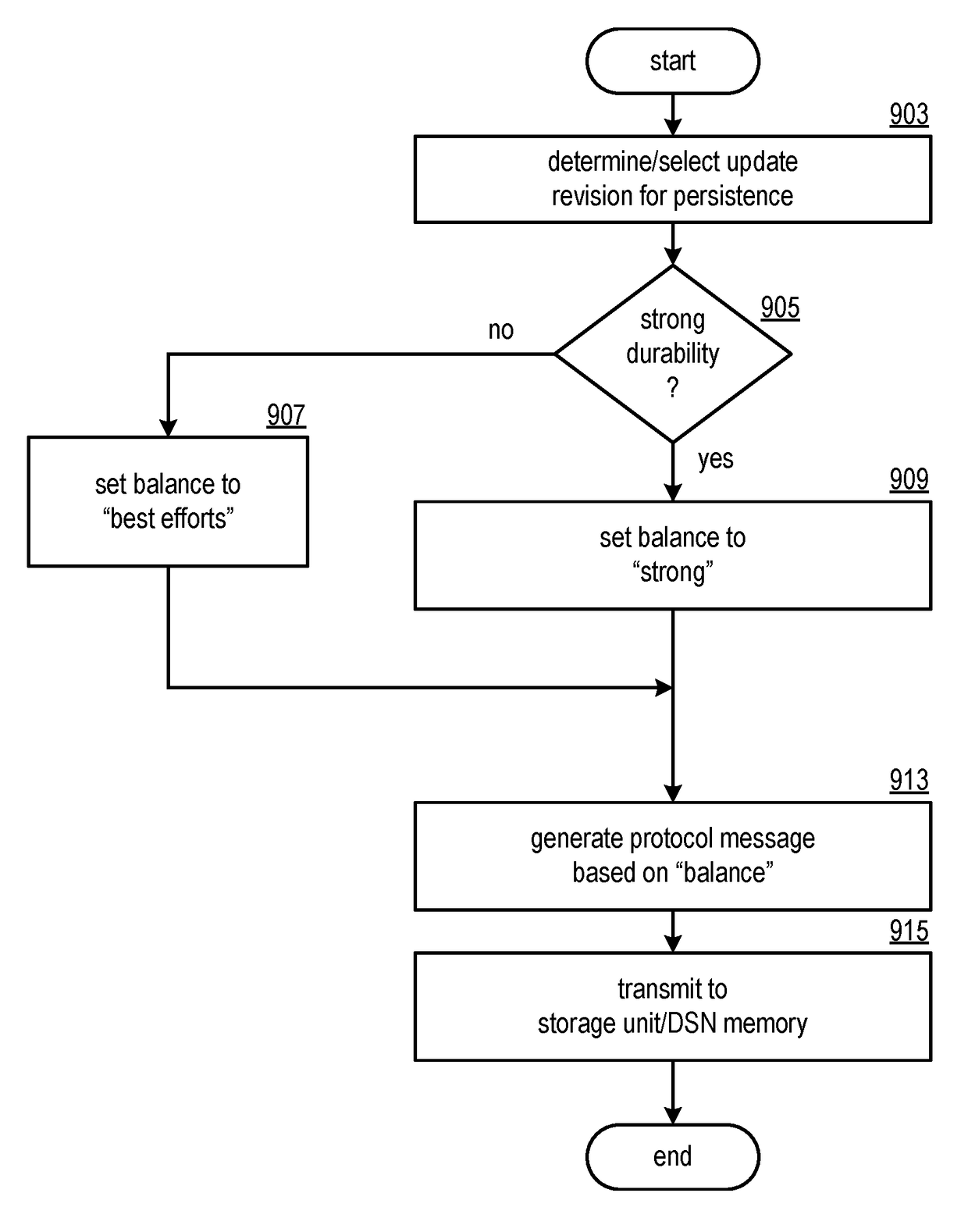

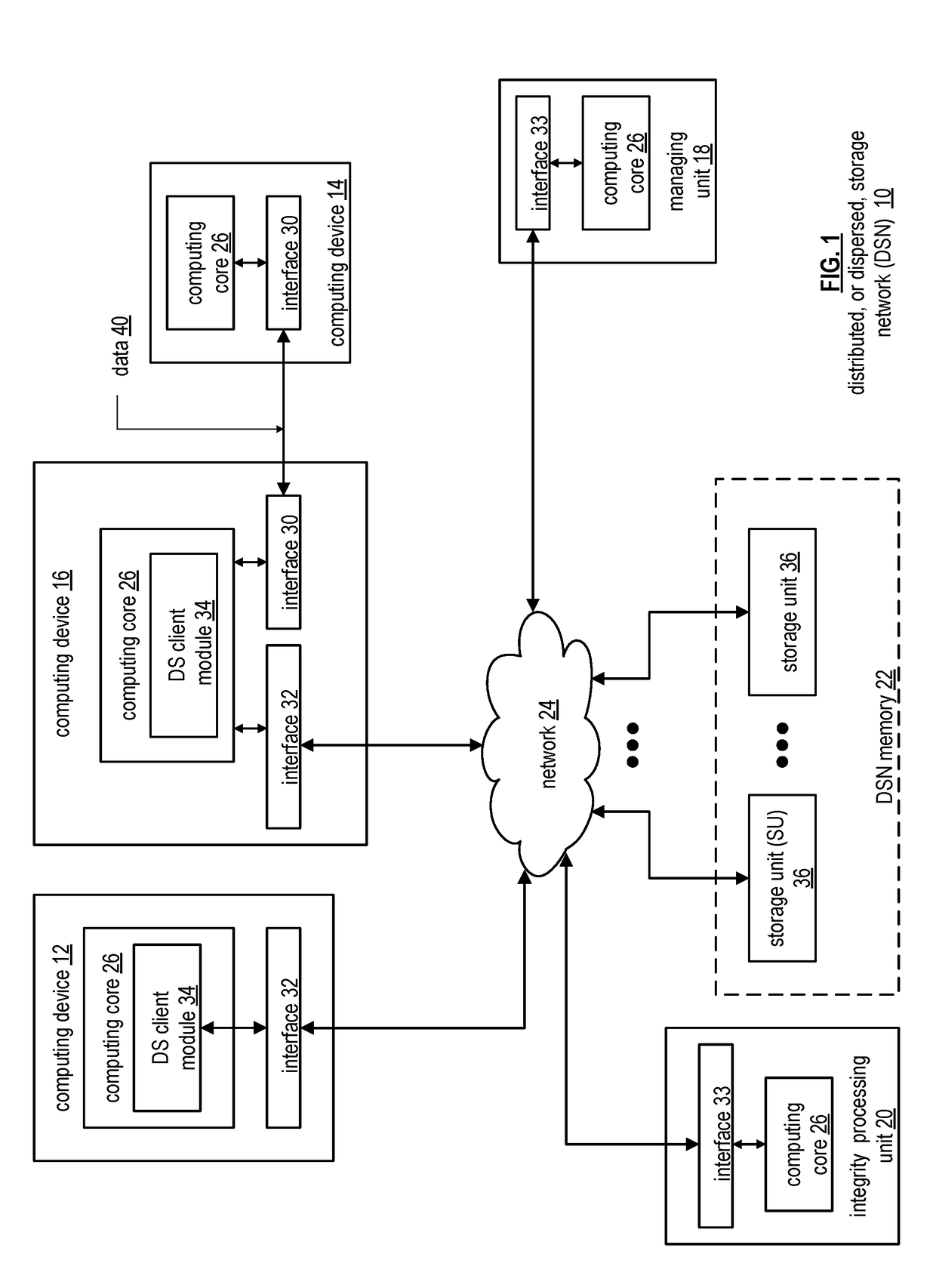

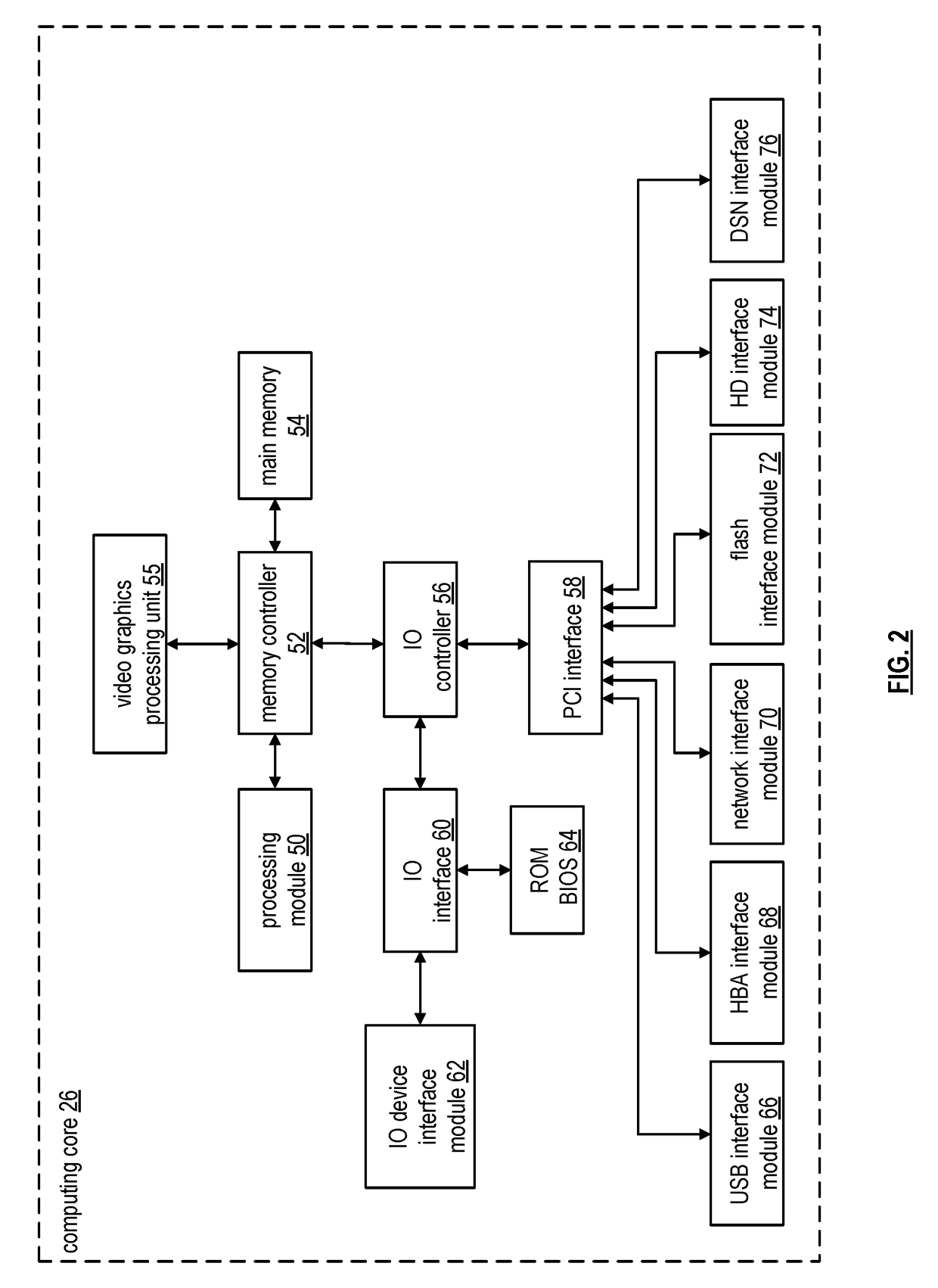

Zone storage - resilient and efficient storage transactions

ActiveUS20180241818A1Input/output to record carriersError detection/correctionMemory processProtocol processing

A distributed storage network (DSN) includes a DSN memory and a distributed storage (DS) processing unit. The DS processing unit determines a particular revision of source data for persistence, and generates a protocol message associated with the particular revision of source data. The protocol message is generated based on a balance between durability and persistence associated with the particular revision. The protocol message is transmitted from the DS processing unit to the DSN memory, and indicates to the DSN memory a particular persistence protocol. The DSN memory process data slices corresponding to the particular revision of source data in accordance with the particular persistence protocol.

Owner:IBM CORP

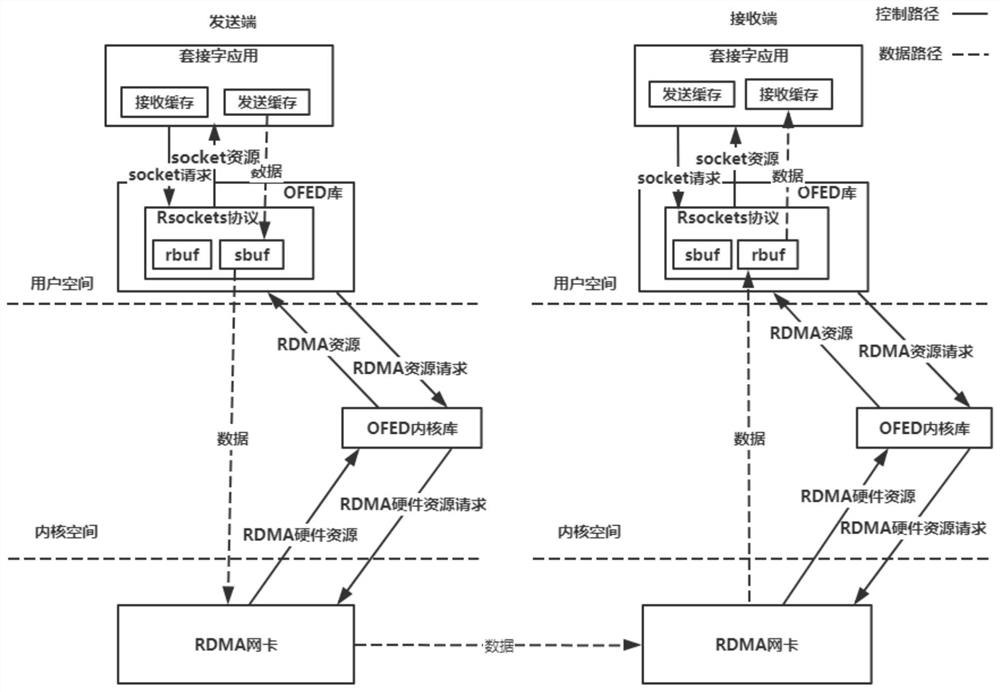

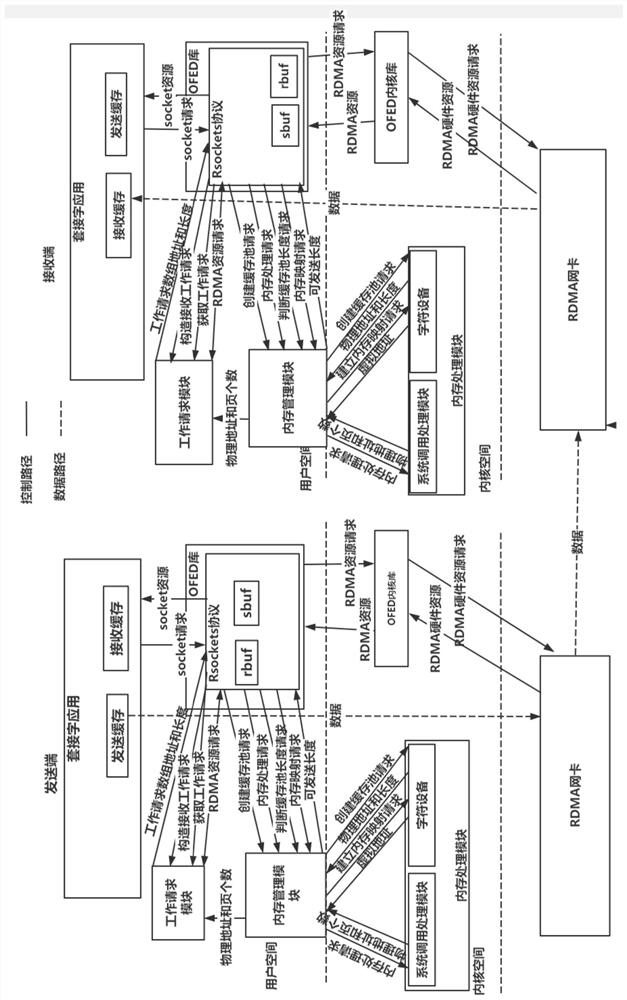

Zero-copy data transmission method based on Rsocket protocol

InactiveCN113064846AEnsure safetyPrevent copyingTransmissionElectric digital data processingMemory processMemory processing

The invention discloses a zero-copy data transmission method based on an Rsocket protocol, and aims to eliminate copy overhead. According to the technical scheme, a zero-copy data transmission system composed of an RDMA transmission system based on the Rsocket protocol, a memory management module, a memory processing module and a work request module is firstly constructed. The sending end socket application and the receiving end socket application create RDMA resources, the memory management module and the memory processing module cooperate to create a cache pool and establish memory mapping for the cache pool, the sending end socket application sends data from a sending cache, and the memory management module and the memory processing module process the data to obtain a physical address and the number of pages. The work request module constructs a corresponding work request, an RDMA network card executes the work request and sends data to a receiving end cache pool, a receiving end memory management module establishes memory mapping between a receiving cache and a data physical address in the cache pool, and the data arrives successfully. According to the invention, zero-copy data transmission is realized.

Owner:CENT SOUTH UNIV +1

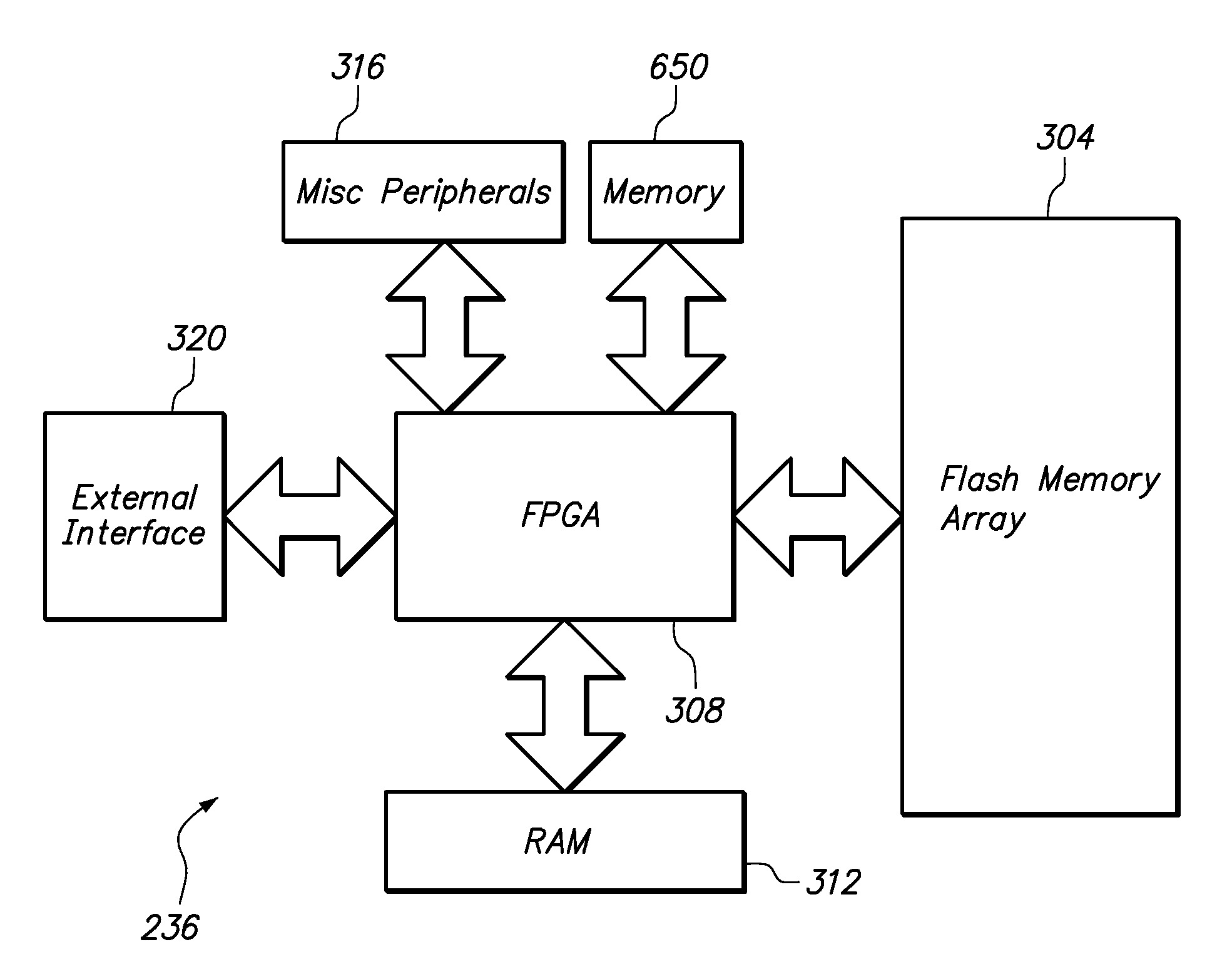

Quick Mounting System and Media With Compatibility and Access Control

InactiveUS20120033947A1Move quicklyAvoiding time-consuming taskTelevision system detailsDigital data processing detailsMemory processComputer hardware

Functionality and control of the media module using a method and apparatus for access and compatibility control is disclosed. The media module interfaces with a camera or other device to store image and audio data from the camera on memory. Access to the media module is controlled by method and system for data encryption or authentication. Encryption or authentication controls access and compatibility with particular camera, camera line, or camera manufacture. The encryption or authentication may also control access to features or functions of the media module. An authentication module comprising an input / output controller, processor and memory processes an authentication request or command to determine if the media module and camera are compatible. The processor may execute software stored on the memory to perform any type of authentication including a hash operation, symmetric key operation, or asymmetric key operation.

Owner:BENBRAHIM JAMAL

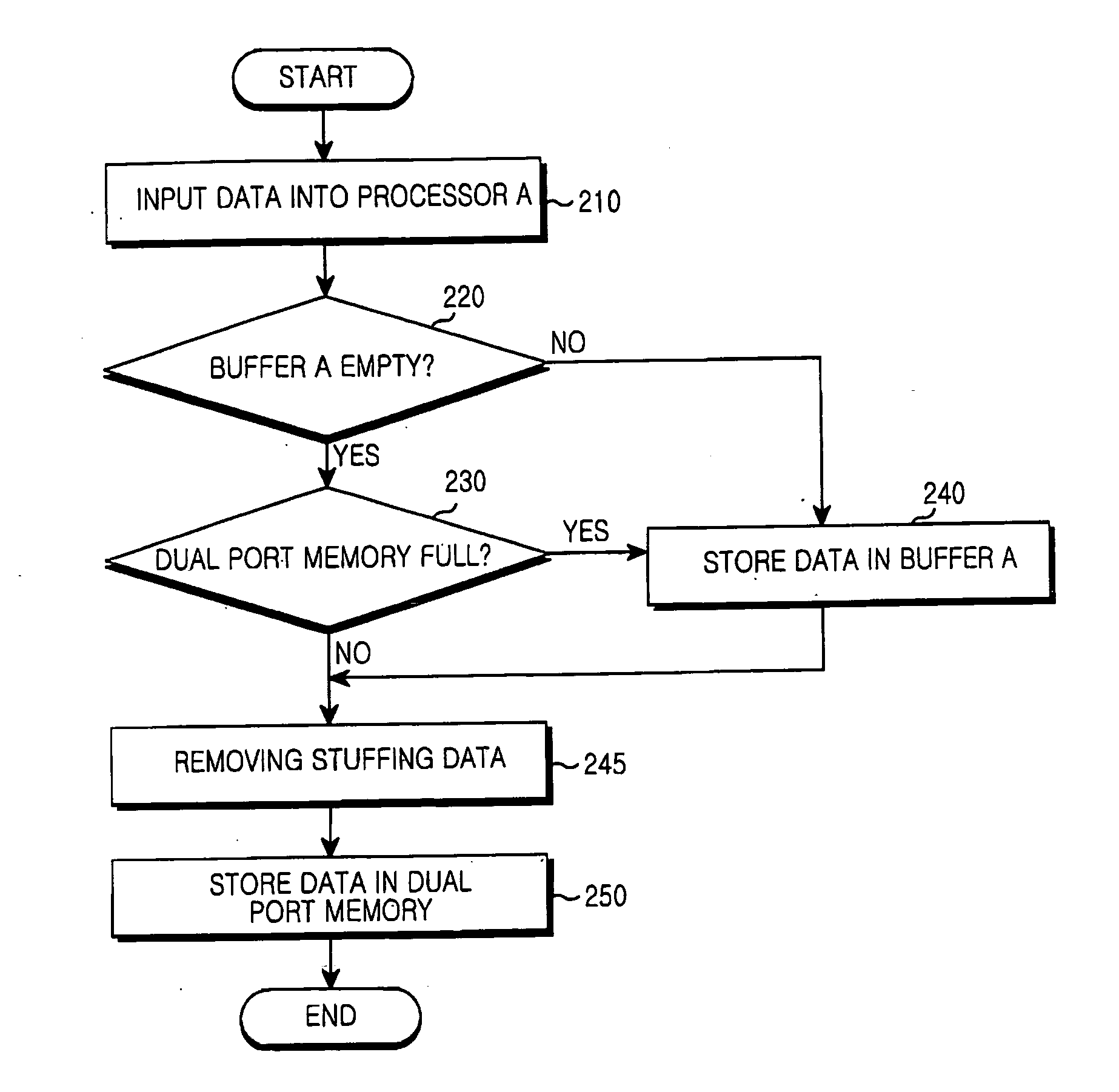

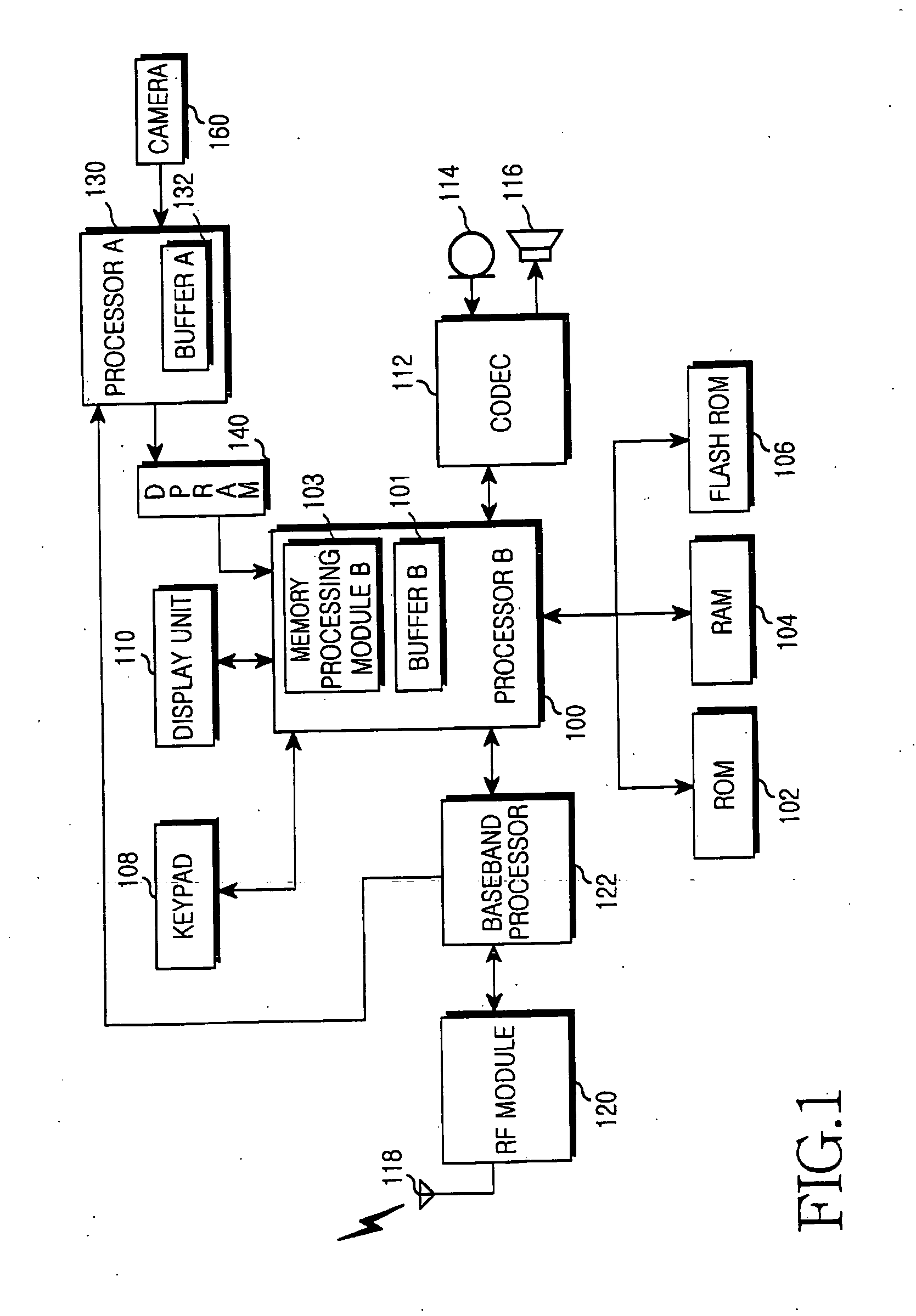

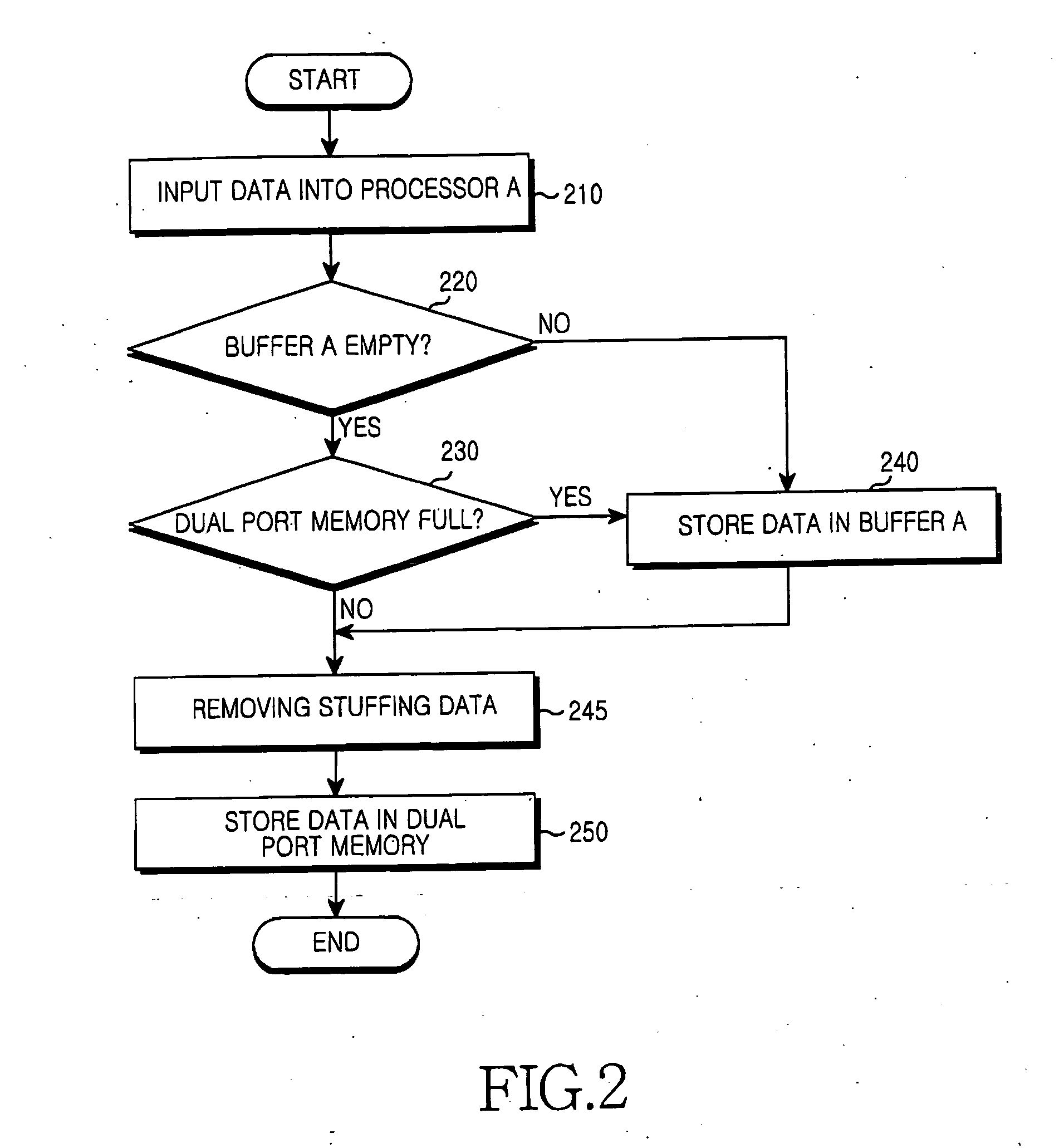

Apparatus and method for controlling dual port memory in a mobile communication terminal with multi processors

InactiveUS20070081412A1Avoid adjustmentTransfer rate is limitedMultiple digital computer combinationsDigital storageMemory processingMemory process

Provided are an apparatus and method for preventing a dual port memory full in a mobile communication terminal with multi processors. The apparatus includes an auxiliary processor having a buffer and storing data in the dual port memory, a main processor having a memory processing module and a buffer and loading the data of the dual port memory, and the dual port memory into which the data from the auxiliary processor and the main processor are loaded. When the dual port memory is used as data exchange units of the multi processors, the synchronization collapse can be prevented, thereby providing the smooth services.

Owner:SAMSUNG ELECTRONICS CO LTD

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com