Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

1017 results about "Market development" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Market development is the process of entering new markets to expand revenue and reduce concentration risk. This involves identifying a target market and finding a way to sell to them.

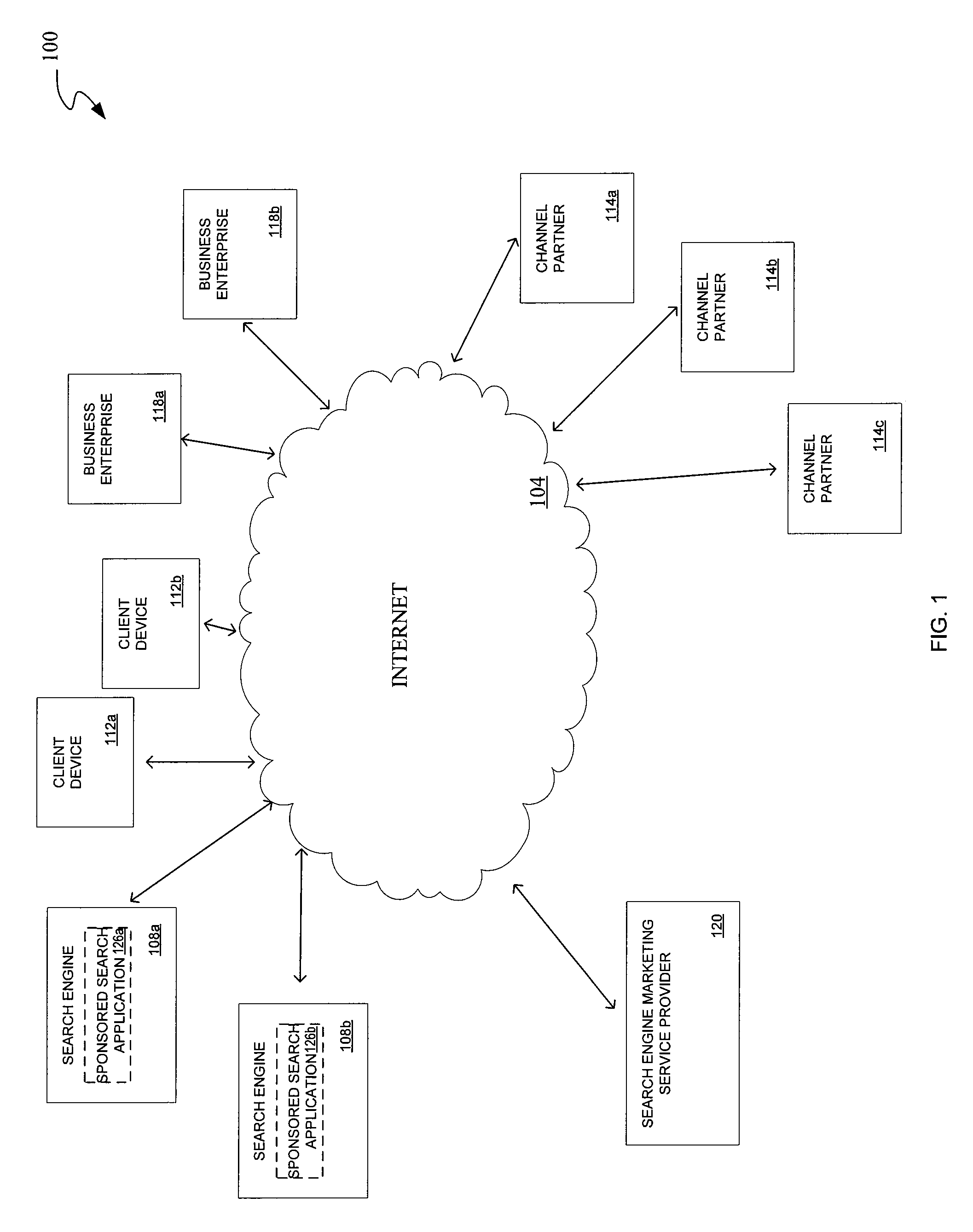

System and method for managing network-based advertising conducted by channel partners of an enterprise

The invention generally relates to a system and method for facilitating cooperative search engine marketing among business entities and their respective channel partners. Embodiments of the invention permit such business enterprises to easily create and distribute approved advertisements and campaign templates, allocate and track the usage of market development funds, monitor the results of sponsored search advertising campaigns instituted by their channel partners, and streamline the reimbursement process for market development funds (MDF). The enterprise may begin the process by creating “ready-made” advertisements and keyword lists with pre-approved content, which helps the enterprise protect brand identity and ensure consistent messaging while making the process of initiating a paid search campaign much easier for the channel partner.

Owner:RIOSOFT HLDG

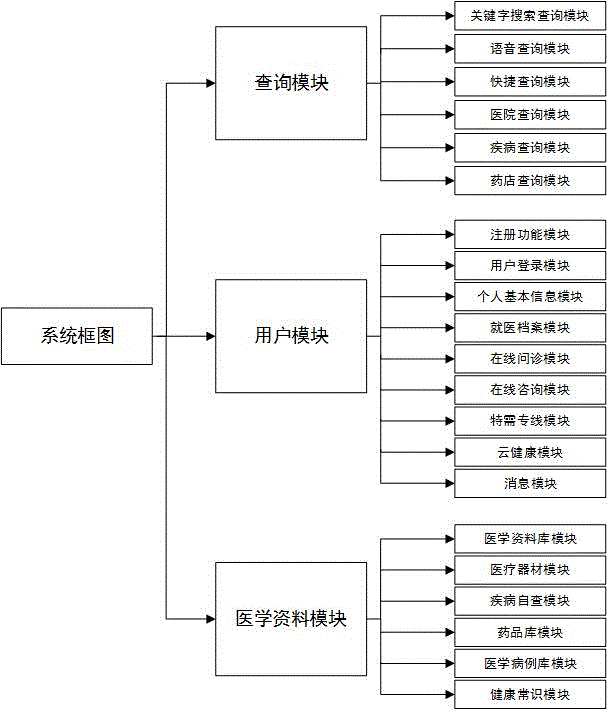

Palm APP based medical service system

ActiveCN105912848AConvenient queryEasy to see a doctorData processing applicationsHealth-index calculationDiseaseMedical record

A palm APP based medical service system includes a query module, a user module, a medicine data module; through connection and information exchange among all the modules, a user can know information about hospitals, diseases and medicine data, and can record personal effective medical history data information; the palm APP based medical service system can effectively integrate all kinds of medical information resources, and integrate guidance, examination, payment, medical history information and medicine knowledge into a whole. The palm APP based medical service system can achieve collection of mobile terminal data through connection of all the databases, can save the time of seeing a doctor, embodies a quick service, and creates favorable conditions for hospital market development.

Owner:广东德澳智慧医疗科技有限公司

Pawpaw leaven of carica papaya and rosaceae plants as well as preparation method and application thereof

InactiveCN102233018AConvenient breastfeedingPromote menstruationNervous disorderMetabolism disorderBiotechnologyFlavor

At present, pawpaw planted in every place of China is used for extracting papain besides preparing Chinese medicinal decoration pieces, preserved fruits, vegetables and fruits, thus nutritional health-care products of pawpaw are nearly not developed. Research on the lactation promoting effect of the pawpaw shows that the pawpaw leaven prepared by fermenting the pawpaw through microbes has comprehensive and rich nutrition and unique flavor and has a remarkable effect of promoting the development of female breast and a unique breast plumping effect of promoting quick recovery of plump, firm, natural and attractive female breast. In conclusion, research and development of the medical health-care products of the pawpaw are at a stage to be developed; the inventor develops the pawpaw leaven with a unique medical health-care effect by fermenting the pawpaw through the microbes; and the pawpaw leaven has a remarkable medical health-care value and a huge economic value, is an innovated invention and an innovated product of deep processing of pawpaw products, and has huge market development space and development prospect.

Owner:李晓青

Plant enzyme probiotic powder and preparation method thereof

InactiveCN104489669AEnhanced Efficacy PropertiesPromote growth and proliferationFood ingredient functionsFood preparationMicroecologyDietary fibre

Owner:SHENZHEN INST OF ADVANCED TECH

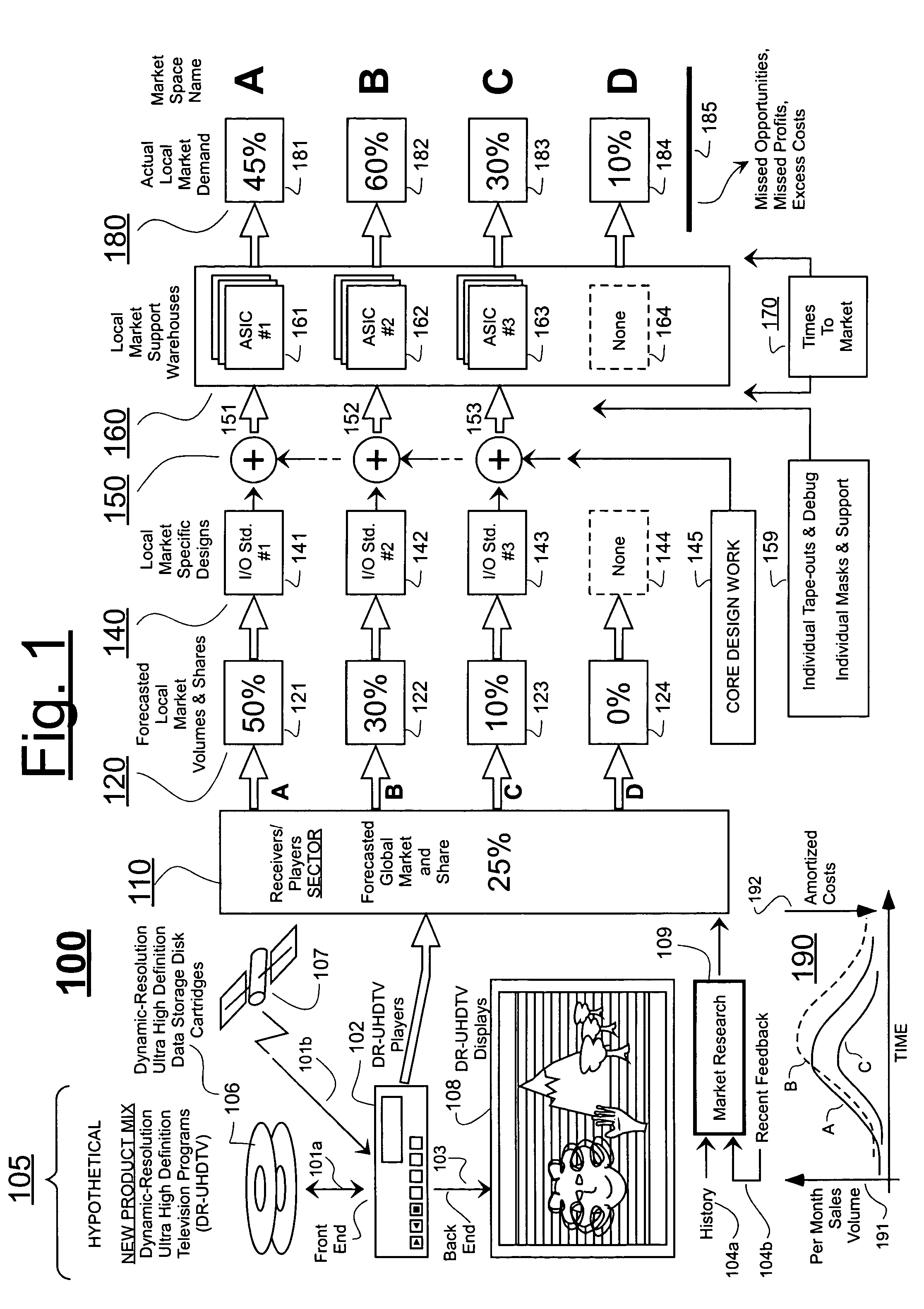

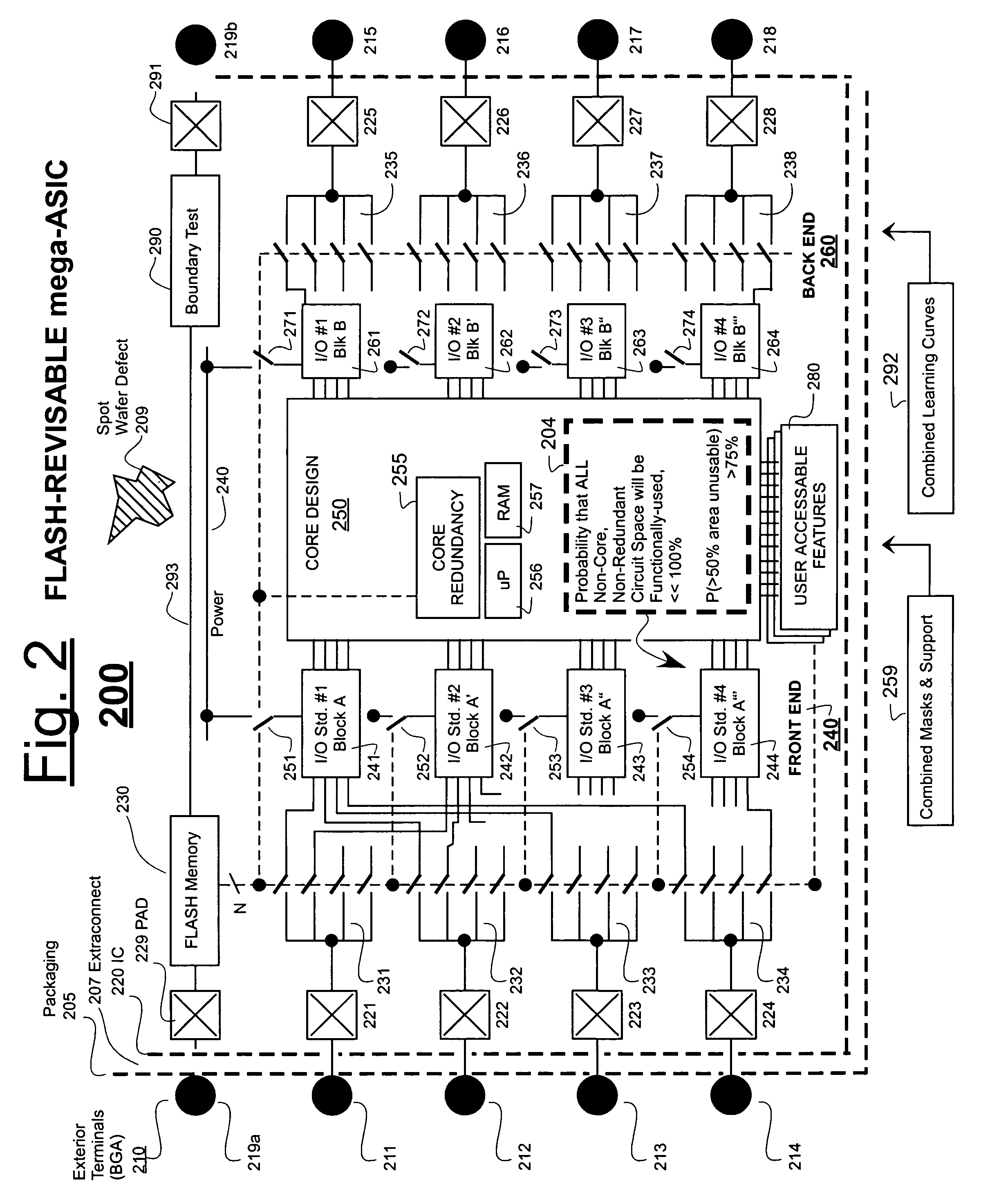

ASICs having more features than generally usable at one time and methods of use

ActiveUS7251805B2Offset drawbackShorten the time to marketSolid-state devicesCAD circuit designChipsetEmbedded system

Owner:SHEYU GROUP

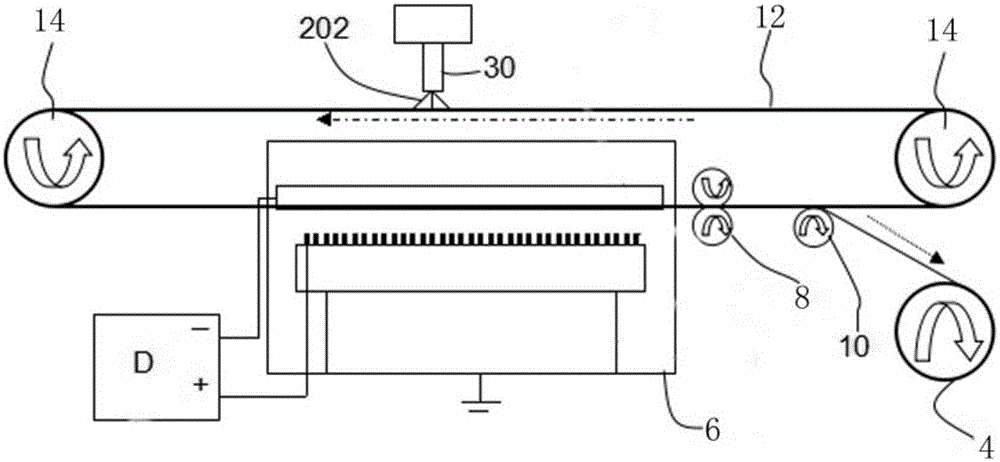

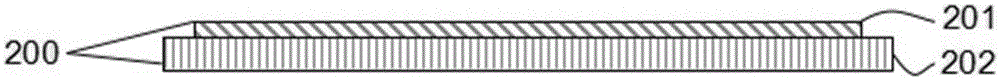

Waterproof and breathable paper diaper base membrane and manufacturing method thereof

ActiveCN105063896ASolve leaking urineSolve the problem of red and swollen buttocksNon-woven fabricsBandagesWater vaporAdult diaper

The invention provides a waterproof and breathable paper diaper base membrane which comprises a base material layer and a waterproof and breathable layer composited with the base material layer. The waterproof and breathable paper diaper base membrane is characterized in that the base material layer is a non-woven fabric fiber layer with the breathability being 100-700 CFM and the thickness being 5-20 GSM, and the waterproof and breathable layer is a nanometer fiber stacking body layer. The invention further provides a manufacturing method of the waterproof and breathable paper diaper base membrane. Hydrophobic high polymer resin is utilized for passing through quantity production high pressure electrostatic spinning equipment, and electrostatic spinning is directly performed on an ultrafine fibber non-woven fabric to form a nanometer fiber stacking body. According to the paper diaper base membrane produced by compositing the nanometer fiber and the ultrafine fiber non-woven fabric, the water pressure resistance can reach more than 4000 mm H2O, meanwhile, the breathability can reach more than 3 CFM, and the water vapor permeance can reach more than 10000 g / cm<2>.24h. A gap for production of the waterproof and breathable base membrane in China is filled, and the problems of urine leakage and red and swollen buttocks caused when a baby wears a paper diaper are completely solved; meanwhile, the base membrane formed by compositing the nanometer fiber and the non-woven fabric can be applied to the market of adult diapers and woman sanitary towels and has the good market development prospect.

Owner:SOOCHOW BOYOO NANO TECH CO LTD

Blueberry freeze-dried powder solid beverage

The invention discloses a blueberry freeze-dried powder solid beverage, and relates to the technical field of health care beverage processing. The beverage is prepared from 15%-30% of whole blueberry freeze-dried powder and 5%-15% of flavoring agents such as white sugar; the beverage is prepared by directly brewing the whole blueberry freeze-dried powder which is taken as raw materials, and a processing technology mainly comprises the procedures of freeze-drying, packaging and sterilizing. The processing technology is simple, the equipment investment is little, the production cost is low, relevant processing technologies are mature, and industrialized production is easy to achieve; whole blueberries are taken as the raw materials and processed through freeze drying at low temperature, and therefore the blueberry freeze-dried powder solid beverage is high in nutritional value, good in healthcare function and suitable for market development tendency.

Owner:SHENYANG AGRI UNIV

Potting nutrient soil

InactiveCN103553769ARich in nutrientsImprove water and fertilizer retention performanceFertilizer mixturesSolubilityGLYCYRRHIZA EXTRACT

The invention relates to the field of plant nutrient soil, and particularly relates to nutrient soil for a potted plant. The potting nutrient soil comprises the following active ingredients in parts by weight: 50-70 parts of needle-point leaf soil, 10-20 parts of chitosan, 5-10 parts of plant ash, 5-10 parts of pine bark, 1-3 parts of slaked lime, 10-20 parts of wormcast, 5-10 parts of river sand, 5-15 parts of bone meal, 2-5 parts of active microorganism, and 0.5-1.2 parts of liquorice. By adopting the technical scheme, the potting nutrient soil has the beneficial effects that the potting nutrient soil is rich in nutrient substances, good in water retention and nutrient preservation properties, good in soil permeability, and low in cost, potted plant can be directly placed in the potting nutrient soil for growth, the potting nutrient soil is high in nutrition value, rich in various mineral substances of calcium, phosphorus and the like, and can continuously provide nutrition. The potting nutrient soil is convenient to use, incapable of causing any environment pollution, good in solubility, popular with potted class, and has a broad market development space.

Owner:溧阳市甜园景观设计工程有限公司

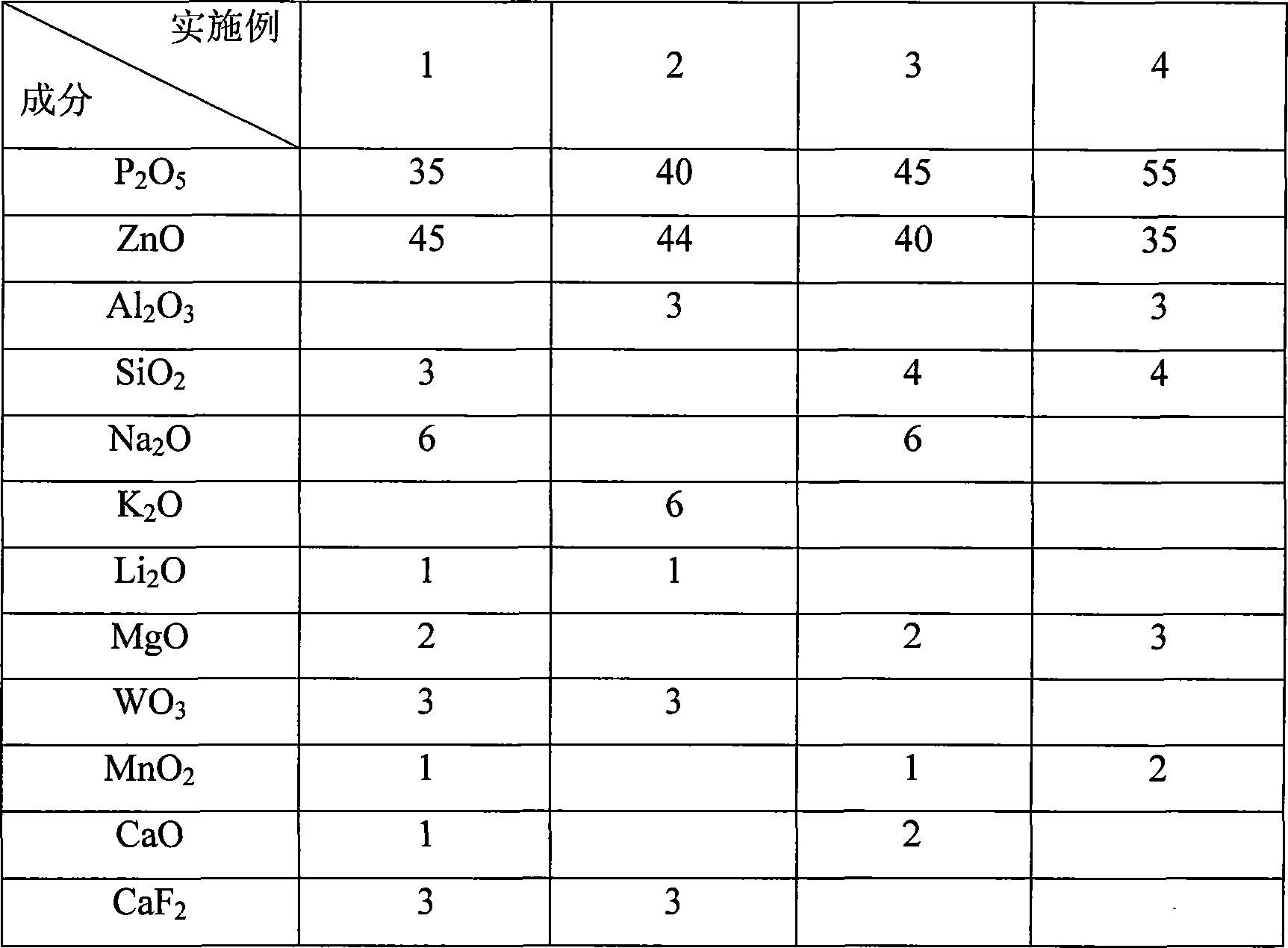

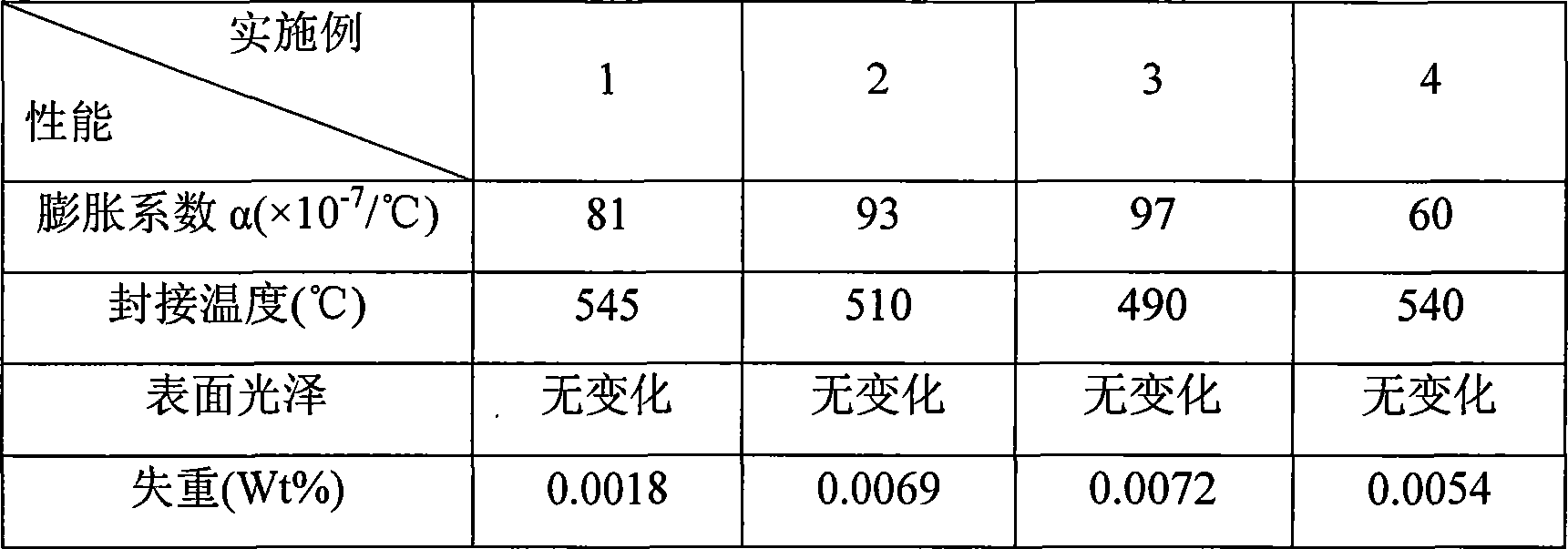

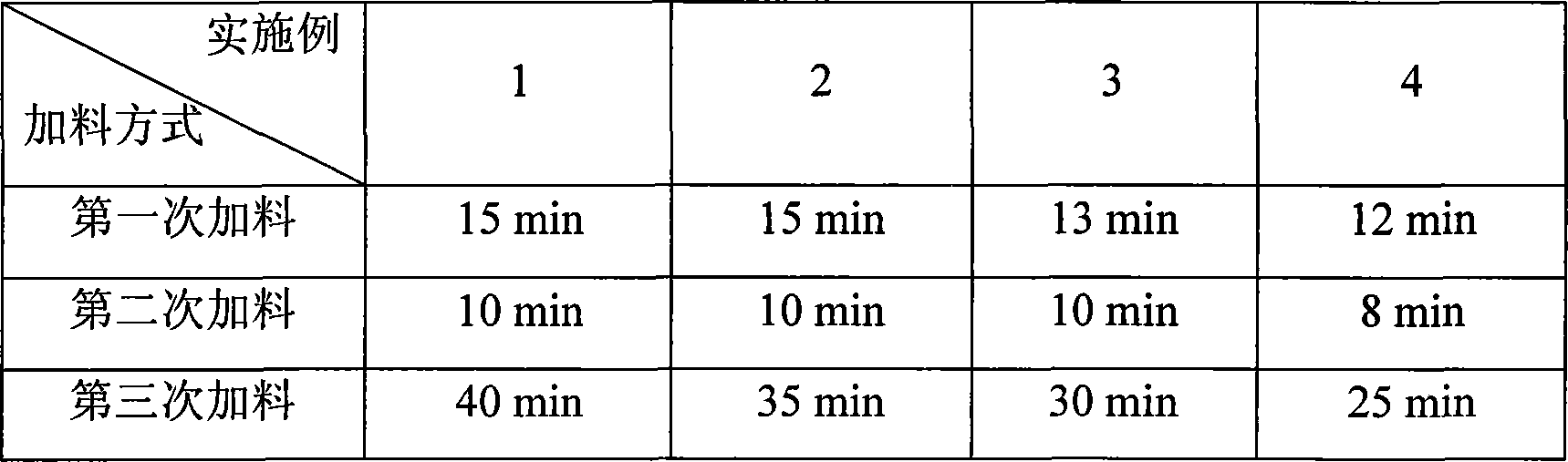

Leadless low-melting glass powder for seal with metal or alloy and preparation method thereof

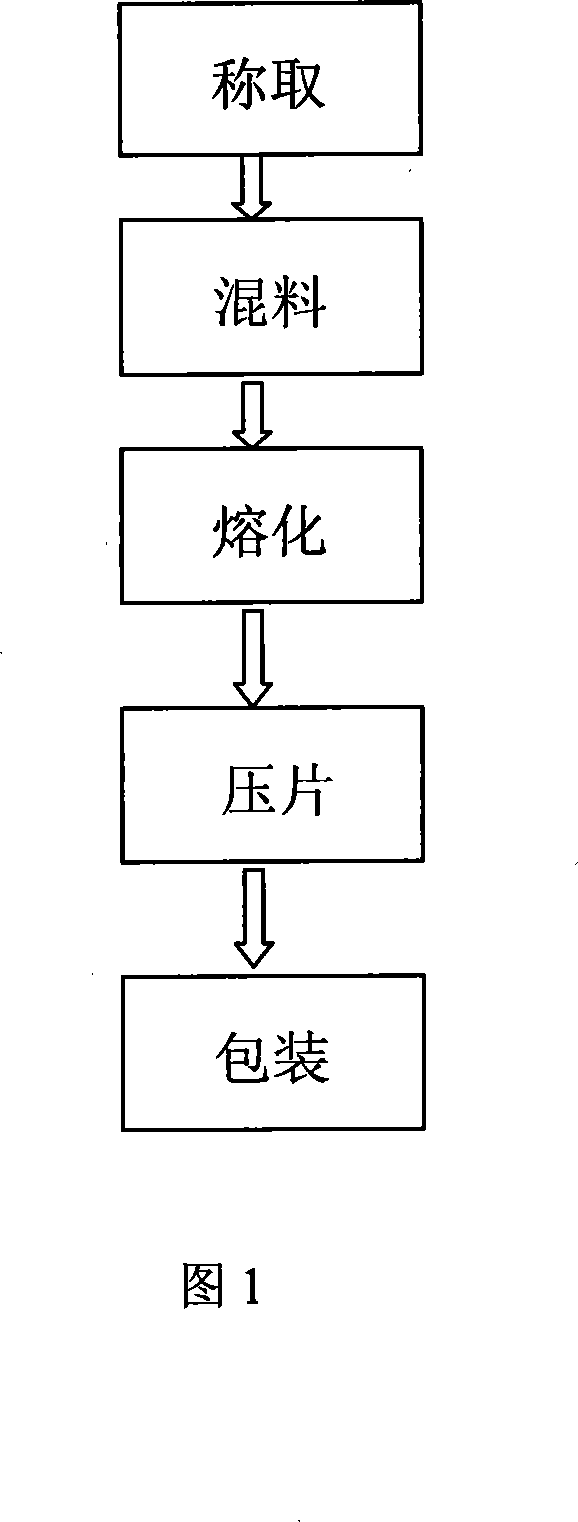

InactiveCN101113073AEasy to adjust thermal expansion coefficientSuitable softening temperatureVitreous BodiesMixed materials

The invention relates to lead-free glass powders with low melting point for sealing of metal or alloy and preparation methods thereof. The glass powder comprises P2O5, ZnO, Al2O3, SiO2, MgO, MnO2, Li2O, WO3, CaF2, Na2O, K2O and CaO. The preparation thereof is divided into the following steps: (1) raw materials are drawn and fully mixed according to weight proportions to make into mixed materials; (2) the mixed materials are heated and melted for 30 minutes to two hours under a temperature ranging from 1000 DEG C to 1350 DEG C; (3) the melted glass liquid is cooled and cured into glass body. The glass powder not only has comparatively ideal heat expansion coefficient, softening temperature and chemical stability but also has simple preparation process, straightforward operation and low cost, which is applicable to the sealing of glass, ceramic, metal and semiconductor and in particular applicable for the sealing of metals of molybdenum family and tungsten family or alloy such as kovar alloy. Also the glass powder is competitive in lead-free production and has wide market development prospect.

Owner:DONGHUA UNIV

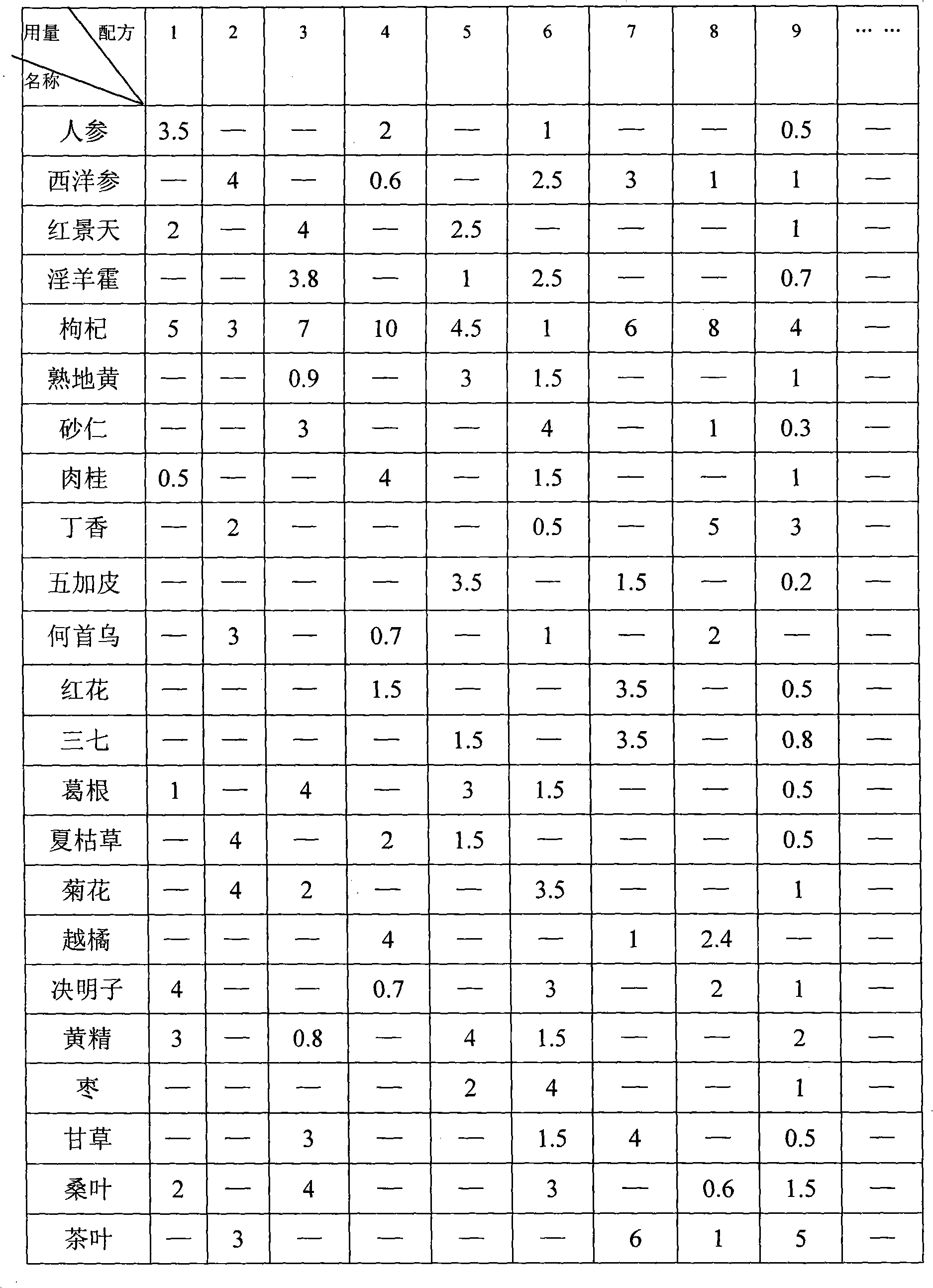

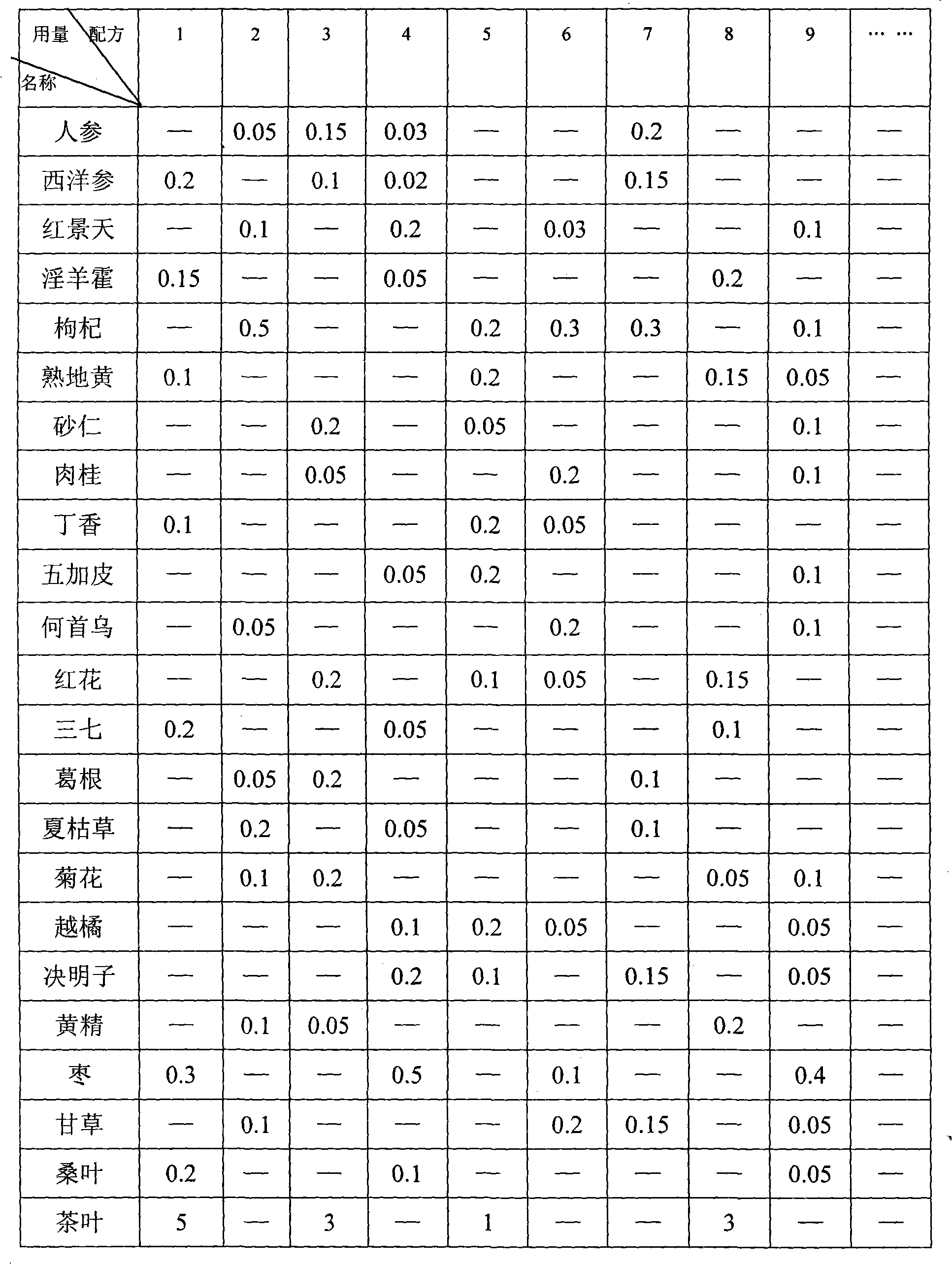

Health beverage

InactiveCN101347244AImprove scienceReliableAlcoholic beverage preparationFood preparationMedicinal herbsFood additive

A health care drink is prepared by combining 22 medicinal herbs and supplementing vitamin, amino acid, food raw materials and a food additive. The health care drink can apply 'Jian' permit, and has the functions of alleviating physical fatigue and asthenopia and strengthening human immunity. The health care drink has wide applicable population, broad market development space and fills up a blank of the health care products.

Owner:曲建波

Salty and sweet olive preserves and production method thereof

The invention discloses salty and sweet olive preserves and a production method thereof. The production method includes processing procedures of fresh olive sorting, selecting, peeling, salting, grading, separating, washing, preserving, baking, separating, packaging and putting in storage. The finished salty and sweet olive preserves are carefully made, have unique shapes, are bright-colored, taste delicate and have bright market development outlook.

Owner:福州市食品工业研究所

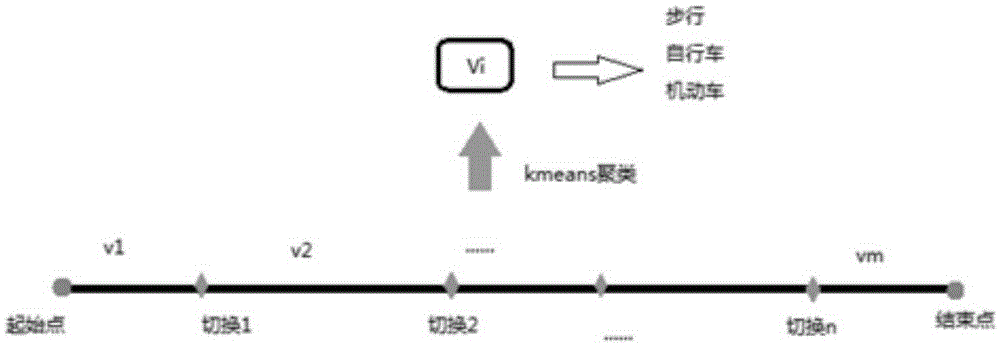

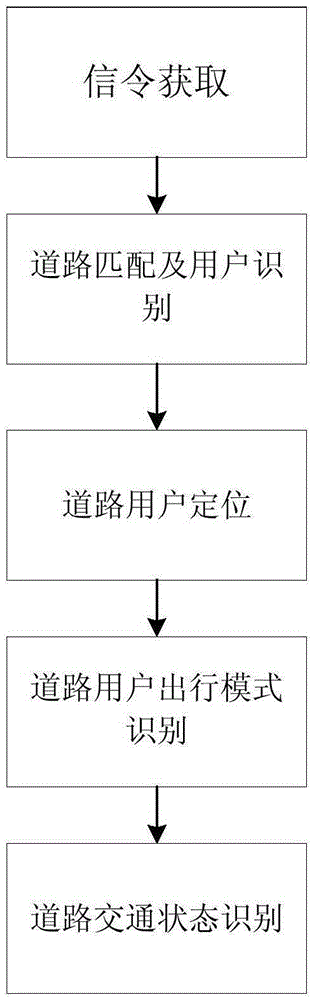

Road state identification method based on mobile phone signal

InactiveCN105243844AEasy accessLow costDetection of traffic movementLocation information based serviceTravel modeRoad traffic

The invention discloses a road state identification method based on mobile phone signals. The method comprises the following steps: firstly, acquiring mobile phone signals; secondly, matching users with roads, and identifying the users and the roads; thirdly, positioning the users on the roads; fourthly, identifying travel modes of the users on the roads; and fifthly, identifying the traffic state of the roads. The advantages are that the method is convenient to obtain and low in cost, has remarkable popularization values and market development potentials, etc.

Owner:SOUTH CHINA UNIV OF TECH

Soap containing vegetable essential oil

The invention discloses a cake of soap with plant essential oil. First geranium essential oil, flores chamomillae oil, honeysuckle essential oil, citronella essential oil, and thyme essential oil etc. are mixed by a certain ratio, then some soap substrate is added and the soap is made. The soap of the invention has the advantages of clearing heat, detoxification, sterilization, stopping itch, clearing body and moisture holding. With simple preparation and distinct effect, the invention has good market development value.

Owner:BEIJING ZHONGKE YONGHE PHARMA TECH

ASICs having more features than generally usable at one time and methods of use

ActiveUS20060080631A1Shorten the time to marketOffset drawbackSolid-state devicesCAD circuit designTime to marketInventory management

More ASIC functionality is crammed into a chip (or chip set) than can probably or definitely be operative at one time when the chip is packaged and inserted into a broader circuit. The excessive ASIC functionality is chosen to cope with different market development probabilities in a host of different market spaces (e.g., in different countries where different interoperability standards are chosen) and a subset of the excessive ASIC functionality is programmably activated in each market space after manufacture. Customer behavior can be fickle. If market trends evolve towards demand for functionality #2 instead of an originally, more expected, functionality #1, the mass produced of the crammed chip (or chip set) is not out of necessarily out of luck. If the mass produced had enough foresight to cram in functionality #2 as well as functionality #1, the producer can programmably activate #2, and deactivate #1 as market demand suddenly shifts in a given market space. In one embodiment, a mega-ASIC with excessive ASIC functionality crammed into it, has a universal core as well as plurality of programmably selectable ASIC function blocks. The ASIC function blocks are programmably activatable and de-activatable so that a mass produced can quickly respond to shifting market demands, thus addresses both time to market and product life issues. The invention allows a small chip designer to simultaneously address more than one market or customer space with one ASIC chip thereby reducing the design cost per product design. By selectively activating the excessive and selectable ASIC functionalities, the small ASIC chip designer can appear to sport different features for different customers and different markets at different times with just one chip, thus he can aggregate the demand of different customers and different markets to achieve economies of scale, and of inventory management and control.

Owner:SHEYU GROUP

Nutritional medicinal granules capable of relieving mental pressure and resisting depression and preparation method thereof

The invention discloses health-care medicinal granules capable of relieving mental pressure and resisting depression. The medicinal granules mainly comprises the following nutritional ingredients: Inca Inchi oil, Inca Inchi polypeptide, plantain powder, soybean polypeptide, L-theanine, passionflower, kendir, licorice root, kudzu root, schisandra fruit extract, deep sea fish oil, tryptophan, tyrosine, folic acid and the like. The method comprises the following steps: carrying out cold pressing and enzymolysis, evenly mixing according to parts by weight, adding emulsifier glycerol monostearate,homogenizing and carrying out spray drying. The nutritional medicinal granules disclosed by the invention have good mouthfeel, and has favorable action on improving depressed people with irritability, great mood fluctuations, obvious energy reduction, causeless continuous fatigue, insomnia, early sleep, hypersomnia, and concentration difficulty or plummet. Compared with products which can only relieve pressure and resist depression or western medicines with side effect, the nutritional medicinal granules have obvious advantages, are a novel health-care solid beverage, and have wide market development and application prospects.

Owner:广州智享生物科技有限公司

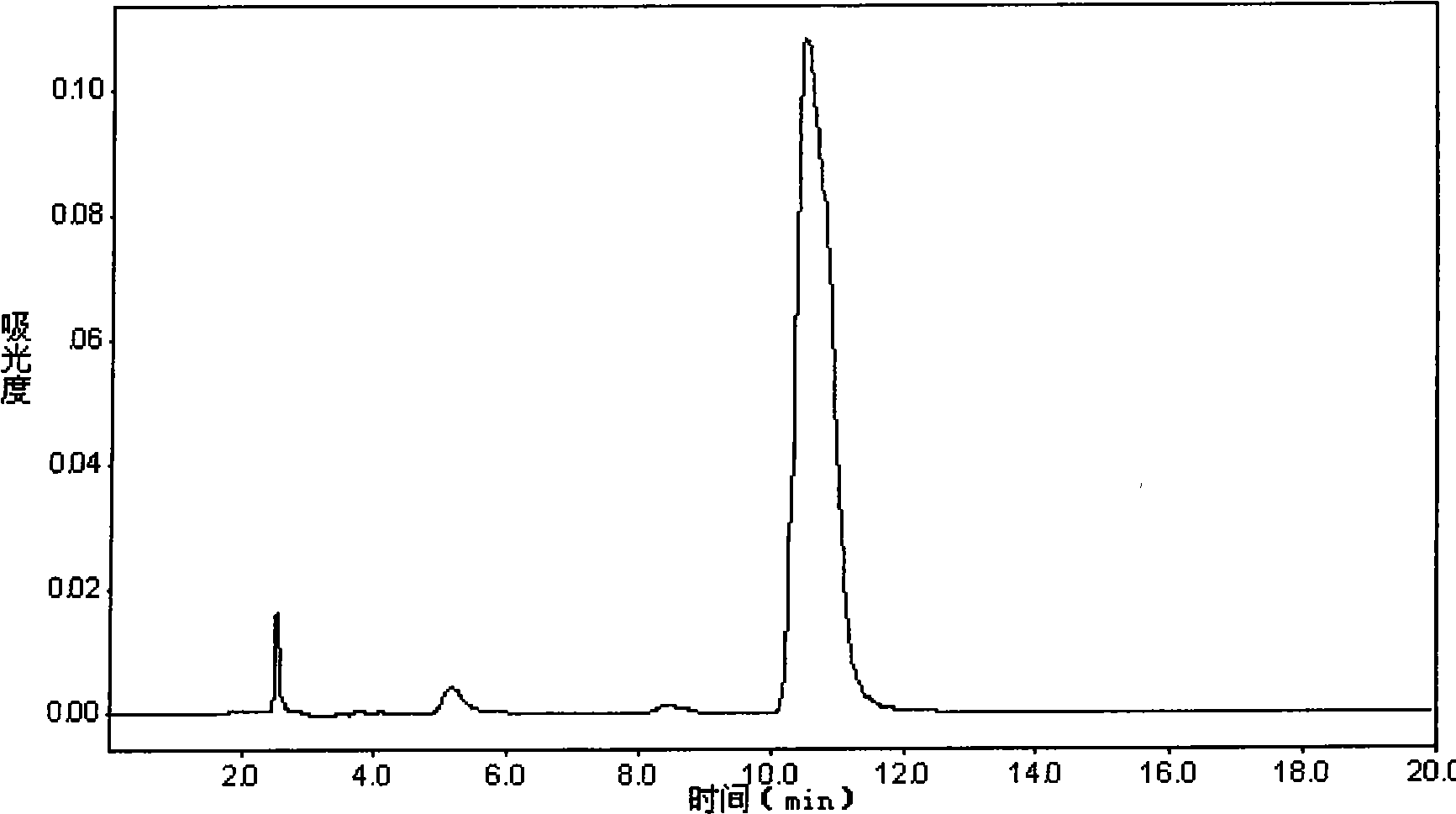

Extraction and purification process for cordycepin in cordyceps militaris link

InactiveCN101508715AMaintain biological activityHigh activitySugar derivativesOther chemical processesPurification methodsRotary evaporator

The invention provides an extraction and purification method of cordycepin from Cordyceps militaris, and belongs to the deep-processing technical field of agricultural products. The method comprises the following steps: crushing Cordyceps militaris raw material, mixing the raw material with water at 1:20 raw material / water ratio, performing ultrasonic extraction, and performing centrifugal filtration on obtained extracting solution and pouring in a macroporous resin column at the adsorption flow of 1.8BV / hr; taking 15% methanol aqueous solution as an eluant to perform resin column elution, and decompressing and condensing obtained eluent at the temperature of 60 DEG C by a rotary evaporator to obtain Cordyceps militaris cordycepin concentrate. The method can help realize aqueous solution extraction of the cordycepin from the Cordyceps militaris raw material at low temperature, and the extraction rate reaches 85%; and polysaccharide and protein can be removed from the extract by macroporous resin separation and purification, thus the content of the cordycepin in the extract can reach 10%. The cordycepin in the Cordyceps militaris product has high activity, can be taken as a raw material for producing cordycepin monomer and can also be directly taken as an additive of health products and functional food, thus the cordycepin has wide market development prospect.

Owner:JIANGSU ACADEMY OF AGRICULTURAL SCIENCES

Skin moisturizer containing rose ferment

InactiveCN104546653ARelieve stressEliminate fatigueCosmetic preparationsToilet preparationsSlagGlycerol

The invention discloses a skin moisturizer containing rose ferment and a preparation method thereof. The skin moisturizer comprises rose ferment, vinegar, glycerol and propylene glycol, and is prepared by the following steps: fresh rose is cleaned, smashed and pulped, a slurry is obtained, and then fruits and vegetables and Chinese herbal medicine are mixed; then water and cellulase powder are added for reacting and resolving, and through yeast fermentation, filtering and slag removing, rose ferment is obtained; then the vinegar, the glycerol and the propylene glycol are added into the rose ferment, uniform stirring and sealing are performed, and still standing is performed for 7 days at the temperature of 25 to 30 DEG C, so as to obtain the skin moisturizer. The skin moisturizer containing rose ferment provided by the invention has the advantages of being free of any preservative components, being inirritative to skin, and playing effects of whitening and delaying senescence, and has a wide market development prospect.

Owner:北海万物盛生物技术开发有限公司

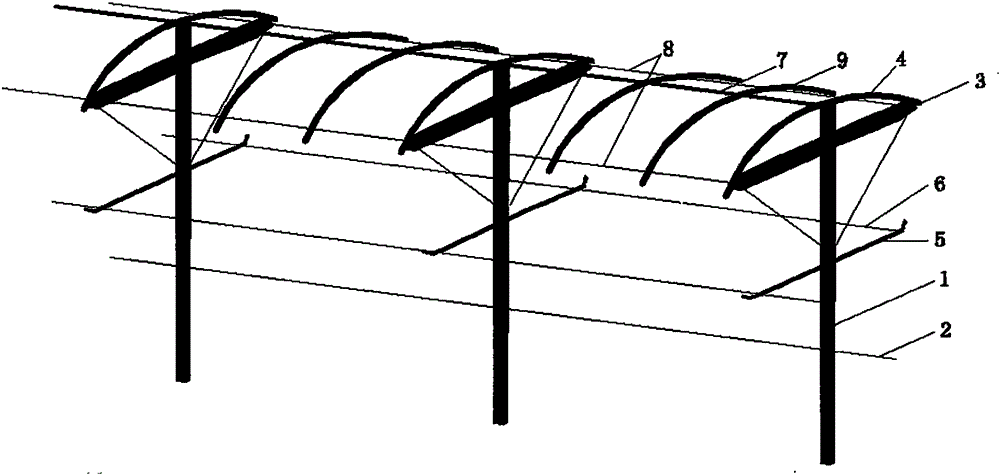

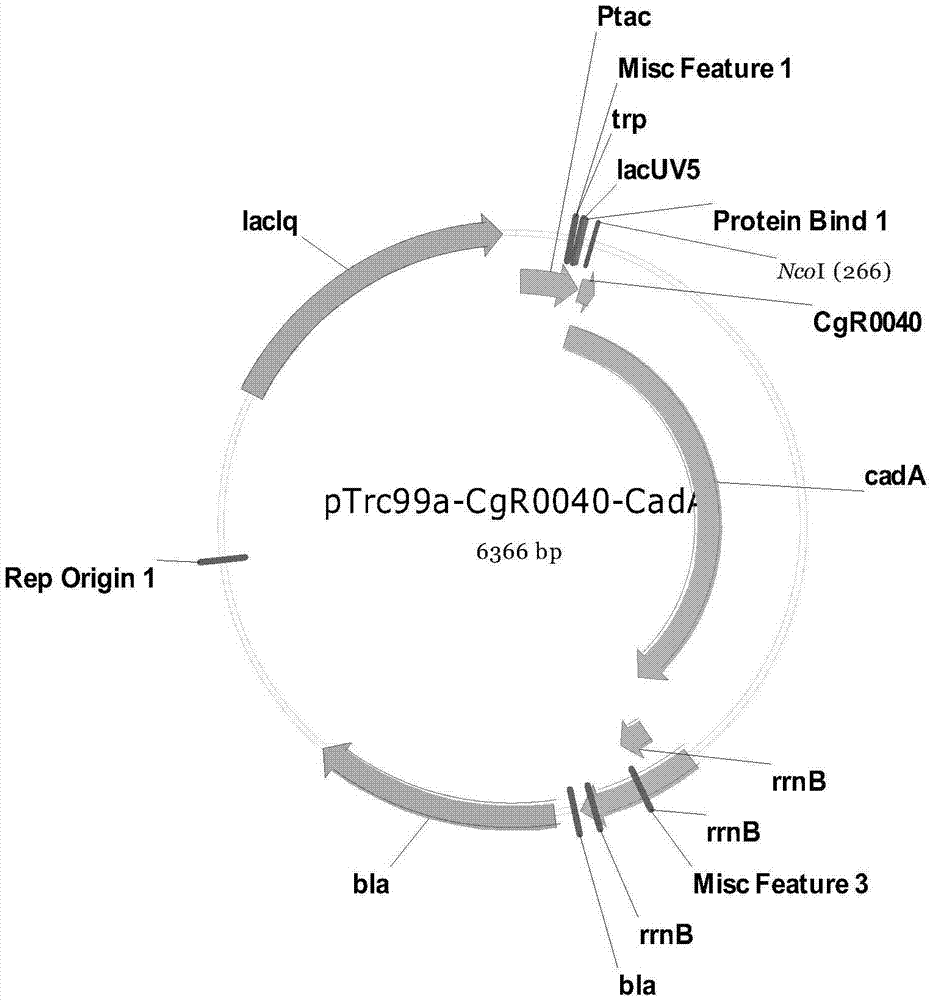

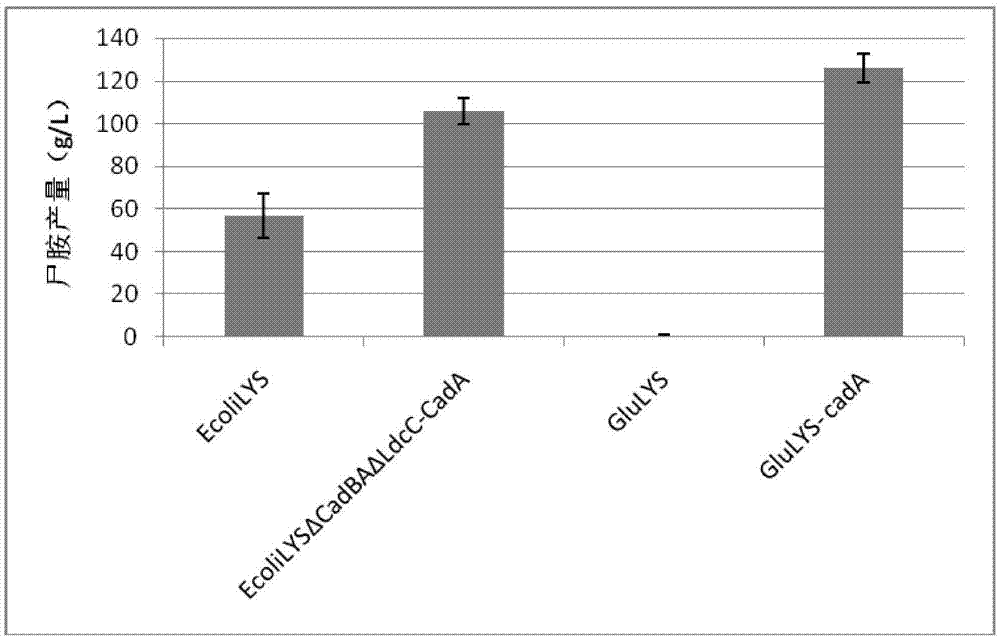

Cadaverine-producing engineering strain

InactiveCN102424811AOversynthesisCurb global warmingBacteriaMicroorganism based processesSynthesis methodsFermentation

The invention relates to a cadaverine-producing engineering strain, a construction method thereof and a method for producing cadaverine by using the strain. Based on a gene engineering technology, an L-lysine decarboxylase gene (cadA / LDC) and a cadaverine-lysine antiporter gene (cadB) are respectively or simultaneously cloned into Corynebacterium glutamicum and subjected to induced coexpression, the lysine is decarboxylated to generate cadaverine under the catalytic action of the CadA enzyme, and the cadaverine is transported out of cells by the CadB protein, thus constructing a high-yield cadaverine-producing engineering strain and establishing a novel one-step cadaverine synthesis method based on the fermentation of Corynebacterium glutamicum. The one-step cadaverine synthesis method based on microbial fermentation provides a new way for large-scale cadaverine production, thereby having great economic benefits and social benefits and wide market development prospects.

Owner:TIANJIN UNIVERSITY OF SCIENCE AND TECHNOLOGY

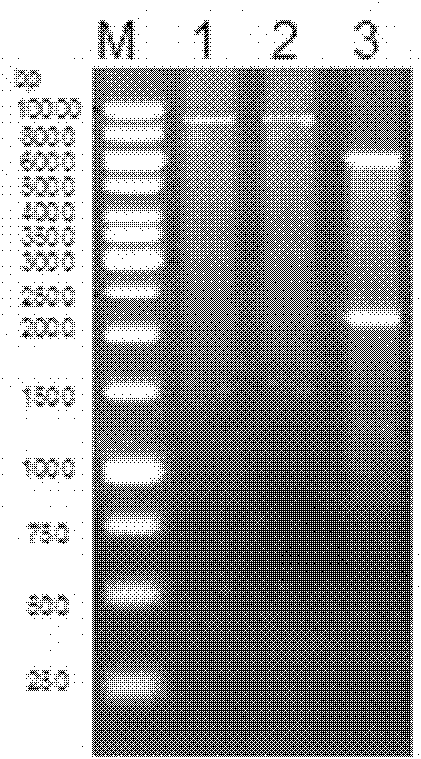

Artificial cultivation method for wild fruit Kadsura coccinea

InactiveCN105284546AImprove the success rate of artificial cultivationRealize large-scale plantingBiocideClimate change adaptationEconomic benefitsPest control

The invention discloses an artificial cultivation method for wild fruit Kadsura coccinea. The method comprises the following steps: selection of an afforestation land, planting, building of a rainproof-sunshade type single trellis, shaping and pruning, pest and disease control, etc. The artificial cultivation method provided by the invention improves the success rate of artificial cultivation of the wild fruit Kadsura coccinea, realizes large-scale plantation of the wild fruit Kadsura coccinea, and has good market development prospects and economic benefits.

Owner:高渐飞

Ligaloes perfumes and method of producing the same

ActiveCN101129316ASimple preparation processSimple recipeCosmetic preparationsToilet preparationsChemistryBenzyl acetone

The invention discloses a linaloe perfume and making method, which is composed of 2. 5-8. 5wt% linaloe oil and 95-105wt% spirit, wherein the linaloe oil is extracted benzine with sesquiterpenes, benzyl acetone, p-methoxy benzyl acetone. The invention has simple preparing technique and formulation with peculiar scent and sedative and tranquilizing effect, which releases working pressure and mood with wide applying scale and good market developing prospect.

Owner:INST OF TROPICAL BIOSCI & BIOTECH CHINESE ACADEMY OF TROPICAL AGRI SCI

Barium crown sealed glass and preparation and application thereof

InactiveCN101113075AEasy to adjust thermal expansion coefficientSuitable softening temperatureVitreous BodiesConductive materials

The invention relates to lead-free sealing glass and a preparation method thereof. The glass contains Bi2O3 of 40-70 percent, B2O3 of 0-30 percent, ZnO of 0-30 percent, Al2O3 of 0-10 percent, SiO2 of 0-10 percent, MgO of 0-15 percent, TiO2 of 0-5 percent, CaO of 0-5 percent, and CuO of 0-5 percent. The preparation method needs the following steps: (1) the materials are weighted according to proportion and mixing the materials completely to make mixture material; (2) the mixture material is melted under 1000-1350 DEG C for 10 minutes to 1 hour; (3) the glass molten preparing is cooled and solidified for making glass body. The sealing glass contains no lead, and has good sealing performance, good sealing fluidity, chemical stability and low expansion coefficient. Meanwhile, the preparation technique is simple, the operation is convenient, the cost is low, and is suitable to be used as sealing glass of glass, ceramic, metal, semi conductive material, and more particularly suitable for the sealing of Al2O3 ceramic base plate (60-70 multiply10-7 / DEG C), and has good competition in lead-free field and good market development prospect.

Owner:DONGHUA UNIV

Preparation method of frozen prepared chicken cutlet

The invention discloses a preparation method of frozen prepared chicken cutlet. The preparation method comprises the following steps: selecting materials, cutting into blocks, preparing a tumbling liquid, tumbling, curing for being tasty, adding cheese, preparing wrapping powder and wrapping pulp, coating the wrapping powder and the wrapping pulp, frying in advance, placing in a dish and quick-freezing, packing, performing metal detection and storing, wherein in the preparation process, the tumbling liquid is prepared from the following components: salt, white granulated sugar, monosodium glutamate, composite phosphate, white pepper powder, garlic powder, and water at the temperature of 0-5 DEG C; and the wrapping powder is prepared from 48-52 parts of wheat flour, 28-32 parts of cassava modified starch, 18-22 parts of sweet potato flour, 0.3-0.7 part of xanthan gum, 0.3-0.7 part of pyrophosphate. The preparation method is applied to processing of frozen prepared food, a product is attractive in appearance, rich in nutrition, delicious, and long in guarantee period, and has a good market development prospect.

Owner:SANTONG WANFU QINGDAO FOOD

Compound active cosmetic collagen powder

The invention discloses a compound active cosmetic collagen powder, particularly discloses a synergetic oral compound active cosmetic collagen powder integrating various functions of remarkably resisting oxidation, whitening skin, moisturizing, dispelling wrinkles and freckles, delaying senescence and the like and belongs to the technical field of nutrient health-care foods. The compound active cosmetic collagen powder is characterized in that active polysaccharides, natural fruit powder and vitamin E are added based on cosmetic collagen and has the advantages of being reasonable in proportioning, strong in pertinence, remarkable in synergy effect, good in taste, convenient to eat, good in safety, free of toxic and side effects, simple in production process, easy to produce, filling market blank and extremely having market development potential.

Owner:北京姿美堂生物技术股份有限公司

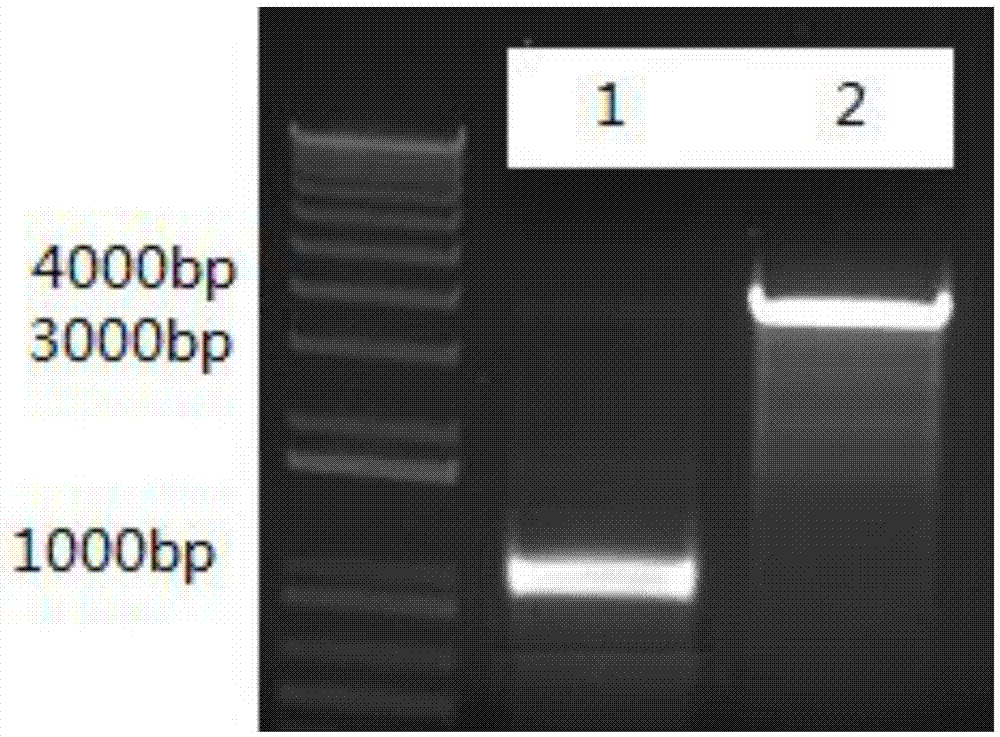

Method for coupled production of cadaverine by using microbial fermentation and microbial conversion

ActiveCN105441497AIncrease productionImprove production efficiencyMicroorganism based processesFermentationEscherichia coliMicrobial transformation

The invention relates to a method for coupled production of cadaverine by using microbial fermentation and microbial conversion. By use of the gene engineering technology, lysine decarboxylase genes with different sources are cloned in Escherichia coli or corynebacterium glutamicum with high yield of lysine for secretory expression, recombinant stains are fermented, the recombinant strains synthesize lysine at the first stage, lysine decarboxylase genes are induced for secretory expression at the second stage, and the lysine is converted into the cadaverine. The method for coupled production of cadaverine by using microbial fermentation and microbial conversion provides a new way for production of the cadaverine, has enormous economic benefit and social benefit and has broad market development prospect.

Owner:TIANJIN UNIVERSITY OF SCIENCE AND TECHNOLOGY

Making method of pleurotus cornucopiae flavored chilli silvery pomfret sauce

InactiveCN105595306ARich sauceWith regulating qi and relieving painFood ingredient functionsNutritive valuesPinellia

The invention discloses a making method of pleurotus cornucopiae flavored chilli silvery pomfret sauce. Pleurotus cornucopiae and silvery pomfret are used as raw materials, pinellia ternate and fragrant sarcococca herb are added at the same time, and the pleurotus cornucopiae flavored chilli silvery pomfret sauce is obtained. The nutritive value of the pleurotus cornucopiae and the silvery pomfret are sufficiently utilized and are compatible with traditional Chinese medicine, synergistic interaction is achieved, and the effects of regulating qi to alleviate pain and tonifying the spleen and reinforcing the stomach are achieved. The finished sauce is strong, bright in color and delicious in taste, has the outstanding healthcare function, and can obviously relieve discomfort of the crowd suffering from dyspepsia and stomach duct and abdomen when eaten for a long time. The making technology is simple, easy to implement, capable of meeting the requirement of market development and capable of achieving large-scale production.

Owner:申健

Black fungus chewing tablets and preparation method thereof

InactiveCN104082706AWith hypolipidemicHypoglycemicFood shapingNon-sugar sweetener food ingredientsFiller ExcipientCyclodextrin

The invention provides a black fungus chewing tablets and a preparation method thereof, wherein the black fungus chewing tablets have functions of reducing blood fat, reducing blood glucose, preventing dental caries and improving functions of intestines and stomachs. The black fungus chewing tablets includes, by weight, 25-35% of black fungus powder planted on logs, 45-62% of a filling agent, 11-15% of a binding agent, 0.2-1.6% of a corrective agent and 1-3% of a lubricant, wherein the filling agent is a mixture composed of one or more of skimmed milk powder, lactose, xylitol, mannitol, modified starch, dextrin, [beta]-cyclodextrin and microcrystalline cellulose. The invention provides the black fungus chewing tablets and the preparation method thereof. Black fungus functional chewing tablets, which are sour-sweet and delicious in taste and is unique in flavors, are prepared. The chewing tablets have functions of reducing blood fat, reducing blood glucose, preventing dental caries and improving functions of intestines and stomachs. A series of products of black fungus is enriched. Transformation approaches of the black fungus resources are increased. A new method for further deep processing the black fungus is provided. The chewing tablets are in conformity with a functional, natural and diversified international developing trend in foods and have a broad market development prospect.

Owner:SHIYAN FULONGSHAN GREEN FOOD DEV CO LTD

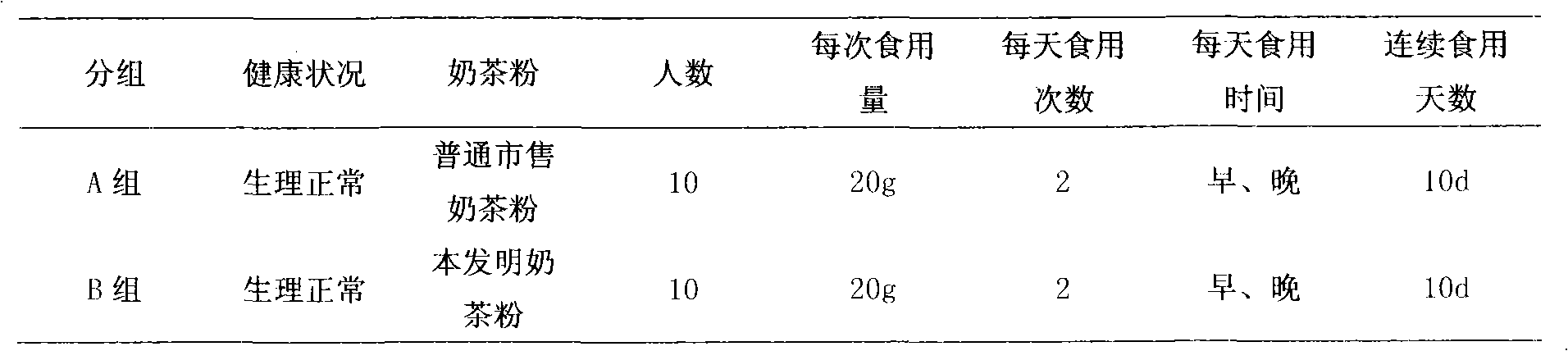

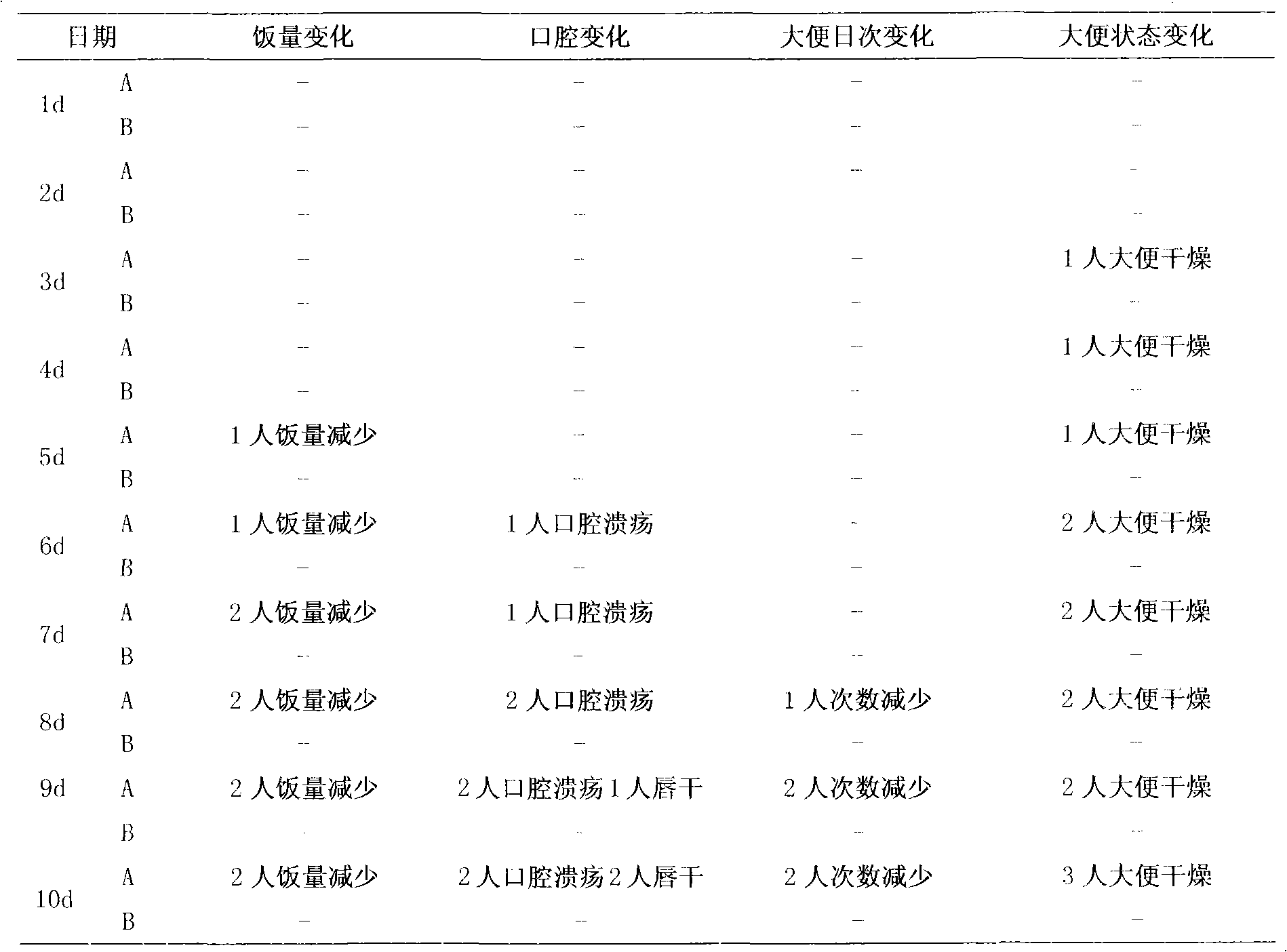

Functional milky tea powder and preparation method thereof

ActiveCN101810223AStrong targetingImprove immunityMilk preparationPre-extraction tea treatmentToxic materialDigestion

The invention discloses functional milky tea powder and a preparation method thereof. The functional milky tea powder is characterized by containing or being strengthened with various nutrients such as taurine, magnesium, zinc, vitamins and the like and integrating various functions of clearing away heat and toxic materials, preventing dental ulcers, invigorating stomachs and promoting digestion, loosening bowels and relieving constipation, lowering blood fat, blood pressure and blood sugar, losing weight, resisting fatigue and the like. The invention has the advantages that the preparation method creatively enables the milky tea powder to be subdivided, has reasonable proportioning, strong pertinence and obvious synergy function and fills the market blank; and the milky tea powder has the characteristics of the mellow and smooth taste of milk, the delicate fragrance of tea and the like and has the advantages of convenient edibility and carrying, simple production process, easy production and very great market development potential.

Owner:呼伦贝尔海乳乳业有限责任公司

Barium crown glass powder for electronic slurry and preparation method thereof

InactiveCN101113074AEasy to adjust thermal expansion coefficientSuitable softening temperatureSlurryThermal expansion

The invention relates to lead-free glass powder used in electronic paste and preparation methods thereof. The lead-free powder at least comprises Bi2O3 of 40-70wt %, B2O3 of 10-40wt %, ZnO of 5-40wt %, Al2O3 of 2-10wt %, and SiO2 of 2-10wt % which are mixed and melt into glass powder. The lead-free sealing glass powder not only has moderate thermal expansion coefficient and softening temperature, excellent chemical stability and simple preparation method, but also is applicable for the sealing of VFD, FED, PDF, CRT and the sealing of anything which has consistent temperature and thermal expansion coefficient; therefore, the invention has powerful competition in the lead-free development and performance and promising market development prospect.

Owner:DONGHUA UNIV

Method for extracting mushroom polysaccharide by using ultra-high pressure

InactiveCN101323649APhysiologically active ingredients unchangedPromote dissolutionOrganic active ingredientsAntiviralsUltra high pressureAdditive ingredient

The invention discloses a method for extracting shiitake polysaccharides from shiitakes, which overcomes the defects that the current extracting method requires long time, has low efficiency and high energy consumption and damages active ingredients of the shiitake polysaccharides. The proposal adopted by the invention comprises the following steps of: crushing the selected dry shiitakes, adding extract, processing under super-high pressure, filtering, concentrating in vacuum, precipitating with alcohol, drying and finally obtaining shiitake polysaccharides. The high pressure is adopted by the invention to hold or relieve pressure of the shiitake extract, increase the differences between osmotic pressures in and out of cells and change the structure of cells, thereby easily dissolving out effective ingredients, keeping the physiologically active ingredients unchanged, killing a part of microorganisms by high-pressure processing and finishing extraction and sterilization in one step. Being a cold extracting technique, the super-high-pressure extracting method generates no high temperature during the whole extraction process, shortens the extracting time to a plurality of minutes and conserves the effective ingredients and has significant economic benefits and broad prospect of market development.

Owner:INFINITUS (CHINA) CO LTD +2

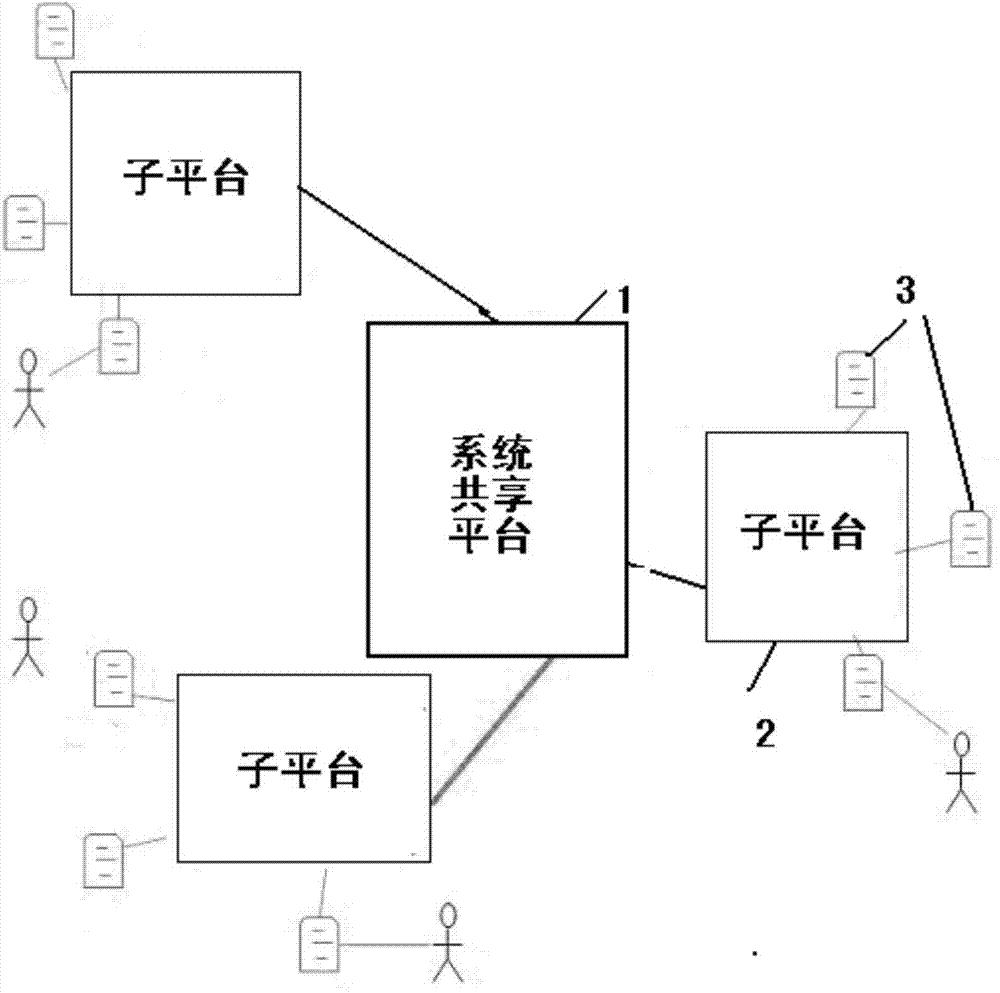

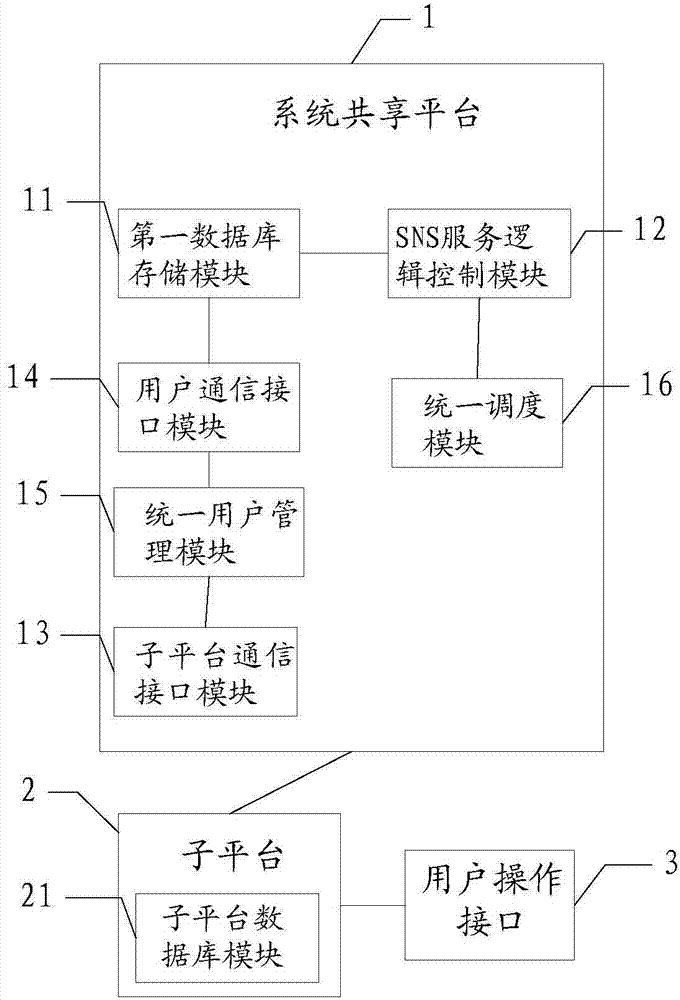

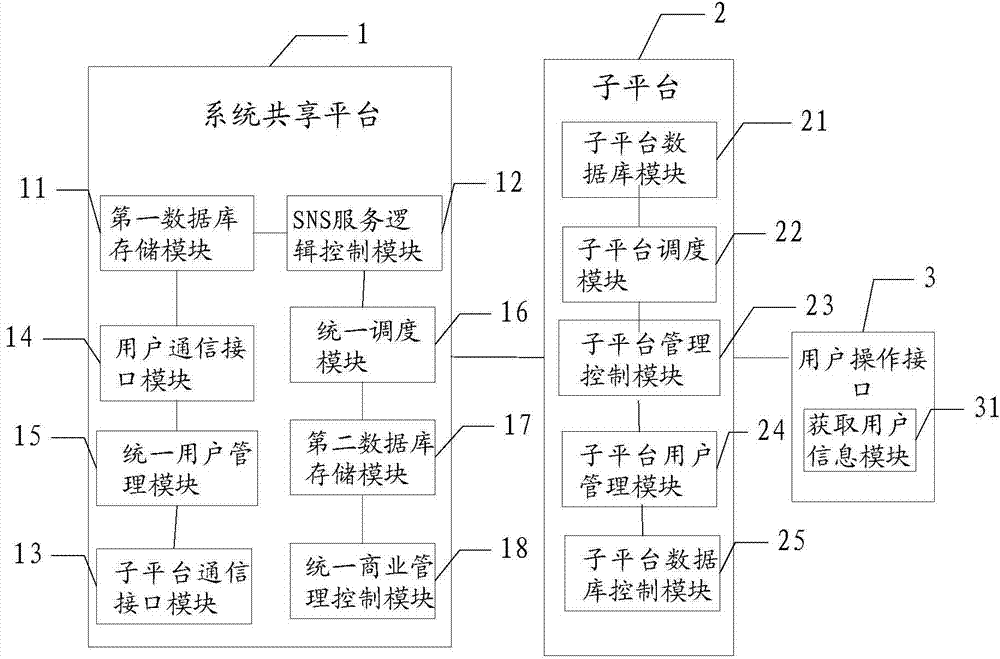

Social network based electronic commerce system

ActiveCN104751348AAchieve sharingLow costMarketingSpecial data processing applicationsE-commerceSocial web

The invention provides a social network based electronic commerce system. The social network based electronic commerce system is designed to comprise a system sharing platform, sub-platforms and a user operation interface which are connected in sequence, wherein the system sharing platform includes information data shared by all sub-platforms, and the information data include specific information required by user information, social information and commodity transaction of all sub-platforms. Therefore, all sub-platforms can obtain the information data of other sub-platforms from the system sharing platform through unified dispatch of the system sharing platform and can also establish social sharing and instant message communication with users registered on the other sub-platforms. Accordingly, sharing of user information data, commodity information data and transaction information is achieved through the different sub-platforms, and the costs for management, market development and marketing of the whole system are saved.

Owner:吴锦锋 +2

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com