Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

4022 results about "Burning out" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

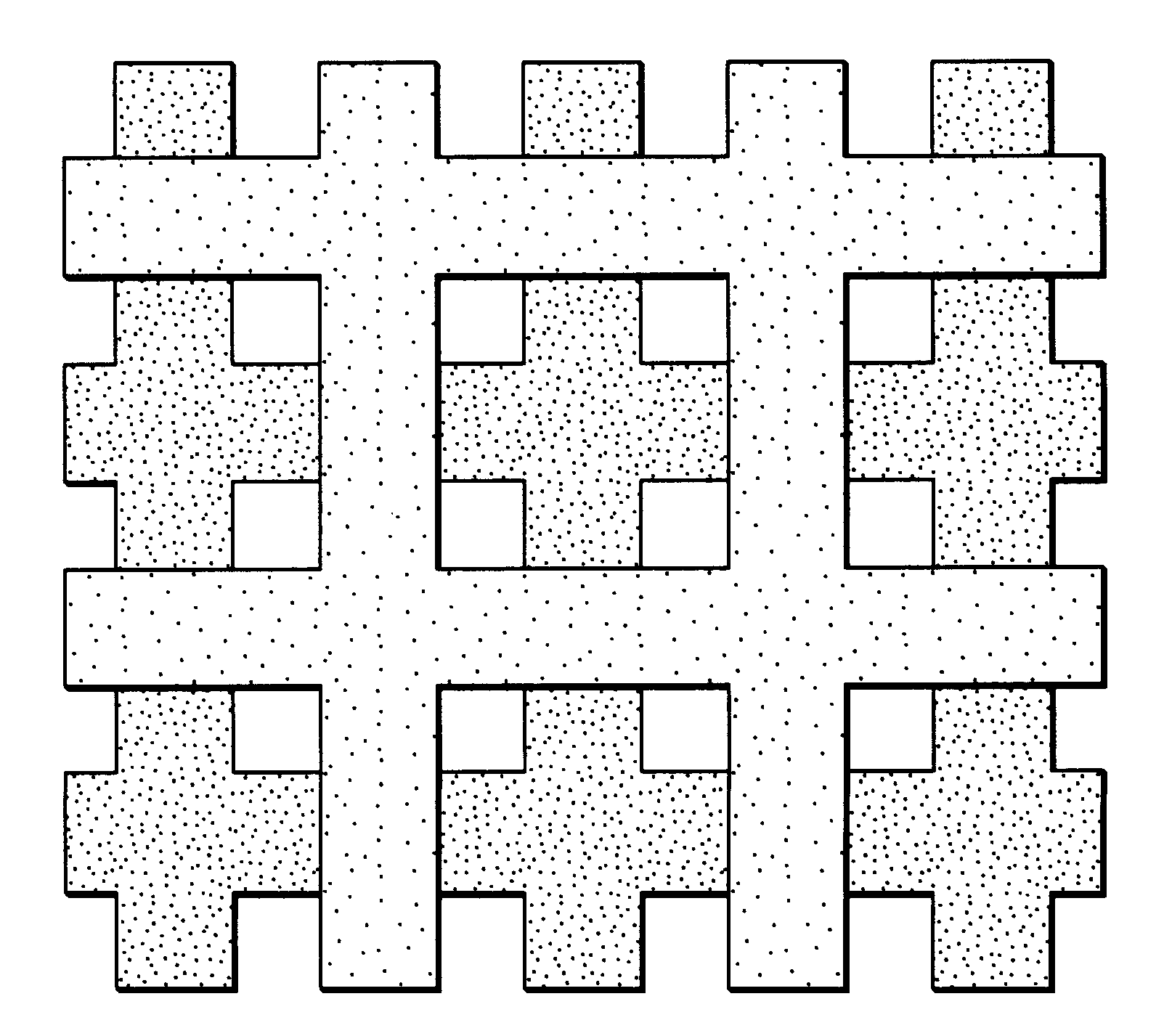

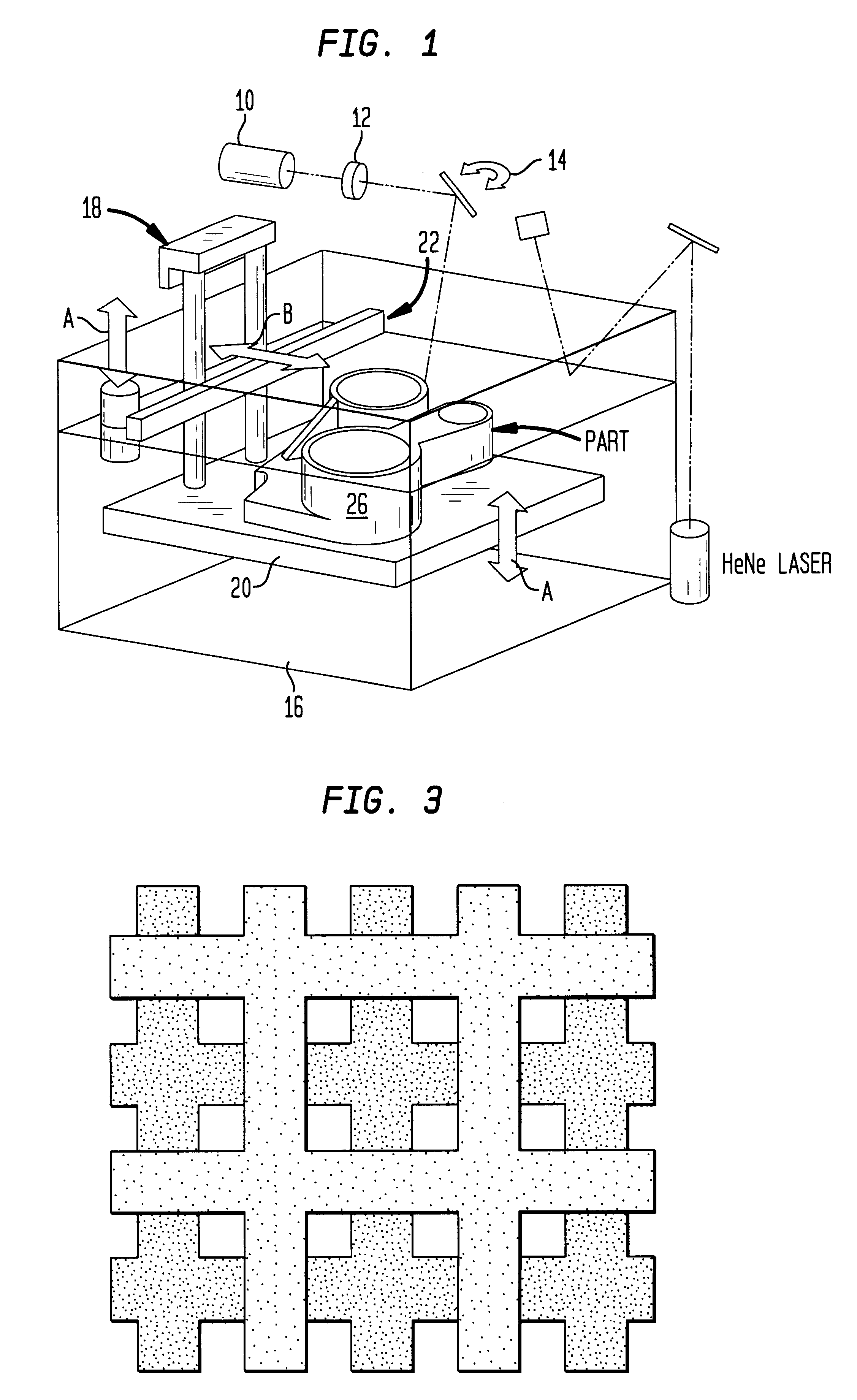

Controlled architecture ceramic composites by stereolithography

InactiveUS6283997B1Quality improvementFast preparationProgramme controlAdditive manufacturing apparatusCeramic compositeMetallurgy

A process for producing a ceramic composite having a porous network. The process includes providing a photocurable ceramic dispersion. The dispersion consists of a photocurable polymer and a ceramic composition. The surface of the dispersion is scanned with a laser to cure the photocurable polymer to produce a photocured polymer / ceramic composition. The photocured composition useful as a polymer / ceramic composite, or the polymer phase can be removed by heating to a first temperature that is sufficient to burn out the photocured polymer. It is then heated to a second temperature that is higher than the first temperature and is sufficient to sinter the ceramic composition to produce a purely ceramic composition having a porous network.Preferably and more specifically, the process uses a stereolithographic technique for laser scanning. The process can form a high quality orthopedic implant that dimensionally matches the bone structure of a patient. The technique relies upon laser photocuring a dense colloidal dispersion into a desired complex three-dimensional shape. The shape is obtained from a CAT scan file of a bone and is rendered into a CAD file that is readable by the stereolithography instrument. Or the shape is obtained directly from a CAD file that is readable by the stereolithography instrument.

Owner:UNITED STATES SURGICAL CORP +2

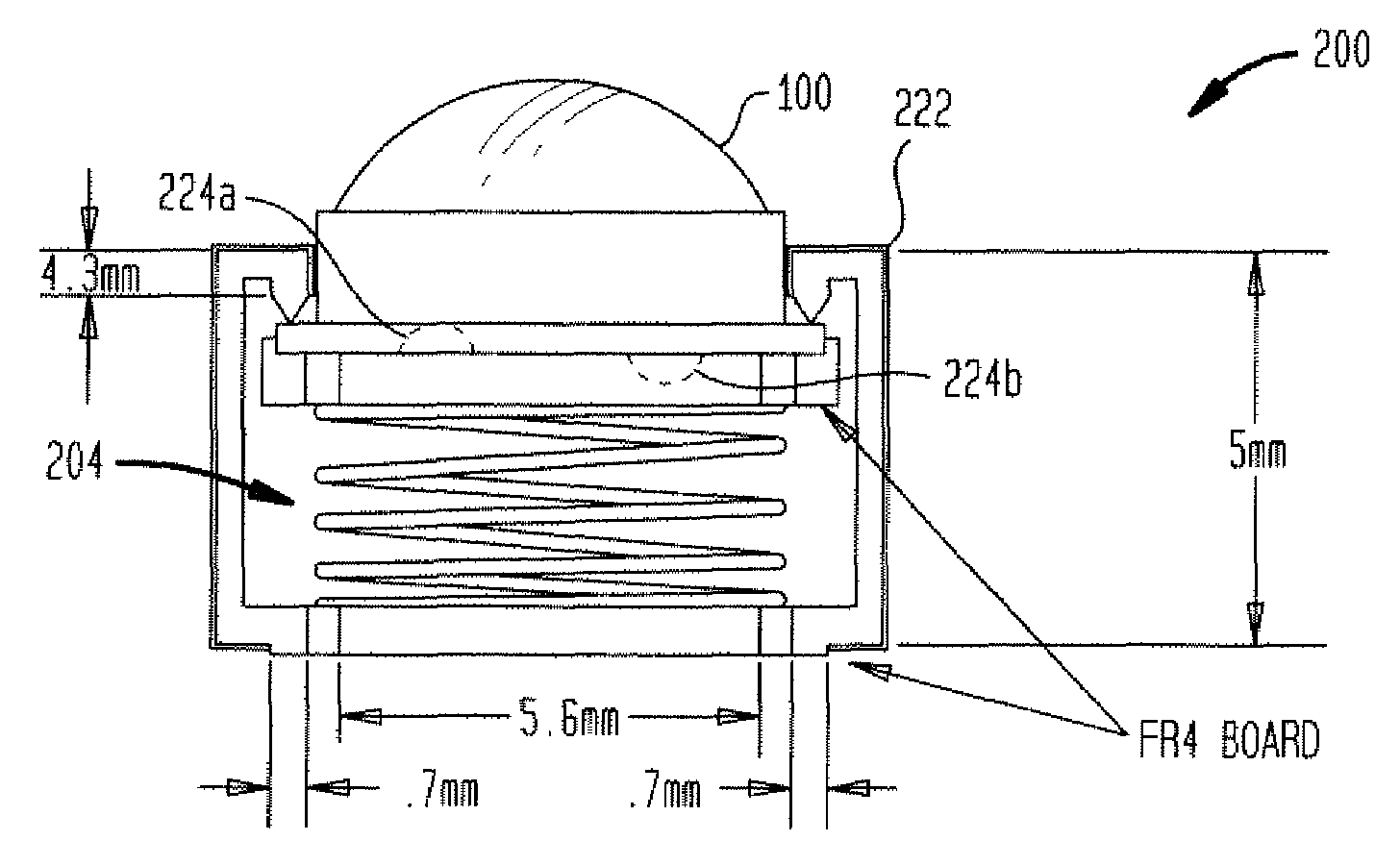

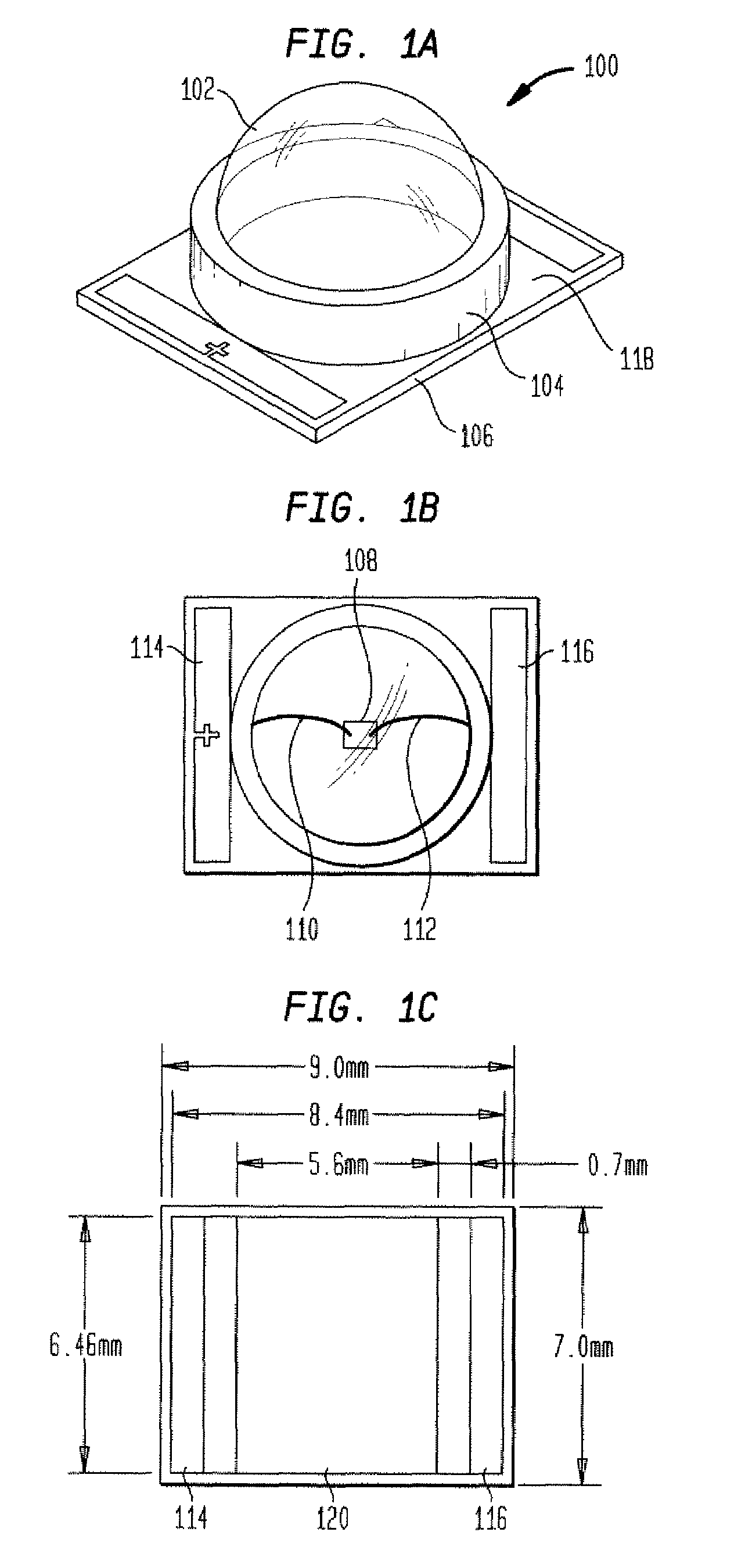

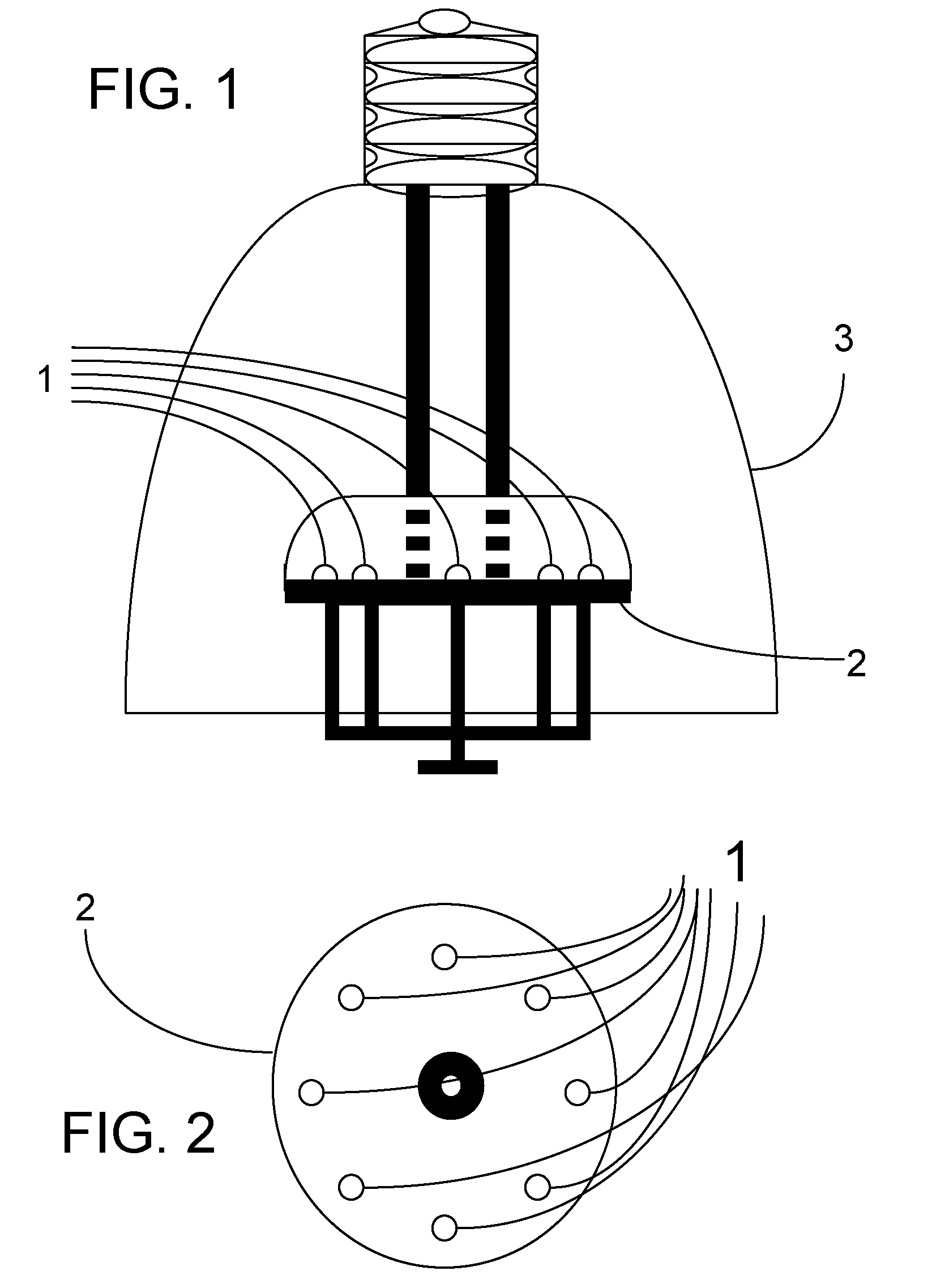

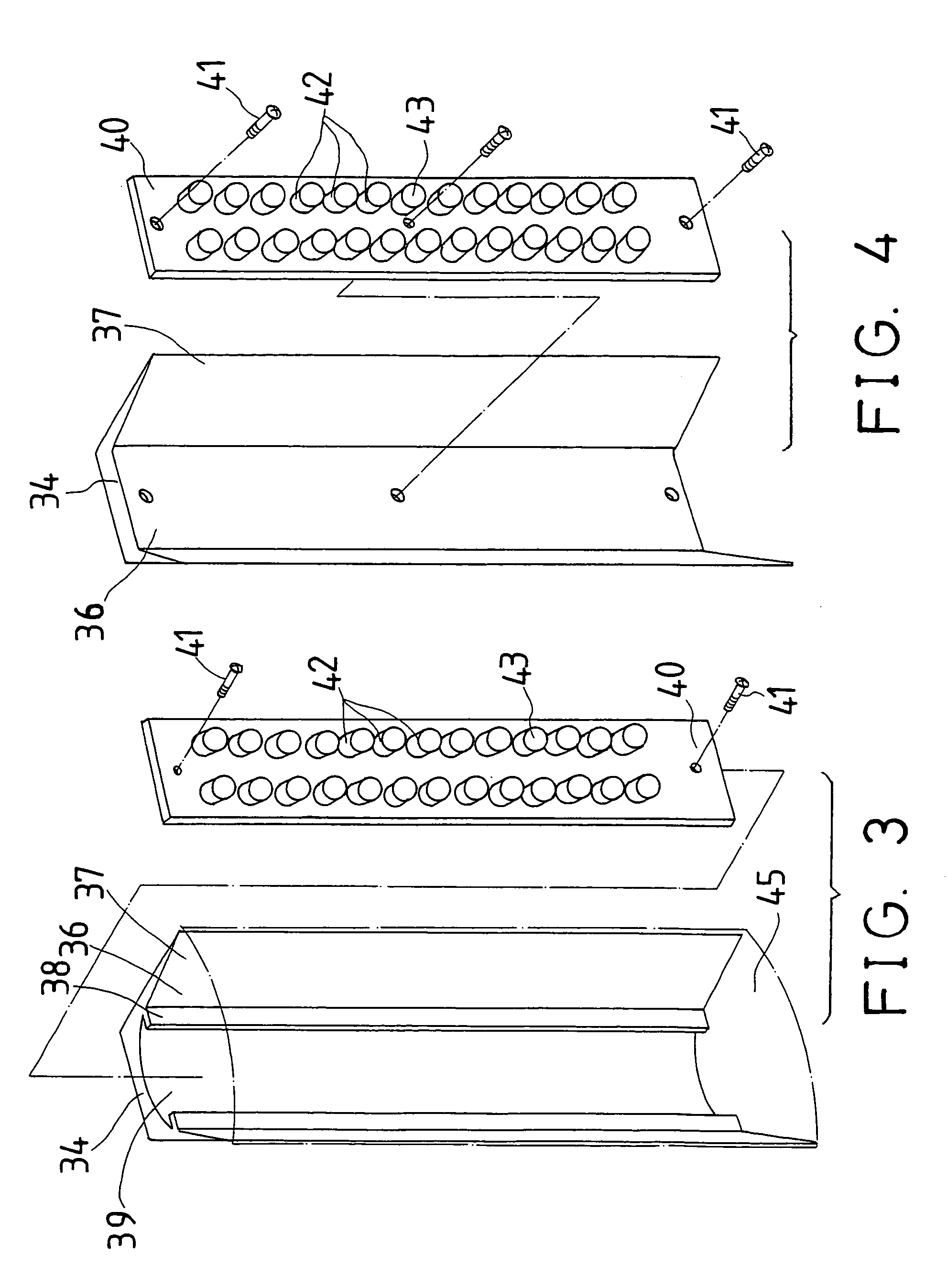

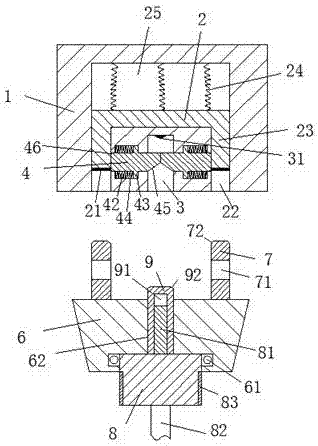

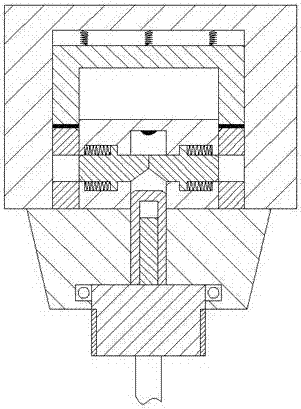

LED socket and replaceable LED assemblies

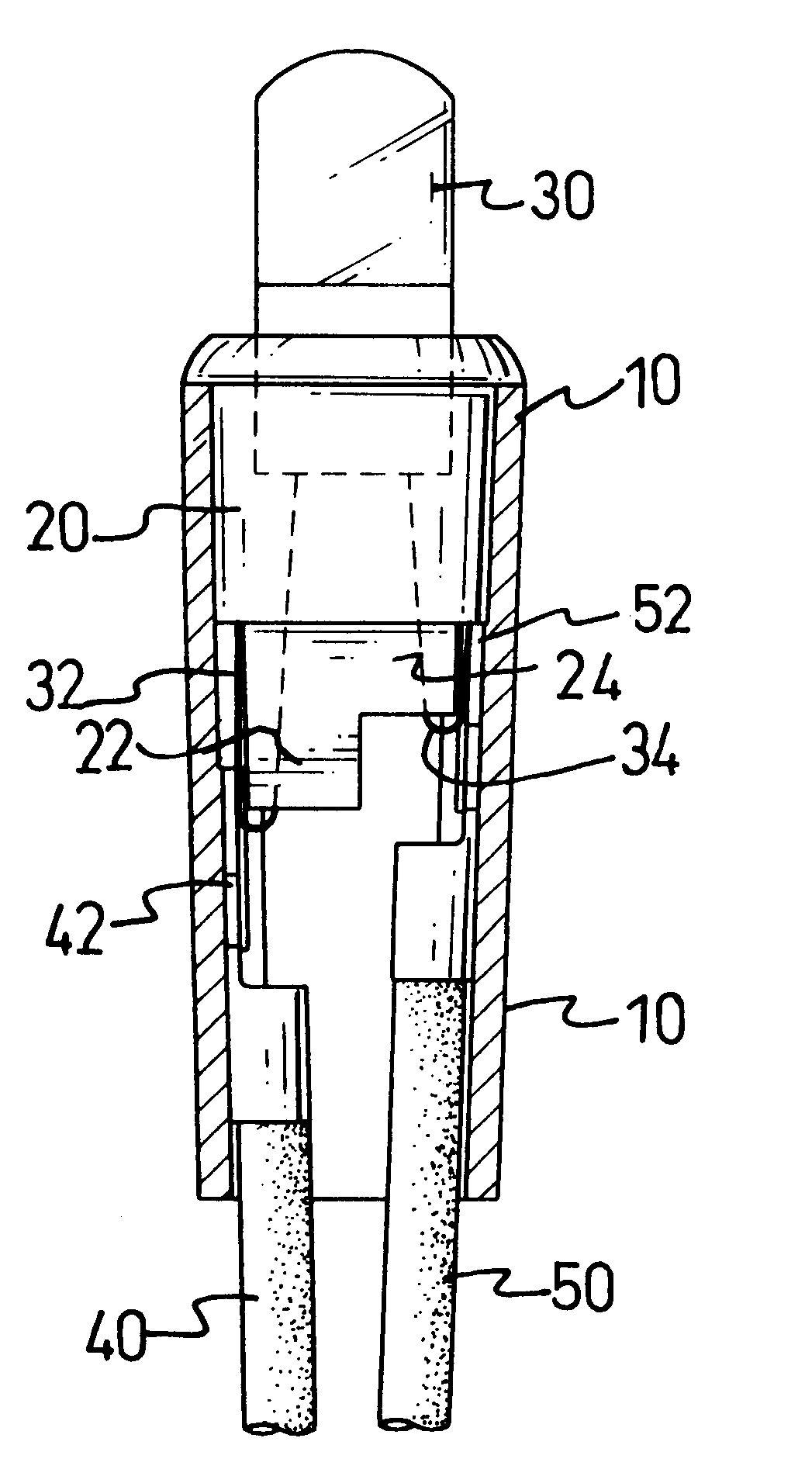

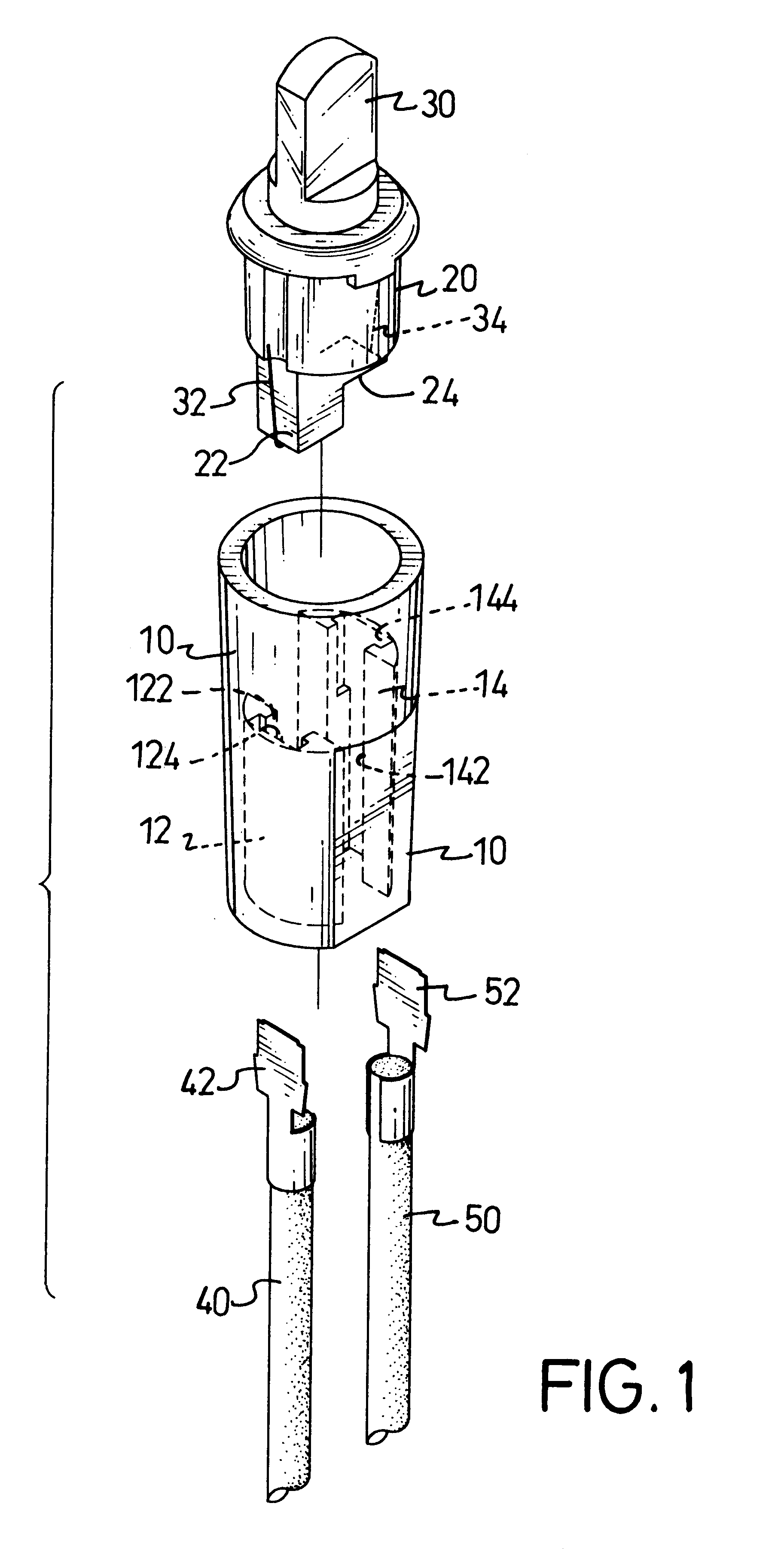

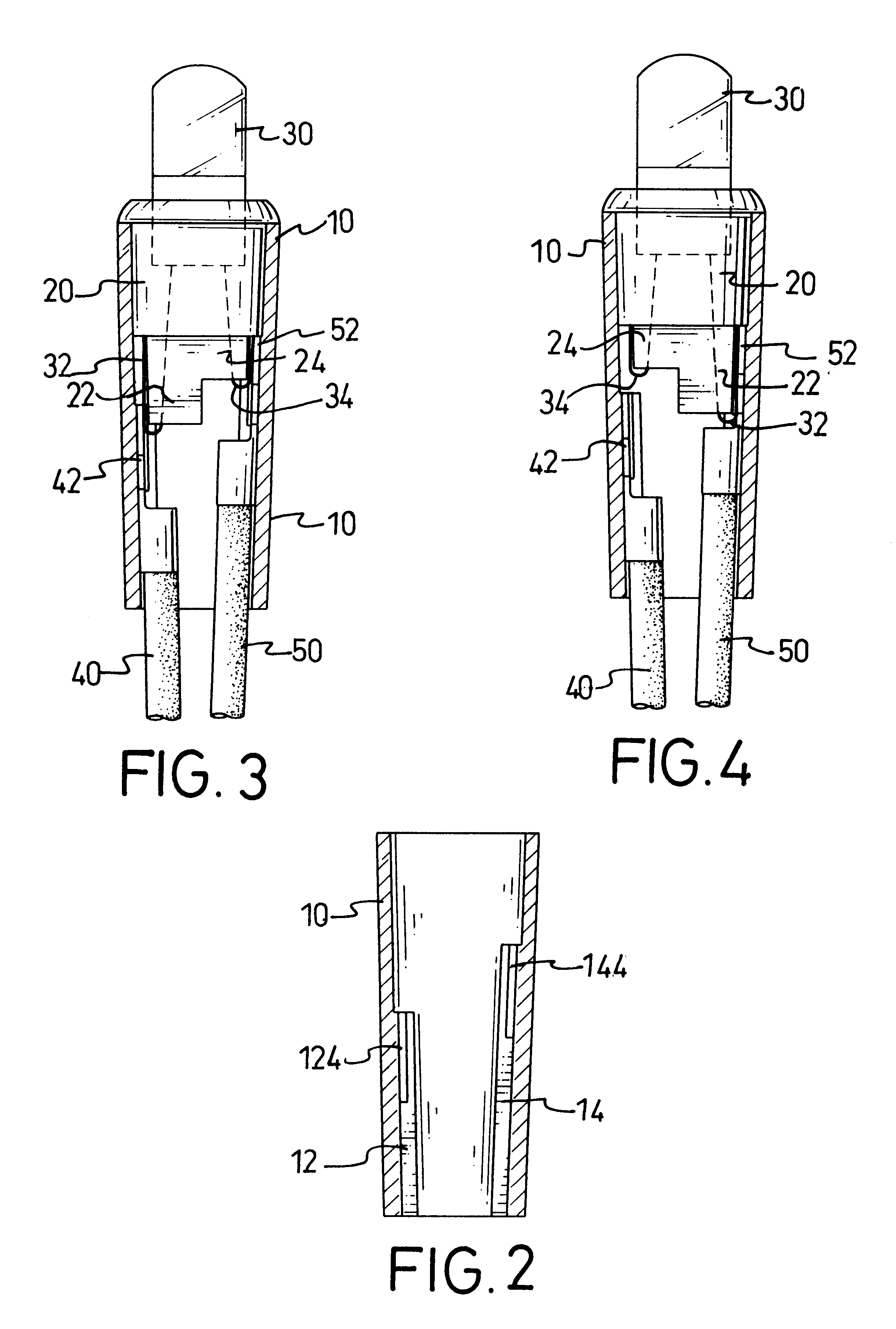

ActiveUS7549786B2Easy to remove and replacePoint-like light sourceLighting support devicesEngineeringSingle lead

Socket arrangements for releasably mounting LEDs and light fixtures or assemblies employing such sockets are described. The socket arrangements facilitate the replacement of LEDs to replace an original LED with a brighter replacement, to change the color of the LED, to replace a single LED with a multiple chip LED, to replace a damaged or burned out LED with a new one, or the like. In further assemblies with plural LEDs, the use of ready release sockets facilitates selective replacement of an LED or LEDs and greatly enhances the flexibility of such units.

Owner:IDEAL IND LIGHTING LLC

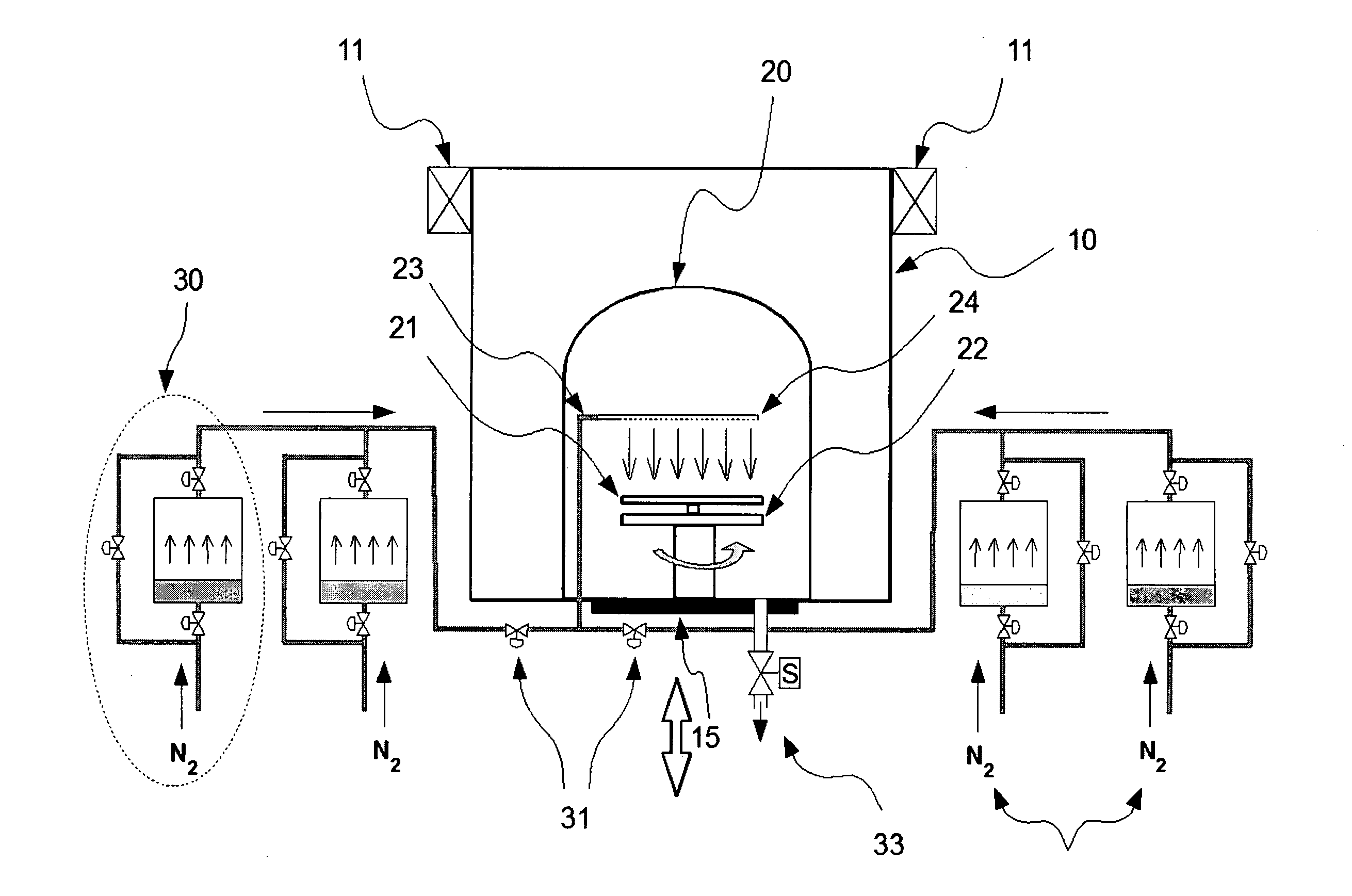

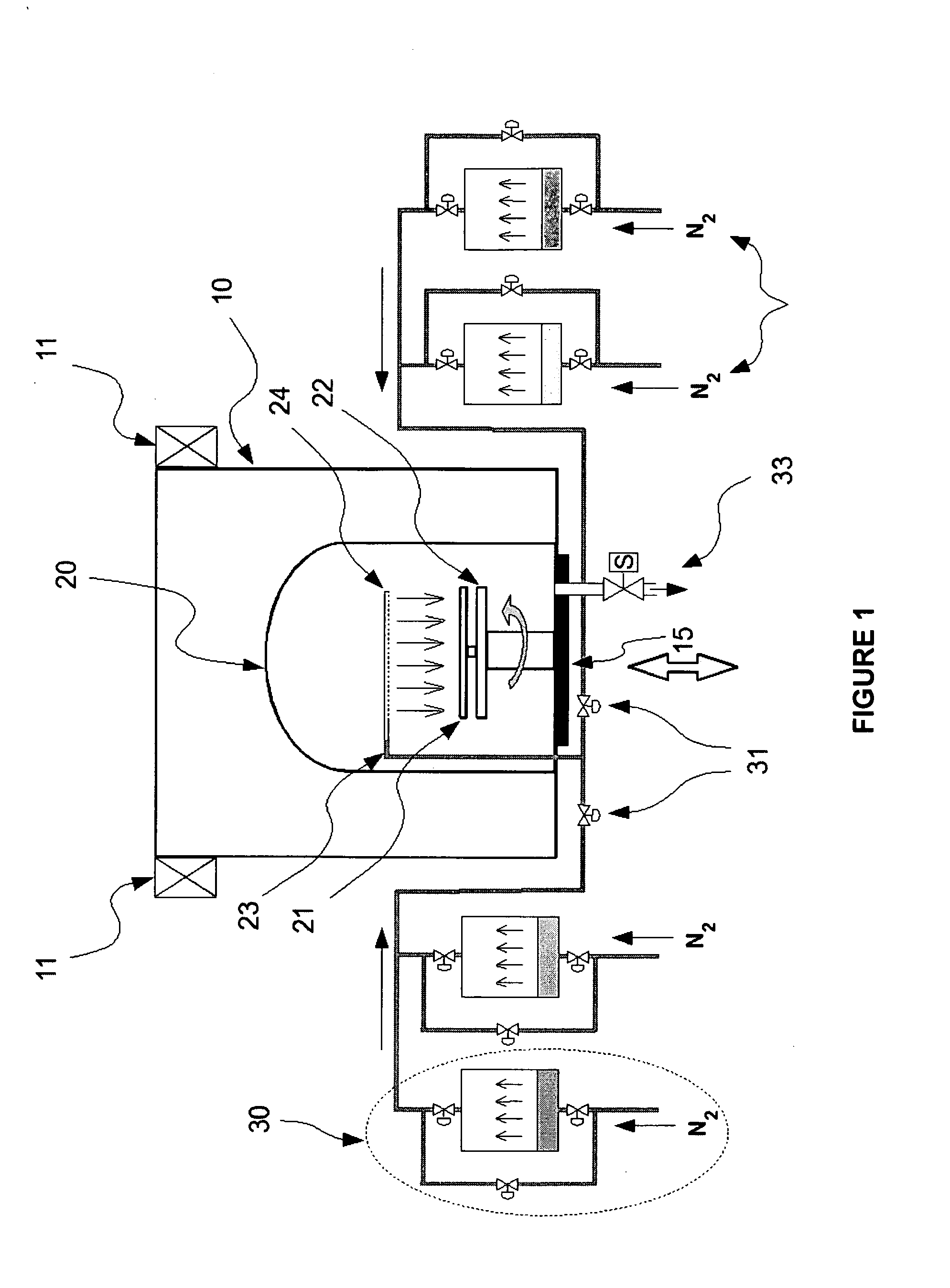

Process and apparatus of combustion for reduction of nitrogen oxide emissions

InactiveUS20030134241A1Special fuel supply arrangementsIndirect carbon-dioxide mitigationNitrogen oxidesControl system

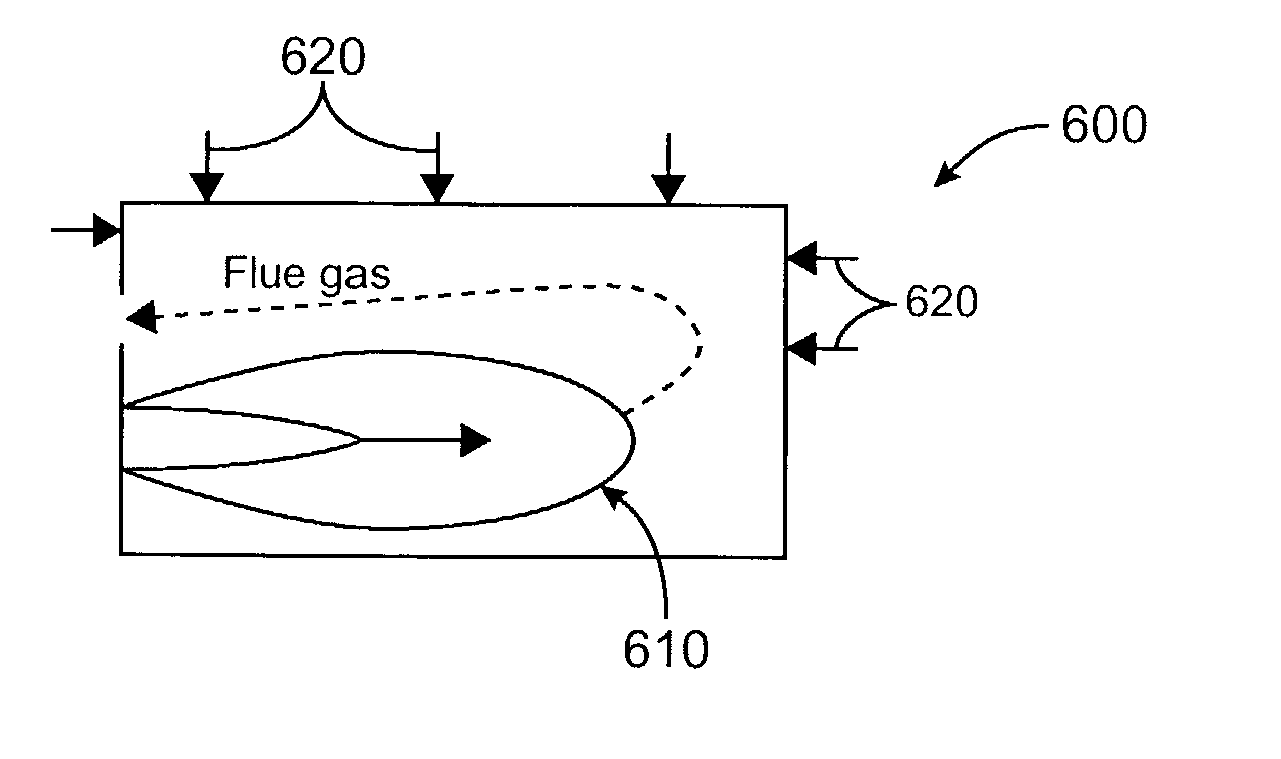

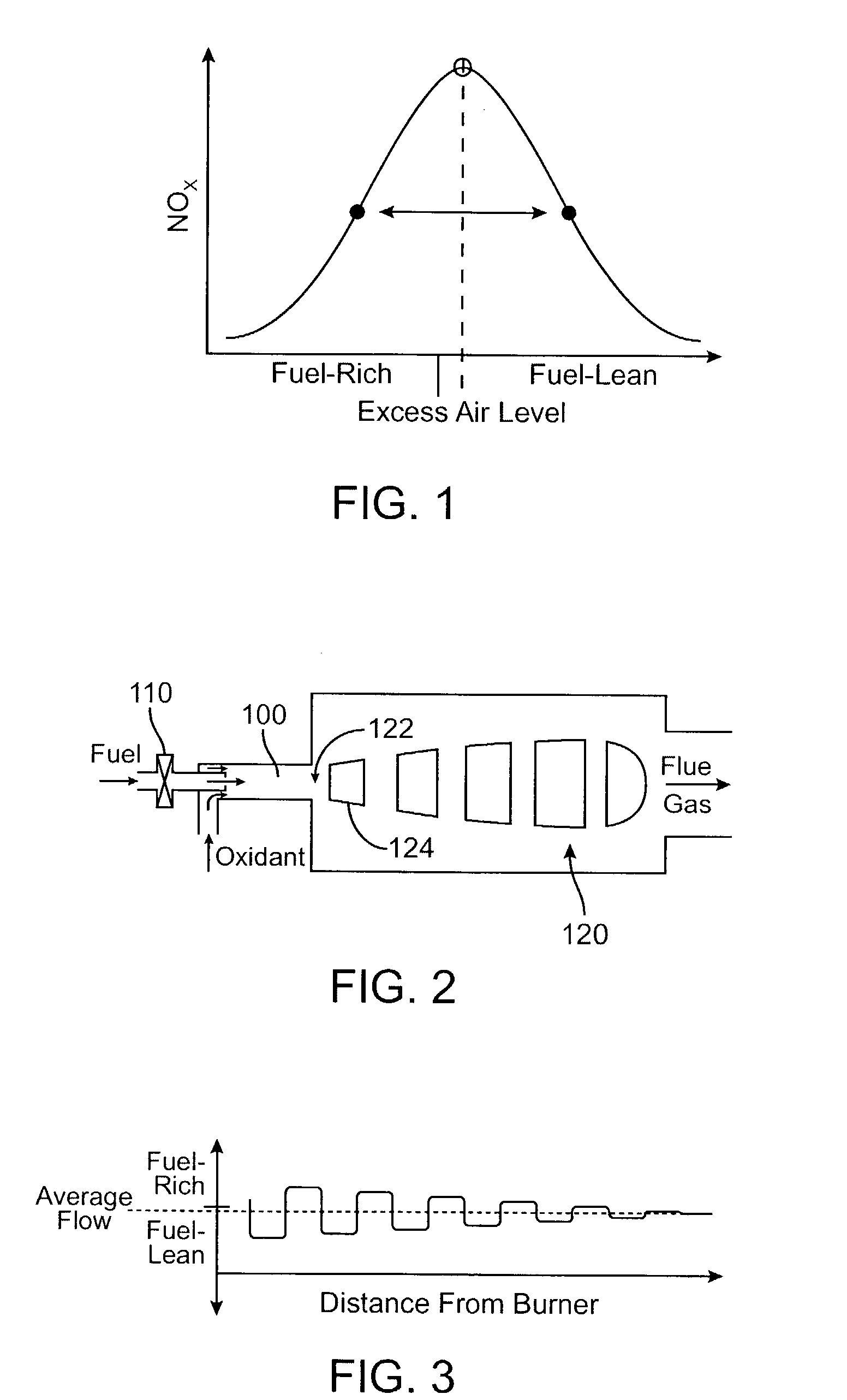

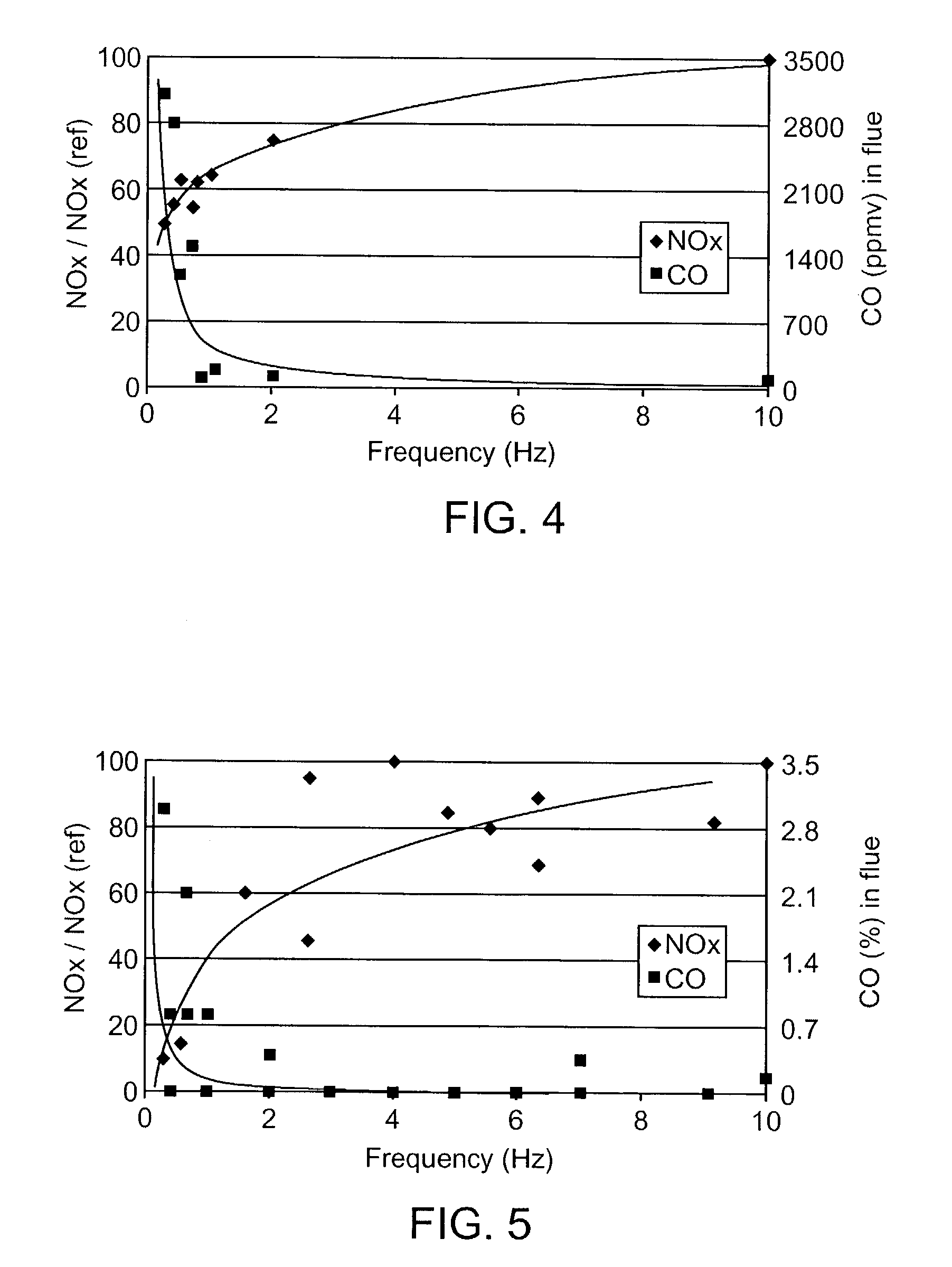

A combustion control system allows the dramatic reduction of NOx emission levels from industrial combustion processes without having recourse to expensive flue gas clean up methods. The system combines the technique of oscillating combustion with an adapted system for post combustion burn out of the excess of CO resulting from the low-NOx combustion zone. A process for fuel combustion includes generating an oscillating combustion zone by oscillating at least one of the fuel flow and the oxidant flow to achieve a reduced nitrogen oxide emission, selecting oscillating parameters and furnace operating parameters to maximize nitrogen oxide reduction efficiency to the detriment of carbon monoxide production, and combusting carbon monoxide downstream of the oscillating combustion zone by injecting a post combustion oxidant.

Owner:MARIN OVIDIU +3

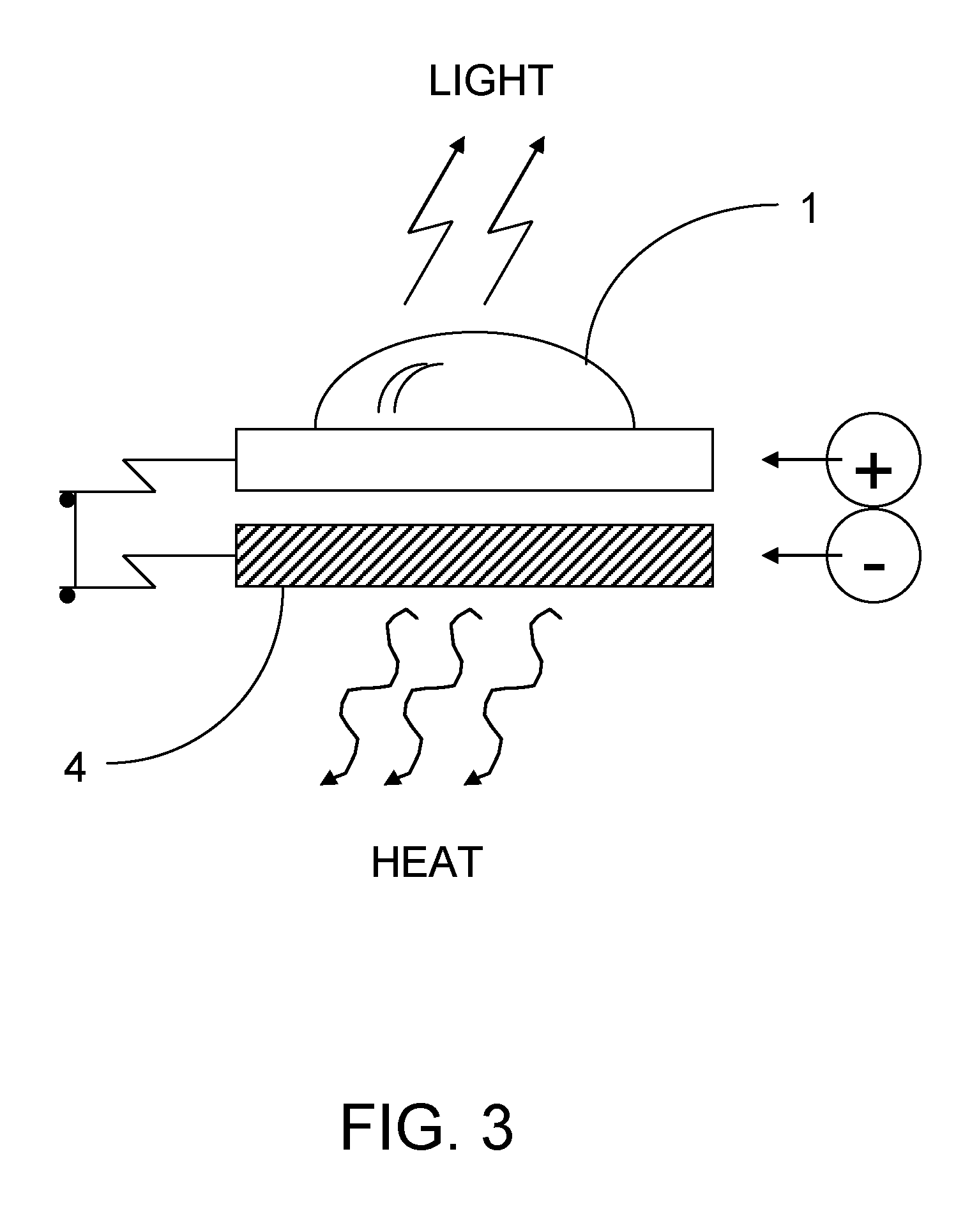

Dynamic heat sink for light emitting diodes

InactiveUS20070102033A1Less power dissipationPoint-like light sourceThermoelectric device with peltier/seeback effectThermoelectric coolingEngineering

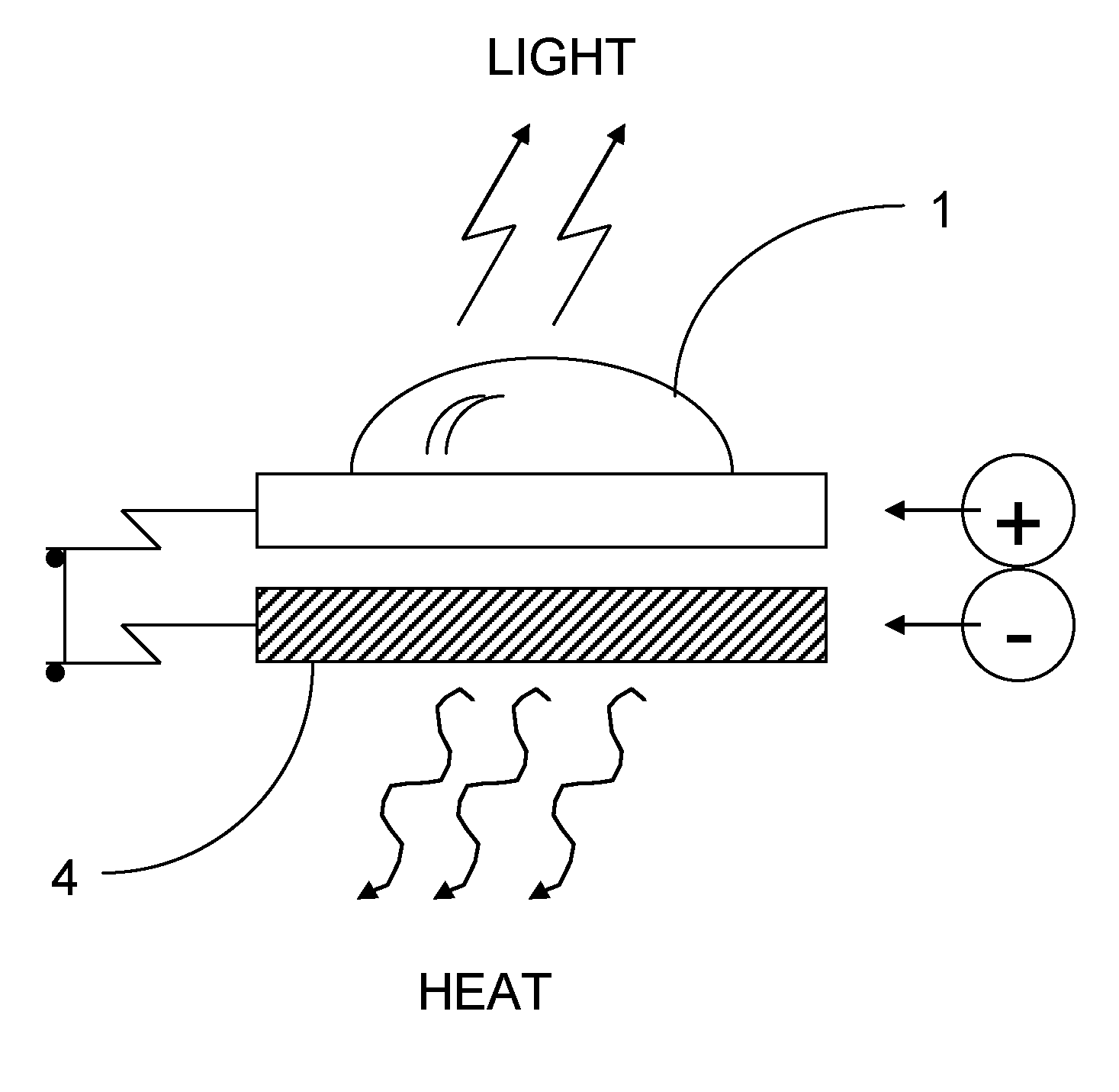

Dynamic heat sink that uses a thermoelectric cooler, such as a Peltier Junction, to move the heat at a LED junction to the other side of the cooling chip. This would allow the LED to run with more current in a much smaller area than a passive metal heat sink without burning out the junctions. The Present Invention would therefore permit a compact light device comprising a plurality of LED's to be constructed. Such a light device would be competitive with standard fluorescent bulbs by outputting light of equivalent brightness with less power dissipation.

Owner:UNIVERSAL MEDIA SYST

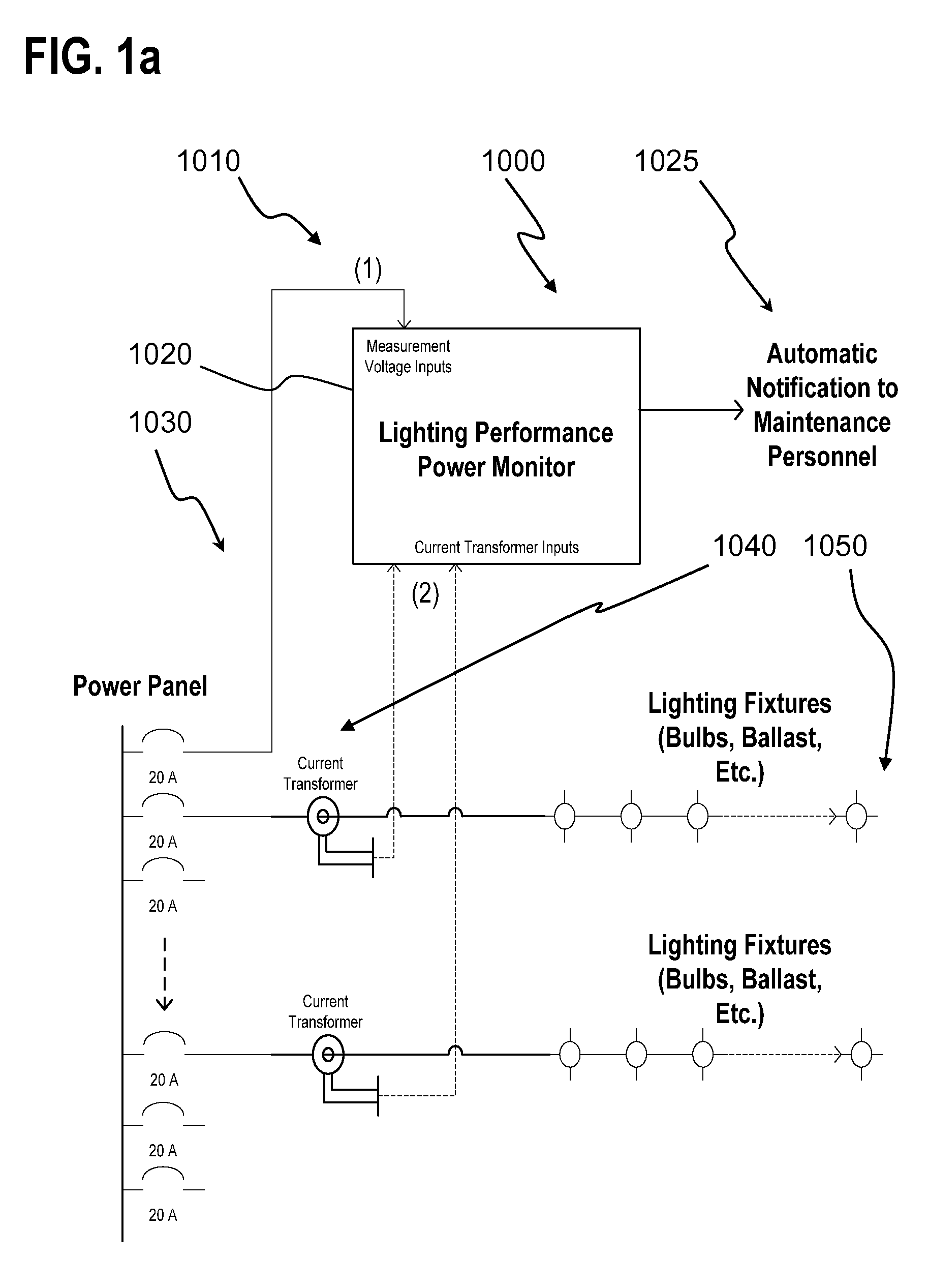

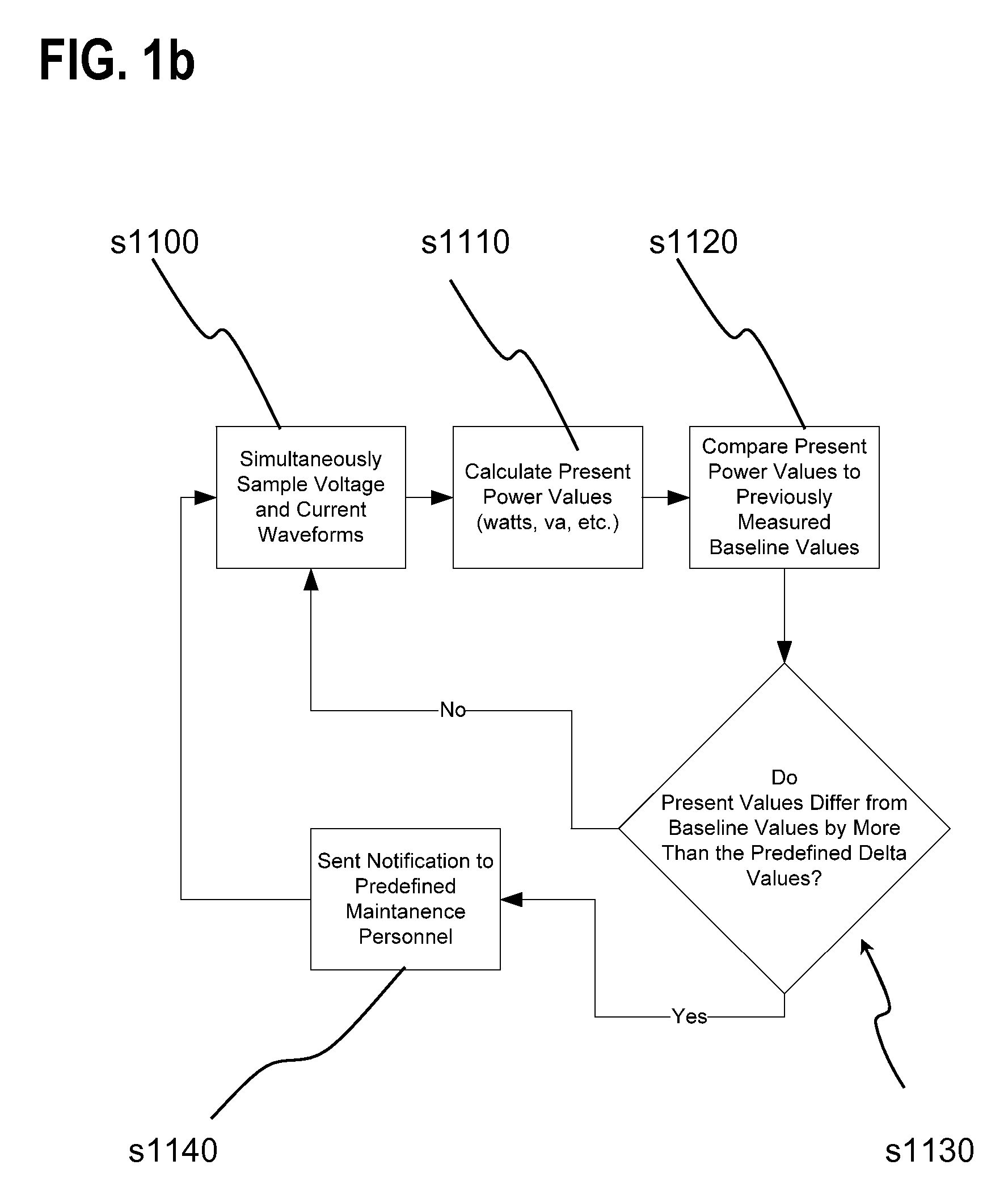

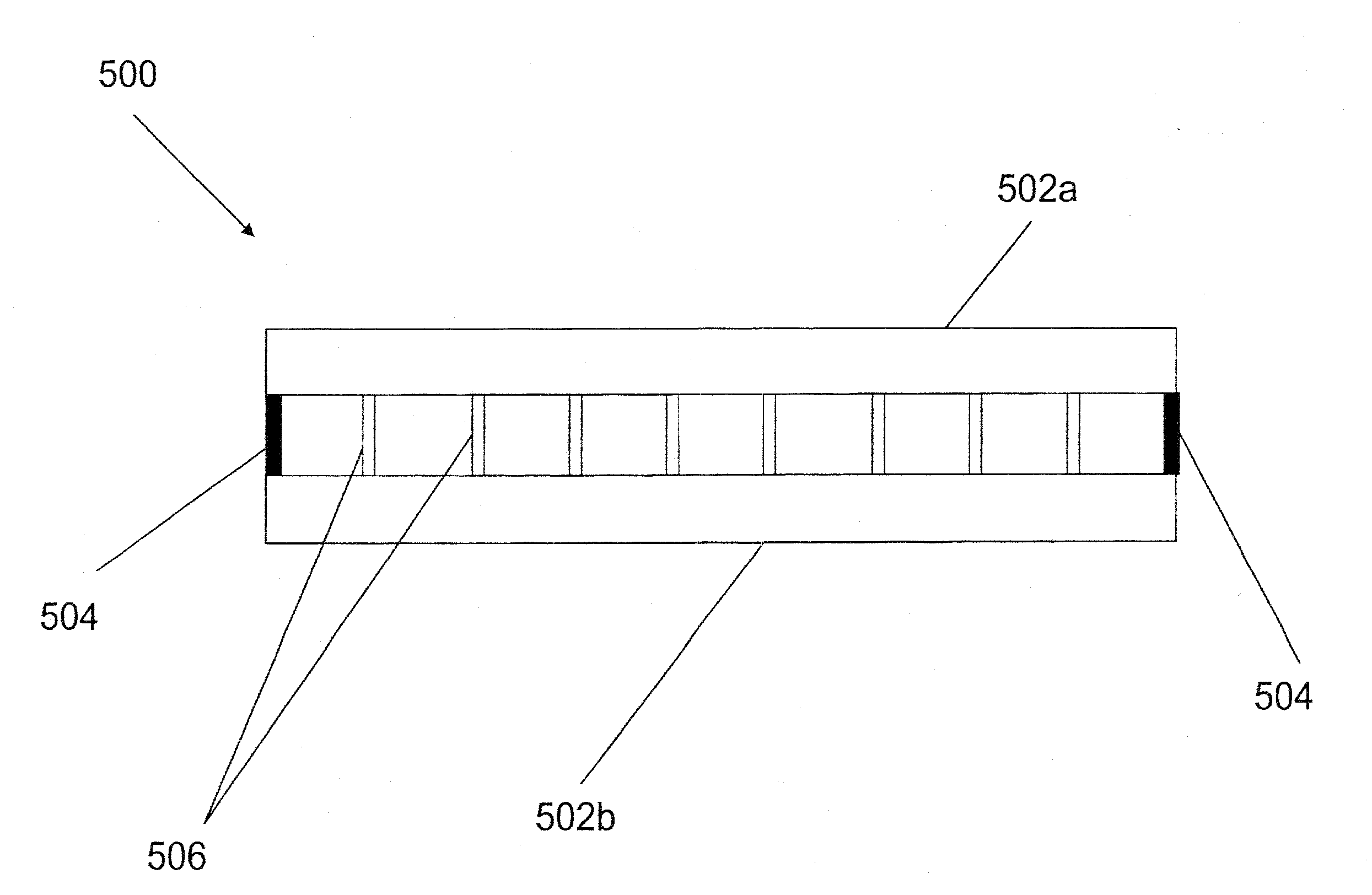

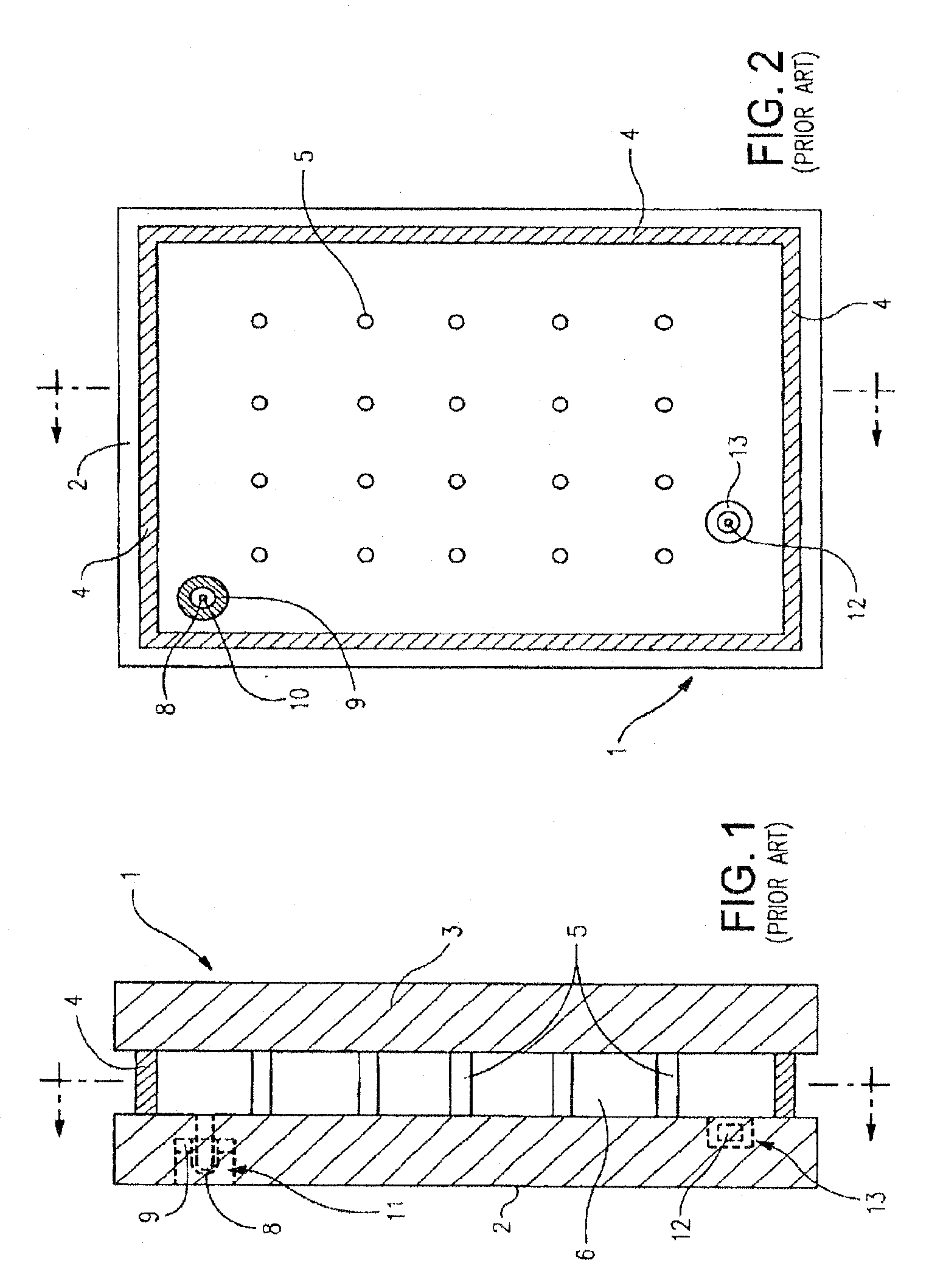

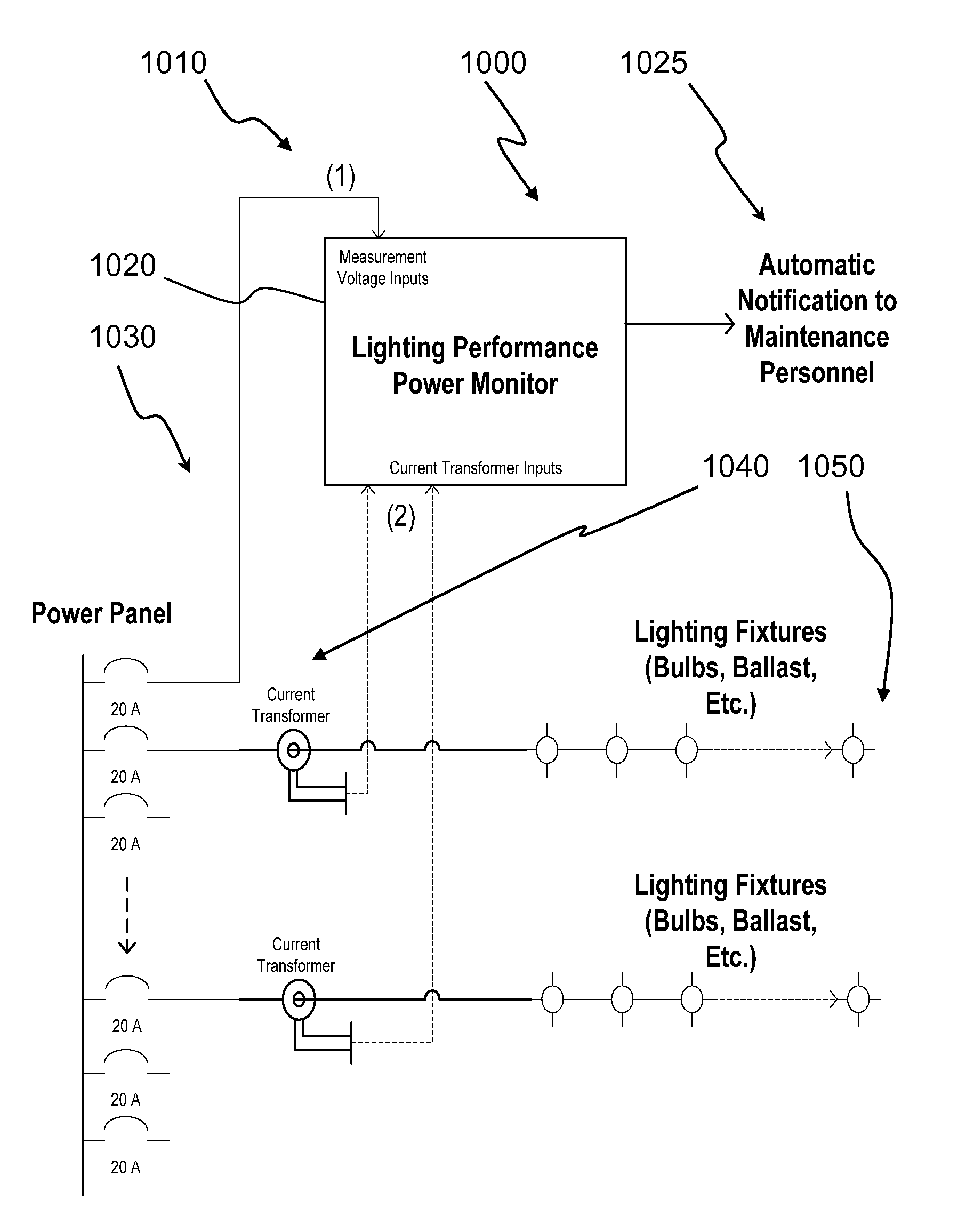

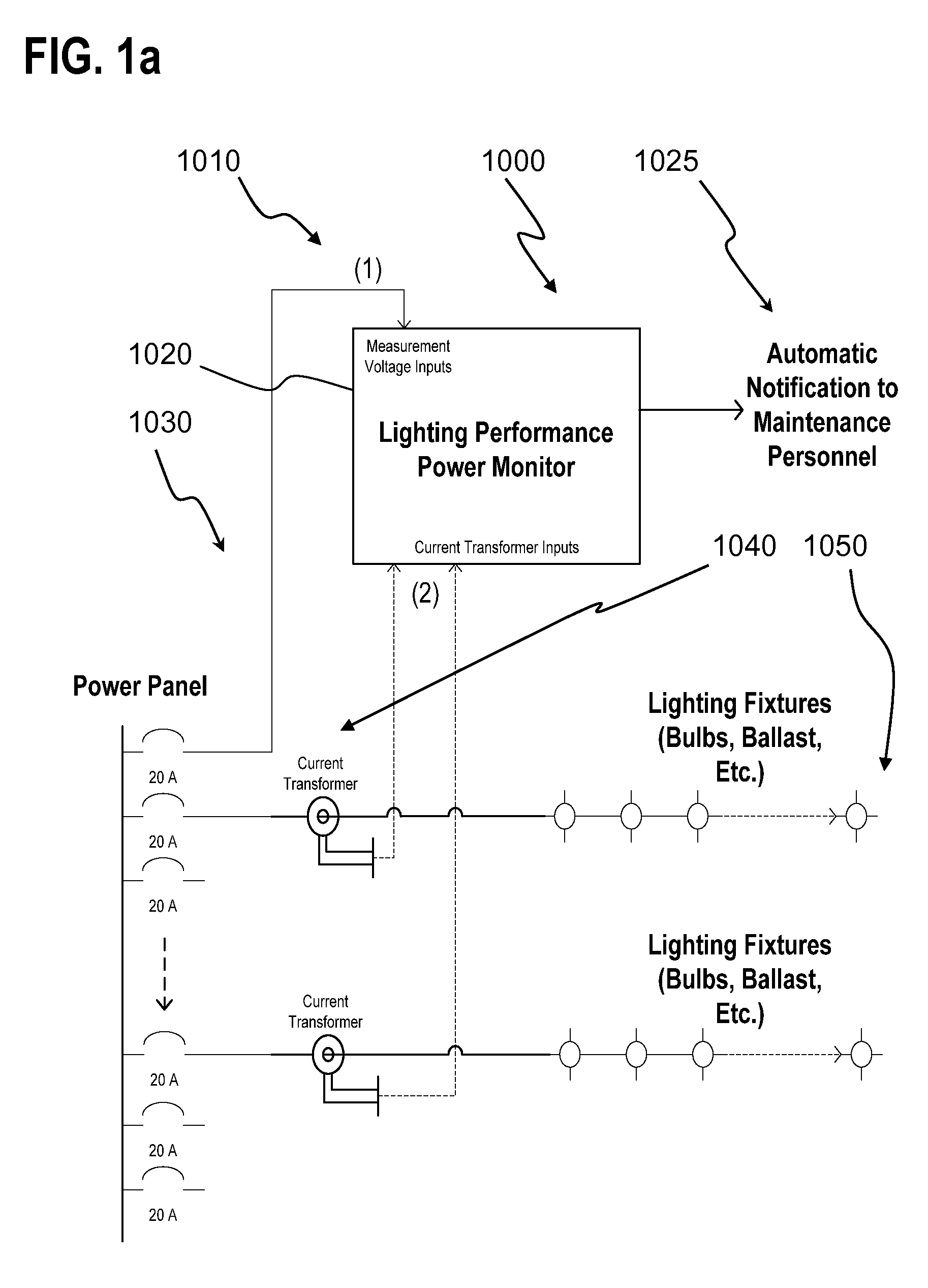

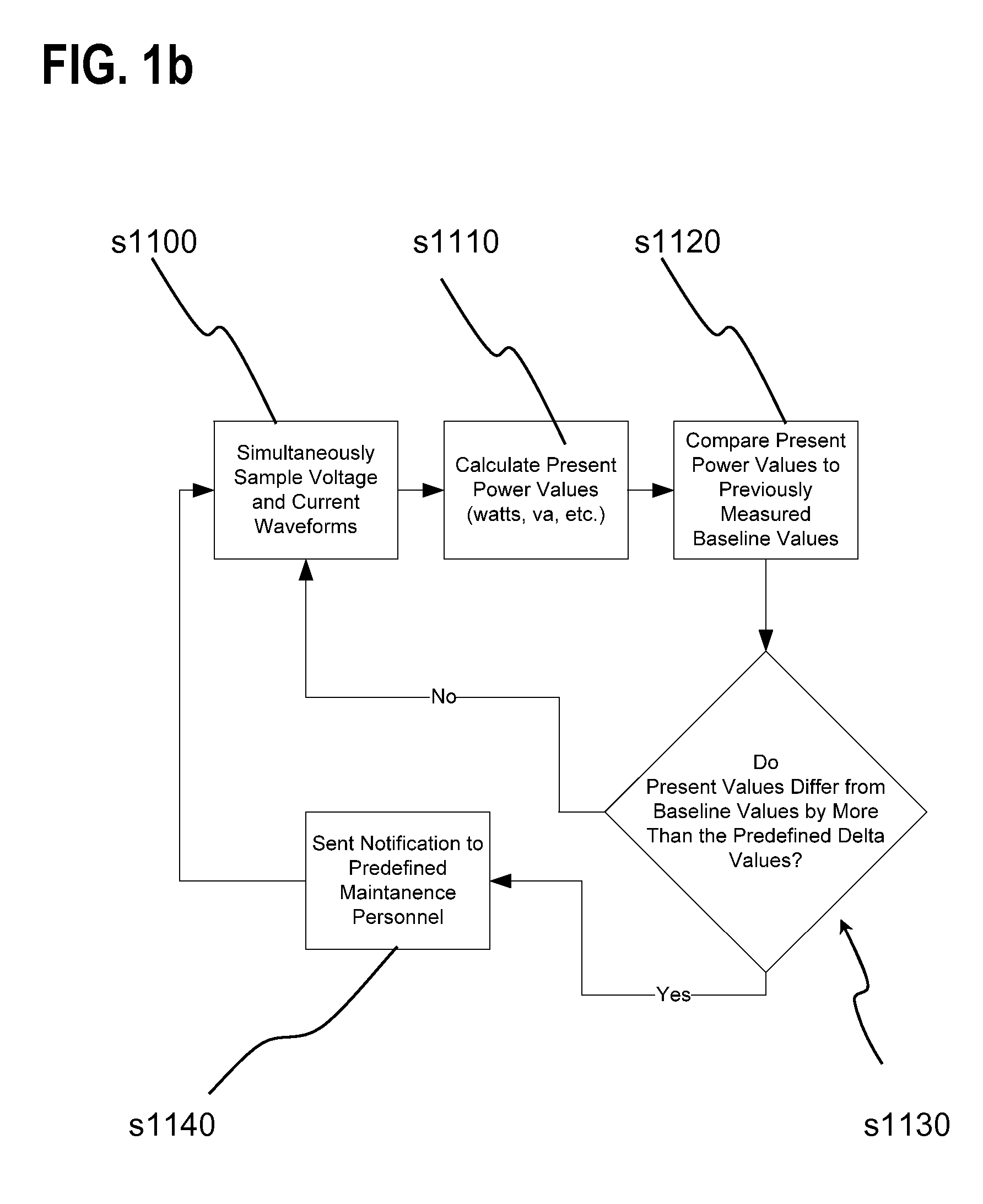

Lighting performance power monitoring system and method with optional integrated light control

ActiveUS7571063B2Save energyLow costLevel controlPower measurement by digital techniqueEngineeringBallast

A light performance monitoring device and optionally integrated controller includes a monitor module that directly monitors energy usage of at least one energy load to generate at least one measurement of energy usage; a storage module stores a series of baseline values of energy usage of the energy load, a comparator module compares energy measurements made at predetermined intervals with the baseline values, and a notification module notifies a designated recipient that there is a deviation from the baseline values consistent with a burned out or non-operational light fixture, including but not limited to light bulbs or ballast devices. A control module optionally integrated with the light performance monitoring device can be operatively coupled to the monitor module to control energy usage by the at least one energy load via a data link in a pre-determined manner that is based on the at least one measurement of energy usage.

Owner:GRIDPOINT

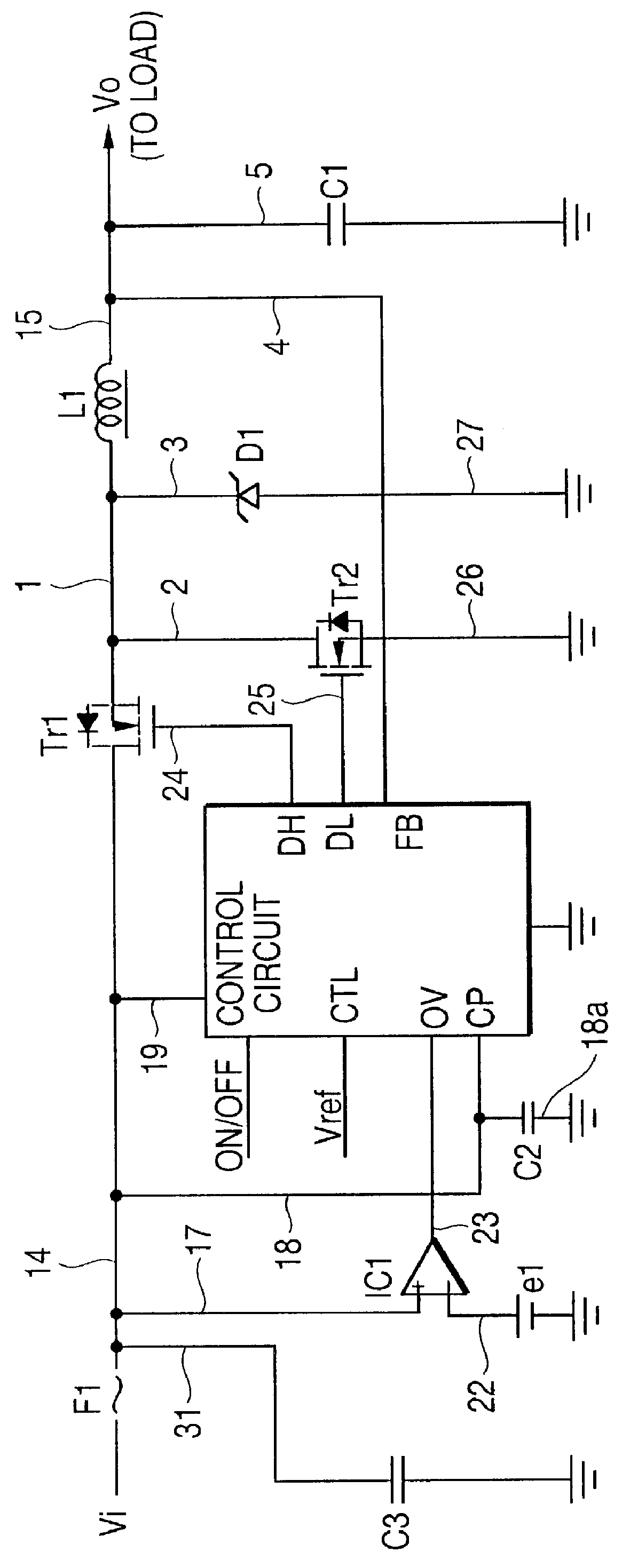

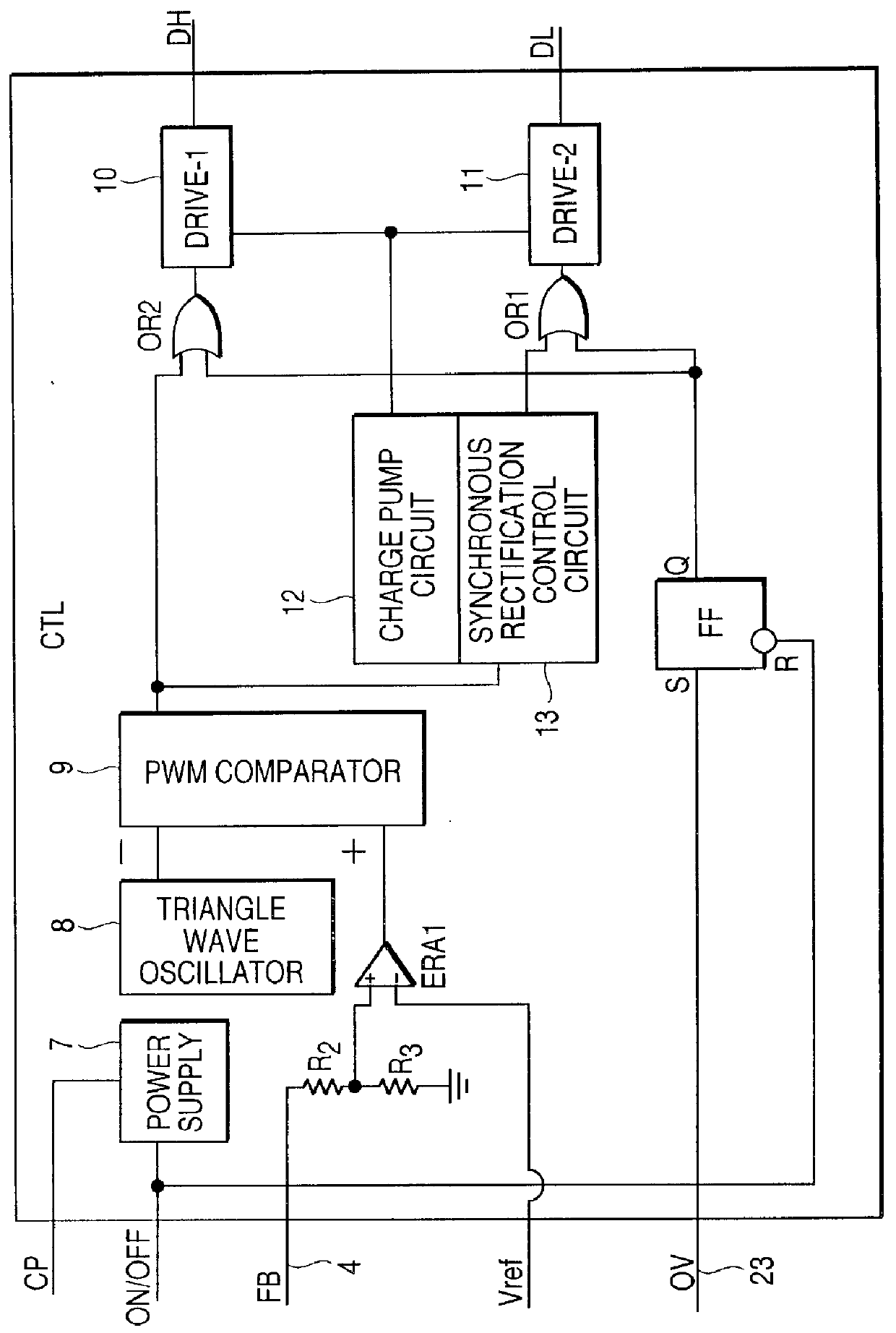

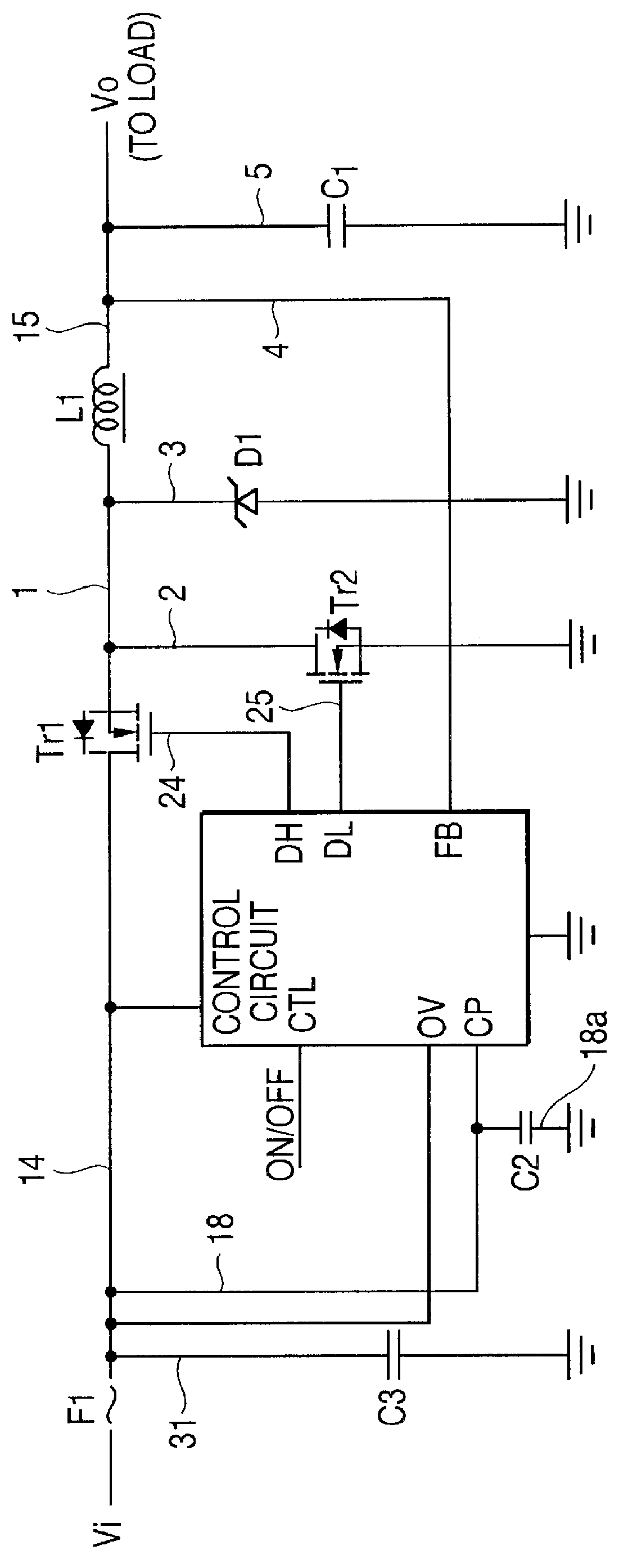

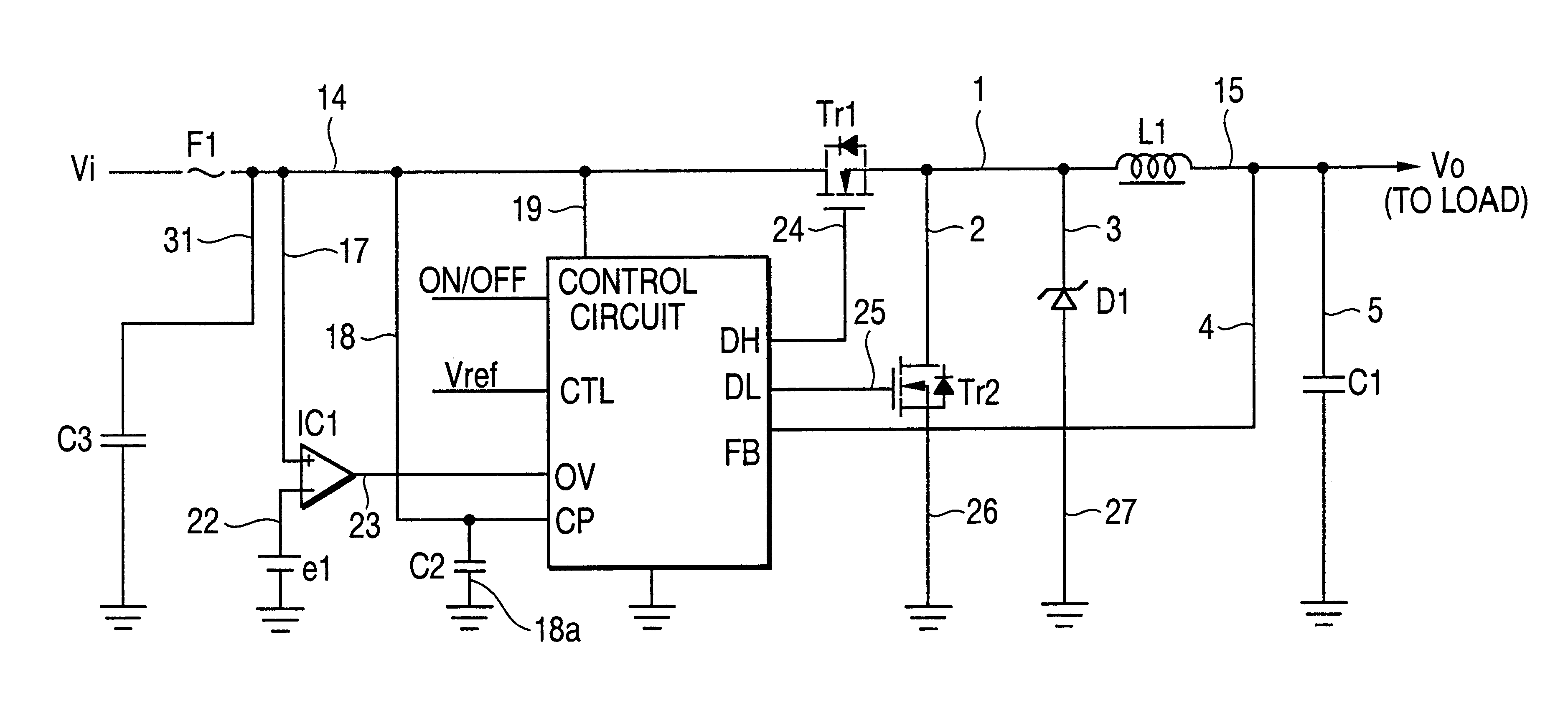

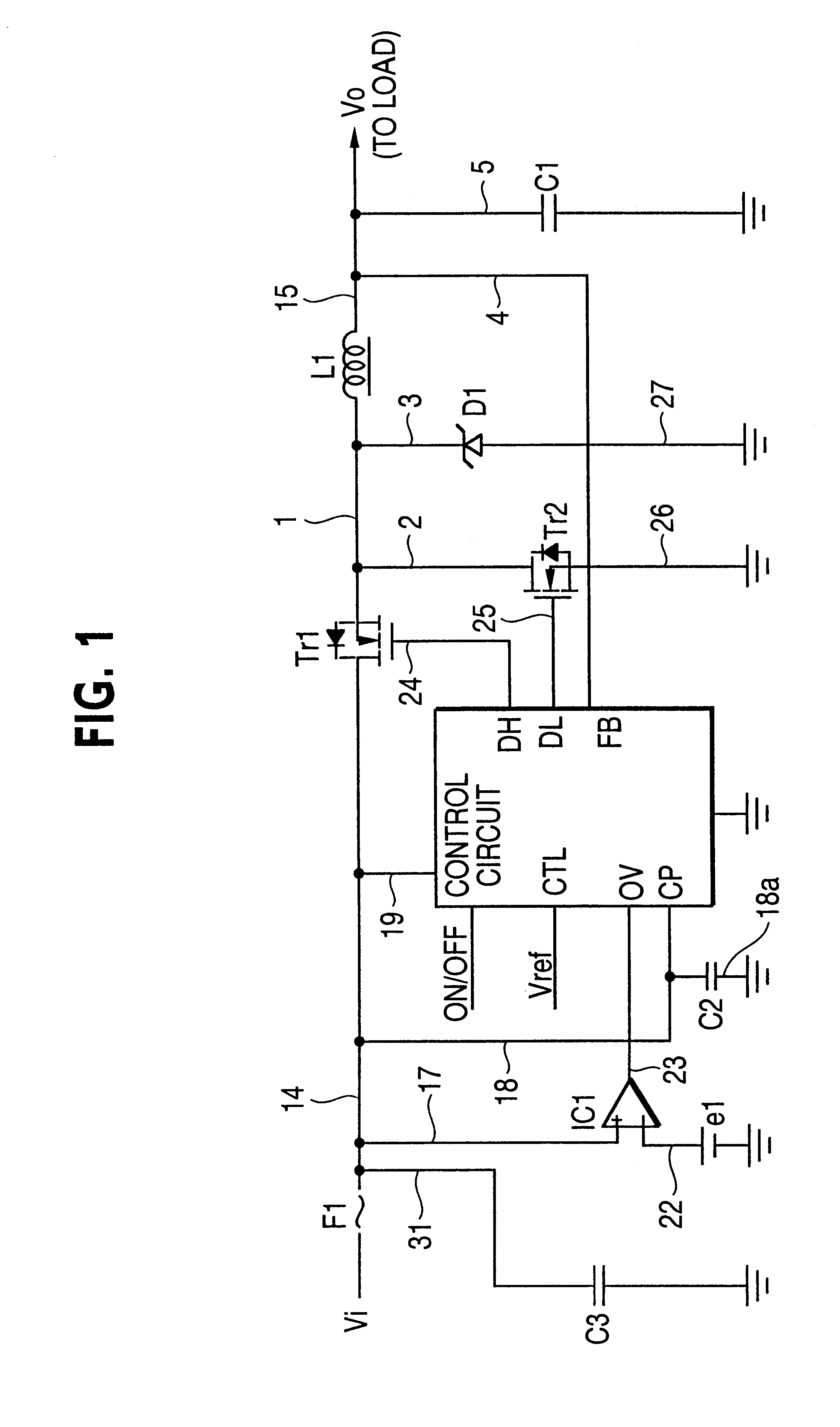

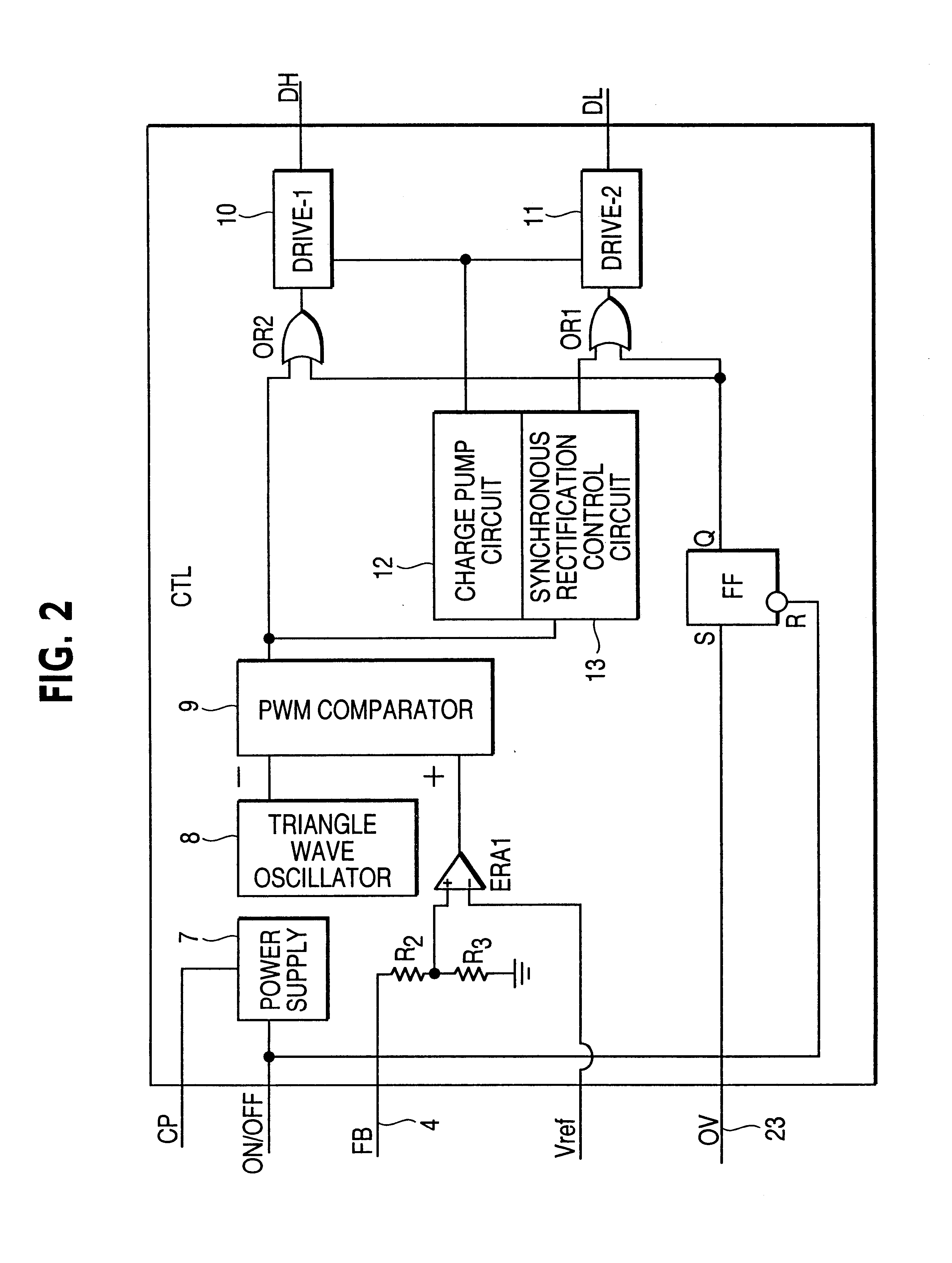

DC-to-DC converter capable of preventing overvoltage

InactiveUS6028755AAvoid Overvoltage ProblemsAvoid fireEfficient power electronics conversionApparatus without intermediate ac conversionOvervoltageEngineering

To avoid burning out a capacitor in a synchronous rectification type DC-to-DC converter due to overvoltages, the synchronous rectification type DC-to-DC converter includes a storage unit storing therein power derived from a power supply, switching elements connecting and disconnecting respective signal paths from power and ground, and a control unit controlling the connecting / disconnecting operations of the switching elements to maintain a voltage output from the storage unit at a predetermined value. The DC / DC converter also includes an overvoltage detecting unit monitoring a voltage derived from the power supply to thereby output an alarm signal when the voltage derived from the power supply exceeds a preselected voltage value, a shortcircuiting unit influencing the connecting conditions of the switching elements when the alarm signal from the overvoltage detecting unit is input therein, whereby the voltage derived from the power supply is shortcircuited, and an interrupting unit interrupting one of the signal paths by the power shortcircuited by the shortcircuiting unit.

Owner:FUJITSU LTD

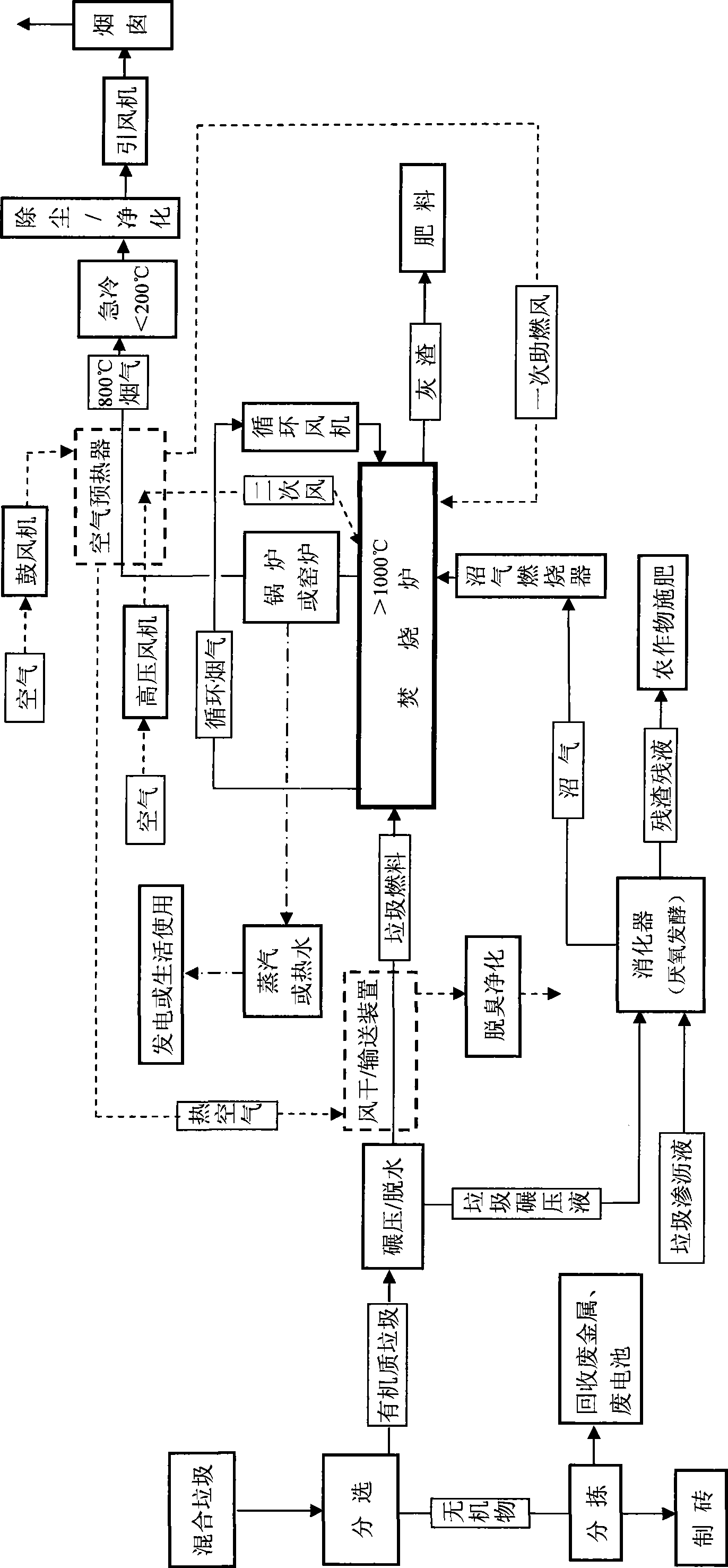

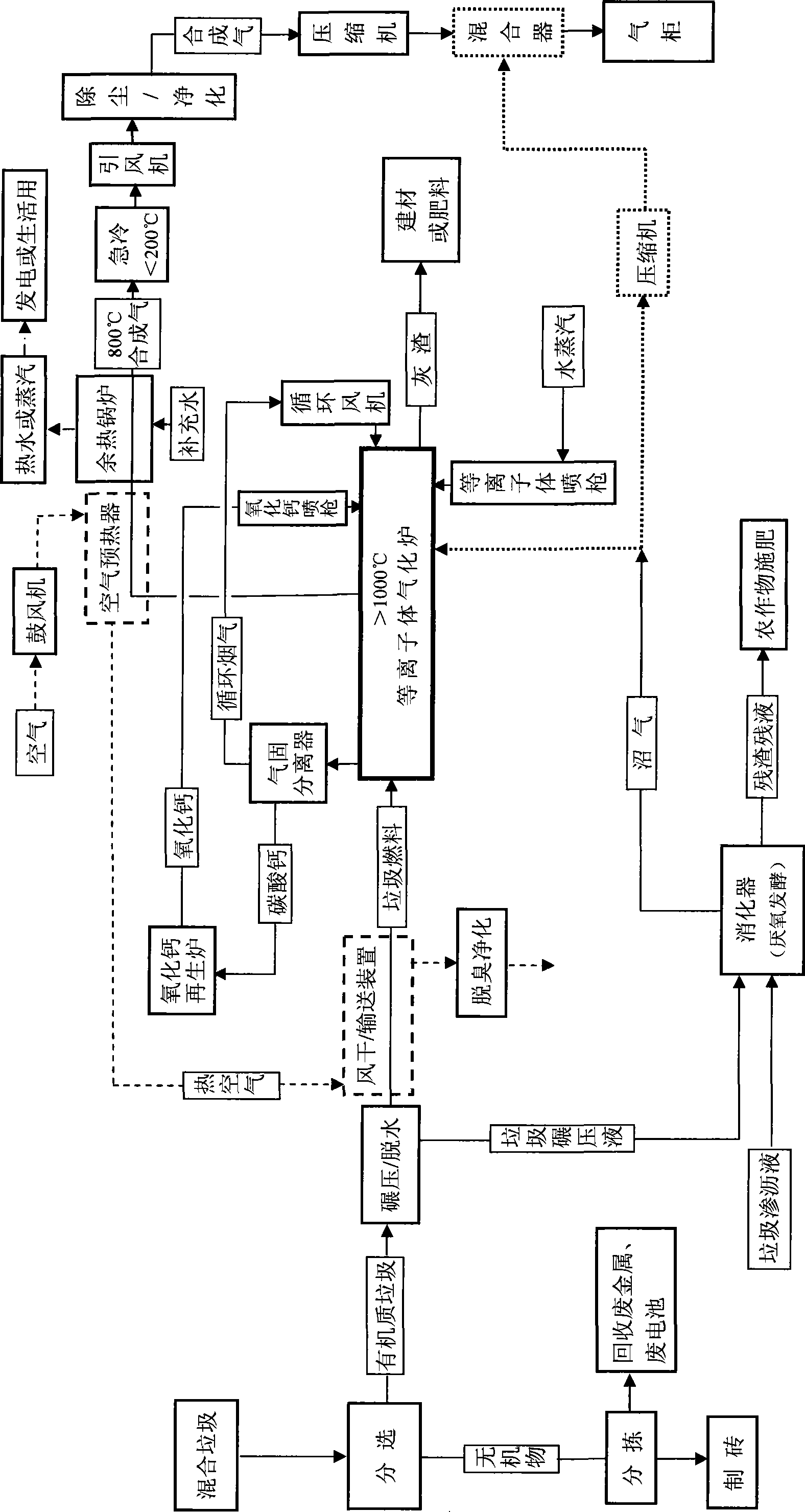

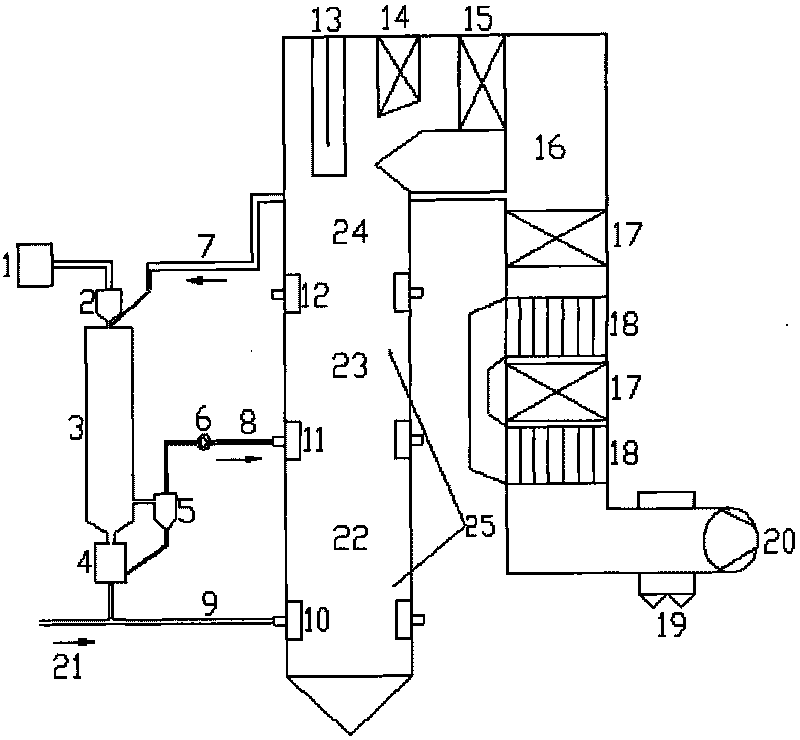

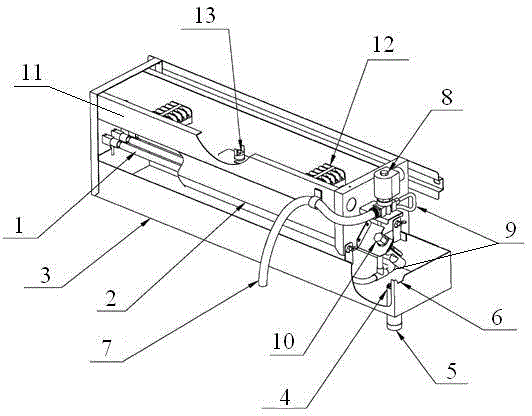

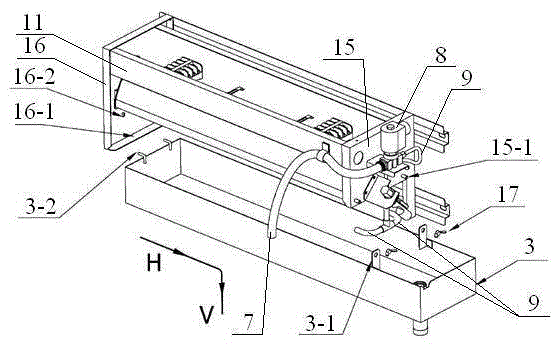

Domestic garbage transformation technique, system and apparatus without conventional fuel for combustion supporting

InactiveCN101468789AReduce pollutant contentLow investment costBio-organic fraction processingSolid waste disposalBrickClean energy

The invention provides a process, a system and equipment for converting household garbage without support combustion of the prior fuels, which relates to a process and equipment for processing garbage. The process is characterized in that the household garbage is sent into a gasification furnace or an incinerator after separating, dehydrating by rolling compaction and air-drying treatment; garbage fuel is converted in the furnace by a mode of gasification or incineration, and is subjected to baking, pyrogenation, gasification and carbon residue burn-out in the furnace; the converted synthesis gas is used for cleaning energy; waste heat of incineration is absorbed by heat-exchange equipment for reclamation; garbage rolling liquid is sent into a digesting machine for anaerobic fermentation so as to produce biogas, the biogas is used as auxiliary fuel of the incinerator, and the digested residue and residual liquid are used for fertilizing crops; and inorganic substances separated from the garbage are used as raw materials to manufacture bricks, and clinker discharged from the incinerator or the gasification furnace is used for producing cement or fertilizer. The process, the system and the equipment comprehensively utilize the garbage so as to achieve complete dissolving treatment, and the equipment has a simple structure and low investment cost, and is easy to popularize..

Owner:周开根

Light device having changeable light members

InactiveUS7014337B2Easy to changeEasy to replaceLighting applicationsNon-electric lightingEngineeringLED lamp

Owner:CHEN CHIA YI

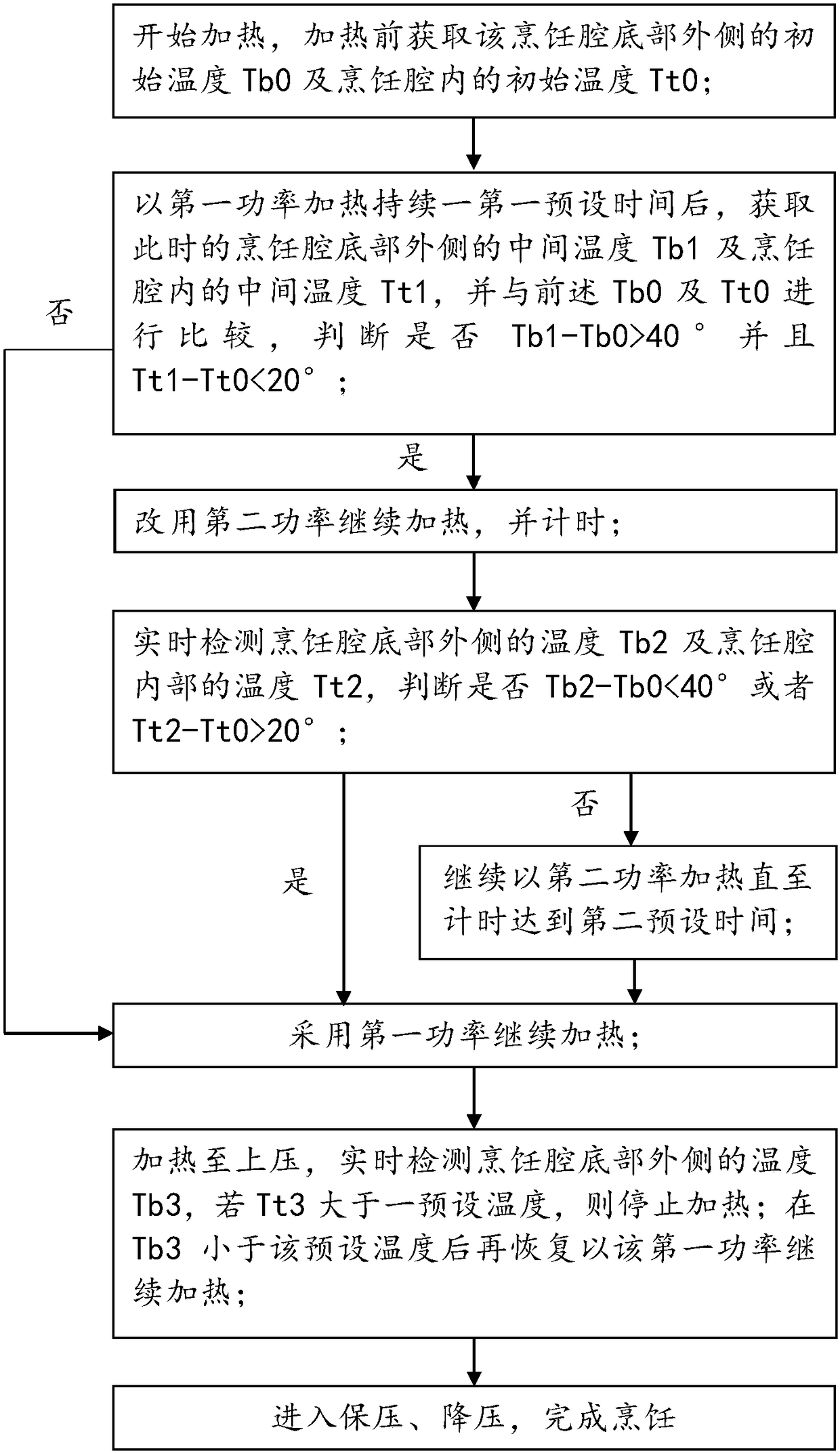

Cooking method and electric pressure cooker adopting cooking method

Owner:ZHEJIANG SHAOXING SUPOR DOMESTIC ELECTRICAL APPLIANCE CO LTD

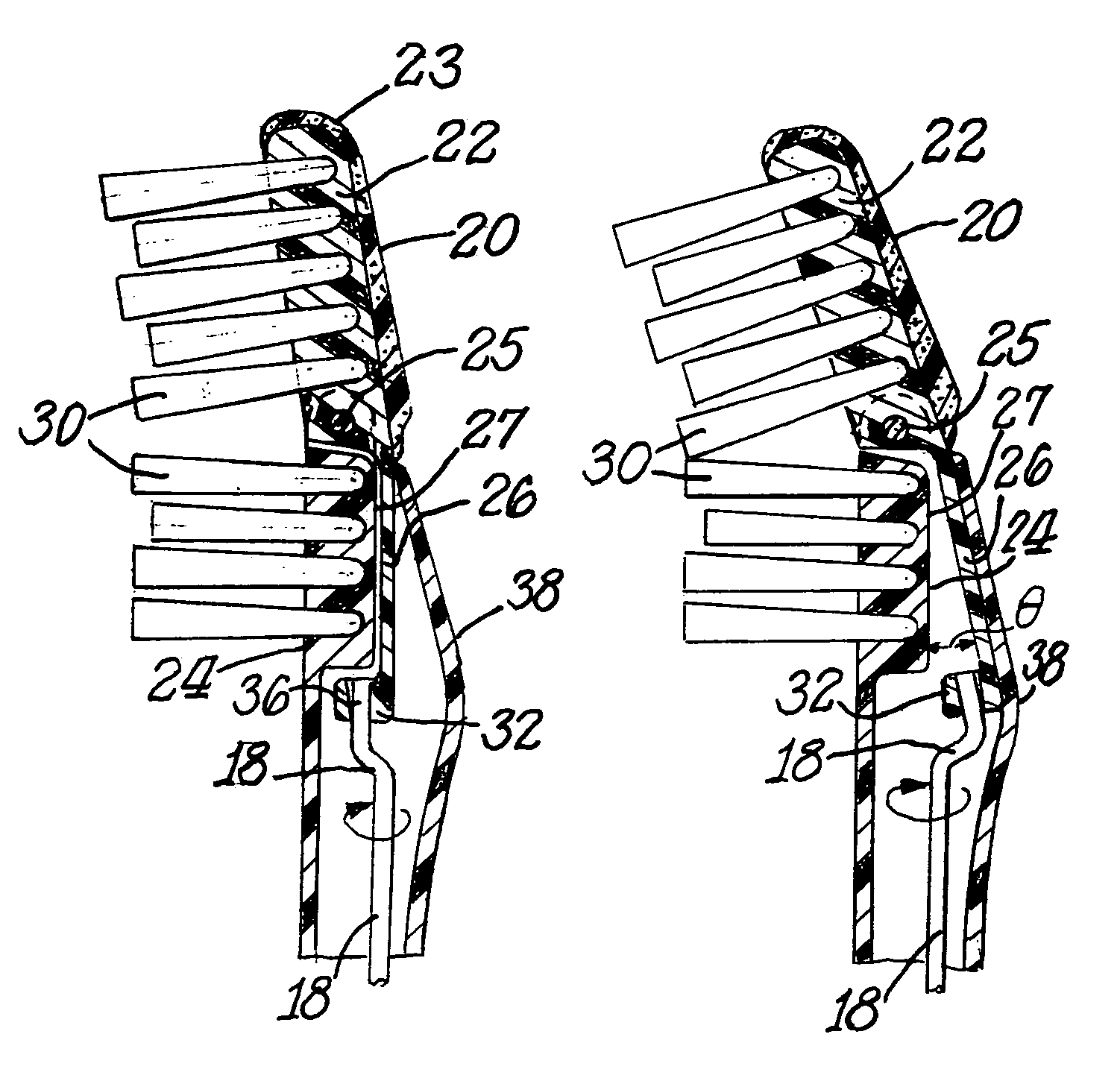

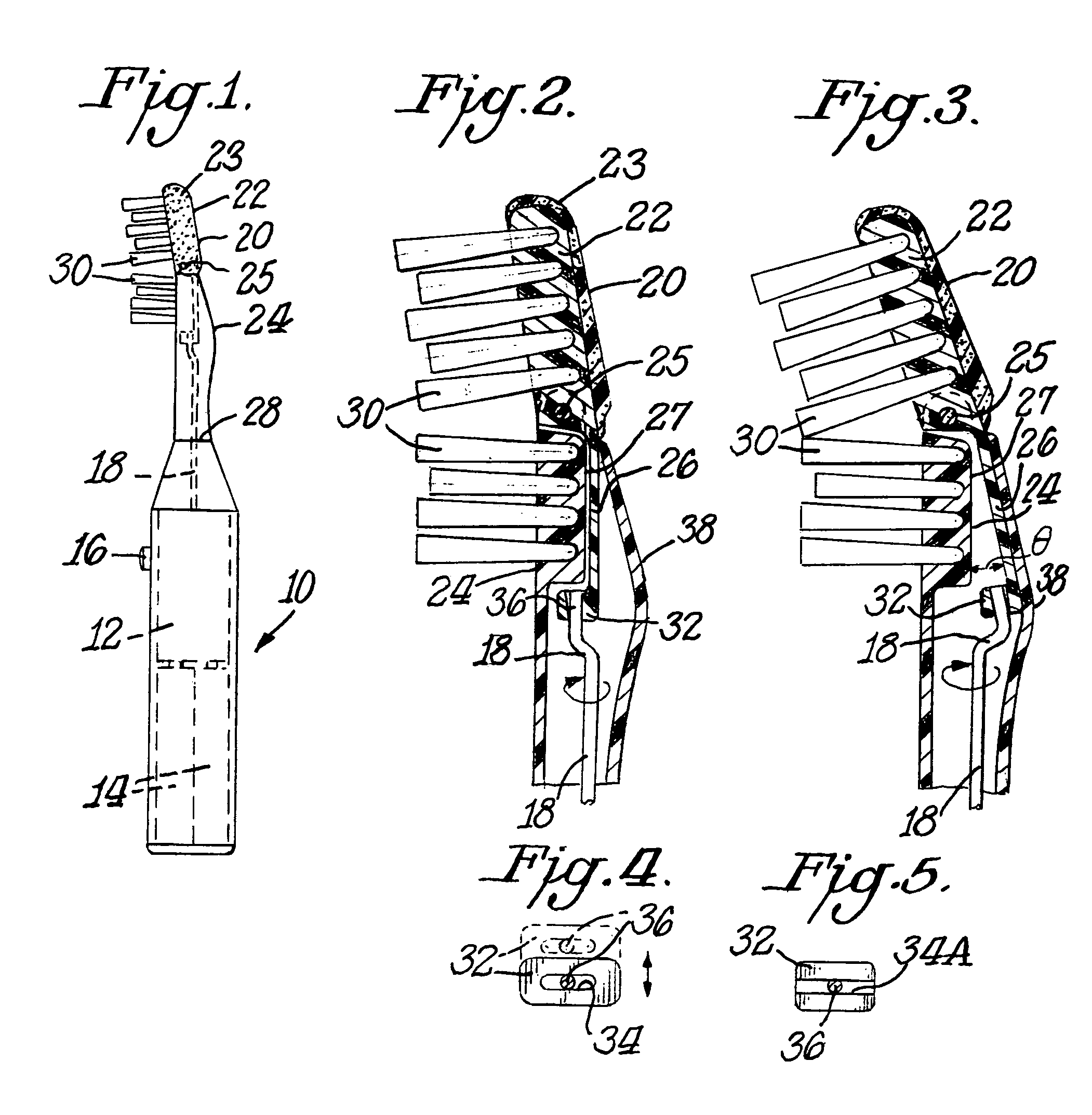

Powered toothbrush

InactiveUS7007332B2Limit its operationLow profileCarpet cleanersBrush bodiesReciprocating motionDrive shaft

A powered toothbrush is disclosed wherein portion of the toothbrush head is movable about a hinge. The movable portion of the head reciprocates about that hinge through the interaction of a flexible extension of that portion containing a slot. Movable within the slot is an offset end of a rotating drive shaft connected to the power source in the toothbrush. Translation of rotation movement of the drive shaft to reciprocating movement of the hinged head is achievable in a manner that the power source is not stalled or burned out if movement of the toothbrush head is prevented or limited.

Owner:COLGATE PALMOLIVE CO

Coefficient of thermal expansion filler for vanadium-based frit materials and/or methods of making and/or using the same

ActiveUS20120213954A1Improve sealingReduce sealClimate change adaptationWindows/door improvementMetal chlorideFrit

Certain example embodiments relate to seals for glass articles. Certain example embodiments relate to a composition used for sealing an insulted glass unit. In certain example embodiments the composition includes vanadium oxide, barium oxide, zinc oxide, and at least one additional additive. For instance, another additive that is a different metal oxide or different metal chloride may be provided. In certain example embodiments, a composition may be combined with a binder solution that substantially or completely burns out by the time the composition is melted. In certain example embodiments, a CTE filler is included with a frit material. In certain example embodiments, a vacuum insulated glass unit includes first and second glass substrates that are sealed together with a seal that includes the above-described composition.

Owner:GUARDIAN GLASS LLC

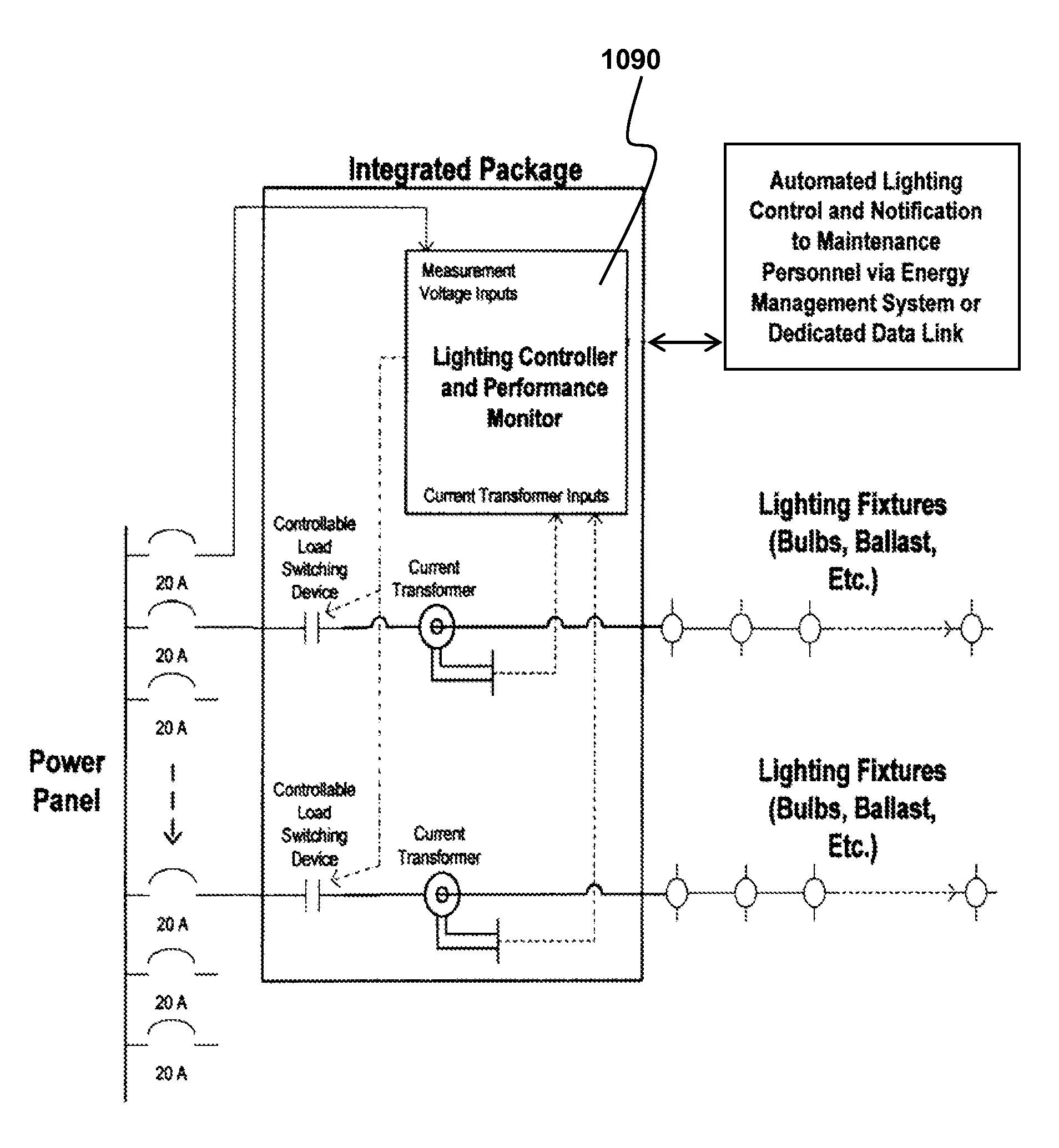

Lighting performance power monitoring system and method with optional integrated light control

ActiveUS20070282547A1Save energyReduce materialLevel controlPower measurement by digital techniqueEngineeringElectric power

A light performance monitoring device and optionally integrated controller includes a monitor module that directly monitors energy usage of at least one energy load to generate at least one measurement of energy usage; a storage module stores a series of baseline values of energy usage of the energy load, a comparator module compares energy measurements made at predetermined intervals with the baseline values, and a notification module notifies a designated recipient that there is a deviation from the baseline values consistent with a burned out or non-operational light fixture, including but not limited to light bulbs or ballast devices. A control module optionally integrated with the light performance monitoring device can be operatively coupled to the monitor module to control energy usage by the at least one energy load via a data link in a pre-determined manner that is based on the at least one measurement of energy usage.

Owner:GRIDPOINT

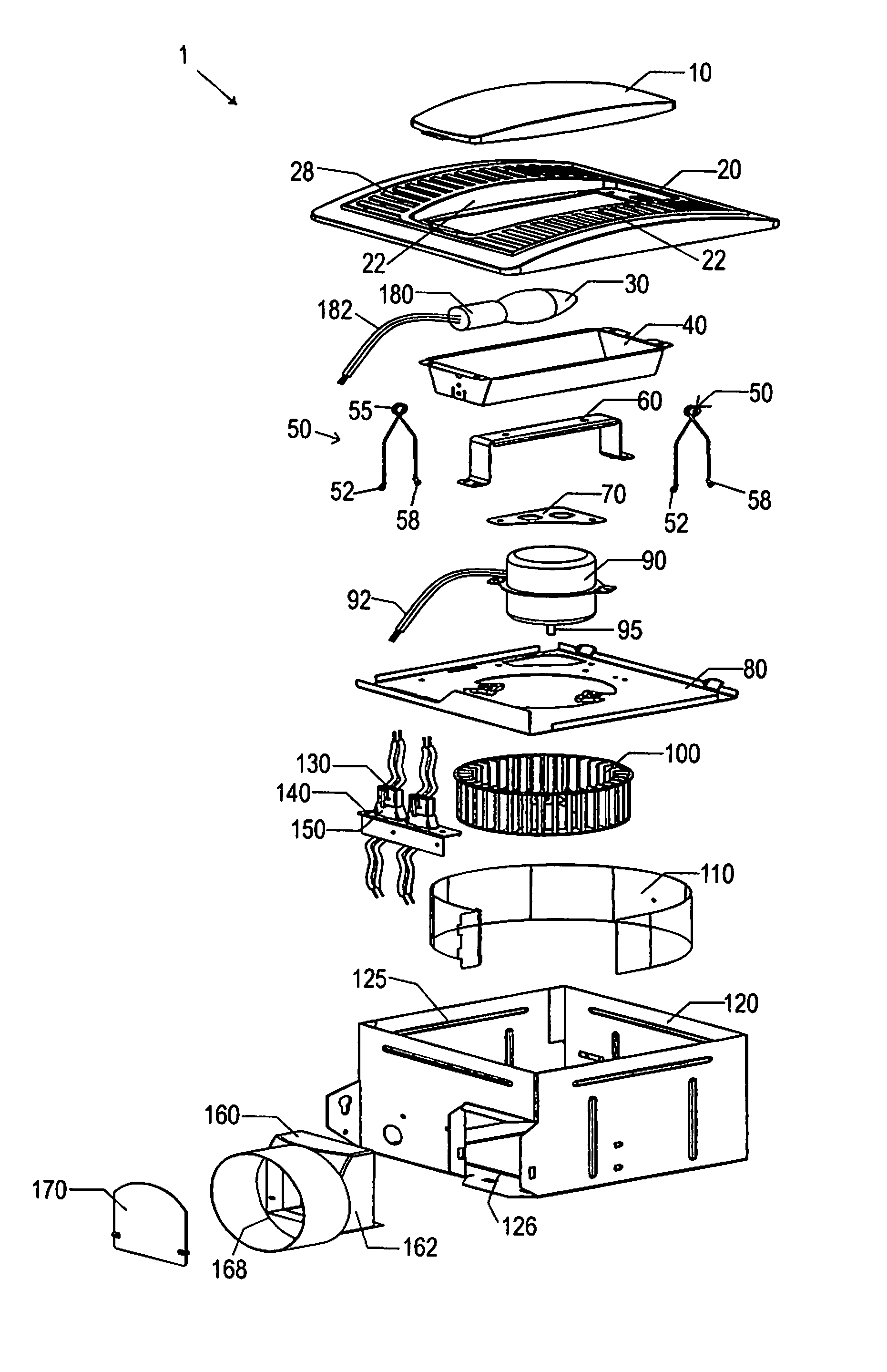

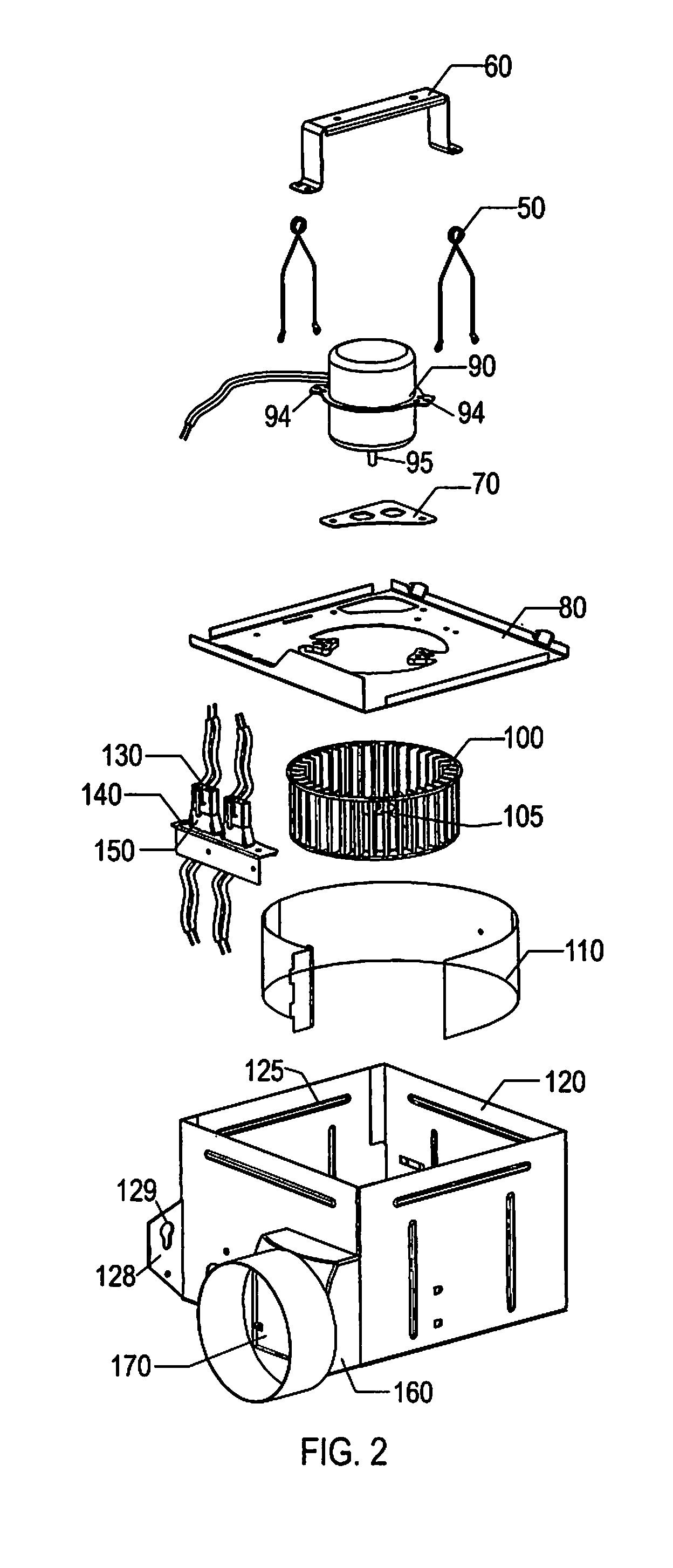

50 CFM bath fans with lens cover and flaps/ears that allow housings to be mounted to joists

InactiveUS9028212B1Minimize excess noiseEasy to disassemblePump componentsEngine componentsImpellerJoist

Apparatus, systems and methods of 50 CFM exhaust and ventilation fans for bathrooms with grill covers having removable light lens covers, and flaps / ears that allow the housings to mount directly to joists and / or other structural members inside of a ceiling or inside of a wall. The housing can include a mounting plate having a motor with attached impeller thereon, wherein the mounting plate with motor and attached impeller and electrical connectors can be removed as a single unit from the housing for accessing and inspecting interior wire connections during inspection and for ease in replacing parts such as burned out motors overtime.

Owner:CHIEN LUEN INDS

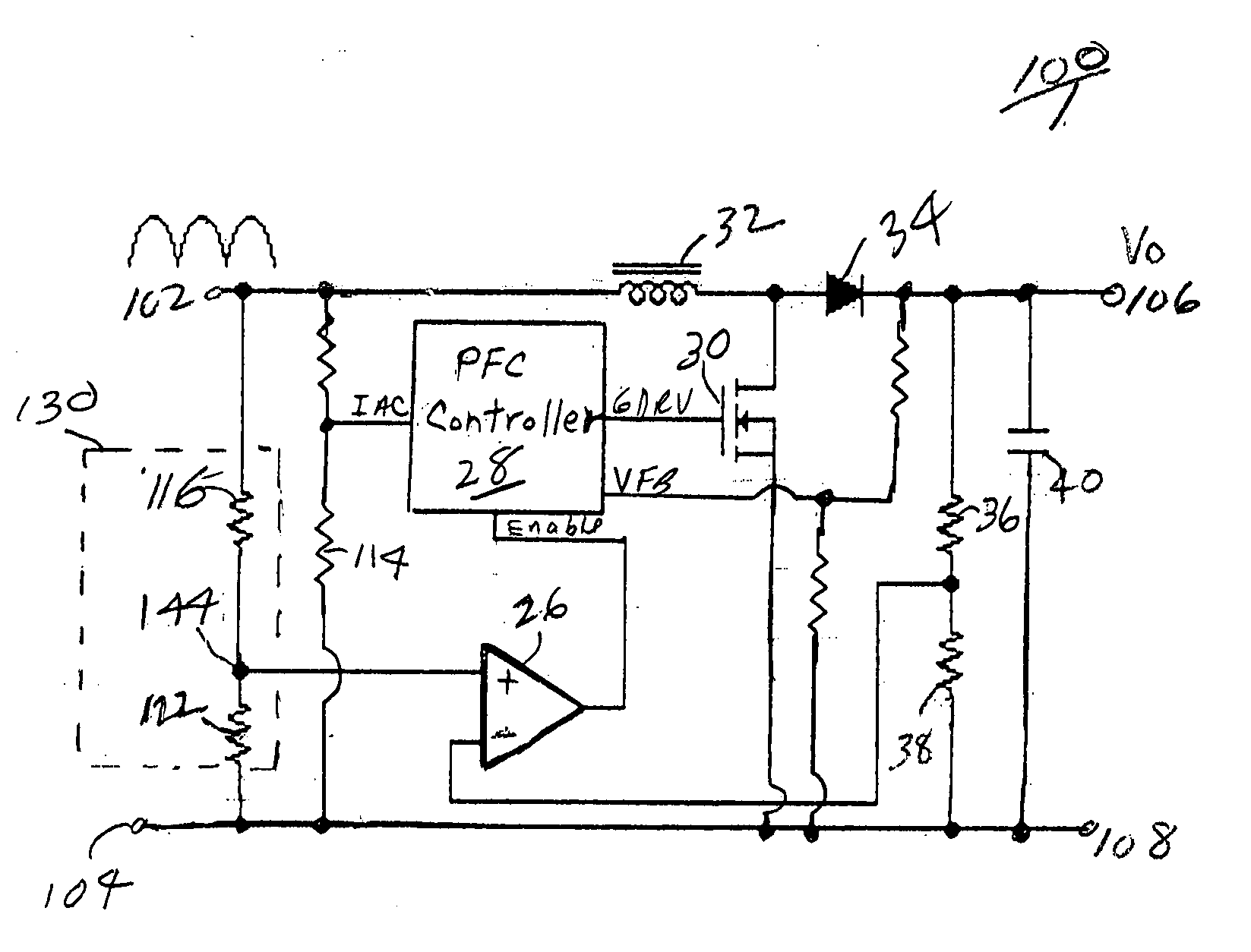

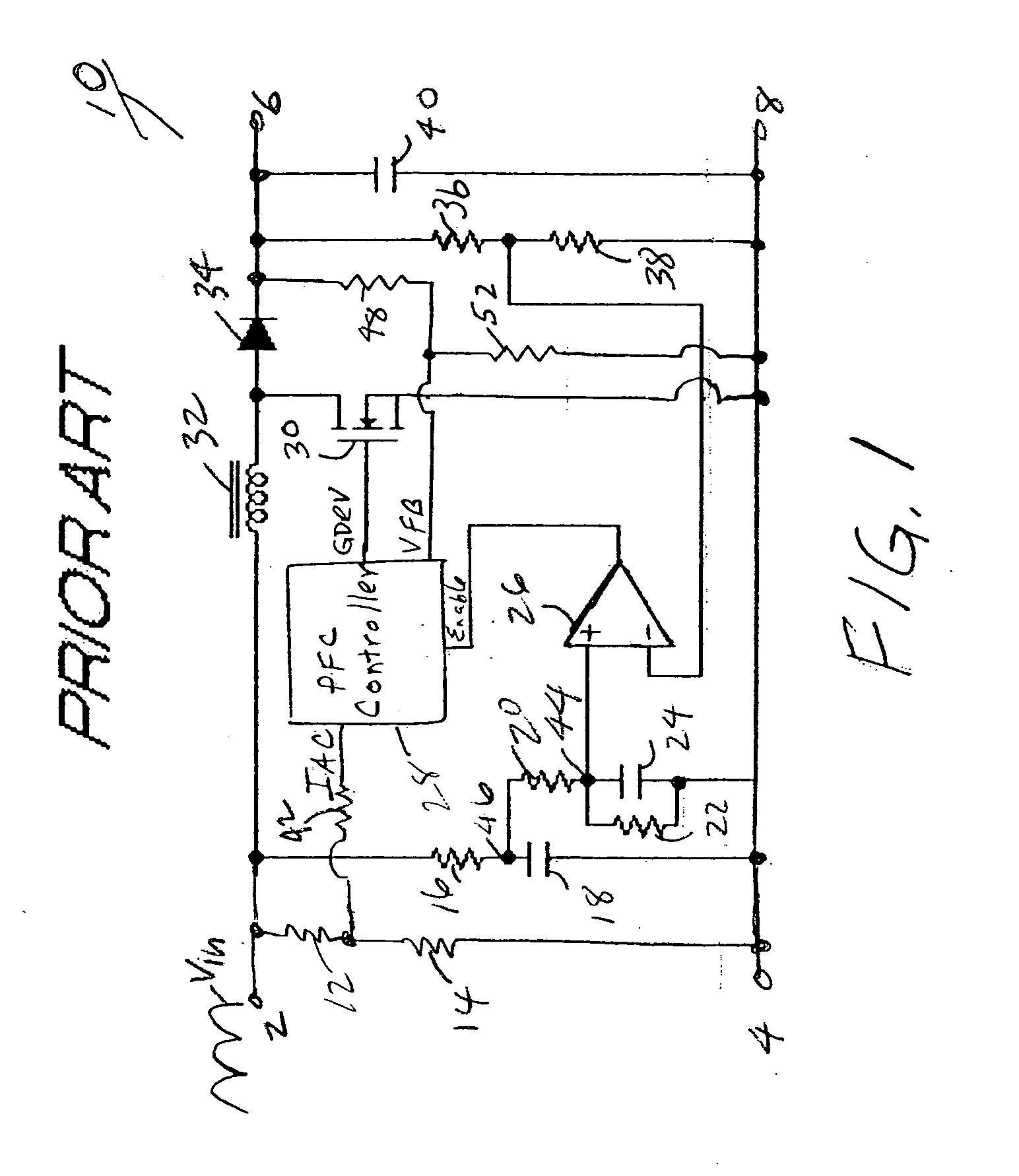

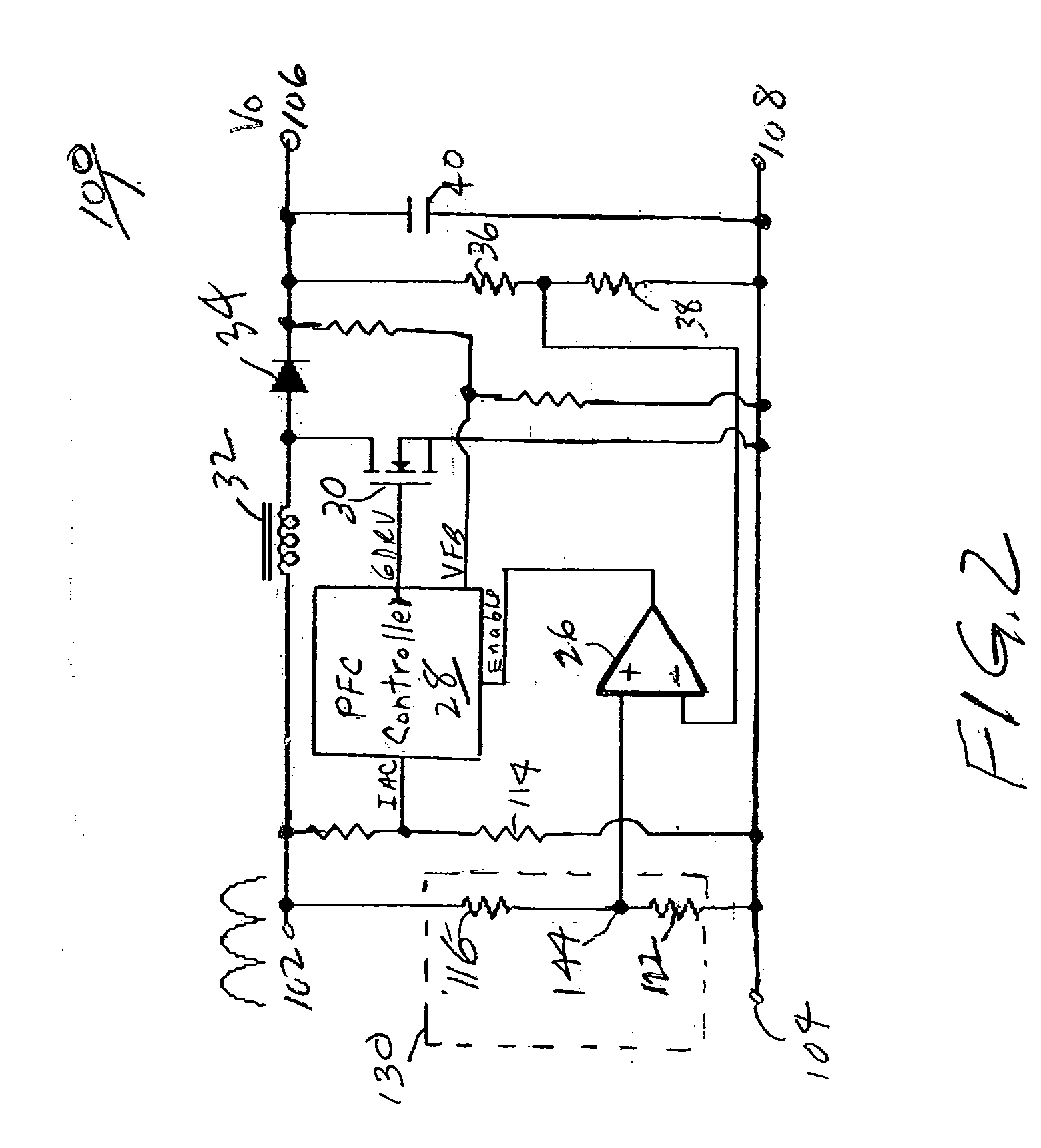

Real-time voltage detection and protection circuit for PFC boost converters

InactiveUS20050269999A1Avoid unnecessary down timeOvercomes drawbackEnergy industryElectric variable regulationPower factorPeak value

A circuit for protection of the operation of power factor correction (PFC) converters from conditions such as input voltage surges that can otherwise cause failure, and to prevent unnecessary down time of the boost converter after a power failure or on startup. The circuit detects the real time rectified input voltage and provides real time comparison of the detected input voltage and the output voltage. The boost function of the PFC is controlled as a function of the output of the comparison circuit so as to quickly inhibit the boost function of the PFC controller thereby disabling boost and protecting the circuit from burning out. The circuit enables the PFC to starts and restart more quickly, even before the output voltage becomes stabilized, since boost is permitted as soon as the output voltage exceeds the real time sampled input voltage. By enabling boost during this period, the circuit eliminates the need to wait at least a few cycle times until the output voltage is higher than the peak of rectified input voltage. In a preferred embodiment, a complementary protection circuit having a voltage clamp is also provided to prevent unnecessary shutdown of the converter.

Owner:ASTEC INT LTD

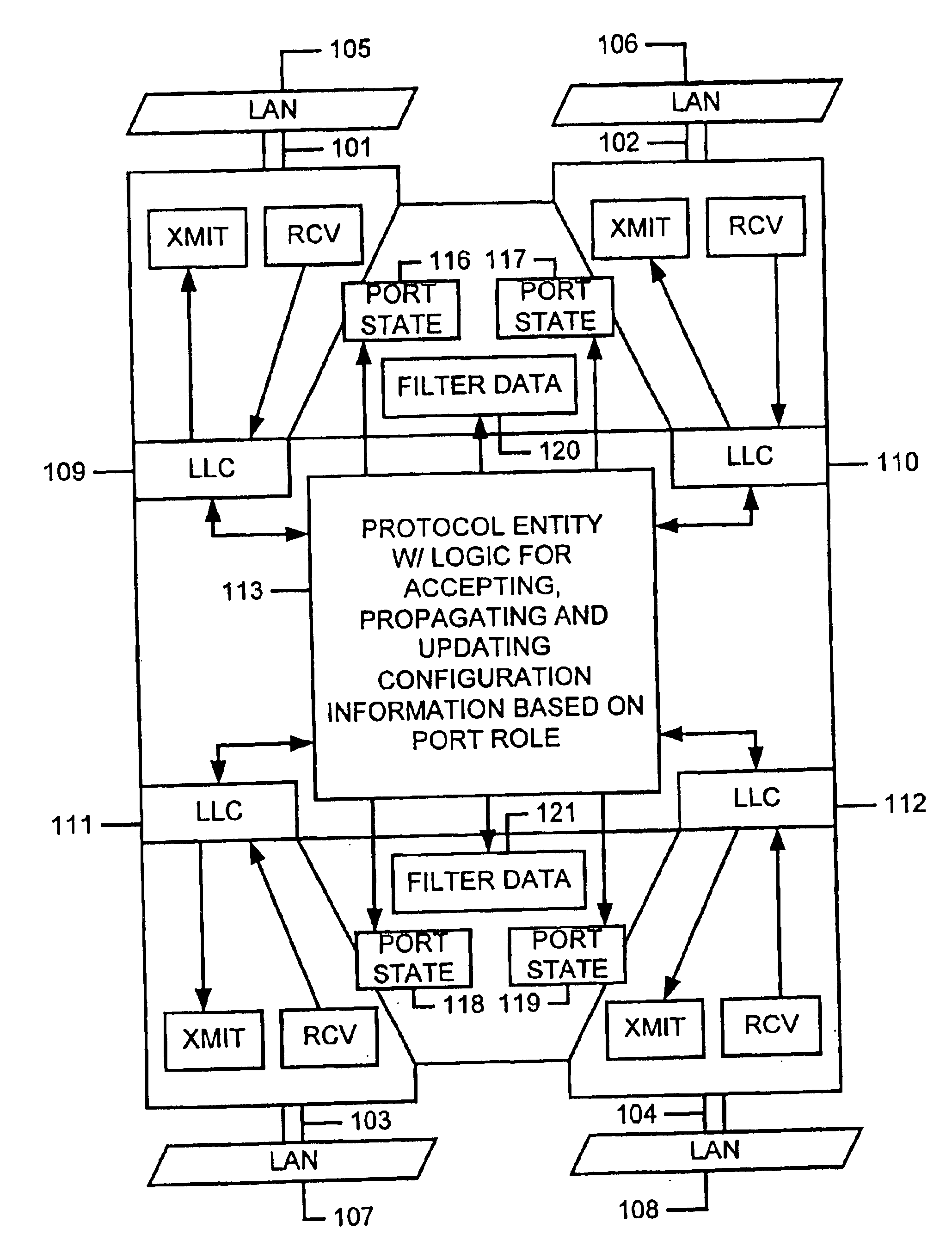

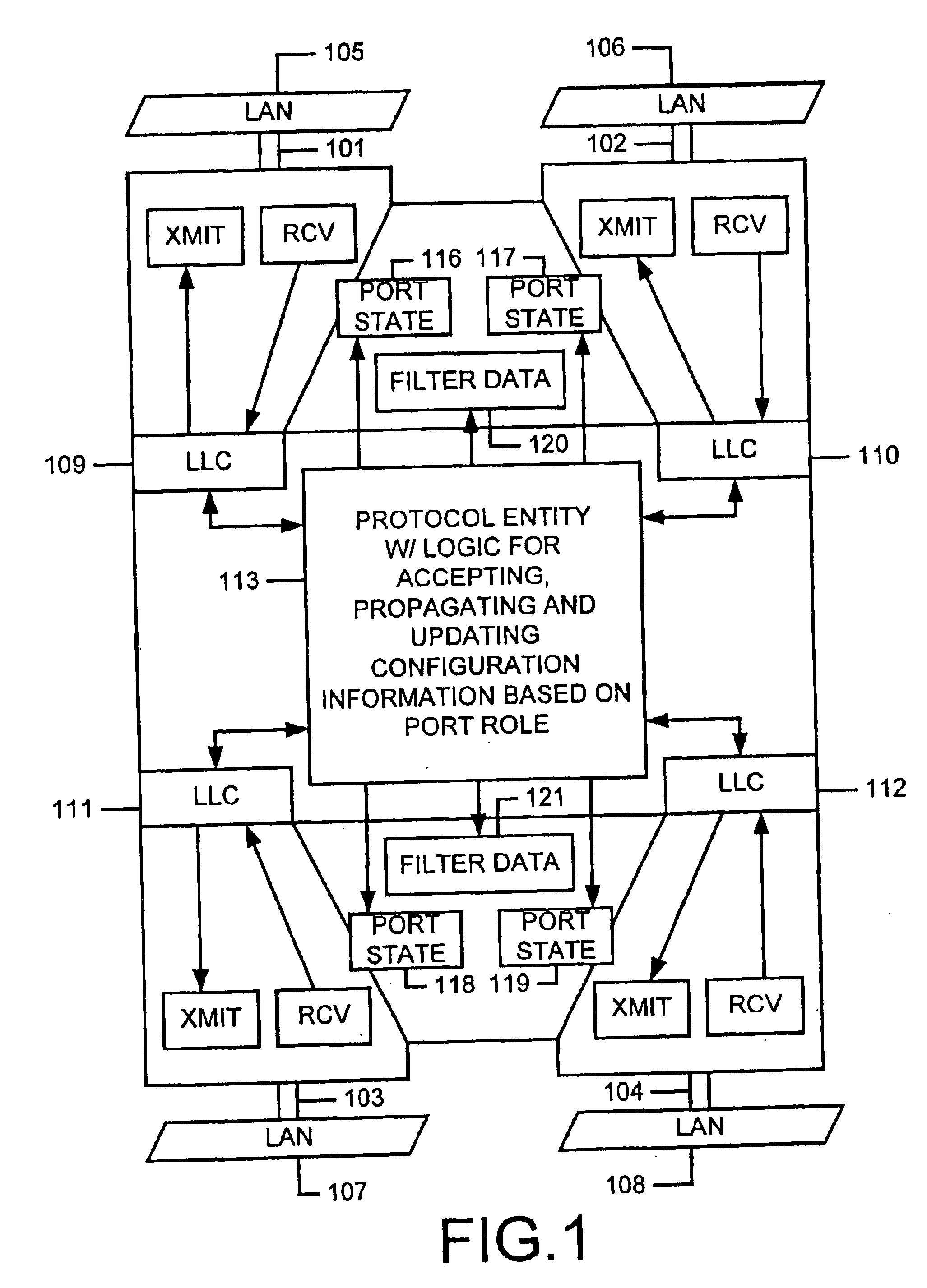

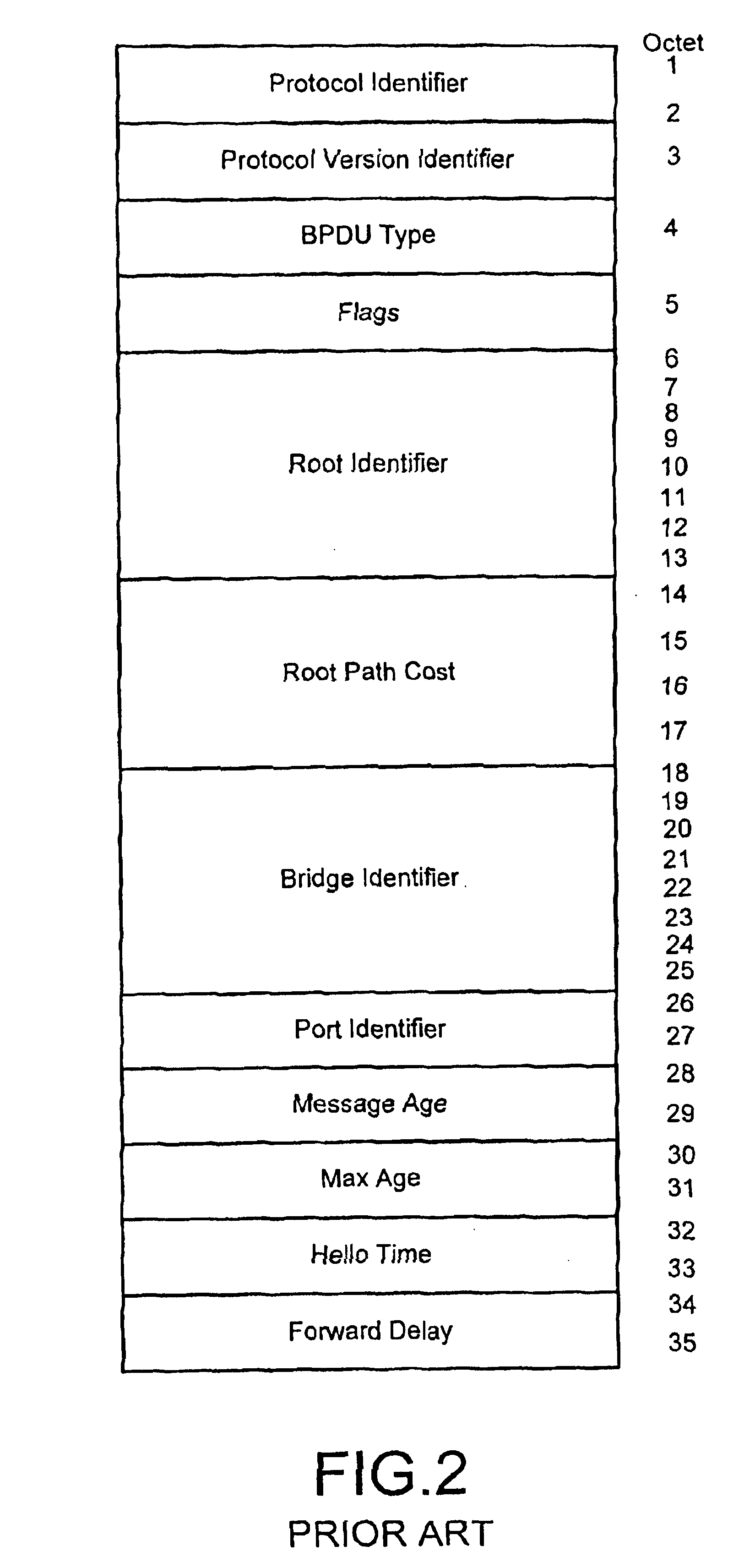

Spanning tree with rapid propagation of topology changes

InactiveUS6882630B1Spread quicklyBad newsNetworks interconnectionInformation propagationProtocol entity

Modifications to the spanning tree algorithm allow bad news to propagate quickly by providing that protocol entities on bridges process inferior information sent by the designated bridge for each LAN. In addition, bridges use per port hello timers to stimulate information propagation, setting it to suit local link characteristics. No changes to the format of bridge protocol data units (BPDUs) as specified in the IEEE Standard 802.1D are required, and the algorithm for computing the topology of the network remains unchanged. Techniques have been adopted for expiring information and recomputing the spanning tree upon detection of link failure, upon receipt of a message having a message age greater than its accompanying maximum age, or if the port hello time algorithm detects a loss of link. Rules for propagating information are provided allowing rapid propagation of changes. Finally, techniques for burning out information in a configuration message are adopted.

Owner:HEWLETT-PACKARD ENTERPRISE DEV LP

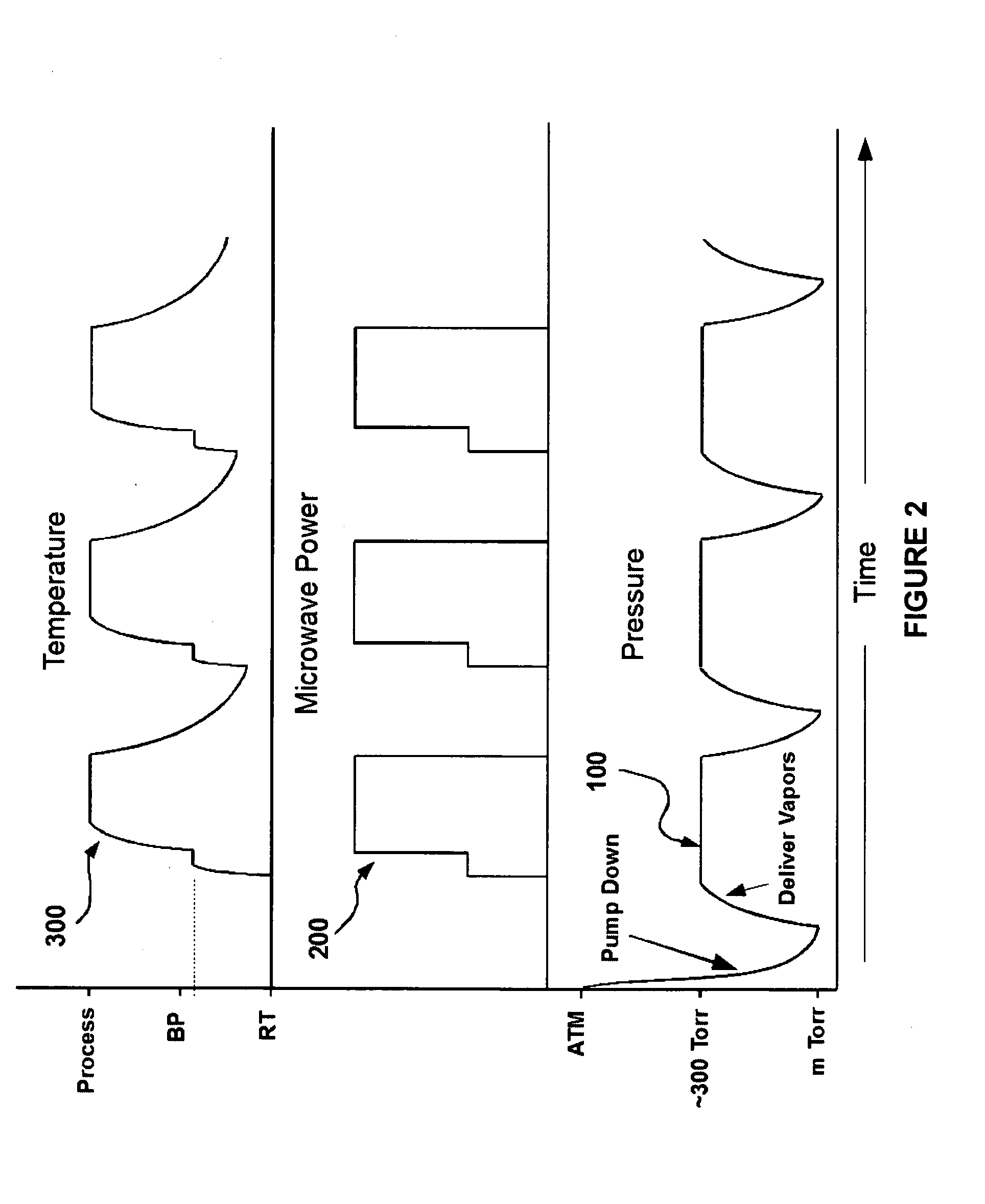

Method and apparatus for microwave treatment of dielectric films

ActiveUS20140322921A1Semiconductor/solid-state device manufacturingMicrowave heatingPorosityBoiling point

A method for processing a dielectric film on a substrate comprises: depositing a porous dielectric film on a substrate; removing the porogen; stuffing the film with a protective polymeric material; performing at least one intermediate processing step on the stuffed dielectric film; placing the film in a microwave applicator cavity and heating to a first temperature to partially burn out the polymeric material; introducing a controlled amount of a polar solvent into the porosity created by the partial burn out; applying microwave energy to heat the film to a second selected temperature below the boiling point of the solvent to clean away remaining polymeric material; and applying microwave energy to heat the film to a third temperature above the boiling point of the solvent to completely burnout the residues of polymeric material. The interaction of the polar solvent with the microwaves enhances the efficiency of the cleaning process.

Owner:APPLIED MATERIALS INC

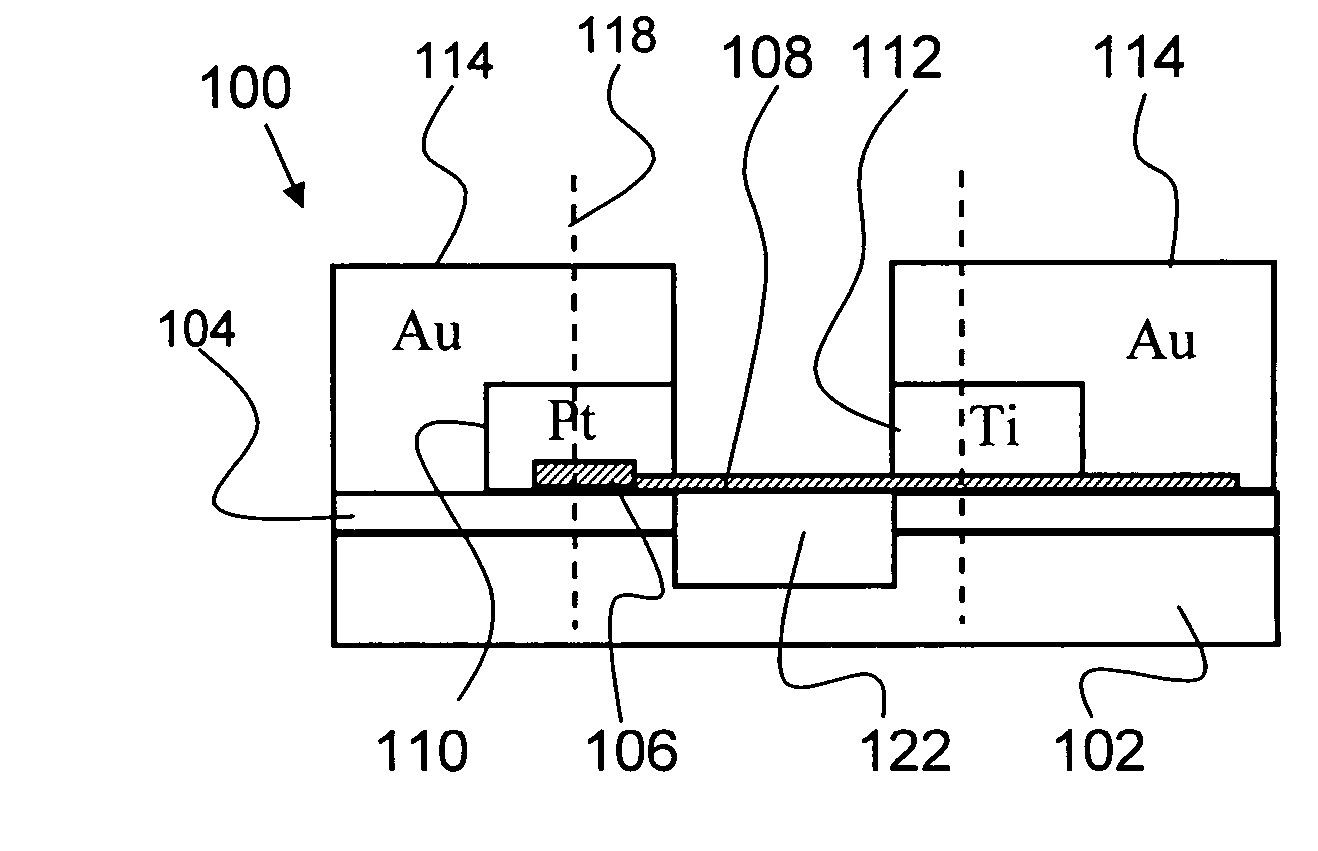

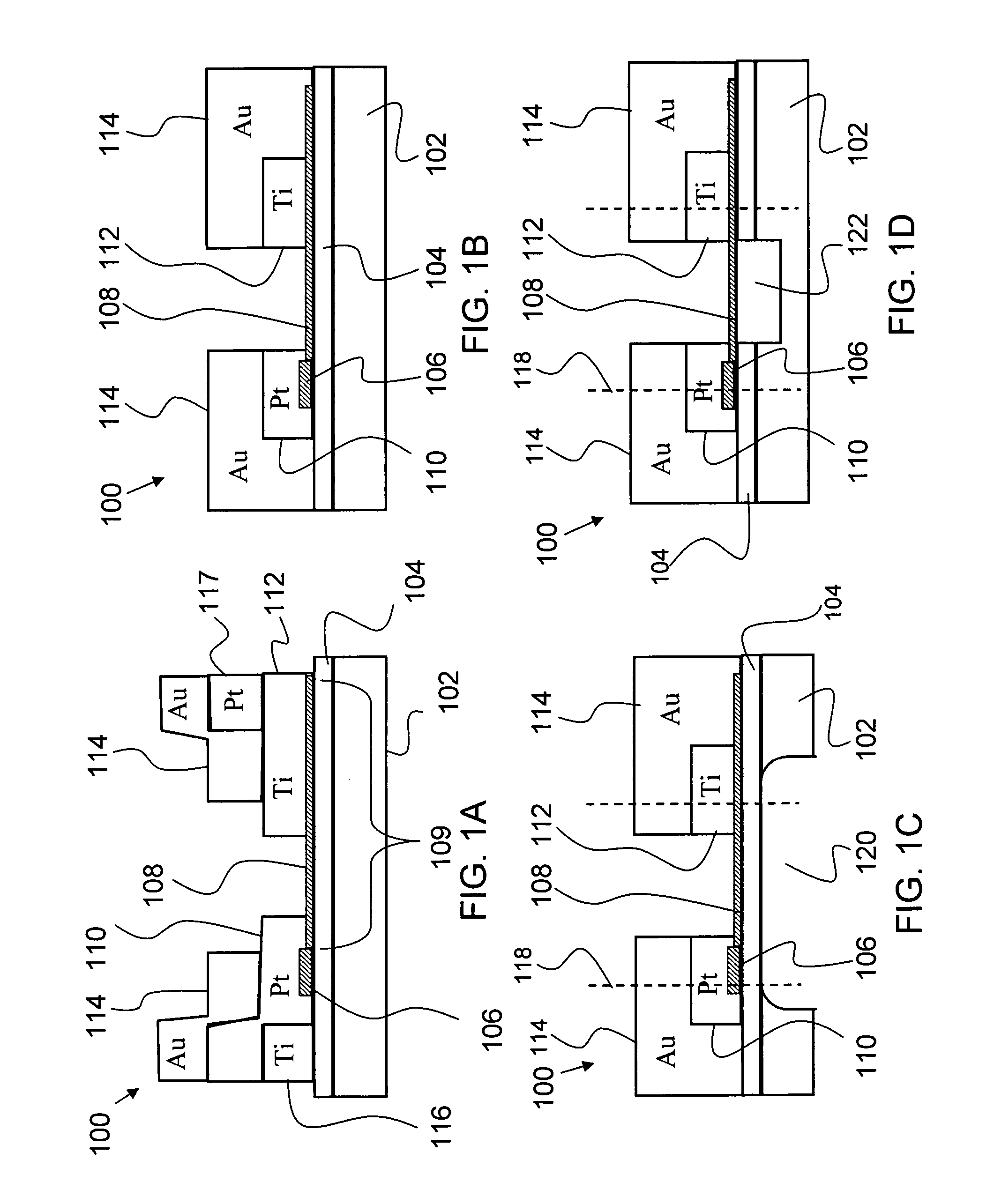

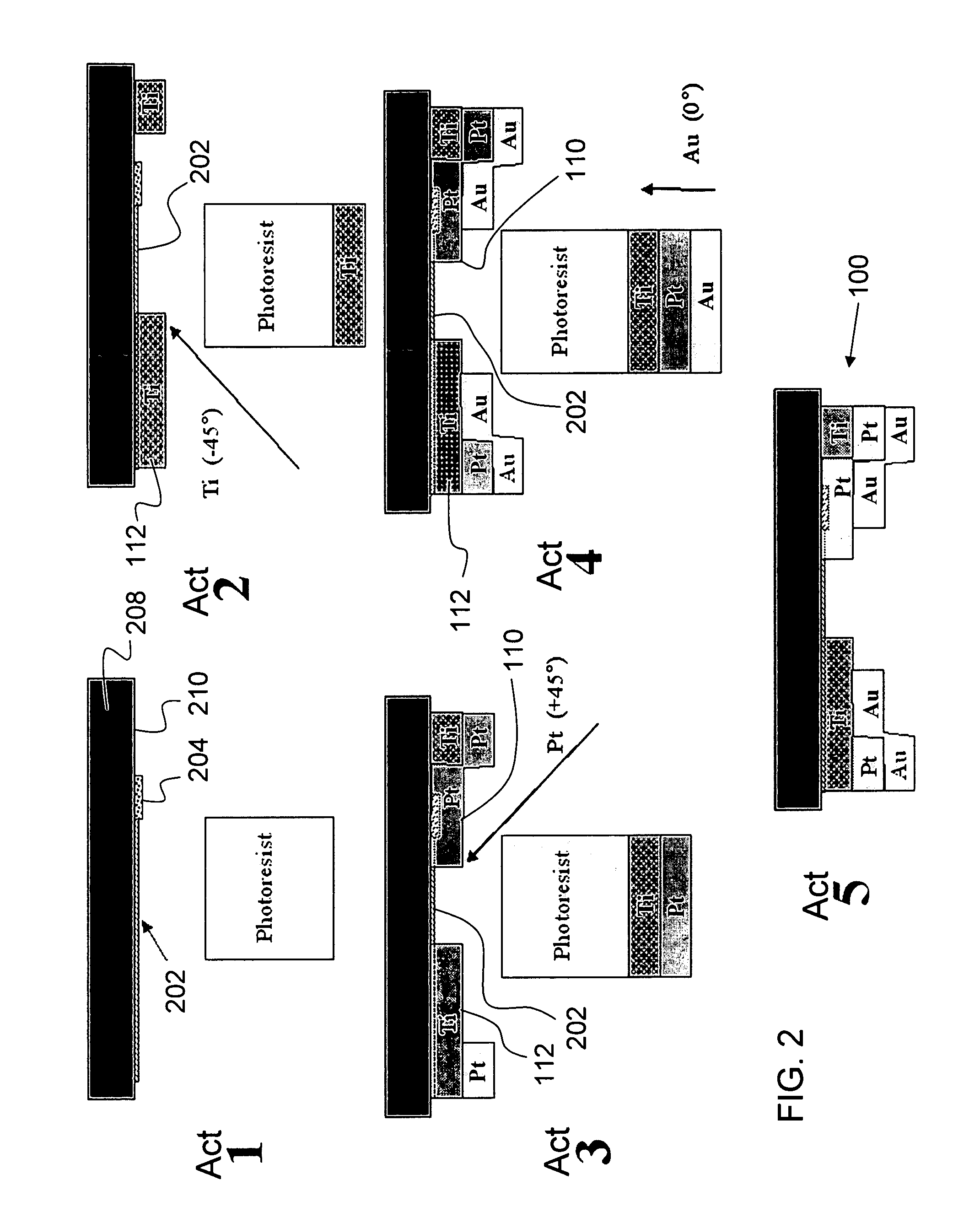

Nanotube Schottky diodes for high-frequency applications

InactiveUS20060261433A1Lower work functionImprove work functionNanoinformaticsSemiconductor/solid-state device manufacturingEvaporationNanotube

Described is a Schottky diode using semi-conducting single-walled nanotubes (s-SWNTs) with titanium Schottky and platinum Ohmic contacts for high-frequency applications. The diodes are fabricated using angled evaporation of dissimilar metal contacts over an s-SWNT. The devices demonstrate rectifying behavior with large reverse-bias breakdown voltages of greater than −15 V. In order to decrease the series resistance, multiple SWNTs are grown in parallel in a single device, and the metallic tubes are burnt-out selectively. At low biases, these diodes showed ideality factors in the range of 1.5 to 1.9. Modeling of these diodes as direct detectors at room temperature at 2.5 terahertz (THz) frequency indicates noise equivalent powers (NEP) comparable to that of the state-of-the-art gallium arsenide sold-state Schottky diodes, in the range of 10-13 W / square-root (√) Hz.

Owner:CALIFORNIA INST OF TECH

Decorative light

A decorative light with an LED as the light source has a socket, two protrusions integrally formed on the inner face of the socket, a base detachably inserted into the socket, an LED mounted on the base, two projections integrally formed on the base for two electrodes of the LED to extend therethrough respectively and two electric wires inserted into second end of the socket, wherein the distances between the end of the socket and each of the protrusions are different from each other, in addition the lengths of each of the projections are different from each other. So that, each electrode of the LED will touch each corresponding wire only in a specific orientation. This can keep the LED from being burned out due to the incorrect connection of the electrodes between the LED and the electric power, and decrease the cost of manufacturing the decorative light with the LED as the light source.

Owner:TSENG WEI JEN

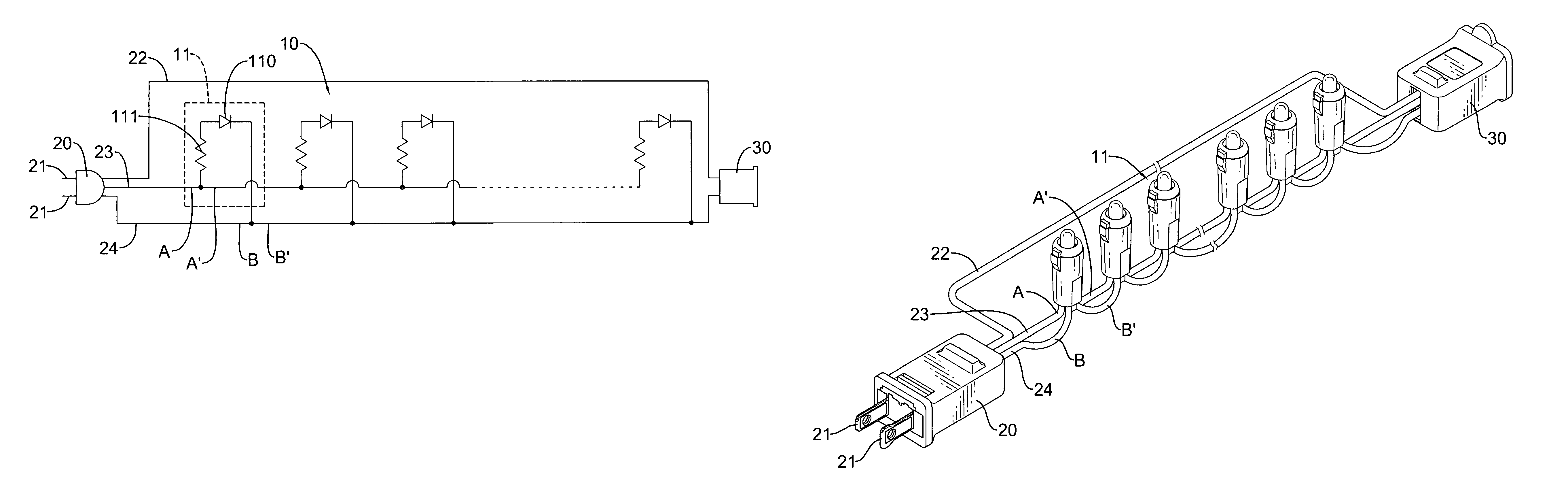

LED-based christmas light string assembly with parallel-wired lighting units

An LED light string assembly has a plug for providing a low DC voltage, an extension socket, a light string connected between the plug and the extension socket. The light string has multiple LED Christmas bulbs connected in parallel. Each LED Christmas bulb includes an LED and a resistor connected in series. Even one of the LED Christmas bulb burns out, all the remaining LED Christmas bulb of the light string will not be affected and still can be normally turned on as required to generate light.

Owner:YANG CHEN SHENG

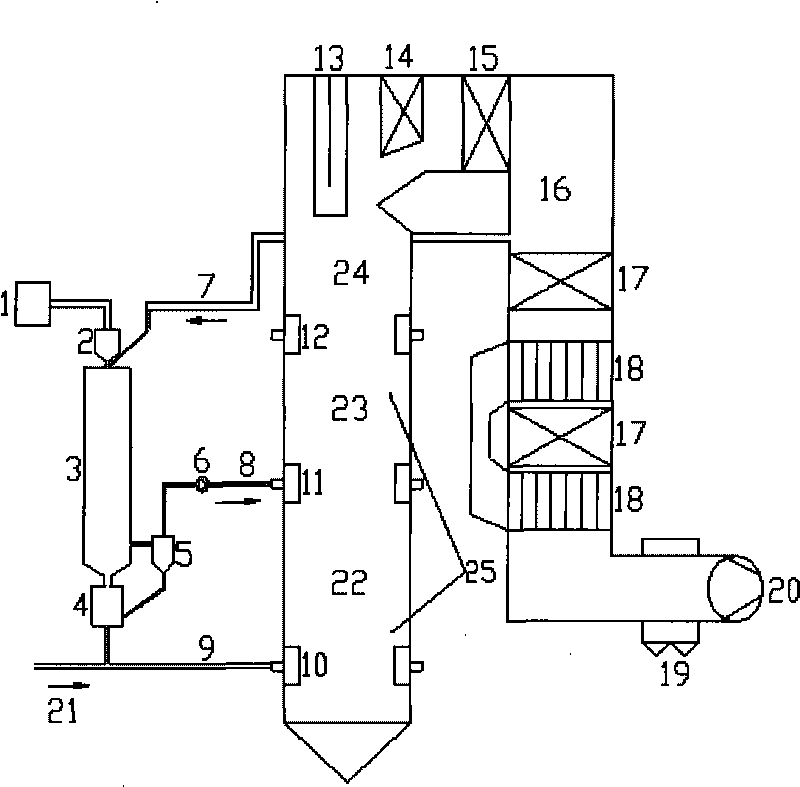

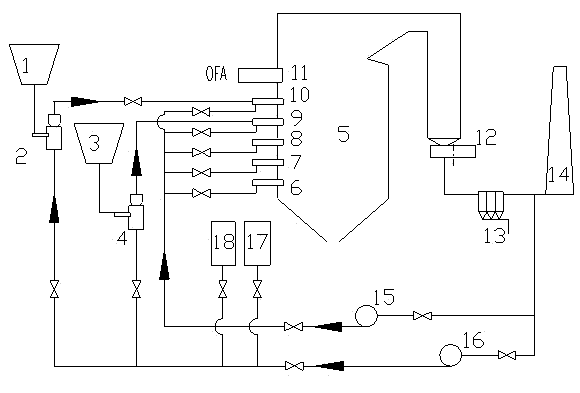

Method and device for burning low NOx by utilizing reburning of pulverized coal pyrolysis gas

InactiveCN101761920AEasy to transformEfficient reductionCombustion apparatusFlue gasProcess engineering

The invention discloses a method and device for burning low NOx by utilizing reburning of pulverized coal pyrolysis gas. The method comprises the following steps: quickly pyrolizing the pulverized coal by utilizing partial hot smoke gas of a tail flue of a pulverized coal boiler entering a pyrolysis reactor; delivering the pulverized coal pyrolysis gas serving as the gas reburning fuel into a reburning area of the pulverized coal boiler to perform high-efficiency NOx reduction, and completely burning the gas reburning fuel subjected to NOx reduction in a burning-out area of the pulverized coal boiler to discharge the low NOx of the pulverized coal boiler; and allowing semicoke which is produced through the pulverized coal pyrolysis to enter a main burning area of the pulverized coal boiler which is carried by primary air to finish burning. The device of the technique mainly comprises a pulverized coal quick pyrolysis device, a pulverized coal flue gas circulating system, a boiler low NOx burning system and a pipeline which is connected with the boiler low NOx burning system. The method and the device have the advantages of simple structure, low investment, high denitration efficiency, and wide application prospect.

Owner:UNIV OF SHANGHAI FOR SCI & TECH

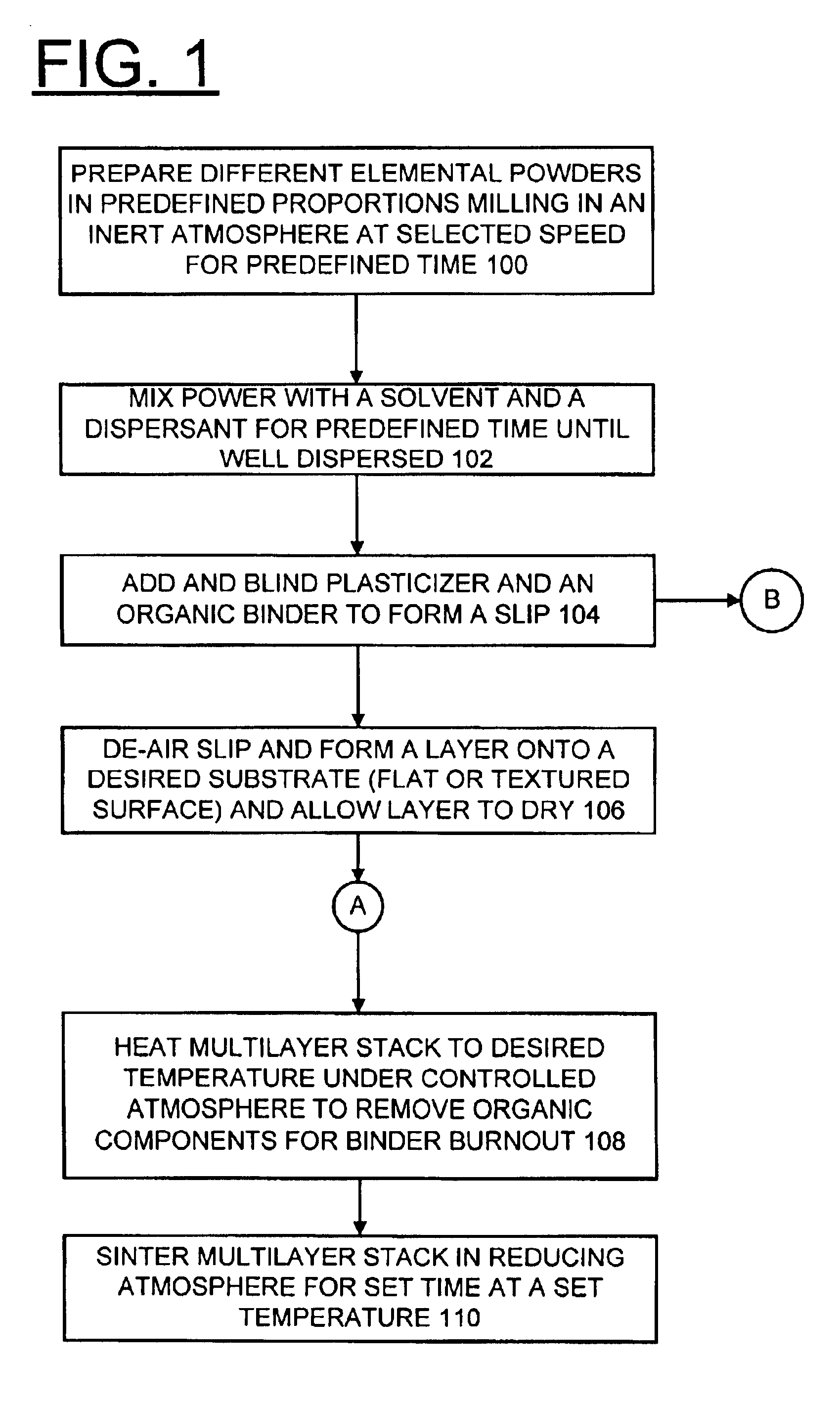

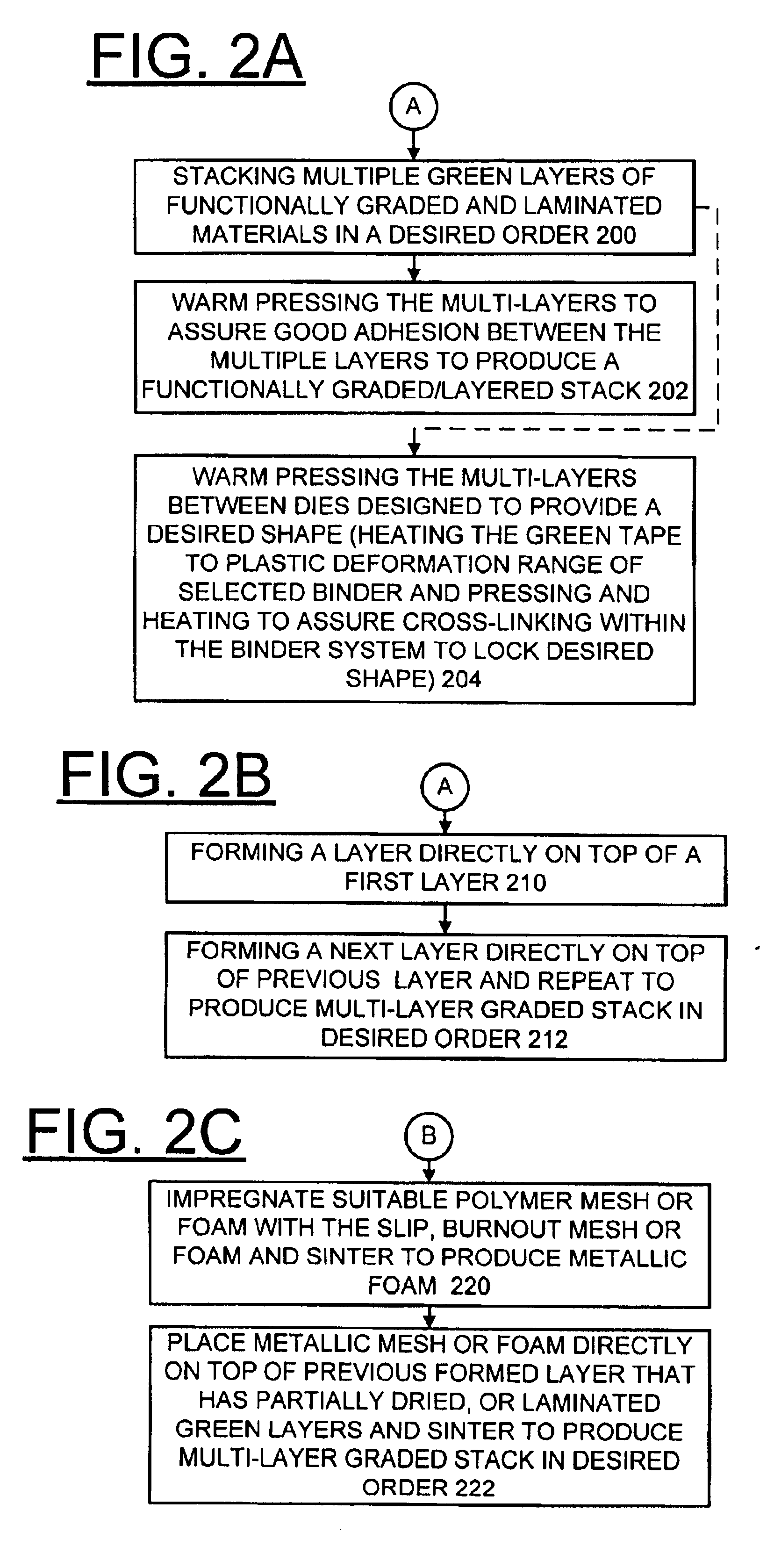

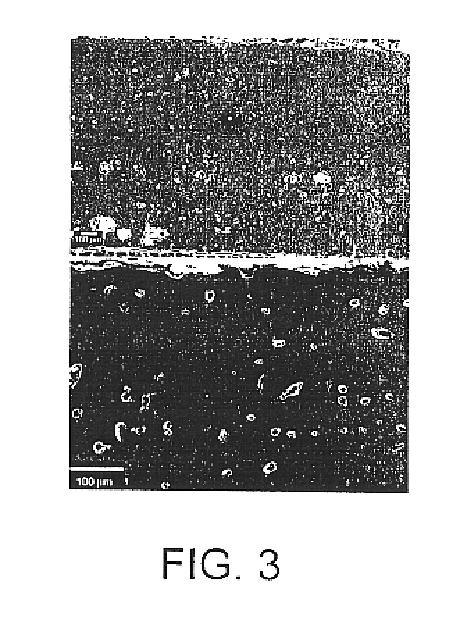

Compositionally graded metallic plates for planar solid oxide fuel cells

A method for preparing compositionally graded metallic plates and compositionally graded metallic plates suitable for use as interconnects for solid oxide fuel cells are provided. The method of the invention, utilizing powder metallurgy, enables making metallic plates of generally any desired composition to meet the corrosion requirements of fuel cells and other applications, and enables making metallic plates of graded composition from one surface of the plate to the other. A powder of the desired alloy composition is obtained, then solvents, dispersants, a plasticizer and an organic binder are added to form a slip. The slip is then formed into a layer on a desired substrate that can be flat or textured. Once dried, the layer is removed from the substrate and the binder is burned out. The layer is sintered in a reducing atmosphere at a set temperature for a predefined duration specific to the materials used and the desired final properties.

Owner:UCHICAGO ARGONNE LLC +1

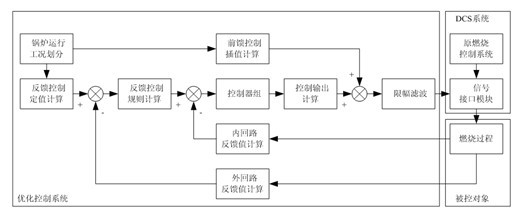

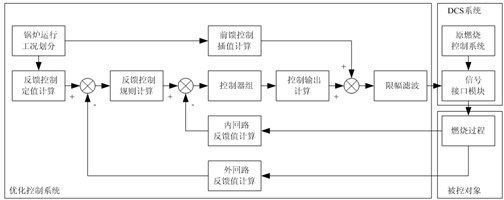

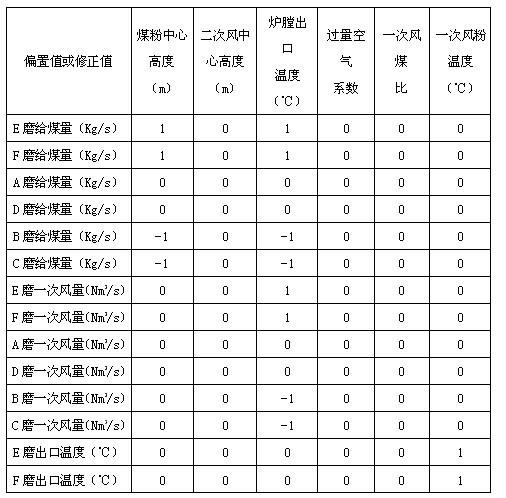

Combustion feedforward and feedback composite optimization controlling method for pulverized coal fired boiler

InactiveCN102425807AImprove combustion efficiencyEmission reductionCombustion regulationCombustorComposite optimization

The invention discloses a combustion feedforward and feedback composite optimization controlling method for a pulverized coal fired boiler. The method is used for realizing dynamic accurate proportioning of wind and coal under a full working condition and in the full combustion process. According to the technical scheme, the method comprises the following steps of: determining feedforward signals according to combustion adjusting experiment data or operation personnel experience, determining feedback signals according to the thermodynamic properties and laws of the boiler, and automatically and accurately adjusting the coal quantity proportion of each burner, the primary air quantity proportion of each coal mill, the outlet temperature of each coal mill and the secondary air quantity and burning-out air quantity proportion of each burner under different working conditions to keep the burning efficiency and the NOX discharge of the boiler in an optimal state. By the method, the advantage of coexistence of a plurality of independent adjusting means of the large pulverized coal fired boiler and the advantages of high dynamic response speed of feedforward control and high static precision of feedback correction control are fully exerted, the pulverized coal fired boiler is close to the optimal state under various working conditions, the burning efficiency of the boiler is improved, and the discharge of NOX is reduced.

Owner:NORTH CHINA ELECTRIC POWER UNIV (BAODING)

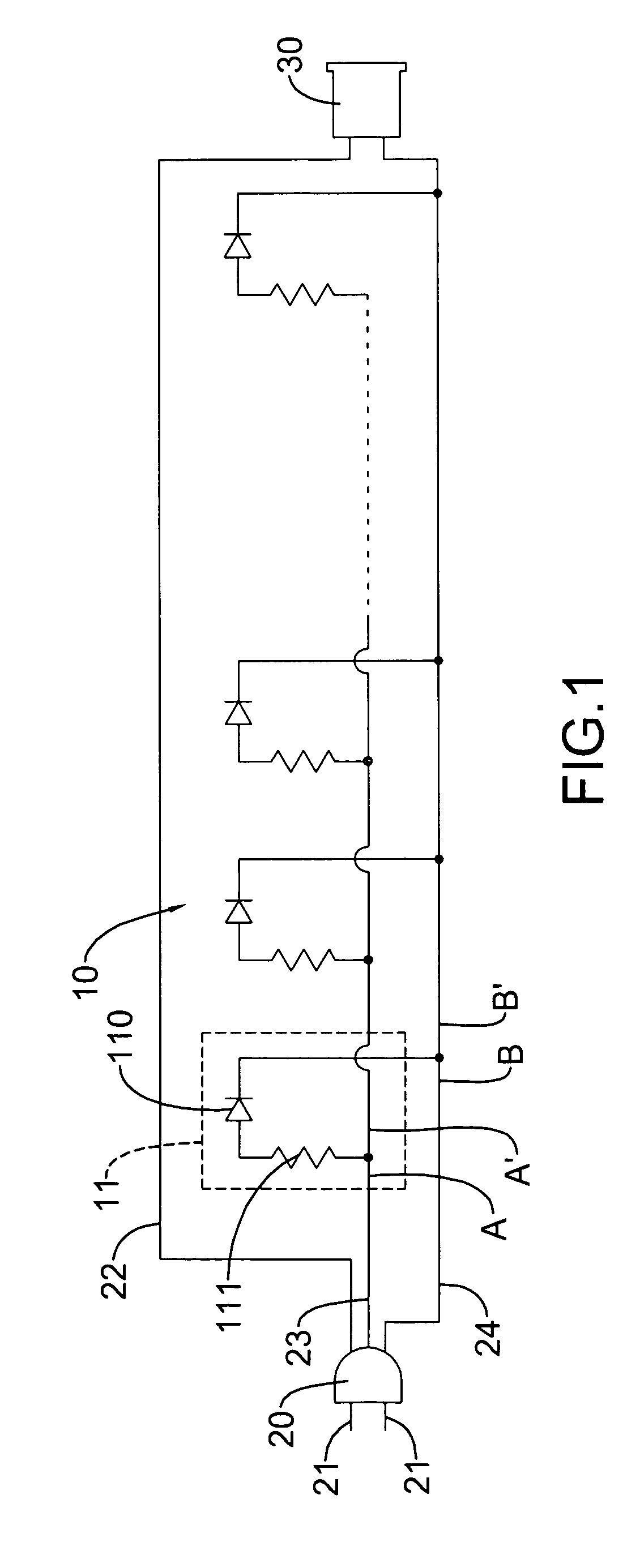

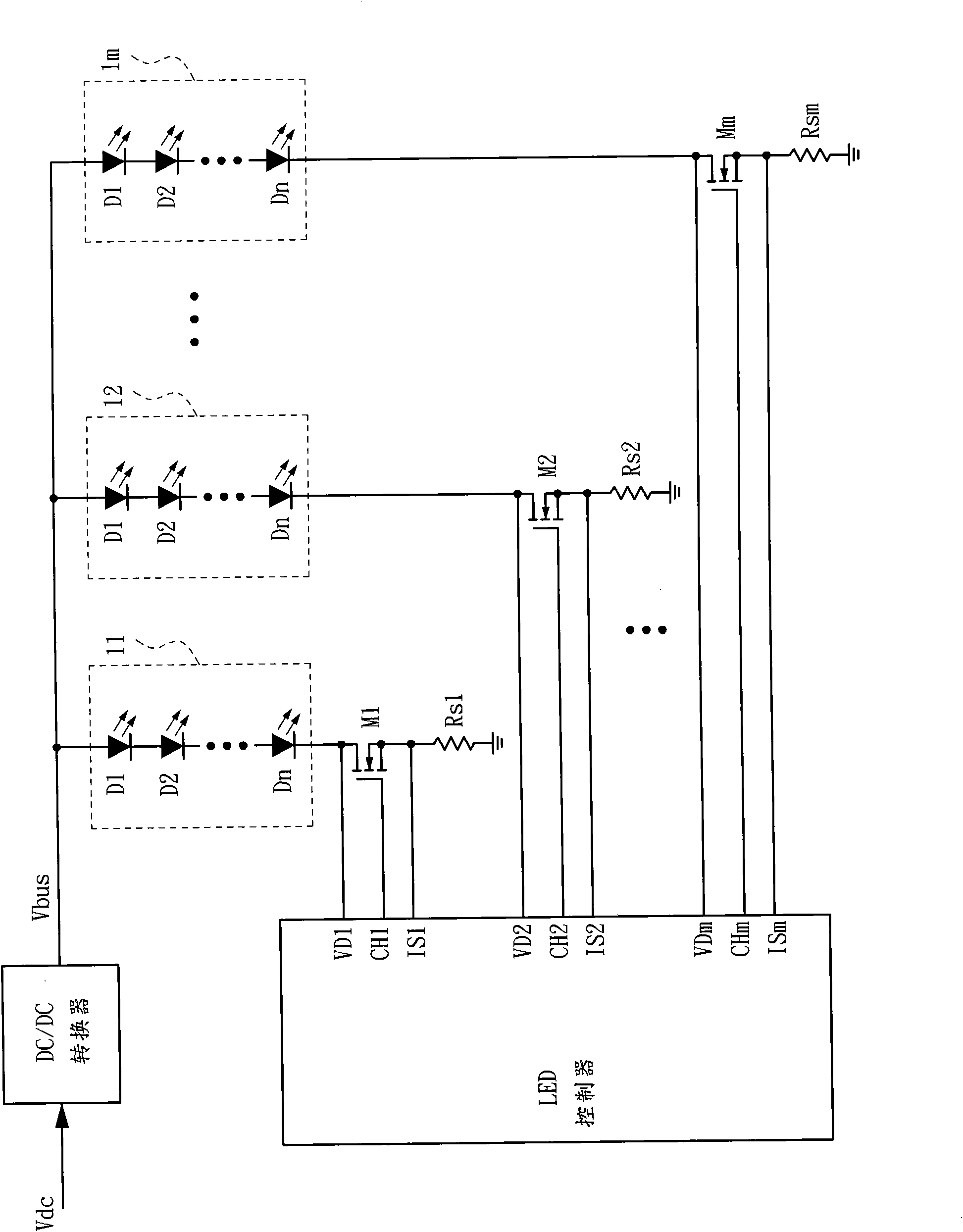

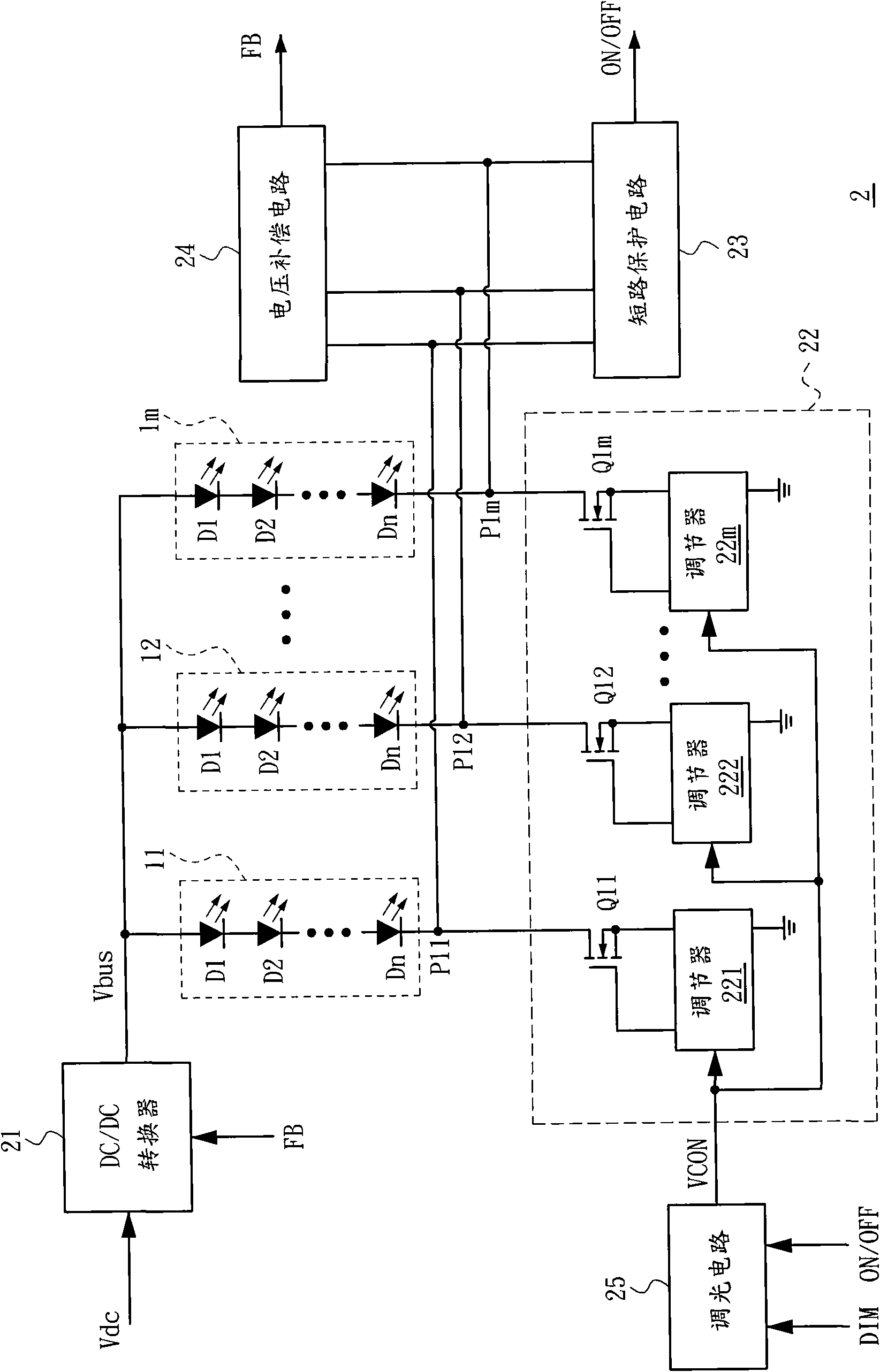

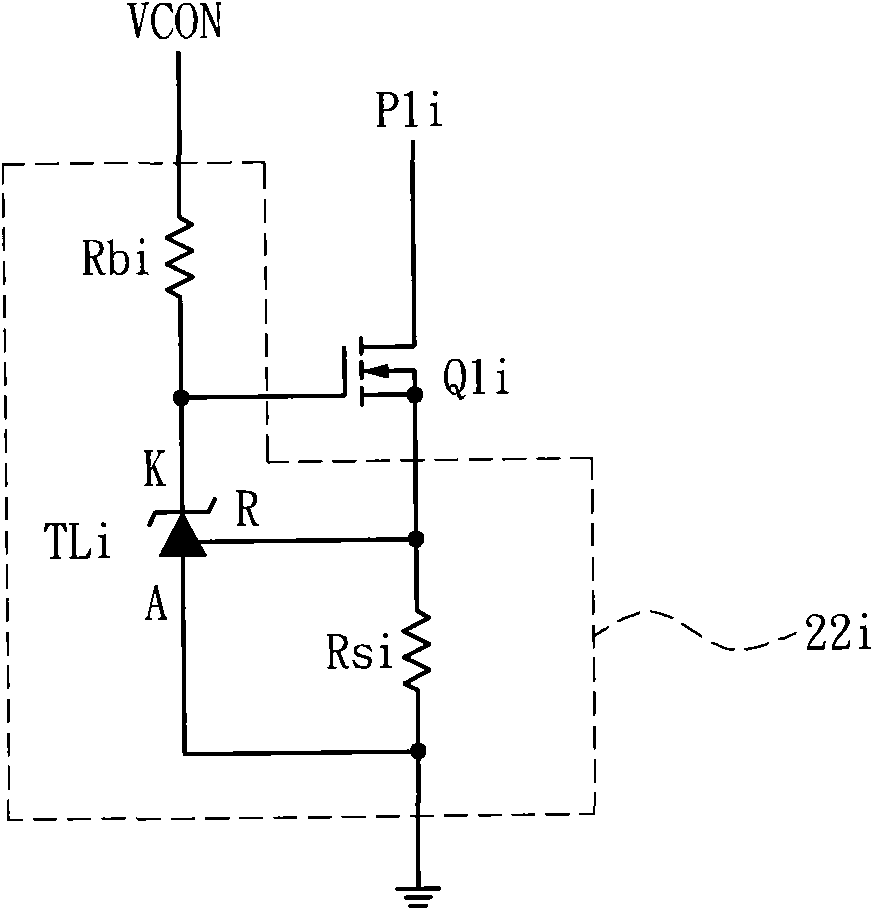

Light-emitting diode driving circuit

InactiveCN102123536ASimple structureLow costElectric light circuit arrangementShort circuit protectionBurning out

The invention provides a light-emitting diode (LED) driving circuit. A second end of each light string is connected with a current balancer in series to perform self-feedback control so as to adjust the current passing through each light string respectively; a voltage compensation circuit is added to finely adjust the voltage of each light string to ensure that each light string with different straight-forward voltage can be completely illuminated; besides, a short circuit protective circuit is added to ensure that the LED driving circuit is turned off when the LED short circuit happens in the light string, so the light string is protected from being burnt out by excess current. The LED driving circuit does not need to adopt a special LED controller, and the framework of the driving circuit is quite simple, so that the cost can be greatly reduced.

Owner:TOP VICTORY INVESTMENTS

DC-to-DC converter capable of preventing overvoltage

InactiveUS6204648B1Avoid Overvoltage ProblemsAvoid fireEfficient power electronics conversionApparatus without intermediate ac conversionOvervoltageConverters

To avoid burning out a capacitor in a synchronous rectification type DC-to-DC converter due to overvoltages, the synchronous rectification type DC-to-DC converter includes a storage unit storing therein power derived from a power supply, switching elements connecting and disconnecting respective signal paths from power and ground, and a control unit controlling the connecting / disconnecting operations of the switching elements to maintain a voltage output from the storage unit at a predetermined value. The DC / DC converter also includes an overvoltage detecting unit monitoring a voltage derived from the power supply to thereby output an alarm signal when the voltage derived from the power supply exceeds a preselected voltage value, a shortcircuiting unit influencing the connecting conditions of the switching elements when the alarm signal from the overvoltage detecting unit is input therein, whereby the voltage derived from the power supply is shortcircuited, and an interrupting unit interrupting one of the signal paths by the power shortcircuited by the shortcircuiting unit.

Owner:FUJITSU LTD

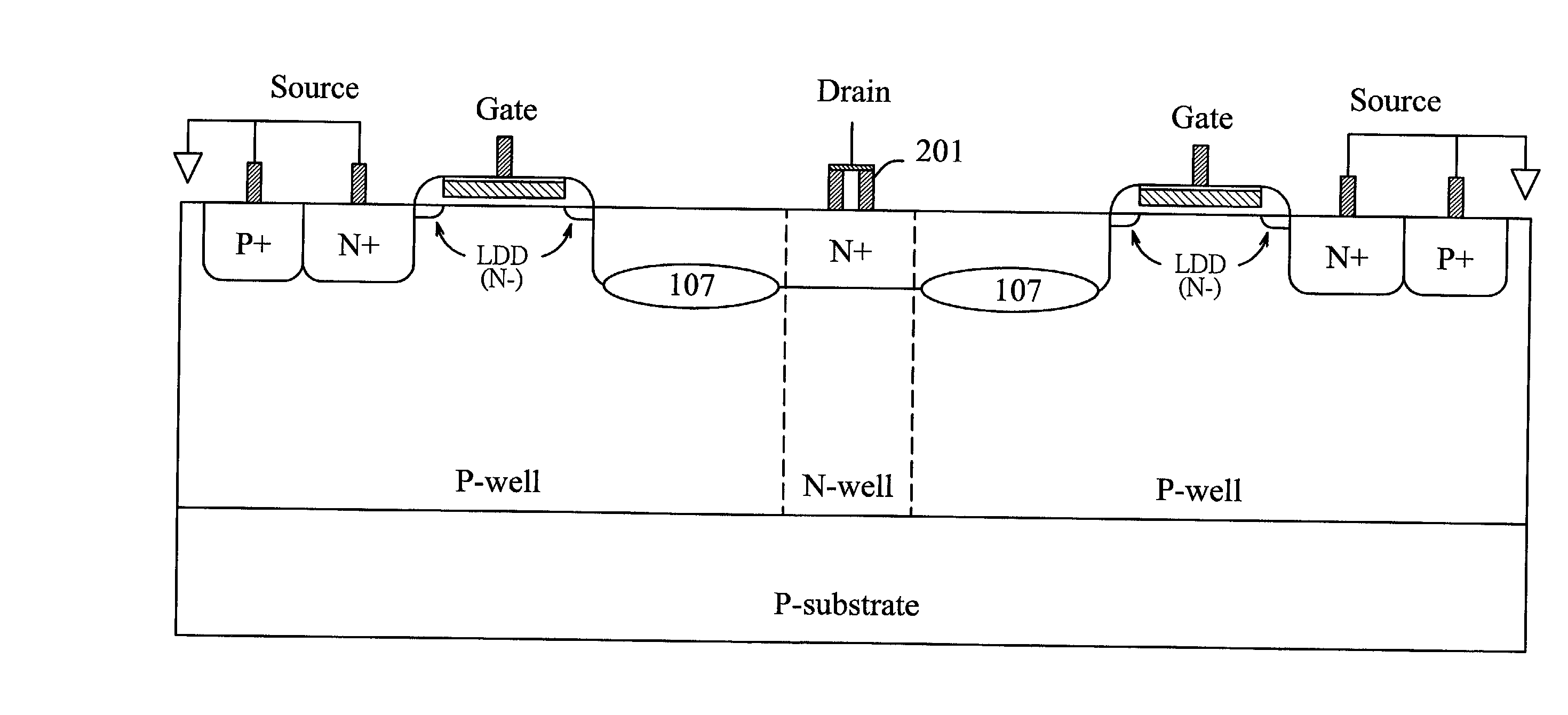

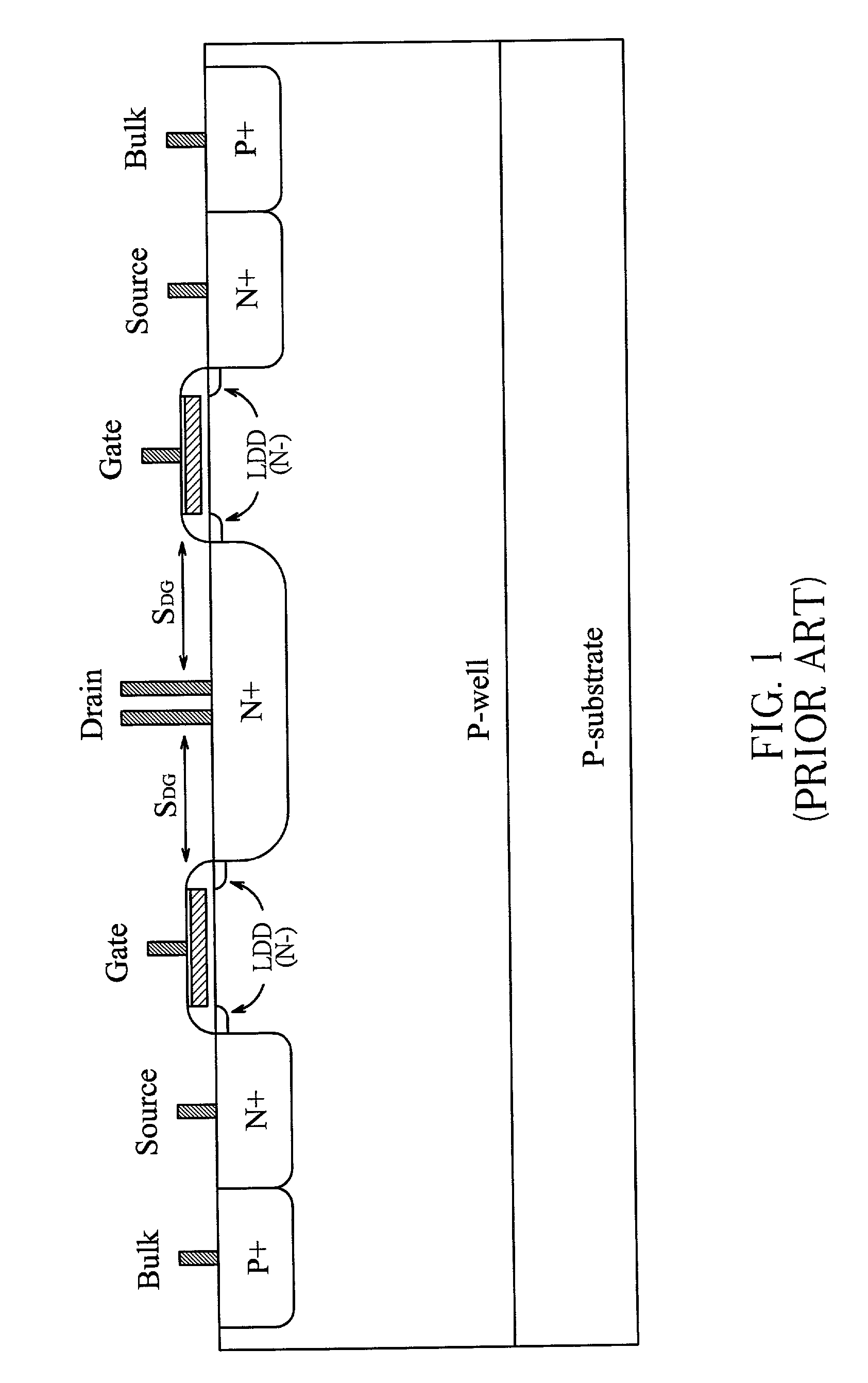

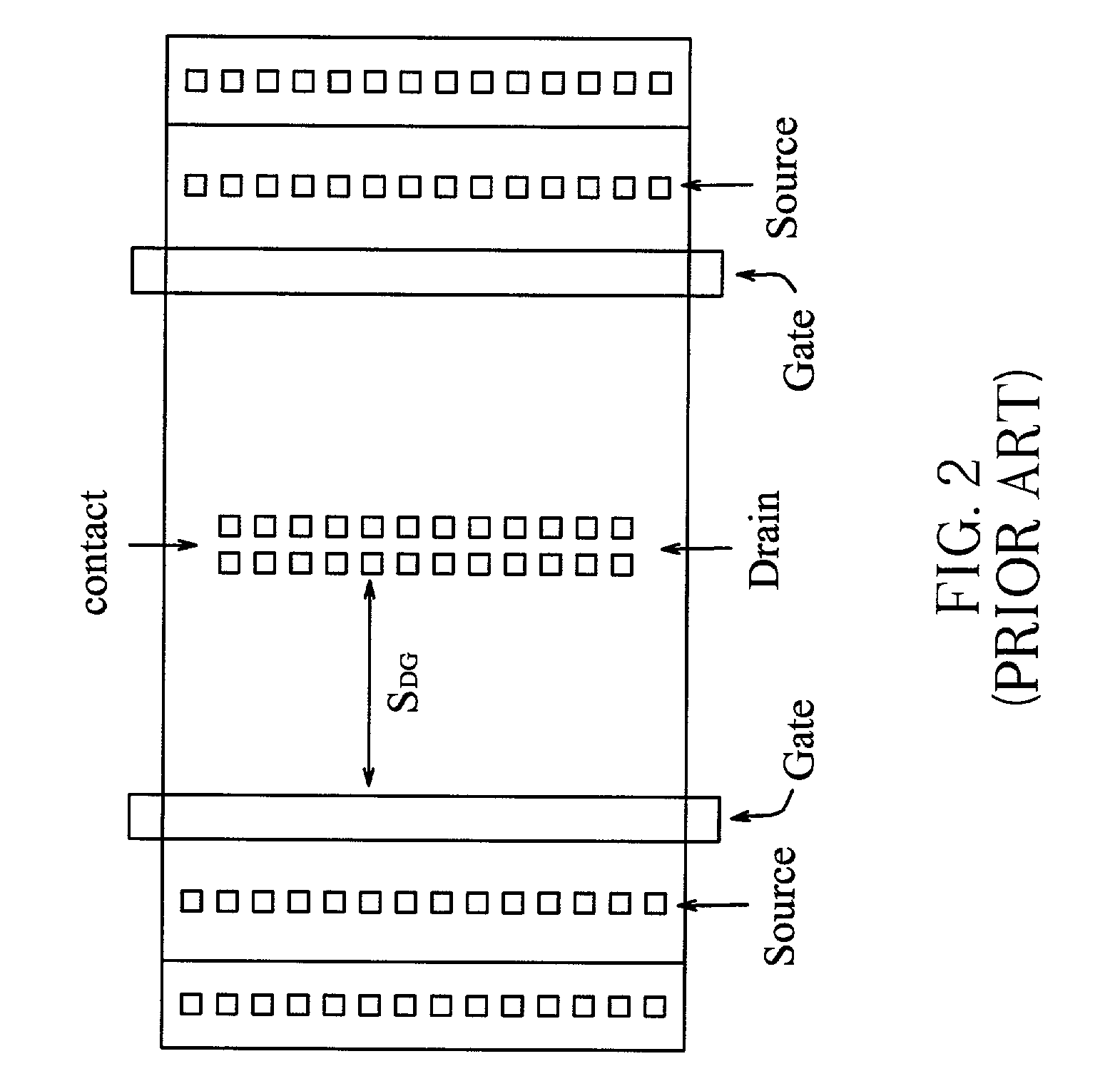

Method for manufacturing semiconductor devices having ESD protection

InactiveUS20020076876A1Solid-state devicesSemiconductor/solid-state device manufacturingEngineeringSemiconductor

A Method for manufacturing semiconductor devices having ESD protection. The method includes the steps of providing a semiconductor substrate having a well region, forming a gate structure on the semiconductor substrate, the gate structure including an oxide layer, a gate electrode on said oxide layer, and two spacer sidewalls, forming a source region within the well region at one side of the gate structure, forming a drain region within the well region at the other side of the gate structure, forming lightly doped source / drain regions in the well region and beneath the spacer walls of the gate structure wherein the lightly doped source / drain regions have the same conductivity type as the drain region and, and performing an implant with the same conductivity type as the well region as to form an ESD implantation region. The ESD implantation region is located under the diffusion region that is between the drain contact and the poly gate of output NMOS, but without covering the region right under the drain contact. Therefore, the ESD current is discharged through the ESD-implanted region to the substrate without causing current crowding under the drain contact as to burn out the drain contact.

Owner:SILICON INTEGRATED SYSTEMS

Infrared humidification device and control method

ActiveCN105650794ASolve the problem of high water quality requirementsAvoid burnsMechanical apparatusSpace heating and ventilation safety systemsWater storage tankWater quality

The invention discloses an infrared humidification device and a control method. The device comprises a plurality of infrared light sources, a lampshade, a water storage structure, a water inlet structure, a water level switch and a controller. The water storage structure comprises a water storage tank, an overflow valve and a drainage pipe. The water inlet structure comprises a water inlet pipe, a water inlet electromagnetic valve and a water injection pipe. On-off of a power supply circuit of the multiple infrared light sources is controlled by the controller, a current transformer is arranged in the power supply circuit of the infrared light sources and used for collecting current values, and the current values are transmitted to the controller. According to the infrared humidification device and the control method, radiant energy of the infrared light sources is adopted for heating and evaporating water, the requirement for water quality is not high, and the application range is wide; the water storage tank is automatically cleaned, the daily maintenance workload is reduced, and the maintenance cost is reduced; and the current values are collected by the current transformer and transmitted to the controller, the controller controls on-off of the power supply circuit of the infrared light sources according to the current values, and the situation that the infrared light sources are burnt out due to abnormal current is avoided, so that the safety and stability of the whole device are improved.

Owner:青岛海信网络能源股份有限公司

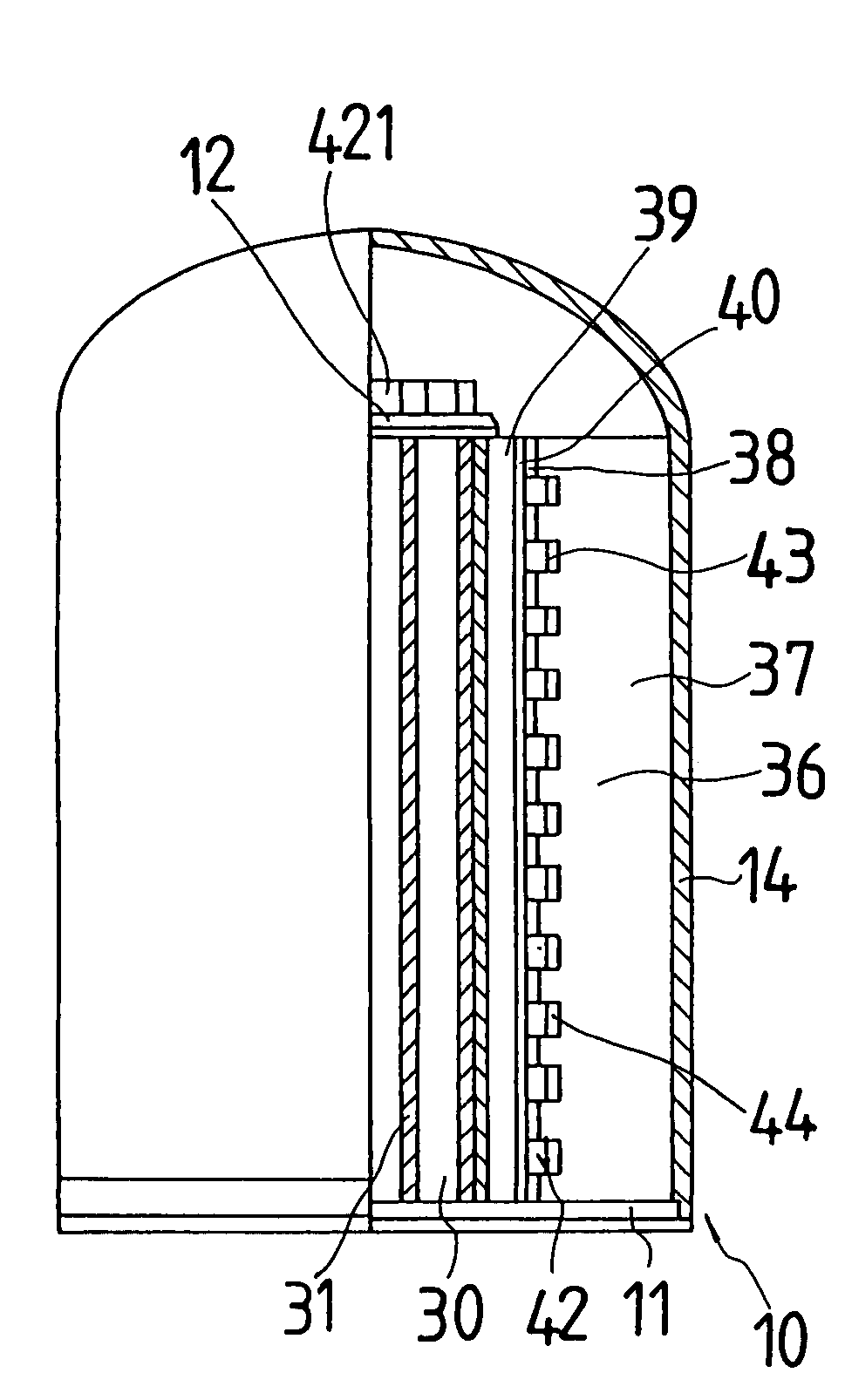

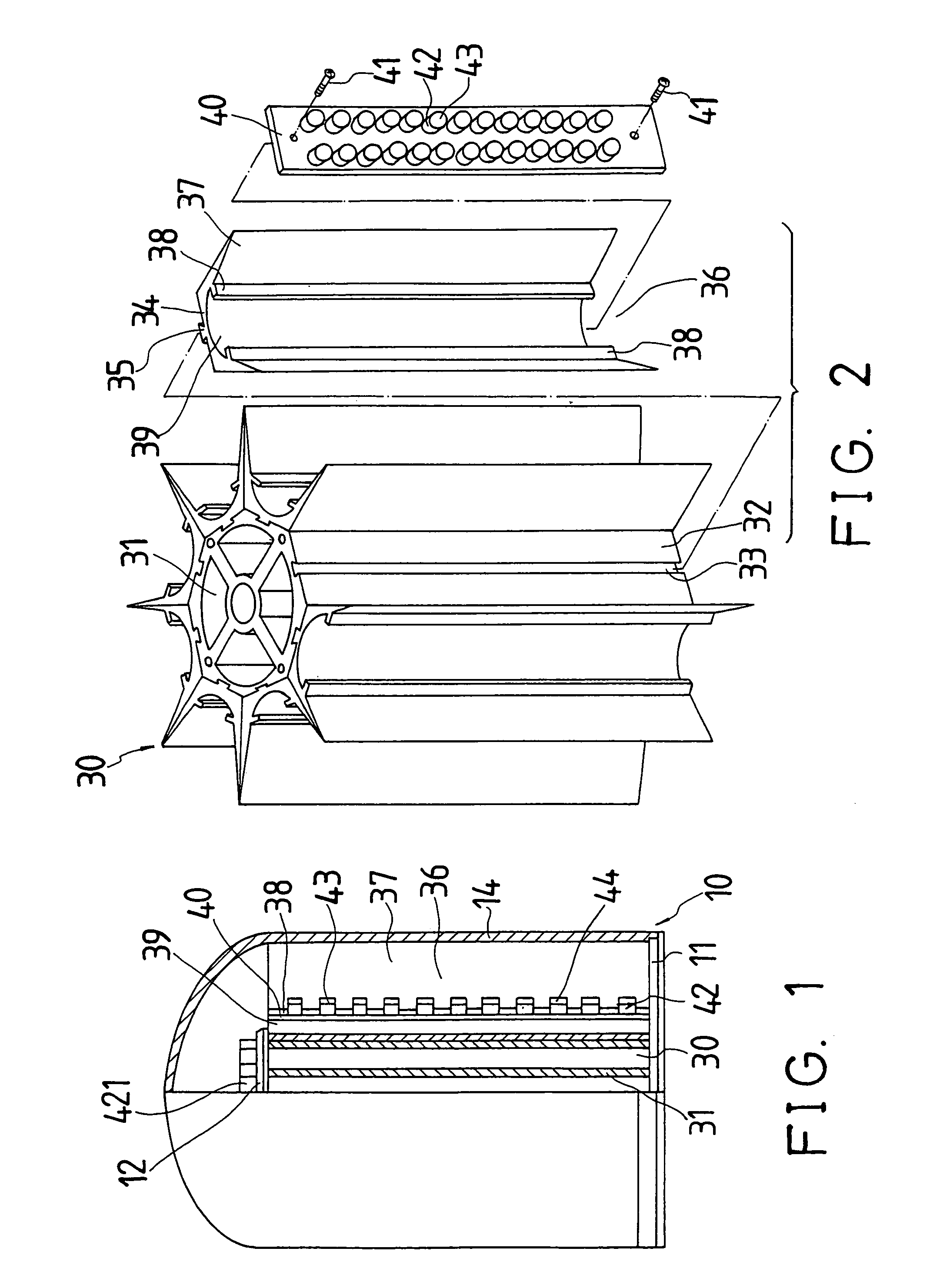

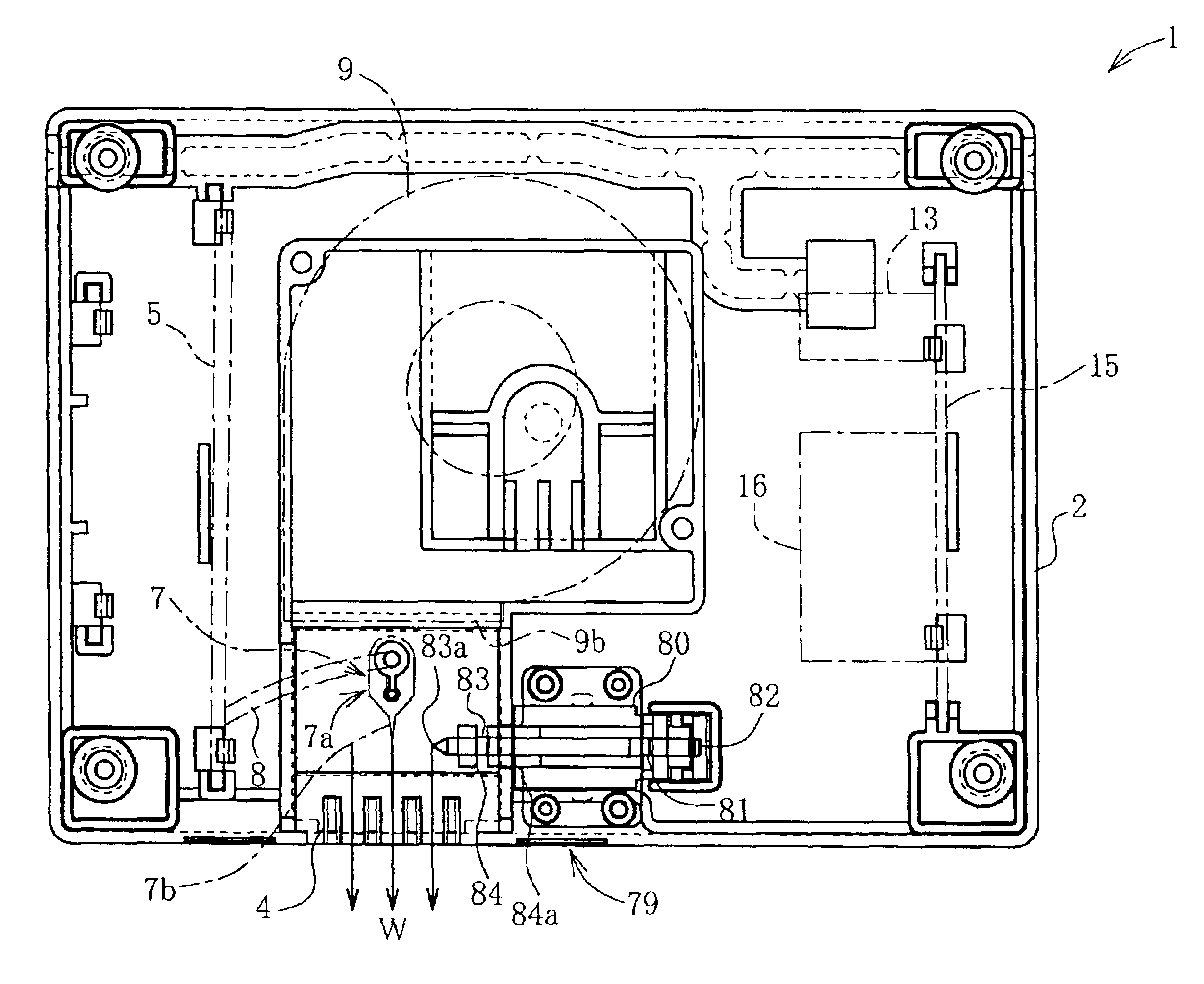

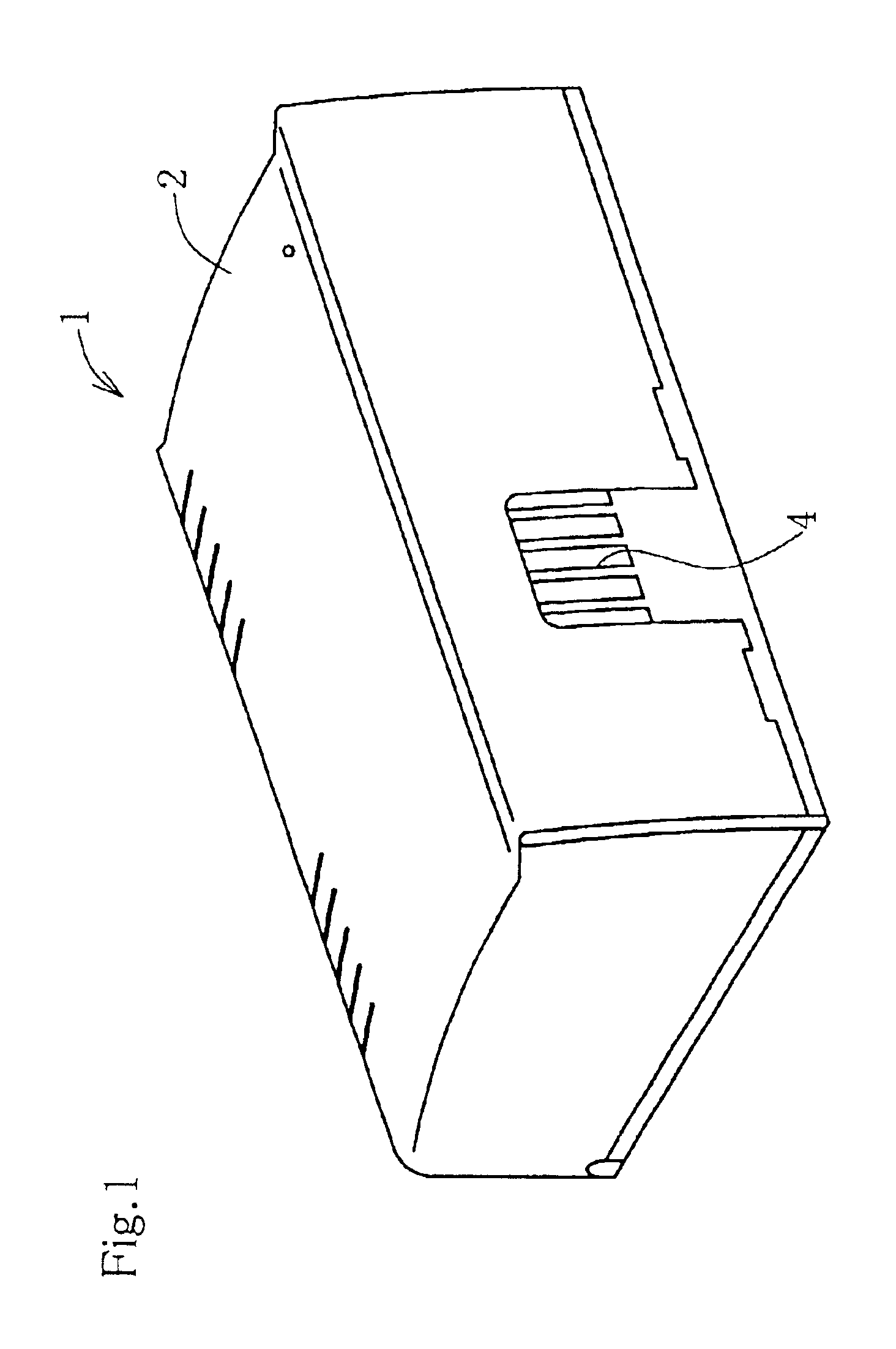

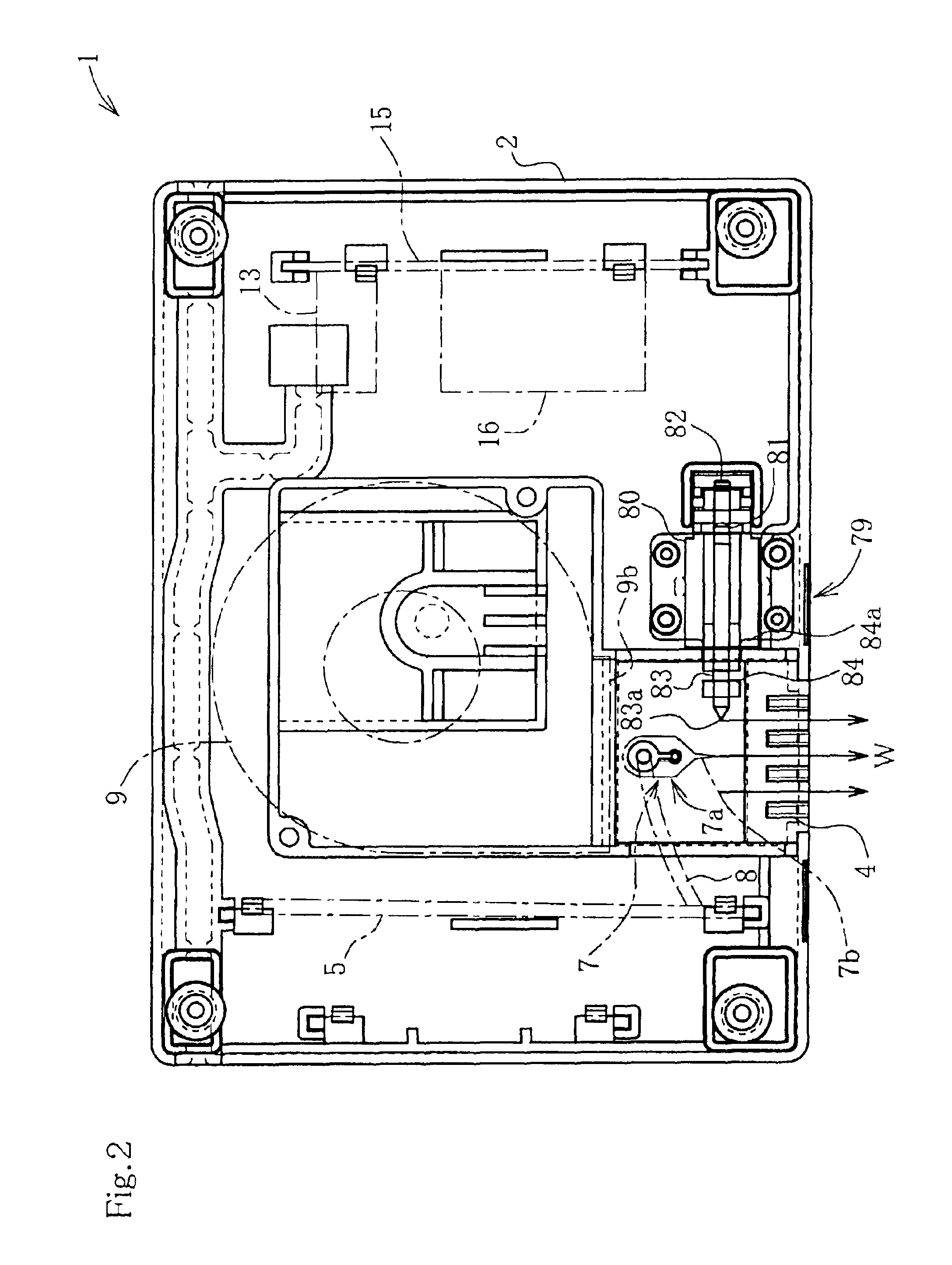

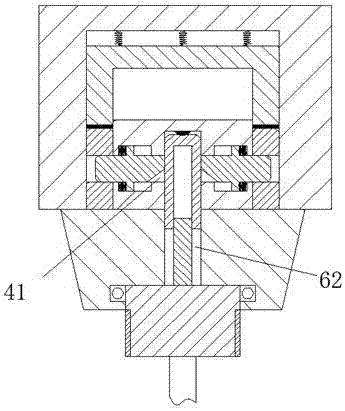

Ion generating apparatus

InactiveUS6791814B2Simple wayAvoid efficiencyLighting and heating apparatusAlternating current plasma display panelsElectricityEngineering

An ion generating apparatus 1 has an electric cleaning mechanism 79 for burning out attachment adhered on an ion generating electrode 7 by electric heating. Adhesion of dirt and the like onto the end portion of the electrode where an electron generation field concentrates will considerably ruin the ion generation efficiency. So that burning out of attachment adhered onto the end portion 7a of the ion generating electrode 7 using the electric cleaning mechanism 79 is extremely effective in terms of avoiding such nonconformity. Object of the cleaning will be attained to a sufficient degree if only the dirt adhered onto the sharpened end portion of the electrode 7, which is responsible for the ion generation, is selectively removed, which is also advantageous in simplifying the apparatus since there is no need to excessively raise the electric heating capacity of the electric cleaning mechanism 79.

Owner:NIHON PACHINKO PARTS

Method for combusting fuel reburning low-nitrogen oxide

ActiveCN102252324AImprove the mixing effectLong reduction reaction timeCombustion apparatusLow nitrogenEvaporation

The invention discloses a method for combusting a fuel reburning low-nitrogen oxide and belongs to a clean combustion method for a coal-fired boiler. Secondary medium air is used as a powder conveying medium of a combustor on the upper layer of the main combustion area of the boiler, coal powder used as a reburning fuel is conveyed into the boiler, the secondary medium air is used as distributed air of the combustor, the secondary air of the combustor on the upper layer is reduced correspondingly, the distributed air in the reburning area is reduced correspondingly, low excess air combustion is formed, the distributed air in a hearth is not enough, and finally over fire air (OFA) complements the required air; and the mixed medium of air and fuel gas is used as the conveying medium of the coal powder of the combustor of the upper layer, and the coal powder with the conventional fineness is conveyed into the boiler from the combustor on the upper layer by using a coal mill and a powder making system and is re-burnt and denitrated, and is burnt out by OFA. The problem that the reburning fuel and the fuel gas are not mixed uniformly, the reduction time is short, and the denitration efficiency is low is solved, the original design working conditions of maximum continuous evaporation capacity of the boiler and the like are not influenced, transformation is easy to realize, and the running cost is low.

Owner:徐州燃烧控制研究院有限公司

Processing method of warp knitting plush fabrics with burning out printing terylens

InactiveCN101876121AImprove the three-dimensional effectIdeal embossing effectPattern makingHeating/cooling textile fabricsPolyesterEngineering

The invention relates to a processing method of warp knitting plush fabrics with burning out printing terylens. The processing method comprises the following steps of: materials selection: selecting DTY (Draw Textured Yarn) terylen low stretch yarns from 75 D to 150 D as felted yarn materials and selecting FDY (Fully Drawn Yarn) semi-dull polyester yarns from 50 D to 100 D as ground yarn materials, wherein the DTY terylen low stretch yarns account for 60-80% of the fabrics by weight percent, and the FDY semi-dull polyester yarns account for 20-40% of the fabrics by weight percent; weaving or slitting after weaving; thermally forming or pretreating after thermally forming; brushing and cropping the front surface or brushing and cropping the back surface, cropping the back surface and pilling; post-forming; burning out printing: carrying out burning out printing on grey fabrics subjected to the post-forming by using a burning out printing alkali slurry; steaming; post-treating; and forming a finished product. By the technical scheme, the fabrics can achieve the advantages of strong third dimension of patterns, ideal sculptured pattern effects and favorable shininess, residues does not generate in the weaving process, which is beneficial to protecting warp knitting machines.

Owner:CHANGSHU XINXIN WARP & KNITTING

Hand-operated power supply plugging connecting device

ActiveCN107154551AImprove stability and securityAvoid Electric Shock AccidentsCoupling device detailsElectric shockBurning out

The invention discloses a hand-operated power supply plugging connecting device. The hand-operated power supply plugging connecting device comprises a power supply body and a plug connected with the power supply body in a cooperated way. The power supply body comprises two plugging grooves, which are in a left-right symmetric arrangement, and have openings facing forwards; and a power supply groove, which is disposed between the two plugging grooves, and has an opening facing forward. The rear end wall of the power supply groove is provided with a power supply contact connected with a power supply. The rear ends of the two plugging grooves are communicated with a sliding groove, A sliding block capable of sliding forwards and backwards is disposed in the sliding groove. The hand-operated power supply plugging connecting device is advantageous in that a structure is simple, production costs are low, power supply is safe and stable, and connecting and disconnecting operation steps are simple, and therefore electric shock accidents in a daily life are effectively reduced, life safety of users is guaranteed, occurrence of electrical equipment power-off accidents caused by wrong kicking and wrong colliding is prevented, the burn-out rate of the electrical equipment is reduced, and popularization and application are facilitated.

Owner:SHANDONG FENGYUAN CHEM CO LTD

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com