Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

55results about How to "Reduce undercutting" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

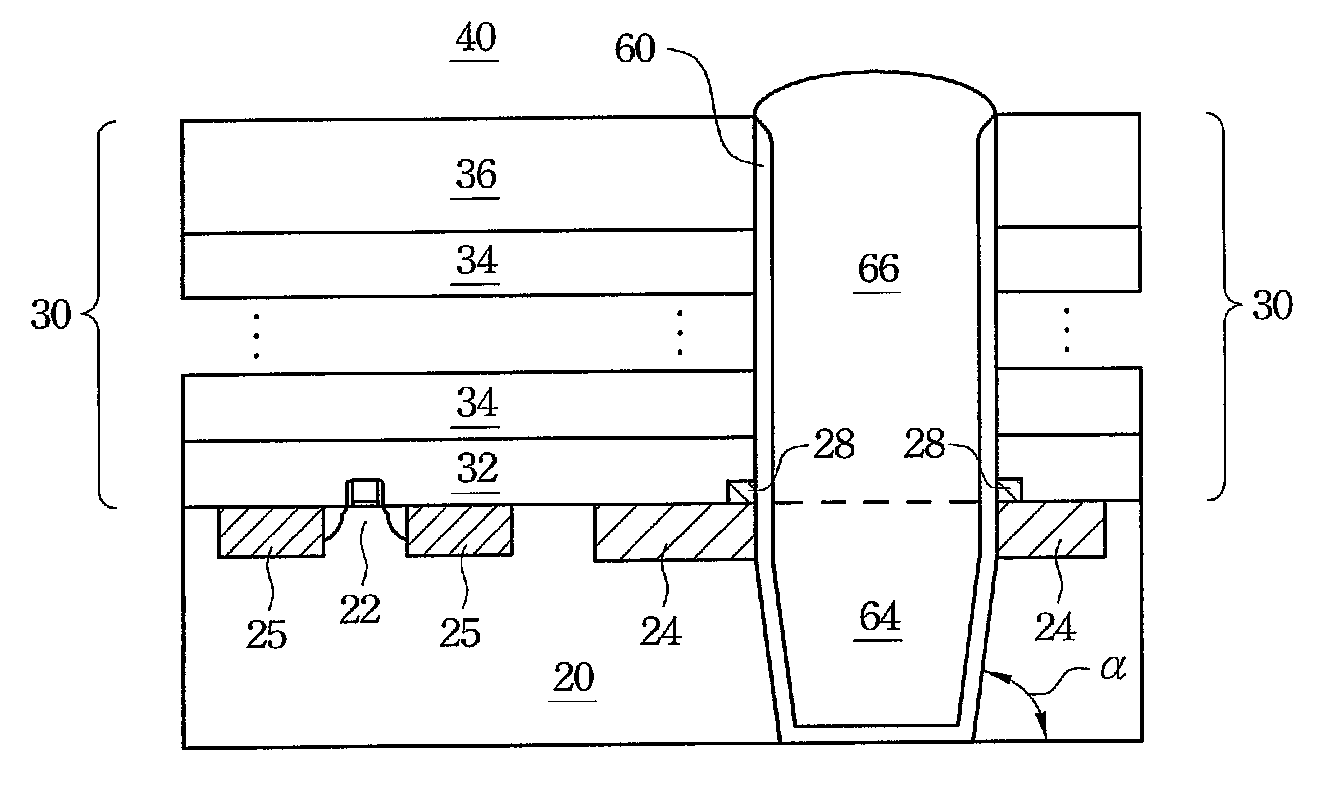

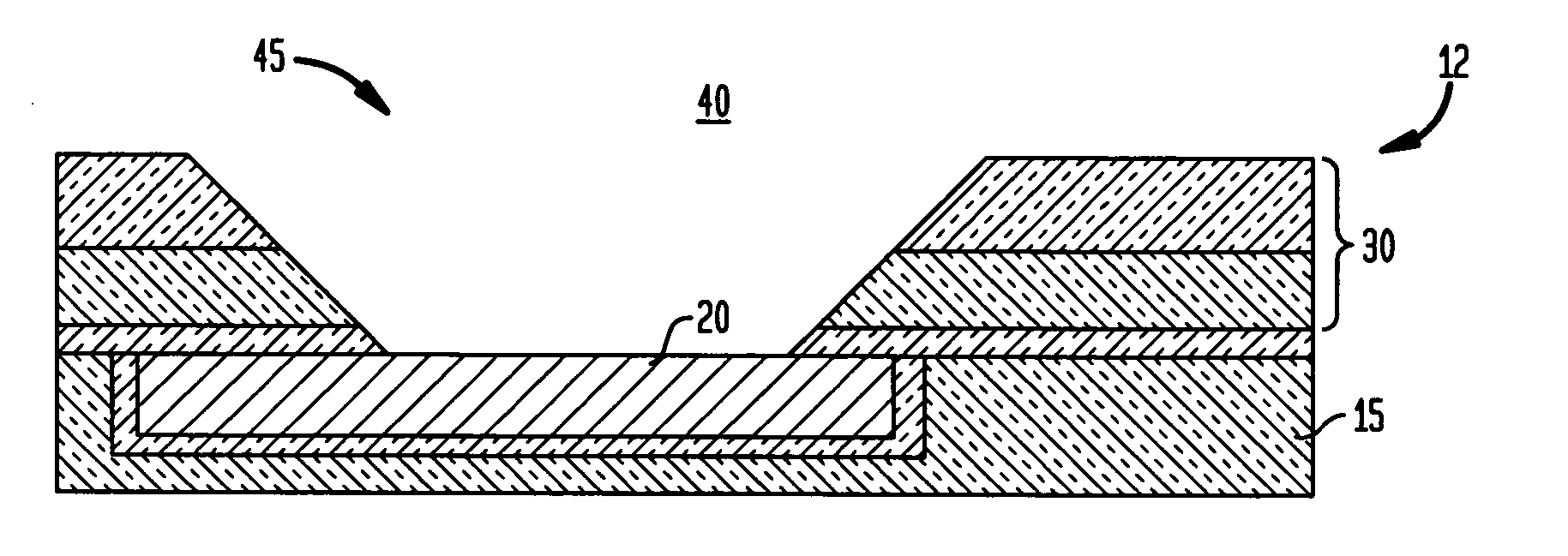

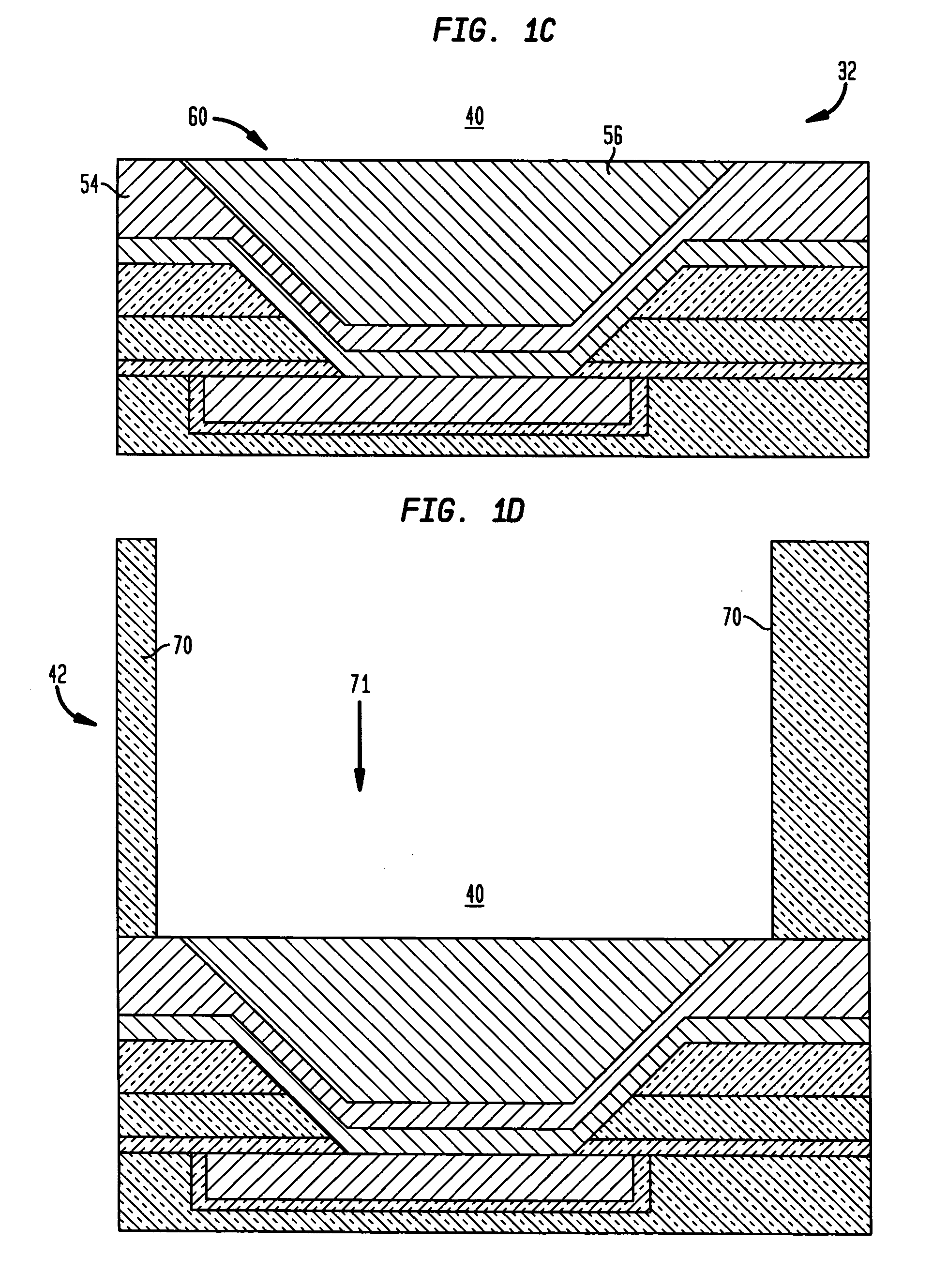

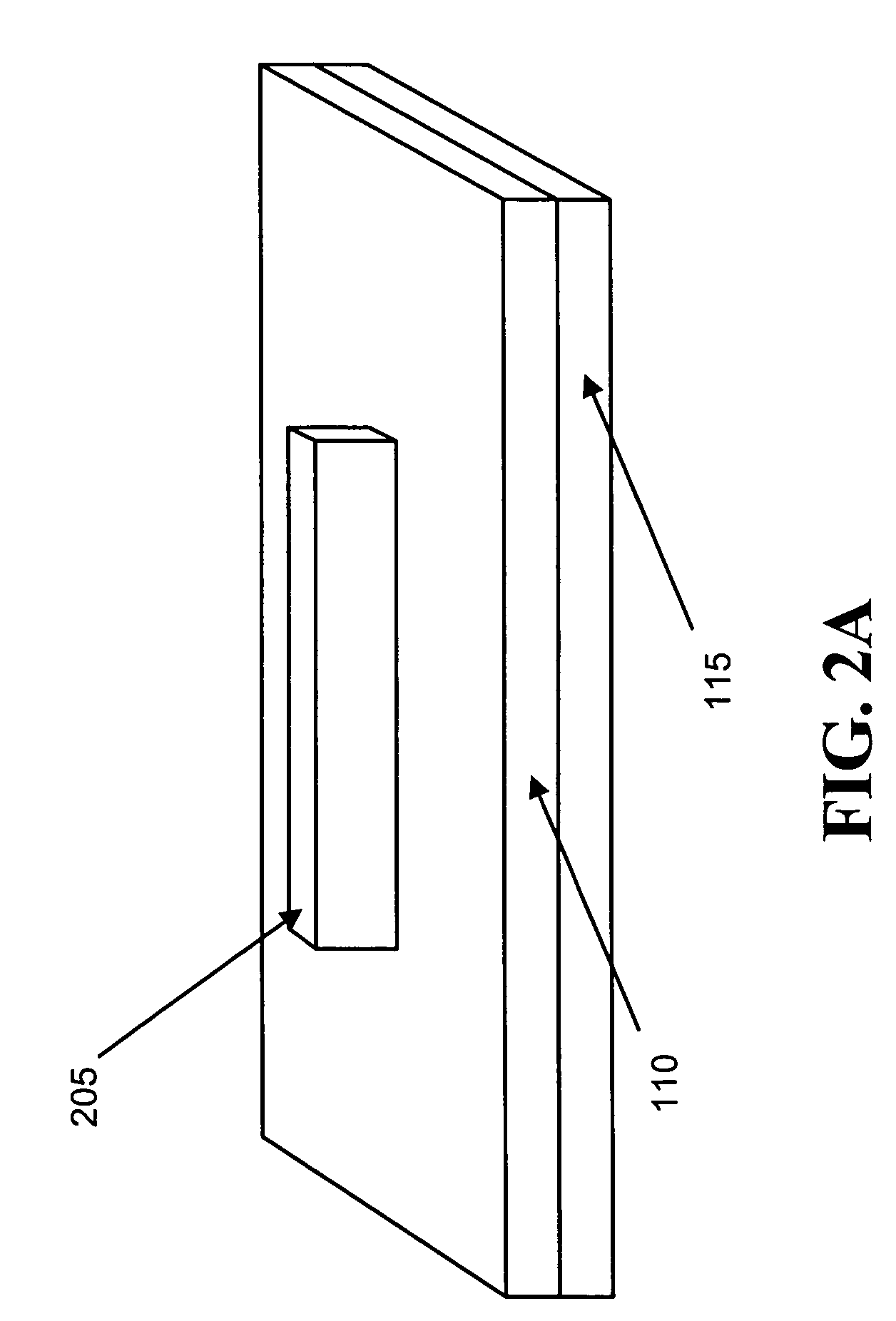

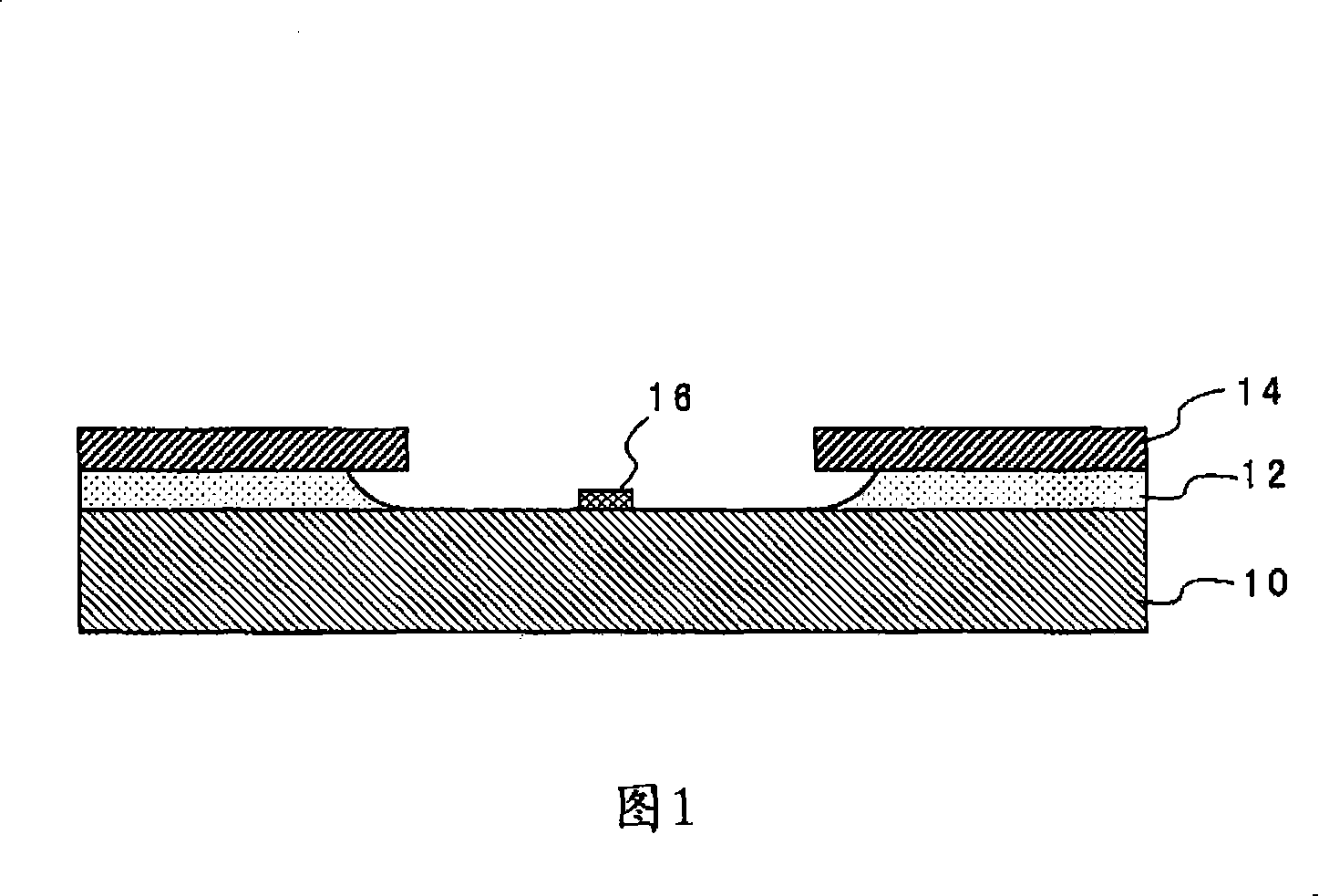

Tapered through-silicon via structure

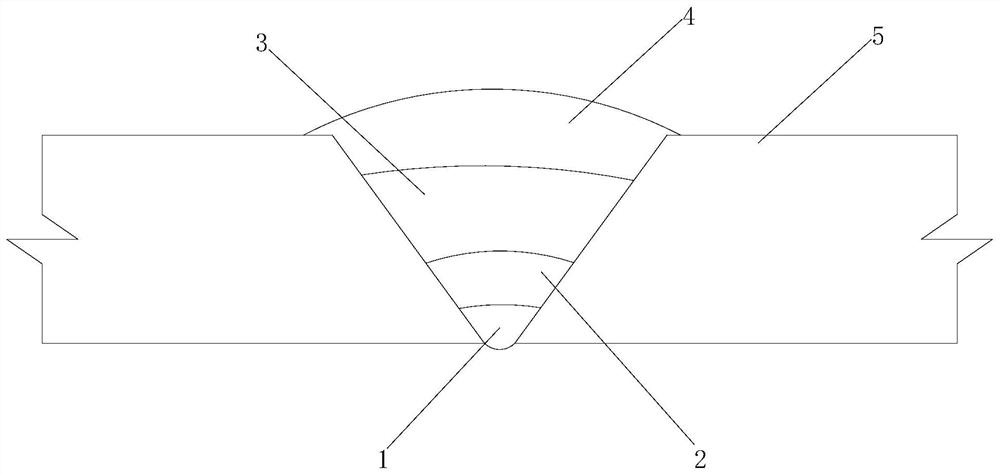

ActiveUS7564115B2Expand coverageReduce undercuttingSemiconductor/solid-state device detailsSolid-state devicesEngineeringDielectric layer

An integrated circuit structure includes a substrate; a through-silicon via (TSV) in the substrate, the TSV being tapered; a hard mask region extending from a top surface of the substrate into the substrate, wherein the hard mask encircles a top portion of the TSV; dielectric layers over the substrate; and a metal post extending from a top surface of the dielectric layers to the TSV, wherein the metal post comprises same materials as the TSV.

Owner:TAIWAN SEMICON MFG CO LTD

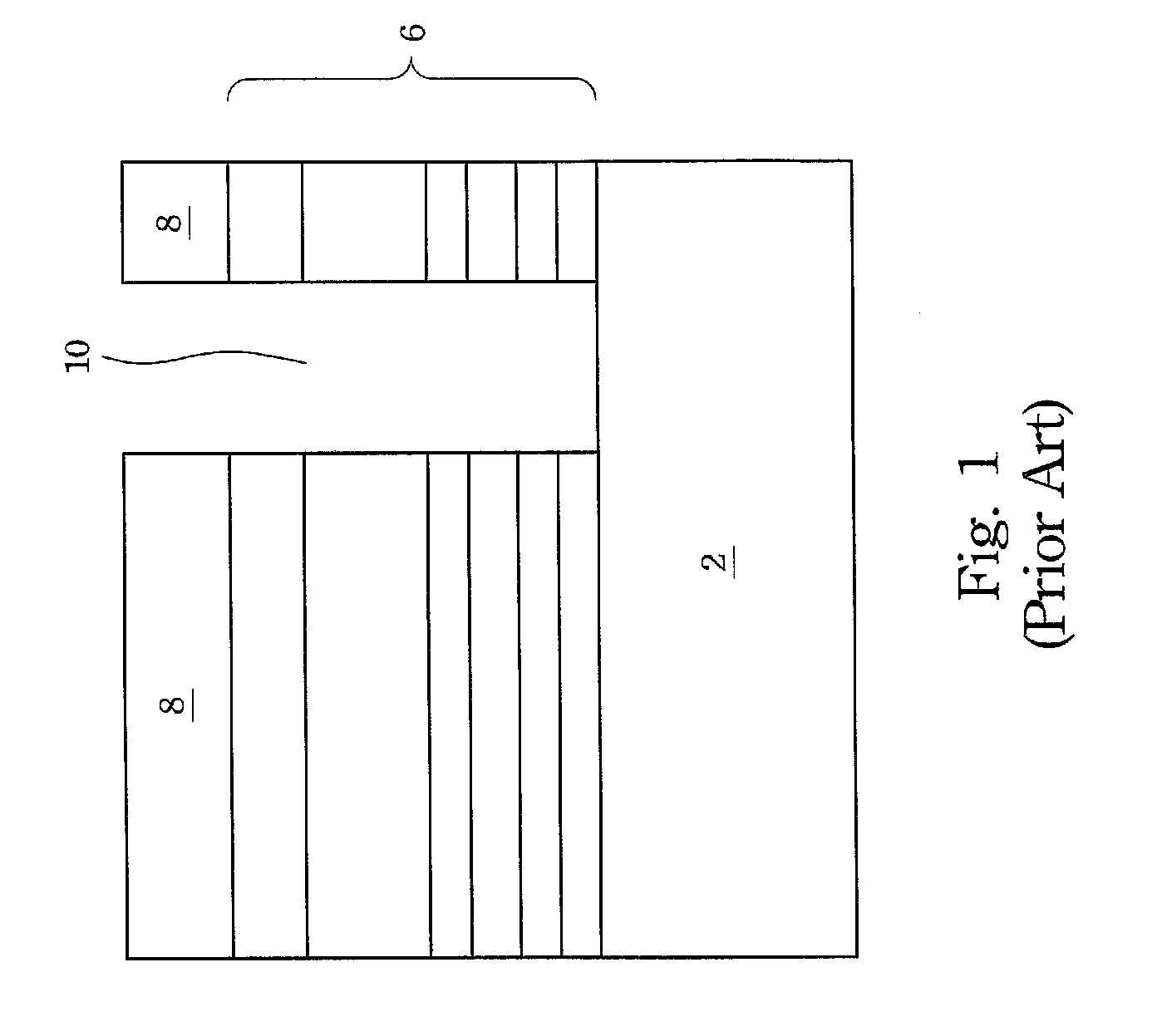

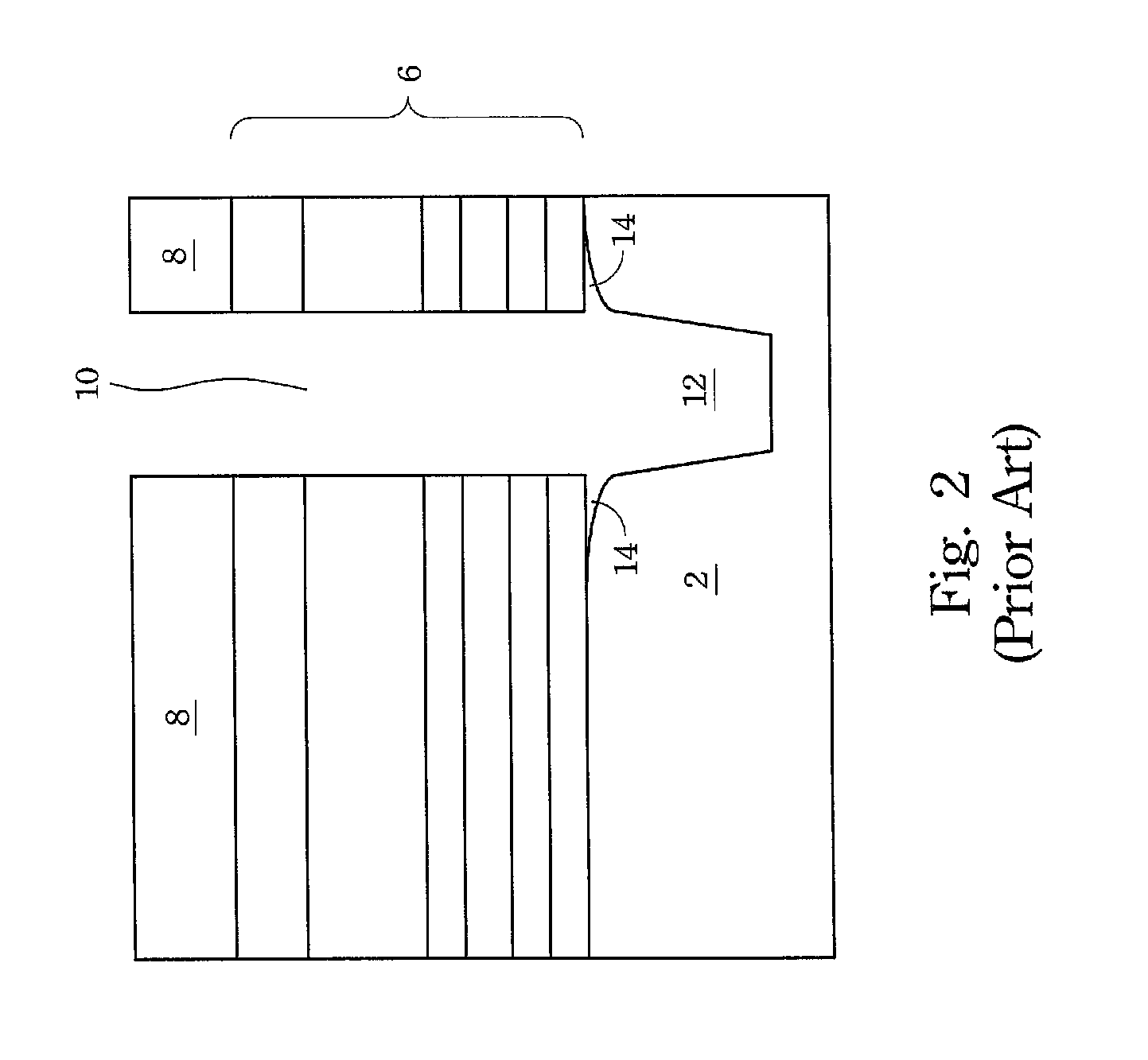

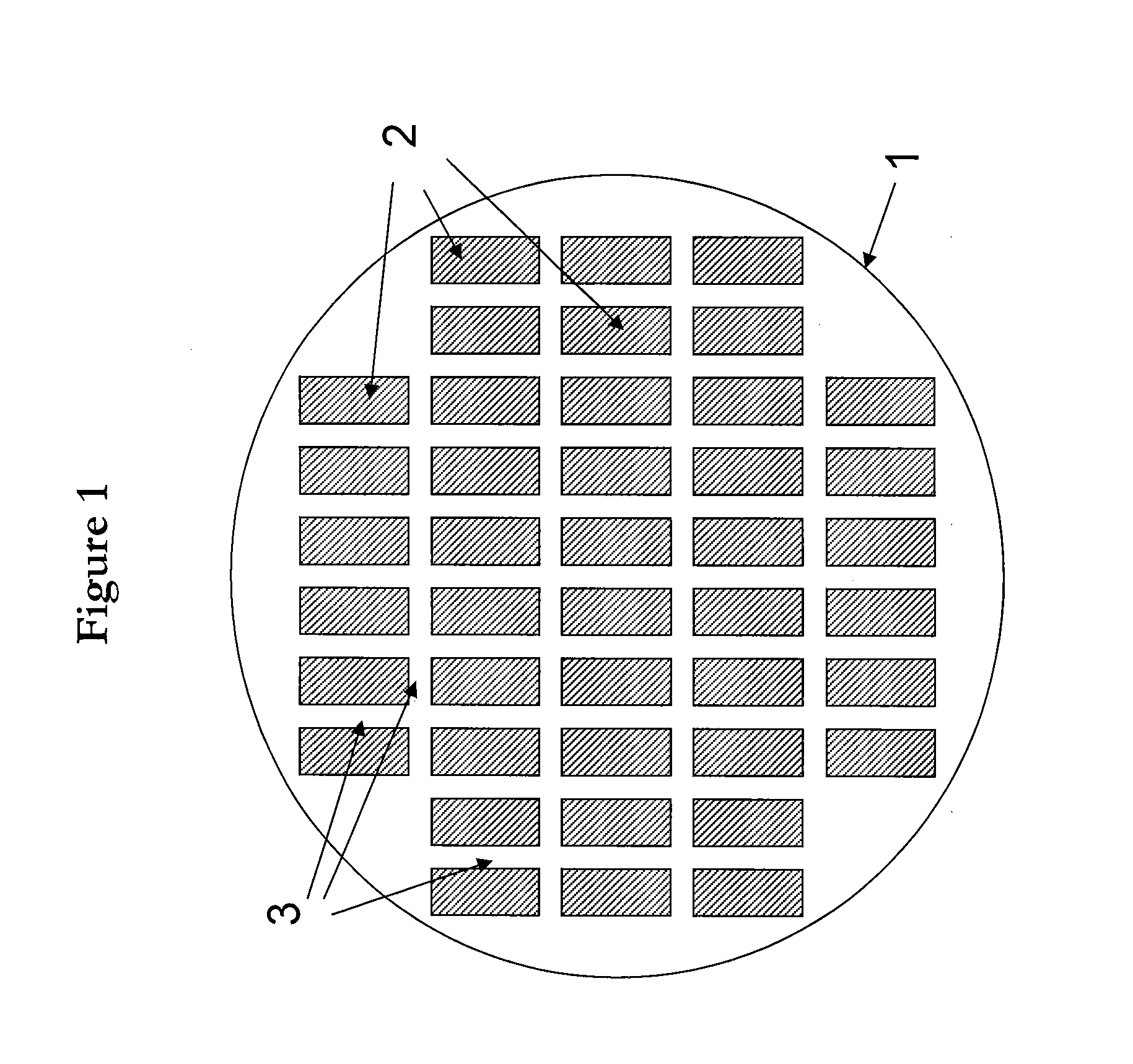

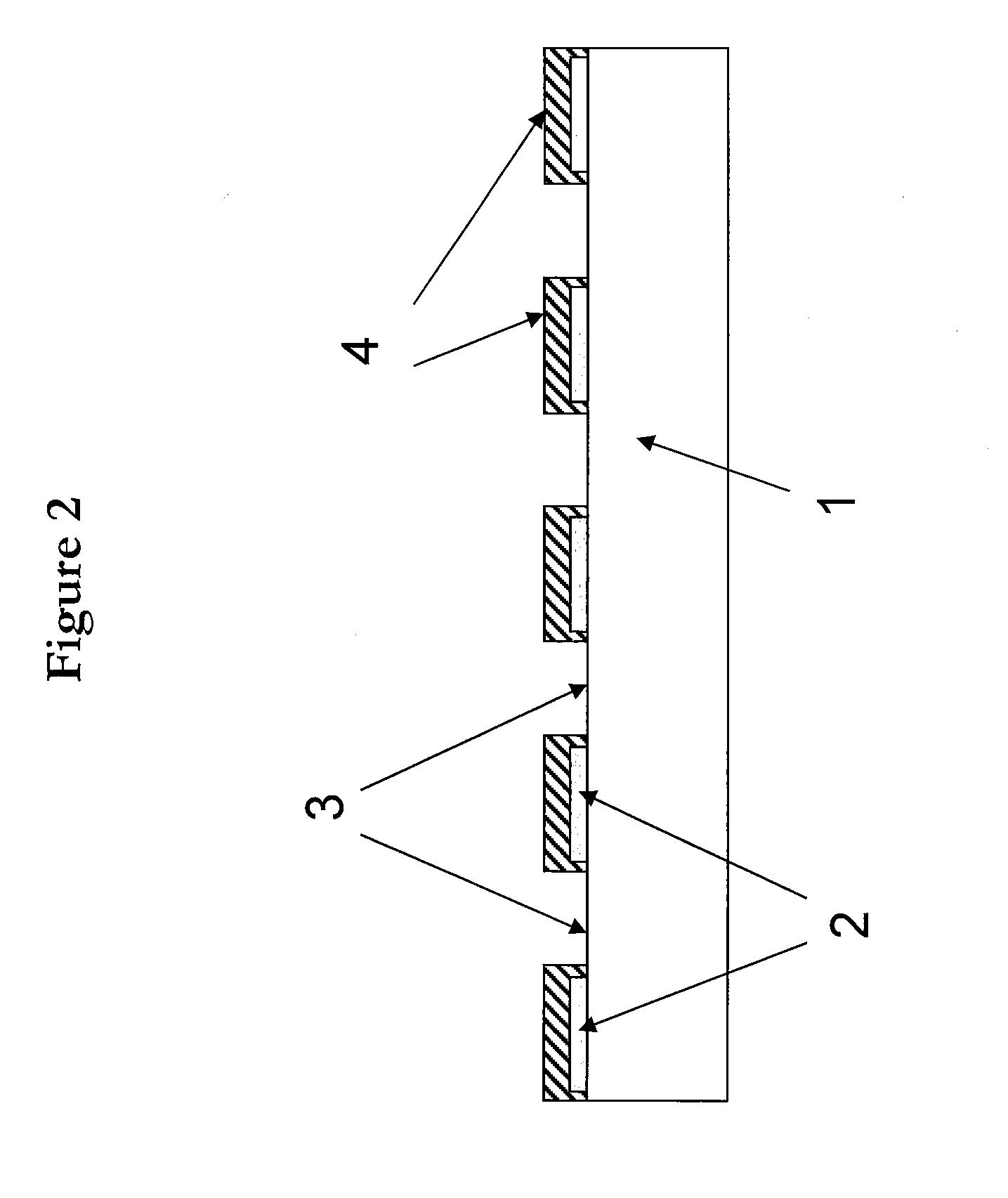

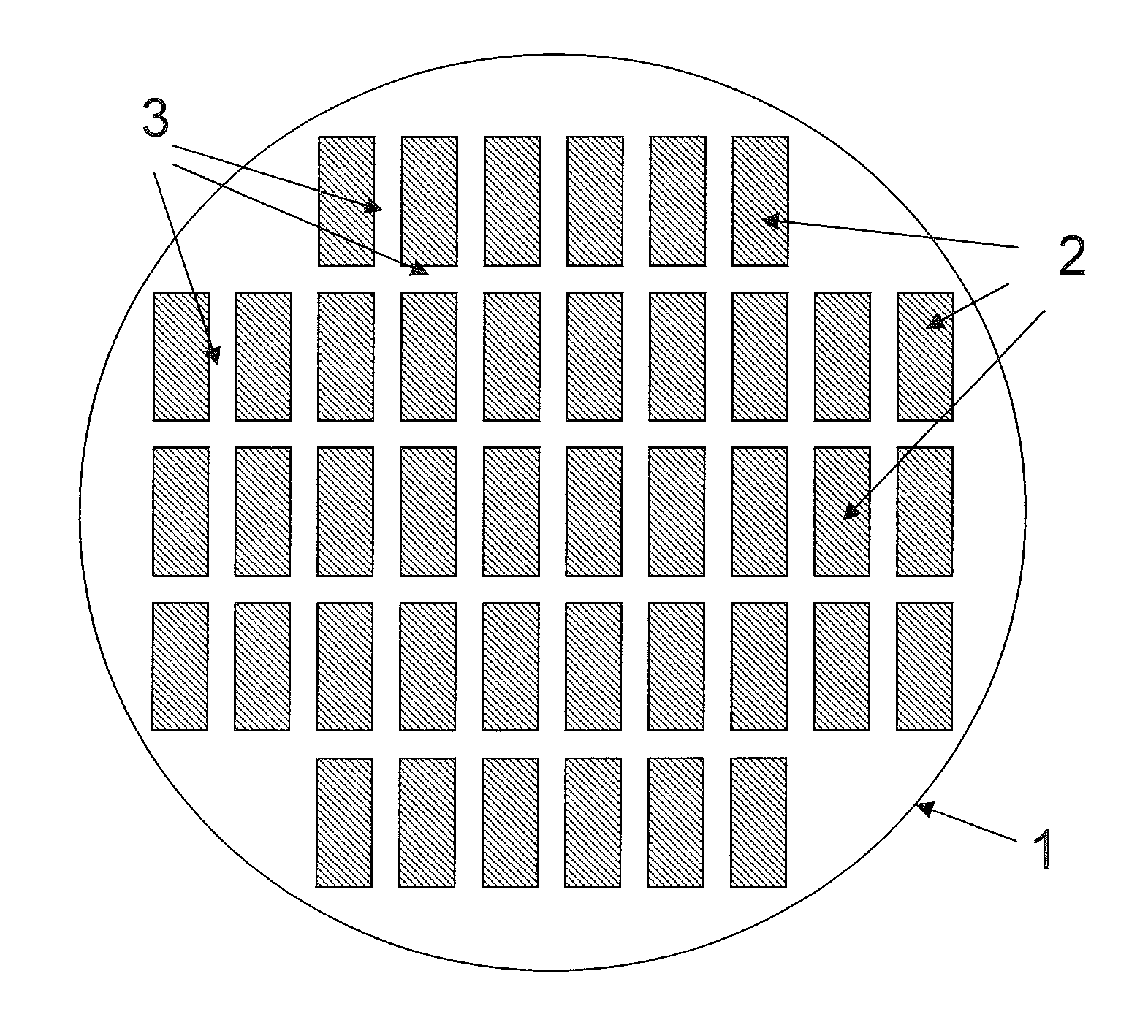

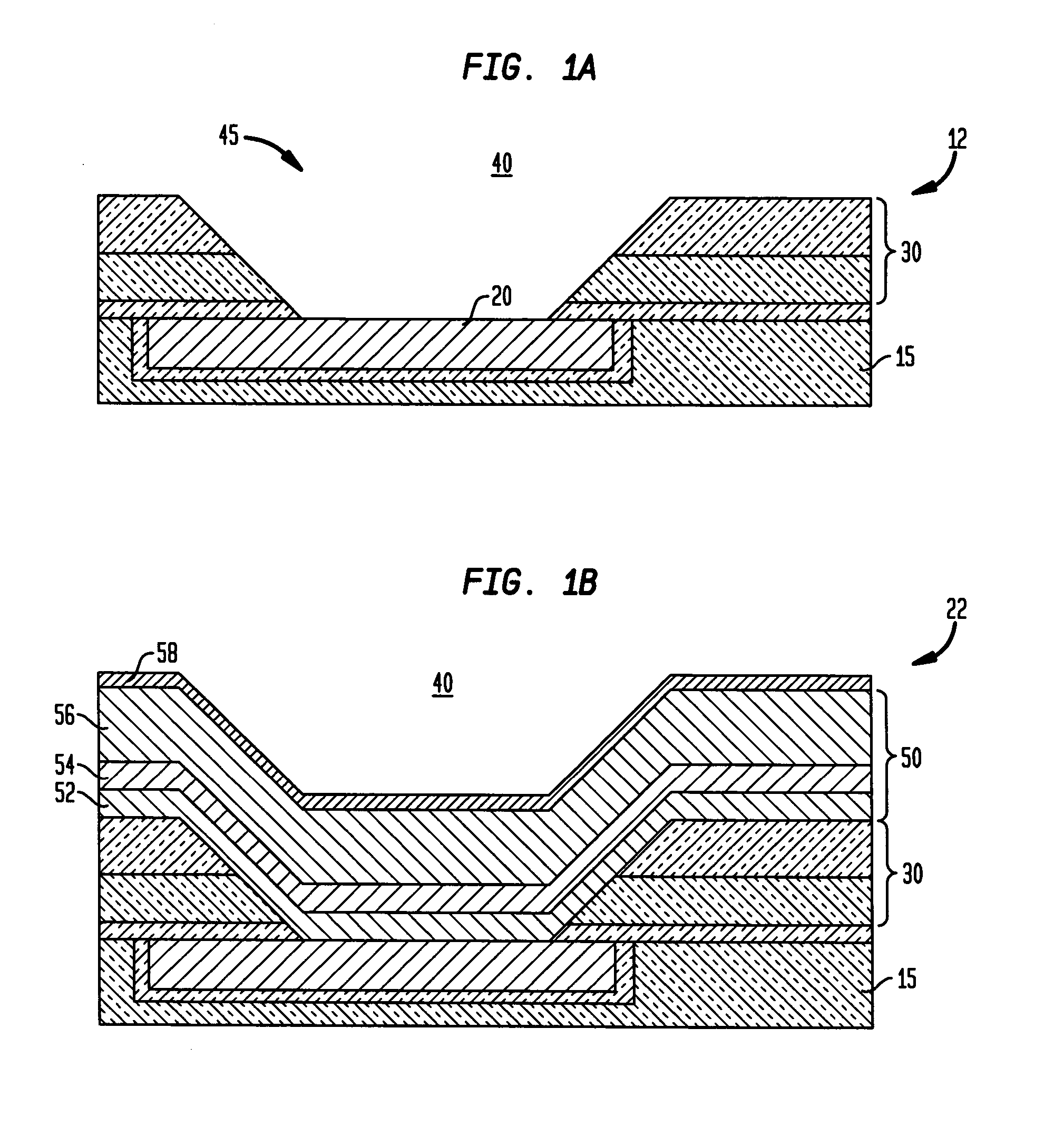

Method and Apparatus for Plasma Dicing a Semi-conductor Wafer

ActiveUS20120238073A1Protection from damageReduce undercuttingElectric discharge tubesSolid-state devicesEngineeringSemiconductor

The present invention provides a method for plasma dicing a substrate. The method comprising providing a process chamber having a wall; providing a plasma source adjacent to the wall of the process chamber; providing a work piece support within the process chamber; placing the substrate onto a support film on a frame to form a work piece work piece; loading the work piece onto the work piece support; providing a cover ring disposed above the work piece; generating a plasma through the plasma source; and etching the work piece through the generated plasma.

Owner:PLASMA THERM

Method and Apparatus for Plasma Dicing a Semi-conductor Wafer

ActiveUS20130065378A1Protection from damageReduce undercuttingElectric discharge tubesSolid-state devicesEngineeringSemiconductor

The present invention provides a method for plasma dicing a substrate. The method comprising providing a process chamber having a wall; providing a plasma source adjacent to the wall of the process chamber; providing a work piece support within the process chamber; placing the substrate onto a support film on a frame to form a work piece work piece; loading the work piece onto the work piece support; providing a cover ring disposed above the work piece; generating a plasma through the plasma source; and etching the work piece through the generated plasma.

Owner:PLASMA THERM

Method and Apparatus for Plasma Dicing a Semi-conductor Wafer

ActiveUS20130230972A1Protection from damageReduce undercuttingElectric discharge tubesSolid-state devicesSemiconductorPlasma cutting

The present invention provides a method for plasma dicing a substrate. The method comprising providing a process chamber having a wall; providing a plasma source adjacent to the wall of the process chamber; providing a work piece support within the process chamber; placing the substrate onto a support film on a frame to form a work piece work piece; loading the work piece onto the work piece support; providing a cover ring disposed above the work piece; generating a plasma through the plasma source; and etching the work piece through the generated plasma.

Owner:PLASMA THERM

Damascene patterning of barrier layer metal for C4 solder bumps

InactiveUS20060016861A1Reduce the amount presentReduce spacingPrinted circuit assemblingSemiconductor/solid-state device detailsEtchingCopper

A system and method for forming a novel C4 solder bump for BLM (Ball Limiting Metallurgy) includes a novel damascene technique is implemented to eliminate the Cu undercut problem and improve the C4 pitch. In the process, a barrier layer metal stack is deposited above a metal pad layer. A top layer of the barrier layer metals (e.g., Cu) is patterned by CMP. Only bottom layers of the barrier metal stack are patterned by a wet etching. The wet etch time for the Cu-based metals is greatly reduced resulting in a reduced undercut. This allows the pitch of the C4 solder bumps to be reduced. An alternate method includes use of multiple vias at the solder bump terminal.

Owner:GLOBALFOUNDRIES INC

Sacrificial oxide for minimizing box undercut in damascene FinFET

ActiveUS7084018B1Reduce buried oxide undercutReducing buried oxide undercutSolid-state devicesSemiconductor/solid-state device manufacturingBuried oxideOxide

A method of reducing buried oxide undercut during FinFET formation includes forming a fin on a buried oxide layer and forming a source region adjacent a first end of the fin and a drain region adjacent a second end of the fin. The method further includes forming a sacrificial oxide layer over the fin and source and drain regions and forming a gate over the fin, wherein the sacrificial oxide layer reduces undercutting of the buried oxide layer during gate formation.

Owner:ADVANCED MICRO DEVICES INC

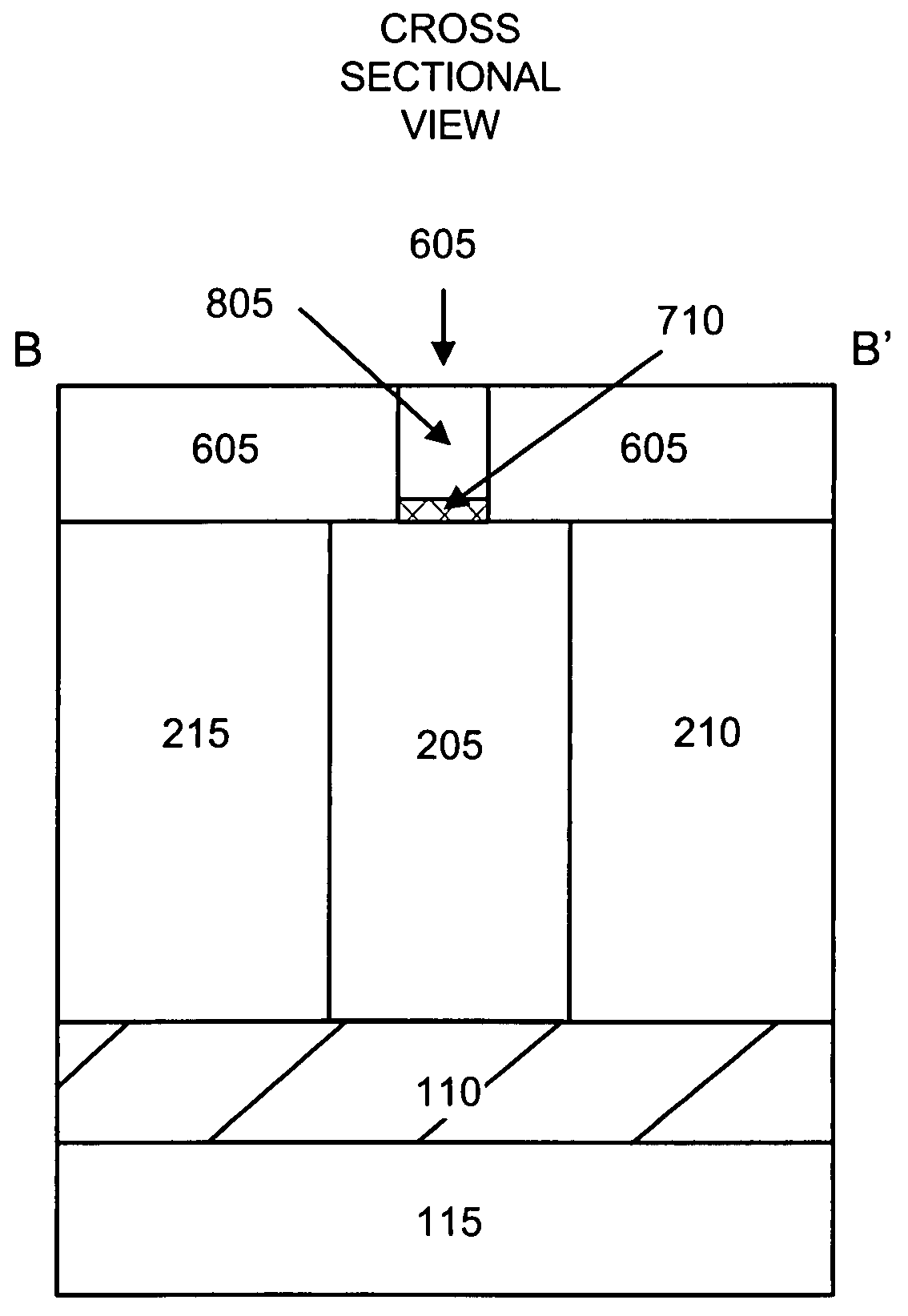

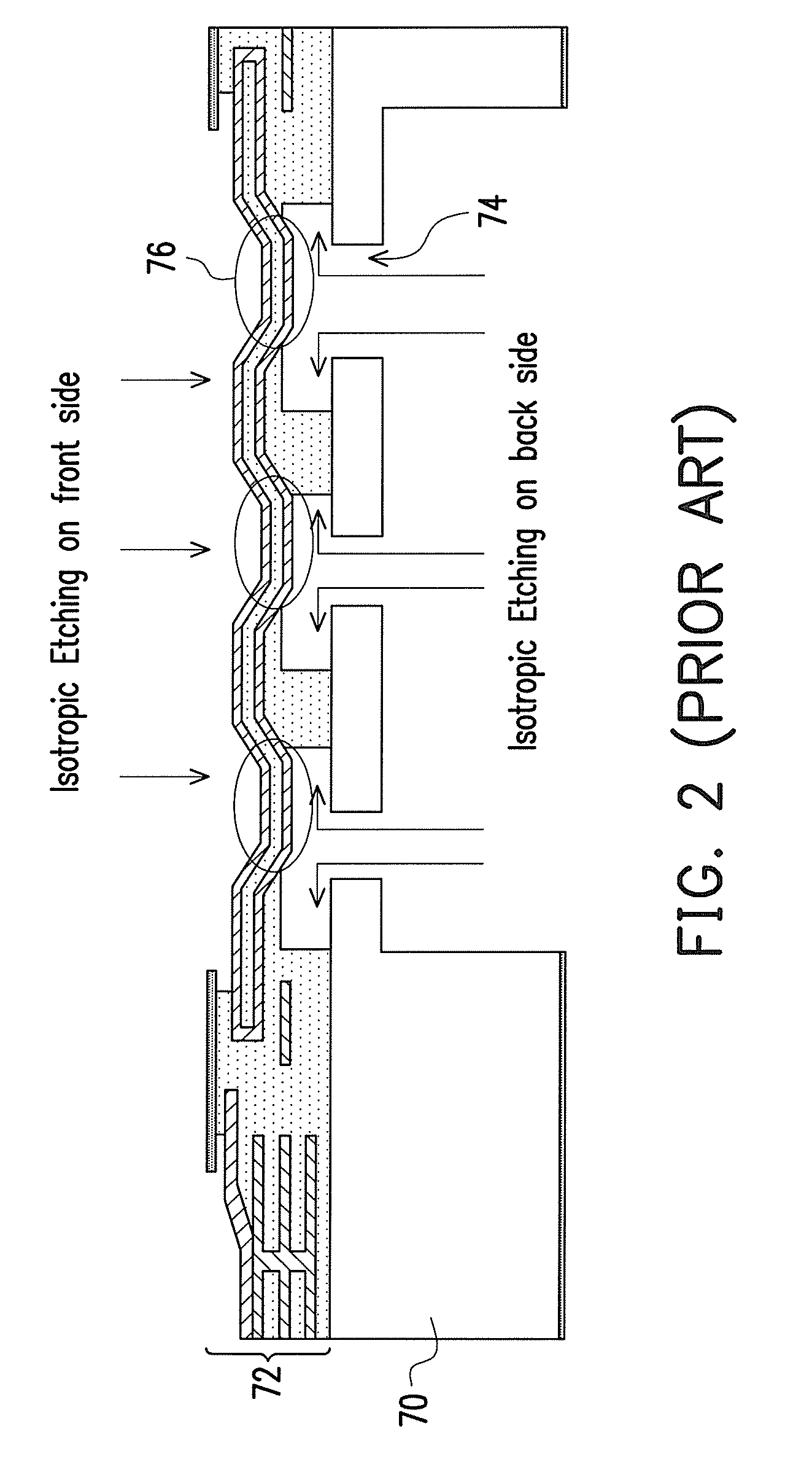

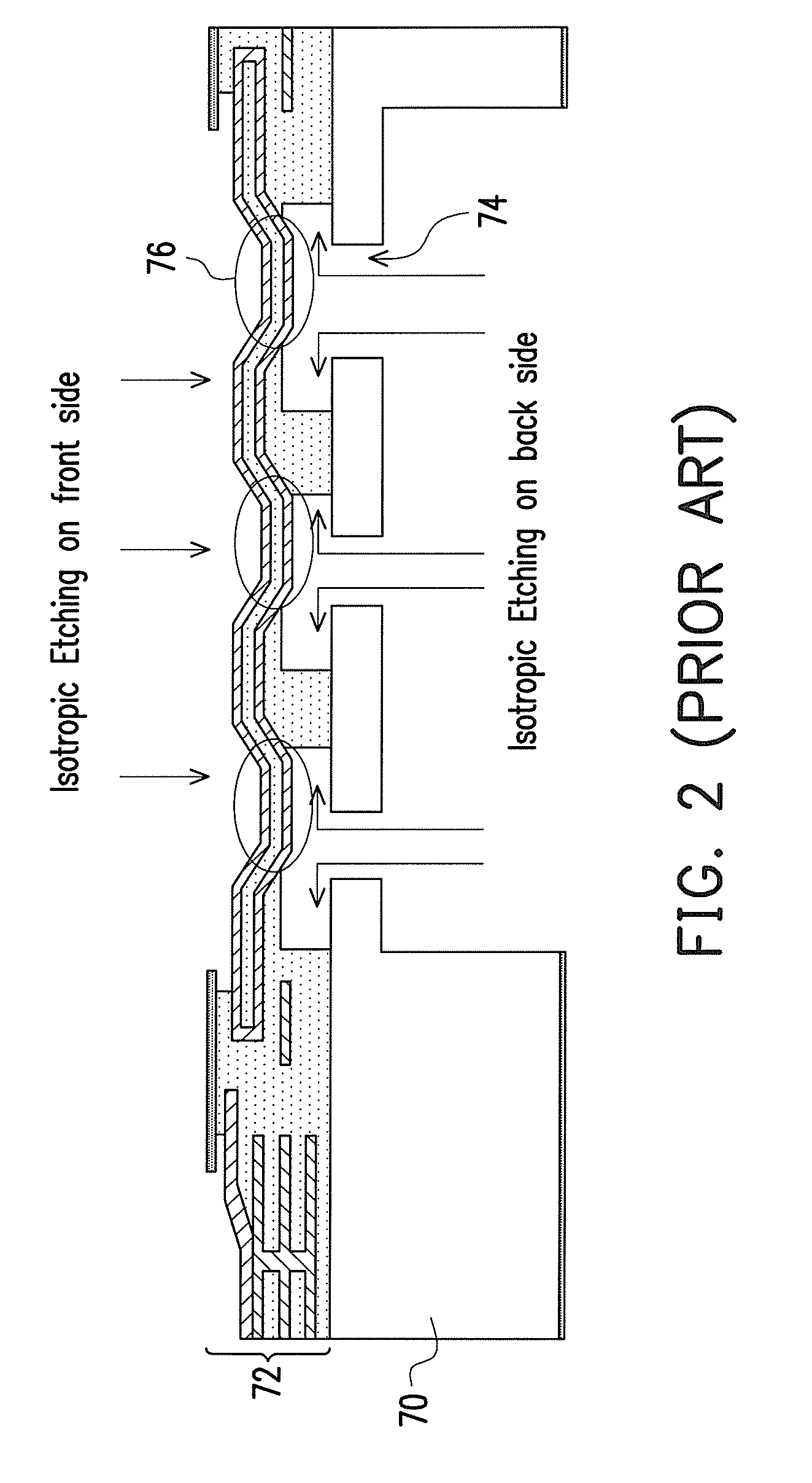

CMOS microelectromechanical system (MEMS) device and fabrication method thereof

ActiveUS20100330722A1Reduce undercuttingReduce harmFluid pressure measurement by electric/magnetic elementsSemiconductor/solid-state device manufacturingCMOSMicroelectromechanical systems

A method for fabricating the MEMS device includes providing a substrate. Then, a structural dielectric layer is formed over the substrate at a first side, wherein a diaphragm is embedded in the structural dielectric layer. The substrate is patterned from a second side to form a cavity in corresponding to the diaphragm and a plurality of venting holes in the substrate. An isotropic etching process is performed from the first side and the second side of the substrate via vent holes to remove a dielectric portion of the structural dielectric layer for exposing a central portion of the diaphragm while an end portion is held by a residue portion of the structural dielectric layer.

Owner:SOLID STATE SYST

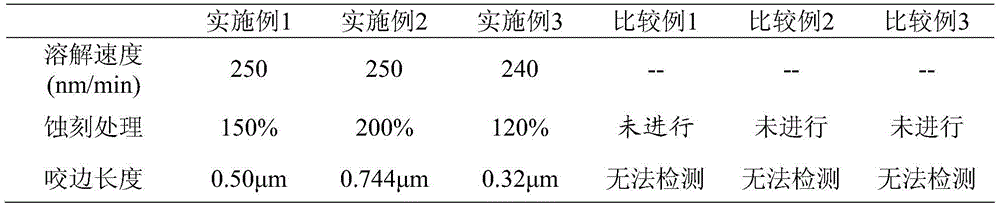

Etchant, replenishment solution and method for producing copper wiring using the same

ActiveUS20050016961A1Reduce undercutReduce undercuttingDecorative surface effectsPhotomechanical apparatusResistChemistry

An etchant for copper and copper alloys, includes an aqueous solution containing: 14 to 155 g / liter of cupric ion source in terms of a concentration of copper ions; 7 to 180 g / liter of hydrochloric acid; and 0.1 to 50 g / liter of azole, the azole including nitrogen atoms only as heteroatoms residing in a ring. A method for producing a wiring by etching of copper or copper alloys, includes the step of: etching a portion of a copper layer on an electrical insulative member that is not covered with an etching resist using the above-described etchant so as to form the wiring. Thereby, a fine and dense wiring pattern with reduced undercut can be formed.

Owner:MEC CO LTD

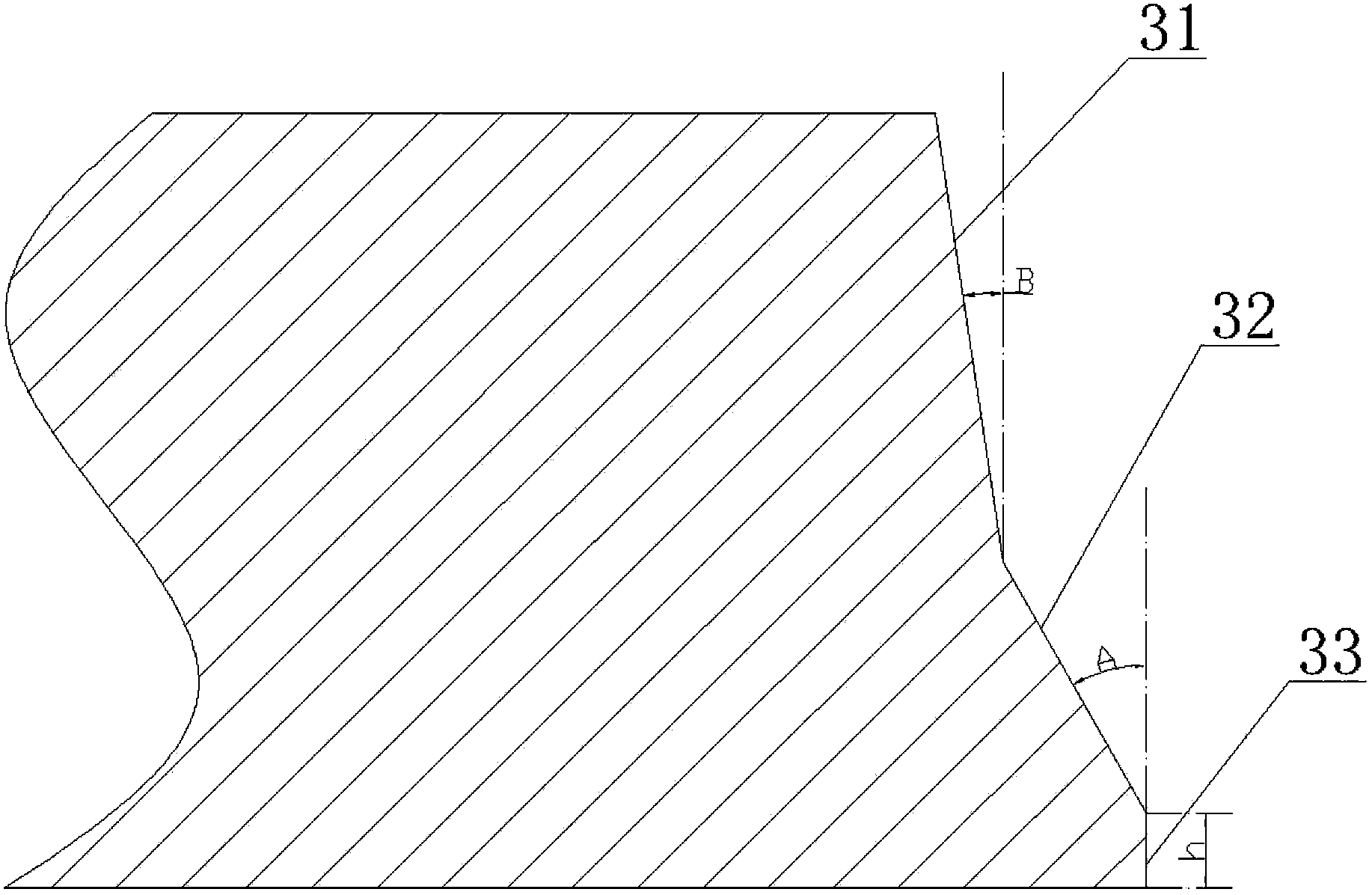

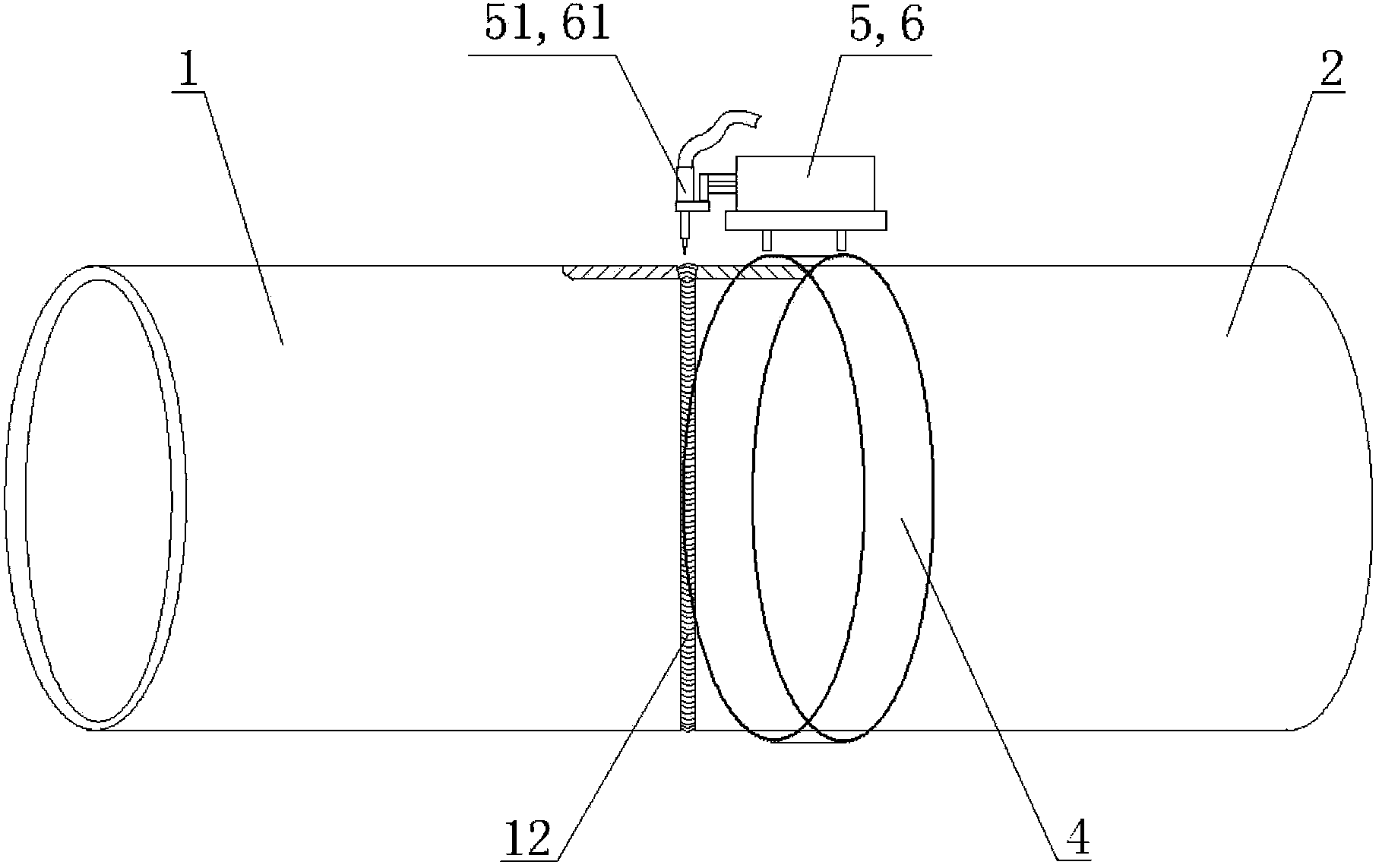

All-position automatic welding method for pipeline circumferential weld

ActiveCN103801796ALow costEasy maintenance and operationArc welding apparatusMetal working apparatusEngineeringWelding defect

The invention discloses an all-position automatic welding method for a pipeline circumferential weld and belongs to the technical field of pipeline circumferential weld welding. The method includes the following steps that firstly, steel pipes needing welding are machined to be provided with groove end faces; secondly, welding technology parameters are typed in a controller program according to the preset welding technology; thirdly, the two welded steel pipes are assembled; fourthly, one of the steel pipes is provided with a welding rail; fifthly, the welding ends of the two steel pipes are preheated before welding; sixthly, a single welding torch is used for performing root welding on grooves; seventhly, a double welding torch is used for performing hot welding, filling welding and cosmetic welding on the grooves. According to the all-position automatic welding method for the pipeline circumferential weld, due to the fact that the groove type is designed, the root welding technology, the filling welding technology and the cosmetic welding technology are adopted, the defects that in the prior art, the welding efficiency is low, a large number of welding materials are consumed, a large number of weld defects exist, the welding joint performance is poor, and the requirement for the operating skills of welders is high; or welding equipment is high in cost, and operating and maintaining are difficult are overcome.

Owner:BC P INC CHINA NAT PETROLEUM CORP +1

Etching liquid for copper nickel multilayer film

The invention relates to etching liquid capable of selectively etching a copper nickel multilayer film in a semiconductor device with an oxide semiconductor layer and the copper nickel multilayer film. The etching liquid contains hydrogen peroxide, an etching inhibitor, a chelating agent, organic acid, a hydrogen peroxide stabilizer, a pH modifier and a water medium; according to total weight of the etching liquid, hydrogen peroxide is 5-30%; according to total weight of the etching liquid, the etching inhibitor is 0.01-5%; according to total weight of the etching liquid, the chelating agent is 0.1-5%; according to total weight of the etching liquid, the organic acid is 1-10%; according to total weight of the etching liquid, the hydrogen peroxide stabilizer is 0.01-0.1%; the content of the pH modifier enables the pH value of the etching liquid to be 3-5; and the balance is the water medium. After etching by the etching liquid, the wiring section shape is excellent, and the undercutting phenomenon can be effectively prevented.

Owner:惠州达诚微电子材料有限公司

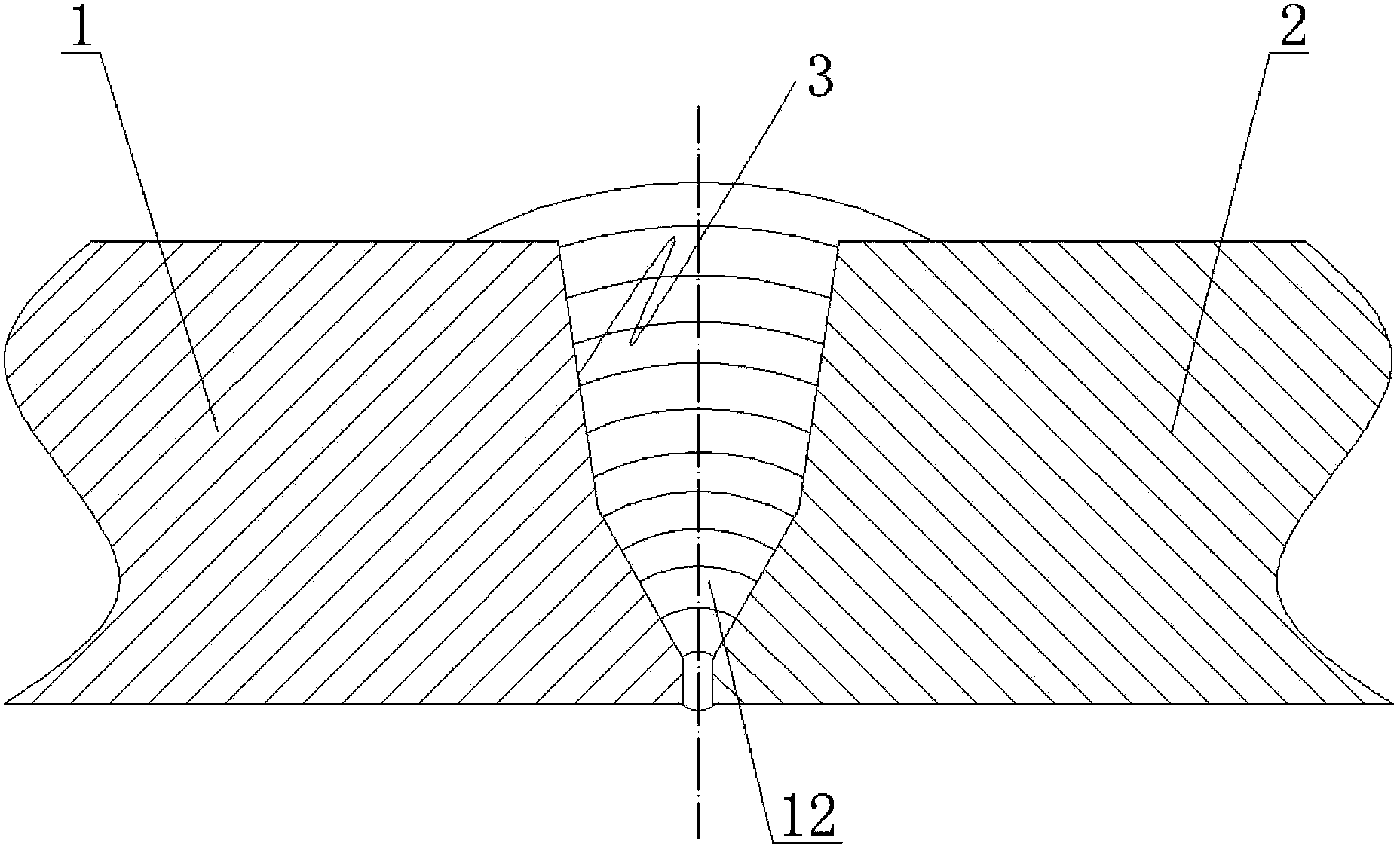

Method for controlling laser welding

ActiveCN105108338AFull flowLower weld stayWelding/soldering/cutting articlesLaser beam welding apparatusHelical lineWeld seam

The invention discloses a method for controlling laser welding. The method comprises the following steps that 1, the weld seam width w of a workpiece to be welded is measured; 2, the locus of laser welding is controlled as x0=x1+delta*cos beta, y0=y1+delta*sin beta, x=x0+R*cos alpha, y=y0+R*sin alpha, wherein w=2R+phi, x0 and y0 serve as coordinates of a point on a straight line, x1 and y1 serve as starting point coordinates of the straight line, delta serves as a point distance of the straight line, beta serves as an inclination angle of the straight line, R serves as a shaking radius, alpha serves as a polar angle, x and y serve as coordinates of a point on a circle (that is a helical line locus), phi serves as a welding point diameter, and delta is smaller than phi. According to the method for controlling laser welding, the locus of a welding helical line is adjusted by adjusting the shaking radius and the point distance for changes of the weld seam width, therefore, a molten pool can flow more fully, the problems of weld seam depression, undercut, point burst and needle holes which are brought by traditional laser welding can be effectively solved, the welding performance is improved, and the quality rate of products is improved.

Owner:UNITED WINNERS LASER CO LTD

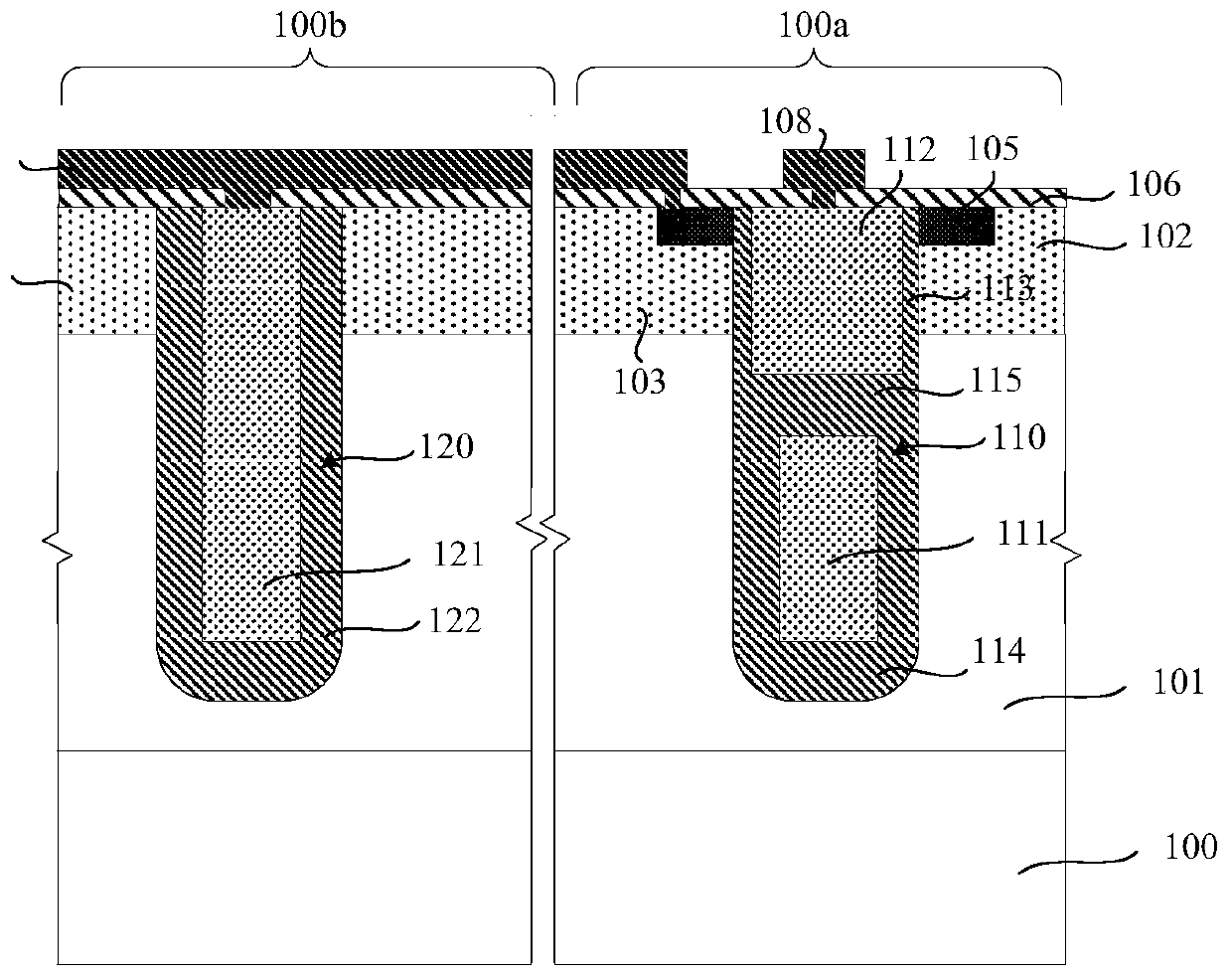

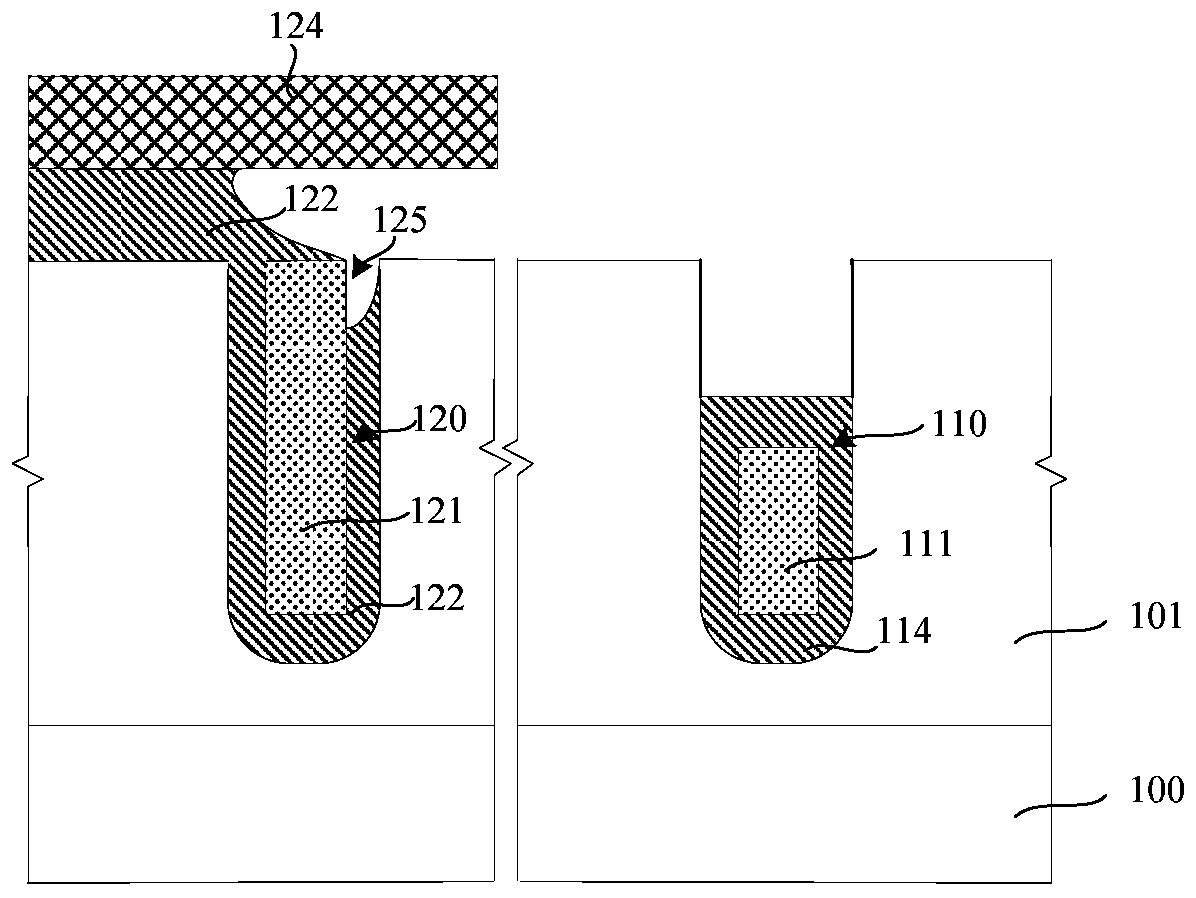

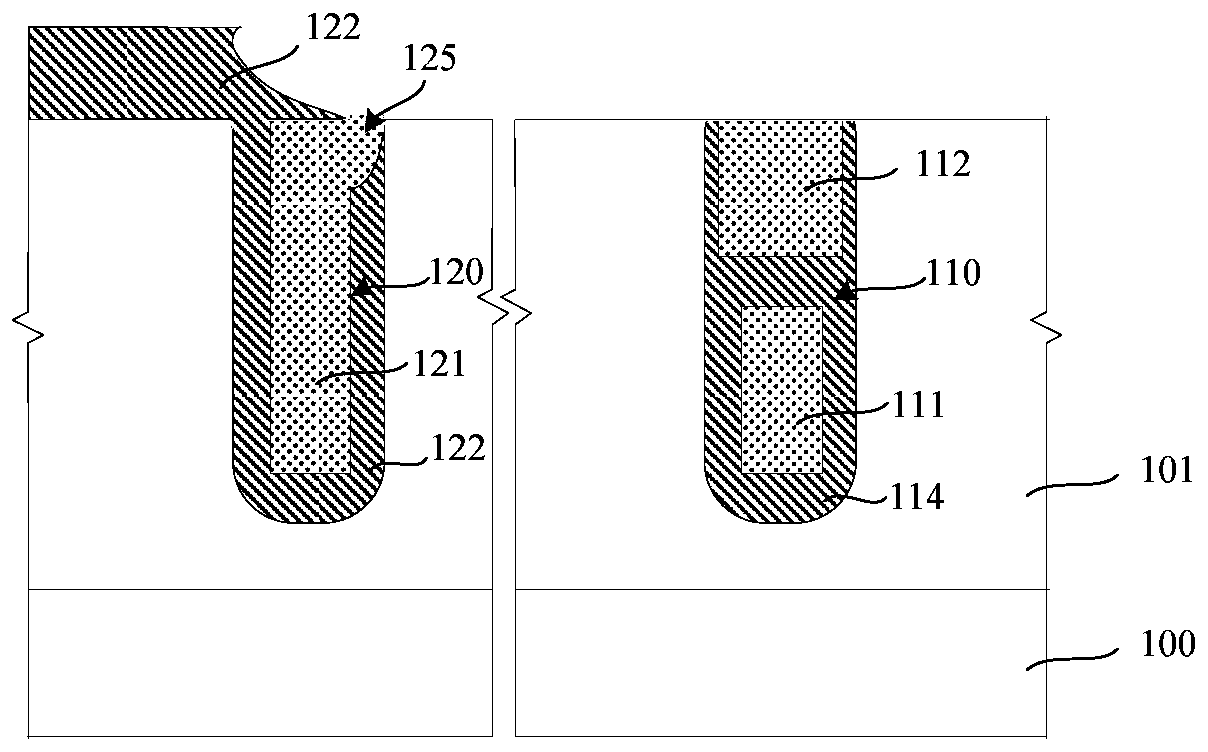

Manufacturing method of shield gate trench power device

PendingCN111081540AShorten process timeAvoid undercutting problemsSemiconductor/solid-state device manufacturingSemiconductor devicesPhysicsElectrically conductive

The invention provides a manufacturing method of a shield gate trench power device. The method comprises the following steps of: providing a substrate, forming at least one first trench in a device unit region of the substrate, forming at least one second trench in an electrode connection region of the substrate, and forming first dielectric layers on the side walls and the bottoms of the first trench and the second trench; forming a shielding gate in the first trench, partially filling the first trench with the shielding gate, and filling the second trench with a conductive material; forminga second dielectric layer which fills the first trench and covers the surface of the substrate and the conductive material; removing the second dielectric layer on the device unit region by adopting adry isotropic etching process, and exposing a part of the first trench; forming a gate in the first trench. According to the invention, before the gate is formed, the second dielectric layer on the device unit region is removed through dry isotropic etching, and part of the first trench is exposed, so that compared with the traditional wet etching removal, the process time is shortened, and the undercutting problem is effectively reduced and even avoided.

Owner:GUANGZHOU CANSEMI TECH INC

Copper-selective etching solution and titanium-selective etching solution

The invention discloses a copper-selective etching solution prepared from a copper oxidizing solution and a copper chelating solution. The copper oxidizing solution is prepared from an oxidizing agent and / or water, the copper chelating solution is prepared from oxalate, amino carboxylic acid and water, and the pH value of the copper-selective etching solution is 6.0-8.5; the copper-selective etching solution can selectively and uniformly etch copper. The invention further discloses a titanium-selective etching solution prepared from a titanium oxidizing solution and a titanium chelating solution. The titanium oxidizing solution is prepared from hydrogen peroxide and / or water, the titanium chelating solution is prepared from a phosphorous acid chelating agent, a copper anticorrosive agent, inorganic base and water, and the pH value of the titanium-selective etching solution is 7-10; the titanium-selective etching solution can selectively and uniformly etch titanium. In the manufacturing process of lead-free solder bumps, lead-free solder bumps with the good size reproducibility can be conveniently and quickly manufactured on a semiconductor substrate by using the copper-selective etching solution and the titanium-selective etching solution for etching.

Owner:XITENG ELECTRONICS TECH SHANGHAI CO LTD

Method for processing micro slot array on borosilicate glass surface

The invention provides a method for processing micro slot array on borosilicate glass surface which comprises sputtering Chromium copper seed layer onto the surface of cleaned boron-silicon glass sheets, forming mask window of processed glass deep groove array through photo-etching, placing the boron-silicon glass sheets into Chromium copper seed layer in the etching solution removing window, striping the analytical pure acetone through ultrasound, employing a plating method for electroplating copper masks, then plating gold masks onto the copper masks, etching continuously so as to obtain micro-trench array with smooth bottoms on the surface of the boron-silicon glass.

Owner:SHANGHAI JIAO TONG UNIV

CMOS microelectromechanical system (MEMS) device and fabrication method thereof

ActiveUS8093119B2Reduce undercuttingReduce harmFluid pressure measurement by electric/magnetic elementsSemiconductor/solid-state device manufacturingCMOSMicroelectromechanical systems

A method for fabricating the MEMS device includes providing a substrate. Then, a structural dielectric layer is formed over the substrate at a first side, wherein a diaphragm is embedded in the structural dielectric layer. The substrate is patterned from a second side to form a cavity in corresponding to the diaphragm and a plurality of venting holes in the substrate. An isotropic etching process is performed from the first side and the second side of the substrate via vent holes to remove a dielectric portion of the structural dielectric layer for exposing a central portion of the diaphragm while an end portion is held by a residue portion of the structural dielectric layer.

Owner:SOLID STATE SYST

Etchant, replenishment solution and method for producing copper wiring using the same

ActiveUS7431861B2Reduce undercuttingDecorative surface effectsPhotomechanical apparatusResistElectricity

An etchant for copper and copper alloys, includes an aqueous solution containing: 14 to 155 g / liter of cupric ion source in terms of a concentration of copper ions; 7 to 180 g / liter of hydrochloric acid; and 0.1 to 50 g / liter of azole, the azole including nitrogen atoms only as heteroatoms residing in a ring. A method for producing a wiring by etching of copper or copper alloys, includes the step of: etching a portion of a copper layer on an electrical insulative member that is not covered with an etching resist using the above-described etchant so as to form the wiring. Thereby, a fine and dense wiring pattern with reduced undercut can be formed.

Owner:MEC CO LTD

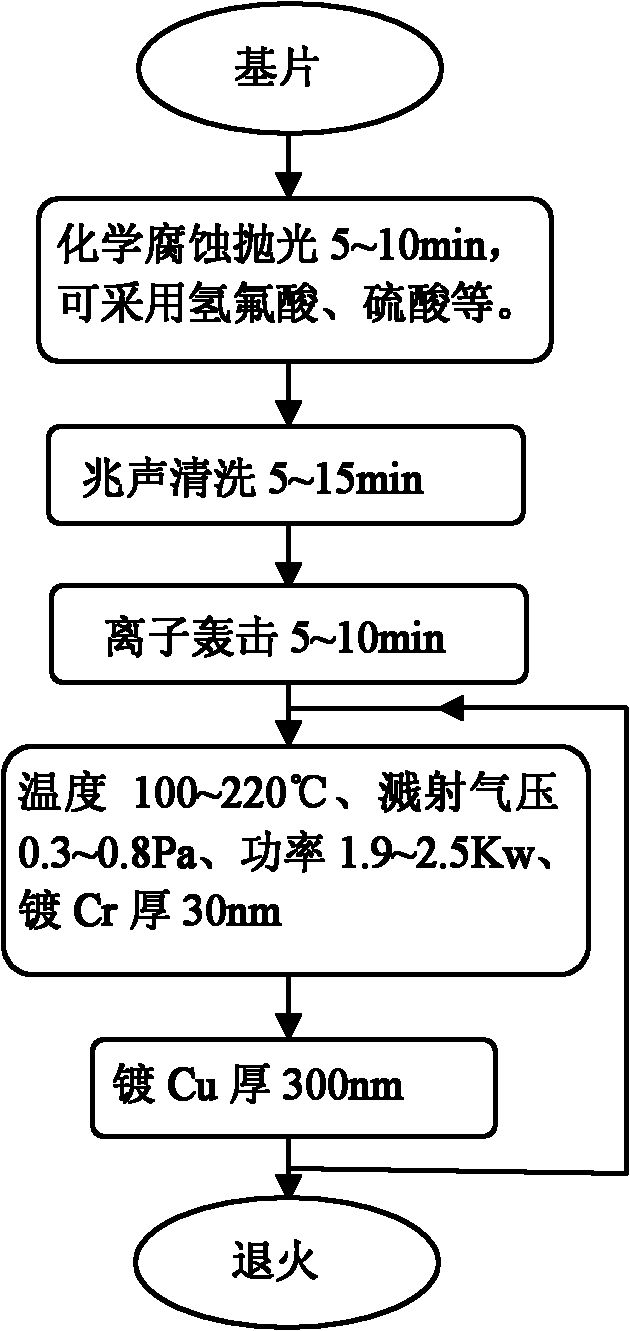

Method for preparing metal mask resistant to corrosion of hydrofluoric acid corrosive liquid

The invention relates to a method for preparing an anticorrosive metal mask, in particular to a method for preparing a metal mask resistant to the corrosion of hydrofluoric acid corrosive liquid. The invention aims to solve the problems of undercut holes, local warping, peeling defects and the like of the conventional corroded mask. The method particularly comprises the following steps of: a, cleaning, namely performing corrosion soaking on a substrate to be coated in hydrofluoric acid and hydrogen peroxide mixed liquid or sulfuric acid and hydrogen peroxide mixed liquid, and performing megasonic cleaning on the substrate; and b, coating, namely (1) performing ion bombardment on Ar on the surface of the substrate; (2) sequentially coating a Cr film and a Cu film on the surface of the substrate under the condition of the temperature of between 100 and 220 DEG C, the sputtering pressure of 0.3 to 0.8 Pa and the sputtering power of 1.9 to 2.5 Kw; and (3) repeating the step (2) to coat the Cr film and the Cu film on the surface of the substrate again to form a double-layered or multilayered Cr / Cu metal mask. The method effectively reduces pinhole undercutting due to fine particles and film layer defects, improves the adhesion of the mask and effectively removes stress.

Owner:BEIJING AUTOMATION CONTROL EQUIP INST

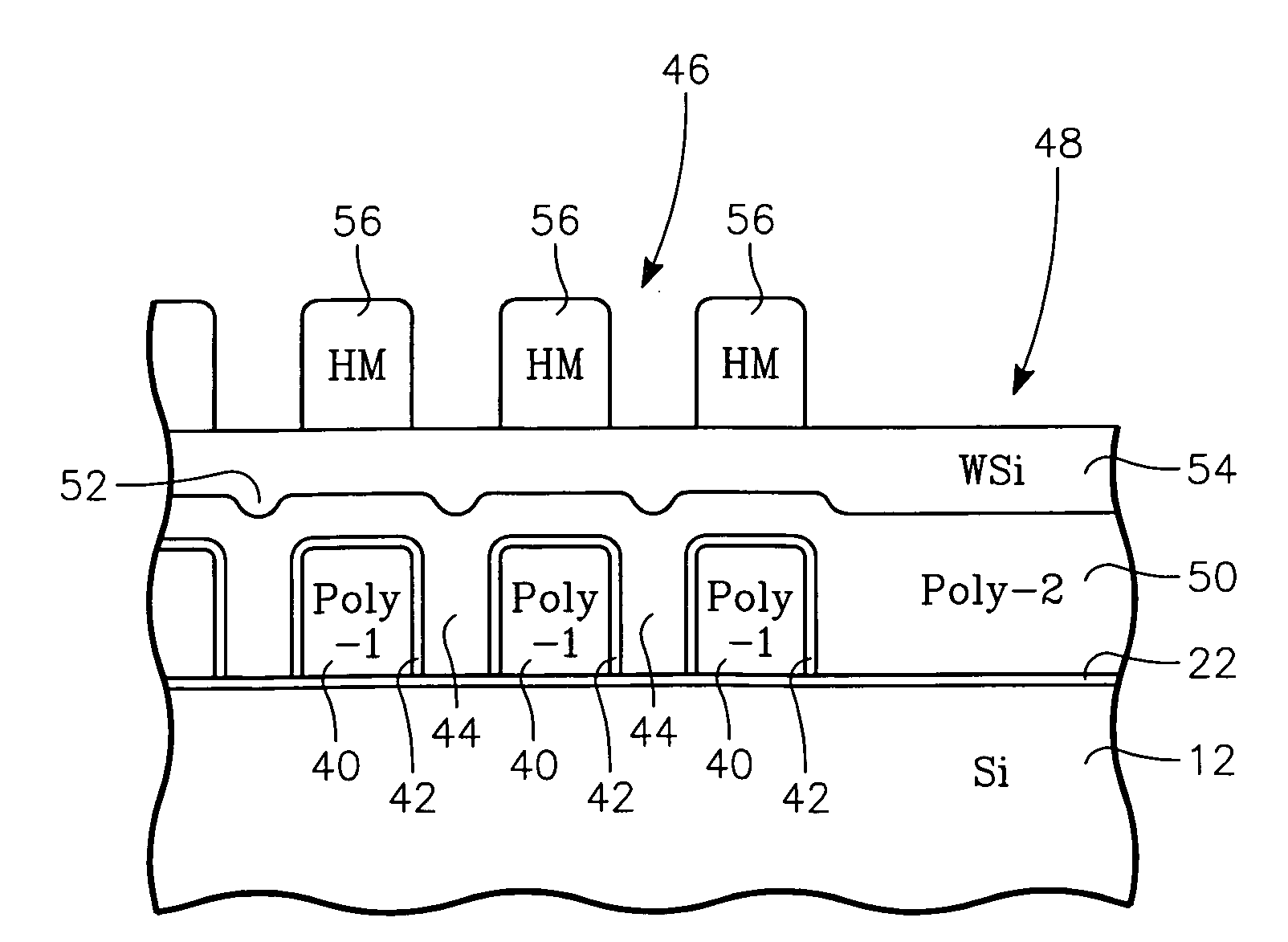

Process including silo-chloro passivation for etching tungsten silicide overlying polysilicon

InactiveUS20070281479A1Reduces depth microloadingHigh selectivityDecorative surface effectsSemiconductor/solid-state device manufacturingNitrogenOxygen

A method of plasma etching tungsten silicide over polysilicon particularly useful in fabricating flash memory having both a densely packed area and an open (iso) area requiring a long over etch due to microloading. Wafer biasing is decreased in the over etch. The principal etchant include NF3 and Cl2. Argon is added to prevent undercutting at the dense / iso interface. Oxygen and nitrogen oxidize any exposed silicon to increase etch selectivity and straightens the etch profile. SiCl4 as an example of a silicon and chlorine containing passivating gas may be added for additional selectivity.

Owner:APPLIED MATERIALS INC

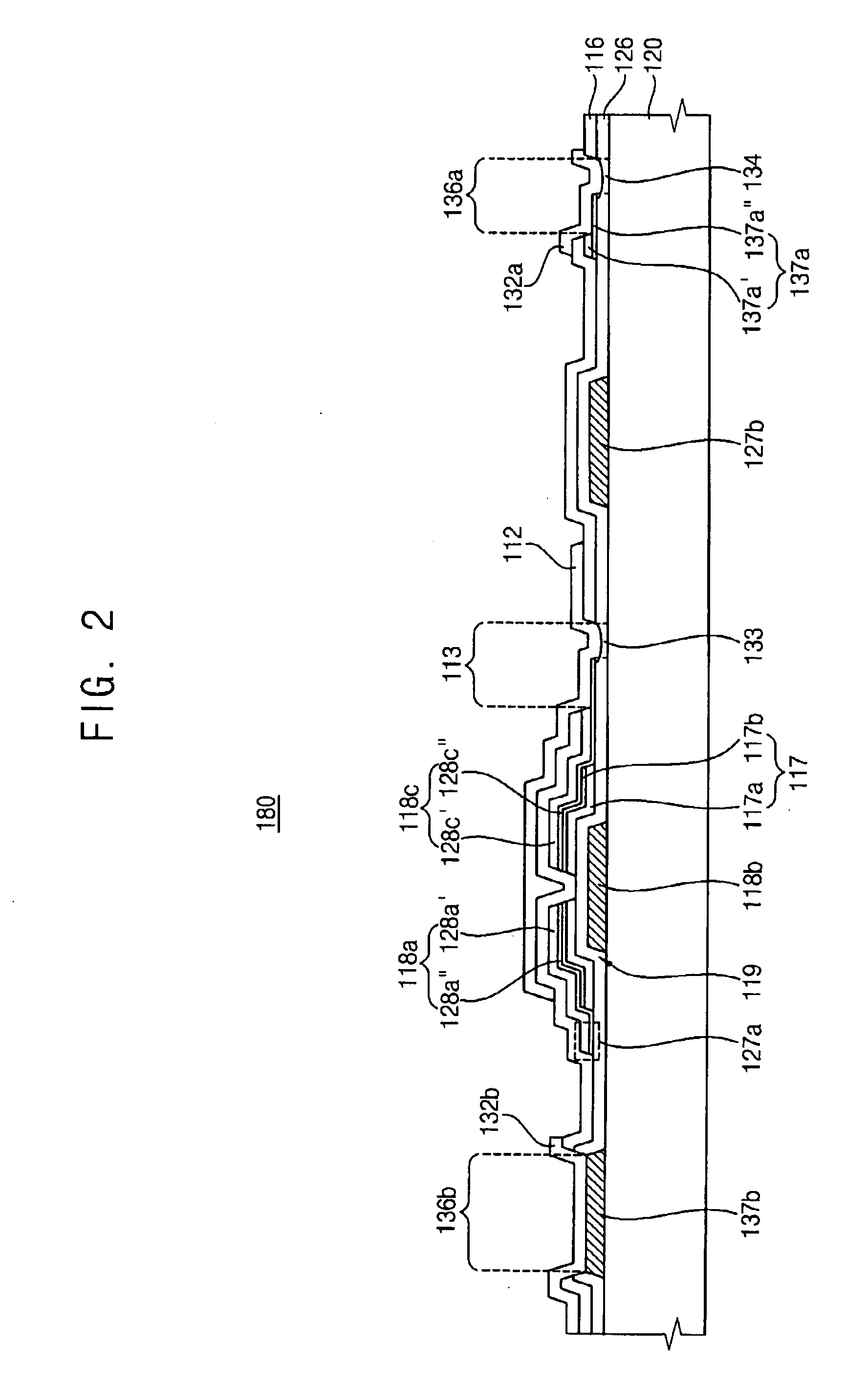

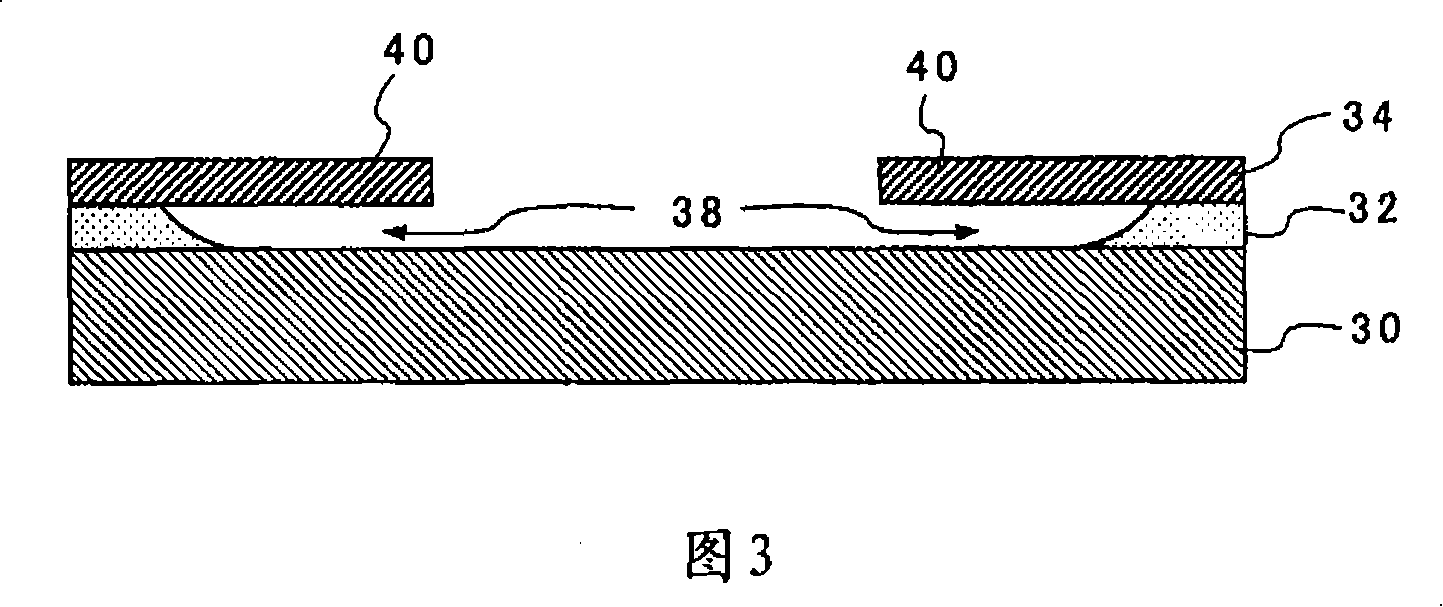

Display substrate, method of manufacturing the same and display device having the same

ActiveUS20070045636A1Improved contact characteristicsImprove image display qualitySolid-state devicesSemiconductor/solid-state device manufacturingDisplay deviceEngineering

A display substrate includes a substrate, a first insulating layer, an undercut compensating member, a first electrode, a second insulating layer and a first conductive pattern. The first insulating layer is formed on the substrate. The undercut compensating member is formed on the first insulating layer. The undercut compensating member has an etching rate smaller than that of the first insulating layer. The first electrode is formed on a portion of the undercut compensating member. The second insulating layer is formed on the first insulating layer. The second insulating layer has a contact hole through which a portion of the first electrode and a remaining portion of the undercut compensating member. The first conductive pattern electrically connected to the first electrode through the contact hole.

Owner:SAMSUNG DISPLAY CO LTD

Prismoid pile and prismoid type pile forest dam

ActiveCN109113029AImprove the state of stressReduce the impact of collisionBarrages/weirsFoundation engineeringStructural engineeringRiver bed

The invention belongs to the technical field of debris flow prevention dams and discloses a prismoid pile and a prismoid type pile forest dam. The prismoid pile comprises a prismoid pile body and a bottom foundation fixed on the bottom surface of the prismoid pile body. The prismoid pile body is fixed on the bottom surface of a debris flow riverbed through the bottom foundation. The water facing surface of the prismoid pile body is two buffer surfaces formed after bending in the flow direction of the debris flow, and the bending lines are distribution buffer edges obliquely arranged in the flow direction of the debris flow. The prismoid type pile forest dam comprises at least one row of prismoid pile groups, and each row of prismoid pile groups comprises a plurality of prismoid pile bodies. By the adoption of the prismoid pile and the prismoid type pile forest dam, the collision impact force, the risk of shearing, the effect of groove bottom erosion, destructiveness of debris flow to structures and possibility of foundation failure are correspondingly reduced.

Owner:四川省交通勘察设计研究院有限公司

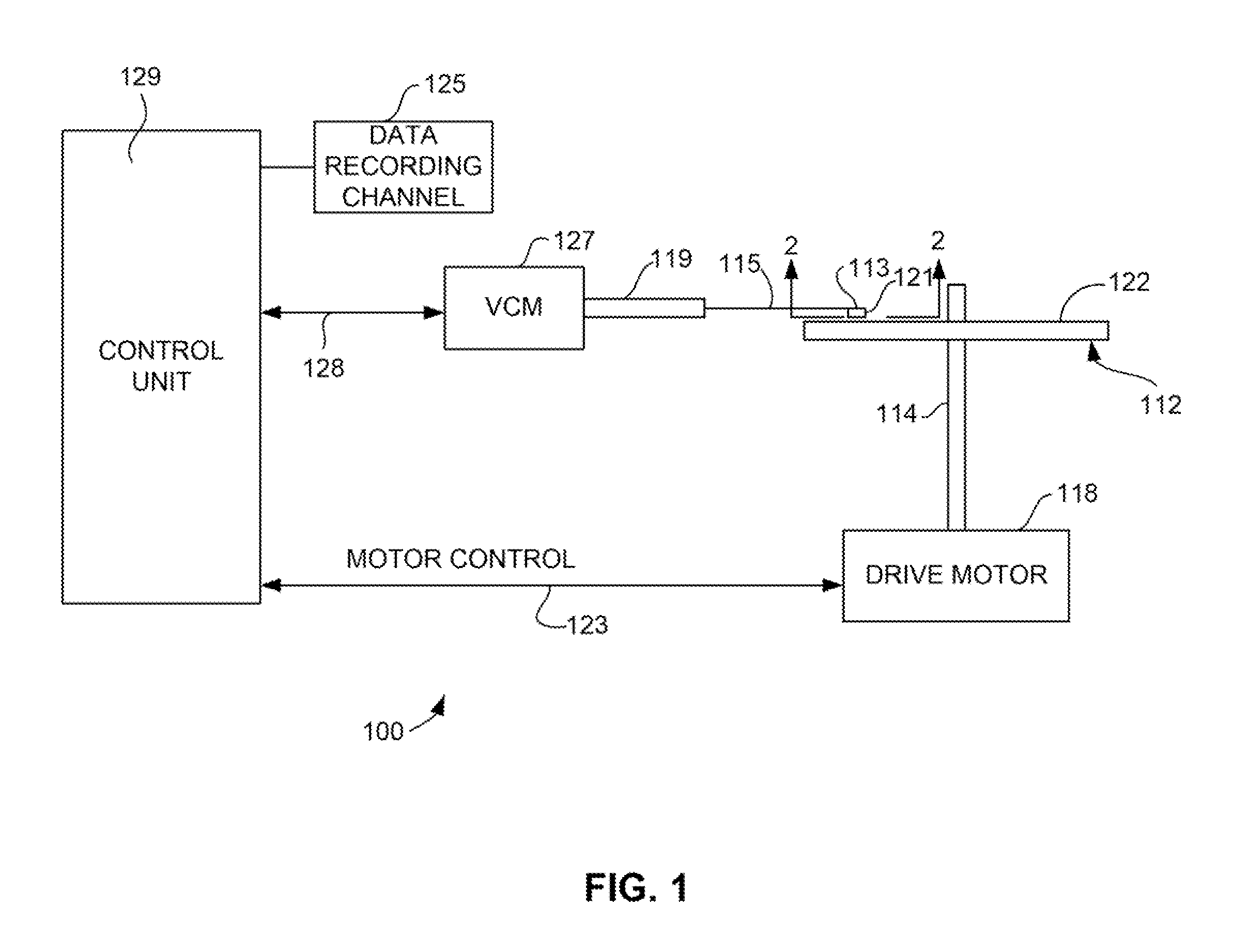

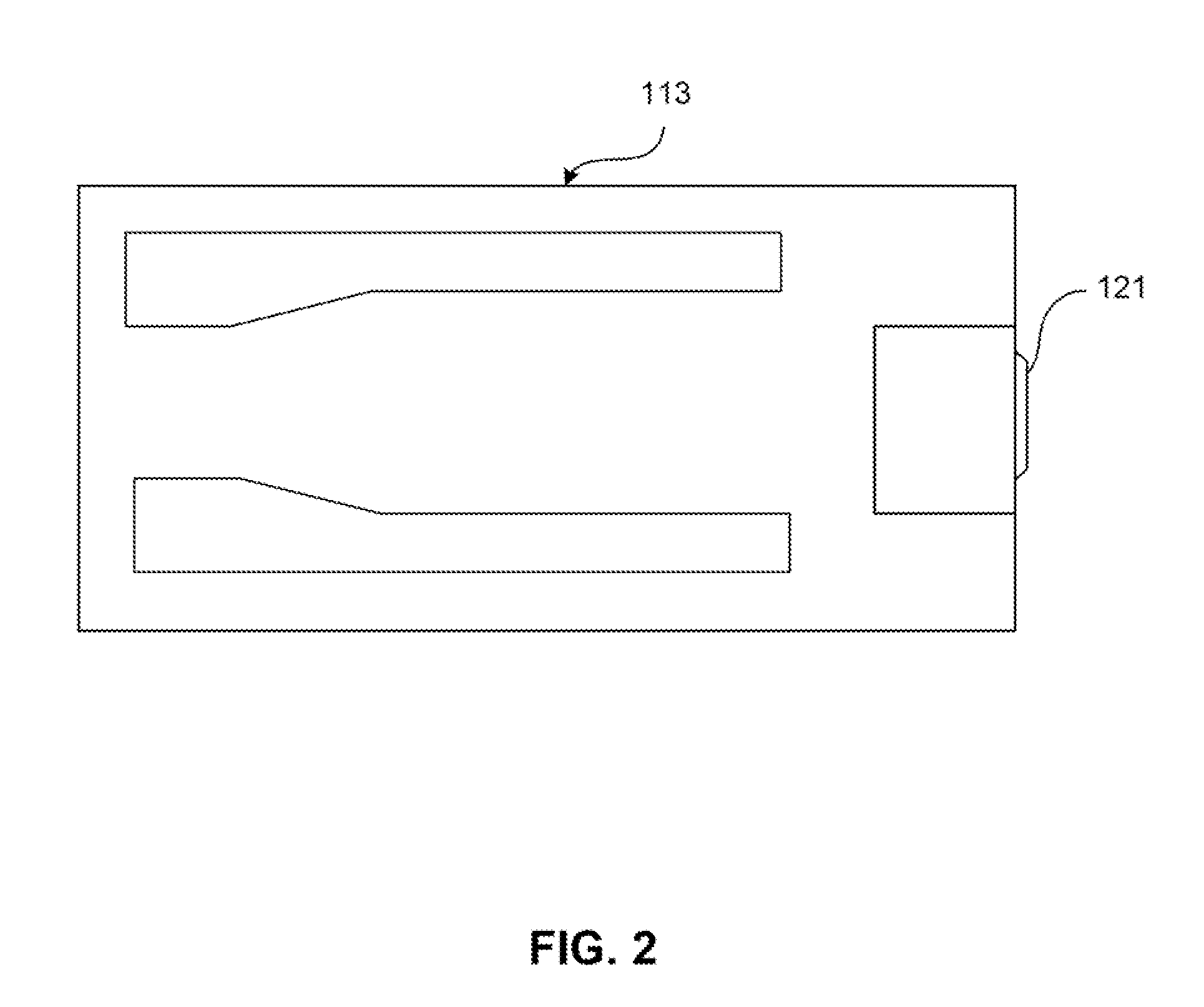

Method for manufacturing a magnetoresistive sensor

InactiveUS20140170774A1Reduce undercuttingMagnetic measurementsSemiconductor/solid-state device manufacturingOptoelectronicsOxygen

A method for manufacturing a magnetic sensor that allows the sensor to be constructed with a very narrow track width and with smooth, well defined side walls. A tri-layer mask structure is deposited over a series of sensor layers. The tri-layer mask structure includes an under-layer, a Si containing hard mask deposited over the under-layer and a photoresist layer deposited over the Si containing hard mask. The photoresist layer is photolithographically patterned to define a photoresist mask. A first reactive ion etching is performed to transfer the image of the photoresist mask onto the Si containing hard mask. The first reactive ion etching is performed in a chemistry that includes CF4, CHF3, O2, and He. A second reactive ion etching is then performed in an oxygen chemistry to transfer the image of the Si containing hard mask onto the under-layer, and an ion milling is performed to define the sensor.

Owner:WESTERN DIGITAL TECH INC

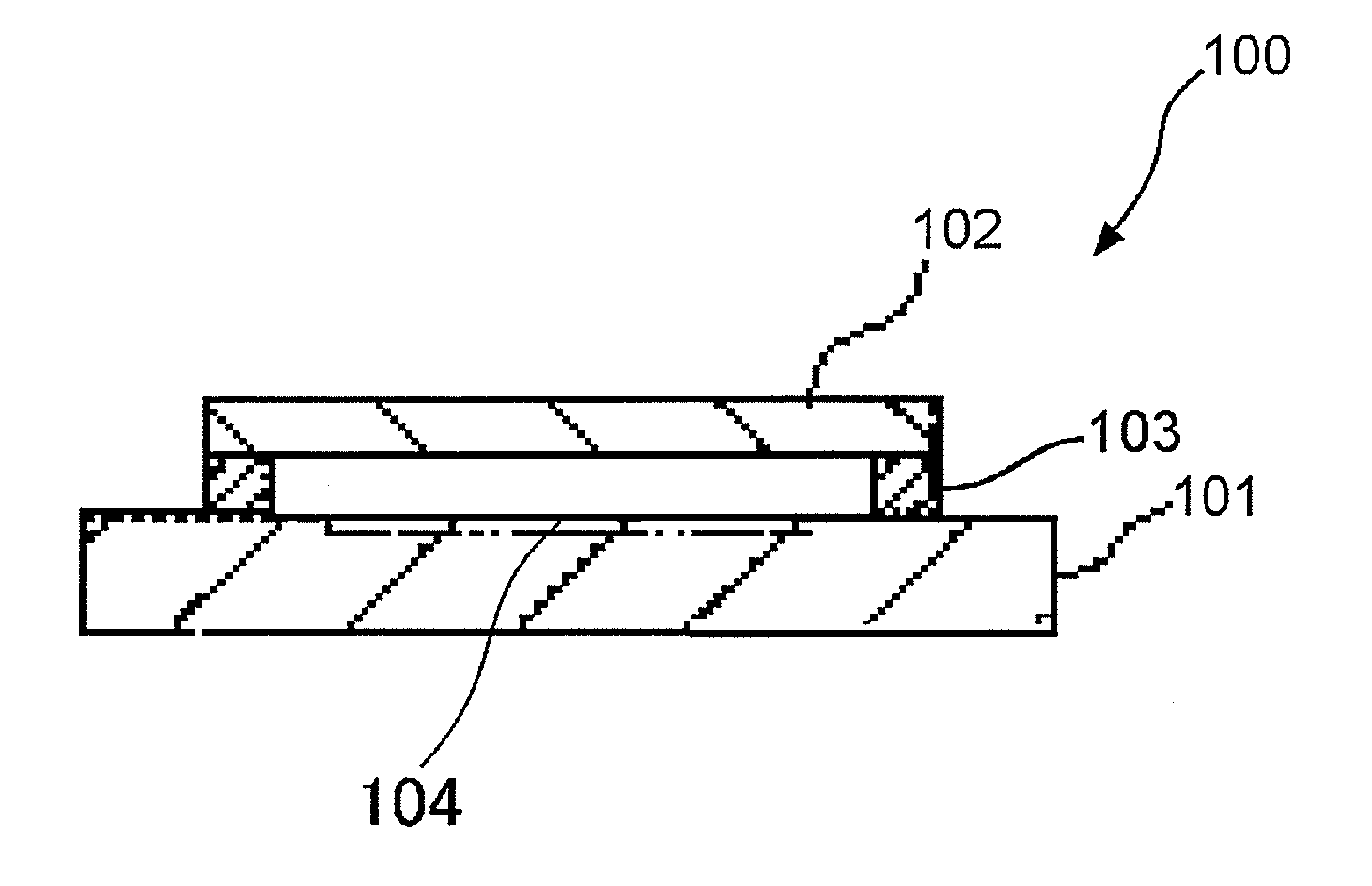

Light-receiving device and method of manufacturing the same

InactiveUS20110101484A1Reduce generationReduce undercuttingSolid-state devicesSemiconductor/solid-state device manufacturingMoisture permeabilityEngineering

There is provided a device including at least one light-receiving unit 11, a base substrate 12A provided with the light-receiving unit 11, a transparent base substrate 13A disposed facing the base substrate 12A and the light-receiving unit 11, and a frame member 14A disposed around the light-receiving unit 11 between the base substrate 12A and the transparent substrate 13A. The frame member 14A consists of a cured resin composition. The resin composition contains an alkali-soluble resin, a photopolymerizable resin and an inorganic filler in 9% or less by weight. The photopolymerizable resin contains an acrylic polyfunctional monomer. The frame member 14A has a moisture permeability of 12 [g / m2·24 h] or more and an elastic modulus of 100 Pa or more at 80 degrees C.

Owner:SUMITOMO BAKELITE CO LTD

Method for manufacturing a magnetoresistive sensor

InactiveUS8796152B2Reduce undercuttingMagnetic measurementsSemiconductor/solid-state device manufacturingResistOxygen

Owner:WESTERN DIGITAL TECH INC

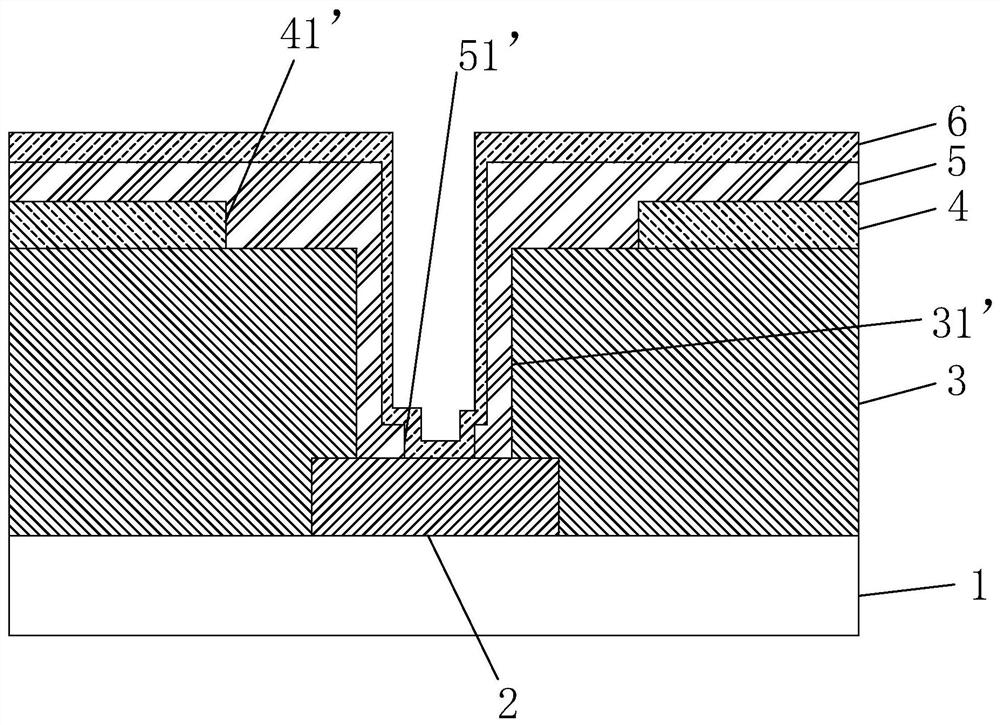

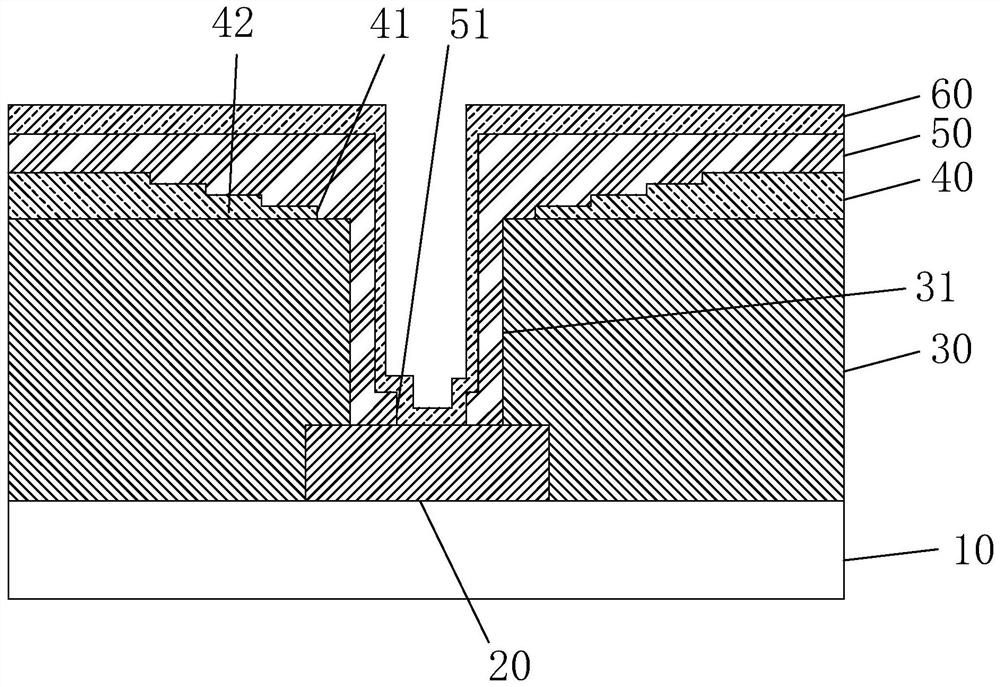

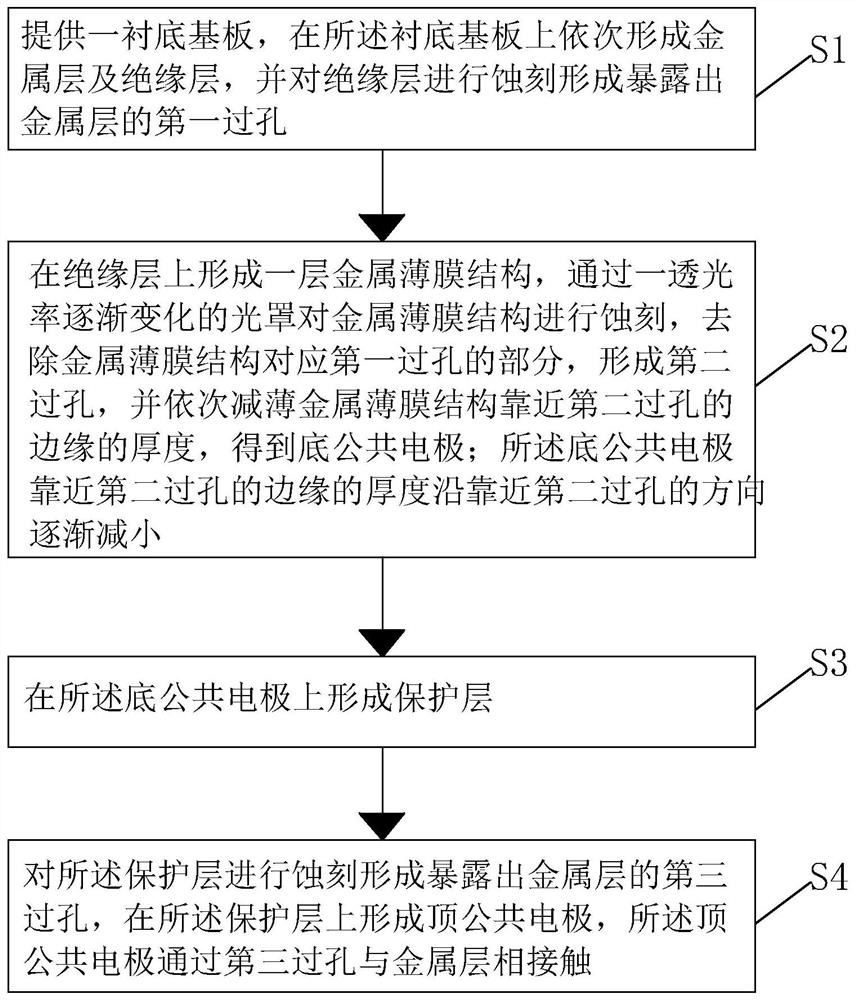

TFT substrate and manufacturing method thereof

ActiveCN108257976AImprove yieldReduce tilt angleSolid-state devicesSemiconductor/solid-state device manufacturingEngineeringLiquid crystal

The invention provides a TFT substrate and a manufacturing method thereof. The TFT substrate comprises a base substrate, a metal layer arranged on the base substrate, an insulating layer arranged on the base substrate and the metal layer, a bottom common electrode arranged on the insulating layer, and a protective layer arranged on the insulating layer and the bottom common electrode. The insulating layer has first via holes exposing the metal layer. The bottom common electrode has second via holes formed in areas corresponding to the first via holes. The thickness of the edge of the bottom common electrode near the second via holes gradually decreases along the direction near the second via holes, so that the upwarp angle of the edge of the bottom common electrode near the second via holes is reduced, and the probability of bottom cutting is reduced. Therefore, the risk of peeling of the film formed on the bottom common electrode is reduced, the yield of the TFT substrate is improved,and the display effect of the LCD panel is good.

Owner:WUHAN CHINA STAR OPTOELECTRONICS TECH CO LTD

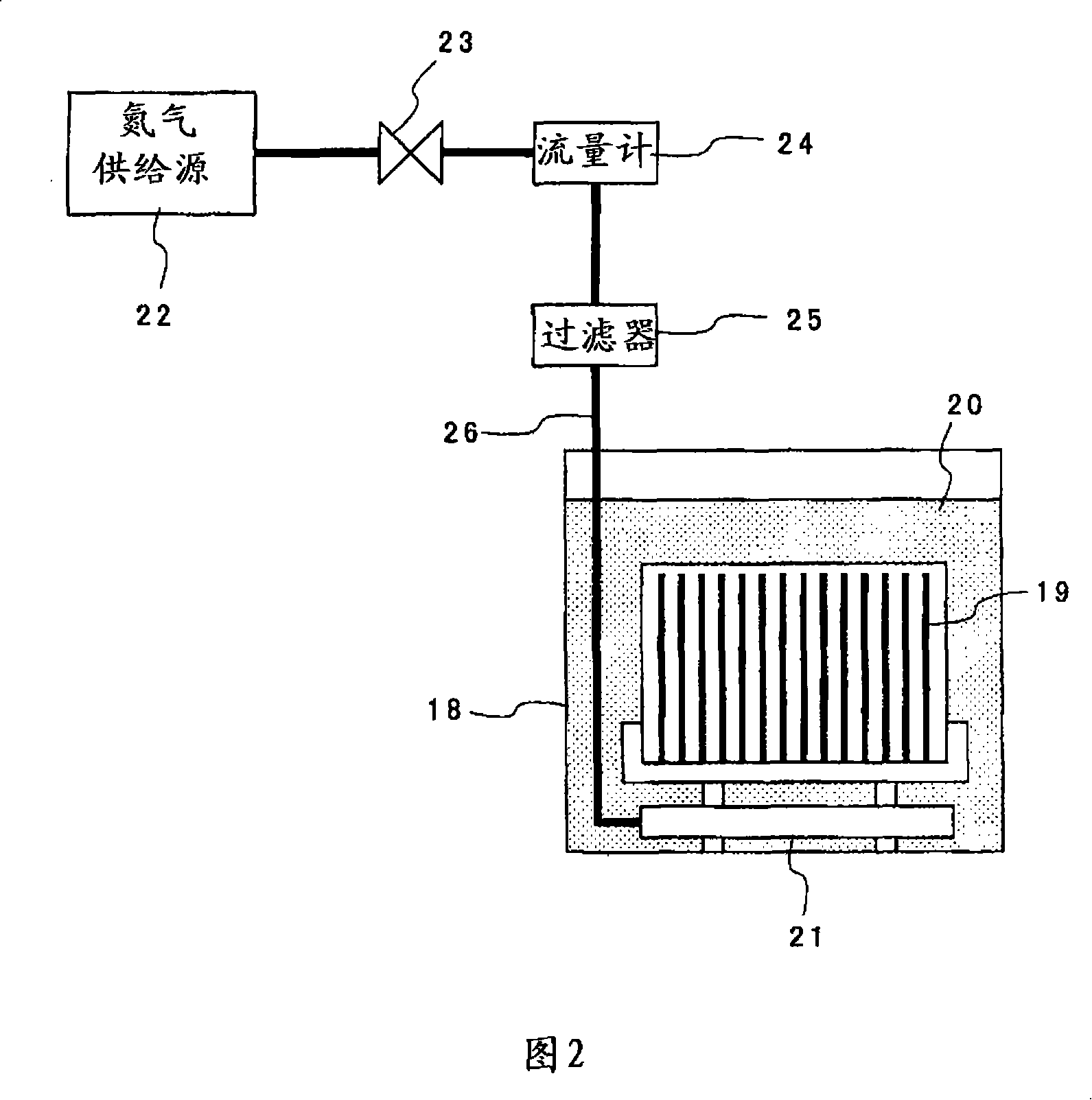

Apparatus for manufacturing semiconductor device, wet etching process device and wet etching process method

InactiveCN101154581AReduce undercuttingInhibition of breakingDecorative surface effectsSemiconductor/solid-state device manufacturingEtchingNitrogen gas

An apparatus according to the present invention, includes an etching solution tank which contains etching solution used for a wet etching process, a wet etching process to a semiconductor wafer being carried out in the etching solution tank; a nitrogen gas supply component which supplies a nitrogen gas (N2), which is used for a wet etching process in the etching solution tank; a flow regulating component which delivers the nitrogen gas (N2) supplied from said nitrogen gas supply component into said etching solution tank during a wet etching process, and which continues to deliver said nitrogen gas into said etching solution tank during a standby phase in which a wet etching process is not being performed; and a bubbling component which bubbles said nitrogen gas (N2), supplied from said nitrogen gas supply component, in said etching solution tank during a wet etching process.

Owner:OKI ELECTRIC IND CO LTD

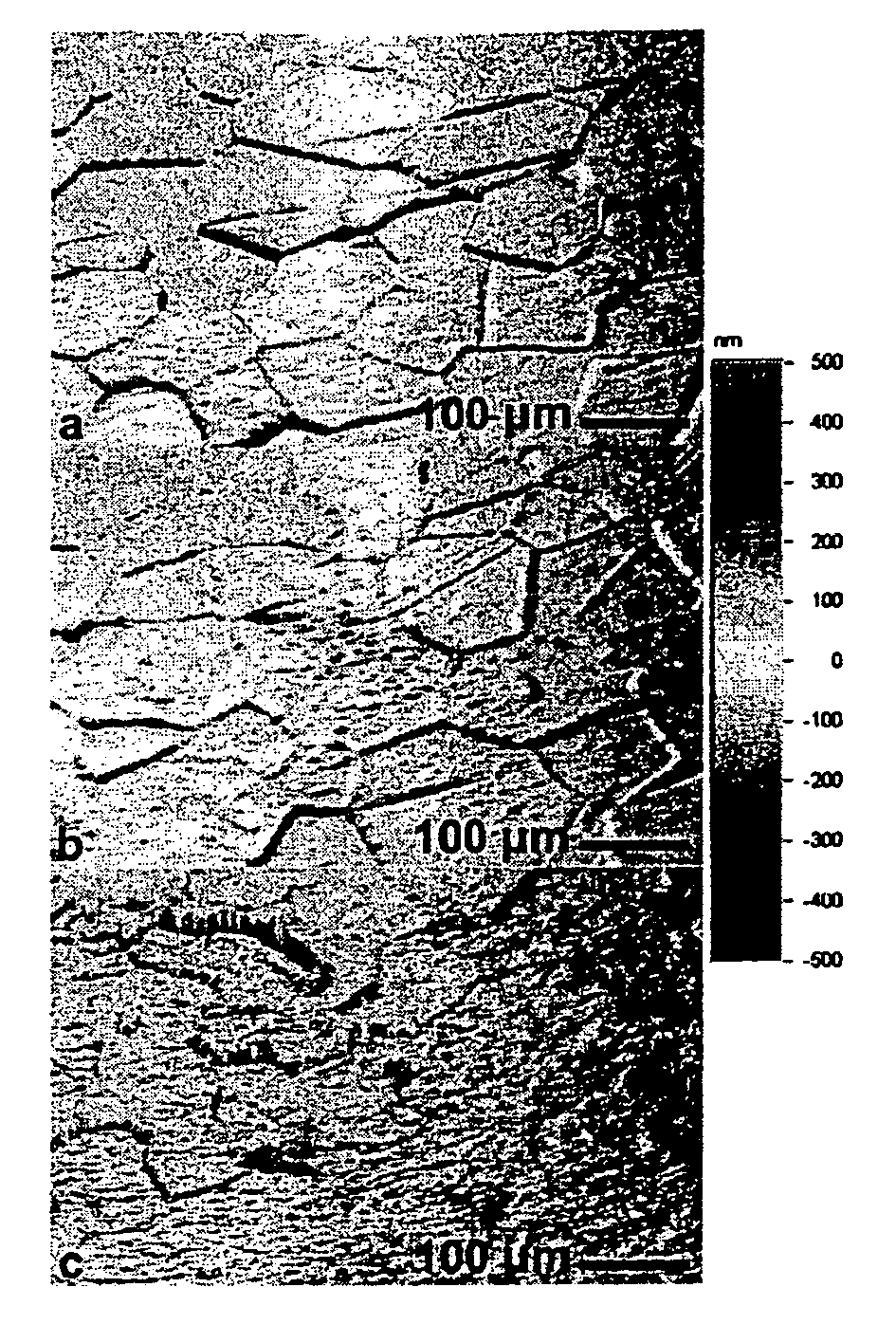

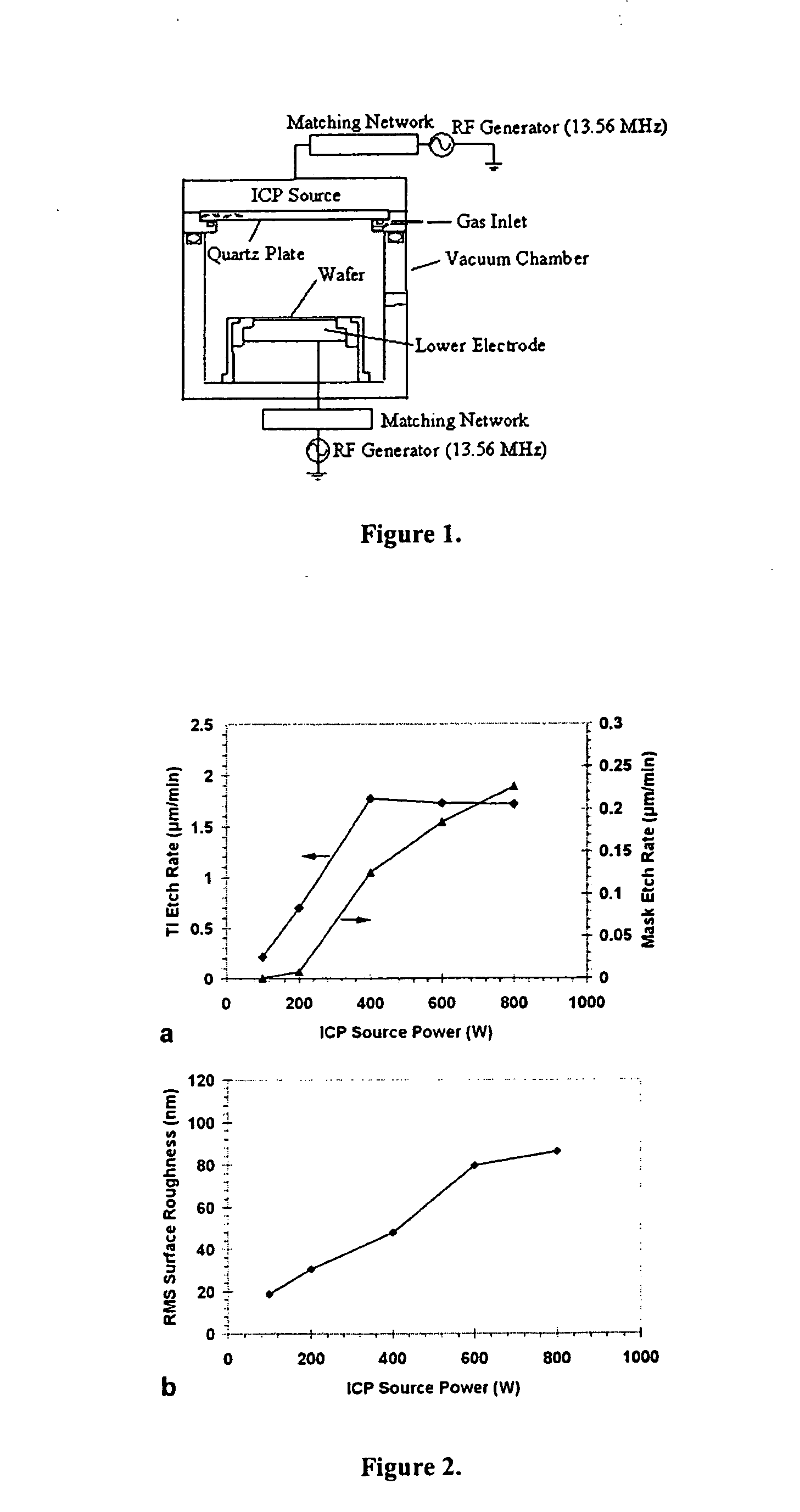

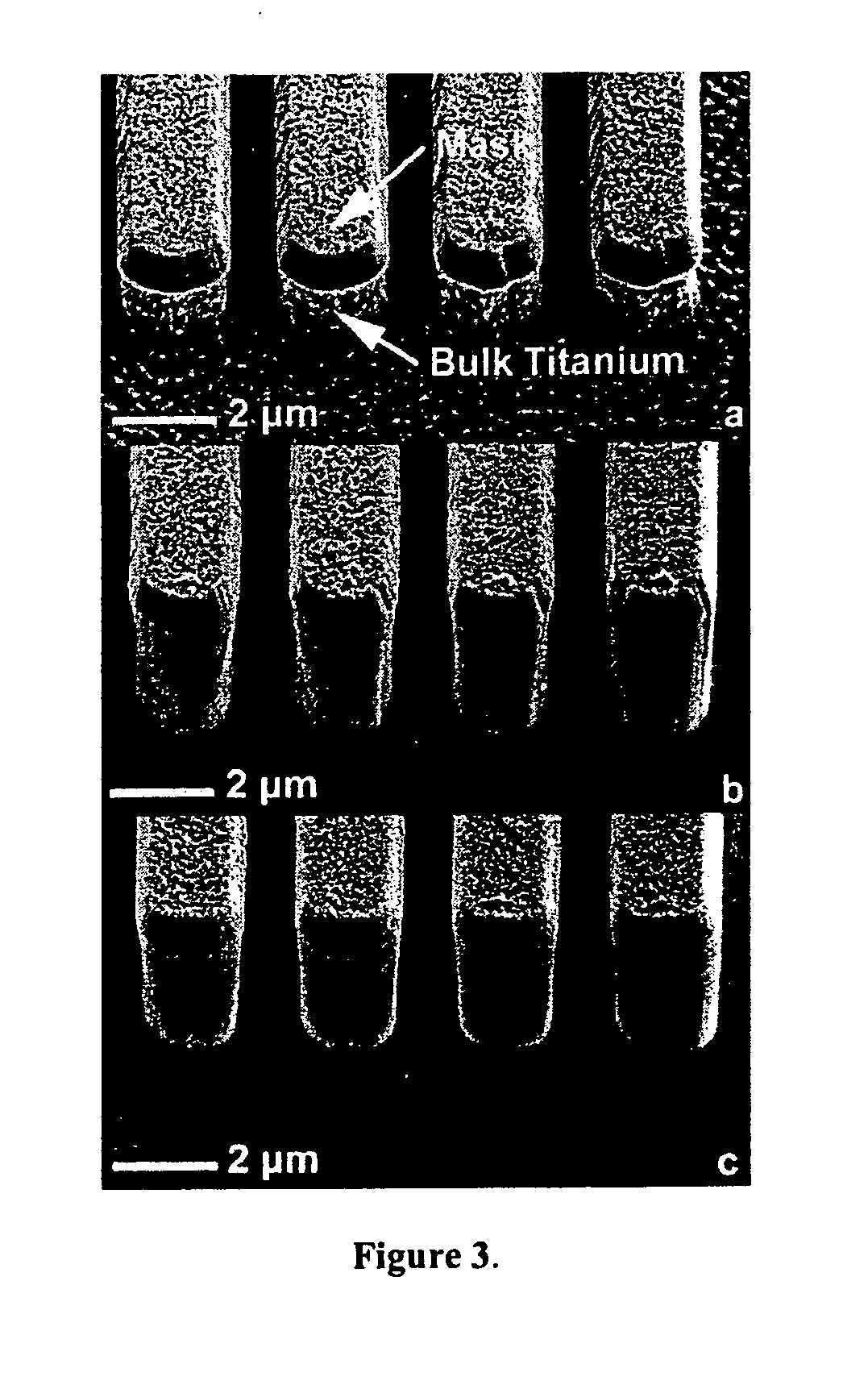

Monocyclic high aspect ratio titanium inductively coupled plasma deep etching processes and products so produced

ActiveUS20100125254A1Reduce undercut pattern tio2 mask workHigh etch rate and surface smoothnessDecorative surface effectsLayered productsMicroelectronicsEtching rate

Monocyclic chlorine based inductively coupled plasma deep etching processes for the rapid micromachining of titanium substrates and titanium devices so produced are disclosed. The method parameters are adjustable to simultaneously vary etch rate, mask selectivity, and surface roughness and can be applied to titanium substrates having a wide variety of thicknesses to produce high aspect ratio features, smooth sidewalls, and smooth surfaces. The titanium microdevices so produced exhibit beneficially high fracture toughness, biocompatibility and are robust and able to withstand harsh environments making them useful in a wide variety of applications including microelectronics, micromechanical devices, MEMS, and biological devices that may be used in vivo.

Owner:RGT UNIV OF CALIFORNIA

Automobile frame welding parameter optimization method

ActiveCN110560847AImprove current regulation efficiencySave adjustment timeArc welding apparatusVehicle componentsAutomotive engineeringFixed frequency

The invention relates to the technical field of software upgrading, and provides an automobile frame welding parameter optimization method. The method comprises the following steps: (1) constructing amathematical model of double-pulse welding current, wherein the mathematical model is represented by the formula; and (2) determining an optimal variable of the continuous adjustment of the welding current in a fixed-frequency mode, wherein the optimal variable is the number n1 of pulses in a strong pulse group and the number n2 of pulses in a weak pulse group. With the automobile frame welding parameter optimization method, the welding reliability of a new energy automobile is improved, and welding parameters are optimized according to the welding mathematical model of the new energy automobile and a related data fitting algorithm, so that the quality of a welding seam is guaranteed, and splashing and undercut phenomena are greatly reduced. In the welding process of a welding machine with the self-learning function, regular and stable current and stable arc length stretching rhythm are ensured, and no arc breaking phenomenon occurs, so that the welding cost of the new energy automobile is reduced.

Owner:奇瑞新能源汽车股份有限公司

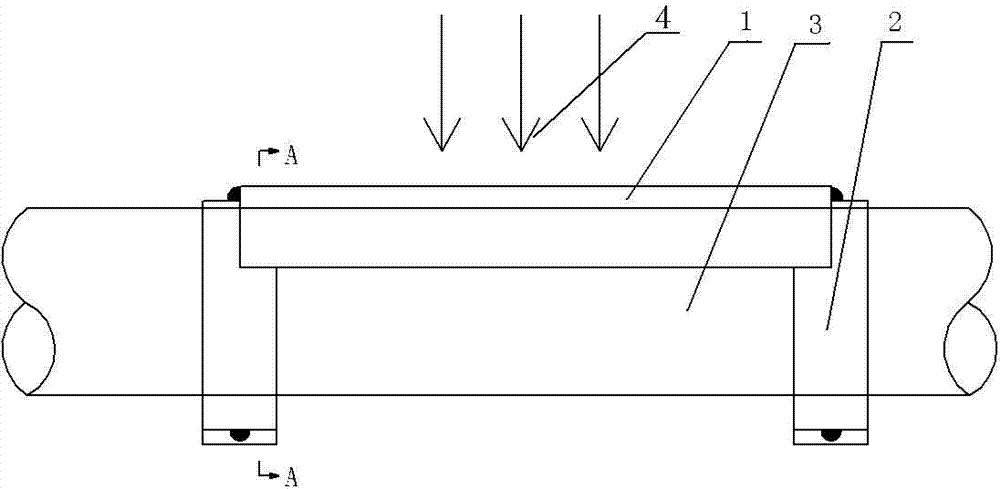

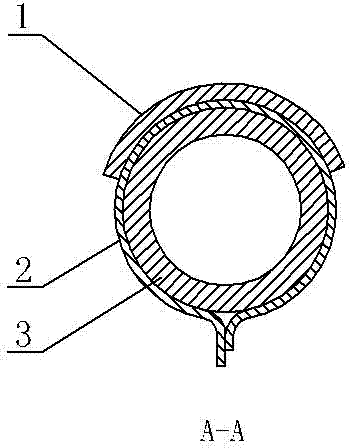

Boiler inside pipe system anti-abrasion cover structure

ActiveCN104329657AReduce hidden dangersImprove wear resistanceFluid heatersBoiler water tubesSpot weldingSystem structure

The invention relates to the technical field of a boiler inside pipe system structure, in particular to a boiler inside pipe system anti-abrasion cover structure with the advantage that phenomena of edge engaging, burn through and the like possibly caused during the spot welding of an anti-abrasion cover can be effectively reduced, the pipe system anti-abrasion capability is enhanced, the pipe system operation time is prolonged, and the boiler pipe system hidden danger is reduced. The boiler inside pipe system anti-abrasion cover structure comprises a pipe and an anti-abrasion cover, and is characterized in that a matched pipe clamp is arranged outside the pipe in a clamping way, and the anti-abrasion cover is fixedly arranged on the pipe clamp in a spot welding way.

Owner:WUXI HUAGUANG BOILER

TFT substrate and manufacturing method thereof

ActiveCN108257976BImprove yieldReduce tilt angleSolid-state devicesSemiconductor/solid-state device manufacturingProtection layerElectrode pair

The invention provides a TFT substrate and a manufacturing method thereof. The TFT substrate comprises a base substrate, a metal layer arranged on the base substrate, an insulating layer arranged on the base substrate and the metal layer, a bottom common electrode arranged on the insulating layer, and a protective layer arranged on the insulating layer and the bottom common electrode. The insulating layer has first via holes exposing the metal layer. The bottom common electrode has second via holes formed in areas corresponding to the first via holes. The thickness of the edge of the bottom common electrode near the second via holes gradually decreases along the direction near the second via holes, so that the upwarp angle of the edge of the bottom common electrode near the second via holes is reduced, and the probability of bottom cutting is reduced. Therefore, the risk of peeling of the film formed on the bottom common electrode is reduced, the yield of the TFT substrate is improved,and the display effect of the LCD panel is good.

Owner:WUHAN CHINA STAR OPTOELECTRONICS TECH CO LTD

Efficient welding method for one side welding both-side formation

InactiveCN111922486AHigh efficiency of single-side welding and double-side formingRealize small angle weldingWorkpiece edge portionsWelding accessoriesEngineeringArc welding

The invention relates to an efficient welding method for one side welding both-side formation. The details of the efficient welding method are as follows: workpiece blanking is carried out; a workpiece after blanking is polished and assembled to form a workpiece to be welded; a digital pulse electric arc welder selects a pulse electric arc mode and completes root pass welding of the workpiece to be welded; then, the digital pulse electric arc welder selects a spray electric arc mode and completes hot weld layer root pass welding of the workpiece to be welded; after hot weld layer root pass welding is completed, the digital pulse electric arc welder selects the spray electric arc mode and completes filling root pass welding of the workpiece to be welded; after filling root pass welding is completed, the digital pulse electric arc welder selects the spray electric arc mode and completes capping root pass welding of the workpiece to be welded; and after welding is over, a power supply isturned off. The efficient welding method can realize one side welding both-side formation, has the advantages of high cladding efficiency and good operability, and solves the technical problems that one side welding both-side formation of traditional TKY welding joints is not high in welding quality, low in operation efficiency and incapable of realizing continuous operation.

Owner:厦门天吴海洋科技有限公司 +1

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com