Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

52results about How to "Reduce read operations" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

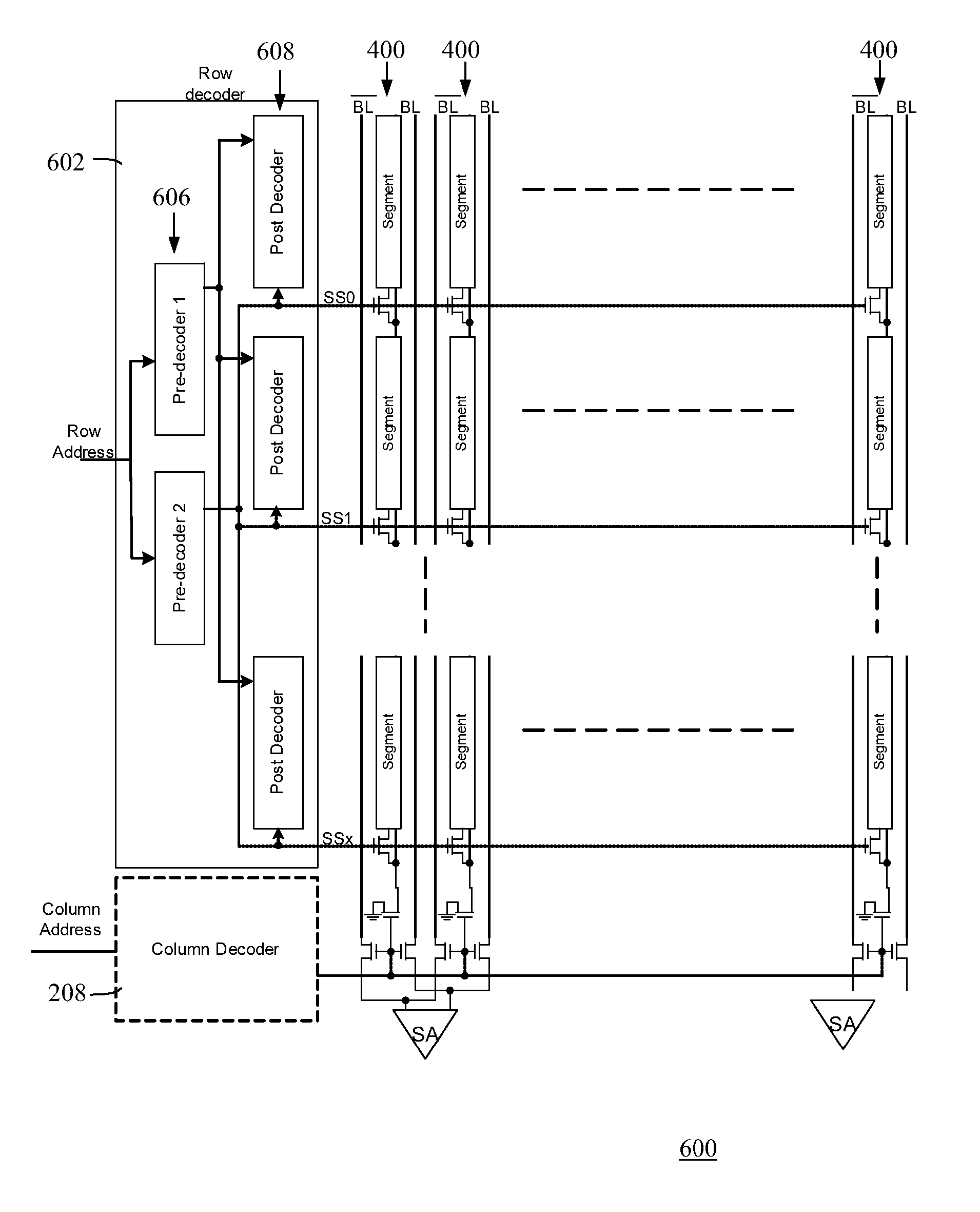

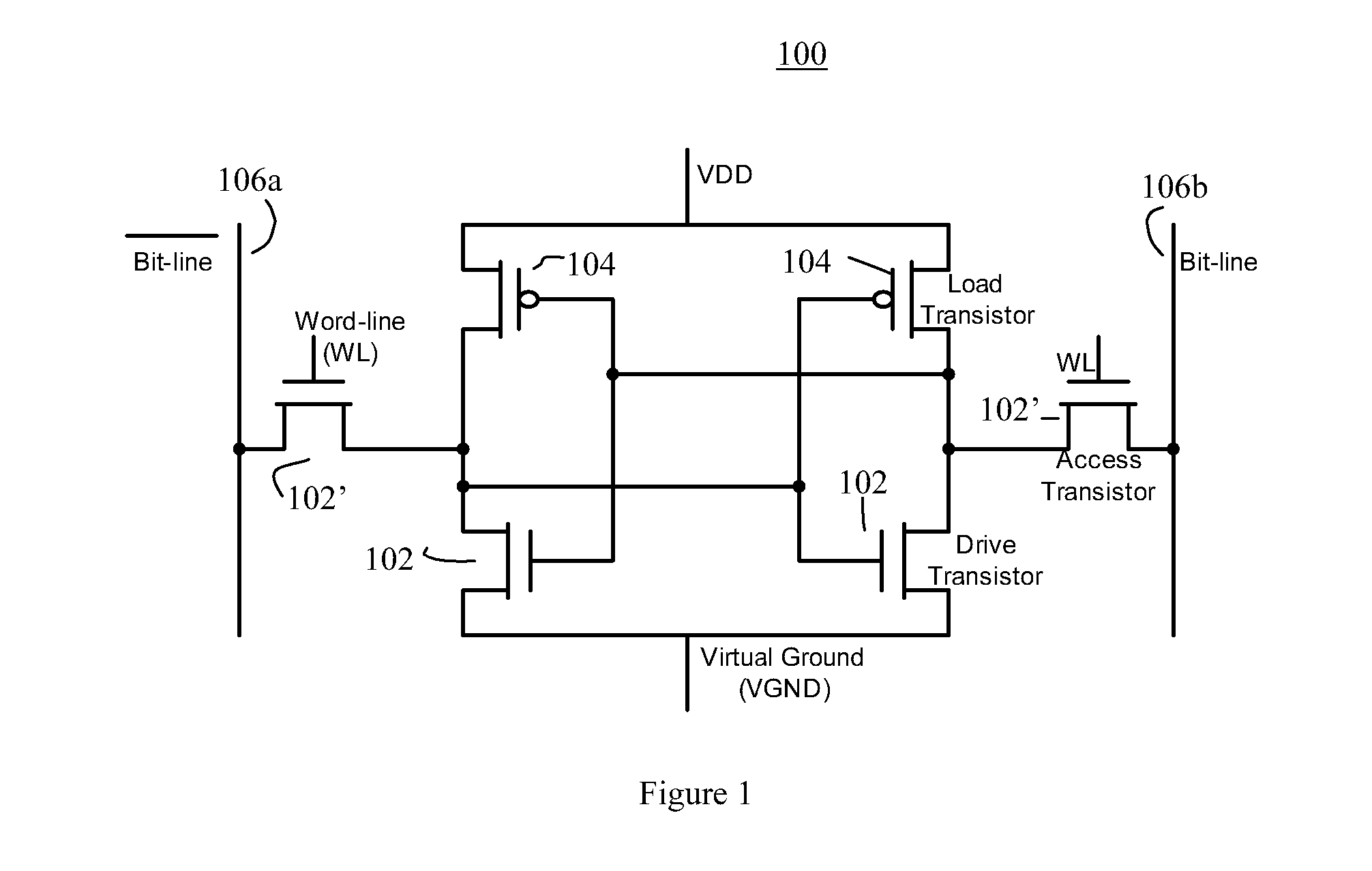

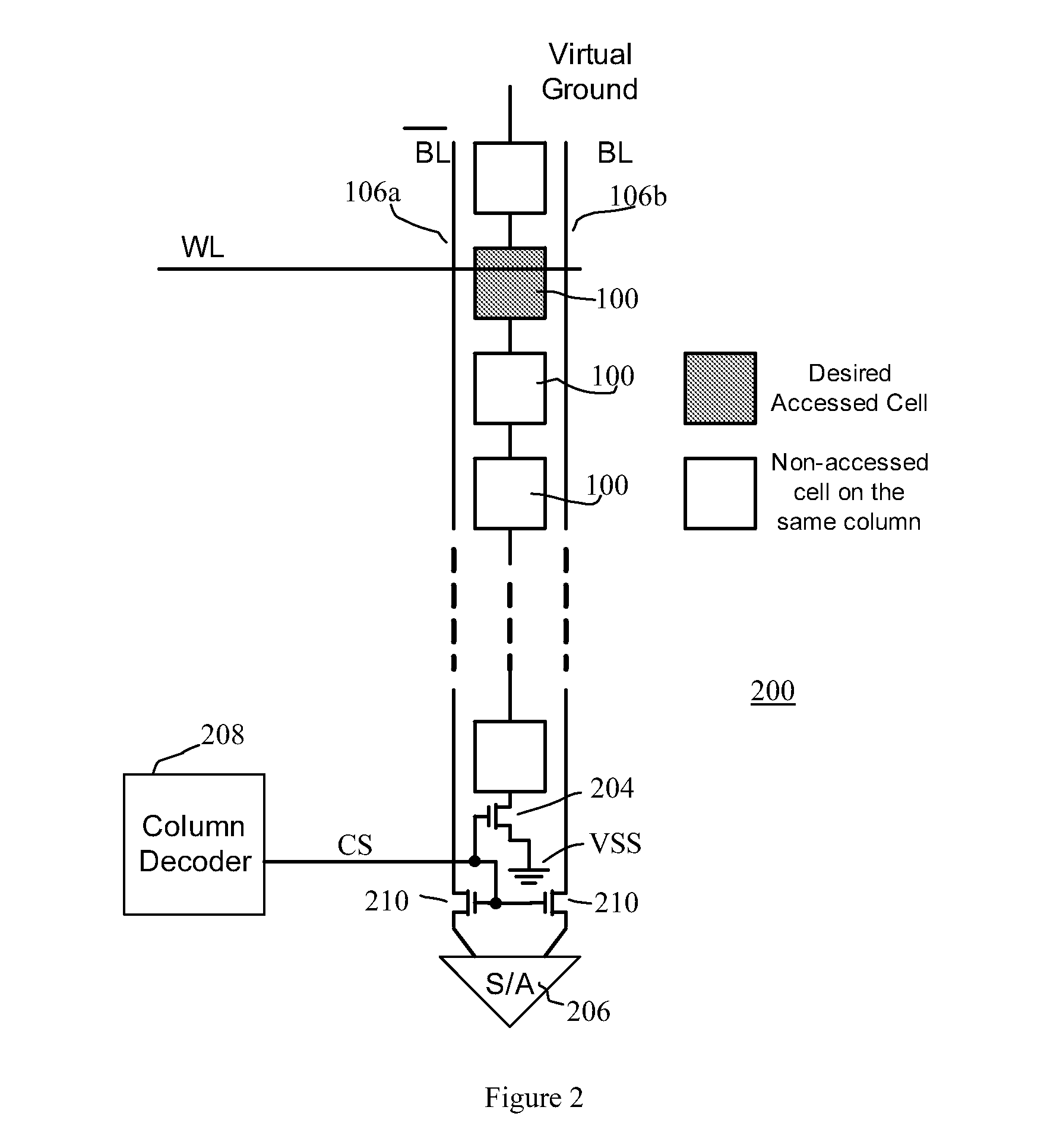

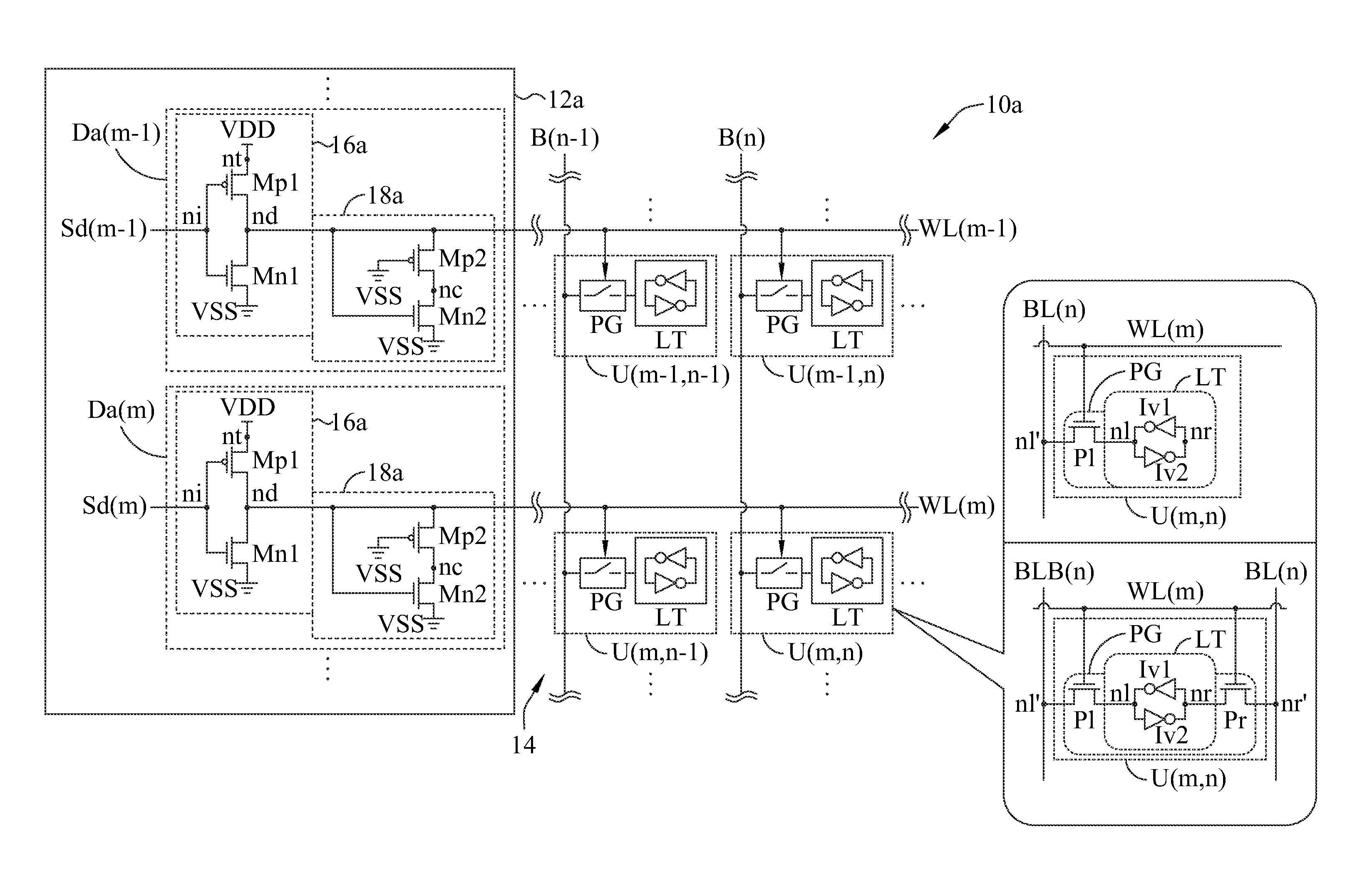

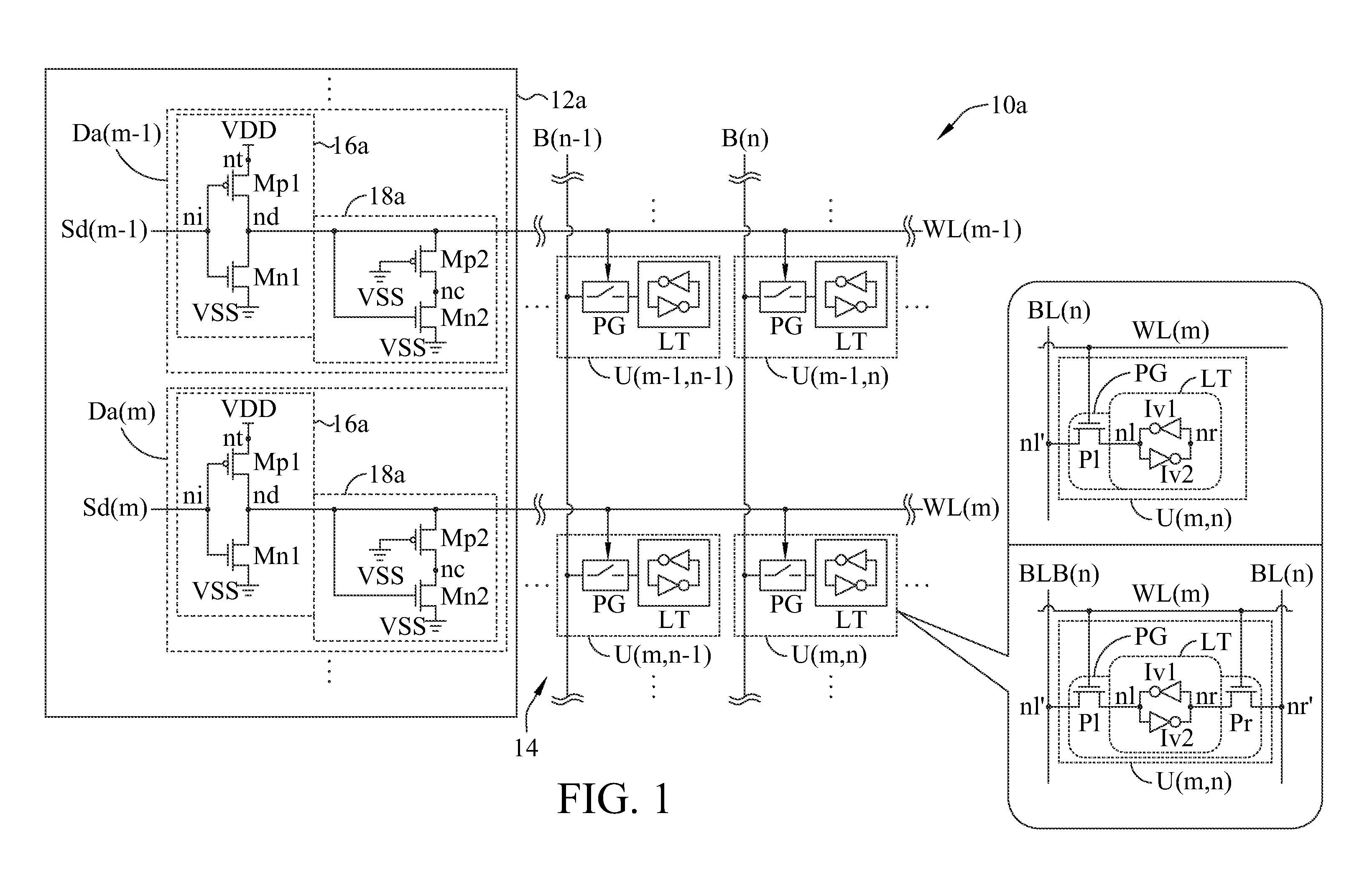

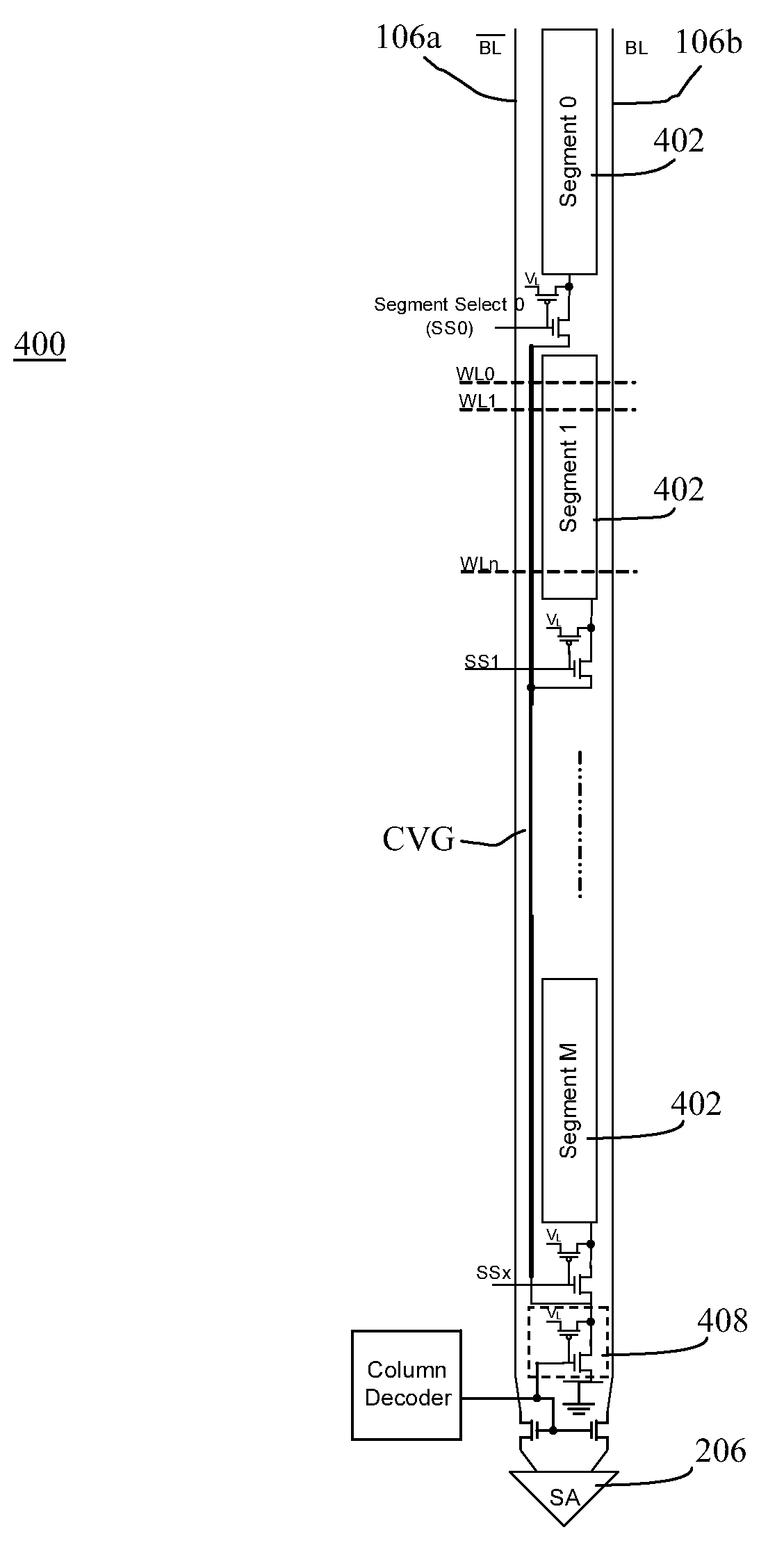

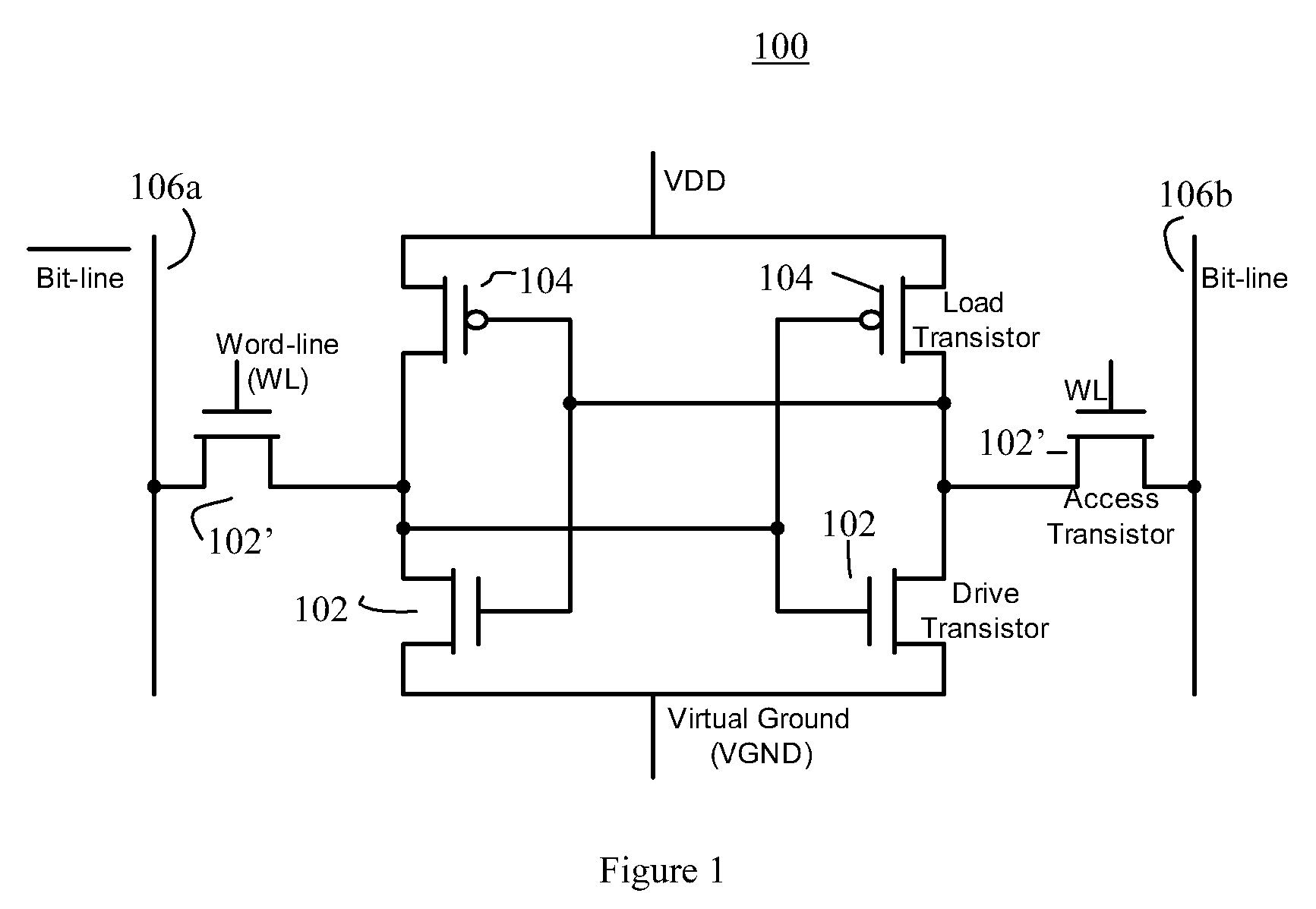

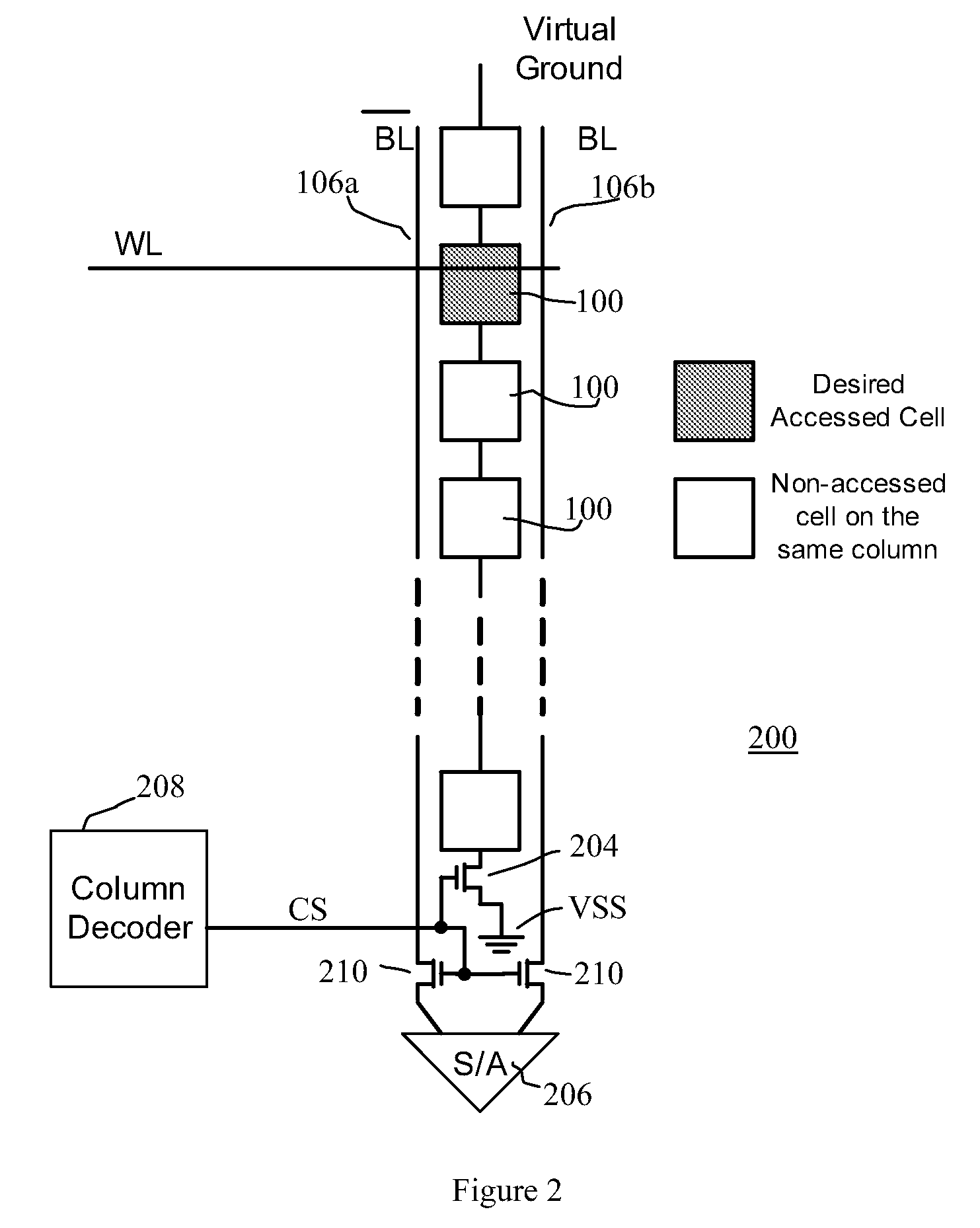

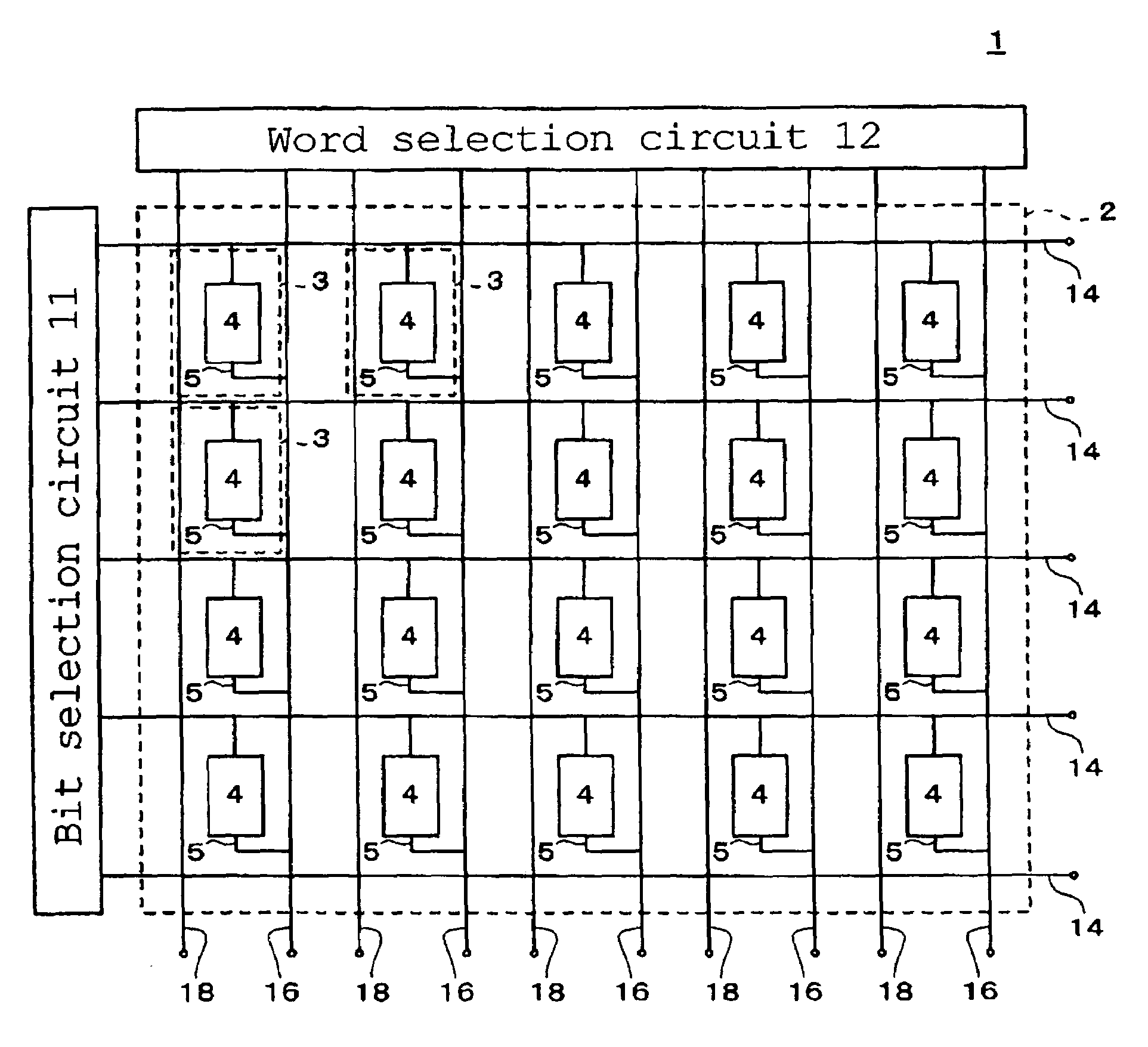

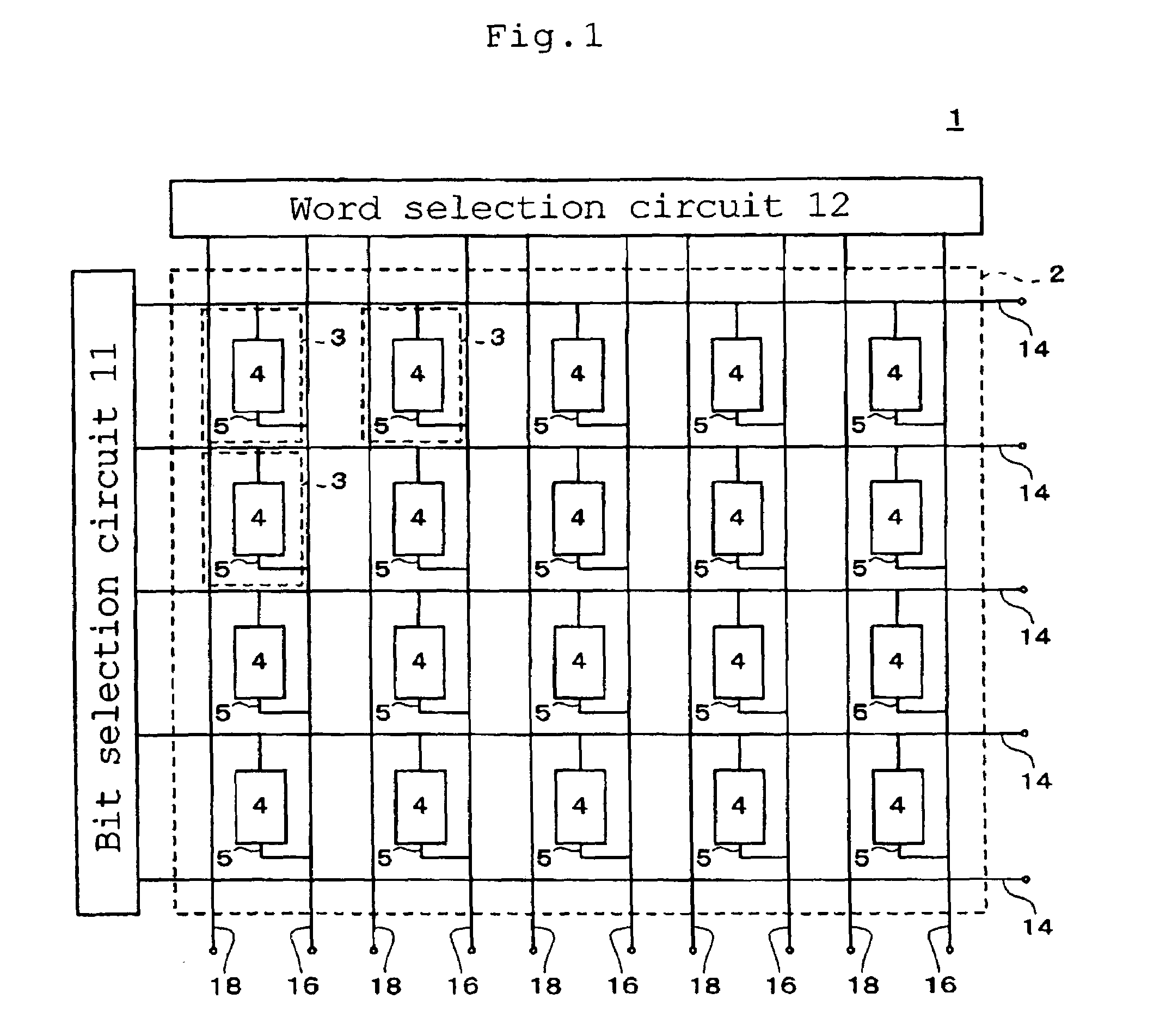

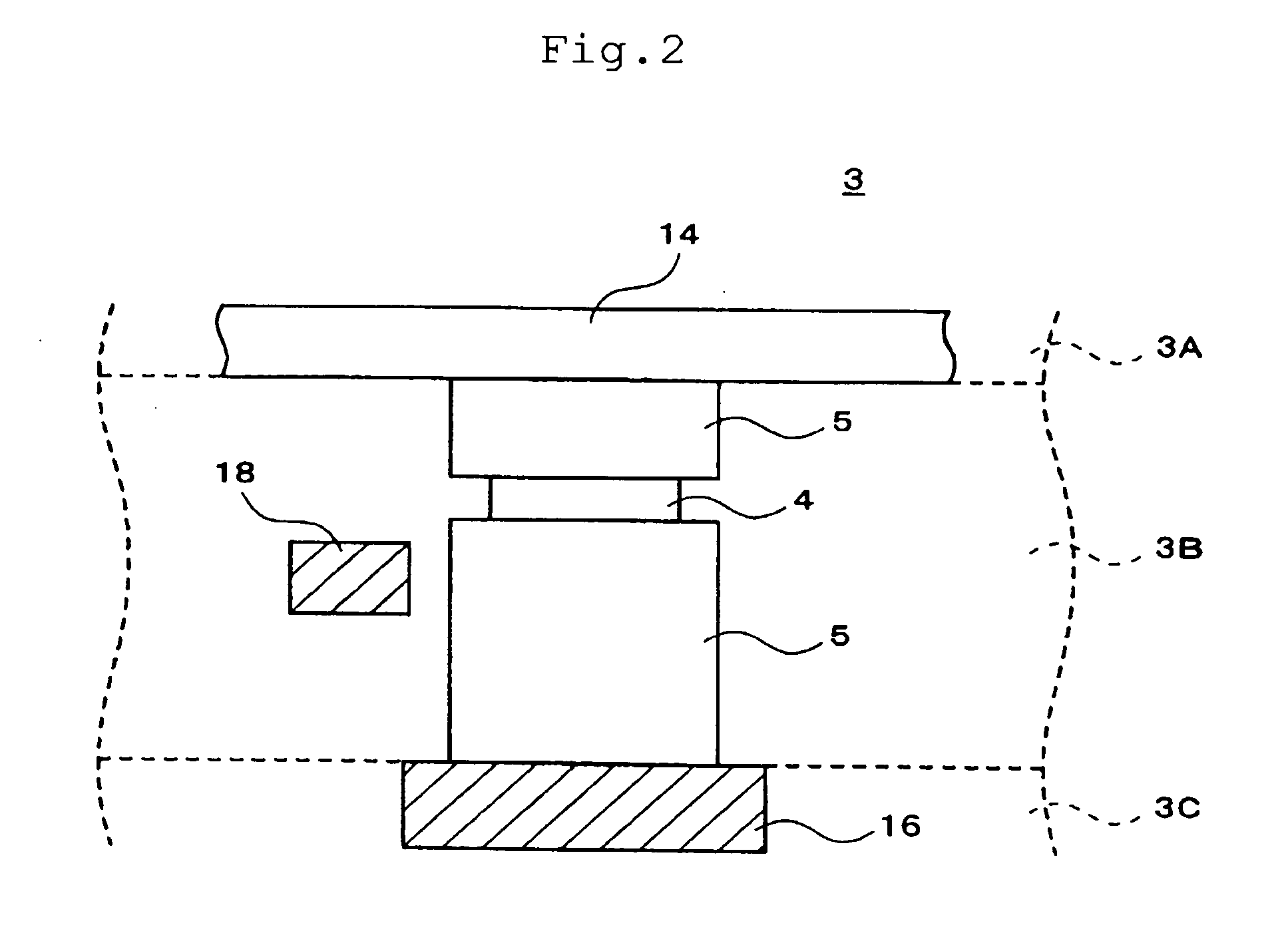

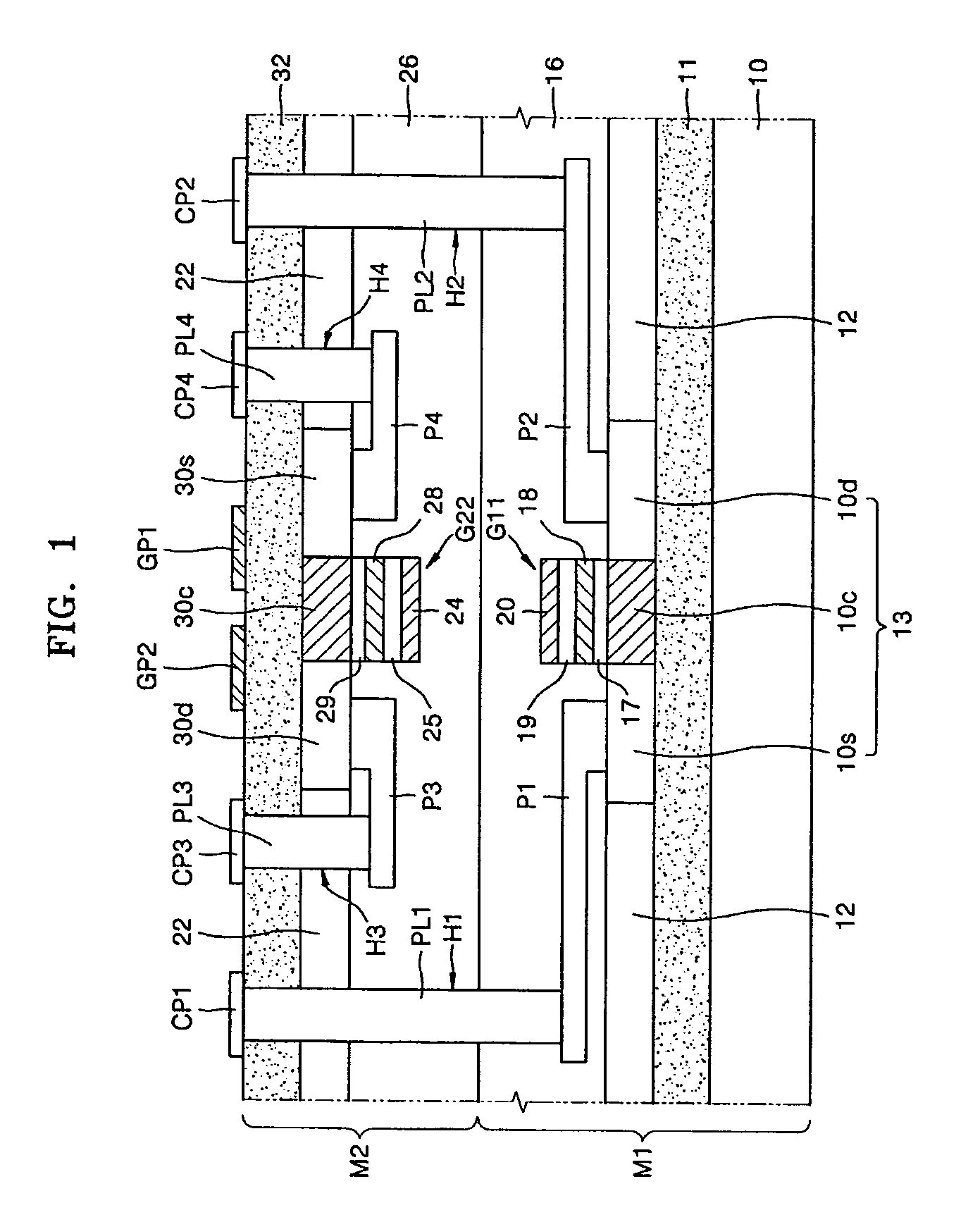

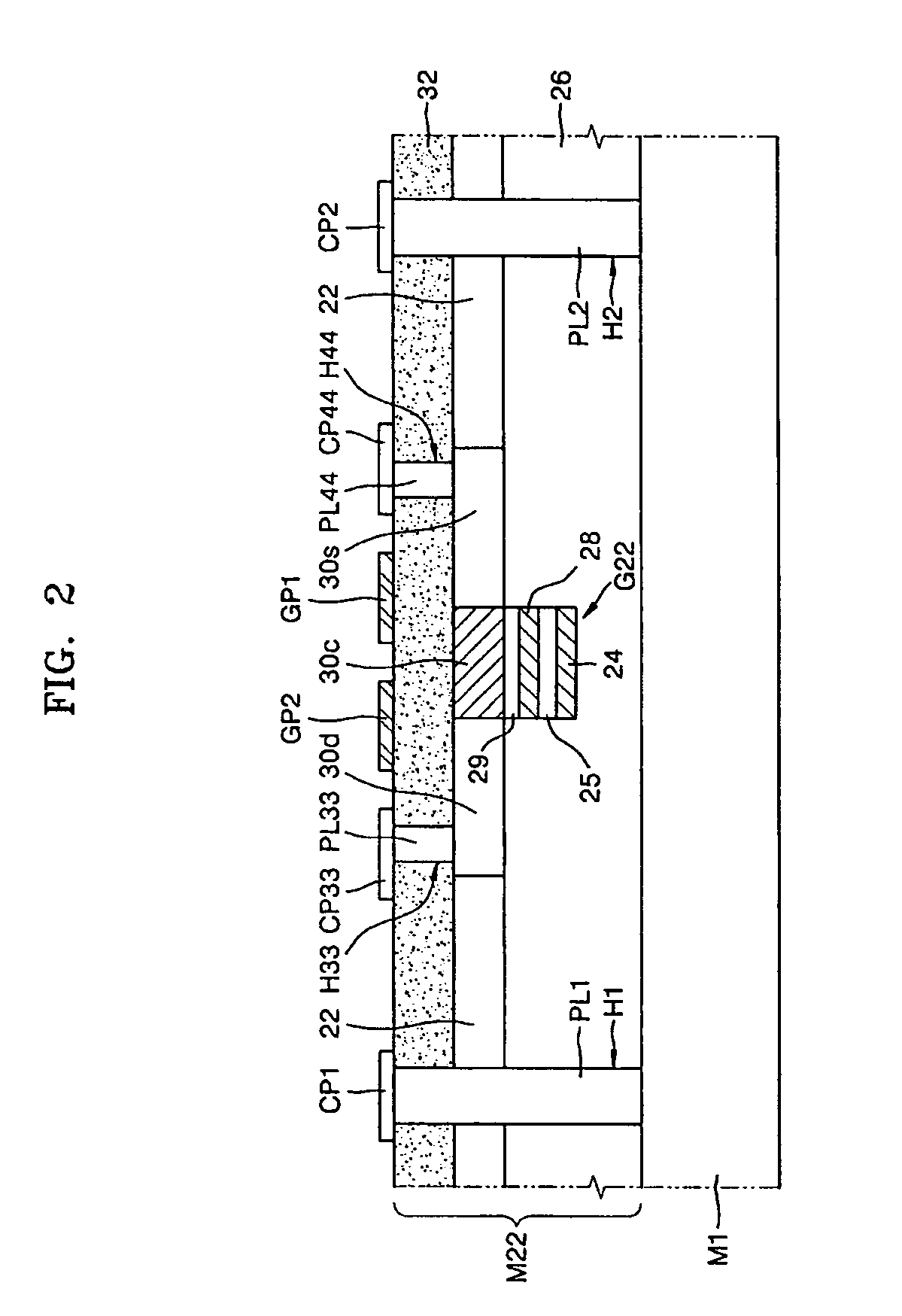

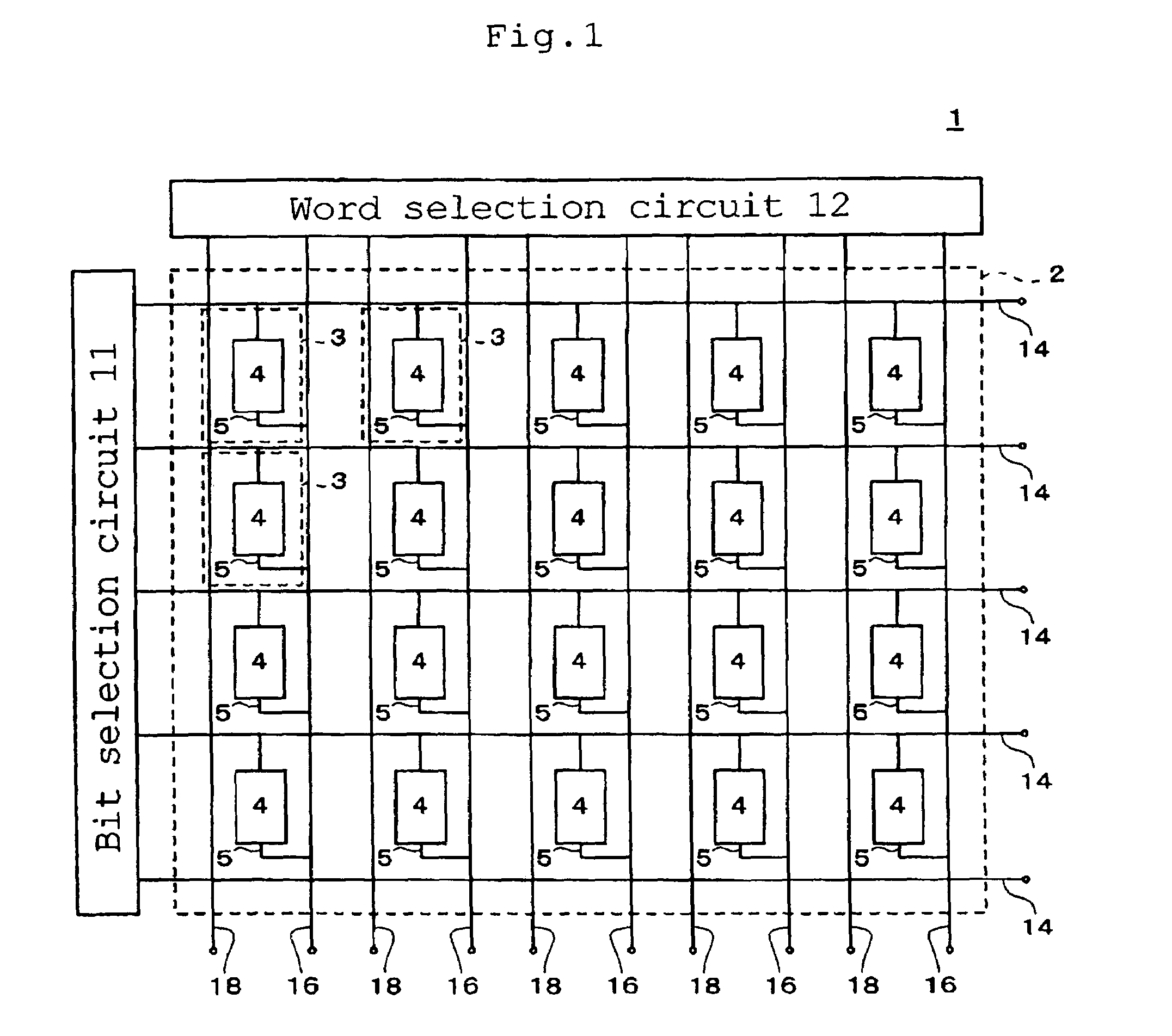

Segmented Column Virtual Ground Scheme In A Static Random Access Memory (SRAM) Circuit

InactiveUS20070217262A1Power write operationTotal current dropRead-only memoriesDigital storageStatic random-access memoryLow voltage

A static random access memory (SRAM) cell array is provided that reduces leakage current. The SRAM cell array is configured in a plurality of columns. Each of the columns comprises: a column virtual ground node; a column switch for selectively coupling the column virtual ground node to one of a ground or a nominal low voltage; and a plurality of segments. Each of the segments comprises: a segment virtual ground node; a plurality of SRAM cells including a virtual ground signal coupled to the segment virtual ground node; and a virtual ground switch for selectively coupling the segment virtual ground node to one of either a nominal low voltage or the column virtual ground node. A method for operating the SRAM cell array is also described.

Owner:SACHDEV MANOJ +1

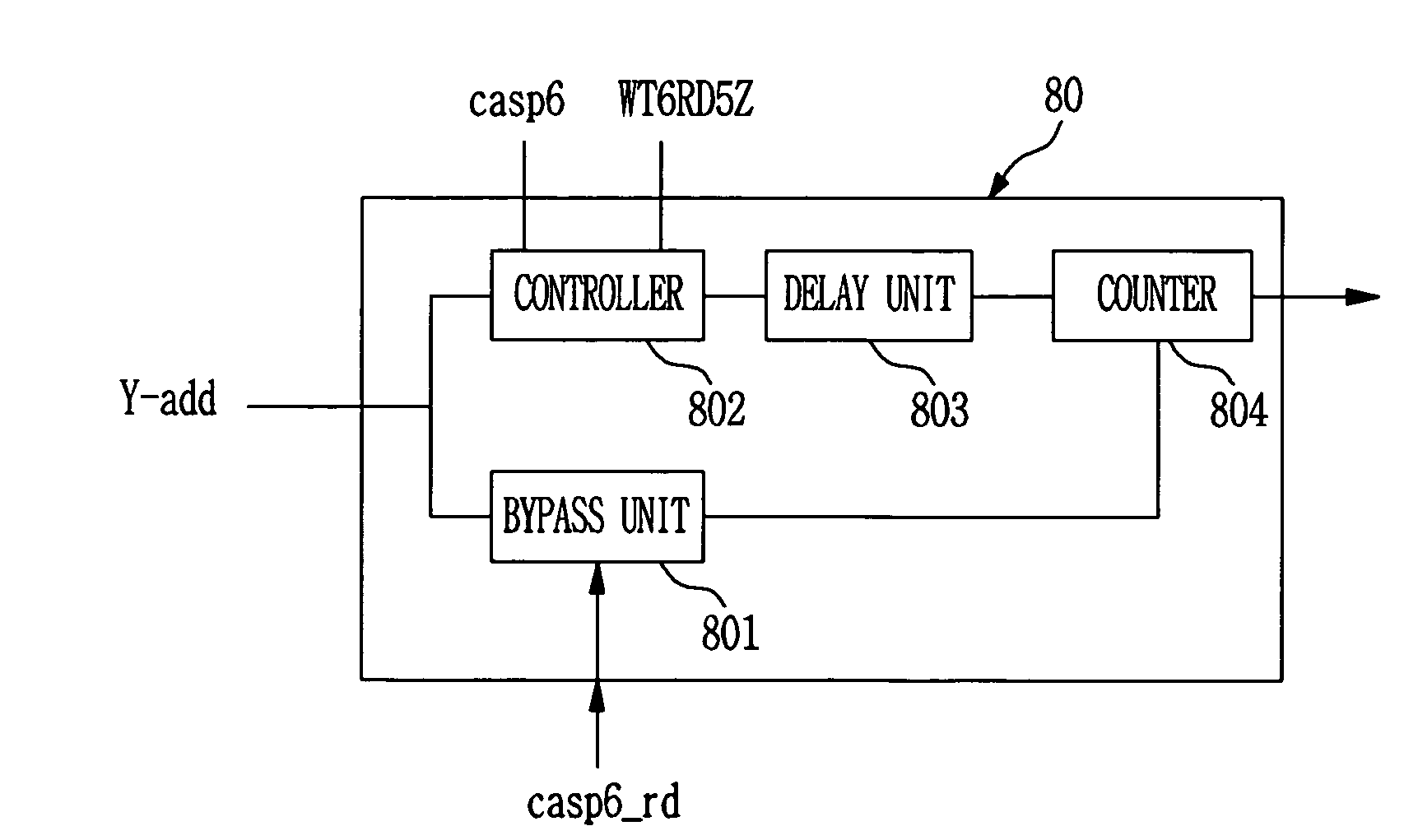

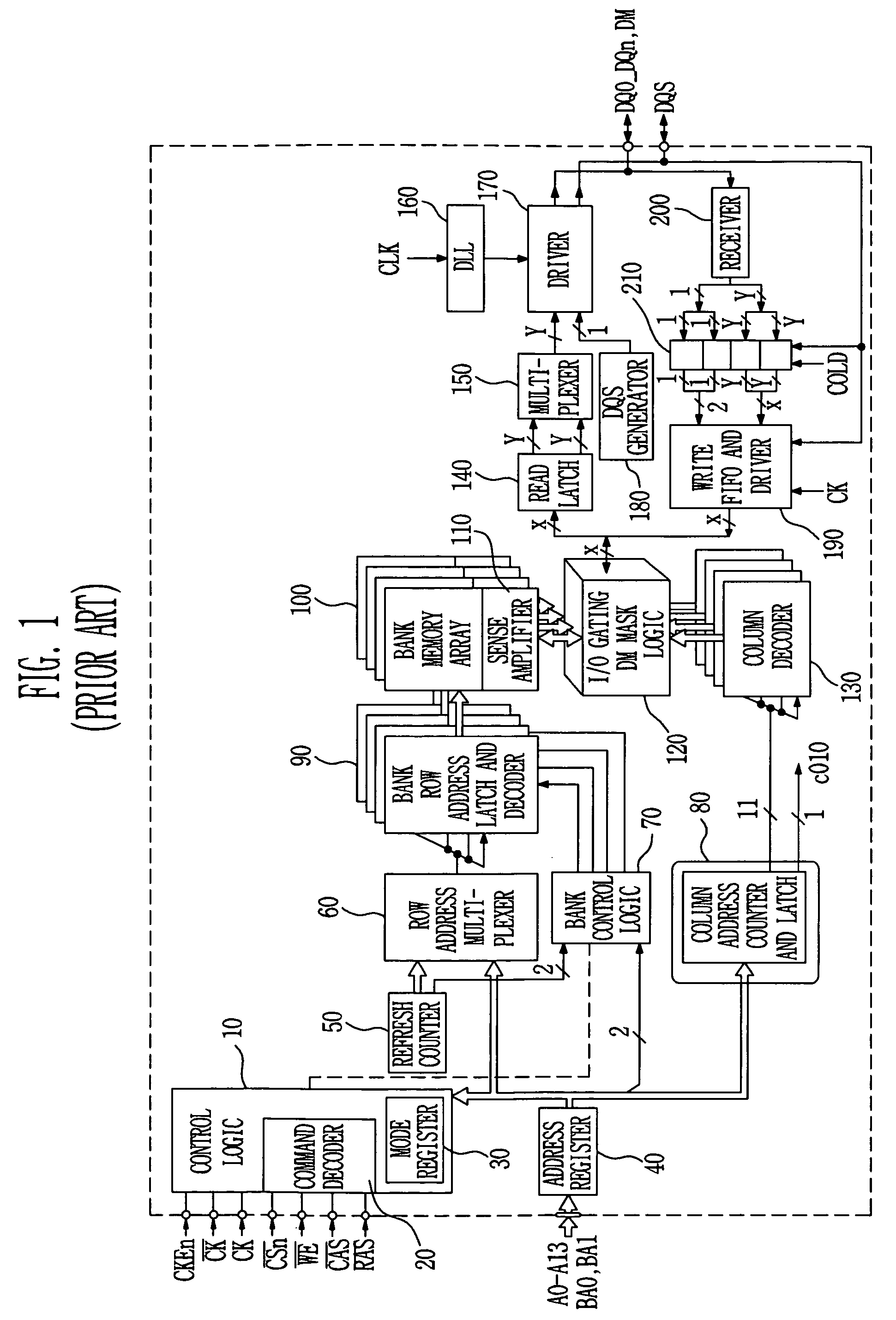

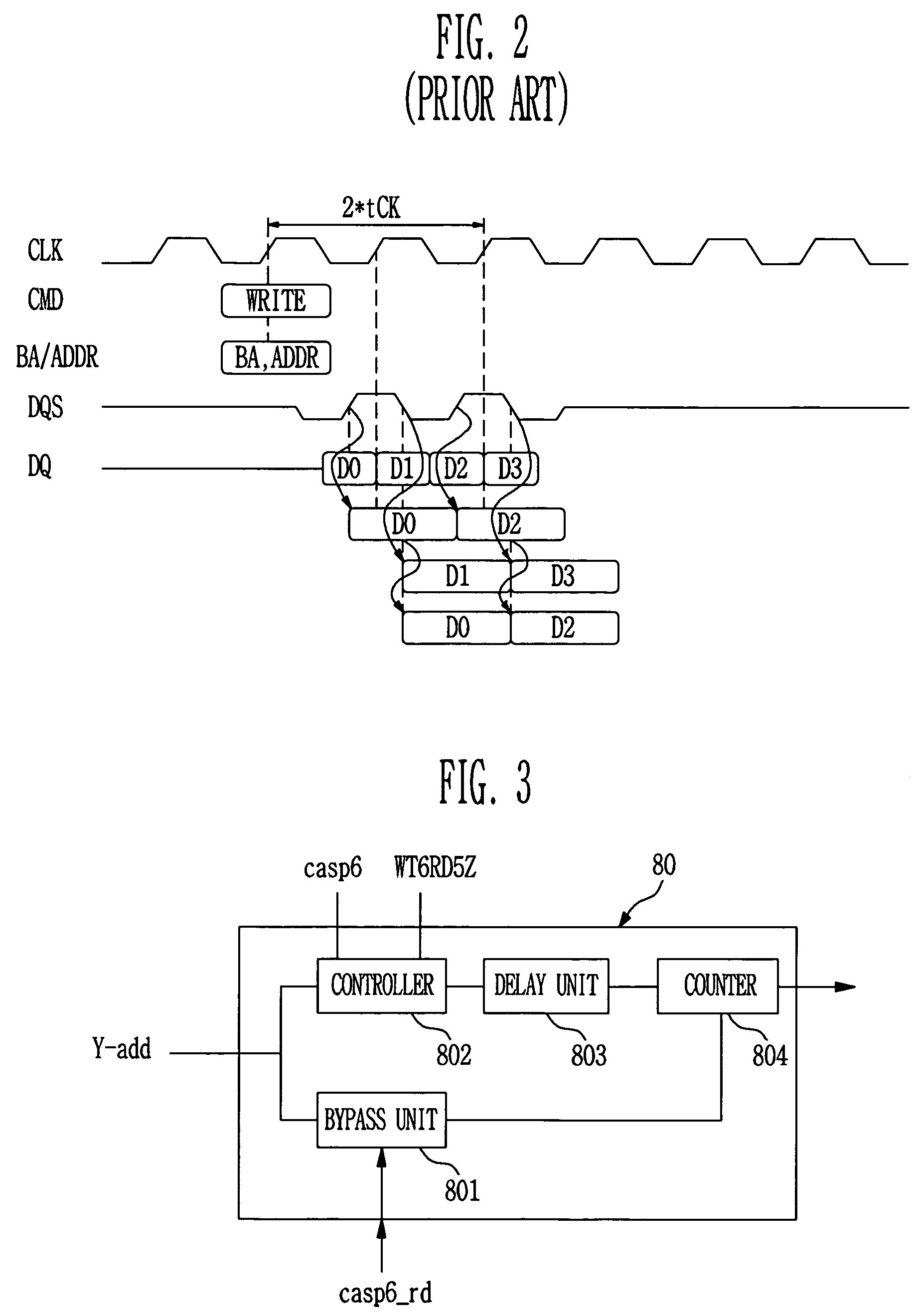

Semiconductor memory device having controller with improved current consumption

InactiveUS7248512B2Total current dropReduce read operationsDigital storageCurrent consumptionComputer science

Owner:SK HYNIX INC

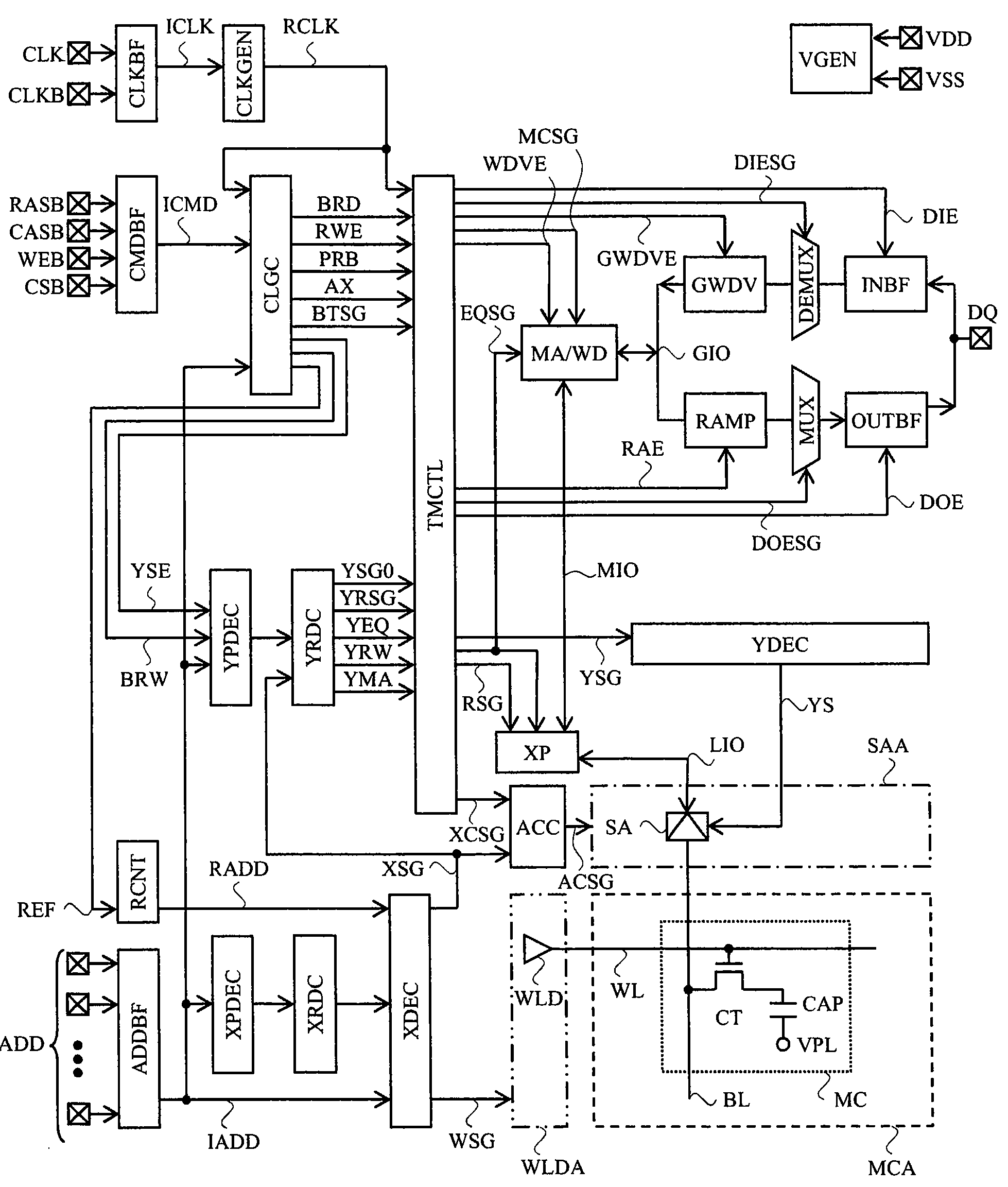

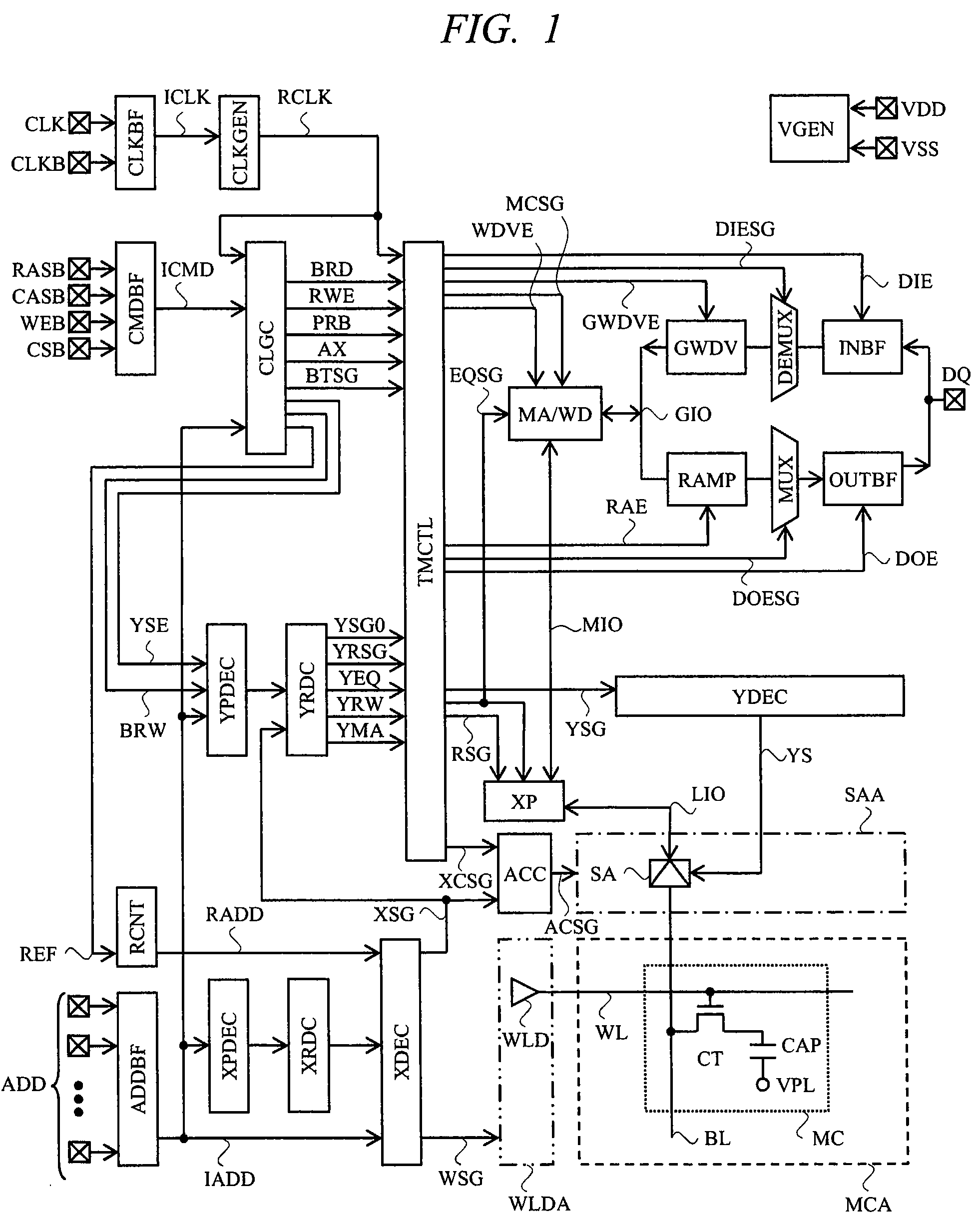

Semiconductor Device

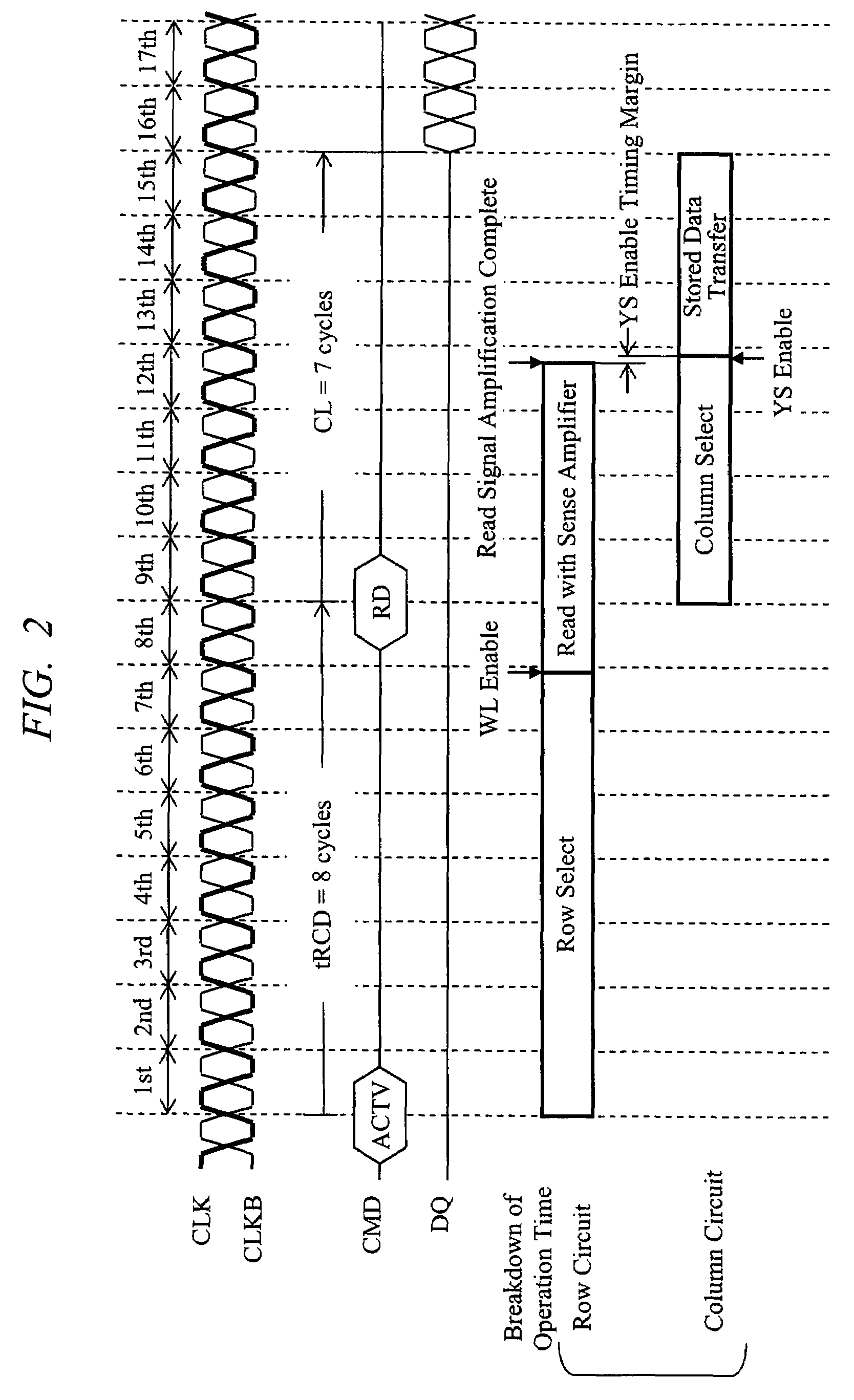

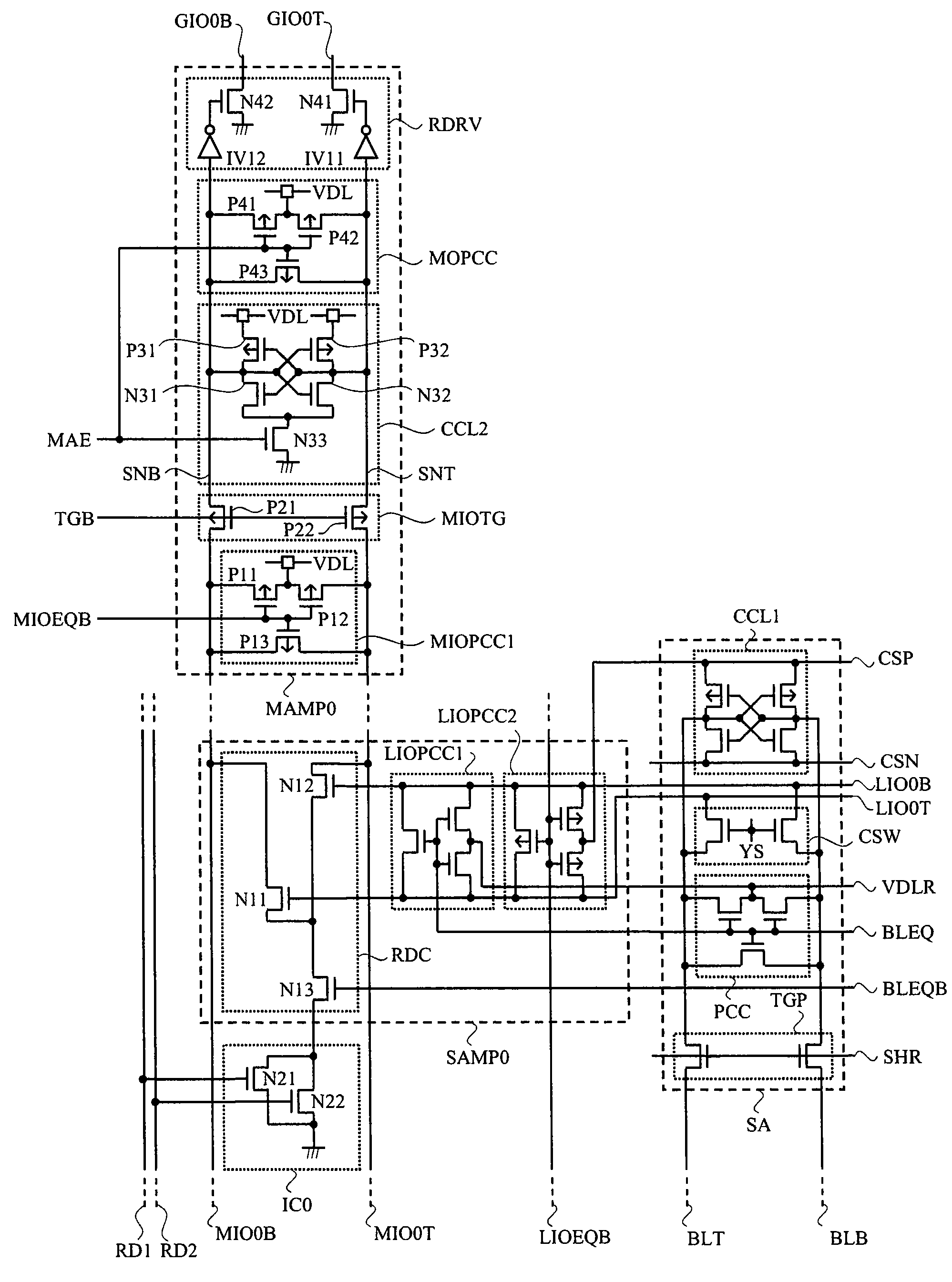

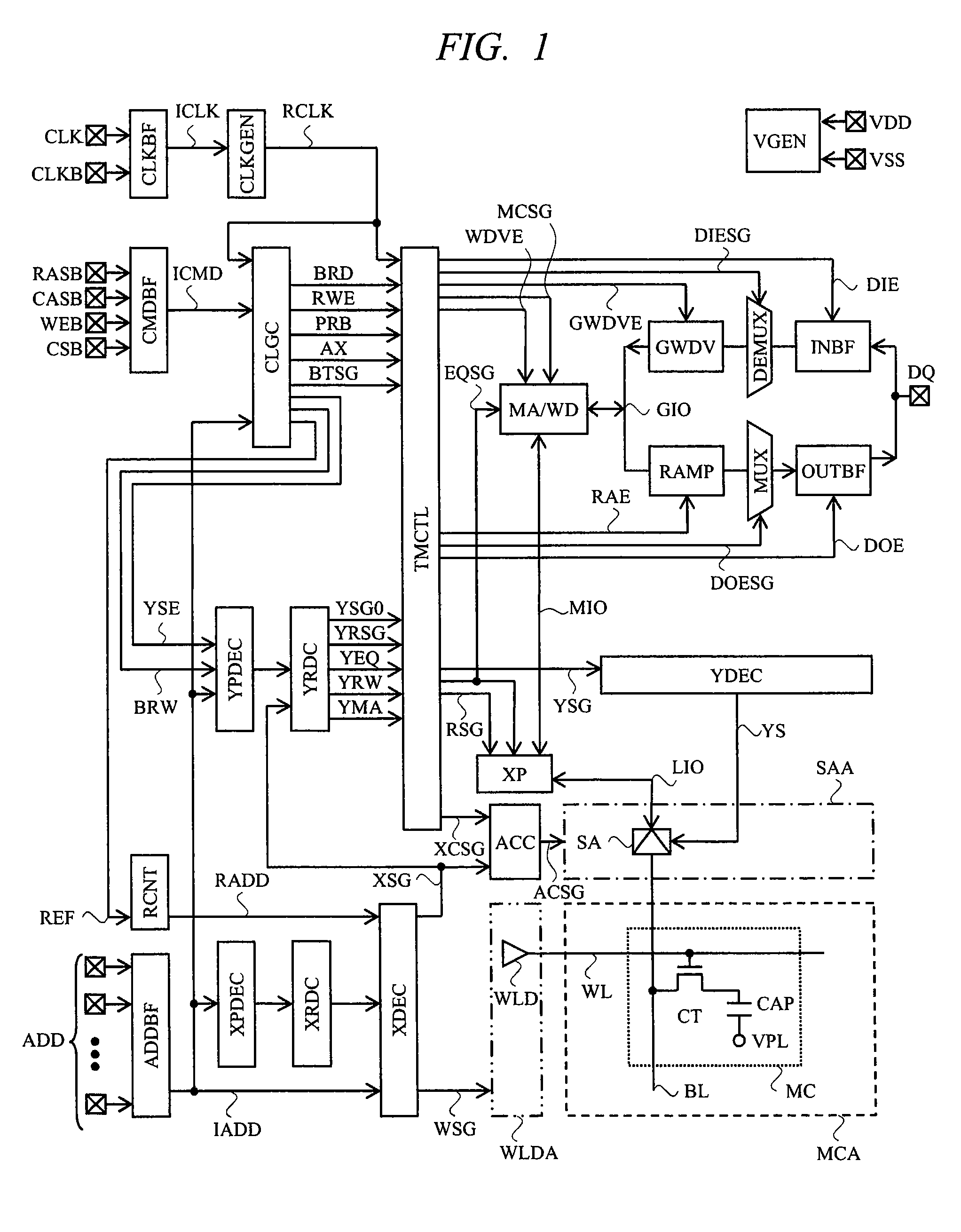

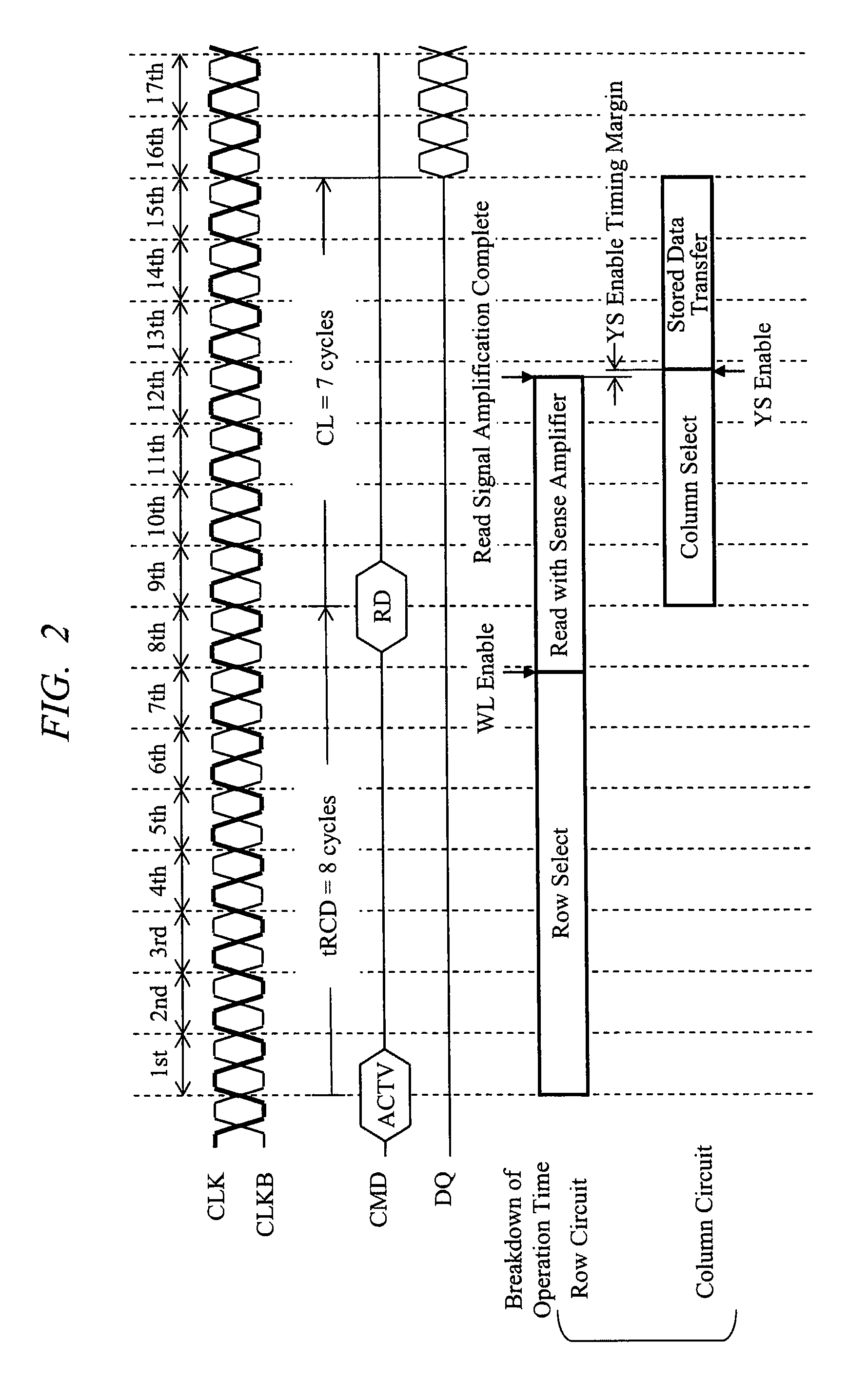

InactiveUS20070147160A1Reduce data transfer timeExpand read operation marginDigital storageSense amplifierInput/output

A column circuit that amplifies signals read from a sense amplifier array SAA to local input / output lines LIO in sub-amplifiers SAMP to transfer the amplified signals to main input / output lines MIO is provided. A current control circuit IC that can set one of two kinds of currents according to read enable signals RD1, RD2 is provided in each sub-amplifier SAMP. The read enable signals RD1, RD2 are generated at timings corresponding to the number of cycles in burst read operation under control of the timing controller. Current in the current control circuit IC is set to be large by the RD1 in burst read operation cycle just after activation of a memory bank, while current in the current control circuit IC is set to be small by the RD2 in the next and subsequent burst read cycles. Accordingly, expansion of an operation margin or reduction of power consumption can be realized in a semiconductor device including a semiconductor memory such as a DRAM.

Owner:LONGITUDE LICENSING LTD

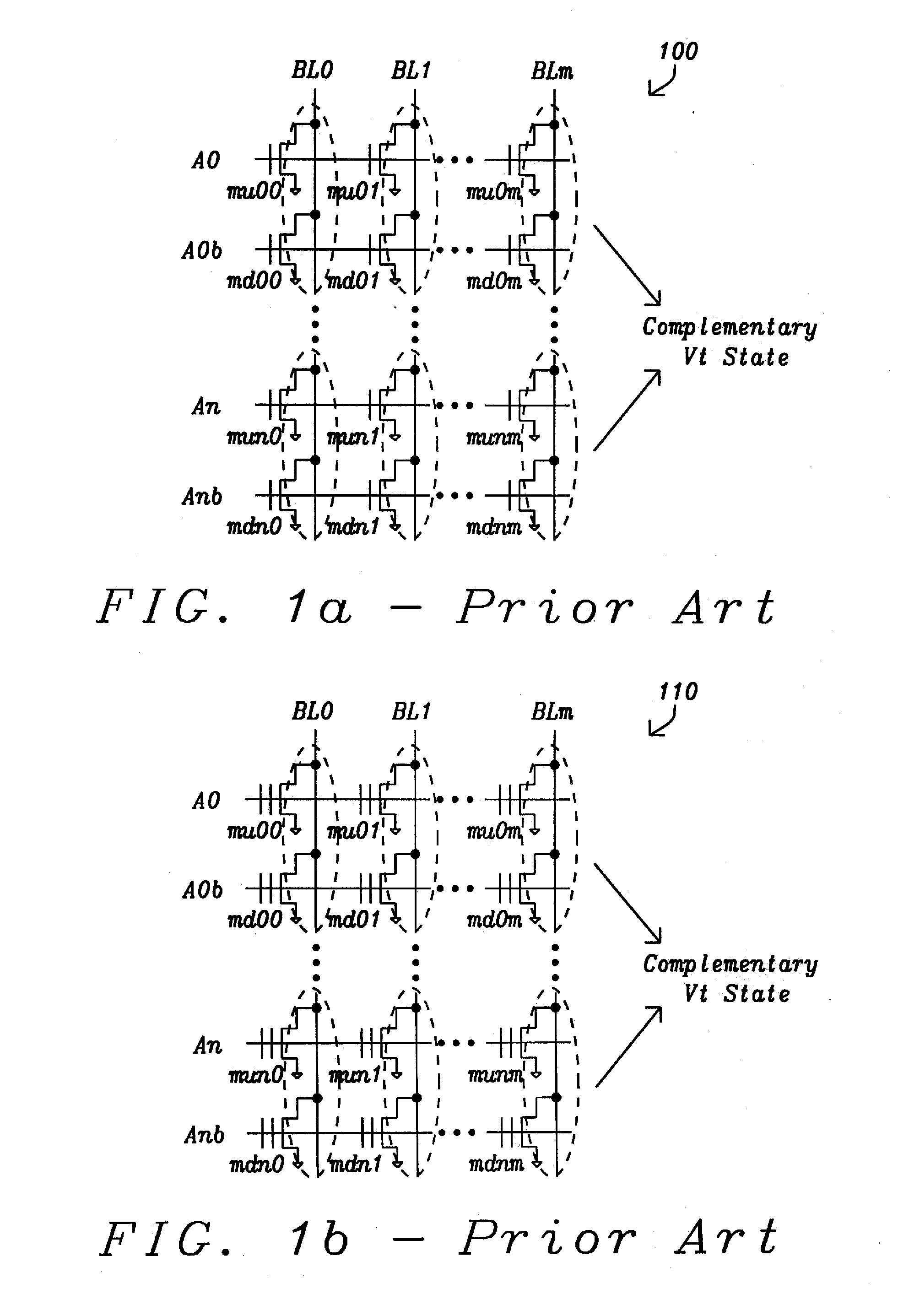

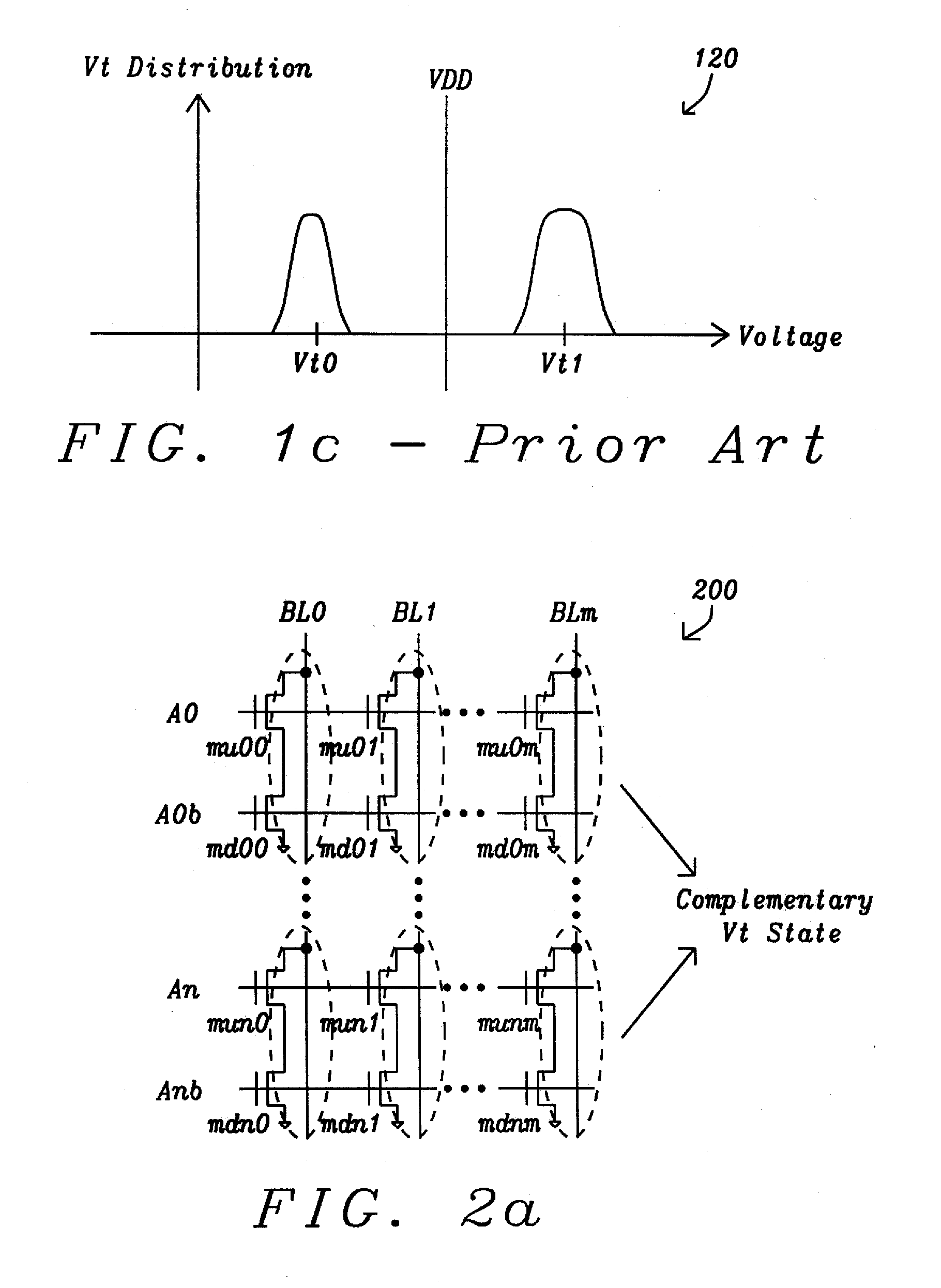

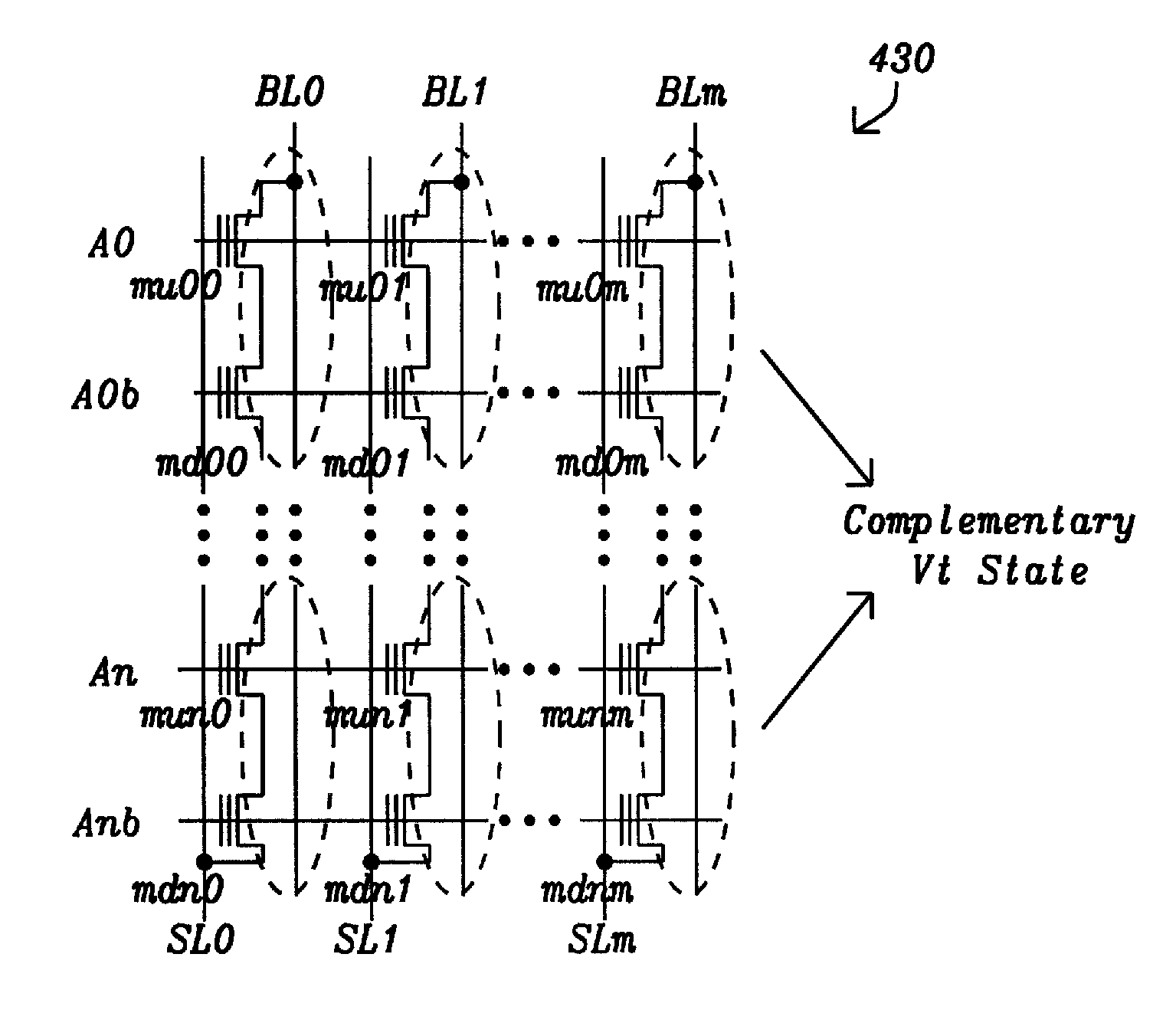

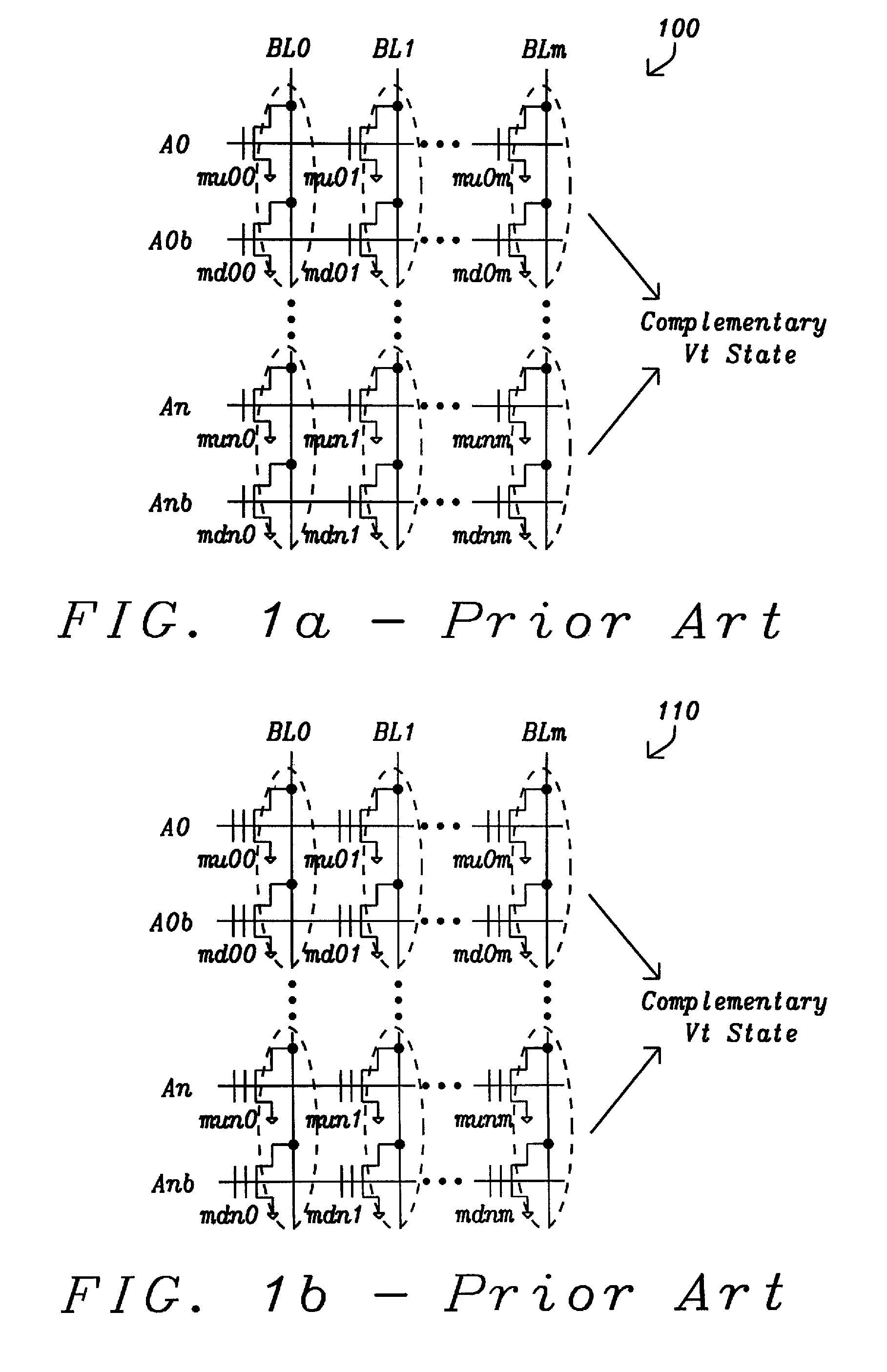

Flexible 2T-Based Fuzzy and Certain Matching Arrays

InactiveUS20120176841A1Reduce noiseImprove good performanceRead-only memoriesDigital storageComputer science

A novel NVM-based 2T or 2nT NAND-cell for a NAND-array for PLD, PAL and matching functions is disclosed. The preferable NVM cell can be ROM or Flash. The 2T flash cell preferably uses FN for both program and erase operation, while 2T ROM cell preferably to use phosphorus for ROM code implant to get negative Vt0.

Owner:APLUS FLASH TECH

Semiconductor memory device with sub-amplifiers having a variable current source

InactiveUS7304910B1Lower performance requirementsShorten operation timeDigital storageHemt circuitsEngineering

A column circuit that amplifies signals read from a sense amplifier array SAA to local input / output lines LIO in sub-amplifiers SAMP to transfer the amplified signals to main input / output lines MIO is provided. A current control circuit IC that can set one of two kinds of currents according to read enable signals RD1, RD2 is provided in each sub-amplifier SAMP. The read enable signals RD1, RD2 are generated at timings corresponding to the number of cycles in burst read operation under control of the timing controller. Current in the current control circuit IC is set to be large by the RD1 in burst read operation cycle just after activation of a memory bank, while current in the current control circuit IC is set to be small by the RD2 in the next and subsequent burst read cycles. Accordingly, expansion of an operation margin or reduction of power consumption can be realized in a semiconductor device including a semiconductor memory such as a DRAM.

Owner:LONGITUDE LICENSING LTD

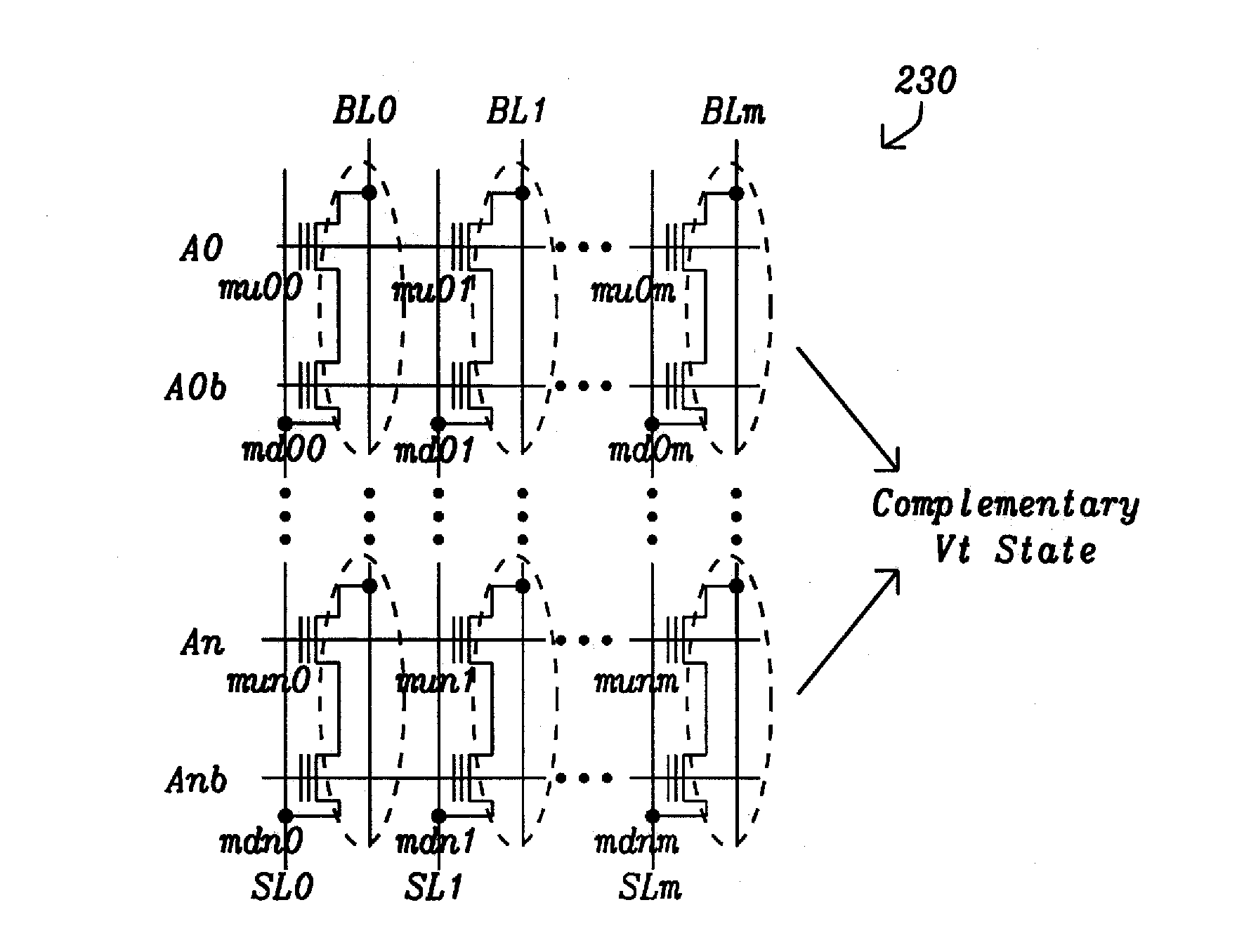

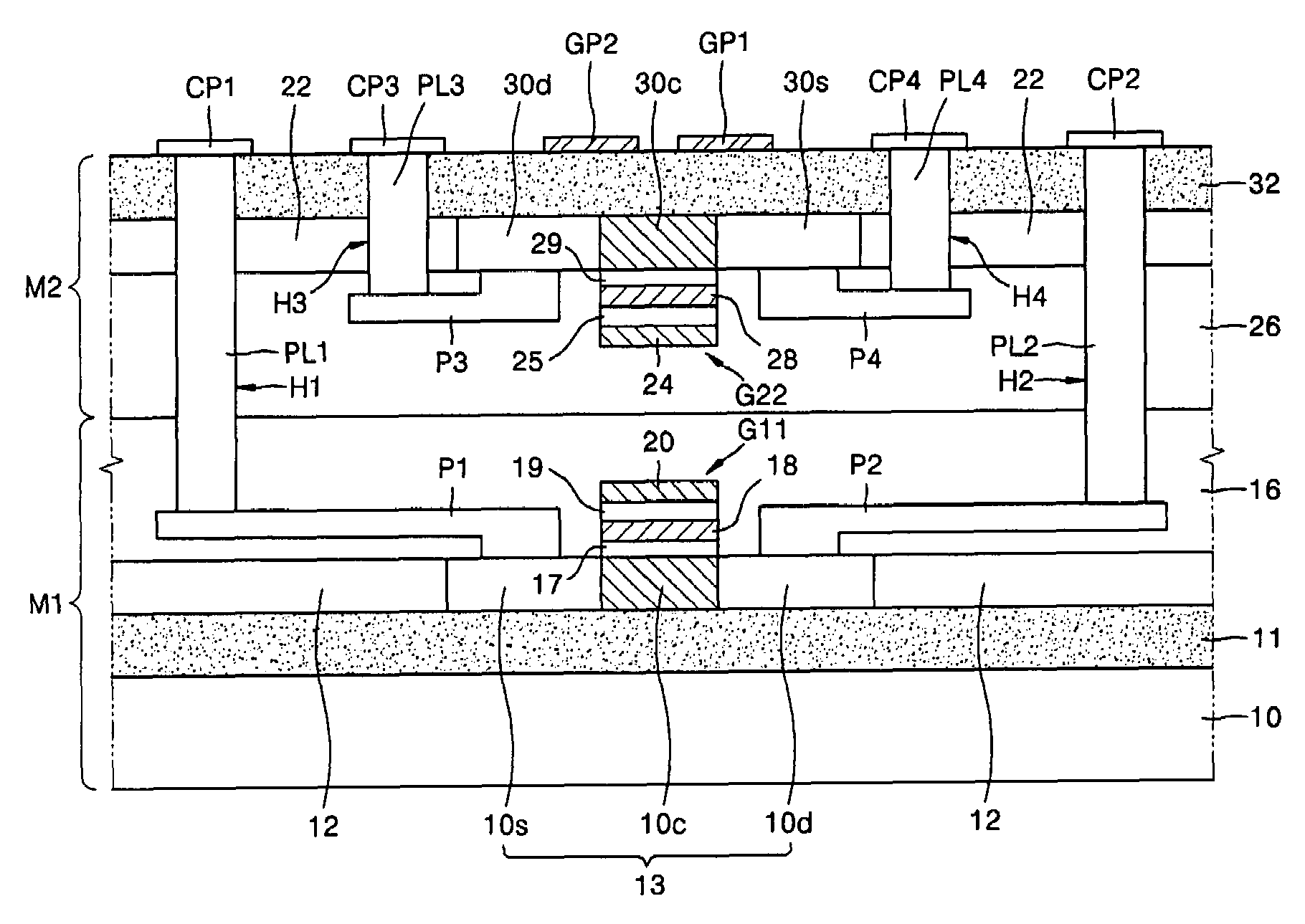

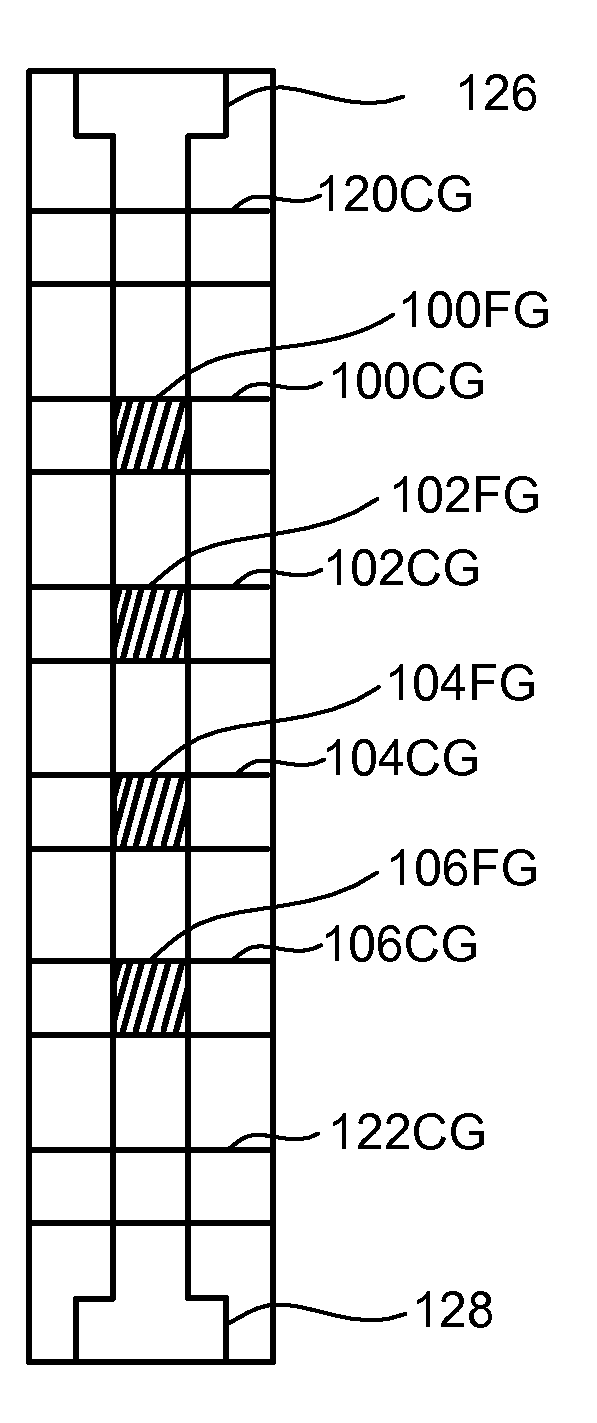

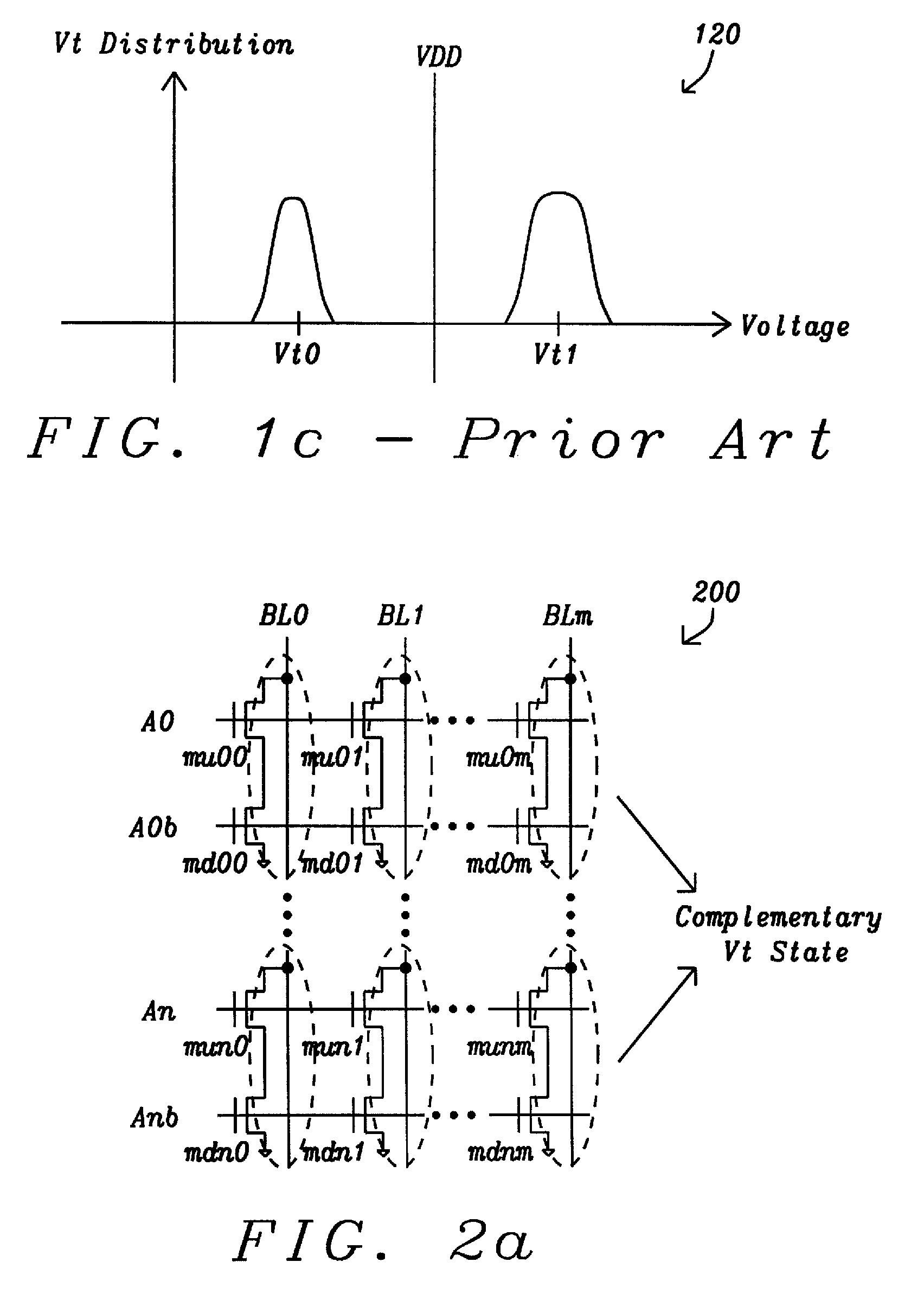

Complementary nonvolatile memory device

ActiveUS7345898B2Increase the number ofReduce read operationsSolid-state devicesRead-only memoriesDevice materialComputer science

Provided are a complementary nonvolatile memory device, methods of operating and manufacturing the same, a logic device and semiconductor device having the same, and a reading circuit for the same. The complementary nonvolatile memory device includes a first nonvolatile memory and a second nonvolatile memory which are sequentially stacked and have a complementary relationship. The first and second nonvolatile memories are arranged so that upper surfaces thereof are contiguous.

Owner:SAMSUNG ELECTRONICS CO LTD

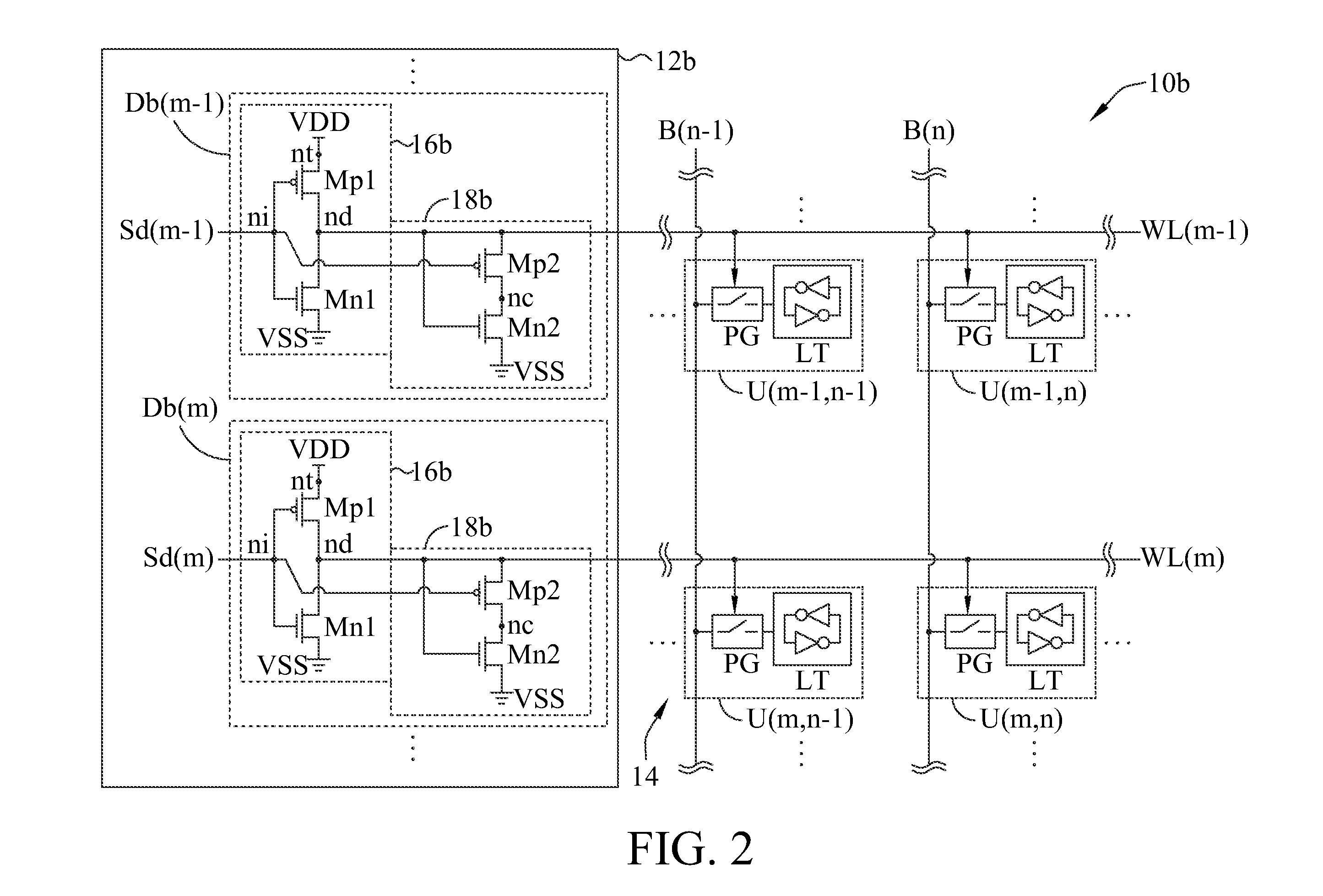

Variation-tolerant word-line under-drive scheme for random access memory

A Random Access Memory (RAM) is provided. The RAM includes a plurality of word-line drivers, at least a first tracking transistor and a second tracking transistor. Each word-line driver has an input node receiving a decoding signal, a power node receiving an operation voltage and a driving node driving a word-line. In an embodiment, the first tracking transistor has two channel terminal nodes respectively coupled to the driving node of one of the word-line driver and a channel terminal node of the second tracking transistor; wherein the first tracking transistor has electronic characteristics tracking those of a driving transistor of word-line driver, and the second tracking transistor has electronic characteristics tracking those of pass-gate transistor(s) in each cell of the RAM.

Owner:FARADAY TECH CORP +1

Segmented column virtual ground scheme in a static random access memory (SRAM) circuit

InactiveUS7372721B2Total current dropReduce voltageRead-only memoriesDigital storageStatic random-access memoryRandom access memory

A static random access memory (SRAM) cell array is provided that reduces leakage current. The SRAM cell array is configured in a plurality of columns. Each of the columns comprises: a column virtual ground node; a column switch for selectively coupling the column virtual ground node to one of a ground or a nominal low voltage; and a plurality of segments. Each of the segments comprises: a segment virtual ground node; a plurality of SRAM cells including a virtual ground signal coupled to the segment virtual ground node; and a virtual ground switch for selectively coupling the segment virtual ground node to one of either a nominal low voltage or the column virtual ground node. A method for operating the SRAM cell array is also described.

Owner:SACHDEV MANOJ +1

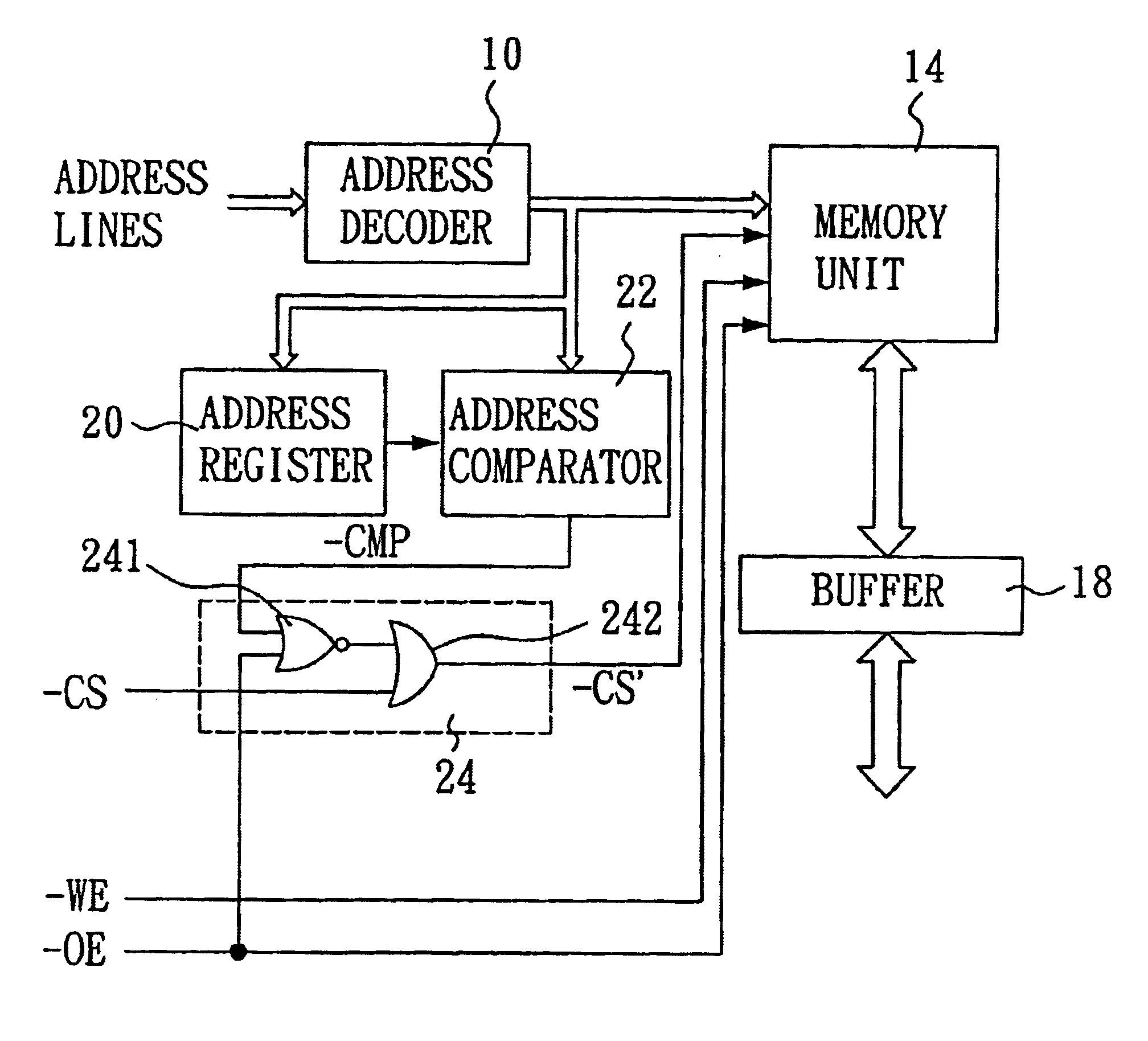

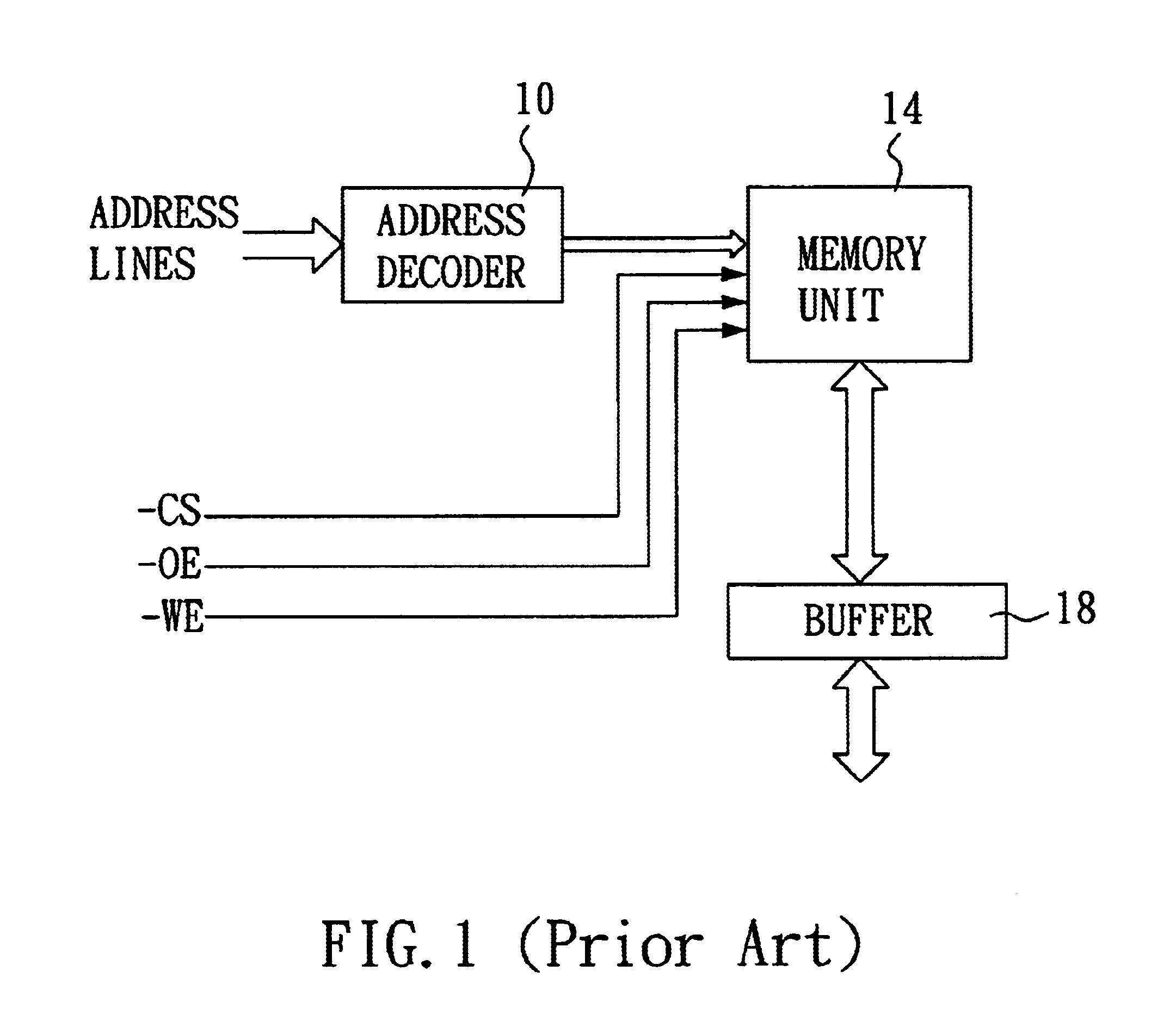

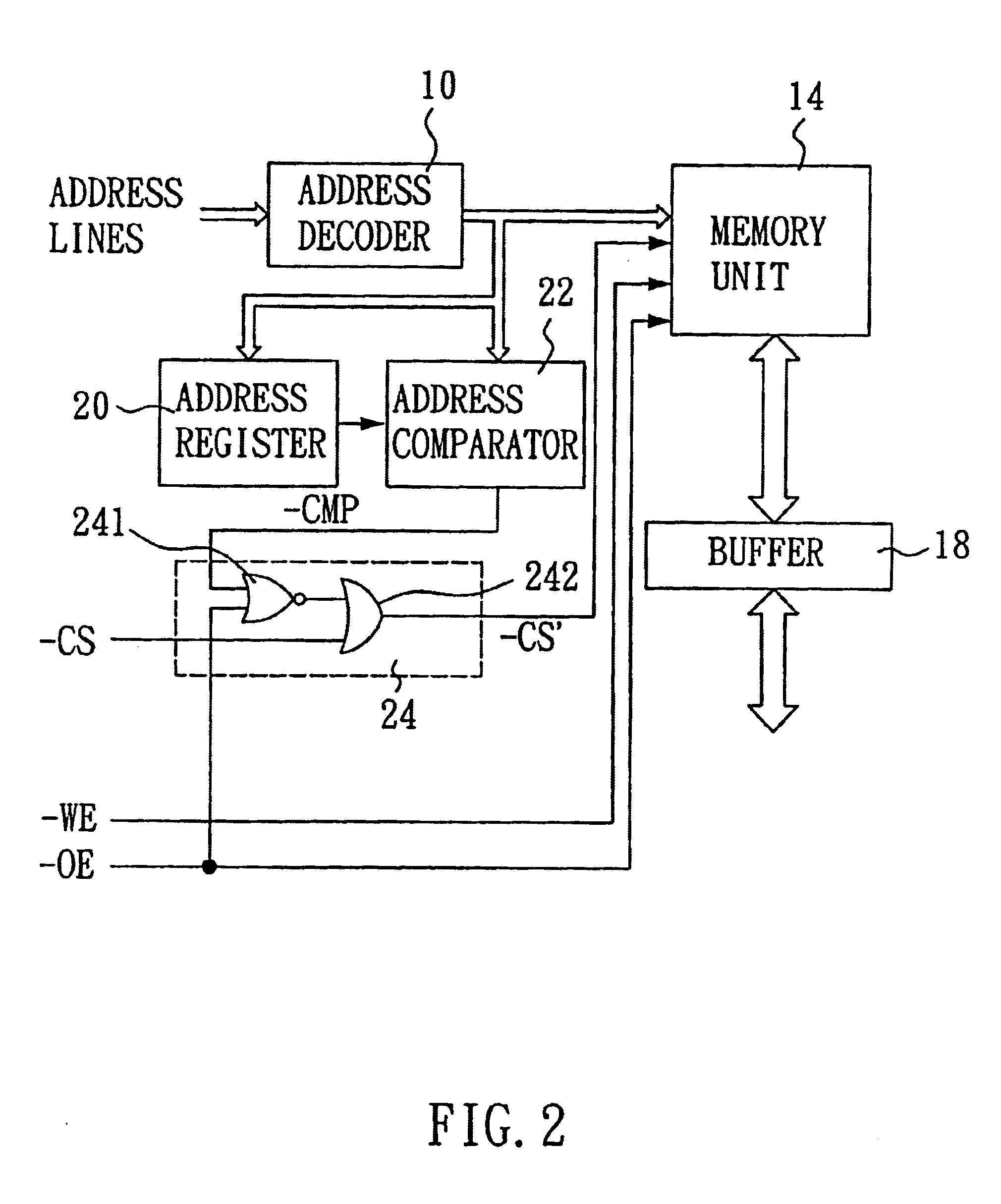

SRAM control circuit with a power saving function

InactiveUS6862242B2Reduce read operationsDigital storageMemory systemsControl circuitComputer science

An SRAM control circuit with a power saving function is disclosed, which uses an address comparator to compare a current address and a previous address in an SRAM read operation. When the two addresses are the same, data is outputted directly from a buffer without enabling a memory unit, thereby saving power.

Owner:SUNPLUS TECH CO LTD

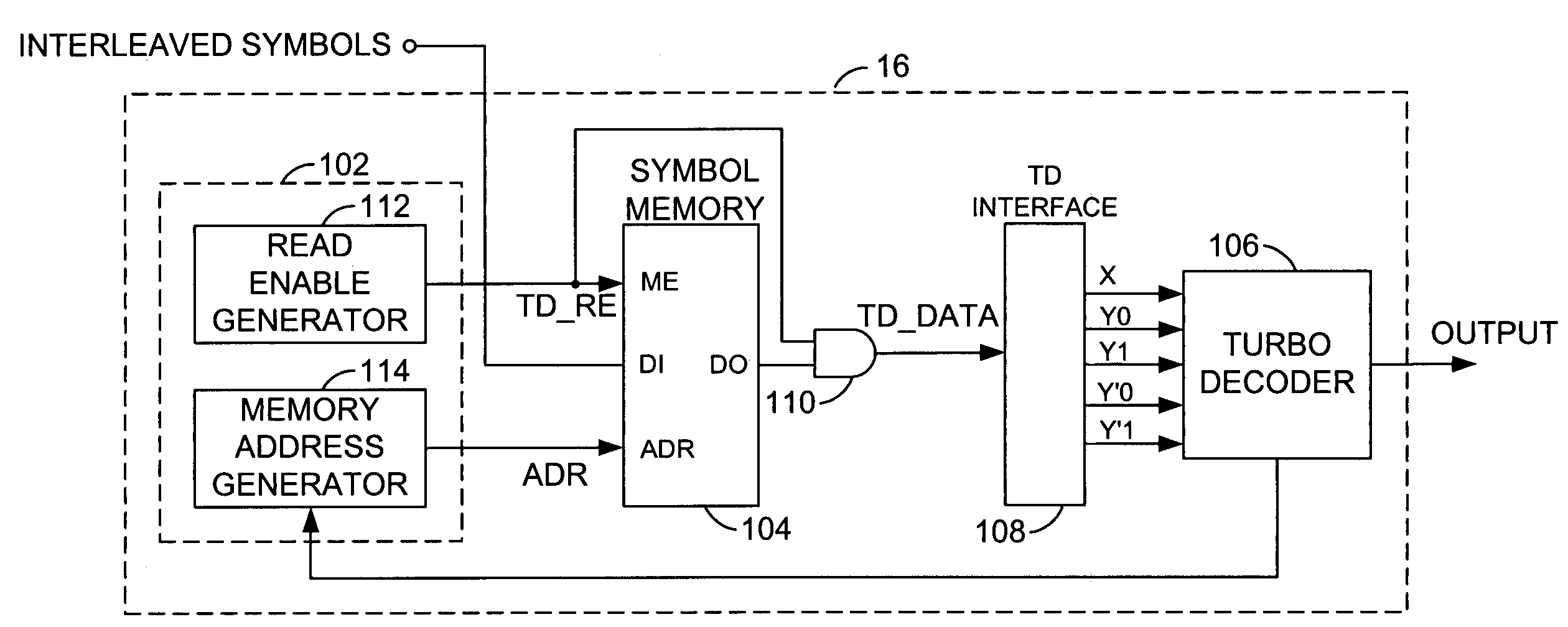

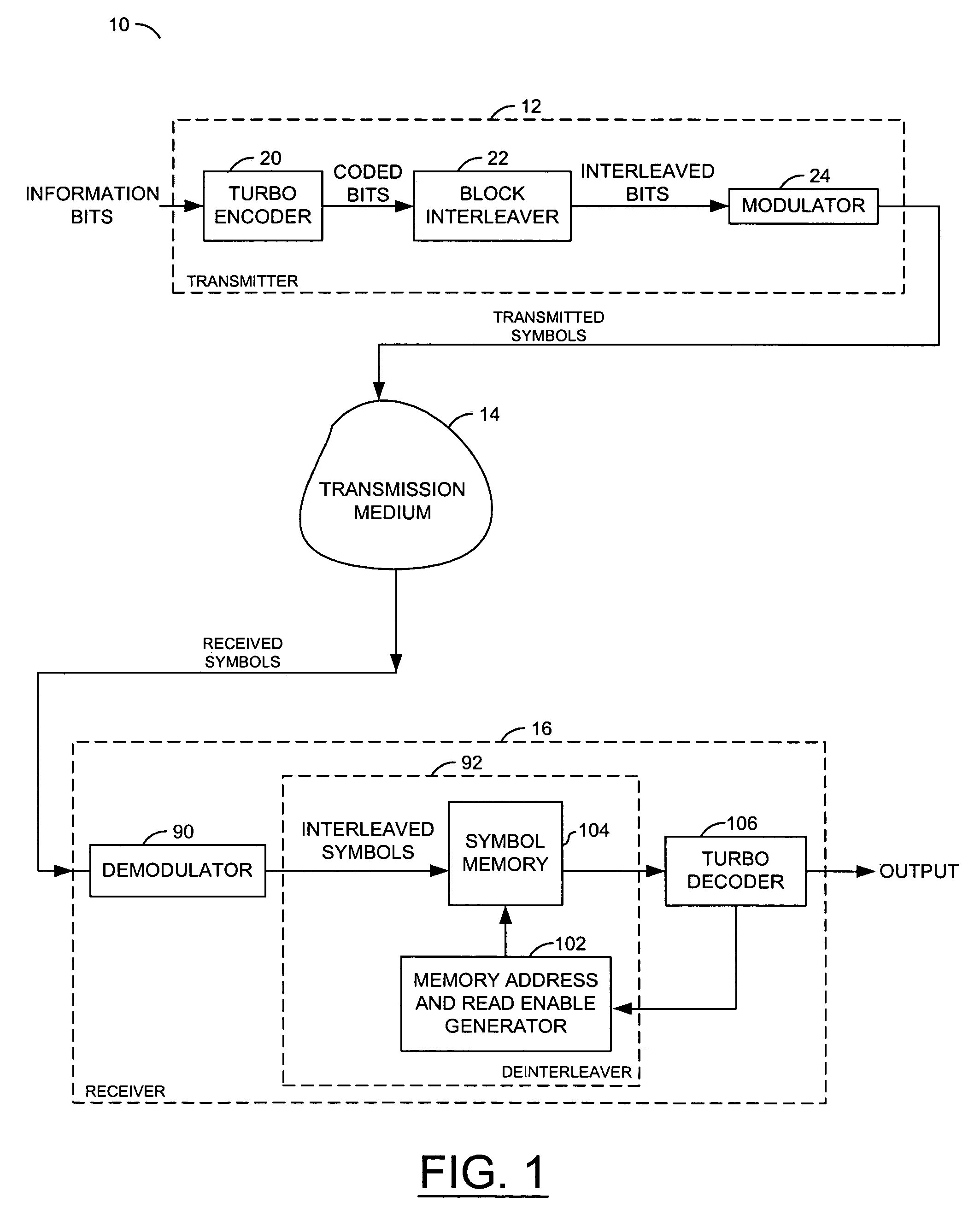

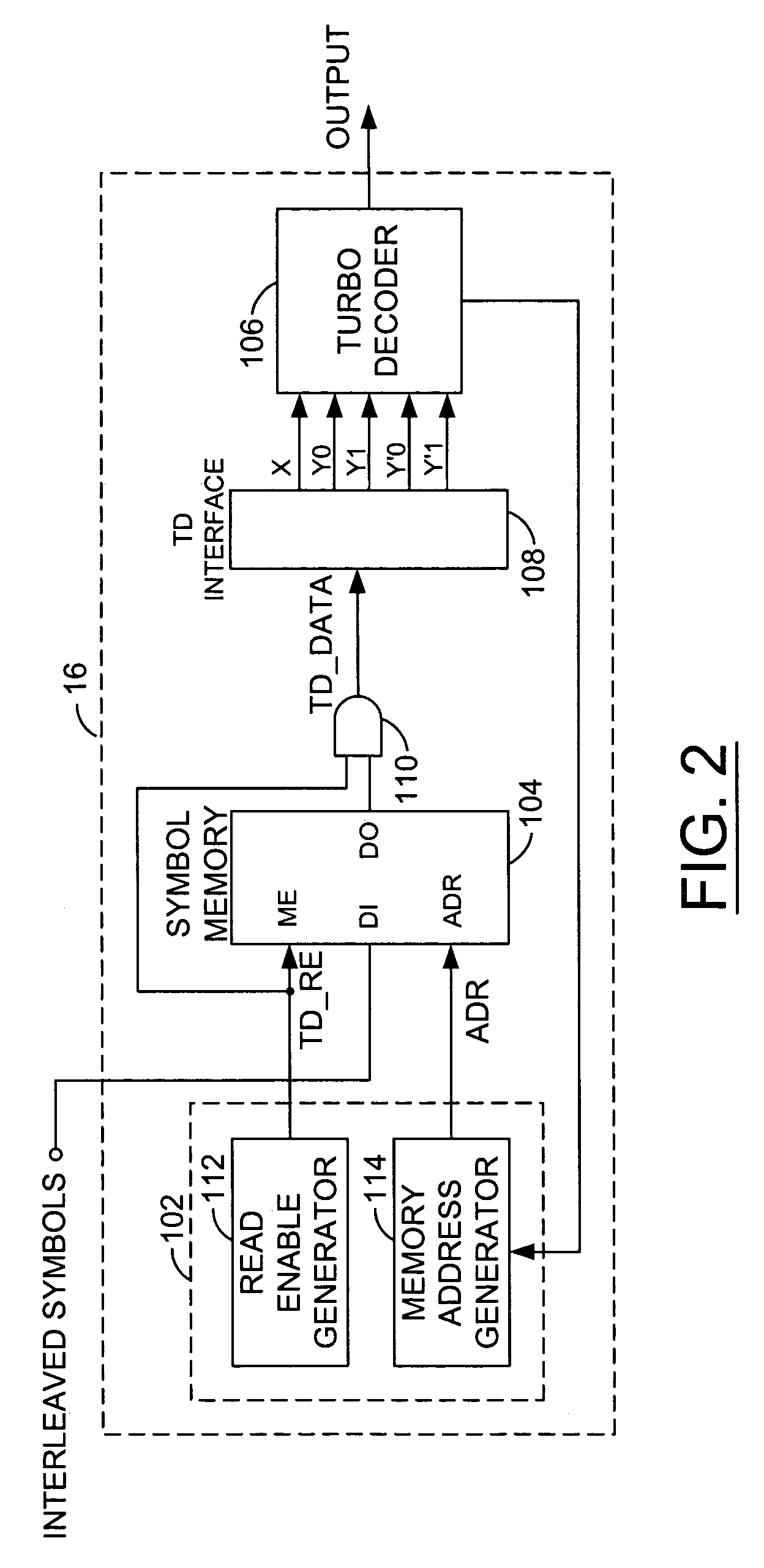

Read enable generator for a turbo decoder deinterleaved symbol memory

InactiveUS7266756B2Reduce read operationsSave powerPulse modulation television signal transmissionTelevision system scanning detailsData signalComputer science

The present invention concerns an apparatus comprising a first circuit, a second circuit and a third circuit. The first circuit may be configured to read a data signal in response to a read enable signal. The second circuit may be configured to generate the read enable signal. The third circuit may be configured to present the data signal in response to a first state of the read enable signal and present a predetermined value in response to a second state of the read enable signal.

Owner:INTEL CORP

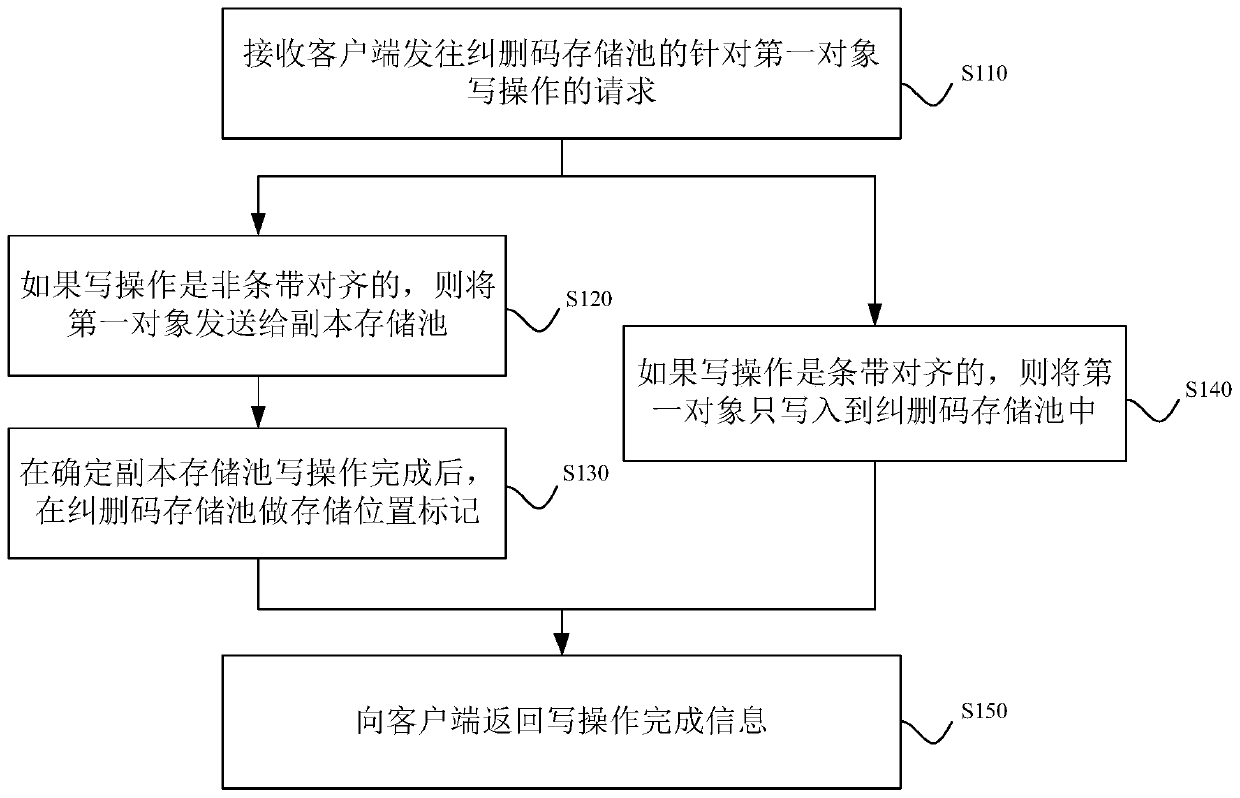

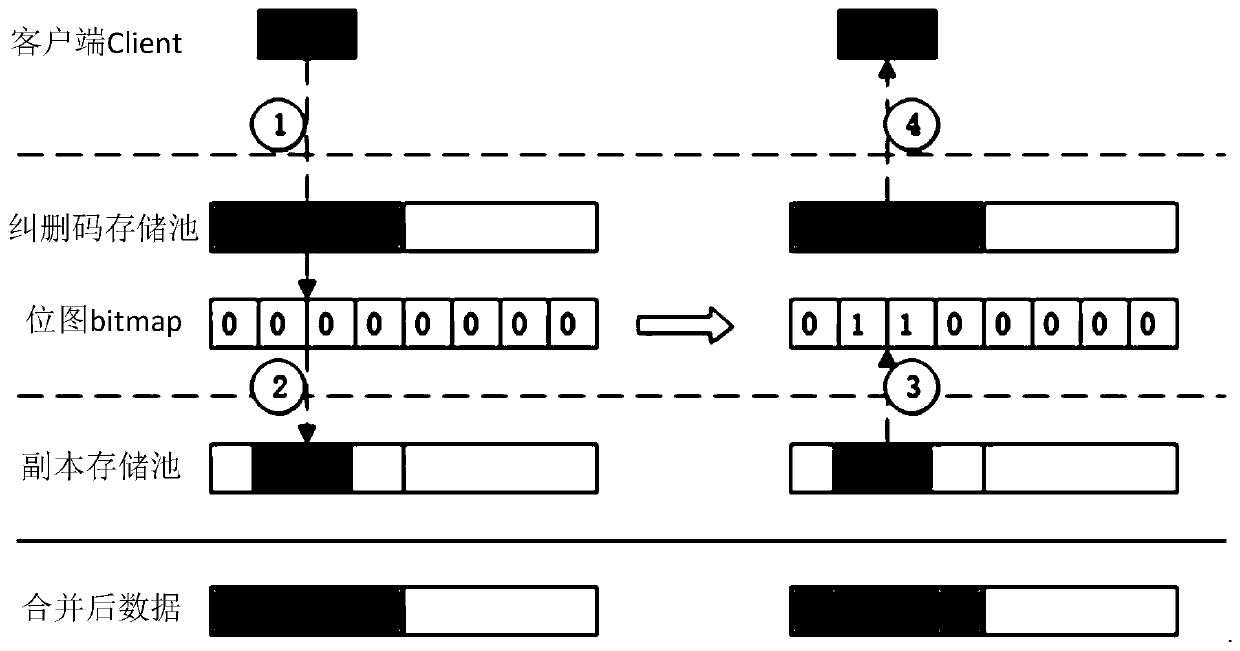

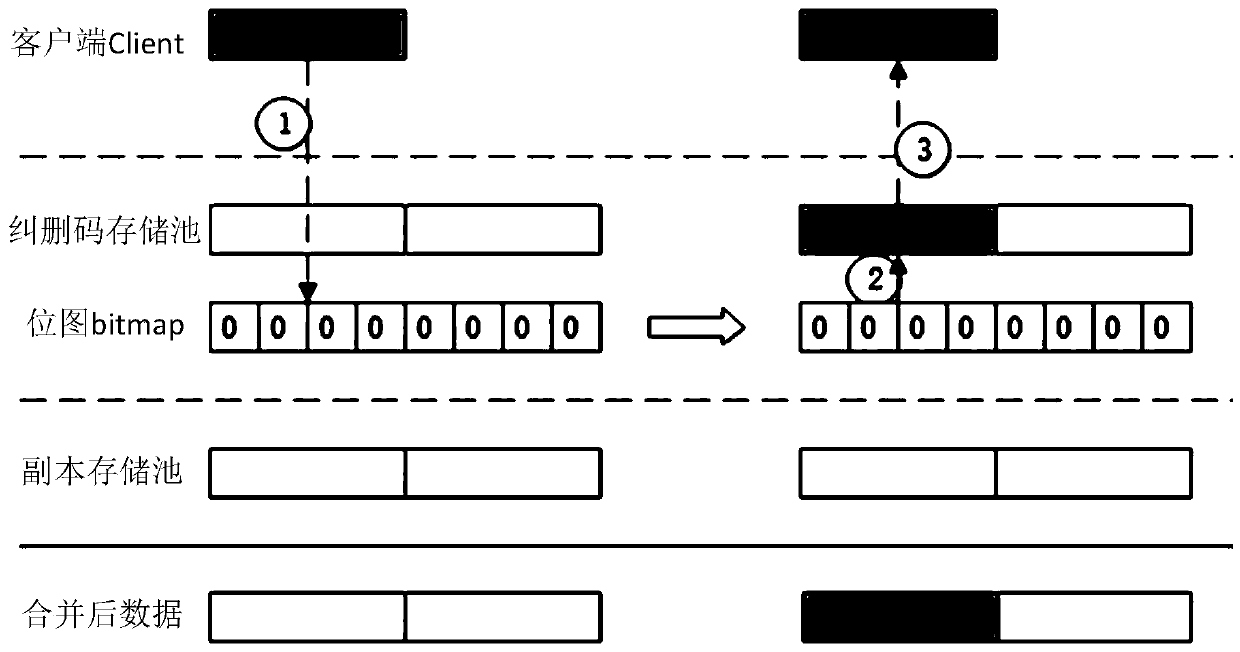

Erasure code operation method, device and equipment and storage medium

PendingCN109901946AReduce overheadReduce read operationsRedundant data error correctionStorage poolOperating system

The invention discloses an erasure code operation method. The method comprises the following steps: receiving a request which is sent to an erasure code storage pool by a client and aims at a first object write operation; If the write operation is non-stripe-aligned, sending the first object to a copy storage pool; After it is determined that the write operation of the copy storage pool is completed, making a storage position mark in the erasure code storage pool; If the write operation is stripe-aligned, only writing the first object into an erasure code storage pool; And returning write operation completion information to the client. By applying the technical scheme provided by the embodiment of the invention, the reading operation additionally introduced by non-strip alignment writing is effectively reduced, the expenditure of a storage system is reduced, and the writing operation performance is improved. The invention further discloses an erasure code operation device and equipmentand a storage medium which have corresponding technical effects.

Owner:SANGFOR TECH INC

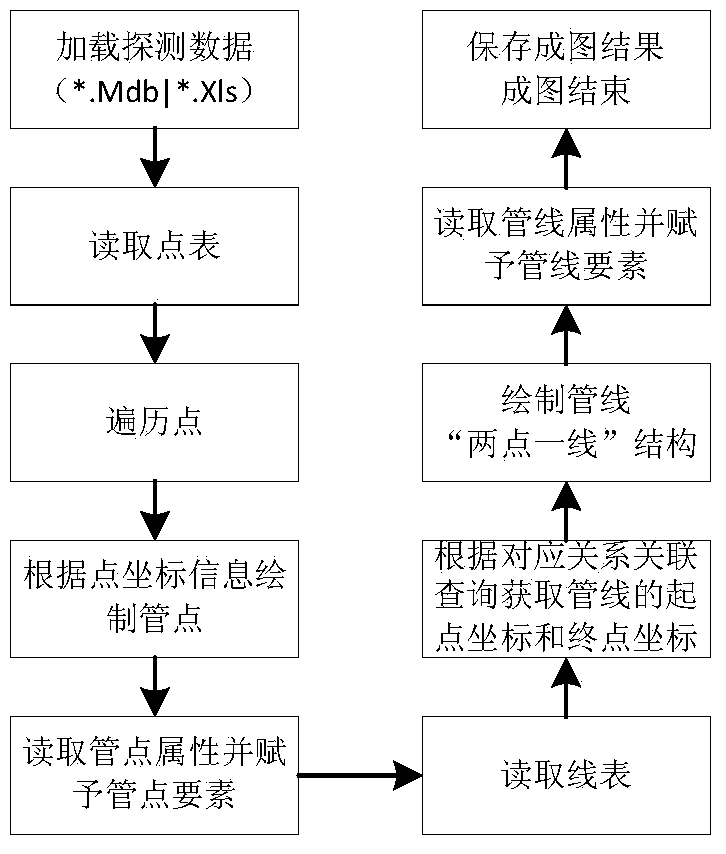

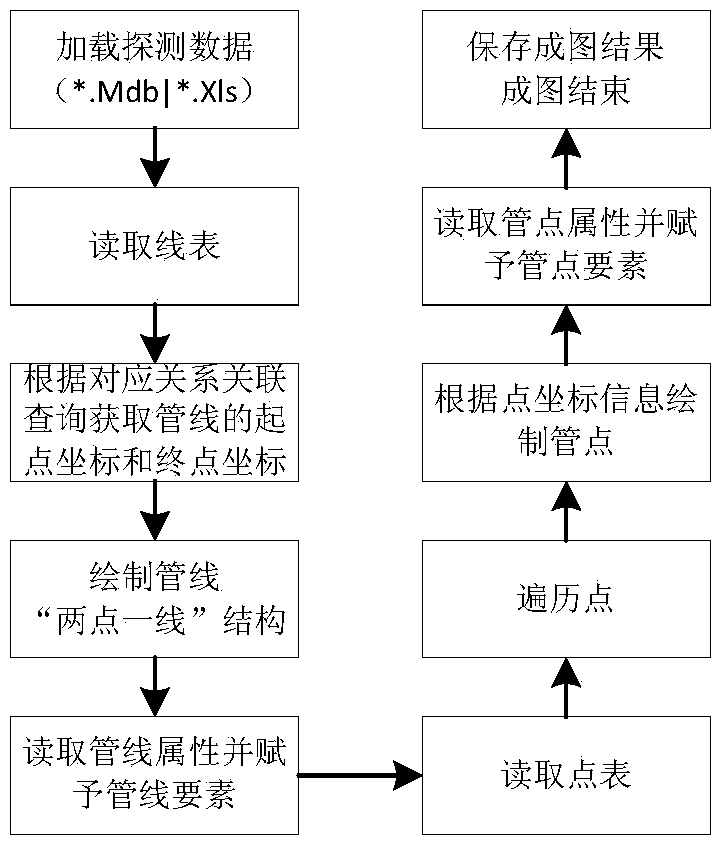

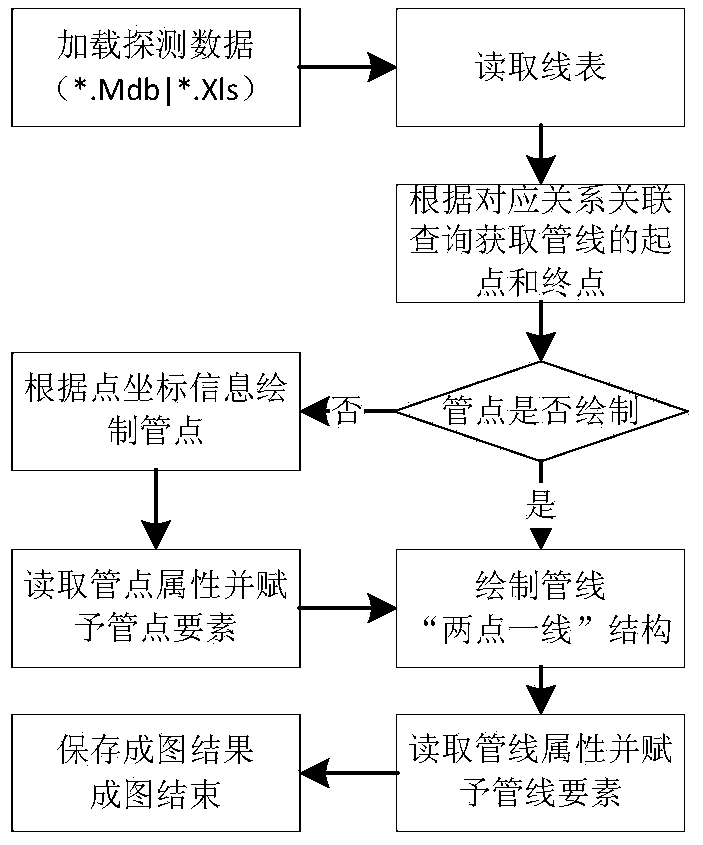

Urban pipe line detection data fast mapping method and system based on GIS platform

ActiveCN103927362AReduce read operationsSimplify the mapping processGeographical information databasesSpecial data processing applicationsLine tubingValue assignment

The invention discloses an urban pipe line detection data fast mapping method and system based on a GIS platform. The method includes the steps that pipe line starting point and ending point coordinate fields are added, and value assignment is carried out on pipe line starting point and ending point coordinates; starting point and ending point coordinate information of pipe lines is directly read during pipe line mapping by carrying out value assignment on all endpoint spatial positions needed by the pipe lines so that the repeated operation of reading the pipe point coordinate information through the relation between the pipe lines and pipe points during mapping can be avoided; pipe line list mapping is carried out, wherein a pipe line list is read and traversed, the pipe lines are drawn, and pipe line attributes are read and assigned to pipe line elements; pipe point list mapping is carried out, wherein a pipe point list is read and traversed, pipe points are drawn according to point coordinate information, and pipe point attributes are read and assigned to pipe point elements; mapping is finished. According to the method, more work is completed before pipe line mapping on the basis that the pipe line mapping principle is understood, so that frequent database reading operation is simplified in the mapping process, especially for mapping with a large data volume.

Owner:TAIHUA WISDOM IND GRP CO LTD

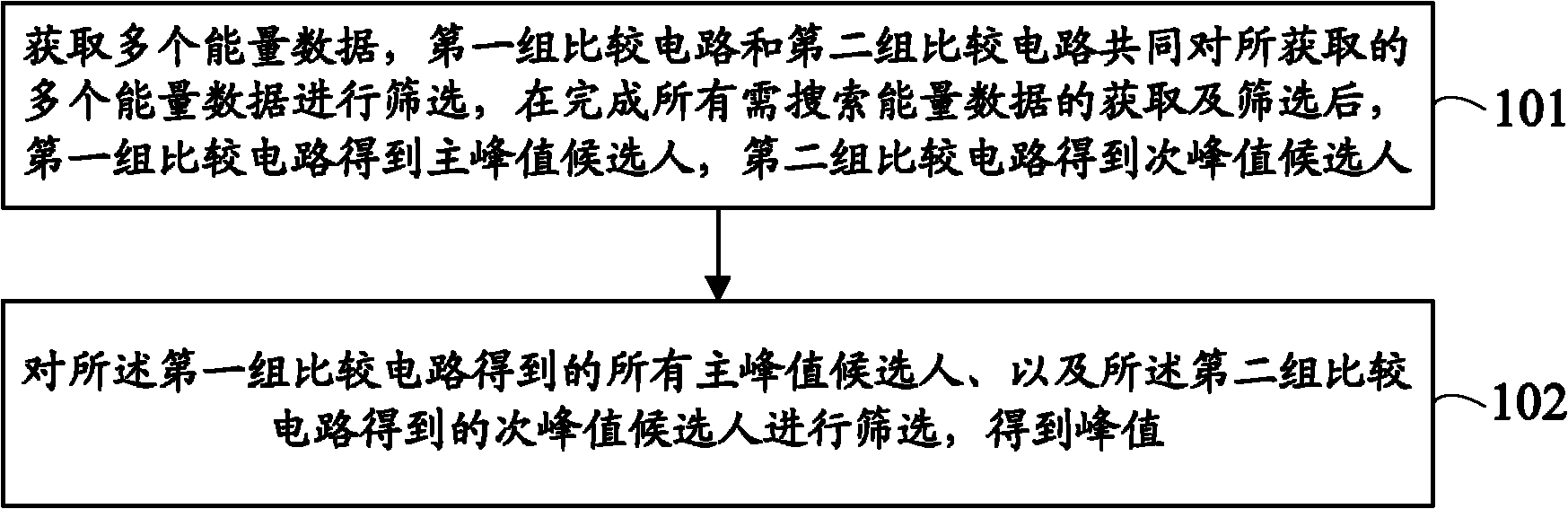

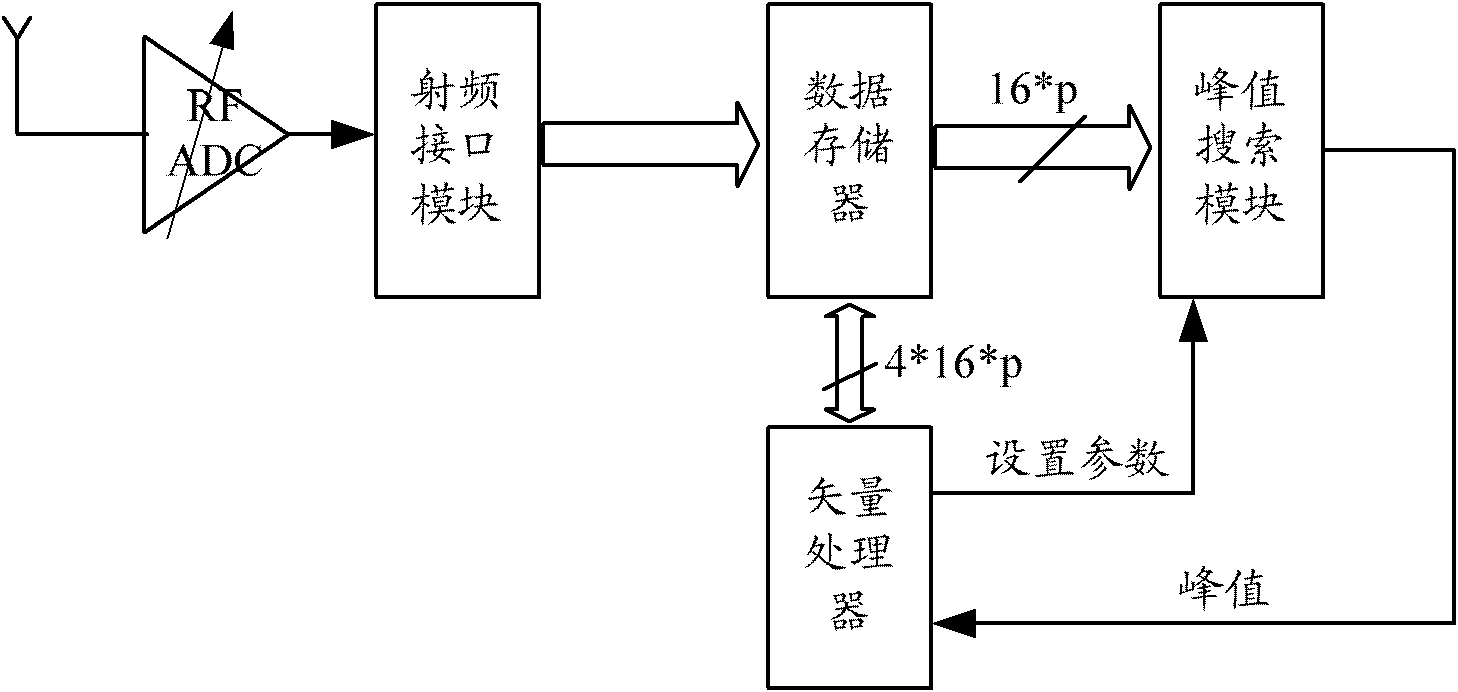

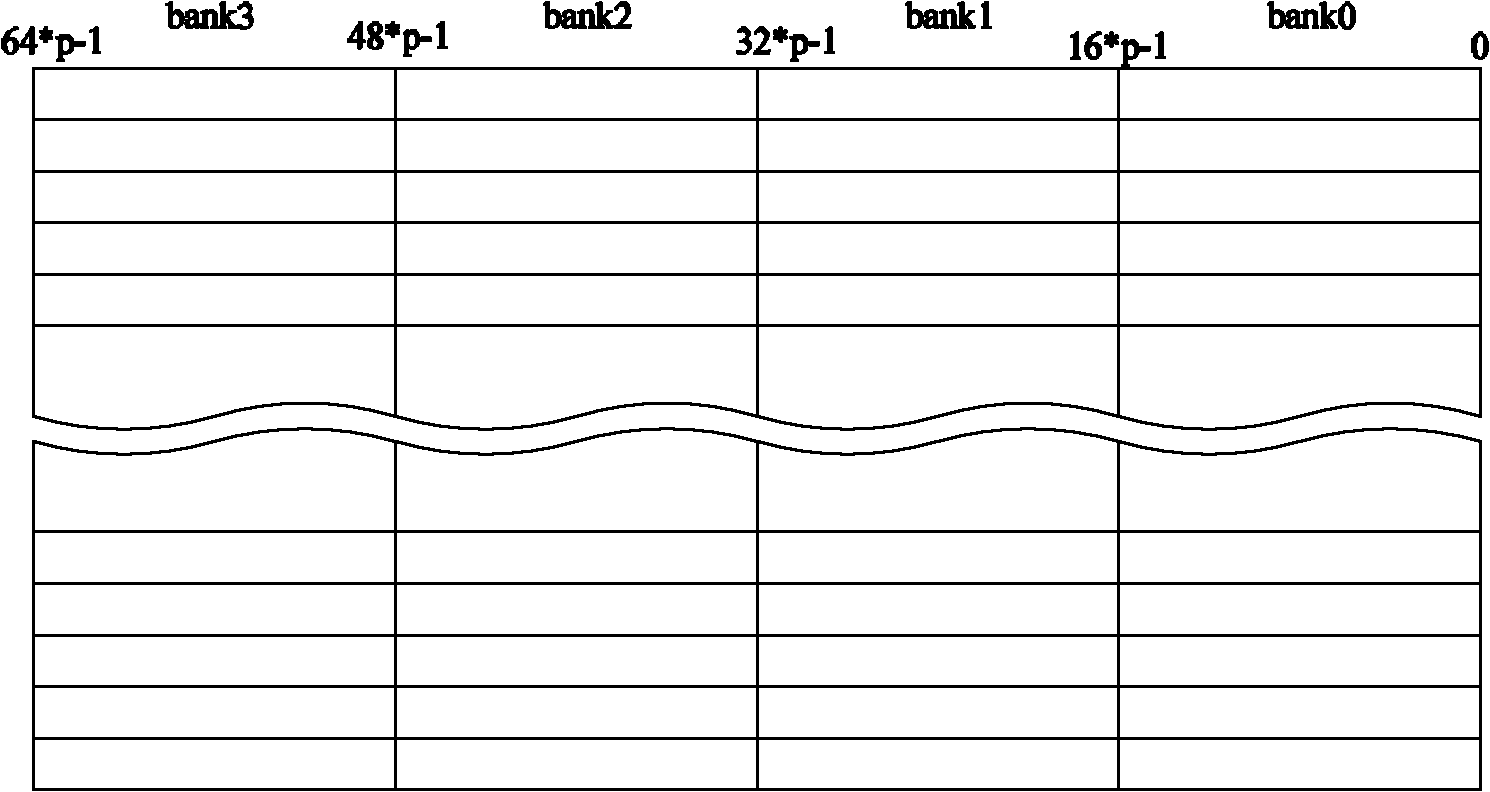

Peak value searching method and device

ActiveCN102185633AAchieving high throughput requirementsReduce read operationsPower managementTransmissionPeak valueTheoretical computer science

The invention discloses a peak value searching method comprising the following steps of: acquiring a plurality of energy data, screening the acquired energy data commonly by a first group of comparison circuits and a second group of comparison circuits, storing main candidate peak values obtained by the first group of comparison circuits after all energy data are acquired and screened, and storing secondary candidate peak values obtained by the second group of comparison circuits; and screening all the main candidate peak values stored by the first group of comparison circuits and all the secondary candidate peak values stored by the second group of comparison circuits, thus obtaining a peak value. The invention further discloses a peak value searching device which is fast in speed and at least can obtain two peak values by each scanning process, thus being capable of saving power consumption and integrating the peak value searching speed and hardware logic resources; besides, a key circuit of the peak value searching device can be realized only by a series of adders and registers, thus being simple and easy to realize, small in area and low in cost.

Owner:SANECHIPS TECH CO LTD

Distributed storage system-oriented erasure coding write buffer method with stream detection technology

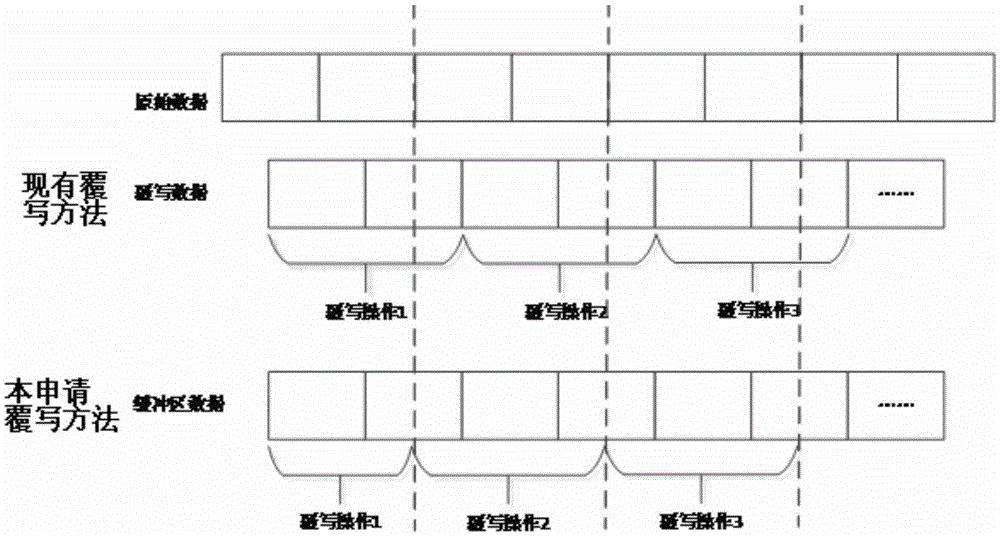

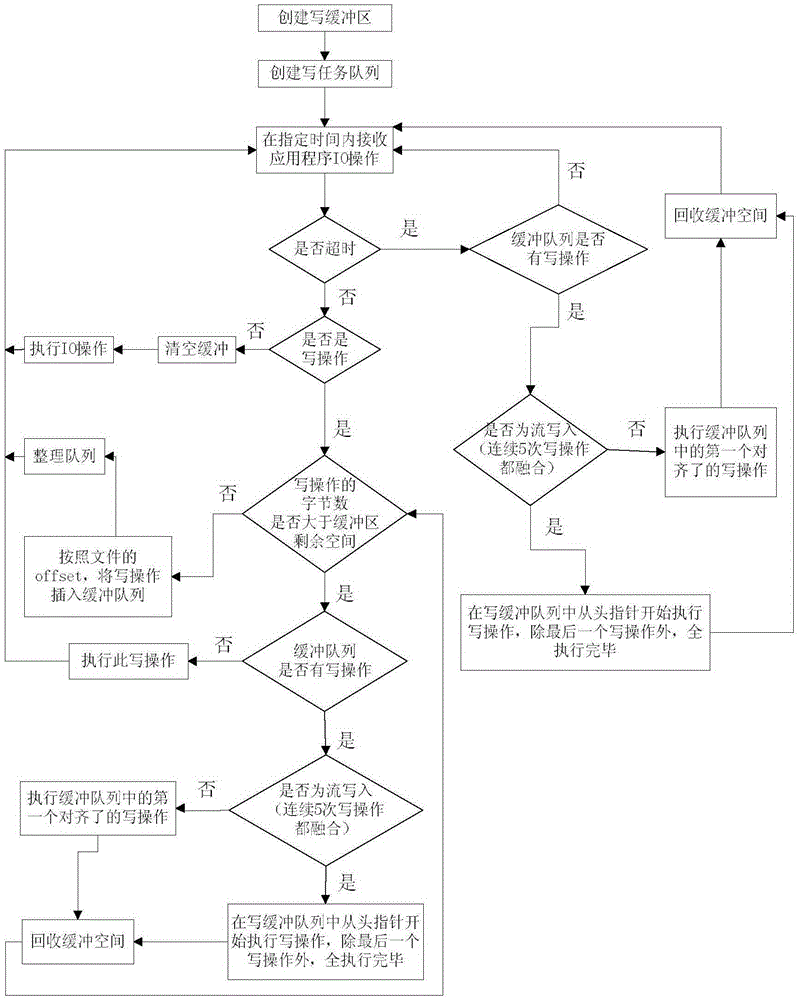

ActiveCN105302660AImprove response speedEasy to operateInput/output to record carriersRedundant data error correctionWrite bufferOriginal data

The invention provides a distributed storage system-oriented erasure coding write buffer method with a stream detection technology. The method comprises the steps that: when overwriting operations are performed on original data, the length of the first-time overwriting operation is from an initial position of data in a buffer layer to a first alignment point, and the length of the last overwriting operation is from a last alignment point to a termination position of the data in the buffer layer; and the lengths of the overwriting operations between the first-time overwriting operation and the last overwriting operation are all equal to the length between the adjacent alignment points, and the positions are aligned. Multiple write operations are combined in the buffer layer, and the write operations of only the head and tail ends of the data in the buffer layer are non-aligned, so that the read operations caused by the non-aligned write operations under the overwriting condition in an erasure coding storage system are reduced, and the command response speed is increased.

Owner:HUNAN ANCUN TECH CO LTD

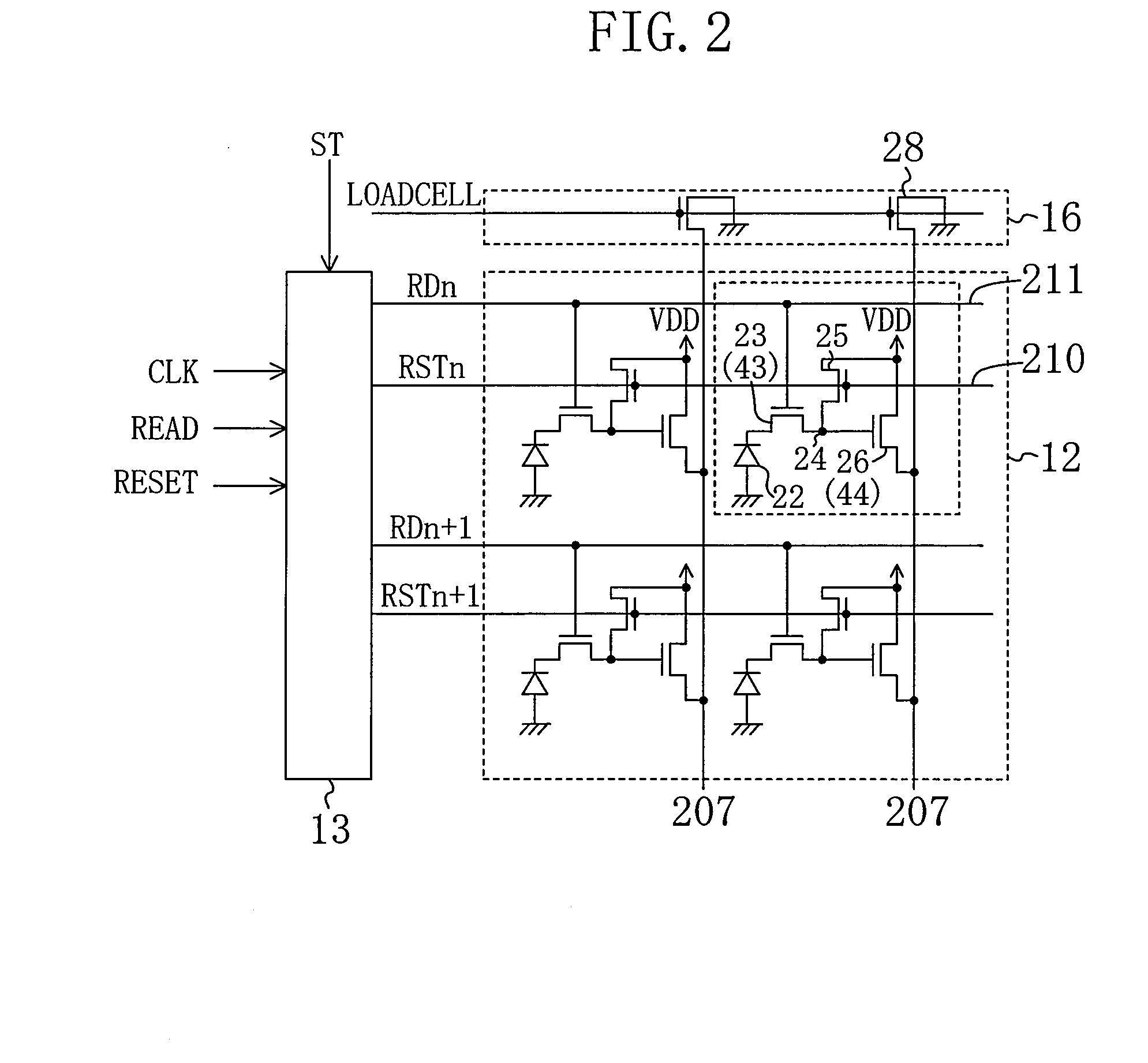

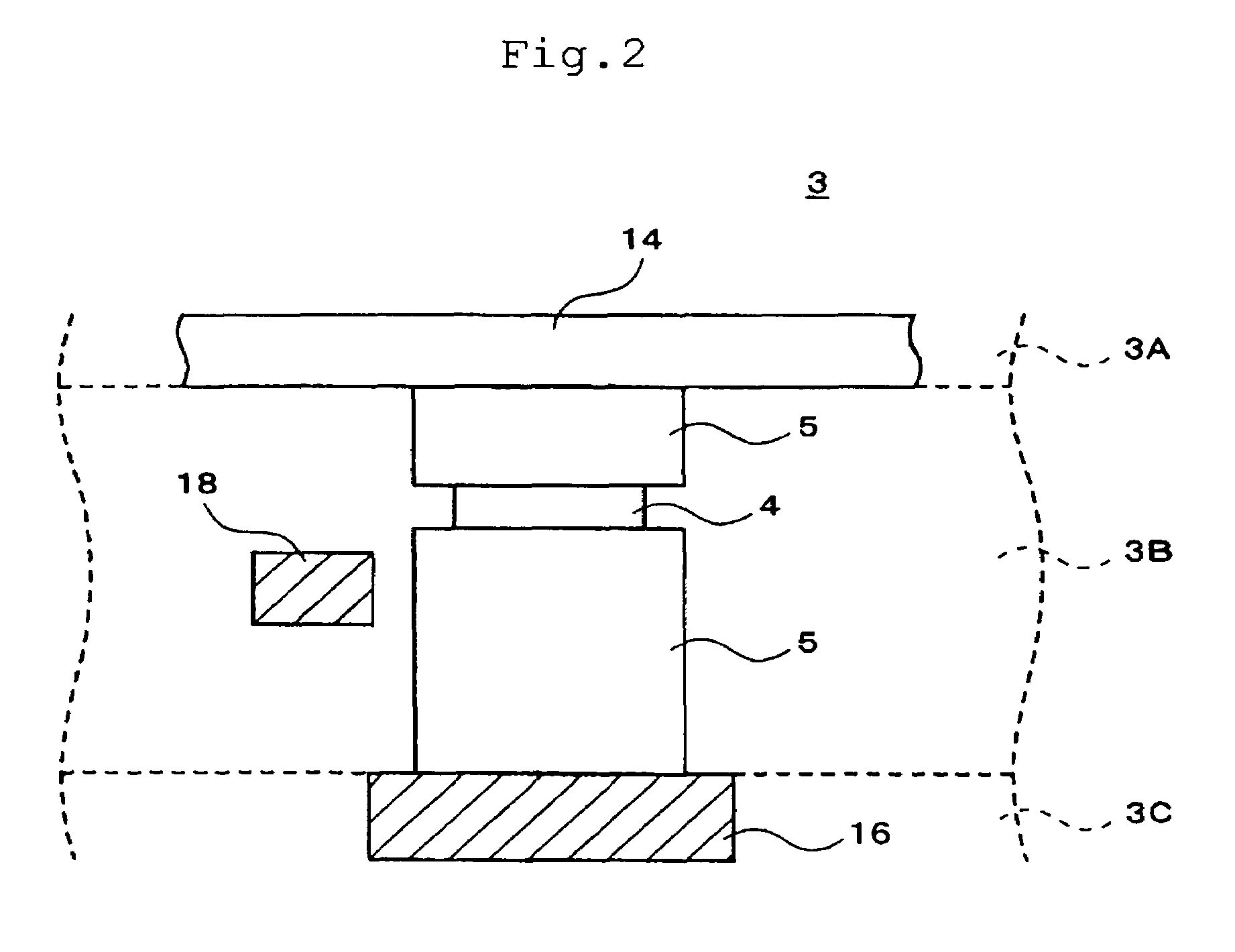

Solid-state imaging device, imaging apparatus and driving method for the same

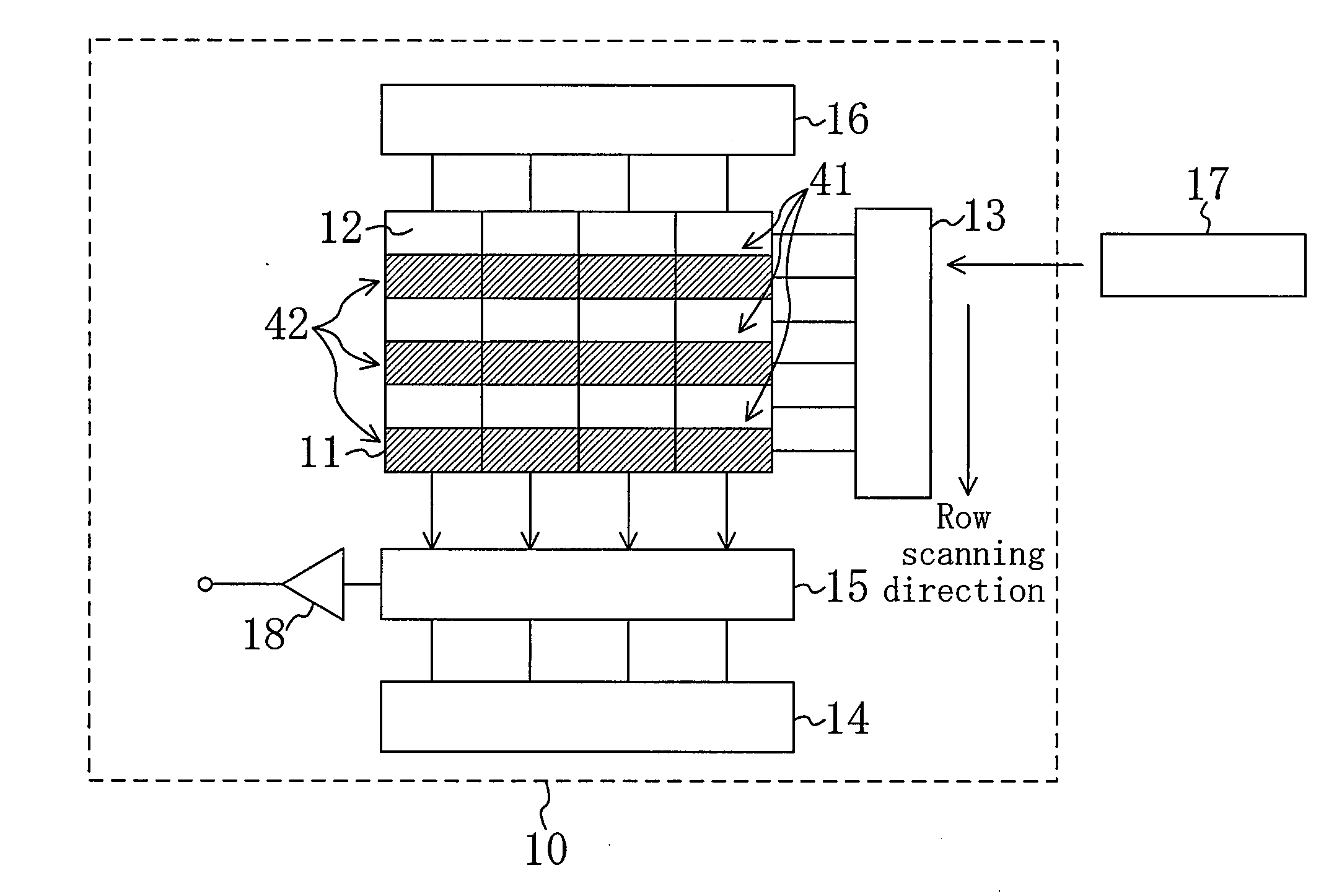

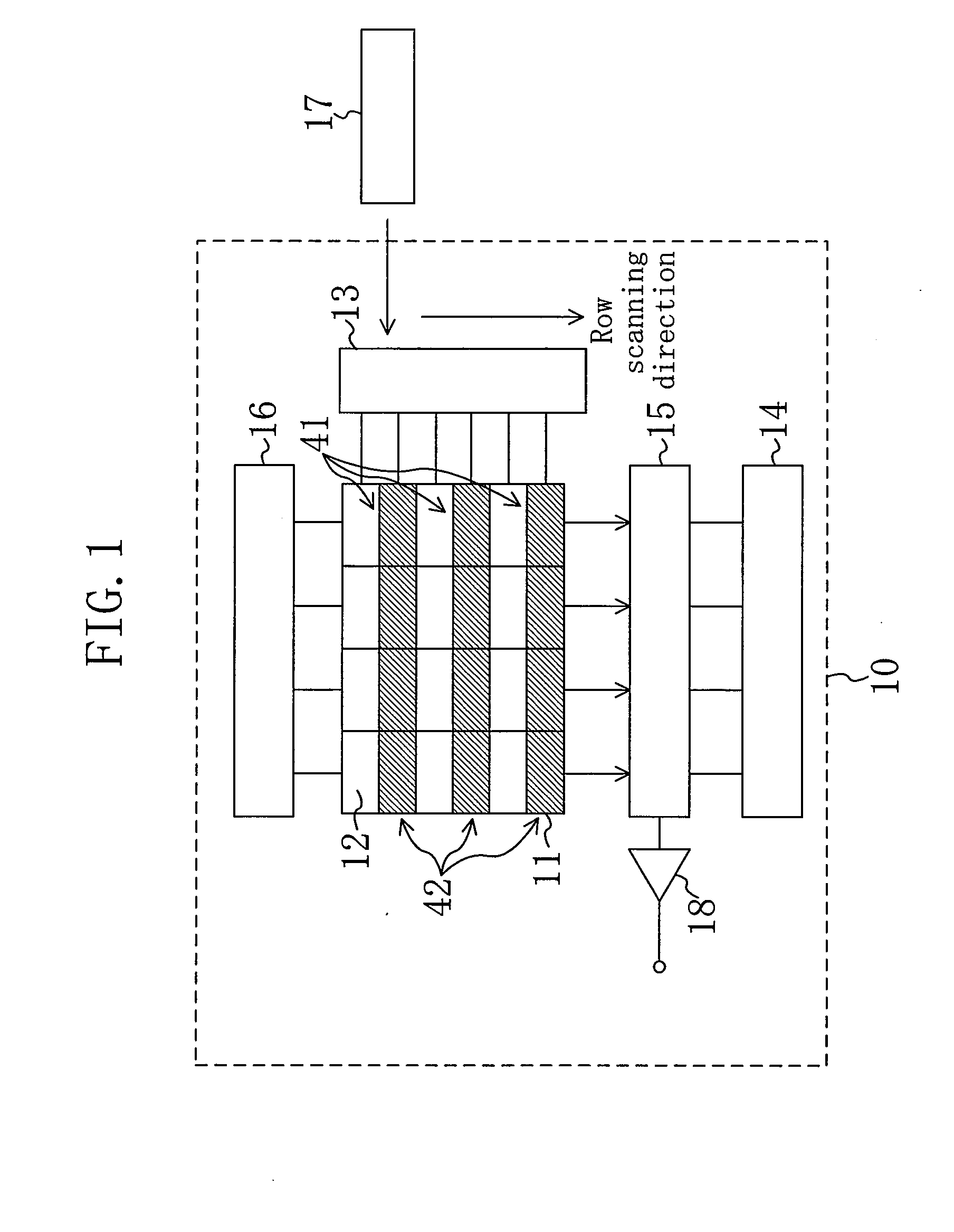

ActiveUS20090040346A1Avoid chargingIncrease frame rateTelevision system detailsTelevision system scanning detailsPhotoelectric conversionEngineering

A solid-state imaging device includes first-group pixels 41, second-group pixels 42 skipped during thinning drive, and a scanning section 13. The scanning section 13 drives each of the first-group pixels 41 to perform read operation of outputting the output signal and initializing the amount of the signal charge accumulated in the photoelectric conversion element to a first level, and also drives each of the second-group pixels 42 to perform discharge operation of initializing the amount of the signal charge accumulated in the photoelectric conversion element to a second level that is higher than the first level and lower than a saturation signal level of the photoelectric conversion element 12.

Owner:PANASONIC SEMICON SOLUTIONS CO LTD

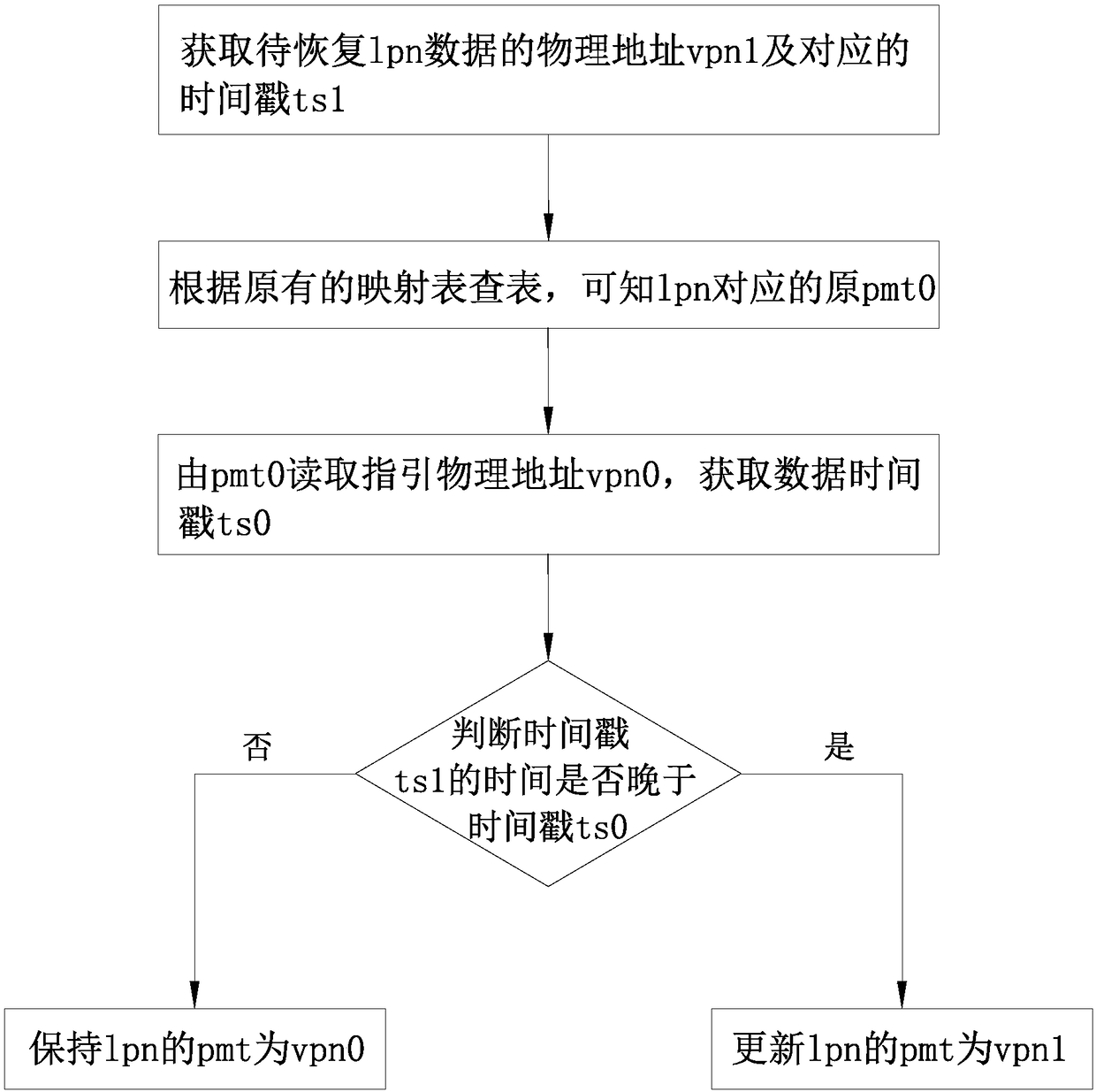

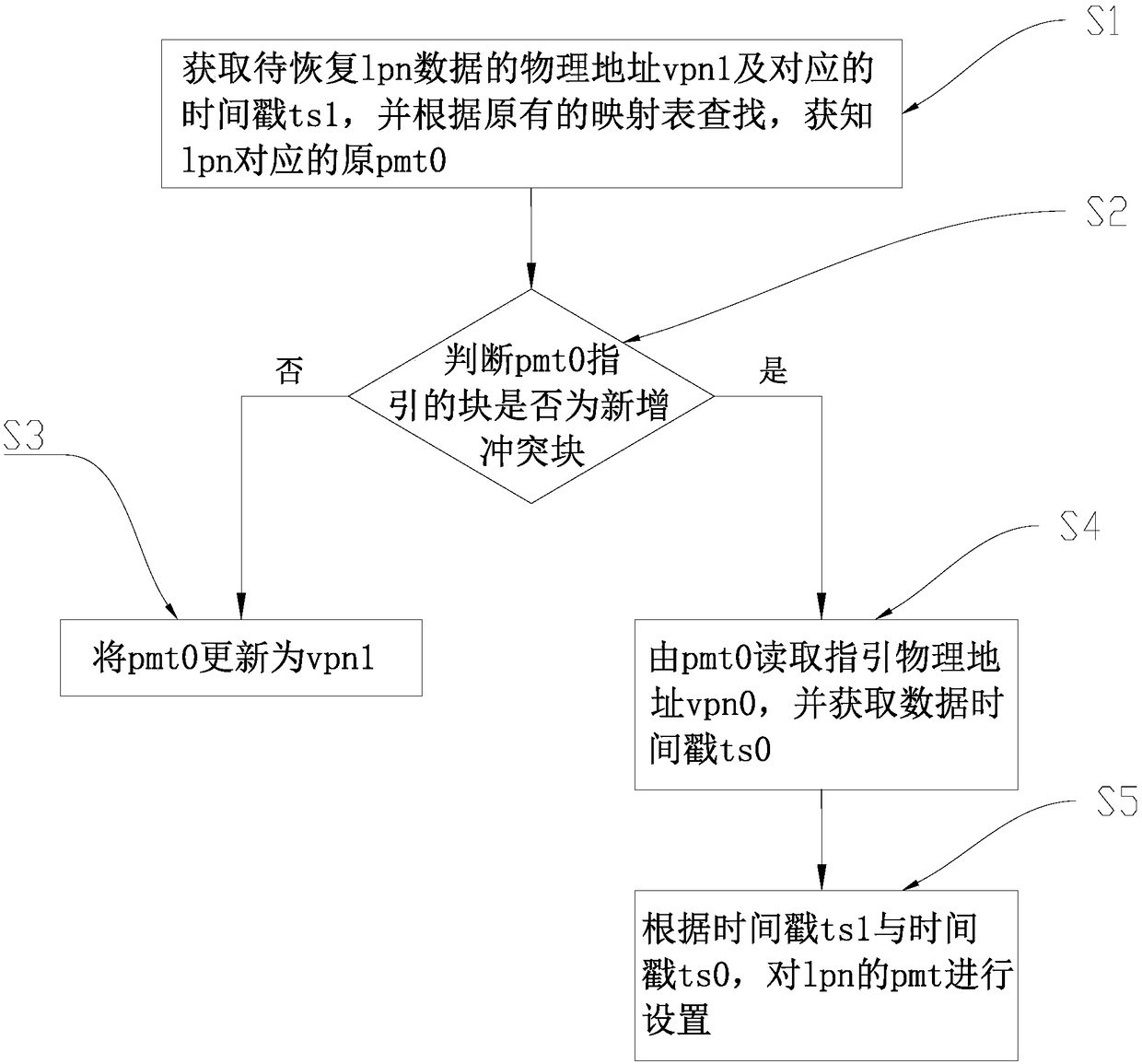

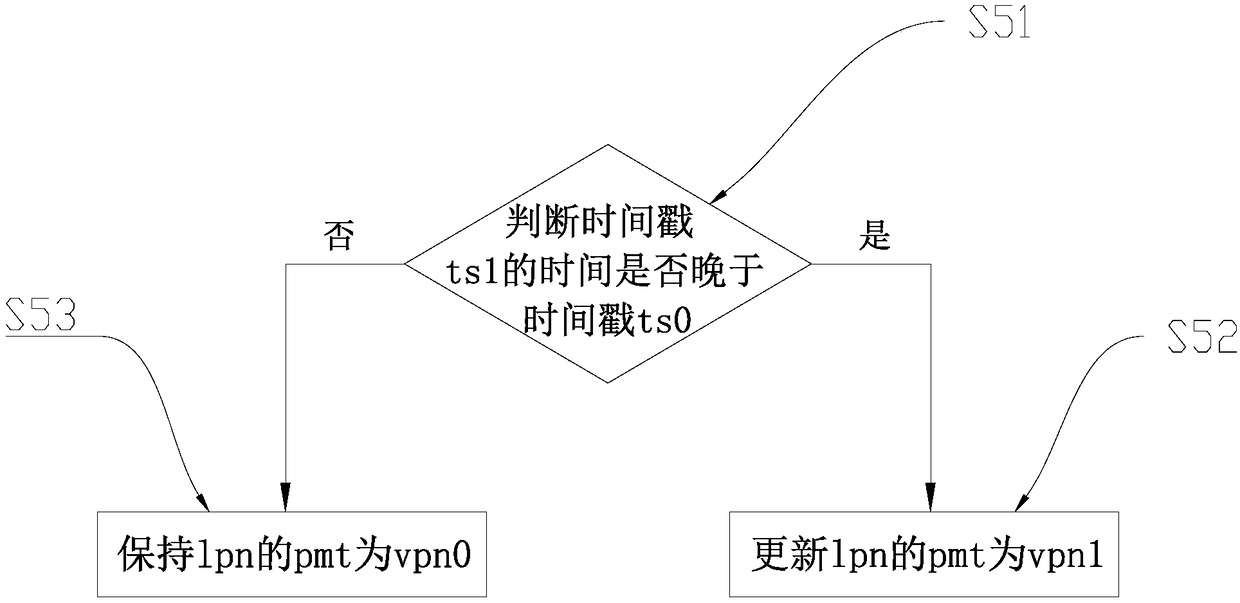

An SSD abnormal power-down recovery method based on block growth record and system thereof

InactiveCN109445987AReduce read operationsRelieve pressureMemory loss protectionMemory adressing/allocation/relocationRecovery methodElectricity

The invention relates to an SSD abnormal power-down recovery method based on block growth record and a system thereof. The SSD abnormal power-down recovery method based on the block growth record comprises the following steps of S1 acquiring the physical address vpn1 of the lpn data to be recovered and the corresponding time stamp ts1, and searching according to the original mapping table to obtain the original pmt0 corresponding to the lpn; S2 judging whether the block indicated by pmt0 is a newly added conflict block; If yes, entering S4; If not, entering S3; S3 updating pmt0 to vpn1; S4 reading the guide physical address vpn0 by pmt0, and obtaining the data timestamp ts0; S5 setting the pmt of the lpn according to the timestamp ts1 and the timestamp ts0. The invention avoids the block-level scanning of the whole disk and rapidly locates the recovered object, reduces the read operation of NAND in the recovery process, greatly improves the efficiency of data recovery, and better meetsthe needs.

Owner:SHENZHEN YILIAN INFORMATION SYST CO LTD

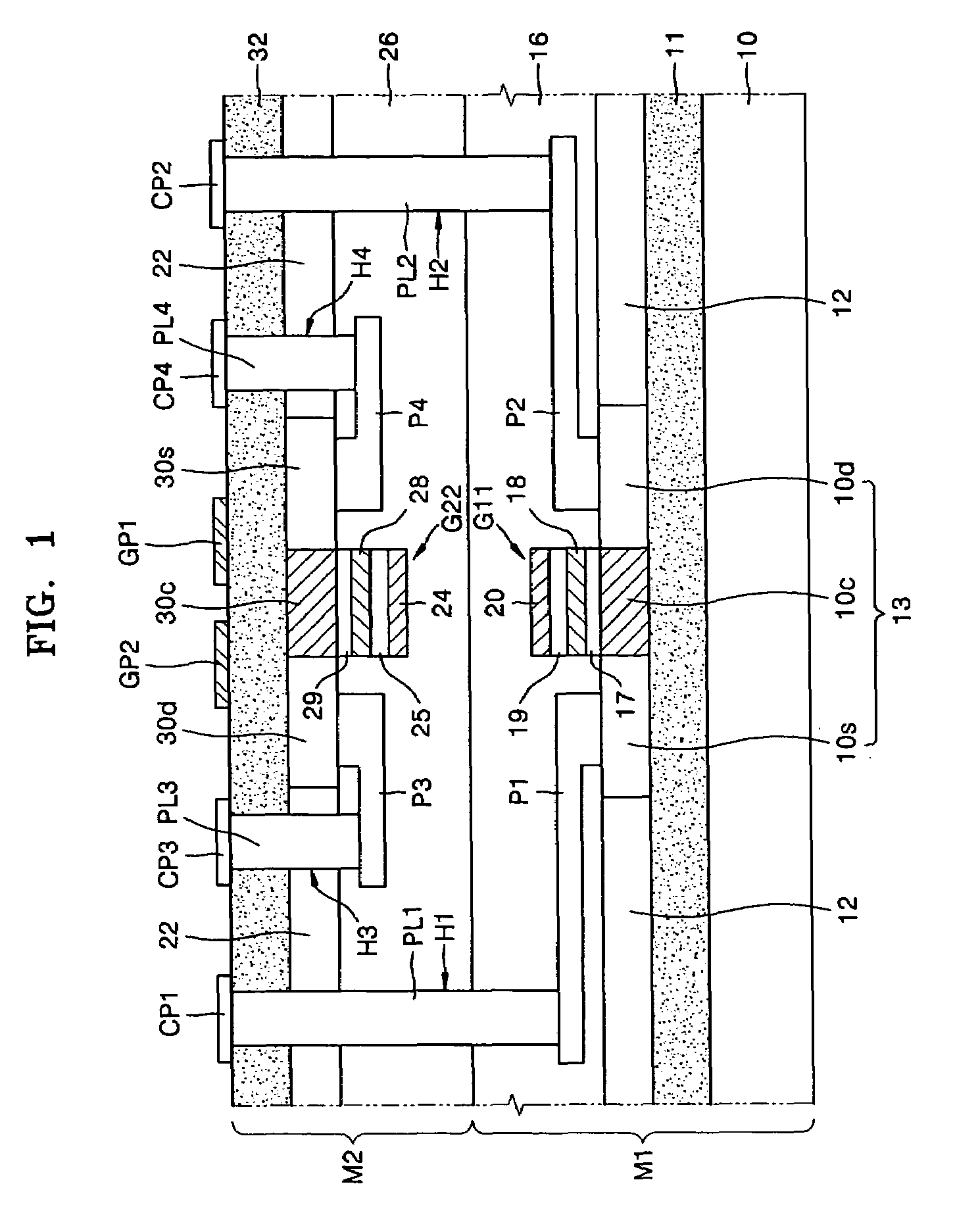

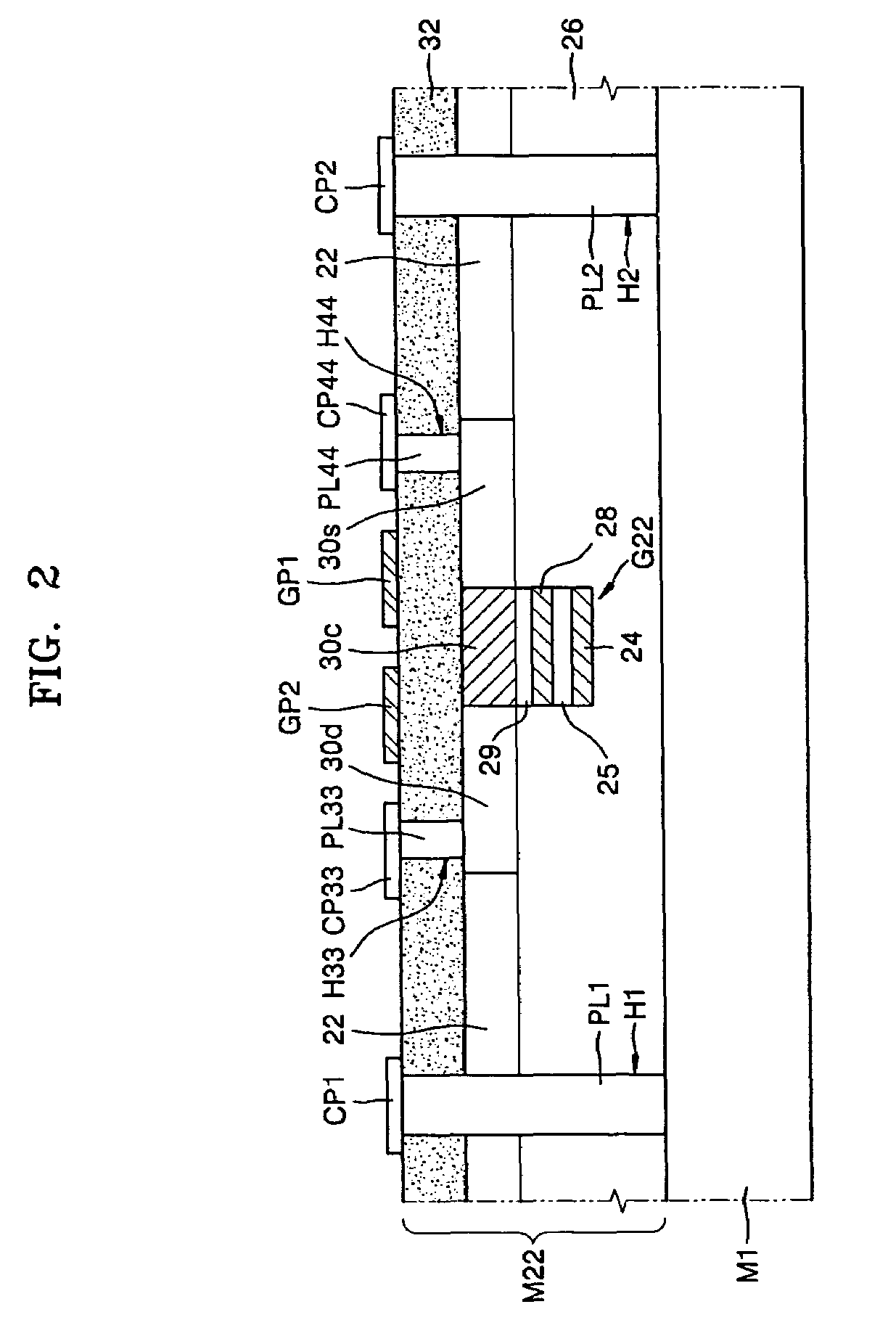

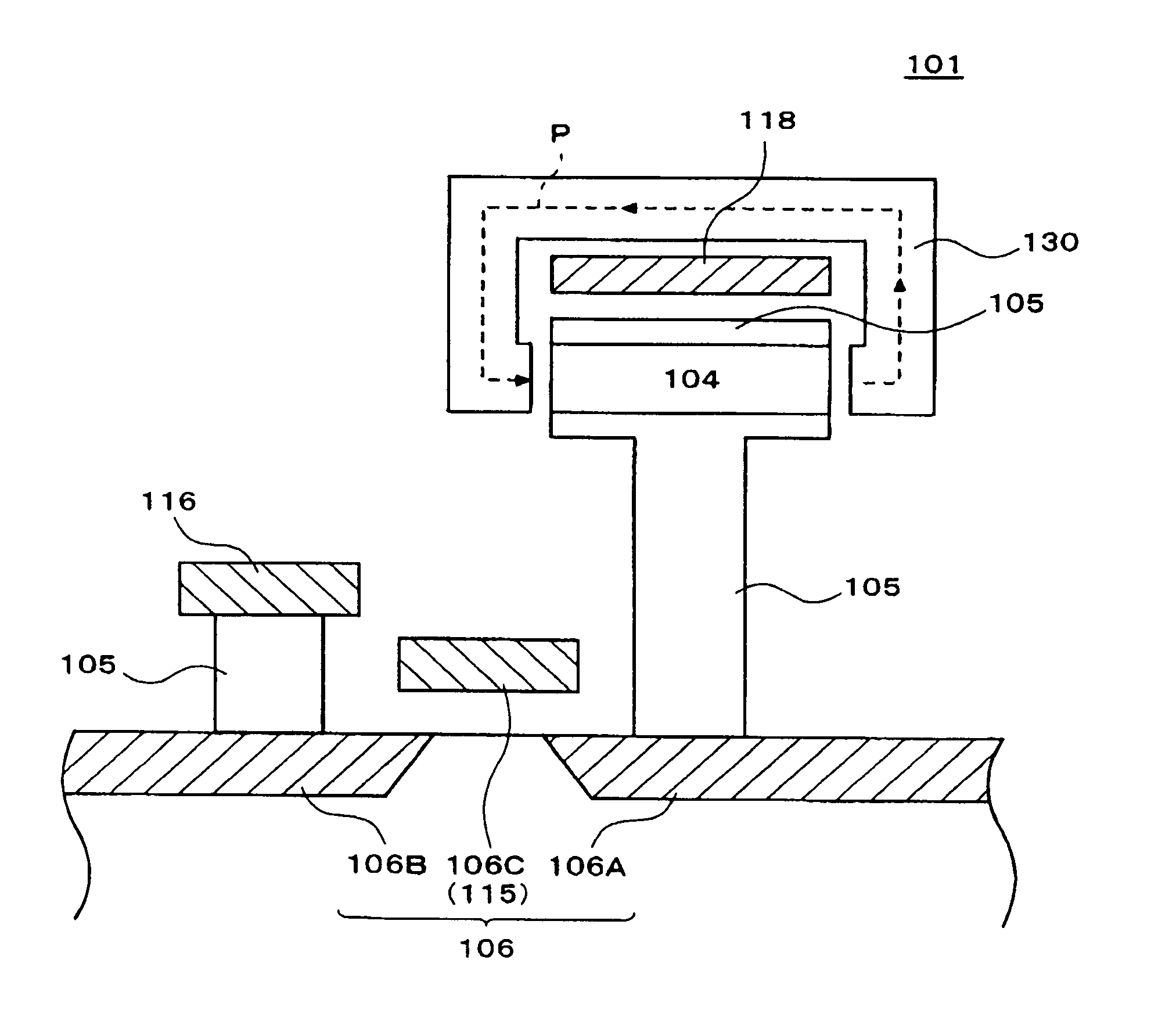

Magnetic memory and method for reading-writing information from-to magnetic storage element

InactiveUS20080037185A1Increase currentReduce read operationsRecord information storageManufacture of flux-sensitive headsMagnetizationMagnetic memory

A magnetic memory is provided in which the margin between a write current and a read current can be reduced. A magnetic storage element includes: a first magnetic layer in which the direction of magnetization can be reversed; a second magnetic layer in which the direction of magnetization is fixed; and a non-magnetic layer which is interposed between the first and second magnetic layers. The write current and the read current are supplied to the magnetic storage element in the stacking direction thereof through a read-write line. Moreover, a bias line which can apply a bias magnetic field to the first magnetic layer during a reading operation is disposed in the vicinity of the magnetic storage element.

Owner:TDK CORPARATION

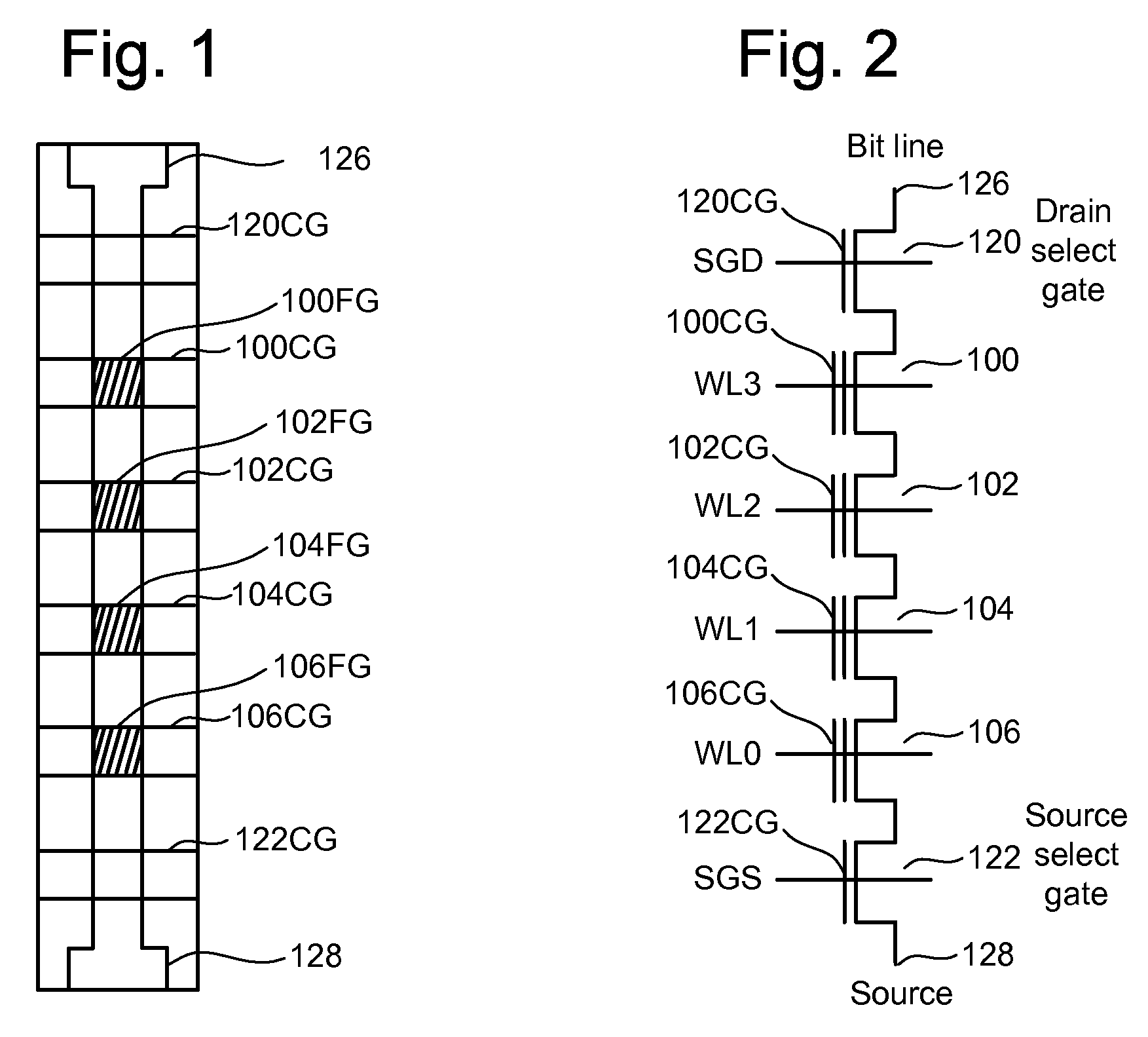

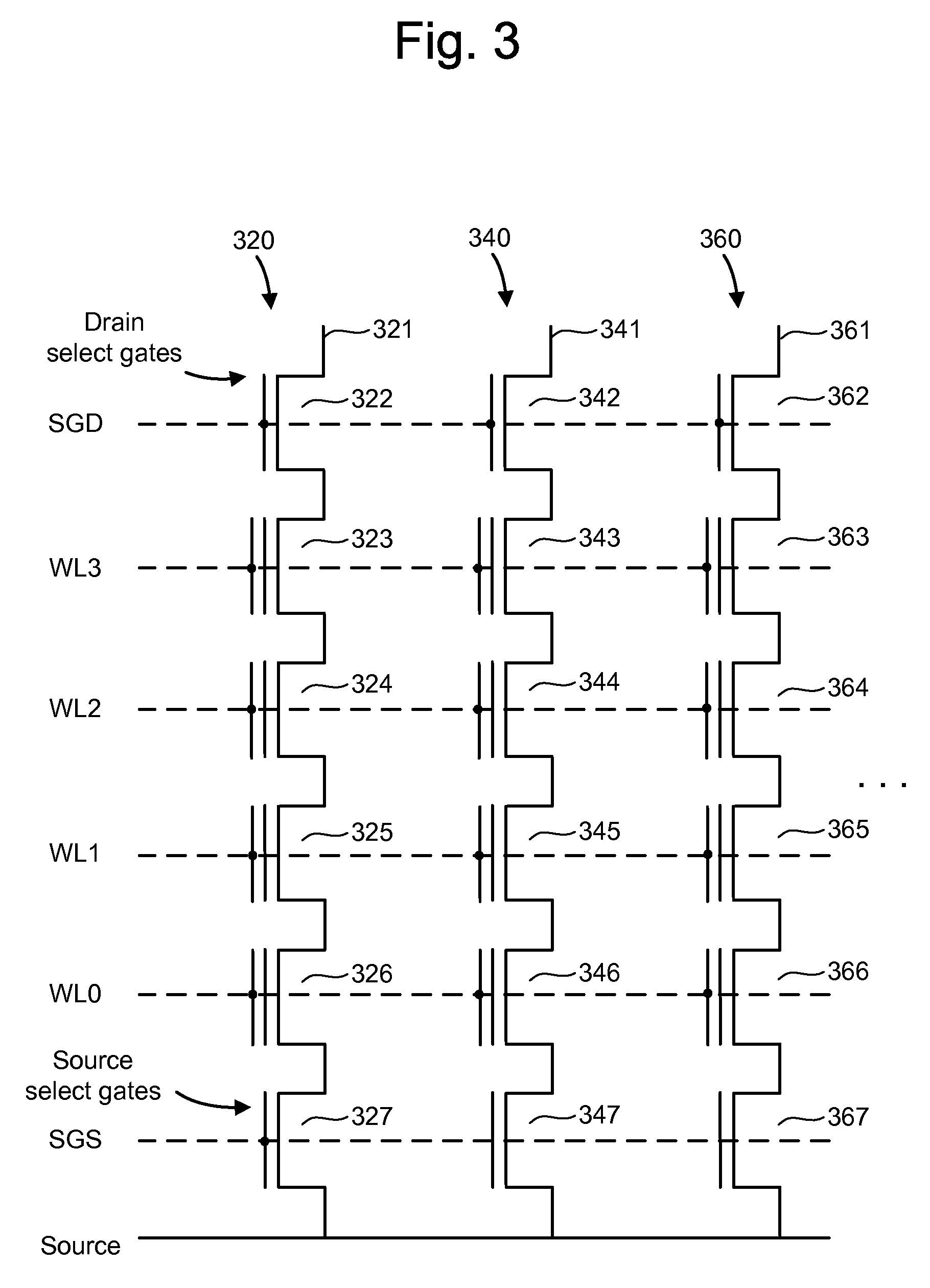

Non-volatile storage with reduced power consumption during read operations

InactiveUS20080266975A1Reduce read operationsReduce power consumptionRead-only memoriesDigital storageProgramming languageEngineering

Owner:SANDISK TECH LLC

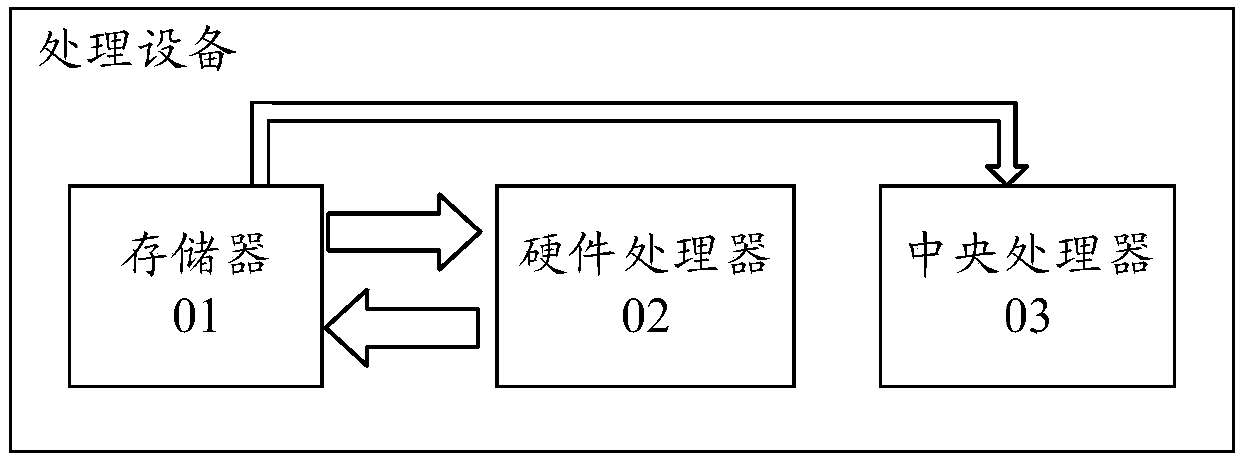

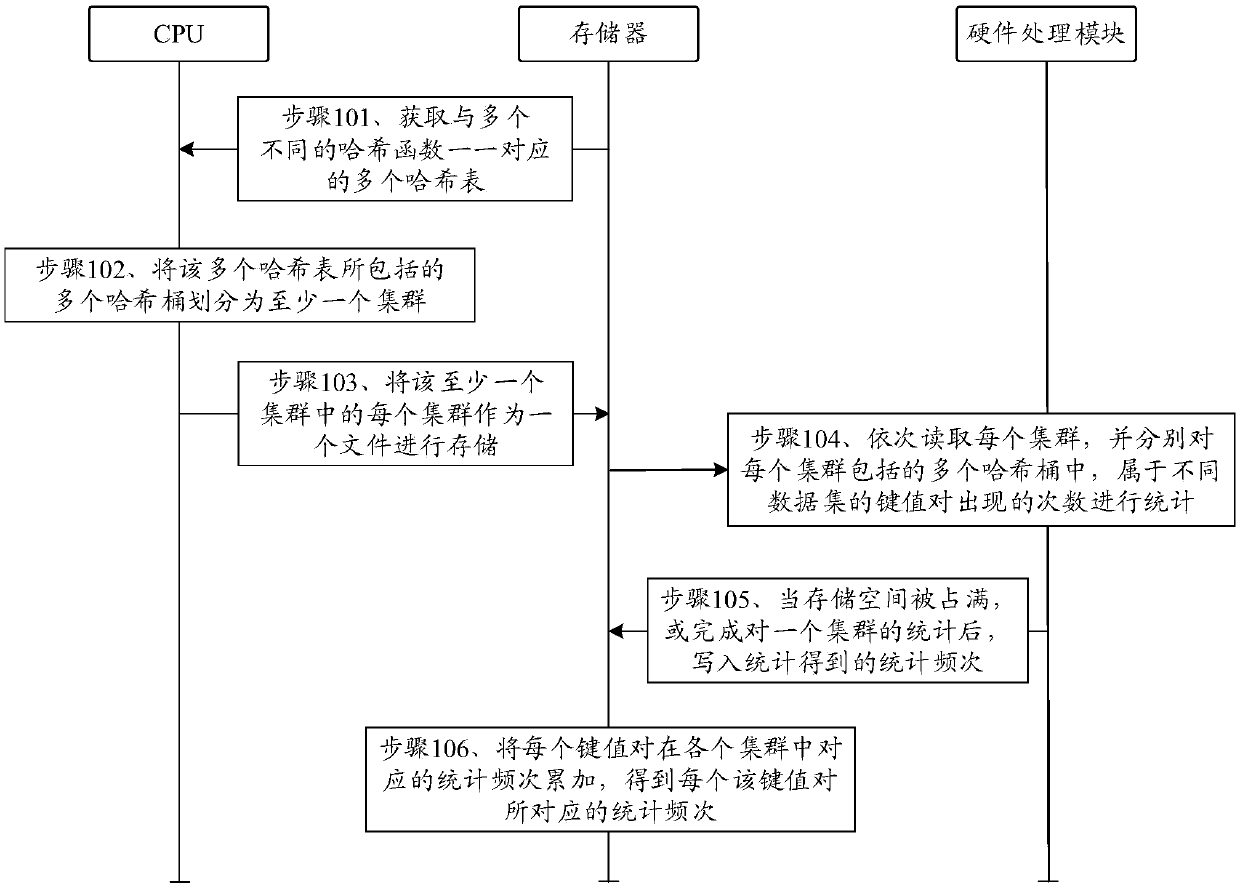

Data similarity determination method and device and processing equipment

ActiveCN110309143AImprove performanceImprove the efficiency of frequency statisticsRelational databasesSpecial data processing applicationsData setAlgorithm

The invention provides a data similarity determination method and device and processing equipment, and relates to the field of data processing. The method comprises: obtaining a plurality of hash tables corresponding to a plurality of different hash functions in a one-to-one mode, wherin each hash table comprises at least one hash bucket, a plurality of key values are recorded in each hash bucket,and the hash values of tuples indicated by the key values are the same; dividing a plurality of hash buckets included in the plurality of hash tables into at least one cluster, wherein each cluster comprises a plurality of hash buckets of which the similarity is greater than a similarity threshold; and counting the occurrence frequency of the key value pairs belonging to different data sets in aplurality of hash buckets included in each cluster to obtain a counting frequency corresponding to each key value pair, wherein the counting frequency is positively correlated with the similarity degree of the tuple pairs indicated by the key value pairs. The data similarity determination method provided by the invention is relatively high in operation efficiency.

Owner:HUAWEI TECH CO LTD

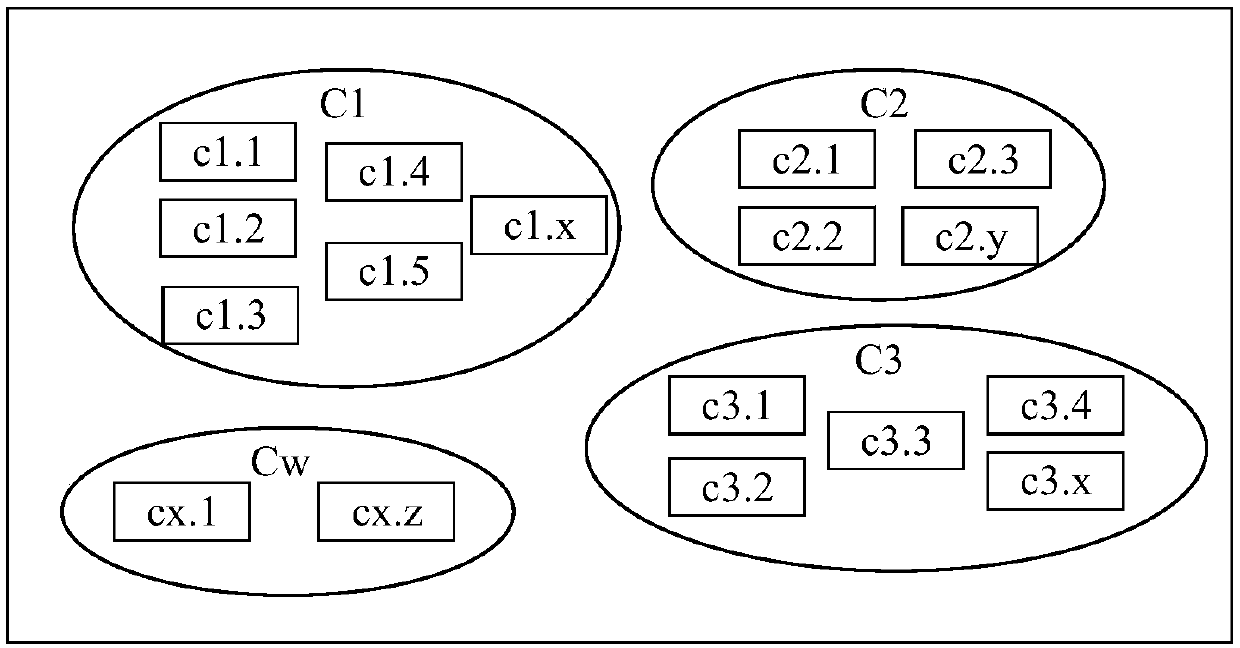

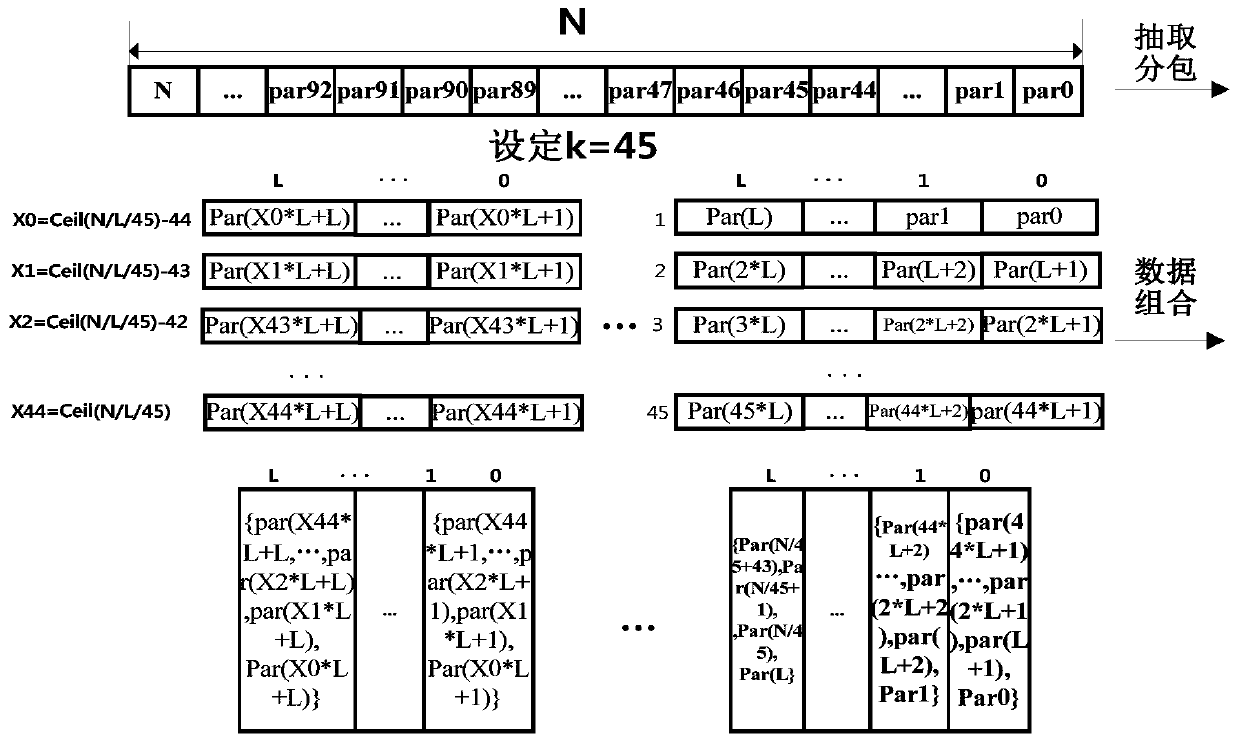

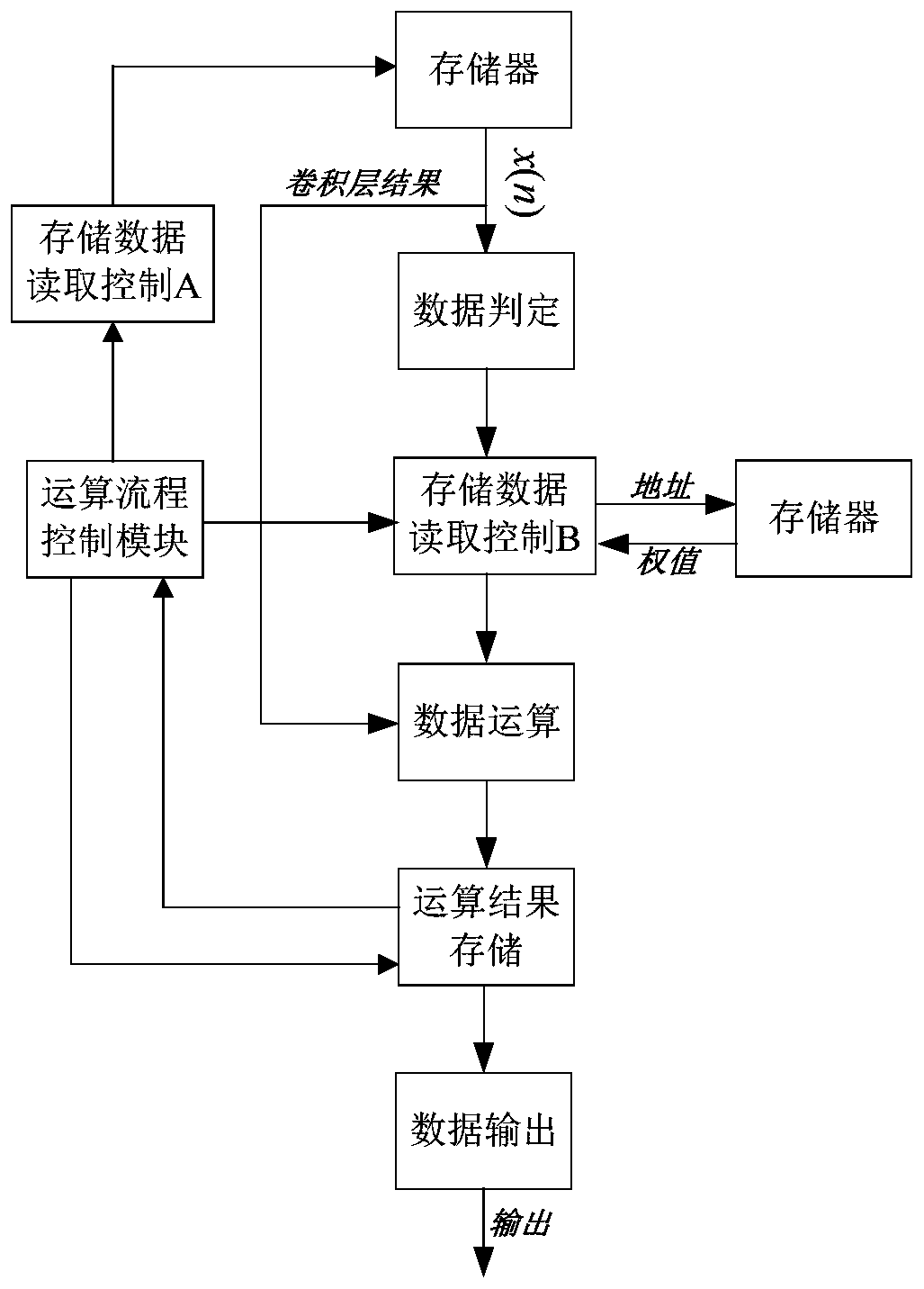

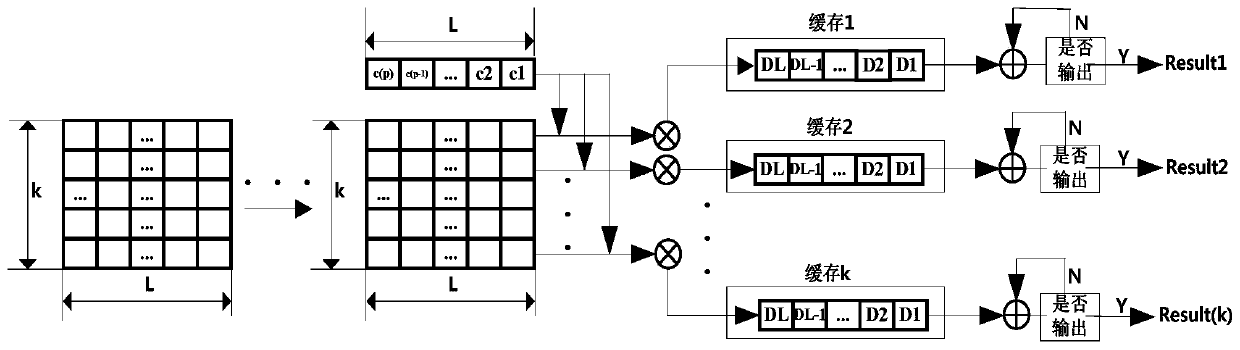

Multi-parallel acceleration method for CNN full connection layer operation

ActiveCN110543936AReduce read operationsImprove access efficiencyNeural architecturesBusiness efficiencyProgrammable logic device

The invention discloses a multi-parallel acceleration method for CNN full-connection layer operation, and the method greatly reduces the reading operation of full-connection layer parameters, effectively saves the energy consumption, and improves the energy efficiency ratio of a system through employing the sparsity characteristics of an operation result of a convolutional neural network and interpreting the numerical value of a convolution layer processing result of the convolutional neural network in advance. By utilizing the characteristics of hardware resource reuse, strong expansion capability and the like of programmable logic devices such as an FPGA and constructing a parallel pipeline multiply-accumulate architecture, the processing time is effectively saved, and the processing efficiency is improved; by comprehensively analyzing factors such as target type data, target characteristic difference and error tolerance in an application process, a processing data format is reasonably set, so that the access efficiency of data and parameters is effectively improved while the processing precision is ensured, and the purpose of multi-parallel acceleration of a full connection layer is achieved.

Owner:BEIJING INST OF SPACECRAFT SYST ENG

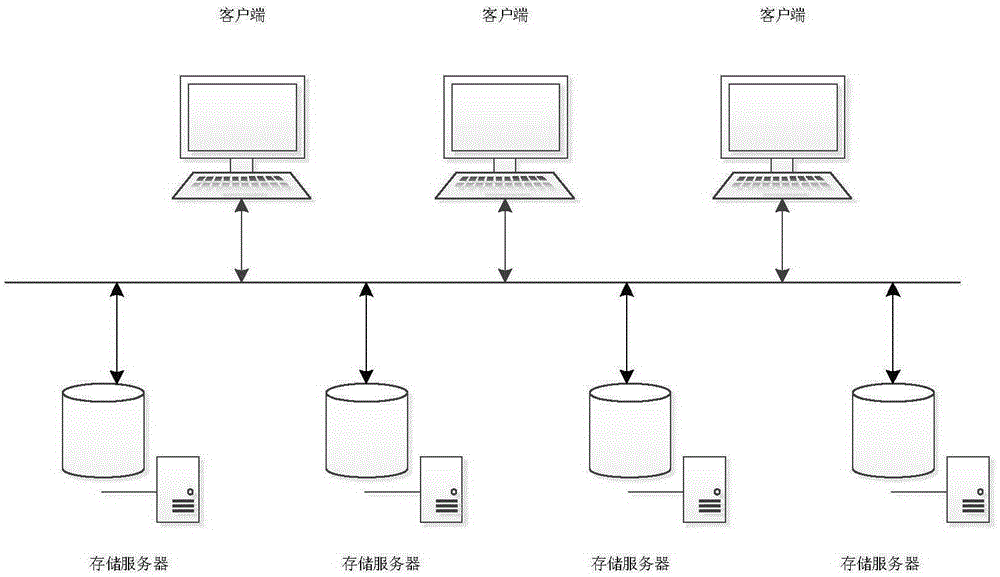

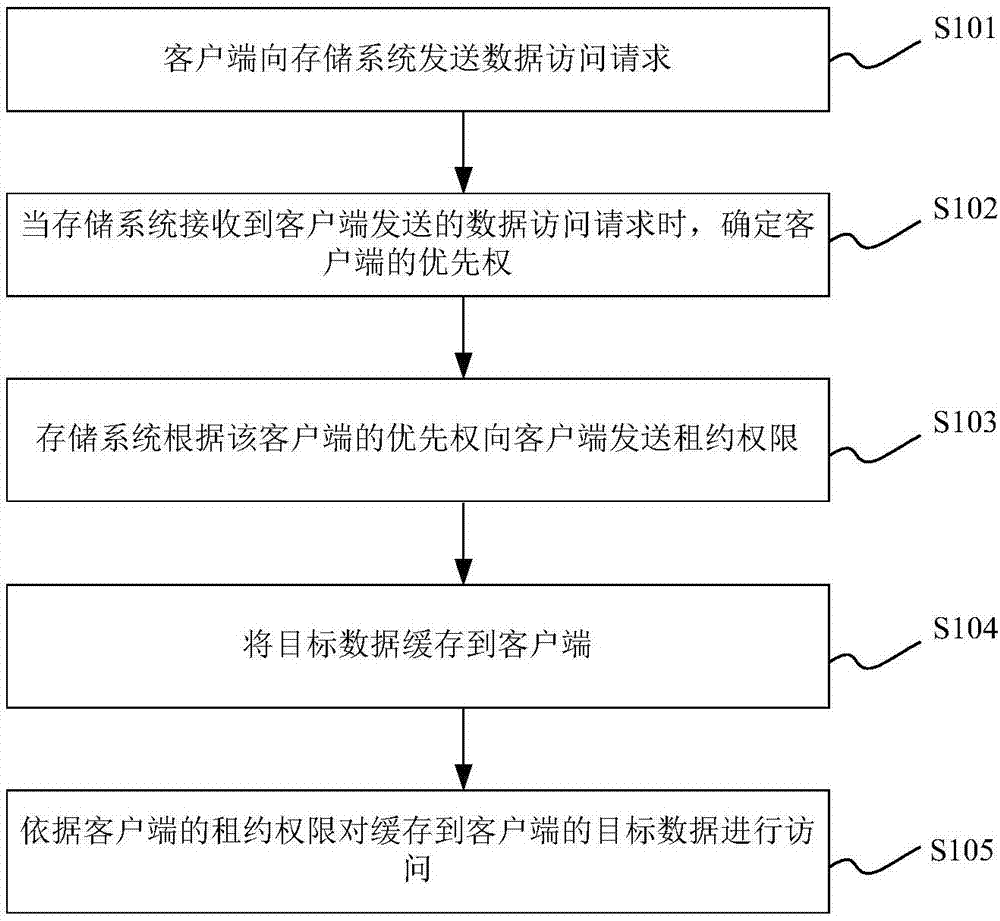

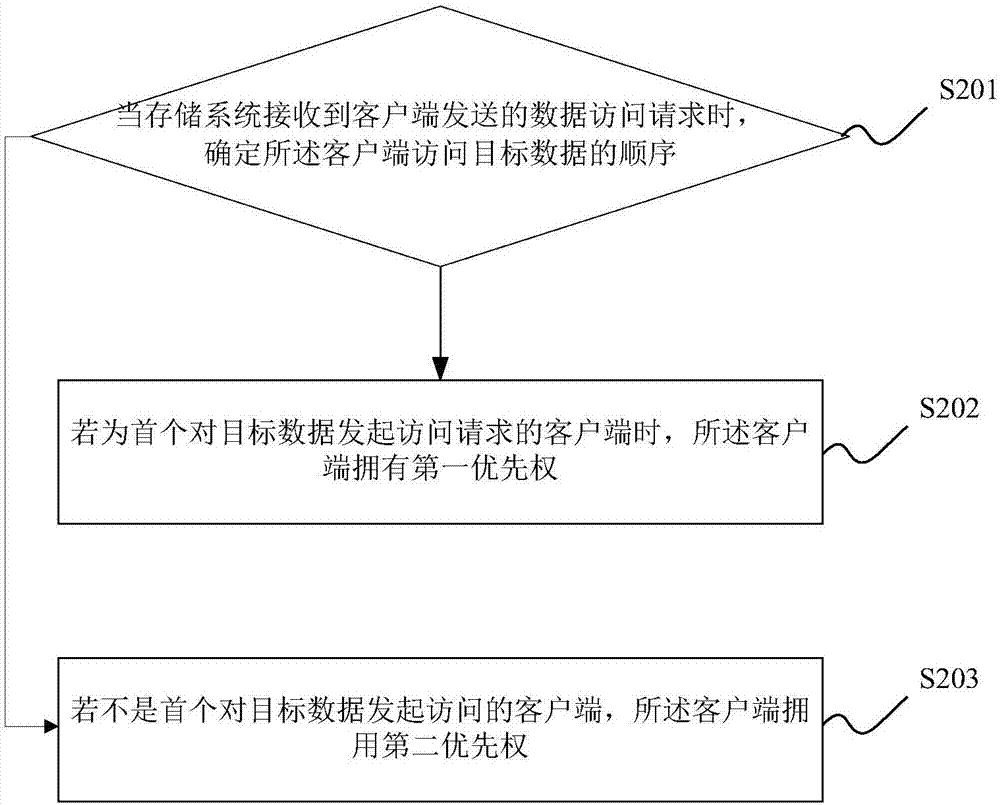

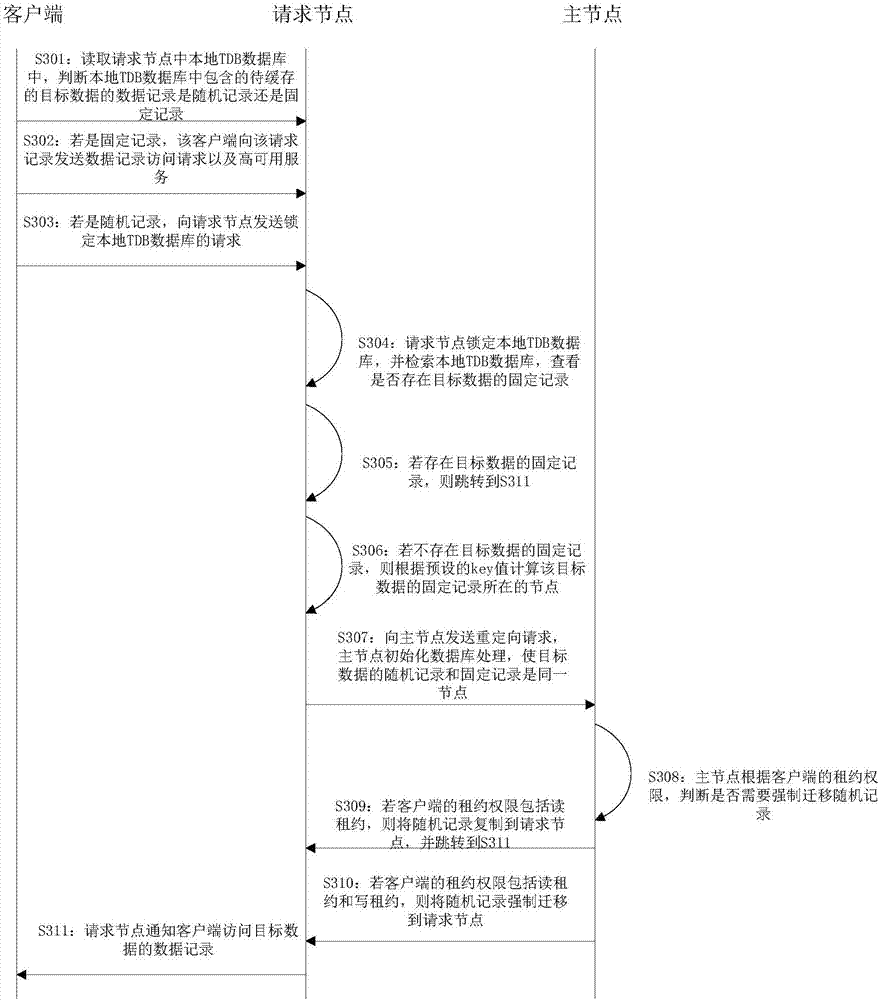

Local caching method and device based on lease lock mechanism

ActiveCN107360245AImprove data access performanceEnsure consistencyTransmissionLocking mechanismData access

The invention discloses a local caching method and device based on a lease lock mechanism. The method comprises the steps of when a storage system receives a data access request sent by a client, determining a priority of the client; sending lease authority to the client according to the priority of the client; and sending target data to the client for caching, thereby enabling the client to operate the cached target data according to the lease authority. Through the lease lock mechanism, the client can cache data in the storage system to the local client, so data exchange processes between the client and a server in which the storage system is located are reduced, read operations for files and the operations for a path list are reduced, paths are shortened, the delay is reduced, and the data access capability of the storage system is improved.

Owner:INSPUR SUZHOU INTELLIGENT TECH CO LTD

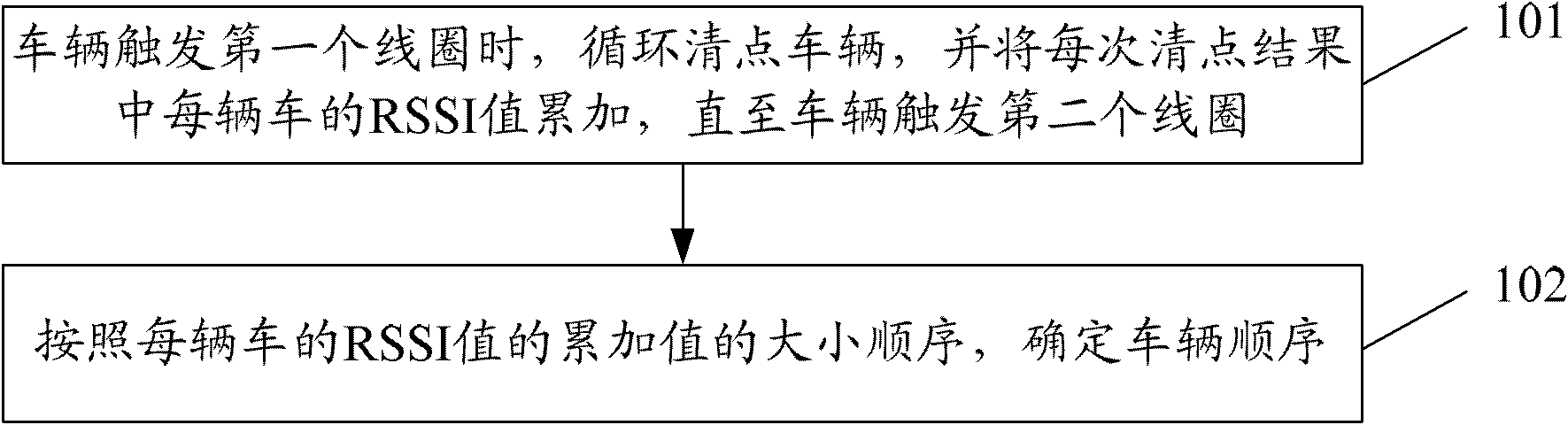

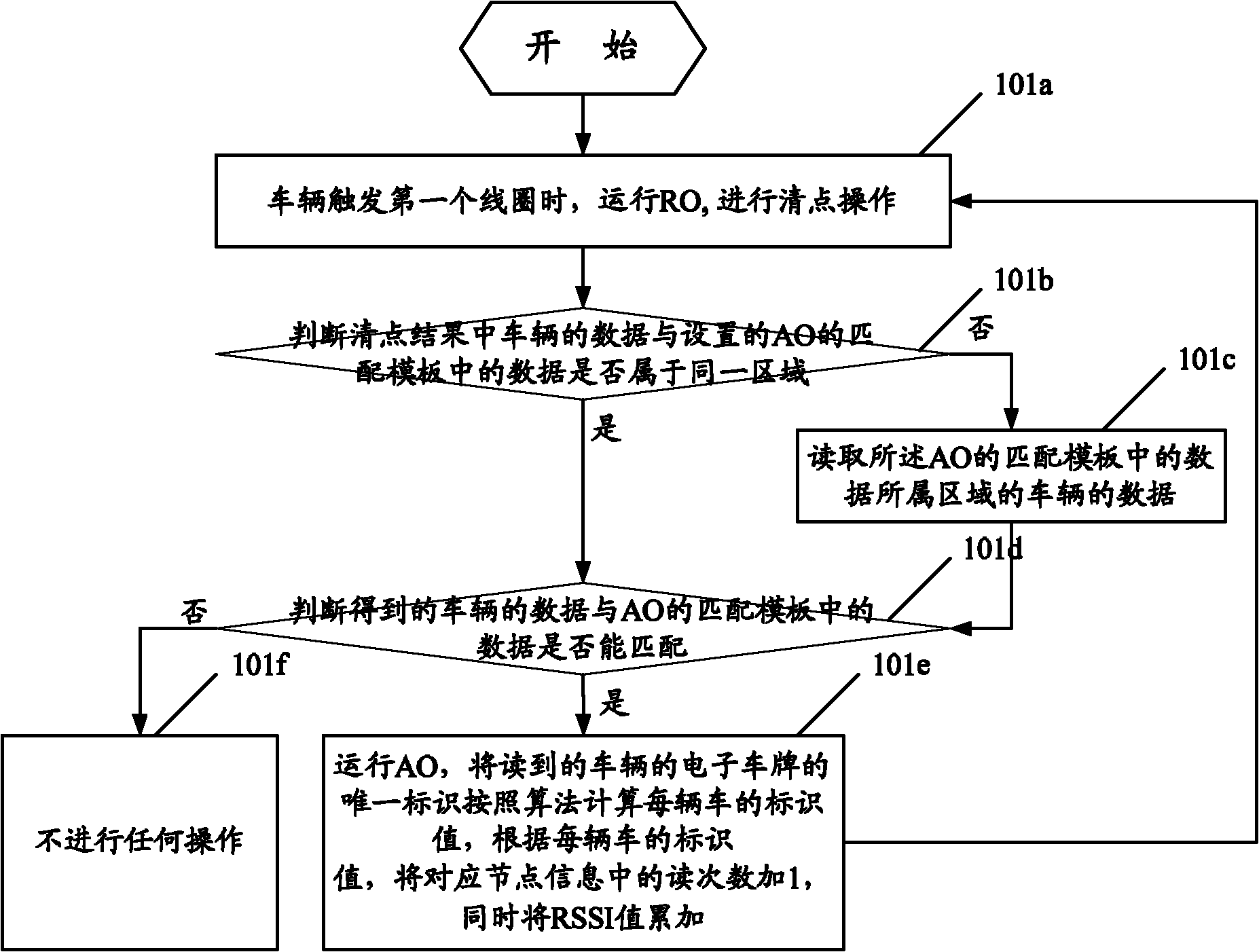

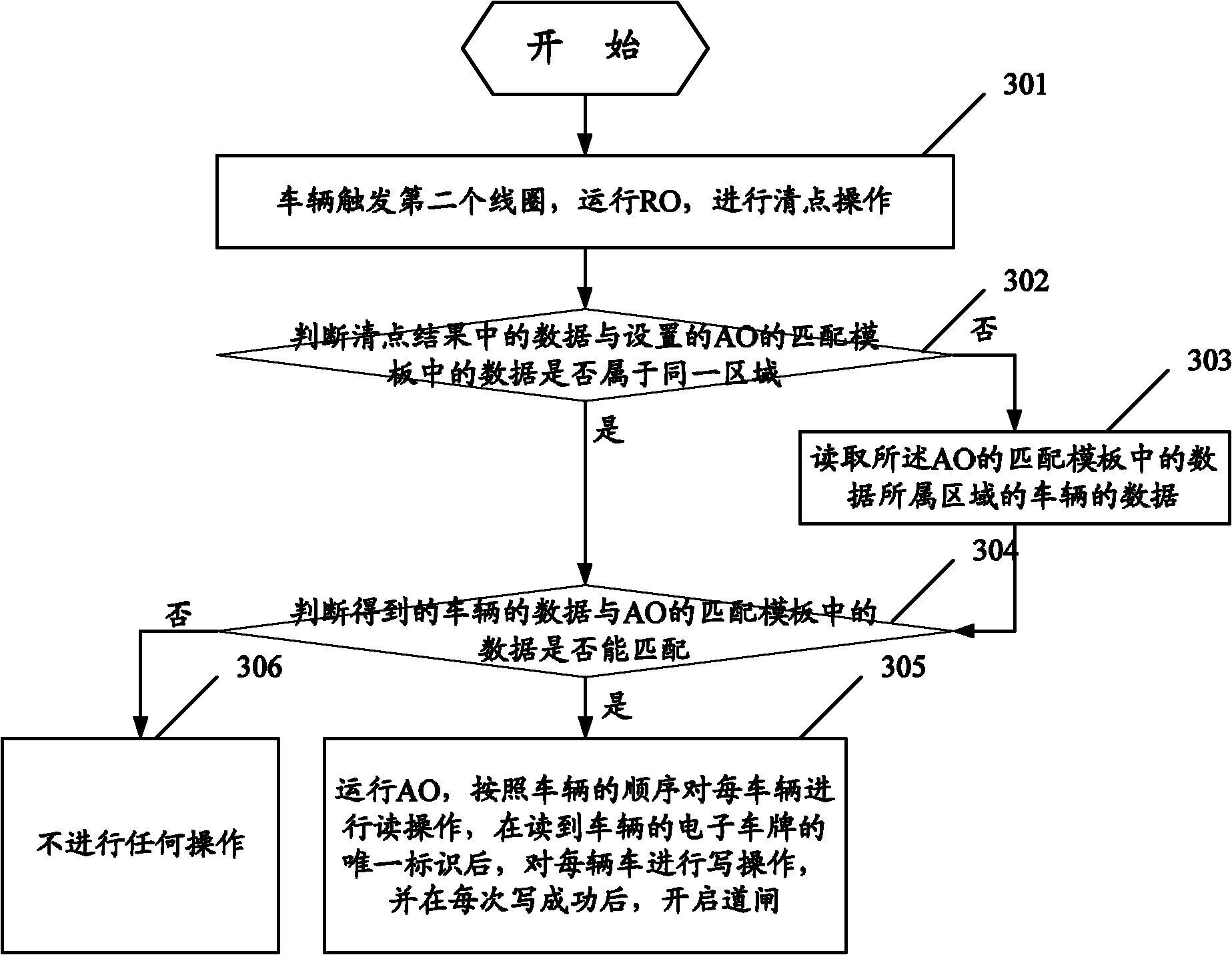

Method and device for identifying vehicle orders

ActiveCN102024136AIncrease success rateReduce read operationsRoad vehicles traffic controlSensing record carriersSignal strengthComputer science

The invention discloses a method for identifying vehicle orders. The method is implemented based on the dispatching of a low level reader protocol (LLRP) and comprises the following steps of: when a vehicle triggers a first coil, checking vehicles circularly; accumulating received signal strength indicator (RSSI) values of each vehicle in a checking result each time until the vehicle triggers a second coil; and determining the vehicle orders according to the magnitude orders of the accommodated values of the RSSI values of each vehicle. The invention also discloses a device for identifying the vehicle orders. By adopting the method and the device, the orders of the vehicles can be identified accurately when a plurality of the vehicles appear in an antenna coverage area at the same time.

Owner:ZTE INTELLIGENT IOT TECH

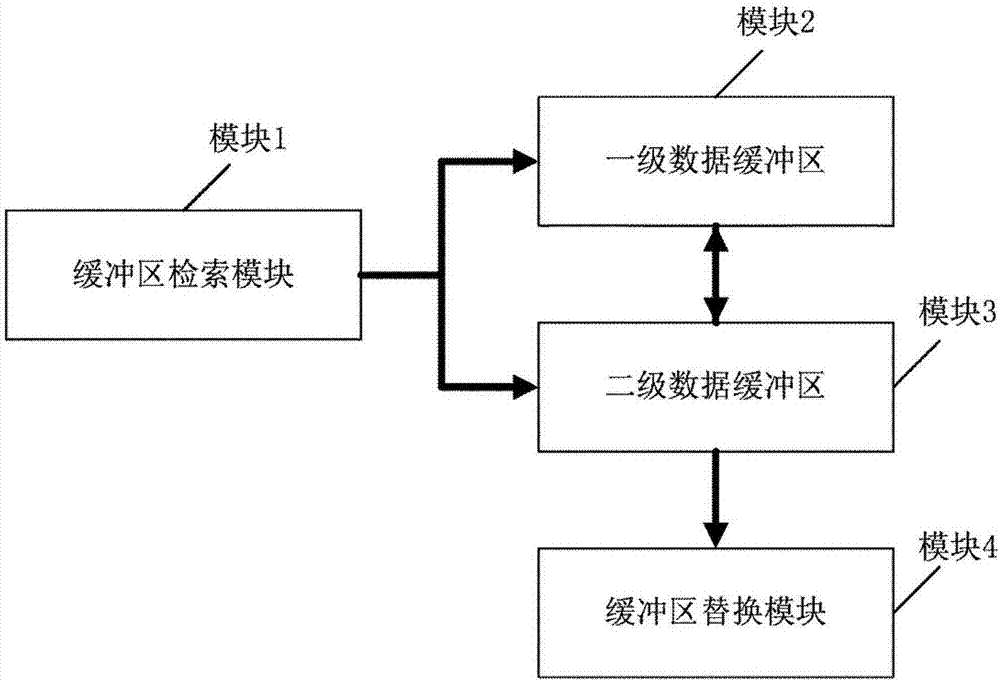

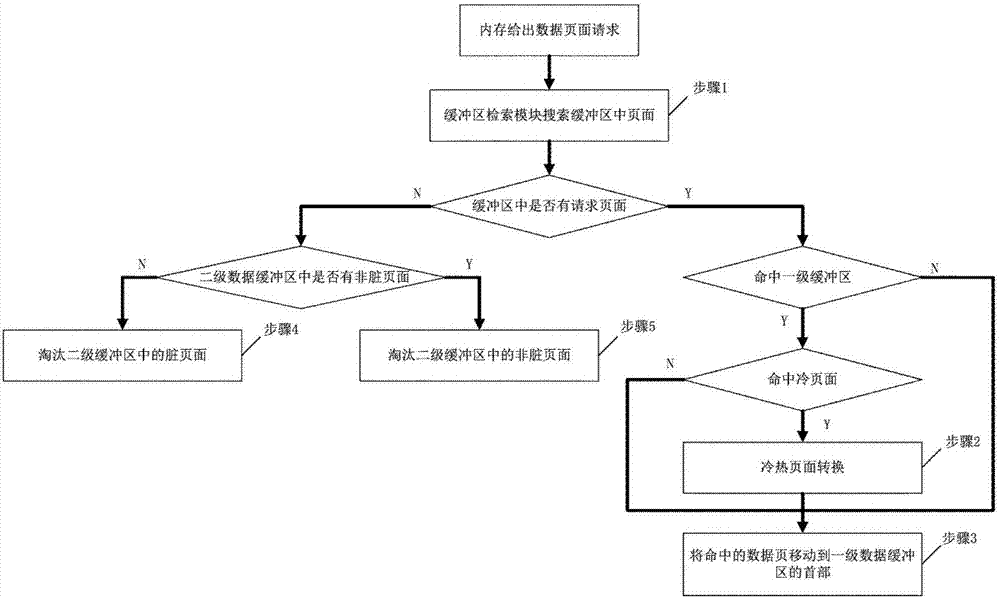

Flash memory data buffer area replacement method based on page access interval

InactiveCN107341112AGuaranteed hit rateReduce write operationsMemory architecture accessing/allocationMemory adressing/allocation/relocationDirty dataReplacement method

The invention discloses a flash memory data buffer area replacement method based on a page access interval. In the method, all data pages cached in the data buffer area are divided into hot dirty data pages, cold dirty data pages, hot clean data pages and cold clean data pages according to access interval characteristics and reading / writing characteristics of the data pages in the buffer area, and all the data pages are managed by using a primary data buffer area and a secondary data buffer area. When the cold data page access interval is less than the last hot data page in an LRU queue of the buffer area, conversion between cold and hot data pages is performed, and meanwhile, the cold data page in the LRU queue of the primary buffer area is moved into the secondary data buffer area. When the data buffer area page needs to be replaced, the cold clean data pages in the secondary buffer area are preferentially shifted out according to an LRU rule, and the influence on performance and service life of a flash memory due to too many times of write-back operations of the dirty data pages of the data buffer area is reduced under the premise of ensuring a hit rate.

Owner:XI AN JIAOTONG UNIV

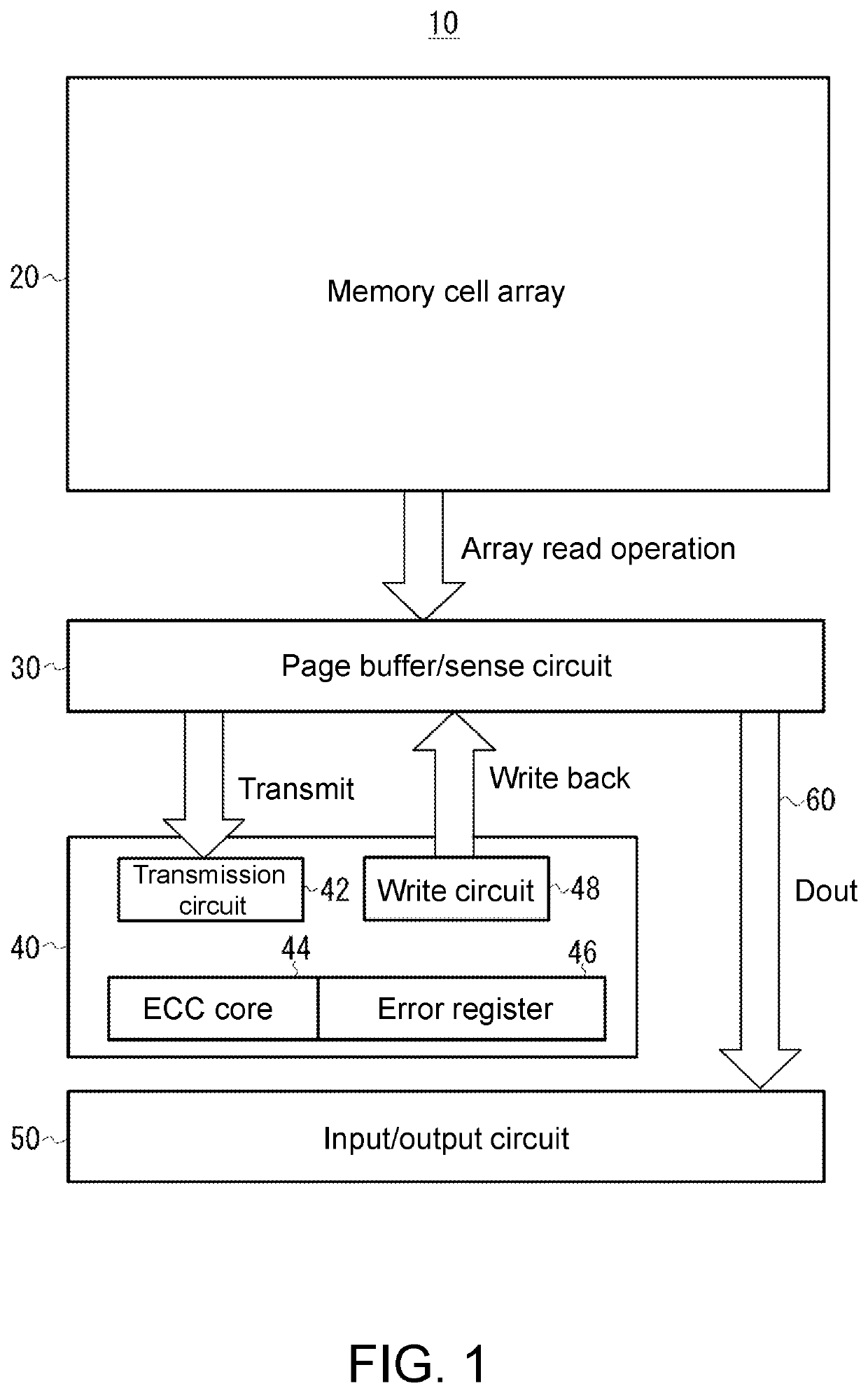

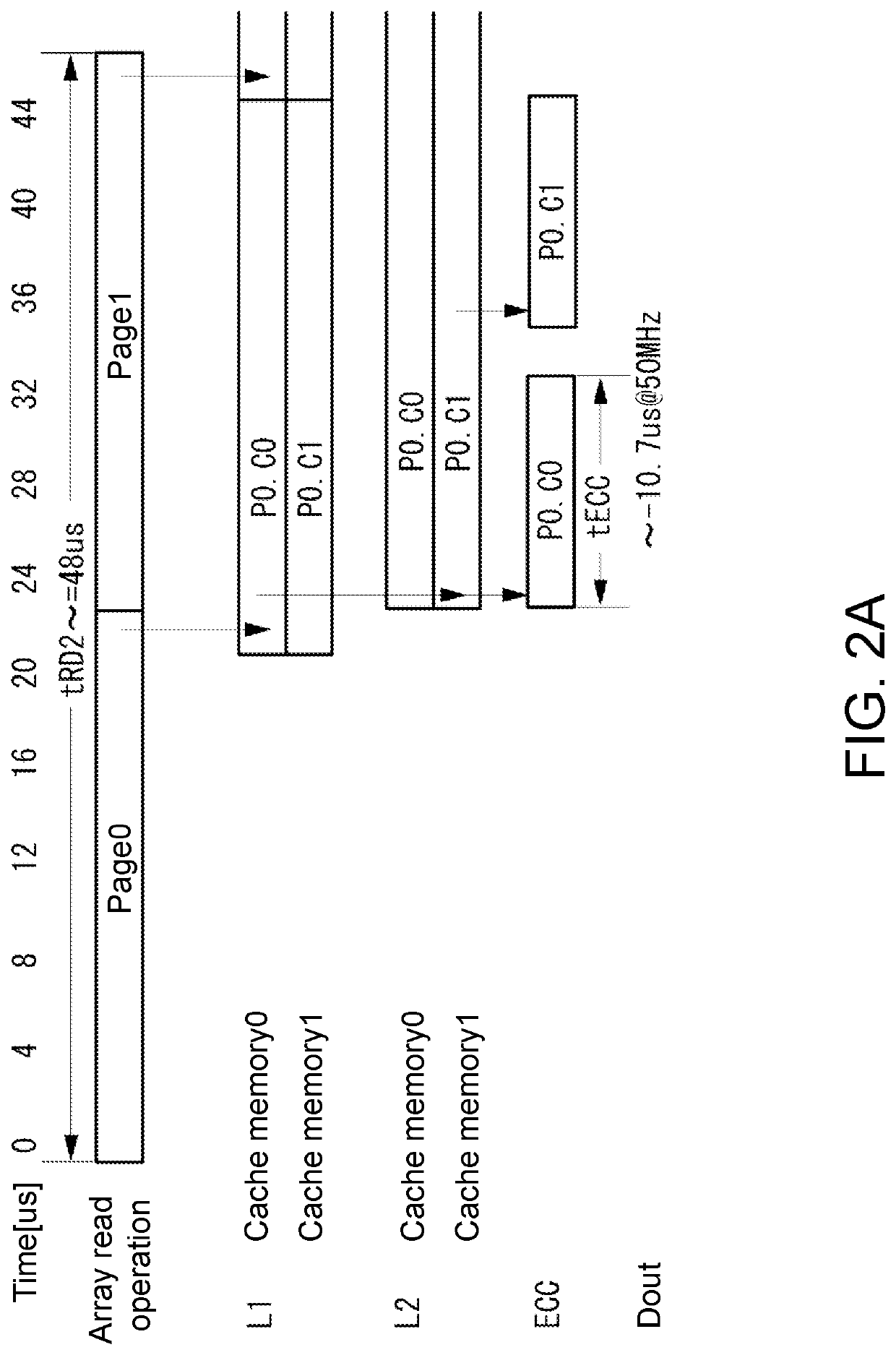

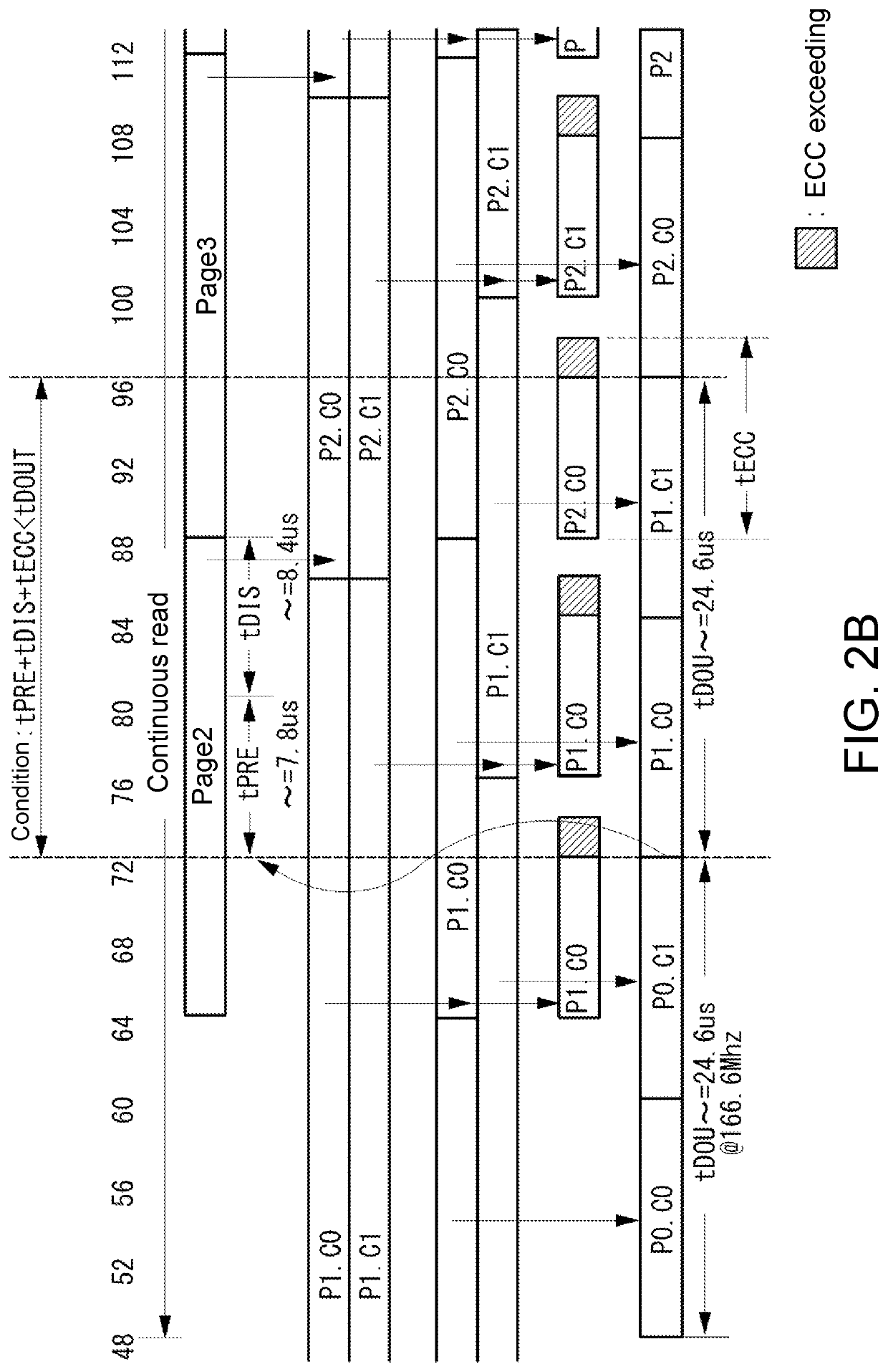

Semiconductor storing apparatus and readout method

ActiveUS20210311826A1Timing errorShorten the timeRead-only memoriesDigital storageMemory cellSemiconductor

A semiconductor storing apparatus capable of shortening a ECC processing time of a readout operation is provided, including a flash memory includes: a memory cell array; a page buffer / sense circuit holding data read out from a selected page of the memory cell array; an error correcting code circuit receiving data from the page buffer / sense circuit and holding error address information of the data; an output circuit selecting data from the page buffer / sense circuit based on a column address, and outputting the selected data to a data bus; and an error correction part correcting data of the data bus based on the error address information.

Owner:WINBOND ELECTRONICS CORP

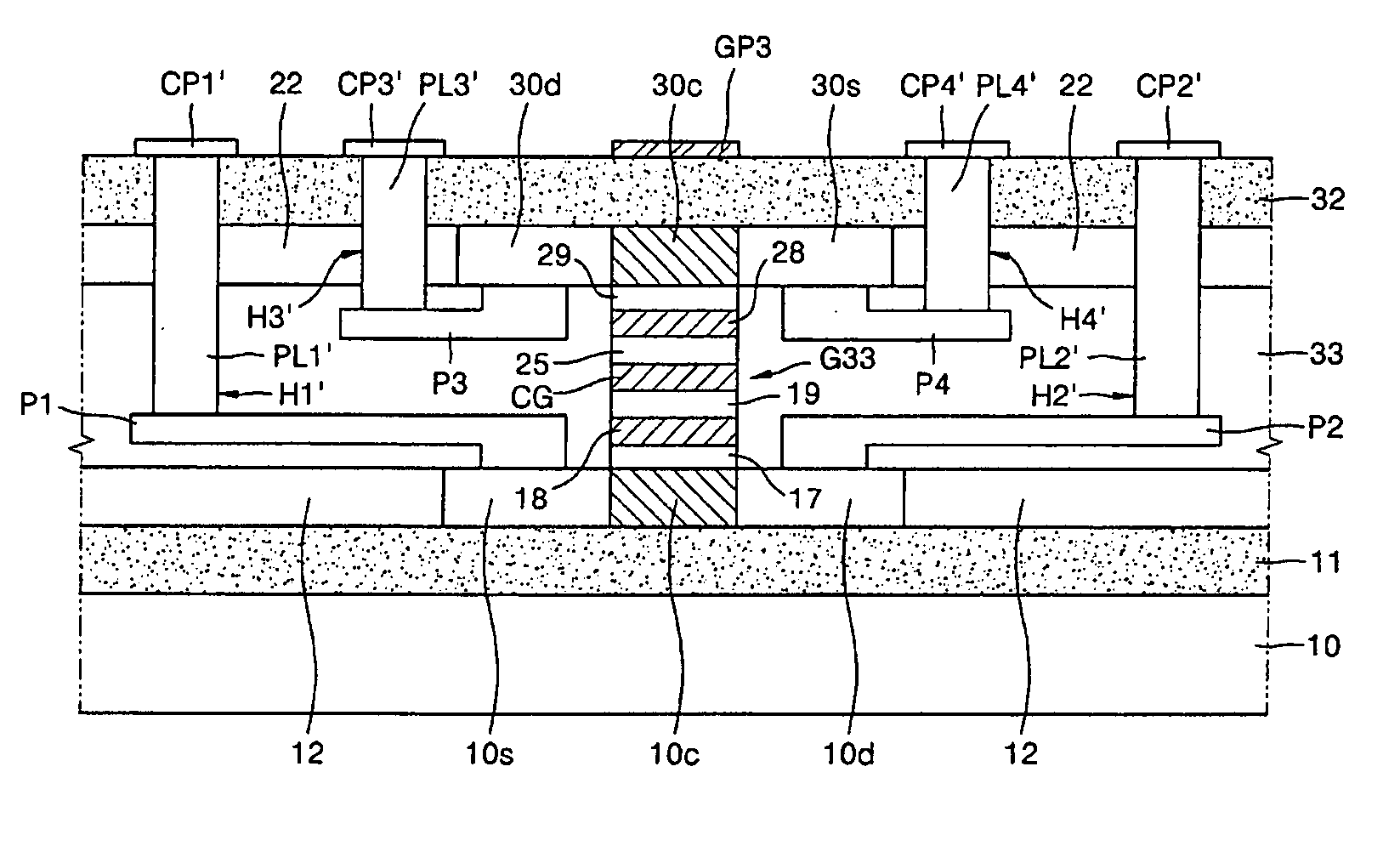

Methods of operating and manufacturing logic device and semiconductor device including complementary nonvolatile memory device, and reading circuit for the same

InactiveUS20080212376A1Increase the number ofReduce read operationsSolid-state devicesRead-only memoriesDevice materialComputer science

Provided are a complementary nonvolatile memory device, methods of operating and manufacturing the same, a logic device and semiconductor device having the same, and a reading circuit for the same. The complementary nonvolatile memory device includes a first nonvolatile memory and a second nonvolatile memory which are sequentially stacked and have a complementary relationship. The first and second nonvolatile memories are arranged so that upper surfaces thereof are contiguous.

Owner:SAMSUNG ELECTRONICS CO LTD

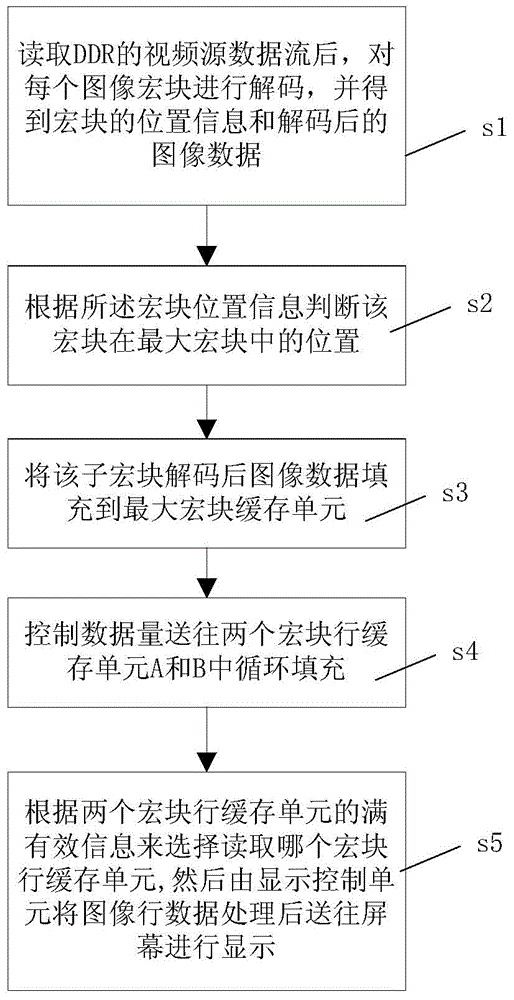

Direct displaying method and device for video decoding

ActiveCN104954798AReduce bandwidth requirementsReduce read operationsDigital video signal modificationData streamDouble data rate

The invention provides a direct displaying method and device for video decoding. The method comprises the following steps: after video source data stream of DDR (double data rate) is read, a macro block of each image is decoded, and location information of the macro block and image data after decoding are obtained; the location of the macro block in a maximum macro block is judged, and a maximum macro block cache unit is filled with image data obtained after the sub macro block is decoded according to the location information; data volume is controlled to be sent to two macro block slice cache units for circulated filling until the whole image is decoded; which macro block slice cache unit is read is selected according to the effective full state of the two macro block slice cache units, and image line data are processed and sent to a screen for display by the aid of a display control unit. According to the direct displaying method, DDR write-back operation of a video decoder and read operation of a display controller on video images in the DDR in the traditional data path are saved, the requirement of the whole decoding display for the bandwidth of the DDR is reduced greatly, and the cost and power consumption of products can be reduced greatly.

Owner:FUZHOU ROCKCHIP SEMICON

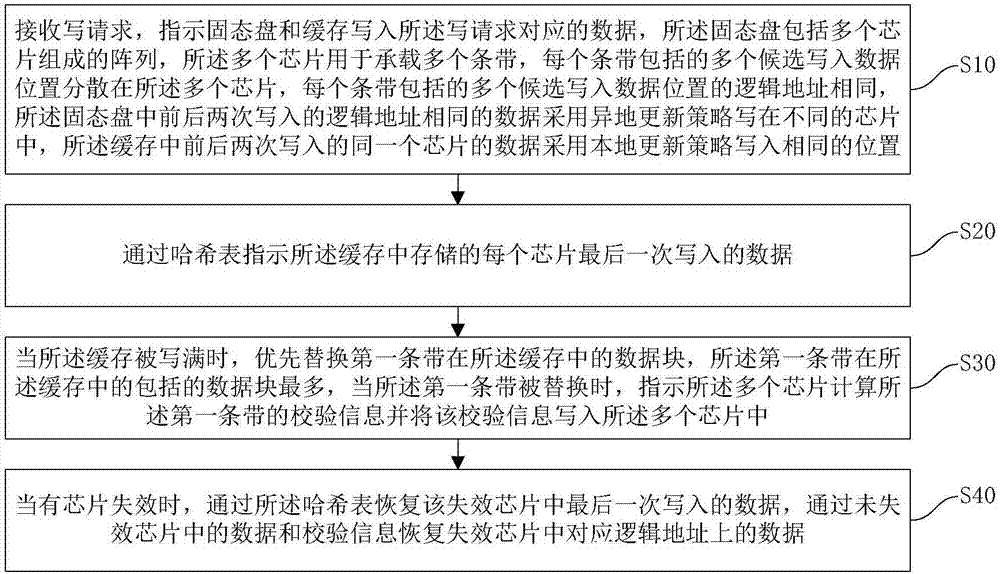

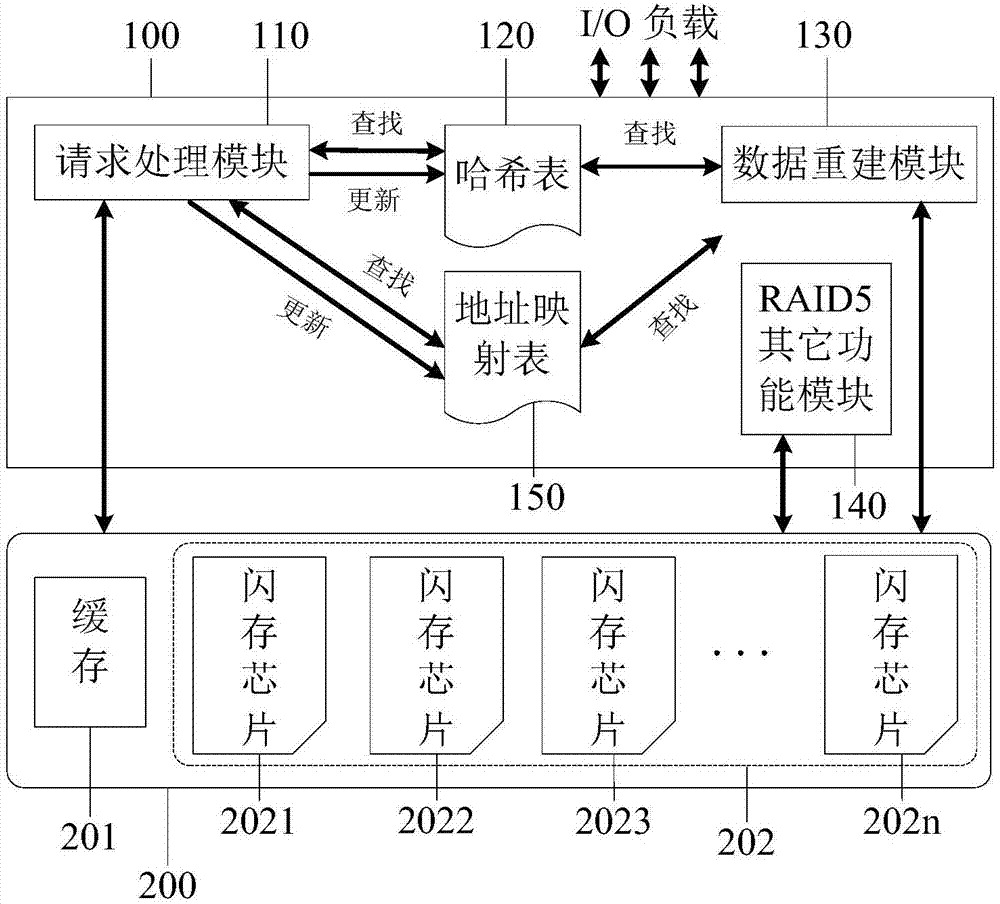

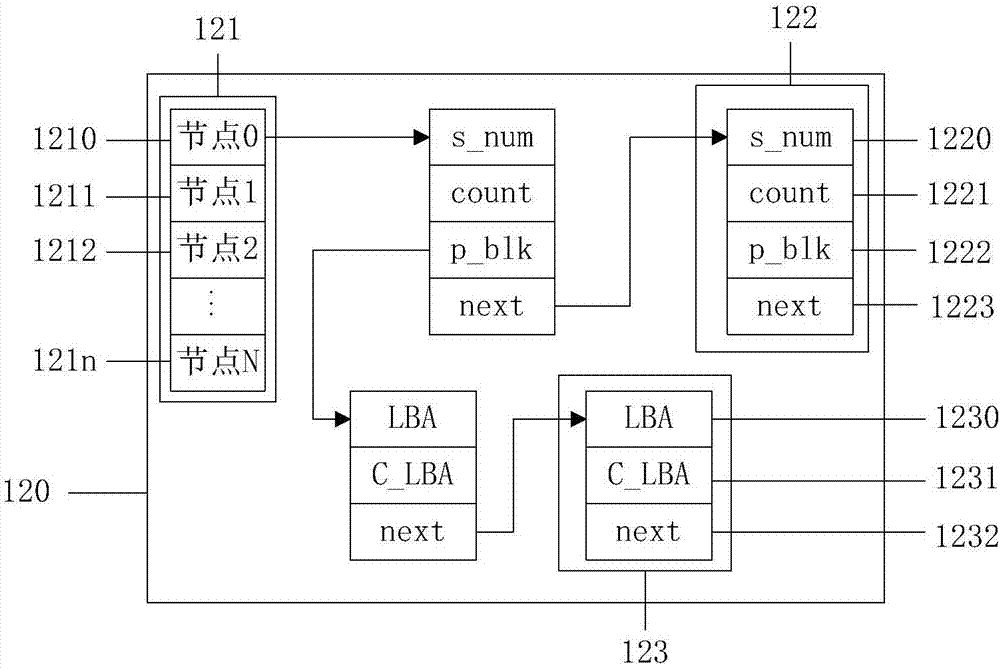

Data processing method and system based on solid state disk array and cache

ActiveCN107402890AReduce read operationsImprove lowercase performanceInput/output to record carriersMemory adressing/allocation/relocationDisk arrayHash table

The invention discloses a data processing method and device based on a solid state disk array and a cache. The method includes: receiving a writing request, and instructing solid state disks and the cache to write data corresponding to the writing request; indicating the data, which is stored in the cache and written by each chip for the last time, through a hash table; preferentially replacing data blocks, which are in the cache and of a first stripe, when the cache is fully written, wherein the included data blocks which are in the cache and of the first stripe are most, and the chips are instructed to calculate verification information of the first stripe and write the verification information into the chips when the first stripe is replaced; and when a failure chip exists, restoring the data, which is written in the failure chip for the last time, through the hash table, and restoring data on a corresponding logical address in the failure chip through the data and the verification information in the non-failure chips. According to the method, verification block updating is delayed through the cache, the small-writing performance of a chip array is improved, and the problem of erasing frequency is alleviated.

Owner:HUAZHONG UNIV OF SCI & TECH

Flexible 2T-based fuzzy and certain matching arrays

InactiveUS8917551B2Reduce read operationsGuaranteed uptimeRead-only memoriesDigital storageComputer science

A novel NVM-based 2T or 2nT NAND-cell for a NAND-array for PLD, PAL and matching functions is disclosed. The preferable NVM cell can be ROM or Flash. The 2T flash cell preferably uses FN for both program and erase operation, while 2T ROM cell preferably to use phosphorus for ROM code implant to get negative Vt0.

Owner:APLUS FLASH TECH

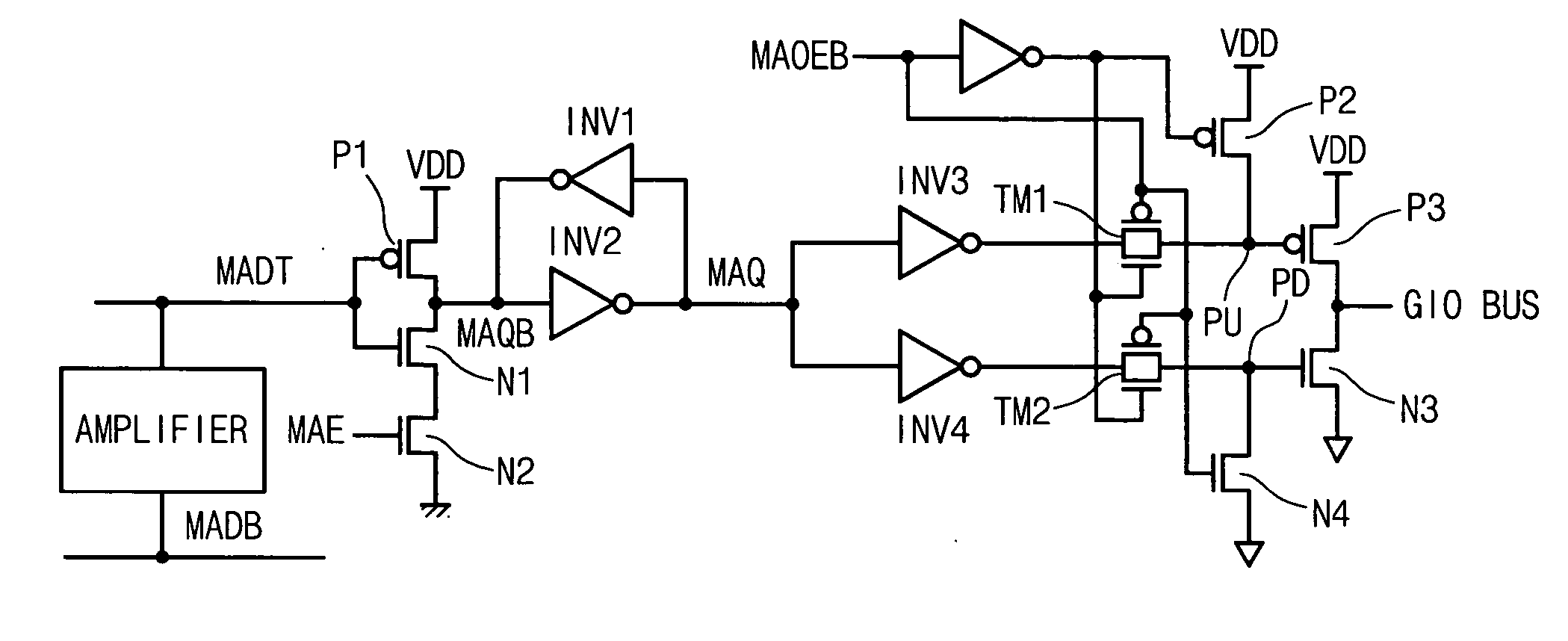

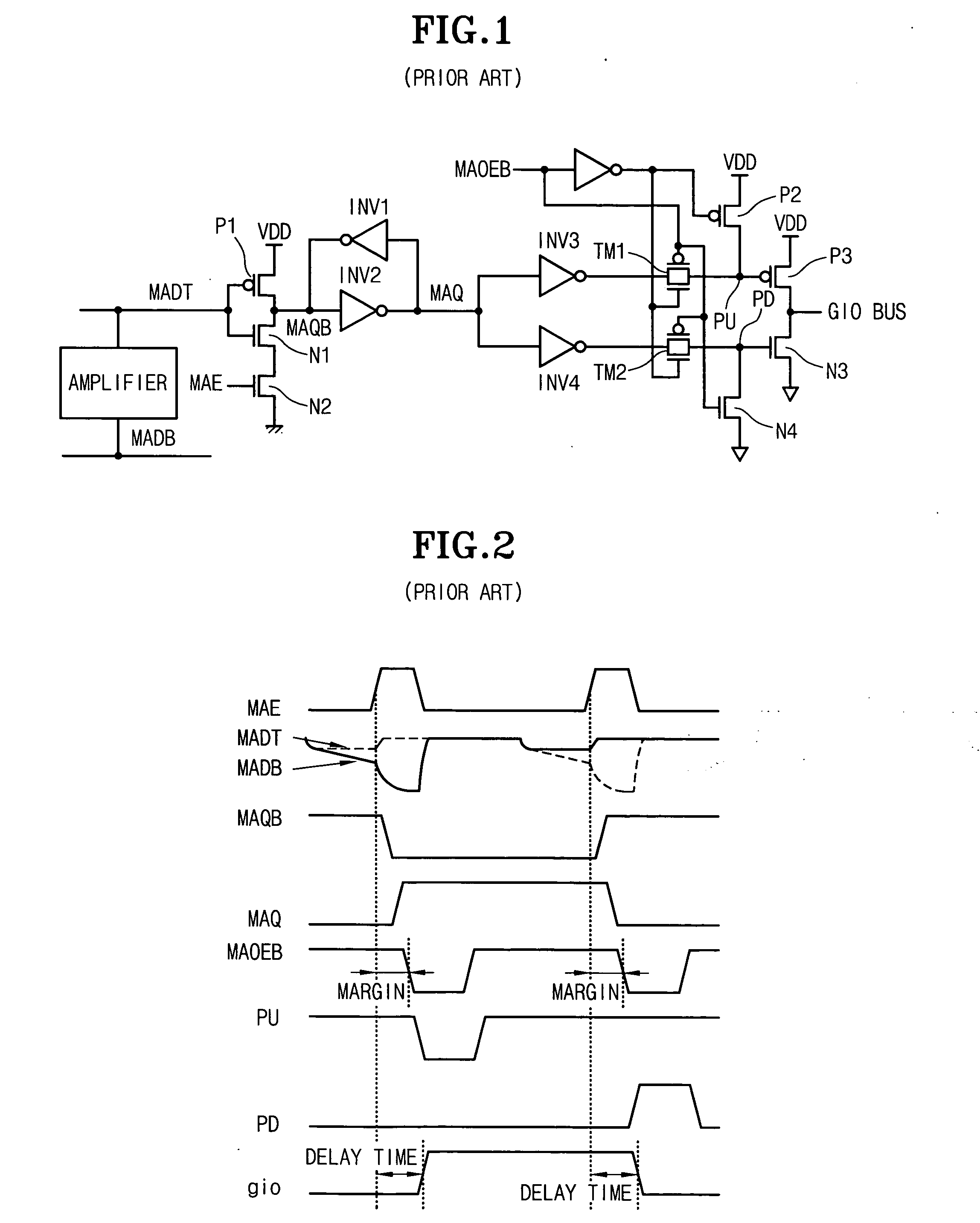

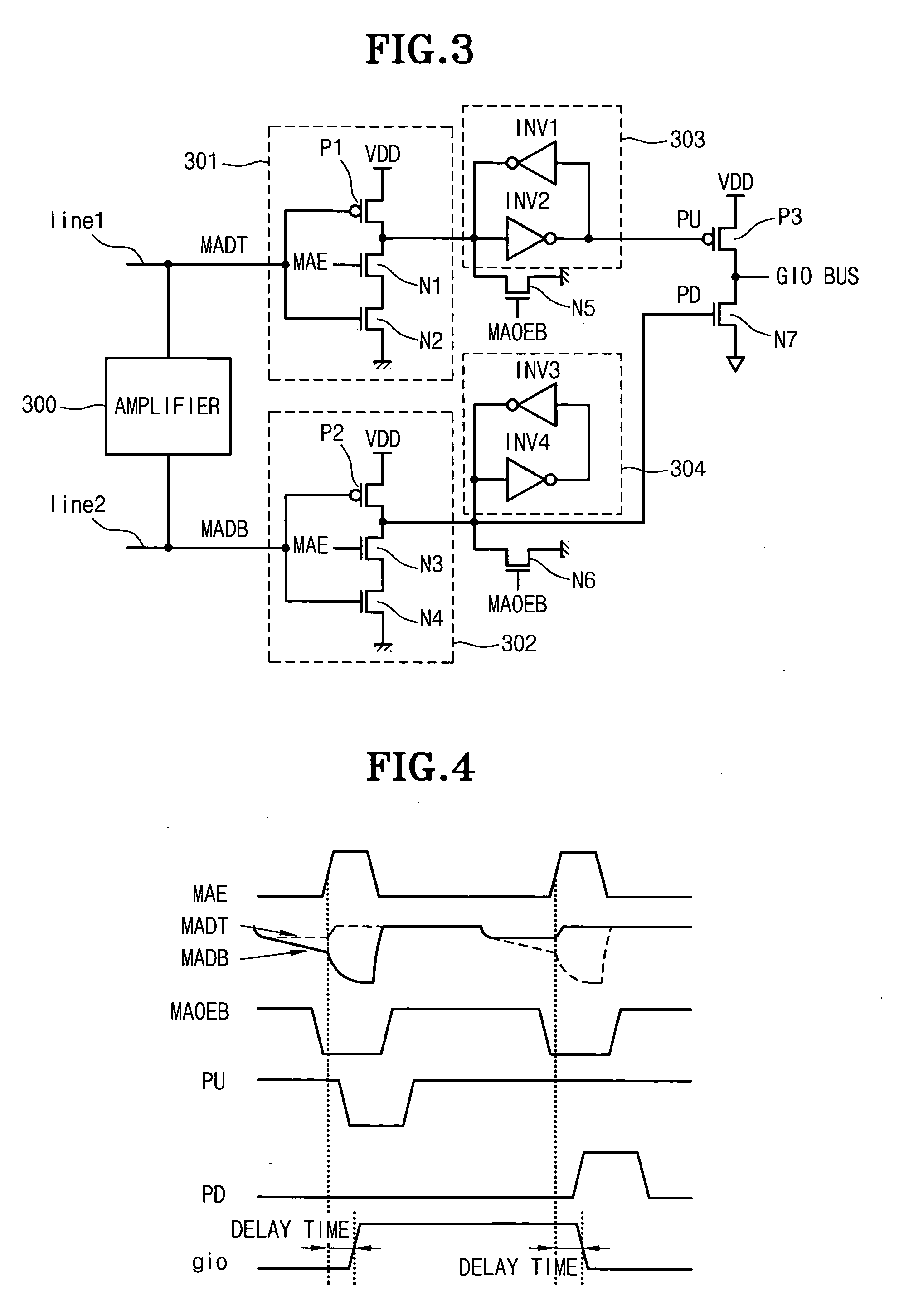

Data output apparatus for memory device

InactiveUS20050237819A1Reduce read operationsIncreased data speedOther accessoriesDigital storageCMOSBit line

The present invention relates to a data output apparatus for a memory device, and more particularly to, a data output apparatus improved a data transferring speed by re-amplifying a data amplified by a bitline sense amplifier and transferring it to global input / output lines. The data output apparatus comprises: first and second local data lines for receiving data transferred from a pair of bitlines of a memory device; an amplifier interposed between the first and second local data lines; a first CMOS buffer means for receiving data on the first local data line; a second CMOS buffer means for receiving data on the second local data line; a first latch means for holding an output signal of the first CMOS buffer means; a second latch means for holding an output signal of the second CMOS buffer means; and a pull-up transistor and a pull-down transistor coupled between a driving voltage and a ground terminal in series. Here, an output signal of the first latch means is applied to a gate of the pull-up transistor, while an output signal of the second latch means is applied to the pull-down transistor.

Owner:INTELLECTUAL DISCOVERY CO LTD

Magnetic memory and method for reading-writing information from-to magnetic storage element

InactiveUS7613034B2Increase currentReduce read operationsRecord information storageManufacture of flux-sensitive headsMagnetic memoryMagnetization

A magnetic memory is provided in which the margin between a write current and a read current can be reduced. A magnetic storage element includes: a first magnetic layer in which the direction of magnetization can be reversed; a second magnetic layer in which the direction of magnetization is fixed; and a non-magnetic layer which is interposed between the first and second magnetic layers. The write current and the read current are supplied to the magnetic storage element in the stacking direction thereof through a read-write line. Moreover, a bias line which can apply a bias magnetic field to the first magnetic layer during a reading operation is disposed in the vicinity of the magnetic storage element.

Owner:TDK CORPARATION

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com