Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

88results about How to "Timing error" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

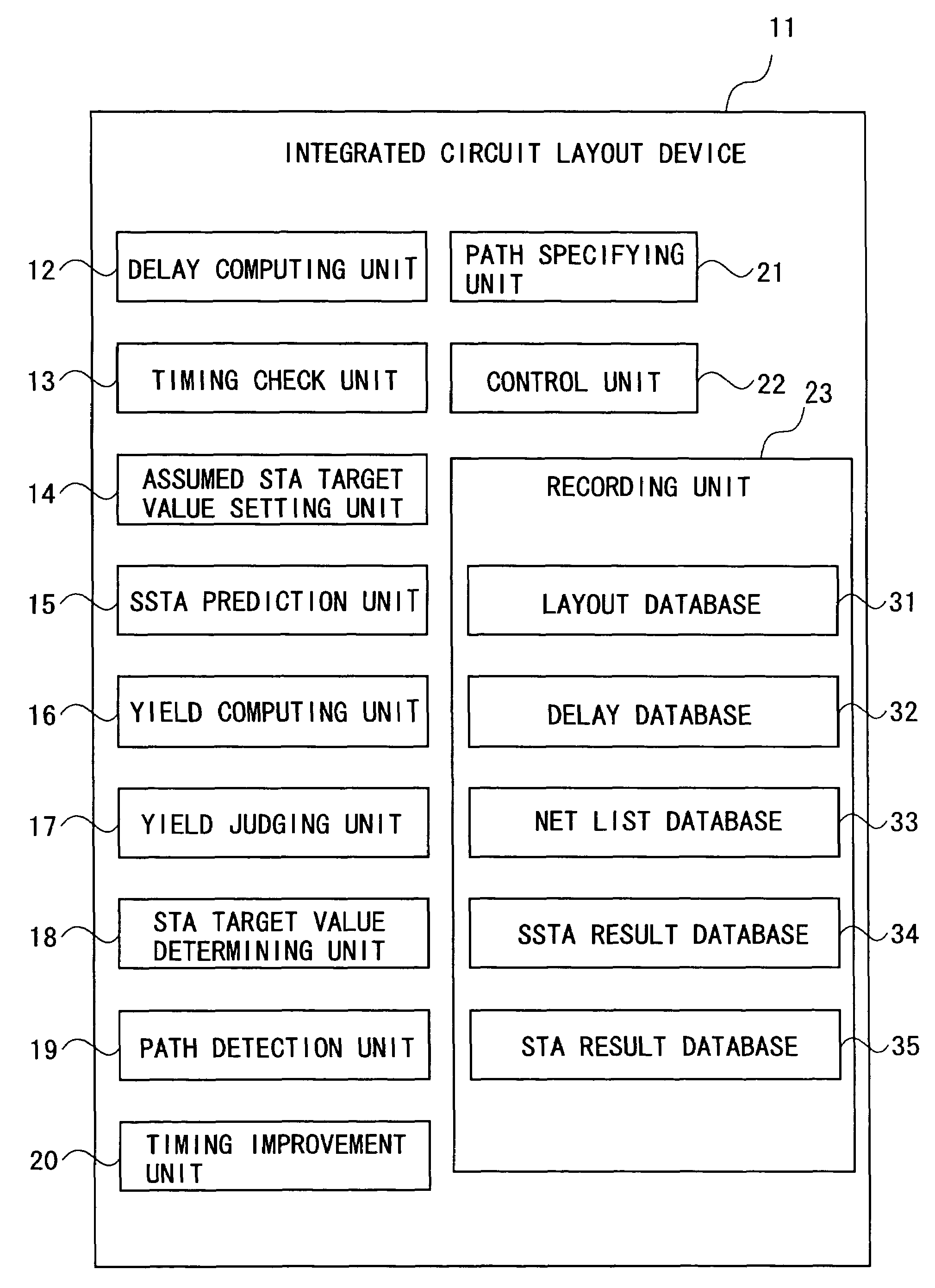

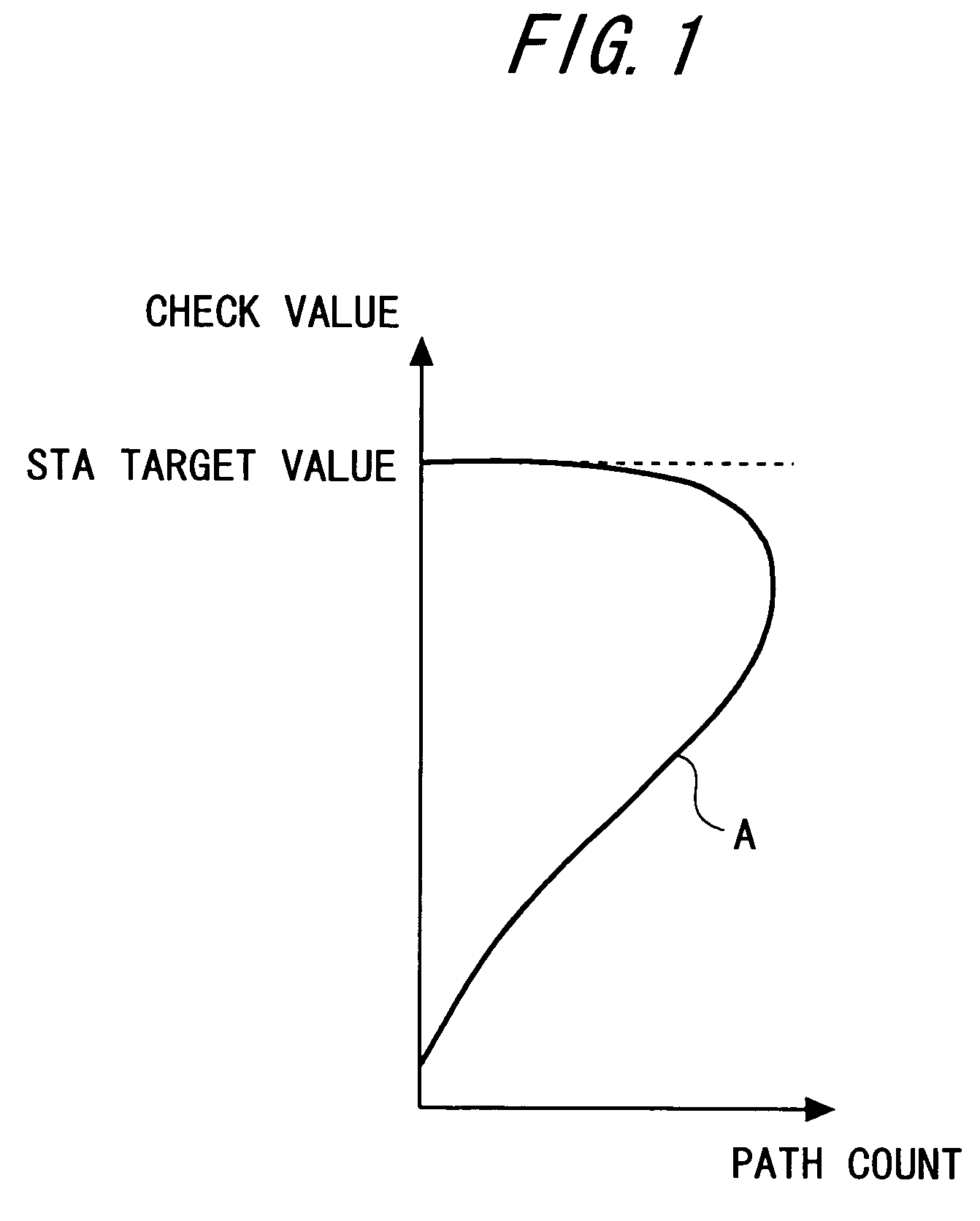

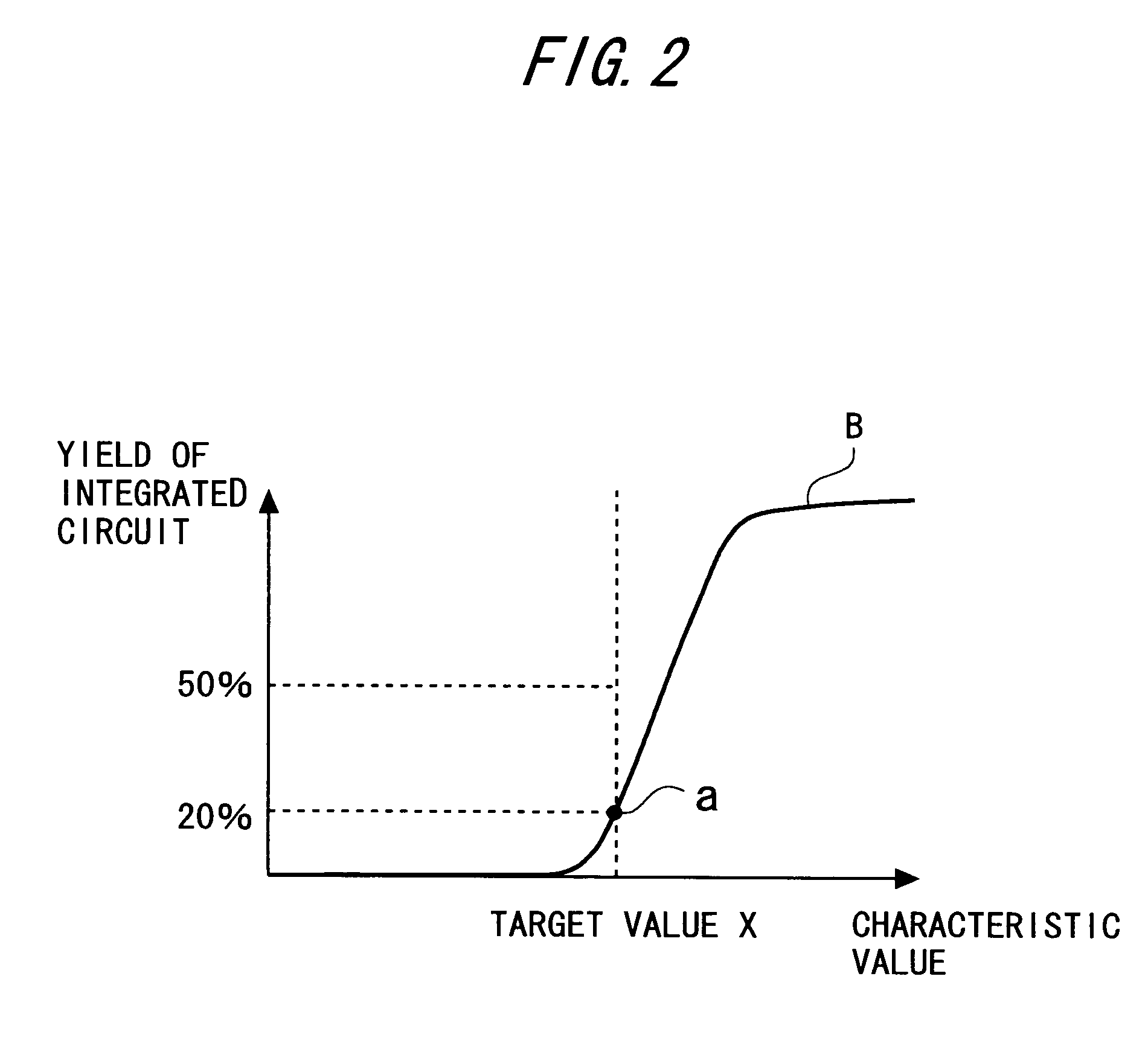

Integrated circuit layout device, method thereof and program thereof

InactiveUS7424694B2Improve timing errorExtension of timeComputer aided designSoftware simulation/interpretation/emulationEngineeringIntegrated circuit layout

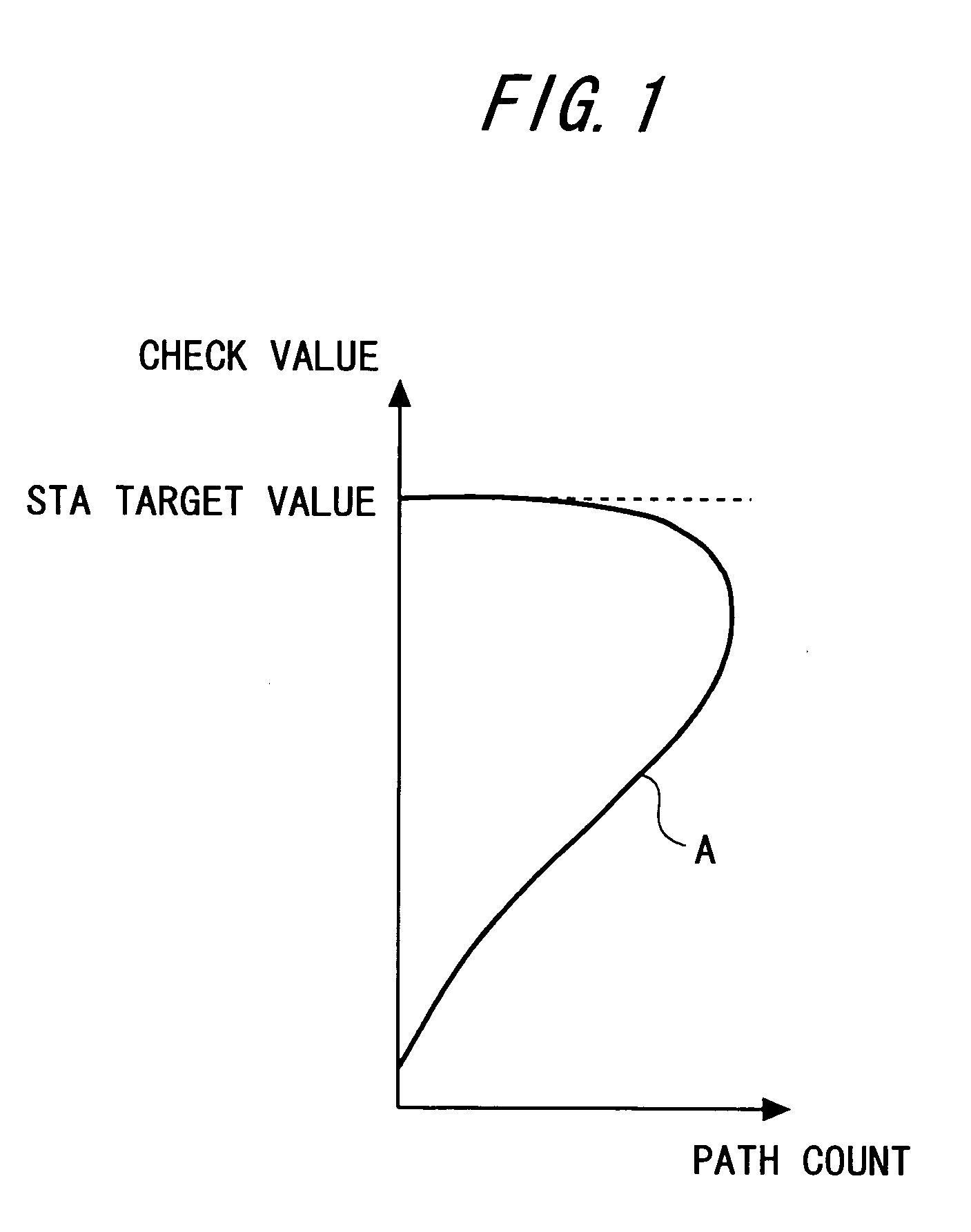

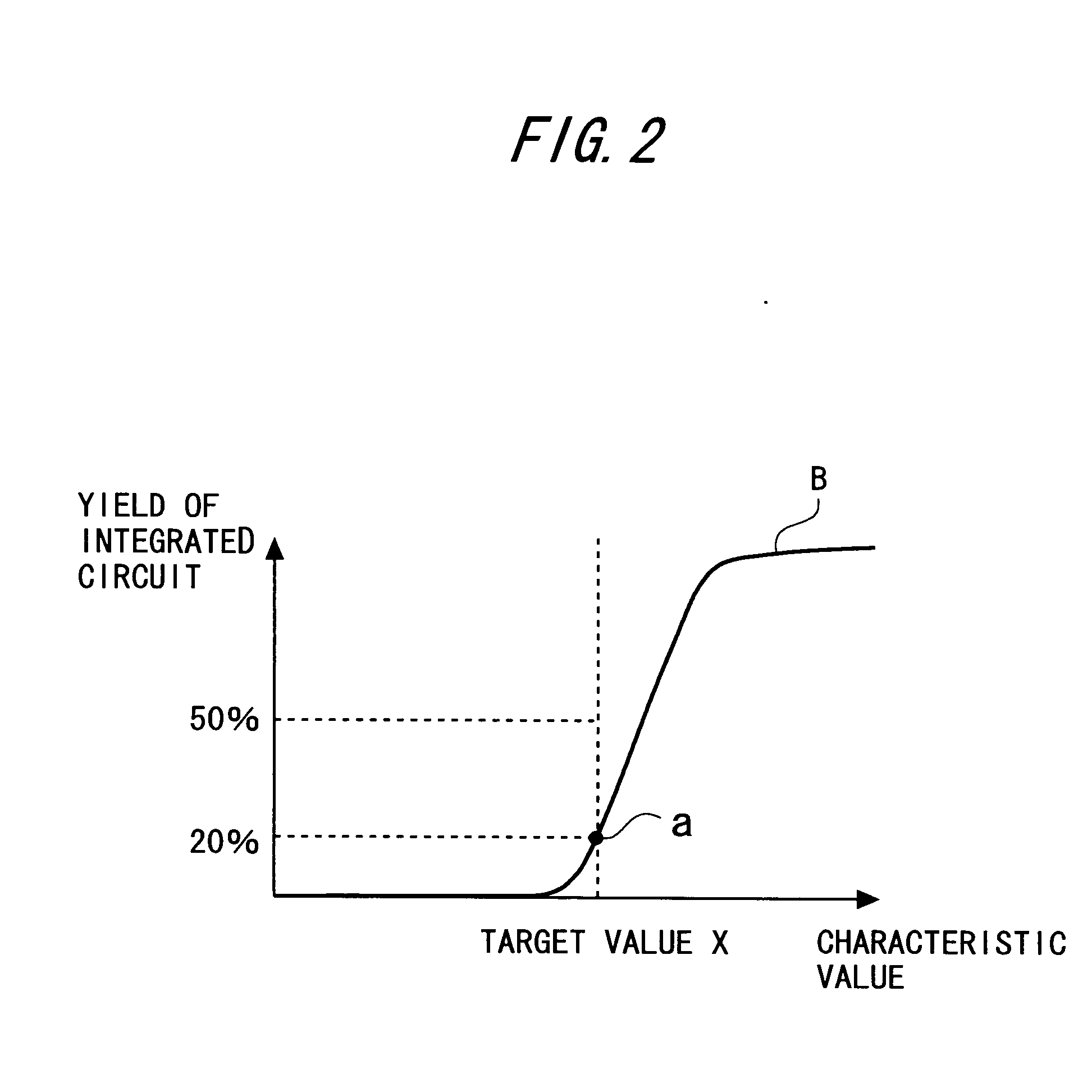

A layout device for an integrated circuit executes calculating a timing value with respect to each wiring path by a analysis based on connection information and delay information of wirings, determining a target value serving as an improvement target of the wiring path, detecting an error wiring path exhibiting the timing value larger than the target value, changing the wiring connection so that the error wiring path shows a timing value smaller than the target value, updating these piece of information into connection information and delay information of the wirings after changing the wiring connection, calculating a distribution about each wiring path by the analysis based on the post-updating connection information and the post-updating delay information of the wirings and a fluctuation factor, calculating a yield of the integrated circuit from the distribution, and judging whether or not the yield is within an allowable range of a predetermined value.

Owner:FUJITSU LTD

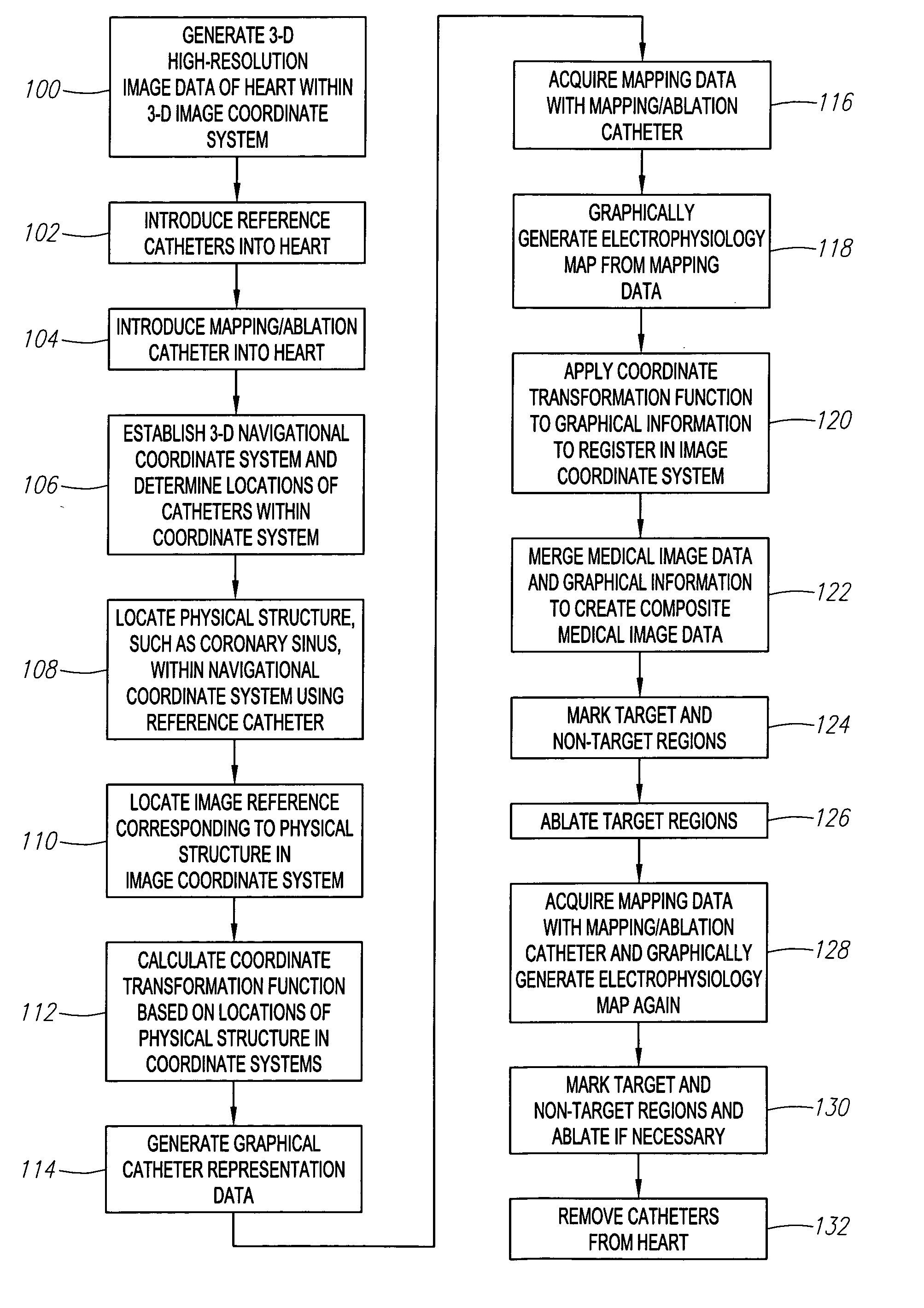

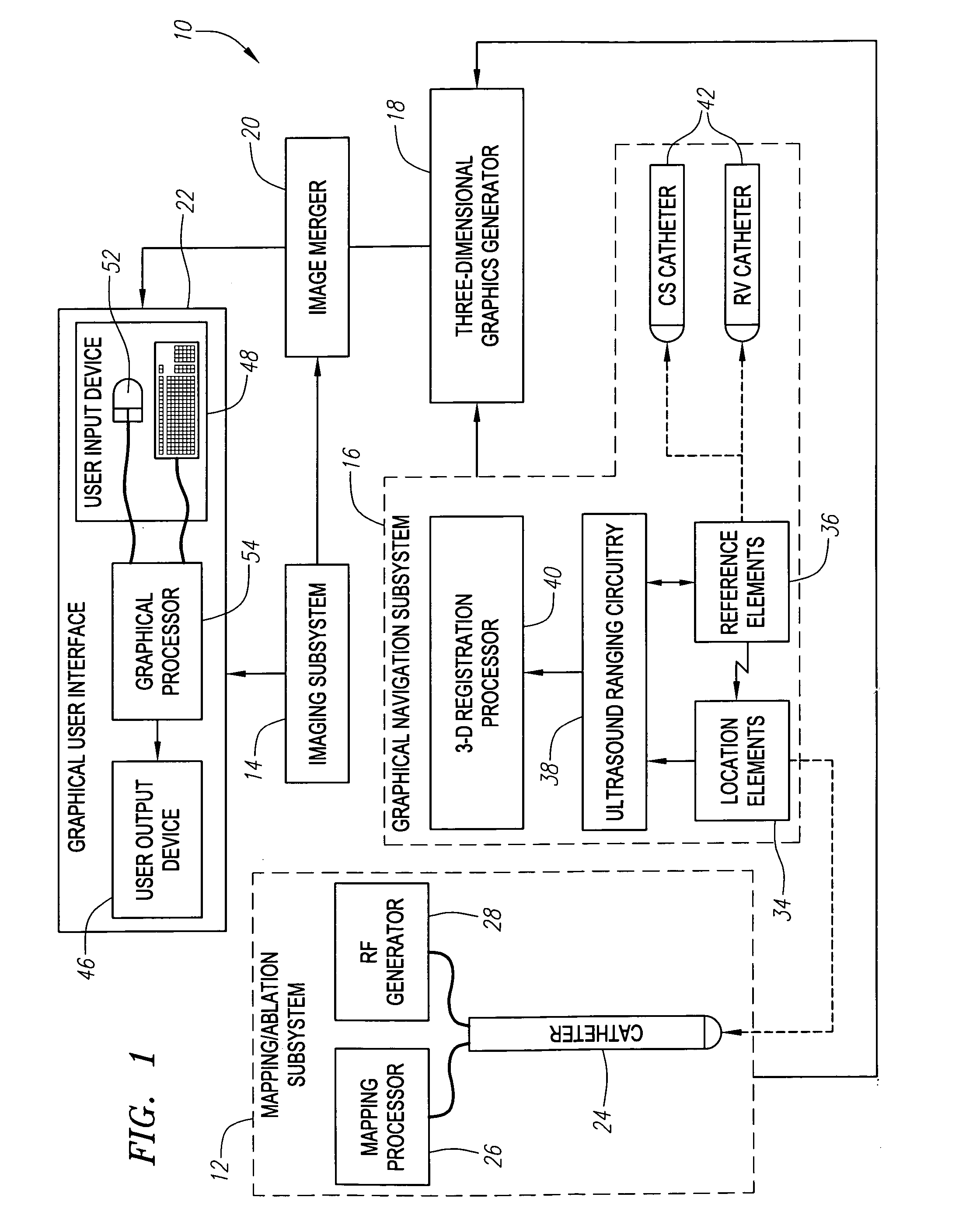

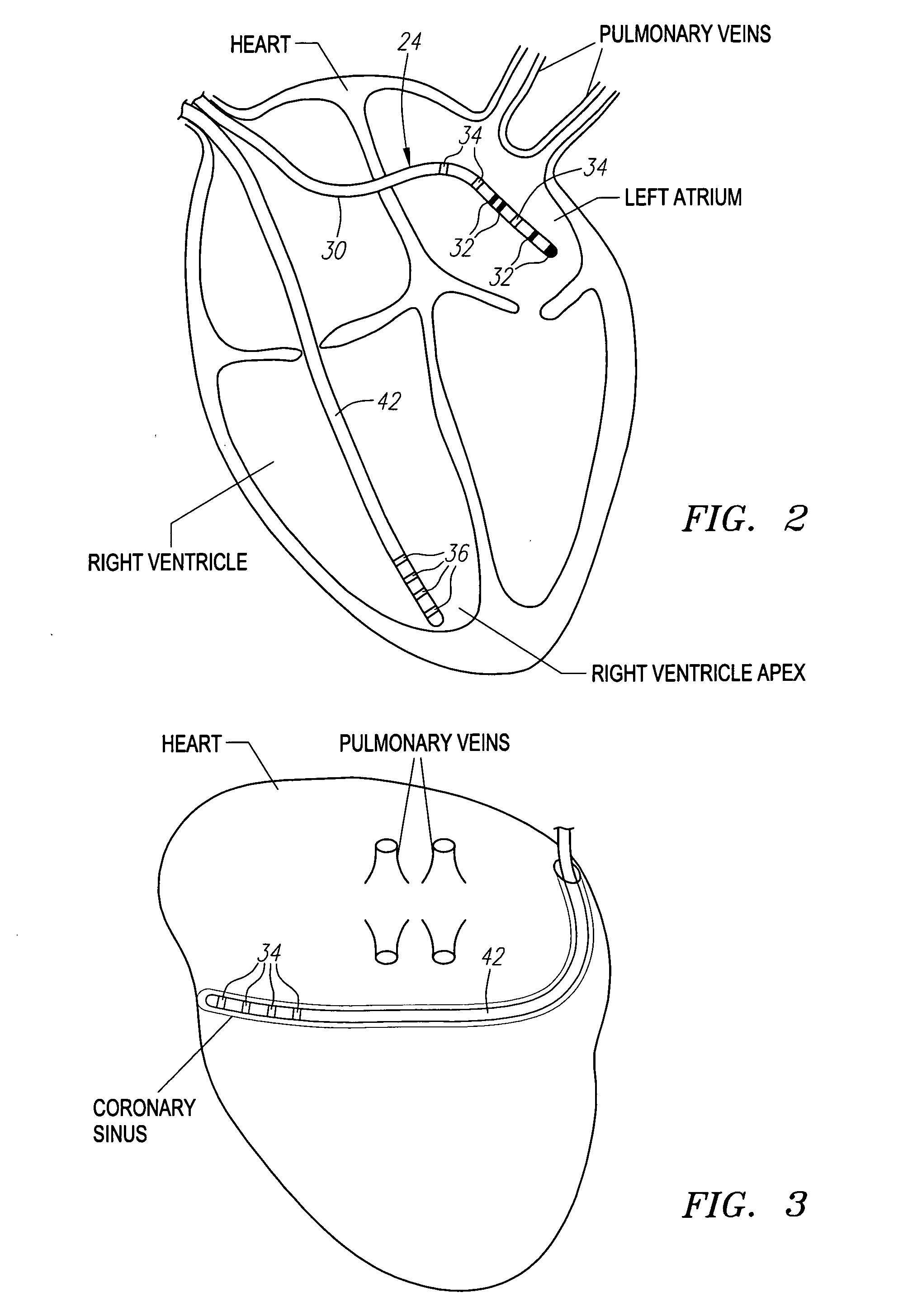

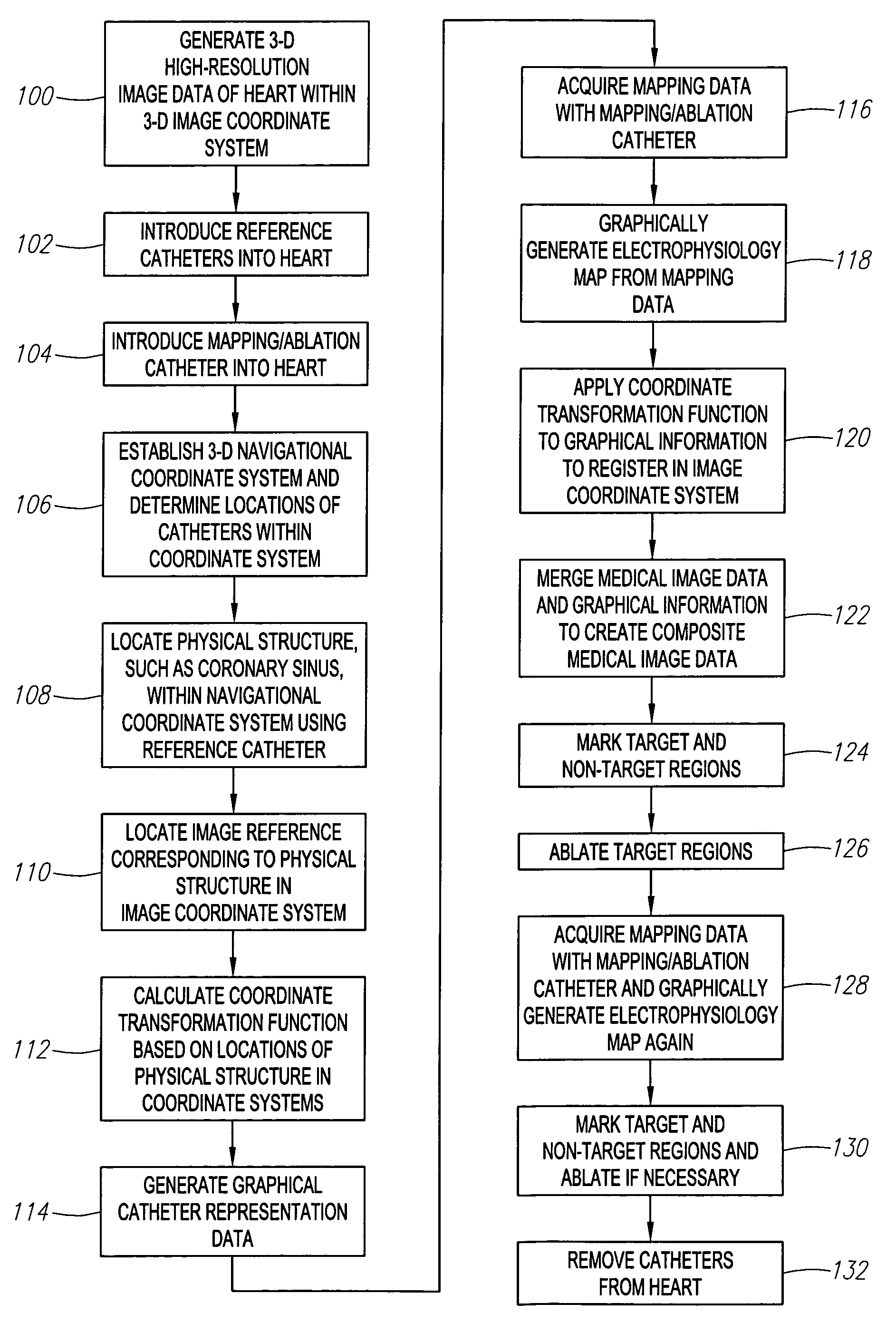

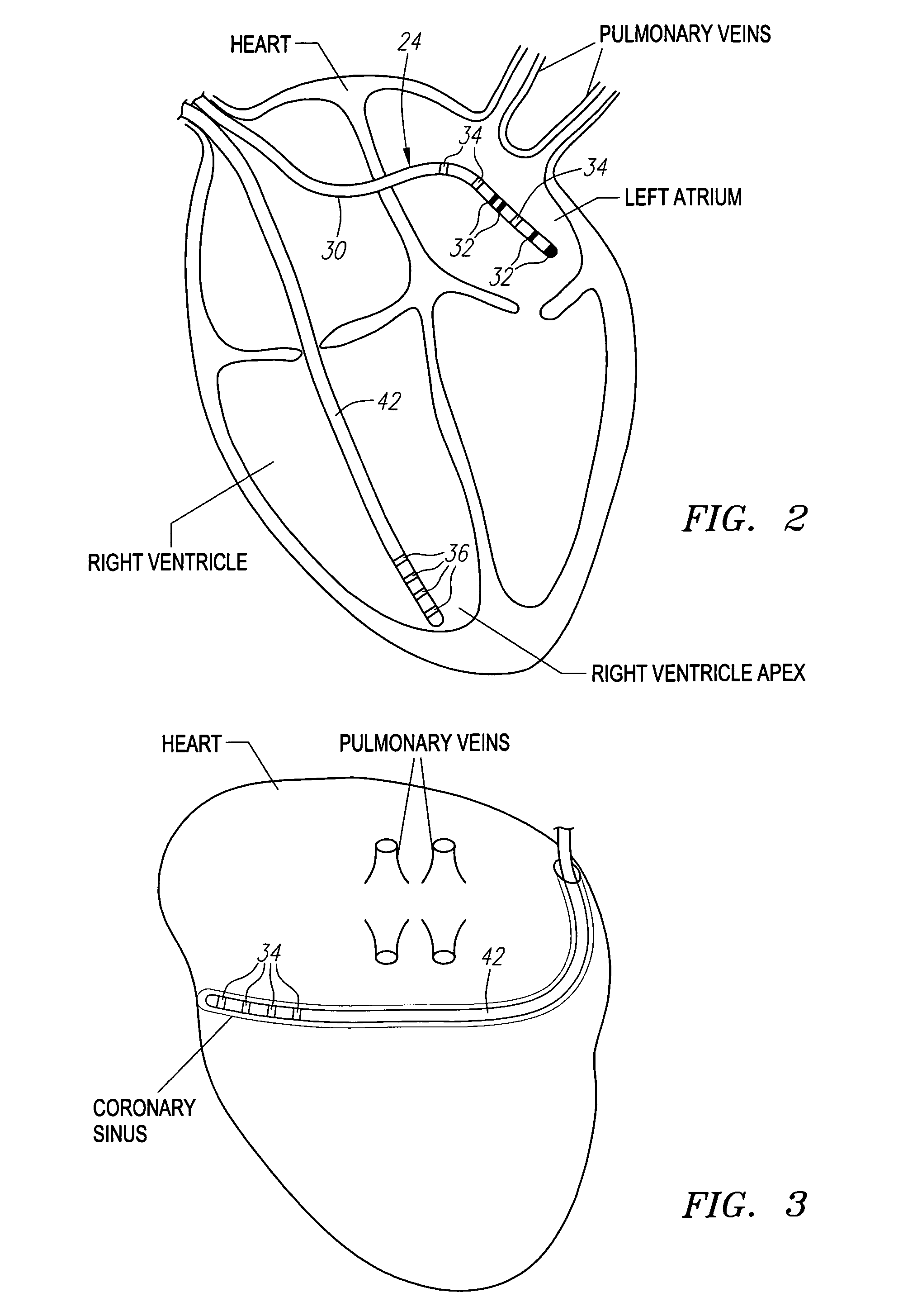

Method and system for registering an image with a navigation reference catheter

ActiveUS20060116575A1Timing errorImage data is accurateUltrasonic/sonic/infrasonic diagnosticsSurgeryGraphicsReference image

Methods and systems for processing and / or superimposing a medical image of an anatomical body (e.g., a heart) with graphical information are provided. Reference elements and / or reference catheter are placed in contact with the anatomical body. A physical structure within a navigational coordinate system is located using the reference elements and / or reference catheter. An image reference within an image coordinate corresponding to the physical structure is located. Location of the image reference can be accomplished, e.g., by displaying the medical image and electronically marking the displayed image reference, or by automatically locating image data corresponding to the image reference. The navigational and image coordinate systems are then registered based on the location of the physical structure within the navigational coordinate system and the location of the image reference within the image coordinate system, which allows graphical information to be accurately merged with the medical image data.

Owner:BOSTON SCI SCIMED INC

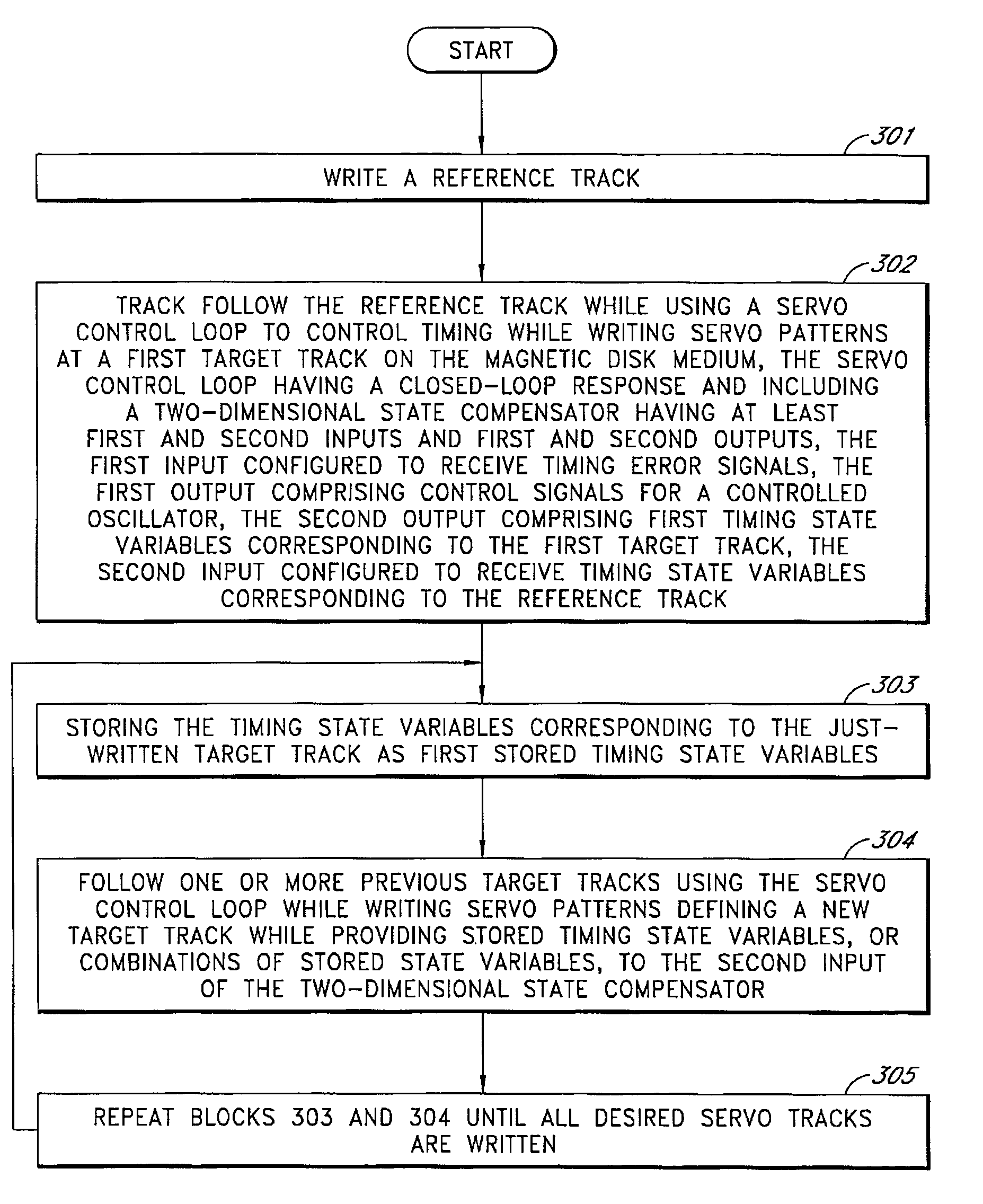

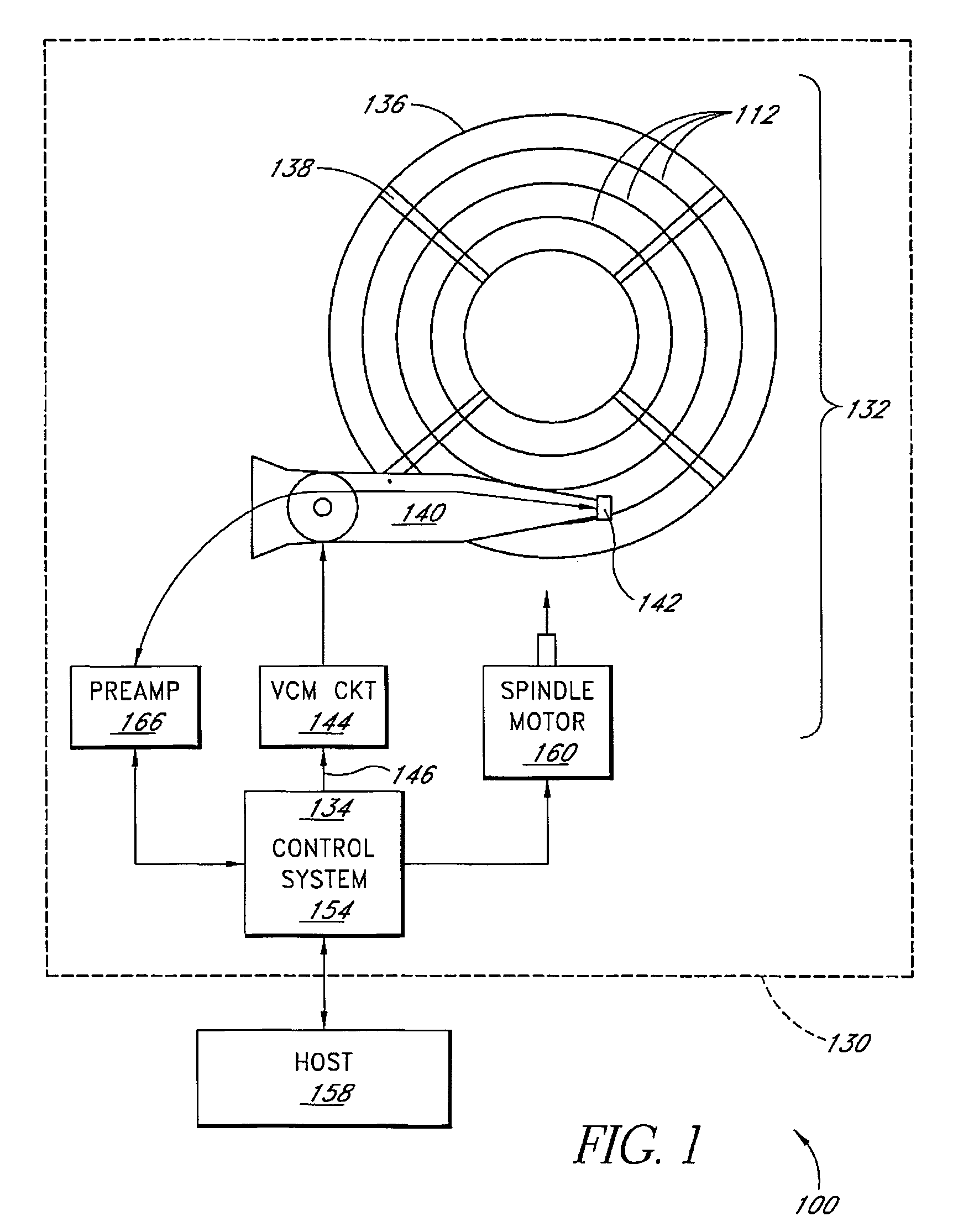

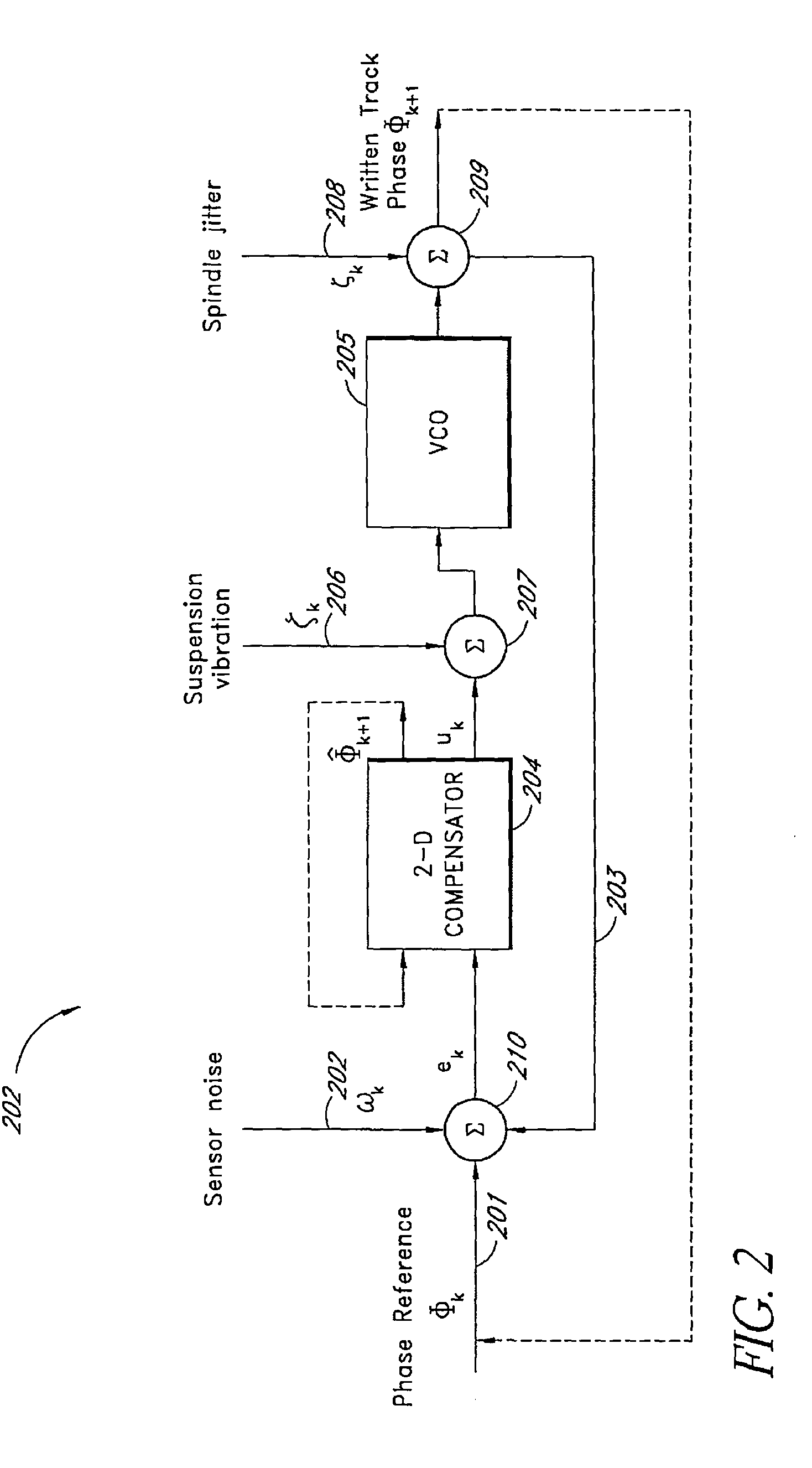

Timing compensation in a self-servowriting system

ActiveUS6924960B1Timing errorRecord information storageAlignment for track following on disksControl signalState variable

A method is disclosed for defining tracks on a rotating magnetic disk medium of a disk drive. Reference tracks are followed using a servo control loop while writing servo patterns defining a first target servo track. The servo control loop includes a two-dimensional digital state compensator having a first input that receives timing error signals, a first output that generates control signals for a controlled oscillator, a second output that generates timing state variables, and a second input that receives stored timing state variables. The first target track is followed using the servo control loop while servo patterns are written, and while the stored timing state variables corresponding to the servo patterns defining the first target track are applied to the second input.

Owner:WESTERN DIGITAL TECH INC

Method and system for registering an image with a navigation reference catheter

ActiveUS7720520B2Image data is accurateTiming errorUltrasonic/sonic/infrasonic diagnosticsSurgeryGraphicsMarine navigation

Methods and systems for processing and / or superimposing a medical image of an anatomical body (e.g., a heart) with graphical information are provided. Reference elements and / or reference catheter are placed in contact with the anatomical body. A physical structure within a navigational coordinate system is located using the reference elements and / or reference catheter. An image reference within an image coordinate corresponding to the physical structure is located. Location of the image reference can be accomplished, e.g., by displaying the medical image and electronically marking the displayed image reference, or by automatically locating image data corresponding to the image reference. The navigational and image coordinate systems are then registered based on the location of the physical structure within the navigational coordinate system and the location of the image reference within the image coordinate system, which allows graphical information to be accurately merged with the medical image data.

Owner:BOSTON SCI SCIMED INC

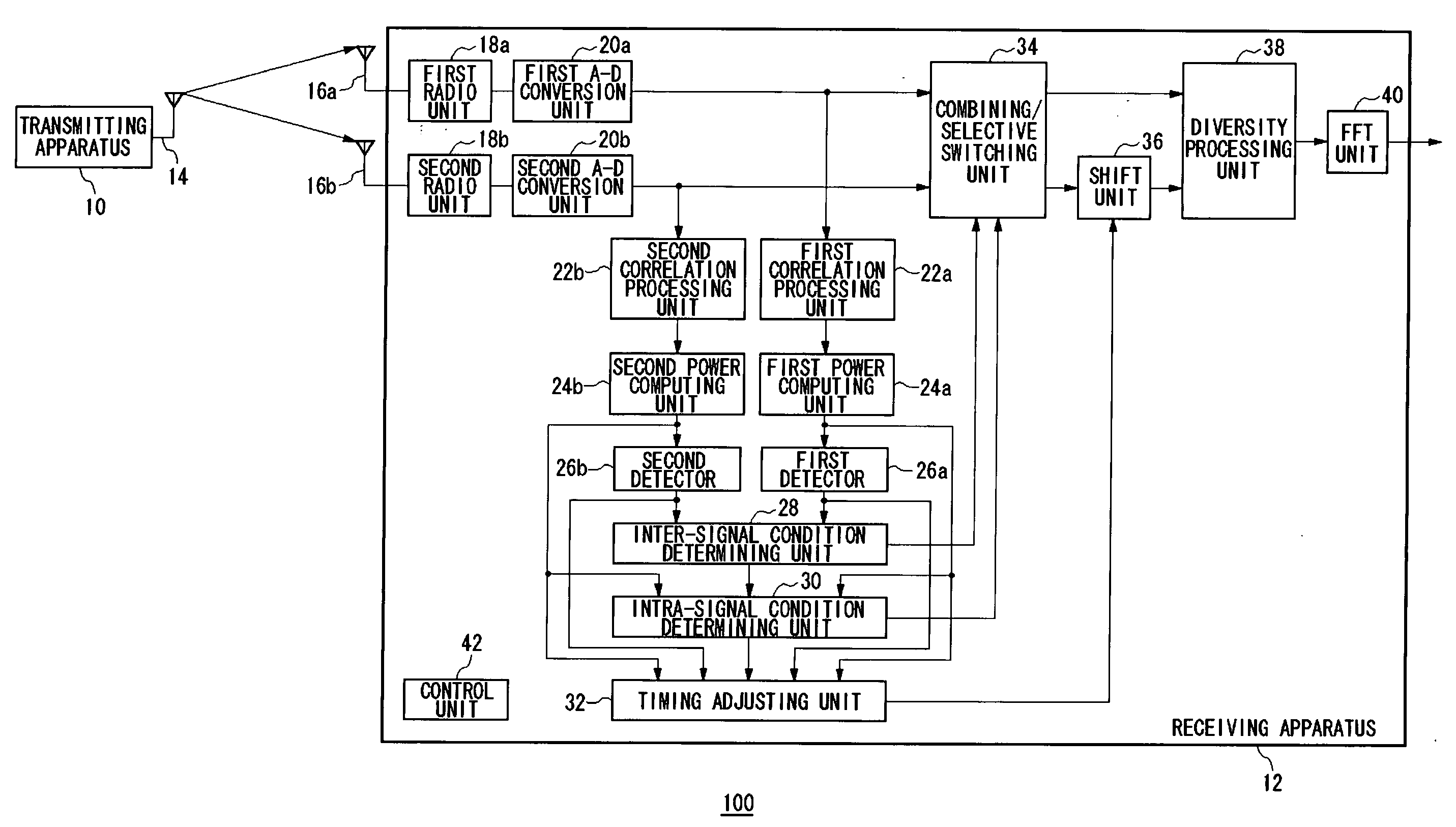

Timing-adjusting method and apparatus, and diversity receivign method and apparatus

InactiveUS20050163261A1Excellent characteristicsLittle timeSpatial transmit diversityPolarisation/directional diversityEngineeringPeak value

An A-D conversion unit performs analog-to-digital conversions on baseband signals. A correlation processing unit carries out a correlation processing. A power computing unit computes the power of correlation values. An inter-signal condition determining unit compares a relationship between the peak of a main signal and the peak of sub-signals to a first condition, and excludes, from combining diversity, baseband signals corresponding to the sub-signals if the relationship does not satisfy the first condition. An intra-signal condition determining unit 30 compares the main signals and sub-signals to a second condition, respectively, and excludes signals from combining diversity if the signals do not satisfy the second condition. A timing adjusting unit adjusts the timing of sub-signals so that the timing thereof comes close to the timing of the main signal. A shift unit shifts the timing of sampled signals corresponding to the sub-signals.

Owner:HERA WIRELESS

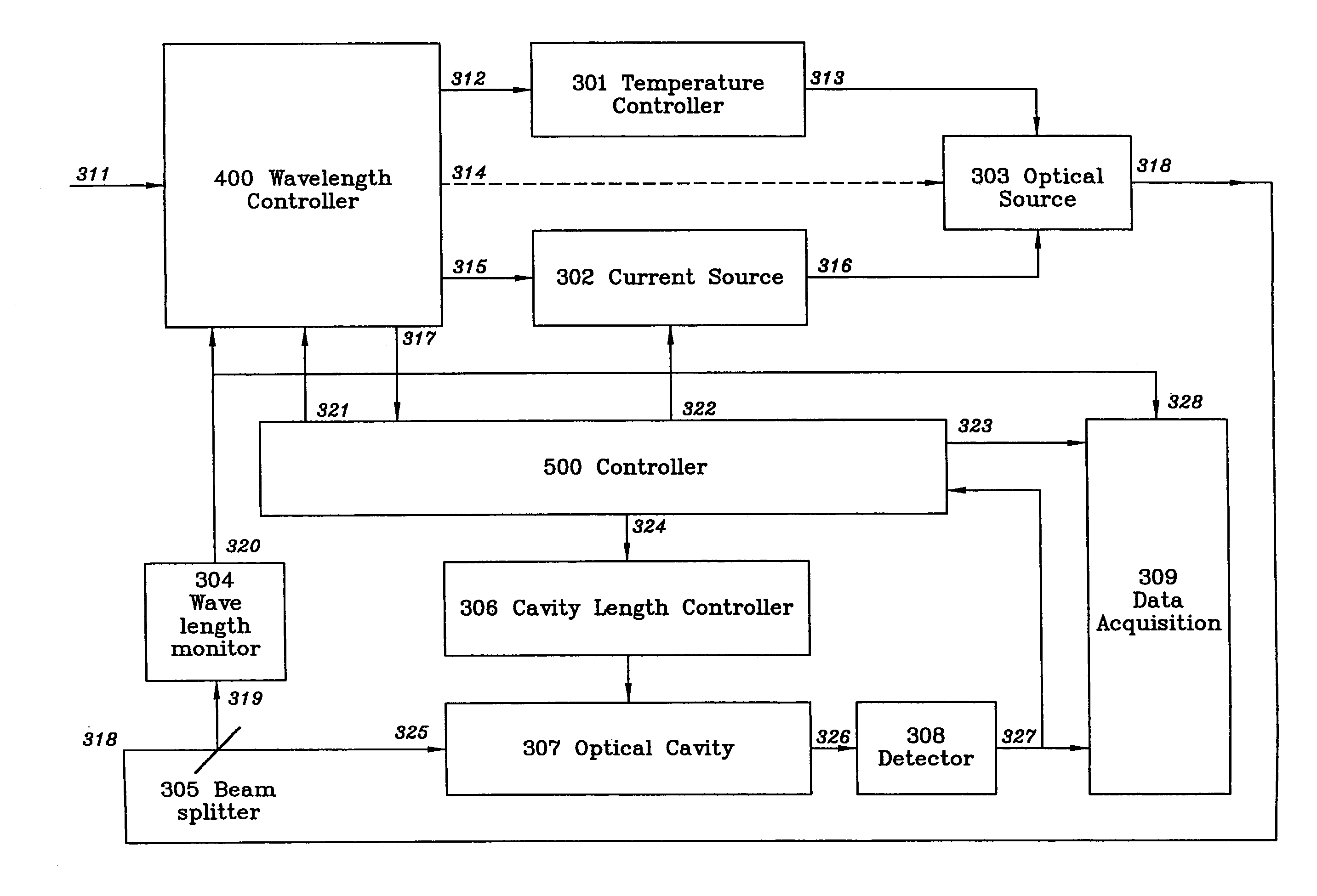

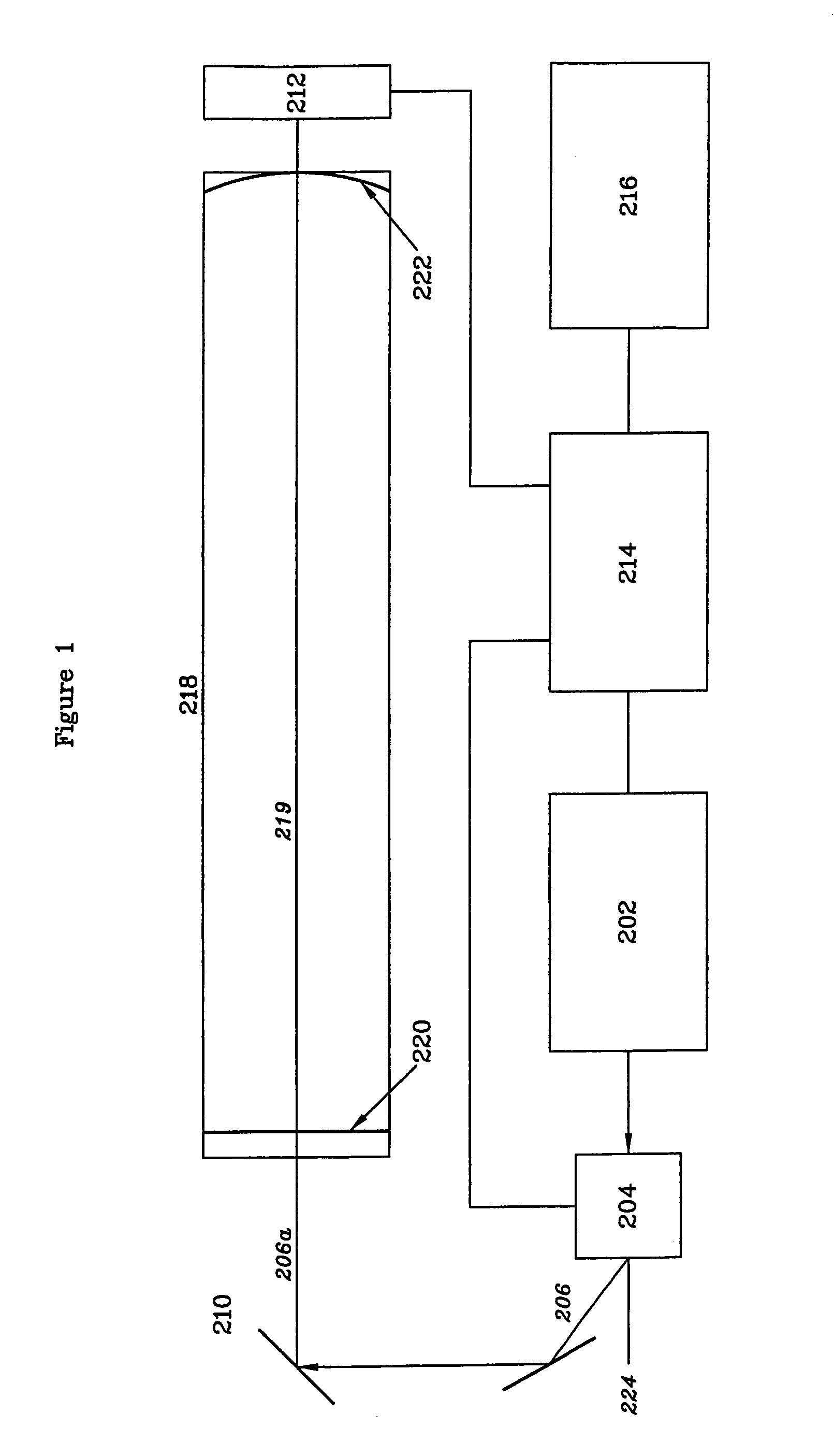

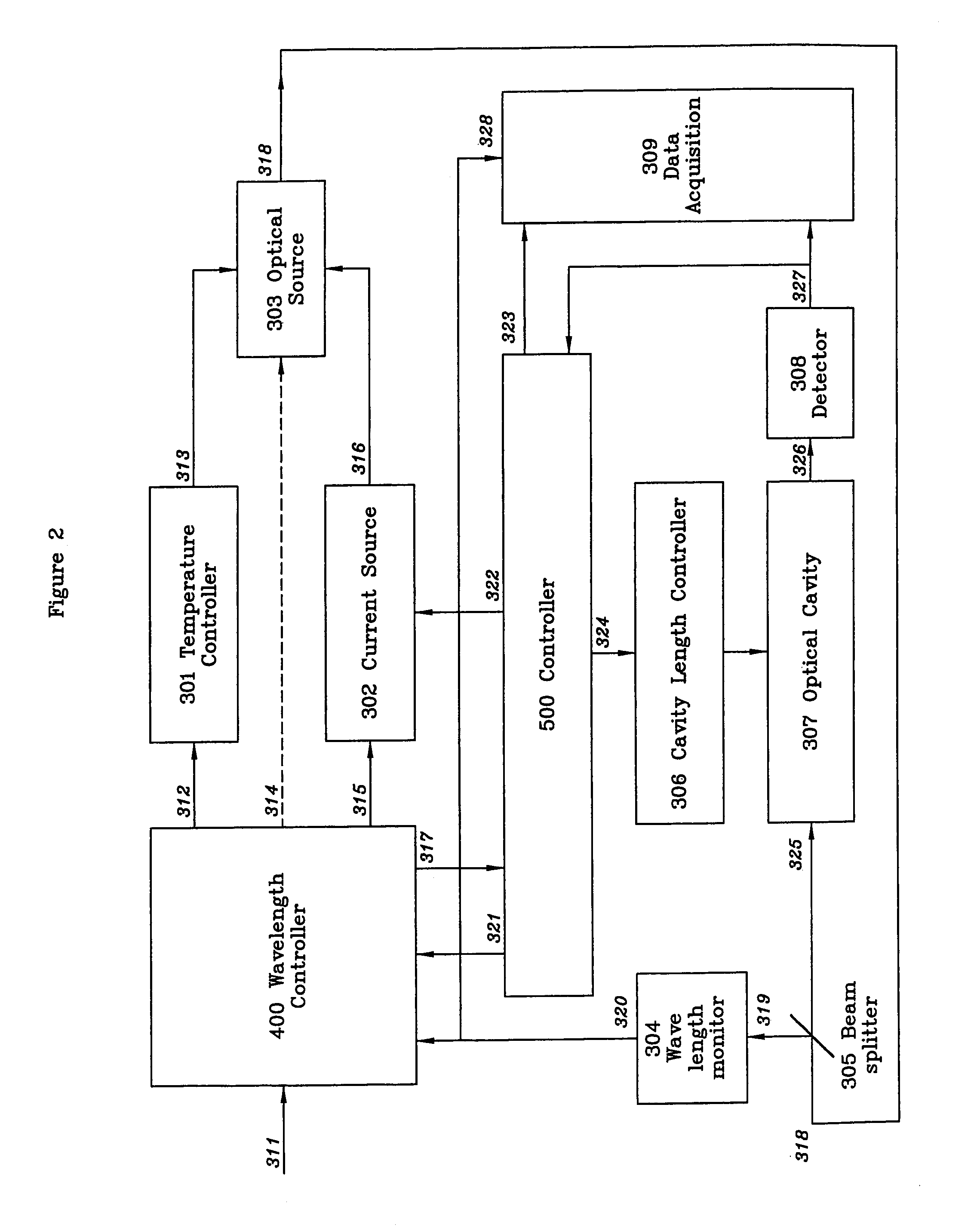

Wavelength control for cavity ringdown spectrometer

ActiveUS7106763B2Easy to controlShort response timeLaser detailsTransmissivity measurementsTarget analysisRing down

A cavity ring-down spectrometer includes:a) multiple detectors for monitoring the intensity of the radiation emitted from the cavity and the wavelength of the radiation injected into the cavity;b) controllers which turn off the radiation into the cavity and precisely adjust the temperature of, and current to, the laser gain medium; andc) means for adjusting the beam path length of the optical cavit to bring the cavity into resonance with the injected radiation. Additionally, disclosed is a method for using the spectrometer to detect a target analyte.

Owner:PICARRO

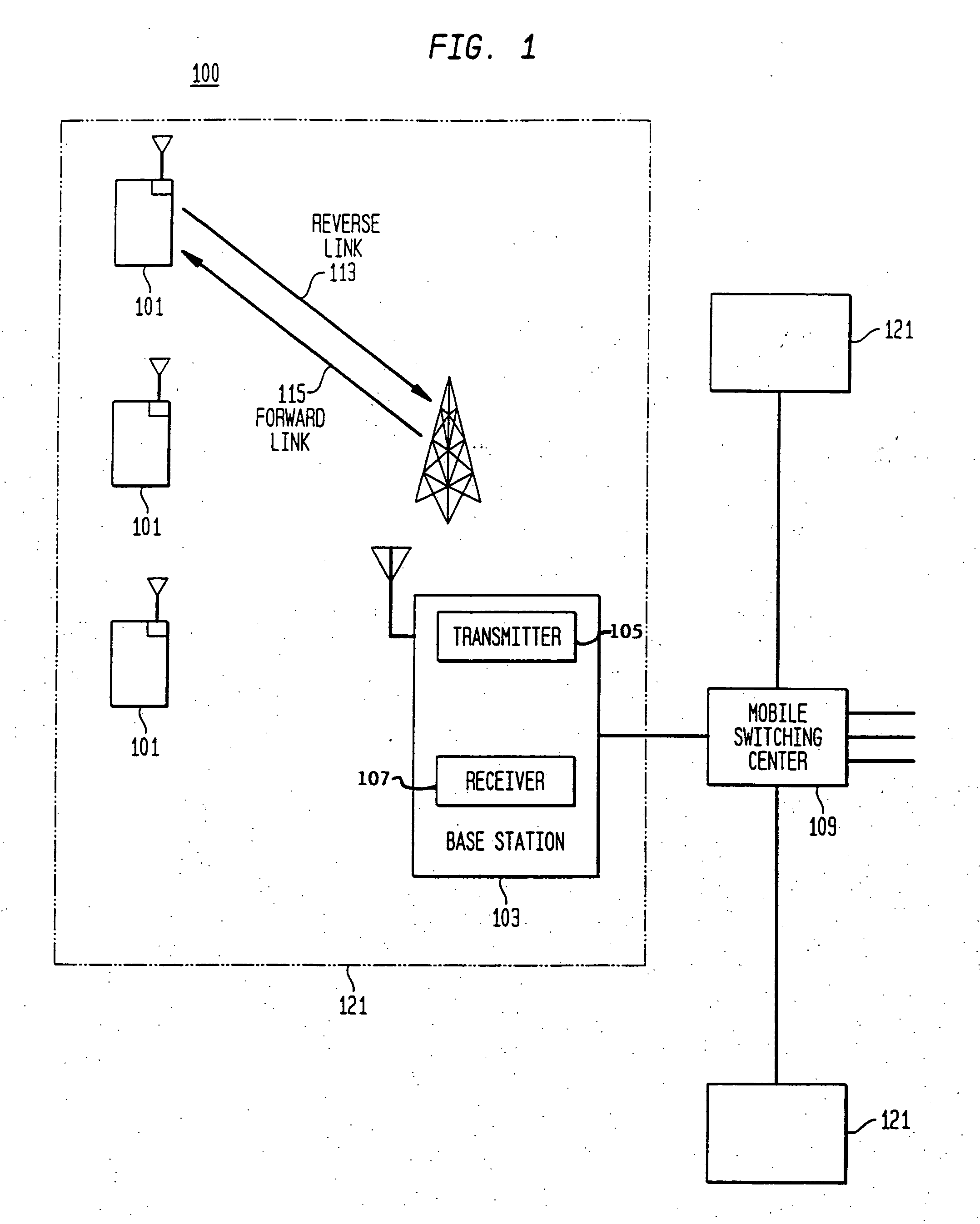

System and method for narrowing the range of frequency uncertainty of a doppler shifted signal

InactiveUS6249539B1Reduce the impactTiming error magnitudeModulated-carrier systemsBeacon systemsCommunications systemHypothesis

A system and method for narrowing the range of frequency uncertainty of a Doppler shifted pilot signal in a satellite or other communications system with relative signal source and receiver motion. The satellite communications system includes a user terminal (for example, a mobile wireless telephone), a gateway (terrestrial base station), and at least one satellite with unknown position and unknown relative velocity. The method includes the steps of shifting the pilot signal over a plurality of frequency hypotheses, coherently accumulating samples of the pilot signal over a plurality of chips, measuring the energy of the accumulated pilot signal samples, accumulating the energy measurements over a plurality of chips to produce an energy accumulation value, and determining which of the plurality of frequency hypotheses results in the highest energy accumulation value.

Owner:QUALCOMM INC

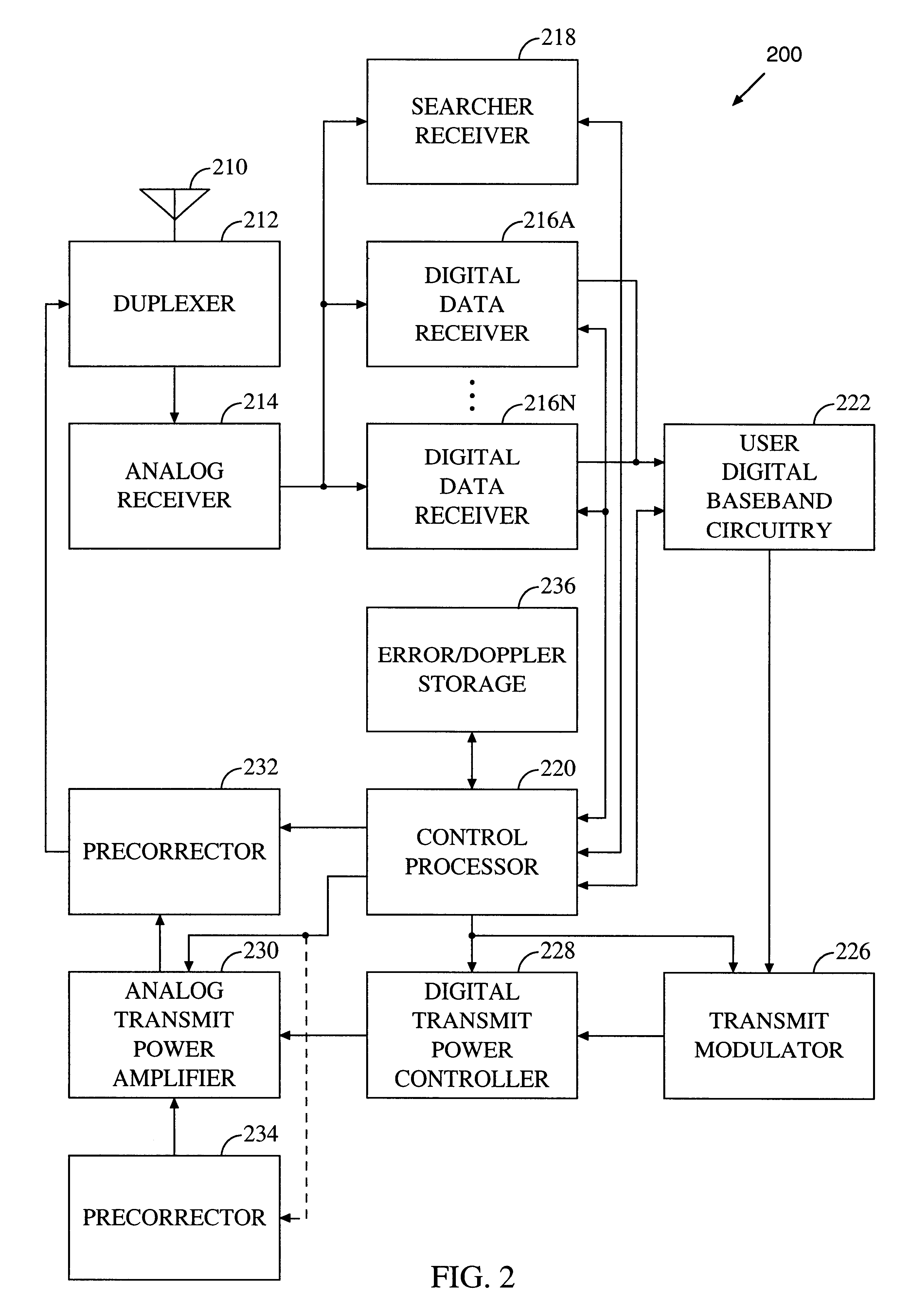

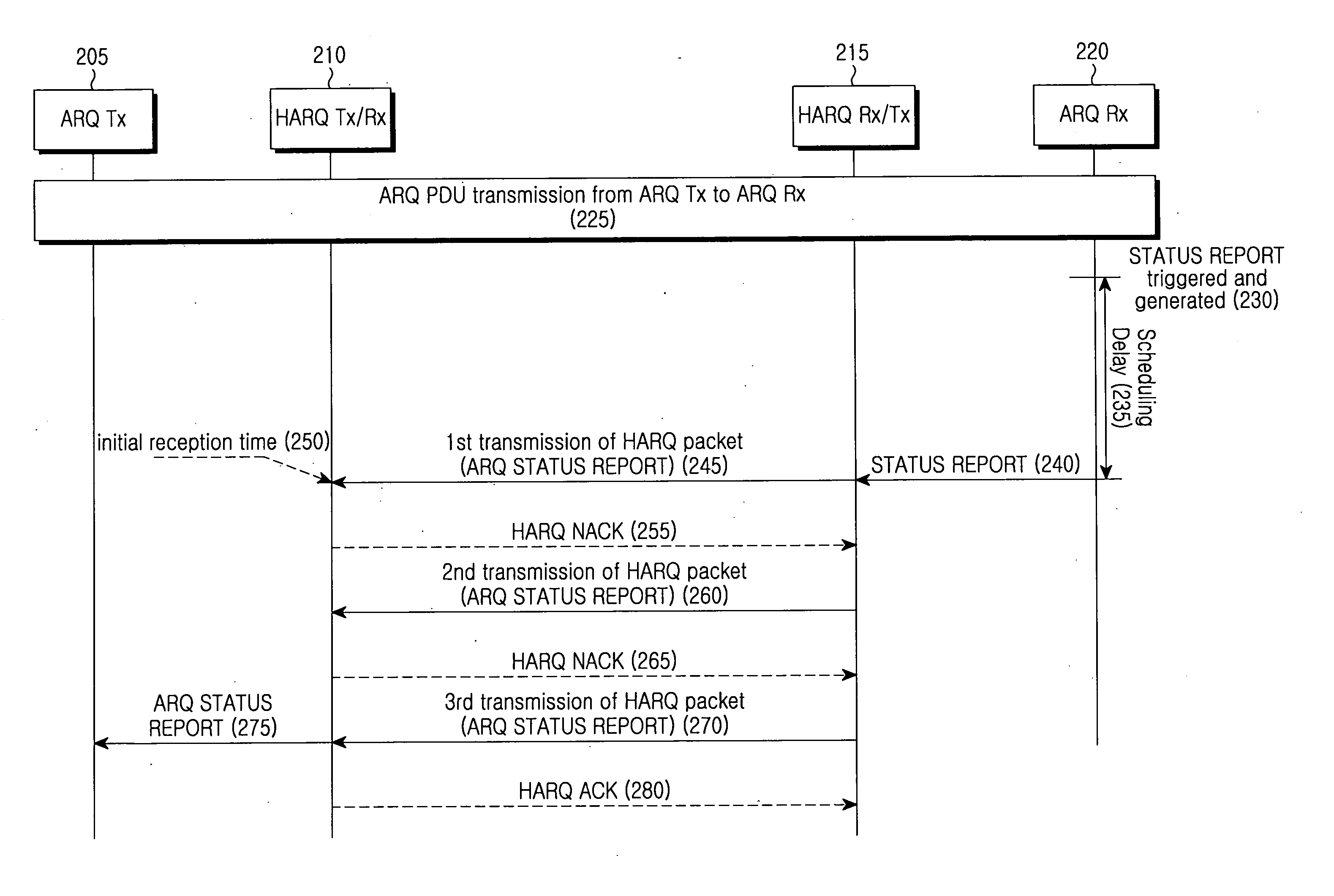

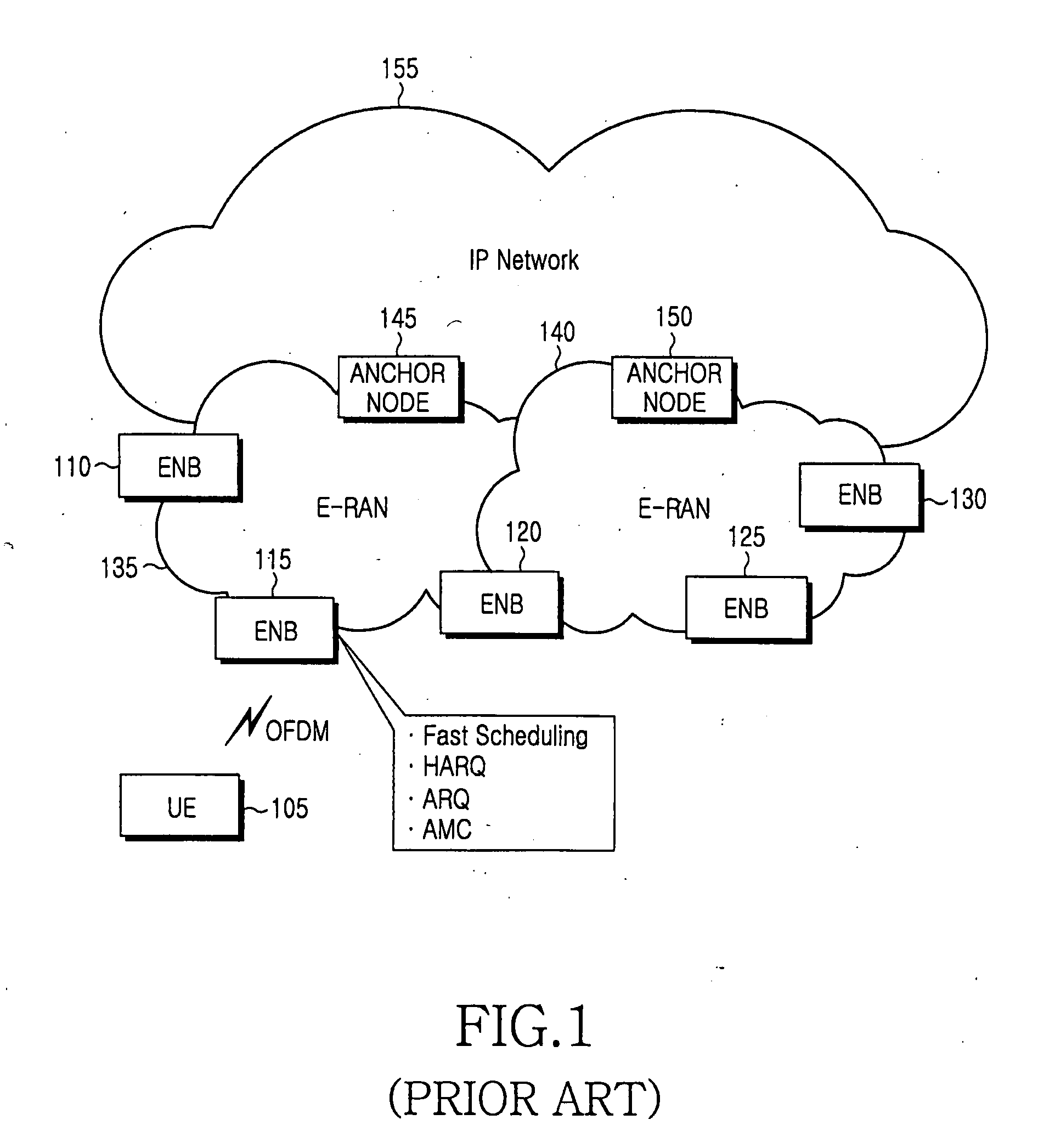

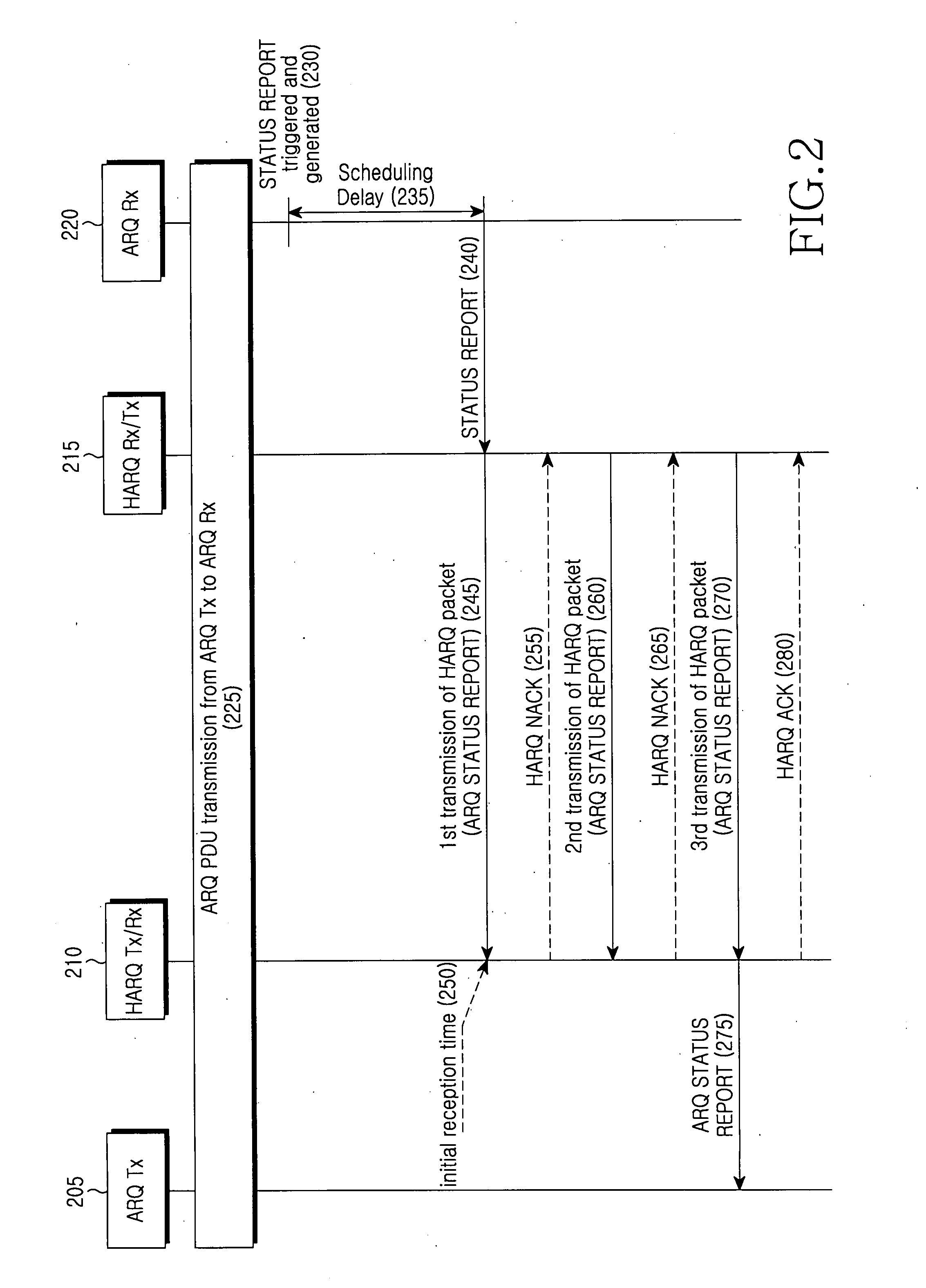

Method and apparatus for transmitting and receiving status report in a mobile communication system

ActiveUS20070283032A1Timing errorError prevention/detection by using return channelMultiple digital computer combinationsAutomatic repeat requestMobile communication systems

A method and apparatus for transmitting / receiving a status report in a mobile communication system where Automatic Repeat reQuest (ARQ) and Hybrid Automatic Repeat reQuest (HARQ) operate together. An ARQ receiving (Rx) entity determines whether transmission of the status report is permitted, if a predetermined status report generation condition is satisfied. If the transmission of the status report is permitted, the ARQ Rx entity generates a status report depending on a reception status of ARQ packets received up to the time the transmission of the status report is permitted, and transmits the generated status report to an ARQ transmitting (Tx) entity through an allocated transmission resource. The ARQ Tx entity determines an initial reception time of an HARQ packet including the status report as a generation time of the status report, and performs retransmission according to the status report.

Owner:SAMSUNG ELECTRONICS CO LTD

Run-time error repairing method, device and system

ActiveUS20150193296A1Timing errorPromote repairNon-redundant fault processingClient-sideError identification

Various embodiments of the present disclosure describe a method, device, and system for repairing run-time errors. The method includes at a client side, obtaining dump file information and version information of an application where a run-time error occurs; calculating the obtained dump file information and version information according to a preset algorithm to get an error identification associated with the run-time error; sending an error report carrying the error identification to an error information acquisition server; receiving a repair application issued by the error information acquisition server according to the error identification; and activating the repair application to perform repairing. When embodiments of the present disclosure are employed, the time required for repairing application run-time errors can be reduced.

Owner:TENCENT TECH (SHENZHEN) CO LTD

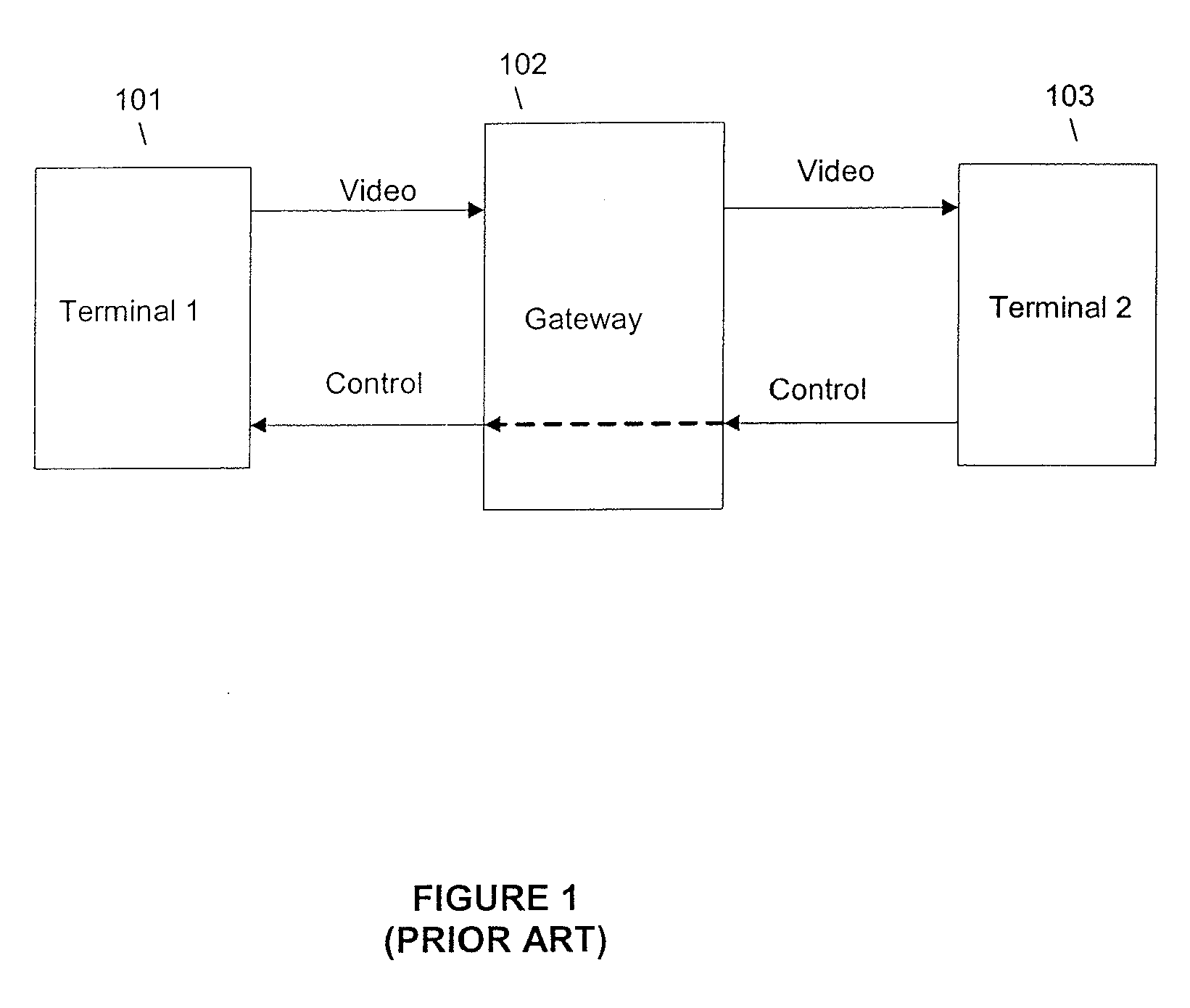

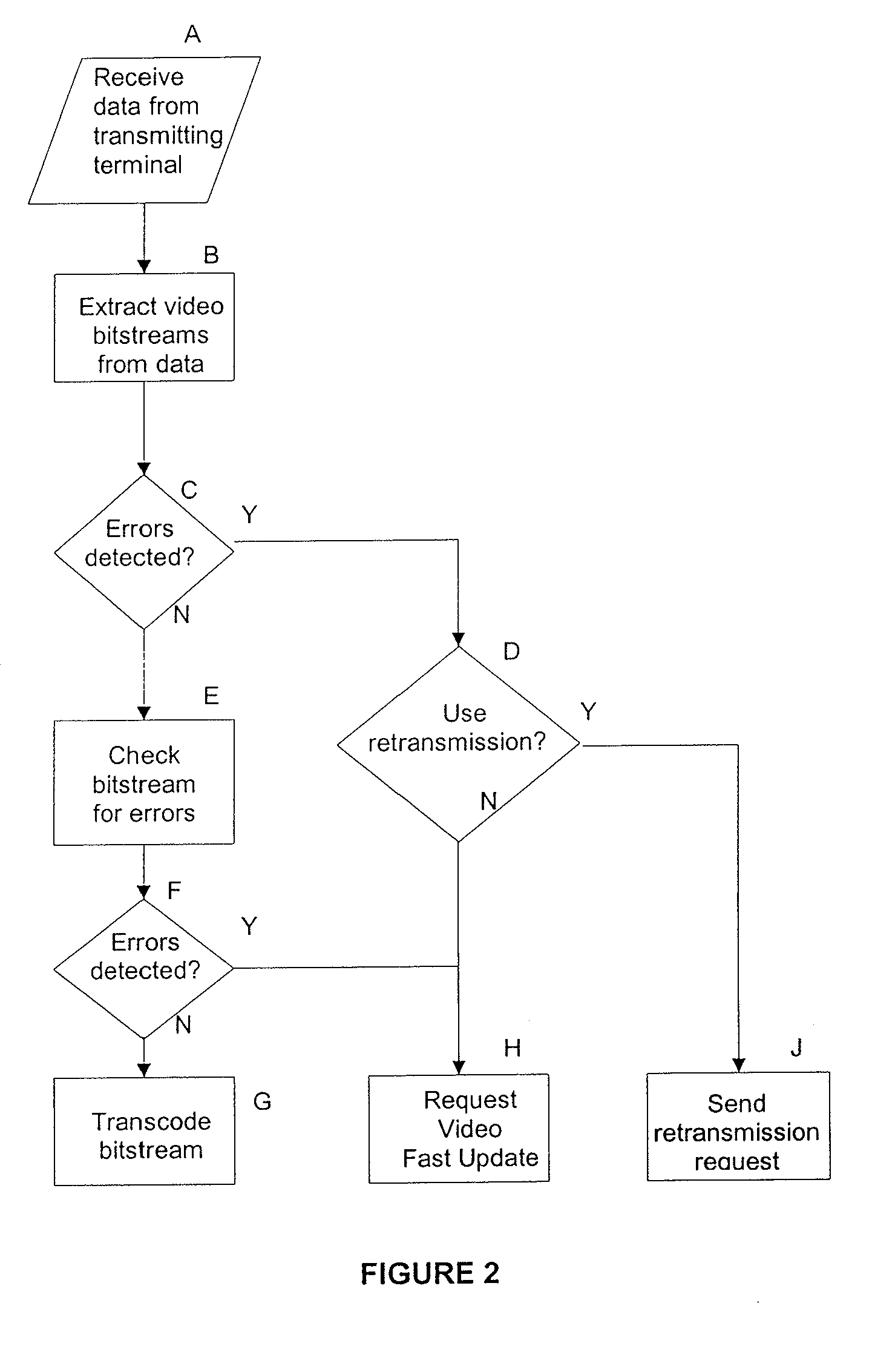

Method and apparatus for handling video communication errors

InactiveUS20090097563A1Function increaseMinimize durationPulse modulation television signal transmissionPicture reproducers using cathode ray tubesVideo bitstreamError processing

A method for handling video bitstream errors in a multimedia gateway device wherein a gateway device detects errors in the incoming video bitstream and sends a signal to the originating device to refresh the bitstream without need of error detection from an end terminating device. When the terminating device signals for the video bitstream to be refreshed, the gateway locally generates and transmits an appropriate refresh frame. The invention allows the gateway to handle errors for devices such as streaming and message servers that have no built-in error handling.

Owner:DILITHIUM NETWORKS PTY LTD

Repeatable timing error correction system for use in a servo writer

InactiveUS7199959B1Minimize timing errorMinimize repeatable timing errorDriving/moving recording headsRecord information storageTiming errorDirect digital synthesizer

A servo writing system for writing servo sectors onto a disk includes a direct digital synthesizer (DDS) that forms a phase and frequency adjustable continuous wave signal based upon a reference digital clock signal. A PLL coupled to the DDS measures repeatable timing errors (RTEs) associated with the continuous wave signal and generates an output clock signal that is used to clock the writing of servo sectors onto the disk. A digital control system is coupled to the DDS and the PLL, which calculates repeatable error compensation adjustment values based on the RTEs measured using the PLL. The compensation adjustment values may be applied to the DDS such that the DDS compensates for the RTEs and such that the output clock signal used to clock the writing of the servo sectors onto the disk includes minimal RTEs.

Owner:WESERN DIGITAL TECH

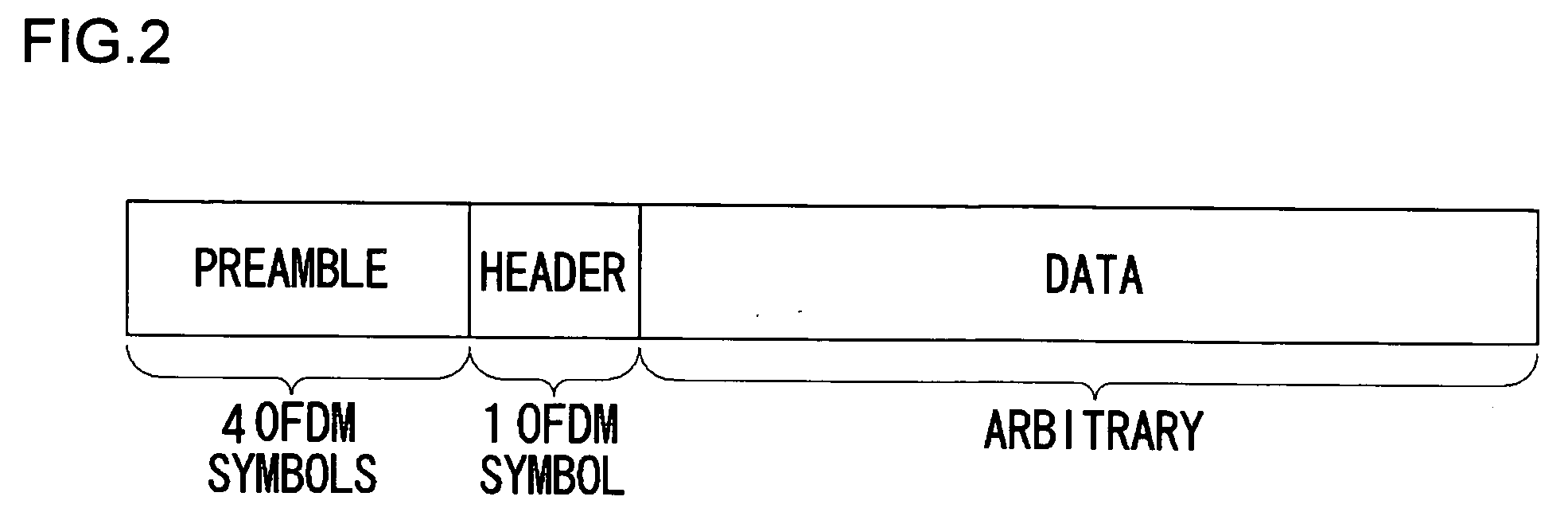

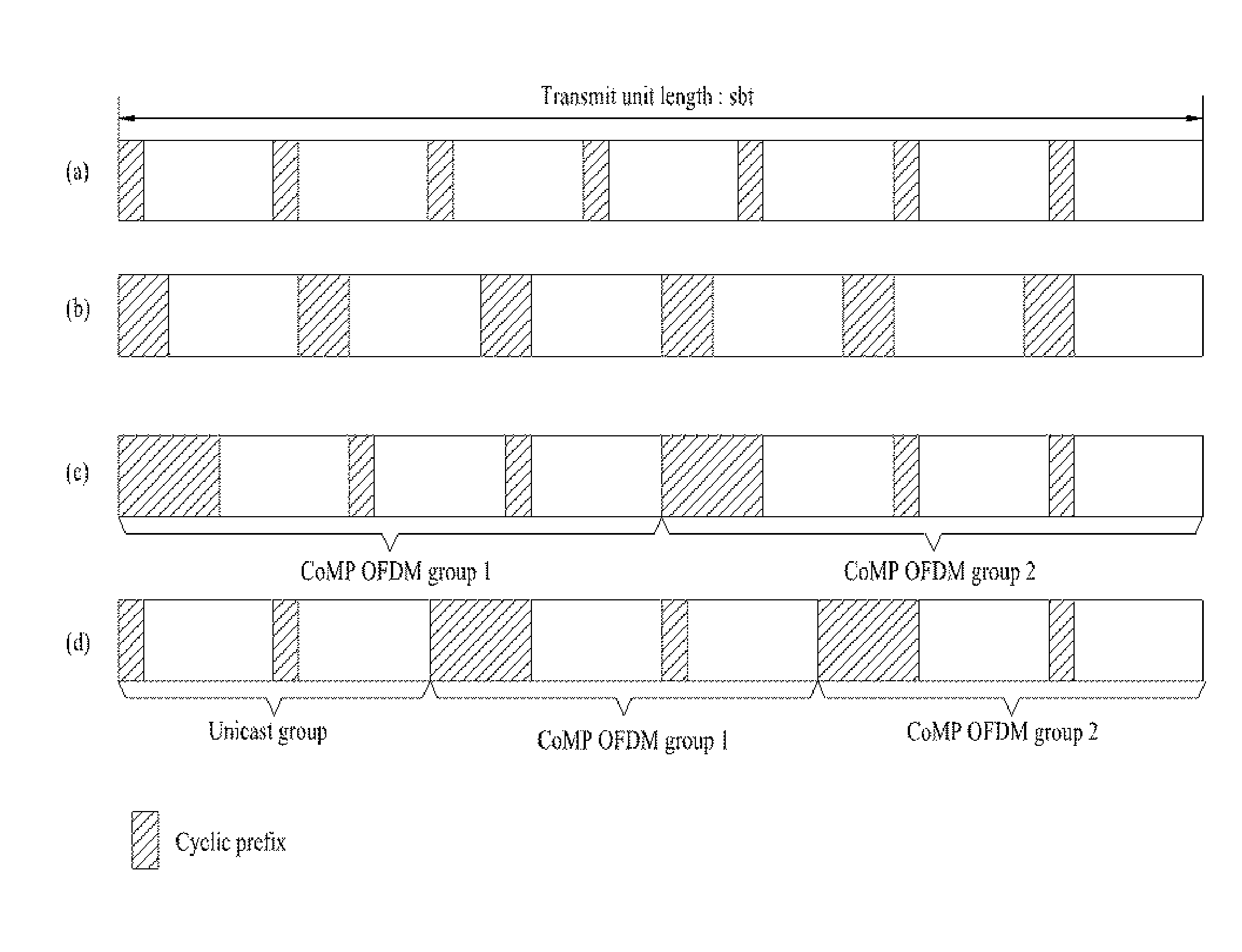

Method of Transmitting and receiving Data in a Wireless System

InactiveUS20110305185A1Timing errorSynchronisation arrangementModulated-carrier systemsCommunications systemDelayed time

A method of transmitting data in a wireless communication is disclosed, by which timing error can be solved in a multi-cell environment. The present invention, in which data is transmitted by a serving cell to a mobile station communicating with a plurality of cells in a wireless communication system, includes receiving information on delay times of signals from the mobile station, wherein the signals are received by the mobile station from the plurality of the cells and transmitting data to the mobile station by inserting a cyclic prefix (CP) having a length determined according to the information on the delay times into the data.

Owner:LG ELECTRONICS INC

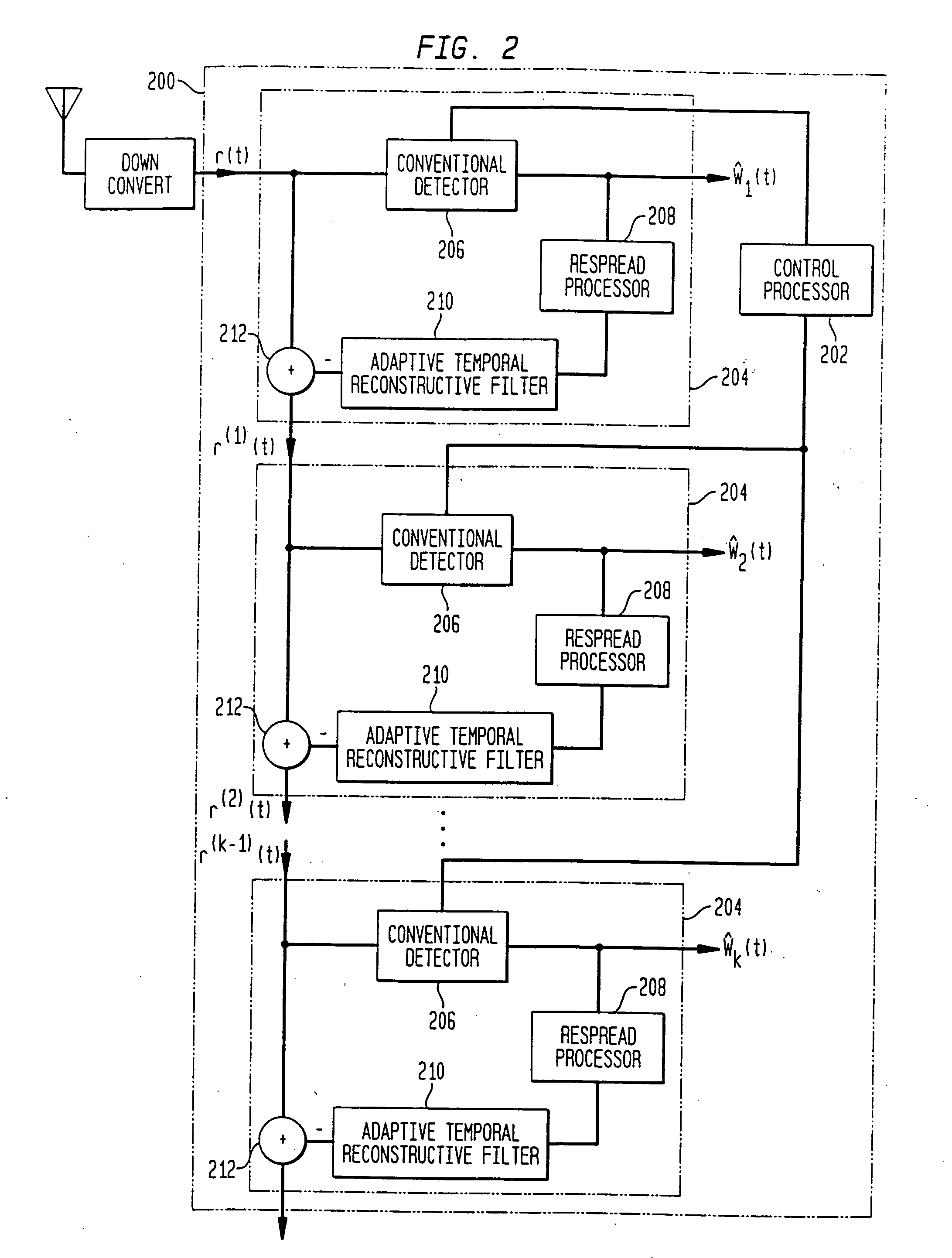

Parallel interference cancellation and minimum cost channel estimation

ActiveUS20050111414A1Minimize residualTiming errorRadio transmissionEngineeringCo-channel interference

Methods and systems in a wireless receiver for enabling the reception of input signals at varied power levels in the presence of co-channel interference utilizing combinations of space-time adaptive processing (STAP), interference cancellation multi-user detection (MUD), and combined STAP / MUD techniques. In MUD, code, timing, and possibly channel information of multiple users are jointly used to better detect each individual user. The novel combination of adaptive signal reconstruction techniques with interference cancellation MUD techniques provides accurate temporal cancellation of interference with minimal interference residuals. Additional methods and systems extend adaptive signal reconstruction techniques to take Doppler spread into account. STAP techniques permit a wireless receiver to exploit multiple antenna elements to form beams in the direction of the desired signal and nulls in the direction of the interfering signals. The combined STAP-MUD methods and systems increase the probability of successful user detection by taking advantage of the benefits of each reception method. An additional method and system utilizes STAP techniques in the case where no pilot signal is available. This method compares the outputs of various hypothesized STAP solutions.

Owner:NYTELL SOFTWARE LLC

Method and system for maintaining a communications protocol session

ActiveUS7089302B1Timing errorMultiple digital computer combinationsTransmissionNetwork Communication ProtocolsDatapath

A method and system is disclosed for maintaining a communications protocol session between a client and server during times of inactivity at the client caused by other processing in the data path following a request by the client. For various client processes that may expire after a specified amount of inactivity during a particular session, an agent of the client in the data path can send a response containing illusory content to the client that causes the client to maintain the current session. The process at the client can ignore this illusory content response but, by processing it, the communications path session between the client and server can be maintained.

Owner:MCAFEE LLC

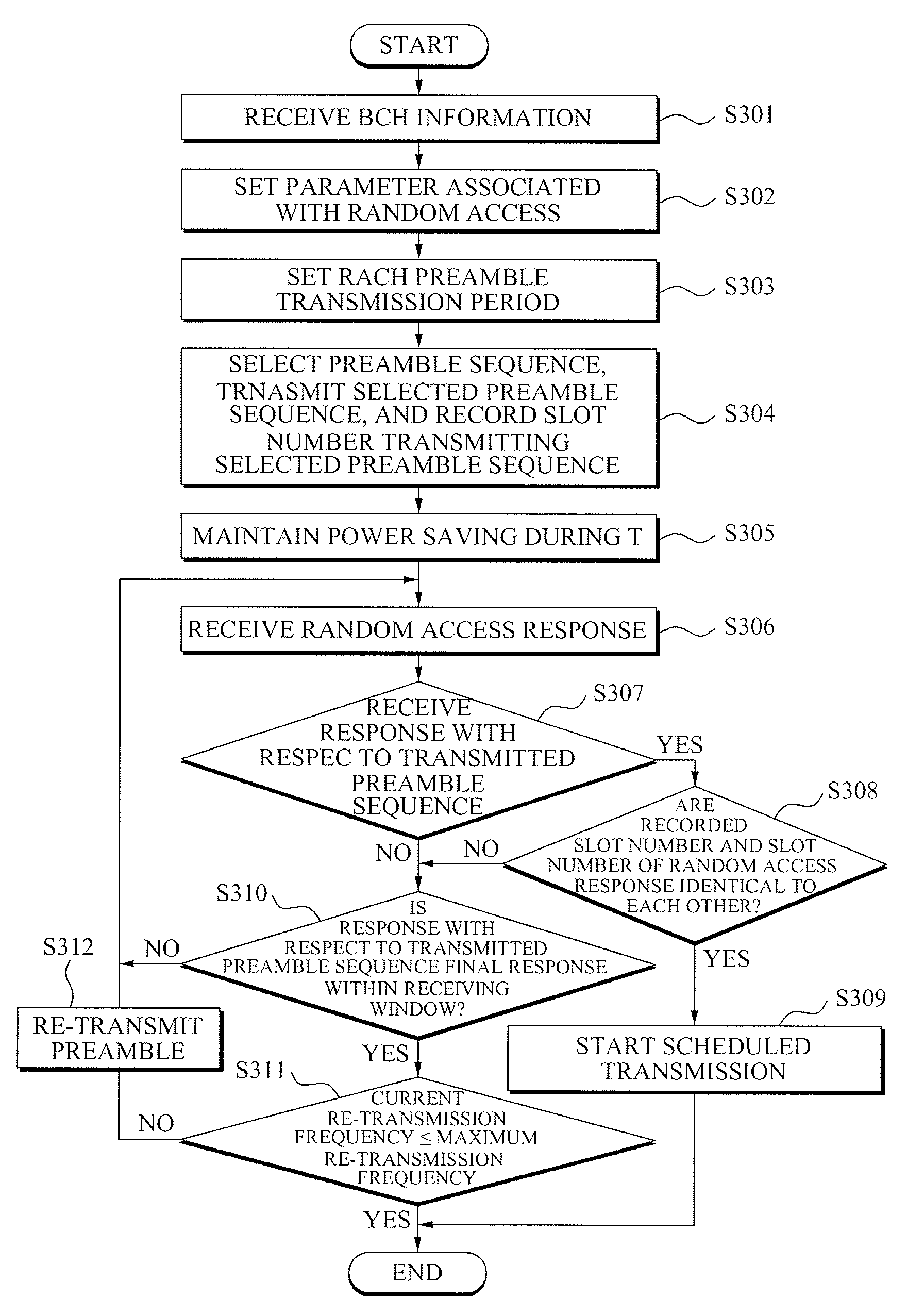

Hierarchical random acces method for wireless communication system having significantly large cell

ActiveUS20100135274A1Improve abilitiesEfficient executionTime-division multiplexRadio transmissionCommunications systemLarge cell

Disclosed is a hierarchical random access method for a wireless communication system having a significantly large cell. According to the present invention, a length of a preamble sequence and a length of a reference slot may be designed based on a terminal having greatest capacity of adjusting a timing error arrived at a base station, and a slot length may be designed to be an integer multiple of the length of the reference slot depending on a timing error correction capacity, thereby enabling terminals to use various slot lengths.

Owner:ELECTRONICS & TELECOMM RES INST

Limited-play optical media with improved shelf-life and playability

InactiveUS20040022986A1Complicated to manufactureIncrease costPhotosensitive materialsLayered productsMetal alloyReflective layer

Limited-play optical medium with improved shelf stability are formed from a plurality of layers, including in sequence: (a) a first substrate layer; (b) a data layer; (c) a reflective layer; (d) a reactive layer comprising a dye having a reduced state and an oxidized state and further comprising an oxidized form of a reducing agent effective to convert the dye from the oxidized state to the reduced state, and (e) a second substrate layer. The dye in the reduced state is substantially transparent to light of wavelengths used to read the optical medium, and the dye in the oxidized state absorbs light of wavelengths used to read the optical medium. The reflective metal layer is formed from a metal or metal alloy that is not significantly oxidized by the oxidized form of the reducing agent. For example, the reflective metal layer is suitably formed from silver or gold.

Owner:GENERAL ELECTRIC CO

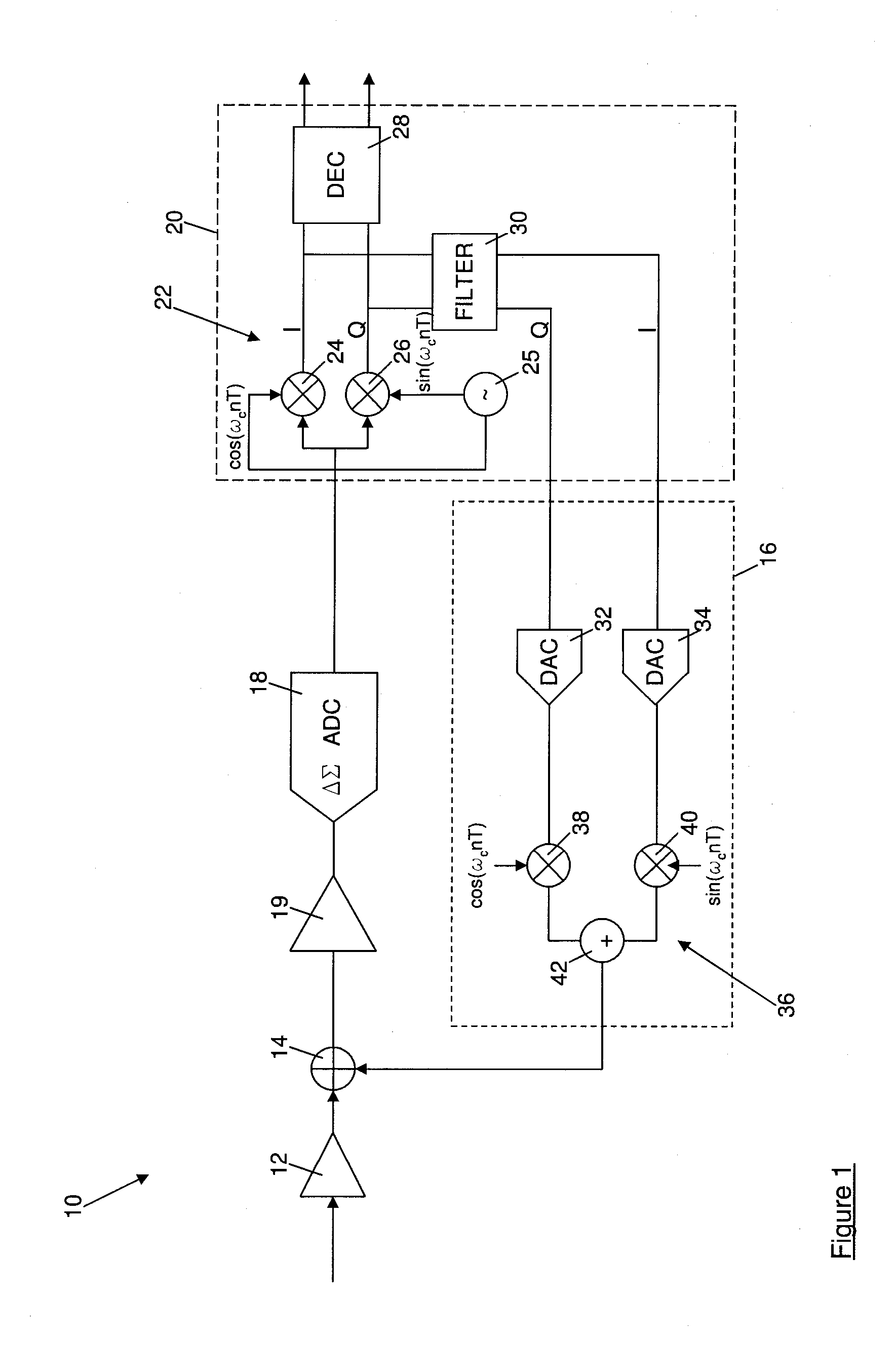

Near field communications receiver

InactiveUS20120322399A1Simple designSimplicity of implementationNear-field transmissionCarrier signalData signal

The present application relates to a near field communications (NFC) receiver in which a received NFC signal comprising a carrier signal onto which a data signal is modulated is digitised and downconverted, and the digitised and downconverted received signal is filtered to recover a digitised and downconverted version of the carrier signal of the NFC signal. This digitised and downconverted version of the carrier signal is converted into an analogue signal which is then upconverted to generate an estimate of the carrier signal, and this estimate is combined with the received NFC signal to suppress or negate, at least partially, the carrier of the received signal.

Owner:QUALCOMM TECH INT

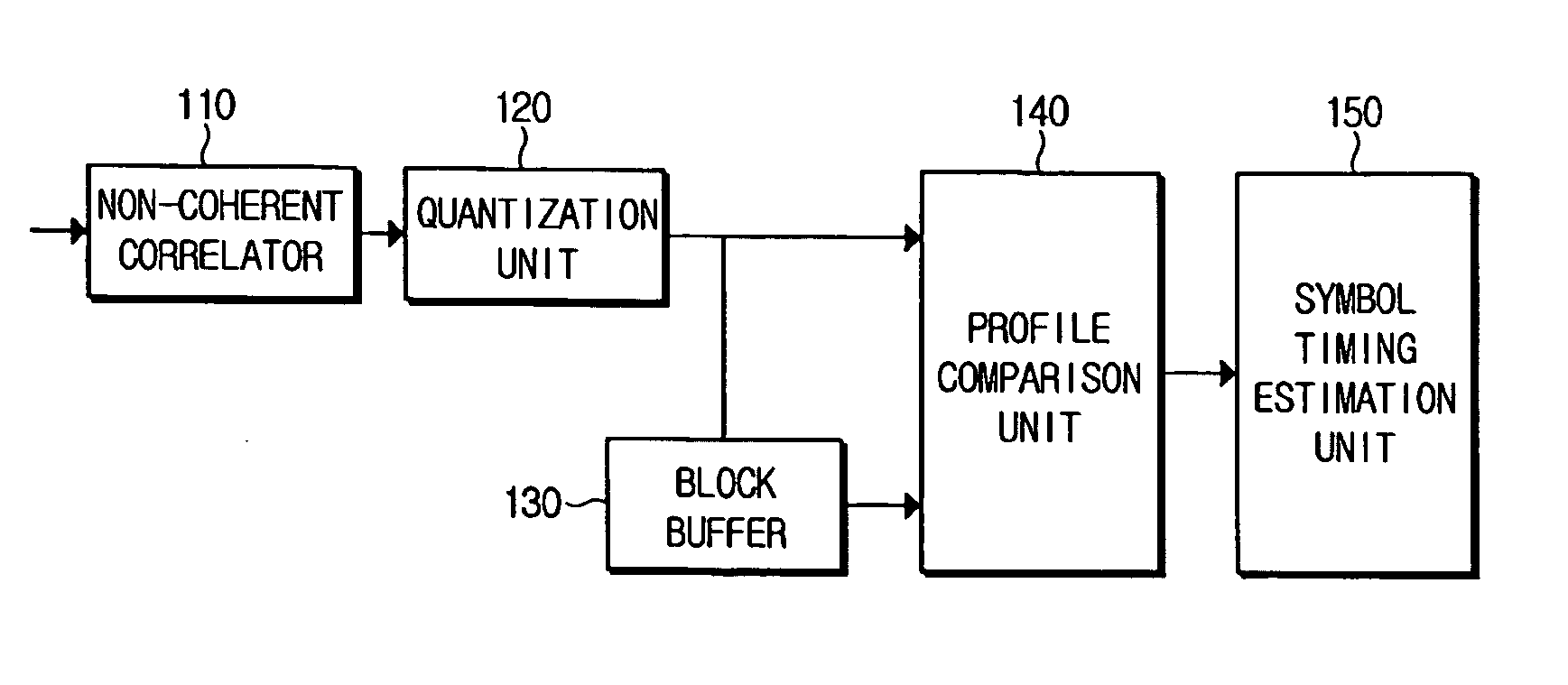

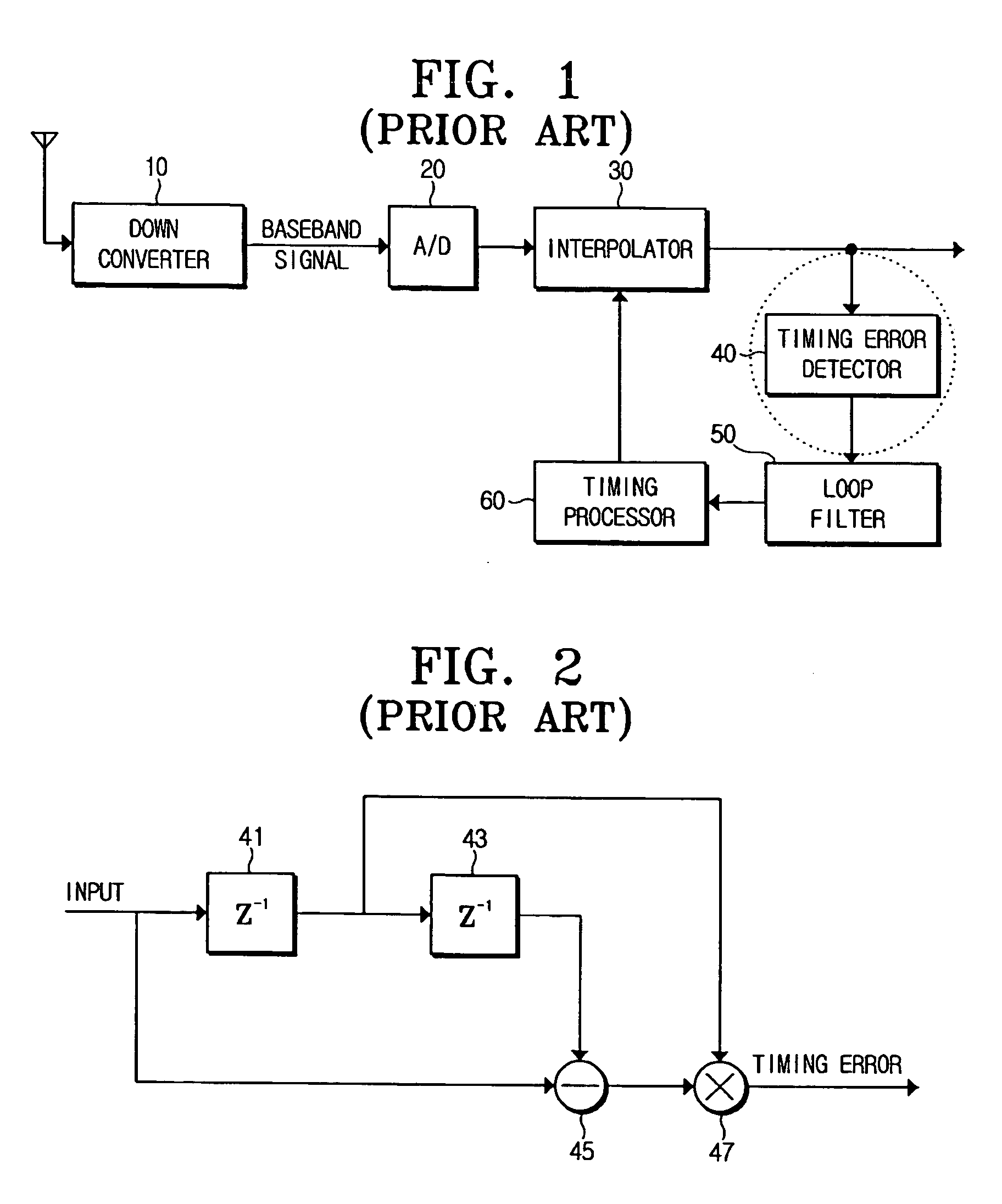

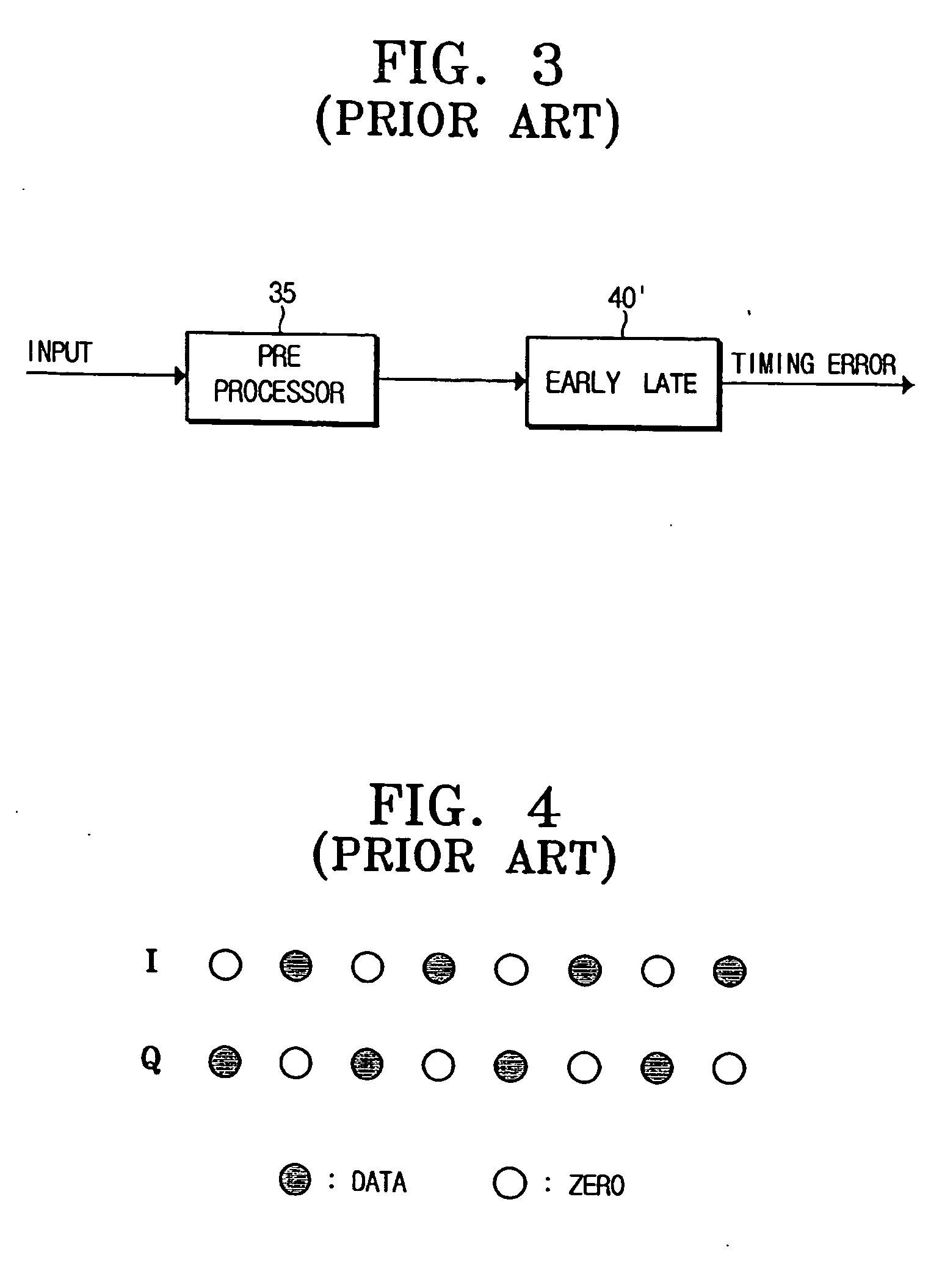

Symbol timing error detector that uses a channel profile of a digital receiver and a method of detecting a symbol timing error

InactiveUS20050286661A1Timing errorReduce the amount requiredError preventionBaseband system detailsCarrier frequency offsetNon coherent

A symbol timing error detector and a method of detecting the symbol timing error that uses a channel profile of a digital receiver. The symbol timing error detector includes a non-coherent correlator to calculate a non-coherent correlation value using pseudo noise (PN) sequence in which a received signal is that is divided into a predetermined number of units to calculate a channel profile, a block buffer to window and store a predetermined portion of the channel profile, a profile comparison unit to compare the channel profile stored in the block buffer with a current channel profile output from the non-coherent correlator using pattern matching, and a symbol timing estimator to detect a symbol index difference determined using the pattern matching of the current channel profile and the stored channel profile as a symbol timing drift. Accordingly, the timing error may be corrected regardless of a carrier frequency offset that results from an effect of a channel environment.

Owner:SAMSUNG ELECTRONICS CO LTD

Method of optimizing signal lines within circuit, optimizing apparatus, recording medium having stored therein optimizing program, and method of designing circuit and recording medium having stored therein program for designing circuit

InactiveUS7032198B2Guaranteed coincidenceEfficient arrangementProgram controlComputer aided designEngineeringDriven element

A method for designing an integrated circuit such as a VLSI circuit, in particular optimizing delay of a signal transmitting through signal lines connecting a signal supplying source to each of elements, whereby skew can be decreased. The method can include determining whether the signal source satisfies a fan-out restriction if the signal source supplies a signal to all of the driven elements which are directly connected to the signal source, dividing the elements into groups so that the fan-out restriction is satisfied in each of the groups and each of the groups has the same or substantially same load capacity, when the signal source does not satisfy the fan-out restriction, and inserting into each group, a buffer having a size which makes the groups of elements satisfy the fan-out restriction. The dividing and the buffer inserting are repeated until a positive determination is delivered on the fan-out restriction.

Owner:SOCIONEXT INC

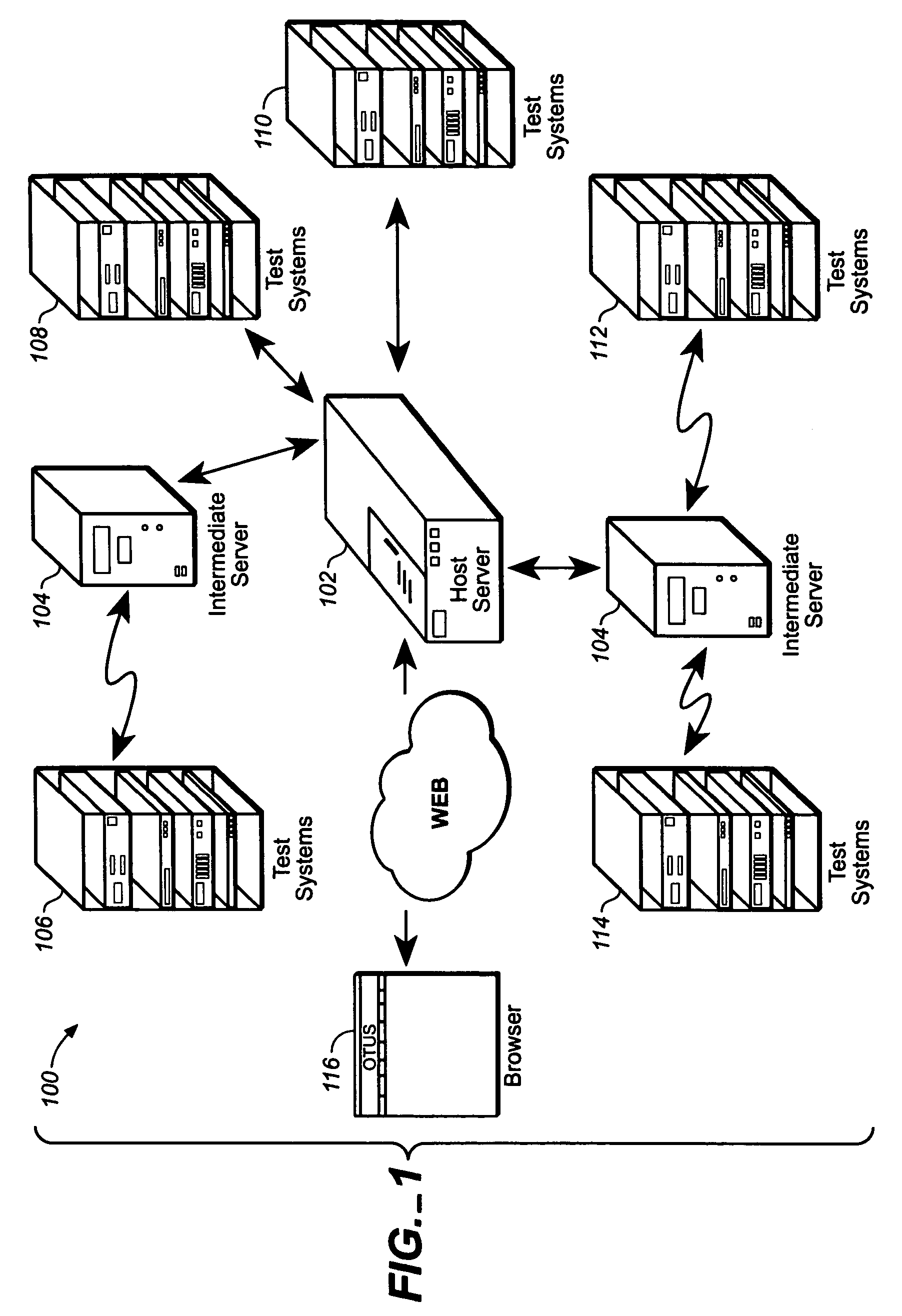

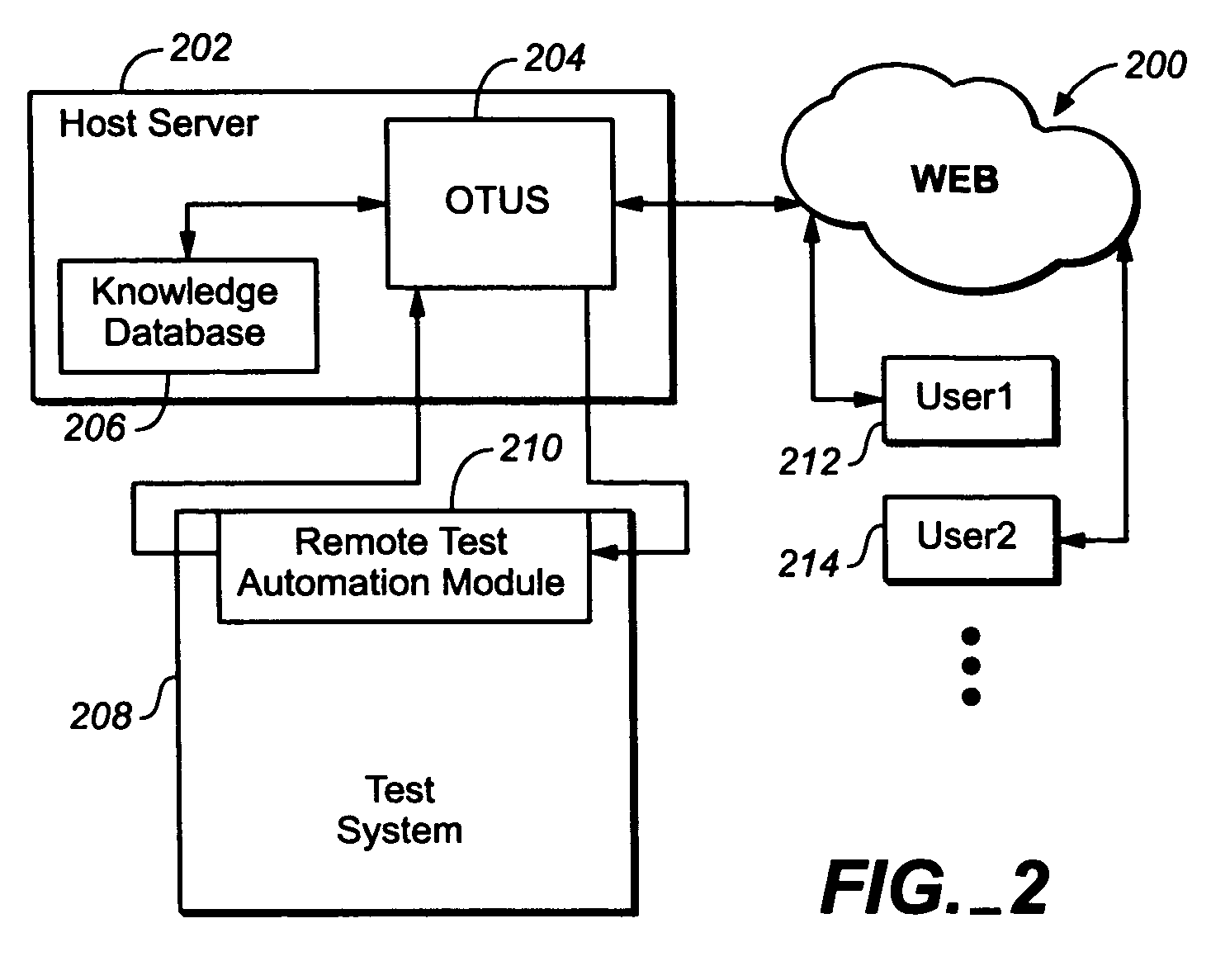

Online testing unification system with remote test automation technology

ActiveUS7673179B2Reduce ambiguityImprove efficiencyDetecting faulty hardware by remote testDetecting faulty hardware using expert systemsRemote systemOnline test

The present invention is directed to an online product validation solution integrating an online testing module configured to assist a user to create test cases and a remote test automation module configured to execute the created test cases on remote test systems. When a user creates a test plan, complete test coverage for the test plan may be ensured and cross-checked with product specifications stored in the knowledge database. Moreover, seamless integration of the online testing module and the remote test automation module may provide a uniform interface for generating both manual and automated test cases. Test case status is reported within the test plan in synchronicity with test case execution.

Owner:NETWORK APPLIANCE INC

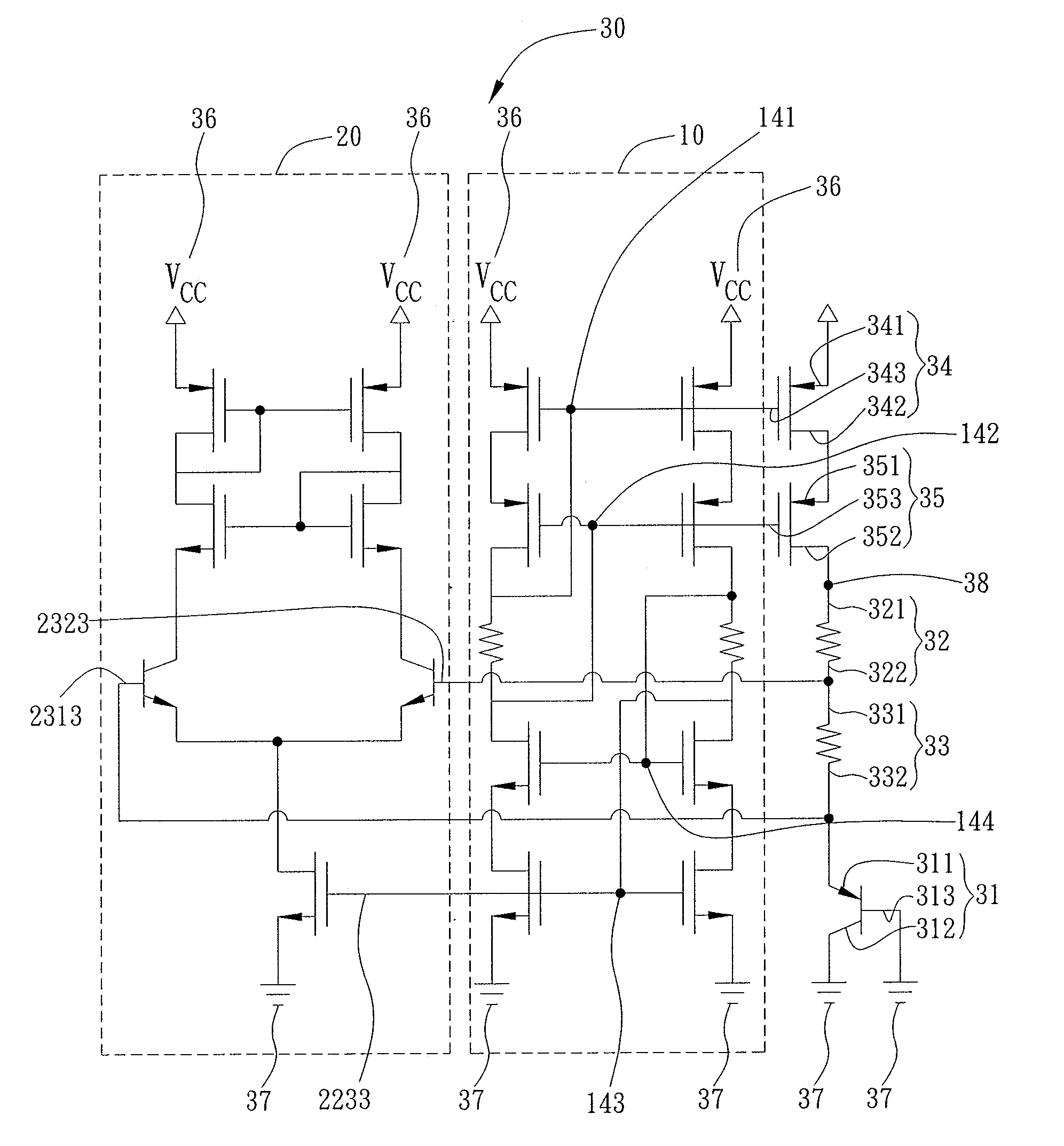

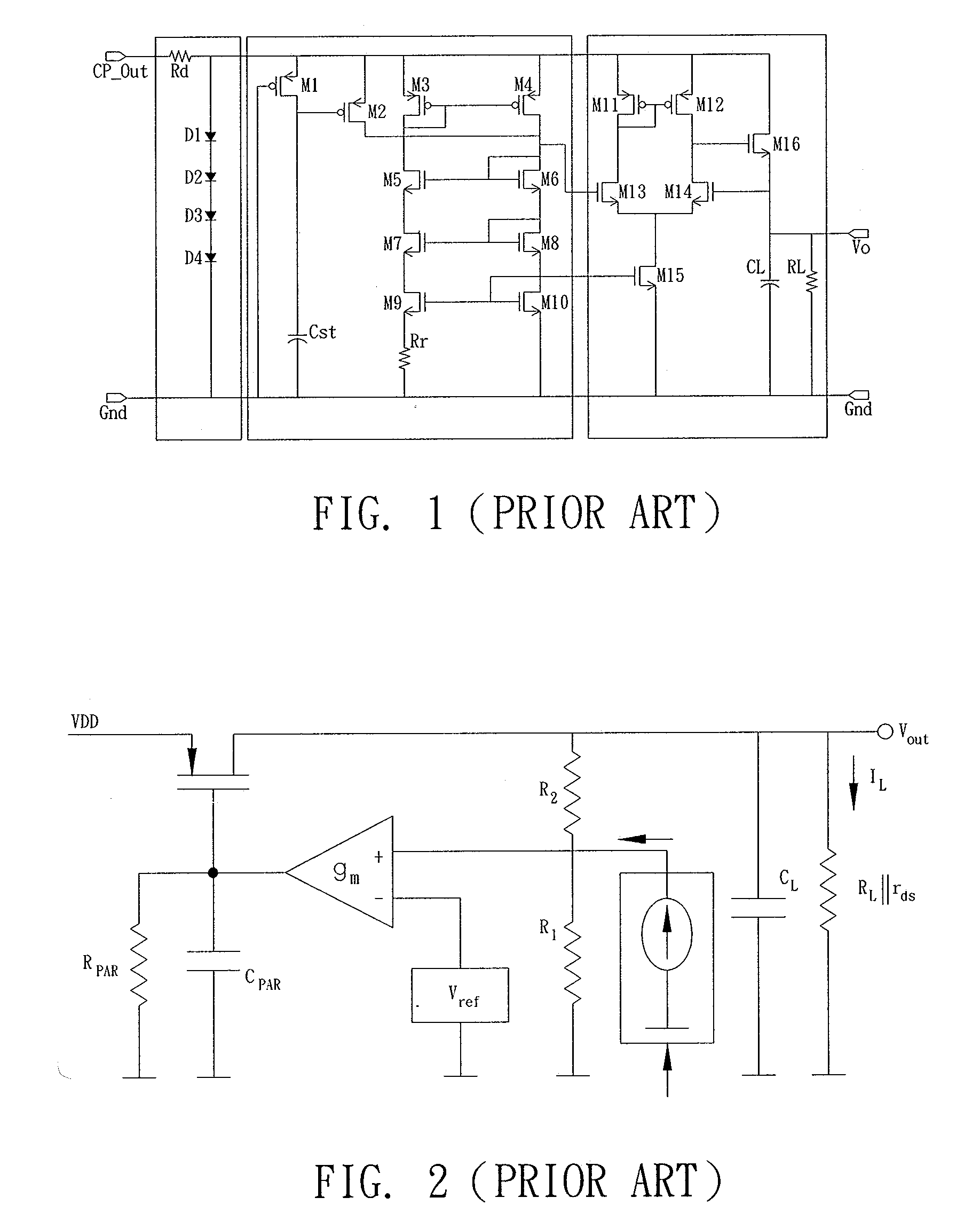

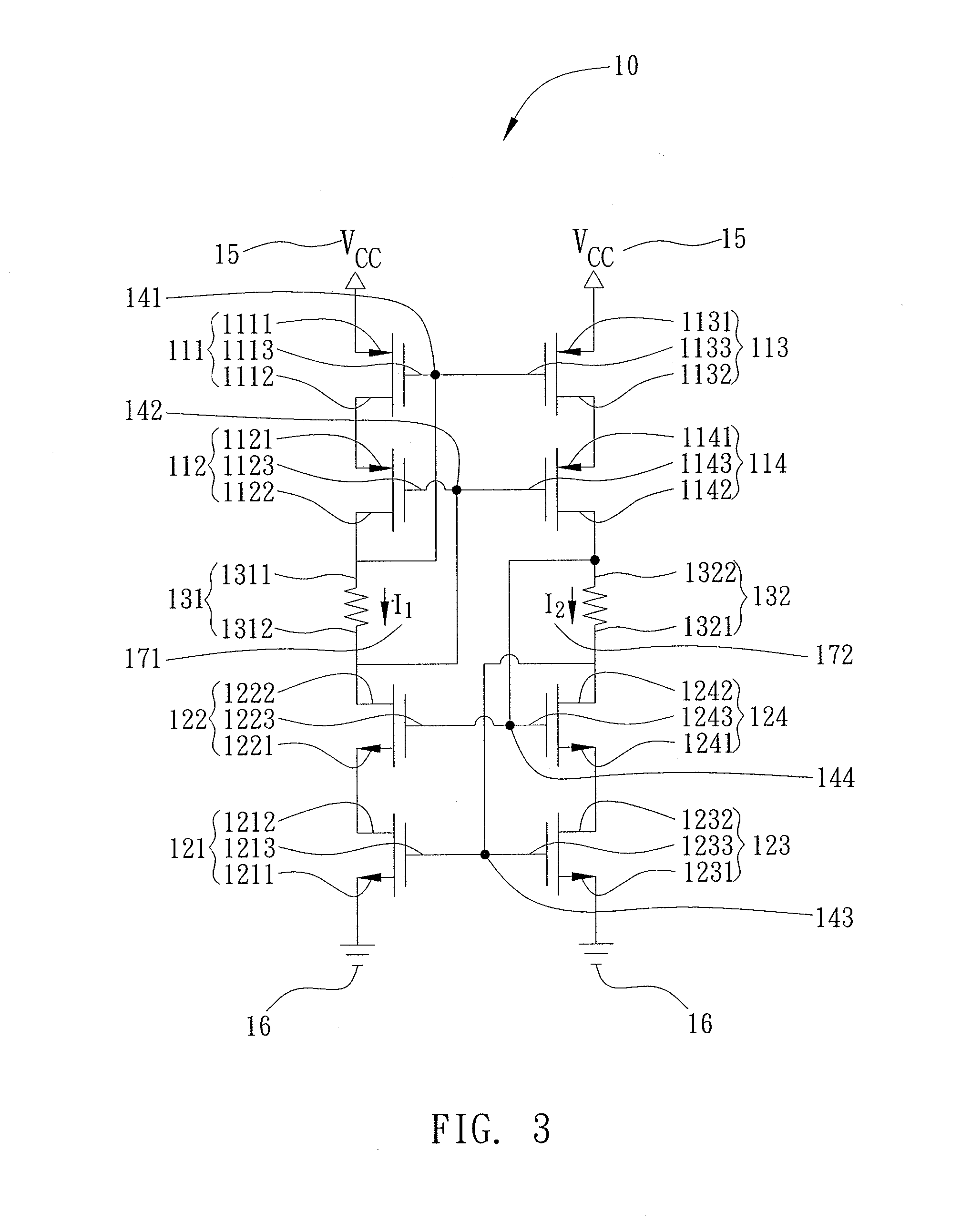

Cascode current mirror circuit, bandgap circuit, reference voltage circuit having the cascode current mirror circuit and the bandgap circuit, and voltage stabilizing/regulating circuit having the reference voltage circuit

InactiveUS20090267585A1Reduce the effect of temperatureMitigate ripple voltage perturbationAmplififers with field-effect devicesAmplifier detailsReference currentCascode current mirror

A cascode current mirror circuit and a bandgap circuit are provided. The circuits are used together and function as a reference voltage circuit. The reference voltage circuit outputs a reference current resistant to temperature variation and ripple-voltage. Accordingly, a voltage stabilizing / regulating circuit corrects error voltage precisely and promptly, and the resultant voltage is temperature insensitive and ripple-voltage-independent.

Owner:NAT TAIWAN UNIV

Integrated circuit layout device, method thereof and program thereof

InactiveUS20070150847A1Improve timing errorExtension of timeComputer aided designSoftware simulation/interpretation/emulationEngineeringIntegrated circuit layout

A layout device for an integrated circuit executes calculating a timing value with respect to each wiring path by a analysis based on connection information and delay information of wirings, determining a target value serving as an improvement target of the wiring path, detecting an error wiring path exhibiting the timing value larger than the target value, changing the wiring connection so that the error wiring path shows a timing value smaller than the target value, updating these piece of information into connection information and delay information of the wirings after changing the wiring connection, calculating a distribution about each wiring path by the analysis based on the post-updating connection information and the post-updating delay information of the wirings and a fluctuation factor, calculating a yield of the integrated circuit from the distribution, and judging whether or not the yield is within an allowable range of a predetermined value.

Owner:FUJITSU LTD

Time-of-flight analyzer

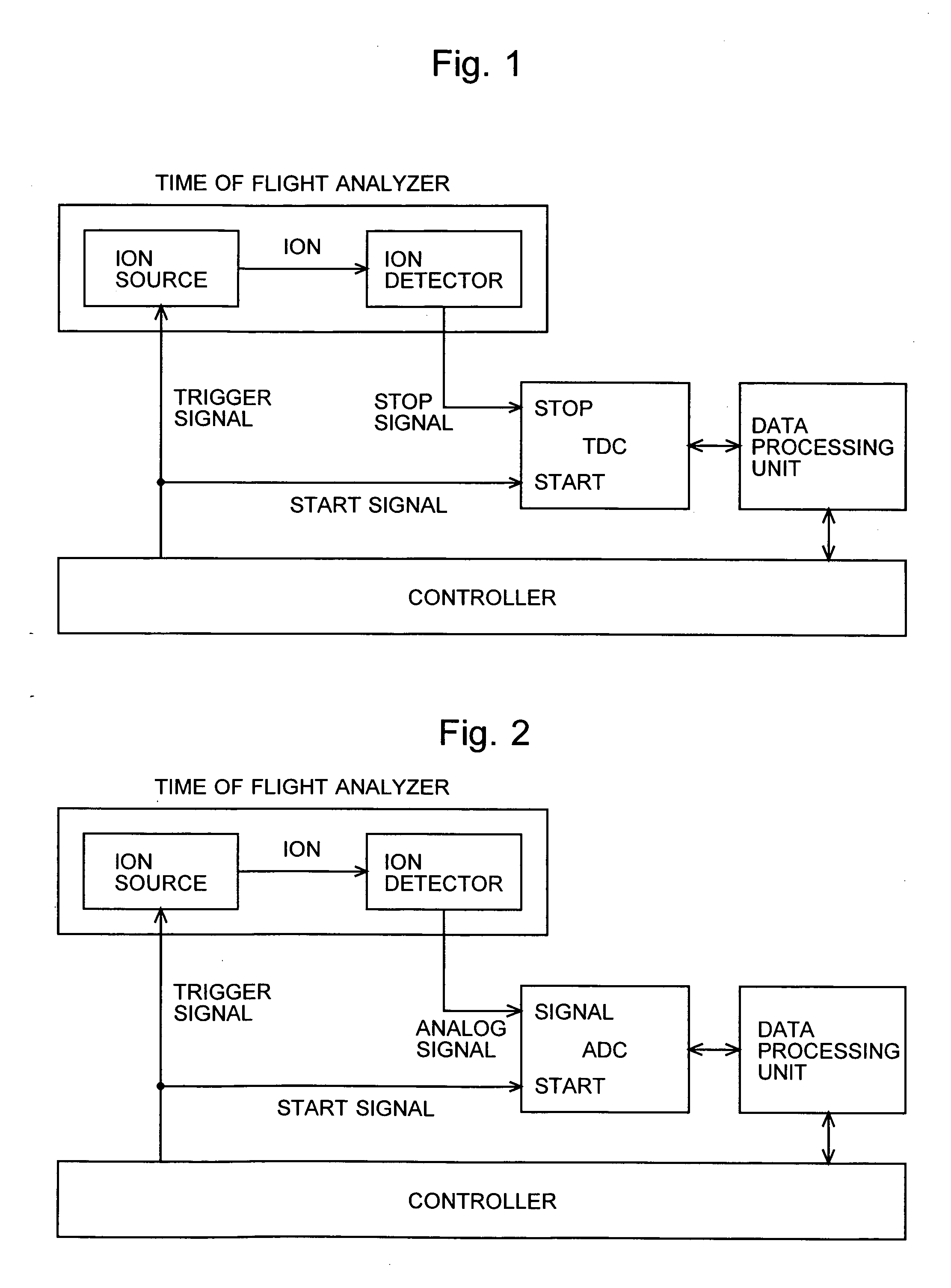

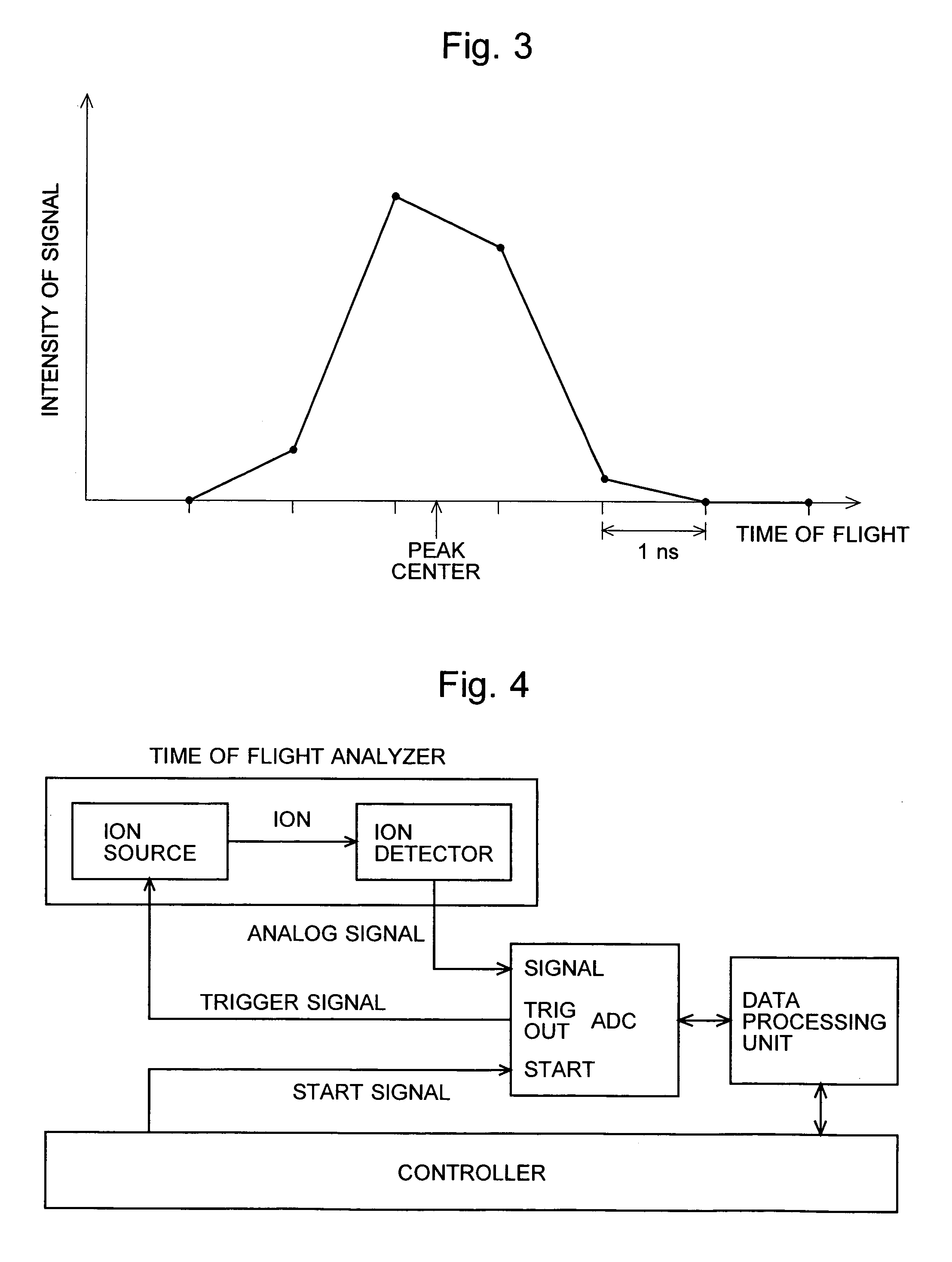

InactiveUS20060016977A1Eliminate timeHigh accuracyTime-of-flight spectrometersIsotope separationTiming errorSynchronism

In order to provide a time of flight analyzer in which the timings of the ion generation and the ion signal recorder are synchronized, and the peak center position can be determined at high accuracy with fewer measurements, the time of flight analyzer of the present invention includes an ion source and an ion signal recorder working on an internal clock, wherein the ion signal recorder generates a trigger signal in synchronism with the internal clock in order to generate ions in the ion source. Since the timing of accelerating ions in the ion source and the timing of digital sampling and recording of the ion signal, which is detected in the ion detector, in the ion signal recorder are synchronized, the timing error occurred in conventional methods can be suppressed.

Owner:SHIMADZU CORP

Synchronization of an external device using a GPS receiver

ActiveUS20070239356A1Variable time delayTiming errorPosition fixationNavigation instrumentsTiming errorData processing

A method for synchronization of an external device's clock 324 with a GPS device 104 is provided. The method can comprise processing one or more data sentences received at the external device 106 from the GPS device to determine a data sentence containing the best available time information that is most accurate among the data sentences. Also, an amount of correction can be determined to compensate for one or more variable time delays introduced by one or more processes. The one or more processes can selected from a group consisting of a process performed by the GPS device t1b, a data sentence transmission from the GPS device to the external device t2b, and a data processing step performed by the external device t3b. A synchronization time using the amount of correction and the best available time information can be provided. The method can further comprise correcting a timing error introduced into time stamp values by the external device clock. This step can include removing an accumulate error by restarting the method after a pre-defined amount of time (e.g., one hour).

Owner:HARRIS GLOBAL COMMUNICATIONS INC

Line path determining method and delay estimating method

InactiveUS6292928B1Timing errorSemiconductor/solid-state device manufacturingCAD circuit designCapacitanceIntegrated circuit

A line capacitance is estimated in consideration of an influence of an adjacent line in rough routing, so that line paths can be determined so as to be free from a timing error. A routing graph is generated from a target integrated circuit, and line paths of cell-to-cell lines are initially determined on the basis of a passage cost set with regard to each of edges of the routing graph. With regard to each edge of the routing graph, the number of cell-to-cell lines passing through the edge is obtained as a line density, and a line capacitance of each line path in view of the influence of an adjacent line is estimated on the basis of the line density. It is verified whether or not there is a timing error with a delay time estimated, and when the integrated circuit does not satisfy a predetermined timing constraint, the line paths are re-determined with the passage cost of each edge allowed to be affected by the line capacitance. Alternatively, allocation to an interconnect layer is changed or a line-to-line distance is increased, so that the integrated circuit can satisfy the timing constraint.

Owner:PANASONIC CORP

Detecting and compensating for erroneous time measurement for mobile device position calculation

A method implemented by an assisted Global Navigation Satellite System (GNSS) server determines a position of a GNSS receiver. The method includes sending a request for measurement information to the GNSS receiver at a first time and receiving the measurement information from the GNSS receiver in response to the request at a second time, where the measurement information includes position measurement data and a corresponding measured time based on satellite signals received by the GNSS receiver. The measured time is determined to be erroneous when it is outside an accurate time range determined based on at least one of the first time and the second time. A substitute time is identified and the position of the GNSS receiver is determined based on the substitute time when the measured time is erroneous.

Owner:TELECOMM SYST INC

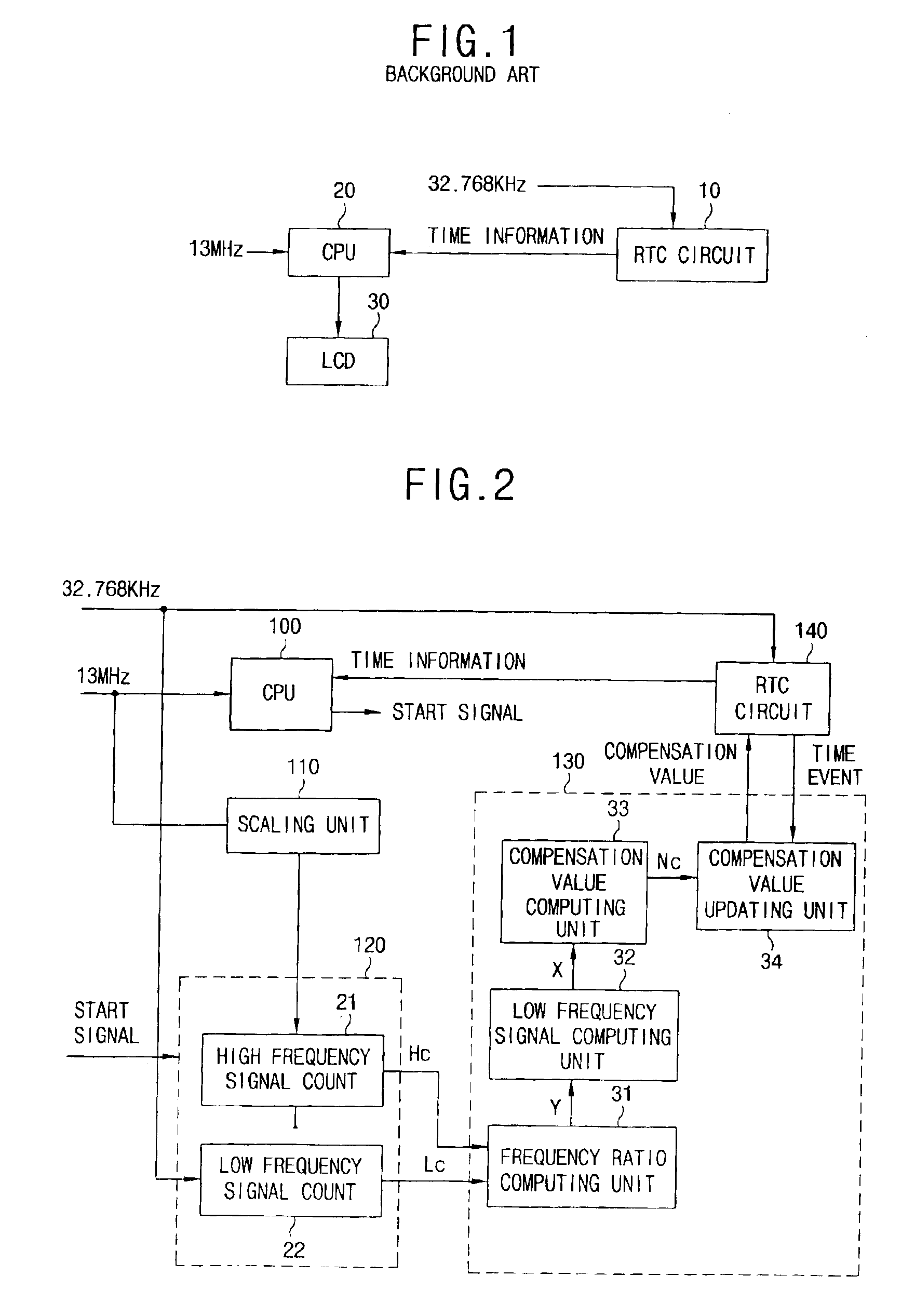

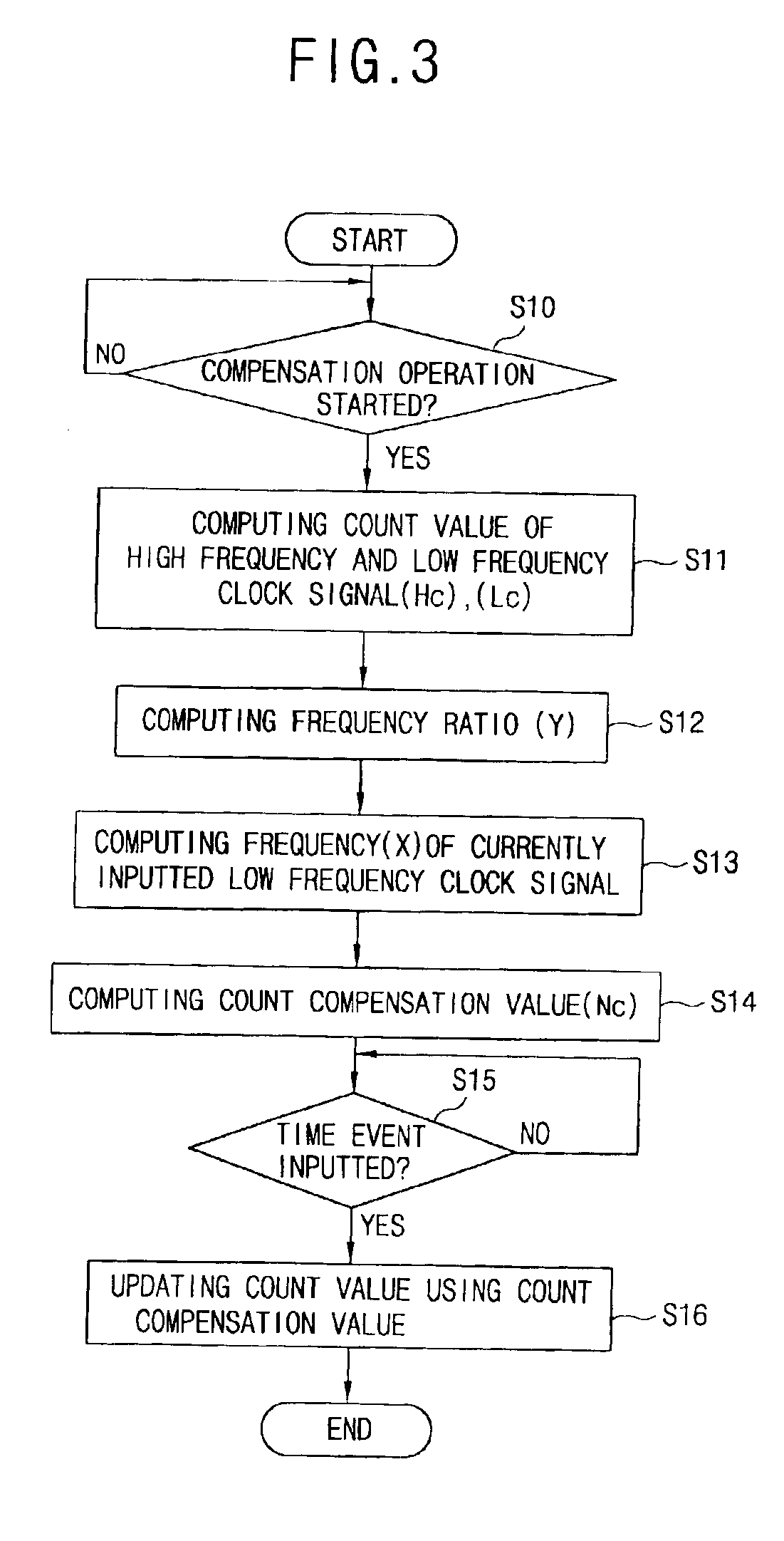

Time error compensating apparatus and method in a terminal

InactiveUS6961287B2Accurate compensationTiming errorFrequency stabilisation mechanismSynchronous motors for clocksTime errorTime information

A time-error-compensating apparatus and method corrects errors in a real-time clock caused by temperature fluctuations or other external influences. The apparatus includes a frequency counting unit which counts a high-frequency clock signal and a low-frequency clock signal, and a time compensating unit which computes a clock count compensation value based on a comparison of the count values of of the low-frequency and high-frequency clock signals. Correcting time using a high-frequency clock is highly desirable because a clock of this type has proven to be accurate in high external stress conditions. Use of this clock also allows the real-time clock to be implemented as a low-frequency, inexpensive low-frequency clock. The method and apparatus are well suited to correcting time information in the terminals of a mobile communications system, or in any other system or device where time tracking is sought.

Owner:LG ELECTRONICS INC

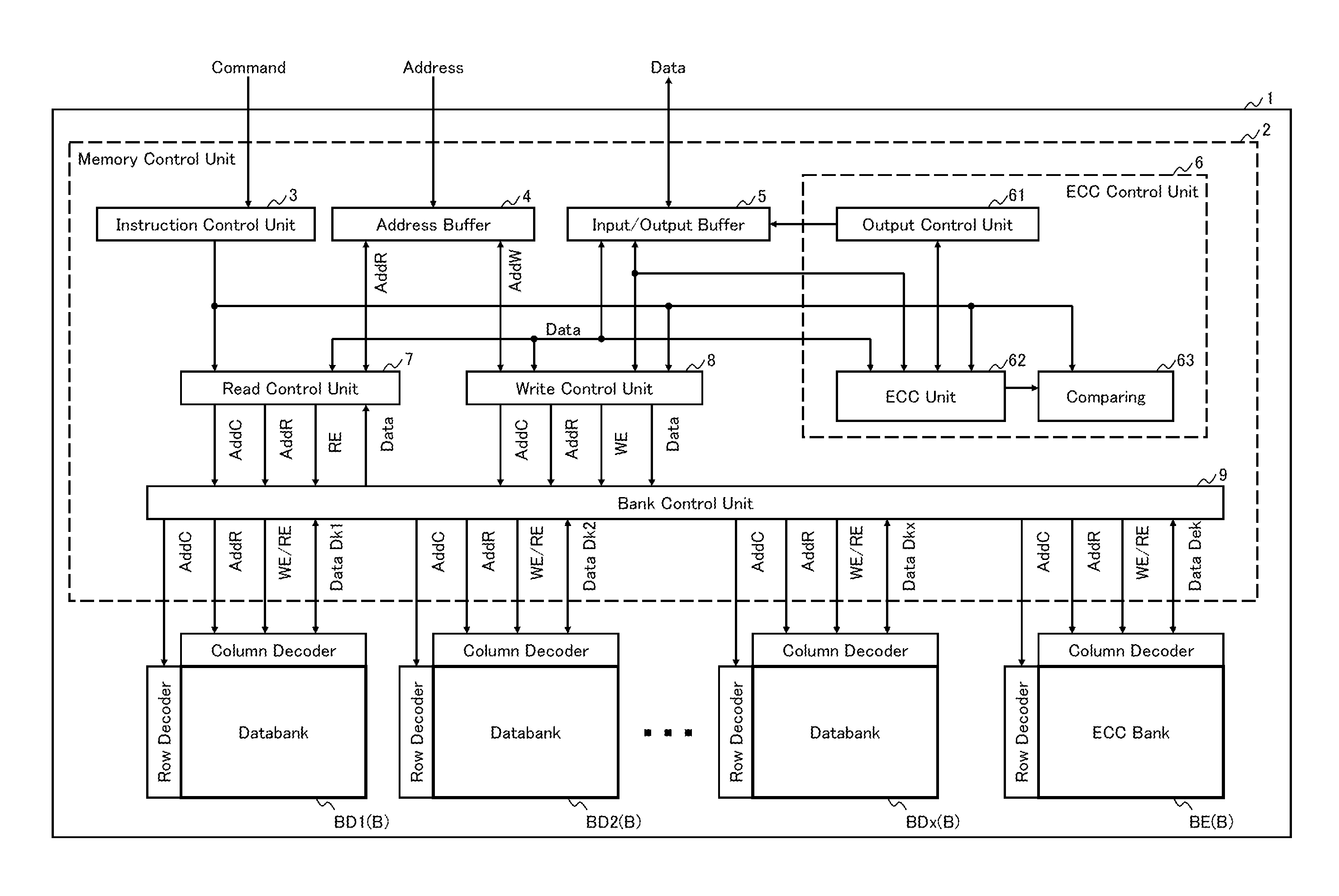

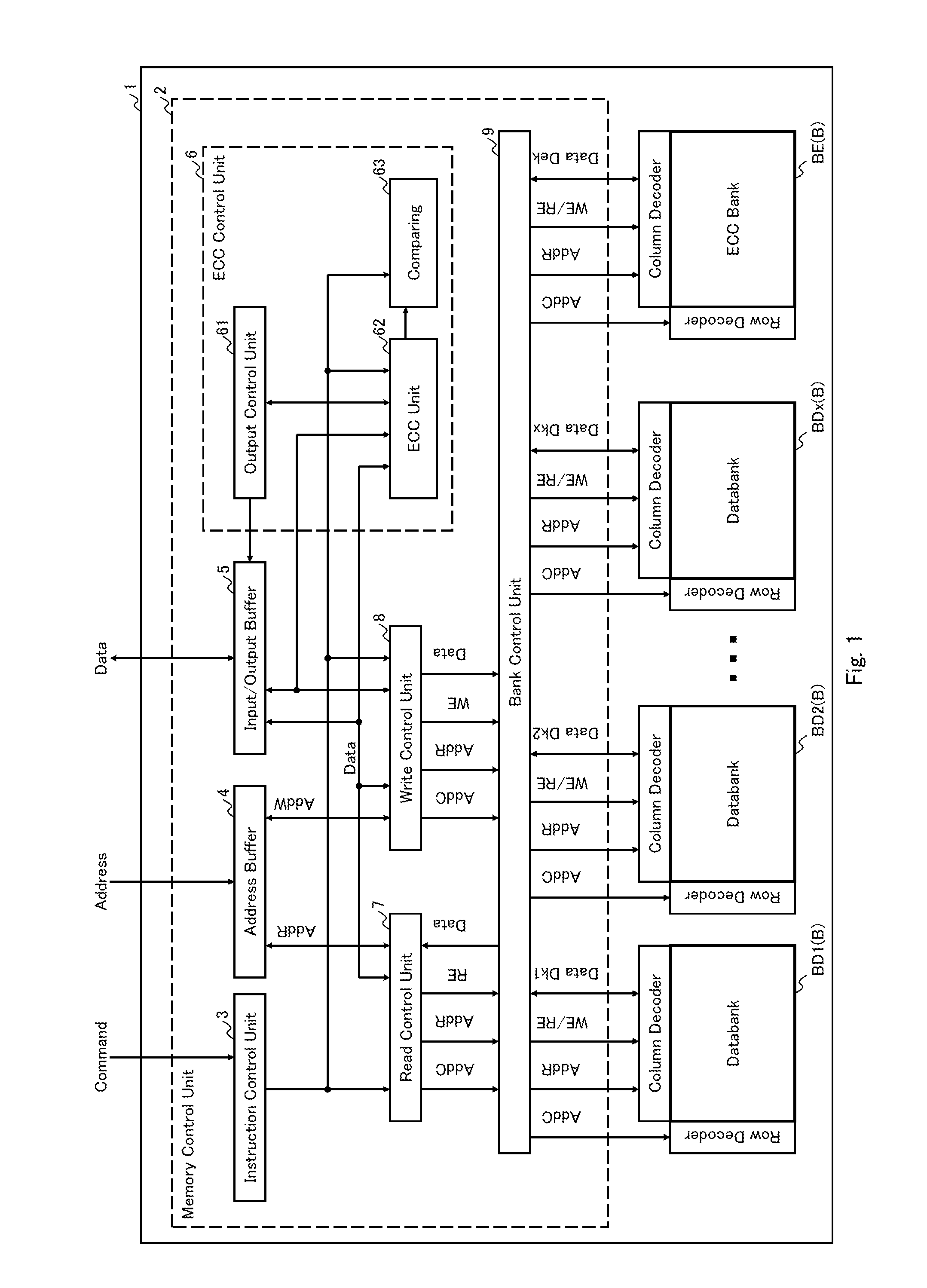

Nonvolatile semiconductor memory device

InactiveUS20120297268A1Reduce processing timeConvenient timeCode conversionDigital storageGeneration processComputer science

The present invention provides a nonvolatile semiconductor memory device that can optimize a timing of performing an error detection and correction process to shorten a processing time. Upon receiving a write request to a memory cell array including a variable resistive element where information is stored based on a resistance state of a variable resistor, an input / output buffer outputs write data to a write control unit and an ECC control unit. The write control unit performs a data write process of writing divided data, obtained by dividing the write data into a predetermined number of data, to the databanks. The ECC control unit generates a first error correction code by performing an error correction code generation process to the write data or the divided data, in parallel with the data write process. The write control unit performs a code write process of writing first test data into an ECC bank.

Owner:SHARP KK

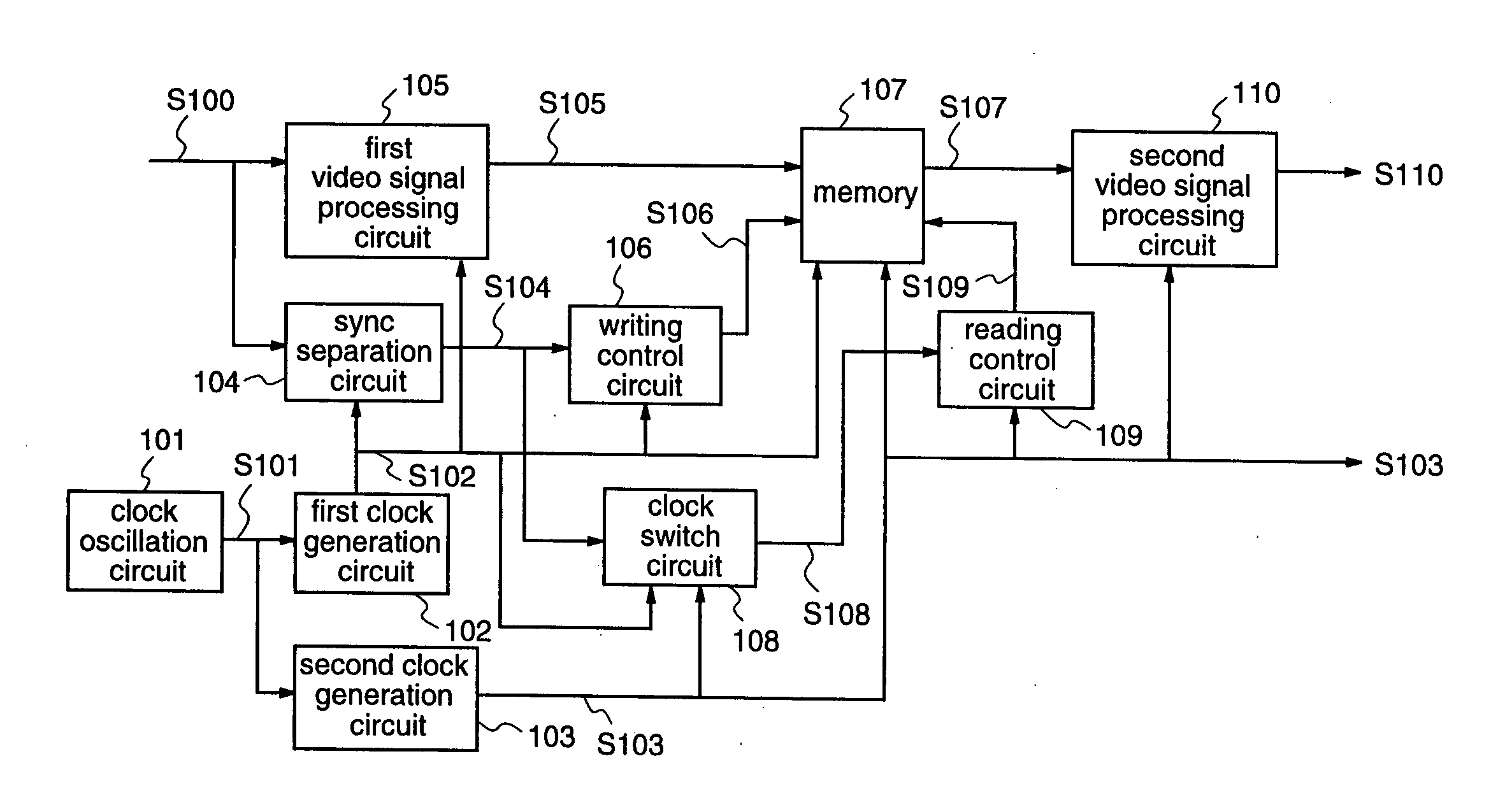

Video signal processing apparatus

InactiveUS20060187349A1Reduce quantization noisePromote generationTelevision system detailsColor signal processing circuitsImage resolutionVideo processing

A video signal processing apparatus is provided with a first clock generation circuit for generating a first clock synchronized with an input signal; a second clock generation circuit for receiving a set value to be a reference of an output frequency, adding the set value for every reference clock, extracting data according to the cumulative value, converting the data into an analog signal, reducing quantization noise, and multiplying the analog signal, thereby to obtain a second clock; and a clock switch circuit for generating a sync signal that is switched to the second clock, by using a sync signal generated with the first clock; and video signal processing is carried out using the second clock that is generated according to the resolution of a pixel display.

Owner:SOCIONEXT INC

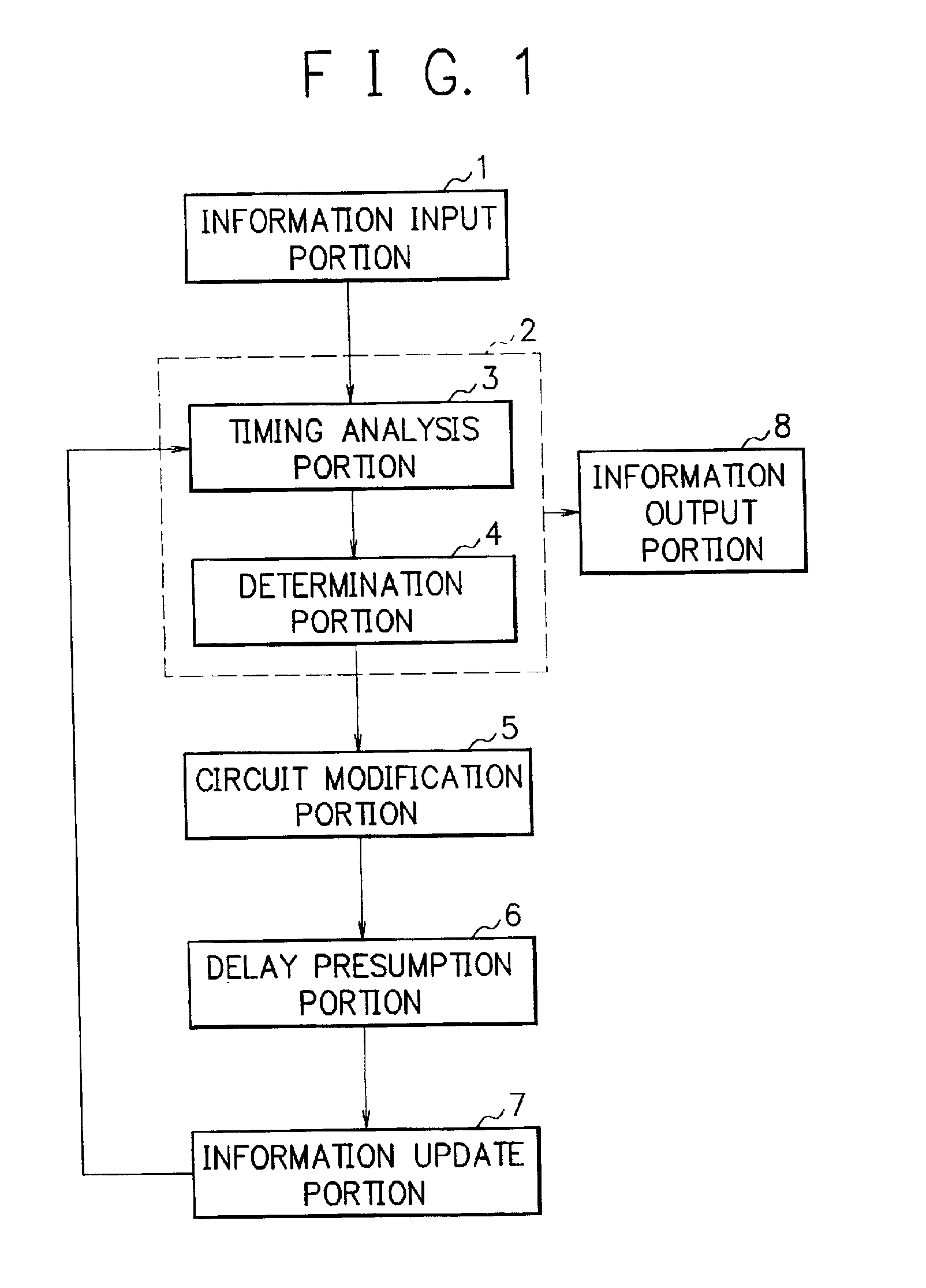

Design system of integrated circuit and its design method and program

InactiveUS6871329B2Timing errorShorten the timeSemiconductor/solid-state device manufacturingCAD circuit designDesign systemsIt design

A circuit modification portion modifies circuit information of an integrated circuit depending on a result of a timing test at a timing test portion to presume delay information at a delay presumption portion by modeling the circuit relating to its modified circuit information. Thereafter updating the circuit information and delay information of the integrated circuit at an information update portion to re-test the timing. This allows to carry out a timing analysis / test of the modified circuit without designing layout with the modified circuit information, which is required in a conventional design method. As a result, the number of designing the layout in the integrated circuit design is reduced to shorten time required for the layout design, which allows to shorten time required for the layout design process (layout design, timing analysis / test, and timing adjustment).

Owner:FUJITSU LTD

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com