Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

209results about How to "More stress" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

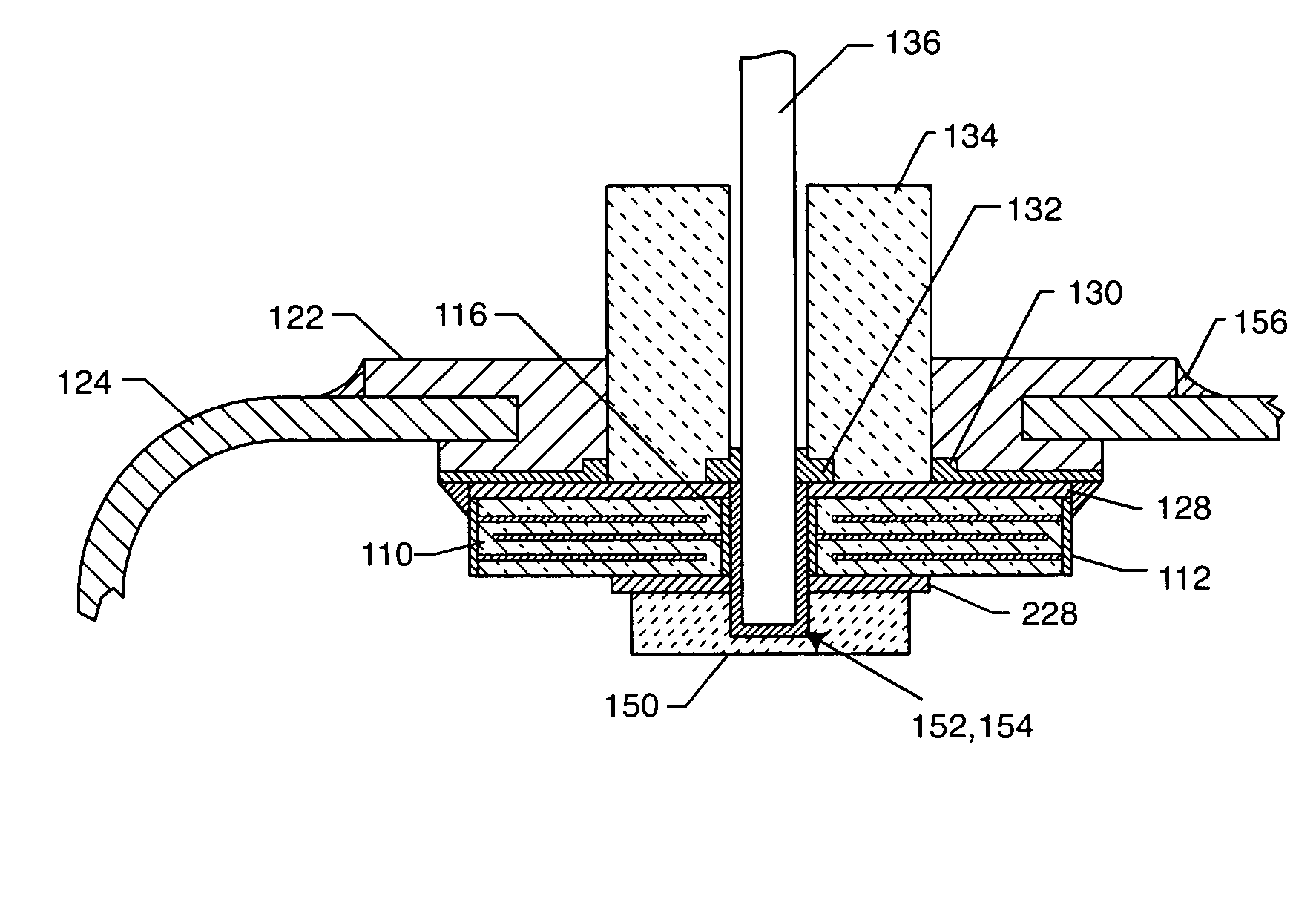

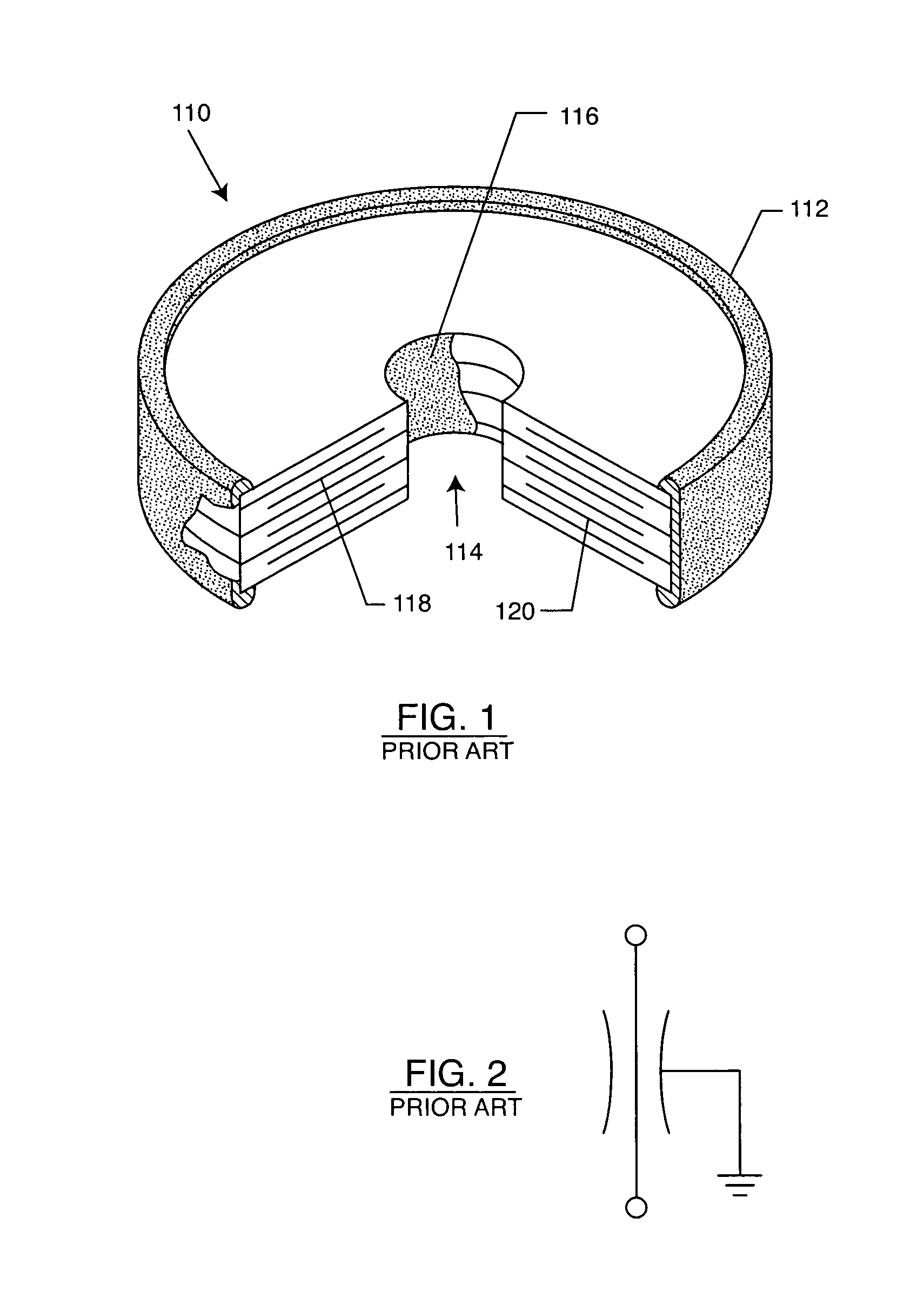

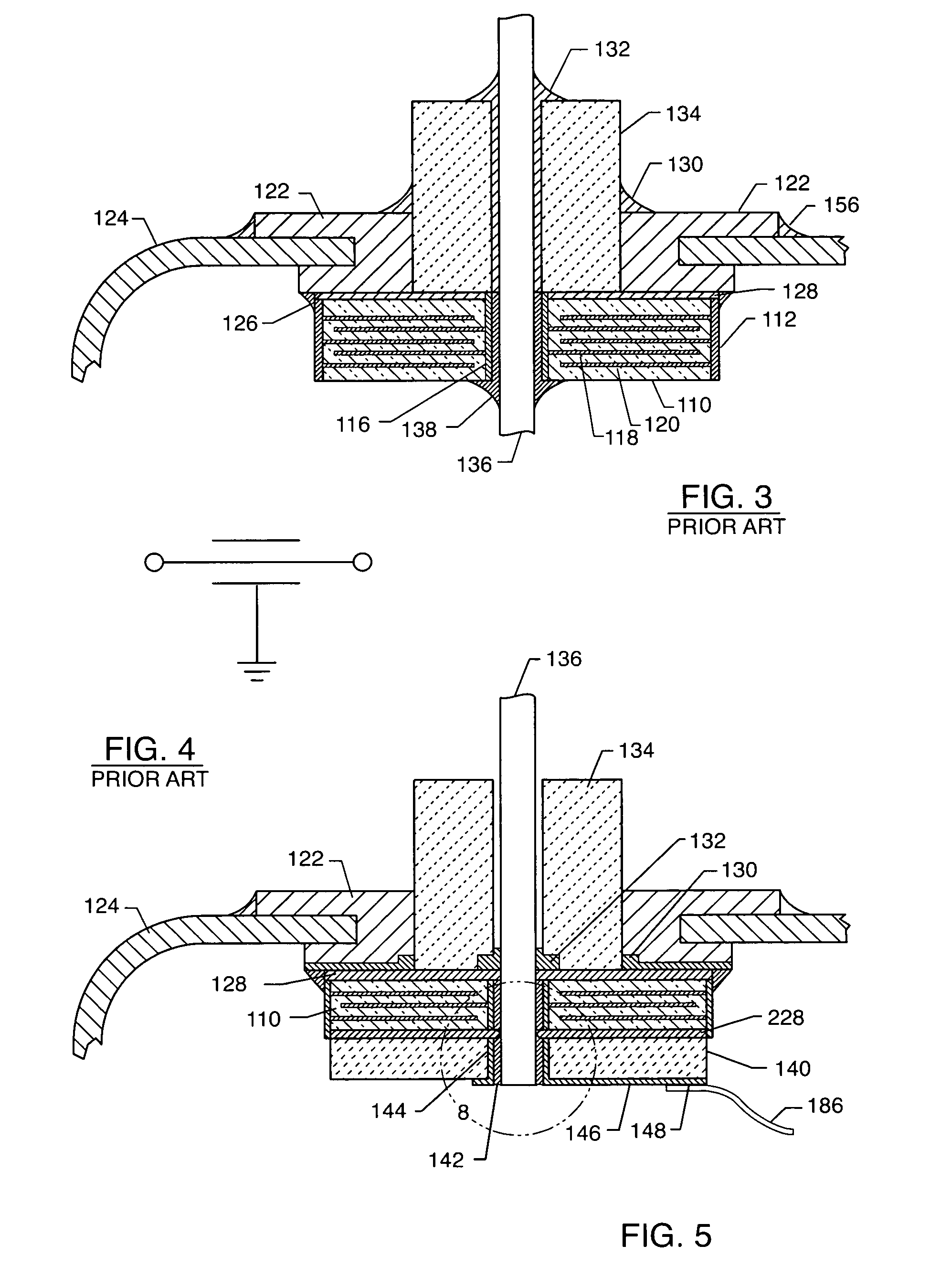

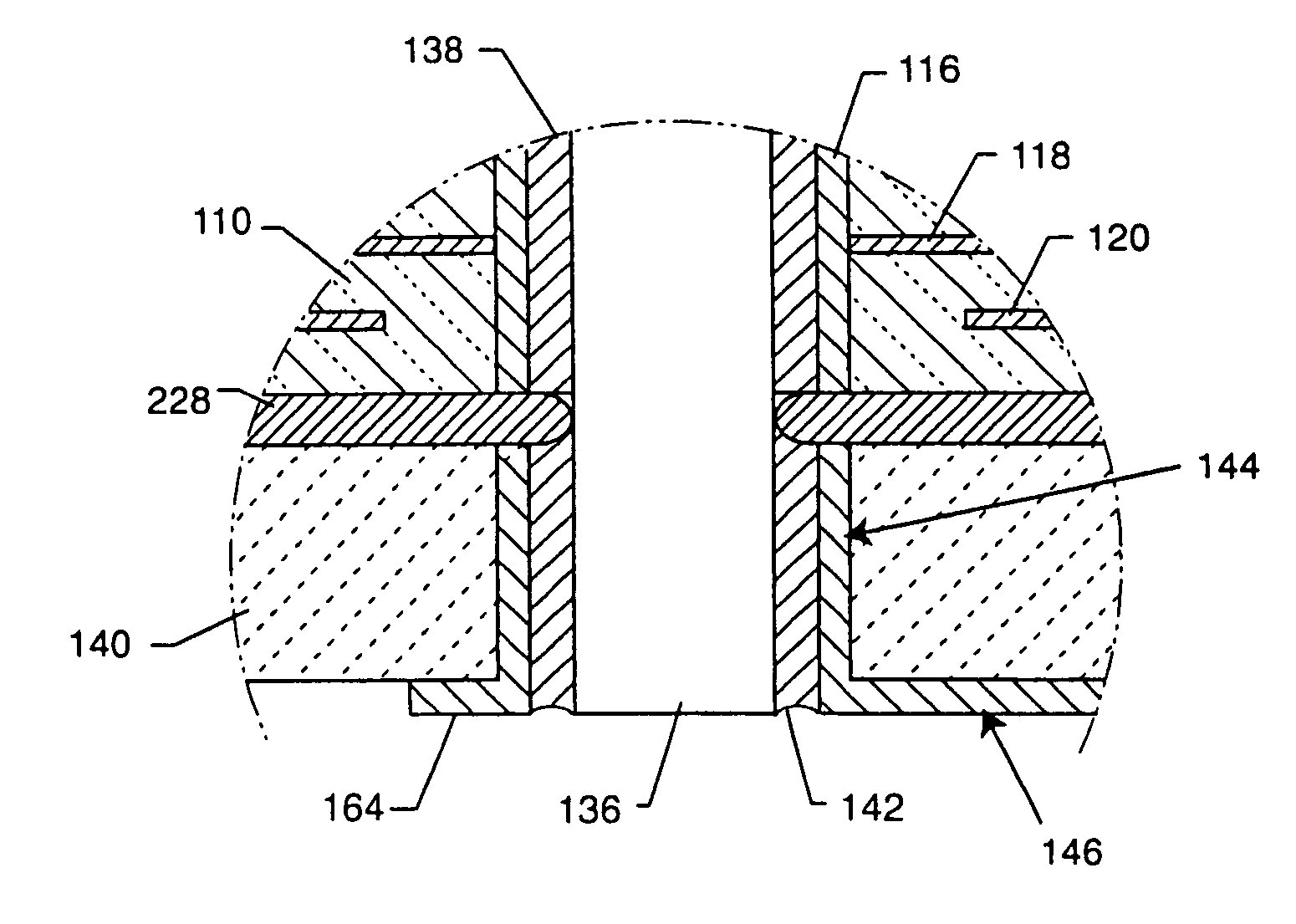

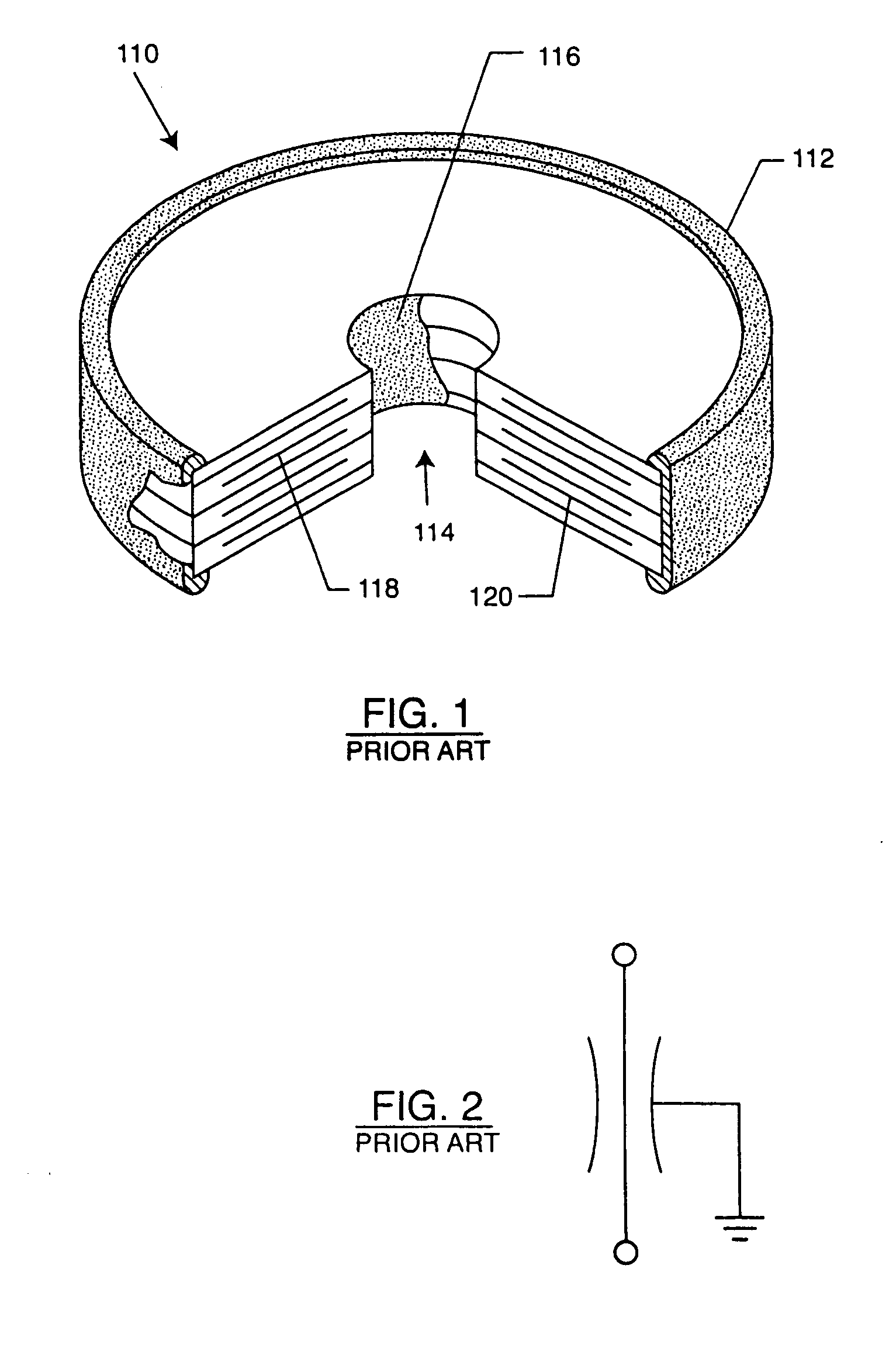

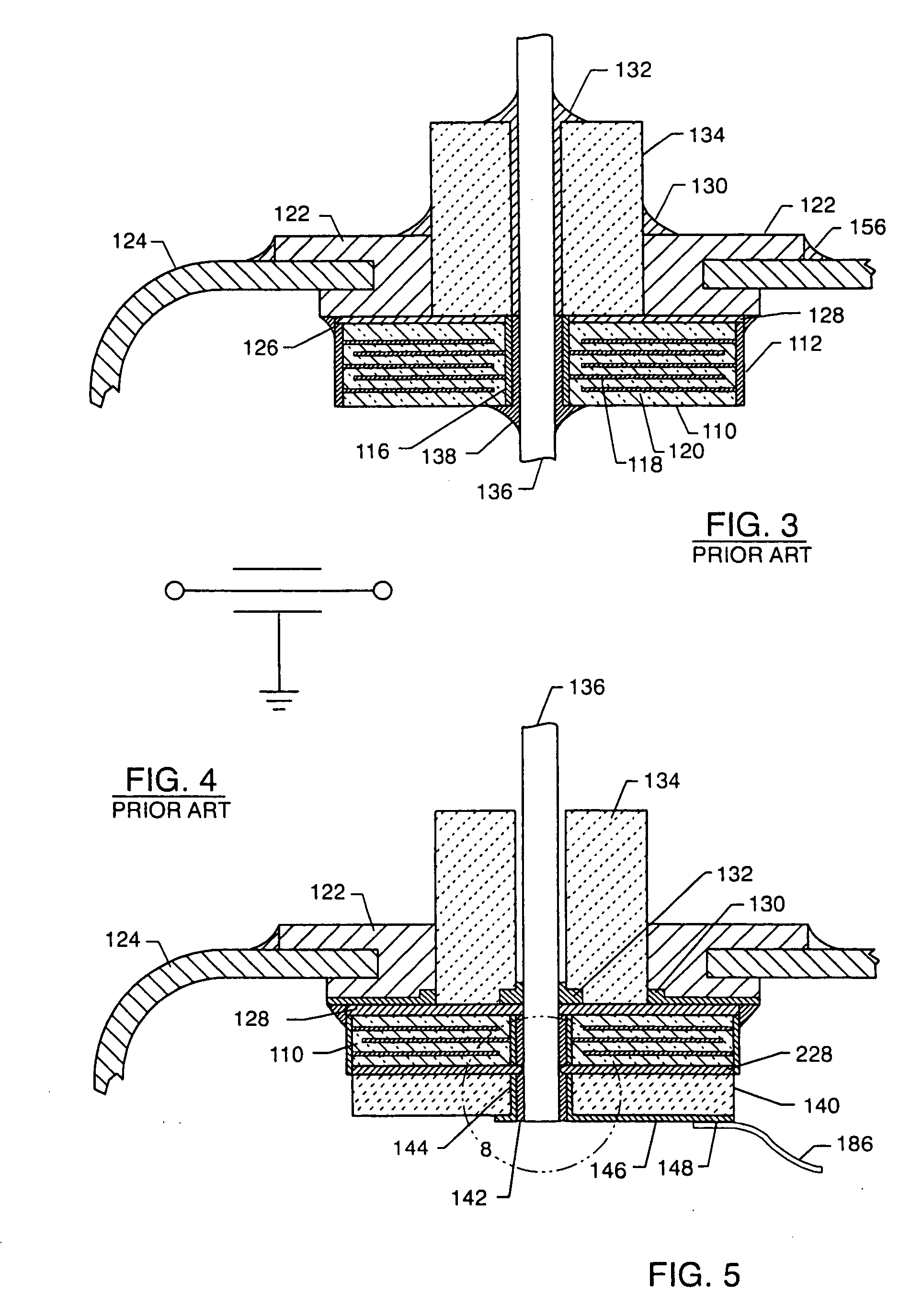

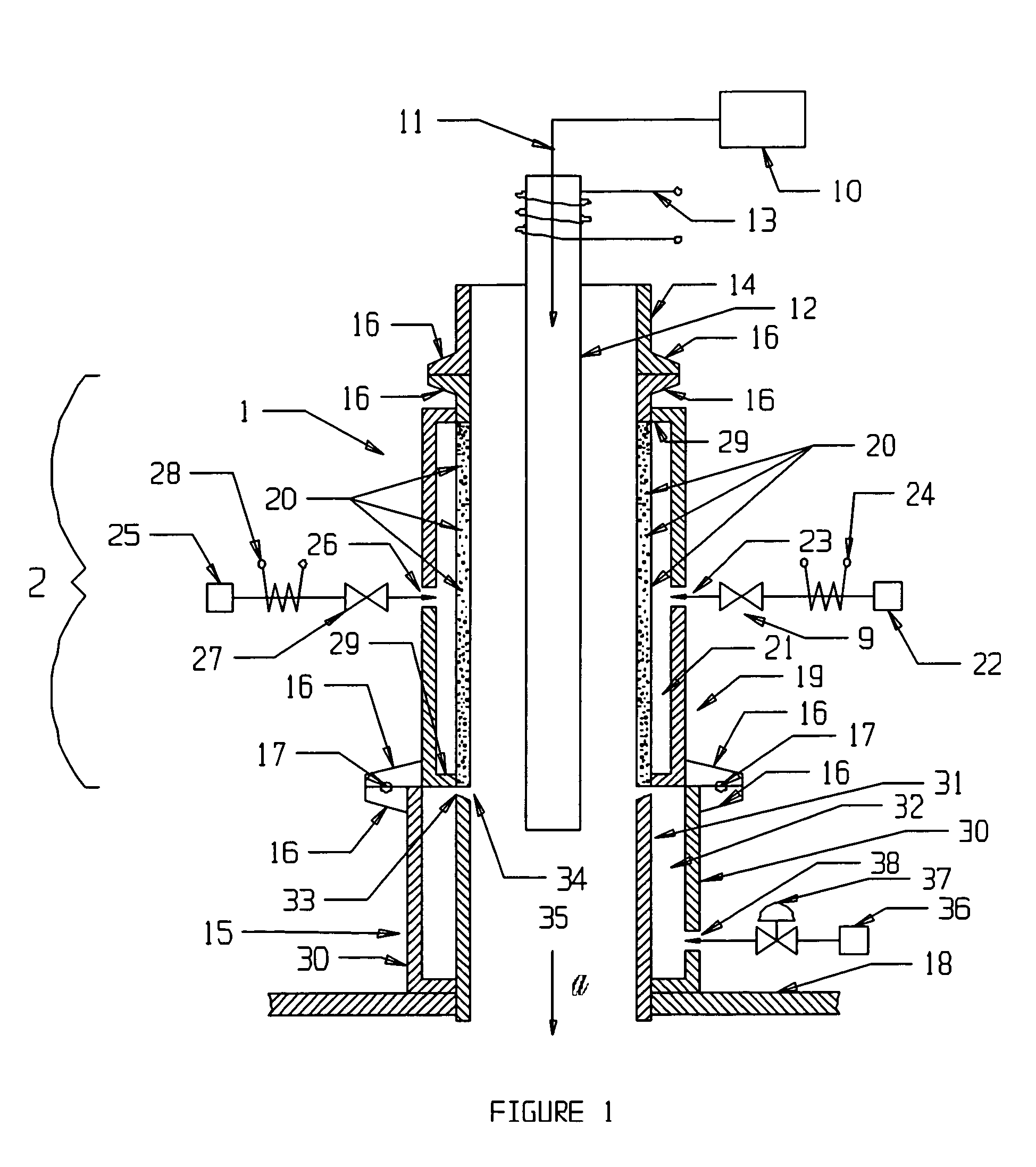

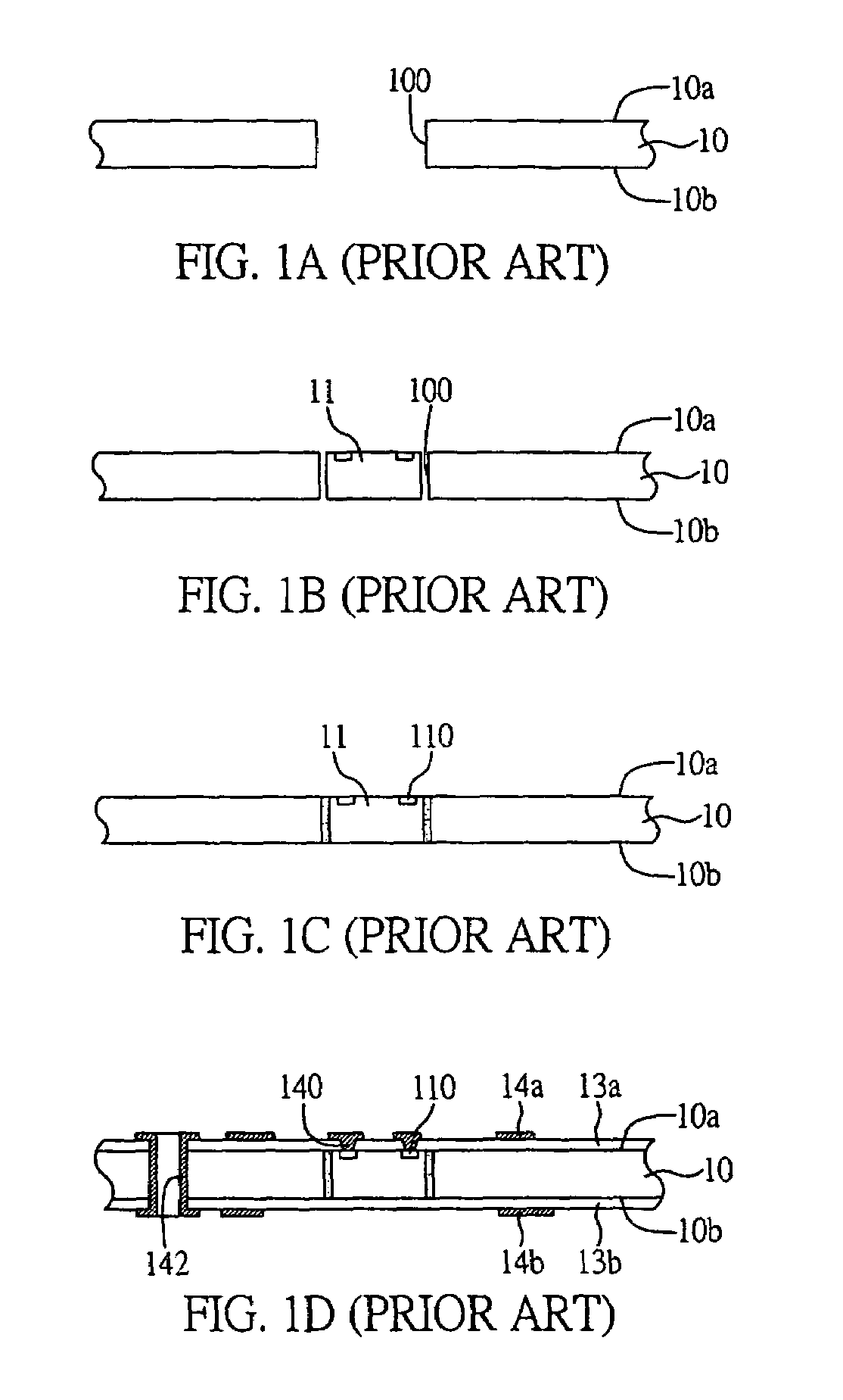

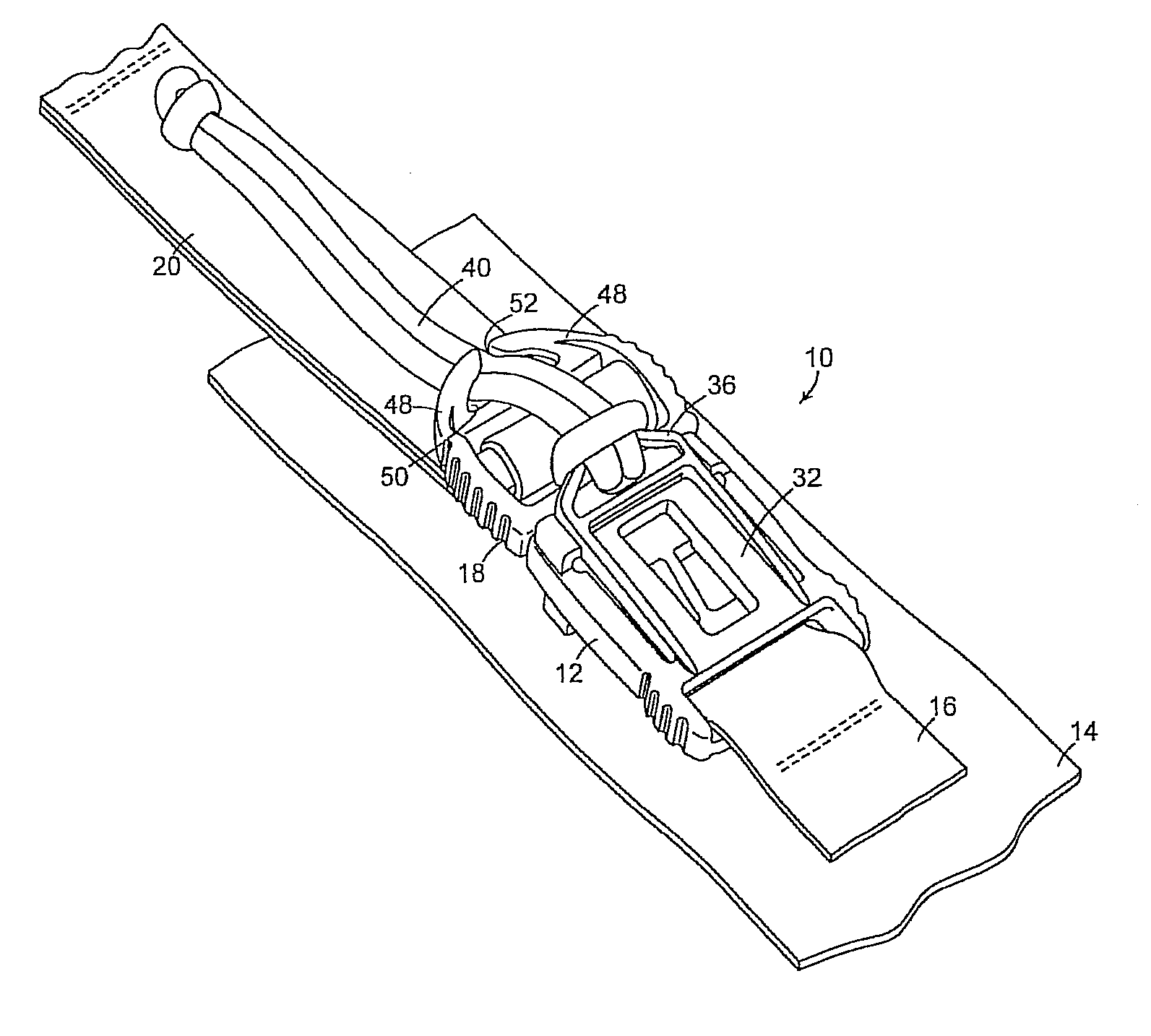

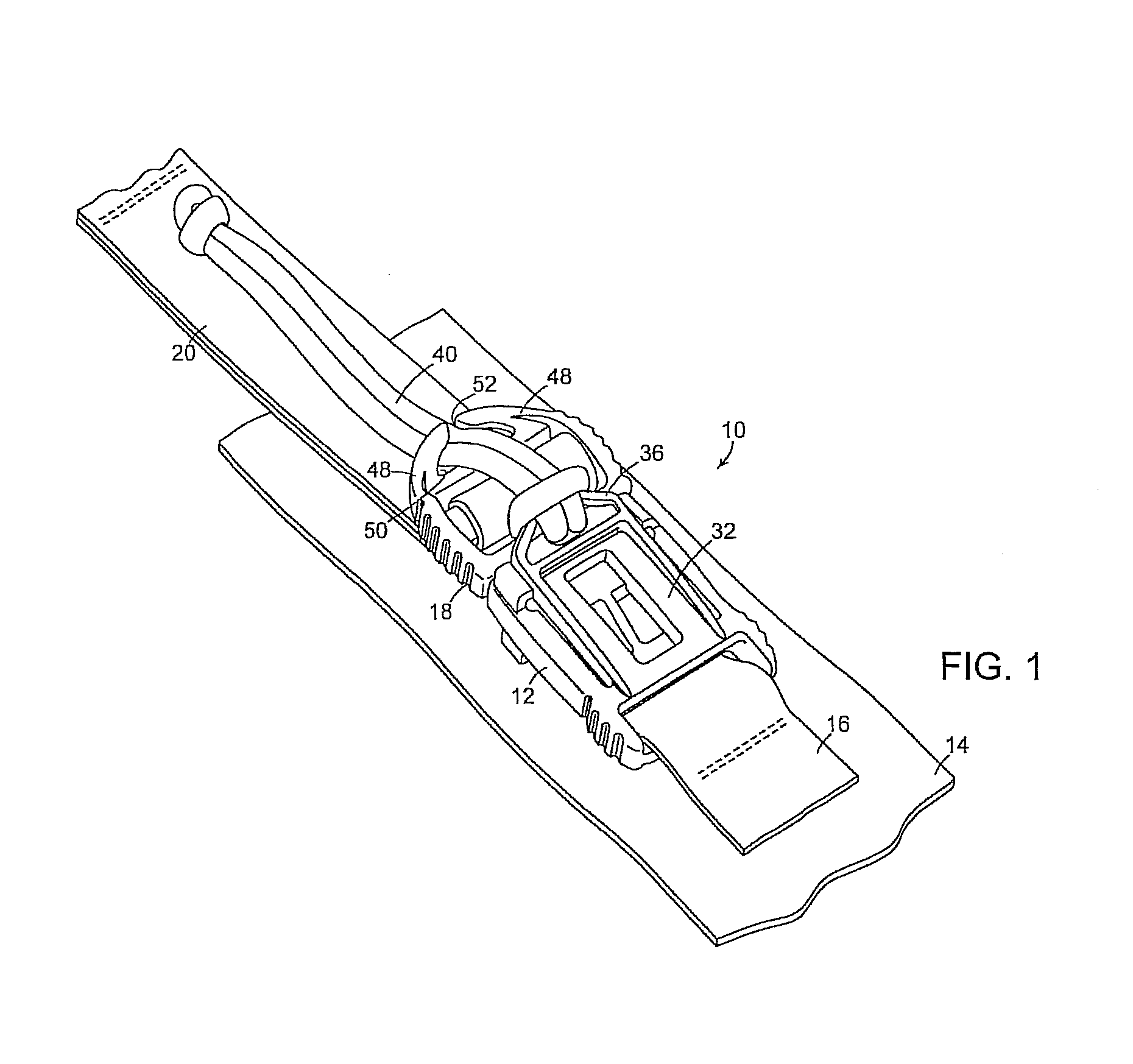

EMI filter terminal assembly with wire bond pads for human implant applications

ActiveUS20050007718A1Avoid crackingAbsorbs stressMultiple-port networksElectrotherapyElectromagnetic interferenceSoldering

An electromagnetic interference filter terminal assembly for active implantable medical devices includes a structural pad in the form of a substrate or attached wire bond pad, for convenient attachment of wires from the circuitry inside the implantable medical device to the capacitor structure via thermal or ultrasonic bonding, soldering or the like while shielding the capacitor from forces applied to the assembly during attachment of the wires.

Owner:WILSON GREATBATCH LTD

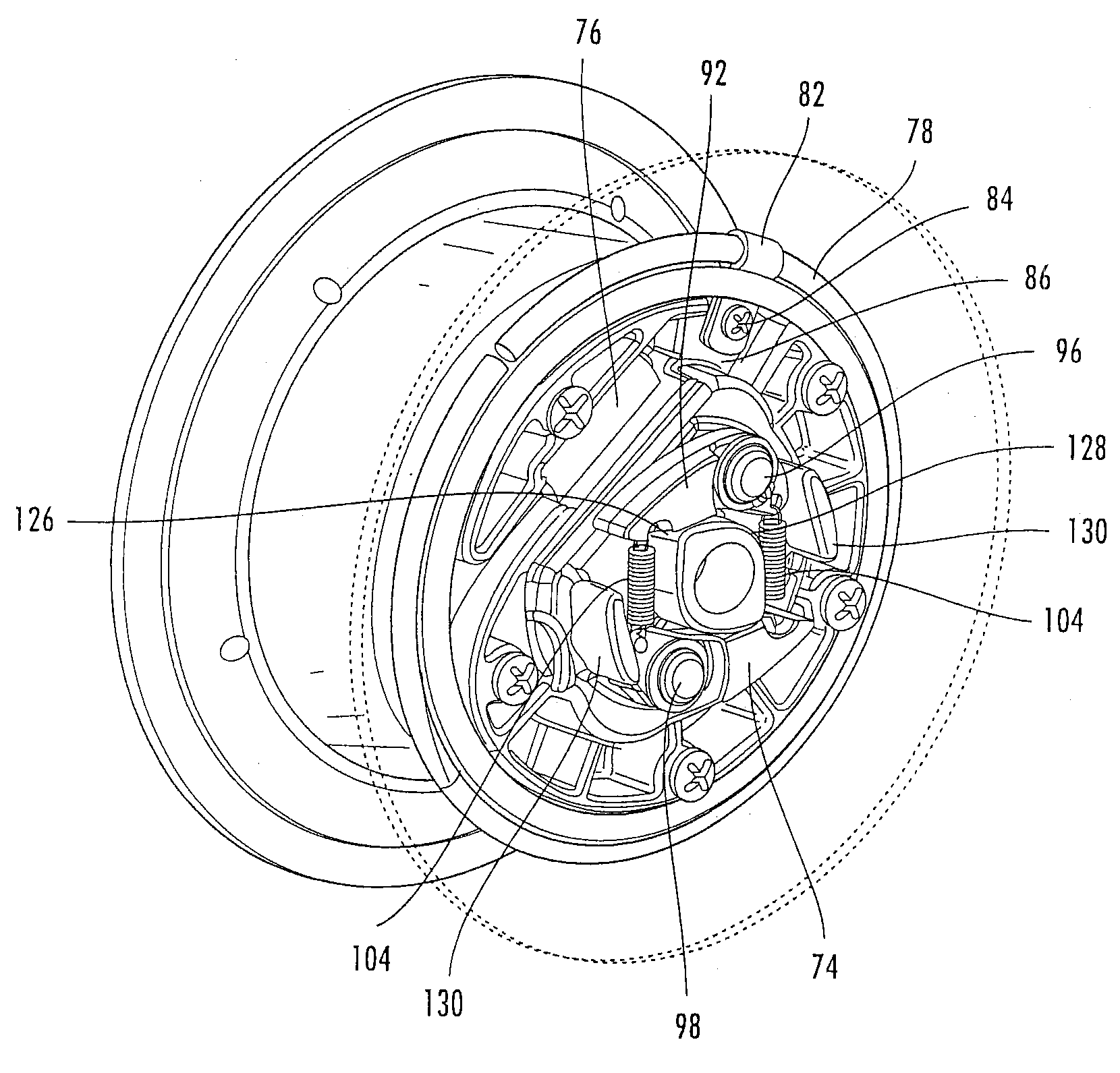

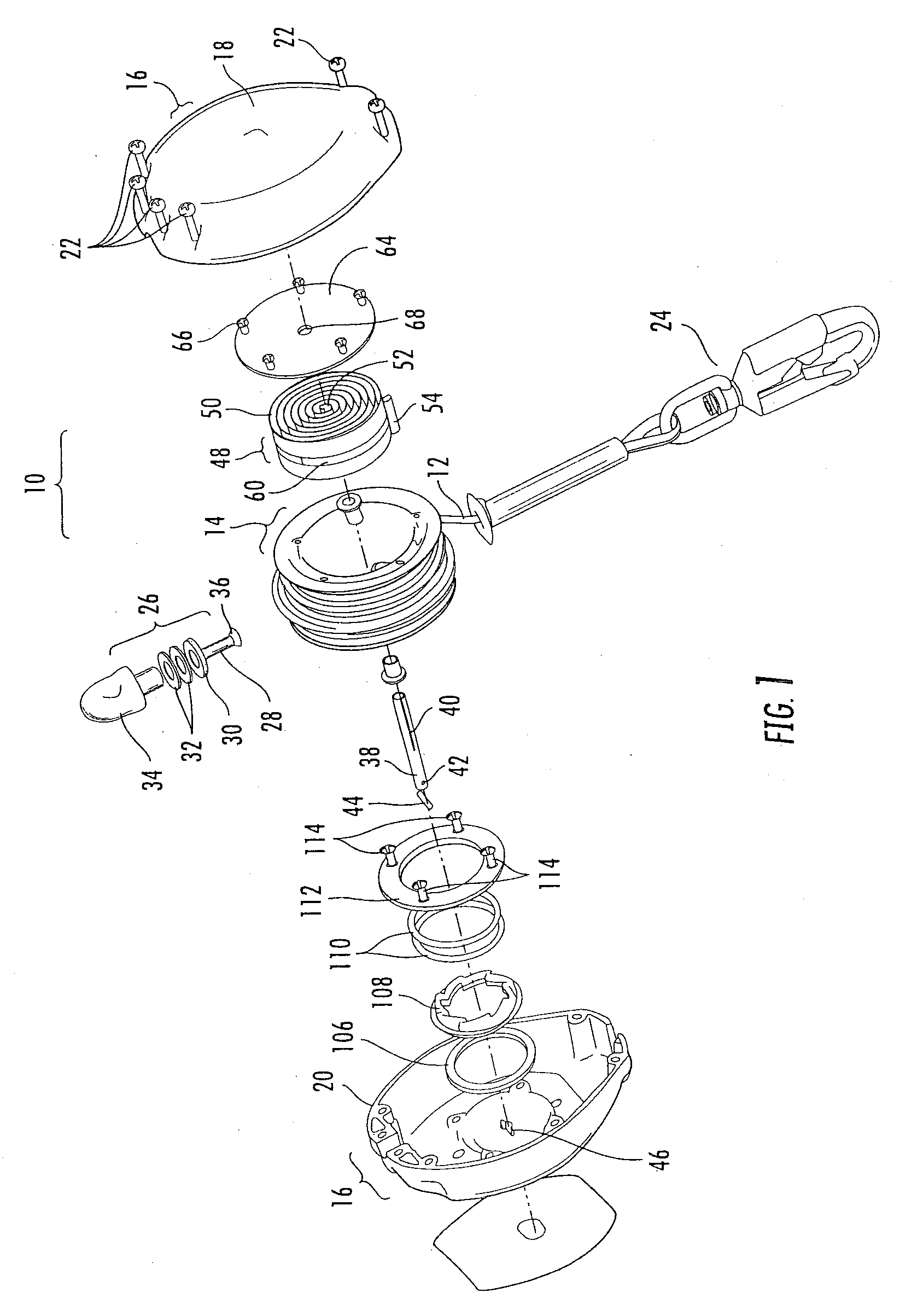

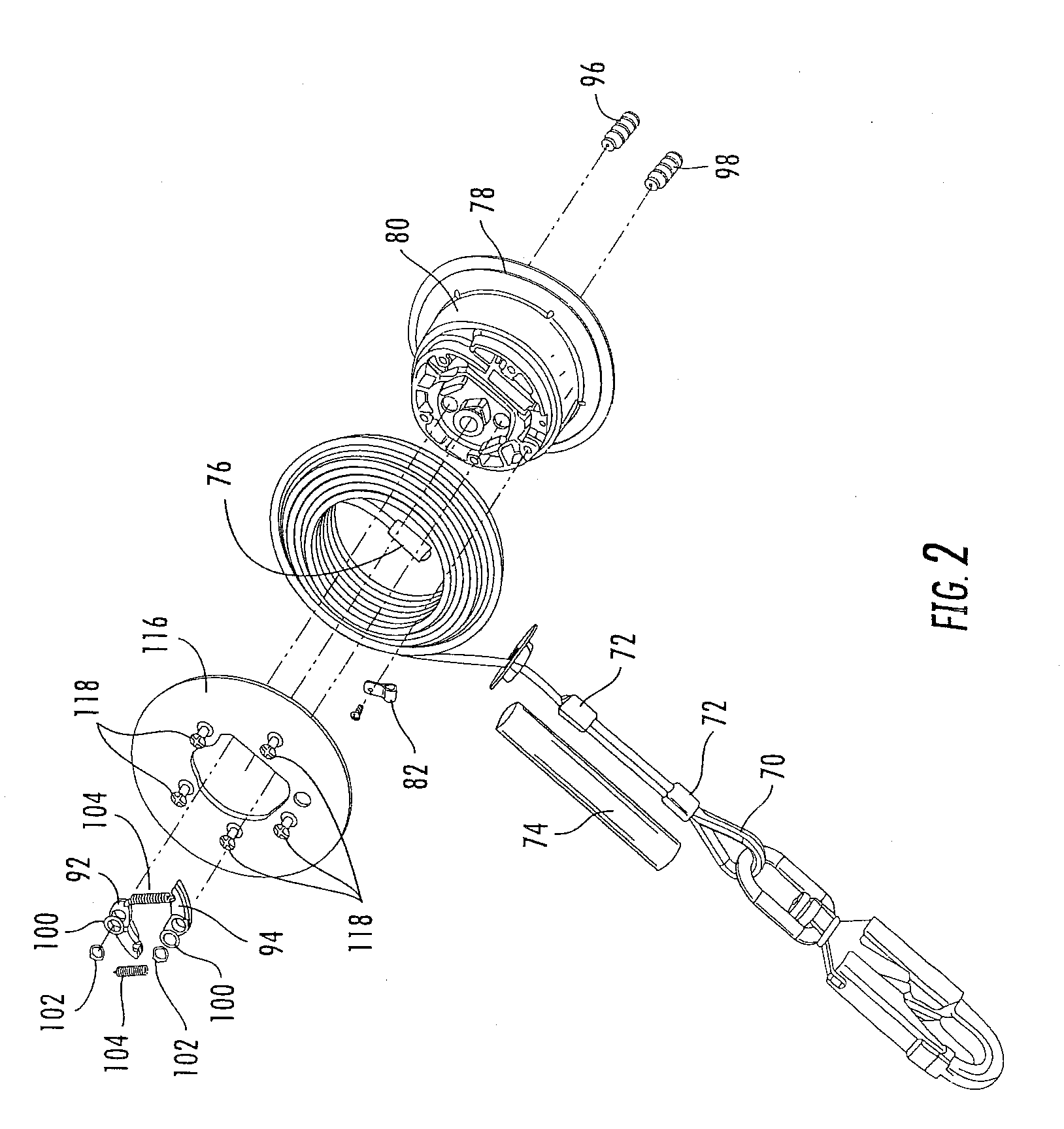

Retractable lifeline safety device

InactiveUS20090178887A1Overcome deficiency and shortcomingReduce manufacturing costSafety beltsBuilding rescueSprocketEngineering

A retractable lifeline safety device usable as heights above the ground. The safety device is attached to the structure on which the worker is performing the task, and a lifeline such as a cable is withdrawn from the housing thereof, the end of which is attached to a belt or harness worn by the worker. The cable may be easily drawn out of the housing in response to the worker moving about normally in the appropriate work space, and the cable is automatically drawn back into the housing of the safety device as the worker draws closer thereto. However, should the worker fall, a brake mechanism within the safety device is automatically engaged by a sprocket and pawl system, stopping the worker's descent.

Owner:SIGMA IND

EMI filter terminal assembly with wire bond pads for human implant applications

ActiveUS20050248907A1More stressImprove featuresAnti-noise capacitorsElectrotherapyElectromagnetic interferenceSoldering

An electromagnetic interference filter terminal assembly for active implantable medical devices includes a structural pad in the form of a substrate or attached wire bond pad, for convenient attachment of wires from the circuitry inside the implantable medical device to the capacitor structure via thermal or ultrasonic bonding, soldering or the like while shielding the capacitor from forces applied to the assembly during attachment of the wires.

Owner:WILSON GREATBATCH LTD

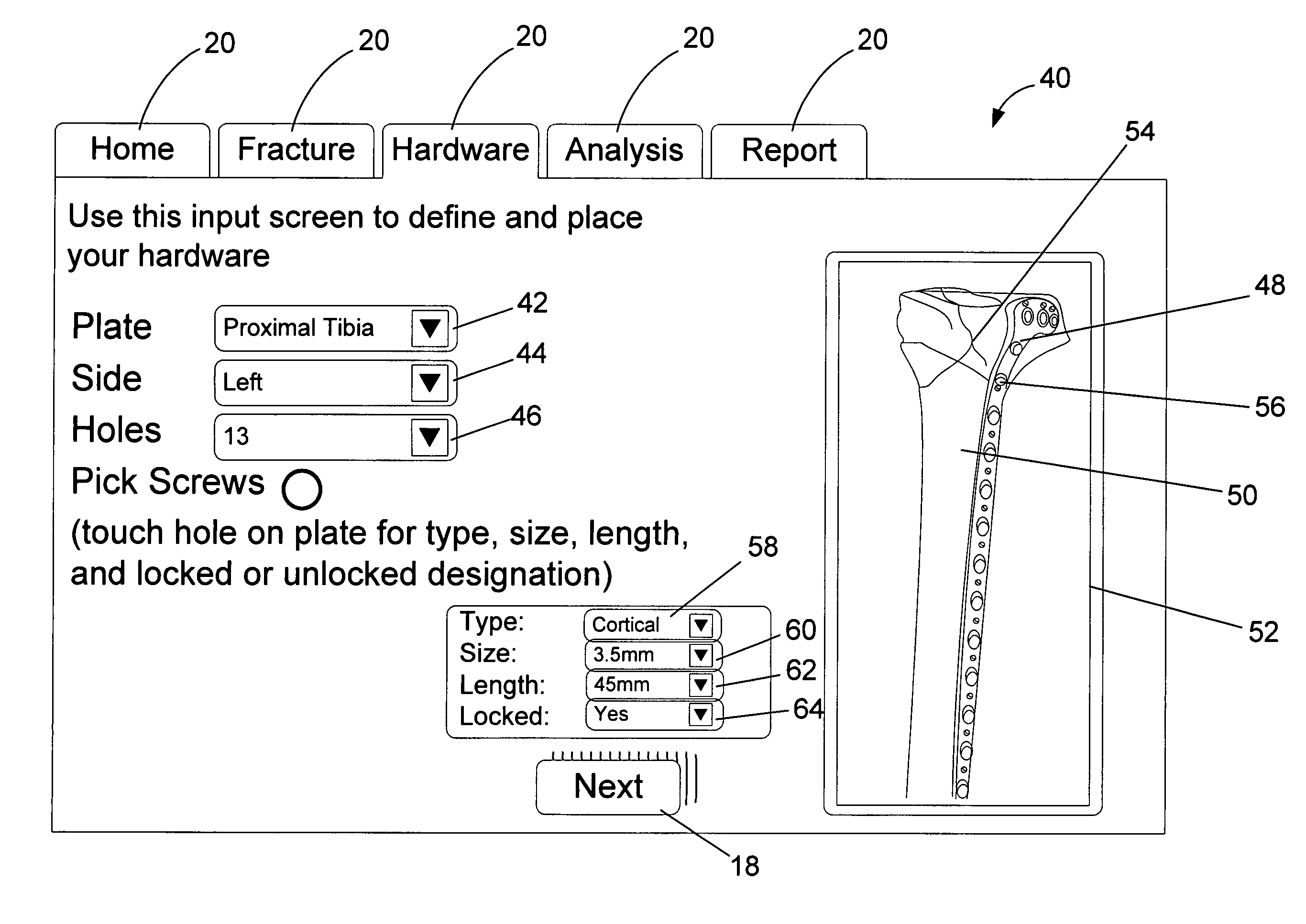

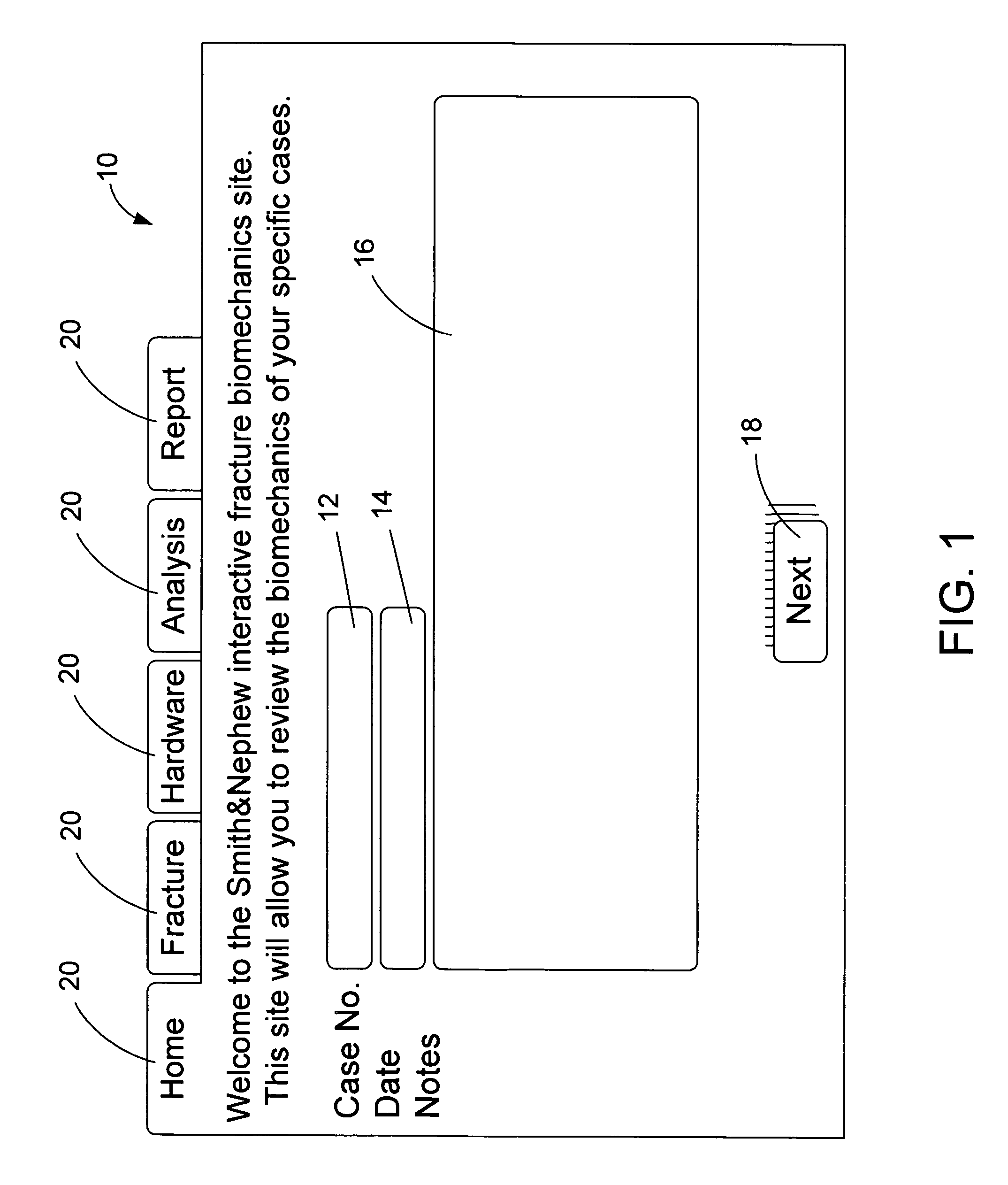

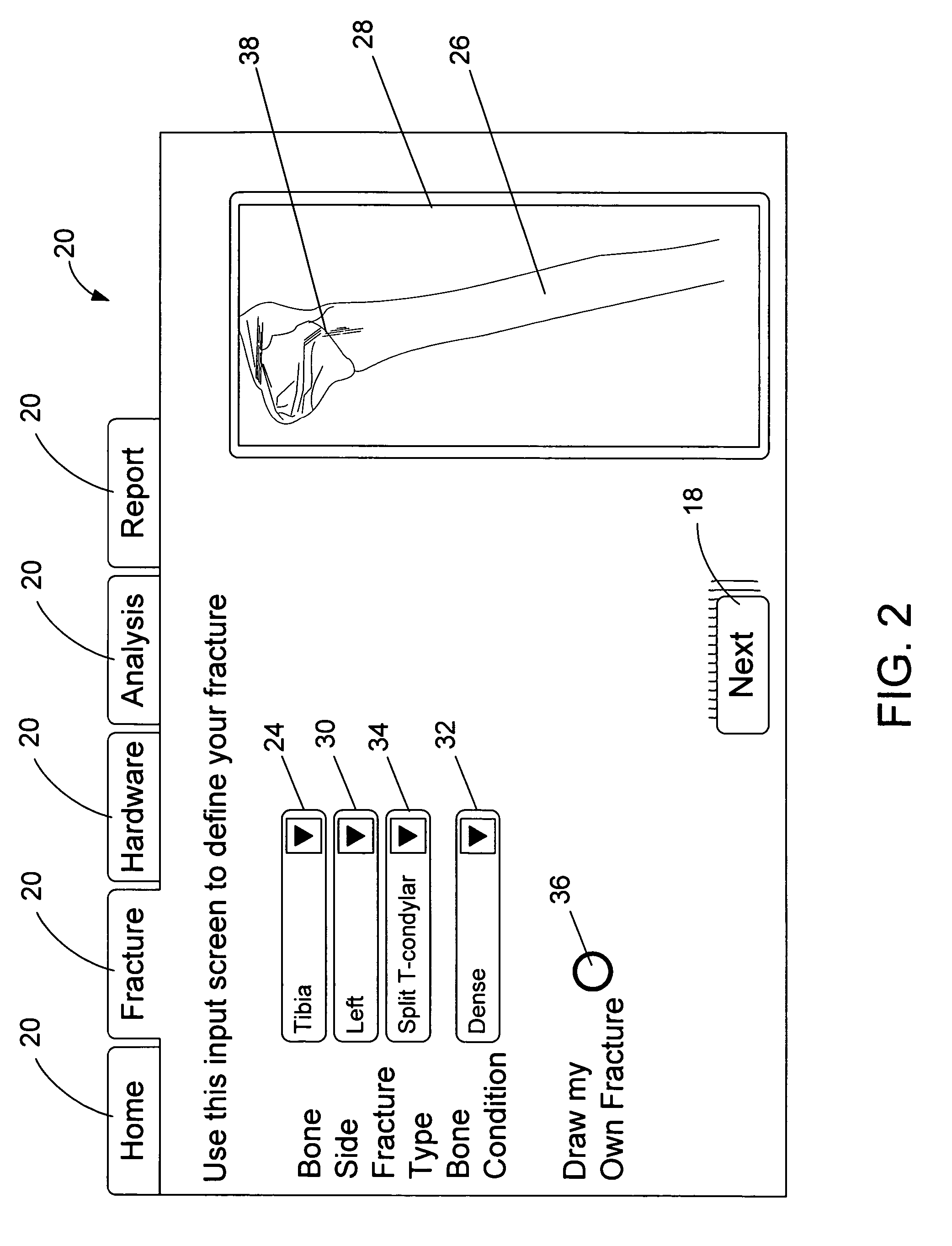

Interactive orthopaedic biomechanics system

Methods of selecting a configuration of fixation and compression screws for a bone plate to be installed on a bone of a patient. A computer or website allows a user to load images of a fractured bone and specify a particular configuration of fixation and compression screws with a plate on the loaded bone. The computer replicates stresses imposed on the bone by regular activities using finite element analysis and provide information about the suitability of the selected configuration.

Owner:SMITH & NEPHEW INC

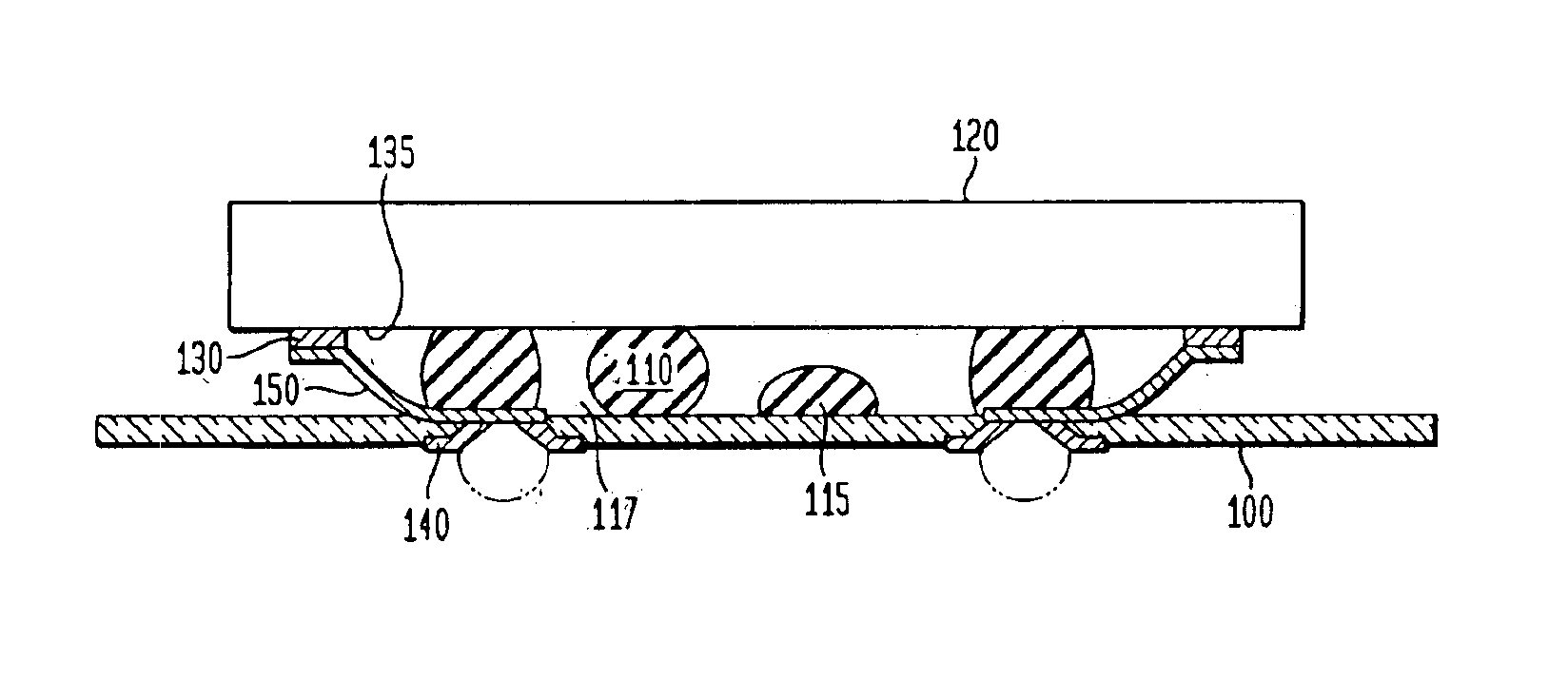

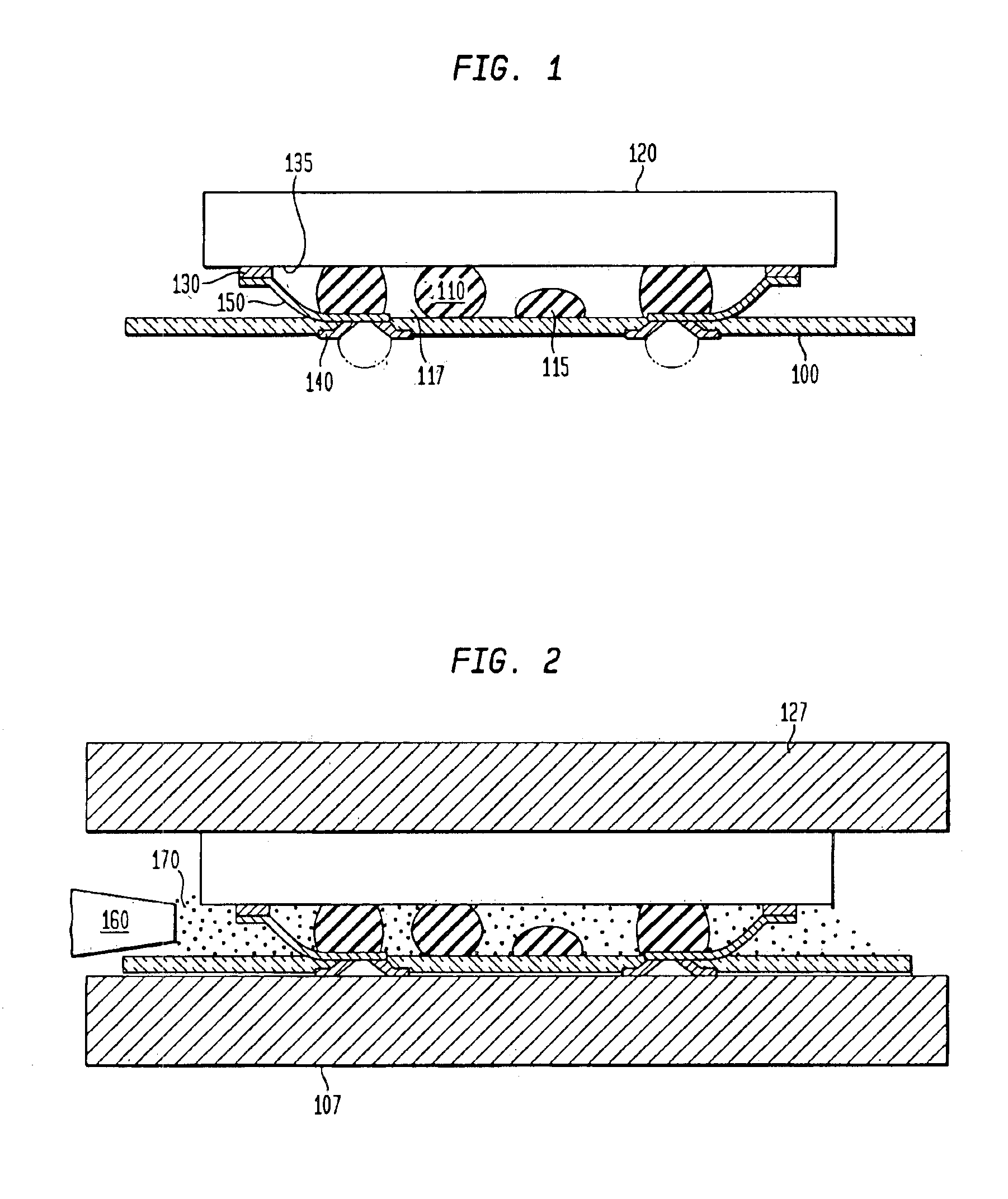

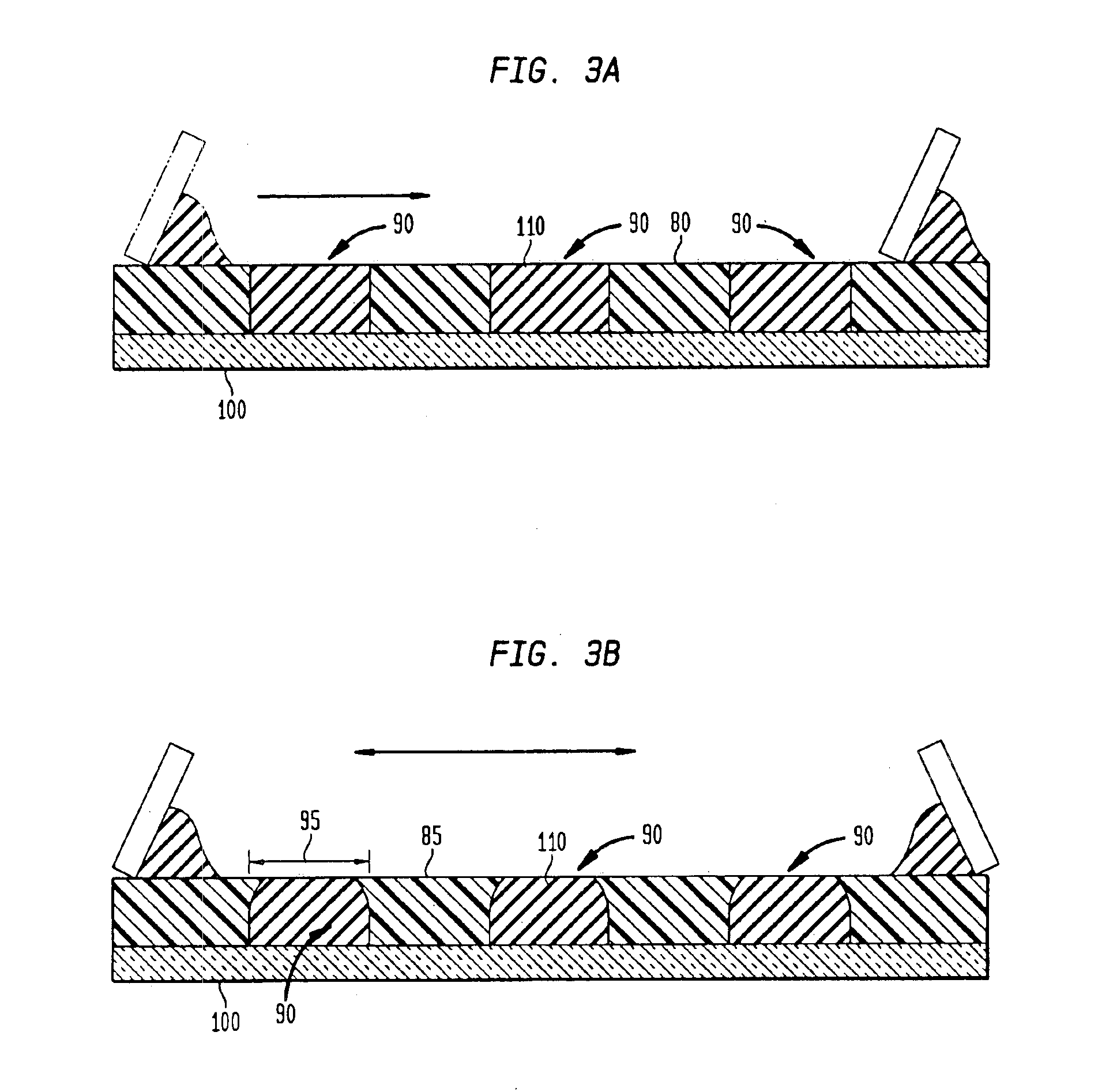

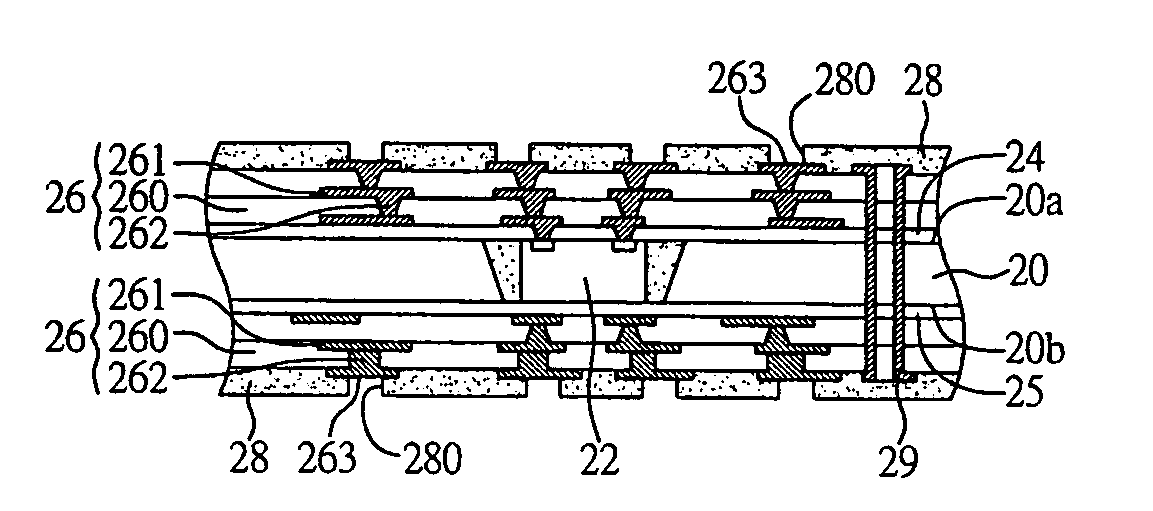

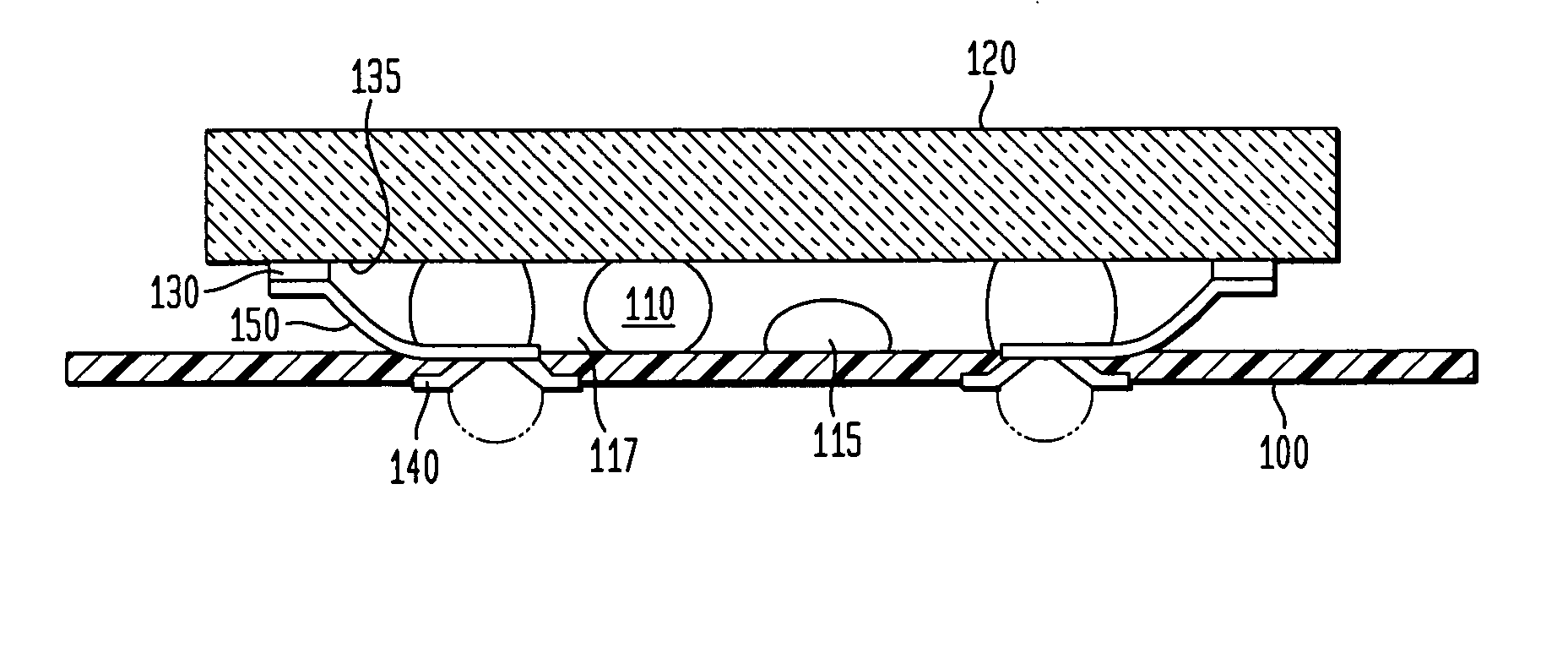

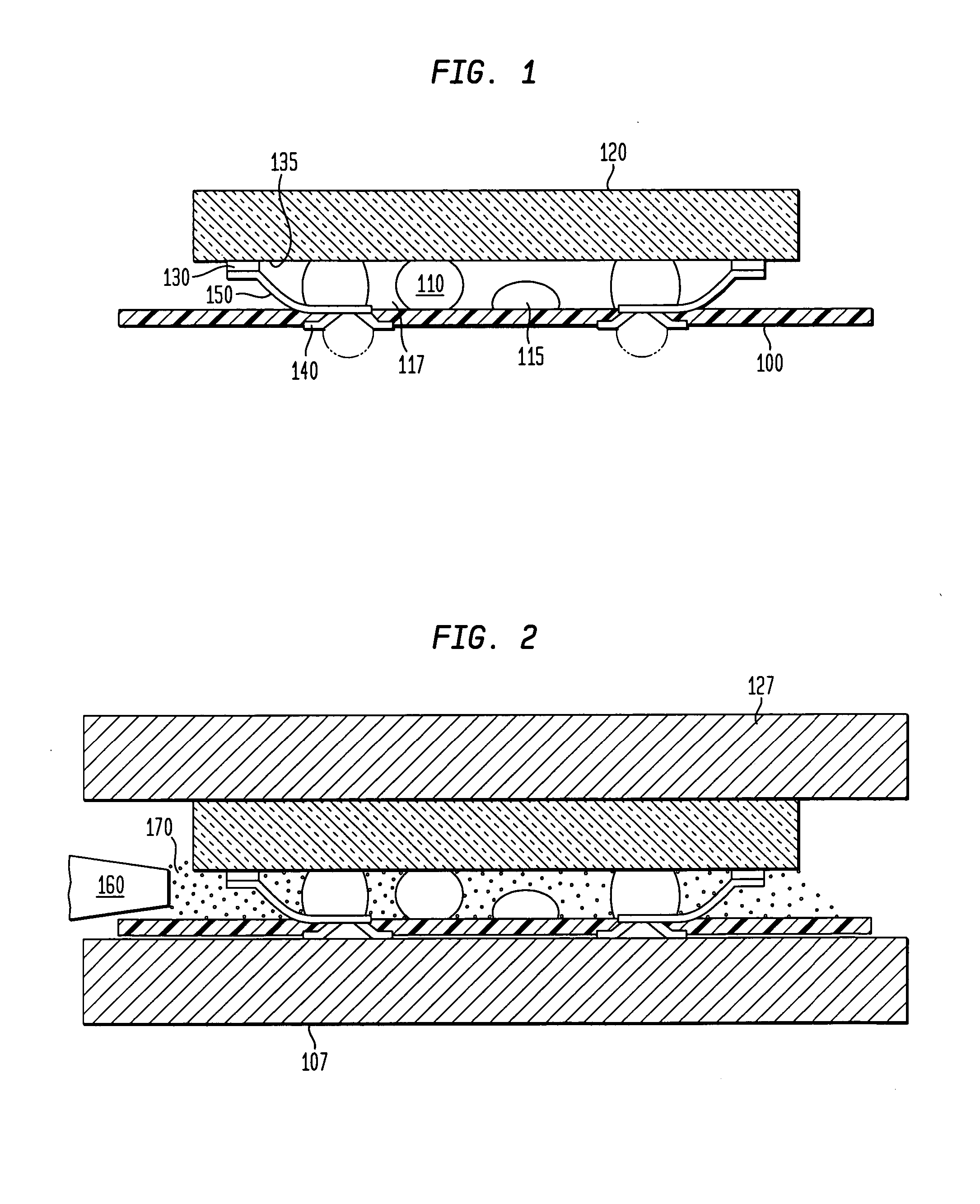

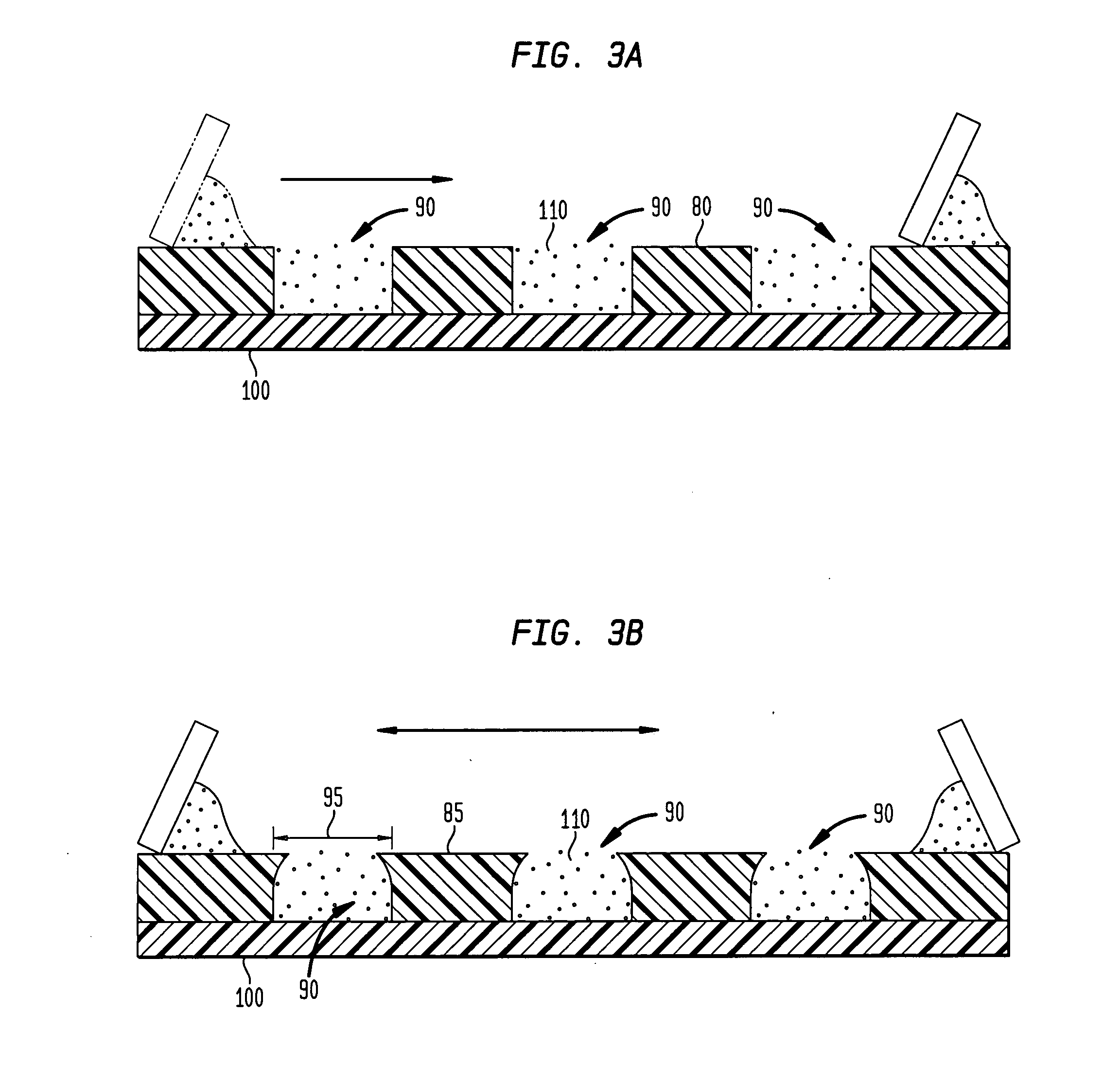

Methods of making microelectronic assemblies including compliant interfaces

InactiveUS6870272B2More stressEfficient packagingPrinted circuit assemblingSemiconductor/solid-state device detailsConductive materialsSilicone Elastomers

An assembly includes a structure, a plurality of terminals and a plurality of compliant pads disposed between said terminals and said structure. The terminals are aligned with at least some of said pads, with the pads providing a standoff between the structure and the terminals. The compliant pads are preferably made of a non-conductive material such as a silicone elastomer.

Owner:TESSERA INC

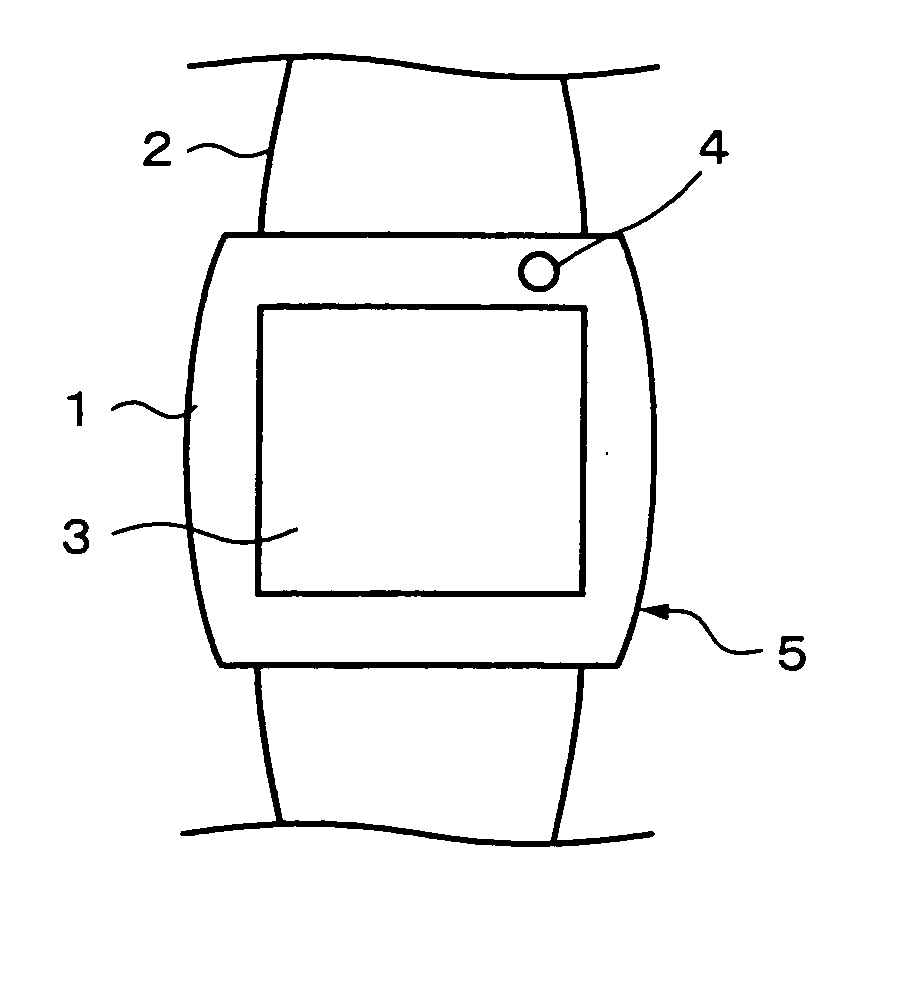

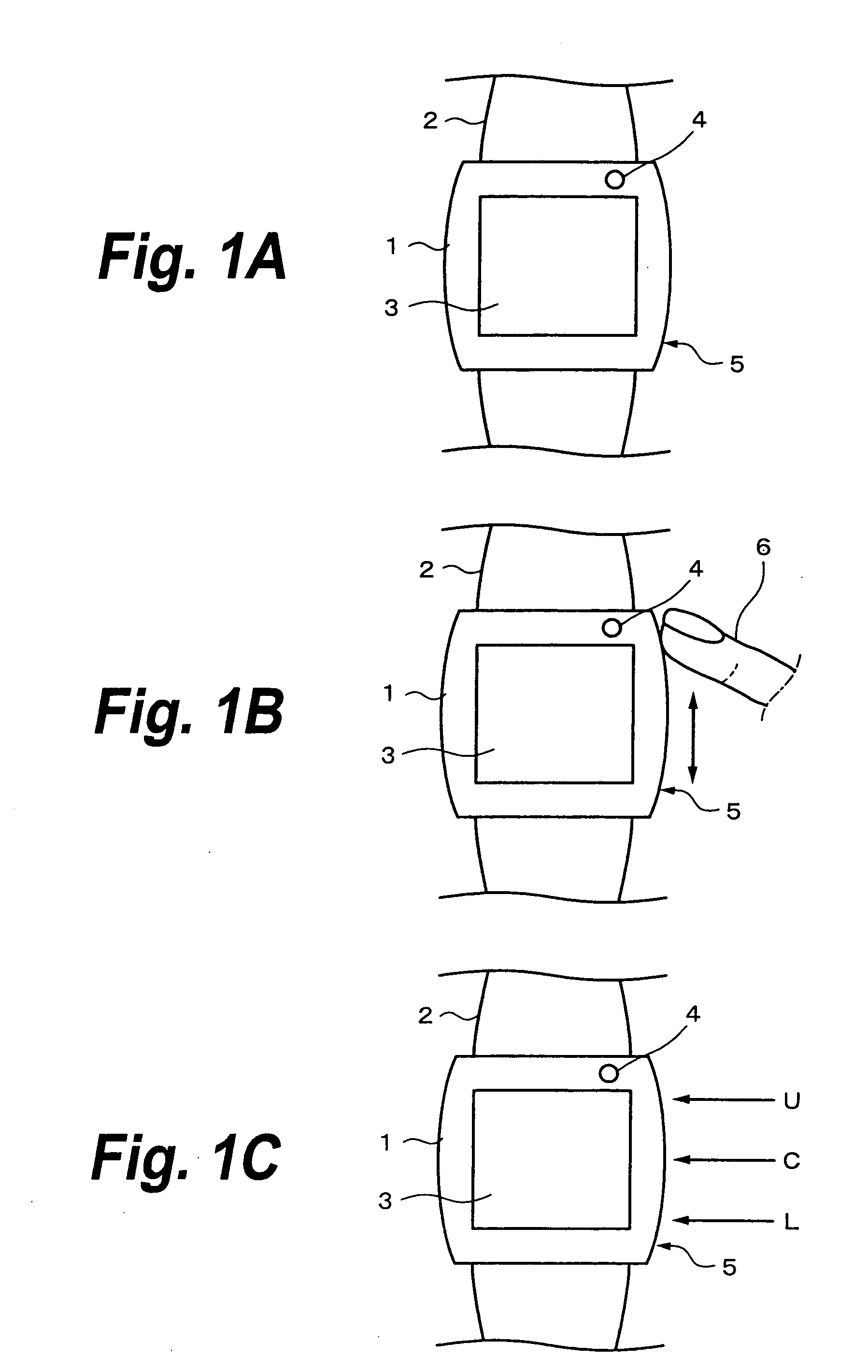

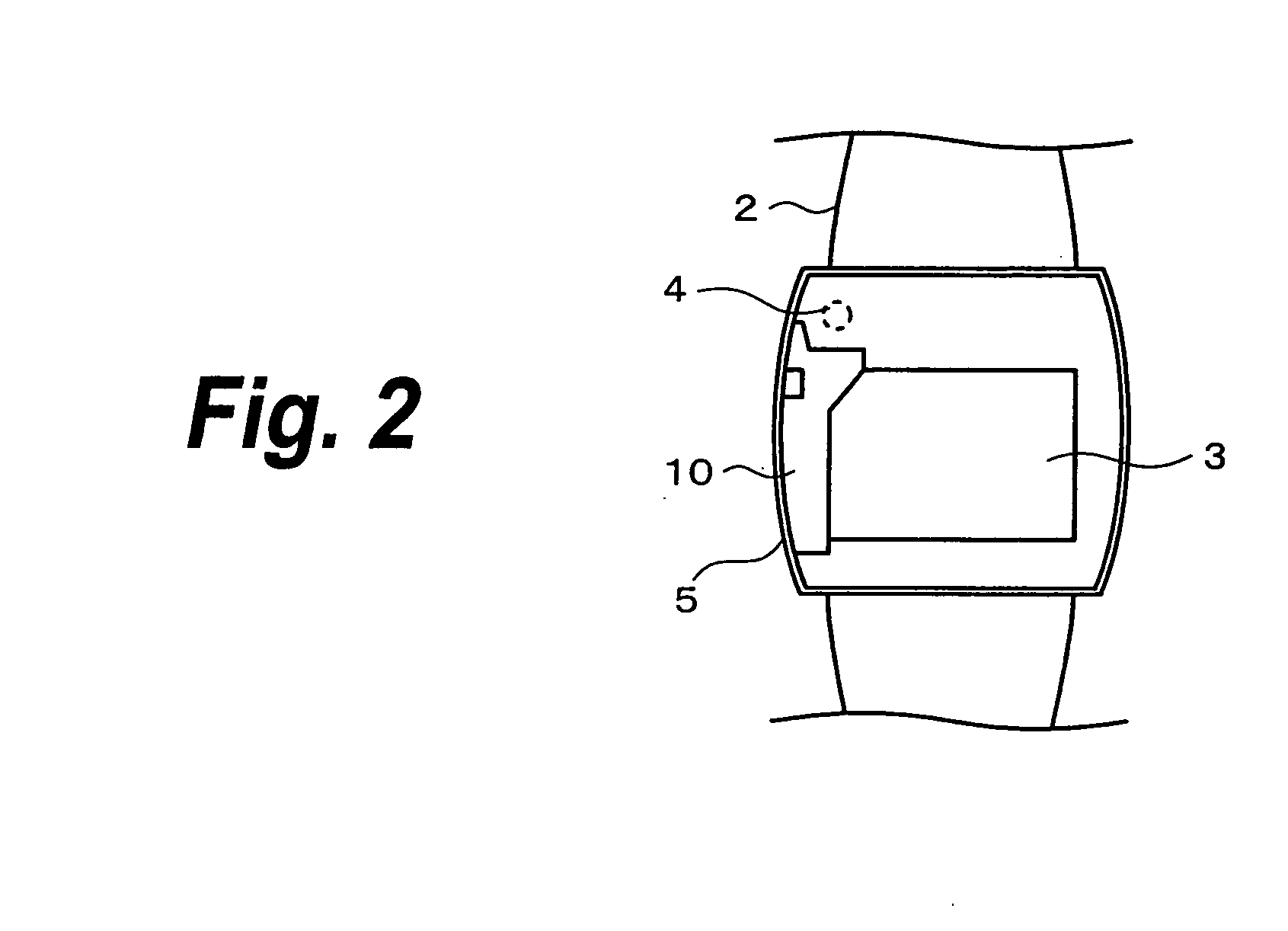

Input device, information terminal device, and mode switching method

InactiveUS20060170649A1Easy to operateRelieve stressInput/output for user-computer interactionTelevision system detailsTerminal equipmentEngineering

A display portion 3 and a camera portion 4 are disposed in a main body 1. A housing of the main body 1 is made of an non-electroconductive material. One side surface of the main body 1 is an information input surface 5 of an input apparatus. Disposed in the housing on the side surface of the information input surface is a light, thin-film shaped electrostatic sensor. By moving a finger tip 6 on the information input surface 5 upward and downward while contacting thereon, a cursor moves on the display portion 3. Tap positions U, C, and L into which the information input surface 5 is divided in its height direction are defined. When each tap position is lightly tapped one time, releasing and touching states of the finger tip 6 are detected by the sensor and a tap operation is recognized. The tap operation includes a confirmation of a menu at the cursor position, a shutter operation, and so forth. The difference of tap positions can be detected by the sensor.

Owner:SONY CORP

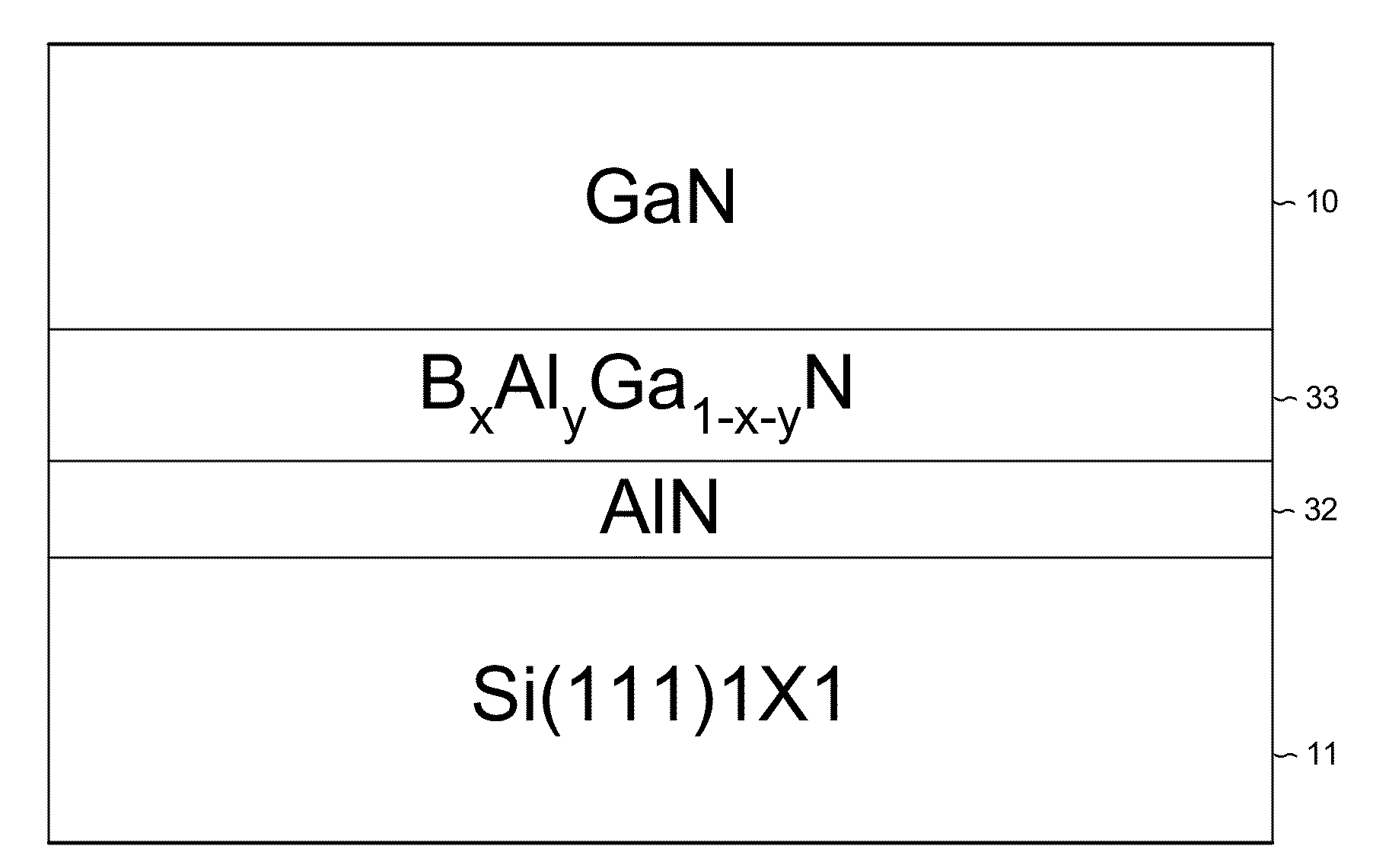

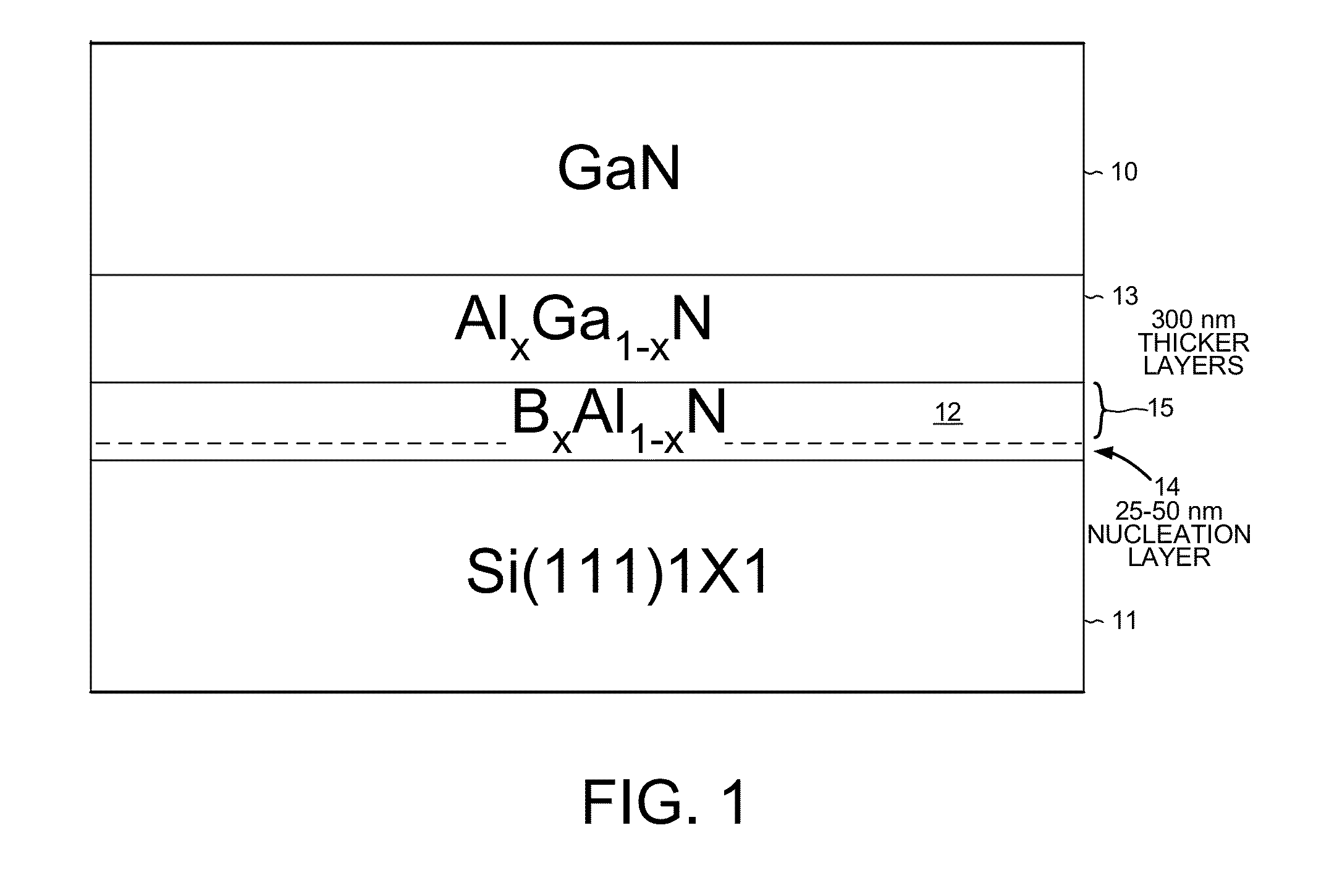

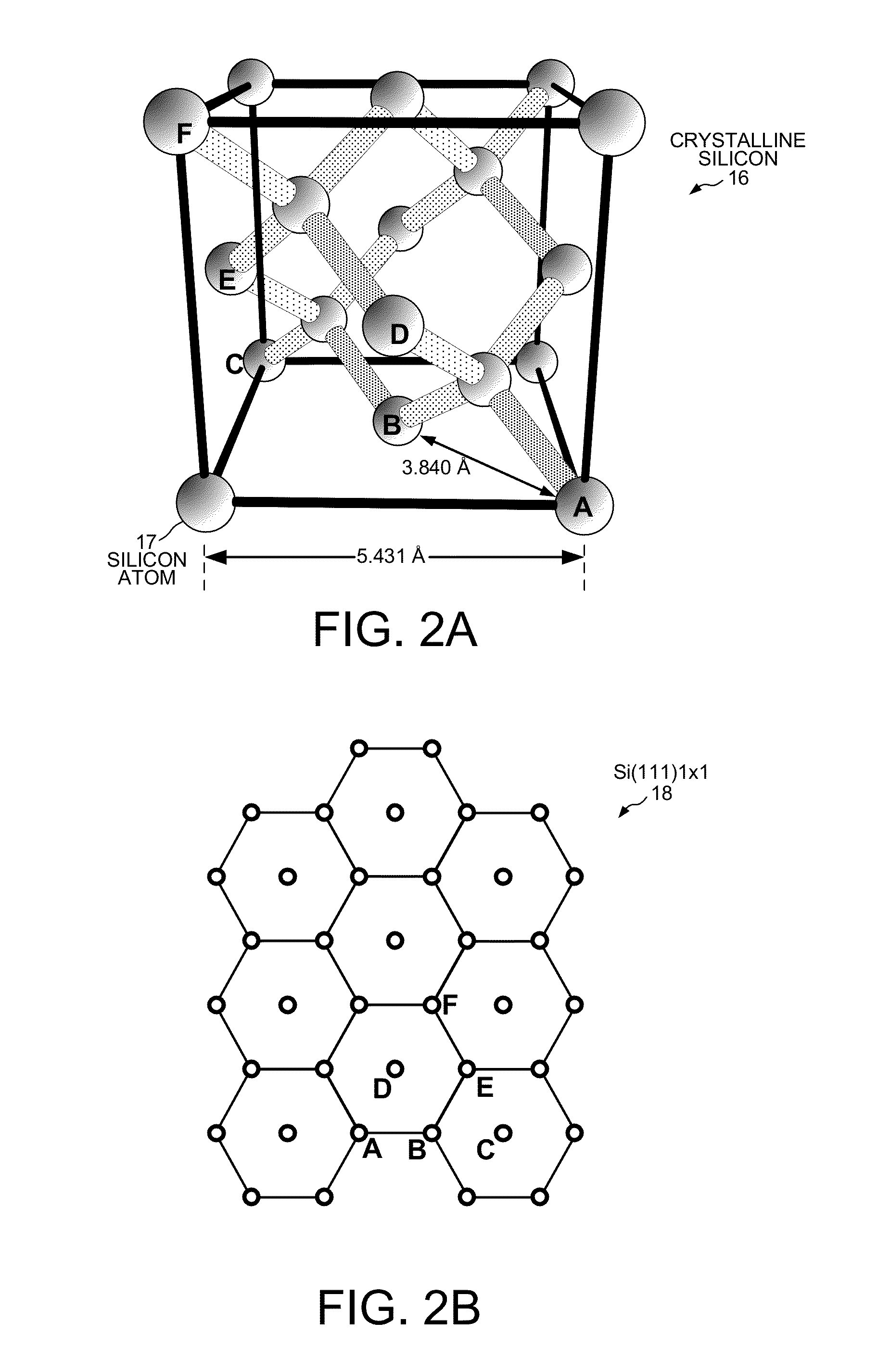

Boron-Containing Buffer Layer for Growing Gallium Nitride on Silicon

InactiveUS20130026482A1Small sizeMore stressSemiconductor/solid-state device manufacturingSemiconductor devicesNitrogenBoron containing

A silicon wafer used in manufacturing GaN for LEDs includes a silicon substrate, a buffer layer of boron aluminum nitride (BxAl1-xN) and an upper layer of GaN, for which 0.35≦x≦0.45. The BAlN forms a wurtzite-type crystal with a cell unit length about two-thirds of a silicon cell unit length on a Si(111) surface. The C-plane of the BAlN crystal has approximately one atom of boron for each two atoms of aluminum. Across the entire wafer substantially only nitrogen atoms of BAlN form bonds to the Si(111) surface, and substantially no aluminum or boron atoms of the BAlN are present in a bottom-most plane of atoms of the BAlN. A method of making the BAlN buffer layer includes preflowing a first amount of ammonia equaling less than 0.01% by volume of hydrogen flowing through a chamber before flowing trimethylaluminum and triethylboron and then a subsequent amount of ammonia through the chamber.

Owner:KK TOSHIBA

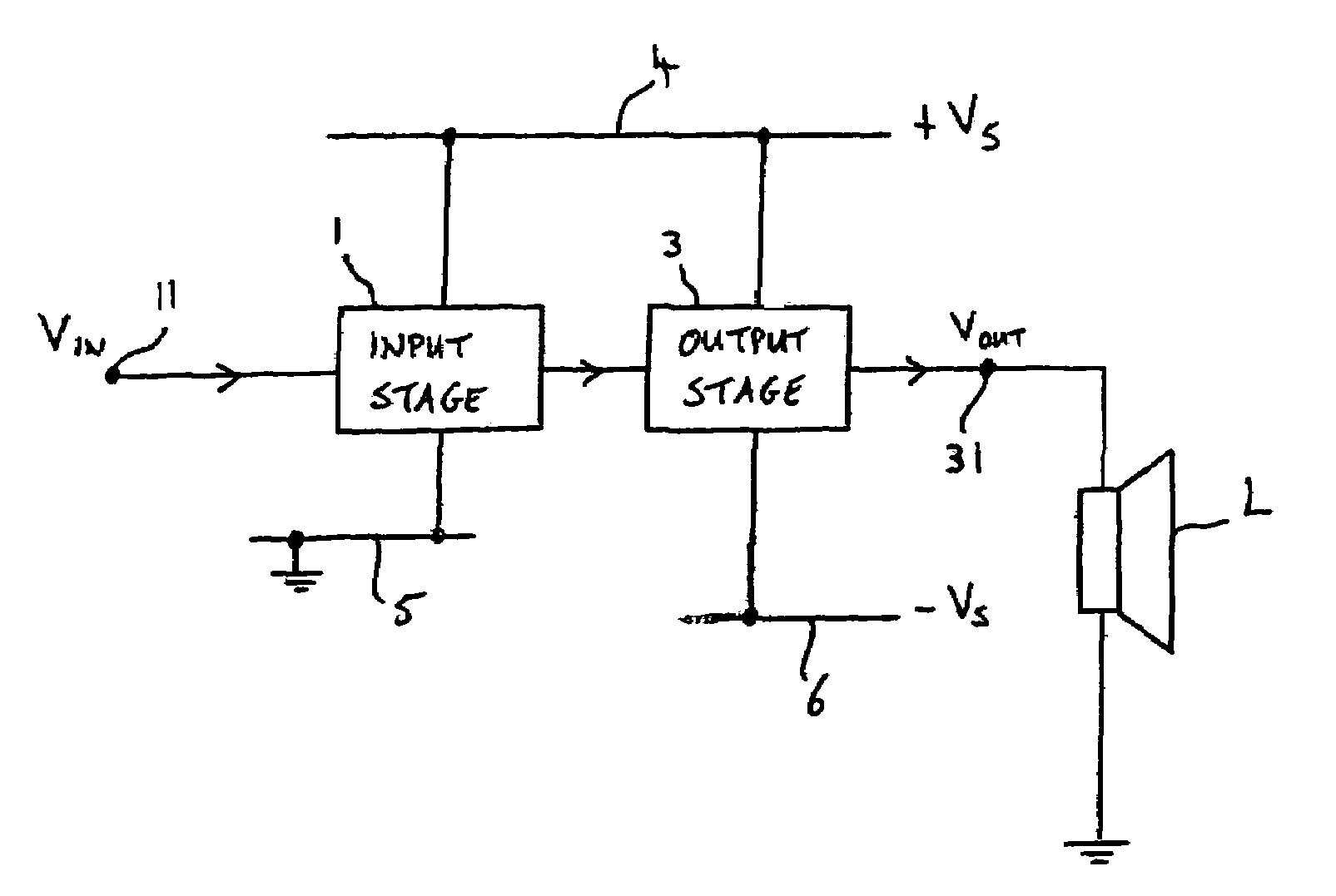

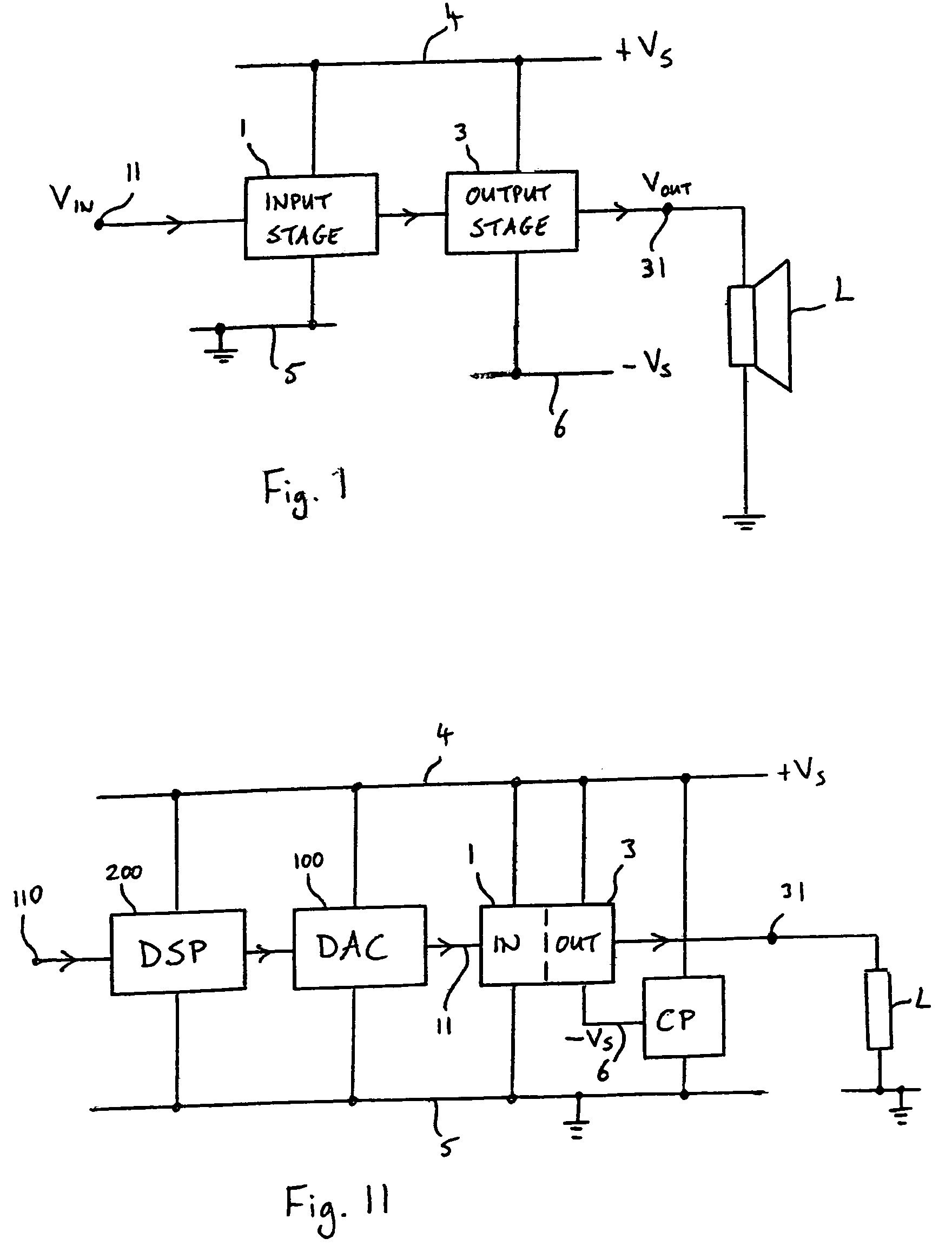

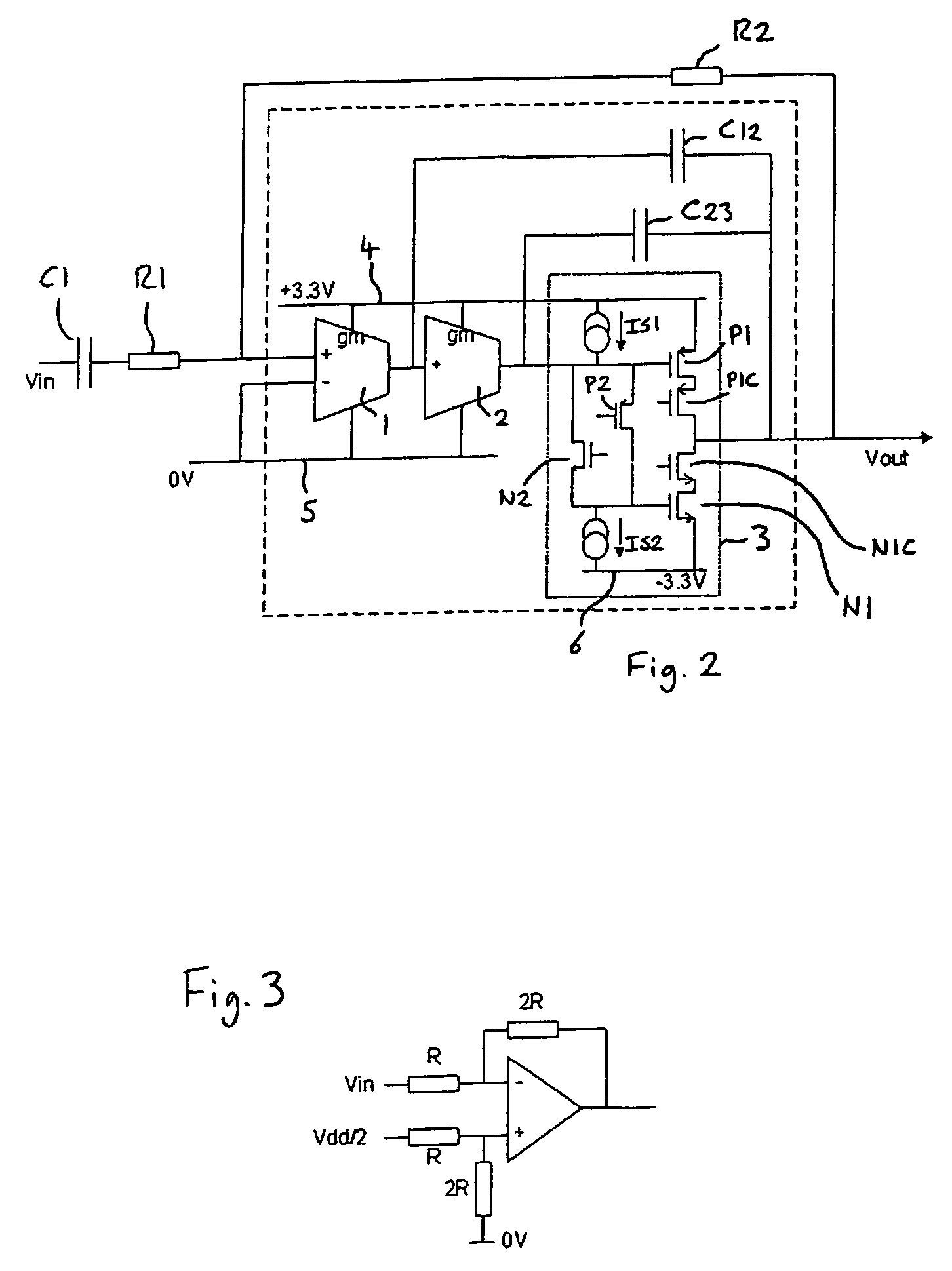

Amplifier

ActiveUS7030699B2Reduce noiseMore stressStereophonic circuit arrangementsLow frequency amplifiersCMOSAudio power amplifier

Owner:CIRRUS LOGIC INC

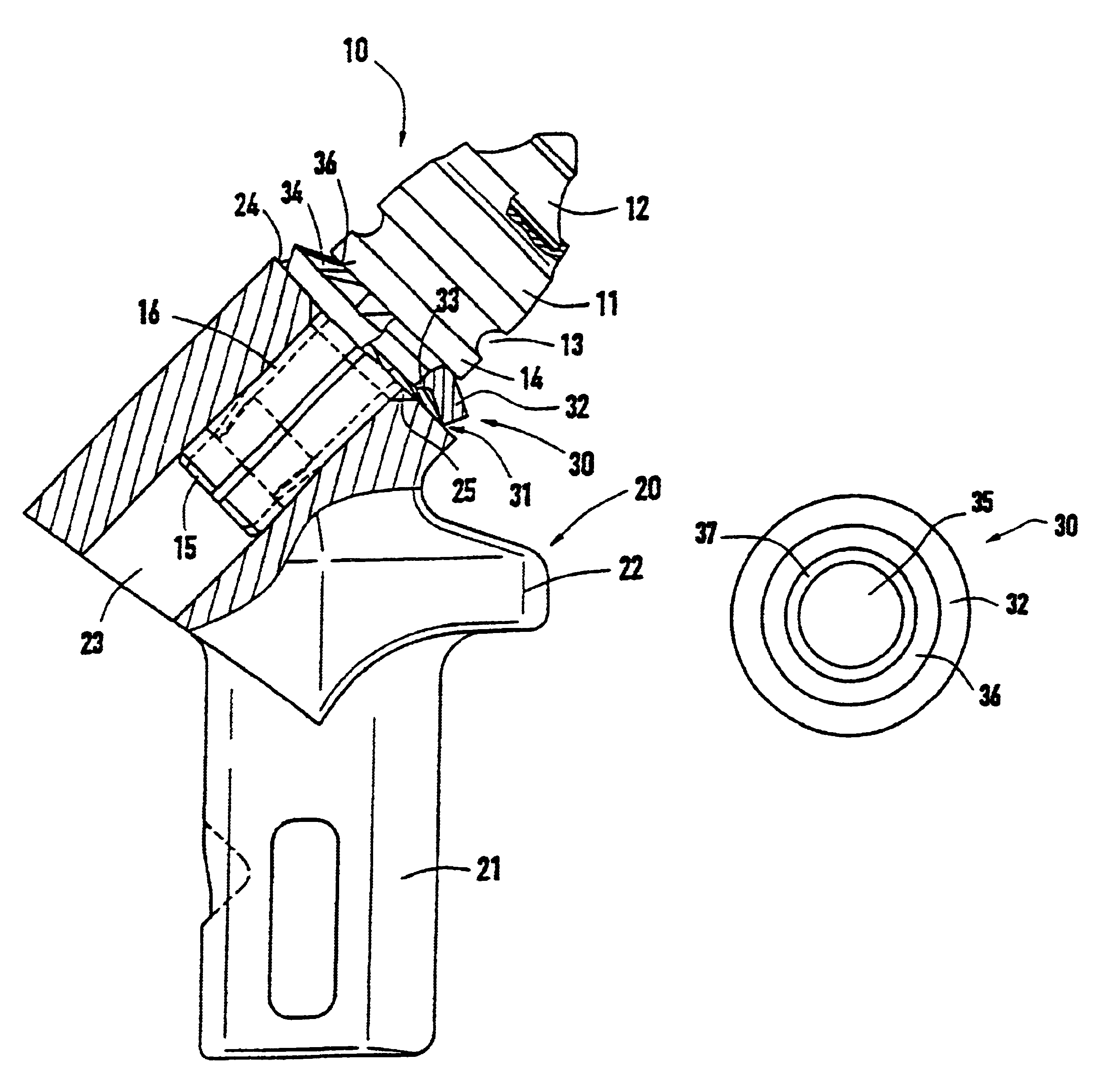

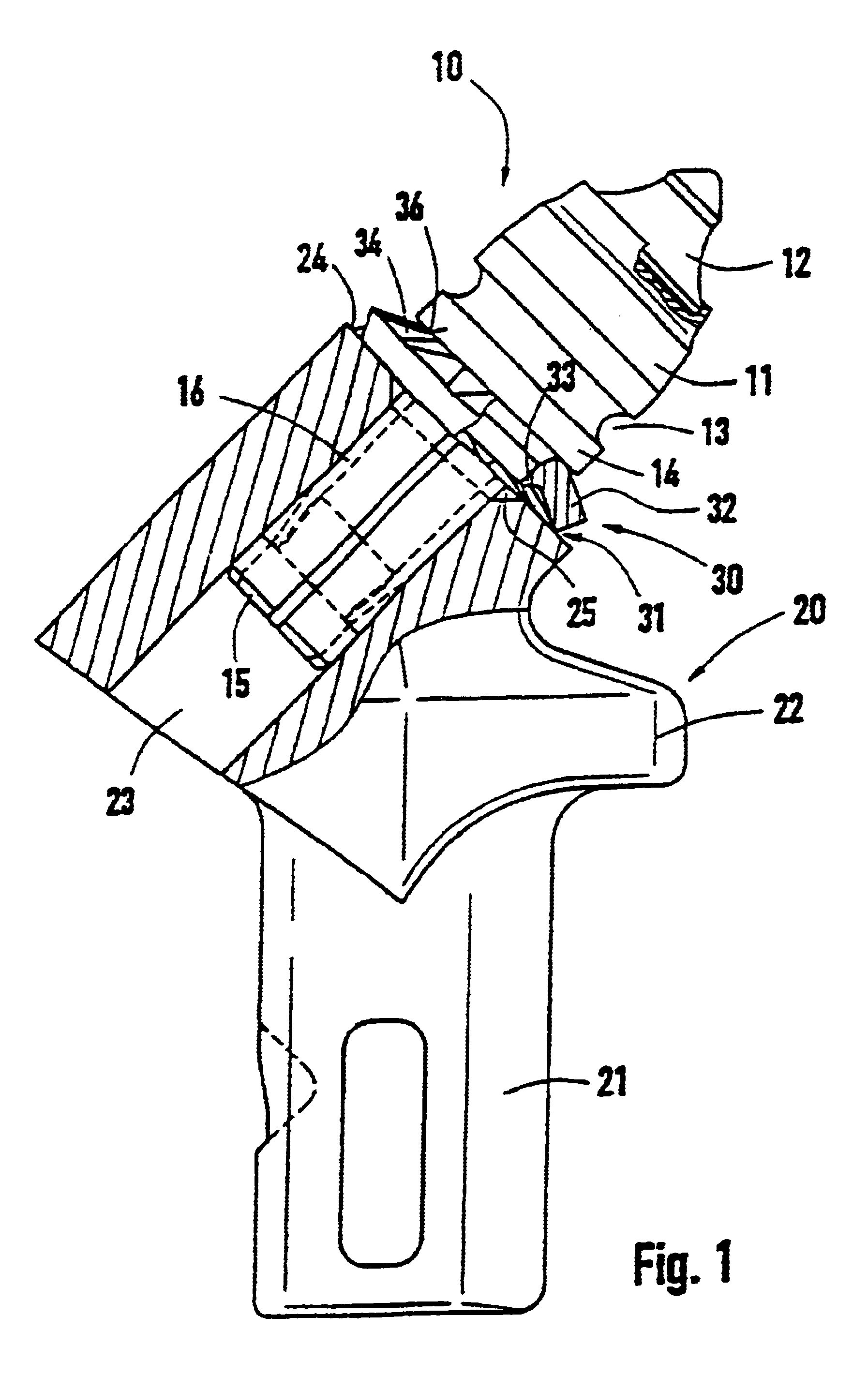

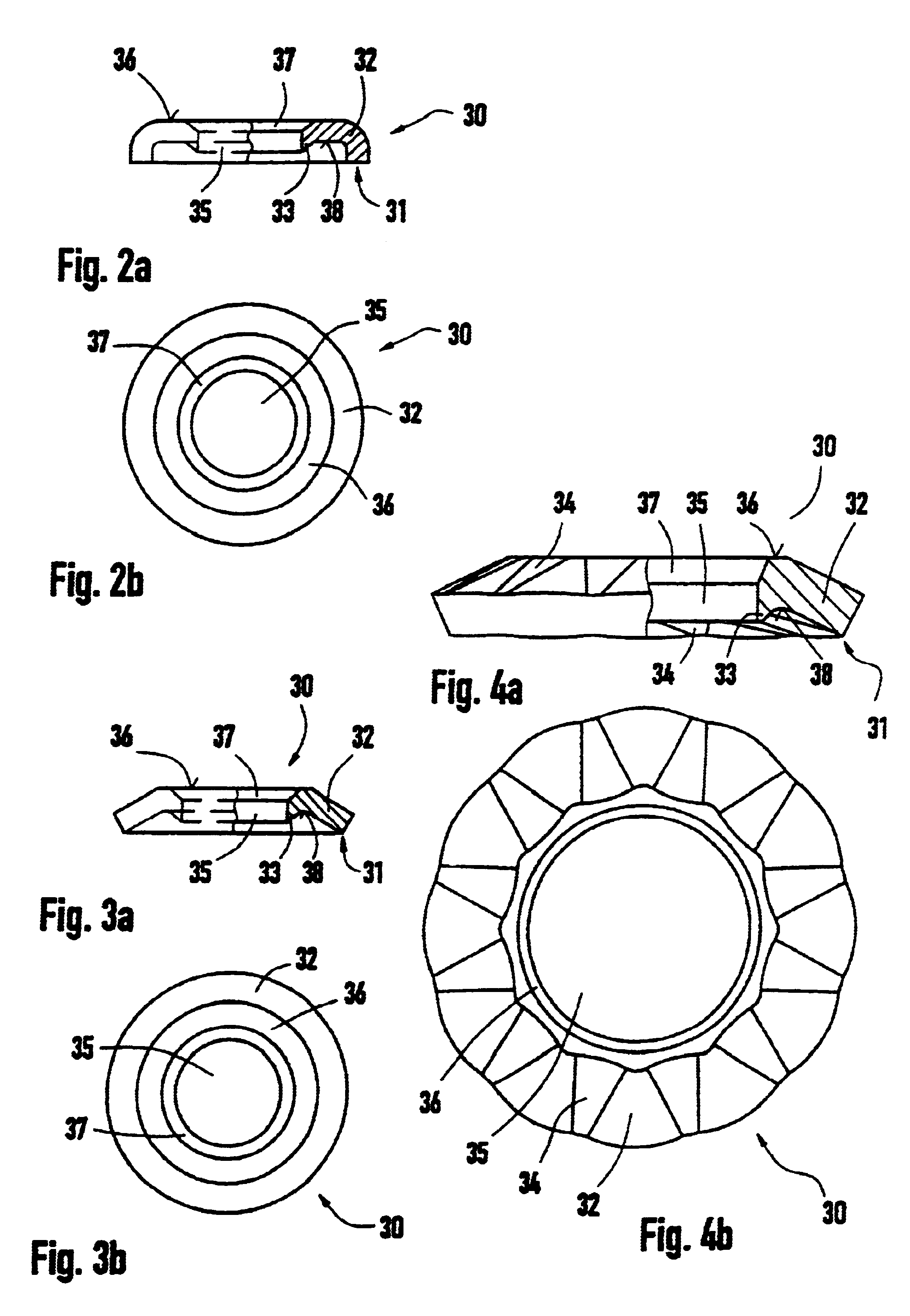

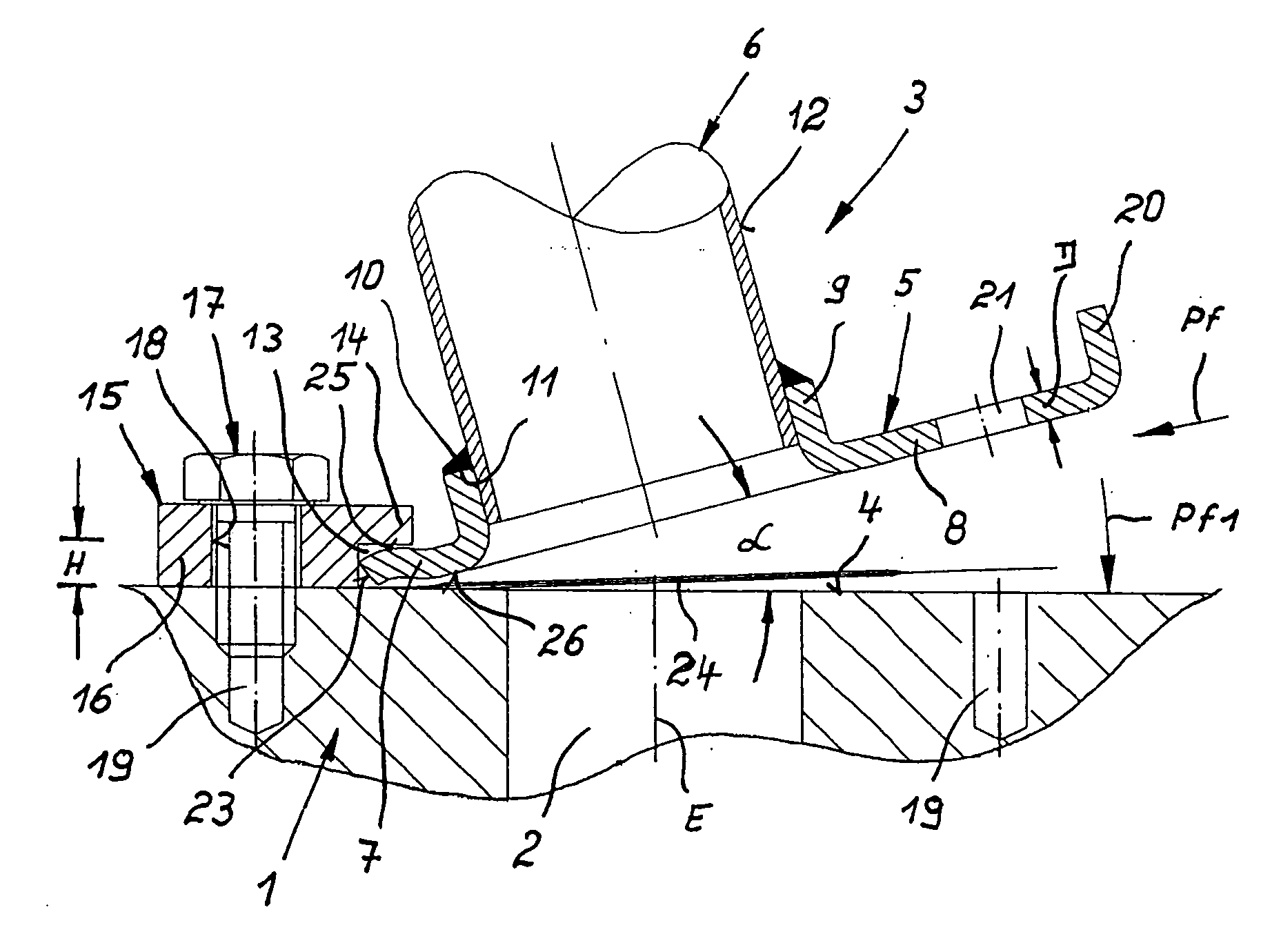

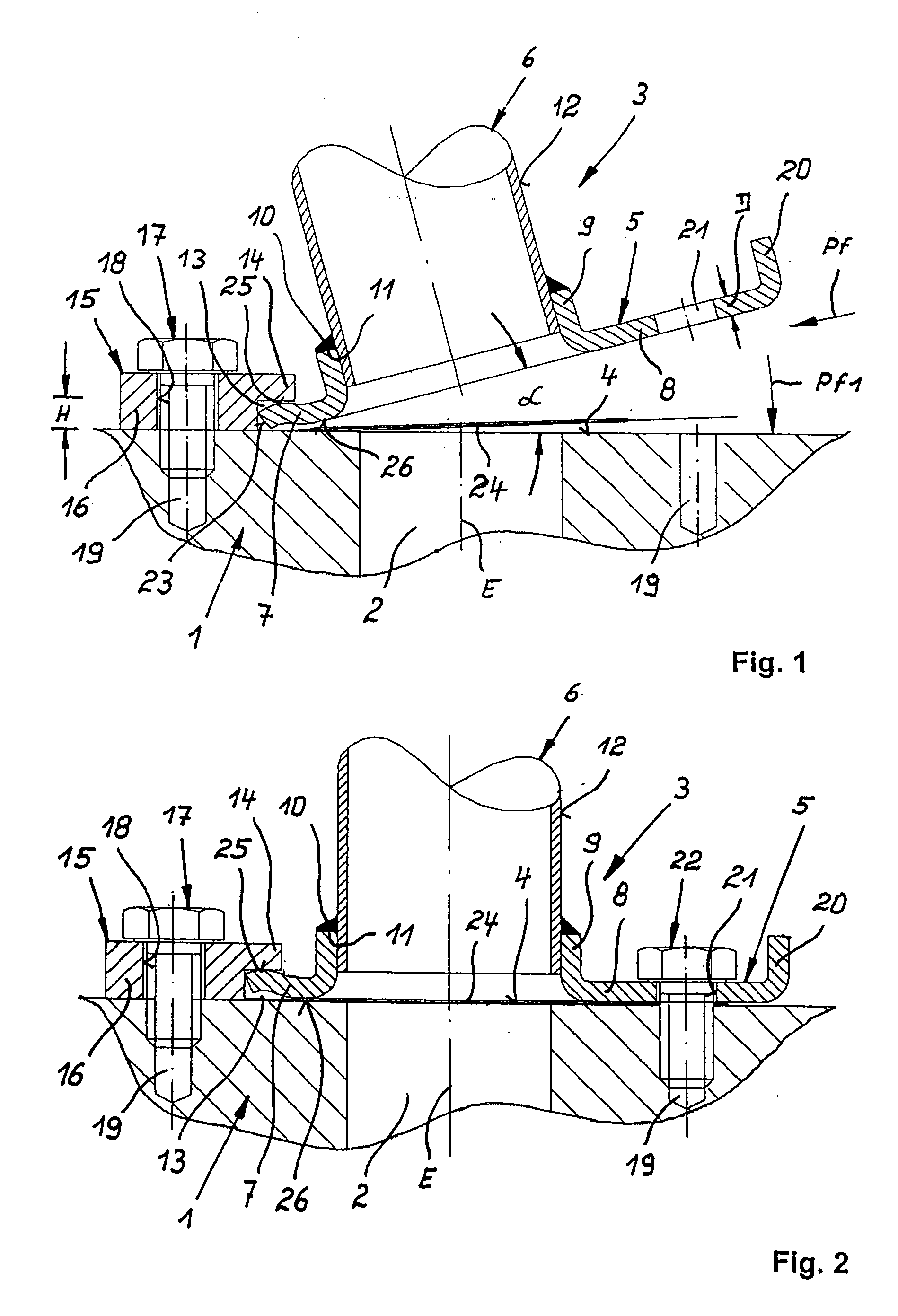

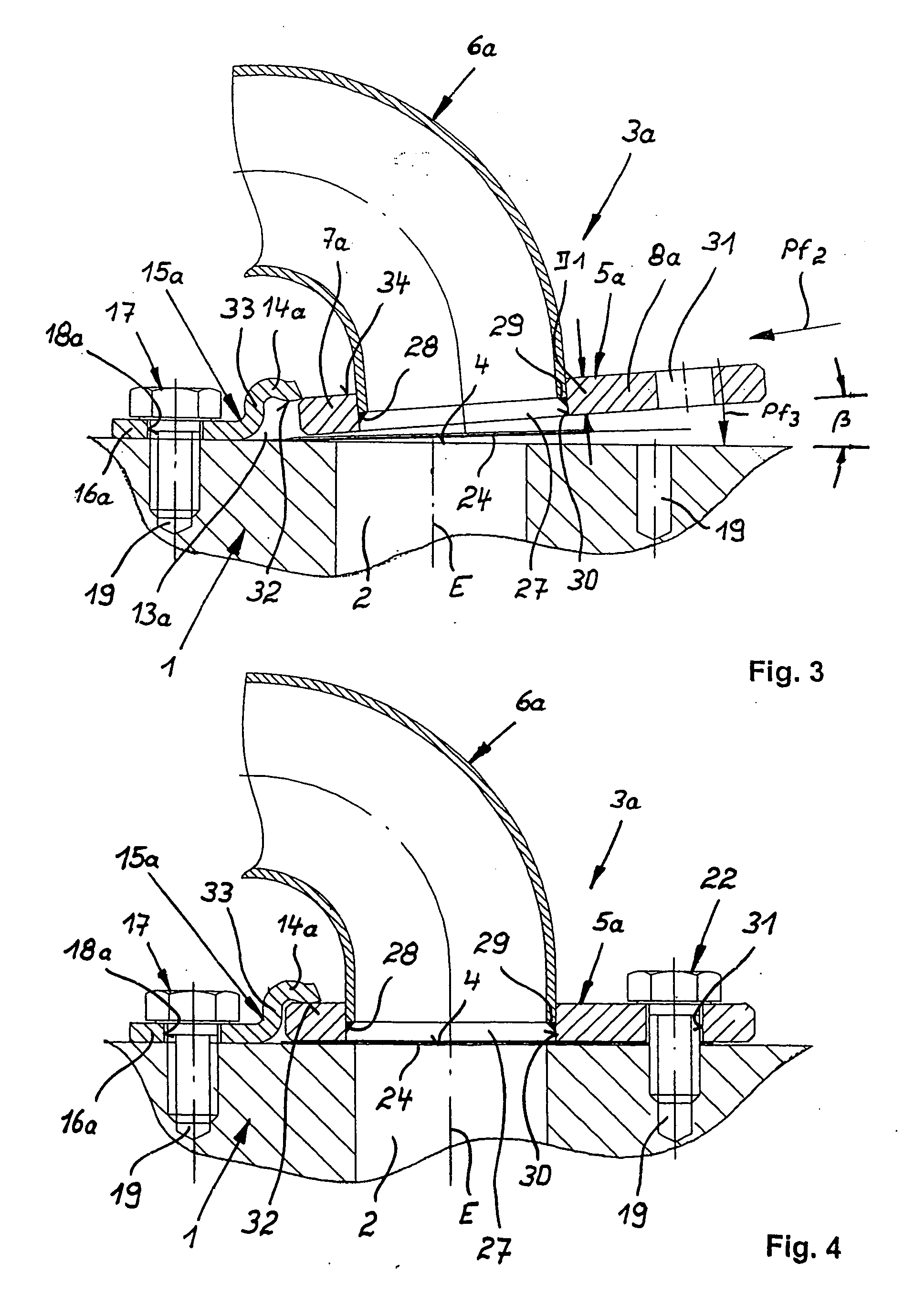

Tool for a street milling, coal-cutting or mining machine

A tool for a street milling, coal-cutting mining machine or the like which includes a chisel with a chisel head and a chisel stem. The chisel stem is rotatably mounted in a receiver of a chisel holder. A perforated wearing protection element is mounted on the chisel head. The chisel head sits closely on the chisel holder while embracing the interposed wearing protection element. This invention achieves improved wearing protection behavior of such a tool. Thus, the inventive wearing protection element has one or more spring elements that elastically support the chisel head by way of the chisel holder.

Owner:BETEK BERGBAU UND HARTMETALLTECHN KARL HEINZ SIMON

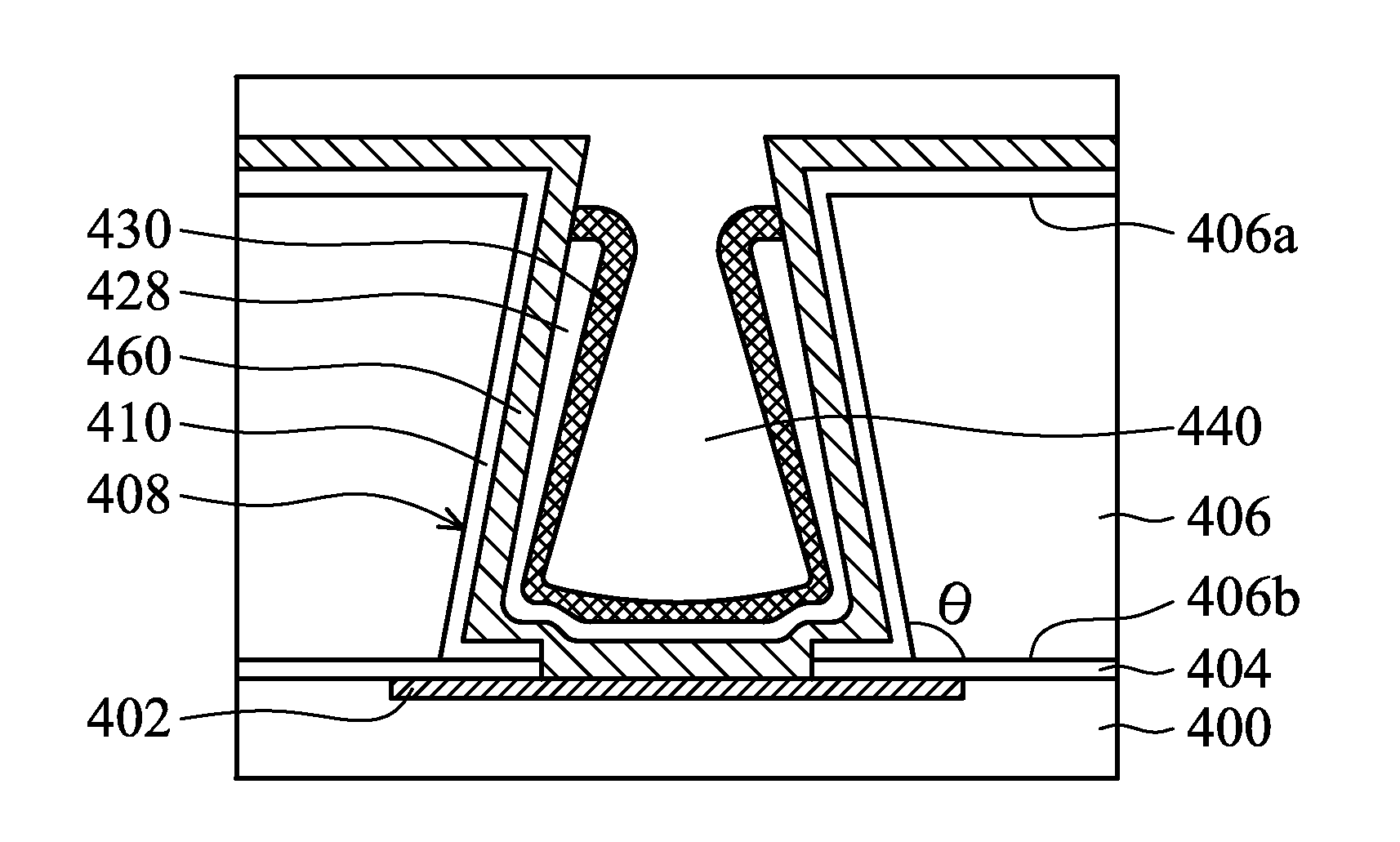

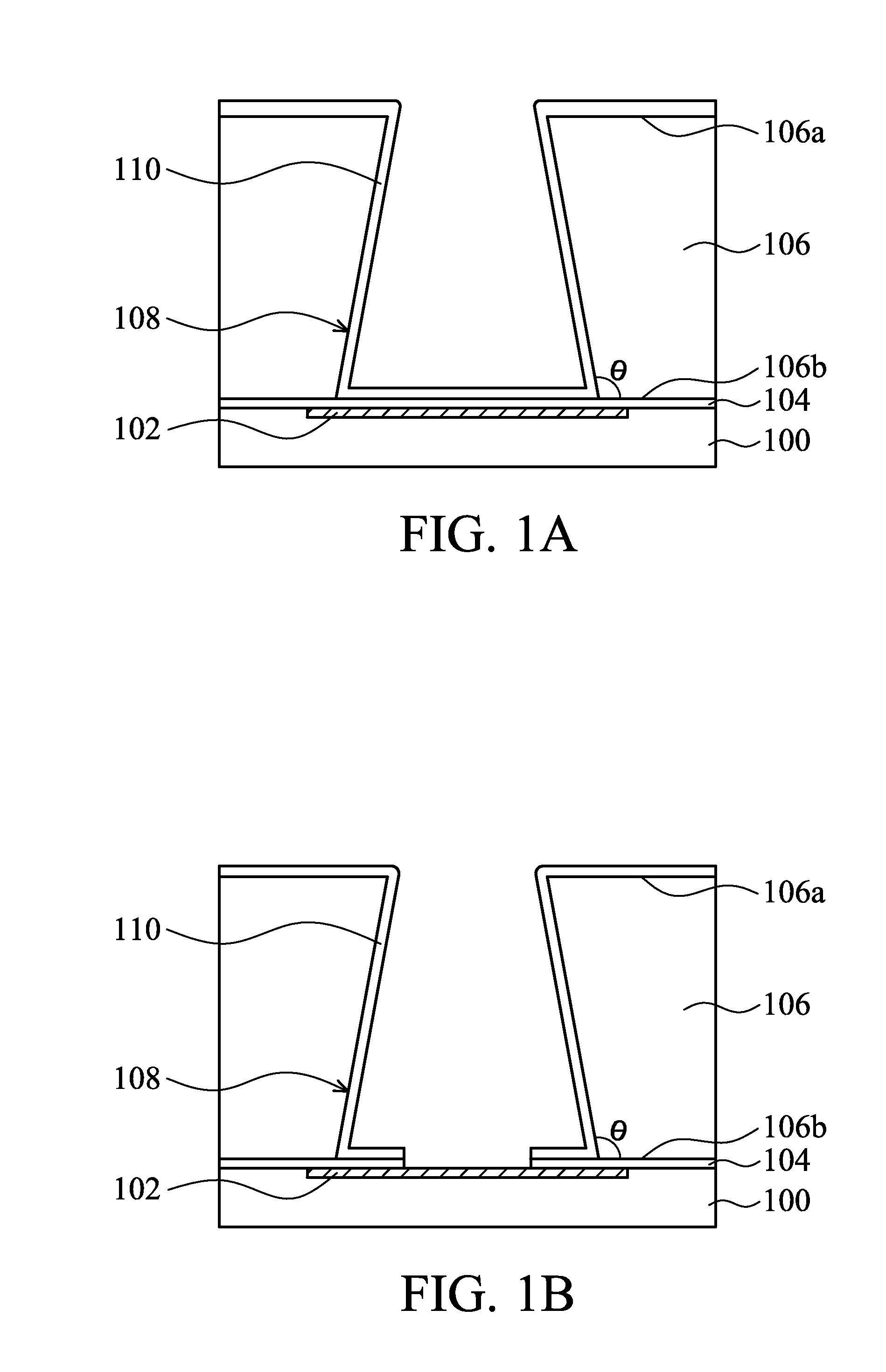

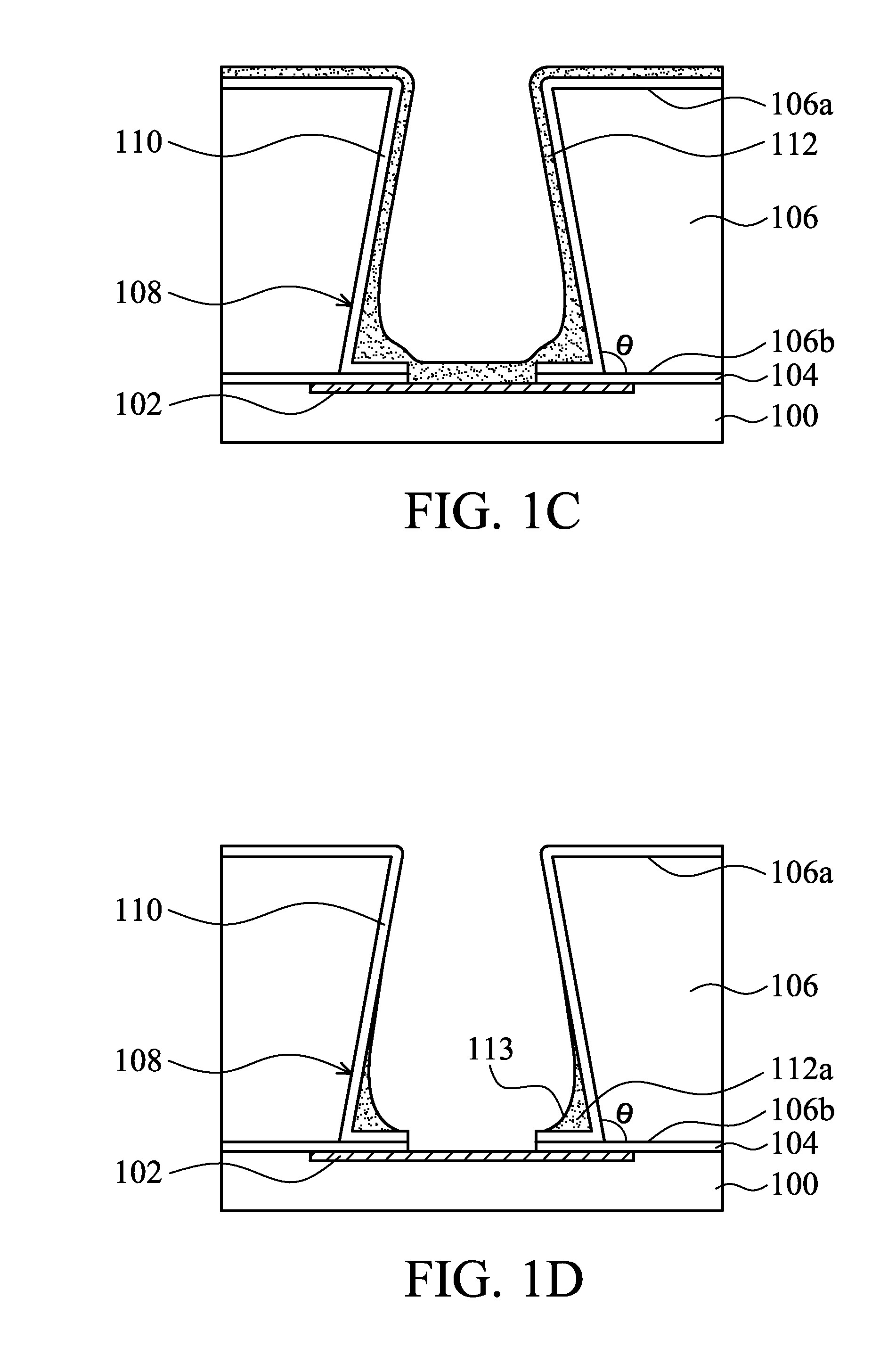

Chip package and method for forming the same

ActiveUS20110193241A1Reduce thicknessImprove reliabilitySemiconductor/solid-state device detailsSolid-state devicesPhysics

According to an embodiment of the invention, a chip package is provided, which includes: a substrate having an upper surface and a lower surface; a hole extending from the upper surface toward the lower surface; an insulating layer located overlying a sidewall of the hole; and a material layer located overlying the sidewall of the hole, wherein the material layer is separated from the upper surface of the substrate by a distance and a thickness of the material layer decreases along a direction toward the lower surface.

Owner:XINTEC INC

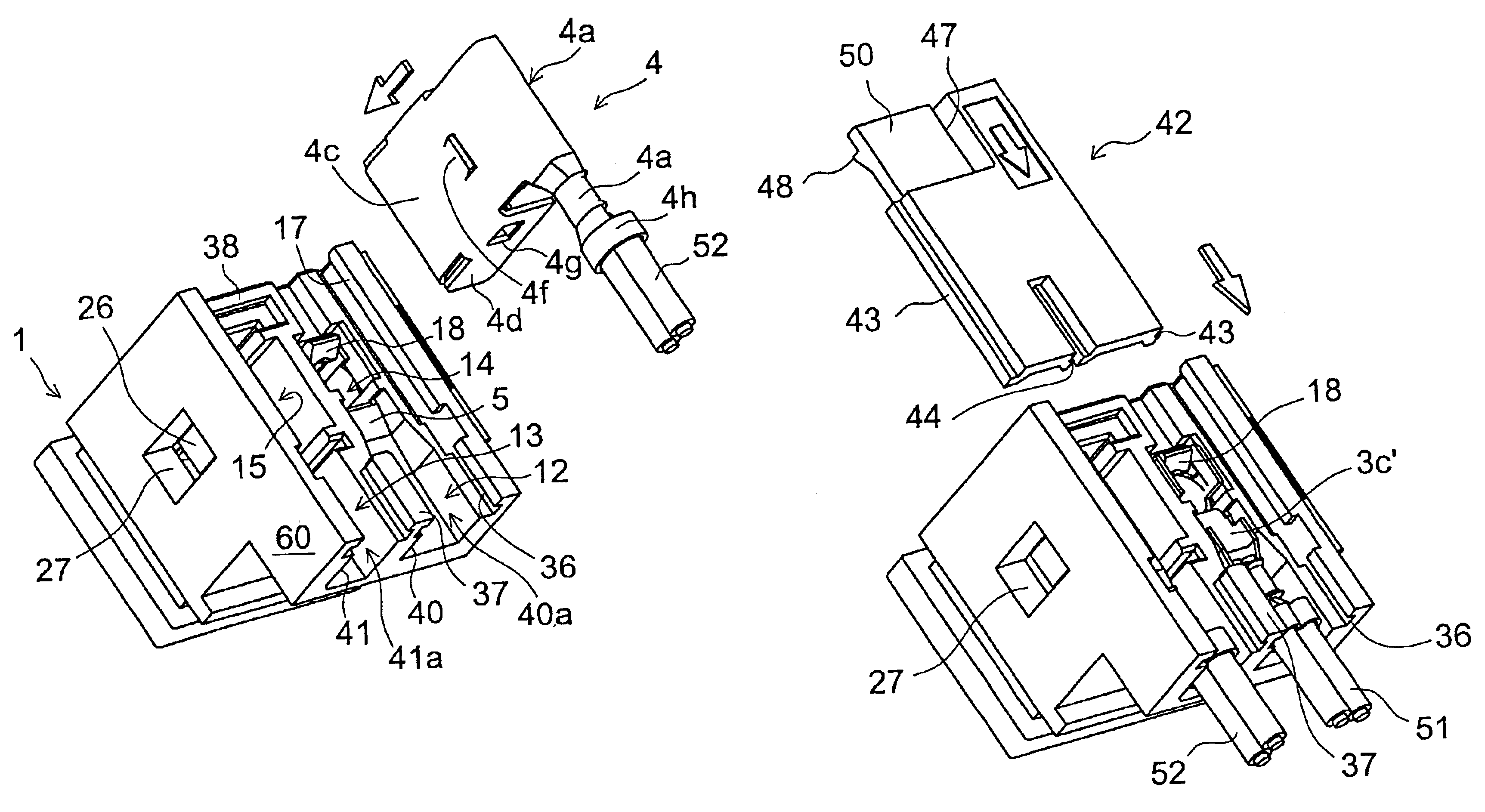

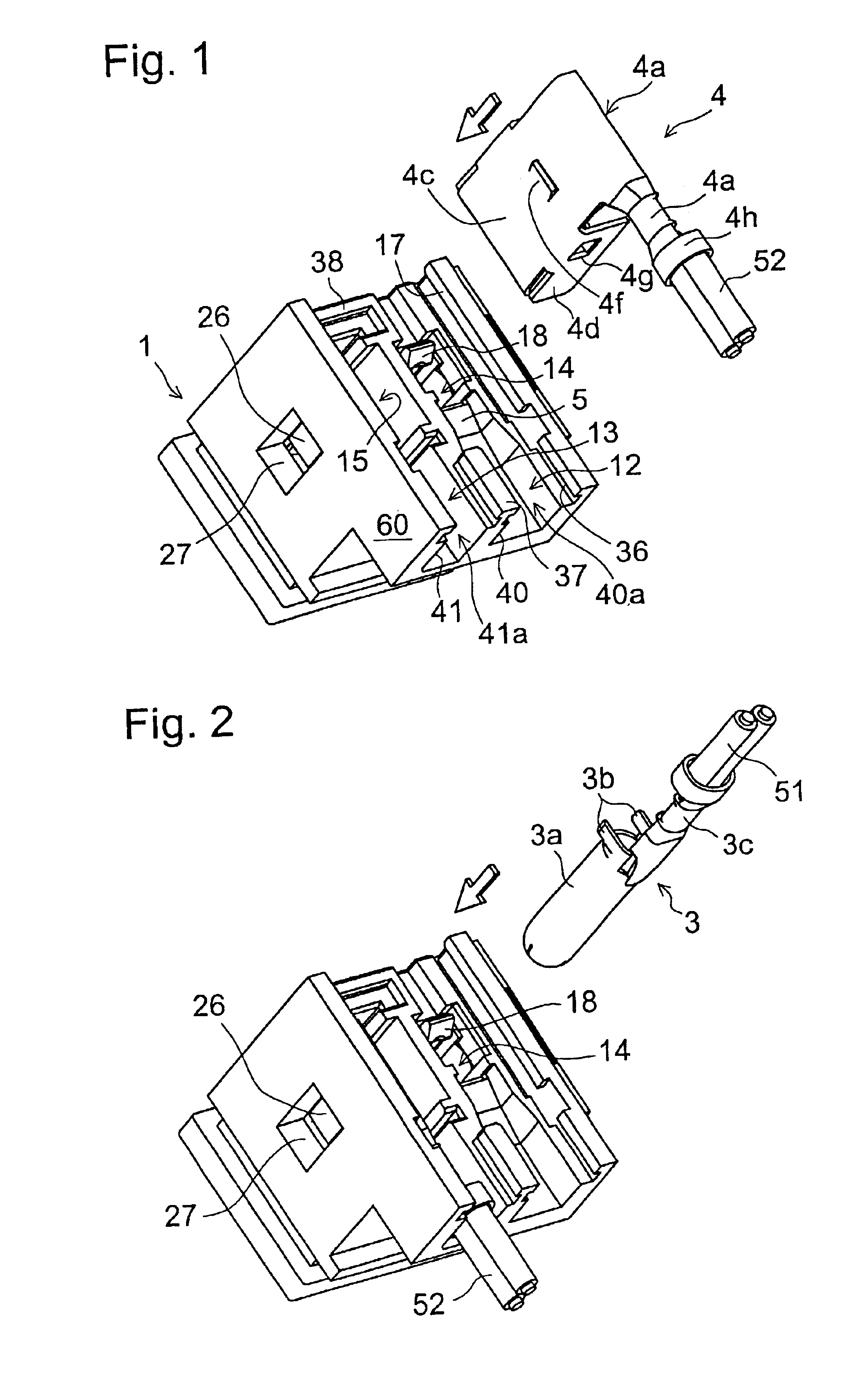

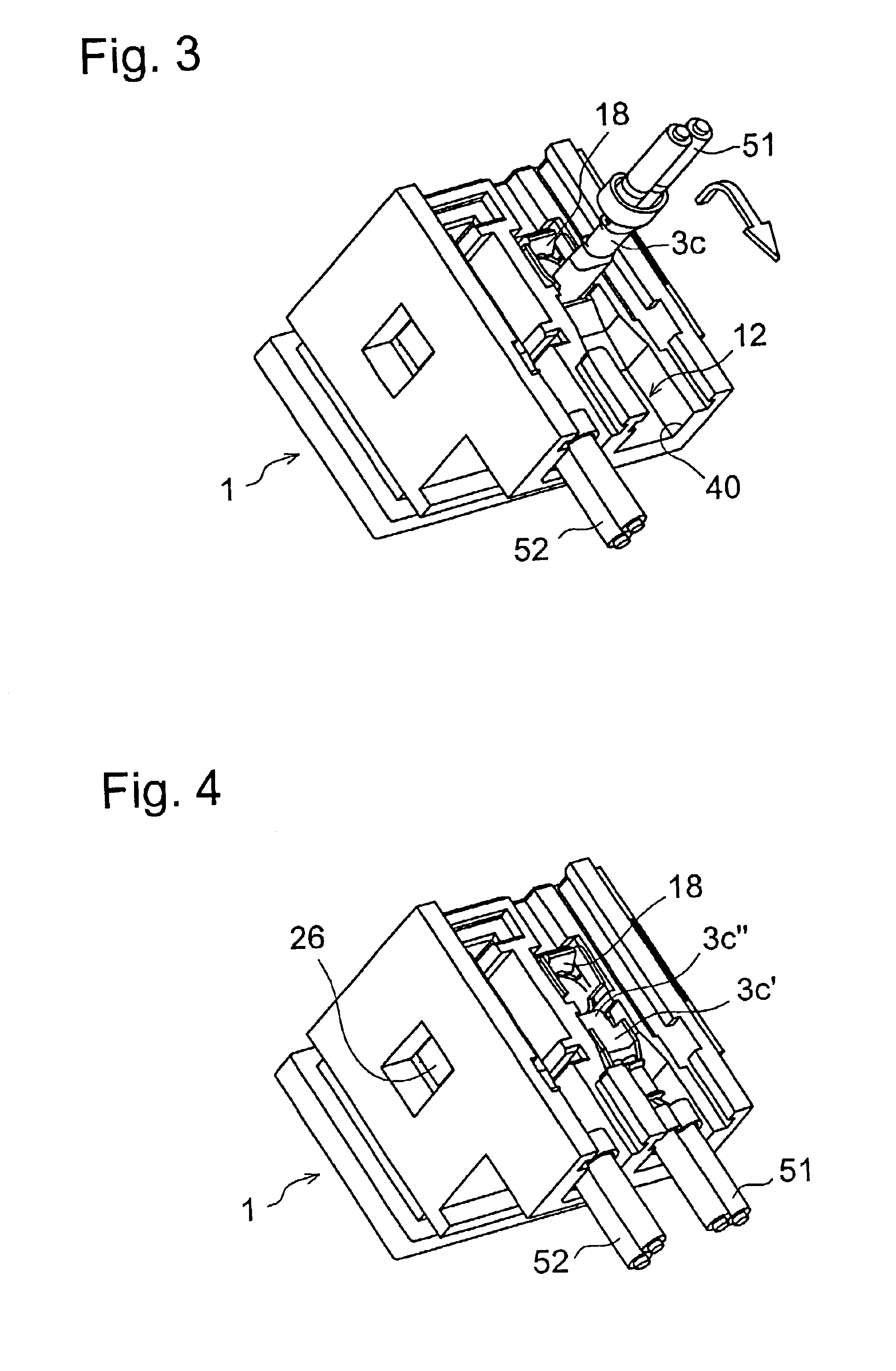

Electric jack

InactiveUS6837745B2Avoid excess mechanical stressImprove productivitySecuring/insulating coupling contact membersCoupling contact membersEngineeringElectrical and Electronics engineering

A jack, which would cause hardly a defective connection even if a mechanical deformation is received when attaching or using it, will be offered. The electric junction of contacts (3), (4) and leads (51), (52) is done by crimping, the crimping portions (3c), (4b) are arranged in a housing (1) of the jack which is not exposed easily to a mechanical deformation, and, in addition, the structure is so made that the mechanical force doesn't work easily on the crimping portions (3c), (4b) also by the leads (51), (52) extending from the jack.

Owner:JST MFG CO LTD

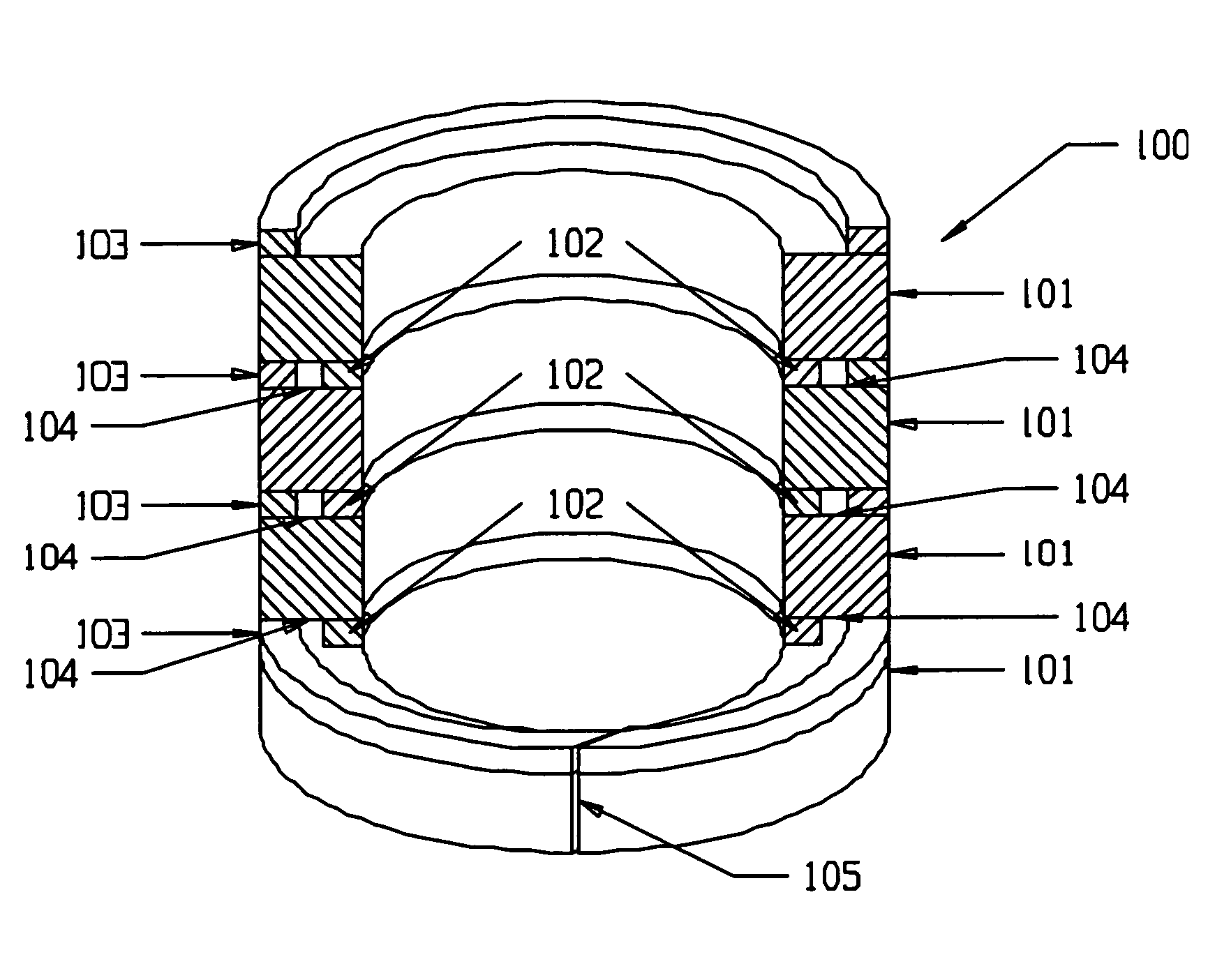

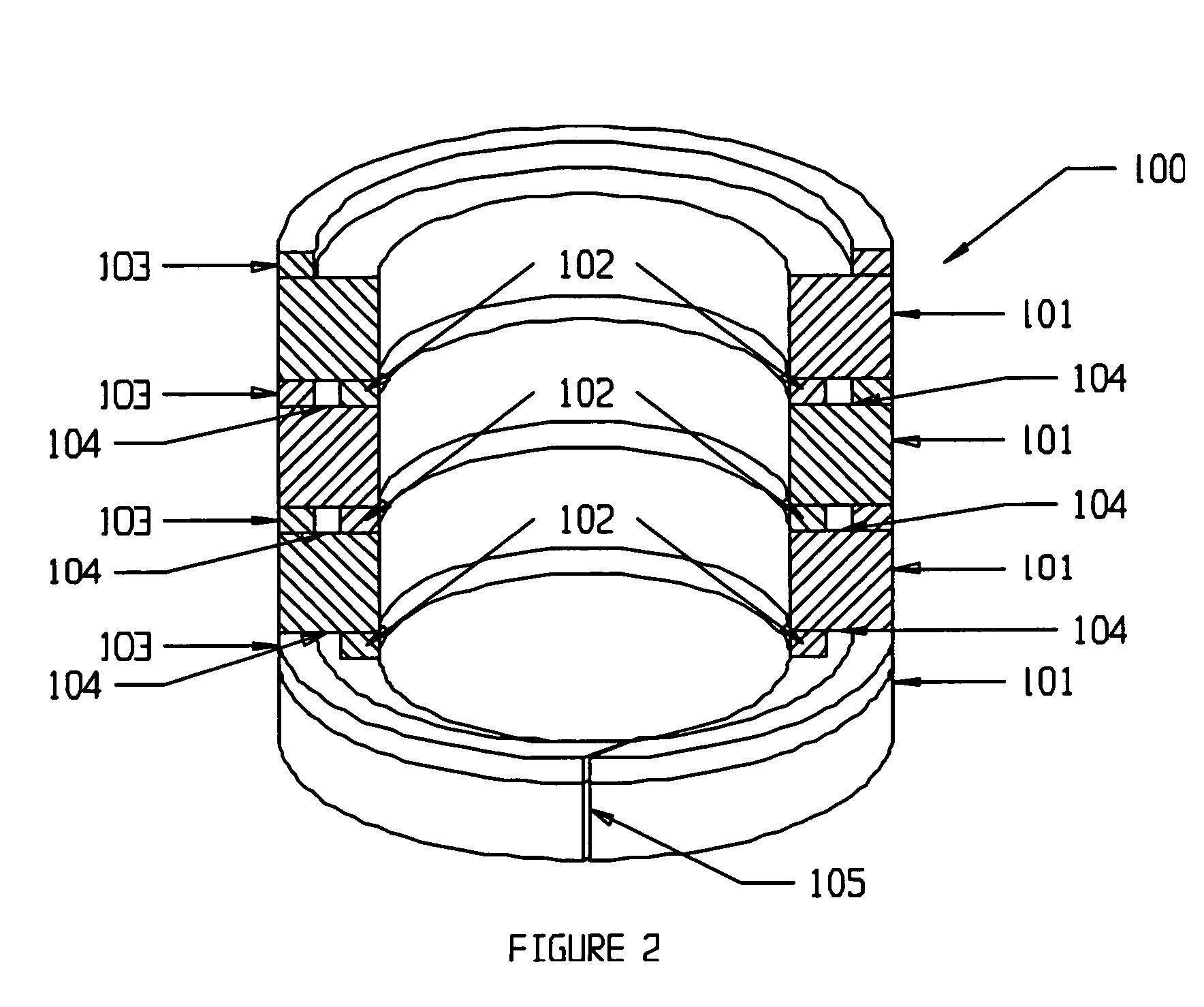

Ceramic foam insulator with thermal expansion joint

InactiveUS7316721B1Easy to useMore stressCombination devicesDispersed particle filtrationThermal expansionCeramic foam

A canister for maintaining entrained particles in a gas stream passing there through. The canister has an outer annular member and an inner porous annular member. The inner porous annular member has rings with at least one expansion zone in each ring. An annular interior volume is between the outer annular member and the inner porous annular member. A gas source is in flow communication with the annular interior volume for providing gas at a pressure sufficient to pass through the inner porous annular member to dislodge particles adhering thereto.

Owner:PORVAIR

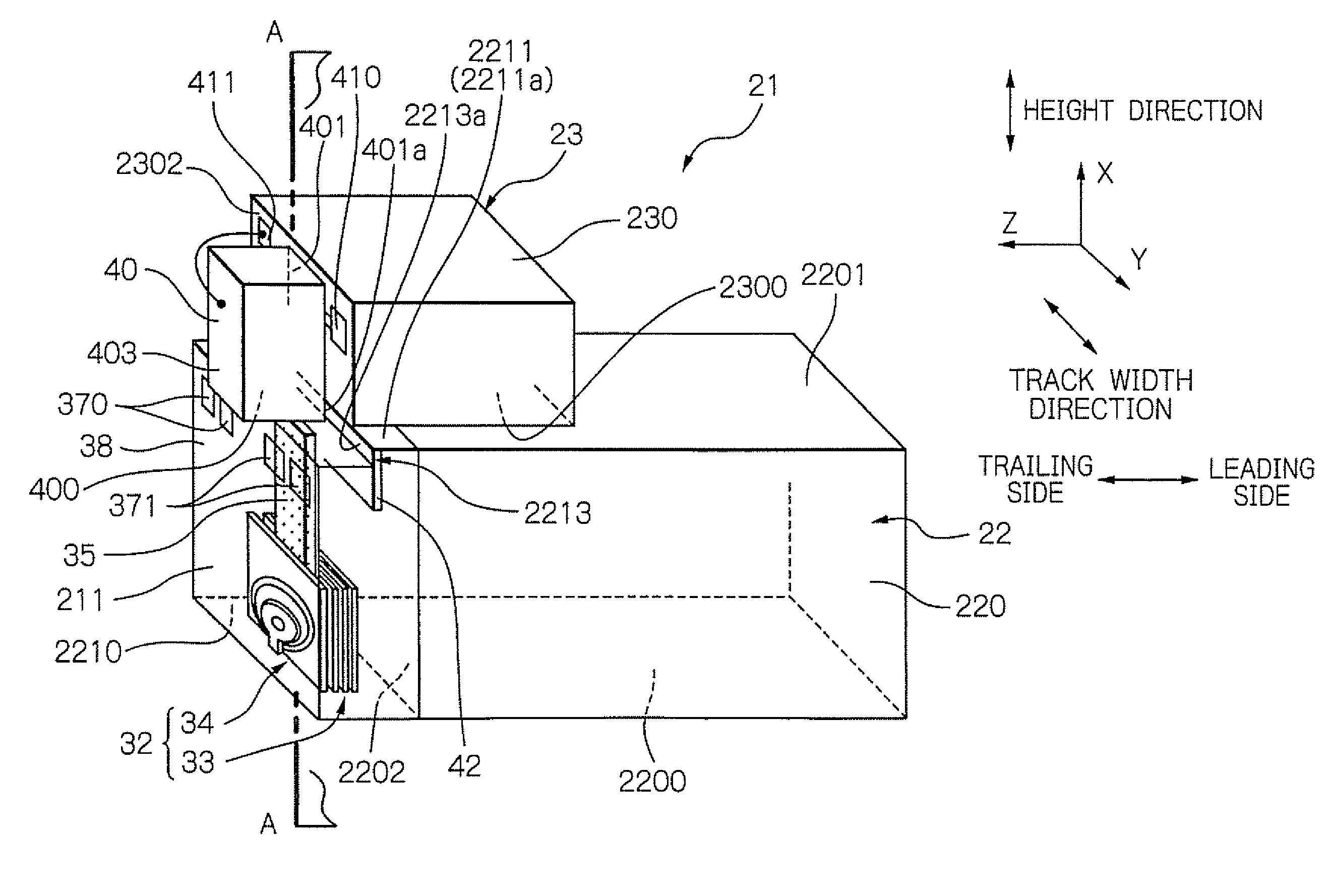

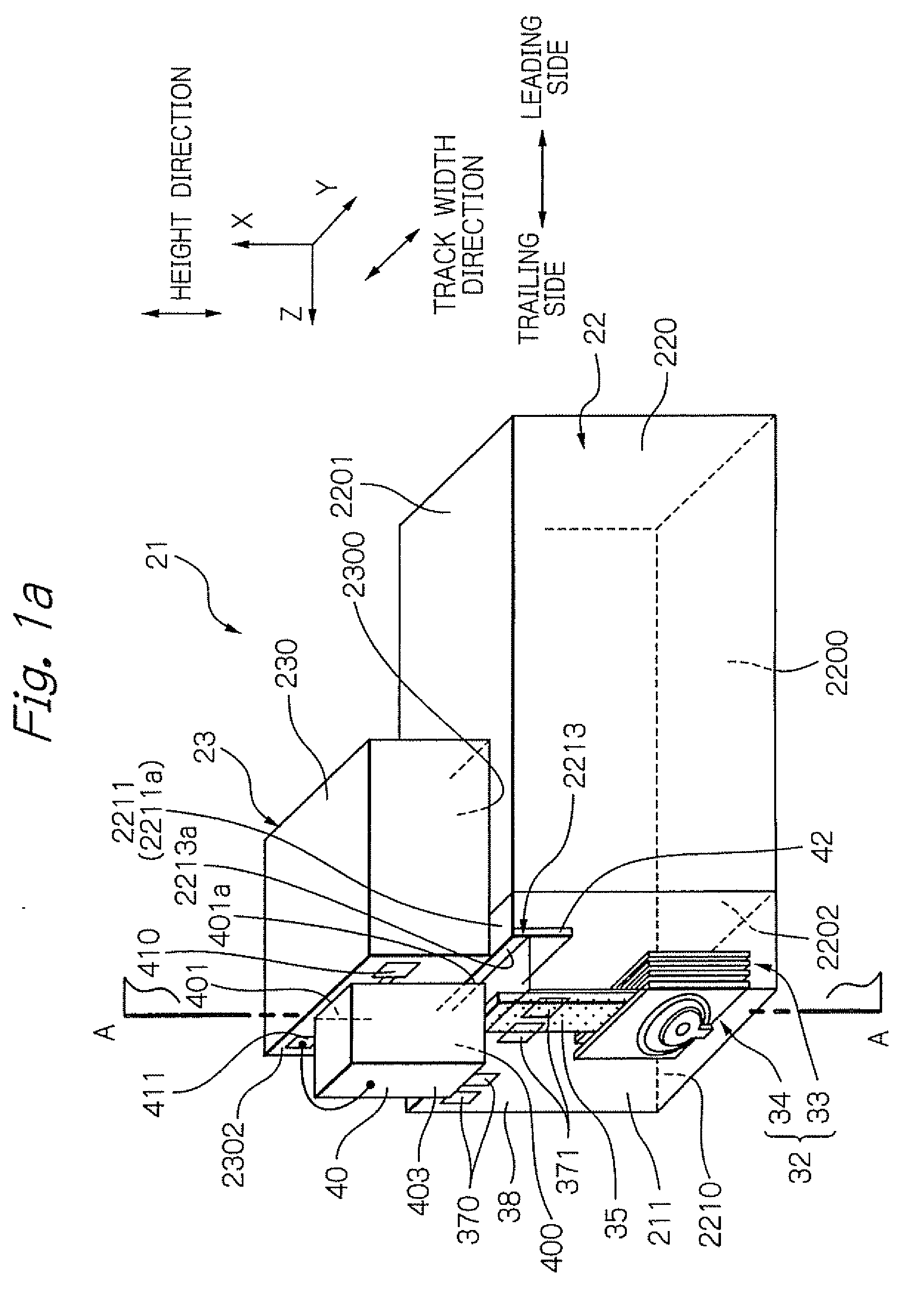

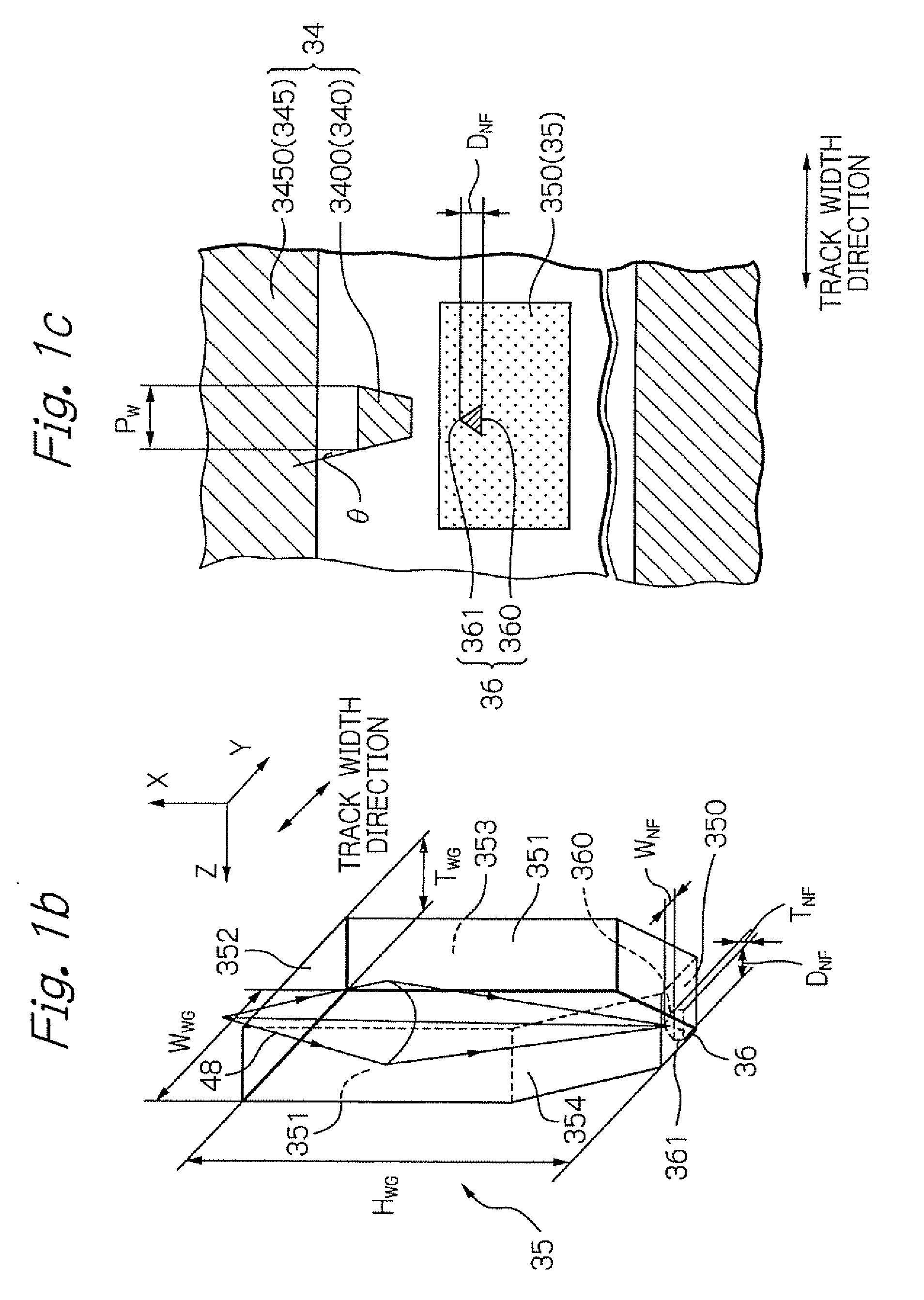

Manufacturing method of heat-assisted magnetic head constituted of slider and light source unit

ActiveUS20090266789A1Easy to joinAvoiding excessive mechanical stressDecorative surface effectsRecord information storageLight sourceEngineering

Provided is a manufacturing method of heat-assisted magnetic recording head, in which a light source unit can be easily joined to a slider with sufficiently high accuracy, under avoiding the excessive mechanical stress. The manufacturing method comprises the steps of: moving relatively the light source unit and the slider, while applying a sufficient voltage between an upper electrode of the light source and an electrode layer provided in the slider; and setting the light source unit and the slider in desired positions in a direction perpendicular to the element-integration surface of the slider substrate. The desired positions are positions where the light source just emits due to a surface contact between: the protruded portion of the lower surface of the light source; and the upper surface of the electrode layer, which is a portion of the wall surface of a step formed on the head part.

Owner:TDK CORPARATION

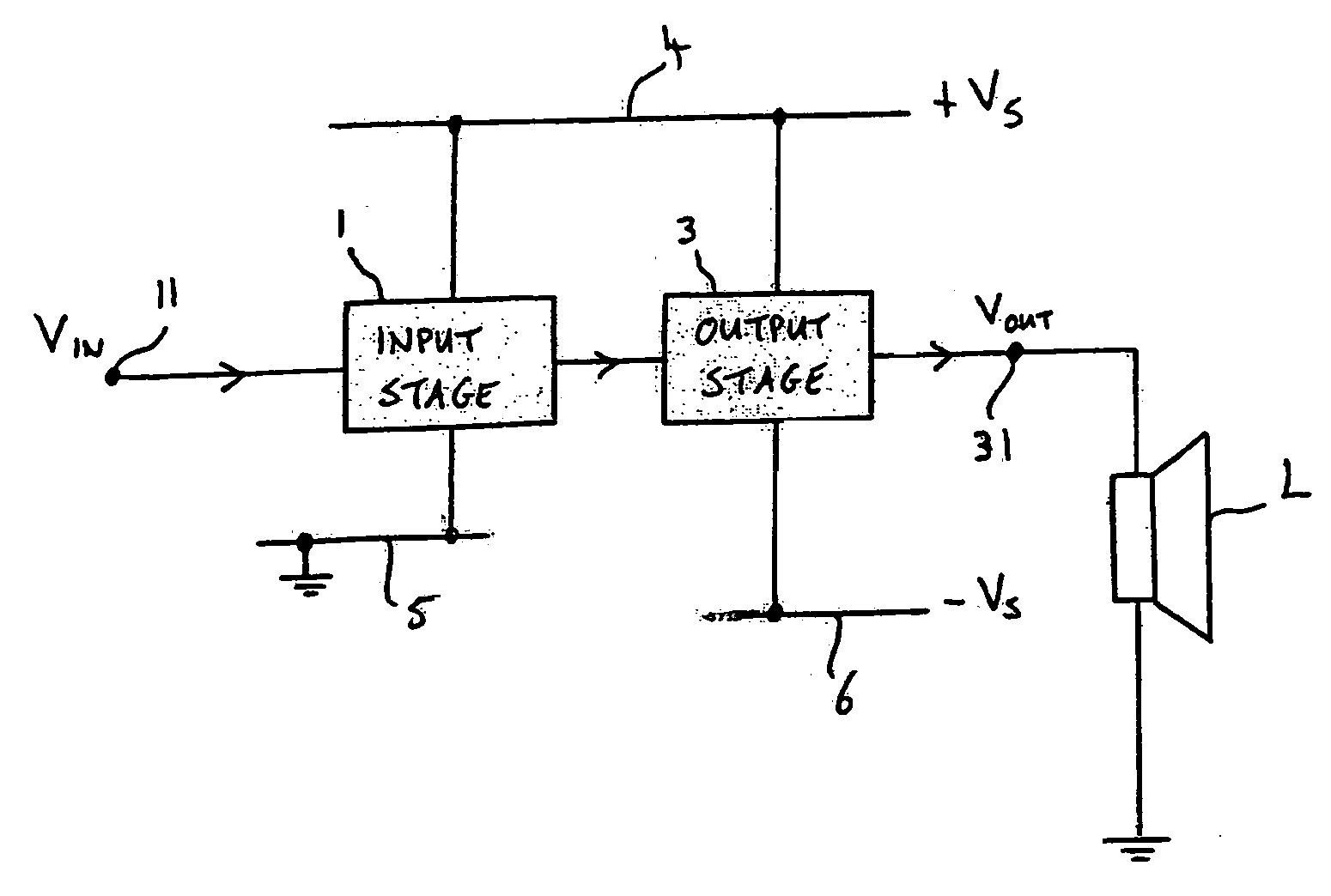

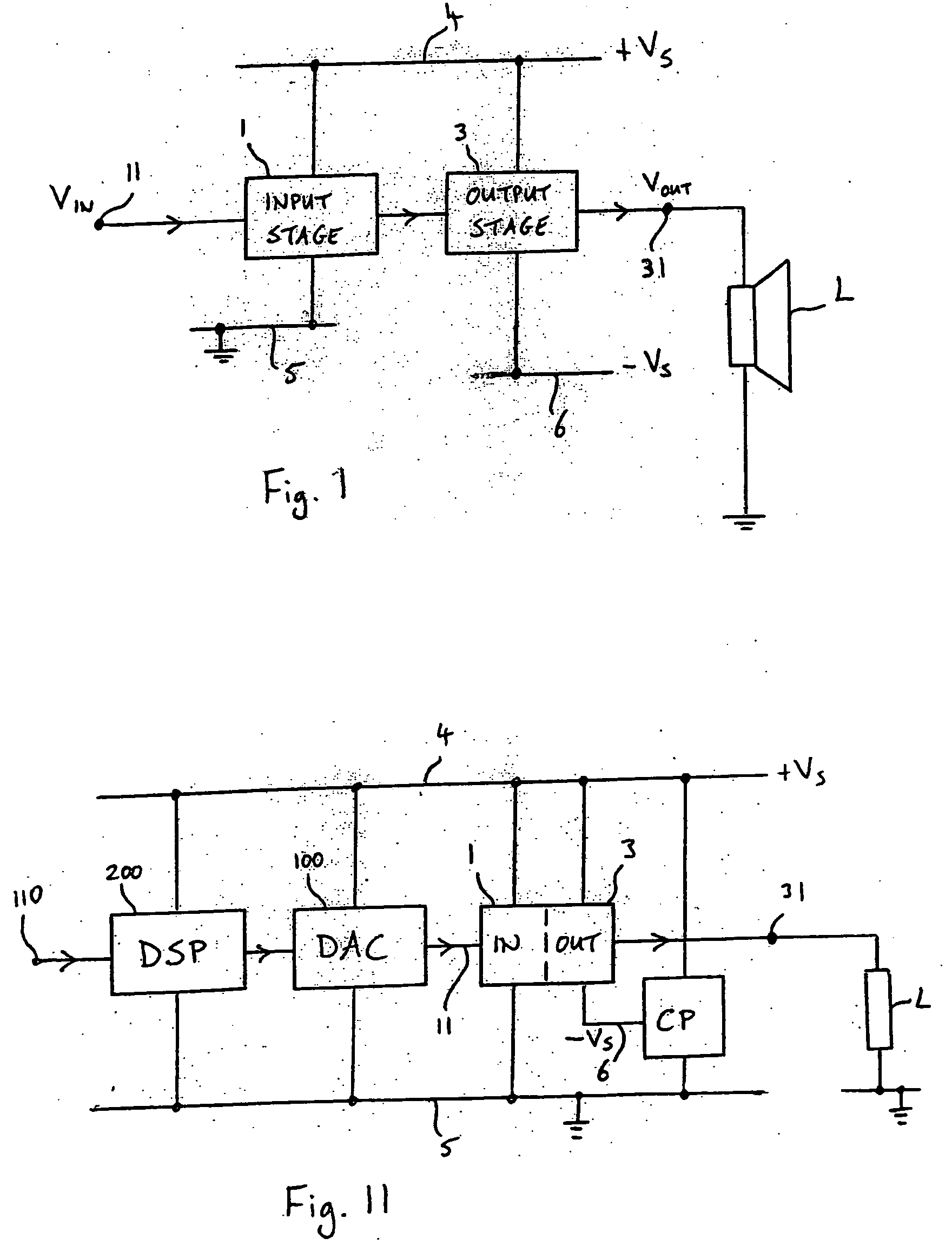

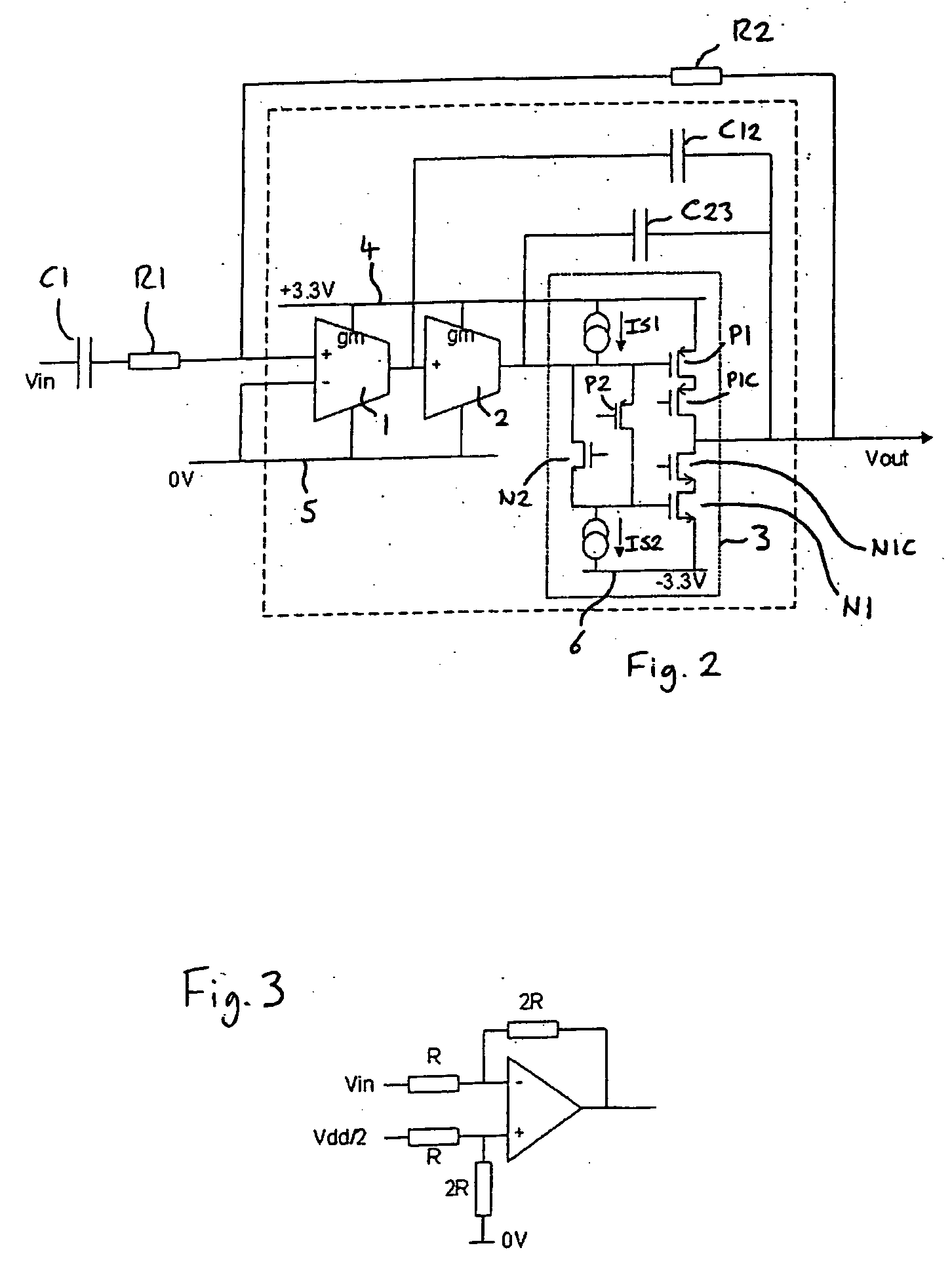

Amplifier

ActiveUS20050110574A1Reduce effectReduce noiseStereophonic circuit arrangementsLow frequency amplifiersCMOSVolt

An amplifier is disclosed, having an input stage connected to an output stage. The input stage is connected between a positive supply rail and a ground rail and has an input terminal arranged to receive an input signal. The output stage is connected between a positive supply rail and a negative supply rail and has an output terminal. The output stage is adapted to generate an output signal, which is dependent on a received input signal, at the output, and is further adapted such that, in use, a quiescent voltage at the output terminal is at a selected value between a voltage on the positive supply rail and a voltage on the negative supply rail. For driving a grounded load, the quiescent output voltage is preferably zero volts. In preferred embodiments, the input and output stages are formed on a common substrate using CMOS technology, the output stage including one or more NMOS devices having a triple-well structure. A corresponding method of driving a grounded load is also disclosed.

Owner:CIRRUS LOGIC INC

Arrangement for securely mounting an exhaust manifold to the cylinder head of an internal combustion engine

InactiveUS20050268602A1More stressProlong lifeFlanged jointsExhaust apparatusCylinder headEngineering

An exhaust manifold has a head flange constructed for receiving at least two exhaust pipes arranged side-by-side, and includes spaced apart first and second longitudinal flange portions. A mounting assembly is provided for sealingly securing the exhaust manifold to a cylinder head of an internal combustion engine and includes a mounting rail formed with a shoulder which laps over the first longitudinal flange portion and contacts the first longitudinal flange portion in a spring-elastic manner. Plural screw fasteners at least indirectly clamp the second longitudinal flange portion to the cylinder head.

Owner:BENTELER AUTOMOBILTECHNIK GMBH

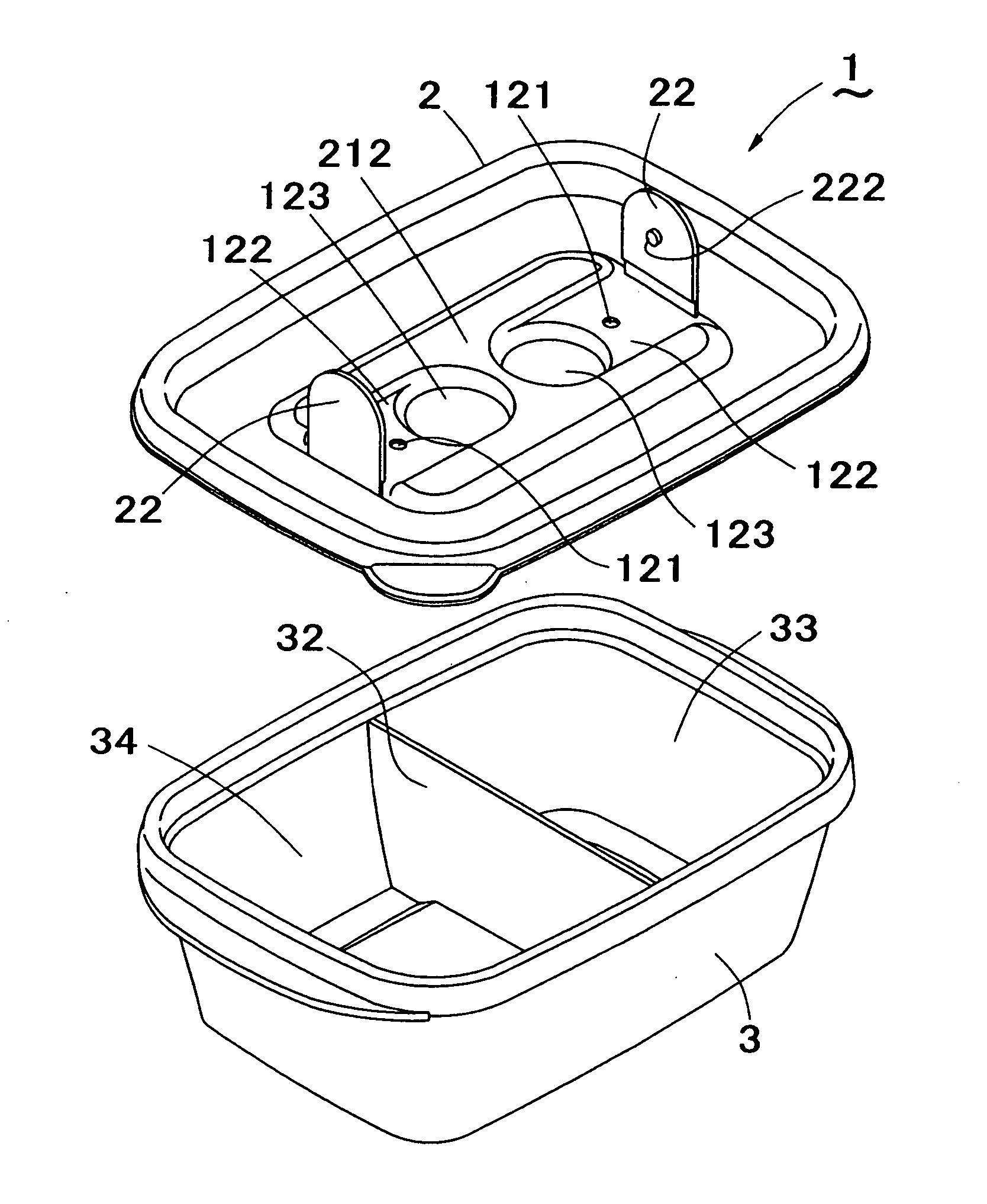

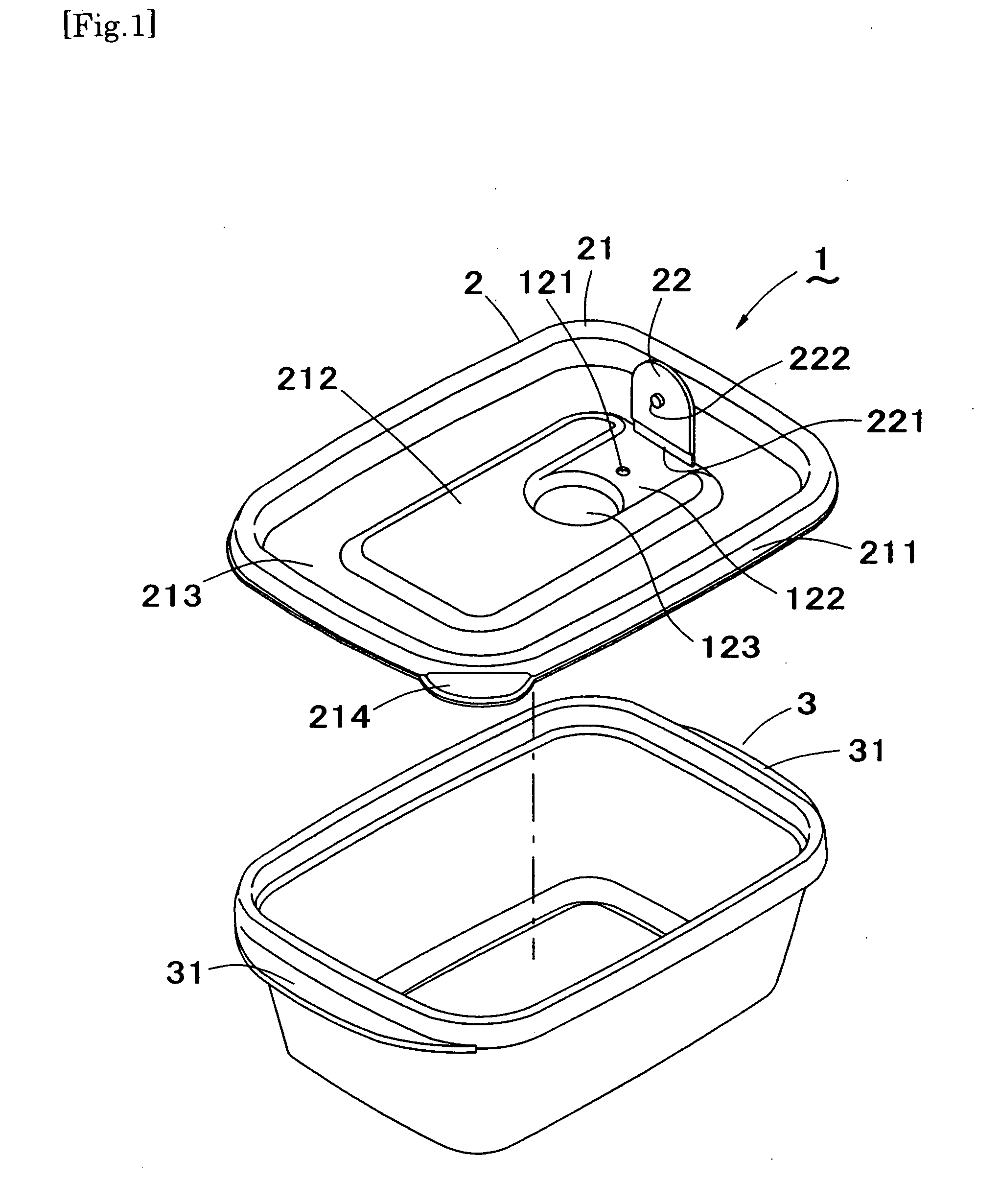

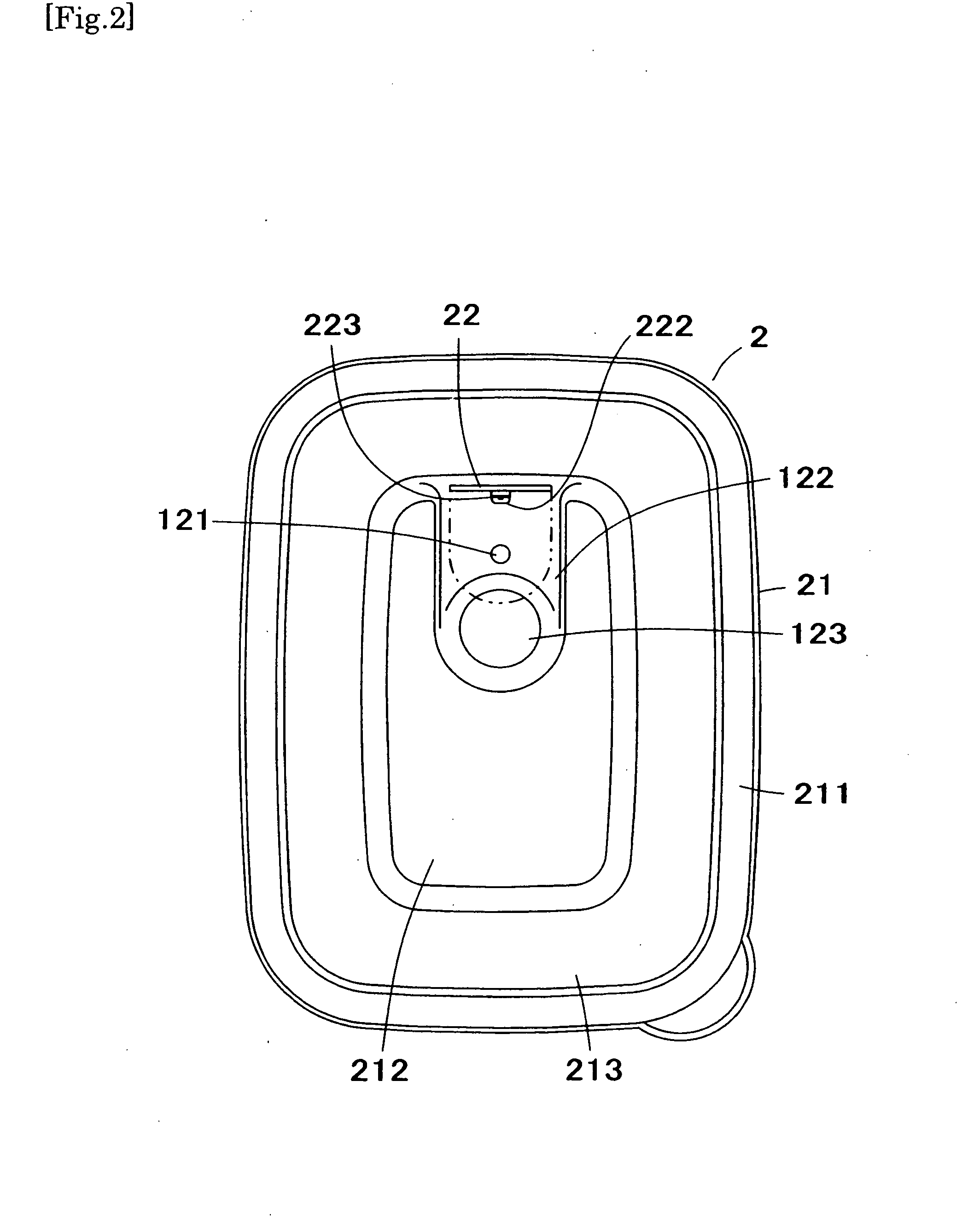

Cover, a container assembly including the cover, a molding device for molding the cover and a method for manufacturing the cover

ActiveUS20090200296A1More stressProlong lifeClosure capsClosure with auxillary devicesMicrowaveCo injection

[Purpose]To provide a container assembly suitable for heating a food stuff therein with a heating device such as a microwave and a cover thereof.[Solution]A cover for covering an opening of a container for a food stuff comprising: a substantially flat cover body including at least one aperture, at least one substantially flat flap including a linear proximal end configured to connect with the cover body, the proximal end allowing the at least one flap to rotate with respect to the cover body, wherein a lower surface of the at least one flap includes a protrusion configured to close the at least one aperture when the at least one flap is at a first position in which the at least one flap is in parallel with the cover body, the cover body and the at least one flap are integrally formed by a co-injection molding.

Owner:IWASAKI IND

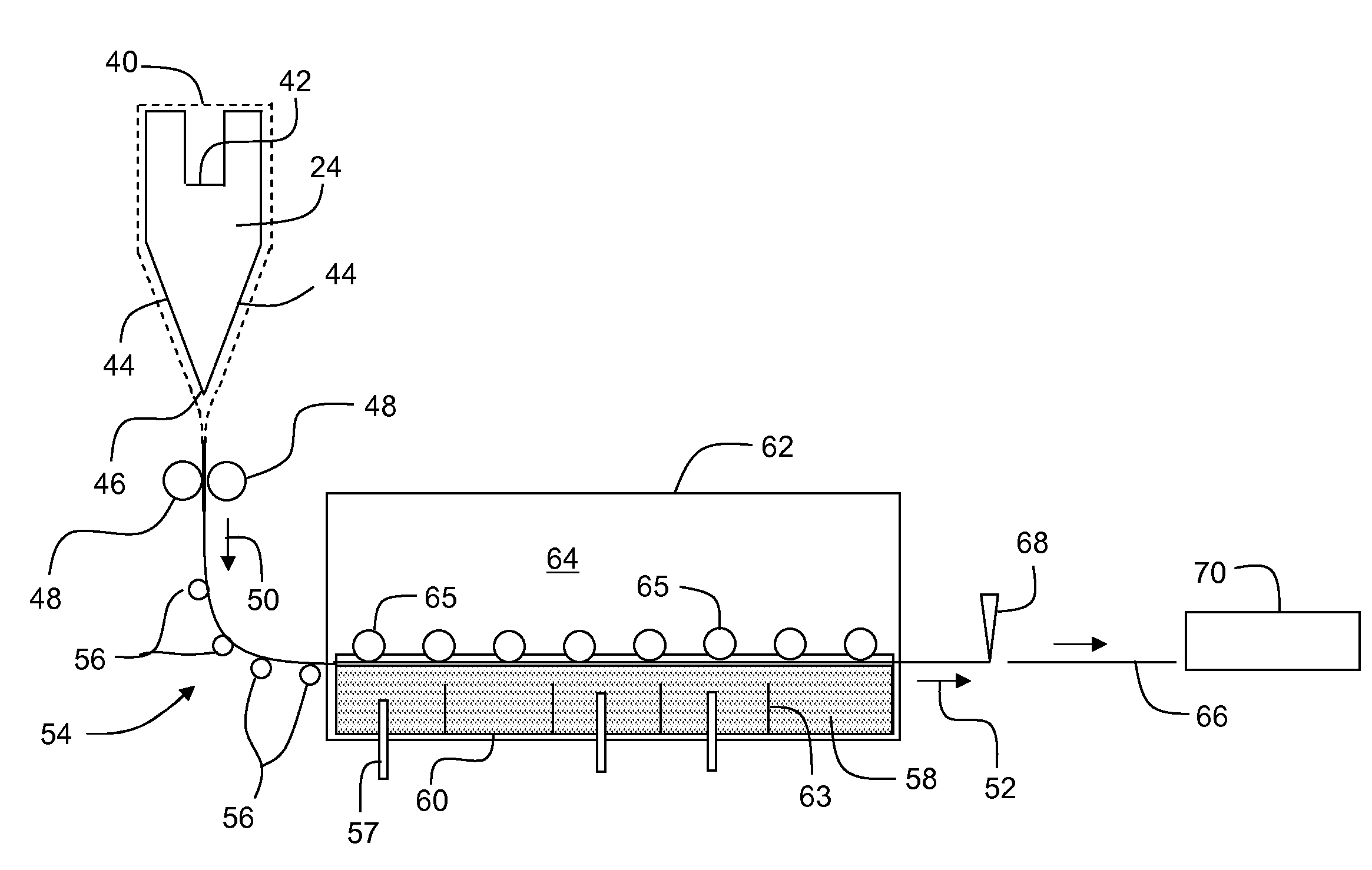

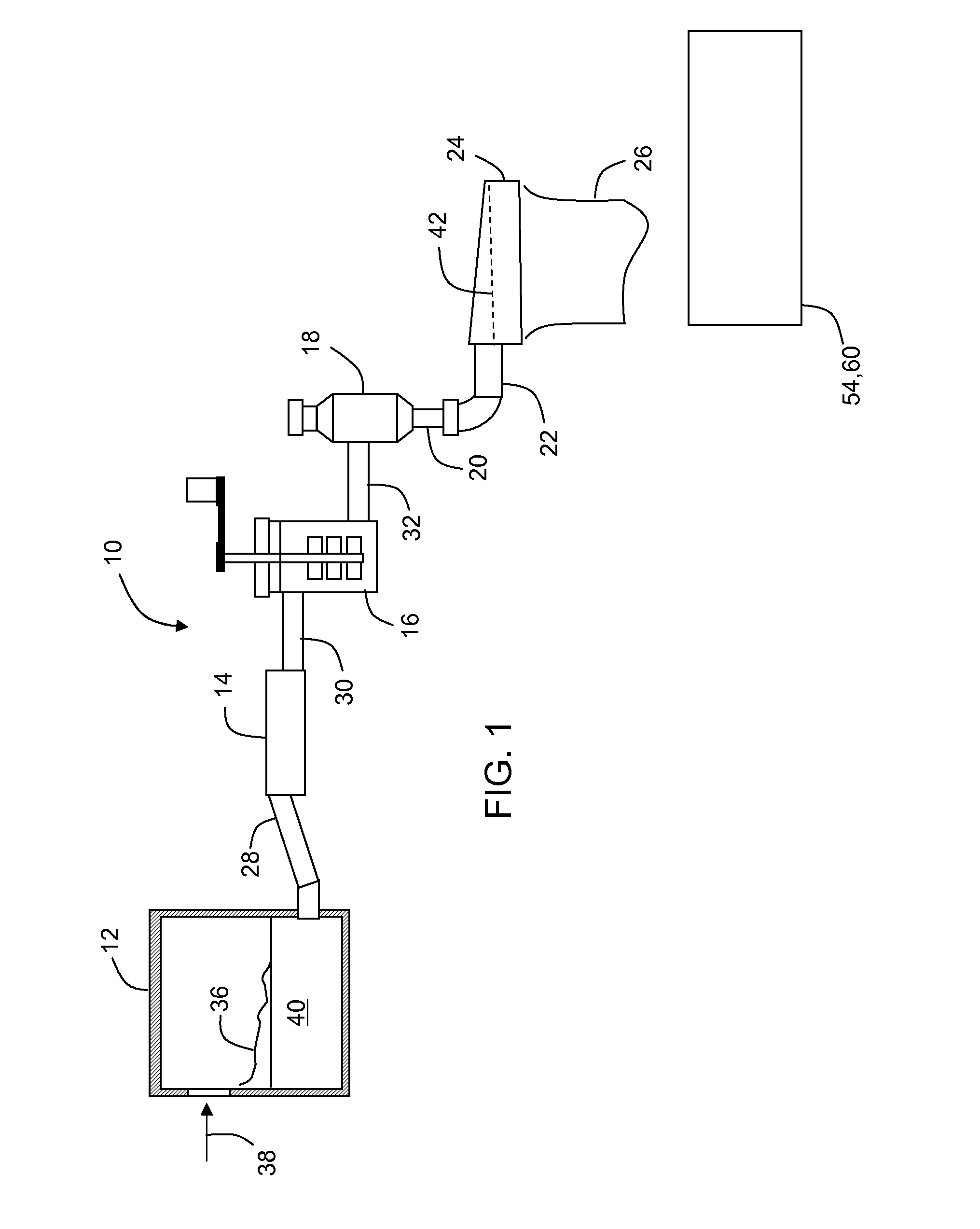

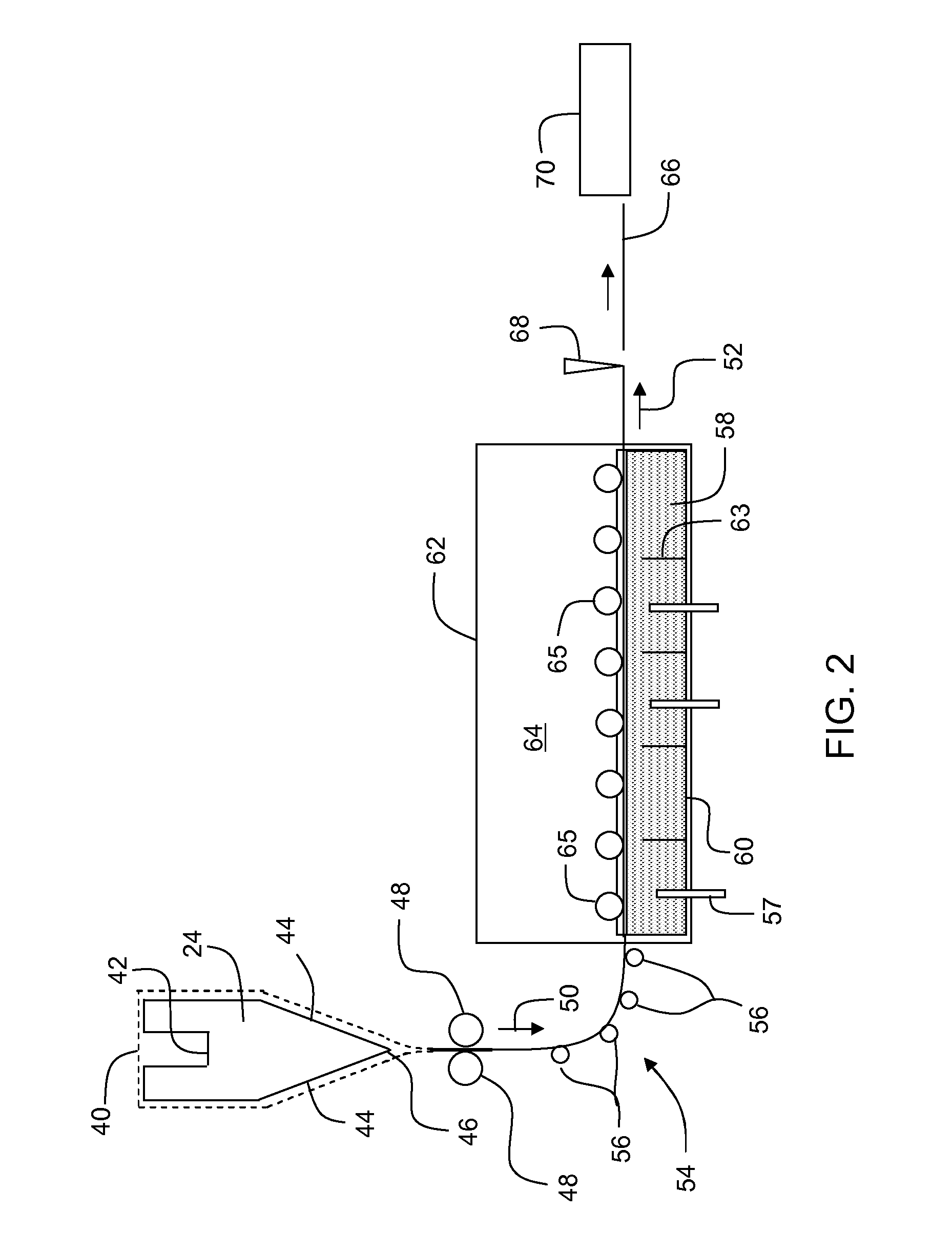

Apparatus and method for forming glass sheets

InactiveUS20130047671A1Increase compressive stressMore stressGlass drawing apparatusGlass forming apparatusGlass sheetMolten metal

Disclosed is a method of reducing the compaction of glass formed by a down draw process. The glass may be a glass sheet or a glass ribbon. Once the glass is formed, it is thermally treated on a molten metal bath for a time and at a temperature effective to reduce the fictive temperature of the glass below a predetermined level. In one embodiment, a glass ribbon is formed in a fusion process and the glass ribbon redirected onto a molten metal bath where the ribbon is thermally treated.

Owner:CORNING INC

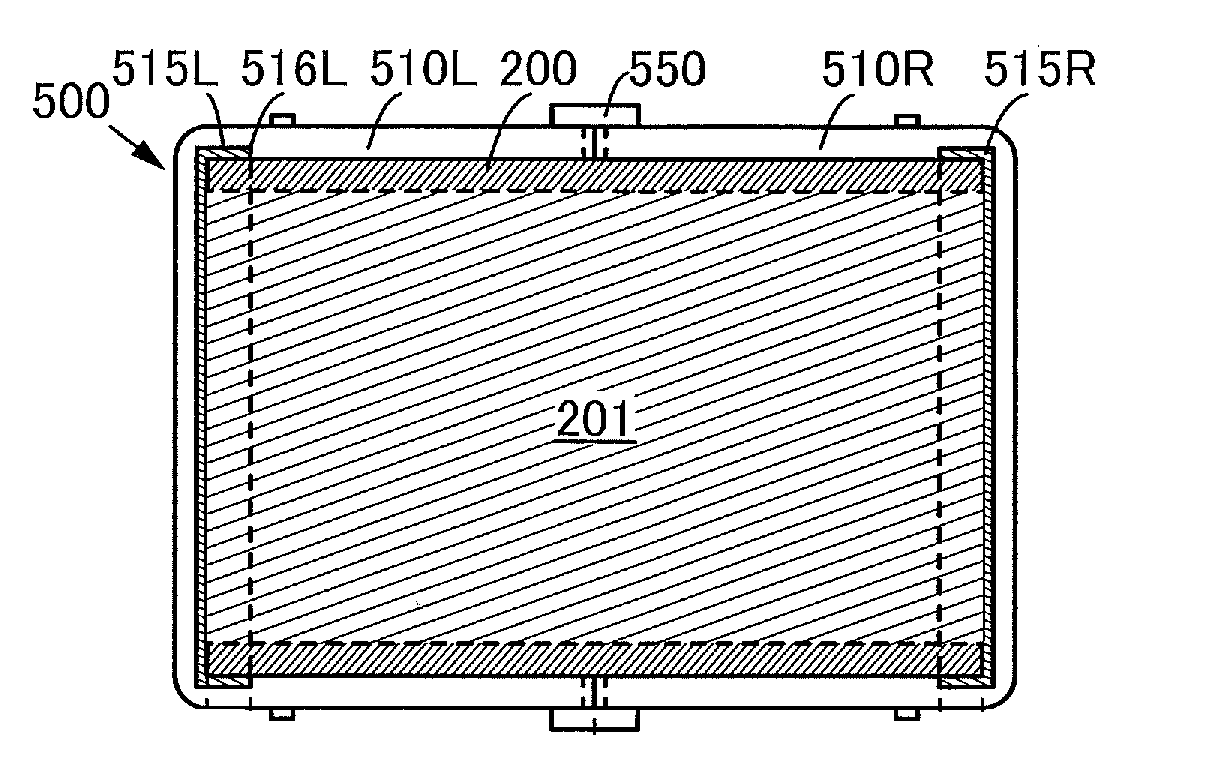

Display device

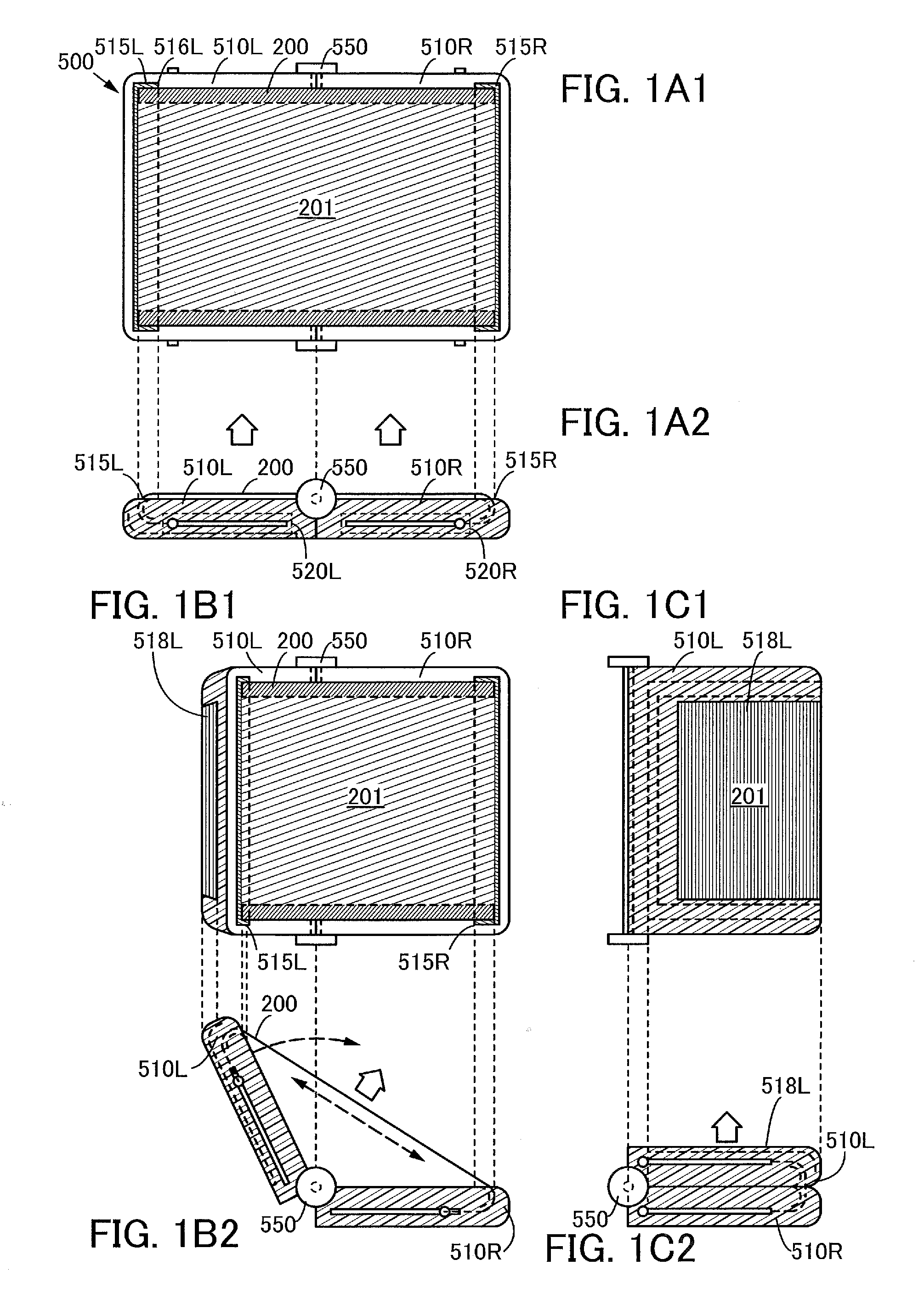

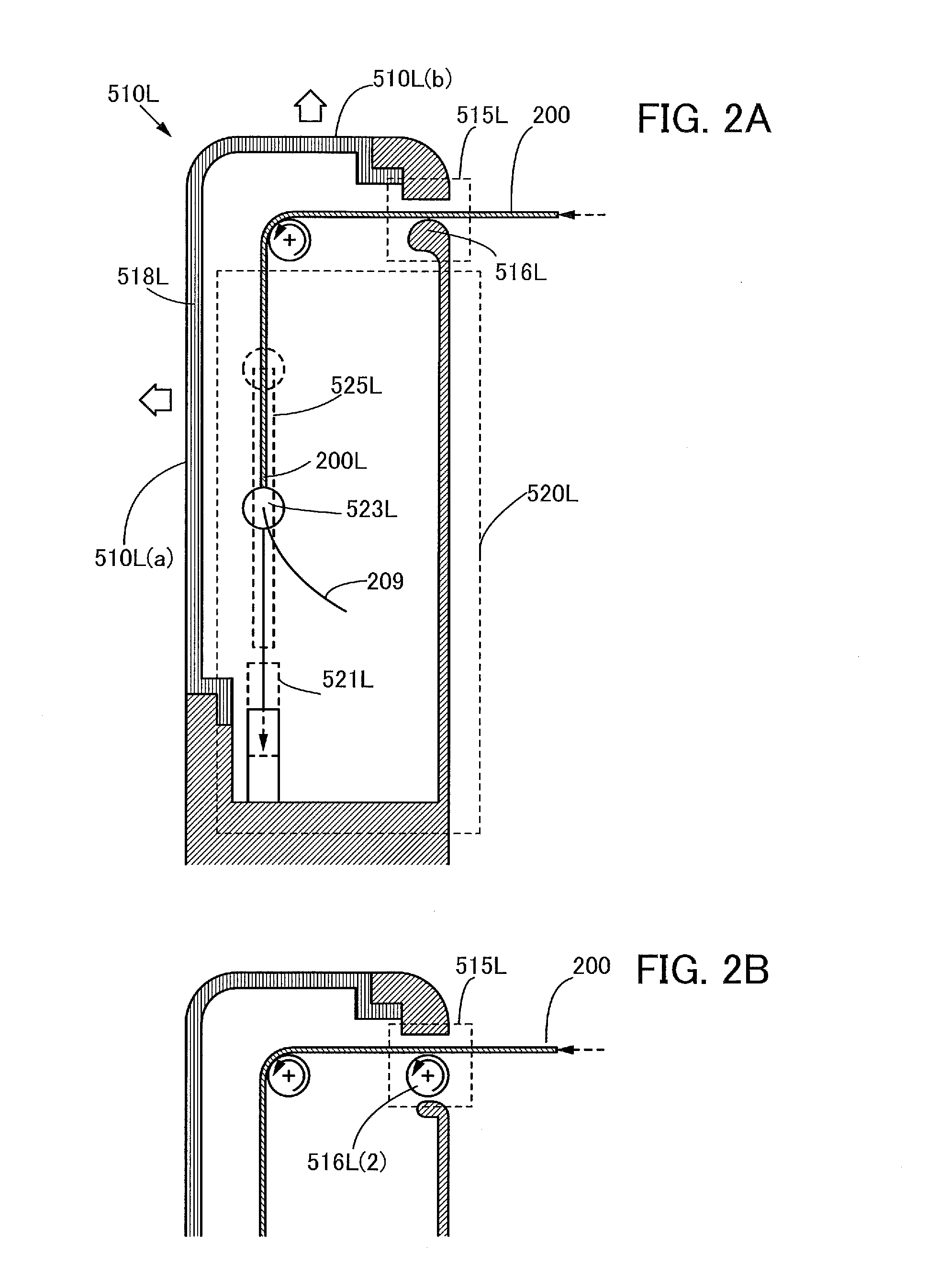

ActiveUS20140321074A1Avoid normal displayMore stressCircuit bendability/stretchabilityDetails for portable computersDisplay deviceLarge screen

A novel foldable and highly portable display device is provided. Further, a novel display device capable of displaying information or the like on a seamless large screen is provided. The display device includes a flexible display panel, a first housing provided with a storage portion that includes a space in which pulled one end of the display panel is stored, a folding mechanism connected to the first housing, and a second housing connected to the folding mechanism. The other end of the display panel is connected to the second housing so that the display panel can be drawn in accordance with an opening operation of the folding mechanism and stored in accordance with a closing operation of the folding mechanism.

Owner:SEMICON ENERGY LAB CO LTD

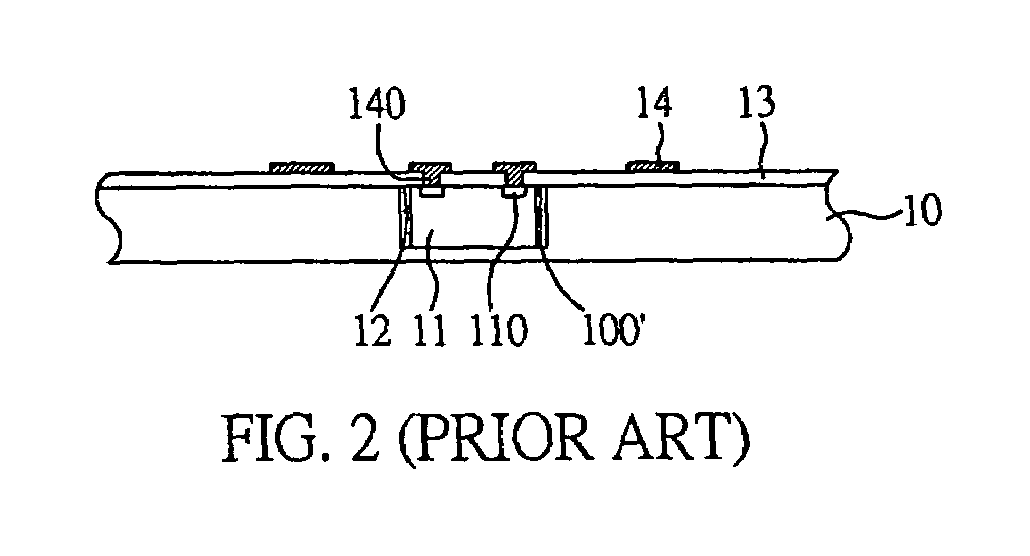

Carrier board structure with semiconductor chip embedded therein

InactiveUS20080054443A1Easy disposalMore stressSemiconductor/solid-state device detailsPrinted circuit aspectsSemiconductor chipBoard structure

A carrier board structure with semiconductor chip embedded therein is proposed. The carrier board structure includes a carrier board having a first surface and a second surface opposed to the first surface, wherein the carrier board including at least one cavity having a chamfer. A semiconductor chip can be easily disposed in the cavity by the chamfer, and an adhesion material can be evenly filled in the cavity by the chamfer, so as to avoid generating air bubbles, voids and reduce stress.

Owner:PHOENIX PRECISION TECH CORP

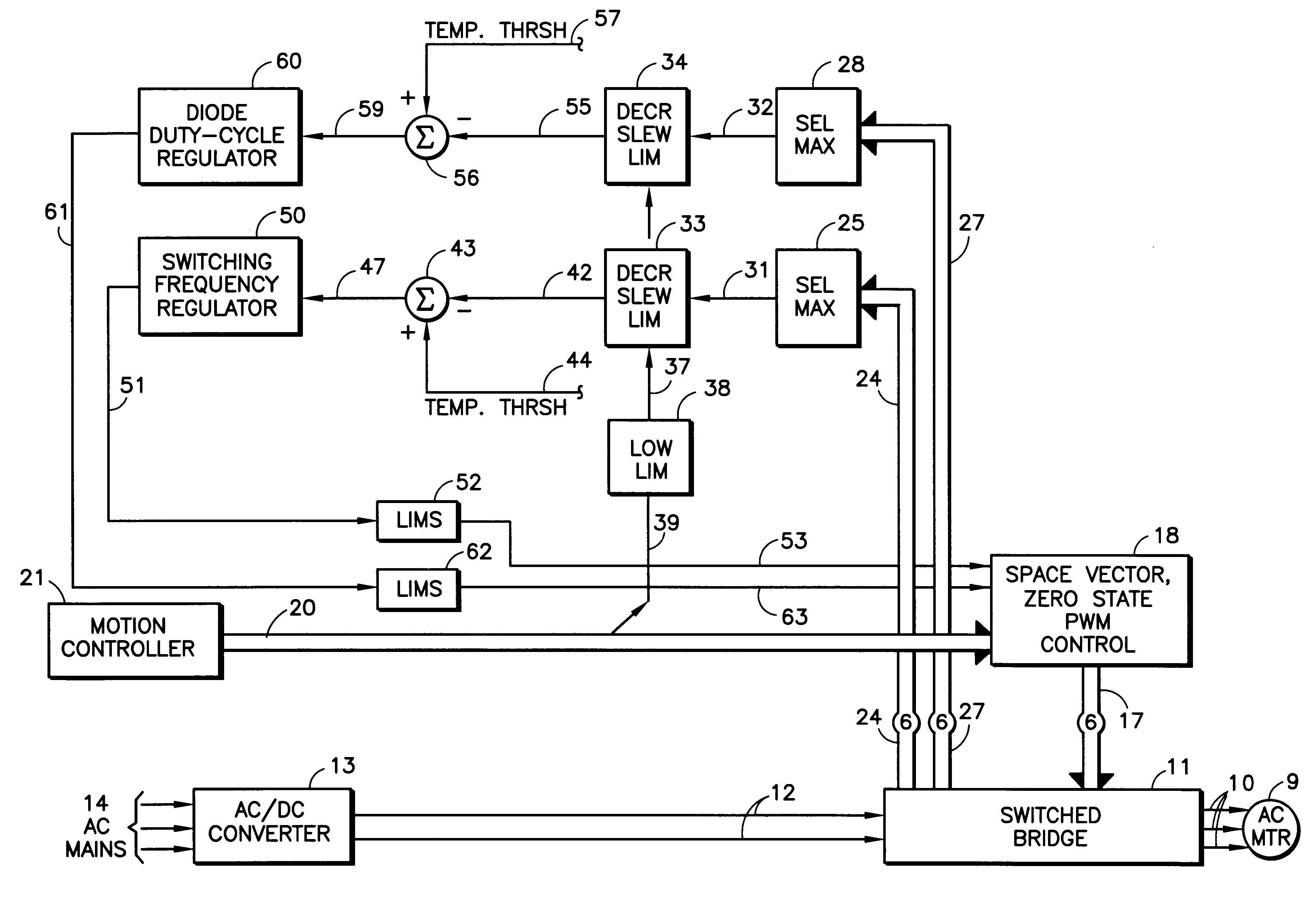

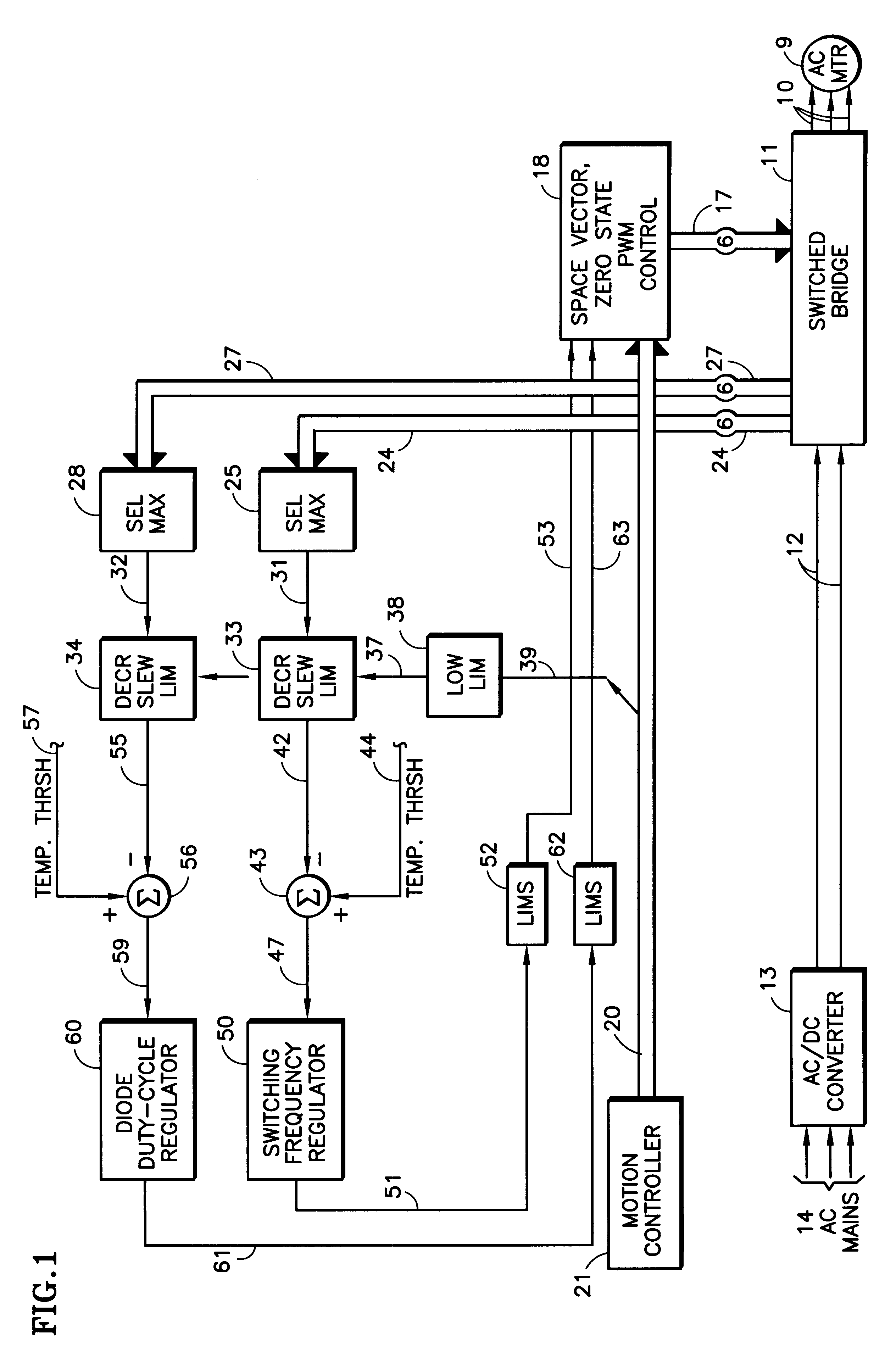

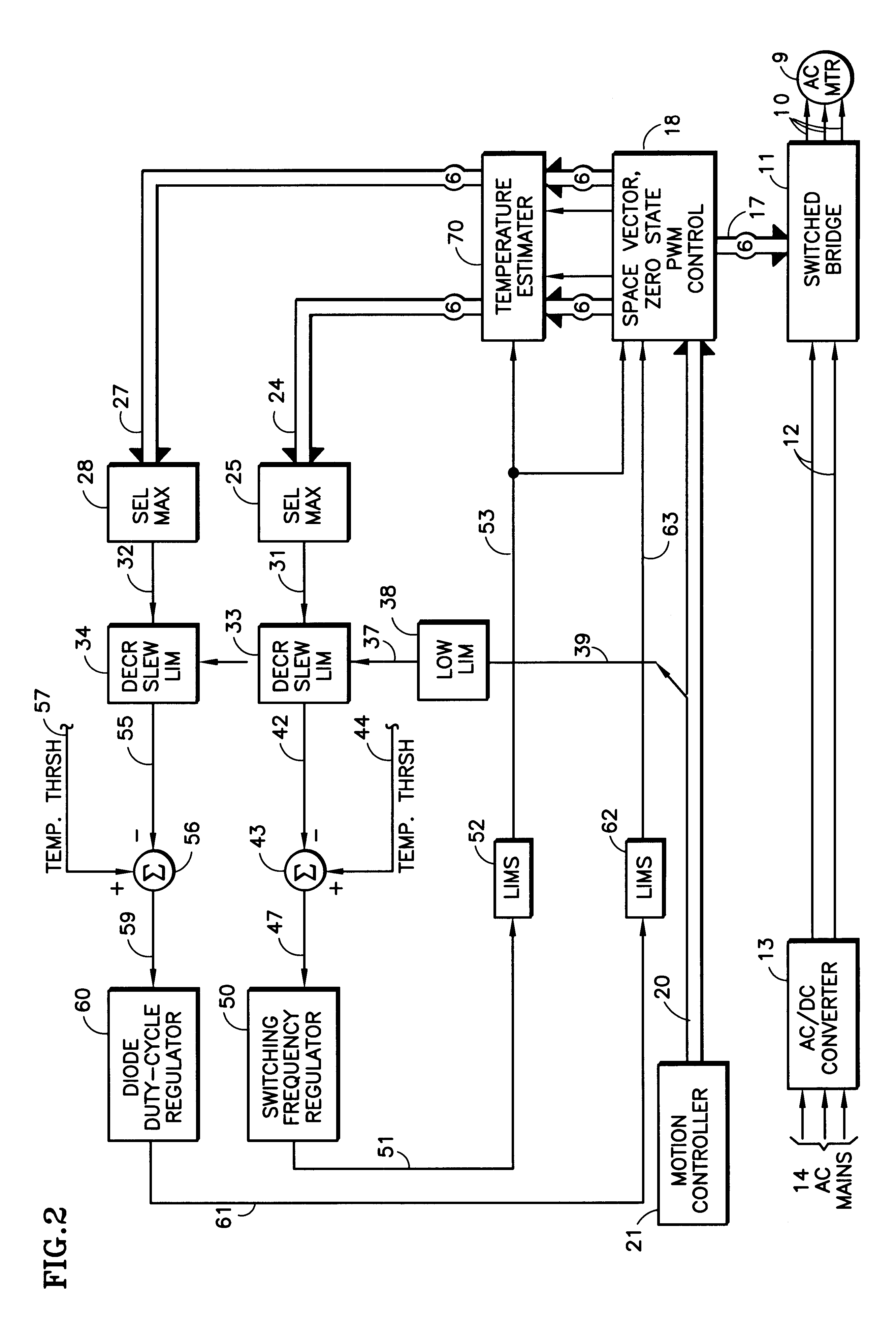

Motor drive parameters

InactiveUS6483271B1More stressReduce mechanical failureSingle-phase induction motor startersAC motor controlMotor speedMotor drive

The temperature (25, 33, 43) of solid state switching devices in variable speed motor drives (11, 18), such as elevator motor drives, are utilized to reduce the load on the drive, by reducing the switching frequency (50) or the commanded load (110). The choice between the preferred non-switching zero state and an alternative zero state is determined (60) by temperature (28, 34, 56) of the switched transistor's anti-parallel diode. The rate of recognizing reduced temperatures is limited (33, 34) to avoid motor speed and / or load variations. The temperature may either be measured (24, 27) or determined (70) from models utilizing manufacturer product specification and normalized thermal transient response from the transistor / diode package to a heat sink.

Owner:OTIS ELEVATOR CO

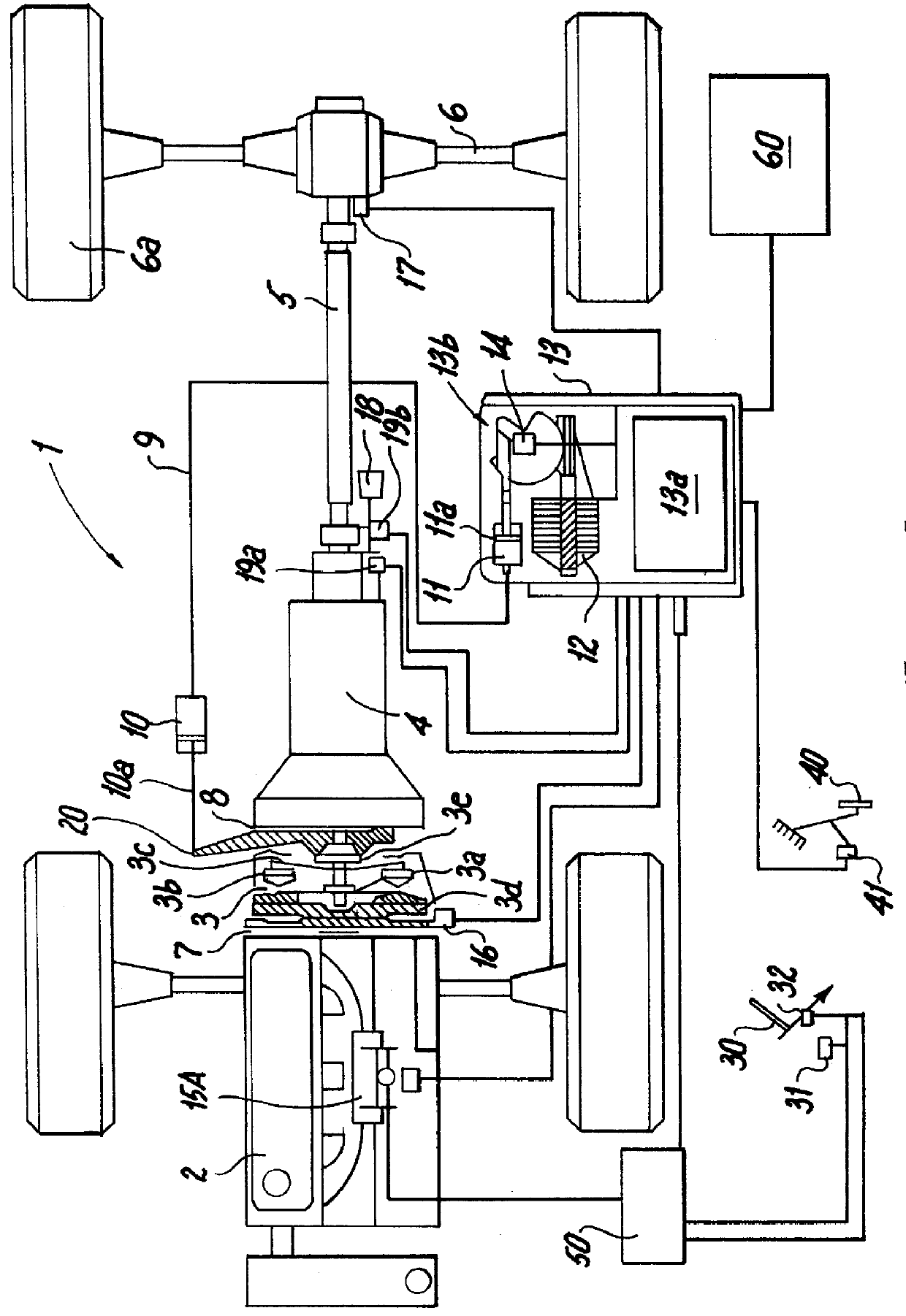

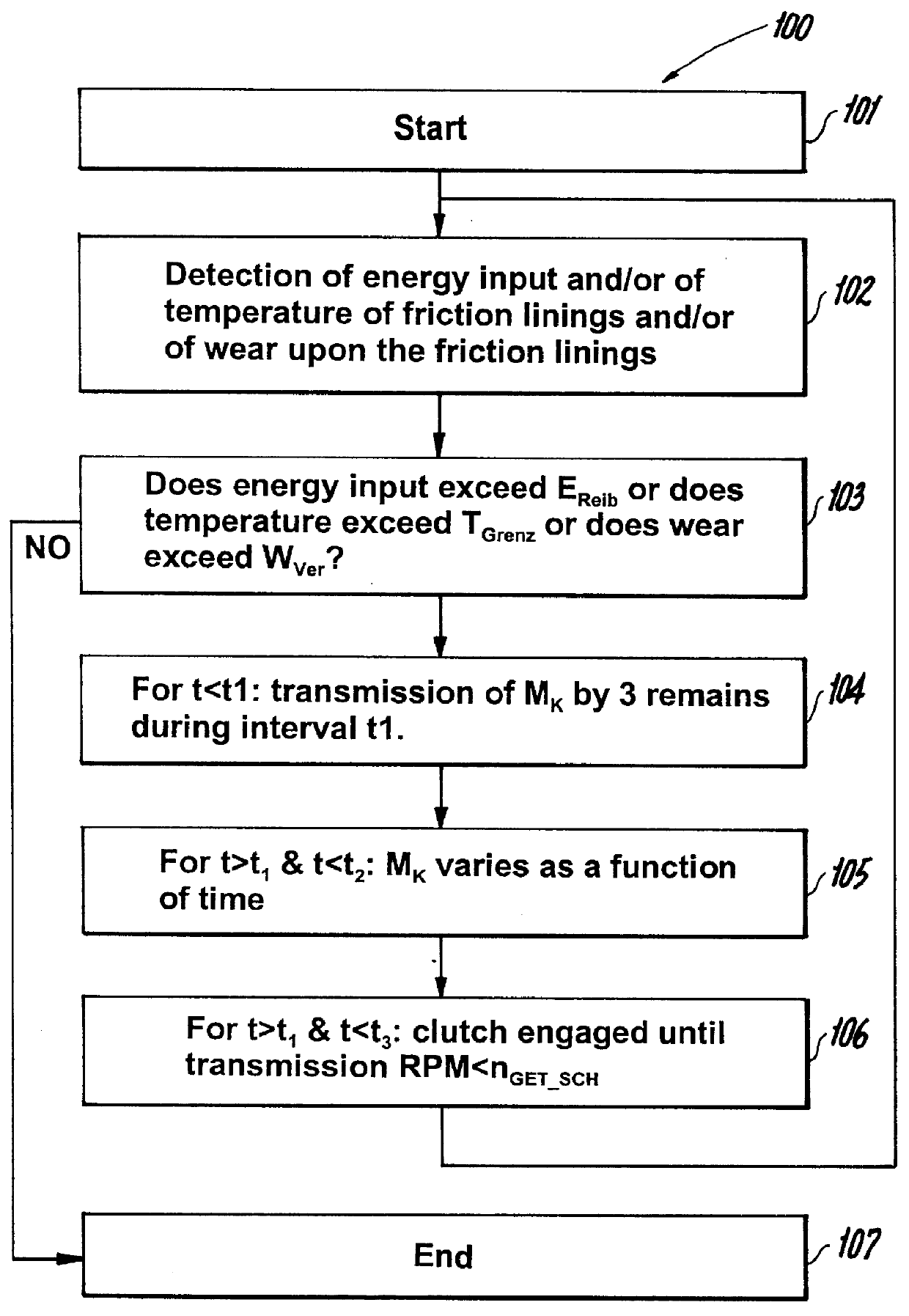

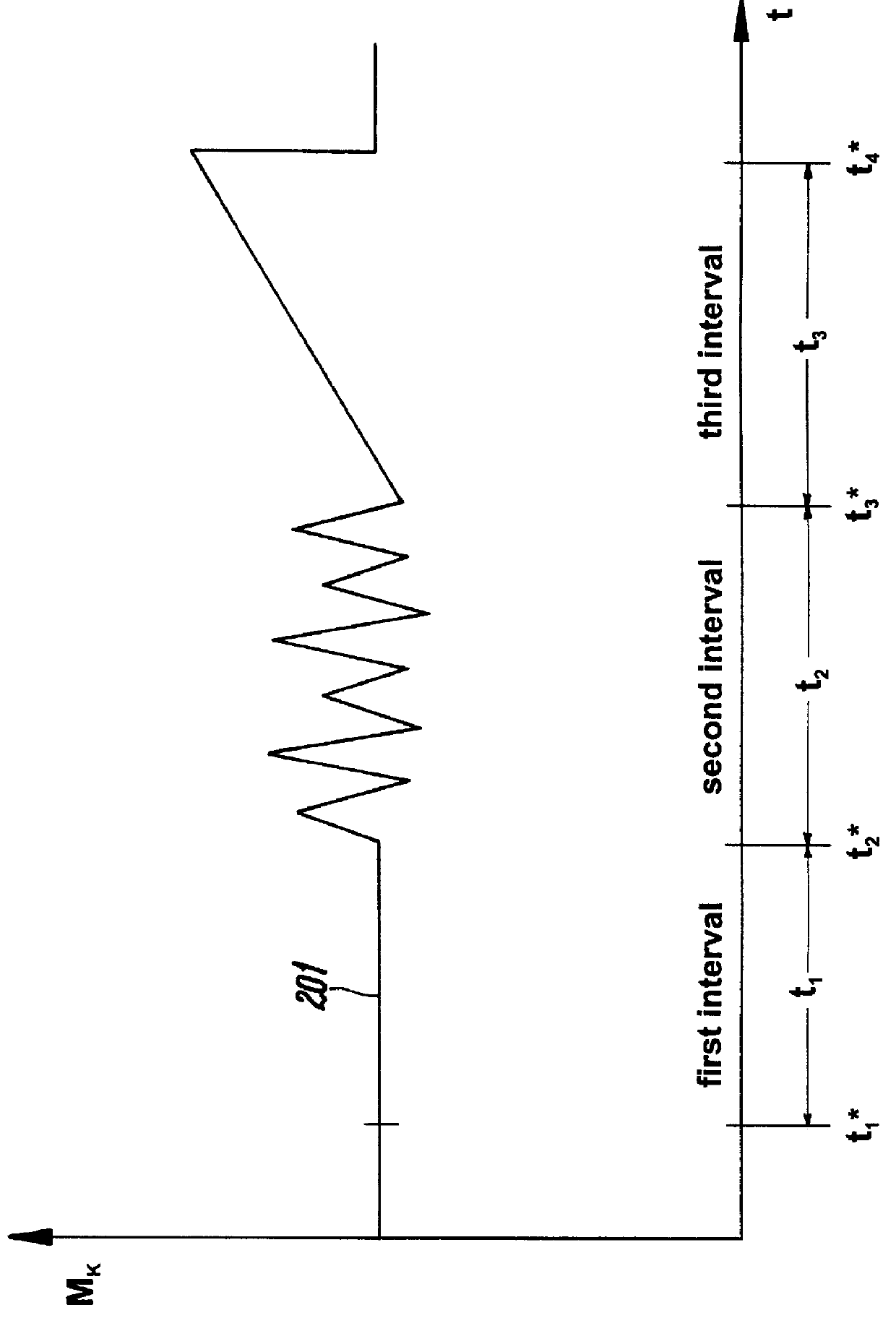

Motor vehicle with a power train having an automated clutch

InactiveUS6113517AOvercomes drawbackMore stressClutchesGearing controlPrime moverControl engineering

The power train of a motor vehicle has an automated clutch which can transmit torque from a prime mover to a transmission in response to signals from an electronic control unit. The latter causes the clutch to transmit a constant torque during a first interval, to thereupon transmit a gently varying torque during a second interval if the operator of the motor vehicle fails to carry out certain necessary operations prior to elapse of the first interval, and to thereafter transmit a pronouncedly varying torque during a third interval if no remedial undertakings were completed during the second interval. The third interval is cut short if the engine tends to choke, and the full or shortened third interval can be followed by a fourth interval corresponding to the first interval or by a further interval corresponding to the second interval.

Owner:LUK GETRIEBE SYST +1

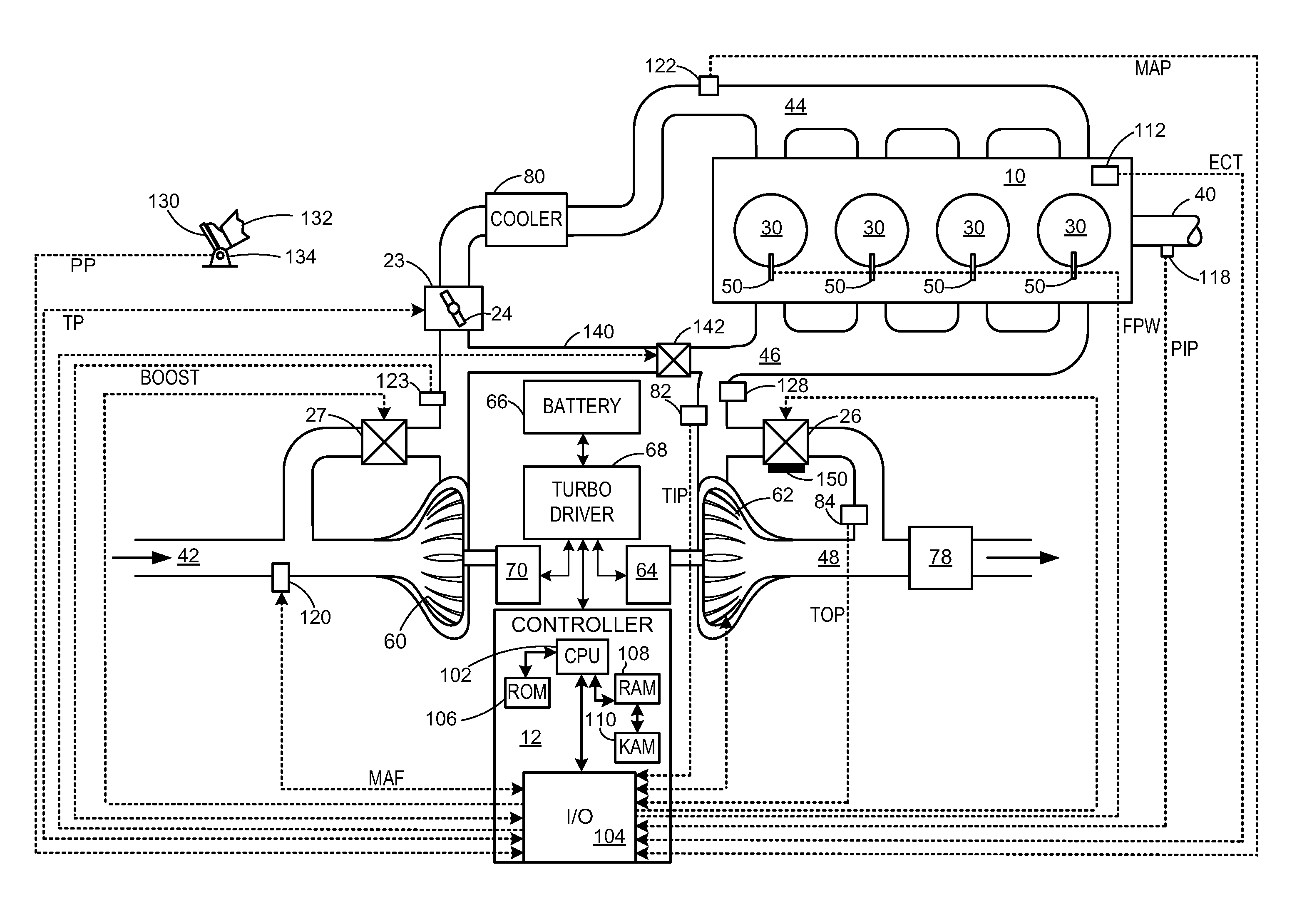

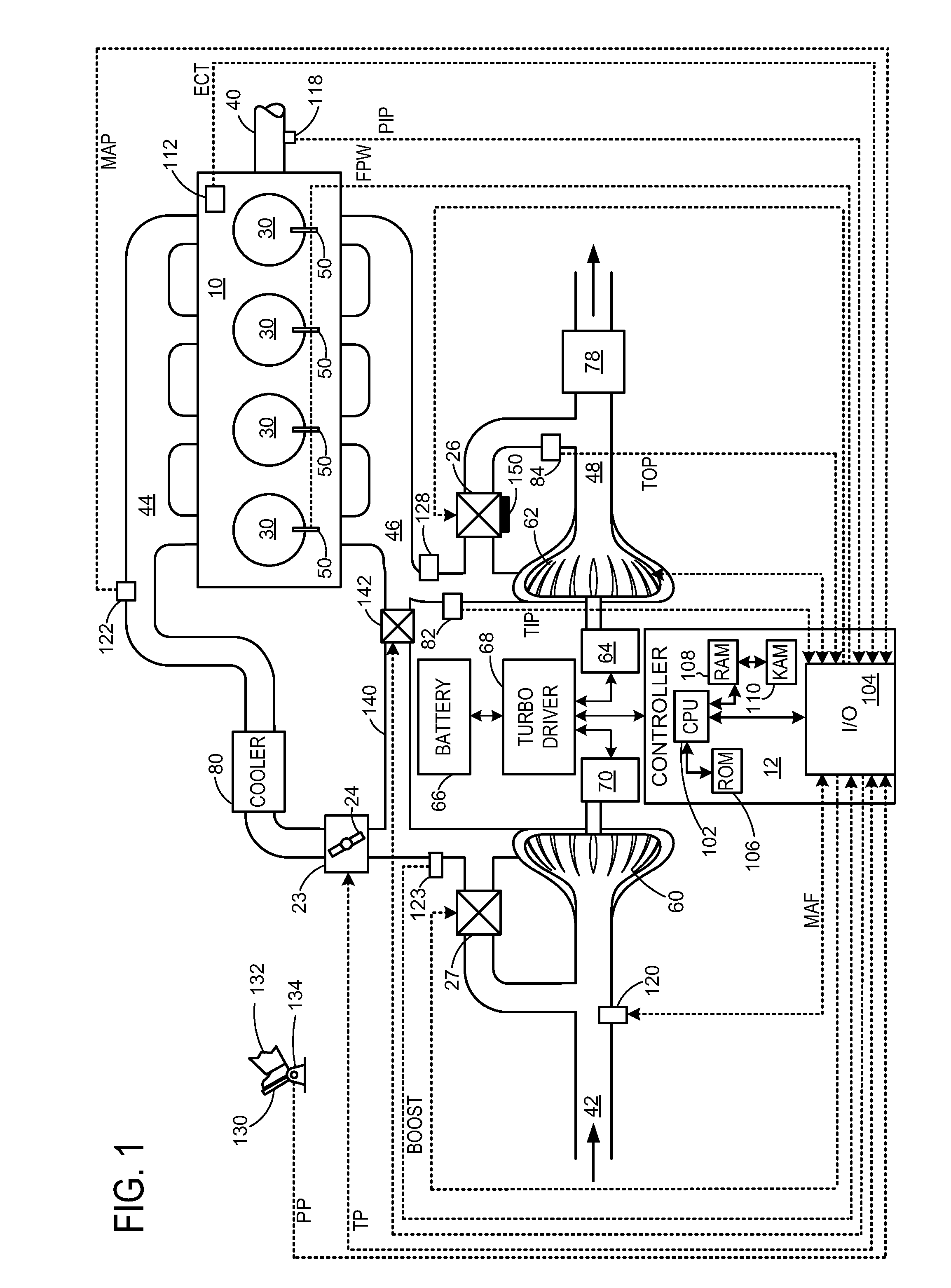

Wastegate control

ActiveUS20160010541A1More mechanical stressIncrease airflowElectrical controlInternal combustion piston enginesPower flowWastegate

Various methods for determining a holding current based on a pressure differential across a wastegate valve are provided. In one example, a method of operating a wastegate comprises determining a holding current with which to hold a wastegate valve at a desired position, the holding current determined based on a pressure differential across the wastegate valve.

Owner:FORD GLOBAL TECH LLC

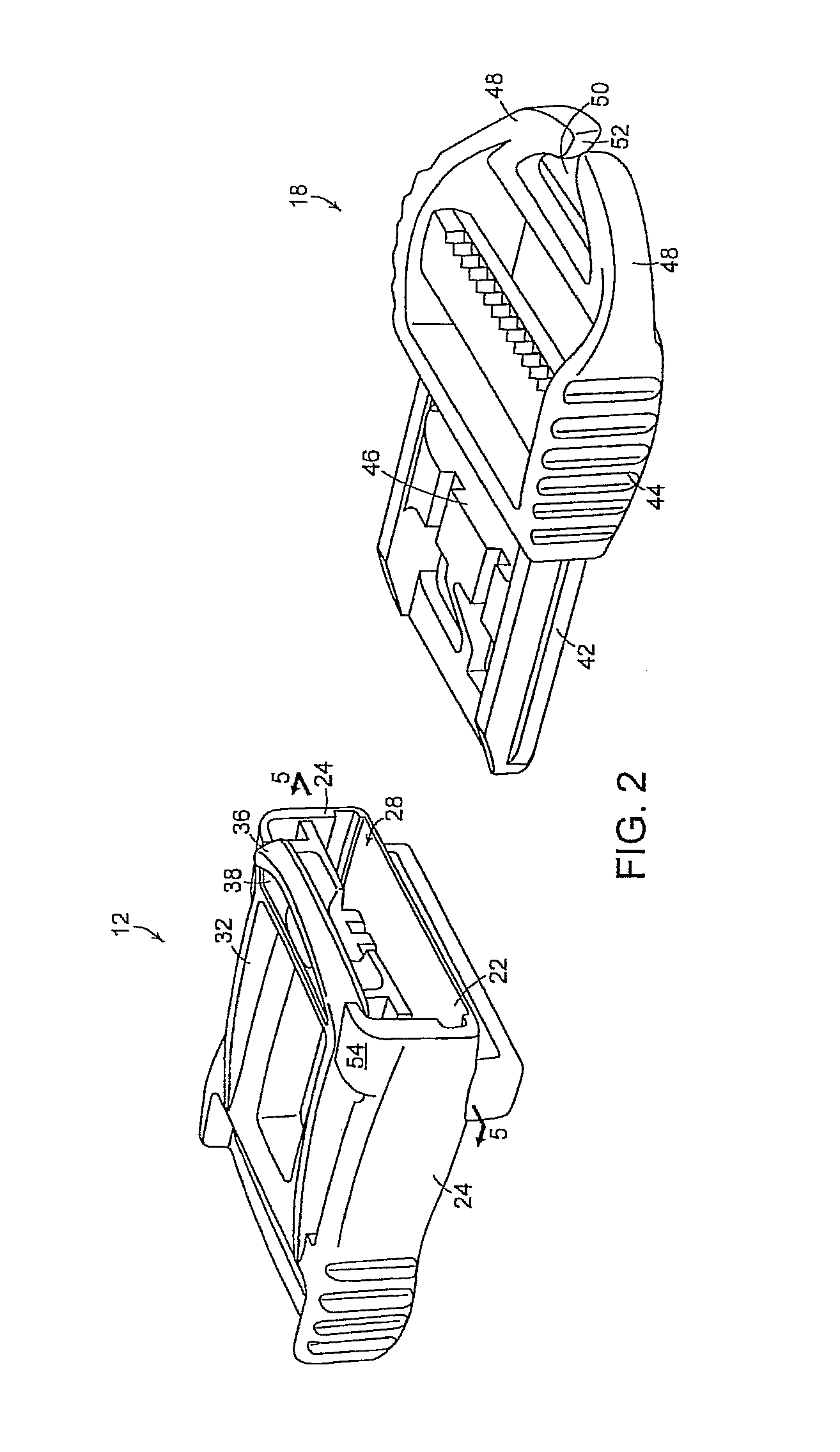

Quick release buckle

Owner:ILLINOIS TOOL WORKS INC

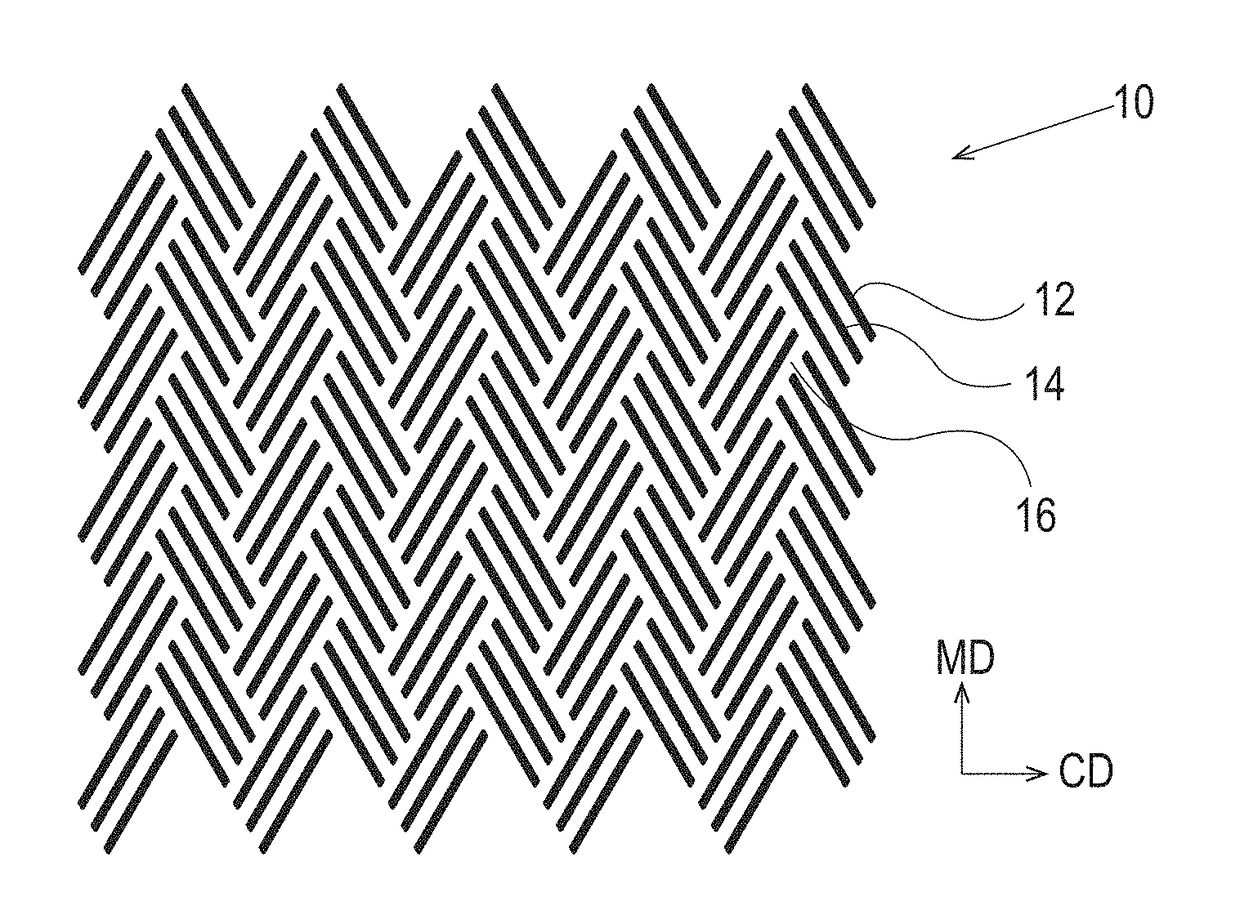

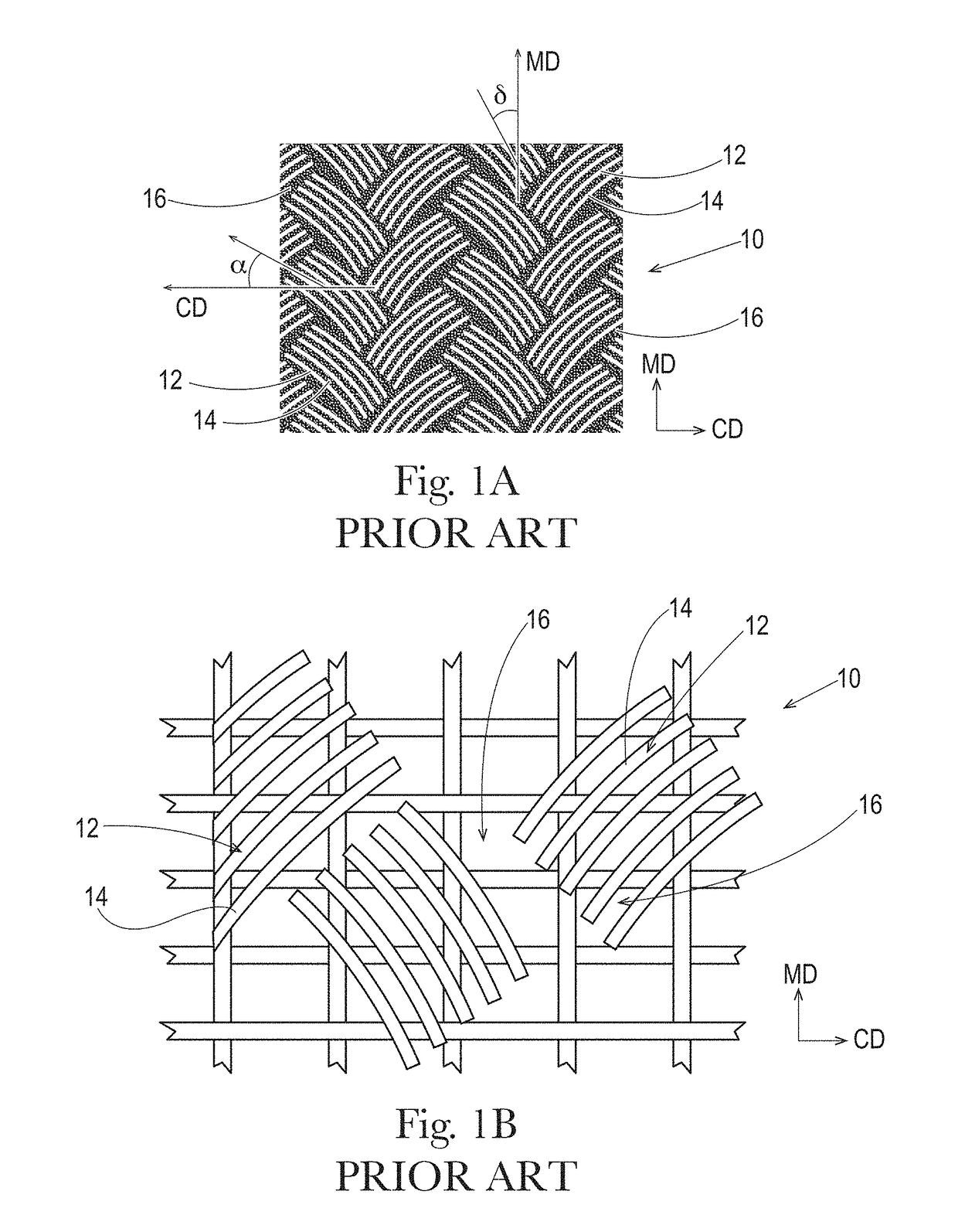

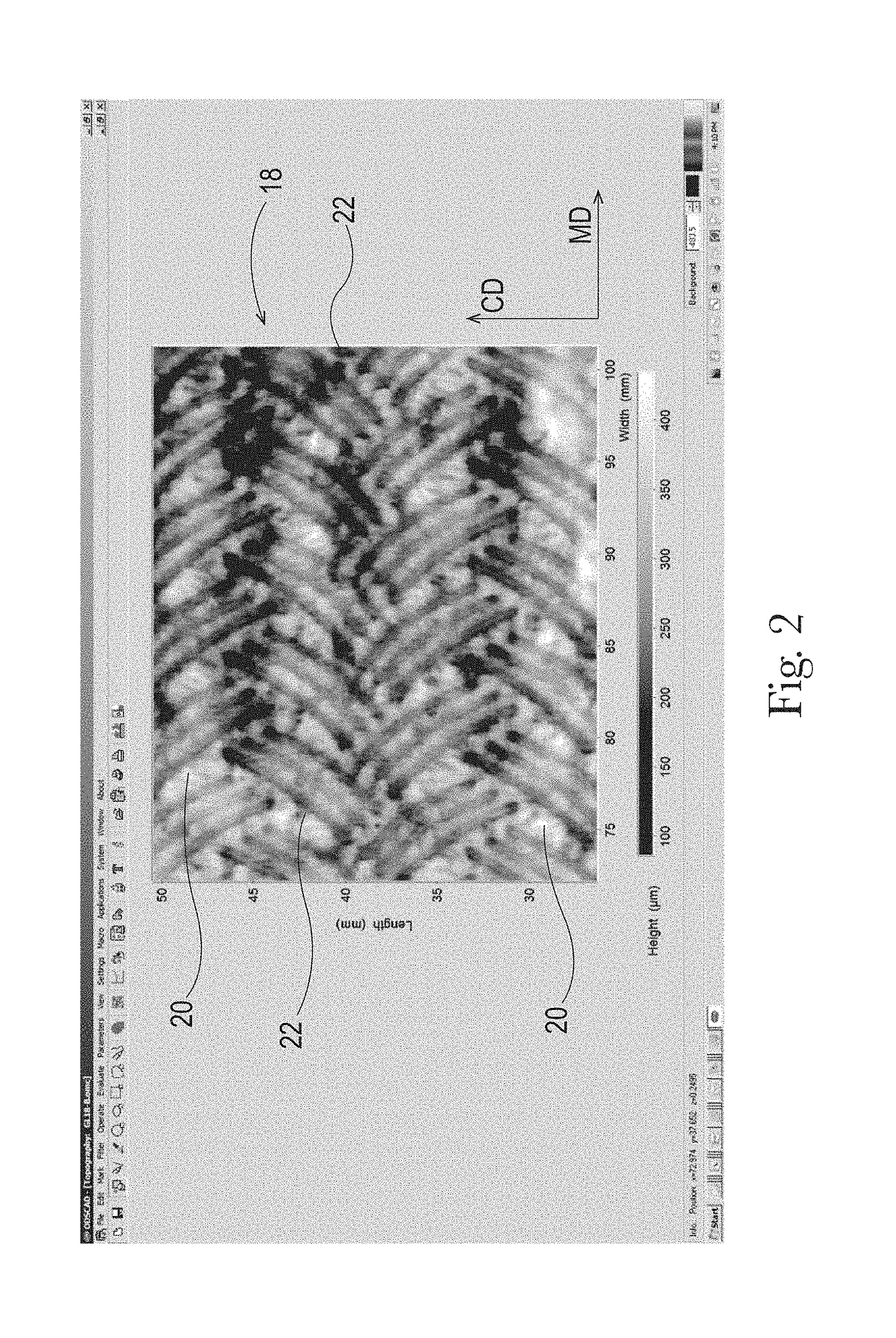

Sanitary Tissue Products

ActiveUS20170306566A1Less stressImprove strength performanceReinforcing agents additionPaper/cardboardFiberBiomedical engineering

Owner:THE PROCTER & GAMBLE COMPANY

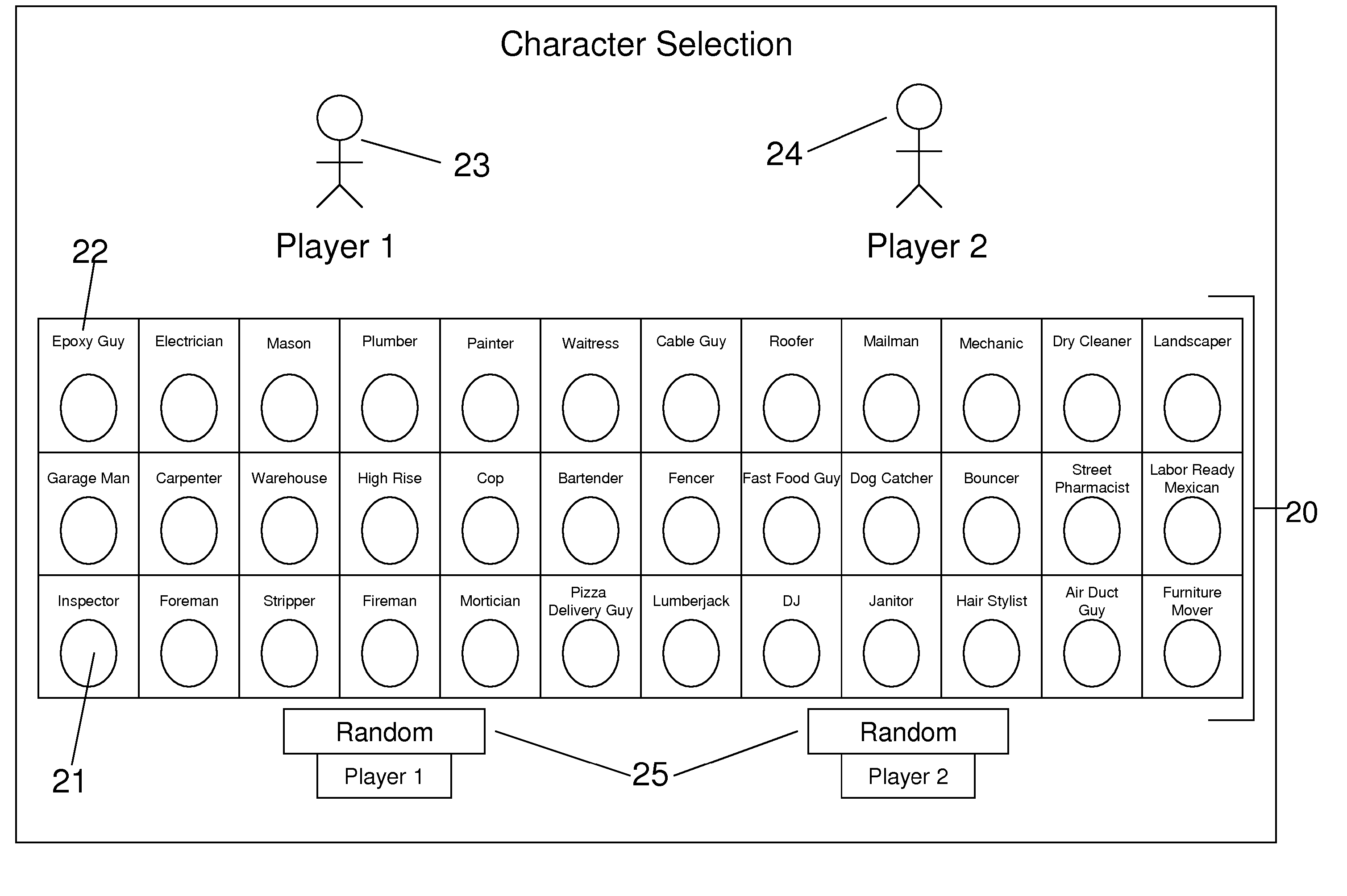

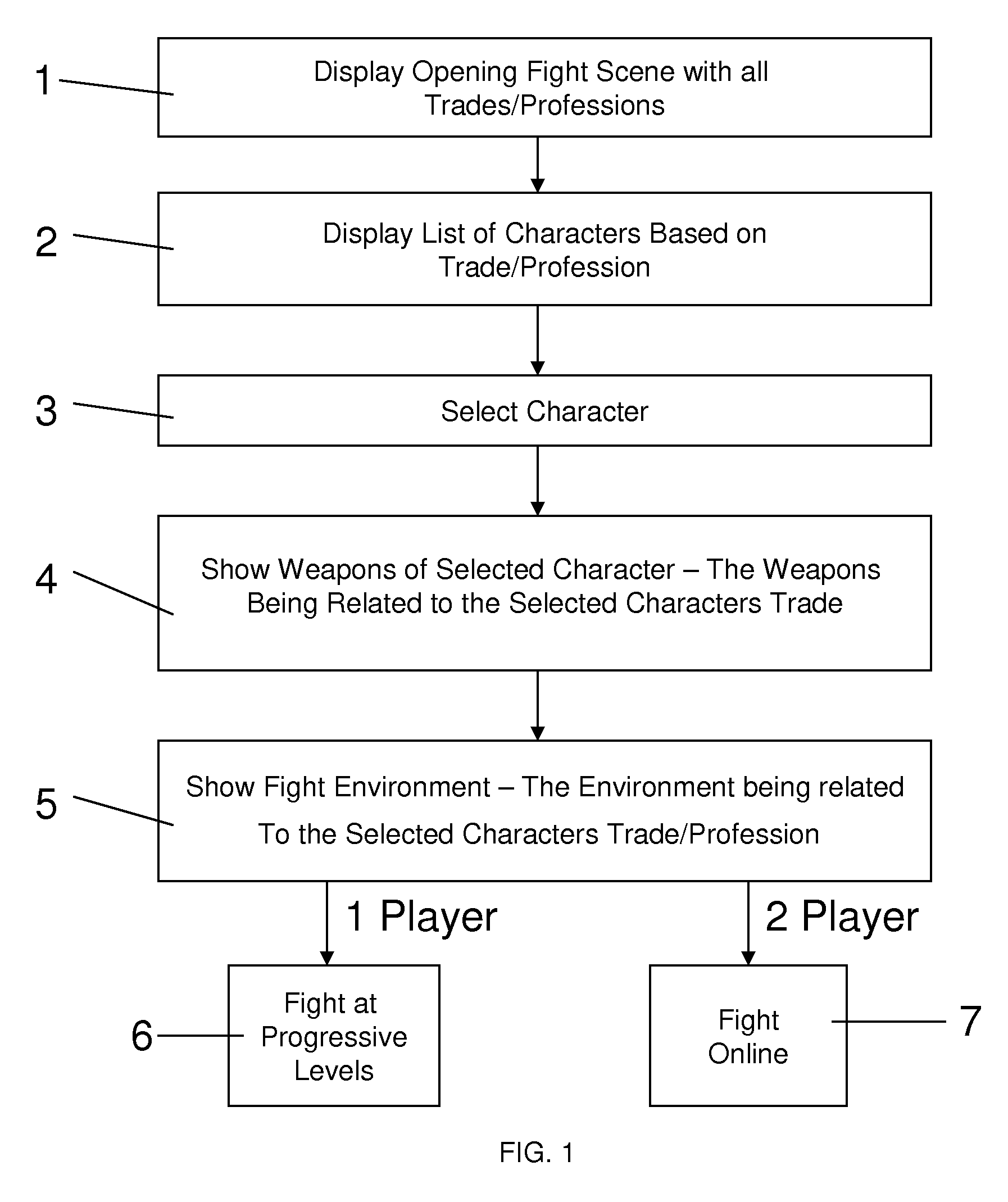

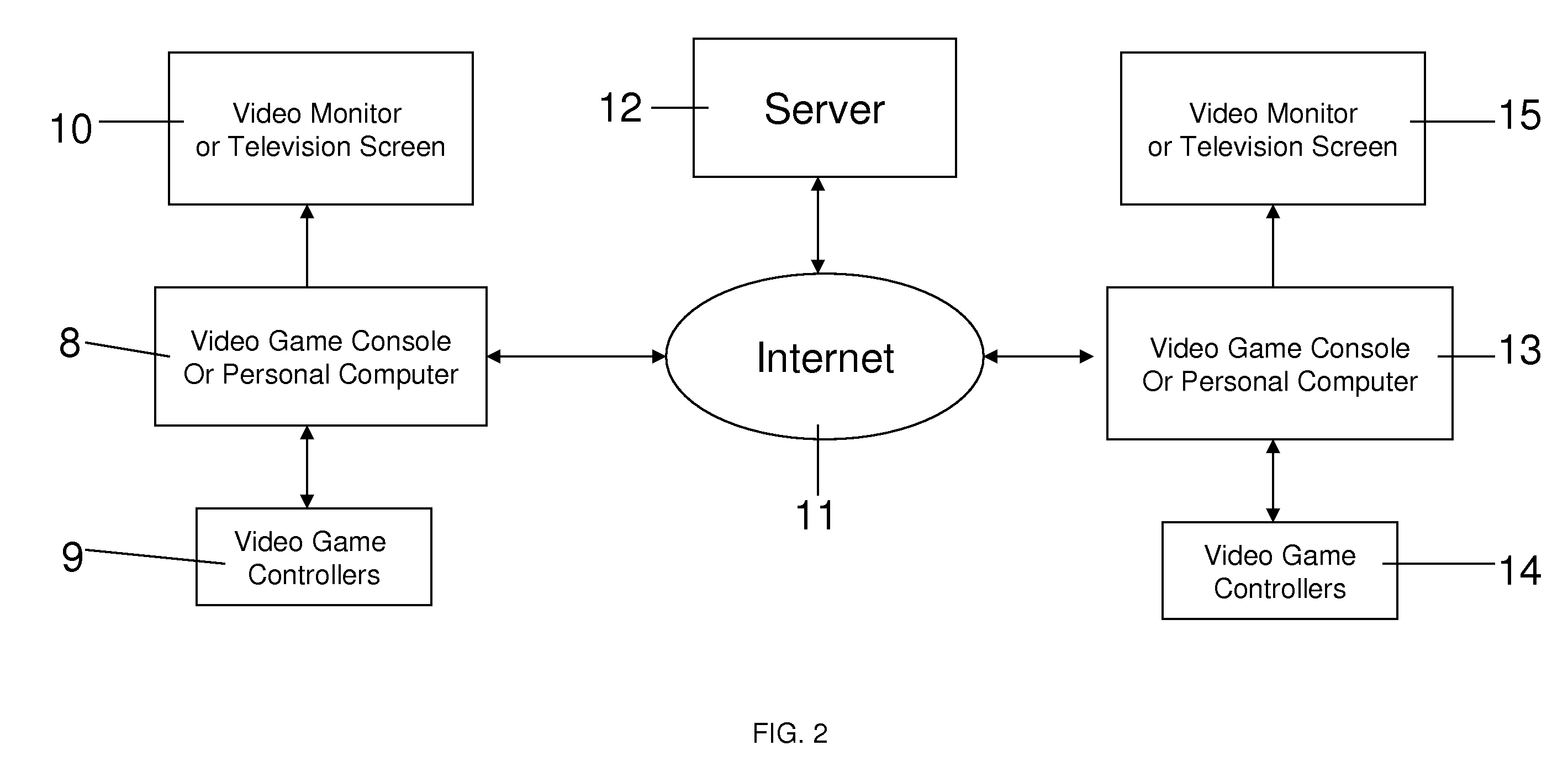

Video Game System and Method with Trade Based Characters, Weapons and Fight Environments

InactiveUS20070060233A1Much needed stress reliefIncrease entertainmentVideo gamesSpecial data processing applicationsComputer scienceVideo game

The disclosure describes a method of video gaming. In a first step, a screen having a plurality of characters is displayed. Each of the plurality of characters represents a trade so that a player can select one of the plurality of characters to generate a selected character. The video game then generates at least one enemy character, a plurality of weapons for use by the selected character in the trade and a fight environment. Then the video game displays the selected character, the at least one enemy character and at least one of the plurality of weapons in the fight environment and controls the actions of the selected character and the at least one of the plurality of weapons in the fight environment based on controls selected by the player.

Owner:LICCARDO ANTHONY J

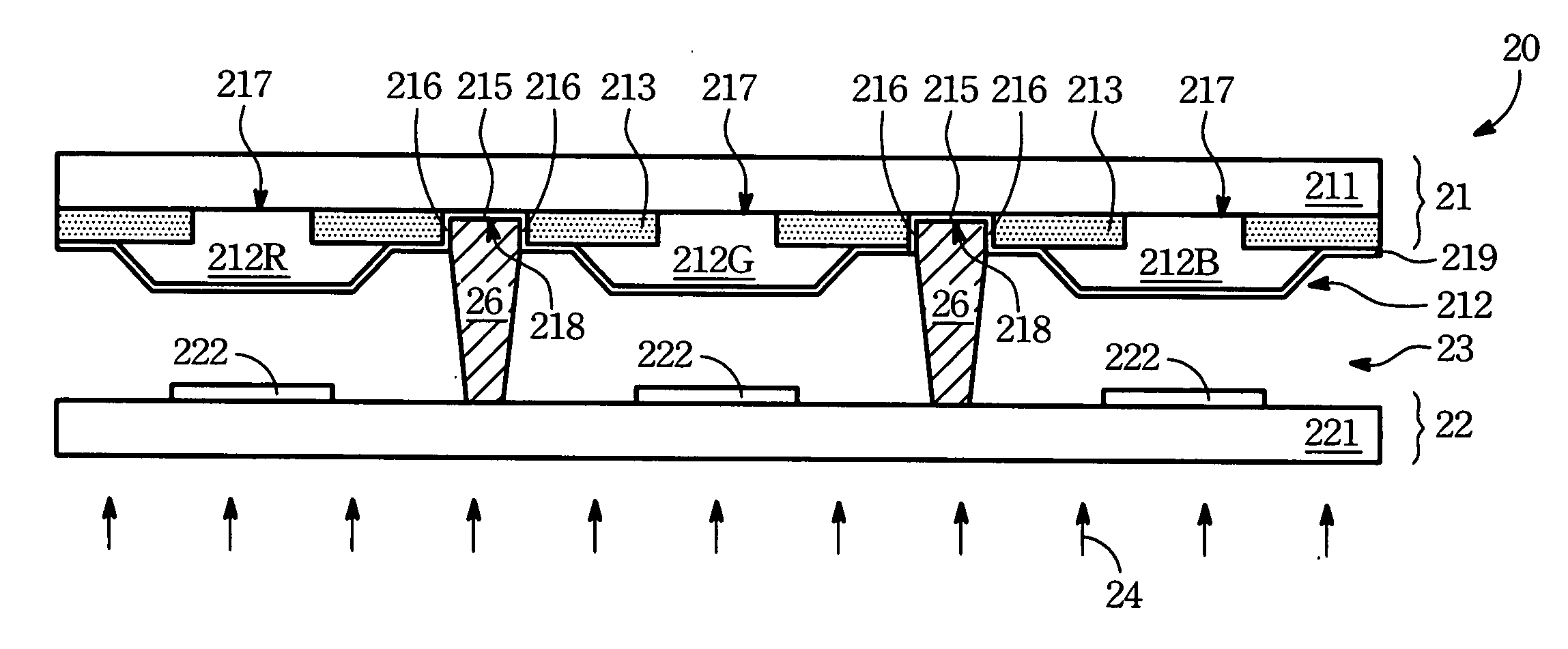

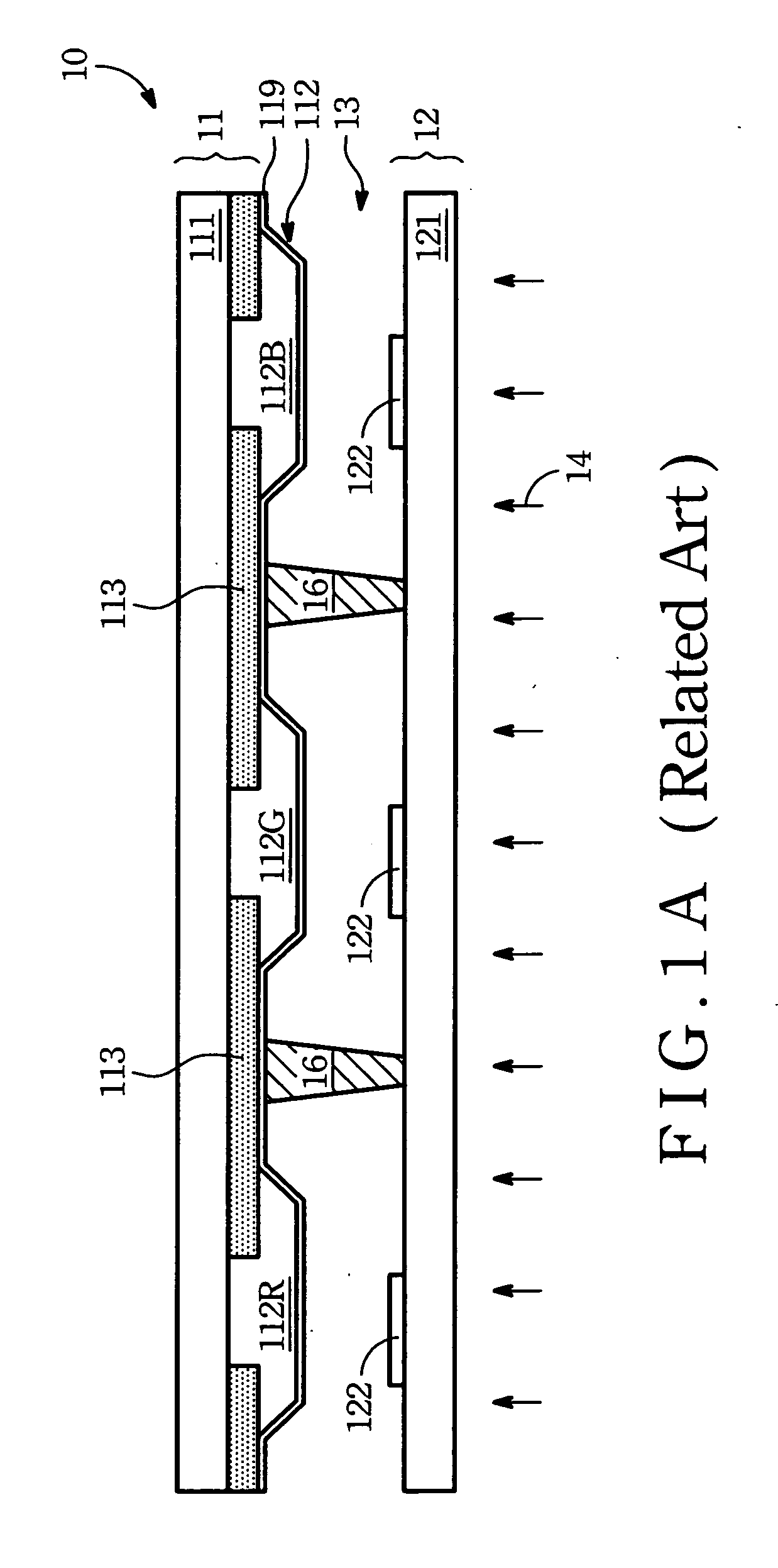

Display panel and color filter therein

InactiveUS20060238694A1Elastic deformation abilityGood deformabilityNon-linear opticsEngineeringBlack matrix

A display panel comprising a first substrate, a second substrate and a plurality of pillar spacers is provided. The first substrate comprises a first base and a black matrix layer with a plurality of openings. The black matrix layer is disposed on the lower surface of the first base. The second substrate is disposed below the first substrate and separated at a predetermined distance from the first substrate. The plurality of pillar spacers for maintaining the predetermined distance. Each of the pillar spacer having a first end and a second end. The first end is inserted into the portion of the plurality of openings, and the second end extends to contact with the second substrate.

Owner:AU OPTRONICS CORP

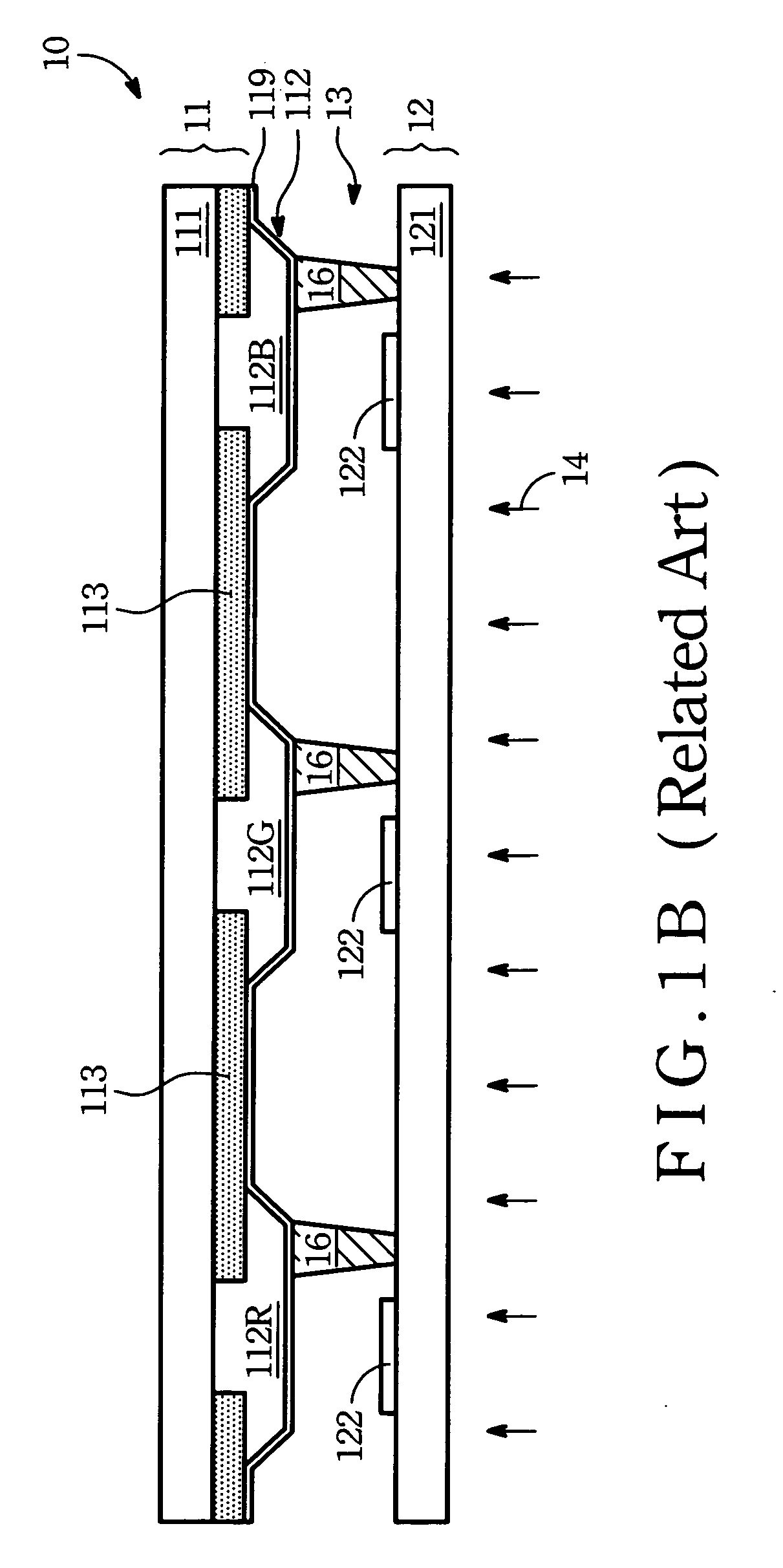

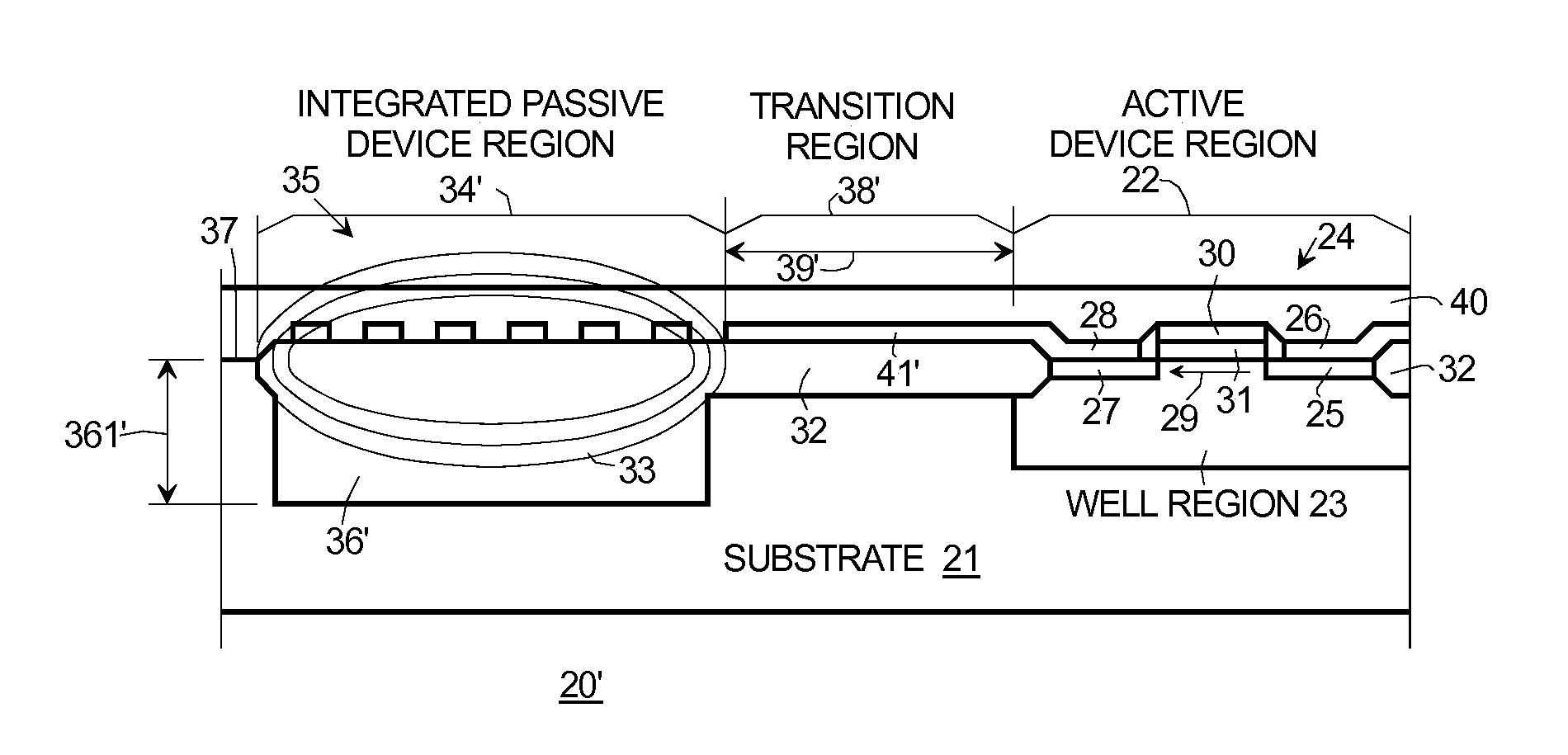

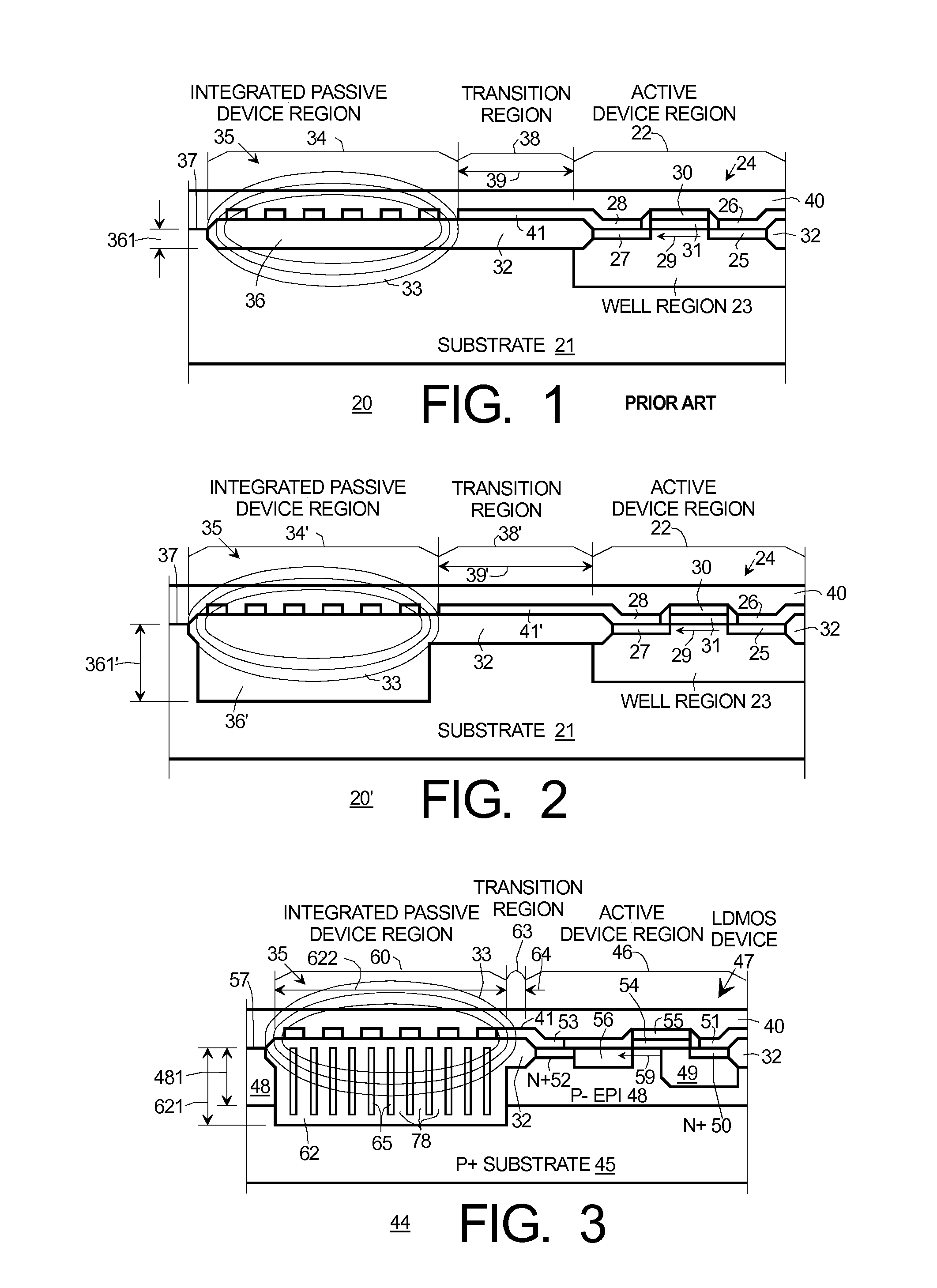

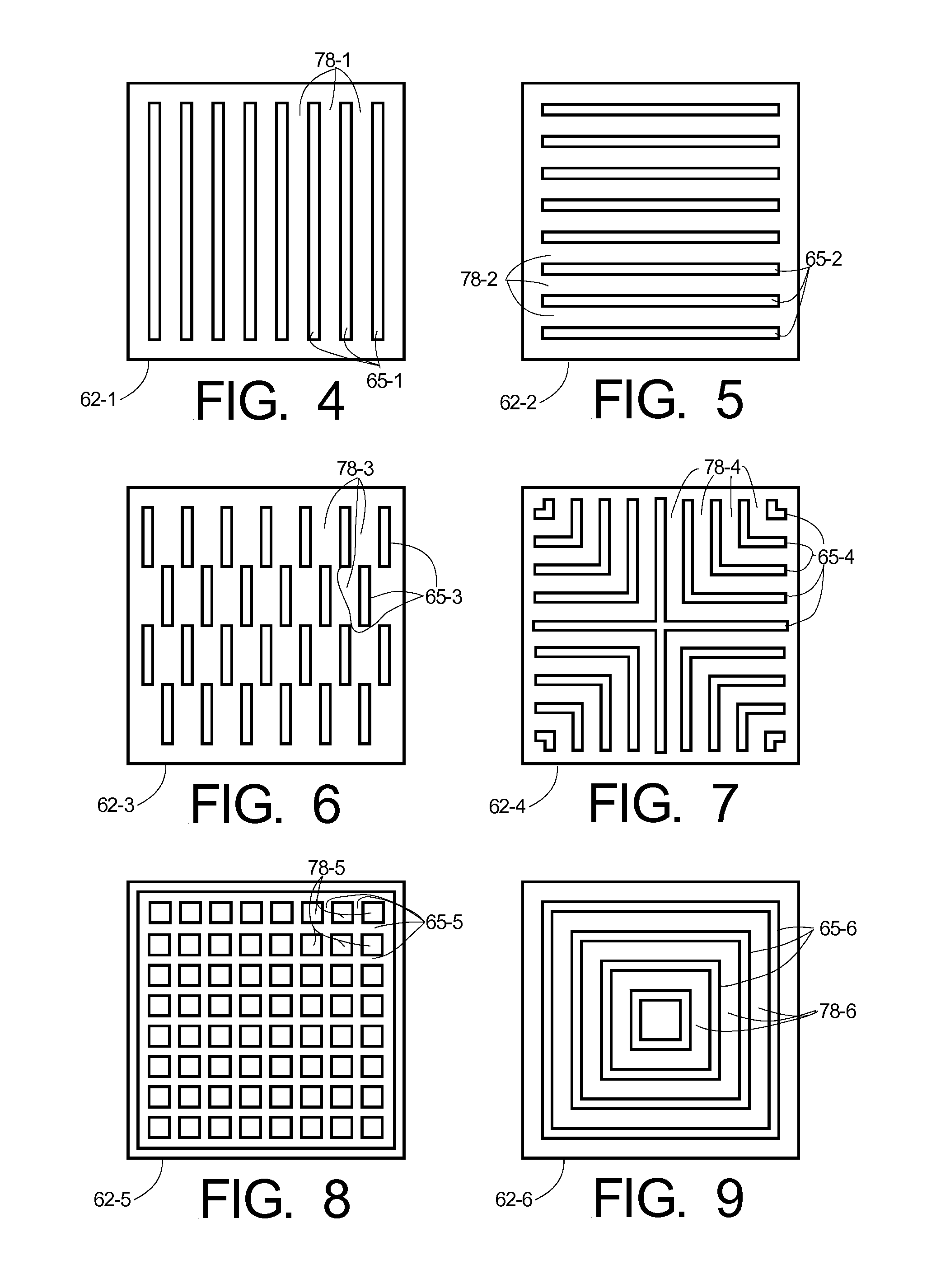

Low loss substrate for integrated passive devices

ActiveUS20100140714A1Convenient planarization polish stop stopConvenient stop etch stopTransistorSolid-state devicesActive devicesEngineering

Electronic elements (44, 44′, 44″) having an active device region (46) and integrated passive device (IPD) region (60) on a common substrate (45) preferably include a composite dielectric region (62, 62′, 62″) in the IPD region underlying the IPD (35) to reduce electromagnetic (E-M) (33) coupling to the substrate (45). Mechanical stress created by plain dielectric regions (36′) and its deleterious affect on performance, manufacturing yield and occupied area may be avoided by providing electrically isolated inclusions (65, 65′, 65″) in the composite dielectric region (62, 62′, 62″) of a material having a thermal expansion coefficient (TEC) less than that of the dielectric material (78, 78′, 78″) in the composite dielectric region (62, 62′, 62″). For silicon substrates (45), non-single crystal silicon is suitable for the inclusions (65, 65′, 65″) and silicon oxide for the dielectric material (78, 78′, 78″). The inclusions (65, 65′, 65″) preferably have a blade-like shape separated by and enclosed within the dielectric material (78, 78′, 78″).

Owner:NXP USA INC

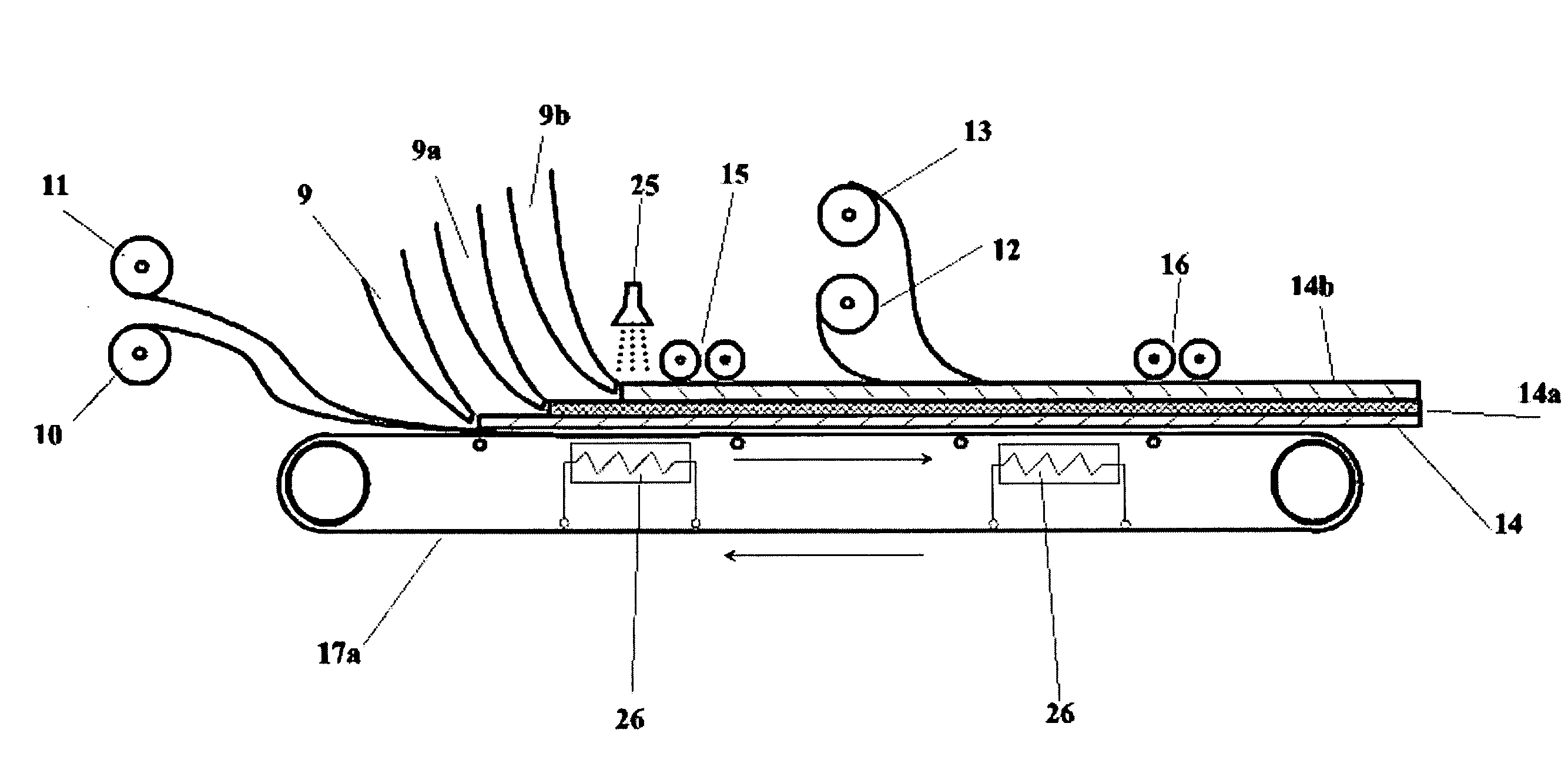

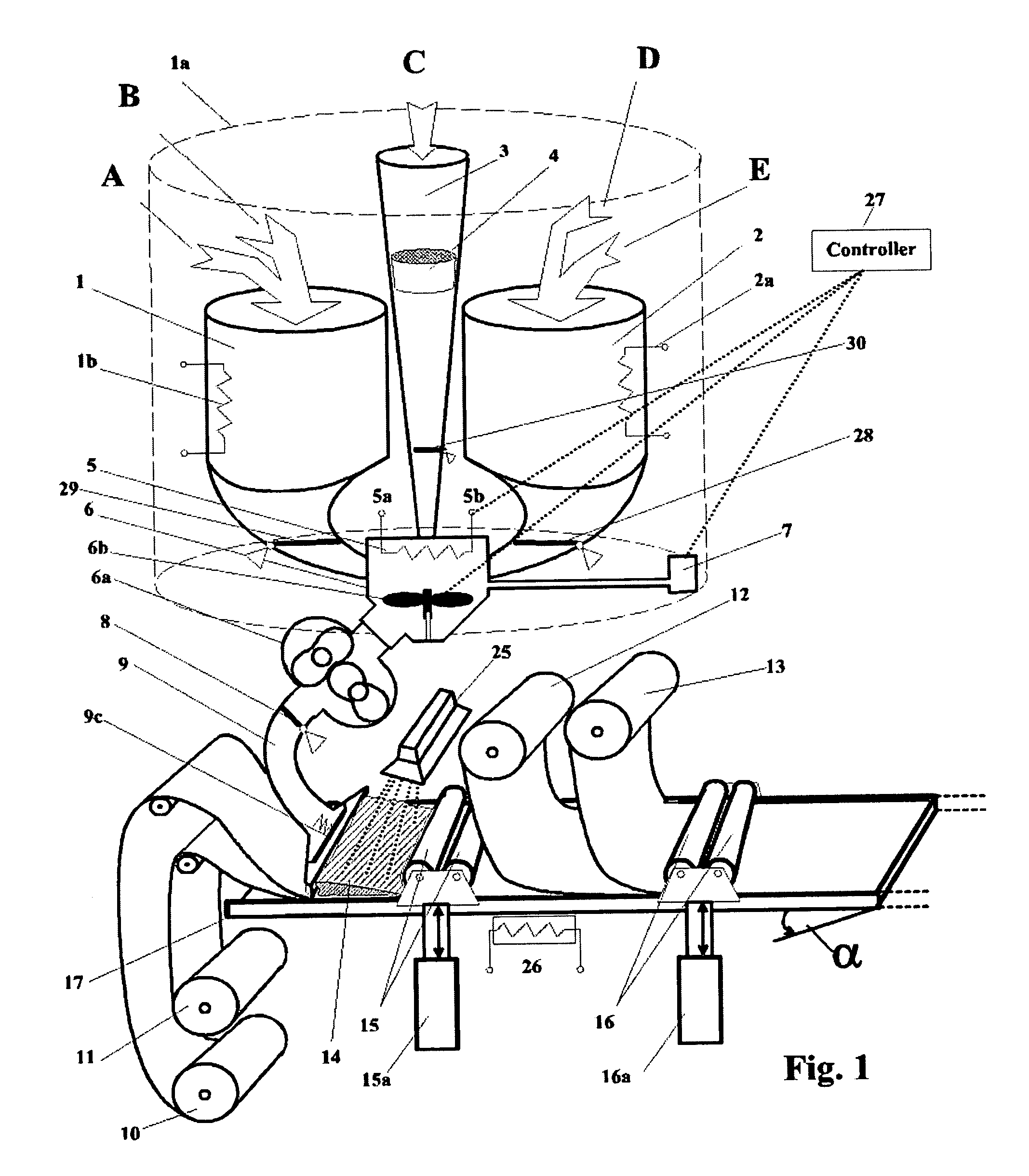

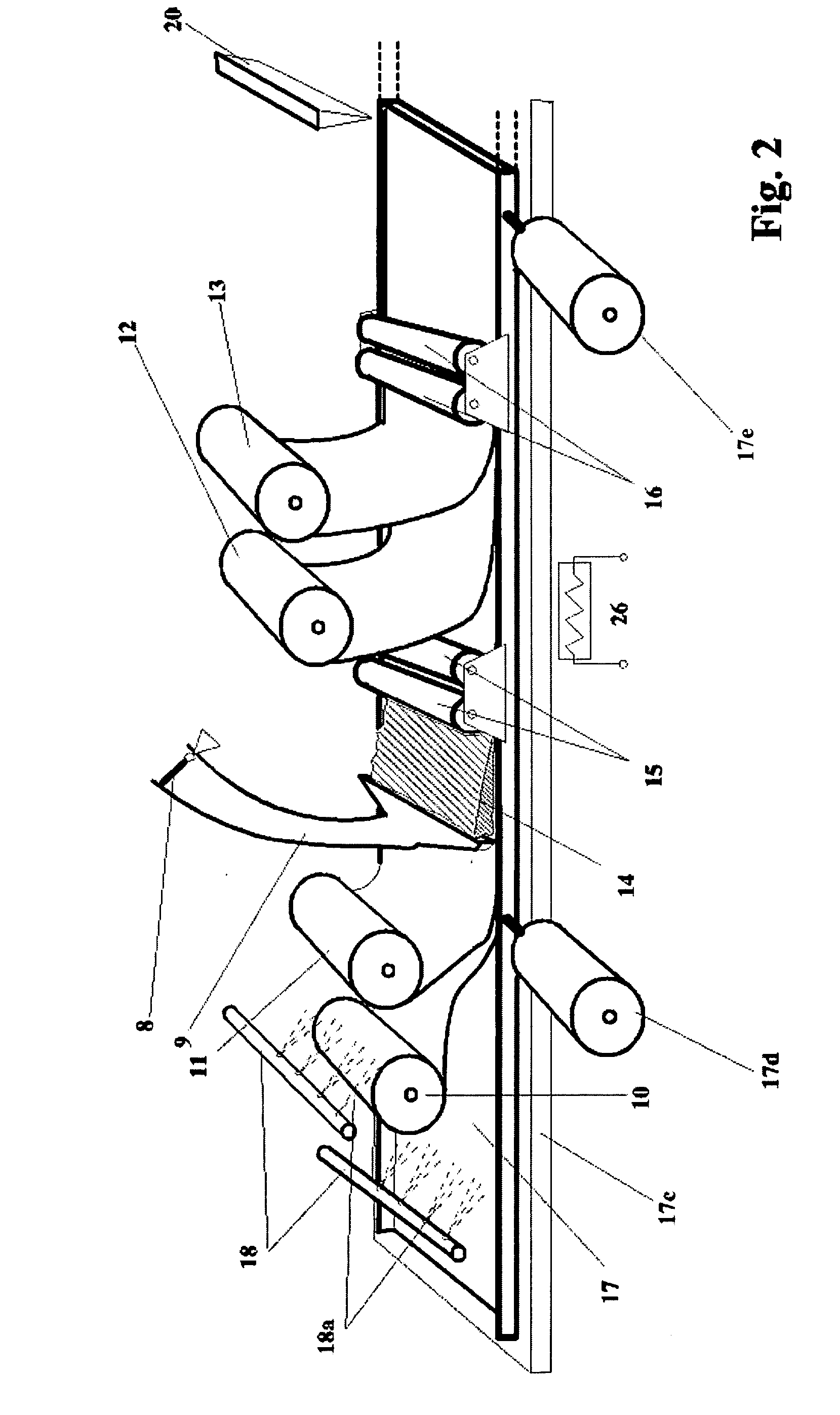

High-performance environmentally friendly building panel and related manufacturing methods

InactiveUS20090133361A1Easily cutMore mechanical stressBuilding repairsBuilding componentsEnvironmentally friendlyFire retardant

Various embodiments of a high-performance environmentally friendly building panel and related manufacturing methods are disclosed. Certain example embodiments described herein relate to various high-performance building panel configurations that utilize at least one engineered mixture produced with a desired thickness, shape and dimension, and manufactured through several preferential manufacturing methods. To selectively enhance some of the high-performance building panel characteristics such as its ability to withstand significant loads, mitigate possible contamination by bacteria growth, as well as its ability to be fire-retardant or fire-suppressant, and other credible operating scenarios the characteristics of different engineered mixtures may be combined during the panel forming process. Some of the manufacturing steps may involve sterilization and utilization of light-sensitive chemicals so as to sterilize as well as to enhance certain thermal-physical and mechanical characteristics of the high-performance building panel.

Owner:SOUTHERN CROSS BUILDING PRODS

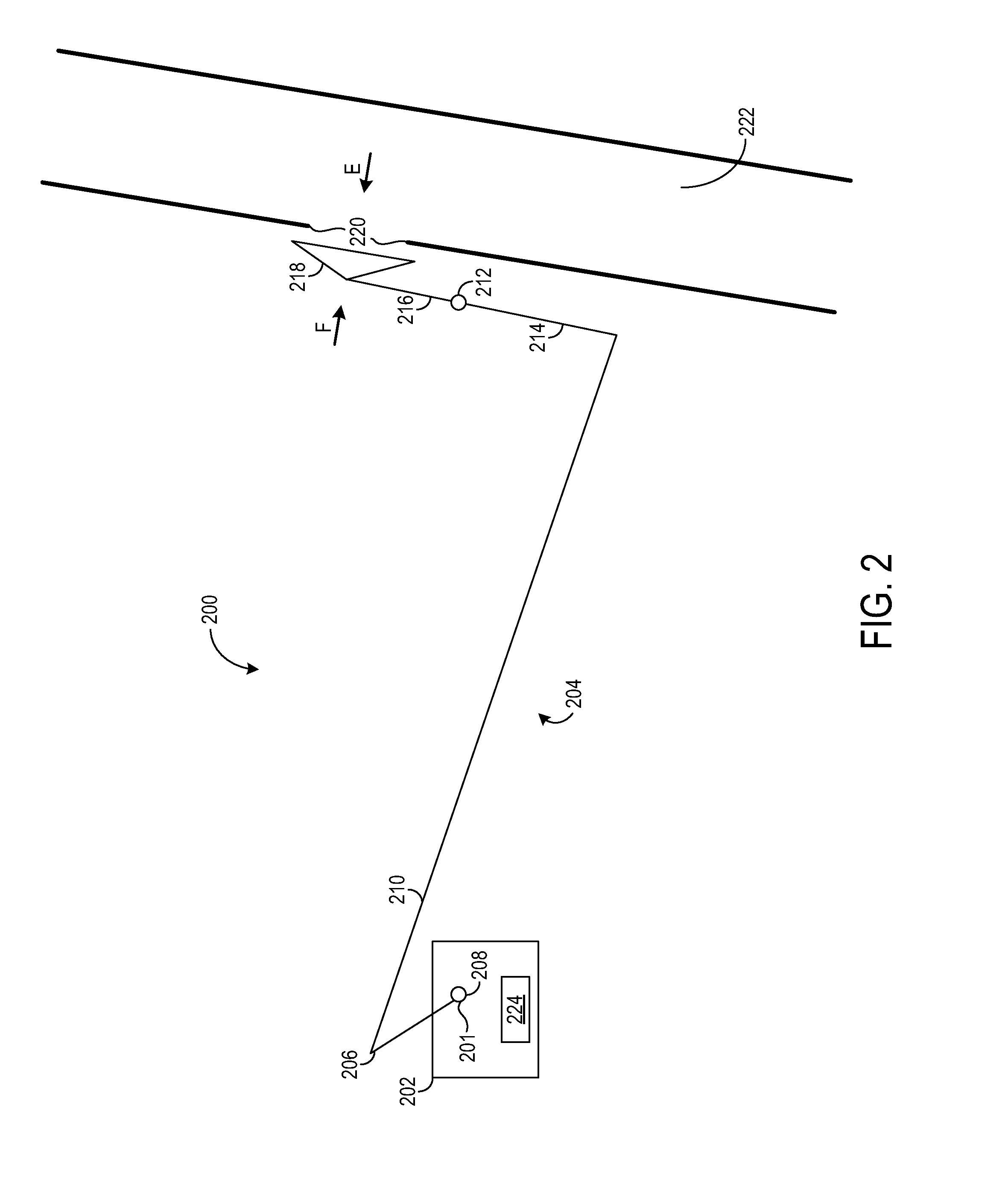

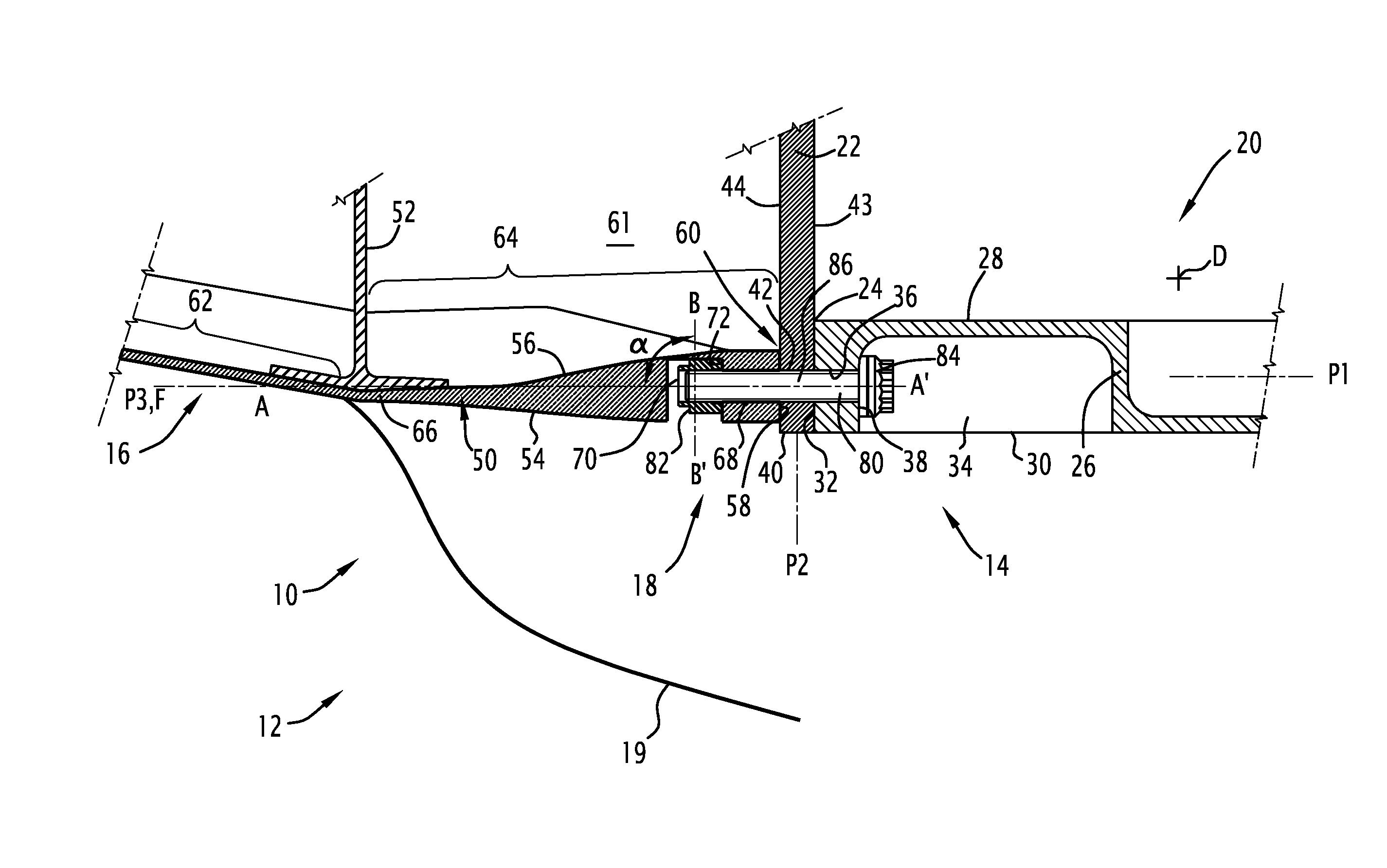

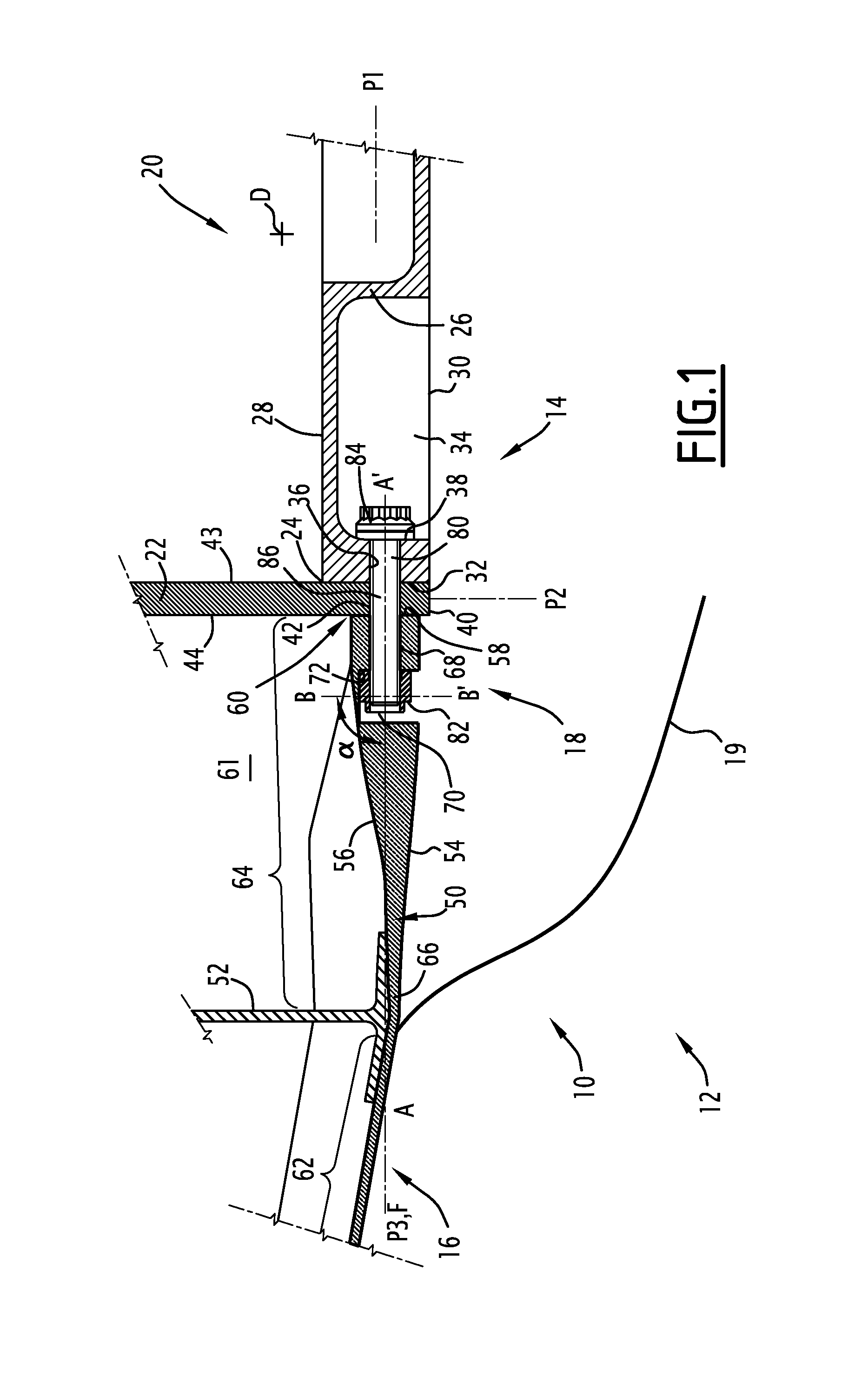

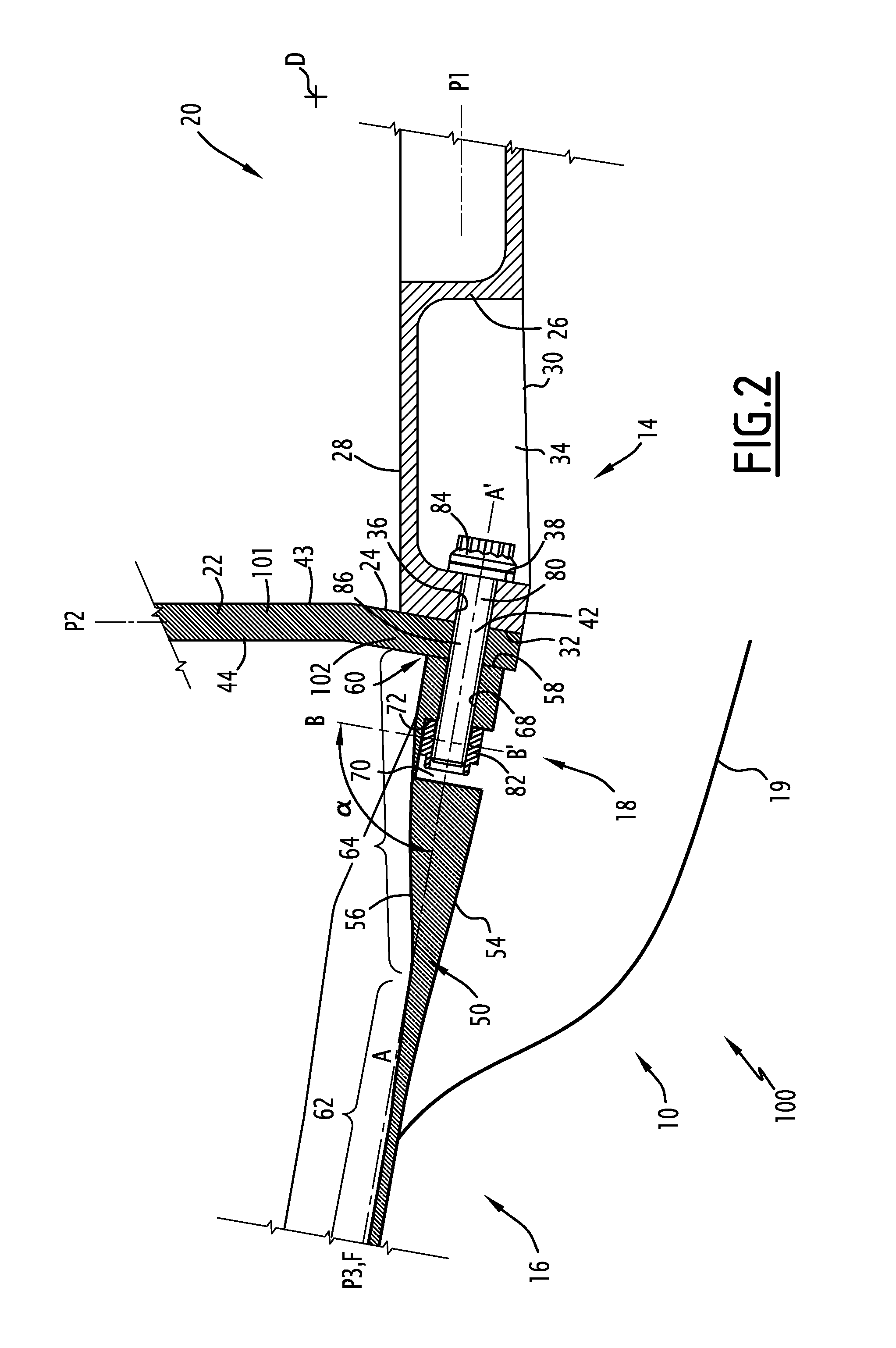

Aircraft structural assembly and associated assembling method

An assembly includes a structural wall and a composite wall extending in the extension of the structural wall and defining a second section positioned facing a first section of the wall. The assembly includes an elongated traction element received in a first passage made in the structural wall, the first passage opening out into the first section and into a cell made in the structural wall. The composite wall defines a second passage opening out into the second section and receiving the elongated element, The assembly includes a locking member added onto the elongated element. The composite wall delimits an access cavity connecting an outer surface of the composite wall to the second passage. The locking member is received into the access cavity.

Owner:DASSAULT AVIATION

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com