Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

1207results about How to "Improve the simulation effect" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

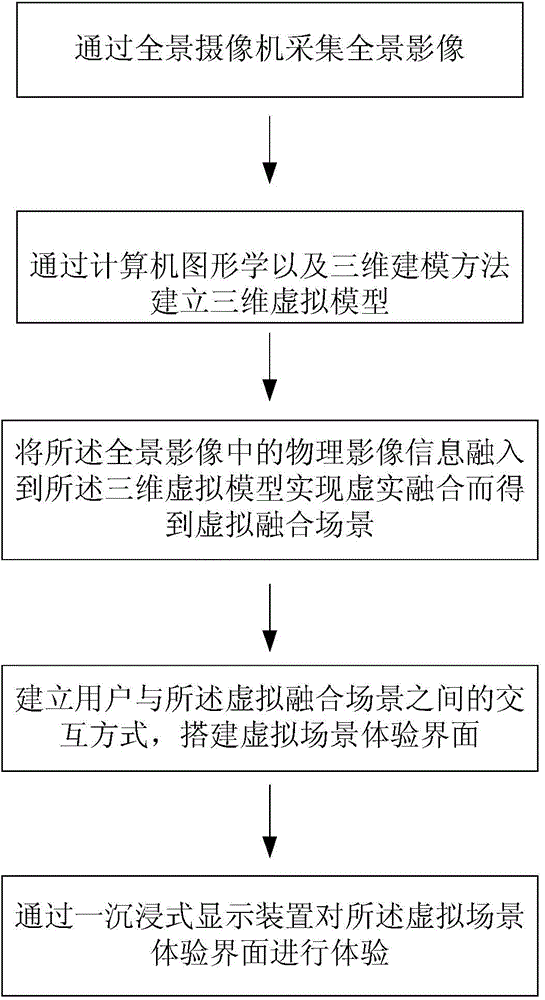

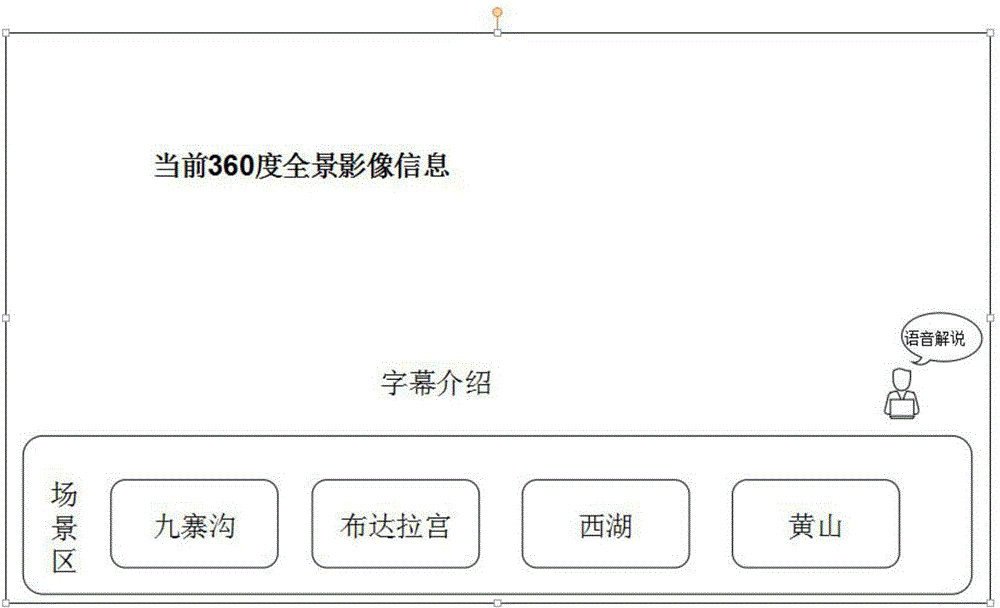

Design method of virtual scene experience system

ActiveCN106157359AAchieve transformationImprove the simulation effect3D modellingComputer graphicsHuman–computer interaction

The invention provides a design method of a virtual scene experience system, comprising the following steps: (a) collecting a panoramic image through a panoramic camera; (b) establishing a 3D virtual model based on the computer graphics and by use of a 3D modeling method; (c) fusing the physical image information in the panoramic image into the 3D virtual model to realize virtual-real fusion and to get a virtual fusion scene; (d) establishing a mode of interaction between users and the virtual fusion scene, and setting up a virtual scene experience interface; and (e) experiencing the virtual scene experience interface through an immersive display device.

Owner:NINGBO INST OF MATERIALS TECH & ENG CHINESE ACADEMY OF SCI

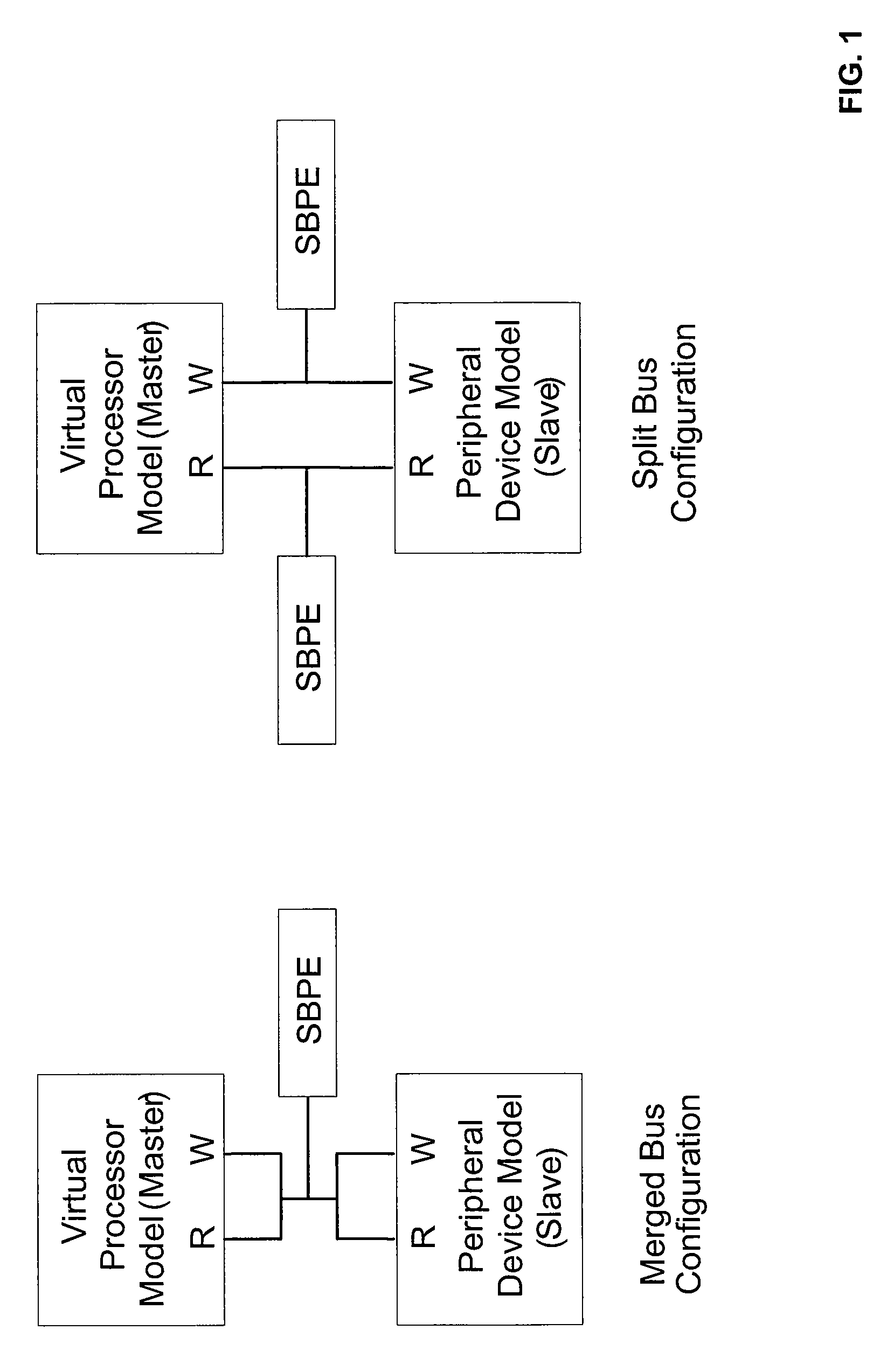

Method and System for Modeling a Bus for a System Design Incorporating One or More Programmable Processors

ActiveUS20080235415A1Without compromising cycle accuracy of dataImprove the simulation effectComputer aided designSpecial data processing applicationsSystems designData set

Systems and methods for modeling a bus for a system design are provided. In an embodiment, the method operates by accepting a virtual bus model, wherein the model simulates behavior for a bus master and slave device, such that the model accurately simulates the timing and behavior of the transfer of data from master to slave, and, from slave to master devices. The method routes a transaction issued by the master device to the slave device. The transaction has storage for transaction data, or a pointer to transaction data, to be transferred through the transaction. The transaction data is transferred in one or more data payloads and the sender of data sets the length of data payloads to be returned. The data payloads are sent from the sender of data to the receiver of data and may contain one or more bus data beats. This method accurately models the bus timing and behavior of the delivery of one or more data beats as one data payload.

Owner:SYNOPSYS INC

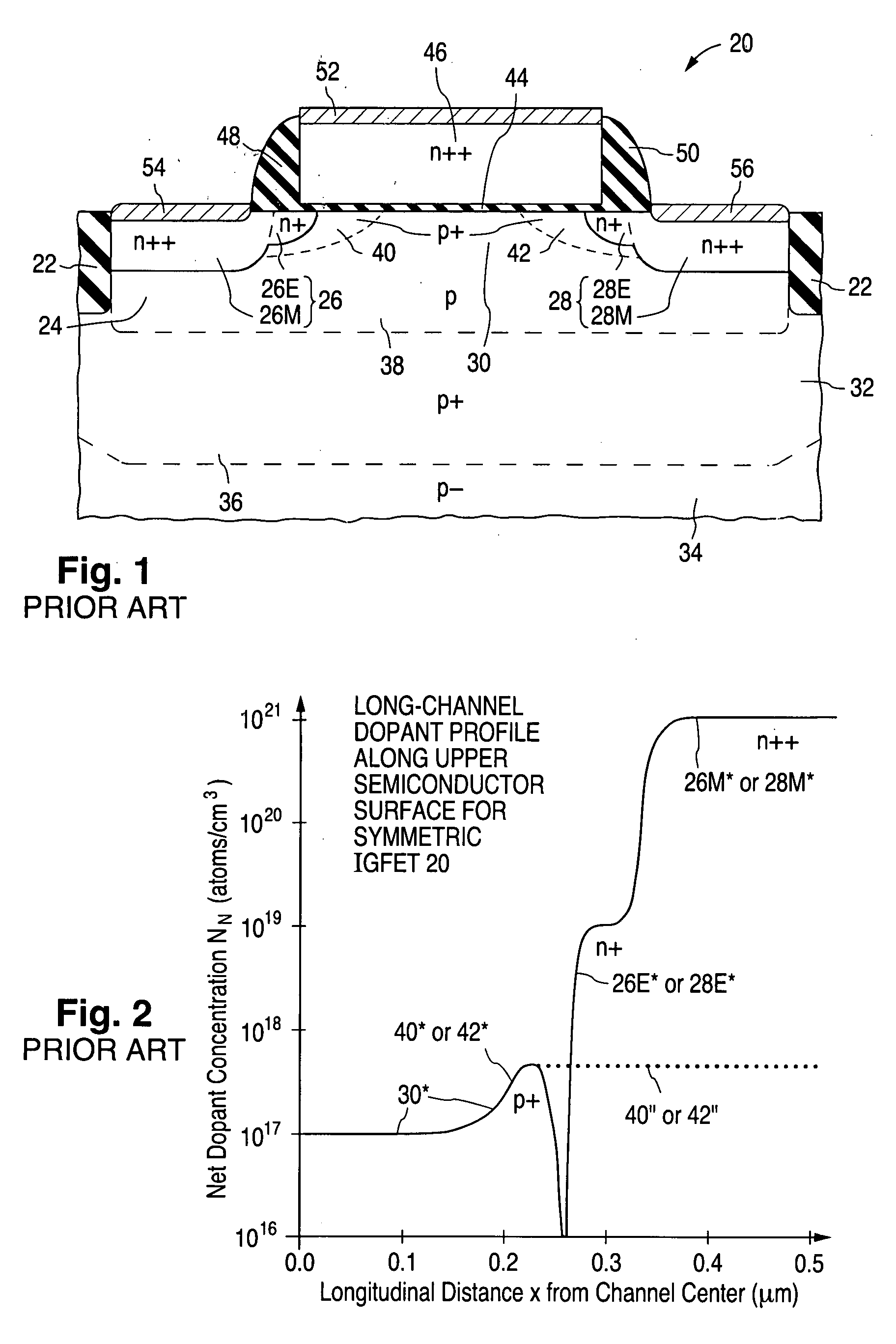

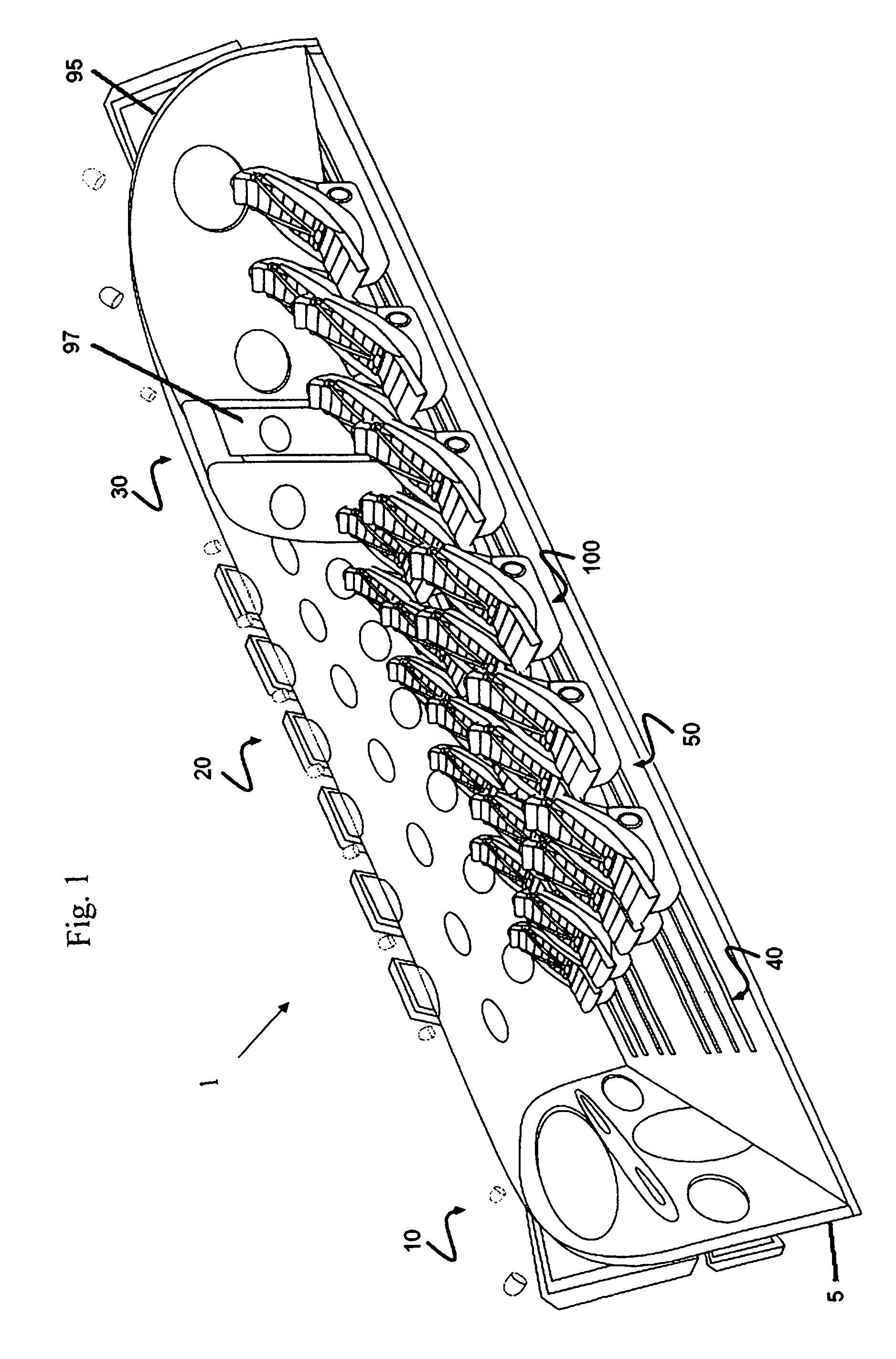

Fabrication of semiconductor architecture having field-effect transistors especially suitable for analog applications

ActiveUS20080311717A1Reduce parasitic capacitanceImprove the simulation effectSolid-state devicesSemiconductor/solid-state device manufacturingDopantParasitic capacitance

An insulated-gate field-effect transistor (100, 100V, 140, 150, 150V, 160, 170, 170V, 180, 180V, 190, 210, 210W, 220, 220U, 220V, 220W, 380, or 480) is fabricated so as to have a hypoabrupt vertical dopant profile below one (104 or 264) of its source / drain zones for reducing the parasitic capacitance along the pn junction between that source / drain zone and adjoining body material (108 or 268). In particular, the concentration of semiconductor dopant which defines the conductivity type of the body material increases by at least a factor of 10 in moving from that source / drain zone down to an underlying body-material location no more than 10 times deeper below the upper semiconductor surface than that source / drain zone. The body material is preferably provided with a more heavily doped pocket portion (120 or 280) situated along the other source / drain zone (102 or 262). The combination of the hypoabrupt vertical dopant profile below the first-mentioned source / drain zone, normally serving as the drain, and the pocket portion along the second-mentioned source / drain zone, normally serving as the source, enables the resultant asymmetric transistor to be especially suitable for high-speed analog applications.

Owner:NAT SEMICON CORP

Fabrication of semiconductor structure in which complementary field-effect transistors each have hypoabrupt body dopant distribution below at least one source/drain zone

ActiveUS7419863B1Reduce parasitic capacitanceImprove the simulation effectSolid-state devicesSemiconductor/solid-state device manufacturingDopantSemiconductor materials

Complementary IGFETs (210W and 220W or 530 and 540) are fabricated so that the body dopant concentration in each IGFET decreases by at least 10 in moving from a subsurface location in the body material of that IGFET up to one of its source / drain zones. Semiconductor dopant, typically a fast-diffusing species such as aluminum, is introduced into starting semiconductor material to form a relatively uniformly doped region that serves as body material (108) for one of the IGFETs. A remaining part of the starting material serves as body material (268) for the other IGFET. Well dopant is introduced into the body material of each IGFET for establishing the requisite body dopant profile. Alternatively, a cavity is formed through an initial structure having body material (108) doped in the preceding way for one of the IGFETs. Semiconductor material is introduced into the cavity to form the body material (568) for the other IGFET.

Owner:NAT SEMICON CORP

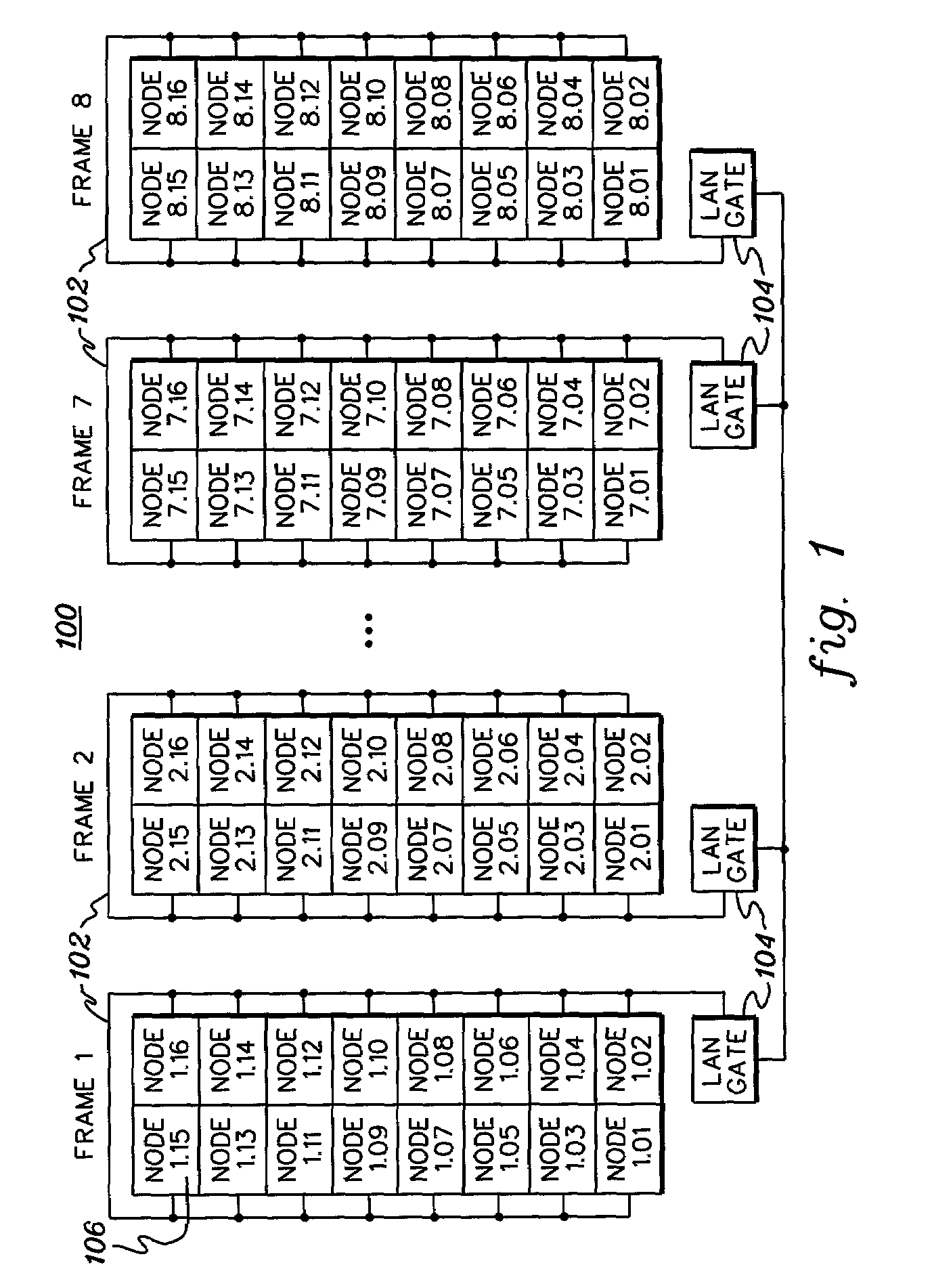

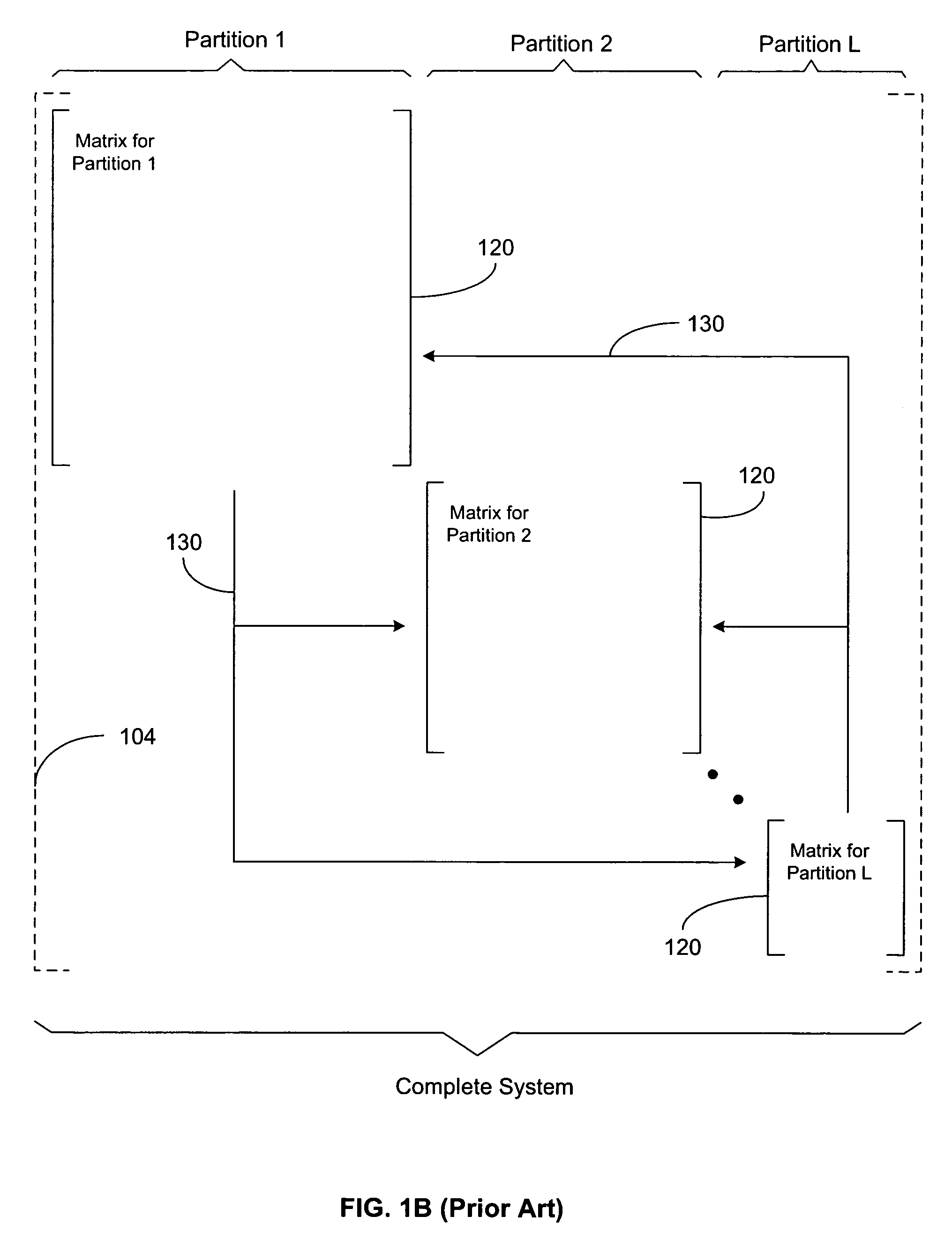

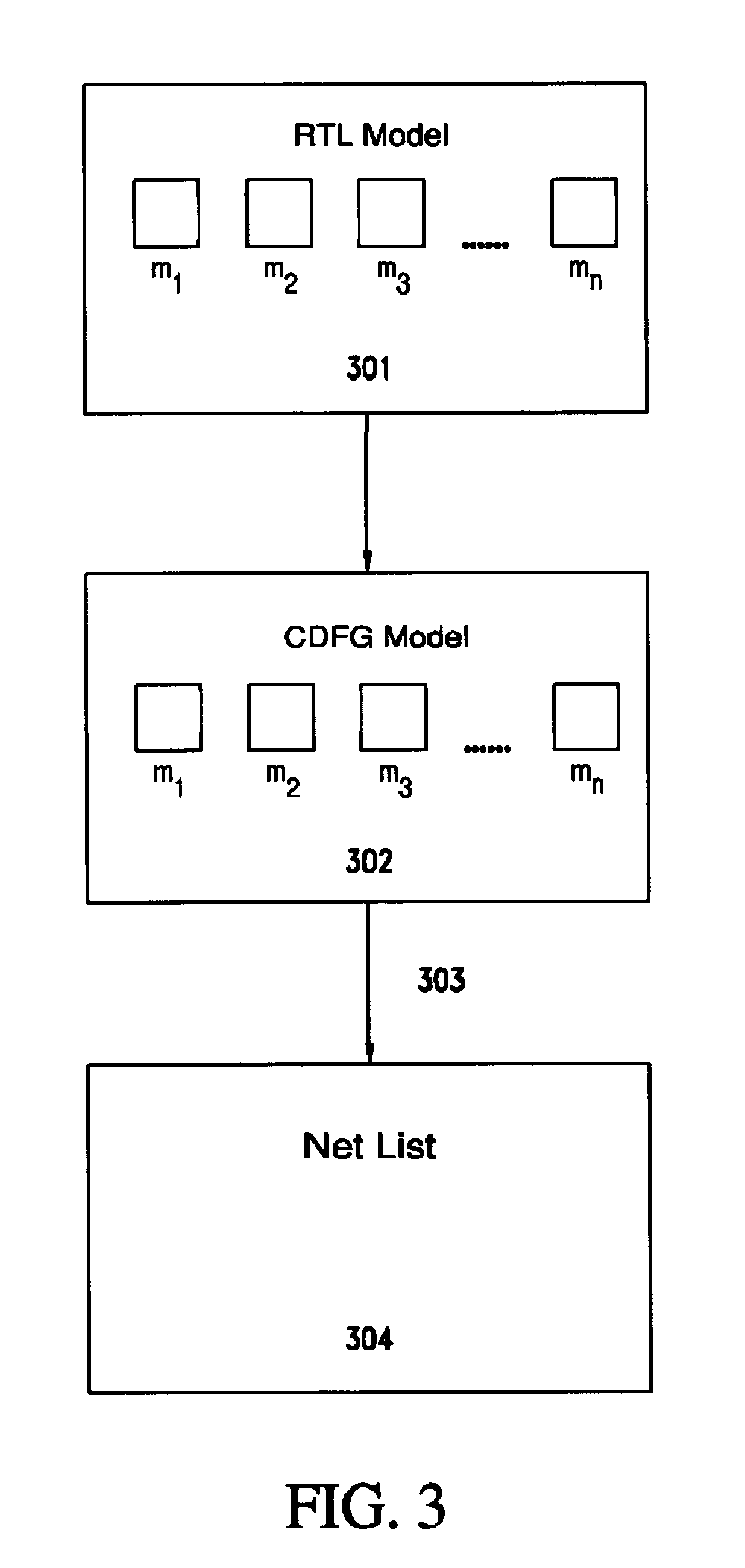

Partitioning a model into a plurality of independent partitions to be processed within a distributed environment

InactiveUS7124071B2High simulationImprove the simulation effectAnalogue computers for electric apparatusCAD circuit designComputer architectureComputational science

A model is partitioned into a plurality of partitions to be processed by a selected number of processors. Since the partitions are substantially independent of one another, the policy employed in the mapping of the partitions to the processors is flexible. Further, in the case in which the model is a chip, at least a portion of the clock and maintenance logic of the chip is also partitioned and mapped to the selected number of processors.

Owner:IBM CORP

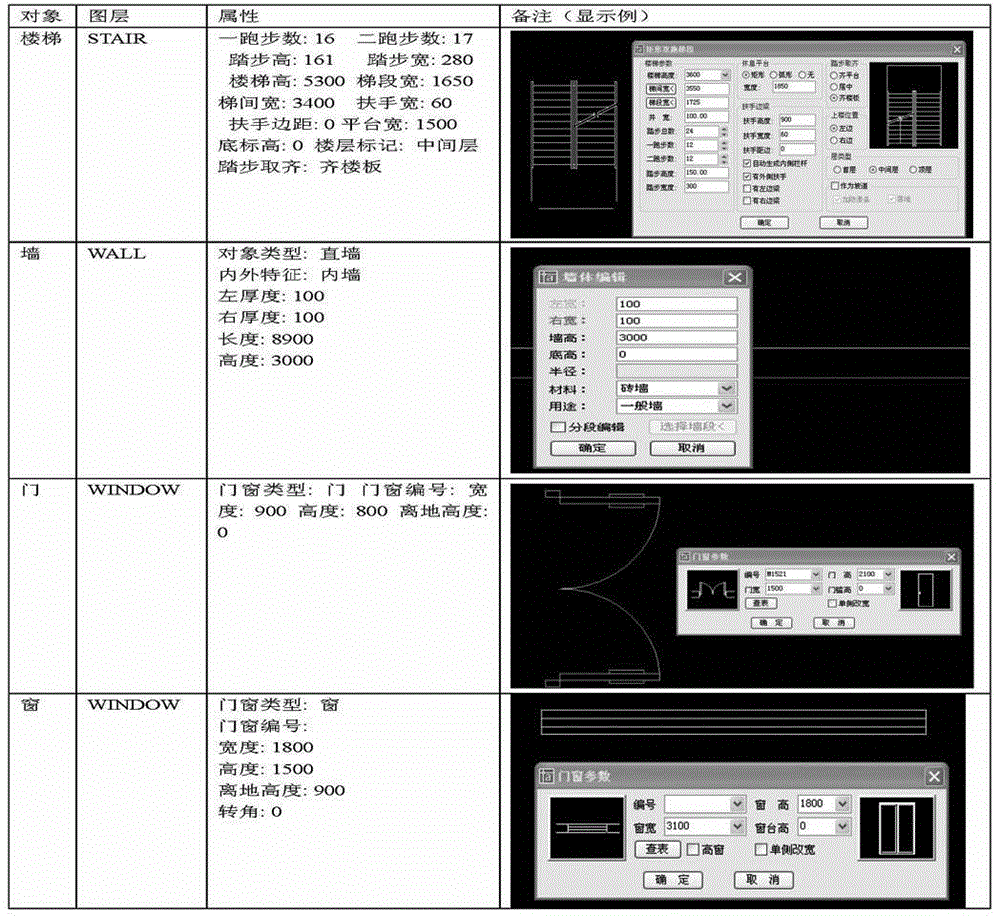

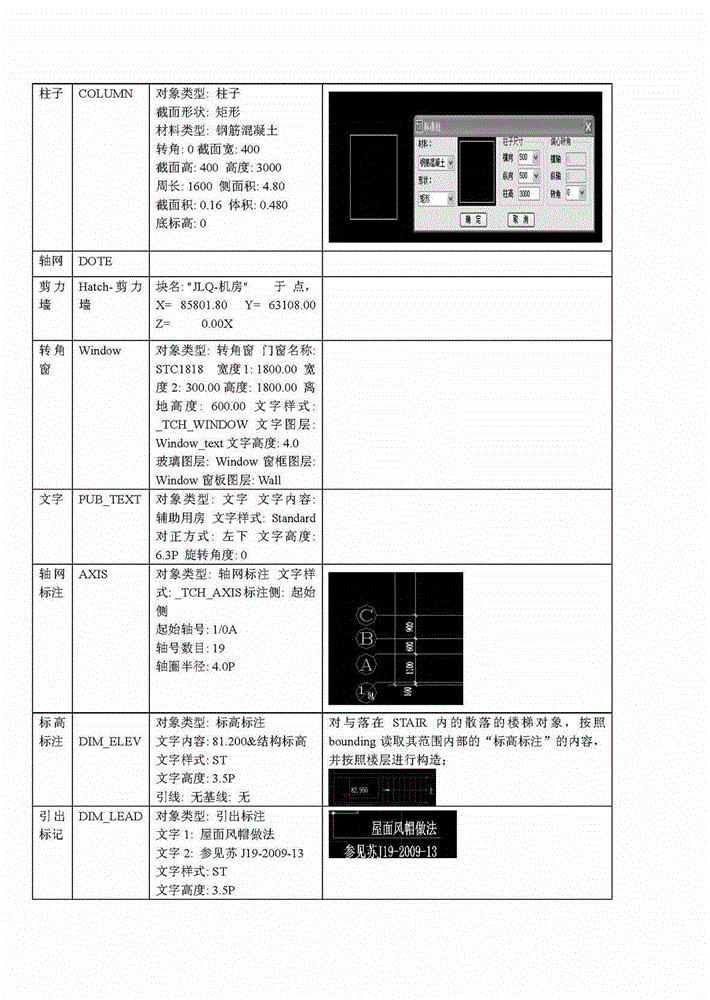

Three-dimensional modeling method for achieving building inside and outside integration in digital map

The invention discloses a three-dimensional modeling method for achieving building inside and outside integration in a digital map and belongs to the technical field of digital map manufacture. The three-dimensional modeling method comprises the steps of firstly, filing building data; then checking building data; extracting data until all data are right; building a data source; generating a MAXScript script according to the data source and using 3DMAX to convert a MAXScript script file into a three-dimensional model; and finally guiding into a map to finish three-dimensional modeling of the building inside and outside integration in the digital map. The three-dimensional modeling method can economically and quickly achieve a three-dimensional digital map with building information and provides decision basis for urban construction and management.

Owner:江苏易图地理信息科技有限公司

Semiconductor architecture having field-effect transistors especially suitable for analog applications

ActiveUS7642574B2Reduce parasitic capacitanceImprove the simulation effectTransistorSolid-state devicesDopantParasitic capacitance

Owner:NAT SEMICON CORP

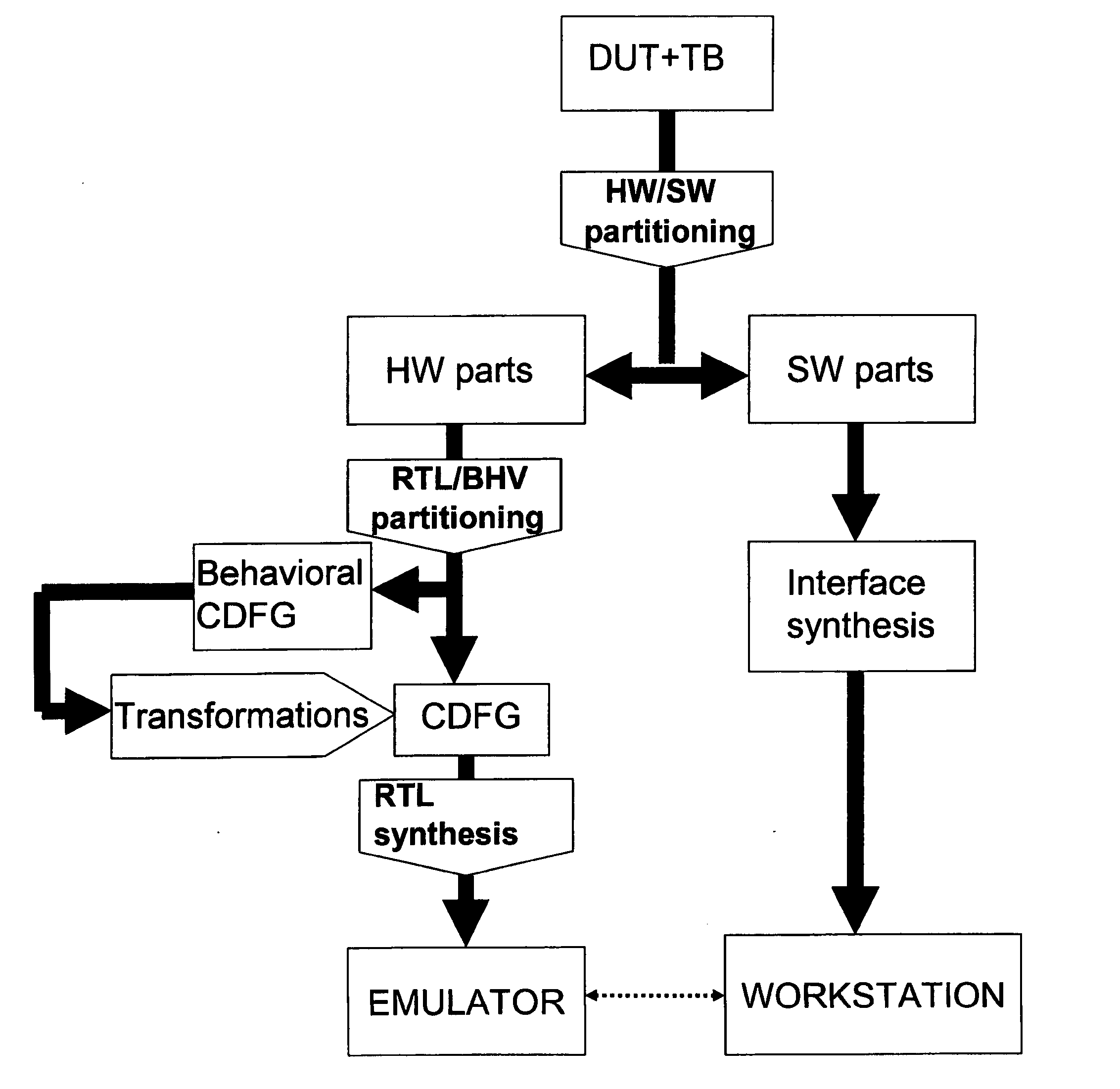

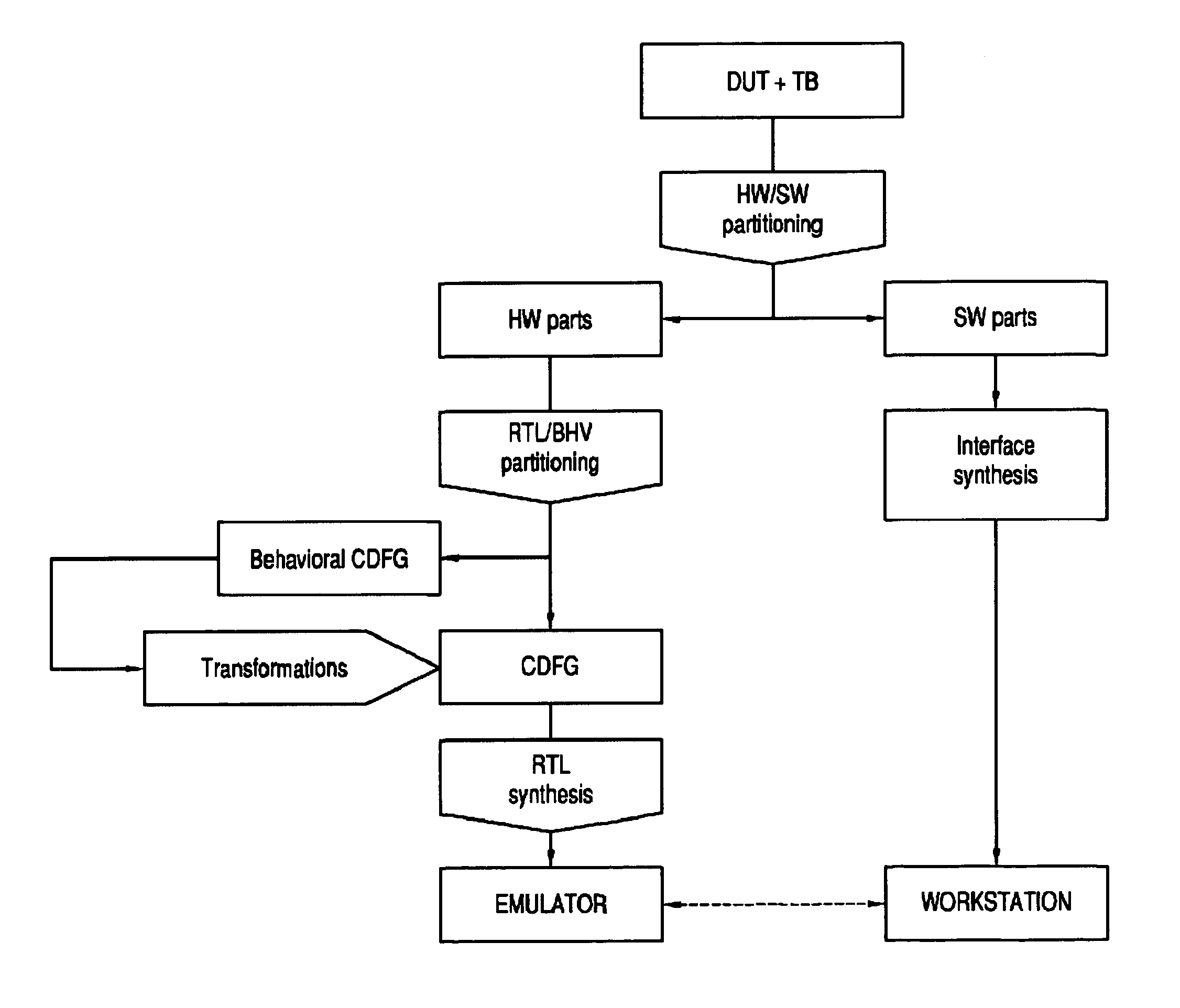

Method and system for hardware accelerated verification of digital circuit design and its testbench

ActiveUS20050144585A1Quick verificationOvercomes drawbackElectrical testingComputer aided designConcurrent computingValidation methods

A system and method is presented for synthesizing both a design under test (DUT) and its test environment (i.e., the testbench for the DUT), into an equivalent structural model suitable for execution on a reconfigurable hardware platform. This may be achieved without any change in the existing verification methodology. Behavioral HDL may be translated into a form that can be executed on a reconfigurable hardware platform. A set of compilation transforms are provided that convert behavioral constructs into RTL constructs that can be directly mapped onto an emulator. Such transforms are provided by introducing the concepts of a behavioral clock and a time advance finite state machine (FSM) that determines simulation time and sequences concurrent computing blocks in the DUT and the testbench.

Owner:SIEMENS PROD LIFECYCLE MANAGEMENT SOFTWARE INC

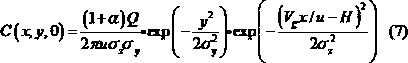

Method for constructing atmospheric pollutant diffusion model

InactiveCN103258116AReduce demandImprove computing efficiencySpecial data processing applicationsICT adaptationDiffusionRectangular coordinates

The invention discloses a method for constructing an atmospheric pollutant diffusion model. The method includes the following steps of establishing three-dimensional space rectangular coordinates, determining factors which influence atmospheric pollution diffusion, simplifying a fundamental form of a Gaussian model, and obtaining the atmospheric pollutant diffusion model. The method can be widely applied to survey regions with various dimensions, and is particularly suitable for medium and small dimensions. Besides, the method is high in computational efficiency, low in requirement to meteorological data, and capable of reflecting a diffusing process of atmospheric pollution to the greatest extent in a simple mode. Under the conditions that a rang is small, a weather field is simple, the underlying surface and topographic conditions are relatively not complex, and secondary pollutant is not considered or processed simply, a concentration field calculated through the method and a concentration field calculated through a complicated numerical method are comparatively fit, errors are mainly derived from input parameters of the model (such as precision degree of pollution source data), the model is simple, input data are less, and programming and developing are convenient.

Owner:STATE GRID CORP OF CHINA +2

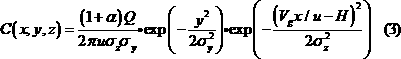

Oil deposit black oil model numerical simulation system

InactiveCN101661514AImprove computing speed and parallel efficiencyIncreased computing speed and simulation capabilitiesSpecial data processing applicationsPetroleumOil field

The invention relates to an oil deposit black oil model numerical simulation system and belongs to the technical field of petroleum extraction. The structure of the system comprises a pretreatment subsystem, serial and parallel simulators and a post-treatment subsystem. Firstly, according to the geological data, production dynamic data, fluid property data and rock seepage property data of the oil deposit, a geological model, a dynamic model, a fluid module and a rock seepage model are established by using the pretreatment subsystem of the system so as to further form a numerical simulation model; secondly, the high-efficiency parallel of the system is used to perform simulation calculation to realize an oil-field development process to obtain models of the deposit at different time; thirdly, the post-treatment module of the system is used to analyze the result of the simulation calculation and the distribution of residual oil in a visual mode and an adjustment scheme for further development of the oil deposit is optimally designed; and finally, an optimal scheme under a current condition is submitted to be implemented on site.

Owner:中国石化股份胜利油田分公司地质科学研究院

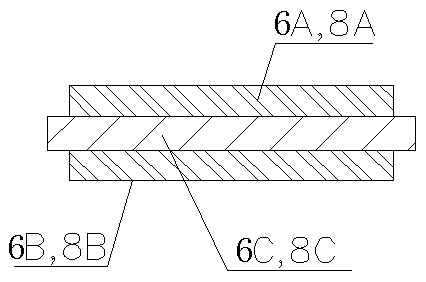

Coal and rock bore hydraulic fracture experimental apparatus

InactiveCN102031954AImprove fracturing effectEasy to take pictures and recordEarth material testingFluid removalPressure systemAcoustic emission

The invention discloses a coal and rock bore hydraulic fracture experimental apparatus, which comprises a sample device system, a confining pressure system, a fracture system, a sealing system and a monitoring system, wherein the sample device system comprises a sample cylinder, the bottom in the sample cylinder is provided with a screen drum of which the bottom is provided with a water outlet pipe, a sample is accommodated in the sample cylinder above the screen drum, and a simulated bore is formed in the sample; the confining pressure system comprises an air filling subsystem and a water filling subsystem; the fracture system comprises a fracture high-pressure water pump of which a water outlet is communicated with the simulated bore through a fracture pipeline; the sealing system comprises a sample cylinder sealing device and an experimental cylinder sealing device; and the monitoring system comprises an acoustic emission sensor arranged on an external wall of the sample cylinder. By the coal and rock bore hydraulic fracture experimental apparatus, a simulated experiment can be performed in a laboratory to investigate the change rules of crack initiation, expansion and extension in the hydraulic fracture process of a coal mine underground coal seam bore, and know a crack extending direction so as to guide field fracture; therefore, the fracture effect is greatly improved.

Owner:HENAN POLYTECHNIC UNIV

Biological ink for 3D printing

ActiveCN105238132AGood biocompatibilityAddressing the lack of suitable rapid-prototyping hydrogelsInksCross-linkSolvent

The invention discloses biological ink for 3D printing. The biological ink for 3D printing comprises water-soluble synthetic polymer with the cross-linking function, water-soluble natural polymer with the cross-linking function, bioactive components capable of spontaneously forming special ultrastructures, cross-linking initiator and solvents and further comprises bioactive components. The biological ink for 3D printing overcomes the defects that traditional 3d printing ink is single in component structure, does not have good biological activity and needs to utilize organic solvents, and it is difficult to take cell compatibility, biological activity and mechanical properties into consideration, the biological ink which has biological activity and the fast curing function at the same time and can form a certain microstructure is obtained, and hydrogel obtained through curing of the ink has controllable mechanical properties, good structural stability and a good fidelity effect.

Owner:SUN YAT SEN UNIV

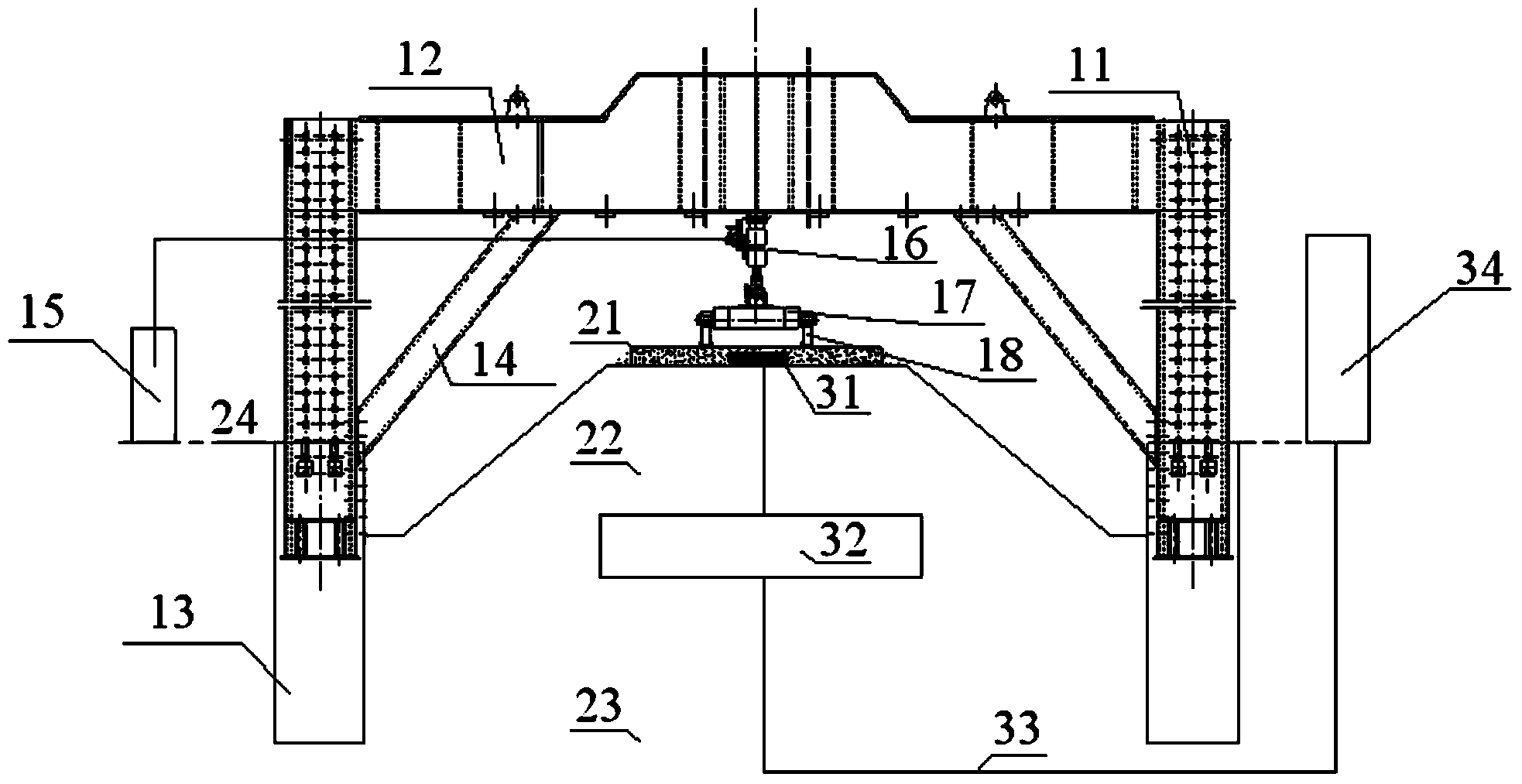

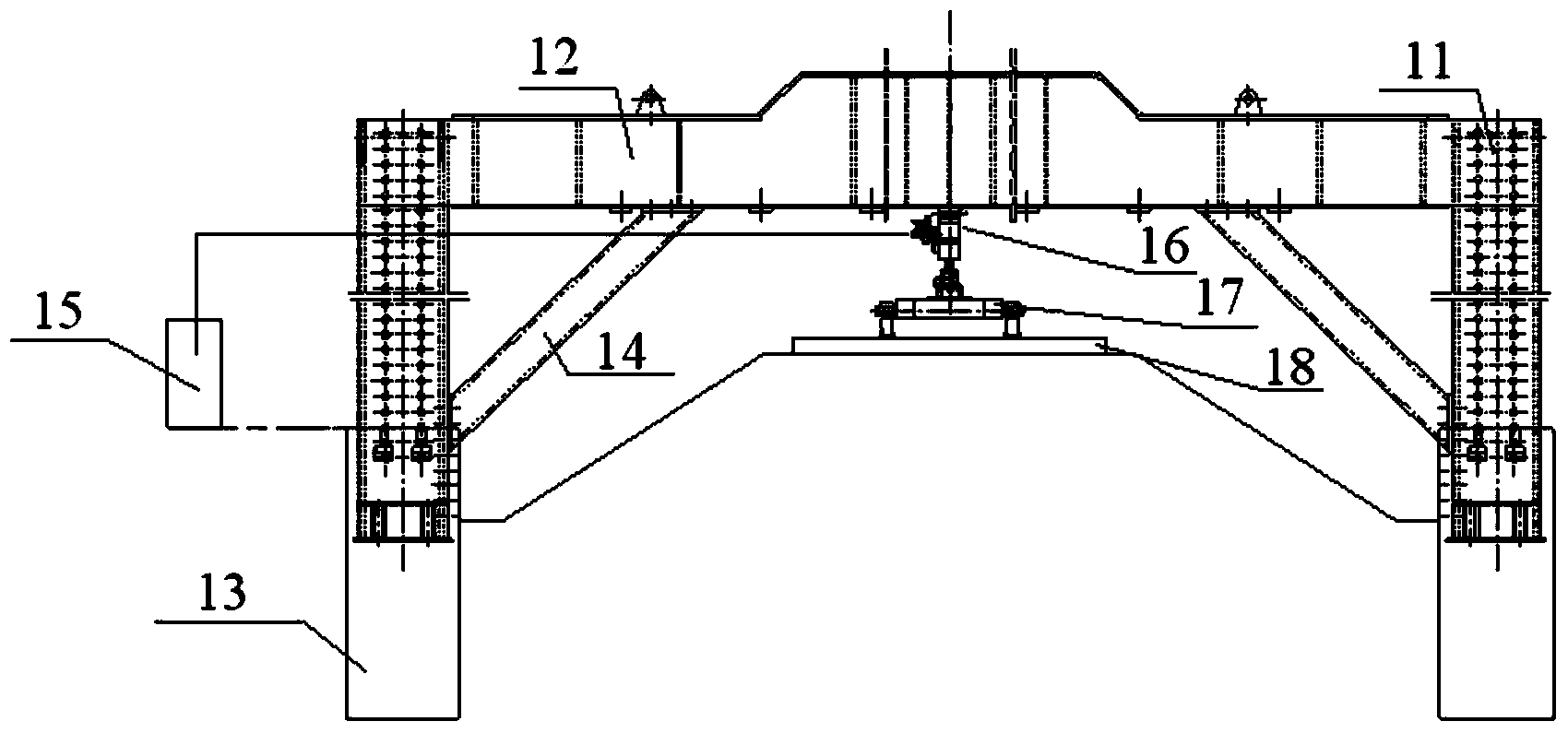

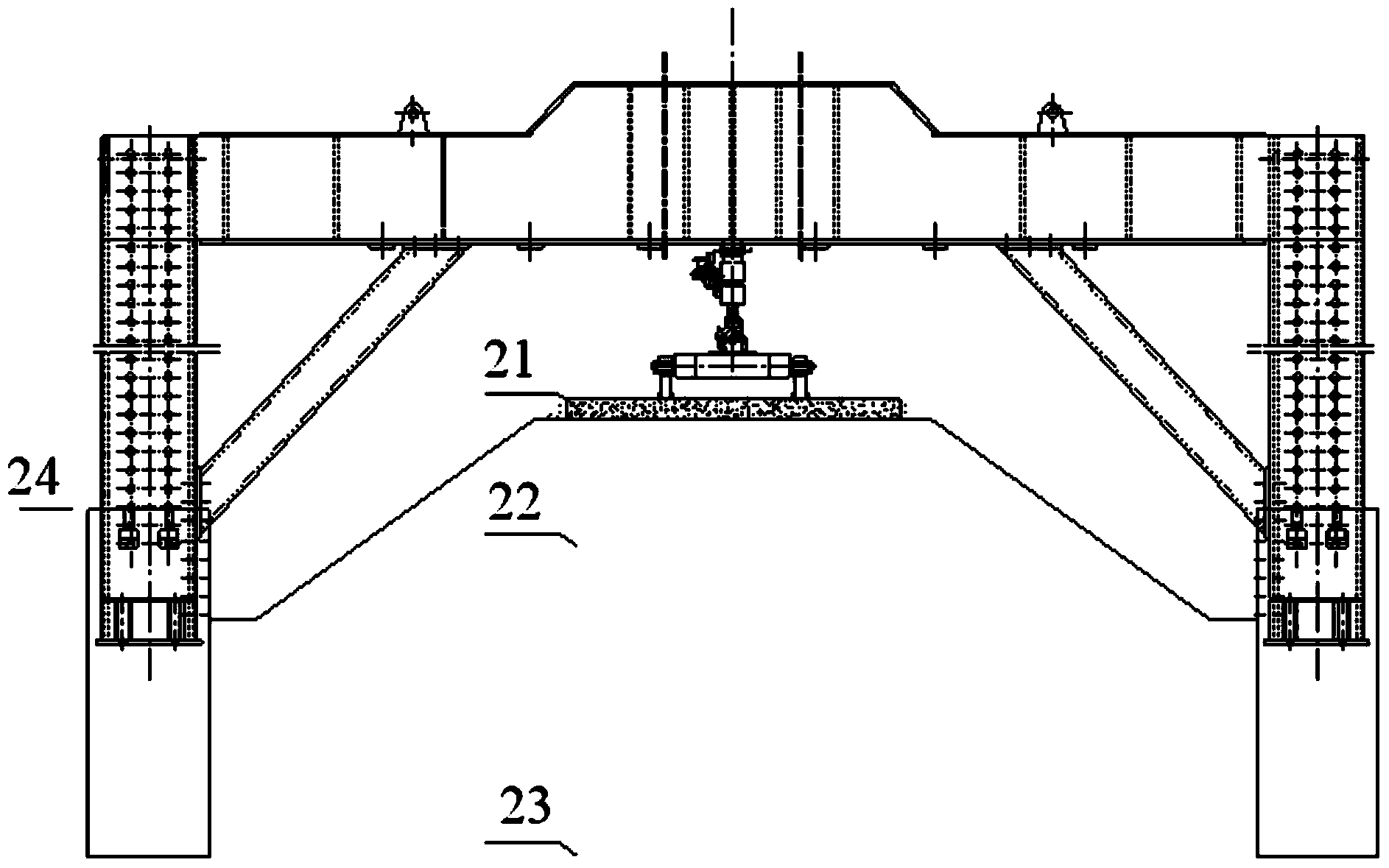

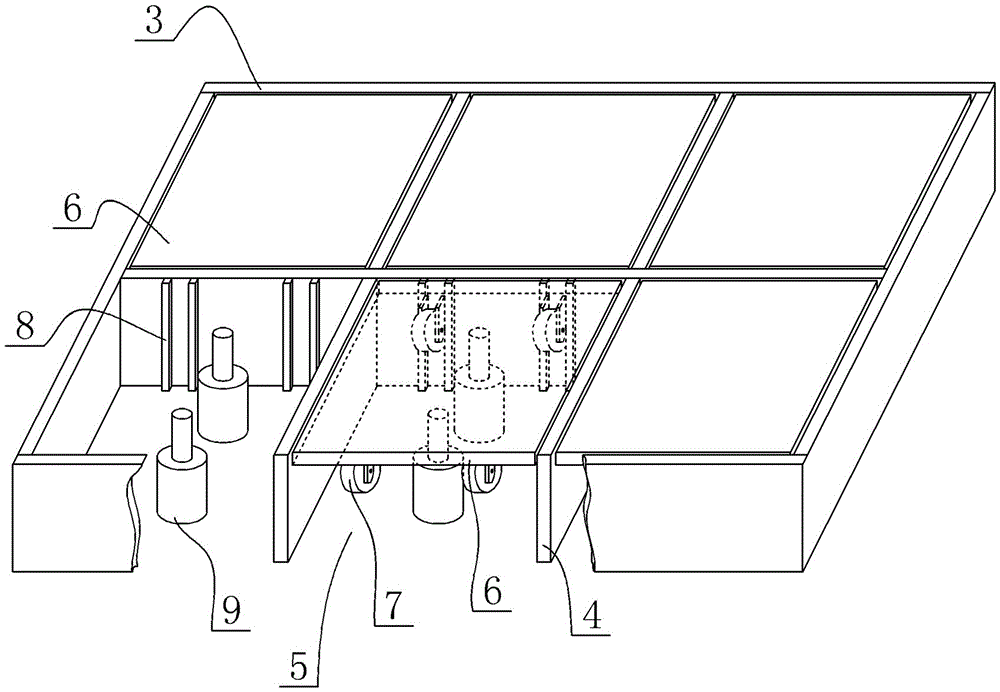

Simulated experiment device for dynamic damages of roadbeds and road surfaces under highway traffic loads

ActiveCN103760045AFulfill loading requirementsReasonable structureMaterial strength using repeated/pulsating forcesControl mannerSimulation

The invention discloses a simulated experiment device for dynamic damages of roadbeds and road surfaces under highway traffic loads. The simulated experiment device is composed of at least one traffic load dynamic loading system, a roadbed-road surface structure and a data acquisition system. Modes for controlling a loading function by a hydraulic oil source system and an MTS servo loading system are adopted, a microcomputer controlled acquisition system controls the vibration waveform of a simulated traffic load and drives an actuator to carry out loading on a loading axis and a loading wheel, the loading wheel transfers dynamic loads to a roadbed part through a road surface structure, and measuring point data of a road surface testing component and a roadbed testing component is intensively controlled, acquired and stored by a microcomputer through data transmission cables. The device disclosed by the invention is reasonable in structure and convenient to operate, and can simulate the needs of a dynamic traffic load simulation test for the long-term behavior of roadbeds and road surfaces acted by a highway traffic load at different speeds and different axle weights.

Owner:湖南省交通科学研究院有限公司

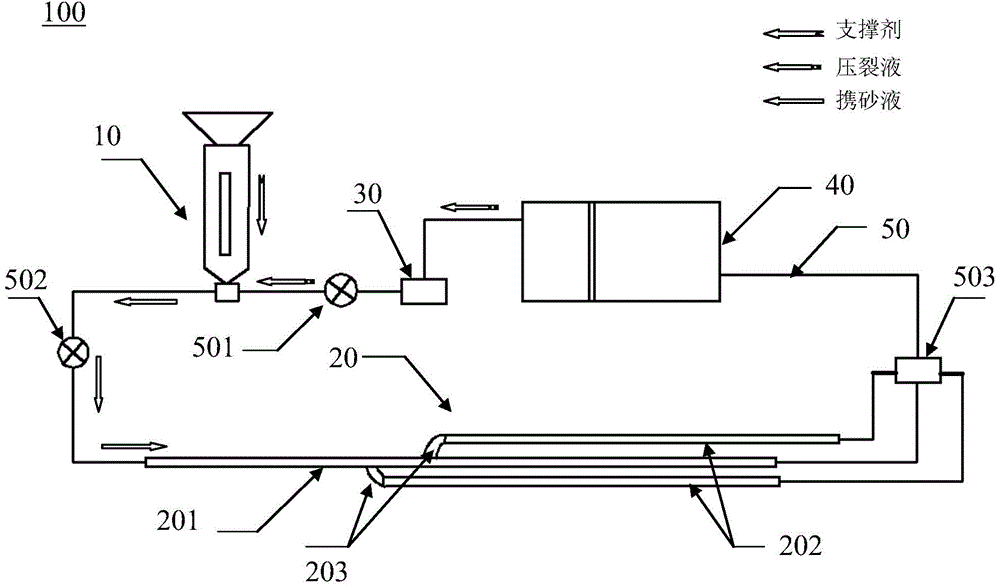

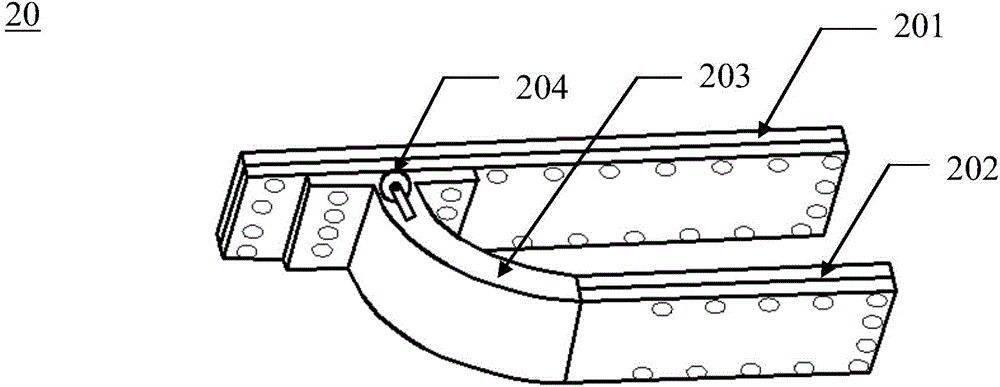

Large-size and multi-crack simulation device and method for propping agent transportation

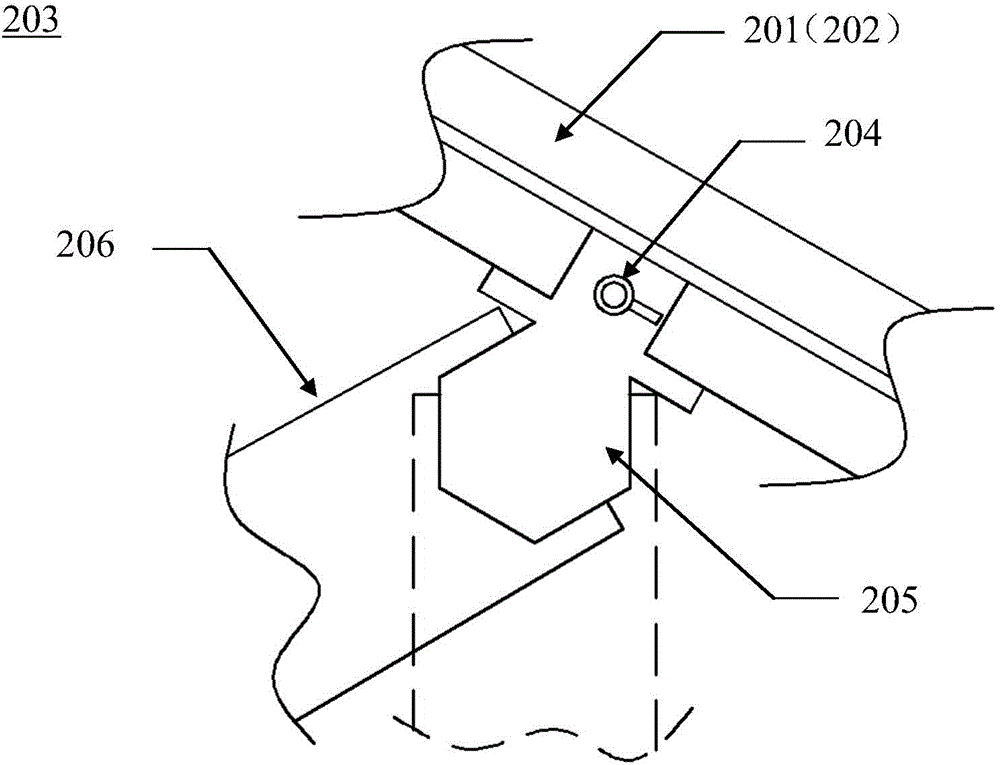

ActiveCN104564048AGood simulation effectImprove experiment performanceHydrodynamic testingBorehole/well accessoriesElectrical and Electronics engineeringControl valves

The invention relates to a large-size and multi-crack simulation device and method for propping agent transportation. The device comprises a crack unit (20), wherein the crack unit (20) comprises a main crack (201) and multi-stage branch cracks (202) arranged on at least one side of the main crack. The device is characterized in that the main crack (201) and the branch cracks (202) are connected through connection parts (203), and the connection parts (203) are provided with control valves (204) which are used for controlling the communicating state between the main crack (201) and the branch cracks. According to the experimental scheme, the control valves (204) are opened or closed, the connection angle between the main crack (201) and the branch cracks (202) is set through angle regulators (205), and the settlement laws of a propping agent in different crack shapes are researched.

Owner:SOUTHWEST PETROLEUM UNIV +1

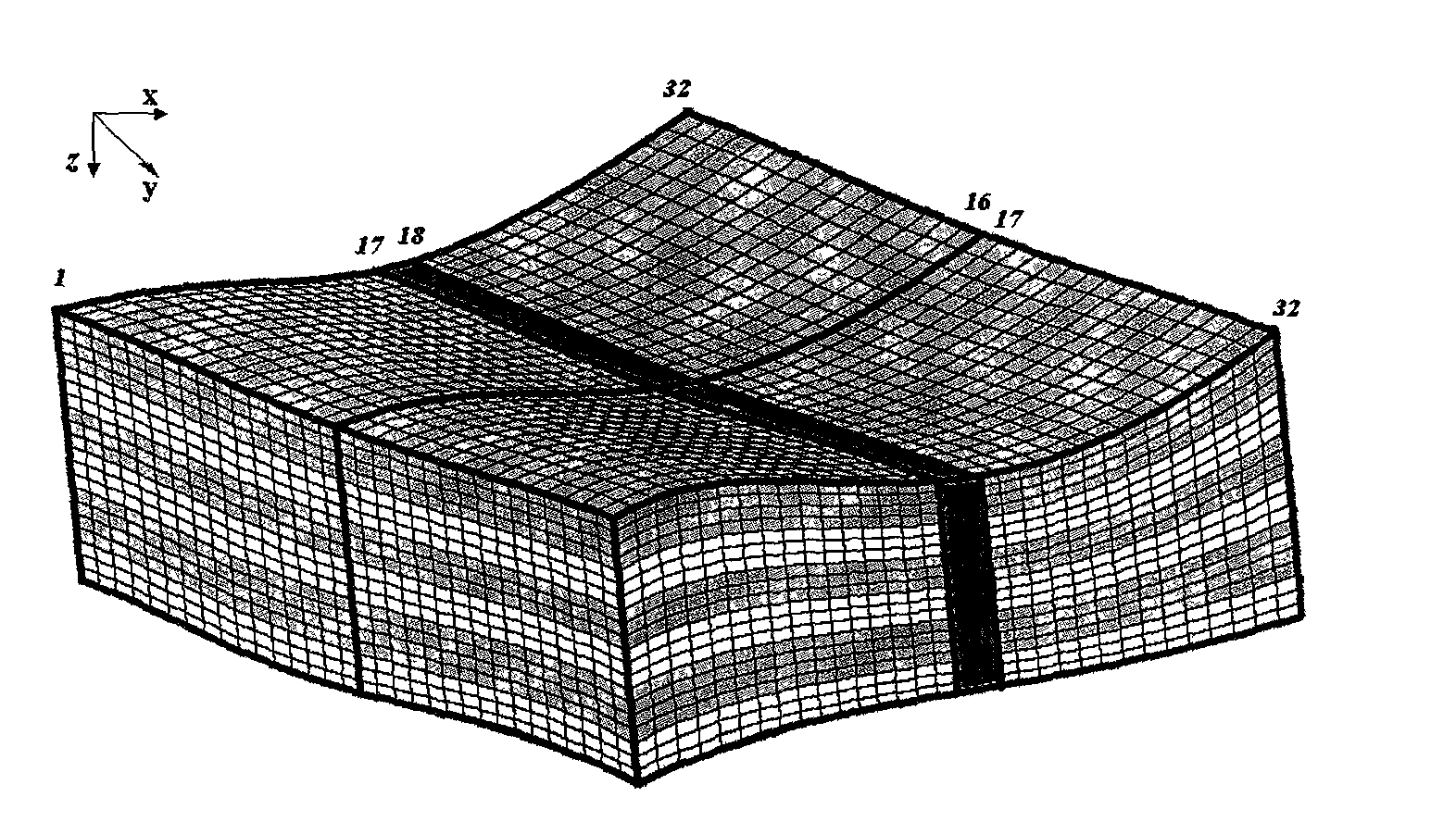

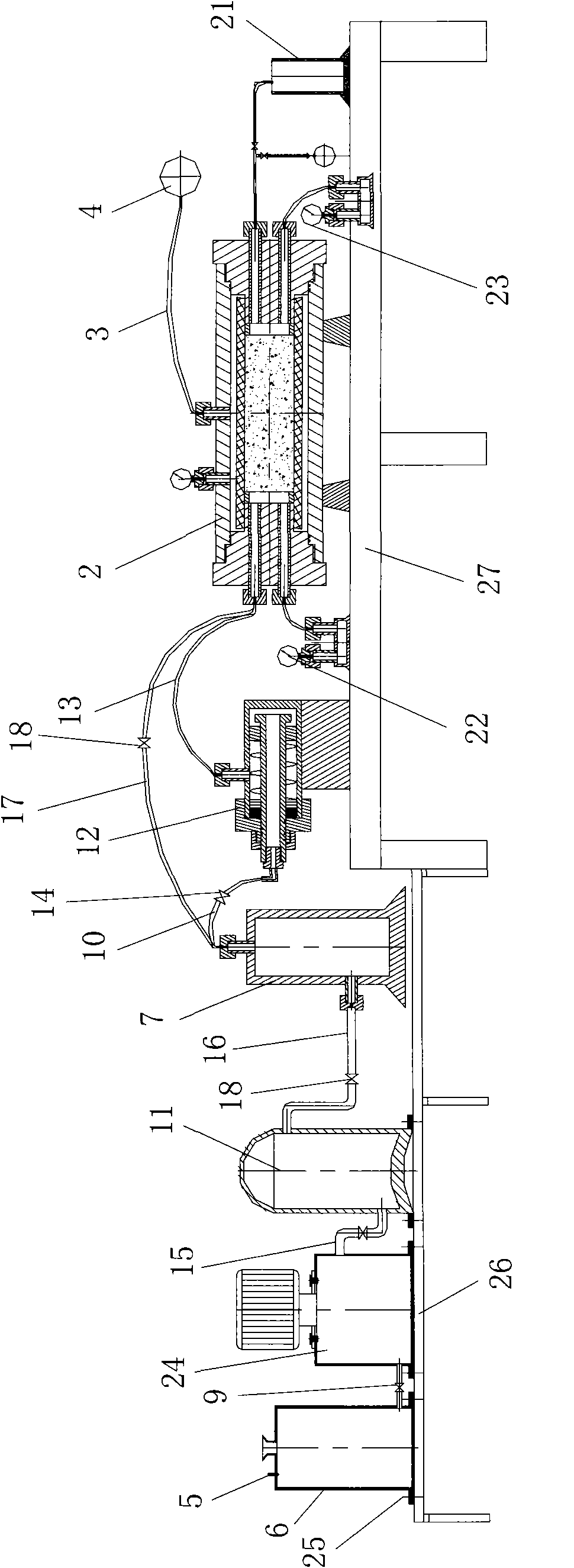

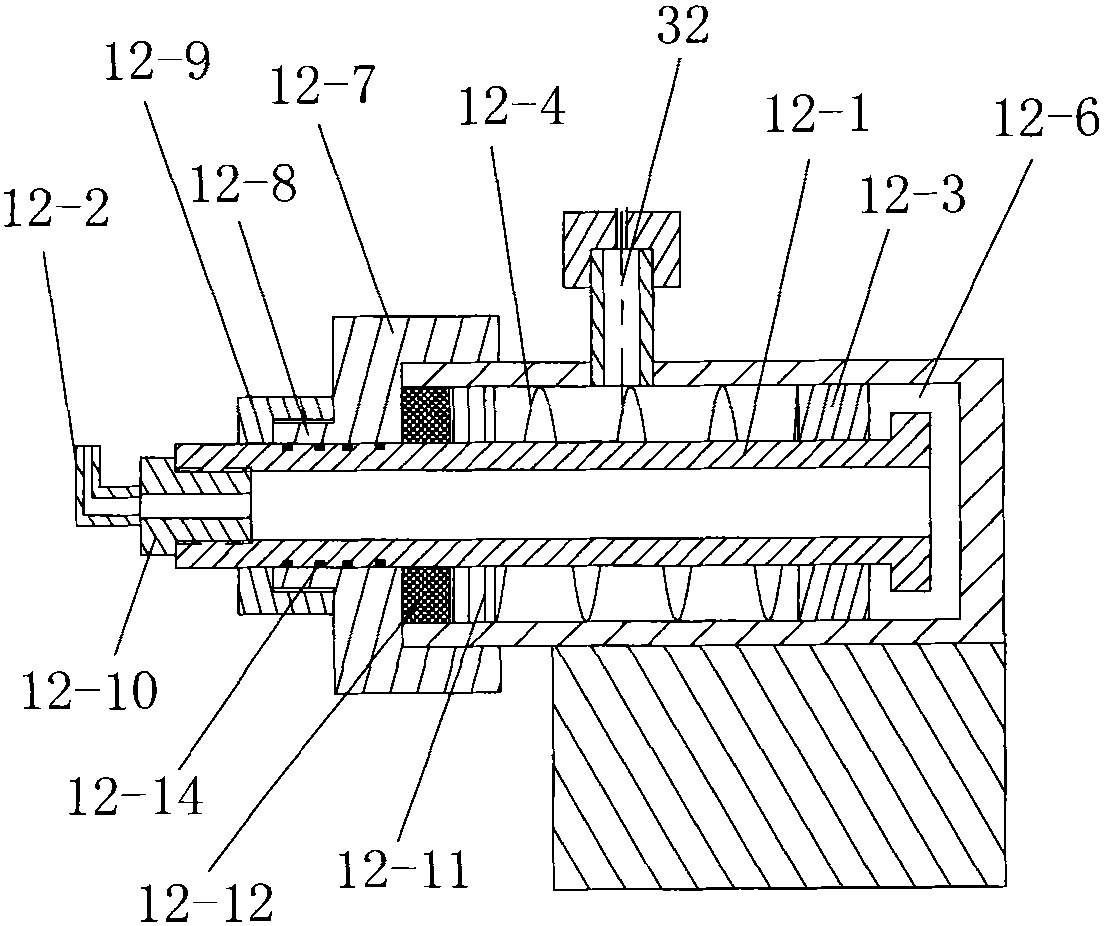

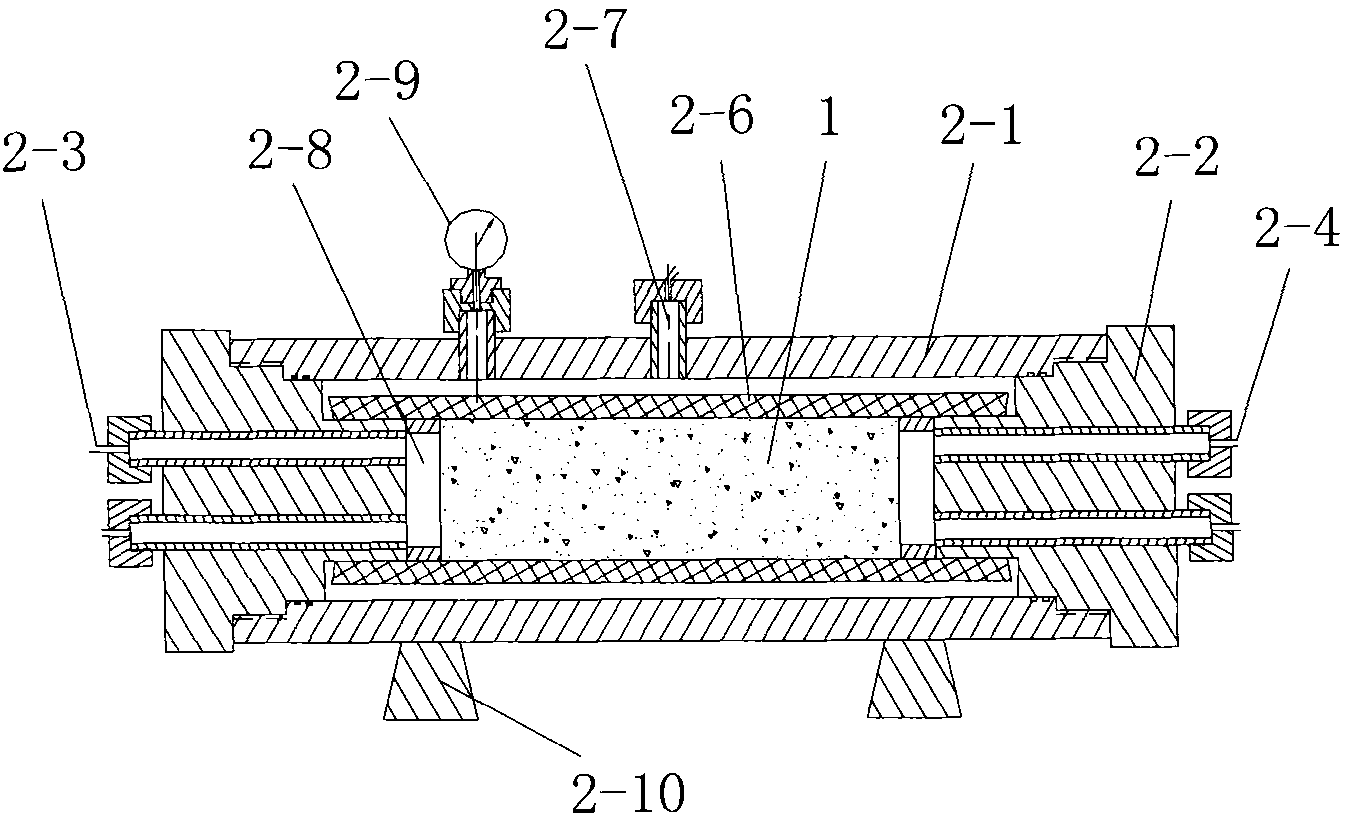

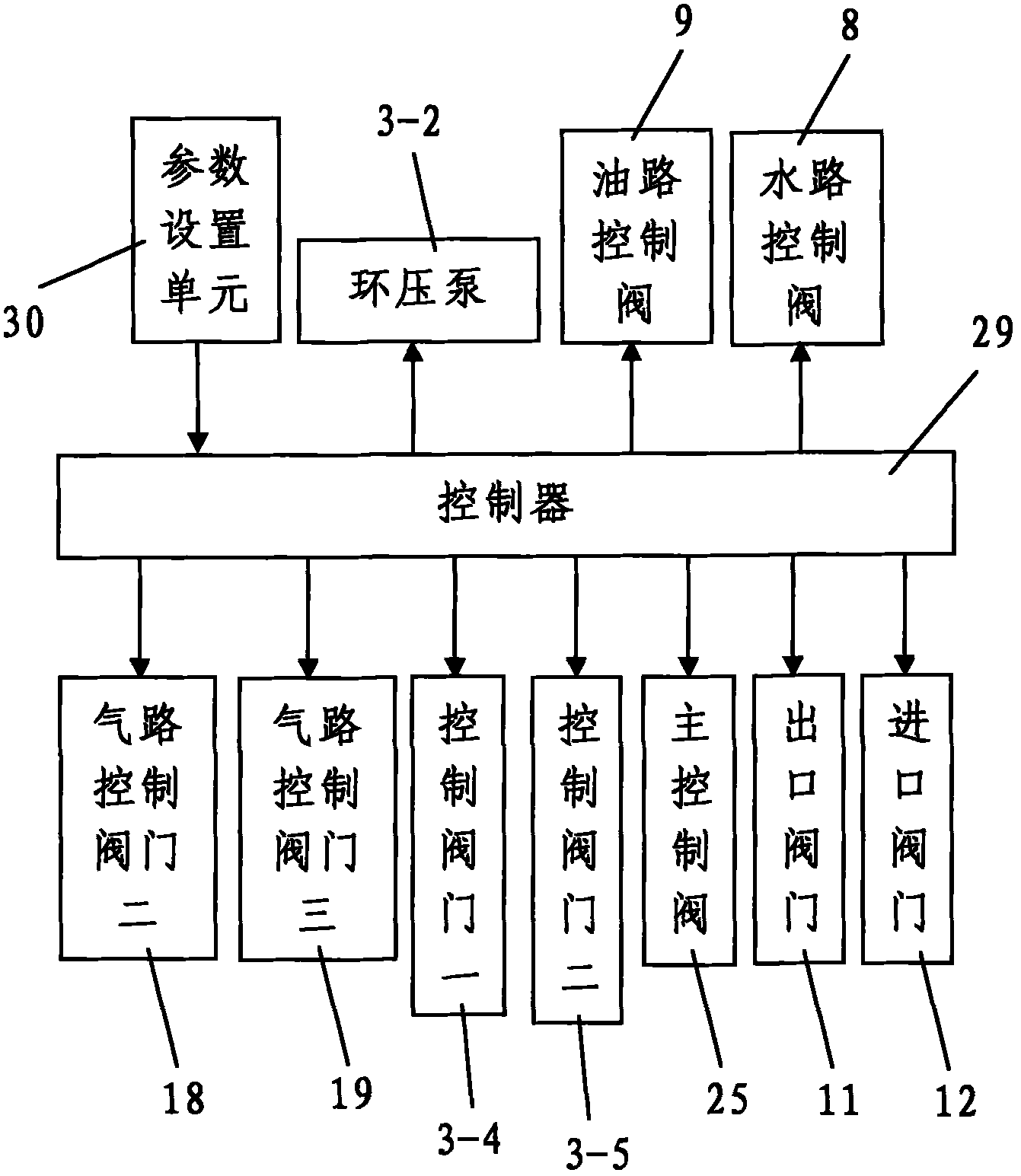

Hydraulic power pulse oil displacement experimental facility and experimental method thereof

ActiveCN101975053AImprove work efficiencyEnhanced overall recoveryFluid removalVibration devicesExperimental methodsWater storage tank

The invention discloses a hydraulic power pulse oil displacement experimental facility and an experimental method thereof. The experimental facility comprises a core clamping device, an annular pressure supply device, a hydraulic power pulse wave generating device, a water storage tank and an oil storage tank which are connected with the liquid inlet of the core clamping device by virtue of a water pipeline and an oil pipeline as well as a liquid container which is connected with the liquid outlet of the core clamping device; wherein the water pipeline and the oil pipeline are all provided with an intermediate container, a pumping device used for generating high pressure liquid flow and an energy storage tank. The experimental method includes the following steps: firstly, oil displacementexperiment is carried out under the condition that no hydraulic power pulse is added; secondly, oil displacement experiment is carried out while frequency and amplitude hydraulic power pulse wave of core are replaced, and meanwhile hydraulic power pulse auxiliary chemical oil displacement experiment is completed; thirdly, data processing is carried out. The invention has reasonable design, mounting convenience, simple operation and good simulation effect, can improve efficiency of oil displacement by water and crude oil recovery ratio, and experiment of hydraulic pulse wave oil displacement and hydraulic pulse wave auxiliary reservoir core oil displacement by water can be realized.

Owner:CHINA UNIV OF PETROLEUM (EAST CHINA)

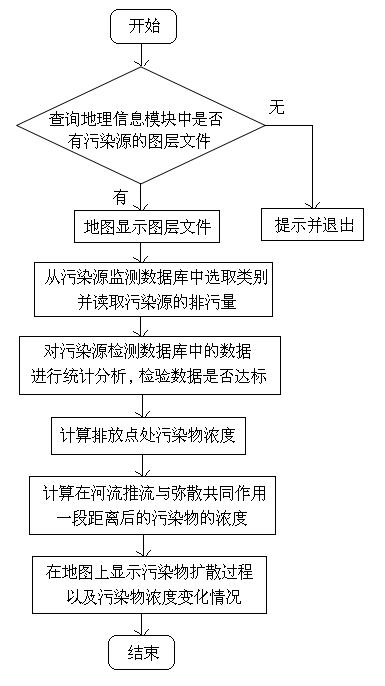

Pollution source management system based on geographic information system (GIS) technology and one-dimensional water quality model and operation method thereof

InactiveCN102184487AAutomatic generatedRealize a reasonable distributionData processing applicationsStatistical analysisWater quality

The invention provides a pollution source management system based on a geographic information system (GIS) technology and a one-dimensional water quality model. The pollution source management system comprises a basic geographic database, a water quality monitoring database, a pollution source monitoring database, a water quality model predicting module, a statistical analysis module and a geographic information system module. The invention also provides an operation method of the pollution source management system based on the GIS technology and the one-dimensional water quality model; and by means of the operation method, the docking between a geographic information system and a management information system is realized to complete the effective management of a large amount of environmental information, analyze the changes in the environmental pollutants, and realize the visualization of a regional environmental pollution status, and thus, the execution of the water environment planning and decision is facilitated.

Owner:EAST CHINA NORMAL UNIV

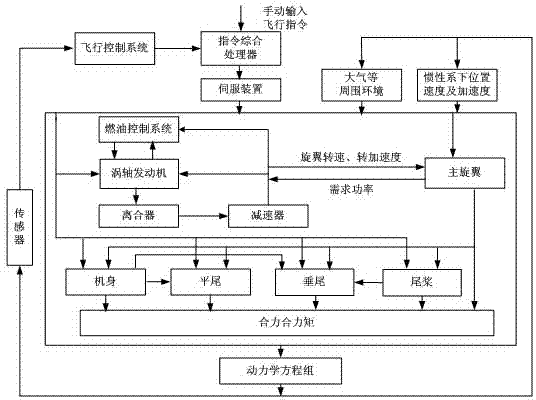

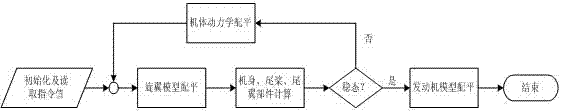

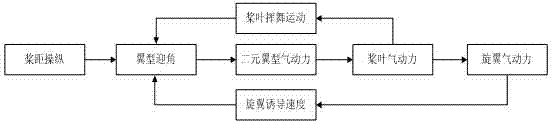

Building method for universal comprehensive models of single-rotor helicopters and turboshaft engines

InactiveCN102520620AVersatilityImprove the simulation effectSimulator controlFiltrationDynamic balance

The invention discloses a building method for the universal comprehensive models of single-rotor helicopters and turboshaft engines. The method includes the building of the non-linear models of a helicopter and an engine, the static trimming of the single-rotor helicopter and the turboshaft engine, the dynamic calculation of the single-rotor helicopter and the turboshaft engine and the actual operation solution of the single-rotor helicopter and the turboshaft engine, wherein the static trimming adopts the Levenberg-Marquarat algorithm, the dynamic calculation adopts the fourth-order Ronge-Kutta method to solve the motion equation system of the helicopter and the single pass algorithm to solve the dynamic balance equation of the turboshaft engine, and the actual operation state solution adopts a modified linear quadratic regulator algorithm to carry out helicopter solution and a cascade PID (Proportion-Integration-Differentiation) plus torque feedforward plus collective pitch compensation and torsional vibration filter method to carry out engine solution and load filtration. The method can meet the test requirements of the universal models and control methods of the single-rotor helicopters and the turboshaft engines, and plays an active role in helping to shorten the development cycle and reduce the test risk and the cost.

Owner:NANJING UNIV OF AERONAUTICS & ASTRONAUTICS

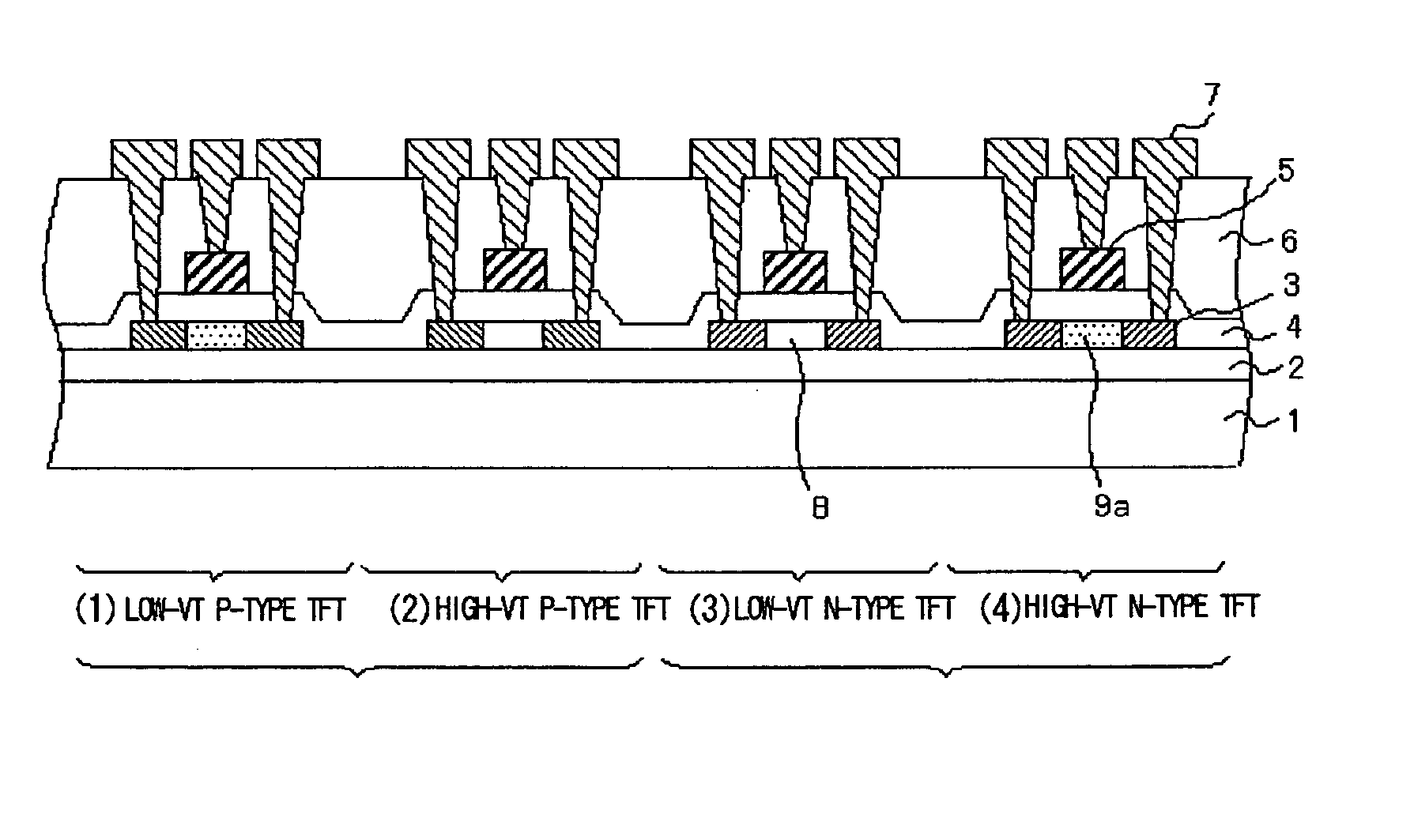

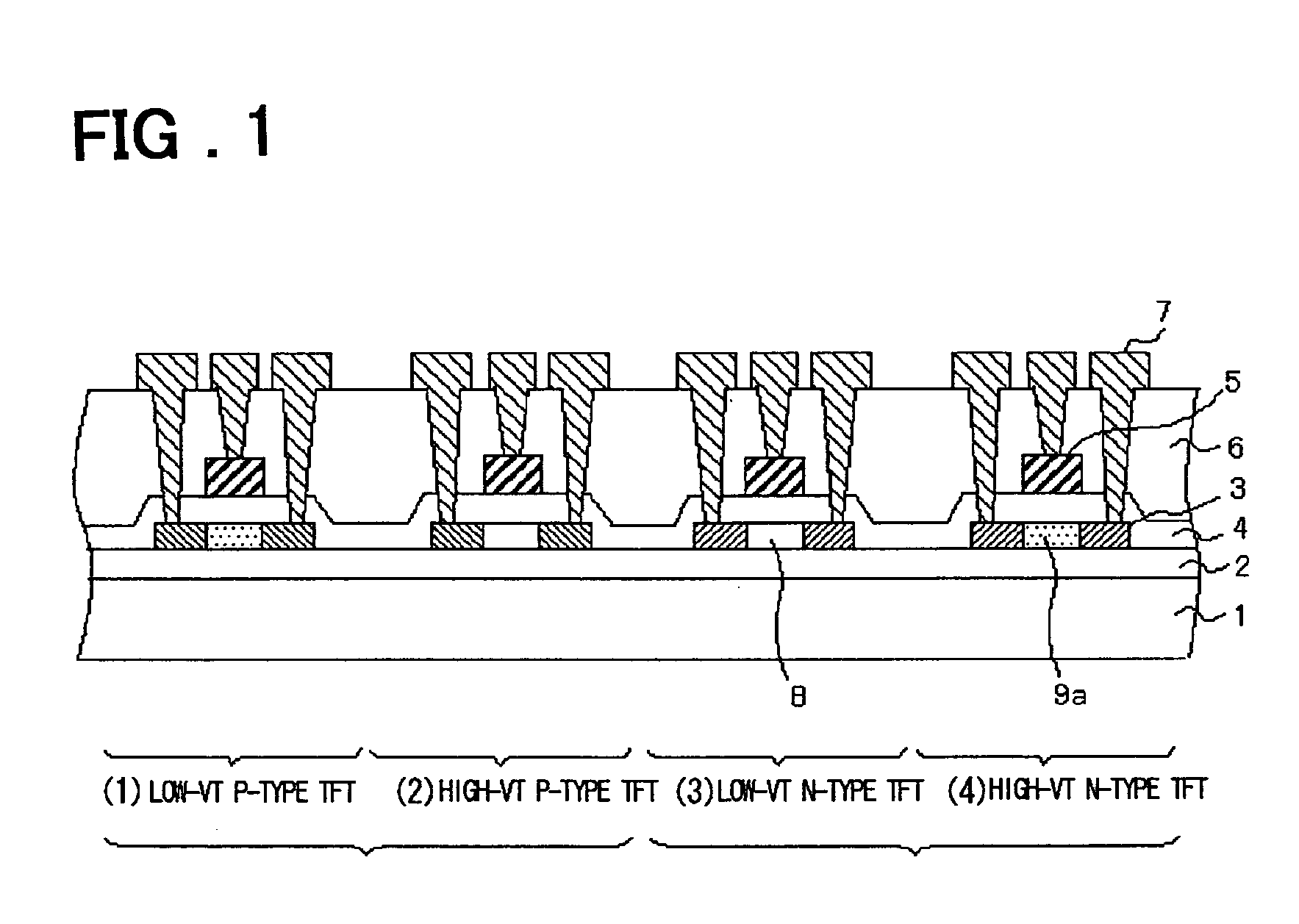

Thin film semiconductor device and manufacturing method

ActiveUS20040046209A1Improve the simulation effectComplicated processingTransistorMultiple input and output pulse circuitsDopantEngineering

When n-channel thin film transistors(TFTs) and p-channel TFTs are formed on a polycrystalline silicon film formed on a glass substrate, a process is included in which P-dopant or N-dopant is introduced at the same time to the channel region of a part of the n-channel TFTs and a part of the p-channel TFTs. In one channel doping operation, a set of low-VT and high-VT p-channel TFTs and a set of low-VT and high-VT n-channel TFTs can be formed. This method is used for forming high-VT TFTs, which can reduce the off-current, in logics and switch circuits and for forming low-VT TFTs, which can enlarge the dynamic range, in analog circuits to improve the performance of a thin film semiconductor.

Owner:HANNSTAR DISPLAY CORPORATION

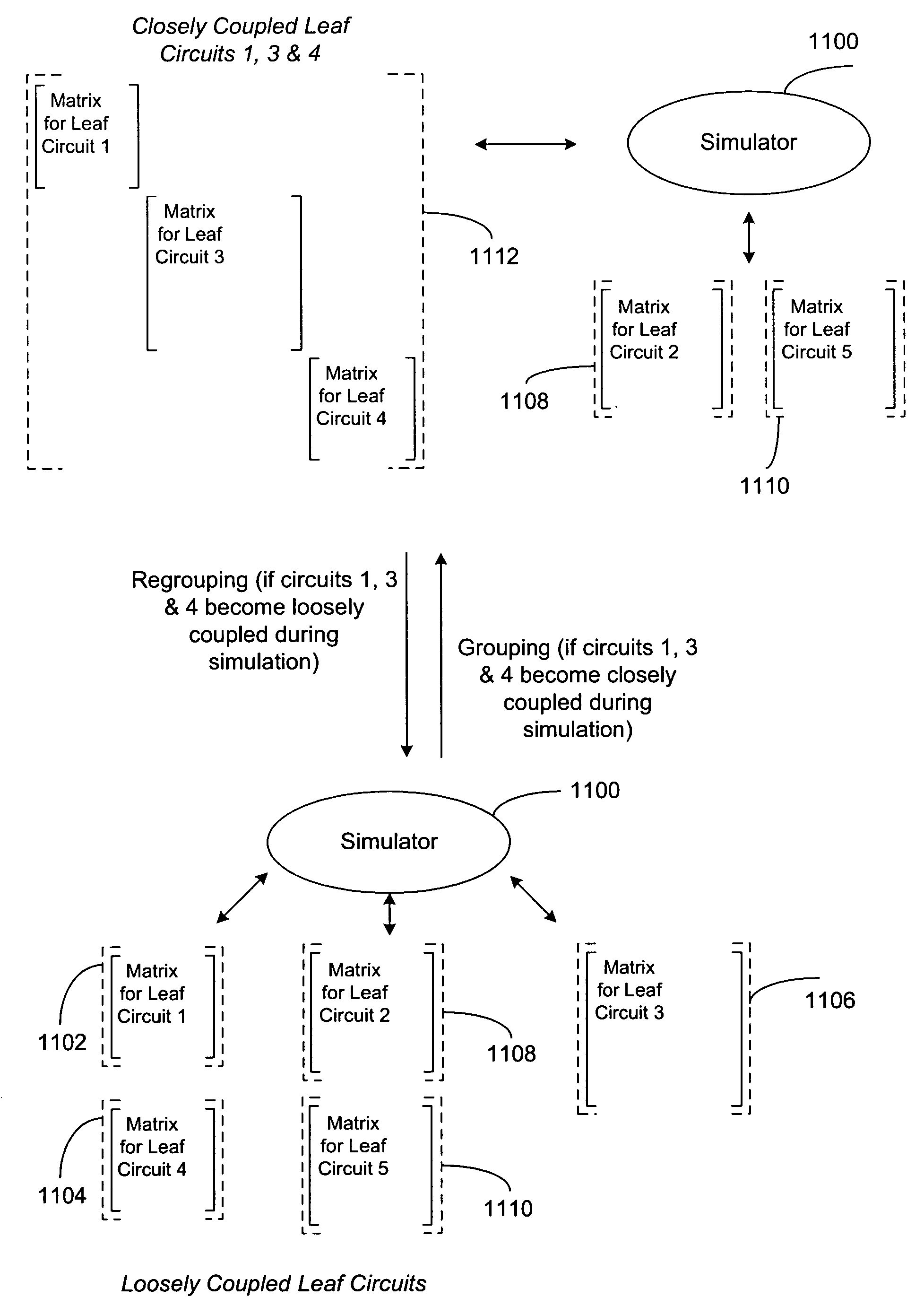

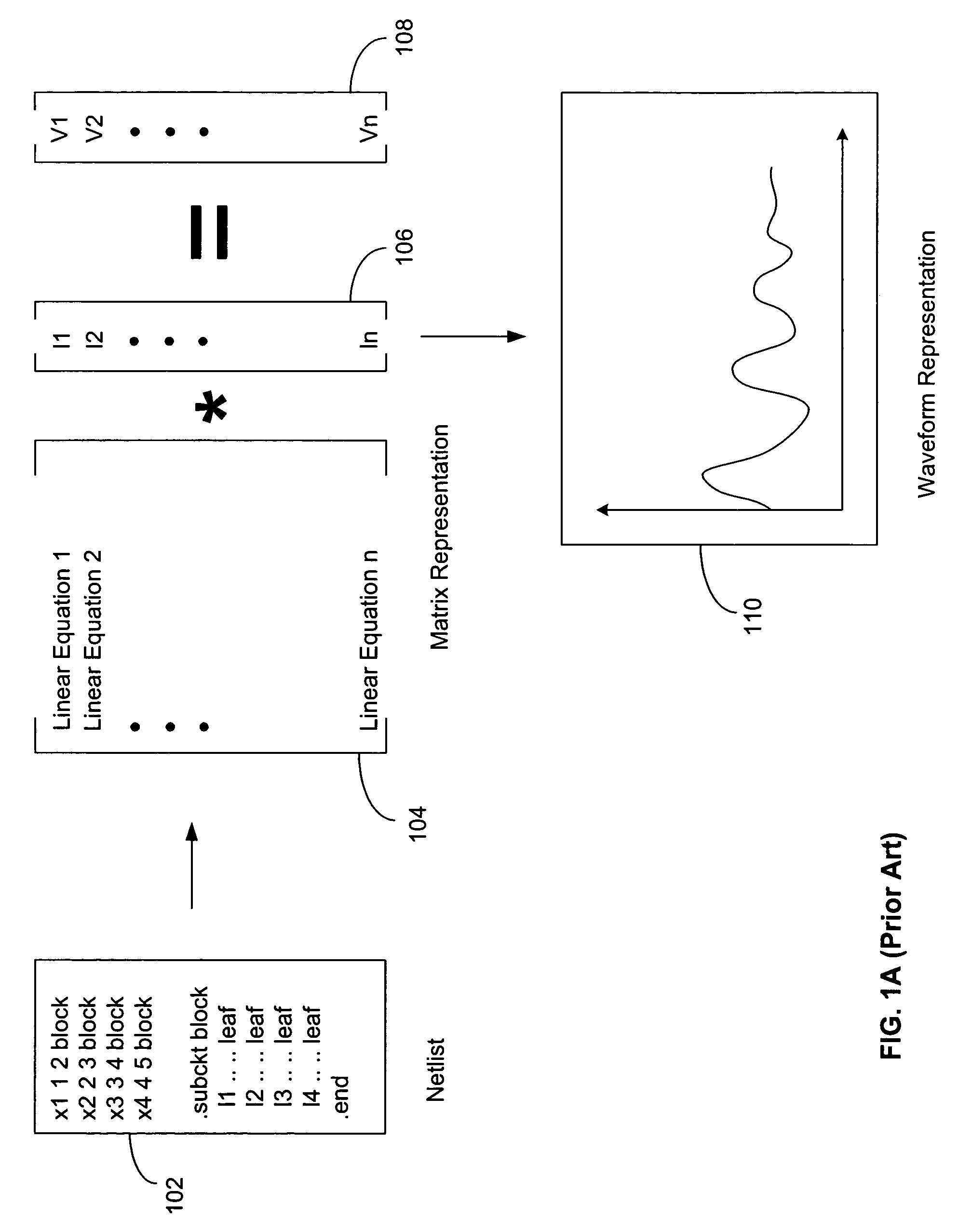

System and method for adaptive partitioning of circuit components during simulation

ActiveUS7024652B1Improve the simulation effectSmall sizeDetecting faulty computer hardwareComputer aided designElectricityEngineering

A system for adaptive partitioning of circuit components during simulating of a circuit having a hierarchical data structure includes a simulator module having one or more computer programs for 1) selecting a group of leaf circuits from the first branch and the second branch for simulation, where each leaf circuit is represented by a matrix comprising a set of equations, 2) determining a strength of coupling between two or more leaf circuits of the group in accordance with a set of predetermined electrical coupling criteria, 3) if two or more leaf circuits are deemed be strongly coupled, combining the corresponding matrix of each strongly coupled leaf circuit into a combined matrix, and 4) performing computation for the two or more strongly coupled leaf circuits in accordance with the combined matrix. The system adaptively adjusts the group circuit matrix for computing a group of circuits according to the strength of coupling between the circuits. Hence, it achieves higher simulation performance by reducing either the size of the solver matrix when the circuits are loosely connected to each other, or by reducing the number of computational repetitions due to the communication of changes of signal conditions between circuits by combining the individual circuit matrices when such circuits are closely coupled to each other.

Owner:CADENCE DESIGN SYST INC

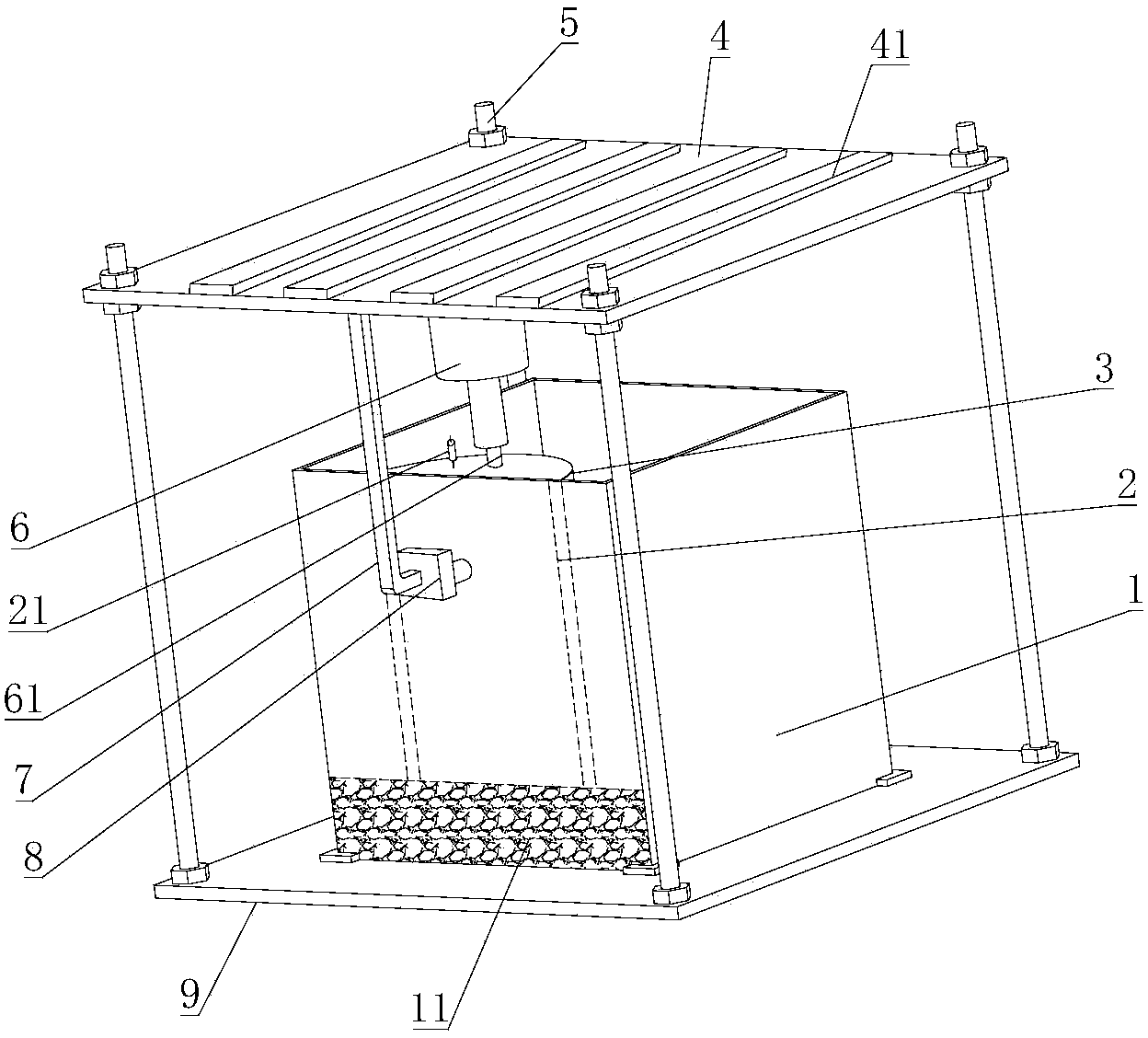

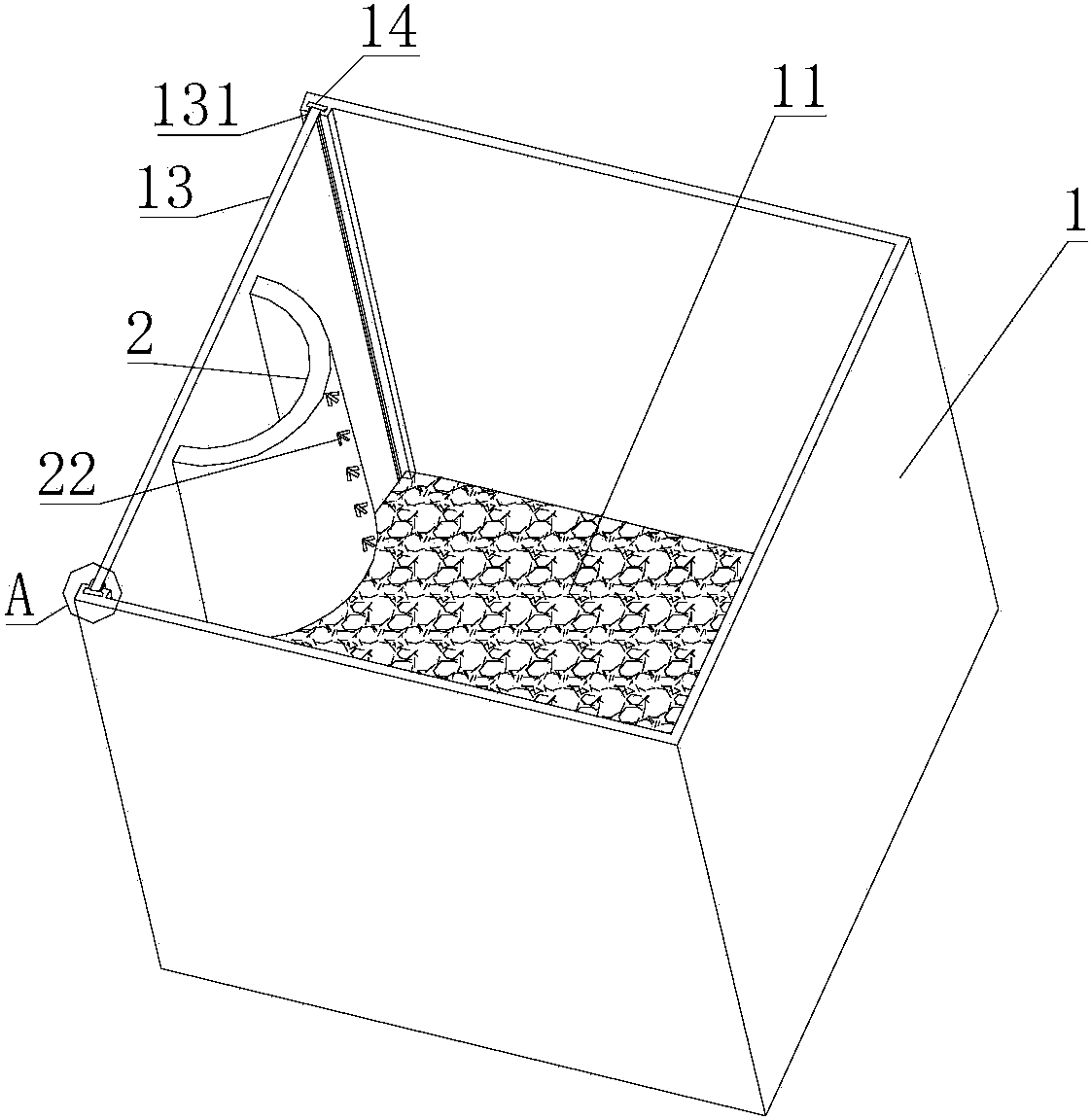

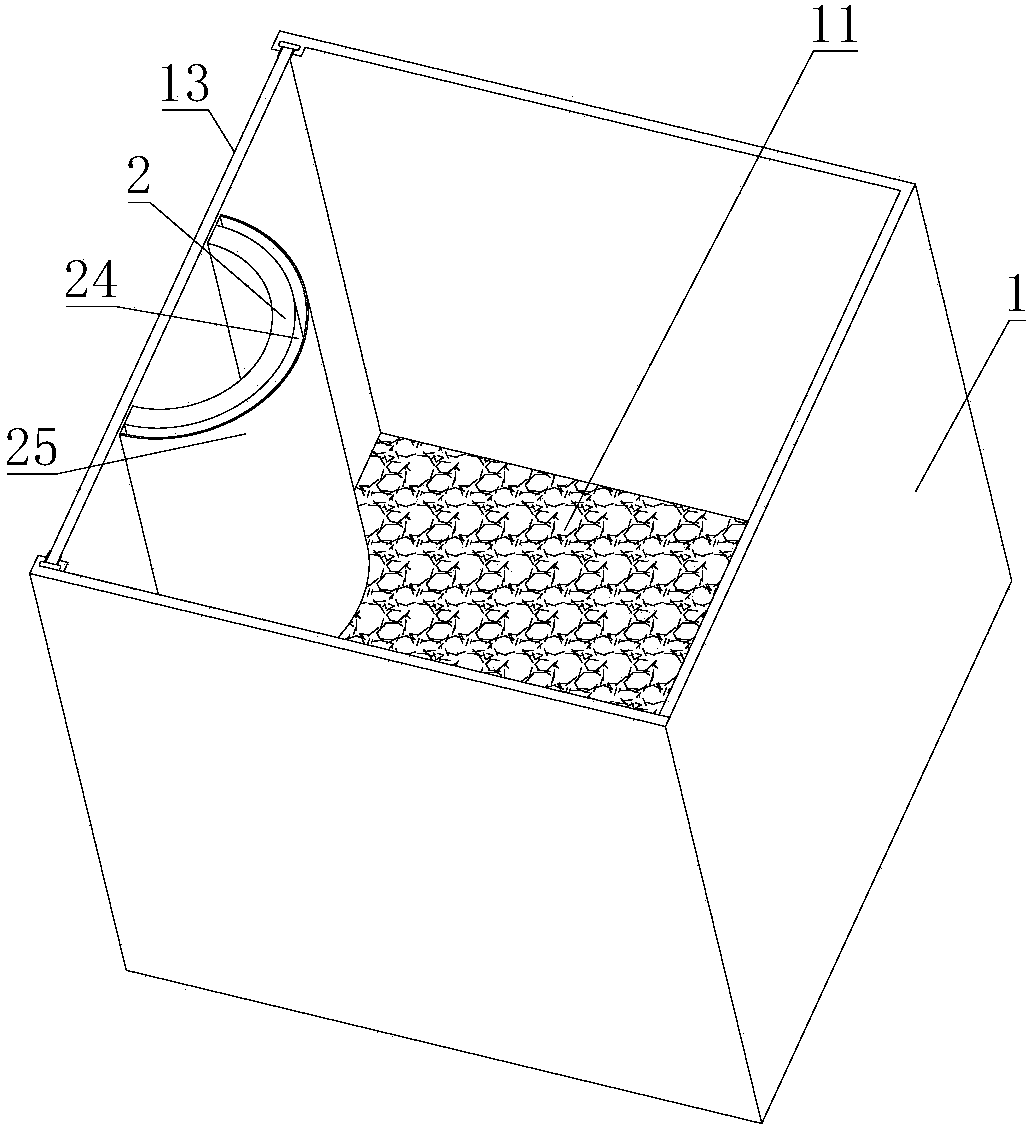

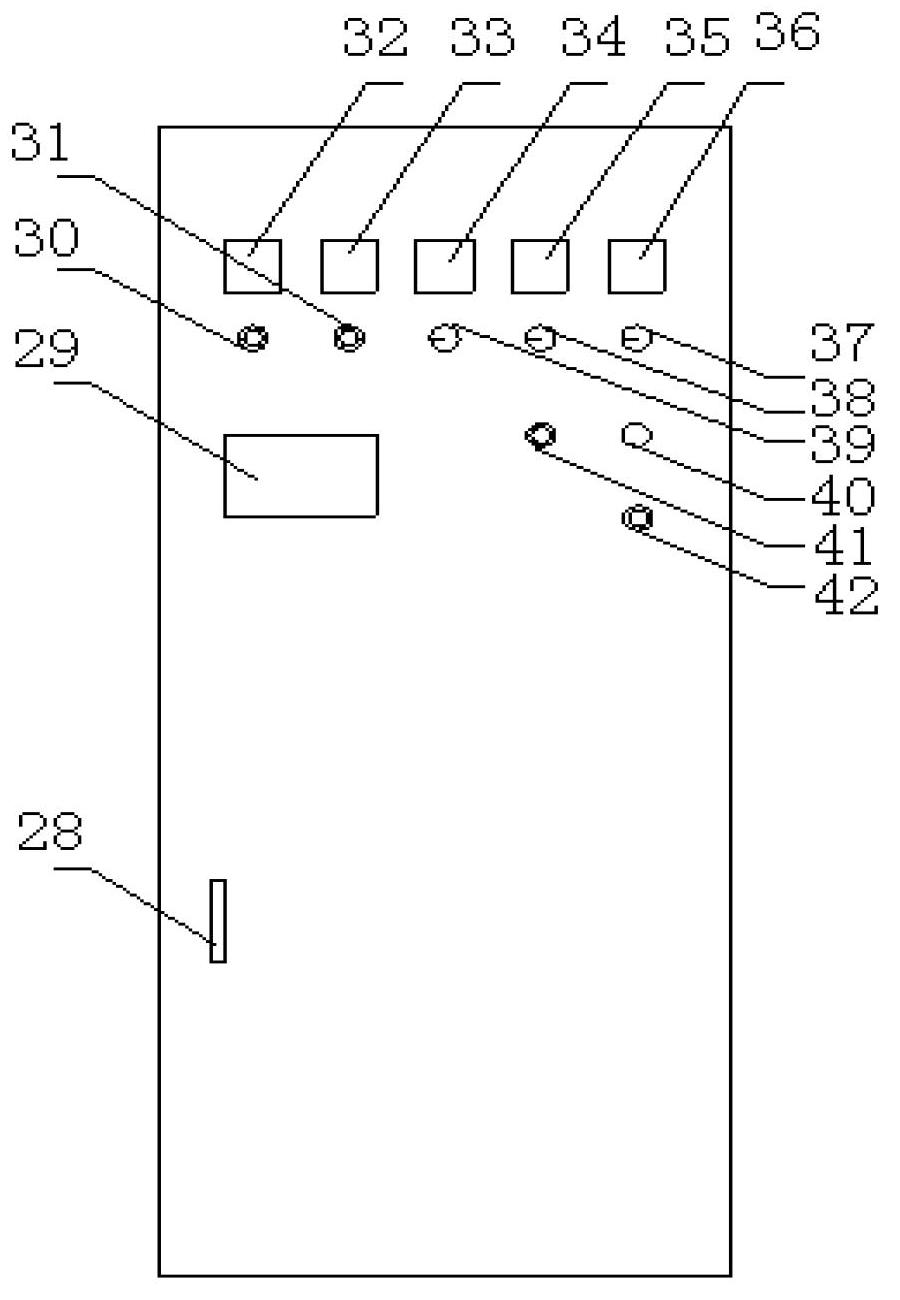

Testing device and method for observing shear deformation failure characteristics between tubular pile and grouting soil body

ActiveCN104374649AEasy to analyzeImprove the simulation effectMaterial strength using steady shearing forcesModel testingMonitoring system

The invention discloses a testing device for observing shear deformation failure characteristics between a tubular pile and a grouting soil body. The testing device comprises a fixing platform, a tubular pile model testing box, a loading mechanism and a monitoring system, wherein the fixing platform comprises a base plate, a top plate and a plurality of connecting screw rods; the tubular pile model testing box comprises a bottom wall, two side walls, a rear wall and a front wall, wherein the front wall is movably arranged between the side walls, and is made of colorless transparent organic glass; the monitoring system comprises a displacement sensor, a pressure sensor and a strain rosette group arranged on the outer surface of the tubular pile; the strain rosette group comprises a plurality of strain rosettes which are uniformly distributed along the central axis direction of the tubular pile, and are connected with an automatic recorder. According to the invention, a semi-circular pipe pile is adopted, so that the shear deformation failure characteristics between the tubular pile and the grouting soil body can be observed conveniently, and the shear resistant intensity between the tubular pile and the grouting soil body can be observed; a camera device is adopted for recording the video of the testing process; the visual testing enables the analysis to be relatively intuitive.

Owner:GUANGZHOU INSTITUTE OF BUILDING SCIENCE CO LTD +1

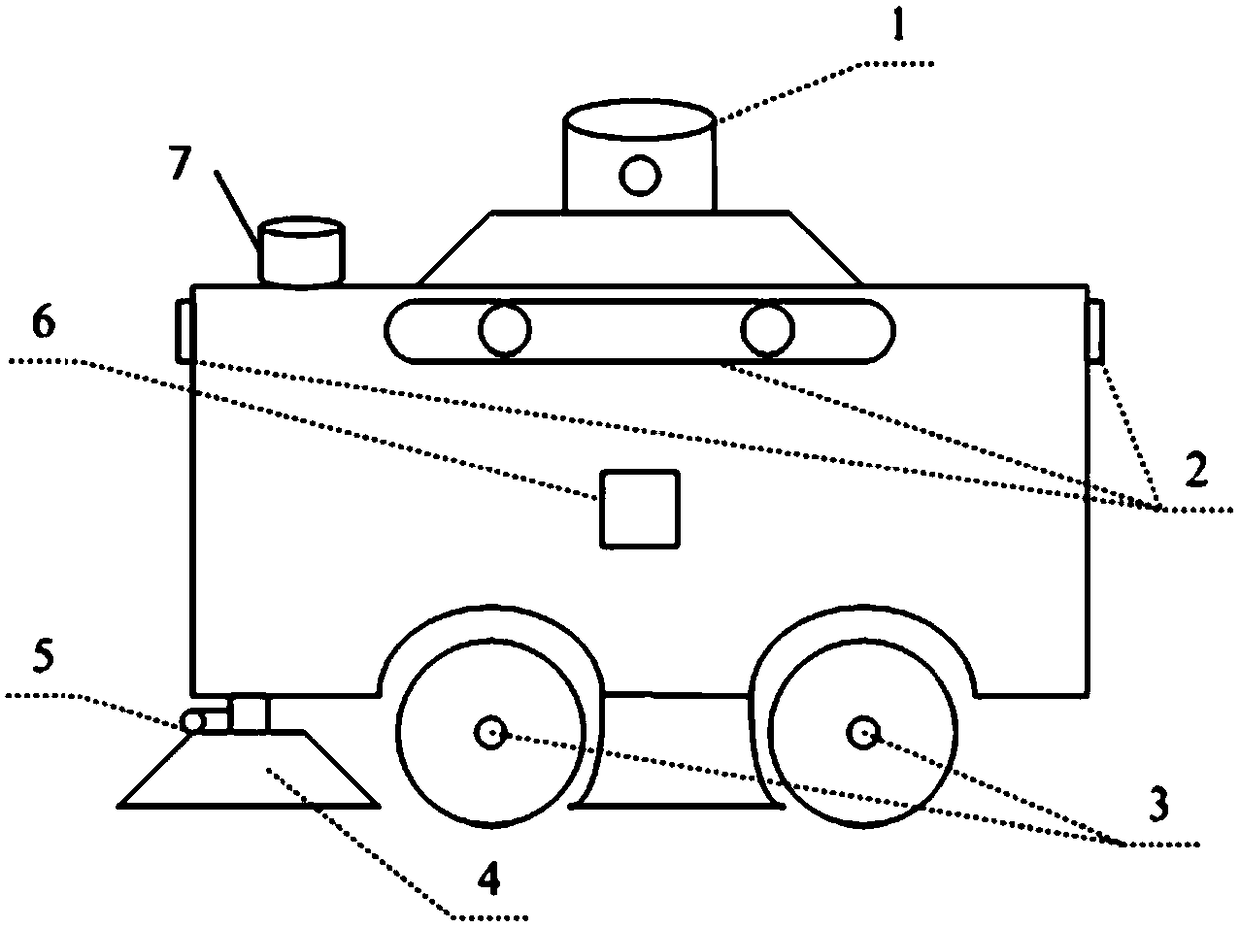

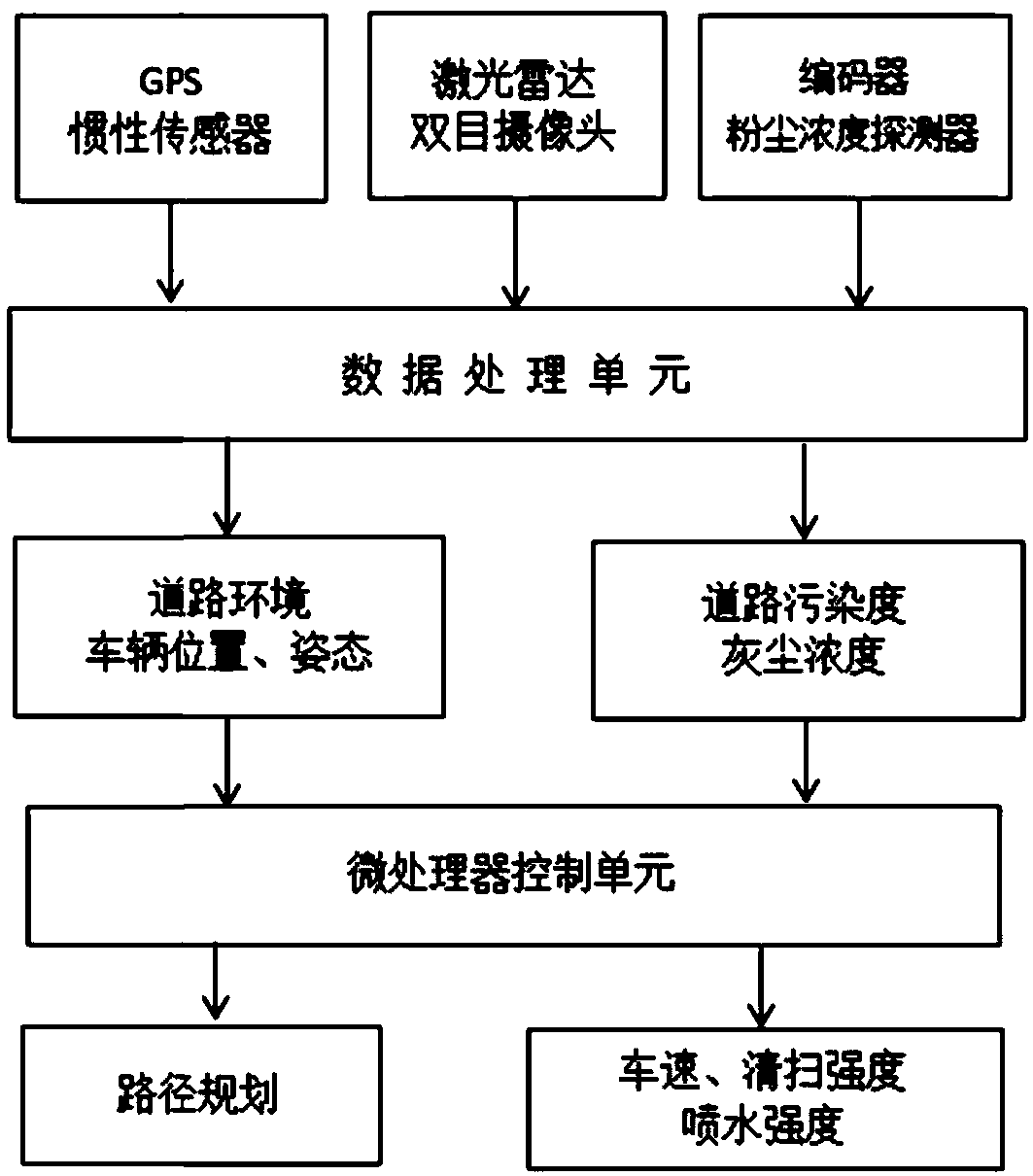

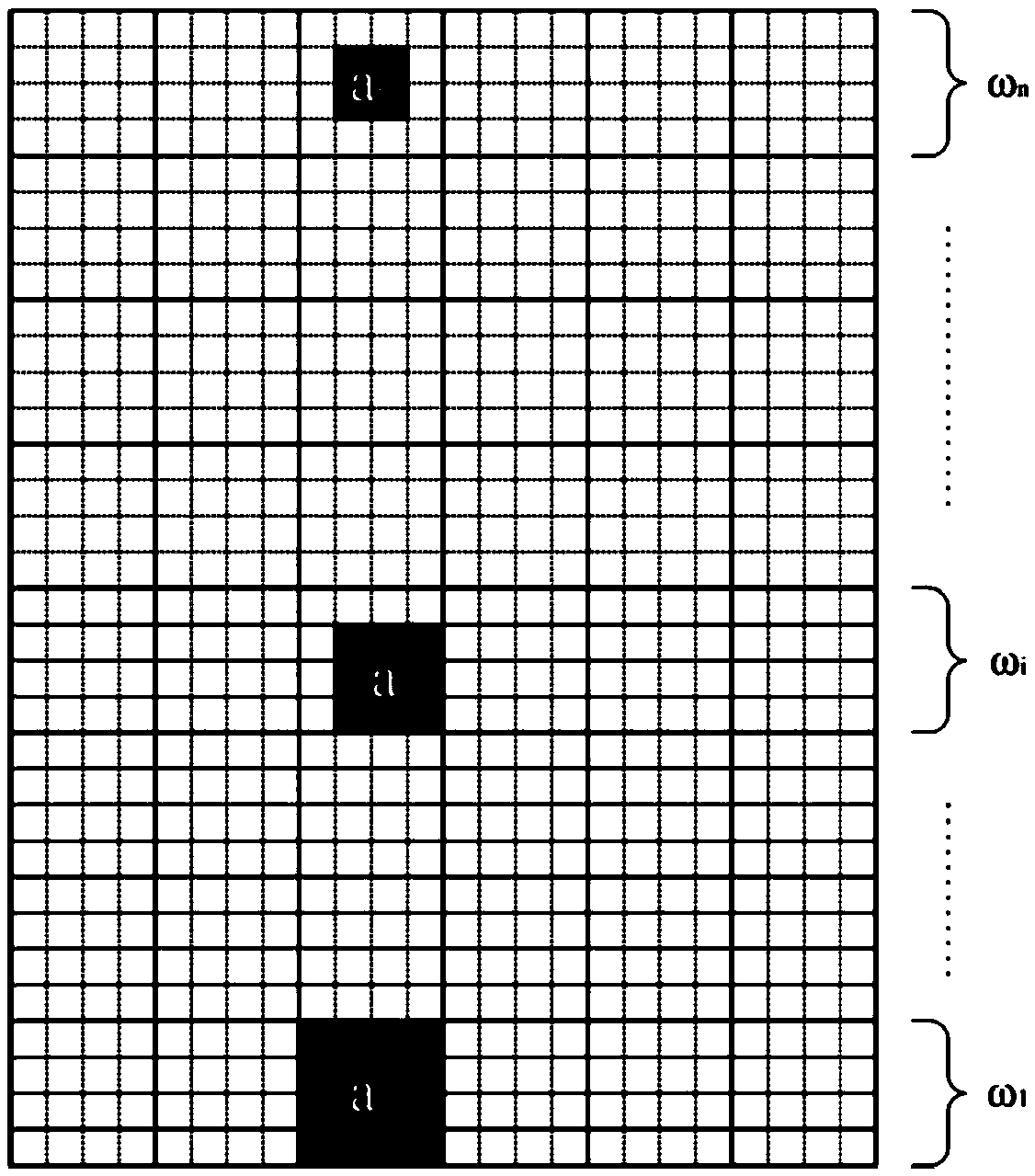

Intelligent road sweeper and a road pollutant identification method and a control method thereof

ActiveCN109024417AGood safety and reliabilityImprove cleaning qualityRoad cleaningPollutantNetwork model

The invention discloses an intelligent road sweeper and a road pollutant identification method and a control method thereof. The road sweeper comprises a road sweeper body, a laser radar, a camera, anencoder, a dust concentration detector, an inertial sensor, a GPS system and a processing controller. A method for identify road pollutants include acquiring RGB images of clean road surface and roadfacilities to be cleaned, convert that acquired RGB images into HSV space, and obtaining a BP neural network model capable of identifying the clean road surface and road facilities; The real-time image information of the road to be cleaned is input to the BP neural network model to identify the pollutants. The method for identifying pollutants such as garbage in the present invention utilizes theHSV feature of a road image, which has a larger information amount of the gray value of the image than that of a single image, and has a better effect for identifying pollutants such as garbage.

Owner:CHANGAN UNIV

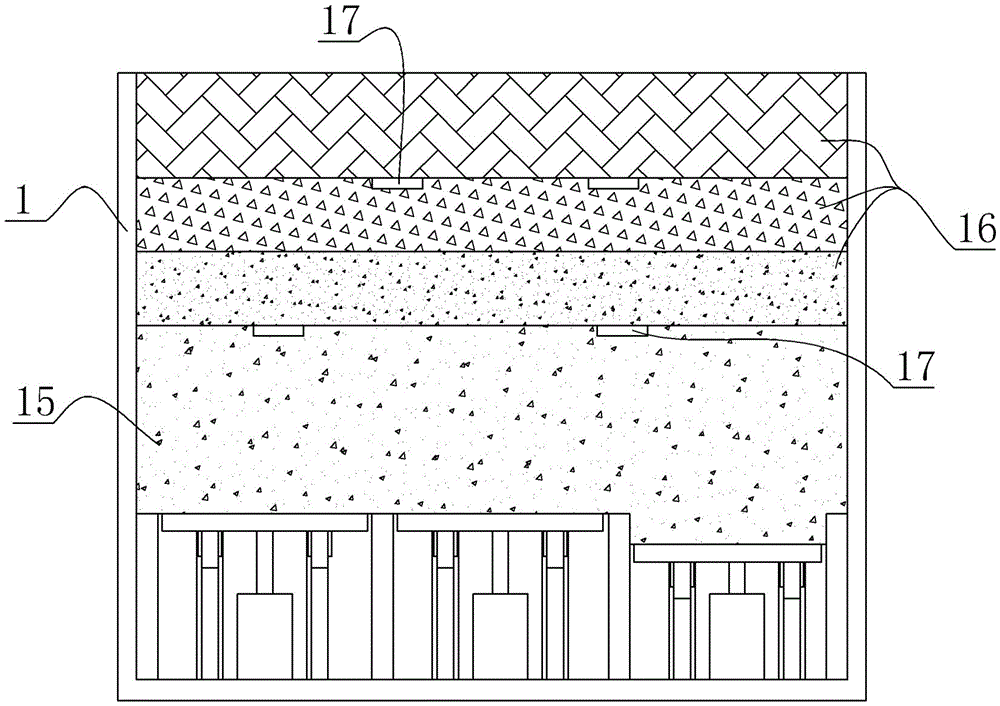

Jack-based experiment model and method for simulating uneven settlement of foundation

InactiveCN105527389AThe data and analysis results are actuallyLow costEducational modelsMaterial analysisEngineeringExperimental model

The invention relates to a jack-based experiment model for simulating the uneven settlement of a foundation. The experiment model comprises a model box with an upper opening and is characterized in that a base frame is arranged at the bottom of the cavity of the model box, the base frame is formed by partition plates, square cells are arranged among the partition plates, a prefabricated plate is arranged in each square cell, and jacks are arranged below each prefabricated plate and connected with a hydraulic system. An experiment method includes the steps of a, building the model box; b, arranging the base frame; c, arranging the jacks and the prefabricated plates; d, filling a foundation layer; e, building an upper engineering structure layer; f, simulating foundation settlement; g, collecting and analyzing data. The experiment model and method has the advantages that the jacks can drive the ascending and descending of the prefabricated plate in the corresponding square cell, and accordingly multipoint uneven settlement simulation of the foundation layer can be achieved; the multipoint uneven settlement of the foundation can be analyzed by collecting and analyzing the data output by sensors, and the experiment model and method is good in simulation effect, low in cost and high in experiment repeatability.

Owner:SHANDONG JIAOTONG UNIV

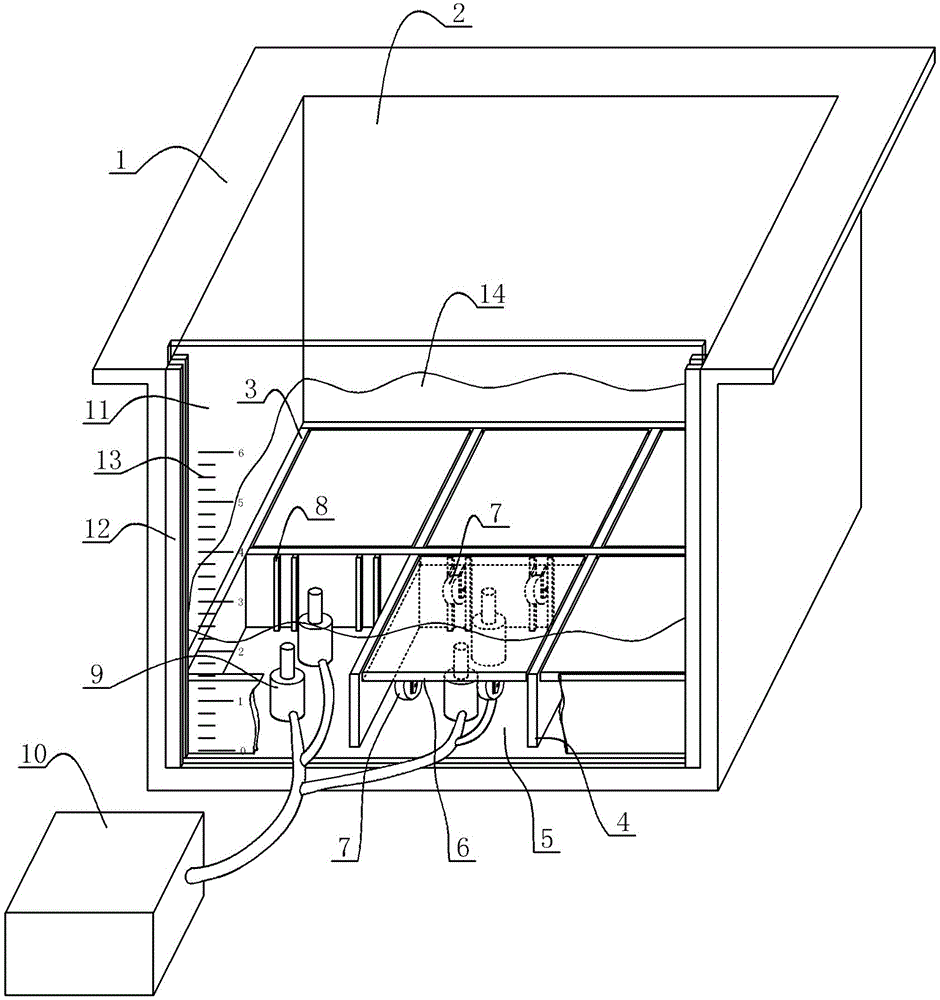

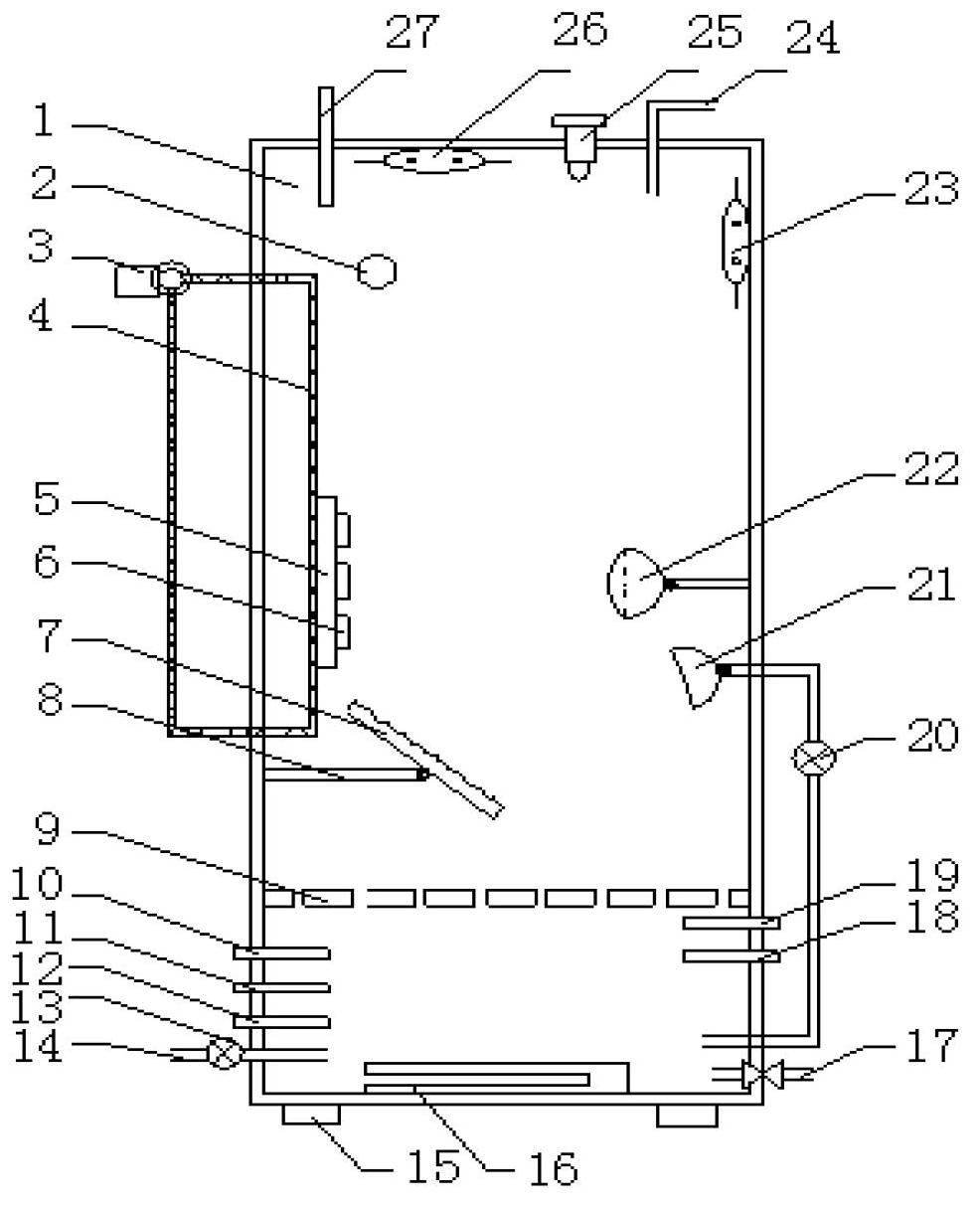

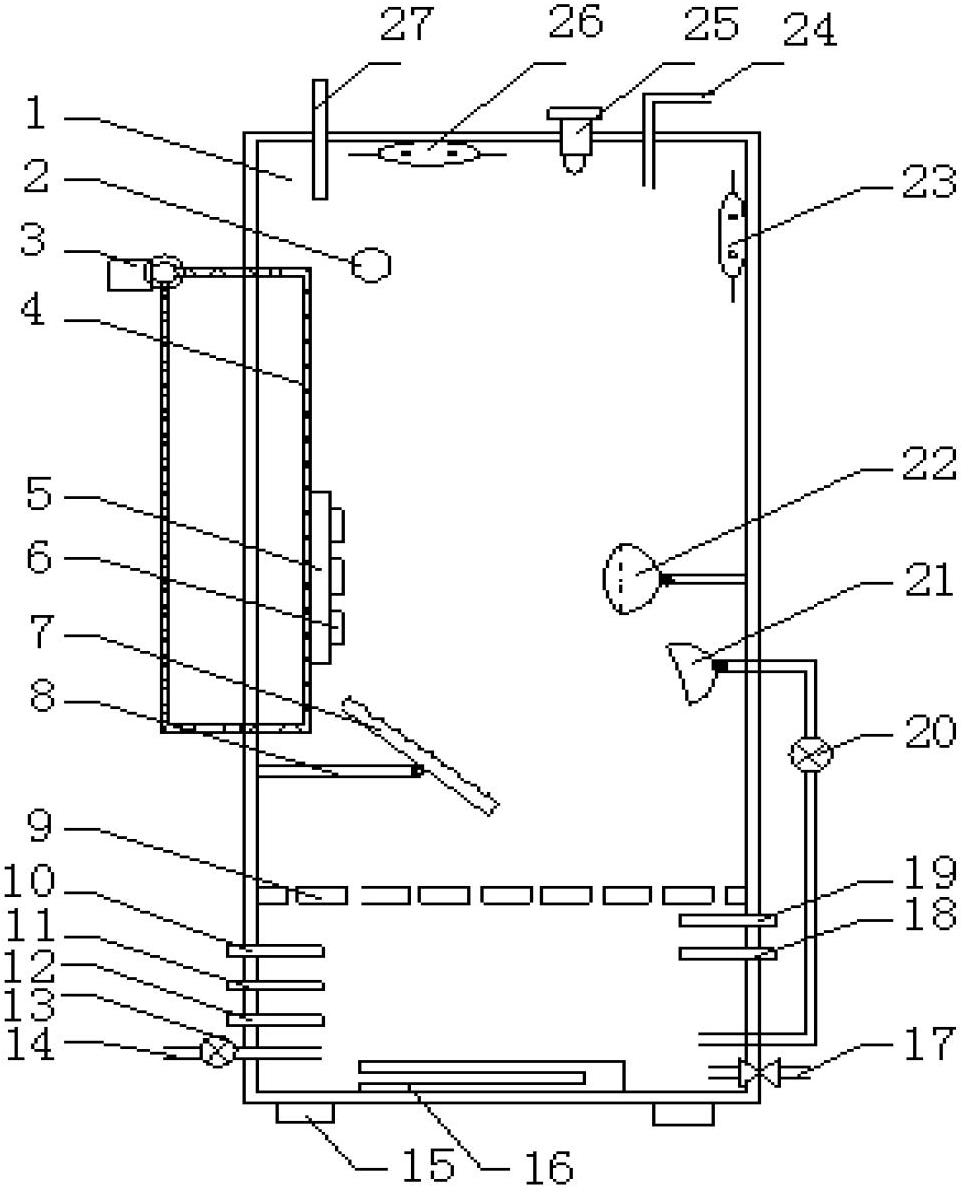

Marine splash environment simulation test device

ActiveCN102680385AImprove the simulation effectComprehensive monitoring of water qualityWeather/light/corrosion resistanceEngineeringMarine equipment

The invention belongs to the technical field of marine equipment, and particularly relates to a marine splash environment simulation test device, wherein stringed testing cable holes are arranged in the upper part of one side surface of the box-structured test box, a frame-structured drive pull rod is arranged on the other side, a splash plate angle adjusting rod is arranged at the lower part, and a splash plate is formed at the inner end of the splash plate angle adjusting rod; sensors and water inlets are arranged on the side surface of a liquid area from top to bottom; a gas exhaust opening, a ventilating and moisture exhausting device, an infrared heating lamp and a box temperature sensor are fixedly and sequentially arranged on the top side surface of the test box body from right to left; and a ultraviolet lamp, an air blower, a nozzle, a water spray pump, a liquid level controller, a dissolved oxygen sensor and a water drain opening are arranged on the opposite side of the test box corresponding to the side surface provided with the drive pull rod. The marine splash environment simulation test device has simple structure and higher automation degree, is convenient to operate, needs no staff attendance, and can simulate marine splash environment in a laboratory, so as to analyze and evaluate the corrosion and aging of the material.

Owner:725TH RES INST OF CHINA SHIPBUILDING INDAL CORP

Method and system for hardware accelerated verification of digital circuit design and its testbench

ActiveUS7257802B2Quick verificationOvercomes drawbackElectrical testingComputer aided designConcurrent computingValidation methods

A system and method is presented for synthesizing both a design under test (DUT) and its test environment (i.e., the testbench for the DUT), into an equivalent structural model suitable for execution on a reconfigurable hardware platform. This may be achieved without any change in the existing verification methodology. Behavioral HDL may be translated into a form that can be executed on a reconfigurable hardware platform. A set of compilation transforms are provided that convert behavioral constructs into RTL constructs that can be directly mapped onto an emulator. Such transforms are provided by introducing the concepts of a behavioral clock and a time advance finite state machine (FSM) that determines simulation time and sequences concurrent computing blocks in the DUT and the testbench.

Owner:SIEMENS PROD LIFECYCLE MANAGEMENT SOFTWARE INC

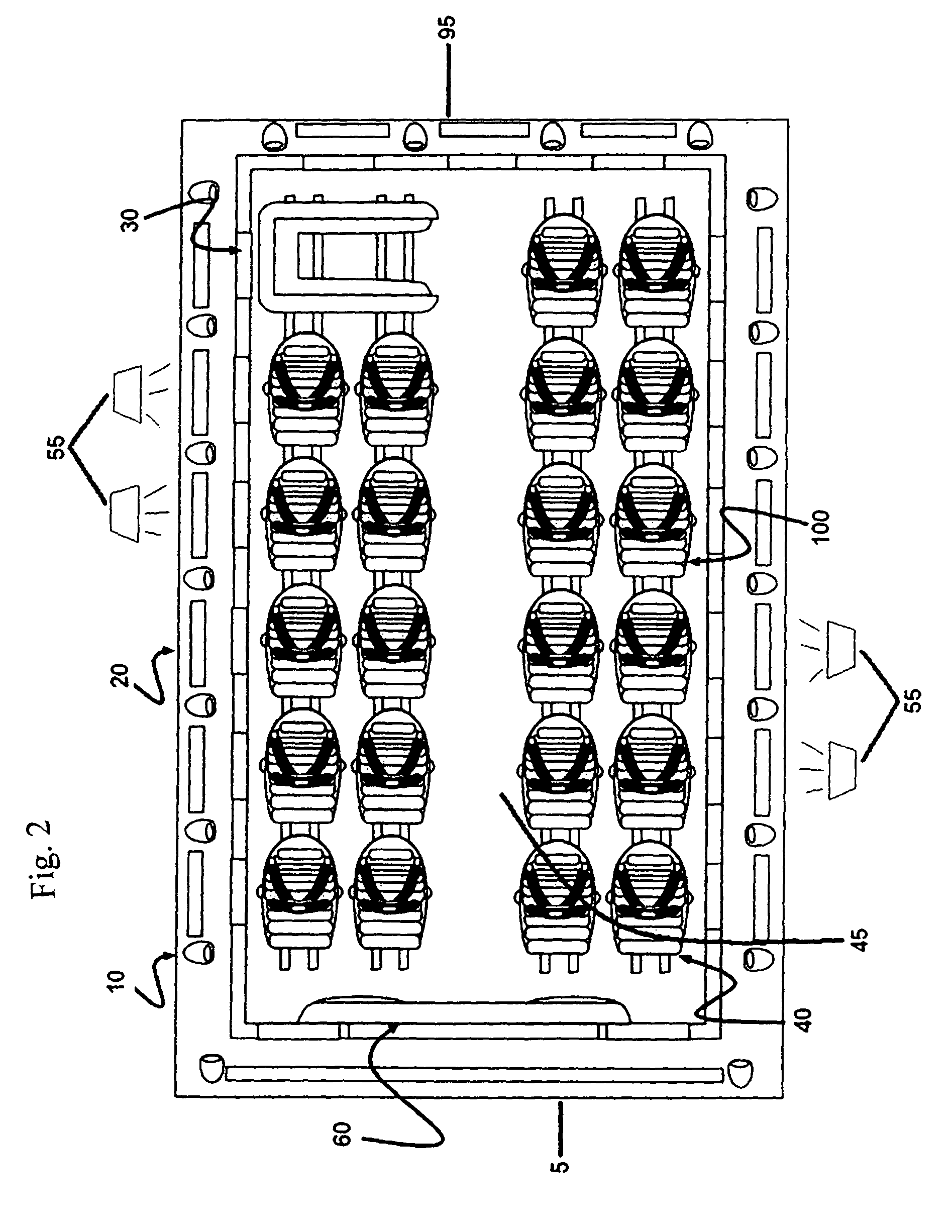

Airborne space simulator with zero gravity effects

InactiveUS8241133B1Real experienceGood effectStage arrangementsRolling drumsInterior spaceMobile vehicle

Systems, devices, apparatus and methods of using a simulator cabin module with an interior space which replicates a space ship, where the simulator module is mounted in a real aircraft, as a real airborne simulator. The aircraft lifts off to provide airborne maneuvers such as parabolic flight paths to cause G force and zero gravity effects to passengers in the cabin module. The cabin module includes rows of seats where passengers experience realistic sounds, lights, different temperatures, and physical effects (vibrations) of space ship liftoffs and space travel by having realistic simulation effects distributed over the seated passengers. Passengers can be seated in special reclinable seats with 5 point harnesses and pilot helmets with operable wireless communications and uniforms to add to the realistic simulation effects. Simulator modules can also be mounted in other moving vehicles, such as but not limited to submersibles, ships, and the like.

Owner:COMM CONCEPTS

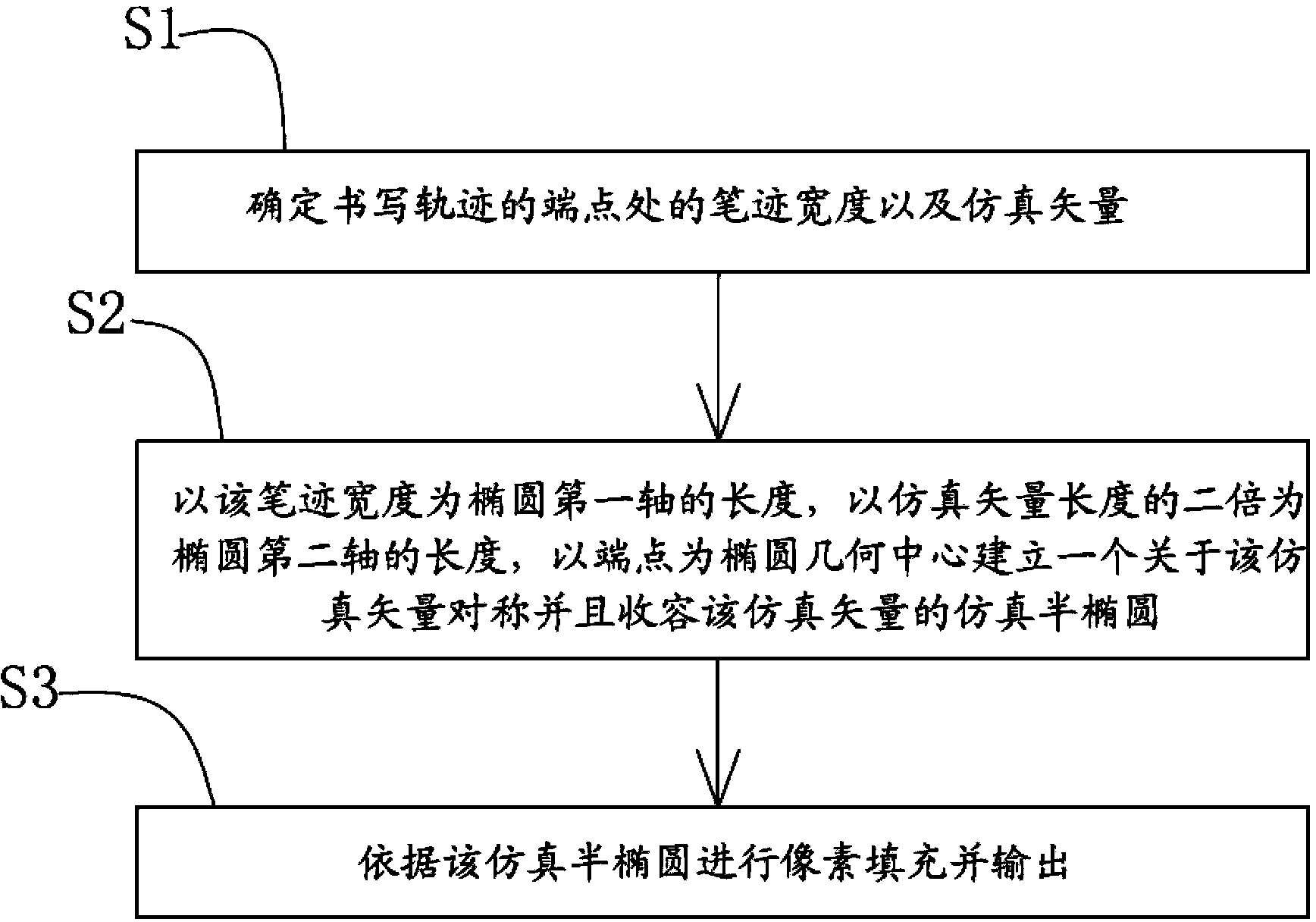

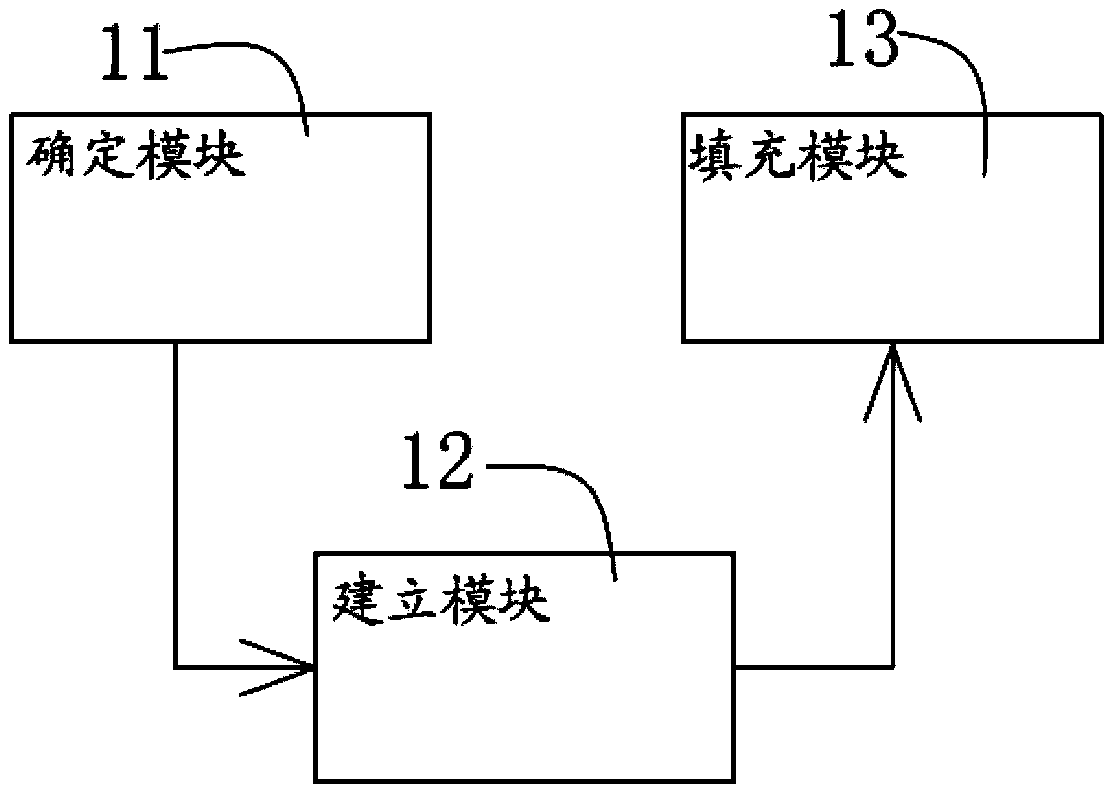

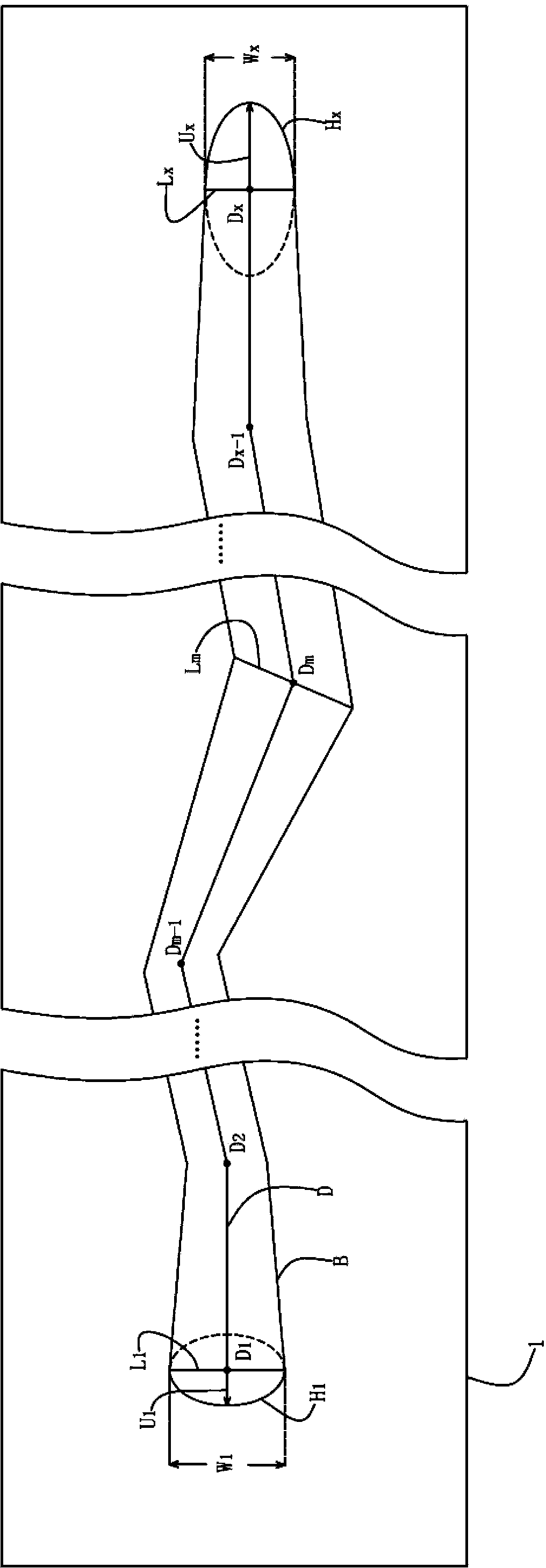

Implementation method and implementation device for original handwriting as well as electronic equipment

ActiveCN104345948AImprove the simulation effectReal simulationInput/output processes for data processingHandwritingEllipse

The invention discloses an implementation method and an implementation device for original handwriting as well as electronic equipment. The implementation method for the original handwriting comprises the following steps: determining a handwriting width and a simulation vector at an end point of a writing track; regarding the handwriting width as a length of a first axis of an ellipse, regarding two times of the length of the simulation vector as a length of a second axis of the ellipse, and regarding the end point as the geometric center of the ellipse to establish a simulated semi-ellipse which is symmetric about the simulation vector and accommodates the simulation vector; filling the simulated semi-ellipse with pixels and outputting. The implementation device for the original handwriting comprises a determination module, an establishment module and a filling module. The electronic equipment for implementing the original handwriting comprises a touch screen, a display screen and a processor, wherein the processor comprises the determination module, the establishment module and the filling module. The implementation method and the implementation device for the original handwriting as well as the electronic equipment disclosed by the invention are good in simulation effect.

Owner:BEIJING ERENEBEN INFORMATION TECH

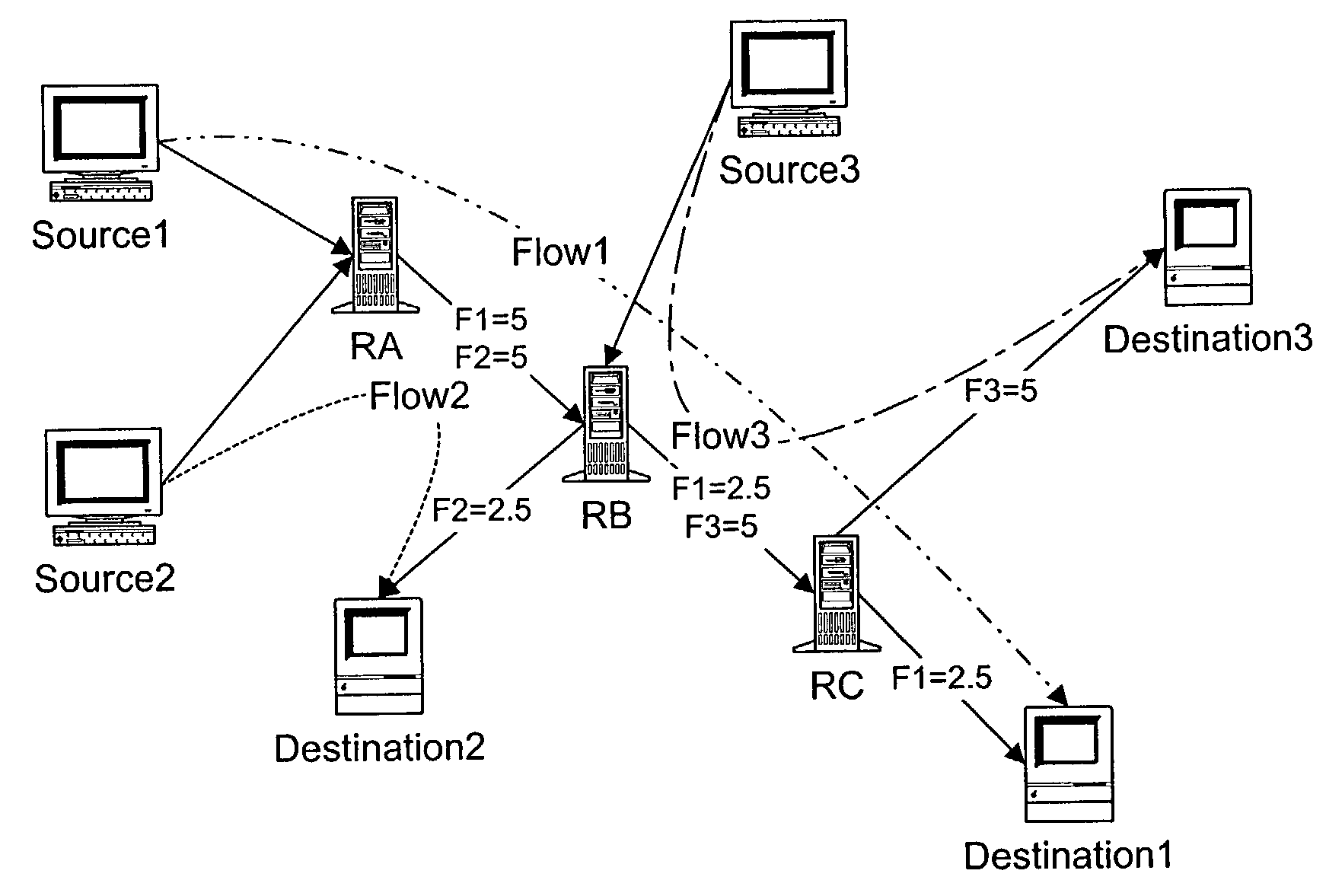

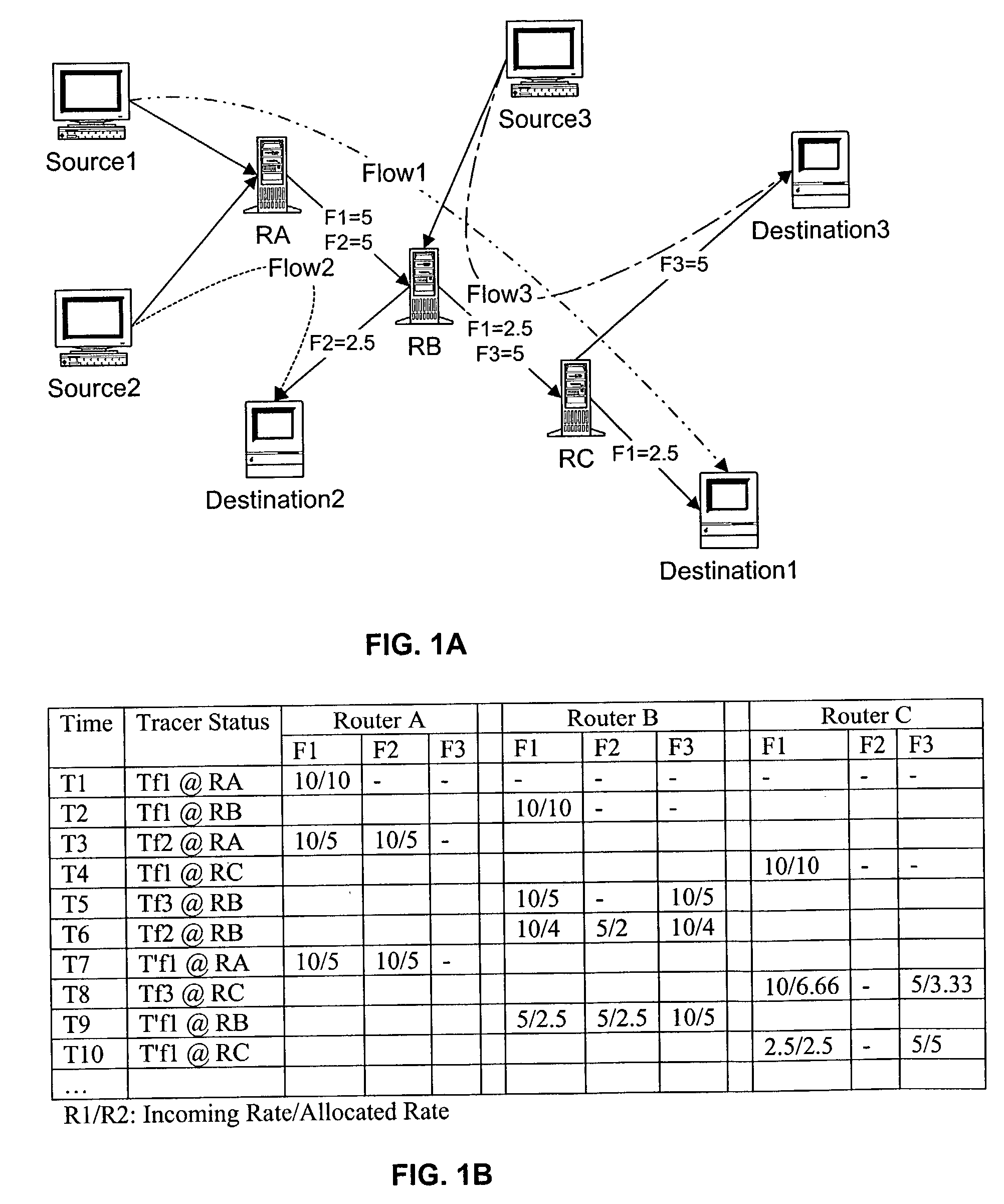

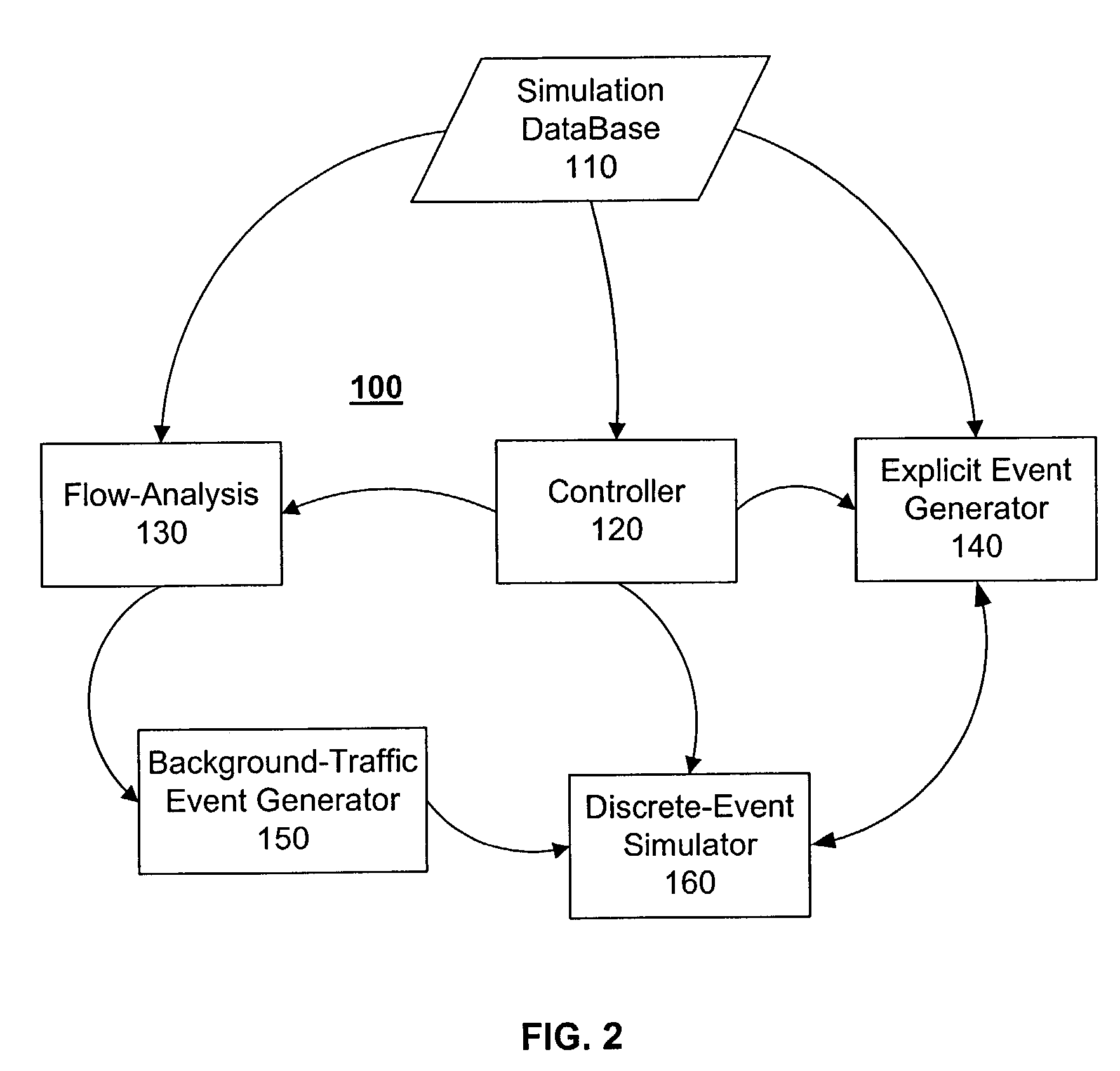

Flow propagation analysis using iterative signaling

ActiveUS7139692B2Efficiently determining the effective throughput of traffic flowsImprove the simulation effectError preventionFrequency-division multiplex detailsTraffic capacityFlow propagation

A method and system for flow propagation analysis uses ‘tracers’ that are iteratively propagated through a simulated network between source and destination elements. These tracers are structured to contain traffic flow information from source to destination, and to reflect changes as the flow is affected by each element along the path from source to destination. The resultant flow information at the destination corresponds to the effective throughput from the source to the destination, and the flow information at the output of each intermediate element in the network corresponds to the potentially achievable throughput through that element for the given source-to-destination flow.

Owner:RIVERBED TECH LLC

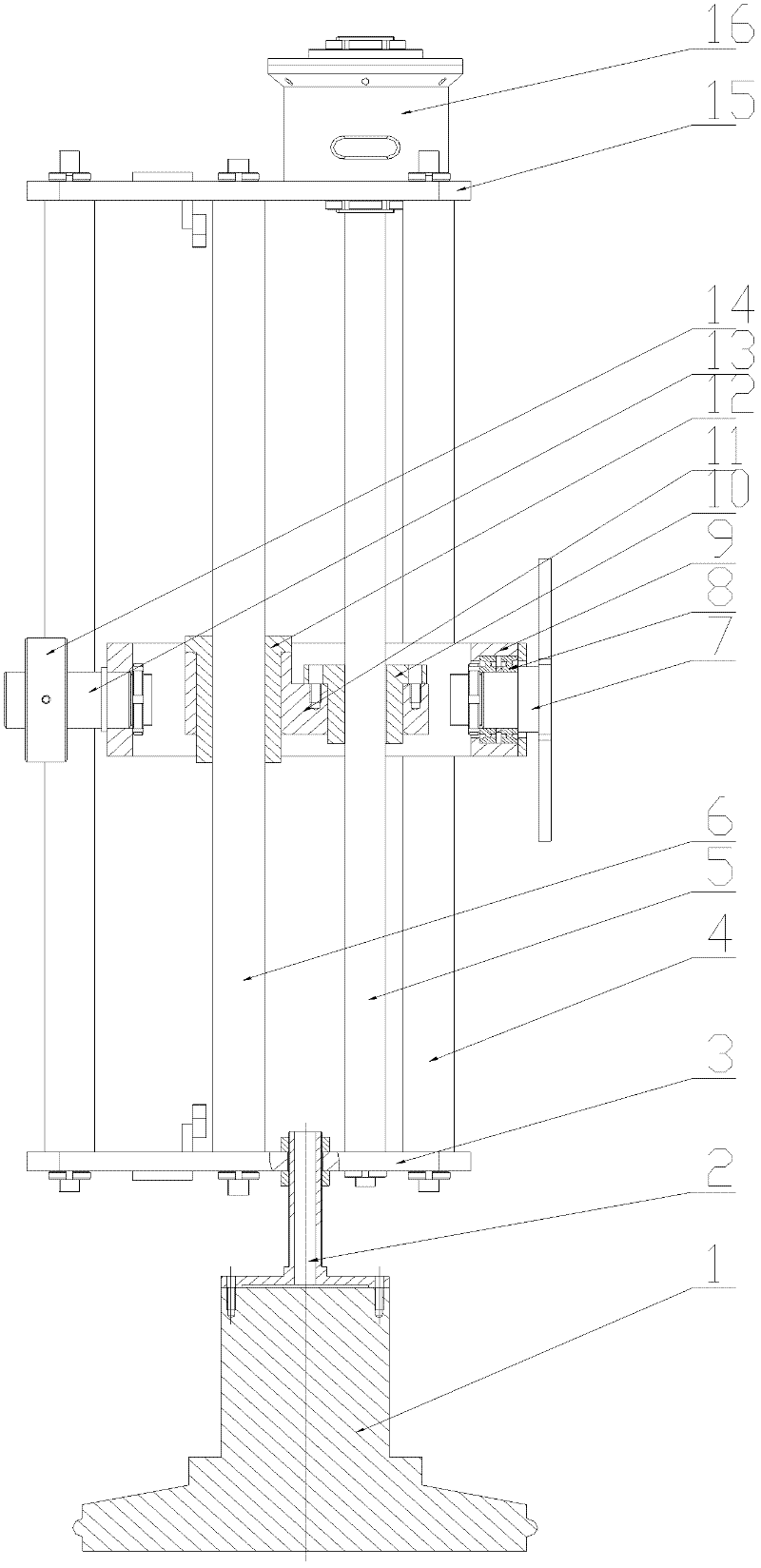

Semi-active six-degree-of-freedom simulation device

The invention provides a semi-active six-degree-of-freedom simulation device, which aims to solve the problems of high manufacturing cost and low safety due to active control over the simulation of a six-degree-of-freedom floating state of a spacecraft under the outer space weightless condition and poor simulation effects and high resistance due to the adoption of a passive control mode. An air foot is connected with a lower connecting plate through a connecting rod; the lower connecting plate is connected with an upper connecting plate through a vertical column; the two ends of a feed rod are connected with the lower connecting plate and the upper connecting plate respectively; a first end of a screw rod is connected with the lower connecting plate; a second end of the screw rod penetrates through the upper connecting plate to be driven by a motor; the screw rod is connected with a sliding block through a nut; the feed rod is connected with the sliding block through a sliding sleeve; the sliding block is connected with pitching shafts on the two sides through a force sensor; a pitching frame is arranged on the pitching shafts through a second bearing; the nut is used for fixing the bearing; and a mounting plate is arranged on the pitching frame through a first bearing. The device has the advantages of active simulation modes and passive simulation modes, and is a six-degree-of-freedom floating state simulation device which has low manufacturing cost and a good simulation effect and is safely used.

Owner:HARBIN INST OF TECH

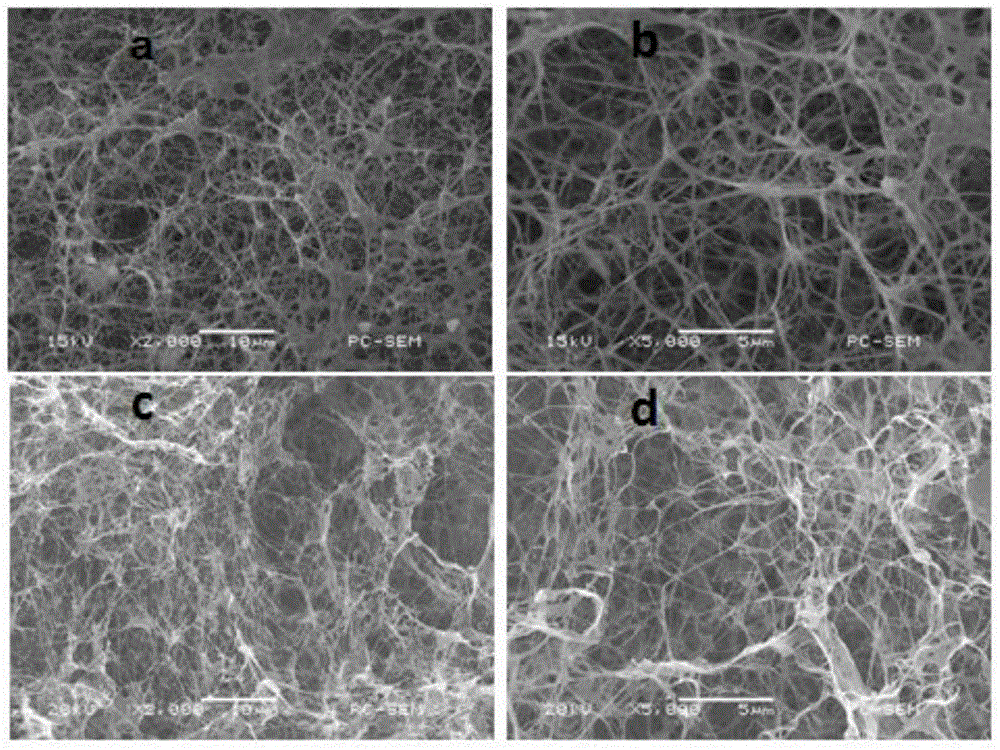

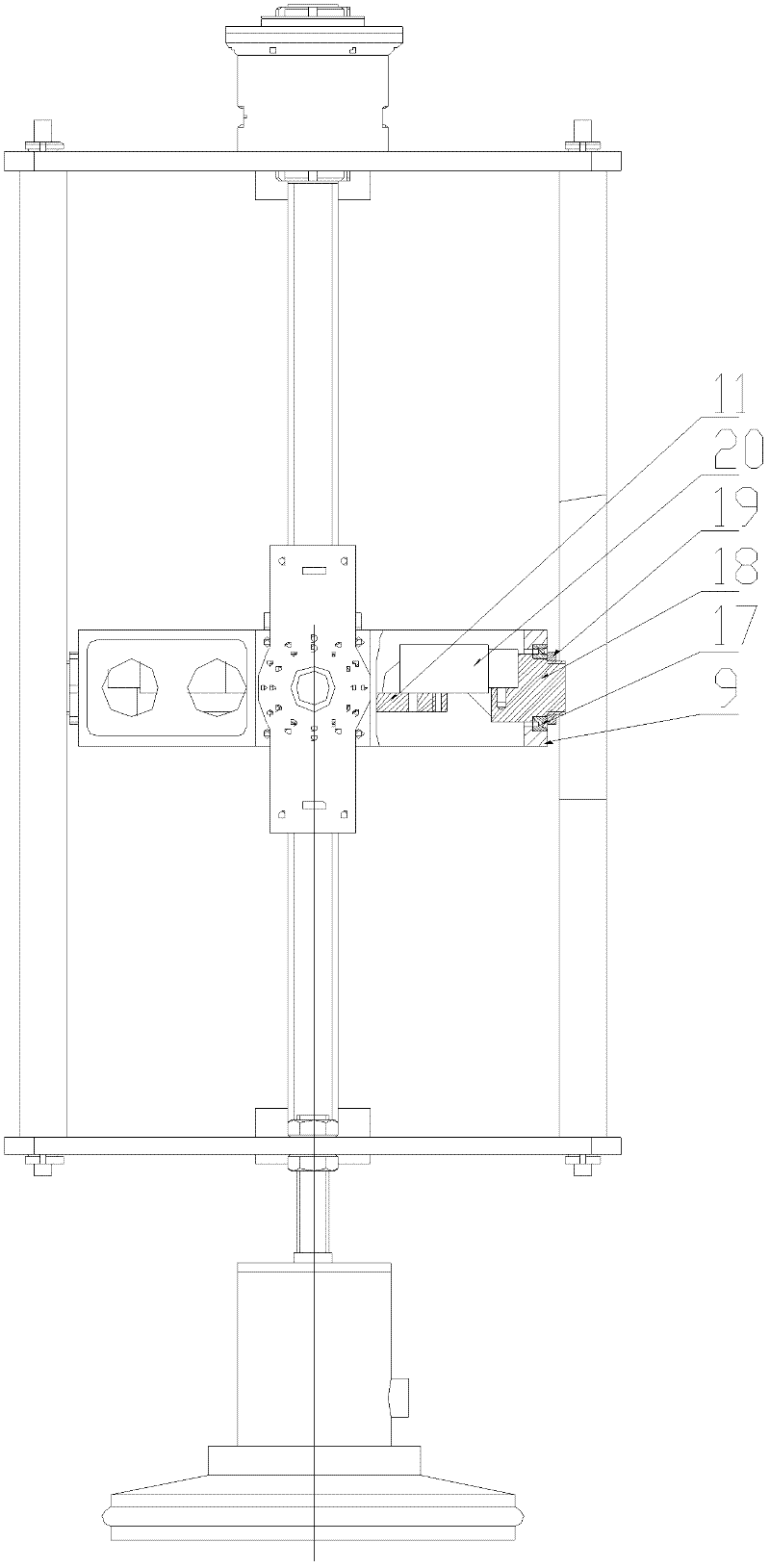

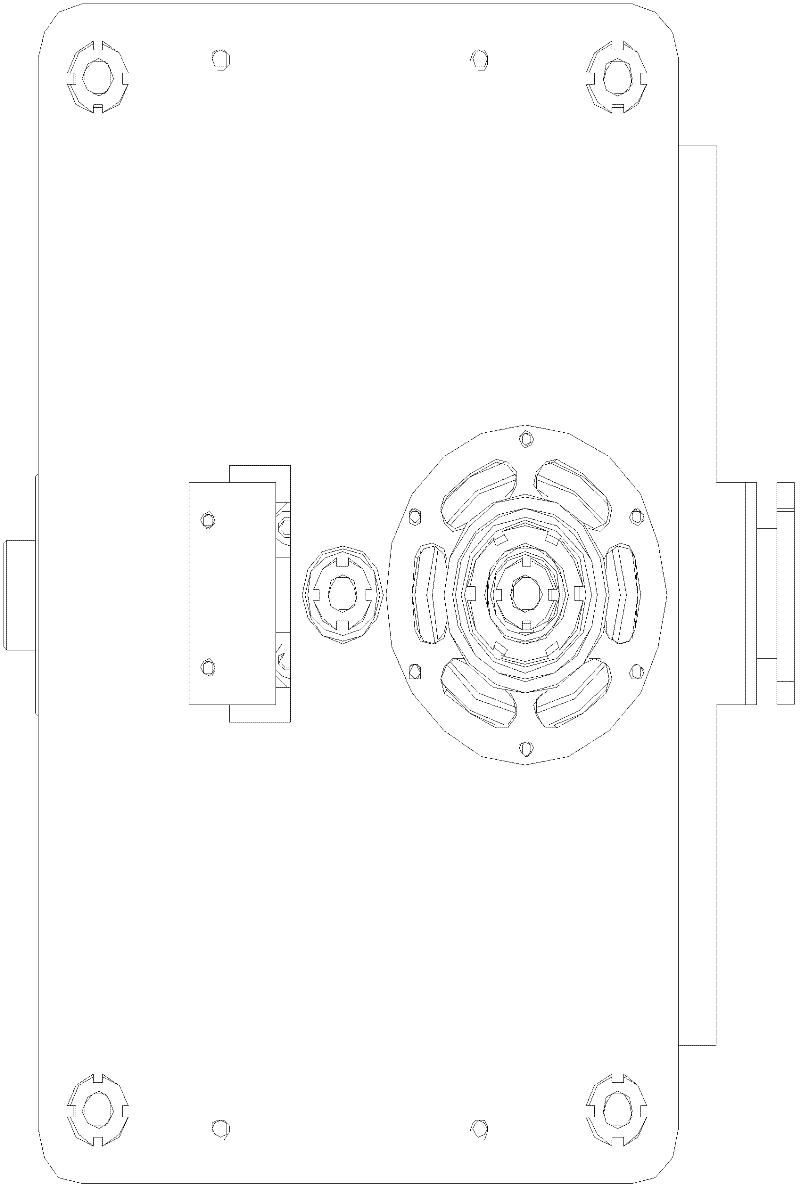

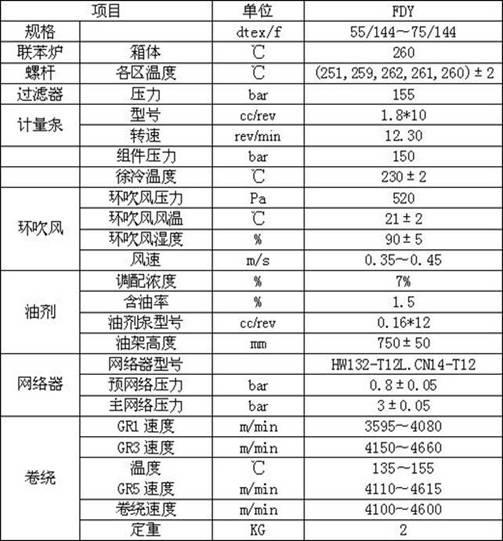

Porous superfine polyamide 6 fully-drawn yarn, preparation method thereof, and equipment thereof

InactiveCN102493016AImprove mixing uniformityImproved pressure stabilityFilament forming substance formingArtificial thread manufacturing machinesYarnAir velocity

The invention relates to a porous superfine polyamide 6 fully-drawn yarn, a preparation method thereof, and equipment thereof. According to the invention, existing FDY production equipment is adopted. A raw material polyamide 6 is sliced and dried; an additive is added on line; the material is subject to screw extrusion and melt extrusion; the material is then cured with a gradually cooling manner and a circular air blow cooling manner; with a reasonably selected spinning temperature of 259-262 DEG C, an air temperature in the circular air blowing process of 19-23 DEG C, a humidity of 85-95%, an air velocity of 0.35-0.45m / s, an oiling and clustering position of 700-800mm, and a winding speed of 4100-4600m / min, the porous superfine polyamide 6 fully-drawn yarn product with a specification of 55dtex / 144f-75dtex / 144f is prepared. Flexible operation is adopted in the preparation method. The preparation method is advantaged in simple technology and low production cost. The product is advantaged in stable performance, good yarn evenness, and good coloration property.

Owner:SUZHOU UNIV

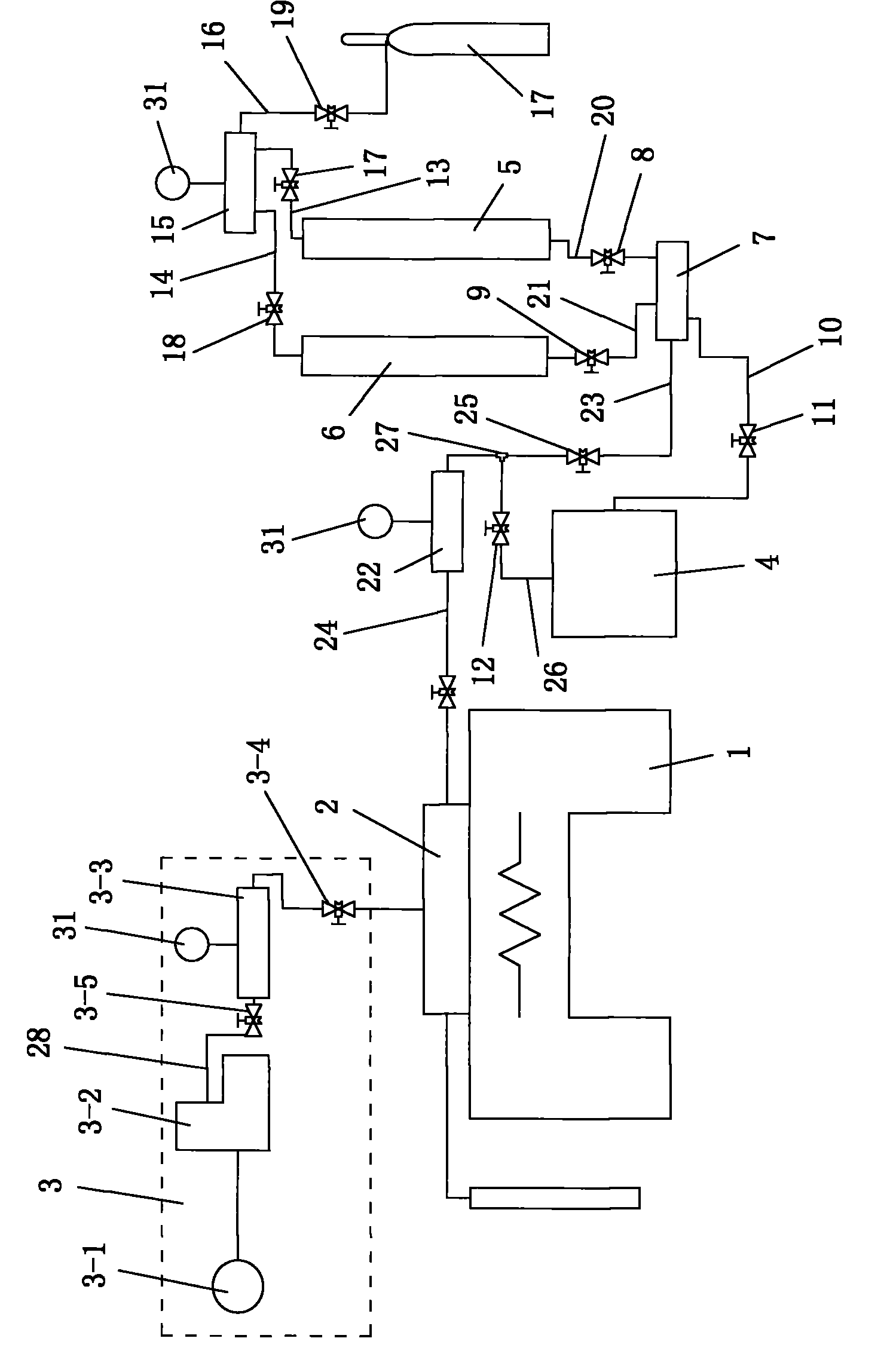

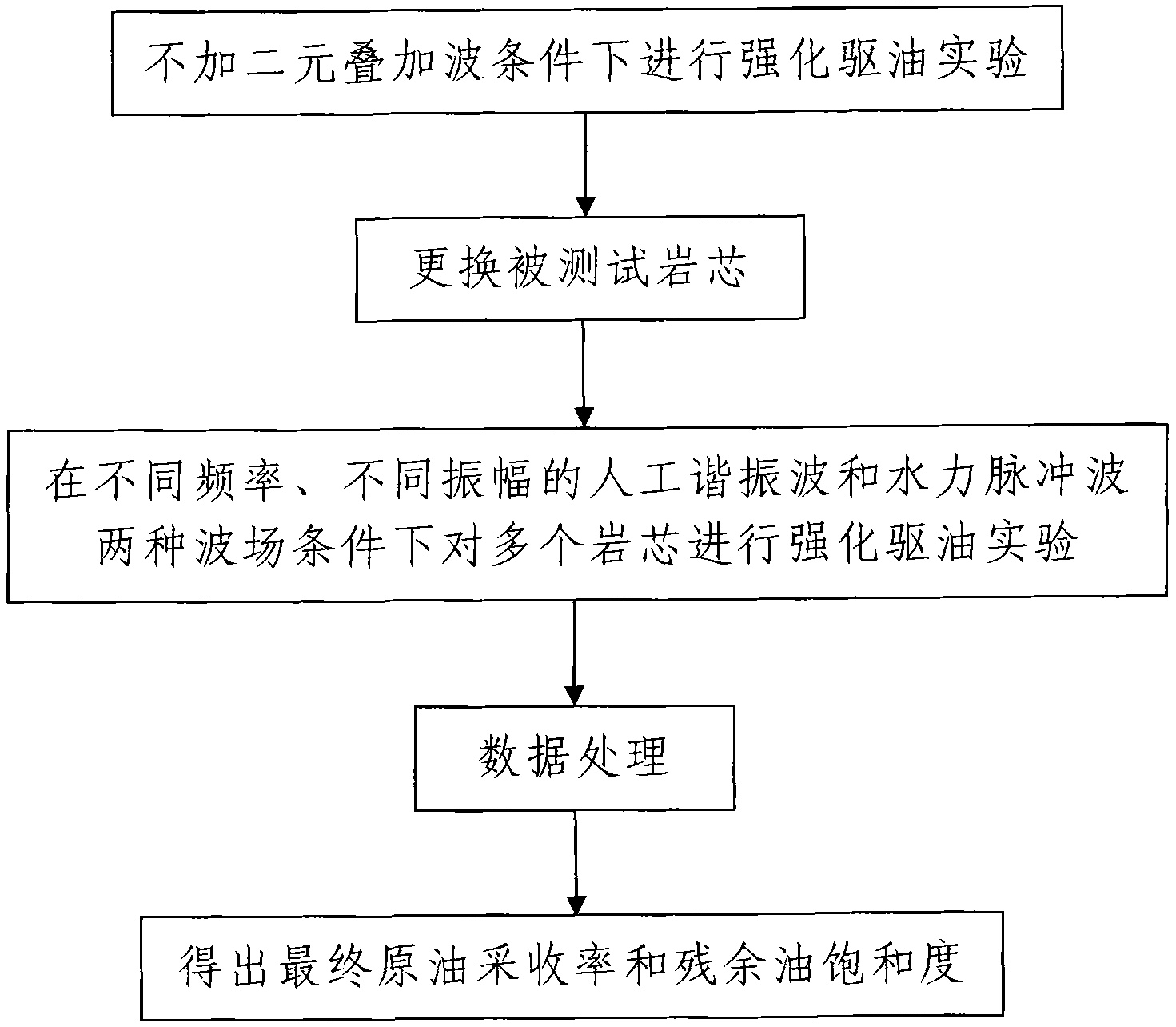

Dualistic superposed wave reinforced oil displacing experiment device and experiment method

The invention discloses a dualistic superposed wave reinforced oil displacing experiment device and an experiment method. The dualistic superposed wave reinforced oil displacing experiment device comprises an artificial resonance wave test table, a rock core holder, a ring-pressure supplying device, a hydraulic impulse wave generator, a high-pressure water tank, a high-pressure oil tank and a liquid container, wherein the hydraulic impulse wave generator is arranged between a liquid outlet of the high-pressure water tank and the rock core holder, the high-pressure water tank and the high-pressure oil tank are connected with a liquid inlet of the rock core holder through a water pipeline and an oil pipeline, the liquid container is connected with the liquid outlet of the rock core holder, middle transition containers are respectively arranged on the water pipeline and the oil pipeline. The experiment method comprises the following steps of: firstly, under the condition of no dualistic superposed waves, carrying out a reinforced oil displacing experiment; secondly, replacing a rock core and carrying out the reinforced oil displacing experiment on a plurality of rock cores under two wave field conditions of artificial resonance waves and hydraulic impulse waves which have different frequencies and amplitudes; and thirdly, processing data. The method has the advantages of rationaldesign, convenient distribution, complete functions, simple and convenient operation and good simulation effect and can test the final recovery ratio and the residual oil saturation of different rockcores under the conditions of two wave fields.

Owner:CHINA UNIV OF PETROLEUM (EAST CHINA)

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com