Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

83results about How to "Improve solder joint reliability" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

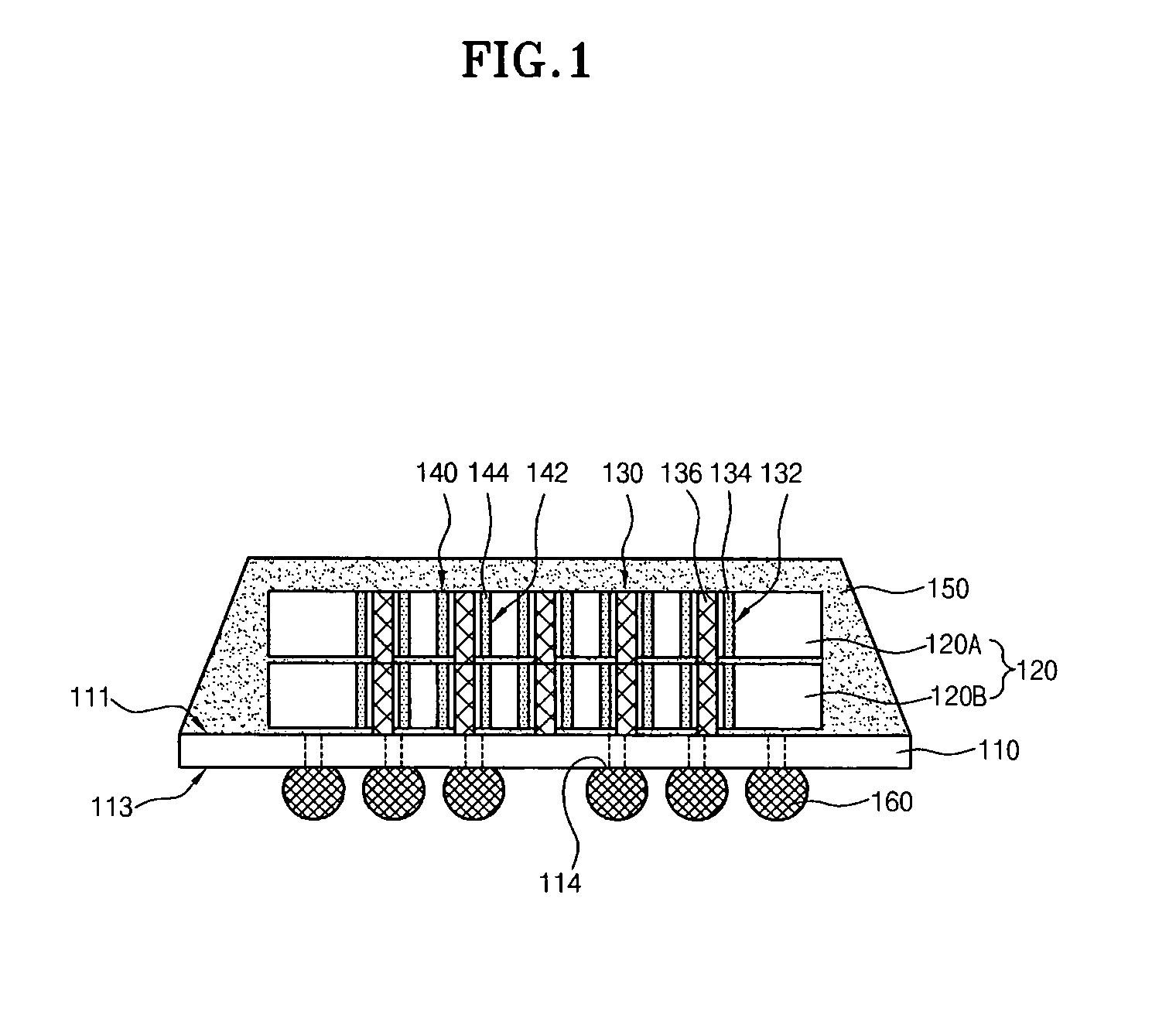

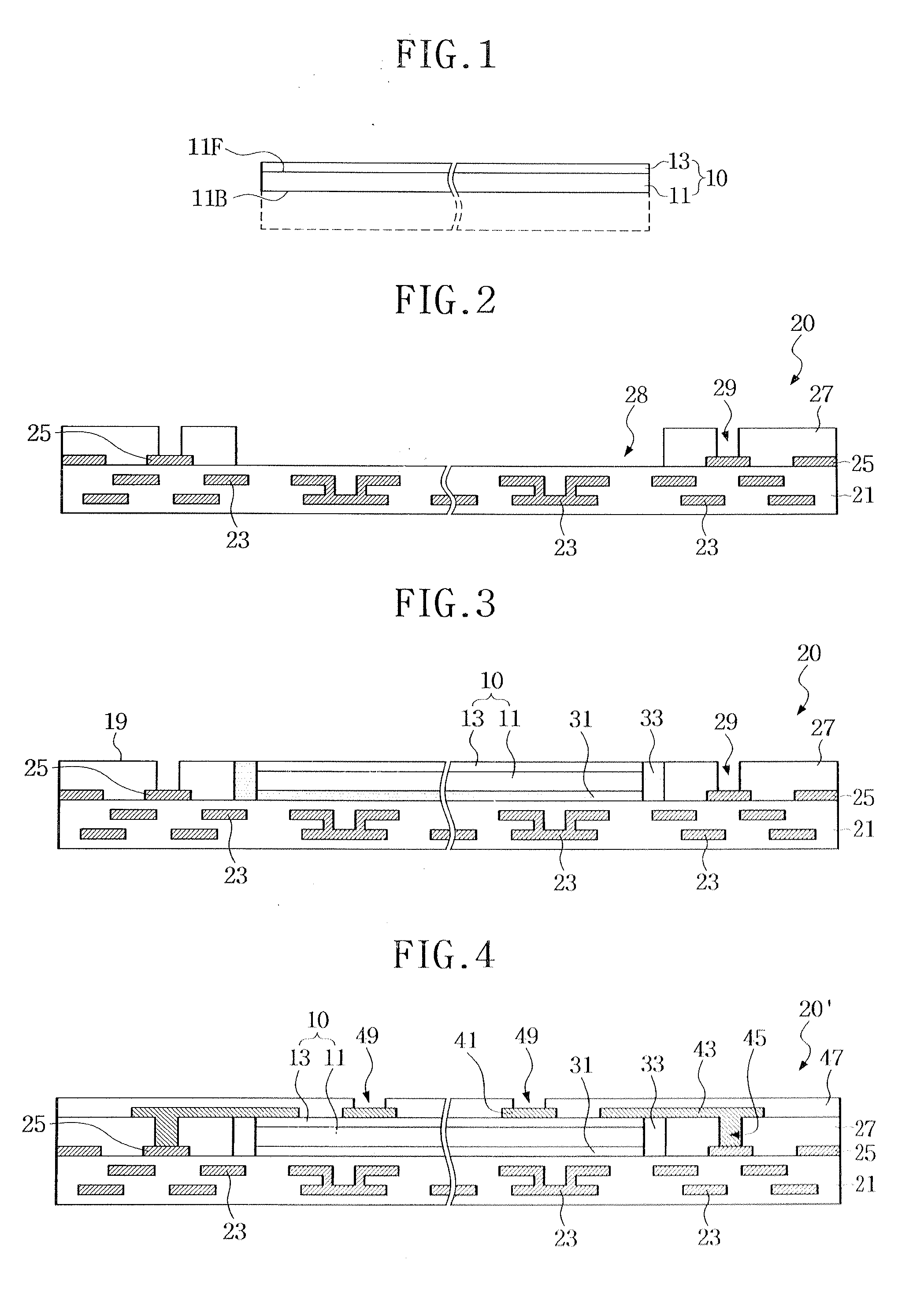

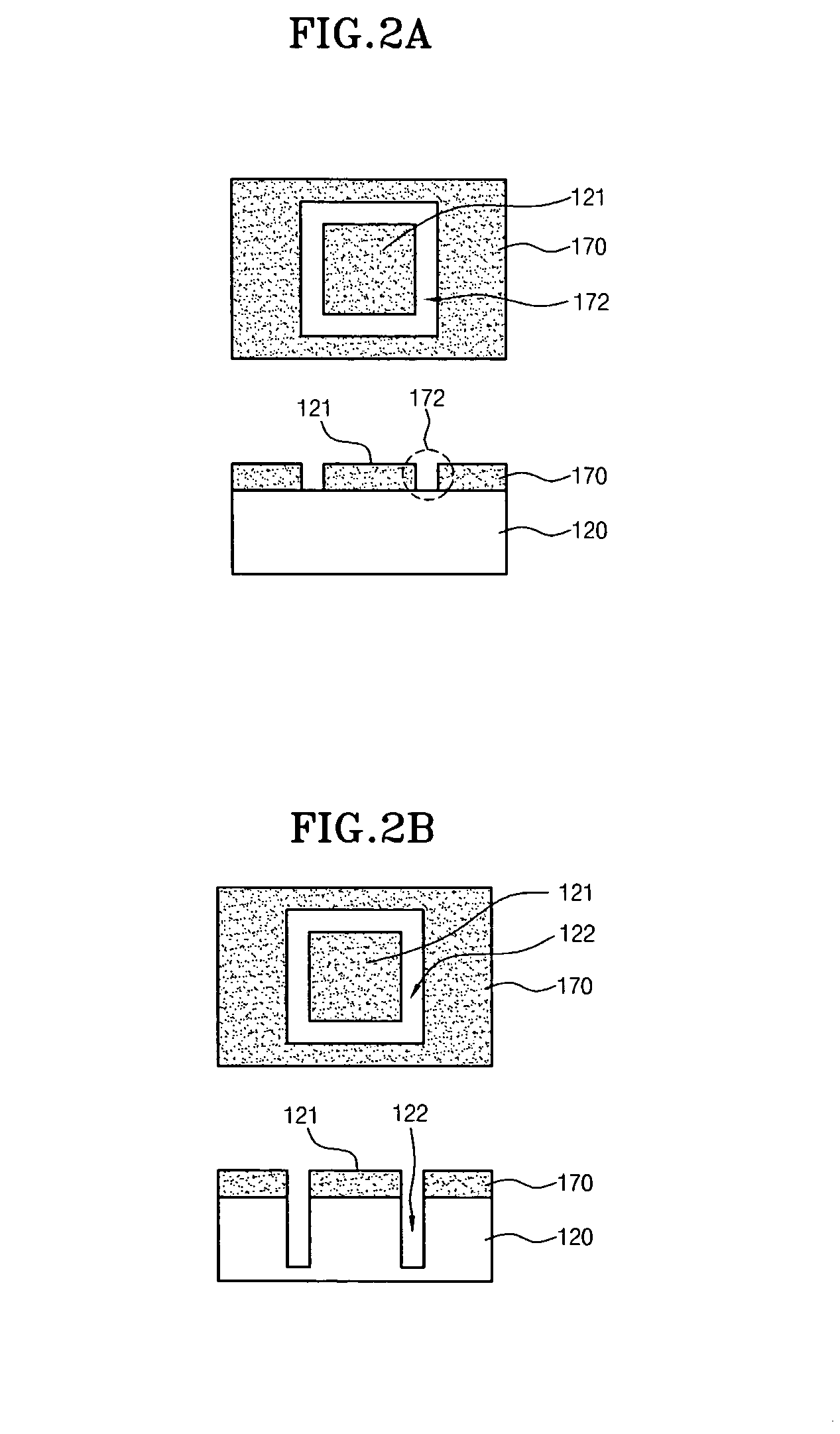

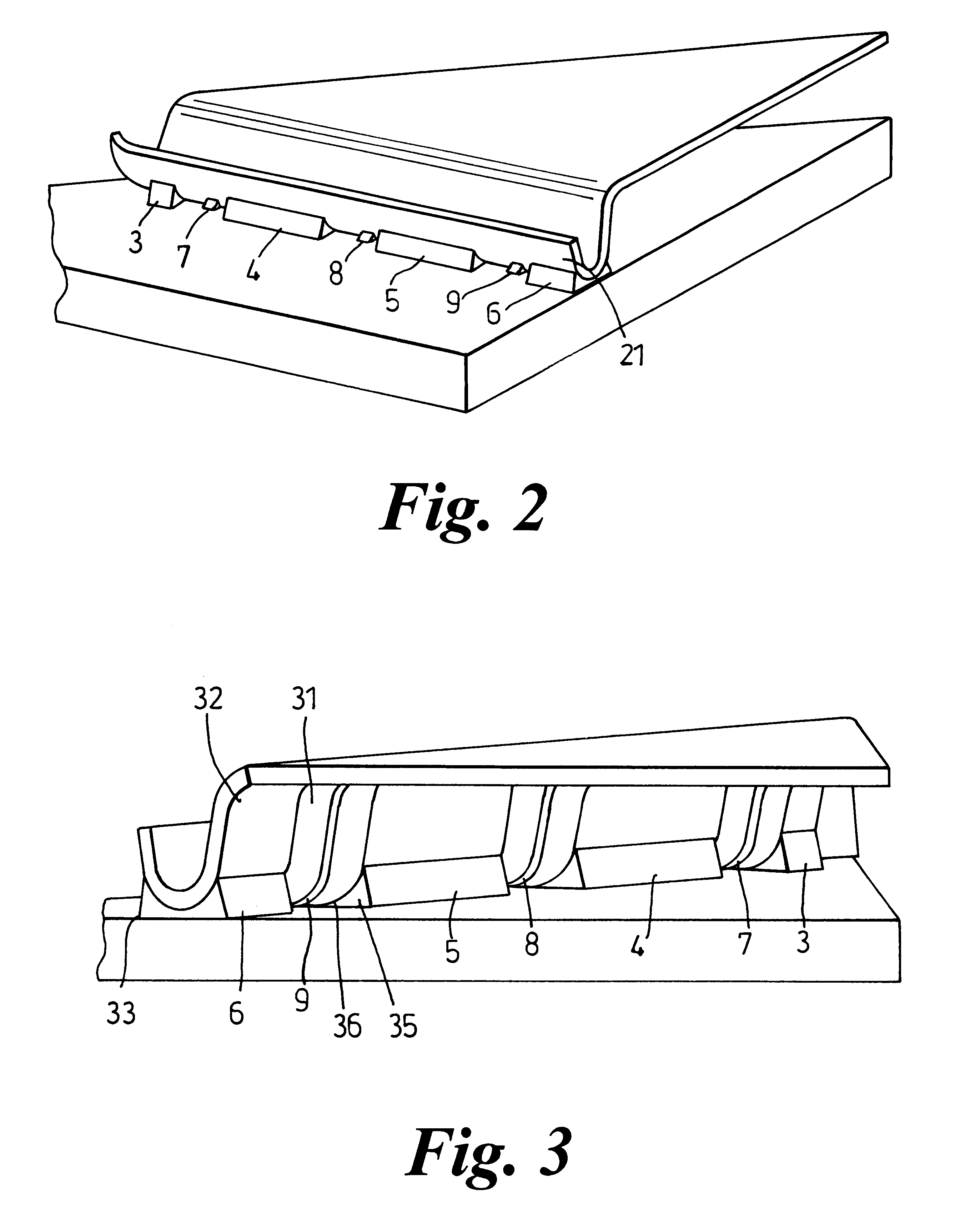

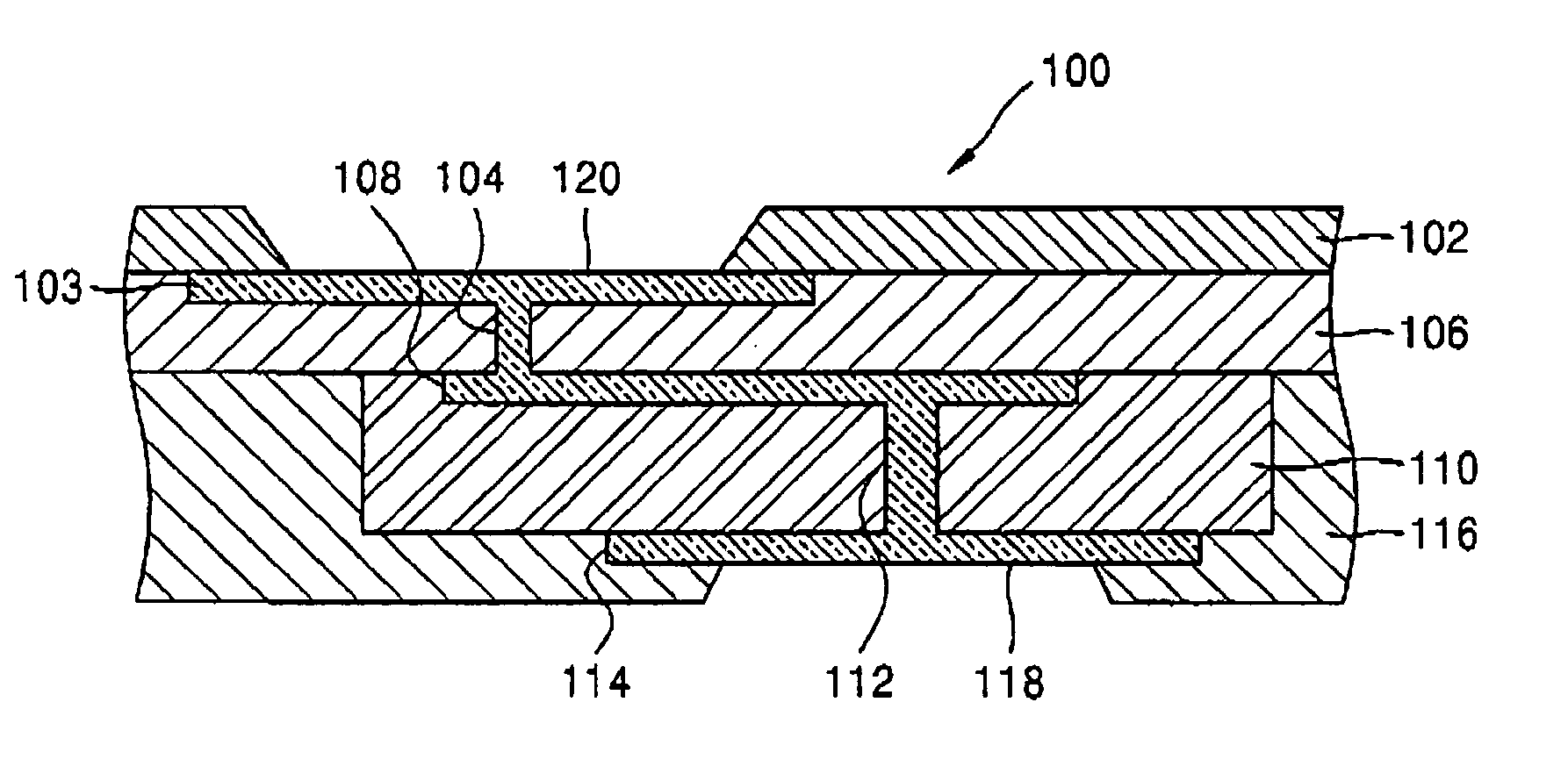

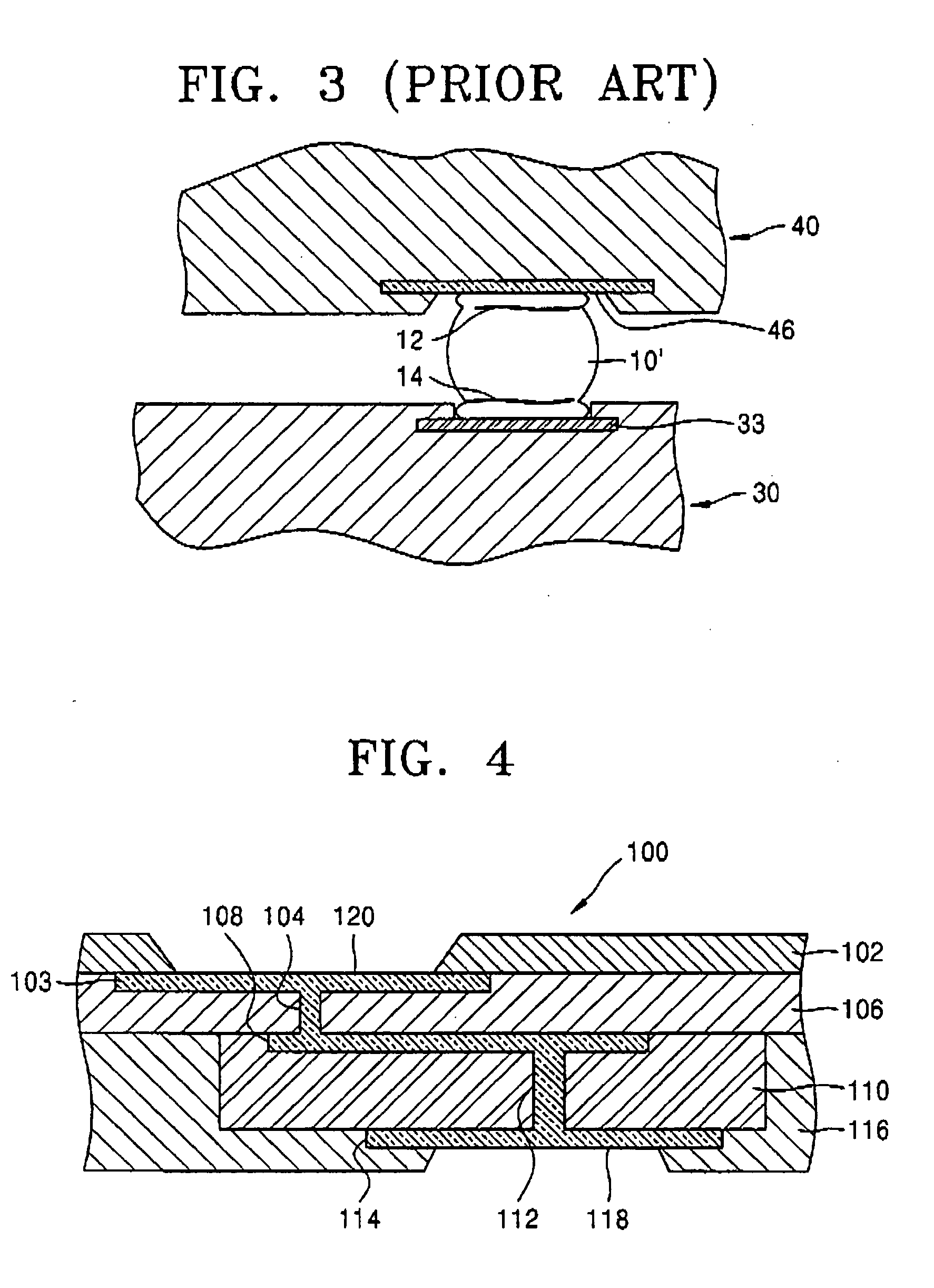

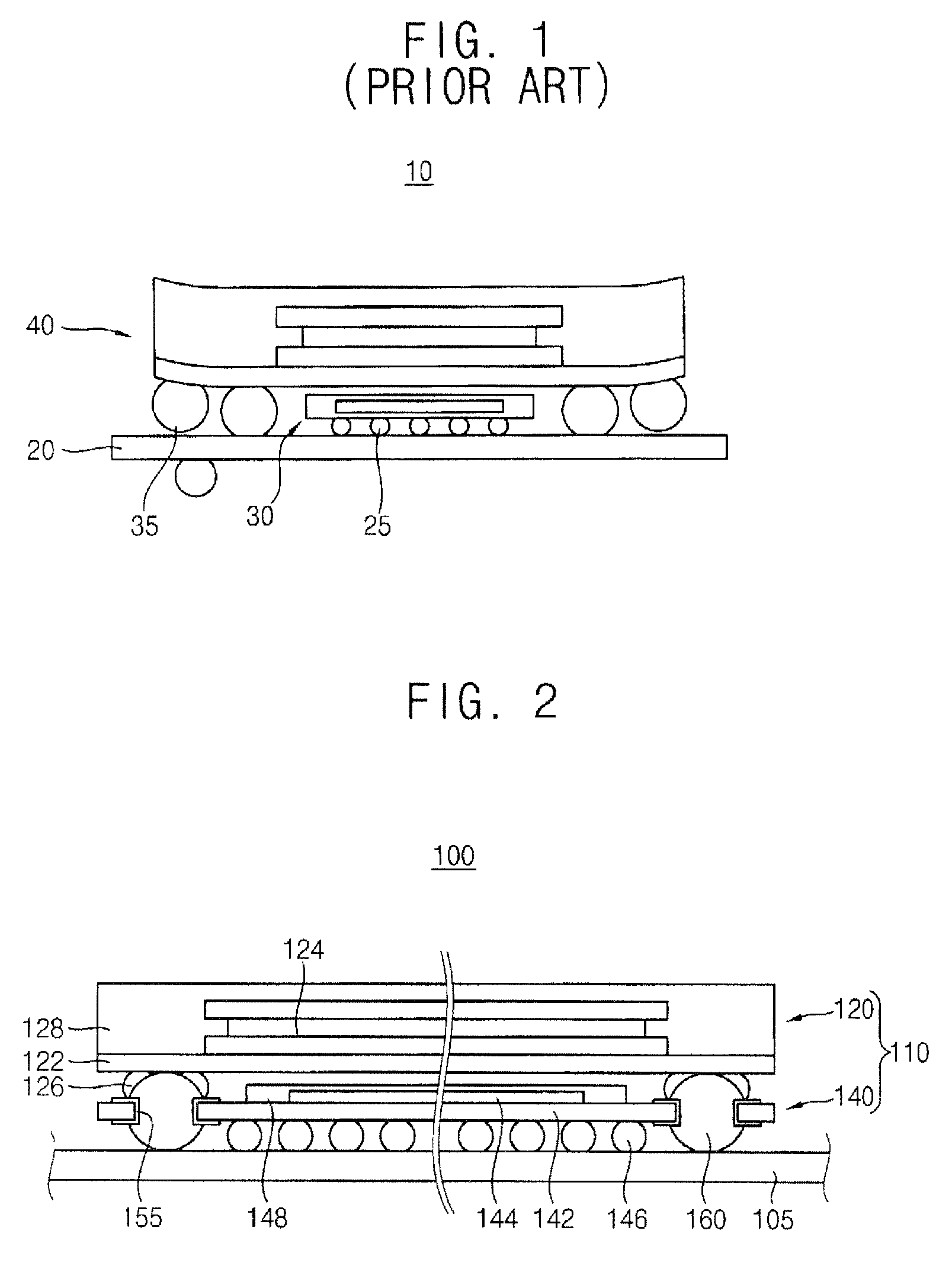

Stack package having guard ring which insulates through-via interconnection plug and method for manufacturing the same

ActiveUS7525186B2Avoid crackingAvoid disconnectionSemiconductor/solid-state device detailsSolid-state devicesSemiconductor chipSolder ball

A stack package comprises a substrate having a circuit pattern; at least two semiconductor chips stacked on the substrate, having a plurality of through-via interconnection plugs and a plurality of guard rings which surround the respective through-via interconnection plugs, and connected with each other by the medium of the through-via interconnection plugs; a molding material for molding an upper surface of the substrate including the stacked semiconductor chips; and solder balls mounted to a lower surface of the substrate.

Owner:SK HYNIX INC

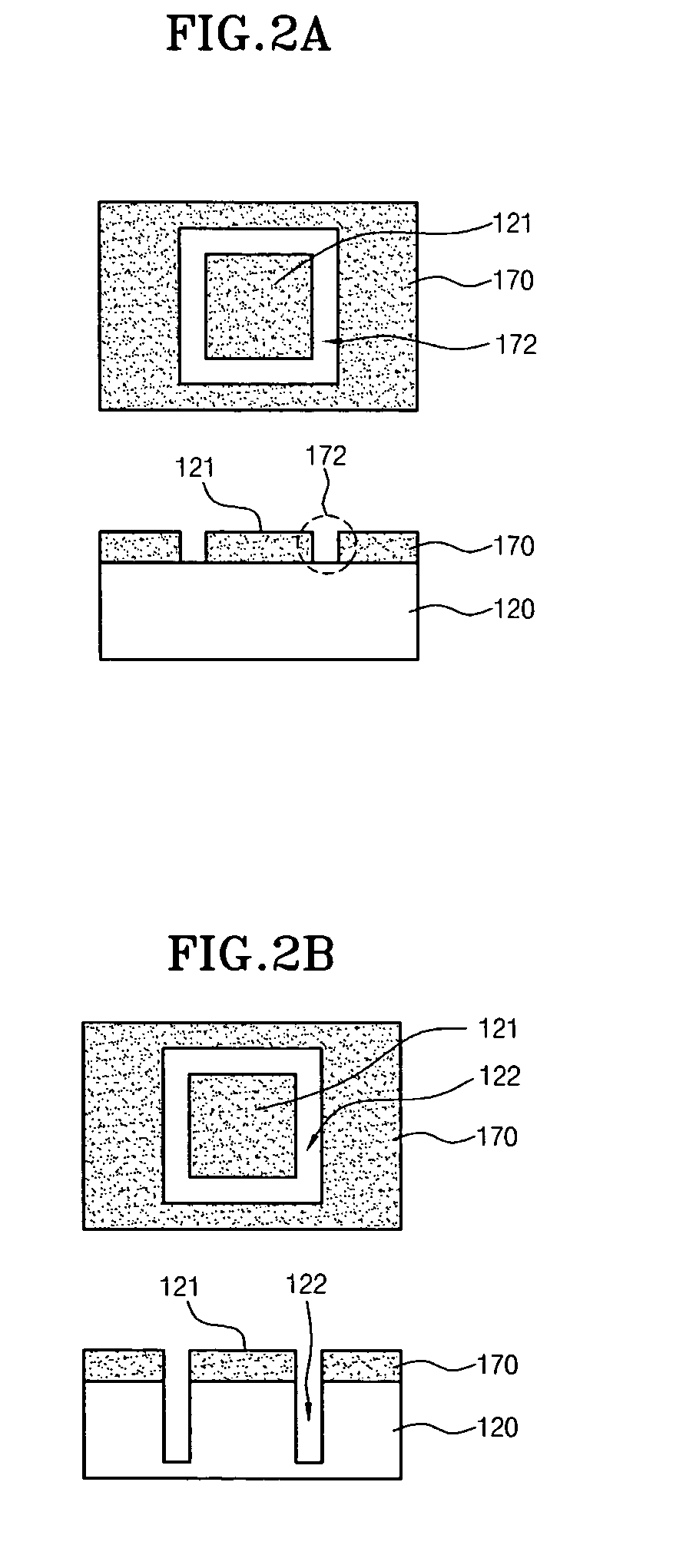

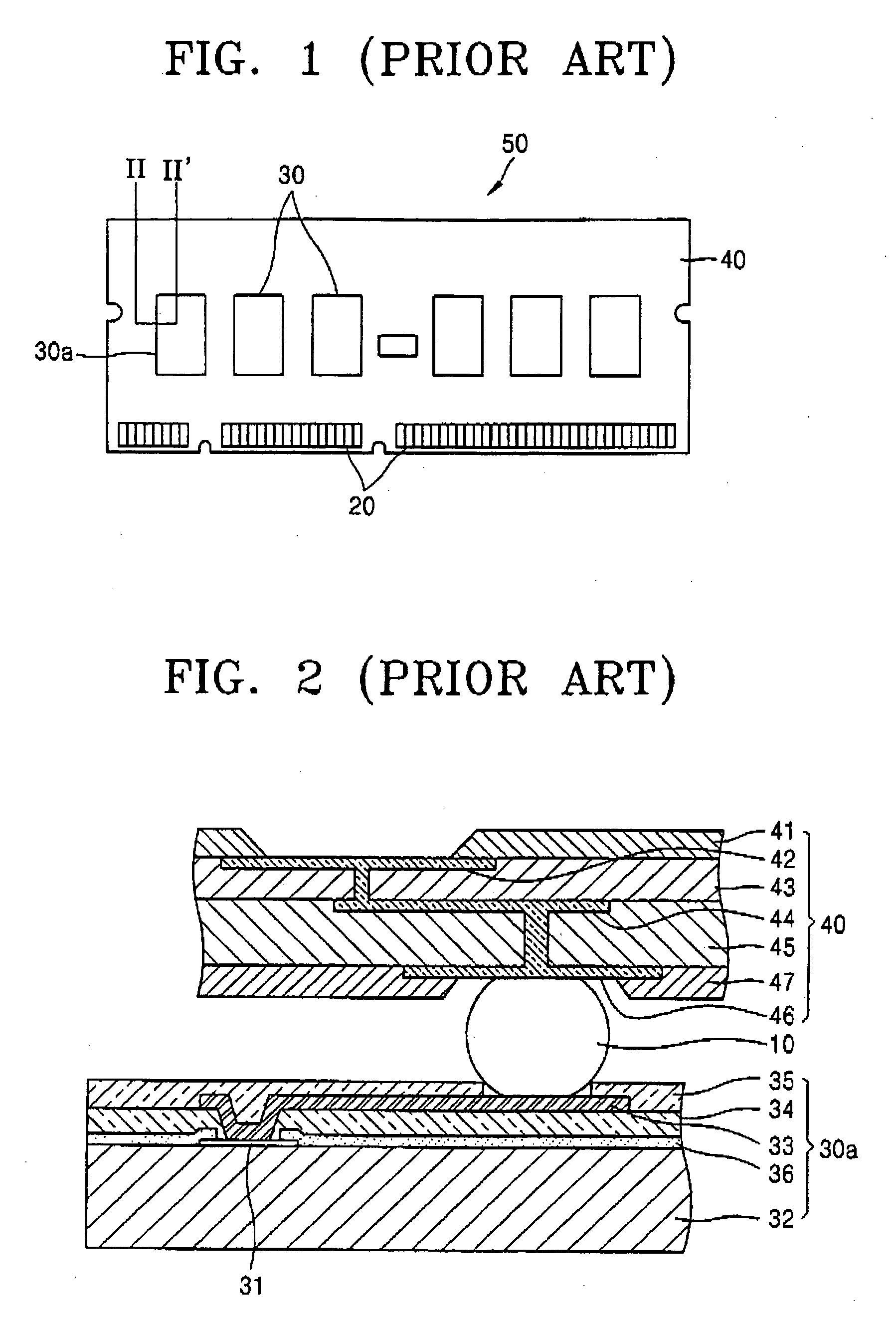

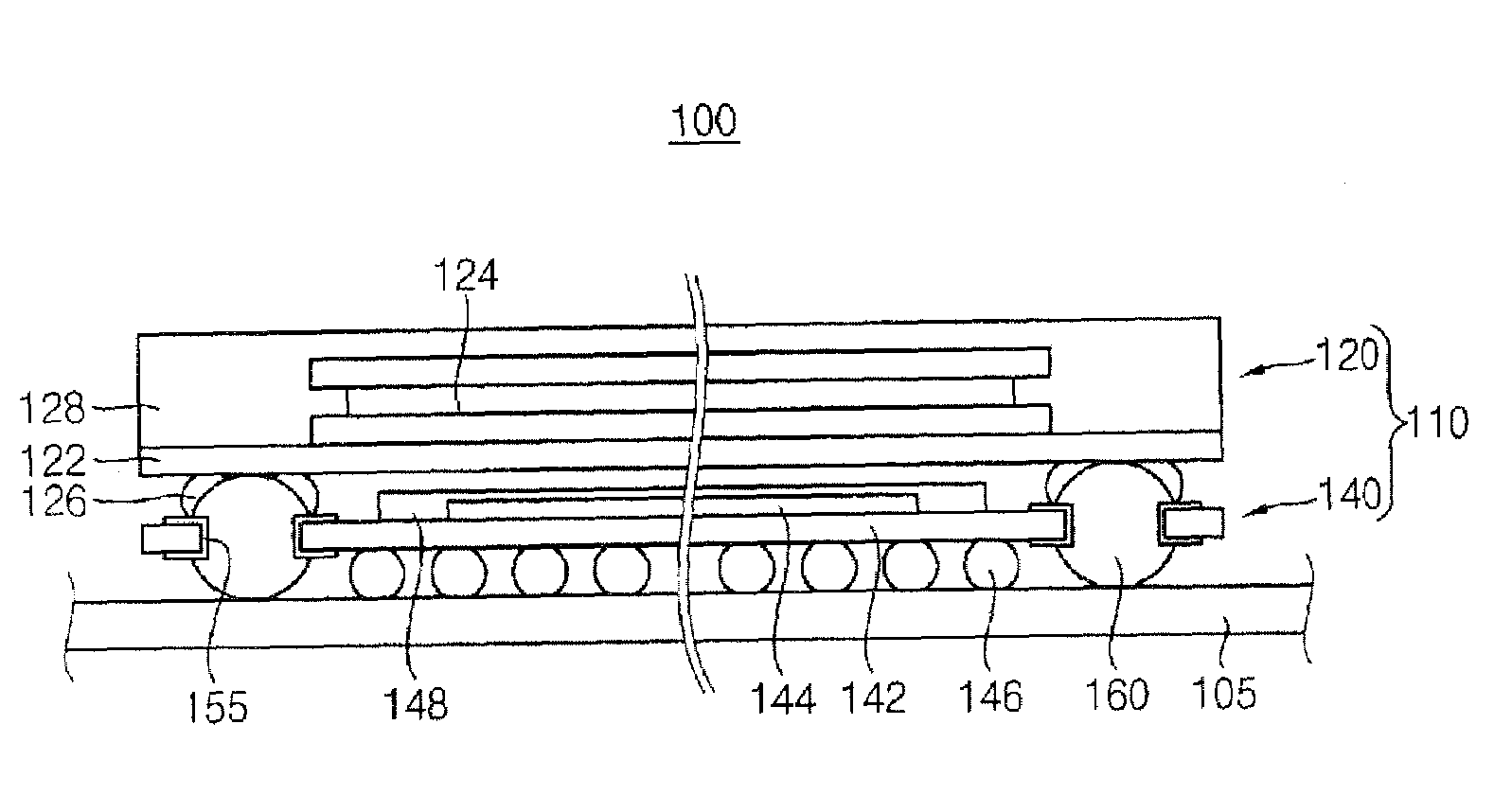

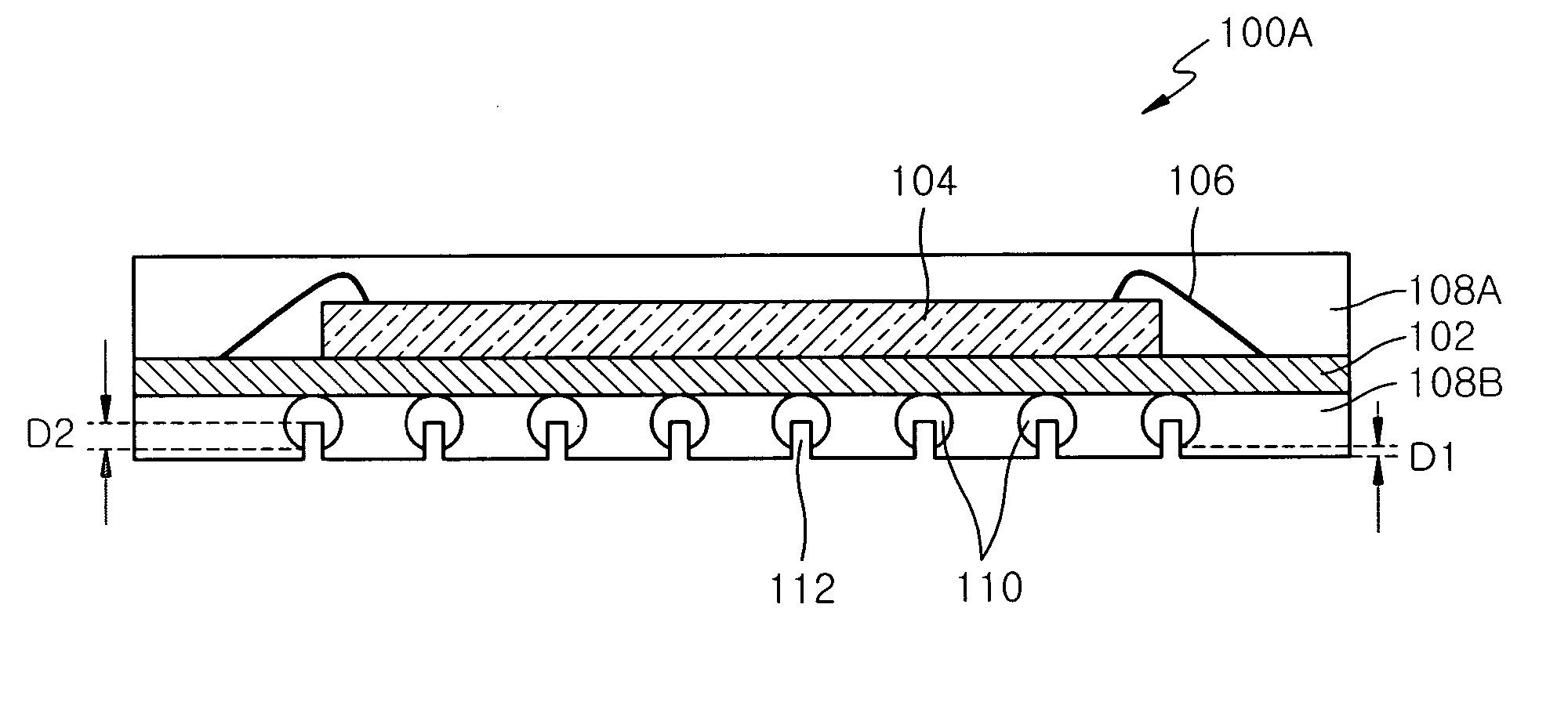

Method of manufacturing semiconductor device with embedded interposer

InactiveUS20100081236A1Improve reliabilityImprove solder joint reliabilitySemiconductor/solid-state device detailsSolid-state devicesPrinted circuit boardEngineering

A method of manufacturing a semiconductor device includes forming printed circuit board (PCB) having an embedded interposer. A semiconductor chip or a semiconductor package is mounted onto the embedded interposer using a conductive adhesive agent. The embedded interposer has substantially the same coefficient of thermal expansion (CTE) as the semiconductor chip. The embedded interposer is formed using a semiconductor wafer.

Owner:SAMSUNG ELECTRONICS CO LTD

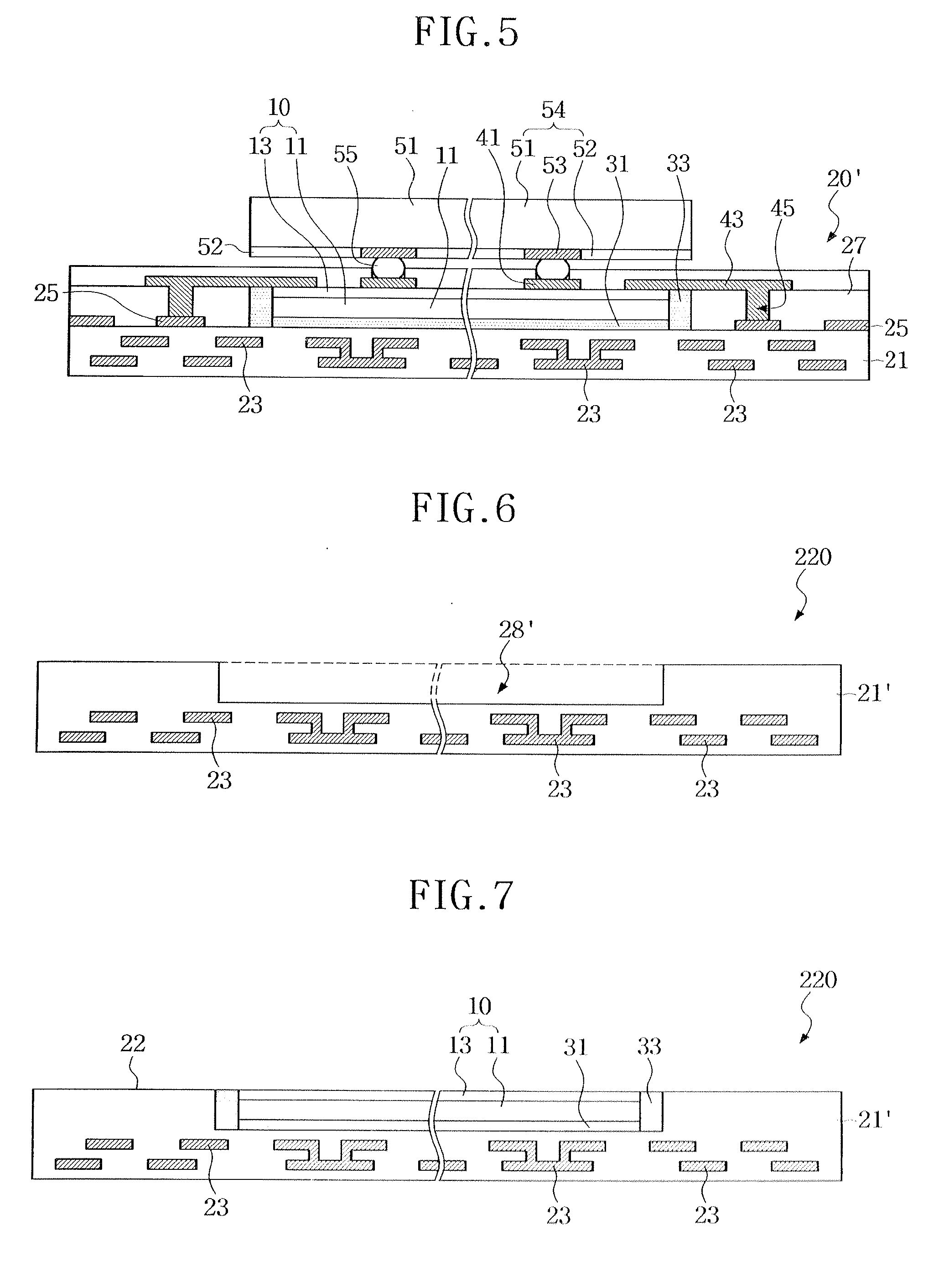

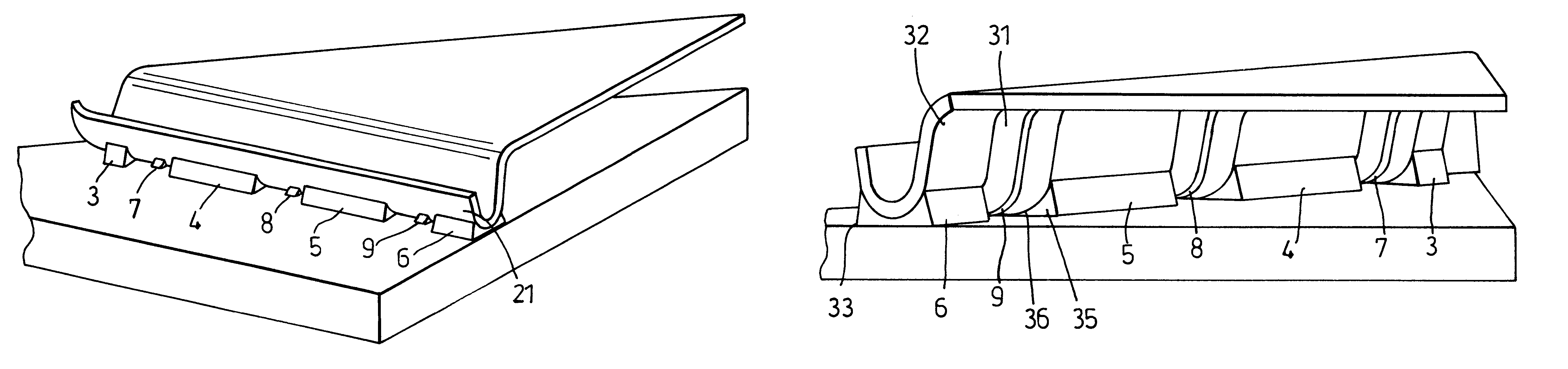

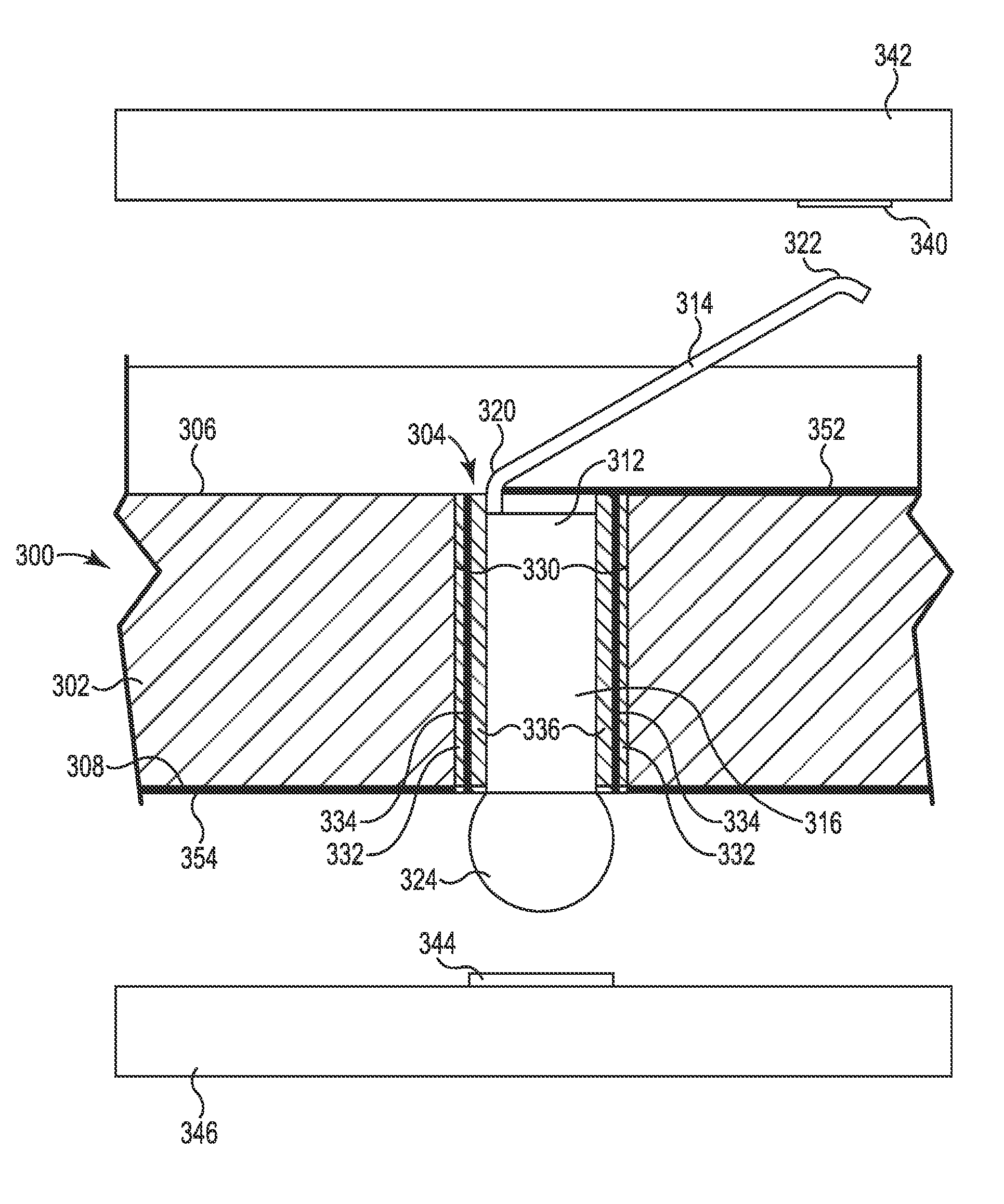

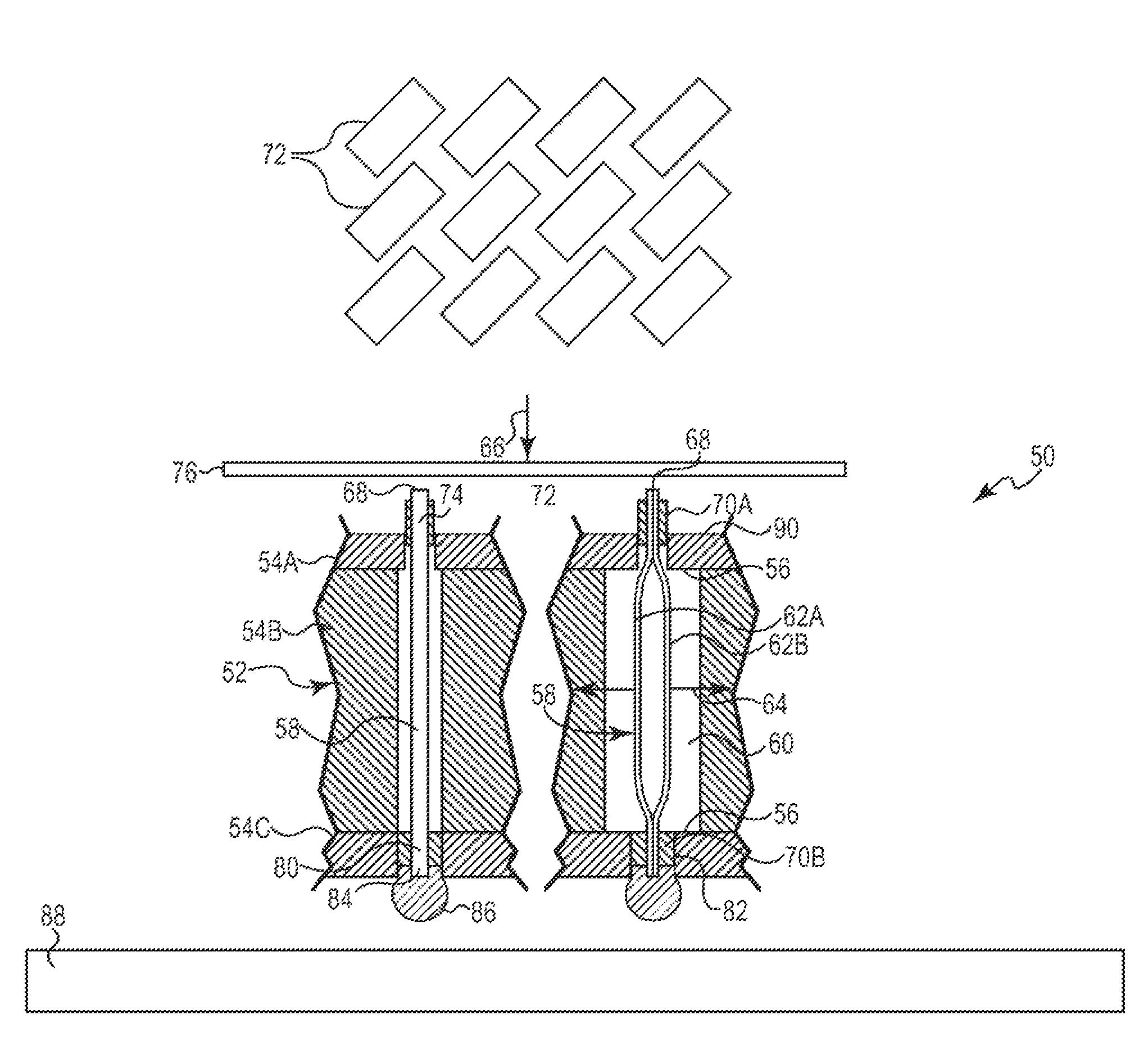

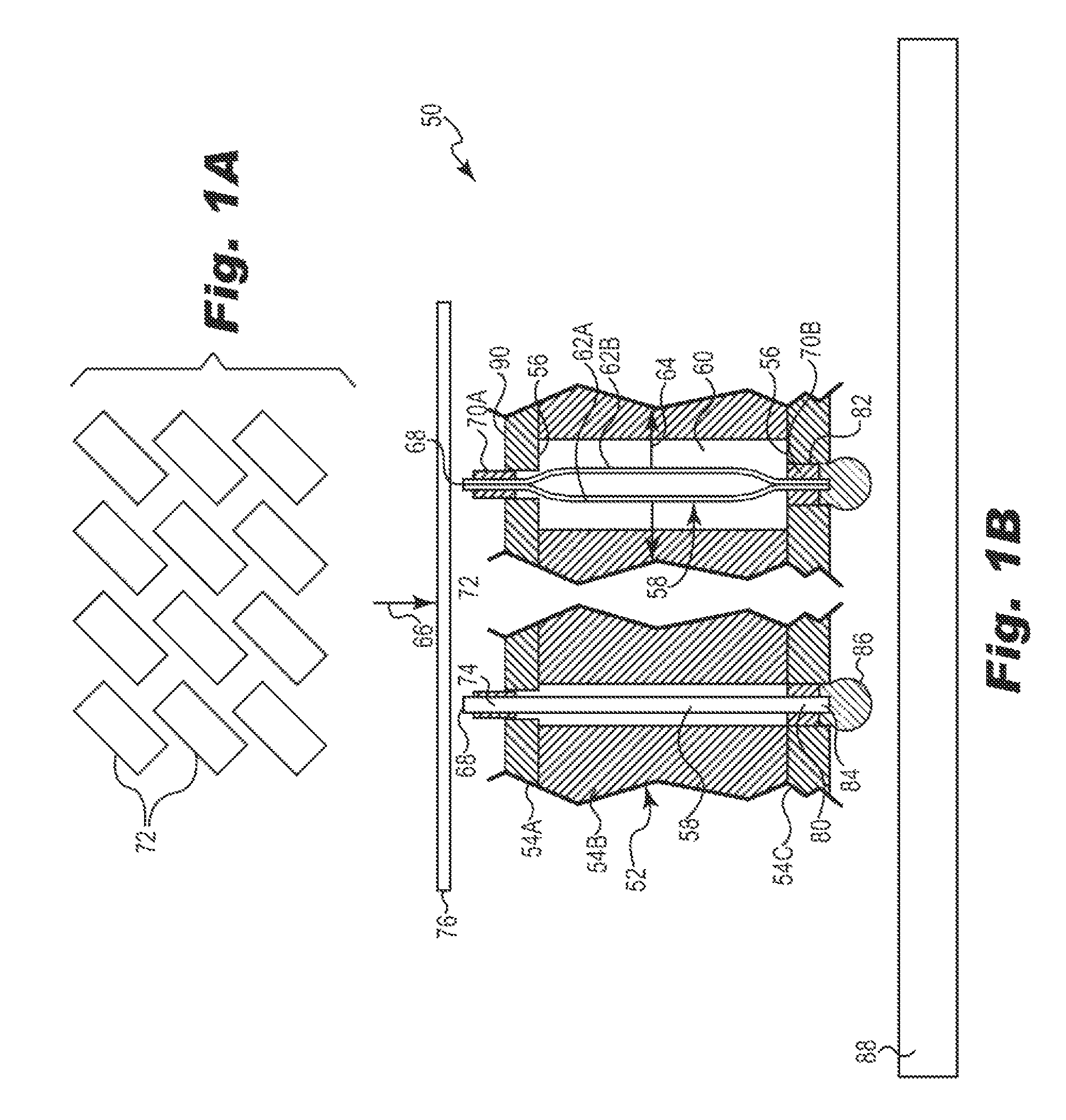

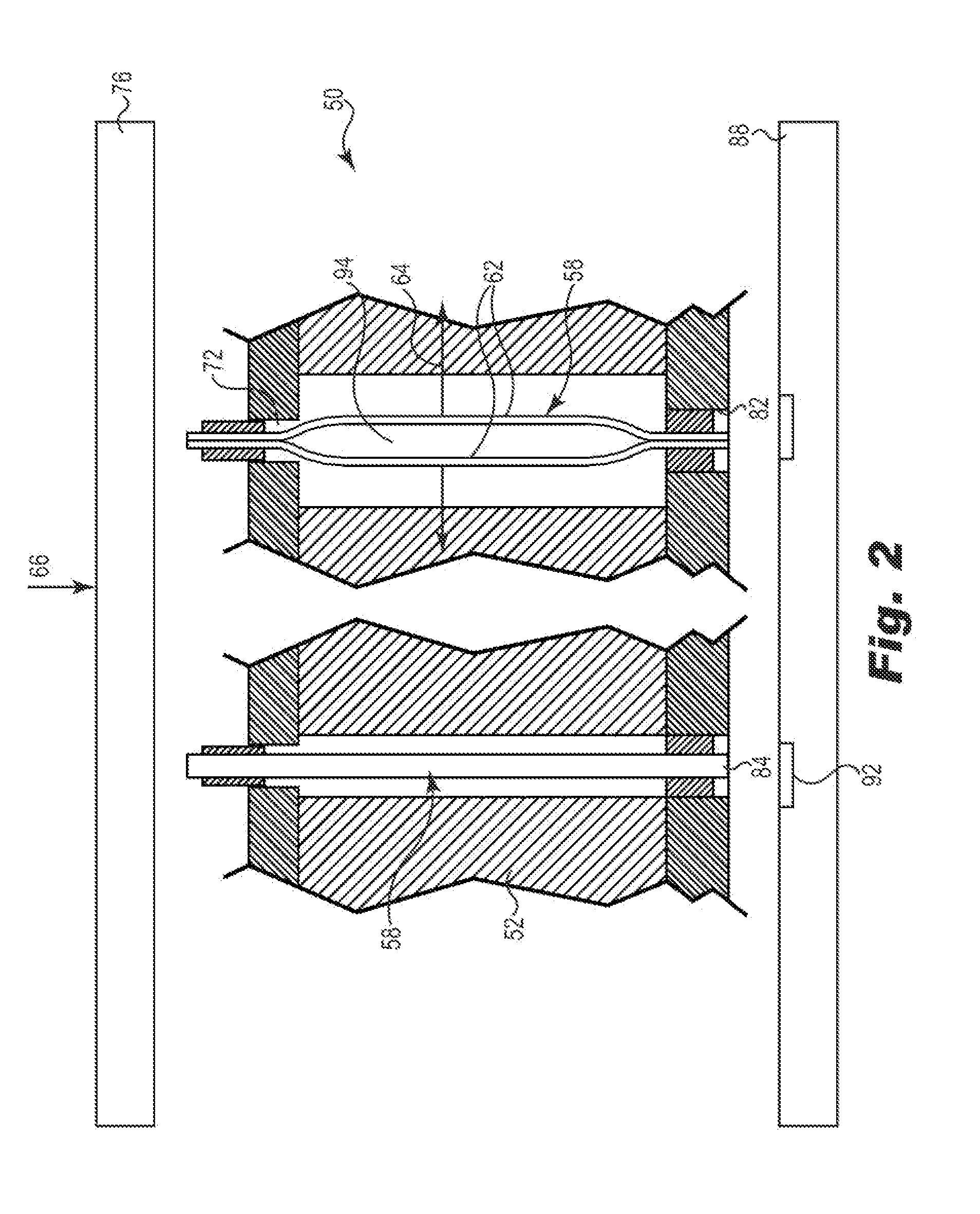

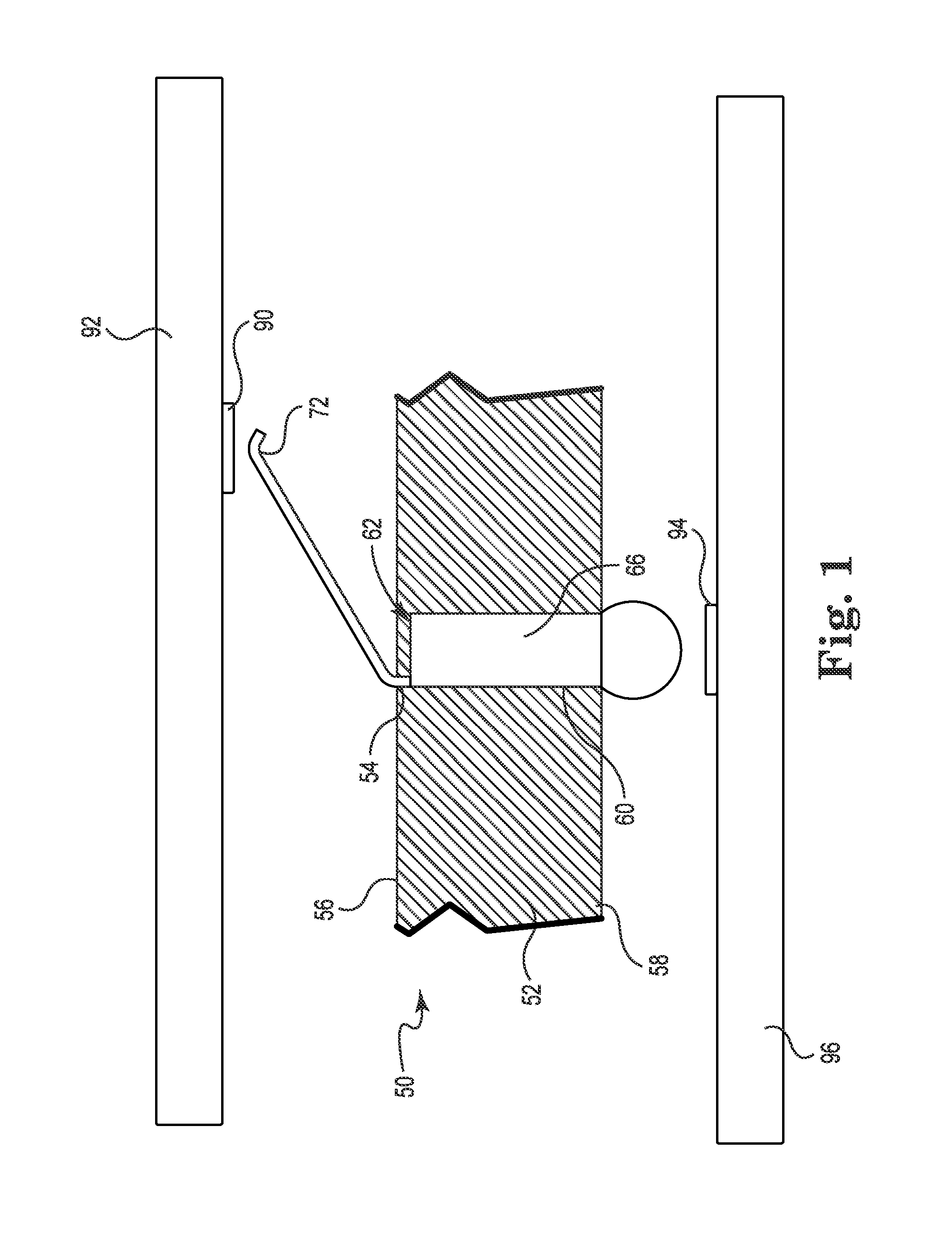

Electrical interconnect IC device socket

ActiveUS20130210276A1Reduce component complexityImprove solder joint reliabilityContact member assembly/disassemblyCoupling contact membersContact padSurface mounting

A surface mount electrical interconnect adapted to provide an interface between contact pads on an LGA device and a PCB. The electrical interconnect includes a socket substrate having a first surface with a plurality of first openings having first cross-sections, a second surface with a plurality of second openings having second cross-sections, and center openings connecting the first and second openings. The center openings include at least one cross-section greater than the first and second cross-sections. A plurality of contact members are located in the socket substrate such that first contact tips are located proximate the first openings, second contact tips are located proximate the second openings, and center portions located in the center openings.

Owner:HSIO TECH

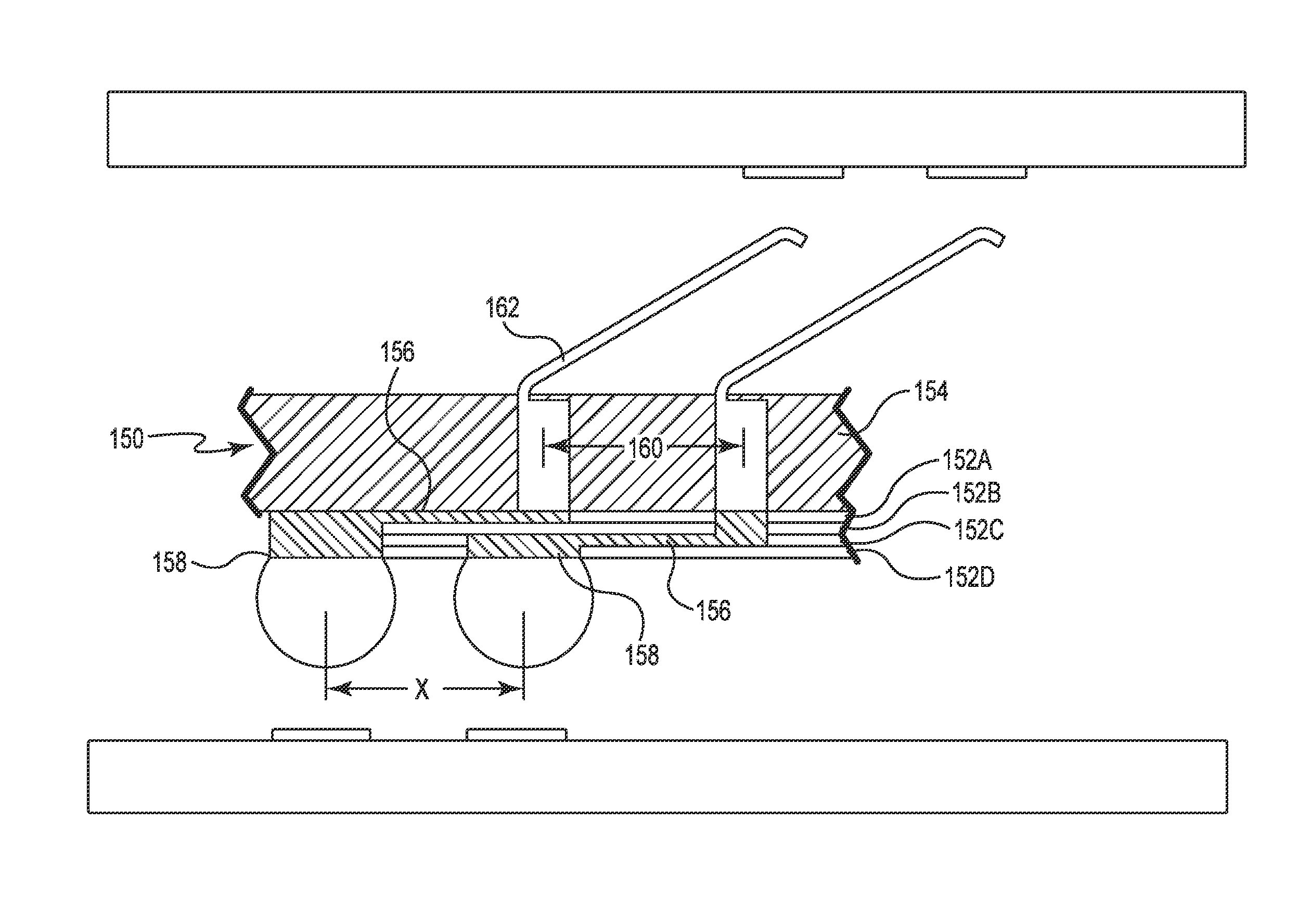

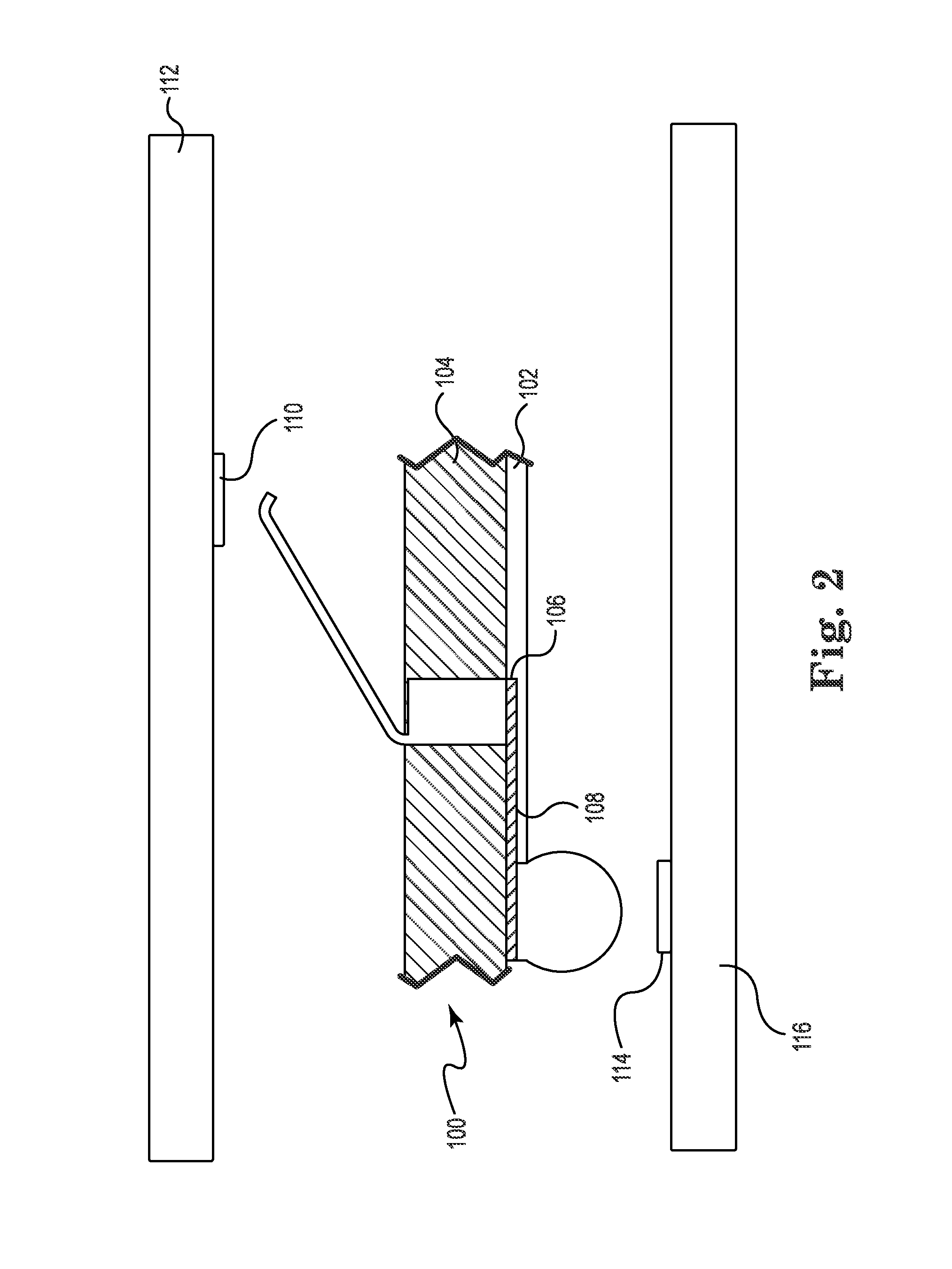

Semiconductor socket

ActiveUS20120051016A1Improve electrical performanceImprove intelligenceElectrically conductive connectionsPrinted circuit aspectsConductive materialsDielectric layer

A semiconductor socket including a substrate with a plurality of through holes extending from a first surface to a second surface. A plurality of discrete contact members are located in the plurality of the through holes. The plurality of contact members each include a proximal end accessible from the second surface, and a distal end extending above the first surface. At least one dielectric layer is bonded to the second surface of the substrate with recesses corresponding to target circuit geometry. A conductive material deposited in at least a portion of the recesses to form conductive traces redistributing terminal pitch of the proximal ends of the contact members.

Owner:HSIO TECH

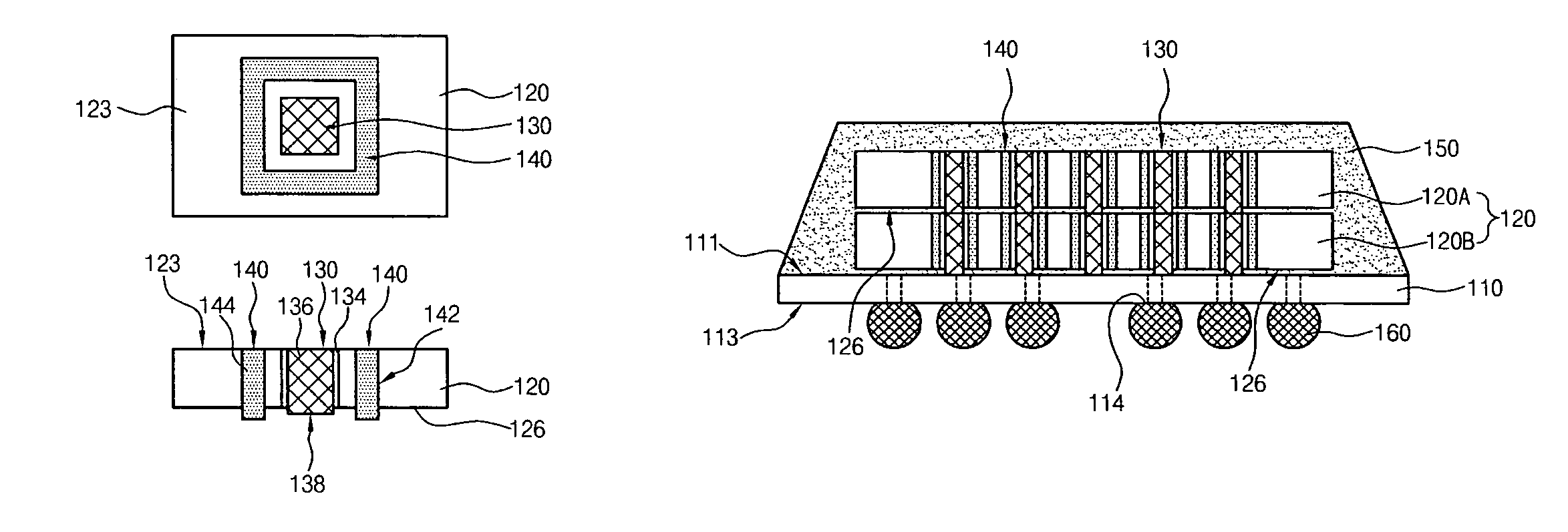

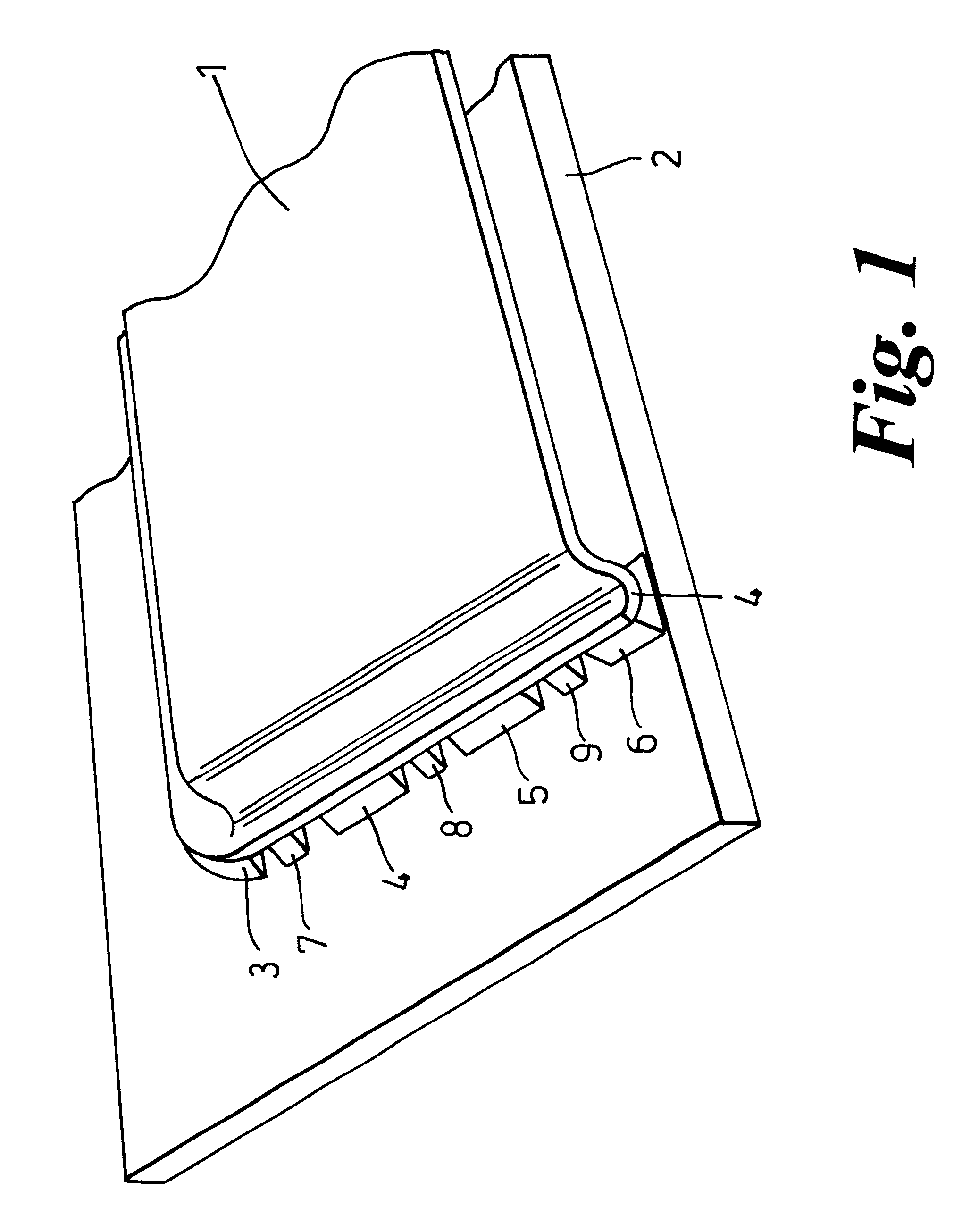

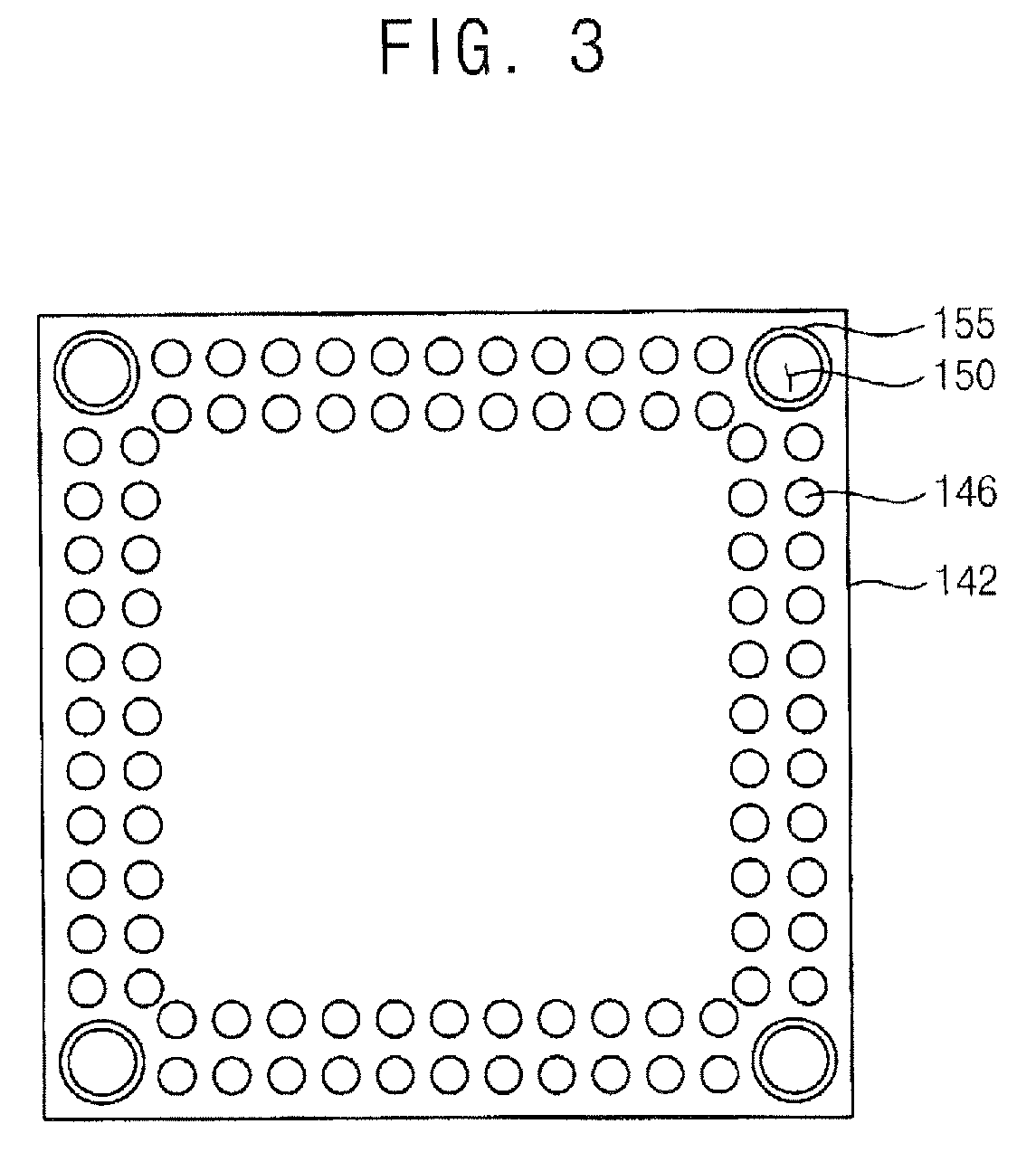

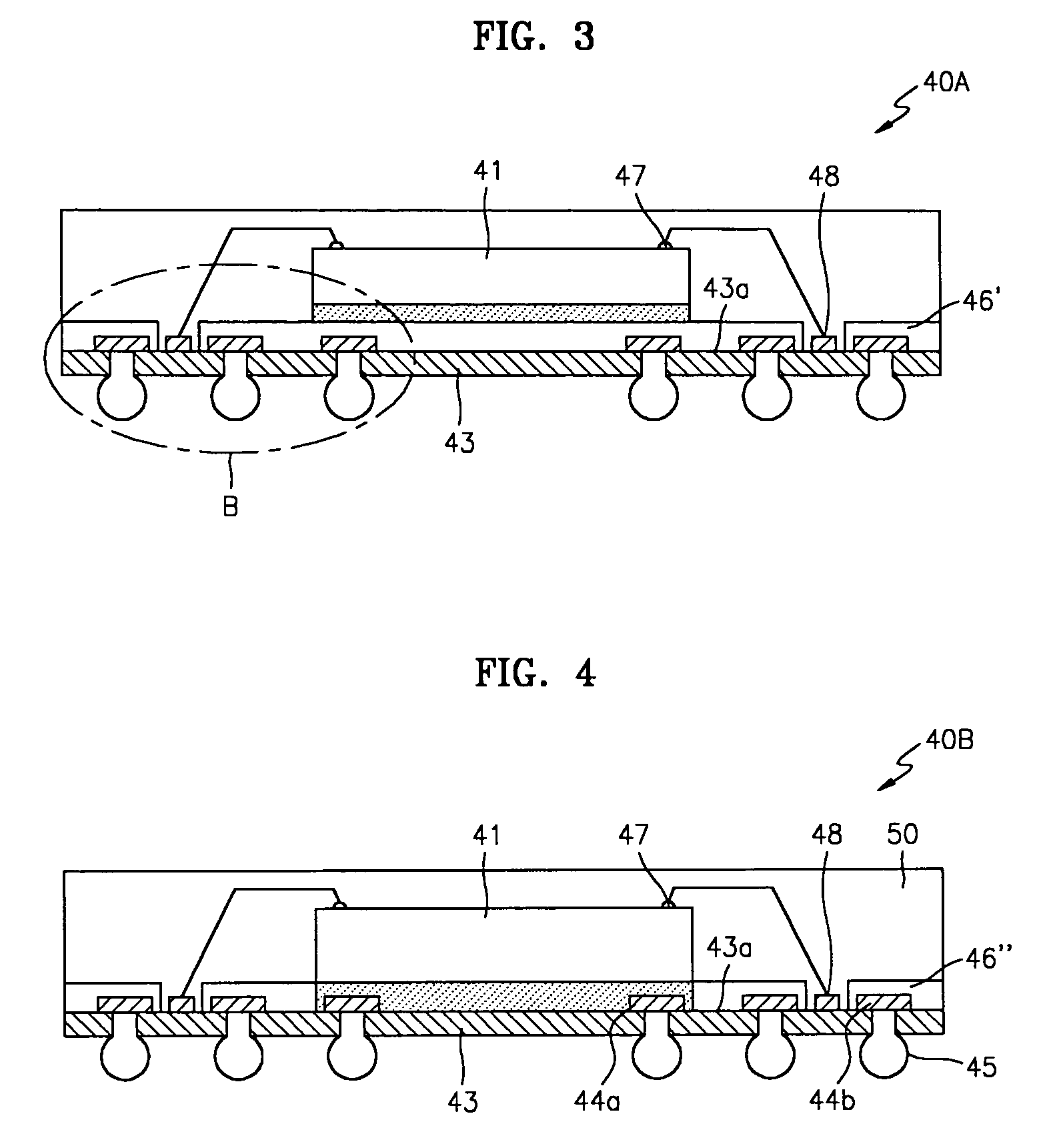

Stack package and method for manufacturing the same

ActiveUS20080079131A1Avoid crackingAvoid disconnectionSemiconductor/solid-state device detailsSolid-state devicesSolder ballSemiconductor chip

A stack package comprises a substrate having a circuit pattern; at least two semiconductor chips stacked on the substrate, having a plurality of through-via interconnection plugs and a plurality of guard rings which surround the respective through-via interconnection plugs, and connected with each other by the medium of the through-via interconnection plugs; a molding material for molding an upper surface of the substrate including the stacked semiconductor chips; and solder balls mounted to a lower surface of the substrate.

Owner:SK HYNIX INC

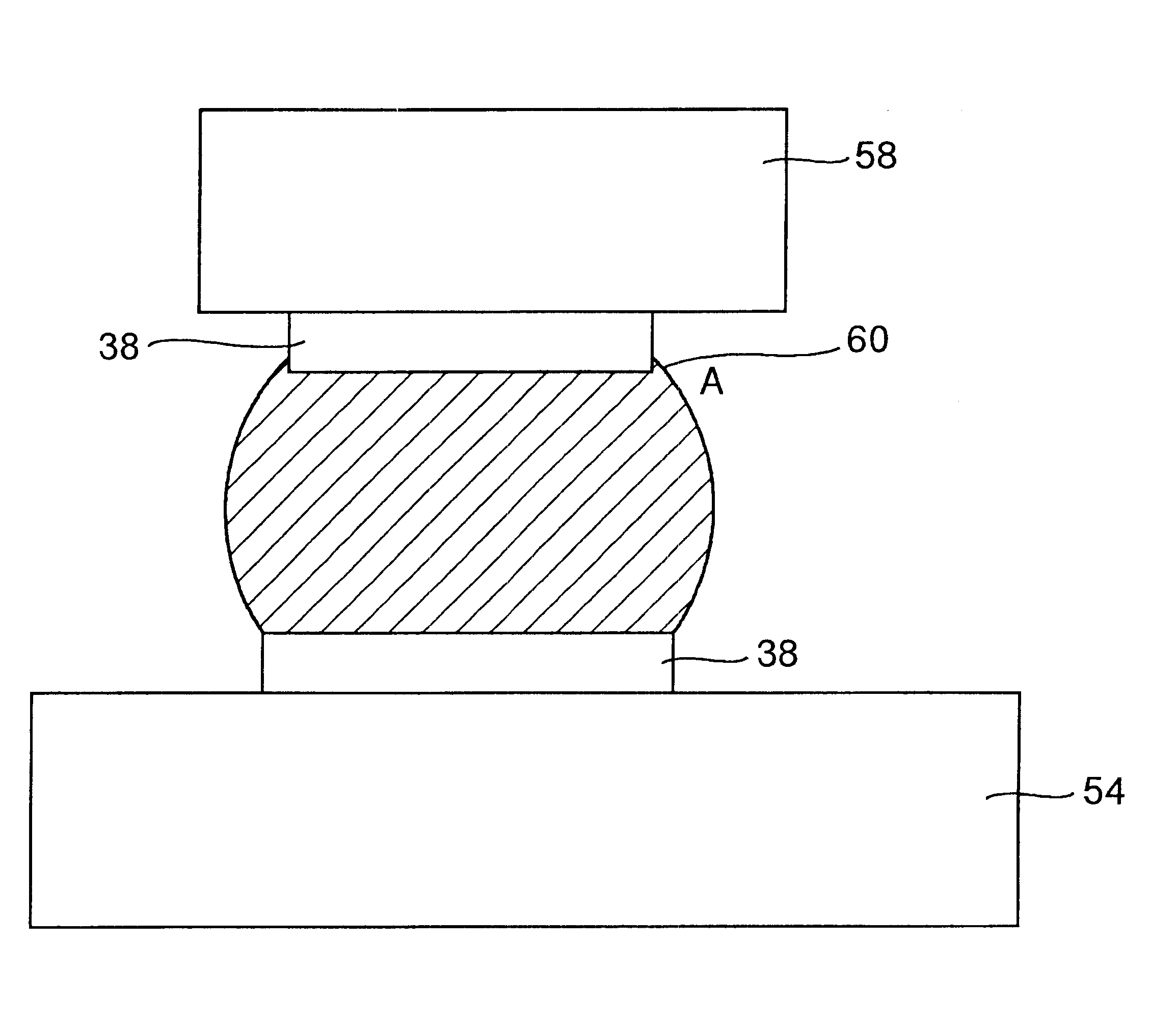

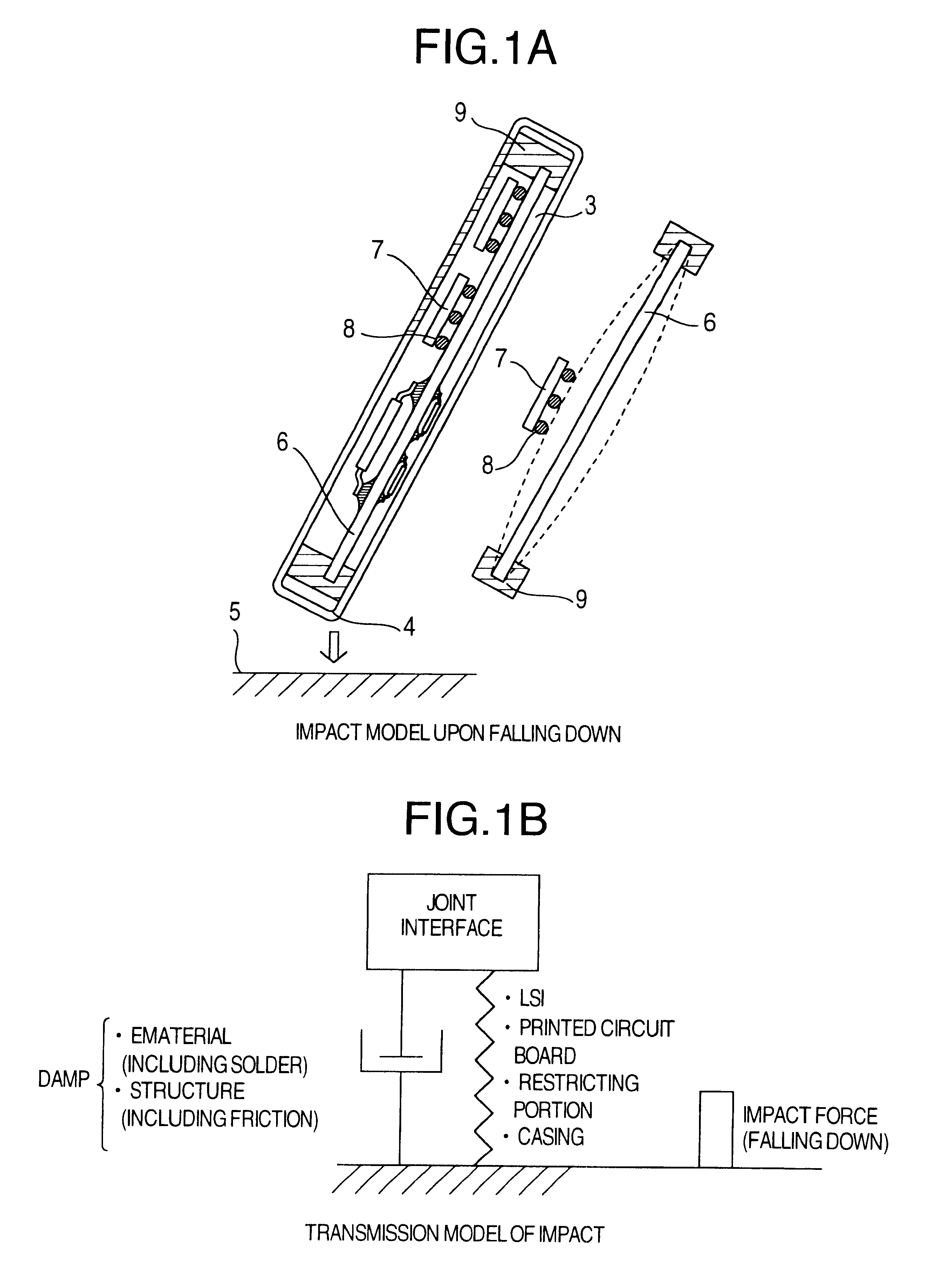

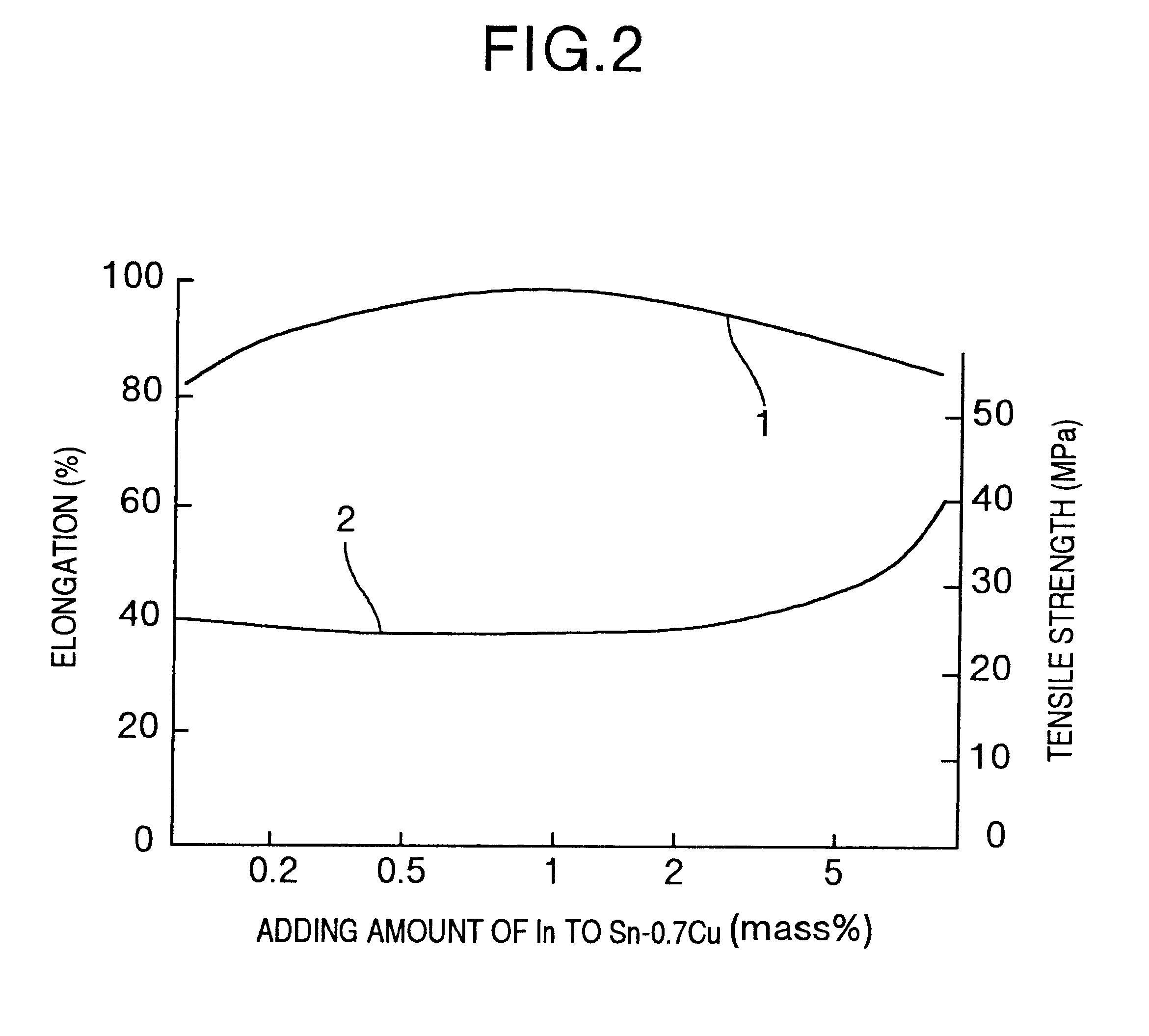

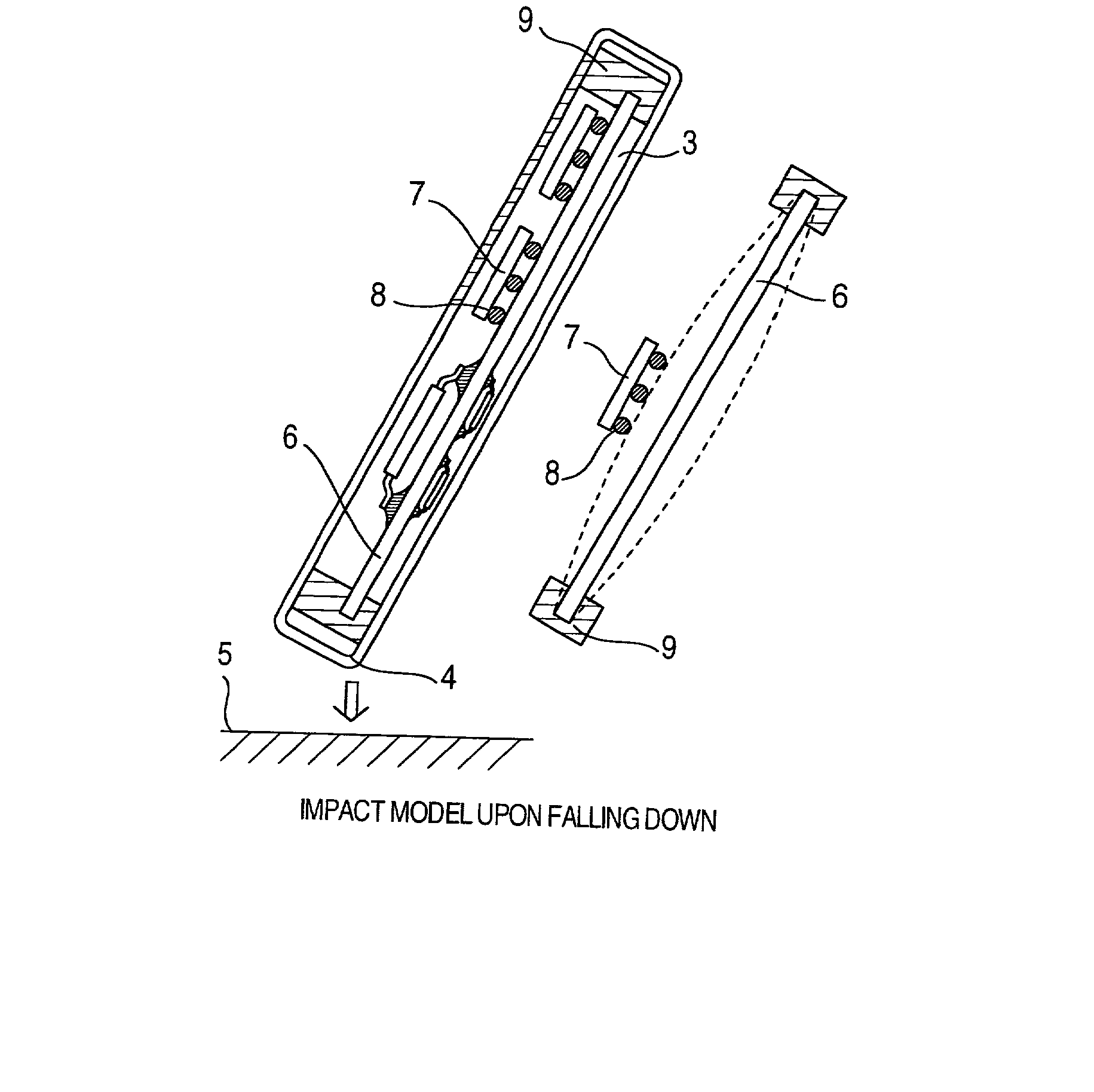

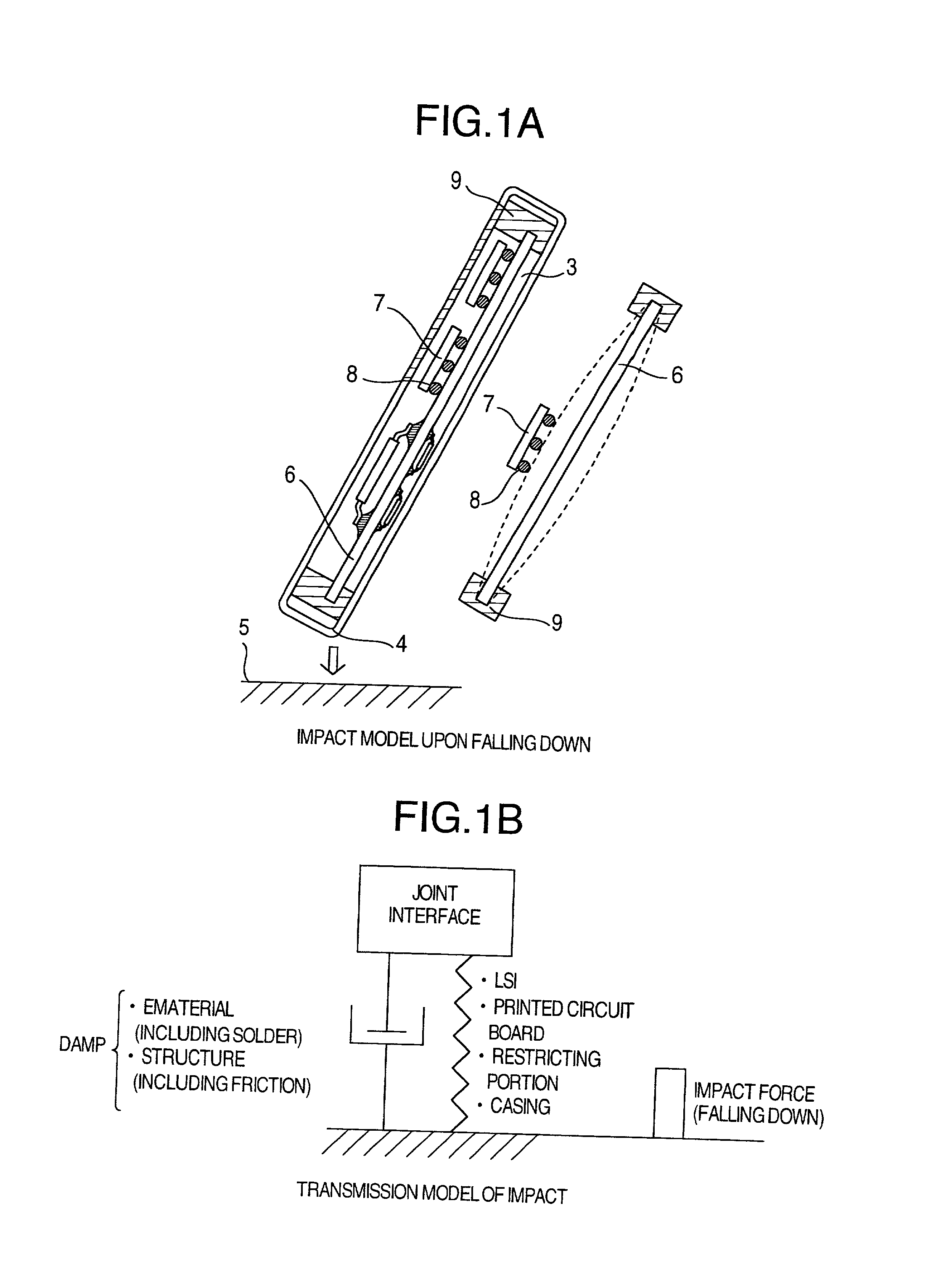

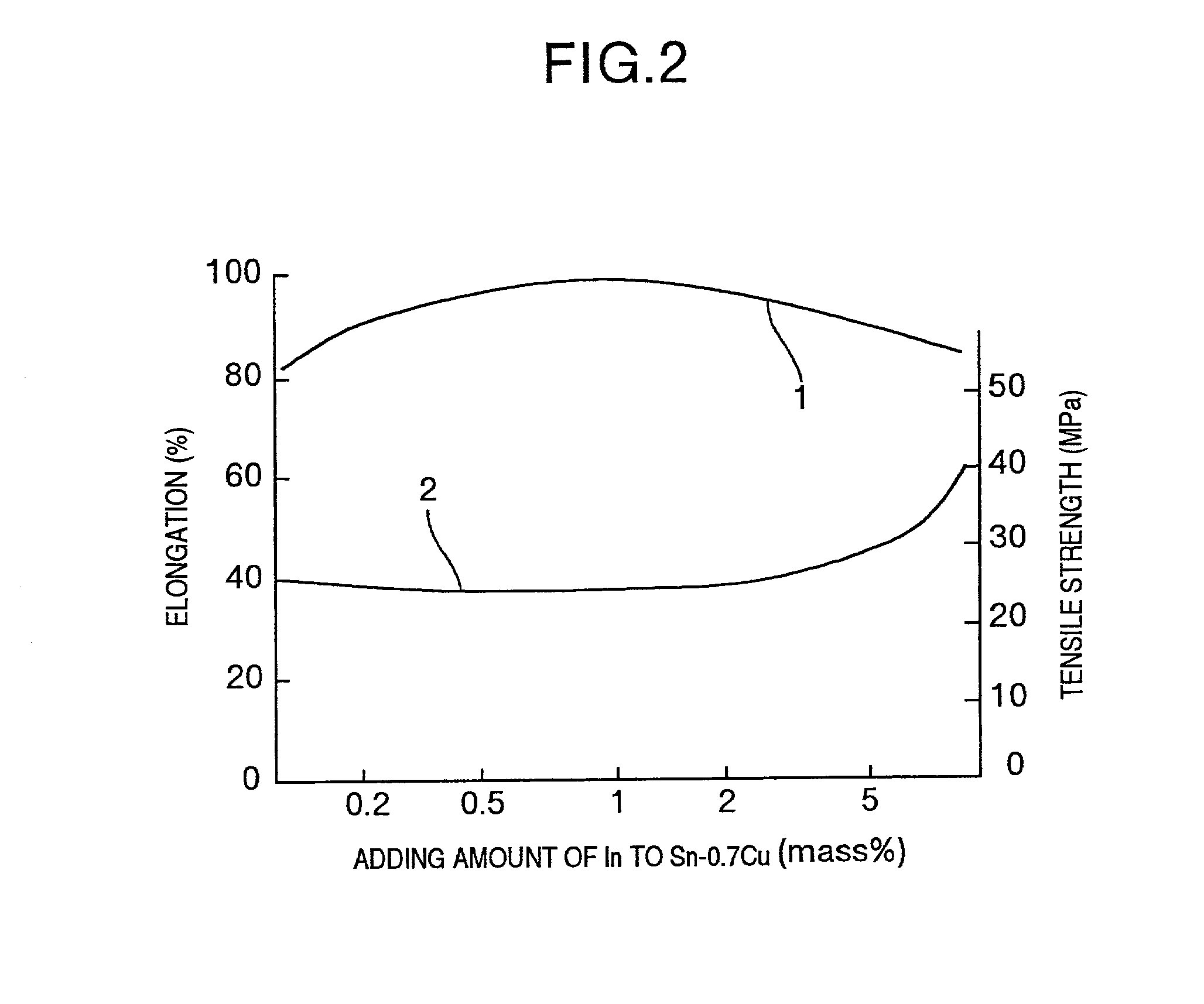

Electron device and semiconductor device

InactiveUS6555052B2Improve solder joint reliabilityEasy to transformSemiconductor/solid-state device detailsSolid-state devicesDevice materialEngineering

An electronic equipment is capable of improving falling down shock resistance or impact resistance in an electronic equipment and of improving reliability of a solder joint in a semiconductor device die-bonded Si chip or the like to which thermal shock causing large deformation may act, bump mounting of BGA, CSP, WPP, flip-chip and so forth, a power module acting large stress and so forth. The electronic equipment has a circuit board and an electronic parts to be electrically connected to an electrode of the circuit board. The electrode of the circuit board and an electrode of the electronic part are connected by soldering using a lead free solder consisted of Cu: 0~2.0 mass %, In: 0.1~10 mass %, and Sn: remaining amount.

Owner:HITACHI LTD

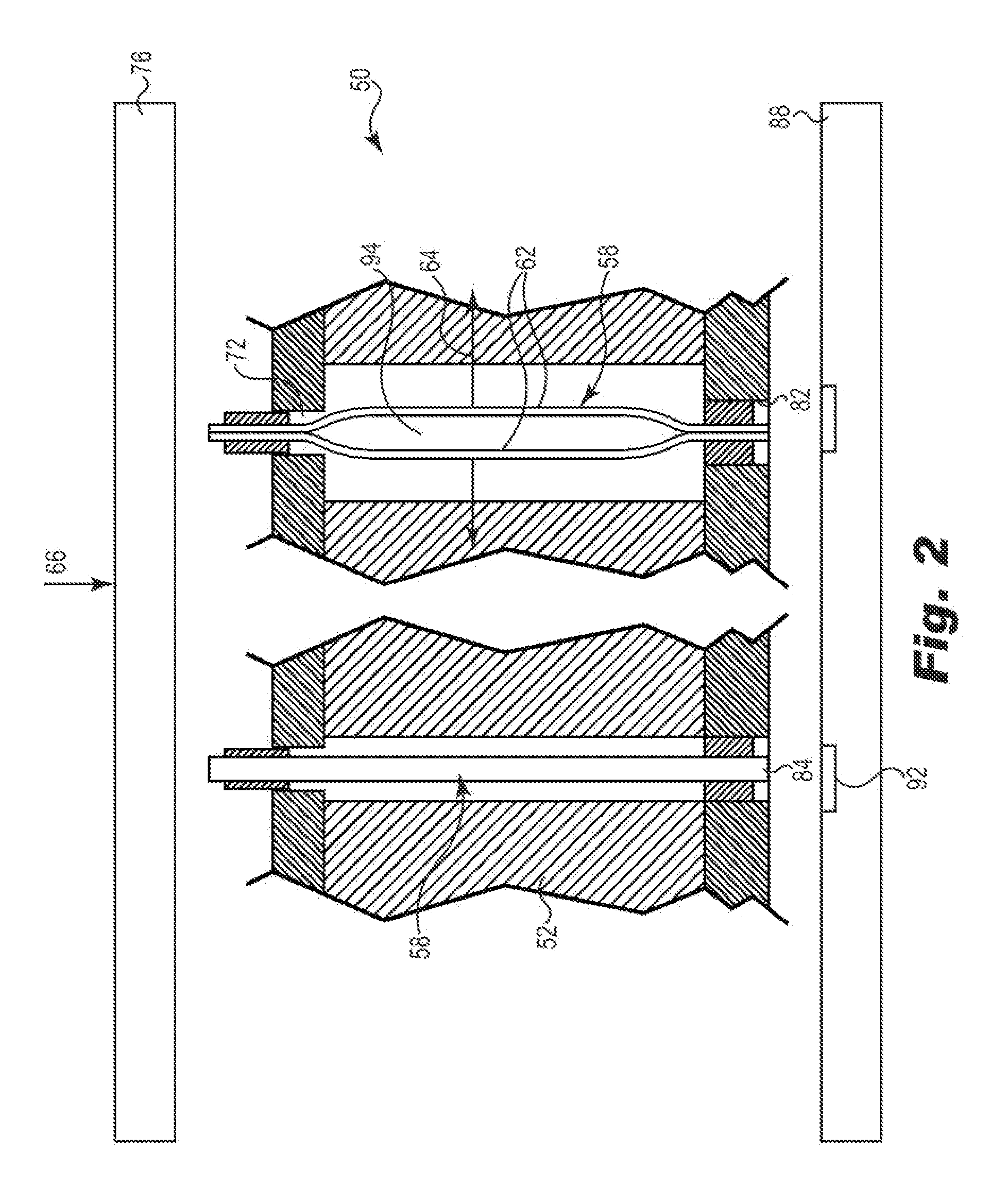

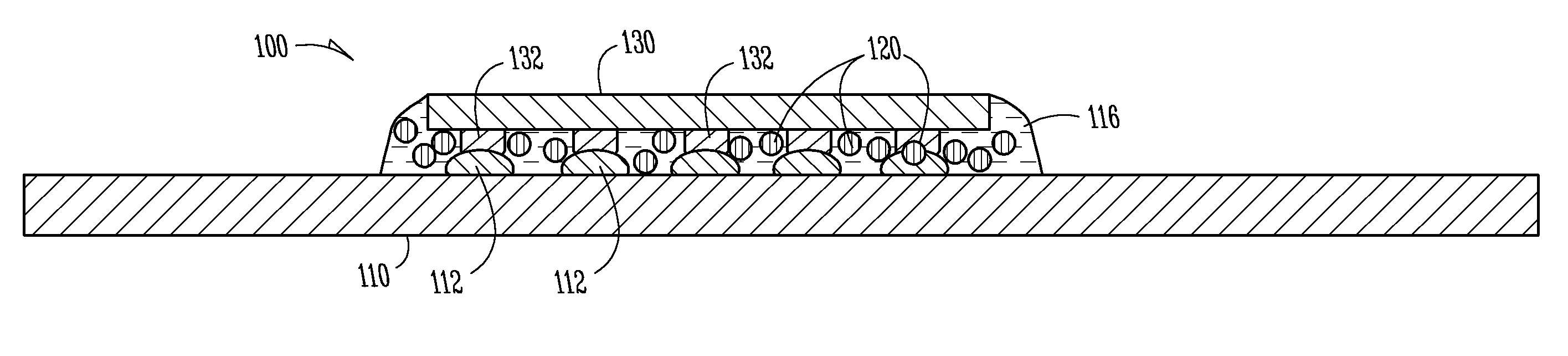

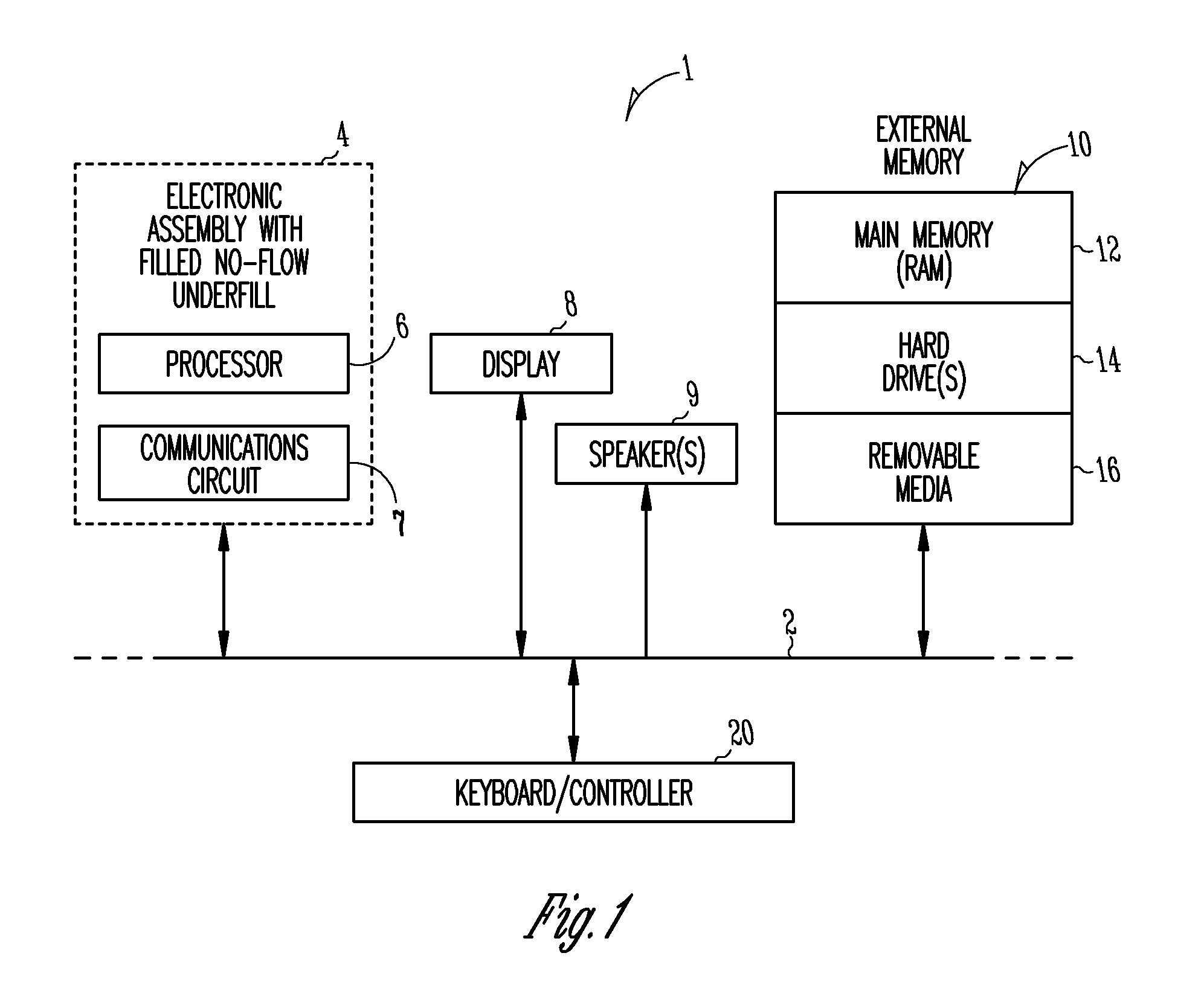

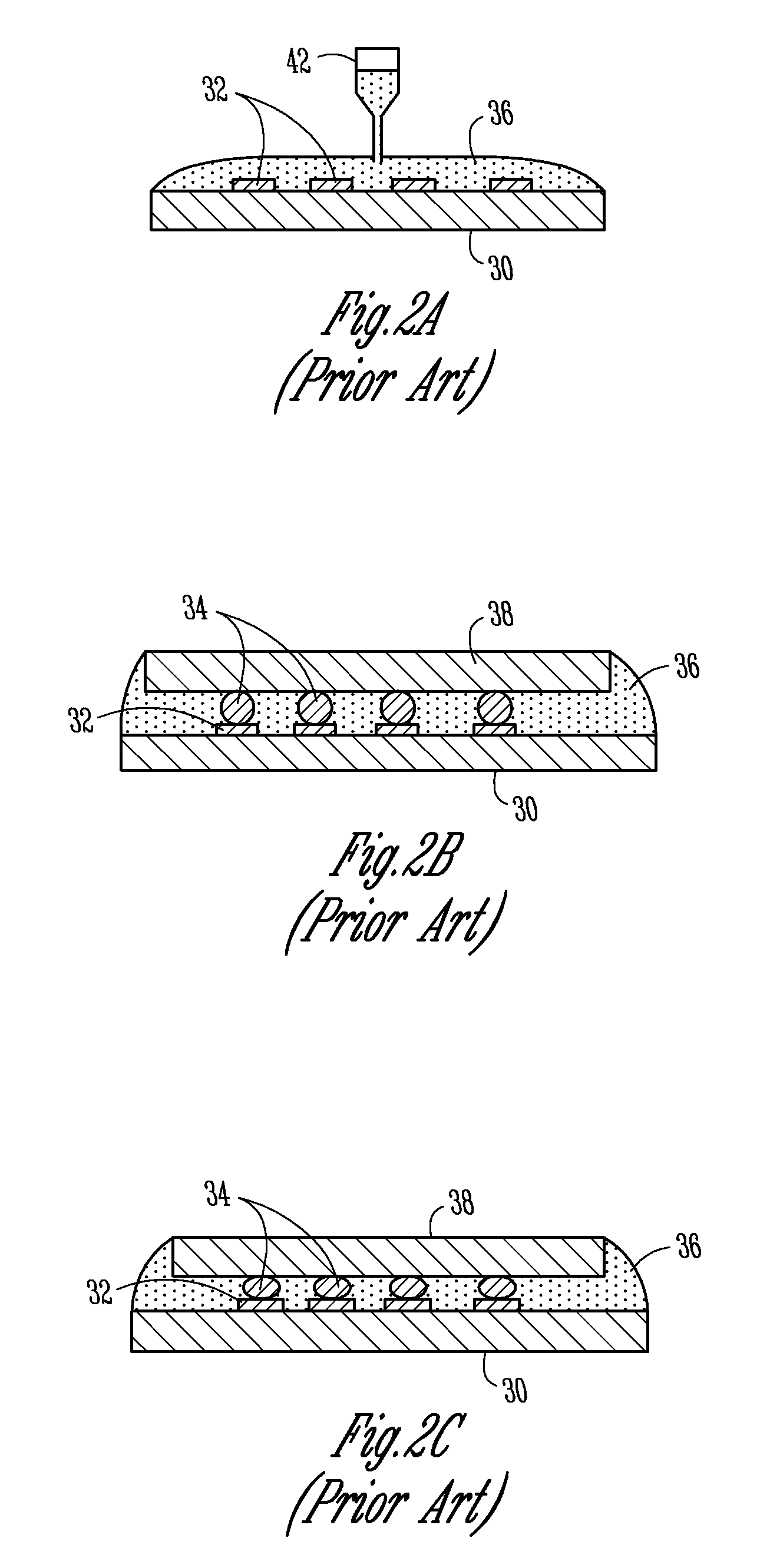

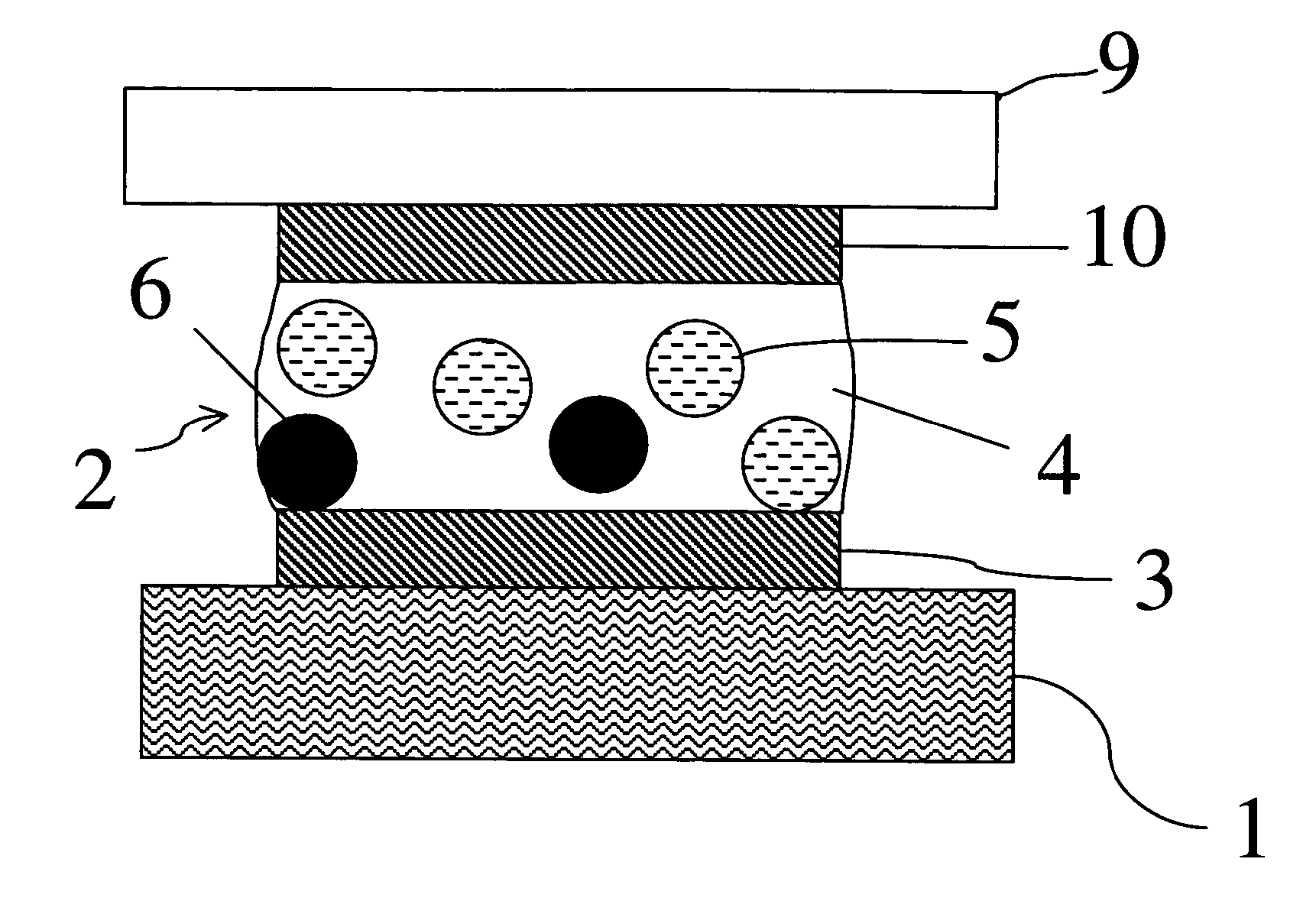

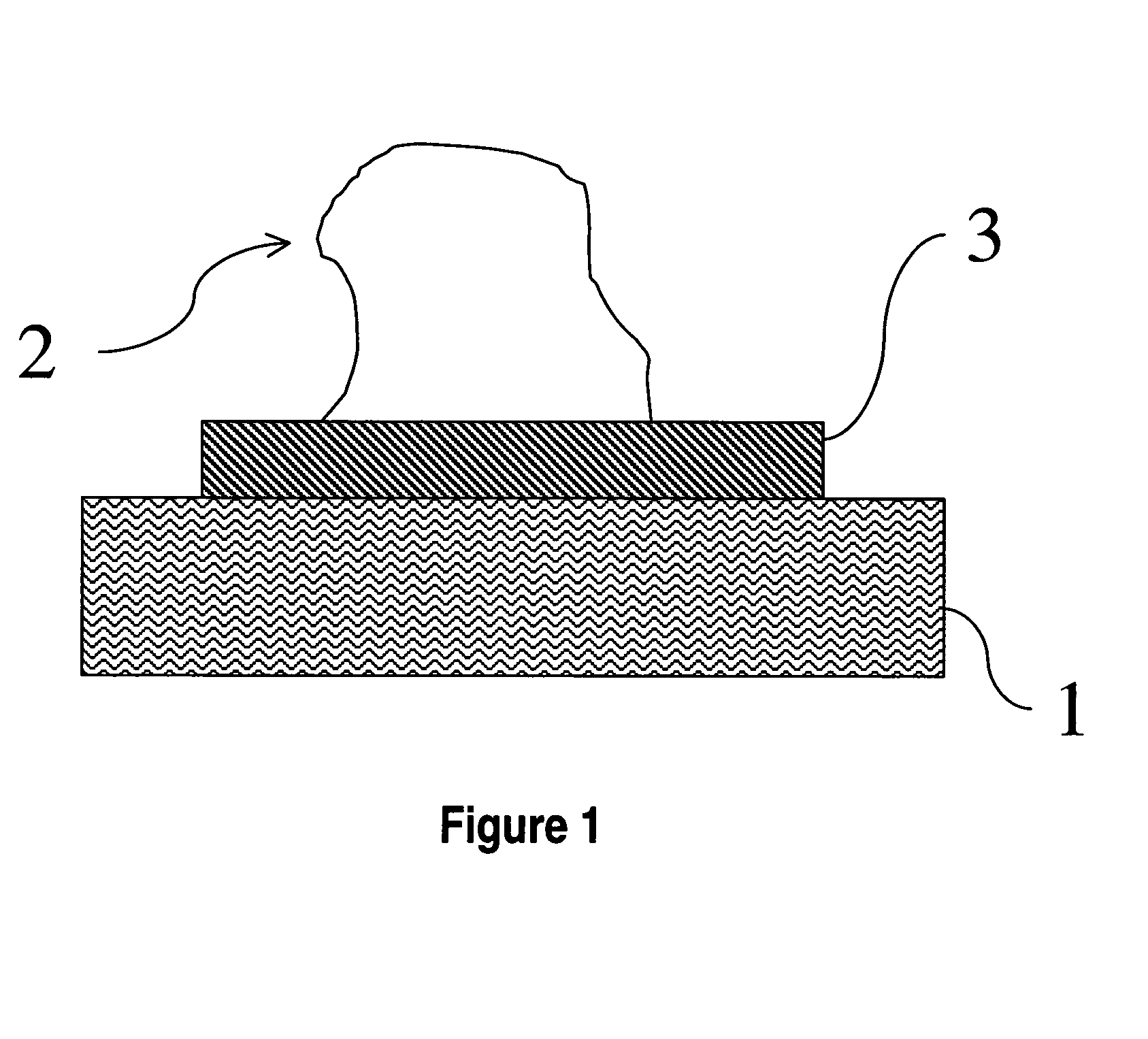

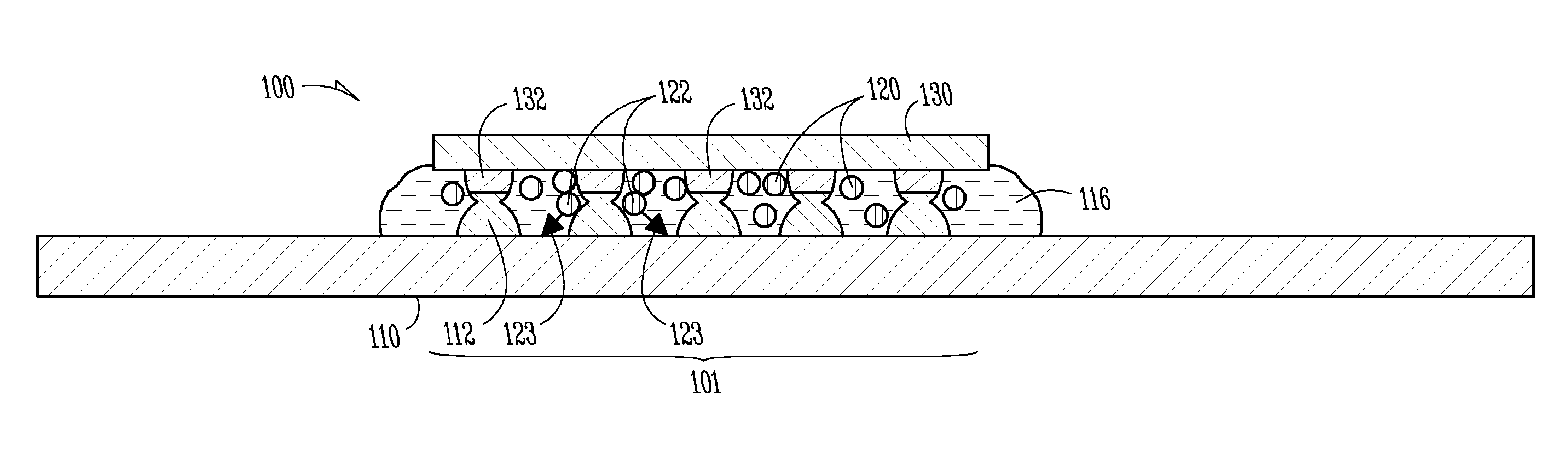

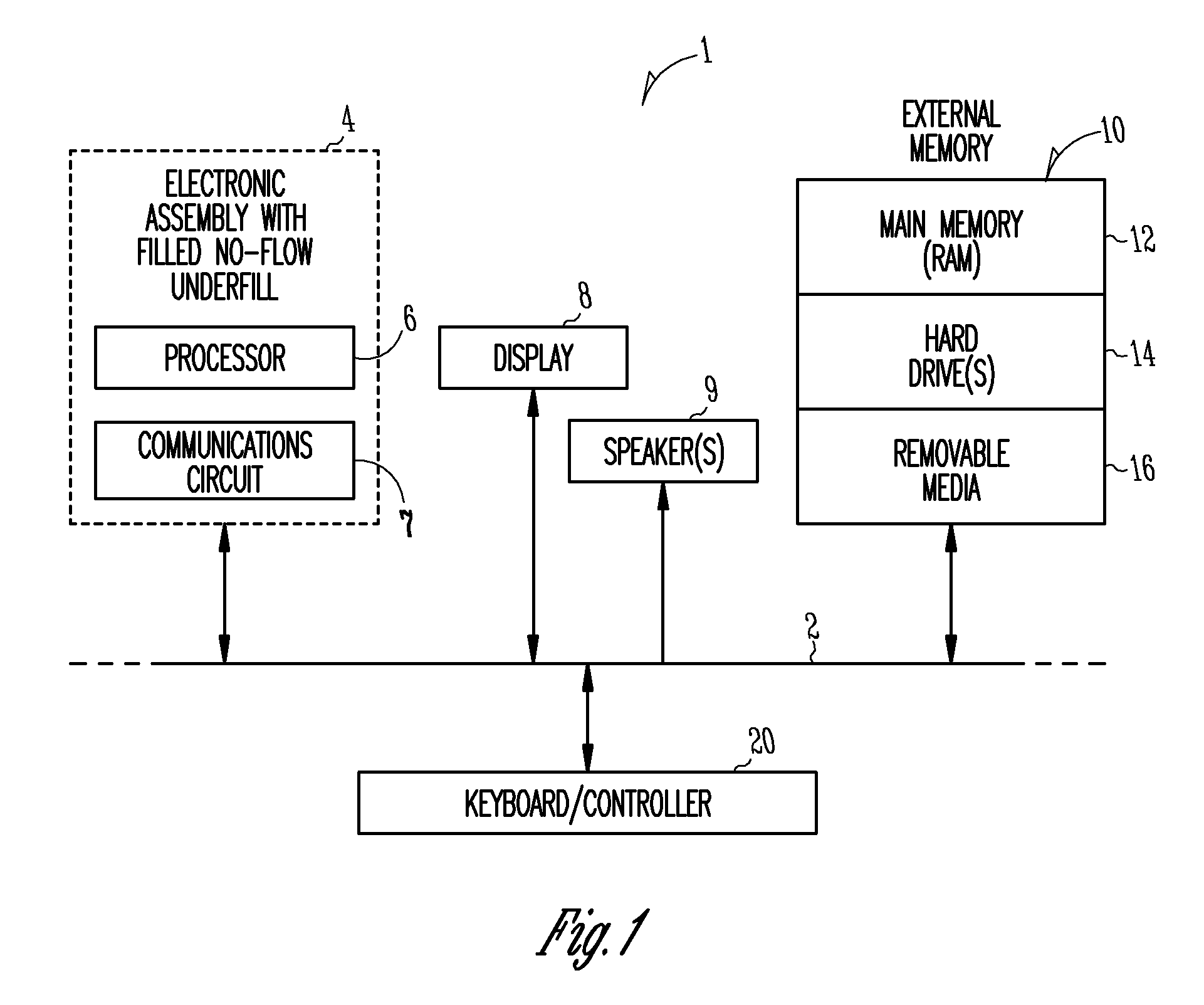

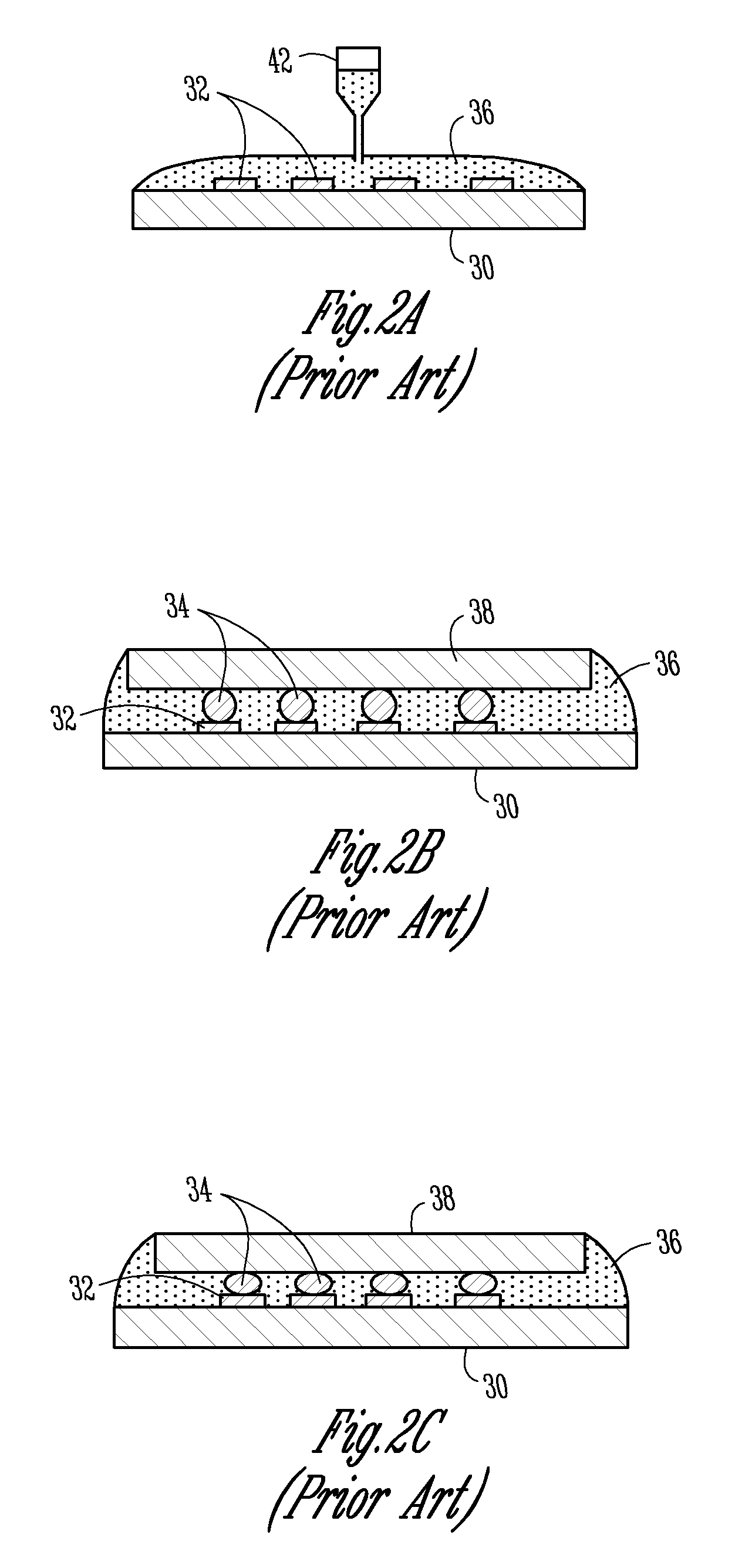

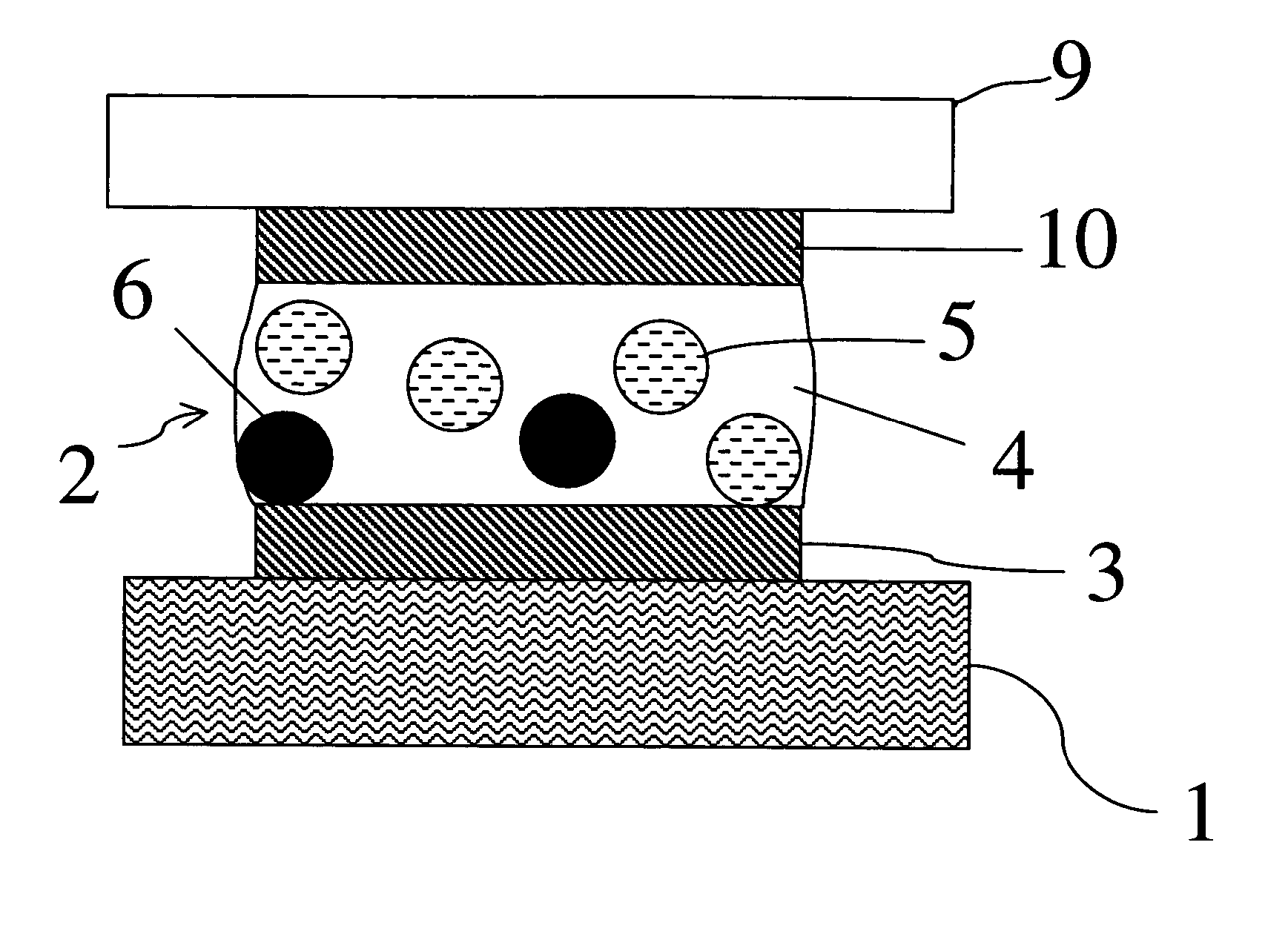

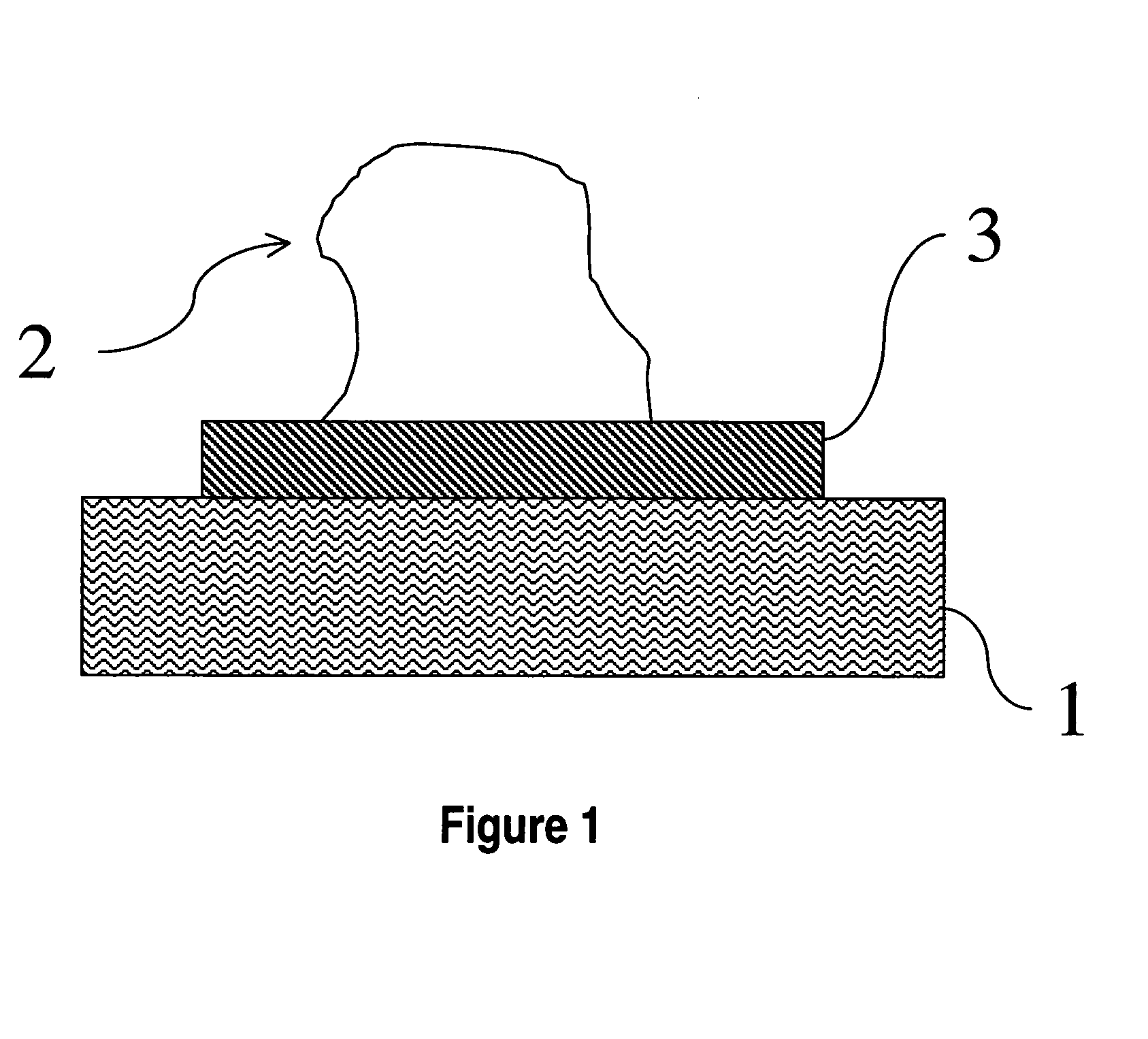

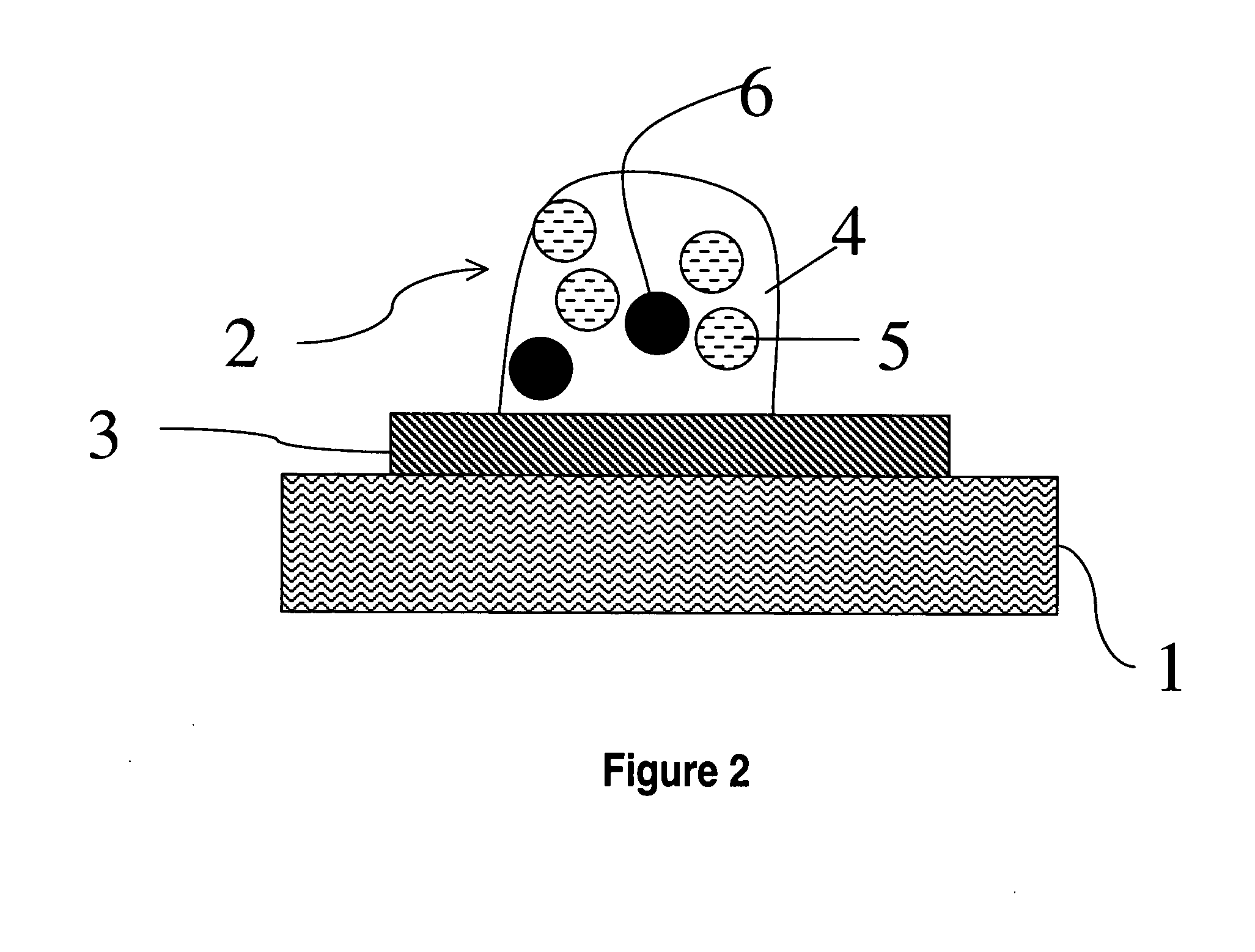

Electronic assemblies with filled no-flow underfill

InactiveUS7323360B2Improve solder joint reliabilityLow viscosityPrinted circuit assemblingSemiconductor/solid-state device detailsSilicon oxideThermal expansion

High yield, high reliability, flip-chip integrated circuit (IC) packages are achieved utilizing a combination of heat and pressure to bond flip-chip die and to cure no-flow underfill material. The underfill comprises a filler or low coefficient of thermal expansion (CTE) material to decrease CTE of the cured underfill. The filler material can be selected from the group comprising silica, silicon oxide, silicon dioxide, silicon nitride, aluminum oxide, aluminum nitride, or a mixture thereof. The filler material may also increase the viscosity of the uncured underfill and / or increase the modulus of elasticity of the cured underfill. In some method embodiments, a thermocompression bonder is used to simultaneously provide solder bump reflow and underfill curing. Application of various methods to a component package, an electronic assembly, and an electronic system are also described.

Owner:MICRON TECH INC

Solder joint reliability

InactiveUS6246011B1Improve solder joint reliabilityEasy alignmentPrinted circuit assemblingElectrically conductive connectionsLife timeElectrical element

An electrical circuit arrangement comprising a circuit board and an electrical component attached thereto by a plurality of solder joints. The sizes of the joints are chosen according to a characteristic (for example the frequency) of signals to be conducted through them. The joint sizes are inversely proportional to the frequency of signals which they are arranged to conduct. The expected fatigue life of the arrangement is greater than one in which all joints are of a smaller size, as required for example for high frequency signals, and this reduces the need for component underfill.

Owner:HANGER SOLUTIONS LLC +1

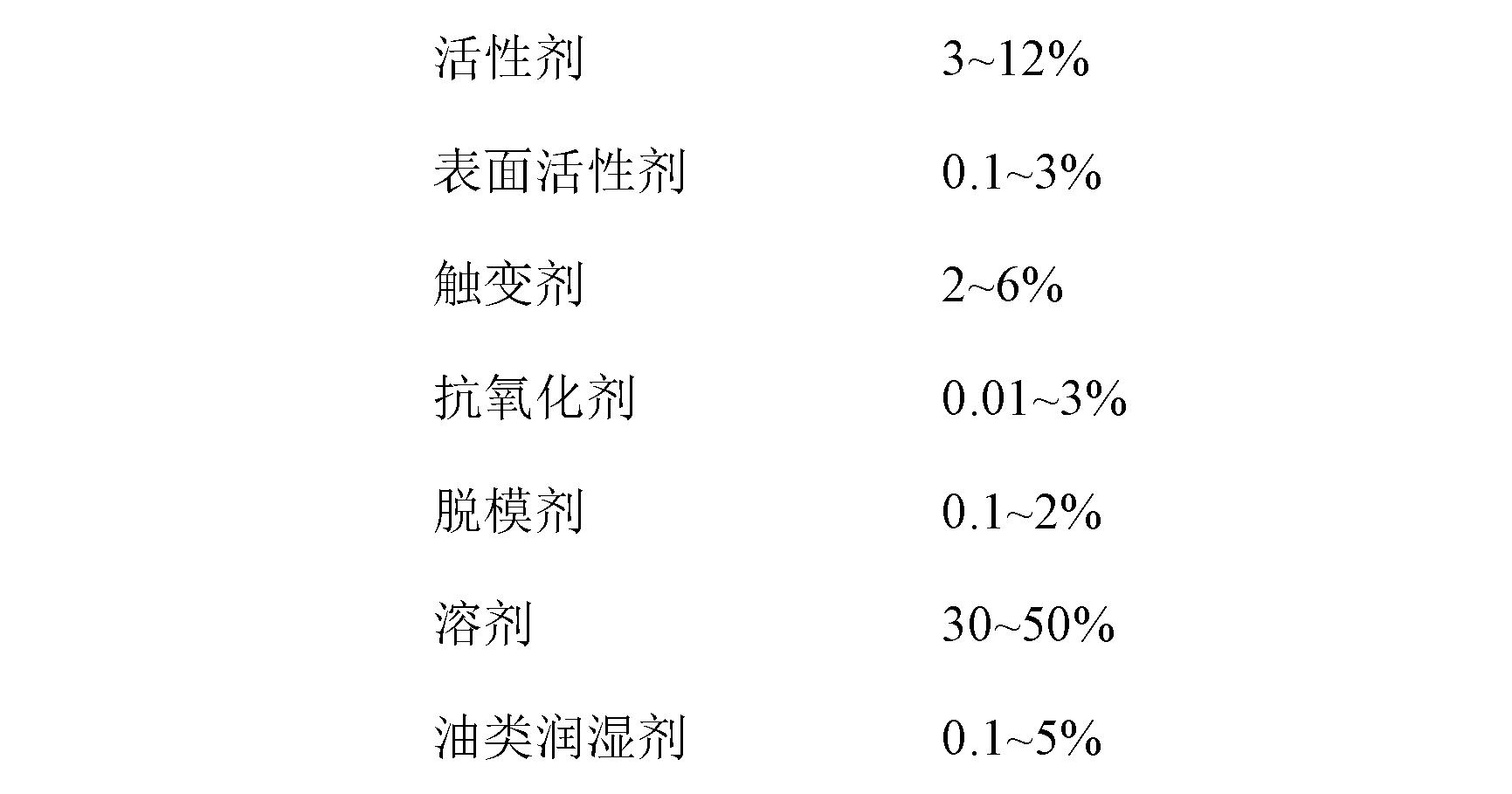

Halogen-free scaling powder used for lead-free solder paste and preparation method thereof

ActiveCN103008921AHigh surface insulation resistanceNo penetrating corrosionWelding/cutting media/materialsSoldering mediaAntioxidantActive agent

The invention relates to a halogen-free scaling powder used for a lead-free solder paste and a preparation method thereof. The halogen-free scaling powder used for the lead-free solder paste is characterized by being composed of the following components by weight percent: 25-55% of modified rosin, 3-12% of active agent, 0.1-3% of surface active agent, 2-6% of thixotropic agent, 0.01-3% of antioxidant, 0.1-2% of release agent, 30-50% of solvent and 0.1-5% of oil wetting agent, wherein the scaling powder does not contain halogen; the activity of the scaling powder can be obviously improved through adding organic carboxylic acid and hydroxy carboxylic acid as the active agent, and combining the active agent with the surface active agent; and in addition, the oil wetting agent is used, so that a layer of thin continuous oil membrane is enabled to cover the surface of a welding spot in a whole reflow soldering technological process of the solder paste, thereby playing an oxygen insulating function, and greatly improving the expansibility and the wetting property. The solder paste prepared by the scaling powder provided by the invention and a tin-silver-copper lead-free solder has the advantages of being good in printing performance, clean in demoulding, good in solderability and strong in wettability, having no penetrability corrosion in a bronze mirror after soldering, being high in soldering spot reliability and excellent in mechanical property, and capability of satisfying the high reliability requirements of high-end electronic products.

Owner:广东中实金属有限公司 +1

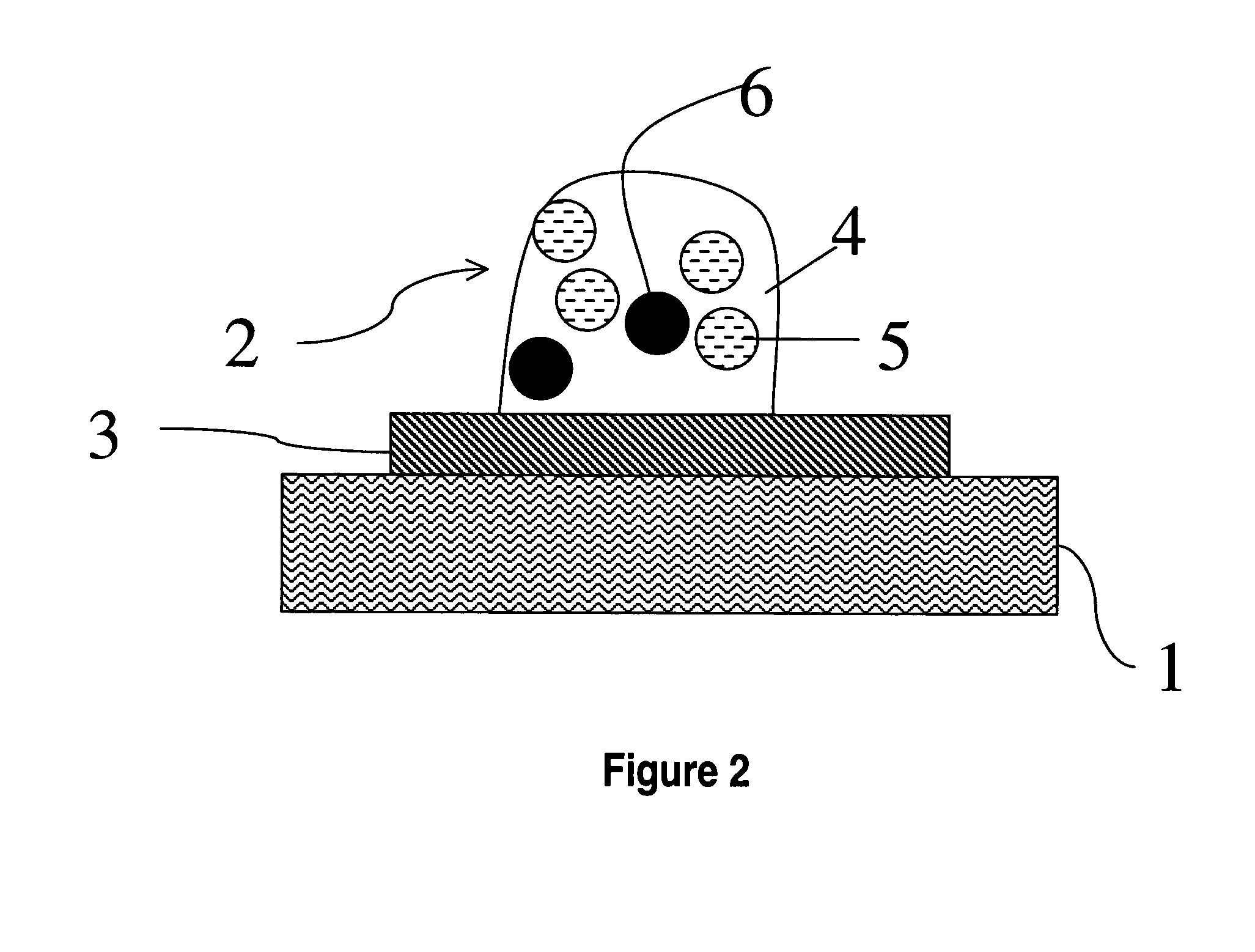

Solder pastes for providing high elasticity, low rigidity solder joints

ActiveUS7017795B2Increase elasticityReduce rigidityPrinted circuit assemblingPrinted circuit aspectsThermal expansionSolder paste

Solder pastes for providing high elasticity, low rigidity solder joints are disclosed. The solder pastes may be used between two parts having large mismatches in their coefficients of thermal expansion and / or when there is a high likelihood of mechanical deformity when the two parts are soldered together. In one particular exemplary embodiment, a solder paste may be realized as a composition comprising a solder powder and high melting temperature particles with a flux, wherein the ratio between solder powder and high melting temperature particles may be between 2:1 and 1:10.

Owner:INDIUM CORP +1

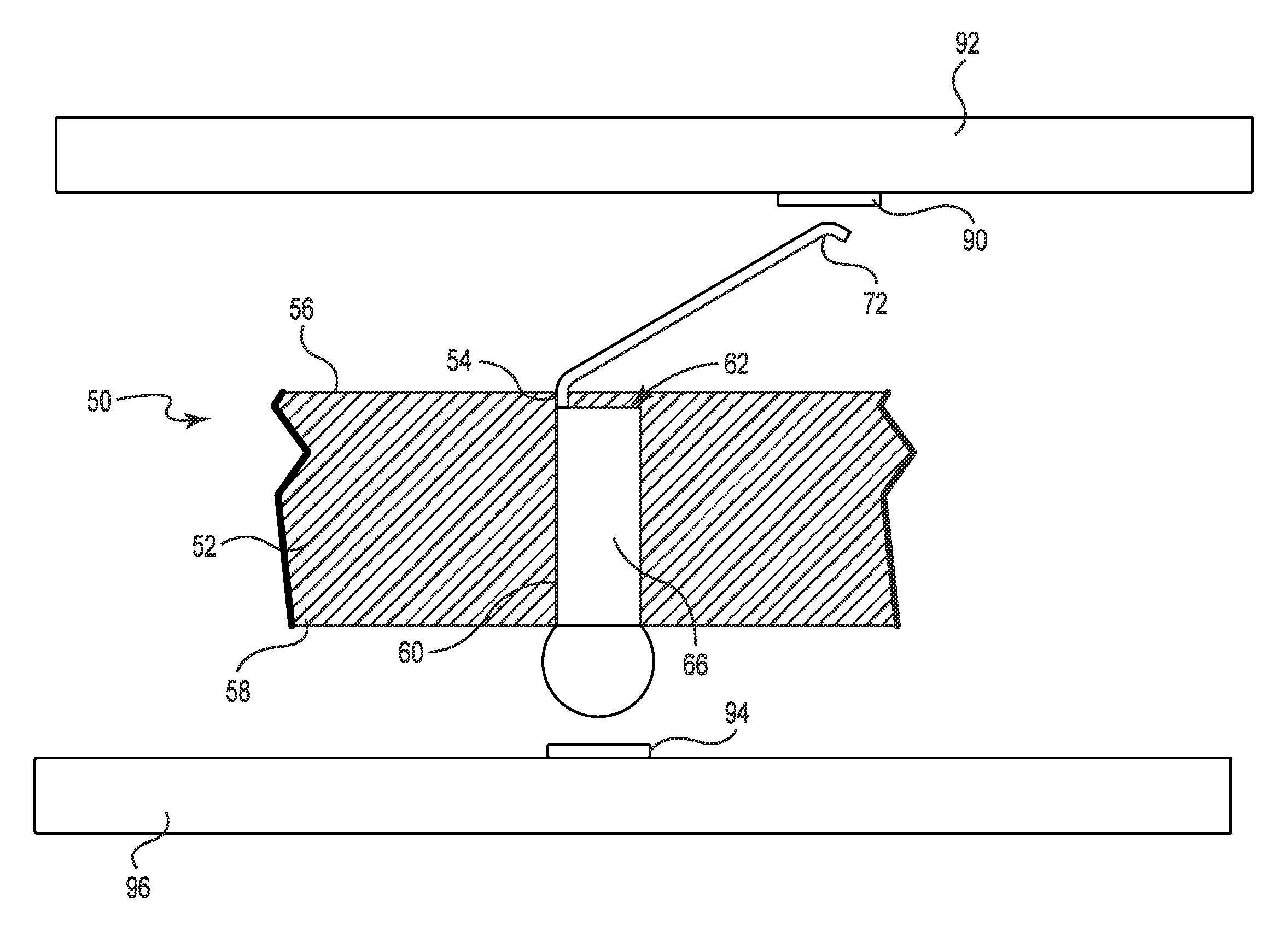

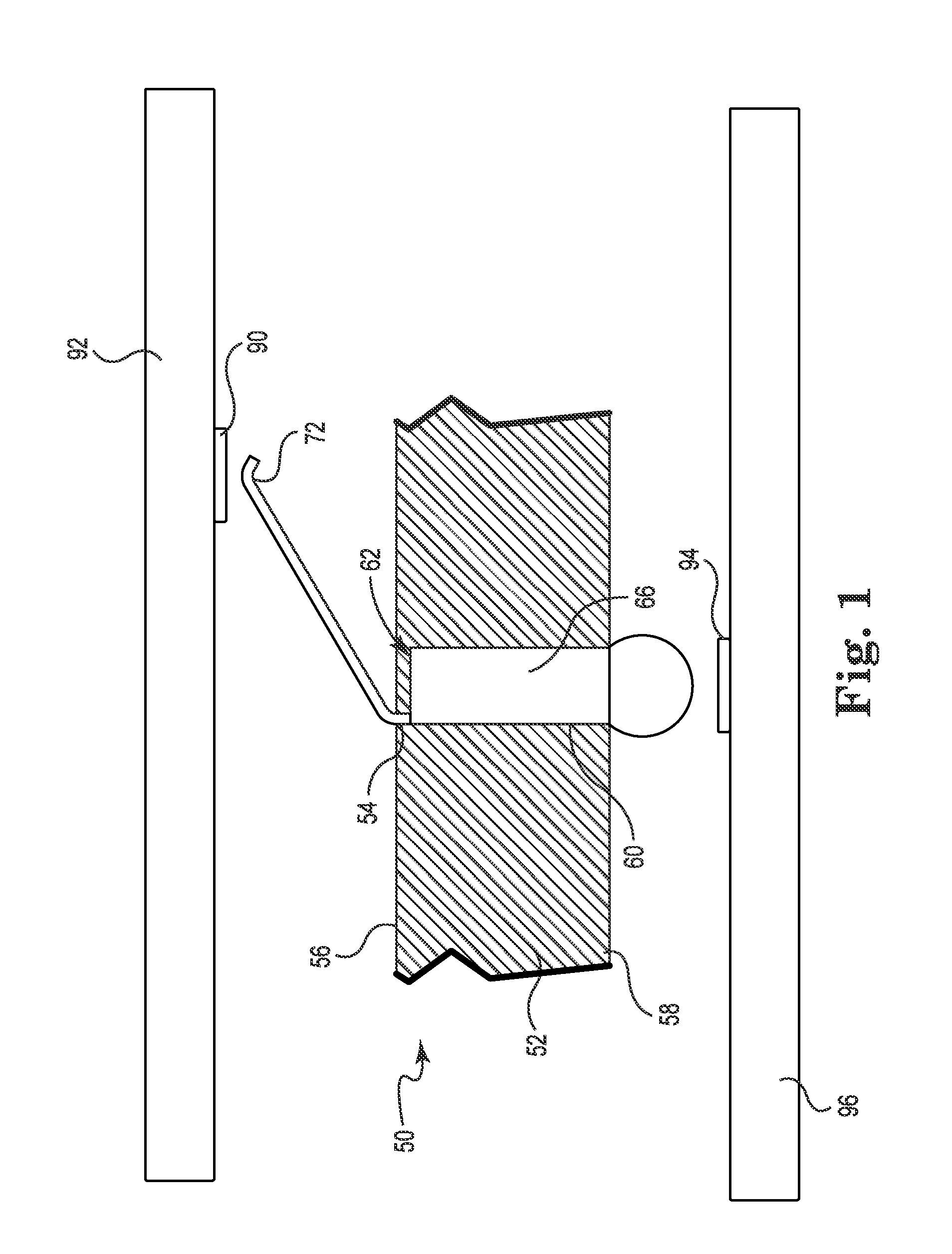

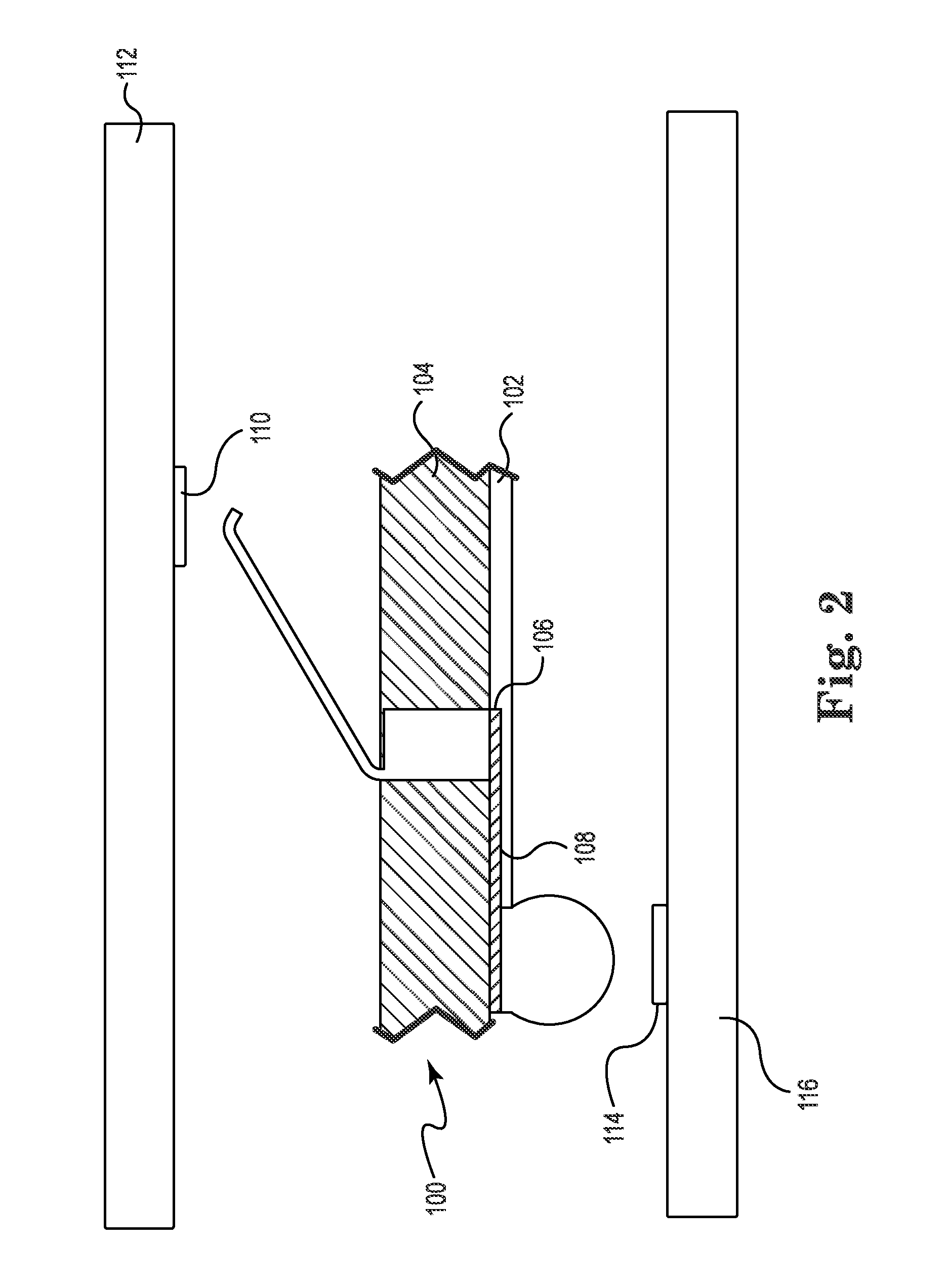

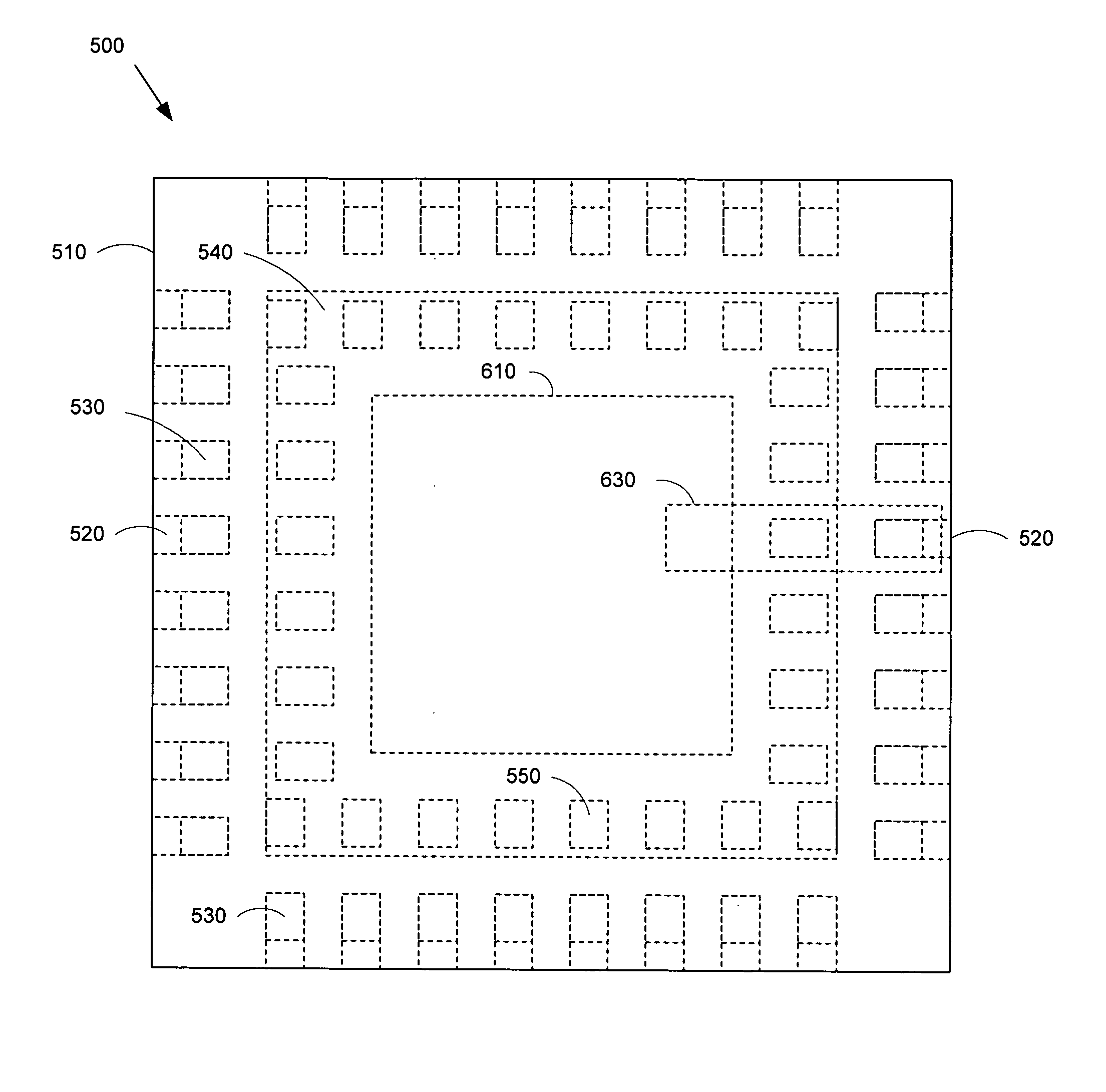

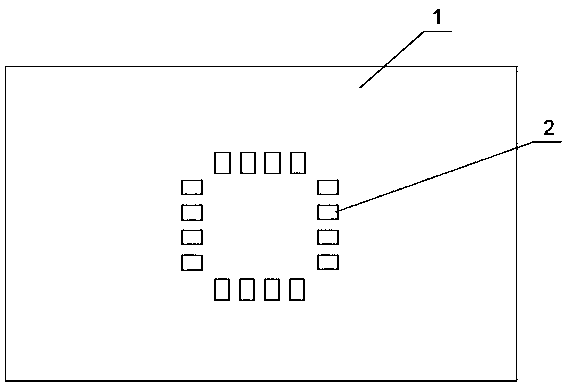

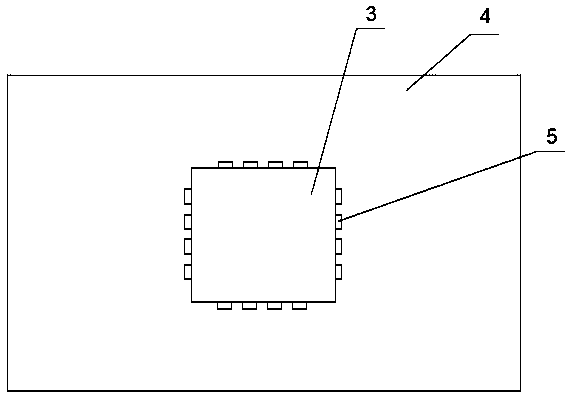

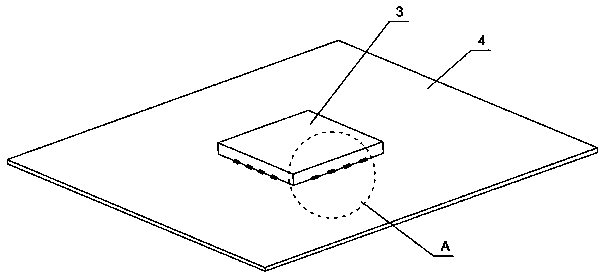

System and method for improving solder joint reliability in an integrated circuit package

ActiveUS20050139972A1Improve solder joint reliabilityHigh solder joint strengthPrinted circuit assemblingFinal product manufactureIntegrated circuit packagingEngineering

A system and method is disclosed for improving solder joint reliability in an integrated circuit package. Each terminal of a quad, flat, non-leaded integrated circuit package is formed having portions that define a solder slot in the bottom surface of the terminal. An external surface of the die pad of the integrated circuit package is also formed having portions that define a plurality of solder slots on the periphery of the die pad. When solder is applied to the die pad and to the terminals, the solder that fills the solder slots increases the solder joint reliability of the integrated circuit package.

Owner:STMICROELECTRONICS SRL

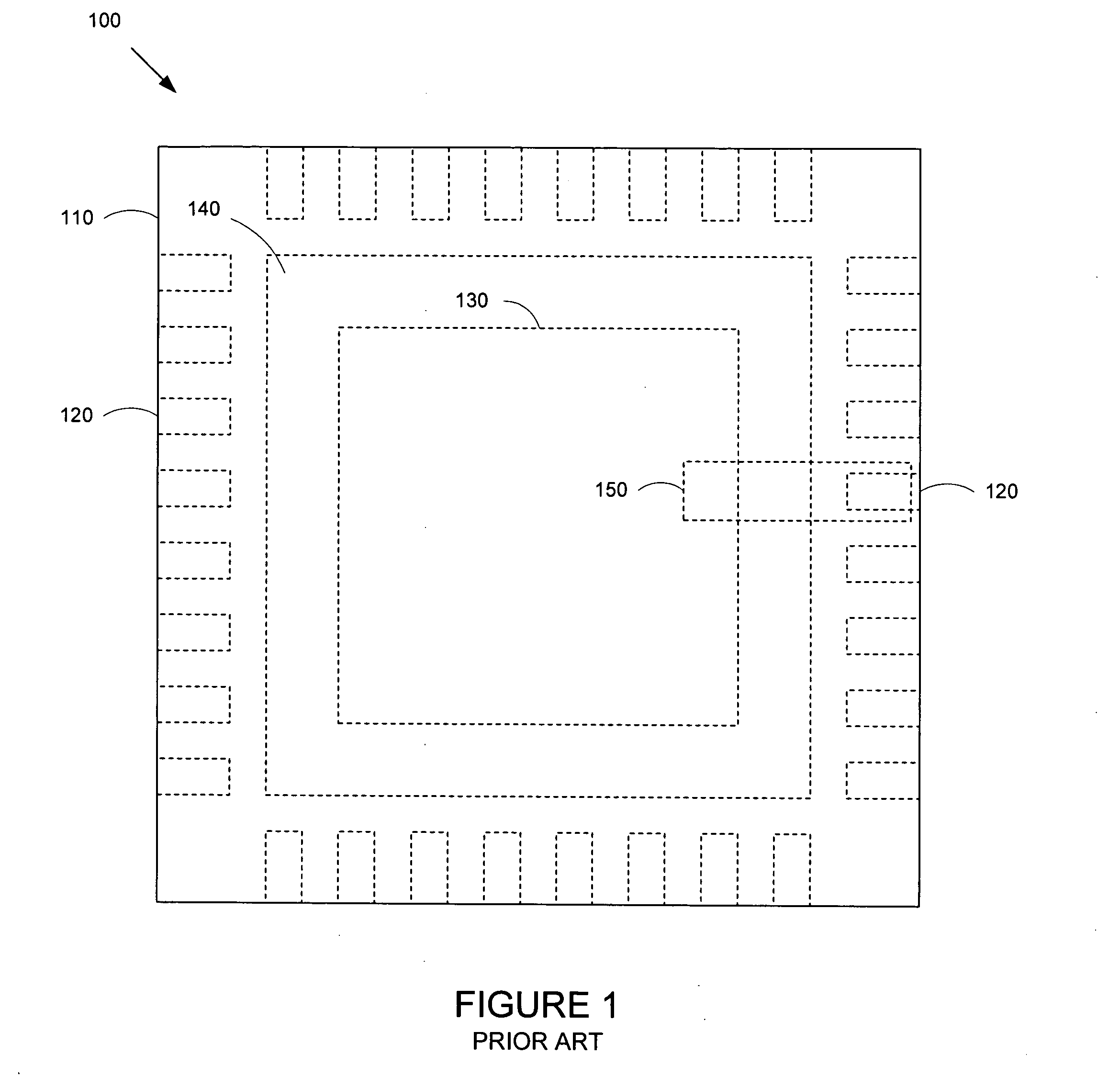

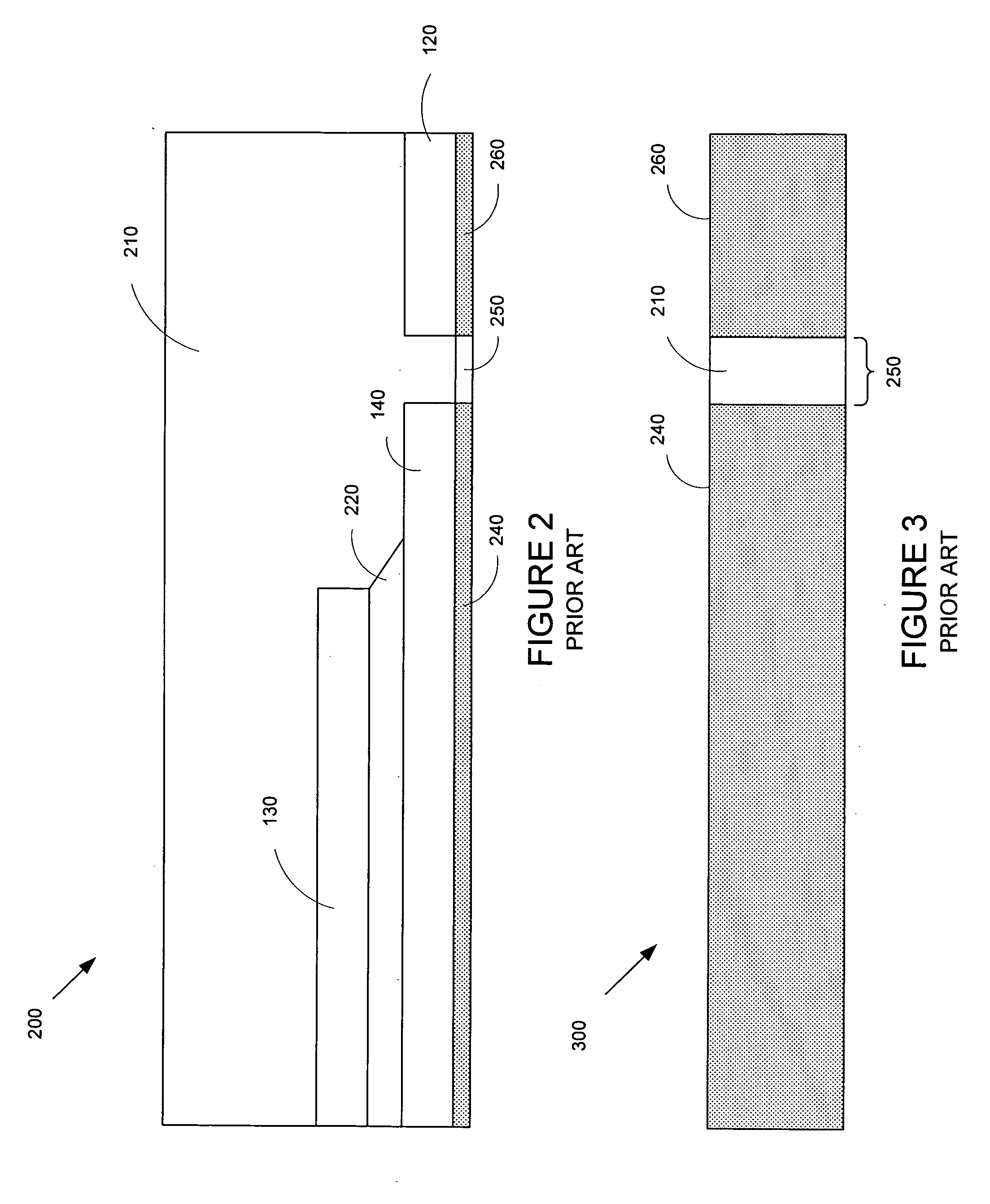

High-reliability solder joint for printed circuit board and semiconductor package module using the same

InactiveUS20050282315A1Improve solder joint reliabilityPrinted circuit assemblingFinal product manufactureSolder ballPrinted circuit board

A printed circuit board and a semiconductor package module using the same in which solder joint reliability (SJR) is improved. The printed circuit board includes: a first terminal exposed to the external of the printed circuit board in a print circuit pattern to be connected to a solder ball of a semiconductor package; a second terminal exposed to the external of the printed circuit board in the printed circuit pattern to be connected to another printed circuit board; and a buffer layer, which is an insulating layer formed adjacent the first terminal, being formed of a thermal absorption material, e.g. an elastomer, configured to absorb thermal stress caused by any difference of coefficients of thermal expansion between the semiconductor package and the first terminal, wherein the printed circuit board is a multi-layered printed circuit board including alternately layered insulators and printed circuit patterns.

Owner:SAMSUNG ELECTRONICS CO LTD

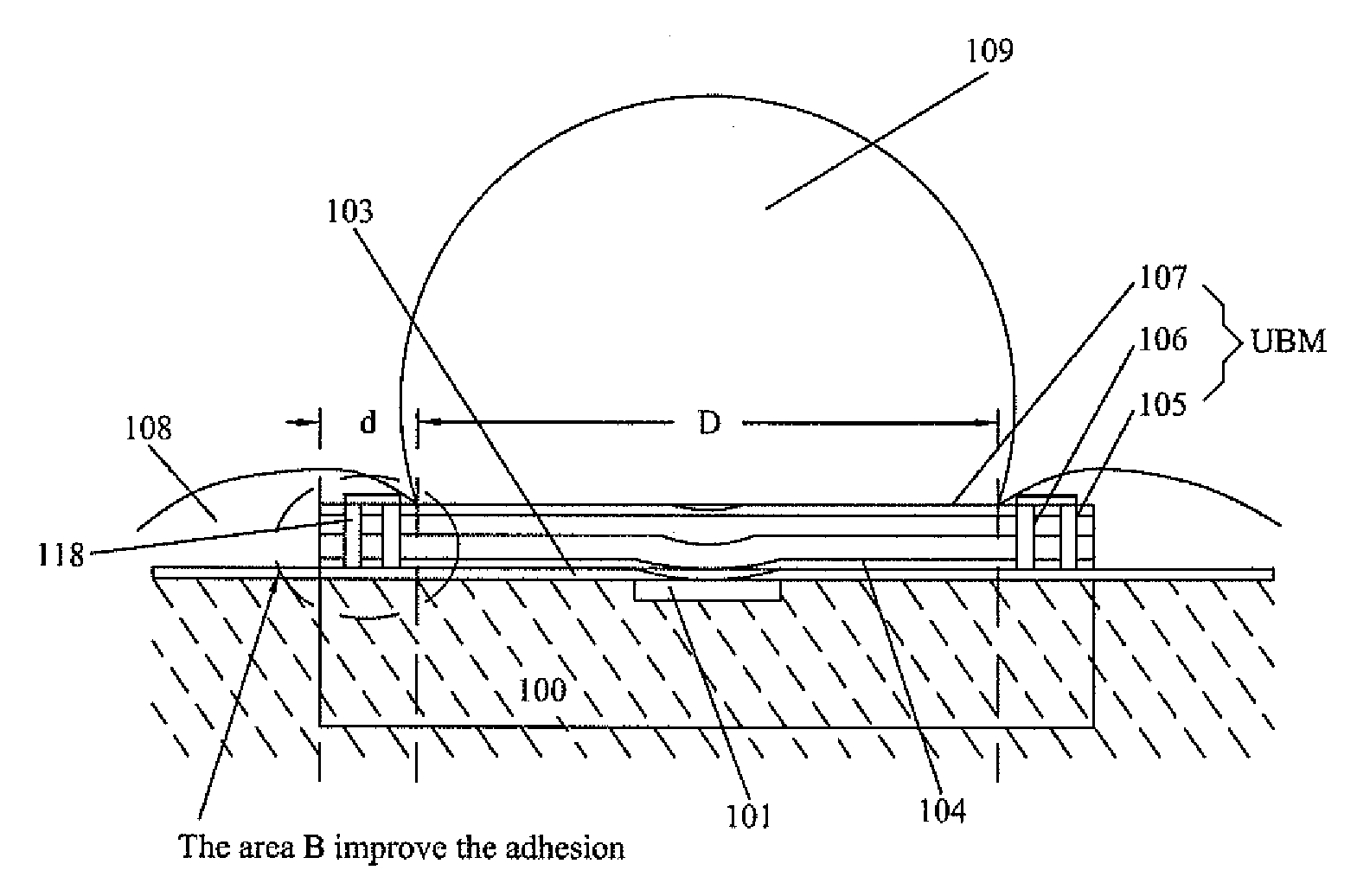

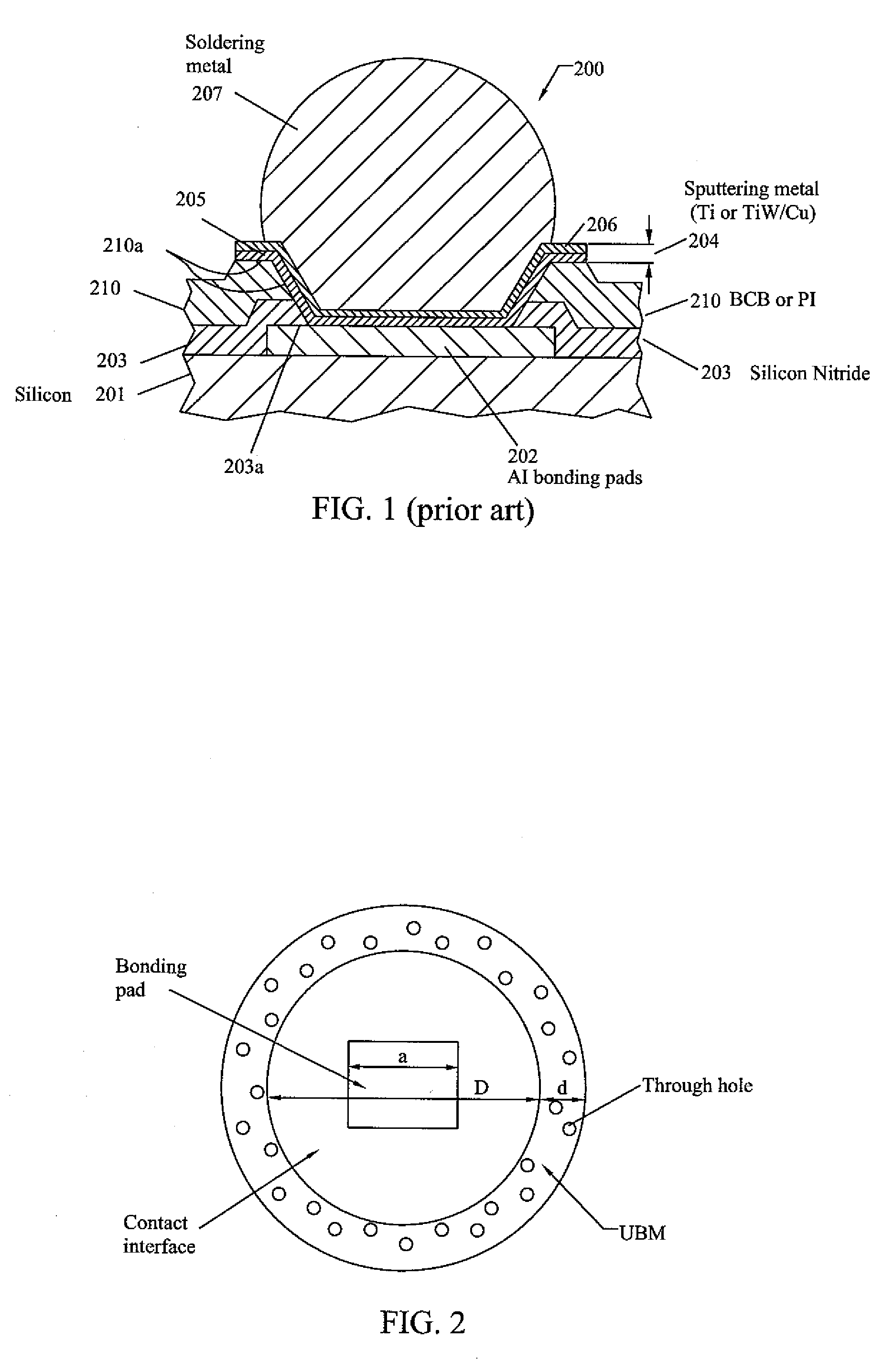

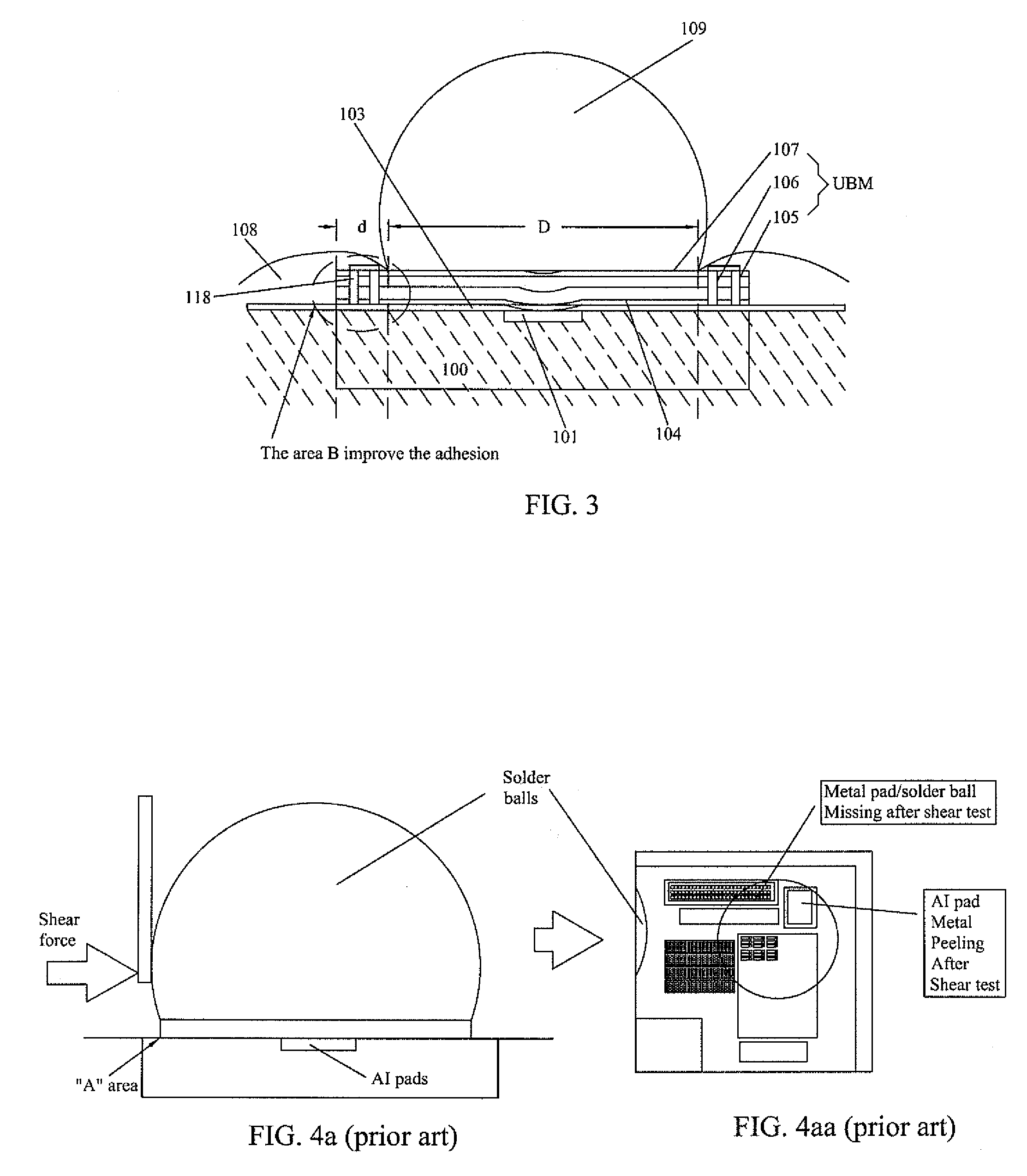

Under bump metallurgy structure of semiconductor device package

InactiveUS20090160052A1High bonding strengthImprove adhesionSemiconductor/solid-state device detailsSolid-state devicesSemiconductor packageEngineering

The under bump metallization (UBM) structure of semiconductor device comprises a substrate having a bonding pad disposed on an active surface; a UBM adhered on the bonding pad, wherein the UBM includes lateral embedded portions and the size of the UBM is larger than the size of the bonding pad; a dielectric layer over the UBM having opening that is smaller than the size of the UBM so as to allow the lateral embedded portions being embedded into the dielectric layer with a desired dimension; and a conductive ball melted on the UBM within the opening defined by the dielectric layer.

Owner:ADVANCED CHIP ENG TECH

Semiconductor socket with direct selective metalization

ActiveUS20150279768A1Improve electrical performanceImprove intelligenceContact member manufacturingSemiconductor/solid-state device detailsEngineeringConductive materials

A semiconductor socket including a substrate with a plurality of through holes extending from a first surface to a second surface. A conductive structure is disposed within the through holes A plurality of discrete contact members are located in the plurality of the through holes, within the conductive structure. The plurality of contact members each include a proximal end accessible from the second surface, and a distal end extending above the first surface. The conductive structure can be electrically coupled to circuit geometry. At least one dielectric layer is bonded to the second surface of the substrate with recesses corresponding to desired circuit geometry. A conductive material deposited in at least a portion of the recesses to form conductive traces redistributing terminal pitch of the proximal ends of the contact members.

Owner:HSIO TECH

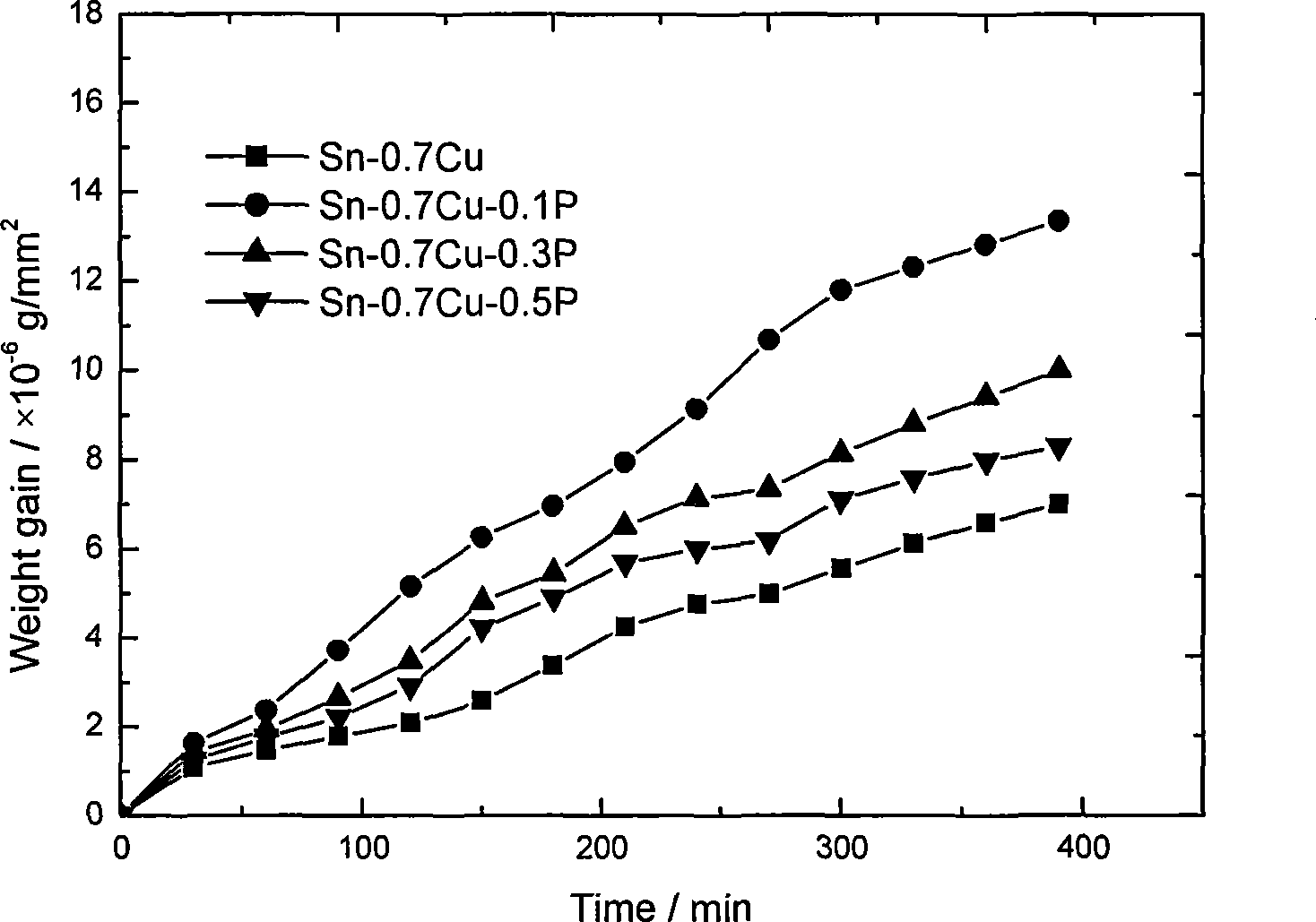

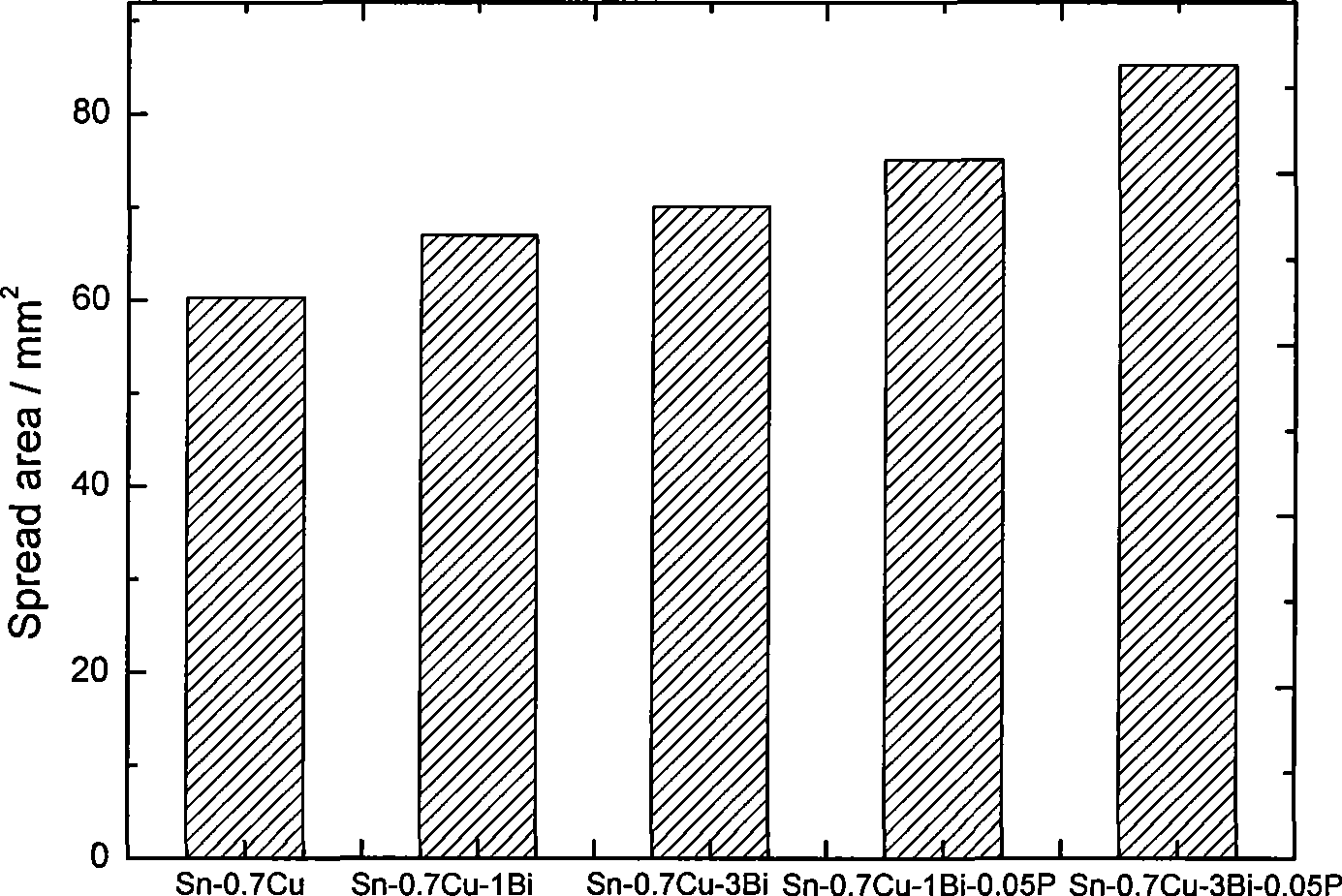

Sn-Cu base leadless solder alloy and preparation method

InactiveCN101381826AImprove wettabilitySmall mechanical propertiesMechanical propertyMaterials science

The invention relates to tin-copper-based lead-free solder alloy and a preparation method thereof. The compositions in mass percentage of the alloy are 0.1 to 1.5 percent of copper, 0.001 to 1 percent of phosphor, 0 to 6 percent of bismuth, 0 to 3 percent of zinc, and the balance being tin. The preparation method comprises the following steps: 3 to 8 percent of the phosphor and 92 to 97 percent of the tin are weighed at first and placed into a graphite crucible; the mixture is covered with protective molten salt and subjected to heat preservation for 30 to 60 minutes at a temperature of between 400 and 550 DEG C; after uniform stirring, casting is performed and tin-copper intermediate alloy is obtained; the tin-copper intermediate alloy is weighed according to the fact that the phosphor occupies 0.001 to 1 percent as calculated by the total mass of 100 percent, and 0.1 to 1.5 percent of the copper, 0 to 6 percent of the bismuth, 0 to 3 percent of the zinc and residual tin are weighed and placed into the graphite crucible; the mixture is covered with the protective molten salt and subjected to heat preservation for 40 to 80 minutes at a temperature of between 450 and 550 DEG C; and after uniform stirring, the mixture is cast into ingots. The preparation method has simple preparation technique and is easy to operate; and the product of the tin-copper-based lead-free solder alloy has the advantages of good wettability, low melting point, good mechanical property, good antioxidation, low cost and so on.

Owner:NANCHANG UNIV

Electronic assemblies and systems with filled no-flow underfill

InactiveUS20070278655A1Improve solder joint reliabilityLow viscositySemiconductor/solid-state device testing/measurementSemiconductor/solid-state device detailsElectronic systemsSilicon oxide

High yield, high reliability, flip-chip integrated circuit (IC) packages are achieved utilizing a combination of heat and pressure to bond flip-chip die and to cure no-flow underfill material. The underfill comprises a filler or low coefficient of thermal expansion (CTE) material to decrease CTE of the cured underfill. The filler material can be selected from the group comprising silica, silicon oxide, silicon dioxide, silicon nitride, aluminum oxide, aluminum nitride, or a mixture thereof. The filler material may also increase the viscosity of the uncured underfill and / or increase the modulus of elasticity of the cured underfill. In some method embodiments, a thermocompression bonder is used to simultaneously provide solder bump reflow and underfill curing. Application of various methods to a component package, an electronic assembly, and an electronic system are also described.

Owner:INTEL CORP

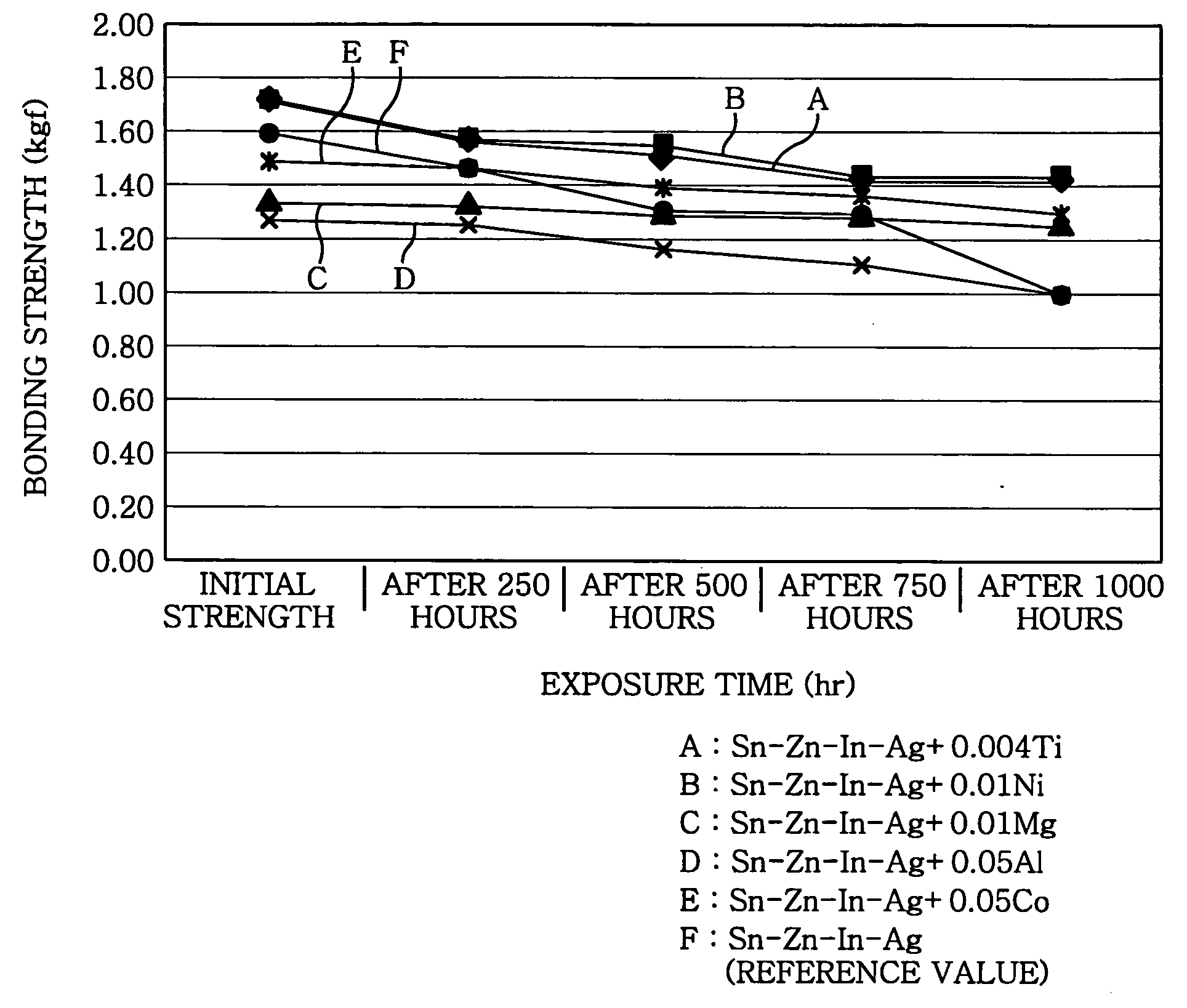

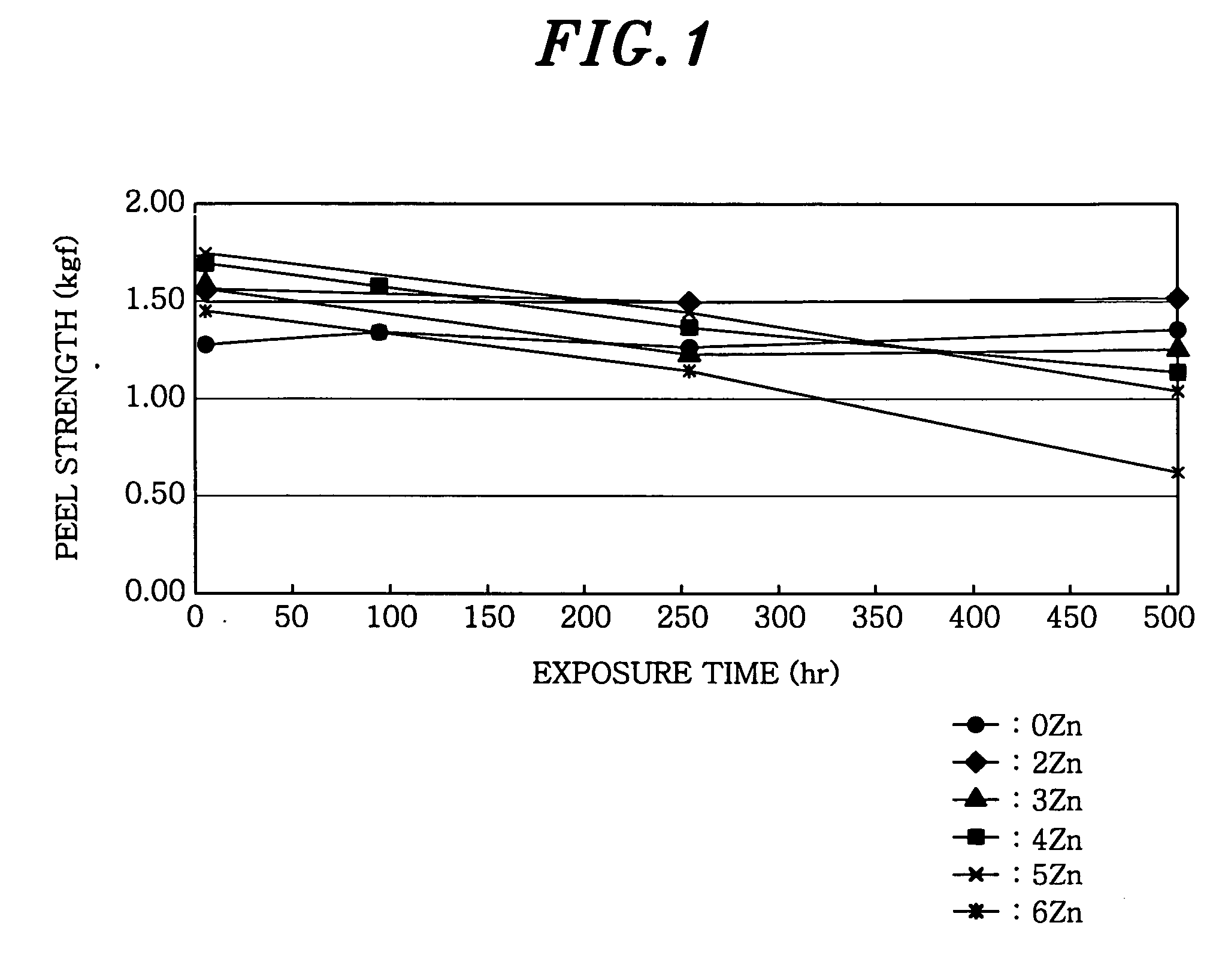

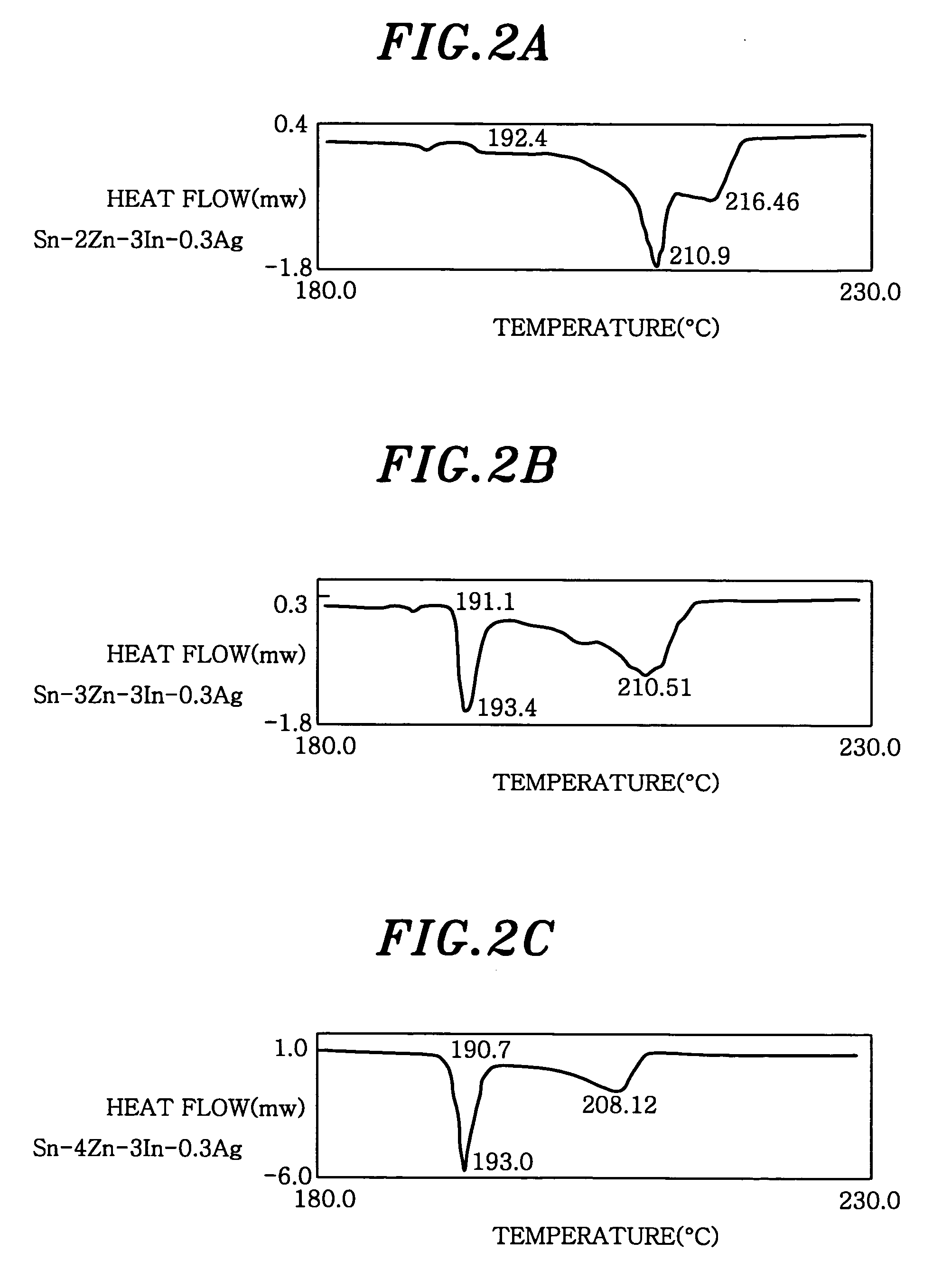

Pb-free solder alloy, and solder material and solder joint using same

InactiveUS20050079092A1Improve solder joint reliabilityWelding/cutting media/materialsSoldering mediaHigh humidityUltimate tensile strength

A solder alloy based on an Sn—Zn—In—Ag system contains, in weight, 3.0%<Zn<5.0%, 0.1%<In<4.0%, 0.1%<Ag<0.4%, and the balance Sn. Therefore, the current Sn—Pb soldering method can be employed as it is. Further, a Pb-free solder material having a solder characteristic with excellent bonding strengths of the parts can be provided. Still further, since a difference between a solidus temperature and a liquidus temperature is small, floating of the parts leads can be suppressed, even in case where packaging processes are performed many times over. Still further, when the joint is exposed to the high temperature and high humidity atmosphere, the bonding strength can be prevented from being lowered.

Owner:PANASONIC CORP

Electrical interconnect IC device socket

ActiveUS9276339B2Reduce component complexityImprove solder joint reliabilityContact member assembly/disassemblyCoupling contact membersContact padSurface mounting

A surface mount electrical interconnect adapted to provide an interface between contact pads on an LGA device and a PCB. The electrical interconnect includes a socket substrate having a first surface with a plurality of first openings having first cross-sections, a second surface with a plurality of second openings having second cross-sections, and center openings connecting the first and second openings. The center openings include at least one cross-section greater than the first and second cross-sections. A plurality of contact members are located in the socket substrate such that first contact tips are located proximate the first openings, second contact tips are located proximate the second openings, and center portions located in the center openings.

Owner:HSIO TECH

Method of forming a semiconductor socket

ActiveUS9320144B2Reduce complexityFirmly connectedPrinted circuit assemblingElectrically conductive connectionsConductive materialsEngineering

Owner:HSIO TECH

Electron device and semiconductor device

InactiveUS20020066583A1Improve solder joint reliabilityEasy to transformSemiconductor/solid-state device detailsSolid-state devicesShock resistanceEngineering

An electronic equipment is capable of improving falling down shock resistance or impact resistance in an electronic equipment and of improving reliability of a solder joint in a semiconductor device die-bonded Si chip or the like to which thermal shock causing large deformation may act, bump mounting of BGA, CSP, WPP, flip-chip and so forth, a power module acting large stress and so forth. The electronic equipment has a circuit board and an electronic parts to be electrically connected to an electrode of the circuit board. The electrode of the circuit board and an electrode of the electronic part are connected by soldering using a lead free solder consisted of Cu: 0~2.0 mass %, In: 0.1~10 mass %, and Sn: remaining amount.

Owner:HITACHI LTD

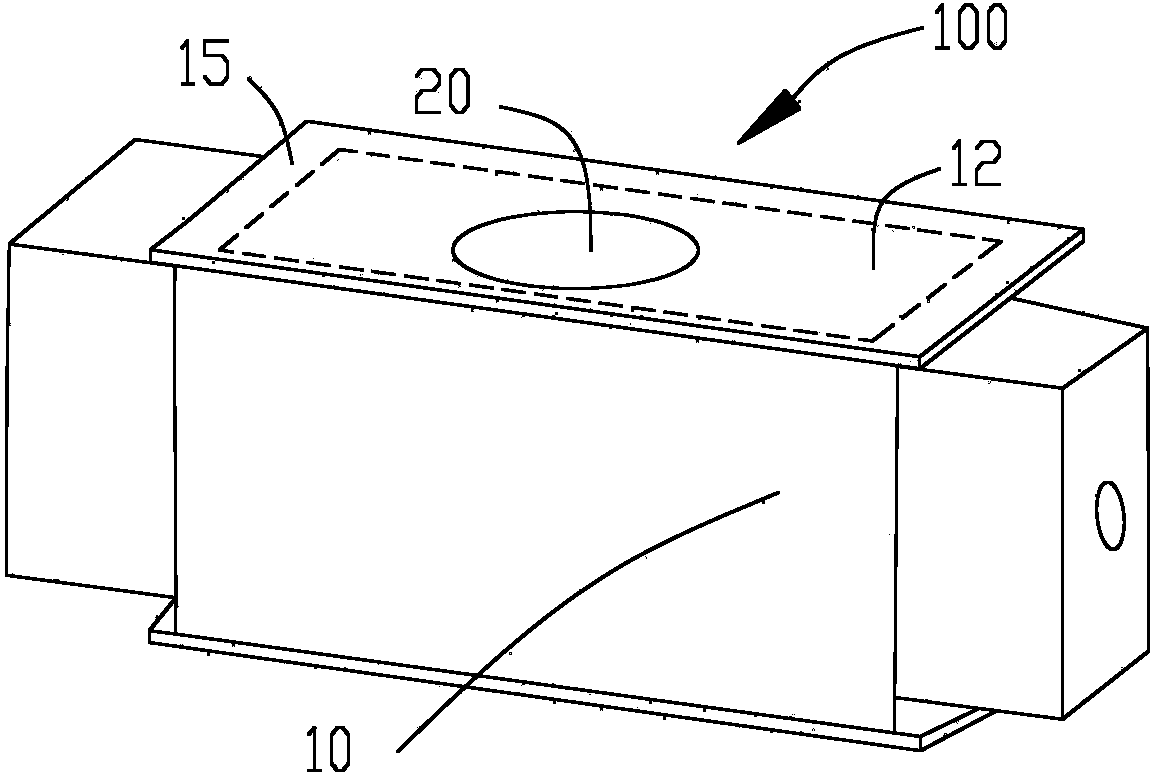

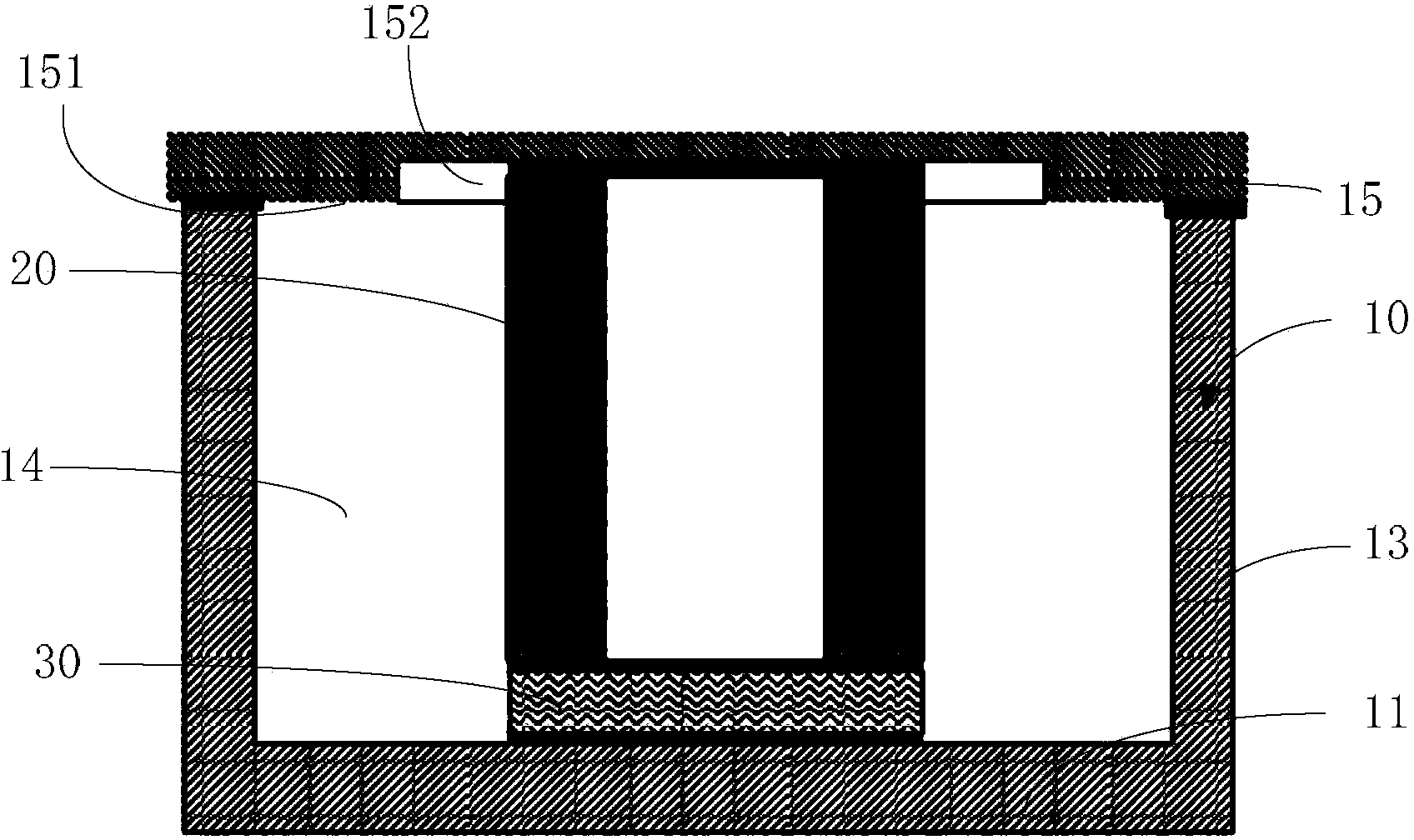

TM (transverse magnetic)-mode dielectric filter

InactiveCN103972618AExtended service lifeImprove solder joint reliabilityWaveguide type devicesDielectricEngineering

The invention provides a TM (transverse magnetic)-mode dielectric filter which comprises a shell, a cover plate, a dielectric filter and a mounting layer. An opening is formed in the shell, the cover plate covers the opening side of the shell, the mounting layer is arranged on the shell, the dielectric filter is positioned between the cover plate and the shell, two opposite ends of the dielectric filter are respectively welded with the cover plate and the mounting layer, and a thermal expansion coefficient of the mounting layer and a thermal expansion coefficient of the cover plate range from a thermal expansion coefficient of the shell and a thermal expansion coefficient of the dielectric filter.

Owner:HUAWEI MACHINERY

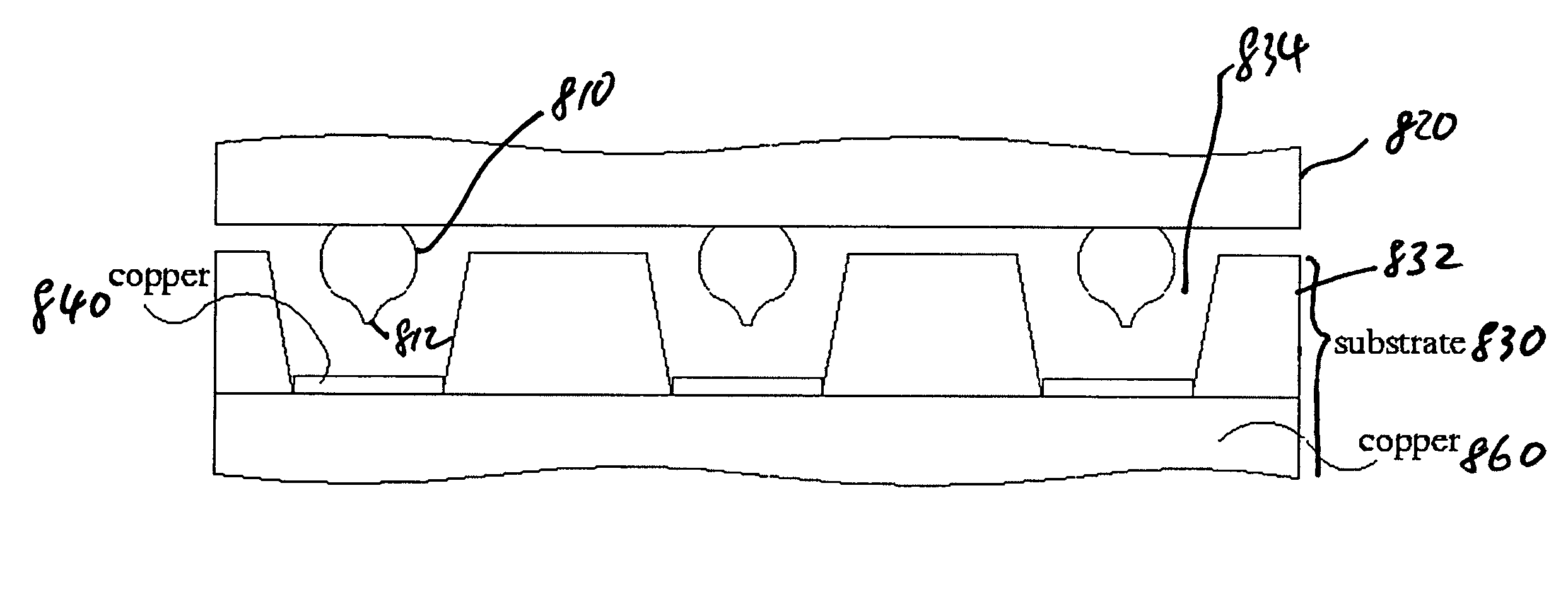

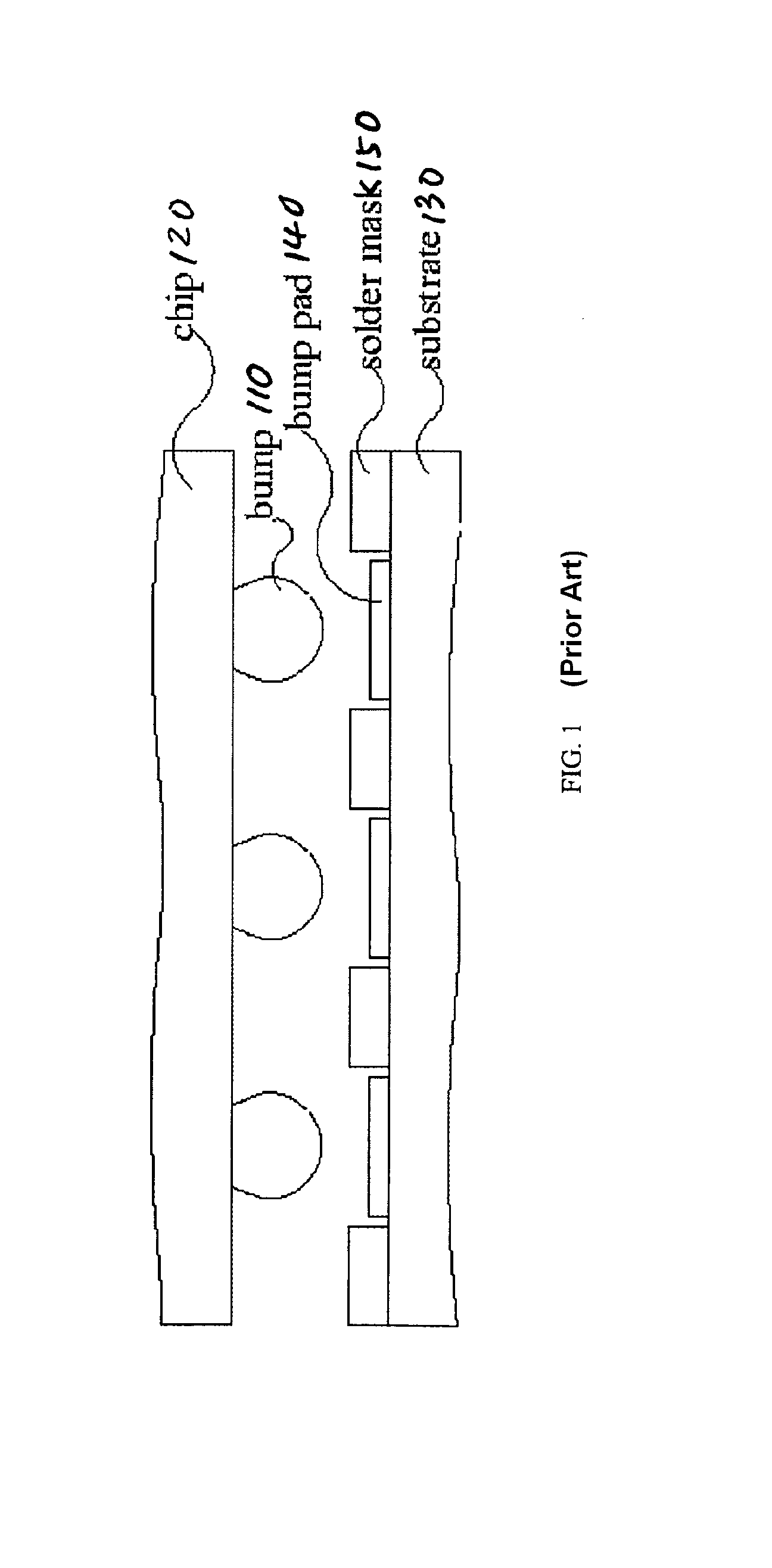

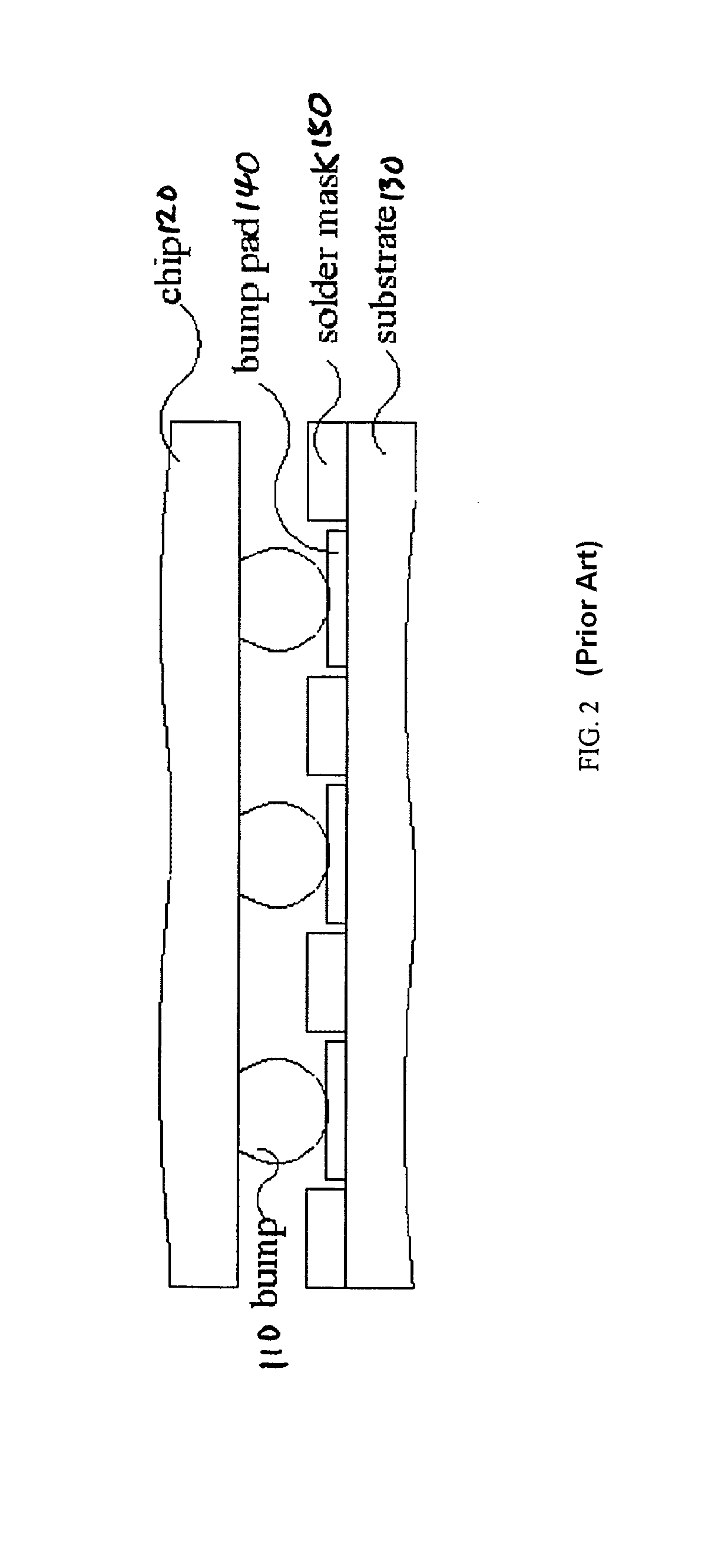

Substrate and process for semiconductor flip chip package

ActiveUS7652374B2Increase contact areaImprove solder joint reliabilityPrinted circuit assemblingSemiconductor/solid-state device detailsElectrical connectionSemiconductor package

A semiconductor package structure for flip chip package includes at least a patterned circuit layer and an insulating layer alternately stacking up each other. The patterned layer includes a plurality of bump pads, and the insulating layer includes a plurality of etching holes. The etching holes and the bump pads are aligned, such that the bump pads are exposed through the etching holes. A plurality of bumps is disposed on the active surface of the chip, which can be obtained by stud bumping. The etching holes are filled with solder paste, and the bumps of the chips penetrate into the solder filled etching holes. Vibration obtained by mechanical equipment, or ultrasonic equipment can be applied to assist the alignment of the bumps to the corresponding bump pads. A reflow process is applied to collapse the solder paste that fills the etching holes to form electrical connection between the bumps and bump pads.

Owner:INTELLECTUAL VENTURES FUND 27

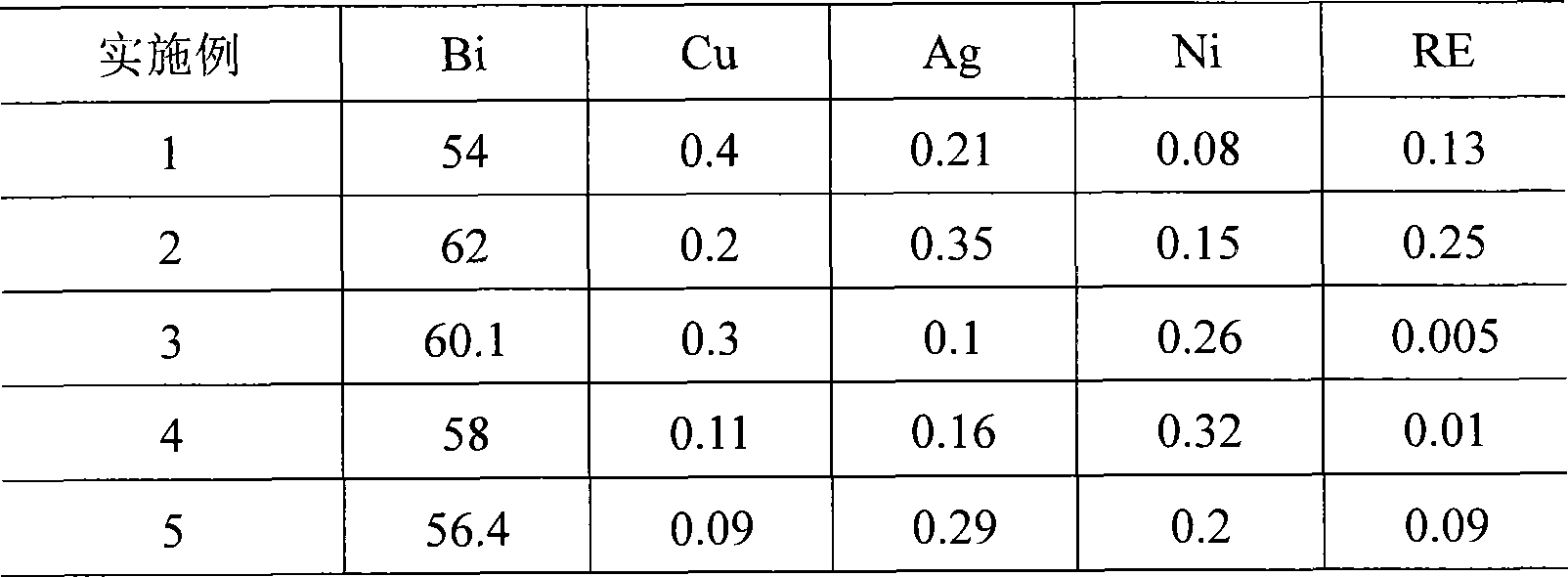

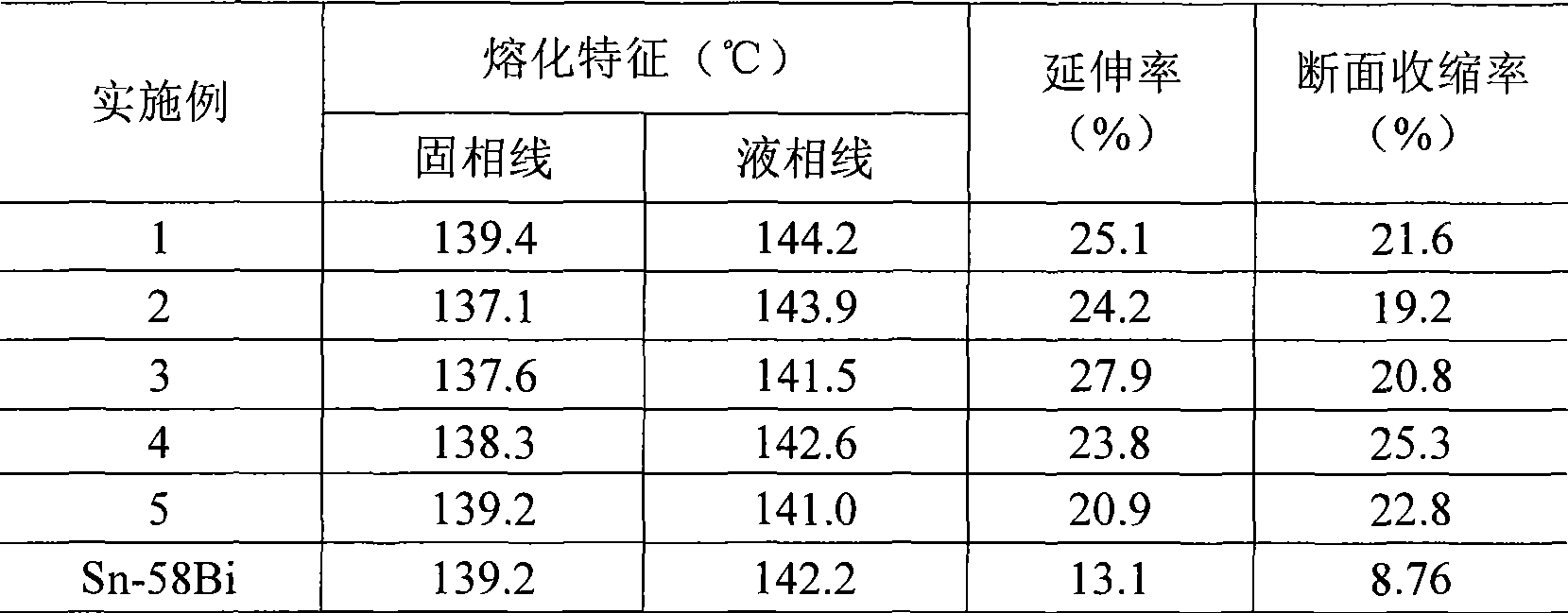

Low melting point lead-free solder alloy

The invention discloses a lead-free solder alloy with a low melting point, which is composed of the following components: 53.0wt percent to 65.0wt percent of Bi, 0.02wt percent to 0.5wt percent of Cu, 0.01wt percent to 0.43wt percent of Ag, 0.01wt percent to 0.4wt percent of Ni, 0.001wt percent to 0.6wt percent of RE, and Sn as the rest. The invention is the lead-free solder alloy of a low melting point that can improve brittleness, enhance tractility and plasticity, be easy to be manufactured into thread-solder and have high reliability of welding spots. The lead-free solder alloy with a low melting point is applied to the welding of heat sensitive components and parts and the step soldering of electronic components and parts.

Owner:GUANGZHOU RES INST OF NON FERROUS METALS

Solder pastes for providing high elasticity, low rigidity solder joints

ActiveUS20050092819A1Increase elasticityReduce rigidityPrinted circuit assemblingPrinted circuit aspectsThermal expansionSolder paste

Solder pastes for providing high elasticity, low rigidity solder joints are disclosed. The solder pastes may be used between two parts having large mismatches in their coefficients of thermal expansion and / or when there is a high likelihood of mechanical deformity when the two parts are soldered together. In one particular exemplary embodiment, a solder paste may be realized as a composition comprising a solder powder and high melting temperature particles with a flux, wherein the ratio between solder powder and high melting temperature particles may be between 2:1 and 1:10.

Owner:INDIUM CORPORATION +1

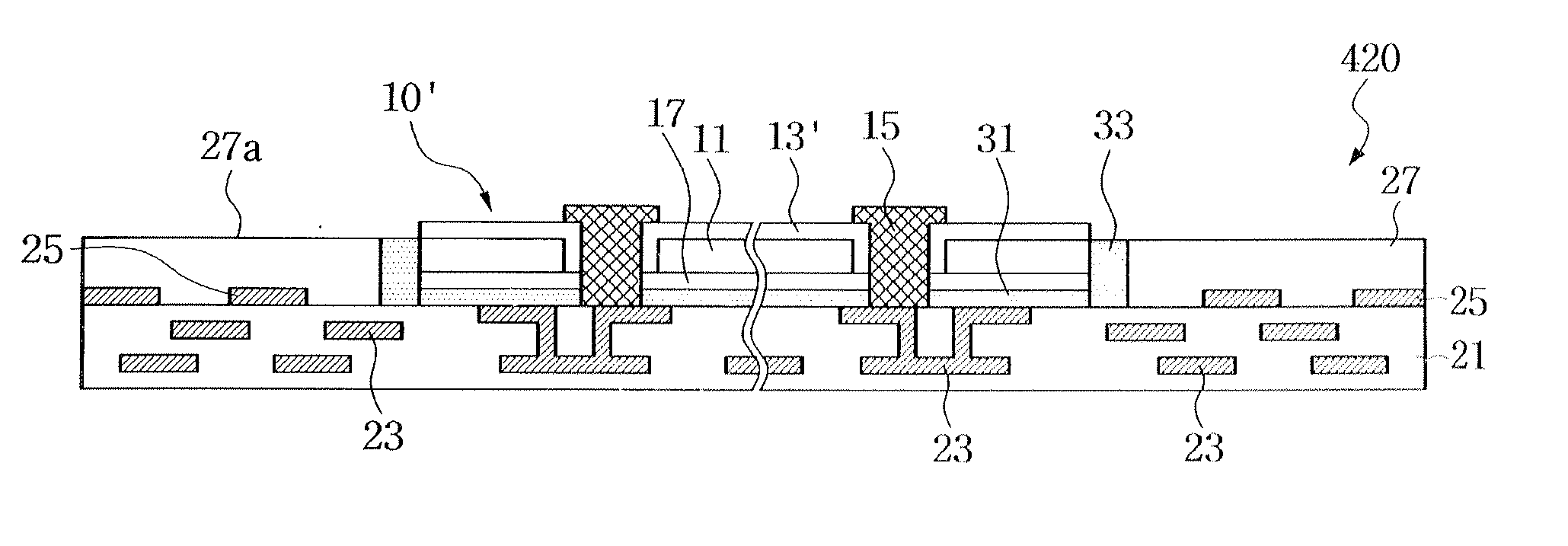

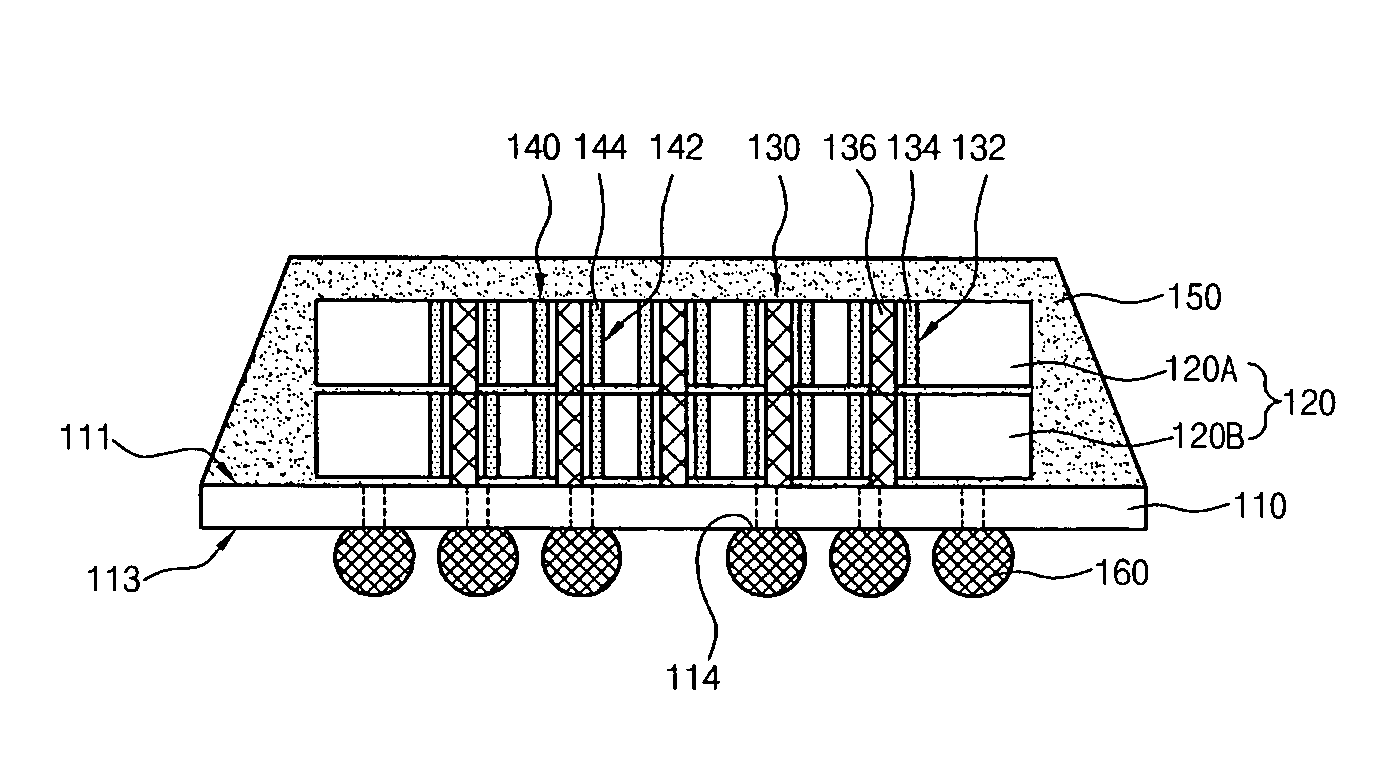

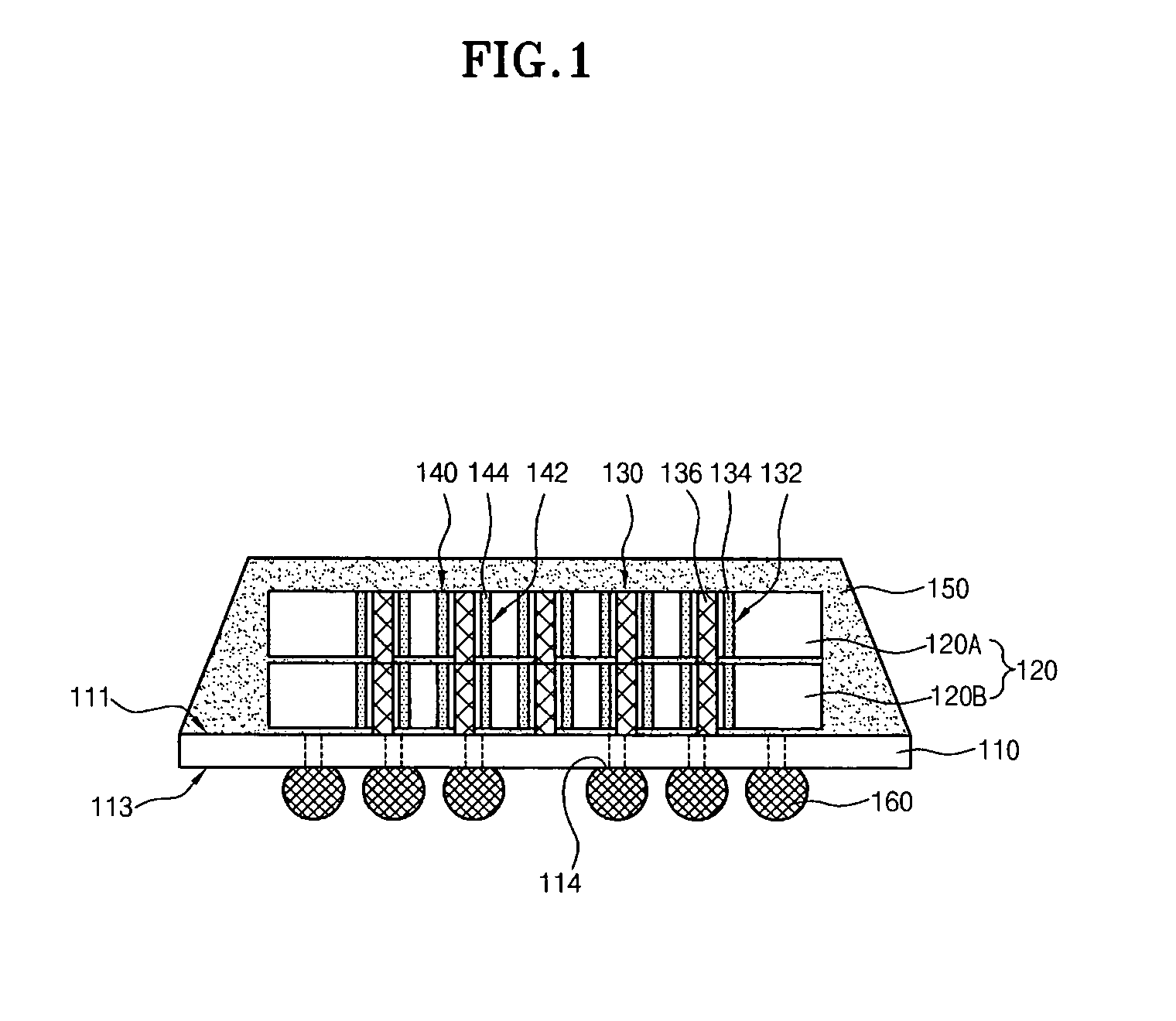

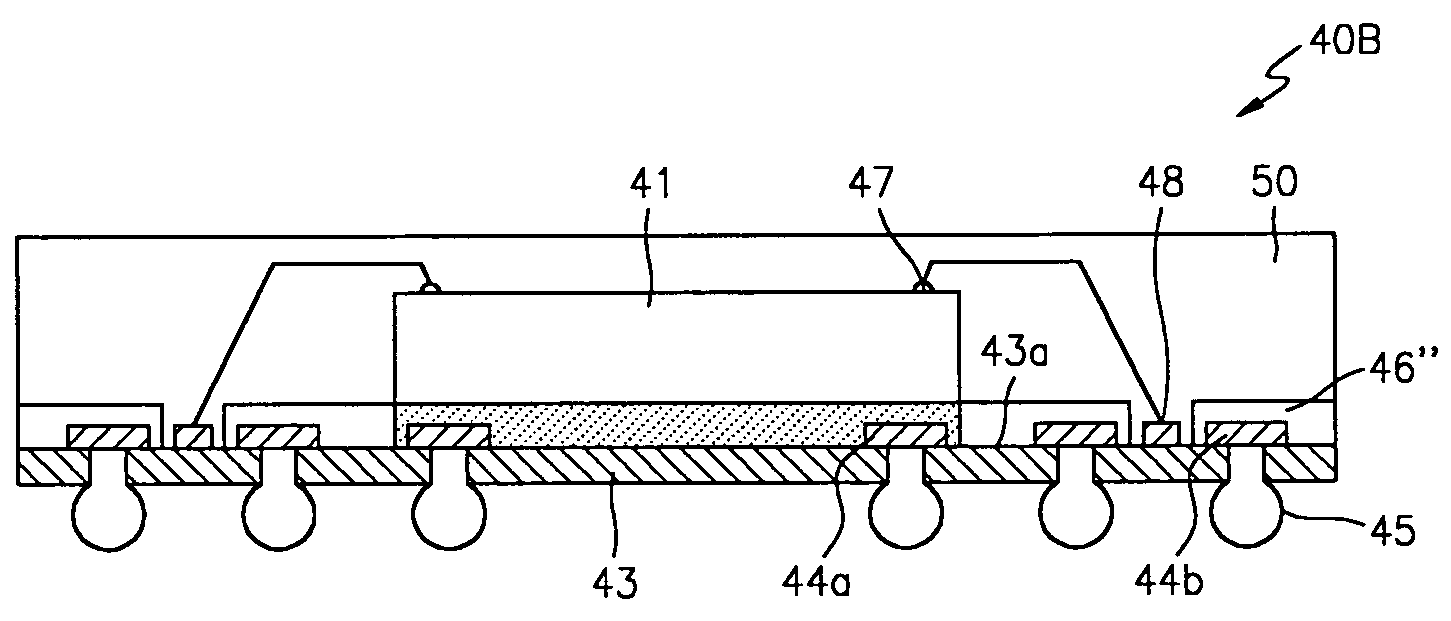

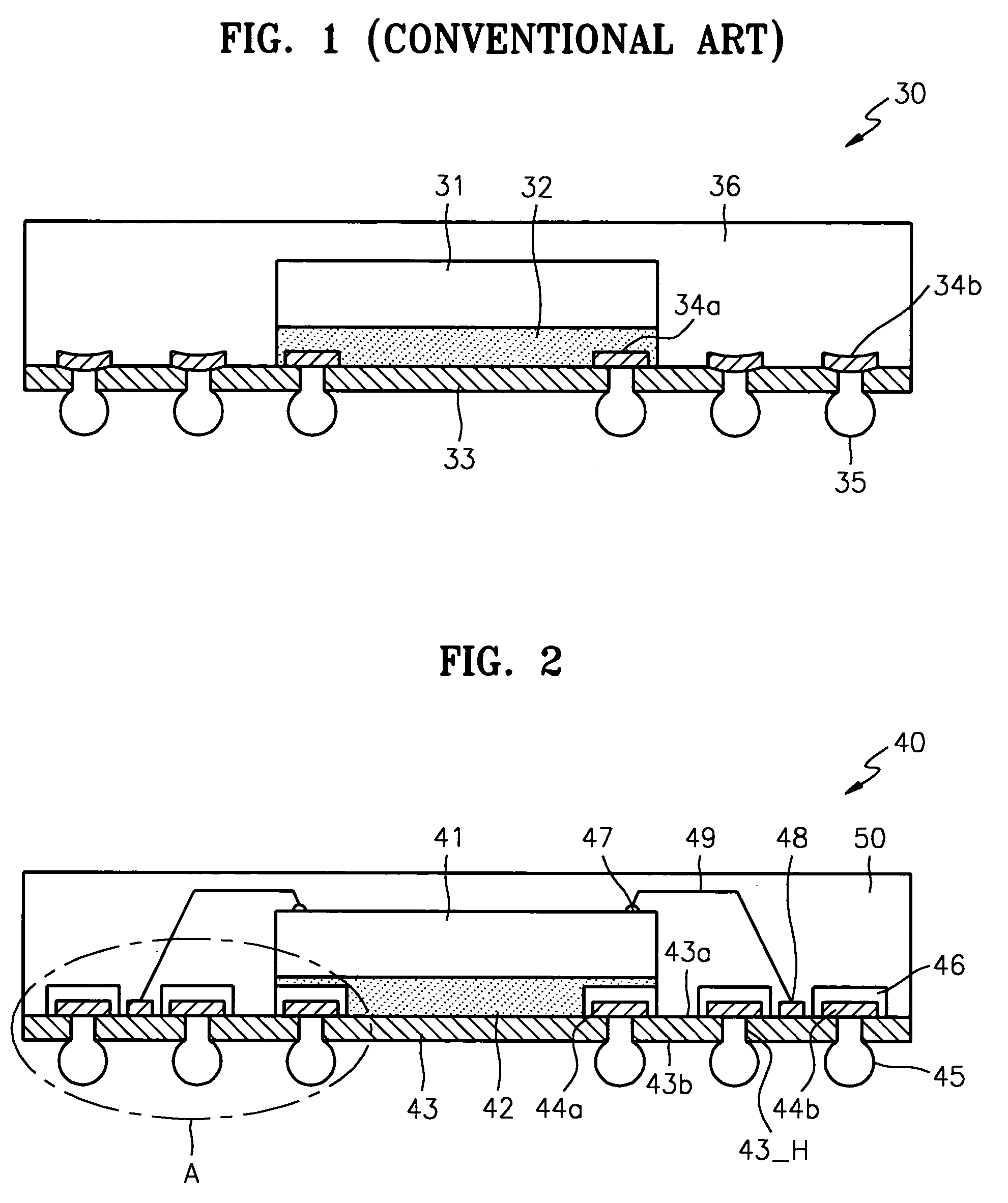

Multi-stacked package and method of manufacturing the same

ActiveUS7566961B2Improve solder joint reliabilityImprove fluencyFinal product manufactureSemiconductor/solid-state device detailsEngineeringMechanical engineering

Owner:SAMSUNG ELECTRONICS CO LTD

Lead frame soldering method

ActiveCN103752970APrevent oxidationImprove solderabilityWelding/cutting media/materialsMetal working apparatusSurface layerSolderability

The invention provides a lead frame soldering method which is characterized in that a nickel base layer is plated on the surface of a lead frame before soldering, a tin surface layer is plated on the surface of the nickel base layer, and then follow-up operation of soldering paste coating and reflow soldering is conducted. By plating the tin surface layer as a protection layer of the nickel base layer, oxidization of the nickel base layer can be prevented, and solderability of the lead frame is improved. Black pads and brittle failure are prevented from happening, interface cavity rate is reduced, and soldering spot reliability is improved. On the basis of the existing lead frame soldering, soldering spot requirements of surface pasting components can be met by changing the plated layers of the lead frame and the content of soldering flux lead (Pb), and other procedures are not required. The whole method is simple and easy to implement and popularize.

Owner:MORNSUN GUANGZHOU SCI & TECH

Ball grid array package having improved reliability and method of manufacturing the same

InactiveUS7071027B2Reduce distortionImprove solder joint reliabilityPrinted circuit assemblingSemiconductor/solid-state device detailsSolder ballEngineering

A ball grid array package utilizing a layer of an elastic insulating material to protect conductive ball lands from deformation during subsequent processing and use of the resulting device and a method of manufacturing the same are disclosed. The elastic insulating layer preferably has a modulus of elasticity no greater than about 20 MPa or less to absorb and or distribute mechanical stress applied to conductive ball lands directly or through solder ball joints or other structures and thereby improve the solder joint reliability (SJR) of the resulting device.

Owner:SAMSUNG ELECTRONICS CO LTD

Board structure, a ball grid array (BGA) package and method thereof, and a solder ball and method thereof

InactiveUS20070102816A1Improve solder joint reliabilityInhibit sheddingFinal product manufactureSemiconductor/solid-state device detailsSolder ballEngineering

A board structure, a ball grid array (BGA) package and method thereof and a solder ball and method thereof. The example solder ball may include a solder portion and a grooved connection portion, formed through a partitioning process, configured to fit a corresponding protruding portion on a board. The example BGA package may include a plurality of the example solder balls. The example board structure may include the example BGA package connected to the board via the grooved connection portions and the protruding portions.

Owner:SAMSUNG ELECTRONICS CO LTD

High-reliability application printed circuit board assembly QFN assembling and welding pretreatment method

ActiveCN110449683AImprove Yield and ReliabilityIncreased stability and longevitySoldering apparatusPrinted circuitsReflow solderingPretreatment method

The invention discloses a high-reliability application printed circuit board assembly QFN assembling and welding pretreatment method. The method comprises the following steps that 1) a carrying plateis manufactured; 2), a mesh plate is manufactured, at least one through hole corresponding to a QFN chip bonding pad is formed in the mesh plate, and the through holes form a through hole array; 3) dehumidification treatment is carried out on a QFN chip; 4), the mesh plate and the carrying plate are cleaned; 5) the mesh plate is placed on the carrying plate, and a soldering paste containing a soldering flux is printed on the carrying plate through the through hole array; 6) the QFN chip is pasted on the carrying plate with the soldering paste by a chip mounter; 7) hot air reflow soldering processing is performed on the carrying plate pasted with the QFN chip; and 8) the carrying plate pasted with the QFN chip is immersed into a cleaning agent so as to dissolve the soldering flux residue, and the QFN chip is separated from the carrying plate to complete the pre-tin coating. According to the method, the weldability of the QFN chip bonding pad is better through the pre-tin coating treatment, the welding qualification rate and reliability of the QFN chip can be improved, the stability and the service life of the printed circuit board assembly with high reliability are improved, and themaintenance cost of the system is reduced.

Owner:嘉兴军胜电子科技有限公司

Tail potting method of cable electric coupler for satellite

ActiveCN103682937ARealize visualizationImprove insulation performanceContact member assembly/disassemblyEpoxyEngineering

The invention provides a tail potting method of a cable electric coupler for a satellite. The method includes the steps that first, E-51 epoxy resin and a curing agent thereof are weighed, the E-51 epoxy resin and the curing agent are mixed according to the proportion that the E-51 epoxy resin to the curing agent is 4 to 1, and a bi-component epoxy resin pouring sealant is manufactured and is filled into a container; afterwards, a stirring defoaming machine is started, and a stirring defoaming program is set; the container filled with the bi-component epoxy resin pouring sealant is placed into the stirring defoaming machine, so that stirring and defoaming are carried out; the bi-component epoxy resin pouring sealant after stirring and defoaming is filled into an injection device, the pouring sealant is manually and slowly poured into the tail portion of the cable electric coupler, whether bubbles generate or not is observed at any time, if the bubbles generate, operation is stopped, the defoaming program is executed again, and operation continues after defoaming; at last, the potted able electric coupler is fixed to be solidified. The tail potting method of the cable electric coupler for the satellite achieves visualization of electric coupler welding spots and has the advantages of improving the reliability of the welding spots, prolonging the service life of cables and lowering the working cost.

Owner:SHANGHAI INST OF SATELLITE EQUIP

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com