Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

58results about How to "Improve ESD resistance" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Liquid crystal display panel

ActiveCN105070239AImprove the efficiency of failure analysisExtended service lifeStatic indicating devicesNon-linear opticsLiquid-crystal displayEngineering

The invention provides a liquid crystal display panel. According to the liquid crystal display panel, each test terminal at the periphery of an array substrate is provided with a switch circuit, when static electricity on the test terminals needs to be released through the switch circuits, all the test terminals are connected with a common electrode wire, and the static electricity is released through the common electrode wire, such that the anti-ESD capability of the test terminals is enhanced, and the service life of the liquid crystal display panel is prolonged.

Owner:WUHAN CHINA STAR OPTOELECTRONICS TECH CO LTD

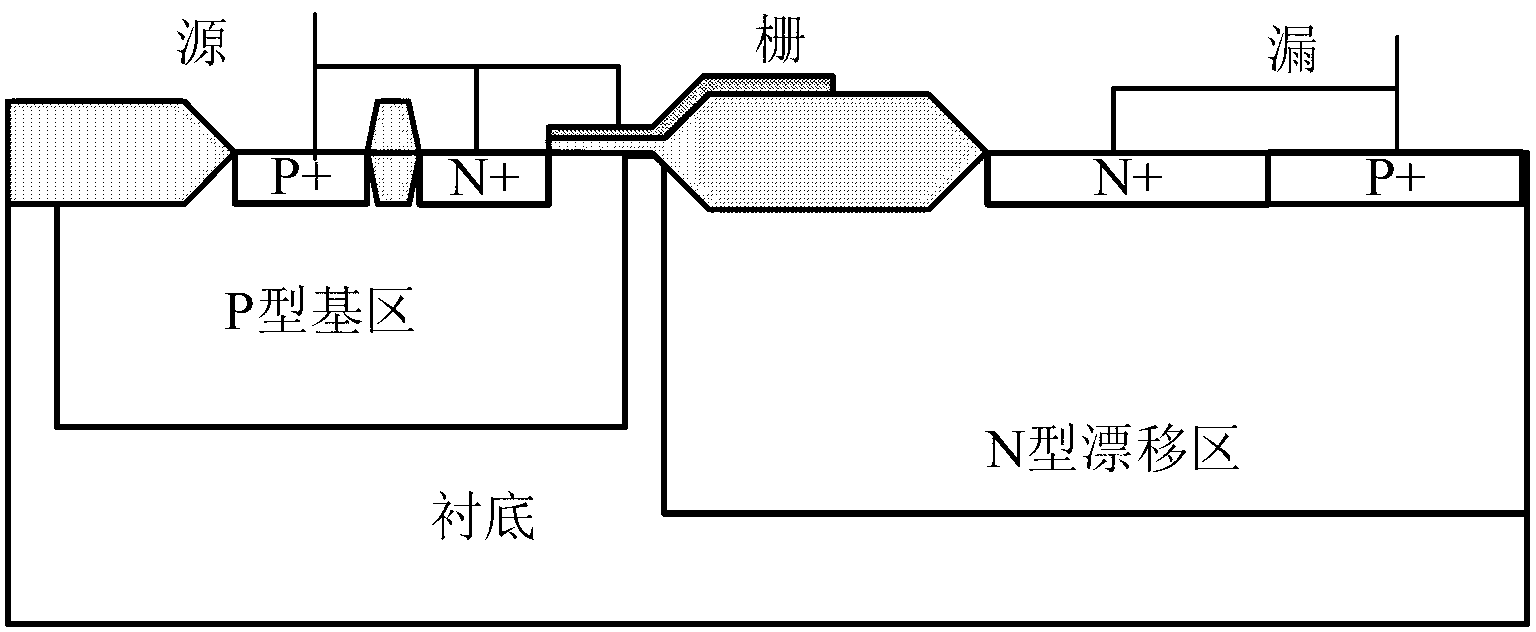

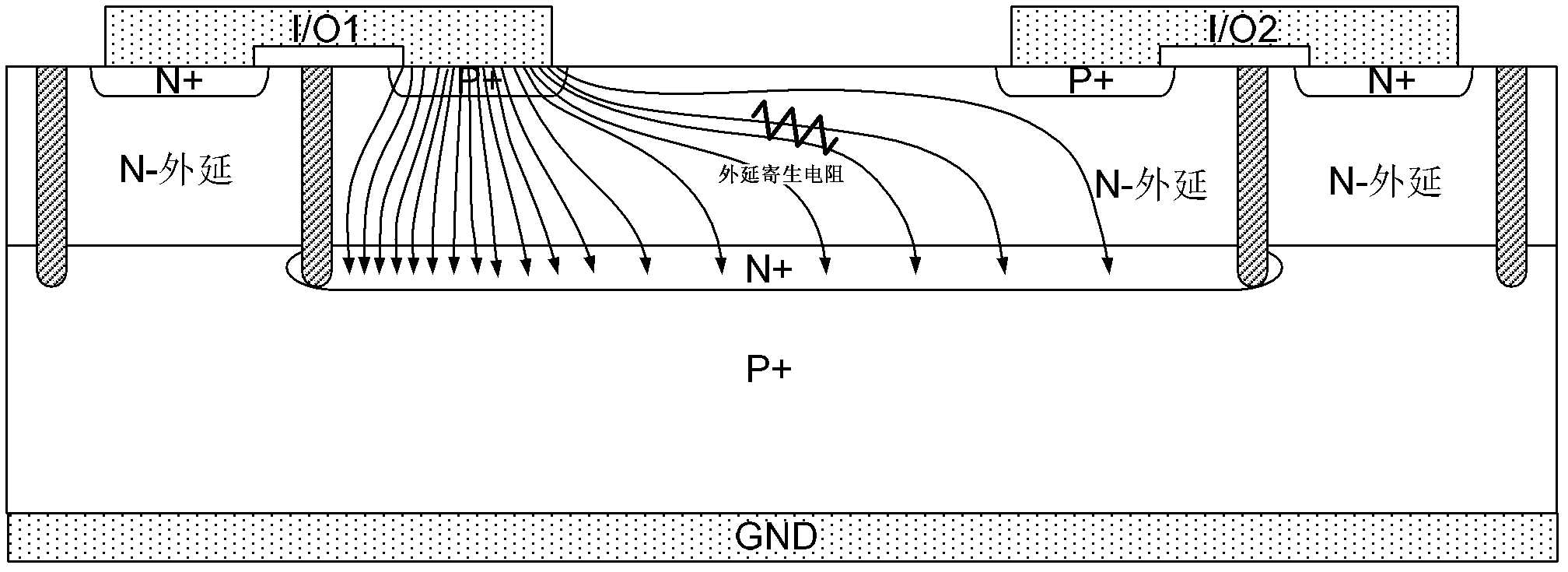

LDMOS SCR for protection against integrated circuit chip ESD

InactiveCN103258814AIncrease the Vhold valueImproves latch-up immunitySemiconductor/solid-state device detailsSolid-state devicesLow voltageHigh voltage

The invention discloses an LDMOS SCR for protection against integrated circuit chip ESD protection and belongs to the technical field of electrons. According to the LDMOS SCR for the protection against the integrated circuit chip ESD, a low-voltage MOS is integrated on the basis of a traditional structure of the LDMOS SCR for the protection against the integrated circuit chip ESD and the low-voltage MOS is used for limiting a hole current injected from the positive electrode of the nested SCR, so that value of the holding voltage Vhold is improved and latch-up immune ability of the LDMOS SCR in high-voltage application is improved. In addition, compared with an ordinary LDMOS, the LDMOS SCR for the protection against the integrated circuit chip ESD is stronger in ability of the protection against the ESD due to the integrated SCR. Besides, the LDMOS SCR for the protection against the integrated circuit chip ESD and the Bipolar CMOS DMOS technology are compatible.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

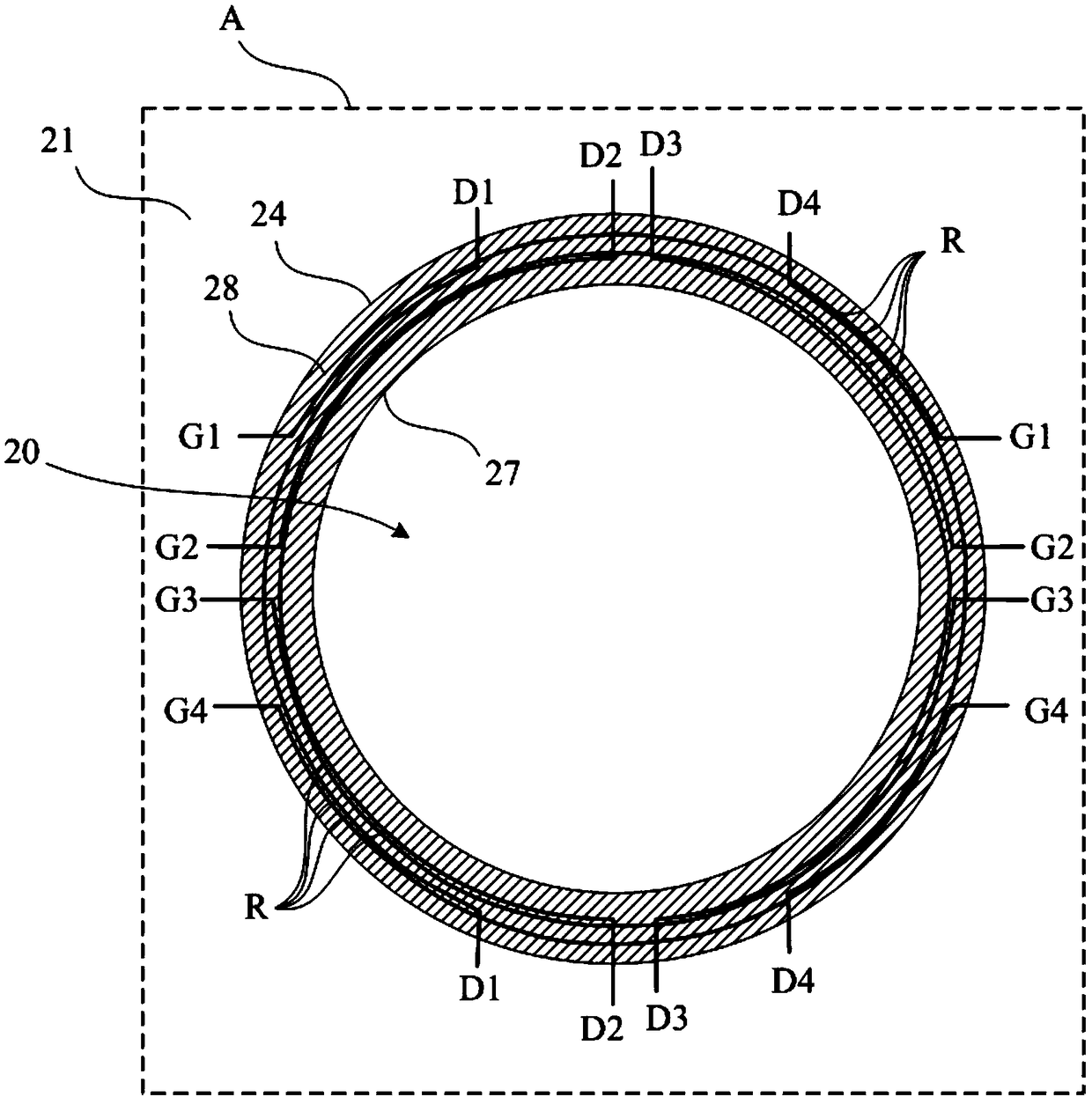

Display panel

InactiveCN108735094AGuaranteed reliabilityImprove ESD resistanceElectrostatic discharge protectionInput/output processes for data processingStaticsElectrostatic discharge protection

The invention discloses a display panel. The display panel is characterized by comprising a display area, a first non-display area, a trepanning, a second non-display area and an anti-static discharging protection circuit, wherein the display area is provided with multiple display units arranged in an array; the first non-display area surrounds the display area; the trepanning is formed in an areain the display area; the second non-display area is located between the display area and the trepanning, and the second non-display area is internally provided with multiple arc-shaped wirings used for being connected with corresponding data cables, gate lines and touch signal lines respectively; the anti-static discharging protection circuit comprises a suspension joint metal wiring, and the suspension joint metal wiring is arranged on the periphery of the trepanning and located in the second non-display area. The anti-static discharging protection circuit is arranged on the second non-display area so as to improve the ESD resistance capacity of the touch signal lines on the second non-display area, thereby ensuring the reliability of the display panel provided with the trepanning in thedisplay area.

Owner:WUHAN CHINA STAR OPTOELECTRONICS TECH CO LTD

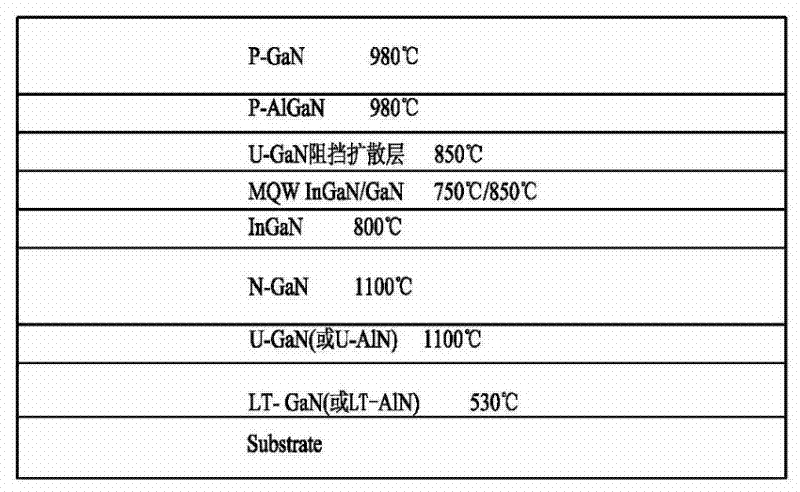

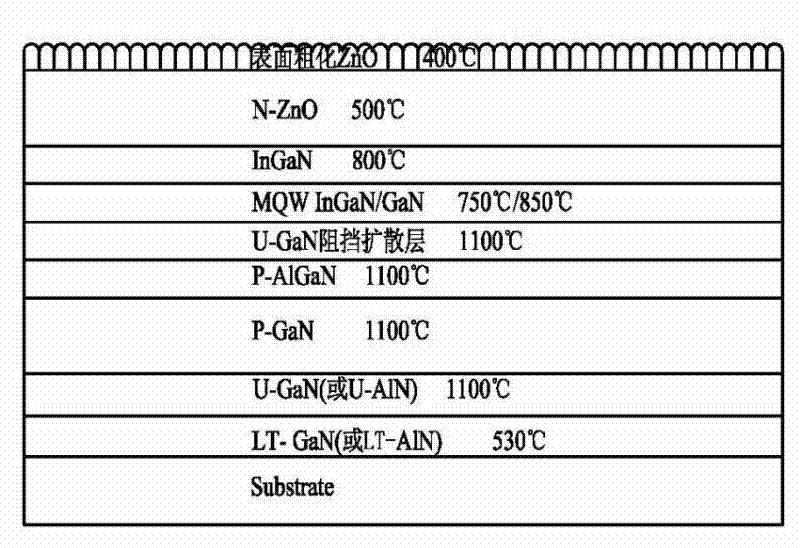

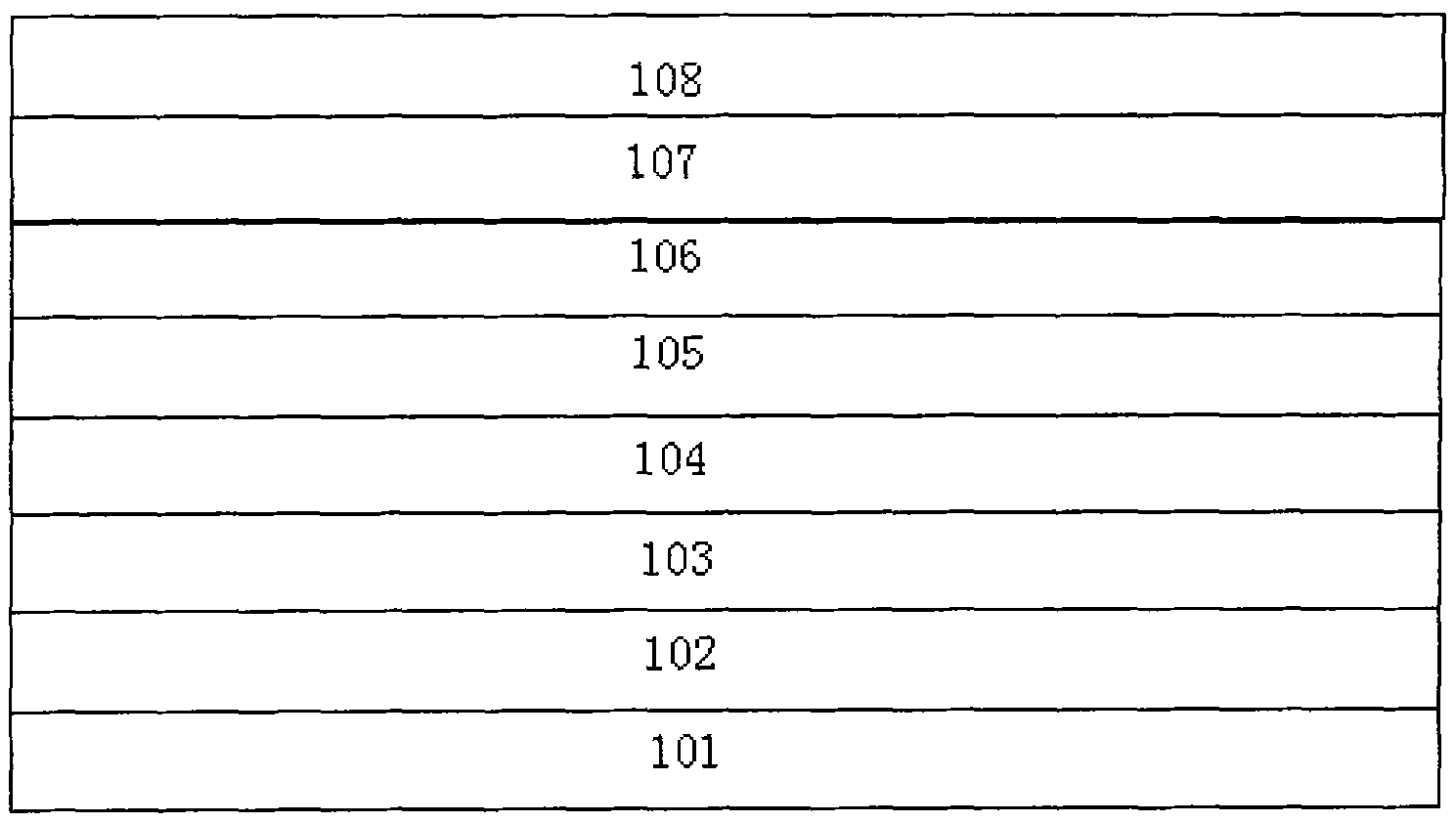

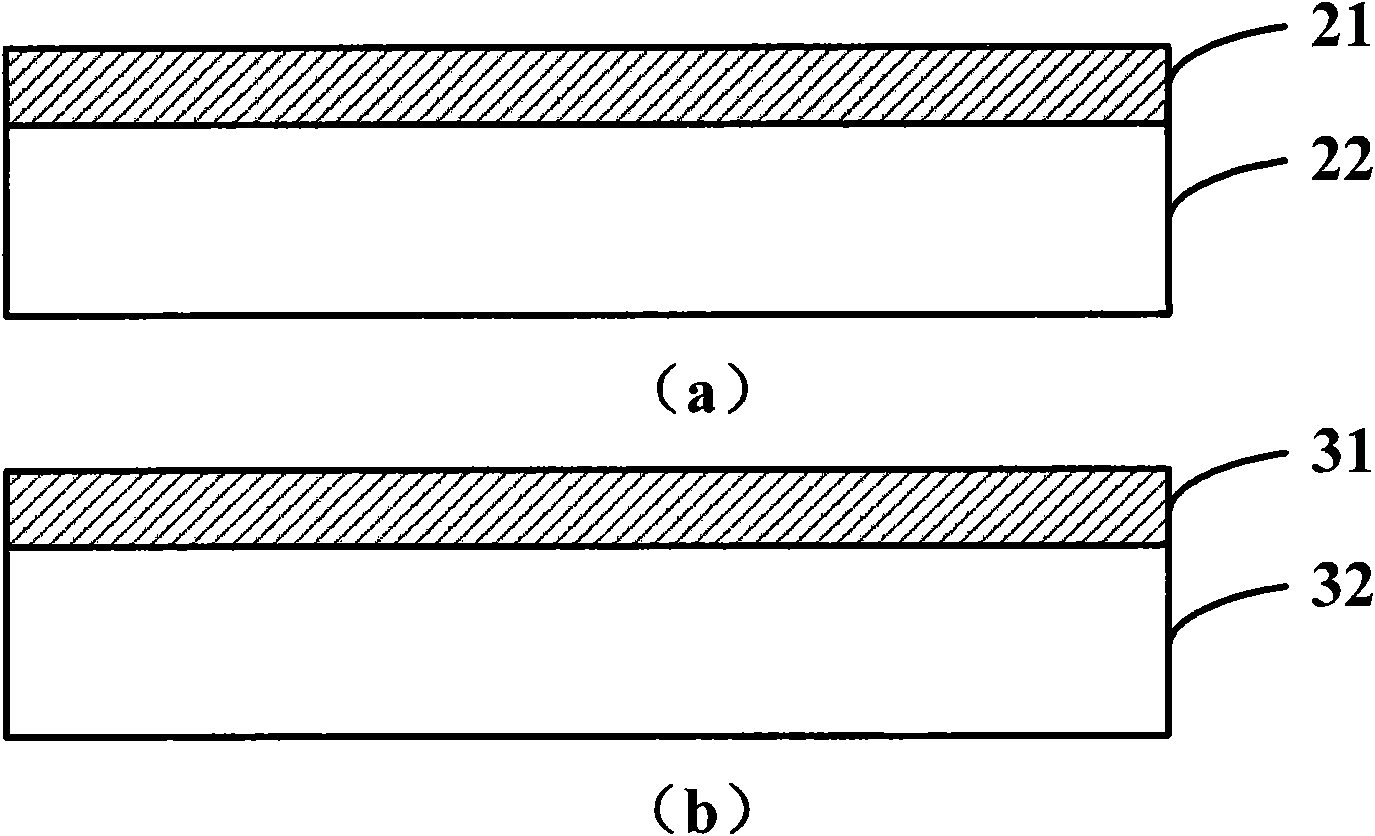

Light-emitting diode (LED) epitaxial structure and manufacturing method thereof

InactiveCN102208503AExcellent ElectricalGood optical performanceSemiconductor devicesQuantum efficiencyOptical property

The invention discloses a light-emitting diode (LED) epitaxial structure and a manufacturing method thereof. The LED epitaxial structure successively comprises an epitaxial substrate, a leukotriene (LT)-GaN nucleating layer, a high-temperature non-doped buffer layer, a P-GaN layer, a P-AlGaN layer, a diffusion barrier layer, a multiple quantum well (MQW) luminous layer, an InGaN current expansion layer, an N-ZnO layer and a surface-coarsened ZnO layer. The manufacturing method comprises the following steps: pre-treating the epitaxial substrate; growing the nucleating layer; growing the buffer layer; growing the P-GaN layer; growing the P-AlGaN layer; growing the diffusion barrier layer; growing the MQW luminous layer; growing the InGaN current expansion layer; growing the N-ZnO layer; and growing the surface-coarsened ZnO layer. By using the LED epitaxial structure obtained by virtue of the manufacturing method provided by the invention, an excellent electrical property and a good optical property are obtained, the internal quantum efficiency and the electronic static discharge (ESD) resistance capability are improved, the lost light caused by total reflection is lowered, the external quantum efficiency is greatly improved, a high-brightness LED is obtained, and the purposes of development and sustainable development of the LED industry are greatly promoted.

Owner:中山大学佛山研究院 +1

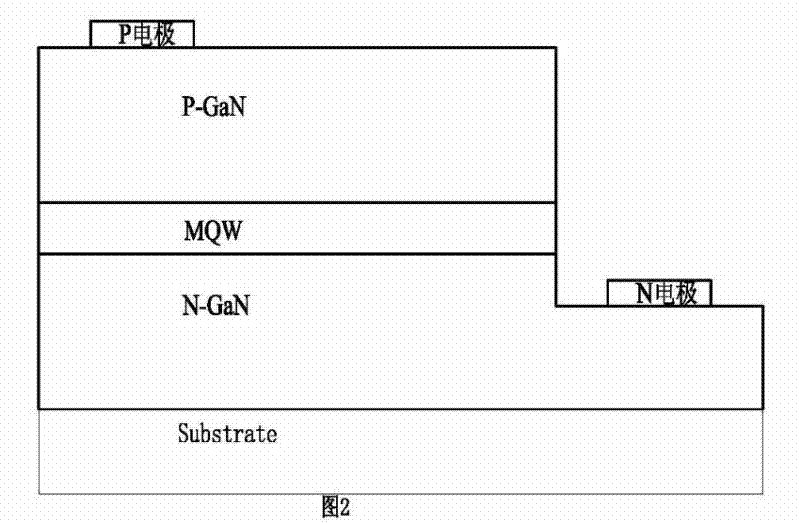

GaN-based light-emitting diode epitaxial wafer and growing method thereof

The invention relates to an LED (Light-Emitting Diode) epitaxial wafer and a growing method thereof, wherein the LED epitaxial wafer comprises two p-type GaN layers, and the growing method of the LED epitaxial wafer comprises the following steps of: when the p-type GaN layers grow, firstly growing a first p-type GaN layer at lower temperature and under lower pressure, and then growing a second p-type GaN layer when the temperature is relatively higher. Because the growing temperature of the first p-type GaN layer is low, an irregular structure is formed behind a quantum well to enable static electricity to be easily dispersed, so that the anti-ESD (Electro-Static discharge) capability of a GaN-based LED chip is improved. The invention has the advantages that the anti-ESD capability of the GaN-based LED chip is improved, the 2000V ESD passing rate of the chip with the size of 300*300mu m<2> can reach 98 percent, and the 4000V ESD passing rate can reach 95 percent.

Owner:DALIAN MEIMING EPITAXIAL WAFER TECH

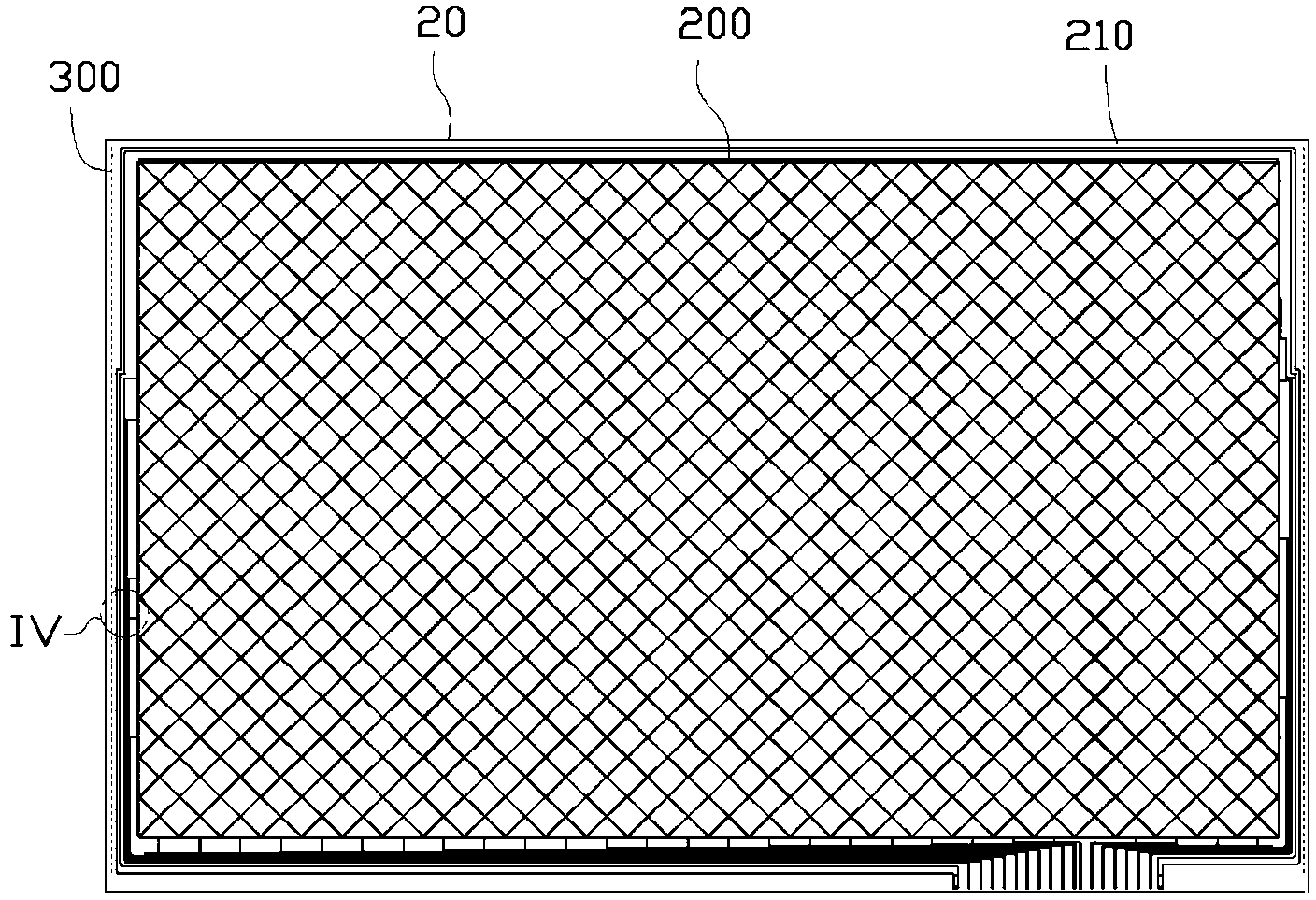

Touch panel and manufacturing method thereof, and touch display device

InactiveCN106201084AImprove ESD resistanceImprove product yieldPrinted circuit aspectsHigh voltage circuit adaptationsTouch panelDisplay device

The invention discloses a touch panel and a manufacturing method thereof, and a touch display device. The touch panel comprises a touch area and a routing area, wherein the routing area surrounds the touch area; the routing area comprises a drive electrode routing and an induction electrode routing; a first ground routing in a loop state surrounds the induction electrode routing, and has an overlapping area with the induction electrode routing; and the first ground routing can lead static electricity generated by the touch panel to the outside. Through the touch panel and the manufacturing method thereof, and the touch display device disclosed by the invention, the static electricity gathered at the edges of a black matrix and a position of an induction electrode can be led out; and thus, the effect of preventing the static electricity from breaking through the BM to cause product badness is achieved.

Owner:BOE TECH GRP CO LTD +1

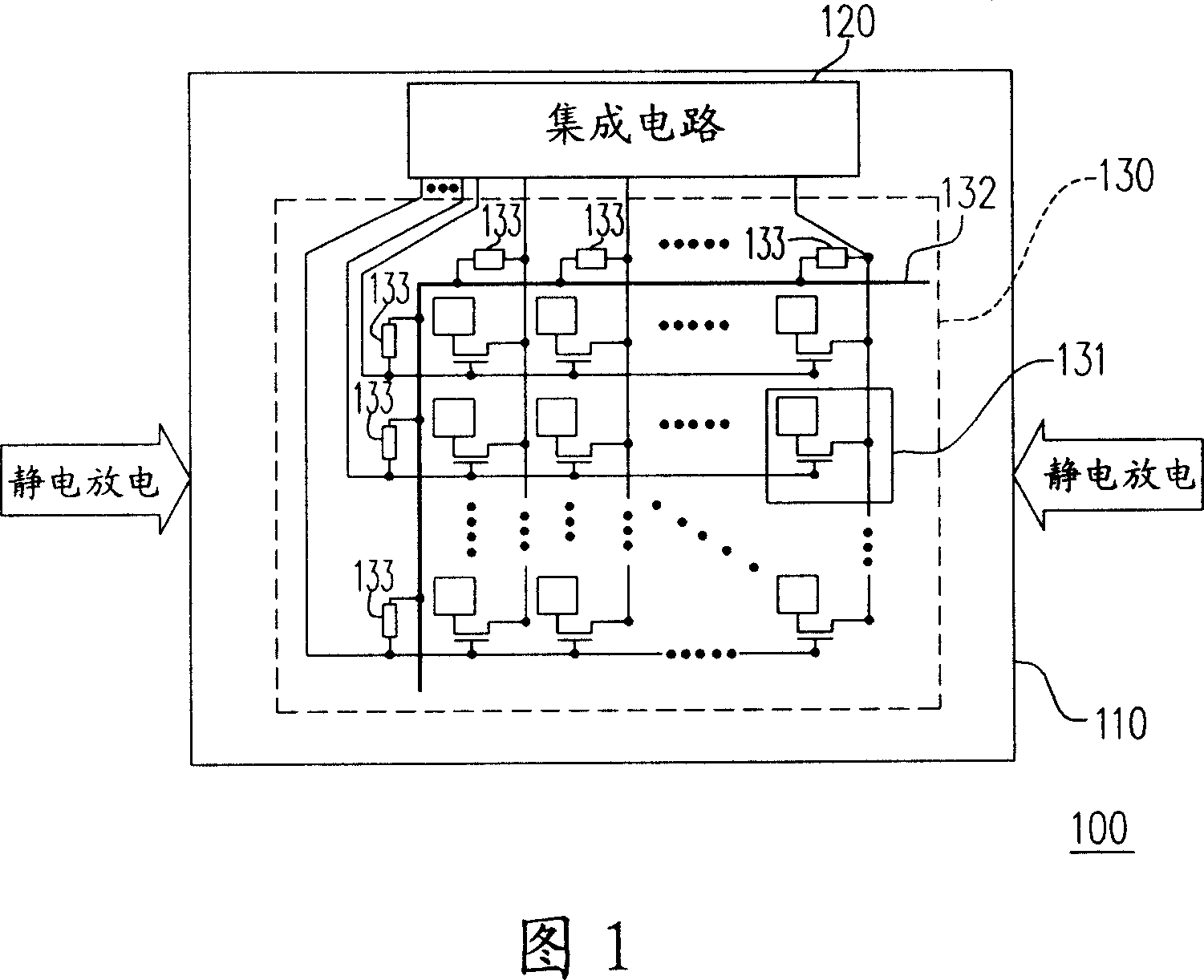

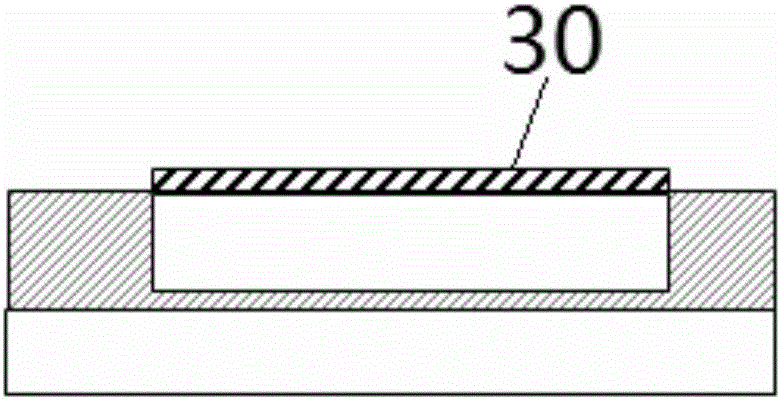

Silicon-on-insulator (SOI) circuit ESD global protecting structure

ActiveCN101562187AImprove collaborationOvercoming the limited ability to discharge ESD currentSemiconductor/solid-state device detailsSolid-state devicesEffusionEngineering

The invention relates to the technical field of semiconductors and discloses a silicon-on-insulator (SOI) circuit ESD global protecting structure comprising the steps: a primary ESD protecting structure and a secondary ESD protecting structure protect an input end; an intelligent resistance ESD protecting structure, an output effusion pipe structure controlled by an RC circuit, and an output ESD protecting structure protect an output end / bi-directional end; a loop effusion pipe protecting structure controlled by the RC circuit and a serial intelligent resistance structure are arranged between a power supply loop and an earth loop, used for protecting the power supply end and the earth end together with a parallel diode structure and assist the input end and the output end / bi-directional end to effuse ESD current. By using the invention, the problems that the SOI chip output end / bi-directional end has poor ESD current effusion capability and a single loop effusion pipe has limit capability for effusing the ESD current are solved so as to enable the ESD protecting capability of an SOI integrated circuit to be completely improved.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

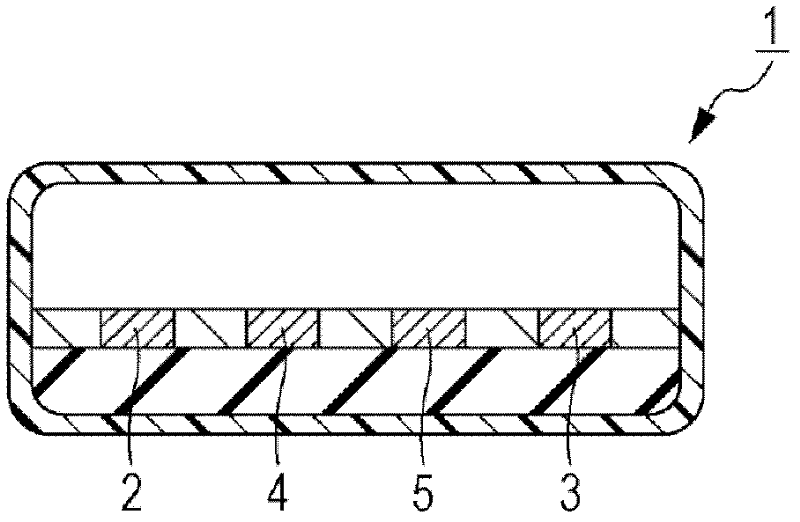

Structure of display panel for improving the static discharge resistance

InactiveCN101035404AImprove ESD resistanceStatic indicating devicesElectrical apparatus contructional detailsEngineeringPixel array

The invention relates to a display panel structure for improving static discharge resistance, comprising first substrate, pixel array region and static discharge protection path, where the pixel array region is arranged on the first substrate, the pixel array region is equipped with at least a pixel cell and at least a data channel, and the static discharge protection path encircles the pixel array region to conduct static current.

Owner:NOVATEK MICROELECTRONICS CORP

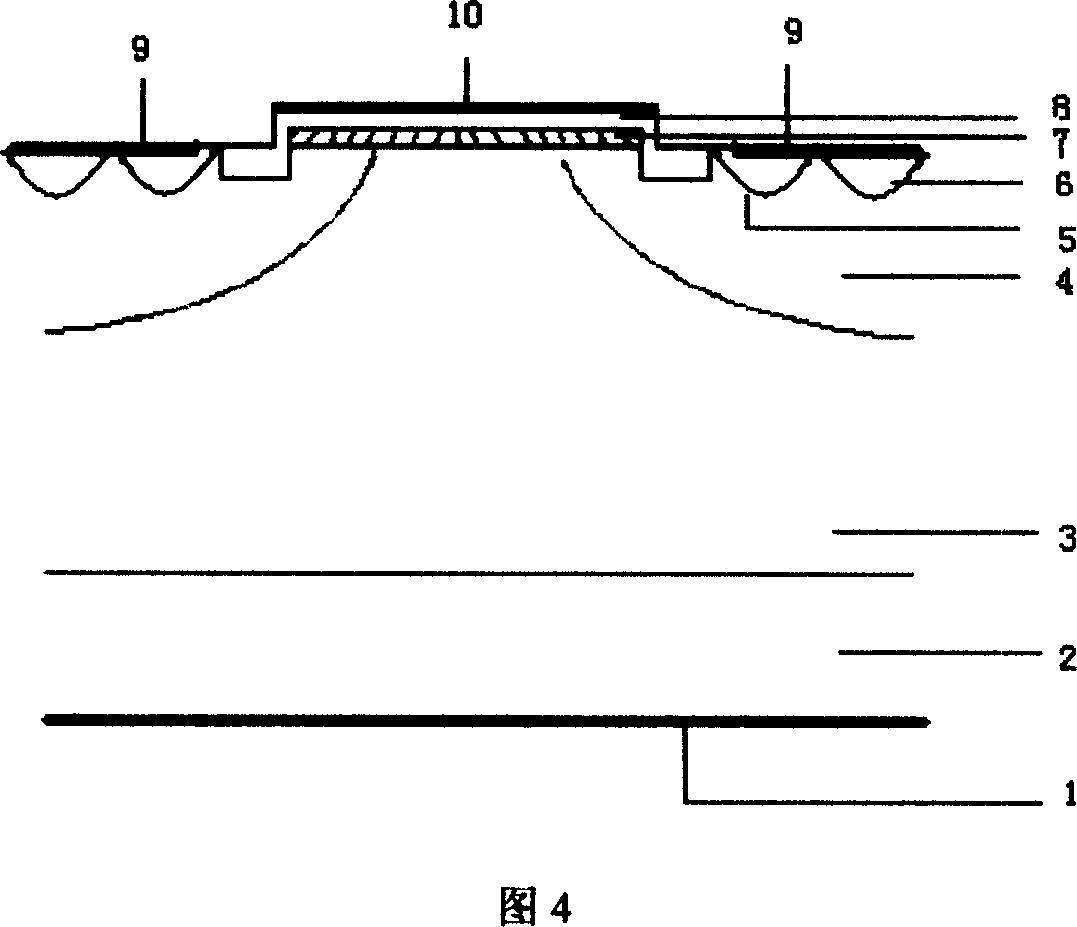

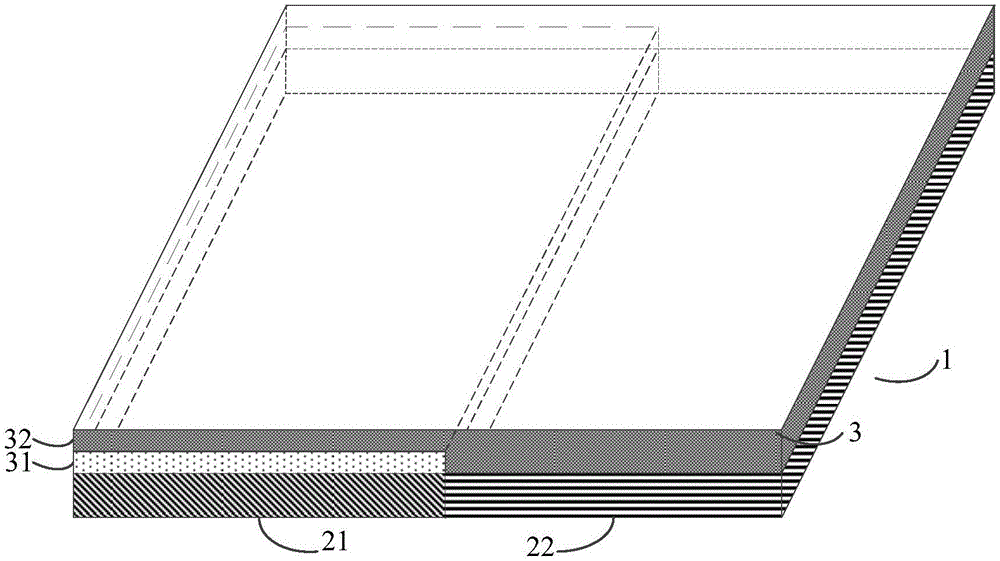

Liquid crystal panel and display device thereof

ActiveCN103278953AImprove ESD resistanceAvoid damageNon-linear opticsLiquid-crystal displayDisplay device

The invention discloses a liquid crystal panel and a display device of the liquid crystal panel. The liquid crystal panel mainly comprises a first substrate, a second substrate and a liquid crystal layer which is filled between the first substrate and the second substrate, wherein the first substrate and the second substrate are oppositely arranged. The liquid crystal panel comprises a display zone and a non-display zone, wherein the non-display zone surrounds the display zone. A first shielding layer is arranged on the non-display zone, far away from one side of the liquid crystal layer, on the first substrate. Compared with the prior art, the first shielding layer is arranged on the non-display zone, far away from the side of the liquid crystal layer, on the first substrate, manufacturing process is relatively simple, and when the liquid crystal panel is interfered by static, the first shielding layer can have the effect of resisting generated static, conductivity of the first shielding layer is utilized to release the generated static, the damage of the static to components inside the liquid crystal panel is reduced, and the capability of resisting ESD of the liquid crystal panel is improved.

Owner:XIAMEN TIANMA MICRO ELECTRONICS

Touch substrate, manufacturing method thereof, and touch screen

ActiveCN106201074AImprove ESD resistancePrevent ESDHigh voltage circuit adaptationsOvervoltage circuit protectionBlack matrixElectrical and Electronics engineering

The invention provides a touch substrate and a manufacturing method thereof, and belongs to the technical field of touch. The touch substrate comprises a touch area and a wiring area positioned around the touch area, wherein the wiring area comprises a black matrix pattern covering the wiring area, conductive routing wires positioned on the black matrix pattern, and a grounded conductive pattern arranged between the two adjacent conductive routing wires positioned on the black matrix pattern. According to the technical scheme provided by the invention, the anti-ESD ability of the touch screen can be improved.

Owner:BOE TECH GRP CO LTD +1

Front electrode structure of schottky diode and process manufacturing method of front electrode structure

InactiveCN102142465AReduce damageImprove ESD resistanceVacuum evaporation coatingSputtering coatingBlocking layerAluminium

The invention discloses a process method for a front electrode of a schottky diode and an electrode structure of the front electrode structure. Besides the normal steps of extending, oxidizing, photoetching for the first time, injecting boron, annealing, photoetching for the second time, etching by using silicon dioxide, depositing a potential barrier, alloying the potential barrier and etching the potential barrier, the method also comprises the following steps of: washing, and evaporating metal Ti (titanium) or V (vanadium) on a contact layer, metal Ni (nickel) on a transitional layer, metal Al (aluminum) on a blocking layer, metal Ni (nickel) on the transitional layer, and metal Ag (argentum) on a conductive layer sequentially in vacuum so as to form a front electrode structure with the electrode metal Ag, Ni, Al, Ni, Ti or V. The invention has the advantages that: during welding or encapsulation, the damage to the silicon surface of an instrument can be reduced under the stress blocking action of Al; a welding pull force and the electro-static discharge resistance of the front electrode structure are improved remarkably.

Owner:HANGZHOU SILAN INTEGRATED CIRCUIT

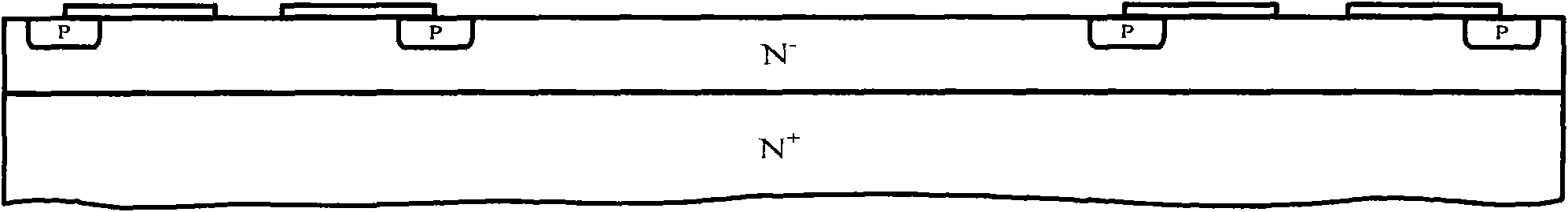

Multi-porous channel current equalizing-based transient voltage suppressor

InactiveCN102593155AShort response timeHigh surge absorption capacitySolid-state devicesSemiconductor devicesPorous channelTransient voltage suppressor

The invention discloses a multi-porous channel current equalizing-based transient voltage suppressor, which comprises a P+ substrate layer and a P- epitaxial layer. An N+ buried layer is arranged between first epitaxial regions and the P+ substrate layer; second epitaxial regions are respectively provided with N+ active injection regions; N wells are respectively embedded on the first epitaxial regions; each N well is provided with a P+ active injection region; the P+ active injection regions are connected with the N+ active injection regions through metal electrodes; the N wells are connected with the N+ active injection regions respectively paved on the first epitaxial regions; and the N+ active injection regions are connected with the N+ buried layer through a plurality of porous channels in which N-type materials are respectively filled. According to the multi-porous channel current equalizing-based transient voltage suppressor disclosed by the invention, electronic static discharge (ESD) current is evenly lead to Zener junctionby adopting the multi-porous channel current equalizing technology, so that the current collected by the Zener nodes is basically the same in density, and thereby, the phenomenon that the partial failure the Zener nodes is caused because of different current densities is avoided, the area utilization ratio of the node is effectively increased, meanwhile, the on resistance is lowered, the clamping feature is improved, and the ESD resistance of devices is enhanced.

Owner:ZHEJIANG UNIV

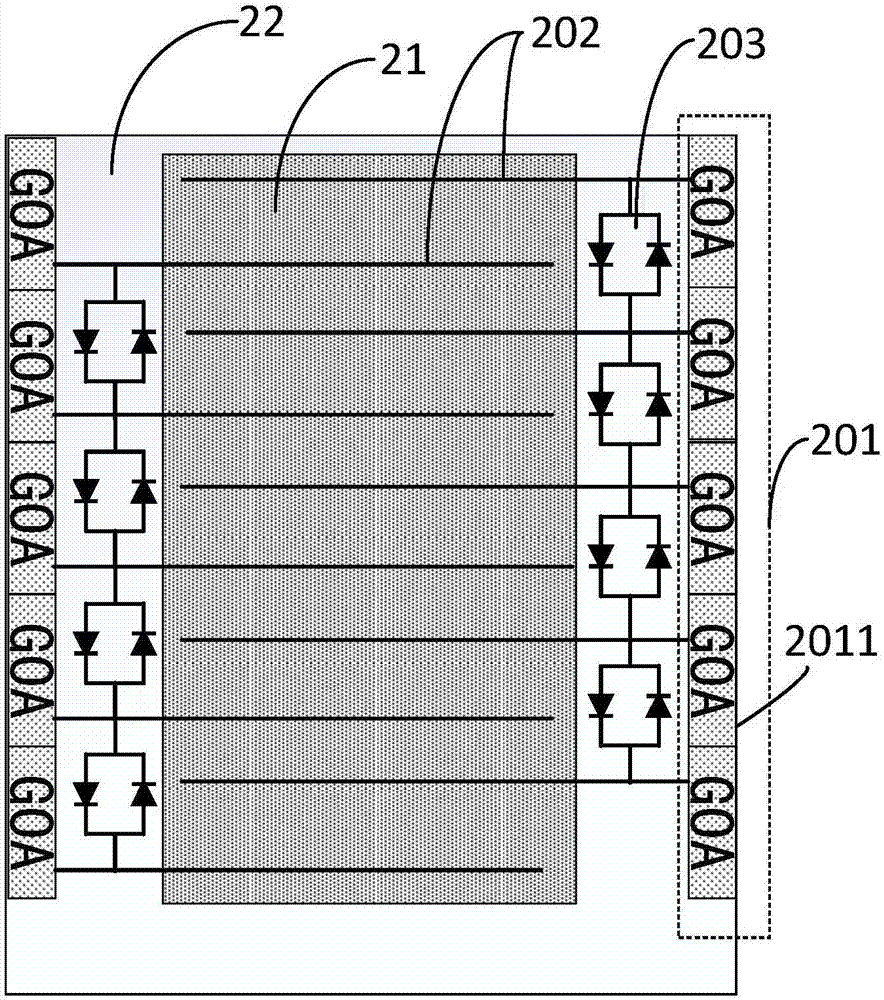

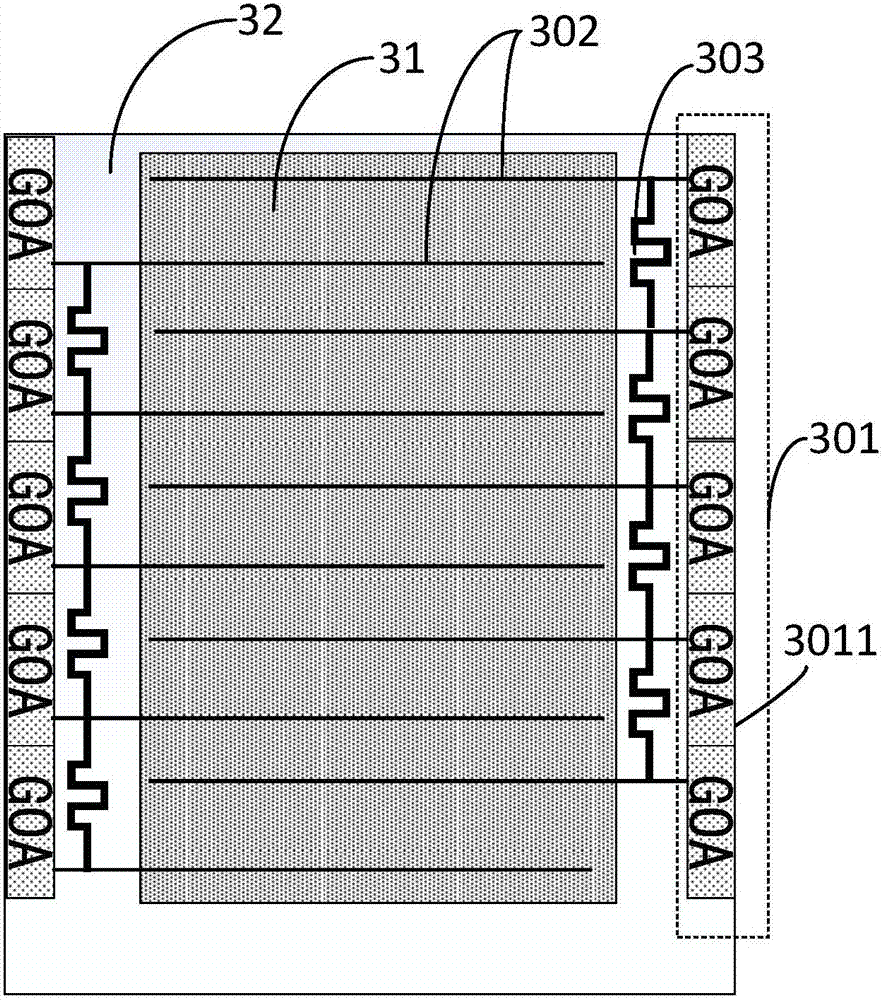

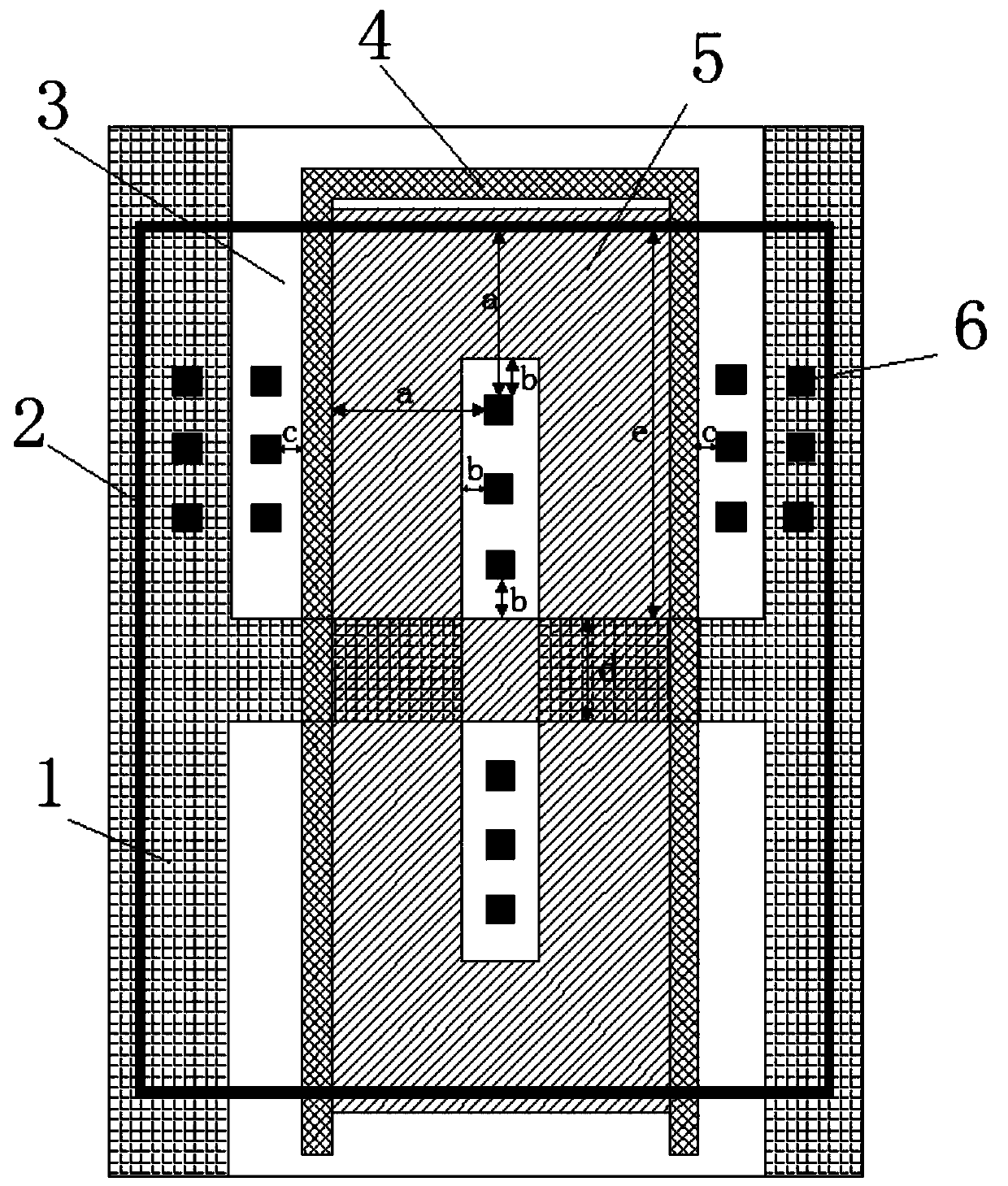

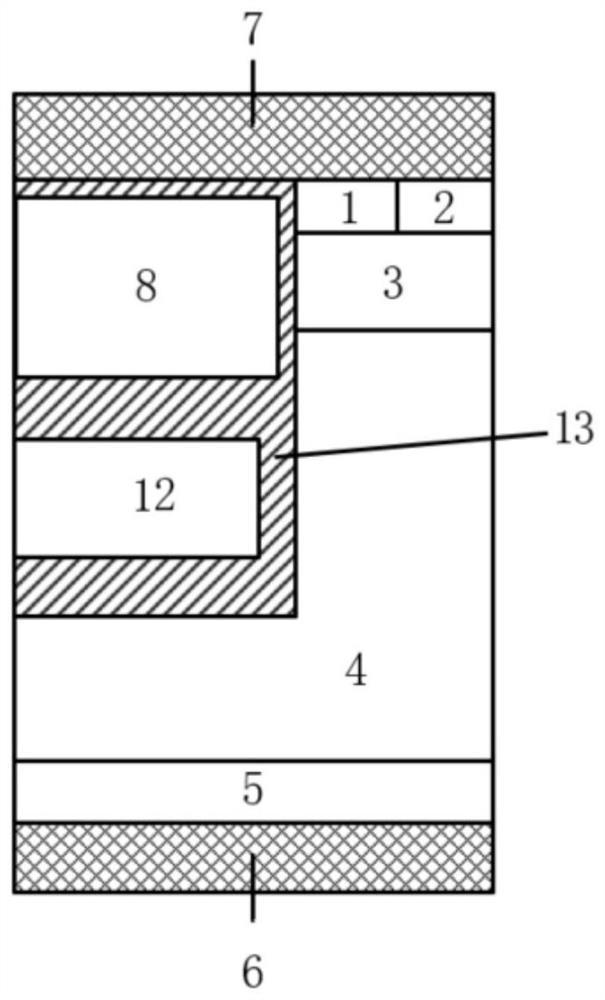

Array substrate and display panel

ActiveCN107505789AImprove ESD resistanceImprove product qualitySolid-state devicesNon-linear opticsElectrical connectionEngineering

The invention discloses an array substrate and a display panel. The array substrate comprises a GOA (gate driver on array) unit, a plurality of grid signal lines and electrostatic conduction devices. The grid signal lines are electrically connected with the GOA unit, and the electrostatic conduction devices are electrically connected among the grid signal lines to realize electrical connection of the grid signal lines. The array substrate has advantages that by the electrostatic conduction devices among the grid signal lines, the grid signal lines are connected together to jointly resist ESD (electrostatic discharge), and accordingly ESD resistance of the array substrate can be evidently improved, and product quality is improved.

Owner:WUHAN CHINA STAR OPTOELECTRONICS TECH CO LTD

Portable information processing device

InactiveCN102448242AImprove ESD resistanceConveying record carriersPrinted circuit aspectsInformation processingElectrostatic discharge

A portable information processing device includes a circuit board portion that has a main body portion side board mounting an electronic circuit thereon and forming a main body portion, and a connector portion side board forming a connector portion for connection to electronic equipment, wherein the main body portion side board mounts an electronic circuit on at least one of a first surface and a second surface opposite to the first surface, and is provided with a main body portion side electro-static discharge line which functions as an electro-static discharge surge arrester at an edge portion of a surface on which at least an electronic circuit is mounted, and wherein the connector portion side board is provided with a connector portion side electro-static discharge line which is connected to the main body portion side electro-static discharge line and functions as an electro-static emission portion. According to the portable information processing device, ESD resistance.

Owner:SONY CORP

Touch substrate, manufacture method thereof, and touch screen

ActiveCN106201134AReduce areaReduced risk of breakdownPhotomechanical apparatusInput/output processes for data processingHuman–computer interactionBlack matrix

The invention provides a touch substrate, a manufacture method thereof, and a touch screen, and belongs to the technical field of touch. The touch substrate comprises a touch area and a black matrix graph which surrounds the touch area; the touch substrate is provided with a plurality of touch electrodes, wherein a virtual electrode graph is formed in each gap between the adjacent touch electrodes; and each virtual electrode graph overlapped between the touch electrodes on the black matrix graph consists of a plurality of mutually-insulated virtual electrode blocks.

Owner:BOE TECH GRP CO LTD +1

A vertical dual diffused MOS power device protected by polysilicon/crystalline silicon ESD structure

InactiveCN1964069AFree from failureAvoid damageSemiconductor/solid-state device detailsSolid-state devicesDouble diffusionP–n junction

The related vertical double-diffusion MOS power device protected by multicrystal silicon / solid silicon ESD structure introduces PN diode for voltage endurance and discharging ESD current. Wherein, the PN junction is formed by the doping multicrystal silicon and doping solid silicon areas from grid / source draw end. This invention can improve device capacity for anti ESD greatly.

Owner:SICHUAN MIANYANG XINYI TECH

Liquid crystal display panel

ActiveCN108873520AEliminate edge red line phenomenonImprove yieldNon-linear opticsLiquid-crystal displayColor film

Owner:WUHAN CHINA STAR OPTOELECTRONICS TECH CO LTD

Resistance structure for improving silicon-on-insulator (SOI) circuit ESD protection network

ActiveCN101562188AAvoid negative effectsEasy to burn problem overcomeSemiconductor/solid-state device detailsSolid-state devicesElectrical resistance and conductanceNegative temperature

The invention relates to the technical field of semiconductors and discloses a resistance structure for improving a silicon-on-insulator (SOI) circuit ESD protection network. By using the conductor characteristics of silicide, the structure solves the problem that a semiconductor current carrier conducting resistance structure enables resistance not to reduce the resistance value and the potential lifting capability of resistance but increase the resistance value and improve the potential lifting capability of the resistance in a large-scale ESD process at high temperature because of the characteristics of the resistance negative temperature generated by the intrinsic ionization effect. In addition, the resistance also has the stable resistance value characteristics after ESD, the problem of the impurity tempering effect generated in the ESD process of the semiconductor current carrier conducting resistance is solved, and the effect on electrical properties of a circuit is further reduced. By using the invention, on one hand, more stable ESD protecting capability can be obtained, on the other hand, the effect on the electrical properties of a circuit by the resistance for protecting the ESD can be reduced when more stable ESD protecting capability is obtained.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

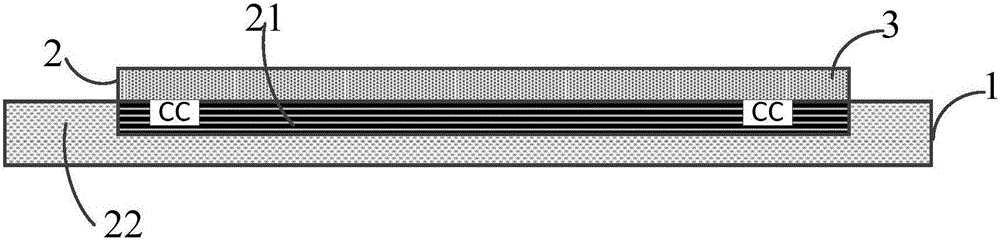

Display apparatus and manufacturing method therefor

ActiveCN105848394AAvoid influenceImprove ESD resistanceElectrostatic discharge protectionCasings with display/control unitsResistConductive materials

Embodiments of the invention provide a display apparatus and a manufacturing method therefor. The manufacturing method comprises the steps of attaching a static shielding layer to an edge region of a connecting line pattern, wherein the connecting line pattern is exposed on a display panel; the static shielding layer is provided with an insulating material region; the insulating material region is in contact with the region where the connecting line pattern is located; and the other region, except the region where the connecting line pattern is located, in the edge region is in contact with a conductive material region on the surface of the static shielding layer. The display apparatus provided by the embodiments of the invention is prepared by the manufacturing method; the anti-ESD (electrostatic discharge) capability of the chip connecting line position on the edge can be improved without increasing technological processes; in addition, the formed material, including the metal static shielding layer, is non-transparent; compared with a photo-sensitive resist, the surface attaching condition of the static shielding layer is easier to detect, and surface flatness defects cannot be formed easily; and the yield and improvement of the performance of the product can be facilitated.

Owner:BOE TECH GRP CO LTD +1

Touch sensor and production method thereof, and touch panel

ActiveCN106293291AImprove ESD resistanceTouch function impactInput/output processes for data processingOptoelectronicsTouch panel

The embodiment of the invention relates to a touch sensor and a production method thereof, and a touch panel. The touch sensor comprises a base plate, an electrode layer, a first insulating layer and a transparent conductive layer, wherein the electrode layer is arranged on the base plate, wherein the electrode layer consists of a first electrode and a second electrode which are isolated from each other; the first insulating layer is arranged on the electrode layer; the transparent conductive layer is arranged on the first insulating layer, wherein the transparent conductive layer consists of a bridging part and an ESD protective part, the bridging part is arranged to be bridged with the first electrode or the second electrode, and the ESD protective part is isolated from the bridging part. According to the touch sensor provided by the embodiment of the invention, the antistatic capability of a functional layer inside the sensor can be improved.

Owner:BOE TECH GRP CO LTD +1

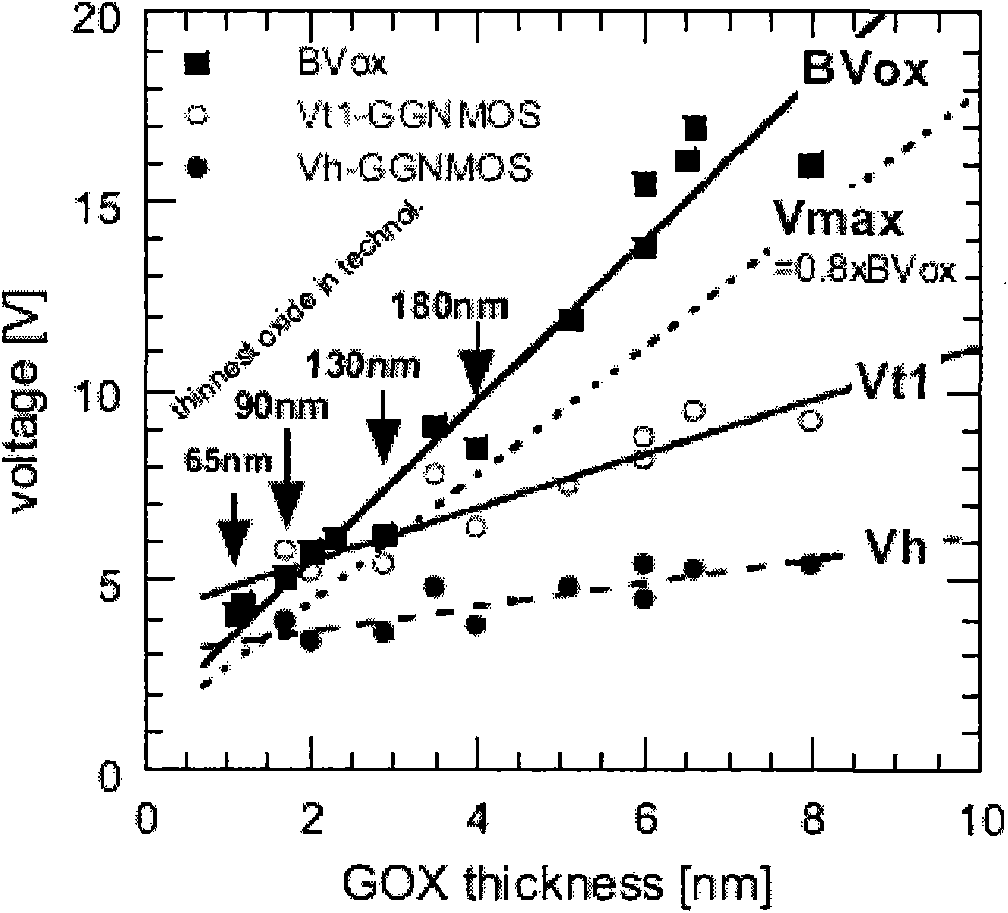

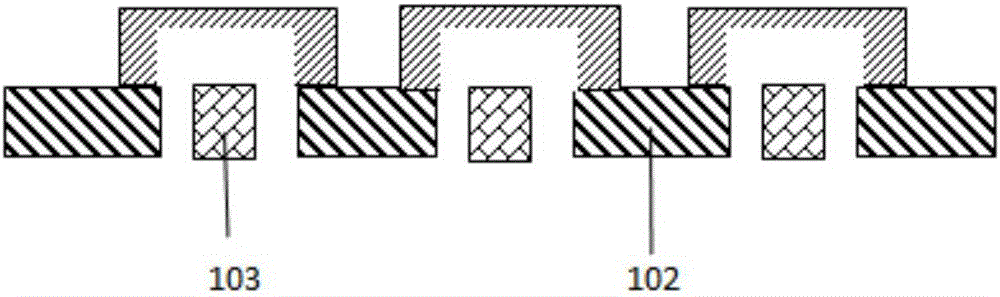

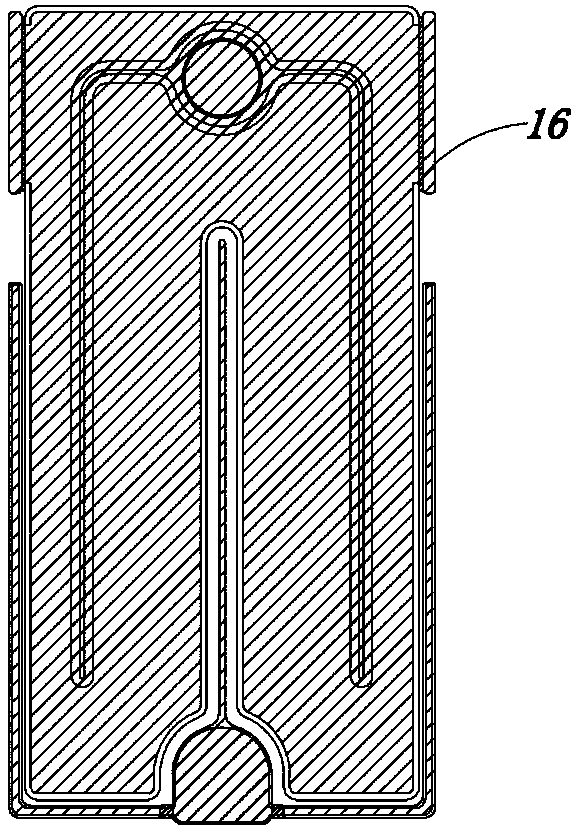

GGNMOS ESD protection device structure based on SOI process

ActiveCN111508951AReduce areaFull body contactTransistorSolid-state devicesGgNMOSCondensed matter physics

The invention discloses a GGNMOS ESD protection device structure based on an SOI technology. The structure comprises an SAB layer, P-type doped source-drain units SP, N-type doped source-drain units SN, a polycrystalline gate POLY, a device active region TO and contact holes W1. P-type doped source and drain units of a strip-type NMOS tube are segmented; the body contact of the device is designedbetween every two sections of P-type doped source-drain units. A P-type doped source and a P-type doped drain of a strip-type NMOS tube are segmented; the body contact of the device is designed between every two P-type doped source drains, the N-type doped source drain units of the strip-type NMOS tube are ingeniously segmented through the structure, the range of an SN injection layer and the range of an SP injection layer are defined by the segments respectively, the process is achieved through photoetching, and by means of the design, on one hand, the area is saved, and on the other hand, the body contact is more sufficient; TLP test evaluation shows that under the same area, the ESD resistance of the SOI GGNMOS device is obviously improved by 1.2 times or above compared with that of a traditional SOI GGNMOS device.

Owner:58TH RES INST OF CETC

SGT MOSFET device with bidirectional ESD protection capability

PendingCN112164721AImprove impactImprove switching characteristicsSolid-state devicesDiodeMOSFETEngineering

Owner:VANGUARD SEMICON CORP

A vertical dual diffused MOS power device protected by polysilicon ESD structure

InactiveCN1964070AAvoid damageImprove ESD resistanceSemiconductor/solid-state device detailsSolid-state devicesDouble diffusionP–n junction

The related vertical double-diffusion MOS power device protected by multicrystal silicon ESD structure introduces PN diode for voltage endurance and discharging ESD current based on general VDMOS. Wherein, the PN junction is formed by different doping multicrystal silicon. This invention can improve device capacity for anti ESD greatly.

Owner:SICHUAN MIANYANG XINYI TECH

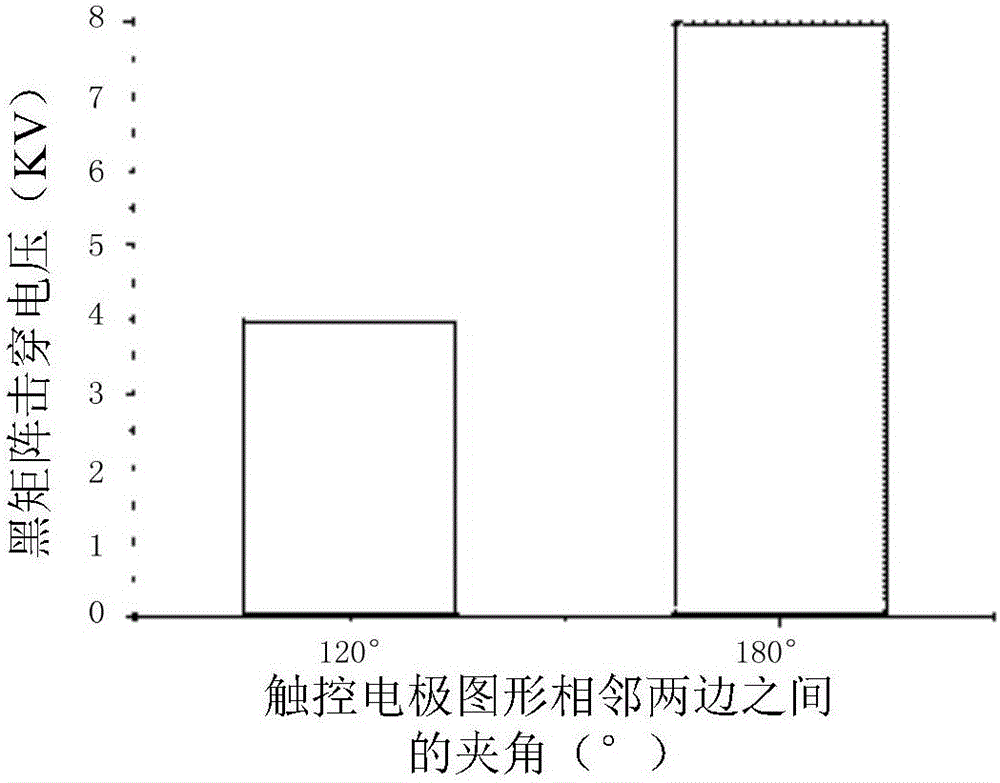

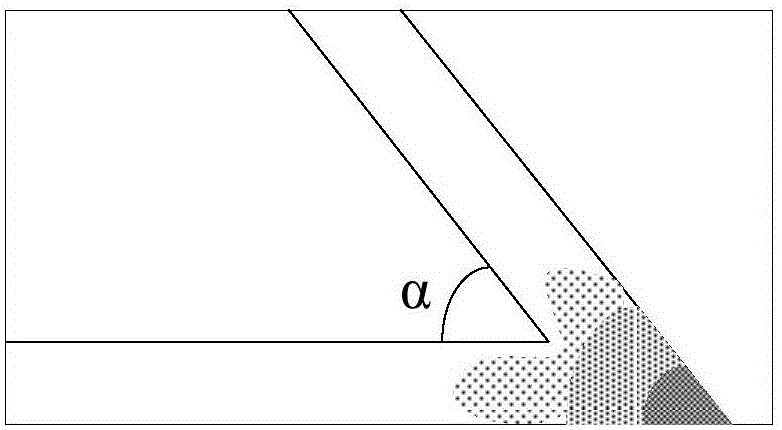

Touch substrate, manufacturing method of touch substrate and touch screen

ActiveCN106201135AReduced risk of breakdownReduce electric field strengthCircuit optical detailsPrinted circuit aspectsGraphicsHuman–computer interaction

The invention provides a touch substrate, a manufacturing method of the touch substrate and a touch screen, and belongs to the technical field of touch. The touch substrate comprises a touch area and a black matrix graphic which encircles the touch area; a plurality of touch electrode graphics are arranged on the touch substrate; each touch electrode graphic comprises a first part which is overlapped on the black matrix graphic; and the included angle between any two adjacent edges of each first part is greater than a preset threshold value. According to the technical scheme of the invention, the anti-ESD ability of the touch screen can be improved.

Owner:BOE TECH GRP CO LTD +1

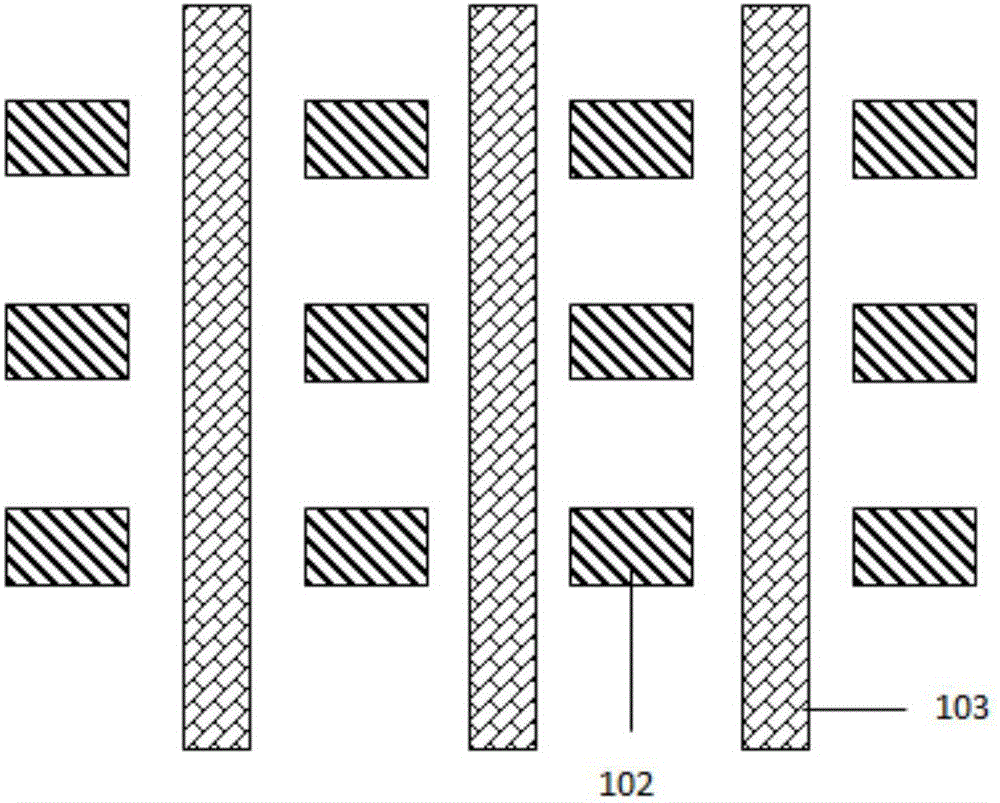

Touch panel and touch display device provided with same

InactiveCN103324343AImprove ESD resistanceReduce misjudgmentInput/output processes for data processingGlass coverDisplay device

Provided are a touch panel and a touch display device provided with the same. The touch panel comprises a touch region and a wiring region located on the periphery of the touch region and surrounding the touch region. The wiring region comprises various conductive signal wires required by the touch panel, at least one starved inspection reference line is arranged in the wiring region, formed by arranging multiple metal blocks at intervals, located on the outer sides of the conductive signal wires in the wiring regions and used in the bonding manufacture process of the display device using the touch panel, and inspectors can conveniently perform starvation inspection by means of a method for inspecting whether optical cement covers the starved inspection reference line or not. The touch panel is provided with one starved inspection reference line in the wiring region, so that the inspectors can conveniently and quickly perform starvation inspection in the bonding manufacture process of the touch panel and a glass cover plate of the touch display device.

Owner:INTERFACE OPTOELECTRONICS SHENZHEN +1

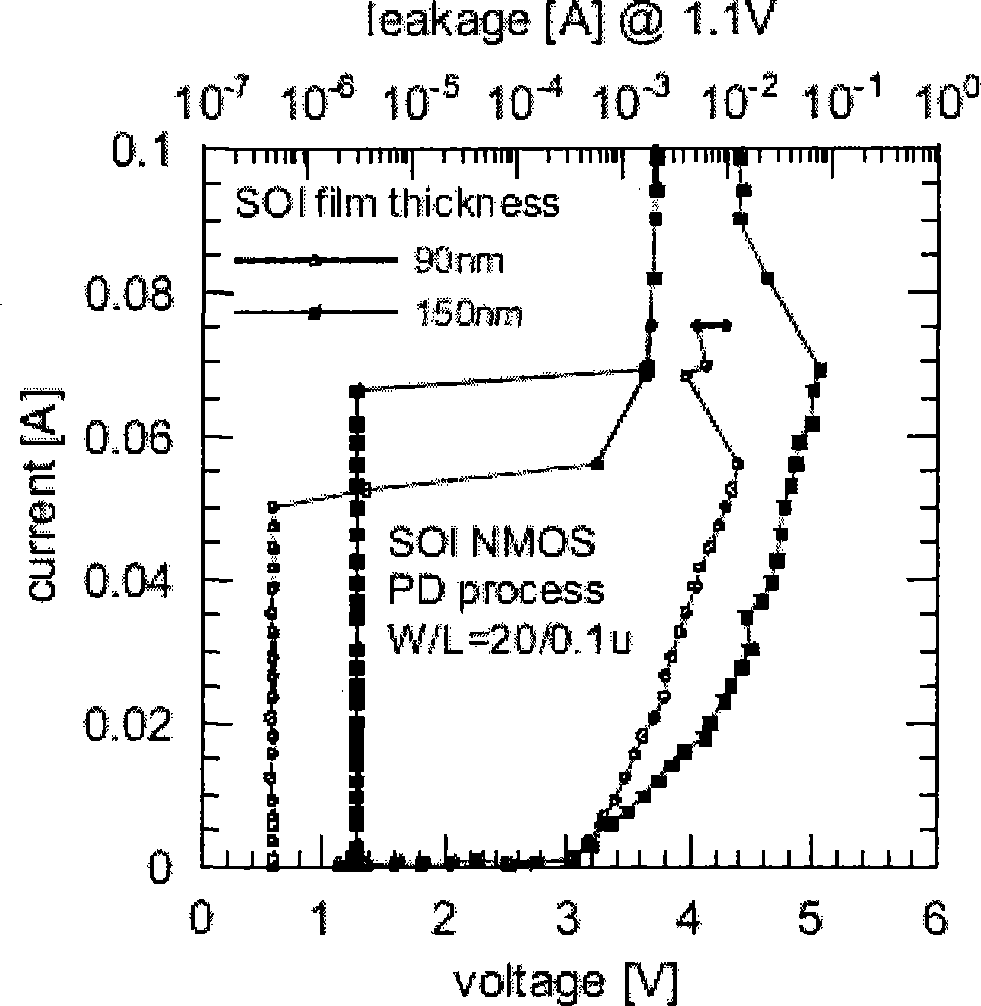

Method for improving ESD protective capability of SOI NMOS device and SOI NMOS device

InactiveCN106129043ALower breakdown voltageImprove ESD resistanceTransistorSemiconductor/solid-state device detailsGate oxidePhotoresist

The invention provides a method for improving an ESD protective capability of an SOI NMOS device and the SOI NMOS device. The method for improving the ESD protective capability of the SOI NMOS device comprises: carrying out well region ion injection and channel ion injection in a silicon top layer of SOI to form a device area; forming a gate oxide layer at the top of the device area; forming a gate structure containing gate side walls on the gate oxide layer through deposition and etching; arranging a photoresist layer on the exposed silicon top layer surface and device area surface and partially removing the photoresist layer from the device area surface so as to partially expose the device area surface; carrying out partial inclined injection by using the photoresist layer to form a partial ESD ion injection area in the device area; and respectively forming a drain electrode and a source electrode in the device area on two sides of the gate structure.

Owner:SHANGHAI HUALI MICROELECTRONICS CORP

Display device and manufacturing method thereof

ActiveCN105848394BImprove ESD resistanceEasy to checkElectrostatic discharge protectionCasings with display/control unitsDisplay deviceEngineering

An embodiment of the present invention provides a display device and a manufacturing method thereof, wherein the manufacturing method includes: attaching an electrostatic shielding layer on the edge area of the connecting line pattern, and the connecting line pattern is exposed on the display panel; wherein the electrostatic shielding The layer has an area of insulating material, the area of insulating material contacts the area where the connection line pattern is located, and the area in the edge area other than the area where the connection line pattern is located contacts the conductive material on the surface of the electrostatic shielding layer. area. The display device provided by the embodiment of the present invention is manufactured by the above manufacturing method. The embodiment of the present invention can improve the anti-ESD capability of the edge chip connection line without increasing the process flow. In addition, the electrostatic shielding layer formed of materials including metal is non-transparent. Compared with photosensitive adhesives, it is easier to check the surface adhesion, and it is not easy to produce surface flatness defects, which is conducive to the improvement of product yield and performance.

Owner:BOE TECH GRP CO LTD +1

LED chip and preparation method thereof

InactiveCN108091638AImprove ESD resistanceImprove reliabilitySemiconductor/solid-state device detailsSolid-state devicesEdge regionEngineering

The invention discloses an LED chip and a preparation method thereof. The LED chip includes a substrate. The substrate includes a middle region and an edge region. The middle region includes a first N-type GaN layer, a first MQW active layer and a first p-type GaN layer in sequence from bottom to top. The edge region includes a second n-type GaN layer, a second MQW active layer, and a second p-type GaN layer in sequence from bottom to top. The first p-type GaN layer is connected with the second n-type GaN layer. The first N-type GaN layer is connected with the second P-type GaN layer. In the invention, the edge portion of the LED chip with poor light emission distribution is independently formed into a micro-diode, the micro-diode forms an anti-parallel structure with the original chip, inthis way, the anti-ESD capability of the LED chip is enhanced and the reliability of the LED chip is improved.

Owner:FOCUS LIGHTINGS SCI & TECH

An ldmos SCR device for integrated circuit chip esd protection

InactiveCN103258814BIncrease the Vhold valueImproves latch-up immunitySemiconductor/solid-state device detailsSolid-state devicesLDMOSCMOS

The invention discloses an LDMOS SCR for protection against integrated circuit chip ESD protection and belongs to the technical field of electrons. According to the LDMOS SCR for the protection against the integrated circuit chip ESD, a low-voltage MOS is integrated on the basis of a traditional structure of the LDMOS SCR for the protection against the integrated circuit chip ESD and the low-voltage MOS is used for limiting a hole current injected from the positive electrode of the nested SCR, so that value of the holding voltage Vhold is improved and latch-up immune ability of the LDMOS SCR in high-voltage application is improved. In addition, compared with an ordinary LDMOS, the LDMOS SCR for the protection against the integrated circuit chip ESD is stronger in ability of the protection against the ESD due to the integrated SCR. Besides, the LDMOS SCR for the protection against the integrated circuit chip ESD and the Bipolar CMOS DMOS technology are compatible.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

Silicon-on-insulator (SOI) circuit ESD global protecting structure

ActiveCN101562187BImprove collaborationOvercoming the limited ability to discharge ESD currentSemiconductor/solid-state device detailsSolid-state devicesEffusionEngineering

The invention relates to the technical field of semiconductors and discloses a silicon-on-insulator (SOI) circuit ESD global protecting structure comprising the steps: a primary ESD protecting structure and a secondary ESD protecting structure protect an input end; an intelligent resistance ESD protecting structure, an output effusion pipe structure controlled by an RC circuit, and an output ESD protecting structure protect an output end / bi-directional end; a loop effusion pipe protecting structure controlled by the RC circuit and a serial intelligent resistance structure are arranged betweena power supply loop and an earth loop, used for protecting the power supply end and the earth end together with a parallel diode structure and assist the input end and the output end / bi-directional end to effuse ESD current. By using the invention, the problems that the SOI chip output end / bi-directional end has poor ESD current effusion capability and a single loop effusion pipe has limit capability for effusing the ESD current are solved so as to enable the ESD protecting capability of an SOI integrated circuit to be completely improved.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com