Method for improving ESD protective capability of SOI NMOS device and SOI NMOS device

A technology for ESD protection and devices, applied in semiconductor/solid-state device components, electric solid-state devices, semiconductor devices, etc., to achieve the effects of reducing breakdown voltage, improving anti-ESD ability, and optimizing tilt angle

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0030] In order to make the content of the present invention clearer and easier to understand, the content of the present invention will be described in detail below in conjunction with specific embodiments and accompanying drawings.

[0031] Figure 2 to Figure 7 Each step of the method for improving the ESD protection capability of the SOI NMOS device according to the preferred embodiment of the present invention is schematically shown.

[0032] Such as Figure 2 to Figure 7 As shown, the method for improving the ESD protection capability of SOI NMOS devices according to a preferred embodiment of the present invention includes:

[0033] The first step: perform well region ion implantation and channel ion implantation (such as figure 2 Shown by the arrow) to form the device region 20;

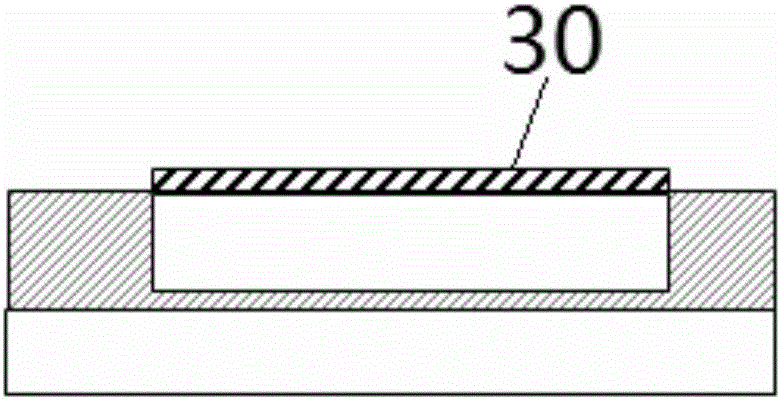

[0034] The second step: forming a gate oxide layer 30 on the top of the device region 20;

[0035] Step 3: forming a gate structure 40 including a gate spacer on the gate oxide layer 30 b...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com