Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

41results about "Catalyst application resist" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

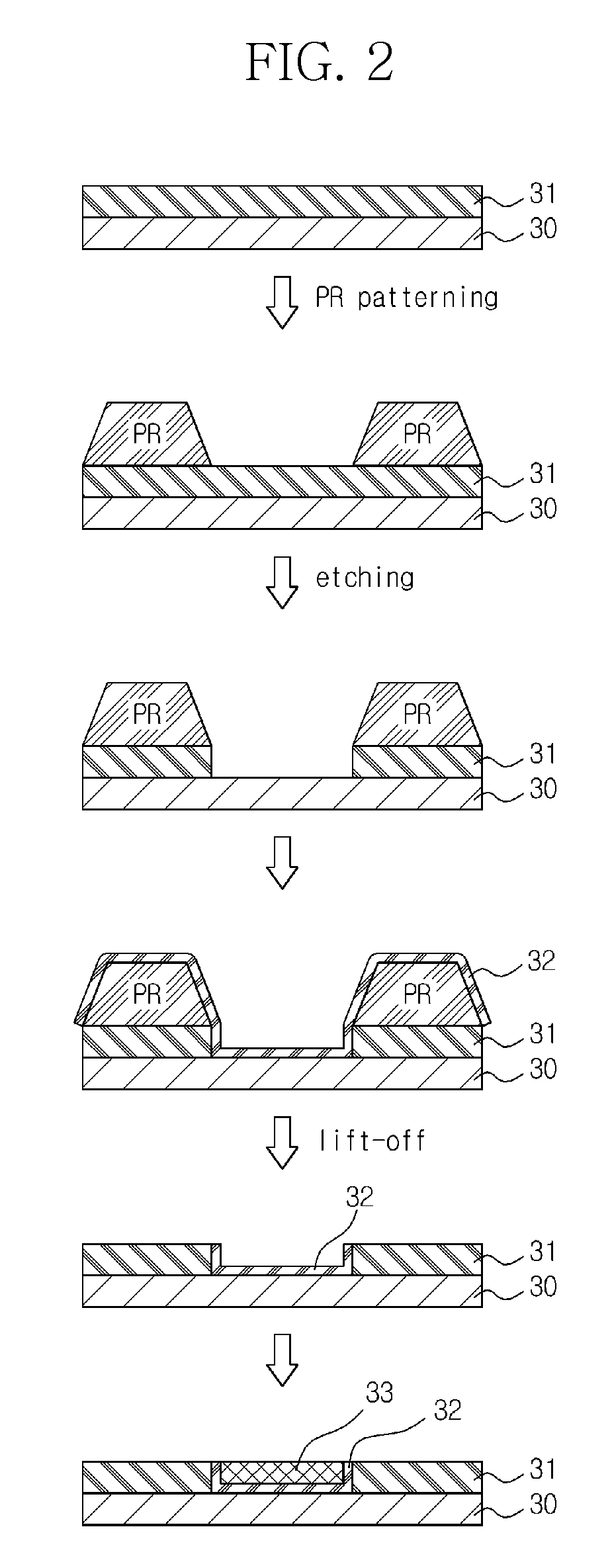

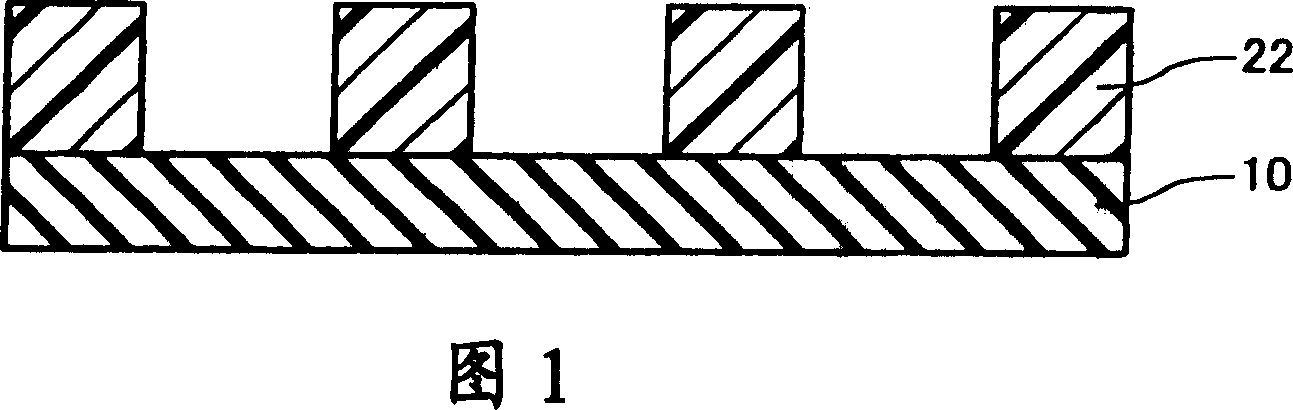

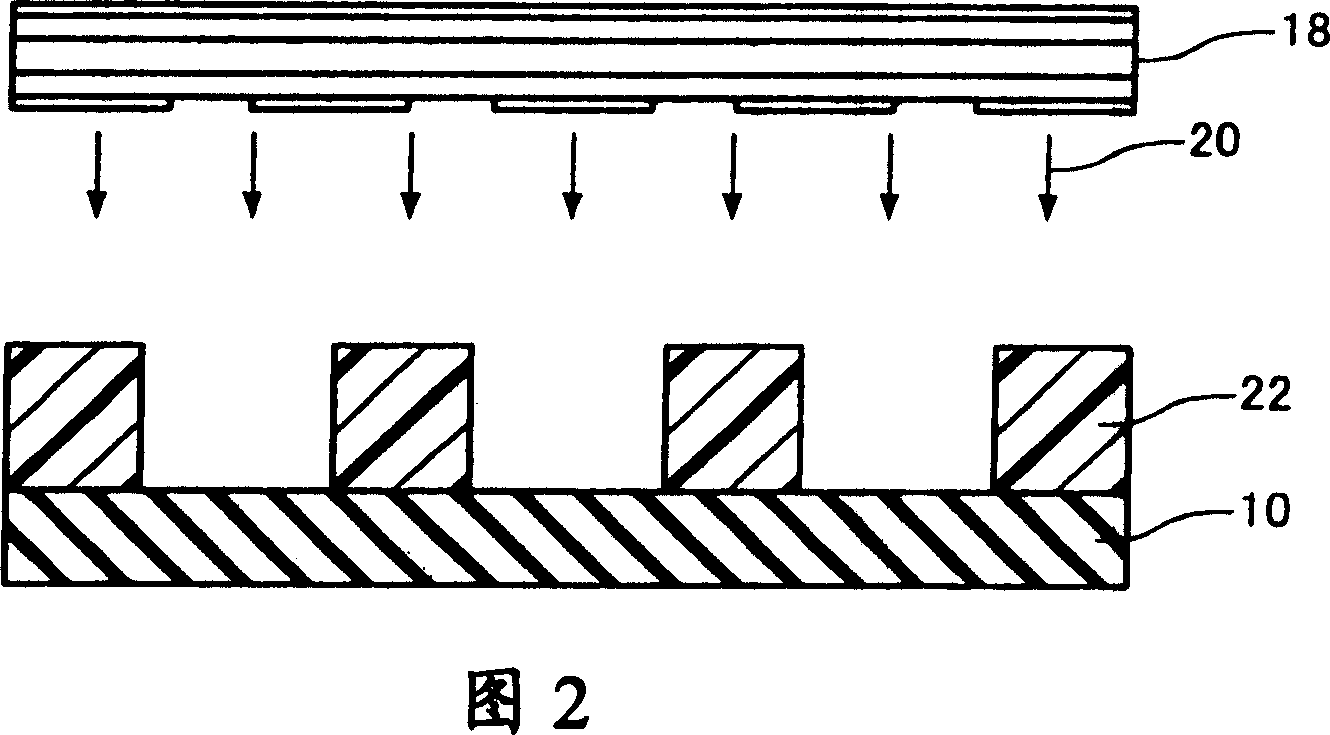

Method of forming metal pattern, patterned metal structure, and thin film transistor-liquid crystal displays using the same

InactiveUS20080314628A1Simple processLow costSolid-state devicesInsulating layers/substrates workingLiquid-crystal displayDielectric substrate

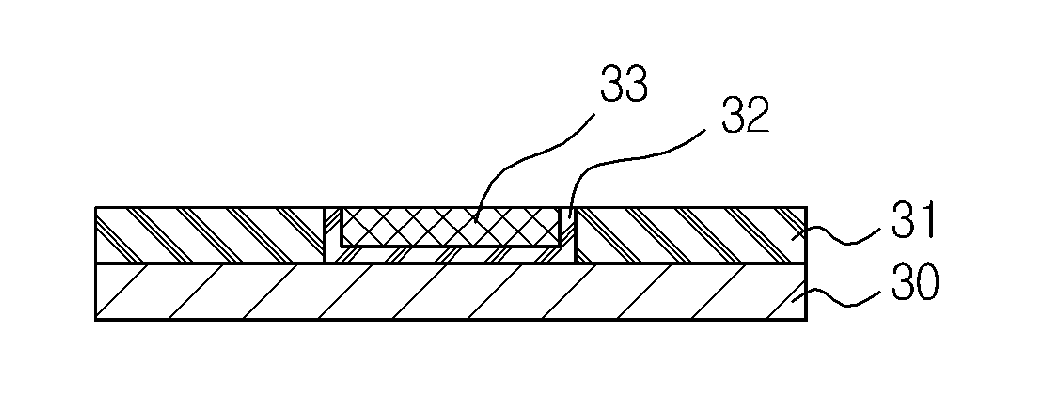

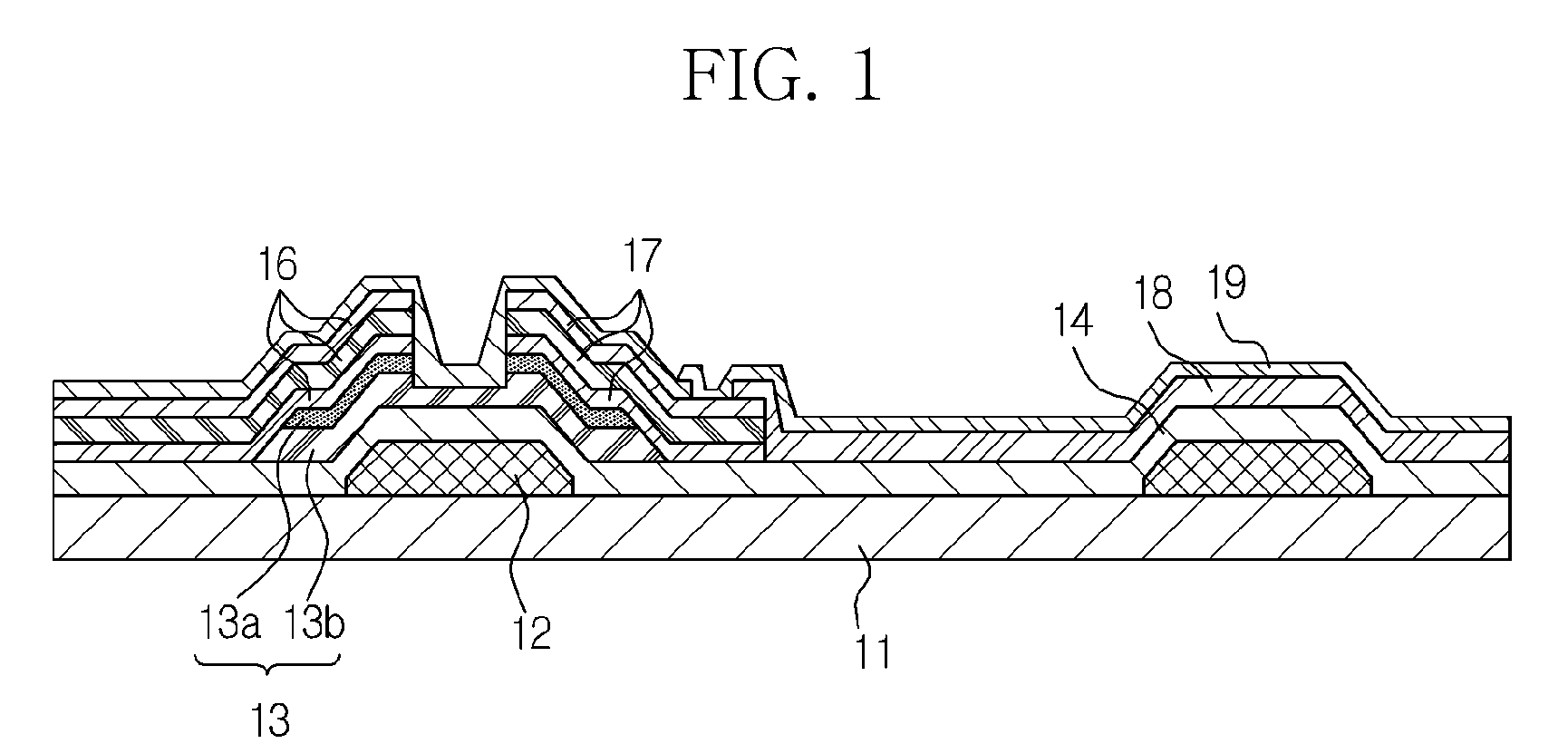

Disclosed is a method of forming a metal pattern, the method comprising depositing a dielectric substrate on a supporting substrate; forming a latent mask pattern of a metal pattern on the dielectric substrate; etching the dielectric substrate exposed by the latent mask pattern; forming a seed layer on the supporting substrate by activating the supporting substrate; removing the latent mask pattern and the portion of the seed layer disposed on the latent mask pattern through a lift-off process; and plating a metal layer on the patterned seed layer.

Owner:SAMSUNG ELECTRONICS CO LTD

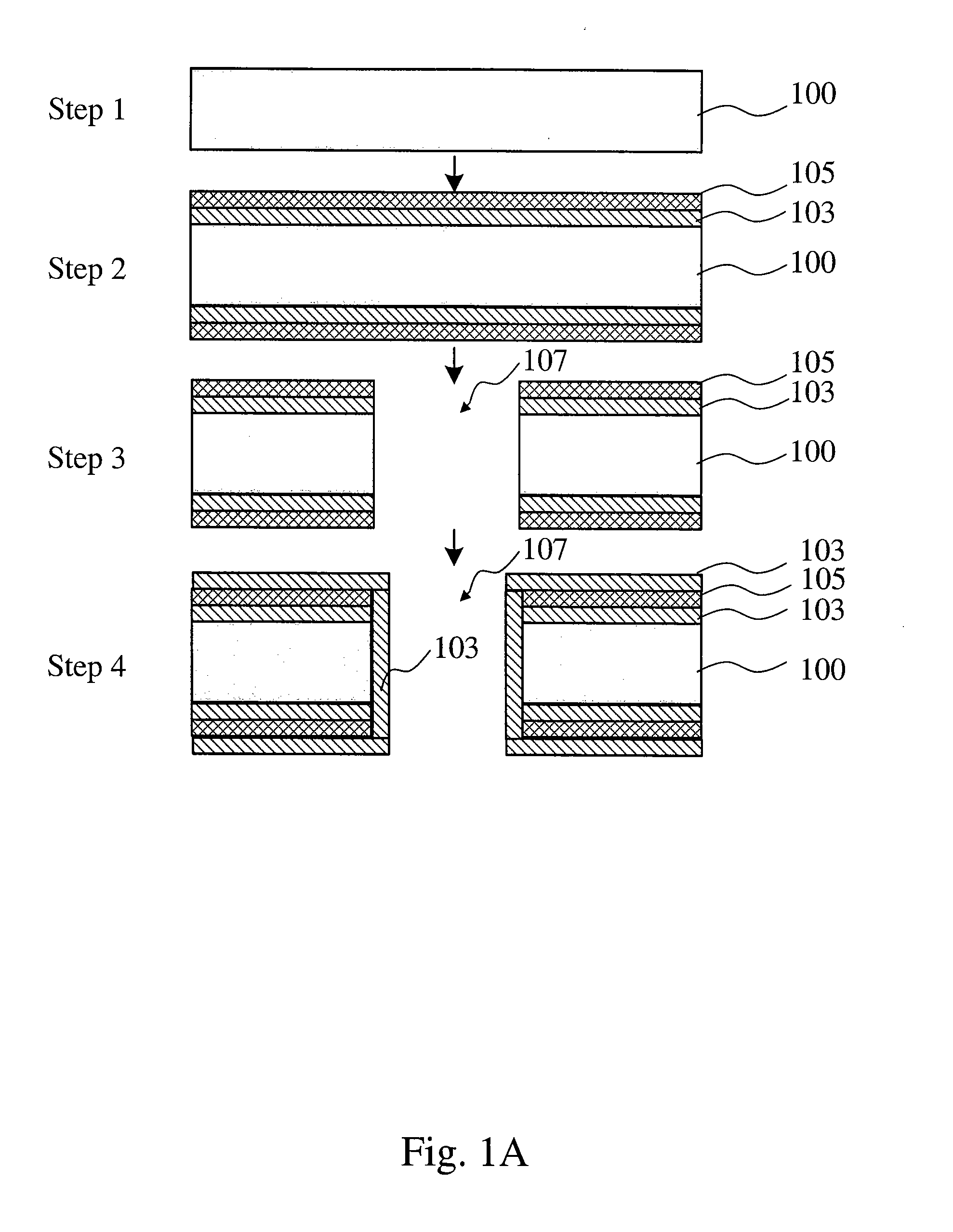

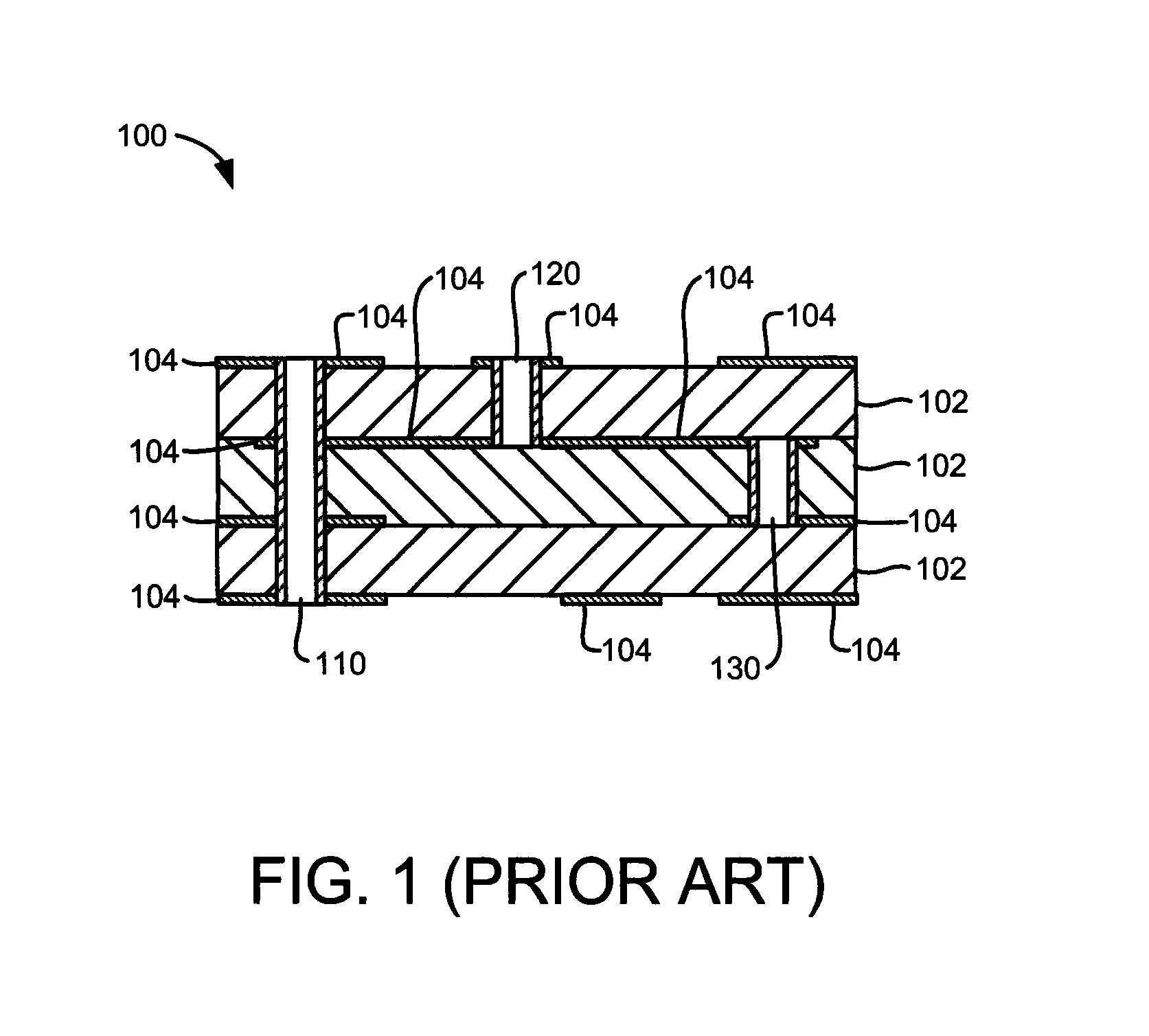

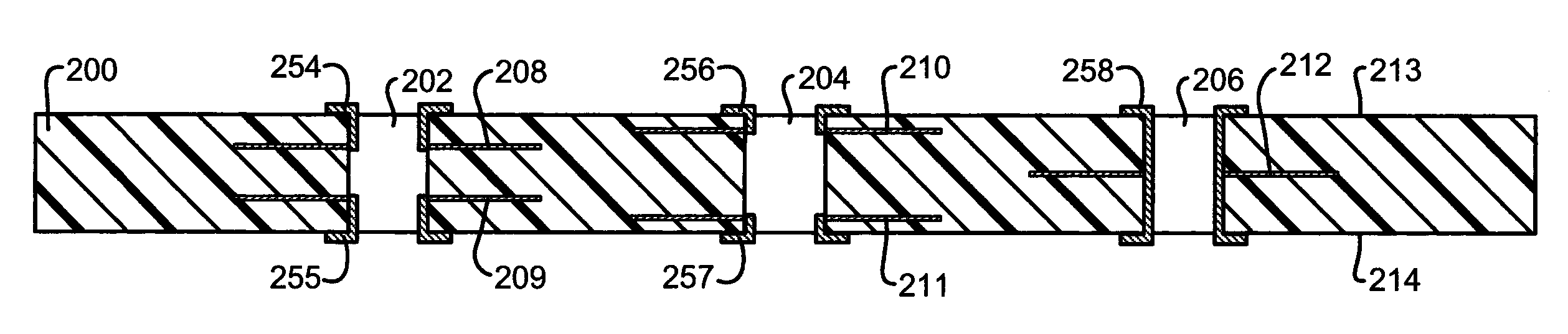

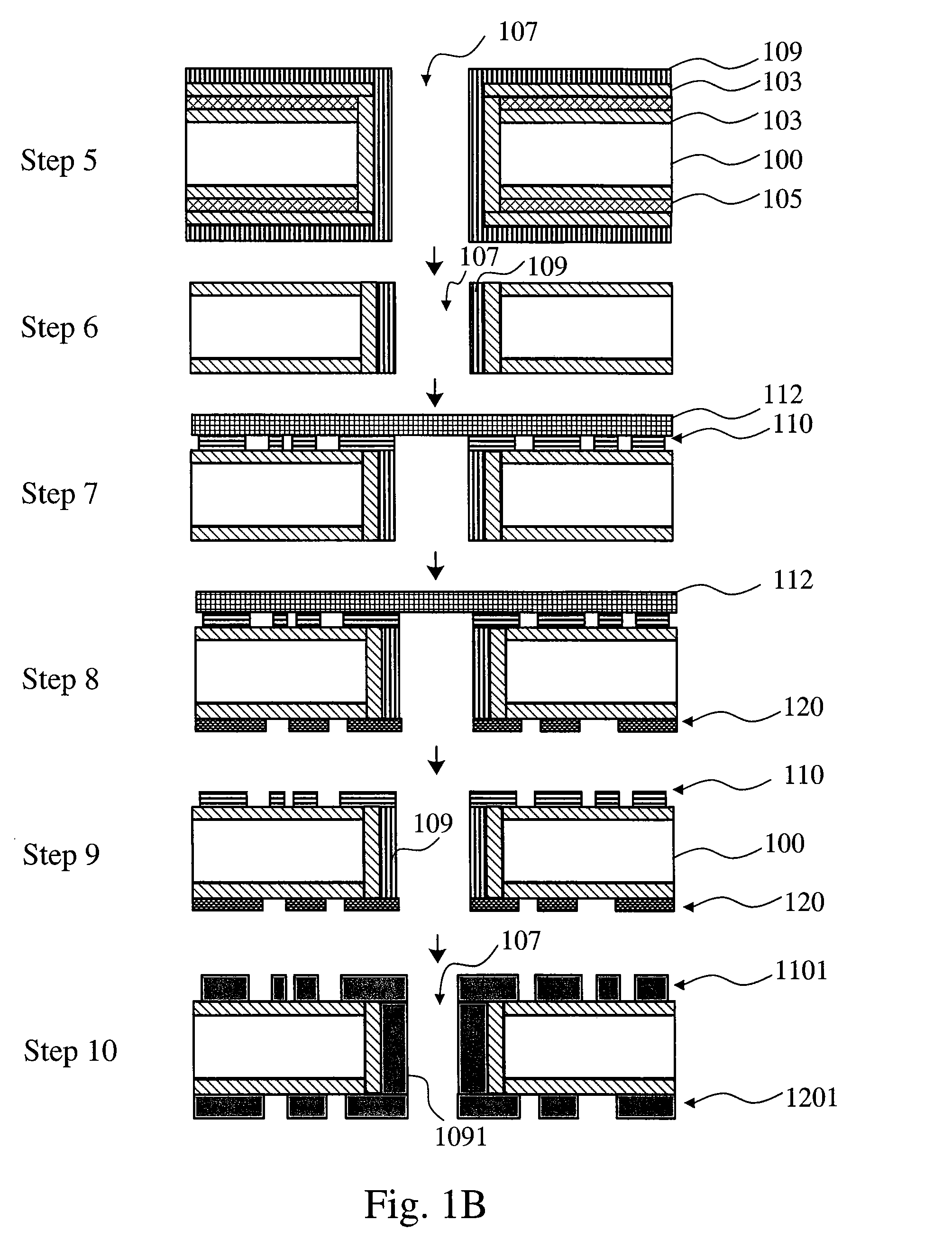

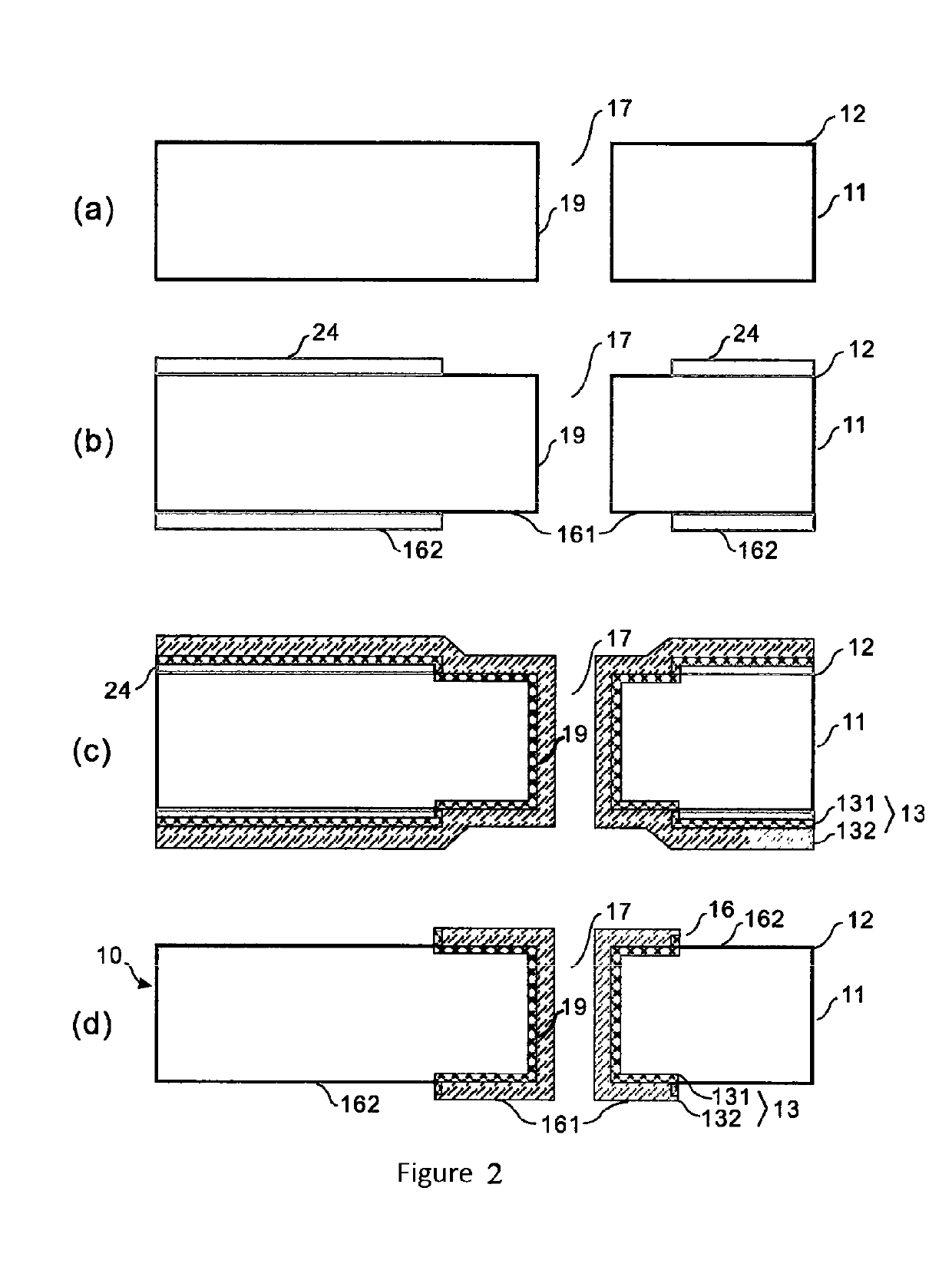

Multi-Layer Printed Circuit Board and Method for Fabricating the Same

ActiveUS20070153488A1Reduce manufacturing costMeet the requirementsConductive pattern formationElectrical connection printed elementsEngineeringPrinted circuit board

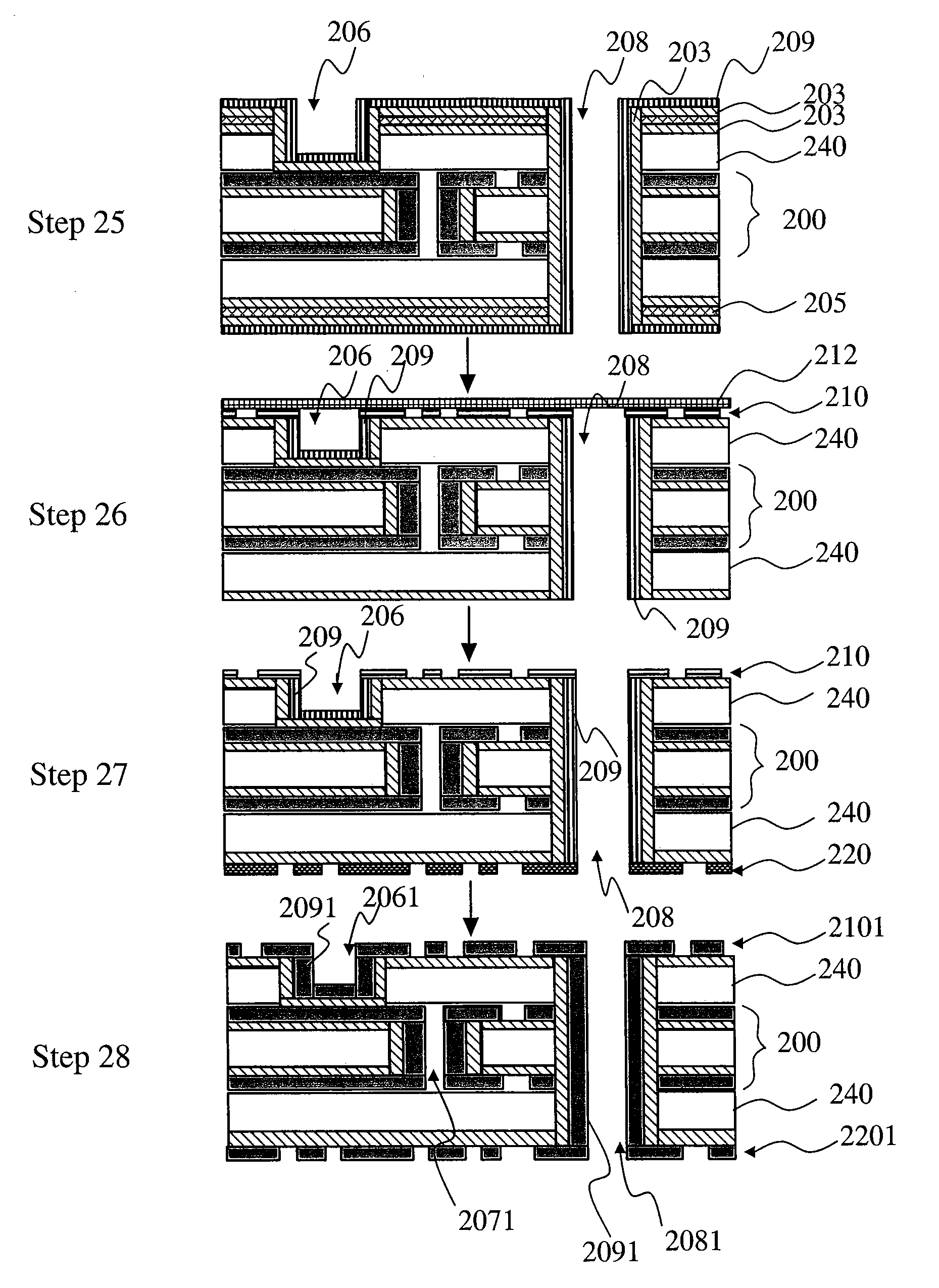

A method for fabricating a double-sided or multi-layer printed circuit board (PCB) by ink-jet printing that includes providing a substrate, forming a first self-assembly membrane (SAM) on at least one side of the substrate, forming a non-adhesive membrane on the first SAM, forming at least one microhole in the substrate, forming a second SAM on a surface of the microhole, providing catalyst particles on the at least one side of the substrate and on the surface of the microhole, and forming a catalyst circuit pattern on the substrate.

Owner:IND TECH RES INST +1

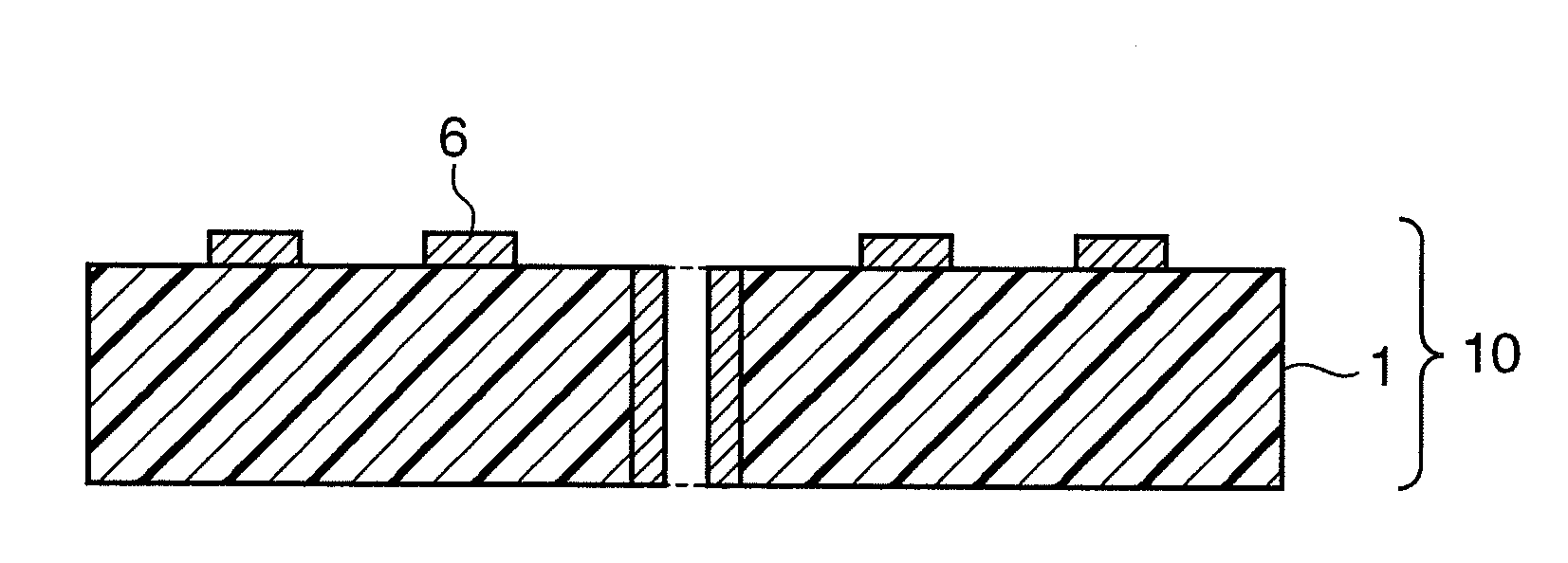

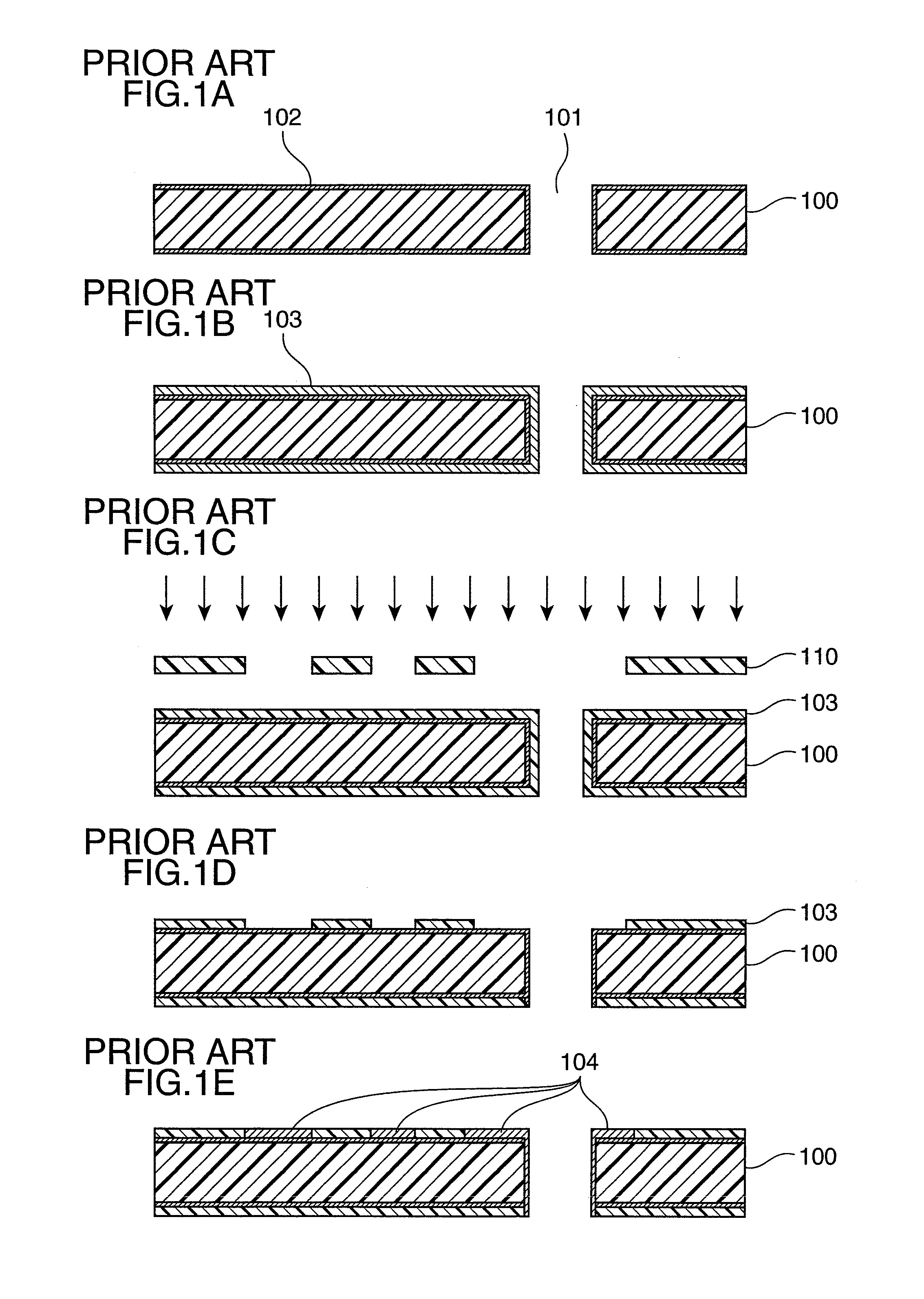

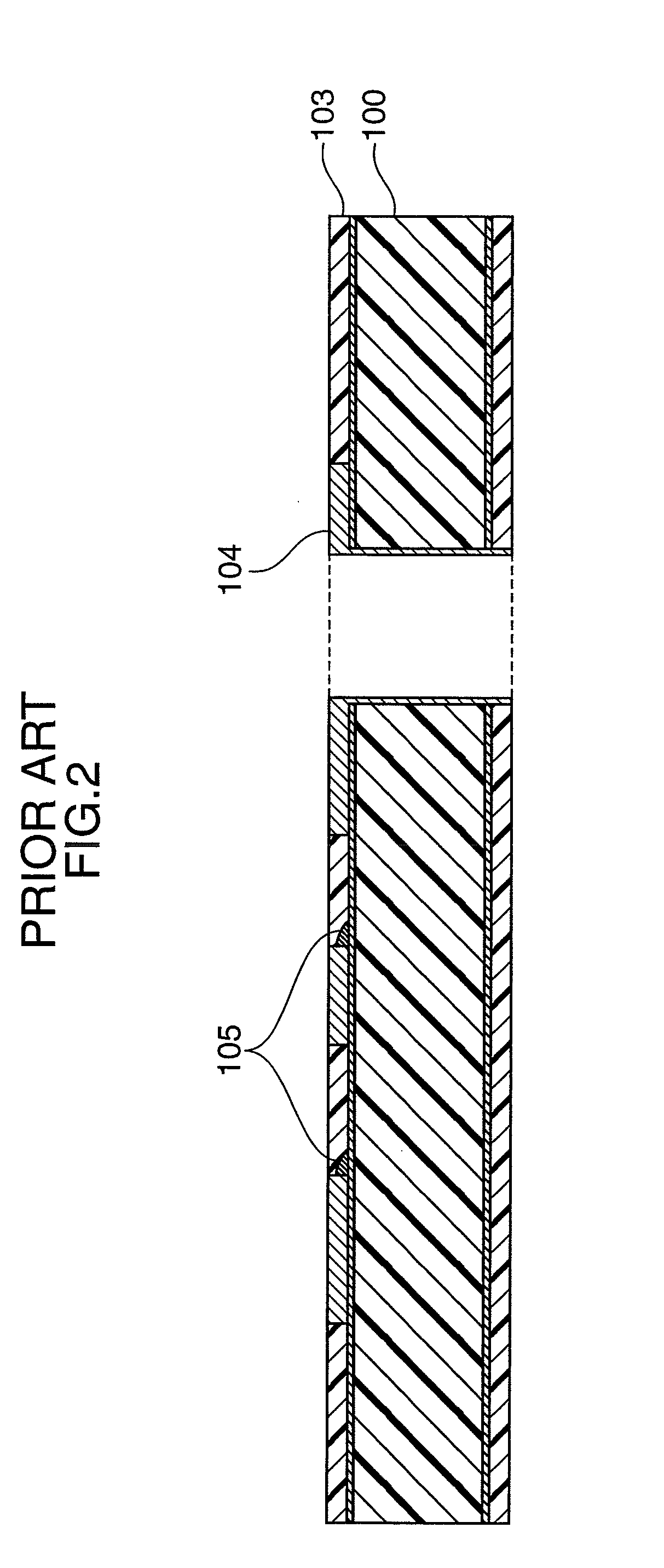

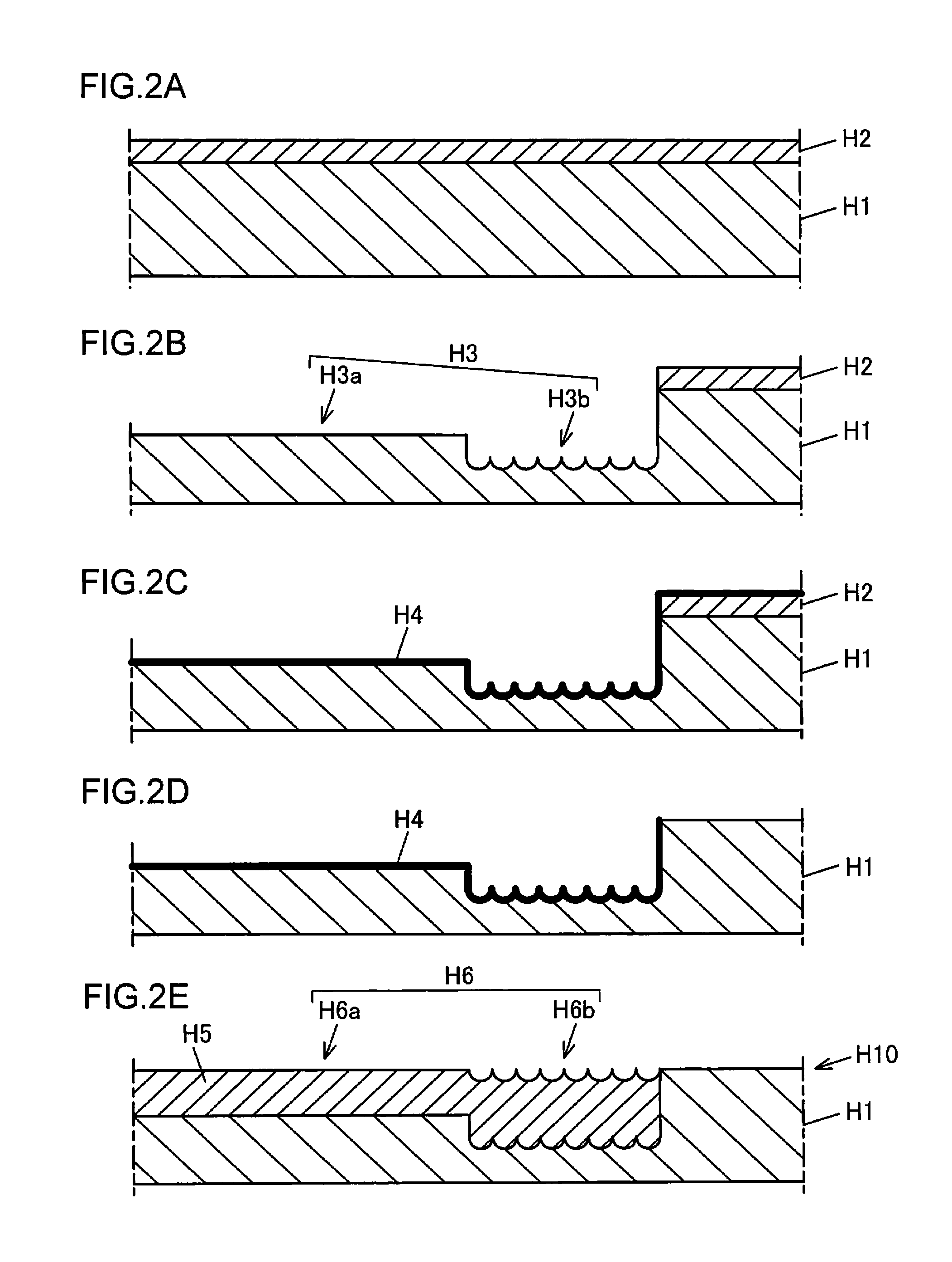

Method of producing circuit board by additive method, and circuit board and multilayer circuit board obtained by the method

InactiveUS20090272564A1Highly accurate preservationPrinted circuit assembling3D rigid printed circuitsEngineeringSubstrate surface

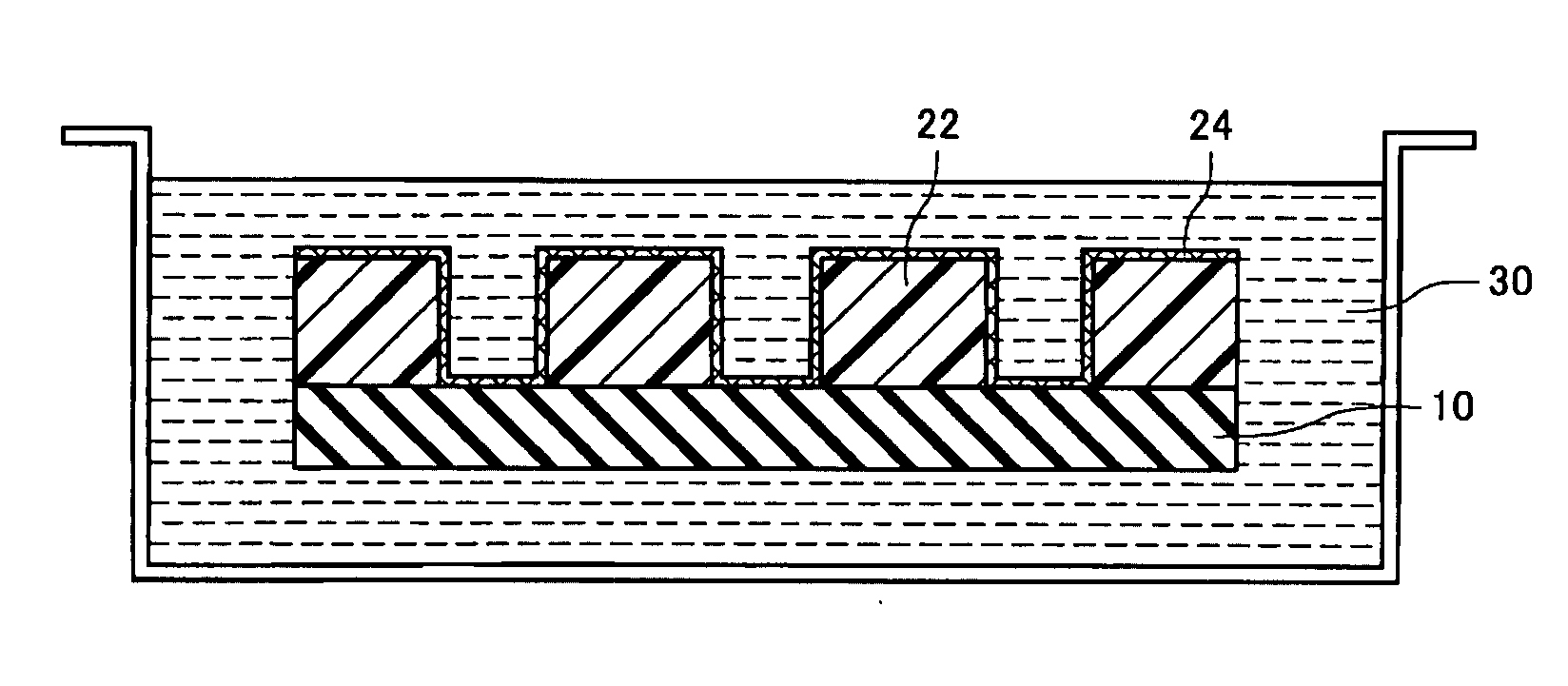

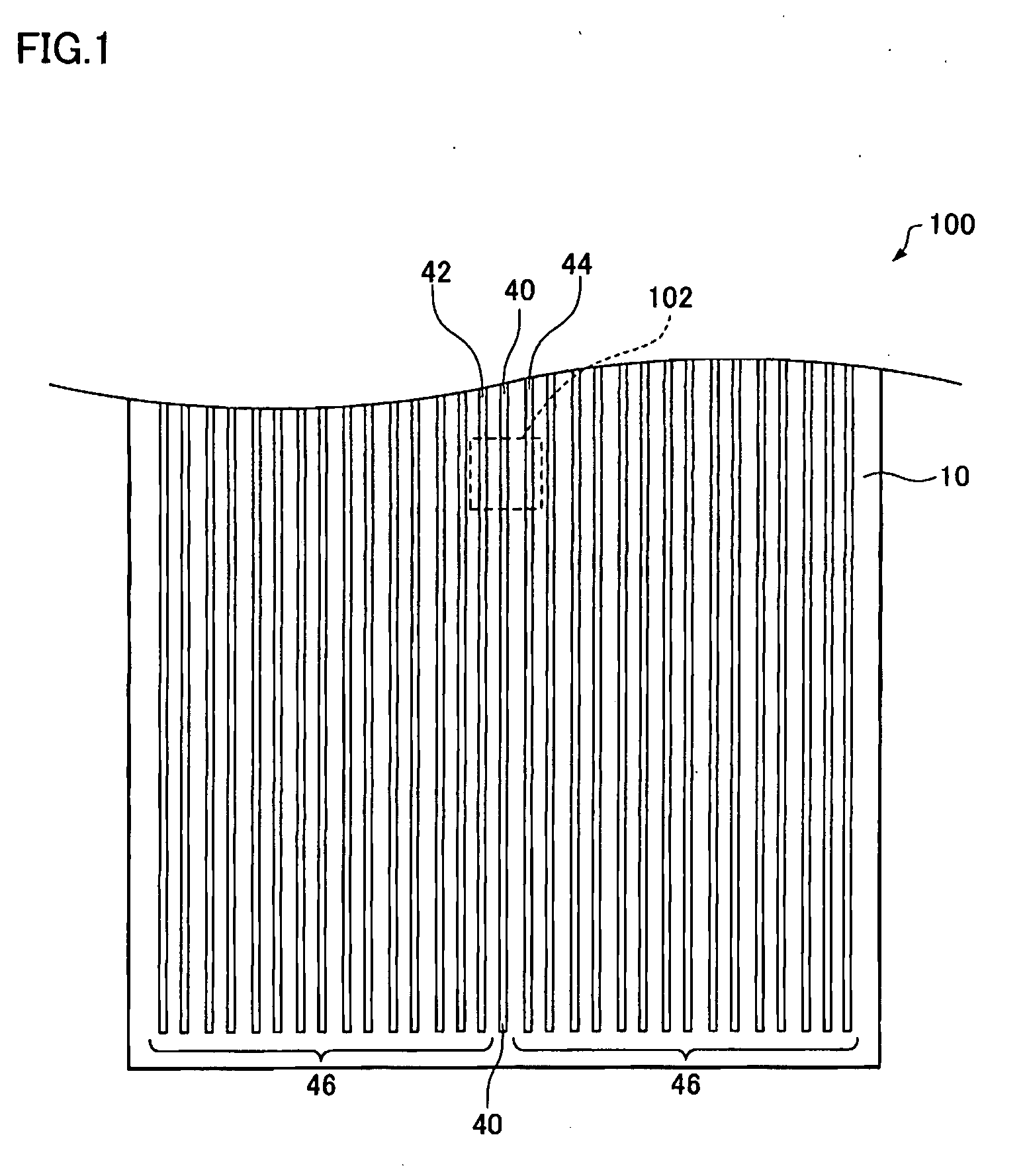

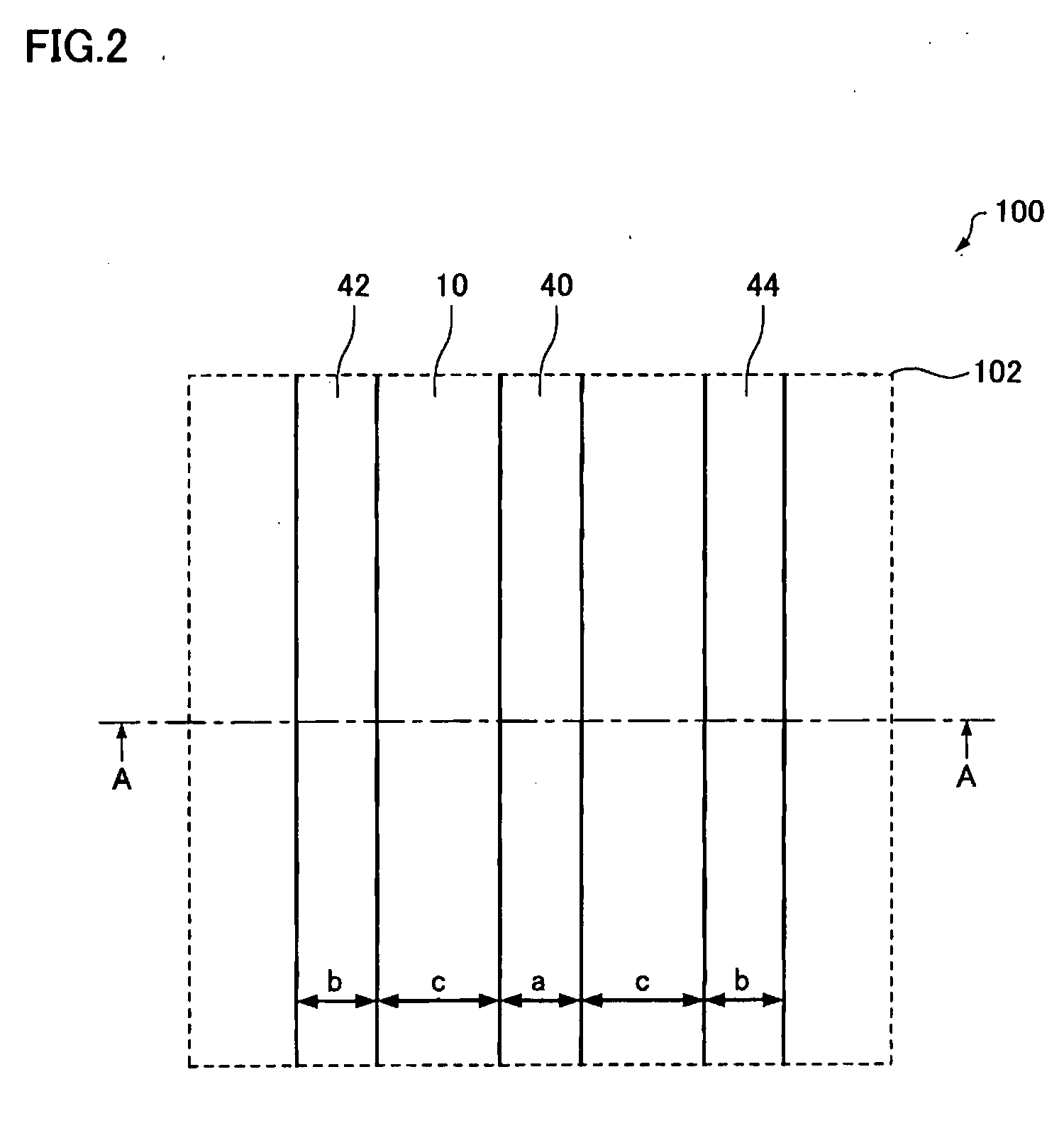

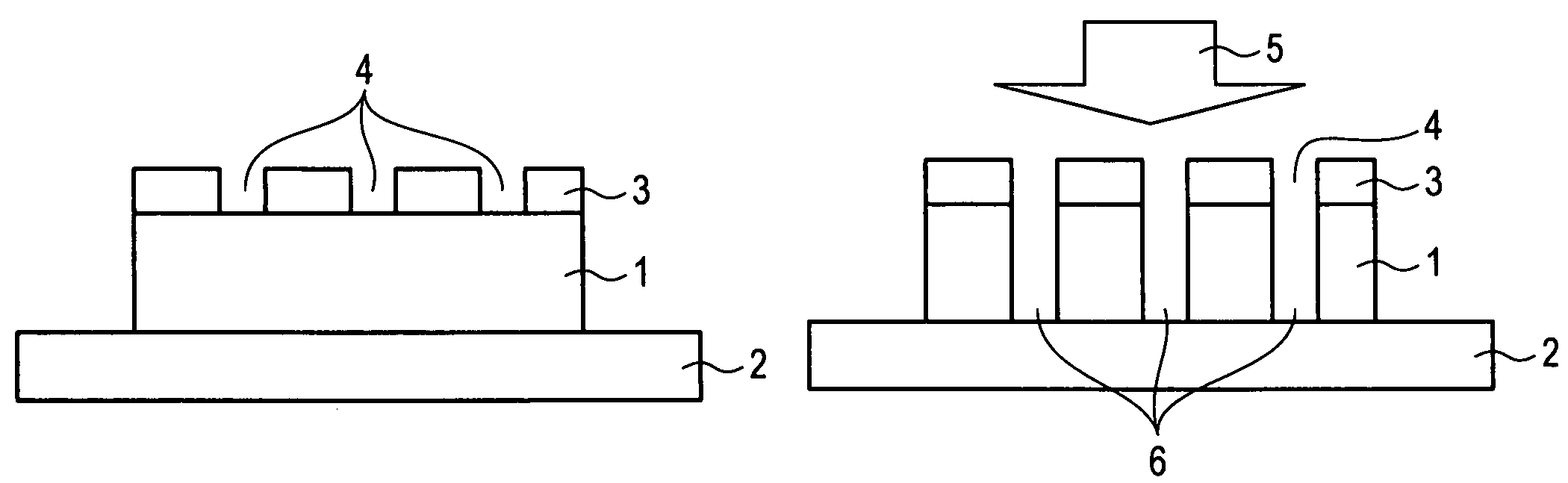

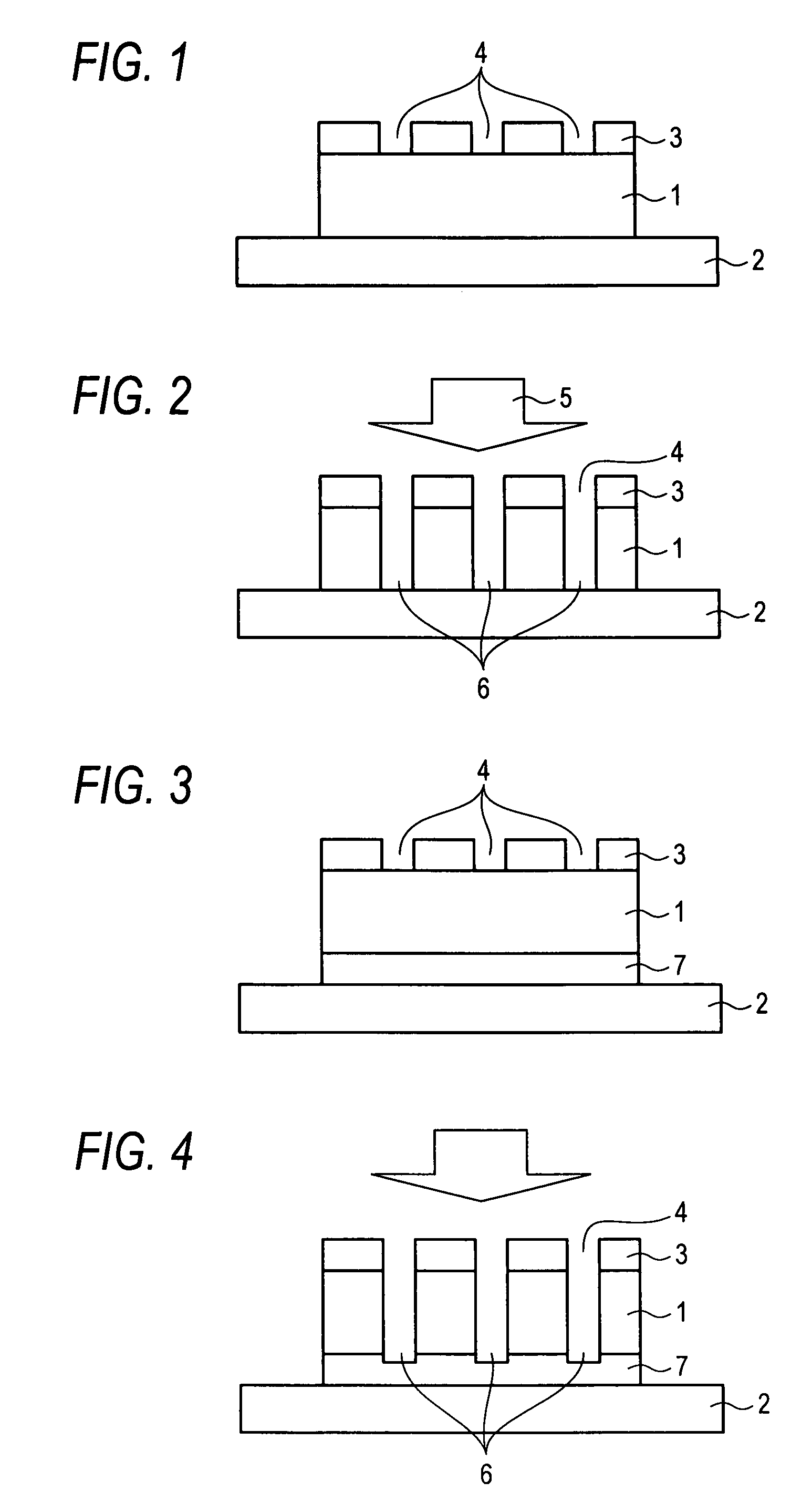

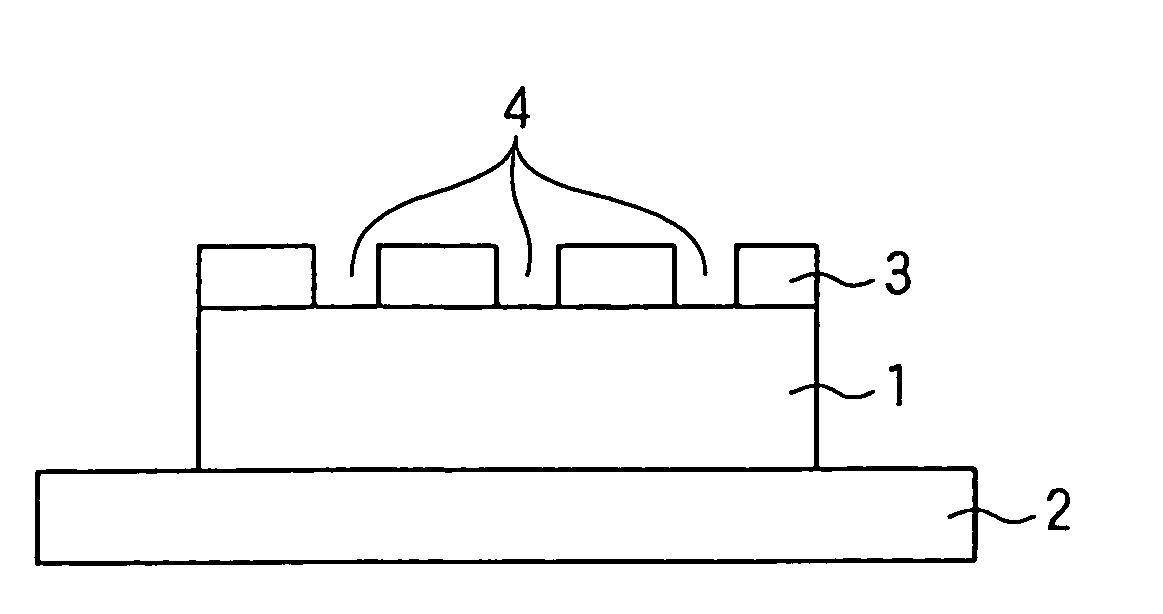

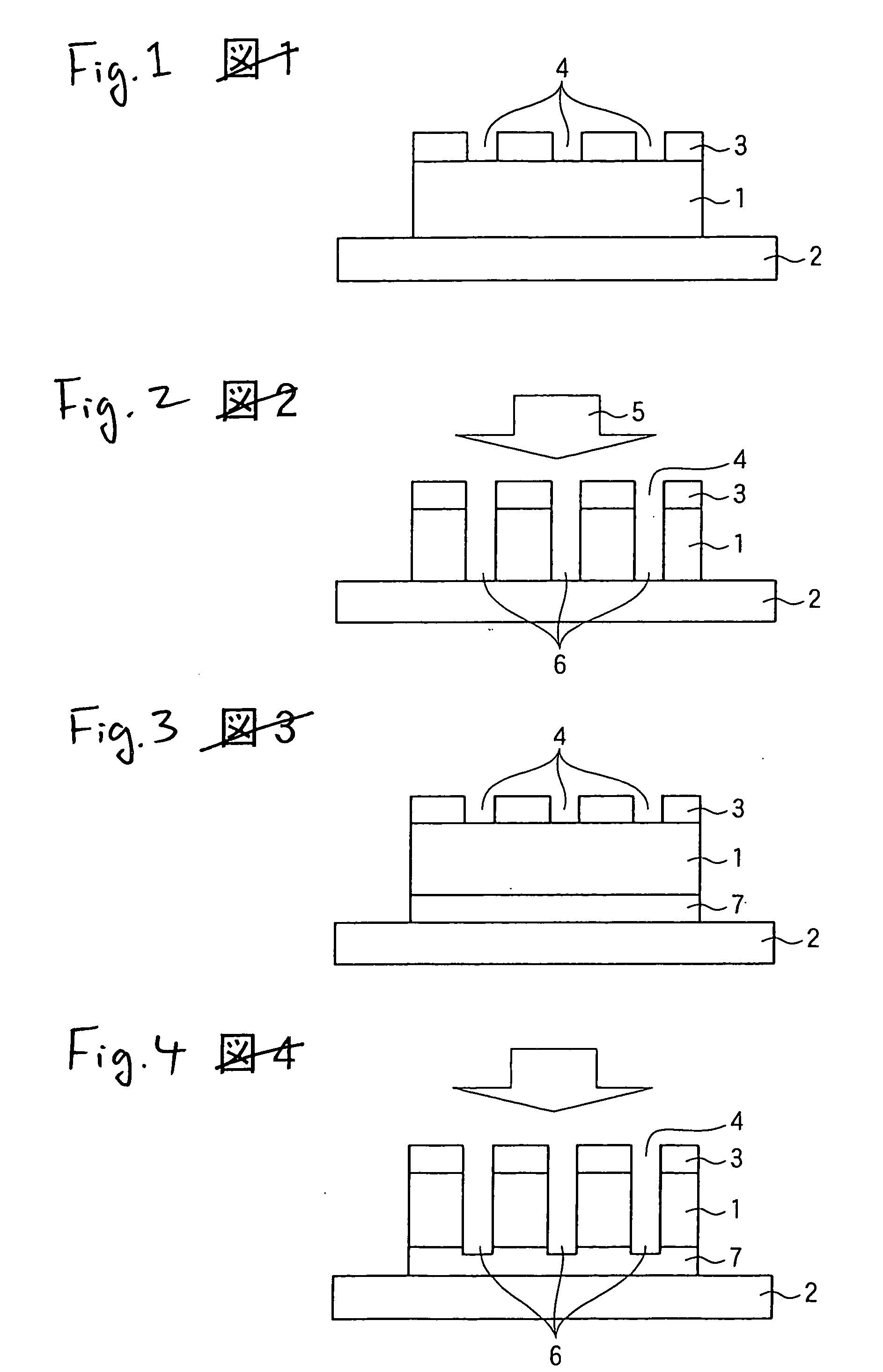

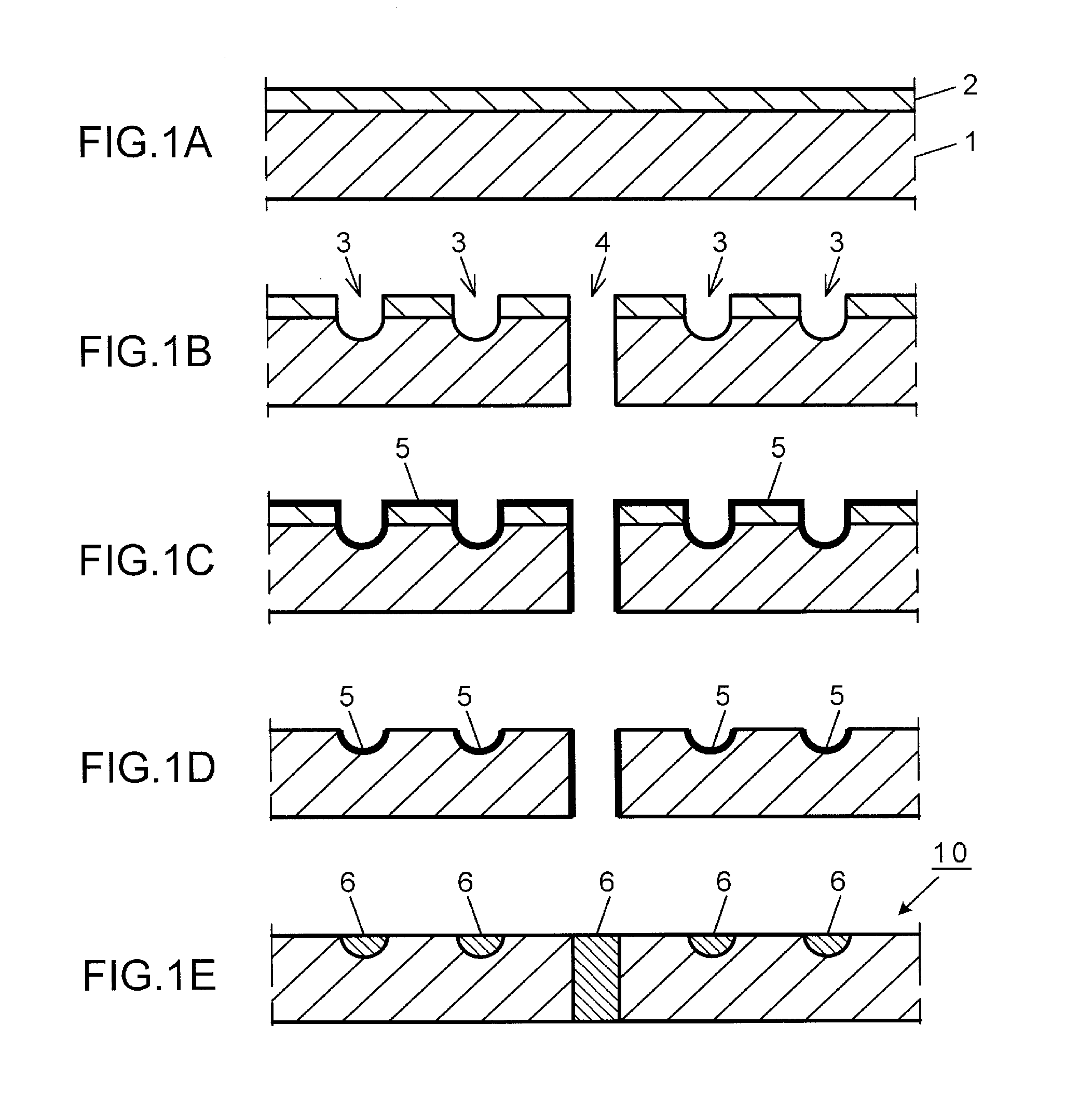

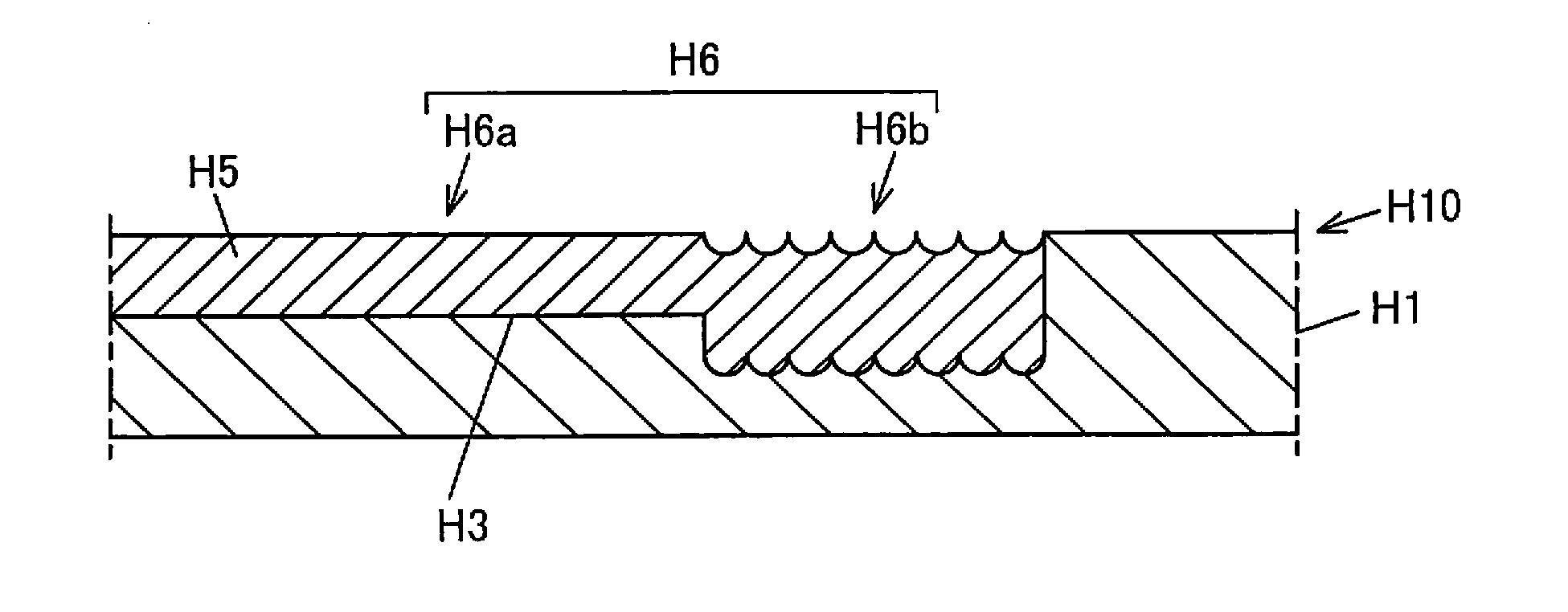

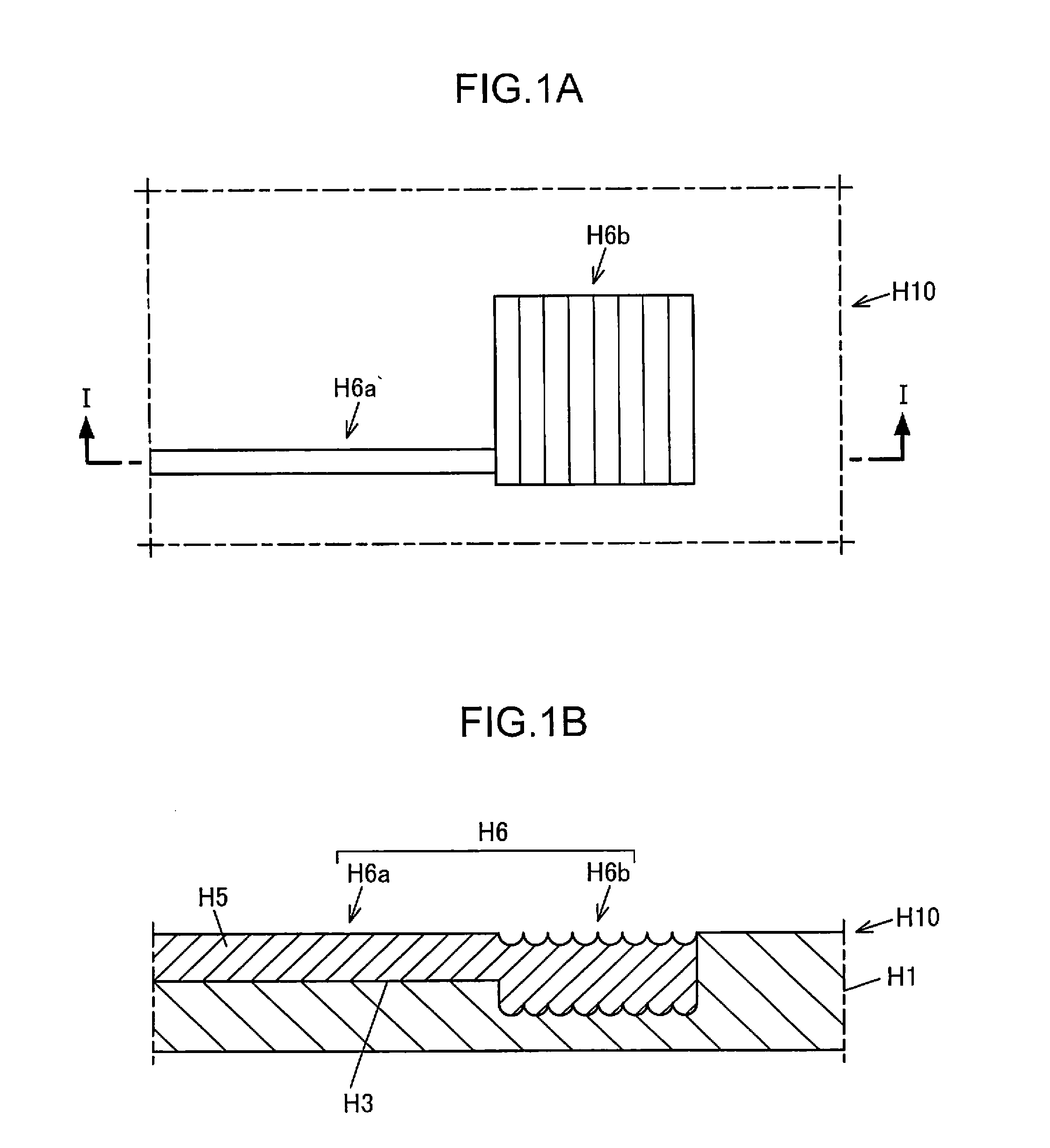

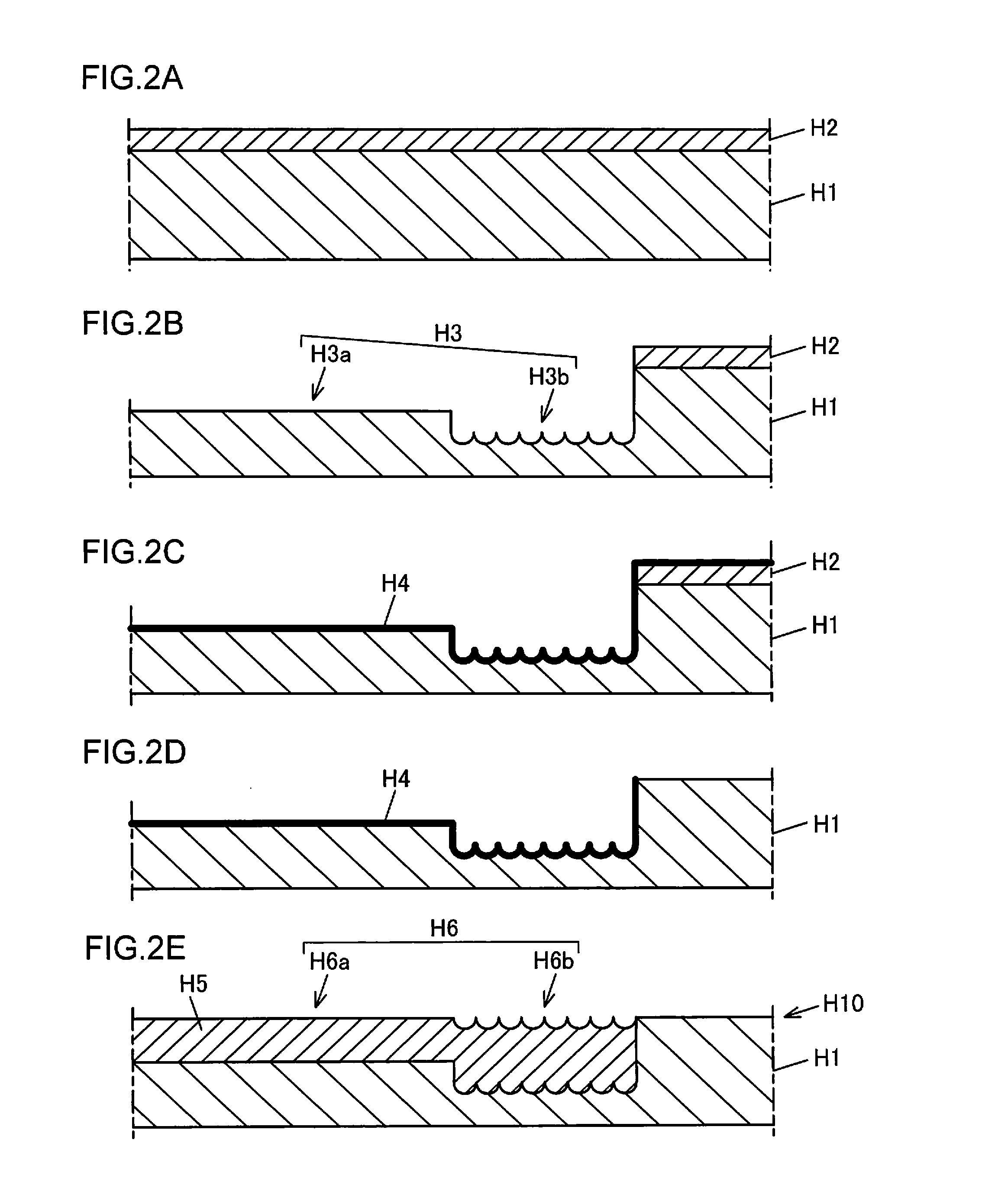

An object of an aspect of the present invention is to provide a method of producing a circuit board that allows highly accurate preservation of the circuit profile and gives a circuit having a desired depth in preparation of a fine circuit by additive process.The method of producing a multilayer circuit board in an aspect of the present invention includes a film-forming step of forming a swellable resin film on the surface of an insulative substrate, a circuit groove-forming step of forming circuit grooves having a depth equal to or greater than the thickness of the swellable resin film on the external surface of the swellable resin film, a catalyst-depositing step of depositing a plating catalyst or the precursor thereof on the surface of the circuit grooves and the surface of the swellable resin film, a film-separating step of swelling the swellable resin film with a particular liquid and then separating the swollen resin film from the insulative substrate surface, and a plating processing step of forming an electrolessly plated film only in the region where the plating catalyst or the plating catalyst formed from the plating catalyst precursor remains unseparated after separation of the swellable resin film.

Owner:PANASONIC CORP

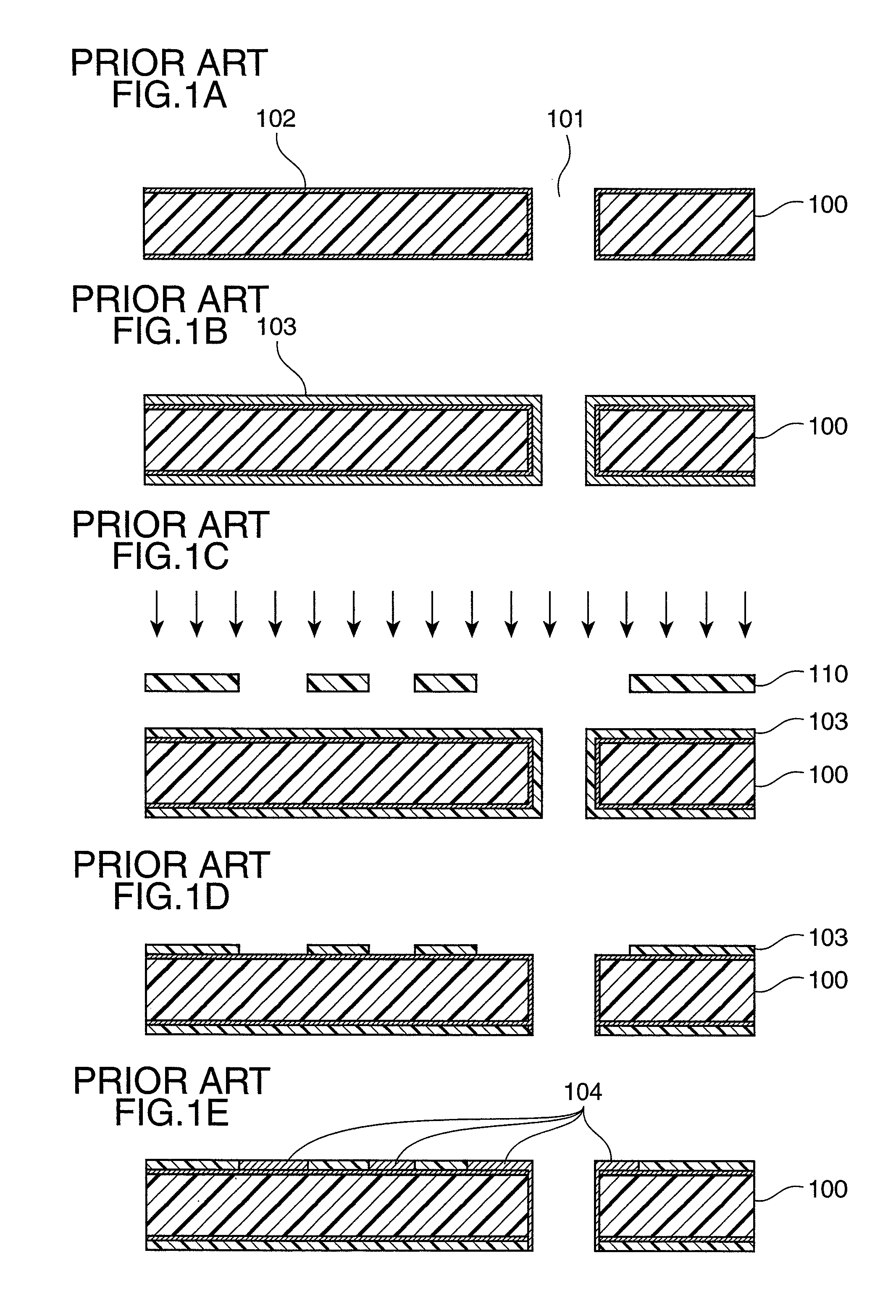

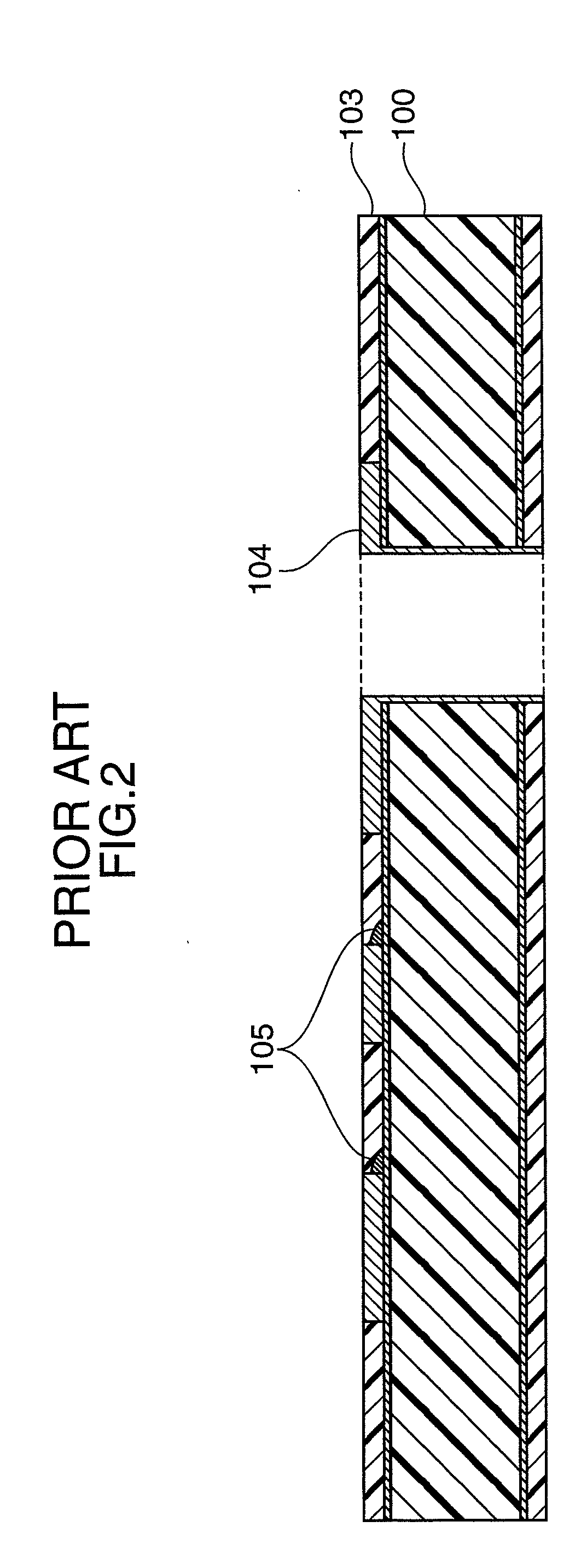

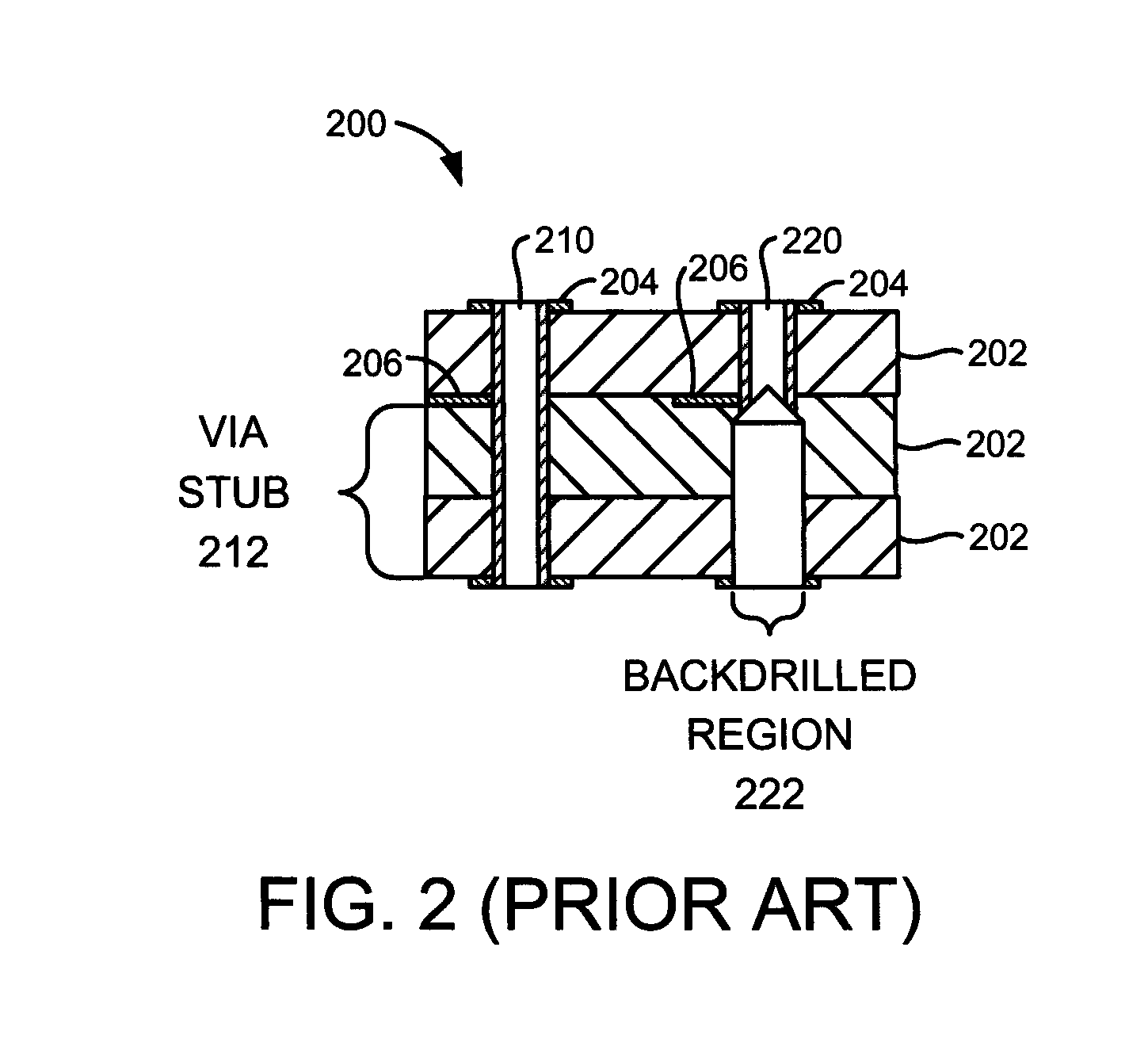

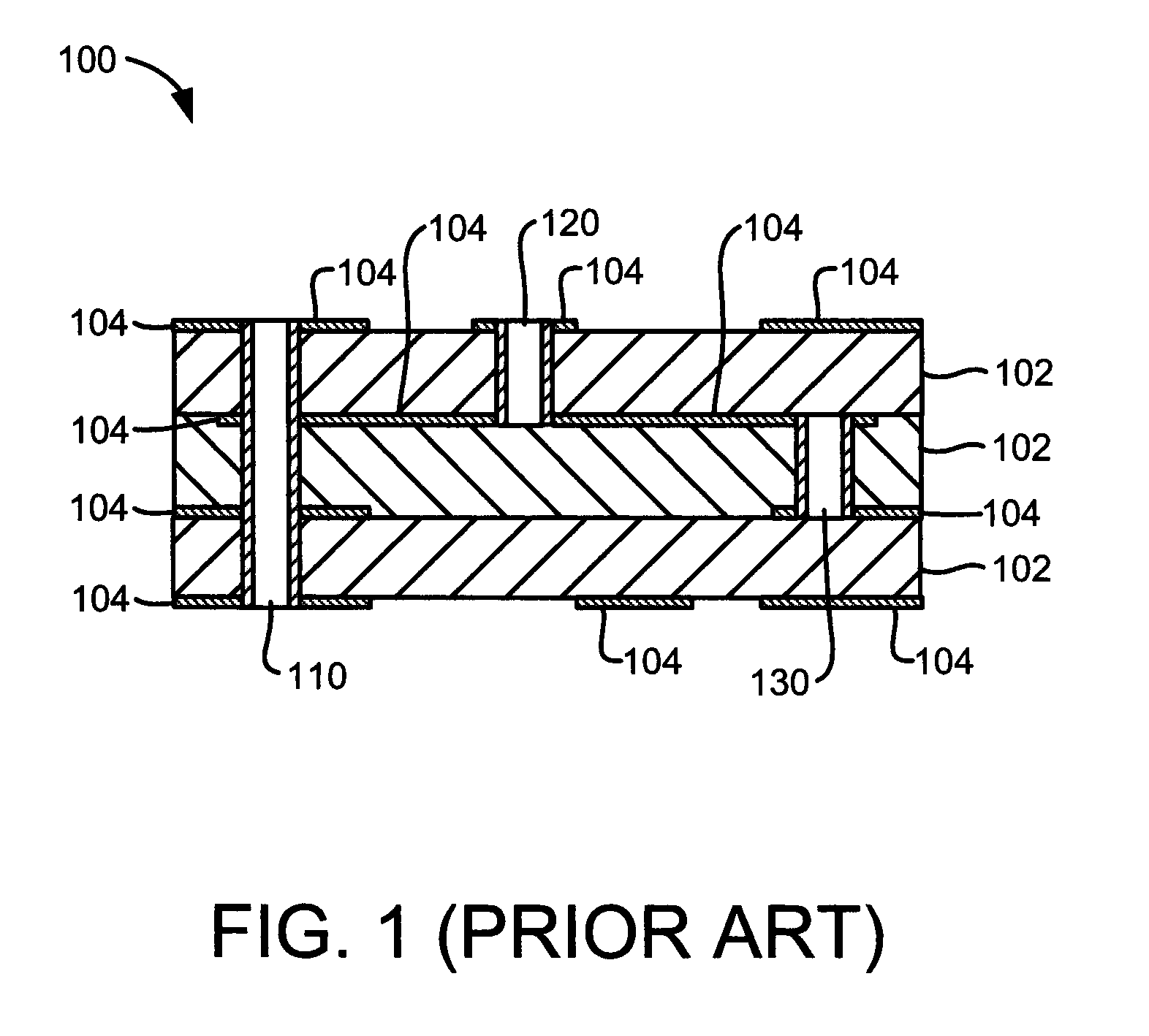

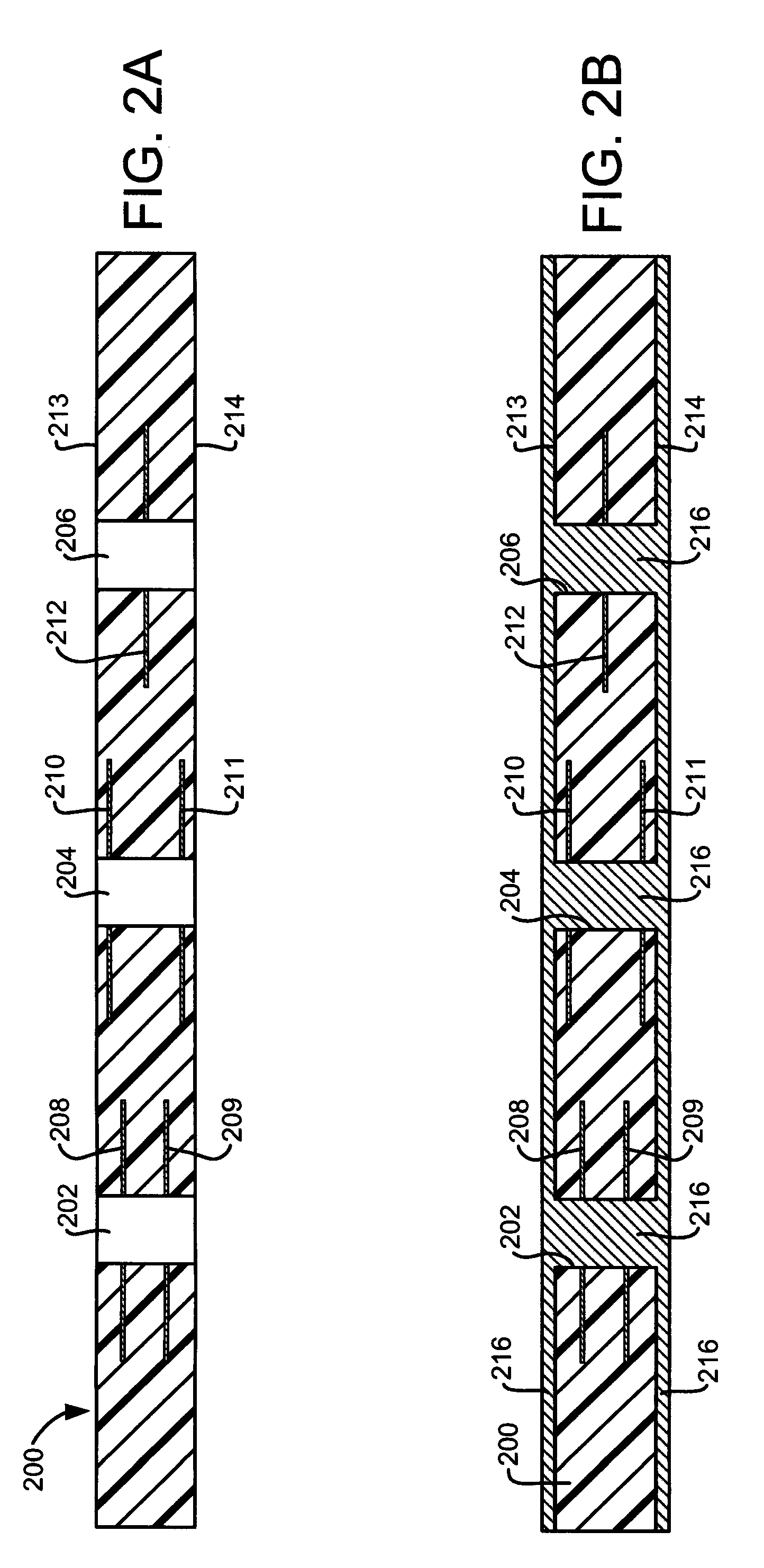

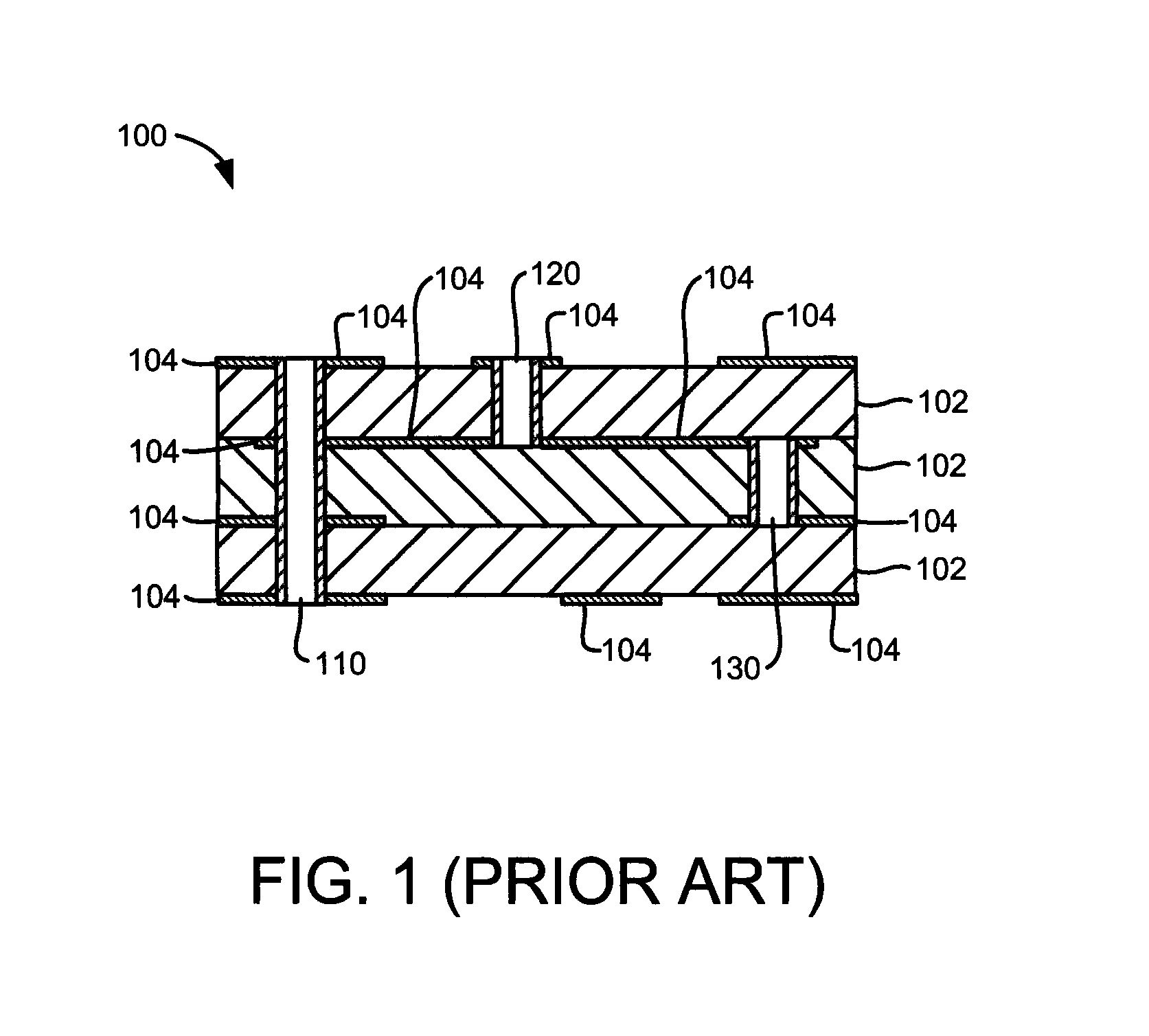

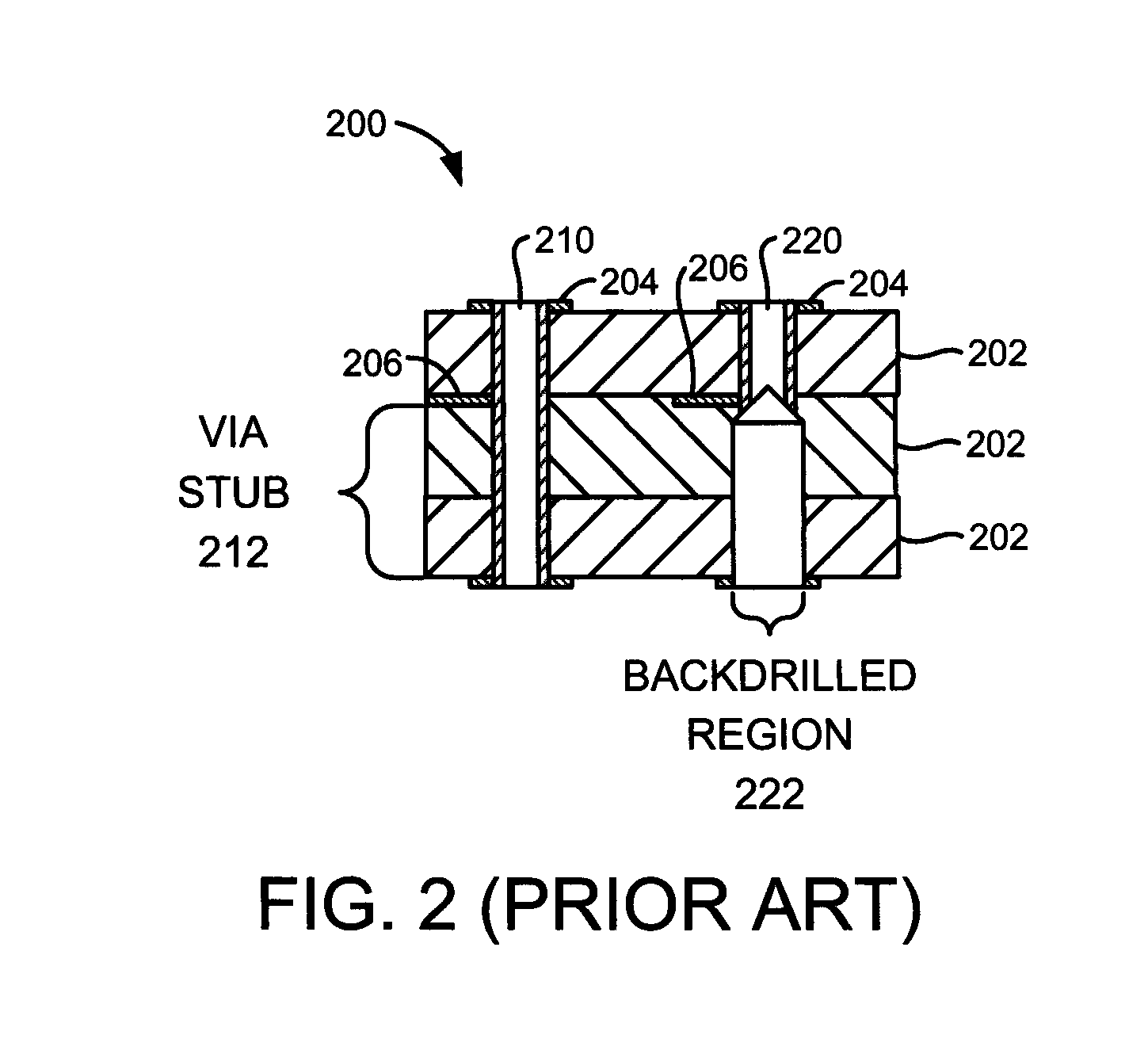

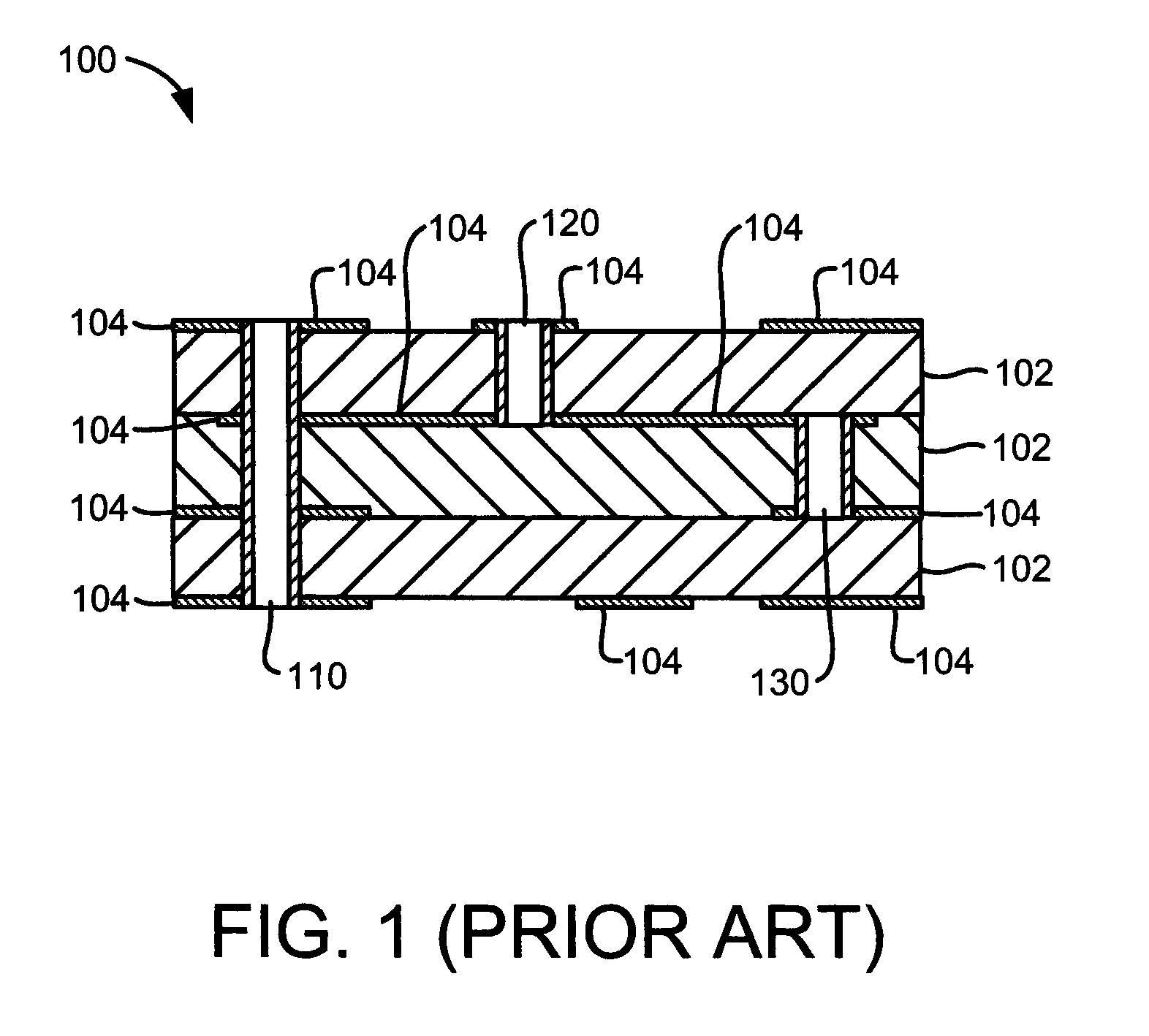

Via Stub Elimination

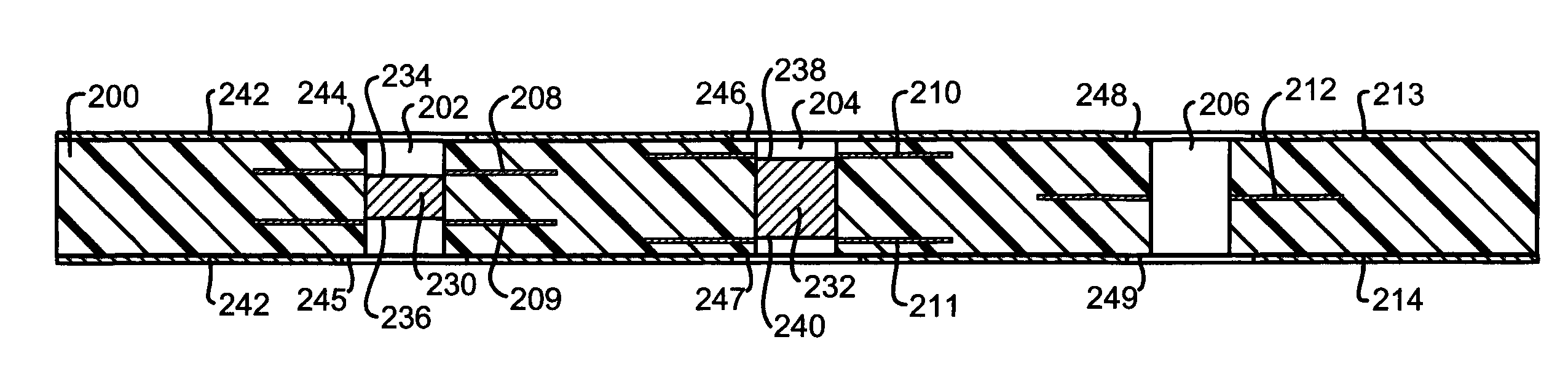

InactiveUS20100044095A1Eliminates costlyTime-consuming to eliminatePrinted circuit assemblingAdditive manufacturing apparatusTime-ConsumingPhotomask

An enhanced mechanism is disclosed for via stub elimination in printed wiring boards (PWBs) and other substrates. In one embodiment, the substrate includes a plurality of insulator layers and internal conductive traces. First and second through-holes extend completely through the substrate and respectively pass through first and second ones of the internal conductive traces, which are at different depths within the substrate. Photolithographic techniques are used to generate plated-through-hole (PTH) plugs of controlled, variable depth in the through-holes before first and second conductive vias are respectively plated onto the first and second through-holes. The depth of these PTH plugs is controlled (e.g., using a photomask and / or variable laser power) to prevent the first and second conductive vias from extending substantially beyond the first and second internal conductive traces, respectively, and thereby prevent via stubs from being formed in the first place. This advantageously eliminates the costly and time consuming process of via stub backdrilling.

Owner:GLOBALFOUNDRIES INC

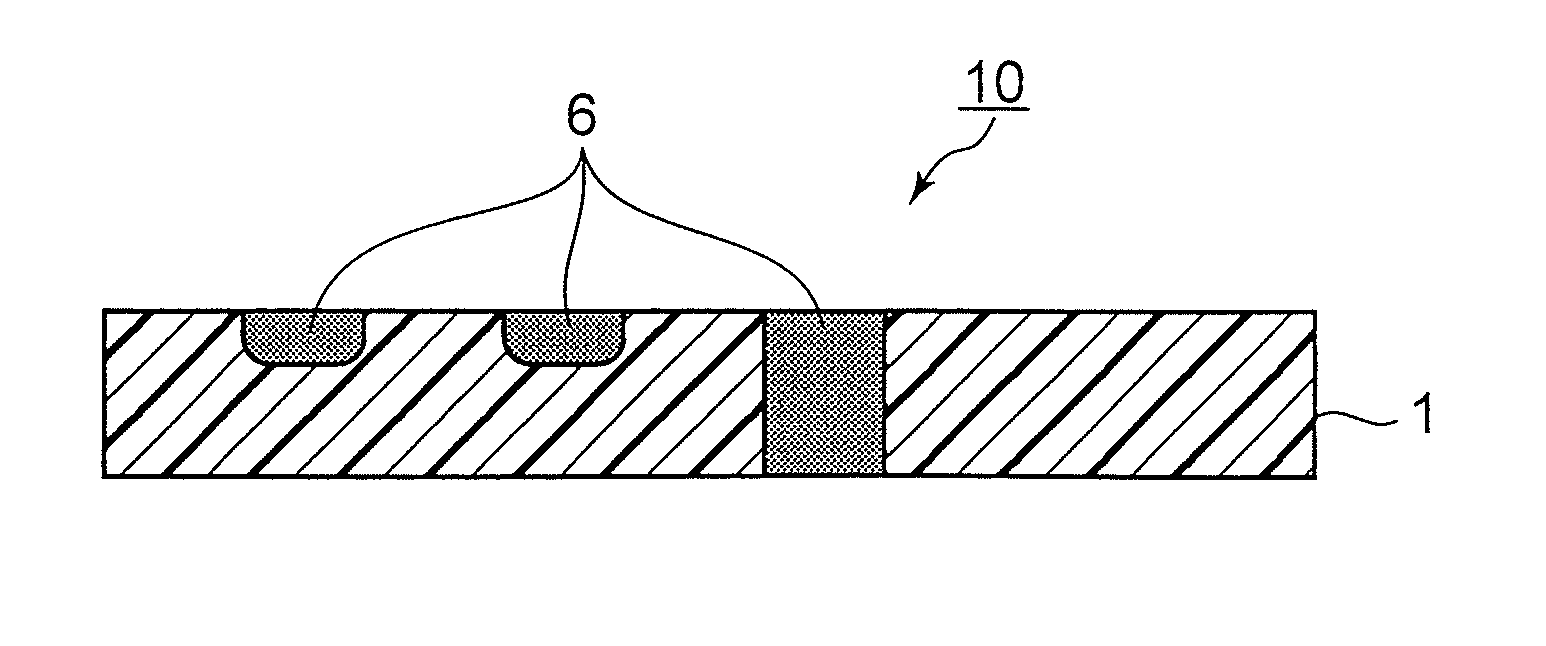

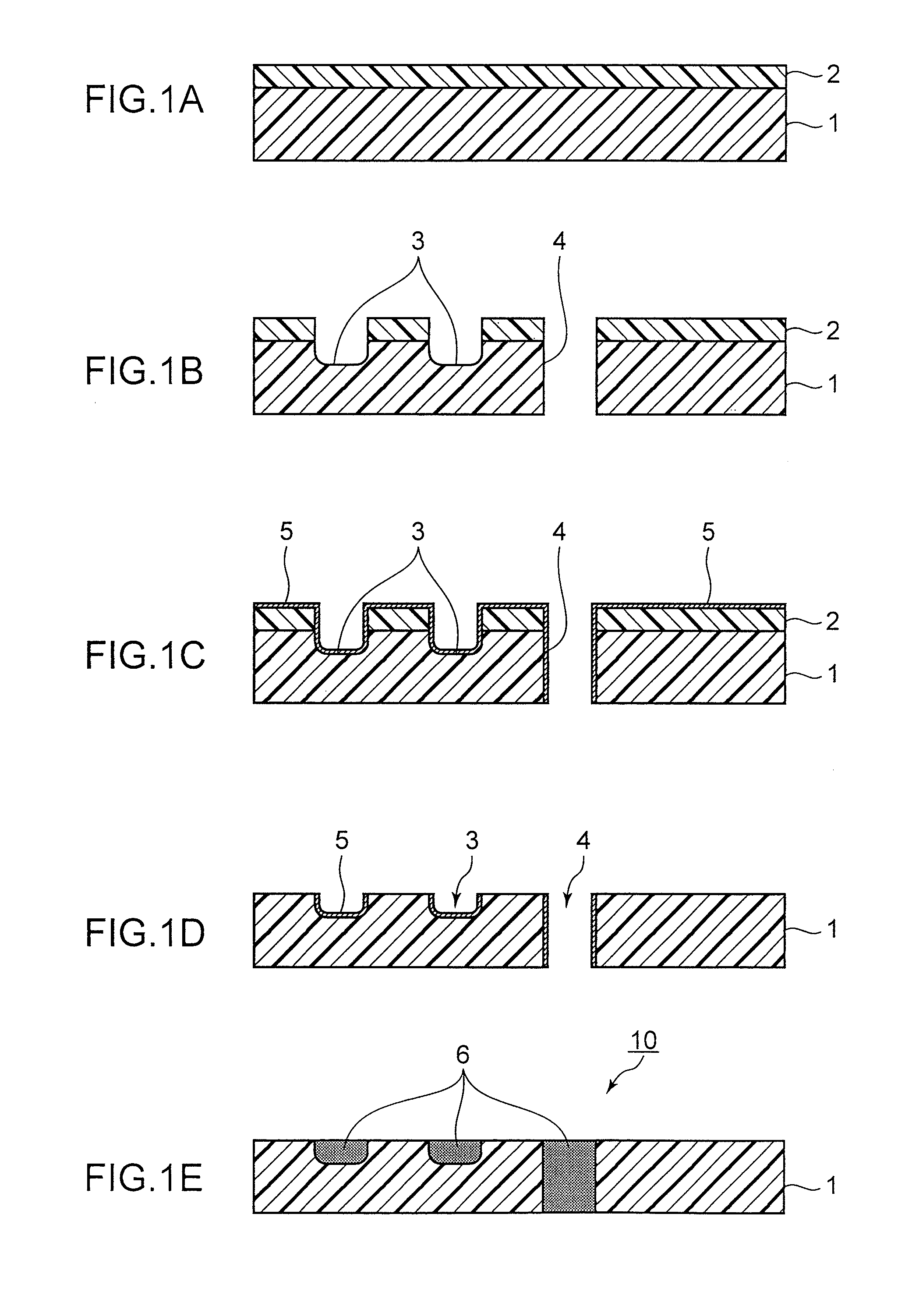

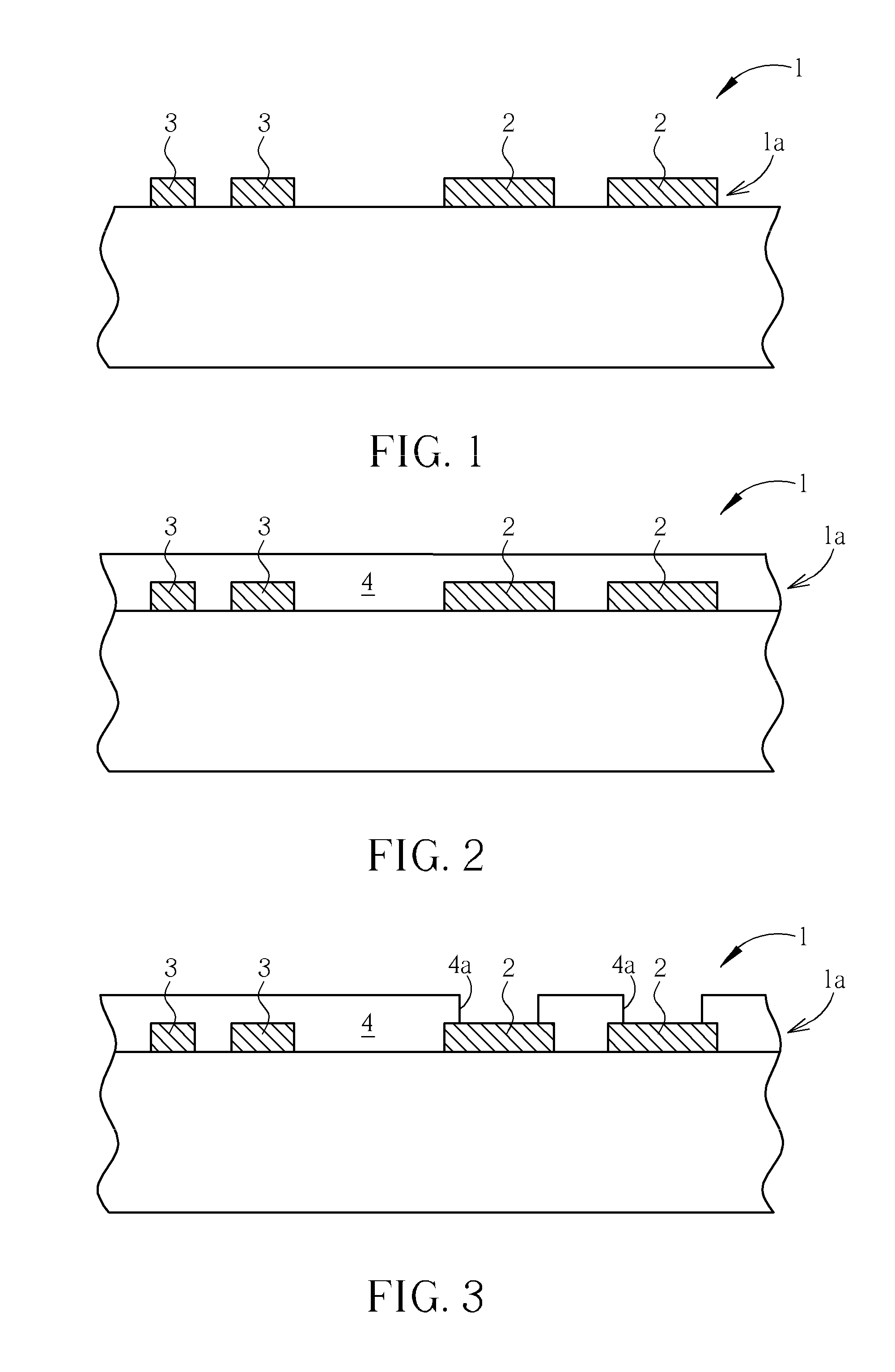

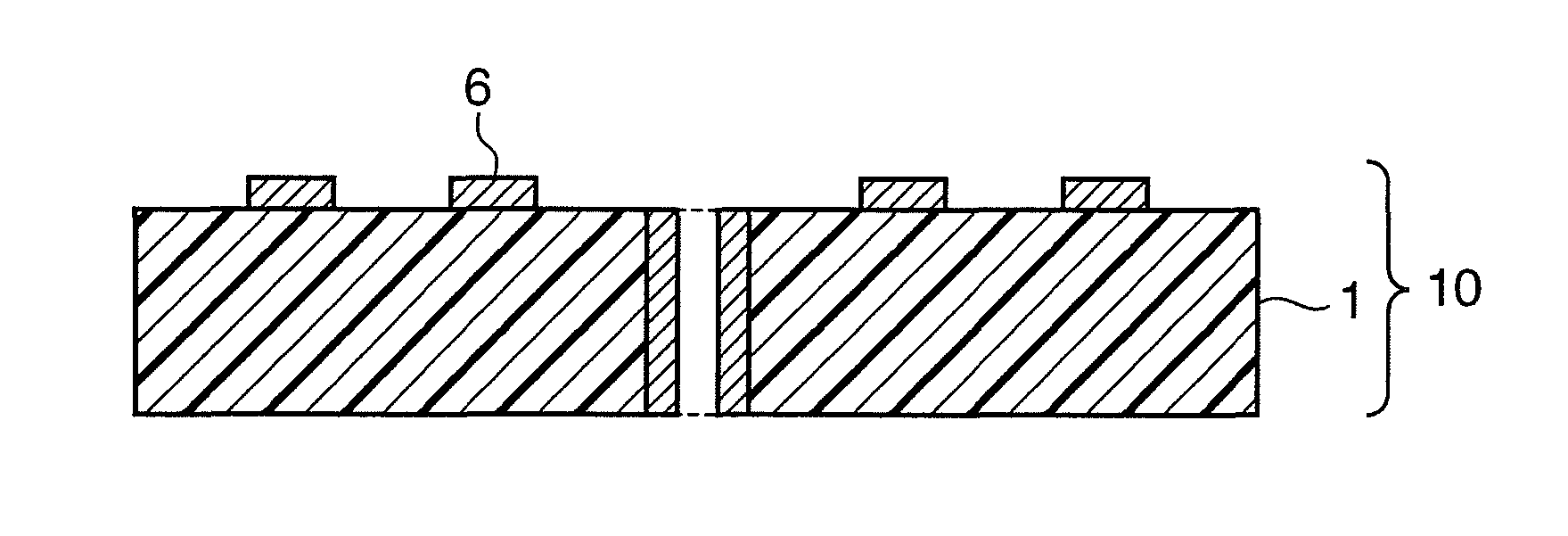

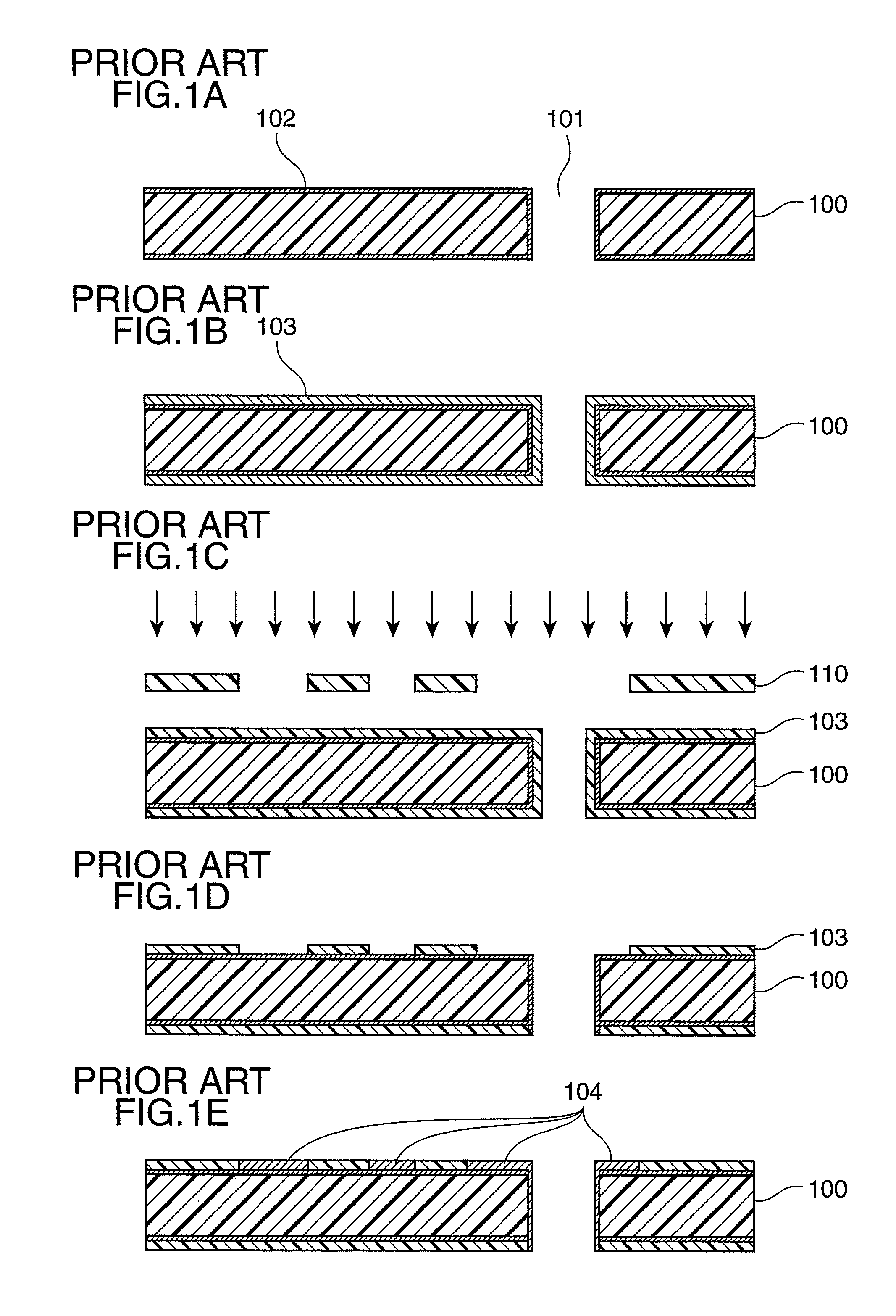

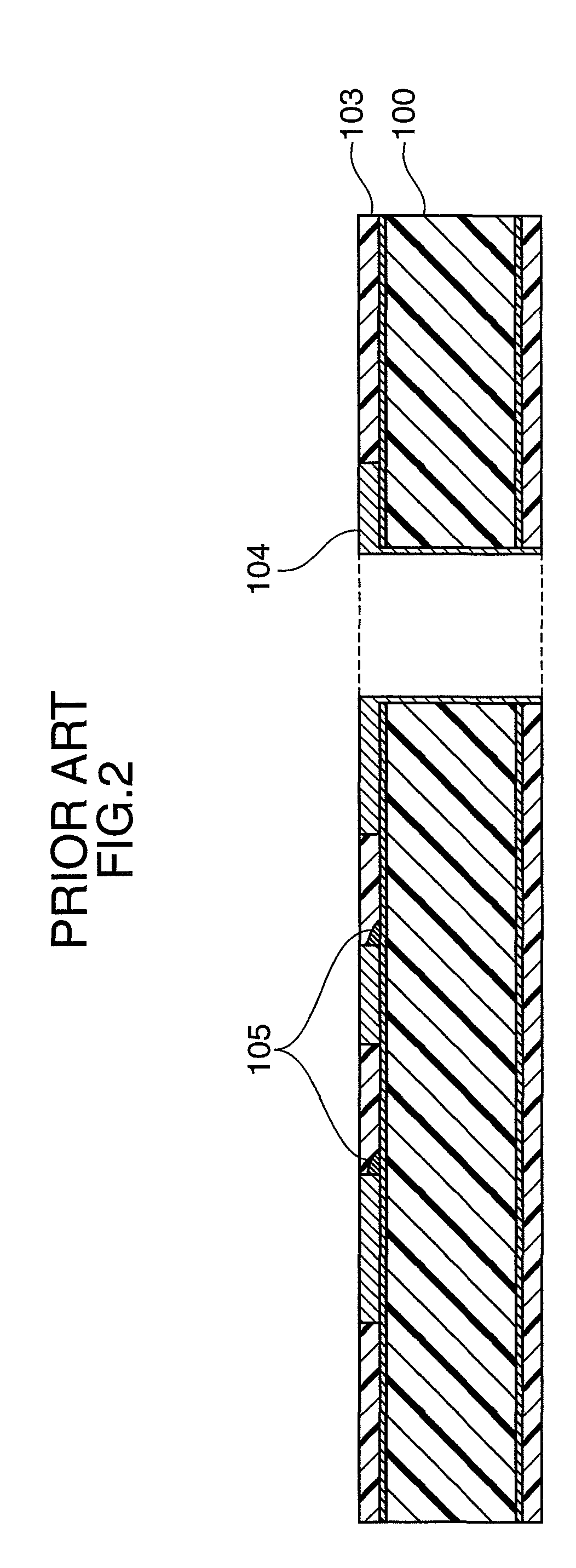

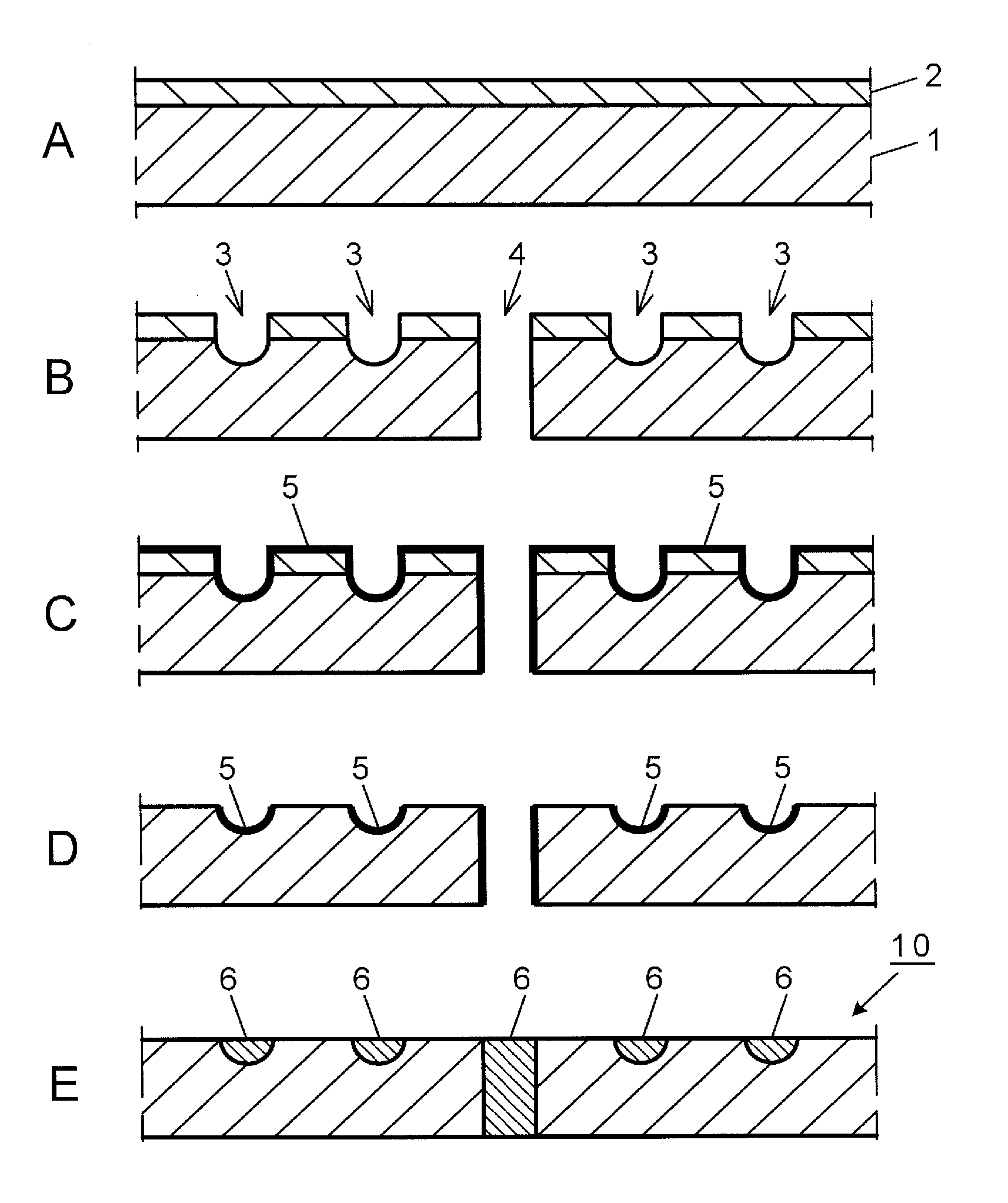

Method of producing circuit board, and circuit board obtained using the manufacturing method

InactiveUS20110247860A1Simple wayRadiation applicationsPretreated surfacesEngineeringElectroless plating

One aspect of the present invention resides in a method of producing a circuit board, including a film-forming step of forming a resin film on a surface of an insulative substrate; a circuit pattern-forming step of forming a circuit pattern portion by forming a recessed portion having a depth equal to or greater than a thickness of the resin film, with an outer surface of the resin film serving as a reference; a catalyst-depositing step of depositing a plating catalyst or a precursor thereof on a surface of the circuit pattern portion and a surface of the resin film; a film-separating step of removing the resin film from the insulative substrate; and a plating step of forming an electroless plating film only in a region where the plating catalyst or the precursor thereof remains after the resin film is separated.

Owner:PANASONIC CORP

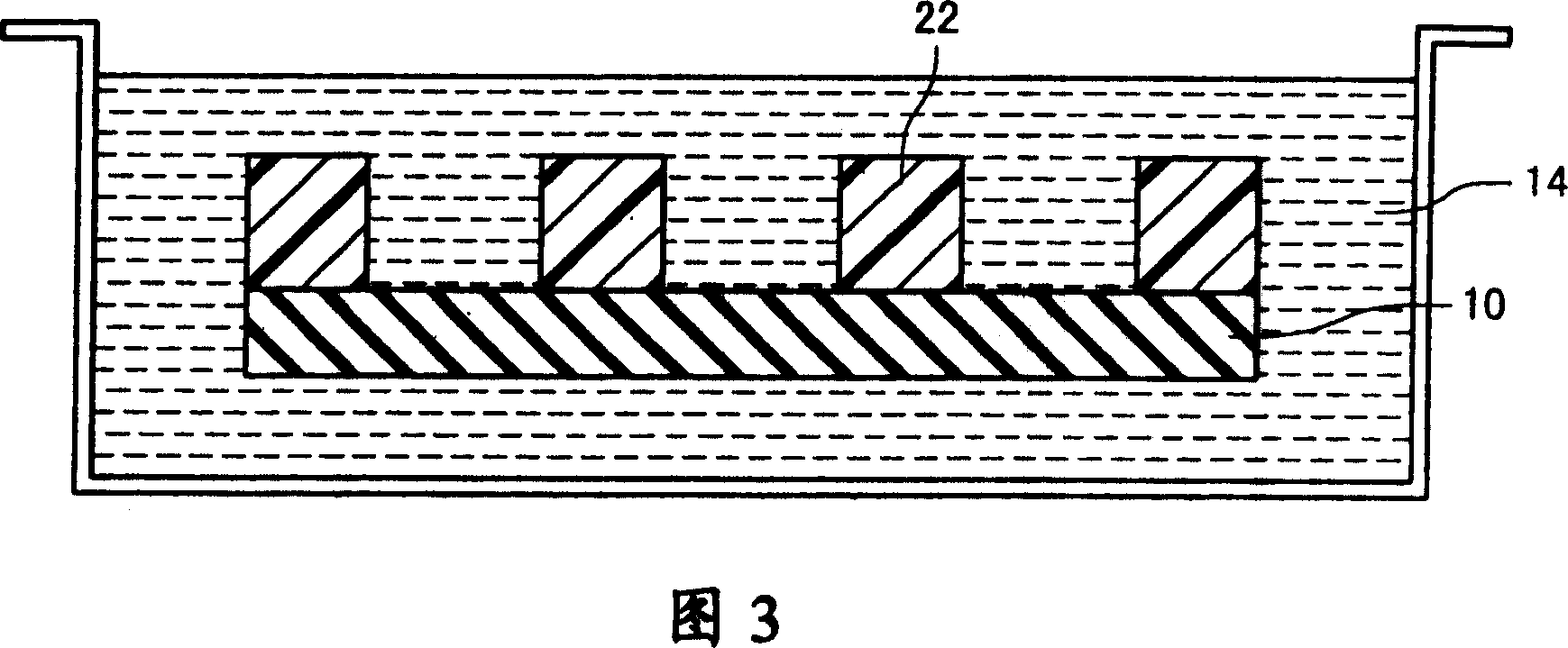

Method of producing circuit board by additive method, and circuit board and multilayer circuit board obtained by the method

The method of producing a multilayer circuit board includes a film-forming step of forming a swellable resin film on the surface of an insulative substrate, a circuit groove-forming step of forming circuit grooves having a depth equal to or greater than the thickness of the swellable resin film on the external surface of the swellable resin film, a catalyst-depositing step of depositing a platingcatalyst on the surface of the circuit grooves and the surface of the swellable resin film, a film-separating step of swelling the swellable resin film with a particular liquid and then separating the swollen resin film, and a plating processing step of forming an electrolessly plated film only in the region where the plating catalyst or the plating catalyst formed from the plating catalyst precursor remains unseparated after separation of the swellable resin film.

Owner:PANASONIC CORP

Solder pad structure for printed circuit boards and fabrication method thereof

A method for fabricating a solder pad structure. A circuit board having thereon at least one copper pad is provided. A solder resist is formed on the circuit board and covers the copper pad. A solder resist opening, which exposes a portion of the copper pad, is formed in the solder resist by laser. The laser also creates a laser activated layer on sidewalls of the solder resist opening. A chemical copper layer is then grown from the exposed copper pad and concurrently from the laser activated layer.

Owner:UNIMICRON TECH CORP

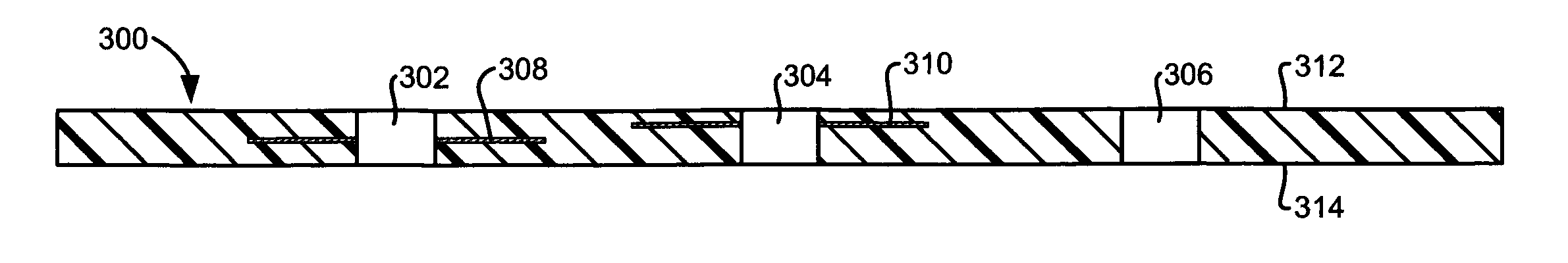

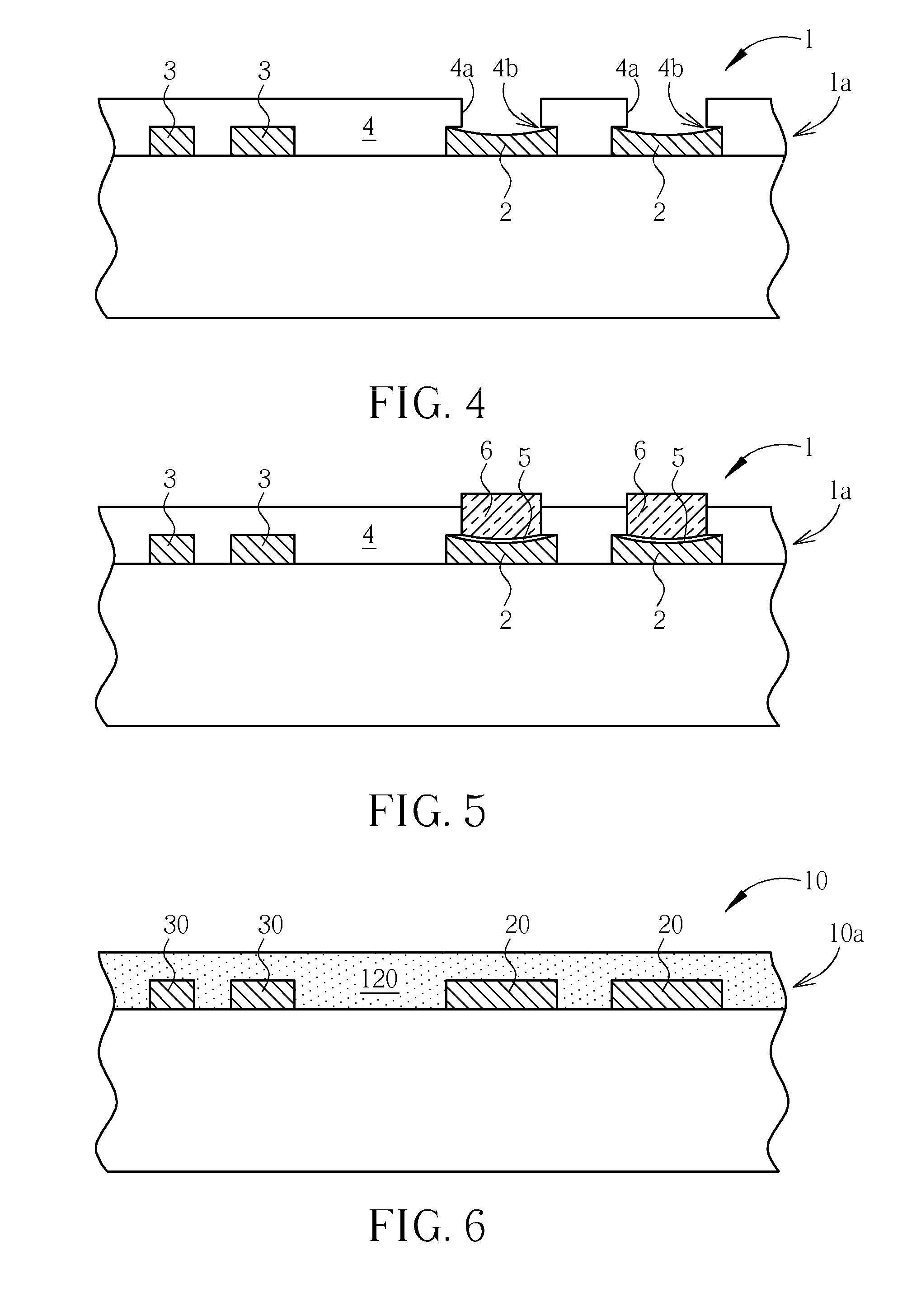

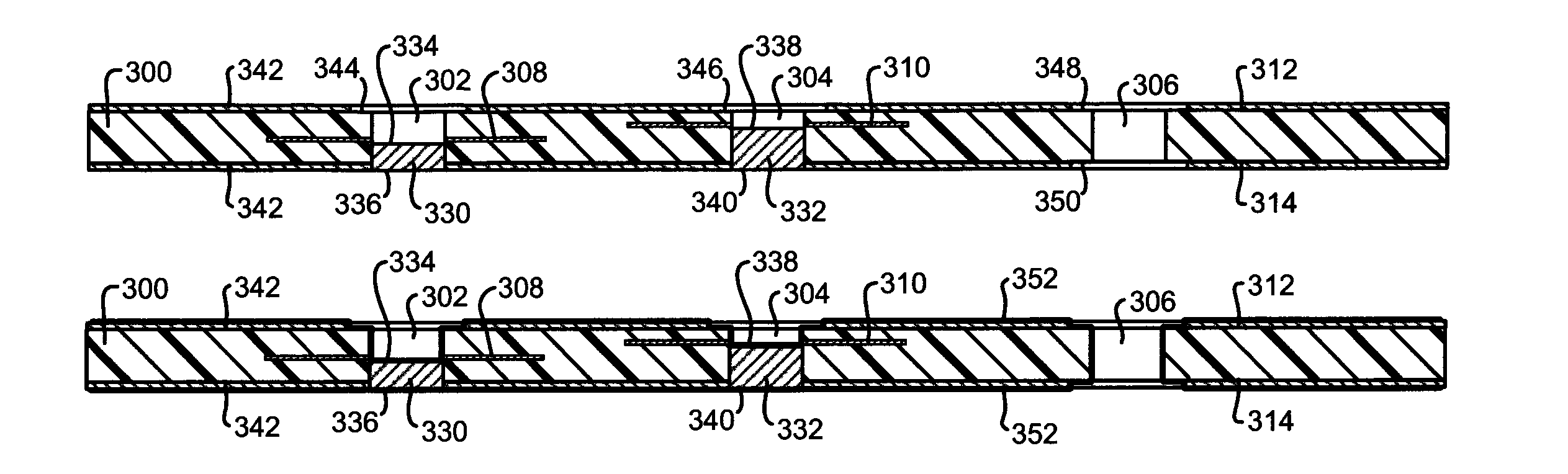

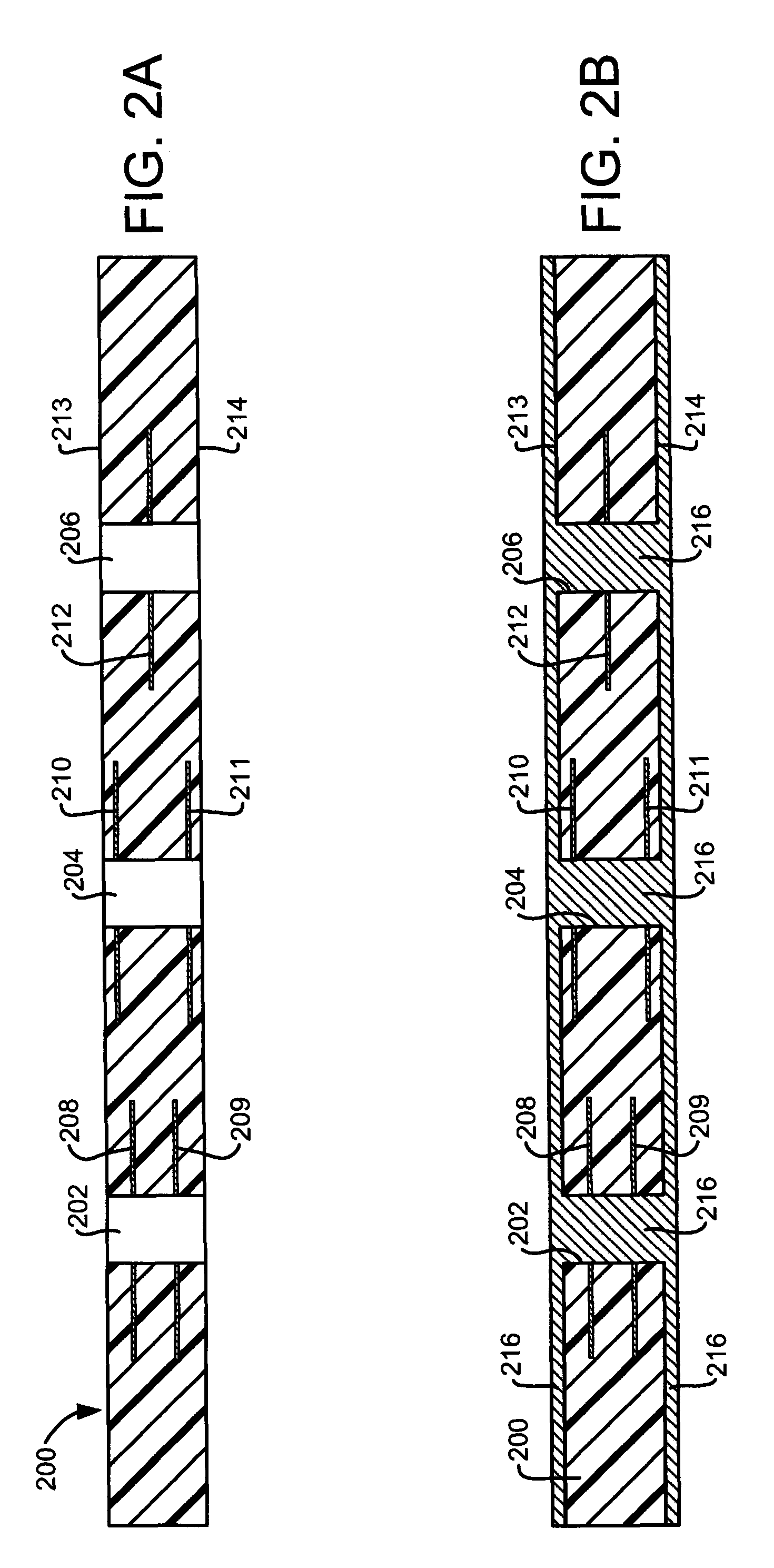

Horizontally Split Vias

InactiveUS20100044096A1Increases (2×) wiring densityRadiation applicationsPretreated surfacesEngineeringVolumetric Mass Density

A mechanism is disclosed for providing horizontally split vias are provided in printed wiring boards (PWBs) and other substrates. In one embodiment, the substrate includes a plurality of insulator layers and internal conductive traces. First and second through-holes extend completely through the substrate and respectively pass through first / second ones and third / fourth ones of the internal conductive traces, which are at different depths within the substrate. Photolithographic techniques are used to generate plated-through-hole (PTH) plugs of controlled, variable depth in the through-holes before first / second conductive vias are plated onto the first through-hole and before third / fourth conductive vias are plated onto the second through-hole. The depth of these PTH plugs is controlled (e.g., using a photomask and / or variable laser power) to prevent the conductive vias from extending substantially beyond their respective internal conductive traces, thereby horizontally spitting the two conductive vias plated onto each of the through-holes. This advantageously increases wiring density up to 2×.

Owner:GLOBALFOUNDRIES INC

Method of producing a circuit board

InactiveUS8240036B2Highly accurate preservationPrinted circuit assembling3D rigid printed circuitsEngineeringAdditive process

An object of an aspect of the present invention is to provide a method of producing a circuit board that allows highly accurate preservation of the circuit profile and gives a circuit having a desired depth in preparation of a fine circuit by additive process.The method of producing a multilayer circuit board in an aspect of the present invention includes a film-forming step of forming a swellable resin film on the surface of an insulative substrate, a circuit groove-forming step of forming circuit grooves having a depth equal to or greater than the thickness of the swellable resin film on the external surface of the swellable resin film, a catalyst-depositing step of depositing a plating catalyst or the precursor thereof on the surface of the circuit grooves and the surface of the swellable resin film, a film-separating step of swelling the swellable resin film with a particular liquid and then separating the swollen resin film from the insulative substrate surface, and a plating processing step of forming an electrolessly plated film only in the region where the plating catalyst or the plating catalyst formed from the plating catalyst precursor remains unseparated after separation of the swellable resin film.

Owner:PANASONIC CORP

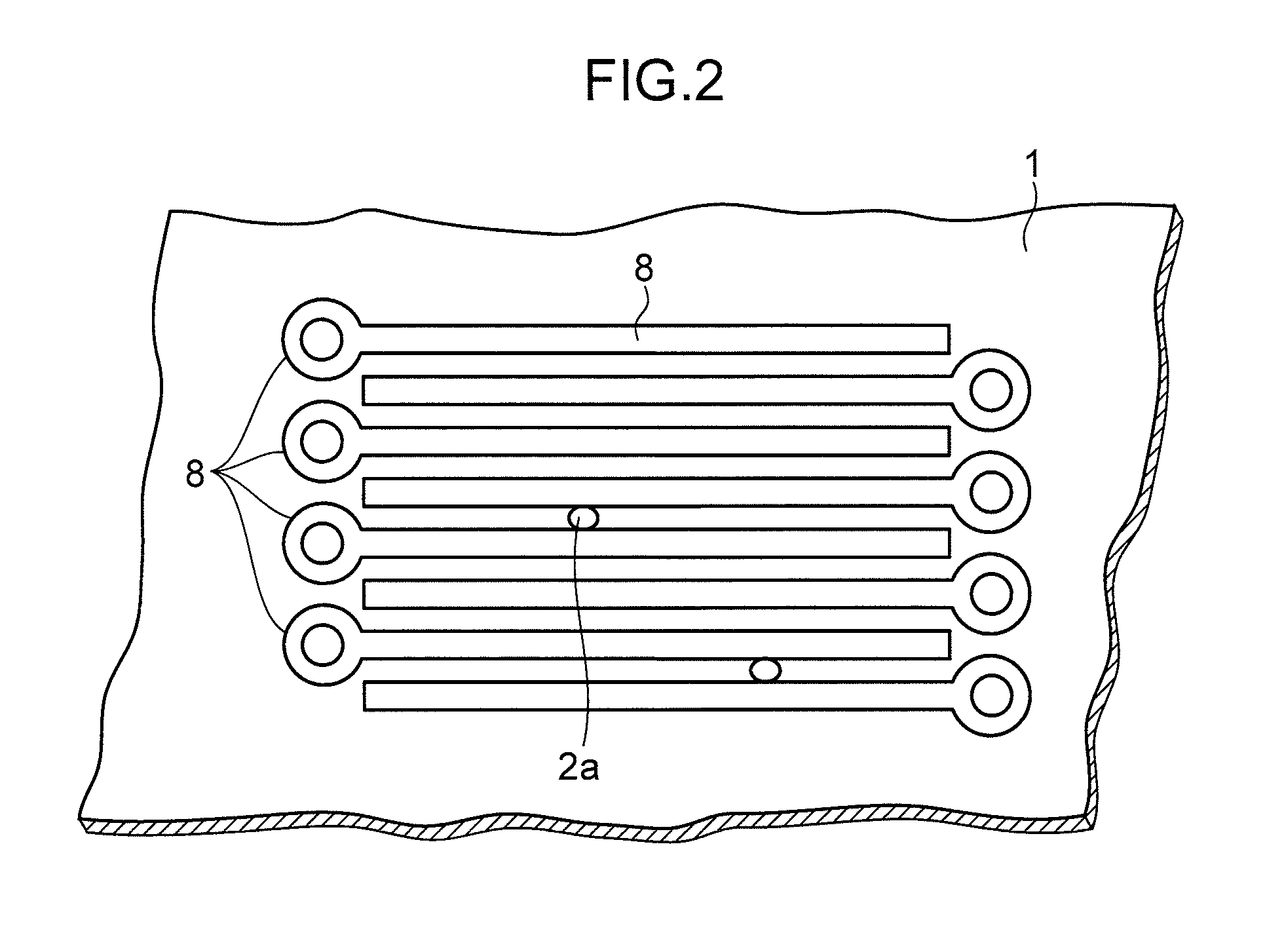

Method of manufacturing interconnect substrate

InactiveUS20070218192A1Printed circuit aspectsLiquid/solution decomposition chemical coatingResistMicrometer

A method of manufacturing an interconnect substrate having a linear interconnect by electroless plating without using a plating resist, the method including: (a) forming a plurality of rows of linear catalyst layers on a substrate; and (b) depositing a metal on the linear catalyst layers by electroless plating to form a plurality of rows of linear metal layers, at least one of the rows of linear catalyst layers having a line width of 2 micrometers or less, and a total line width of the linear catalyst layers on the substrate being 10 micrometers or more.

Owner:SEIKO EPSON CORP

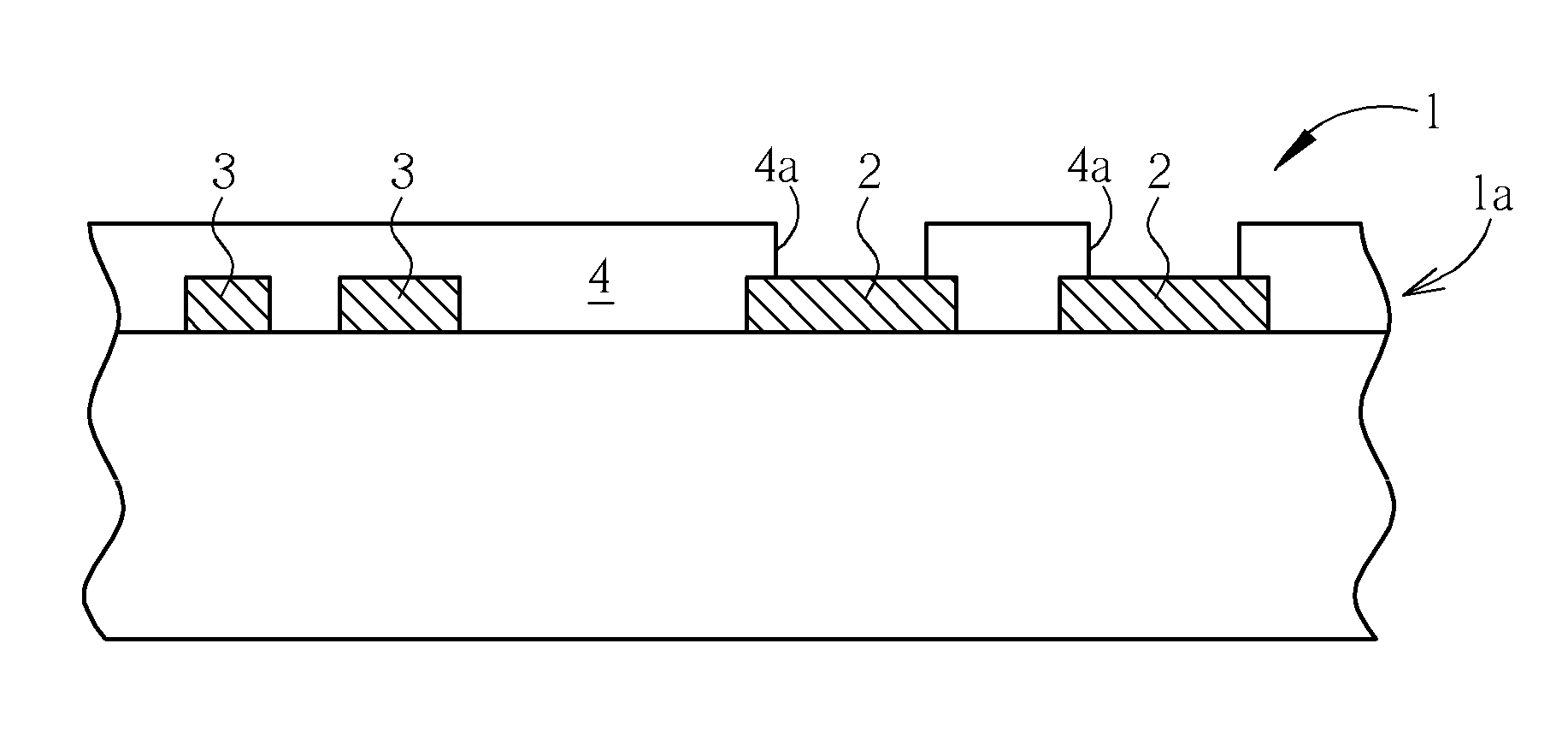

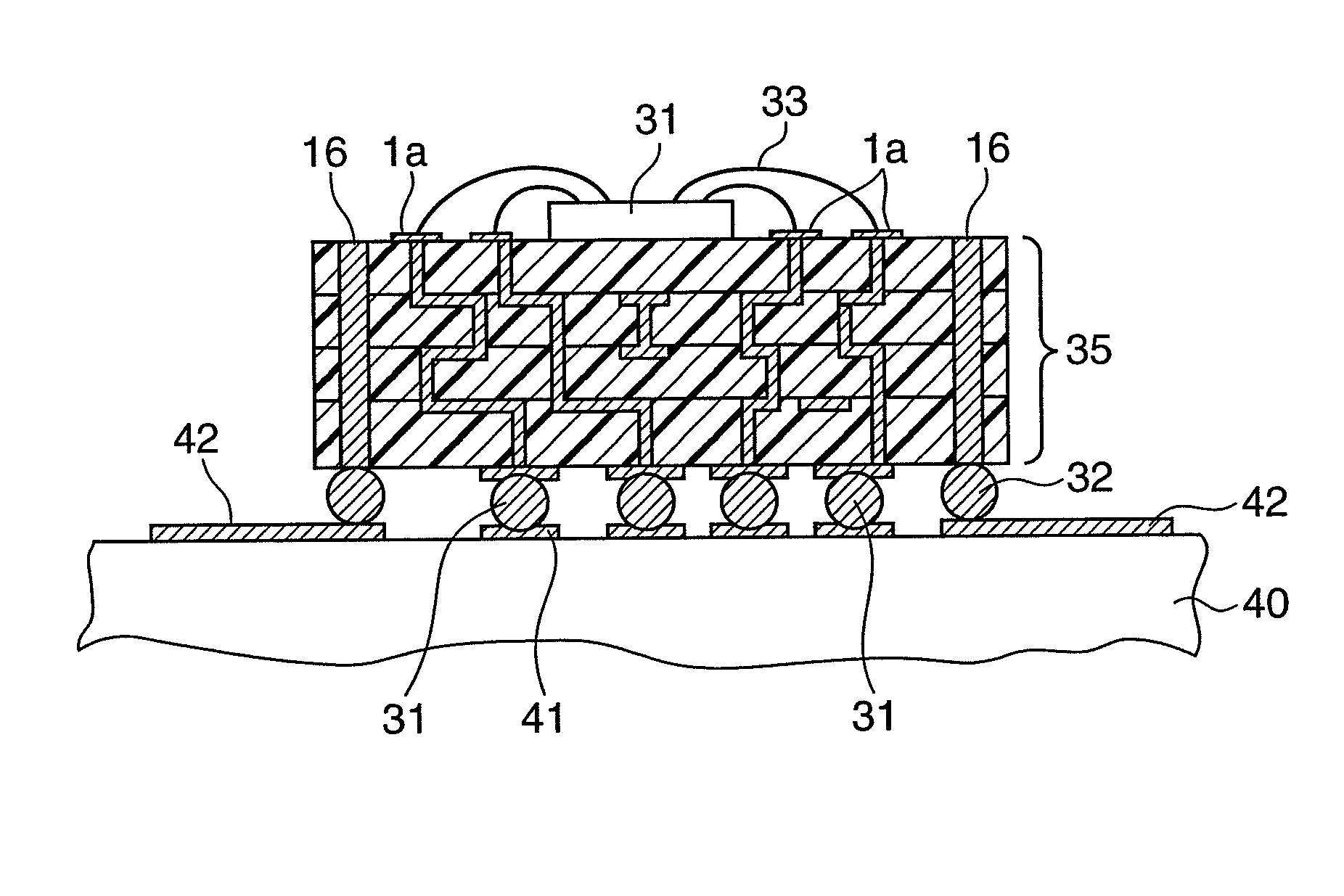

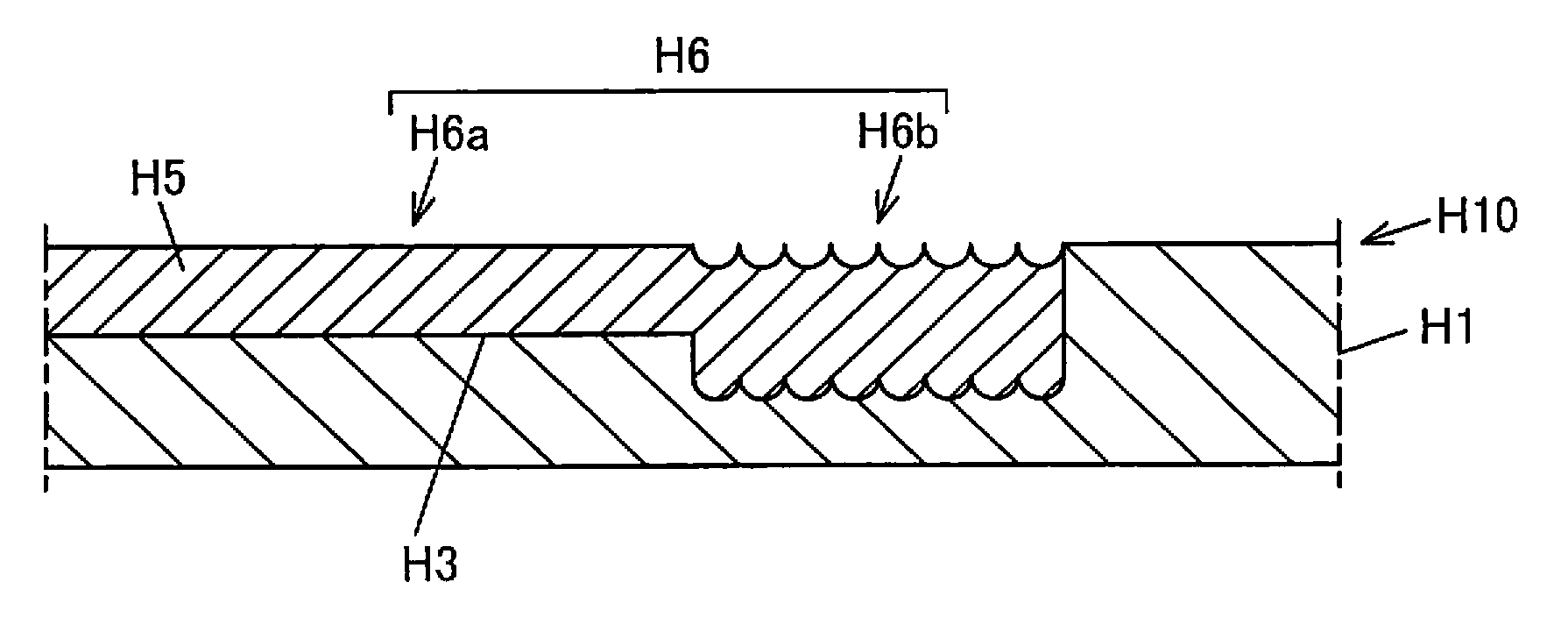

Circuit board, and semiconductor device having component mounted on circuit board

ActiveUS8929092B2Low reliabilityReduce adhesionFinal product manufactureSemiconductor/solid-state device detailsElectrical conductorSurface roughness

A circuit board includes an electric circuit having a wiring section and a pad section in the surface of an insulating base substrate. The electric circuit is configured such that a conductor is embedded in a circuit recess formed in the surface of the insulating base substrate, and the surface roughness of the conductor is different in the wiring section and the pad section of the electric circuit. In this case, it is preferable that the surface roughness of the conductor in the pad section is greater than the surface roughness of the conductor in the wiring section.

Owner:PANASONIC CORP

Method for via stub elimination

InactiveUS8230592B2Eliminates costlyTime-consuming to eliminatePrinted circuit assemblingAdditive manufacturing apparatusTime-ConsumingPhotomask

An enhanced mechanism is disclosed for via stub elimination in printed wiring boards (PWBs) and other substrates. In one embodiment, the substrate includes a plurality of insulator layers and internal conductive traces. First and second through-holes extend completely through the substrate and respectively pass through first and second ones of the internal conductive traces, which are at different depths within the substrate. Photolithographic techniques are used to generate plated-through-hole (PTH) plugs of controlled, variable depth in the through-holes before first and second conductive vias are respectively plated onto the first and second through-holes. The depth of these PTH plugs is controlled (e.g., using a photomask and / or variable laser power) to prevent the first and second conductive vias from extending substantially beyond the first and second internal conductive traces, respectively, and thereby prevent via stubs from being formed in the first place. This advantageously eliminates the costly and time consuming process of via stub backdrilling.

Owner:GLOBALFOUNDRIES INC

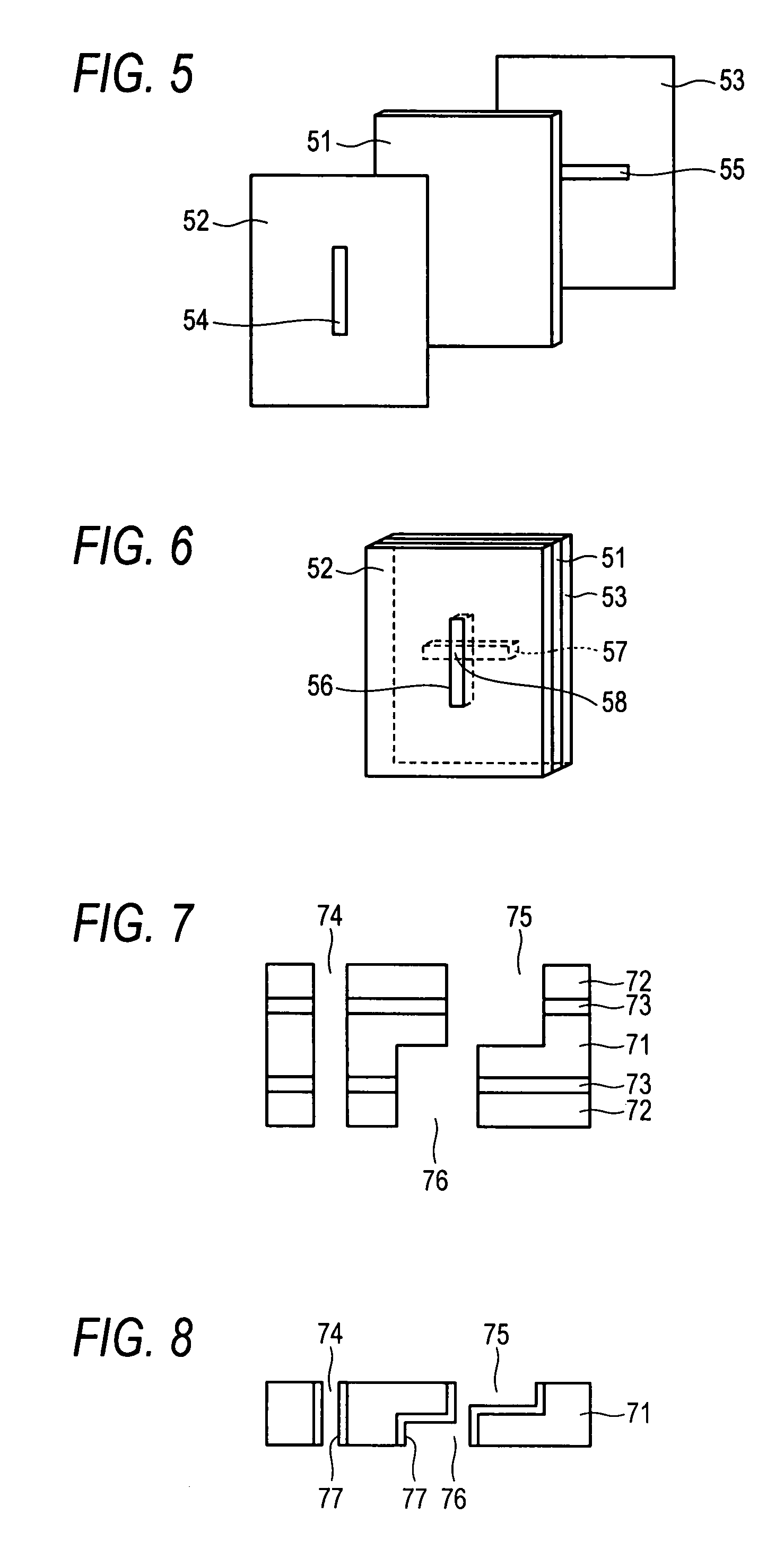

Method for manufacturing patterned porous molded product or nonwoven fabric, and electric circuit component

InactiveUS7586047B2Avoid damageNot easy to cutPorous dielectricsPaper/cardboard articlesNonwoven fabricMaterials science

An object of the present invention is to provide a method for manufacturing a porous material in which complicated and fine through portions, recessed portions, and the like have been patterned. It is to provide a patterned porous molded product or nonwoven fabric, in which a plated layer has been selectively formed on the surfaces of the through portions and the recessed portions.With the invention, a mask having through portions in a pattern is placed on at least one side of the porous molded product or the nonwoven fabric. A fluid or a fluid containing abrasive grains is sprayed from above the mask, thereby to form through portions or recessed portions, or both of them, to which the opening shape of each through portion of the mask has been transferred, in the porous molded product or the nonwoven fabric. The invention provides a porous molded product or a nonwoven fabric in which a plated layer has been selectively formed on the surfaces of the through portions or the recessed portions, or both of these, an electric circuit component, or the like.

Owner:SUMITOMO ELECTRIC IND LTD

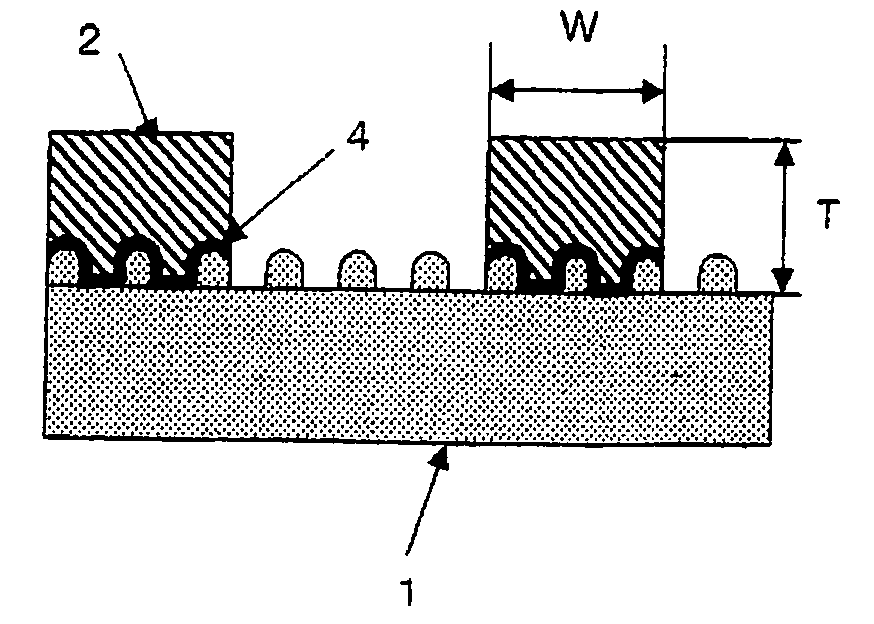

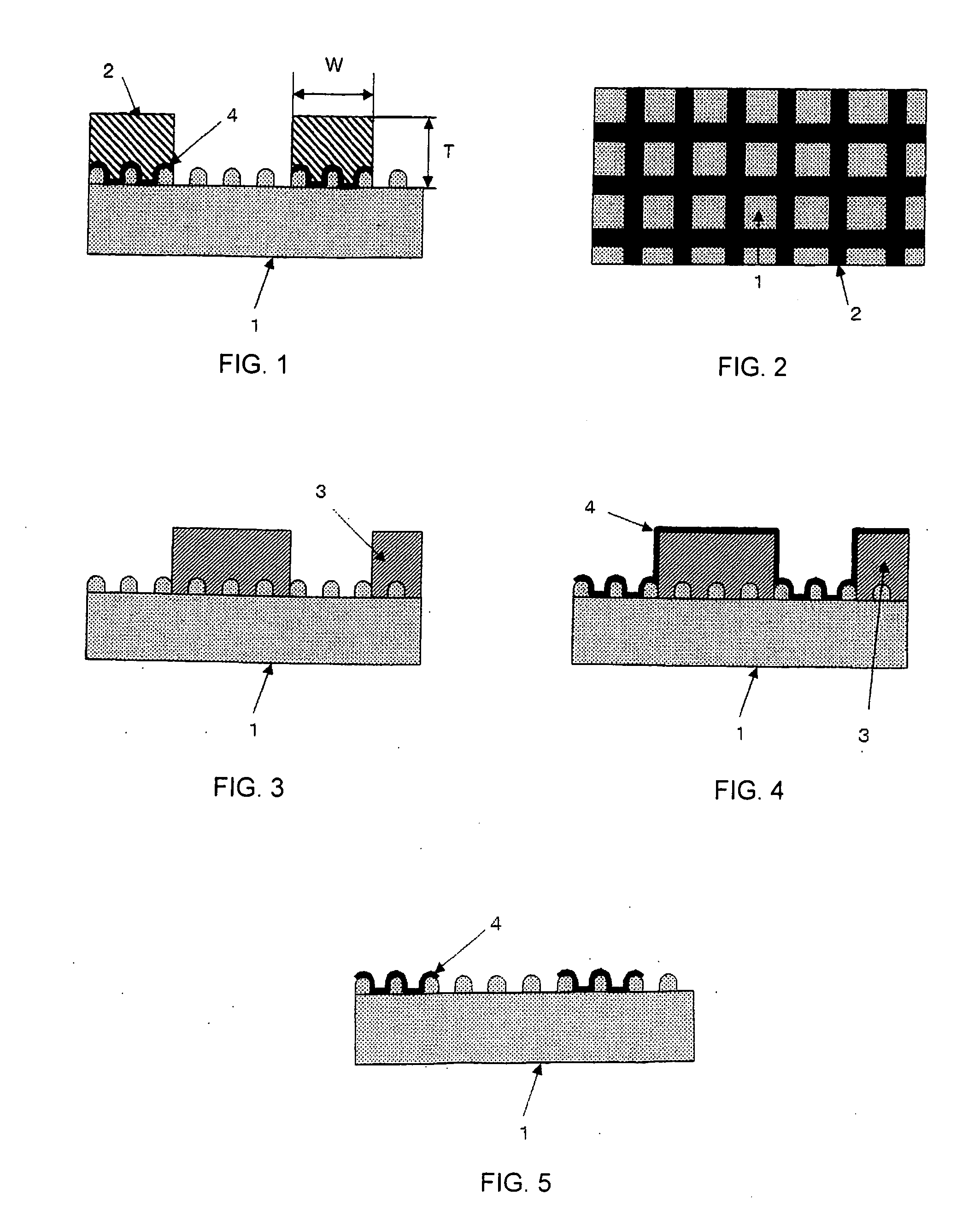

Transparent electrically conductive film and process for producing the same

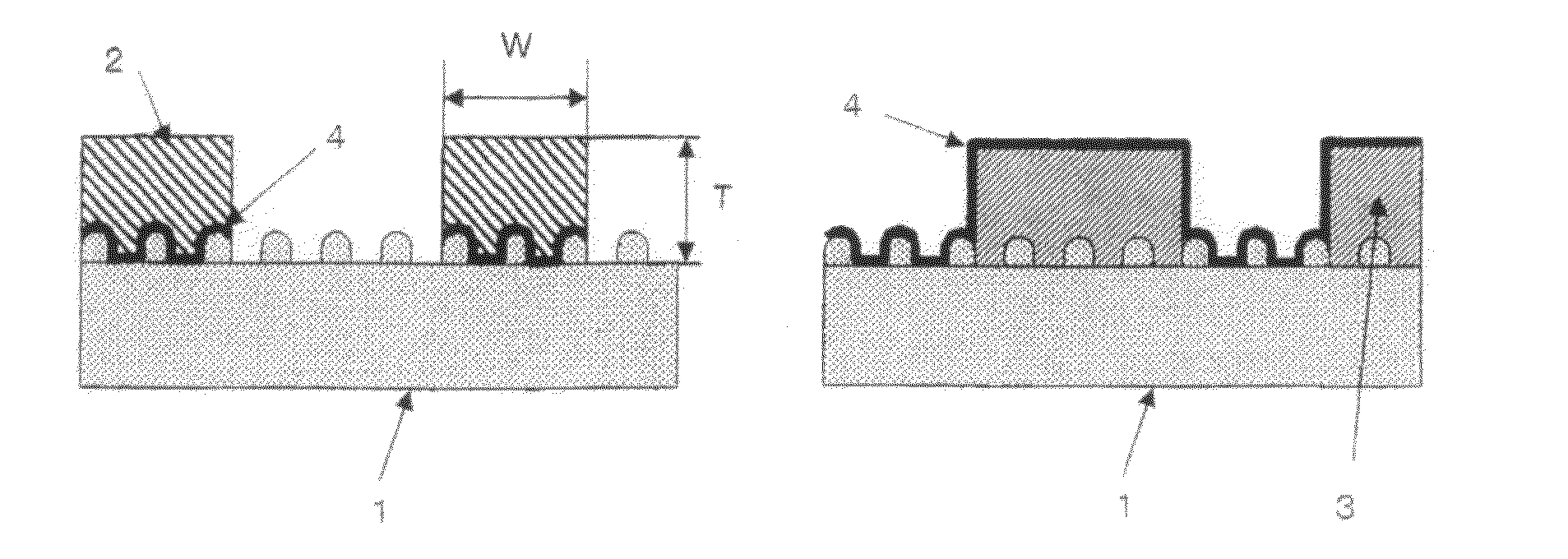

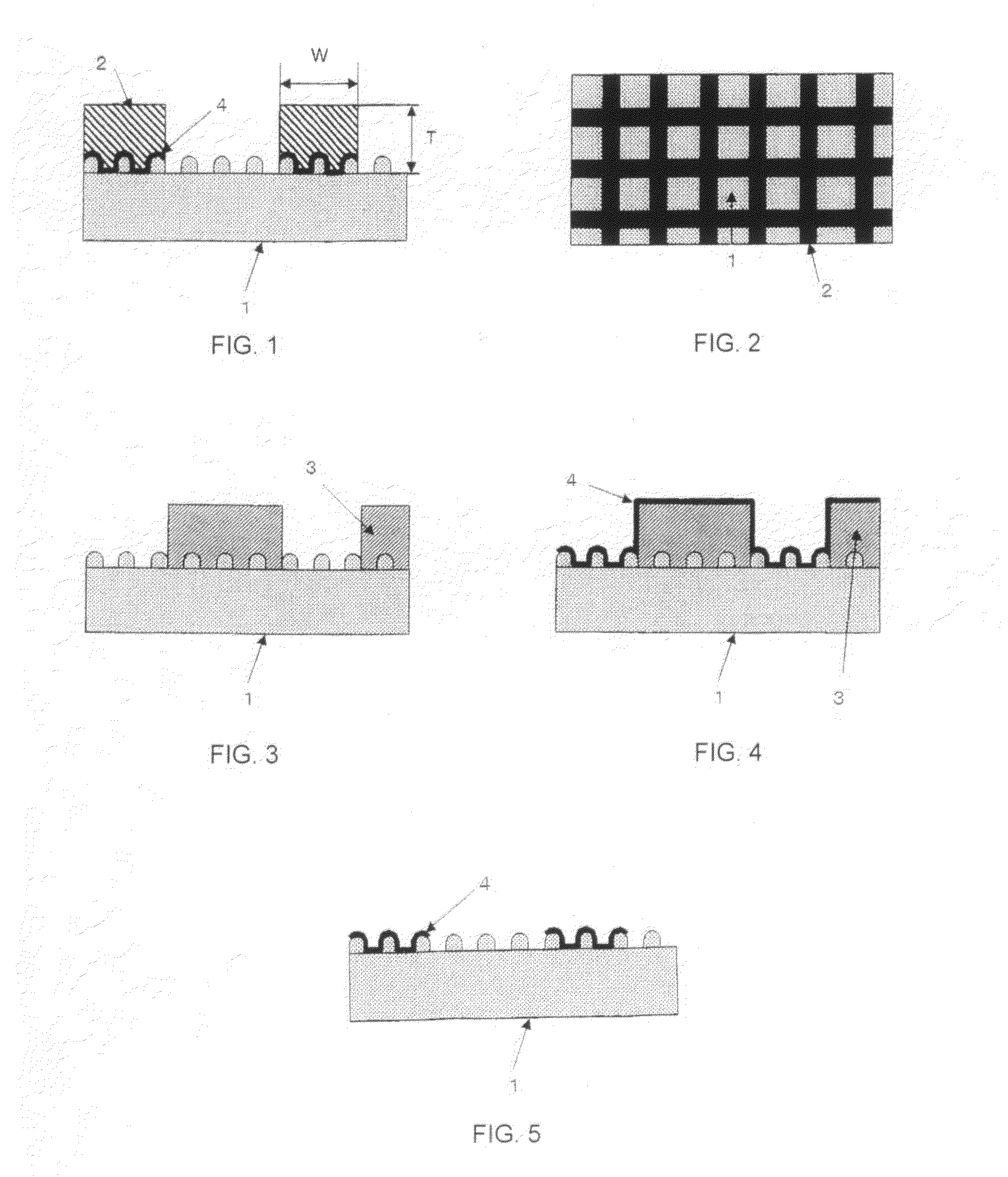

InactiveUS20090042150A1Improve conductivityHigh yieldConductive layers on insulating-supportsMagnetic/electric field screeningResistForming face

This invention provides a transparent electrically conductive film, which, while maintaining the light transparency of a transparent film, has excellent electrical conductivity, can be utilized for electromagnetic wave shielding, and does not cause inclusion of air bubbles in the lamination onto other base material, and a process for producing the same. The production process comprises the steps of forming a large number of concaves and convexes having an average height of not more than 0.1 μm on both sides or one side of a transparent film, forming a resist layer having a pattern shape opposite to the electrically conductive part in the electrically conductive film on the transparent film on its concave-convex side, applying a catalyst for plating onto the resist layer-formed face, separating the resist layer, forming a metal layer by plating, and blackening the metal layer, the metal layer satisfying 1≦W / T≦500 wherein W represents the width of the metal layer and T represents the height of the metal layer.

Owner:SEIREN CO LTD

Method for manufacturing patterned porous molded product or nonwoven fabric, and electric circuit component

InactiveUS20070160810A1Avoid damageSuitable for mass productionPorous dielectricsPaper/cardboard articlesNonwoven fabricMaterials science

An object of the present invention is to provide a method for manufacturing a porous material in which complicated and fine through portions, recessed portions, and the like have been patterned. It is to provide a patterned porous molded product or nonwoven fabric, in which a plated layer has been selectively formed on the surfaces of the through portions and the recessed portions. With the invention, a mask having through portions in a pattern is placed on at least one side of the porous molded product or the nonwoven fabric. A fluid or a fluid containing abrasive grains is sprayed from above the mask, thereby to form through portions or recessed portions, or both of them, to which the opening shape of each through portion of the mask has been transferred, in the porous molded product or the nonwoven fabric. The invention provides a porous molded product or a nonwoven fabric in which a plated layer has been selectively formed on the surfaces of the through portions or the recessed portions, or both of these, an electric circuit component, or the like.

Owner:SUMITOMO ELECTRIC IND LTD

Method of producing circuit board

InactiveUS8272126B2Highly accurate preservationPrinted circuit assembling3D rigid printed circuitsEngineeringAdditive process

An object of an aspect of the present invention is to provide a method of producing a circuit board that allows highly accurate preservation of the circuit profile and gives a circuit having a desired depth in preparation of a fine circuit by additive process.The method of producing a multilayer circuit board in an aspect of the present invention includes a film-forming step of forming a swellable resin film on the surface of an insulative substrate, a circuit groove-forming step of forming circuit grooves having a depth equal to or greater than the thickness of the swellable resin film on the external surface of the swellable resin film, a catalyst-depositing step of depositing a plating catalyst or the precursor thereof on the surface of the circuit grooves and the surface of the swellable resin film, a film-separating step of swelling the swellable resin film with a particular liquid and then separating the swollen resin film from the insulative substrate surface, and a plating processing step of forming an electrolessly plated film only in the region where the plating catalyst or the plating catalyst formed from the plating catalyst precursor remains unseparated after separation of the swellable resin film.

Owner:PANASONIC CORP

Resin composition and method for producing circuit board

ActiveUS20130337188A1Improve absorption rateImprove circuit board productivityLight absorption dielectricsRadiation applicationsUv absorberWavelength

The present invention relates to a resin composition which includes a copolymer consisting of a first monomer containing a monomer unit having at least one carboxyl group and a second monomer copolymerizable with the first monomer, and also includes an ultraviolet absorber. The resin composition used is a resin composition for which, when ∈1 represents an absorbance coefficient per unit weight of a resin film 2 in a solution prepared by dissolving, in a solvent, the resin film 2 formed by application of the resin composition as a liquid, ∈1 at a light wavelength at which the resin film 2 is to be irradiated is at least 0.01 (L / (g·cm)).

Owner:PANASONIC CORP

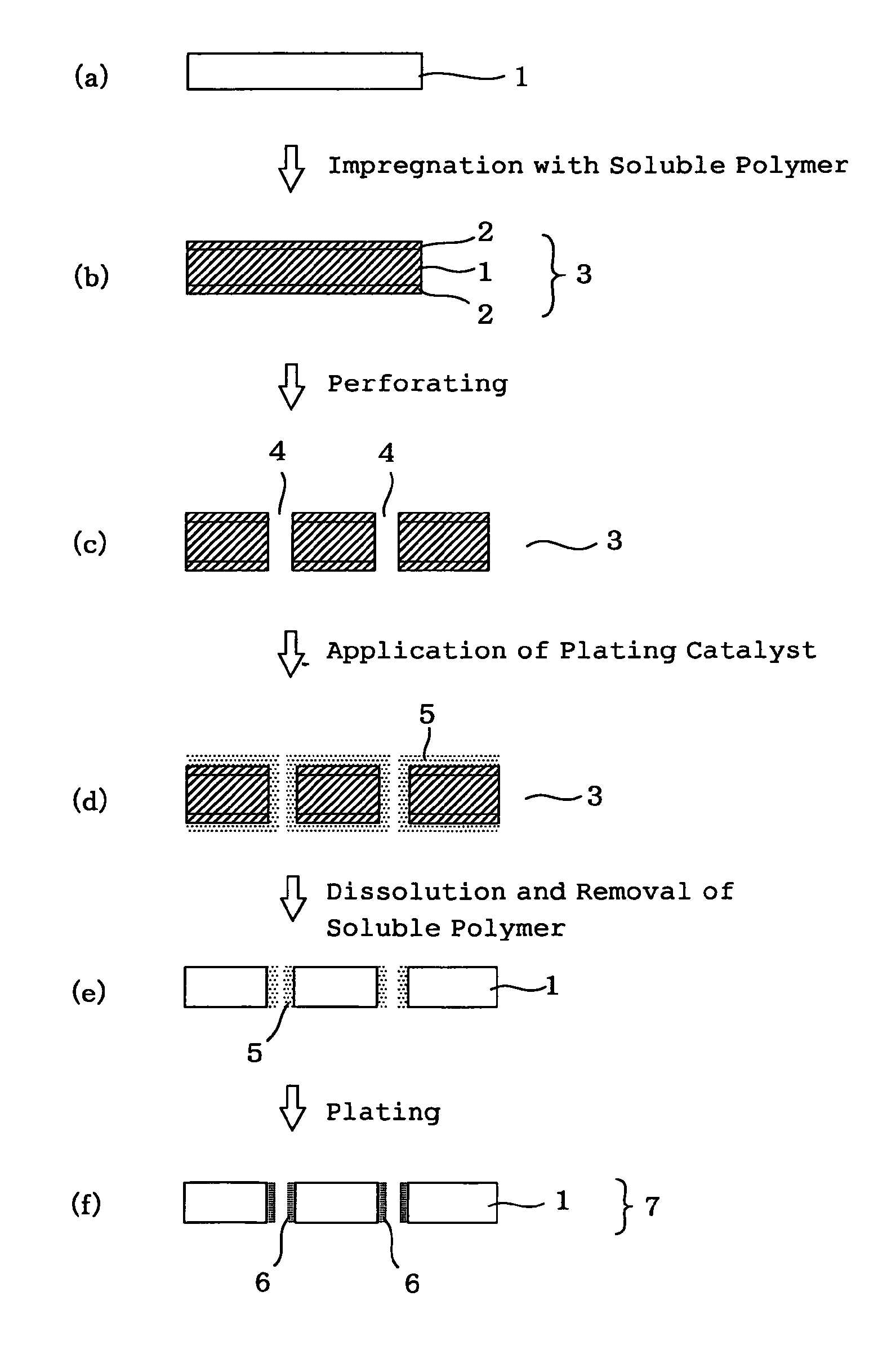

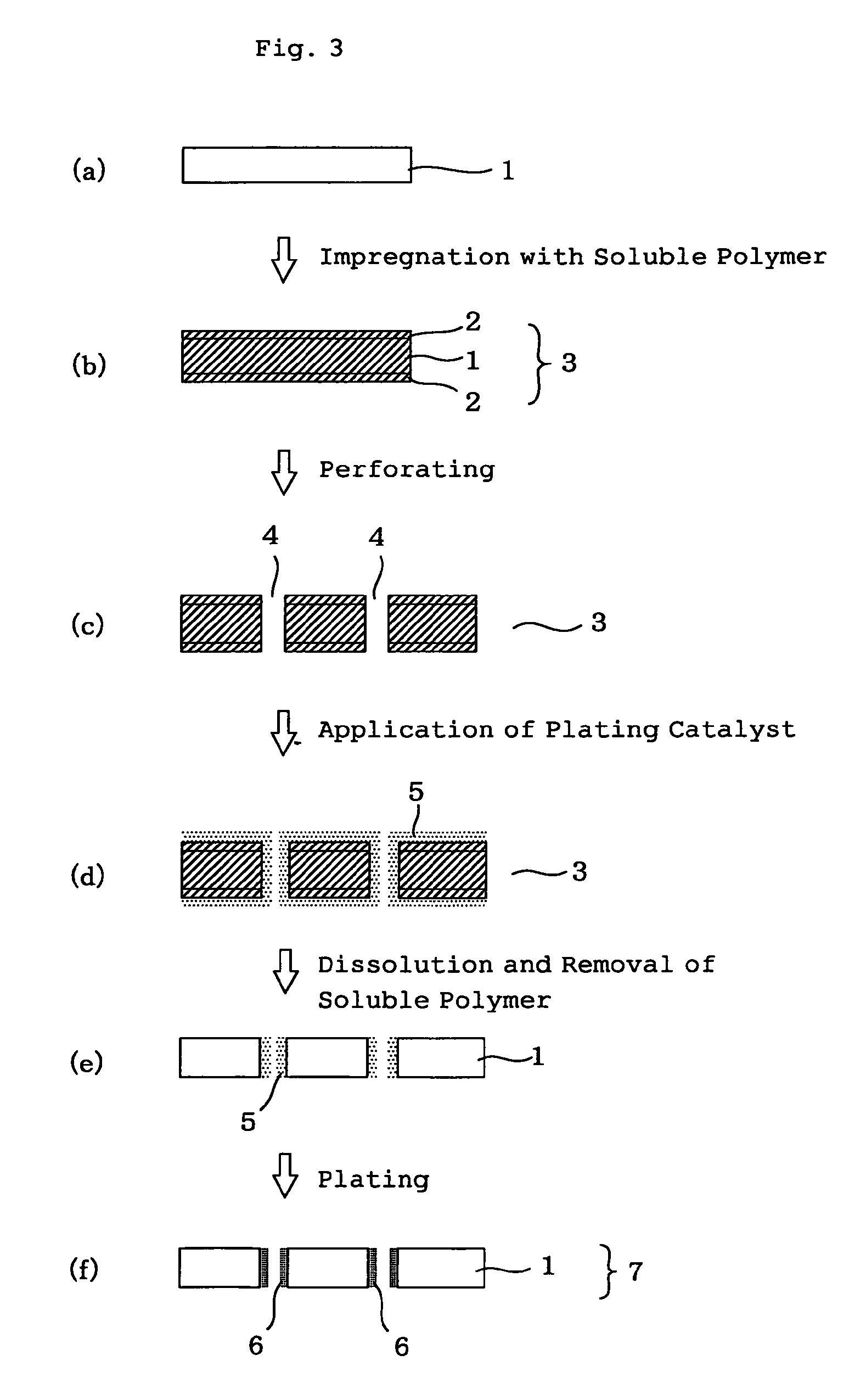

Perforated porous resin base material and production process of porous resin base with inner wall surfaces of perforations made conductive.

InactiveUS8147911B2Use of materialIncrease elasticityPorous dielectricsSemiconductor/solid-state device manufacturingMaterial PerforationPolyresin

A production process of a perforated porous resin base, comprising Step 1 of impregnating the porous structure of a porous resin base with a liquid or solution; Step 2 of forming a solid substance from the liquid or solution impregnated; Step 3 of forming a plurality of perforations extending through from the first surface of the porous resin base having the solid substance within the porous structure to the second surface in the porous resin base; and Step 4 of melting or dissolving the solid substance to remove it from the interior of the porous structure, and a production process of a porous resin base with the inner wall surfaces of the perforations made conductive, comprising the step of selectively applying a catalyst only to the inner wall surfaces of the perforations to apply a conductive metal to the inner wall surfaces.

Owner:SUMITOMO ELECTRIC IND LTD

Circuit board, and semiconductor device having component mounted on circuit board

ActiveUS20150156873A1Low reliabilityReduce adhesionInsulating substrate metal adhesion improvementFinal product manufacturePower semiconductor deviceElectrical conductor

Owner:PANASONIC CORP

Method of forming a substrate having a plurality of insulator layers

InactiveUS8136240B2Increases (2×) wiring densityRadiation applicationsPretreated surfacesEngineeringPhotolithography

A mechanism is disclosed for providing horizontally split vias in printed wiring boards (PWBs) and other substrates. In one embodiment, the substrate includes a plurality of insulator layers and internal conductive traces. First and second through-holes extend completely through the substrate and respectively pass through first / second ones and third / fourth ones of the internal conductive traces, which are at different depths within the substrate. Photolithographic techniques are used to generate plated-through-hole (PTH) plugs of controlled, variable depth in the through-holes before first / second conductive vias are plated onto the first through-hole and before third / fourth conductive vias are plated onto the second through-hole. The depth of these PTH plugs is controlled (e.g., using a photomask and / or variable laser power) to prevent the conductive vias from extending substantially beyond their respective internal conductive traces, thereby horizontally spitting the two conductive vias plated onto each of the through-holes. This advantageously increases wiring density up to 2×.

Owner:GLOBALFOUNDRIES INC

Method of manufacturing wiring substrate

InactiveCN101035414ASemiconductor/solid-state device manufacturingLiquid/solution decomposition chemical coatingResistPalladium

A method of manufacturing an interconnect substrate by electroless plating which causes a metal to be deposited without using a plating resist, the method including: (a) immersing a substrate in a catalyst solution including palladium, hydrogen peroxide, and hydrochloric acid to form a catalyst layer on the substrate; and (b) depositing a metal on the catalyst layer by immersing the substrate in an electroless plating solution to form a metal layer.

Owner:SEIKO EPSON CORP

Production method for pattern-worked porous molding or nonwoven fabric, and electric circuit components

InactiveCN1910013ADamage will notLow costPorous dielectrics3D rigid printed circuitsPolymer scienceNonwoven fabric

Owner:SUMITOMO ELECTRIC IND LTD

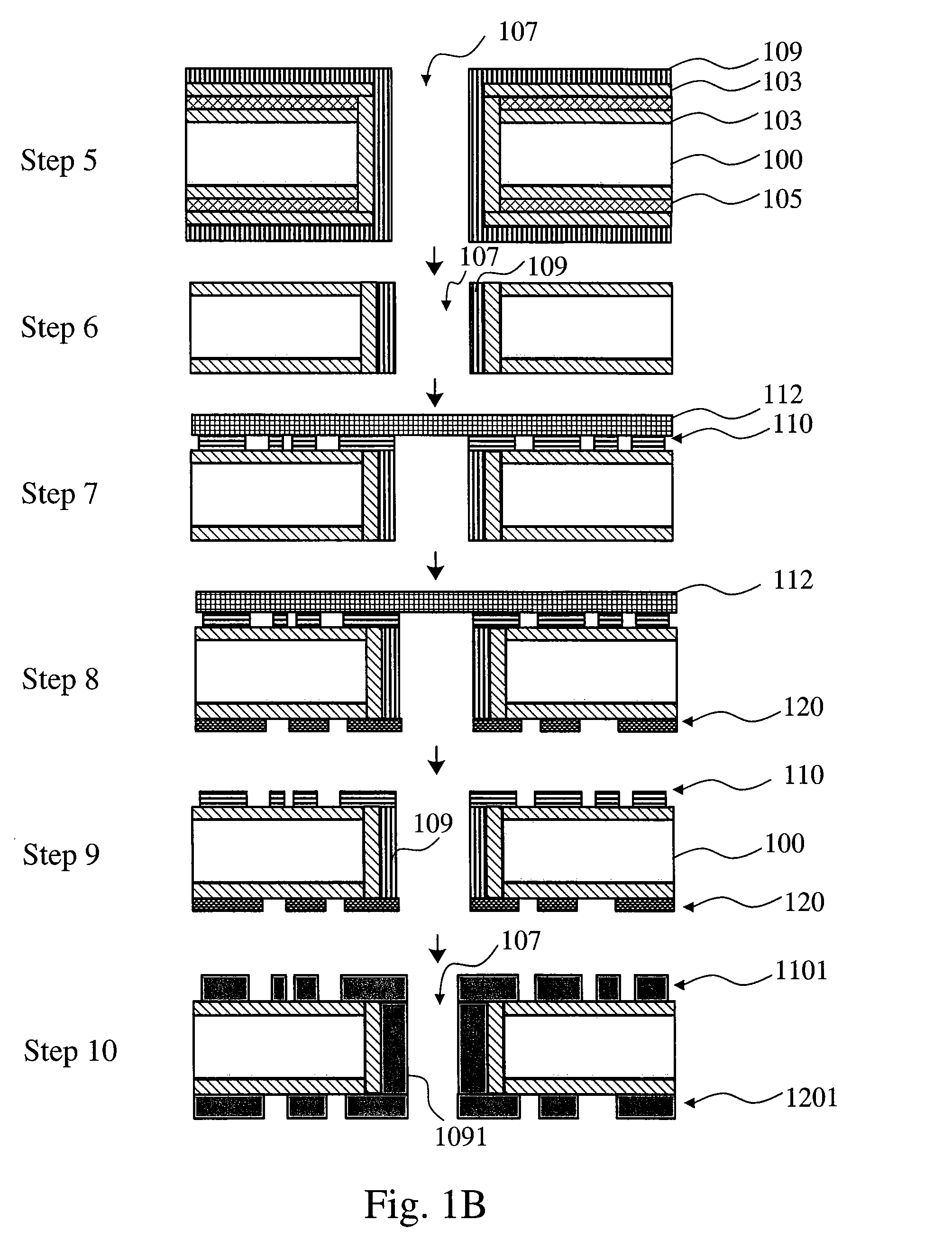

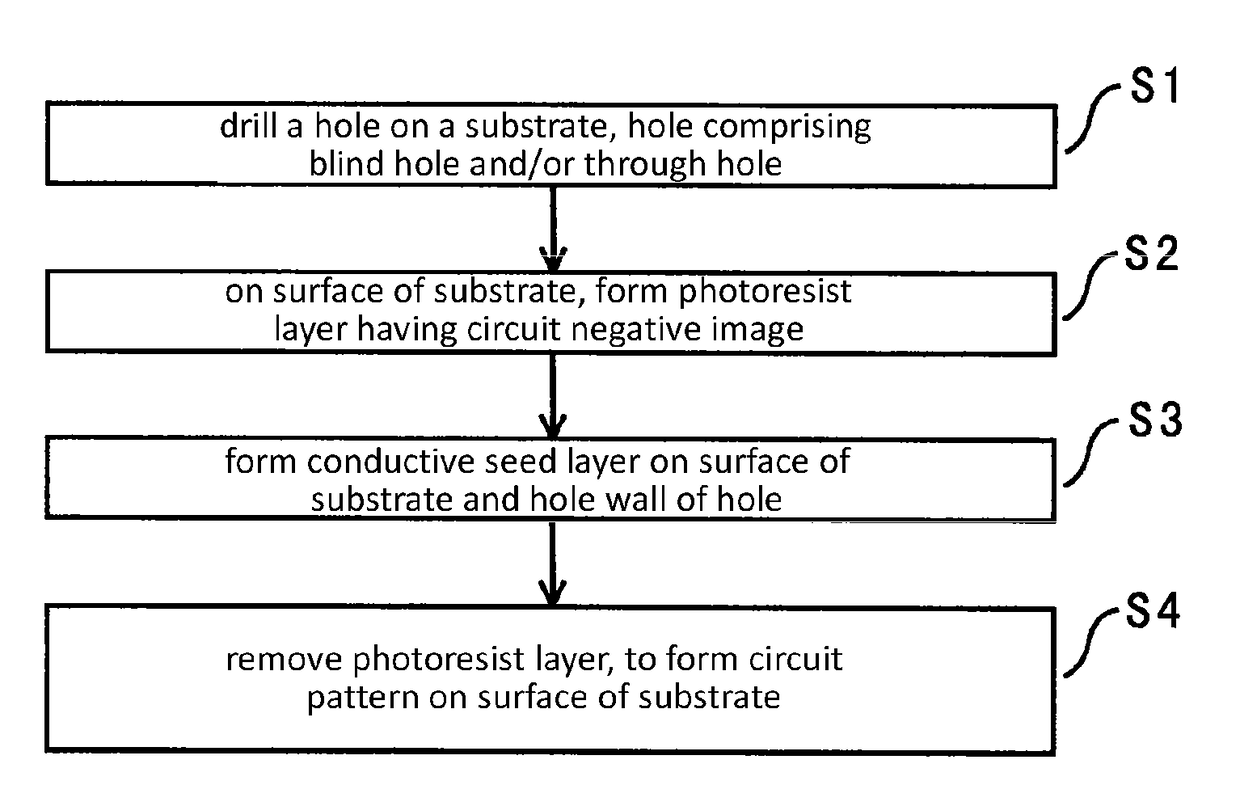

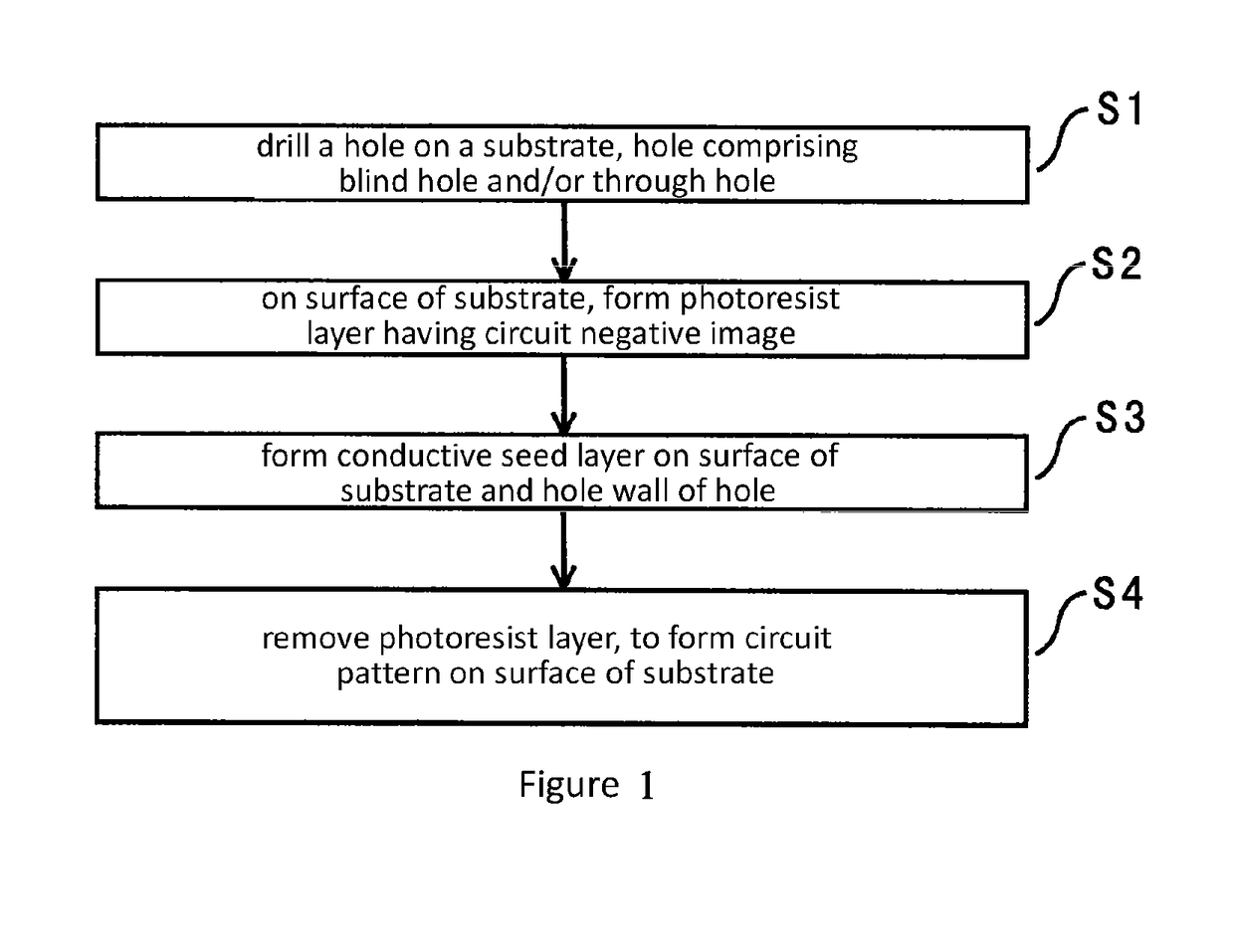

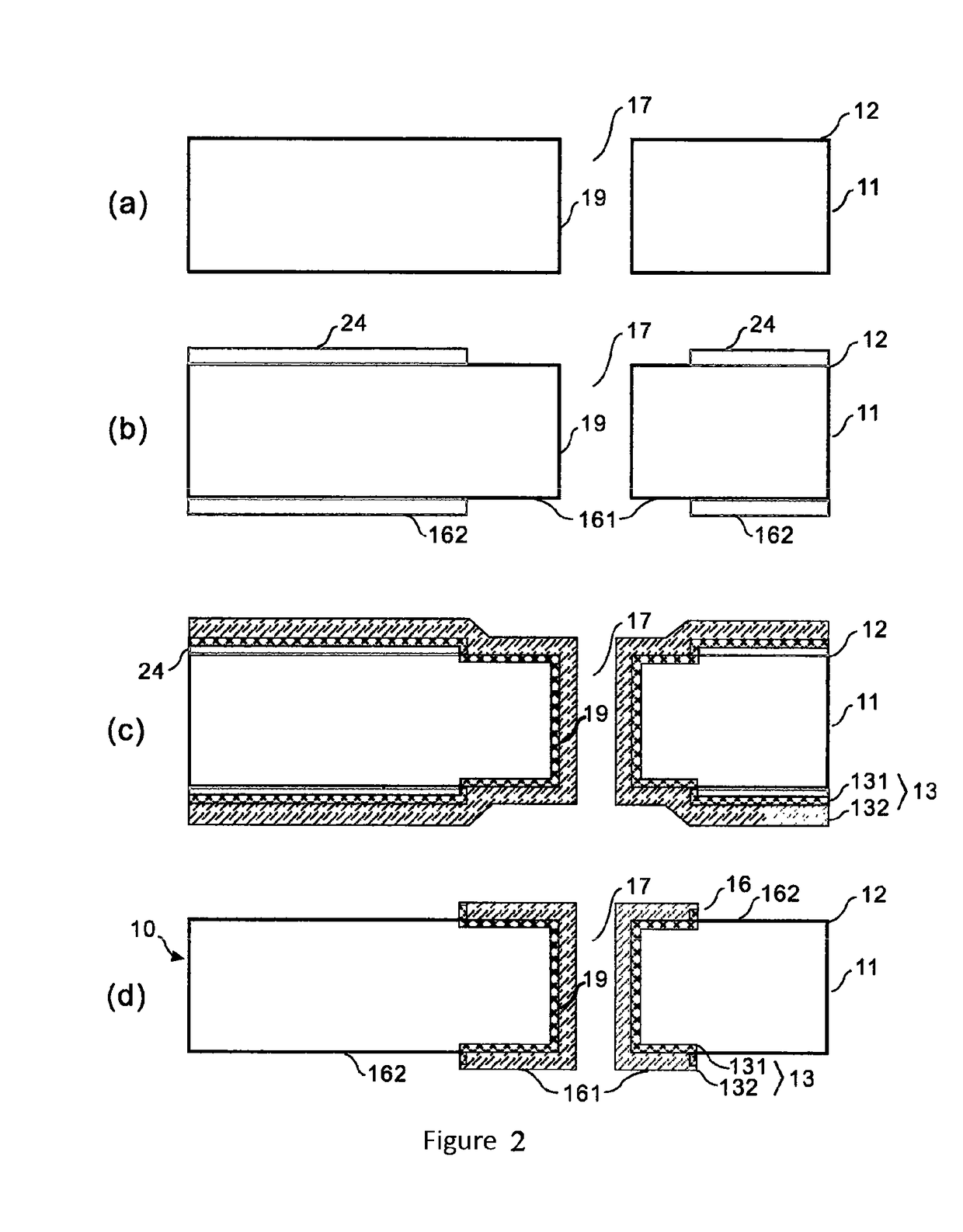

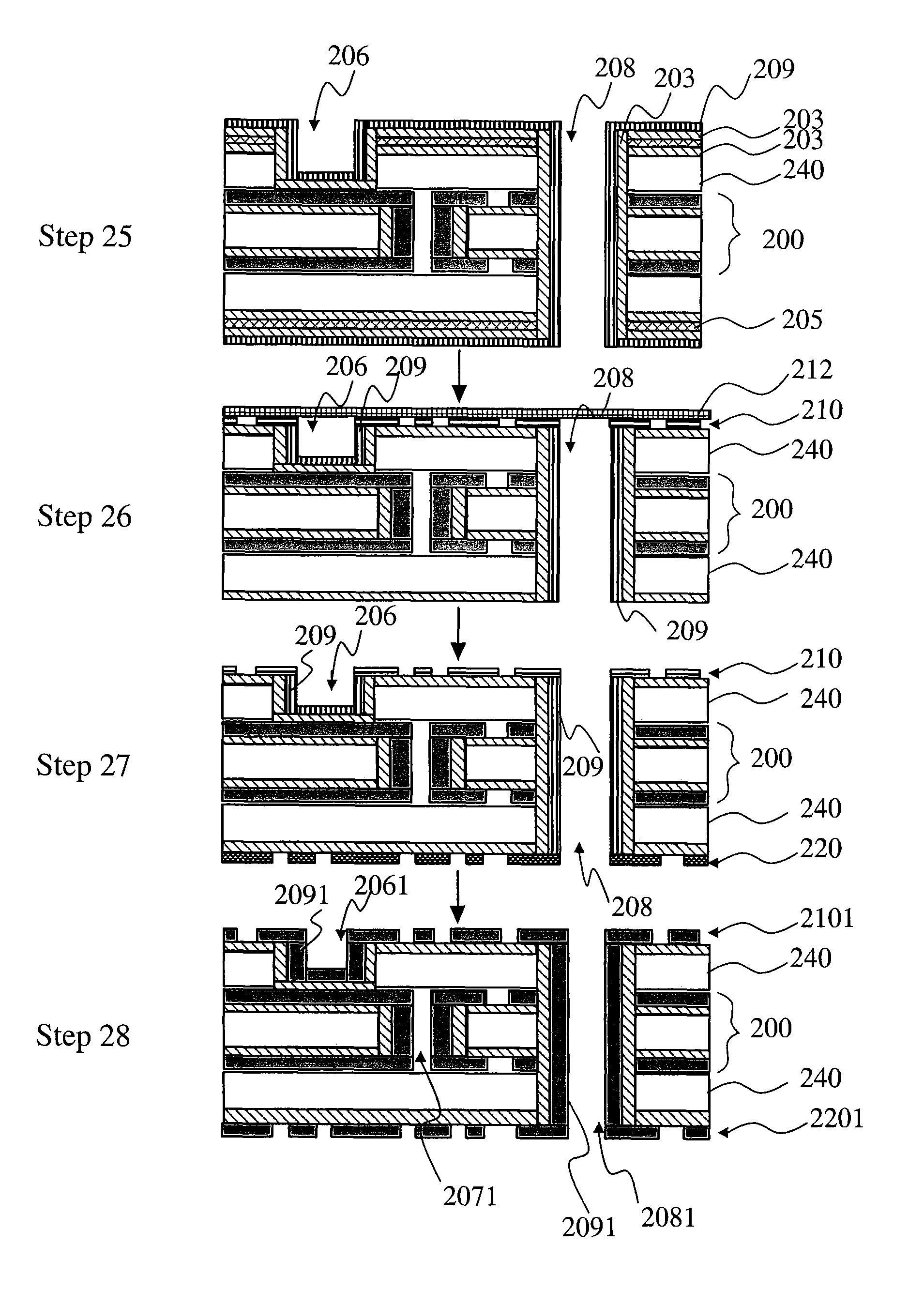

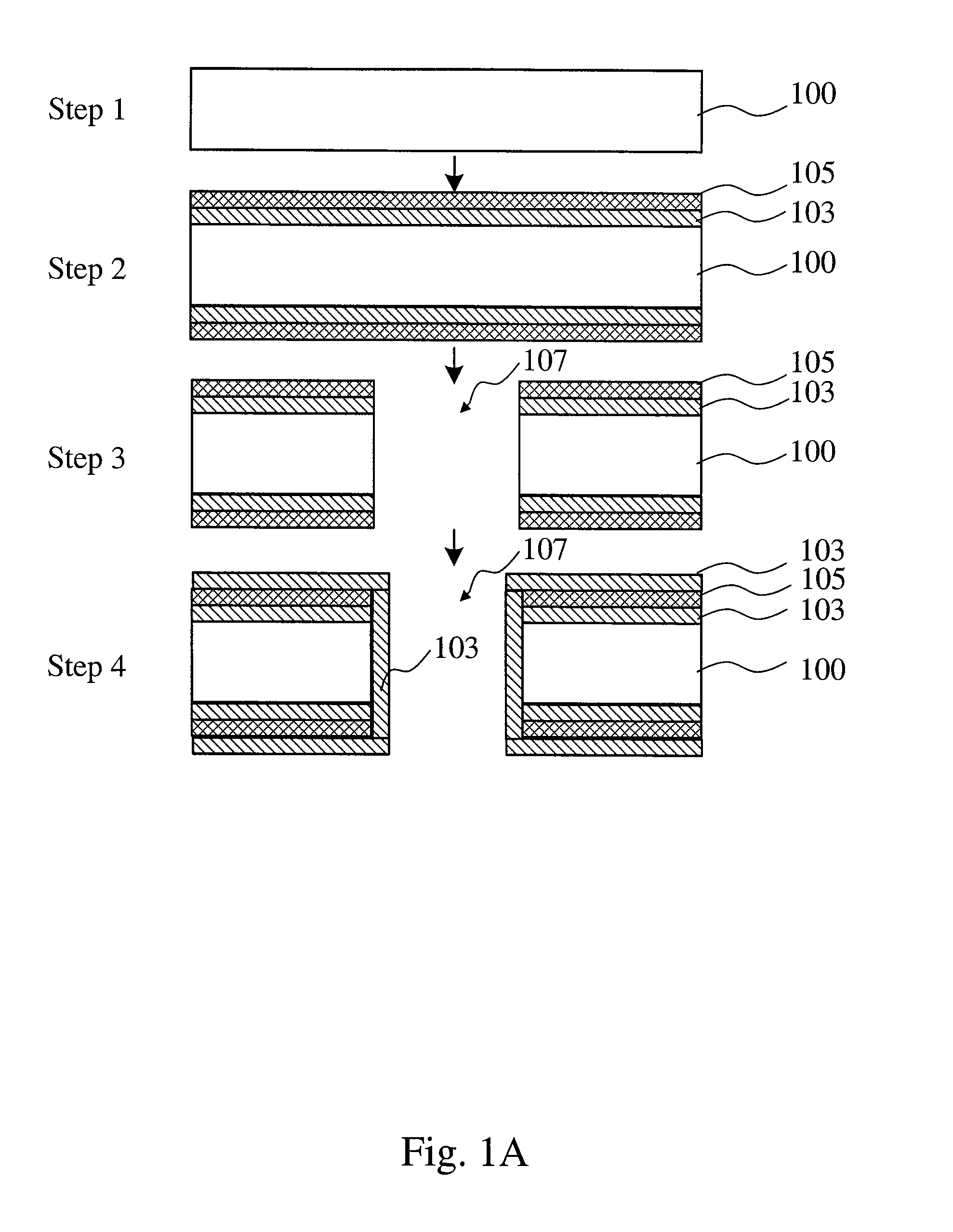

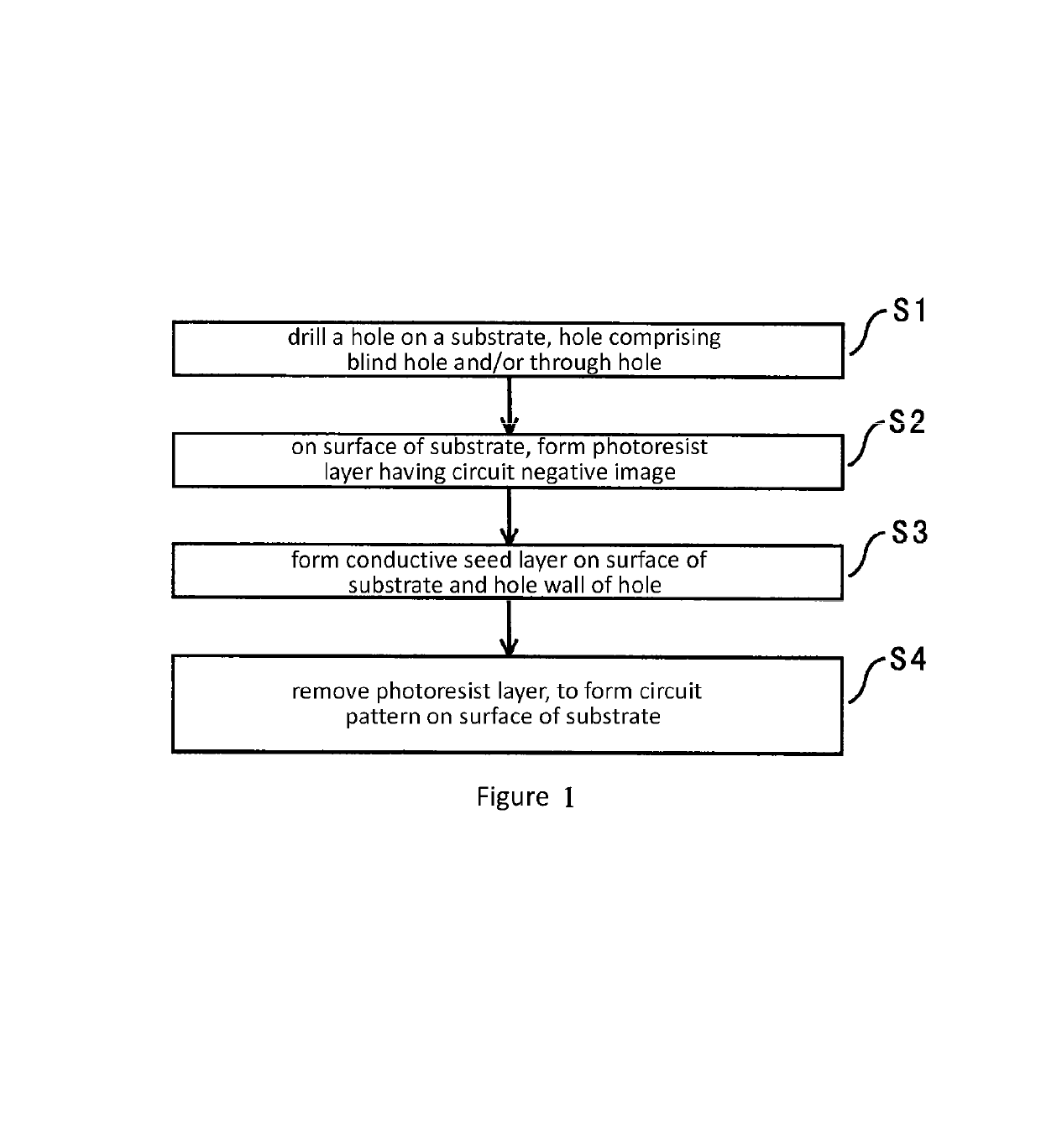

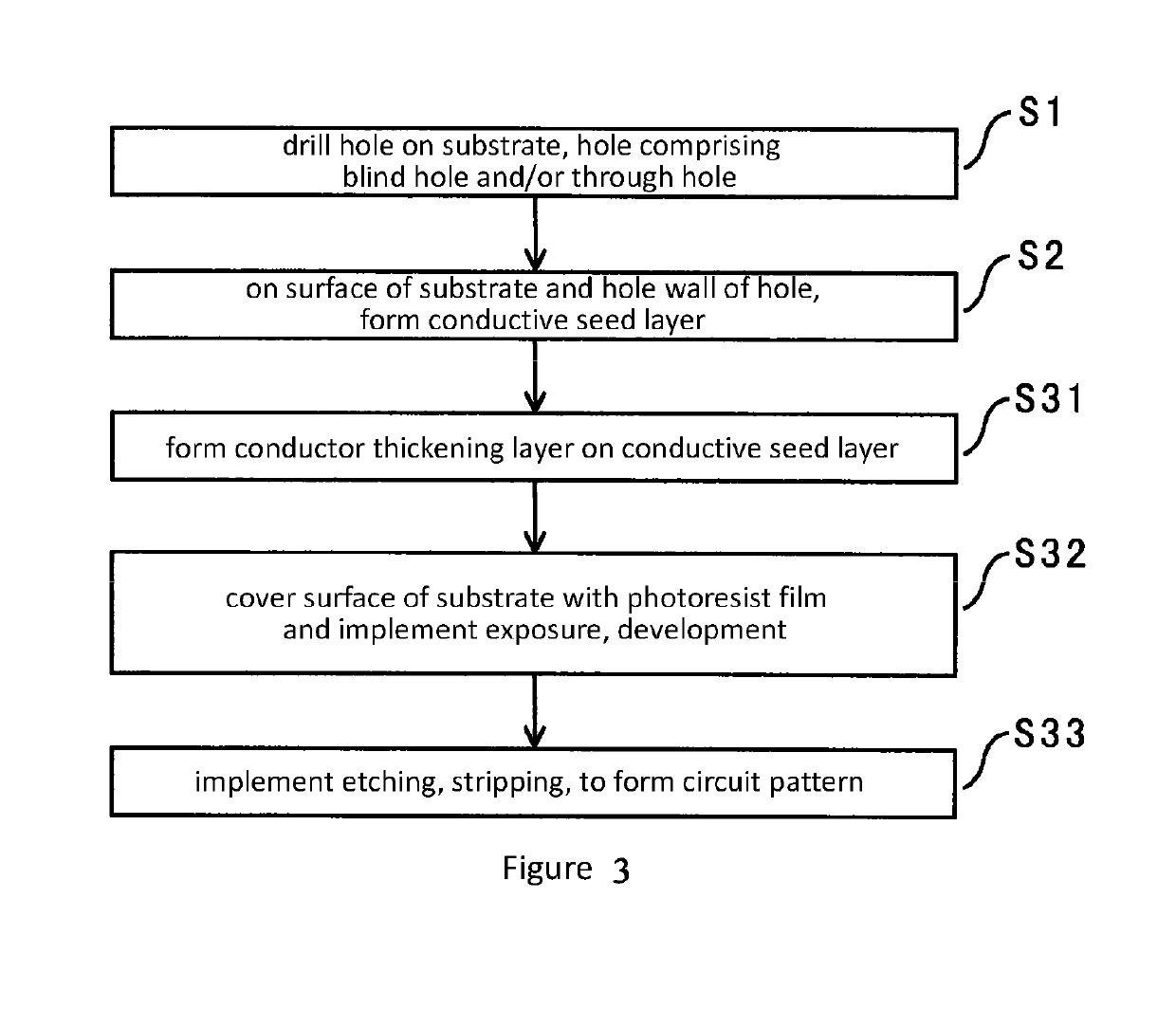

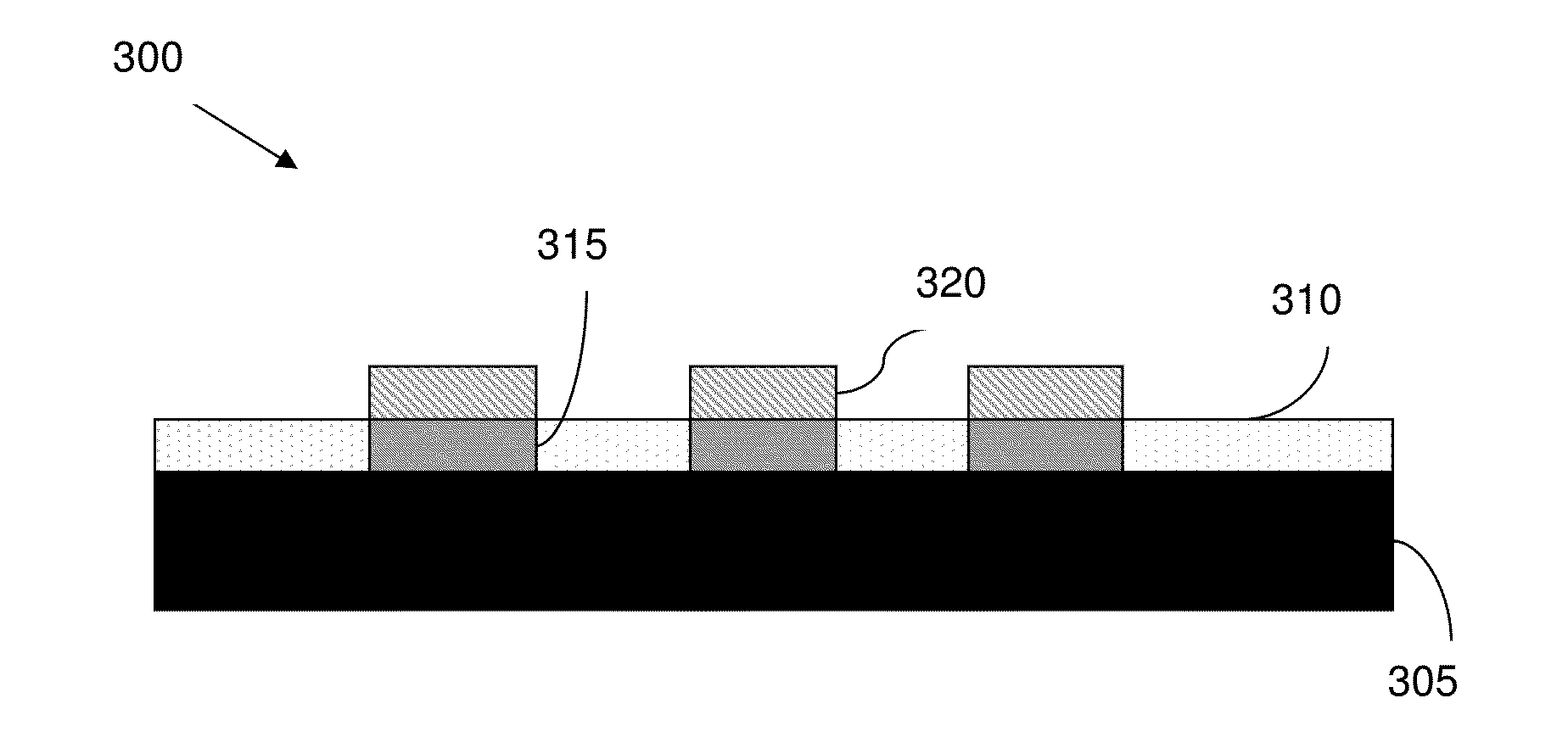

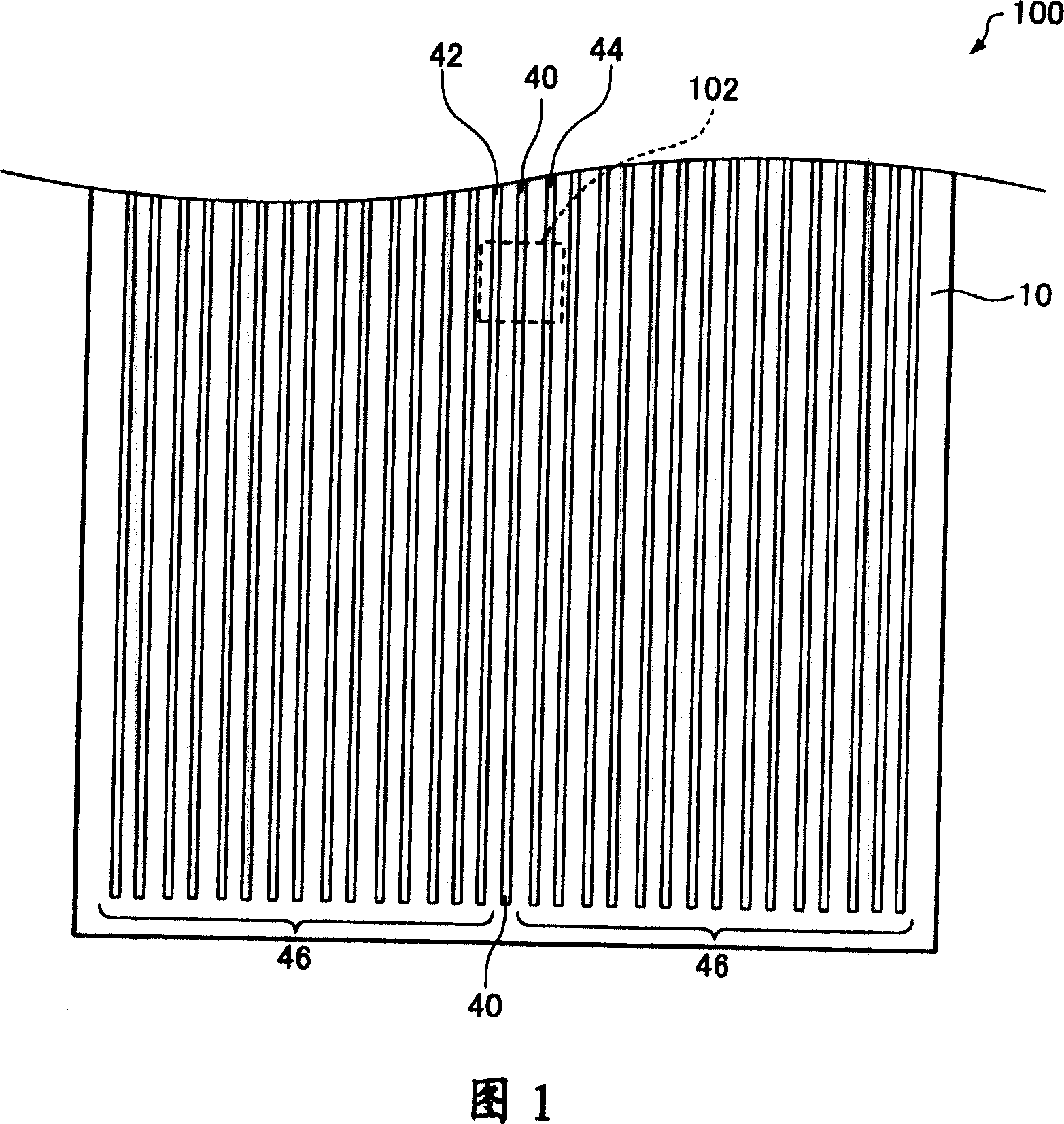

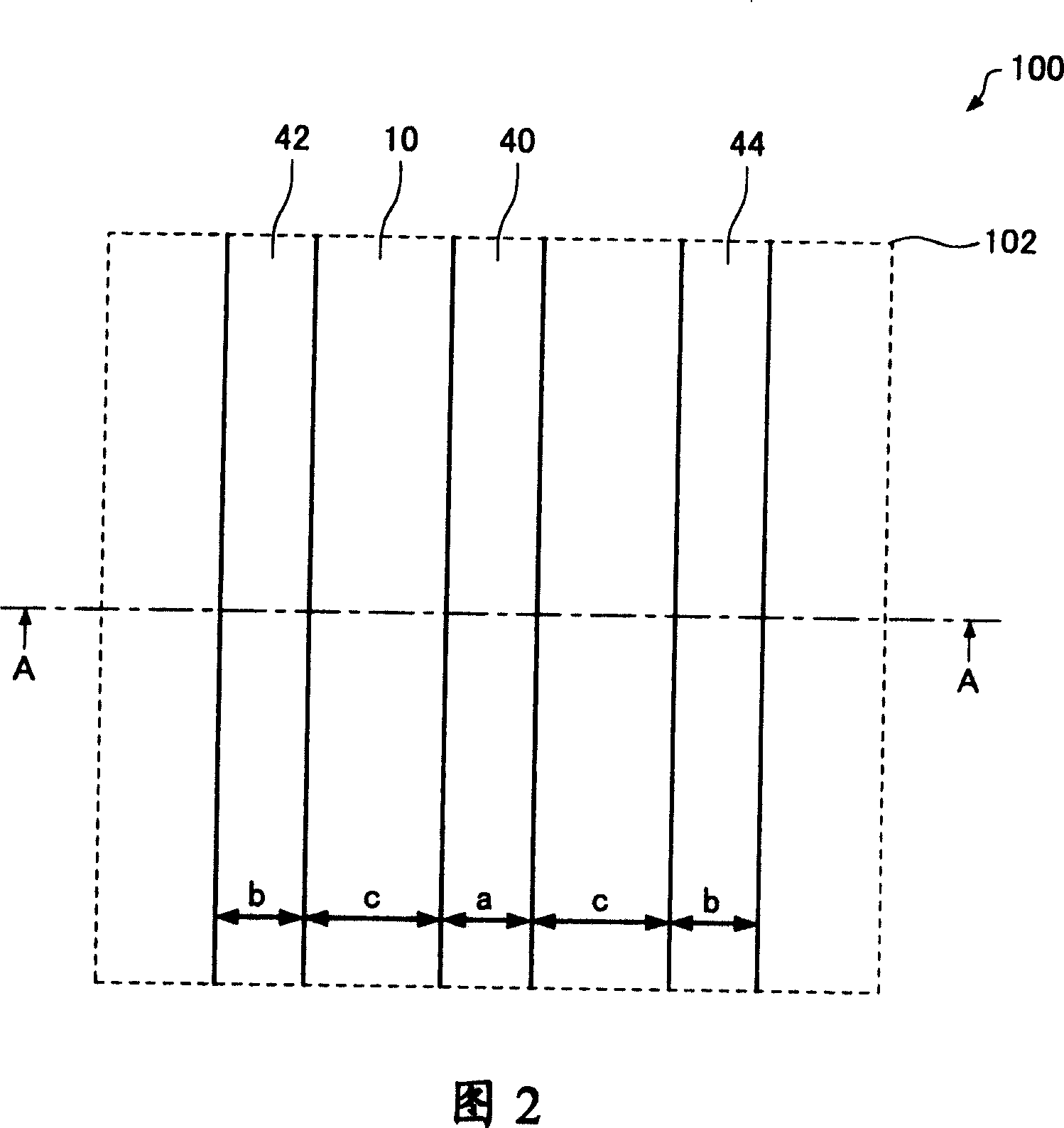

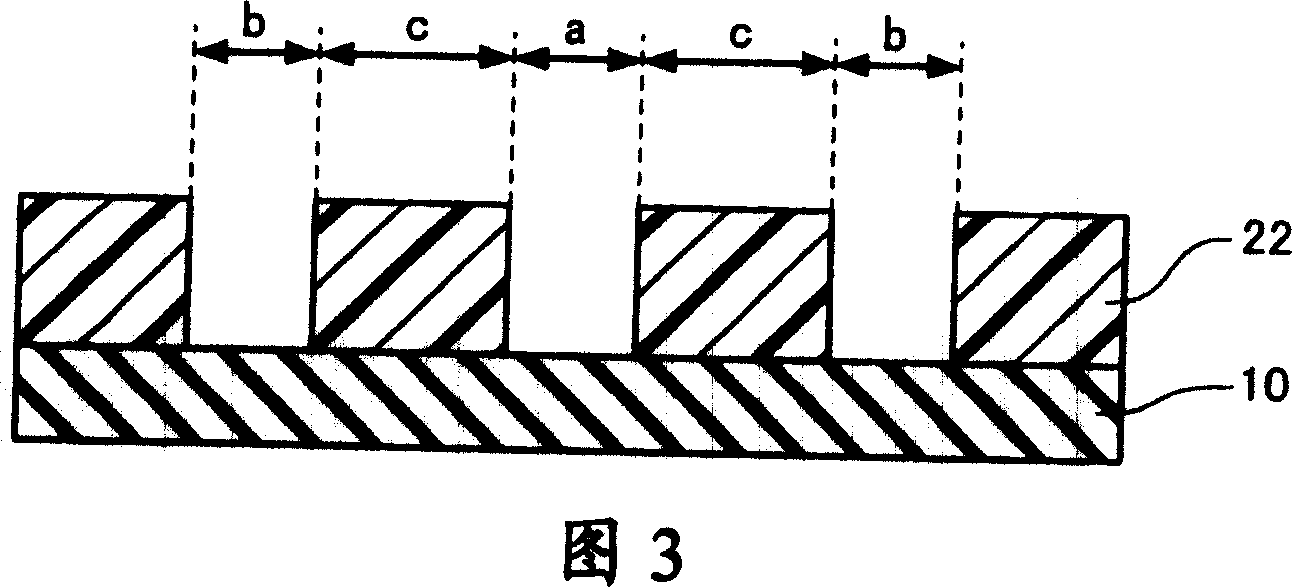

Single-layer circuit board, multi-layer circuit board, and manufacturing methods therefor

ActiveUS20180324958A1The production process is simpleImprove conduction abilityPrinted circuit aspectsVacuum evaporation coatingConductive materialsEngineering

A single-layer circuit board, multi-layer circuit board, and manufacturing methods therefor. The method for manufacturing the single-layer circuit board (10) comprises the following steps: drilling a hole on a substrate (11), the hole comprising a blind hole and / or a through hole (S1); on a surface (12) of the substrate, forming a photoresist layer having a circuit negative image (S2); forming a conductive seed layer on the surface (12) of the substrate and a hole wall (19) of the hole (S3); removing the photoresist layer, and forming a circuit pattern on the surface (12) of the substrate (S4), wherein Step S3 comprises implanting a conductive material below the surface (12) of the substrate and below the hole wall (19) of the hole via ion implantation, and forming an ion implantation layer as at least part of the conductive seed layer.

Owner:RICHVIEW ELECTRONICS CO LTD

Multi-layer printed circuit board and method for fabricating the same

ActiveUS7834274B2Reduce manufacturing costMeet the requirementsConductive pattern formationElectrical connection printed elementsEngineeringPrinted circuit board

A method for fabricating a double-sided or multi-layer printed circuit board (PCB) by ink-jet printing that includes providing a substrate, forming a first self-assembly membrane (SAM) on at least one side of the substrate, forming a non-adhesive membrane on the first SAM, forming at least one microhole in the substrate, forming a second SAM on a surface of the microhole, providing catalyst particles on the at least one side of the substrate and on the surface of the microhole, and forming a catalyst circuit pattern on the substrate.

Owner:IND TECH RES INST +1

Single-layer circuit board, multi-layer circuit board, and manufacturing methods therefor

ActiveUS10321581B2The production process is simpleImprove conduction abilityPrinted circuit aspectsVacuum evaporation coatingConductive materialsEngineering

Owner:RICHVIEW ELECTRONICS CO LTD

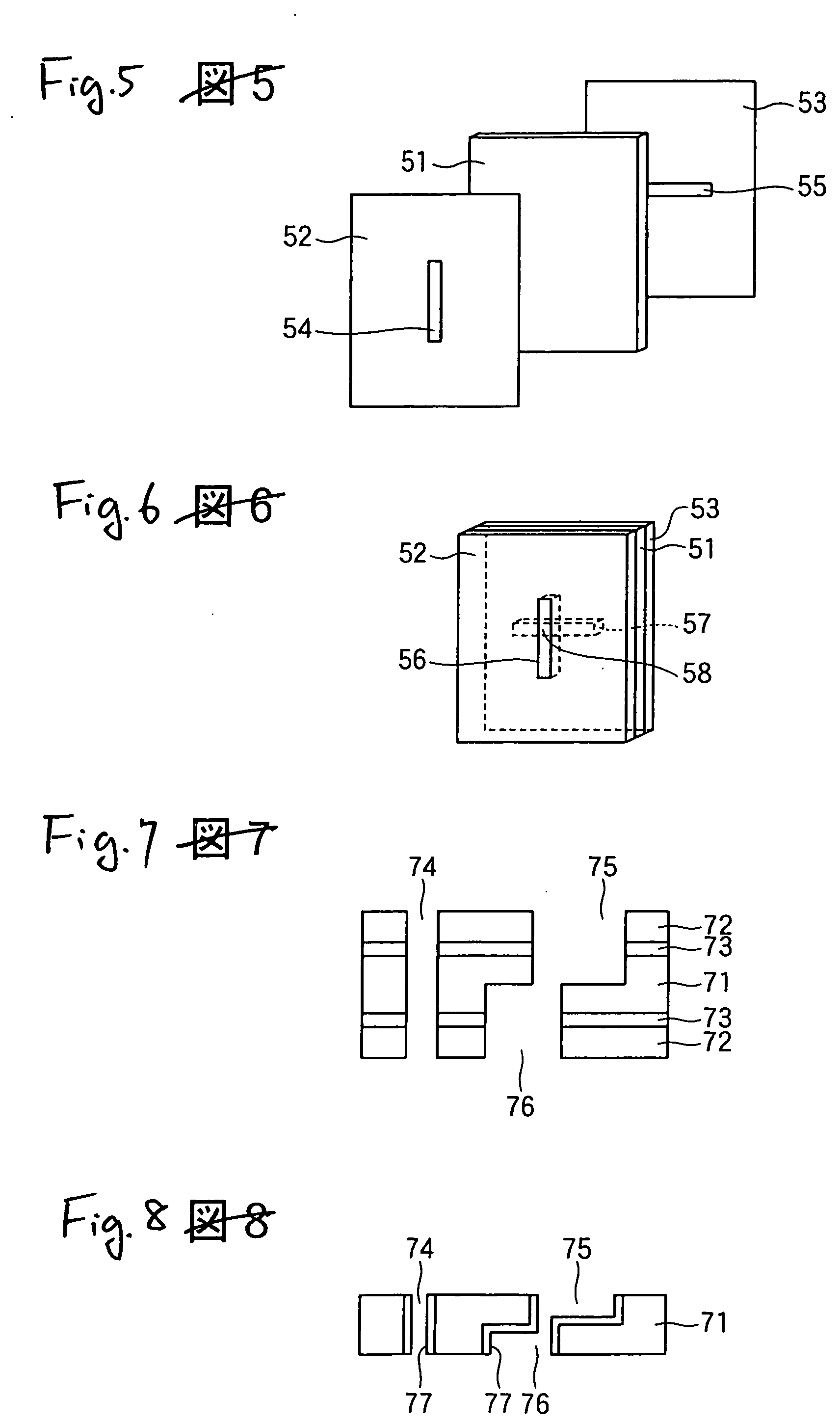

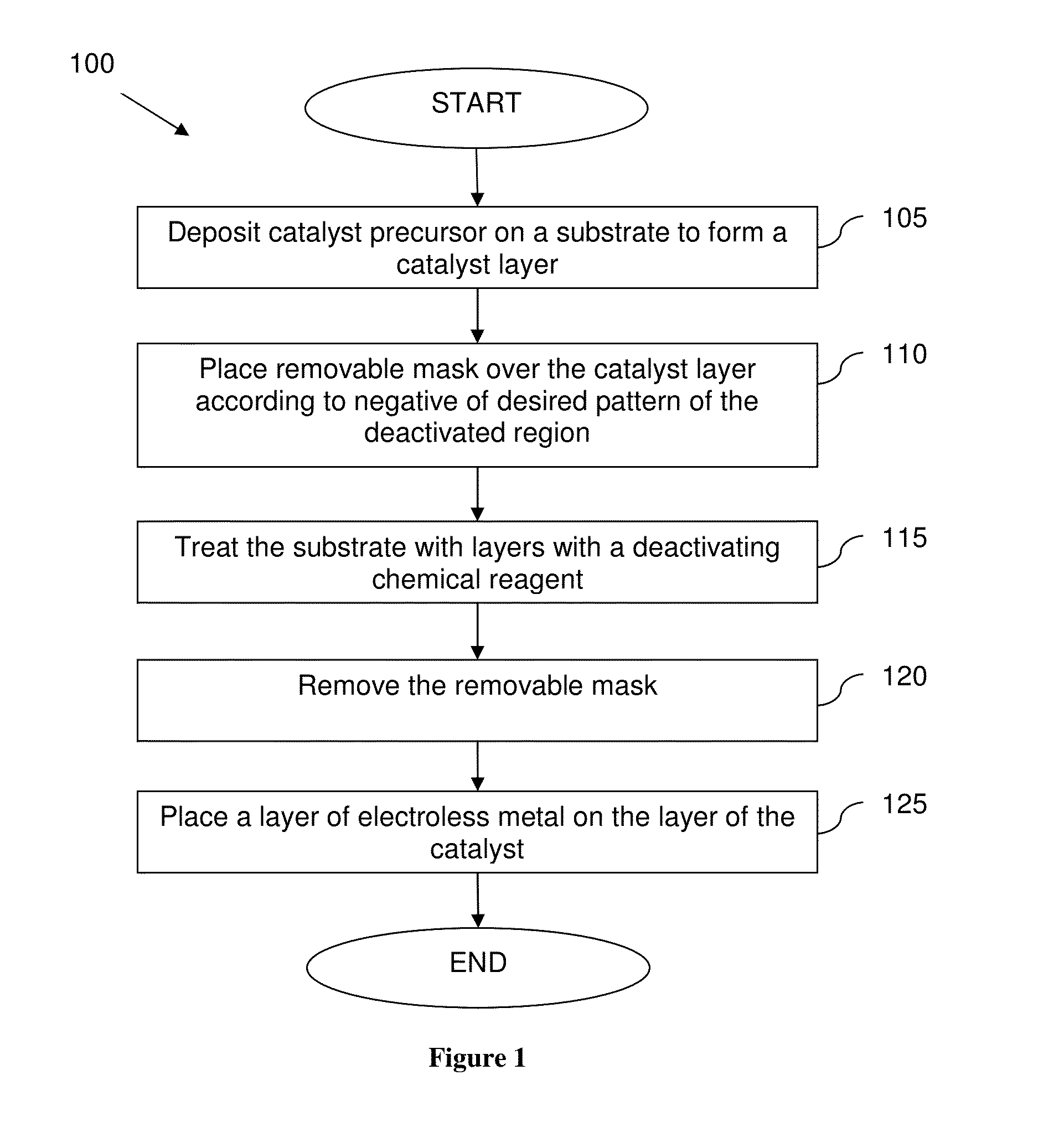

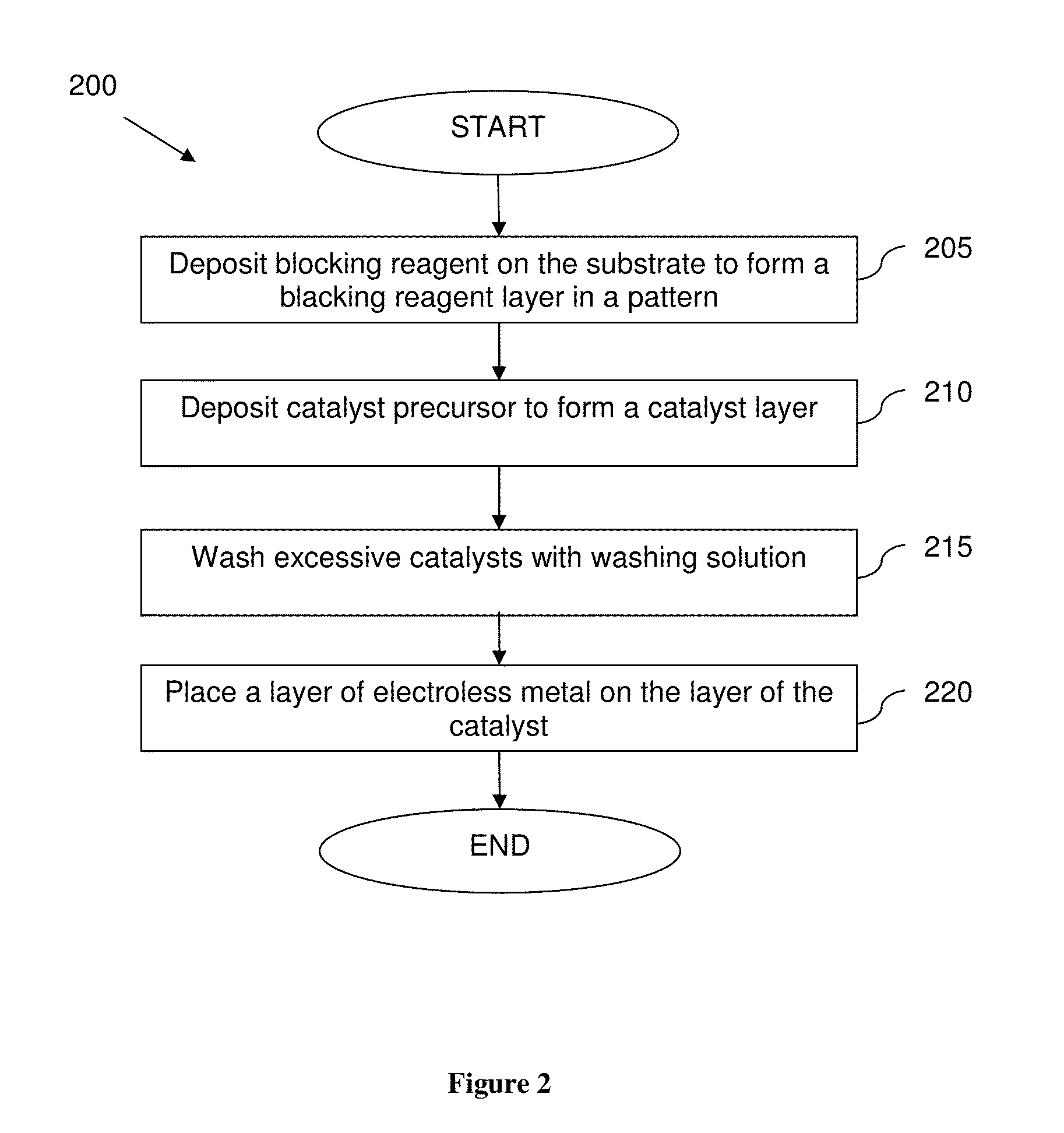

Patterning of electroless metals by selective deactivation of catalysts

ActiveUS20160113121A1Liquid/solution decomposition chemical coatingSolid/suspension decomposition chemical coatingElectroless nickelMetal

Methods and devices for patterning electroless metals on a substrate are presented. An active catalyst layer on the substrate can be covered with a patterned mask and treated with a deactivating chemical reagent, which deactivates the catalyst layer not covered by the mask. Once the patterned mask is removed, the electroless metal layer can be placed to have a patterned electroless metals. Alternatively, a substrate can be coated with a blocking reagent in a pattern first to inhibit formation of the catalyst layer before a catalyst layer can be placed over the blocking agent layer and then electroless metal layer is placed on the catalyst layer. The pattern of the blocking reagent acts as a negative pattern of the final conductive line pattern.

Owner:AVERATEK

Method for the manufacture of printed circuit boards with integral plated resistors

InactiveCN1689381ALiquid/solution decomposition chemical coatingPrinted resistor incorporationEngineeringBiological activation

The present invention is a process for manufacturing resistors integral with the printed circuit board by plating the resistors onto the insulative substrate. The invention uses a mask during the activation step so as to selectively activate only selected portions of the surface thus enabling smaller areas to be plated on the printed circuit board because no plating mask is used. The process of the present invention produced printed circuit boards having greater uniformity and reliability as compared to the prior art.

Owner:MACDERMID INC

Transparent electrically conductive film and process for producing the same

InactiveUS7883837B2Improve conductivityHigh yieldConductive layers on insulating-supportsPhotosensitive materialsResistForming face

This invention provides a transparent electrically conductive film, which, while maintaining the light transparency of a transparent film, has excellent electrical conductivity, can be utilized for electromagnetic wave shielding, and does not cause inclusion of air bubbles in the lamination onto other base material, and a process for producing the same. The production process comprises the steps of forming a large number of concaves and convexes having an average height of not more than 0.1 μm on both sides or one side of a transparent film, forming a resist layer having a pattern shape opposite to the electrically conductive part in the electrically conductive film on the transparent film on its concave-convex side, applying a catalyst for plating onto the resist layer-formed face, separating the resist layer, forming a metal layer by plating, and blackening the metal layer, the metal layer satisfying 1≦W / T≦500 wherein W represents the width of the metal layer and T represents the height of the metal layer.

Owner:SEIREN CO LTD

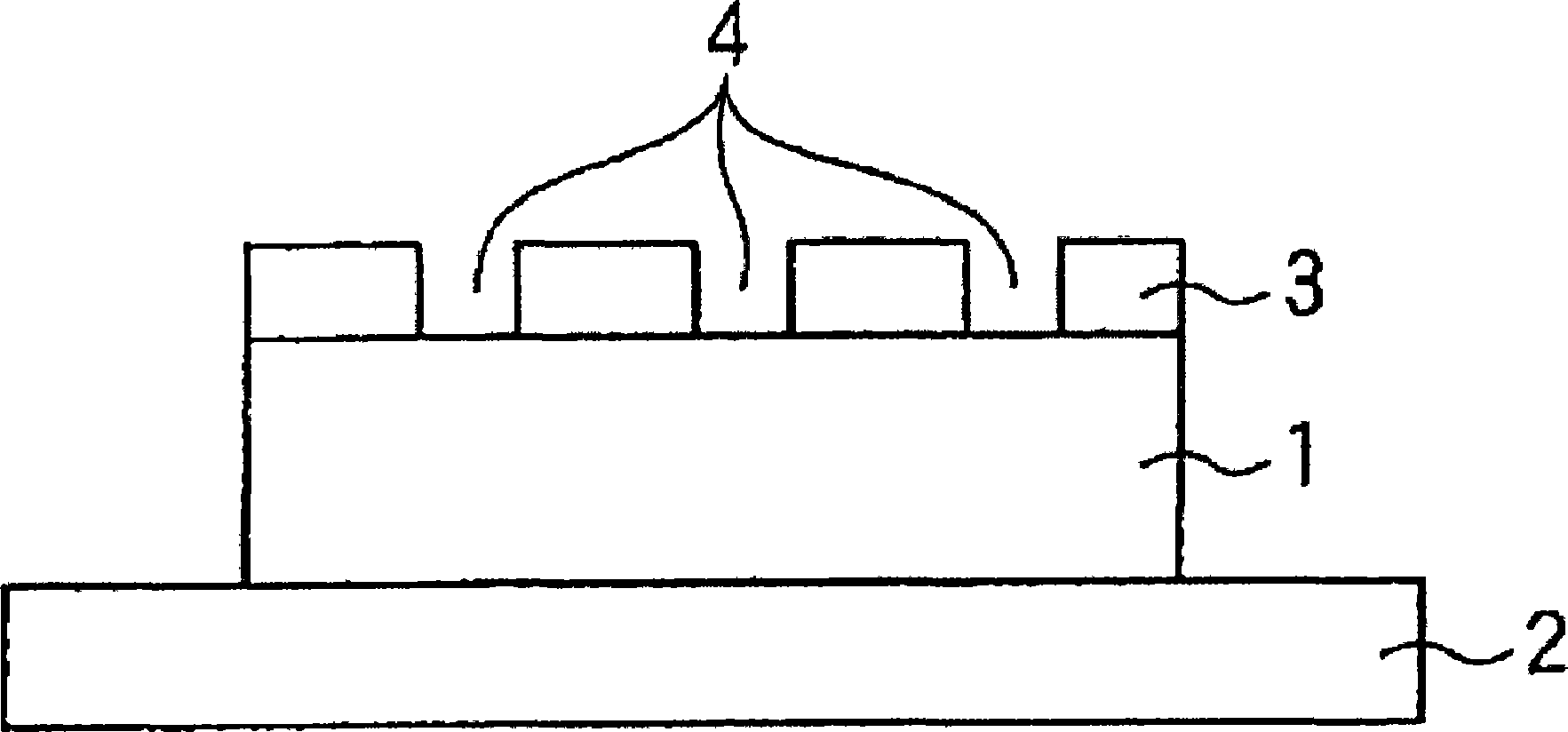

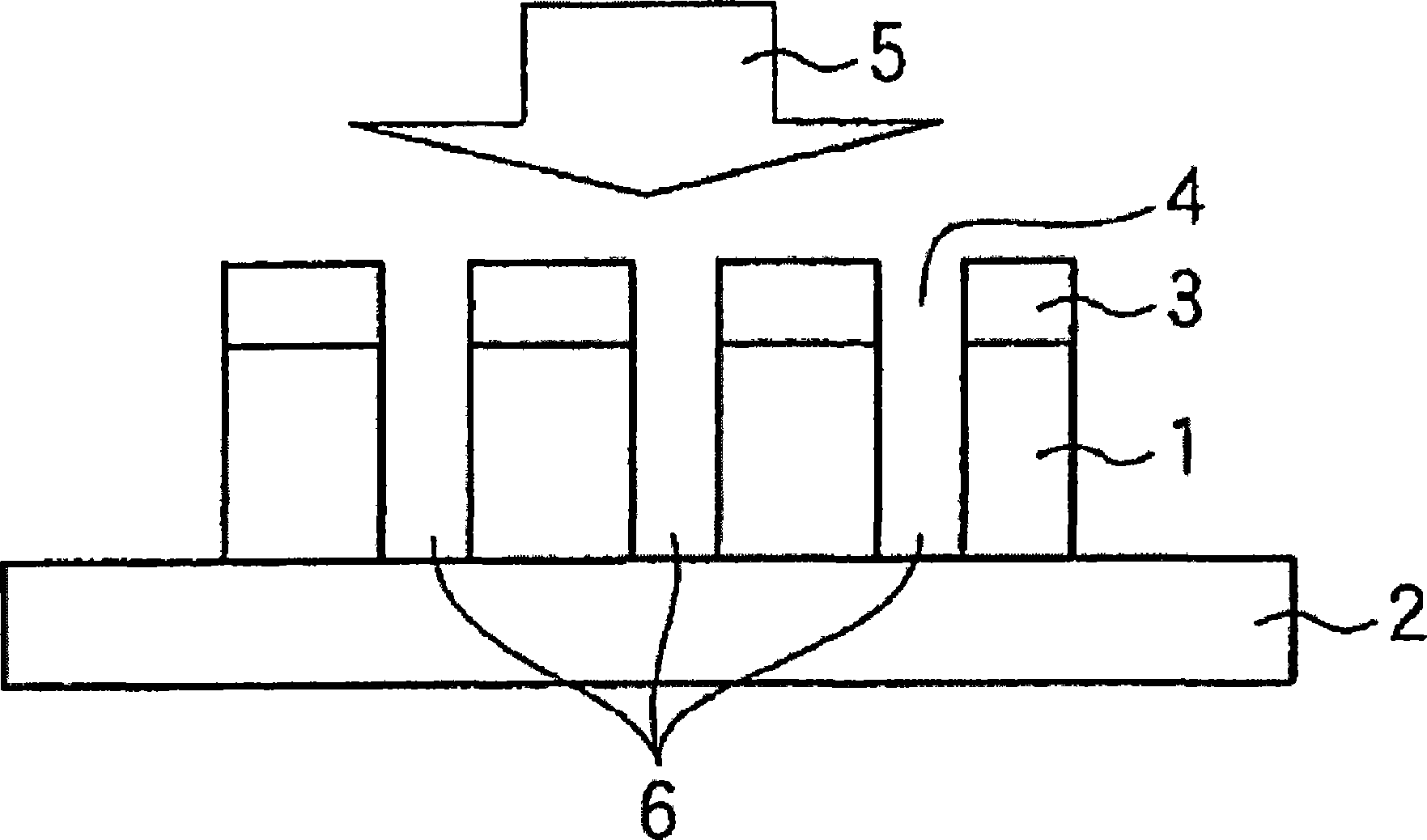

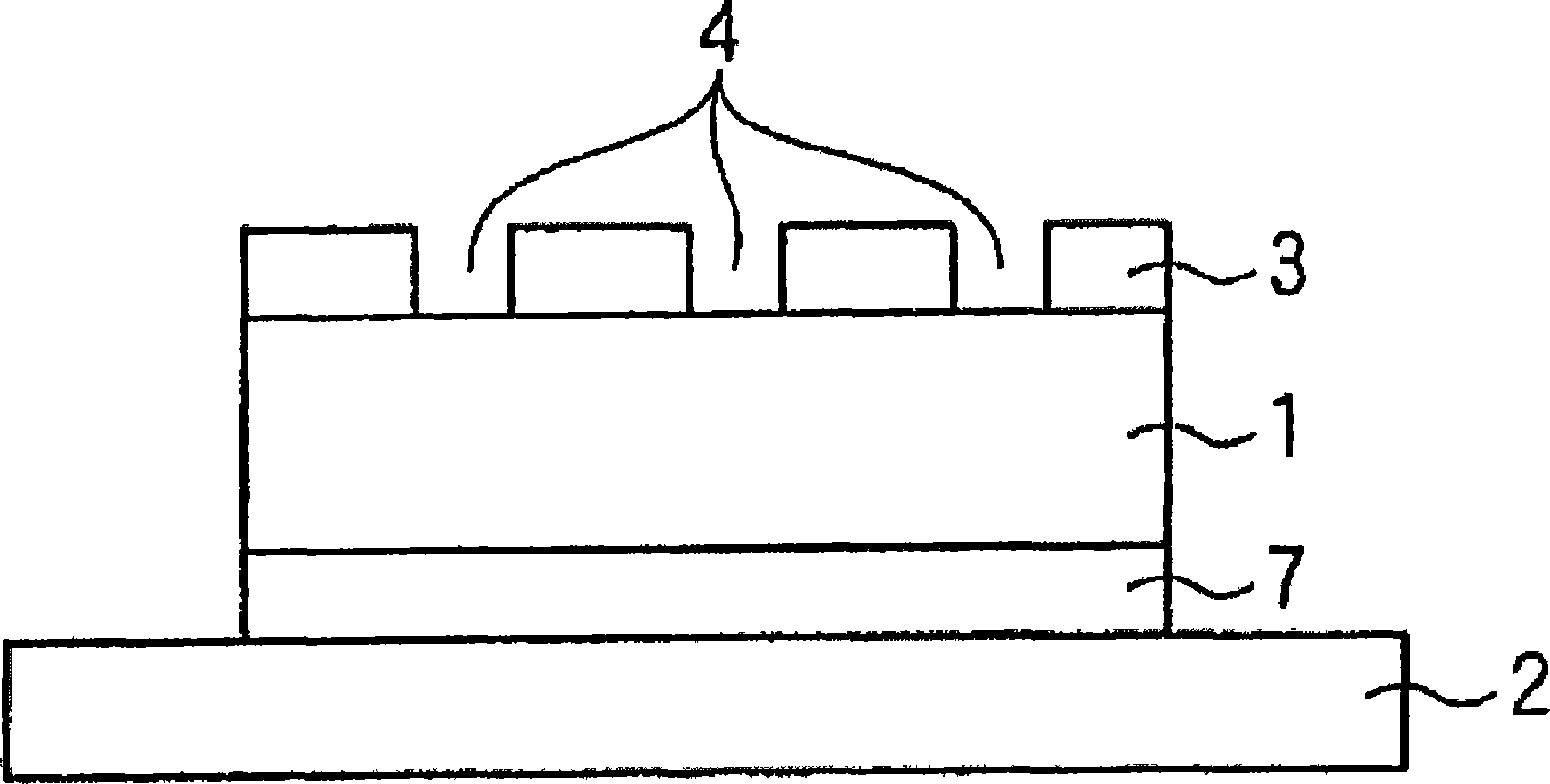

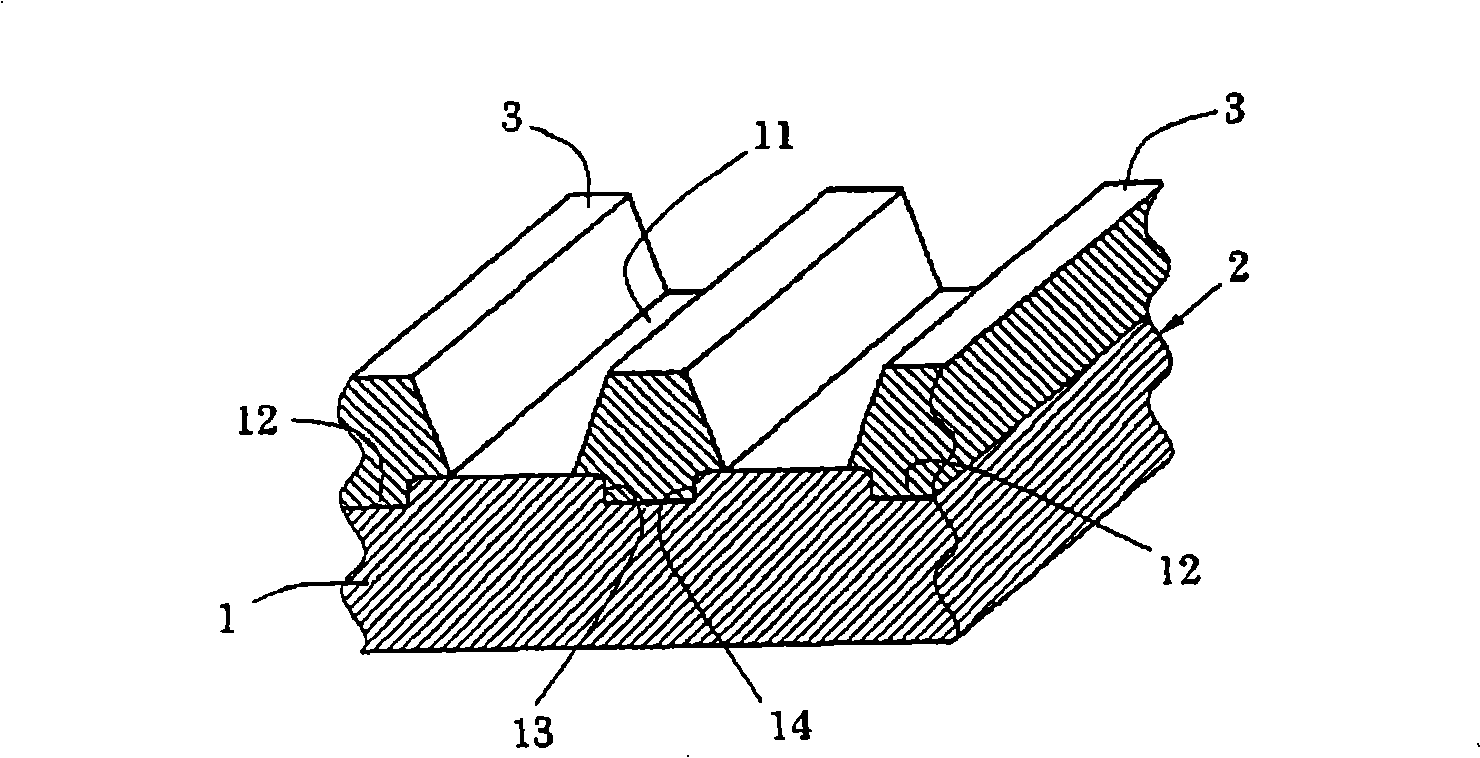

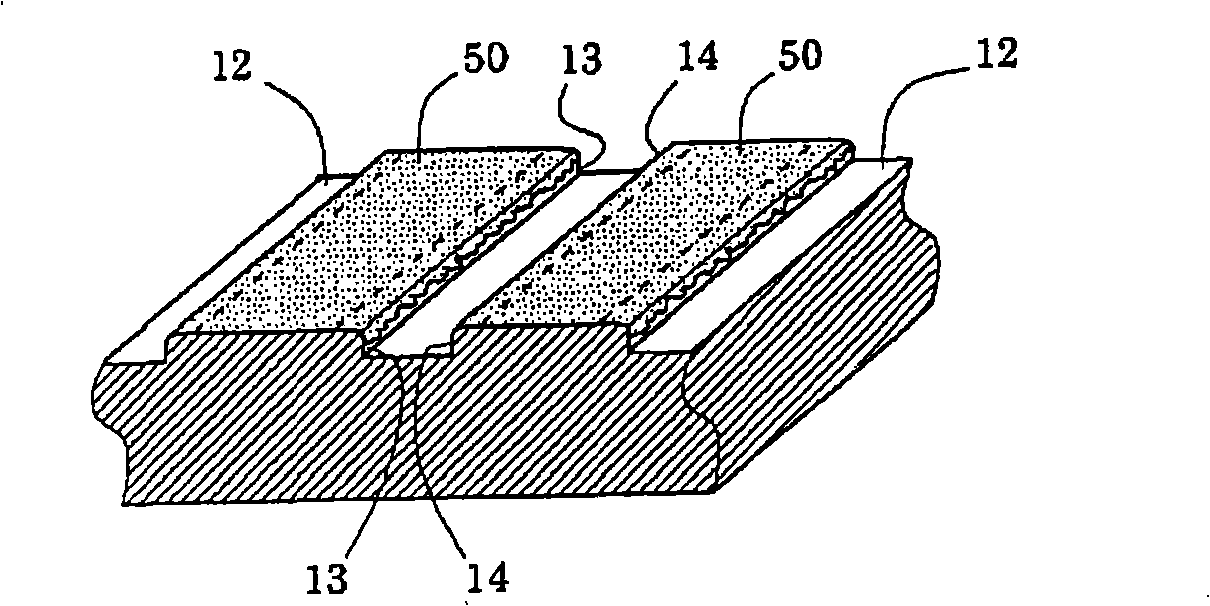

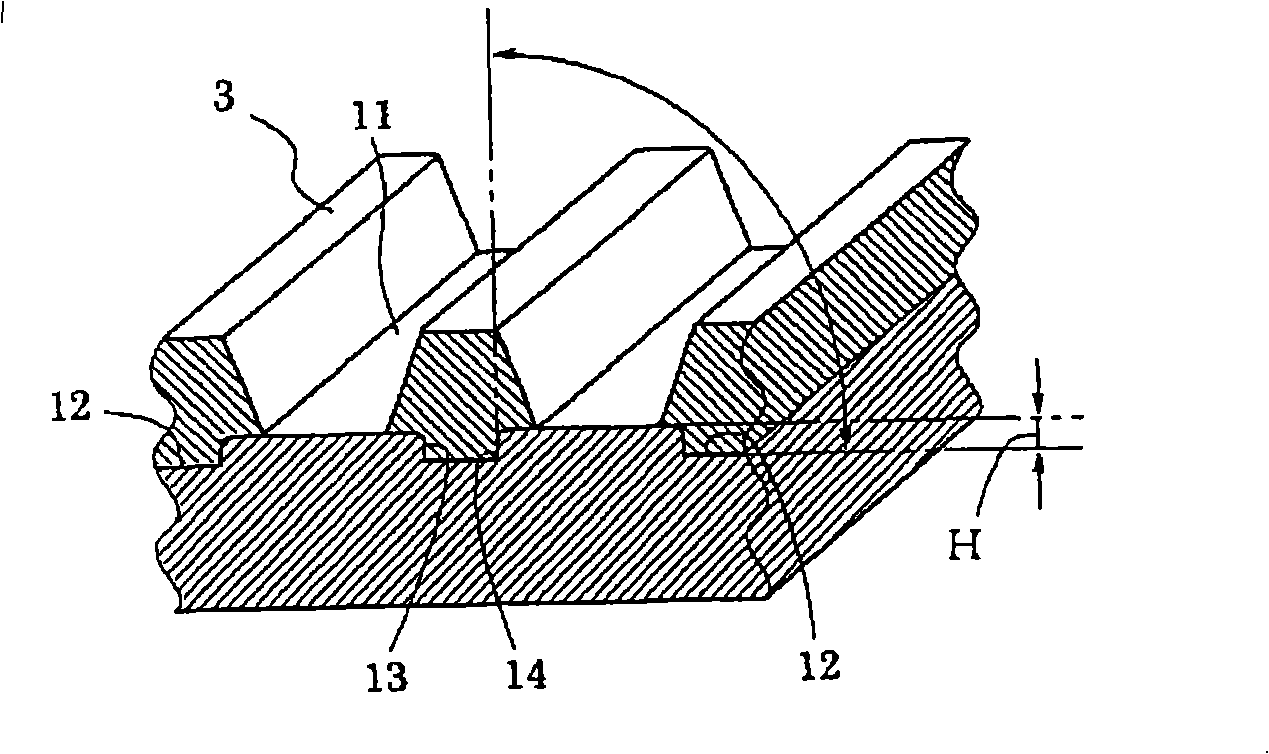

Molding circuit component and process for producing the same

InactiveCN101263751AAvoid short circuitBroaden the field of usePrinted circuit aspectsHigh voltage circuit adaptationsForming faceLiquid temperature

The range of selection of the material for a primary substrate and the material for a resin mask in a secondary substrate can be broadened, and short circuiting of a circuit can be reliably prevented. The shape of a primary substrate (1) is such that a circuit forming face (11) is in a convex form and a circuit non-forming face (12) is in a concave form, the difference in level between the circuit forming face (11) and the circuit non-forming face (12) is 0.05 mm, and the angle of side walls (13, 14) connecting the circuit forming face to the circuit non-forming face is 90 . In order to apply a catalyst, a palladium catalyst solution was immersed in a bath having a water depth of 500 mm at a liquid temperature of 40 C for 5 min. Thereafter, a resin mask (3) is dissolved and removed, followed by electroless plating. As a result, the catalyst solution penetrates up to a part in which the creeping distance could have been increased, that is, up to both side walls (13, 14). That is, the catalyst penetration can be prevented, and short circuiting between conductive layers (50), that is, between circuits, can be prevented.

Owner:SANKYO KASEI CO LTD

Method of manufacturing wiring substrate

InactiveCN101035413APrinted circuit aspectsLiquid/solution decomposition chemical coatingResistLine width

Owner:SEIKO EPSON CORP

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com