Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

43 results about "Time Stamp Counter" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

The Time Stamp Counter (TSC) is a 64-bit register present on all x86 processors since the Pentium. It counts the number of cycles since reset. The instruction RDTSC returns the TSC in EDX:EAX. In x86-64 mode, RDTSC also clears the higher 32 bits of RAX and RDX. Its opcode is 0F 31. Pentium competitors such as the Cyrix 6x86 did not always have a TSC and may consider RDTSC an illegal instruction. Cyrix included a Time Stamp Counter in their MII.

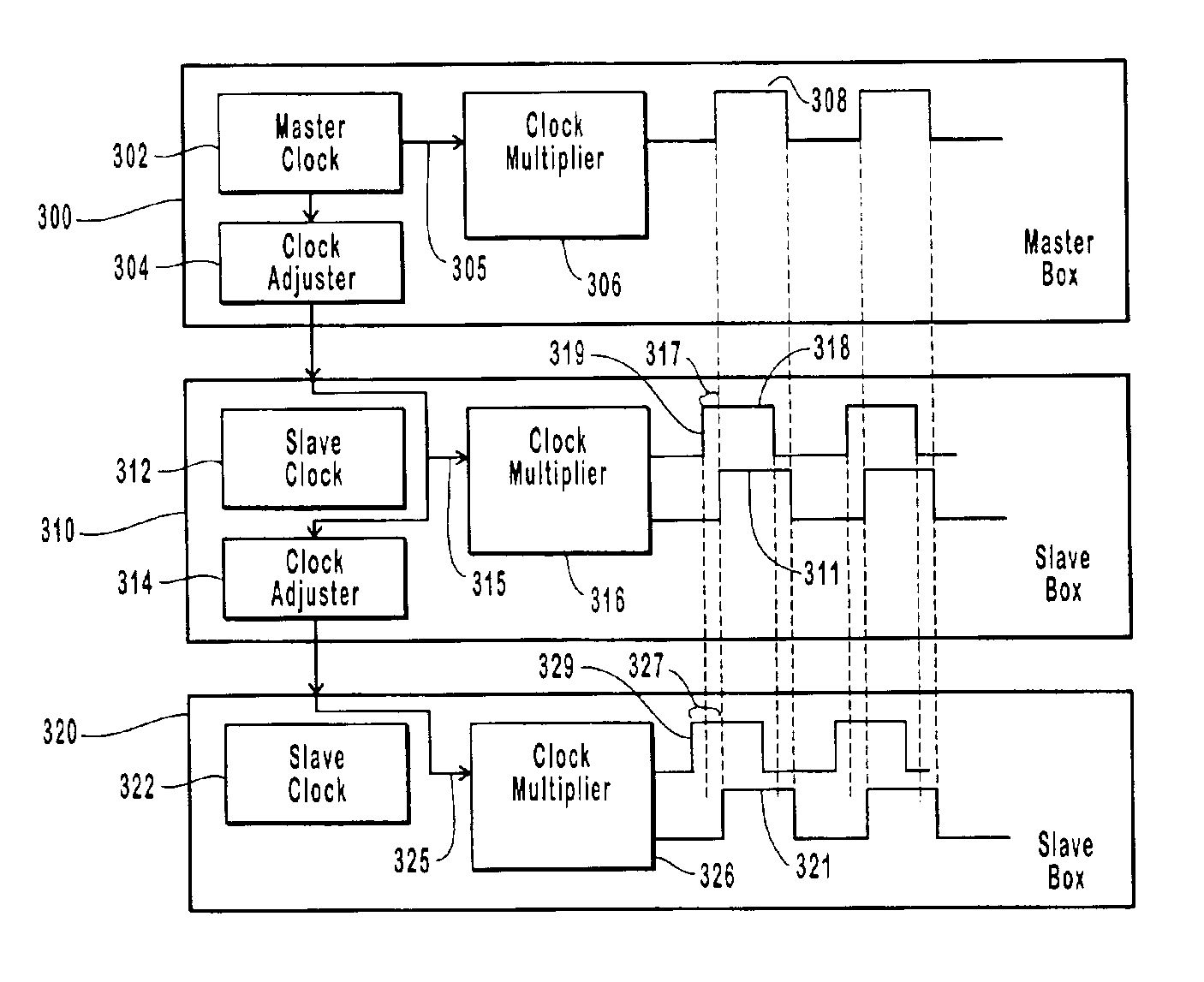

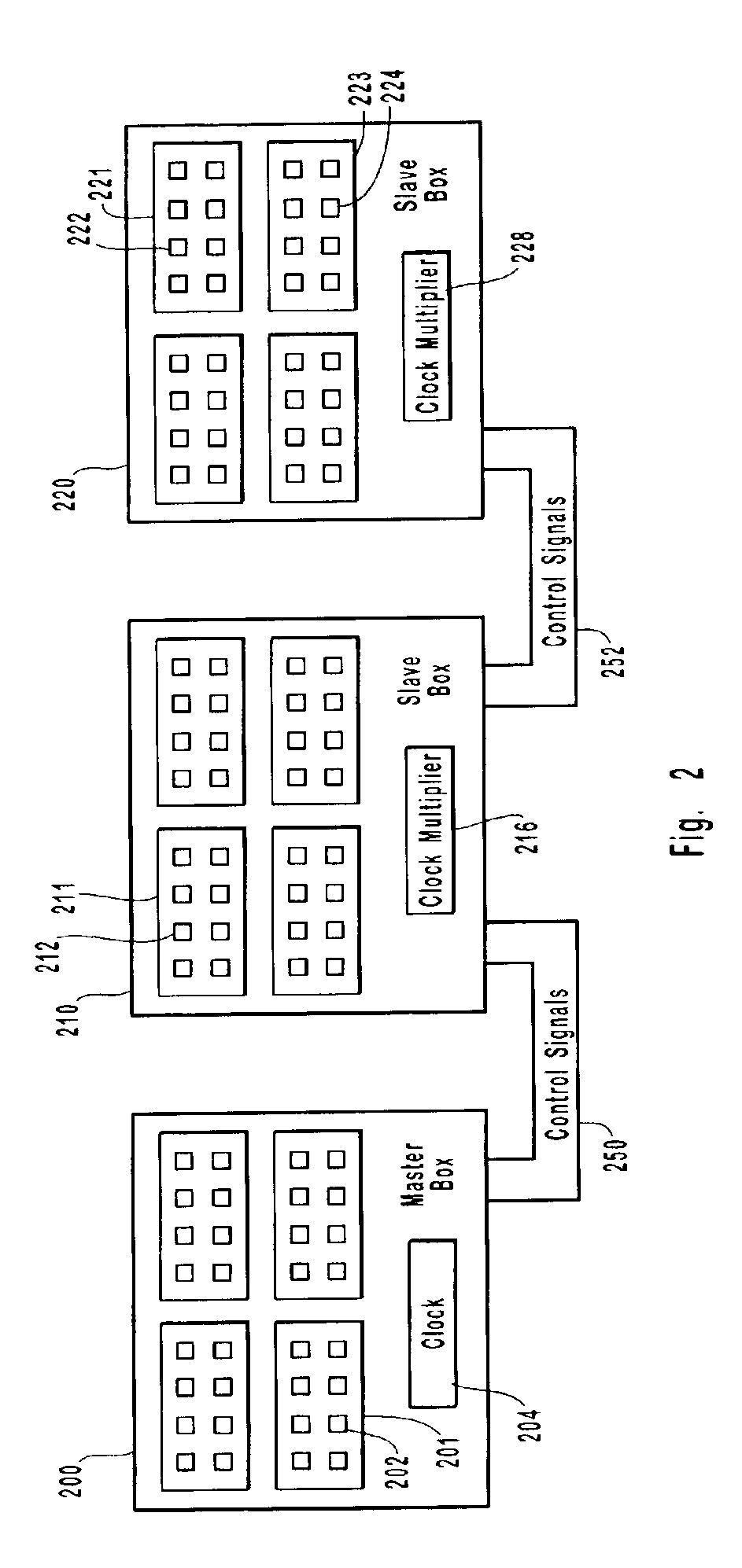

Systems and methods for synchronizing time stamps

ActiveUS6941482B2Error preventionFrequency-division multiplex detailsControl signalFrequency multiplier

Systems and methods for synchronizing time stamp counters of ports in a domain and for starting, stopping and triggering the ports in the domain at substantially the same time. A master box is connected with at least one slave box and the ports on the connected boxes are logically grouped in domains. The master box generates a clock signal that is adjusted and distributed to the slave boxes. The clock signal thus received by the slave boxes drives a clock multiplier that in turn drives the time stamp counters of the ports in the domains across the respective boxes. The time stamps of ports within a domain are synchronized because they are driven by the clock signal from the master box. The ports in a particular domain can be started, stopped and triggered using control signals that are similarly distributed from the master box to the slave boxes.

Owner:VIAVI SOLUTIONS INC

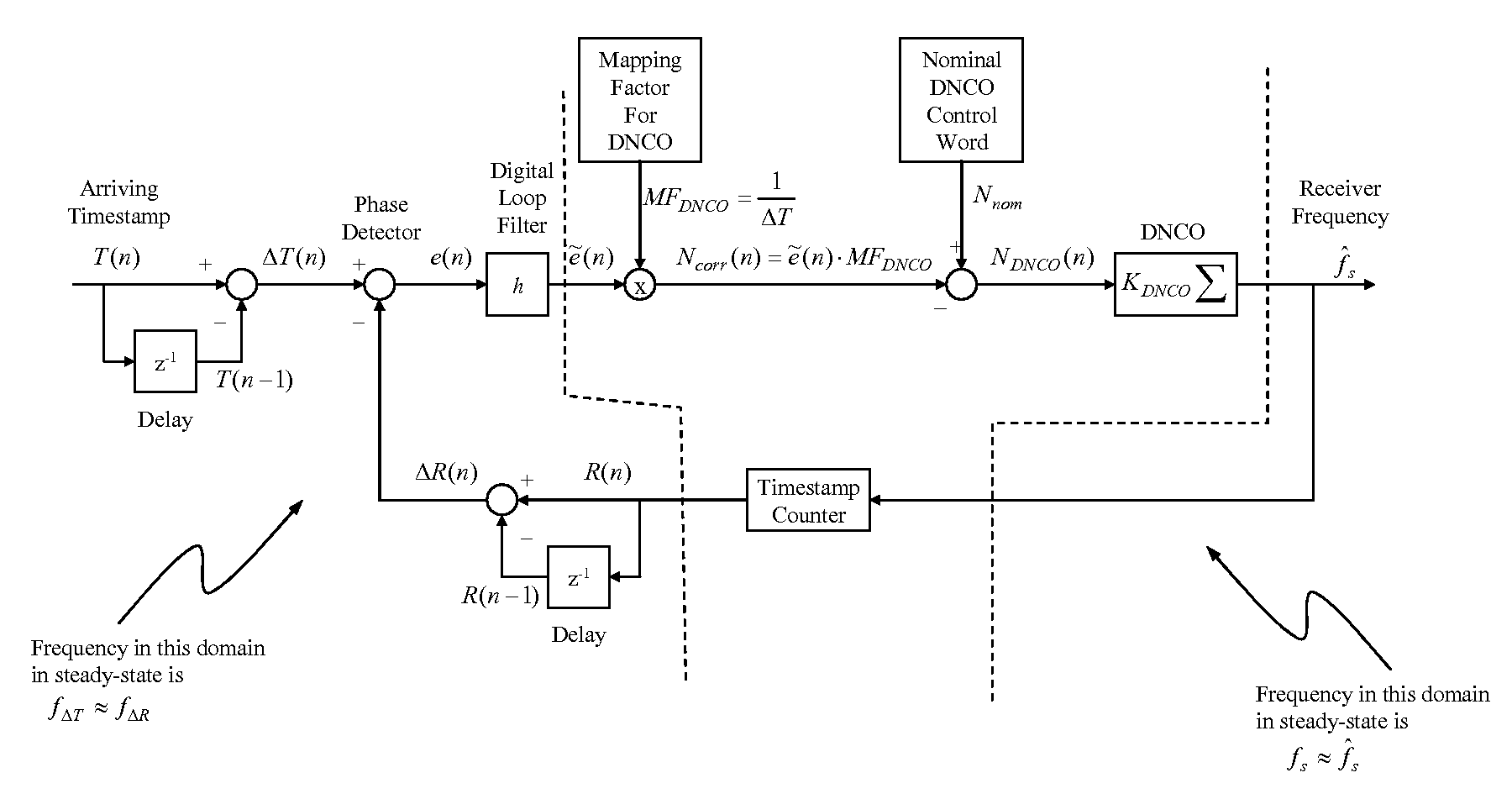

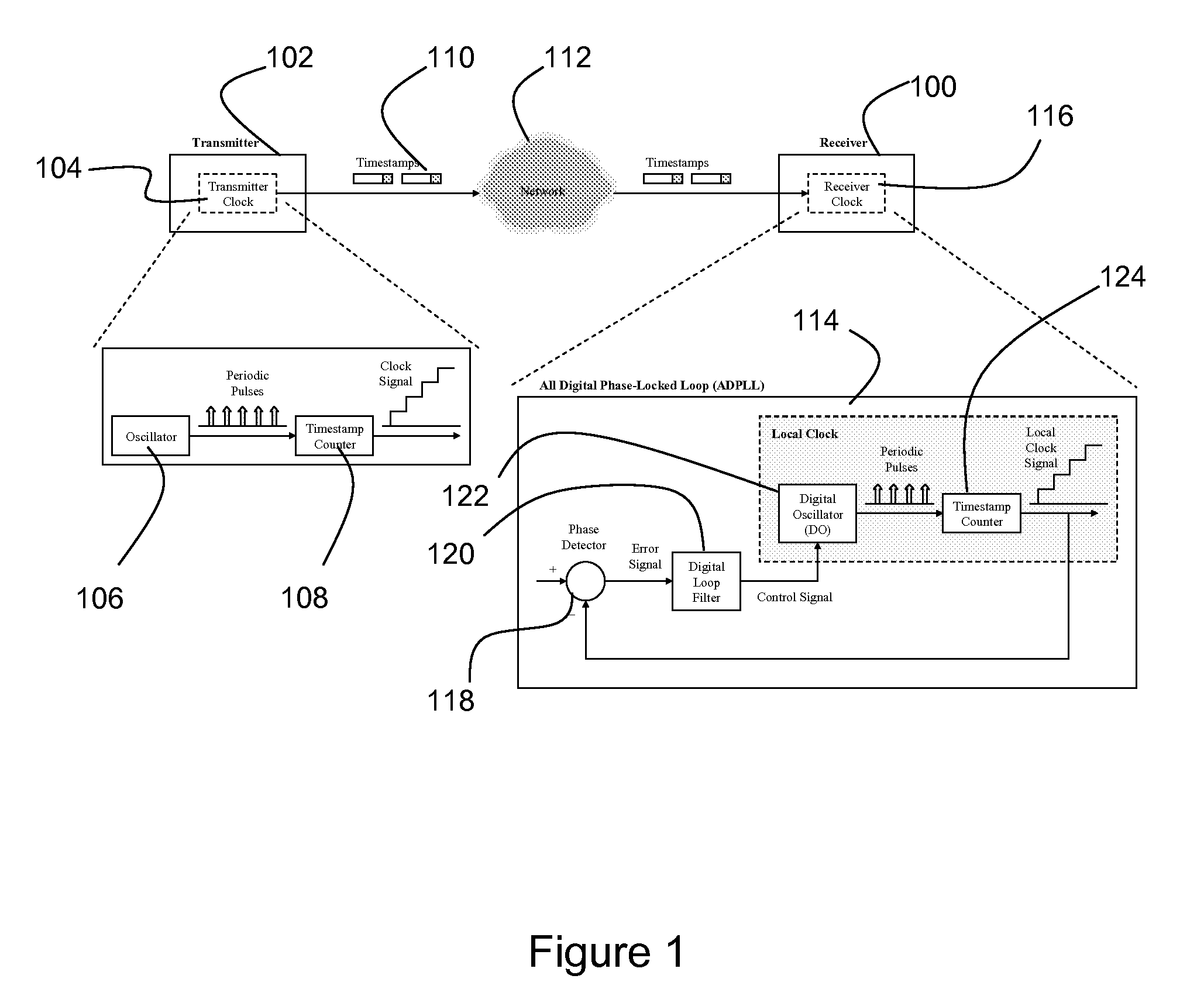

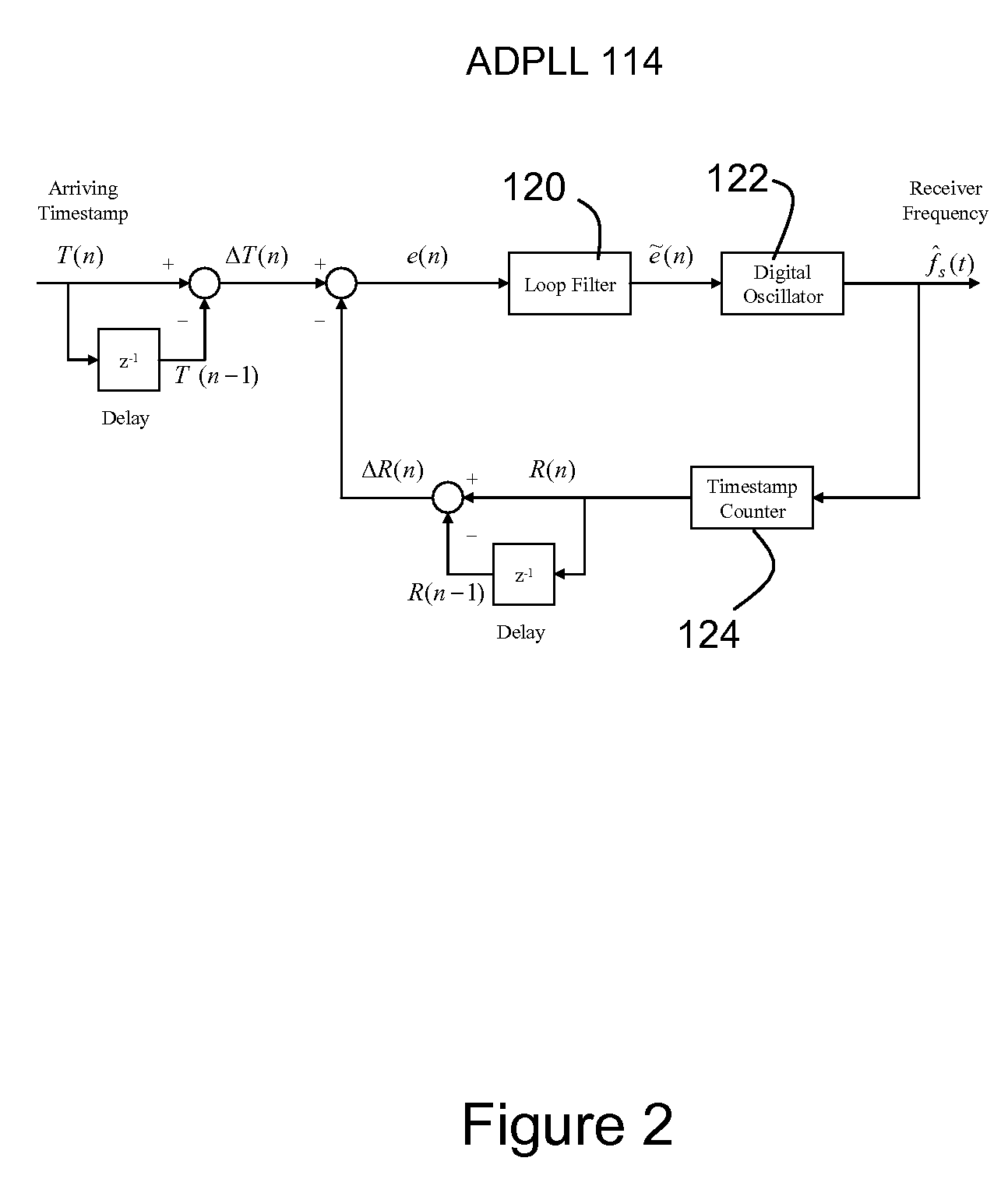

Timestamp-based all digital phase locked loop for clock synchronization over packet networks

ActiveUS7656985B1Reduce jitterReduce noiseFrequency-division multiplex detailsModulated-carrier systemsPhase detectorLoop filter

A timestamp-based all digital phase locked loop is utilized for clock synchronization for Circuit Emulation Service (“CES”) over packet networks. The all digital phase locked loop at a CES receiver includes a phase detector, a loop filter, a digital oscillator and a timestamp counter. The all digital phase locked loop enables the CES receiver to synchronize a local clock at the receiver with a clock at a CES transmitter, where indications of transmitter clock signals are communicated to the receiver as timestamps. The phase detector is operable to compute an error signal indicative of differences between the timestamps and a local clock signal. The loop filter is operable to reduce jitter and noise in the error signal, and thereby produce a control signal. The digital oscillator is operable to oscillate at a frequency based at least in-part on the control signal, and thereby produce a digital oscillator output signal. The timestamp counter operable to count pulses in the digital oscillator output signal, and output the local clock signal.

Owner:CIENA

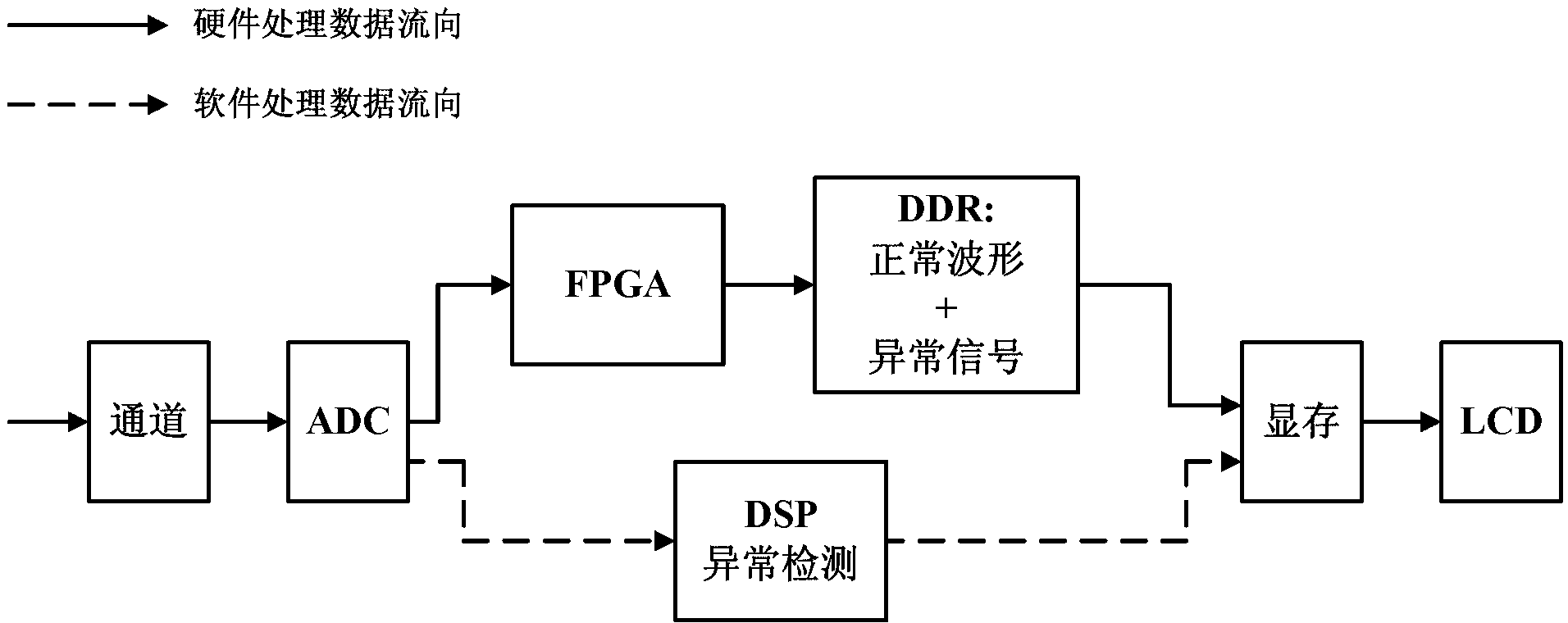

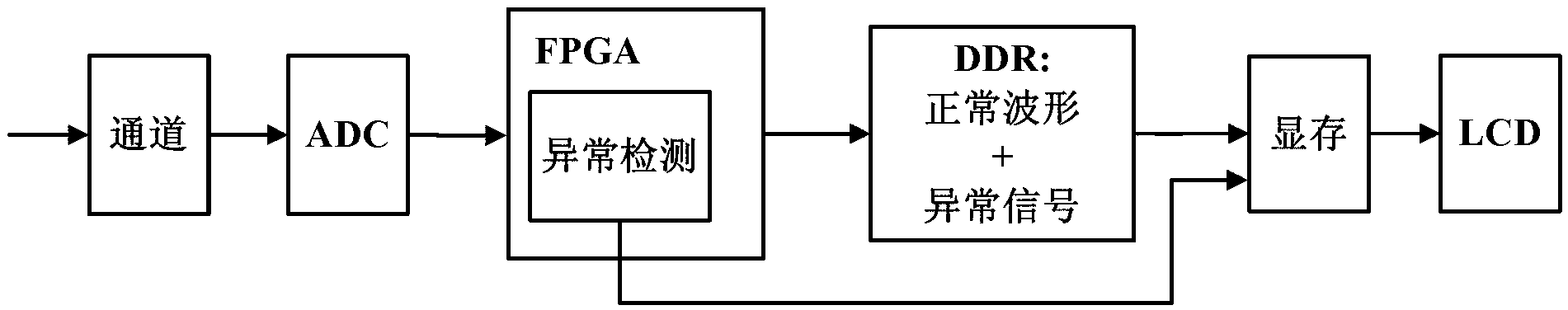

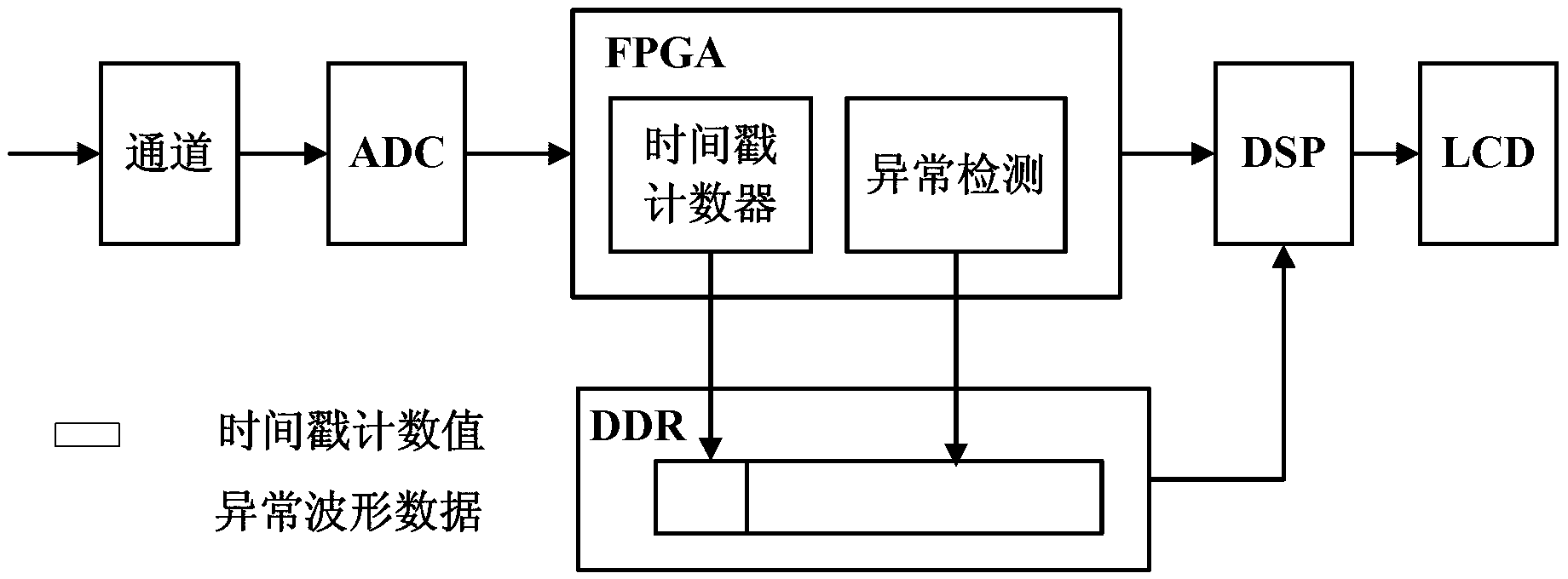

Abnormal waveform recording method for oscilloscope with high capture rate

InactiveCN103308738AImprove capture abilityRealize time positioningDigital variable displayDouble data rateReal-time clock

The invention discloses an abnormal waveform recording method for an oscilloscope with a high capture rate. The method comprises the following steps: arranging a time stamp counter in an FPGA (Field Programmable Gate Array); binding a time stamp with a real-time clock at a DSP (Digital Signal Processor) end; comparing waveform data acquired by using the FPGA with an abnormal waveform detection template; when an abnormal waveform appears, storing abnormal waveform data and a corresponding time stamp in a DDR (Double Data Rate); and calculating the generation time of the abnormal waveform data via a corresponding relation between the time stamp and the real-time clock at the DSP end so as to realize time positioning of abnormal waveforms. According to the method, only abnormal waveform data are stored, and normal waveform data are not stored, so that the abnormal waveform capturing capacity can be increased; and meanwhile, time positioning of abnormal waveforms is also realized, and manual observation and recording are not required. Abnormal waveforms can be displayed by adopting multiple display modes, so that abnormal waveforms can be analyzed conveniently.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

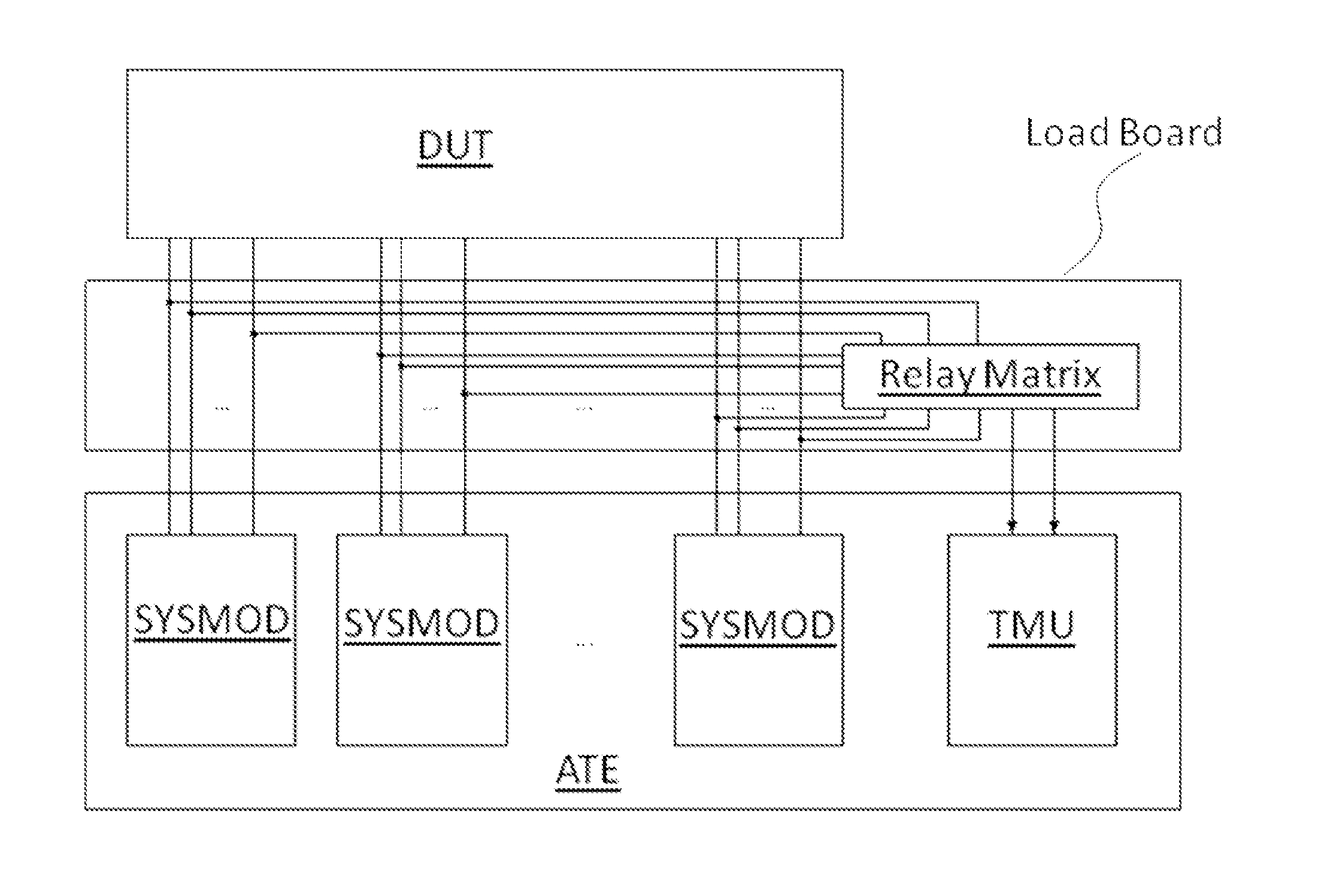

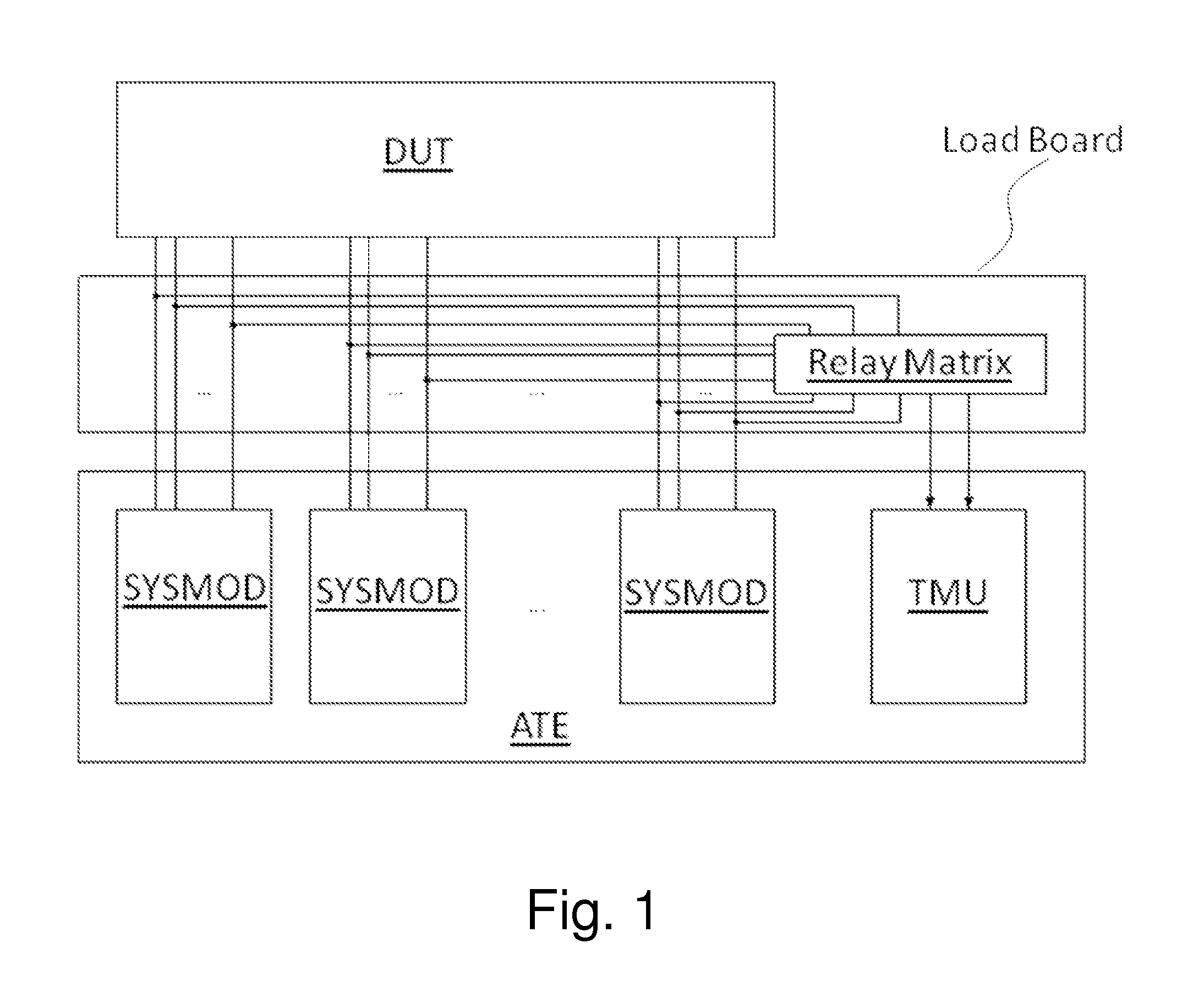

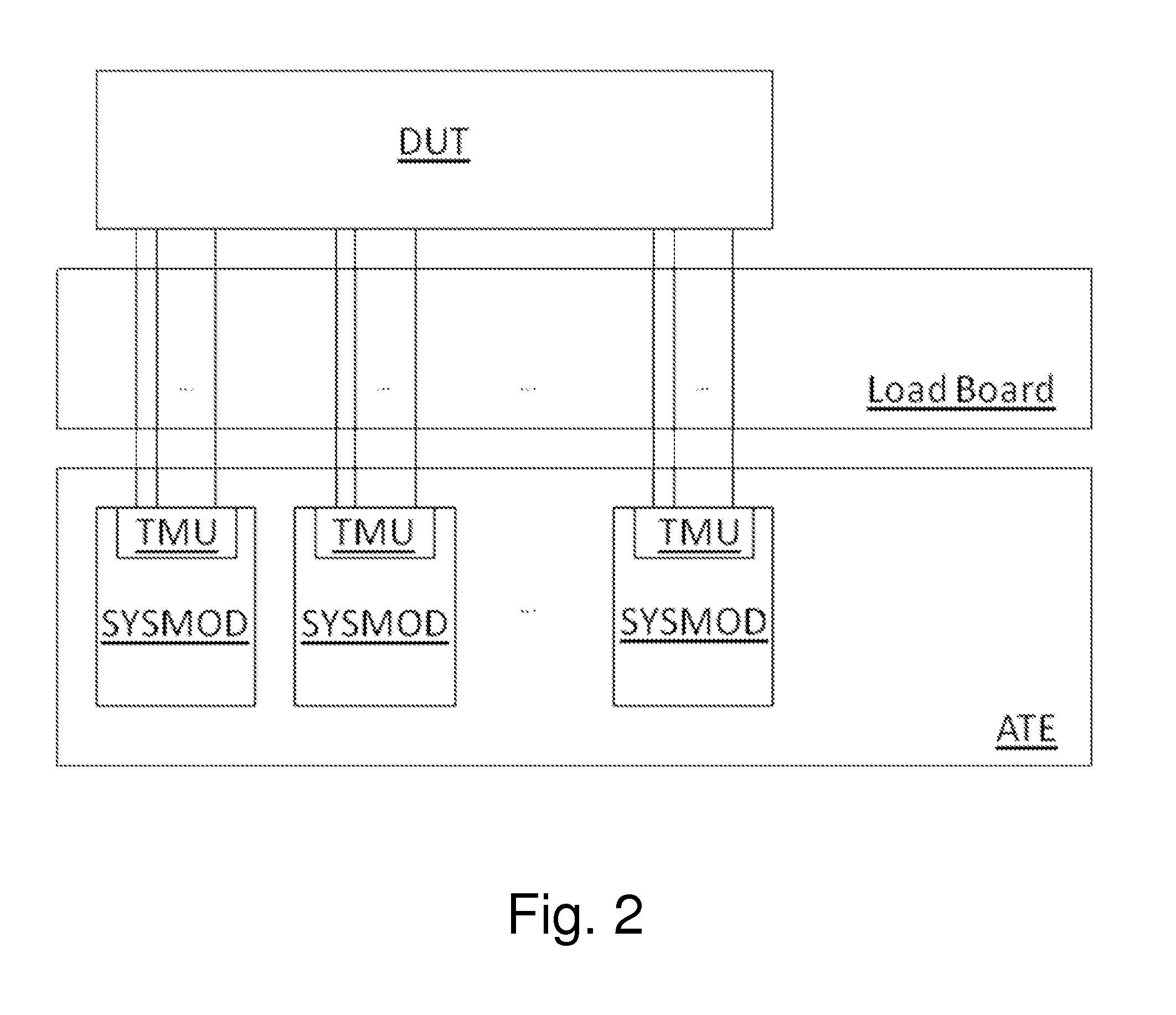

Method and apparatus for complex time measurements

ActiveUS20120010857A1Reduce resolutionHigh resolutionElectrical testingDigital computer detailsAutomatic test equipmentComputer module

Apparatus used in an automatic test equipment, comprising a plurality of system modules. Each system module comprises a Time Measurement Unit. The Time Measurement Unit comprises a Global Time Stamping Module. The Global Time Stamping Module comprises a plurality of Global Time Stamping Cores that comprising: an information receiving section for receiving at least two information, an event receiving section for receiving at a Core Input events, an event determining section for determining events of interest from said received events appearing on said Core Input, and an instructing section for instructing a Time Stamp Memory to record a current status of a Time Stamp Counter corresponding to the Clock Information, if an event of interest is determined. The Global Time Stamping Module further comprises a supplying section for supplying said plurality of Global Time Stamping Cores with a common time base.

Owner:ADVANTEST CORP

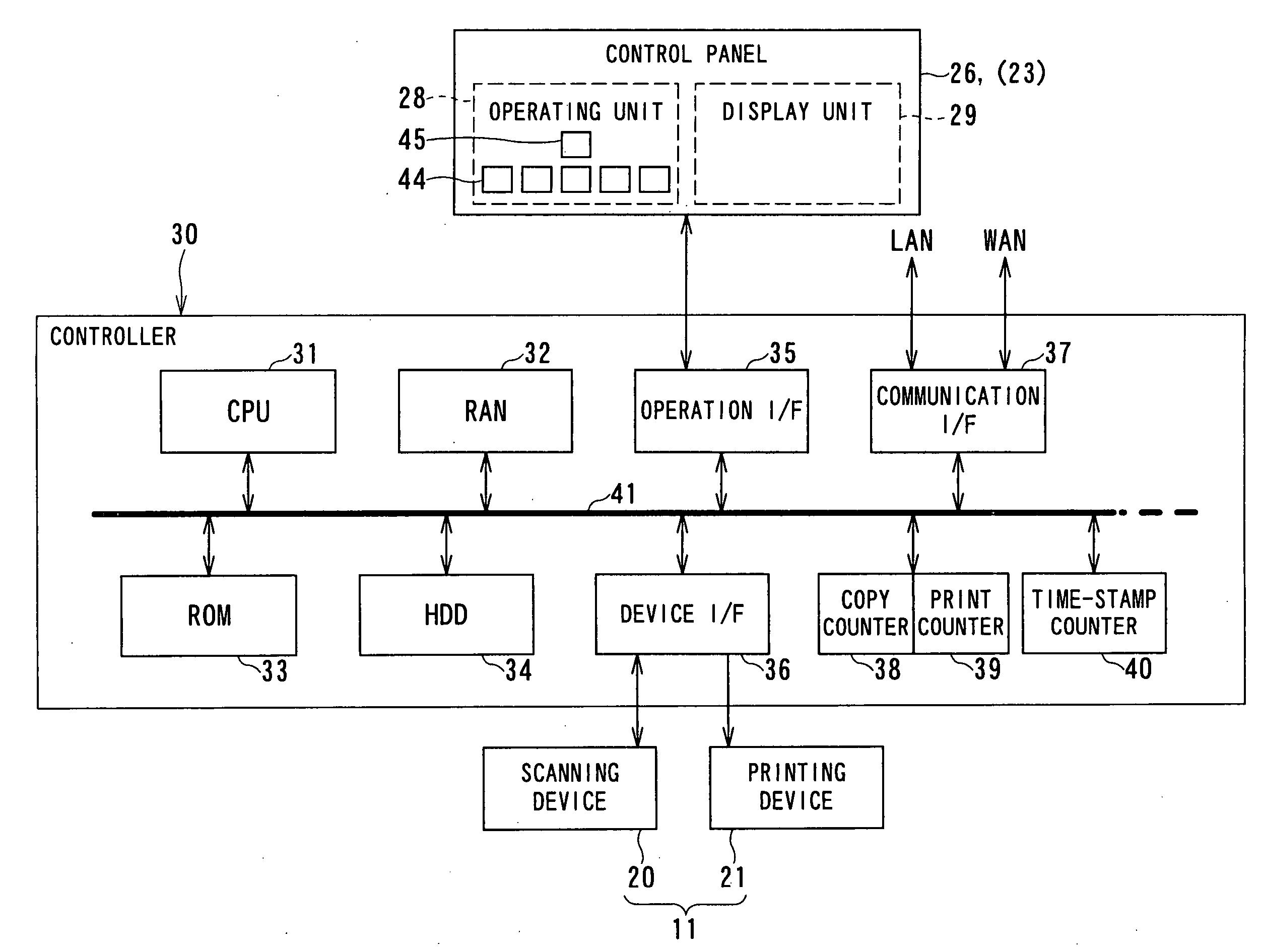

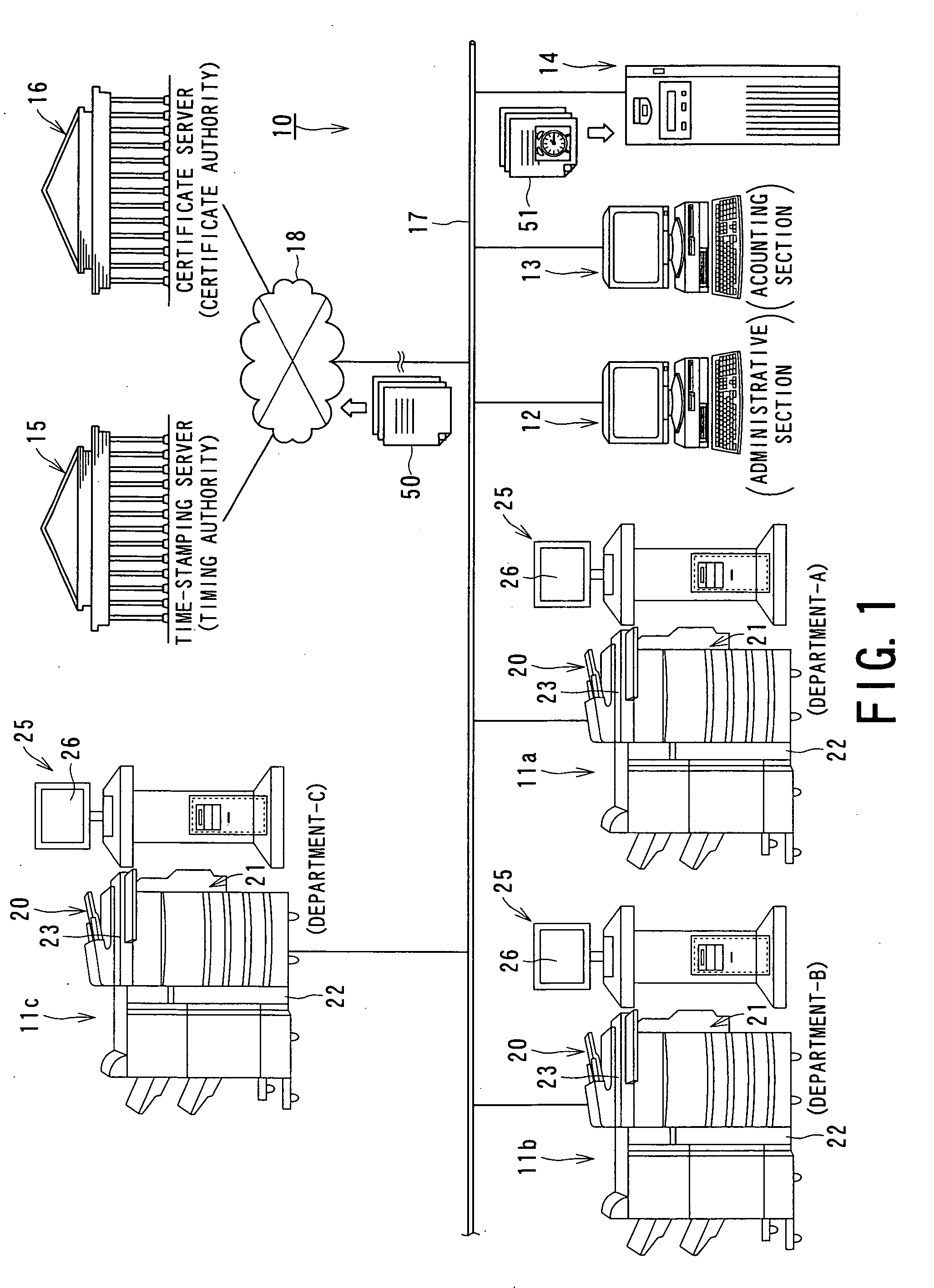

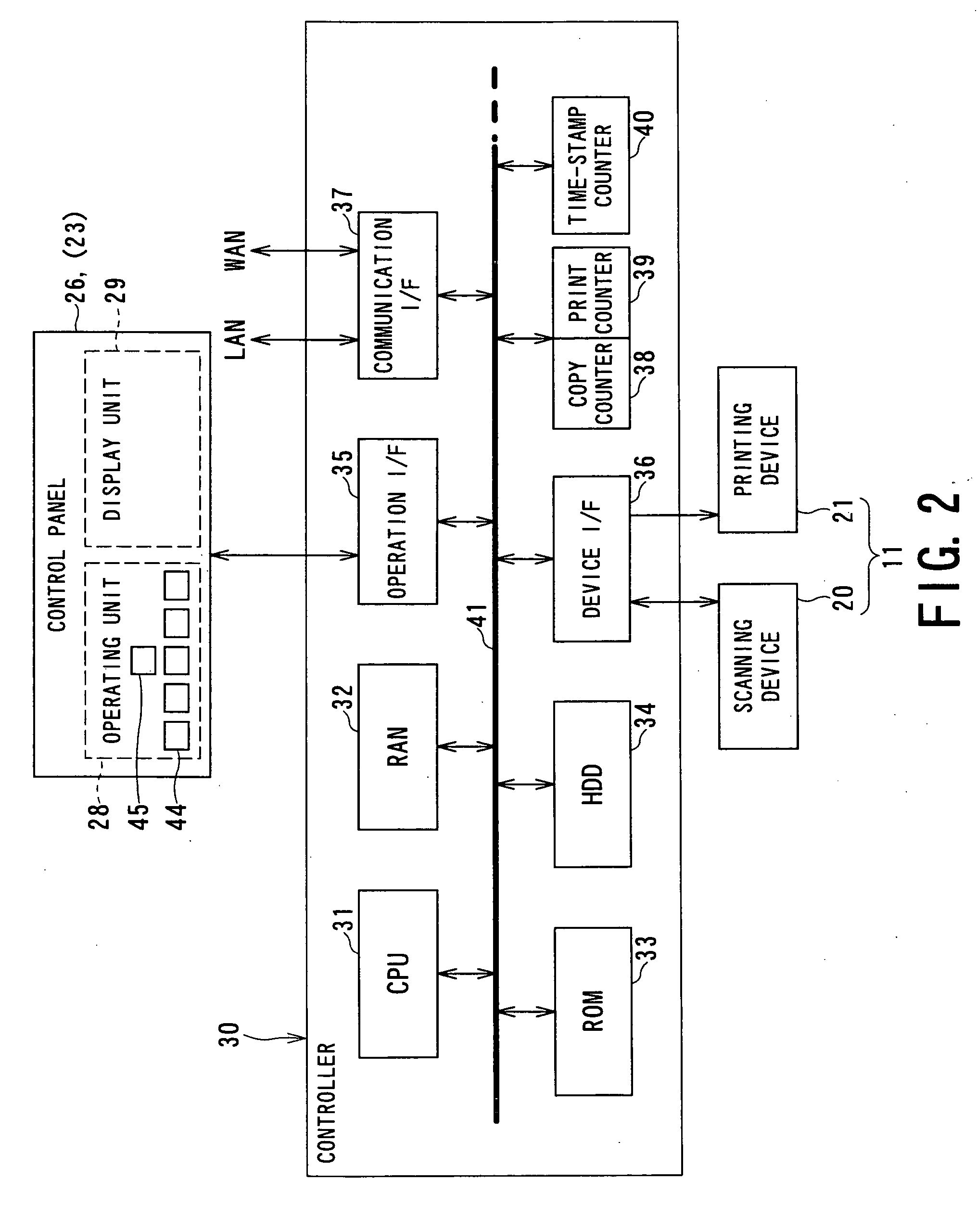

Device management system

InactiveUS20060221405A1The process is convenient and fastSmooth managementDigital data protectionOffice automationElectronic formPaper document

A device management system includes one or a plurality of scanning devices for reading and converting a document image of a contract document, an approval document, a receipt, or the like into electronic form to generate scanned document data; a time-stamping server for adding a time stamp to the scanned document data; a time-stamp counter included in each of the scanning devices for counting the number of times the time stamp is used; a document management server for receiving and storing the time-stamped scanned document data; a control panel for causing one of the scanning devices to perform scanning operation; and an administrative PC connected to each of the scanning devices and collectively managing the number of times the time stamp is used by the scanning devices.

Owner:KK TOSHIBA +1

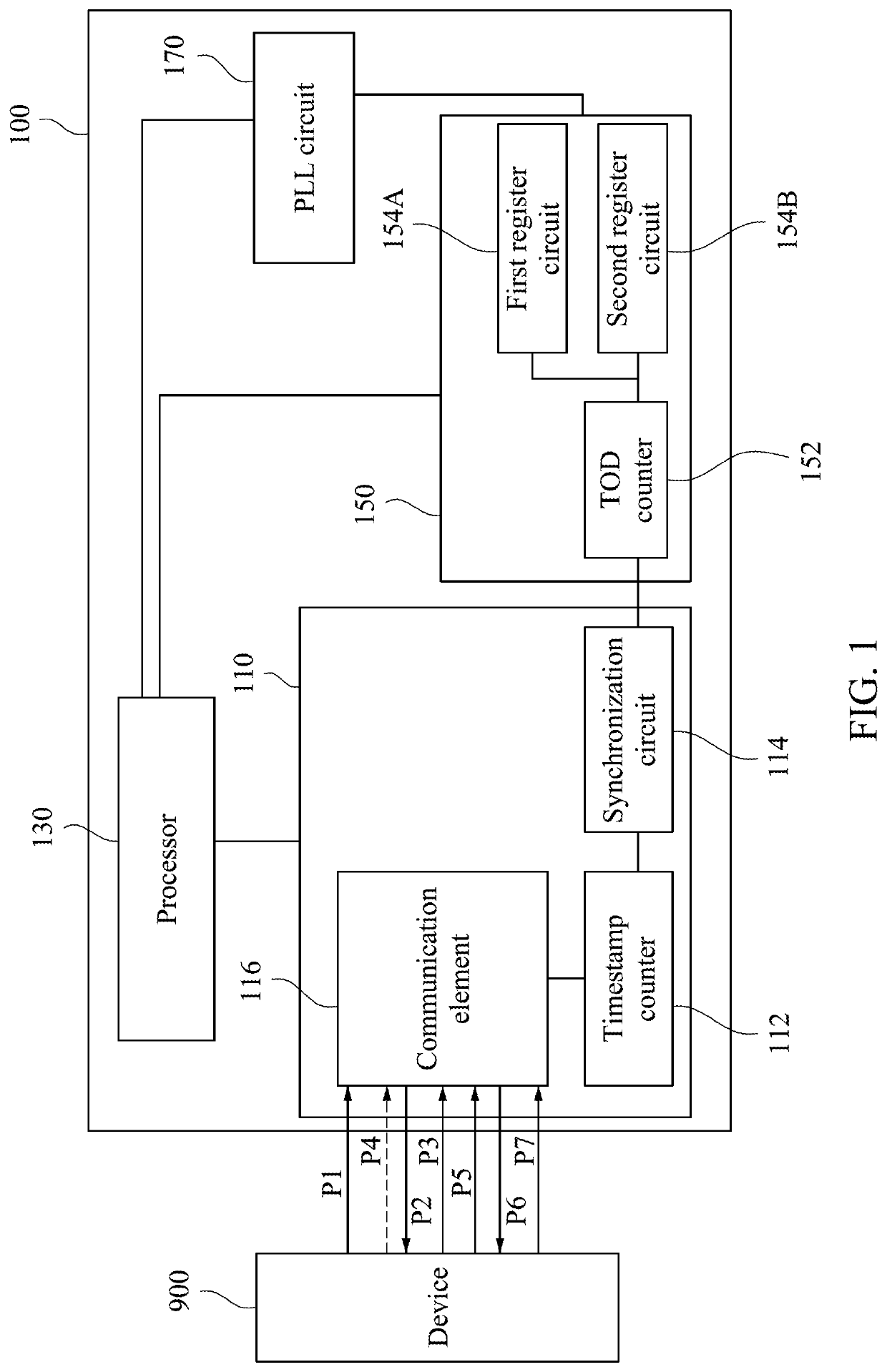

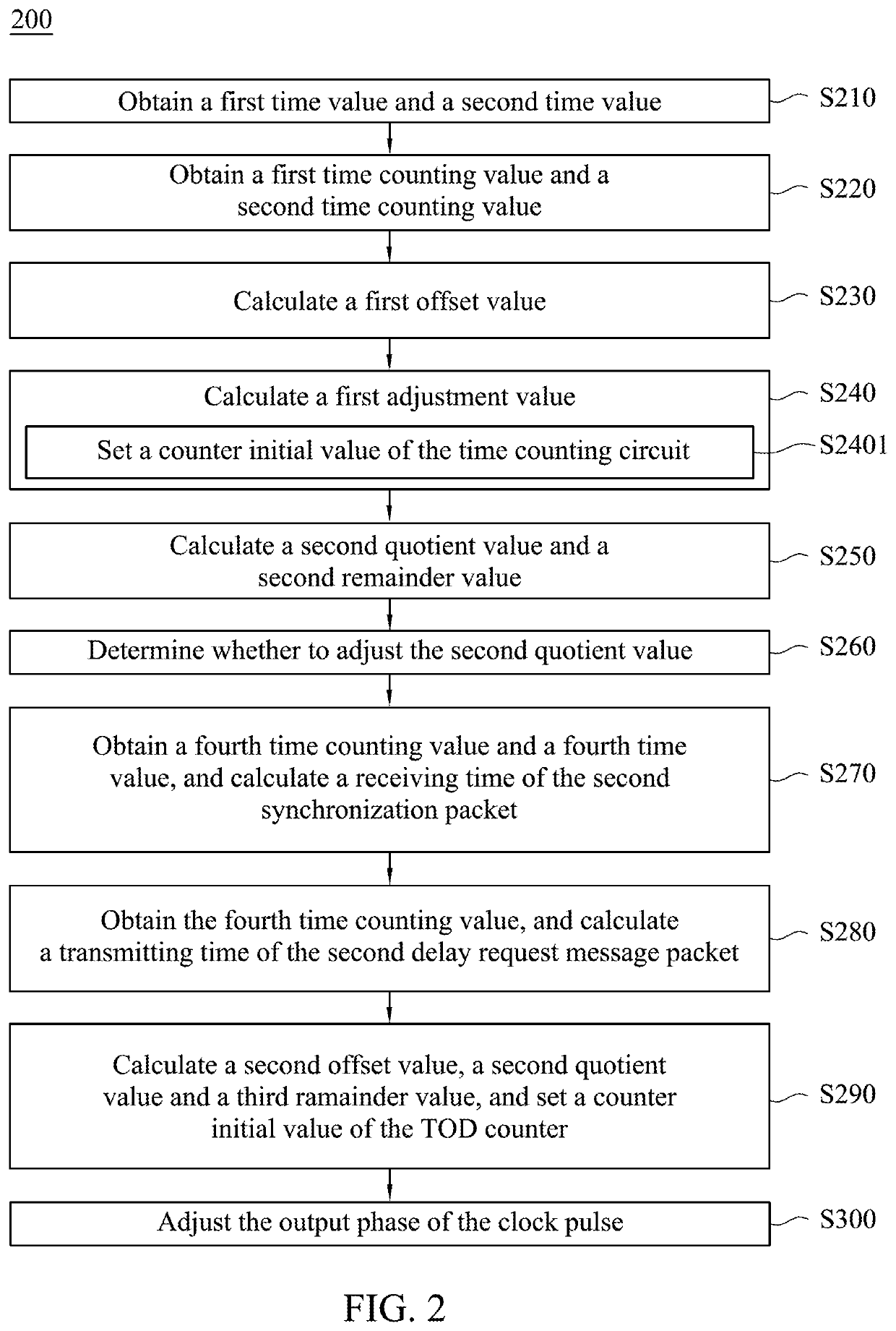

Time synchronization device and time synchronization method

ActiveUS20200127752A1Ensure correct executionTime synchronization can be performed more preciselyTime-division multiplexEngineeringComputer science

A time synchronization device performs a time synchronization process with a device that provides first and second time values. The time synchronization device includes a packet processing circuit, a time counting circuit, and a processor. The packet processing circuit includes a timestamp counter having an N-bit length, and the packet processing circuit provides first to third time counting values. The processor calculates the first offset value based on the first and second time values and the first and second time counting values; calculates the first adjustment value based on the first offset value and the reciprocal of the frequency of the time counting circuit; calculates a second quotient value and a second remainder value based on the first adjustment value and the N-bit length; and calculates the receiving time of the second synchronization packet based on the N-bit length, the second quotient value, and the third time counting value.

Owner:ACCTON TECHNOLOGY CORPORATION

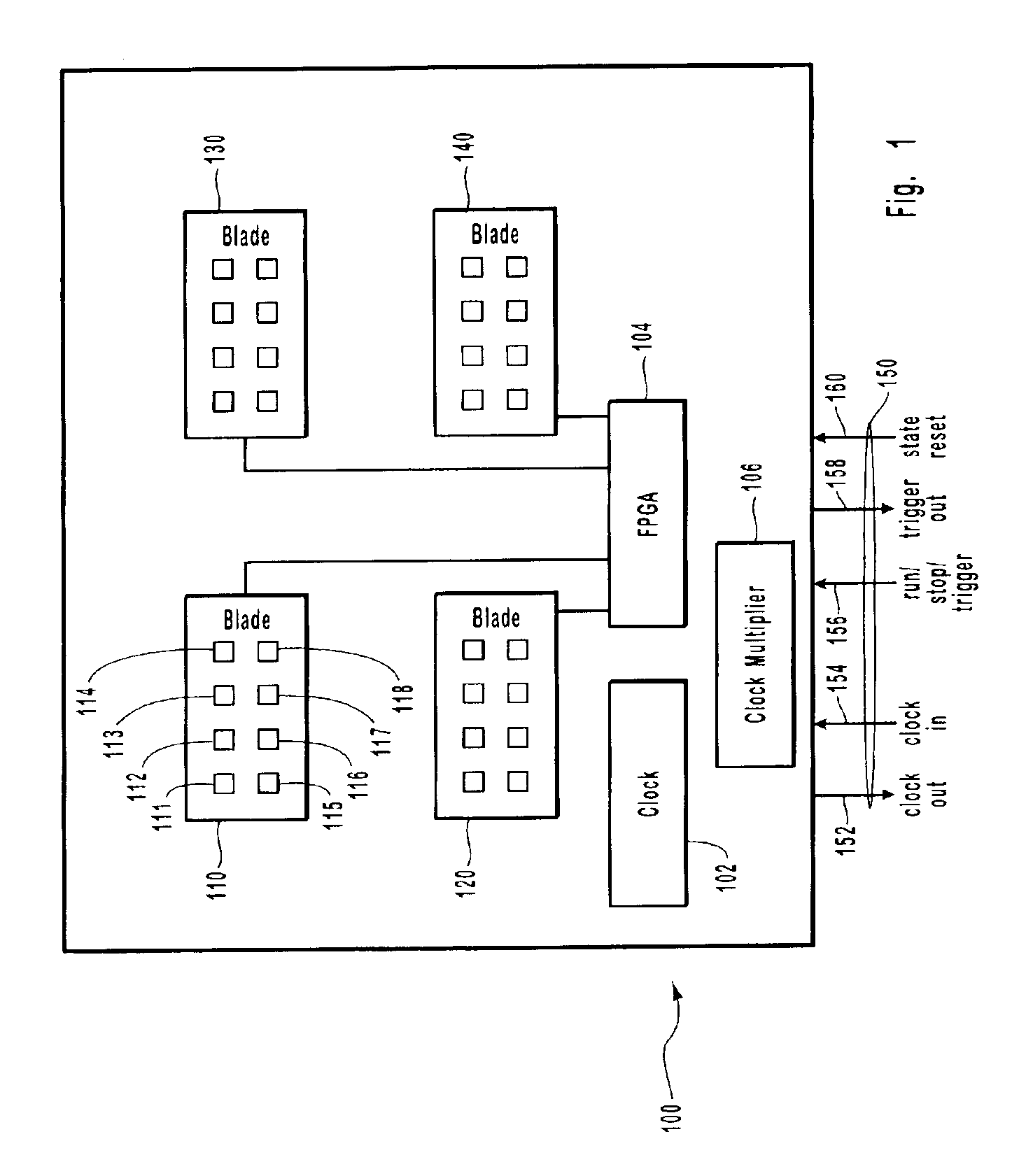

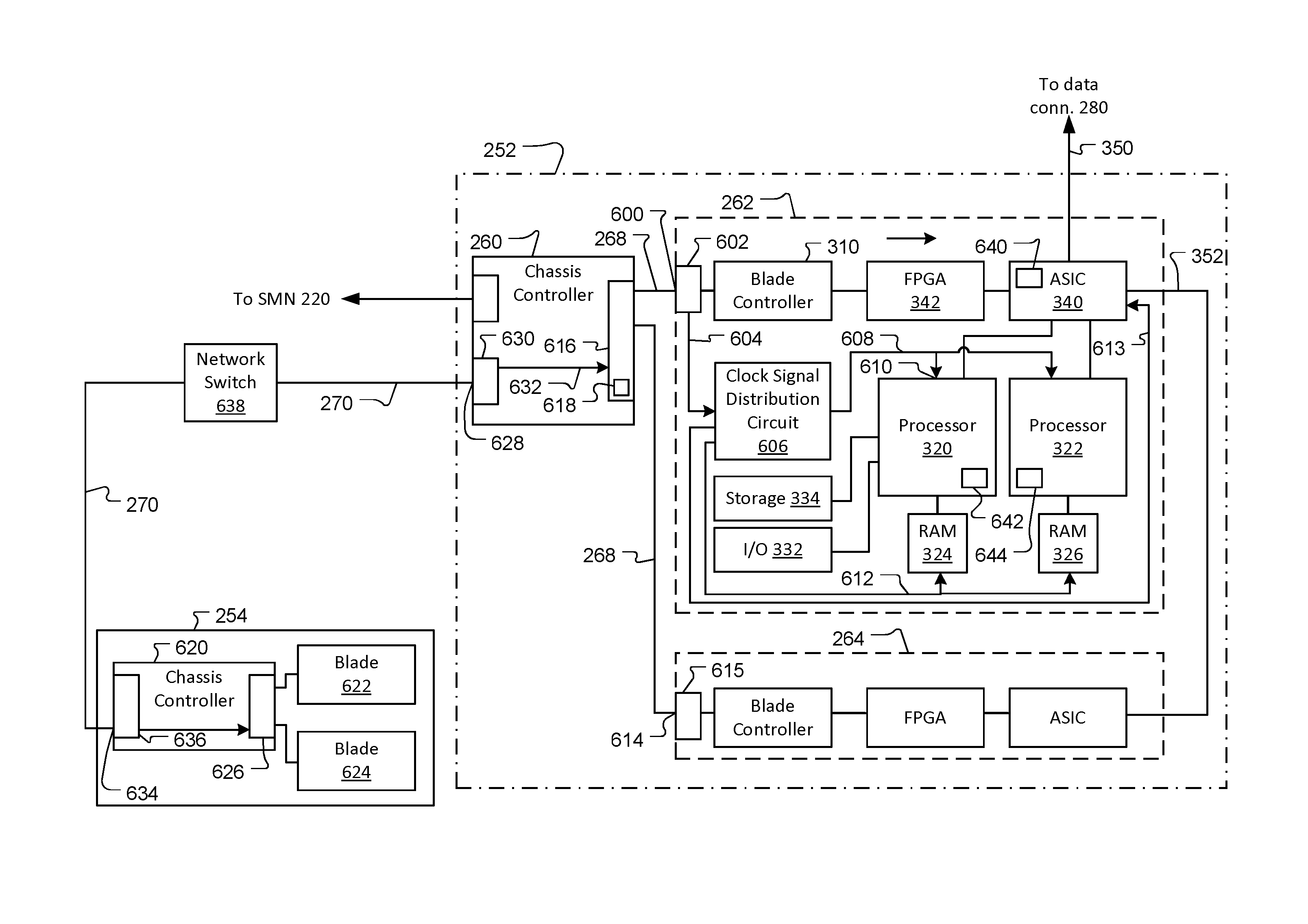

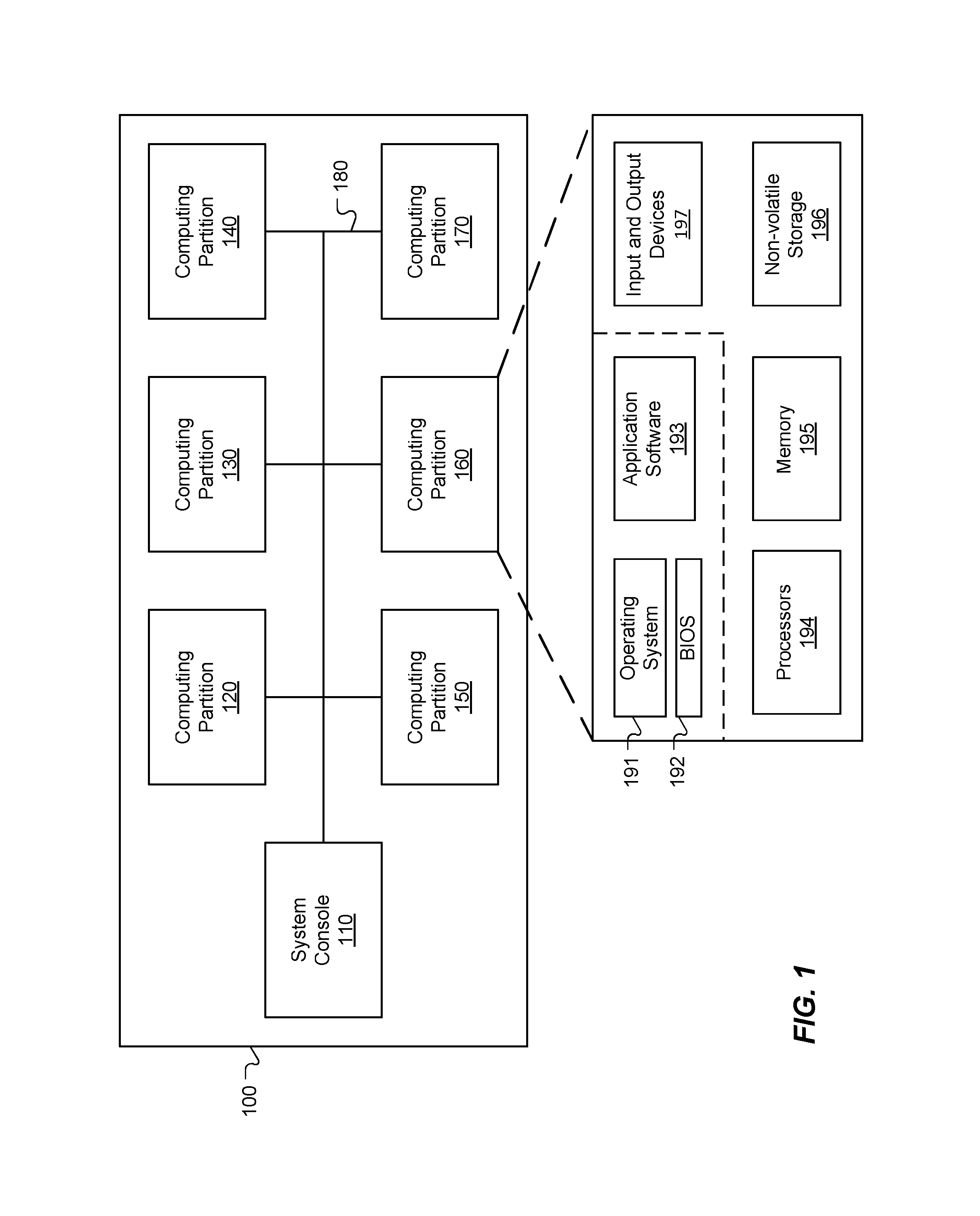

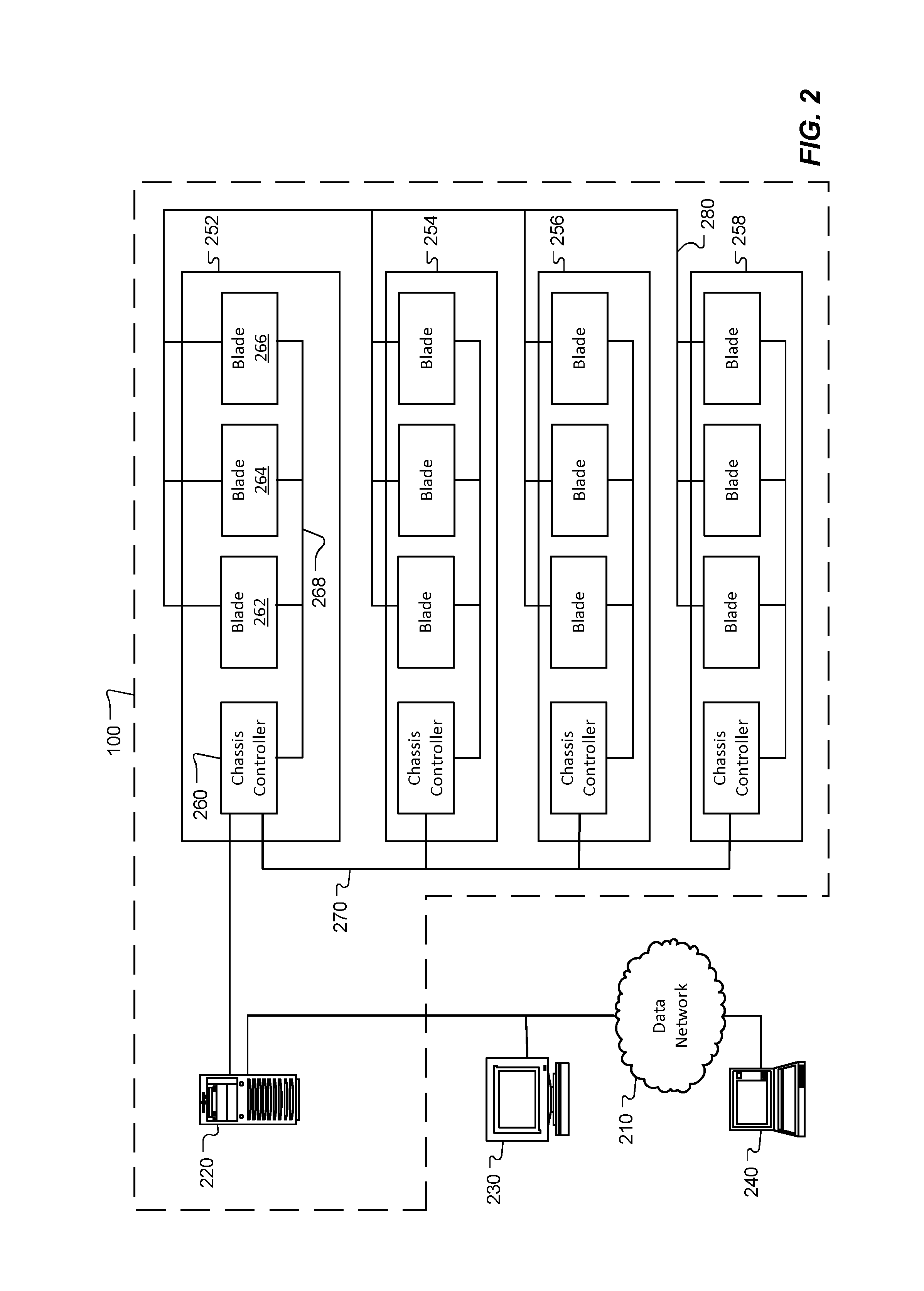

Global synchronous clock circuit and method for blade processors

ActiveUS9104343B2Time-division multiplexGenerating/distributing signalsCommunications systemComputer science

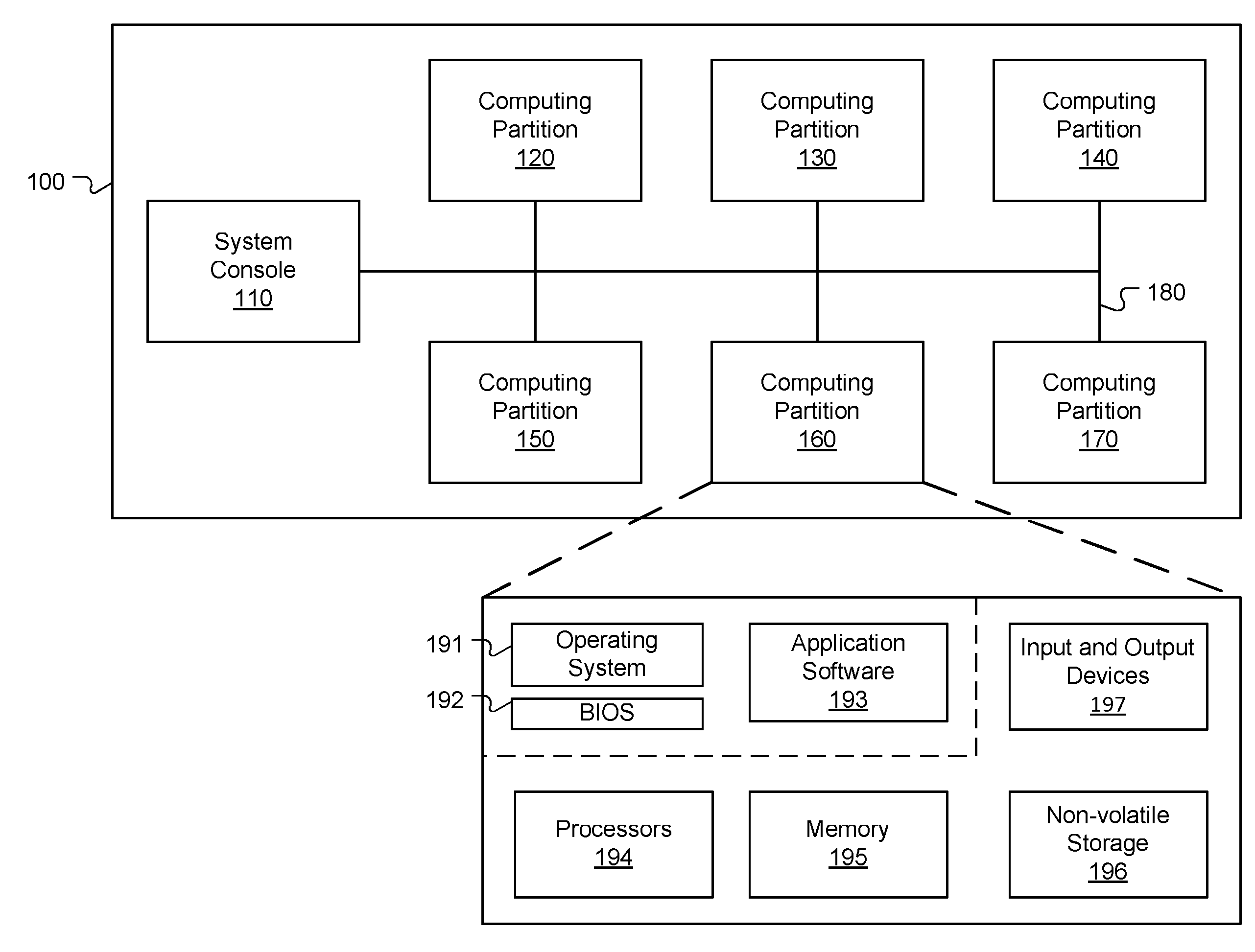

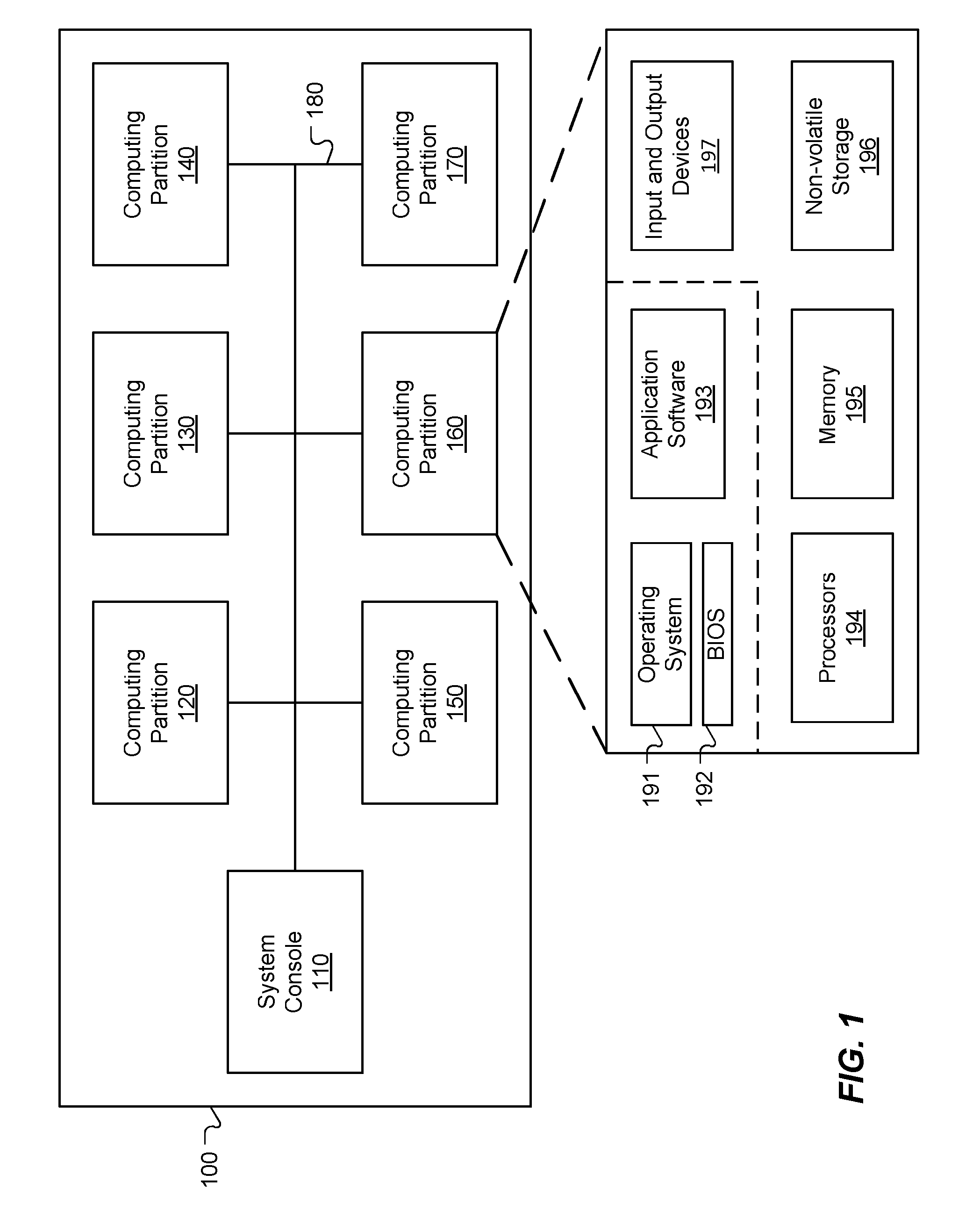

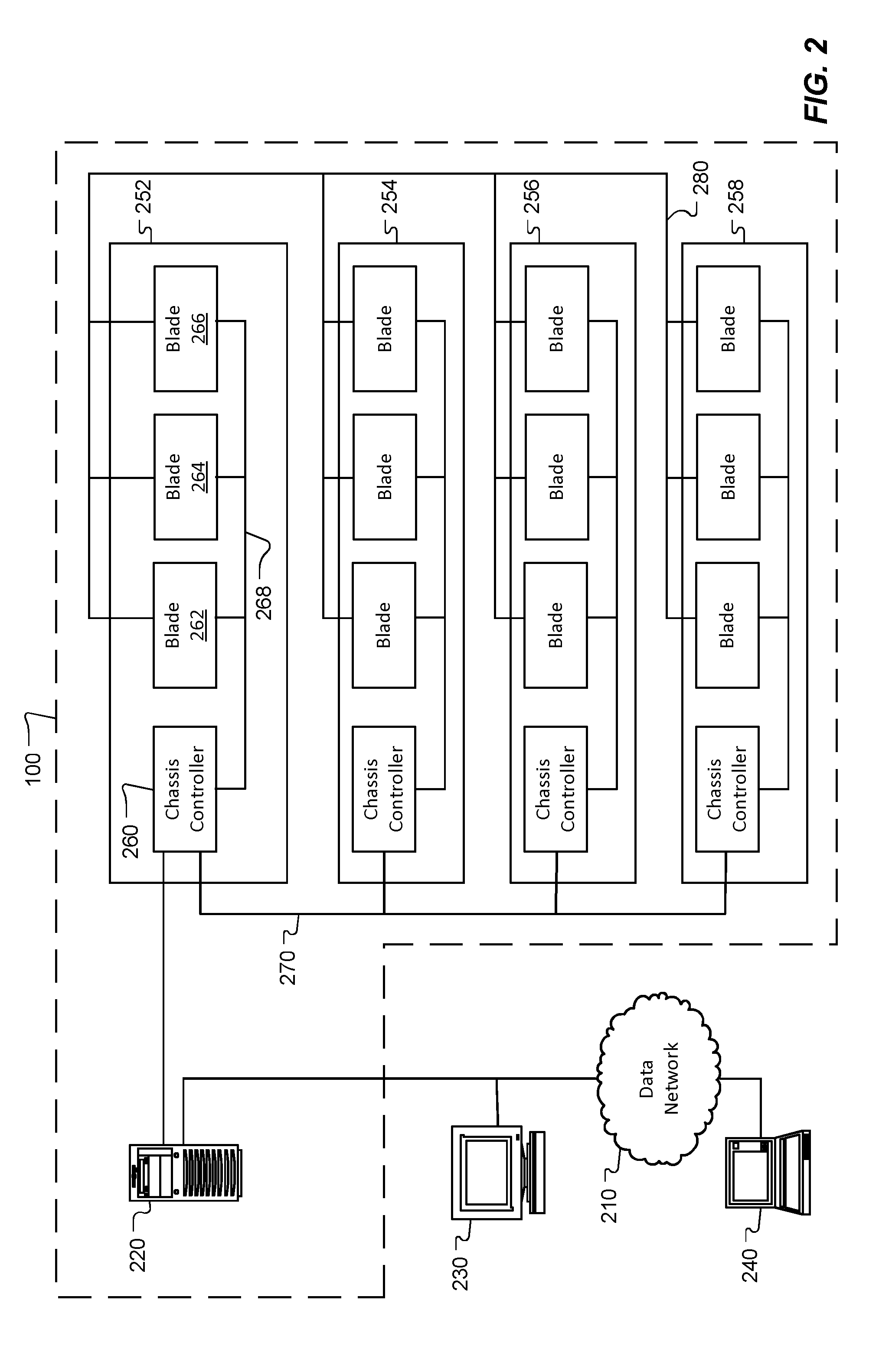

Processor clock signals are generated for each processor in a HPC system, such that all the processor clock signals are of the same frequency. Furthermore, as part of a startup (boot) procedure, a process sets all time stamp counters (TSCs) of the processors, such they indicate identical times. Each blade of the HPC system recovers a recovered clock signal from a synchronous communication network, to which the blade is coupled. The blade generates a processor clock from the recovered clock signal and provides the processor clock to processor(s) on the blade. Each chassis is coupled to a second, system-wide, synchronous communication network, and each chassis synchronizes its chassis synchronous communication network with the system-wide synchronous communication system. Thus, all the processor clock signals are generated with the same frequency.

Owner:HEWLETT-PACKARD ENTERPRISE DEV LP

Consistent distributed timestamp counters

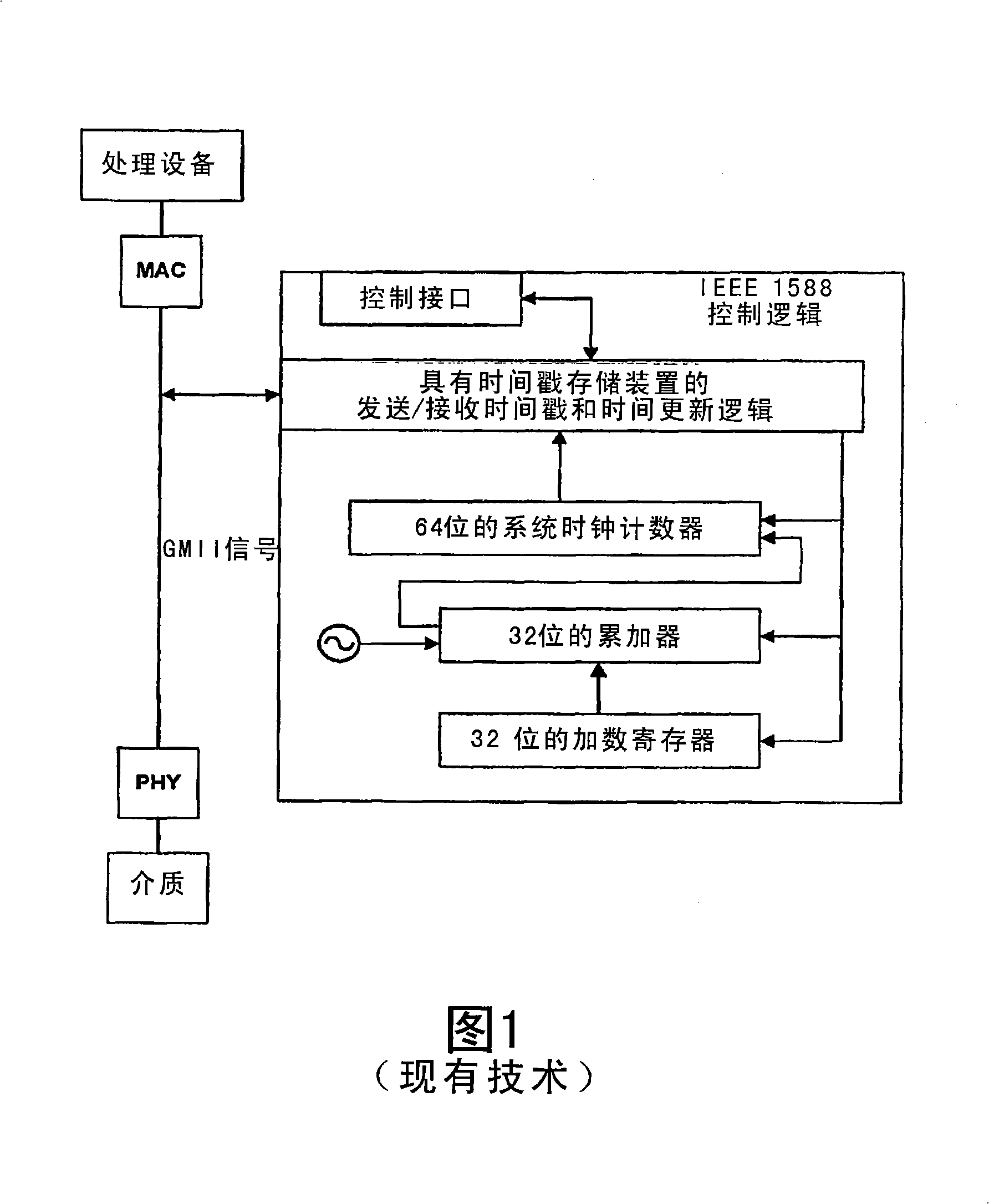

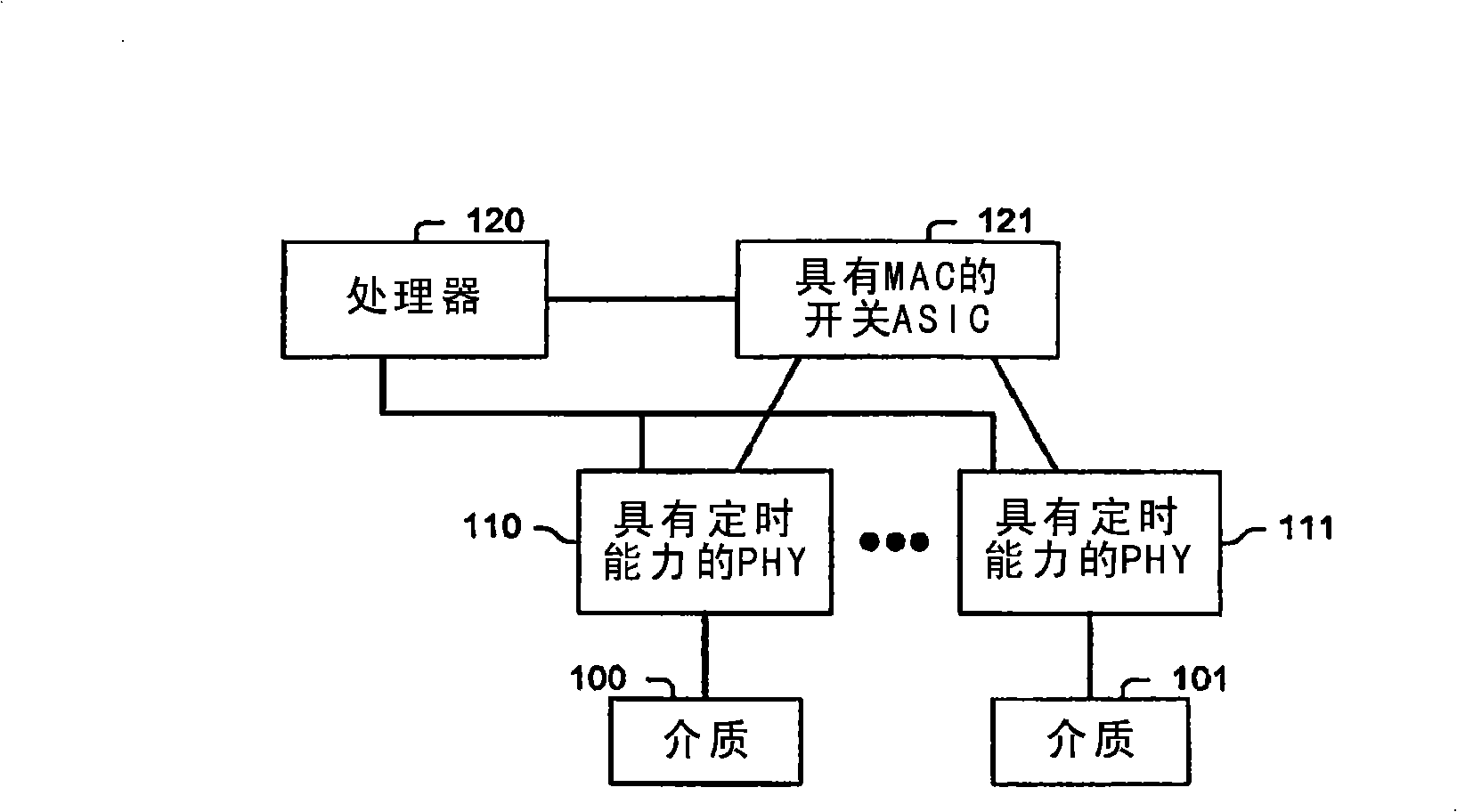

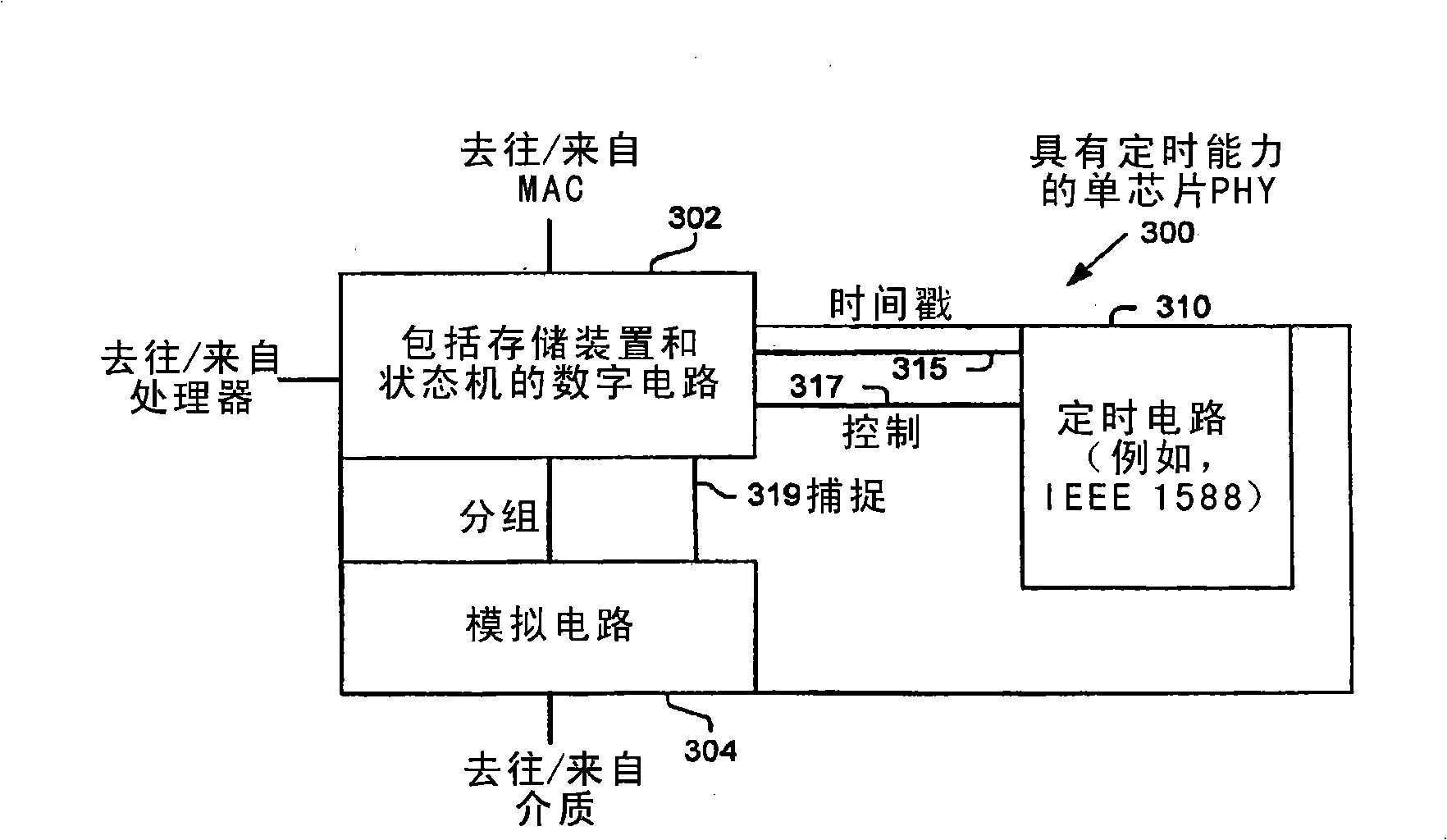

When timestamp counters are distributed among multiple physical devices, variances in their timestamp values can occur, such as, but not limited to those cause by variances among clocks in these different devices, different routing delays, different components, etc. These differences may be same, but still not allow high enough precision, especially as packet and processing rates continue to increase (which also causes clocking rates of devices to increase). One implementation distributes a time advance signal to each of these devices, which each device independently uses to determine when to advance its timestamp counter in response to its clock signal. These timestamps may be generated according to IEEE 1588 Standard for a Precision Clock Synchronization Protocol for Networked Measurement and Control Systems; and / or Physical Layer Transceivers (PHYs) may be disposed in each of the different physical devices.

Owner:CISCO TECH INC

Global Synchronous Clock

ActiveUS20140281656A1Time-division multiplexGenerating/distributing signalsCommunications systemComputer science

Processor clock signals are generated for each processor in a HPC system, such that all the processor clock signals are of the same frequency. Furthermore, as part of a startup (boot) procedure, a process sets all time stamp counters (TSCs) of the processors, such they indicate identical times. Each blade of the HPC system recovers a recovered clock signal from a synchronous communication network, to which the blade is coupled. The blade generates a processor clock from the recovered clock signal and provides the processor clock to processor(s) on the blade. Each chassis is coupled to a second, system-wide, synchronous communication network, and each chassis synchronizes its chassis synchronous communication network with the system-wide synchronous communication system. Thus, all the processor clock signals are generated with the same frequency.

Owner:HEWLETT-PACKARD ENTERPRISE DEV LP

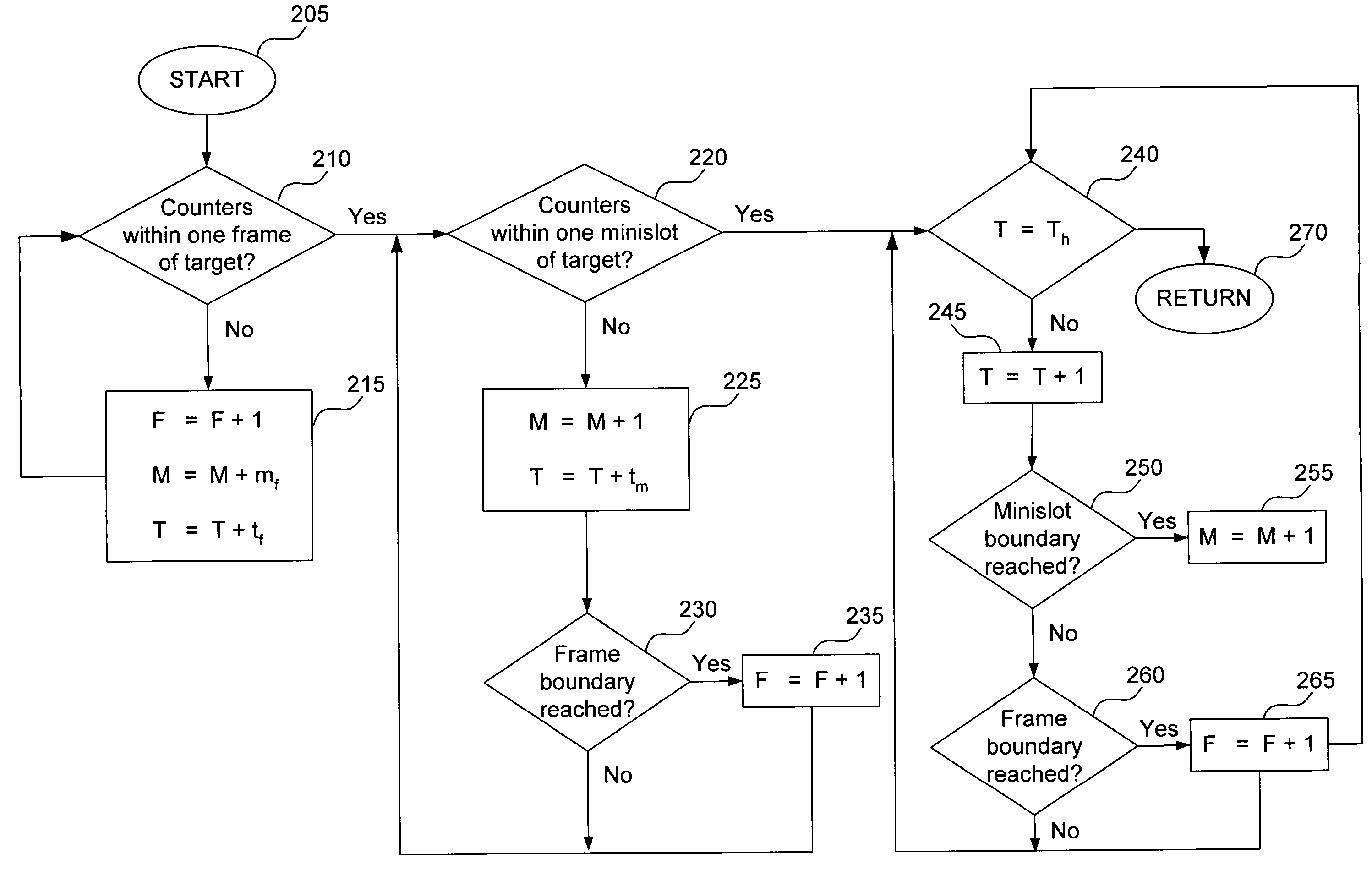

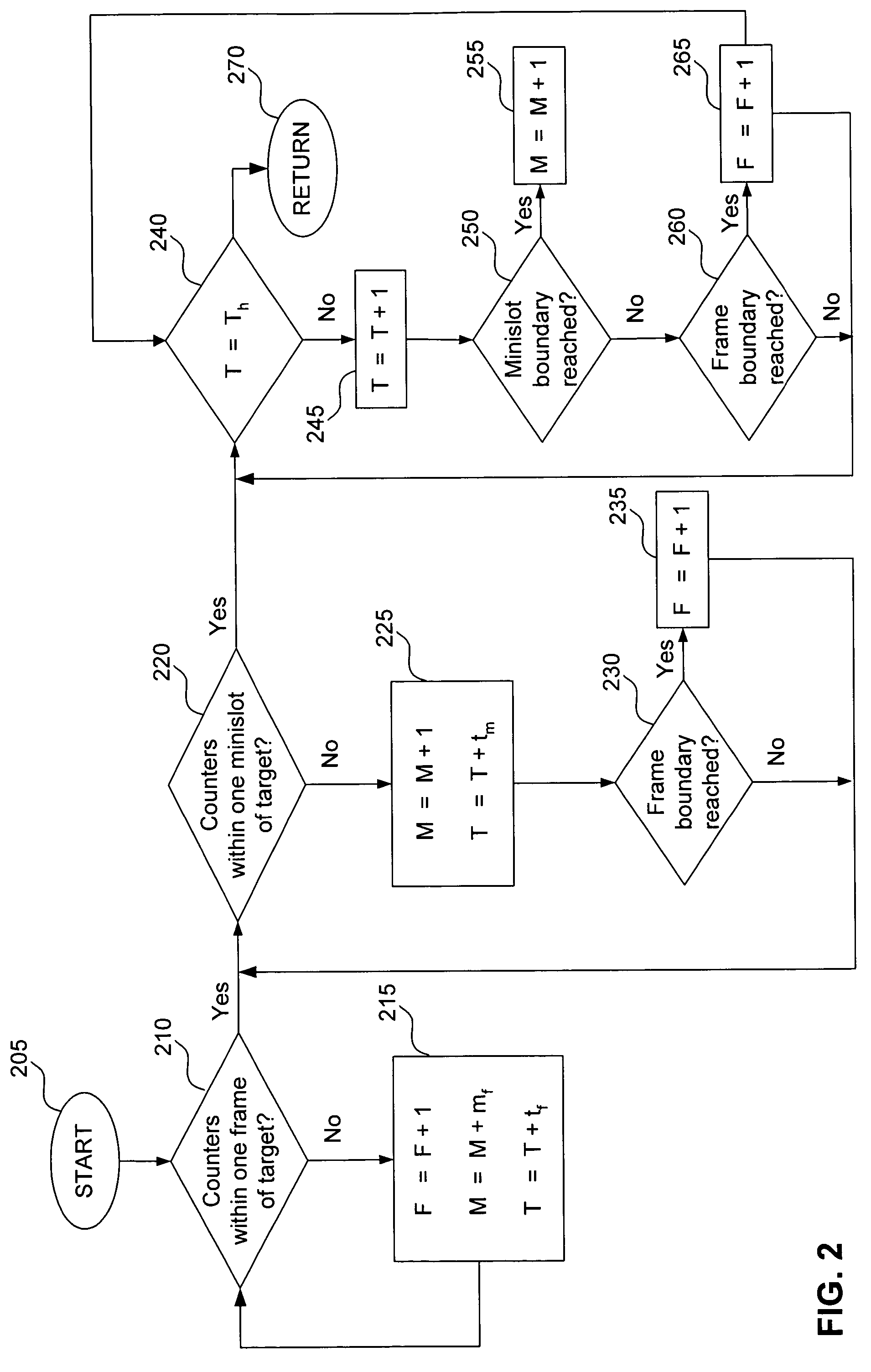

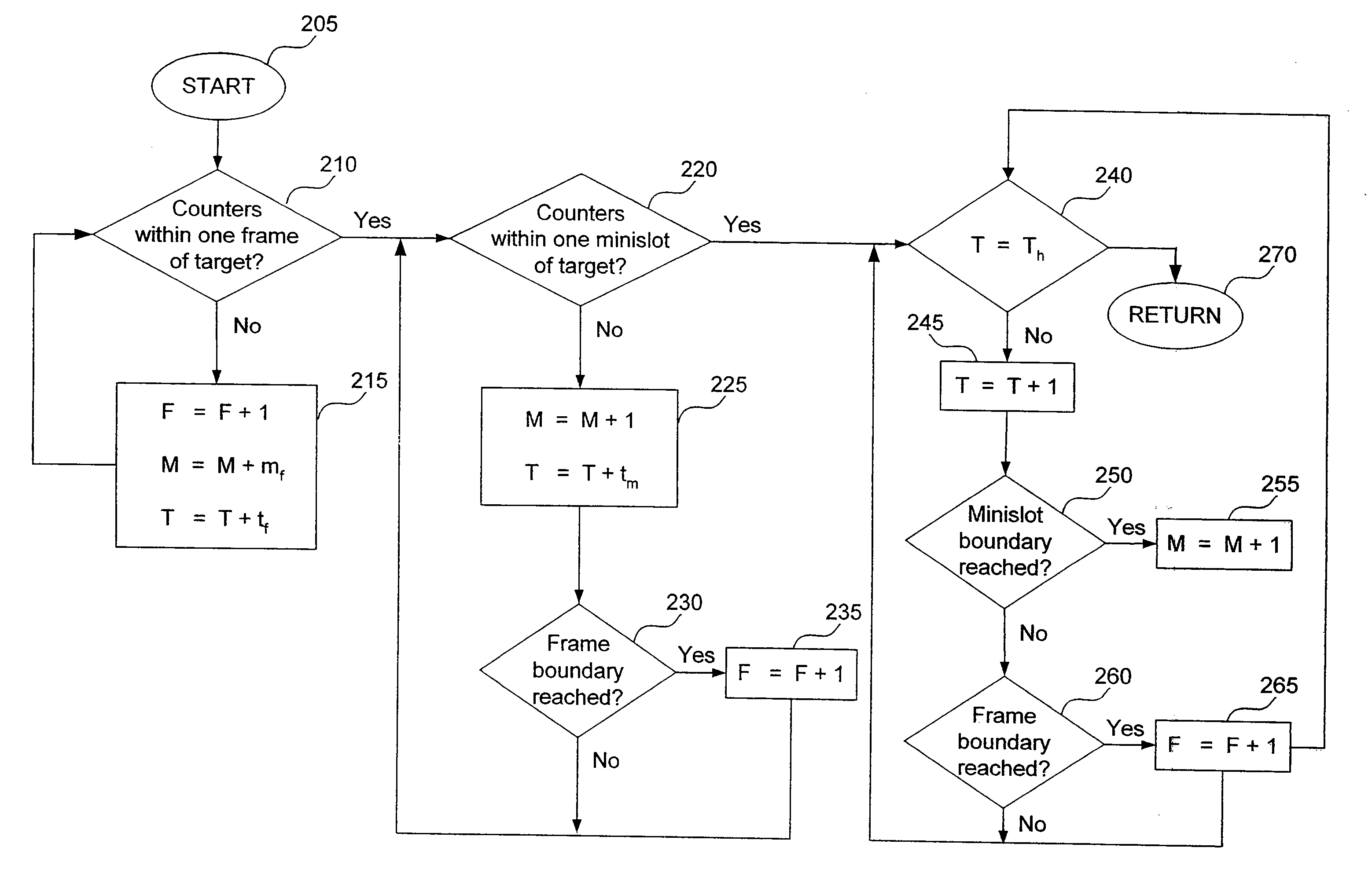

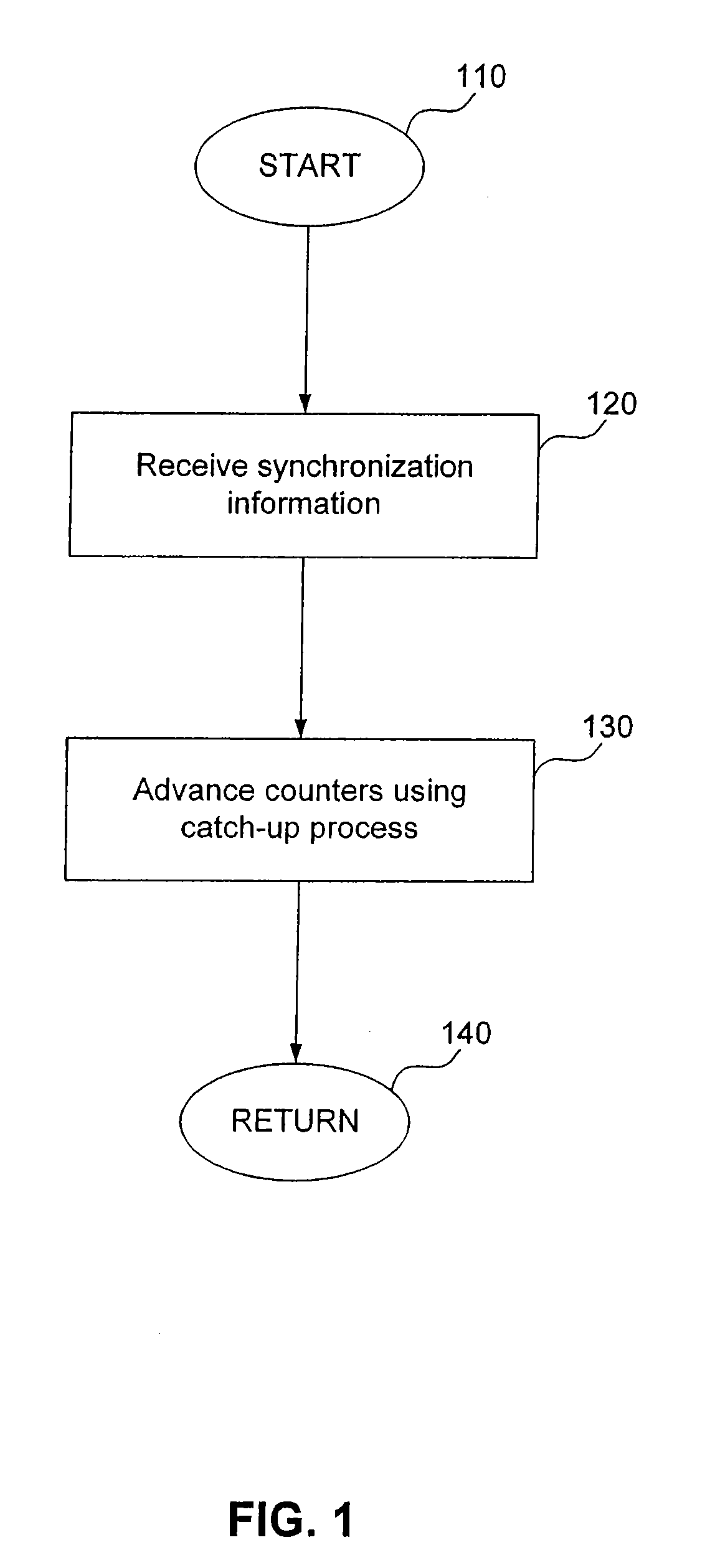

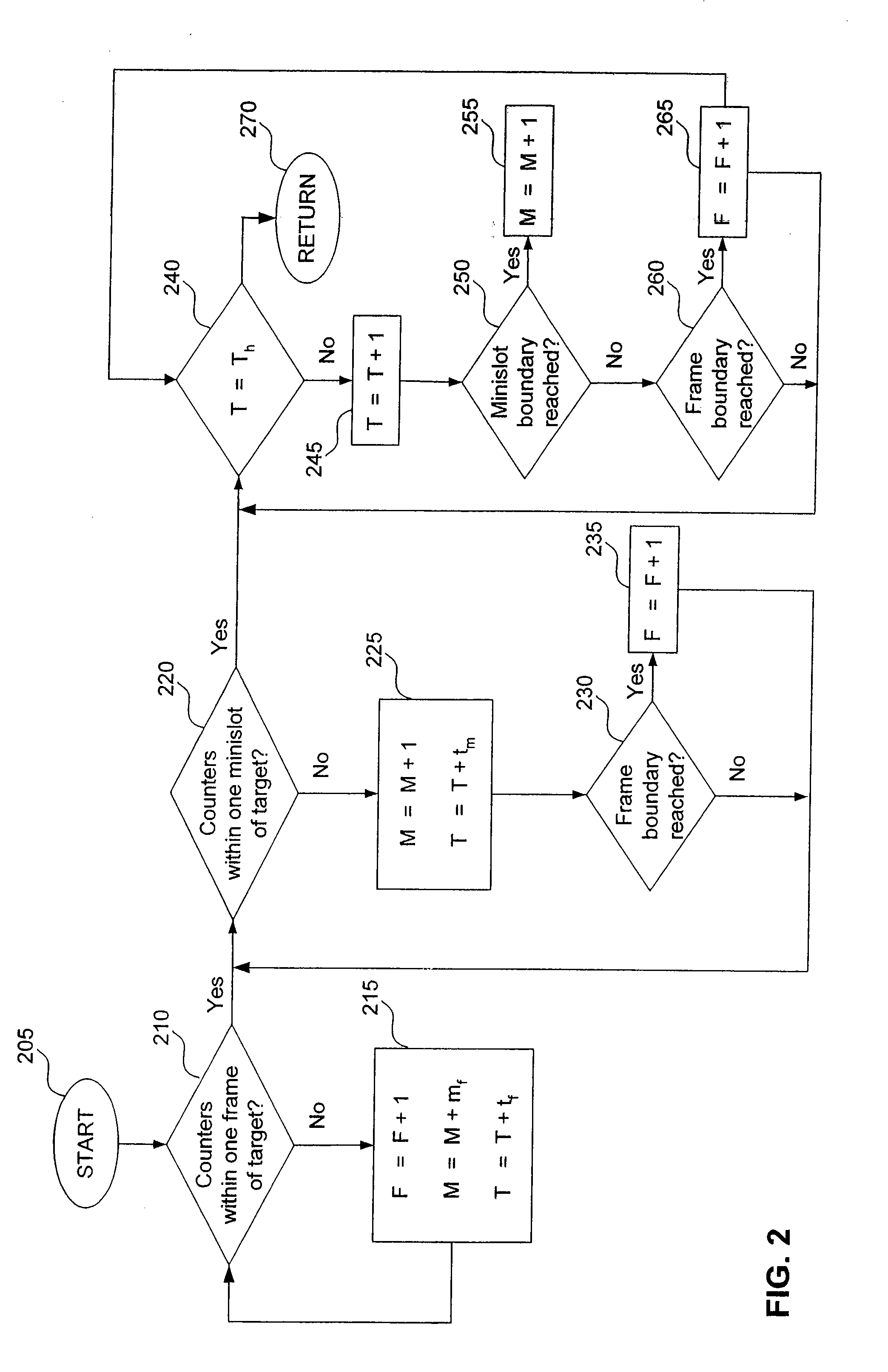

Method for synchronization through accelerated advance of counters

InactiveUS7260165B2Time-division multiplexTwo-way working systemsComputer hardwareTerminal equipment

A method for synchronizing counters in a terminal device, such as a cable modem in a DOCSIS-based system, with those of an administrative device, such as a headend. A cable modem advances its frame counter. With each increment of the frame counter, the cable modem's minislot counter advances by an amount equal to the number of minislots per frame. Likewise, with each increment of the frame counter, the cable modem's timestamp counter is incremented by the number of timestamps per frame. This continues until the counters at the cable modem are within one frame of the headend's counters. The minislot counter is then incremented. With each increment of the minislot counter, the timestamp counter is incremented by an amount equal to the number of timestamps per minislot. This continues until the cable modem's counters are within a minislot of the headend's counters. The timestamp counter is then incremented until the cable modem's counters match those of the headend.

Owner:AVAGO TECH WIRELESS IP SINGAPORE PTE

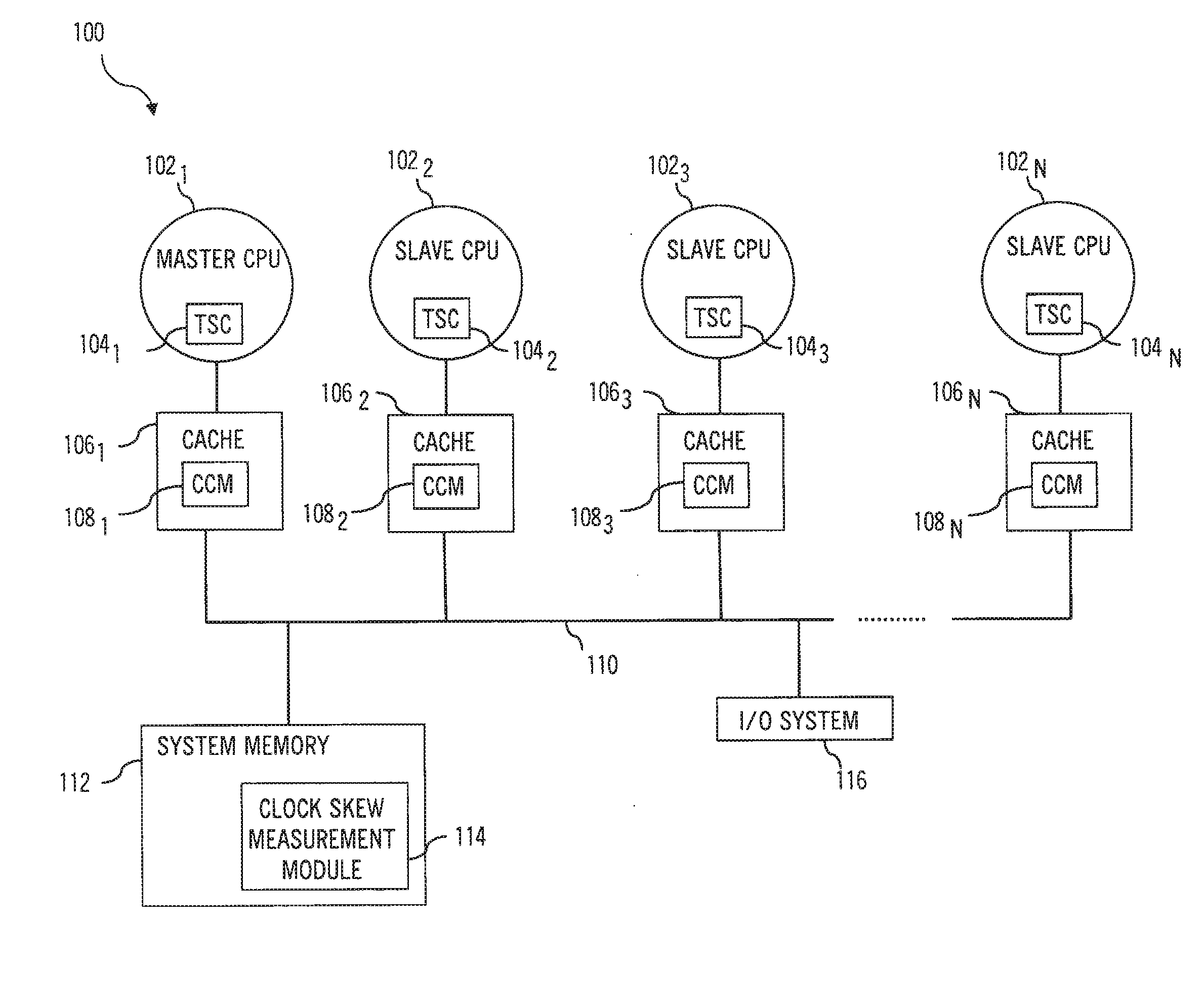

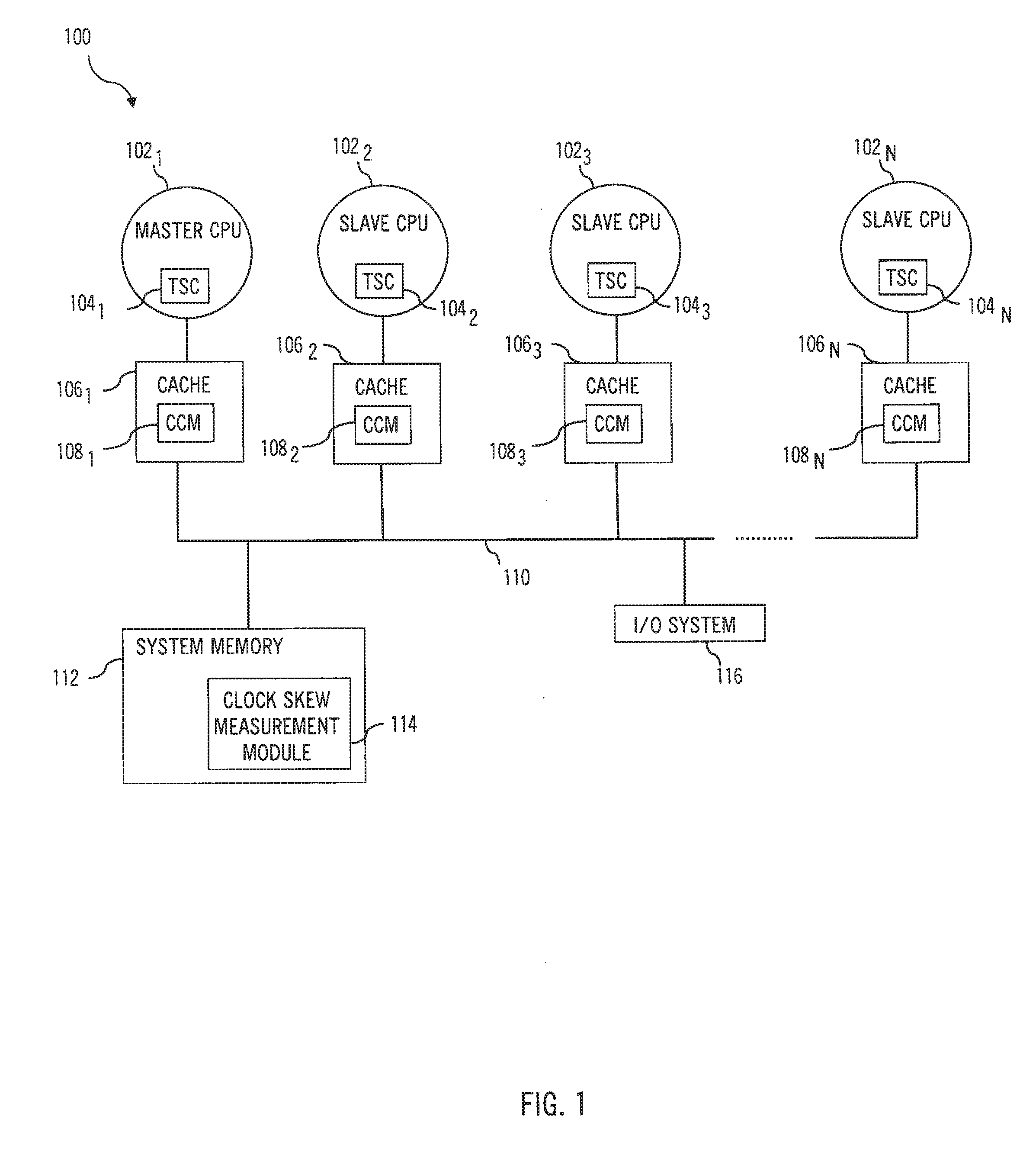

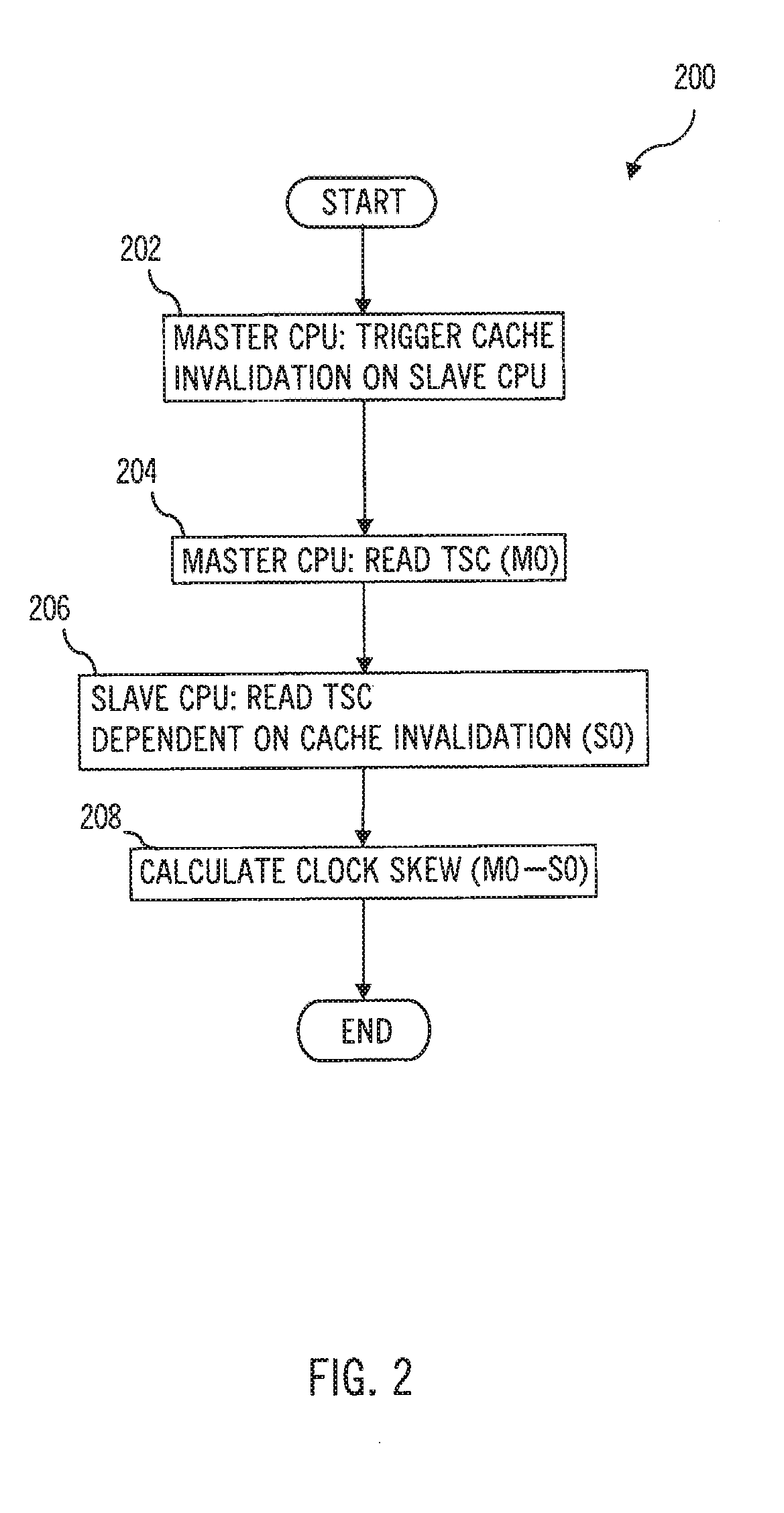

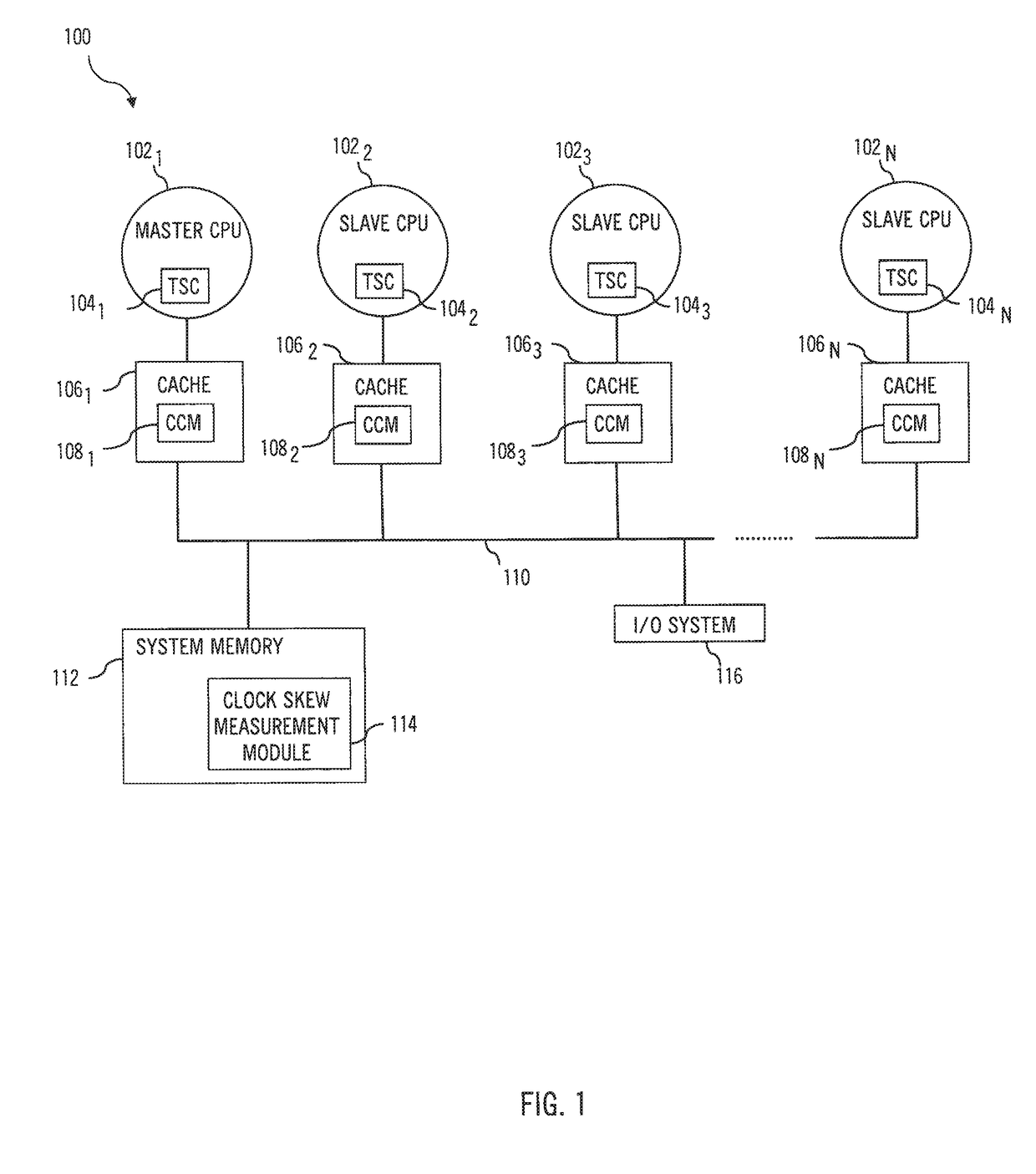

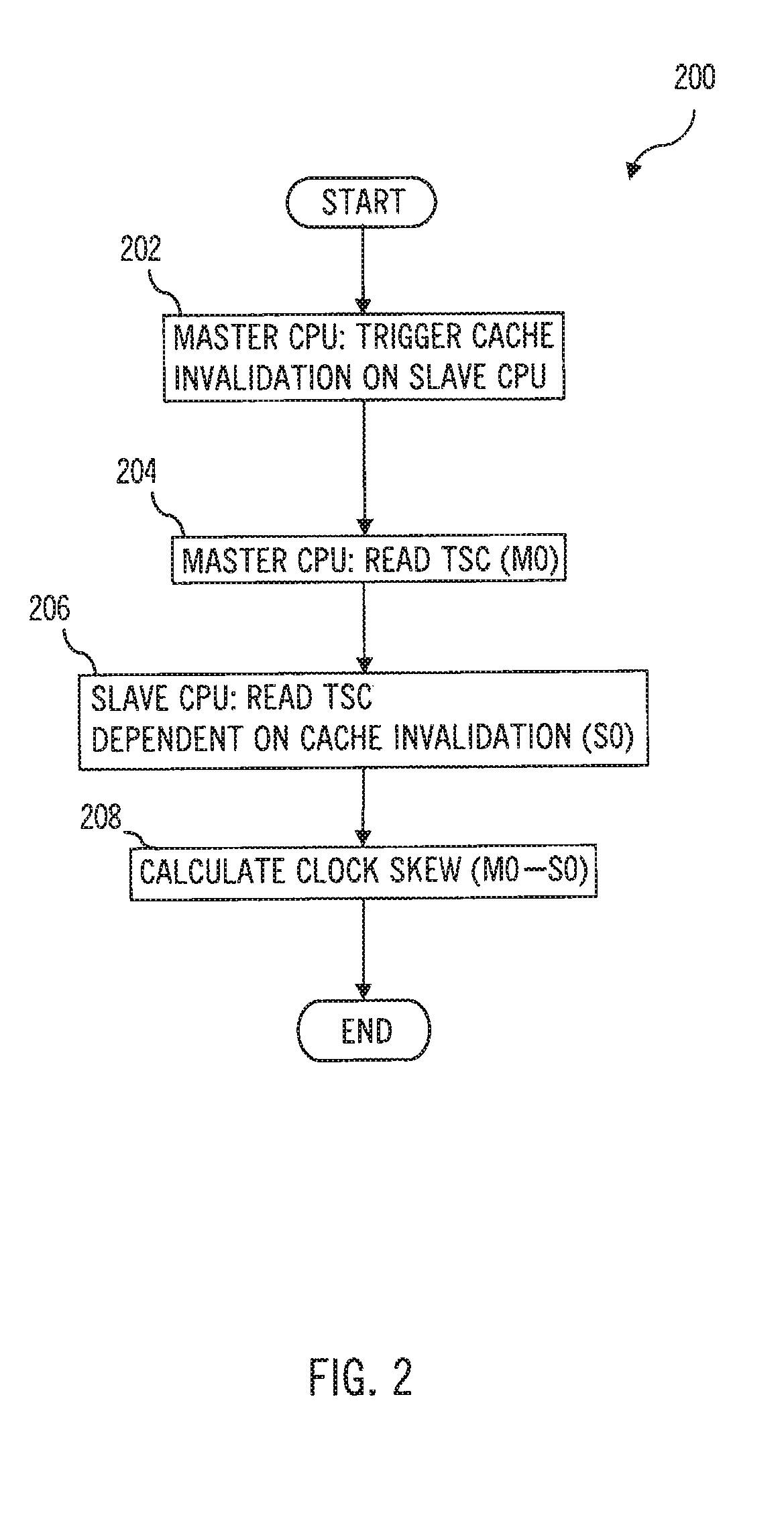

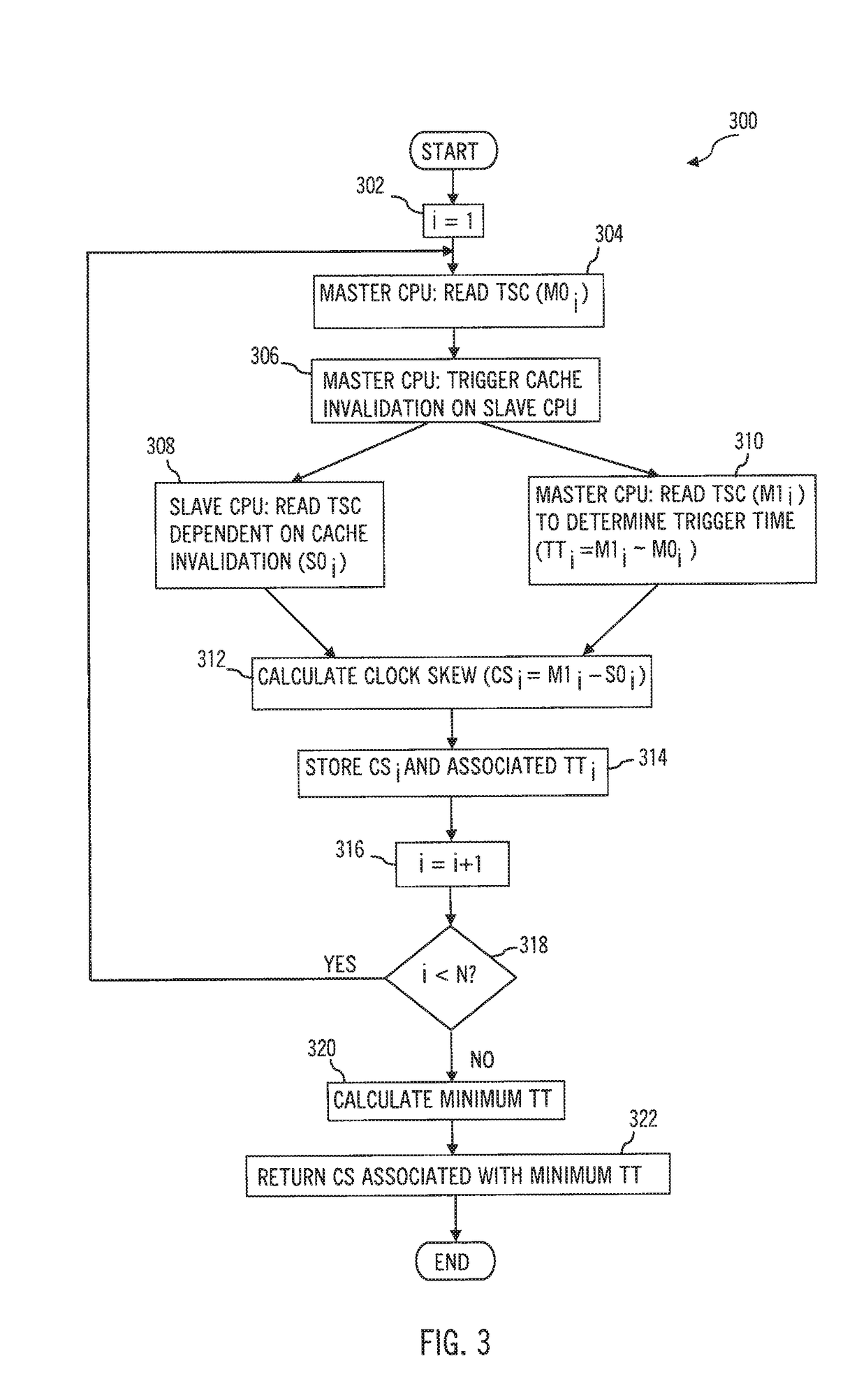

Clock skew measurement for multiprocessor systems

ActiveUS20100275053A1Accurate measurementIntroduces delayError detection/correctionMemory adressing/allocation/relocationMulti processorTime Stamp Counter

Systems and methods (“utility”) for providing more accurate clock skew measurements between multiple CPUs in a multiprocessor computer system by utilizing the cache control or management protocols of the CPUs in the multiprocessor system. The utility may utilize a time stamp counter (TSC) register of the CPUs in the multiprocessor computer system to detect the clock skew between the various CPUs in the system. Further, the delay between measurements of the TSC registers of the CPUs may be minimized by utilizing the features of the hardware cache control or management protocols of the computer system, thereby providing more accurate clock skew measurements.

Owner:ORACLE INT CORP

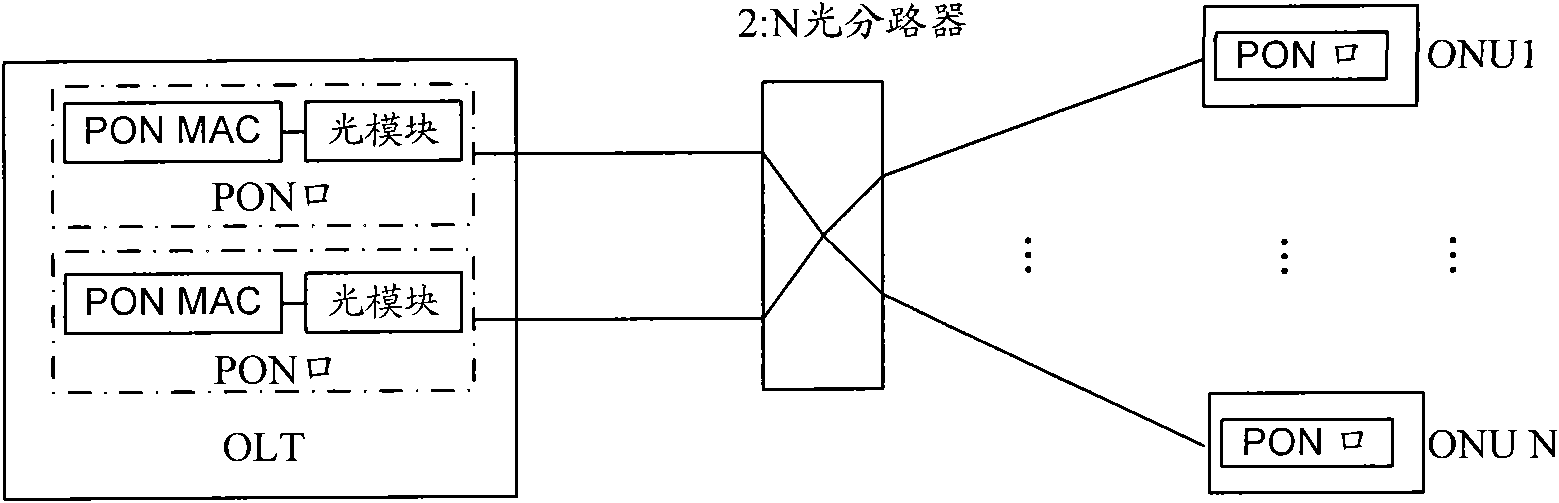

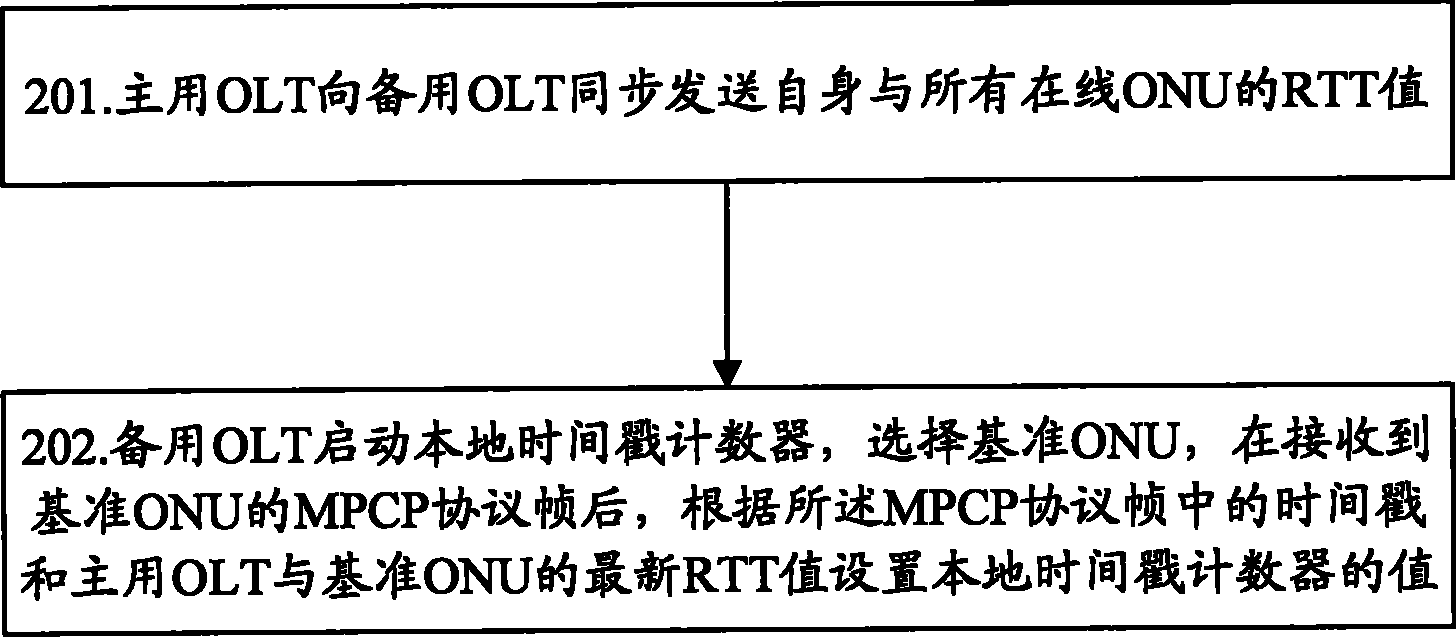

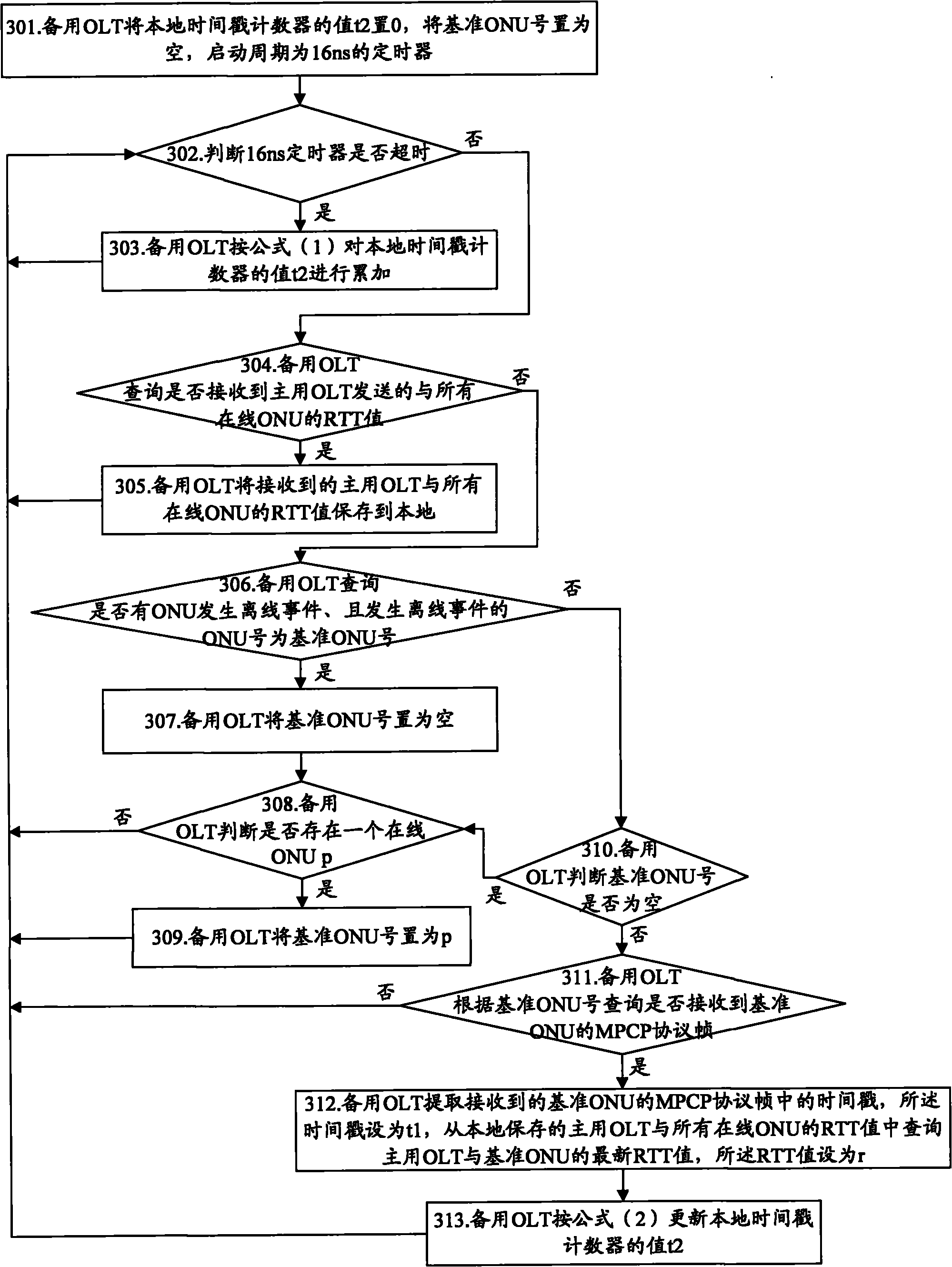

Method and system for realizing timestamp synchronization of active and standby optical line terminals

InactiveCN102377556APrevent offlineLower requirementMultiplex system selection arrangementsTime-division multiplexData synchronizationOptical network unit

The invention discloses a method for realizing the timestamp synchronization of an active optical line terminal (OLT) and a standby OLT. The method comprises that: the active OLT synchronously transmits round trip time (RTT) values with all online optical network units (ONU) to the standby OLT; and the standby OLT selects a reference ONU, and sets a value of a local timestamp counter according to a timestamp in a multipoint control protocol (MPCP) frame and an RTT value of the active OLT with the reference ONU after receiving the MPCP frame of the reference ONU. The invention simultaneously discloses a system for realizing the timestamp synchronization of the active and standby OLTs. By the scheme provided by the invention, timestamp counters of the active and standby OLTs in an Ethernet passive optical network (EPON) backbone optical fiber protection system can be effectively synchronized, and the offline state of the ONU caused by timestamp drift in handover can be avoided, thereby ensuring that the handover can be finished quickly. Moreover, requirements on the ONUs are relatively lower, and compatibility with all conventional ONU equipment can be achieved.

Owner:ZTE CORP

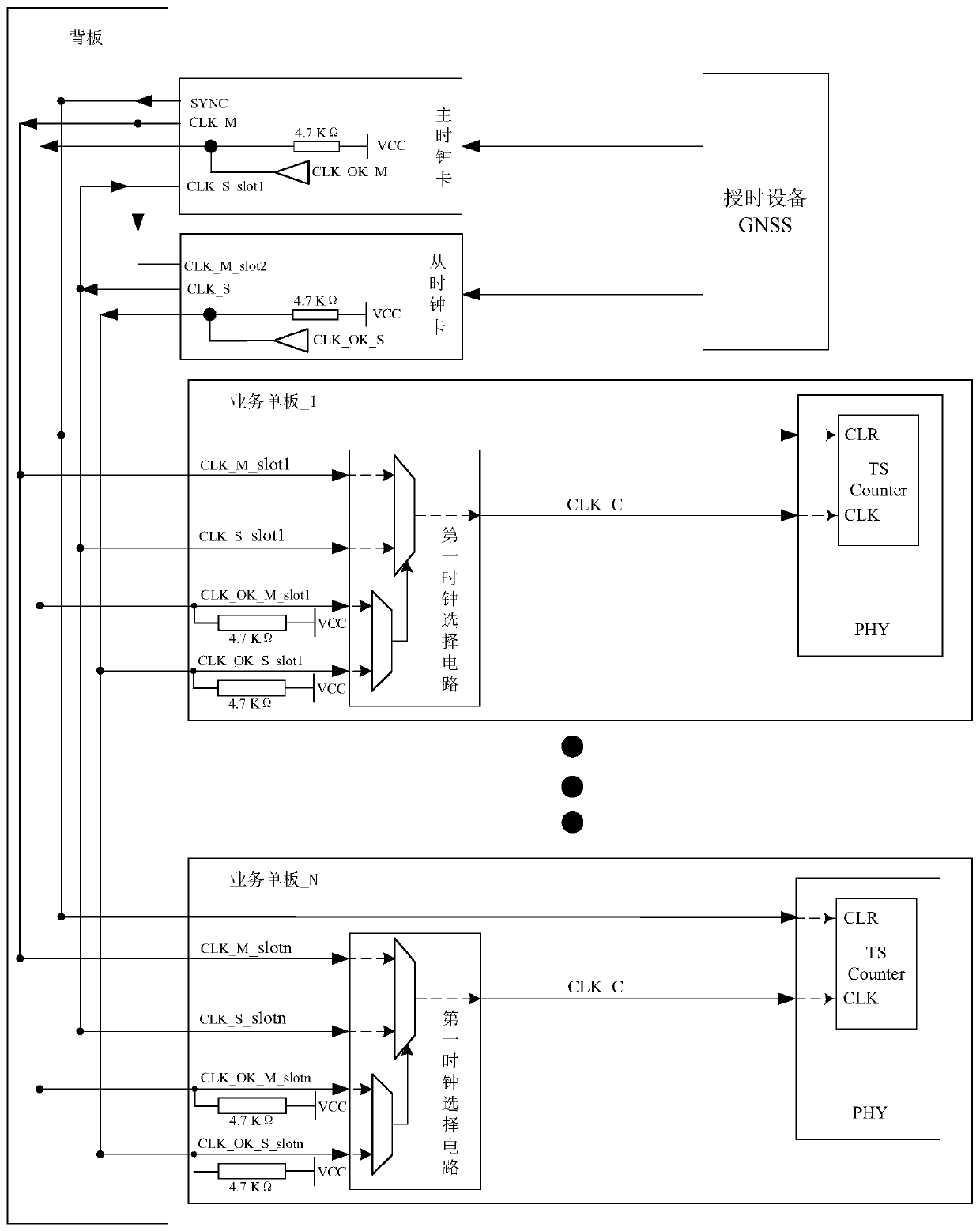

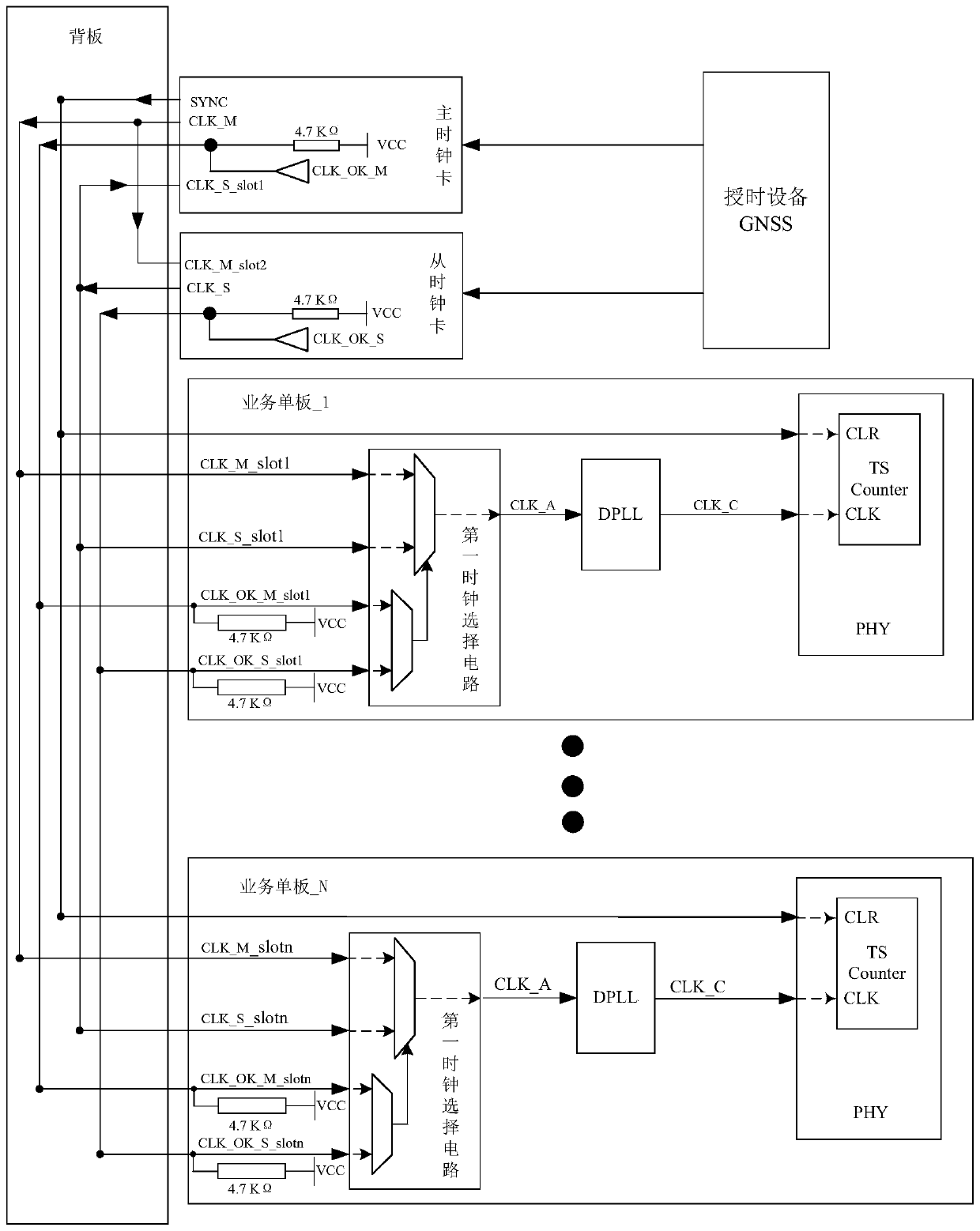

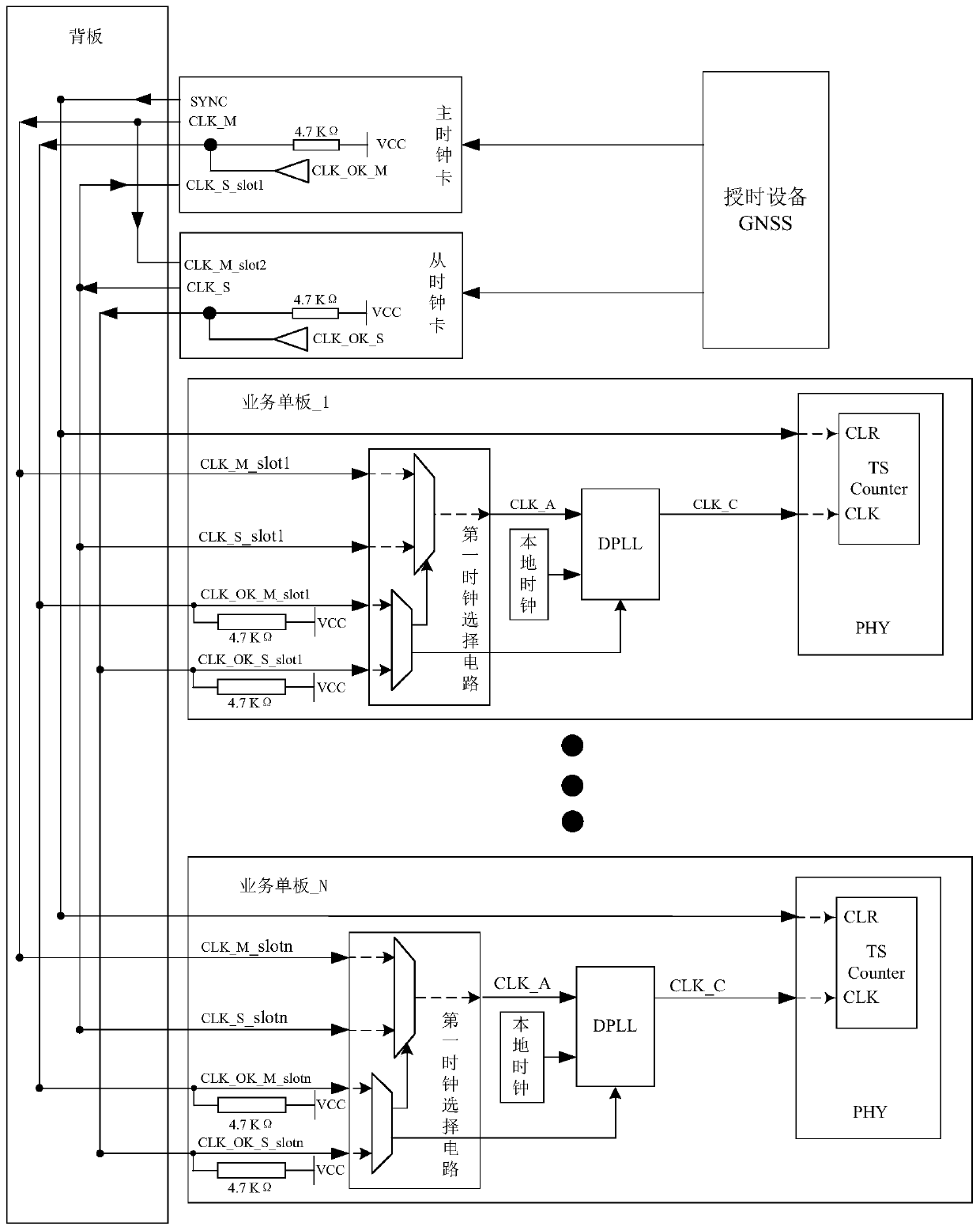

PTP clock synchronization system and clock synchronization method

PendingCN111181555AGuaranteed accuracyTroubleshoot valid clock signal inputPulse automatic controlSlave clockPHY

The invention discloses a PTP clock synchronization system. The system includes a master clock board and a slave clock board; a plurality of service single boards which are used for receiving a masterclock signal output by the master clock board and a slave clock signal output by the slave clock board; and a backboard which is used for forming signal connection leads among the master clock board,the slave clock board and the service single boards. Each service single board comprises a first clock selection unit used for determining one clock signal as a working clock signal according to thecurrent states of the master clock state signal and the slave clock state signal; and a digital phase-locked loop which is used for carrying out phase locking on the received working clock signal andthen generating an effective clock signal of a timestamp counter of the physical PHY chip. The invention also discloses a PTP clock synchronization method. According to the system and the method provided by the invention, a stable and effective clock signal can be provided for the timestamp counter of each service single board PHY chip in the clock board switching process.

Owner:RAISECOM TECH

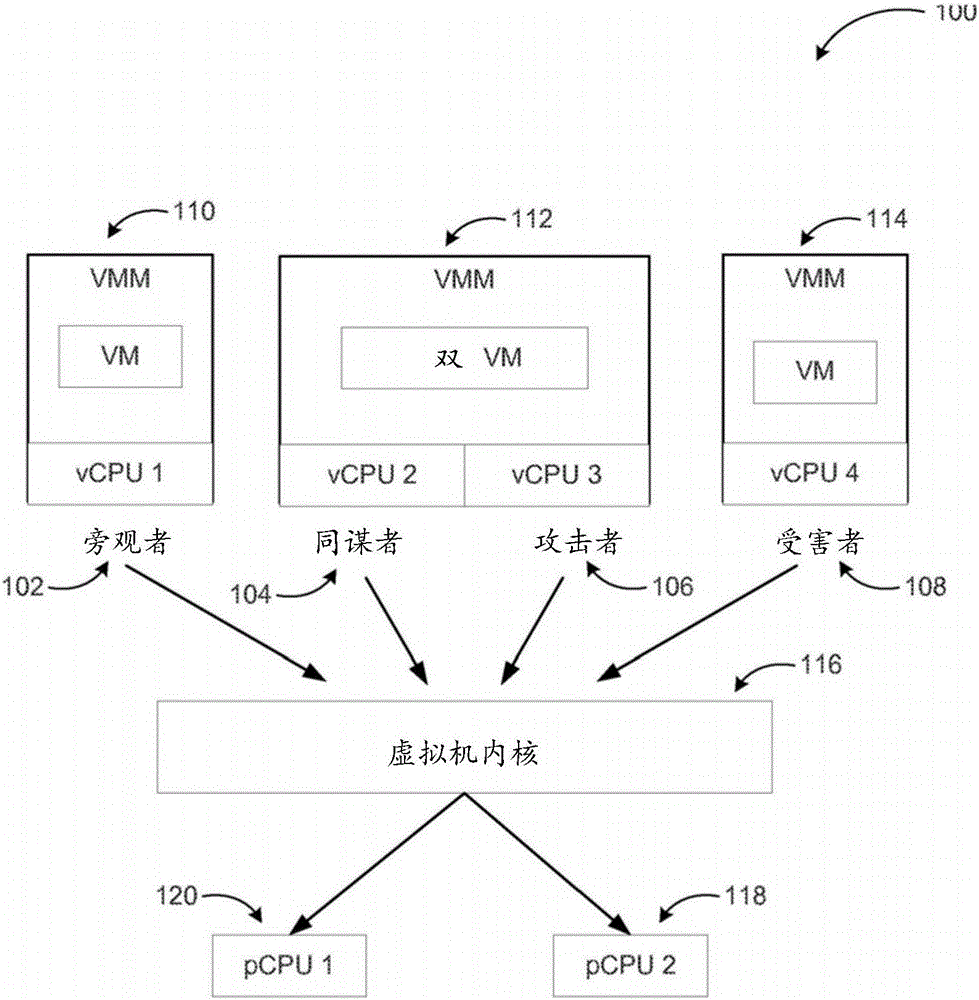

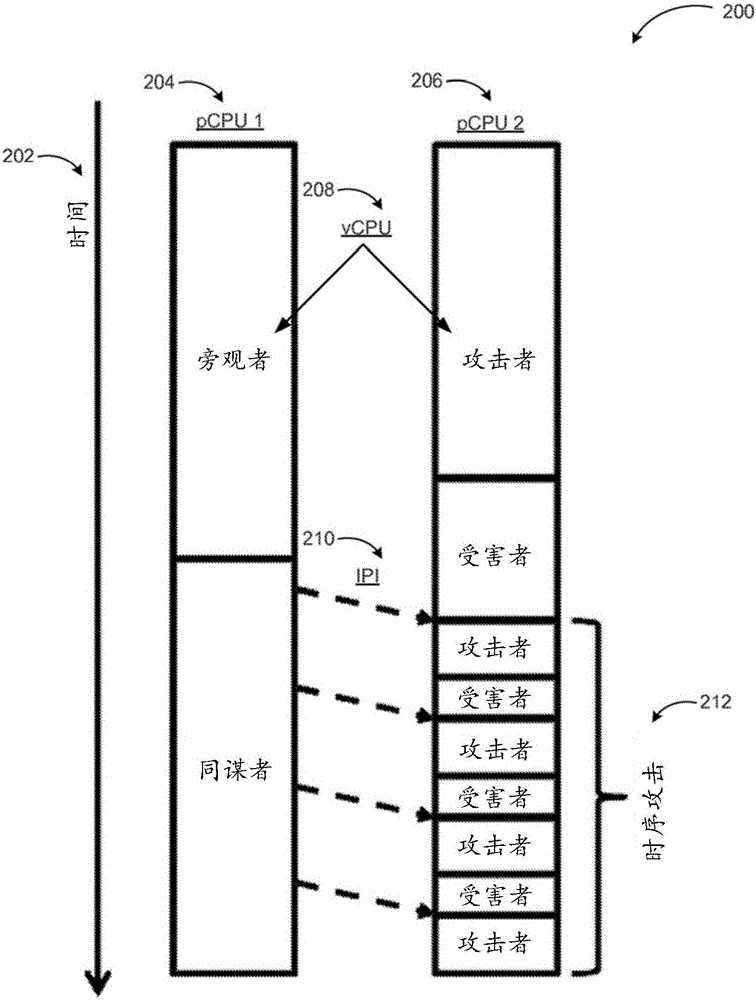

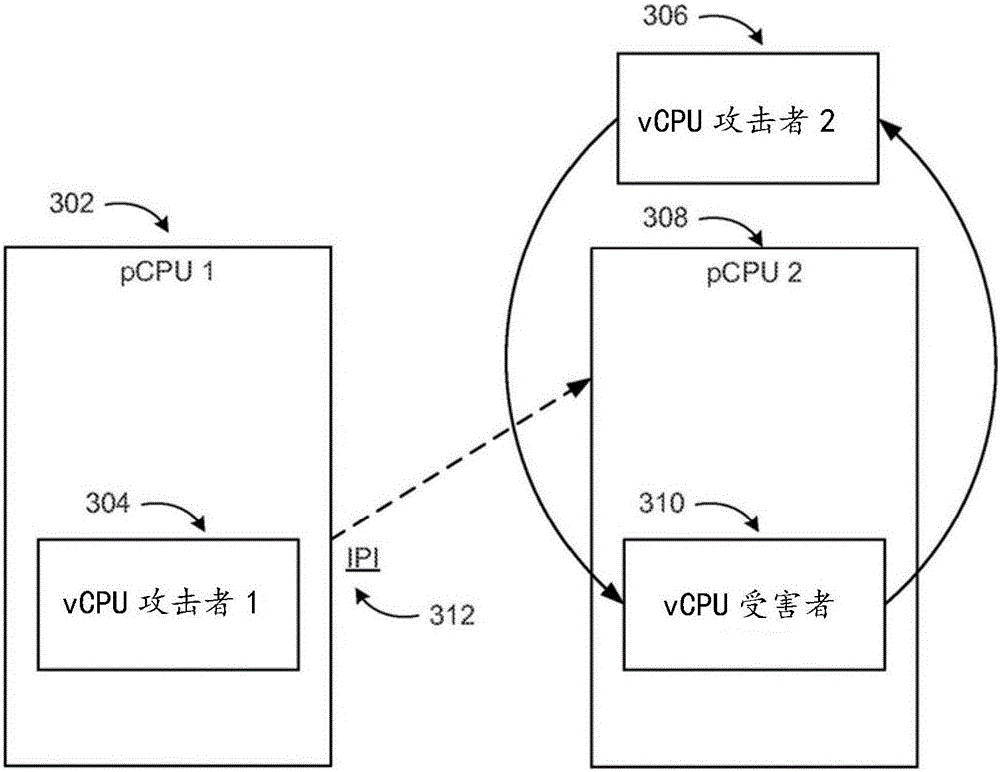

Detection of side channel attacks between virtual machines

InactiveCN105917345APlatform integrity maintainanceProgram controlInter-processor interruptComputer science

Technologies are directed to a detector to identify a side channel attack between virtual machines. According to some examples, an inter-processor interrupt (IPI) rate of a first virtual machine (VM), a time stamp counter (TSC) rate of a second VM, and a cache miss ratio (CMR) of a third VM may be monitored. A side channel attack may then be detected based on the IPI rate, the TSC rate, and the CMR.

Owner:EMPIRE TECH DEV LLC

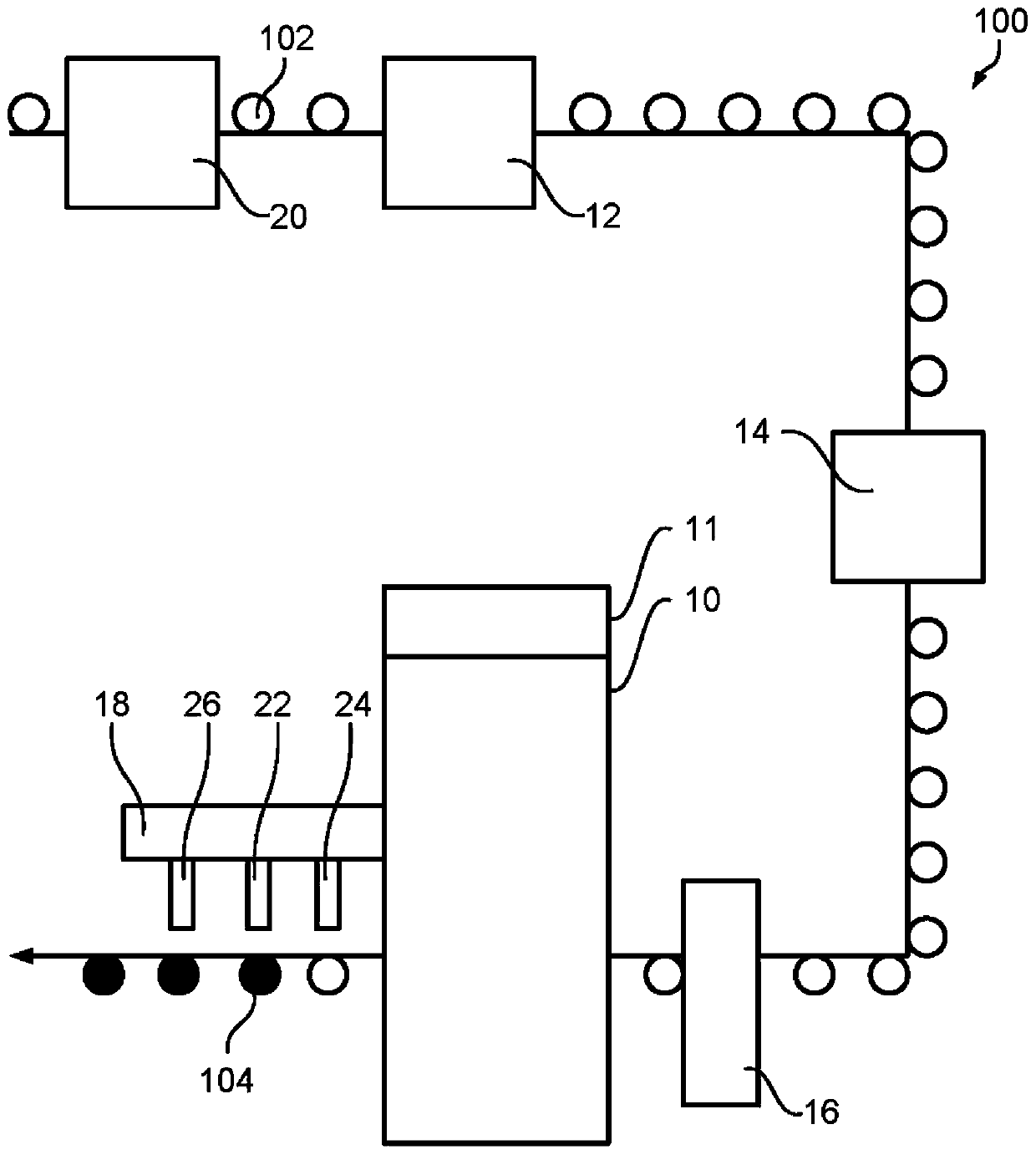

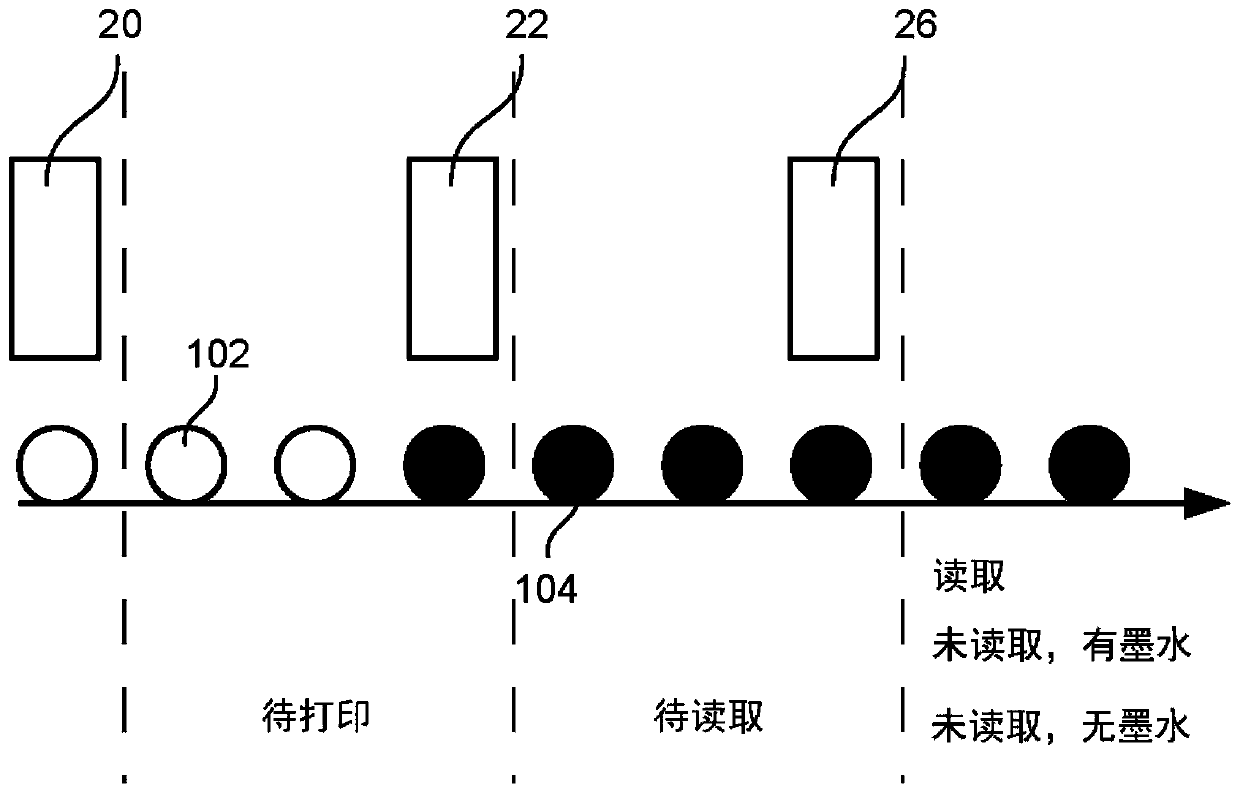

System and method for tracing a product item

ActiveCN110073300ALow costReduce investmentData processing applicationsTotal factory controlControl cellTimestamping

The present application concerns a system for tracing a product item (102, 104) on a production line (100) comprising a control unit (10) and a timestamp counter (11), wherein the control unit (10) isconfigured to receive a product signal related to the product item (102, 104) from at least one peripheral device (12, 14, 16, 18, 20, 22, 24, 26). According to the invention, the control unit (10) is further configured to carry out the method steps of receiving a plurality of product signals each relating to a product item (102, 104) and a peripheral device (12, 14, 16, 18, 20, 22, 24, 26), generating a plurality of event signals, wherein each event signal is based on one of the product signals, arranging the event signals in a sequence corresponding to an order in which the product signalswere received, and associating a timestamp generated by the timestamp counter (11) with the sequence.

Owner:SICPA HLDG SA

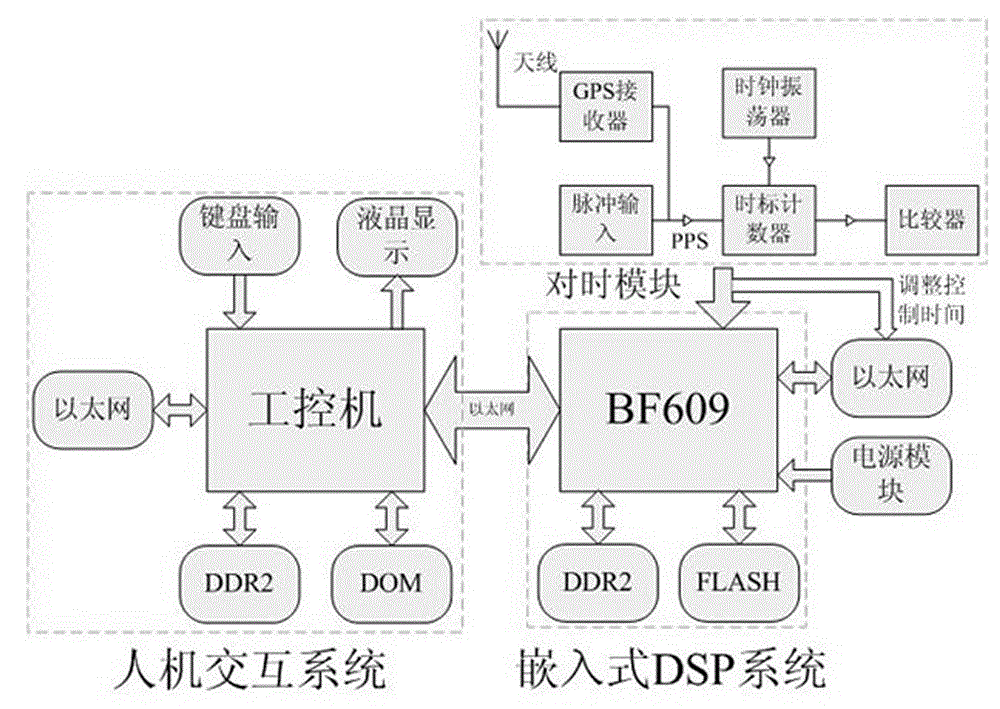

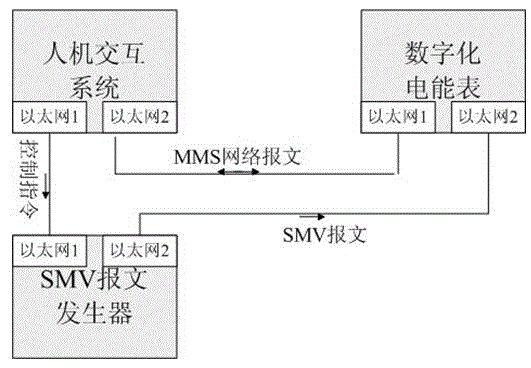

SMV packet generator for digital energy meter communication protocol test

InactiveCN104836706ARealize the control functionReal-time display of sending statusData switching networksLiquid-crystal displayPacket generator

The invention provides an SMV packet generator for a digital energy meter communication protocol test. The SMV packet generator comprises a man-machine interactive system which comprises an industrial control machine which is externally connected to a first DDR2, a DOM, an input keyboard, an LCD and a first Ethernet module respectively, an embedded DSP system which comprises a BF609 module which is externally connected to a second DDR2, a FLASH and a second Ethernet module respectively, a time set module which comprises an antenna, a GPS receiver, a time stamp counter and a comparator which are connected in order, and a power supply module. The output end of the comparator is connected to the embedded DSP system. The time stamp counter is also externally connected to a pulse input module and a clock oscillator at the same time. Both the first Ethernet module and the second Ethernet module are provided with two paths of Ethernet interfaces. The man-machine interactive system, the embedded DSP system and a digital energy meter are in mutual communication and connection through the Ethernet. The SMV packet generator can be used in a digital energy meter communication protocol test, and the technical parameters of synchronization time delay, dispersion and sampling rate can be flexibly controlled.

Owner:ELECTRIC POWER RES INST OF GUANGDONG POWER GRID

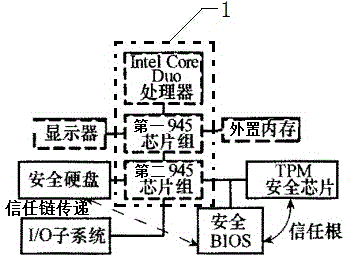

Trusted secure simulation computer

The invention discloses a trusted secure simulation computer, comprising a secure mainboard platform, a TPM secure chip, a secure BIOS, a secure hard disk and an I / O subsystem. The secure mainboard platform is composed of an Intel Core Duo processor and an Intel 9456 chip. The I / O subsystem comprises a high-speed digital to analog conversion D / A card, a high-speed analog to digital conversion A / D card and a digital input and output D / D card. The TPM secure chip communicates with the secure BIOS through a trust root. The secure hard disk communicates with the secure BIOS through trust chain transmission. According to the trusted secure simulation computer provided by the invention, a high-precision time counter is employed; a binary time stamp counter based on GPU main frequency exists in the Intel Core Duo processor; the nanosecond level control time is obtained through utilization of a product of the counter and the clock cycle of a CPU; and the relatively high guarantee for real-time synchronization control and communication of the simulation computer and an externally connected device is provided.

Owner:HARBIN GUANGKAI TECH DEV

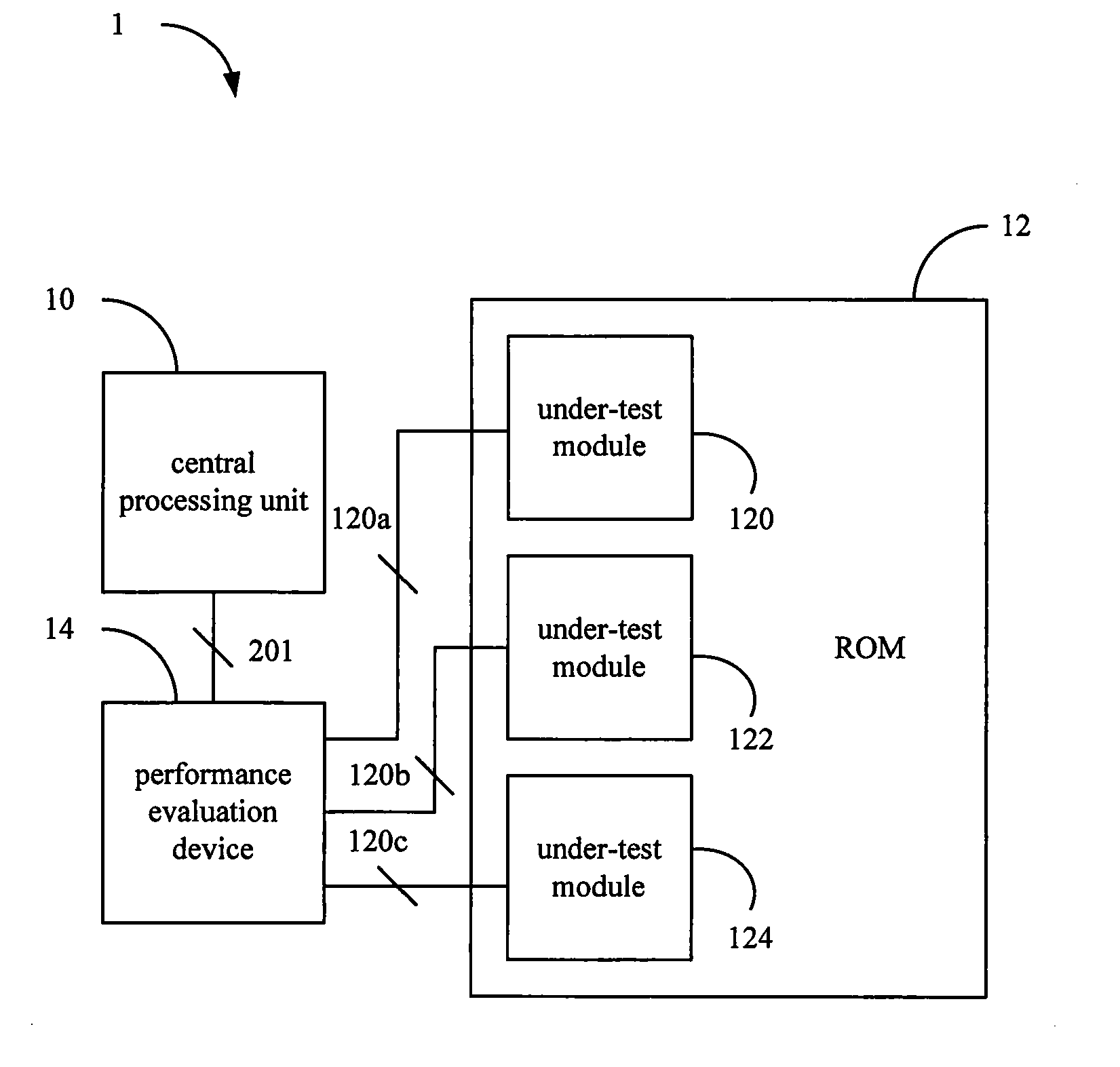

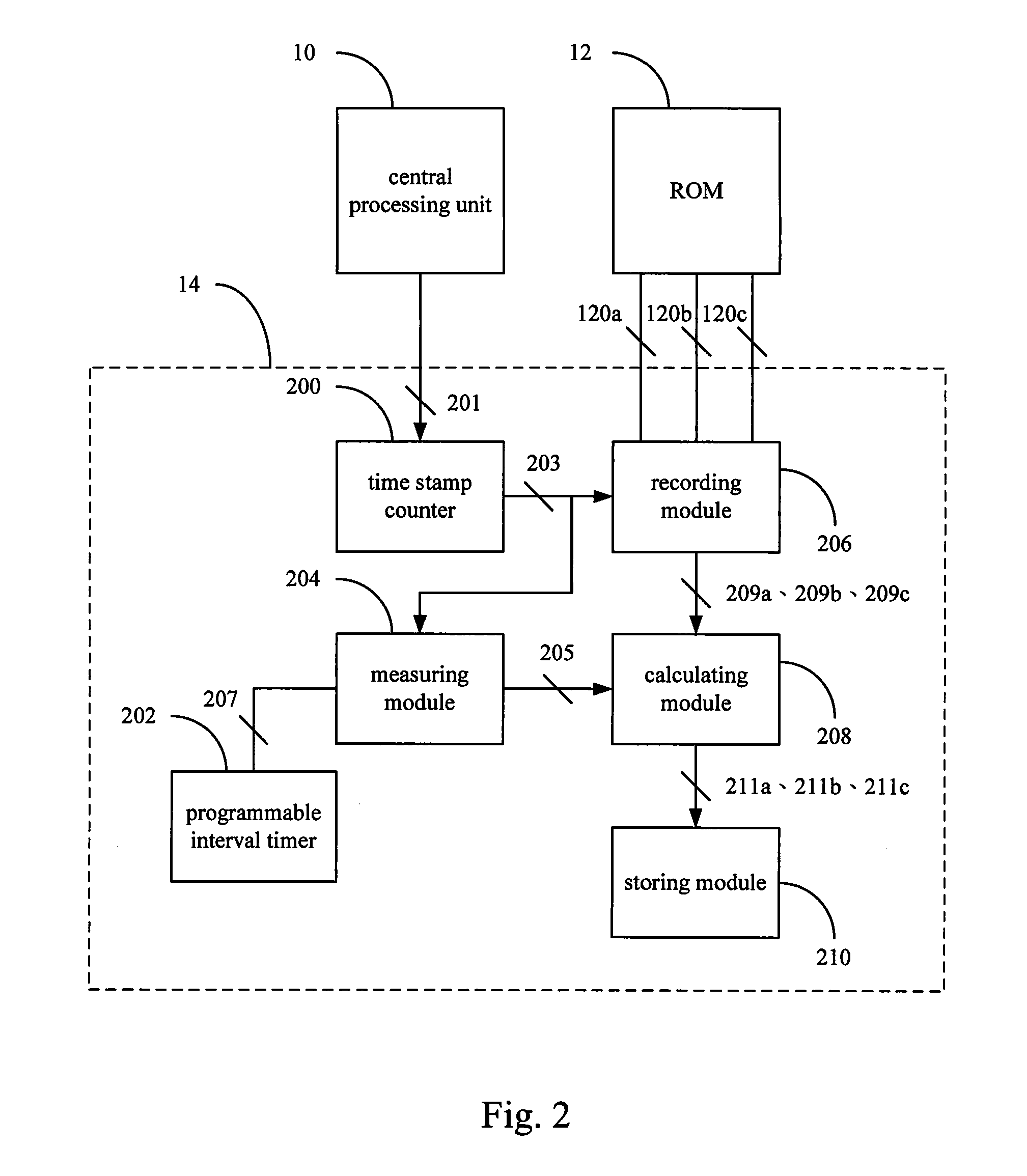

Performance evaluation device and performance evaluation method

A performance evaluation device and a performance evaluation method to evaluate at least one under-test module in a ROM of an electronic device are provided. The performance evaluation device comprises a time stamp counter, a measuring module, a recording module and a calculating module. The time stamp counter increments every time period to generate a time-stamp-number. The measuring module measures a unit-time time-stamp-number during a unit time to further calculates the time period. The recording module records a begin time-stamp-number when the at least one under-test module begins the operation and a finish time-stamp-number when the at least one under-test module finishes the operation. And the calculating module calculates an operation time data according to a difference between the begin time-stamp-number and the finish time-stamp-number and the time period.

Owner:INVENTEC CORP

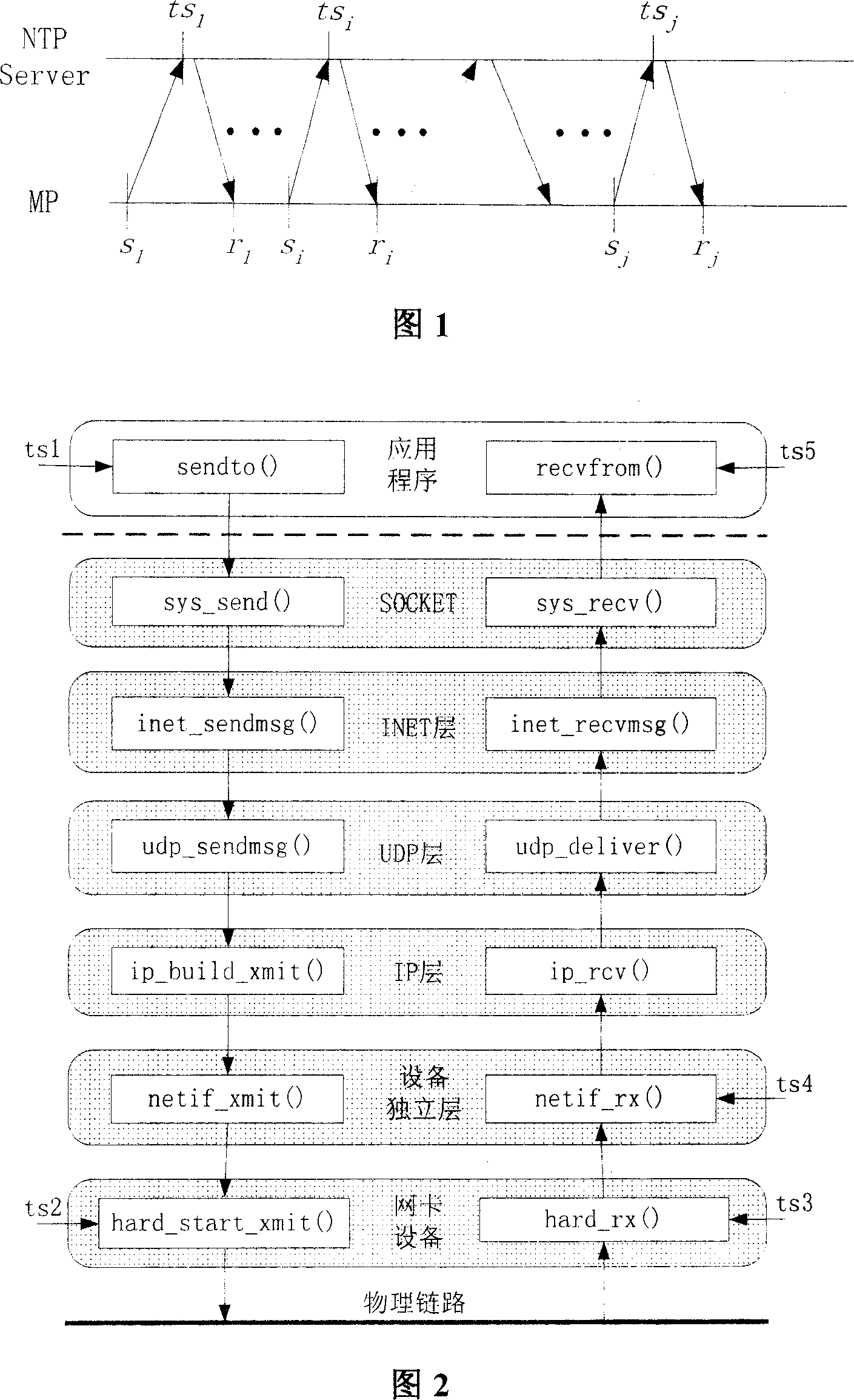

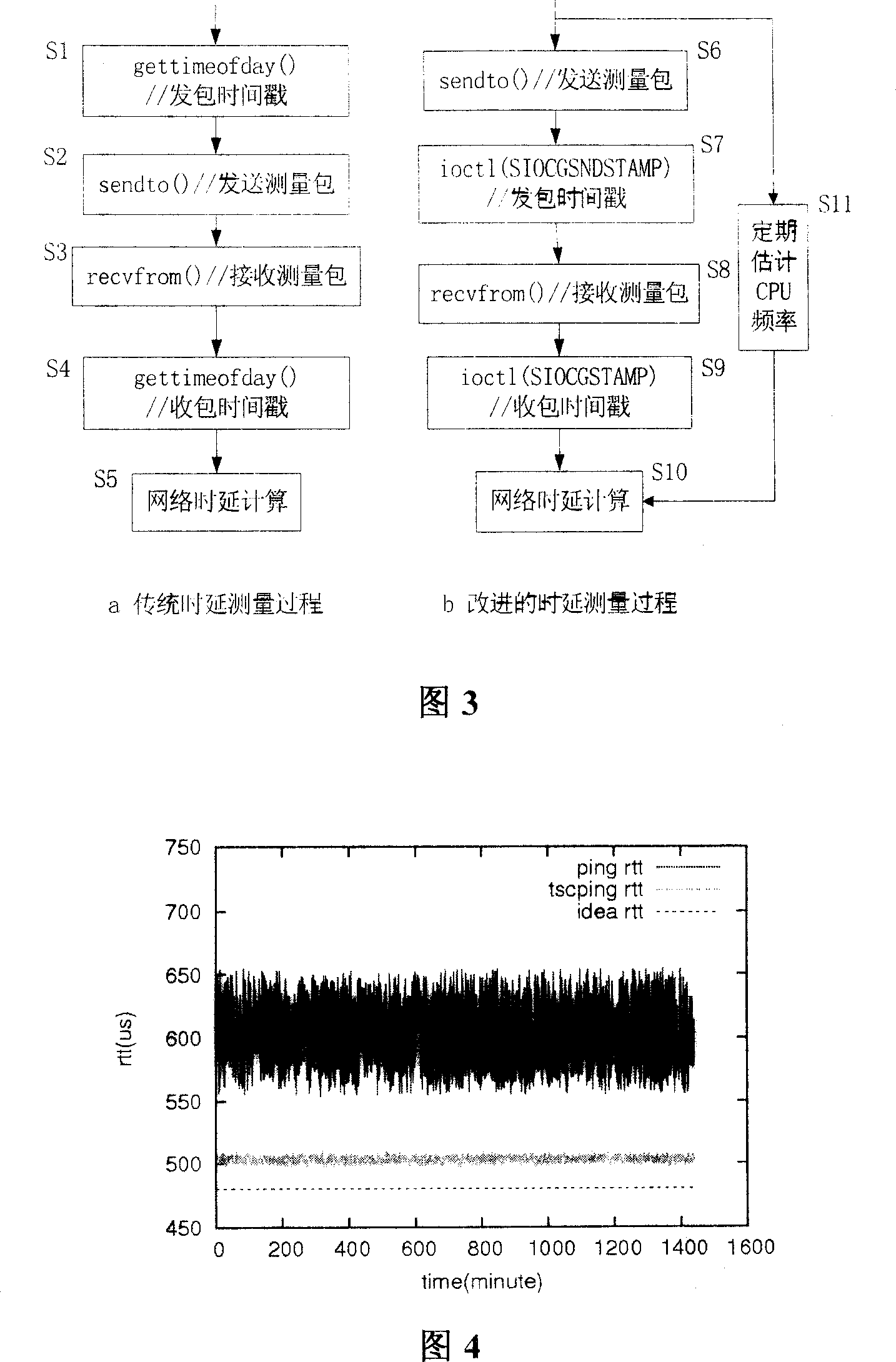

High precision network delay measuring method based on universal PC

InactiveCN100334846CHigh resolutionReduce cost of measurementData switching networksOperational systemTime delays

A method for measuring time delay of high accurate network based on universal PC includes utilizing software and hardware structural frame of universal PC to replace operation system clock by time - tag counter in CPU for timing and to estimate CPU frequency periodically for eliminating off clock error of measurement, revising operation system kernel to transfer time - tag recording position of packet receiving and packet sending from measuring program to network card drive and to read out packet receiving and packet sending time - tag recorded by network card drive directly from measuring program for eliminating off position error of measurement.

Owner:HUNAN UNIV

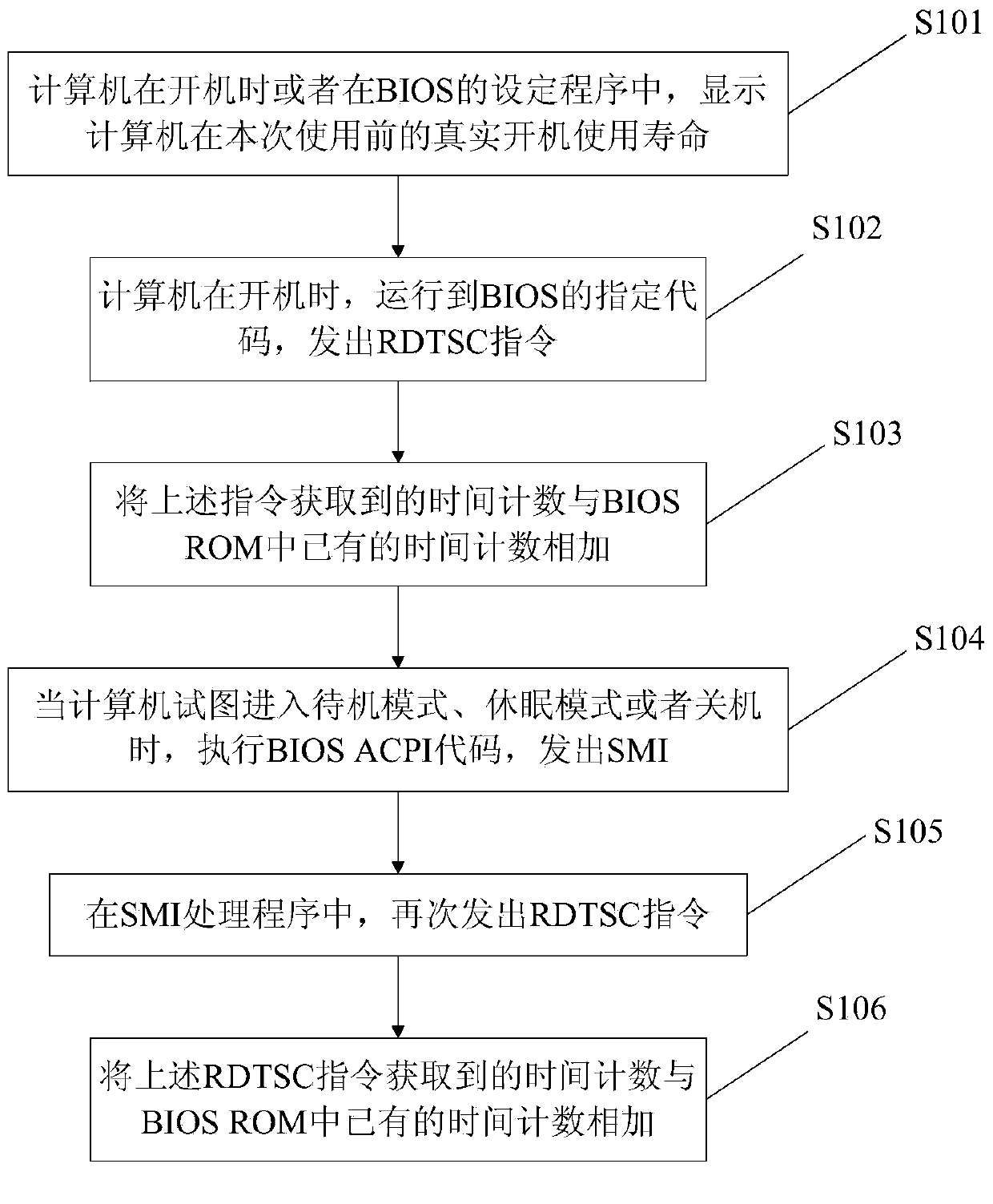

Method and system for recording real startup service life of computer

InactiveCN103425567AMaster usageReduce maintenanceHardware monitoringProgram loading/initiatingAdvanced Configuration and Power InterfaceStructure of Management Information

The invention discloses a method for recording real startup service life of a computer. The method comprises the following steps: during computer startup, transmitting an RDTSC (Read Time Stamp Counter) command after running to a specified code of a BIOS (Basic Input Output System); adding time count acquired by using the command with existing time count in a BISO ROM (Read Only Memory); when the computer attempts to enter a standby mode, or a hibernation mode or is turned off, executing a BISO ACPI (Advanced Configuration and Power Interface) code and transmitting SMI (Structure of Management Information); retransmitting a RDTSC command in an SMI processing producer; adding the time count acquired by using the retransmitted RDTSC command with the existing time count of the BIOS ROM. According to the method for recording real startup service life of the computer related to the invention, the real startup service life of the computer can be acquired.

Owner:HEFEI LCFC INFORMATION TECH

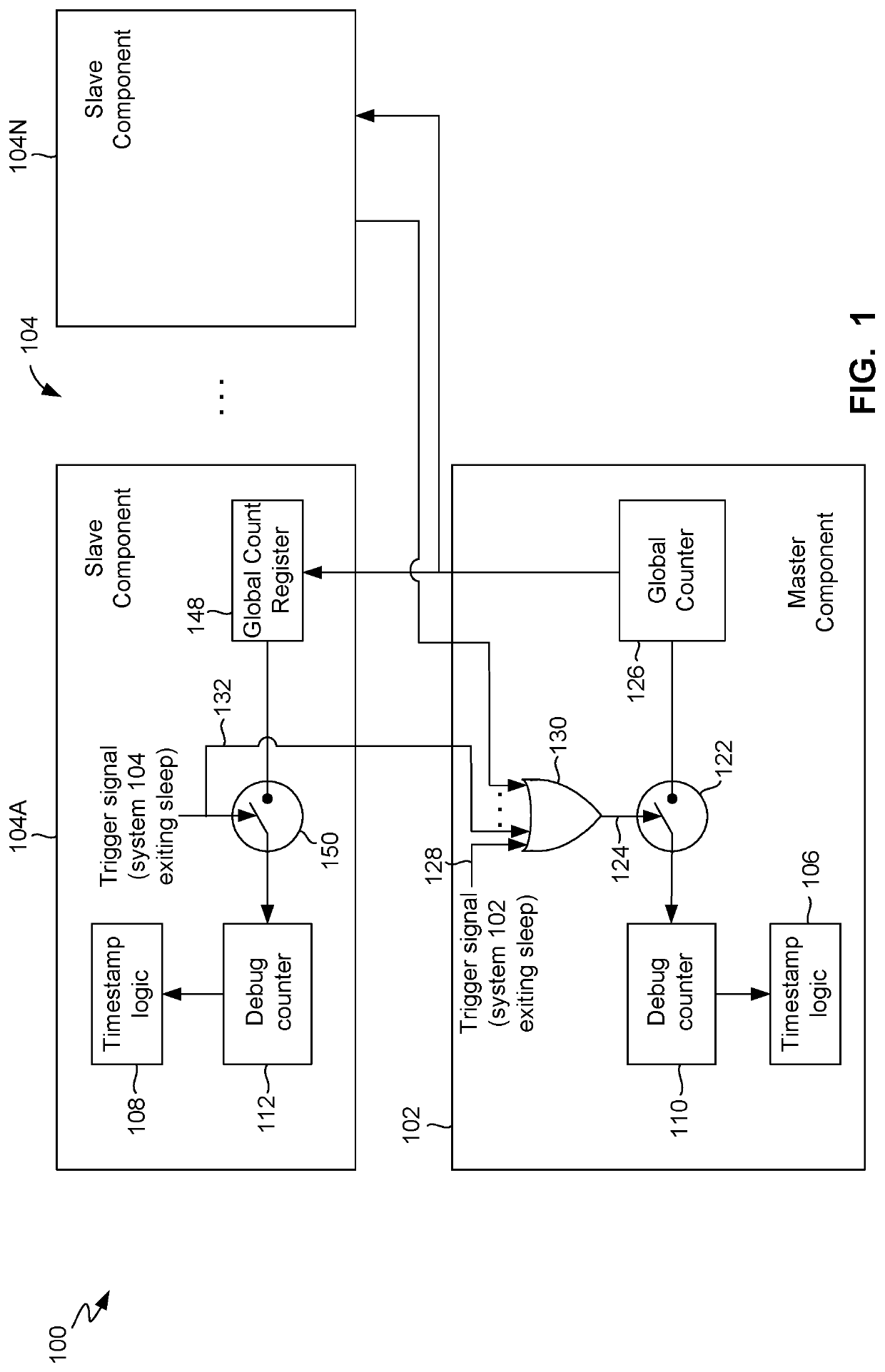

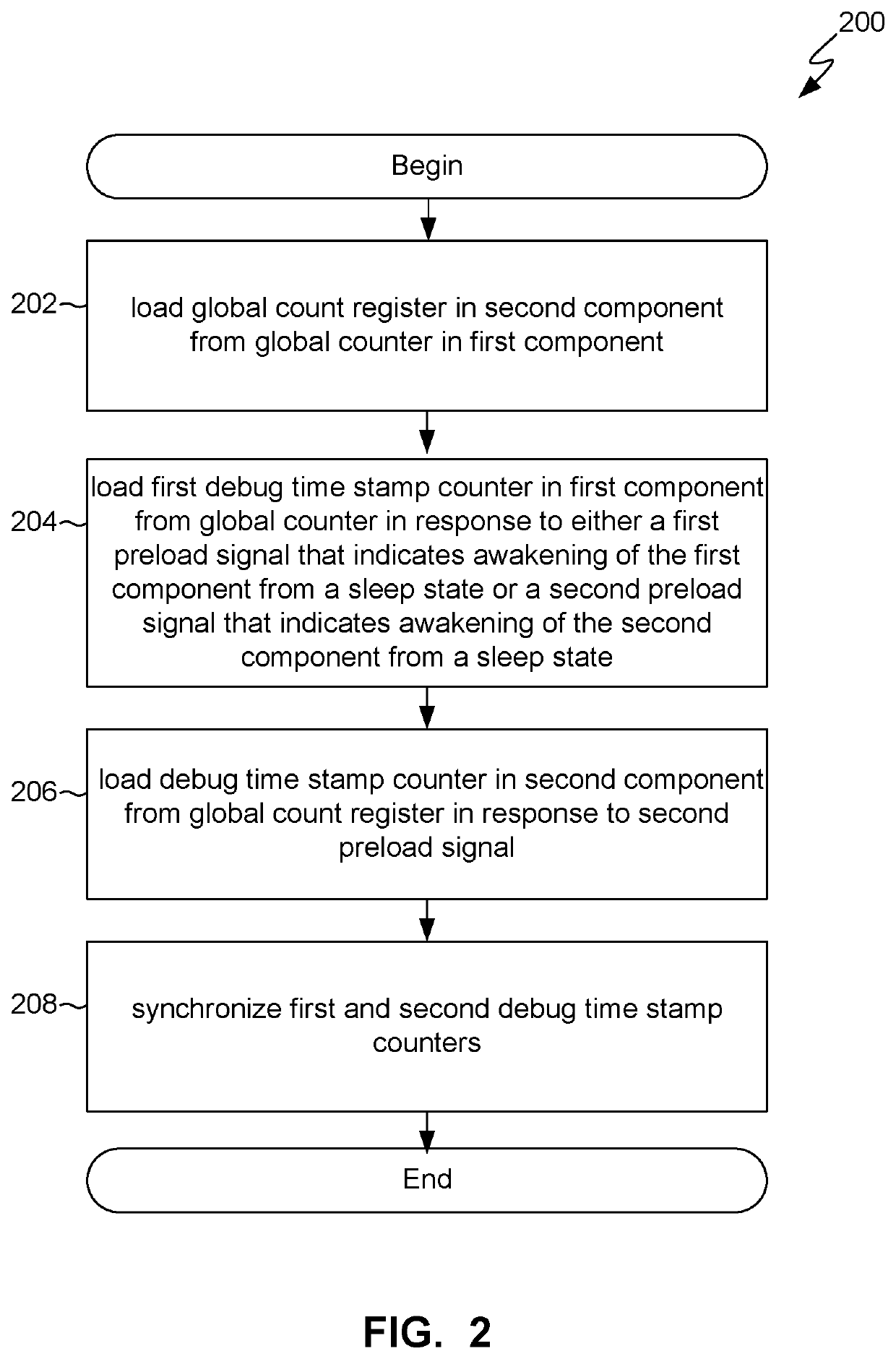

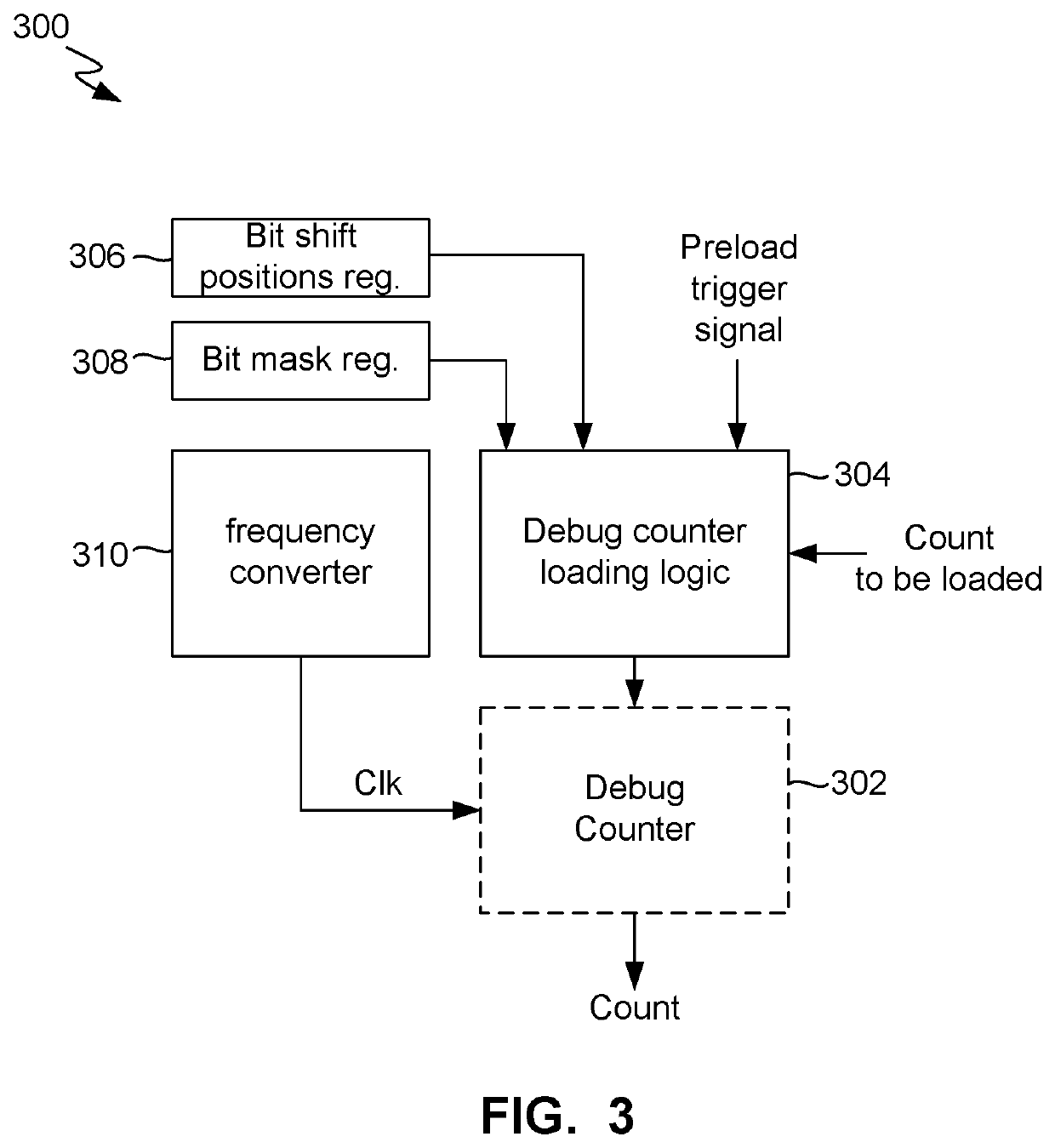

Debug trace time stamp correlation between components

ActiveUS11320855B1Error detection/correctionGenerating/distributing signalsComputer hardwareSleep state

Debug time stamp counters in a computing device may be synchronized based on signals indicating awakening of a component of the computing device from a sleep state. A count from a global counter in a first component may be loaded into a replica global counter in a second component. The count from the global counter may be loaded into a first debug time stamp counter in the first component in response to a first preload signal indicating awakening of the first component from a sleep state or in response to a second preload signal indicating awakening of the second component from a sleep state. The count from the replica global counter may be loaded into a second debug time stamp counter in the second component in response to the second preload signal.

Owner:QUALCOMM INC

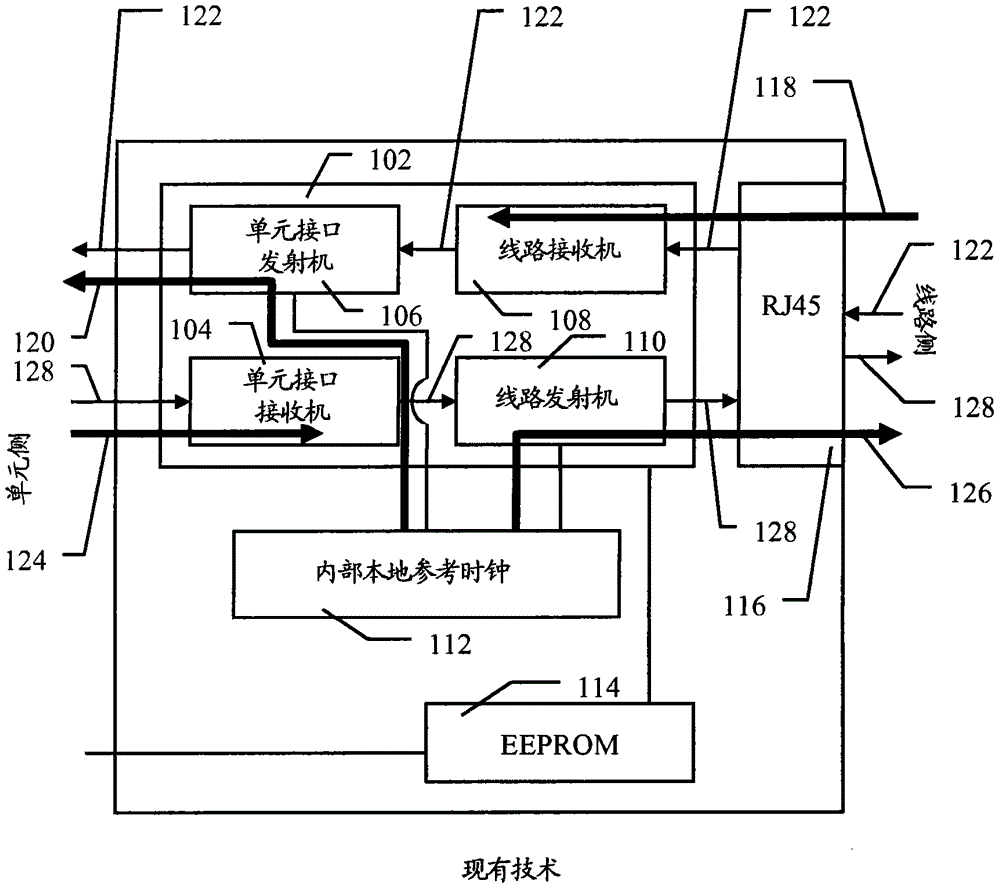

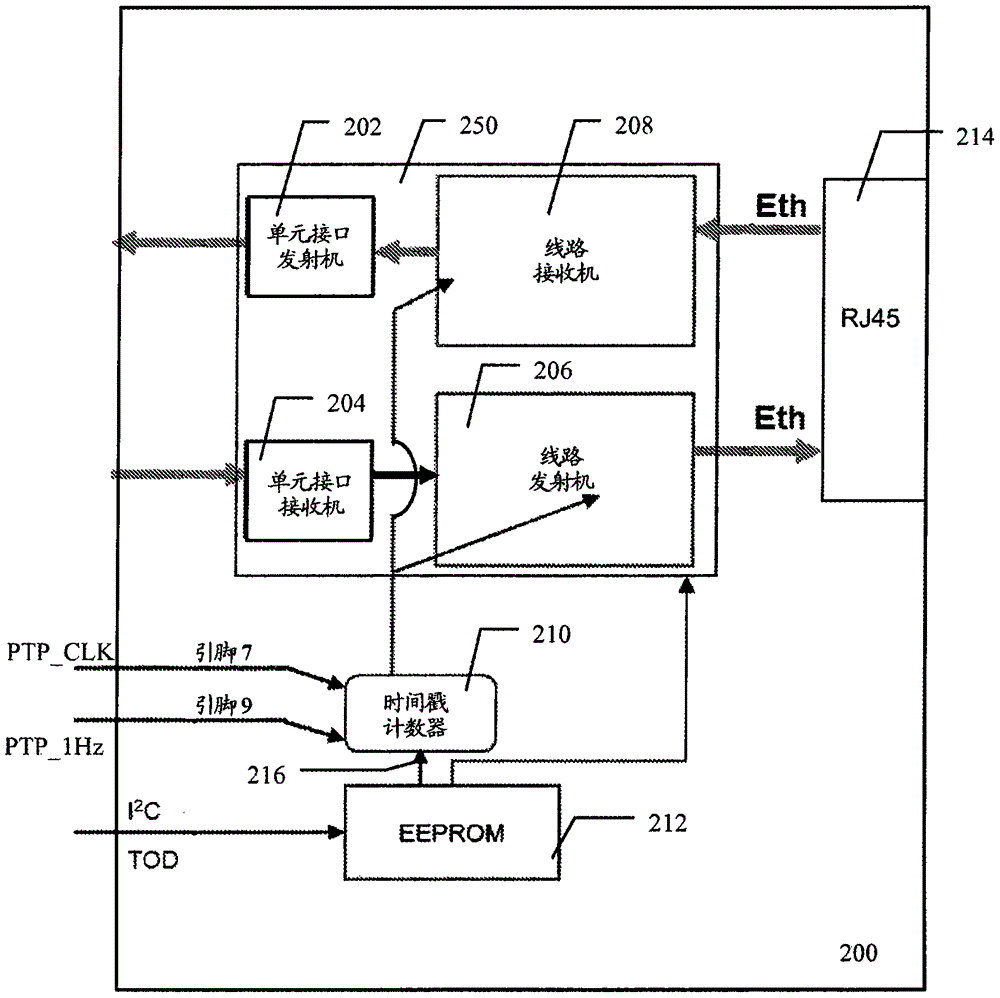

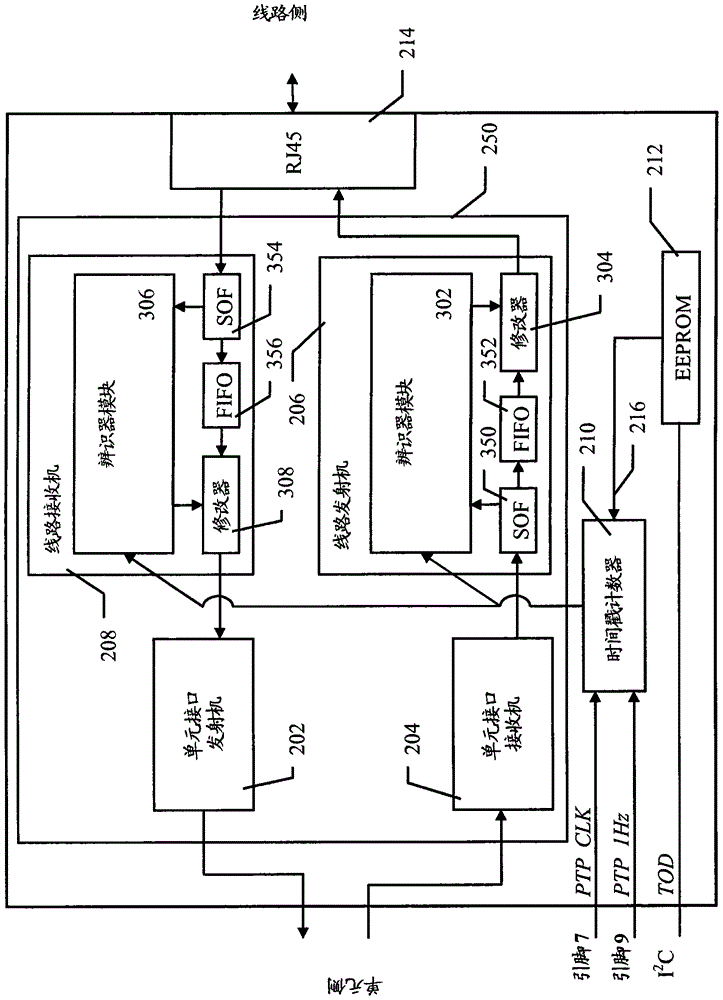

Time synchronous pluggable transceiver

The invention discloses a pluggable transceiver module (200) comprising a line receiver (208) connected to a unit interface transmitter (202), a line transmitter (206) connected to a unit interface receiver (204) and a timestamp counter (210) adapted to generate counter values based on clock signals received from an external source and to send the counter values to the line transmitter (206) and to the line receiver (208). The line transmitter (206) and the line receiver (208) are adapted to associate timing packets in a stream of data packets transmitted and received by the pluggable transceiver module (200) with counter values output by the timestamp counter (210).

Owner:TELEFON AB LM ERICSSON (PUBL)

Clock skew measurement for multiprocessor systems

ActiveUS8122278B2Accurate measurementIntroduces delayError detection/correctionData resettingMulti processorComputerized system

Systems and methods (“utility”) for providing more accurate clock skew measurements between multiple CPUs in a multiprocessor computer system by utilizing the cache control or management protocols of the CPUs in the multiprocessor system. The utility may utilize a time stamp counter (TSC) register of the CPUs in the multiprocessor computer system to detect the clock skew between the various CPUs in the system. Further, the delay between measurements of the TSC registers of the CPUs may be minimized by utilizing the features of the hardware cache control or management protocols of the computer system, thereby providing more accurate clock skew measurements.

Owner:ORACLE INT CORP

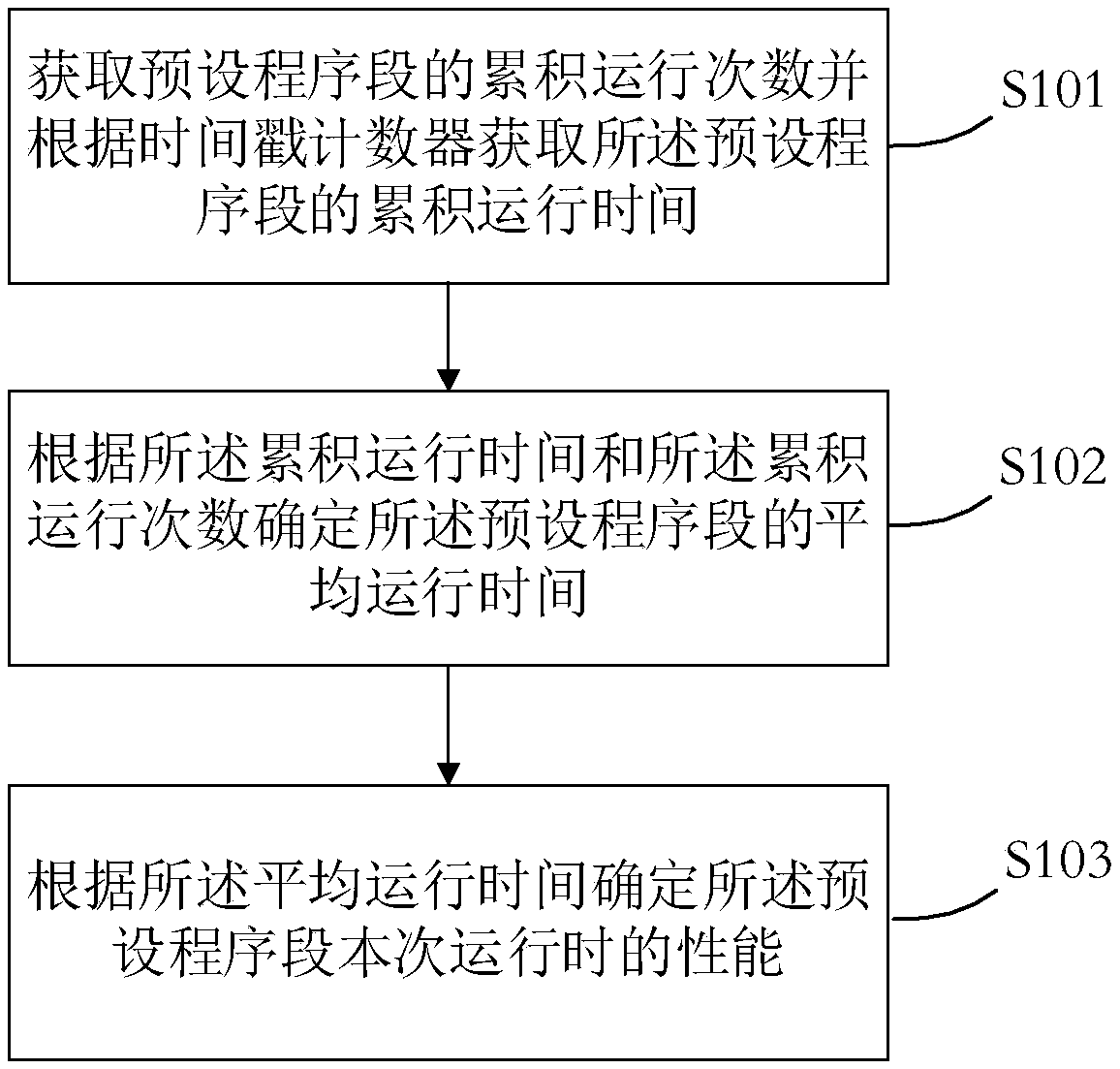

A method and apparatus for acquiring program segment performance

InactiveCN109460347ASolve the problem of locating program segments with performance defectsImprove versatilityHardware monitoringProgram segmentCpu load

The present application provides a method and apparatus for acquiring the performance of a program segment. The method includes: acquiring the cumulative running times of a preset program segment andacquiring the cumulative running time of the preset program segment according to a timestamp counter; Acquiring an average running time of the preset program segment according to the cumulative running time and the cumulative running times; Determining the performance of the preset program segment at the current run time according to the average run time. The method provided by the present application has good generality, is not affected by any CPU load, and can be applied across platforms. The problem of locating segments with performance flaws in complex programs is solved. Because the method adopted is not affected by the environment, it can be applied to the kernel state or the application state.

Owner:BEIJING TOPSEC NETWORK SECURITY TECH +2

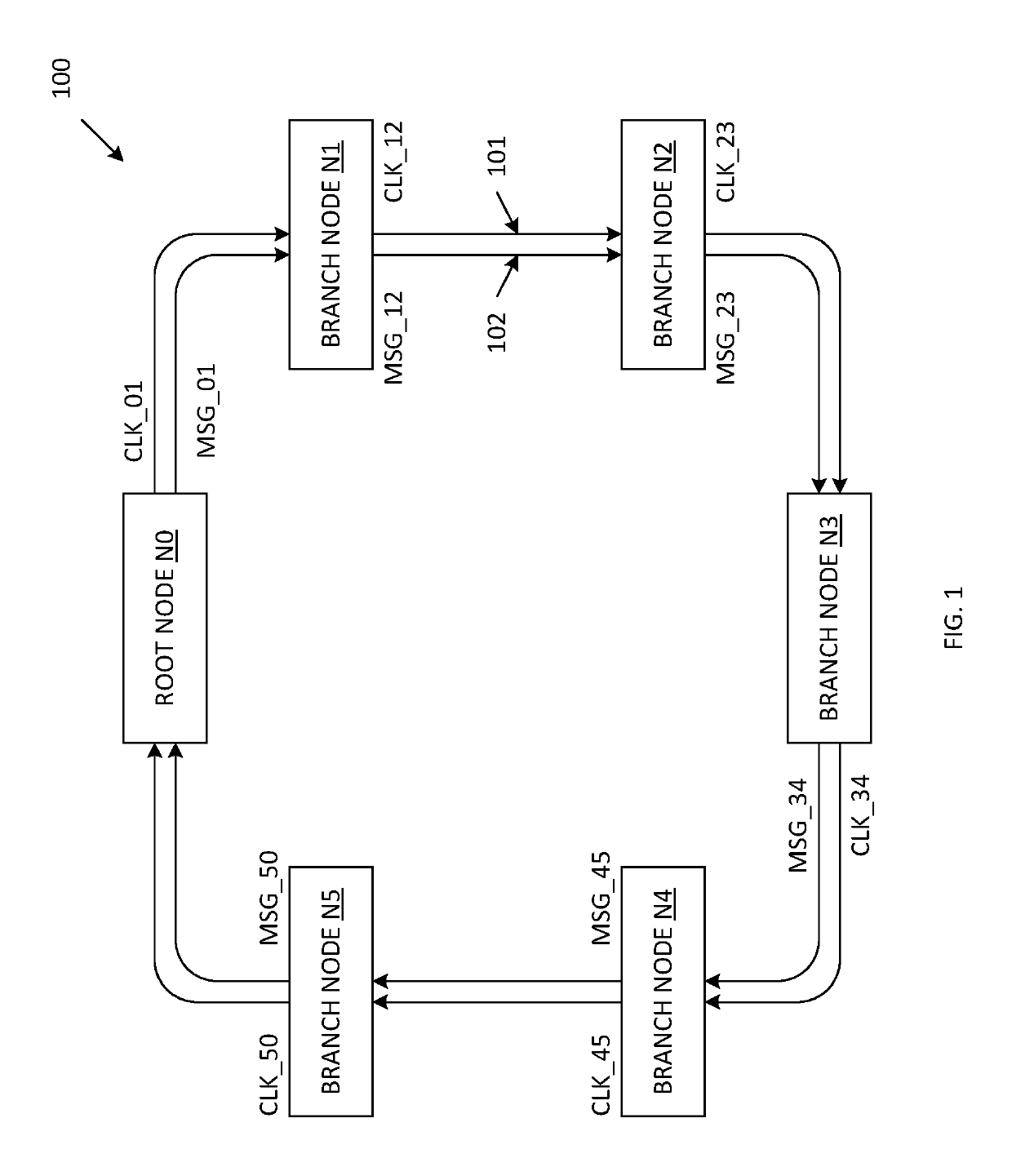

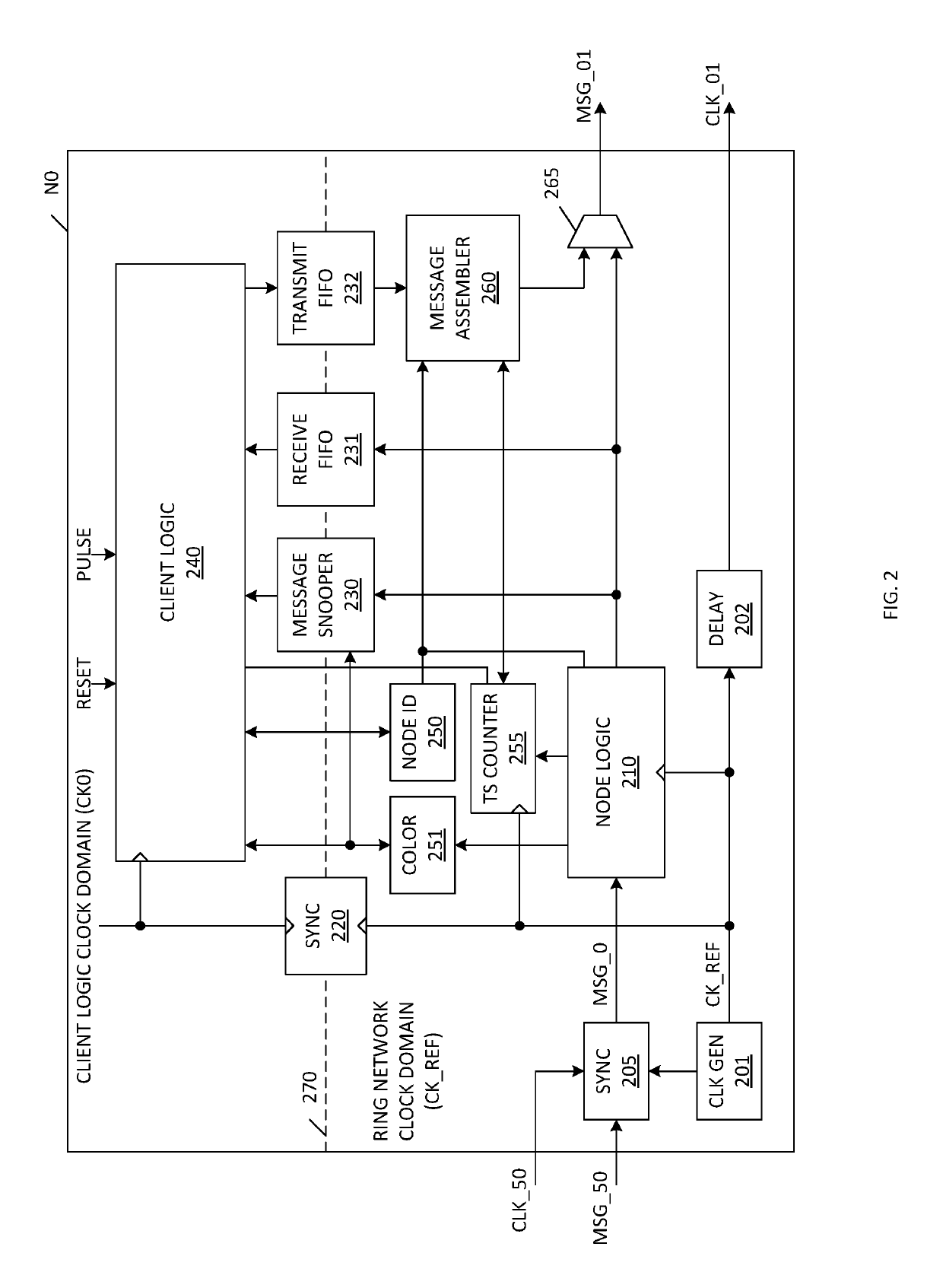

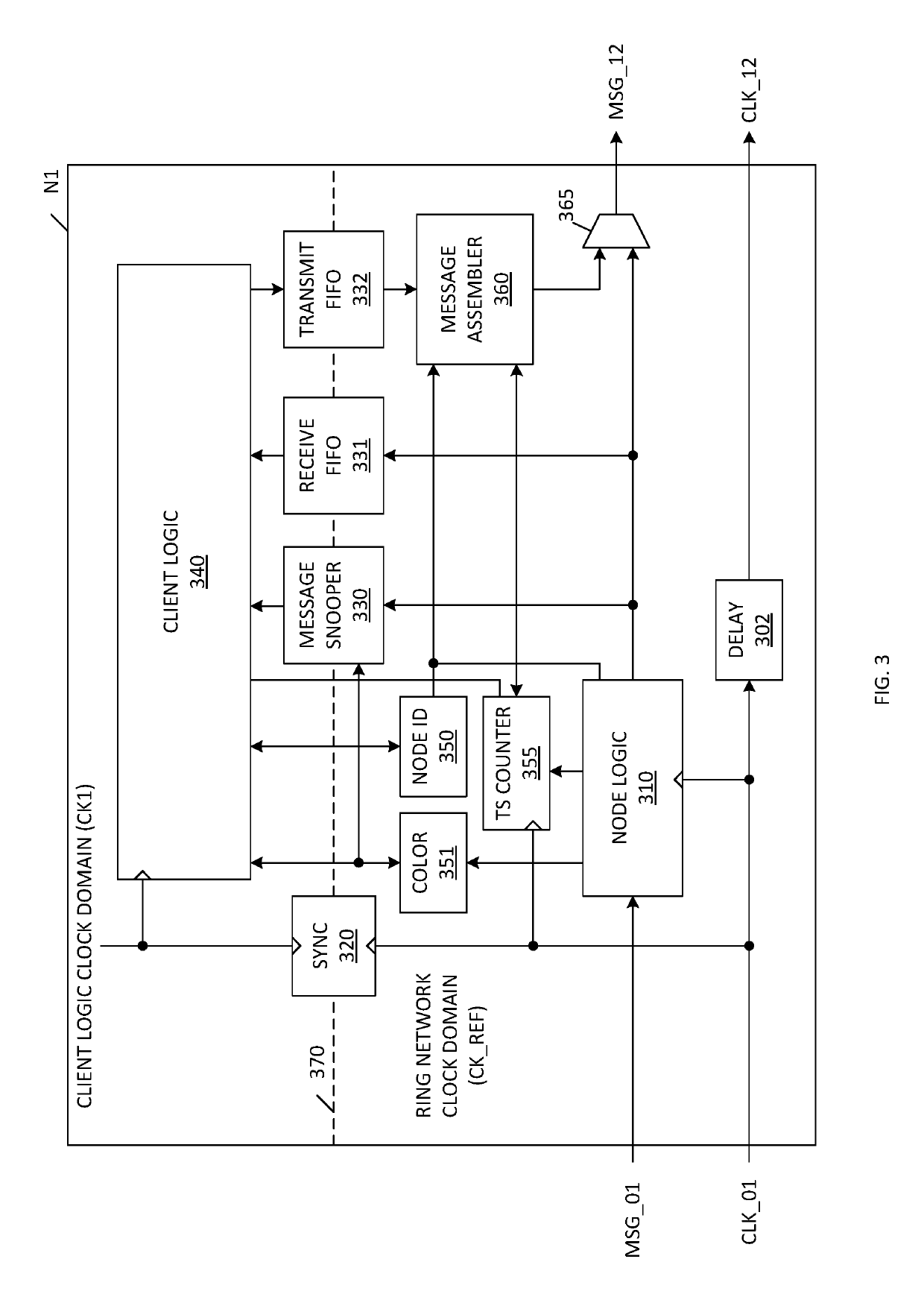

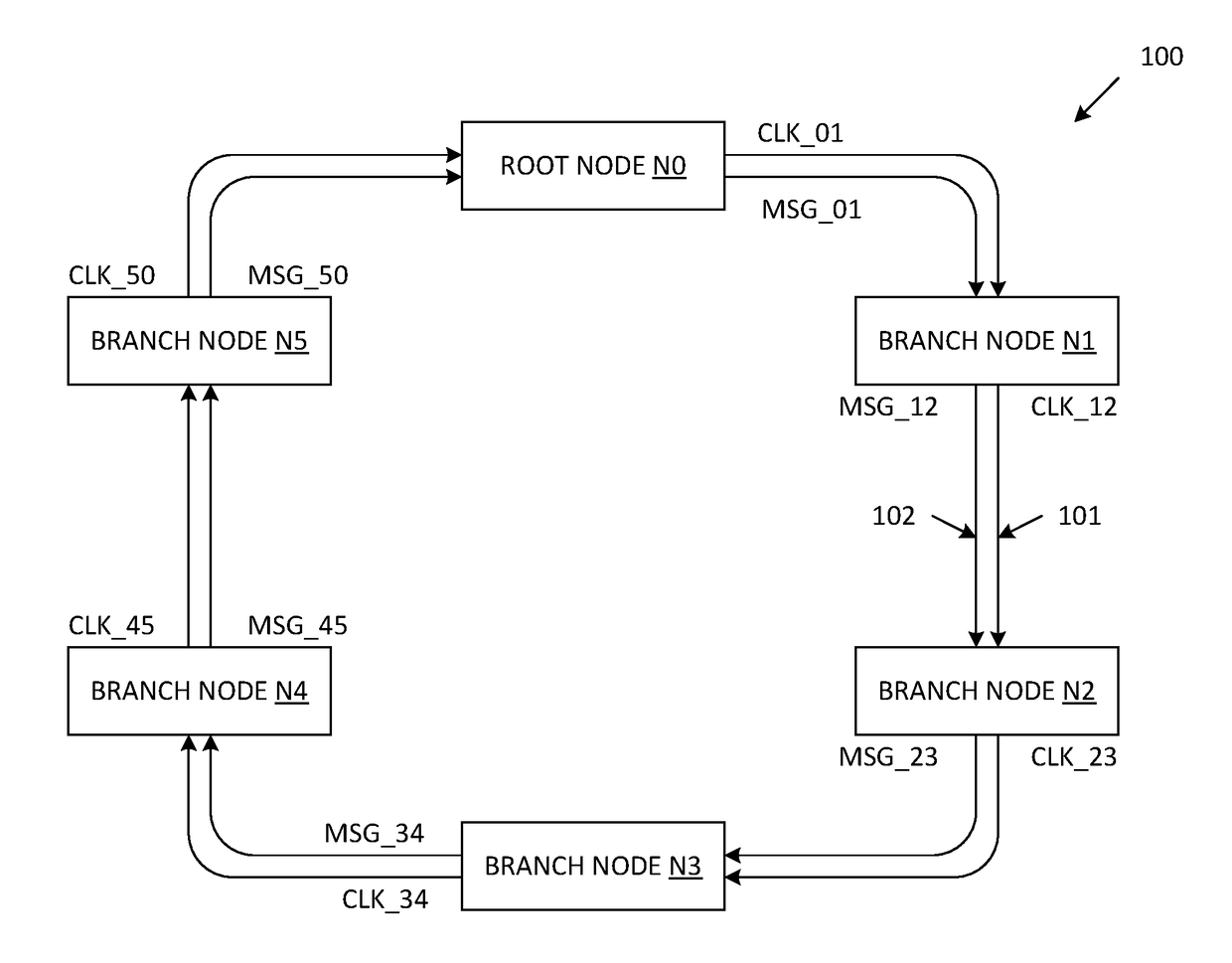

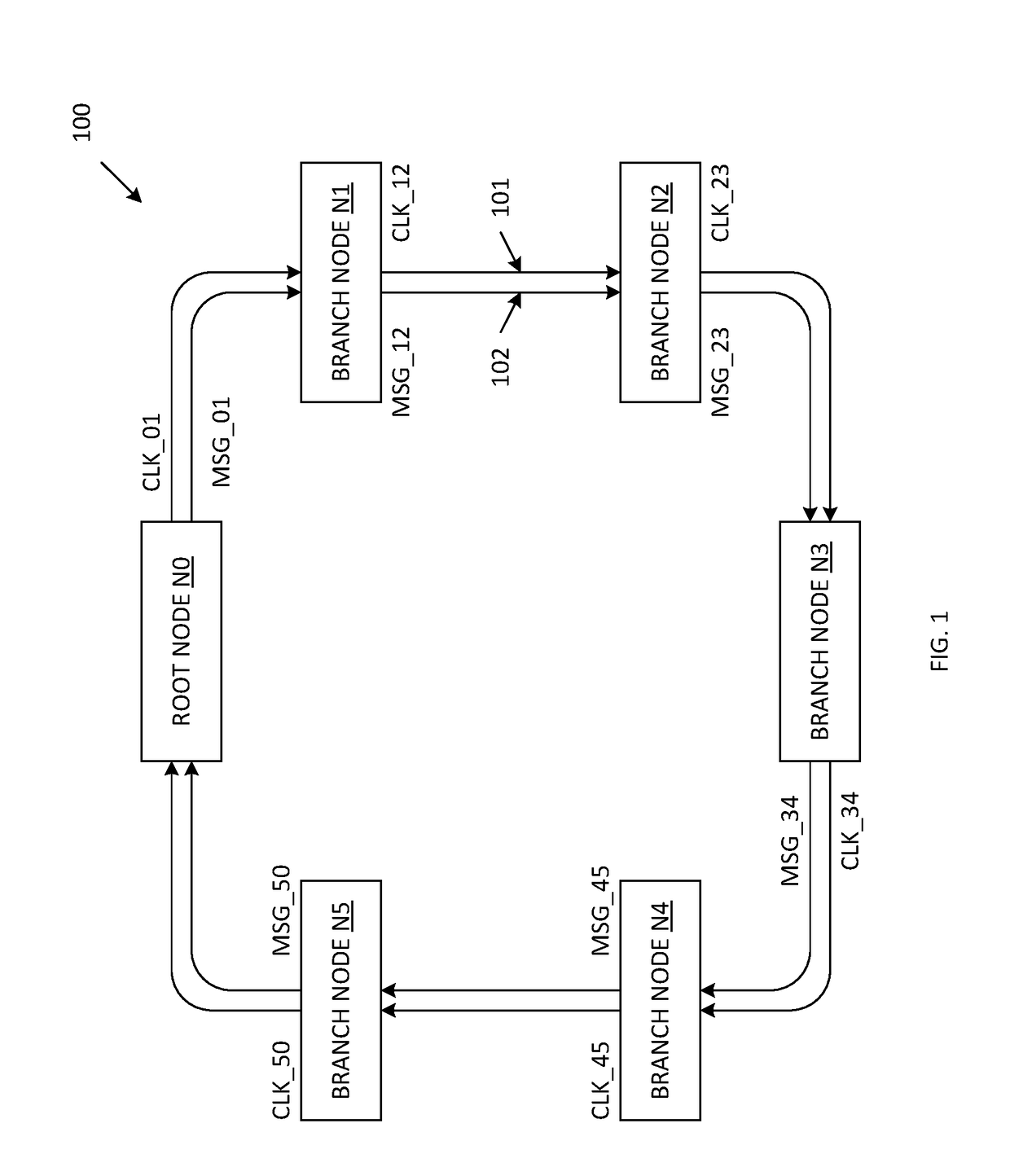

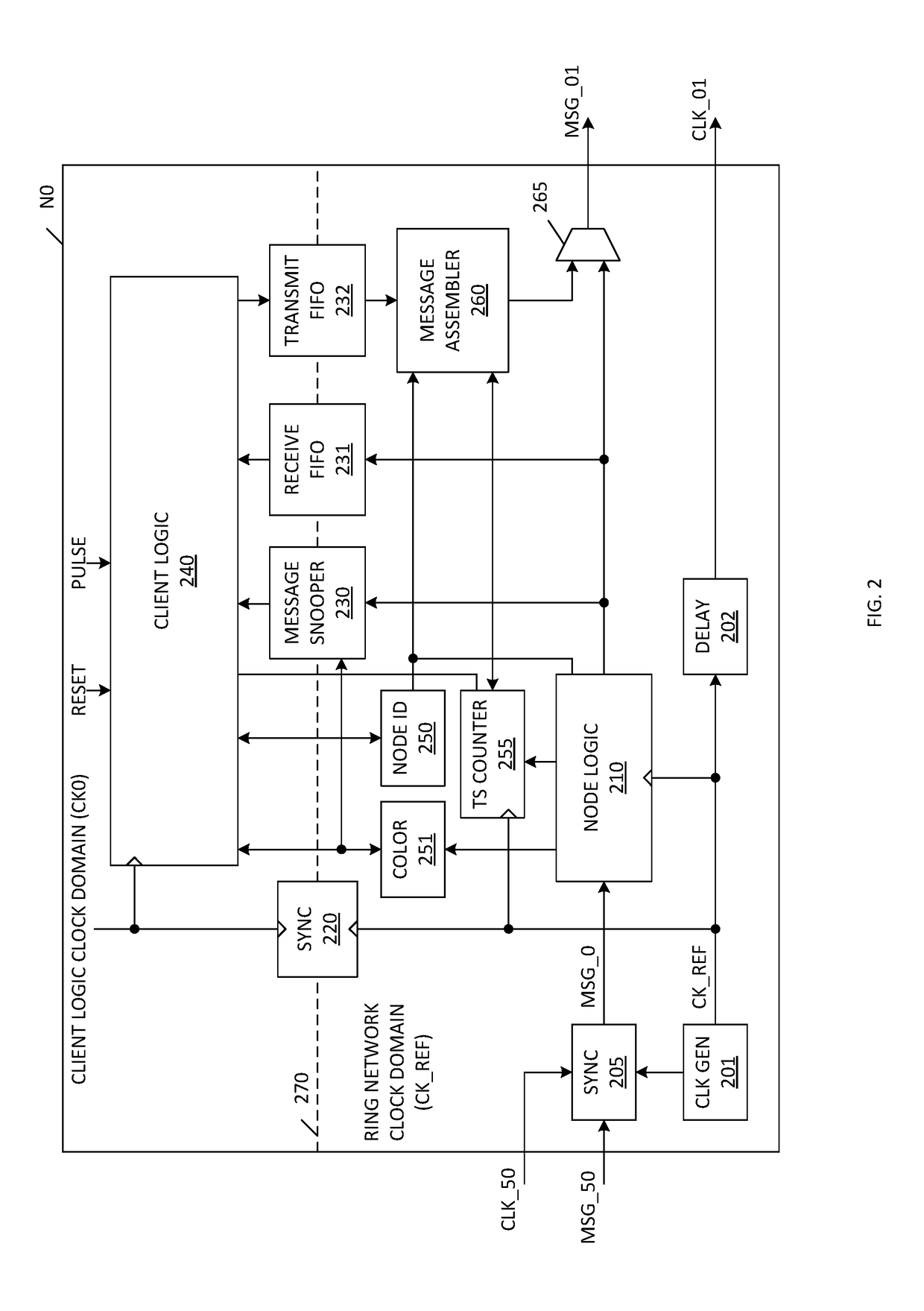

Distributed control synchronized ring network architecture

ActiveUS10411910B2Simple physical implementationGuaranteed high speed operationSynchronisation information channelsTime-division multiplexHigh bandwidthClock tree

A ring network architecture includes multiple communication nodes configured in a ring. Wave pipelining is used to provide for high bandwidth and low latency on-chip communications. Each node implements a source-synchronized clocking scheme, such that there is no need to build an extensive low skew clock-tree across a large die area. A single reference clock signal is generated within a root node, and is routed through each of the nodes of the ring network in a unidirectional manner. Each node includes a timestamp counter and a color bit register, which store values that enable the node to resolve ordered transaction messages issued by the other nodes in a precise order, even though the nodes are operating independently, and receive the various transaction messages in totally different timing orders. Because the control logic is distributed among the nodes, no centralized controller is necessary.

Owner:DEGIRUM CORP

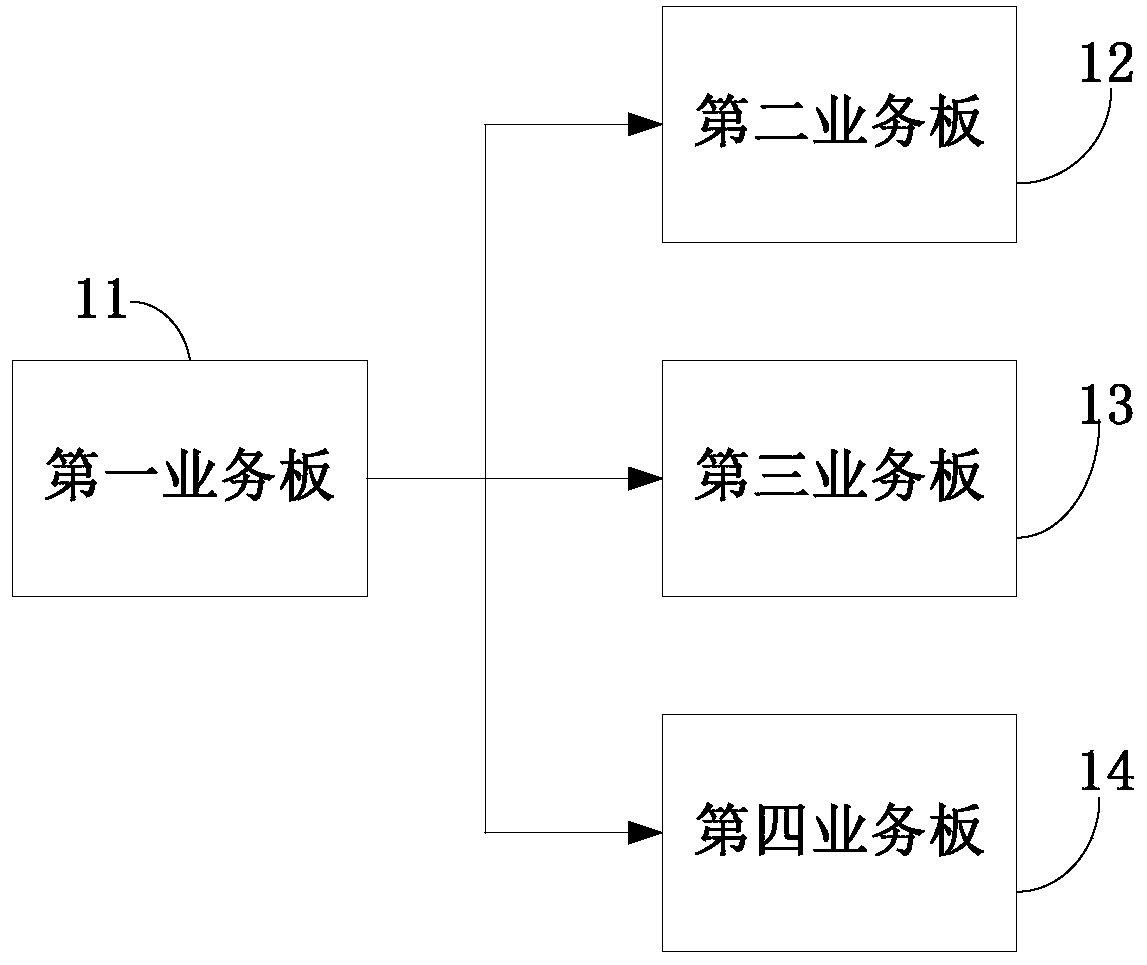

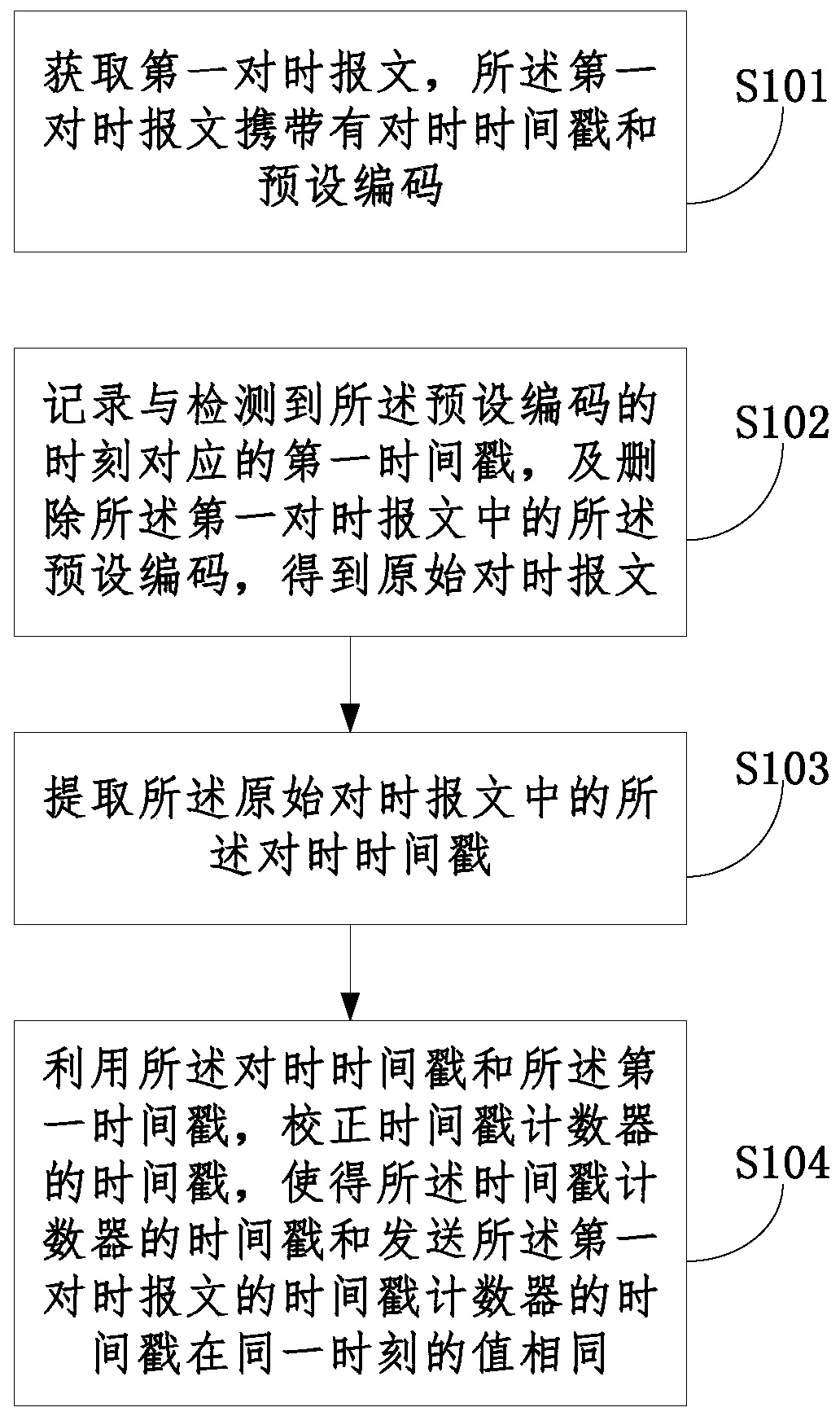

Time correction method, device and system and storage medium

ActiveCN111385049AMitigate inaccuraciesImprove accuracyTime-division multiplexData switching networksComputer hardwareTime information

The invention relates to a time correction method, device and system and a storage medium, and the method comprises the steps: obtaining a first time synchronization message which carries a time synchronization timestamp and a preset code; recording a first timestamp corresponding to the moment when the preset code is detected, and deleting the preset code in the first time tick message to obtainan original time tick message; extracting a time synchronization timestamp in the original time synchronization message; and correcting the timestamp of the timestamp counter by using the time synchronization timestamp and the first timestamp, so that the timestamp of the timestamp counter and the timestamp of the timestamp counter sending the first time synchronization message have the same valueat the same moment. According to the method, the problem that the time information transmitted between the cross-service sub-frames is inaccurate in the prior art can be relieved, and the accuracy ofthe time information transmitted between the cross-service sub-frames is improved.

Owner:ZTE CORP

Method for synchronization of wireless devices through accelerated advance of counters

InactiveUS20080013661A1Time-division multiplexTwo-way working systemsComputer hardwareTerminal equipment

A method for synchronizing counters in a wireless terminal device with those of an administrative device. A wireless terminal device advances its frame counter. With each increment of the frame counter, the wireless terminal device minislot counter advances by an amount equal to the number of minislots per frame. Likewise, with each increment of the frame counter, the wireless terminal, device's timestamp counter is incremented by the number of timestamps per frame. This continues until the counters at the wireless terminal device are within one frame of the administrative device's counters. The minislot counter is then incremented. With each increment of the minislot counter, the timestamp counter is incremented by an amount equal to the number of timestamps per minislot. This continues until the wireless terminal devices counters are within a minislot of the administrative device's counters. The timestamp counter is then incremented until the wireless terminal device's counters match those of the administrative device.

Owner:AVAGO TECH WIRELESS IP SINGAPORE PTE

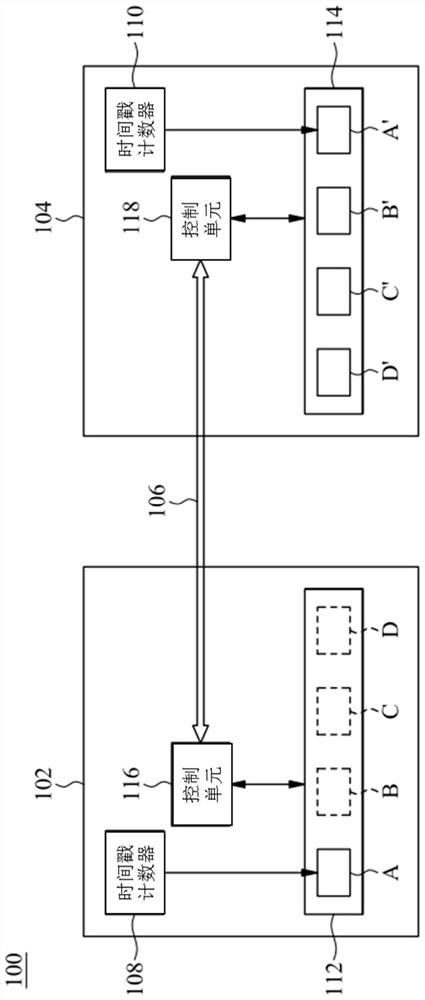

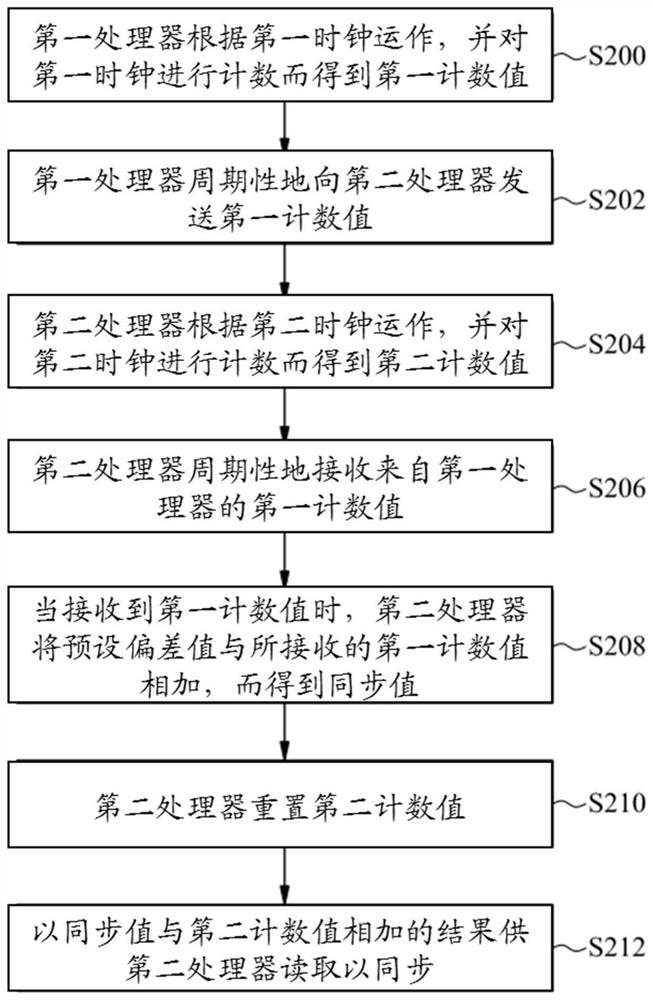

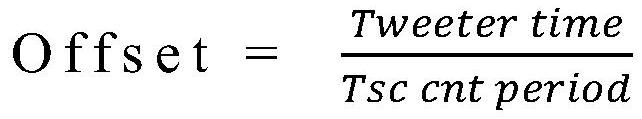

Electronic device with multiple processors and synchronization method of processors

ActiveCN112162591AEliminate counting errorsEliminate signal delayGenerating/distributing signalsCommunication interfaceComputer architecture

The invention relates to an electronic device with multiple processors and a synchronization method of the processors. The electronic device comprises a first processor, a second processor and a communication interface. The first processor operates according to a first clock and has a first time stamp counter for counting the first clock to obtain a first count value. The second processor operatesaccording to a second clock and has a second time stamp counter for counting the second clock to obtain a second count value. The communication interface is coupled between the first processor and the second processor. The first processor periodically transmits the first count value to the second processor through the communication interface. When the second processor receives the first count value, the second processor adds a preset deviation value and the received first count value of the first processor to obtain a synchronization value, resets the second count value, and then reads an addition result of the synchronization value and the second count value for synchronization.

Owner:VIA ALLIANCE SEMICON CO LTD

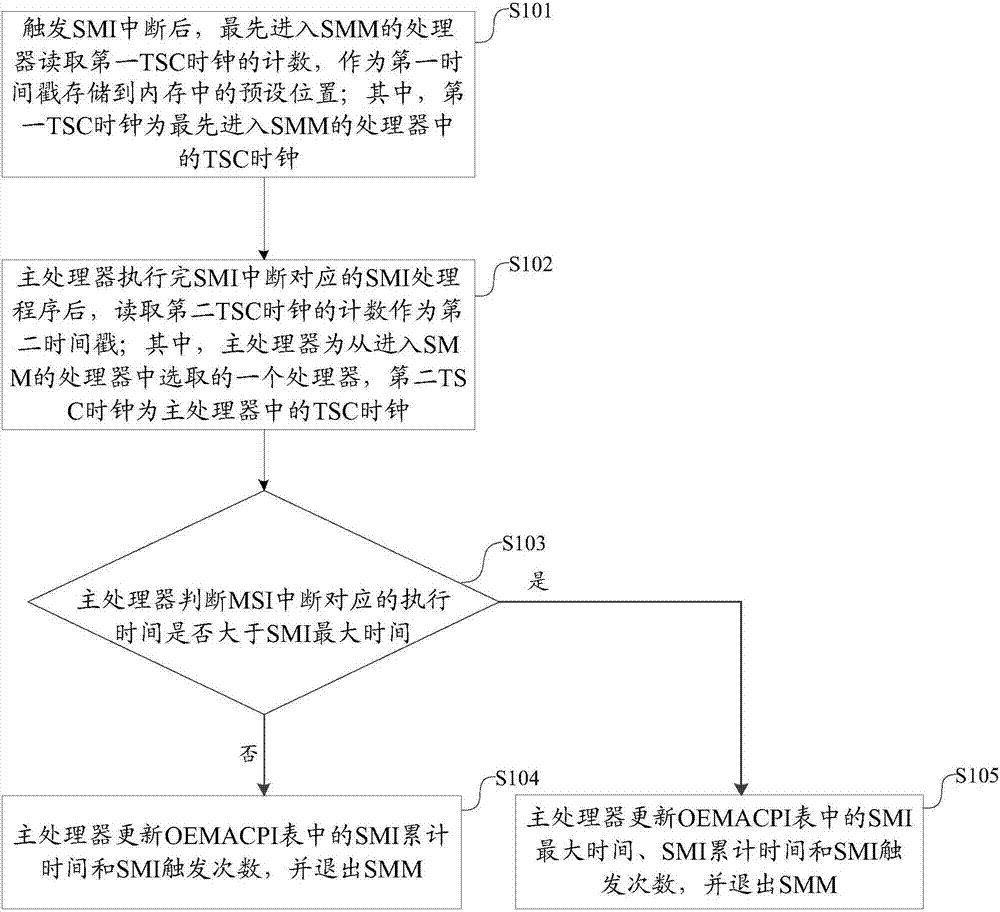

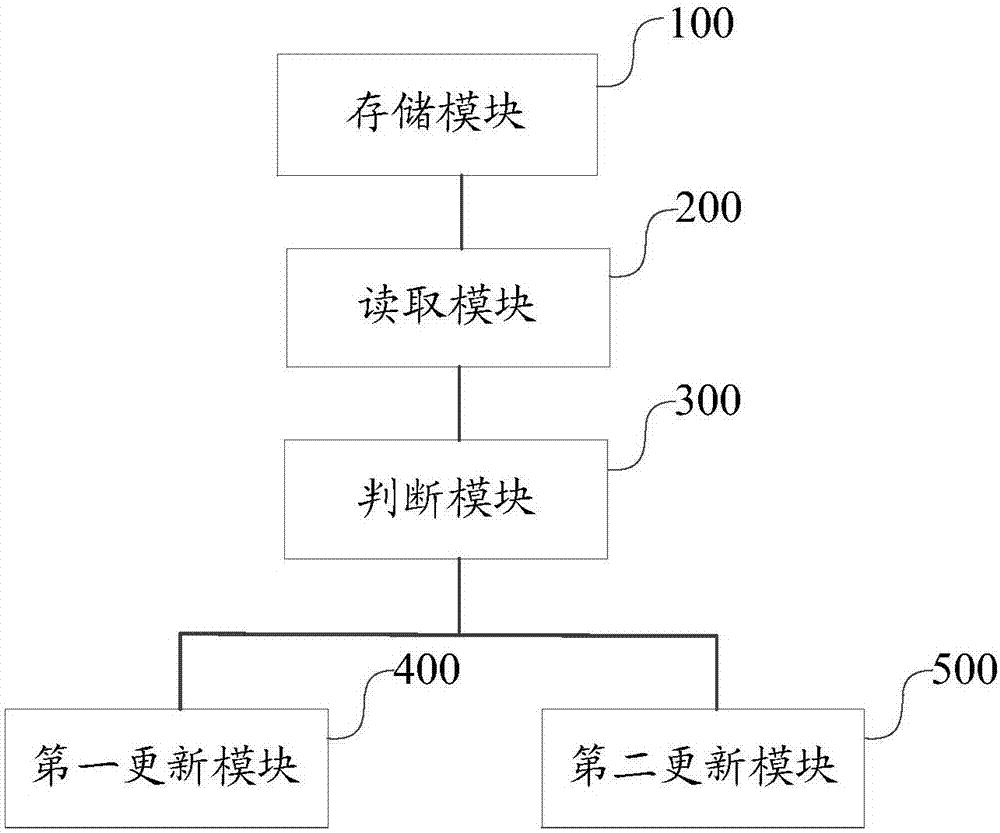

Method and device for measuring system manager interrupt time

ActiveCN107423206AHigh precisionReduce access latencyHardware monitoringAdvanced Configuration and Power InterfaceOriginal equipment manufacturer

The invention discloses a method and a device for measuring the system manager interrupt time. The method includes triggering SMI (system manager interrupt), and then reading the count of first TSC (time stamp counter) clocks in processors of SMM (system management modes); executing SMI processing programs corresponding to the SMI by the aid of main processors and then reading the count of second TSC clocks; judging whether the execution time corresponding to the SMI is longer than the maximum SMI time or not; updating the maximum SMI time, the SMI cumulative time and SMI trigger frequencies in OEMACPI (original equipment manufacturer advanced configuration and power interface) tables if the execution time corresponding to the SMI is longer than the maximum SMI time, and quitting the SMM. The count of the first TSC clocks is used as preset locations for storing first time stamps in memories. The count of the second TSC clocks is used as second time stamps. The method and the device have the advantages that the execution time of the SMI is acquired by the aid of the TSC clocks, accordingly, access delay can be shortened, the accuracy of the obtained execution time of the SMI can be improved, and parameters stored in the OEMACPI tables can be analyzed by operating systems and can be used for measuring the system performance.

Owner:SUZHOU LANGCHAO INTELLIGENT TECH CO LTD

Distributed Control Synchronized Ring Network Architecture

ActiveUS20180145849A1High bandwidthLower latencySynchronisation information channelsTime-division multiplexHigh bandwidthProcessor register

A ring network architecture includes multiple communication nodes configured in a ring. Wave pipelining is used to provide for high bandwidth and low latency on-chip communications. Each node implements a source-synchronized clocking scheme, such that there is no need to build an extensive low skew clock-tree across a large die area. A single reference clock signal is generated within a root node, and is routed through each of the nodes of the ring network in a unidirectional manner. Each node includes a timestamp counter and a color bit register, which store values that enable the node to resolve ordered transaction messages issued by the other nodes in a precise order, even though the nodes are operating independently, and receive the various transaction messages in totally different timing orders. Because the control logic is distributed among the nodes, no centralized controller is necessary.

Owner:DEGIRUM CORP

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com