Time synchronous pluggable transceiver

A transceiver and time stamp technology, applied in synchronization devices, multiplexing communication, time division multiplexing systems, etc., can solve the problems of damaging the synchronous Ethernet clock chain and affecting the performance of the IEEE1588 standard.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0025] For the sake of brevity, all references to Ethernet below refer to electrical Ethernet unless optical Ethernet is specifically mentioned.

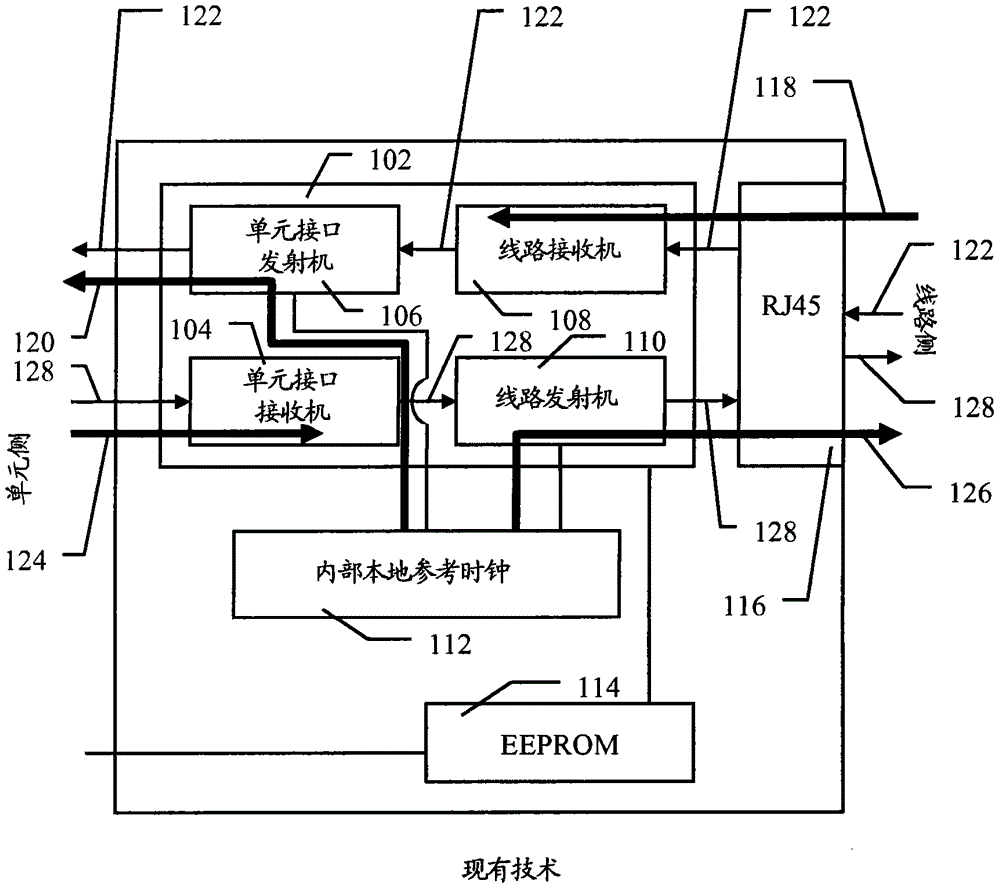

[0026] As mentioned earlier, in Electrical Ethernet SFPs, Ethernet signal processing at the physical layer breaks the Synchronous Ethernet (syncE) clock chain. figure 1 This situation is illustrated, where the figure depicts a basic block diagram of a known Electrical Ethernet SFP.

[0027] Physical layer (PHY) preprocessing in the SFP results in the inability to provide recovered SyncE timing in the receive direction to the near-end Ethernet line card located at the SFP host device, and this portion of the electronics on the SFP printed circuit board is marked as 102. Such as figure 1 As shown, electrical Ethernet frame 122 arrives at SFP 110 via RJ45 jack 116 . These electrical Ethernet frames 122 have SyncE timing indicated here at 118 . While the electrical Ethernet frame 122 is propagated through the electronics (line recei...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com