Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

143 results about "Self-aligned gate" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

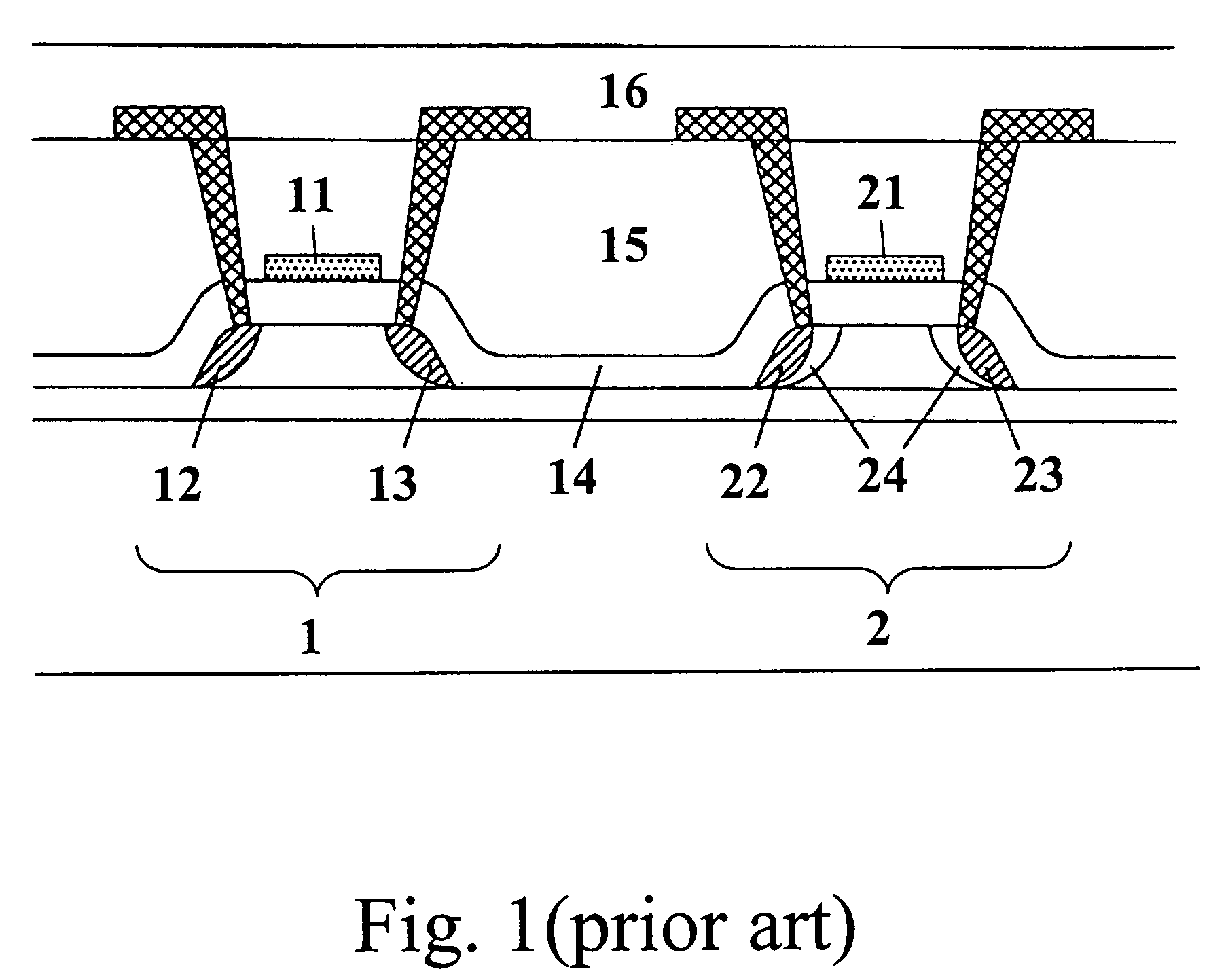

In electronics, a self-aligned gate is a transistor manufacturing feature whereby a refractory gate electrode region of a MOSFET (metal–oxide–semiconductor field-effect transistor) is used as a mask for the doping of the source and drain regions. This technique ensures that the gate will slightly overlap the edges of the source and drain.

Tunneling effect transistor with self-aligned gate

ActiveUS7700466B2Semiconductor/solid-state device detailsSemiconductor/solid-state device manufacturingField-effect transistorP–n junction

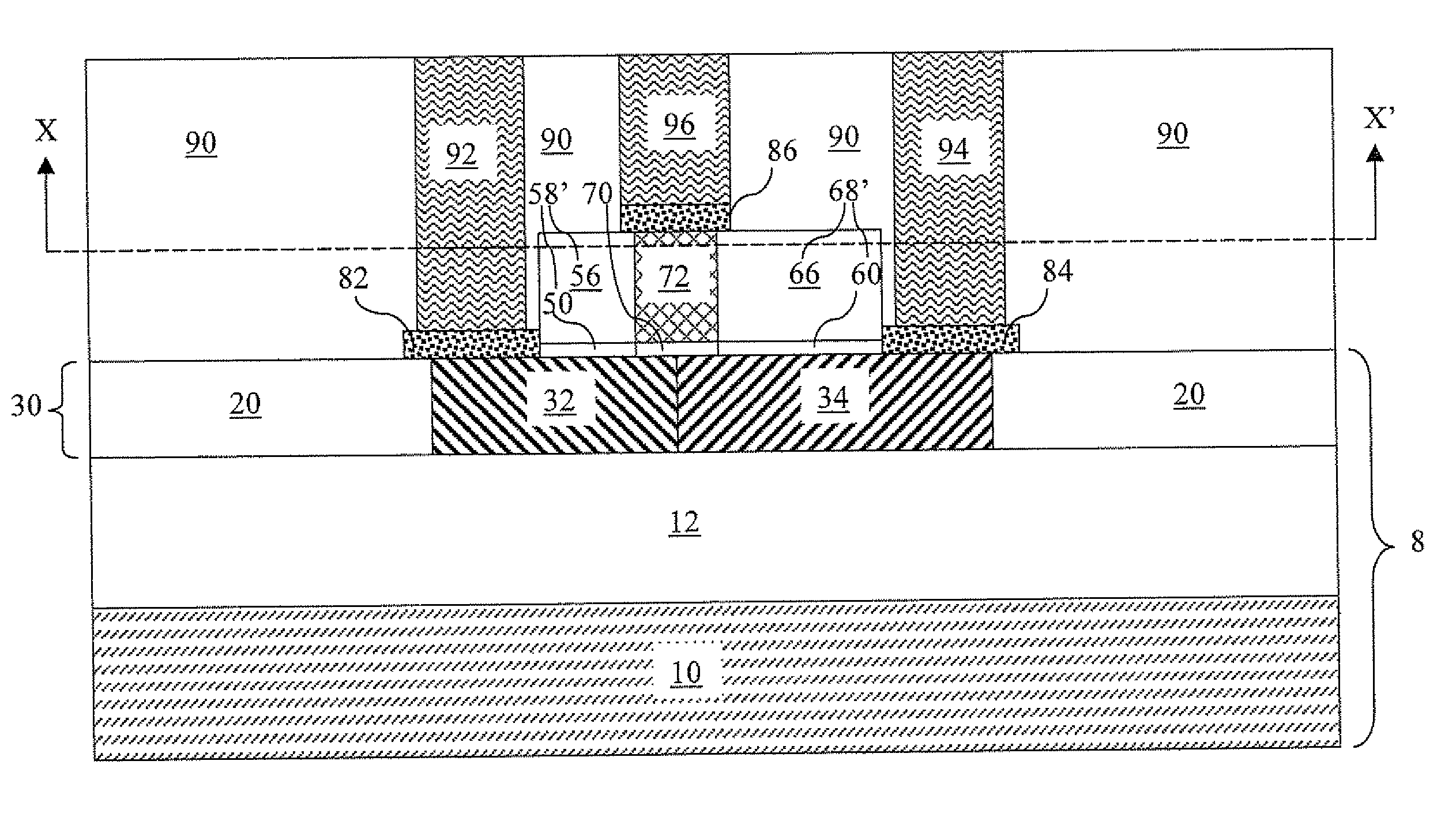

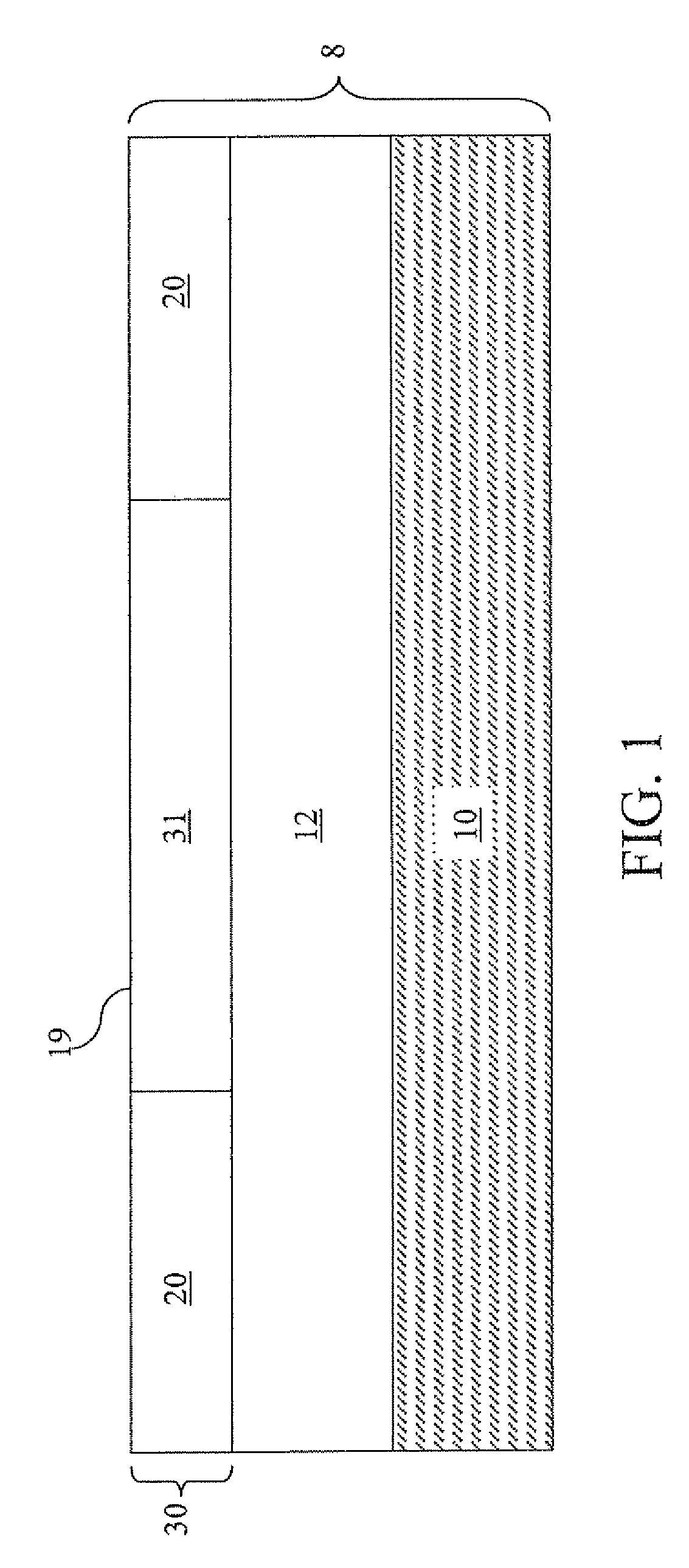

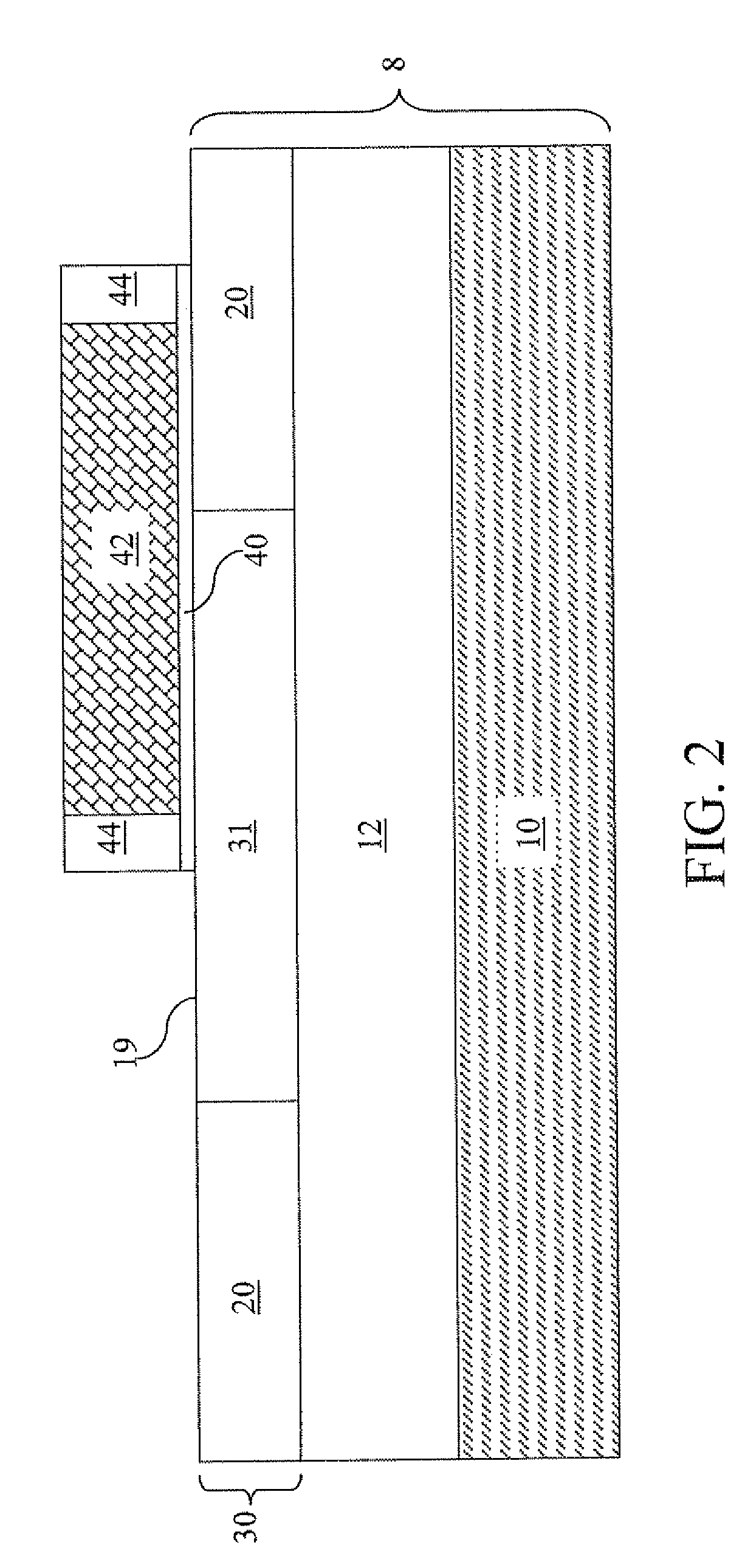

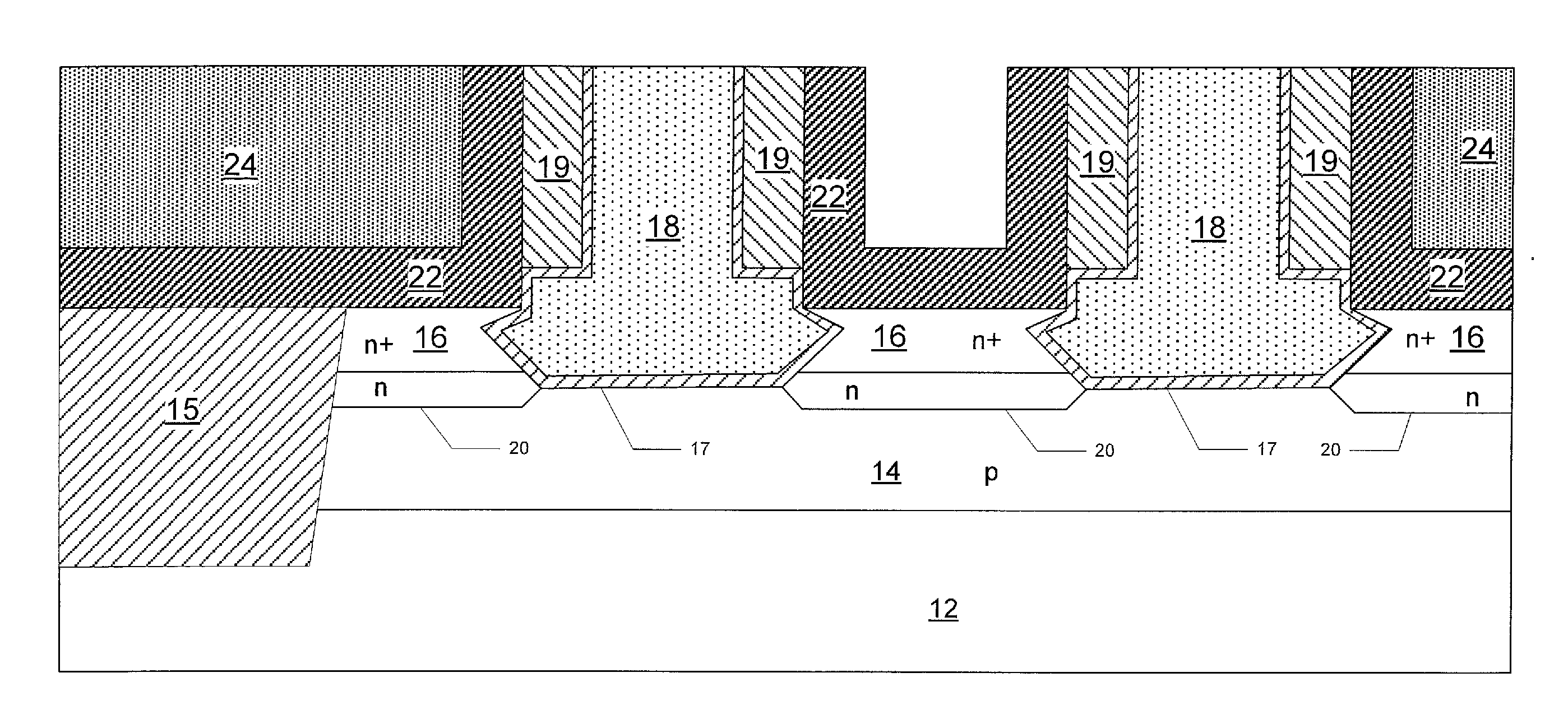

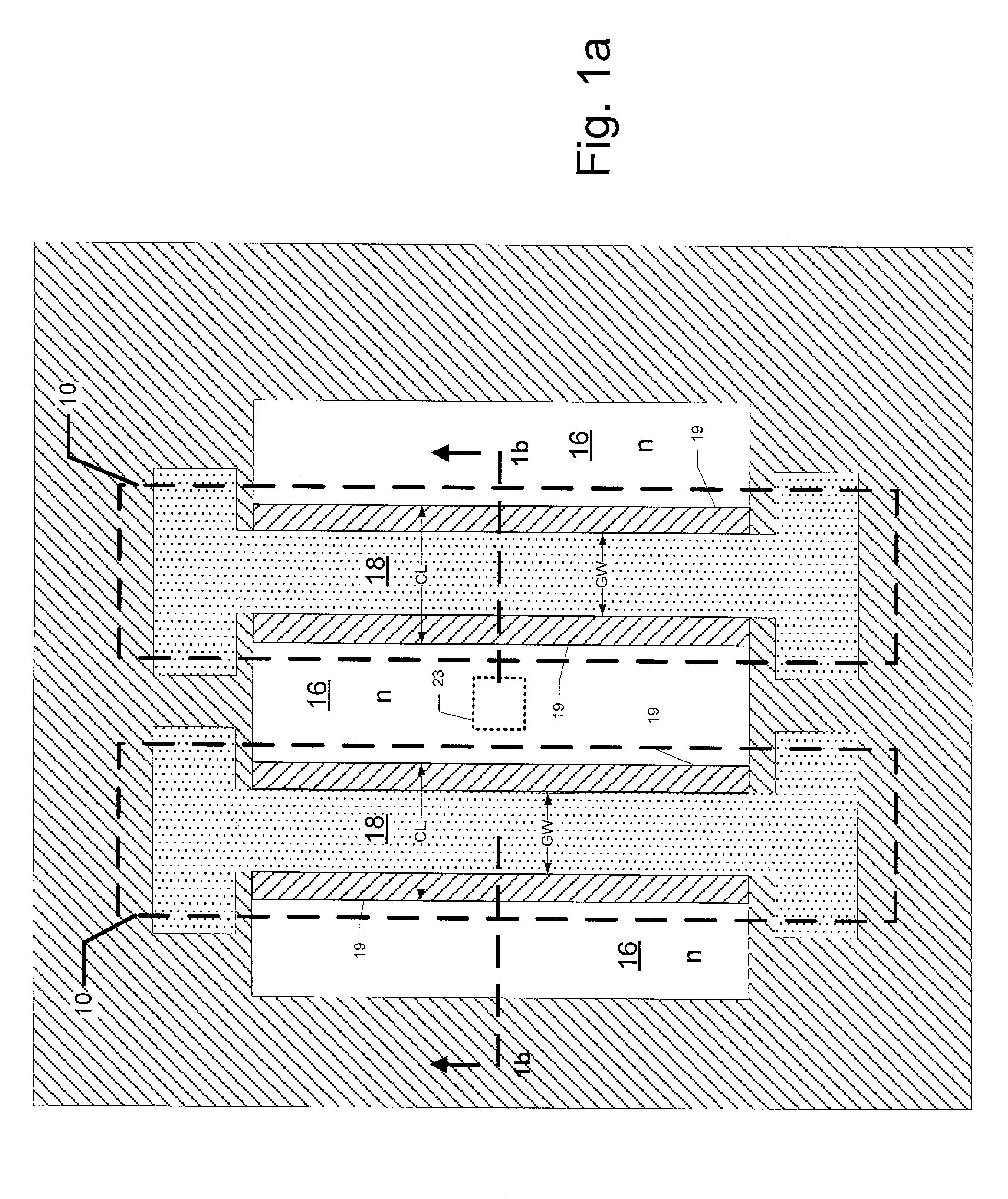

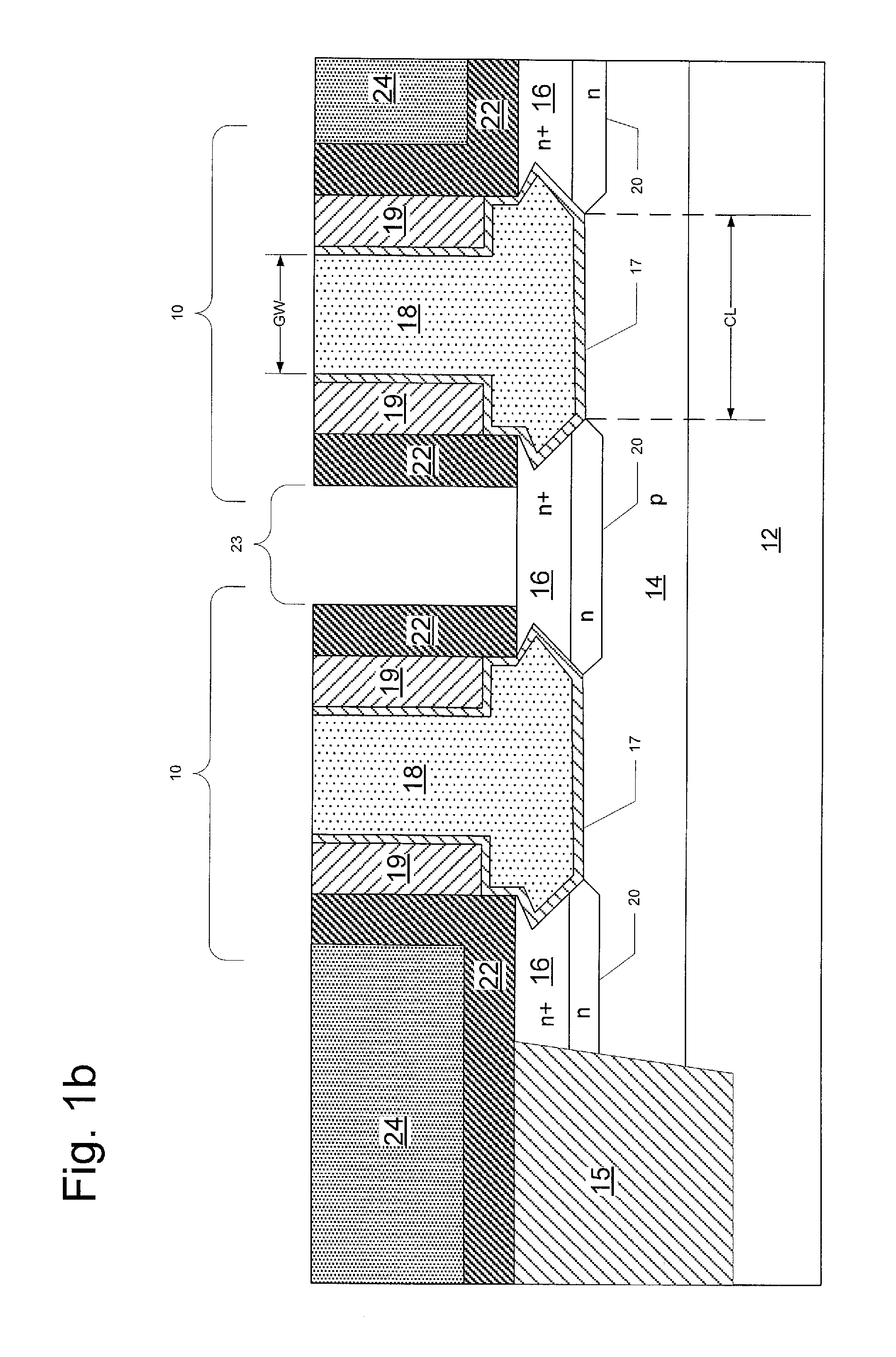

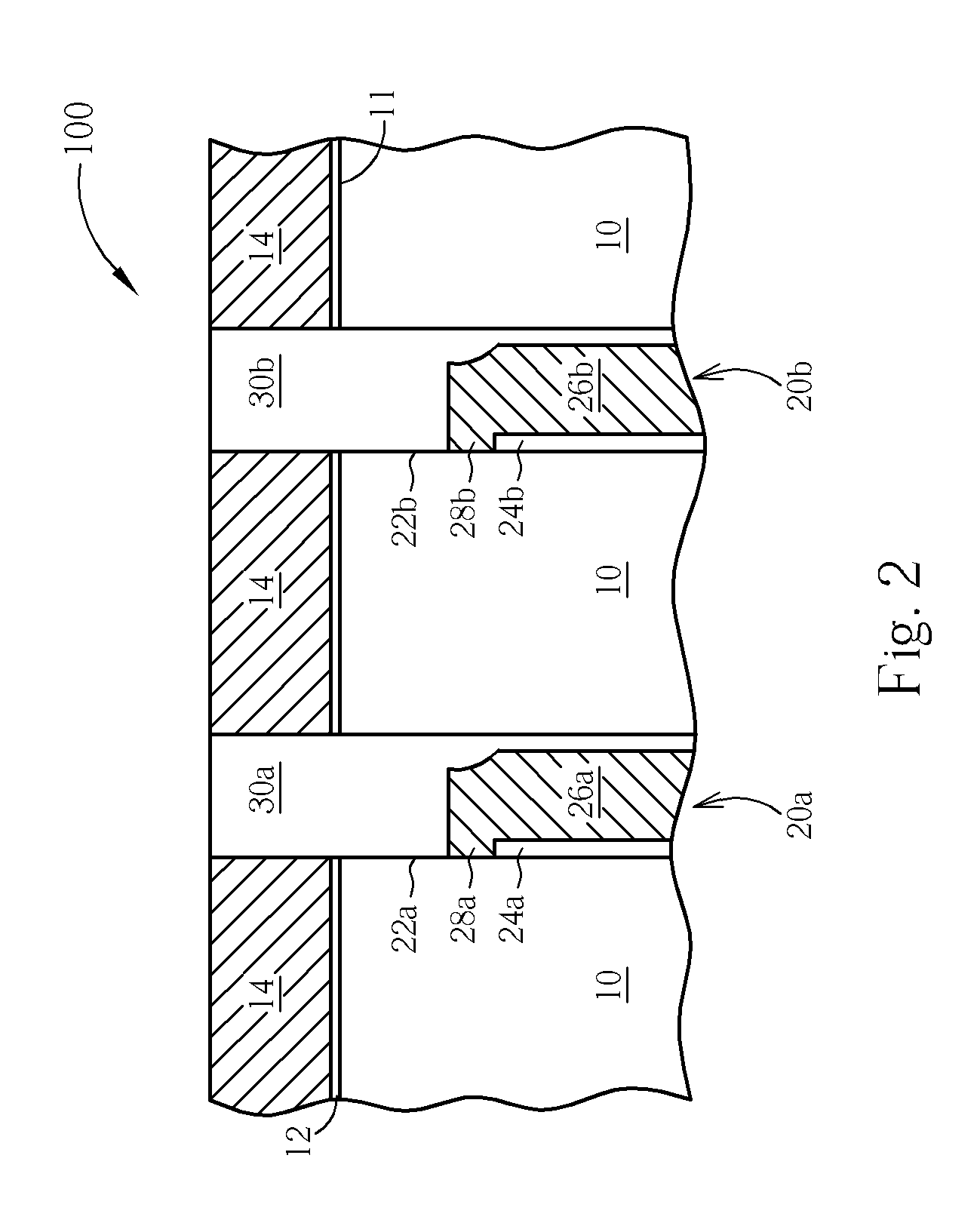

In one embodiment, a mandrel and an outer dummy spacer may be employed to form a first conductivity type region. The mandrel is removed to form a recessed region wherein a second conductivity type region is formed. In another embodiment, a mandrel is removed from within shallow trench isolation to form a recessed region, in which an inner dummy spacer is formed. A first conductivity type region and a second conductivity region are formed within the remainder of the recessed region. An anneal is performed so that the first conductivity type region and the second conductivity type region abut each other by diffusion. A gate electrode is formed in self-alignment to the p-n junction between the first and second conductivity regions. The p-n junction controlled by the gate electrode, which may be sublithographic, constitutes an inventive tunneling effect transistor.

Owner:TWITTER INC

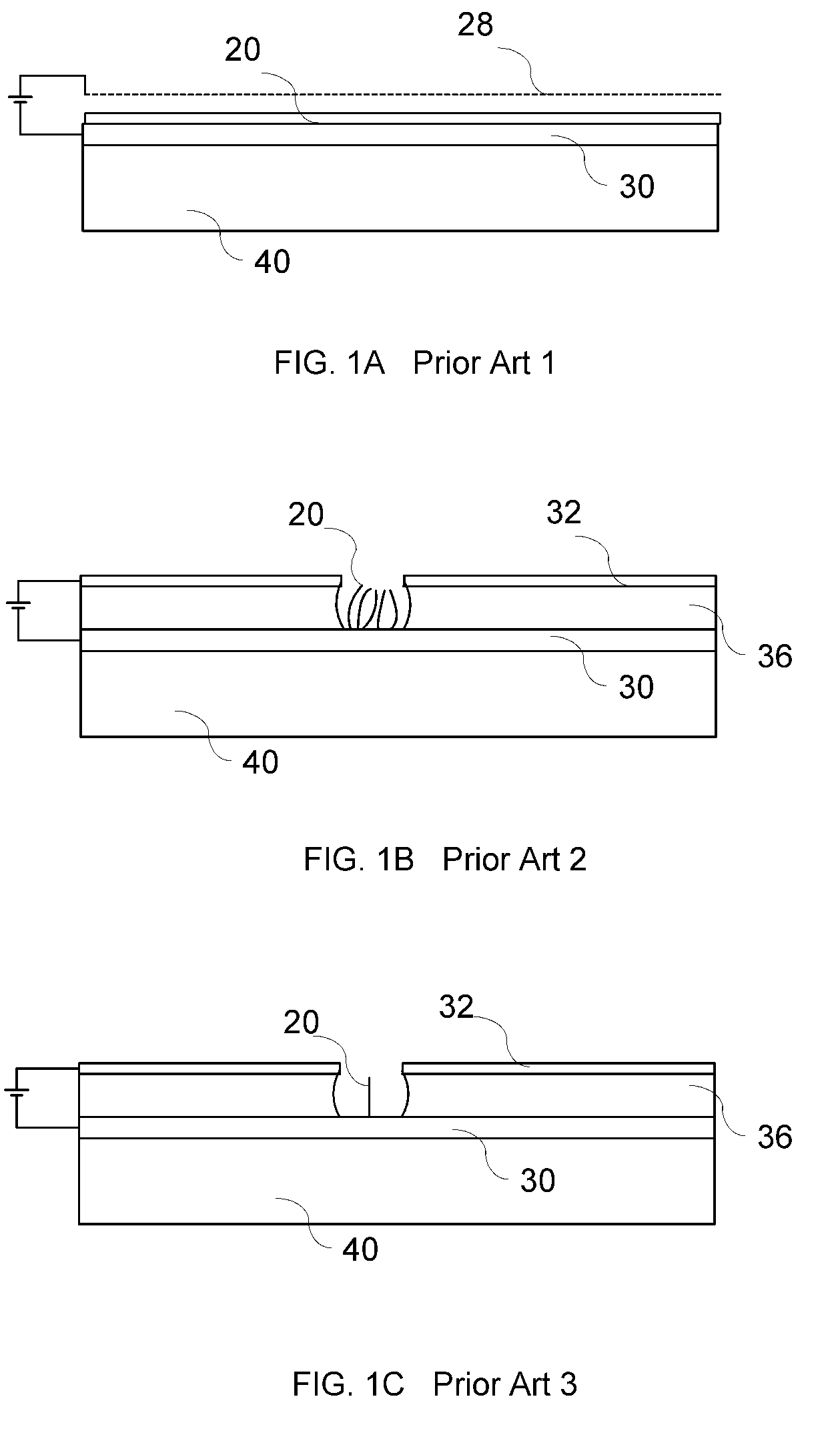

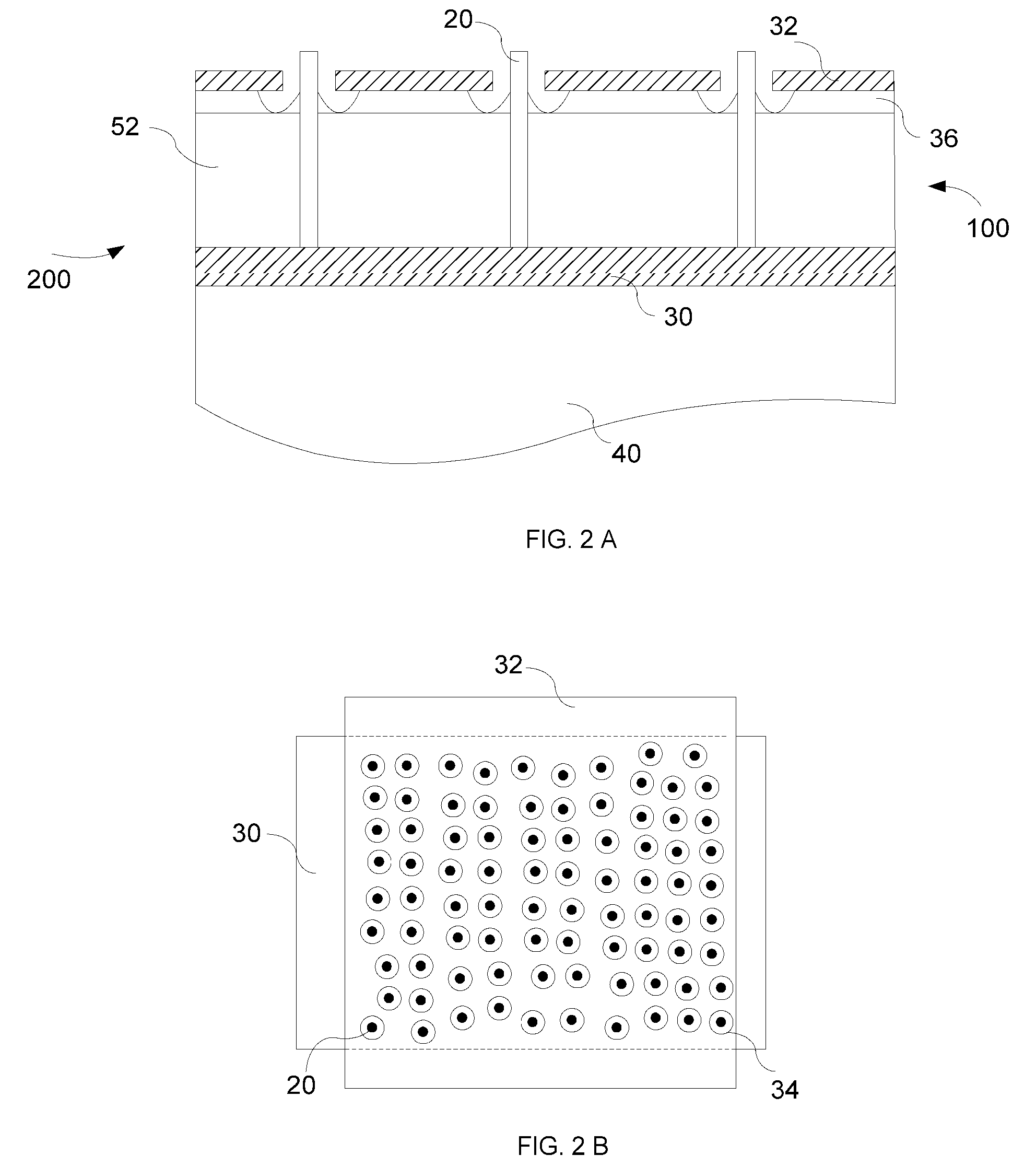

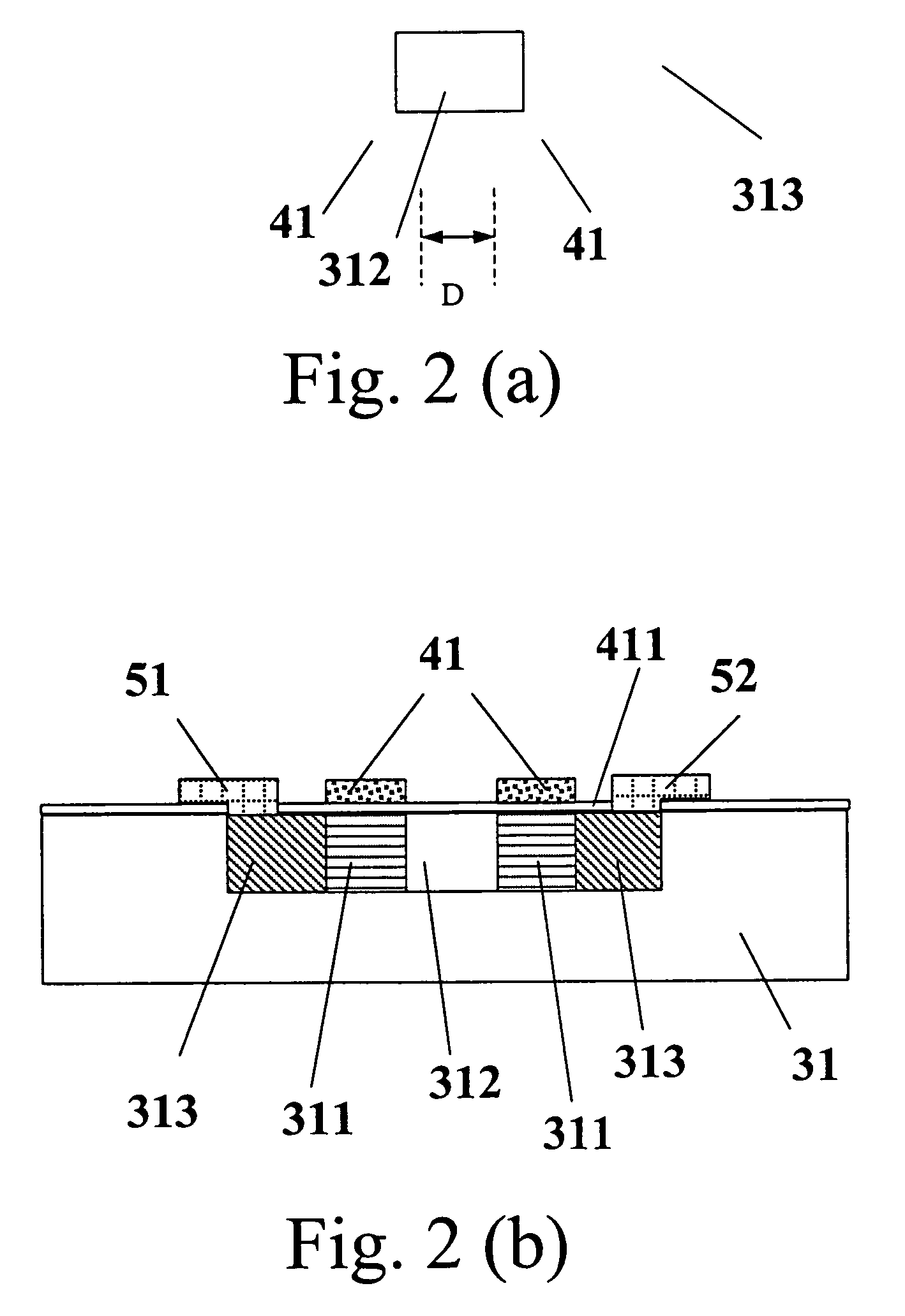

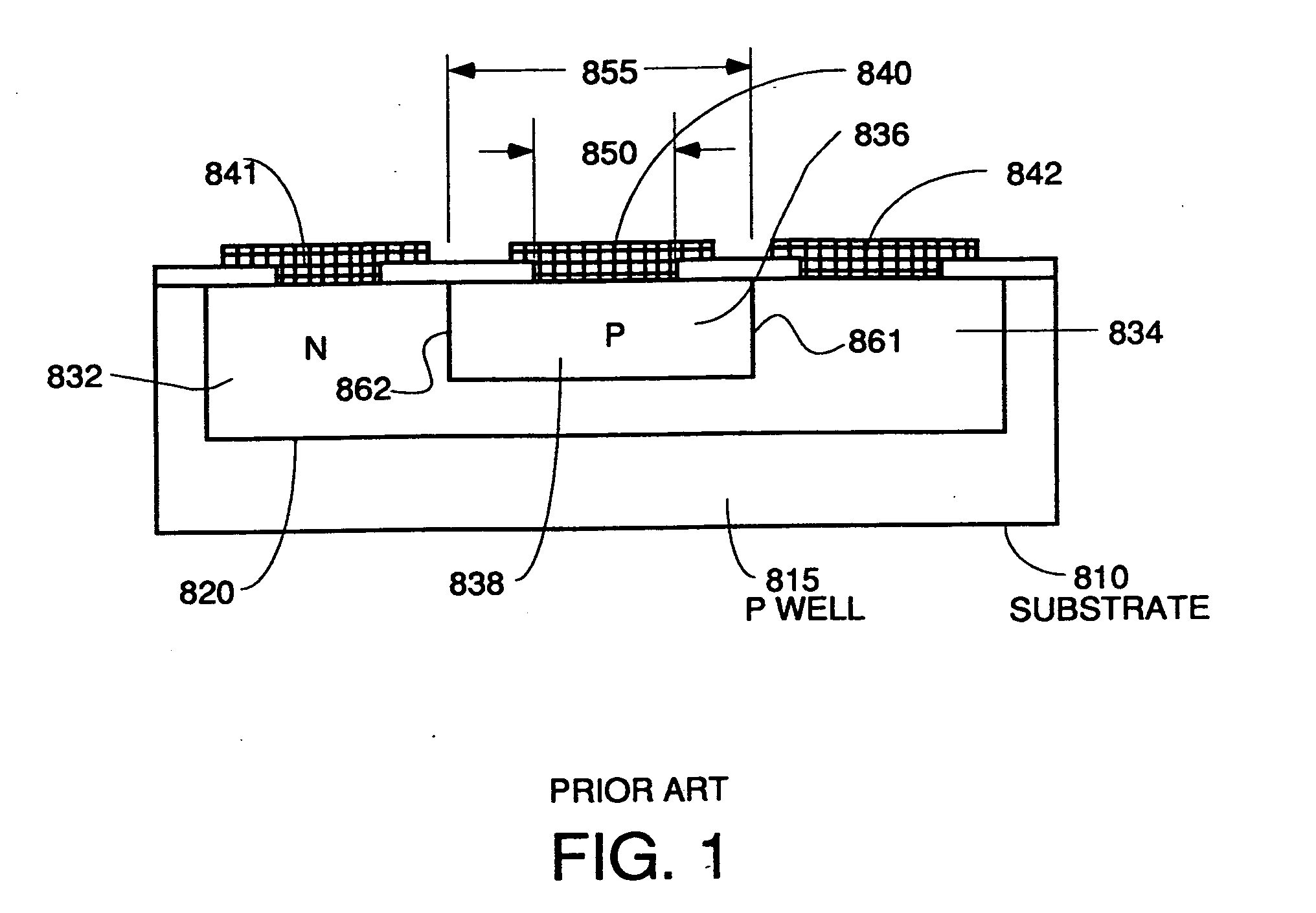

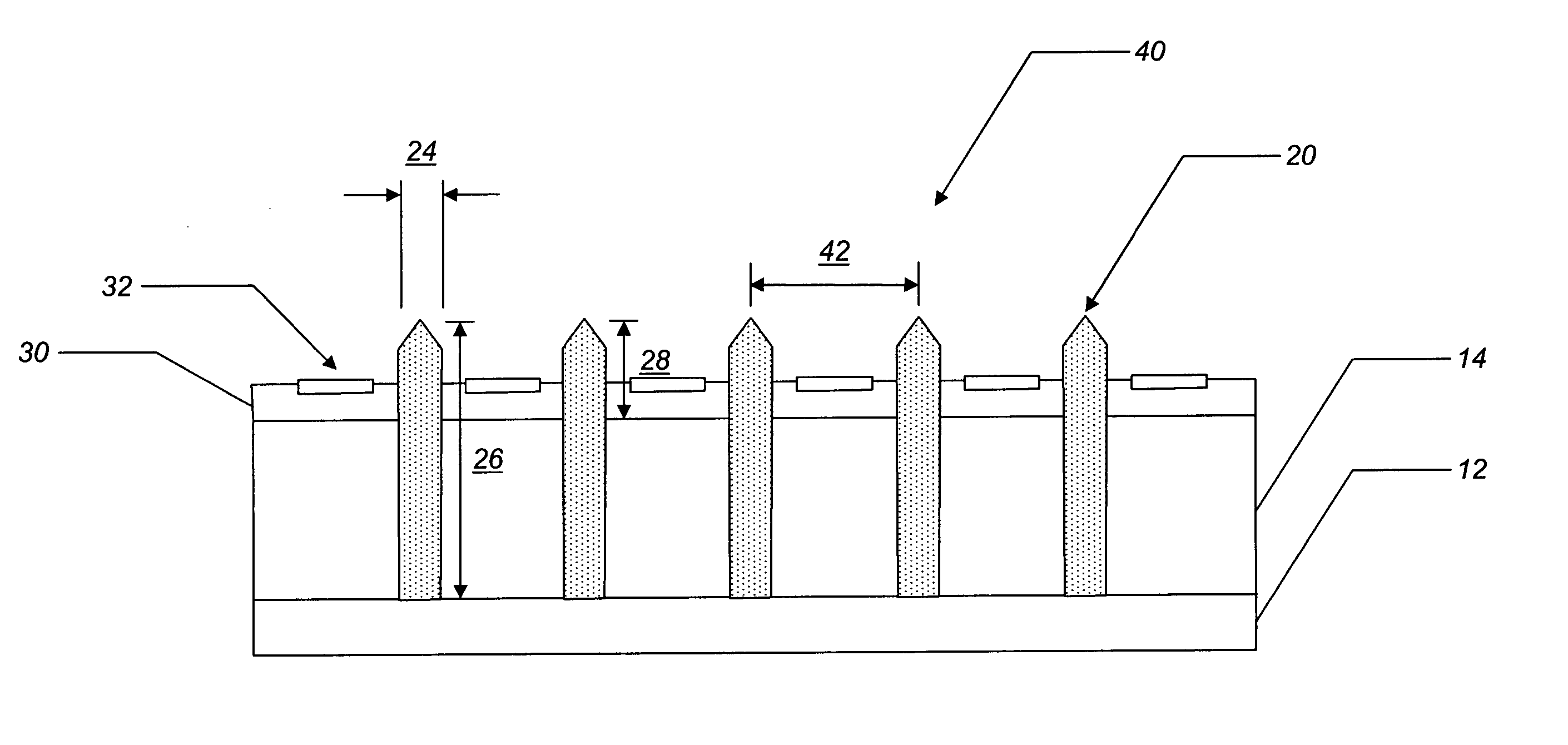

Low voltage electron source with self aligned gate apertures, fabrication method thereof, and luminous display using the electron source

InactiveUS20050127351A1Narrow diameterHigh densityNanoinformaticsThermionic cathodesHigh current densityHigh energy

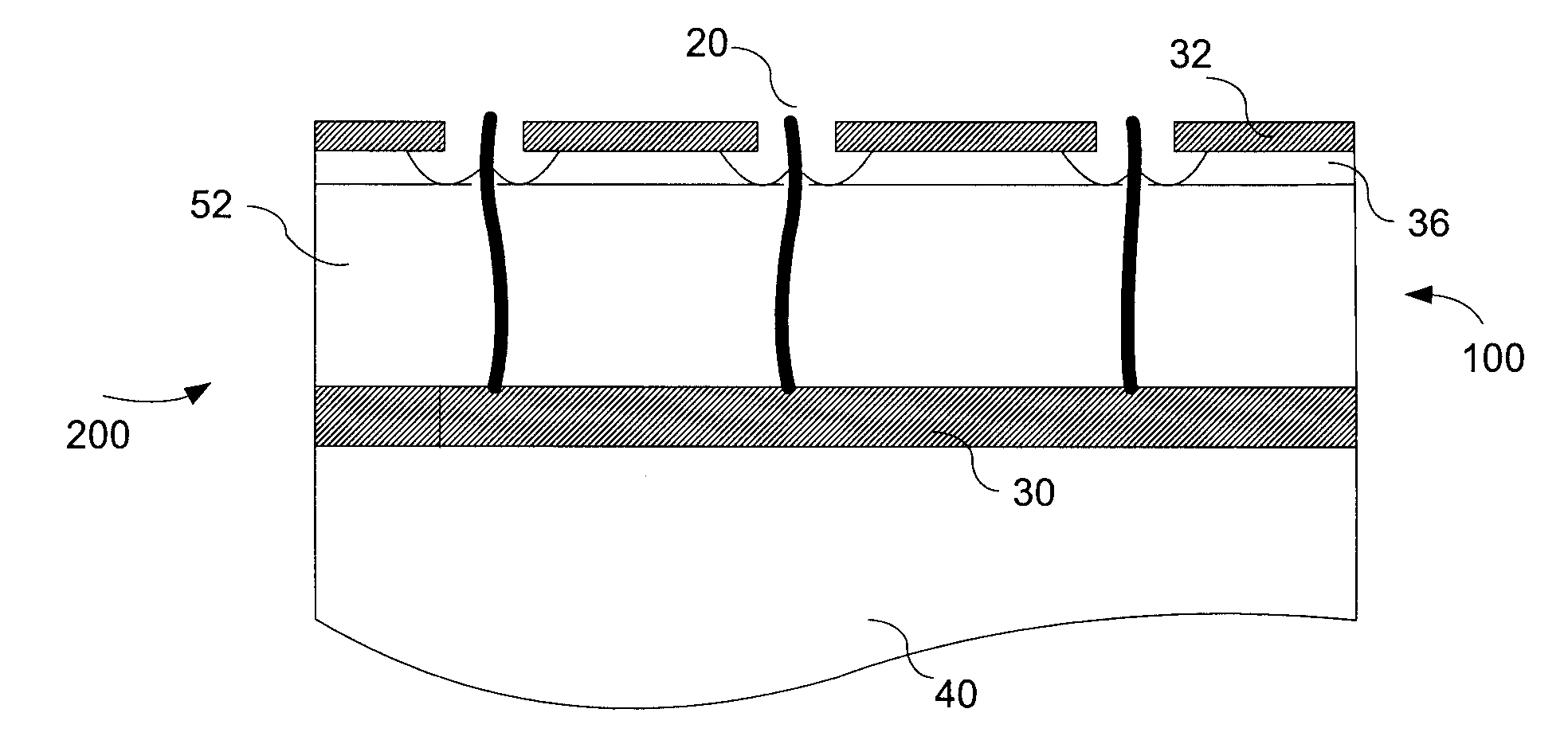

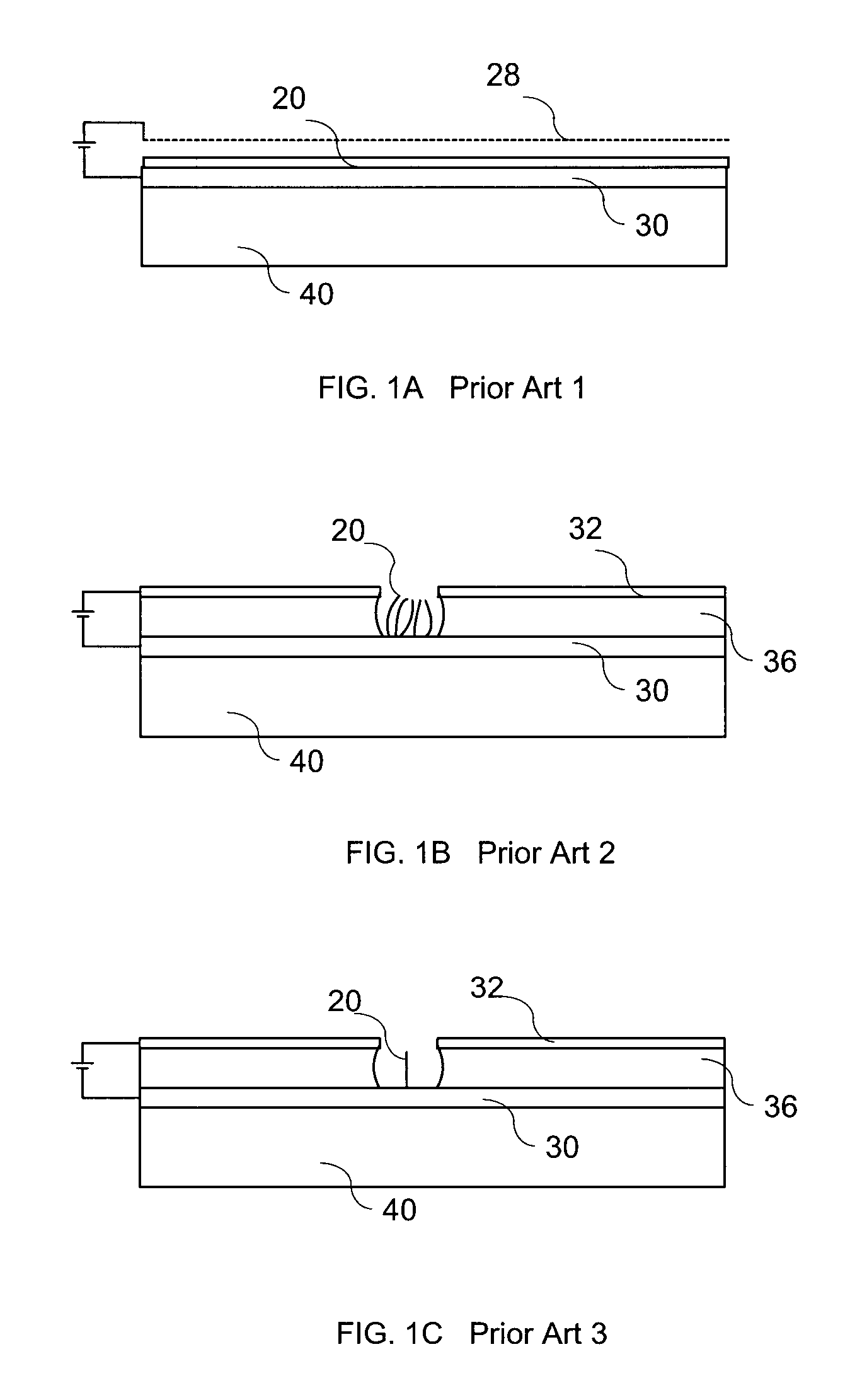

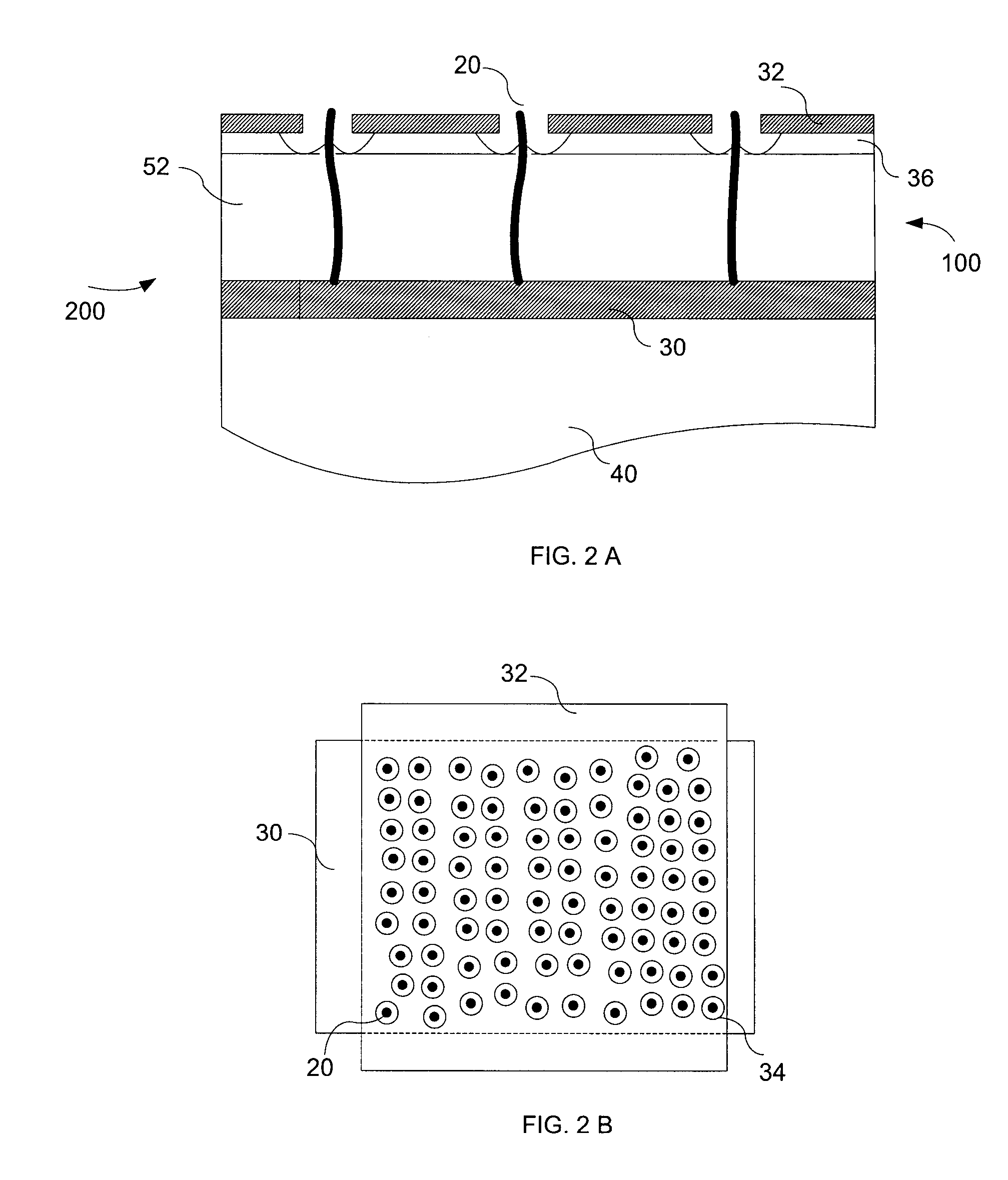

An electron source include a first cathode electrode disposed over a substrate and terminated to provide electrons; an emitter layer disposed over the cathode electrode and formed from one or plurality vertically aligned and mono-dispersed nano-structures that are truncated to the same length, embedded in a solid matrix and protruding above the surface for emitting electrons; an insulator disposed over the emitter layer and having one or plurality of apertures, each is self-aligned with and exposes one nano-structure in the emitter layer; and a second gate electrode disposed over the insulator, having one or plurality of apertures self-aligned with the apertures in the insulator and terminated to extract electrons from the exposed nano-structures through the apertures. The gate aperture is substantially less than one micrometer and the gated nano-structures can have a density on the order of 108 / cm2. Such an electron source can be modulated with an extra low voltage, emits electrons with high current density and high uniformity, and operates with high energy-efficiency and long lifetime.

Owner:TOLT ZHIDAN LI

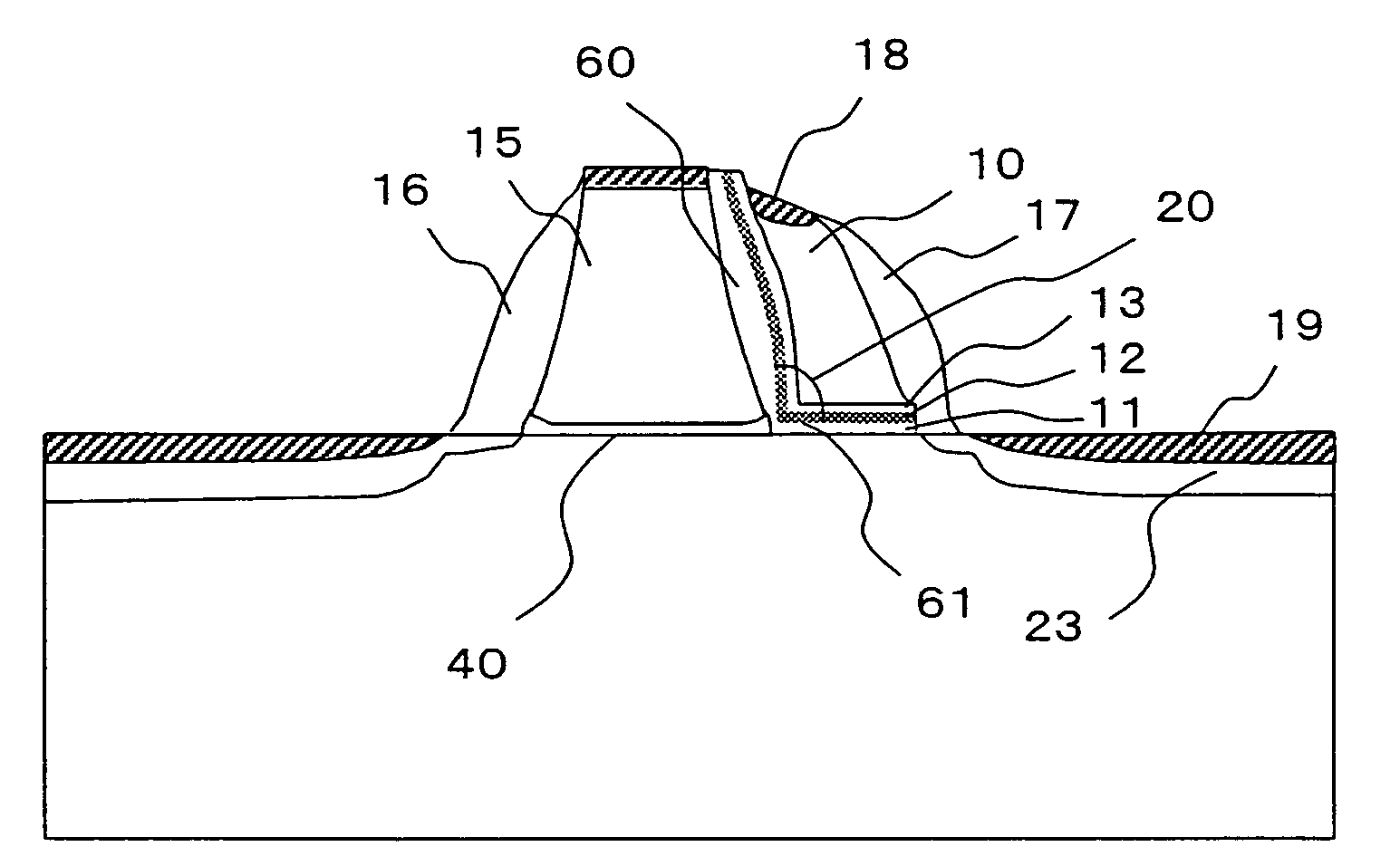

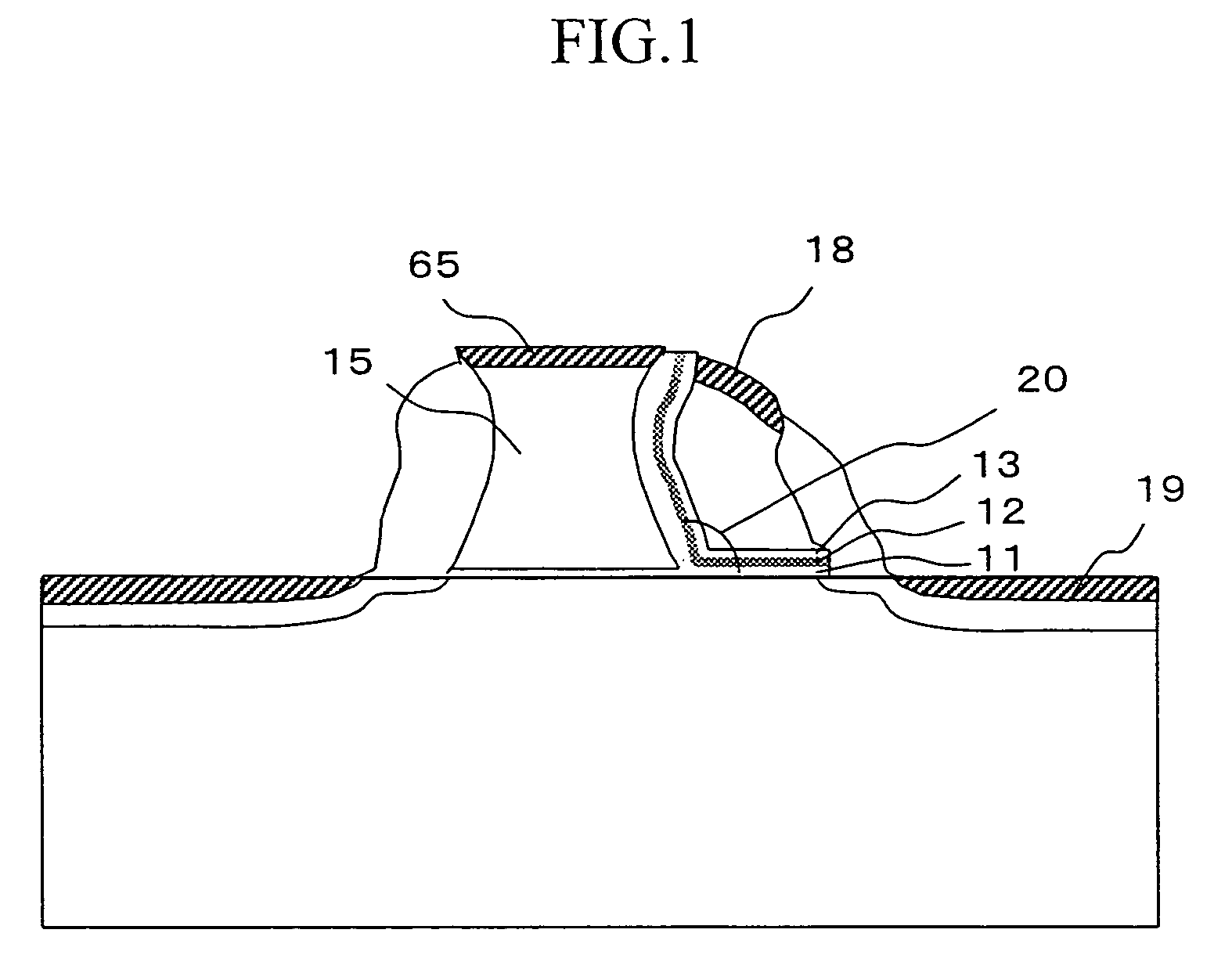

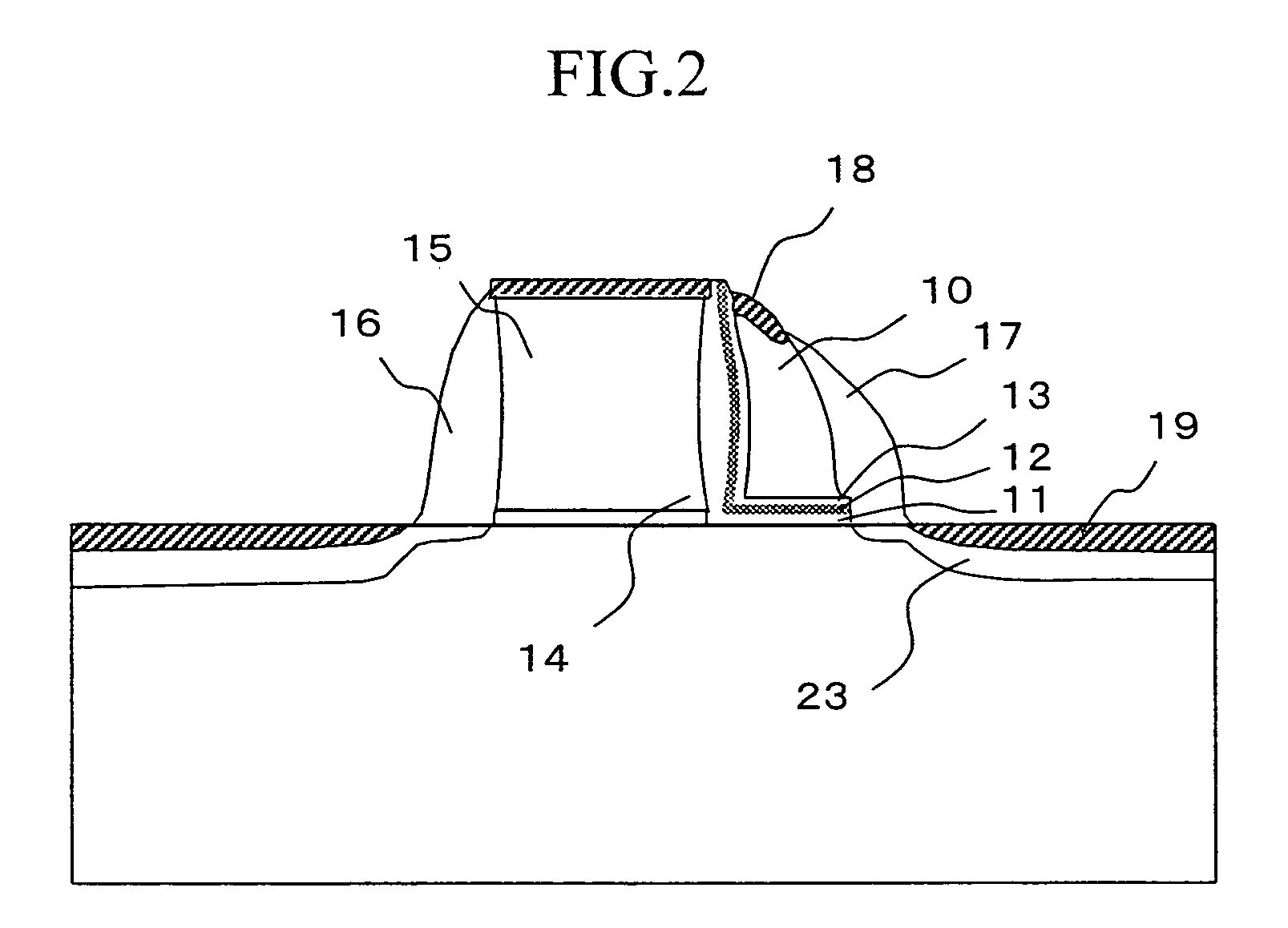

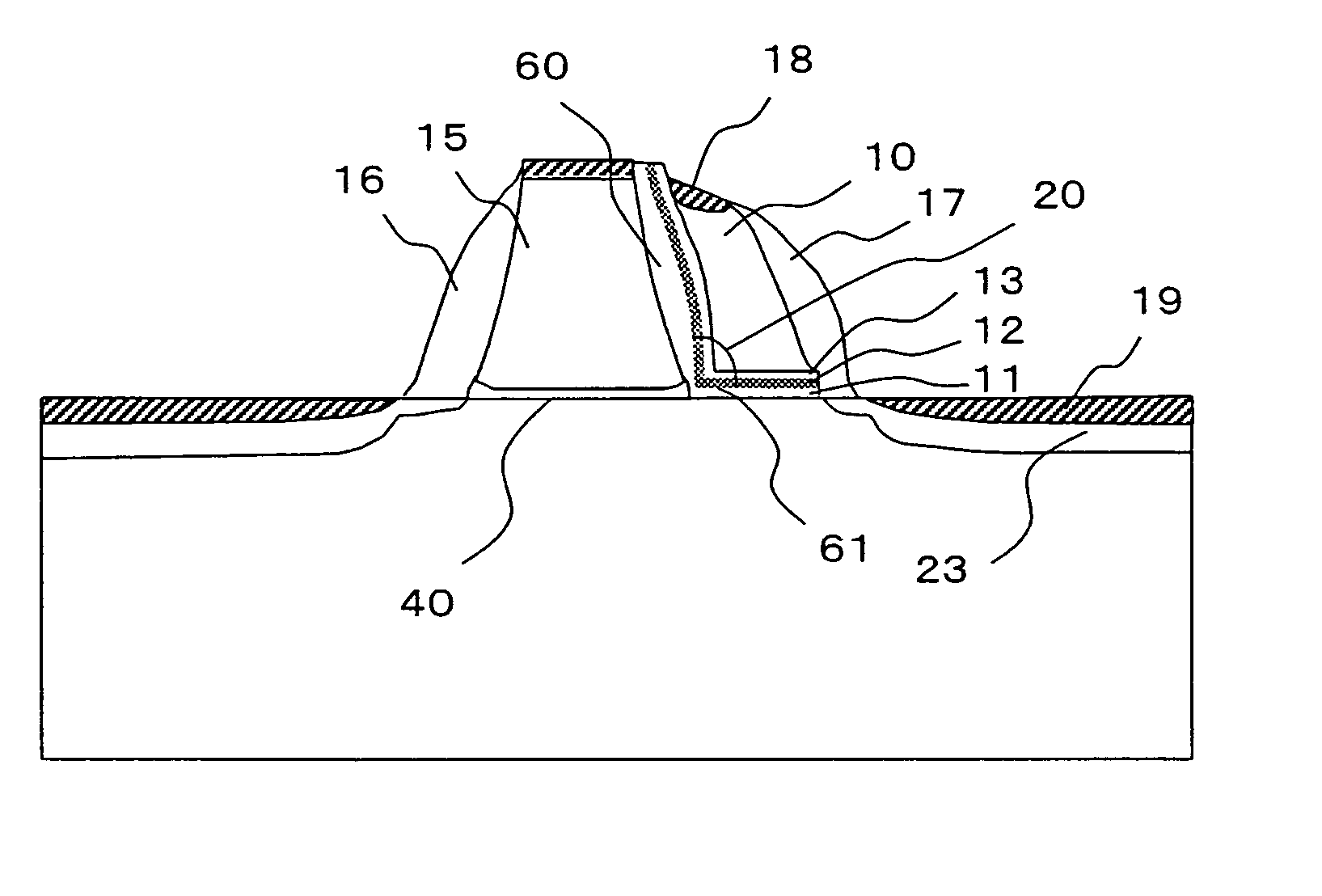

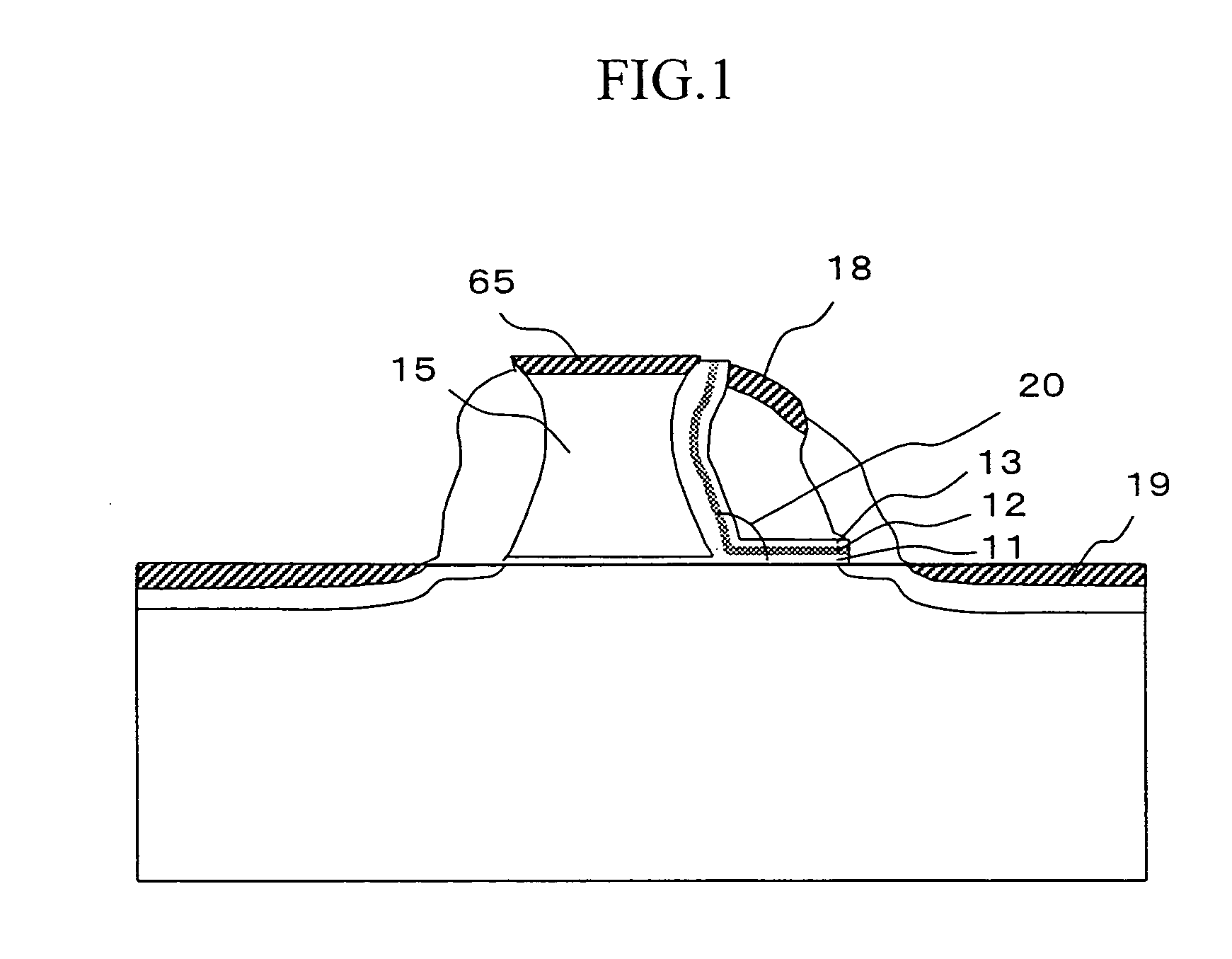

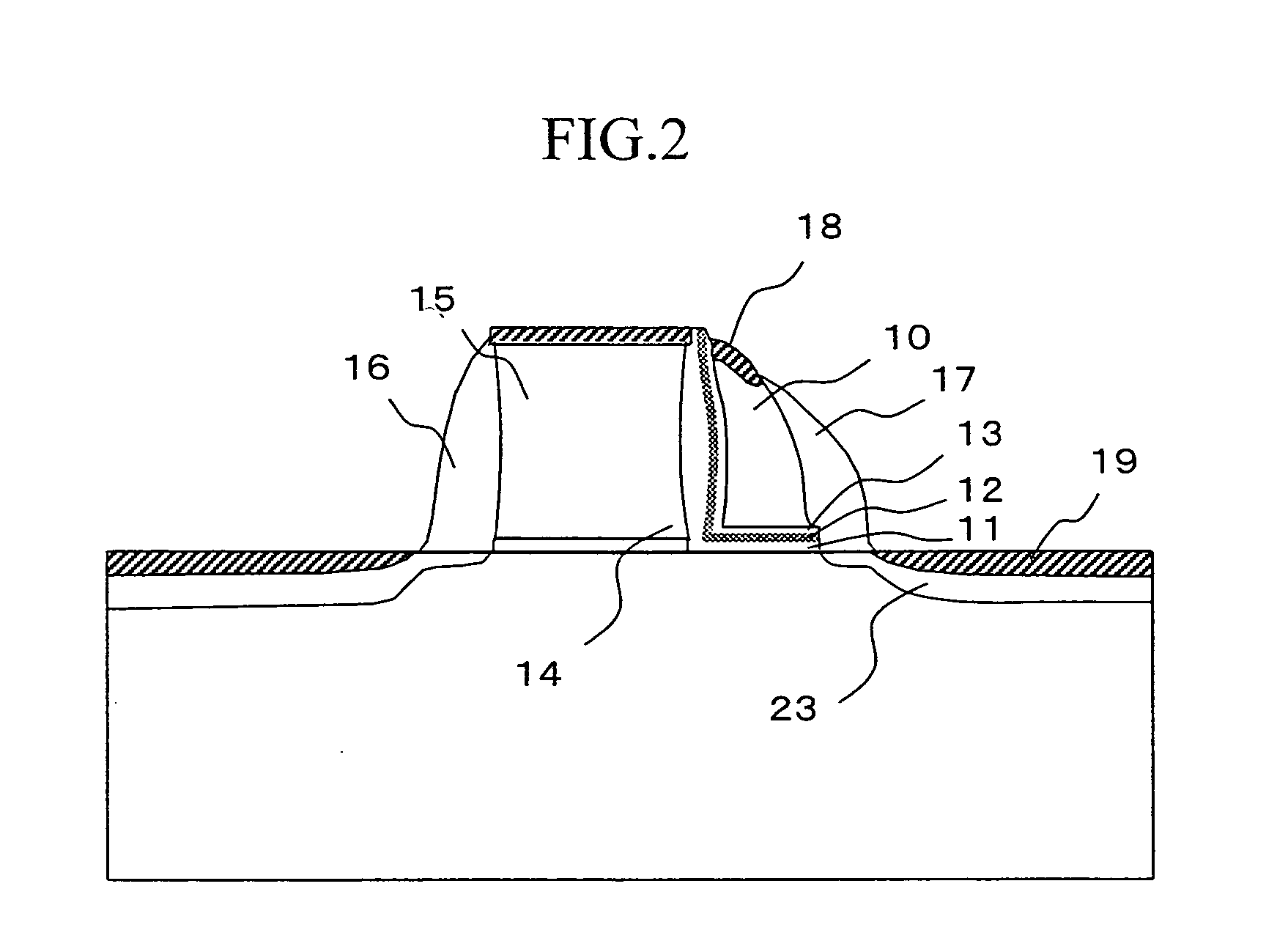

Nonvolatile semiconductor memory device with tapered sidewall gate and method of manufacturing the same

ActiveUS7235441B2Increase deposition thicknessReduce thicknessTransistorSolid-state devicesSalicideEngineering

In a split gate type nonvolatile memory cell in which a MOS transistor for a nonvolatile memory using a charge storing film and a MOS transistor for selecting it are adjacently formed, the charge storing characteristic is improved and the resistance of the gate electrode is reduced. In order to prevent the thickness reduction at the corner portion of the charge storing film and improve the charge storing characteristic, a taper is formed on the sidewall of the select gate electrode. Also, in order to stably perform a silicide process for reducing the resistance of the self-aligned gate electrode, the sidewall of the select gate electrode is recessed. Alternatively, a discontinuity is formed between the upper portion of the self-aligned gate electrode and the upper portion of the select gate electrode.

Owner:RENESAS ELECTRONICS CORP

Graphene transistor with a self-aligned gate

ActiveUS20120056161A1Semiconductor/solid-state device manufacturingSemiconductor devicesConductive materialsDeposition process

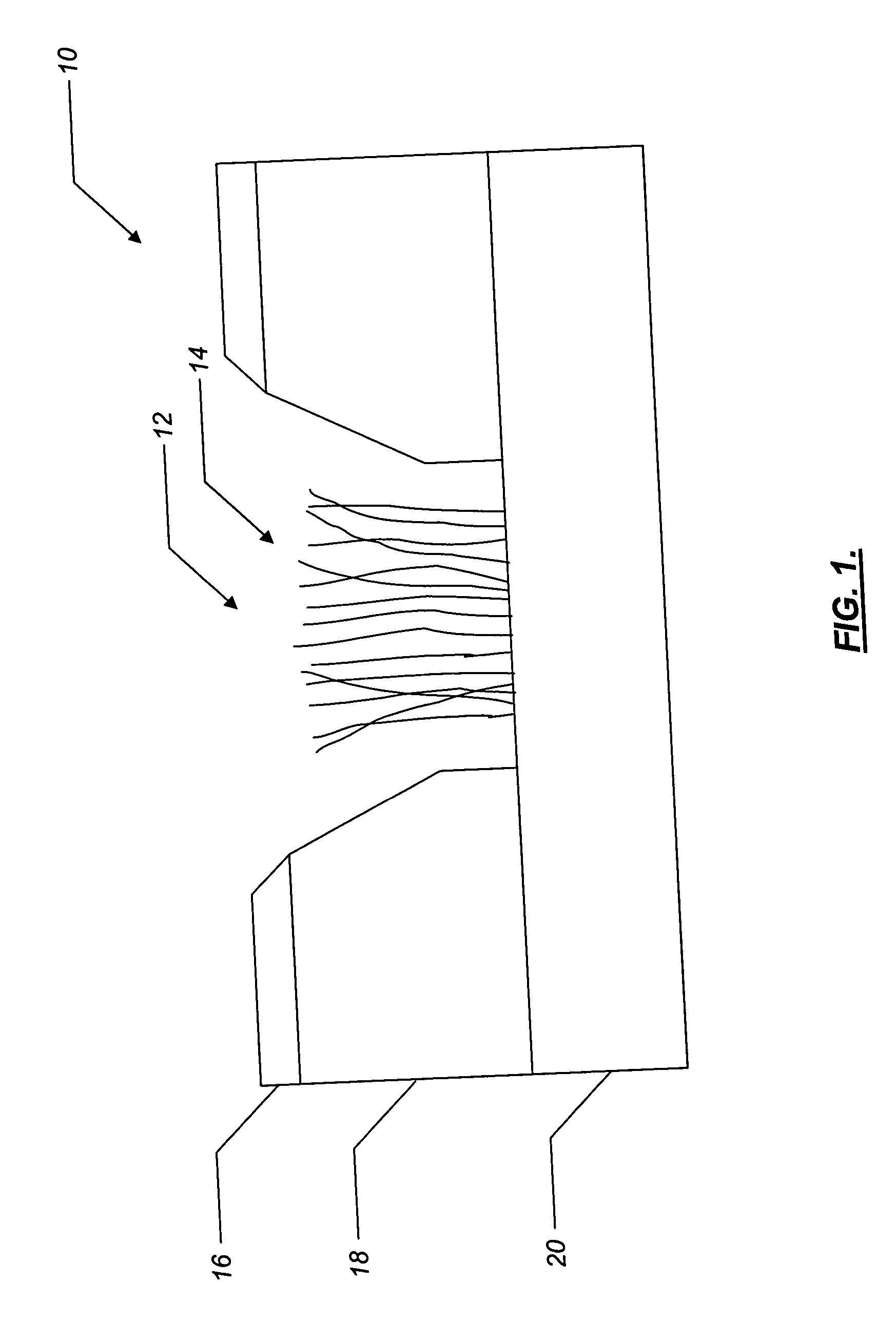

A graphene-based field effect transistor includes source and drain electrodes that are self-aligned to a gate electrode. A stack of a seed layer and a dielectric metal oxide layer is deposited over a patterned graphene layer. A conductive material stack of a first metal portion and a second metal portion is formed above the dielectric metal oxide layer. The first metal portion is laterally etched employing the second metal portion, and exposed portions of the dielectric metal oxide layer are removed to form a gate structure in which the second metal portion overhangs the first metal portion. The seed layer is removed and the overhang is employed to shadow proximal regions around the gate structure during a directional deposition process to form source and drain electrodes that are self-aligned and minimally laterally spaced from edges of the gate electrode.

Owner:GLOBALFOUNDRIES US INC

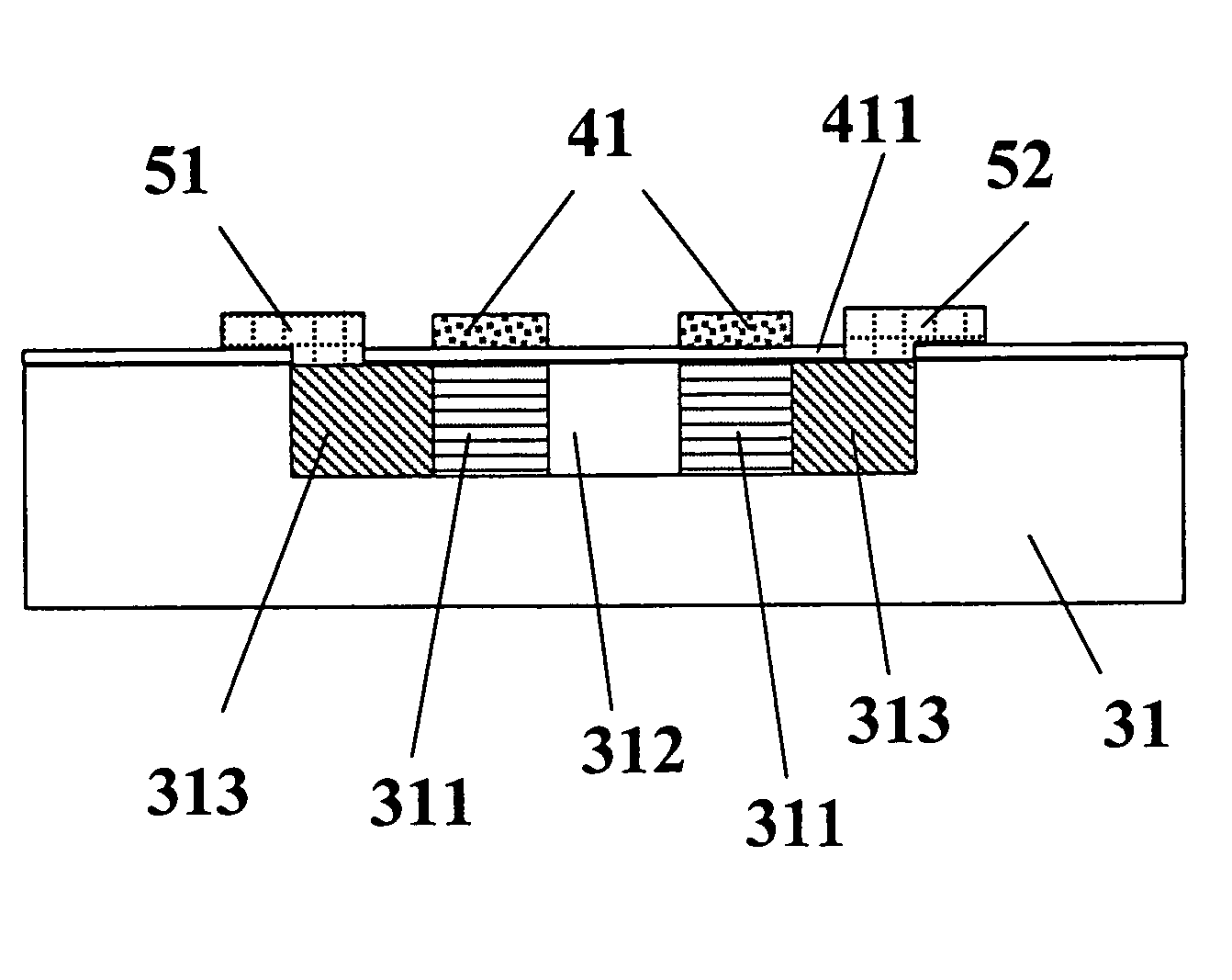

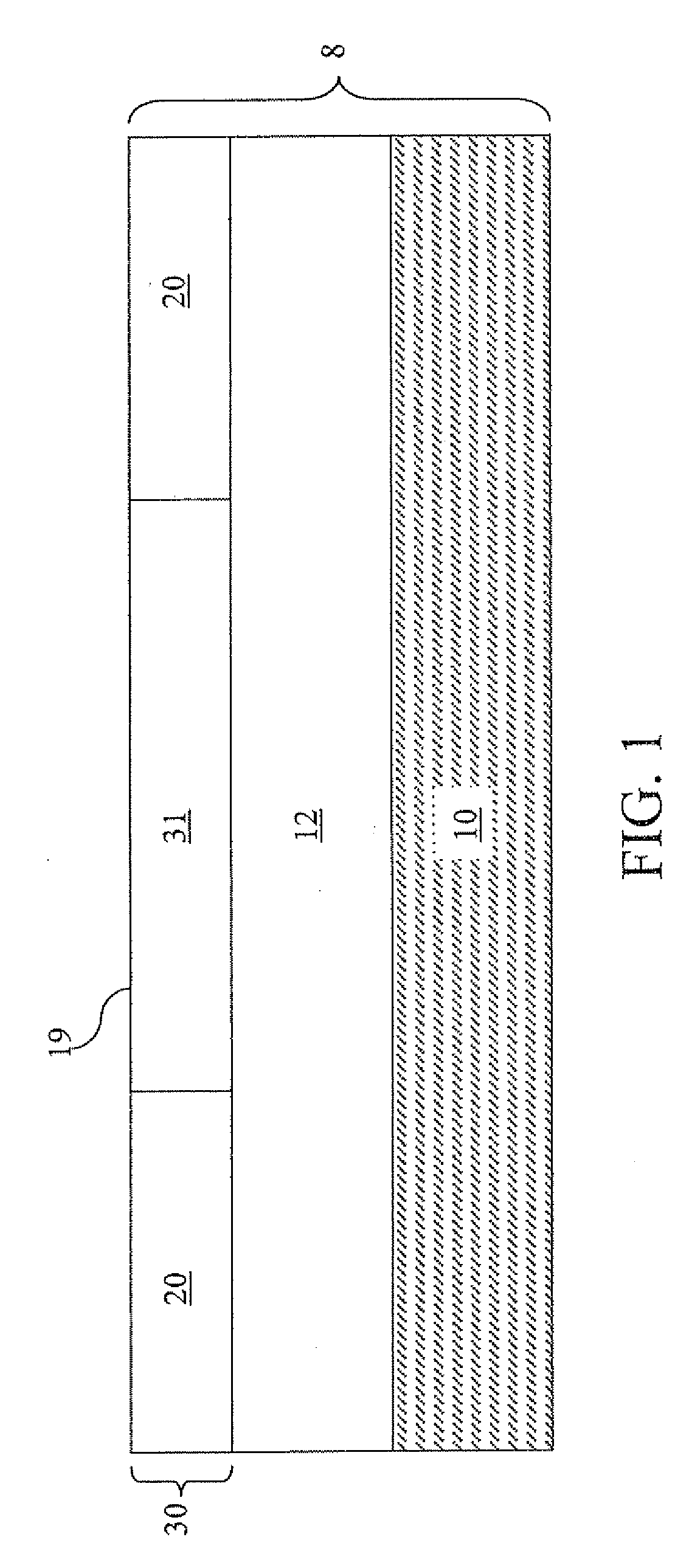

Thin film transistor with self-aligned intra-gate electrode

InactiveUS7009204B2Minimizes problemGood imaging propertiesTransistorSolid-state devicesActive-matrix liquid-crystal displayLiquid-crystal display

A thin film transistor for use in an active matrix liquid crystal display includes a substrate, a source and a drain regions, and at least a gate electrode. The substrate includes therein a plurality of intrinsic regions, at least one first doped region and two second doped regions. The first doped region is disposed between the plurality of intrinsic regions. The plurality of intrinsic regions are linked together to form a connection structure via the first doped region, and the two second doped regions are disposed at both ends of the connection structure, respectively. The source and the drain regions are coupled to the two second doped regions disposed at both ends of the connection structure, respectively. The gate electrode is disposed over the plurality of intrinsic regions, such that the periphery of each of the plurality of intrinsic regions and the periphery of a corresponding gate electrode are substantially aligned with each other.

Owner:INNOLUX CORP

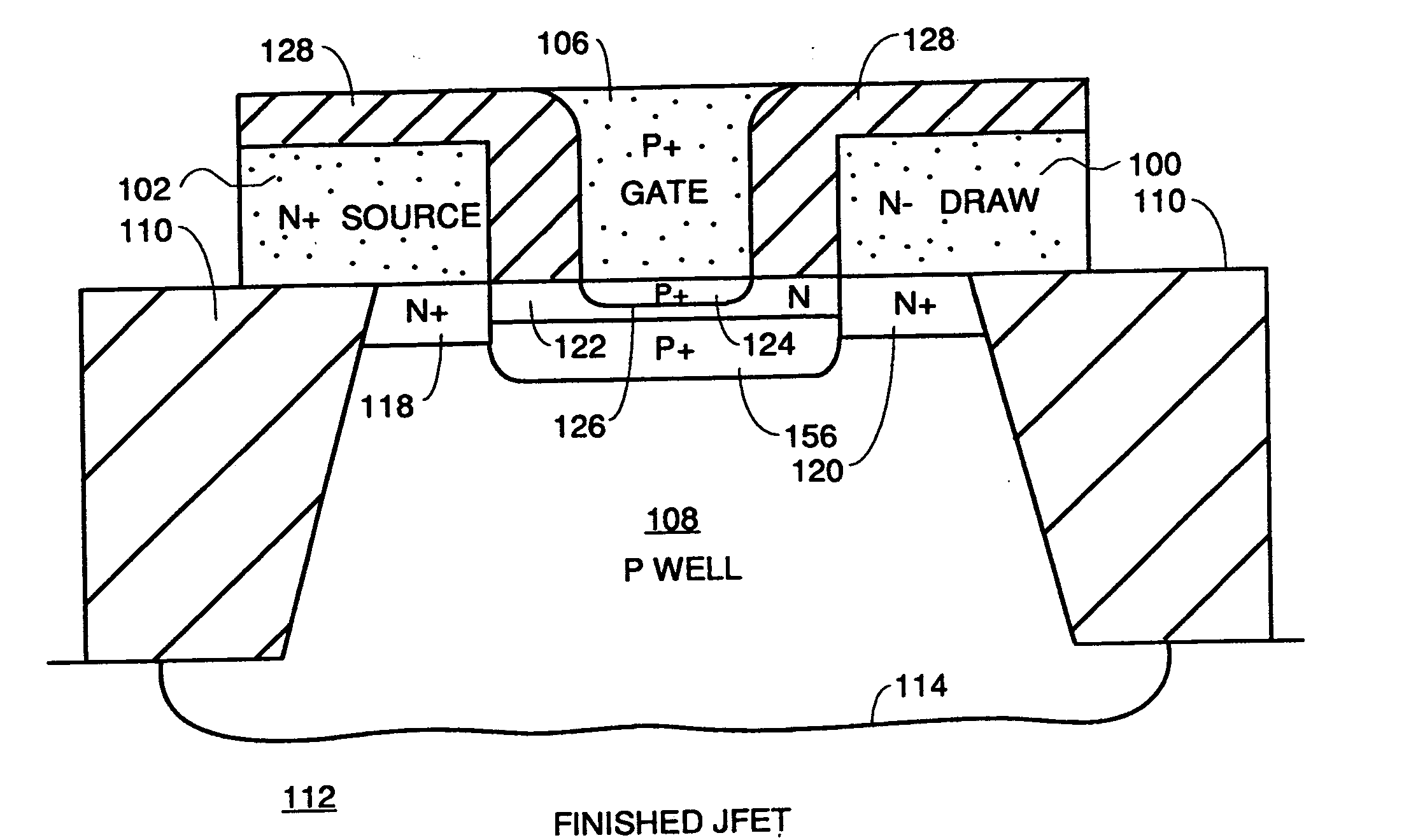

Self aligned gate JFET structure and method

A JFET integrated onto a substrate having a semiconductor layer at least and having source and drain contacts over an active area and made of first polysilicon (or other conductors such as refractive metal or silicide) and a self-aligned gate contact made of second polysilicon which has been polished back to be flush with a top surface of a dielectric layer covering the tops of the source and drain contacts. The dielectric layer preferably has a nitride cap to act as a polish stop. In some embodiments, nitride covers the entire dielectric layer covering the source and drain contacts as well as the field oxide region defining an active area for said JFET. An embodiment with an epitaxially grown channel region formed on the surface of the substrate is also disclosed.

Owner:MIE FUJITSU SEMICON

Nonvolatile semiconductor memory device with tapered sidewall gate and method of manufacturing the same

ActiveUS20050085039A1Increase currentRun at high speedTransistorSolid-state devicesSalicideEngineering

In a split gate type nonvolatile memory cell in which a MOS transistor for a nonvolatile memory using a charge storing film and a MOS transistor for selecting it are adjacently formed, the charge storing characteristic is improved and the resistance of the gate electrode is reduced. In order to prevent the thickness reduction at the corner portion of the charge storing film and improve the charge storing characteristic, a taper is formed on the sidewall of the select gate electrode. Also, in order to stably perform a silicide process for reducing the resistance of the self-aligned gate electrode, the sidewall of the select gate electrode is recessed. Alternatively, a discontinuity is formed between the upper portion of the self-aligned gate electrode and the upper portion of the select gate electrode.

Owner:RENESAS ELECTRONICS CORP

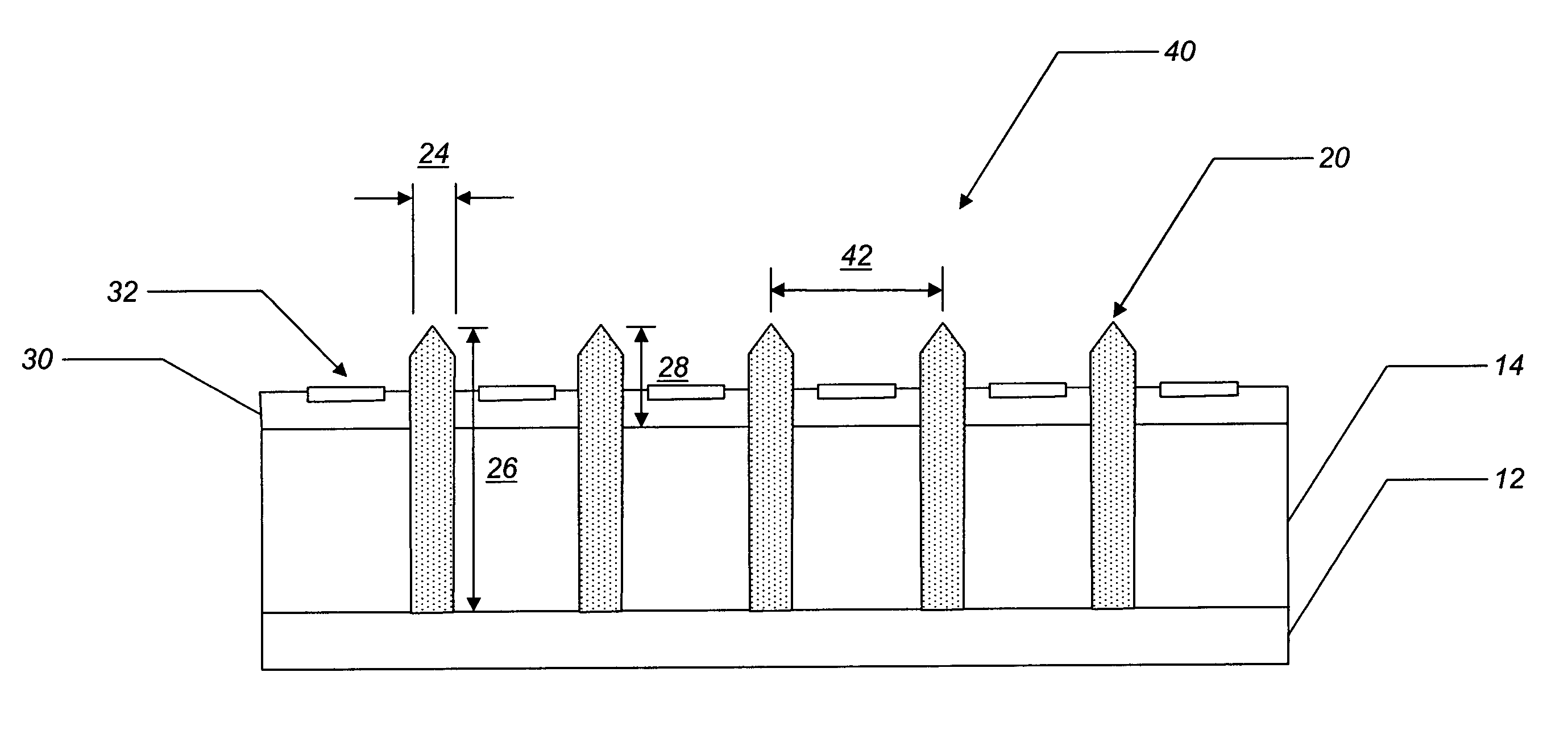

Self-aligned gated rod field emission device and associated method of fabrication

ActiveUS20050067935A1Discharge tube luminescnet screensLamp detailsCylindrical channelField emission device

A self-aligned gated field emission device and an associated method of fabrication are described. The device includes a substrate and a porous layer disposed adjacent to the surface of the substrate, wherein the porous layer defines a plurality of substantially cylindrical channels, each of the plurality of substantially cylindrical channels aligned substantially parallel to one another and substantially perpendicular to the surface of the substrate. The device also includes a plurality of substantially rod-shaped structures disposed within at least a portion of the plurality of substantially cylindrical channels defined by the porous layer and adjacent to the surface of the substrate, wherein a portion of each of the plurality of substantially rod-shaped structures protrudes above the surface of the porous layer. The device further includes a gate dielectric layer disposed on the surface of the porous layer, wherein the gate dielectric layer is disposed between the plurality of substantially rod-shaped structures. The device still further includes a conductive layer selectively disposed on the surface of the gate dielectric layer, wherein the conductive layer is selectively disposed between the plurality of substantially rod-shaped structures.

Owner:GENERAL ELECTRIC CO

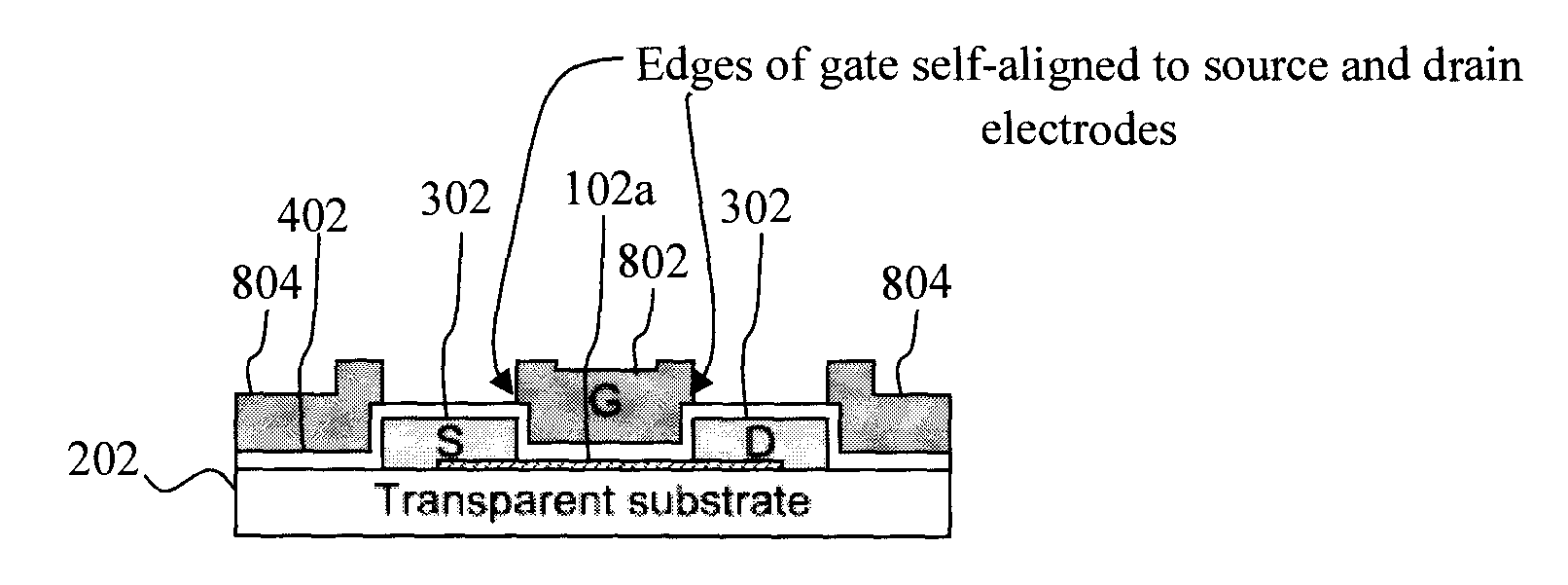

Graphene and Nanotube/Nanowire Transistor with a Self-Aligned Gate Structure on Transparent Substrates and Method of Making Same

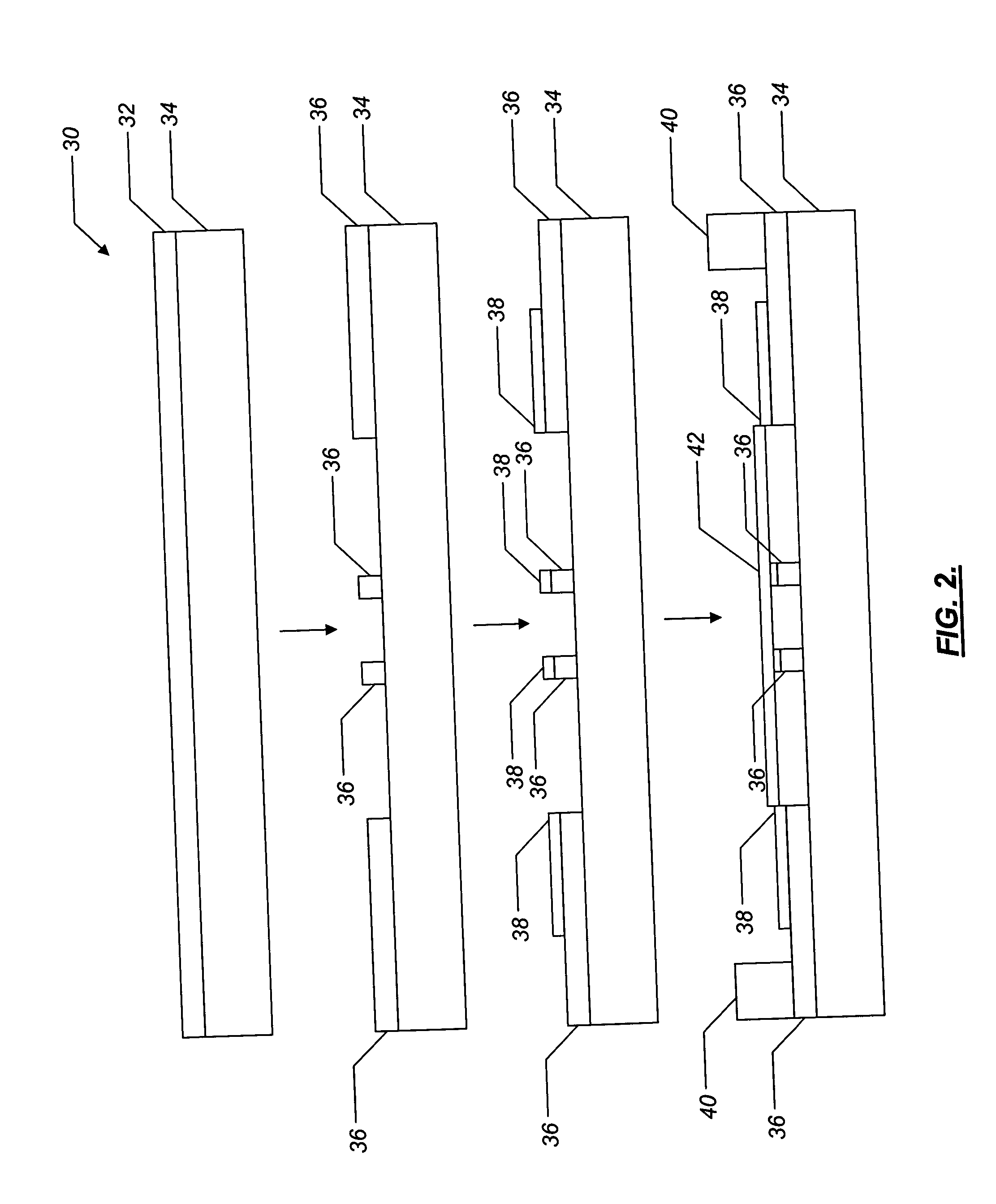

Transistor devices having a self-aligned gate structure on transparent substrates and techniques for fabrication thereof are provided. In one aspect, a method of fabricating a transistor device includes the following steps. A channel material is formed on a transparent substrate. Source and drain electrodes are formed in contact with the channel material. A dielectric layer is deposited on the channel material. A photoresist is deposited on the dielectric layer and developed using UV light exposure through the transparent substrate. A gate metal(s) is deposited on the exposed portions of the dielectric layer and the undeveloped portions of the photoresist. The undeveloped portions of the photoresist are removed along with portions of the gate metal over the source and drain regions to form a gate of the device on the dielectric layer over the channel material which is self-aligned to the source and drain electrodes.

Owner:GLOBALFOUNDRIES US INC

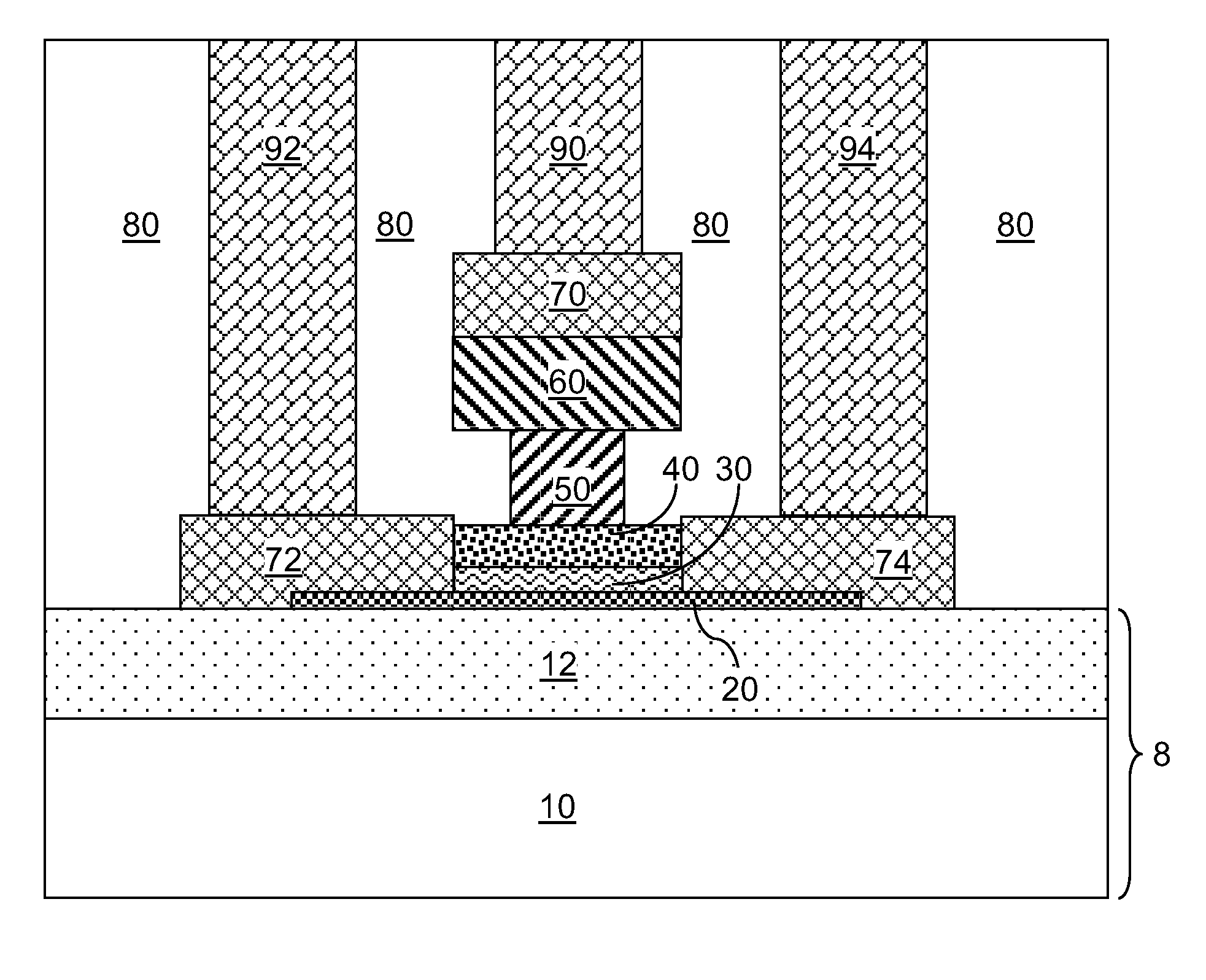

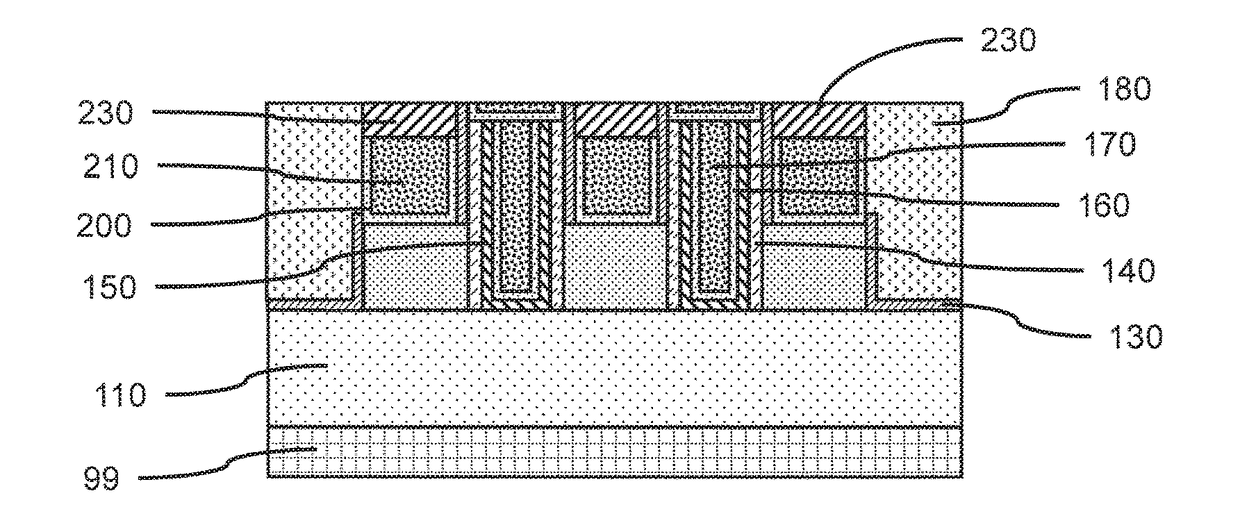

Borderless contact for replacement gate employing selective deposition

ActiveUS8232607B2Preventing electrical shortTransistorSemiconductor/solid-state device manufacturingSelf-assembled monolayerConductive materials

A self-aligned gate cap dielectric can be employed to form a self-aligned contact to a diffusion region, while preventing electrical short with a gate conductor due to overlay variations. In one embodiment, an electroplatable or electrolessly platable metal is selectively deposited on conductive materials in a gate electrode, while the metal is not deposited on dielectric surfaces. The metal portion on top of the gate electrode is converted into a gate cap dielectric including the metal and oxygen. In another embodiment, a self-assembling monolayer is formed on dielectric surfaces, while exposing metallic top surfaces of a gate electrode. A gate cap dielectric including a dielectric oxide is formed on areas not covered by the self-assembling monolayer. The gate cap dielectric functions as an etch-stop structure during formation of a via hole, so that electrical shorting between a contact via structure formed therein and the gate electrode is avoided.

Owner:AURIGA INNOVATIONS INC

Method for fabricating a self aligned contact which eliminates the key hole problem using a two step spacer deposition

InactiveUS6214715B1Enhance the imageEasy to integrateSolid-state devicesSemiconductor/solid-state device manufacturingBit lineSemiconductor structure

This invention provides a method for forming a self aligned contact without key holes using a two step sidewall spacer deposition. The process begins by providing a semiconductor structure having a device layer, a first inter poly oxide layer (IPO-1), and a conductive structure (such as a bit line) thereover, and having a contact area on the device layer adjacent to the conductive structure. The semiconductor structure can further include an optional etch stop layer overlying the first inter poly oxide layer. The conductive structure comprises at least one conductive layer with a hard mask thereover. A first spacer layer is formed over the hard mask and the IPO-1 layer and anisotropically etched to form first sidewall spacers on the sidewalls of the conductive structure up to a level above the bottom of the hard mask and below the level of the top of the hard mask such that the profile of the first sidewall spacers are not concave at any point. A second spacer layer is formed over the first sidewall spacers and anisotropically etched to form second sidewall spacers, having a profile that is not concave at any point. A second inter poly oxide layer is formed over the second sidewall spacers, the hard mask, and the IPO-1 layer, whereby the second inter poly oxide layer is free from key holes. A contact opening is formed in the second inter poly oxide layer and the first inter poly oxide layer over the contact area. A contact plug is formed in the contact openings.

Owner:TAIWAN SEMICON MFG CO LTD

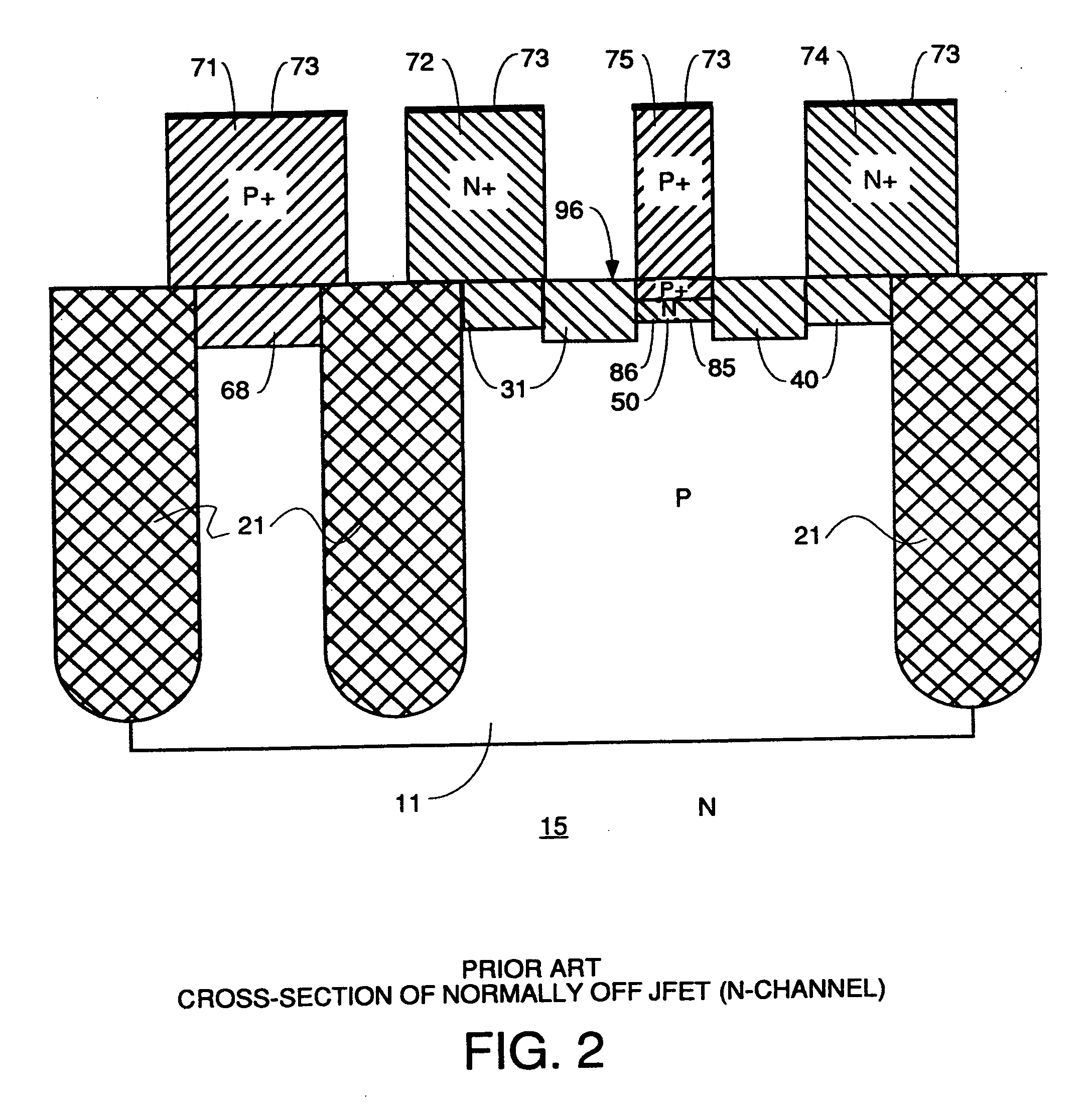

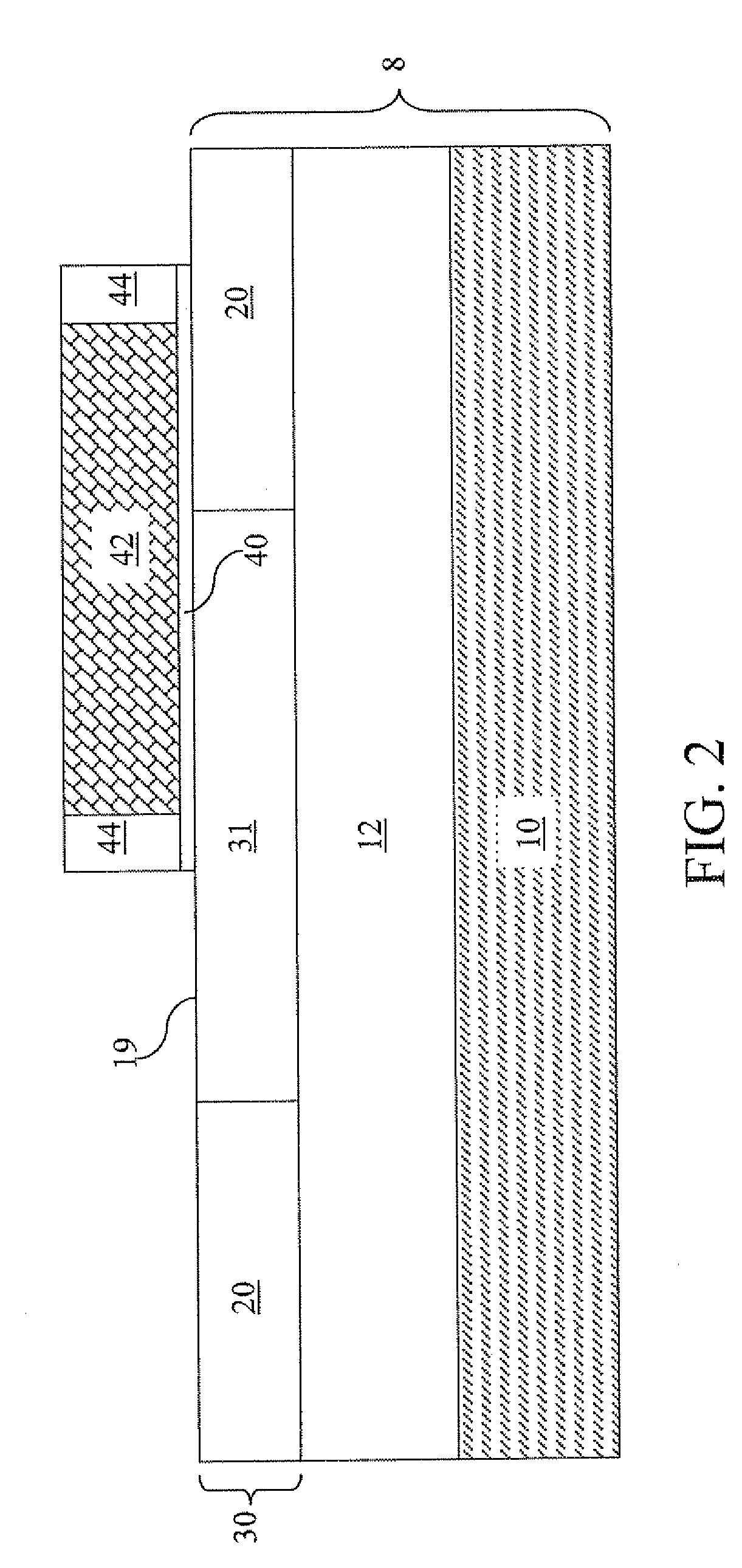

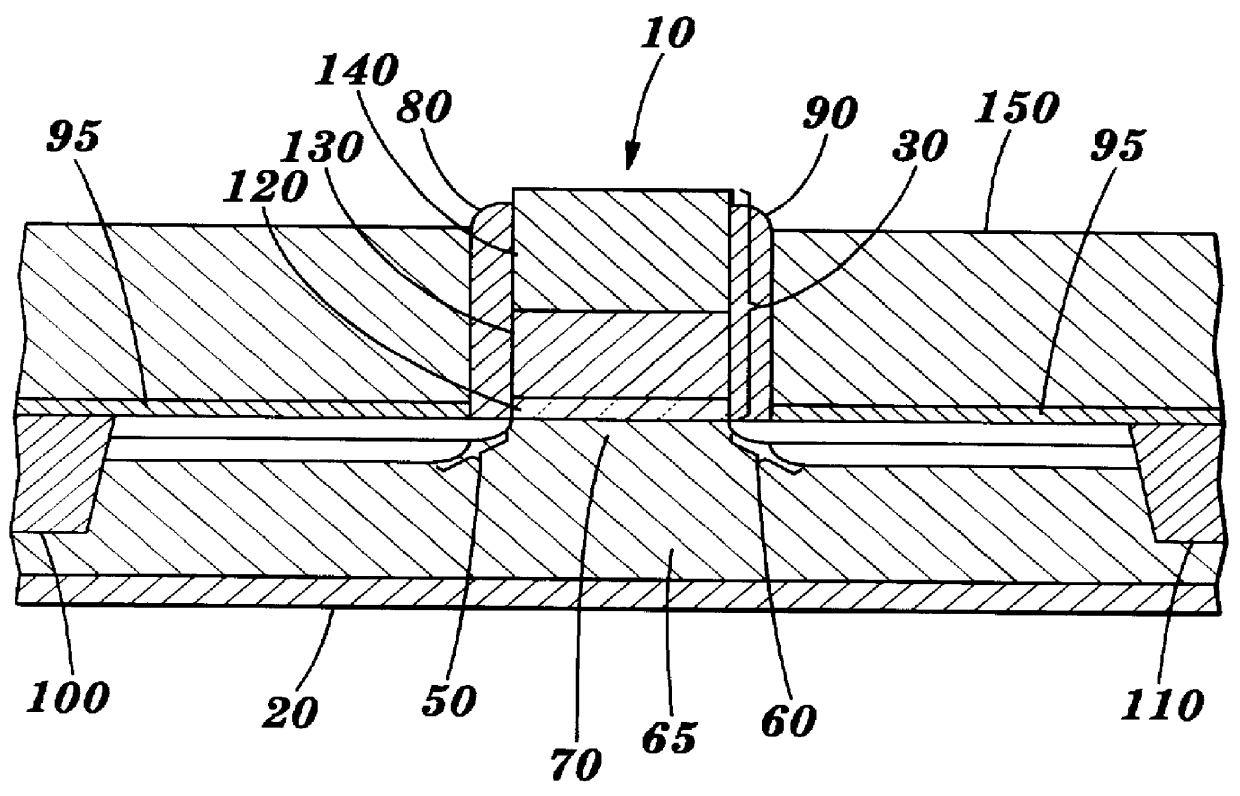

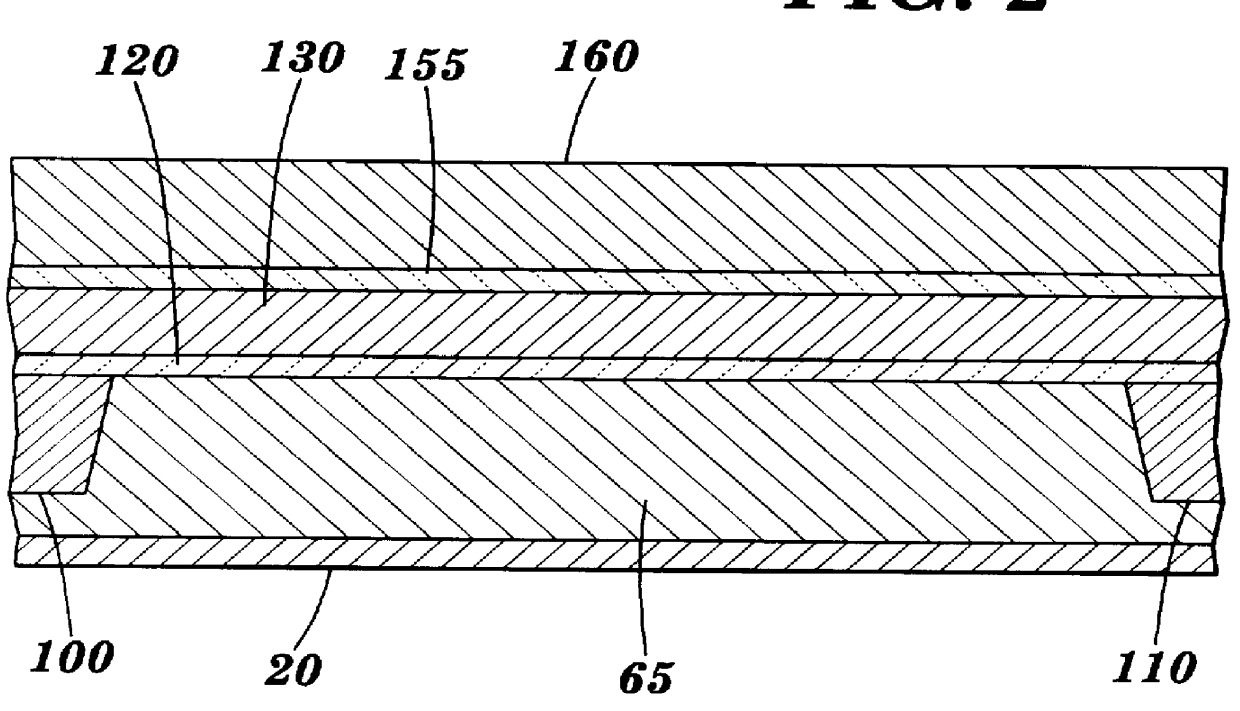

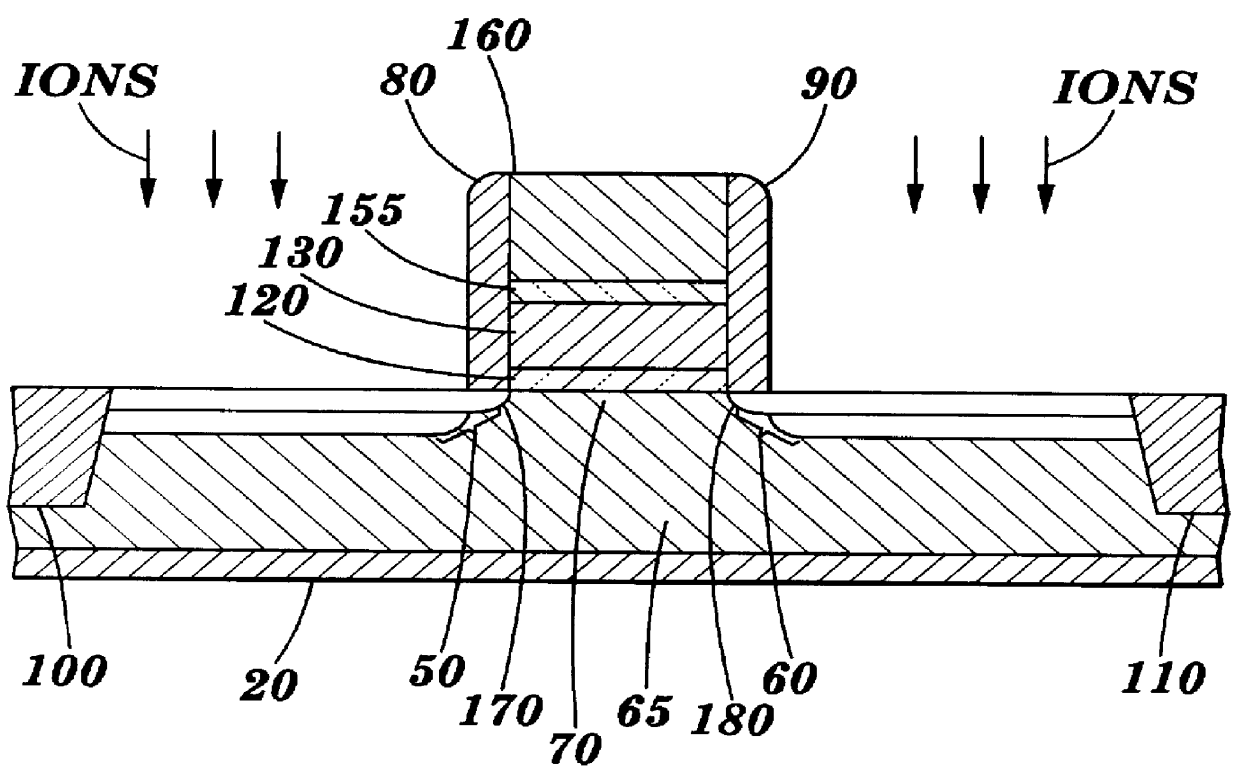

Self-aligned gate MOSFET with separate gates

A structure and method of manufacturing a double-gate integrated circuit which includes forming a laminated structure having a channel layer and first insulating layers on each side of the channel layer, forming openings in the laminated structure, forming drain and source regions in the openings, removing portions of the laminated structure to leave a first portion of the channel layer exposed, forming a first gate dielectric layer on the channel layer, forming a first gate electrode on the first gate dielectric layer, removing portions of the laminated structure to leave a second portion of the channel layer exposed, forming a second gate dielectric layer on the channel layer, forming a second gate electrode on the second gate dielectric layer, doping the drain and source regions, using self-aligned ion implantation, wherein the first gate electrode and the second gate electrode are formed independent of each other.

Owner:GLOBALFOUNDRIES INC

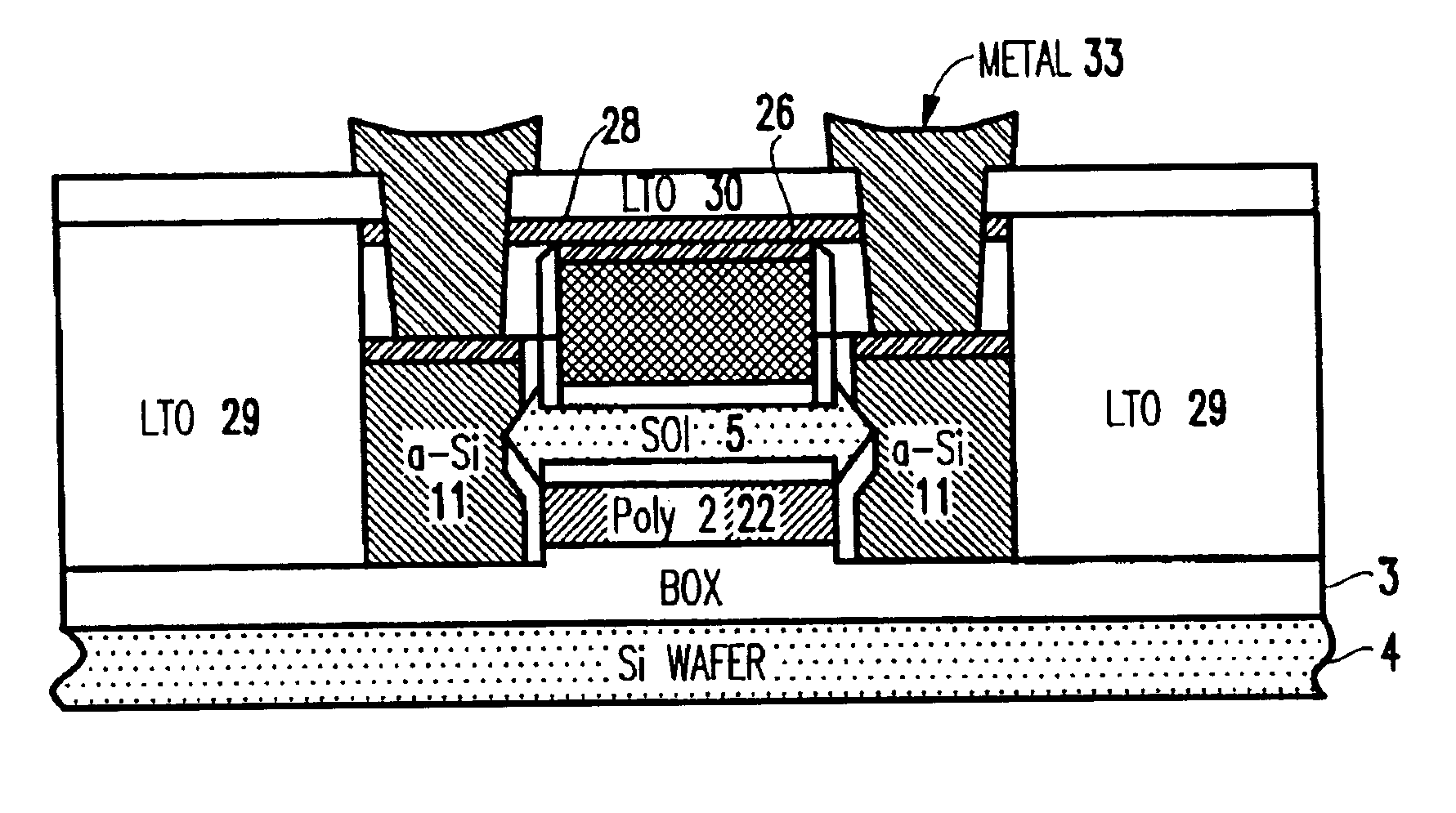

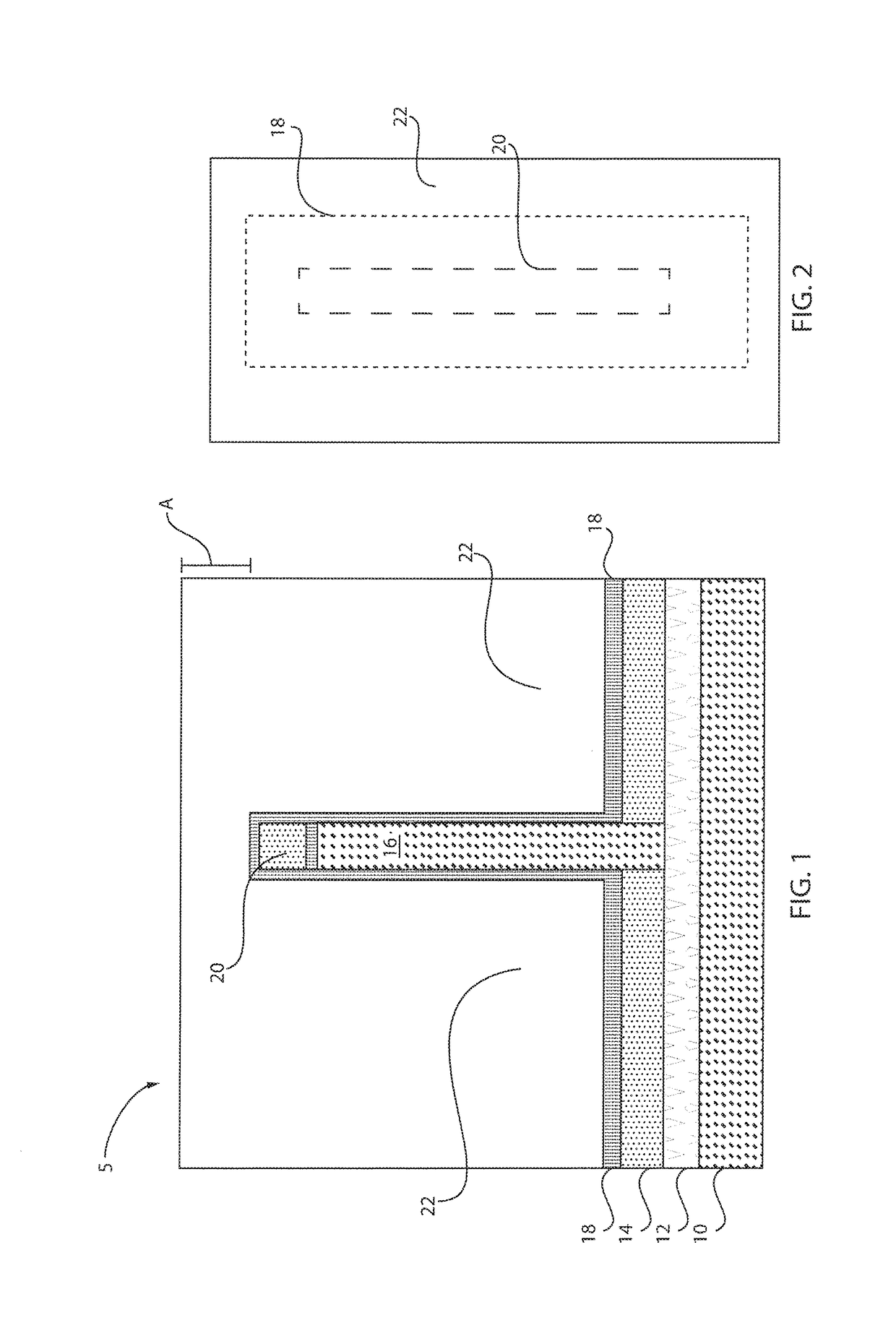

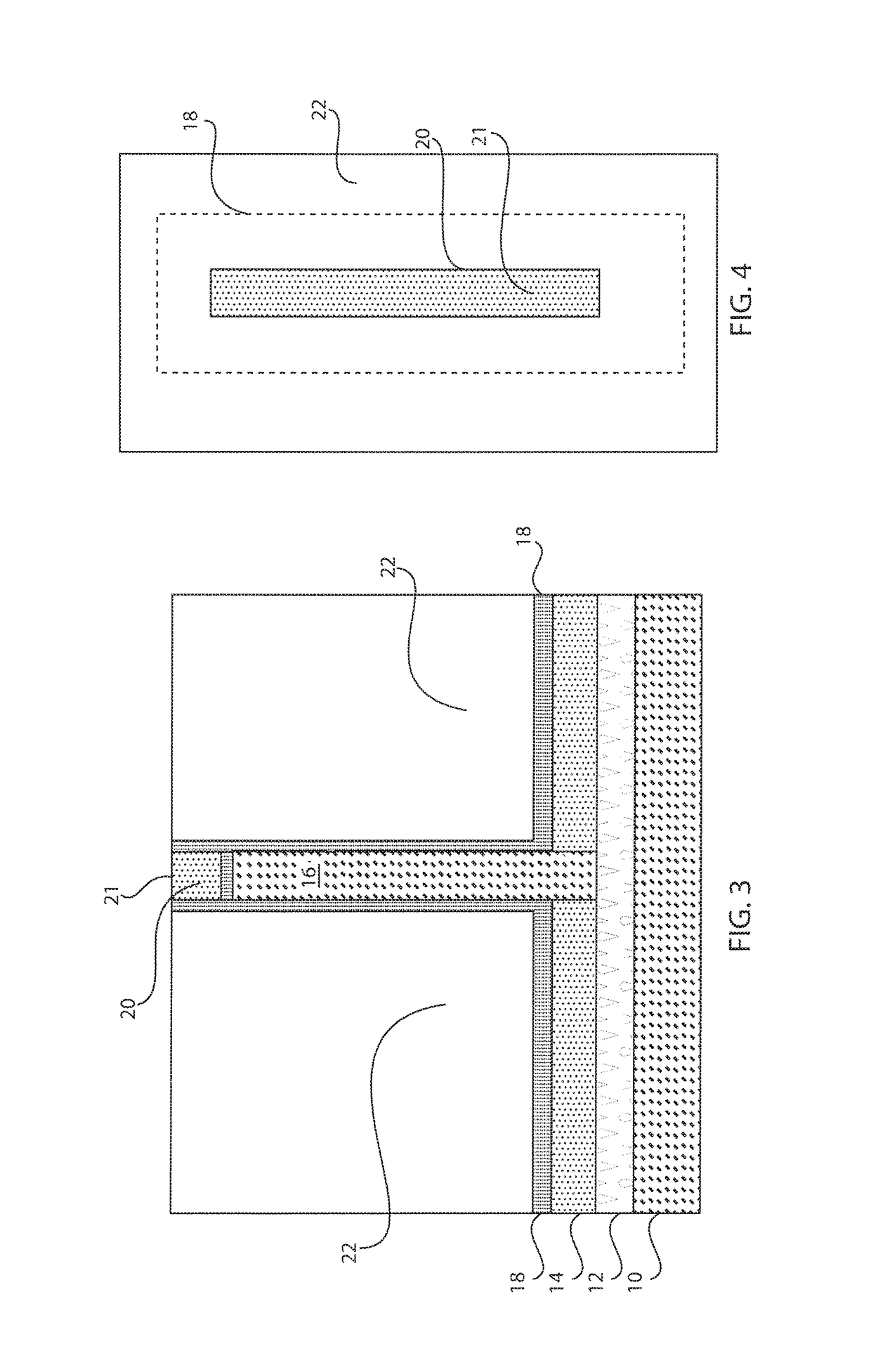

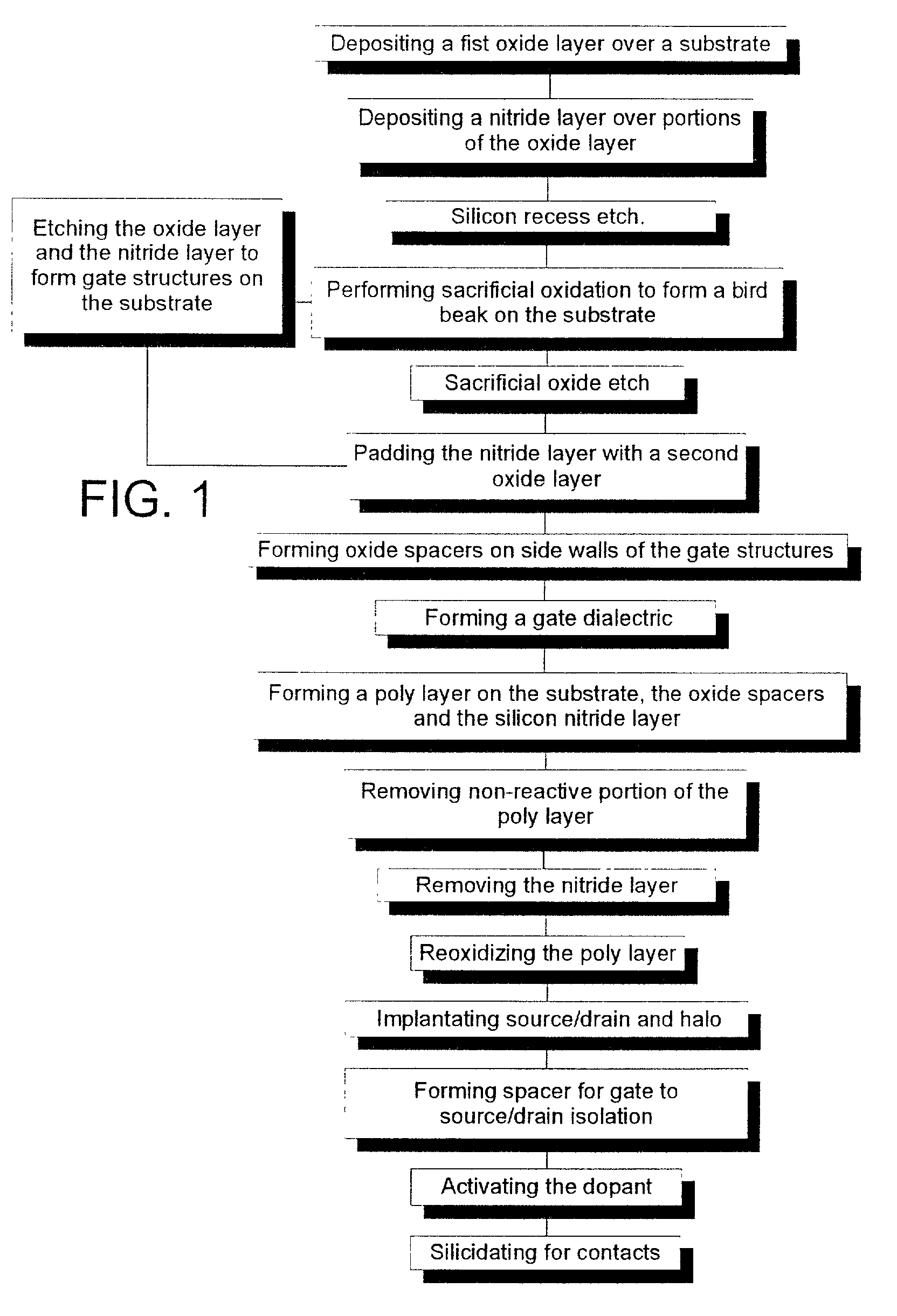

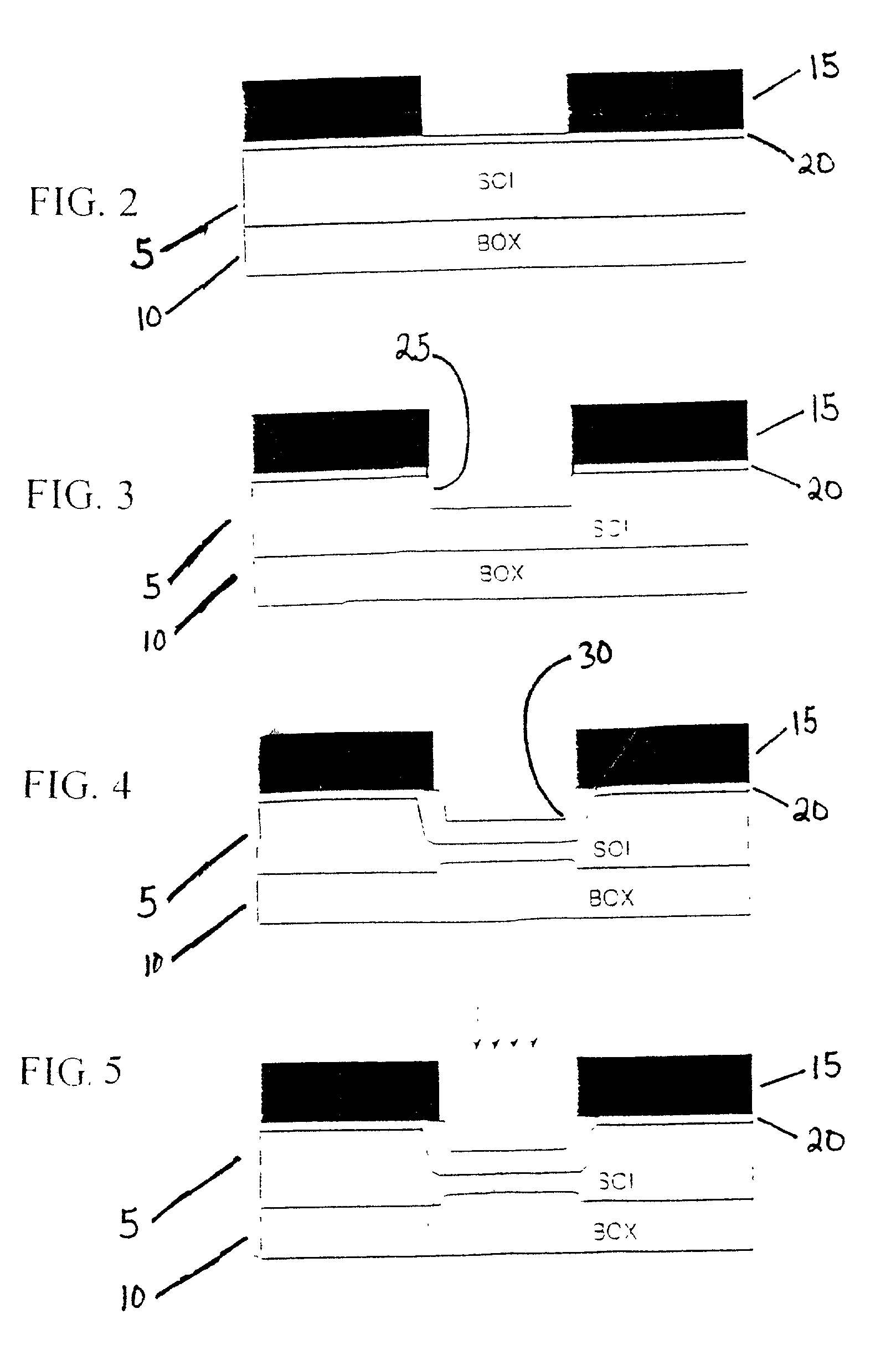

CMOS structure with non-epitaxial raised source/drain and self-aligned gate and method of manufacture

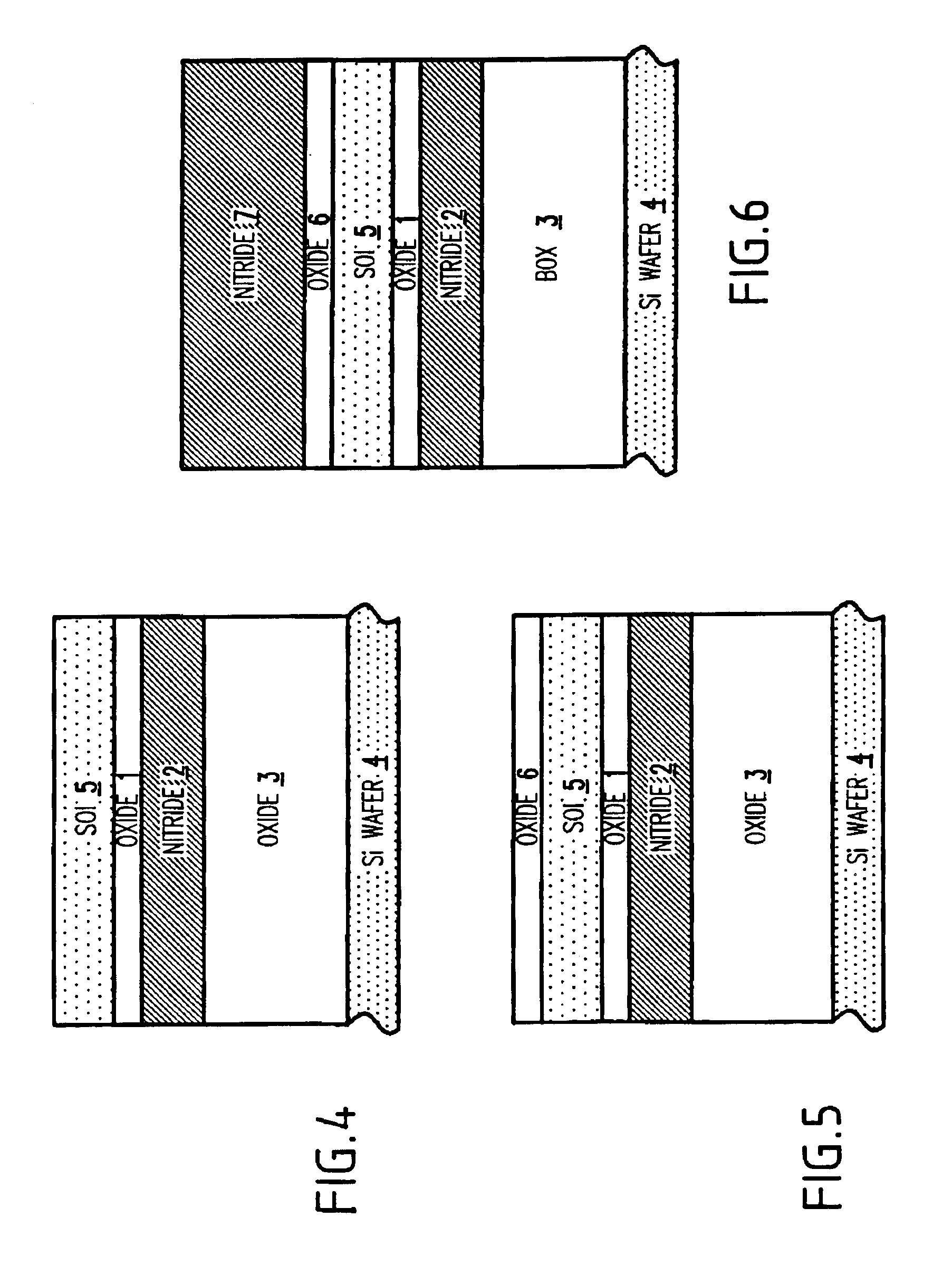

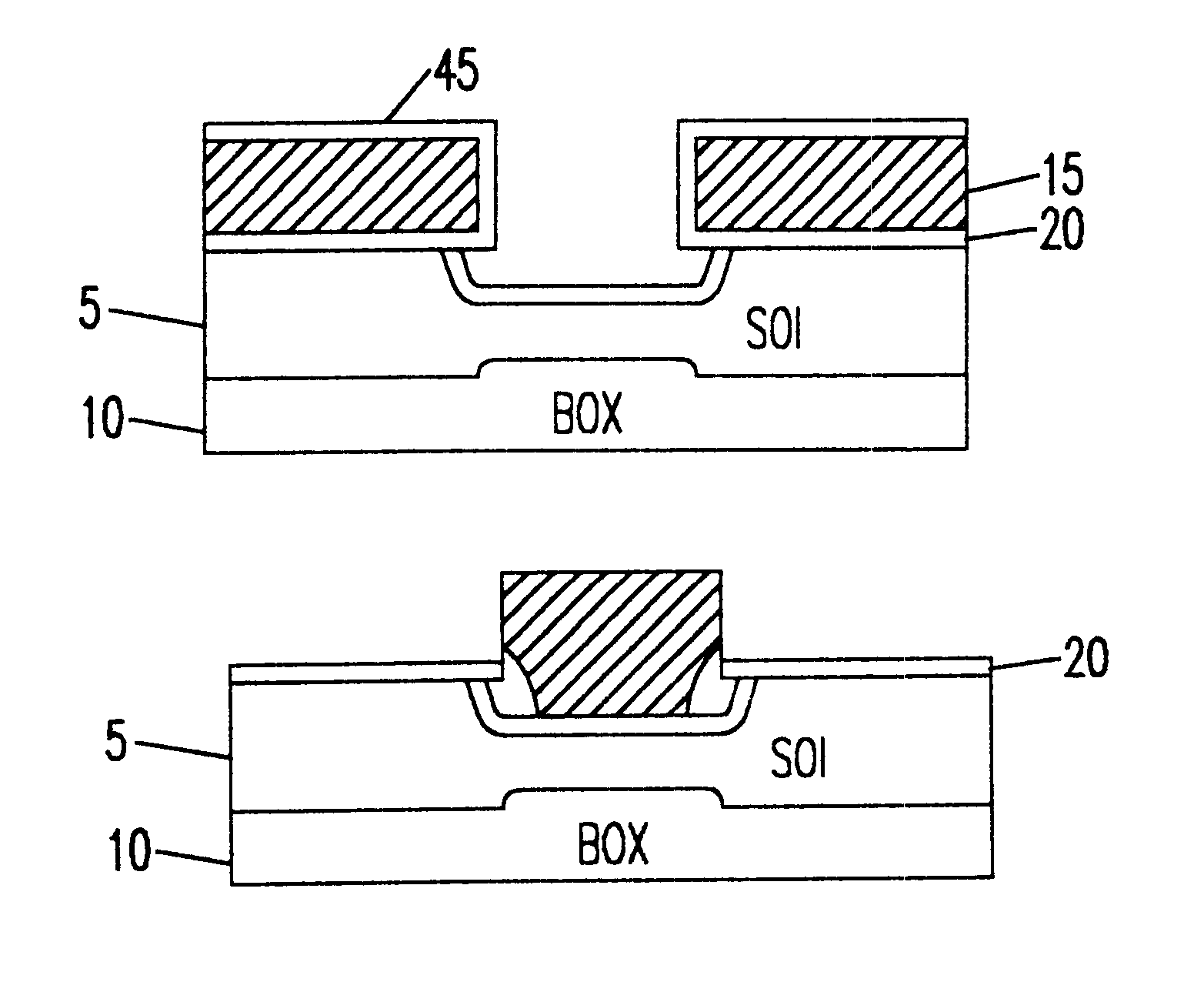

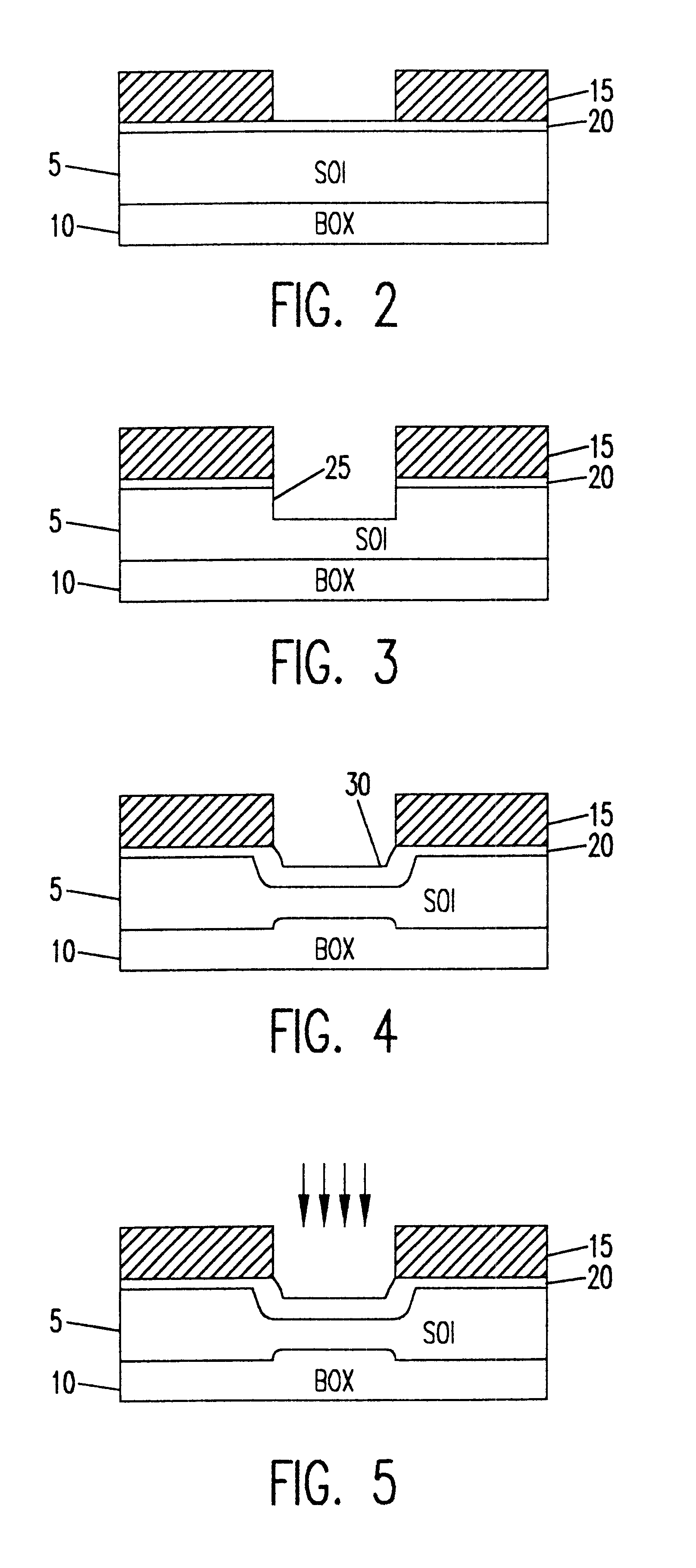

A CMOS structure and method of achieving self-aligned raised source / drain for CMOS structures on SOI without relying on selective epitaxial growth of silicon. In the method, CMOS structures are provided by performing sacrificial oxidation so that oxidation occurs on the surface of both the SOI and BOX interface. This allows for oxide spacer formation for gate-to-source / drain isolation which makes possible raised source / drain fabrication without increasing contact resistance.

Owner:INT BUSINESS MASCH CORP

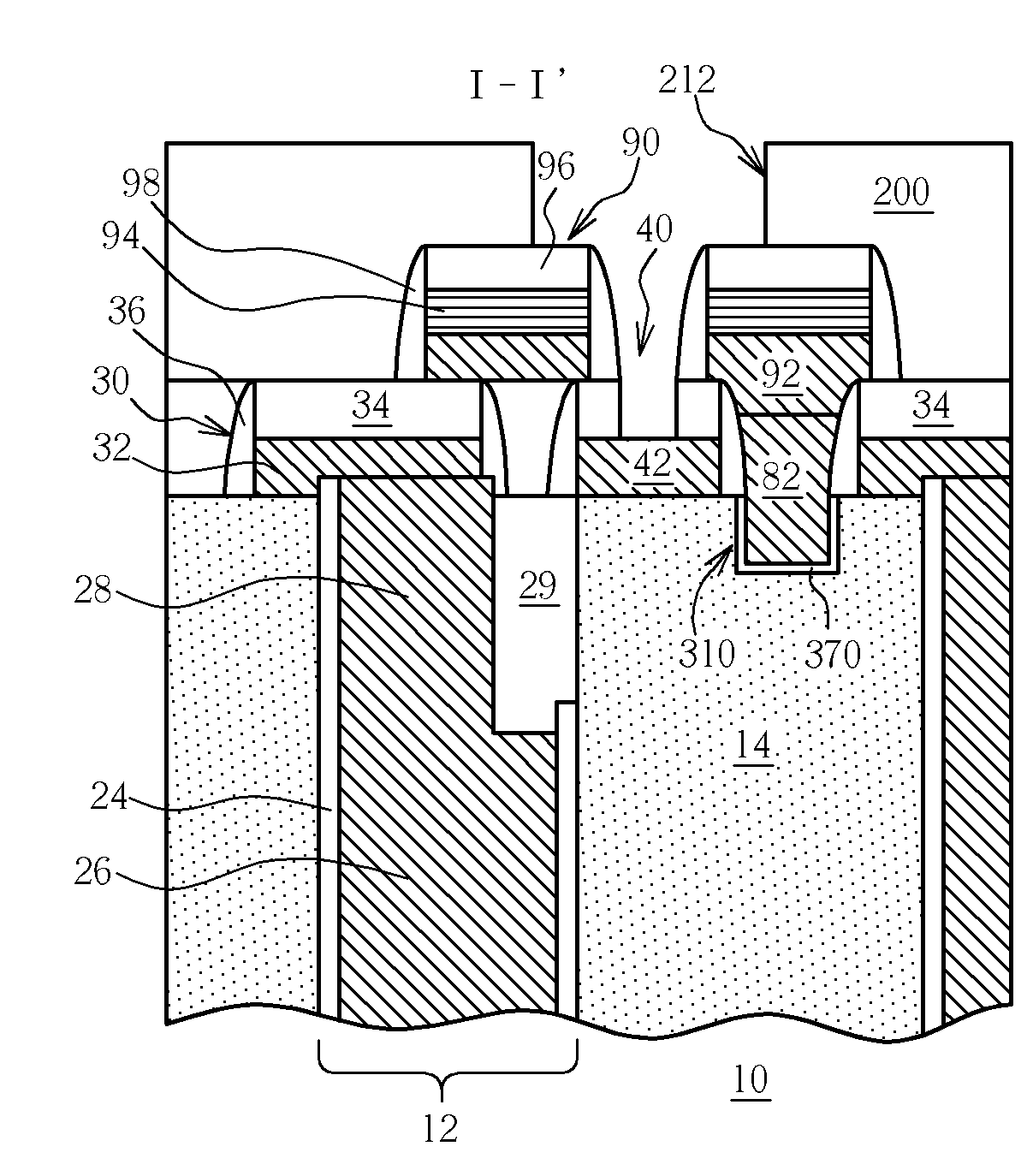

Recessed Channel Insulated-Gate Field Effect Transistor with Self-Aligned Gate and Increased Channel Length

ActiveUS20140159142A1Increase channel lengthSuppression of short channel effectsSemiconductor/solid-state device manufacturingSemiconductor devicesGate dielectricCrystal orientation

A metal-oxide-semiconductor transistor (MOS) and method of fabricating the same, in which the effective channel length is increased relative to the width of the gate electrode. A dummy gate electrode overlying dummy gate dielectric material is formed at the surface of the structure, with self-aligned source / drain regions, and dielectric spacers on the sidewalls of the dummy gate structure. The dummy gate dielectric underlies the sidewall spacers. Following removal of the dummy gate electrode and the underlying dummy gate dielectric material, including from under the spacers, a silicon etch is performed to form a recess in the underlying substrate. This etch is self-limiting on the undercut sides, due to the crystal orientation, relative to the etch of the bottom of the recess. The gate dielectric and gate electrode material are then deposited into the remaining void, for example to form a high-k metal gate MOS transistor.

Owner:TEXAS INSTR INC

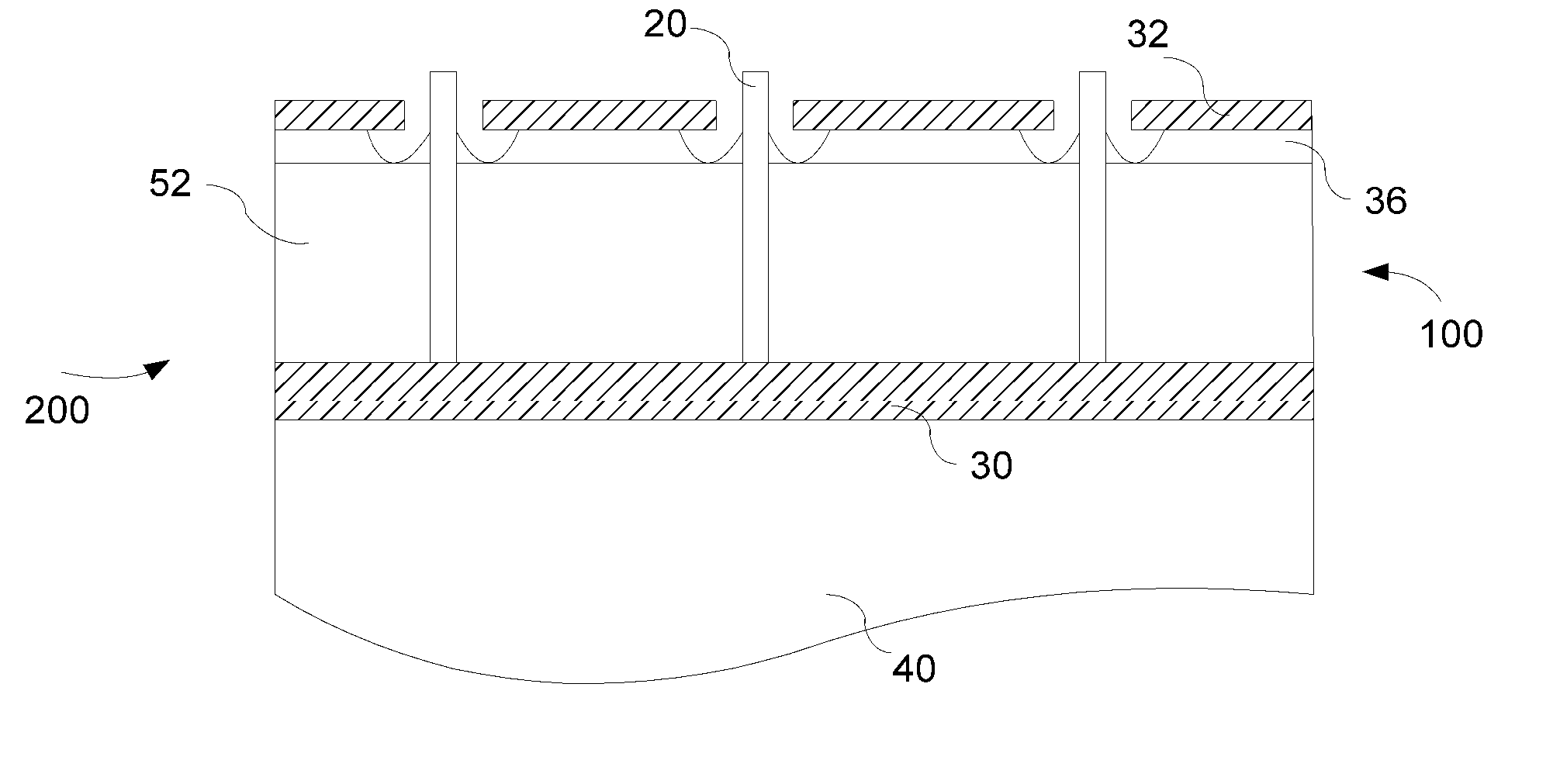

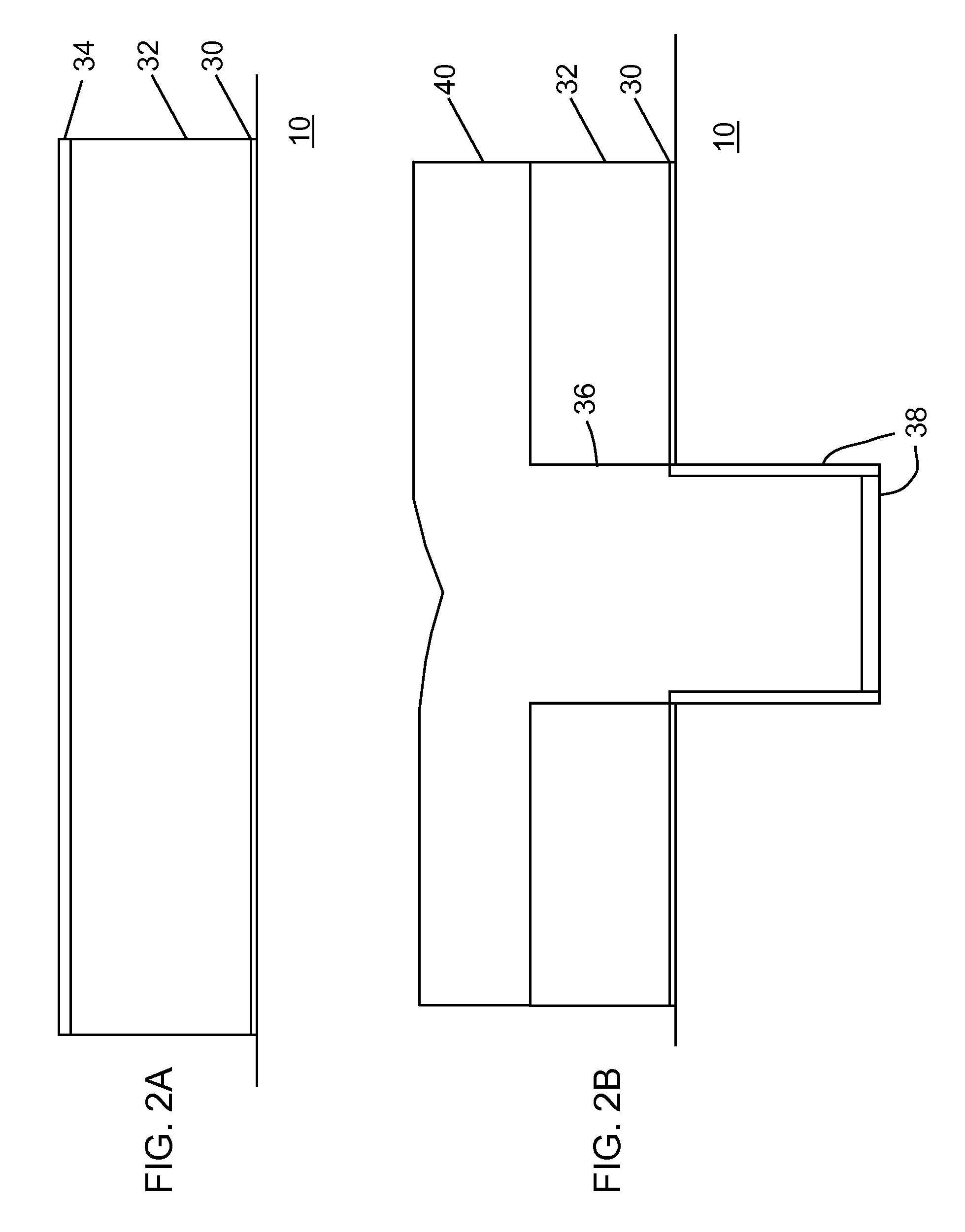

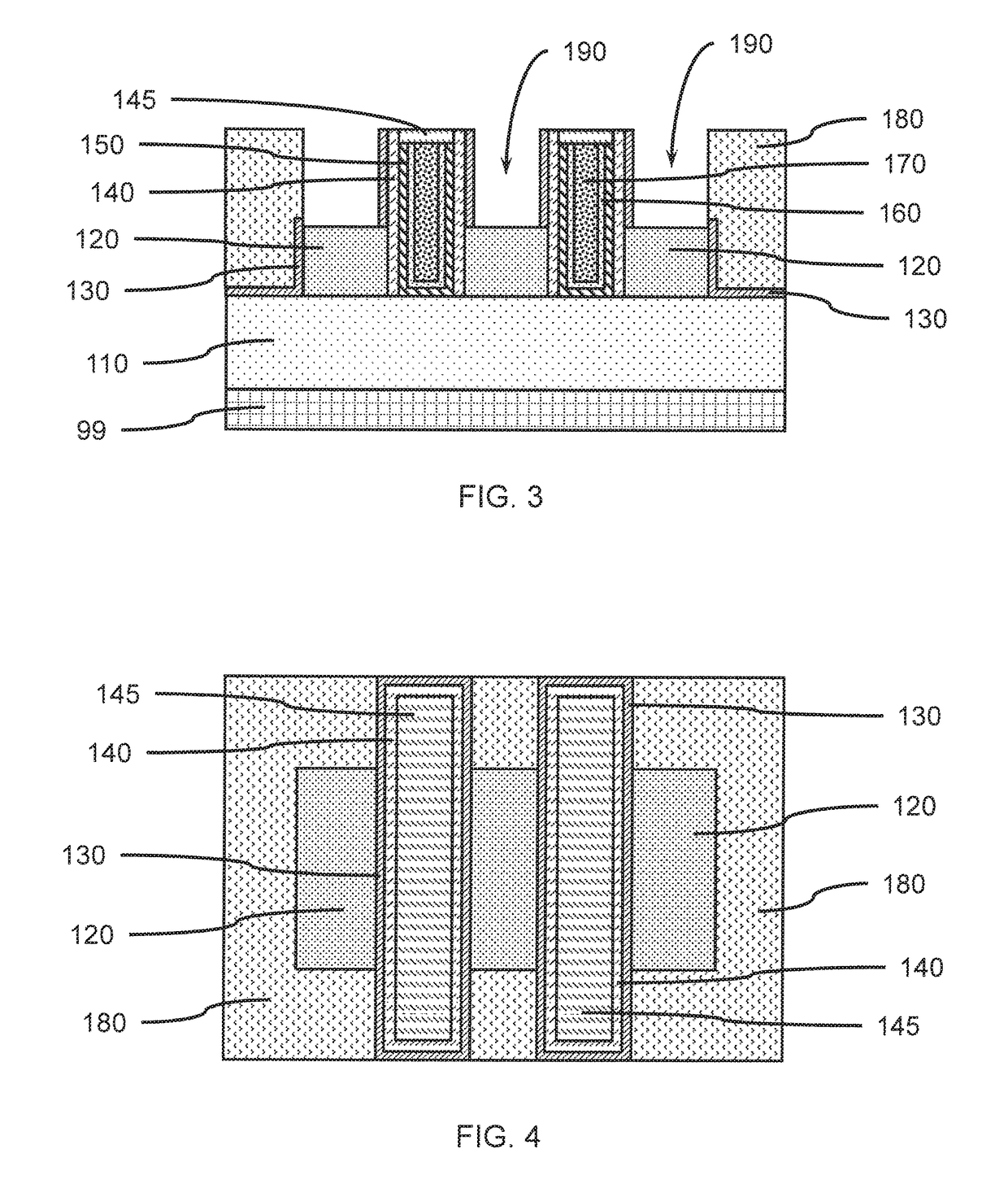

Fabrication of self-aligned gate contacts and source/drain contacts directly above gate electrodes and source/drains

ActiveUS20180211874A1Semiconductor/solid-state device detailsSolid-state devicesEngineeringActive layer

A method of forming an active device having self-aligned source / drain contacts and gate contacts, including, forming an active area on a substrate, where the active area includes a device channel; forming two or more gate structures on the device channel; forming a plurality of source / drains on the active area adjacent to the two or more gate structures and device channel; forming a protective layer on the surfaces of the two or more gate structures, plurality of source / drains, and active layer; forming an interlayer dielectric layer on the protective layer; removing a portion of the interlayer dielectric and protective layer to form openings, where each opening exposes a portion of one of the plurality of source / drains; forming a source / drain contact liner in at least one of the plurality of openings; and forming a source / drain contact fill on the source / drain contact liner.

Owner:IBM CORP

Self-aligned gate isolation

Embodiments of the invention include a circuit with a transistor having a self-aligned gate. Insulating isolation structures may be formed, self-aligned to diffusions. The gate may then be formed self-aligned to the insulating isolation structures.

Owner:INTEL CORP

Self-aligned gated carbon nanotube field emitter structures and associated methods of fabrication

InactiveUS20050067936A1Simple and cost-effective and efficientDischarge tube luminescnet screensElectric discharge tubesElectrical conductorField line

A method for fabricating a self-aligned gated carbon nanotube field emitter structure includes providing a substrate, depositing a dielectric material on the surface of the substrate and depositing a conductor layer on the surface of the dielectric material. The method also includes selectively etching the conductor layer to form an opening and selectively etching the dielectric material to form a micro-cavity. The method further includes depositing a base layer structure in the micro-cavity adjacent to the surface of the substrate, wherein the base layer structure has a substantially conical shape, and depositing a catalyst on a portion of the surface of the base layer structure, wherein the catalyst is suitable for growing at least one carbon nanotube. The method still further includes applying an electrical potential to the substrate and the conductor layer, wherein the electrical potential generates a plurality of electrical field lines that are deflected around the surface of the base layer structure, and wherein the plurality of electrical field lines have a strength that is greatest in a direction substantially perpendicular to the surface of the substrate. Finally, the method includes growing at least one carbon nanotube from the catalyst in the presence of the plurality of electrical field lines, wherein the at least one carbon nanotube is grown in a direction substantially perpendicular to the surface of the substrate.

Owner:GENERAL ELECTRIC CO

Method for fabricating recessed gate mos transistor device

A method of fabricating self-aligned gate trench utilizing TTO poly spacer is disclosed. A semiconductor substrate having thereon a pad oxide layer and pad nitride layer is provided. A plurality of trench capacitors are embedded in a memory array region of the semiconductor substrate. Each of the trench capacitors has a trench top oxide (TTO) that extrudes from a main surface of the semiconductor substrate. Poly spacers are formed on two opposite sides of the extruding TTO and are used, after oxidized, as an etching hard mask for etching a recessed gate trench in close proximity to the trench capacitor.

Owner:NAN YA TECH

Low voltage electron source with self aligned gate apertures, fabrication method thereof, and devices using the electron source

InactiveUS20090039754A1Narrow distributionHigh densityControl electrodesDischarge tube luminescnet screensNano structuringElectron source

A method of fabricating an electron source having a self-aligned gate aperture is disclosed. A substrate is deposited on a first conductive layer. Over the first conductive layer an emitter layer is deposited. The emitter layer includes one or a plurality of spaced-apart nano-structures and a solid surface with nano-structures protruding above the surface. An insulator is conformally deposited over the emitter layer surface and forms a post from each protruding nano-structure. A second conductive layer is deposited over the insulator and the second conductive layer and the insulator are removed from the nano-structures such that apertures are formed in the second conductive layer and at least the ends of the nano-structures are exposed at the centers of said apertures.

Owner:TOLT ZHIDAN L

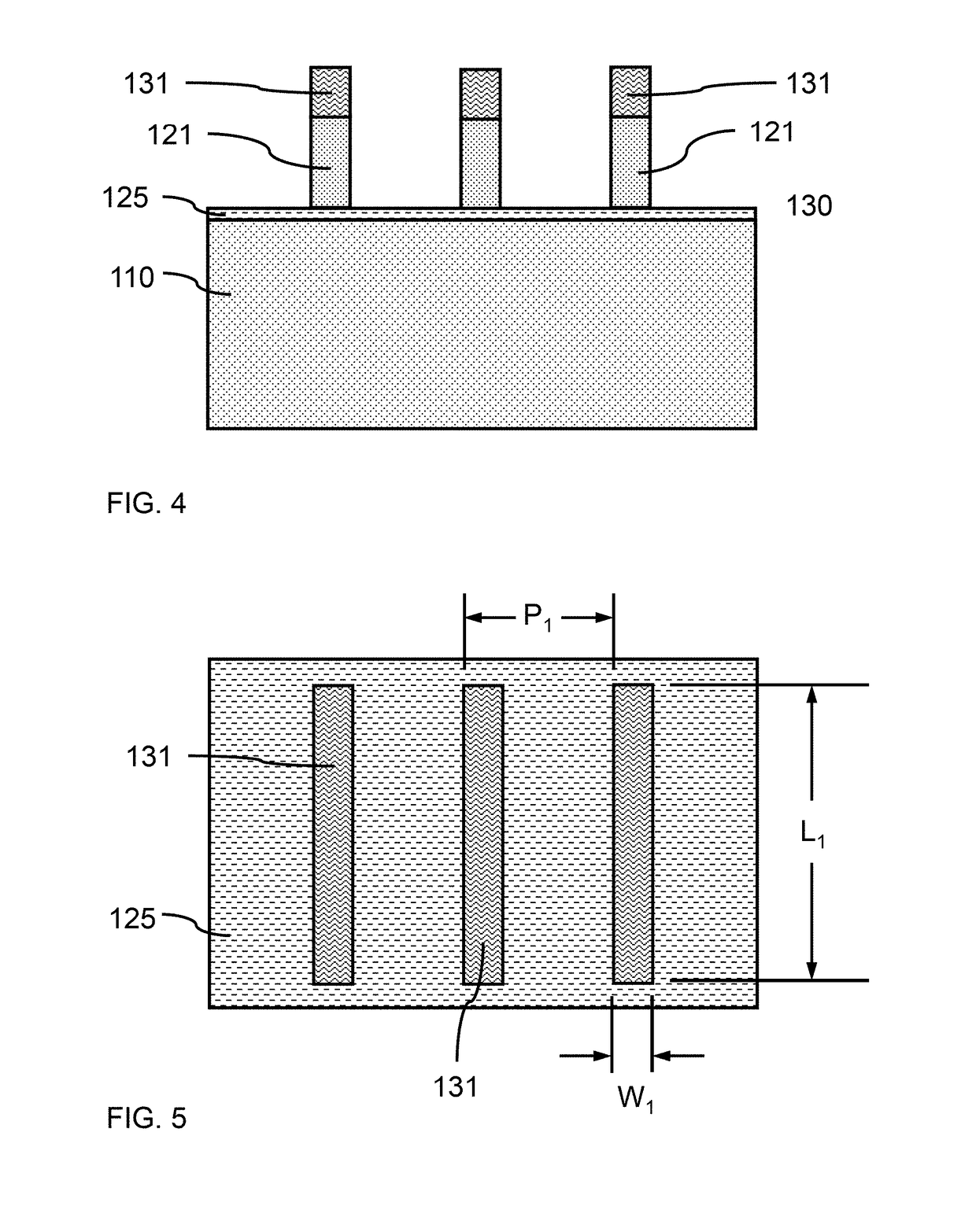

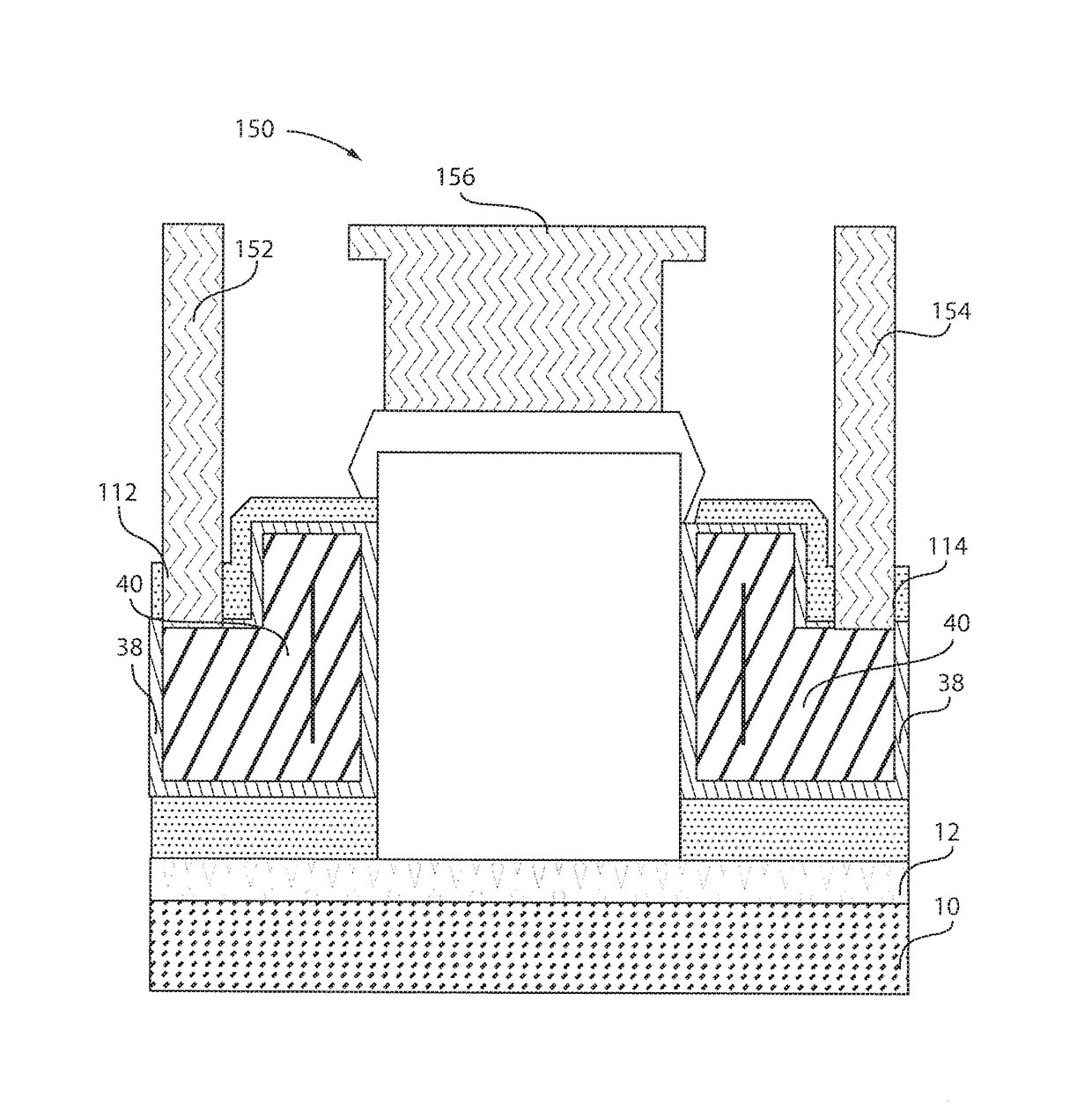

Fabrication of a vertical fin field effect transistor (vertical finfet) with a self-aligned gate and fin edges

ActiveUS20170358660A1Semiconductor/solid-state device manufacturingSemiconductor devicesGate dielectricSelf-aligned gate

A method of forming a vertical fin field effect transistor with a self-aligned gate structure, comprising forming a plurality of vertical fins on a substrate, forming gate dielectric layers on opposite sidewalls of each vertical fin, forming a gate fill layer between the vertical fins, forming a fin-cut mask layer on the gate fill layer, forming one or more fin-cut mask trench(es) in the fin-cut mask layer, and removing portions of the gate fill layer and vertical fins not covered by the fin-cut mask layer to form one or more fin trench(es), and two or more vertical fin segments from each of the plurality of vertical fins, having a separation distance, D1, between two vertical fin segments.

Owner:IBM CORP

Tunneling effect transistor with self-aligned gate

ActiveUS20090026491A1Semiconductor/solid-state device detailsSemiconductor/solid-state device manufacturingEngineeringField-effect transistor

In one embodiment, a mandrel and an outer dummy spacer may be employed to form a first conductivity type region. The mandrel is removed to form a recessed region wherein a second conductivity type region is formed. In another embodiment, a mandrel is removed from within shallow trench isolation to form a recessed region, in which an inner dummy spacer is formed. A first conductivity type region and a second conductivity region are formed within the remainder of the recessed region. An anneal is performed so that the first conductivity type region and the second conductivity type region abut each other by diffusion. A gate electrode is formed in self-alignment to the p-n junction between the first and second conductivity regions. The p-n junction controlled by the gate electrode, which may be sublithographic, constitutes an inventive tunneling effect transistor.

Owner:TWITTER INC

Non-volatile memory cell with self aligned floating and erase gates, and method of making same

A memory device, and method of making the same, in which a trench is formed into a substrate of semiconductor material. The source region is formed under the trench, and the channel region between the source and drain regions includes a first portion that extends substantially along a sidewall of the trench and a second portion that extends substantially along the surface of the substrate. The floating gate is disposed in the trench, and is insulated from the channel region first portion for controlling its conductivity. The control gate is disposed over and insulated from the channel region second portion, for controlling its conductivity. The erase gate is disposed at least partially over and insulated from the floating gate. The erase gate includes a notch, and the floating gate includes an edge that directly faces and is insulated from the notch.

Owner:SILICON STORAGE TECHNOLOGY

Method of forming self-aligned gates and transistors

InactiveUS20080318377A1Solid-state devicesSemiconductor/solid-state device manufacturingResistContact pad

Method for fabricating a self-aligned gate of a transistor including: forming a plurality of deep trench capacitors in a substrate, concurrently forming a surface strap and a contact pad on a surface of the substrate, wherein a spacing between the surface strap and the contact pad exposes a portion of an active area, filling the spacing with a dielectric layer, forming a photoresist pattern on the substrate, wherein the photoresist has an opening situated directly above the spacing between the surface strap and the contact pad, etching away the dielectric layer and a portion of a shallow trench isolation region through the opening thereby forming an upwardly protruding fin-typed channel structure, forming a gate dielectric layer on the upwardly protruding fin-typed channel structure, and forming a gate on the gate dielectric layer.

Owner:NAN YA TECH

Transistor with integrated poly/metal gate electrode

InactiveUS6118163ATransistorSemiconductor/solid-state device manufacturingElectrical conductorDielectric layer

An integrated circuit transistor and method of making the same are provided. The transistor includes a substrate, first and second source / drain regions, and a gate electrode stack coupled to the substrate. The gate electrode stack is fabricated by forming a first insulating layer on the substrate, forming a first conductor layer on the first insulating layer, and forming a metal layer on the first conductor layer. A second insulating layer, such as an interlevel dielectric layer, is coupled to the substrate adjacent to the gate electrode stack. Sidewall spacers and LDD processing may be incorporated. The transistor and method integrate metal and polysilicon into a self-aligned gate electrode stack.

Owner:ADVANCED MICRO DEVICES INC

Replacement metal gate scheme with self-alignment gate for vertical field effect transistors

ActiveUS9960254B1Maximizing effective device widthImprove device performanceSolid-state devicesSemiconductor/solid-state device manufacturingSelf-aligned gateField-effect transistor

A method is presented for forming a semiconductor structure. The method includes forming a fin structure over a substrate, forming a dummy gate over the fin structure, and etching the dummy gate by a first amount to expose a top portion of the fin structure. The method further includes forming a first dielectric layer adjacent the exposed top portion of the fin structure, forming a spacer adjacent the first dielectric layer contacting the fin structure, and etching the dummy gate by a second amount. The method further includes depositing a second dielectric layer to encapsulate the remaining dummy gate, depositing an inter-level dielectric (ILD) over the second dielectric layer, depositing at least one hard mask to access the dummy gate, stripping the dummy gate to form at least one recess, and filling the at least one recess with a high-k metal gate (HKMG).

Owner:IBM CORP

Fabrication of self-aligned gate contacts and source/drain contacts directly above gate electrodes and source/drains

ActiveUS20180211875A1Semiconductor/solid-state device detailsSolid-state devicesEngineeringActive layer

A method of forming an active device having self-aligned source / drain contacts and gate contacts, including, forming an active area on a substrate, where the active area includes a device channel; forming two or more gate structures on the device channel; forming a plurality of source / drains on the active area adjacent to the two or more gate structures and device channel; forming a protective layer on the surfaces of the two or more gate structures, plurality of source / drains, and active layer; forming an interlayer dielectric layer on the protective layer; removing a portion of the interlayer dielectric and protective layer to form openings, where each opening exposes a portion of one of the plurality of source / drains; forming a source / drain contact liner in at least one of the plurality of openings; and forming a source / drain contact fill on the source / drain contact liner.

Owner:IBM CORP

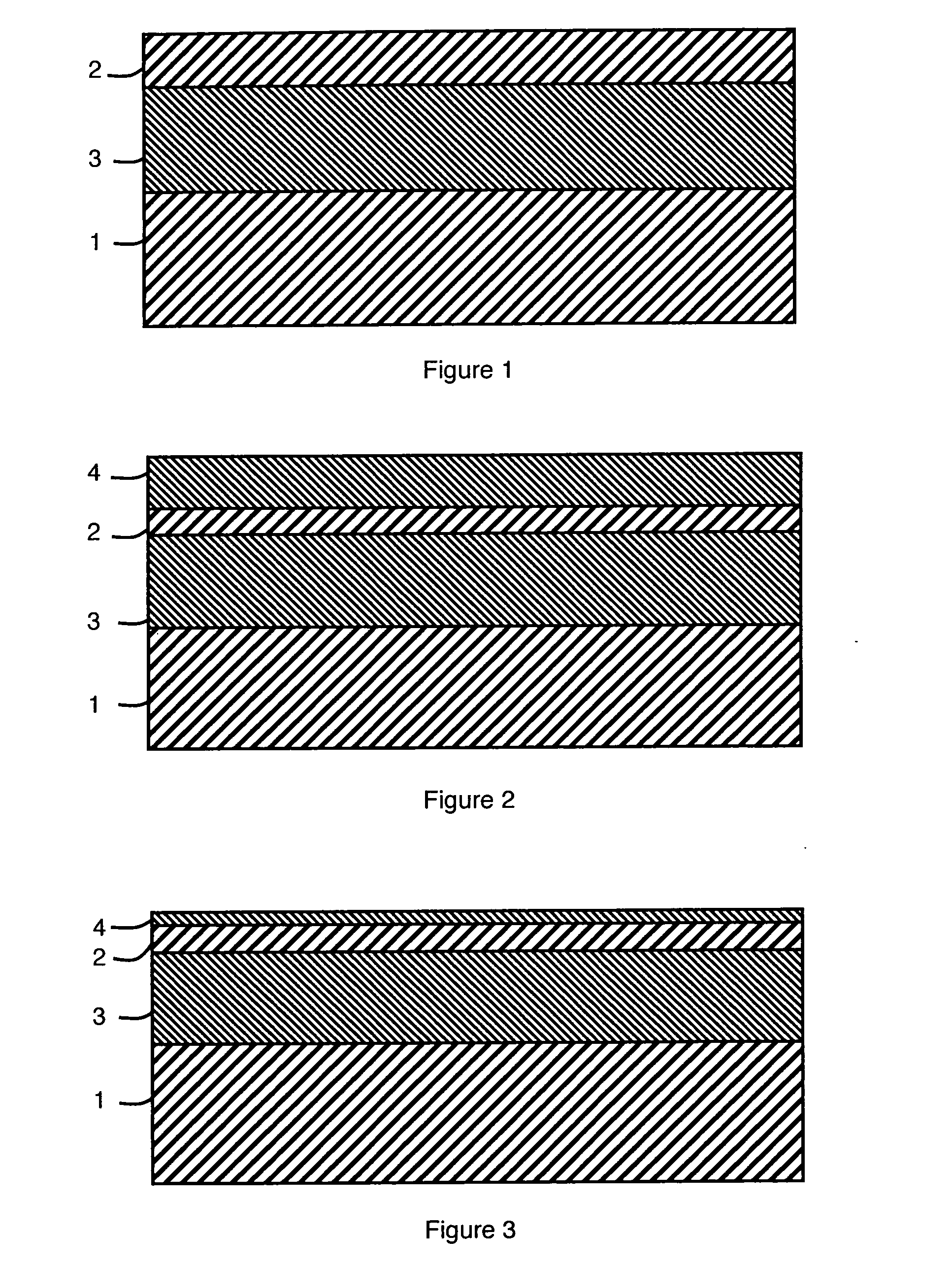

Process for Fabricating a Field-Effect Transistor with Self-Aligned Gates

InactiveUS20090011562A1Solid-state devicesSemiconductor/solid-state device manufacturingAmorphous siliconSource area

A first gate, formed on a substrate, is surmounted by a hard layer designed, with first spacers surrounding the first gate, to act as etching mask to bound the channel and a pad that bounds a space subsequently used to form a gate cavity. The hard layer is preferably made of silicon nitride. Before flipping and bonding, a bounding layer, preferably made of amorphous silicon or polysilicon, is formed to bound drain and source areas. After flipping and bonding of the assembly on a second substrate, a second gate is formed in the gate cavity. At least partial silicidation of the bounding layer is then performed before the metal source and drain electrodes are produced.

Owner:COMMISSARIAT A LENERGIE ATOMIQUE ET AUX ENERGIES ALTERNATIVES

CMOS structure with non-epitaxial raised source/drain and self-aligned gate and method of manufacture

A CMOS structure and method of achieving self-aligned raised source / drain for CMOS structures on SOI without relying on selective epitaxial growth of silicon. In the method, CMOS structures are provided by performing sacraficial oxidation so that oxidation occurs on the surface of both the SOI and BOX interface. This allows for oxide spacer formation for gate-to-source / drain isolation which makes raised source / drain fabrication without increasing contact resistance possible.

Owner:IBM CORP

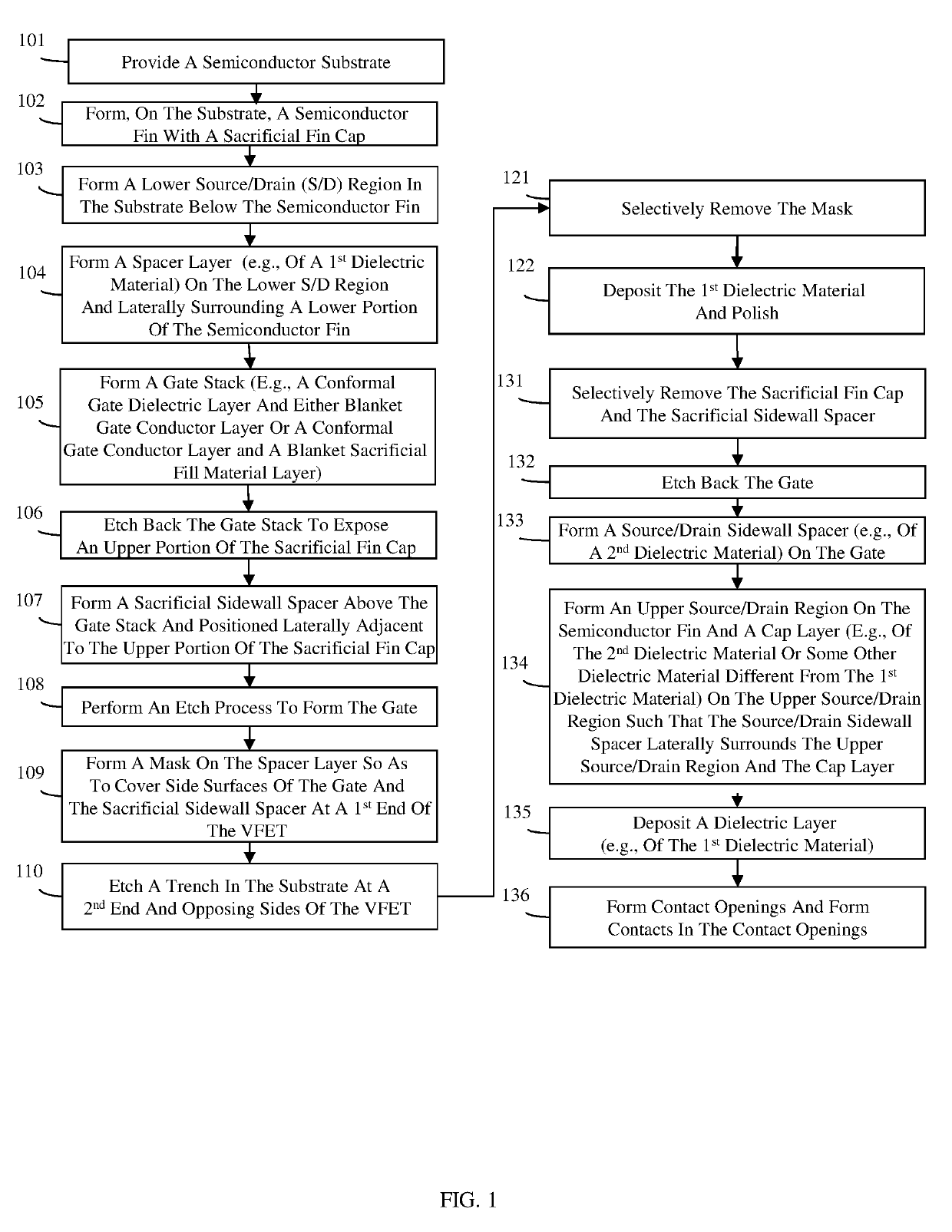

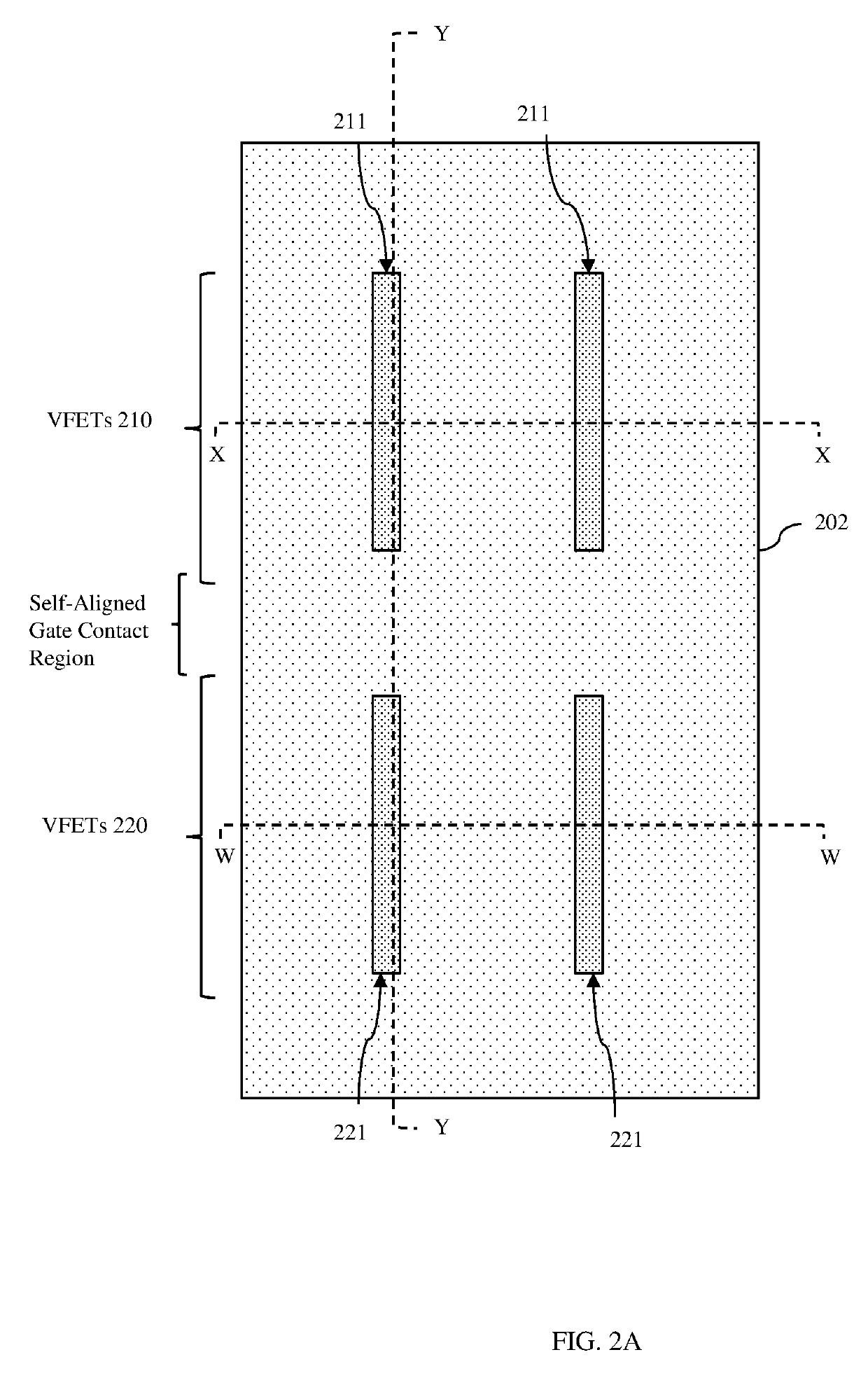

Methods of forming vertical field effect transistors with self-aligned contacts and the resulting structures

ActiveUS10461186B1TransistorSemiconductor/solid-state device manufacturingField-effect transistorVertical field

Disclosed are methods wherein vertical field effect transistor(s) (VFET(s)) and isolation region(s) are formed on a substrate. Each VFET includes a fin extending vertically between source / drain regions, a spacer layer and a gate around the fin, and a source / drain sidewall spacer around an upper source / drain region. Optionally, a gate sidewall spacer is adjacent to the gate at a first end of the VFET. An isolation region is adjacent to the gate at a second end and opposing sides of the VFET and extends into the substrate. Contacts are formed including a lower source / drain contact (which is adjacent to the first end of the VFET and is self-aligned if the optional gate sidewall spacer is present) and a self-aligned gate contact (which extends into the isolation region at the second end of the VFET and contacts a side surface of the gate). Also disclosed are structures formed according to the methods.

Owner:GLOBALFOUNDRIES US INC

Self-aligned gated rod field emission device and associated method of fabrication

ActiveUS7239076B2Small emitter tipSimple and efficientDischarge tube luminescnet screensLamp detailsCylindrical channelField emission device

A self-aligned gated field emission device and an associated method of fabrication are described. The device includes a substrate and a porous layer disposed adjacent to the surface of the substrate, wherein the porous layer defines a plurality of substantially cylindrical channels, each of the plurality of substantially cylindrical channels aligned substantially parallel to one another and substantially perpendicular to the surface of the substrate. The device also includes a plurality of substantially rod-shaped structures disposed within at least a portion of the plurality of substantially cylindrical channels defined by the porous layer and adjacent to the surface of the substrate, wherein a portion of each of the plurality of substantially rod-shaped structures protrudes above the surface of the porous layer. The device further includes a gate dielectric layer disposed on the surface of the porous layer, wherein the gate dielectric layer is disposed between the plurality of substantially rod-shaped structures. The device still further includes a conductive layer selectively disposed on the surface of the gate dielectric layer, wherein the conductive layer is selectively disposed between the plurality of substantially rod-shaped structures.

Owner:GENERAL ELECTRIC CO

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com