Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

226results about How to "Small package" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

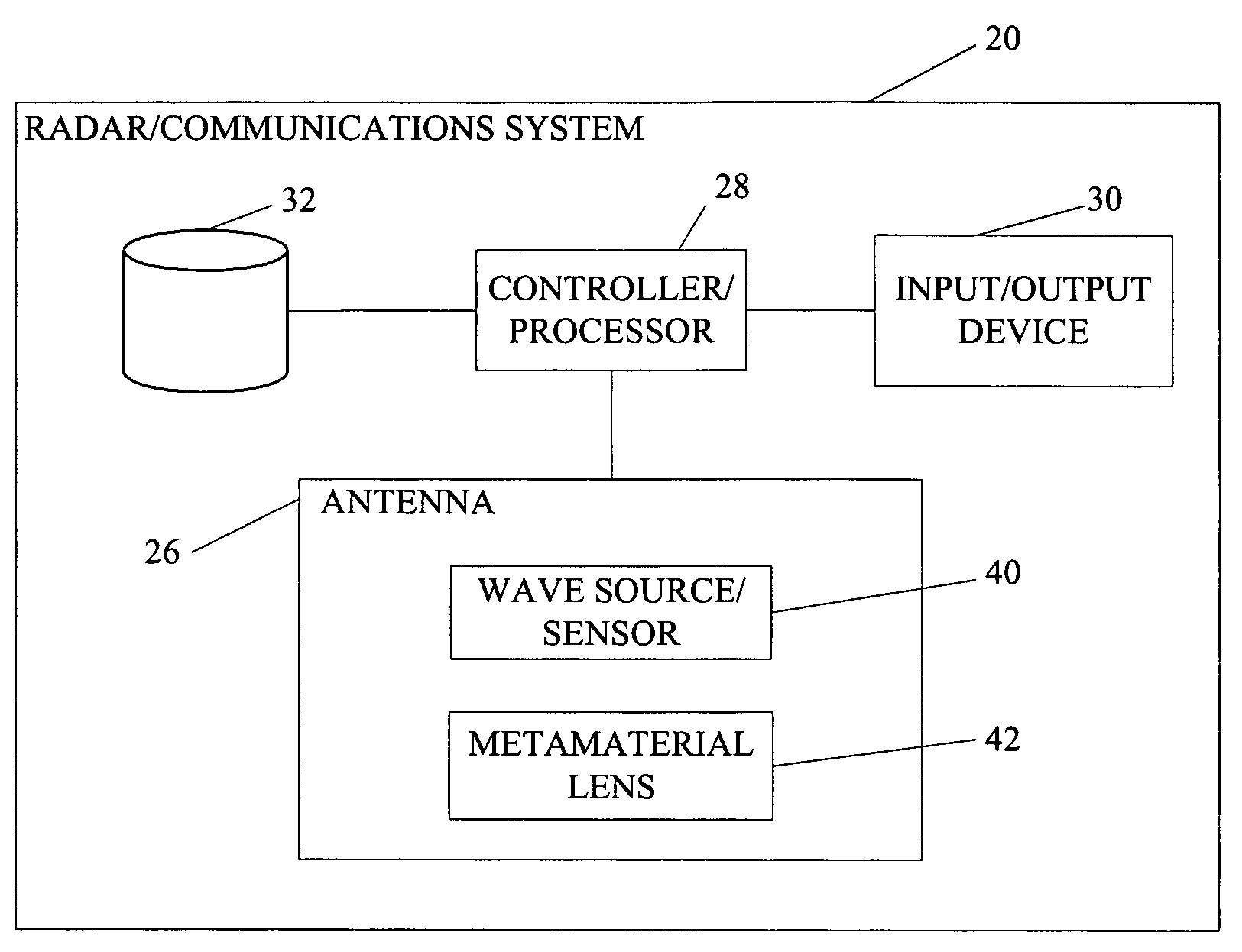

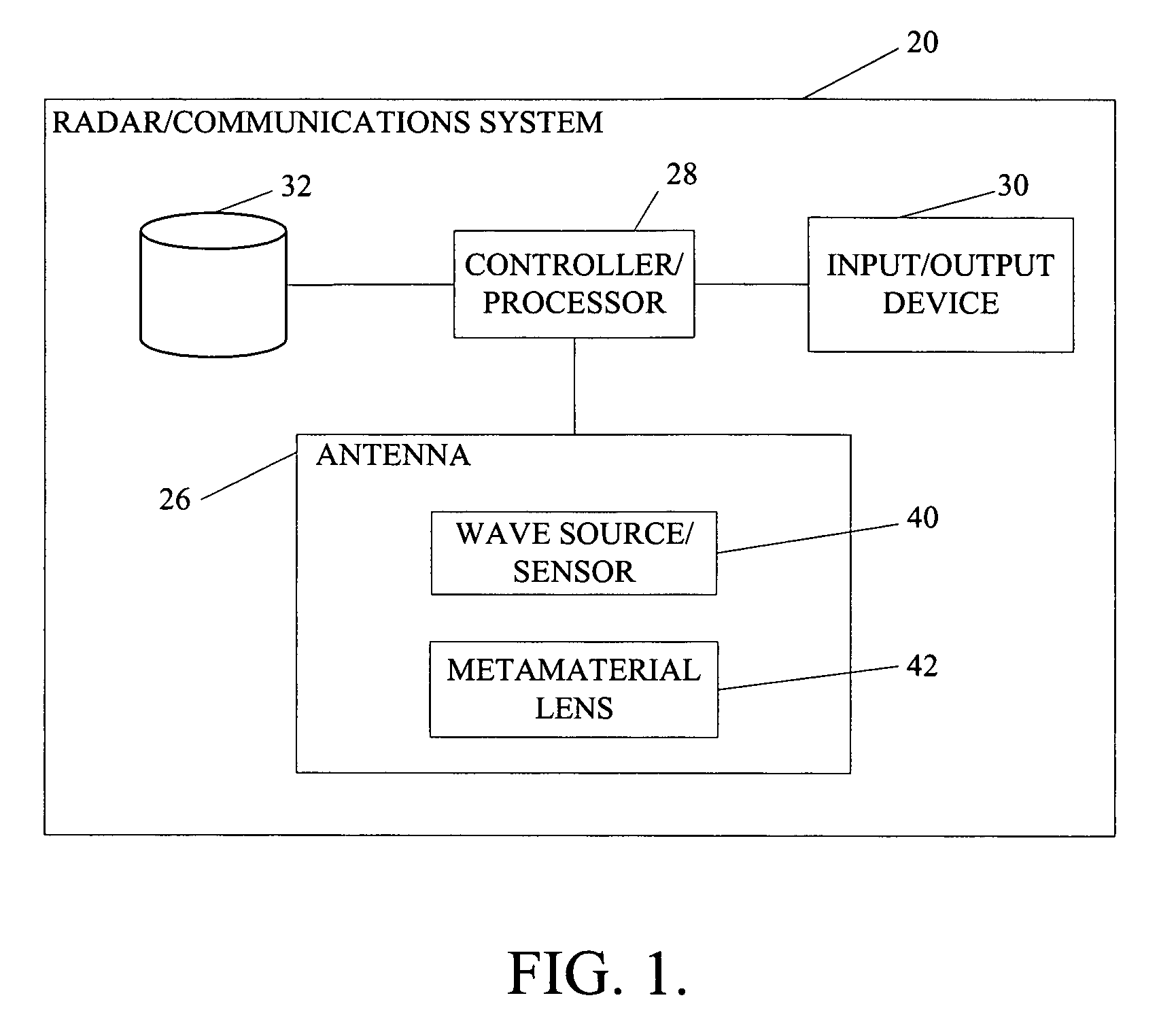

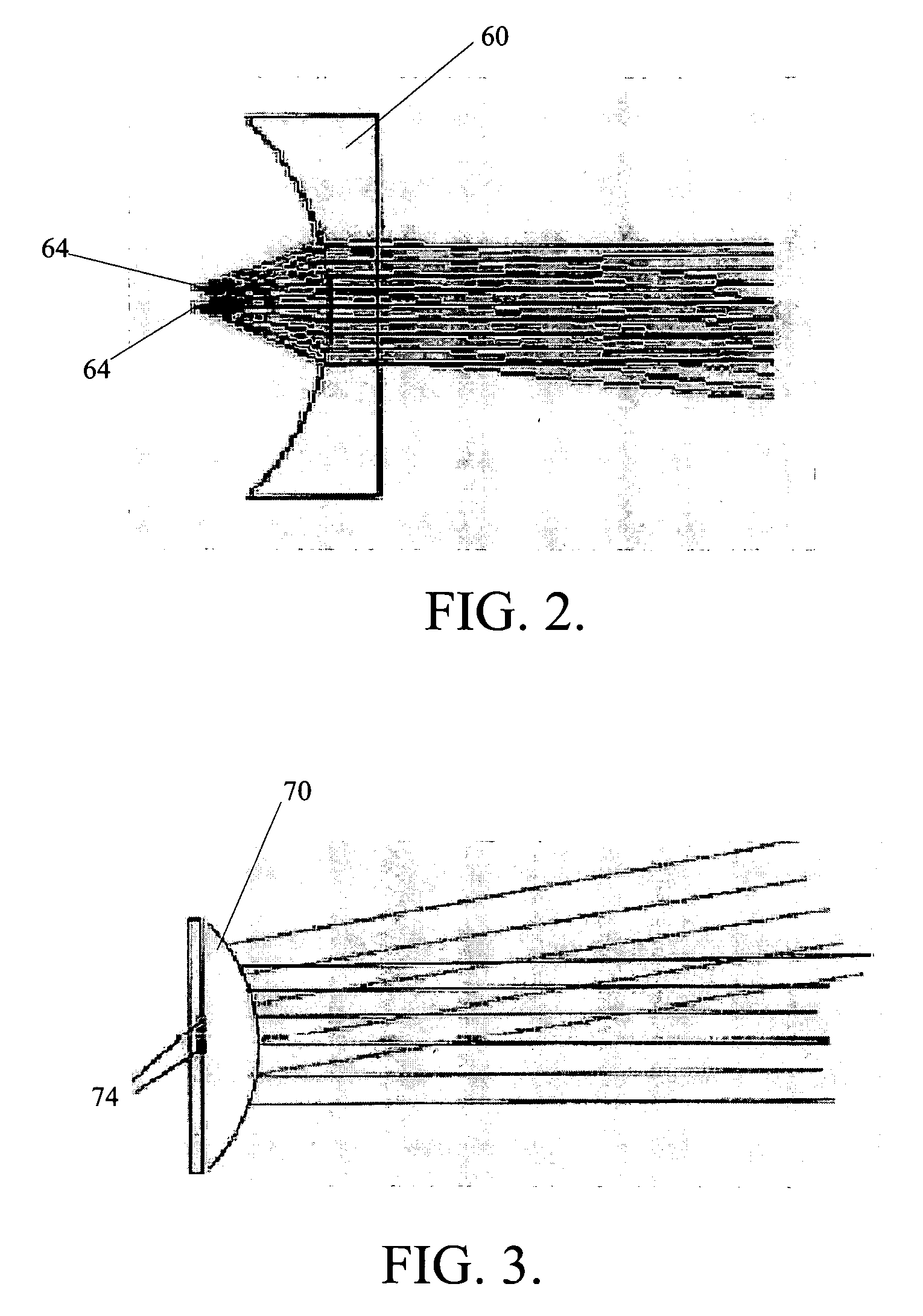

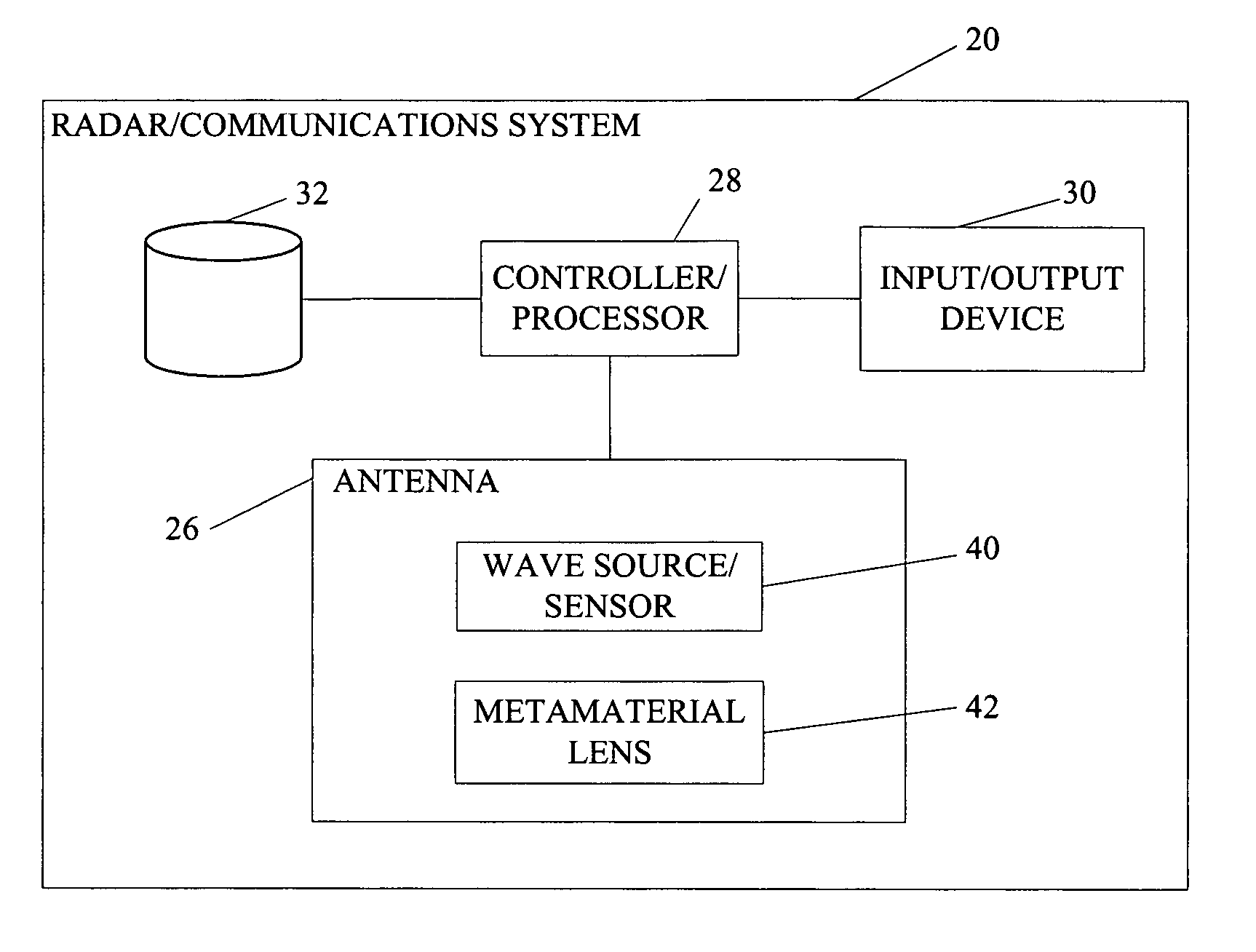

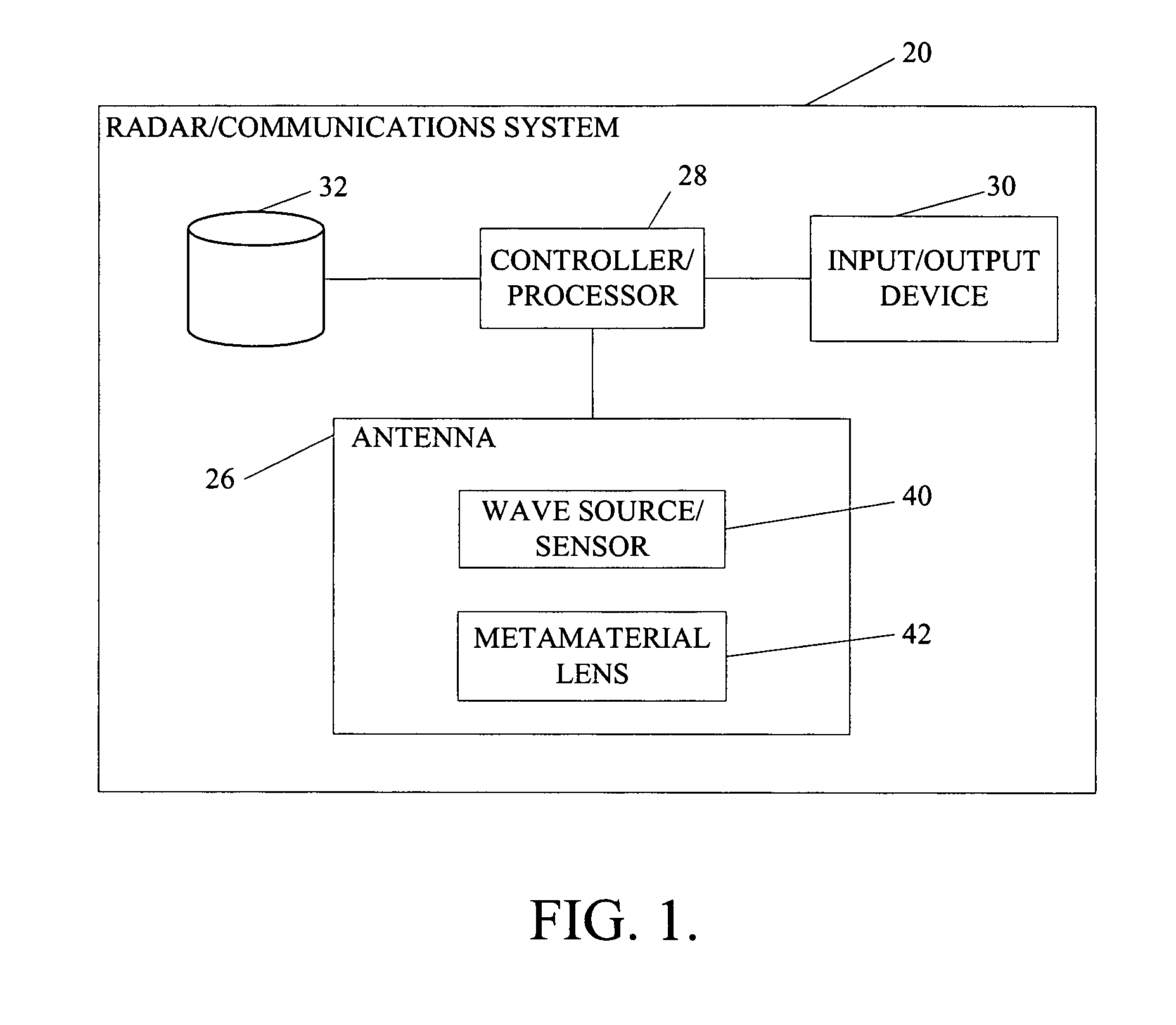

Metamaterial scanning lens antenna systems and methods

The present invention is directed to systems and methods for radiating radar signals, communication signals, or other similar signals. In one embodiment, a system includes a controller that generates a control signal and an antenna coupled to the controller. The antenna includes a first component that generates at least one wave based on the generated control signal and a metamaterial lens positioned at some predefined focal length from the first component. The metamaterial lens directs the generated at least one wave.

Owner:THE BOEING CO

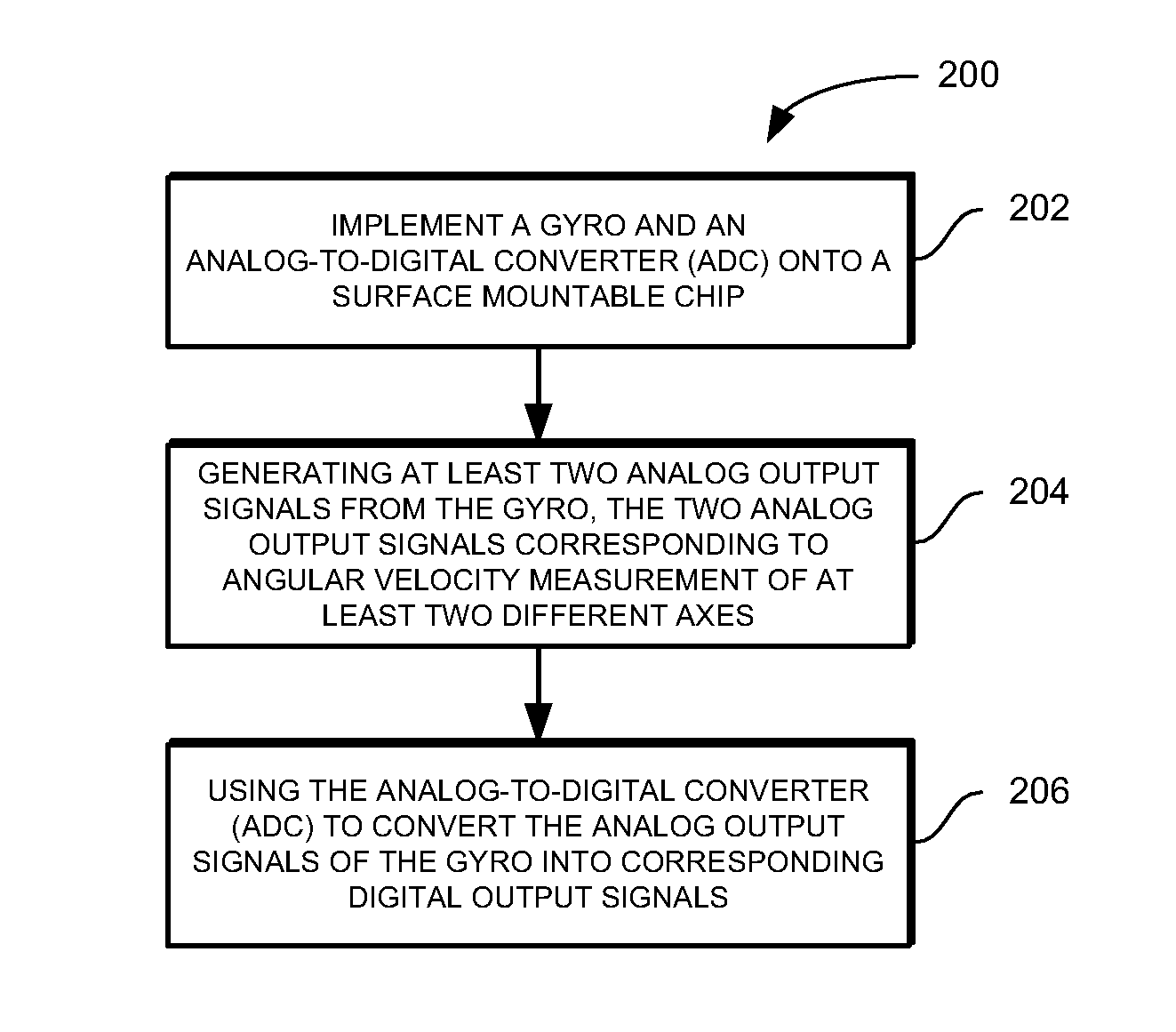

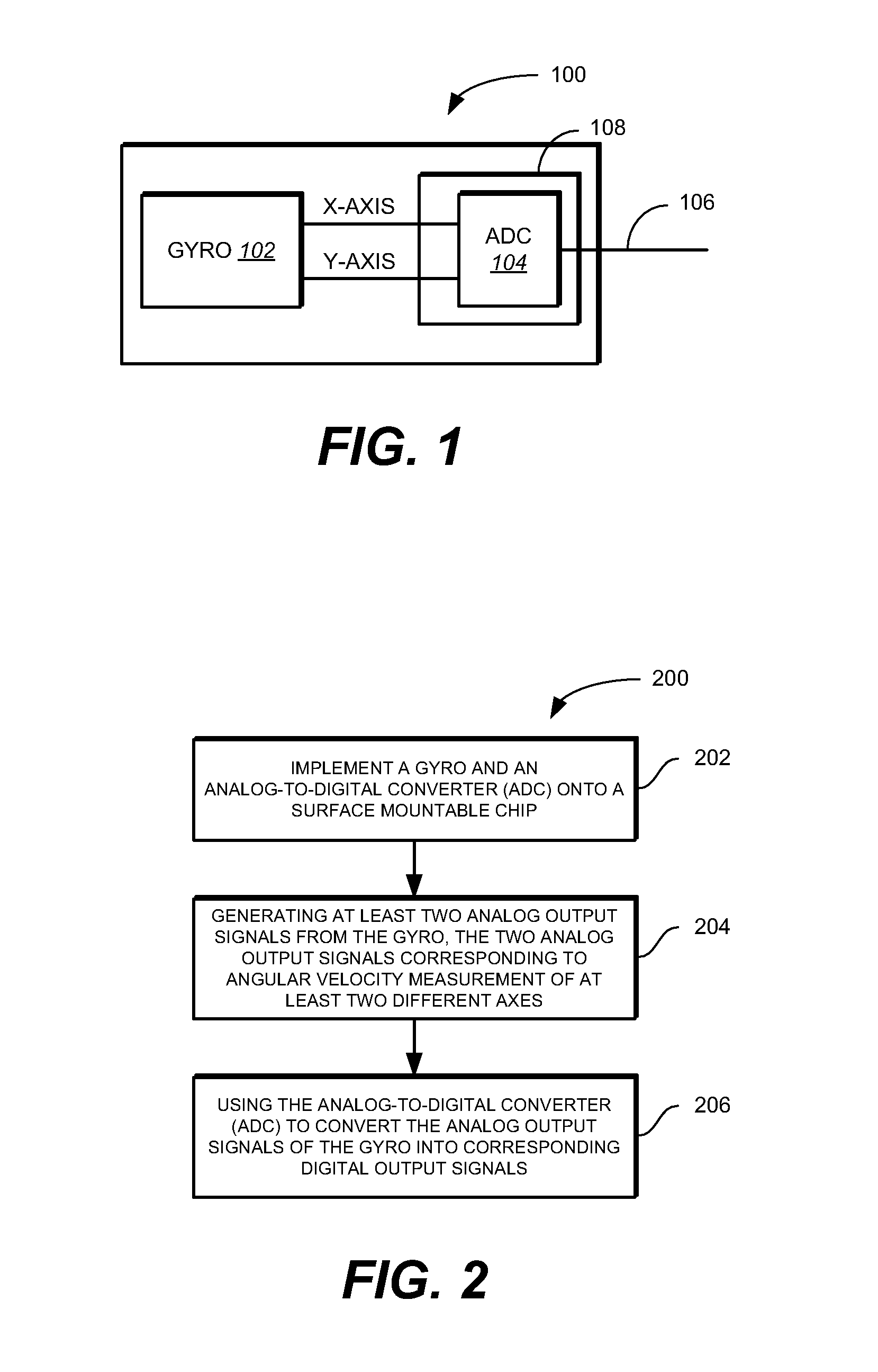

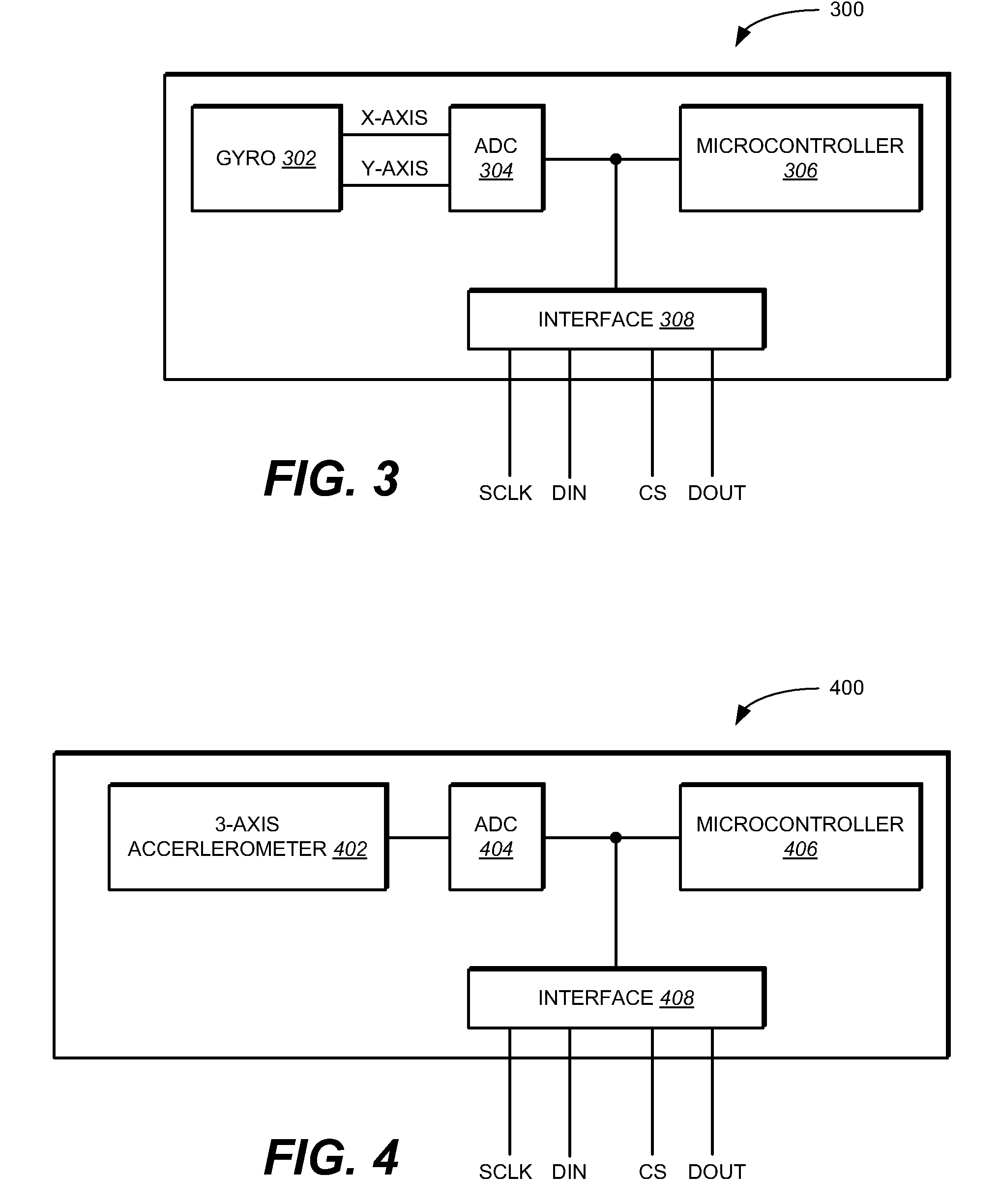

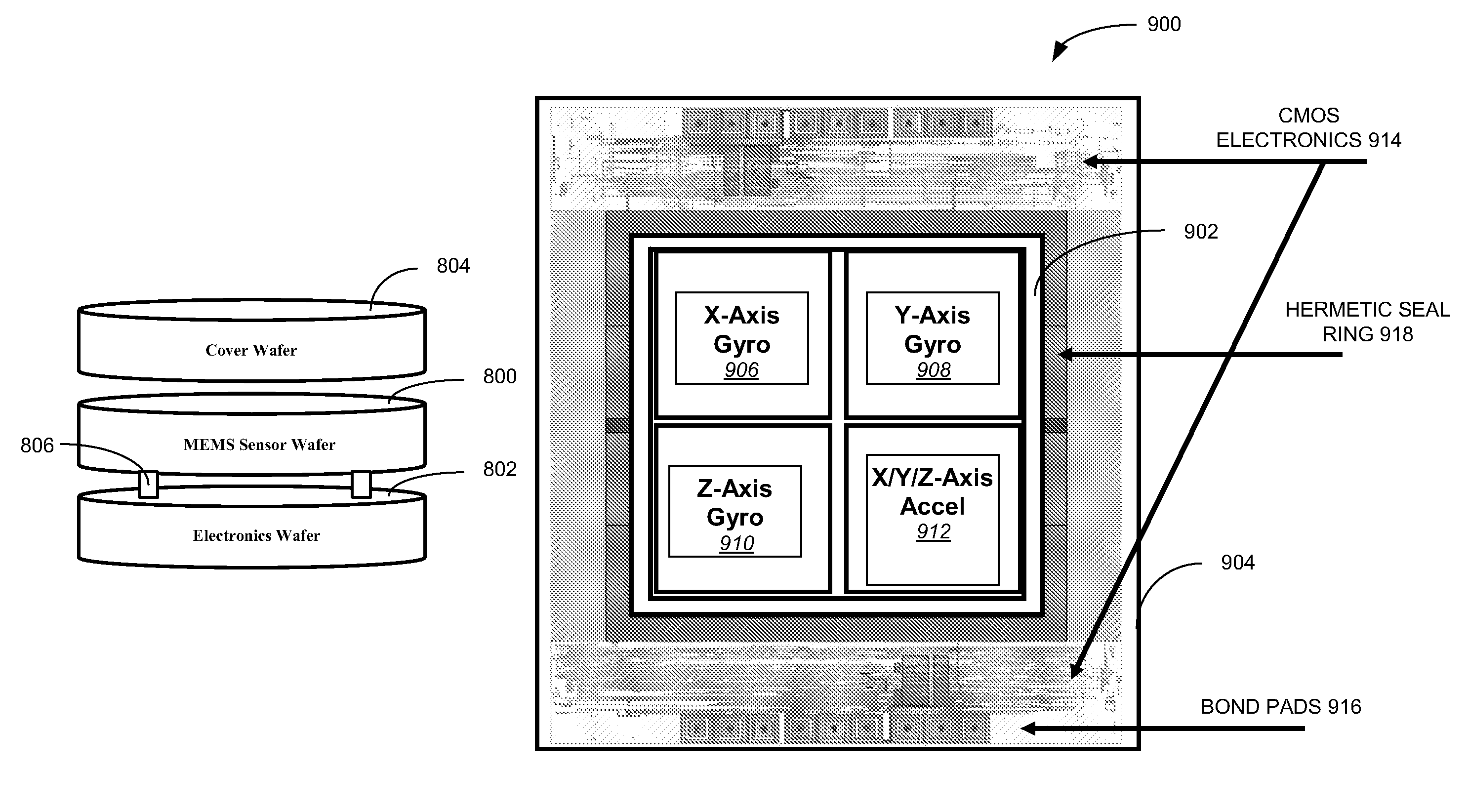

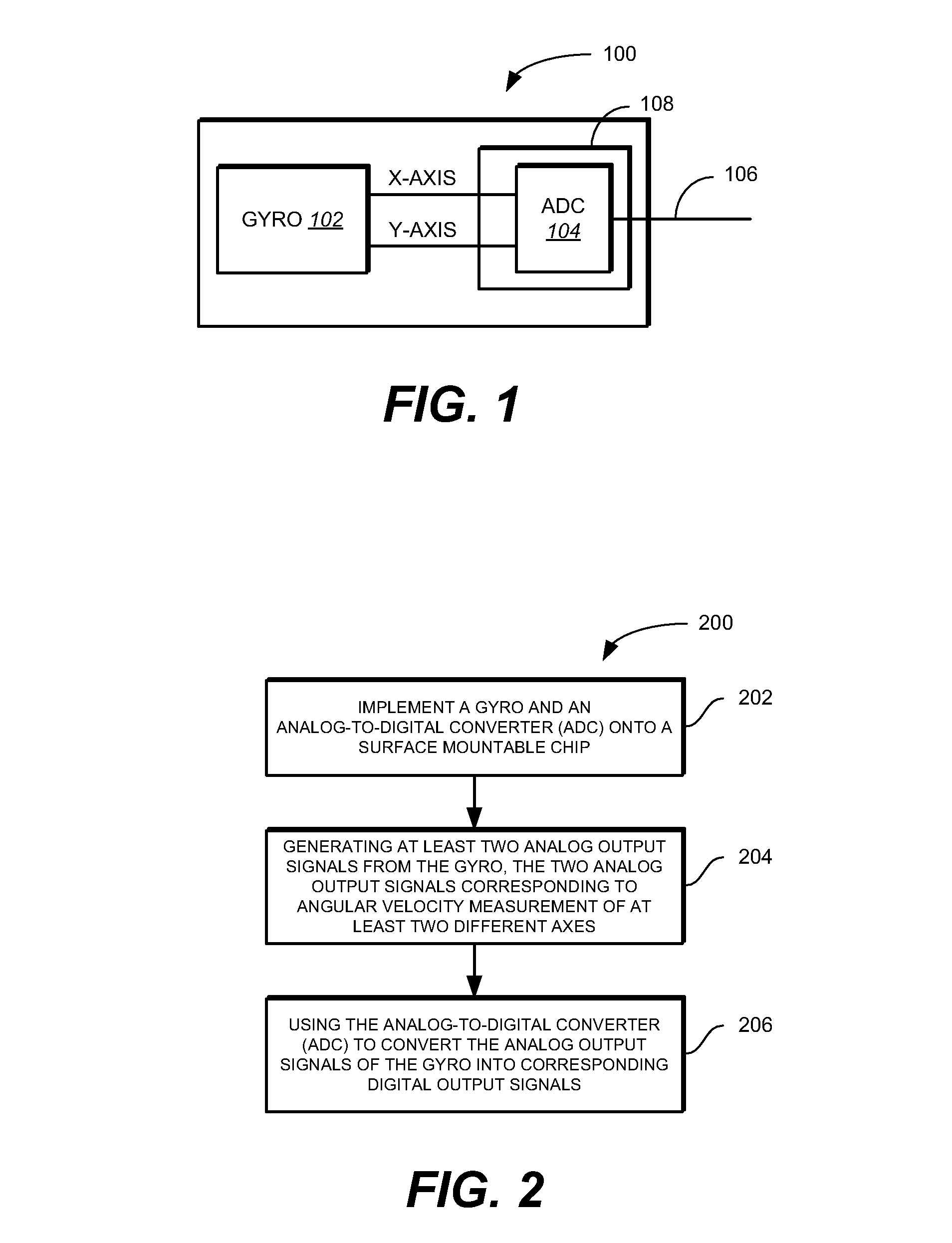

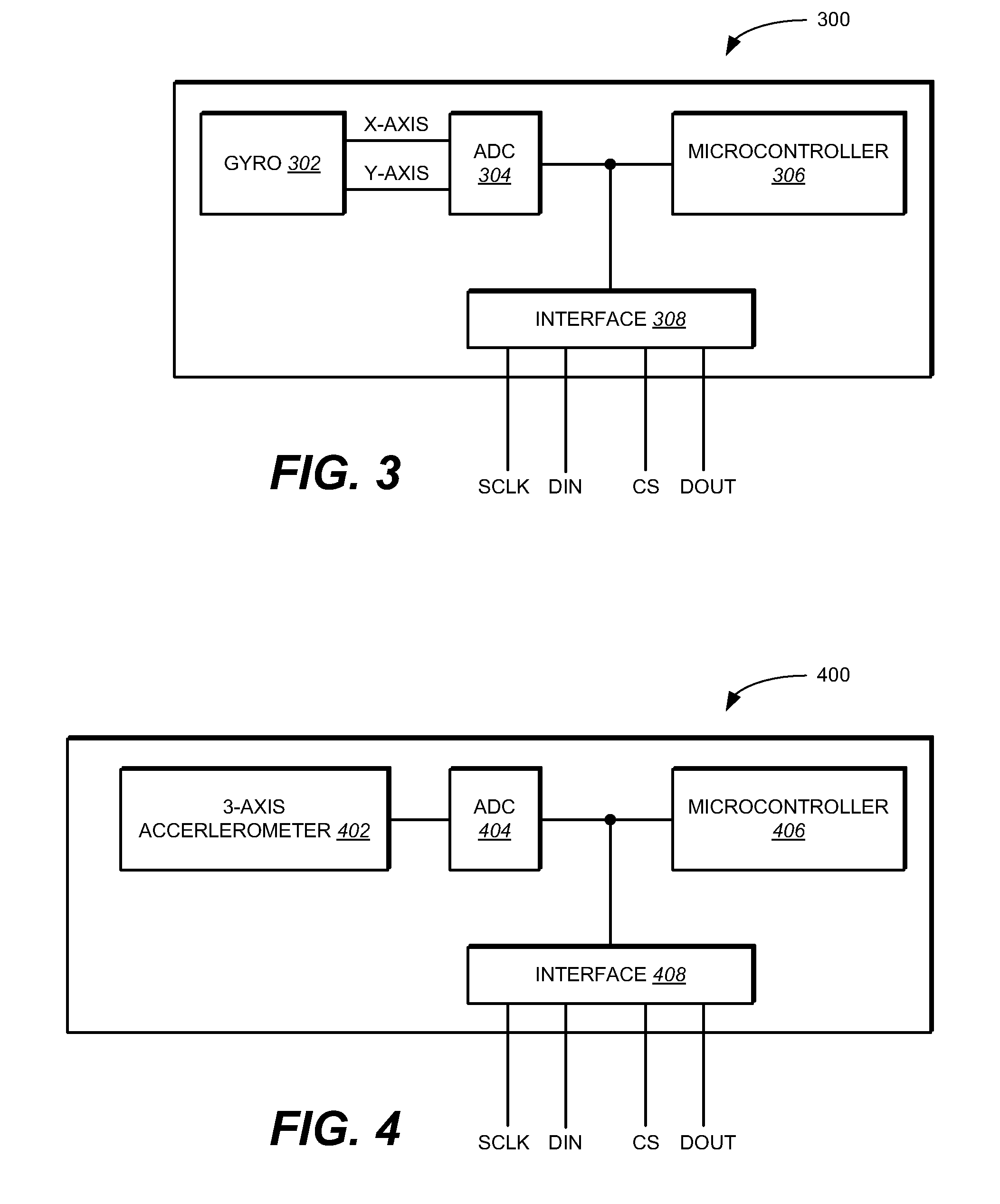

Integrated Motion Processing Unit (MPU) With MEMS Inertial Sensing And Embedded Digital Electronics

ActiveUS20090007661A1Small packageLower performance requirementsElectric signal transmission systemsAcceleration measurement using interia forcesMotion processingAccelerometer

A module operable to be mounted onto a surface of a board. The module includes a linear accelerometer to provide a first measurement output corresponding to a measurement of linear acceleration in at least one axis, and a first rotation sensor operable to provide a second measurement output corresponding to a measurement of rotation about at least one axis. The accelerometer and the first rotation sensor are formed on a first substrate. The module further includes an application specific integrated circuit (ASIC) to receive both the first measurement output from the linear accelerometer and the second measurement output from the first rotation sensor. The ASIC includes an analog-to-digital converter and is implemented on a second substrate. The first substrate is vertically bonded to the second substrate.

Owner:INVENSENSE

Integrated motion processing unit (MPU) with MEMS inertial sensing and embedded digital electronics

ActiveUS8250921B2Low costSmall packageElectric signal transmission systemsSpeed/acceleration/shock instrument detailsMotion processingAccelerometer

Owner:INVENSENSE

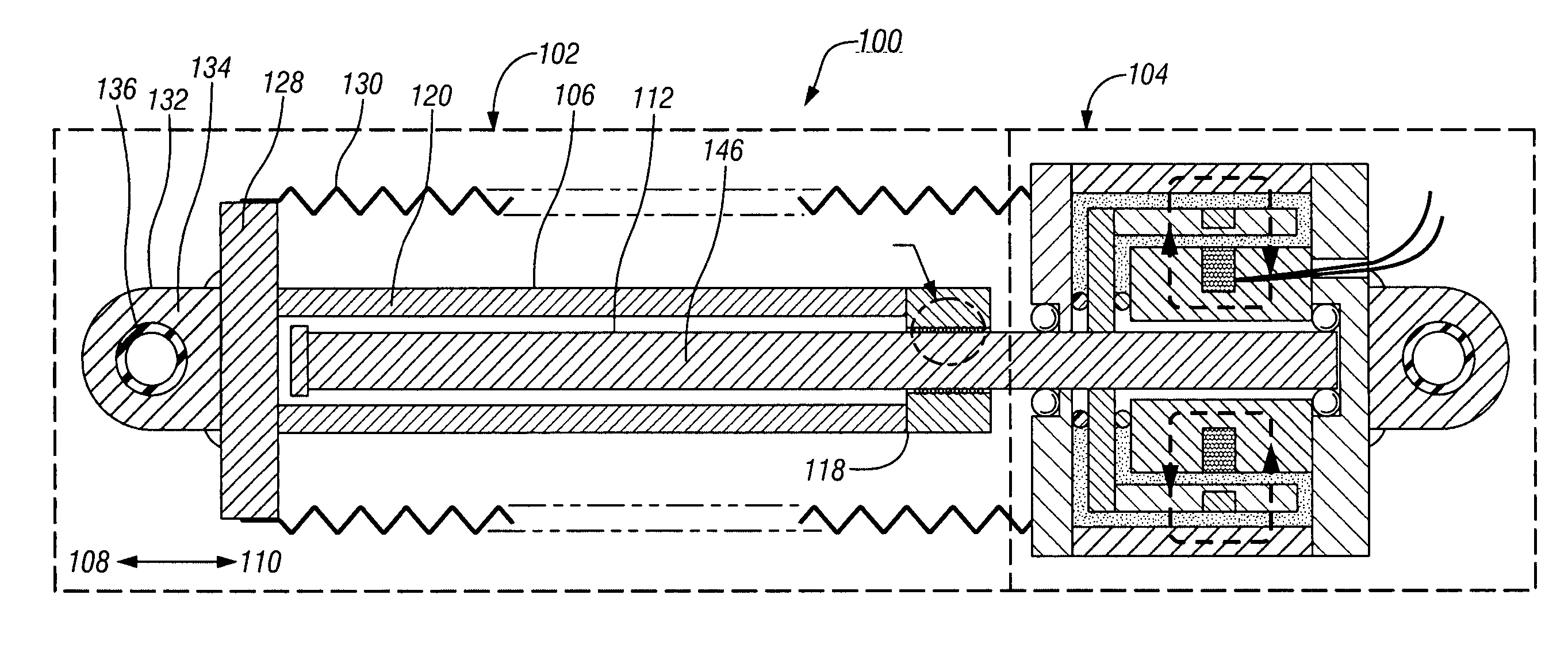

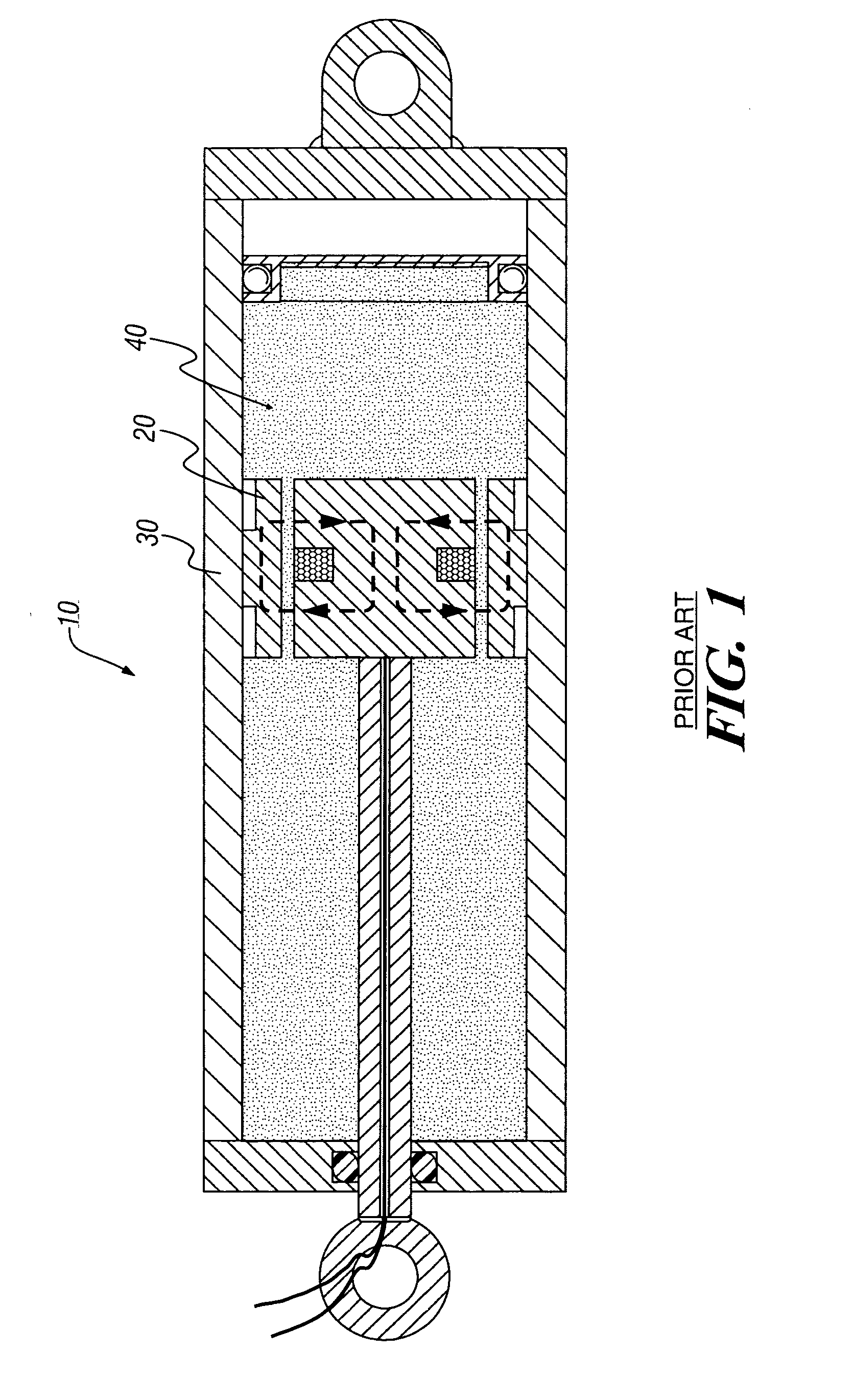

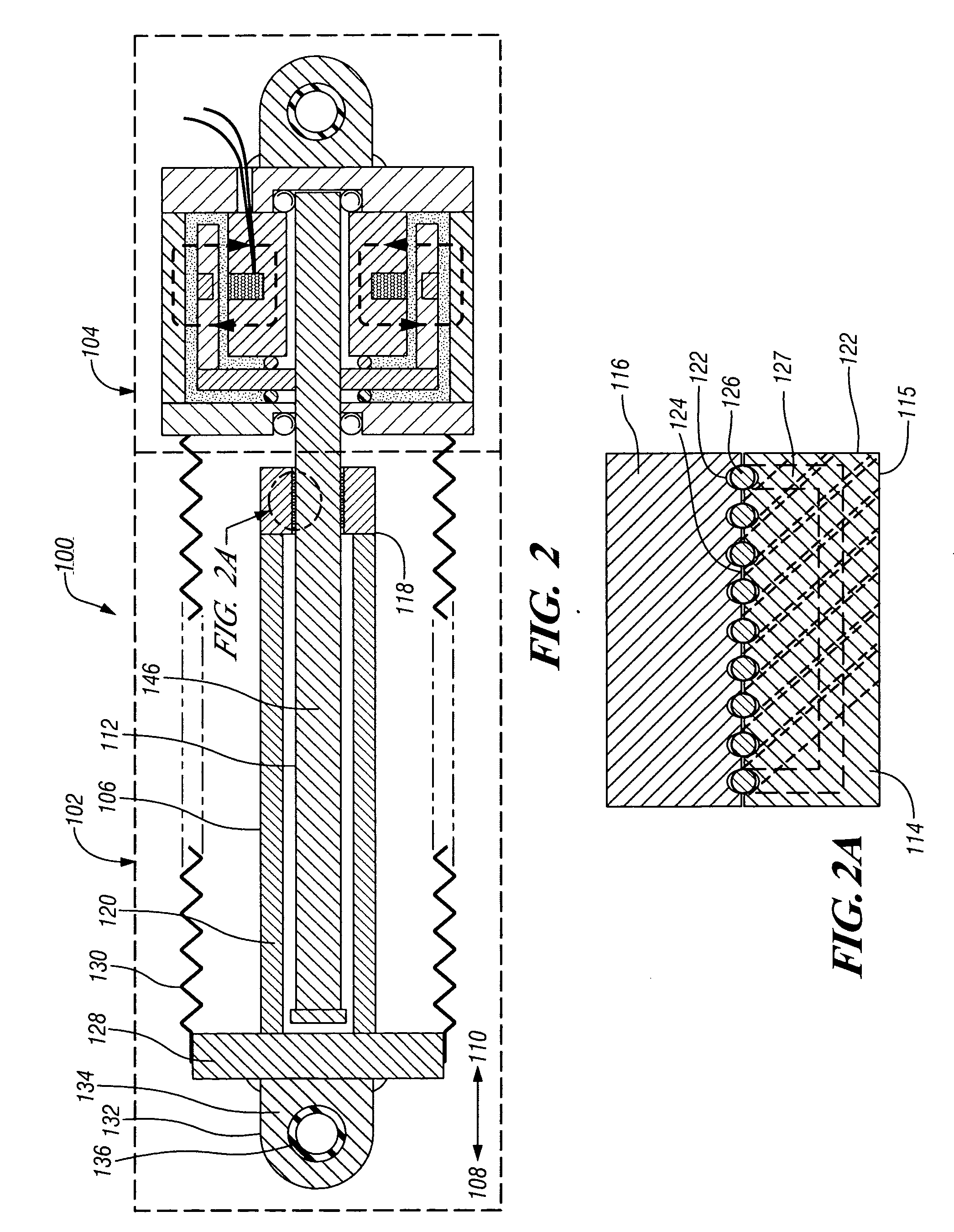

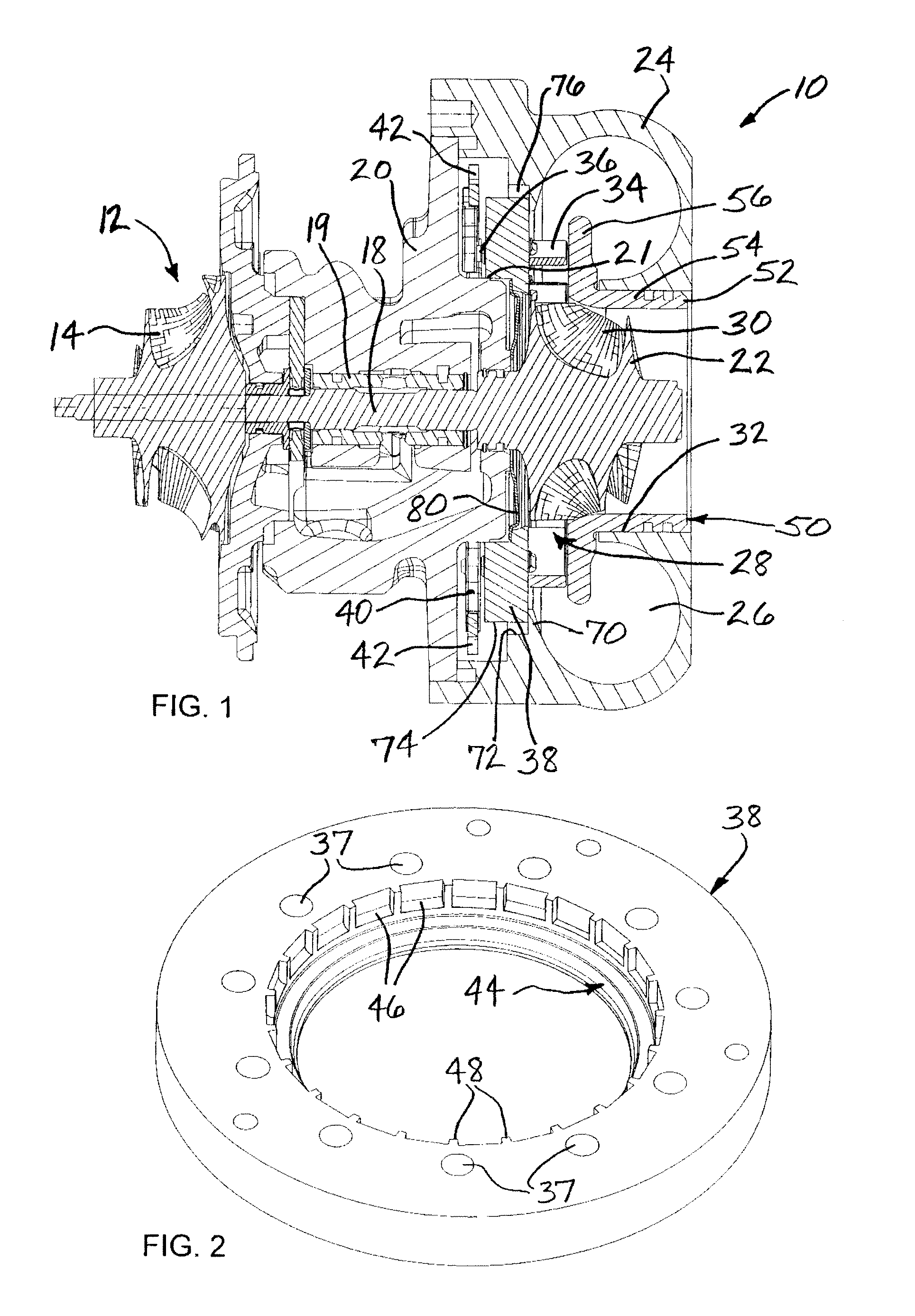

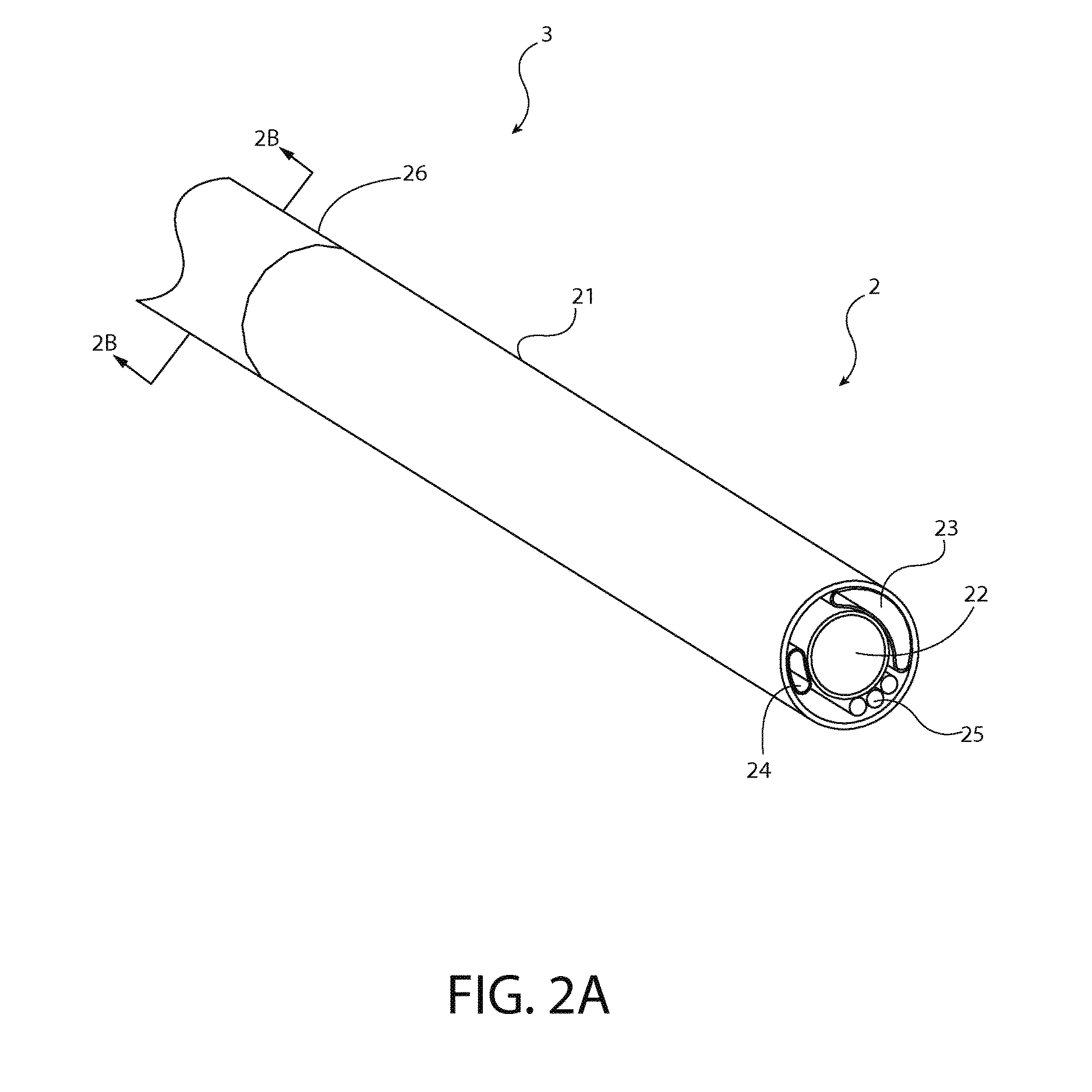

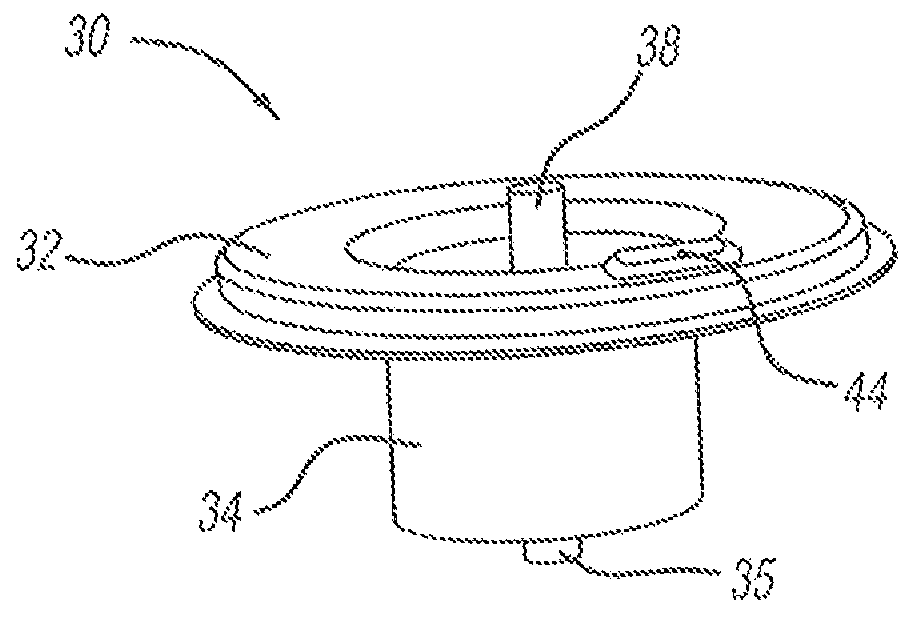

Fluid damper having continuously variable damping response

ActiveUS20050121269A1Reduce manufacturing costLower the volumeSpringsNon-rotating vibration suppressionMagnetorheological fluidEngineering

An improved damping apparatus that utilizes a fluid having a viscosity that may be varied by the application of an electromagnetic field, such as a magnetorheological fluid or an electrorheological fluid, to provide the damping response. The damping apparatus includes a linear to rotary conversion mechanism which comprises a translatable member that is adapted for linear translation in a forward and a reverse direction and a rotatable member comprising a rotatable shaft that is rotatably coupled to the translatable member; wherein translation of the translatable member in one of the forward or the reverse directions produces a forward or a reverse rotation of the rotatable member and shaft, respectively. The damping apparatus also includes a damping mechanism which comprises a hub that is fixed to the shaft, a means for generating a variable electromagnetic field in response to an applied electrical signal that may be continuously varied in response to an input signal that is representative of a desired damping force and a fluid having a viscosity that may be continuously varied by application of the electromagnetic field that is in touching contact with the hub. Application of the variable electromagnetic field to the fluid produces changes in the viscosity of the fluid that in turn provides variable resistance to rotation of the hub and resistance to translation of the translatable member, thereby providing a damping apparatus with a continuously variable damping response.

Owner:GM GLOBAL TECH OPERATIONS LLC

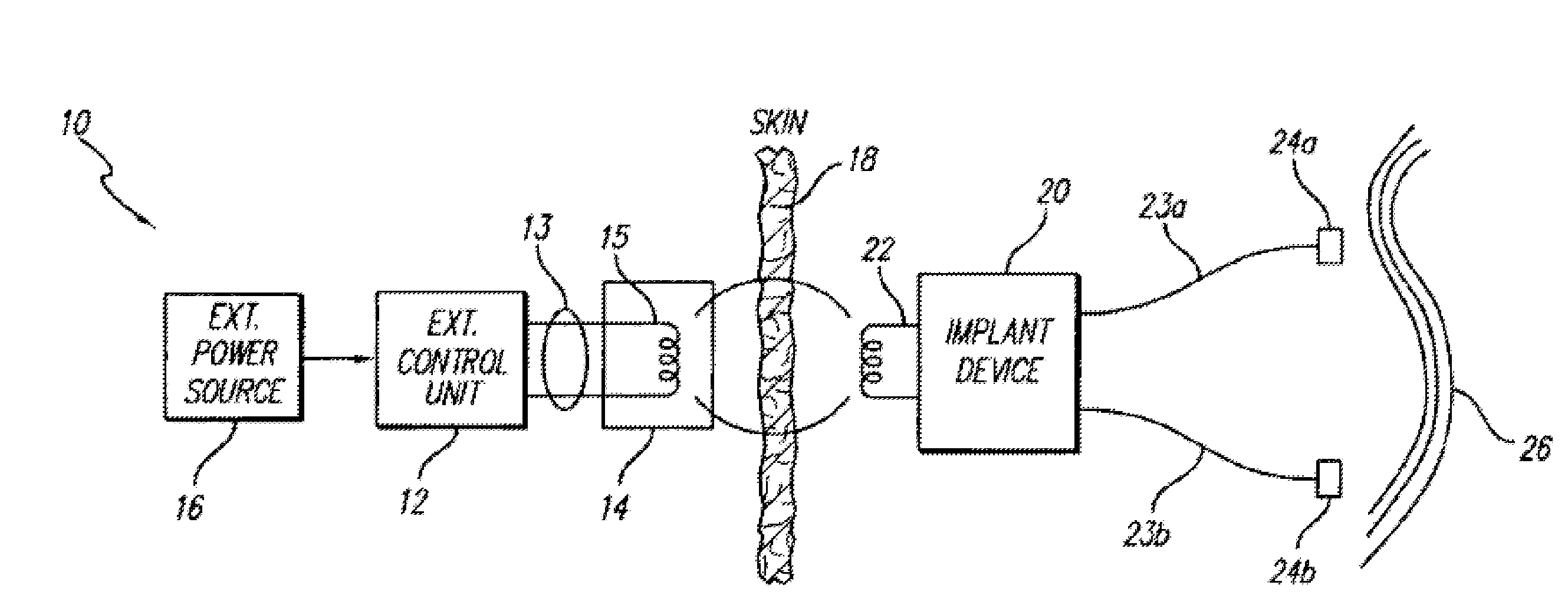

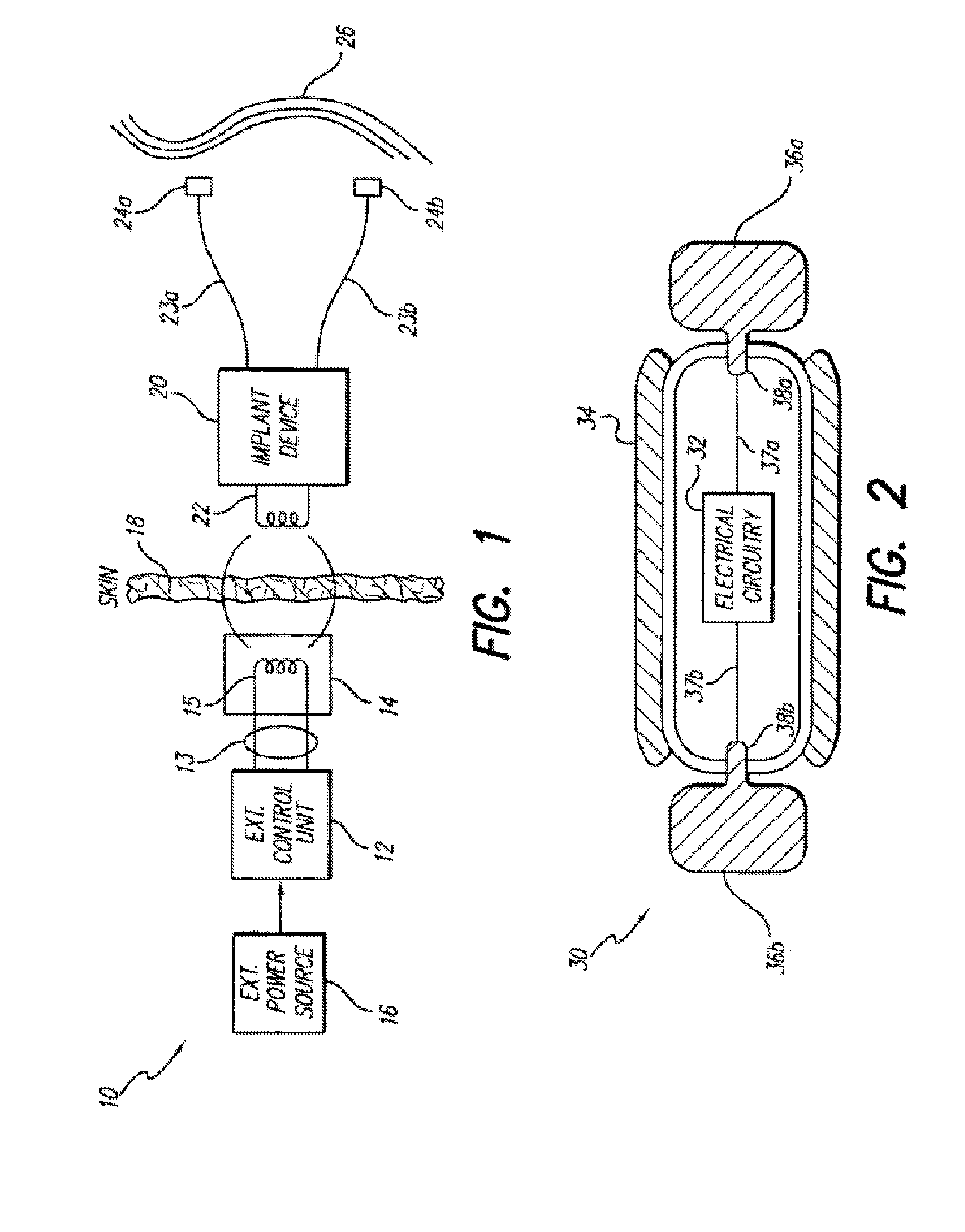

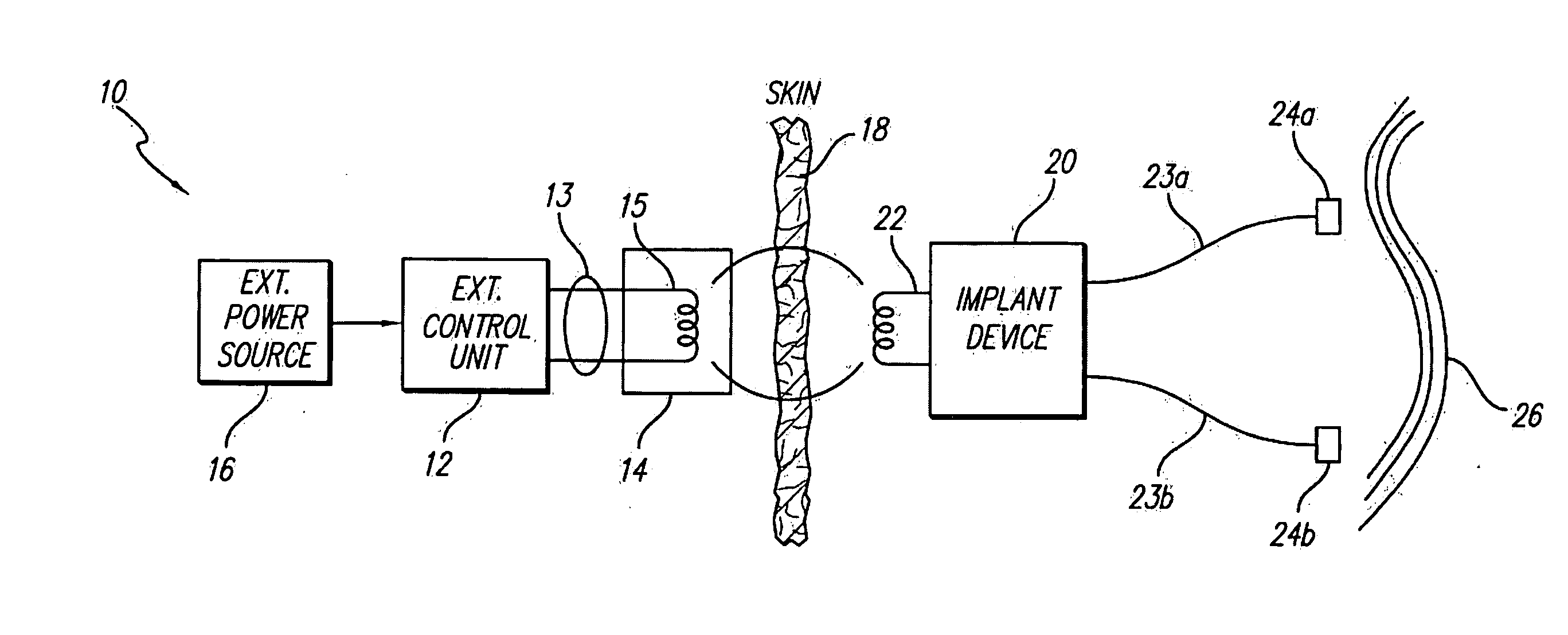

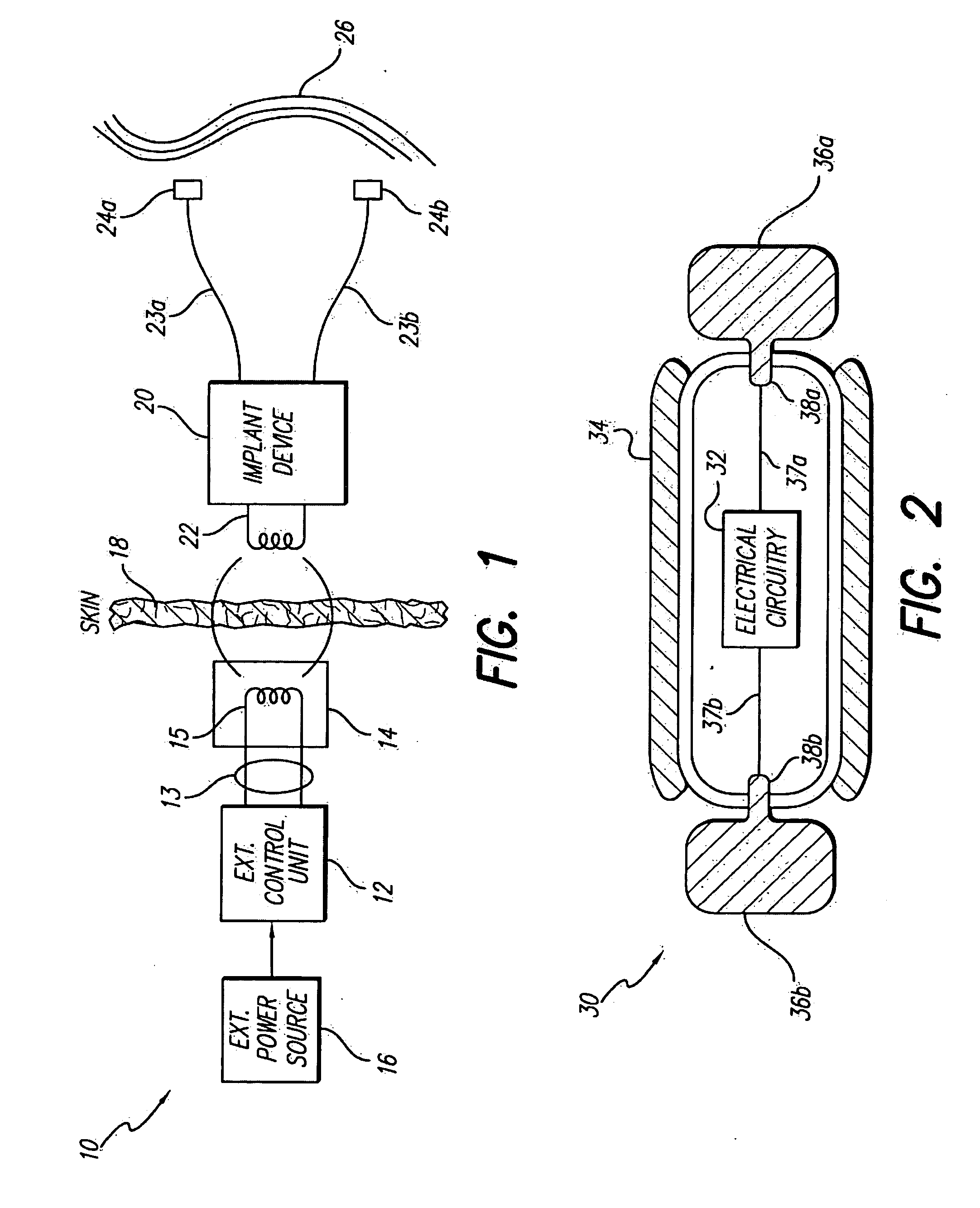

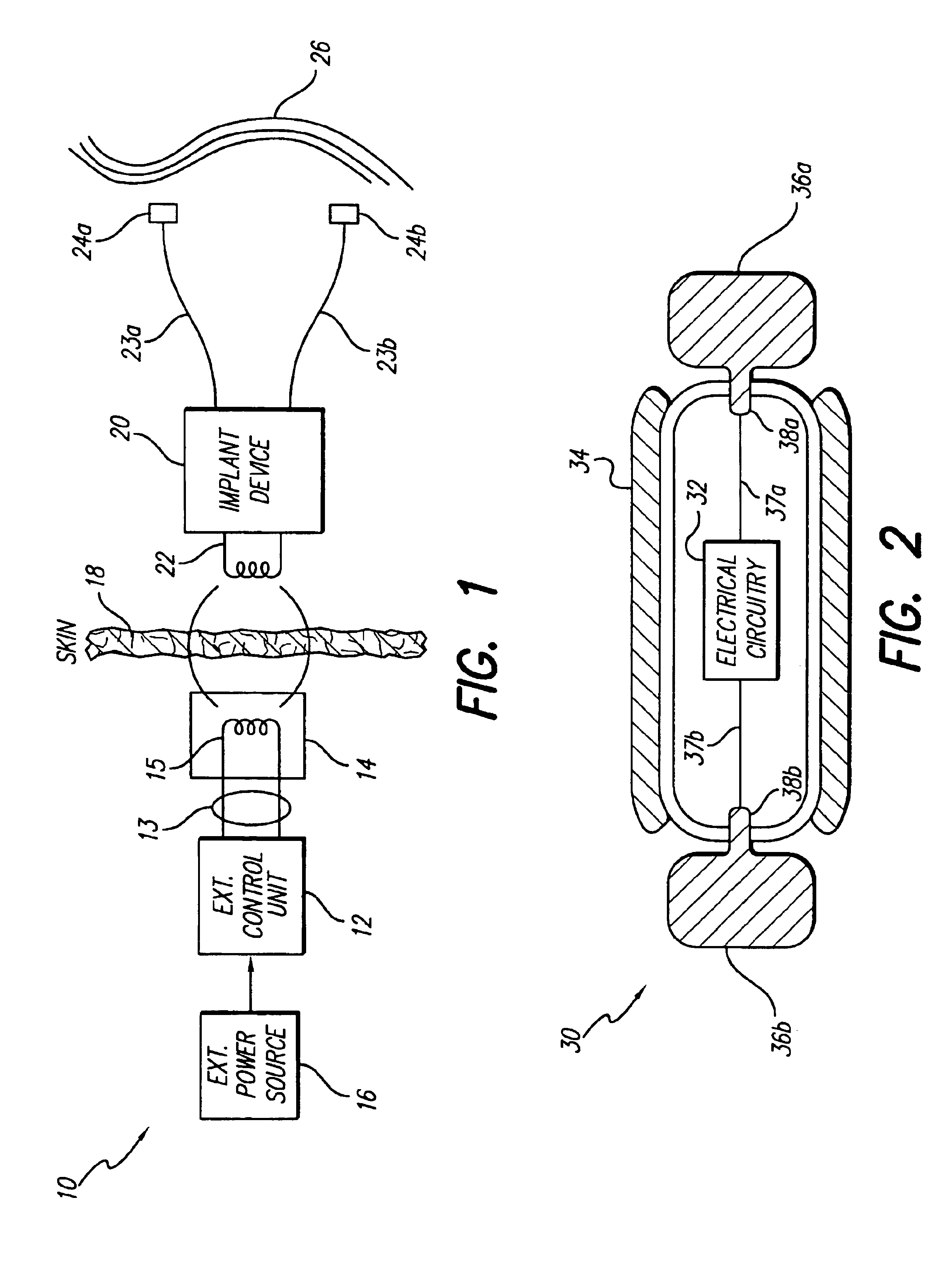

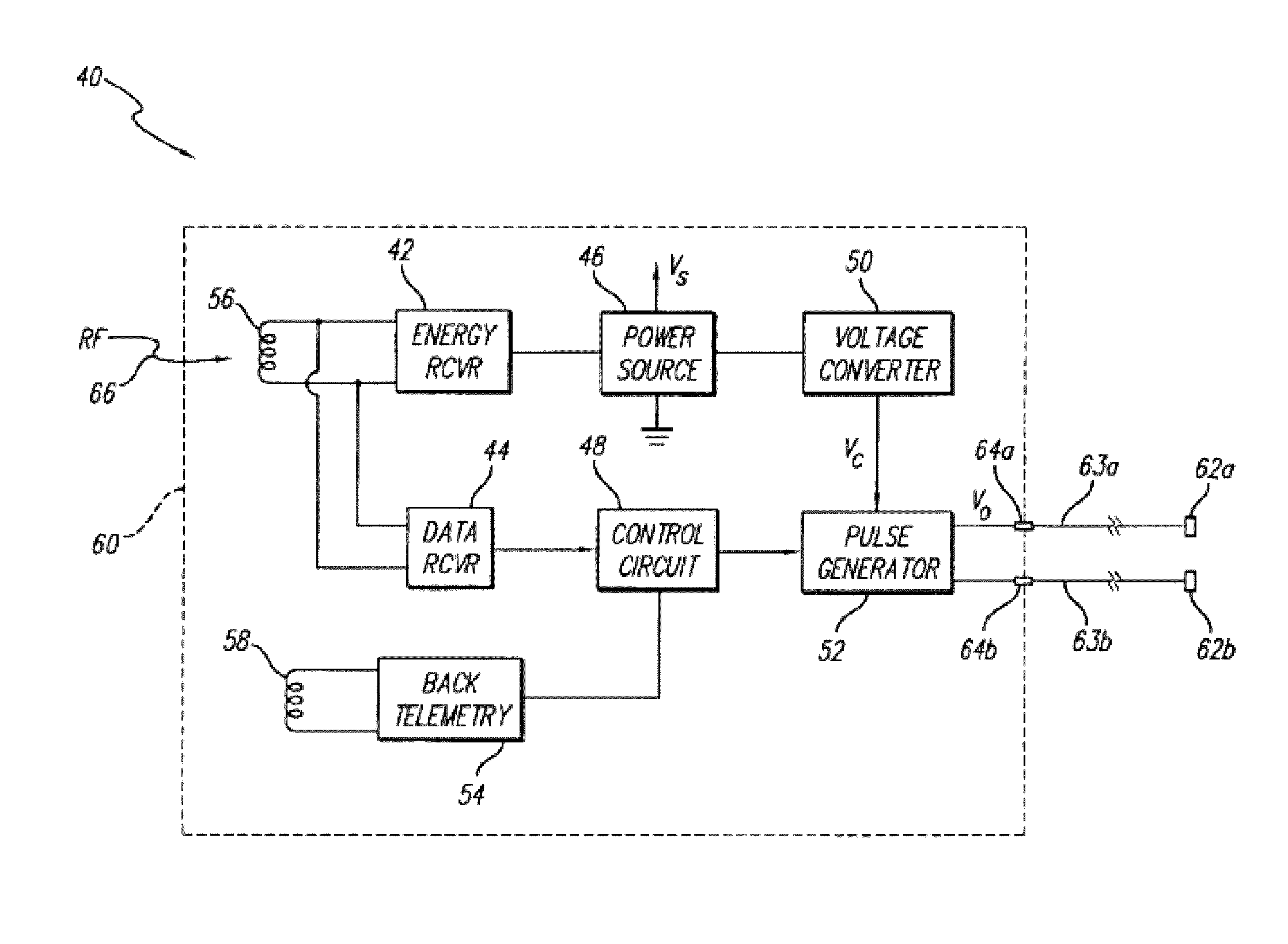

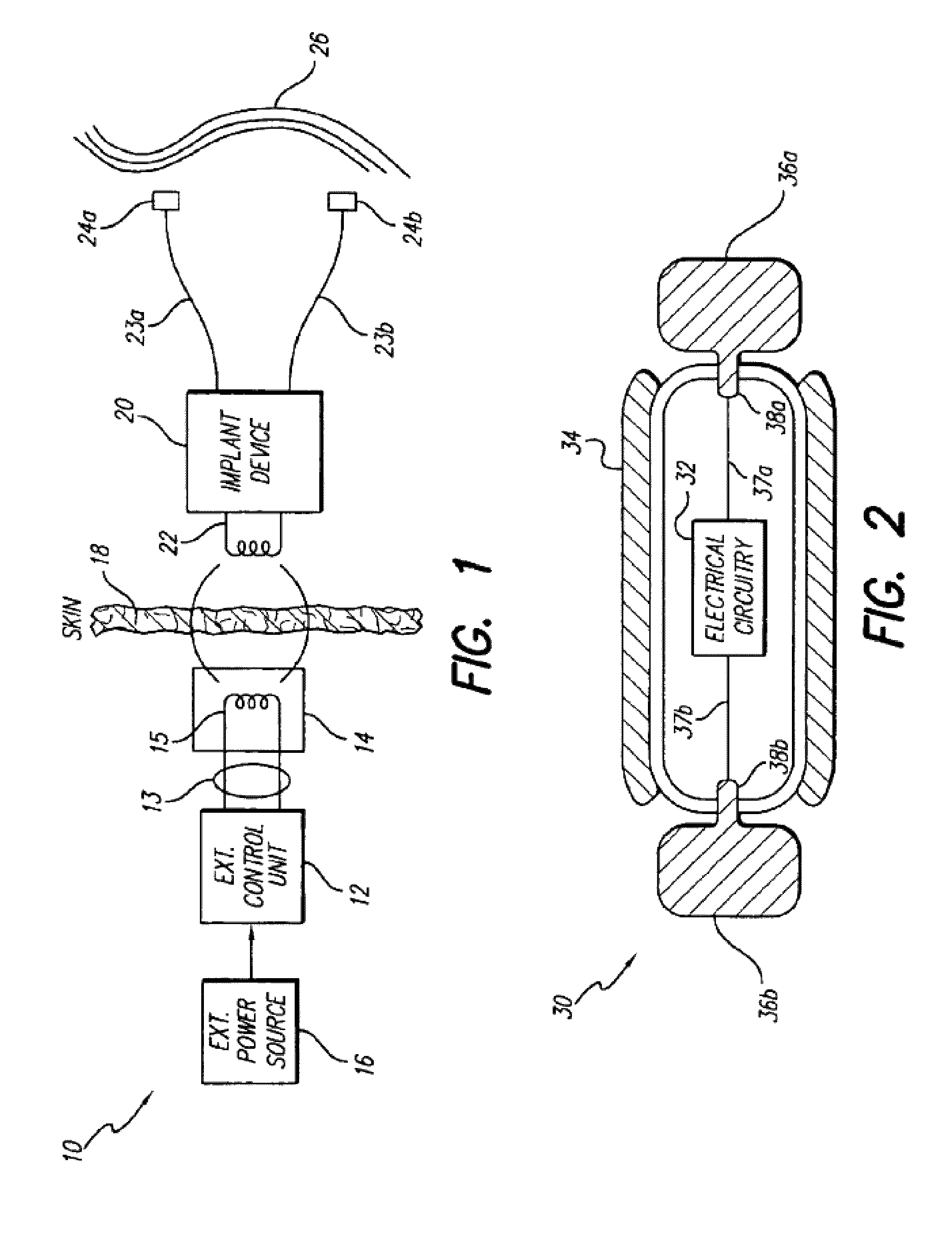

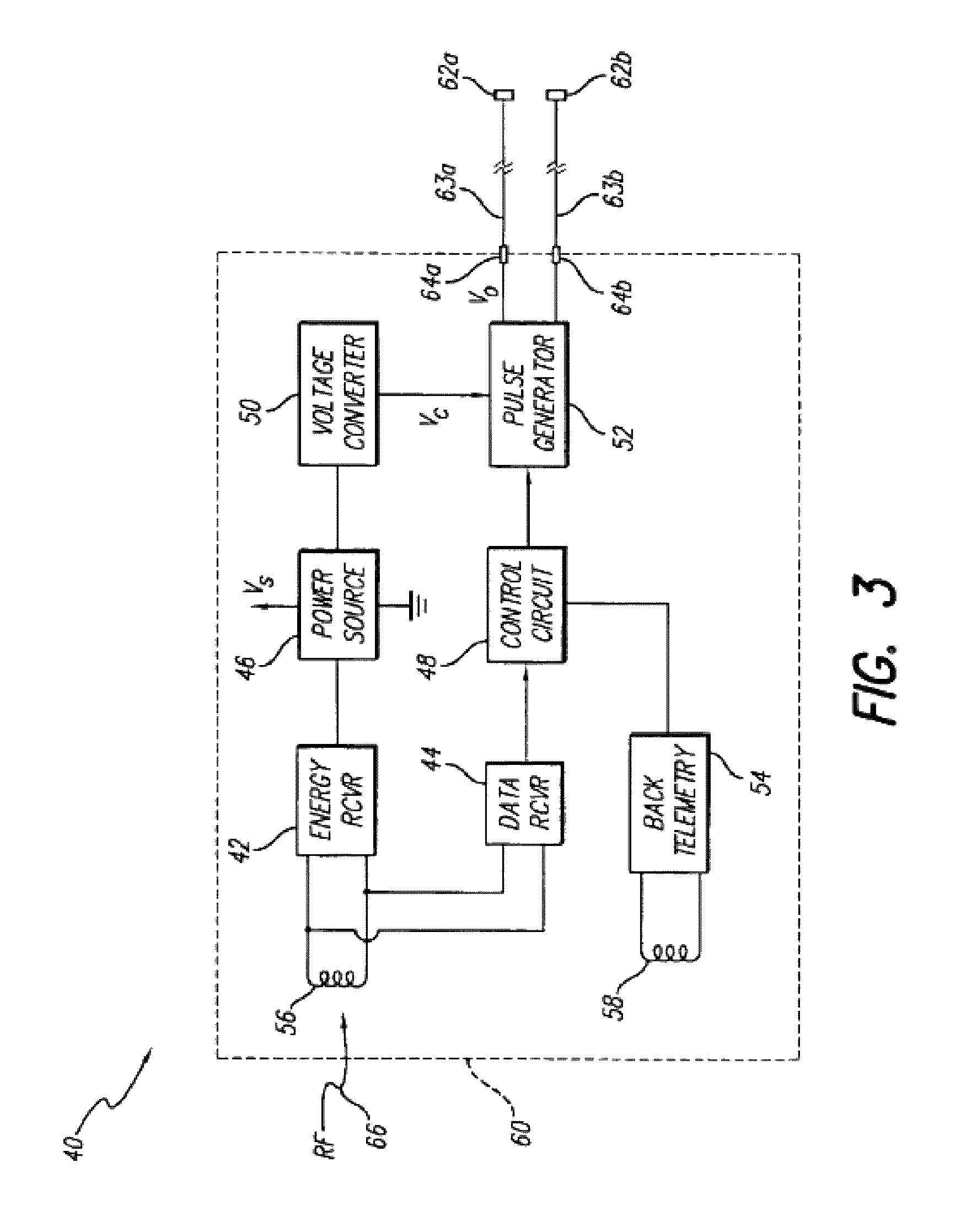

Implantable Medical Device with Single Coil for Charging and Communicating

A combination charging and telemetry circuit for use within an implantable device, such as a microstimulator, uses a single coil for both charging and telemetry. In accordance with one aspect of the invention, one or more capacitors are used to tune the single coil to different frequencies, wherein the coil is used for multiple purposes, e.g., for receiving power from an external source and also for the telemetry of information to and from an external source.

Owner:BOSTON SCI NEUROMODULATION CORP

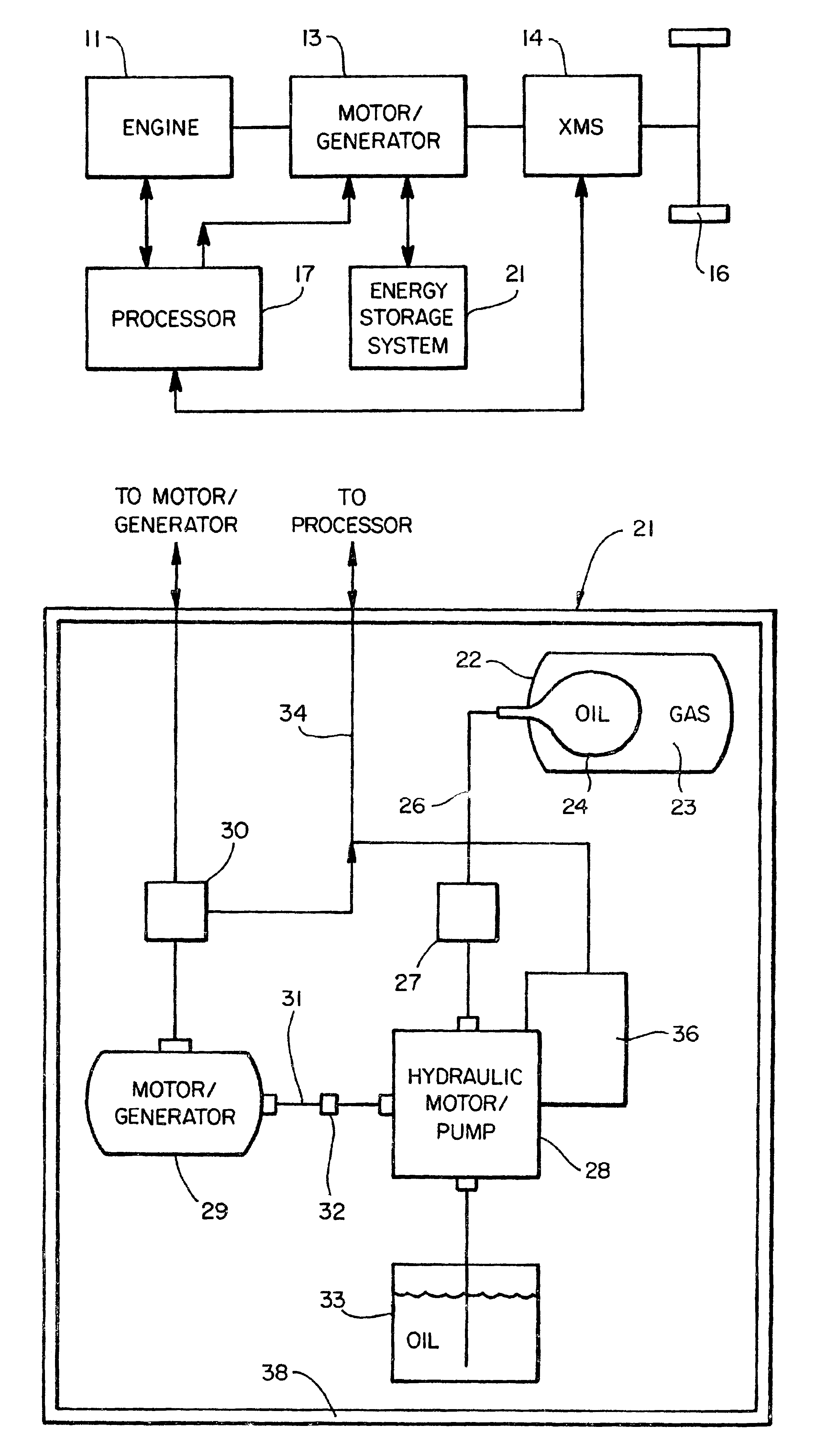

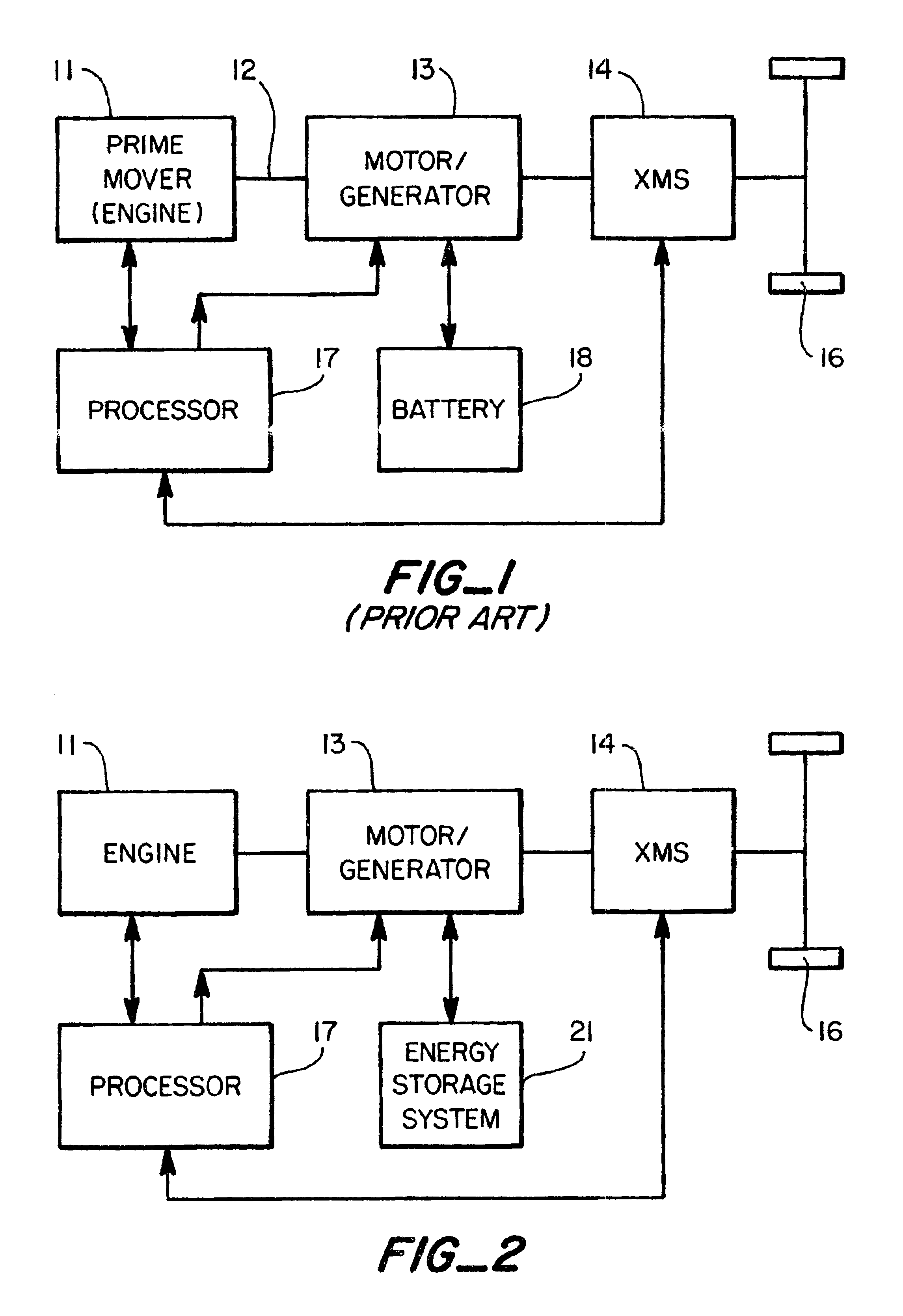

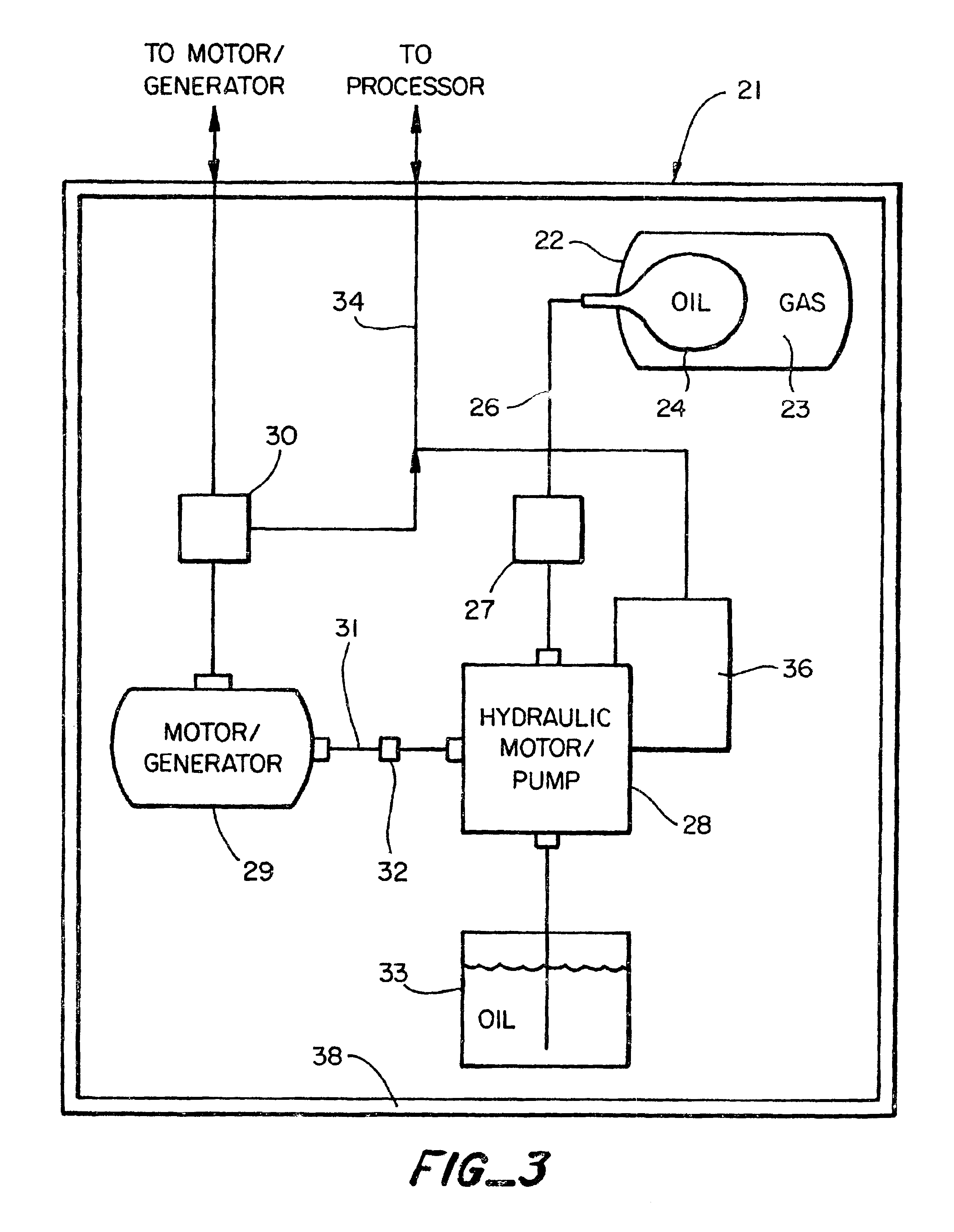

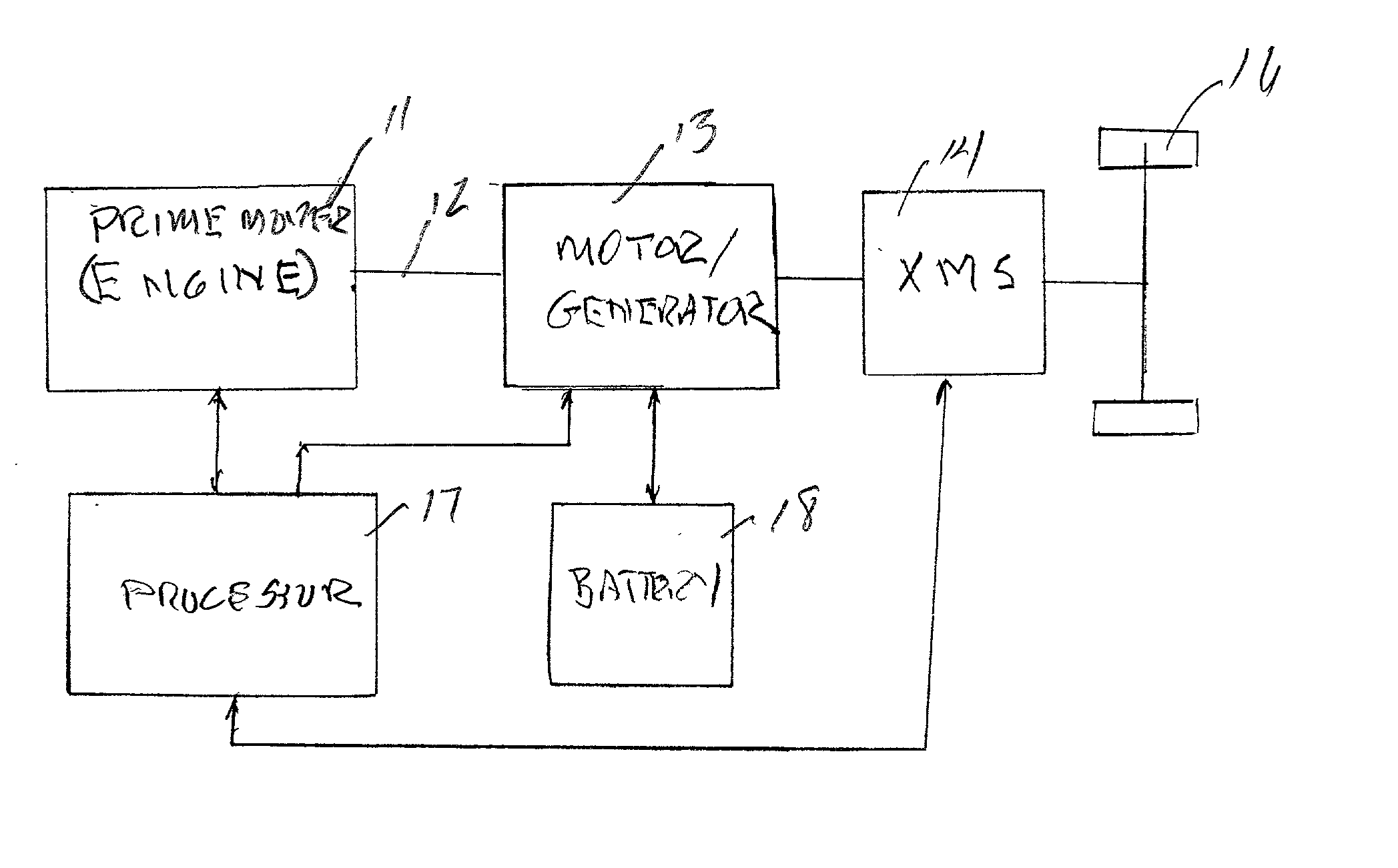

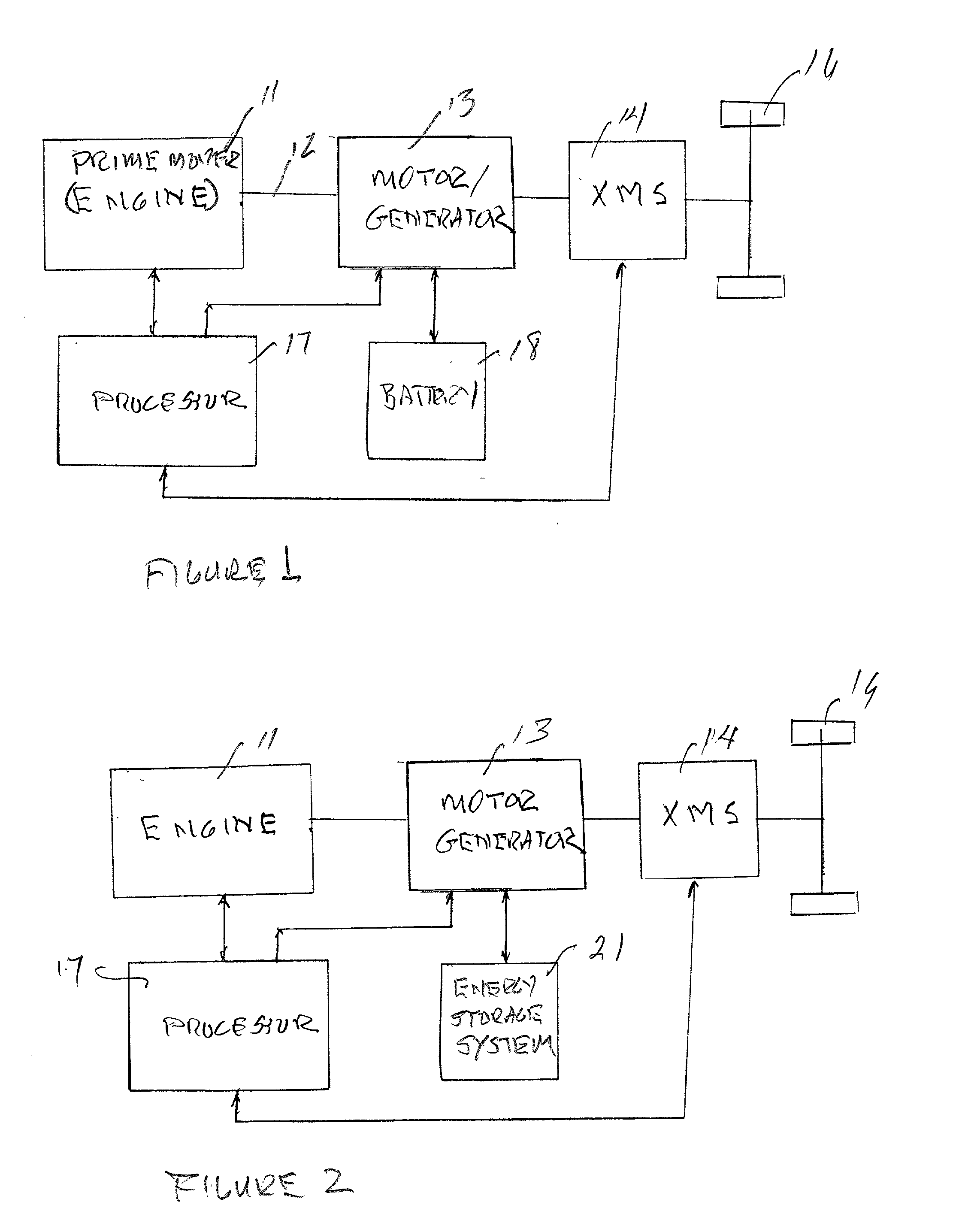

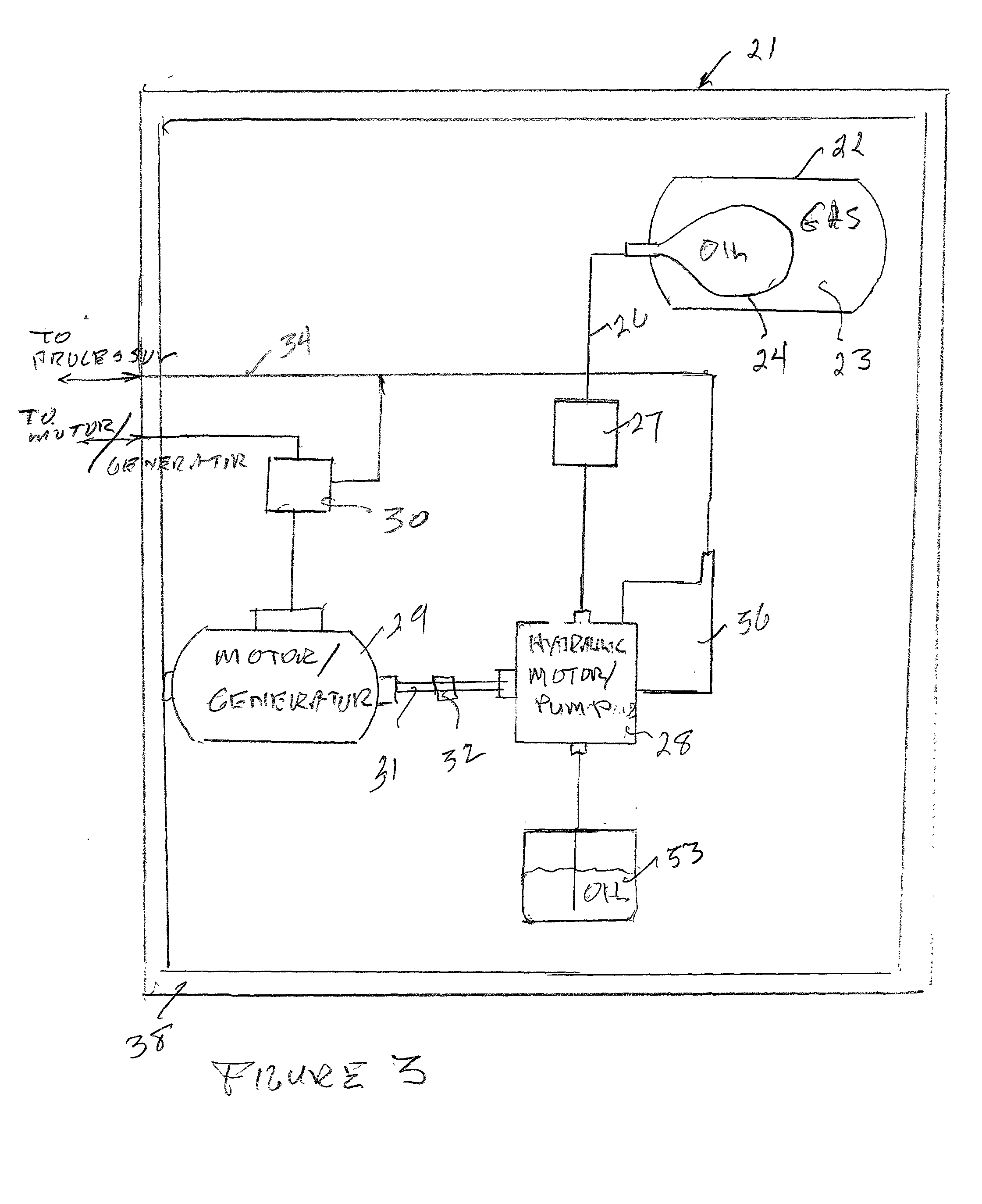

Hybrid vehicle and energy storage system and method

InactiveUS6834737B2Conveniently and inexpensively adaptableSmall packageReciprocating combination enginesAuxillary drivesStored energyPower mode

A system for providing a hybrid vehicle with a practical source of auxiliary power. The system includes two electric motor / generators connected to each other in such a fashion so that when one electric motor / generator functions as a motor, the other becomes a generator with their roles being reversed depending on whether the system is in an auxiliary power mode or energy storage mode. Connected to one motor / generator is the vehicle drive train. Connected to the other motor / generator is a pressure energy storage system, which in the energy storage mode converts the force of rotation into pressurized gas for storage in an energy system and delivered in the form of electric current by the one motor / generator, and in the energy delivery mode converts the stored energy of the energy storage system into electric current for delivery to the one motor / generator which is part of the vehicle drive train to provide auxiliary power for practical hybrid vehicles.

Owner:BLOXHAM STEVEN R

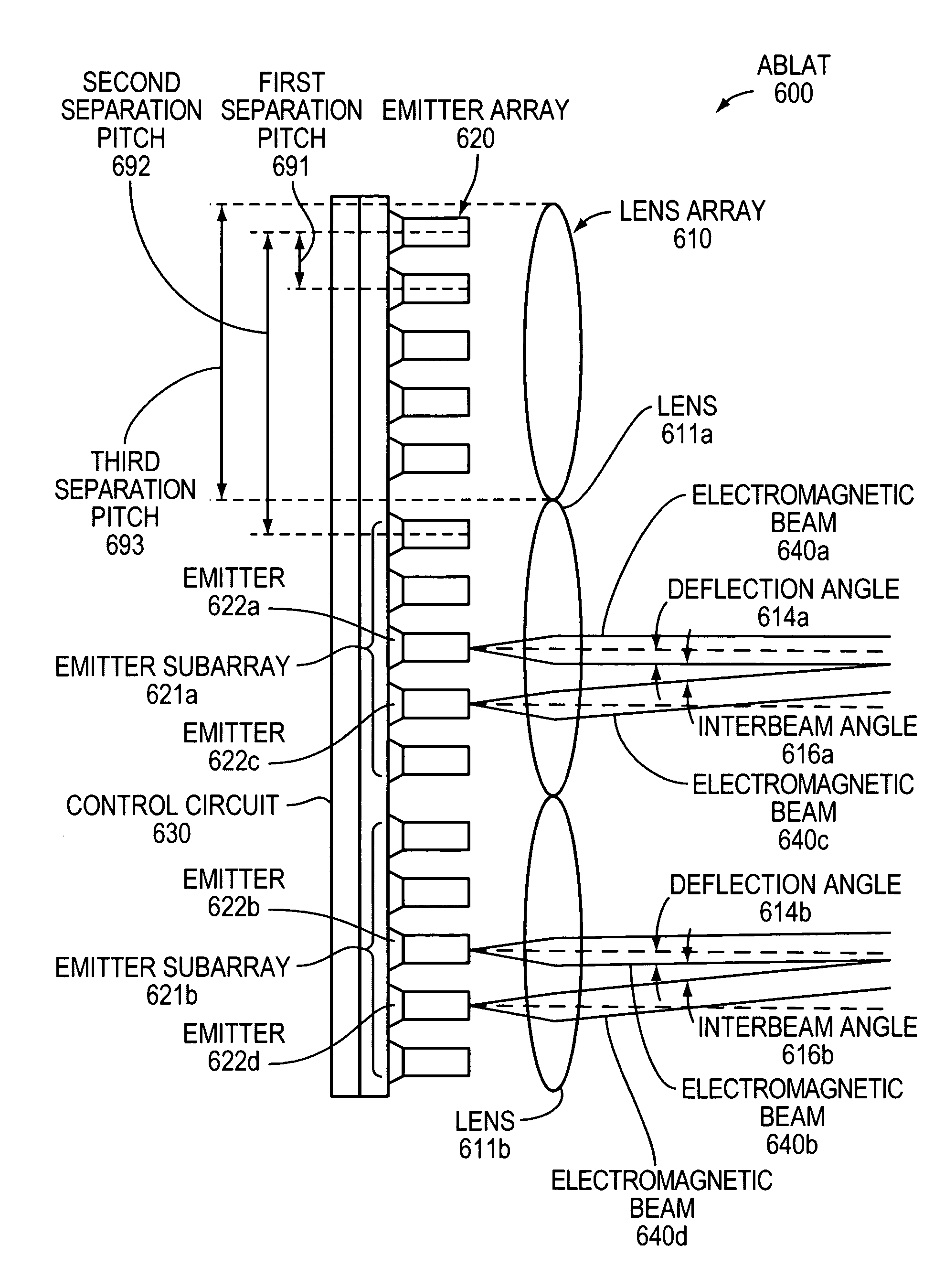

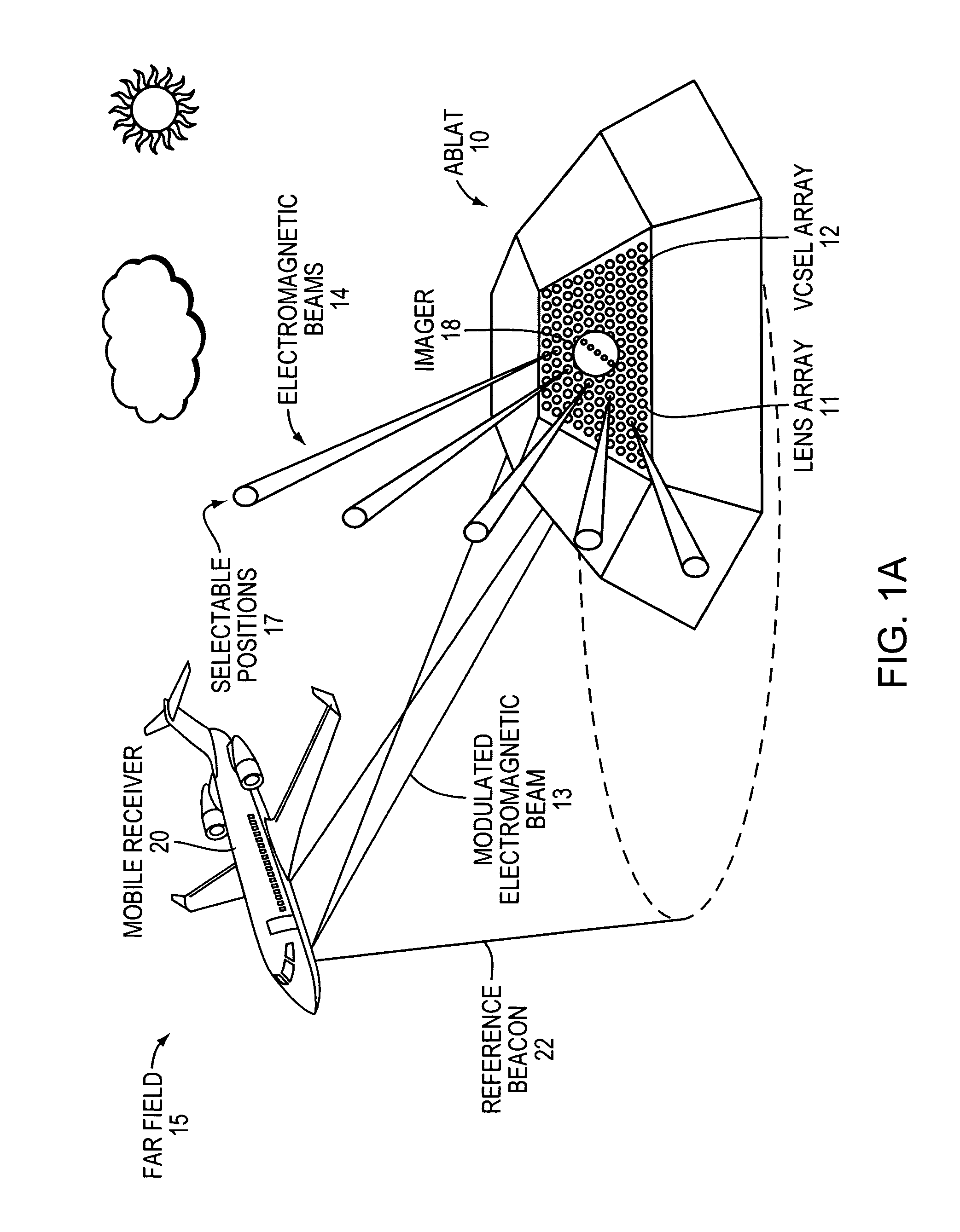

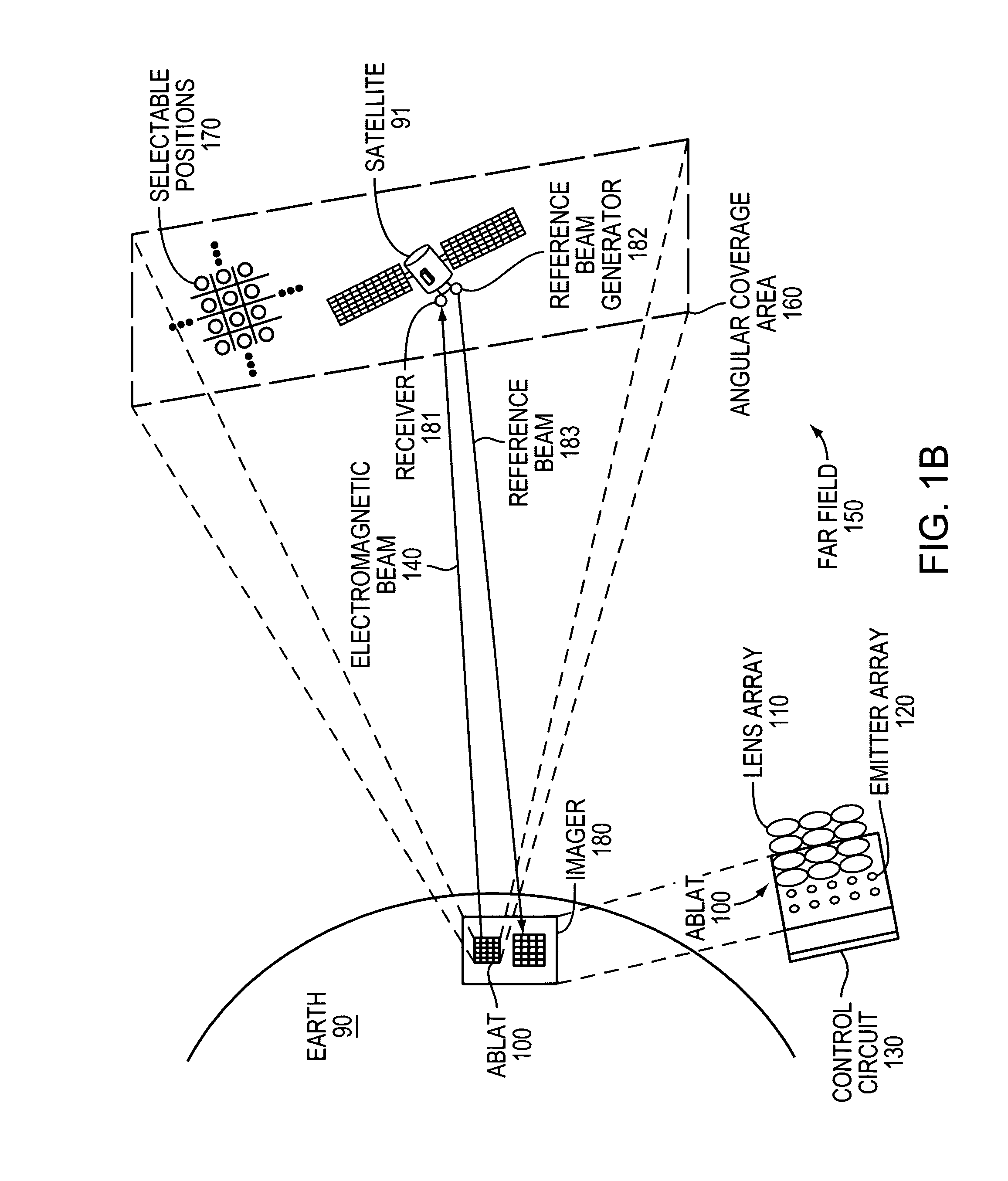

Agile-beam laser array transmitter

ActiveUS20100046953A1Turn fasterWide field of viewWave based measurement systemsWavelength-division multiplex systemsLaser arrayColor printing

An Agile-Beam Laser Array Transmitter (ABLAT) uses an array of emitters and an array of lenses to project electromagnetic beams over a wide angular coverage area in the far field. Differences in the separation pitches of the two arrays allows the ABLAT to project beams to contiguous and / or overlapping positions, depending on the ratio of the separation pitches and the lens focal length. Compared to other beam steering technology, the ABLAT is a smaller, lighter, and more efficient means of projecting beams over wider angular coverage areas. Various embodiments can be used in any beam steering application, including, but not limited to: free-space optical communications; light detection and ranging (lidar); optical scanning (e.g., retinal or bar-code scanning); display projection; image capture; optical character recognition; scanning laser microscopy; non-destructive testing; printing; facsimiles; map making; web inspection; color print processing; phototypesetting and platemaking; laser marking; material processing; DNA analysis; and drug discovery.

Owner:MASSACHUSETTS INST OF TECH

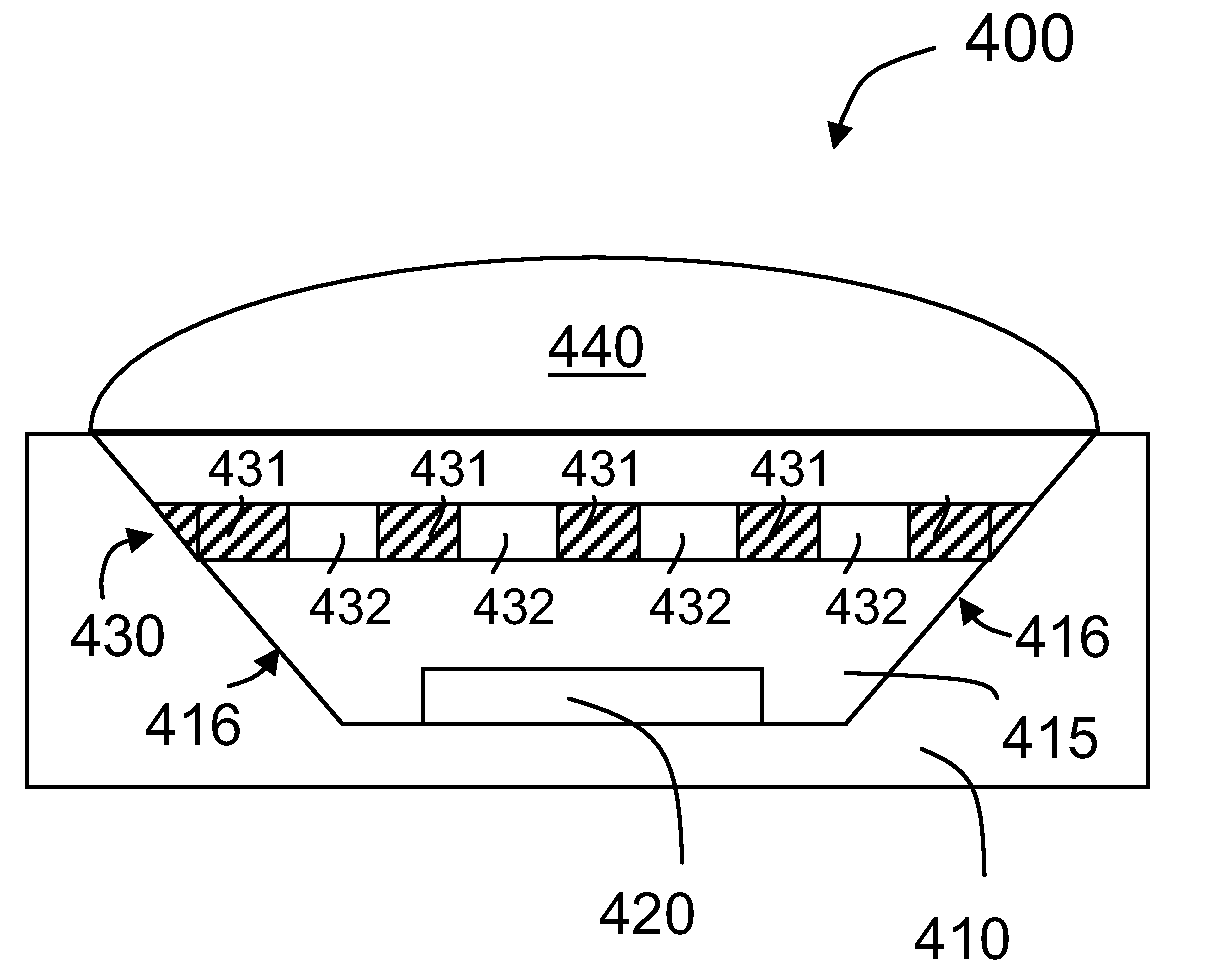

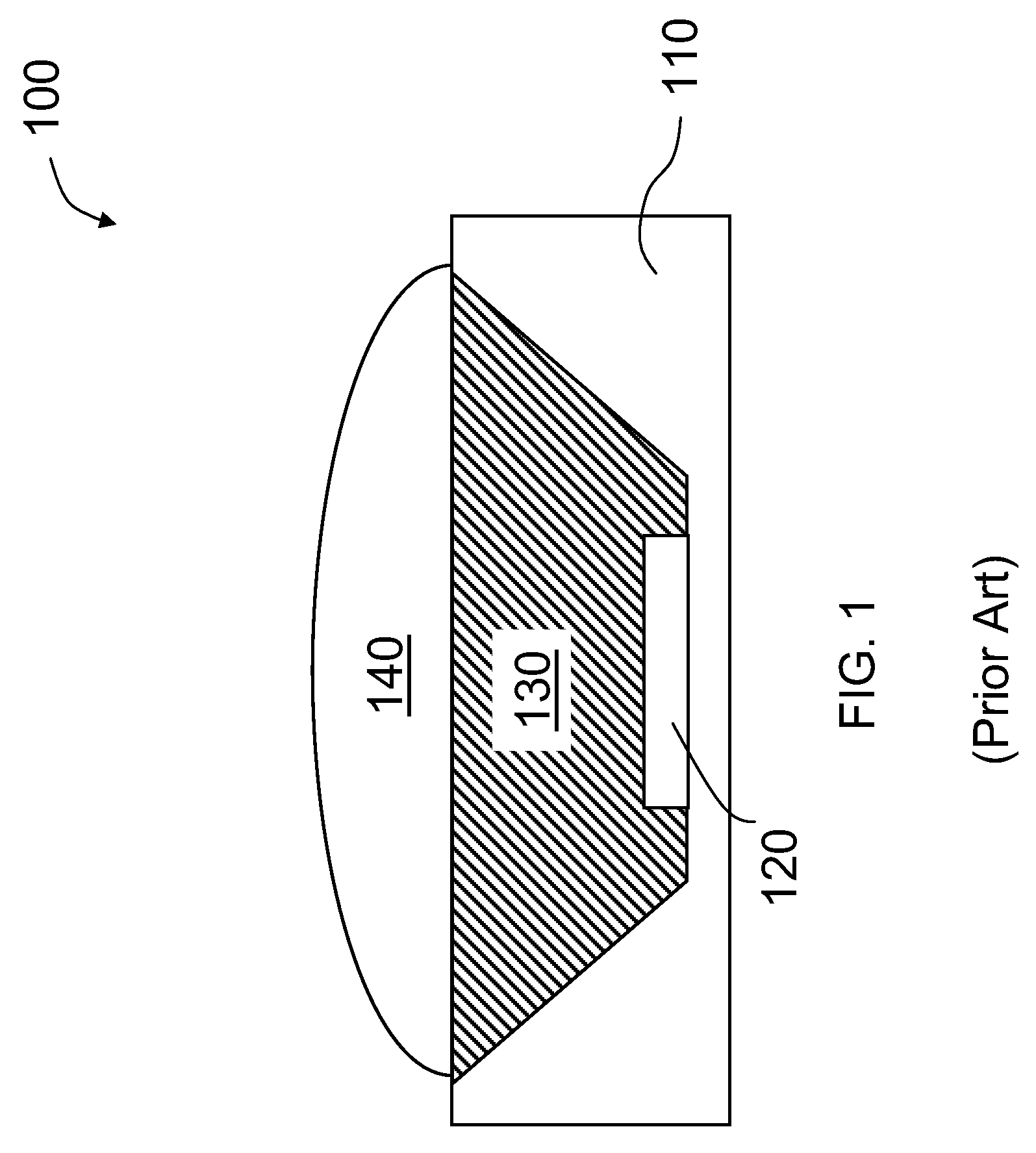

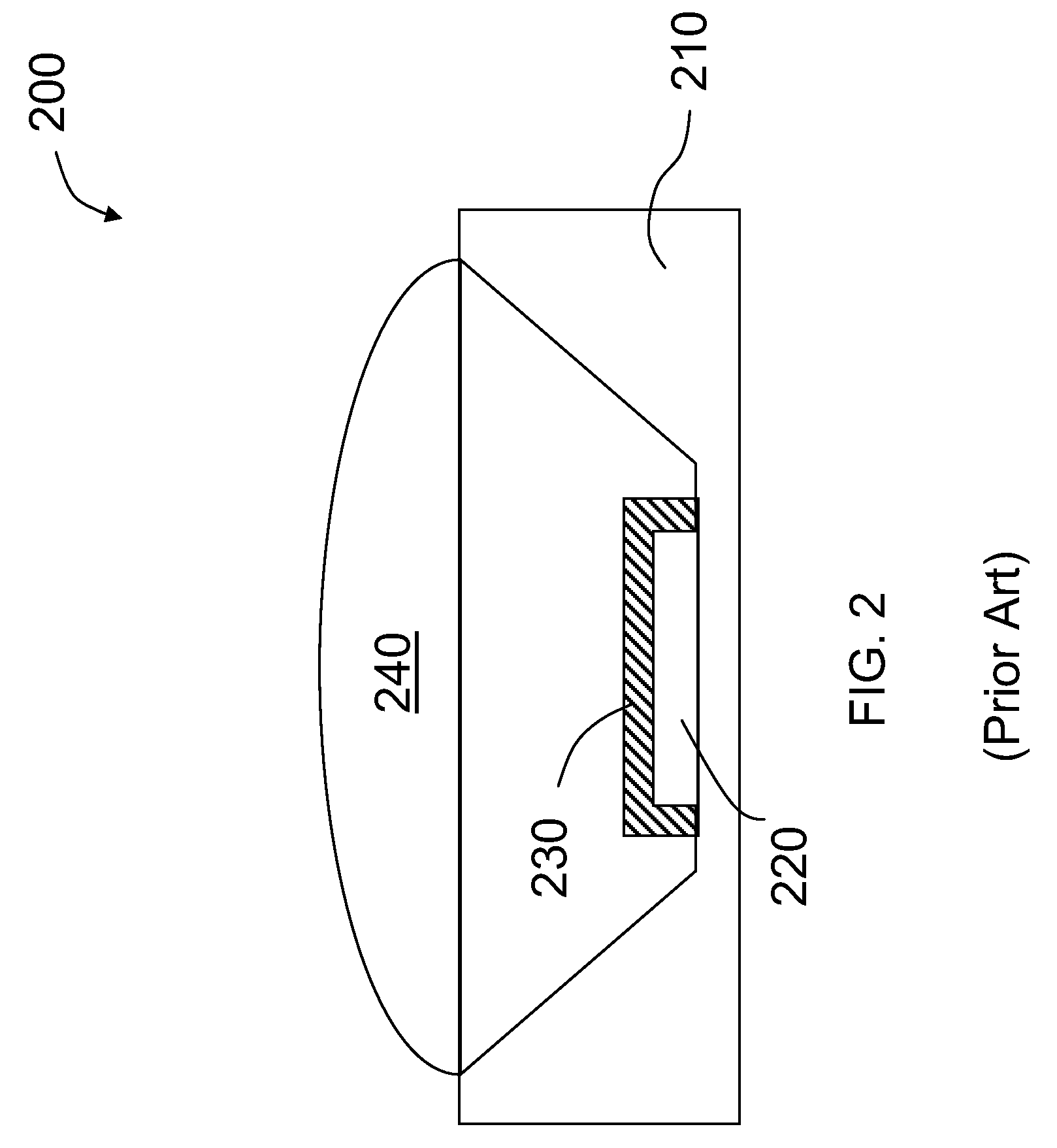

LED with light-conversion layer

InactiveUS20100117106A1Maximize yellow light outputUniform white lightSemiconductor/solid-state device manufacturingSemiconductor devicesEpoxyLight equipment

A lighting apparatus includes a light-emitting diode (LED). A light-conversion layer having multiple non-overlapping regions overlies the light-emitting diode. The light-conversion layer includes at least one first region and at least one second region. In the lighting apparatus, the light-emitting diode is configured to emit light of a first color, the at least one first region is substantially transparent to light of the first color, and the at least one second region converts light of the first color to light of a second color. In an embodiment, the light-conversion layer is configured such that the lighting apparatus provides substantially uniform light of a third color. In some embodiments, the second region includes a phosphor-containing material, and the first region includes silicone or epoxy. In an example, the lighting apparatus uses a blue LED in conjunction with a yellow phosphor material to produce white light.

Owner:LEDENGIN

Submerged rotor electric water pump with structural wetsleeve

ActiveUS20140017073A1Reduced volume and massLess componentsPump componentsBlade accessoriesEngineeringElectrical and Electronics engineering

Owner:HANON SYST EFP CANADA LTD

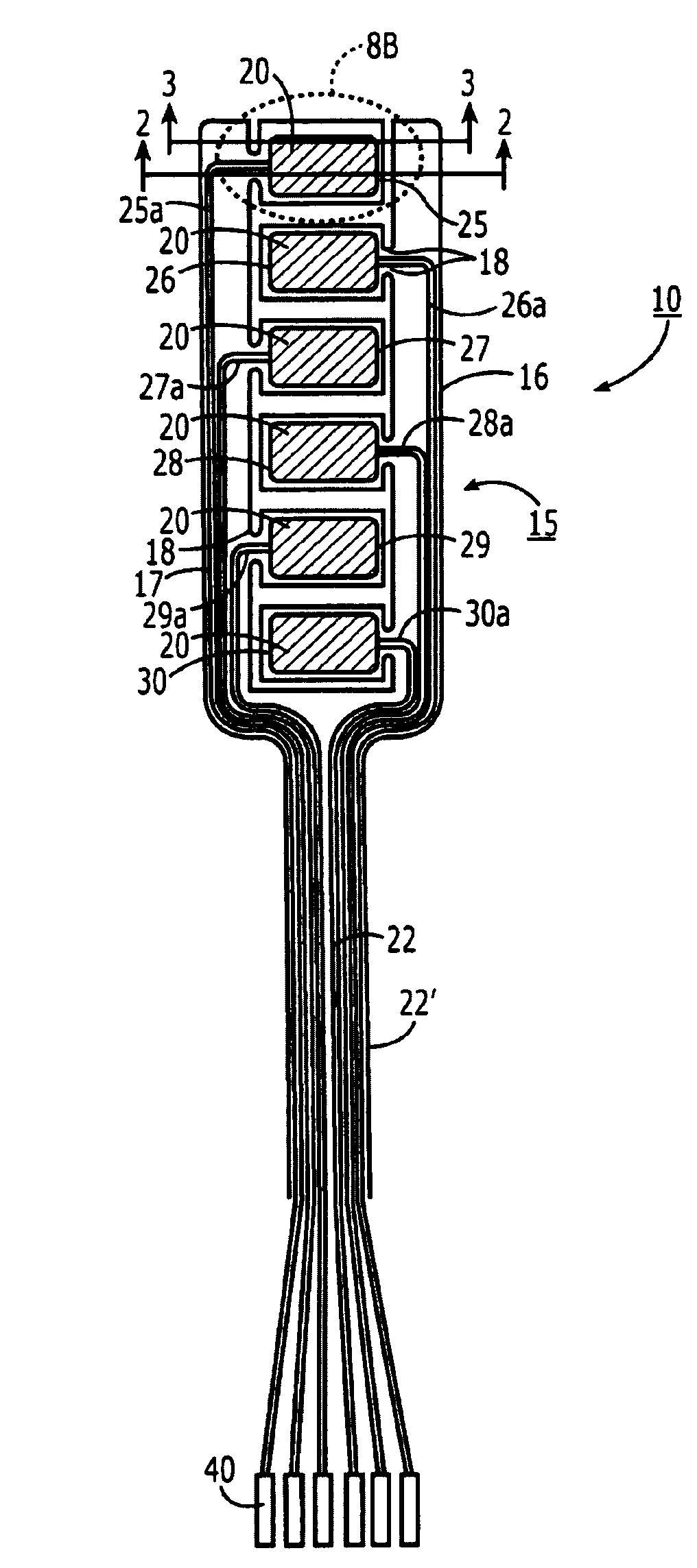

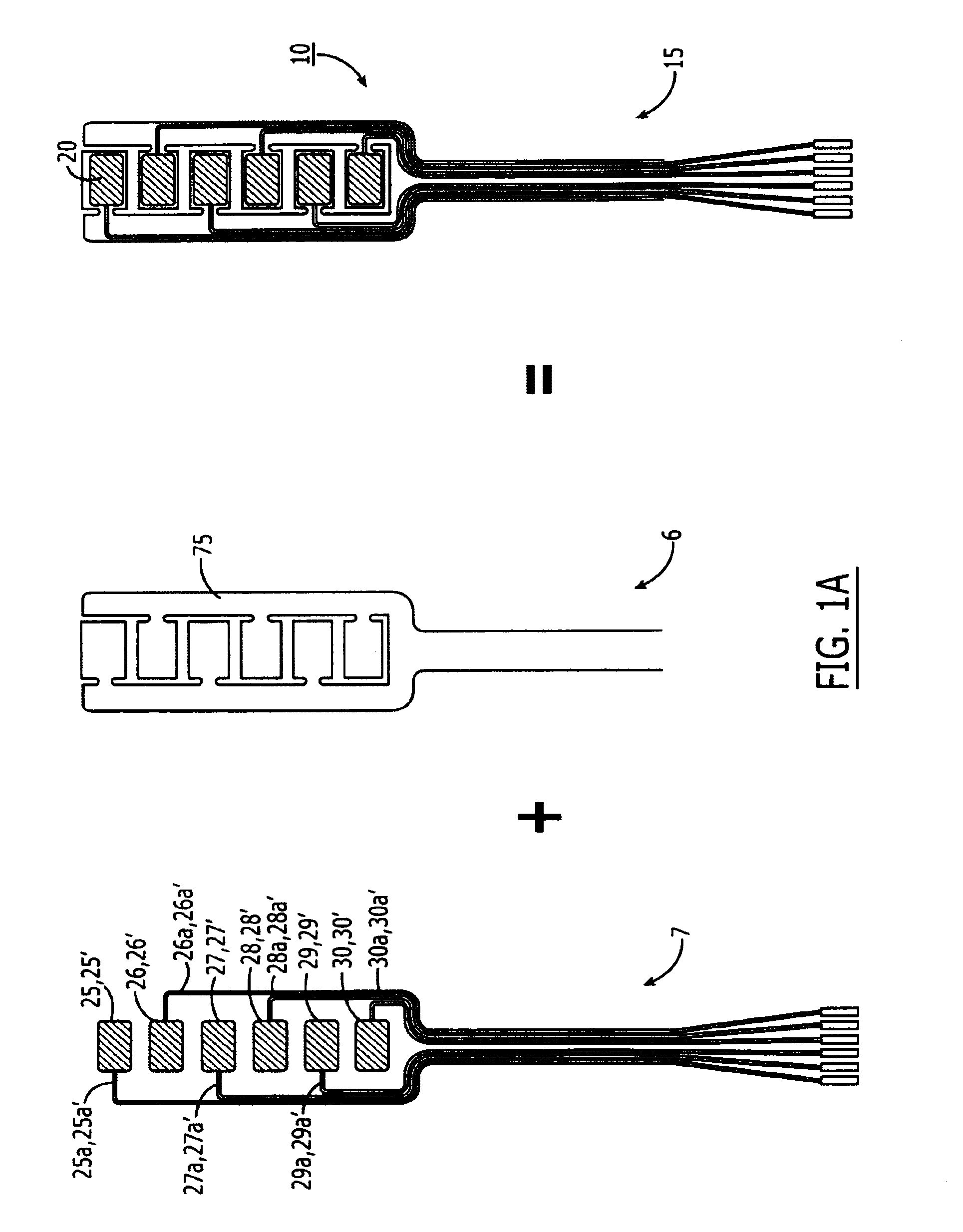

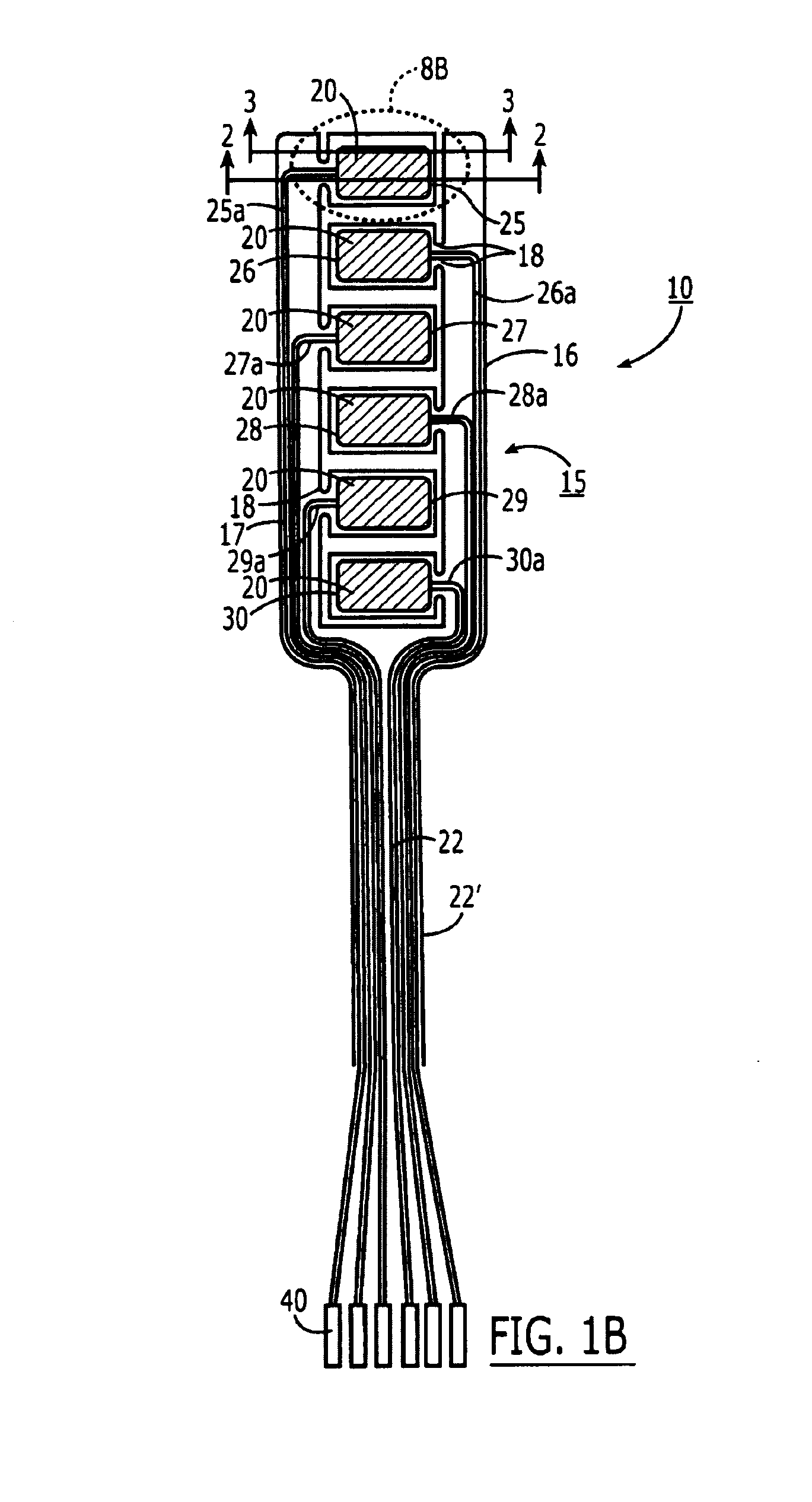

Low profile acoustic sensor arry and sensors with pleated transmission lines and related methods

InactiveUS7037268B1Facilitate flexural responseEasy to operateUltrasonic/sonic/infrasonic diagnosticsMeasurement of fluid loss/gain rateSensor arrayAcoustic array

A low profile acoustic array (10) is configured to selectively respond to shear waves while rejecting compression wave energy in the frequency range of interest. One sensor array is configured as a linear strip with a frame segment having at least one longitudinally extending rail and a plurality of sensor elements (20) extending therefrom. These sensor elements have a resilient core and opposing PDVF outer layers configured with opposing polarities onto the core. The linear strip array also includes a pair of separate electrical signal transmission paths. The transmission lines can include a series of undulations formed thereon to help minimize undesired mechanical crossover between sensors. A carrier member can be configured to be detachably releasable carries the discrete sensors to maintain the positional alignment until they are secured to a patient.

Owner:HARRIS CORP

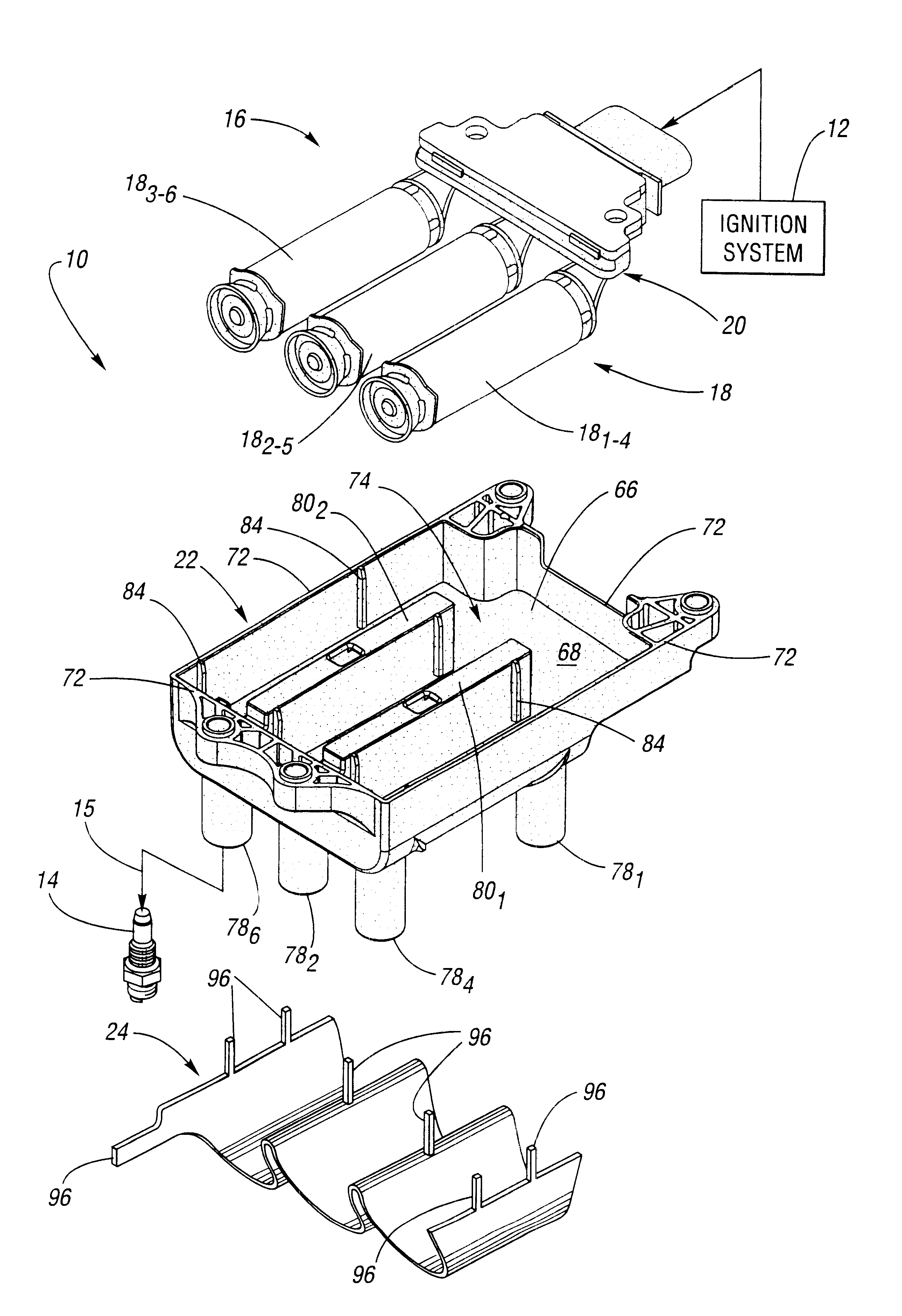

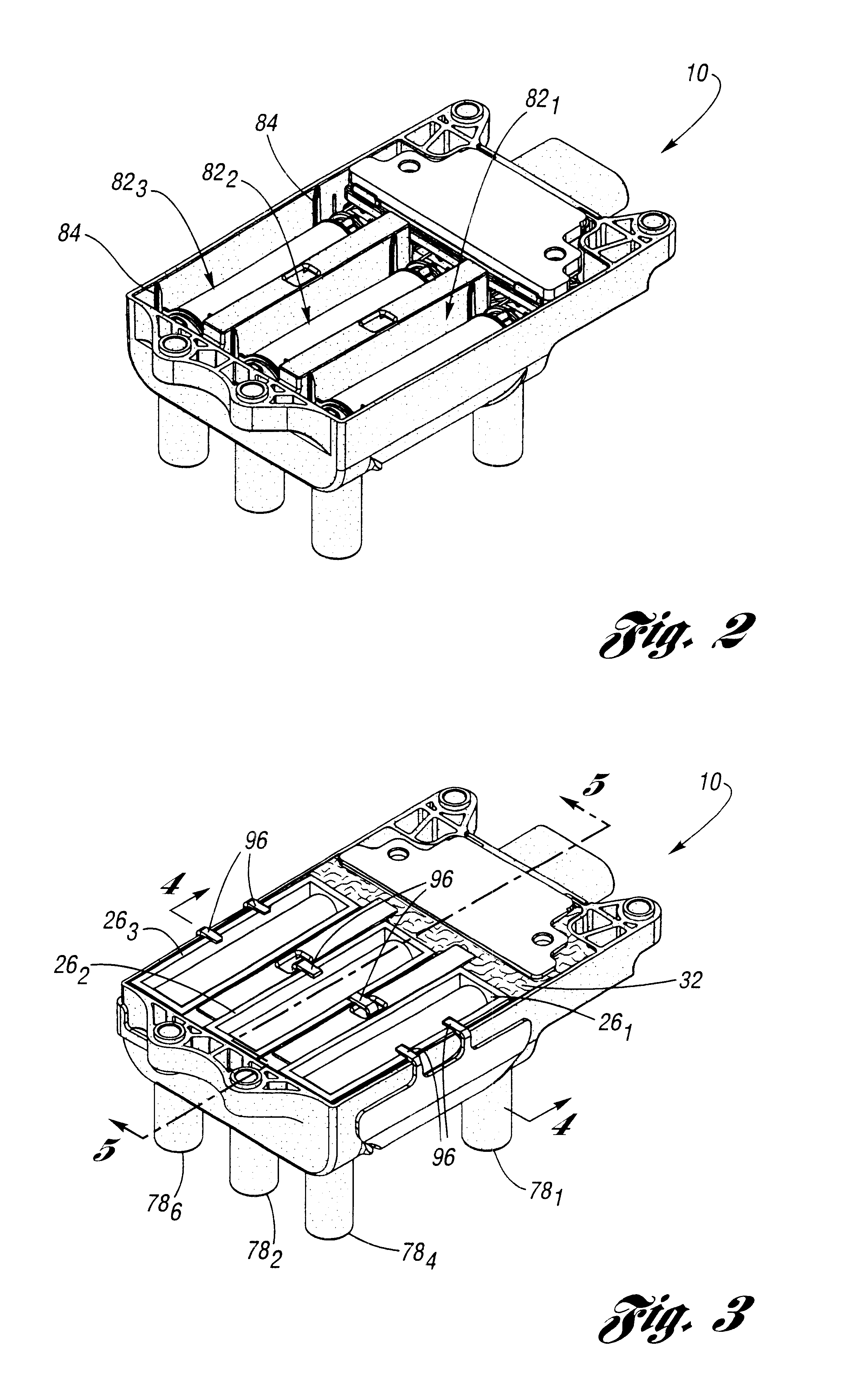

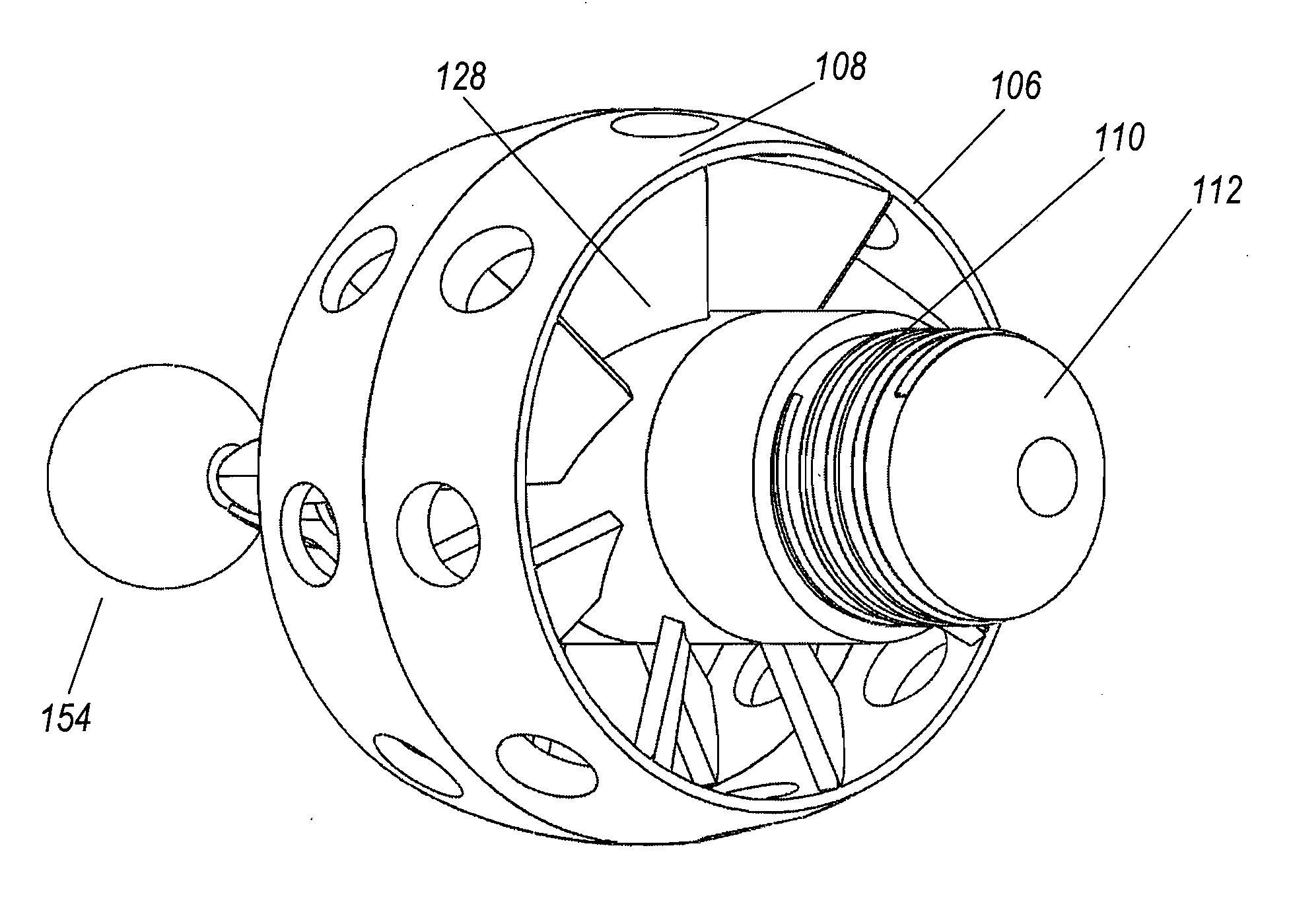

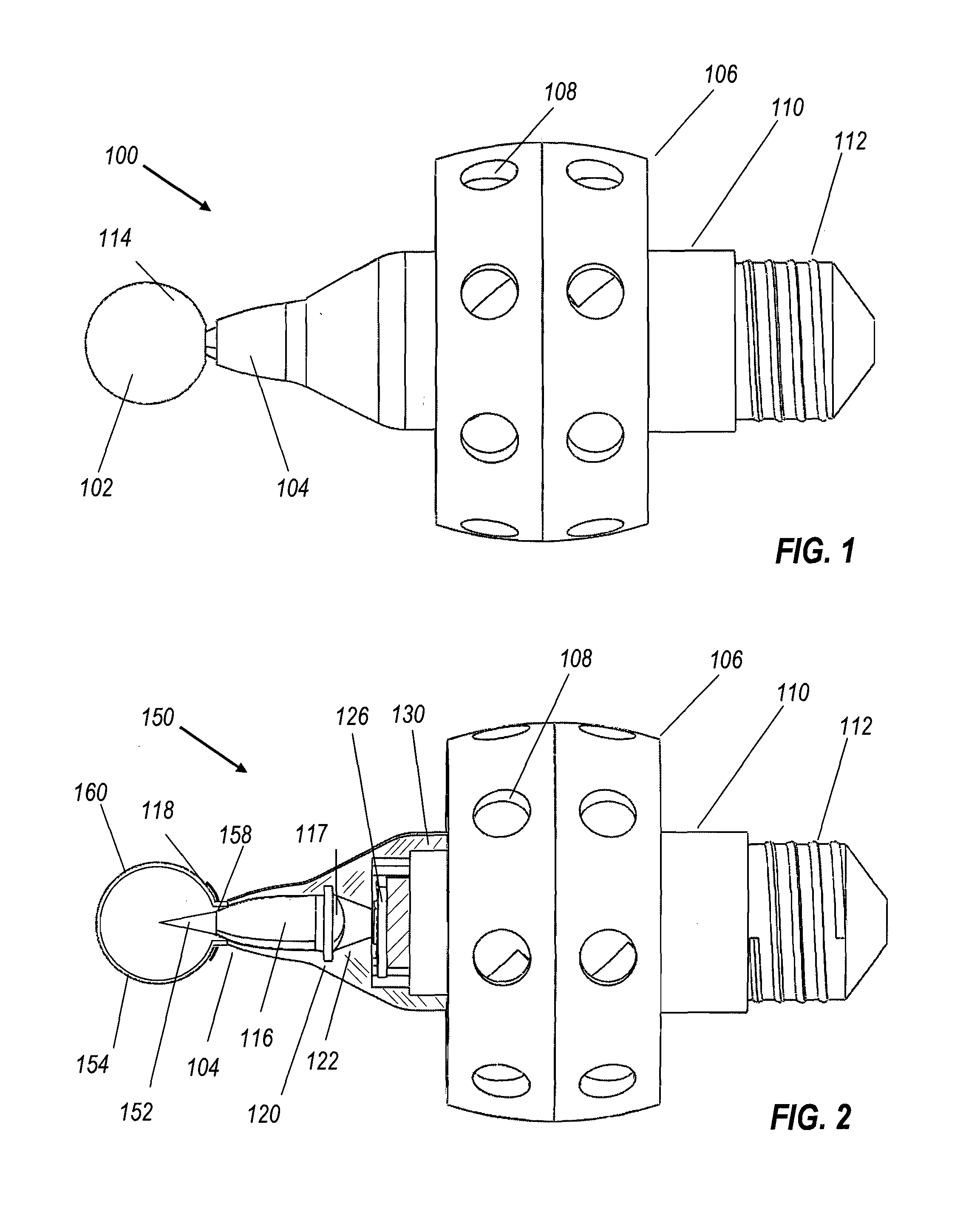

Separate mount ignition coil utilizing a progressive wound secondary winding

InactiveUS6556118B1Eliminate failure modesSmall sizeTransformersTransformers/inductances casingsElectricityIgnition coil

An ignition coil assembly includes a core formed of magnetically-permeable material extending along a main axis, a primary winding disposed about the core, a secondary winding disposed on a secondary winding spool wherein at least one of the secondary winding leads is connected to a high-voltage connector terminal portion of the ignition coil assembly configured for connection to a remotely disposed spark plug, a case formed of electrical insulating material, and a magnetically-permeable shield disposed outwardly of the case. The secondary winding is progressively wound on the secondary winding spool, thereby eliminating failure modes associated with the segment-wound secondary windings, and, eliminating the need for pole pieces in the magnetic circuit, thereby reducing components, cost, weight, and size of the ignition coil assembly.

Owner:DELPHI TECH INC

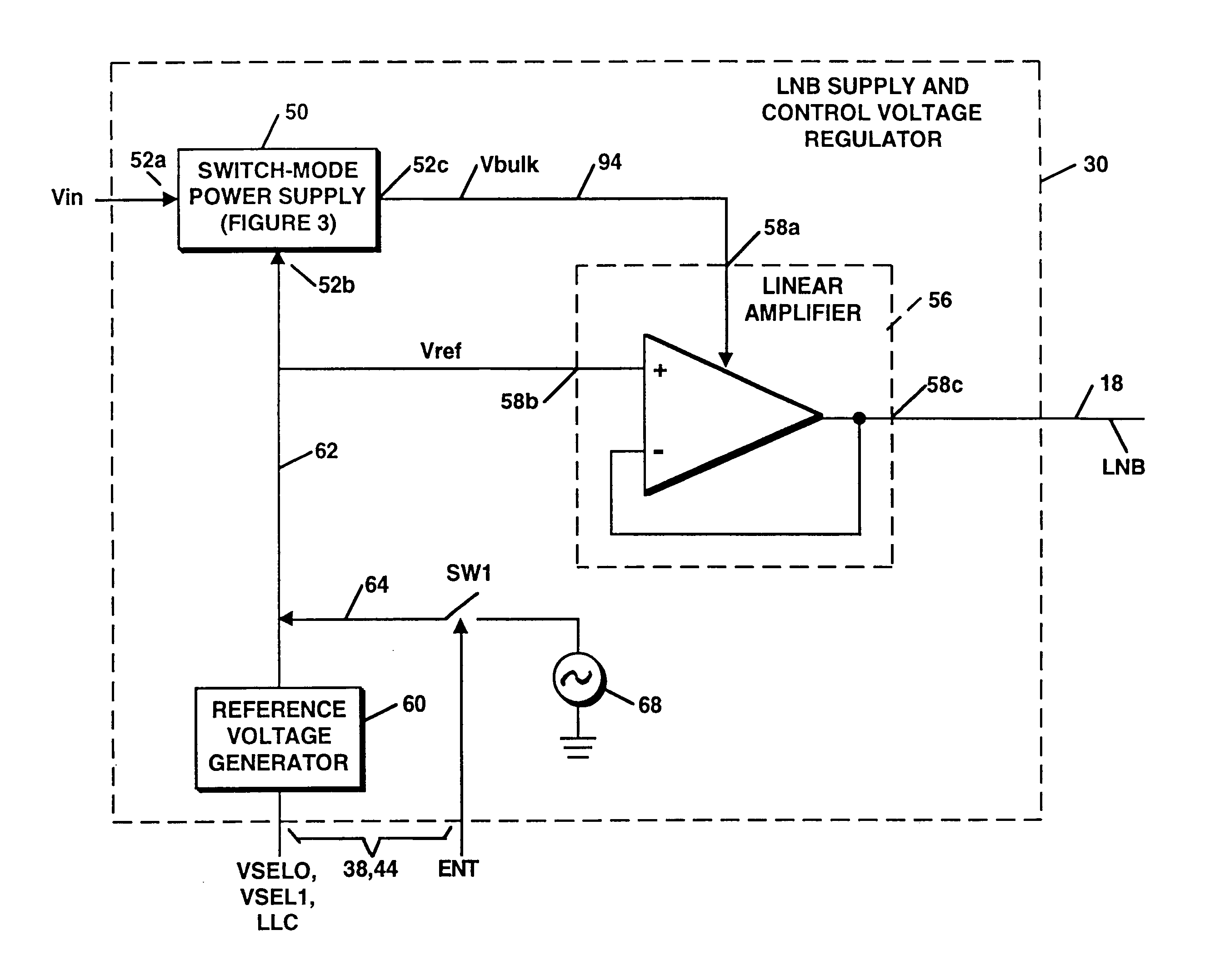

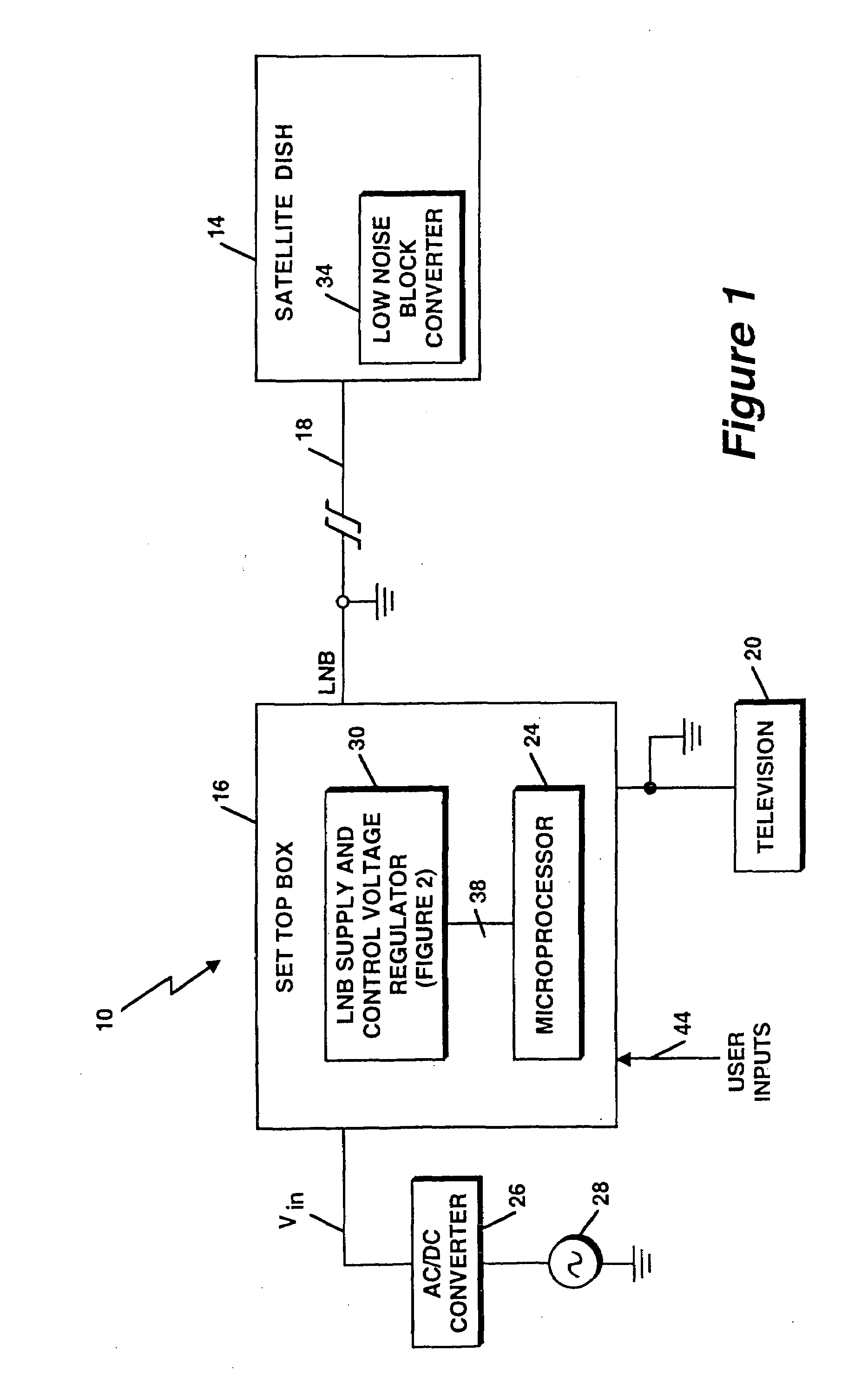

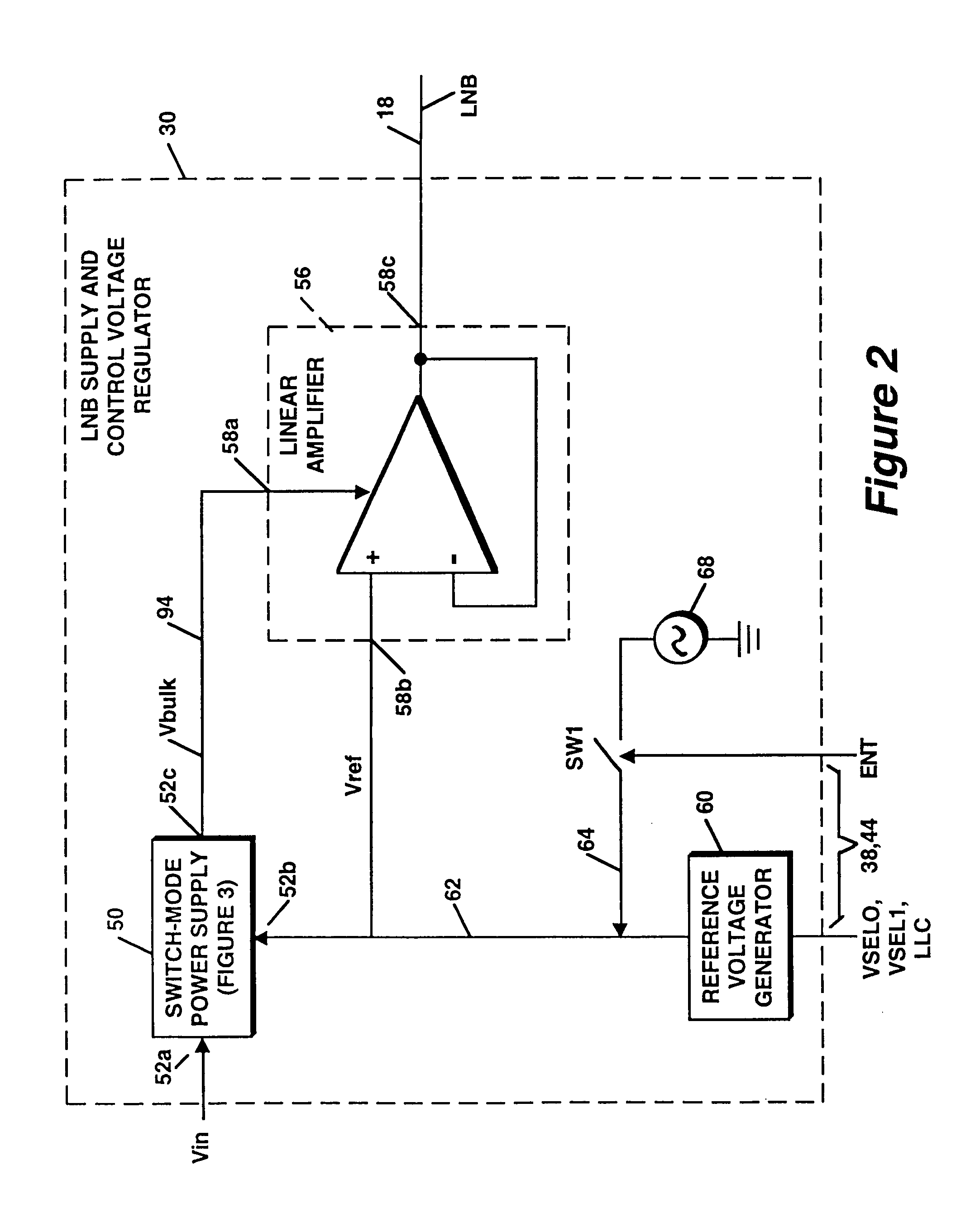

Low noise block supply and control voltage regulator

InactiveUS7207054B1Minimize voltage dropReduce heat sinkAmplifier modifications to reduce non-linear distortionGHz frequency transmissionLow noiseConverters

A low power circuit for providing power and control signals to a low noise block converter of a satellite receiver over a single coaxial cable includes a tracking switch-mode power supply. The power and control signals have a DC voltage level selected from a plurality of DC voltage levels and are modulated by an analog AC tone signal. The switch-mode power supply provides a regulated output voltage which tracks the selected DC voltage level. The regulated output voltage provides the input voltage to an adjustable linear amplifier which generates an output voltage having the selected DC voltage level modulated by the analog AC tone signal.

Owner:ALLEGRO MICROSYSTEMS INC

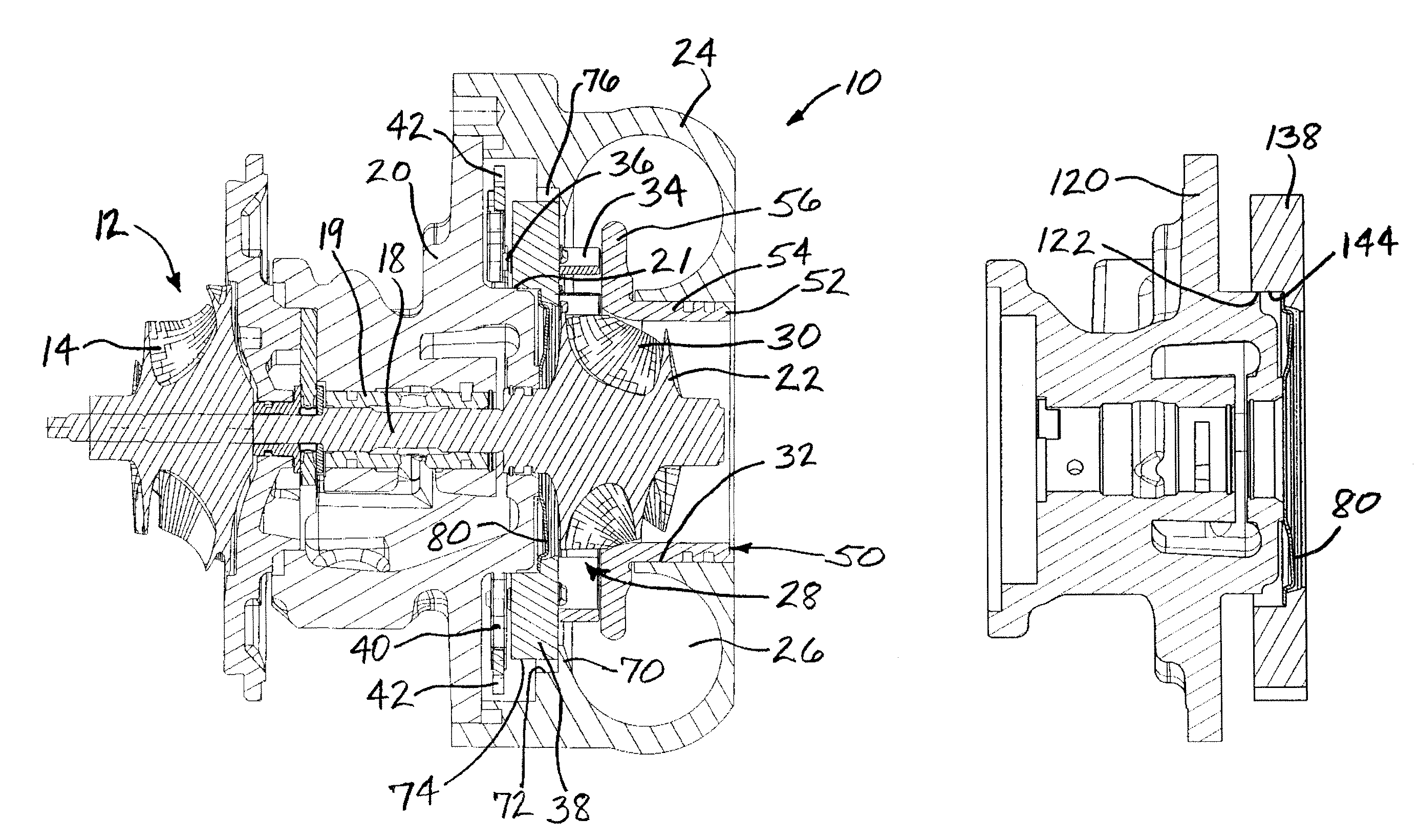

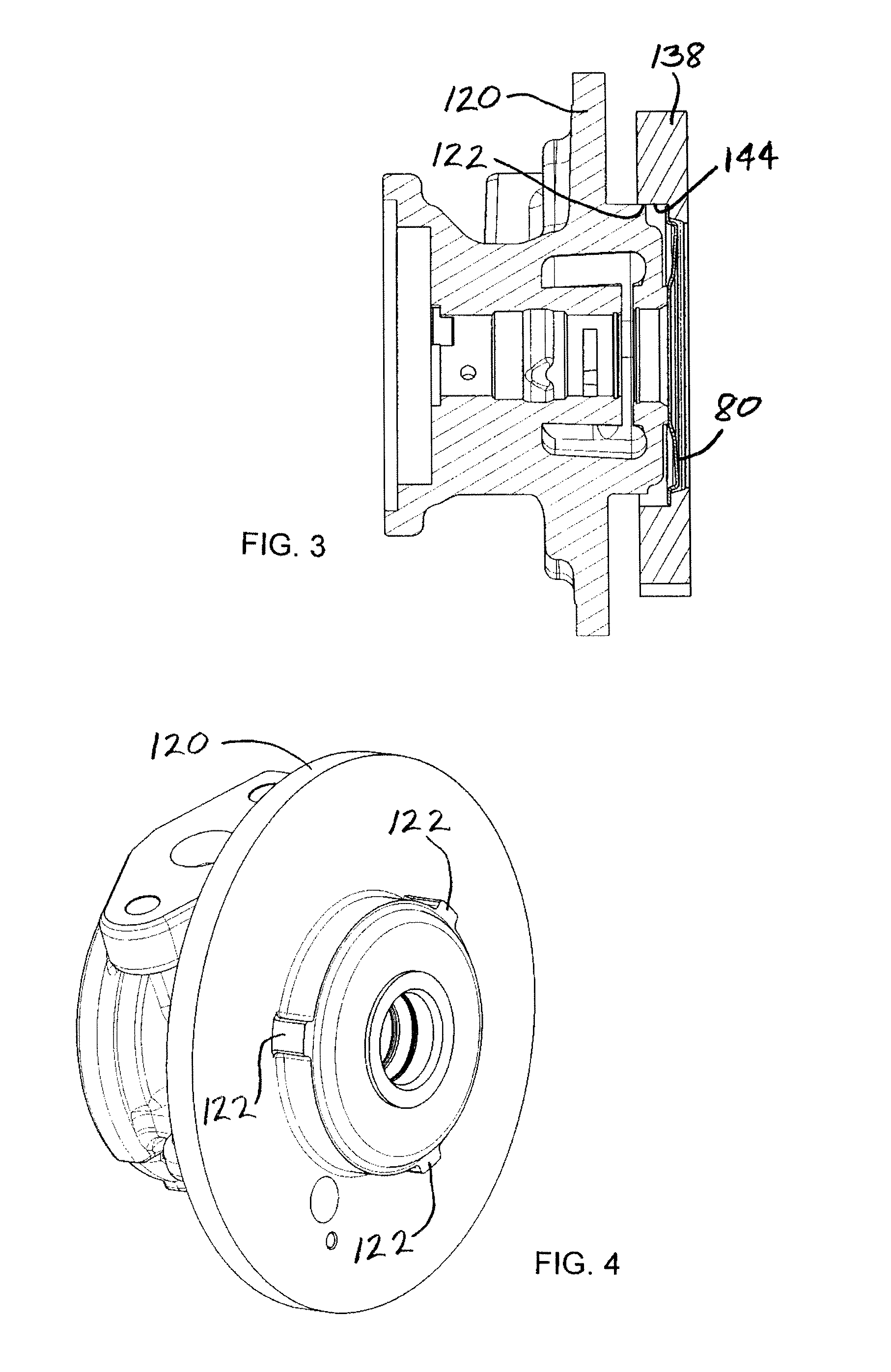

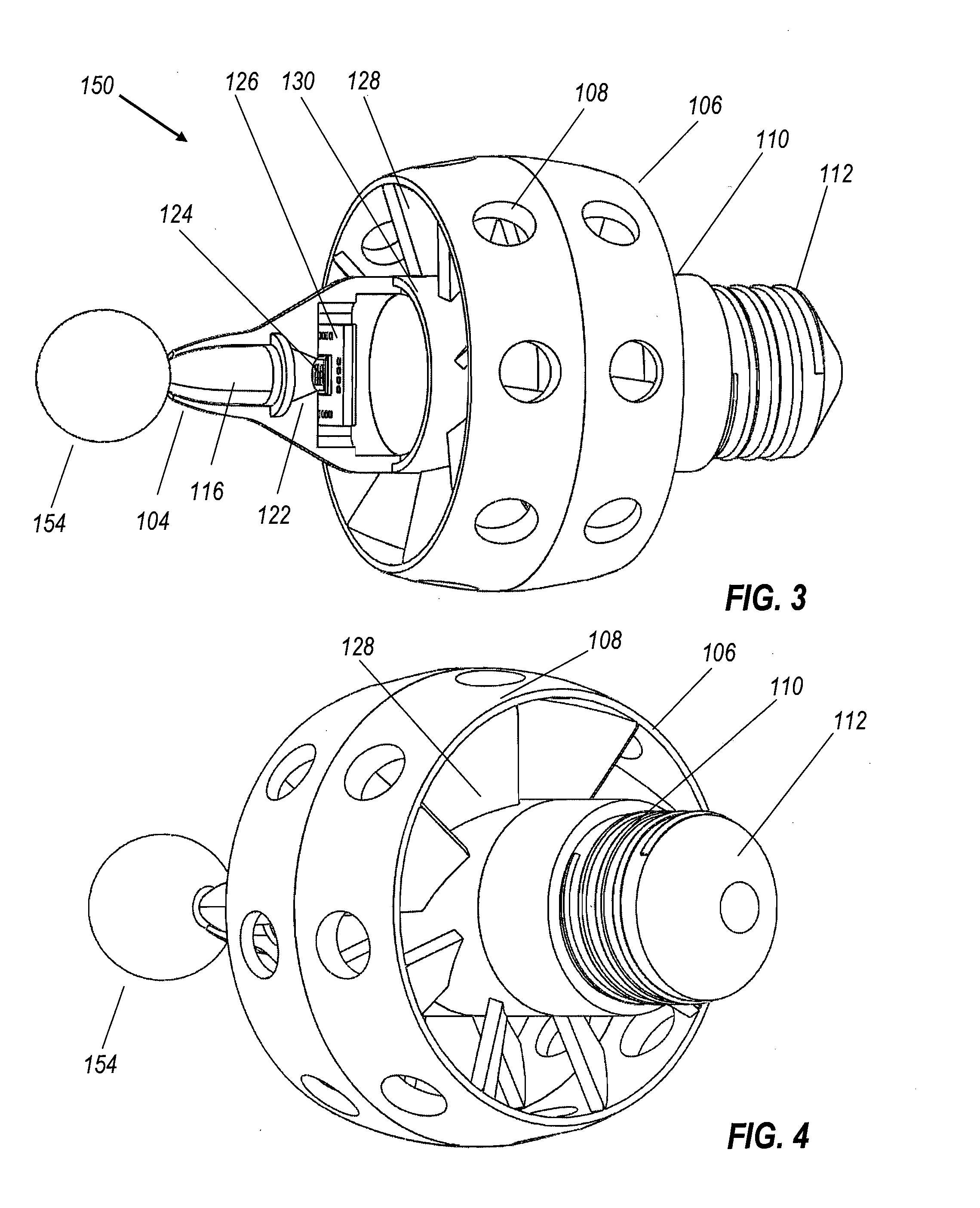

Variable-nozzle cartridge for a turbocharger

ActiveUS7559199B2Reduce the overall diameterLow costWind motor controlPump componentsTurbochargerEngineering

A variable-nozzle turbocharger includes a cartridge containing a variable vane mechanism connected between the center housing and the turbine housing. The cartridge comprises an annular nozzle ring supporting an array of rotatable vanes, an insert having a tubular portion sealingly received into the bore of the turbine housing and having a nozzle portion extending radially out from one end of the tubular portion and being axially spaced from the nozzle ring with the vanes therebetween, and a plurality of spacers connected between the nozzle portion of the insert and the nozzle ring. The turbine housing has a surface that directly contacts a surface of the nozzle ring that axially faces the insert for axially locating the nozzle ring relative to the turbine housing. A radial gap is defined between the turbine housing and the nozzle ring to allow radial movement of the nozzle ring relative to the turbine housing.

Owner:GARRETT TRANSPORATION I INC

Metamaterial scanning lens antenna systems and methods

InactiveUS20060028385A1Negative index of refractionSolve the power is smallAntennasControl signalRadar signals

The present invention is directed to systems and methods for radiating radar signals, communication signals, or other similar signals. In one embodiment, a system includes a controller that generates a control signal and an antenna coupled to the controller. The antenna includes a first component that generates at least one wave based on the generated control signal and a metamaterial lens positioned at some predefined focal length from the first component. The metamaterial lens directs the generated at least one wave.

Owner:THE BOEING CO

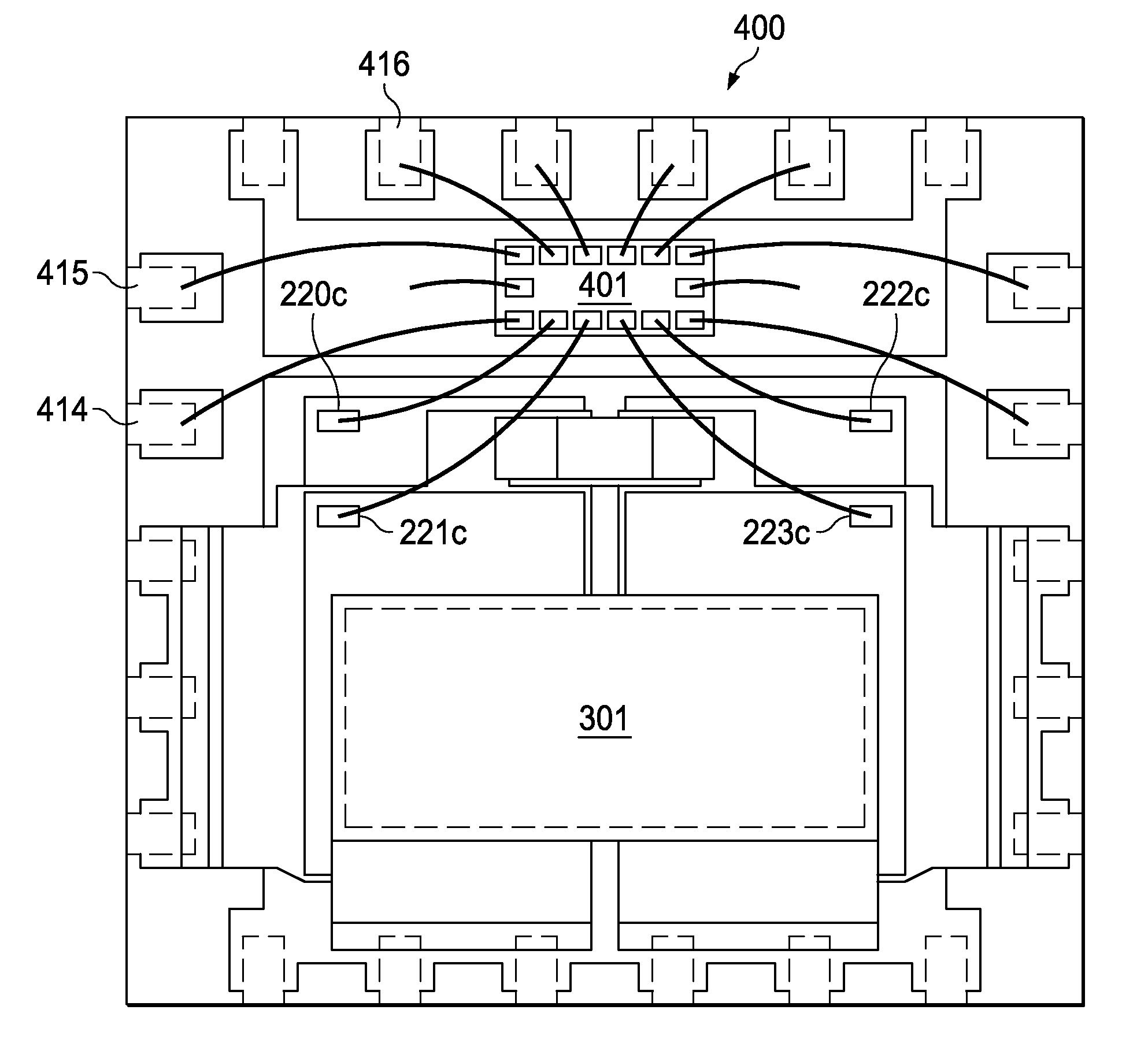

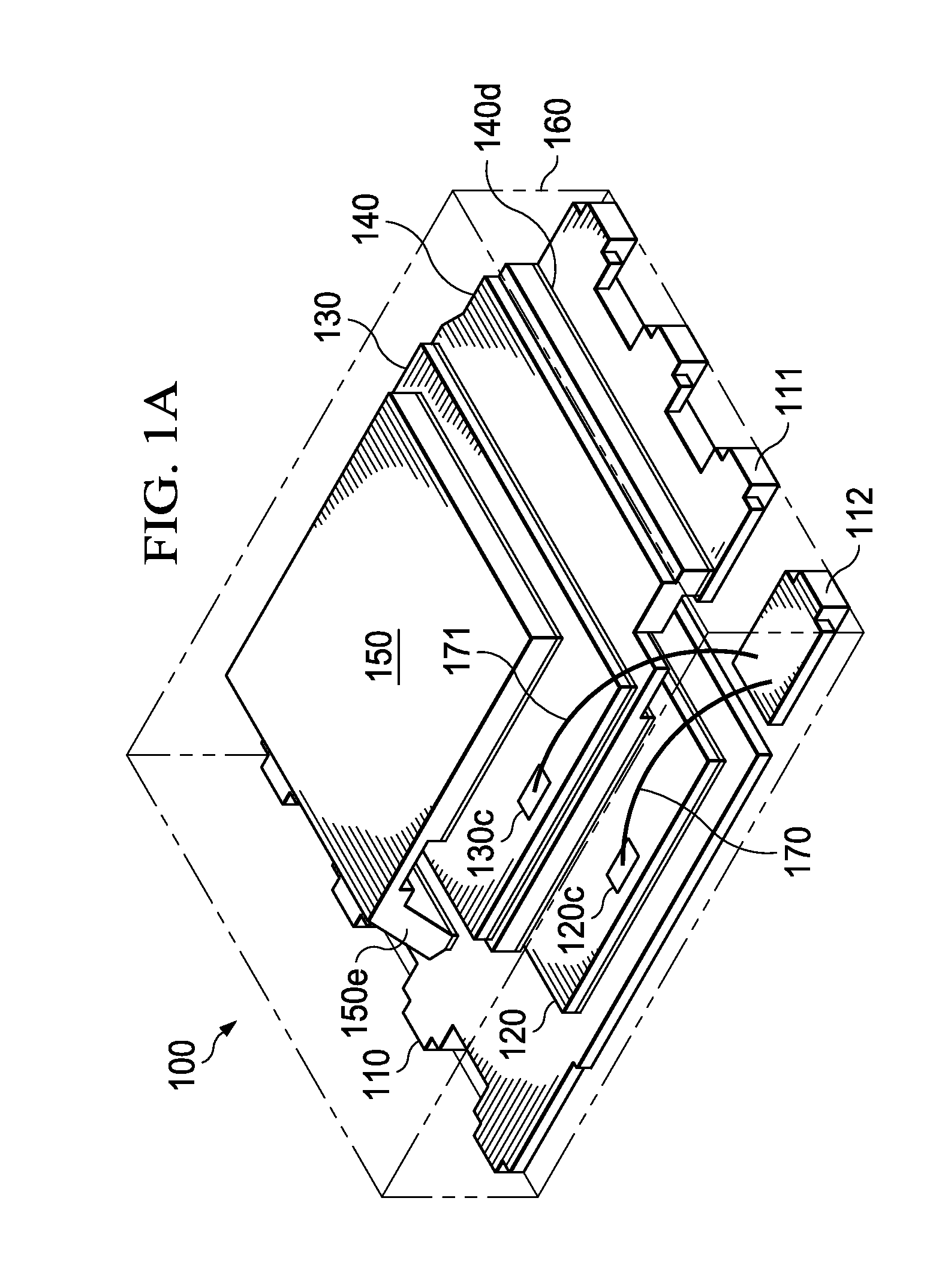

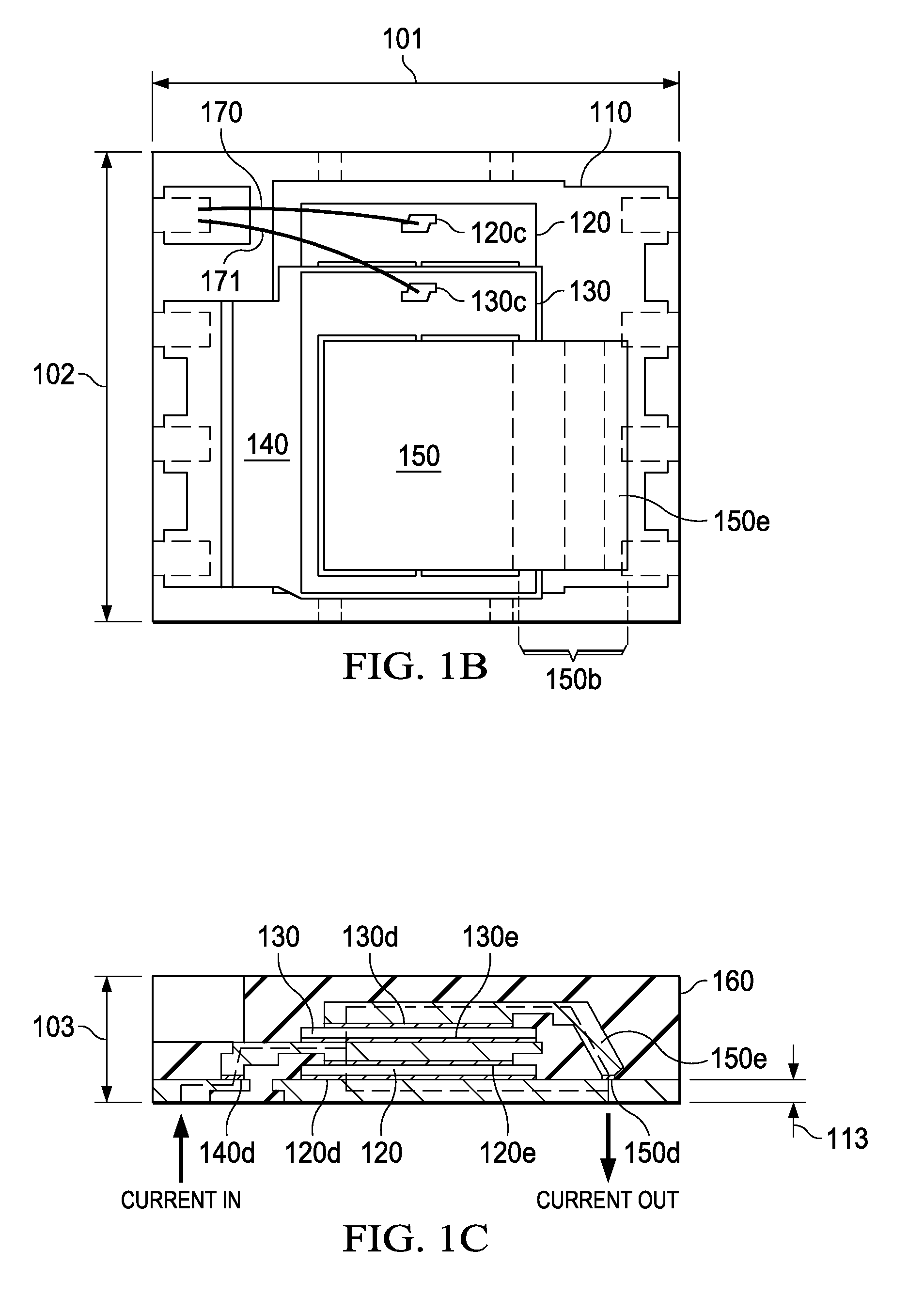

Vertically Stacked Power FETS and Synchronous Buck Converter Having Low On-Resistance

InactiveUS20140063744A1Improve power densityReduce power consumptionSemiconductor/solid-state device detailsSolid-state devicesBuck converterMetal

A power FET (100) comprising a leadframe including a pad (110), a first lead (111), and a second lead (112); a first metal clip (150) including a plate (150a), an extension (150b) and a ridge (150c), the plate and extension spaced from the leadframe pad and the ridge connected to the pad; a vertically assembled stack of FET chips in the space between the plate and the pad, the stack including a first n-channel FET chip (120) having the drain terminal on one surface and the source and gate terminals on the opposite surface, the drain terminal attached to the pad, the source terminal attached to a second clip (140) tied to the first lead; and a second n-channel FET chip (130) having the source terminal on one surface and the drain and gate terminals on the opposite surface, the source terminal attached to the second clip, its drain terminal attached to the first clip; wherein the drain-source on-resistance of the FET stack is smaller than the on-resistance of the first FET chip and of the second FET chip.

Owner:TEXAS INSTR INC

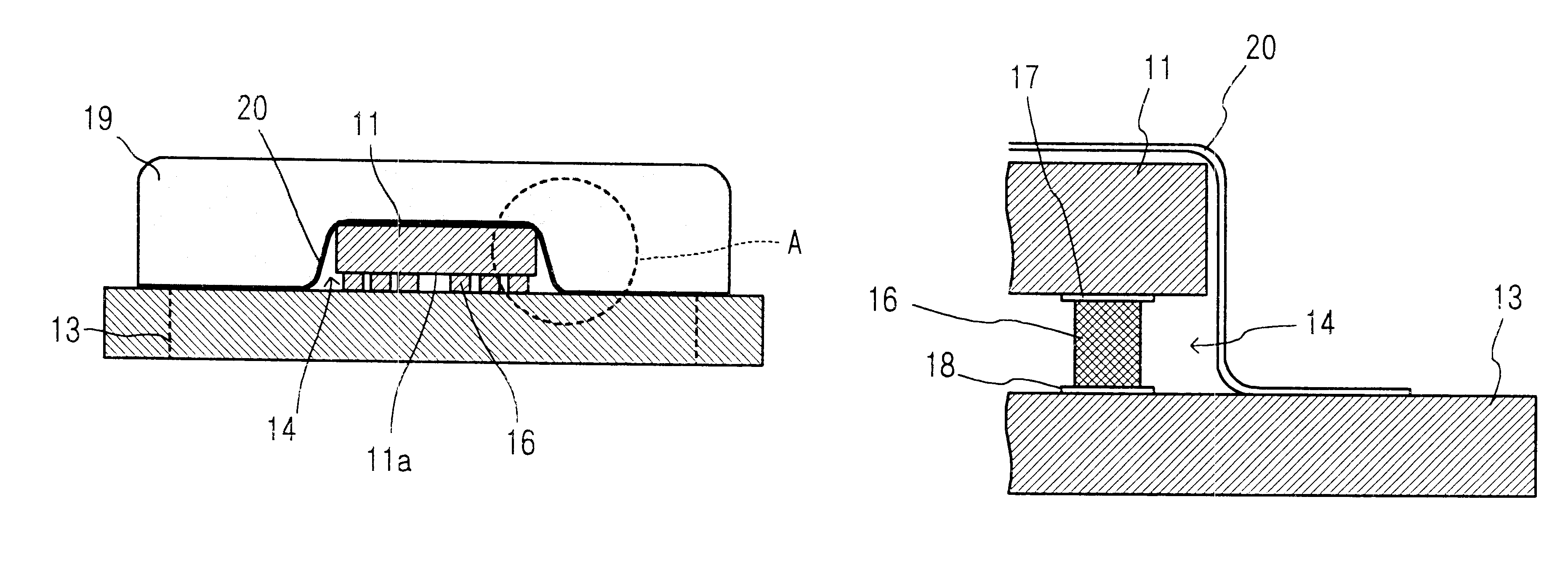

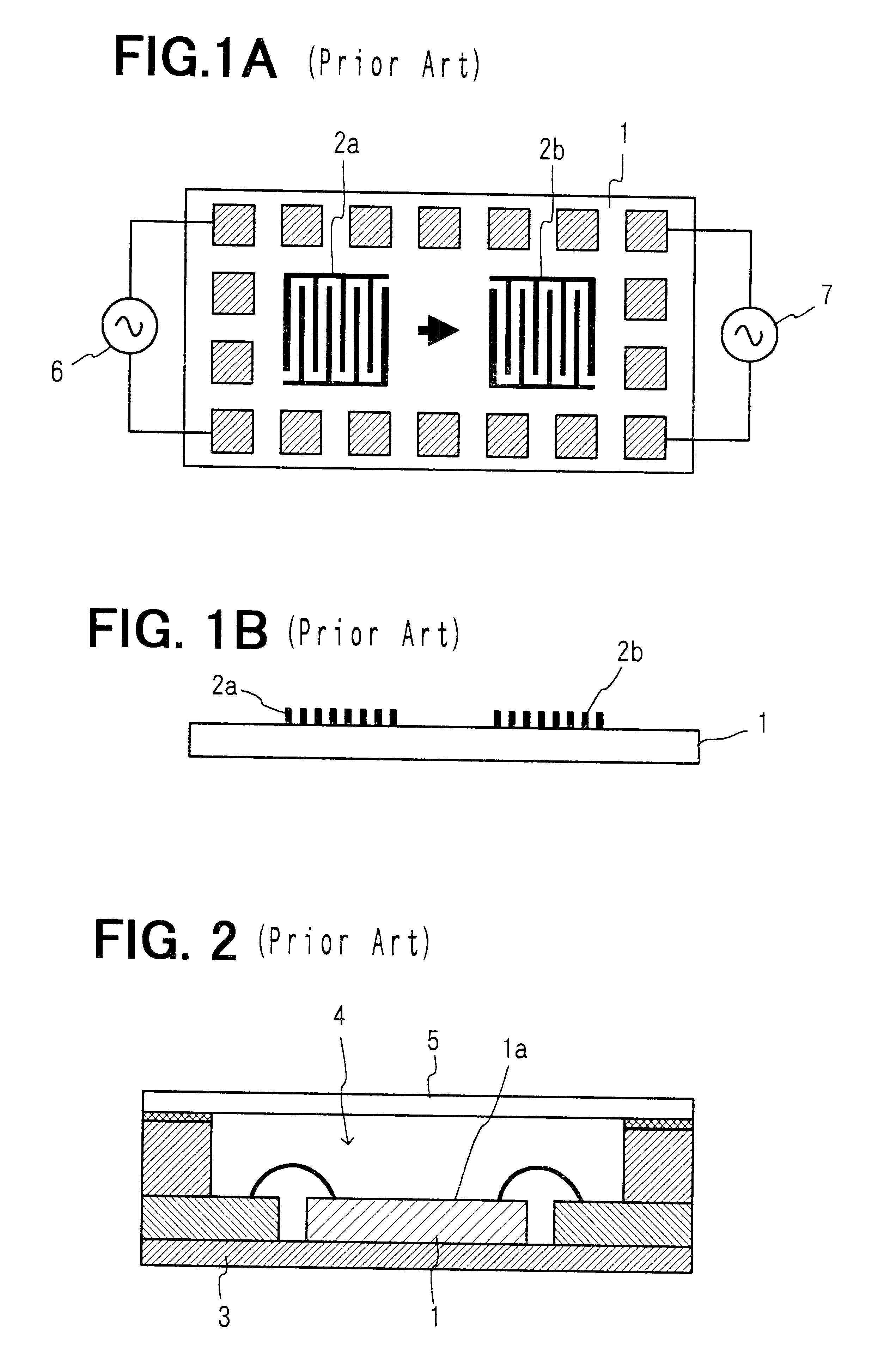

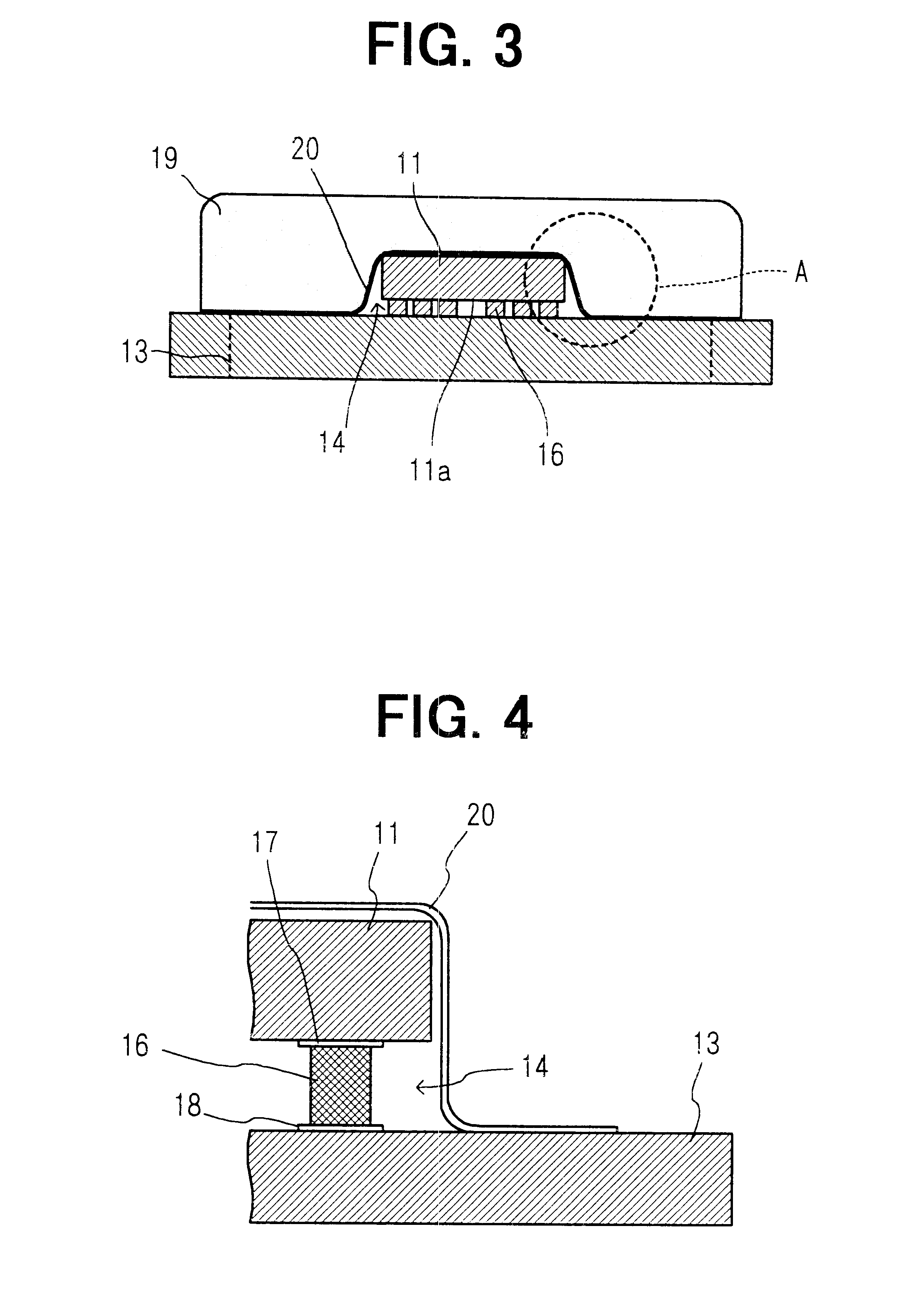

Surface-acoustic wave device package

InactiveUS6329739B1MiniaturizationSmall packagePiezoelectric/electrostriction/magnetostriction machinesImpedence networksAcoustic waveEngineering

A surface-acoustic-wave device package includes a cover film which covers a piezoelectric substrate to provide an air gap around the functional surface of the surface-acoustic-wave device. The surface-acoustic-wave device package also includes a seal material which is provided over the cover film to seal the surface-acoustic-wave device.

Owner:HANGER SOLUTIONS LLC

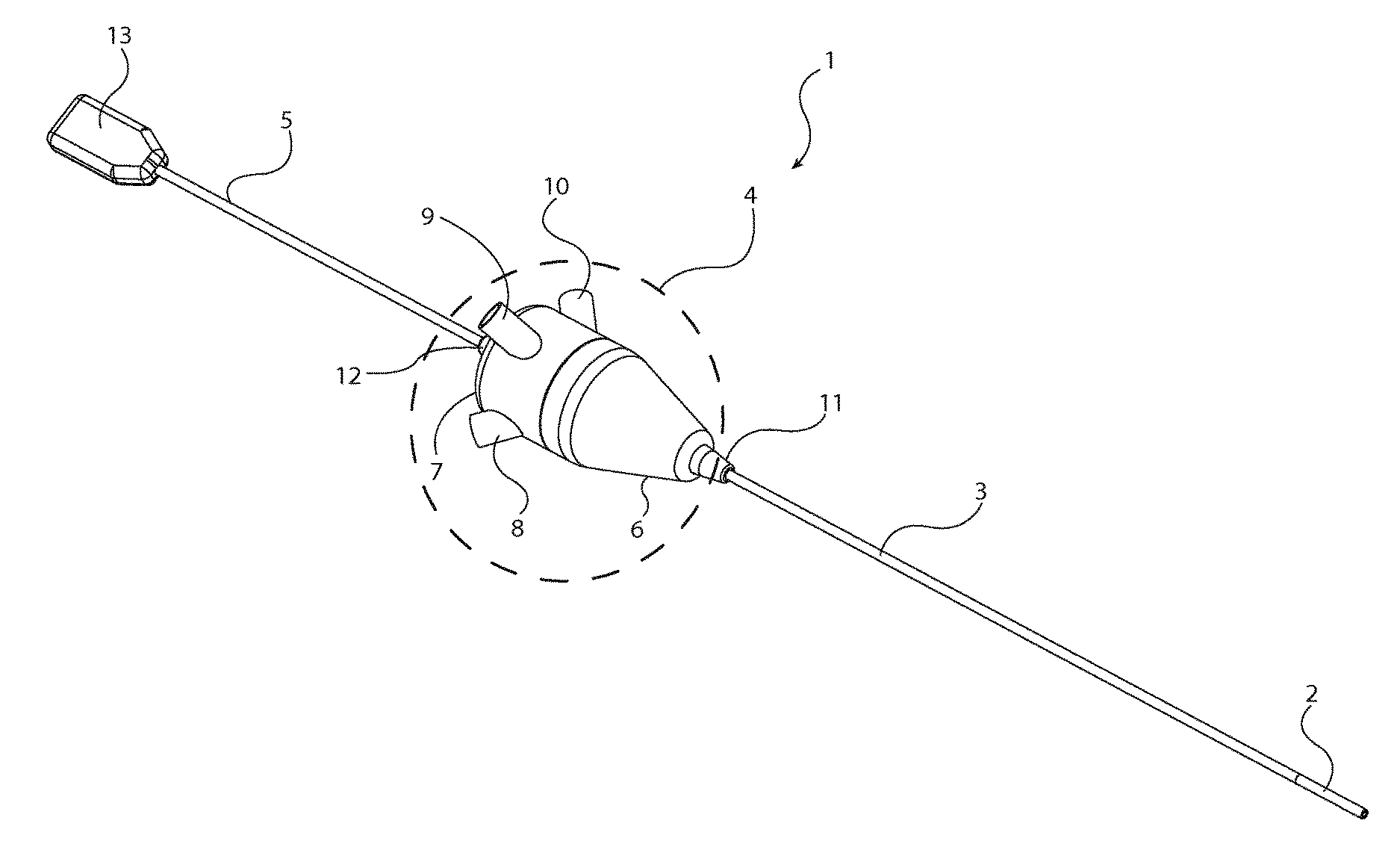

Endoscope with Variable Profile Tip

ActiveUS20170035277A1Without increasing overall sizeLow profileSurgeryEndoscopesLight guideEngineering

A single-use electronic endoscope has a hub, a shaft extending from the hub, flexible or rigid as desired, and an expandable distal tip extending from the shaft. Within the distal tip, an image sensor provides a field of view external from the endoscope. Illuminating elements or light guides within the distal tip emit light to illuminate the field of view. The distal tip also has a variable profile working channel that permits tools to be passed from the hub and into the field of view. The expandable working channel changes cross-sectional shape from a generally noncircular shape to a shape to accommodate the cross-sectional shape of the tool when expanded.

Owner:ENLIGHTENVUE INC

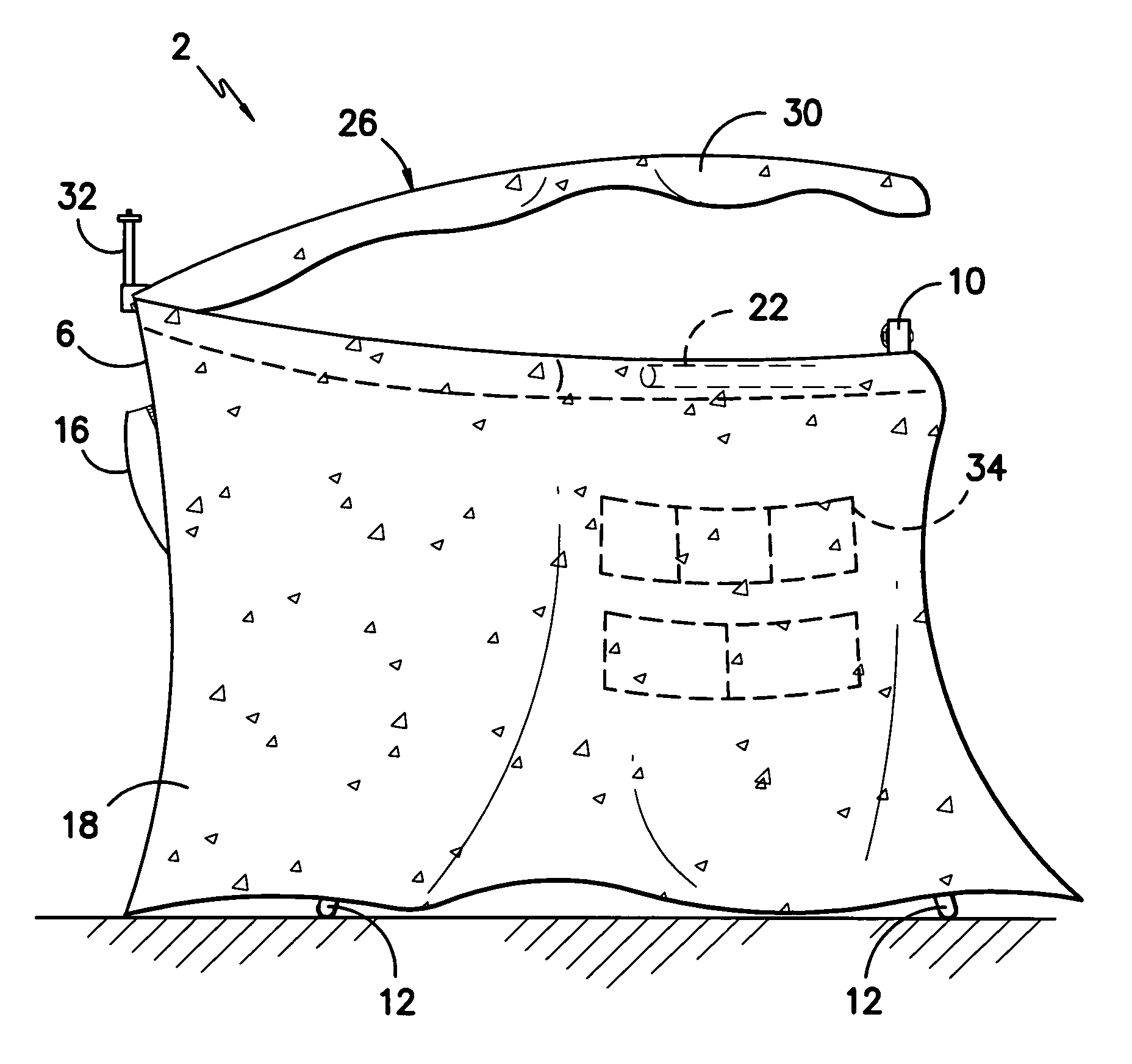

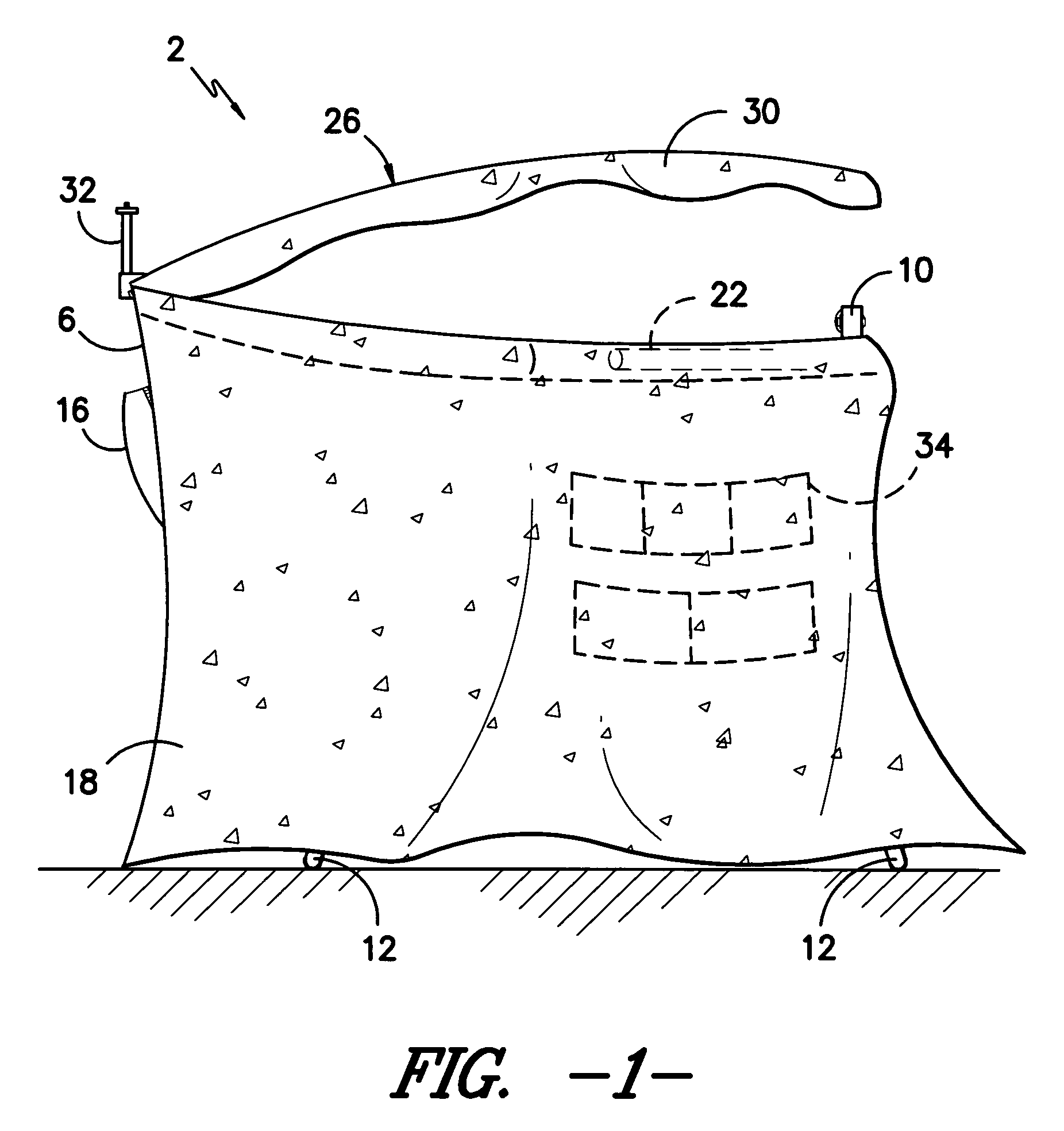

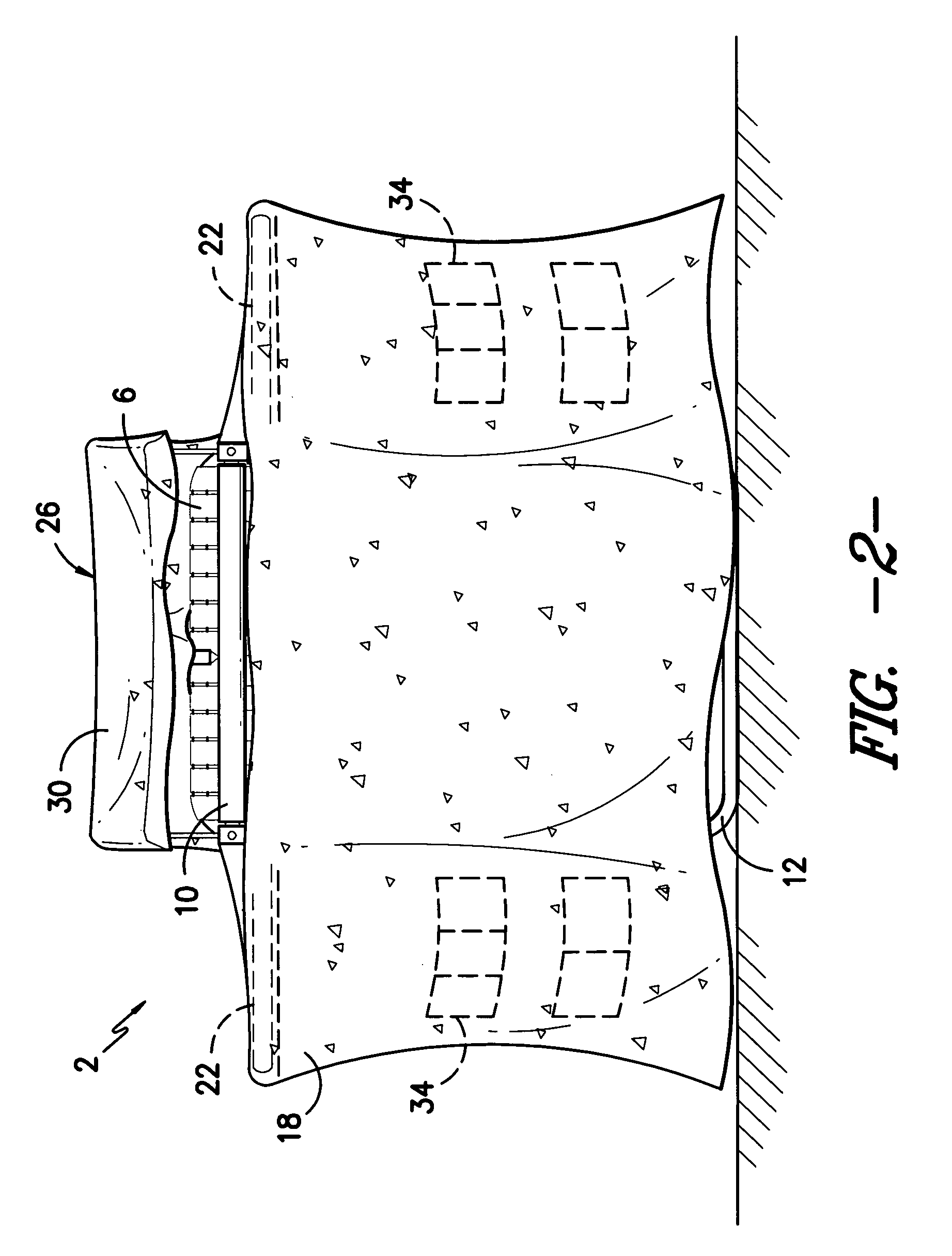

Portable hunting chair and blind

InactiveUS7997291B2Reduce manufacturing costEasy to disassembleVehicle seatsAnimal huntingEngineeringMechanical engineering

A hunting chair with a hunting blind attachment that encircles the chair is disclosed, as well as an attachable camouflage roof covering, all of which may be folded and disassembled in such a way that it fits into a self-contained pack that may be carried on a hunter's back. The chair includes an adjustable, pivoting backrest, a pivoting gun rest with telescoping legs for height adjustment, folding legs, a pouch to contain the disassembled elements, and shoulder straps for carrying the apparatus. In its disassembled state, the roof poles, roof fabric, and blind fabric are packed into a pouch on the back side of the backrest, and the chair is folded into a carrying position. Detachable shoulder straps may be attached to the underside of the seat section, so that the entire chair and blind combination may be carried on a hunter's back into the field.

Owner:GRESSETTE III F REEVES +2

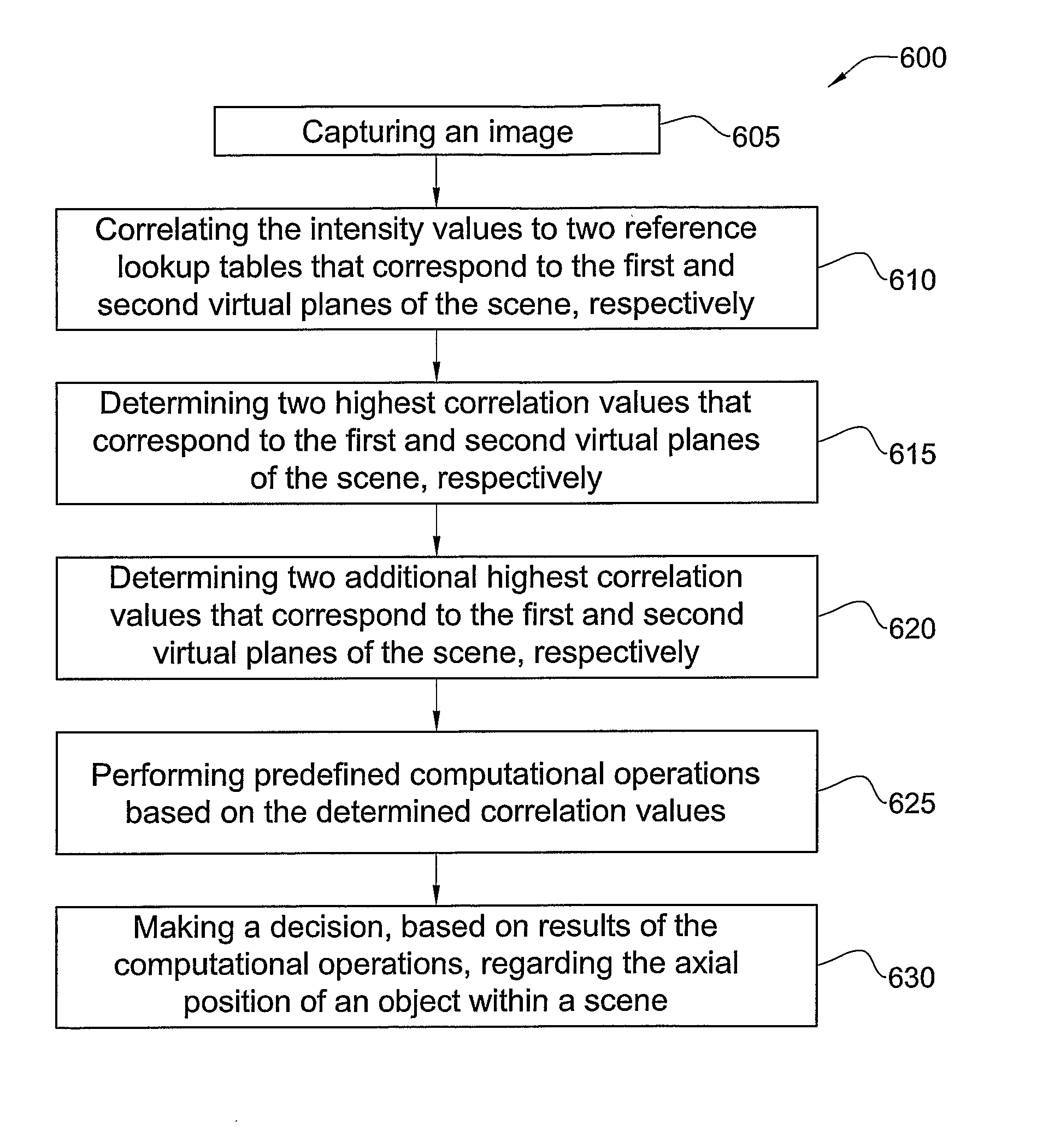

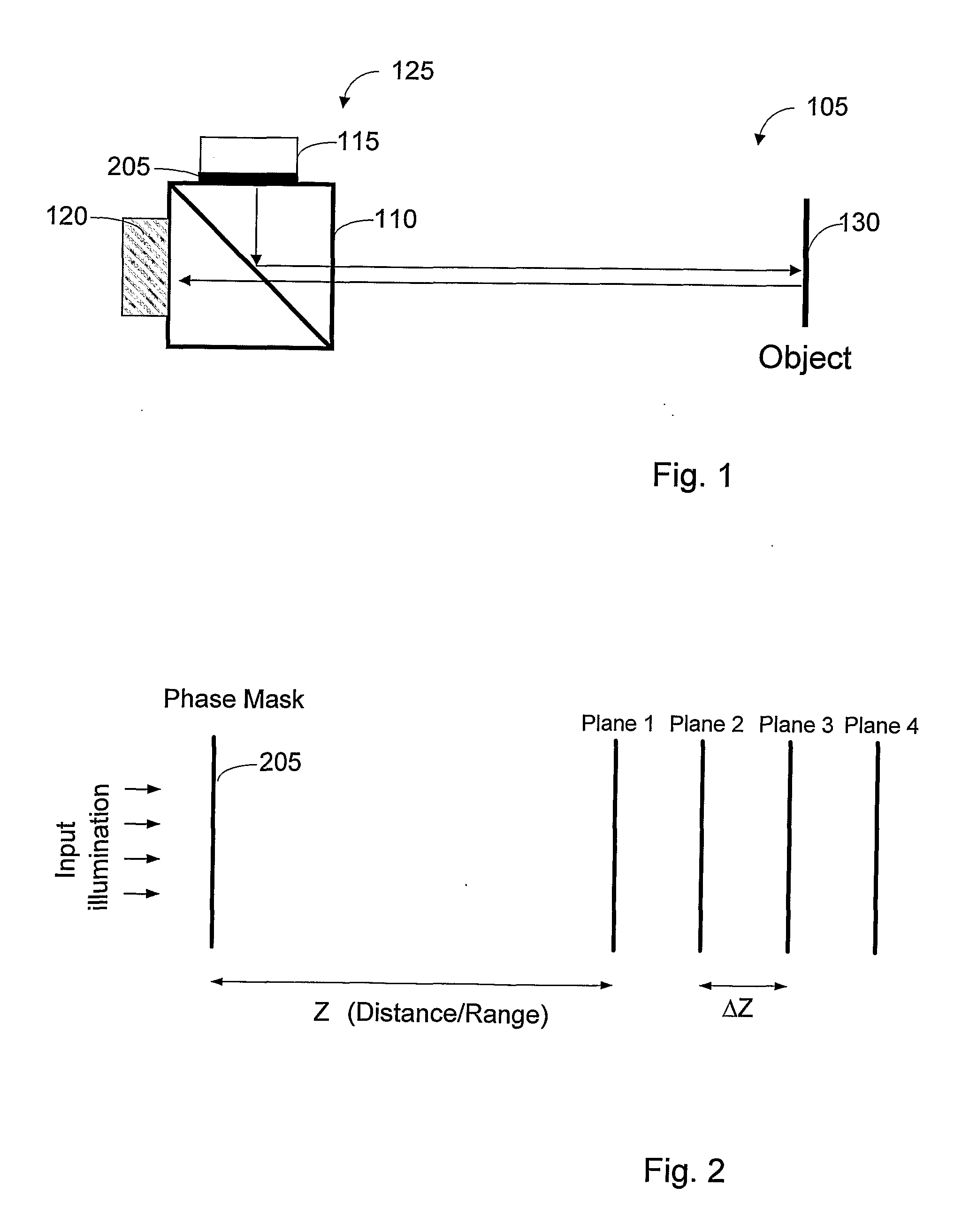

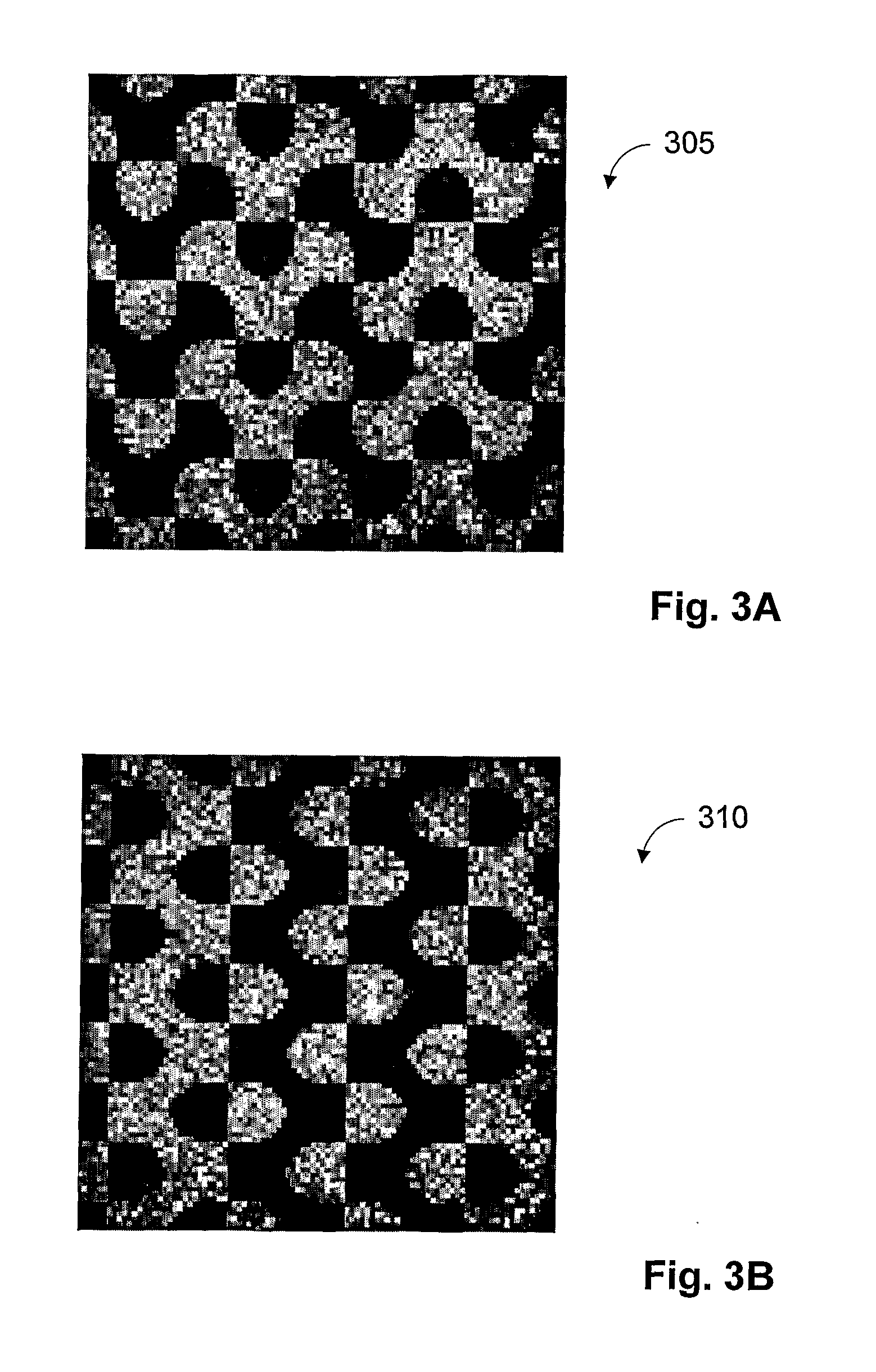

Method and system for providing three-dimensional and range inter-planar estimation

InactiveUS20110181704A1Small packageEliminate requirementsImage analysisCharacter and pattern recognitionComputer visionCharacteristic type

A system, apparatus and method of performing 3-D object profile inter-planar estimation and / or range inter-planar estimation of objects within a scene, including: providing a predefined finite set of distinct types of features, resulting in feature types, each feature type being distinguishable according to a unique bi-dimensional formation; providing a coded light pattern having multiple appearances of the feature types; projecting the coded light pattern, having axially varying intensity, on objects within a scene, the scene having at least two planes, resulting in a first plane and a second plane; capturing a 2-D image of the objects having the projected coded light pattern projected thereupon, resulting in a captured 2-D image, the captured 2-D image including reflected feature types; determining intensity values of the 2-D captured image; and performing 3-D object profile inter-planar estimation and / or range inter-planar estimation of objects within the scene based on determined intensity values.

Owner:MANTIS VISION

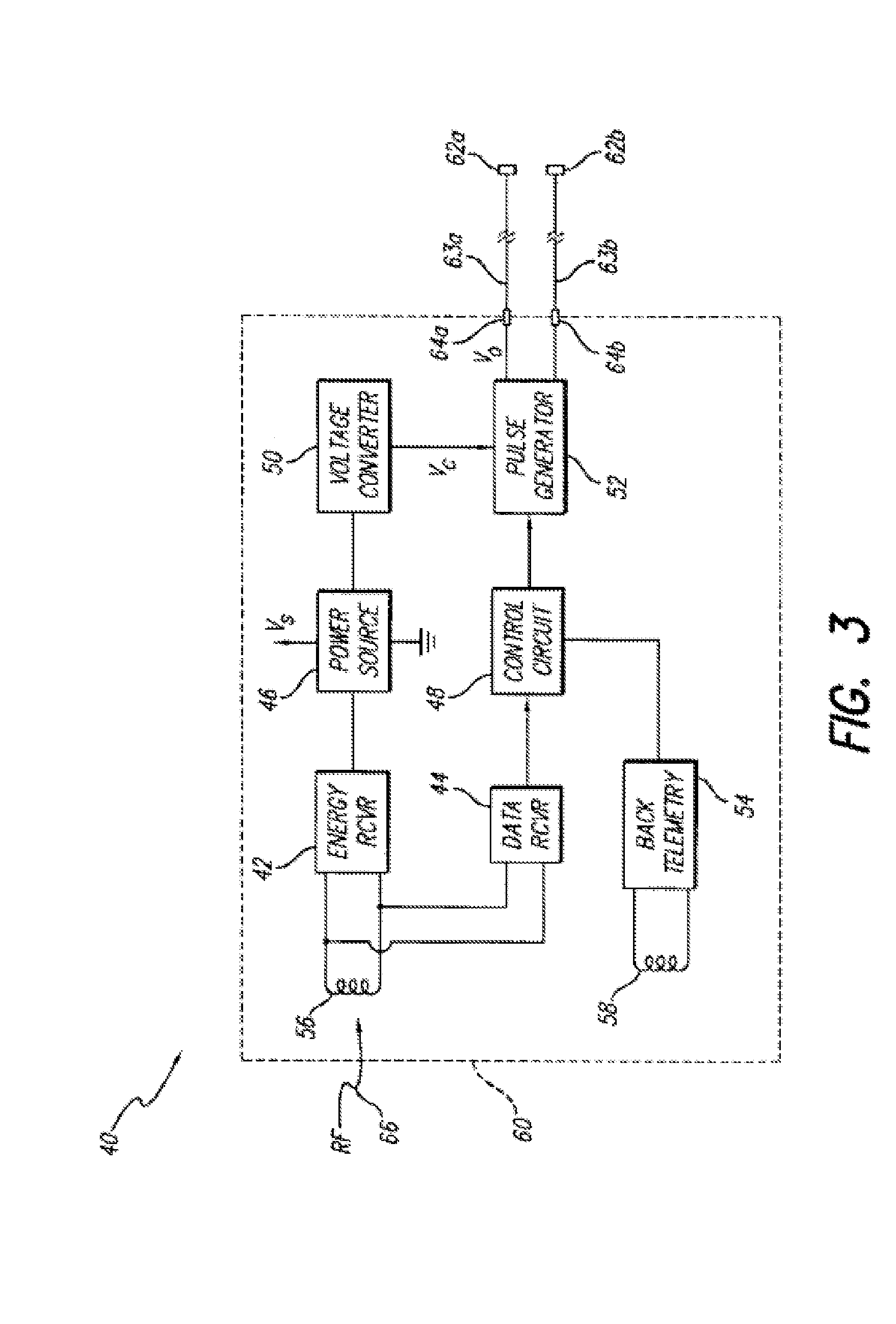

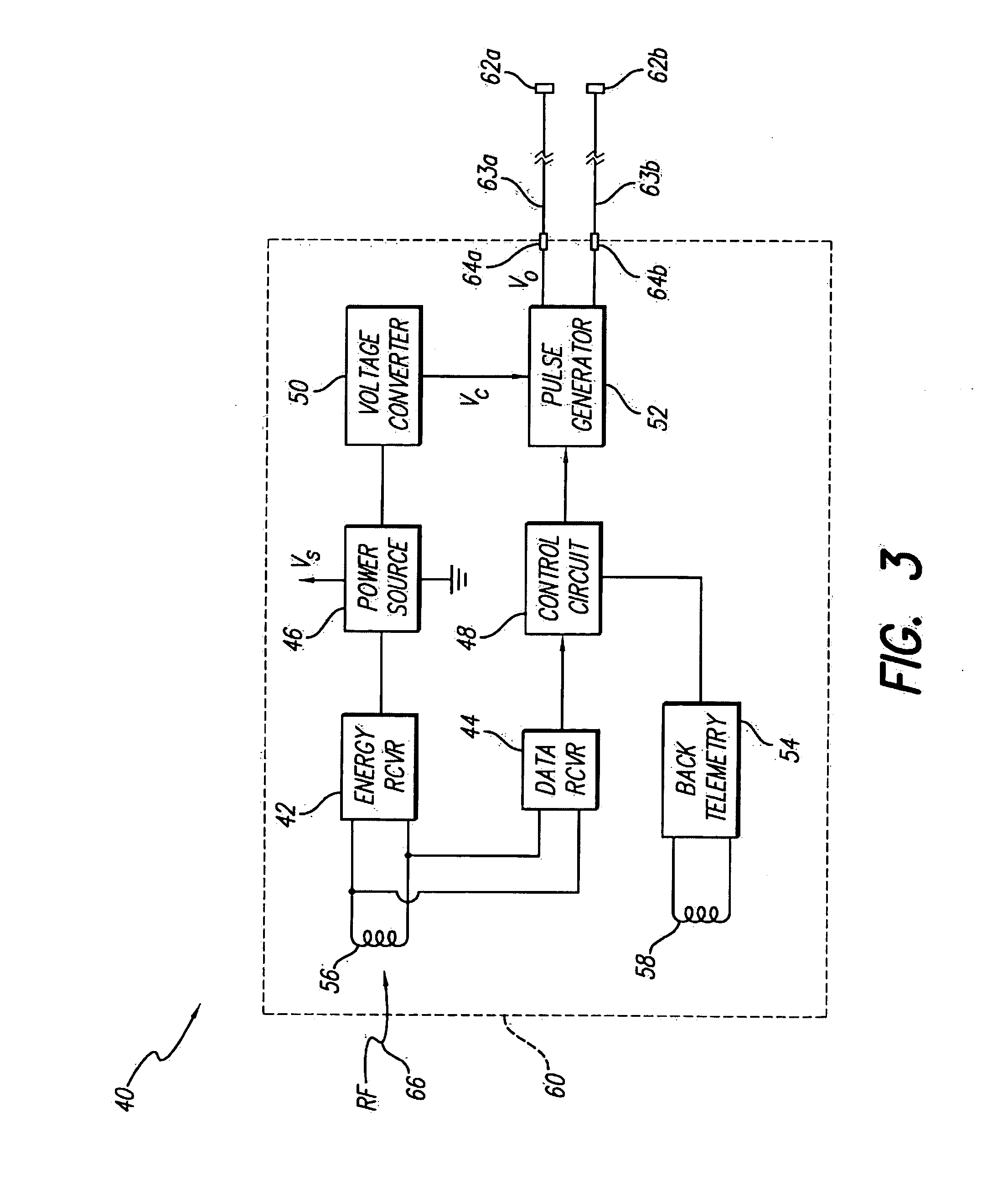

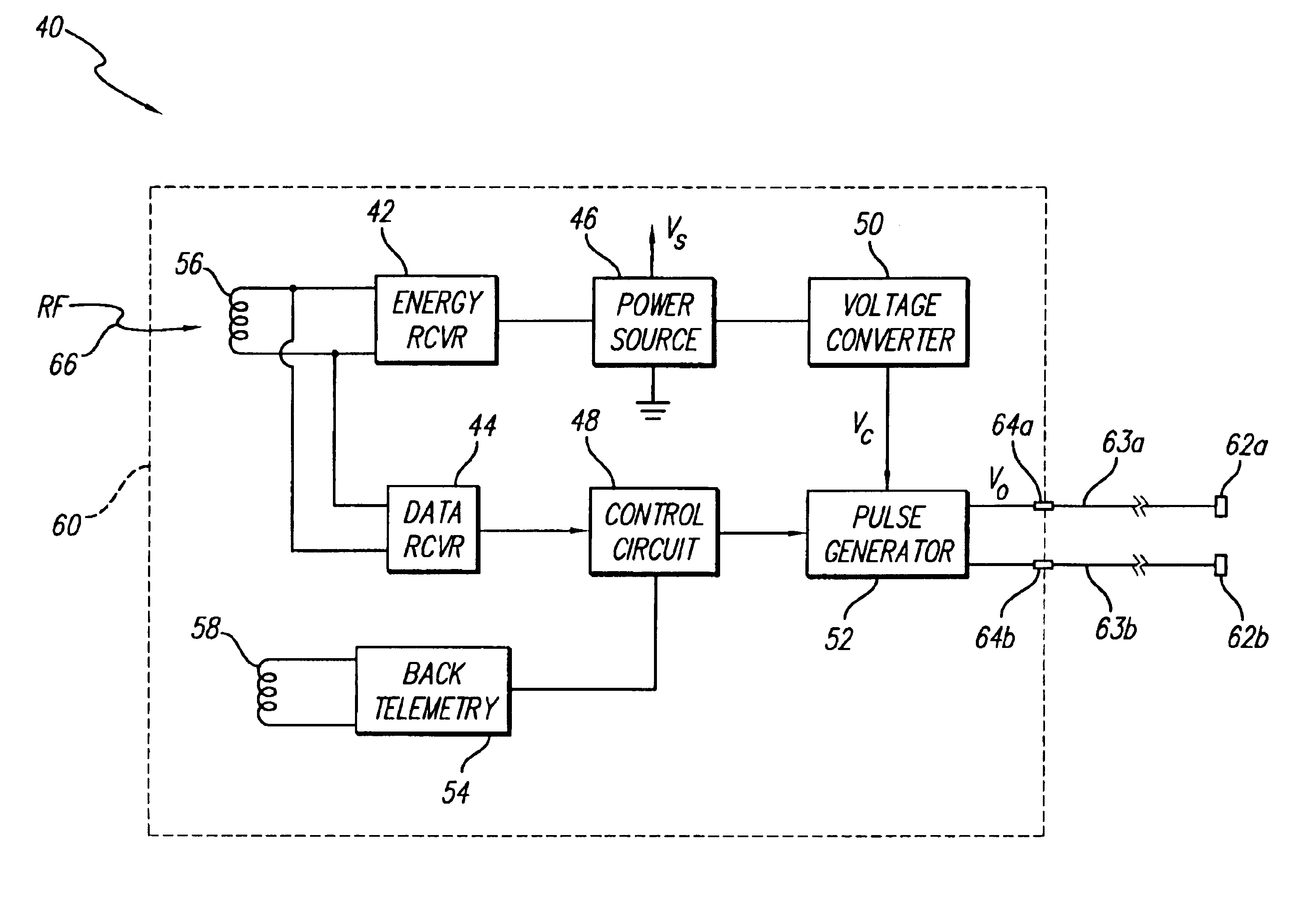

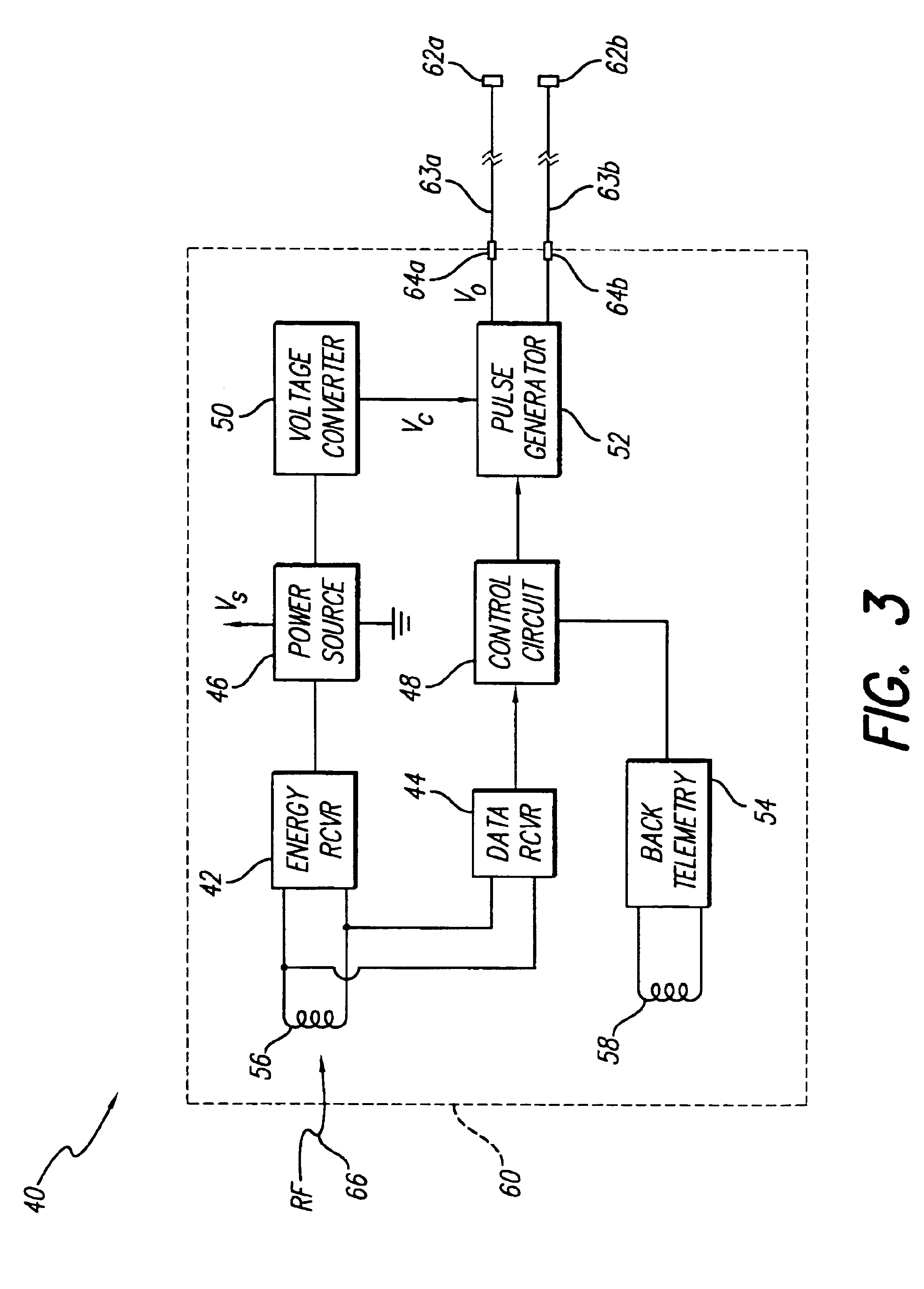

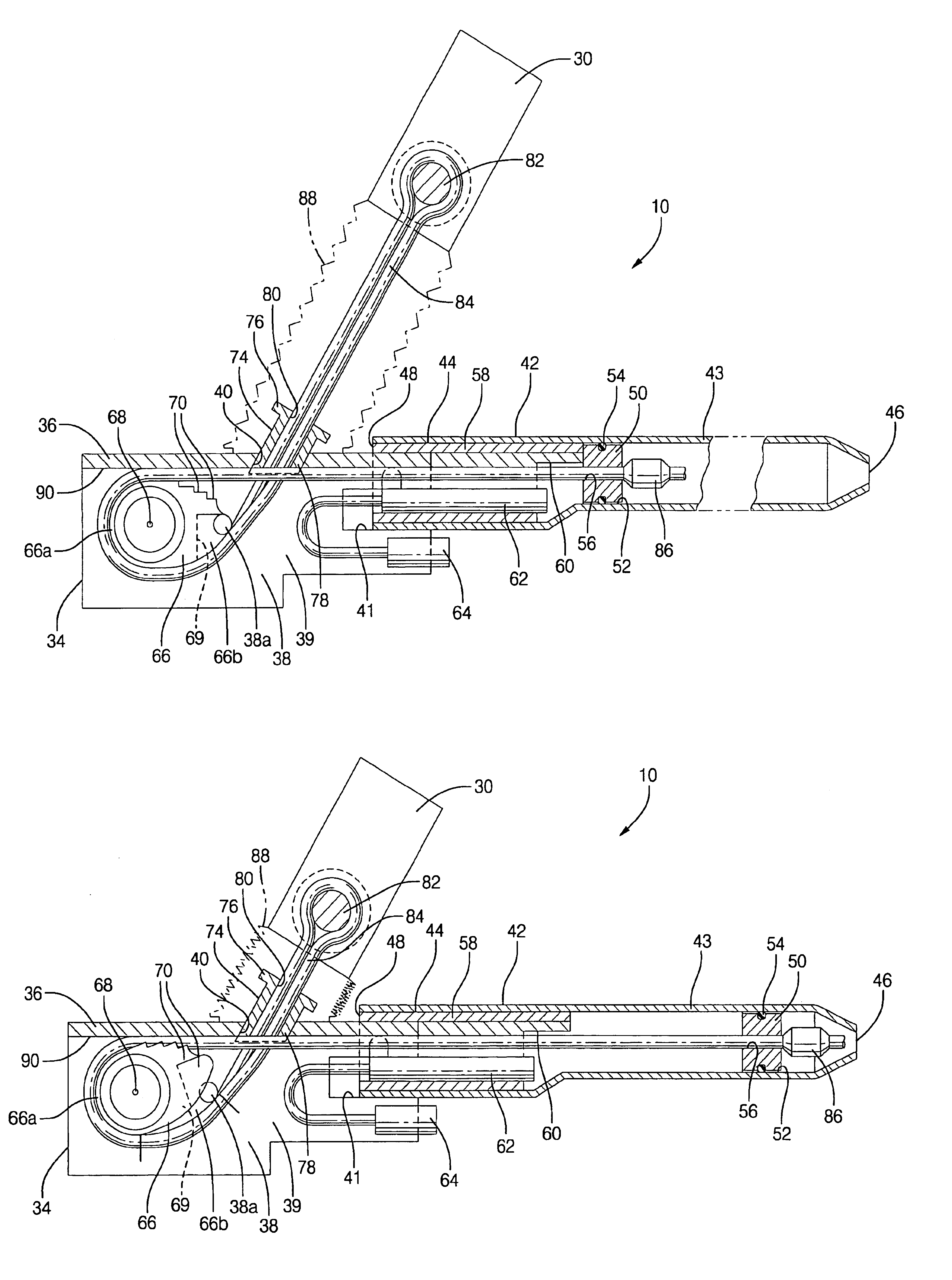

Voltage converter for implantable microstimulator using RF-powering coil

InactiveUS20050131496A1Minimizes numberSmall and more densely packedElectrotherapyTime multiplexingPower control

A combination, voltage converter circuit for use within an implantable device, such as a microstimulator, uses a coil, instead of capacitors, to provide a voltage step up and step down conversion functions. The output voltage is controlled, or adjusted, through duty-cycle modulation. In accordance with one aspect of the invention, applicable to implantable devices having an existing RF coil through which primary or charging power is provided, the existing RF coil is used in a time-multiplexing scheme to provide both the receipt of the RF signal and the voltage conversion function. This minimizes the number of components needed within the device, and thus allows the device to be packaged in a smaller housing or frees up additional space within an existing housing for other circuit components. In accordance with another aspect of the invention, the voltage up / down converter circuit is controlled by a pulse width modulation (PWM) low power control circuit. Such operation allows high efficiencies over a wide range of output voltages and current loads.

Owner:BOSTON SCI NEUROMODULATION CORP

Dimmable LED lamp

InactiveUS20100289395A1Small packageImprove efficiencyLight source combinationsDischarge tube luminescnet screensLED lampLightness

An LED-powered replacement for the conventional incandescent screw-in light bulb comprises a phosphor coated sphere emitting white light into the same spherical pattern as a frosted incandescent bulb. In one embodiment inside the hollow sphere there is a dielectric cone emitting blue light, which causes the phosphor coating to glow. The blue light comes into the cone from a dielectric totally internally reflecting concentrator (DTIRC), which receives light from a conical reflector surrounding an LED array. The array has blue chips for energizing the phosphor and red chips for supplementing the phosphor light, enabling separate electronic control of the color temperature as well as the overall luminosity of the LED Lamp. Both blue and red chips are controlled by a quantum dimmer.

Owner:LIGHT PRESCRIPTIONS INNOVATORS

Hybrid vehicle and energy storage system and method

InactiveUS20020074175A1Conveniently and inexpensively adaptableSmall packageAuxillary drivesReciprocating combination enginesStored energyPower mode

A system for providing a hybrid vehicle with a practical source of auxiliary power. The system includes two electric motor / generators connected to each other in such a fashion so that when one electric motor / generator functions as a motor, the other becomes a generator with their roles being reversed depending on whether the system is in an auxiliary power mode or energy storage mode. Connected to one motor / generator is the vehicle drive train. Connected to the other motor / generator is a pressure energy storage system, which in the energy storage mode converts the force of rotation into pressurized gas for storage in an energy system and delivered in the form of electric current by the one motor / generator, and in the energy delivery mode converts the stored energy of the energy storage system into electric current for delivery to the one motor / generator which is part of the vehicle drive train to provide auxiliary power for practical hybrid vehicles.

Owner:BLOXHAM STEVEN R

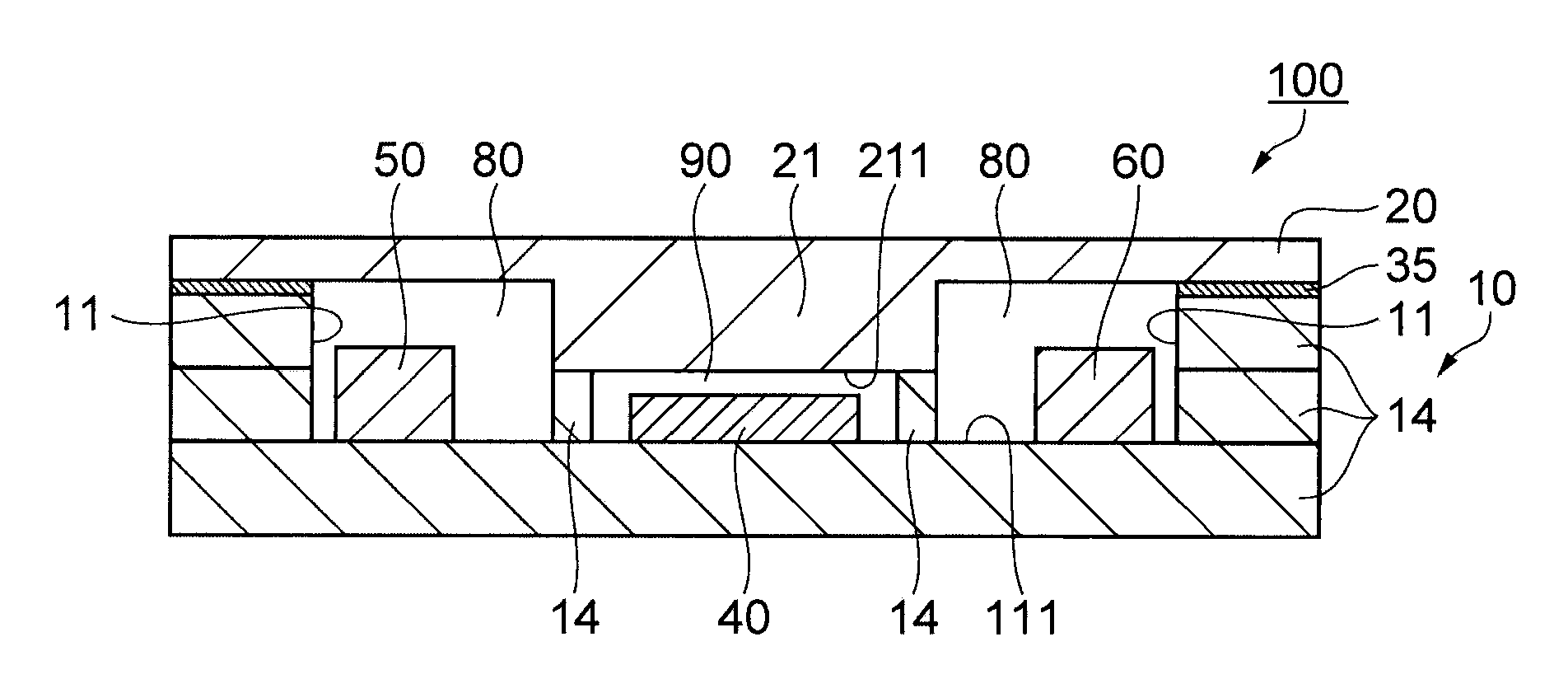

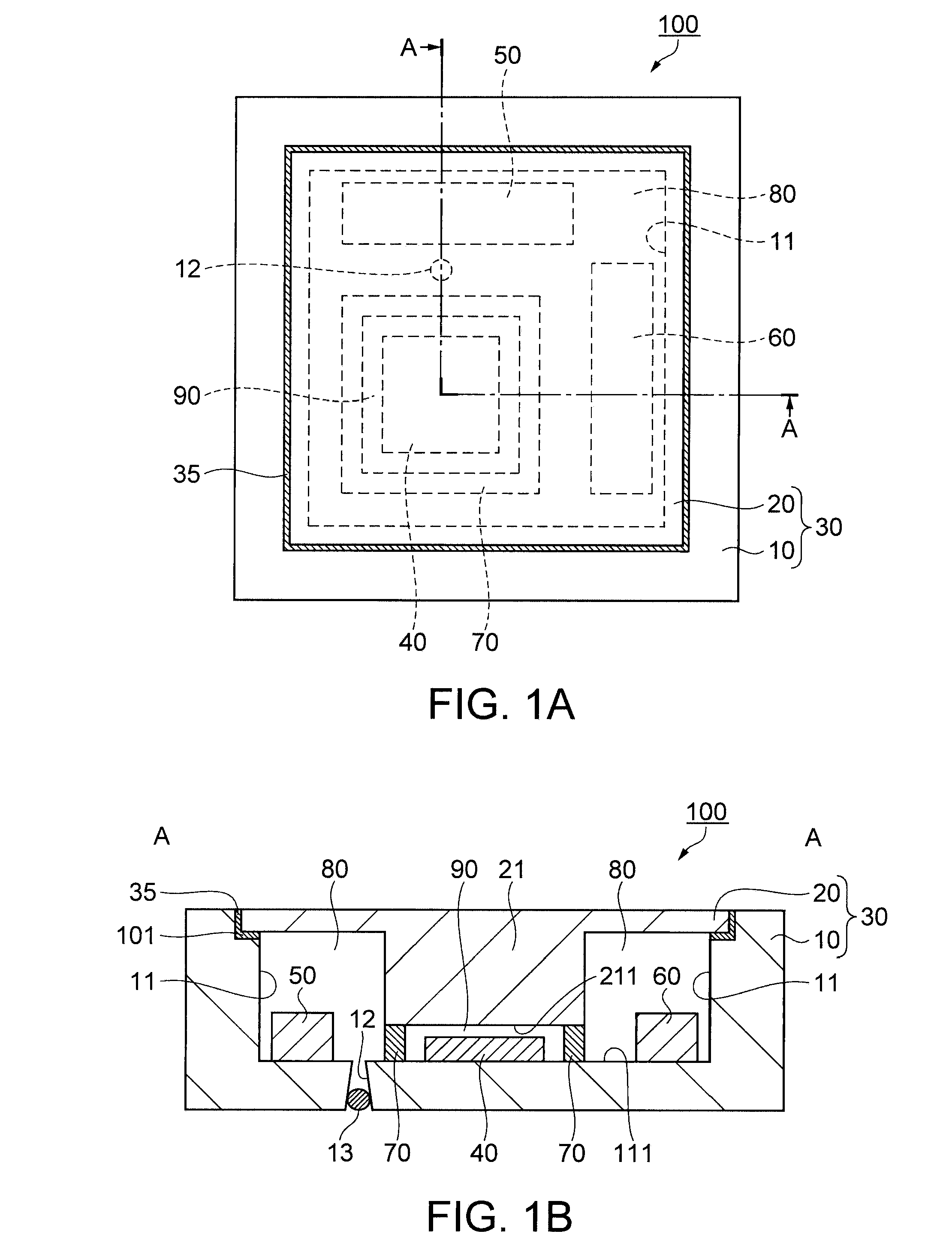

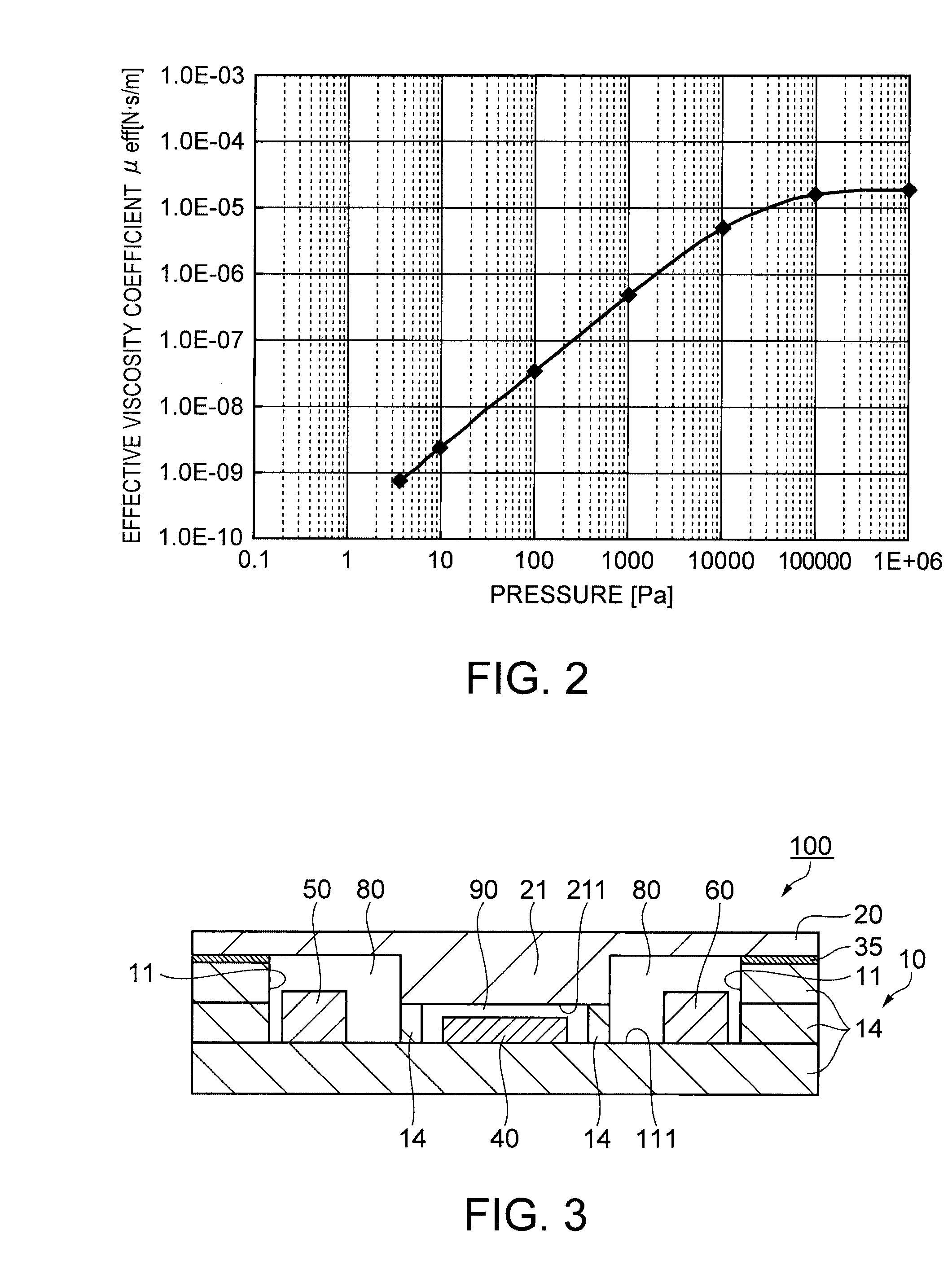

Composite sensor and electronic device

ActiveUS8342021B2Improve featuresSmall packageAcceleration measurement using interia forcesSolid-state devicesAngular velocityEngineering

A composite sensor includes: a package including a container and a lid; a plurality of spaces that is partitioned by at least the container and the lid, and has different pressures, the plurality of the spaces including a first space sealed at around an atmospheric pressure and a second space sealed at a depressurized state; an acceleration sensor element disposed in the first space; and a vibration type angular velocity sensor element disposed in the second space. In the sensor, the first space has a volume smaller than a volume of the second space.

Owner:138 EAST LCD ADVANCEMENTS LTD

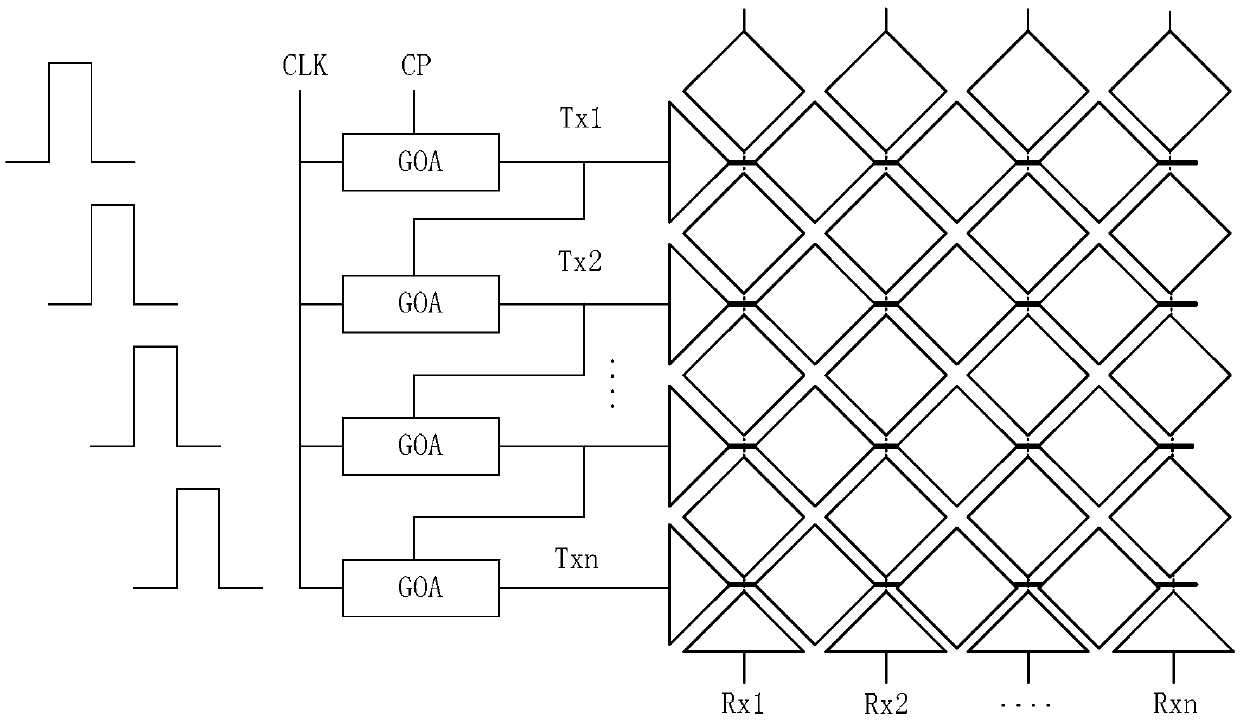

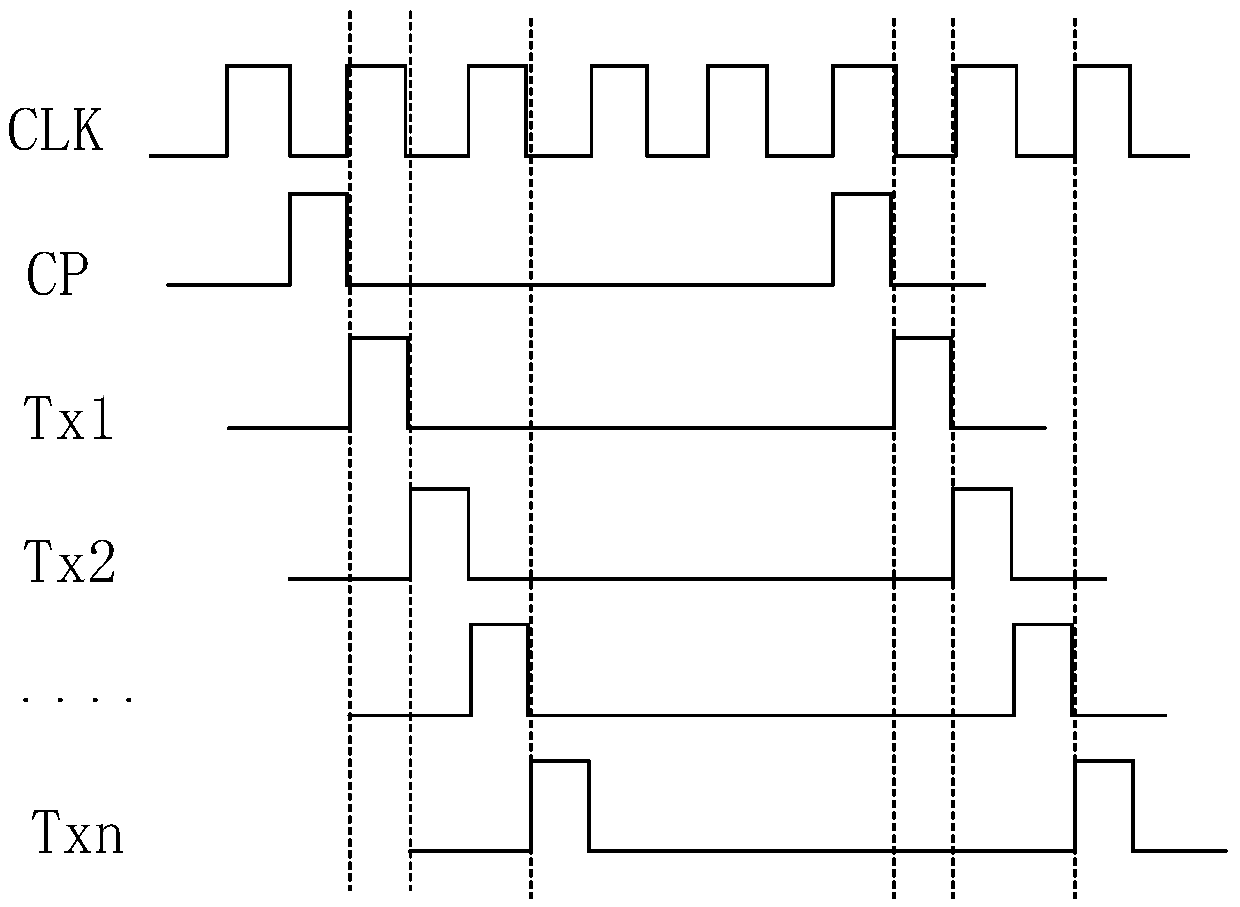

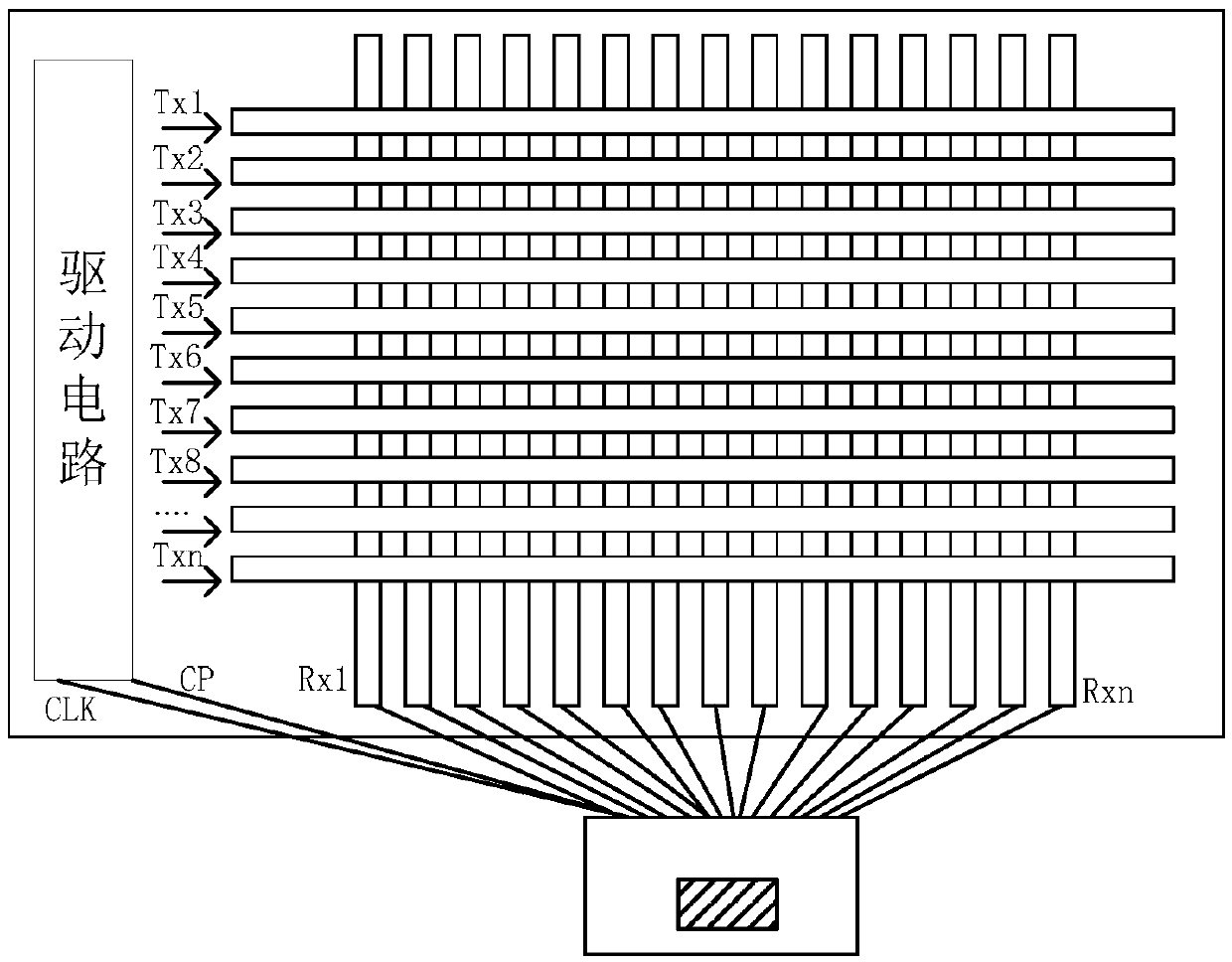

Touch display panel, driving method thereof and detecting method of induction signals

ActiveCN105528118AImprove reporting rateReduce scan timeInput/output processes for data processingEngineeringReporting rate

The invention discloses a touch display panel, a driving method thereof and a detecting method of induction signals, relates to the field of display and solves the problems that the report rate is influenced due to long scanning period and thin film transistors in a visible range are prone to electrical conductivity reduction. A plurality of touch driving electrodes and touch induction electrodes are arranged in a touch area of the touch display panel, and a driving unit is arranged on the edge; the driving unit comprises a first gate driving circuit to an Nth gate driving circuit which are coupled sequentially in a cascading manner, the enable end of the first gate driving circuit is connected with a field synchronizing signal line arranged on the edge of the touch display panel, and the output end of the (N-1)th gate driving circuit is connected to the enable end of the Nth gate driving circuit adjacently connected with the (N-1)th gate driving circuit; the input ends of the first gate driving circuit to the Nth gate driving circuit are connected with a driving signal line respectively, and the output ends of the first gate driving circuit to the Nth gate driving circuit are coupled with the corresponding touch driving electrodes respectively.

Owner:BOE TECH GRP CO LTD +1

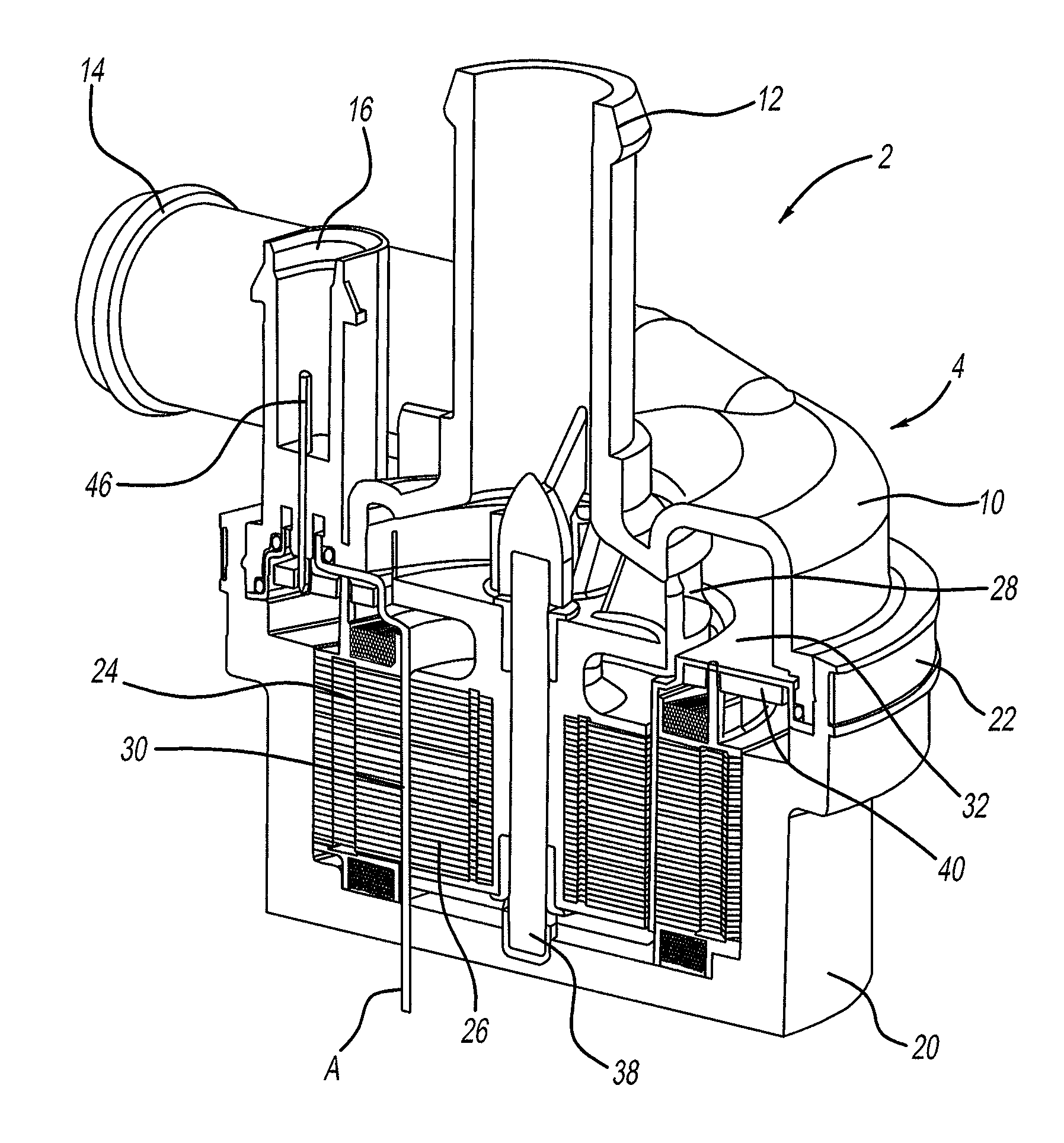

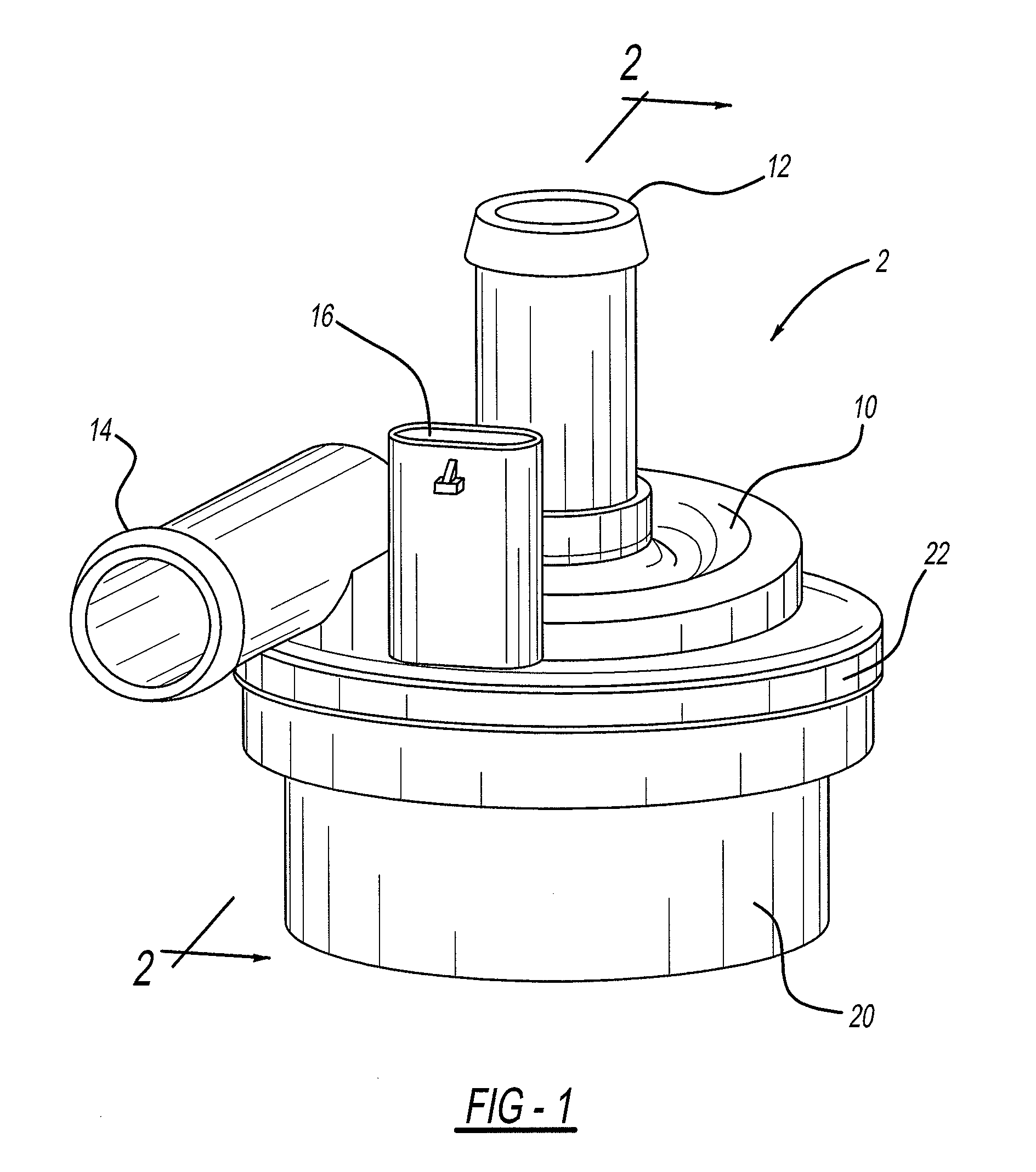

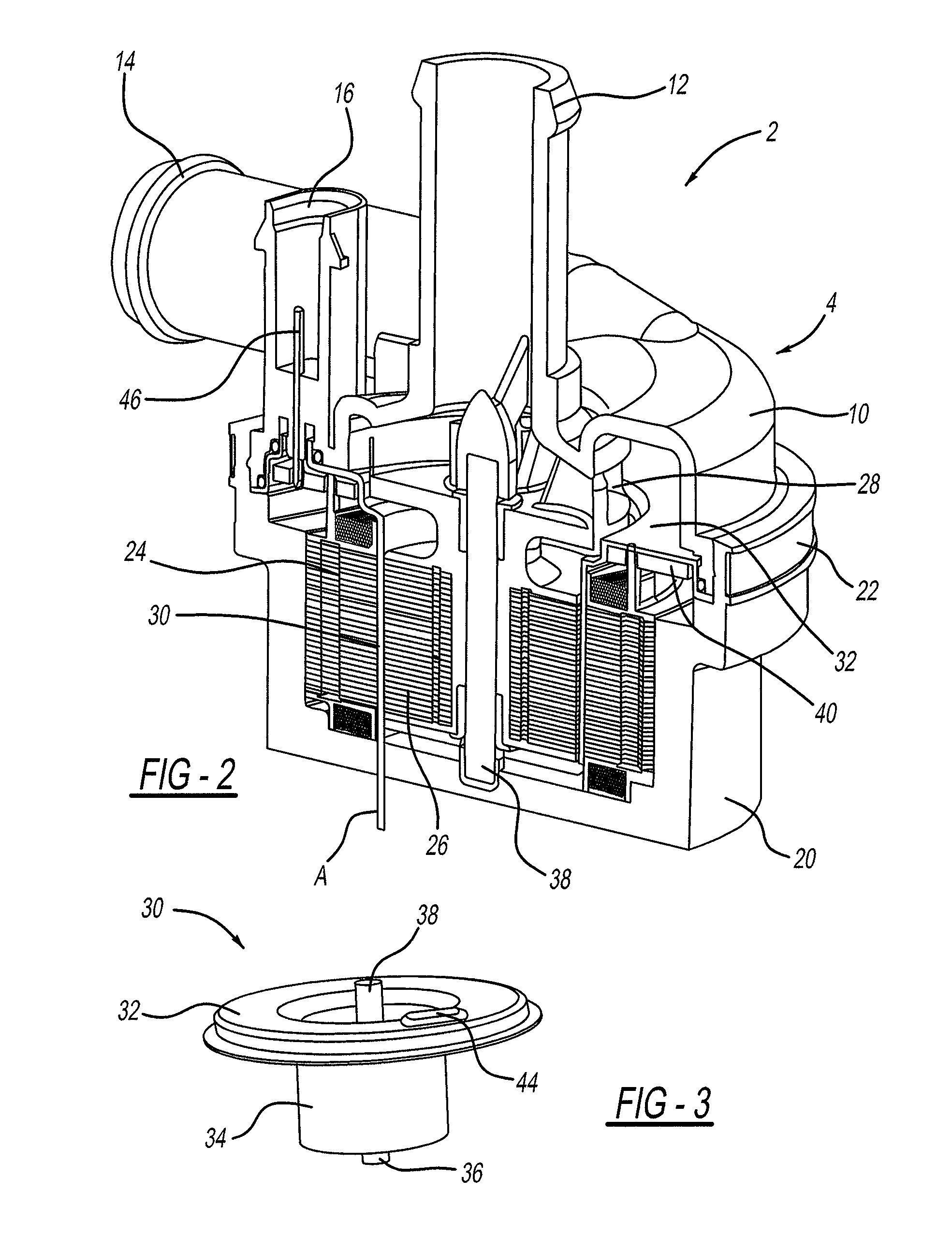

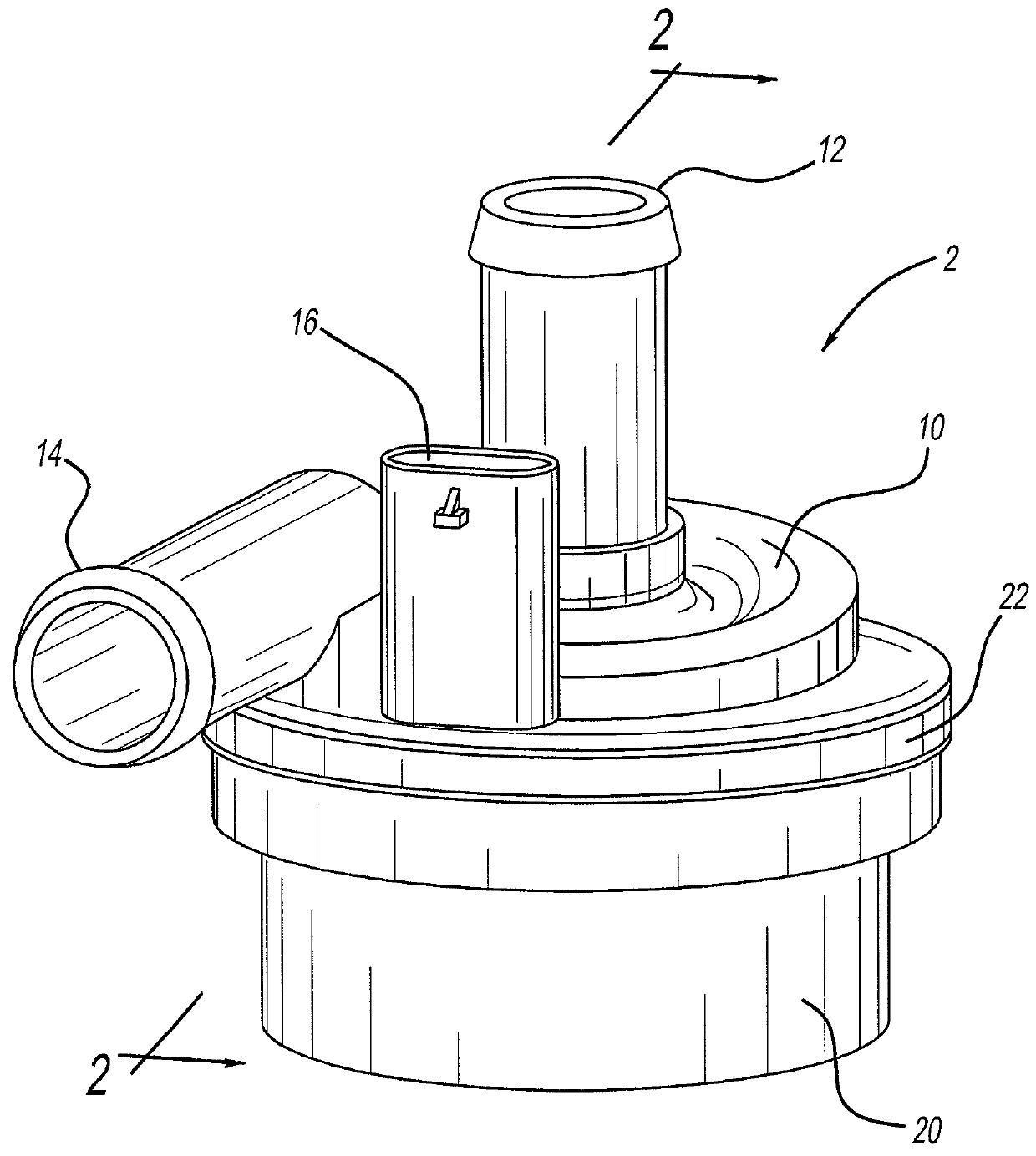

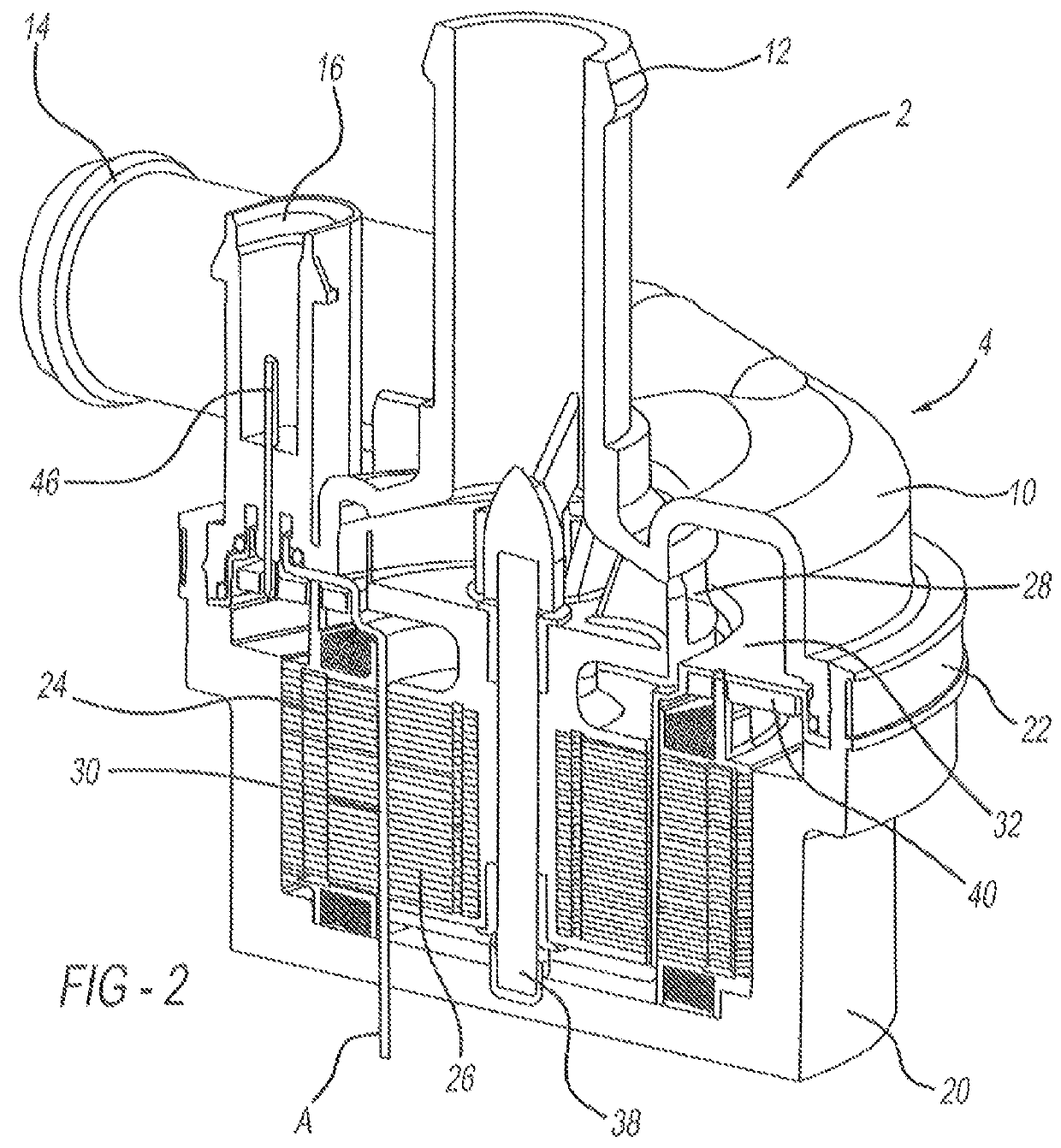

Submerged rotor electric water pump with structural wetsleeve

ActiveUS9360015B2Reduced volume and massLess componentsPump componentsPump installationsEngineeringMechanical engineering

An electric water pump, and more specifically an electric water pump having an improved wet sleeve so that the water pump is free of a housing. The electric water includes a pump rotor having a shaft. A wetsleeve surrounds the rotor and has a cap, a sleeve that houses the rotor, and a seat in communication with the shaft of the rotor so that the seat assists in supporting the shaft a stator. Surrounding the wet sleeve and the rotor is a volute covering an upper portion of the rotor, wet sleeve, and stator. The electric water pump further includes a rubber boot covering a lower portion of the rotor, wet sleeve, and stator and is in communication with the volute forming a cover.

Owner:HANON SYST EFP CANADA LTD

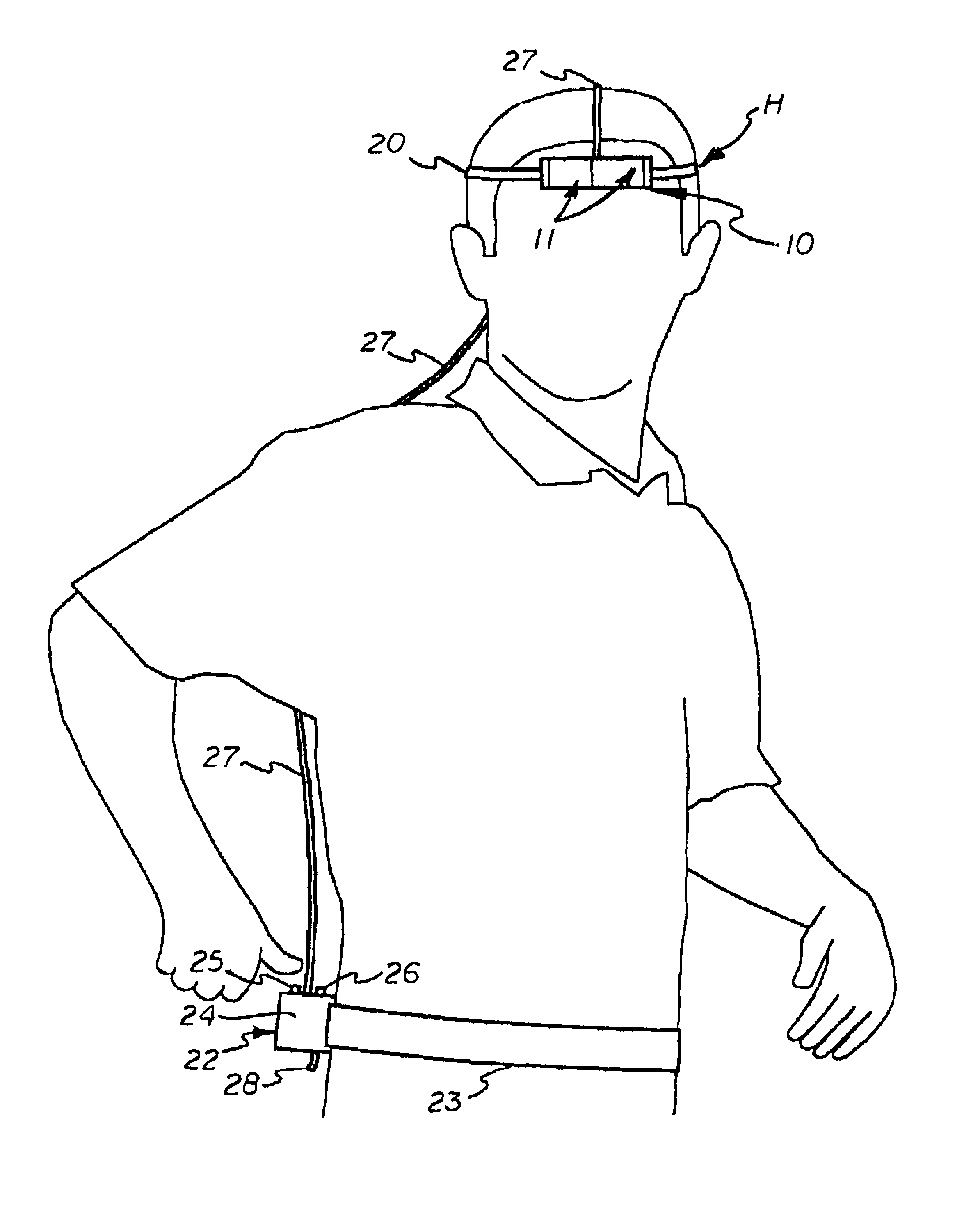

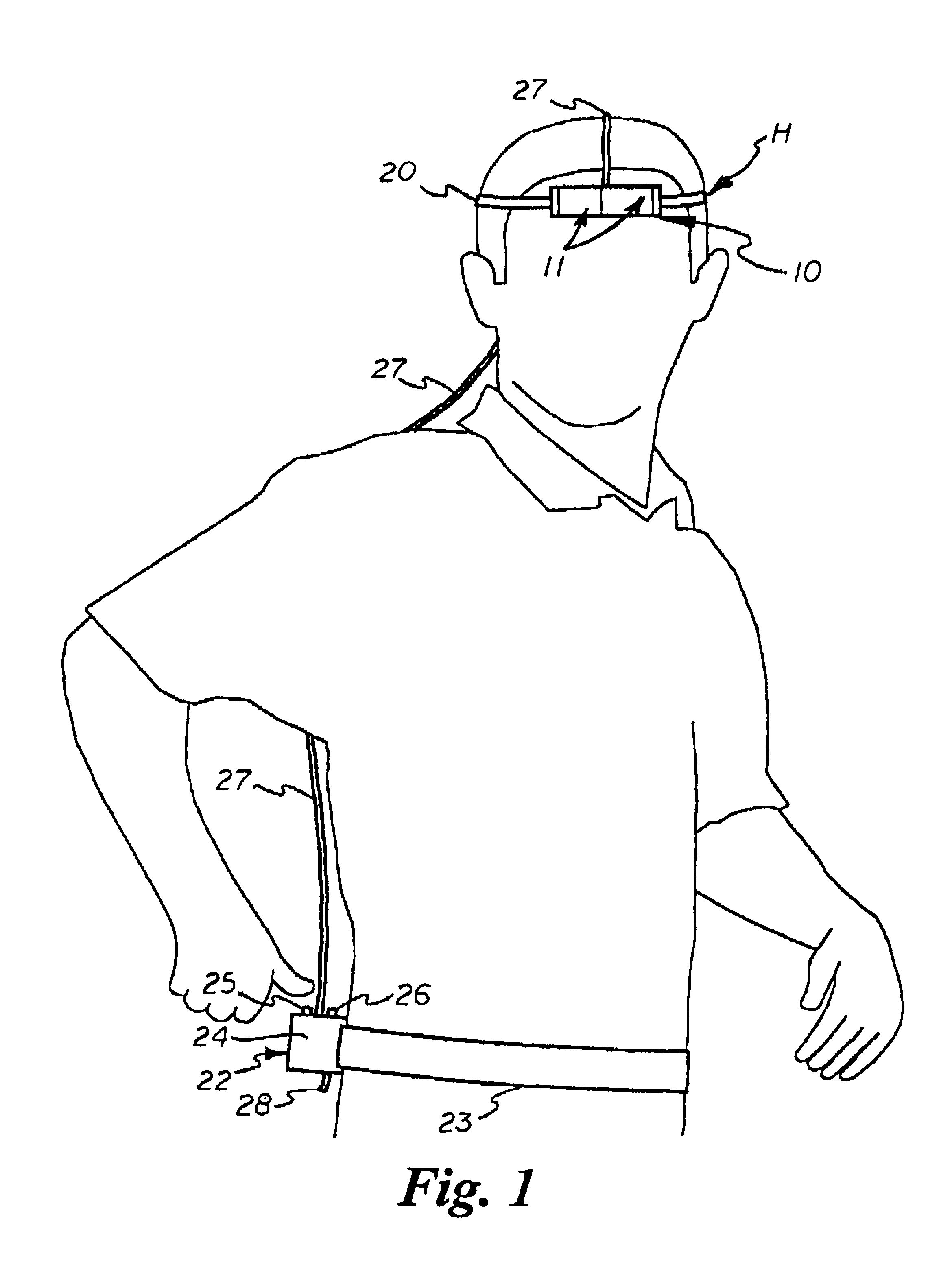

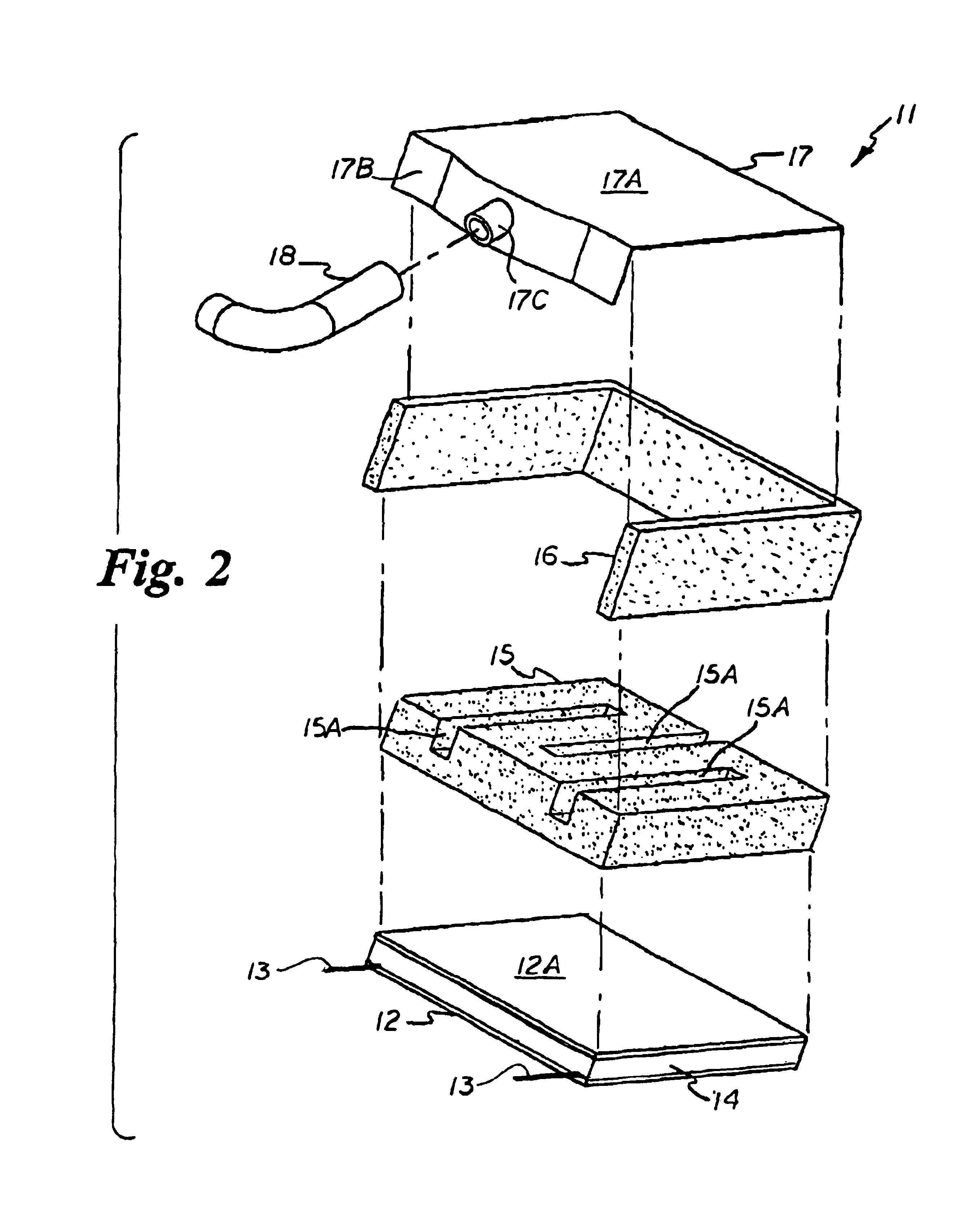

Solid state heat pump appliance with carbon foam heat sink

InactiveUS6948322B1Less power to operateImprove heat transfer efficiencyThermoelectric device with peltier/seeback effectDomestic cooling apparatusAir filterPorous carbon

A thermionic heating and cooling device for heating or cooling a portion of a user's body utilizes thermal diodes having a first surface in thermal contact with a flexible thermal transfer band strapped to a portion of the user's body and a second surface spaced apart therefrom with a thermally conductive porous carbon foam heat sink secured to their second surface which is partially enclosed by a shroud and a surrounding air filter. A small enclosure worn by the user contains an air pump, a battery and a switch. A flexible conduit connects the air pump and shroud and draws ambient air through the porous carbon foam medium. The thermal diodes are connected to the battery by leads extending through the conduit. A voltage bias between the diode surfaces creates a cold surface and hot surface opposite each other and causes electrons to flow in one direction and transfer heat from the first surface to the second and into the heat exchanger, and the heat is prevented from returning to the first surface.

Owner:GIBLIN PERCY

Voltage converter for implantable microstimulator using RF-powering coil

InactiveUS6856838B2Wide rangeThe process is compact and efficientElectrotherapyConvertersHemt circuits

A combination, voltage converter circuit for use within an implantable device, such as a microstimulator, uses a coil, instead of capacitors, to provide a voltage step up and step down conversion functions. The output voltage is controlled, or adjusted, through duty-cycle modulation. In accordance with one aspect of the invention, applicable to implantable devices having an existing RF coil through which primary or charging power is provided, the existing RF coil is used in a time-multiplexing scheme to provide both the receipt of the RF signal and the voltage conversion function. This minimizes the number of components needed within the device, and thus allows the device to be packaged in a smaller housing or frees up additional space within an existing housing for other circuit components. In accordance with another aspect of the invention, the voltage up / down converter circuit is controlled by a pulse width modulation (PWM) low power control circuit. Such operation allows high efficiencies over a wide range of output voltages and current loads.

Owner:BOSTON SCI NEUROMODULATION CORP

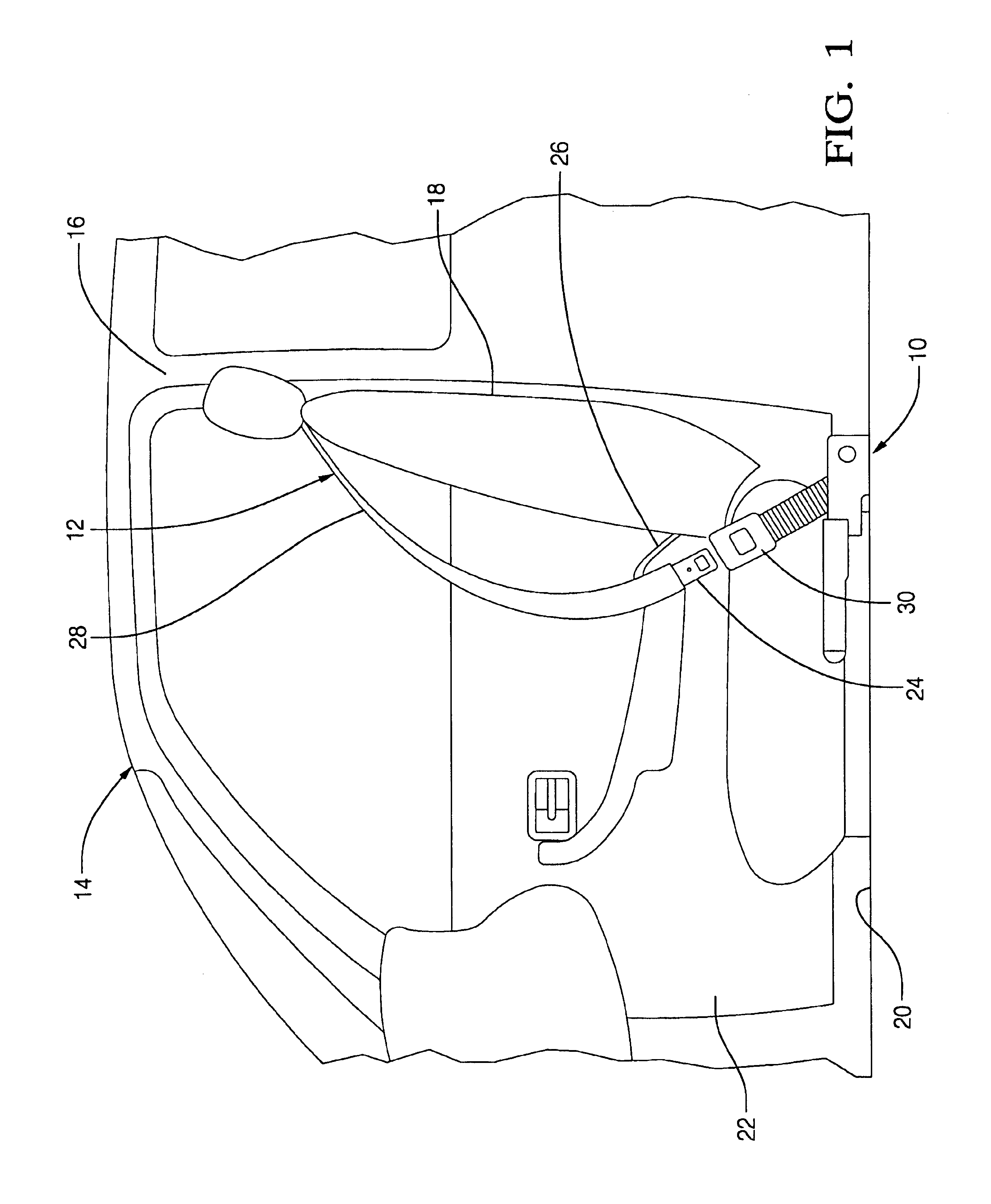

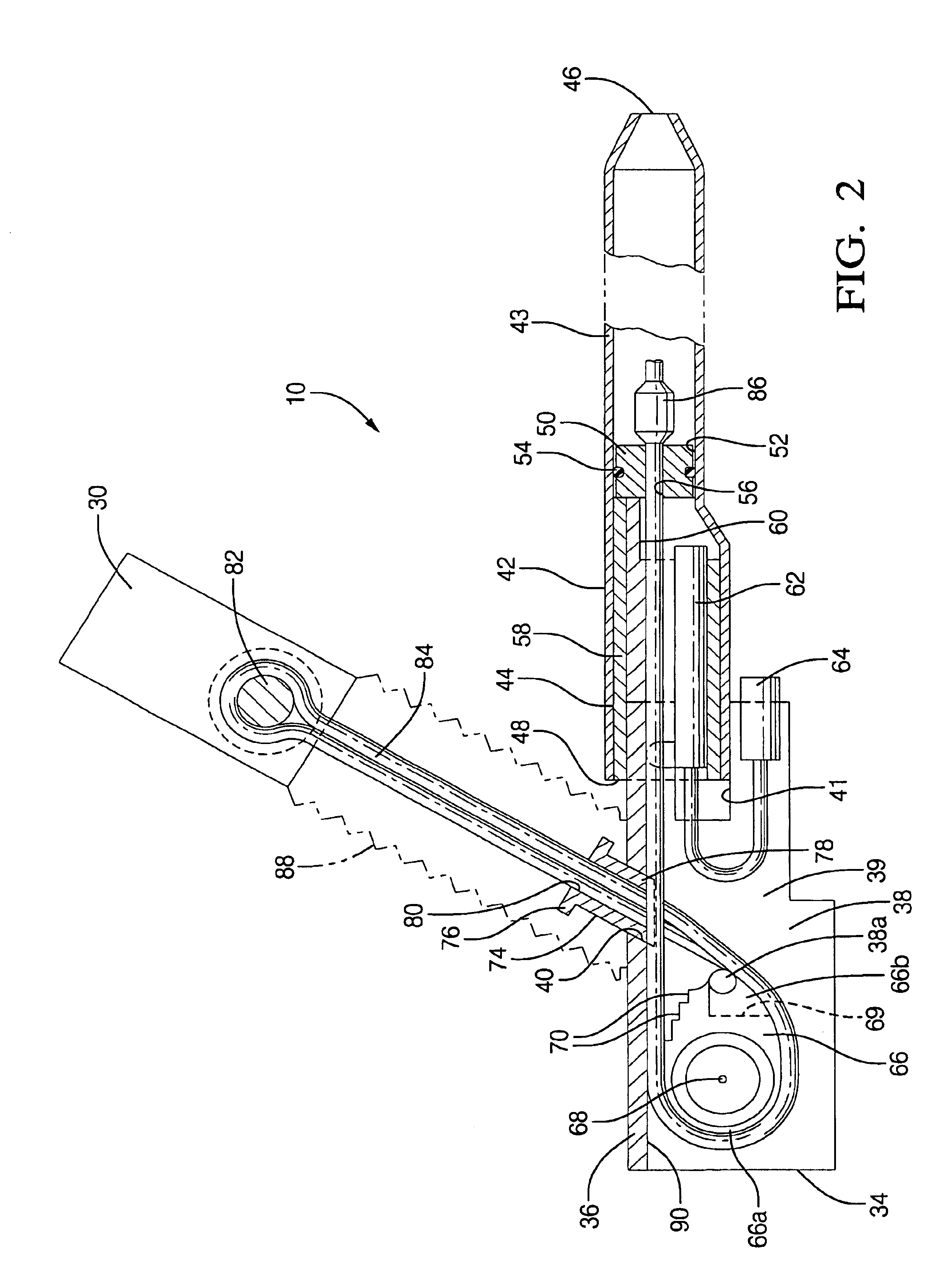

Seat restraint tensioner

A seat restraint tensioner for a seat restraint system in a vehicle includes a cable having a first end and a second end. The first end is operatively connected to a seat restraint of the seat restraint system. The seat restraint tensioner also includes a movable mechanism connected to the second end of the cable to apply a force for tightening the seat restraint when activated. The seat restraint tensioner further includes a rotatable cam cooperating with the cable to generate a clamping force toward the seat restraint to clamp the cable between the cam and a clamping surface to prevent reverse travel of the cable after tightening the seat restraint.

Owner:AUTOLIV DEV AB

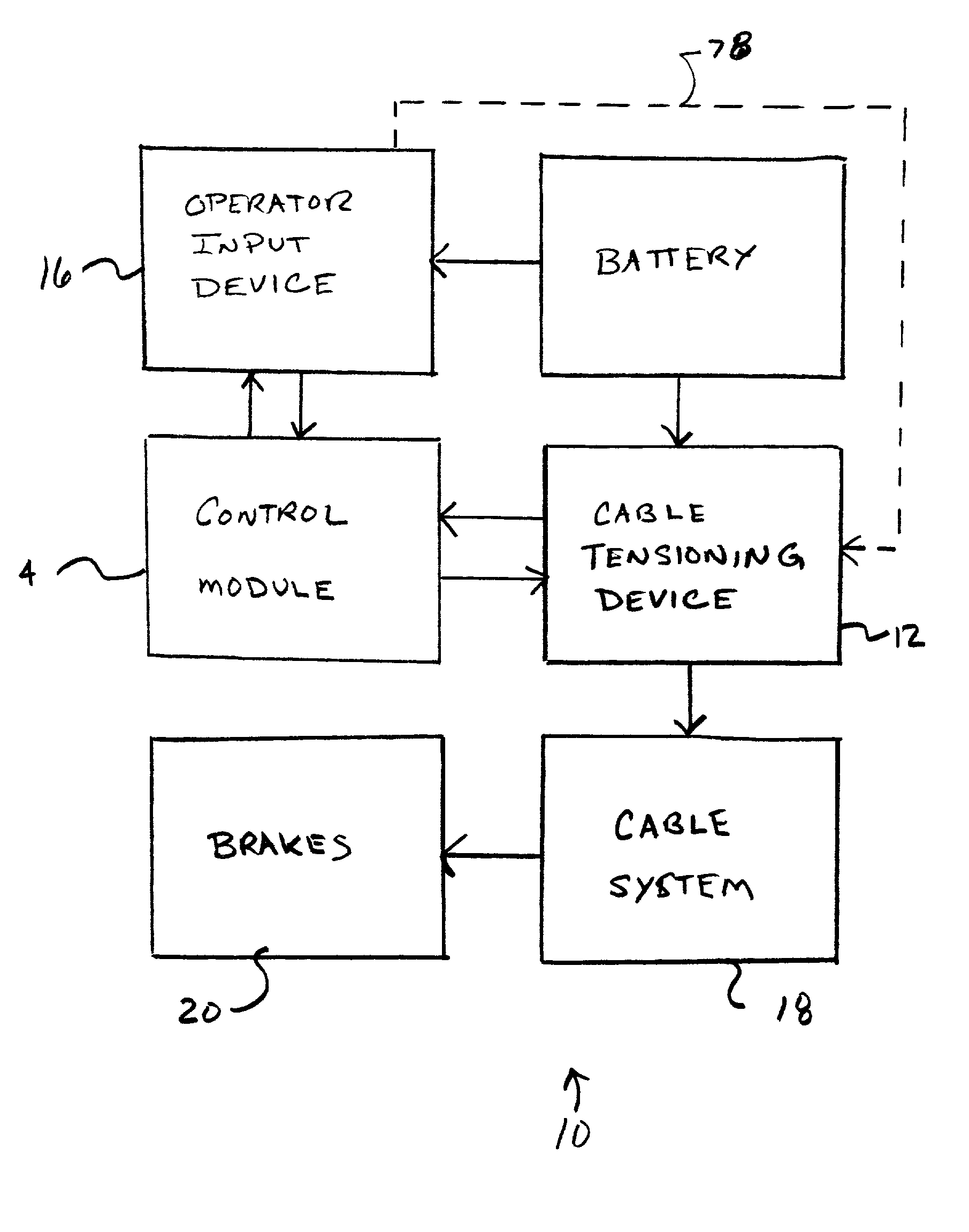

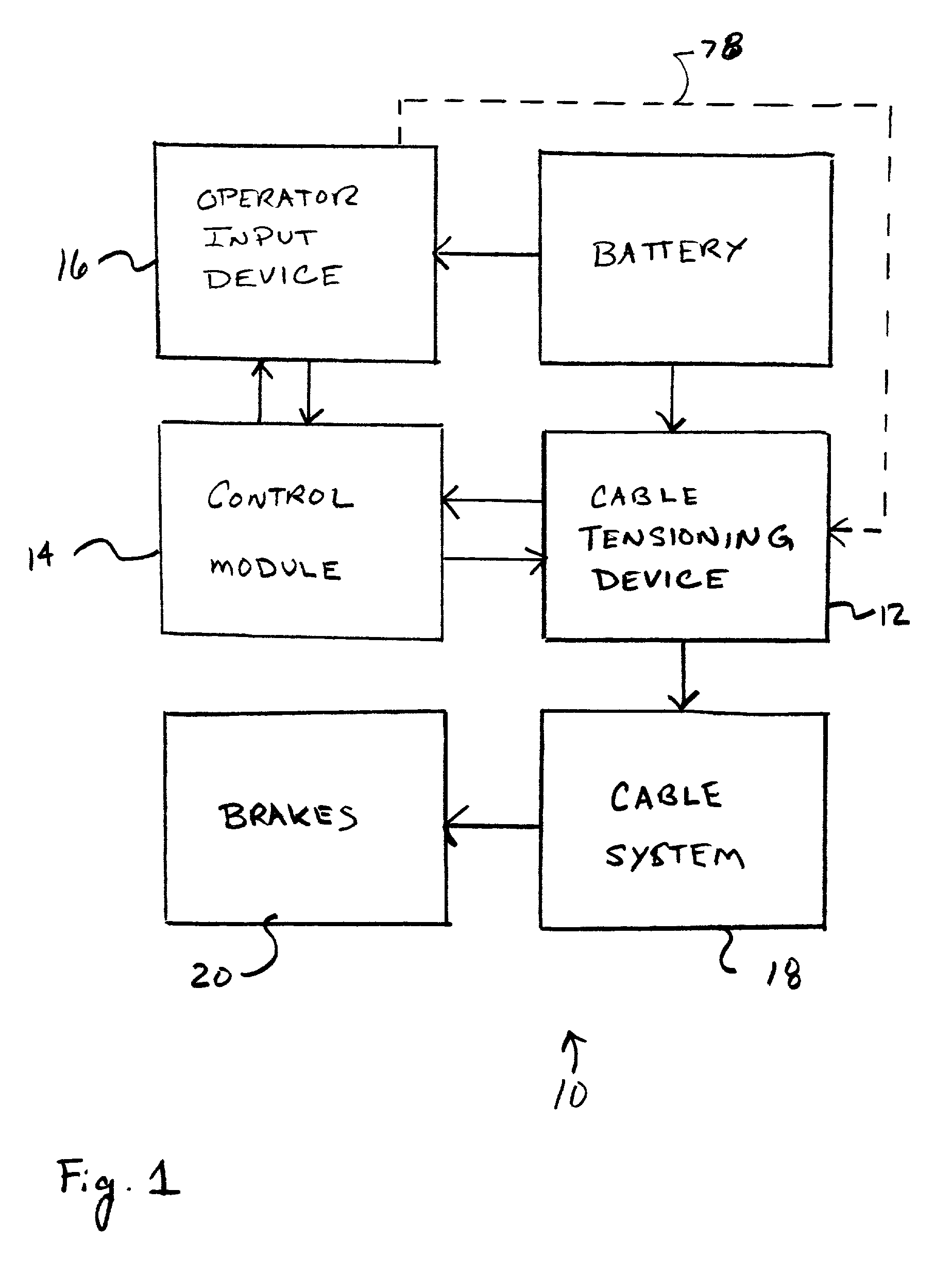

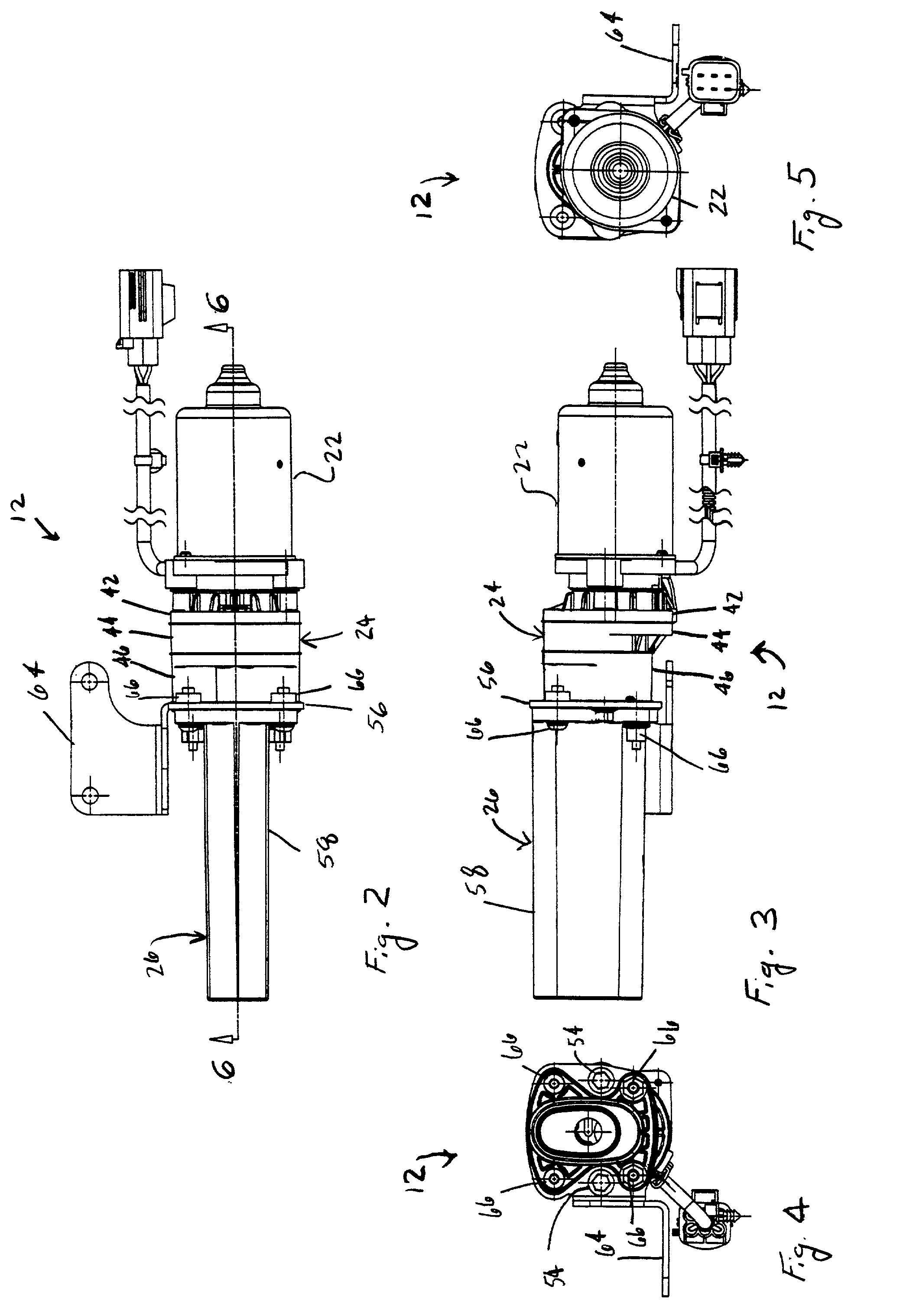

Electric parking brake

InactiveUS20020066626A1Quality improvementLight weightBraking action transmissionMechanically actuated brakesLinear motionElectric parking brake

An electric parking brake assembly includes an electric motor having an output shaft, a control module coupled to the electric motor for controlling the electric motor and a transmission coupling a threaded lead screw to the output shaft of the electric motor. The transmission preferably includes a gear train having a plurality of helical gears and the lead screw and the output shaft are preferably coaxial. A stationary elongate guide shaft extends substantially parallel to and spaced apart from the lead screw. A drive nut has a lead screw bore threadably receiving the lead screw therein and a guide shaft bore slidingly receiving the elongate guide shaft therein. The drive nut also has a cable attachment for attaching a brake cable to the drive nut. The cable attachment has a central axis offset from a central axis of the lead screw and is preferably located midway between the lead screw bore and the guide shaft bore. The control module controls the electric motor such that rotation of the output shaft causes motion of the transmission and rotation of the lead screw, rotation of the lead screw causes linear motion of the drive nut along the lead screw and the guide shaft, and linear motion of the drive nut causes tensioning and untensioning of the brake cable. The assembly preferably includes a manual override device operatively connected to the lead screw. The manual override device selectively causes manual rotation of the lead screw, rotation of the lead screw causes linear motion of the drive nut, and linear motion of the drive nut causes tensioning and untensioning of the brake cable.

Owner:DURA GLOBAL TECH

Implantable medical device with single coil for charging and communicating

InactiveUS8155752B2Minimizes numberSmall and more densely packedElectrotherapyEngineeringSingle coil

A combination charging and telemetry circuit for use within an implantable device, such as a microstimulator, uses a single coil for both charging and telemetry. In accordance with one aspect of the invention, one or more capacitors are used to tune the single coil to different frequencies, wherein the coil is used for multiple purposes, e.g., for receiving power from an external source and also for the telemetry of information to and from an external source.

Owner:BOSTON SCI NEUROMODULATION CORP

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com