Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

40results about How to "Reduced risk of splintering" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

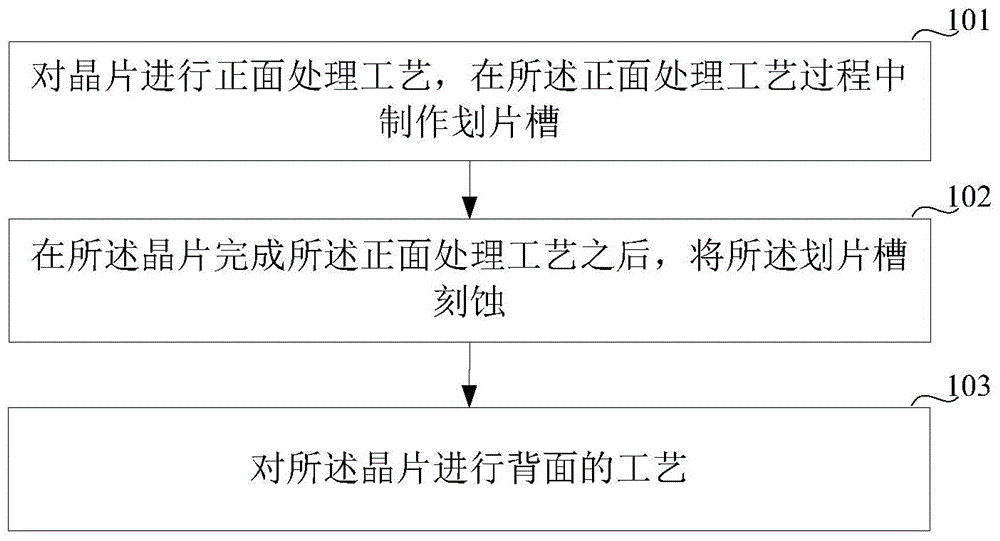

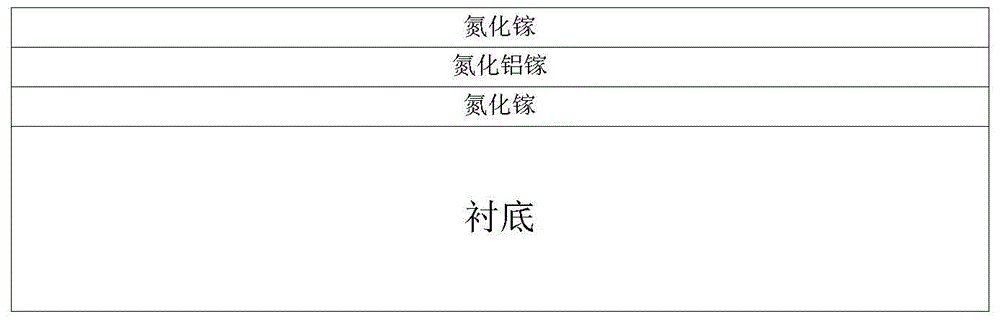

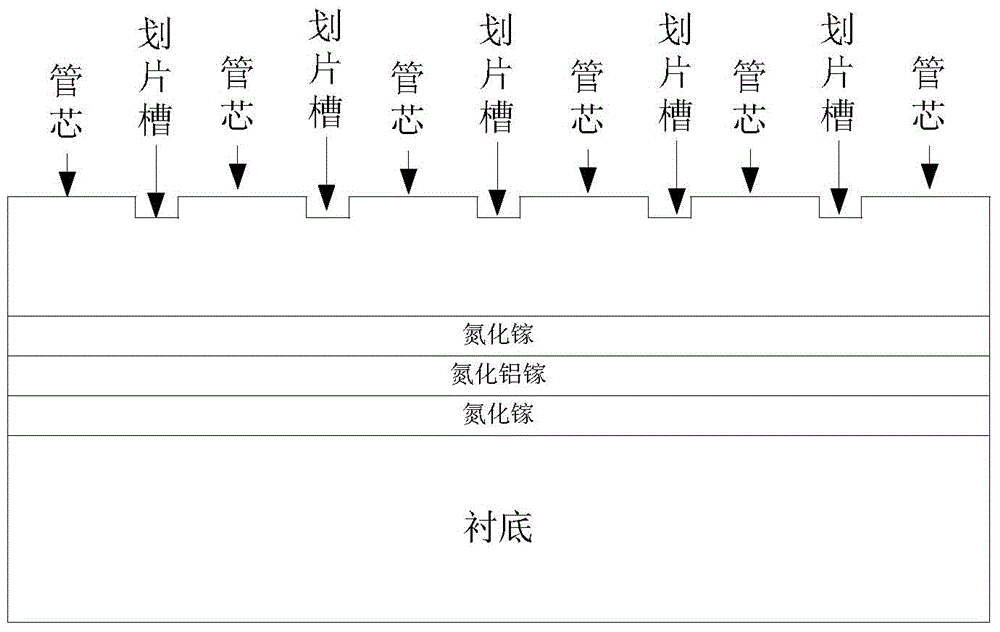

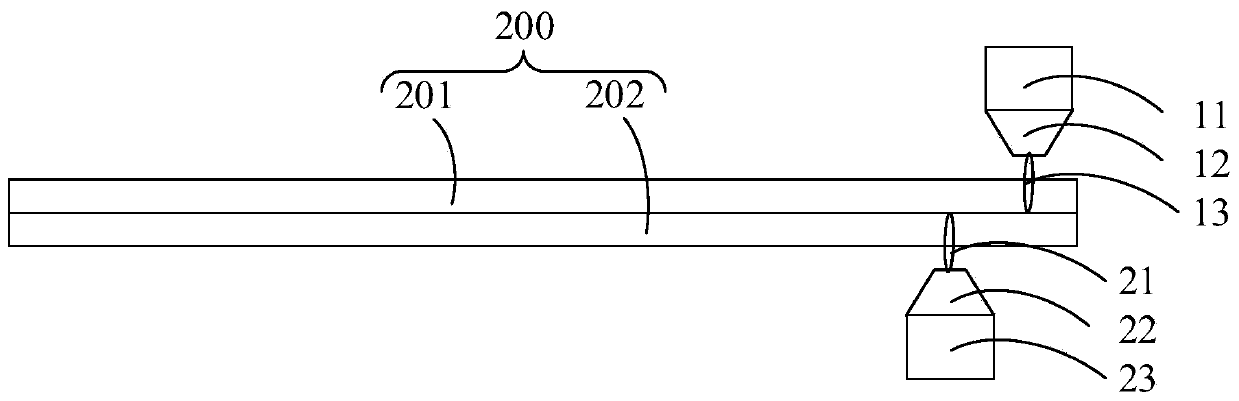

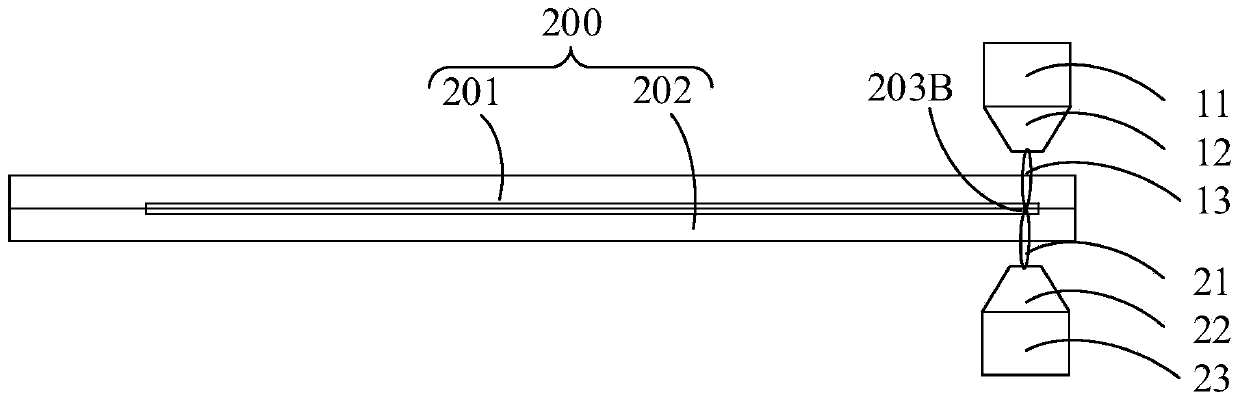

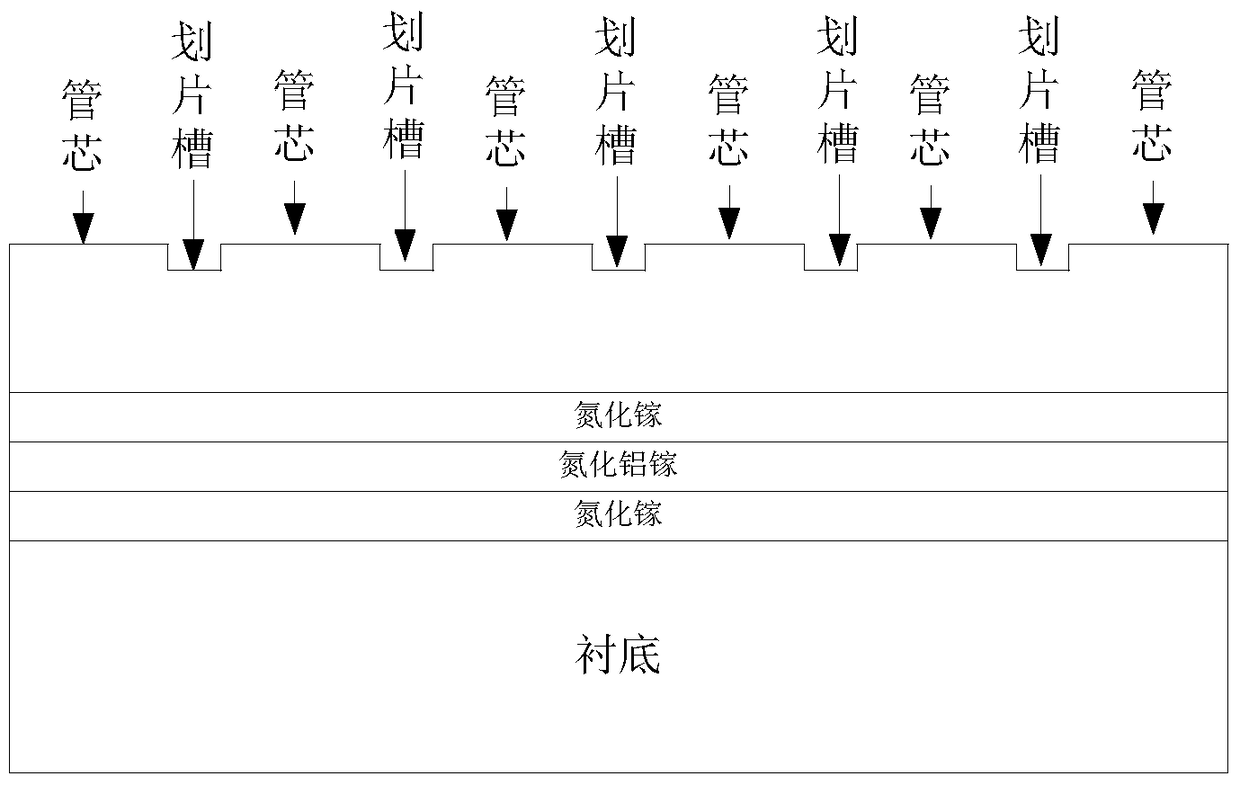

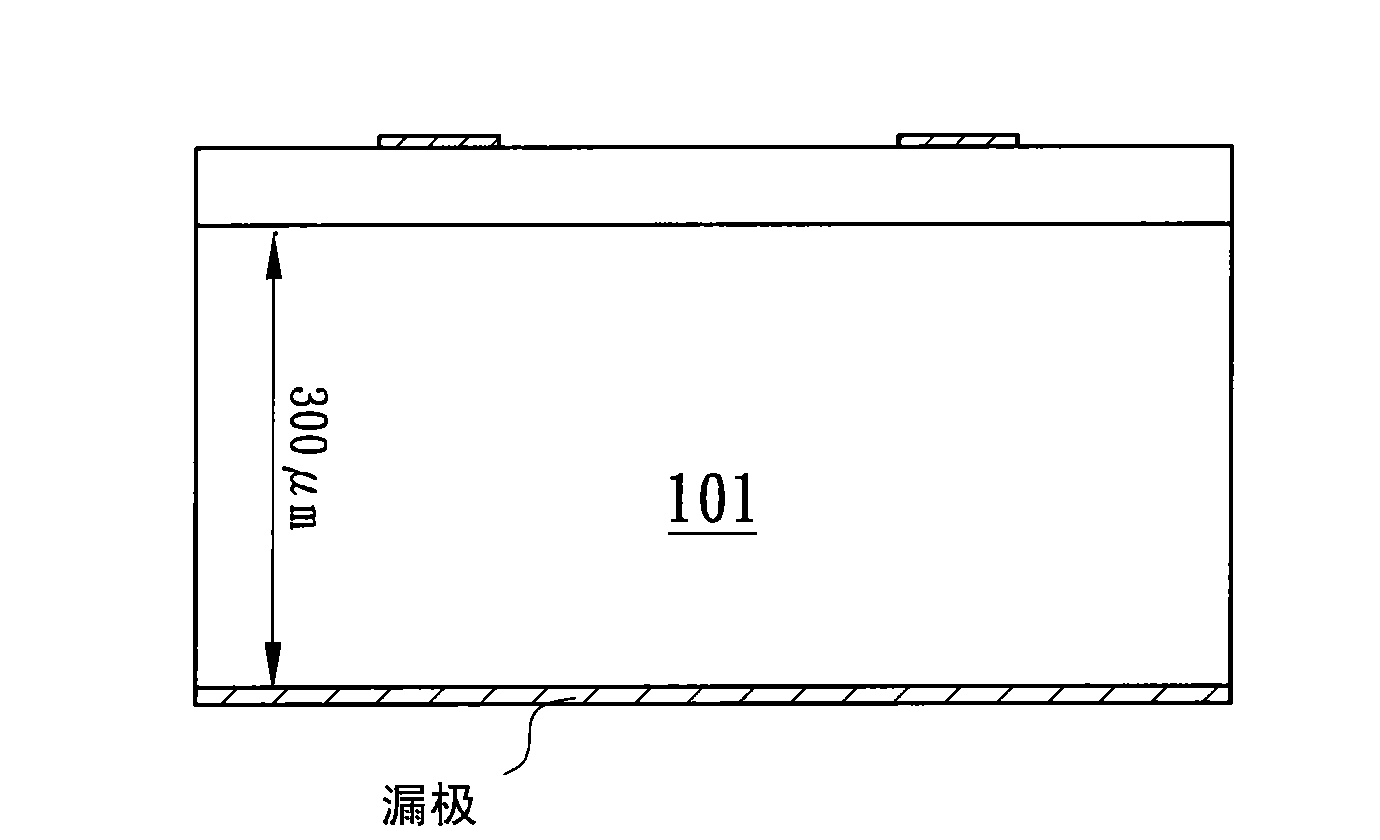

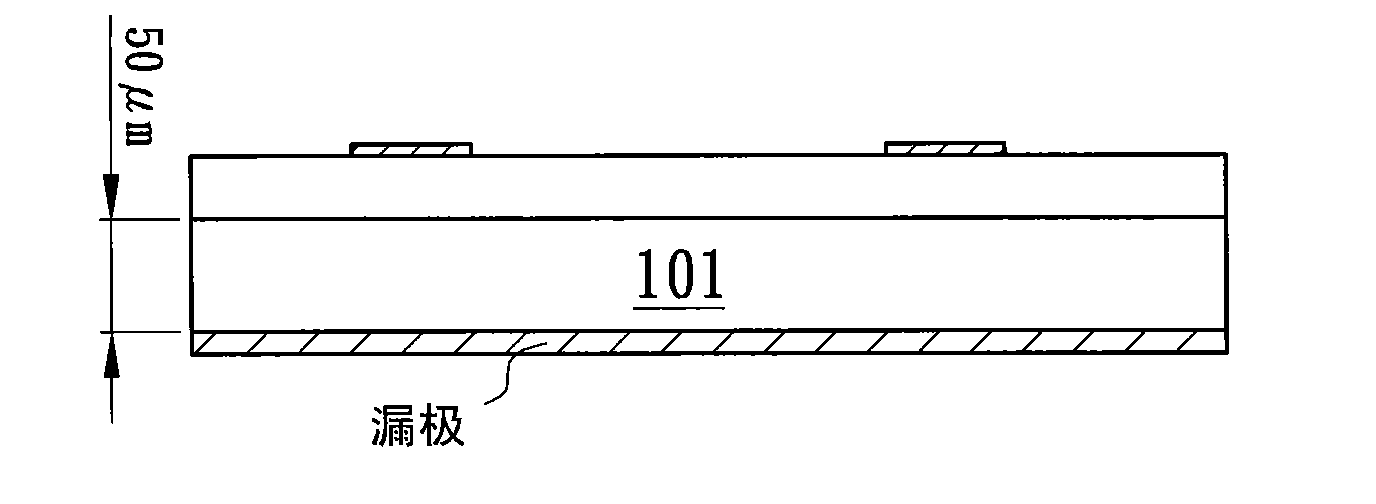

Wafer tapeout method

ActiveCN105448648AReduced risk of splinteringSemiconductor/solid-state device manufacturingEngineeringSemiconductor technology

An embodiment of the invention relates to the technical field of a semiconductor and especially relates to a wafer tapeout method so as to improve stress status of a wafer. The method comprises the following steps: carrying out front-side treatment process on the wafer to prepare scribing grooves in the front-side treatment process; after the front-side treatment process of the wafer, etching the scribing grooves; and carrying out back-side process on the wafer. The scribing grooves are etched after the front-side treatment process, so that the stress inside the wafer can be released, and the risk of wafer fragmenting and breaking in the follow-up process, such as back thinning, is reduced greatly.

Owner:FOUNDER MICROELECTRONICS INT

Elastic buffering decorating plate

Owner:ZHEJIANG CHANGXING BOTA BUILDING MATERIALS CO LTD

Lamination technology of film photovoltaic assembly

ActiveCN104900756AReduce the probability of air bubblesReduced risk of splinteringFinal product manufactureLaminationVacuum pumpingAtmospheric pressure

The invention relates to a lamination technology of a film photovoltaic assembly. The lamination technology comprises the flows of 1) preparing a battery chip; 2) leading a transmission structure; 3) laying a connection film layer; 4) laying a backboard package; 5) laminating a battery assembly; and 6) completing the battery assembly. In the flow 5), the lamination temperature is controlled between 160 and 165 DEG C, the lamination time is kept within 6-8 min, the vacuum-pumping time is controlled within 3 to 5 min, the laminating vacuum degree is kept between 0 and 50 Pa, and the laminating pressure is controlled between 0.4 and 0.6 that of the atmospheric pressure. The qualified rate and production efficiency of products are effectively improved, and the film photovoltaic assembly of higher reliability, longer service life and high stability and consistency can be obtained in the lamination process via optimization.

Owner:HANERGY MOBILE ENERGY HLDG GRP CO LTD

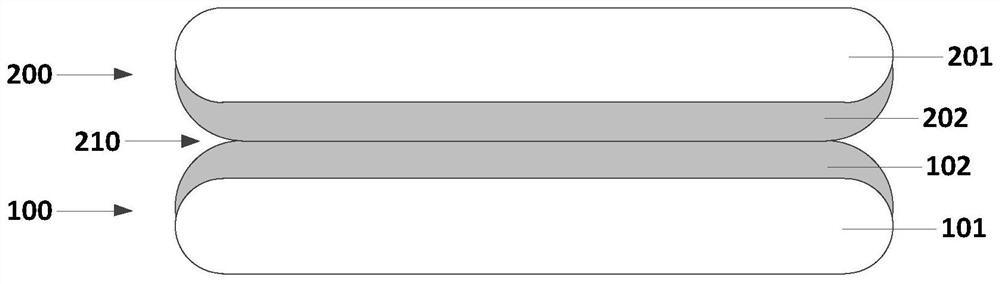

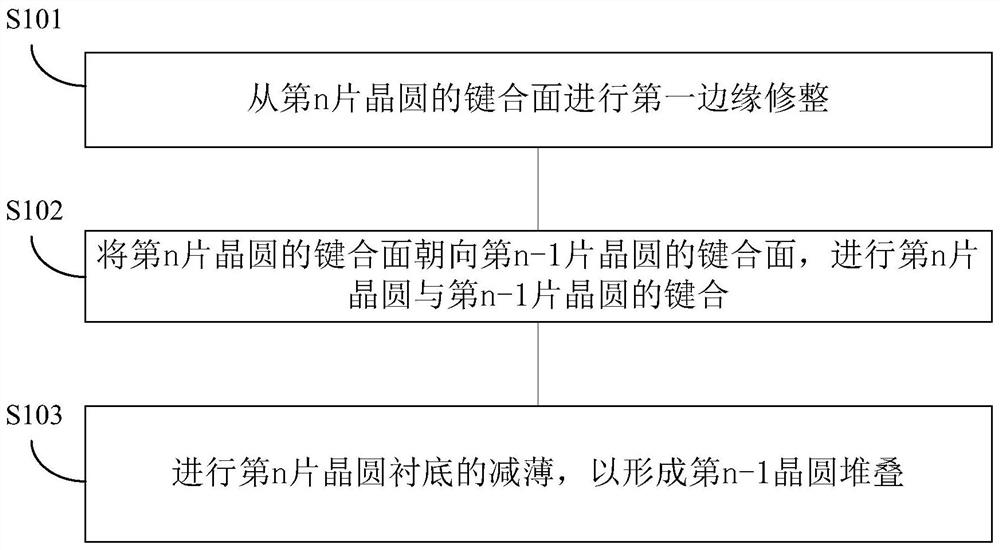

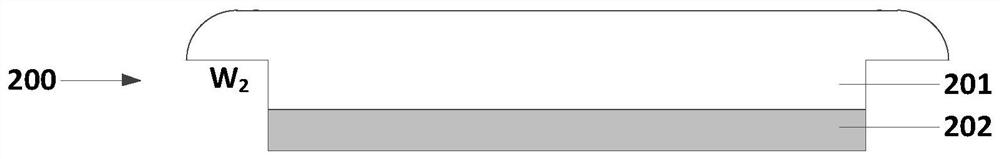

Bonding structure and manufacturing method thereof

ActiveCN110189985AHigh bonding strengthImprove reliabilitySemiconductor/solid-state device detailsSolid-state devicesWafer stackingEngineering

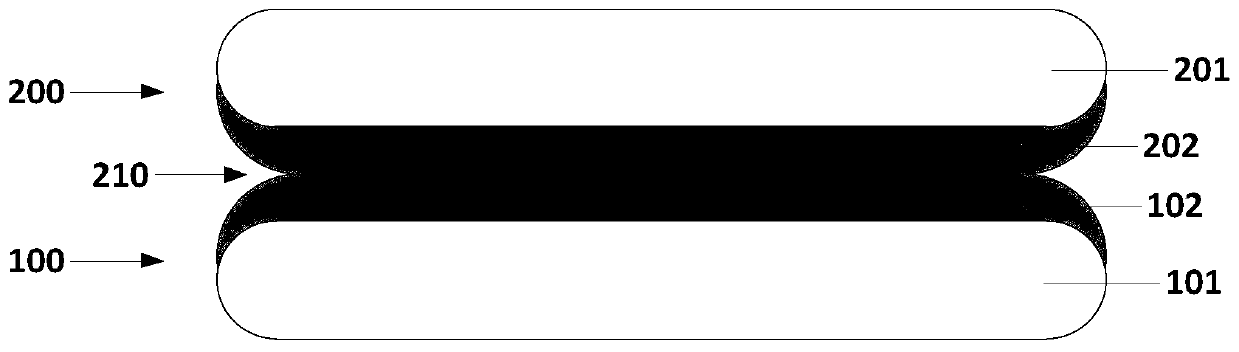

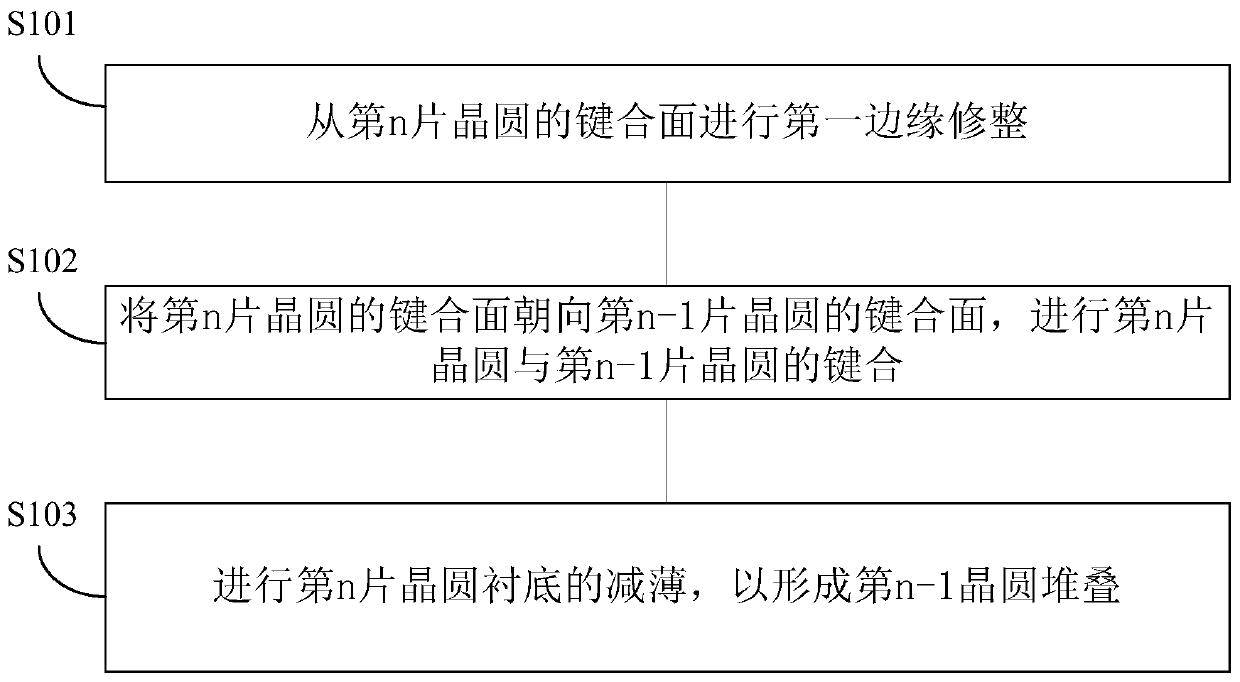

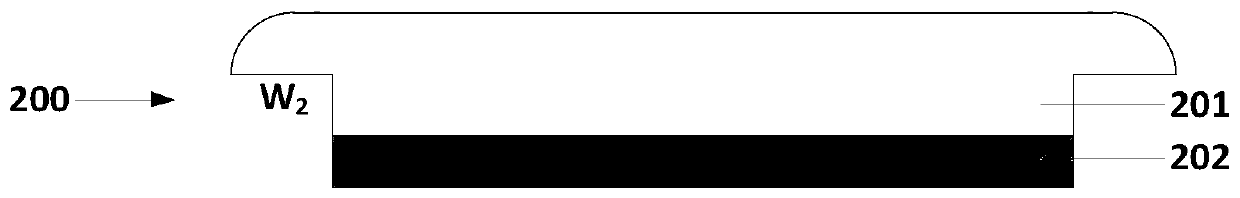

The invention provides a bonding structure and a manufacturing method thereof. When bonding of the nth wafer and the (n-1)th wafer is performed, the first edge trimming can be performed from the bonding surface of the nth wafer, the width of the first edge trimming is Wn, and the width of the first edge trimming can be gradually increased along with the increase of the n, this is because that thewafer edge is not flat enough to form a gap between the wafers during bonding. After the edge of the wafer is trimmed, the uneven part at the edge of the nth wafer can be removed, the bonding surfaceof the nth wafer faces the bonding surface of the (n-1)th wafer to perform bonding of the nth wafer and the (n-1)th wafer to reduce the possibility of a gap formed between the bonding surfaces of thewafers, improve the bonding strength between the adjacent wafers, the nth wafer substrate is thinned to form the (n-1)th wafer stack, due to the fact that the bonding strength between the adjacent wafers is large, the formed wafer stack is high in reliability, and the risk of cracking is low.

Owner:WUHAN XINXIN SEMICON MFG CO LTD

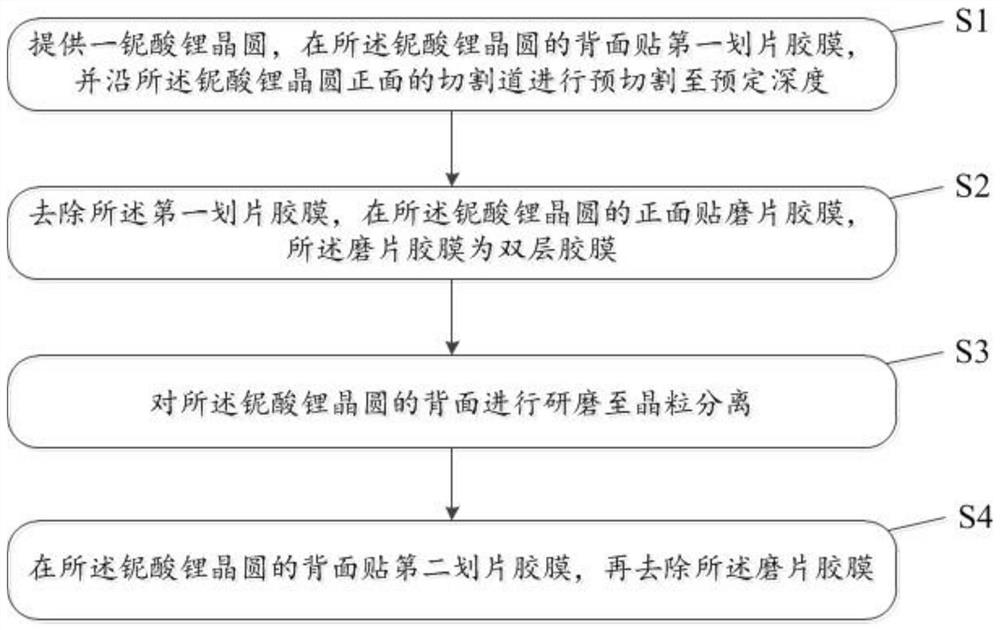

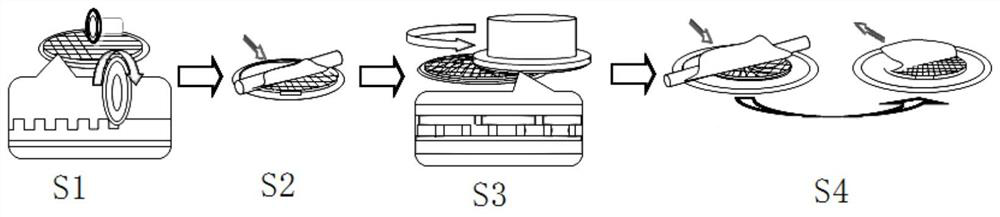

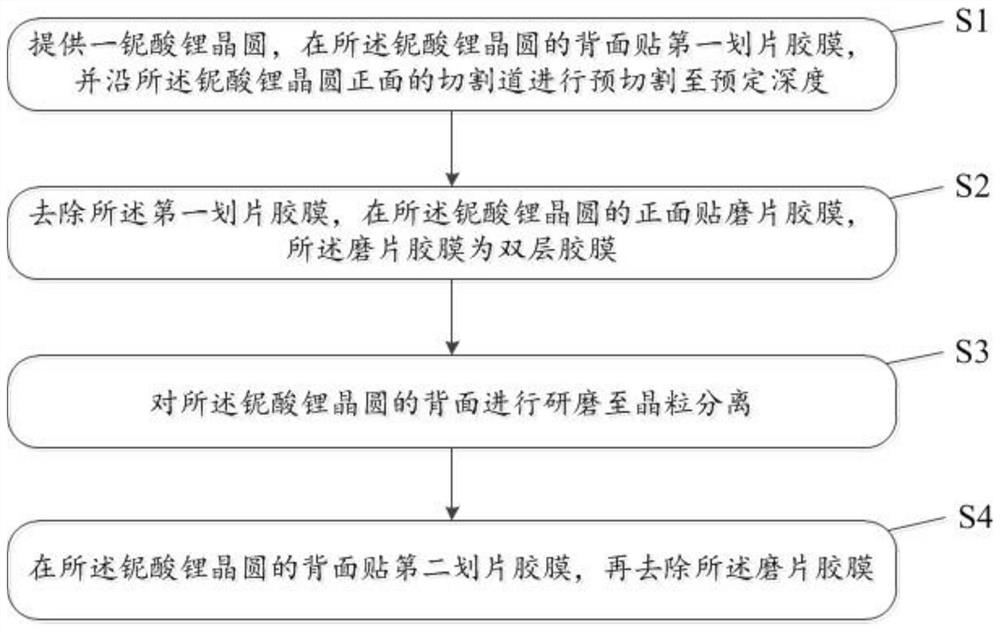

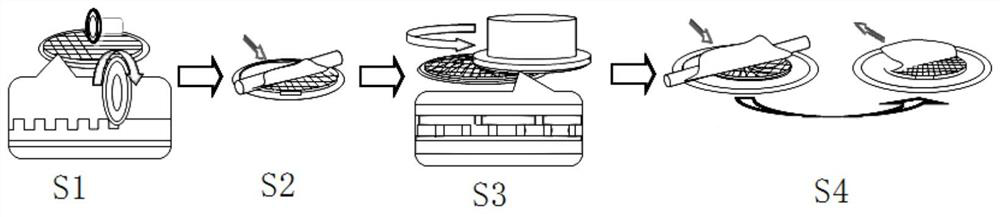

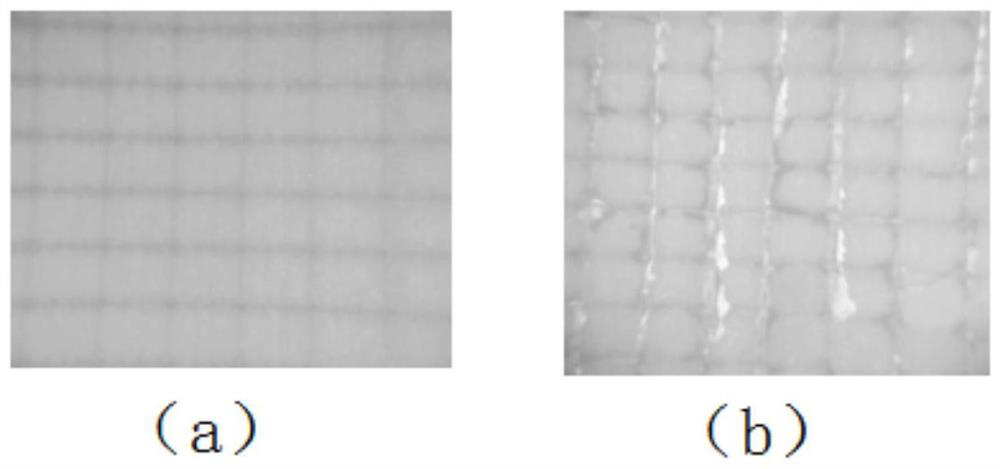

Thinning method of lithium niobate wafer

ActiveCN111900078AImprove qualityImprove reliabilitySolid-state devicesSemiconductor/solid-state device manufacturingBi layerWafer

The invention discloses a thinning method of a lithium niobate wafer, and belongs to the technical field of chip packaging. The thinning method of the lithium niobate wafer comprises the following steps: providing the lithium niobate wafer, pasting a first scribing adhesive film on the back surface of the lithium niobate wafer, and pre-cutting to a predetermined depth along a cutting channel on the front surface of the lithium niobate wafer; removing the first scribing adhesive film, and pasting an abrasive disc adhesive film on the front surface of the lithium niobate wafer, the abrasive discadhesive film being a double-layer adhesive film; grinding the back surface of the lithium niobate wafer until crystal grains are separated; and pasting a second scribing adhesive film on the back surface of the lithium niobate wafer, and then removing the grinding adhesive film. According to the invention, the pre-grinding cutting process of the lithium niobate wafer is realized. The phenomena of brittle failure, deep sub-surface damage layer, large cracks on the front and back surfaces of the chip and the like in the abrasive cutting process of the lithium niobate wafer in the prior art areavoided, the cracks on the front and back surfaces of the chip can be controlled within 10 microns, and the quality of a lithium niobate chip packaging product is ensured.

Owner:NINGBO CHIPEX SEMICON

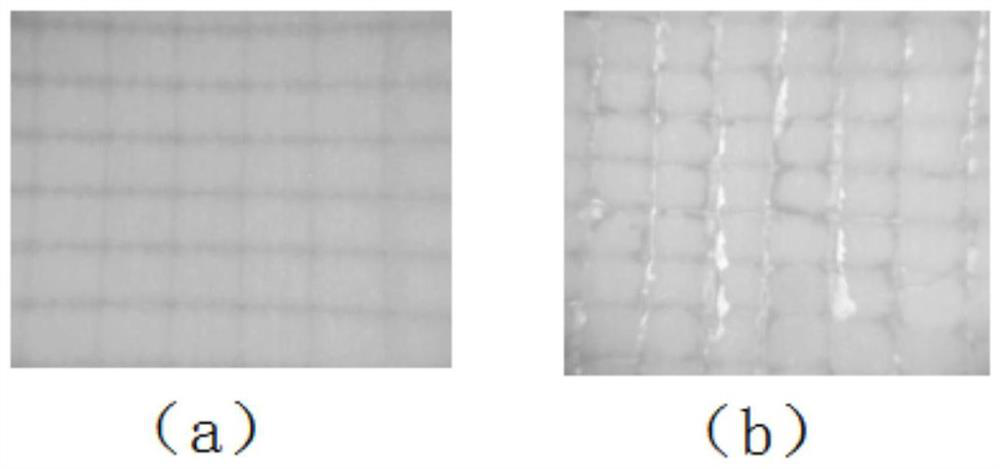

Cutting mechanism and method and display panel

ActiveCN109794984AAvoid breakingGuaranteed normal cuttingMetal working apparatusColor filmOutput device

The invention provides a cutting mechanism and method and a display panel. The cutting mechanism comprises a first output device and a second output device; the first output device drives a first cutting wheel to move along a first path to cut an array substrate of the display panel; the second output device drives a second cutting wheel to move along a second path to cut a color film substrate ofthe display panel; and in a first superposition section, the second path coincides with the first path to enable the first cutting wheel and the second cutting wheel to jointly cut sealing rubber onan edge between the array substrate and the color film substrate. The cutting mechanism and method and the display panel have the advantage that the display panel is prevented from breaking during piece split due to the fact that the sealing rubber is subjected to double-surface cutting or the sealing rubber is completely cut.

Owner:HKC CORP LTD

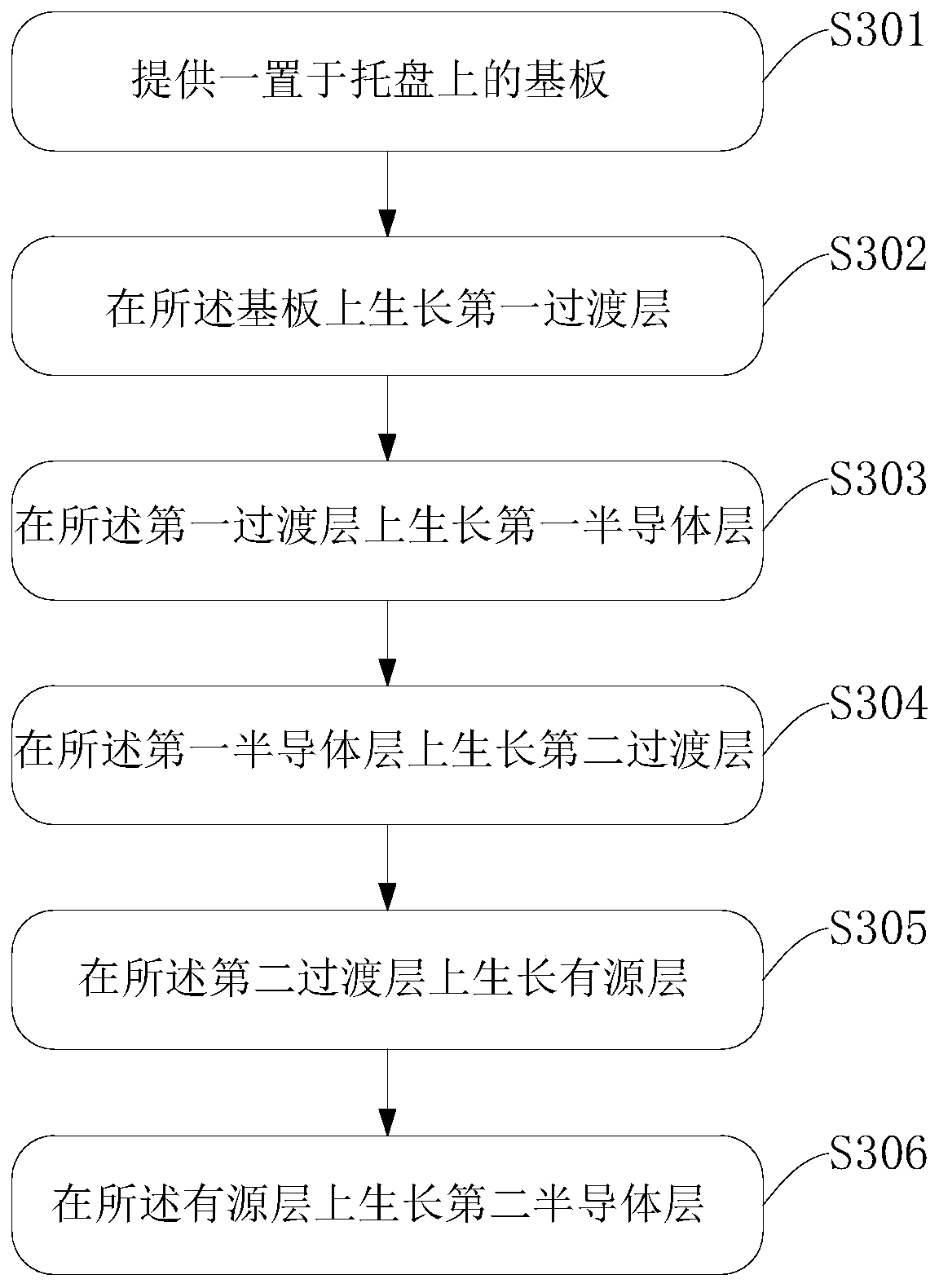

A kind of wafer tape-out method

ActiveCN105448648BReduced risk of splinteringSemiconductor/solid-state device manufacturingEngineeringFlow sheet

An embodiment of the invention relates to the technical field of a semiconductor and especially relates to a wafer tapeout method so as to improve stress status of a wafer. The method comprises the following steps: carrying out front-side treatment process on the wafer to prepare scribing grooves in the front-side treatment process; after the front-side treatment process of the wafer, etching the scribing grooves; and carrying out back-side process on the wafer. The scribing grooves are etched after the front-side treatment process, so that the stress inside the wafer can be released, and the risk of wafer fragmenting and breaking in the follow-up process, such as back thinning, is reduced greatly.

Owner:FOUNDER MICROELECTRONICS INT

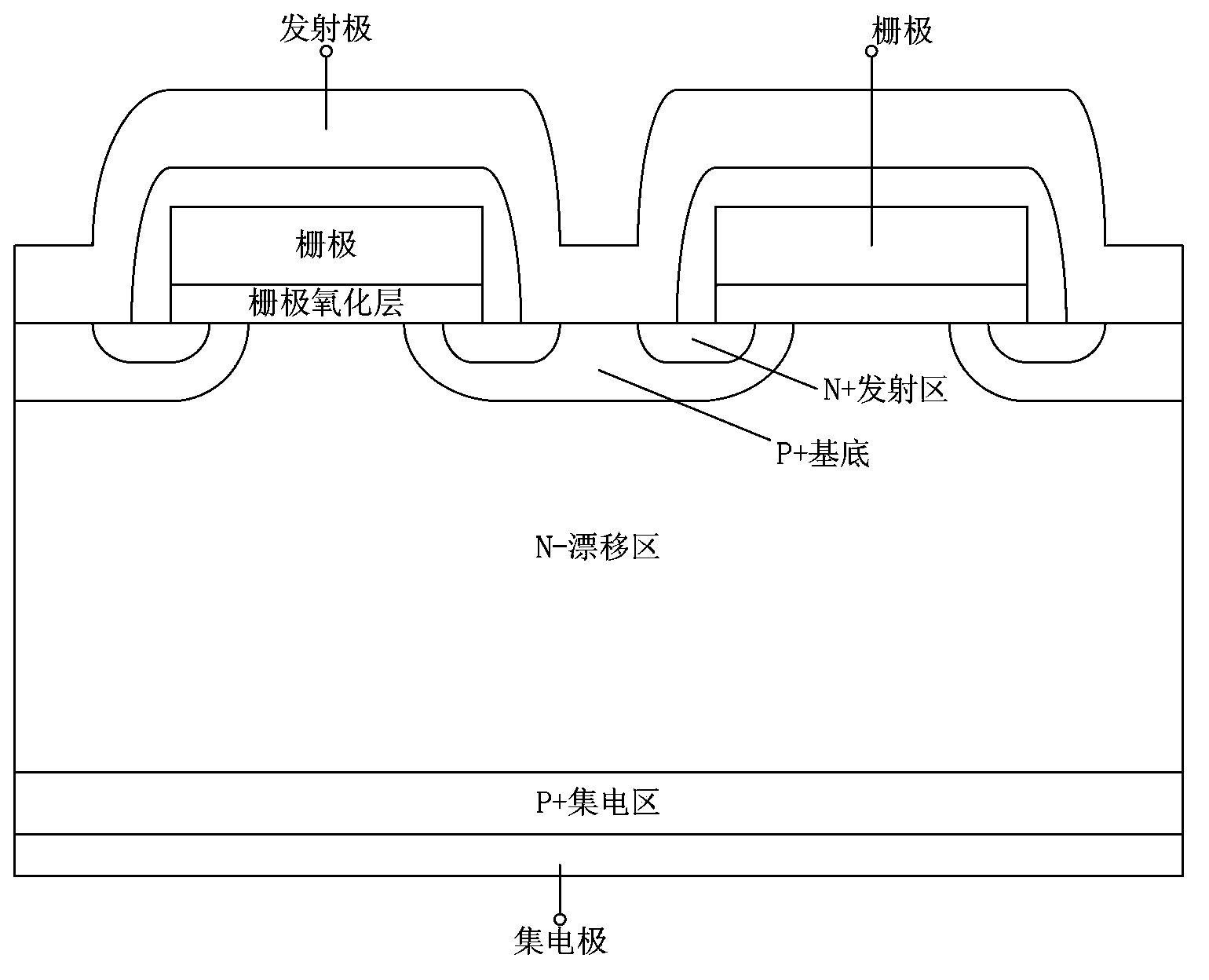

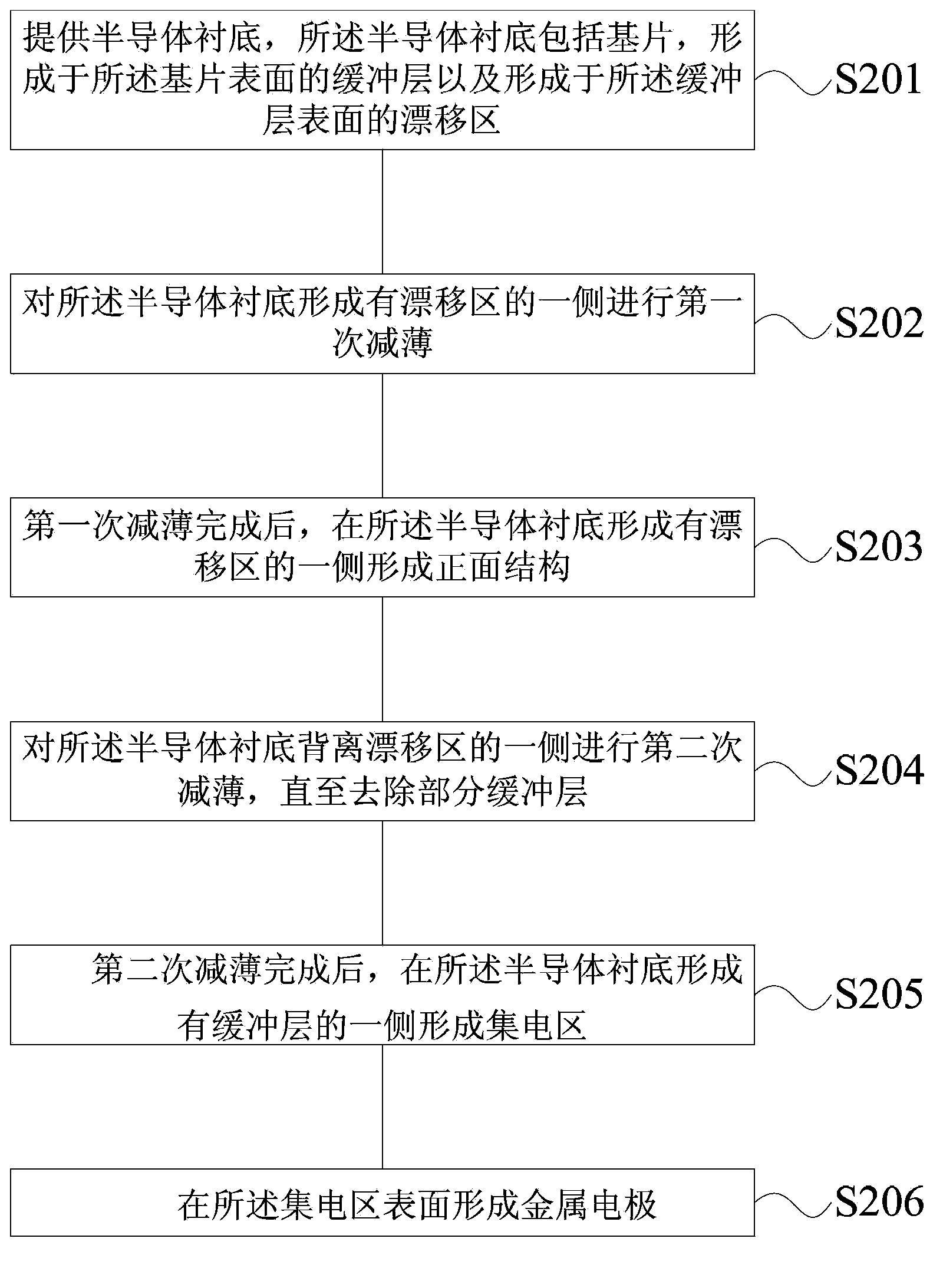

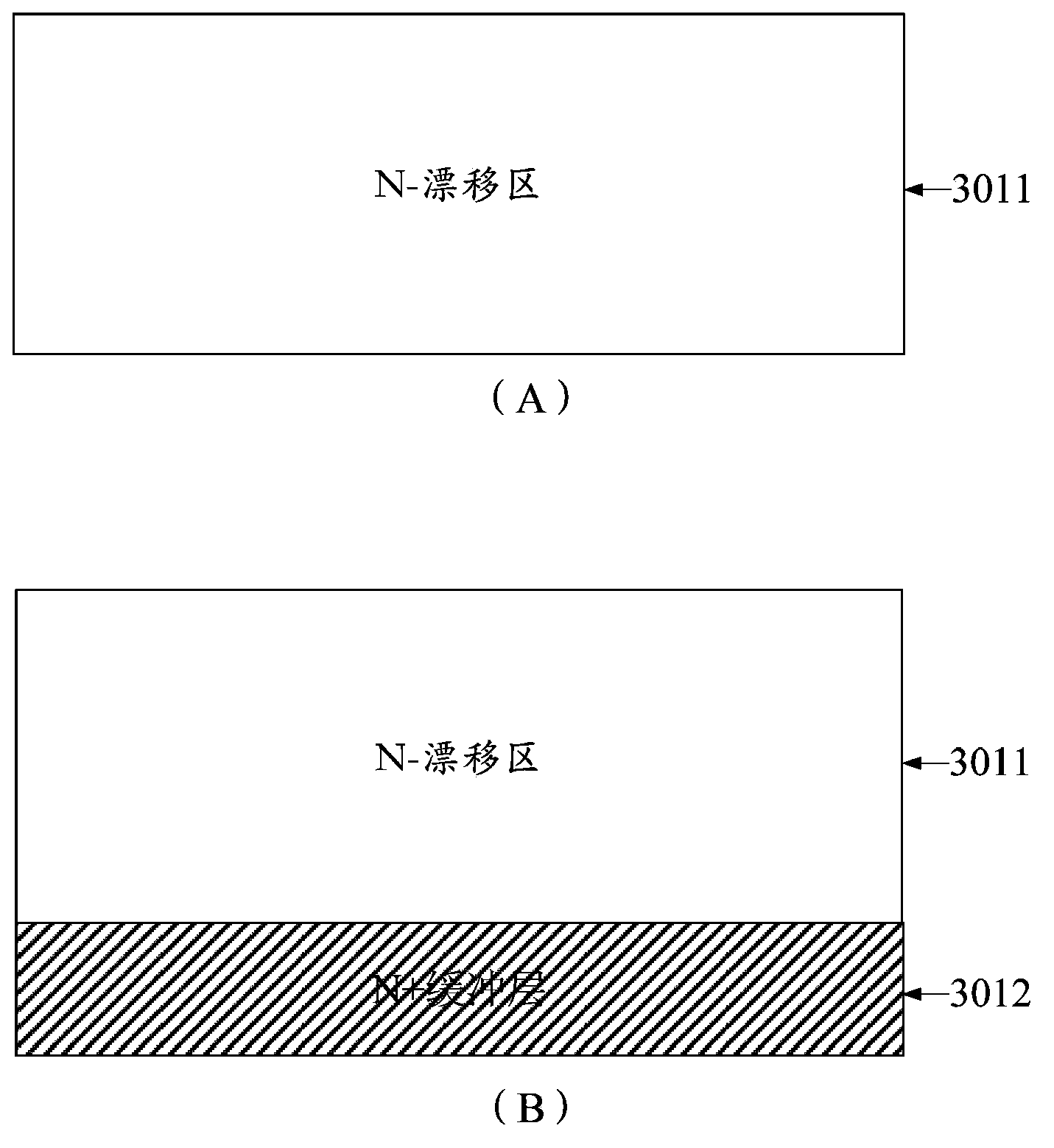

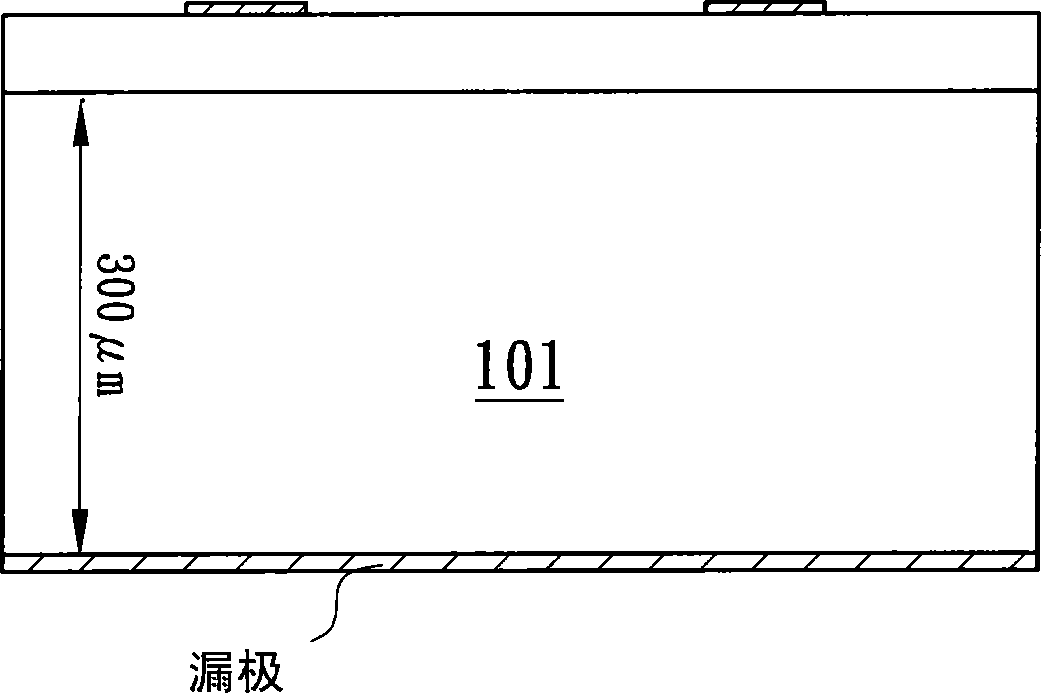

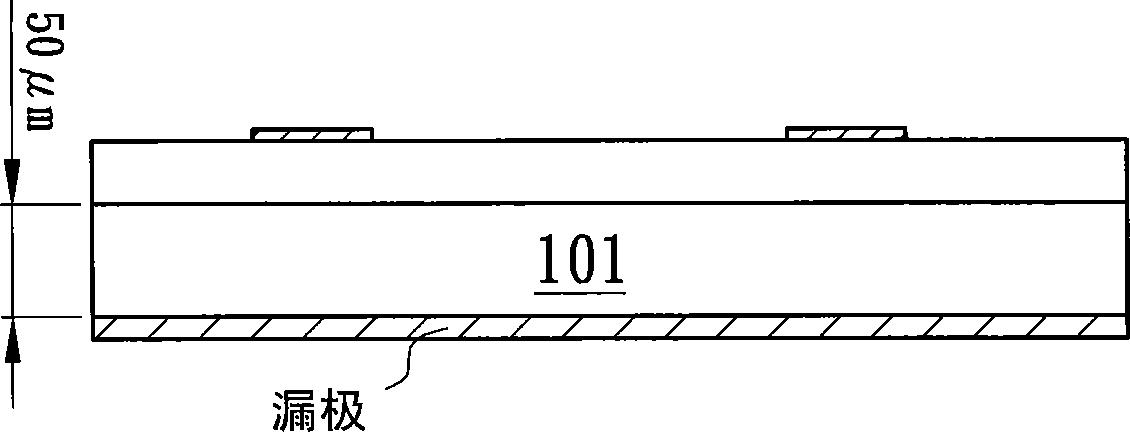

Punch-through IGBT and manufacturing method thereof

InactiveCN103854997AReduce processing difficultyIncreasing the thicknessSemiconductor/solid-state device manufacturingSemiconductor devicesEngineeringThinning

The invention discloses a punch-through IGBT and a manufacturing method of the punch-through IGBT. The method comprises the steps of providing a semiconductor substrate, wherein the semiconductor substrate comprises a substrate, a buffer layer formed on the surface of the substrate and a drift region formed on the surface of the buffer layer; conducting first-time thinning on the side, provided with the shift region, of the semiconductor substrate; after the first-time thinning is completed, forming a front face structure on the side, provided with the shift region, of the semiconductor substrate; conducting second-time thinning on the side, away from the shift region, of the semiconductor substrate until part of buffer layer is removed; after second-time thinning is completed, forming a collector region on the side, provided with the buffer layer, of the semiconductor substrate, and forming a metal electrode on the surface of the collector region. According to the manufacturing method of the punch-through IGBT, the manufacturing difficulty of the punch-through IGBT is reduced, and particularly the manufacturing difficulty of the thinner low-medium voltage punch-through IGBT is reduced.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI +2

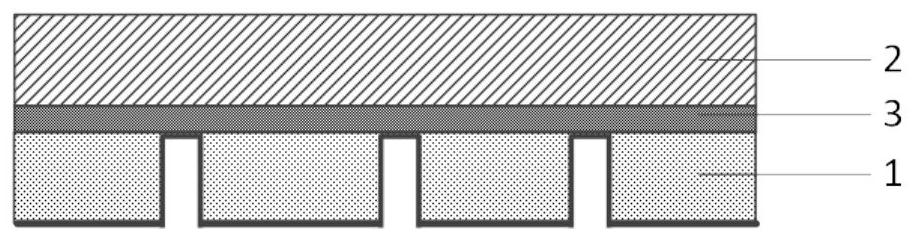

Semiconductor structure with low resistance substrate and low power loss

InactiveCN102651359ALower resistanceReduce power lossSemiconductor/solid-state device detailsSolid-state devicesSemiconductor structureEngineering

The invention provides a semiconductor structure with a low resistance substrate and low power loss. The semiconductor structure comprises a semiconductor unit, a first conductive structure, a first conductive material and a second conductive structure, wherein the semiconductor unit is provided with a substrate, and the substrate is positioned at one side of the semiconductor unit and is provided with at least one hole; the first conductive material is positioned in the hole in a filling-in or underfilling way, and the first conductive structure is positioned on one surface of the side of the semiconductor unit; and the second conductive structure is positioned on the surface of the other side of the semiconductor unit different from the semiconductor substrate. The semiconductor structure can effectively reduce the resistance of the substrate, and further reduce the power loss during the breakover on the semiconductor structure, and also has a longer service life. In addition, without adding additional equipment, the advantages of the current packaging factory capacity can be continuously utilized, so that the power loss and potential die crack risks are further reduced.

Owner:NIKO SEMICON

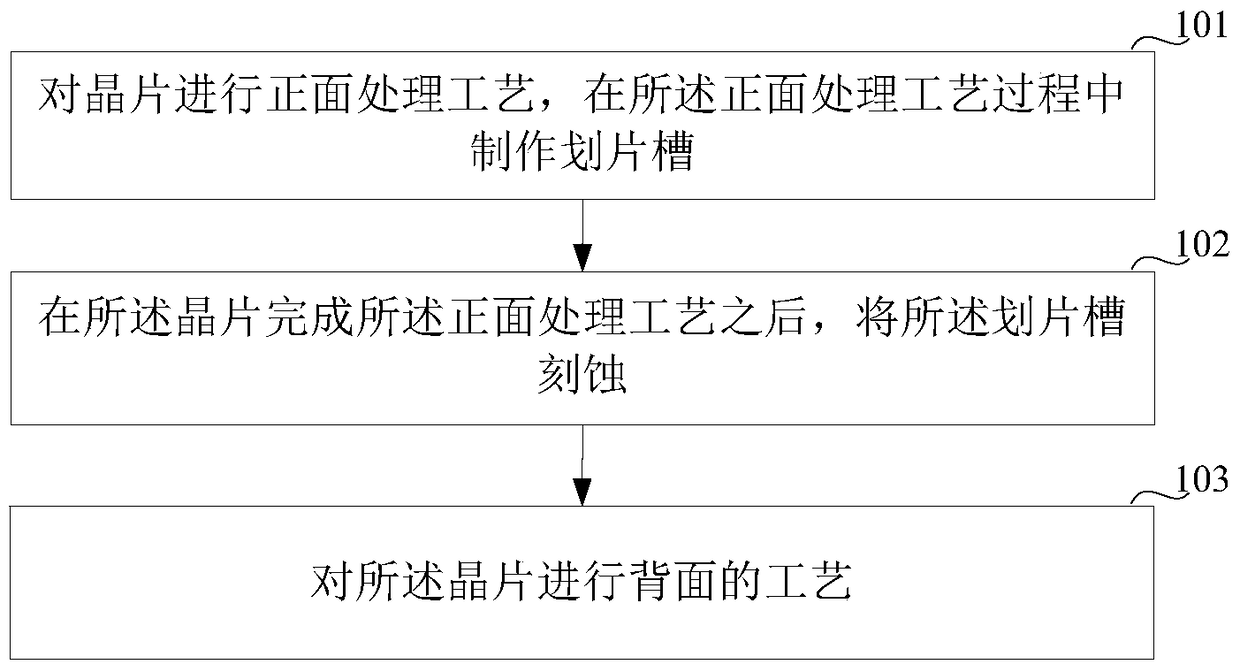

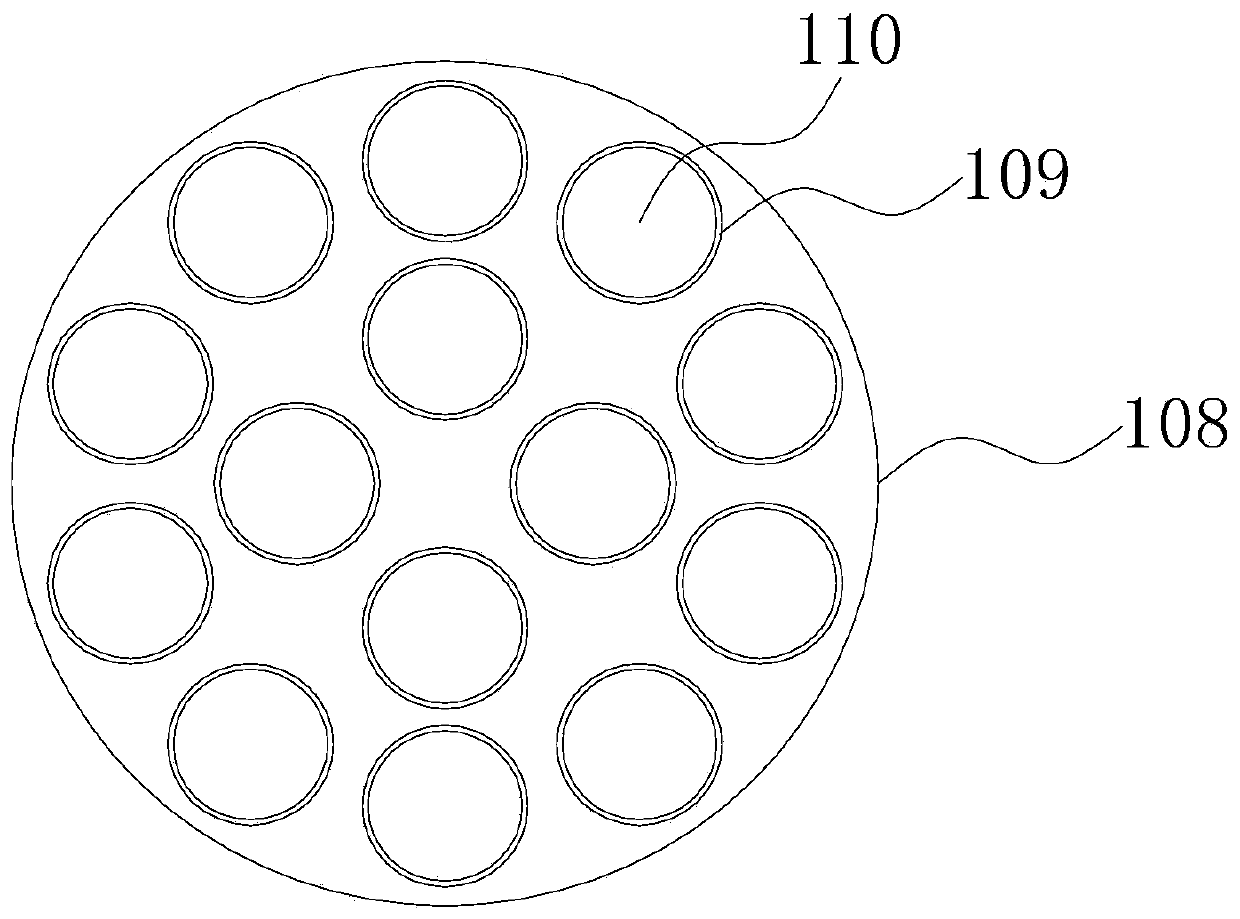

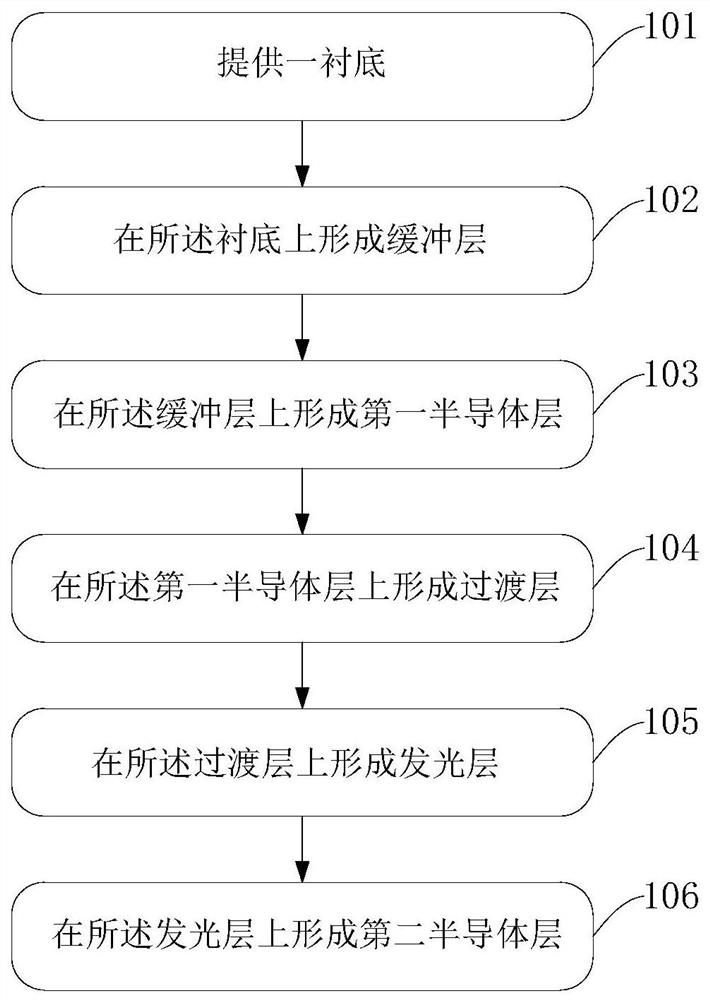

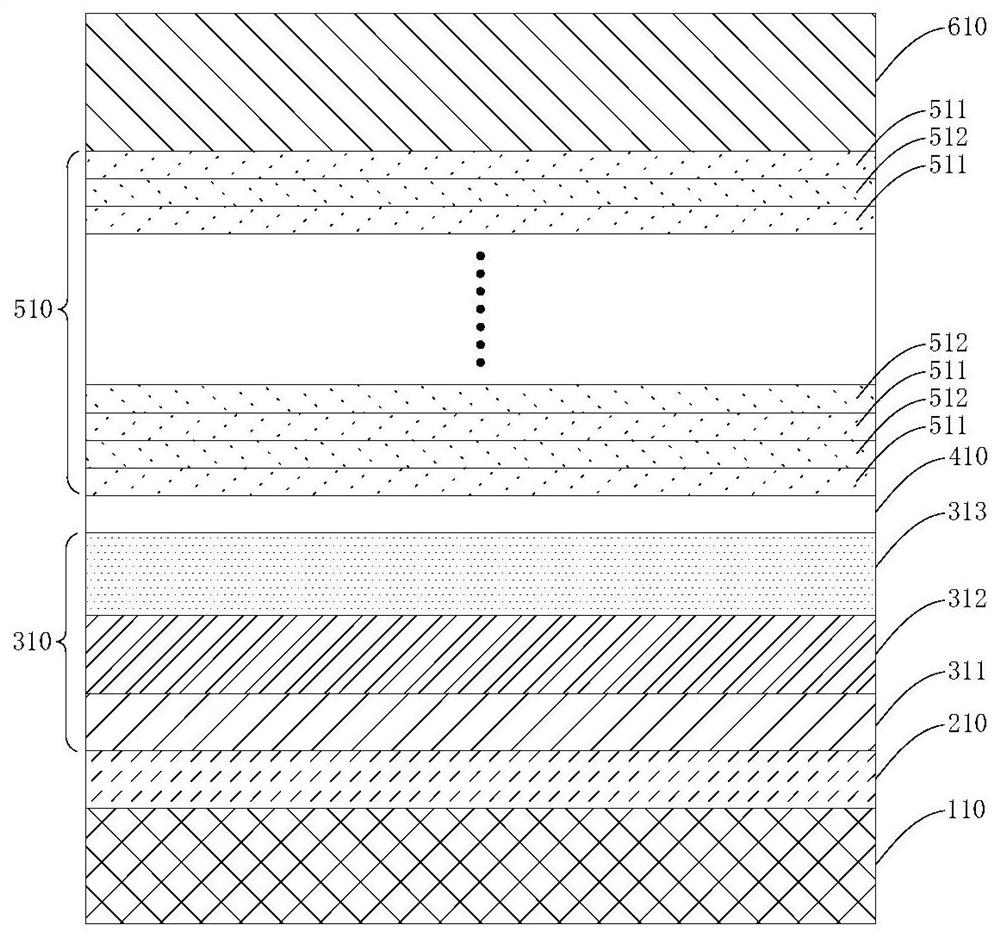

Preparation method of epitaxial structure for medical sterilization and disinfection

InactiveCN110854245AReduced risk of splinteringShorten transition timeSemiconductor/solid-state device manufacturingLight therapyIndiumActive layer

The invention provides a preparation method of an epitaxial structure for medical sterilization and disinfection. The method comprises steps of providing a substrate arranged on a tray; growing a first transition layer on the substrate; growing a first semiconductor layer on the first transition layer; growing a second transition layer on the first semiconductor layer; growing an active layer on the second transition layer; growing a second semiconductor layer on the active layer. The second transition layer comprises front barrier layers and front well layers which are alternately stacked, the aluminum content in the front barrier layers is gradually increased along with the thickness, the indium content in the front well layer is gradually reduced along with the thickness, and the tray rotation speed in the growth process of the first semiconductor layer is the same as the tray rotation speed in the growth process of the second transition layer. The method is advantaged in that the conversion time from the first semiconductor layer to the second transition layer can be reduced, and the cracking risk in the conversion process of different steps is reduced.

Owner:李丹丹

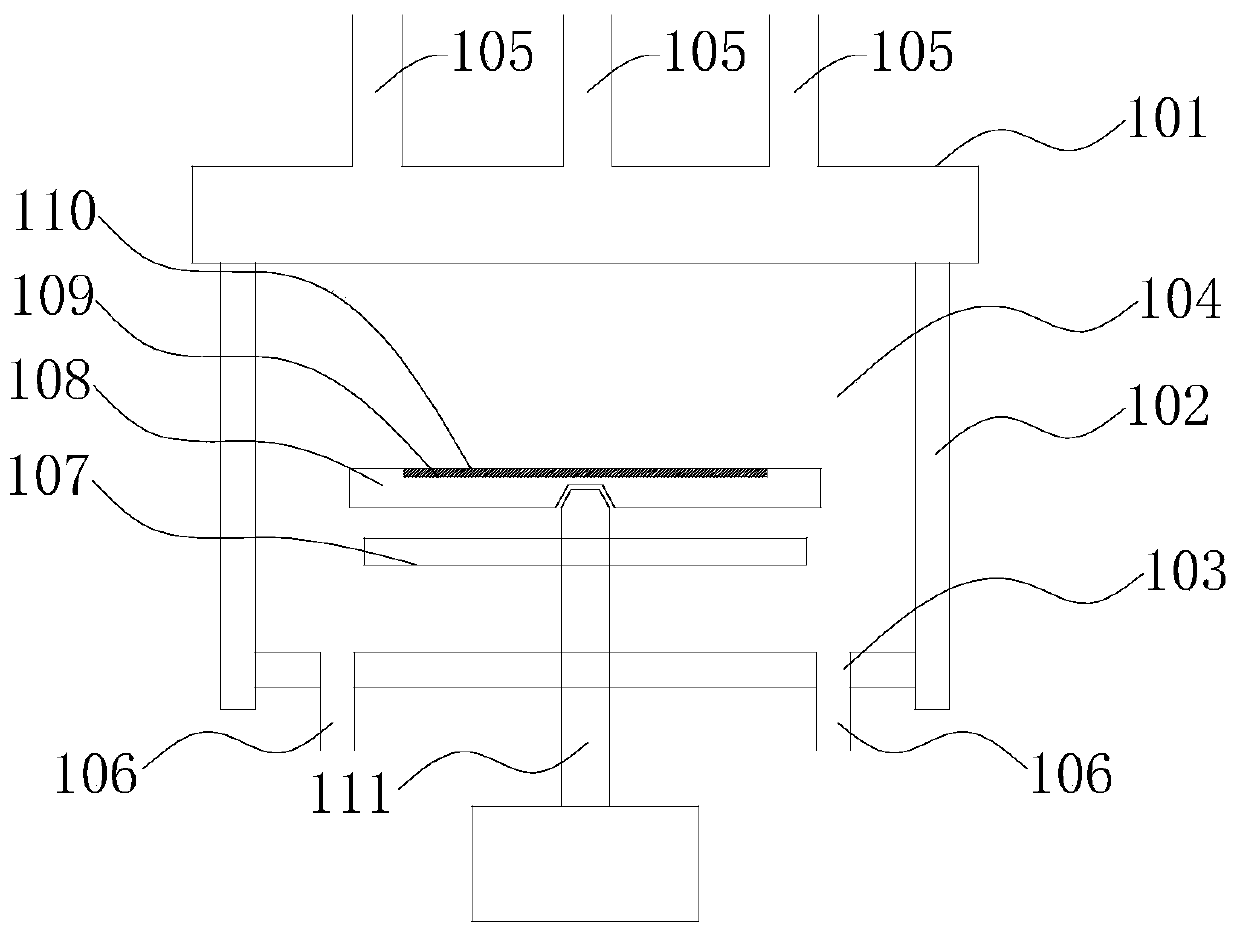

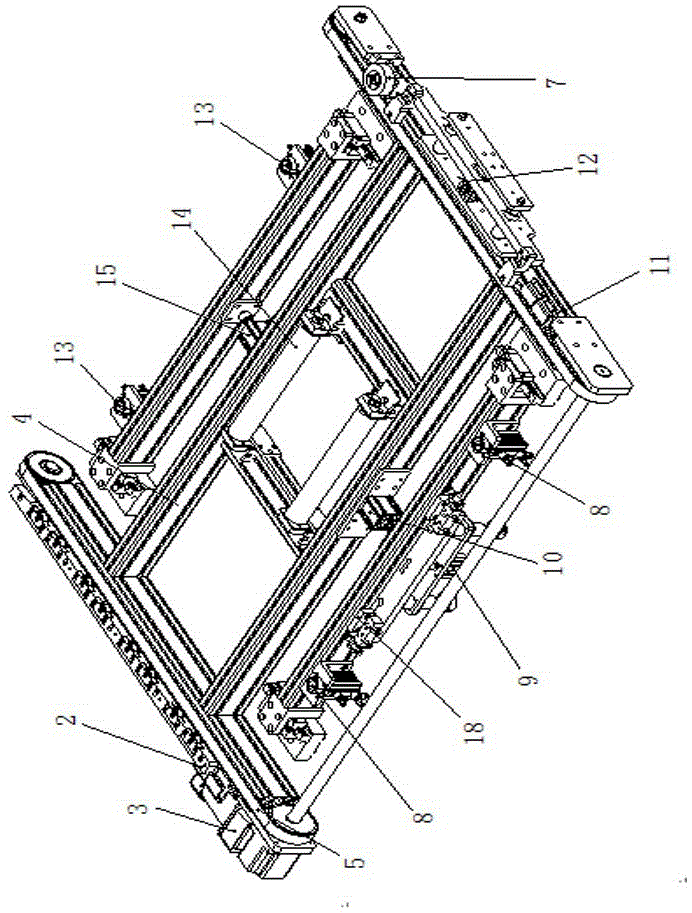

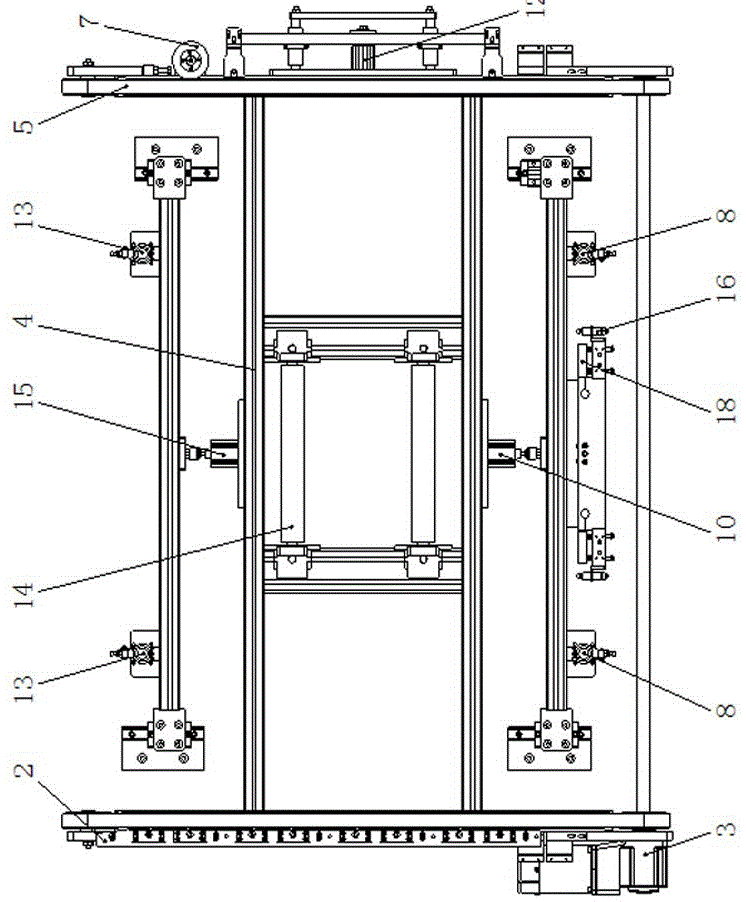

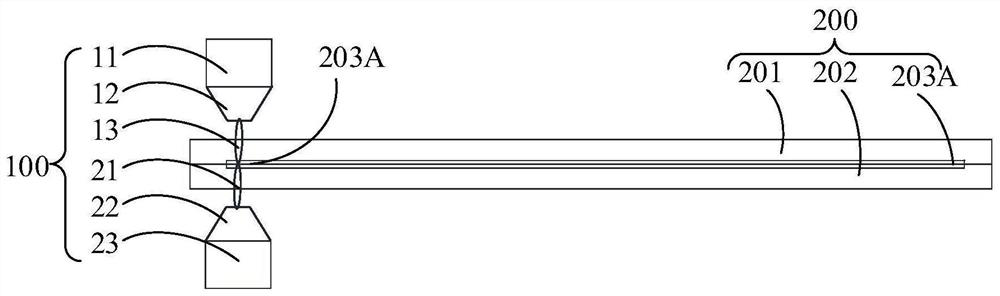

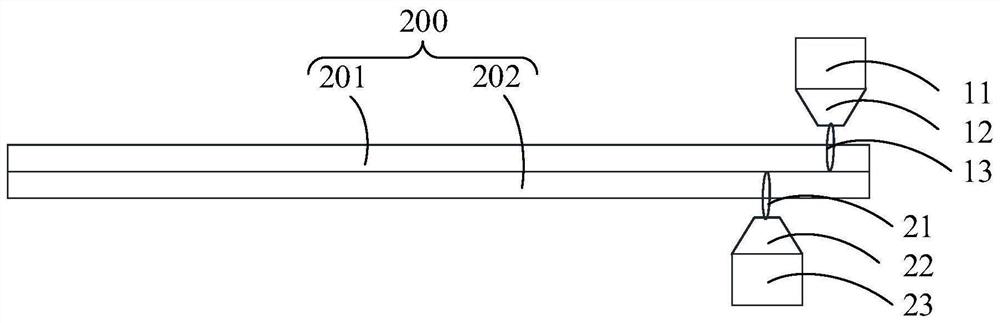

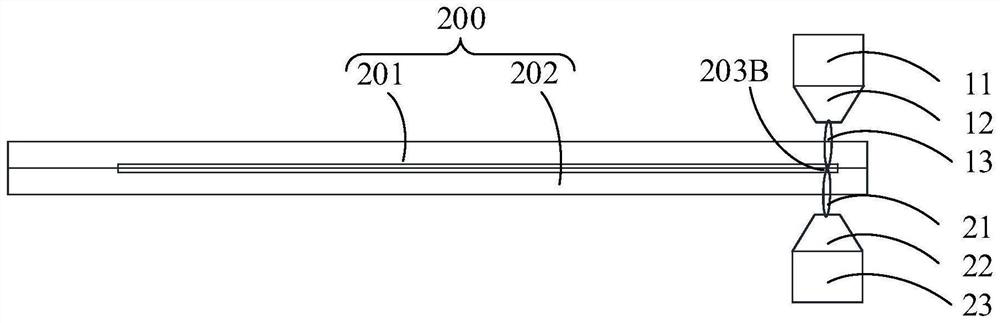

Mobile positioning mechanism for large support plate

ActiveCN106340481AMoving the carrier board saves time and effortSave human effortSolid-state devicesSemiconductor/solid-state device manufacturingEngineeringSolar cell

The invention discloses a mobile positioning mechanism for a large support plate, and relates to the technical field of automatic solar cell panel loading and unloading equipment. Synchronous belts are arranged on the two sides of a mainframe, and are driven by a motor to drive the support plate to move. A guide wheel plate is installed outside a synchronous belt on one side of the mainframe, a sensor is installed on the outer front side of the synchronous belt on the other side of the mainframe, and a side compressing guiding wheel is installed on the rear end of the synchronous belt on the other side of the mainframe. A support roller is installed on the central section of the mainframe, and a front blocking cylinder, a front elevating cylinder and a front compaction cylinder are installed on the front portion of the mainframe. A side compaction cylinder is installed on the side portion of the mainframe, and a rear blocking cylinder and a rear compaction cylinder are installed on the rear portion of the mainframe. The mobile positioning mechanism saves manpower, improves work efficiency and accurately positions a support plate. Splinter risk during subsequent support plate placing is reduced. The mobile positioning mechanism is safe and reliable and is easy for promotion and use.

Owner:山东昆仲信息科技有限公司

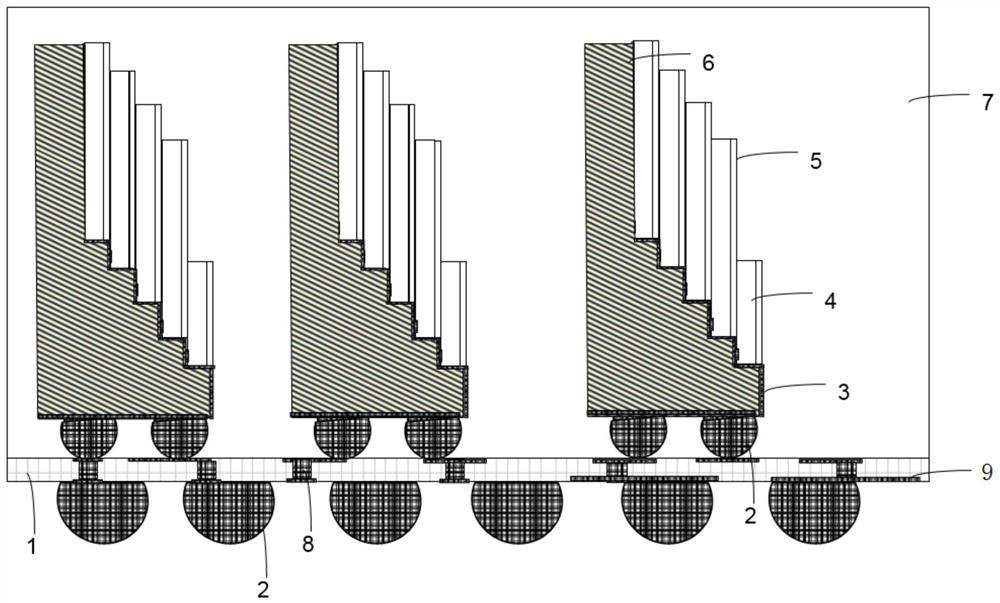

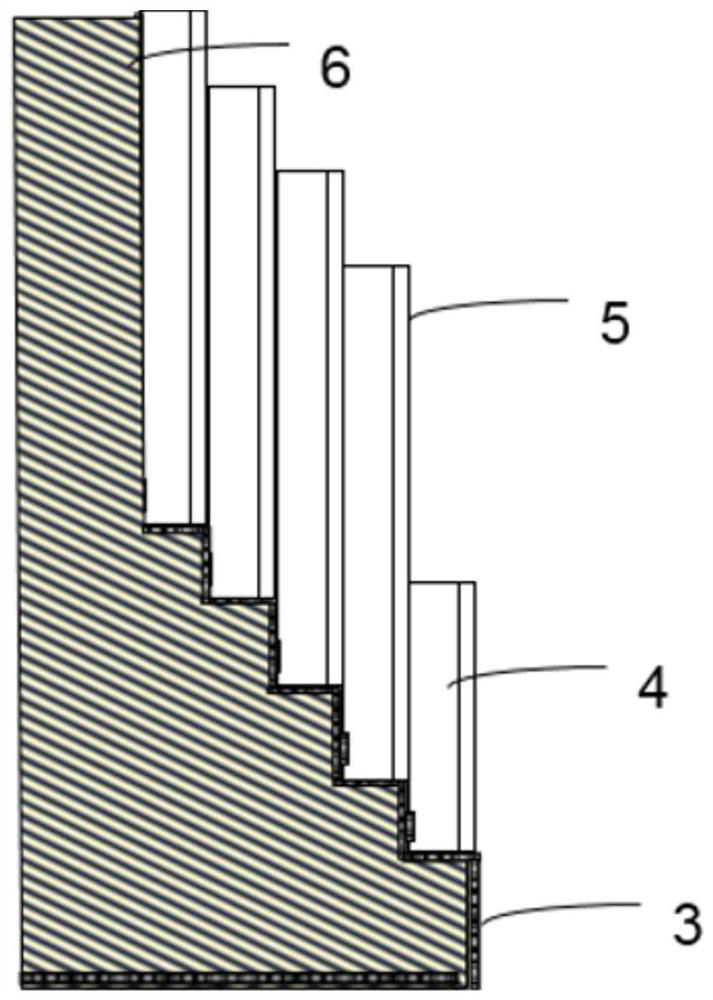

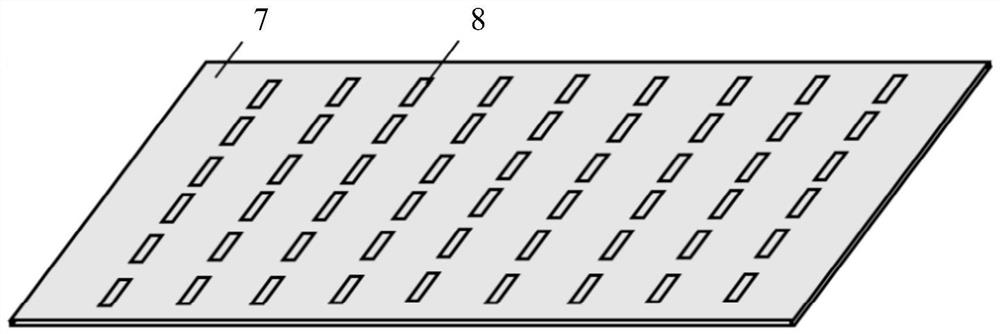

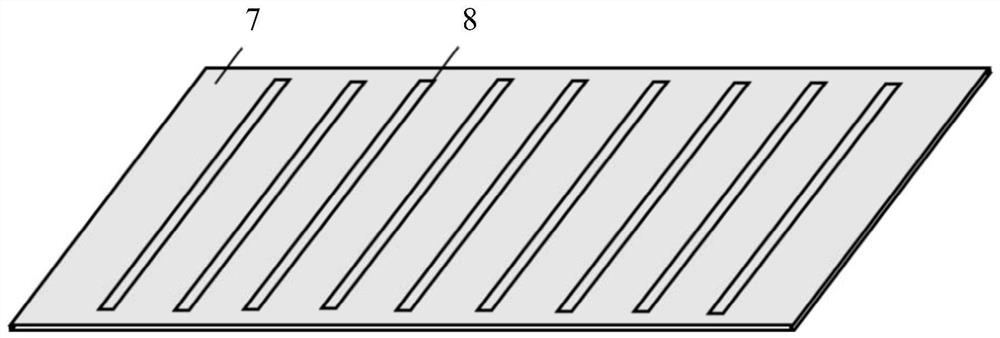

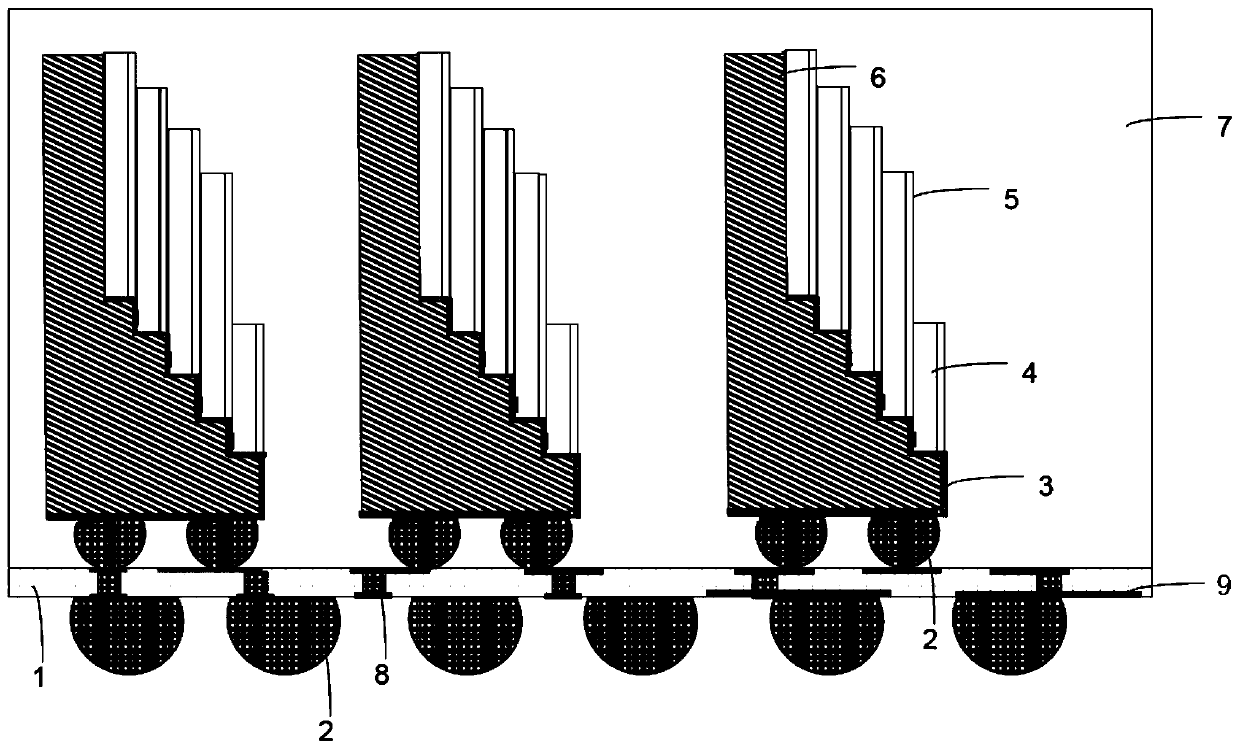

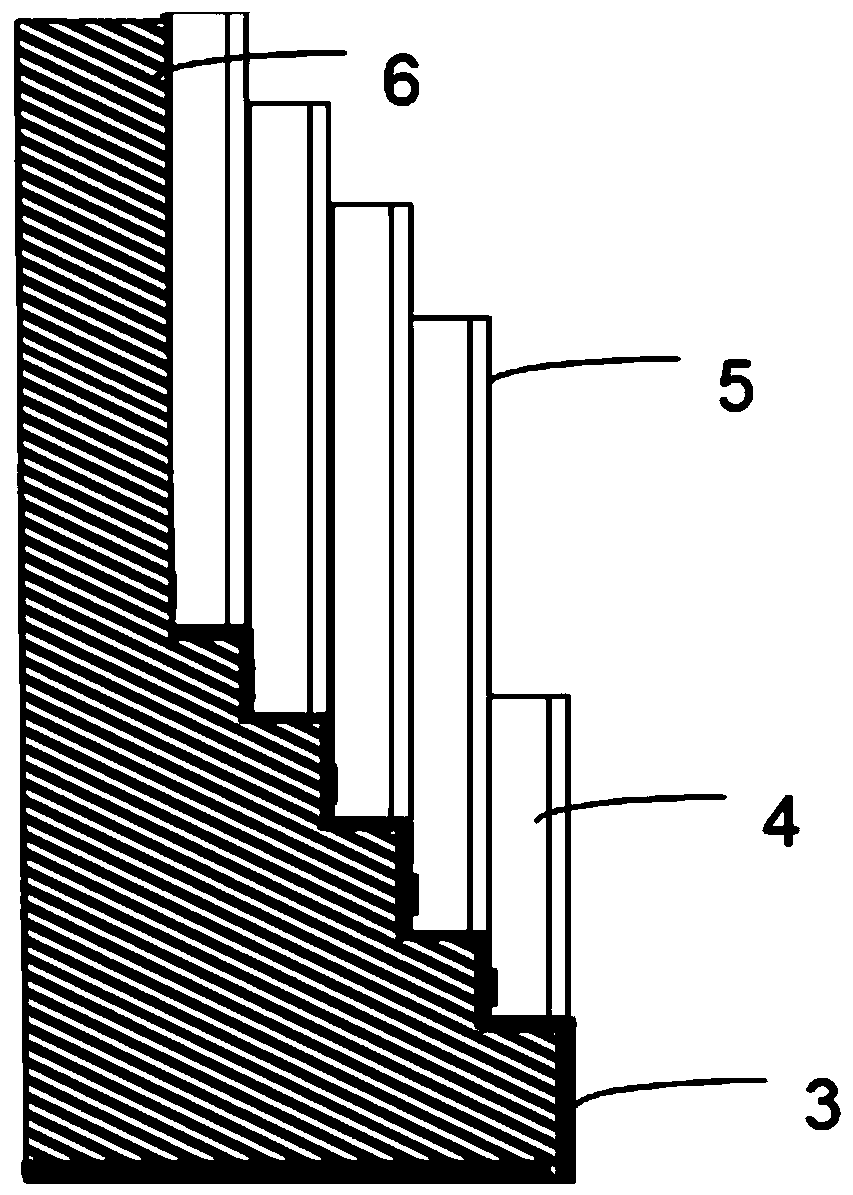

A modular multi-chip packaging structure and packaging method thereof

ActiveCN111063664BReduce package sizeReduced risk of splinteringSemiconductor/solid-state device detailsSolid-state devicesPlastic packagingEngineering

The invention discloses a modular multi-chip packaging structure and a packaging method thereof. A plurality of packaging units are arrayed on a substrate, and the packaging unit is formed by a plurality of chips stacked in steps. The lead ends of the chips stacked in steps are located on the steps. On the surface, the lead ends of multiple chips are connected by chip wiring, and the chips do not need to be wired, which reduces the packaging volume of the chip and avoids the loss of electrical performance on the wirebond line. The plastic package is plastic-sealed. The bottom of the first plastic package is provided with an etched circuit connected to the chip wiring, and the connecting wiring is arranged on the substrate. The etched circuit at the bottom of the first plastic package is connected to the connection wiring on the substrate. Multiple packaging units are sealed on the substrate, and the chips are vertically placed on the substrate after plastic packaging. The independent modules can be packaged together to integrate different functions, which breaks the limitations of traditional multi-chip packaging, and has a simple structure. The connection is stable.

Owner:华天科技(南京)有限公司

Photovoltaic module

PendingCN112133781AReduced risk of splintersSecure connectionPhotovoltaic energy generationSemiconductor devicesPhysicsElectrical and Electronics engineering

The invention discloses a photovoltaic module, and the photovoltaic module comprises a plurality of battery pieces and a plurality of interconnection structural parts. Two adjacent battery pieces in the plurality of battery pieces are respectively a first battery piece and a second battery piece; each interconnection structural part comprises a light reflecting section and connecting sections, theconnecting sections comprise a first connecting section and a second connecting section, the first connecting section and the second connecting section are connected to the two ends of the light reflecting section respectively, at least one part of the first connecting section is in a flat shape, and at least one part of the second connecting section is in a flat shape; the reflecting section isnon-flat, the reflecting section and the second connecting section are both connected to the front surface of the first battery piece, and at least one part of the first connecting section is connected to the back surface of the second battery piece. According to the photovoltaic module provided by the invention, the reflecting sections can be prevented from being positioned on the back surface ofthe battery piece, so that the risk of battery piece cracking can be effectively reduced, firm connection with the front surface of the battery piece can be realized, and the reliability of the photovoltaic module is improved.

Owner:CSI CELLS CO LTD +1

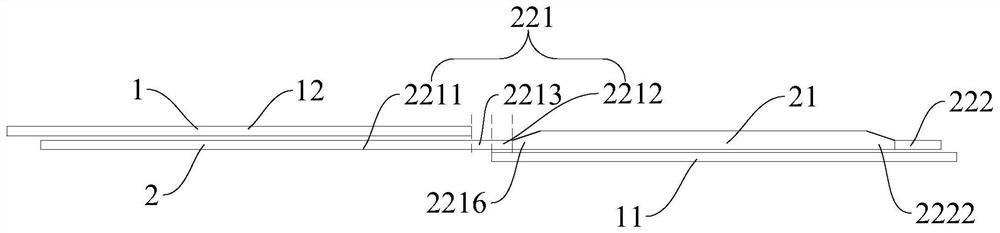

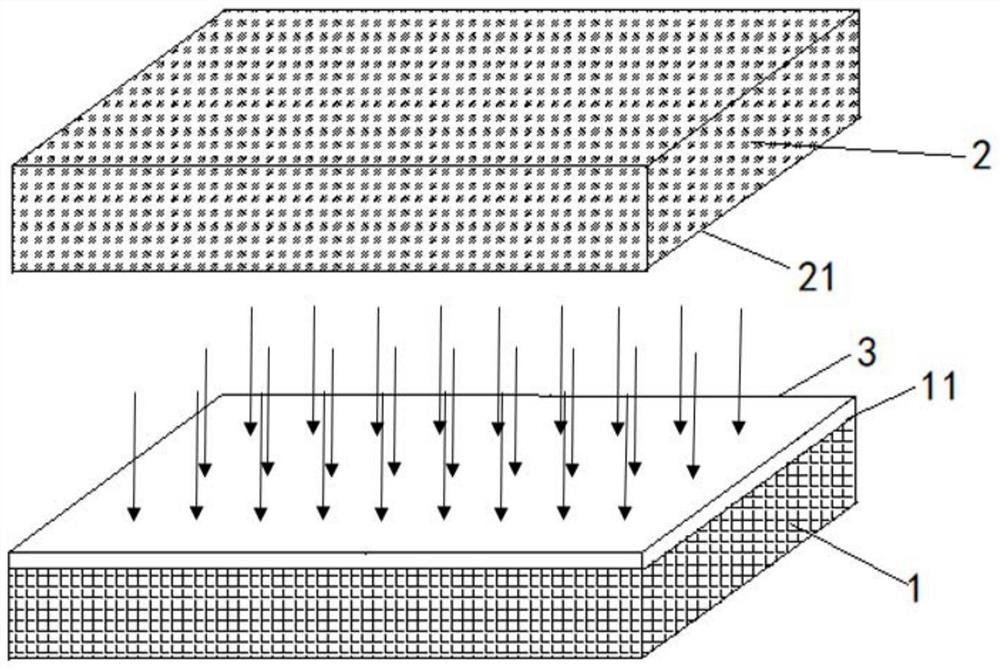

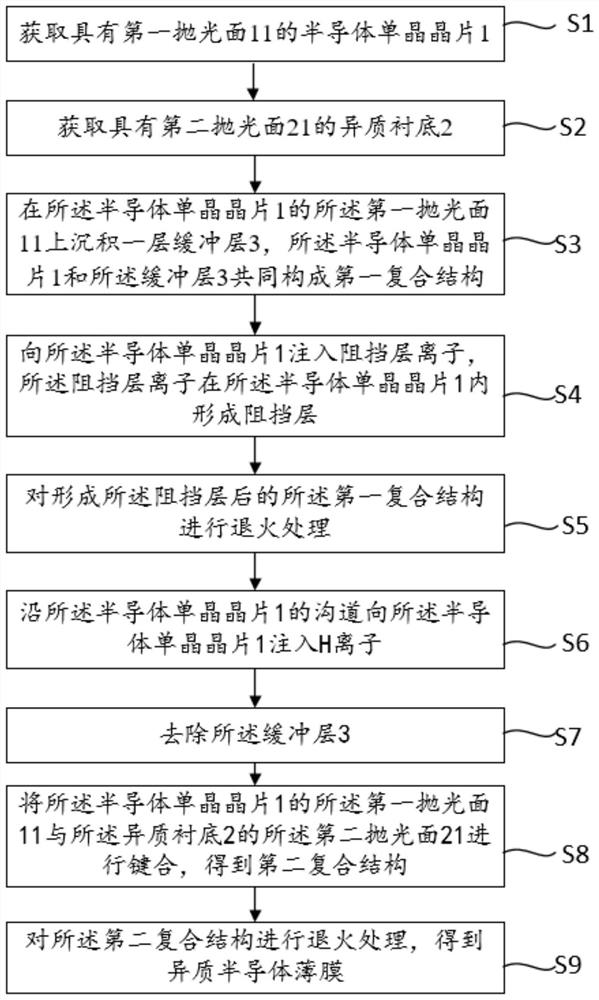

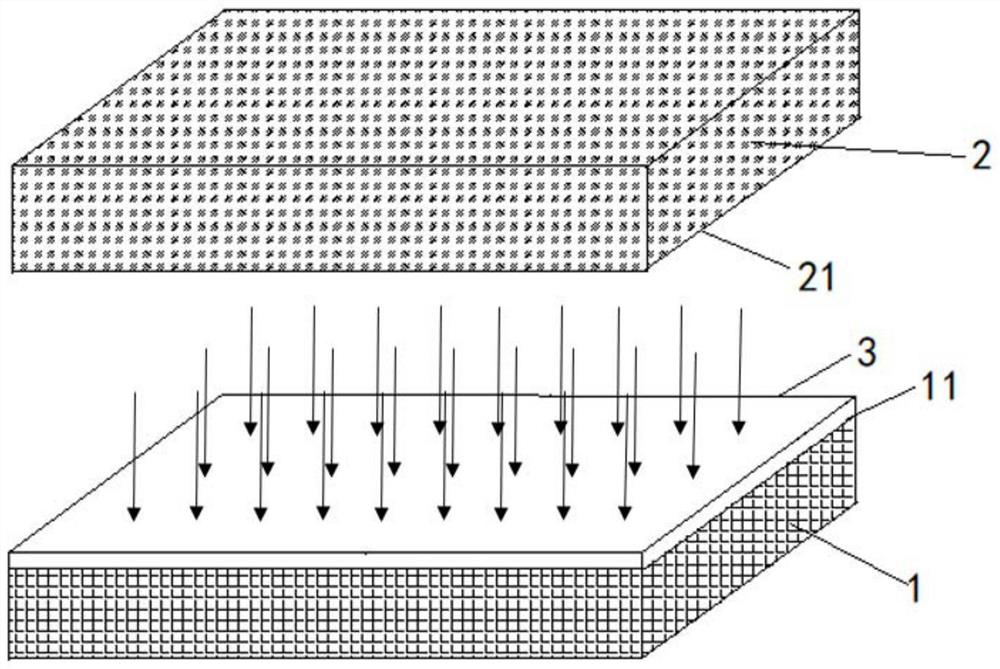

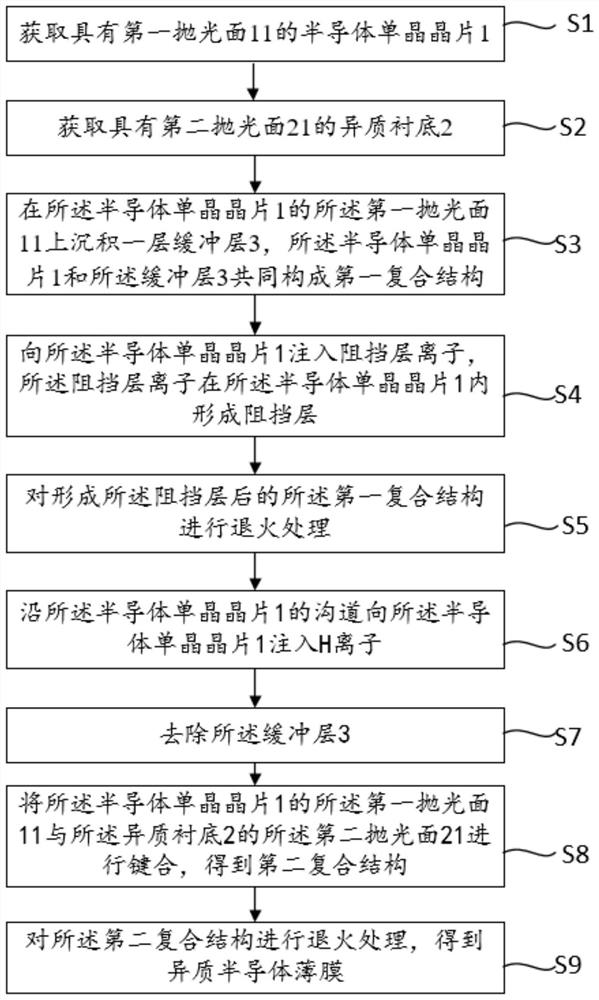

Heterogeneous semiconductor film and preparation method thereof

ActiveCN111834205AQuality improvementImprove material propertiesSolid-state devicesSemiconductor/solid-state device manufacturingWaferingSingle crystal

The invention discloses a preparation method of a heterogeneous semiconductor film. The preparation method comprises the steps of obtaining a semiconductor single crystal wafer with a first polished surface; obtaining a heterogeneous substrate with a second polished surface; depositing a buffer layer on the first polished surface of the semiconductor single crystal wafer to form a first compositestructure; injecting barrier layer ions into the semiconductor single crystal wafer to form a barrier layer; conducting annealing treatment; injecting H ions into the semiconductor single crystal wafer along a channel of the semiconductor single crystal wafer, wherein the atomic number of the H ions is less than that of the barrier layer ions, and the injection energy is greater than that of the barrier layer ions; removing the buffer layer; bonding the semiconductor single crystal wafer with the heterogeneous substrate to obtain a second composite structure; and conducting annealing treatmentto obtain the heterogeneous semiconductor film. According to the method, the barrier layer ions are injected into the semiconductor single crystal wafer to form the barrier layer so as to capture theH ions, so that damage caused by ion stripping is reduced, and the utilization rate of the H ions and the quality of the film are greatly improved.

Owner:SHANGHAI INST OF MICROSYSTEM & INFORMATION TECH CHINESE ACAD OF SCI

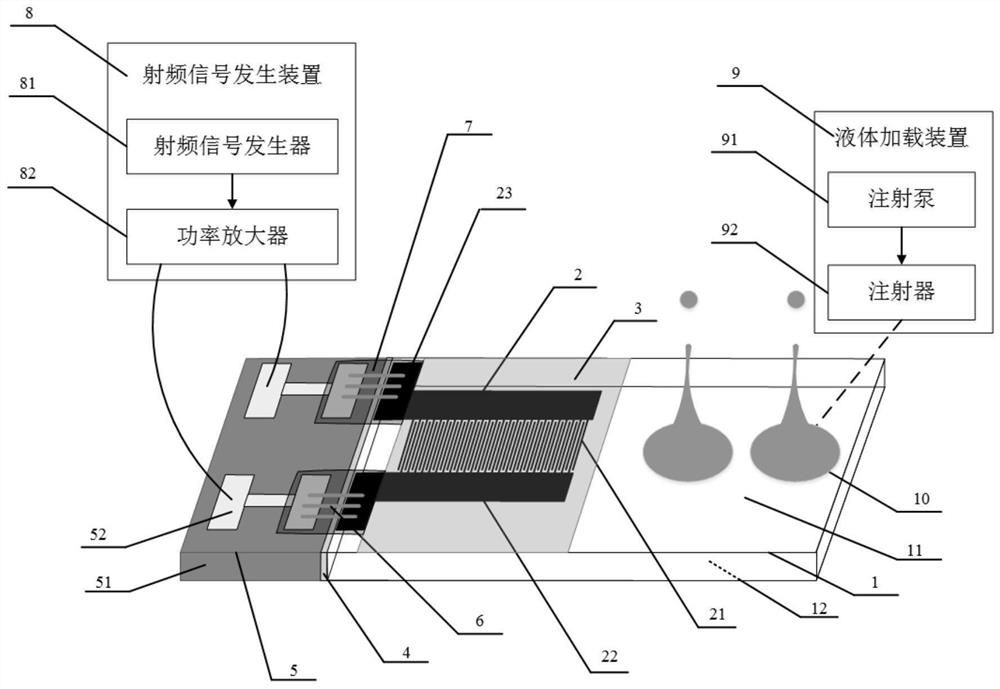

Droplet jetting device and related method

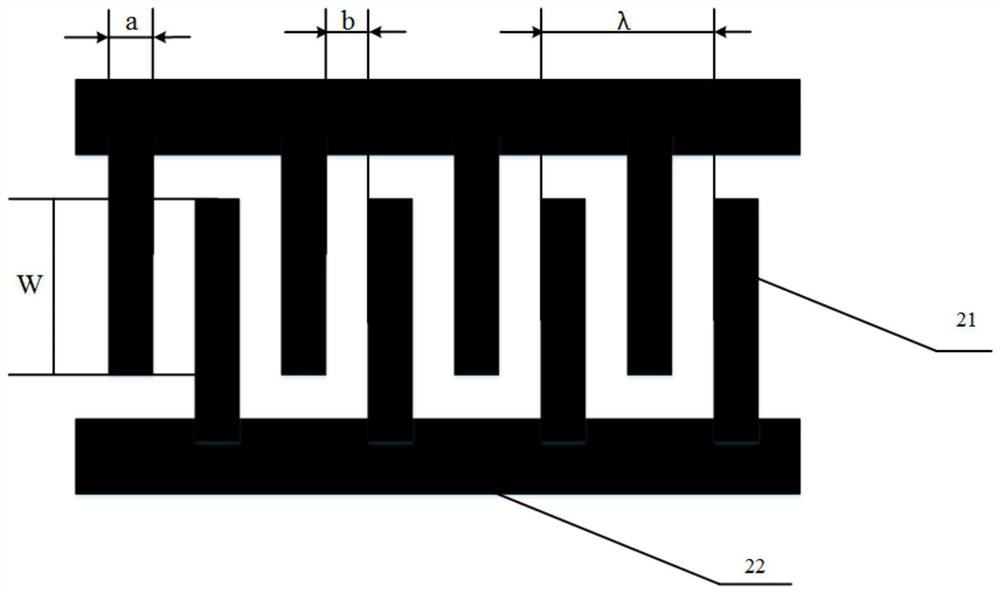

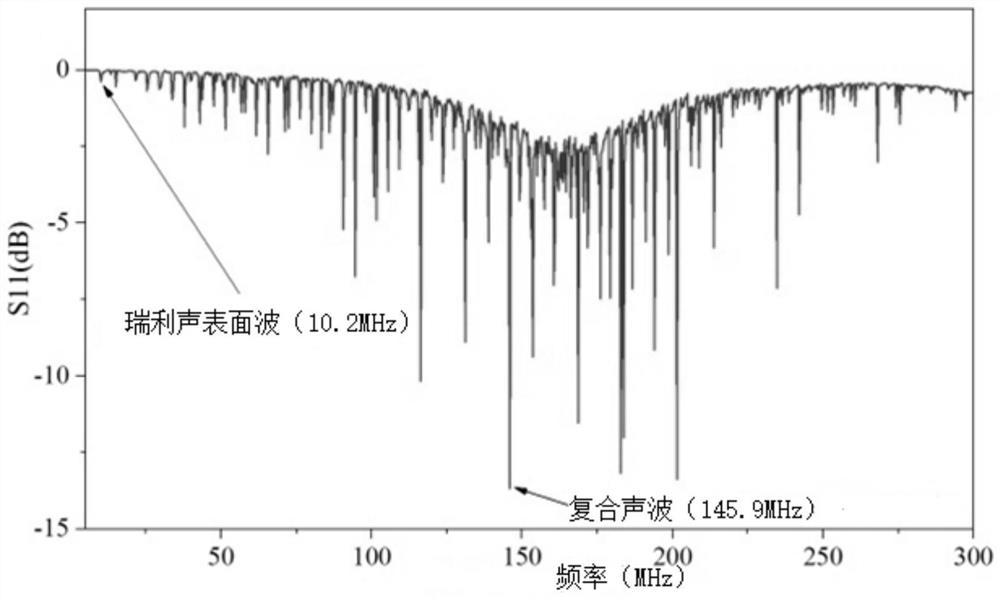

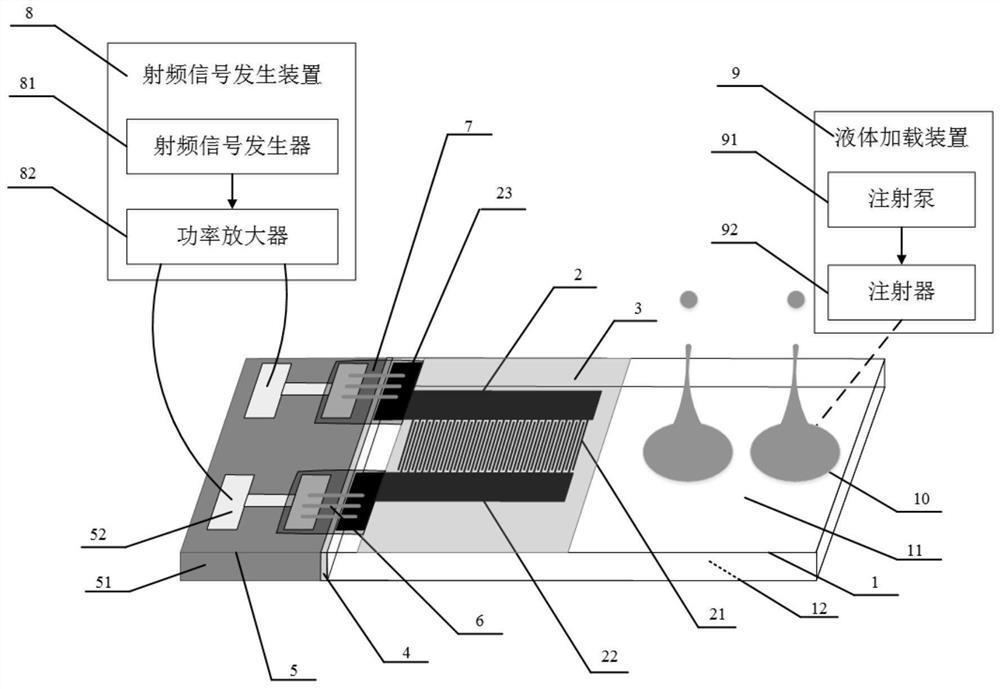

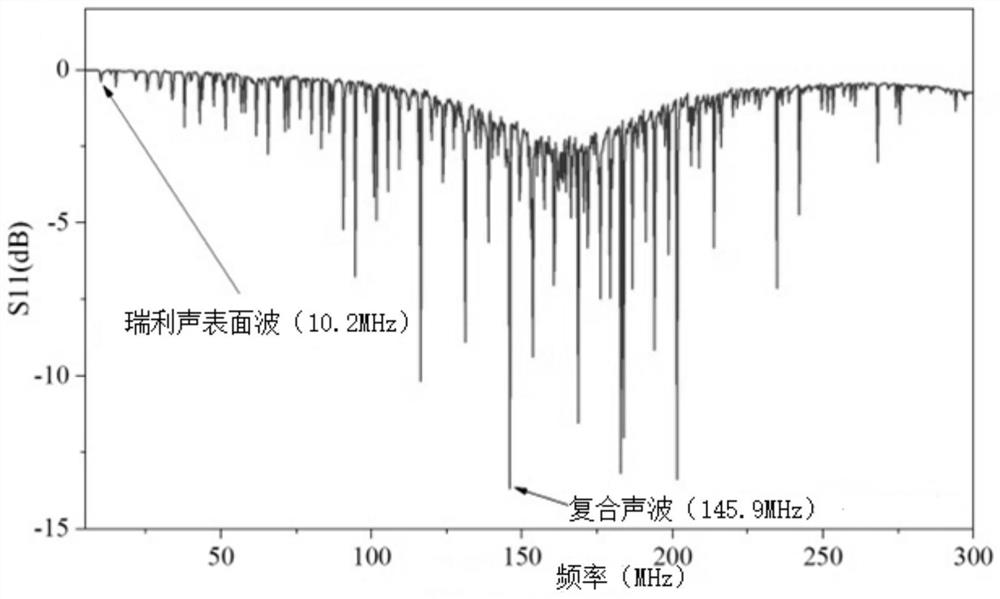

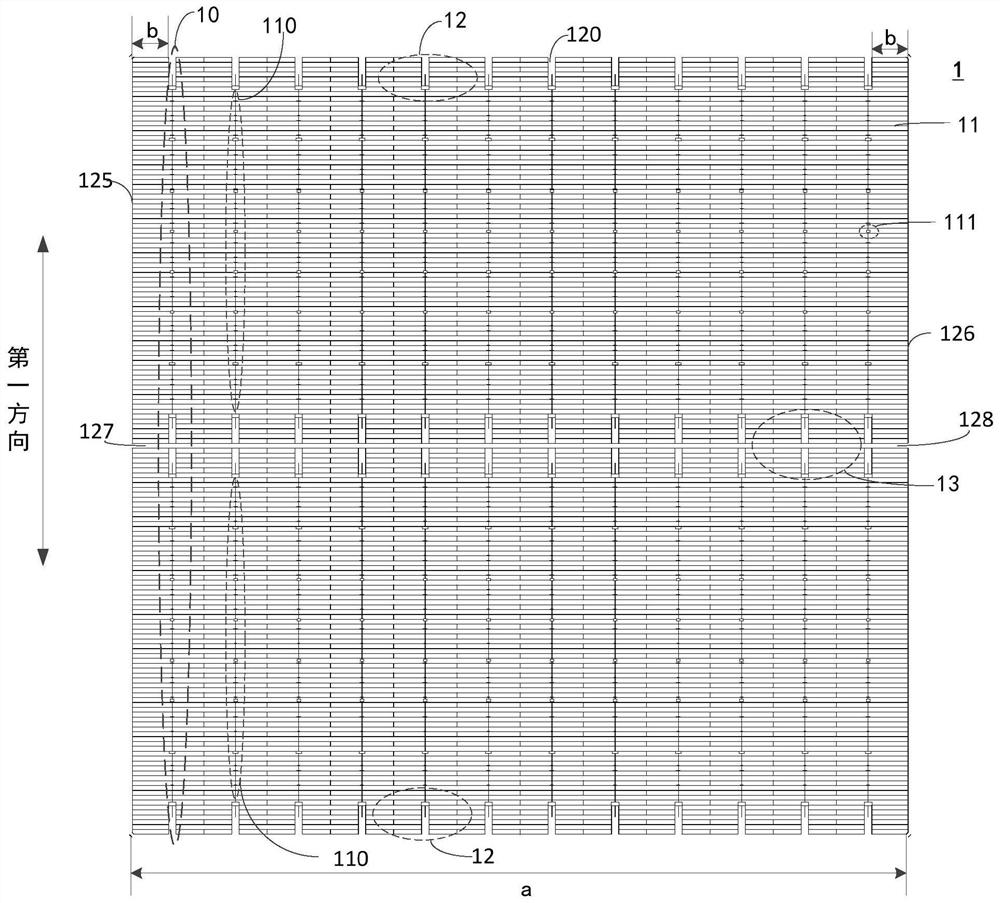

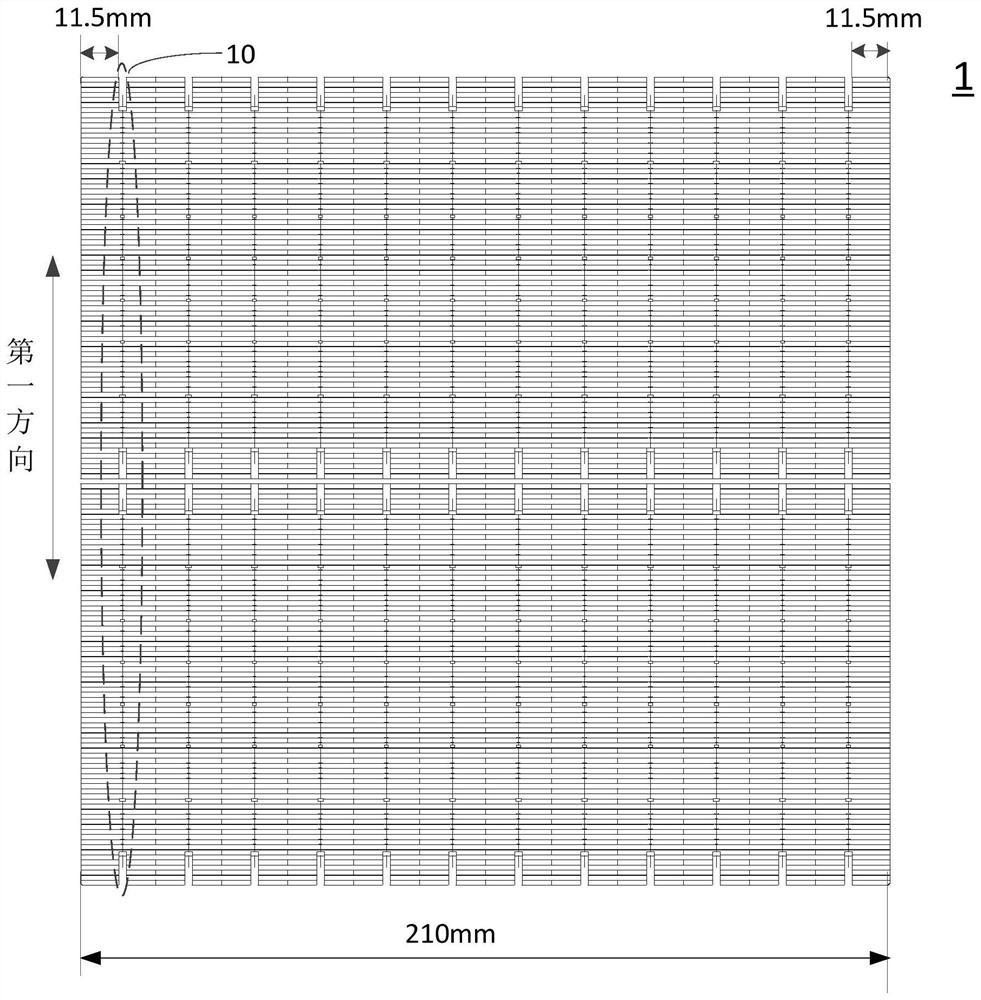

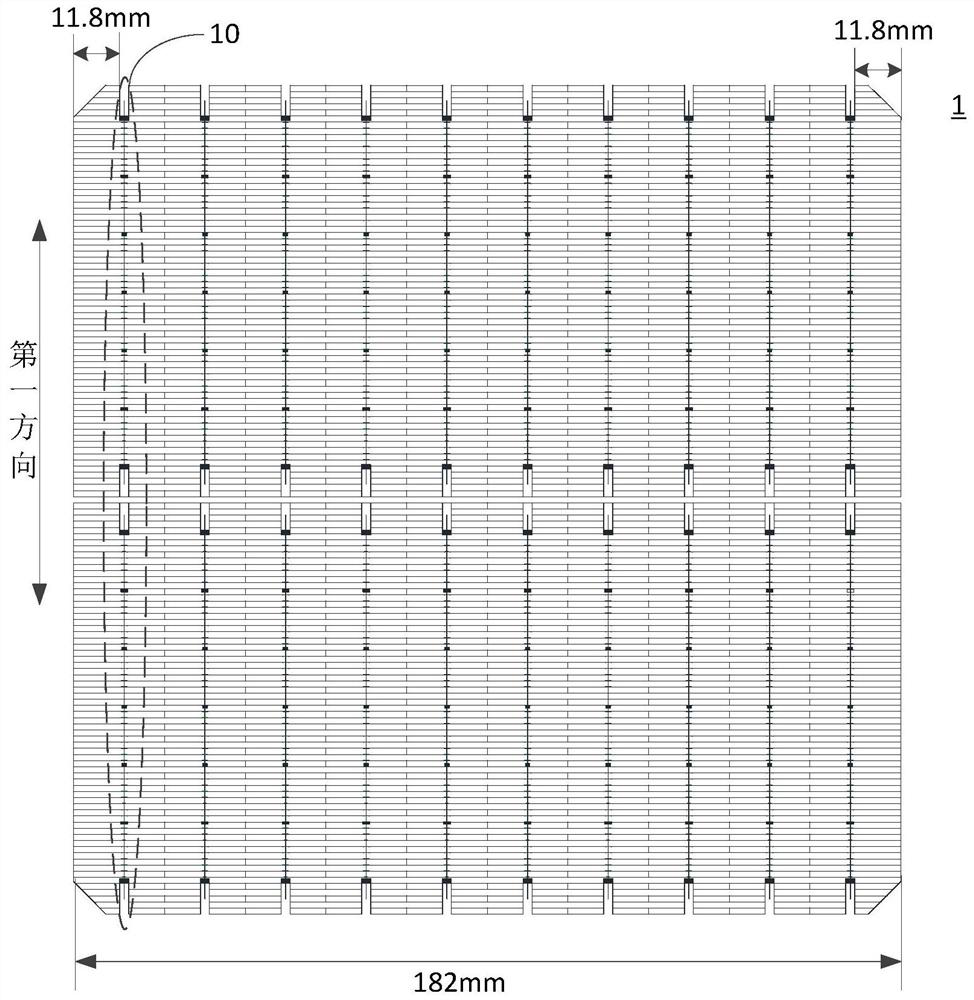

ActiveCN112916286AJet stabilityEasy to useLiquid spraying apparatusRadio frequency signalMechanical engineering

The invention provides a droplet jetting device and a related method. The droplet jetting device comprises a piezoelectric chip and an interdigital transducer arranged on the upper surface of the piezoelectric chip, the ratio of the thickness of the piezoelectric chip to the period of the interdigital transducer is 1-3, the interdigital transducer is driven by a radio frequency signal to excite surface acoustic waves and bulk acoustic waves in the piezoelectric chip, and the surface acoustic waves and the bulk acoustic waves are reflected on the upper surface and the lower surface of the piezoelectric chip to generate composite acoustic waves so as to drive to-be-driven liquid on a liquid attachment area to stretch in the direction perpendicular to the surface of the piezoelectric chip to form a liquid column, so that the liquid column generates a liquid drop pinch-off effect at the end part, and a single liquid drop is ejected, the liquid attachment area is located on the upper surface and / or the lower surface of the piezoelectric chip and corresponds to the area covered by the surface acoustic wave generated by the interdigital transducer propagating along the surface of the piezoelectric chip. The problems that a device is complex in structure, high in cost, low in efficiency and inconvenient to achieve on-demand jetting are solved.

Owner:HARBIN INST OF TECH SHENZHEN GRADUATE SCHOOL

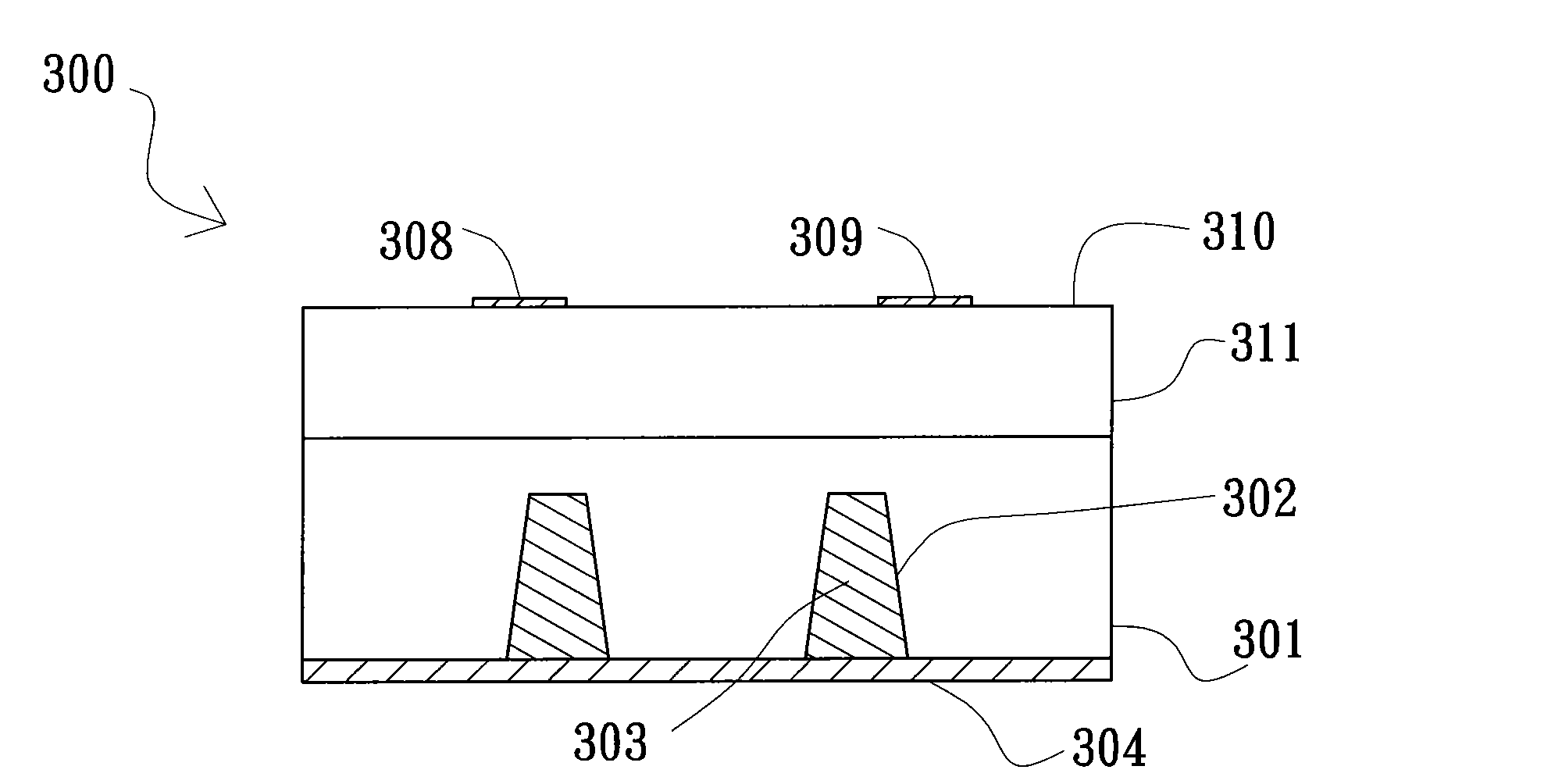

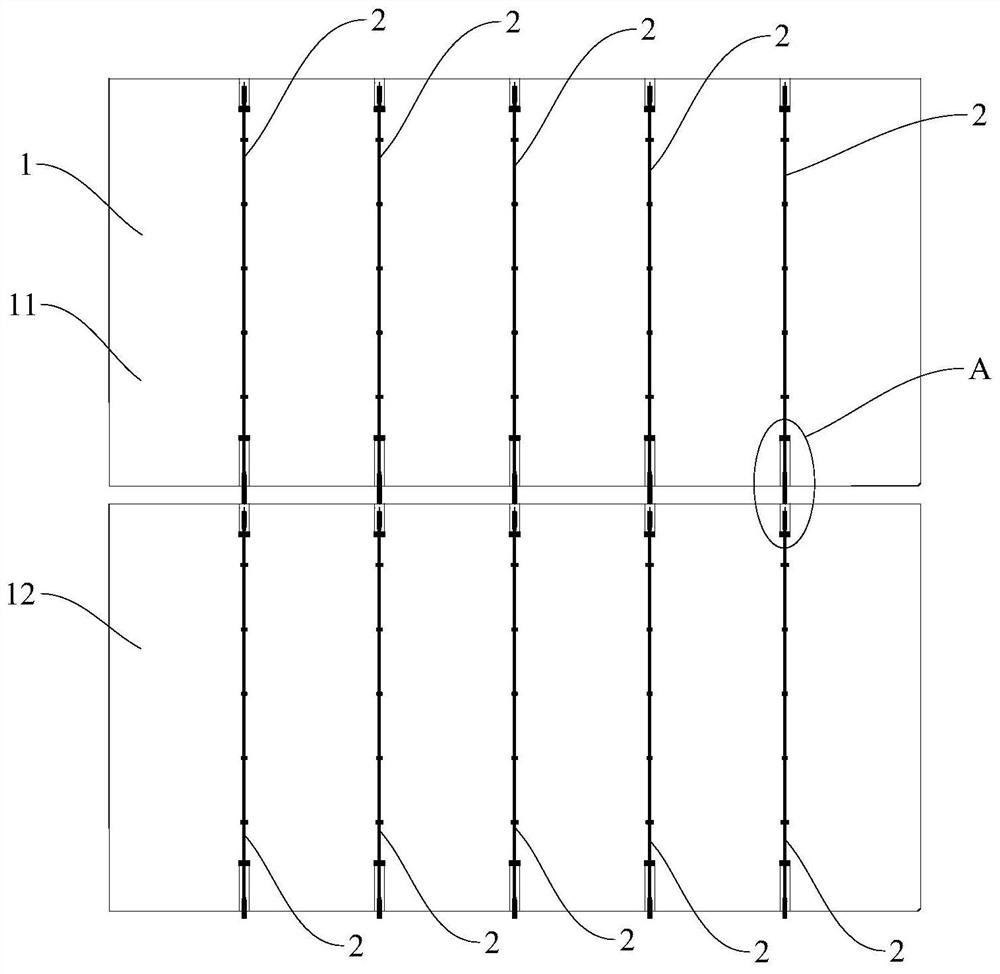

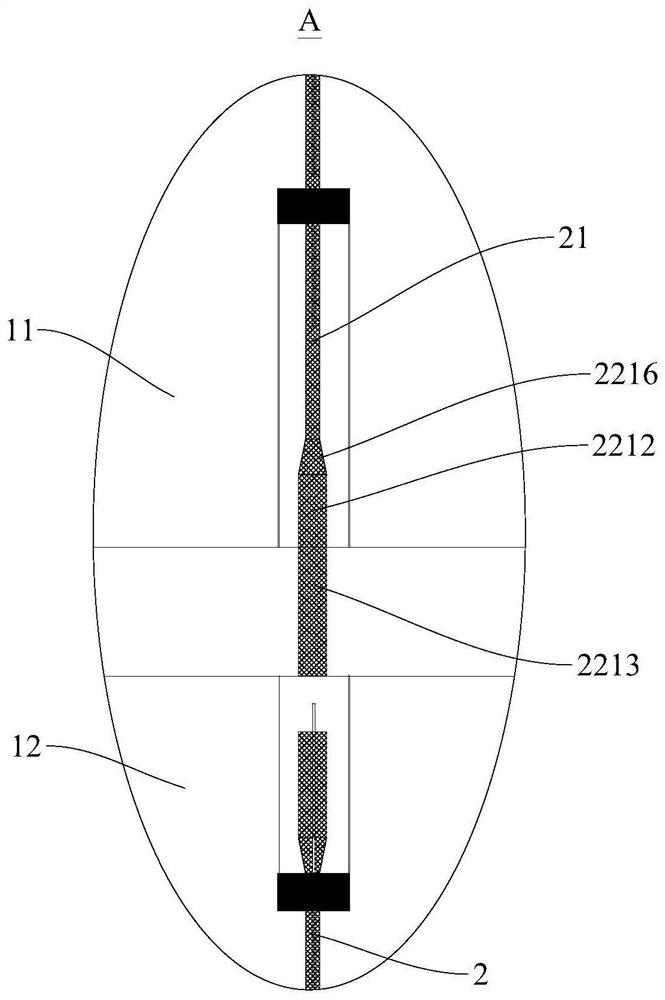

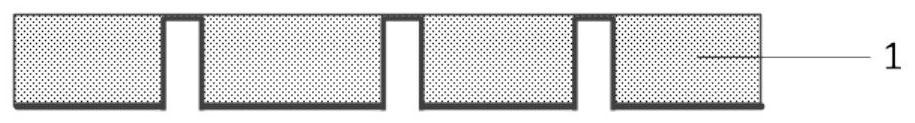

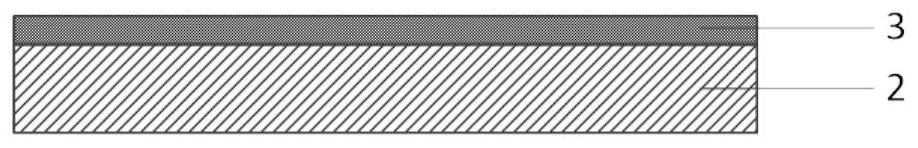

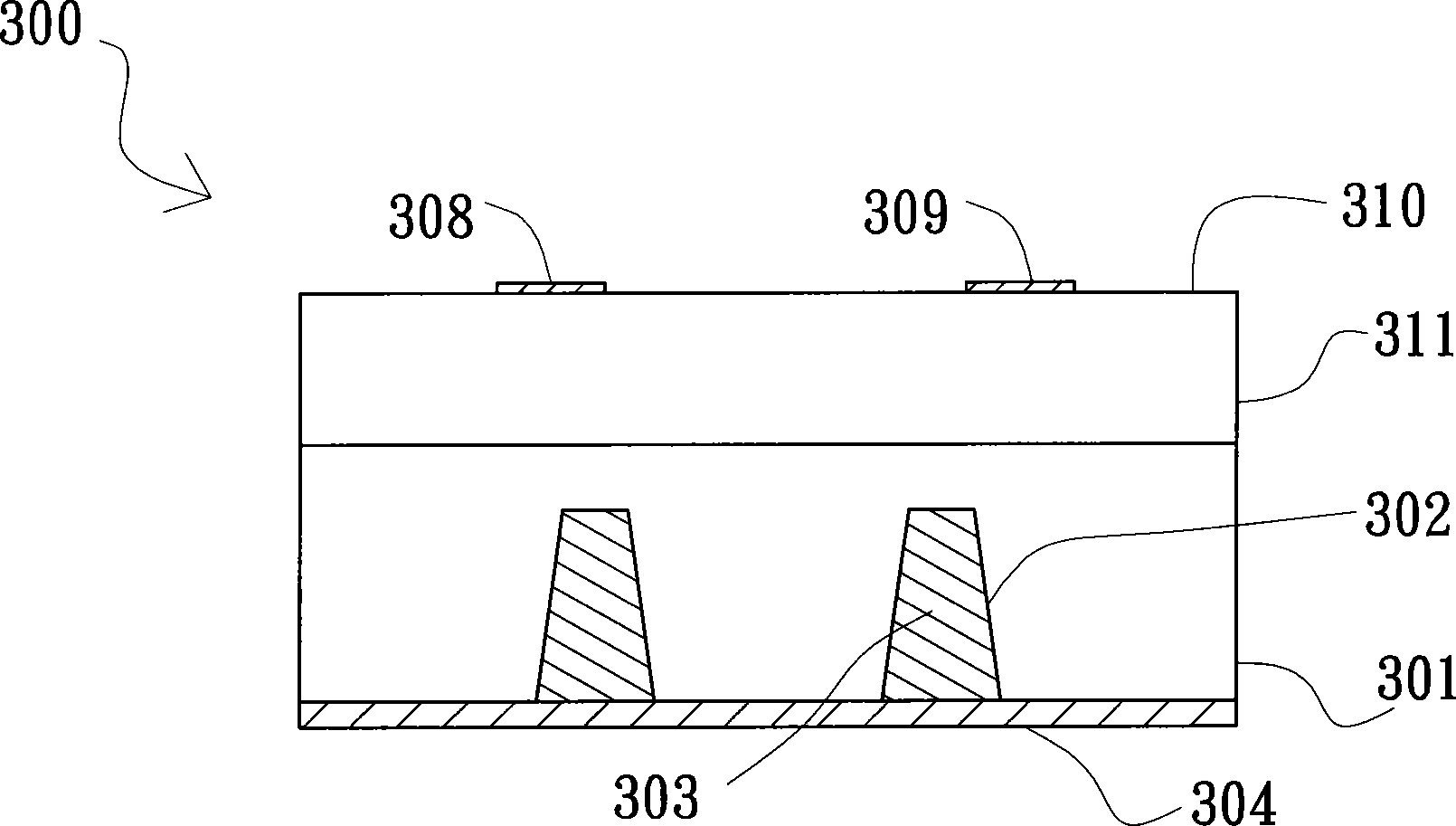

A holding method for ultra-thin semiconductor wafers in semiconductor integration process

ActiveCN109494182BSo as not to damageReduced risk of splinteringSolid-state devicesSemiconductor/solid-state device manufacturingWaferEngineering physics

The present application discloses a method for holding an ultra-thin semiconductor wafer (1) in a semiconductor integration process. The main steps comprise: 1) spin-coating a first temporary bonding adhesive (3) on a front surface of a first temporary carrier (2); 2) bonding a front surface of an ultra-thin semiconductor wafer to the front surface of the first temporary carrier; 3) spin-coating a second temporary bonding adhesive (5) on a front surface of a second temporary carrier (4); 4) bonding a rear surface of the ultra-thin semiconductor wafer to the front surface of the second temporary carrier; 5) separating the ultra-thin semiconductor wafer from the first temporary carrier; 6) fabricating an integrated interconnection structure; 7) performing a bonding integration process; and 8) separating the integrated wafer from the second carrier. Two types of temporary bonding adhesives having different softening temperatures are used in conjunction with two temporary carriers, and a temporary bonding process and a bonding release process are used, thereby ensuring that the ultra-thin semiconductor wafer is supported by the temporary carrier during three-dimensional integration processes such as transferring, holding, interconnection structure fabrication, and bonding, and effectively reducing the risk of wafer cracking during the integration process.

Owner:南京中电芯谷高频器件产业技术研究院有限公司

Semiconductor structure with low resistance substrate and low power loss

InactiveCN102651359BLower resistanceReduce power lossSemiconductor/solid-state device detailsSolid-state devicesSemiconductor structureConductive materials

The invention provides a semiconductor structure with a low resistance substrate and low power loss. The semiconductor structure comprises a semiconductor unit, a first conductive structure, a first conductive material and a second conductive structure, wherein the semiconductor unit is provided with a substrate, and the substrate is positioned at one side of the semiconductor unit and is provided with at least one hole; the first conductive material is positioned in the hole in a filling-in or underfilling way, and the first conductive structure is positioned on one surface of the side of the semiconductor unit; and the second conductive structure is positioned on the surface of the other side of the semiconductor unit different from the semiconductor substrate. The semiconductor structure can effectively reduce the resistance of the substrate, and further reduce the power loss during the breakover on the semiconductor structure, and also has a longer service life. In addition, without adding additional equipment, the advantages of the current packaging factory capacity can be continuously utilized, so that the power loss and potential die crack risks are further reduced.

Owner:NIKO SEMICON

A kind of thinning method of lithium niobate wafer

ActiveCN111900078BImprove qualityImprove reliabilitySolid-state devicesSemiconductor/solid-state device manufacturingWaferPhysical chemistry

The invention discloses a method for thinning a lithium niobate wafer, which belongs to the technical field of chip packaging. The thinning method of the lithium niobate wafer of the present invention comprises the following steps: providing a lithium niobate wafer, pasting the first dicing adhesive film on the back side of the lithium niobate wafer, and The dicing road is pre-cut to a predetermined depth; the first dicing film is removed, and a grinding film is attached to the front of the lithium niobate wafer, and the grinding film is a double-layer film; the back of the lithium niobate wafer is Grinding until the grains are separated; sticking a second dicing film on the back of the lithium niobate wafer, and then removing the grinding film. The invention realizes the cutting process of the lithium niobate wafer before grinding, and avoids the brittle failure, deep subsurface damage layer, and large cracking of the front and back sides of the cutting lithium niobate wafer in the prior art during grinding and cutting. Phenomenon, and the cracking of the front and back of the chip can be controlled within 10um, which is conducive to ensuring the quality of lithium niobate chip packaging products.

Owner:NINGBO CHIPEX SEMICON

led manufacturing process

ActiveCN111244232BAchieve growthReduce interface stressSemiconductor devicesPhysical chemistrySemiconductor

Owner:江西通利晟电子科技有限公司

Cutting mechanism, cutting method and display panel

ActiveCN109794984BAvoid breakingGuaranteed normal cuttingMetal working apparatusColor filmStructural engineering

The invention provides a cutting mechanism and method and a display panel. The cutting mechanism comprises a first output device and a second output device; the first output device drives a first cutting wheel to move along a first path to cut an array substrate of the display panel; the second output device drives a second cutting wheel to move along a second path to cut a color film substrate ofthe display panel; and in a first superposition section, the second path coincides with the first path to enable the first cutting wheel and the second cutting wheel to jointly cut sealing rubber onan edge between the array substrate and the color film substrate. The cutting mechanism and method and the display panel have the advantage that the display panel is prevented from breaking during piece split due to the fact that the sealing rubber is subjected to double-surface cutting or the sealing rubber is completely cut.

Owner:HKC CORP LTD

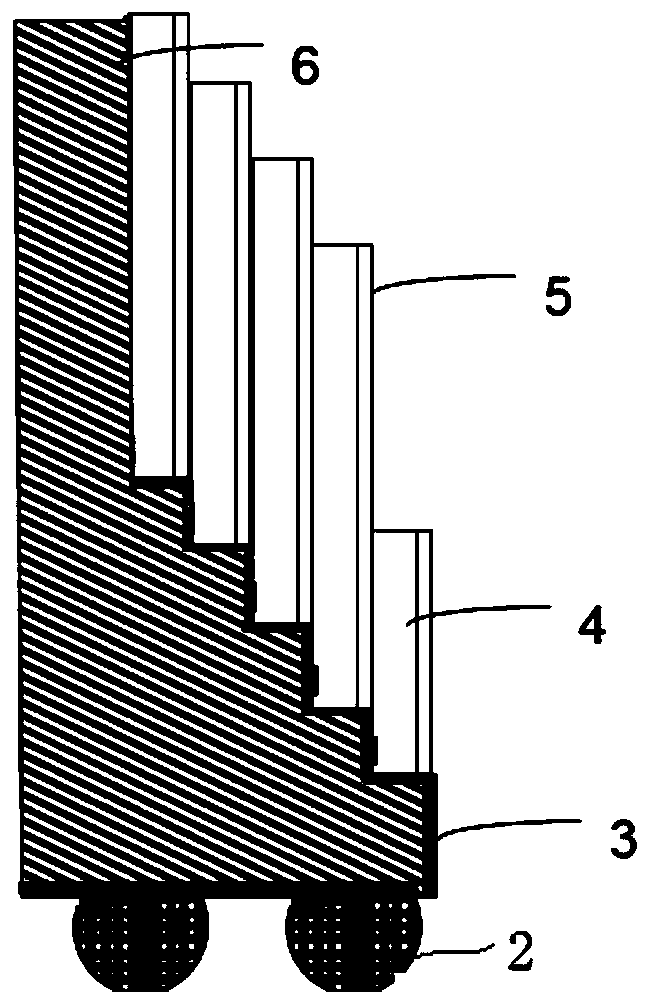

Solar cell and preparation method thereof

ActiveCN112909102AReduce usageReduce weightFinal product manufacturePhotovoltaic energy generationElectrical batteryEngineering

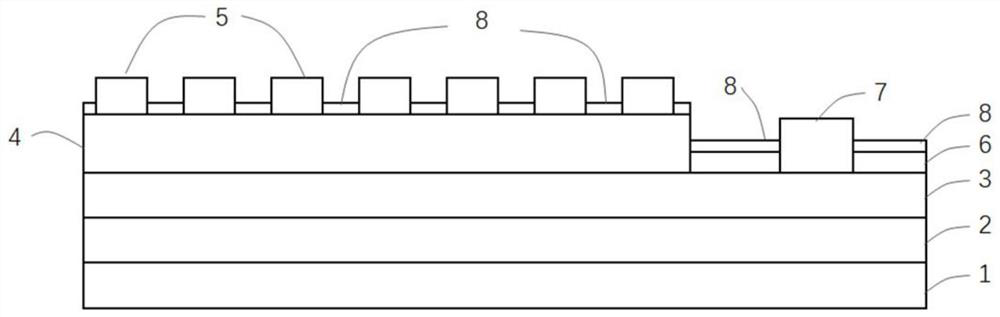

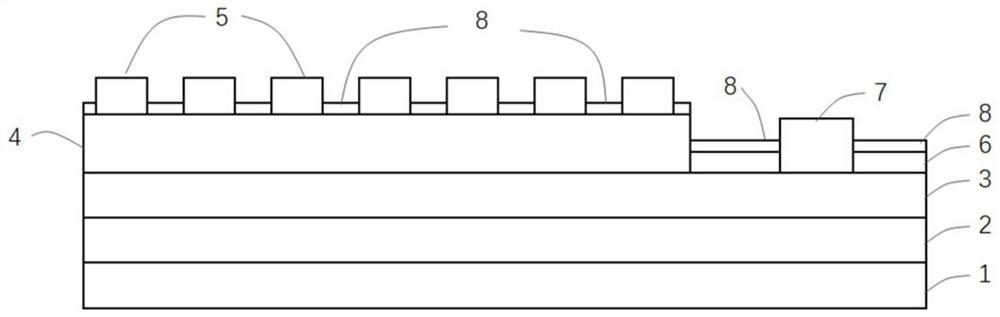

The invention provides a solar cell and a preparation method thereof. The solar cell is characterized in that the solar cell comprises a flexible substrate (1); a bonding layer (2), arranged on the surface of the flexible substrate (1); a back metal layer (3), arranged on the surface of the bonding layer (2); a battery material layer (4), arranged on the surface of the back metal layer (3); front electrode layers (5), arranged on the surface of the battery material layer (4) at equal intervals; a cut-off layer (6), arranged on the surface of the back metal layer (3), and the cut-off layer (6) being adjacent to the battery material layer (4); a back electrode (7) embedded in the cut-off layer (6); and anti-reflection film layers (8), arranged on the surface of the cell material layer (4) outside the front electrode layer (5) and the surface of the cut-off layer (6) outside the back electrode (7). The solar cell preparation method provided by the invention is low in cost, high in yield and high in power-to-weight ratio.

Owner:ZHONGSHAN DEHUA CHIP TECH CO LTD

A droplet ejection device and related method

ActiveCN112916286BJet stabilityEasy to useLiquid spraying apparatusRadio frequency signalEngineering

The present disclosure provides a droplet ejection device and related methods. The droplet ejection device comprises: a piezoelectric chip, an interdigital transducer arranged on the upper surface of the piezoelectric chip; the ratio of the thickness of the piezoelectric chip to the period of the interdigital transducer is 1 to 3 ; The interdigital transducer excites surface acoustic waves and bulk acoustic waves in the piezoelectric chip under the drive of radio frequency signals, and the surface acoustic waves and the bulk acoustic waves are reflected on the upper and lower surfaces of the piezoelectric chip to generate recombination Acoustic waves, to drive the liquid to be driven on the liquid attachment area to stretch along the direction perpendicular to the surface of the piezoelectric chip to form a liquid column, so that the liquid column will have a droplet pinch-off effect at the end, and a single droplet will be ejected; the liquid The attachment area is located on the upper surface and / or the lower surface of the piezoelectric chip corresponding to the area covered by the propagation of the surface acoustic wave generated by the interdigital transducer along the surface of the piezoelectric chip. It solves the problems of complicated device structure, high cost, low efficiency, and inconvenient realization of on-demand injection.

Owner:HARBIN INST OF TECH SHENZHEN GRADUATE SCHOOL

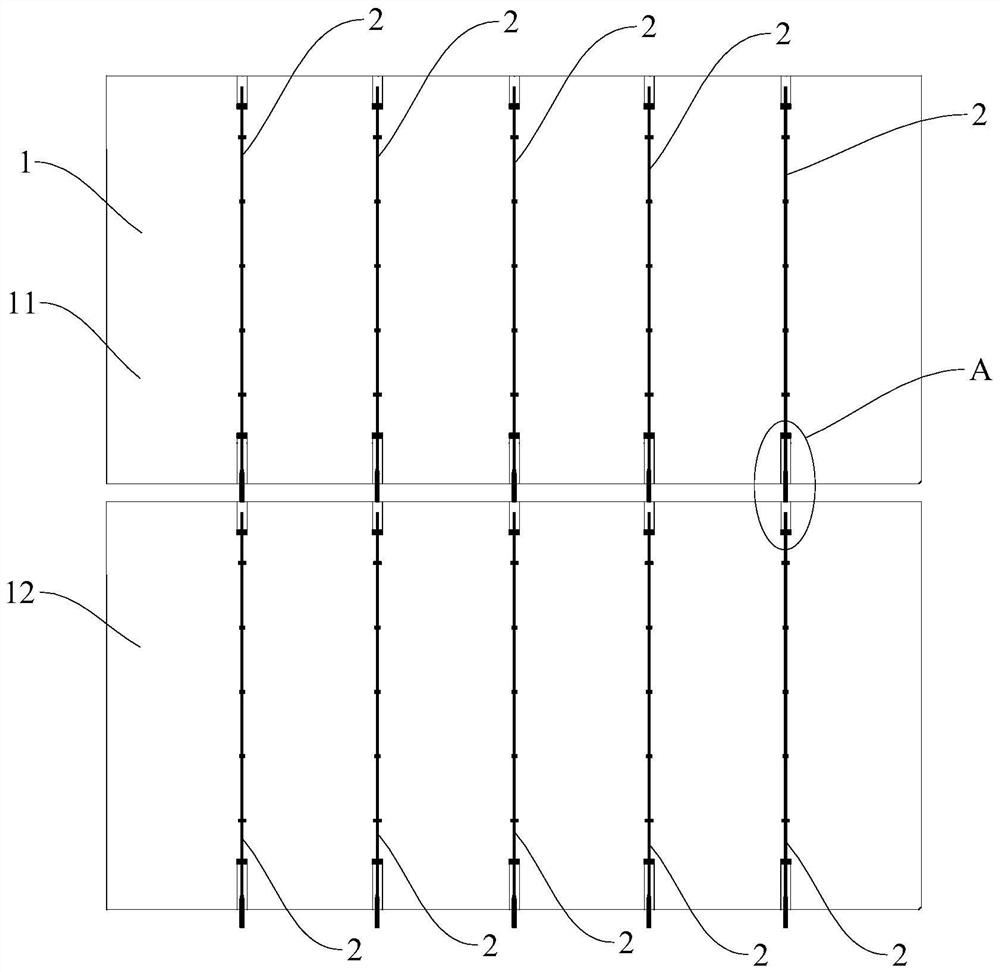

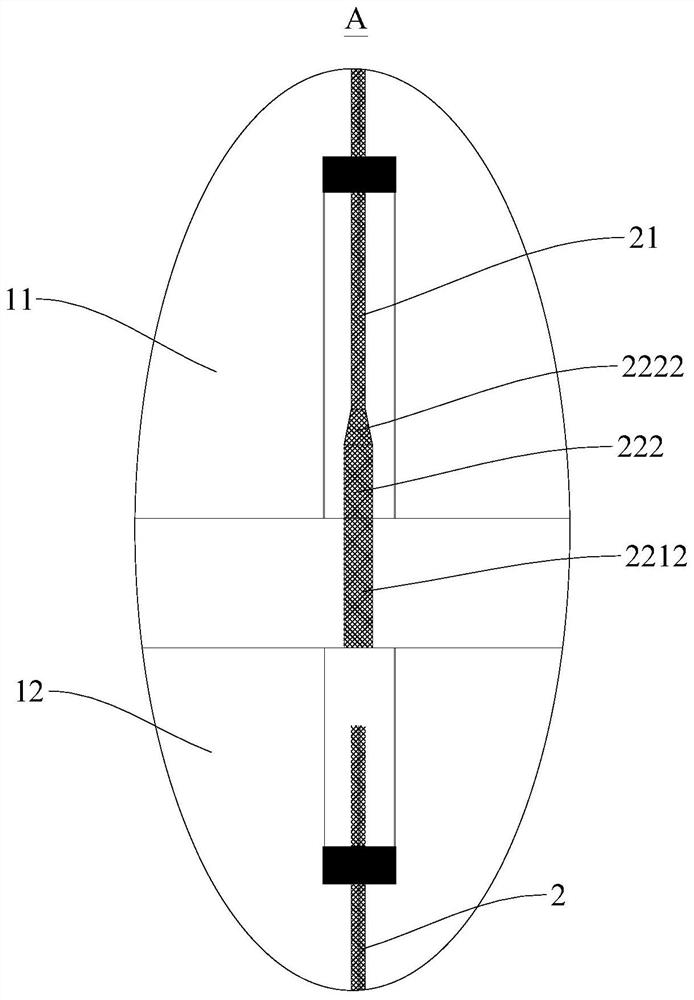

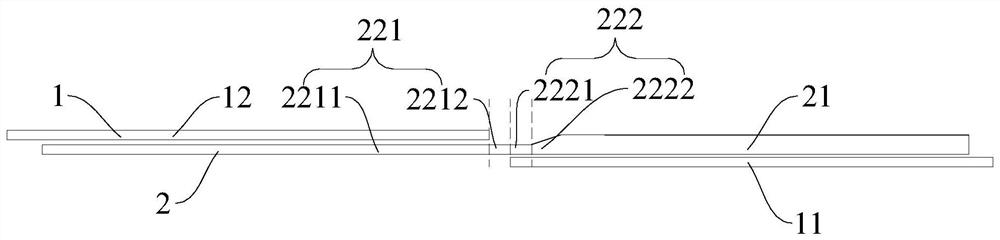

Solar cell and photovoltaic module

PendingCN114512553ARelieve pressureReduced risk of splinteringSemiconductor devicesElectrical batterySolar cell

The invention discloses a solar cell and a photovoltaic module, the cell comprises a plurality of main grid lines and auxiliary grid lines, the plurality of main grid lines are arranged in parallel on the front surface of the cell and extend along the first direction of the cell; a plurality of auxiliary grid lines are arranged in parallel and are vertically intersected with the main grid lines; wherein the first distance between the main grid line arranged close to the first edge of the battery piece and the first edge is larger than or equal to 10 mm, and the first edge is the edge, extending in the first direction, of the battery piece. The solar cell provided by the embodiment of the invention can reduce the risk of layer fracture.

Owner:CSI CELLS CO LTD +1

A kind of solar cell module and preparation method

ActiveCN111293190BImprove reliabilityReduced risk of splinteringFinal product manufacturePhotovoltaic energy generationElectrical batterySolar battery

The application discloses a solar cell module and its preparation method, which belongs to the technical field of solar cells, and solves the problem of external force at the edge of the overlapping area of the solar cell module in the prior art during the preparation process of the solar cell module and in the lamination process. It is prone to cracks or even slivers, and the problem of inconvenient processing. The preparation method of the present application includes the following steps: sequentially laying the first encapsulation film, the battery string, the second encapsulation film and the front cover on the rear cover to obtain a laminate; laminating the laminate to obtain a solar cell The assembly; the battery string includes a plurality of battery sheets connected in a head-to-tail overlapping manner; the first encapsulation film includes a main body and a plurality of local protrusions arranged on the main body and corresponding to the overlapping areas of the battery sheets, and / or Alternatively, the second encapsulation film includes a main body and a plurality of local protrusions disposed on the main body and corresponding to overlapping regions of the battery sheets. This application can be used for solar power generation.

Owner:晶澳(扬州)新能源有限公司

Modular multi-chip packaging structure and packaging method thereof

ActiveCN111063664AReduce package sizeAvoid lostSemiconductor/solid-state device detailsSolid-state devicesBond lineEngineering

The invention discloses a modular multi-chip packaging structure and a packaging method thereof. A plurality of packaging units arrayed on a substrate are packaging units formed by a plurality of chips which are stacked in a stepped manner. The lead ends of the chips stacked in a stepped manner are positioned on the surfaces of the steps, and the lead ends of the plurality of chips are connected through chip wiring. Chip routing is not needed, the packaging volumes of the chips are reduced, and the loss of the electrical property on a wire bond line is avoided. Plastic packaging is carried outon the step surfaces on one sides of the lead ends of the plurality of chips through a first plastic packaging body. An etching circuit connected with the chip wiring is arranged at the bottom of thefirst plastic packaging body, connection wiring is arranged on the substrate, and the etching circuit at the bottom of the first plastic packaging body is connected with the connection wiring on thesubstrate. Finally, the plurality of packaging units are packaged on the substrate through a second plastic packaging body, and the chips are vertically arranged on the substrate after plastic packaging. Different functions can be integrated by packaging the independent modules together, the limitation of traditional multi-chip packaging is well broken through, the structure is simple, and the connection is stable.

Owner:华天科技(南京)有限公司

Photovoltaic module

PendingCN112133782AReduced risk of splintersSecure connectionPhotovoltaic energy generationSemiconductor devicesMaterials scienceEngineering physics

The invention discloses a photovoltaic module, and the photovoltaic module comprises a plurality of battery pieces and a plurality of interconnection structural parts; and two adjacent battery piecesin the plurality of battery pieces are respectively a first battery piece and a second battery piece; each interconnection structural part comprises a light reflecting section and connecting sectionswhich are connected with each other, the connecting sections comprise a first connecting section and a second connecting section, the first connecting section and the light reflecting section are connected to the two ends of the second connecting section respectively, the first connecting section is flat, and at least one part of the second connecting section is flat; the reflecting section is non-flat, the reflecting section and the second connecting section are both connected to the front surface of the first battery piece, and at least one part of the first connecting section is connected to the back surface of the second battery piece. According to the photovoltaic module provided by the invention, the reflecting section can be prevented from being positioned on the back surface of thebattery piece, the risk of battery piece cracking is effectively reduced, firm connection between the interconnection structural member and the front surface of the battery piece can be realized, andthe reliability of the photovoltaic module is improved.

Owner:CSI CELLS CO LTD +1

A kind of solar cell and preparation method thereof

ActiveCN112909102BReduce usageReduce weightFinal product manufacturePhotovoltaic energy generationEngineeringSolar battery

The invention provides a solar cell and a preparation method thereof. A solar cell, characterized in that it comprises a flexible substrate (1); an adhesive layer (2) placed on the surface of the flexible substrate (1); a back metal layer (3) arranged on the surface of the adhesive layer (2) The battery material layer (4) that is arranged on the surface of the back metal layer (3); the front electrode layer (5) that is arranged on the surface of the battery material layer (4) at equal intervals; the cut-off layer ( that is arranged on the surface of the back metal layer (3) 6), and the cut-off layer (6) is adjacent to the battery material layer (4); the back electrode (7) embedded in the cut-off layer (6); the battery material layer ( 4) the surface, and the anti-reflection film layer (8) on the surface of the cut-off layer (6) other than the back electrode (7). The solar cell preparation method provided by the invention has low cost, high yield rate and high power-to-weight ratio.

Owner:ZHONGSHAN DEHUA CHIP TECH CO LTD

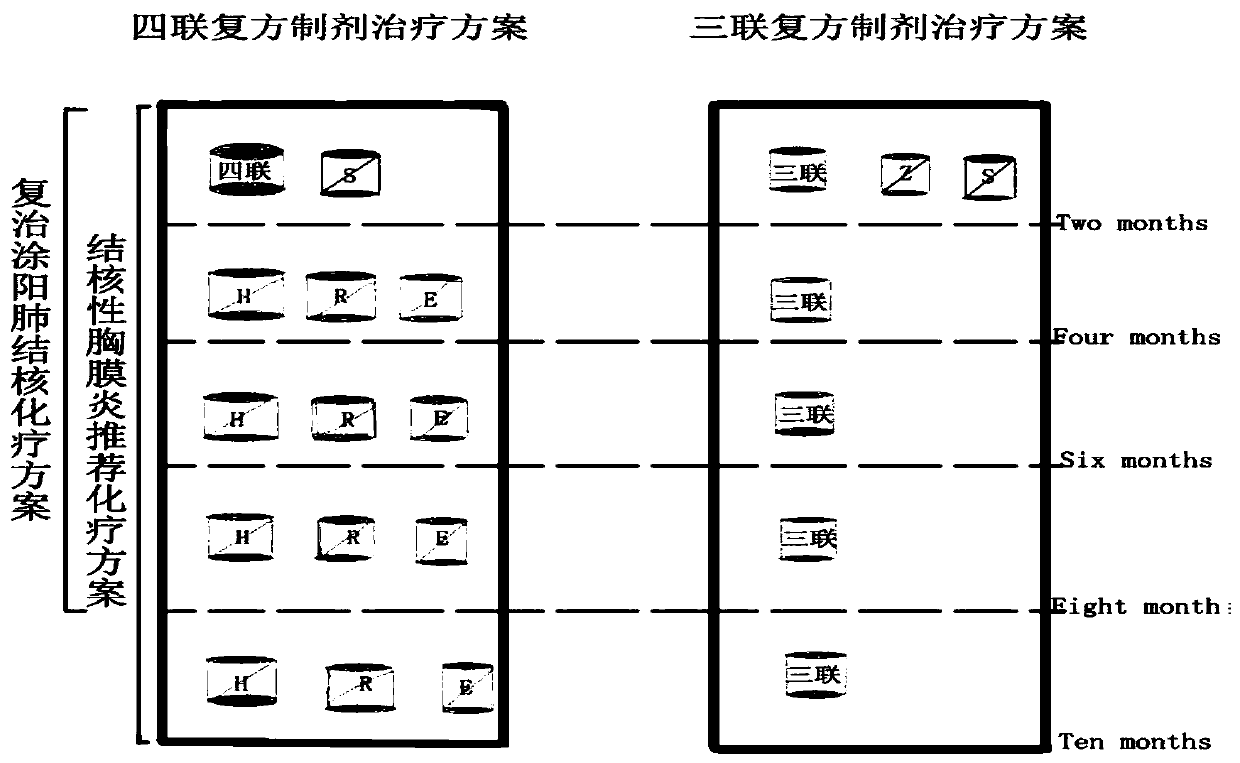

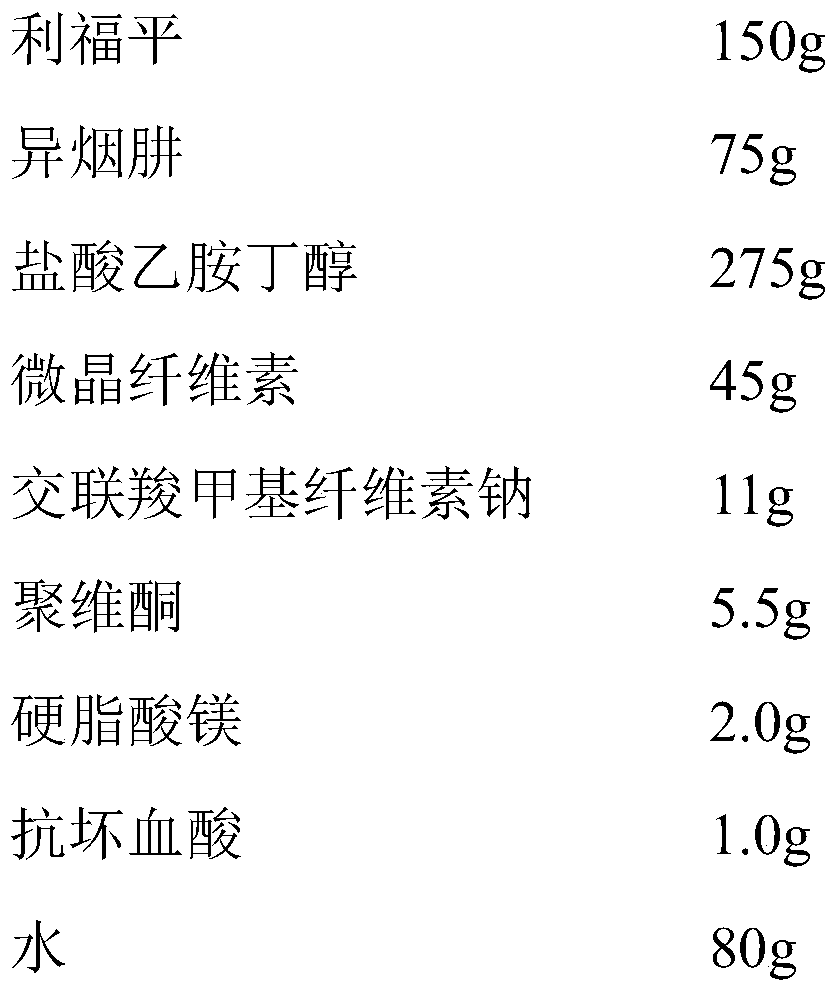

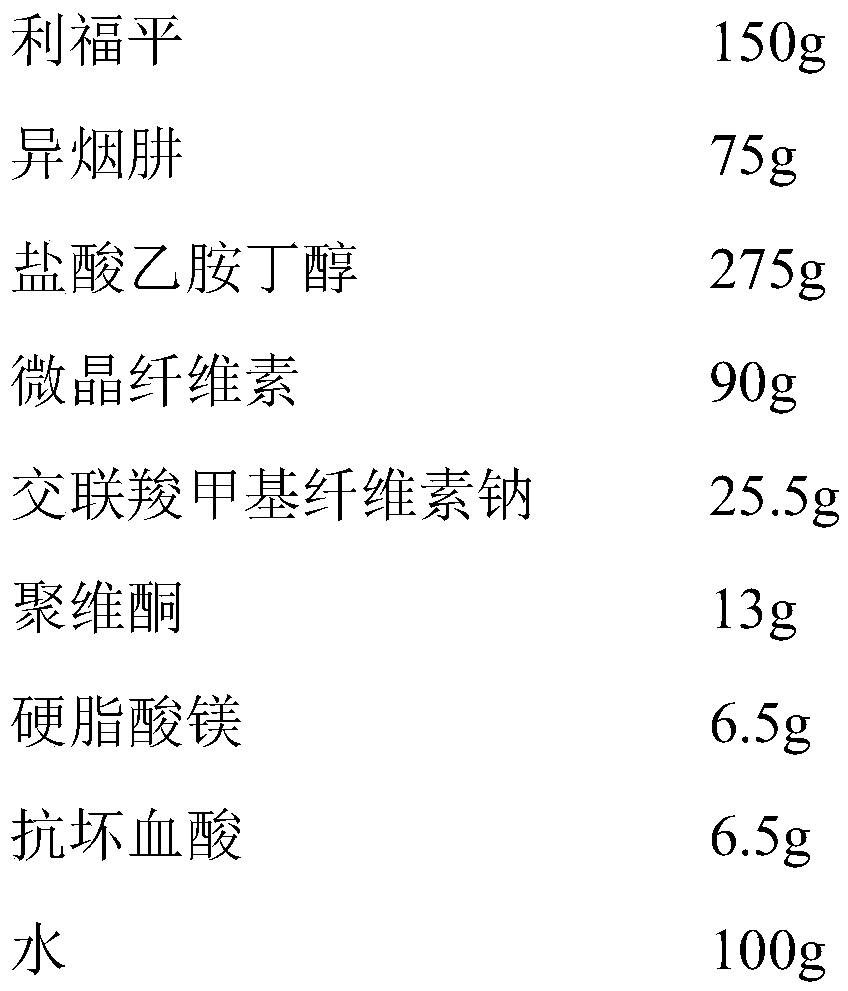

Composition for preparing triple compound preparation for treatment of pulmonary tuberculosis and preparation method and application of composition

The invention belongs to the technical field of pharmaceutical preparation and particularly relates to a composition for preparing a triple compound preparation for treatment of pulmonary tuberculosis, a preparation method and application of the composition and a prepared medicine. The composition comprises rifampicin, isoniazide, ethambutol or pharmaceutically acceptable ethambutol salt and an analogue thereof. Compared with a quadruple compound preparation, the triple compound preparation which is a triple compound tablet is small in size, easy to swallow, low in cracking risk and convenientfor patients to take and is applicable to the whole treatment period of recurrent smear-positive pulmonary tuberculosis and tuberculous pleuritis. By adoption of the preparation, tablet intake and pharmaceutical adjuvant amount can be sharply reduced, and accordingly compliance of the patients can be improved while drug resistance is reduced.

Owner:CHONGQING HUAPONT PHARMA

Bonding structure and manufacturing method thereof

ActiveCN110189985BHigh bonding strengthImprove reliabilitySemiconductor/solid-state device detailsSolid-state devicesWafer stackingEngineering

The present application provides a bonding structure and a manufacturing method thereof. When bonding the nth wafer to the n-1th wafer, the first edge trimming can be performed from the bonding surface of the nth wafer. , the width of the first edge trimming is W n , as n increases, the first edge trimming width can gradually increase, this is because the edge of the wafer is usually not smooth enough, resulting in gaps in the wafer during bonding, after edge trimming of the wafer, The uneven part at the edge of the n-th wafer can be removed, and the bonding surface of the n-th wafer faces the bonding surface of the n-1-th wafer, and the n-th wafer and the n-1-th Wafer bonding, reducing the possibility of gaps between wafer bonding interfaces, improving the bonding strength between wafers, and then thinning the n-th wafer substrate to form the n-1th wafer stack , due to the stronger bonding strength between adjacent wafers, the resulting wafer stack has higher reliability and lower risk of splitting.

Owner:WUHAN XINXIN SEMICON MFG CO LTD

A kind of heterogeneous semiconductor thin film and preparation method thereof

ActiveCN111834205BQuality improvementImprove material propertiesSolid-state devicesSemiconductor/solid-state device manufacturingChemical physicsWafering

The invention discloses a method for preparing a heterogeneous semiconductor thin film, comprising: obtaining a semiconductor single crystal wafer with a first polished surface; obtaining a heterogeneous substrate with a second polished surface; After depositing a layer of buffer layer on the top to form the first composite structure; implanting barrier layer ions into the semiconductor single crystal wafer to form a barrier layer; annealing treatment; implanting H ions into the semiconductor single crystal wafer along the channel of the semiconductor single crystal wafer, the H ion The atomic number is smaller than the atomic number of the barrier layer ions, and the implantation energy is greater than the implantation energy of the barrier layer ions; the buffer layer is removed; the semiconductor single crystal wafer is bonded to the heterogeneous substrate to obtain the second composite structure; annealing treatment is obtained to obtain the heterogeneous semiconductor film. The invention forms a barrier layer in the semiconductor single crystal wafer by implanting barrier layer ions to trap H ions, thus reducing damage caused by ion stripping, thereby greatly improving the utilization rate of H ions and the quality of the film.

Owner:SHANGHAI INST OF MICROSYSTEM & INFORMATION TECH CHINESE ACAD OF SCI

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com