Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

303results about How to "Reduce parasitic inductance" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

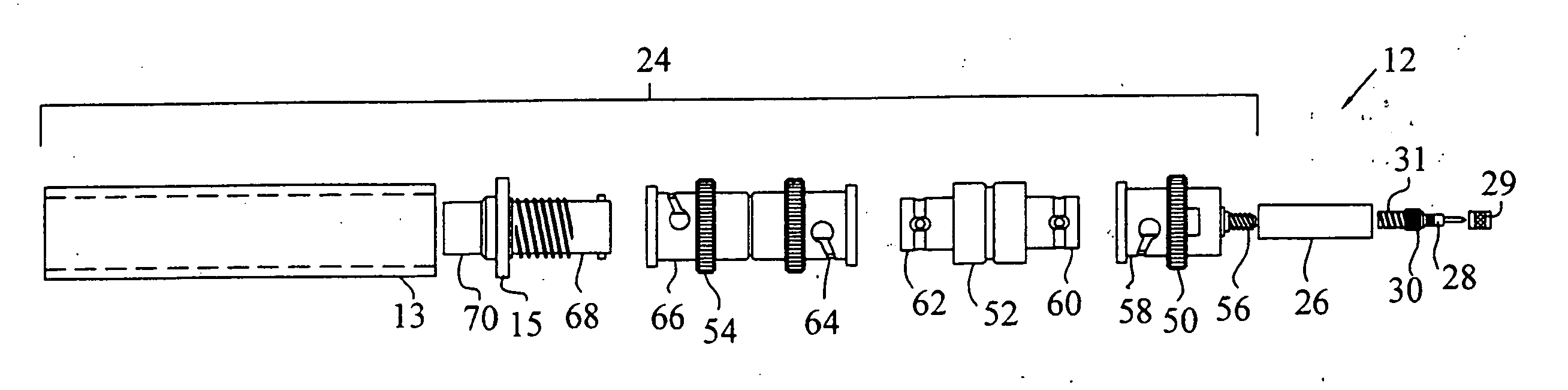

Ultra-broadband differential voltage probes

ActiveUS7015709B2Reduce parasitic inductanceError minimizationElectrical testingMeasurement leads/probesElectricityElectrical conductor

Passive balanced probes are disclosed for use with a signal analysis device. The probes are very low cost relative to typical commercially available probes and provide an extremely flat response over a frequency range of approximately 0 to at least 1.5 gigahertz. The probes include a probe body constructed primarily from conventional components, a first surface mount resistor electrically connected between a probe tip and a center conductor, and two surface mount resistors electrically connected and parallel between the center conductor and a conductive shield. The probes further include a coaxial cable for connection to an instrument combiner or other instrument connection device.

Owner:APTIV TECH LTD

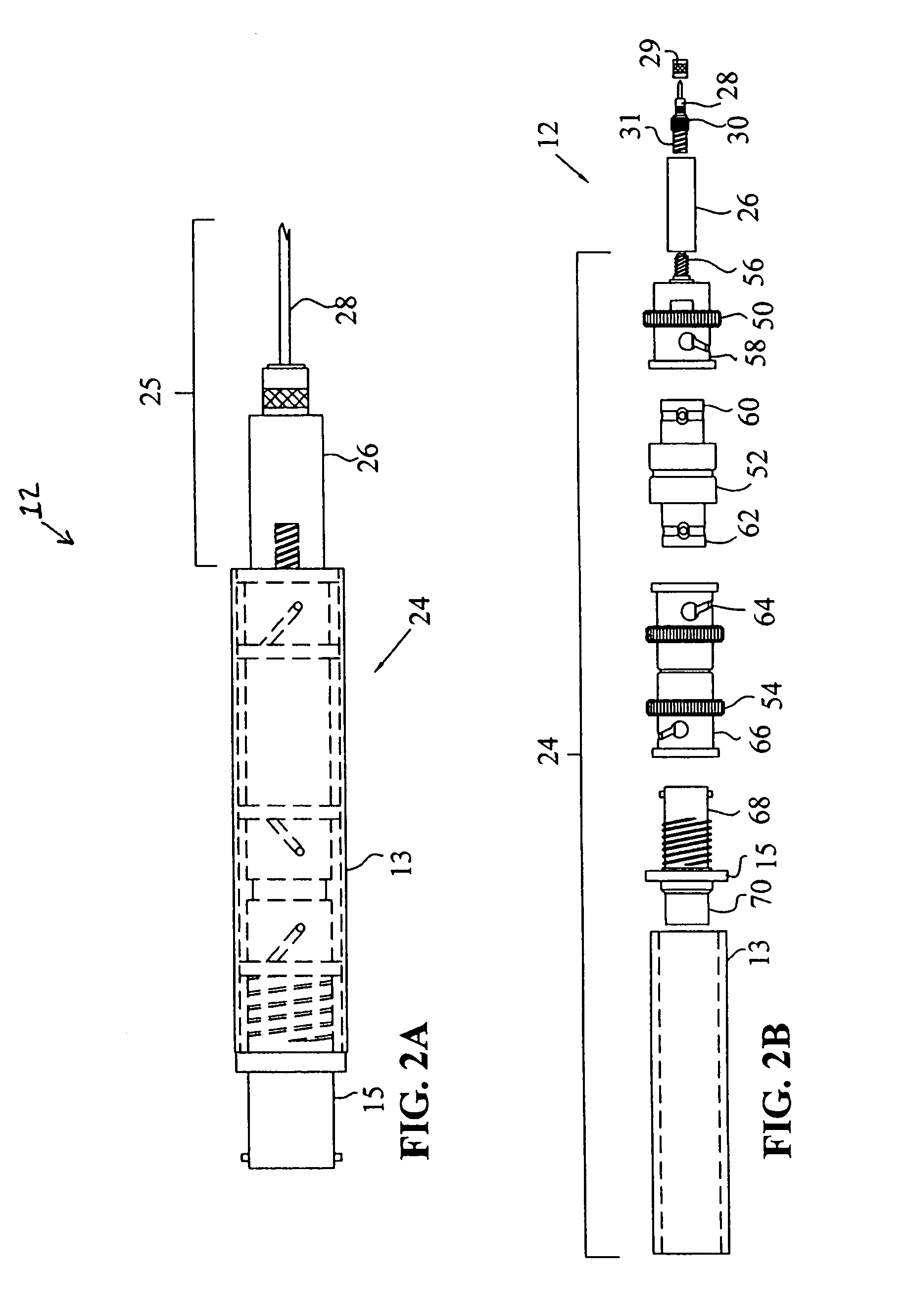

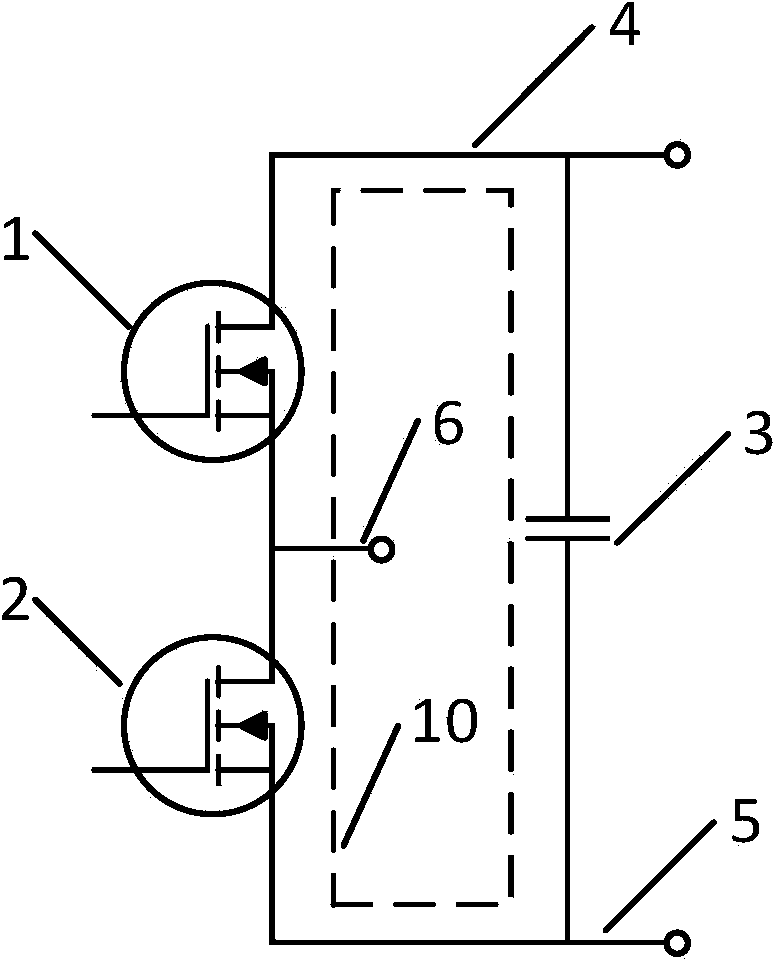

High-reliability MOSFET drive circuit

The invention relates to a drive circuit applied to a power switch tube MOSFET, in particular to a drive circuit of a silicon carbide MOSFET, and belongs to the technical field of drive circuits. The drive circuit aims to solve the problem that when an MOSFET in an existing drive circuit is turned off, the reliability is poor. The drive circuit comprises a PWM control circuit, a drive pulse amplifying circuit, a drive resistor Rg, a first diode D1, a resistor R1, a PNP triode Qoff, a second diode D2 and a capacitor C. According to the drive circuit, the PNP triode Qoff, the resistor R1 and the capacitor C form an MOSFET turn-off circuit; when the MOSFET is turned off quickly, a gate pole positive voltage spike caused by Miller currents is effectively suppressed; meanwhile, a gate pole negative voltage spike can also be suppressed through the second diode D2 and the capacitor C, it is guaranteed that the MOSFET is turned off safely and reliably, and the performance advantages of the silicon carbide MOSFET can be given to full play.

Owner:NANJING UNIV OF AERONAUTICS & ASTRONAUTICS

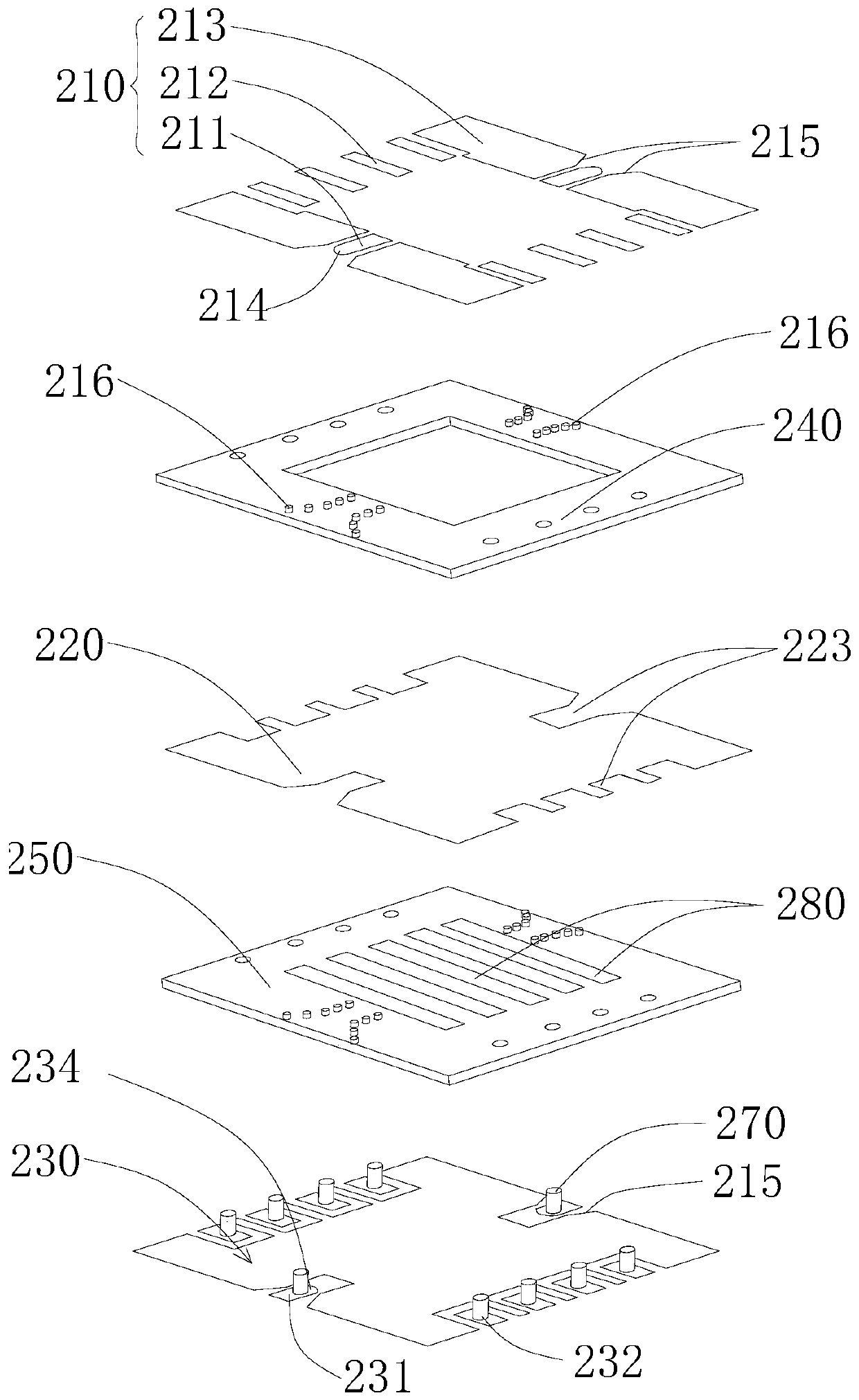

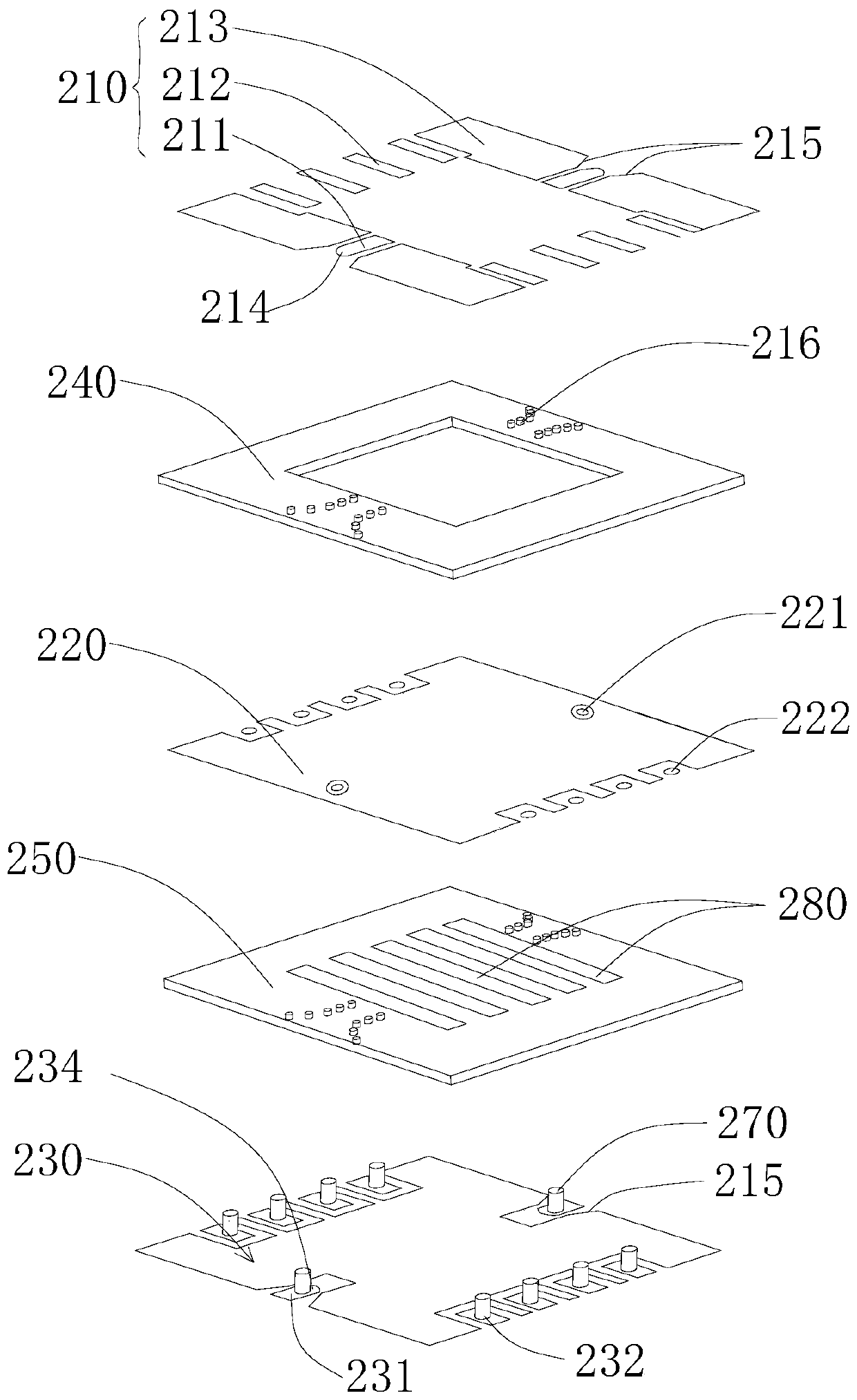

Millimeter wave frequency band amplifier chip packaging structure and manufacturing method thereof

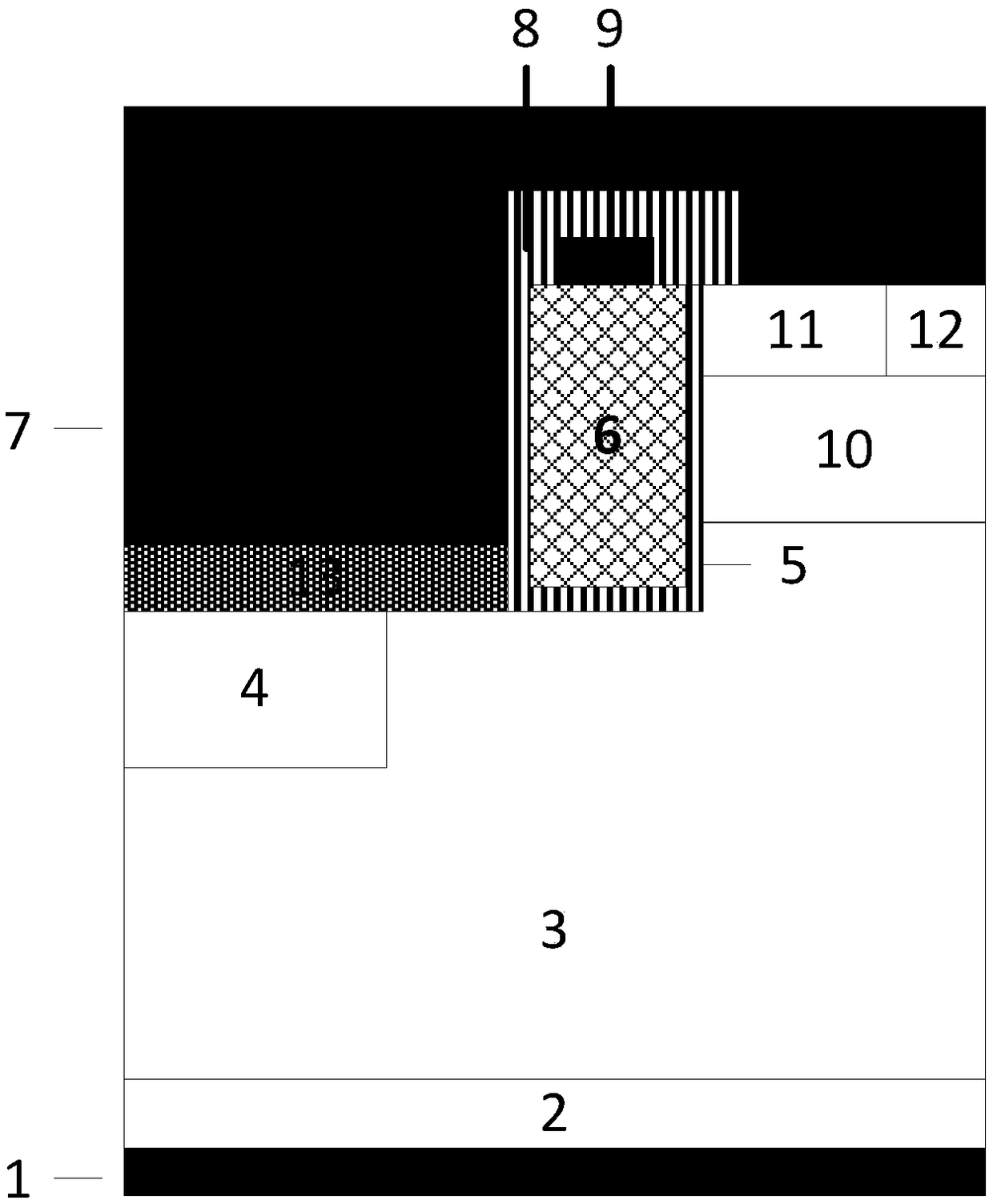

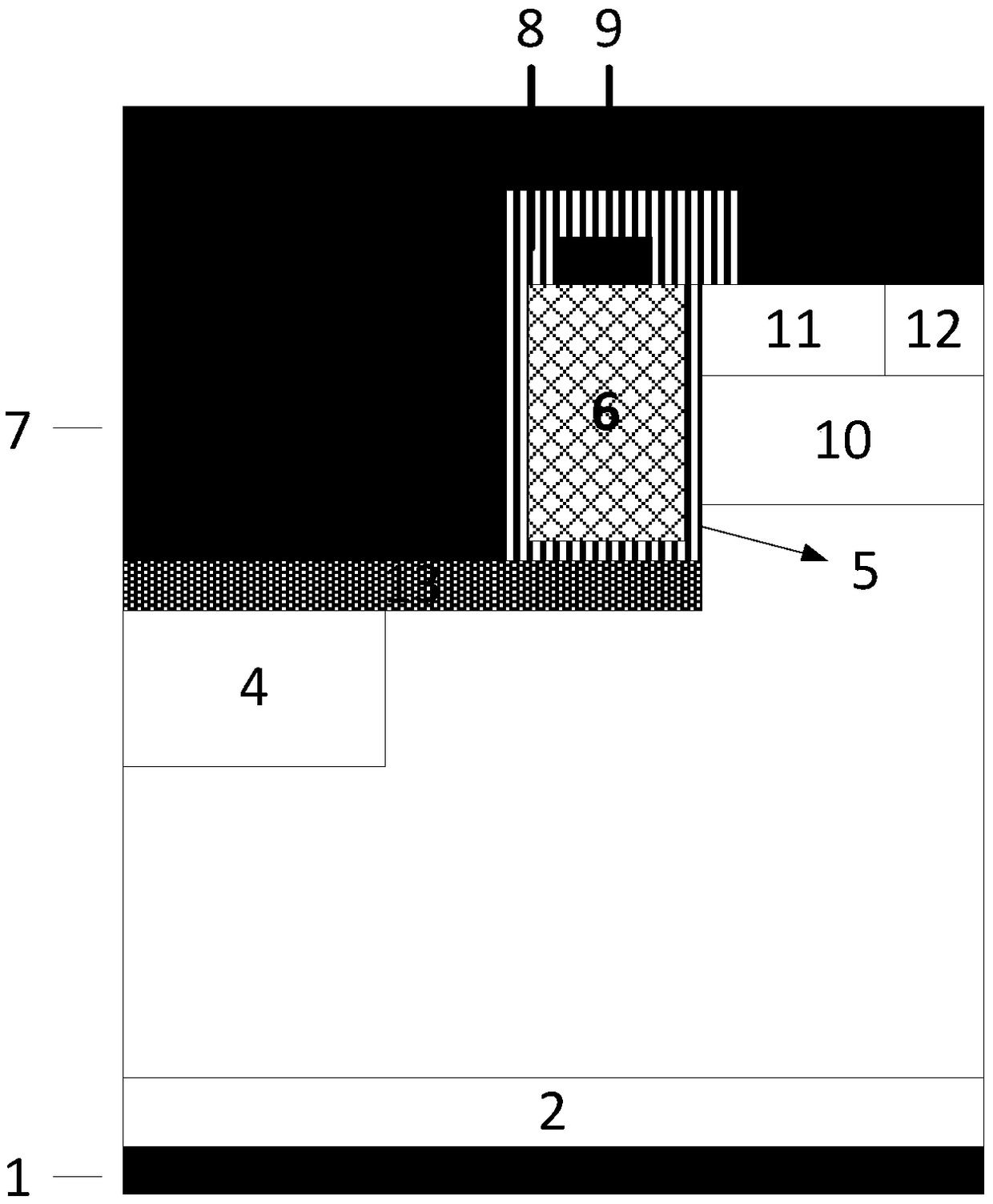

PendingCN110739288AImprove transmission performanceImprove your own RF performanceSemiconductor/solid-state device detailsSolid-state devicesMillimetre waveRadio frequency

The invention provides a millimeter wave frequency band amplifier chip packaging structure and a manufacturing method thereof and relates to the technical field of chip packaging. The structure comprises a chip, a packaging substrate and a sealing cover, wherein the packaging substrate is provided with a first metal layer, a first dielectric layer, a second metal layer, a second dielectric layer and a third metal layer which are sequentially stacked from top to bottom, the sealing cover is arranged on the packaging substrate and used for sealing the packaging substrate, and the sealing cover is provided with an inner cavity with a downward opening. The millimeter wave frequency band amplifier chip packaging structure is advantaged in that the packaging substrate and the sealing cover are combined, an accommodating groove is formed in the packaging substrate so that the chip is accommodated, the connection length between the chip and the packaging substrate is effectively shortened, theparasitic inductance is conveniently reduced, and the transmission capability of the chip is improved; the sealing cover with the inner cavity enables connection between a chip direct-current port ofthe chip and the packaging substrate to be in direct contact with air, so loss of a high-frequency band is reduced, and radio frequency performance of the chip is improved.

Owner:NORTH-CHINA INTEGRATED CIRCUIT CO LTD

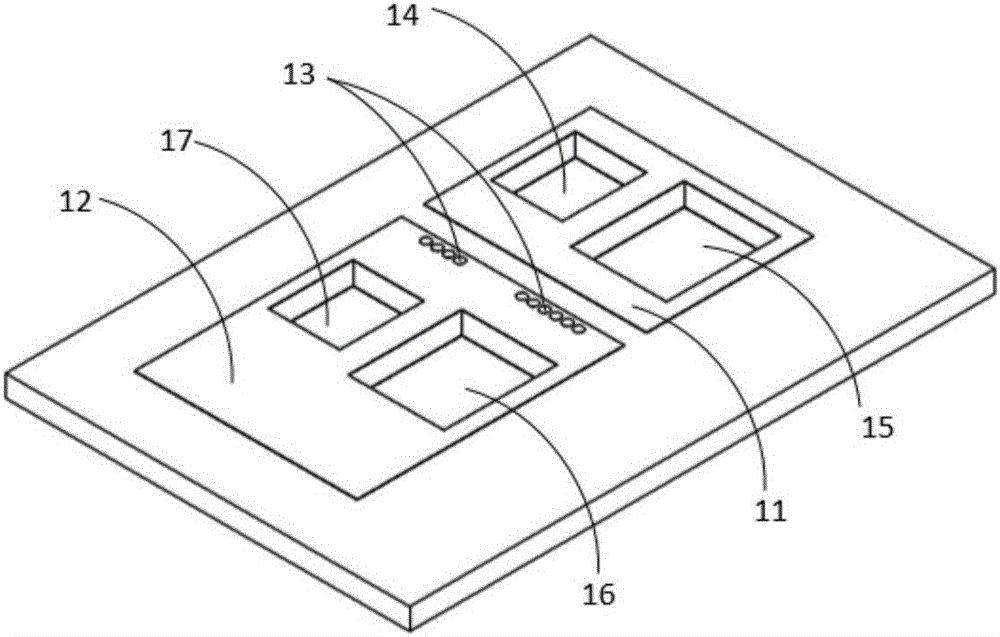

Substrate embedded power device packaging structure and manufacturing method thereof

InactiveCN109727969AReduce parasitic inductanceImprove cooling efficiencySemiconductor/solid-state device detailsSolid-state devicesResistInterconnection

The invention discloses a substrate embedded power device packaging structure comprising: a substrate having a metalized through hole and a first power chip embedding slot; a first power chip disposedin the first power chip embedding slot; a photo-imageable dielectric (PID) covering the upper and lower sides of the substrate, and provided with an upper opening and a lower opening at positions corresponding to the metalized through hole and the electrode of the first power chip; an upper metal layer disposed on the upper surface of the PID and in the upper opening, and in electric interconnection to the first surface electrode of the first power chip and the metalized through hole; a lower metal layer disposed on the lower surface of the PID and in the lower opening, and in electric interconnection to the second surface electrode of the first power chip and the metalized through hole; an upper solder resist layer covering the upper metal layer; a lower solder resist layer covering thelower metal layer; and a metalized bonding pad.

Owner:NAT CENT FOR ADVANCED PACKAGING

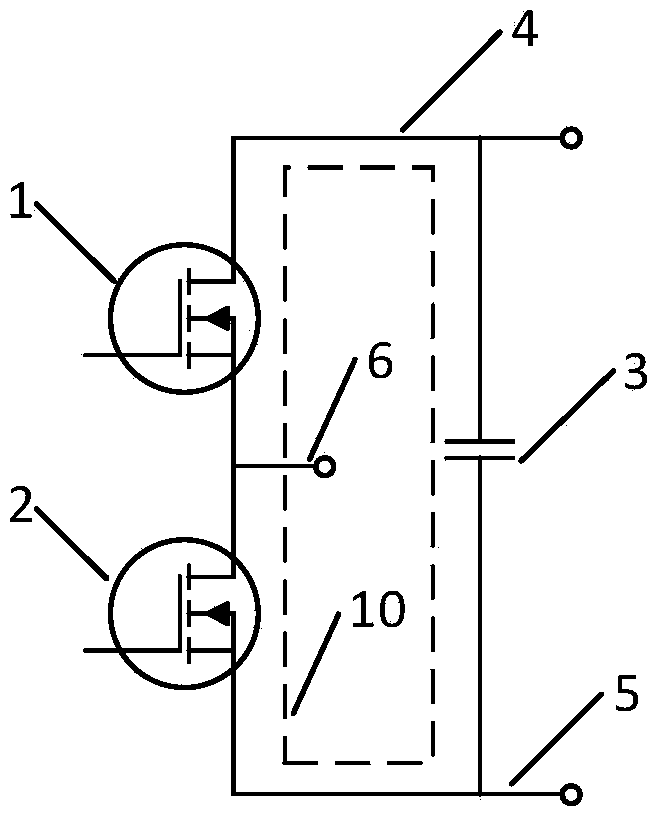

Double-surface low-parasitic inductance GaN power integrated module

ActiveCN104112718AReduce areaReduce parasitic inductanceSemiconductor/solid-state device detailsSolid-state devicesCapacitanceHigh frequency power

The invention discloses a double-surface low-parasitic inductance GaN power integrated module. The double-surface low-parasitic inductance GaN power integrated module comprises an upper bridge arm apparatus, a lower bridge arm apparatus and a bus capacitor. The upper bridge arm apparatus and the lower bridge arm apparatus are LGA packaged GaN apparatuses, and the bus capacitor uses chip packaging. One apparatus is arranged at the front surface of a substrate while the other is arranged at the reverse surface of the substrate, and the source electrode of the upper bridge arm apparatus is opposite to the drain electrode of the lower bridge arm apparatus and directly connected with the drain electrode of the lower bridge arm apparatus through holes. The bus capacitor is arranged at two sides of the upper bridge arm apparatus. The arrangement mode of the double-surface low-parasitic inductance GaN power integrated module is capable of effectively reducing the area of a high-frequency power loop and completely uses the crossed structure of LGA packaging drain electrodes and source electrodes to form a plurality of crossed and parallel high-frequency power current loops, and accordingly the parasitic inductance of the high-frequency power loops is greatly lowered, and the over-voltage and oscillation are effectively reduced in the switching process.

Owner:XI AN JIAOTONG UNIV

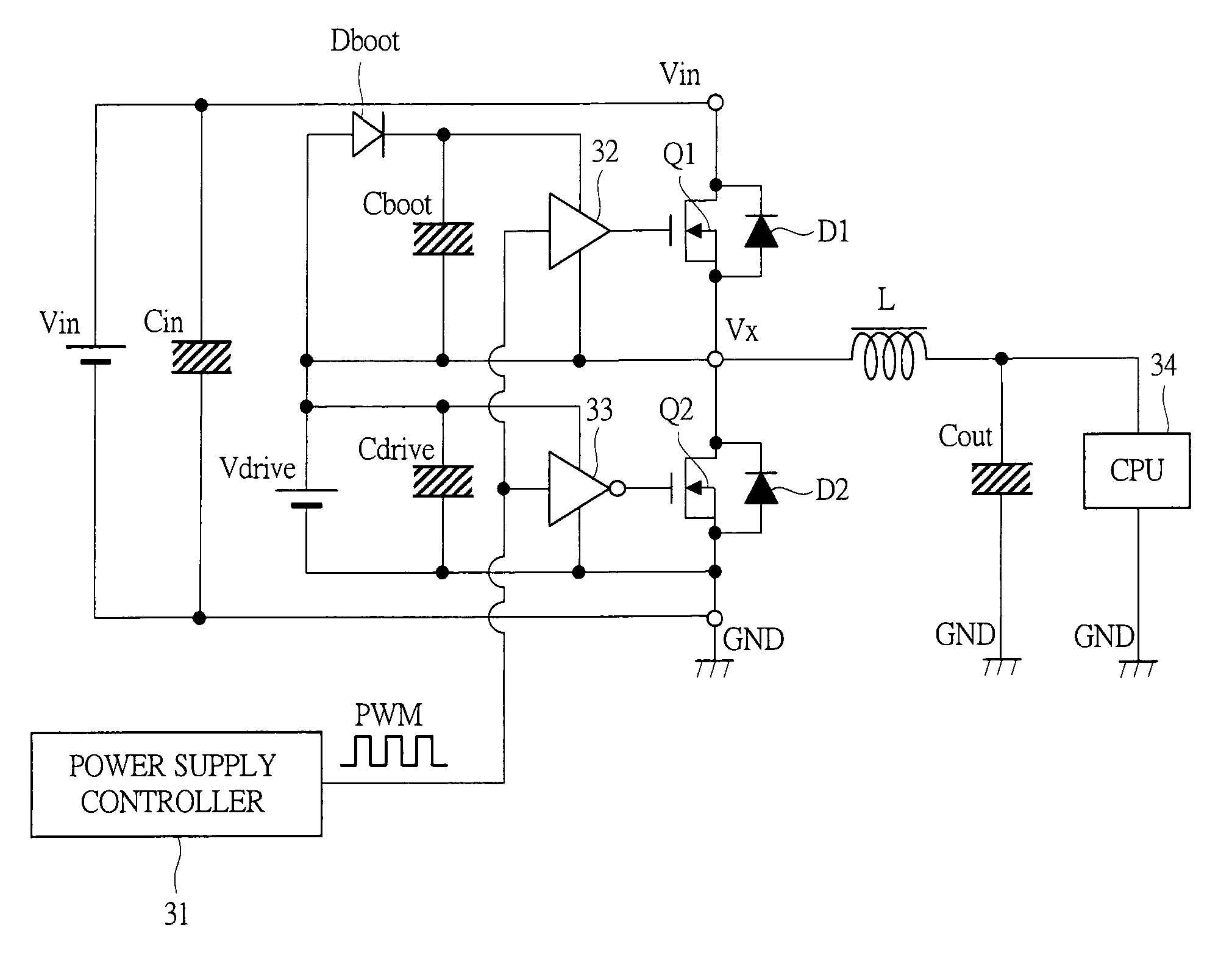

Semiconductor device

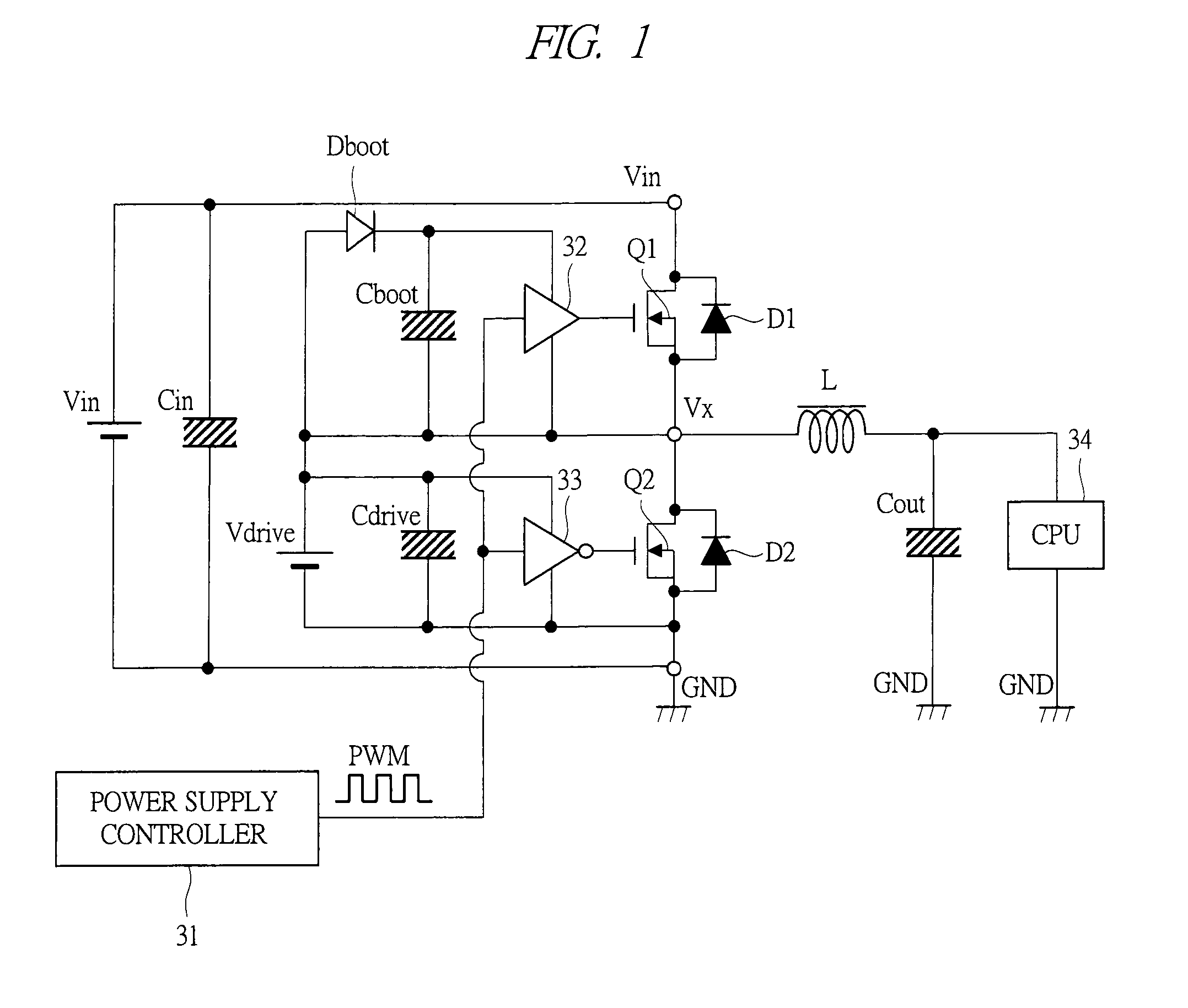

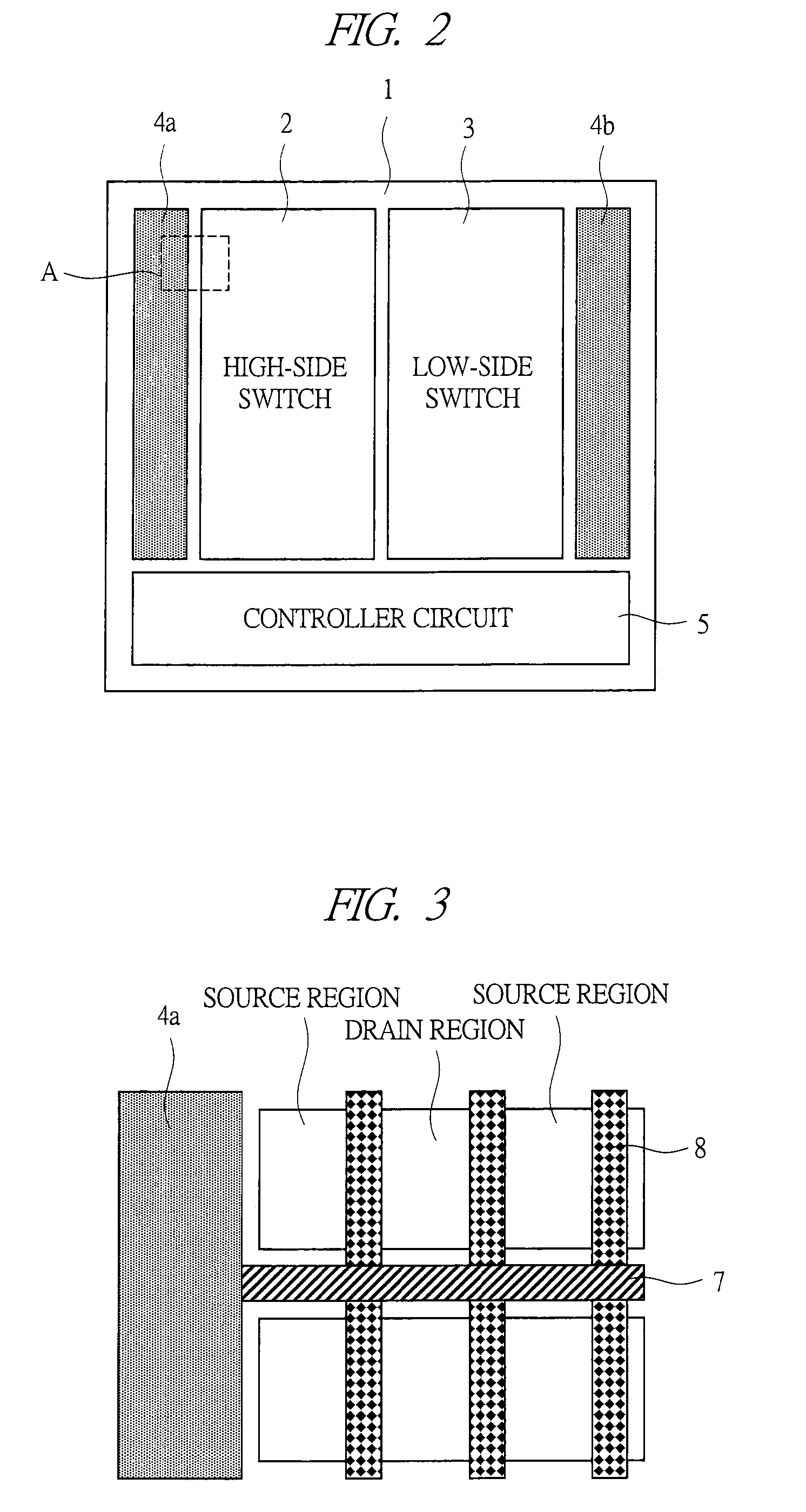

InactiveUS20100001790A1Reduce parasitic inductanceConversion efficiency be highTransistorConversion constructional detailsCapacitanceEngineering

In a semiconductor device, a high-side driver is arranged in a region closer to a periphery of a semiconductor substrate than a high-side switch, and a low-side driver is arranged in a region closer to the periphery of the semiconductor substrate than the low-side switch. By this means, a path from a positive terminal of an input capacitor to a negative terminal of the input capacitor via the high-side switch and the low-side switch is short, a path from a positive terminal of a drive capacitor to a negative terminal of the drive capacitor via the low-side driver is short, and a path from a positive terminal of a boot strap capacitor to a negative terminal of the boot strap capacitor via the high-side driver is short, and therefore, the parasitic inductance can be reduced, and the conversion efficiency can be improved.

Owner:RENESAS ELECTRONICS CORP

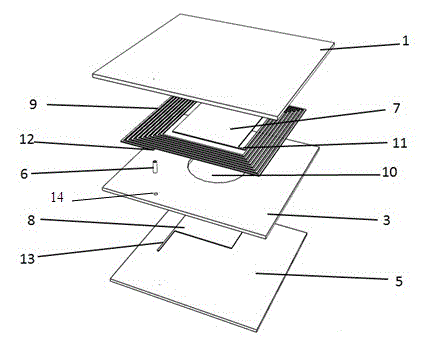

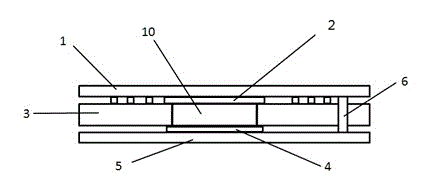

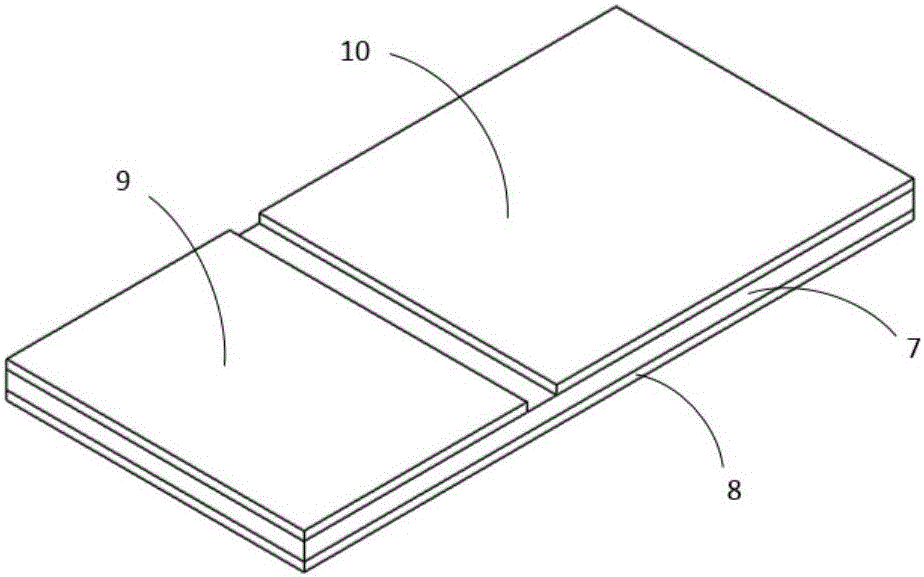

Flexible-substrate-based passive wireless pressure sensor with self-packaging function

InactiveCN103148977AProtection capacitorProtection inductanceFluid pressure measurement using capacitance variationCapacitanceEngineering

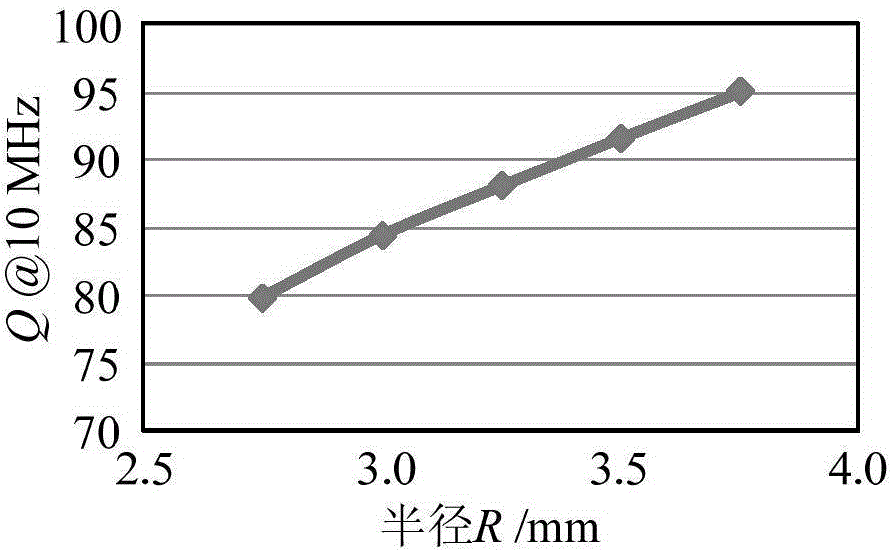

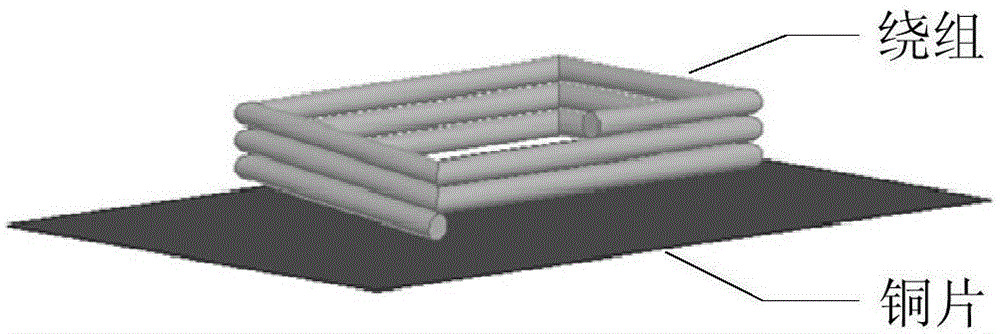

The invention discloses a flexible-substrate-based passive wireless pressure sensor with a self-packaging function. The pressure sensor comprises an upper flexible substrate, an upper metal layer, a middle flexible substrate, a lower metal layer and a lower flexible substrate, which are sequentially arranged from top to bottom and fixedly connected. An electric through hole and a cavity are formed in the middle flexible substrate. The upper metal layer comprises a planar inductance coil and a capacitor upper polar plate positioned on the middle part of the planar inductance coil. An inner connector of the planar inductance coil is connected with the capacitor upper polar plate. The lower metal layer comprises a capacitor lower polar plate opposite to the upper plate capacitor and an interconnecting wire connected with the capacitor upper polar plate. The sizes of the capacitor upper polar plate and capacitor lower polar plate are the same. An outer connector of the planar inductance coil of the upper metal layer is connected with the interconnecting wire of the lower metal layer through a conductive medium column in the electric through hole. The cavity of the middle flexible substrate is positioned between the capacitor upper polar plate and capacitor lower polar plate. The pressure sensor has the high performance of self packaging, non-contact, high sensitivity and high quality factor.

Owner:SOUTHEAST UNIV

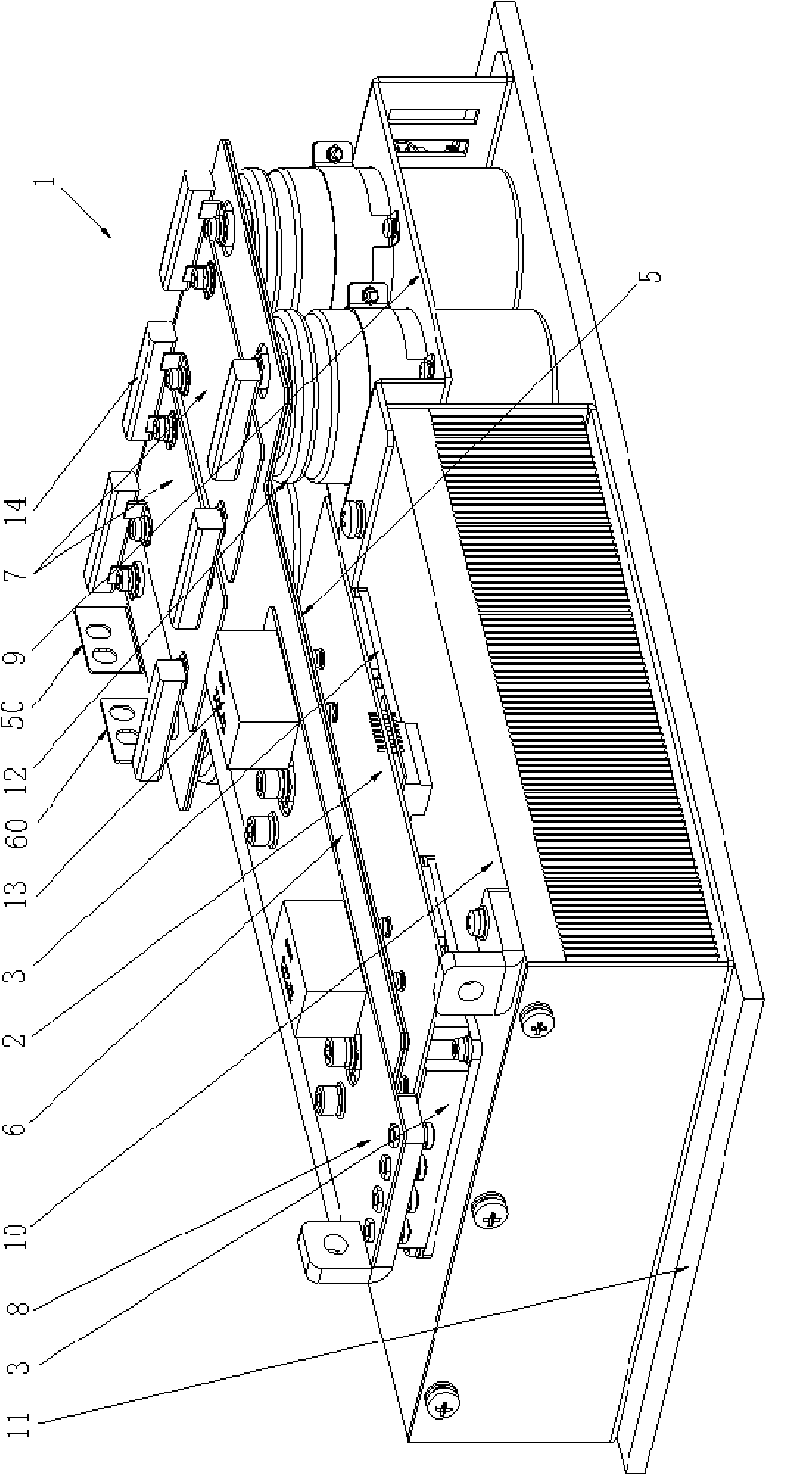

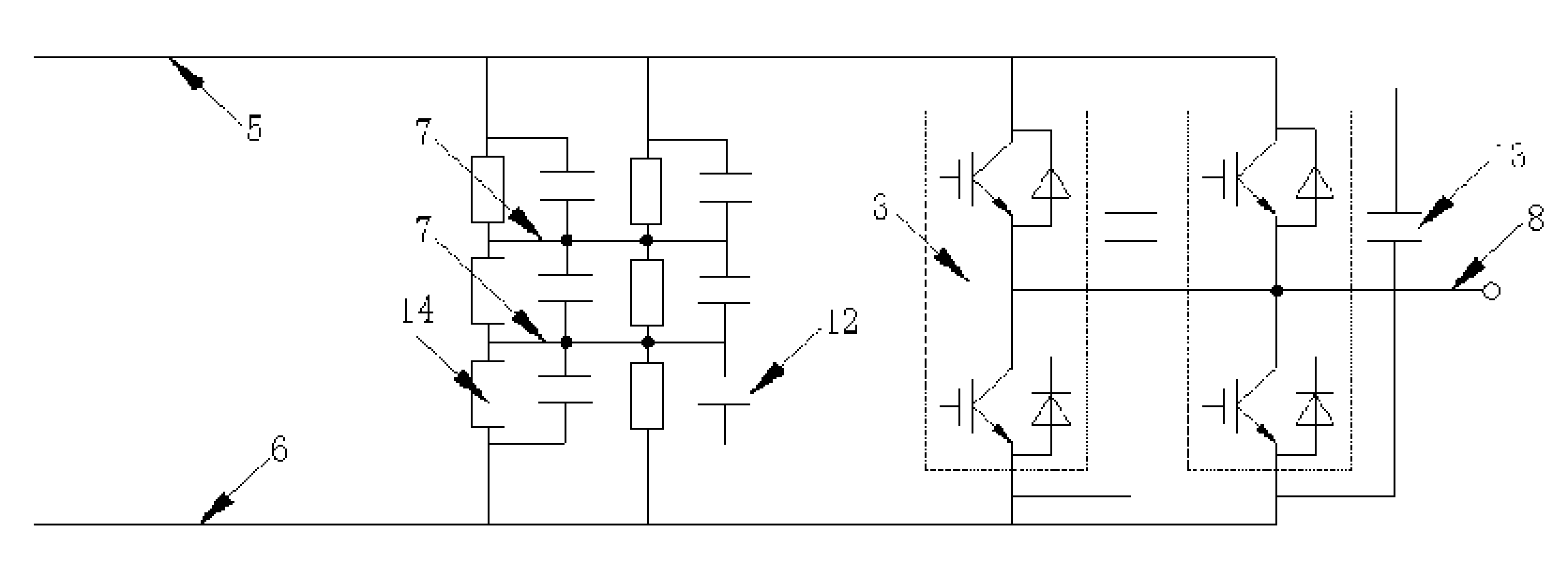

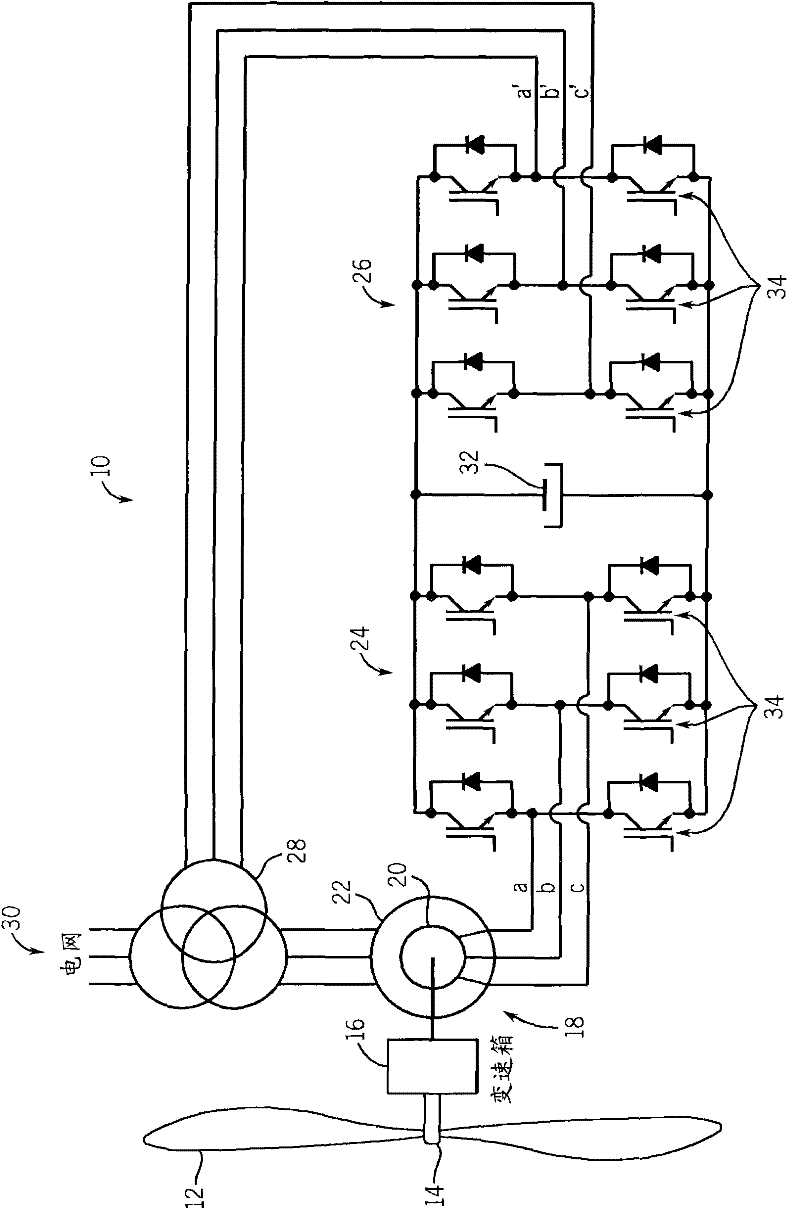

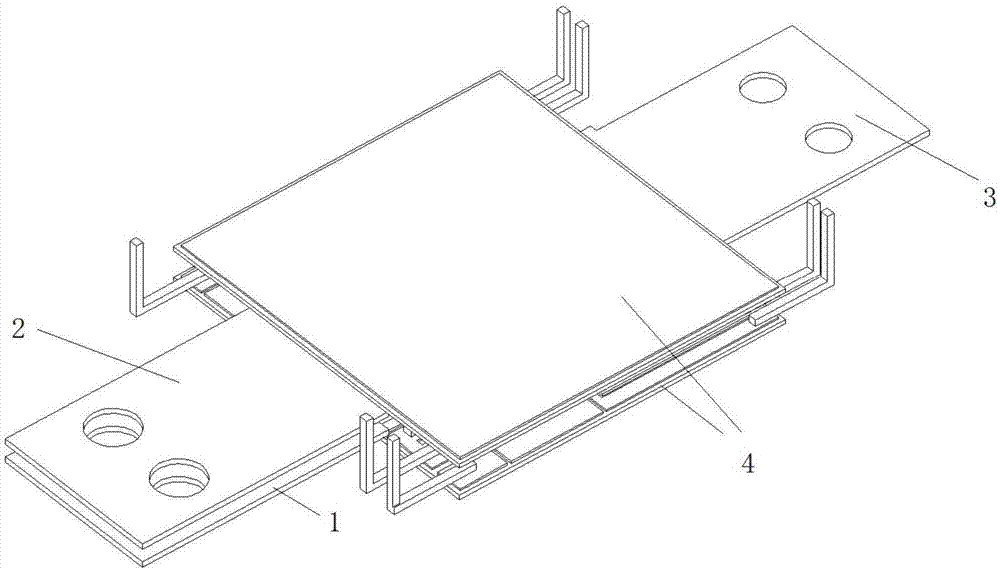

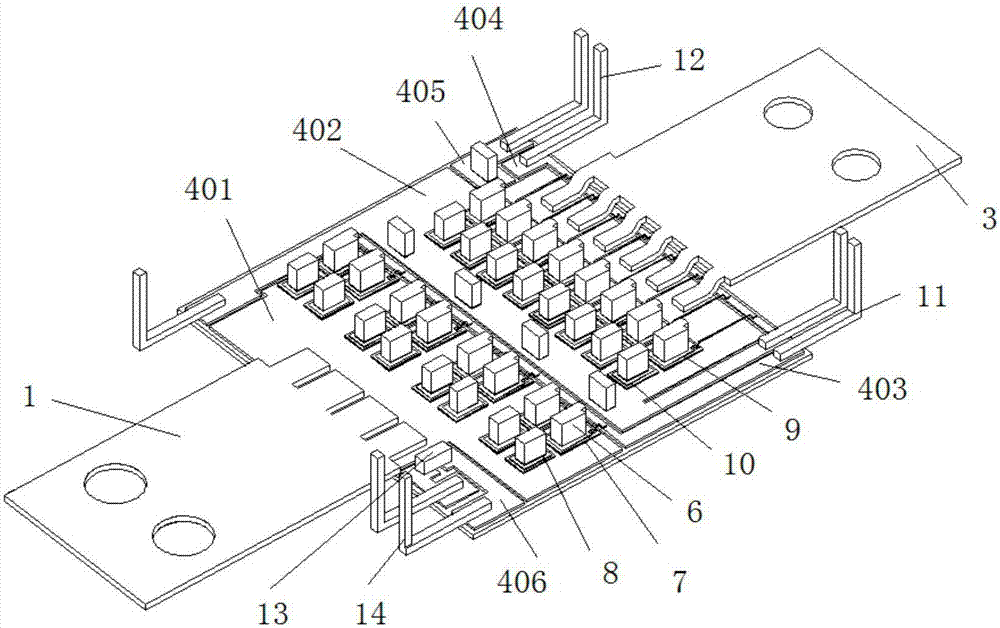

Variable frequency control power module of wind power generator

InactiveCN101826837ALarge current contact surfaceSimple and reliable electrical connectionAC motor controlFailure rateBusbar

The invention relates to a doubly-fed variable frequency control power module structure of a wind power generator. Aiming at the high failure rate caused by an electrical structure of the traditional variable frequency control power module of a wind power generator, a doubly-fed variable frequency control power module of a wind power generator is disclosed, which comprises a converter, a positive DC (Direct Current) busbar, a negative DC busbar, an interconnecting busbar and an AC (Alternating Current) busbar. The positive DC busbar and the negative DC busbar are used for transferring DC, the AC busbar is used for transferring AC, the interconnecting busbar is used for electrical connection of a filter circuit; the converter is connected with the positive DC busbar, the negative DC busbar and the AC busbar, and the positive DC busbar and the negative DC busbar respectively consist of two DC conducting plates which are piled up and isolated by insulating materials. The invention is mainly used for variable frequency control of a large-power wind power generator, and has the advantages of simple and reliable electrical connection, convenient installation and practicality.

Owner:四川吉风电源科技有限公司

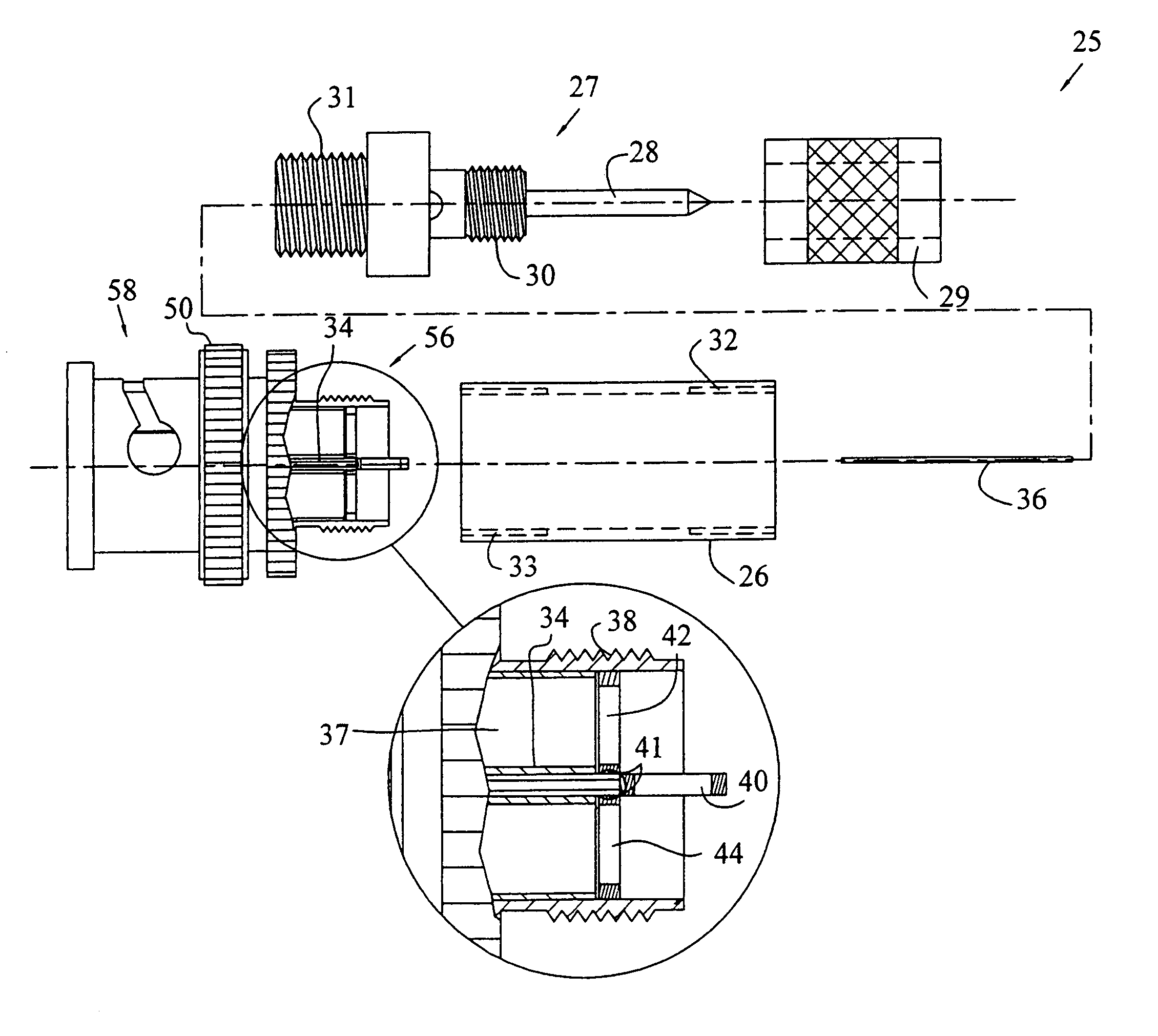

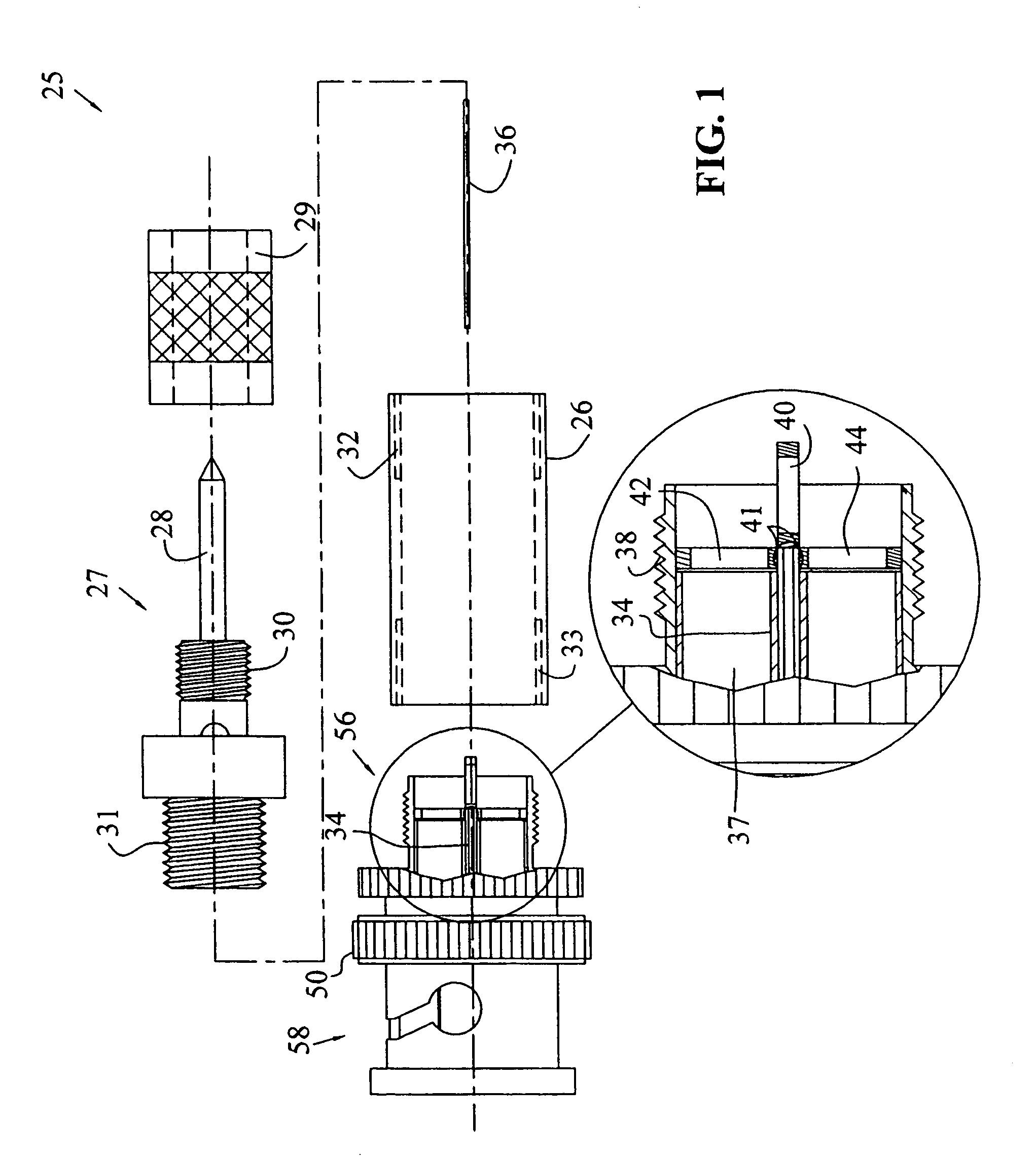

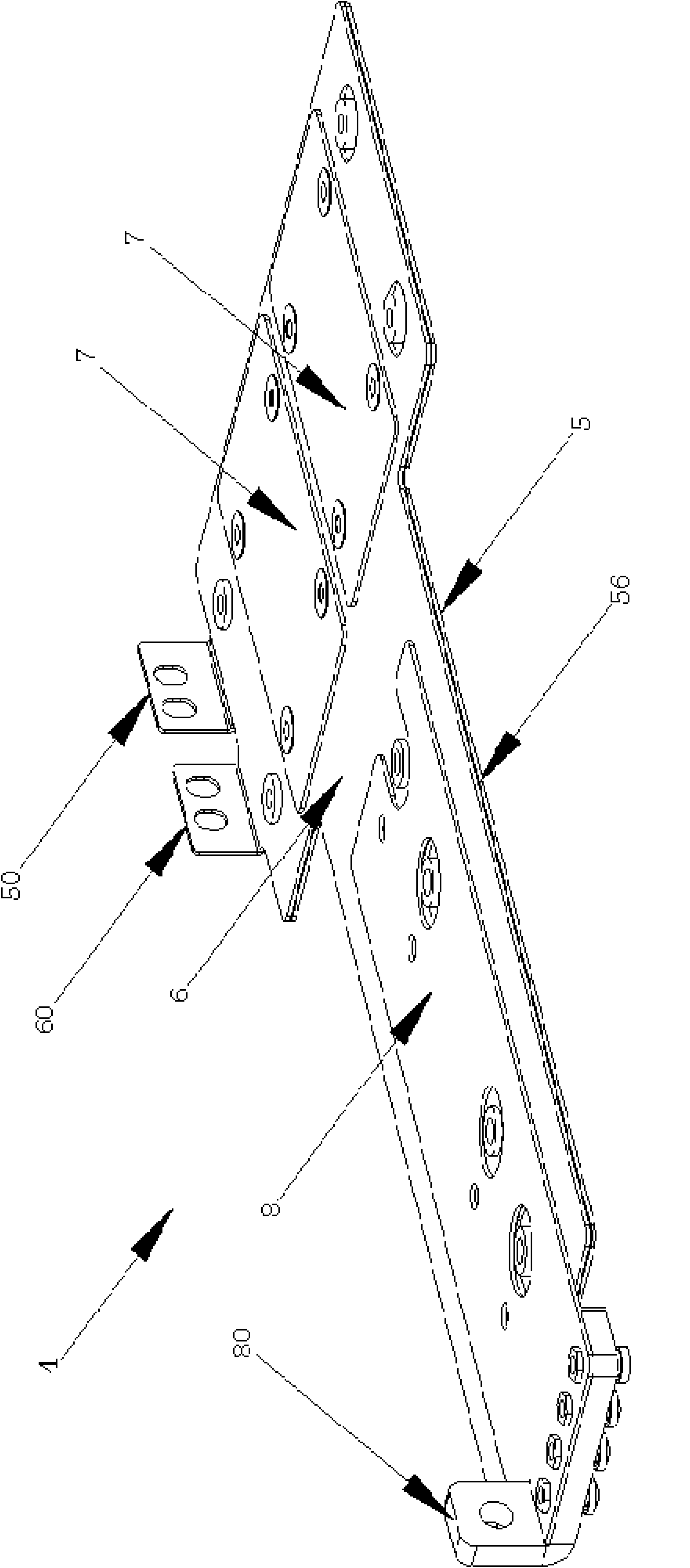

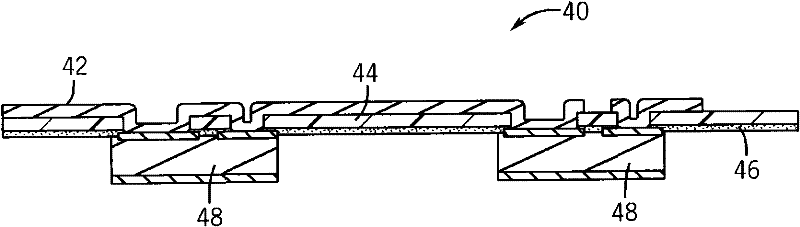

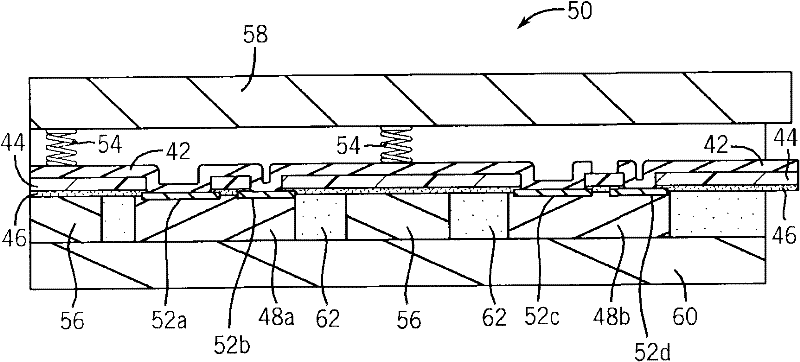

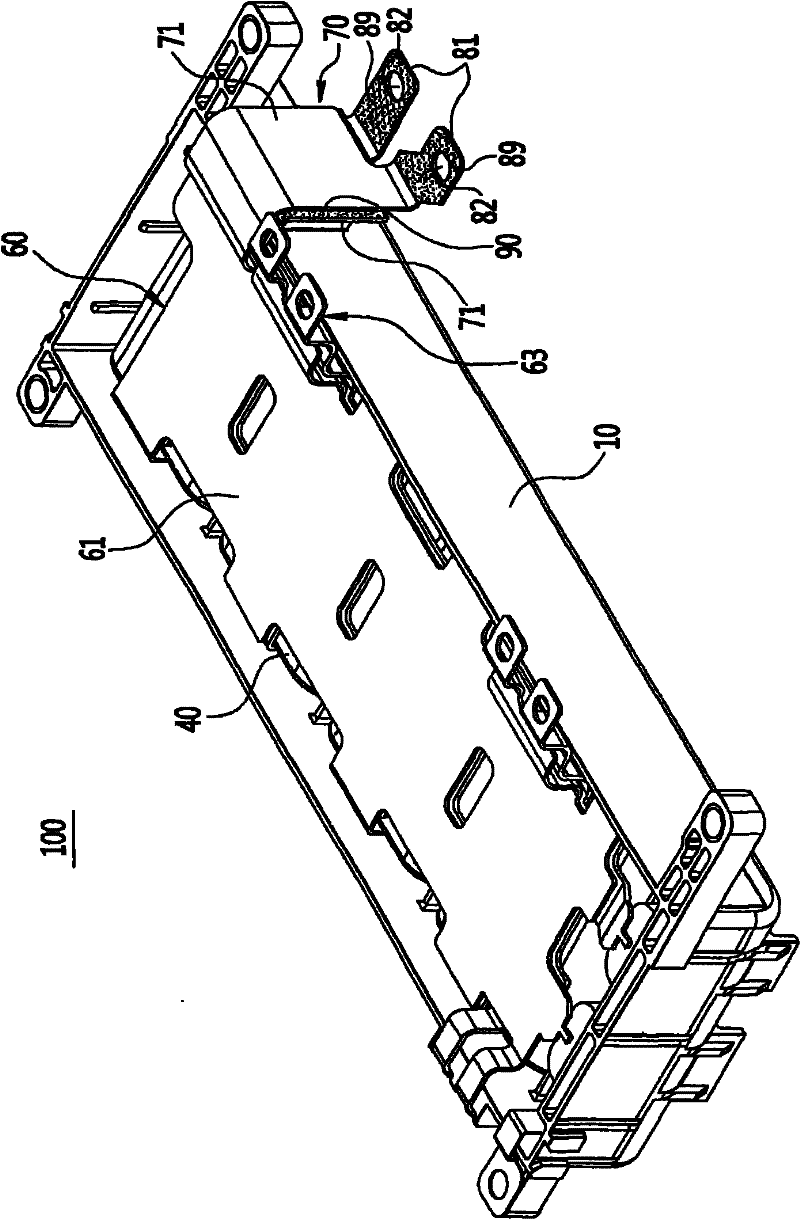

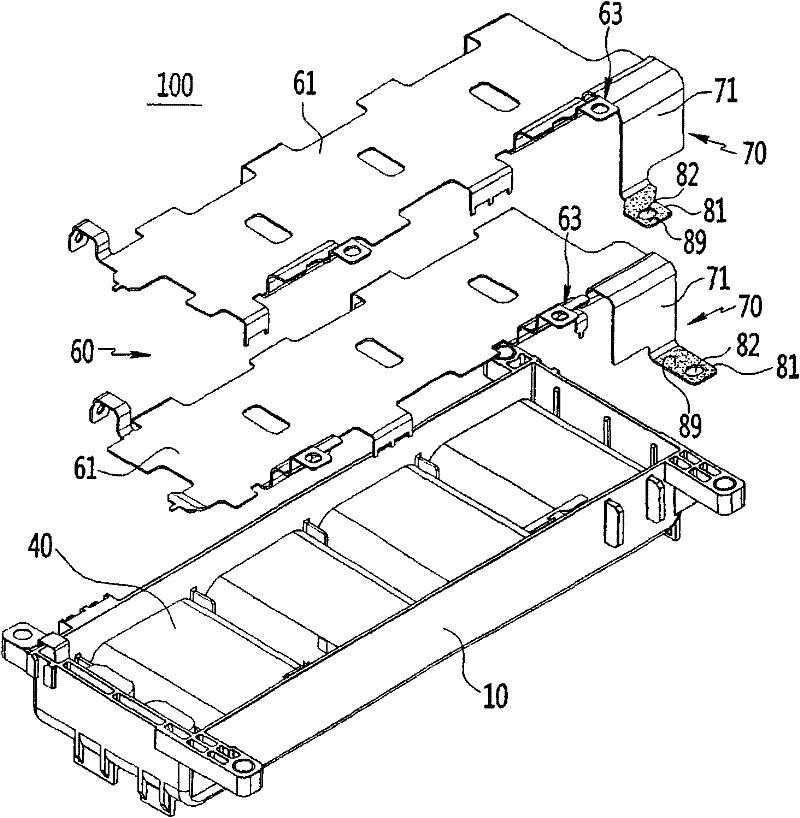

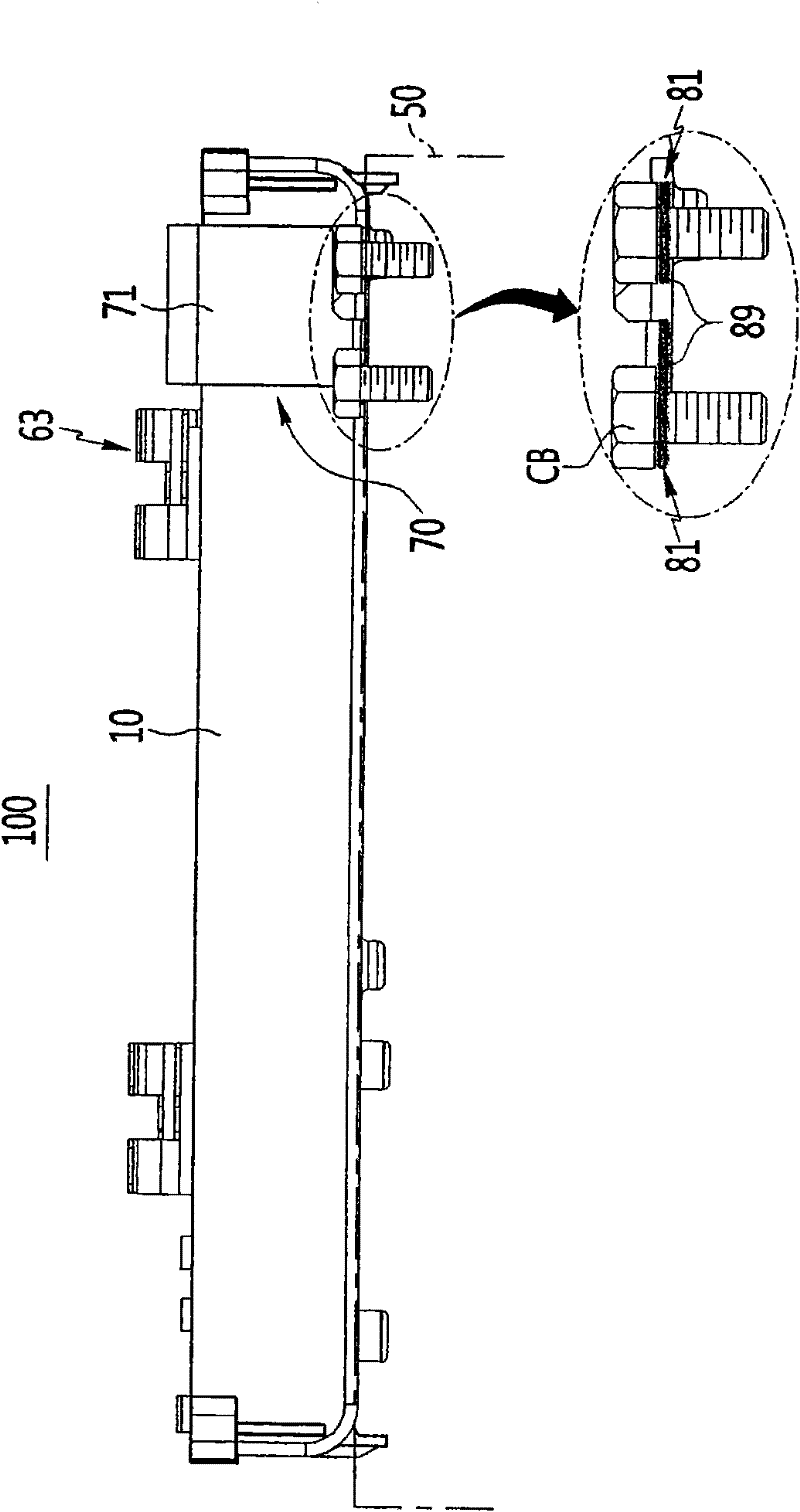

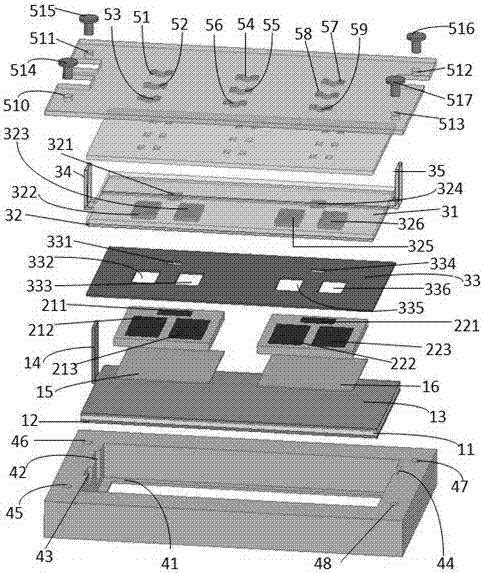

Press-pack module with power overlay interconnection

ActiveCN102237344AImprove power densityImprove reliabilitySemiconductor/solid-state device detailsSolid-state devicesSemiconductor packageComputer module

Systems and methods for utilizing power overlay (POL) technology and semiconductor press-pack technology to produce semiconductor packages (50, 70, 78, 80, 90, 100, 110, 120) with higher reliability and power density are provided. A POL structure (40) may interconnect semiconductor devices (48) within a semiconductor package (50, 70, 78, 80, 90, 100, 110, 120), and certain embodiments may be implemented to reduce the probability of damaging the semiconductor devices (48) during the pressing of the conductive plates (58, 60). In one embodiment, springs (54) and / or spacers (56) may be used to reduce or control the force applied by an emitter plate (58) onto the semiconductor devices (48) in the package (50, 70, 78, 80, 90, 100, 110, 120). In another embodiment, the emitter plate (58) may be recessed to exert force on the POL structure (40), rather than directly against the semiconductor devices (48). Further, in some embodiments, the conductive layer (42) of the POL structure (40) may be grown to function as an emitter plate (58), and regions of the conductive layer (40) may be made porous to provide compliance.

Owner:GENERAL ELECTRIC RENOVABLES ESPANA SL

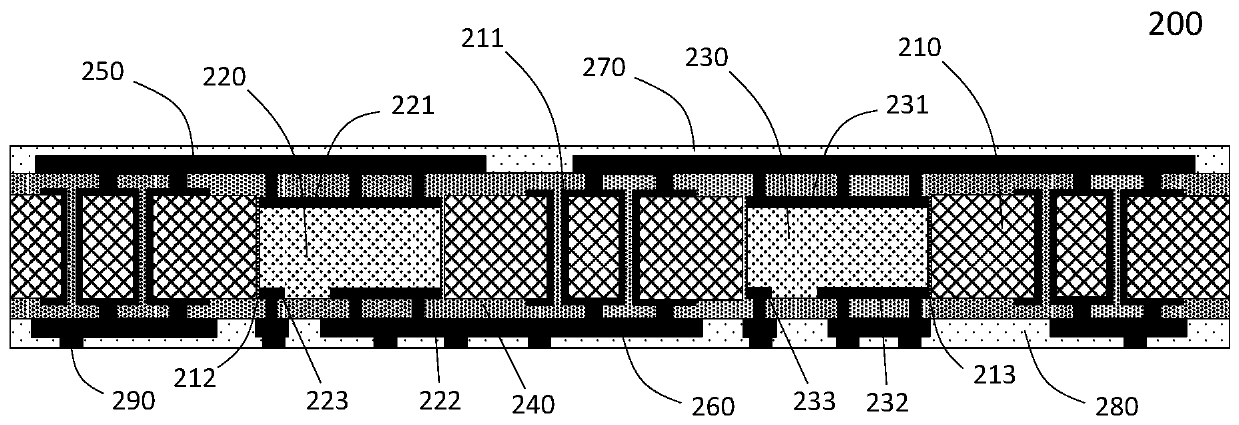

Double-sided cooling power module based on multi-area parallel arrangement

PendingCN107369657AReduce the commutation circuit areaReduce parasitic inductanceSemiconductor/solid-state device detailsSolid-state devicesCooling powerPositive power

The invention discloses a double-sided cooling power module based on multi-area parallel arrangement. A metal insulating substrate connected with a negative power terminal is provided with annular insulating slots, and metal layers surrounded in the annular insulating slots are connected with upper half bridge chips through metal blocks and are connected with lower half bridge chips through metal blocks; or, a metal insulating substrate connected with a positive power terminal is provided with annular insulating slots, and lower half bridge chips and upper half bridge chips are sintered on metal layers surrounded in the annular insulating slots. Two metal insulating substrates are laminated, annular insulating slots are arranged in one metal insulating substrate, and metal layers and metal blocks are sintered inside the power module, and therefore, the area of a commutation circuit is reduced and the parasitic inductance of the module is greatly reduced. Moreover, the positive and negative power terminals laminated can be easily connected with an external bus, the area of the metal layers is increased as much as possible, the lead resistance of the module is reduced, and the parasitic inductance is significantly reduced.

Owner:YANGZHOU GUOYANG ELECTRONICS CO LTD

Capacitors for vehicle inverters

InactiveCN102280247AReduce short circuitAvoid damageMultiple fixed capacitorsConversion constructional detailsElectricityPower inverter

The present invention provides a capacitor for an inverter of a vehicle comprising a case; a plurality of capacitor unit modules; positive and negative bus plates that are disposed in the case to be connected to the capacitor unit modules; and a power module corresponding to the unit modules, wherein that the unit modules are insulated from each other through an insulating material, and wherein the bus plates each comprise a bus bar that overlaps with the other bus bar and is electrically connected to the power module.

Owner:HYUNDAI MOTOR CO LTD +1

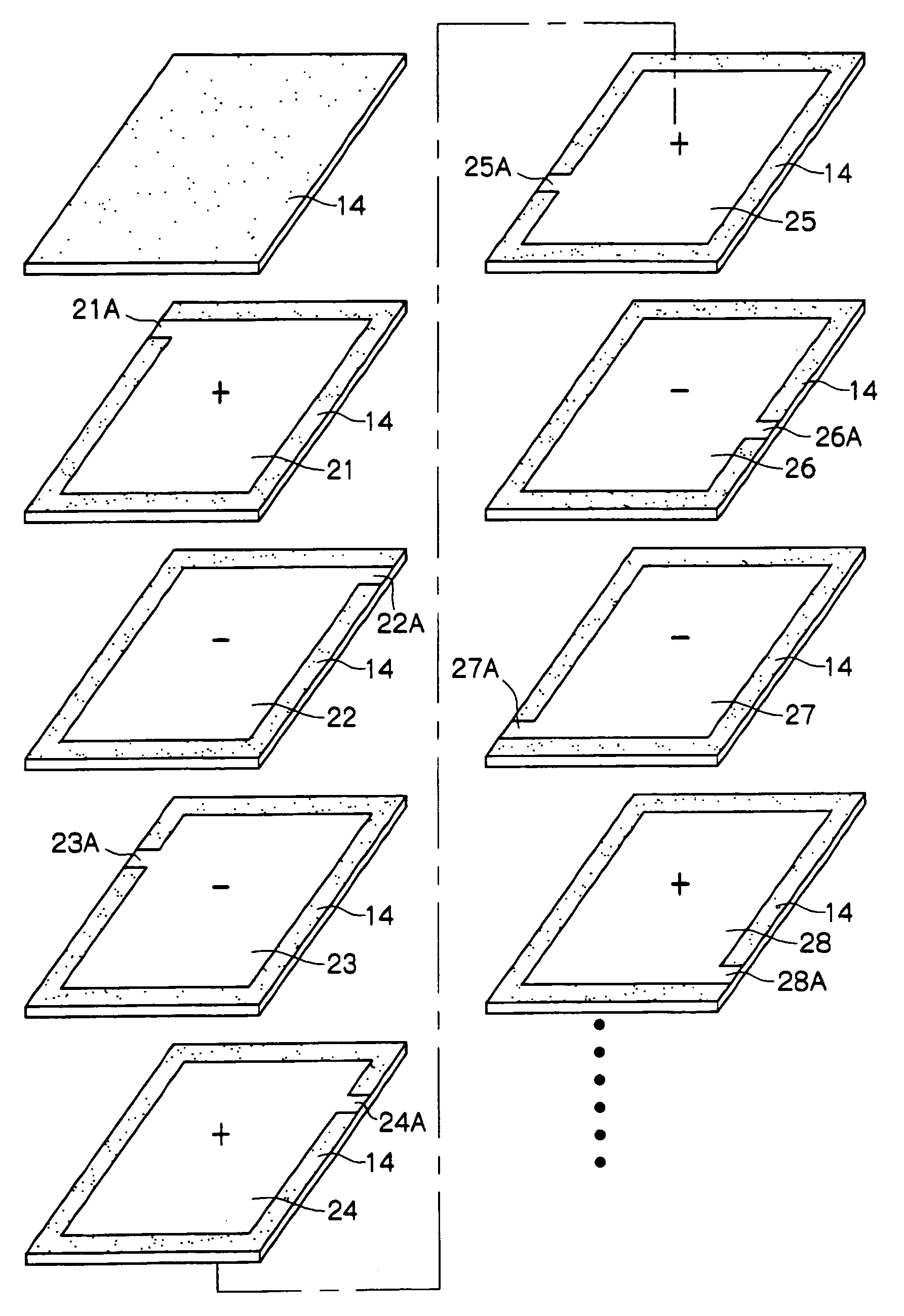

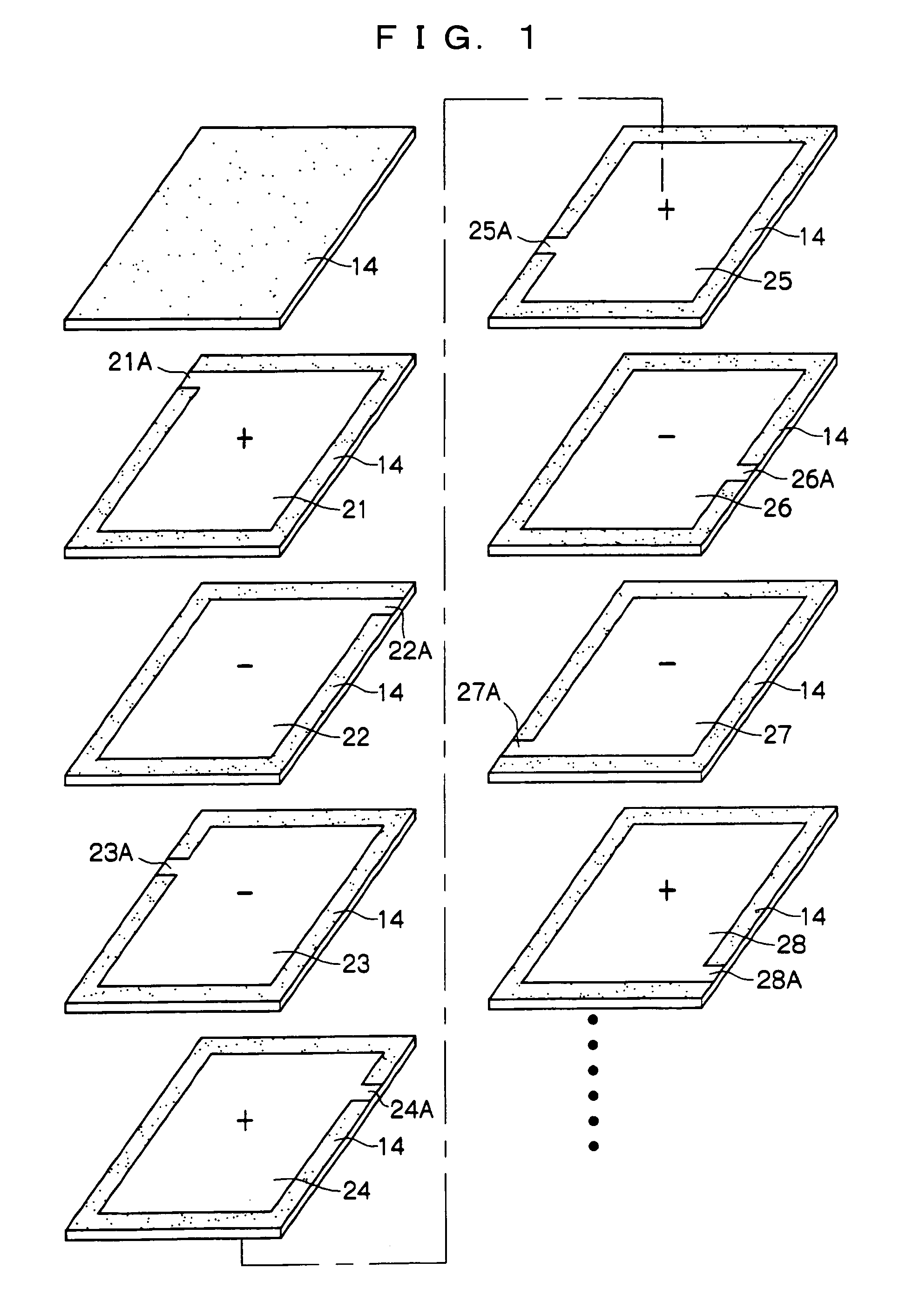

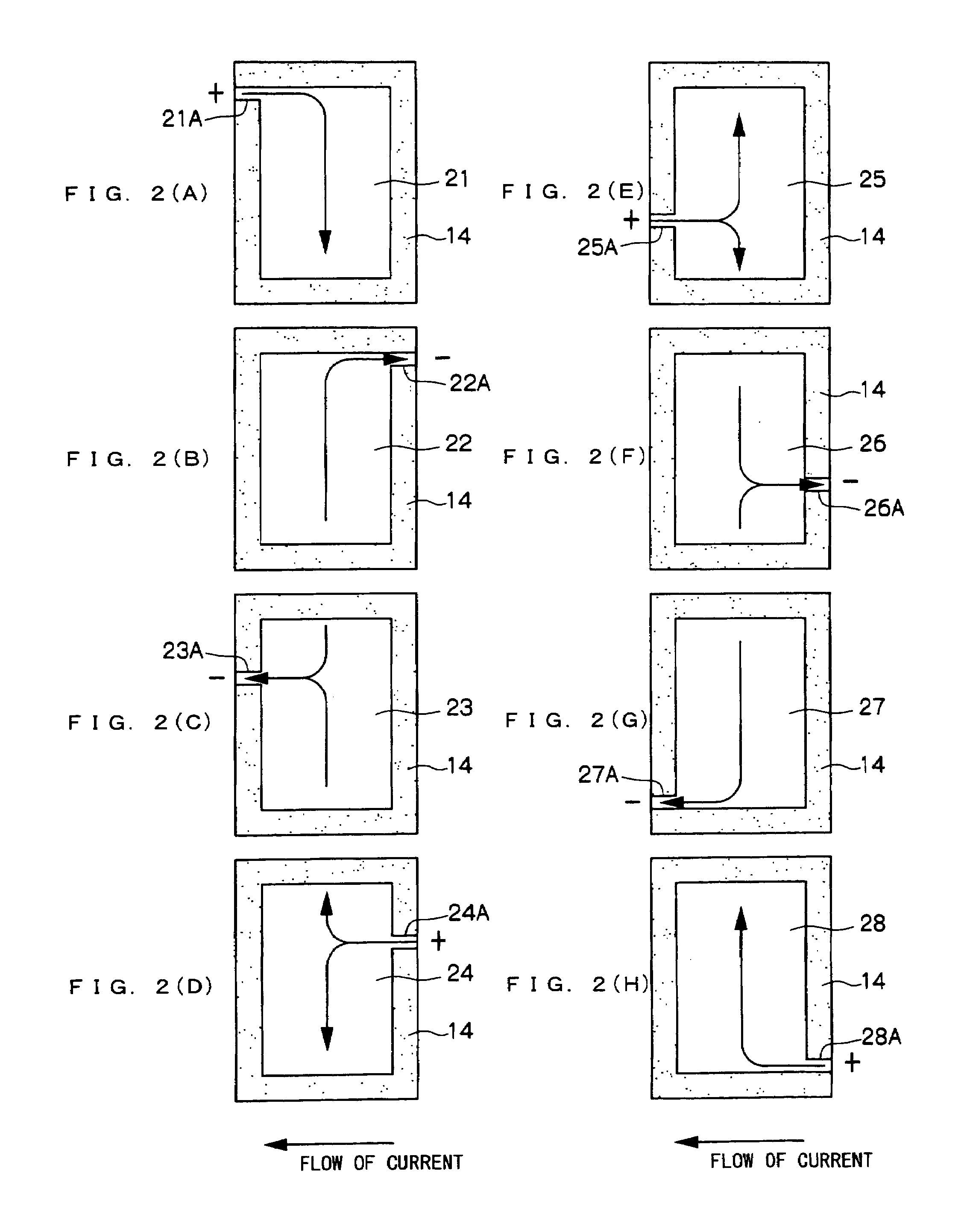

Multilayer capacitor

ActiveUS7050289B2Reduce parasitic inductanceEquivalent series inductance (ESL) is reducedMultiple fixed capacitorsDoors/windowsElectrical conductorElectrical polarity

A multilayer capacitor includes: a dielectric element; a pair of first internal conductors with same polarity disposed in the dielectric element to be adjacent to each other while being separated from each other by the dielectric layer; first leadout portions led out from the pair of first internal conductors respectively, one being provided for each of the first internal conductors; a pair of second internal conductors with same polarity disposed in the dielectric element to be adjacent to each other while being separated from each other by the dielectric layer; and second leadout portions led out from the pair of second internal conductors respectively, one being provided for each of the second internal conductors, wherein the first leadout portion and the second leadout portion led out respectively from the first internal conductor and the second internal conductor disposed adjacent to each other are led out to substantially the same positions in side faces facing each other of the dielectric element, respectively. Therefore, a multilayer capacitor capable of reducing equivalent series inductance to reduce voltage fluctuation of a power source of a CPU is obtained.

Owner:TDK CORPARATION

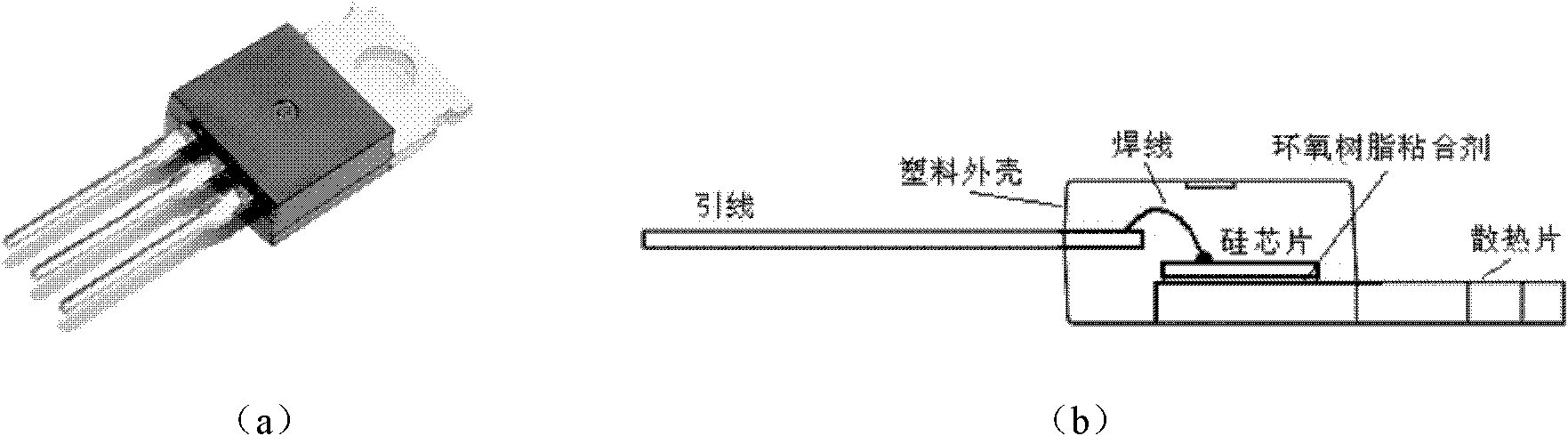

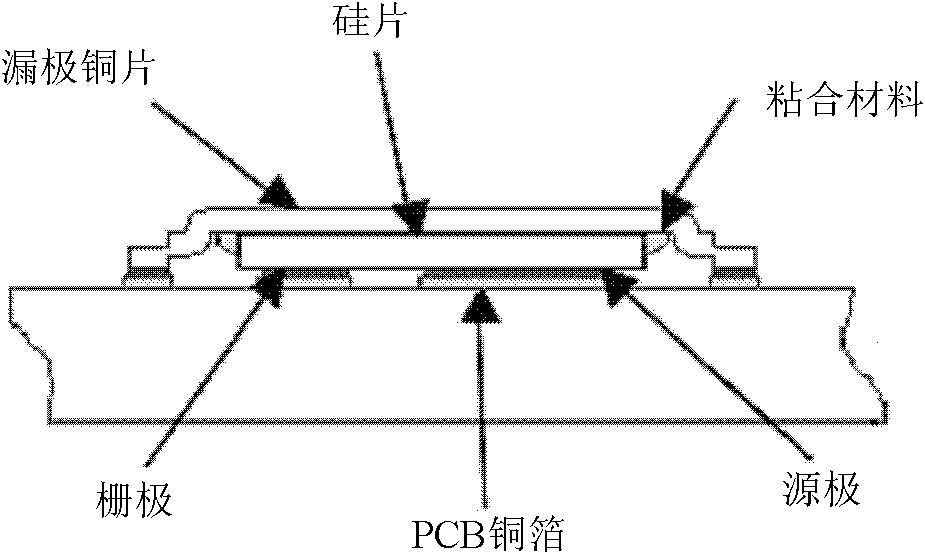

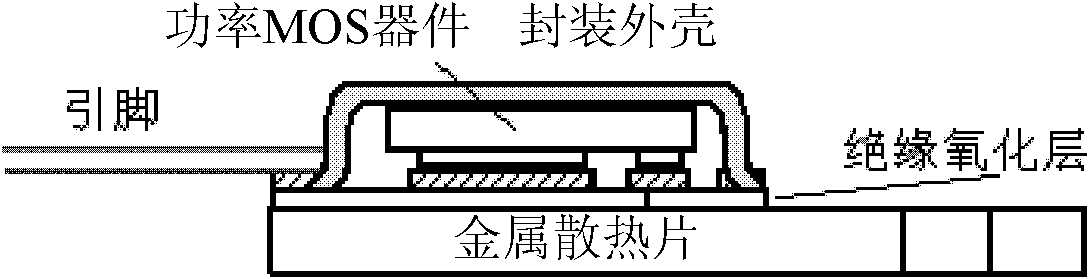

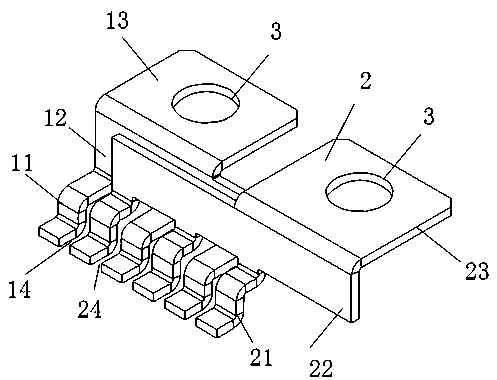

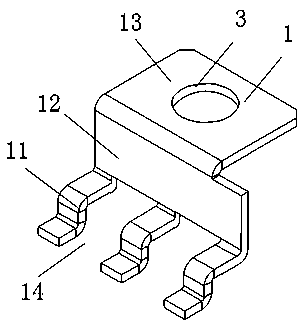

Low-heat-resistance packaging structure of power MOS (Metal Oxide Semiconductor) device

ActiveCN102201449AImprove performanceSolve the problem of excessive thermal resistanceSemiconductor/solid-state device detailsSolid-state devicesPower semiconductor deviceHeat resistance

The invention discloses a low-heat-resistance packaging structure of a power MOS (Metal Oxide Semiconductor) device, belonging to the technical field of power semiconductor devices. In the invention, the silicon chip flip bridge clip technology and the conventional TO packaging technology are combined, and a flip heat-radiation structure is used so that the heat generated by the power MOS device directly flows to a metal heat sink, the problem of overhigh heat resistance caused by the conventional TO packaging of the power MOS device is solved; the large area contact of the bridge clip technology achieves the reduction of the heat resistance, the increment of the current capacity and the decrement of the parasitic inductance. The low heat resistance packaging structure of the power MOS device, provided by the invention, has the appearance of the conventional TO packaging; the power MOS device with excellent performance is packaged without adding the packaging equipment, but only properly increasing the related equipment of the bridge clip and the flip technique. The low heat resistance packaging structure of the power MOS device, provided by the invention, has about 80% of reducedheat resistance, about two times of increased current capacity and largely reduced parasitic inductance compared with the conventional TO packaging structure through the proving of the actual testing.

Owner:广东成利泰科技有限公司

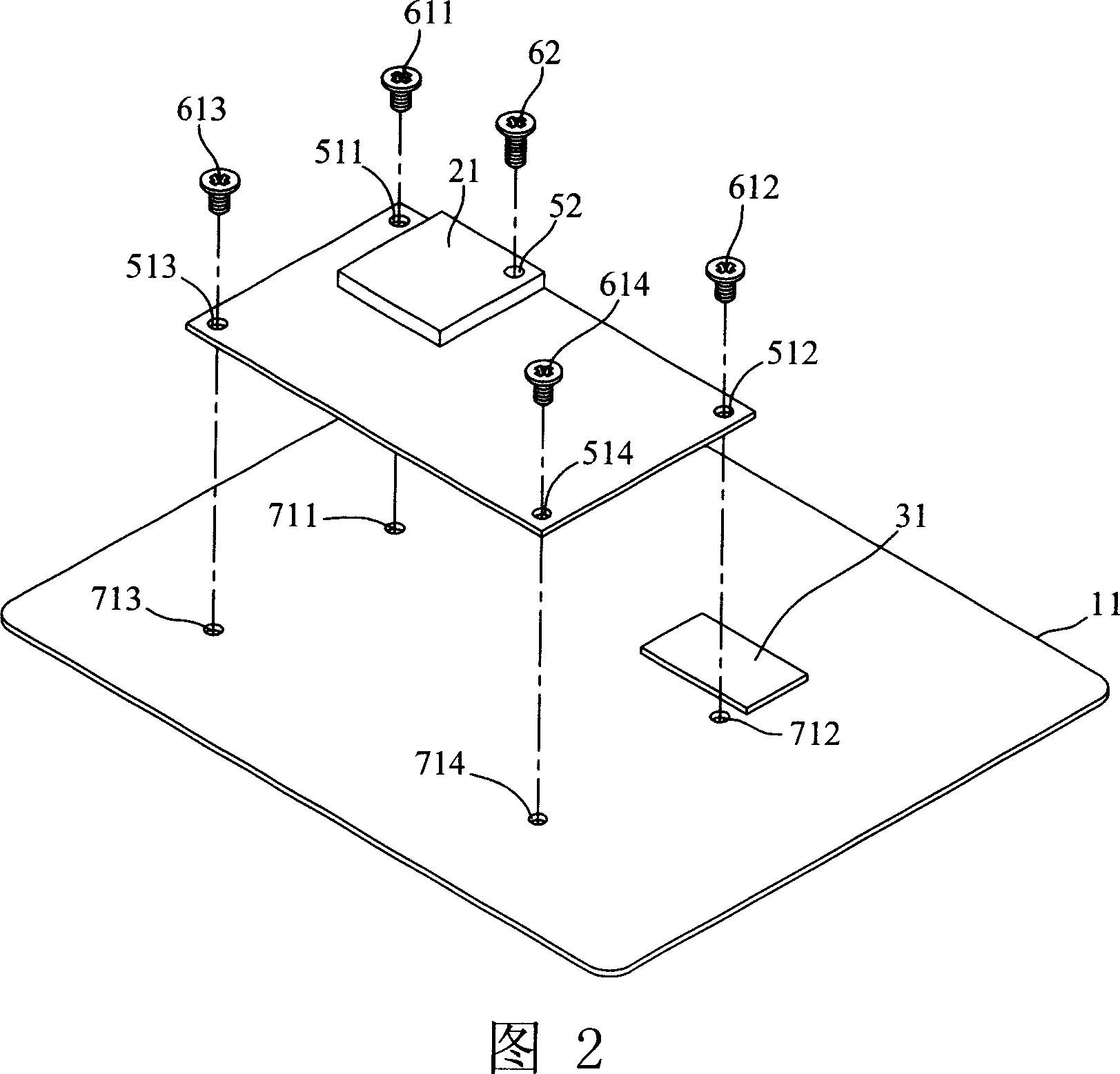

Circuit board for reducing electromagnetic interference of electronic product

InactiveCN101005730AReduce parasitic inductanceReduce electromagnetic interferenceMagnetic/electric field screeningPrinted circuit non-printed electric components associationElectromagnetic interferenceEngineering

The invention is used for reducing the radiation emission of circuit board caused by the signals passing through the parasitic inductance. It removes the layout of ground trace from the circuit layout, and uses metal plate and metal screw instead of the ground race. Due to removing of twist ground trace, the radiation emission is reduced.

Owner:MITAC COMP (SHUN DE) LTD +1

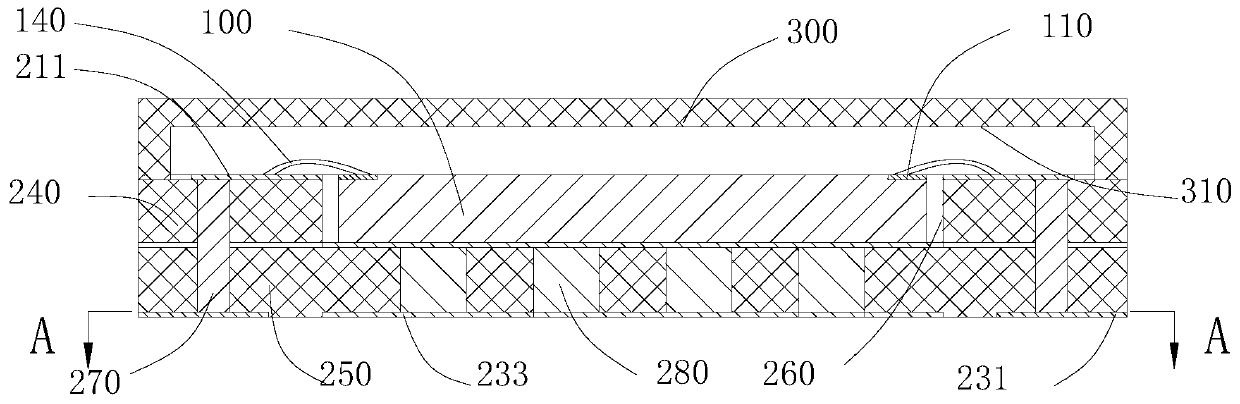

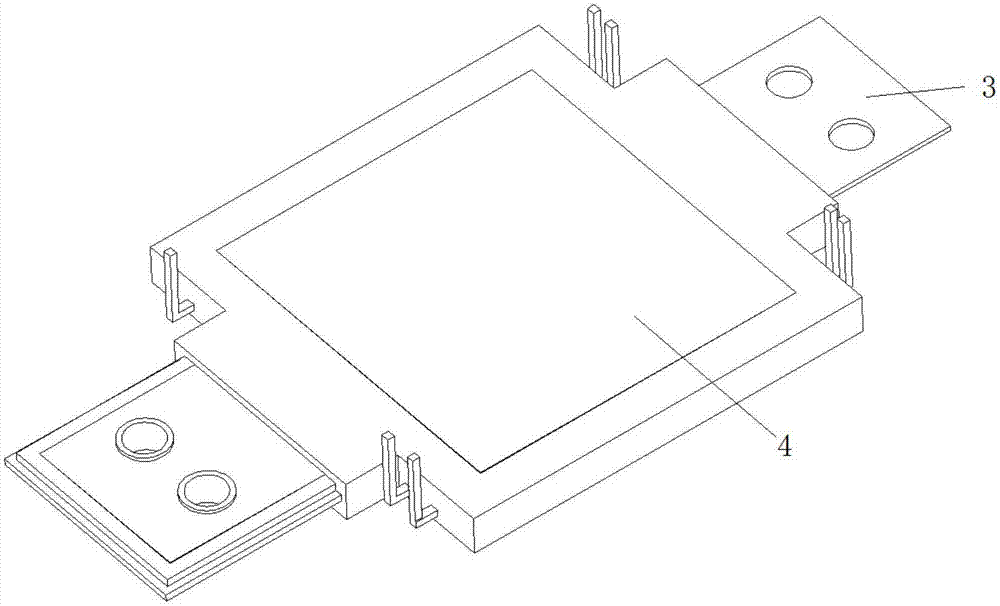

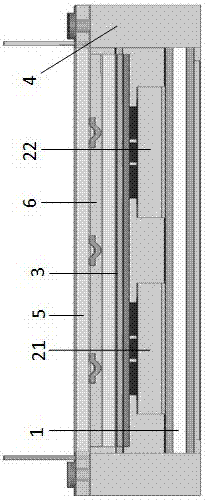

Packaging structure of power module

PendingCN106997871AImprove performanceImprove reliabilitySemiconductor/solid-state device detailsSolid-state devicesPower flowCarrying capacity

The invention discloses a packaging structure of a power module. The packaging structure comprises a lower layer metal direct bonded ceramic circuit board, a packaged power device chip, an upper layer metal direct bonded ceramic circuit board, an upper cover plate and an insulating shell, wherein an electrode on the lower surface of the packaged power device chip is fixed on the lower layer ceramic circuit board through solder; the upper layer ceramic circuit board is inversely arranged on the packaged power device chip, and is in contact with an electrode on the upper surface of the packaged power device chip through a convex contact on the metal layer thereof; and the upper cover plate applies downward pressure to the upper layer ceramic circuit board through a compression spring to ensure tight contact between the convex contact and the electrode. By virtue of the packaging structure of the power module disclosed by the invention, lead bonding in the conventional power module packaging can be avoided, so that current carrying capacity is improved; and in addition, the packaging structure is simple and compact in structure, easy to realize, high in power device compatibility, and capable of improving heat dissipation of the power module and enhancing reliability of the power module.

Owner:杨杰

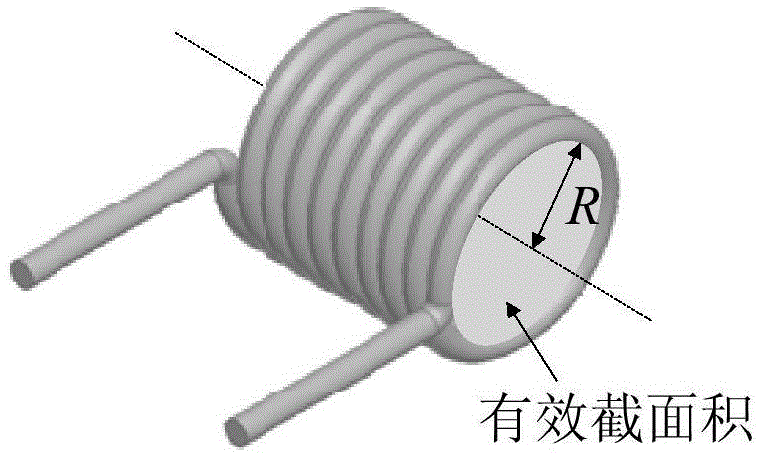

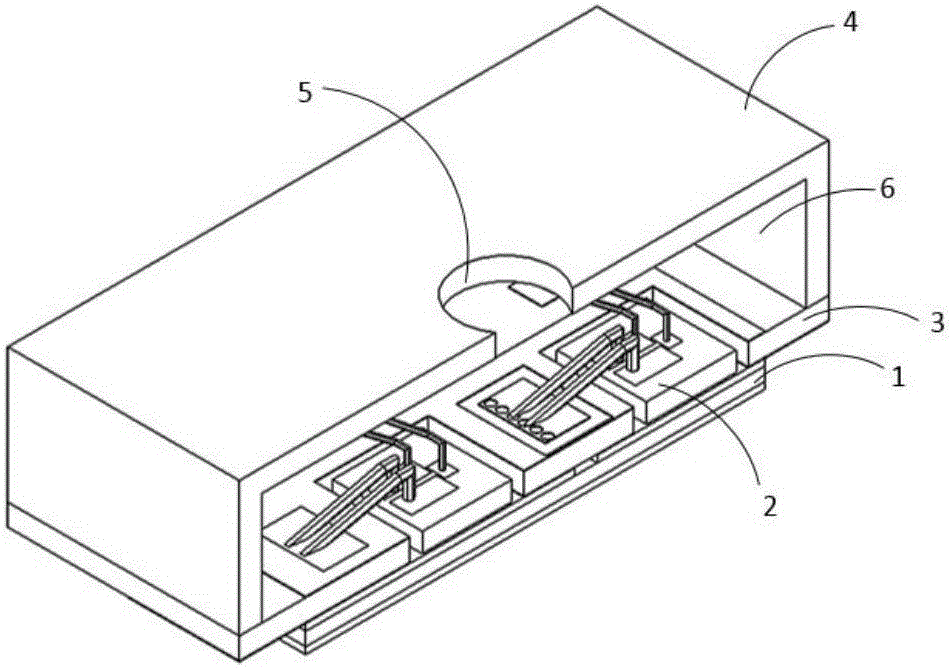

3D integrated framework of ultrahigh frequency power converter

ActiveCN104934209AReduce volumeImprove power densityTransformers/inductances coils/windings/connectionsFixed signal inductancesTransformerEngineering

The invention provides a 3D integrated framework of an ultrahigh frequency power converter. The 3D integrated framework comprises a PCB circuit layer and a winding unit erected on the PCB circuit layer. The winding unit is connected with the PCB circuit layer through a wire. The winding unit comprises winding layers formed on a first insulating layer and a first soft magnetic thin film layer formed on a second insulating layer. The first soft magnetic thin film layer is arranged below the winding layers in a laminated mode to be used for achieving magnetic shielding between the winding layers and the PCB circuit layer. Compared with the prior art, by the adoption of 3D integration, the size of the converter is reduced, and the power density is increased; soft magnetic materials are adopted to form the magnetic shielding layer, magnetic field interference between windings and the PCB circuit layer and between the windings and external metal is solved, the Q value of the windings is increased, the alternating current resistance and high-frequency loss of an inductor and a transformer are reduced, and the working efficiency of the converter is improved; a plane magnetic element is further adopted, and the miniaturization and flattening of products are guaranteed; temperature rising of the magnetic element is reduced greatly, and the working environment of a semiconductor device is improved.

Owner:MORNSUN GUANGZHOU SCI & TECH +1

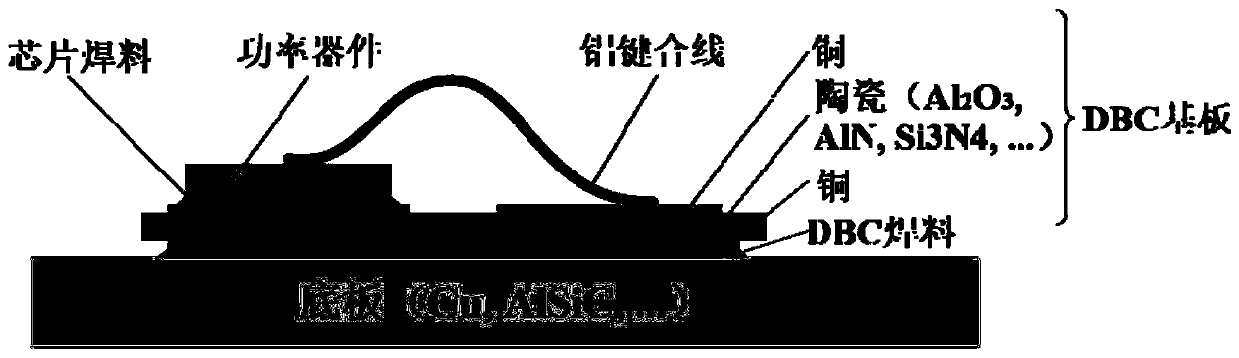

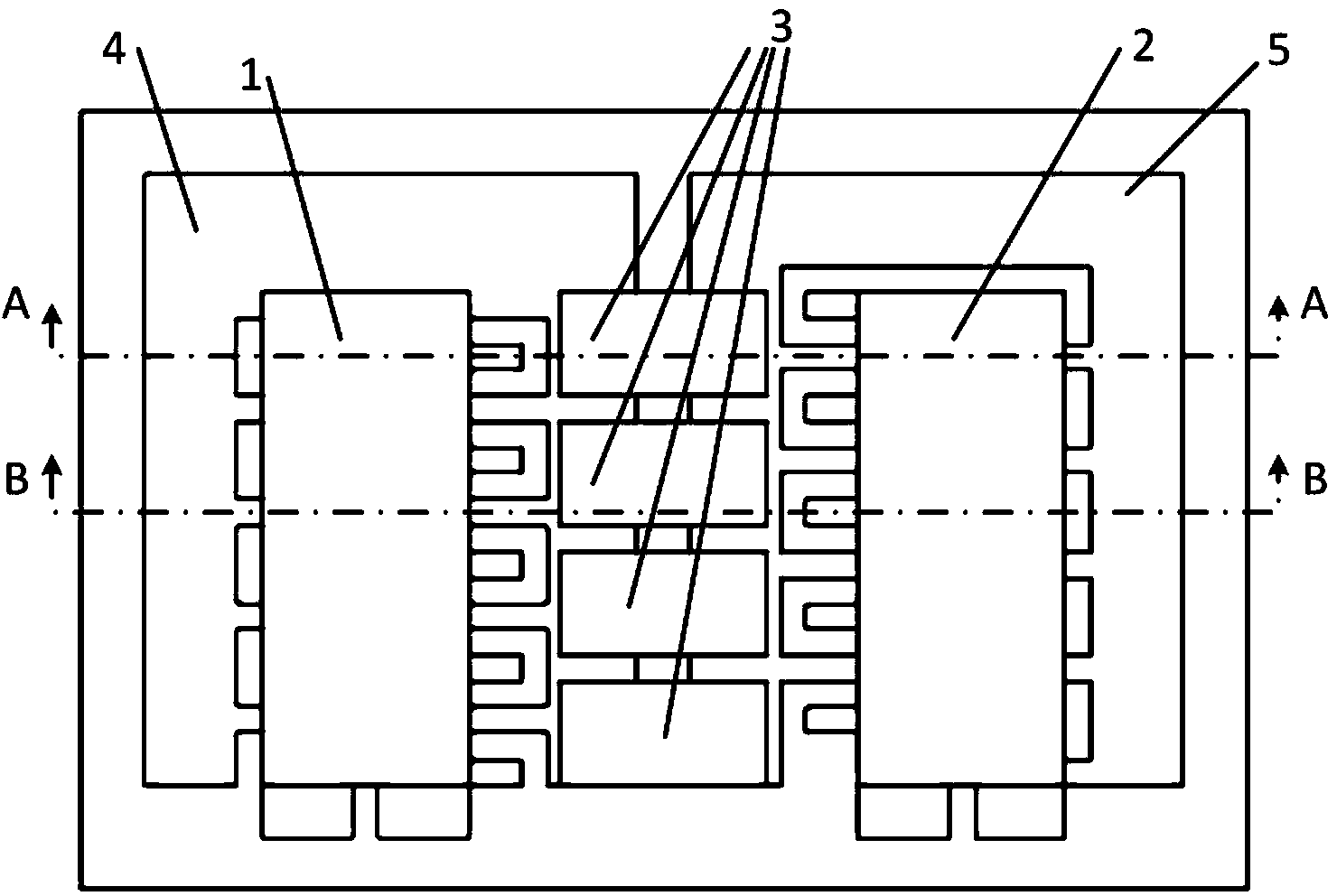

Packaging structure and packaging method for silicon carbide power device

ActiveCN105914185AReduce areaReduce parasitic inductanceSemiconductor/solid-state device detailsSolid-state devicesOvervoltageDBc

The invention discloses a packaging structure and a packaging method for a silicon carbide power device. The packaging structure comprises a direct bond copper (DBC) ceramic substrate, a silicon carbide power device, a PCB, leads and a shell and forms a half-bridge circuit structure formed by the silicon carbide power device. According to the packaging structure and the packaging method provided by the invention, the area of a power circuit can be effectively reduced, conductors with opposite current flowing directions are formed during a commutation process by a switch transistor, mutual inductance offset is used for reducing parasitic inductance of a commutation circuit, and overvoltage and oscillation during the switching process can be effectively reduced; driving signal leads adopt a Kelvin connection mode and are vertical to power leads, a role of effectively reducing coupling between a driving circuit and a power circuit is played, and driving stability is enhanced; the DBC substrate and the PCB are welded thoroughly, and packaging reliability is enhanced; and power terminals and signal terminals are directly included in the PCB, thereby reducing contact resistance and parasitic inductance brought by extra terminals and achieving effects of reducing the cost.

Owner:HUAZHONG UNIV OF SCI & TECH

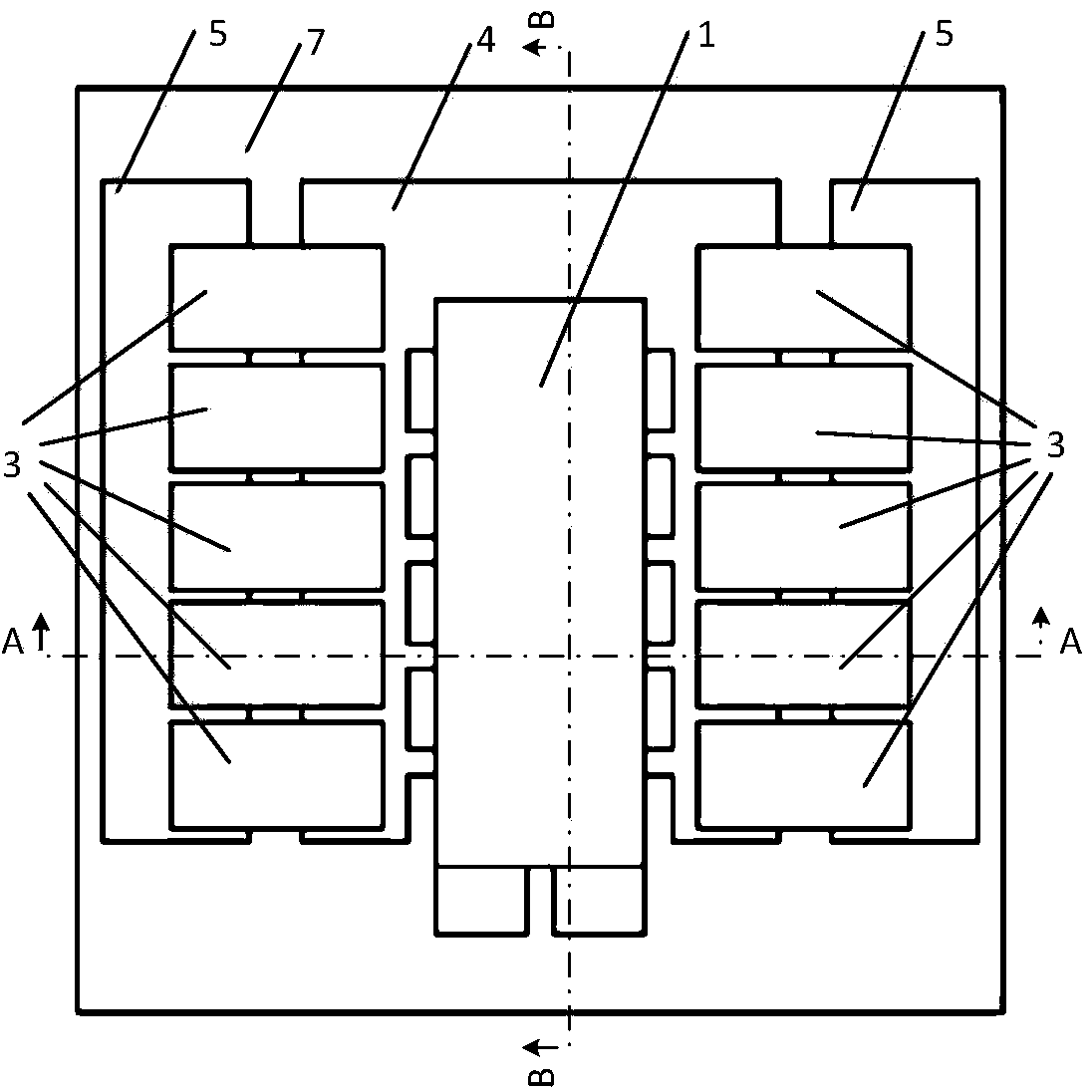

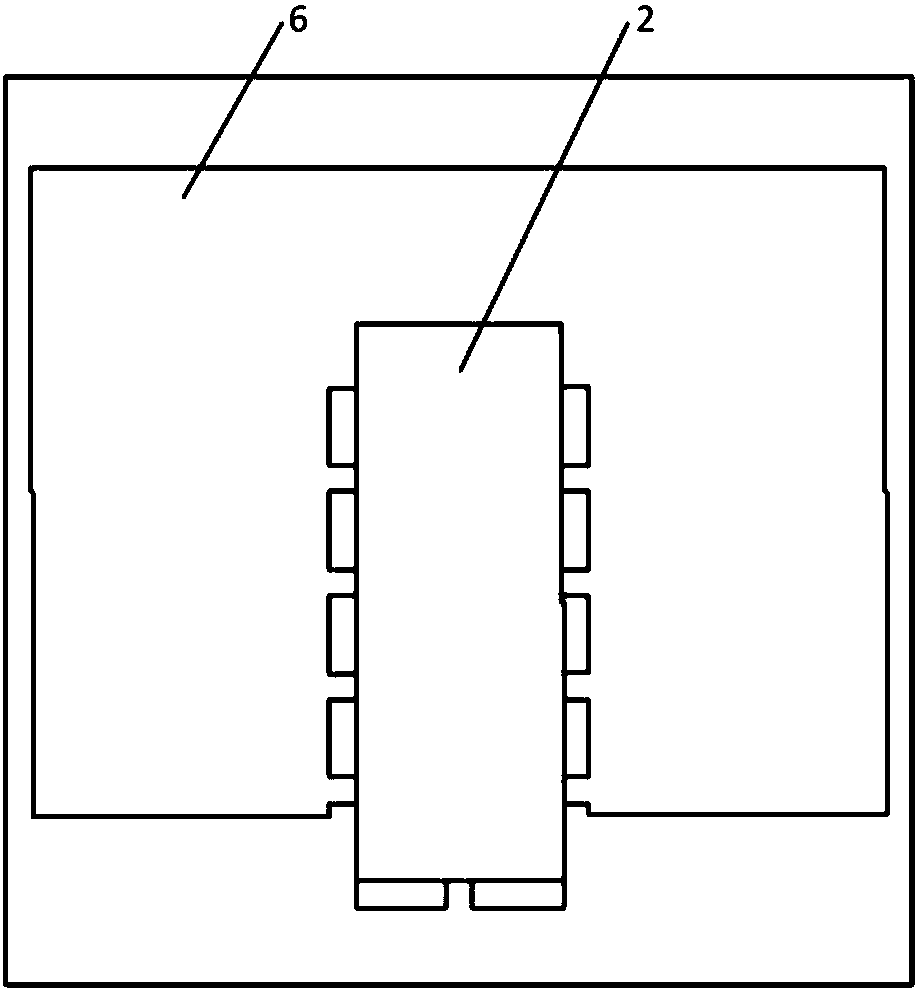

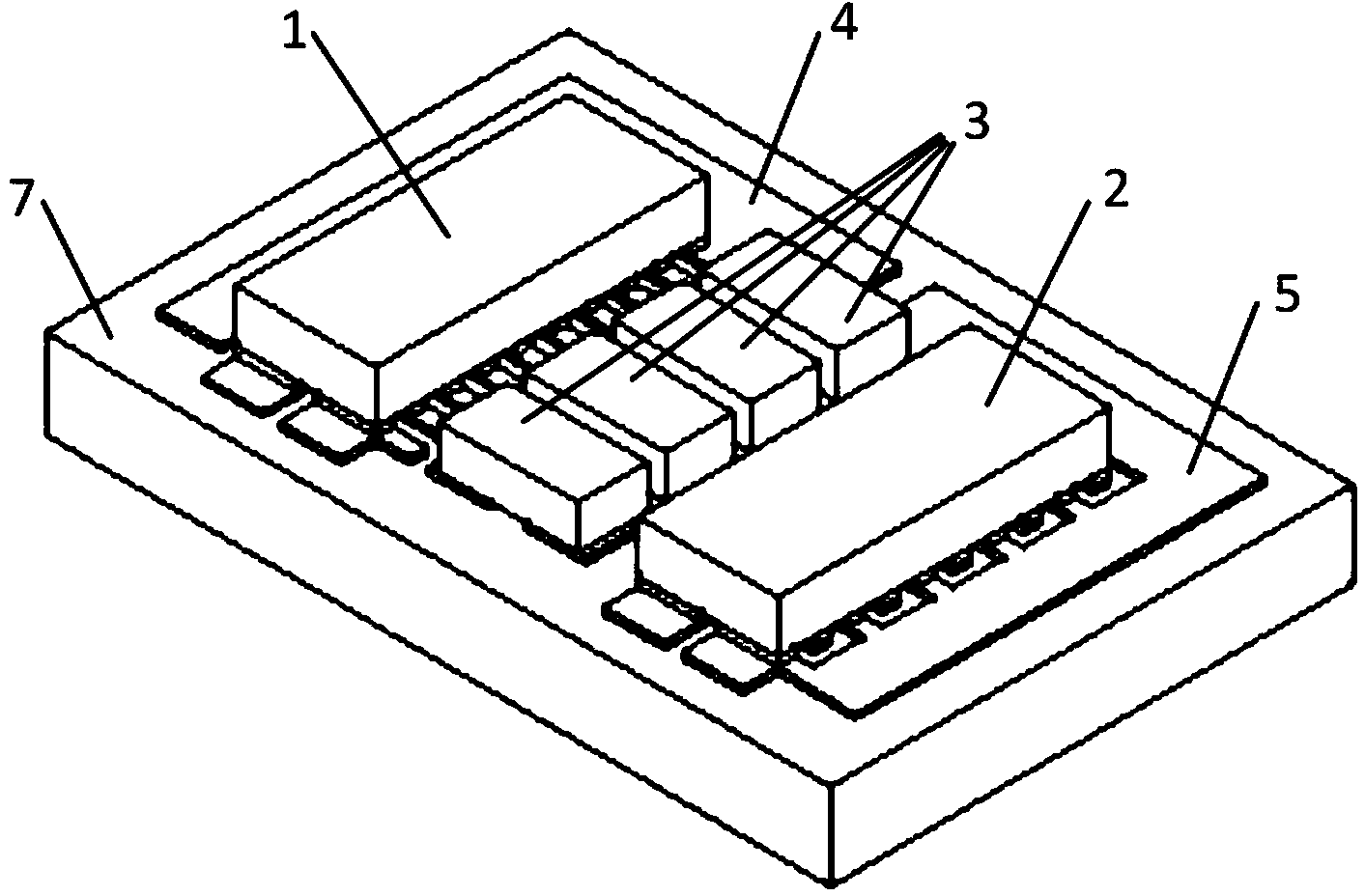

Low-parasitic-inductance GaN power integration module arranged in middle of shunt capacitor

ActiveCN104143547AReduce areaReduce parasitic inductanceEfficient power electronics conversionSolid-state devicesOvervoltageCapacitance

The invention provides a low-parasitic-inductance GaN power integration module arranged in the middle of a shunt capacitor. The module comprises an upper bridge arm device, a lower bridge arm device and a plurality of bus capacitors. The upper bridge arm device and the lower bridge arm device are LGA packaged GaN devices. The bus capacitors are surface mount devices. The two GaN devices are arranged side by side. The bus capacitors are placed between the two GaN devices in parallel. All source electrode pins of the upper bridge arm device and all drain electrode pins of the lower bridge arm deice are connected to an inner conducting layer through via holes. According to the layout way, the area of a high-frequency power loop can be effectively reduced, so that the parasitic inductance of the high-frequency power loop is obviously reduced, and the overvoltage and oscillation produced in the switching process are reduced.

Owner:XI AN JIAOTONG UNIV

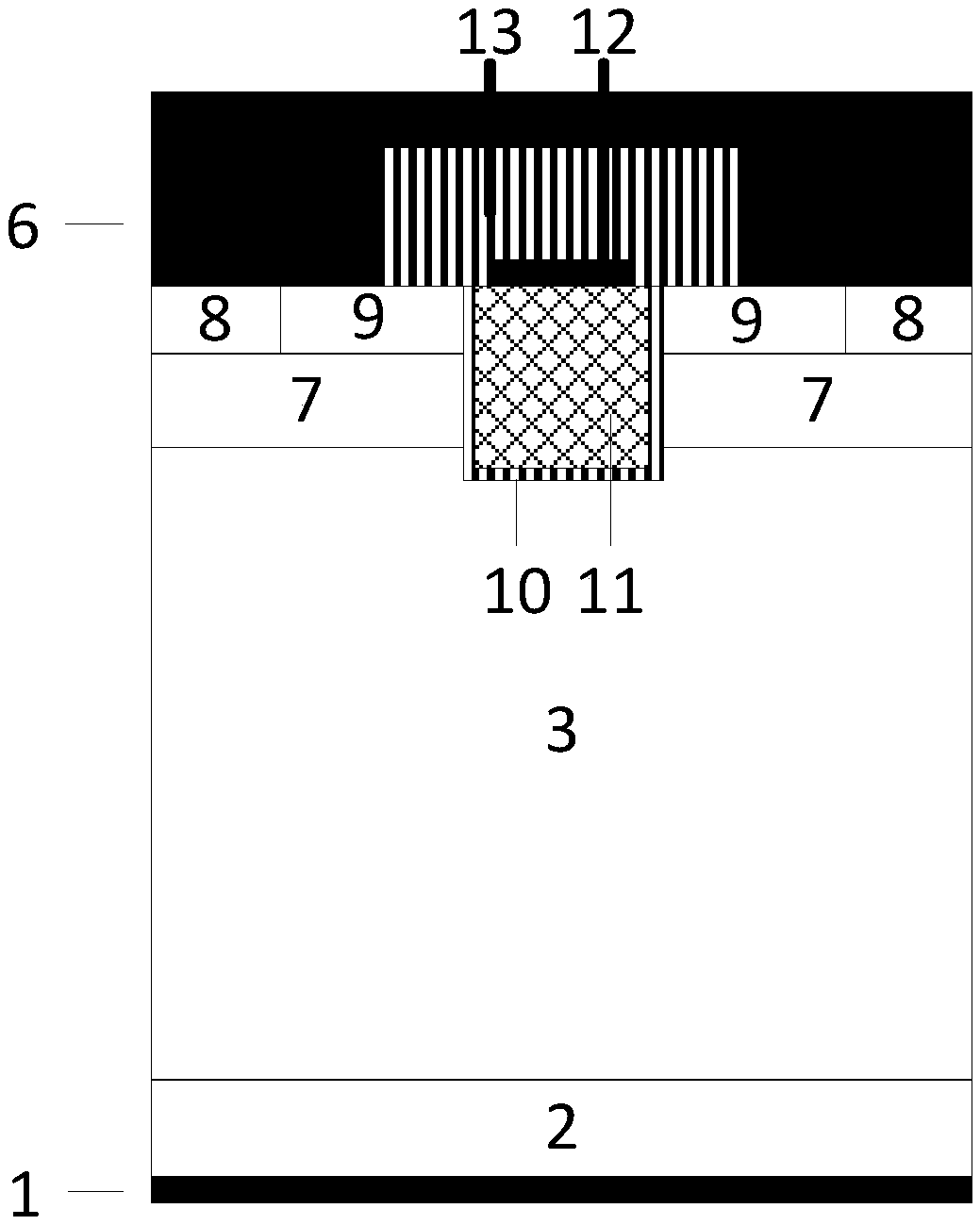

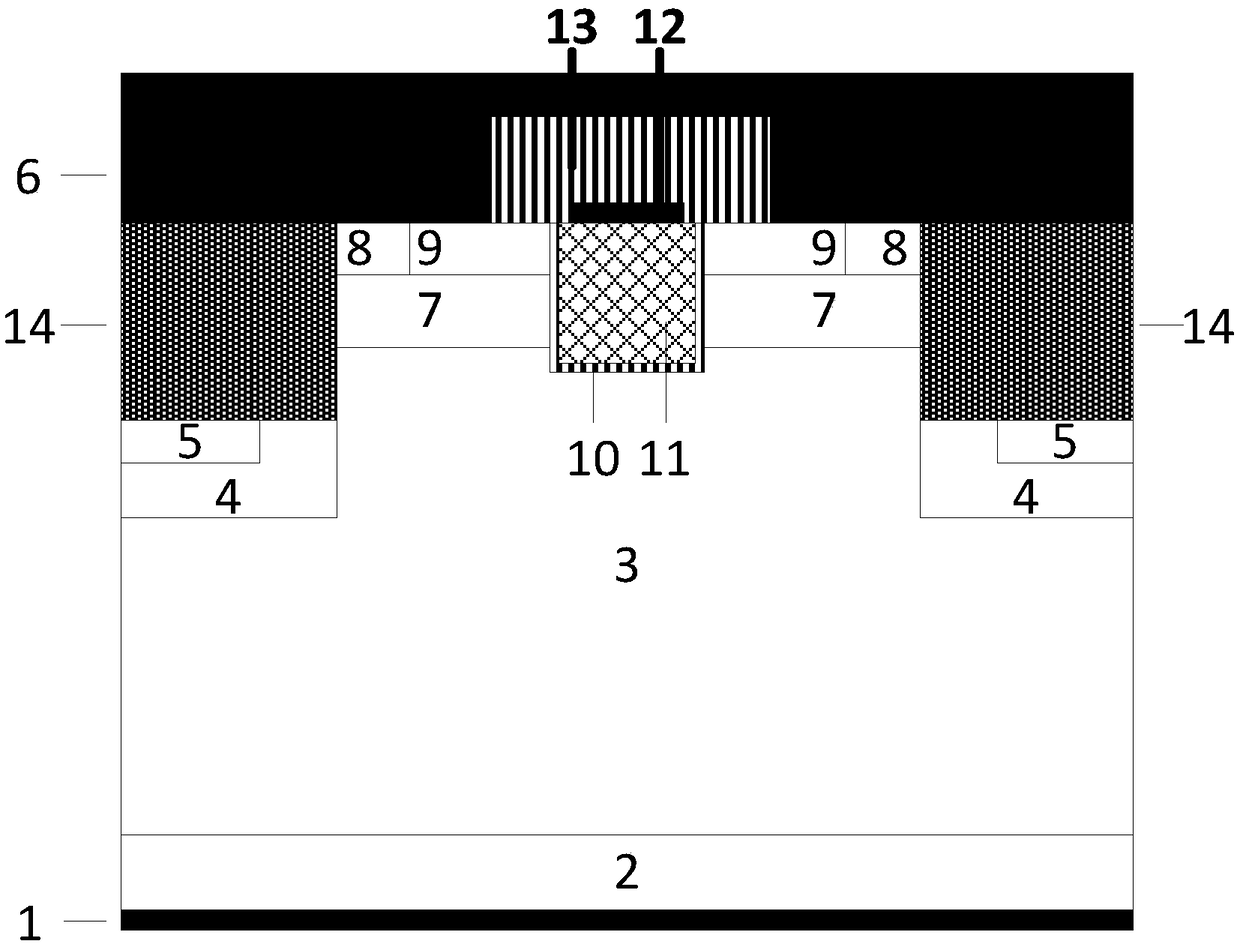

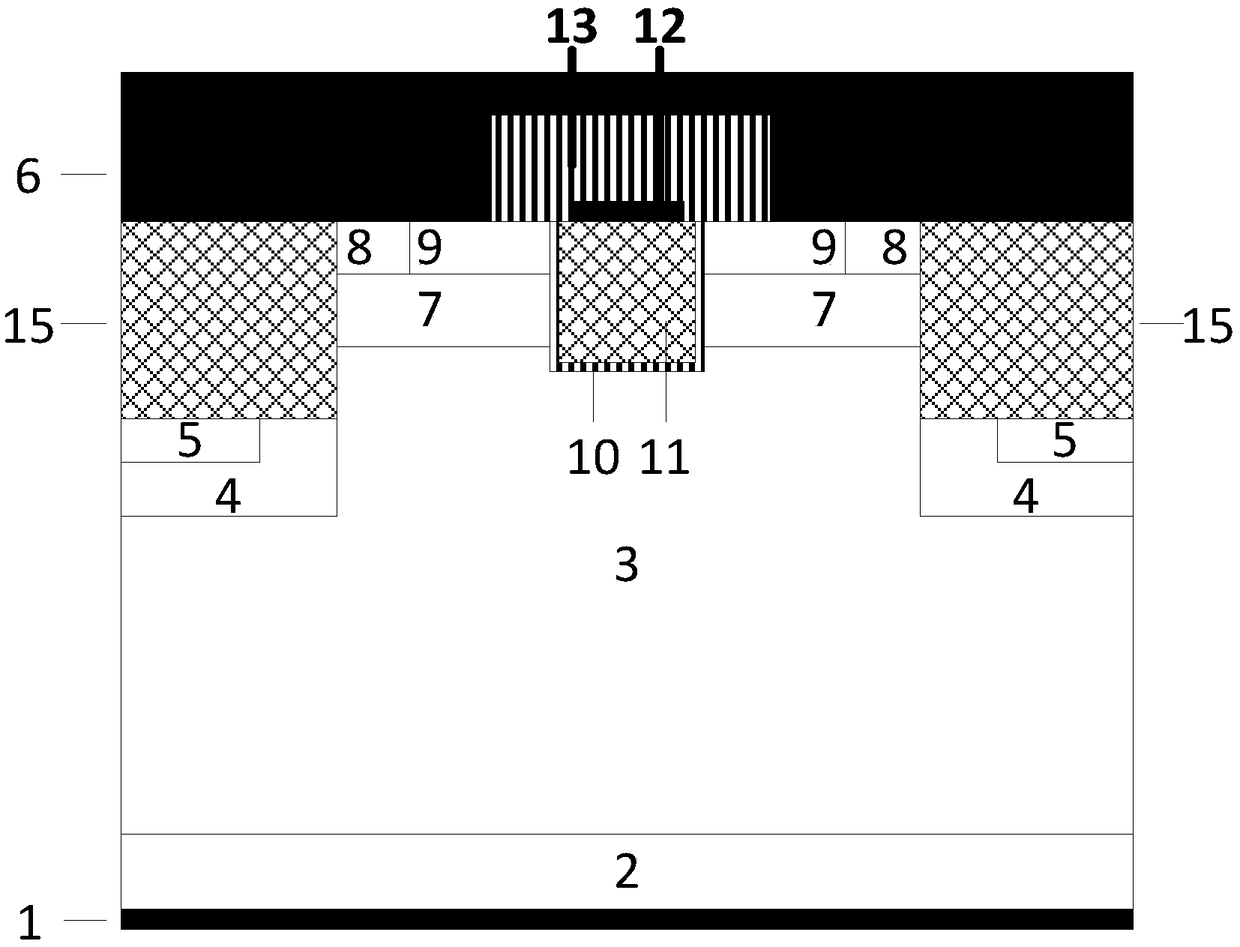

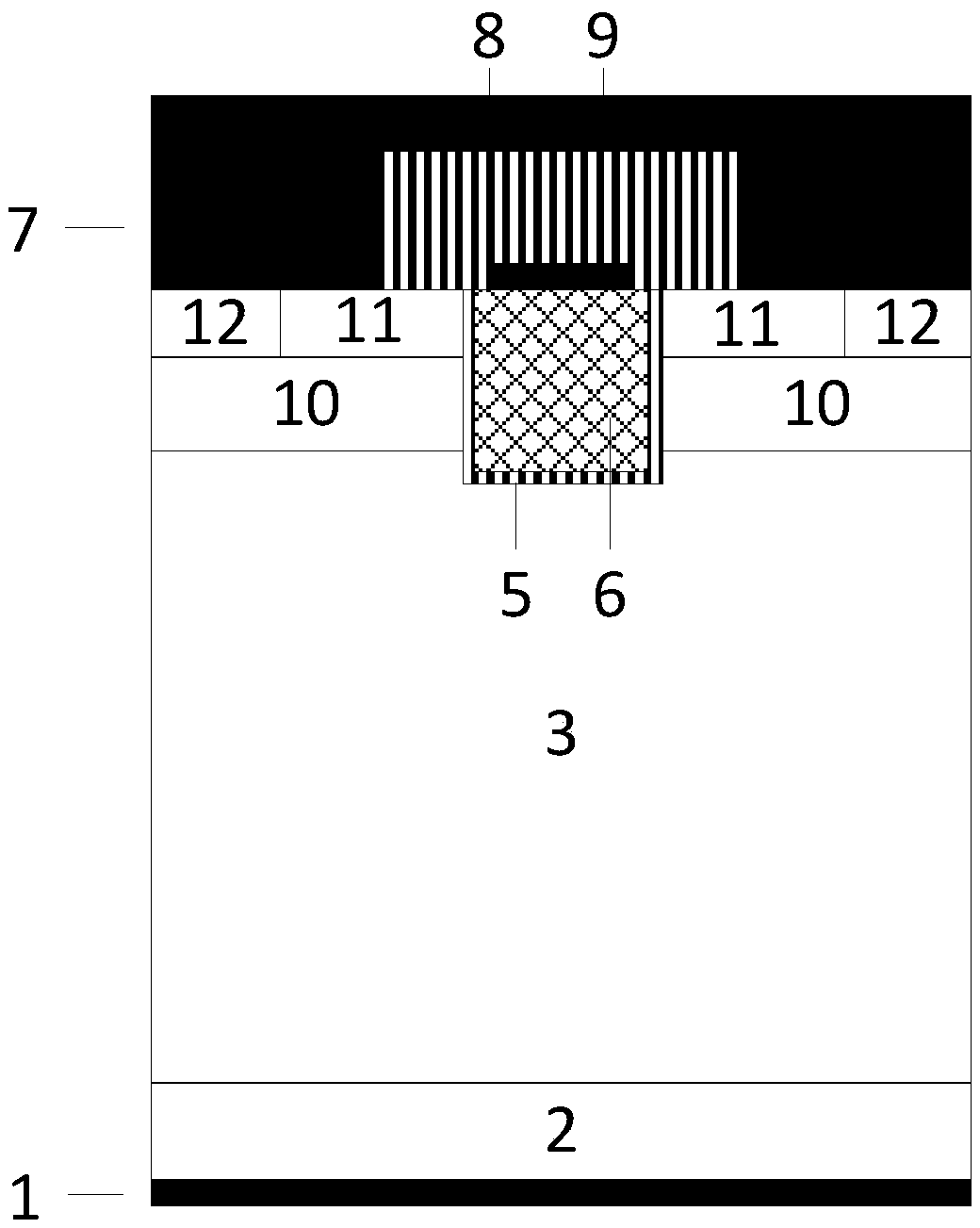

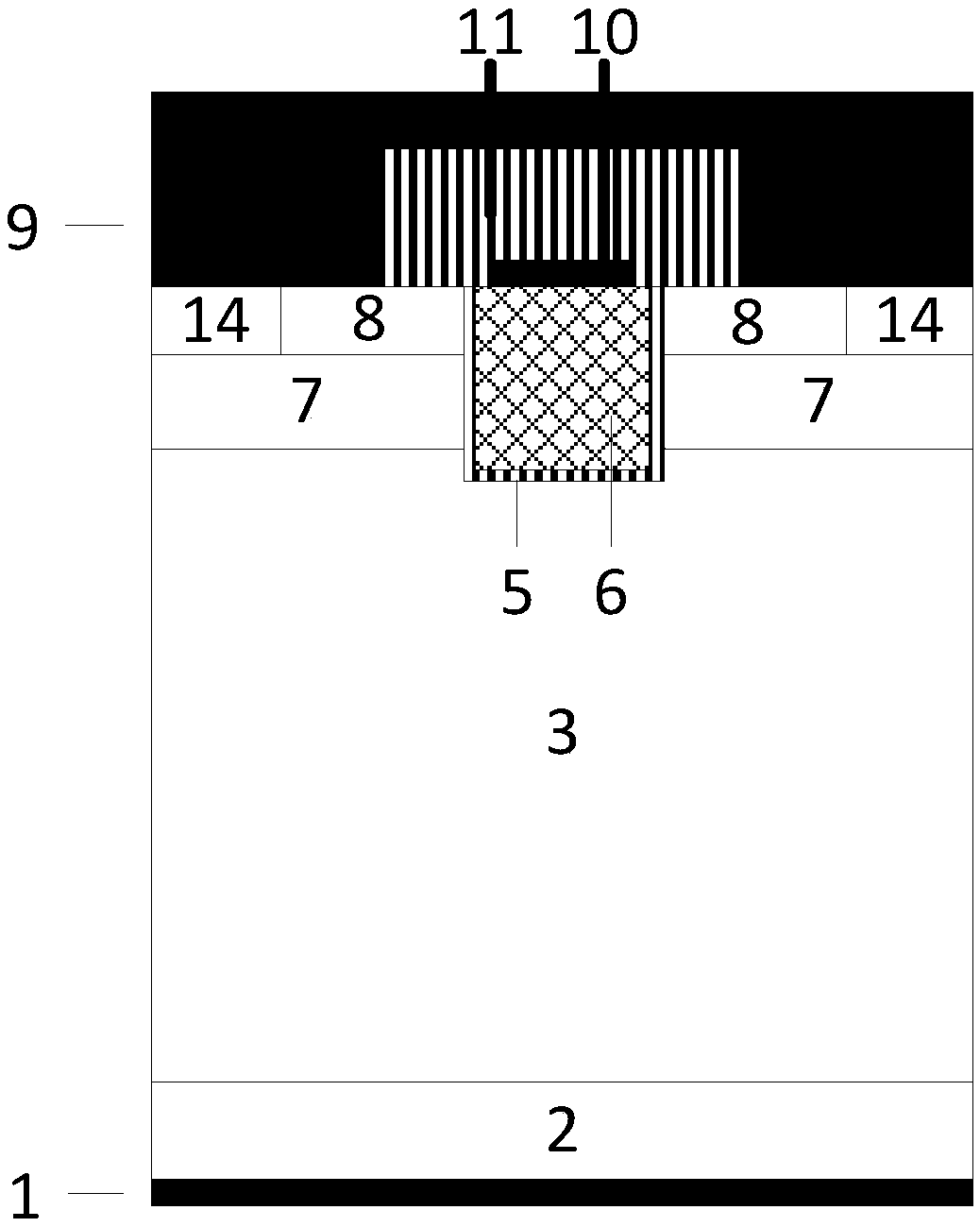

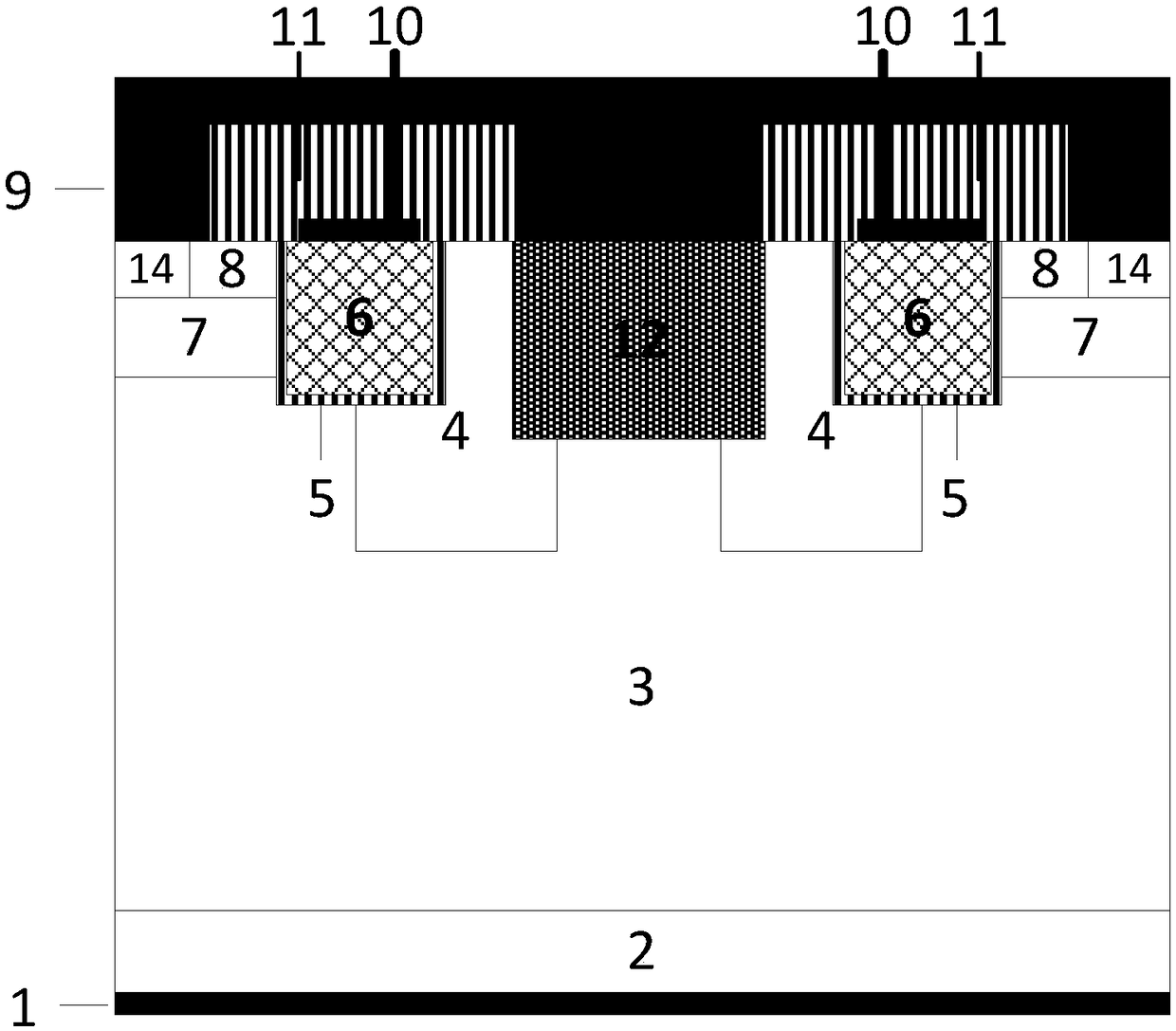

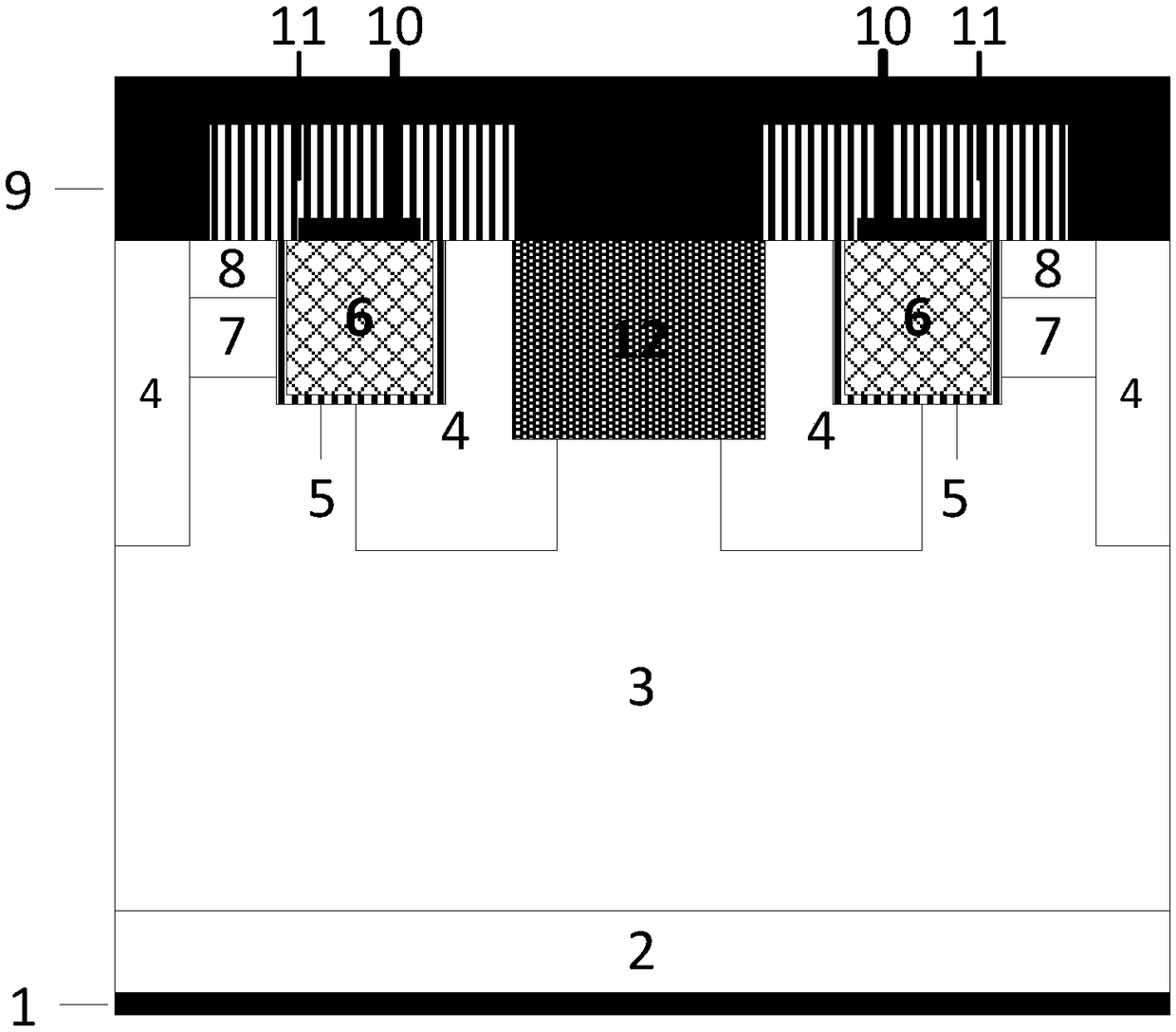

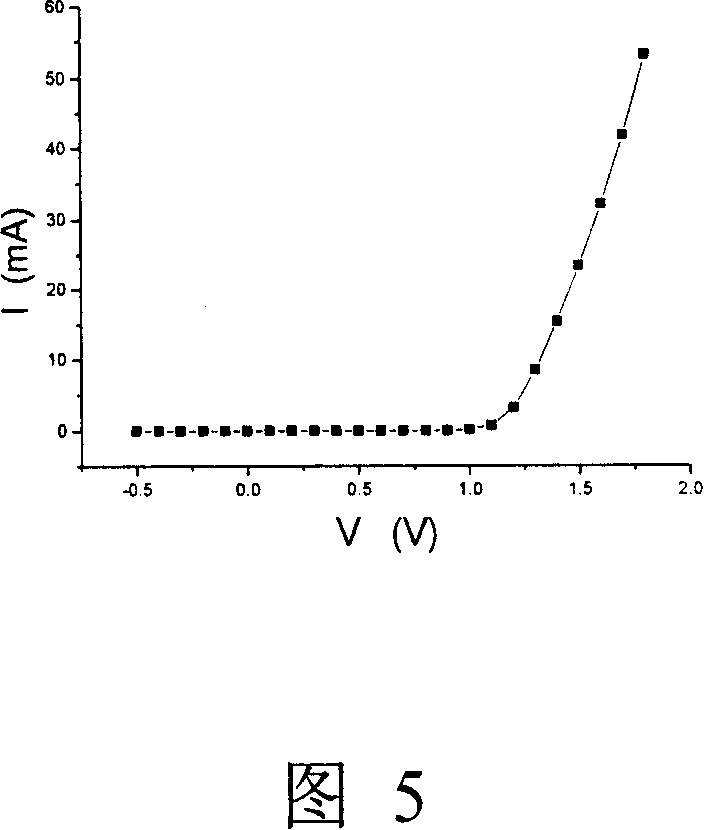

Silicon carbide MOSFET device and manufacturing method thereof

ActiveCN108807504AImprove leakageReduce leakageSemiconductor/solid-state device manufacturingSemiconductor devicesCarbide siliconMOSFET

The invention provides a silicon carbide MOSFET device and a manufacturing method thereof. Silicon carbide deep P injection is performed in a specified region, groove etching and deposition of metal or polysilicon are performed above a silicon carbide deep P doped region, and the deposited metal or polysilicon is in direct contact with the silicon carbide N-epitaxy to form a Schottky contact or aSi / SiC heterojunction contact having rectifying characteristics. Therefore, the integration of multiple sub-rectifiers is achieve while optimizing the basic performance of the conventional silicon carbide UMOSFET, the working performance of the third quadrant of the device is greatly optimized, the gate-drain capacitance of the device is reduced and the switching speed of the device is improved.

Owner:HANGZHOU SILICON-MAGIC SEMICON TECH CO LTD

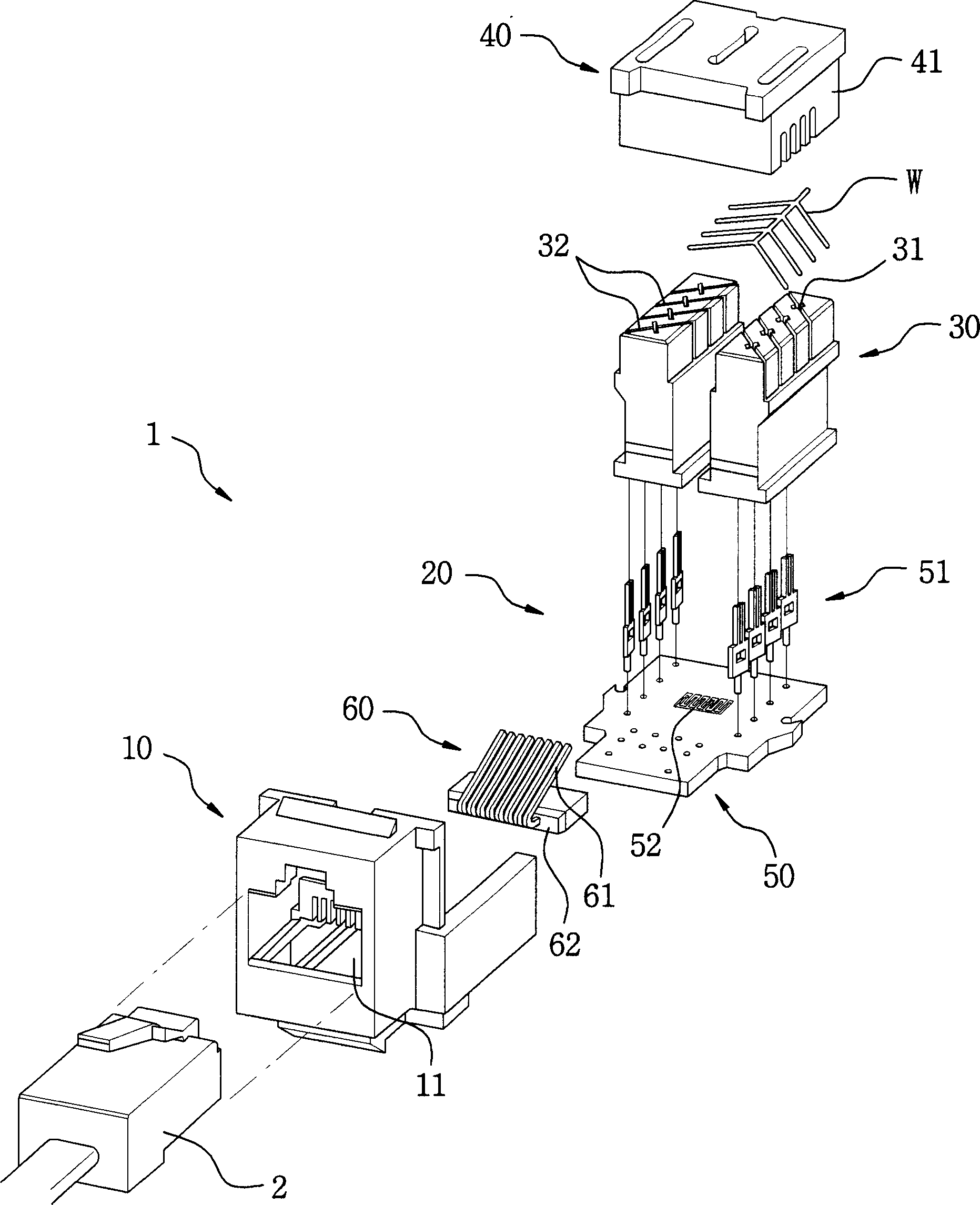

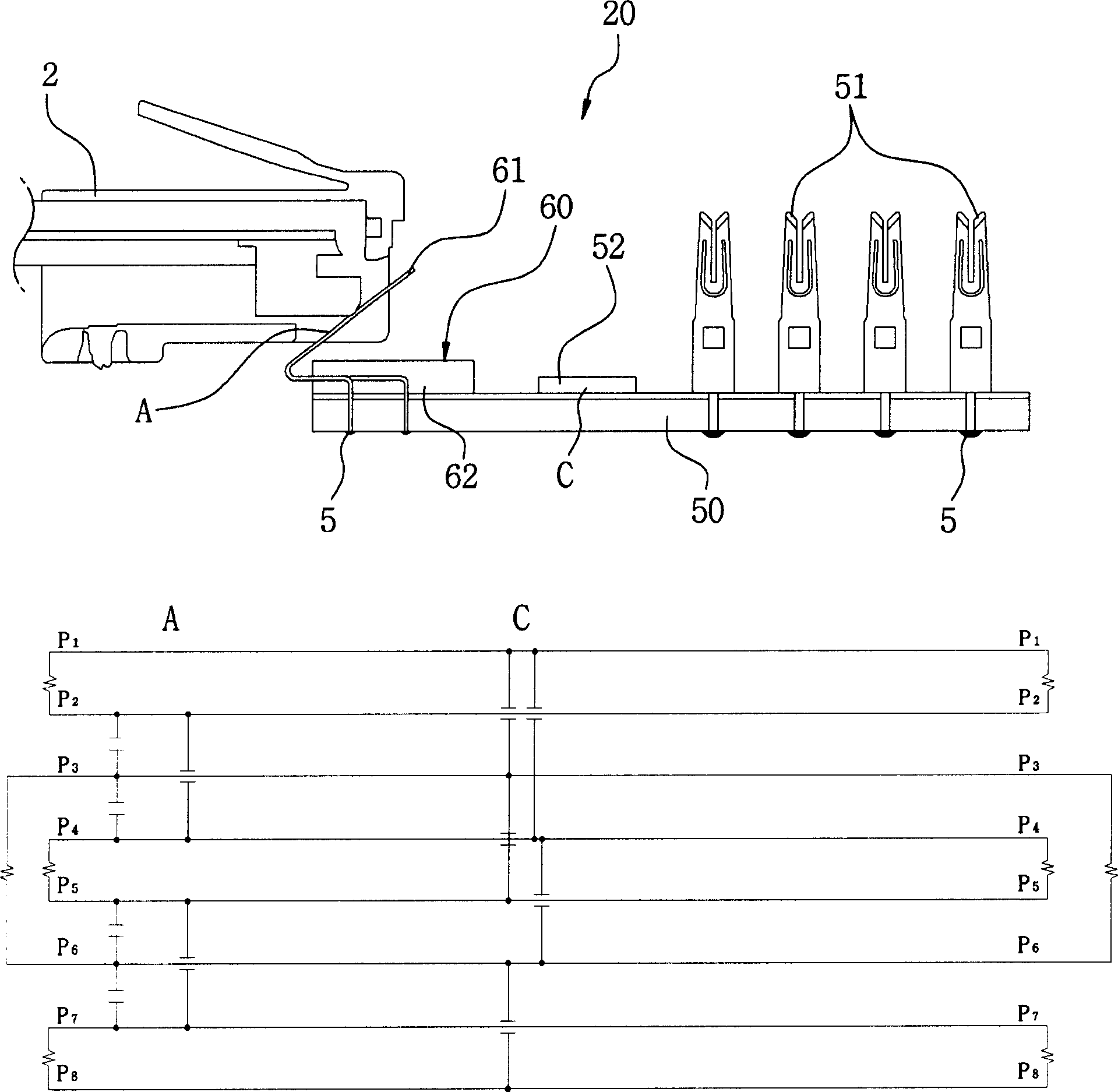

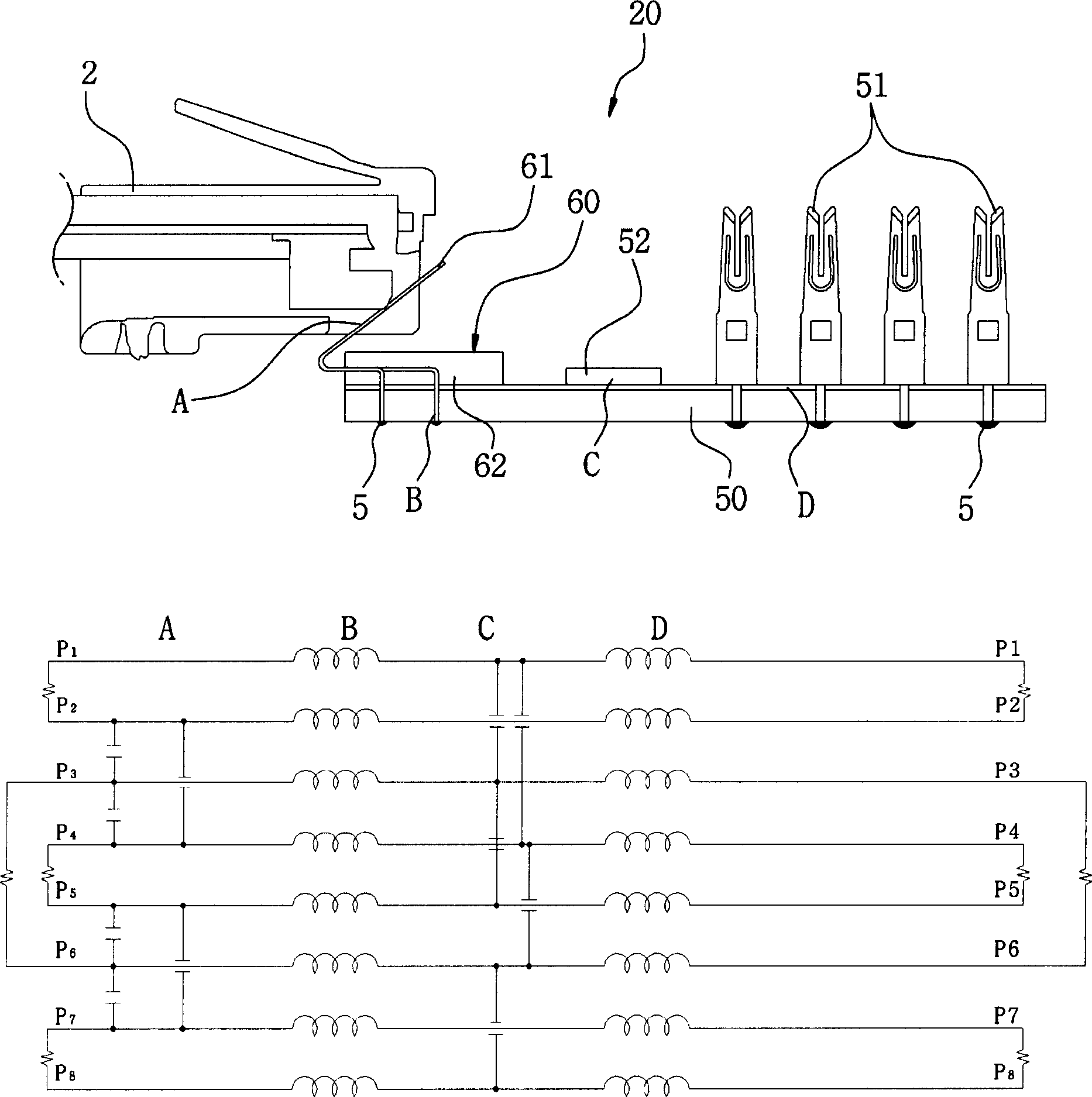

Crosstalk canceling pattern for high-speed communications and modular jack having the same

InactiveCN1808788AReduce parasitic inductanceReduce foulingCoupling for high frequencySoil-shifting machines/dredgersParasitic capacitanceEngineering

The invention relates to a modular socket used for high-speed communication; in particular, a compensation capacitor is arranged on a transmission line to eliminate the interference generated by the parasitic capacitance between adjacent bolts, meanwhile a high-speed communication interference compensation pattern for a second compensation capacitor and a modular socket containing the pattern arealso arranged on the transmission line. The high-speed communication interference compensation pattern and the modular socket containing the pattern include the following units: a casing formed by a bolt buckle positioned at the lower end of a plug faucet and used for fixing the bolt and a combination guiding plate; a multilayer structure type printed circuit board with a plurality of bolts and IDC terminals communicated and combined at the upper part and with a plurality of compensation capacitors; a lower connecting block with the bottom surface combined with the printed circuit board and insliding combination along the combination guiding plate of the casing; and an upper connecting block combined with the upper part of the lower connecting block, cutting a UTP cable leaded from the rear part and connecting the pieces of the UTP cable to the IDC terminals.

Owner:DAE EUN ELECTRONICS

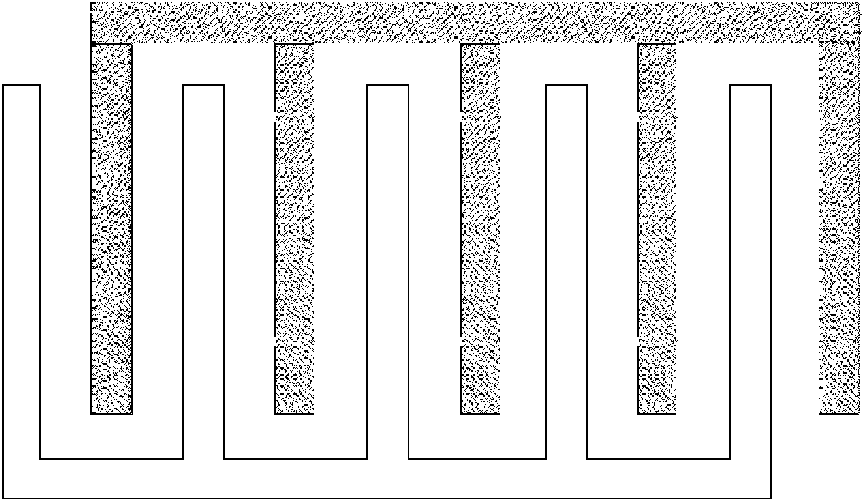

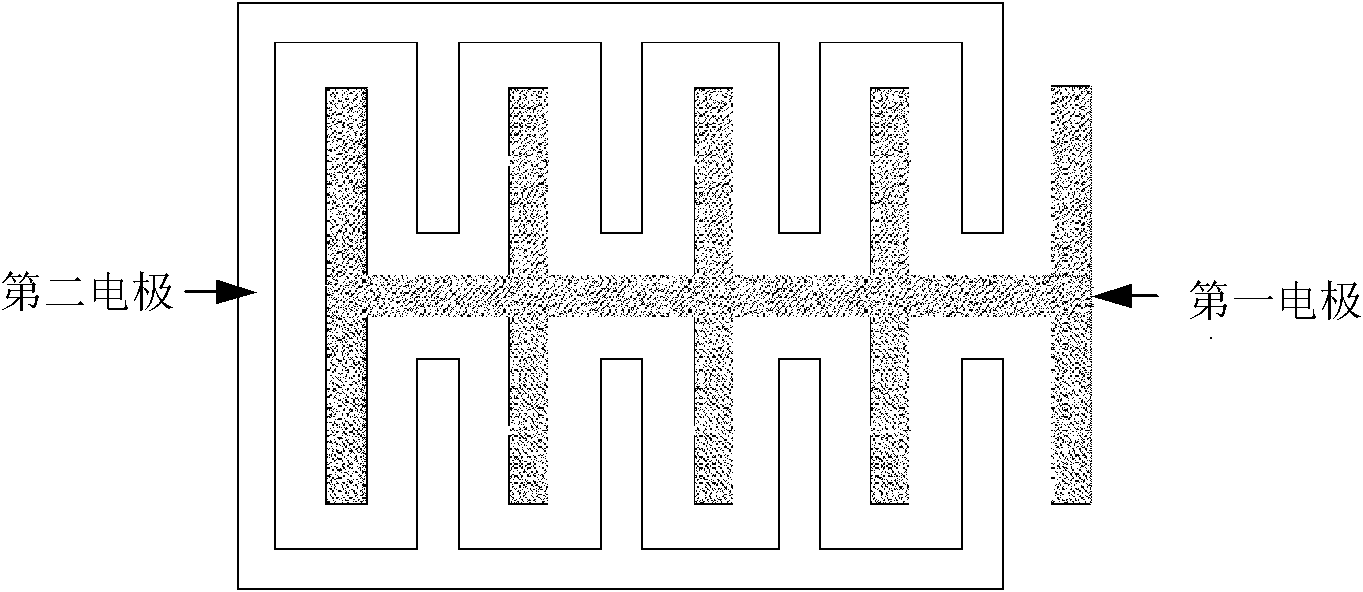

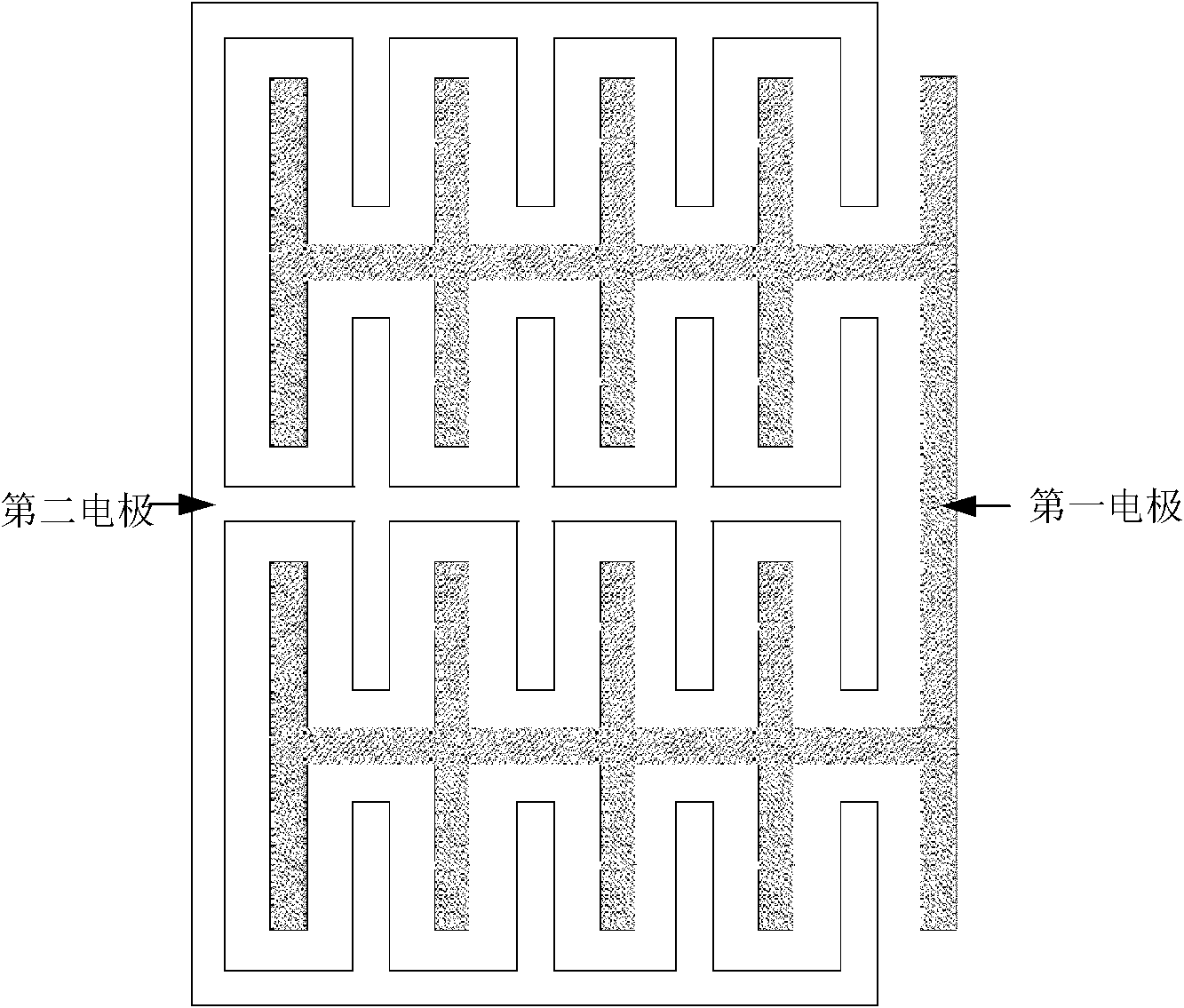

Metal-oxide-metal capacitor structure

InactiveCN102487055AReduce difficultyReduce parasitic inductanceSemiconductor/solid-state device detailsSolid-state devicesCapacitanceEngineering

The invention discloses a metal-oxide-metal capacitor structure. The capacitor structure is characterized in that on the same-layer metal, a first electrode of a capacitor consists of a first group of metal strips which are mutually parallel, and the first group of metal strips which are mutually parallel are connected with a metal strip vertical to the first group of metal strips which are mutually parallel; or the first electrode of the capacitor consists of a stack-shaped metal strip; on the same-layer metal, a second electrode of the capacitor consists of a second group of metal strips which form an interpolation structure with the first electrode of the capacitor; and the same-layer metal structure is a minimum repeating unit so as to form an MOM (Metal-Oxide-Metal) capacitor structure. According to the metal-oxide-metal capacitor structure, by utilization of a symmetric structure, the parasitic inductance and resistance of pole plates at the two ends of the MOM capacitor are effectively reduced, and the application range of the MOM capacitor is expanded; and simultaneously, the structure is used as a unit, and the capacitor with large capacitance is formed by utilizing repeated parallel connection of the unit structures, so that the difficulty in establishing a radio-frequency MOM capacitance model is reduced.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

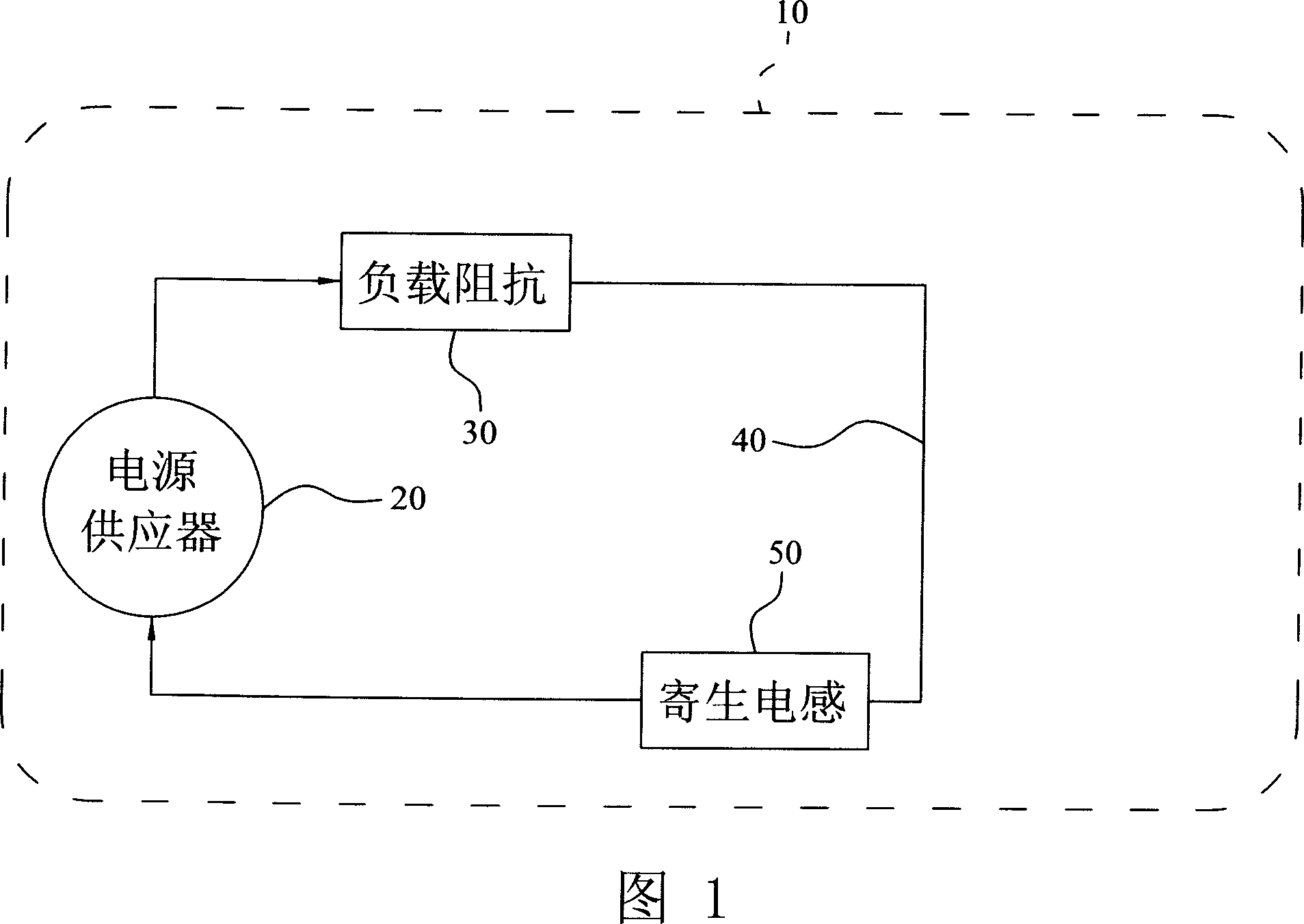

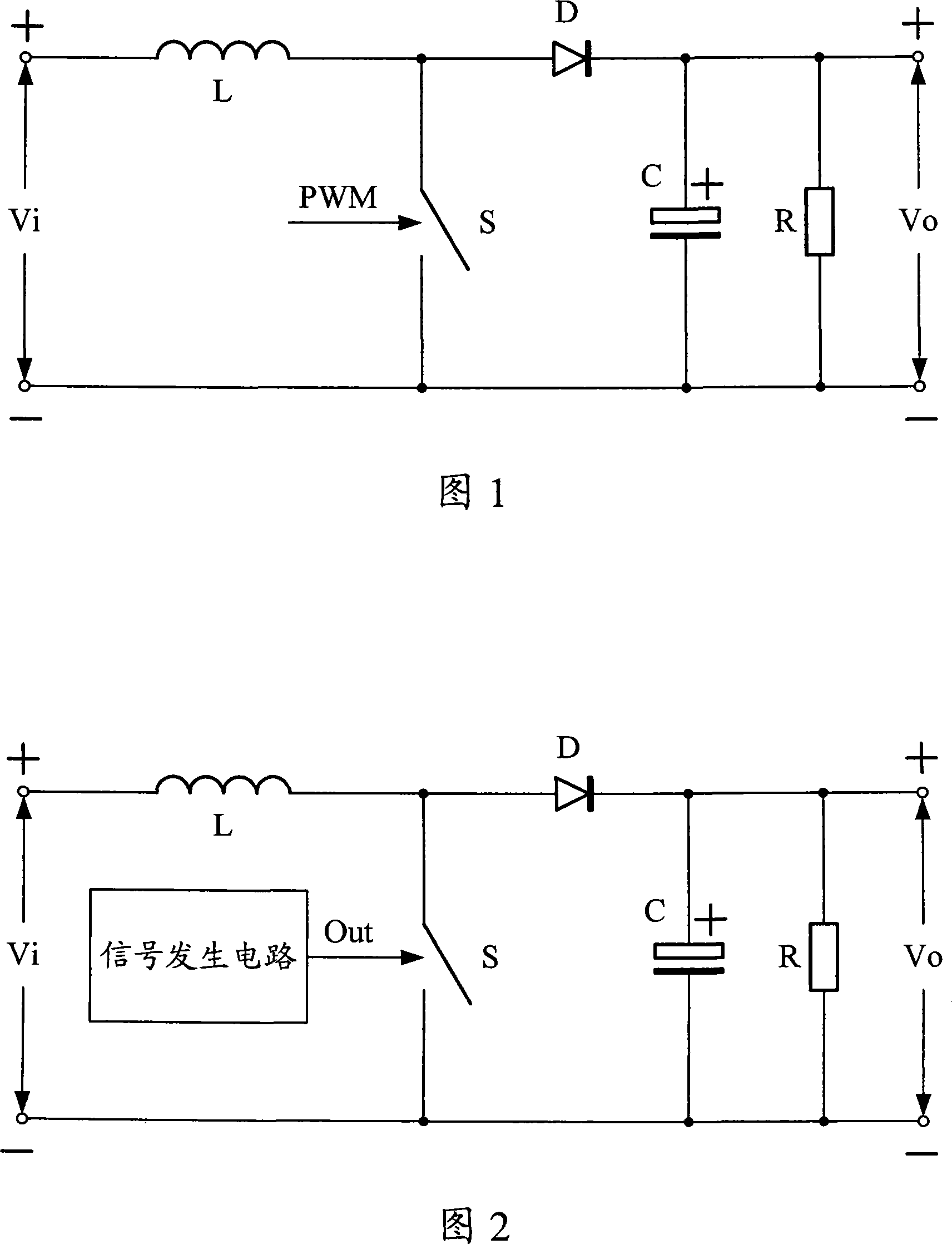

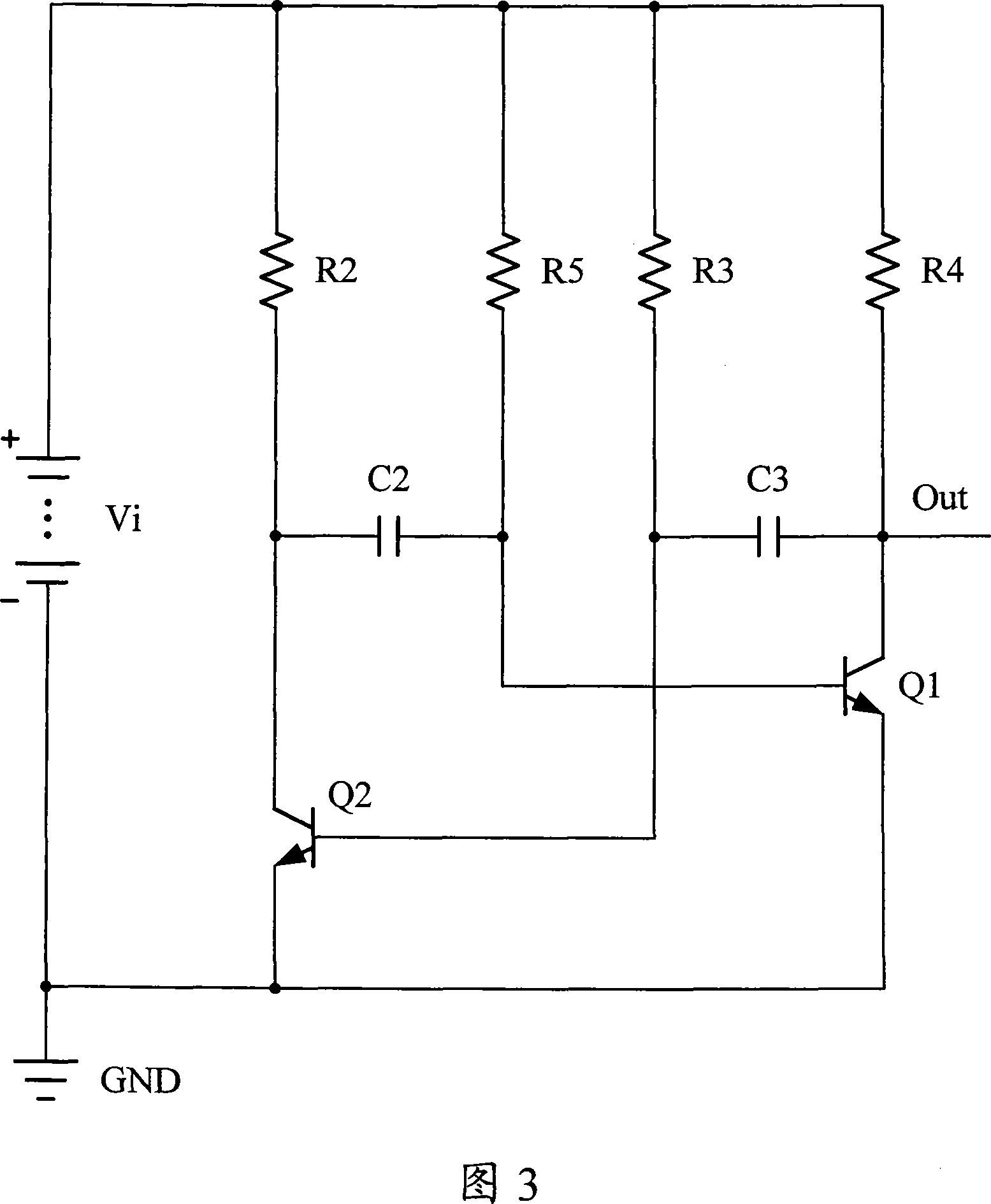

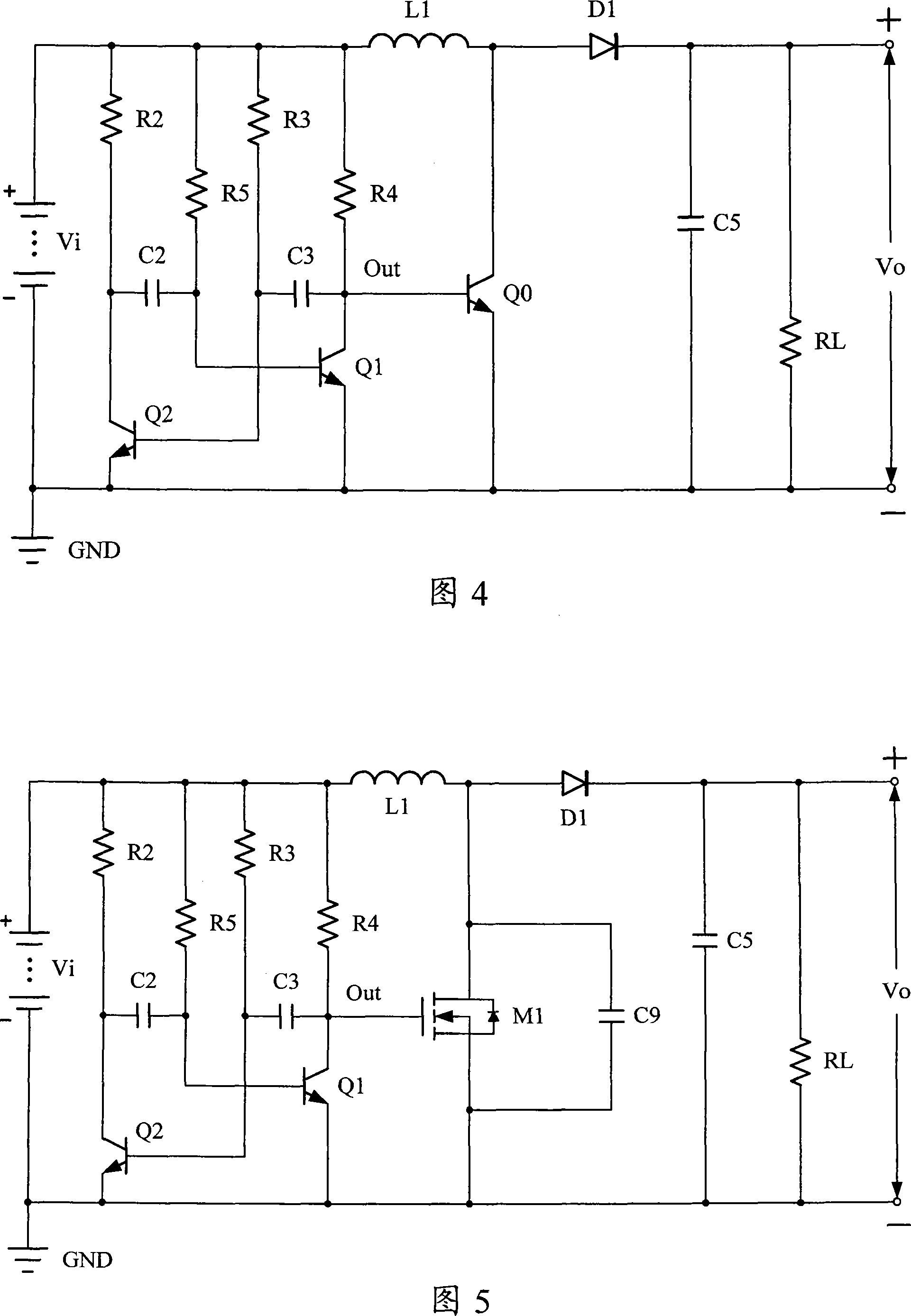

Boosted circuit

InactiveCN101232239AReduce parasitic inductanceReduce capacitanceApparatus without intermediate ac conversionEngineeringVoltage

The invention discloses a voltage booster circuit, the development cost and the maintenance cost of which are lower. The voltage booster circuit comprises a switch, and further has a signal generating circuit, wherein the signal generating circuit outputs a pulse signal to control the opening and the closing of the switch. The invention is widely applied to consumption electronic products.

Owner:新奇点智能科技集团有限公司

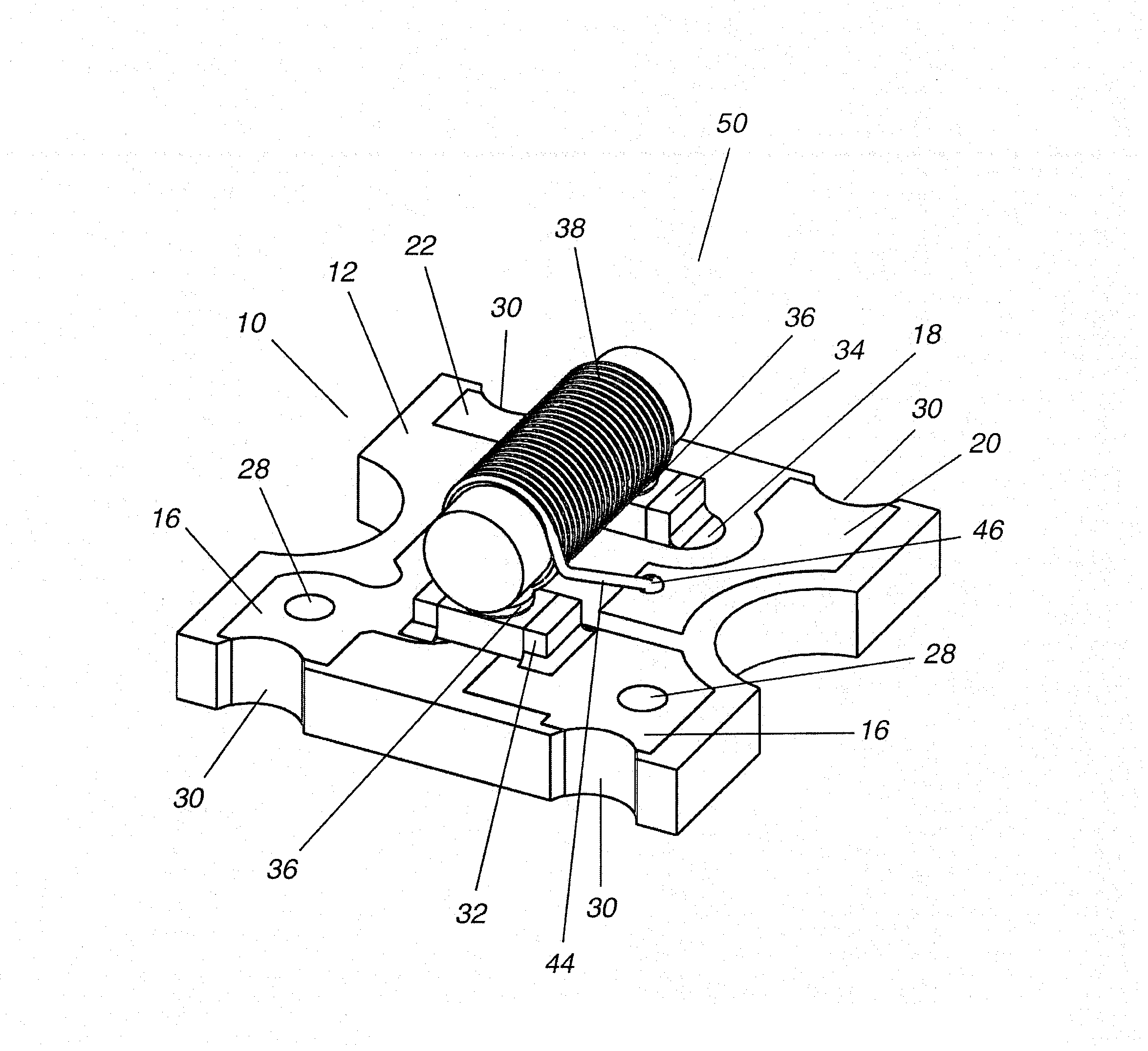

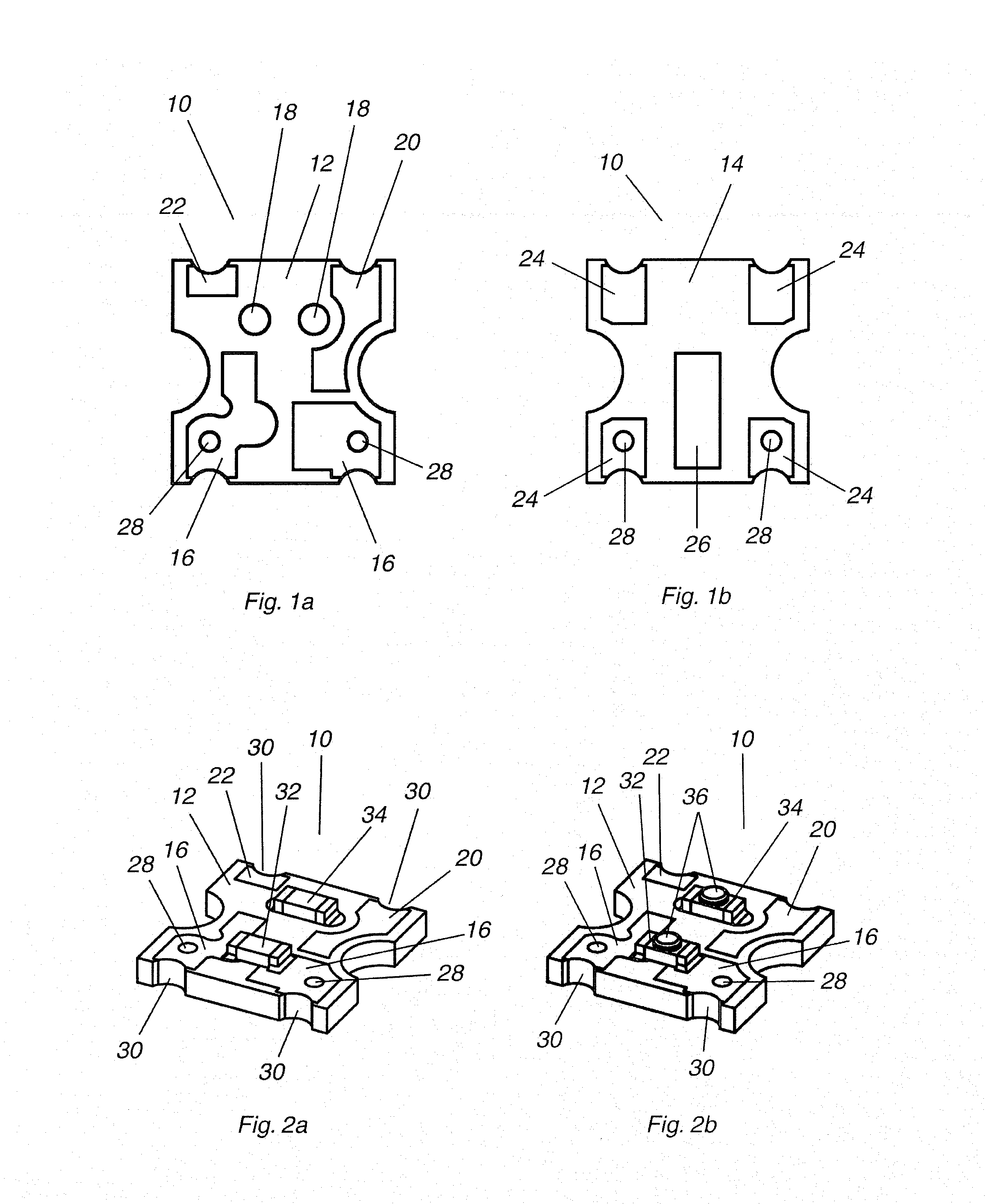

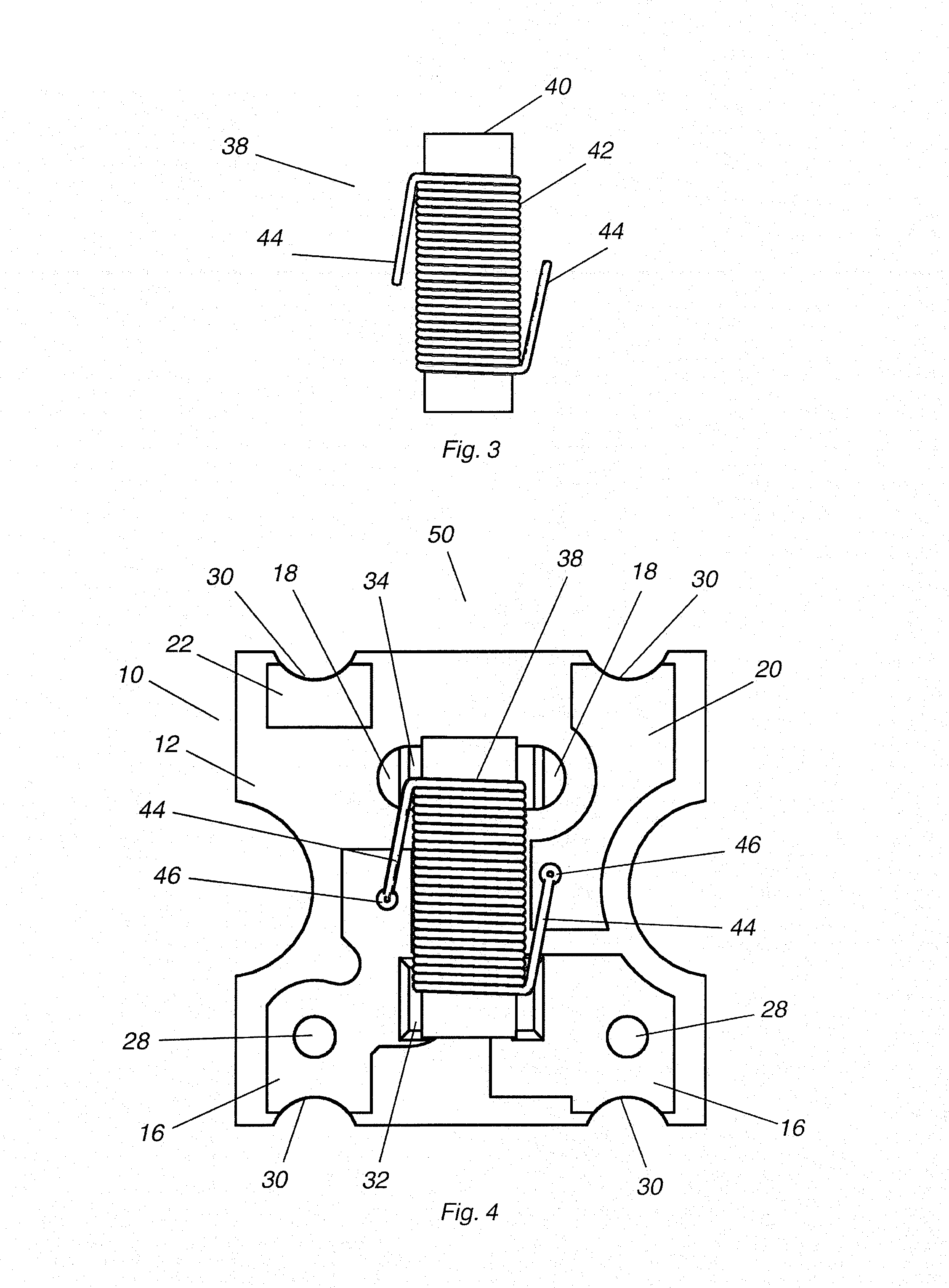

Surface mount bias tee

ActiveUS8644029B1Extend frequency rangeIncrease mechanical retentionFinal product manufacturePrinted circuit aspectsInductorPrinted circuit board

A miniaturized wideband surface mount bias tee comprises a printed circuit board with a functioning first capacitor and a dummy second capacitor, and an inductor bonded atop the two capacitors. The capacitors, adhesive and solder are depositable by standard surface mount pick and place machinery. The inductor wires are bonded to one of the first capacitor bonding pads and to an inductor bonding pad. The circuit element bonding pads include portions bordering the pc board edges and are conductively connected to bonding pads on the bottom face of the pc board. Conductive thru-vias for the first capacitor bonding pads reduce parasitic inductance and extend the operating frequency range. A flat-topped insulating cap encloses the bias tee sides and top. The cap forms an air gap between the inductor and circuit elements and provides a surface for manipulating the bias tee with present-day assembly equipment.

Owner:SCI COMPONENTS

A silicon carbide MOSFET device and a manufacturing method thereof

ActiveCN109192779AGood long-term application reliabilityImprove pressure resistanceSemiconductor/solid-state device manufacturingDiodeMOSFETHeterojunction

The invention provides a silicon carbide MOSFET device and a manufacturing method thereof. The invention improves device structure design and finally integrates Schottky contact or heterojunction contact with rectifying characteristics on the basis of traditional silicon carbide UMOSFET structure. At that same time of optimize the basic characteristics of the traditional silicon carbide UMOSFET structure, the improvement realize the integration of multi-sub rectifier devices, greatly optimizes the work performance of the third quadrant of the device, and in addition, the invention also optimizes the dynamic performance of the device, and has shorter switching time; In addition, the invention also has the characteristics of simple process and easy realization.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

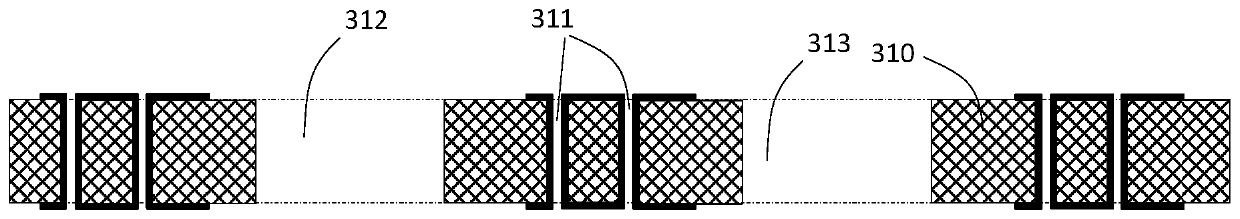

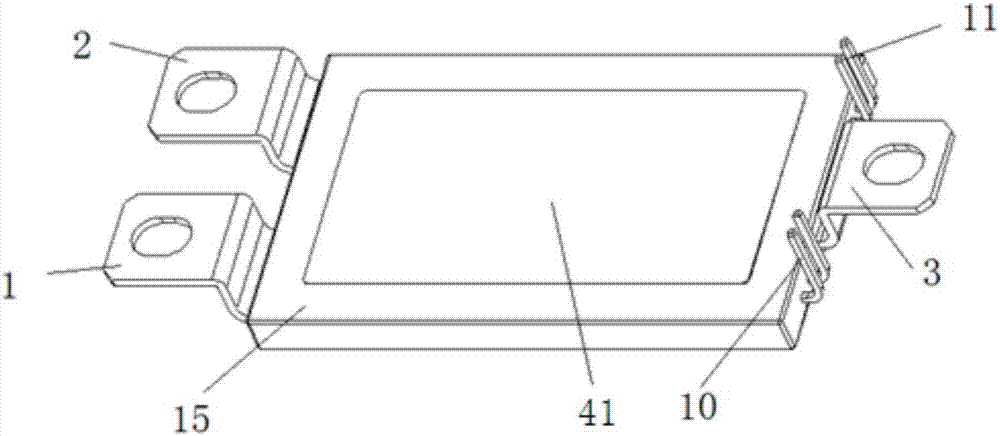

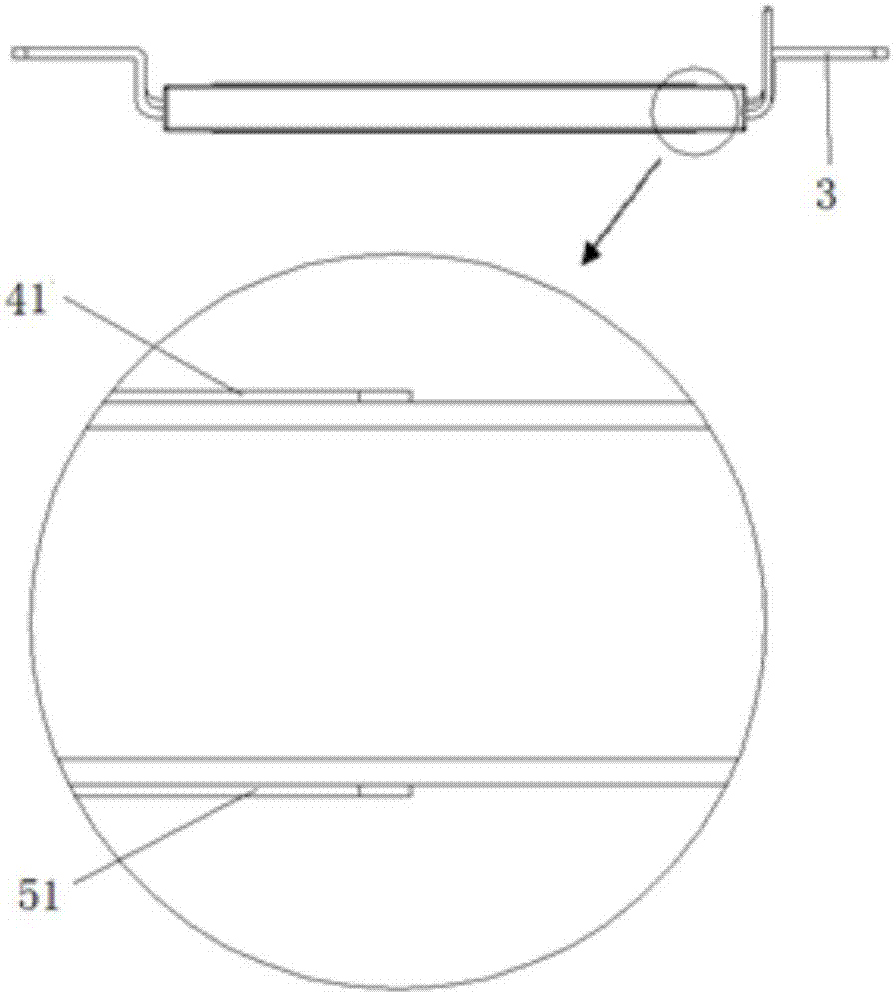

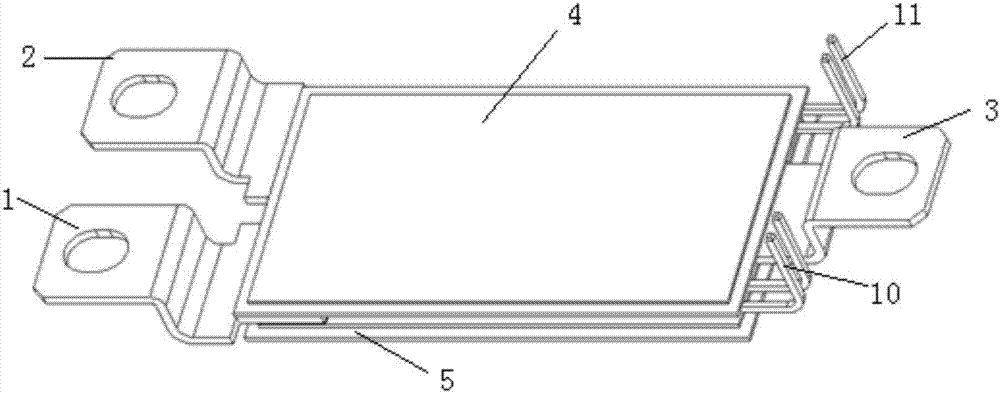

Power module low-inductance lead terminal

InactiveCN105514072AReduce parasitic inductanceGuaranteed versatilitySemiconductor/solid-state device detailsSolid-state devicesDBcBusbar

The invention discloses a power module low-inductance lead terminal. The lead terminal comprises a first lead terminal body and a second lead terminal body which are connected with a positive busbar and a negative busbar of an external power source of a power module. The first lead terminal body comprises a plurality of first lead terminal pins, first supporting parts and first fixed connecting parts which are connected sequentially. The second lead terminal body comprises a plurality of second lead terminal pins, second supporting parts and second fixed connecting parts which are connected sequentially. The first lead terminal pins of the first lead terminal body and the second lead terminal pins of the second lead terminal body are arranged in a staggered mode. The pins of the two terminal bodies are located on the same straight line so as to reduce terminal parasitic inductance, and correspondingly, copper foil on the DBC is designed to be in a staggering shape, so that interconnection is achieved; the parallel crossing structure is adopted in the positive and negative terminal bodies, the loop area of the power lead terminal is reduced, and parasitic inductance of the power terminal bodies is greatly reduced, is about 11.9 nH, and is only half of that of a general power lead terminal; meanwhile, the occupied distance of the two lead terminal bodies on the power module is saved.

Owner:南京银茂微电子制造有限公司

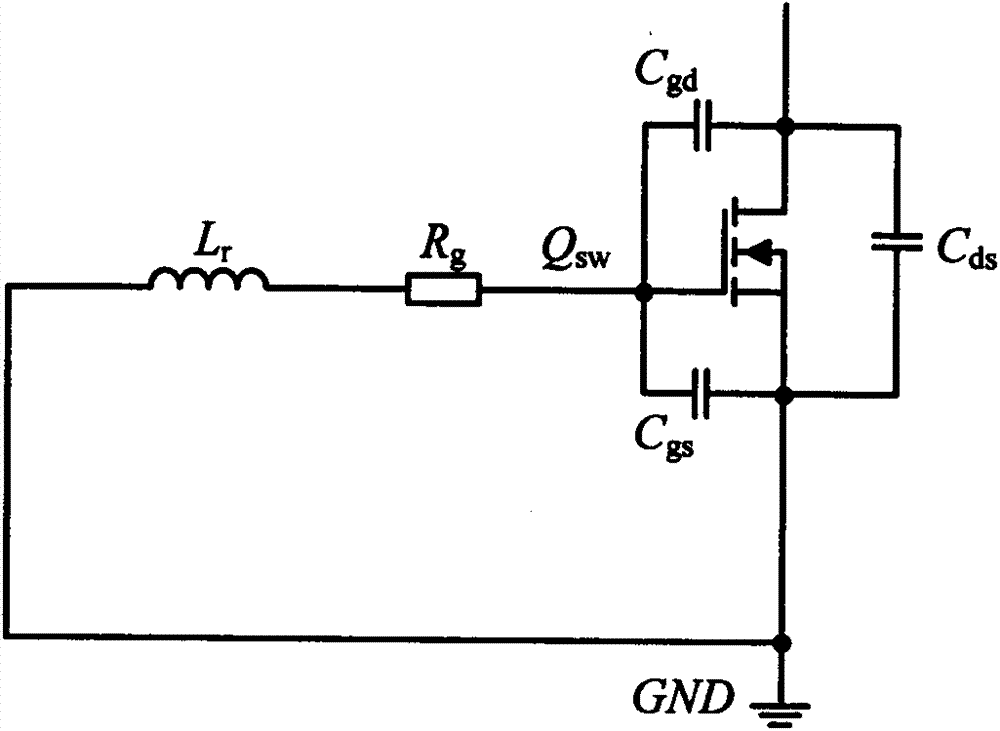

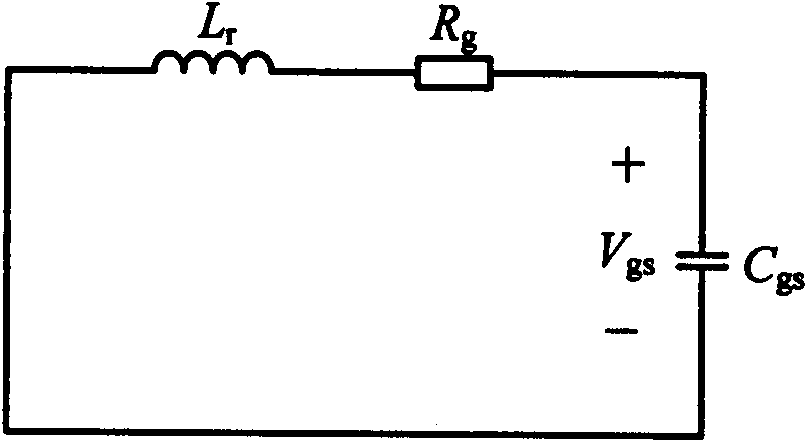

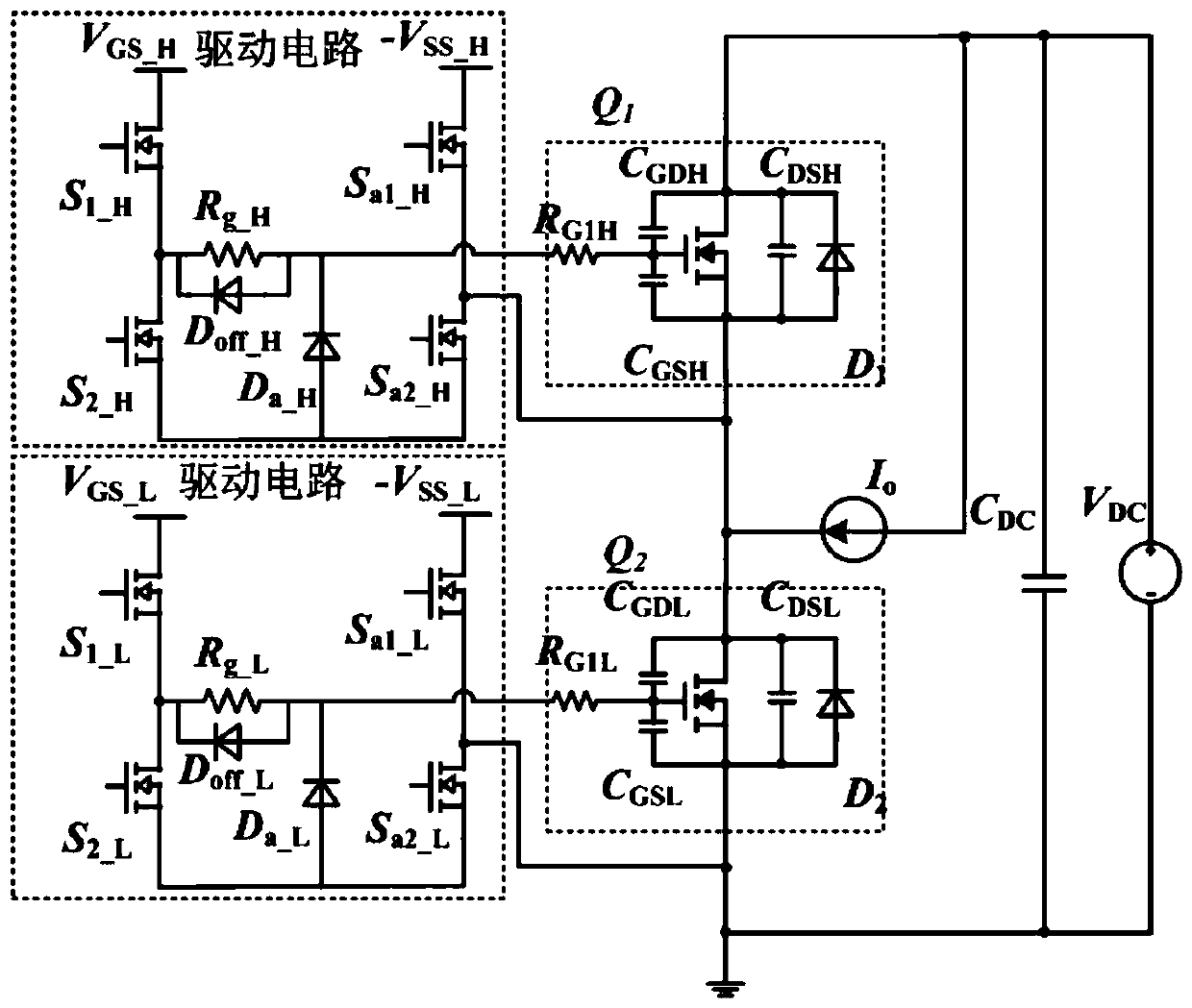

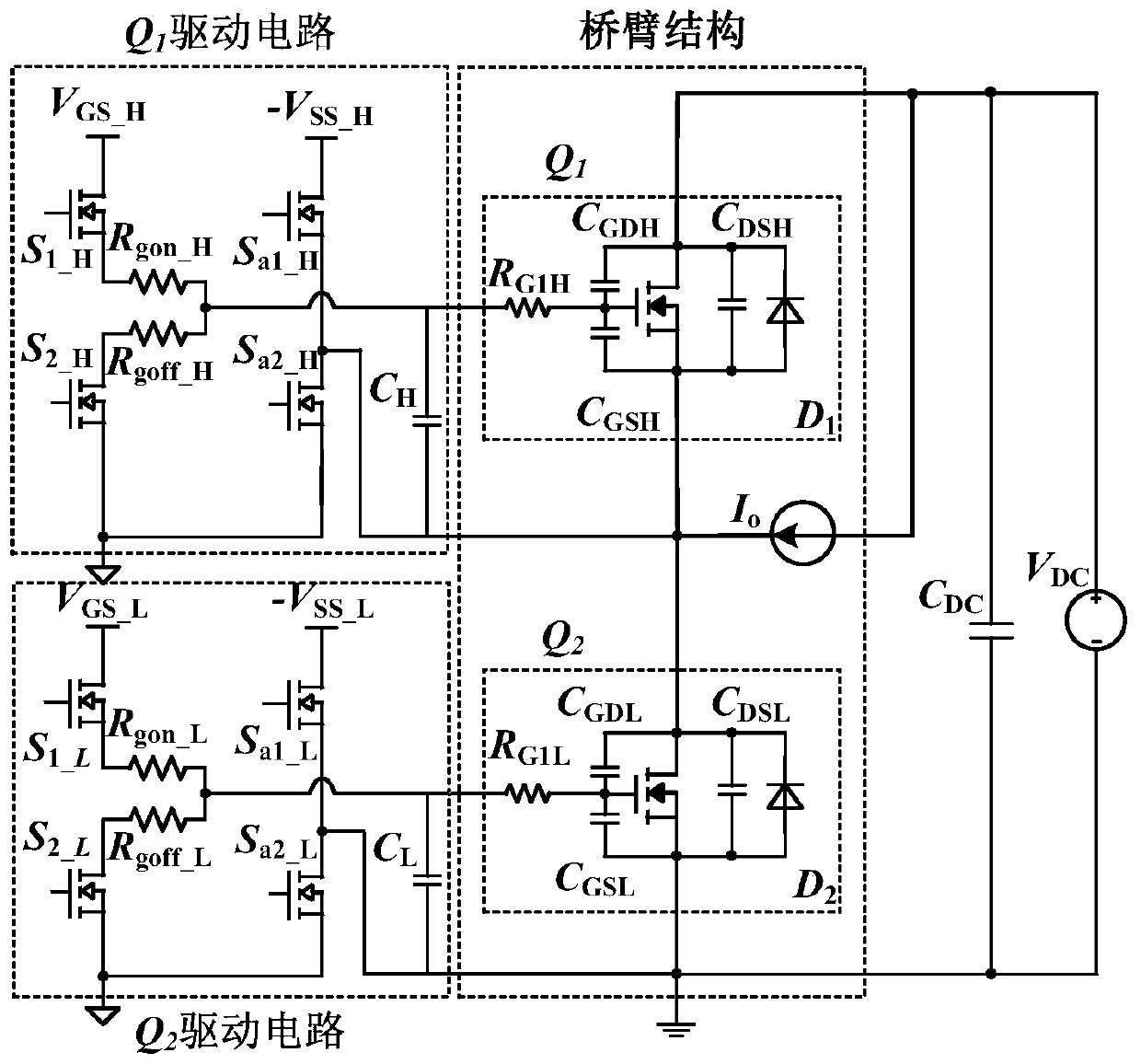

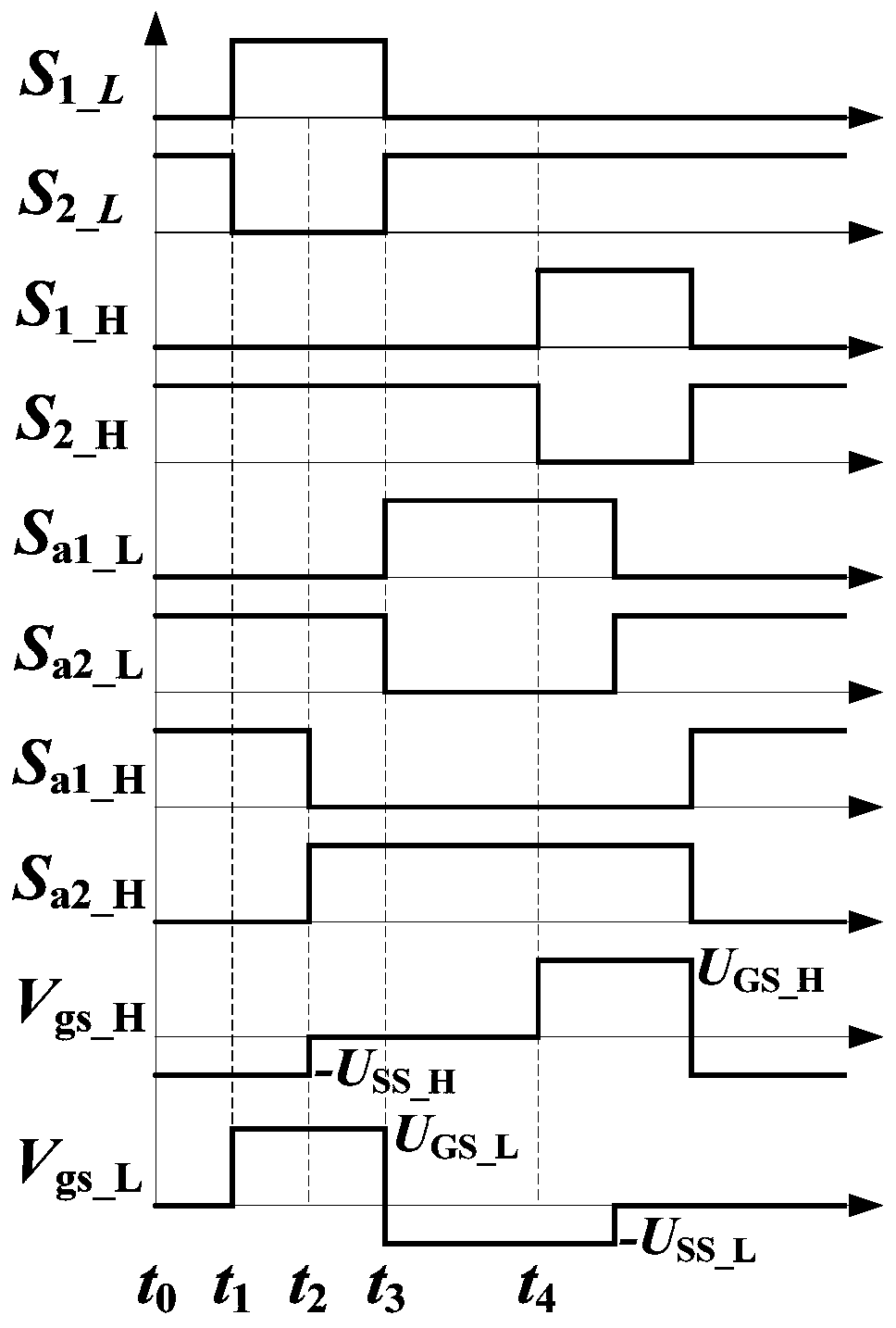

SiC power device driving circuit capable of suppressing bridge arm crosstalk and control method thereof

PendingCN110492728AReduce the impactSuppress bridge arm crosstalk problemEfficient power electronics conversionPower conversion systemsCapacitanceEngineering

The invention discloses a SiC power device driving circuit capable of suppressing bridge arm crosstalk and a control method thereof. The driving circuit comprises a G-pole driving circuit, an S-pole driving circuit and a capacitor arranged between the G-pole driving circuit and the S-pole driving circuit. The G-pole drive circuit comprises a positive voltage power supply, a first G-pole switch tube, a second G-pole switch tube, a switch-on resistor and a switch-off resistor, wherein the first G-pole switch tube, the second G-pole switch tube, the switch-on resistor, the switch-off resistor andthe second G-pole switch tube are used for controlling the G-pole voltage state and are sequentially connected in series. The S-pole drive circuit comprises a negative voltage power supply, a first S-pole switch tube and a second S-pole switch tube, wherein the first S-pole switch tube and the second S-pole switch tube control the S-pole voltage state. The negative-voltage power supply, the firstS-pole switch tube and the second S-pole switch tube are sequentially connected in series. According to the invention, the influence of the gate-source parallel capacitor on the switching speed is reduced, and the problem of bridge arm crosstalk is effectively inhibited.

Owner:ELECTRIC POWER RES INST OF STATE GRID ZHEJIANG ELECTRIC POWER COMAPNY

Silicon carbide MOSFET device and manufacturing method thereof

The invention provides a silicon carbide MOSFET device and a manufacturing method thereof. Discontinuous gate structures are formed on the basis of the common silicon carbide MOSFET structure, two silicon carbide deep P injection regions are introduced between the two gate structure and metal or polycrystalline silicon is introduced between the two silicon carbide deep P injection regions. The metal or the polycrystalline silicon directly contacts the silicon carbide N-epitaxy so as to form the Schottky contact or the heterojunction contact having the rectification characteristic. The improvement greatly optimizes the conventional silicon carbide UMOSFET basic characteristics, realizes integration of multiple sub-rectifiers and greatly optimizes the third quadrant performance of the device. Meanwhile, the silicon carbide MOSFET device has the characteristics of low Miller capacitance, simple process and easy implementation.

Owner:UNIV OF ELECTRONIC SCI & TECH OF CHINA

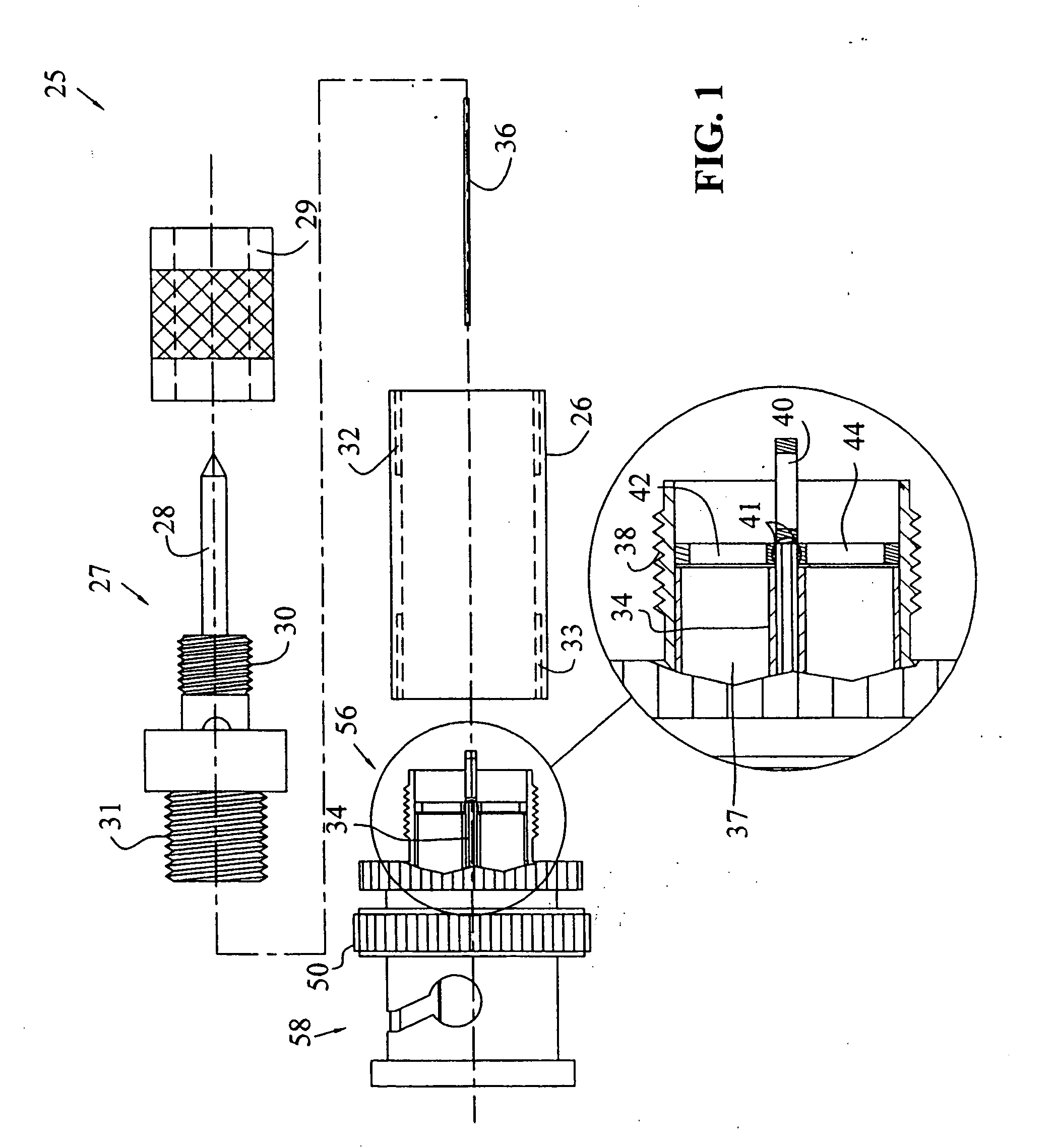

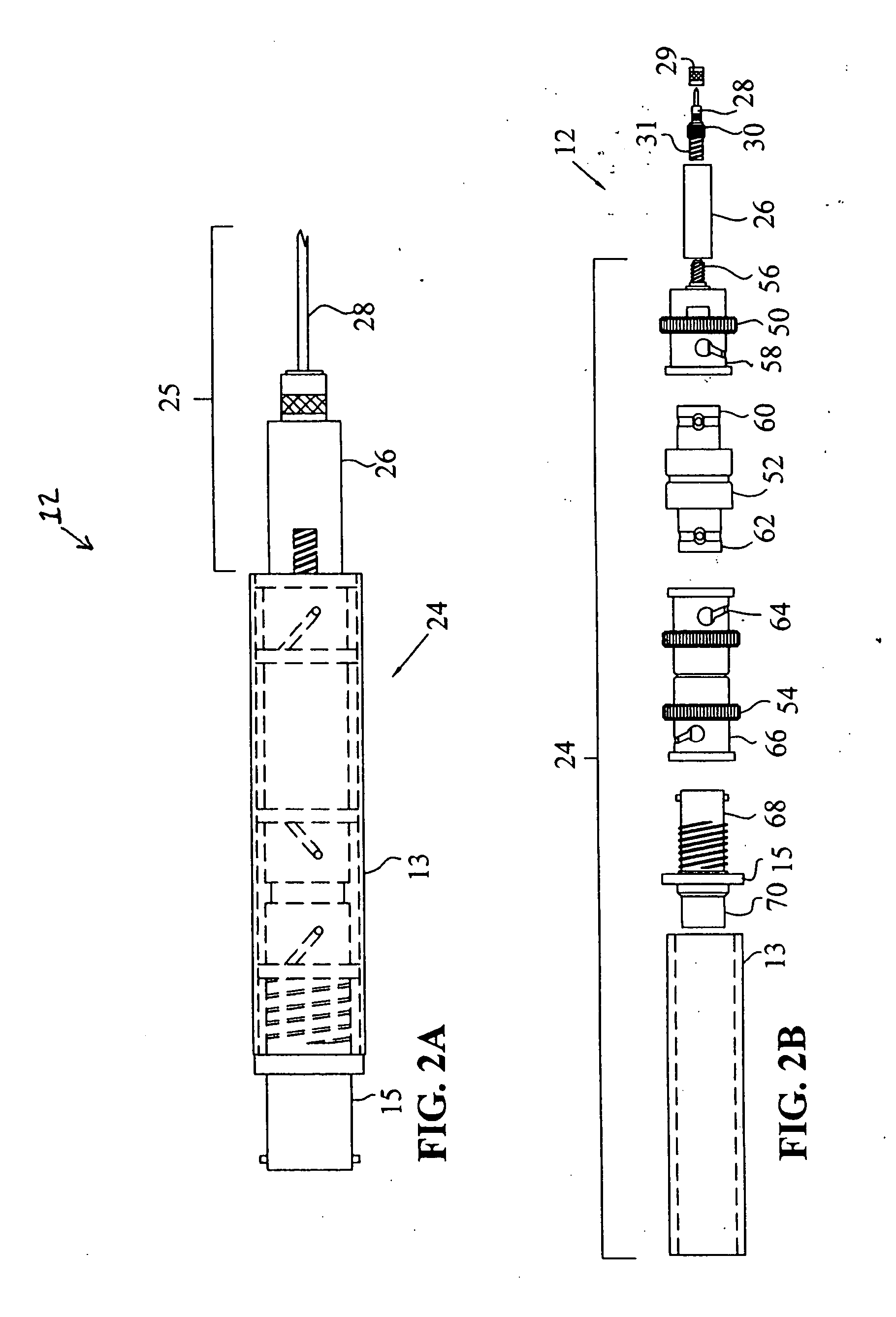

Ultra-broadband differential voltage probes

ActiveUS20050253603A1Minimize parasitic inductanceMinimize capacitanceElectrical testingMeasurement leads/probesElectricityCoaxial cable

Passive balanced probes are disclosed for use with a signal analysis device. The probes are very low cost relative to typical commercially available probes and provide an extremely flat response over a frequency range of approximately 0 to at least 1.5 gigahertz. The probes include a probe body constructed primarily from conventional components, a first surface mount resistor electrically connected between a probe tip and a center conductor, and two surface mount resistors electrically connected and parallel between the center conductor and a conductive shield. The probes further include a coaxial cable for connection to an instrument combiner or other instrument connection device.

Owner:APTIV TECH LTD

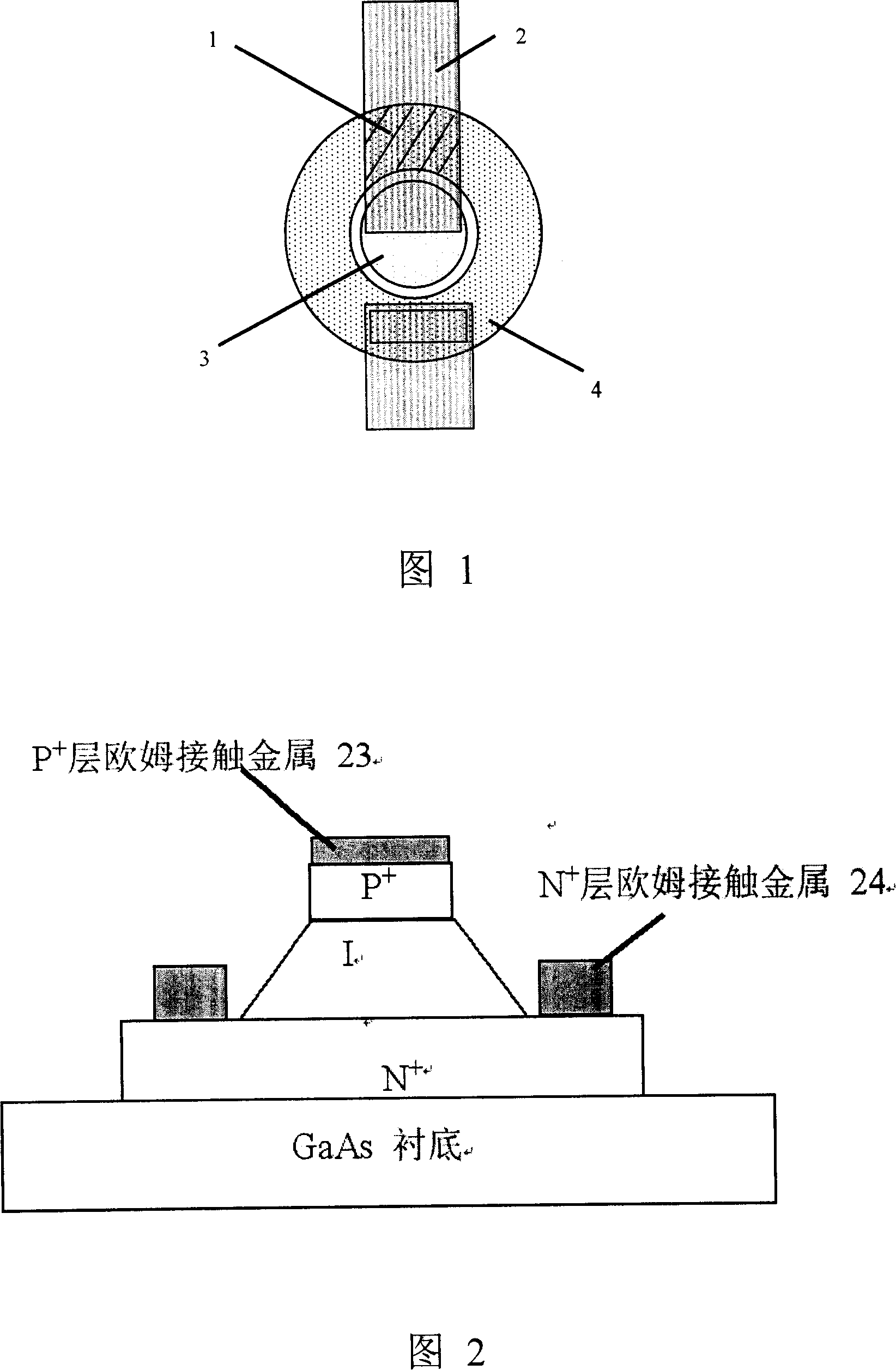

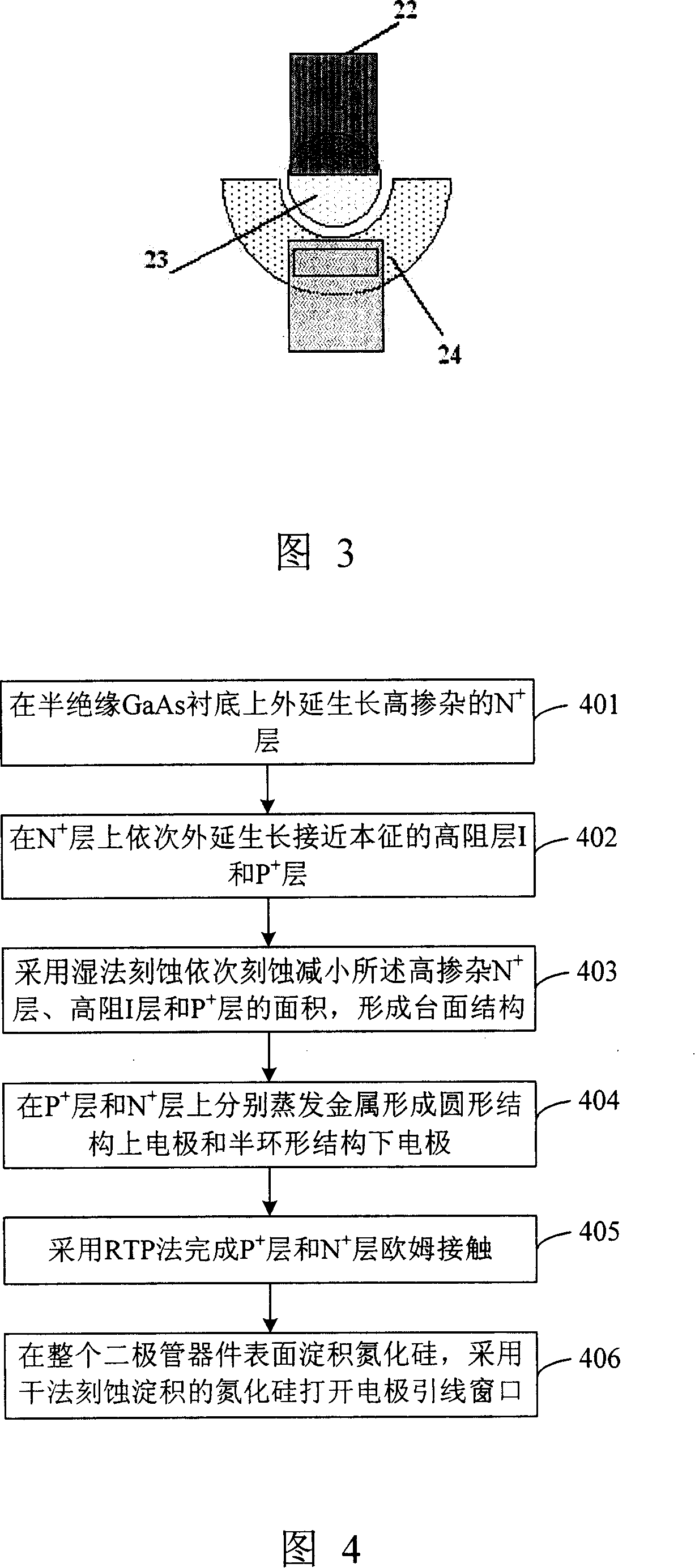

Gallium arsenide PIN diode and preparation method thereof

ActiveCN101140955AReduce parasitic capacitanceRealize the process is simpleSemiconductor/solid-state device manufacturingSemiconductor devicesMaterials scienceAir bridge

The invention discloses a GaAs PIN diode, which comprises: a semi-insulating GaAs underlay for supporting the whole GaAs diode; a high doped layer N growing in extension on the semi-insulating GaAs underlay, resistive formations I and P close to eigen growing in extension in turn on the high doped layer N; By wet process and etching, the areas of the said high doped layer N, resistive formations I and P reduced in turn to form a mesa structure; a top electrode of the round structure formed by metal evaporator on layer P; a semi-orbicular bottom electrode formed by metal evaporator on layer N. The invention also discloses a manufacturing method of GaAs PIN diode. The invention efficiently lowers the parasitic capacitance of the PIN diode without increasing the difficulty of the process and simultaneously greatly shortens the microstrip line connected with the top electrode. The spurious inductance brought by the invention can be greatly reduced or even omitted without using the air-bridge process. The invention has the advantages of easy making, better high frequency characteristic, which is easy to realize the single scale integration.

Owner:北京中科微投资管理有限责任公司

Double-surface heat-dissipation and high-reliability power module

PendingCN107195623AReduce parasitic inductanceReduced risk of crackingSemiconductor/solid-state device detailsSolid-state devicesNegative powerEngineering

The invention discloses a double-surface heat-dissipation and high-reliability power module. The double-surface heat-dissipation and high-reliability power module comprises a positive power terminal, a negative power terminal, an output power terminal, a bottom metal insulating substrate and a top metal insulating substrate; the bottom metal insulating substrate and the top metal insulating substrate are laminated; an output local metal layer is arranged on the bottom metal insulating substrate or the top metal insulating substrate; the output power terminal is connected to a chip connection block through the output local metal layer; and the chip connection block is electrically connected with a chip on the bottom metal insulating substrate and a chip on the top metal insulating substrate. By means of the double-surface heat-dissipation and high-reliability power module disclosed by the invention, the loop parasitic inductance is greatly reduced; interconnection is realized by adoption of a material matched with the thermal expansion coefficient of the chip; the cracking risk of a welding layer can be reduced; the reliability of the power module can be improved; the volume of the power module is reduced; the cost is reduced; the weight is lightened; the module is particularly suitable for encapsulation of a SiC power chip; and thus, the discharge capacity is sufficiently improved.

Owner:YANGZHOU GUOYANG ELECTRONICS CO LTD

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com