Power module low-inductance lead terminal

A technology of lead terminals and power modules, applied in the field of low inductance lead terminals of power modules, can solve the problems of increasing the operating frequency and switching speed of the module, large parasitic inductance of the module, and failure of the chip, and achieves the effect of reducing the parasitic inductance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

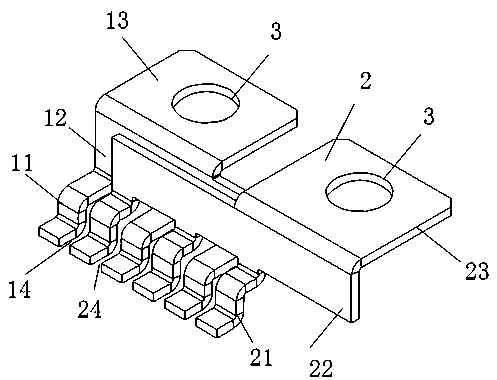

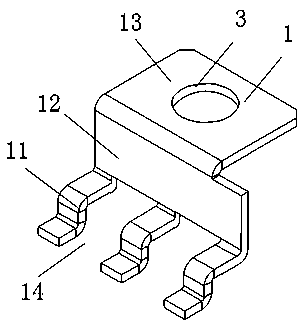

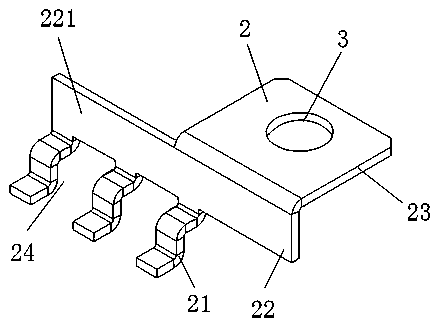

[0028] In order to deepen the understanding of the present invention, the present invention will be further described below in conjunction with the accompanying drawings and embodiments, which are only used to explain the present invention and do not limit the protection scope of the present invention.

[0029] like Figure 5 As shown, it is designed for the DC lead terminals of the power module. It is composed of a pair of parallel and coplanar power terminals 1' and 2'. Due to the large distance between them, the area surrounded by the two terminals is large, and its parasitic inductance is large. After the numerical value Simulation analysis shows that its parasitic inductance is 24.2nH.

[0030] In order to reduce the parasitic inductance of the lead terminals, it is common practice to reduce the distance between the terminals as Figure 6 As shown, it consists of a pair of parallel and coplanar power terminals 1'' and 2'' with small spacing, but this has a limited effect...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com