Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

60results about How to "Improve retention characteristics" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

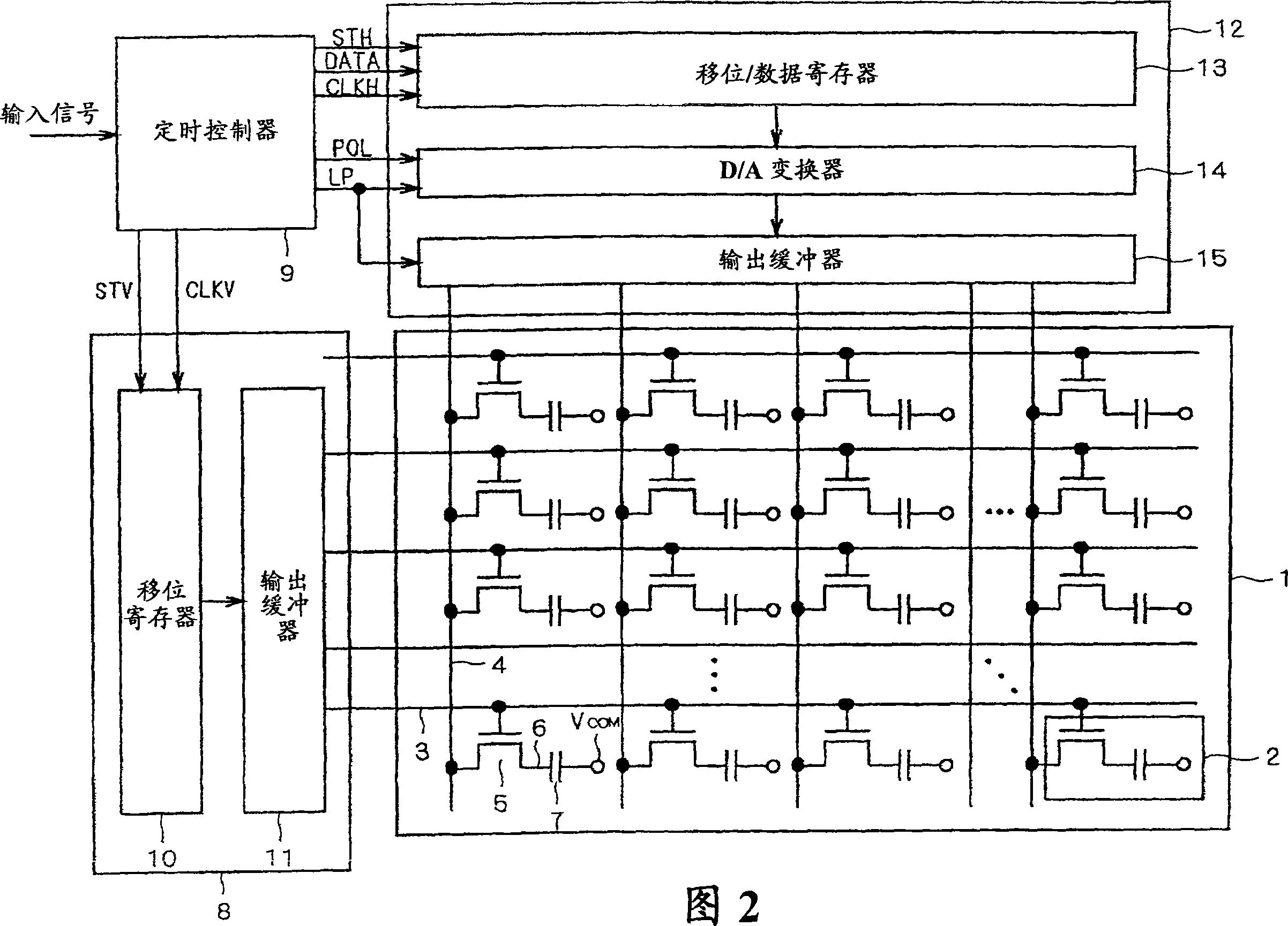

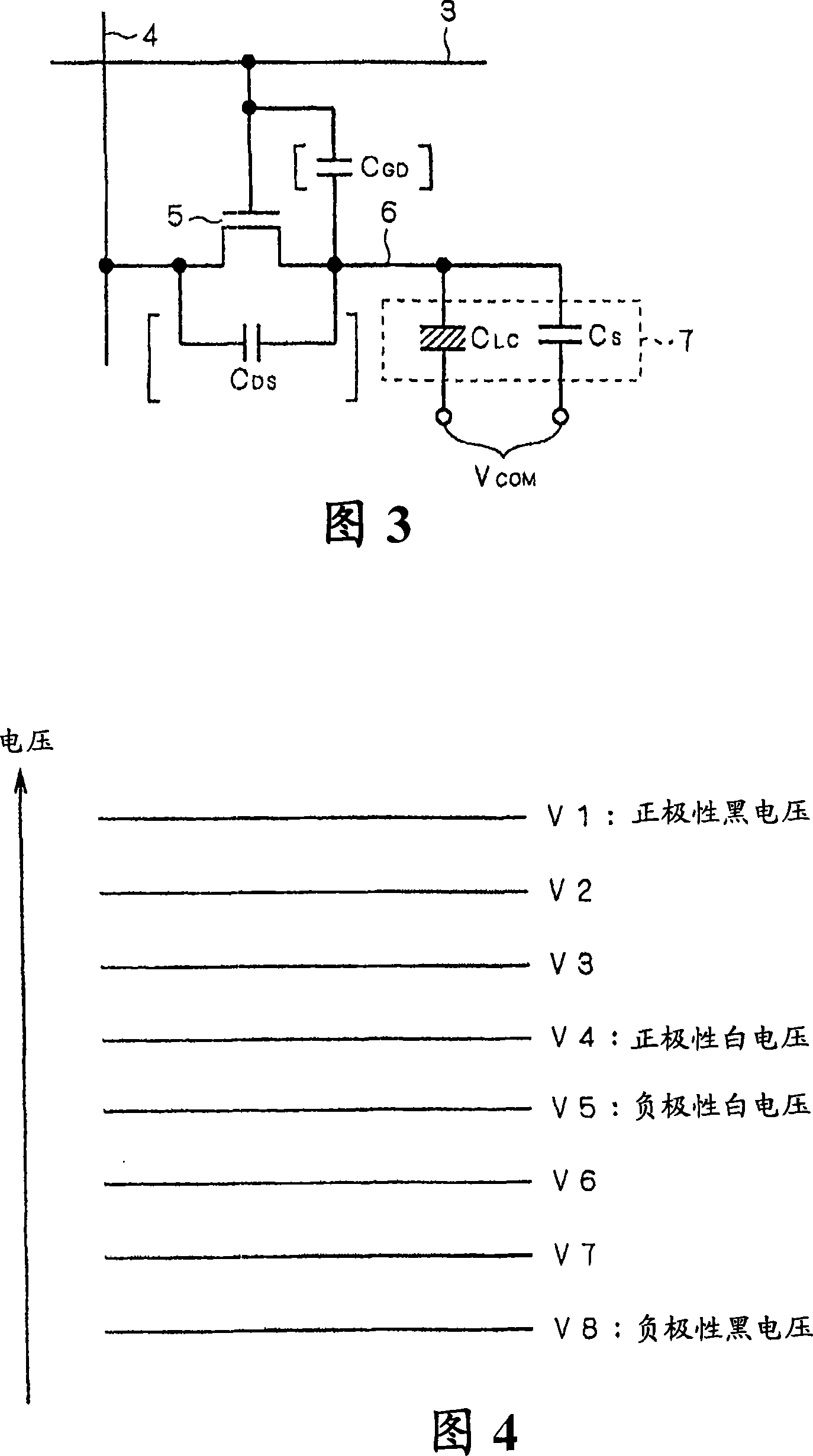

Liquid crystal display device and method of driving the same

InactiveUS20070296661A1Improve featuresReduce power consumptionStatic indicating devicesNon-linear opticsElectricityDriver circuit

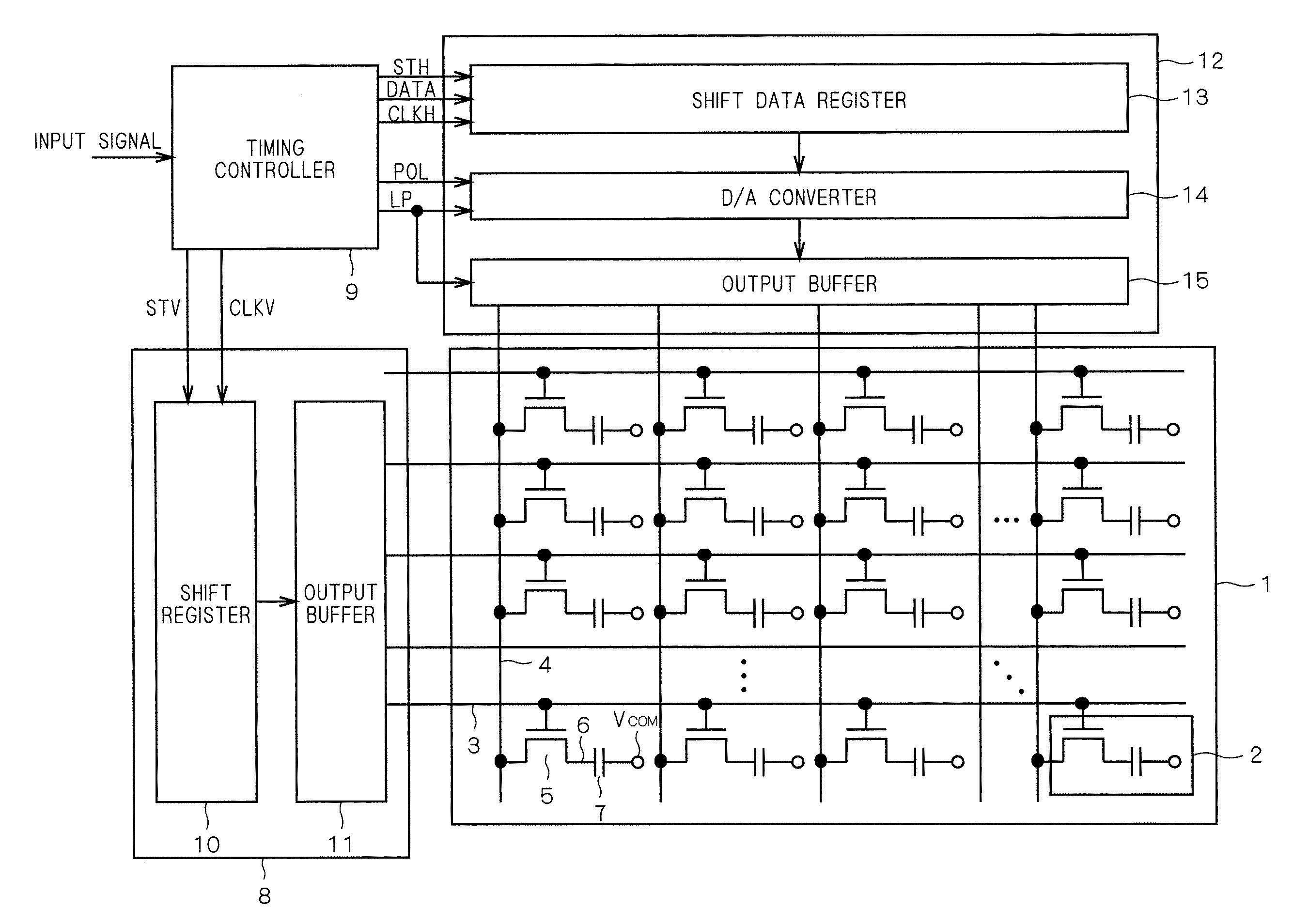

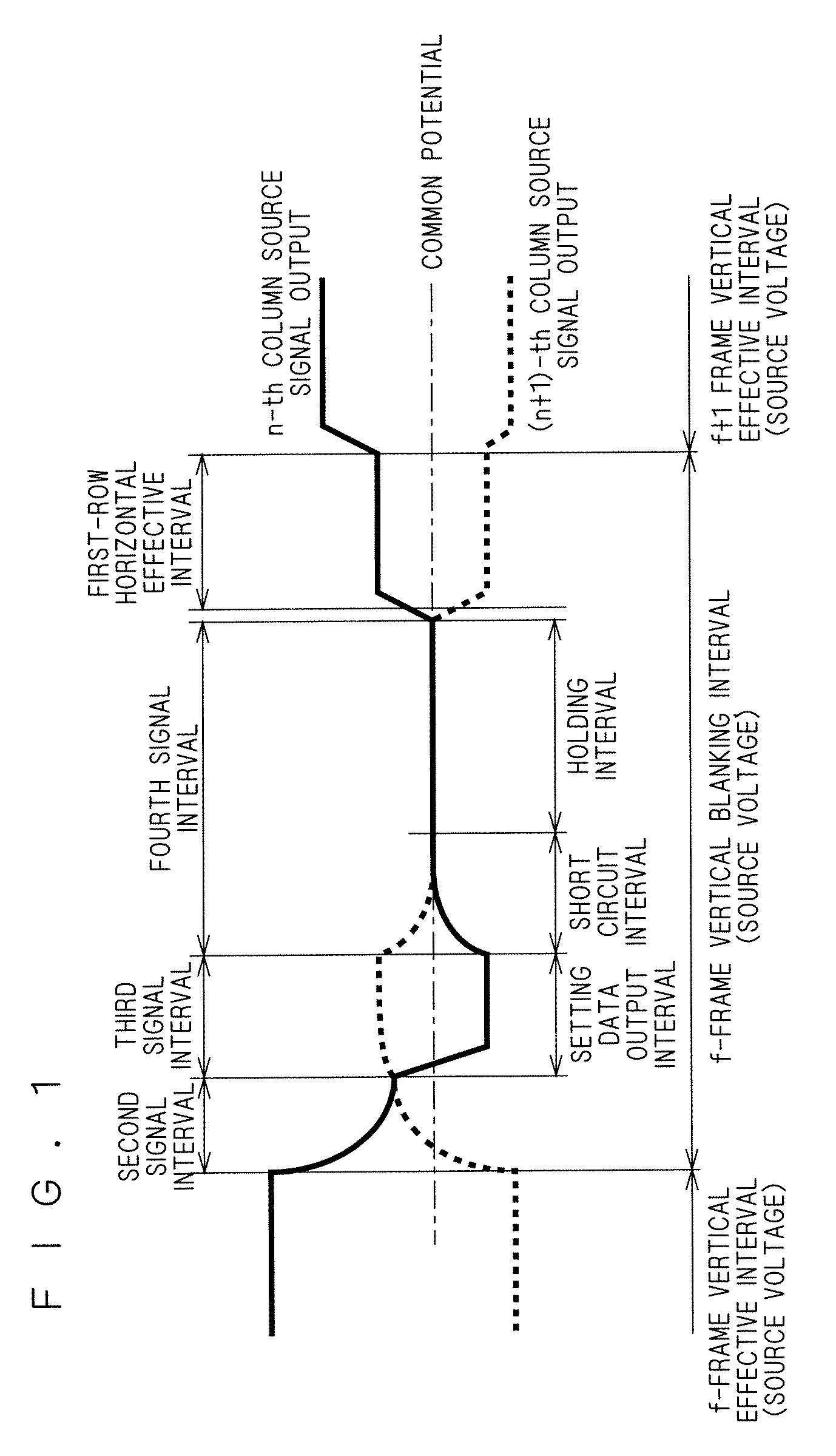

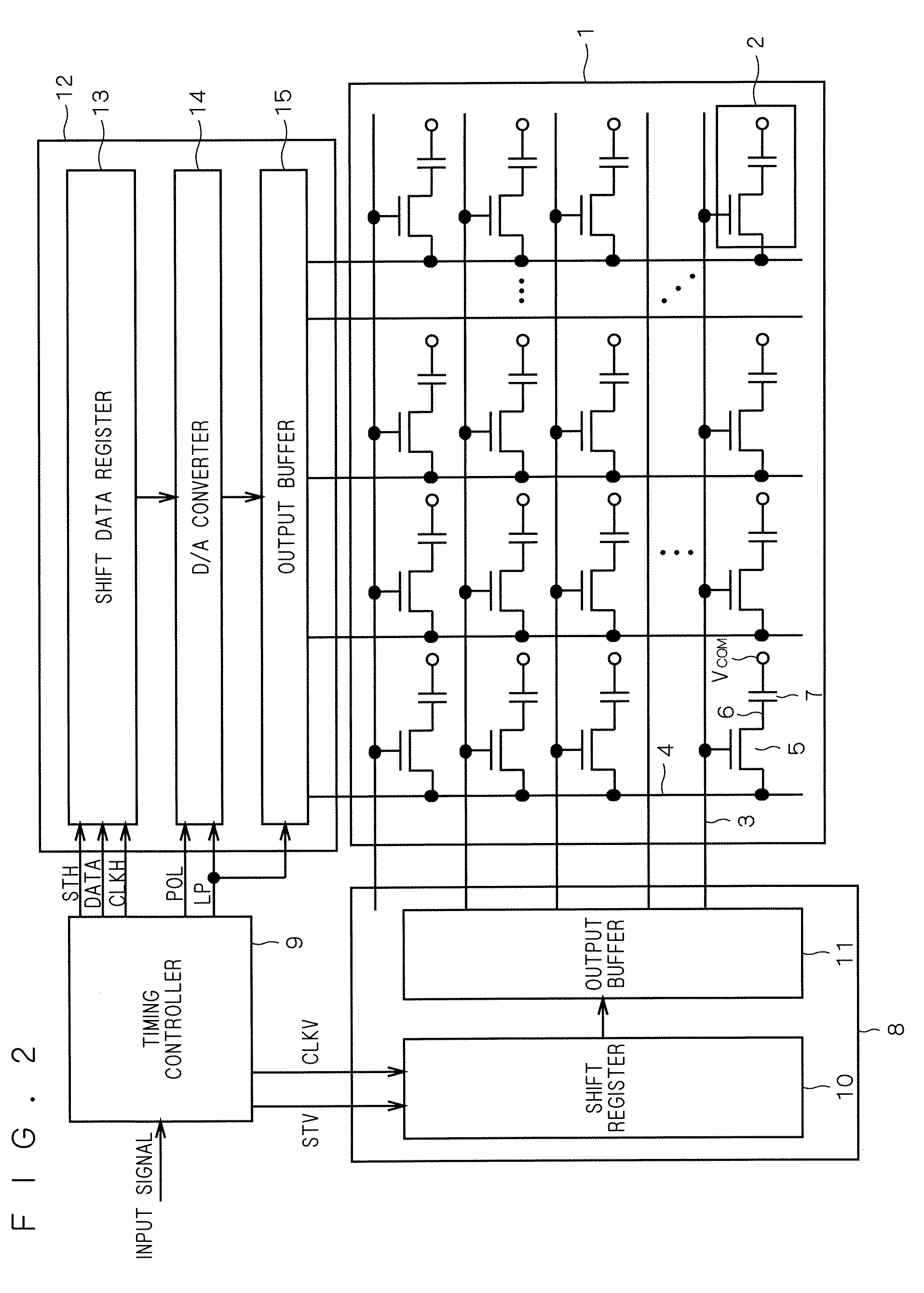

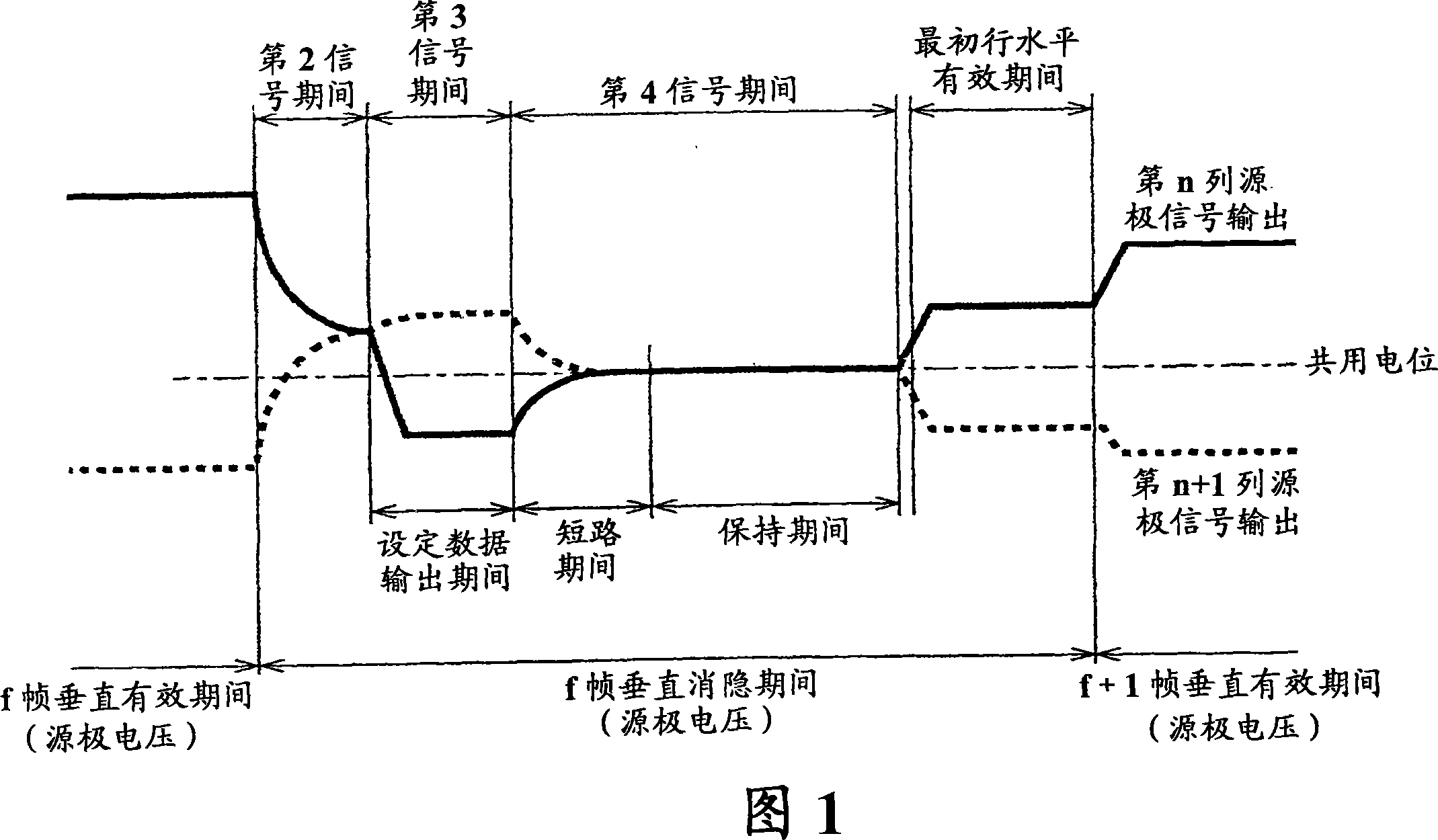

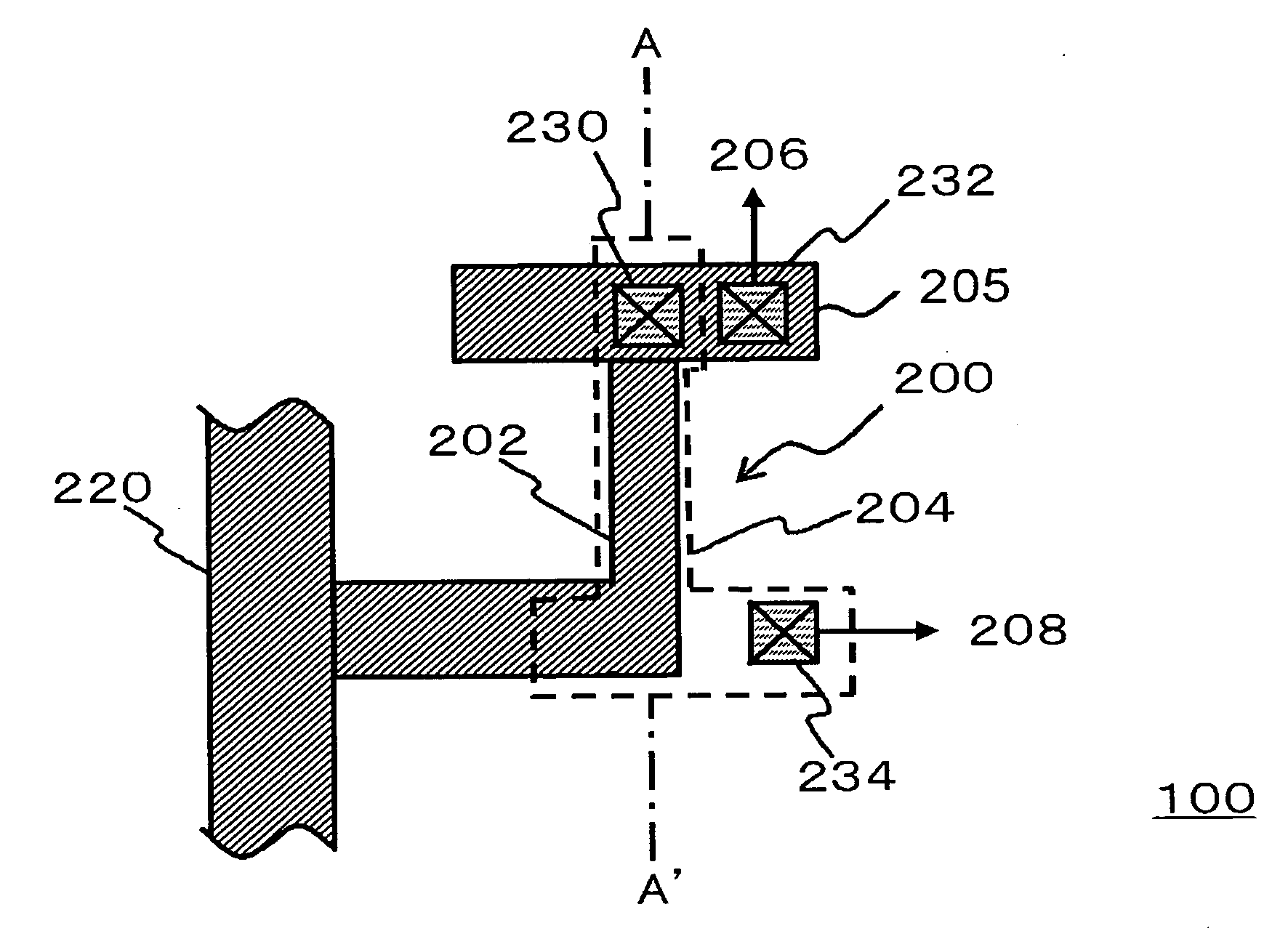

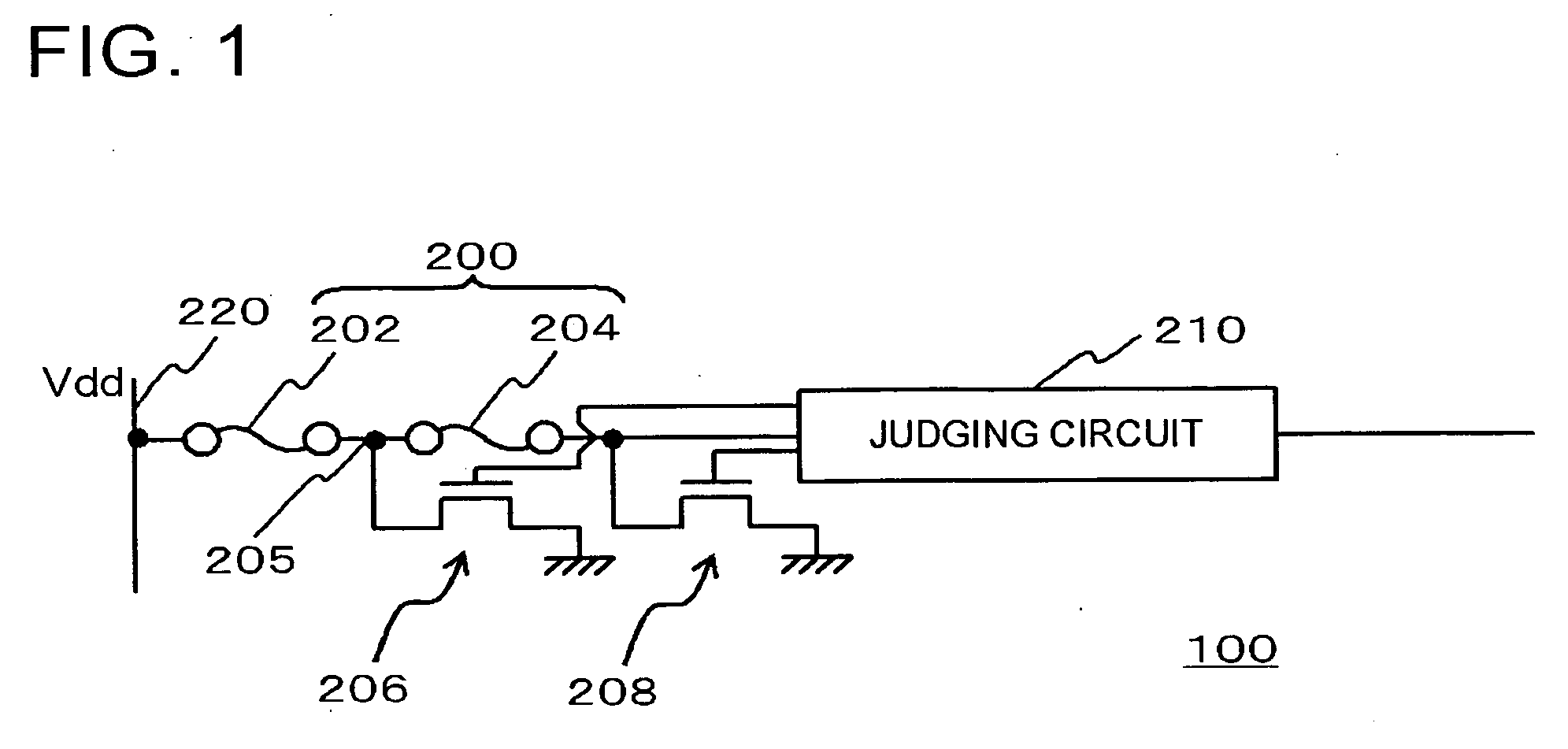

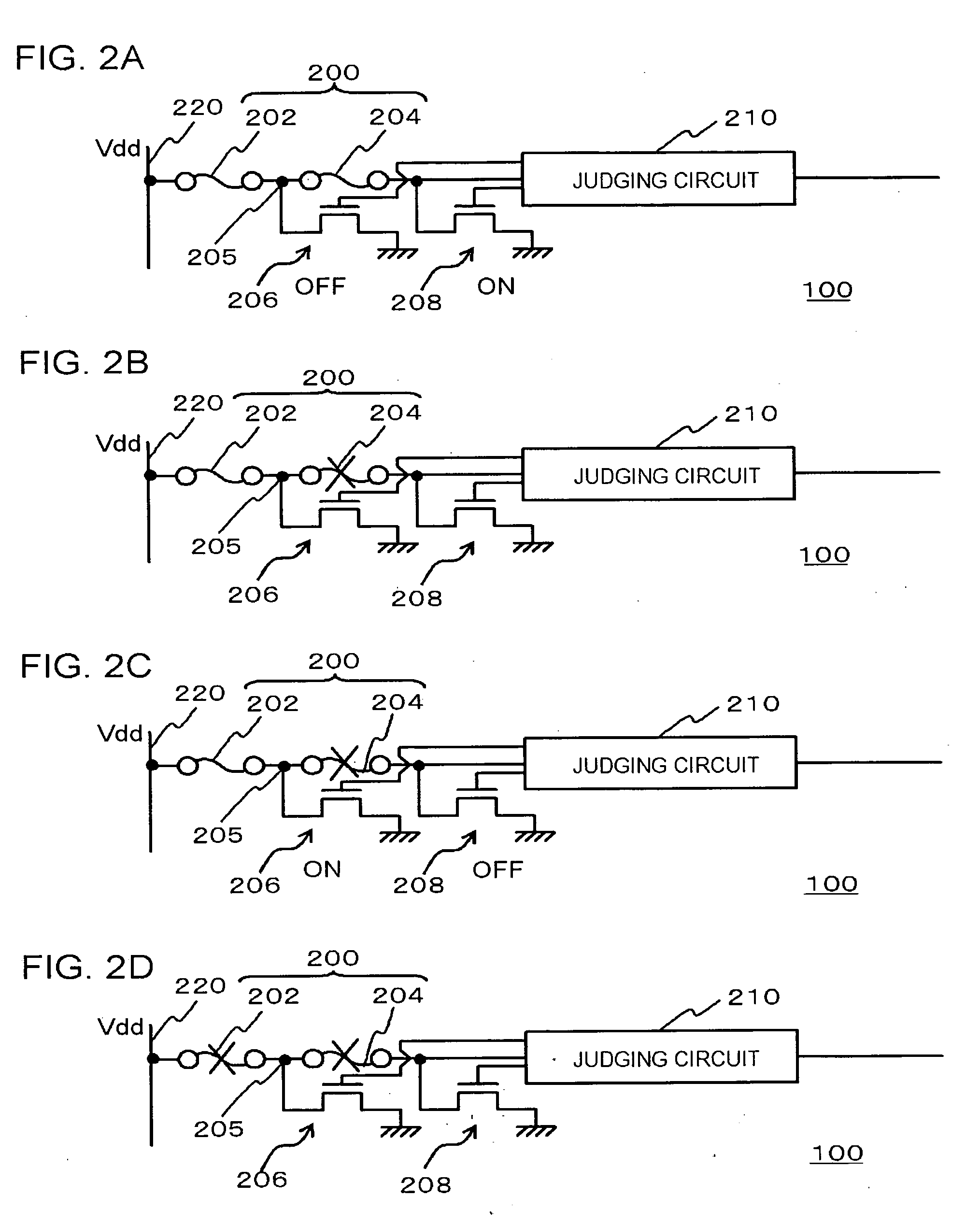

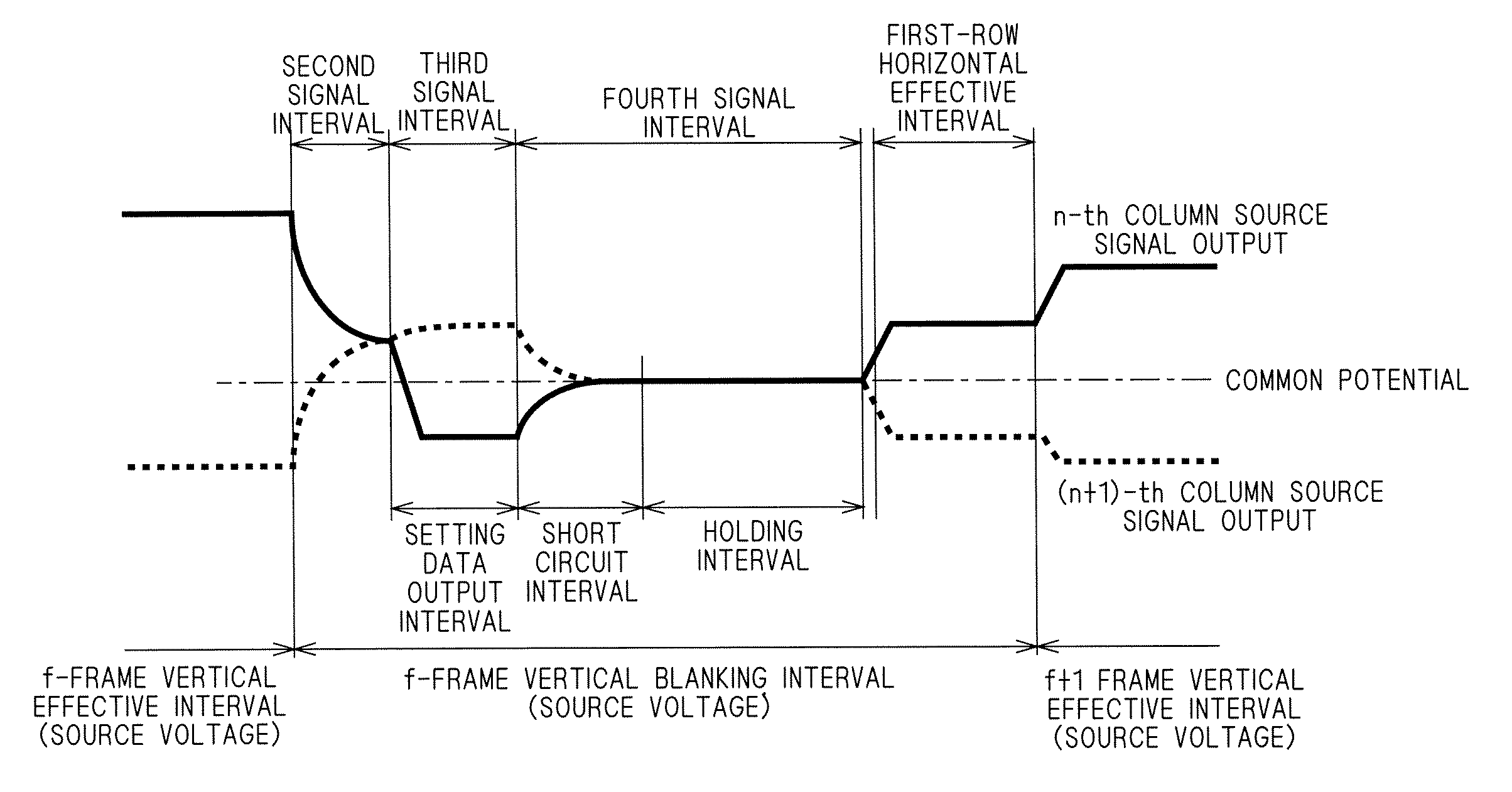

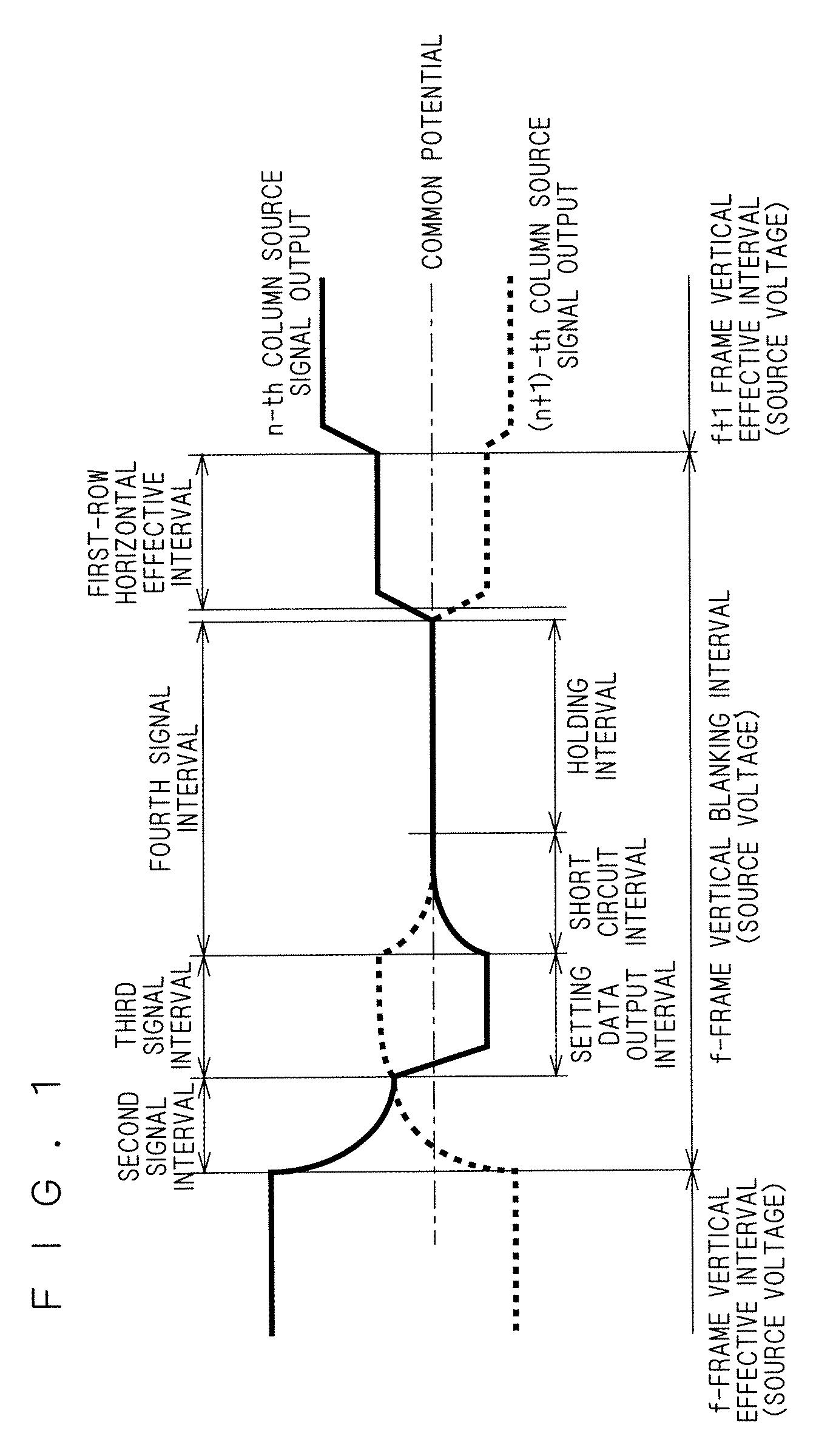

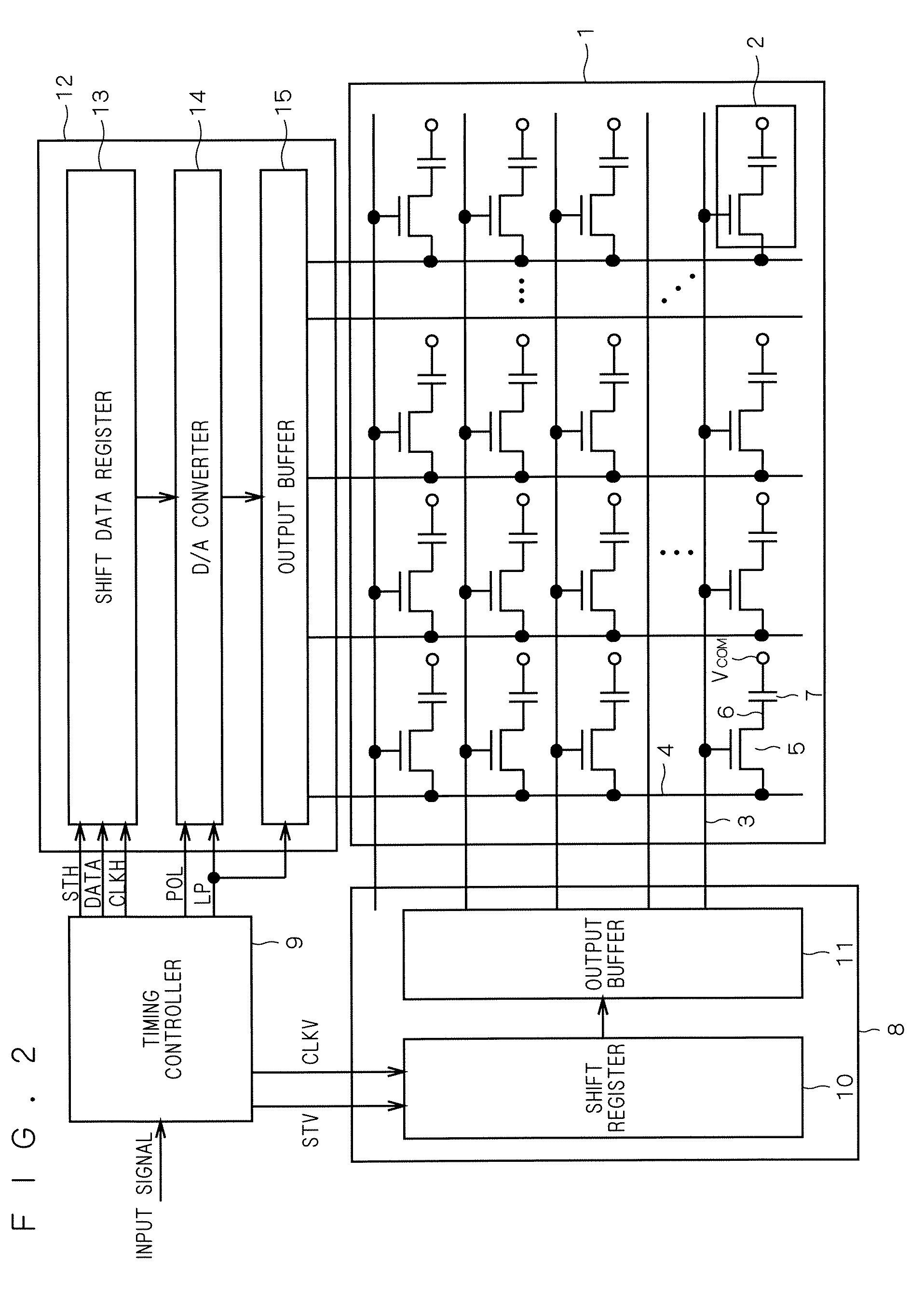

A liquid crystal display device includes pixels, gate lines and source lines, active elements, a gate driver circuit, a source driver circuit, and a timing controller circuit. The source driver circuit conducts a prescribed operation of supplying the source signals of positive polarity and negative polarity having a prescribed voltage to the source lines during a vertical blanking interval, and electrically cutting the source lines off after the supply of the source signals while establishing a short circuit between adjoining source lines supplied with the source signals of opposite polarities, thereby causing the source lines to hold a prescribed DC voltage value.

Owner:MITSUBISHI ELECTRIC CORP

Liquid crystal display device and driving method

InactiveCN101097390AReduce problem sizeImprove retention characteristicsStatic indicating devicesNon-linear opticsDriver circuitLiquid-crystal display

A liquid crystal display device includes pixels, gate lines and source lines, active elements, a gate driver circuit, a source driver circuit, and a timing controller circuit. The source driver circuit conducts a prescribed operation of supplying the source signals of positive polarity and negative polarity having a prescribed voltage to the source lines during a vertical blanking interval, and electrically cutting the source lines off after the supply of the source signals while establishing a short circuit between adjoining source lines supplied with the source signals of opposite polarities, thereby causing the source lines to hold a prescribed DC voltage value.

Owner:MITSUBISHI ELECTRIC CORP

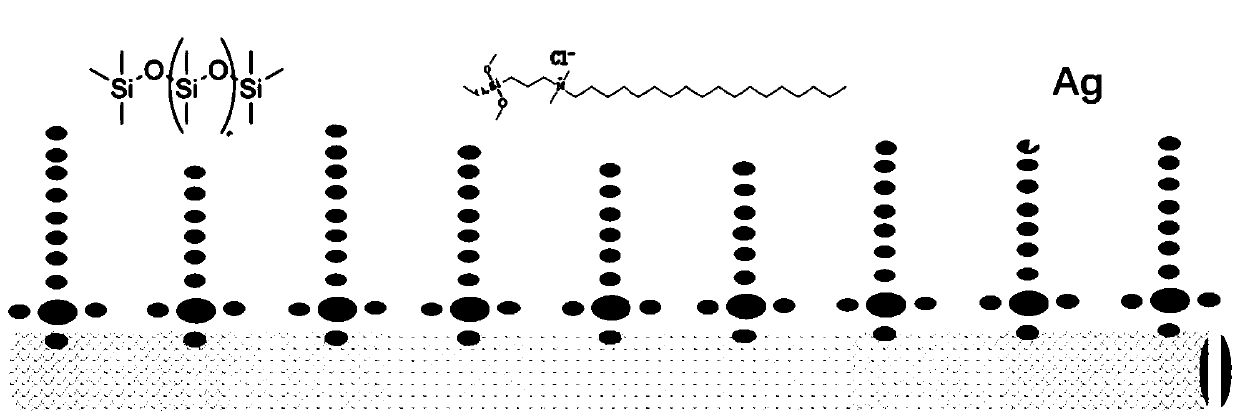

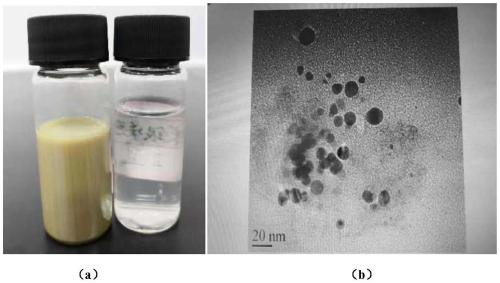

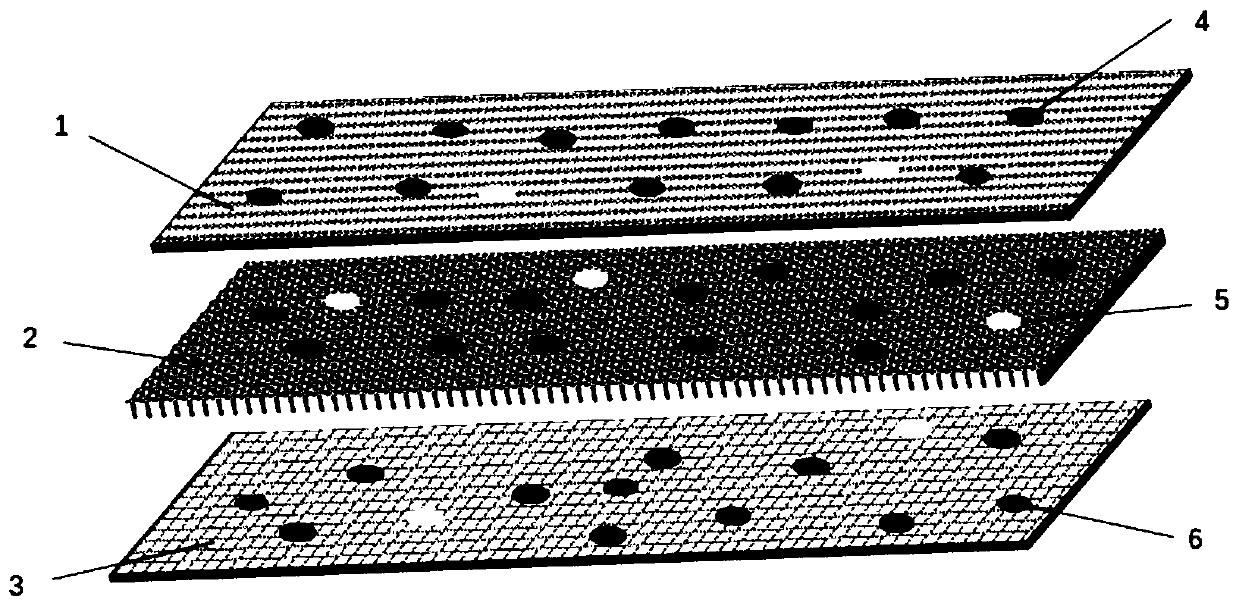

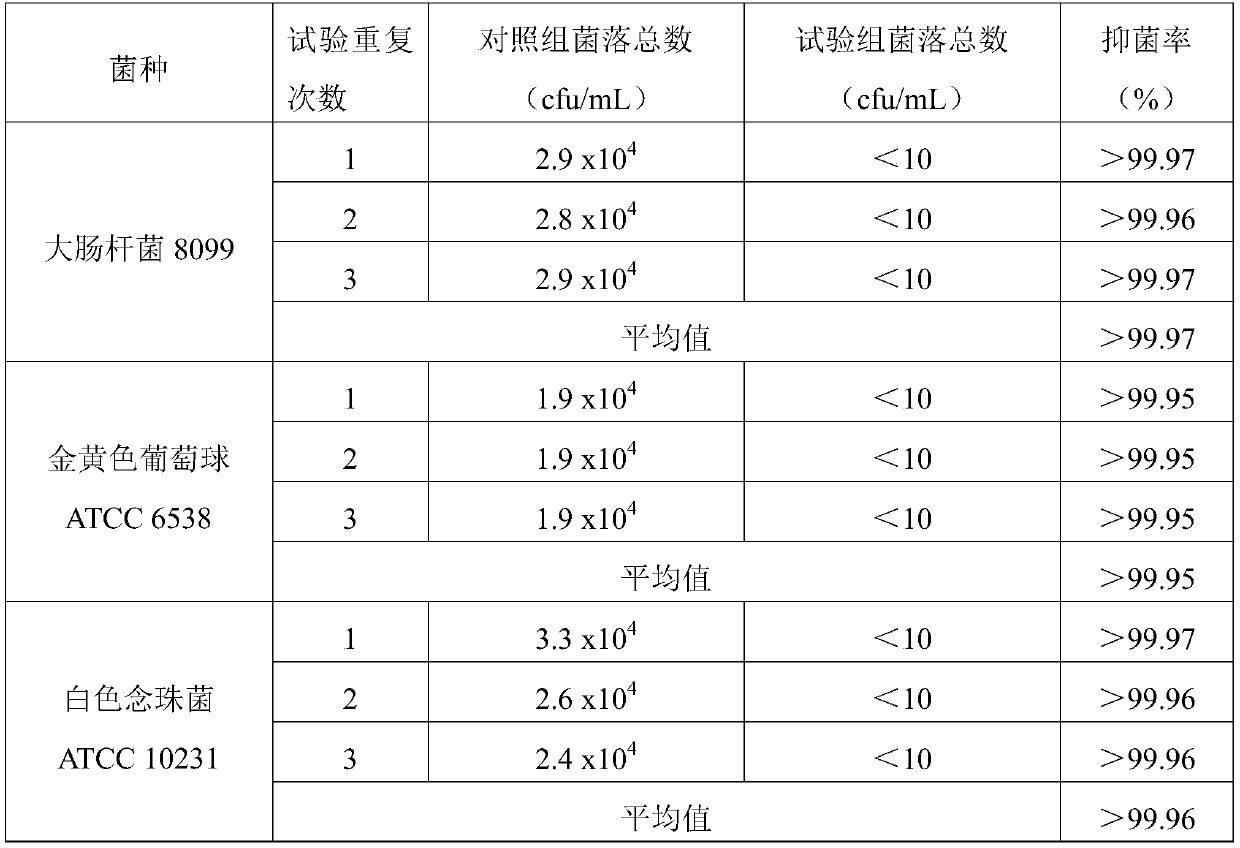

Non-dissolution type long-acting antibacterial protective non-woven fabric and preparation method and application thereof

ActiveCN111424432AWill not damage the structureImprove breathabilityMaterial nanotechnologyBiochemical fibre treatmentAntibacterial activityNonwoven fabric

The invention belongs to the technical field of antibacterial materials, and discloses a non-dissolution type long-acting antibacterial protective non-woven fabric and a preparation method and application thereof. The preparation method comprises the following steps that antibacterial liquid is evenly sprayed on a non-woven fabric or the non-woven fabric is soaked in the antibacterial liquid, andorganic silicon molecular polymerization is carried out to enhance the binding force of non-woven fabric fiber and antibacterial active substances; and high-temperature setting is performed, and the antibacterial active substances such as ammonium salt and nano-silver are loaded on the surface of the non-woven fabric in a directional mode to prepare the antibacterial protective non-woven fabric, wherein the antibacterial liquid comprises nano-silver gel, quaternary ammonium salt, organic silicon, an auxiliary agent and water. According to the method, the high-activity quaternary ammonium saltand the nano-silver are loaded on the surface of the non-woven fabric fiber to form an ultra-thin positively charged antibacterial layer through chemical bonding of the organic silicon on the surfaceof the polymer fiber, the structure of the non-woven fabric fiber is basically not damaged, the good air permeability is maintained, meanwhile, the rejection rate of the protective non-woven fabric can be remarkably improved, and masks prepared from the non-woven fabric can be repeatedly used.

Owner:SOUTH CHINA UNIV OF TECH +1

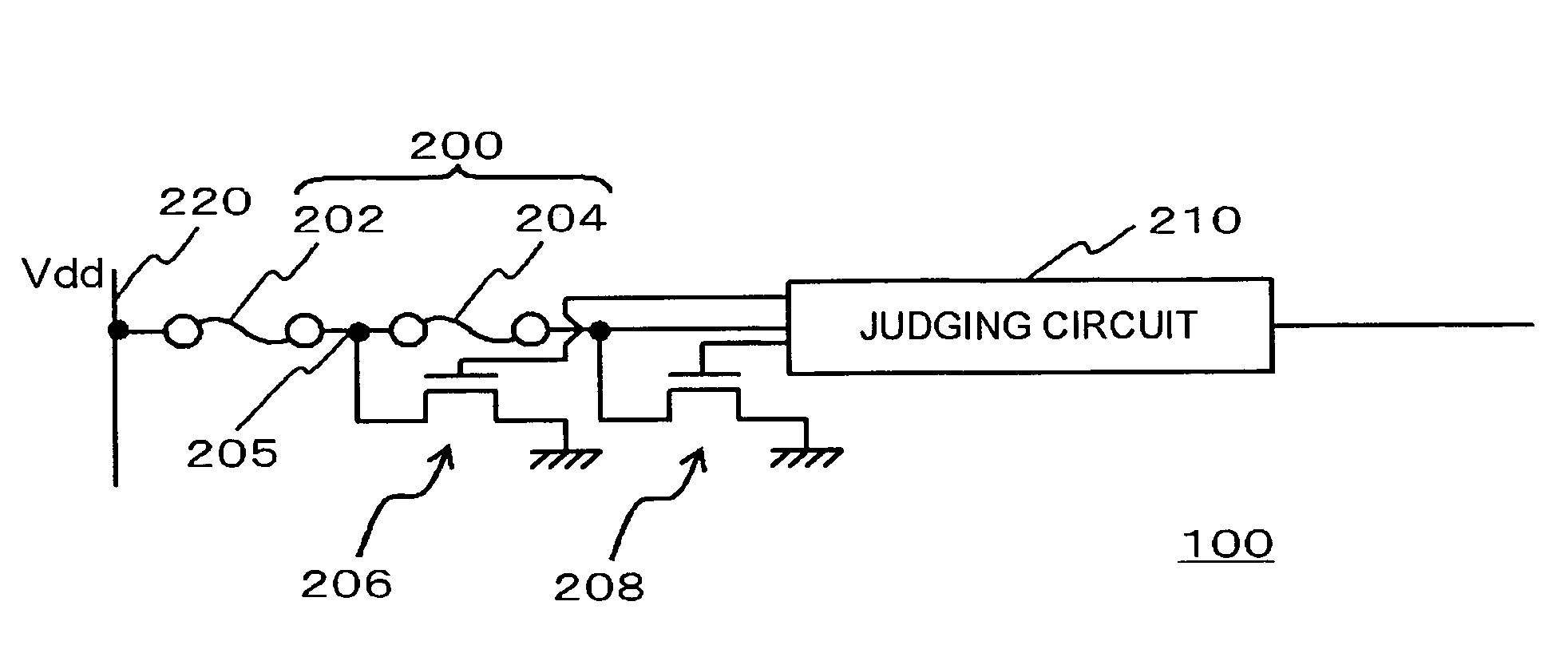

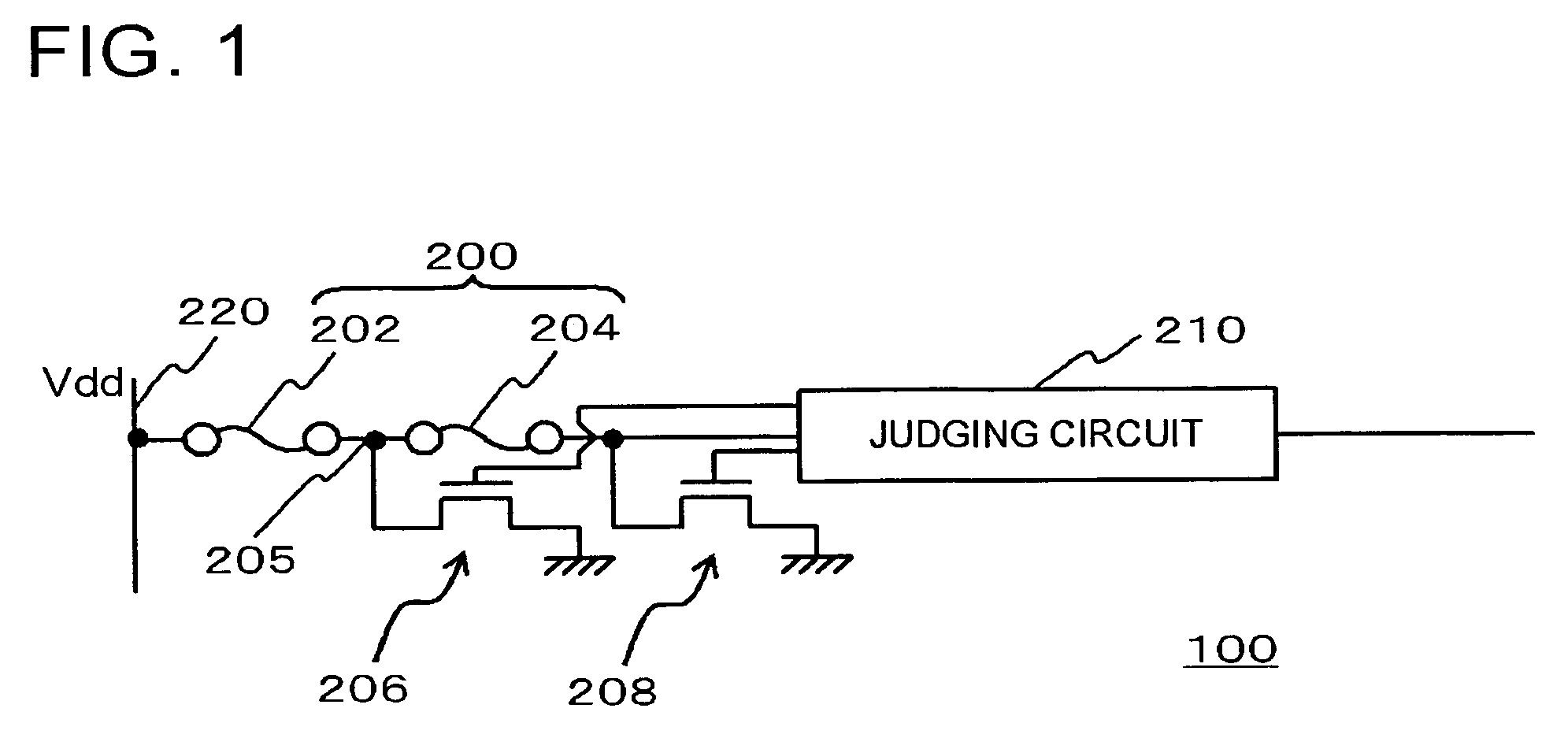

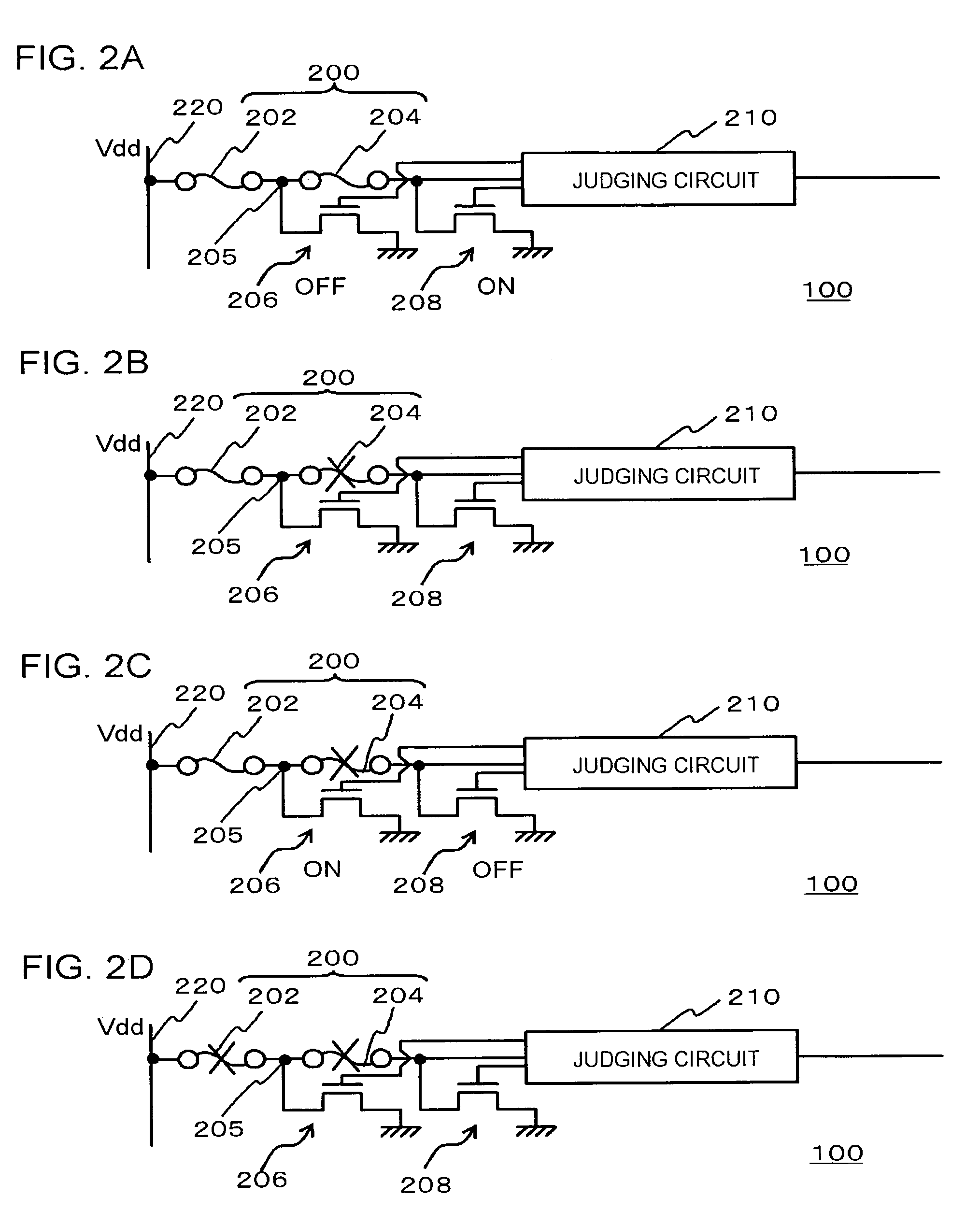

Semiconductor device and method of fabricating the same

InactiveUS7529147B2Reduce rateImprove retention characteristicsSemiconductor/solid-state device detailsSolid-state devicesElectric fusesEngineering

The semiconductor device has a semiconductor substrate; an electric fuse provided on the semiconductor substrate, and having a first fuse link and a second fuse link connected in series; and a terminal provided between the first fuse link and the second fuse link, wherein the first fuse link and the second fuse link are configured as being different from each other in current value necessary for blowing.

Owner:RENESAS ELECTRONICS CORP

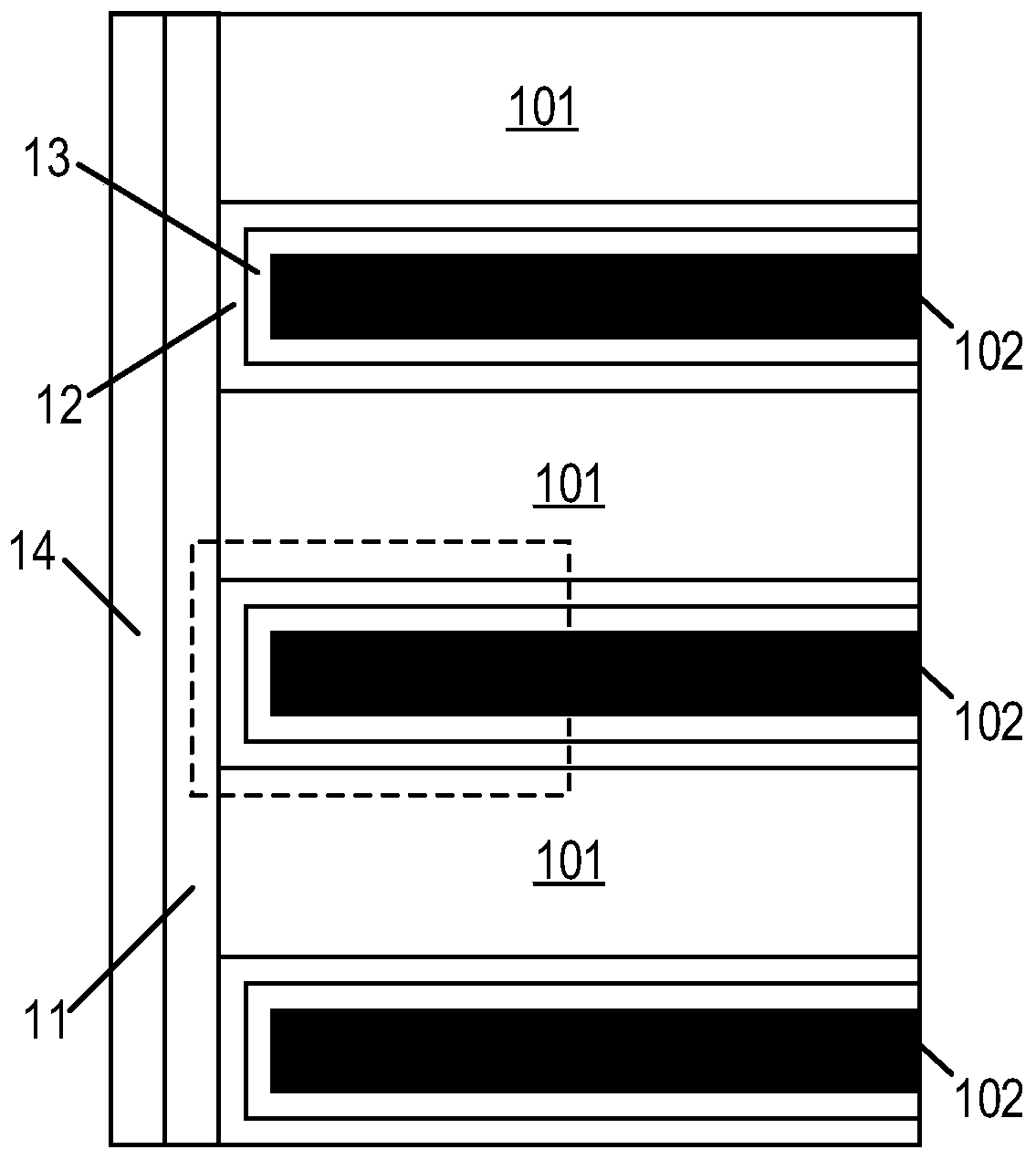

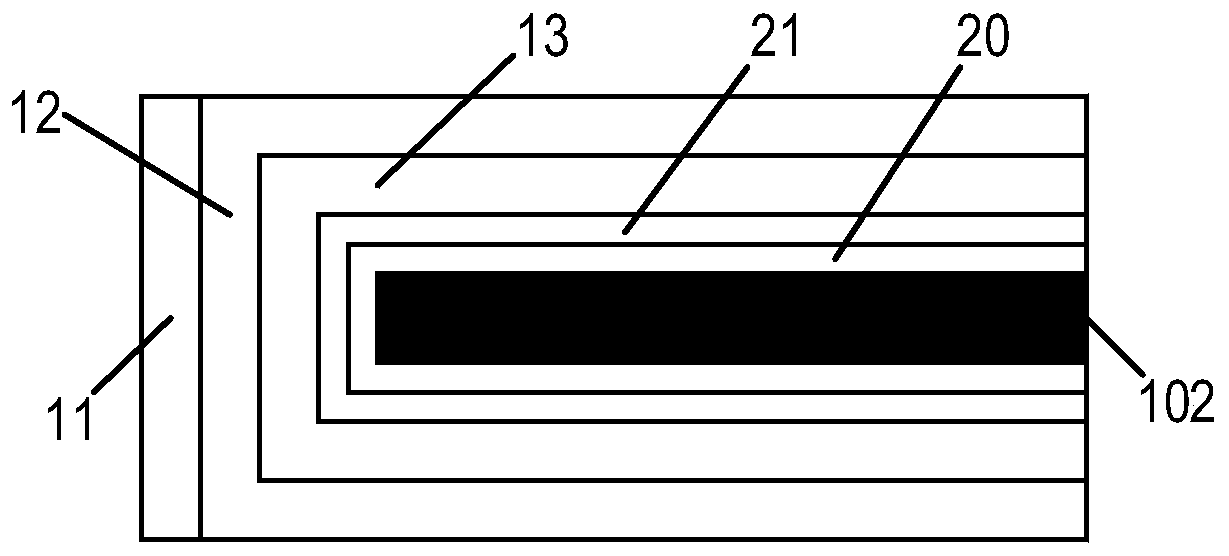

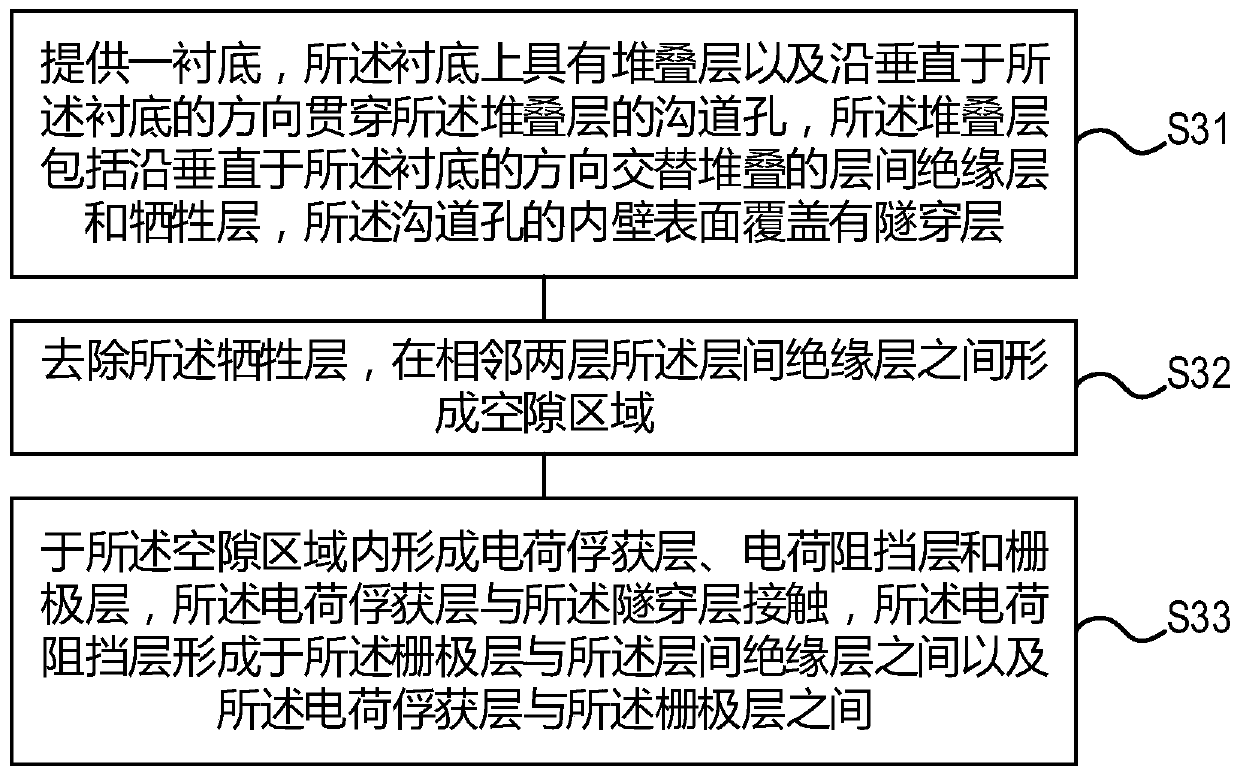

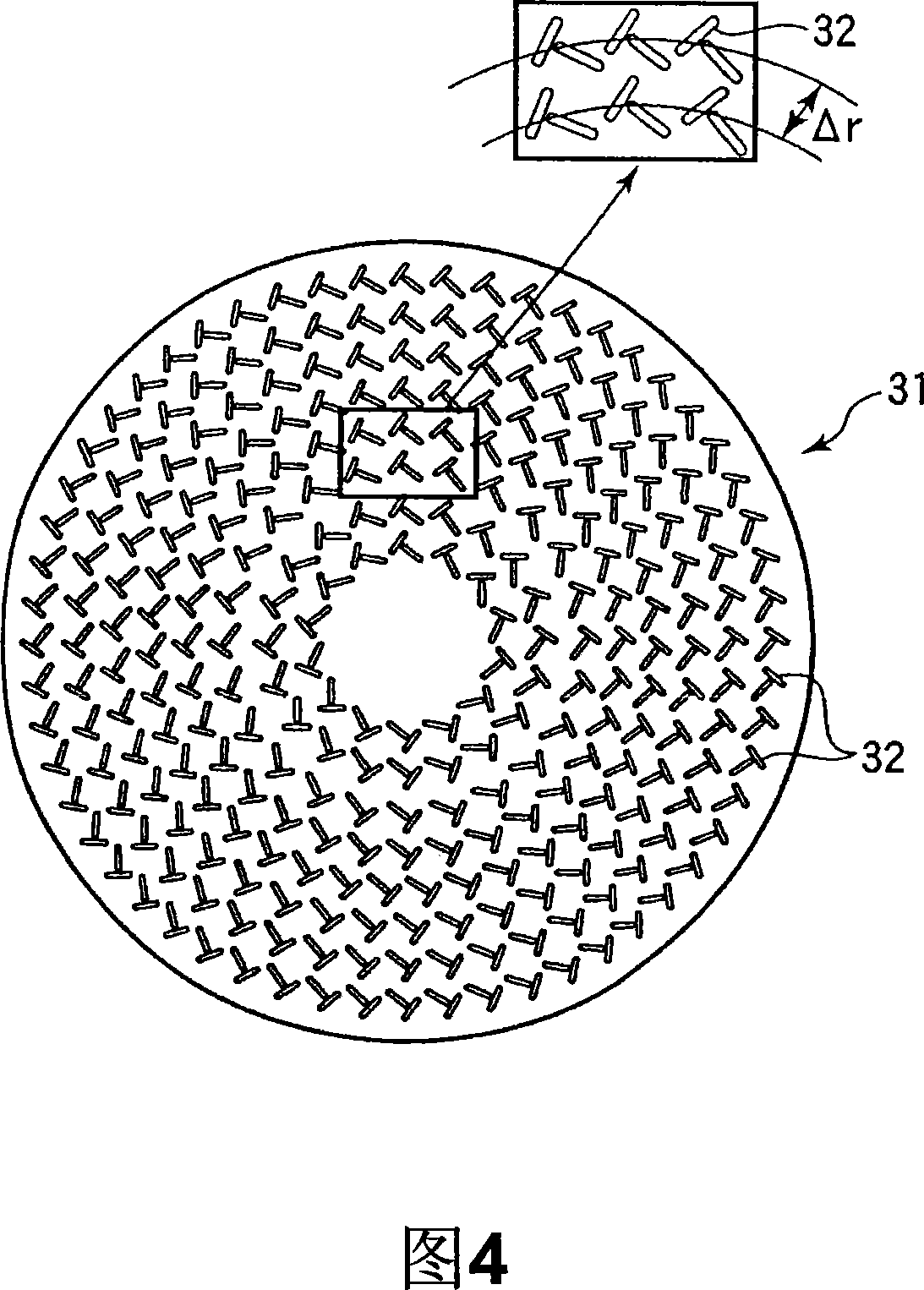

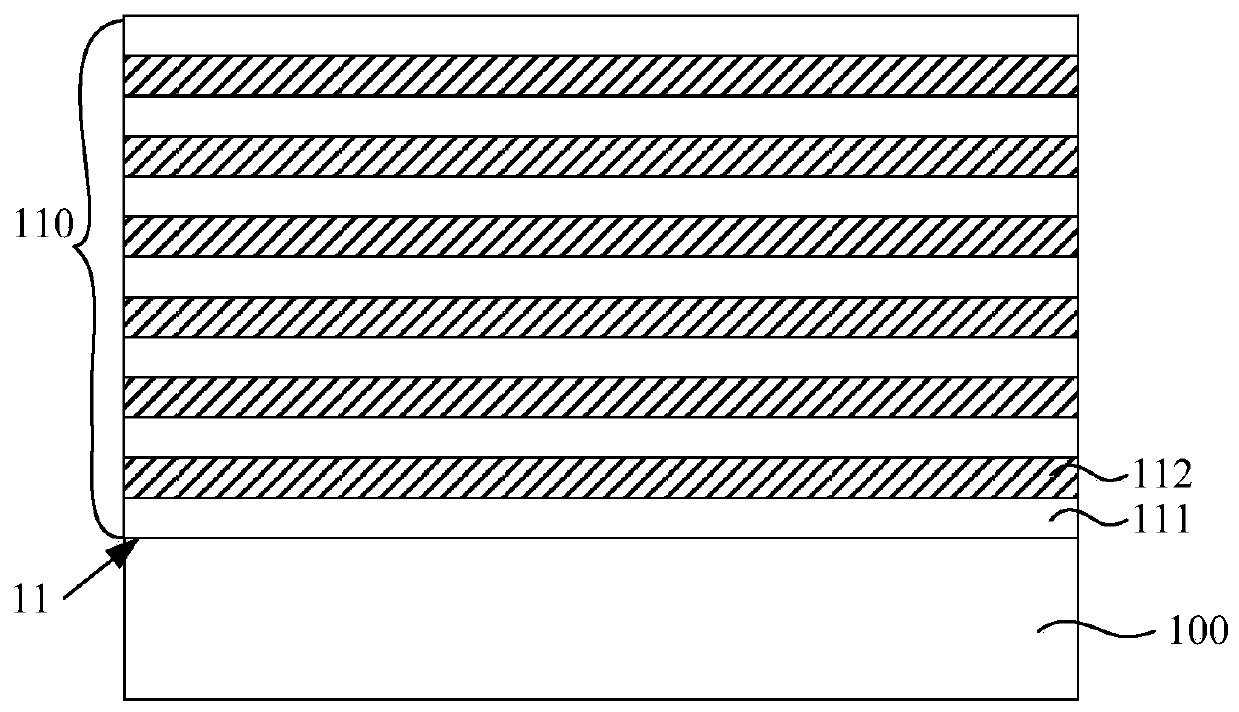

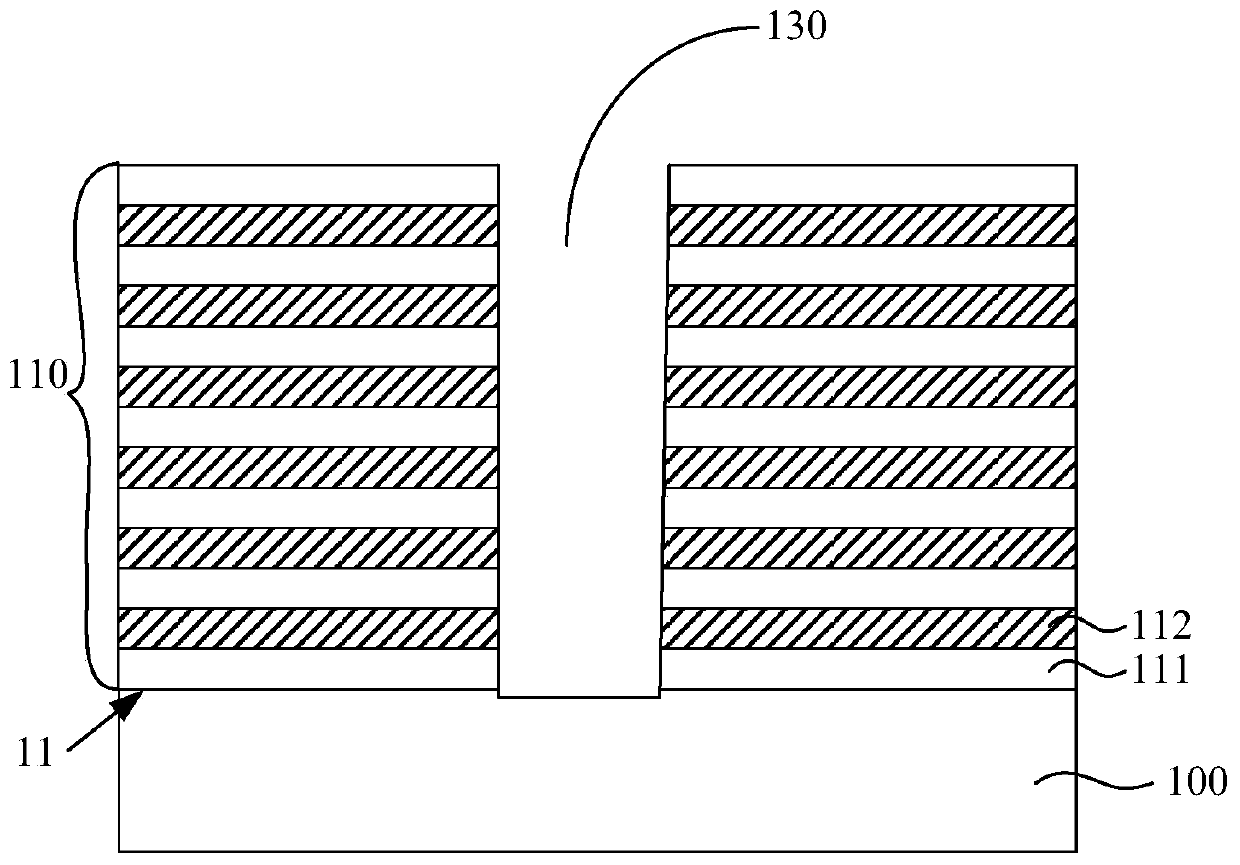

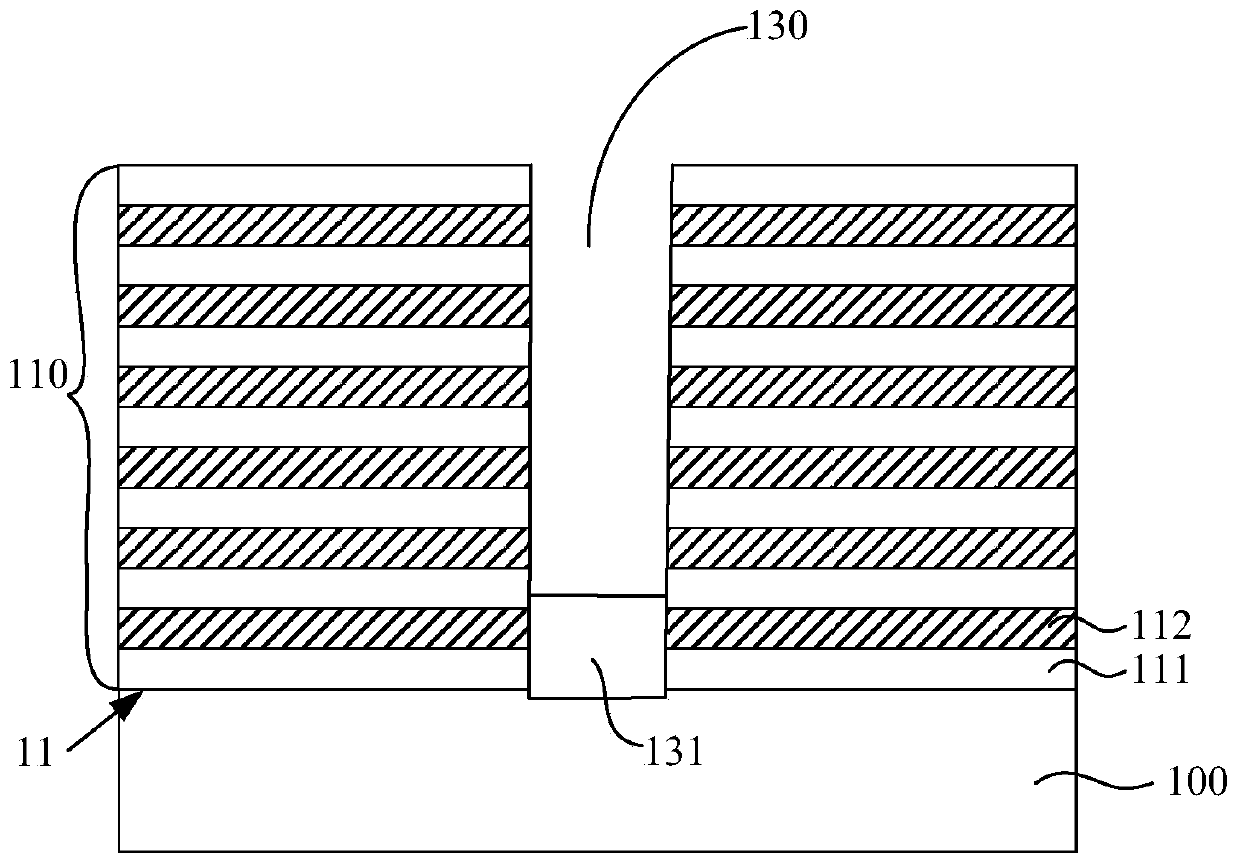

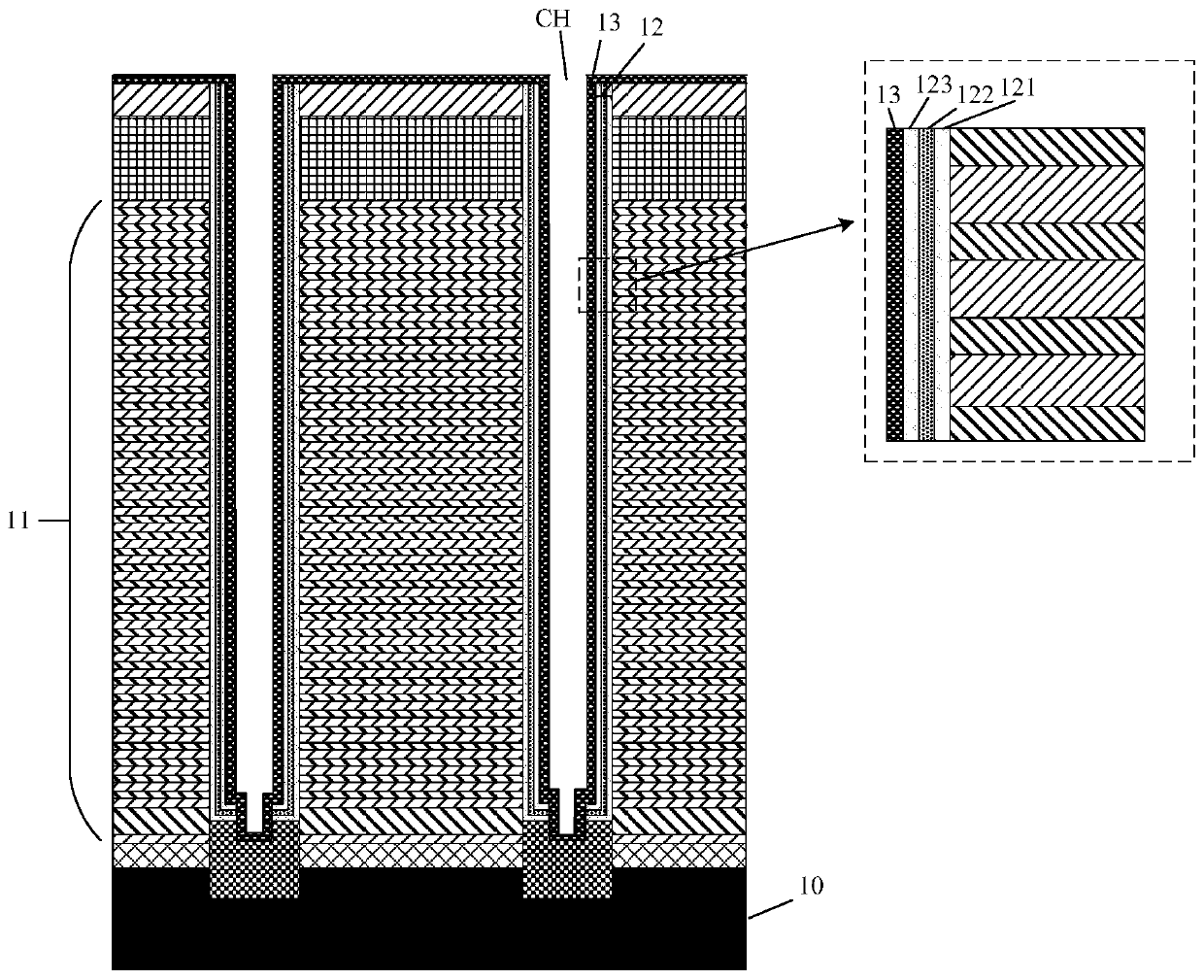

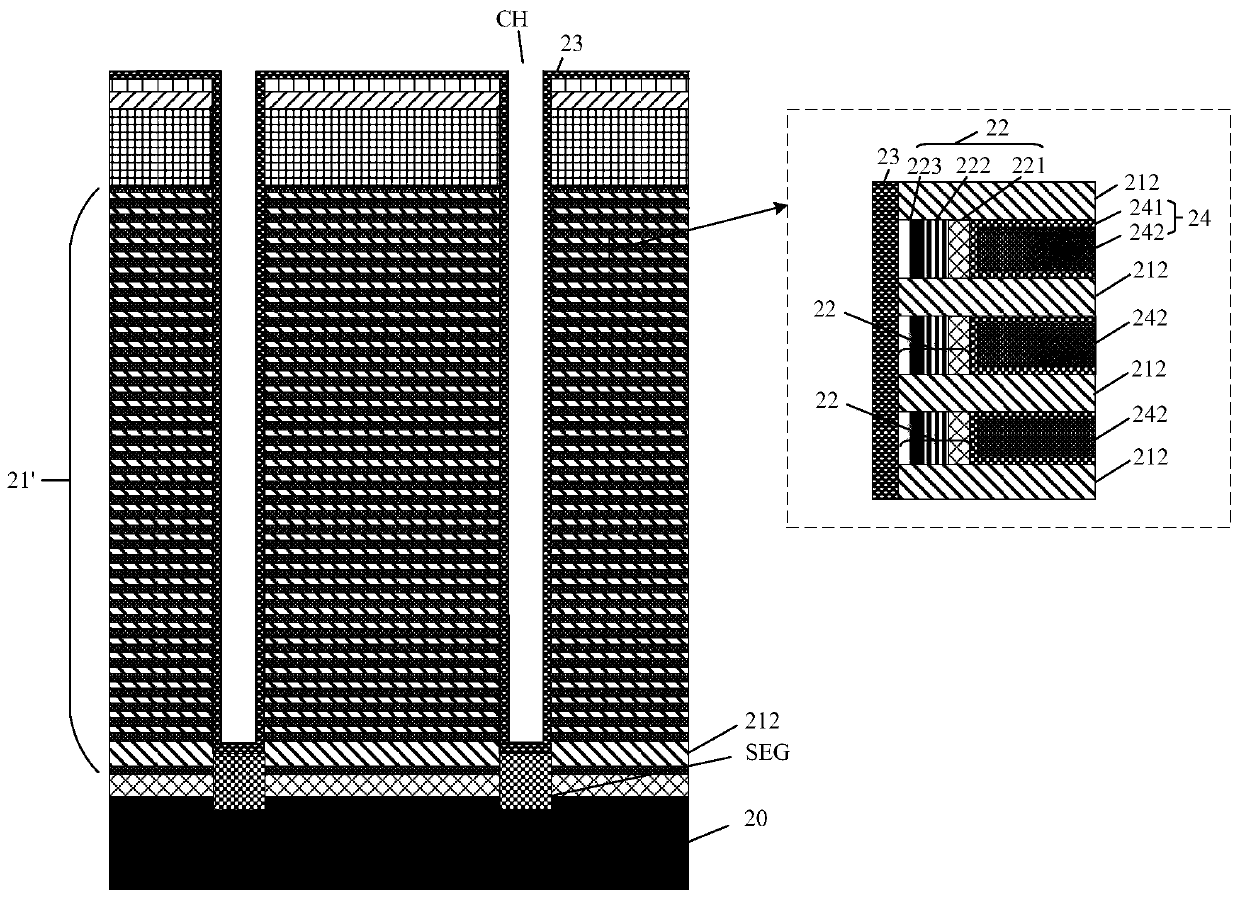

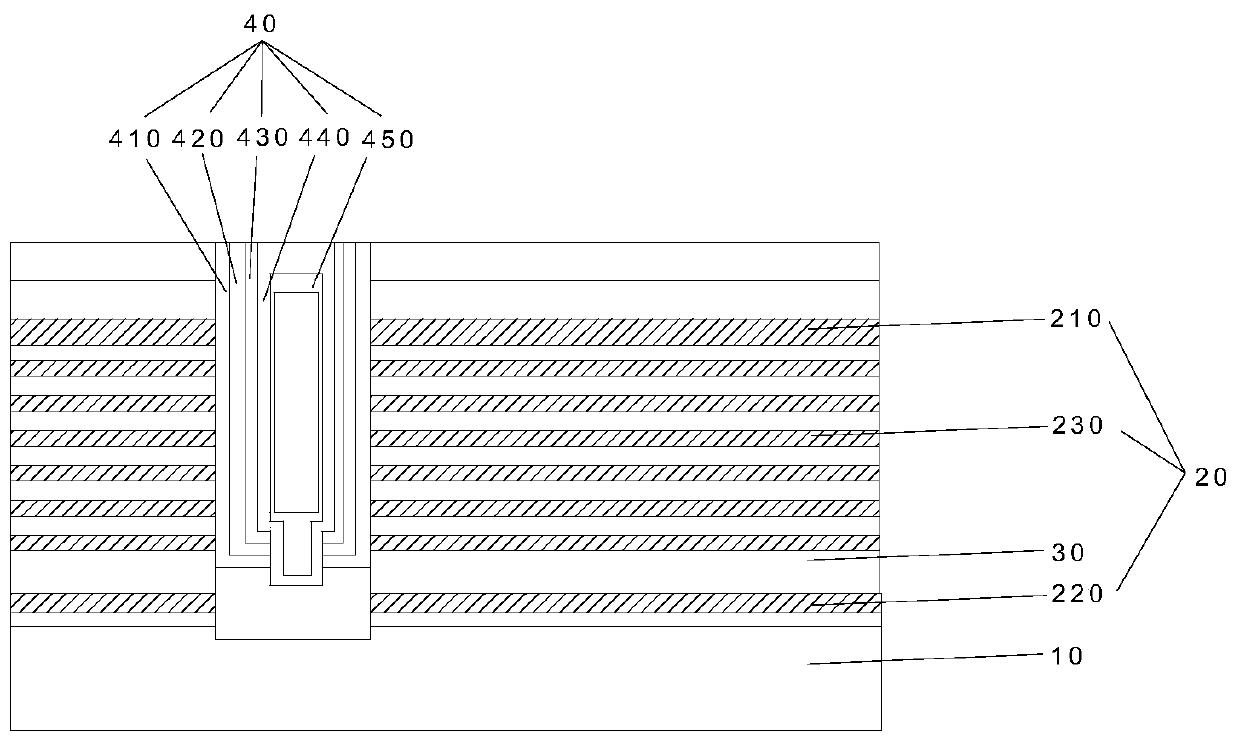

Three-dimensional memory and manufacture method thereof

ActiveCN109887922AImprove retention characteristicsInhibit migrationSolid-state devicesSemiconductor devicesInsulation layerCharge carrier

The invention relates to the technical field of semiconductor manufacture, in particular to a three-dimensional memory and a manufacture method thereof. The three-dimensional memory comprises a substrate, a tunneling layer, a plurality of charge capture layers and a plurality of charge barrier layers, wherein the substrate is provided with a stacking structure and channel holes which penetrate through the stacking structure along a direction vertical to the substrate, the stacking structure comprises interlayer insulation layers and grid electrode layers, and the interlayer insulation layers and the grid electrode layers are alternately stacked along a direction vertical to the substrate; the tunneling layer covers the inner wall surface of the channel holes; each charge capture layer is positioned between two adjacent interlayer insulation layers and is in contact with the tunneling layer; and each charge barrier layer is positioned between each grid electrode layer and each interlayer insulation layer as well as each charge capture layer and each grid electrode layer. By use of the three-dimensional memory, the migration of current carriers in the charge capture layers along a channel direction can be prevented, and the retention characteristics of the three-dimensional memory are improved.

Owner:YANGTZE MEMORY TECH CO LTD

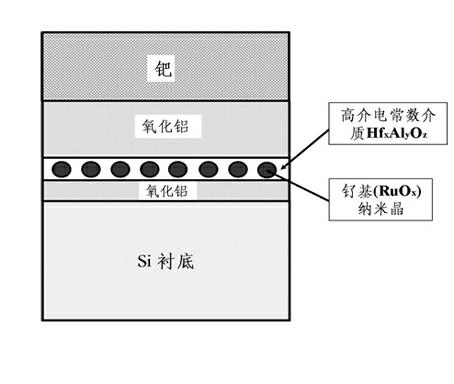

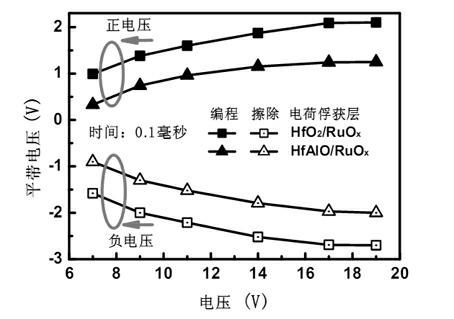

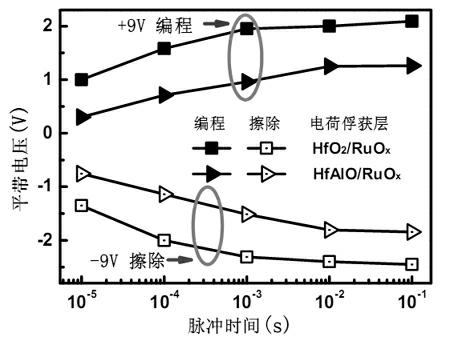

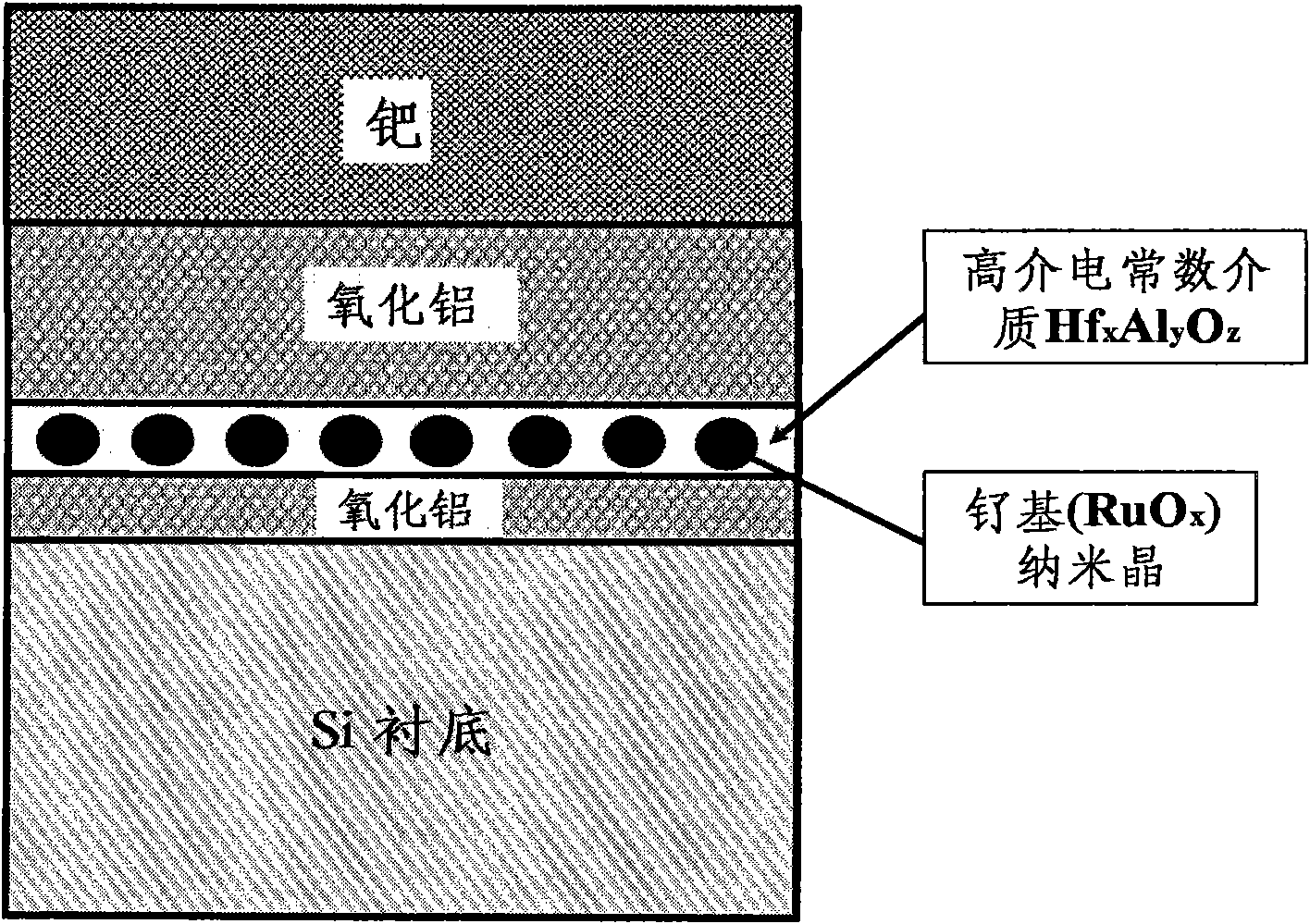

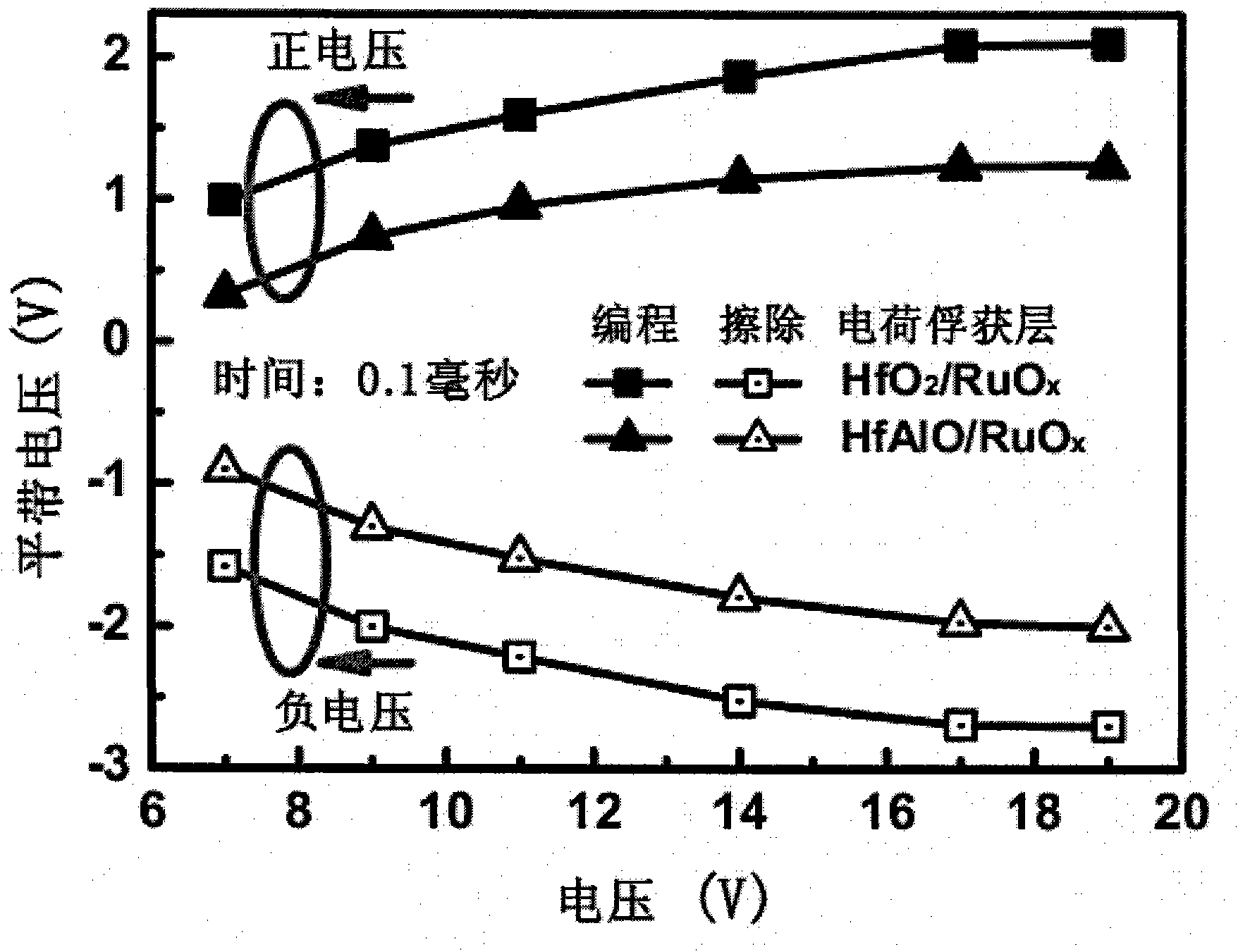

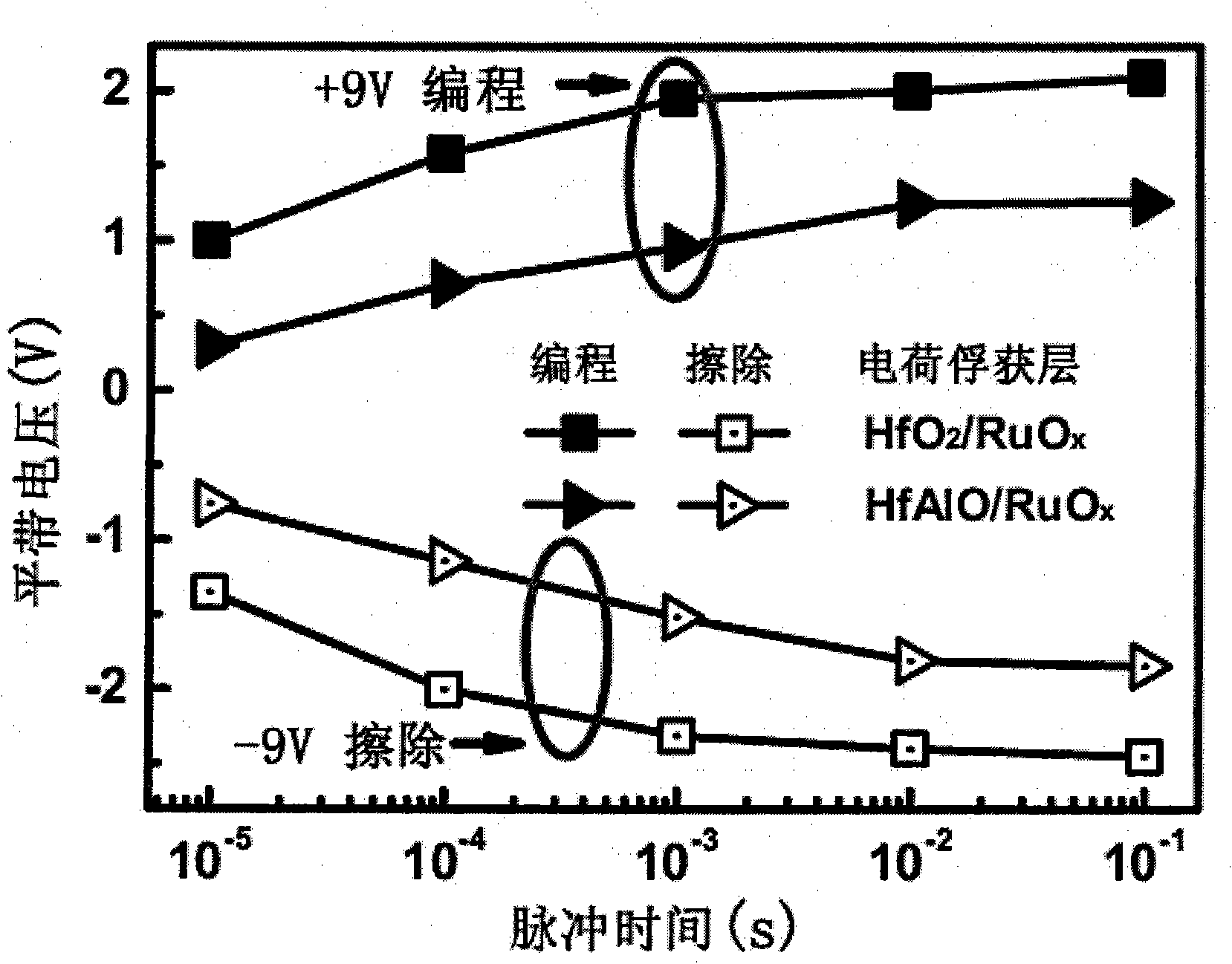

Gate stack structure suitable for semiconductor flash memory device and manufacturing method of gate stack structure

The invention relates to a gate stack structure suitable for a semiconductor flash memory device and a manufacturing method of the gate stack structure. In the gate stack structure, a P-type monocrystalline silicon wafer with crystallographic orientation of 100 is used as a substrate; and an Al2O3 film used as a charge tunneling layer, ruthenium-based RuOx nano-crystals used as a first charge trapping layer, a high dielectric constant HfxAlyOz film used as a second charge trapping layer, an Al2O3 film used as a charge barrier layer and an upper electrode layer are arranged on the substrate from bottom to top sequentially. In the invention, the ruthenium-based RuOx nano-crystals have high thermal stability and are difficult to diffuse at high temperature; the high dielectric constant HfxAlyOz film has higher charge trap density; and an upper electrode is made of metal palladium and has a higher work function. Therefore, the gate stack structure disclosed by the invention has wide application prospect in a nano-crystal memory capacitor.

Owner:FUDAN UNIV

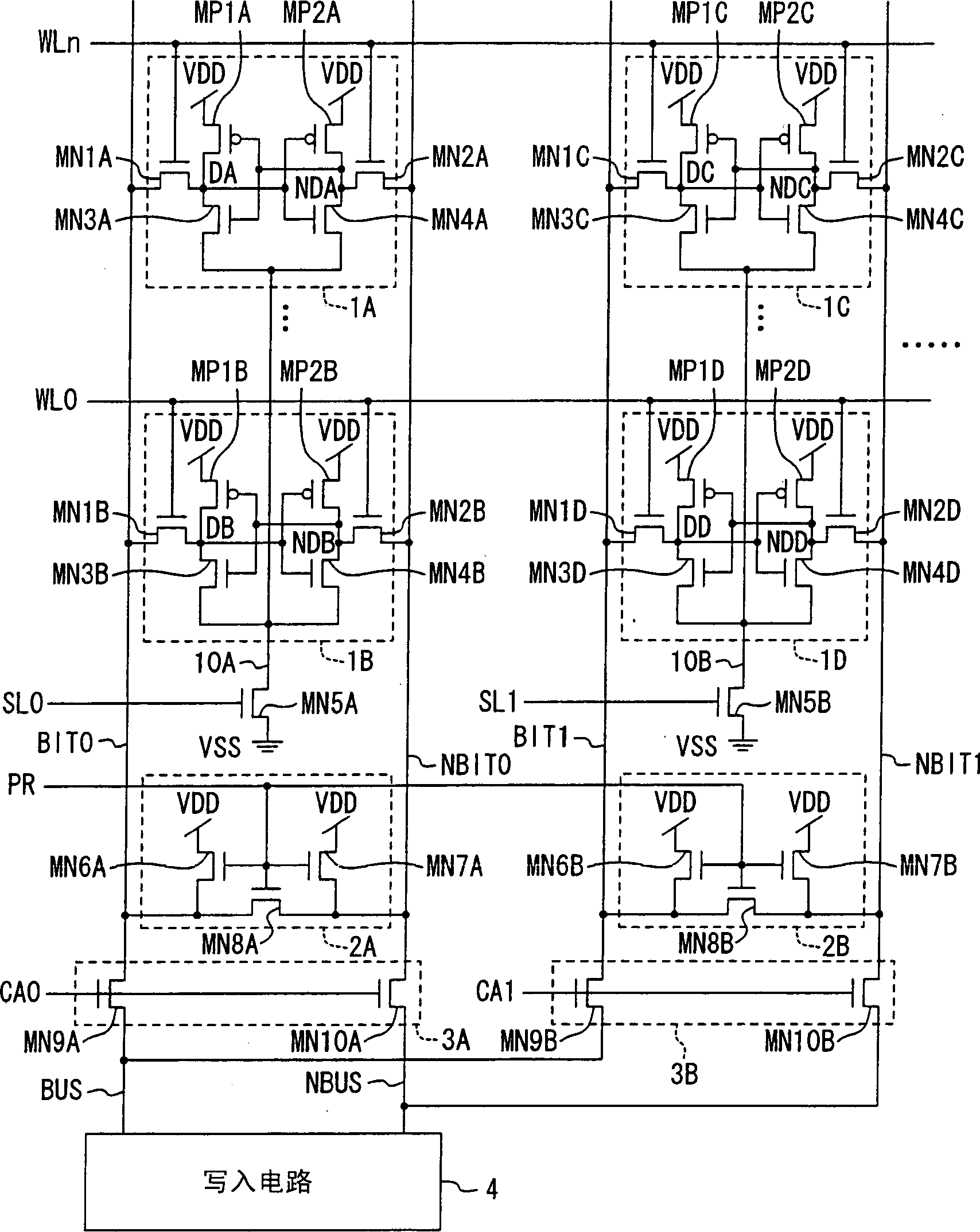

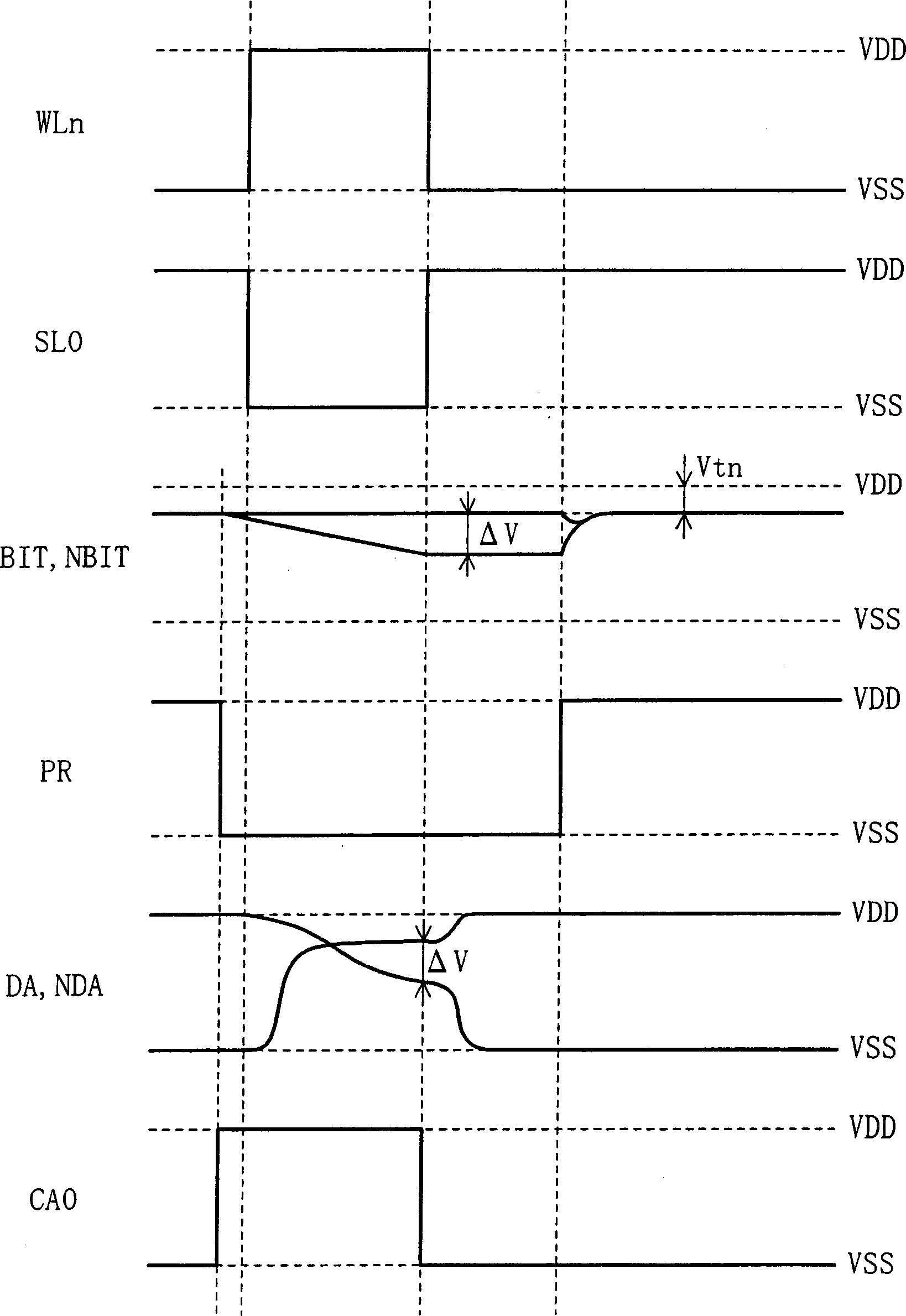

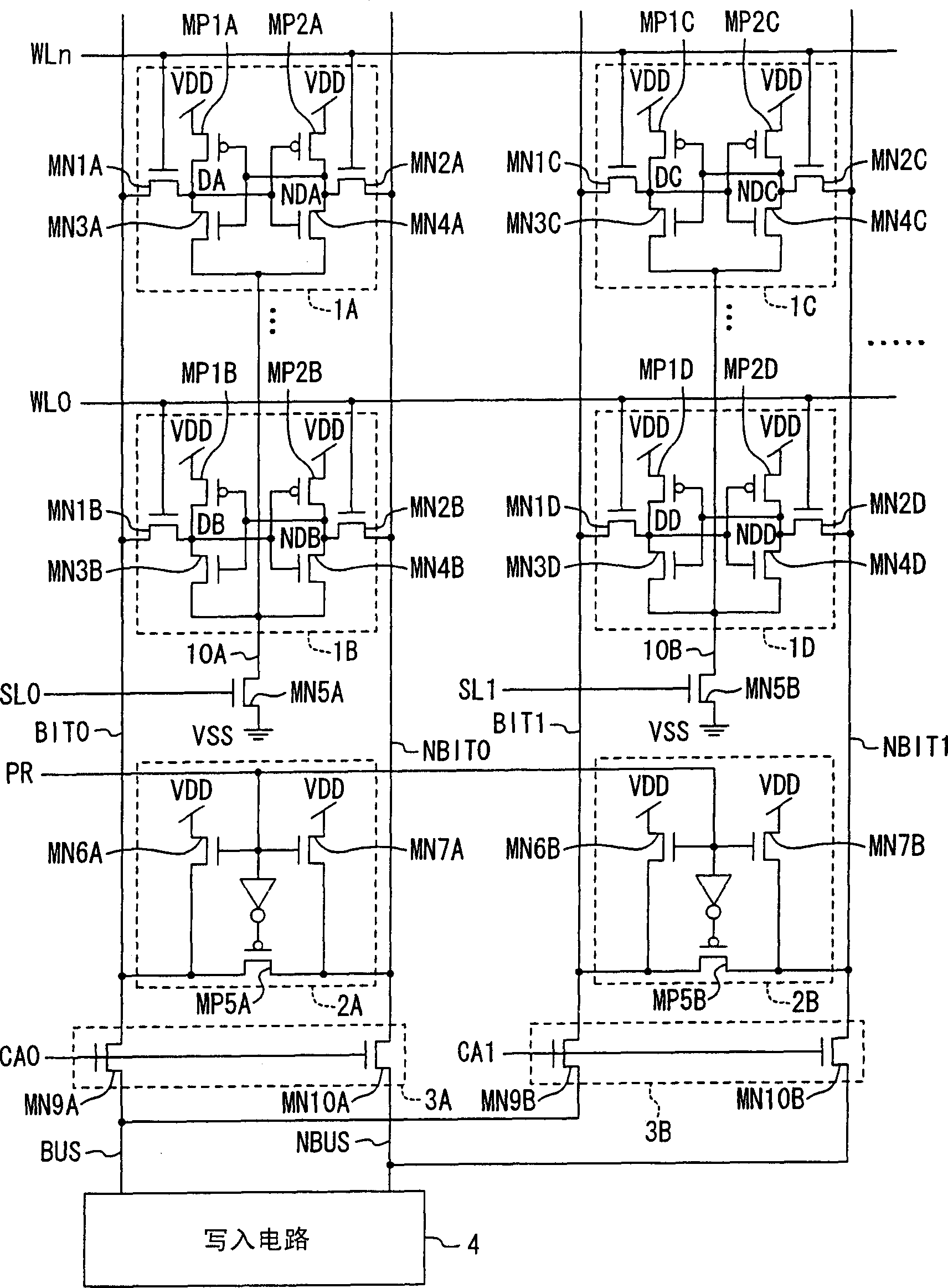

Semiconductor storage

InactiveCN1516196AGuaranteed dataReduce current consumptionSolid-state devicesDigital storageBit lineLow voltage

The respective sources of drive transistors included in memory cells that are located in each of multiple columns and connected to a corresponding one of bit line pairs are connected commonly to a low voltage power supply VSS via an assertion transistor. When data is written, the assertion transistor for the memory cells connected to a selected one of the bit line pairs and located in the identical column is negated, so that the sources of the drive transistors in the memory cells in that column are allowed to float. Consequently, even with a low power supply voltage, it is possible to write the data into a single selected memory cell, while data in the unselected memory cells can be retained favorably.

Owner:SOCIONEXT INC

Gate stack structure for semiconductor flash memory device and preparation method thereof

InactiveCN101887910AHigh densityControl thicknessNanoinformaticsSolid-state devicesManufacturing technologyTrapping

The invention belongs to the technical field of manufacturing technology of semiconductor integrated circuits, and in particular relates to a gate stack structure for a flash memory device and a preparation method thereof. The gate stack structure comprises an Al2O3 thin film, ruthenium-based nanocrystals, a HfxAlyOz thin film, an Al2O3 thin film and a top electrode layer from bottom to top in turn by taking a silicon slice in P-type (100) crystal orientation as a substrate, wherein the Al2O3 thin film is used as a charge tunneling layer; the ruthenium-based nanocrystals are used as a first charge trapping layer; the HfxAlyOz thin film is used as a second charge trapping layer; and the Al2O3 thin film is used as a charge barrier layer. In the invention, the ruthenium-based nanocrystals have high thermal stability and are difficult to diffuse at a high temperature; the HfxAlyOz thin film has high charge trapping density; and the top electrode is made of metal palladium and has large work function. Thus the gate stack structure has broad application prospect in nanocrystalline memory capacitors.

Owner:FUDAN UNIV

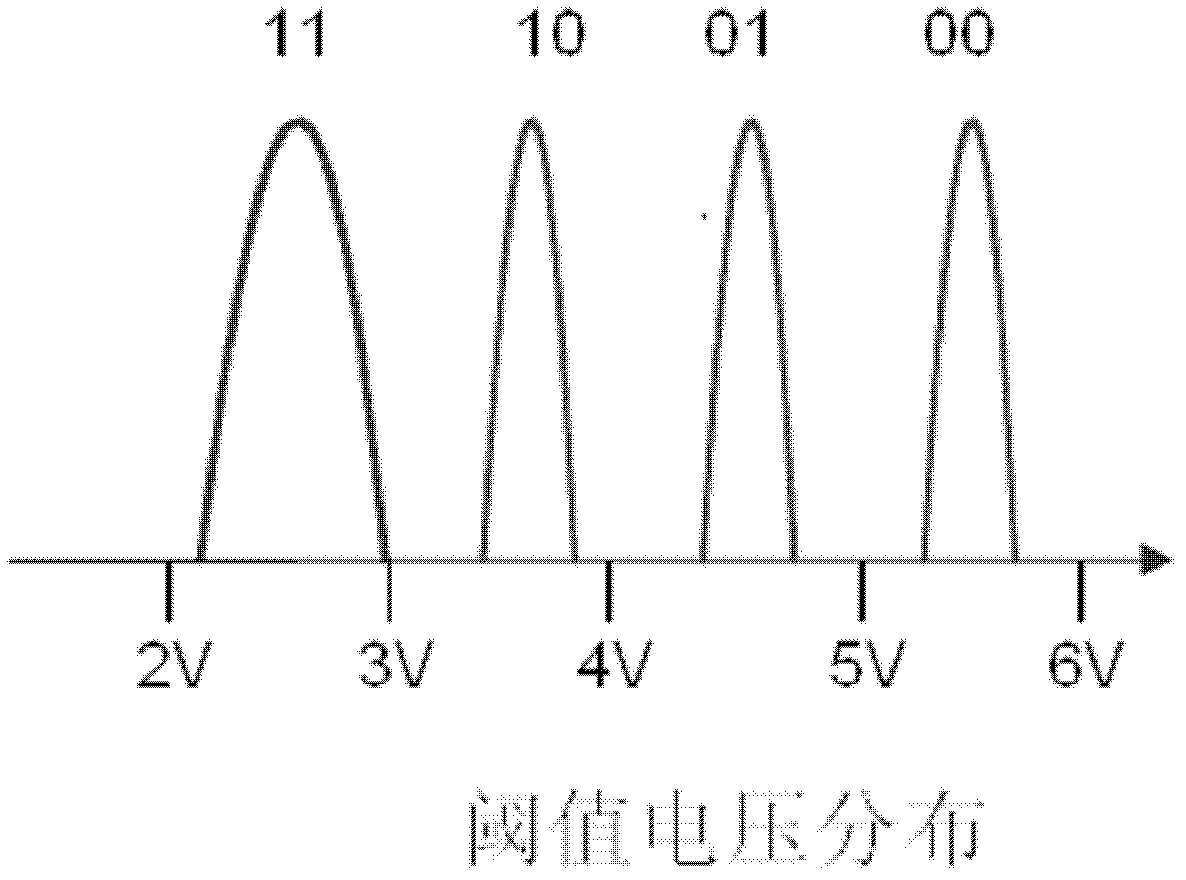

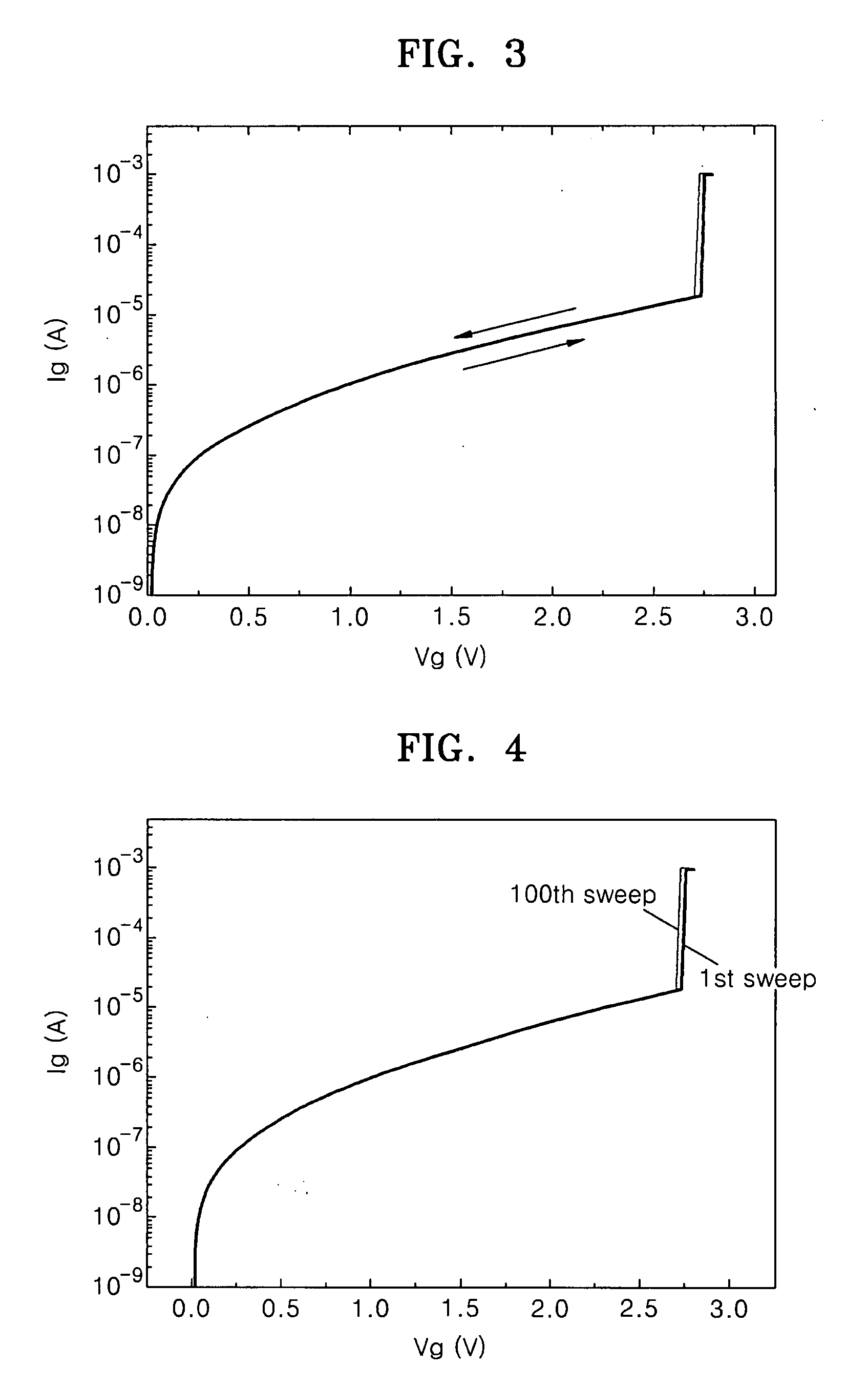

Operation method for increasing high-density storage characteristic of non-volatile flash memory

ActiveCN102509559AIncrease spacingLess likely to overlapRead-only memoriesHigh densityComputer science

The invention relates to an operation method for increasing a high-density multi-valued storage characteristic of a non-volatile flash memory. The operation method comprises the following steps of: (1), adjusting an initial state of a local captured type non-volatile flash storage unit to threshold voltage of minus 2V to minus 1 V at first: adjusting to the threshold voltage by adopting a bilateral belt-belt tunnelling hot hole injection (BBHH) erasing method; and then carrying out a transient FN operation so as to promote charges in a channel to be distributed uniformly; (2), repetitively carrying out the step (1) for many times, wherein the initial state is adjusted to the threshold voltage of minus 2V to minus 1 V through the bilateral BBHH and FN operation steps, and the fact that the threshold voltage in a channel region is same everywhere is finally realized; (3), taking the threshold as the multi-valued storage initial state, and carrying out a multi-valued unitary programming operation on an NOR type local captured storage unit; and (4), carrying out a -FN process for a short time at one time after achieving a programming state. The operation method disclosed by the invention is capable of increasing holding characteristic and tolerance characteristic of a storage device.

Owner:NANJING UNIV

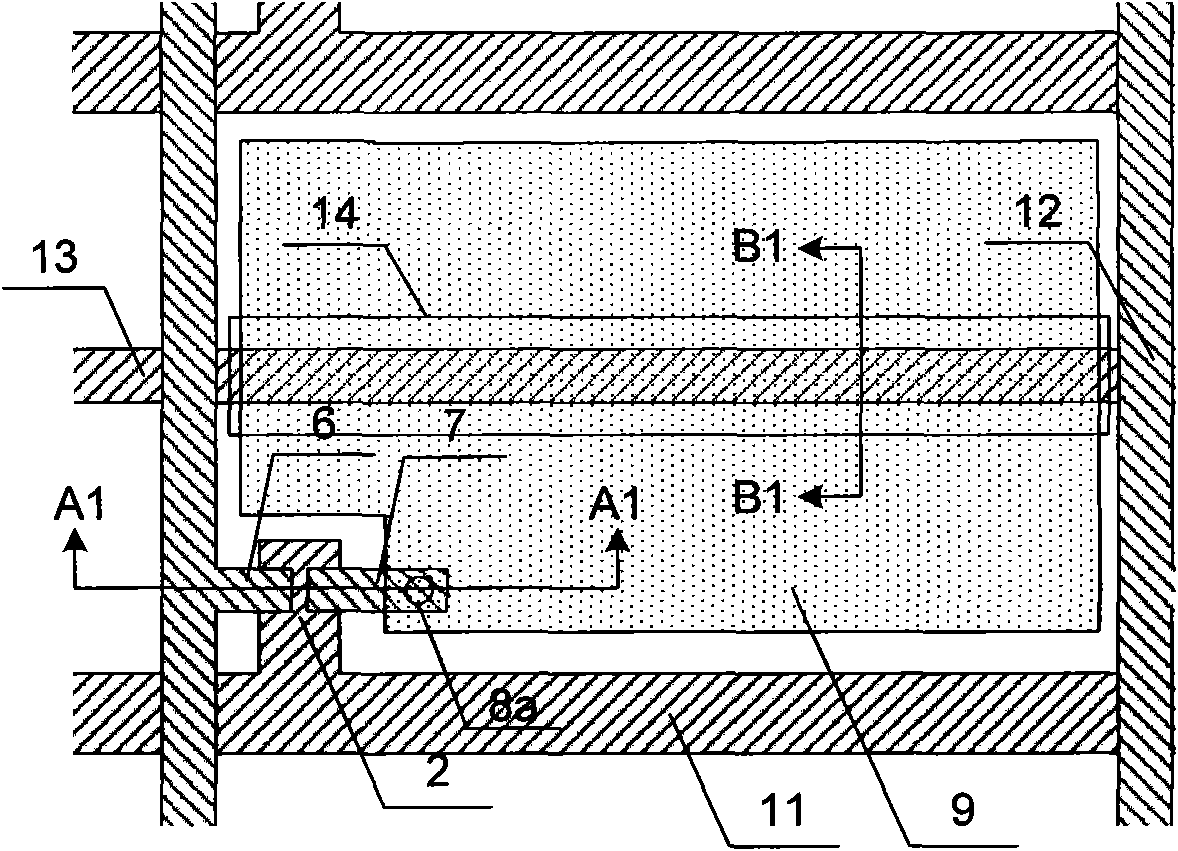

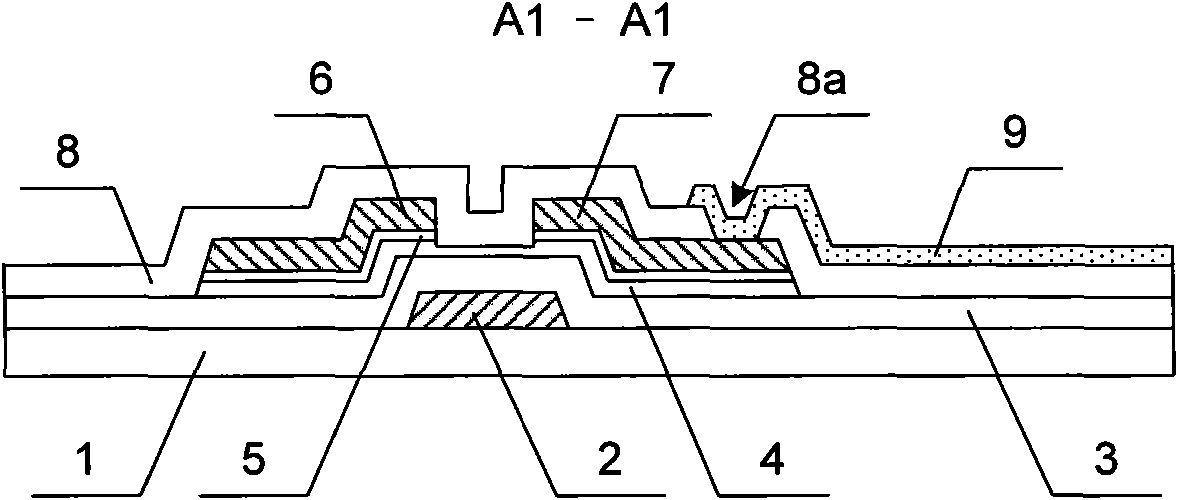

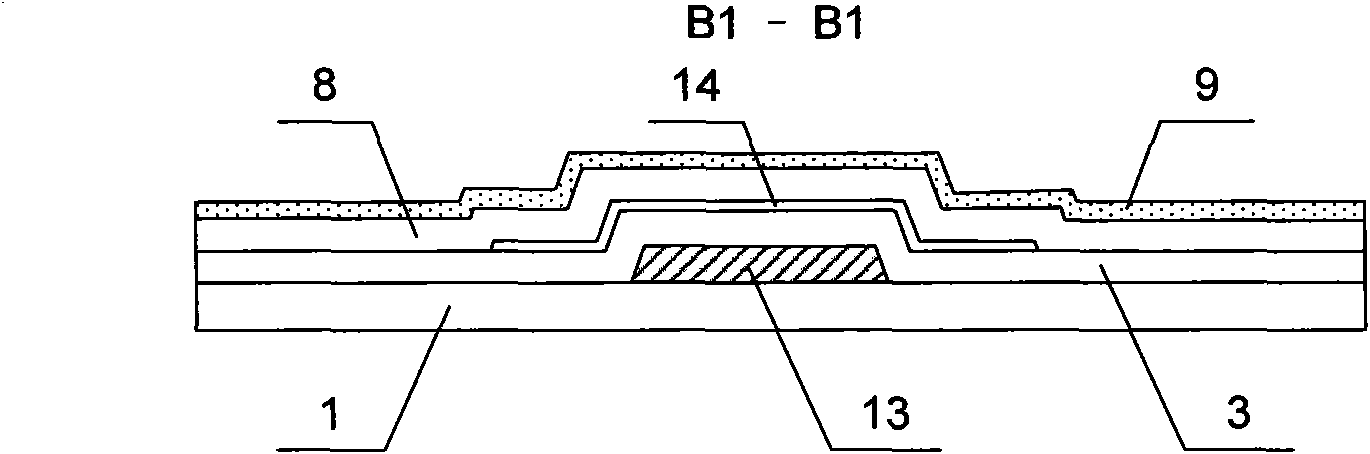

TFT-LCD array substrate and making method thereof

InactiveCN101957525AImprove working characteristicsReduce capacitanceSemiconductor/solid-state device manufacturingNon-linear opticsCapacitanceCapacitor

The invention relates to a TFT-LCD array substrate and a making method thereof. The array substrate comprises a gate line, a data line, a thin film transistor, a pixel electrode and a common electrode line, wherein the gate line, the data line and the thin film transistor are formed on the substrate, and the pixel electrode and the common electrode line form a storage capacitor, a pulse electrodeis arranged between the common electrode line and the pixel electrode and is used for enabling the storage capacitor to have a first capacitance value when the pixel electrode is started to be charged and enabling the storage capacitor to have a second capacitance value when pixel electrode charging is finished, and the first capacitance value is smaller than the second capacitance value. In the invention, because the pulse electrode is arranged between the common electrode line and the pixel electrode, on the one hand, the storage capacitor has the smaller capacitance value when pixel electrode charging is started so as to lower load of the thin film transistor and enhance the charging capability of the thin film transistor, and on the other hand, the storage capacitor has the larger capacitance value when pixel electrode charging is finished to strengthen the holding property of voltage of the pixel electrode and lower the leaping voltage of the pixel electrode at the moment that the thin film transistor is closed.

Owner:BOE TECH GRP CO LTD +1

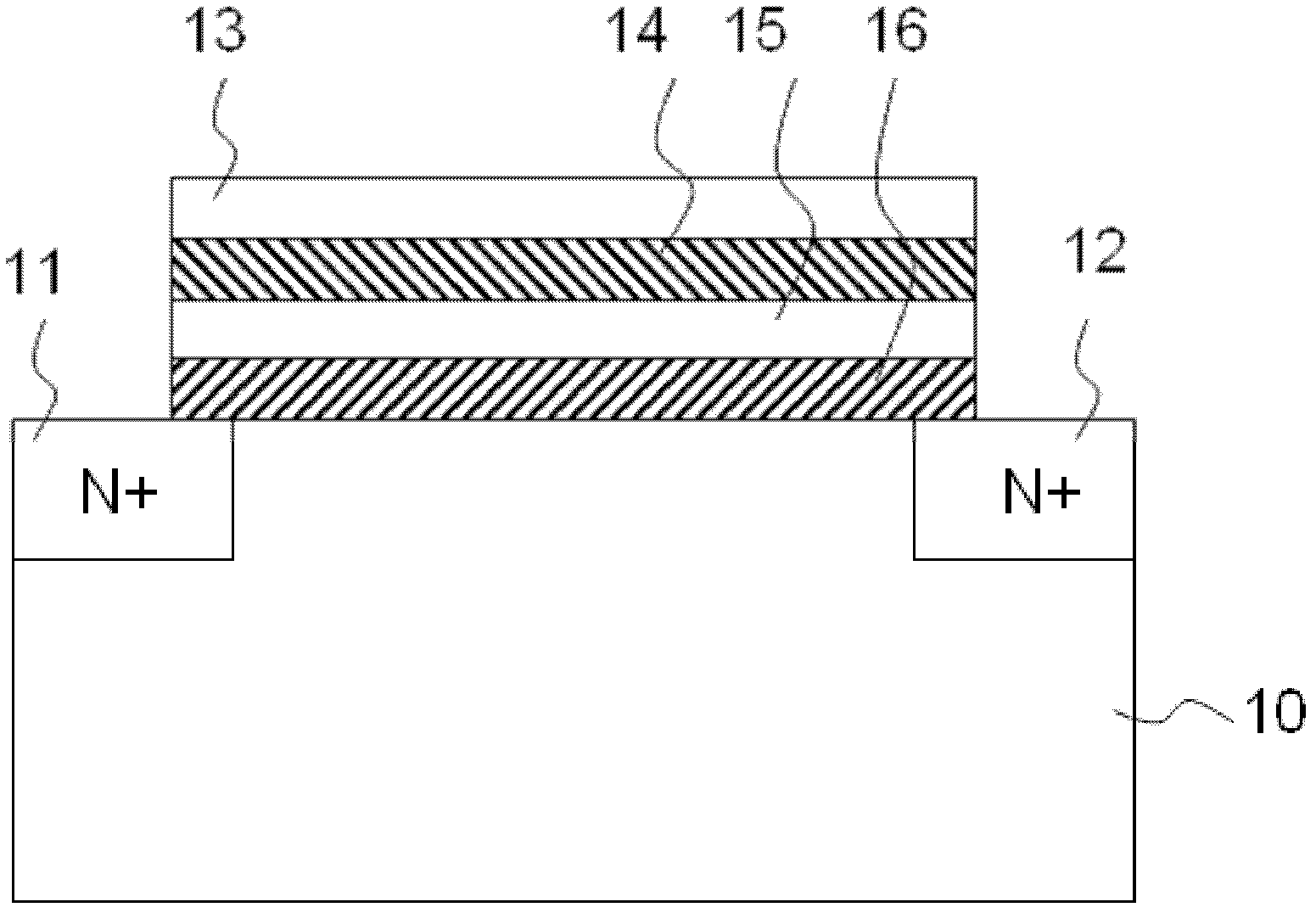

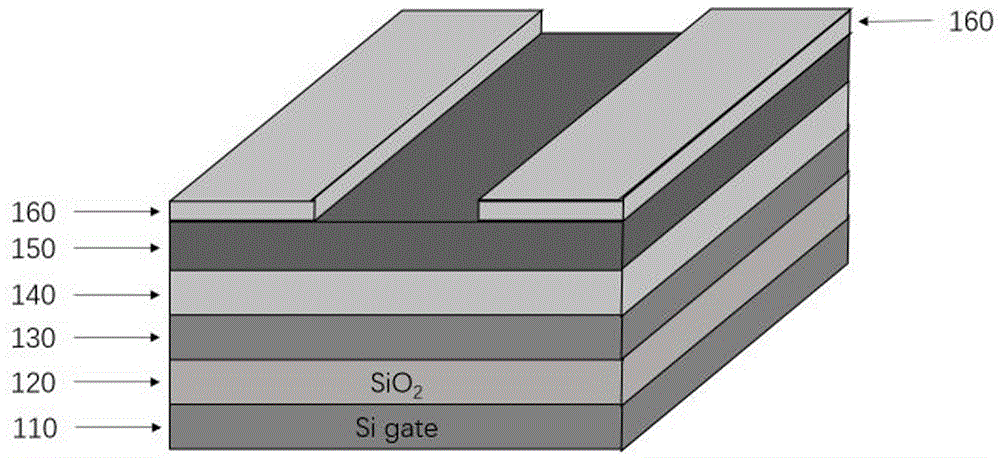

Method for improving properties of non-volatile floating-gate organic thin film transistor type memorizer

InactiveCN106299122AImprove performanceImprove retention characteristicsSolid-state devicesSemiconductor/solid-state device manufacturingQuantum wellBottom gate

The invention relates to a method for improving properties of a non-volatile floating-gate organic thin film transistor type memorizer, and provides a non-volatile floating-gate organic thin film transistor type memorizer with a bottom-gate top contact structure. According to the non-volatile floating-gate organic thin film transistor type memorizer with the bottom-gate top contact structure, a charge storage layer adopts an organic insulation polymer film doped with quantum dot material; the quantum dot material is of a core-shell structure, and the highest occupied molecular orbital of the nuclear material is higher than that of a shell material, the lowest unoccupied molecular orbital of the nuclear material is lower than that of the shell material, a quantum well is formed between the nuclear material and the shell material, so that the captured electric charges are limited in the nuclear material, the electric charge capture ability of the charge storage layer is improved, and then the memory window of the non-volatile floating-gate organic thin film transistor type memorizer is increased, retention characteristics thereof are significantly improved. The provided method is simple, easy to operate, low in invested cost and enhances the memory property of the memorizer.

Owner:FUZHOU UNIV

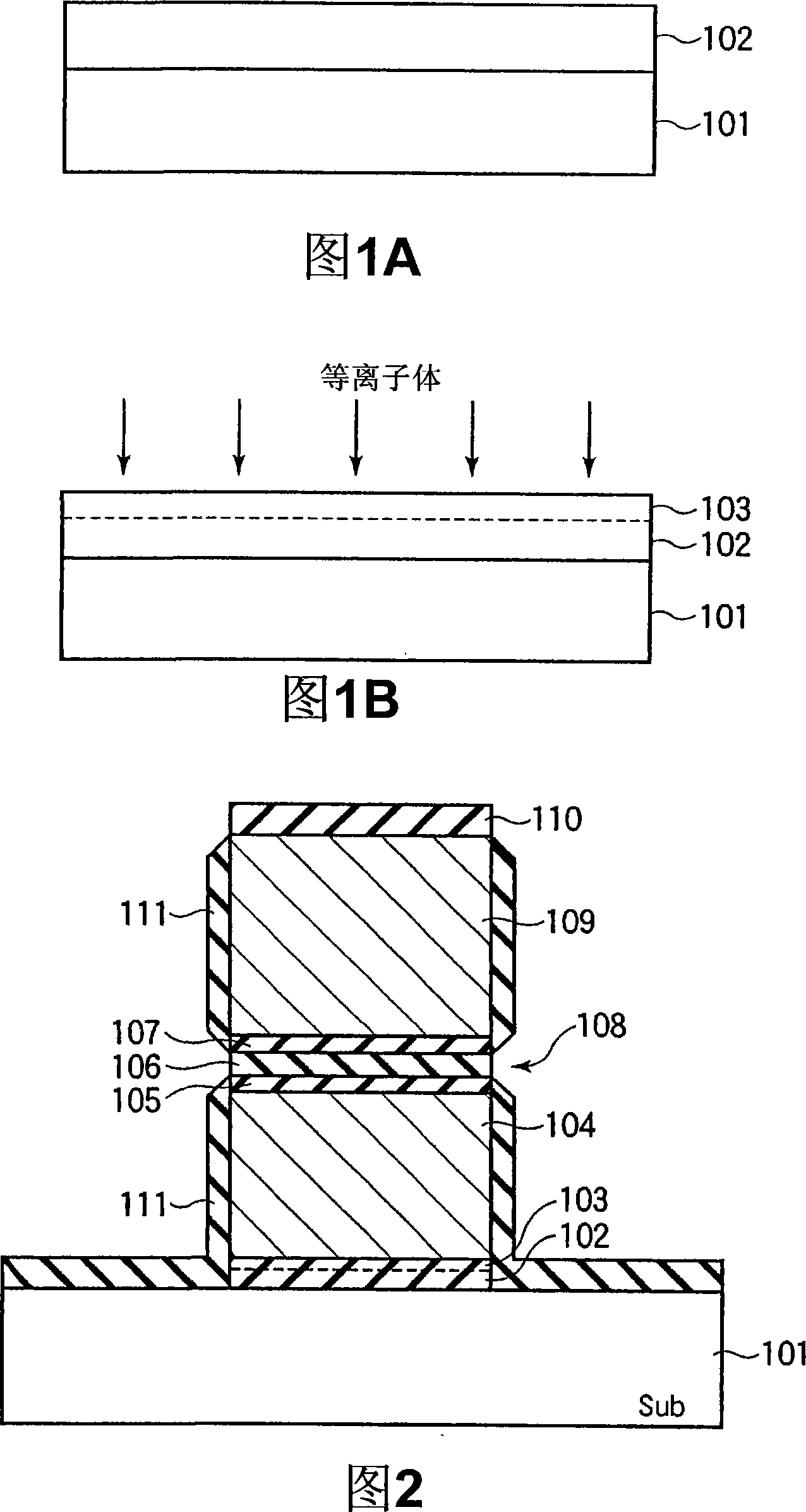

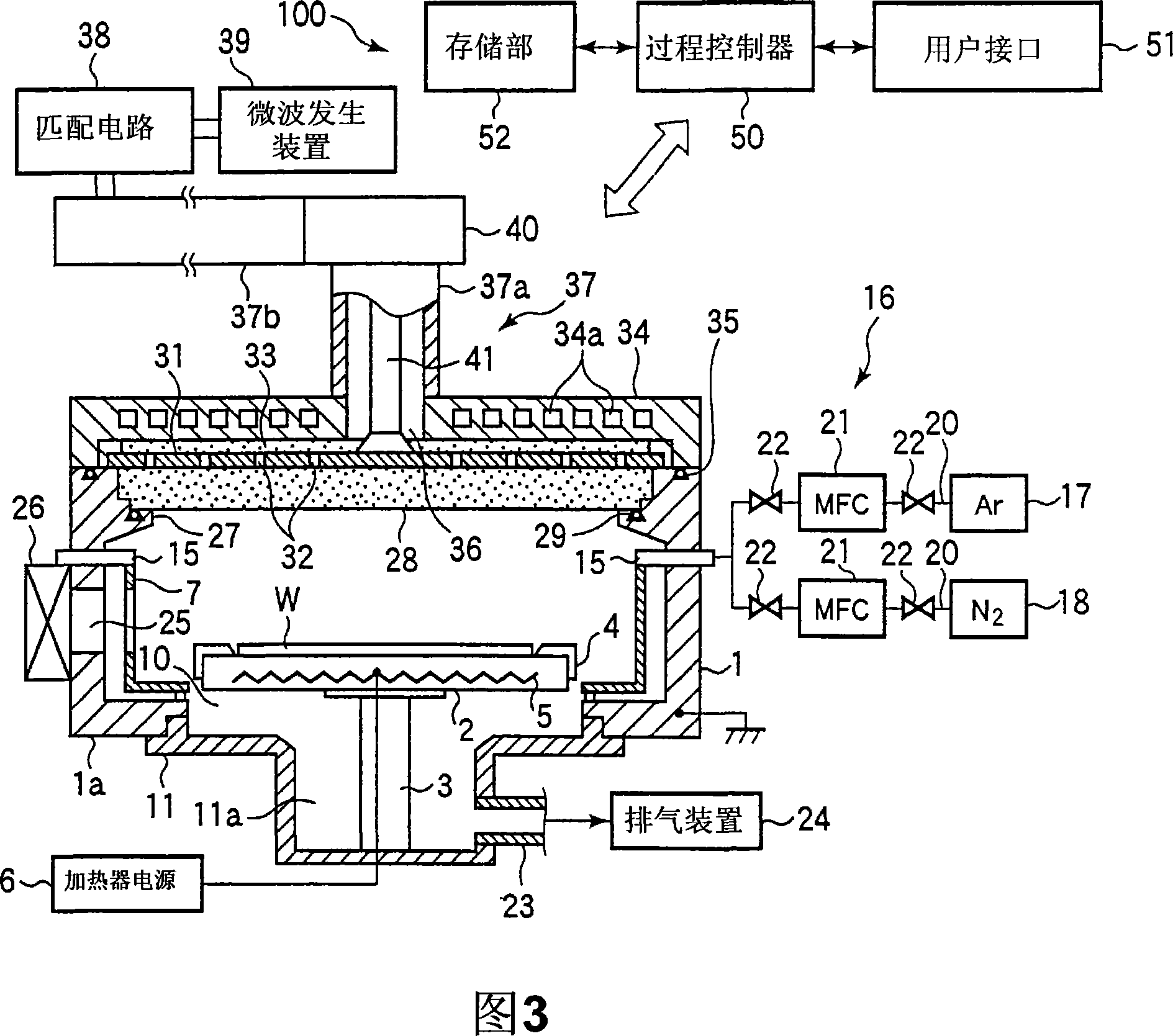

Method for nitriding tunnel oxide film, method for manufacturing non-volatile memory device, non-volatile memory device, control program and computer-readable storage medium

InactiveCN101095224AHigh quality film qualityIncrease freedomTransistorSolid-state devicesNitrogen gasPlasma processing

When nitriding a tunnel oxide film in a non-volatile memory device, a nitrided region is formed in the surface portion of the tunnel oxide film by a plasma processing using a process gas containing a nitrogen gas.

Owner:TOKYO ELECTRON LTD

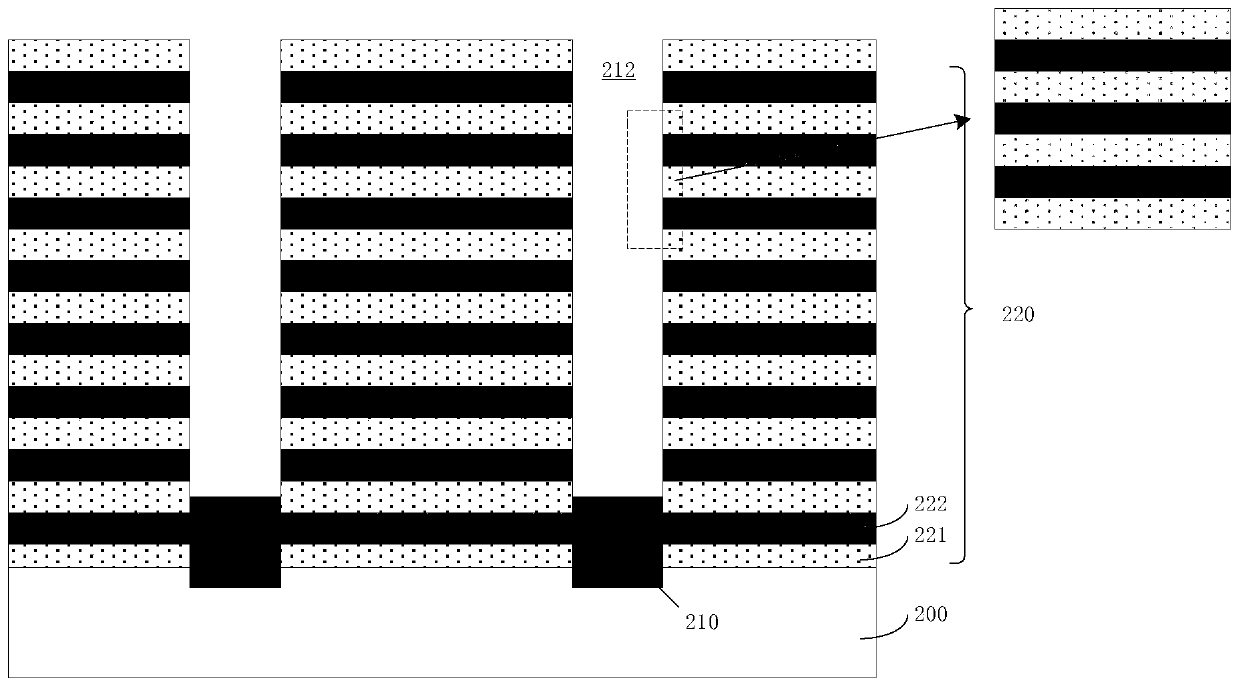

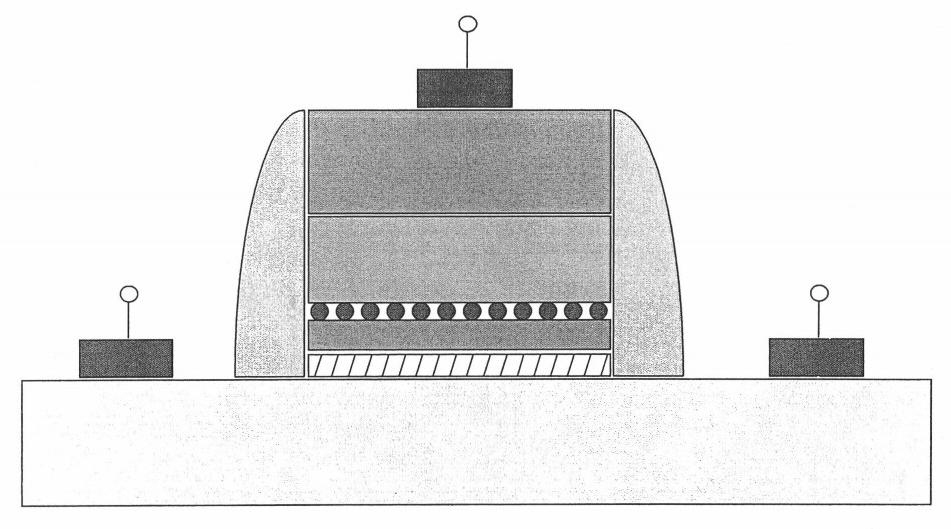

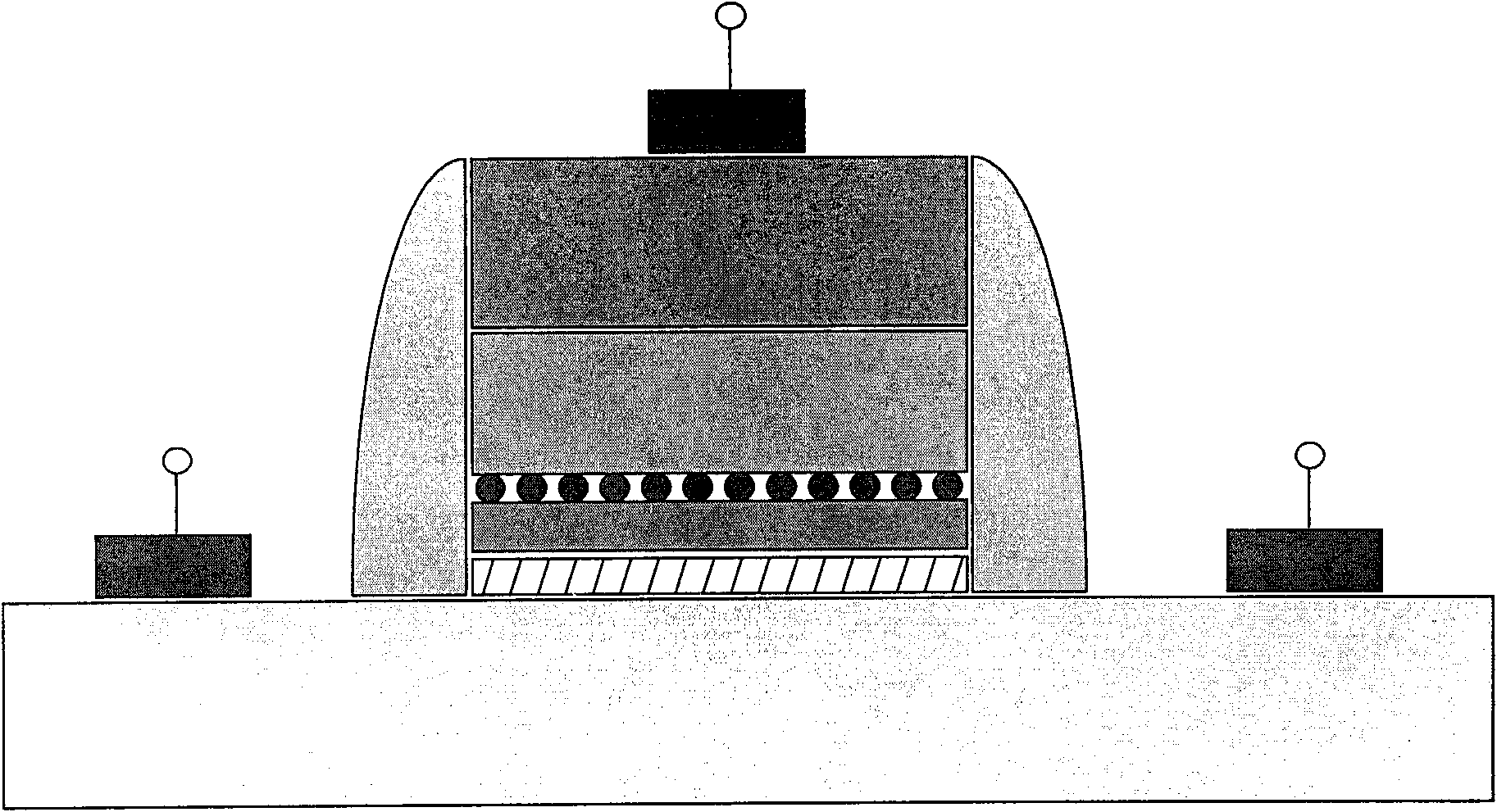

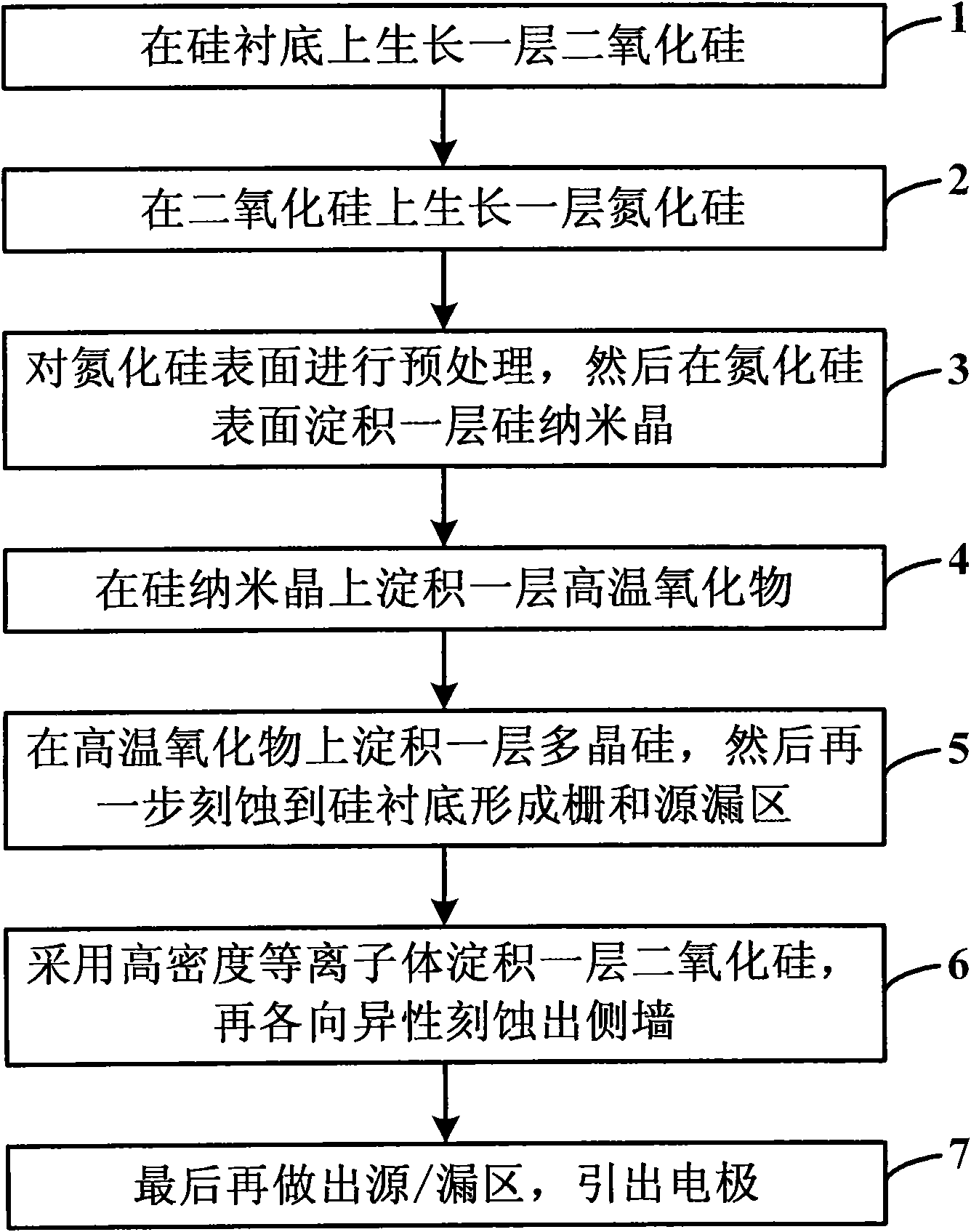

Multi-layer floating gate nonvolatile memory structure and production method thereof

InactiveCN101814505AHigh densityIncrease storage windowSolid-state devicesSemiconductor/solid-state device manufacturingSilicon nanocrystalsSilicon dioxide

The invention discloses a multi-layer floating gate nonvolatile memory structure and a production method thereof, wherein the multi-layer floating gate nonvolatile memory structure comprises a silicon substrate, a silicon dioxide layer, a silicon nanocrystals / high temperature oxide multilayer structure, a polysilicon layer, a silicon dioxide layer, grid and source / drain region formed by sculpturing on the silicon substrate, and a side wall formed by sculpturing on the silicon dioxide layer. The invention solves the defects because the traditional Flash technology node can downsized, utilizes the multi-layer floating gate to storage charge to enhance a storage window, so that the reliability of the floating grid for storing charge can be increased and the retention performance of a floating device can be improved.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

Three-dimensional NAND type ferroelectric memory, manufacturing method and operation method

ActiveCN110071117AElectric field regulationEnhanced electric fieldSolid-state devicesDigital storageGate dielectricFerroelectric relaxor

The invention provides a three-dimensional NAND type ferroelectric memory, a manufacturing method and an operation method; the three-dimensional NAND type ferroelectric memory takes the inherent electric field adjusting effect of a ring gate device into consideration, namely compared with a flat-plate laminated gate, in a ring gate dielectric laminated layer, the electric field is enhanced in thedielectric layer with small radius and the electric field is weakened in the dielectric layer with large radius; a ferroelectric layer is integrated on the small-radius inner ring of the ring gate, and a dielectric layer is integrated on the outer ring of the large radius, so that the electric field distribution is effectively adjusted, the electric field of the dielectric layer is reduced, and the electric field of the ferroelectric layer is enhanced, and therefore the reliability of the ferroelectric memory is effectively improved, namely, the storage window is enlarged, the durability of the device is improved, and the retention characteristic of the device is improved.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

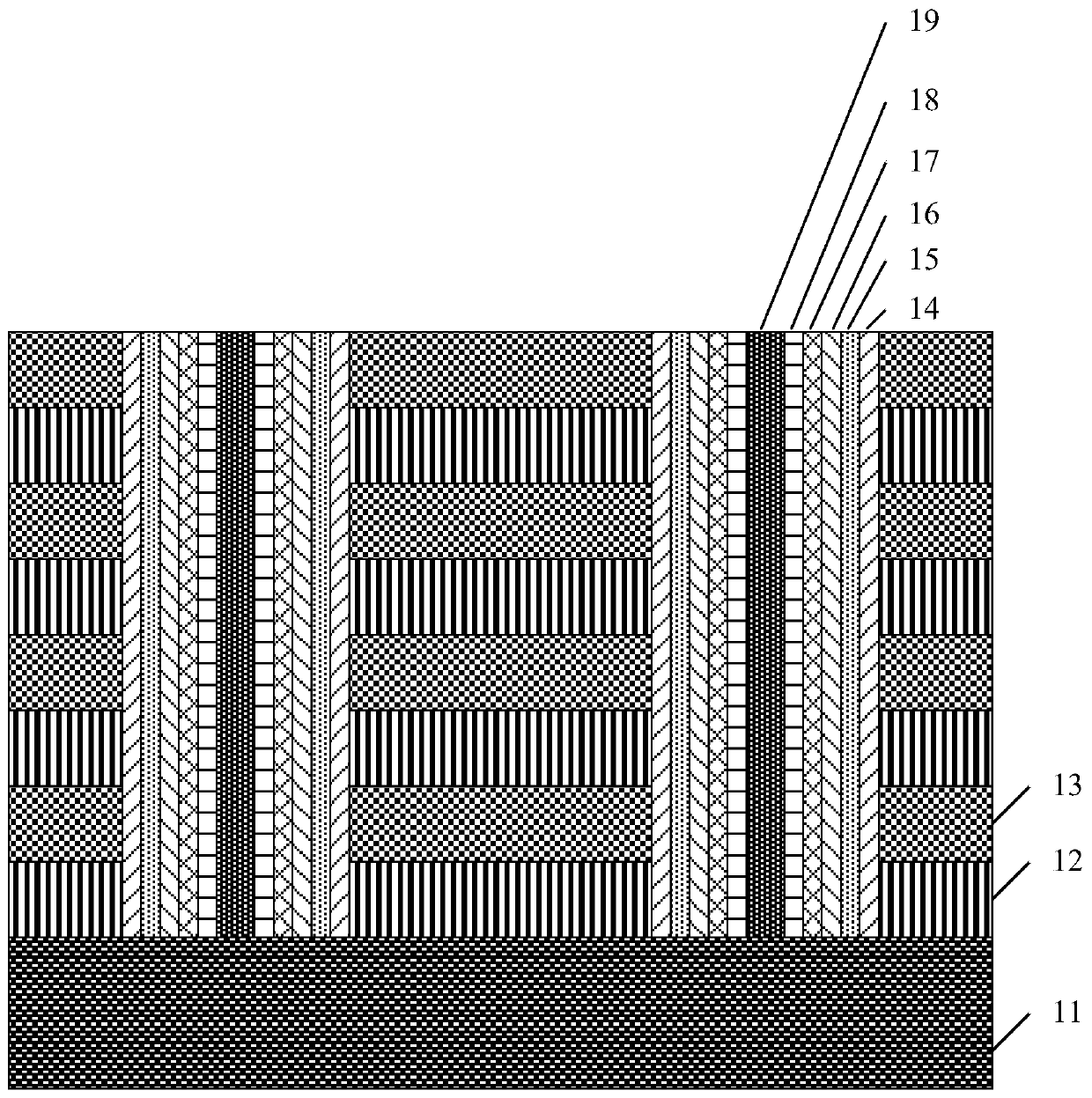

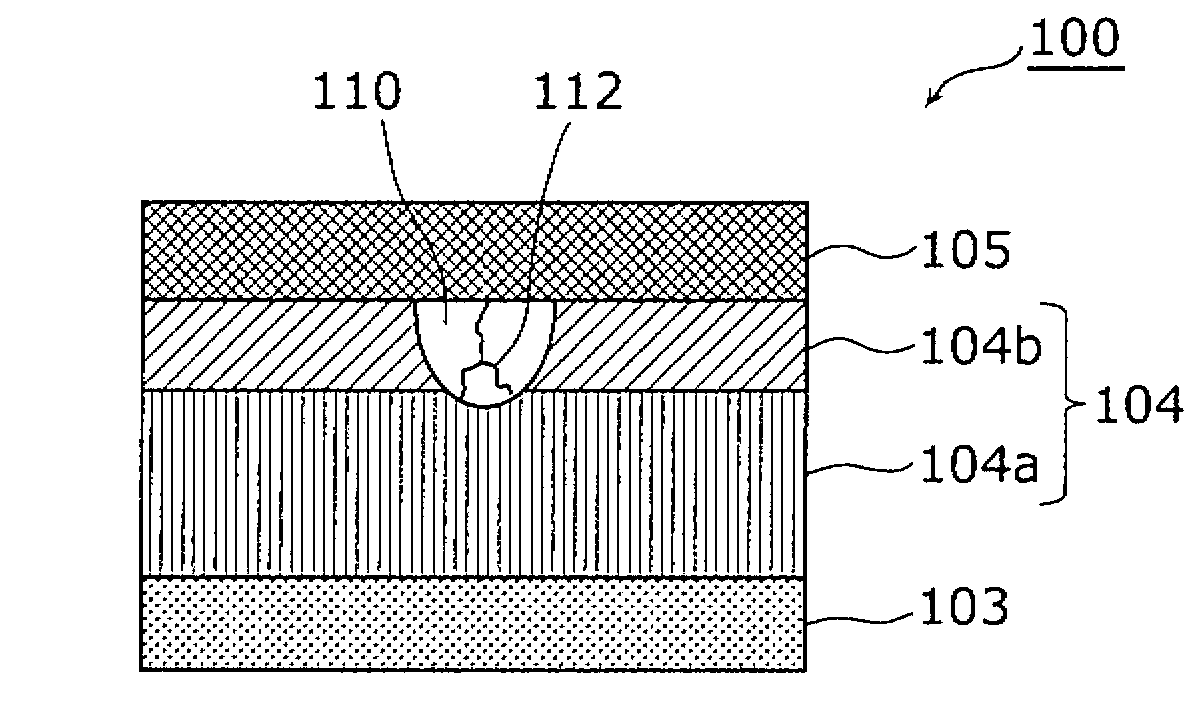

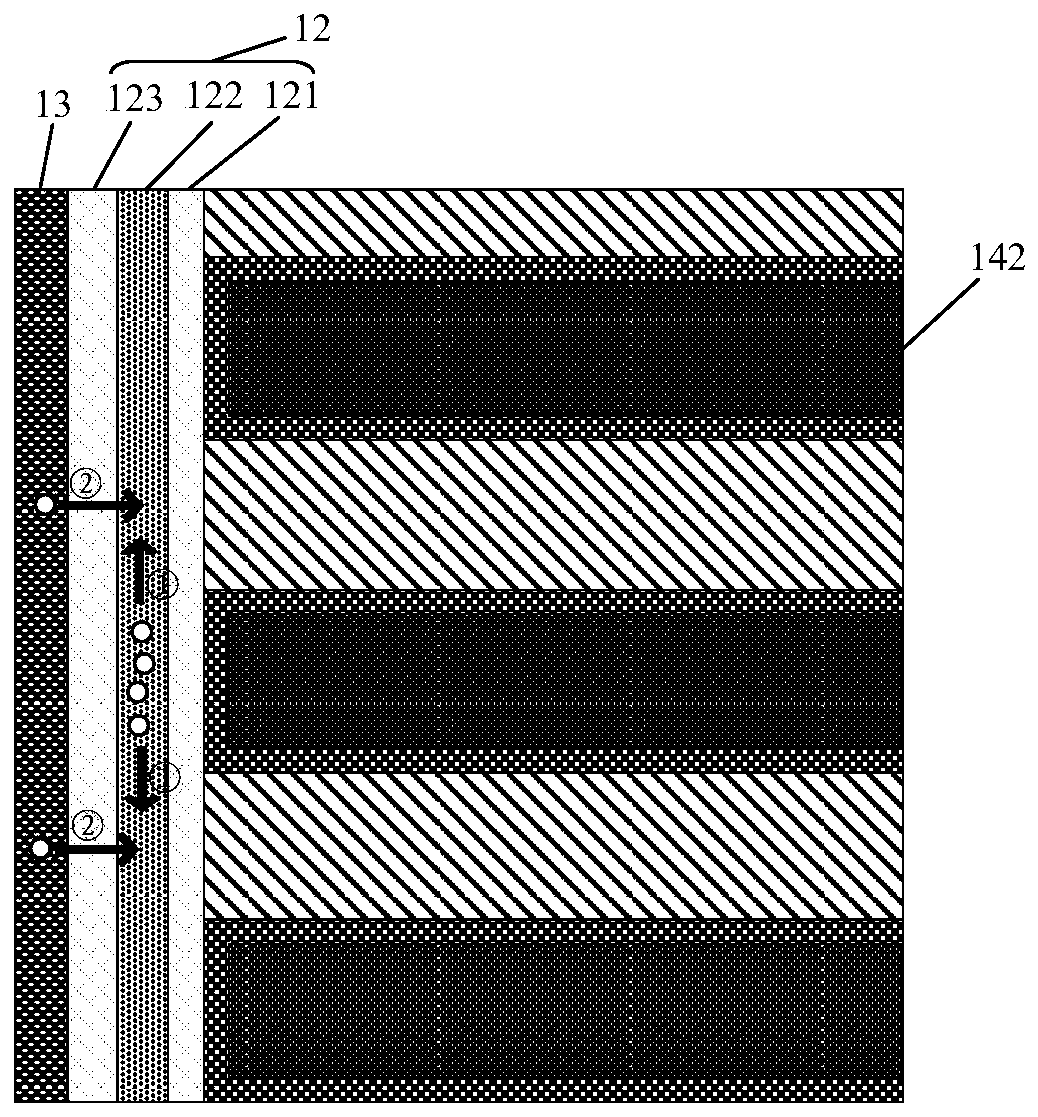

Semiconductor structure and forming method thereof

ActiveCN110112136APrevent proliferationImprove retention characteristicsSolid-state devicesSemiconductor devicesSemiconductor structureDiffusion barrier

The invention relates to a semiconductor structure and a forming method thereof. The semiconductor structure comprises a substrate, wherein a stacked structure is formed on the surface of the substrate; a channel hole penetrating through the stacked structure to the surface of the substrate; a functional sidewall covering the sidewall of the channel hole and including an electron barrier layer, anelectron capturing layer and a tunneling layer which are successively stacked from the sidewall of the channel hole to the inside of the channel hole; and a diffusion barrier layer between the electron barrier layer and the electron capturing layer and / or between the electron capturing layer and the tunneling layer. The semiconductor structure has high retention characteristics.

Owner:YANGTZE MEMORY TECH CO LTD

Method for writing data in nonvolatile storage element, and nonvolatile storage device

InactiveCN103314411AImprove retention characteristicsSuppresses the effect of swingingDigital storageVoltage pulseElectrical polarity

Provided is a method for writing data in a nonvolatile storage element, wherein it is possible to inhibit the effects from fluctuations in resistance. The method involves: a first application step (S120) in which a first voltage pulse for changing the resistance state of a nonvolatile storage element (100) from a first state to a second state is applied; a second application step (S121) in which a second voltage pulse having the same polarity as the first voltage pulse and a smaller absolute voltage value than the first voltage pulse is applied; a determination step (S122) in which it is determined whether or not the resistance state of the nonvolatile storage element (100) is the second state; and a third application step (S123) in which a third voltage pulse for changing the resistance state of the nonvolatile storage element from the first state to the second state is applied when it is determined that the resistance state of the nonvolatile storage element (100) is not the second state.

Owner:PANASONIC CORP

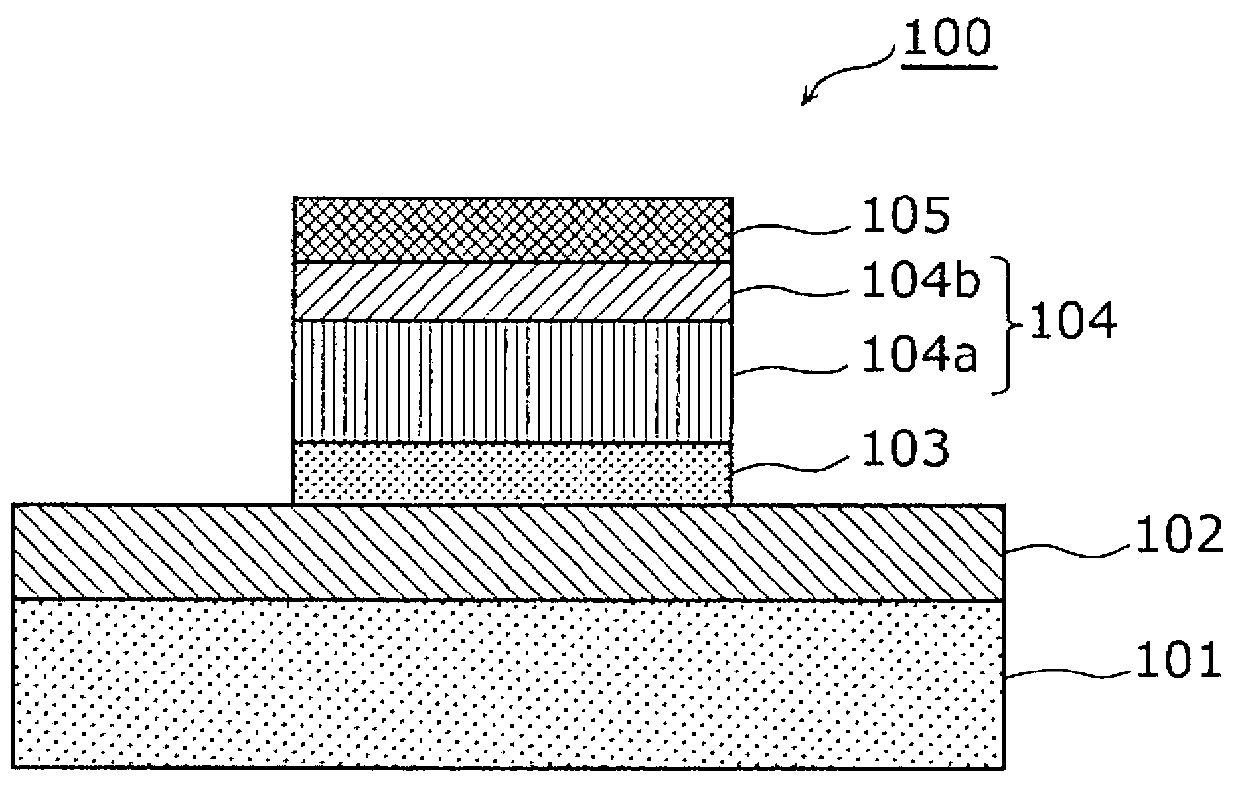

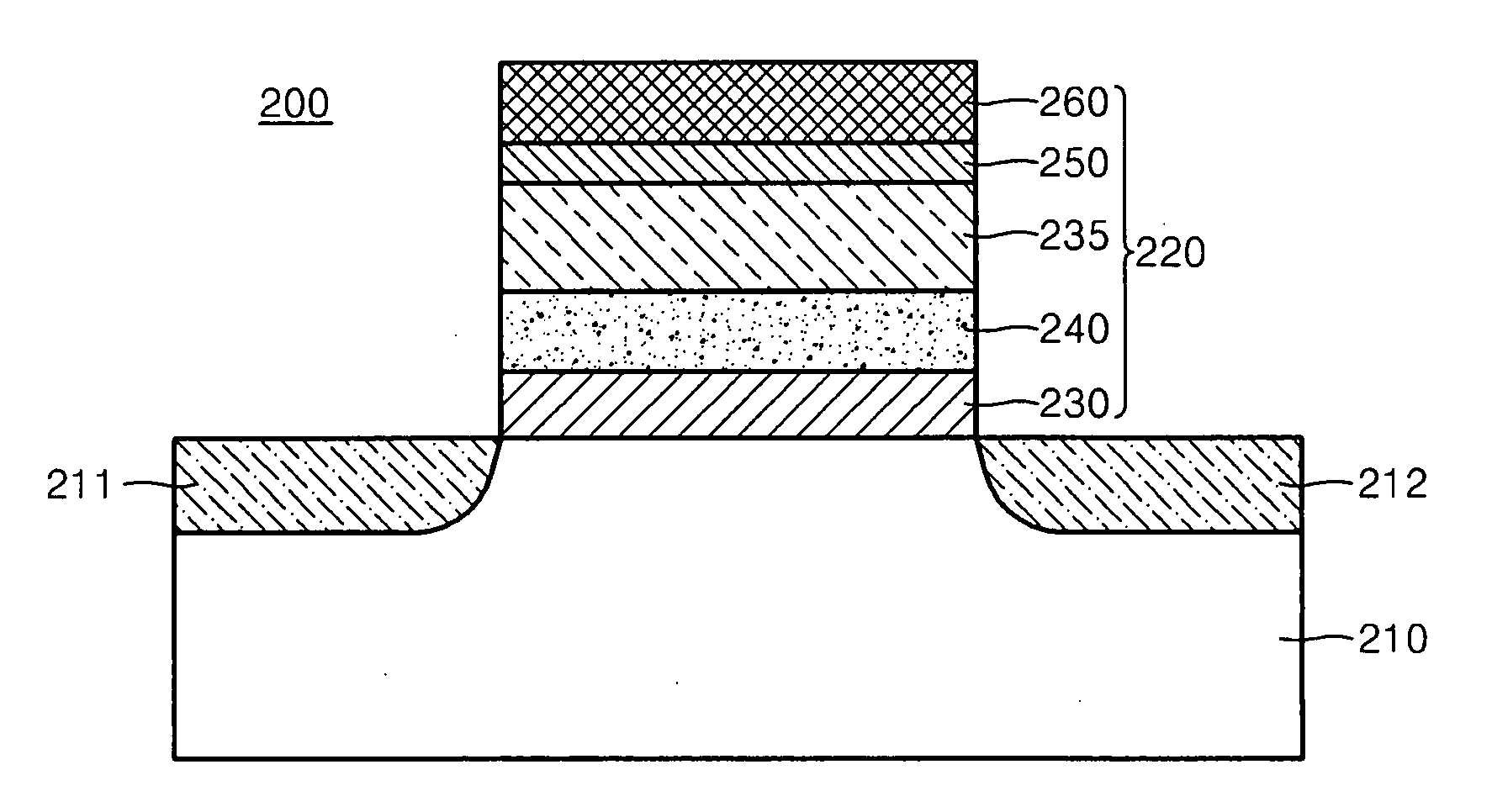

Non-volatile memory device including metal-insulator transition material

InactiveUS20080157186A1Increase write speedImprove retention characteristicsSemiconductor/solid-state device manufacturingSemiconductor devicesGate stackMetal–insulator transition

A non-volatile memory device including a metal-insulator transition (MIT) material is provided. The non-volatile memory device includes a gate stack having a tunneling layer, a charge trap layer, a blocking layer and a gate electrode formed on a substrate, wherein at least one of the tunneling layer and the blocking layer is formed of an MIT (metal-insulator transition) material.

Owner:SAMSUNG ELECTRONICS CO LTD

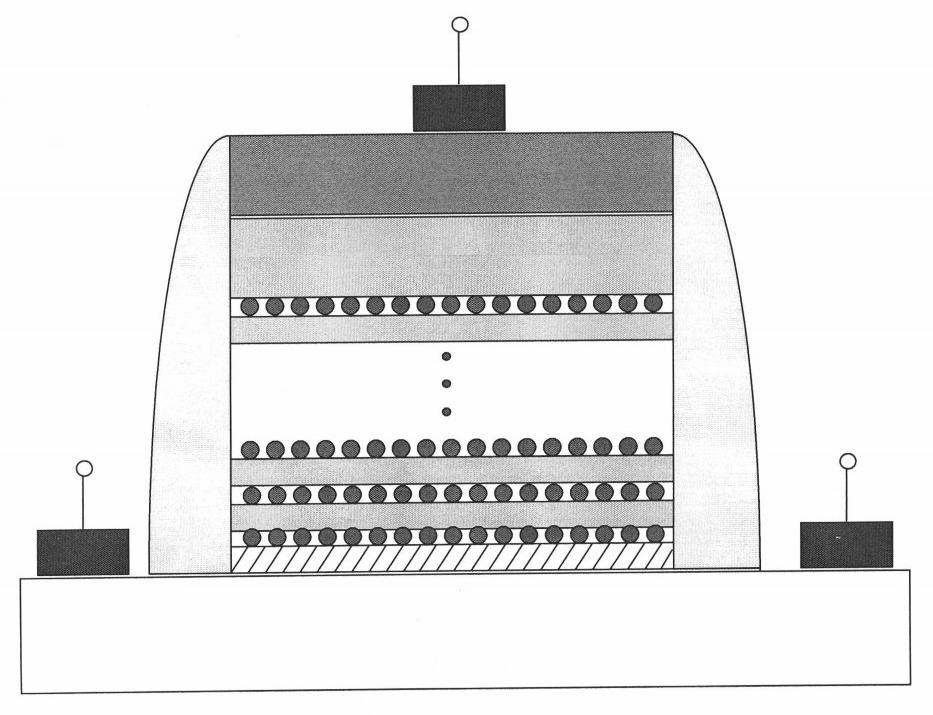

Three-dimensional memory and preparation method thereof

InactiveCN110010617AImprove retention characteristicsQuality improvementSolid-state devicesSemiconductor devicesComputer scienceDielectric layer

The invention discloses a three-dimensional memory and a preparation method thereof. The three-dimensional memory comprises a stacked structure and channel through holes penetrating the stacked structure, wherein the stacked structure comprises a plurality of storage units and interlayer dielectric layers which are alternately stacked, and each storage unit comprises a storage device layer and a gate layer which are arranged in order from inside to outside in the radial directions of the channel through holes.

Owner:YANGTZE MEMORY TECH CO LTD

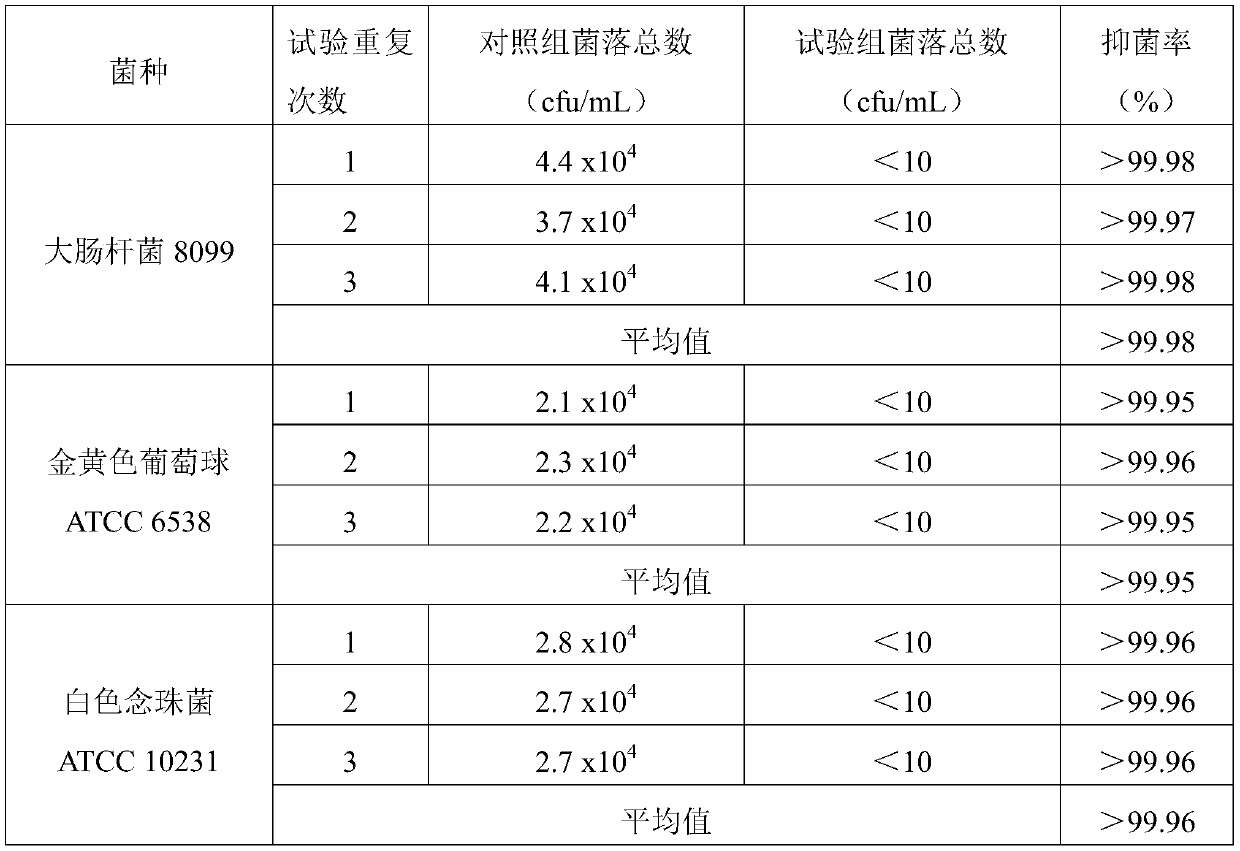

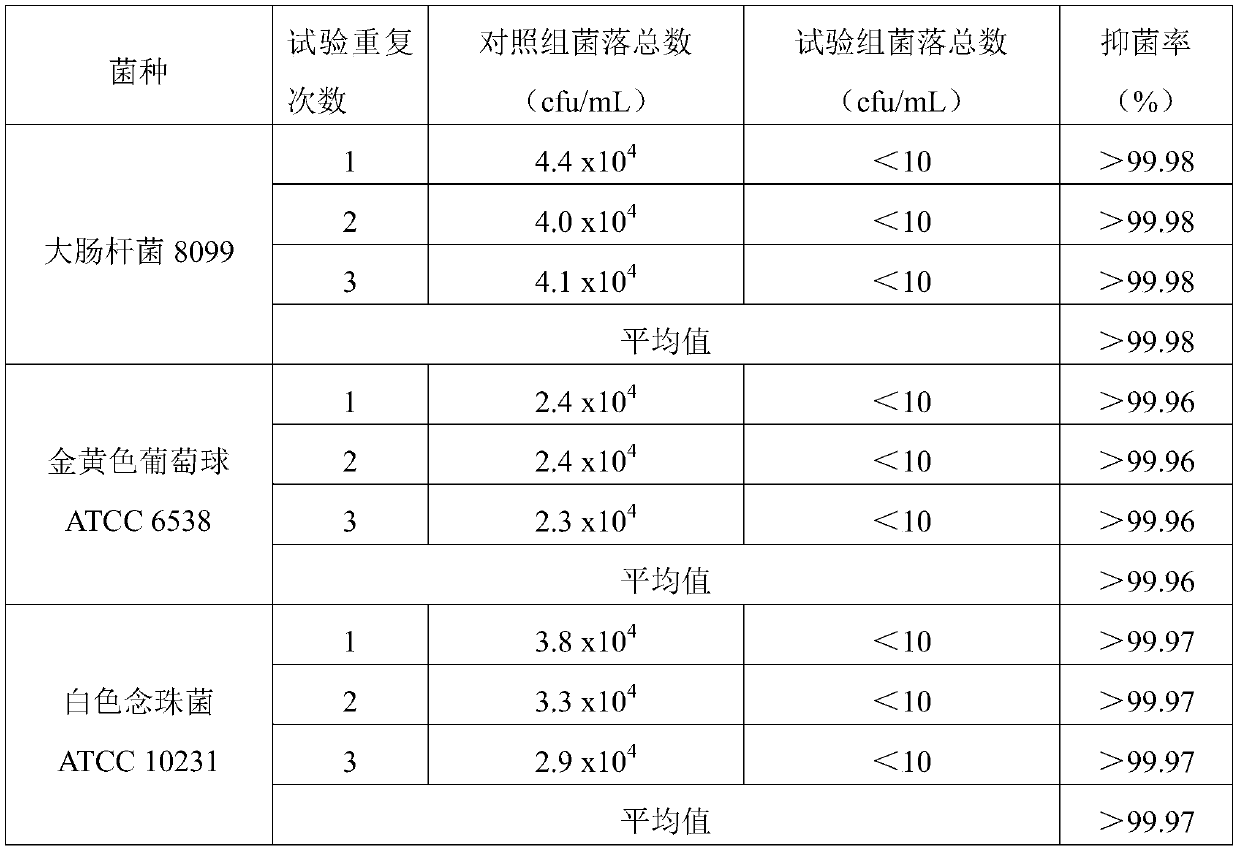

Long-acting antibacterial and virus-killing hygienic protection article spray and application thereof

ActiveCN111226993AImprove breathabilityImprove the efficiency of sand-killing virusBiocideDisinfectantsMethyl palmoxiratePropanediol

The invention belongs to the technical field of antibiosis and disinfection of hygiene protection articles. The invention relates to a spray, and particularly discloses a long-acting antibacterial andvirus-killing hygienic protection article spray and application thereof. The formula of the spray comprises the following components in percentage by silver concentration: 0.01 to 1.0 percent of polyhexamethylene biguanide hydrochloride, 0.001 to 0.1 percent of nano-silver gel, 0.5 to 5 percent of quaternary ammonium salt, 0.0001 to 0.001 percent of melaleuca alternifolia oil, 2 to 15 percent oforganic silicon, 1 to 10 percent of propylene glycol and the balance of water. The spray for the protective articles is lasting in antibacterial effect, the spray is uniformly sprayed on the surfacesof the used sanitary protective articles until the sanitary protective articles are wet, and the sanitary protective articles can be reused after being dried. After the mask treated by the protectivearticle spray is washed with water for three times, the antibacterial rate is kept at 95% or above under the condition of keeping good air permeability.

Owner:SOUTH CHINA UNIV OF TECH +1

Conductive bridge semiconductor component and manufacturing method therefor

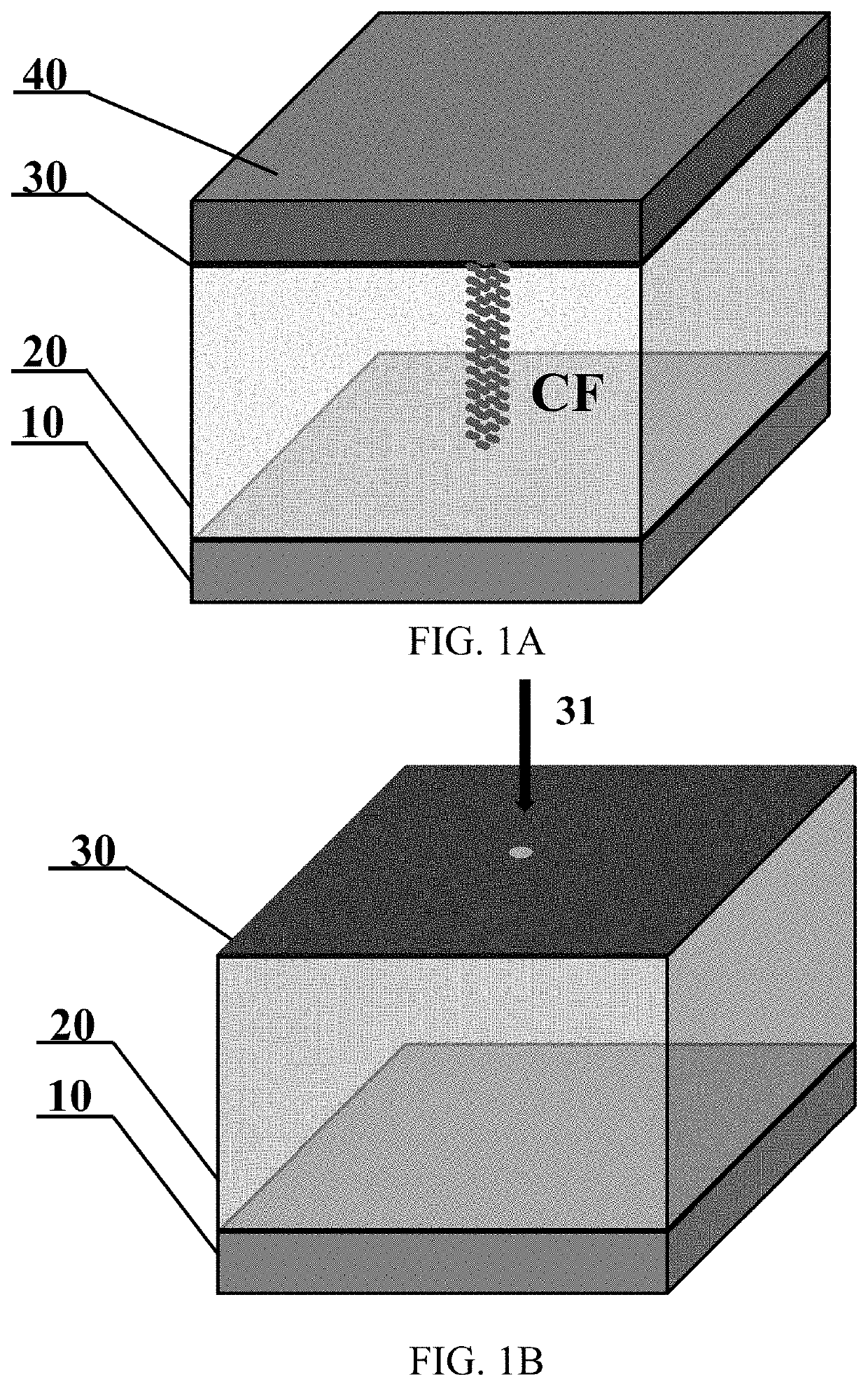

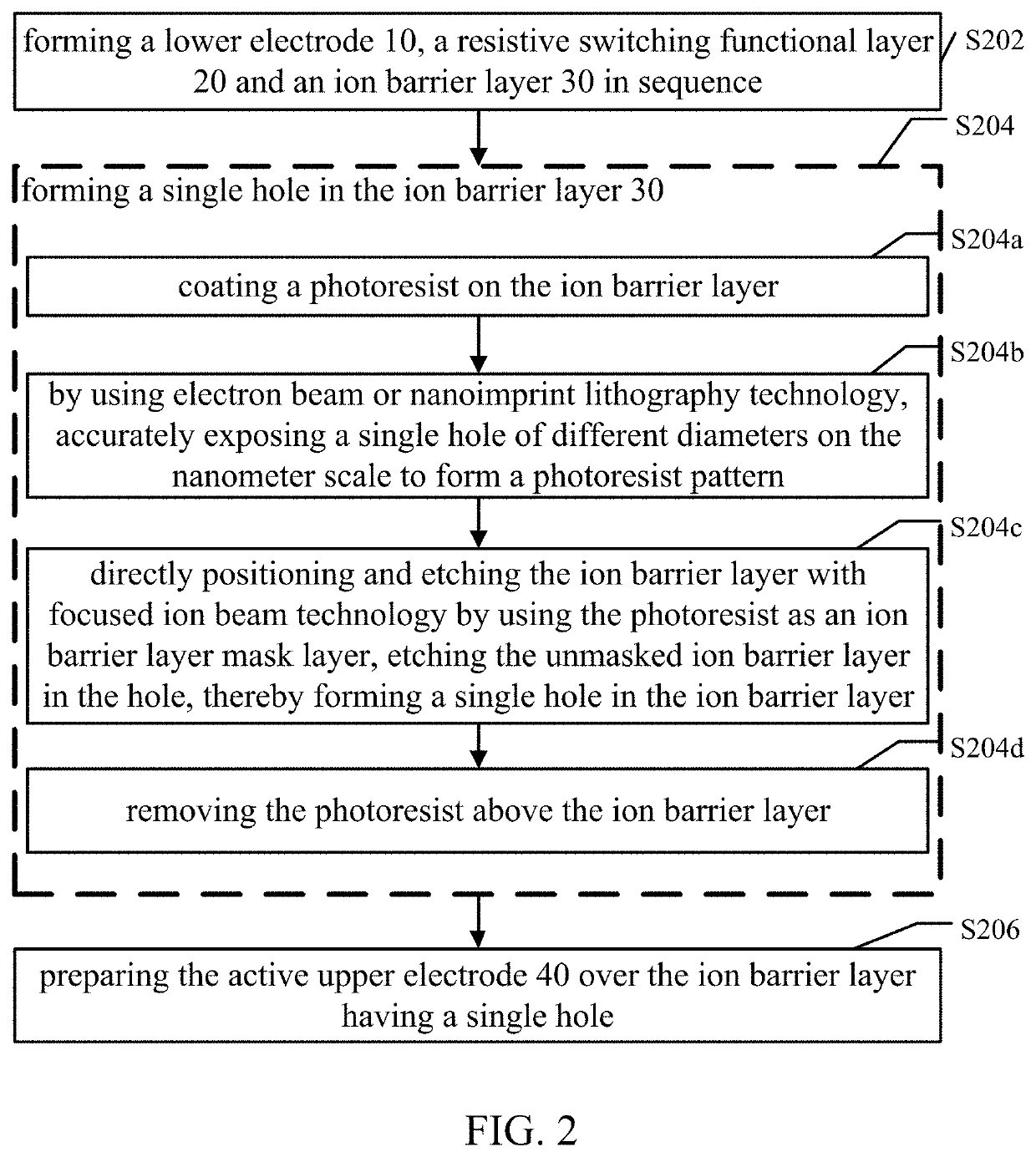

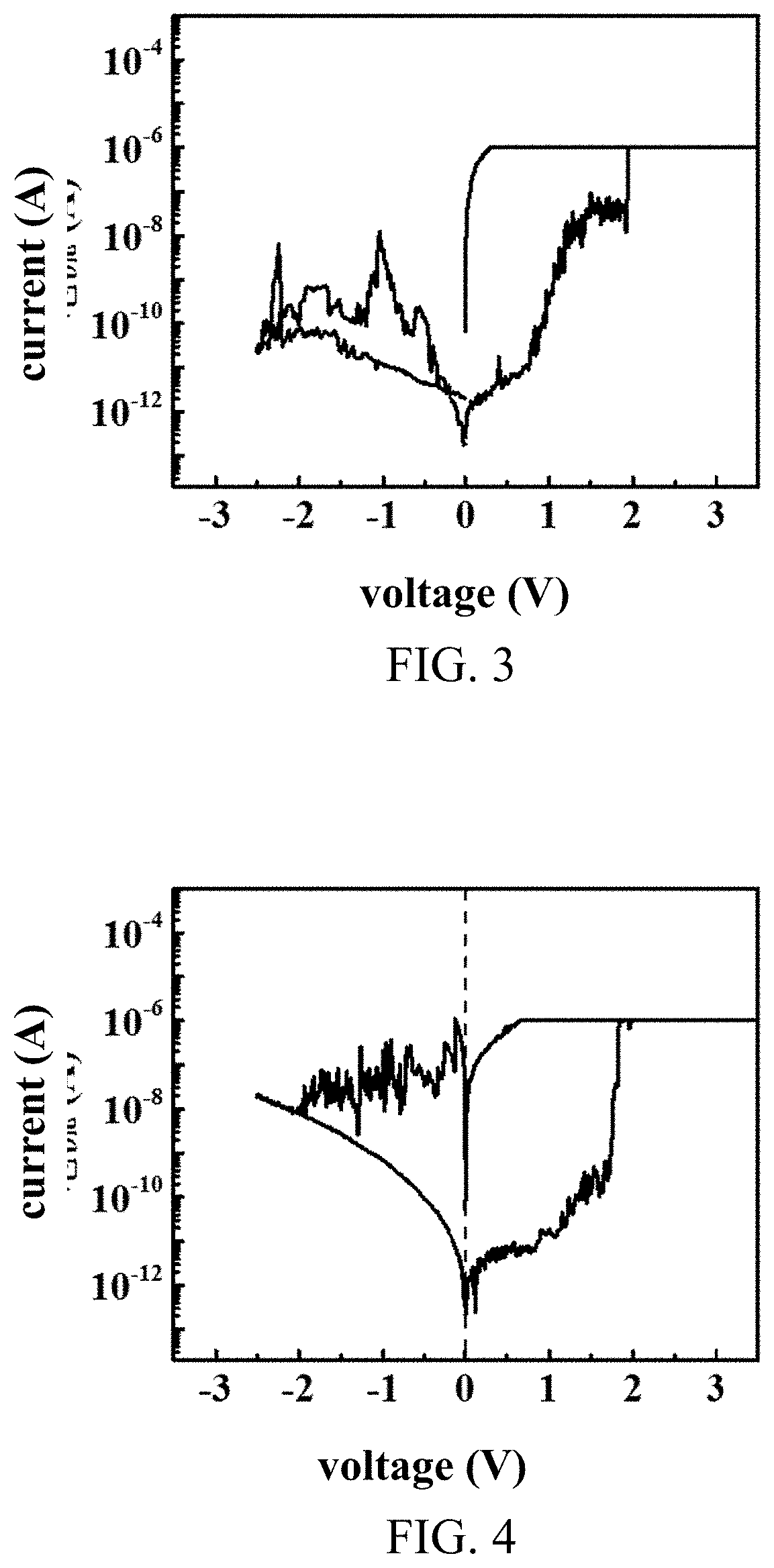

ActiveUS20200066984A1Easy to controlFacilitate concentrated distribution of conductive pathSemiconductor devicesDriving currentDevice material

The present disclosure provides a conductive bridge semiconductor device and a method of manufacturing the same. The conductive bridge semiconductor device includes a lower electrode, a resistive switching functional layer, an ion barrier layer and an active upper electrode from bottom to top, wherein the ion barrier layer is provided with certain holes through which active conductive ions pass. Based on this structure, the precise designing of the holes on the barrier layer facilitates the modulation of the quantity, size and density of the conduction paths in the conductive bridge semiconductor device, which enables that the conductive bridge semiconductor device can be modulated to be a nonvolatile conductive bridge resistive random access memory or a volatile conductive bridge selector. Based on the above method, ultra-low power nonvolatile conductive bridge memory and high driving-current volatile conductive bridge selector with controllable polarity are completed.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

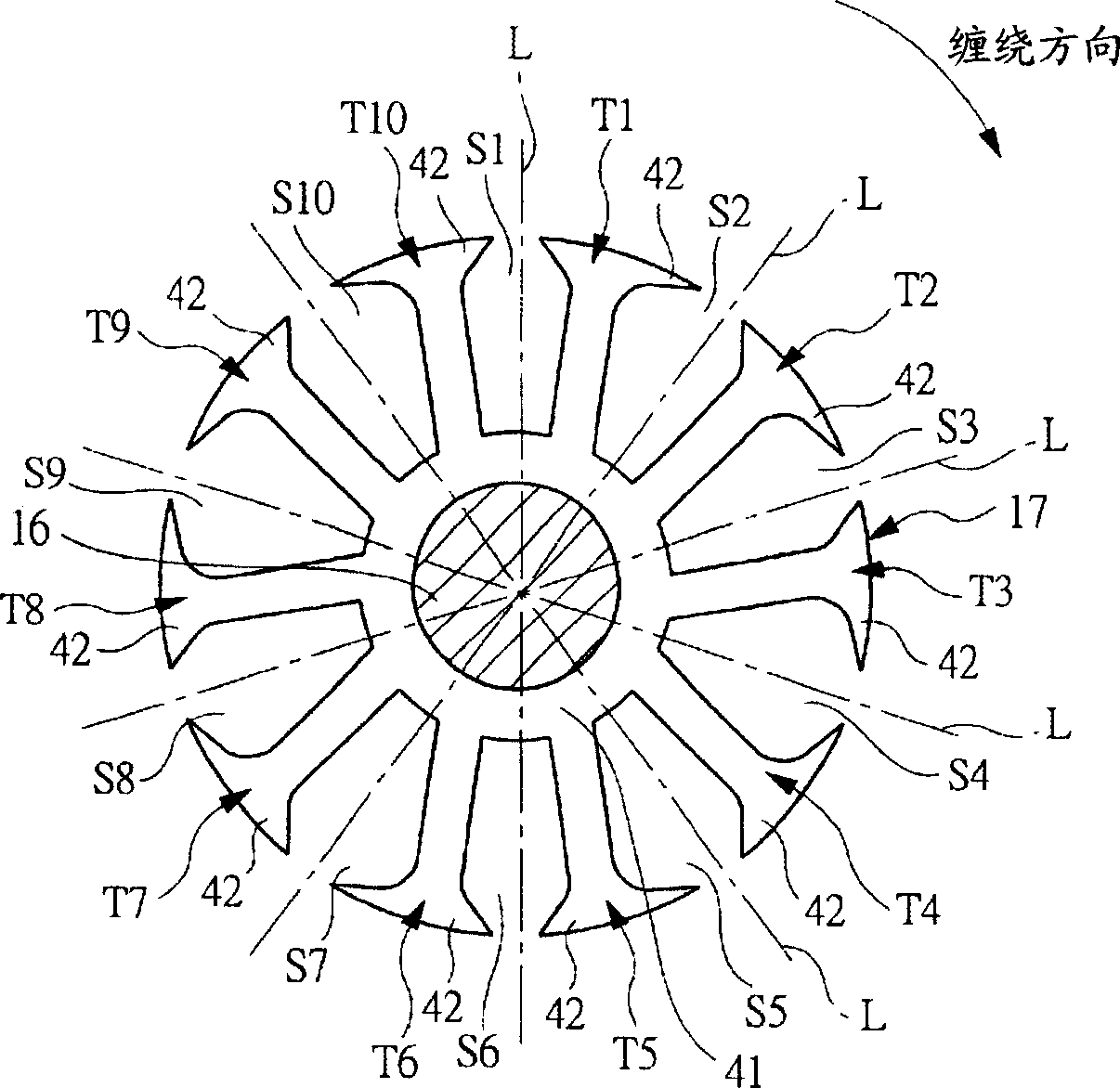

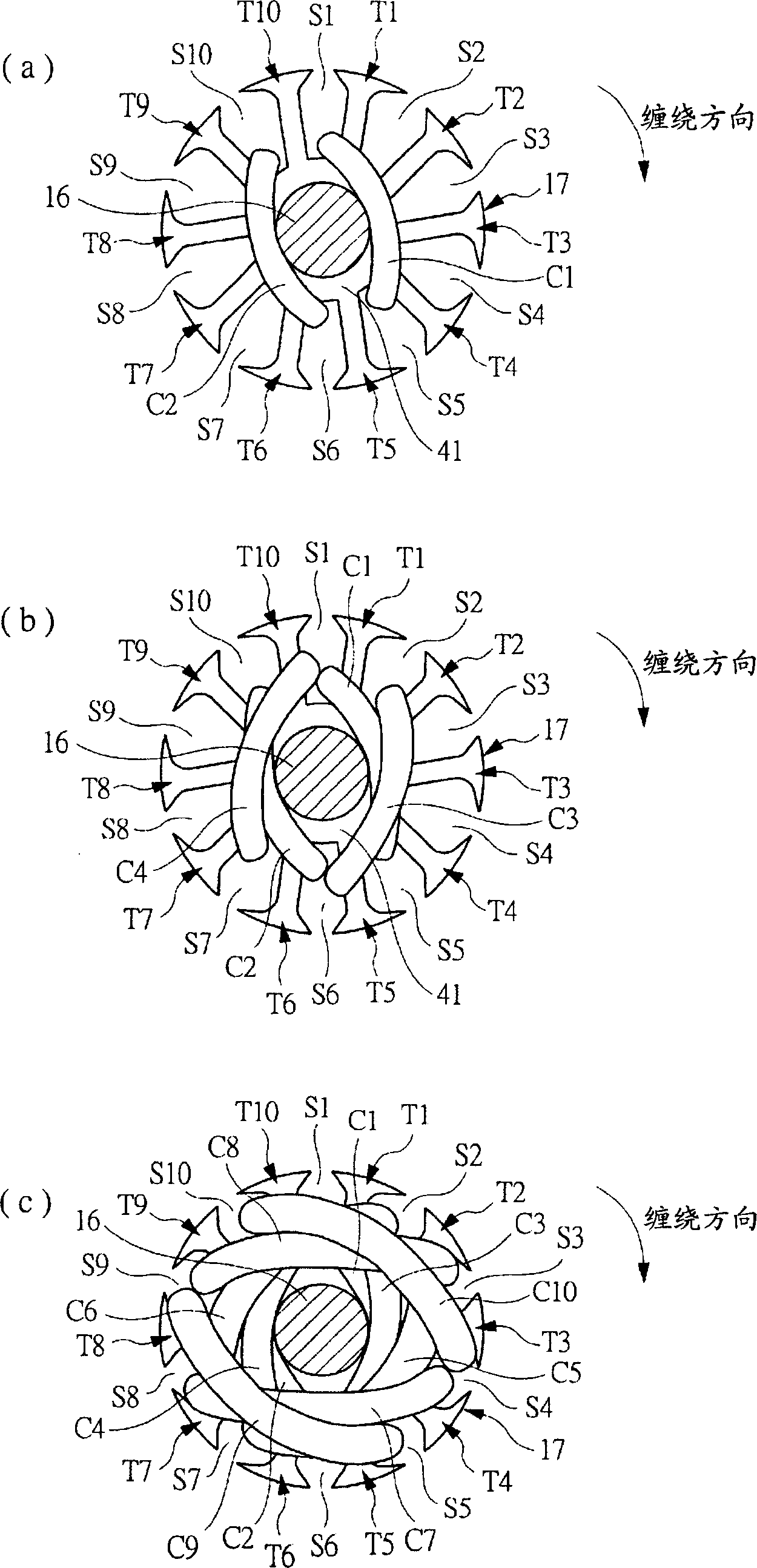

Electric motor

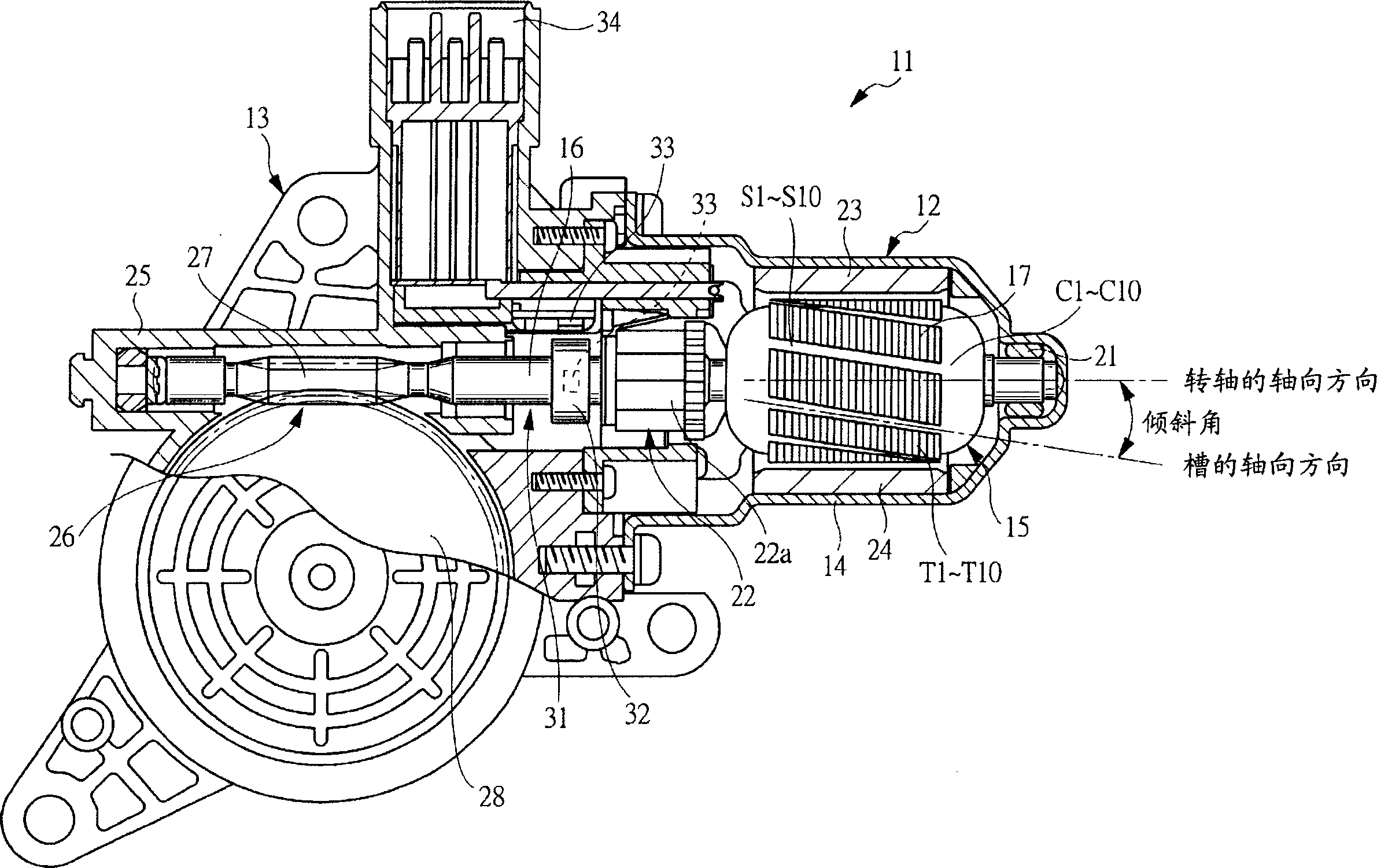

InactiveCN1849738AIncrease the stack factorImprove efficiencyMagnetic circuit rotating partsMechanical energy handlingElectric machineFill factor

A motor includes an armature rotatably accommodated in a motor housing, and a pair of magnets fixed on the inner surface of the motor housing. The armature has an armature core (17) fixed on a rotating shaft (16) and windings accommodated in ten slots (S1-S10) formed in the armature core (17). These slots (S1-S10) have four different shapes, thereby increasing the fill factor of the individual windings. Since the respective slots ( S1 - S10 ) are inclined in the rotational direction with respect to the axial direction of the rotating shaft ( 16 ), the magnetic imbalance caused by the different-shaped slots ( S1 - S10 ) can be made uniform.

Owner:MITSUBA CORP

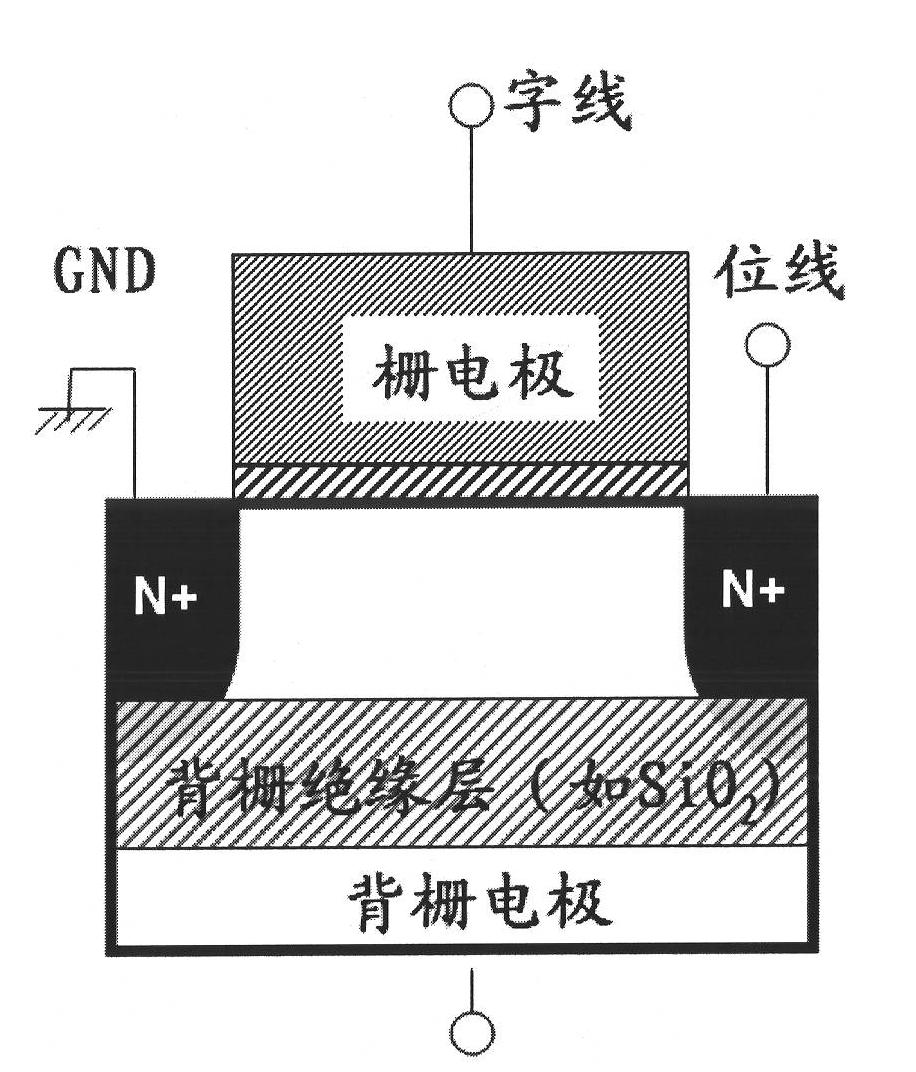

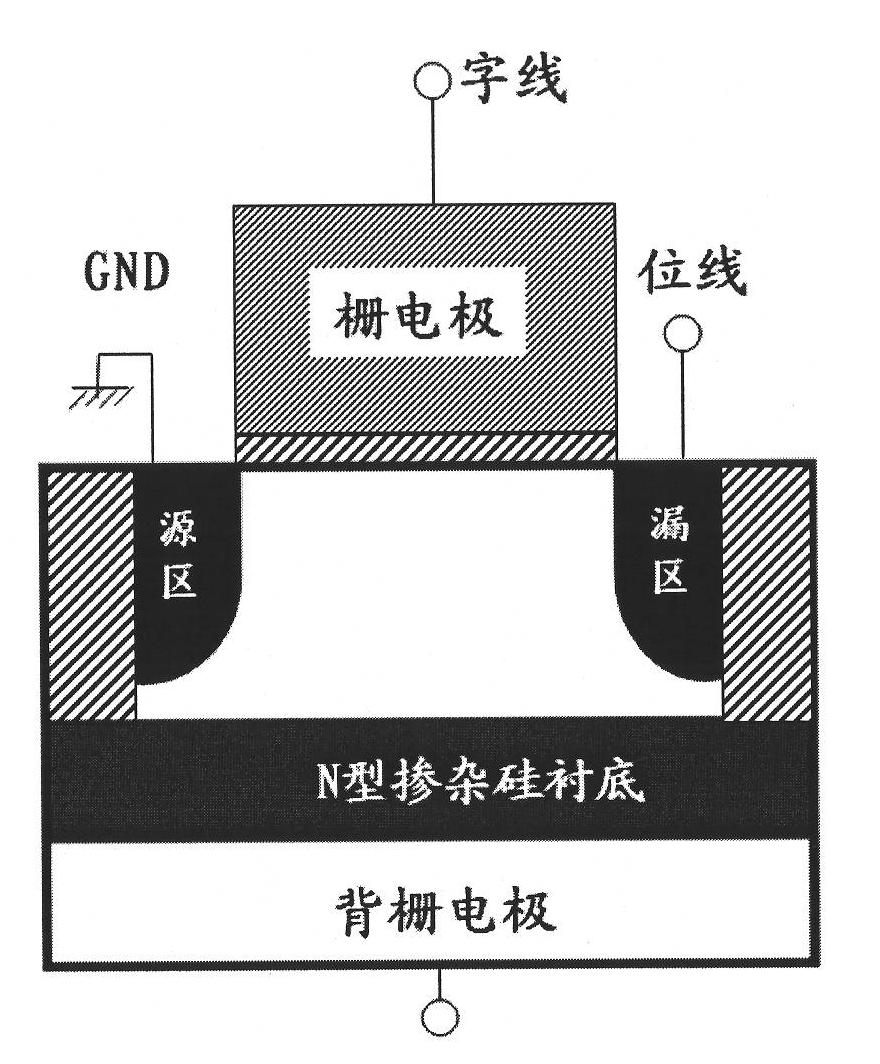

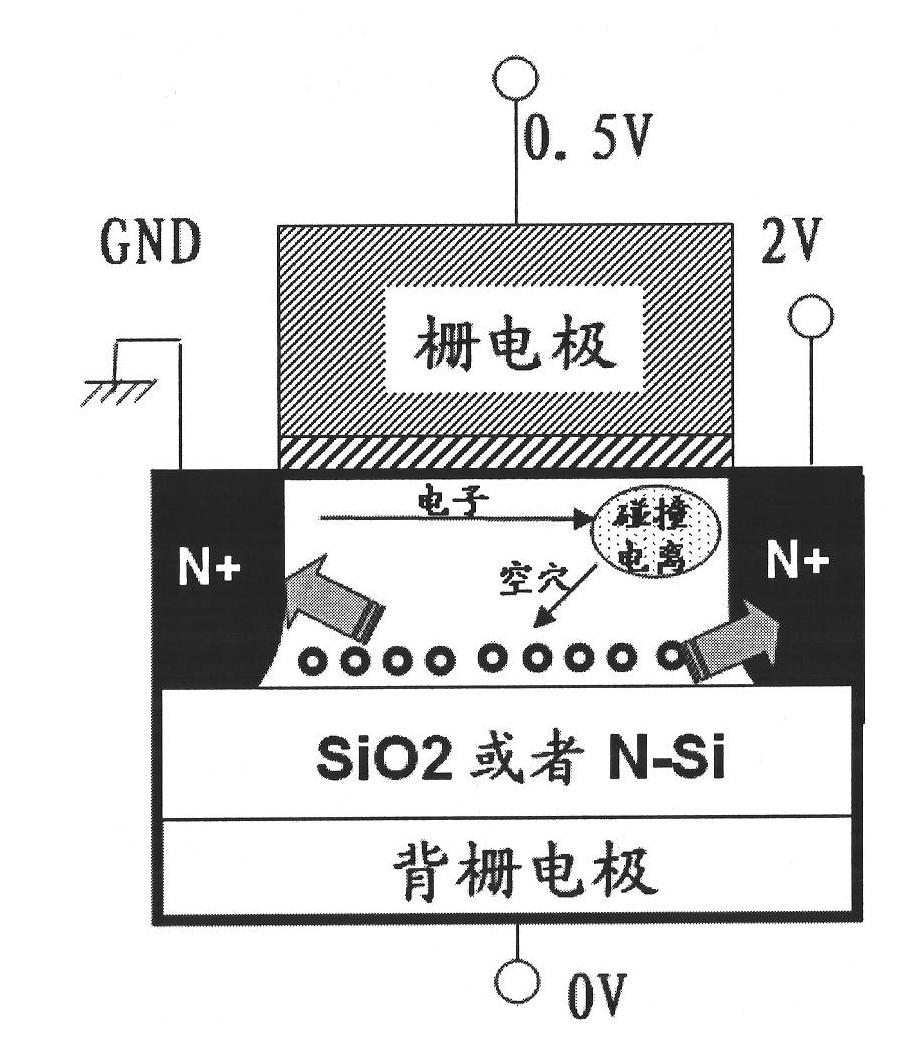

Semiconductor memory cell, device and preparation method thereof

ActiveCN102468303AReduce movement speedExtended hold timeTransistorSemiconductor/solid-state device manufacturingFloating body effectSource area

The invention discloses a semiconductor memory cell, a device and a preparation method thereof. The semiconductor memory cell comprises: a substrate, a channel region located above the substrate, a grid region located above the channel region, a source area and leakage area located above the substrate and on two sides of the channel region, a buried layer located between the substrate and the channel region and is made by a material whose forbidden bandwidth is narrower than the forbidden bandwidth of the channel region material. Because the forbidden bandwidth of the buried layer is narrower than the forbidden bandwidth of the channel region material, a hole barrier is formed in the buried layer so that the hole stored in the buried layer is difficult to be leaked out facing the barrier. By using the method of the invention, information maintaining time of the memory cell using a floating body effect can be increased.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

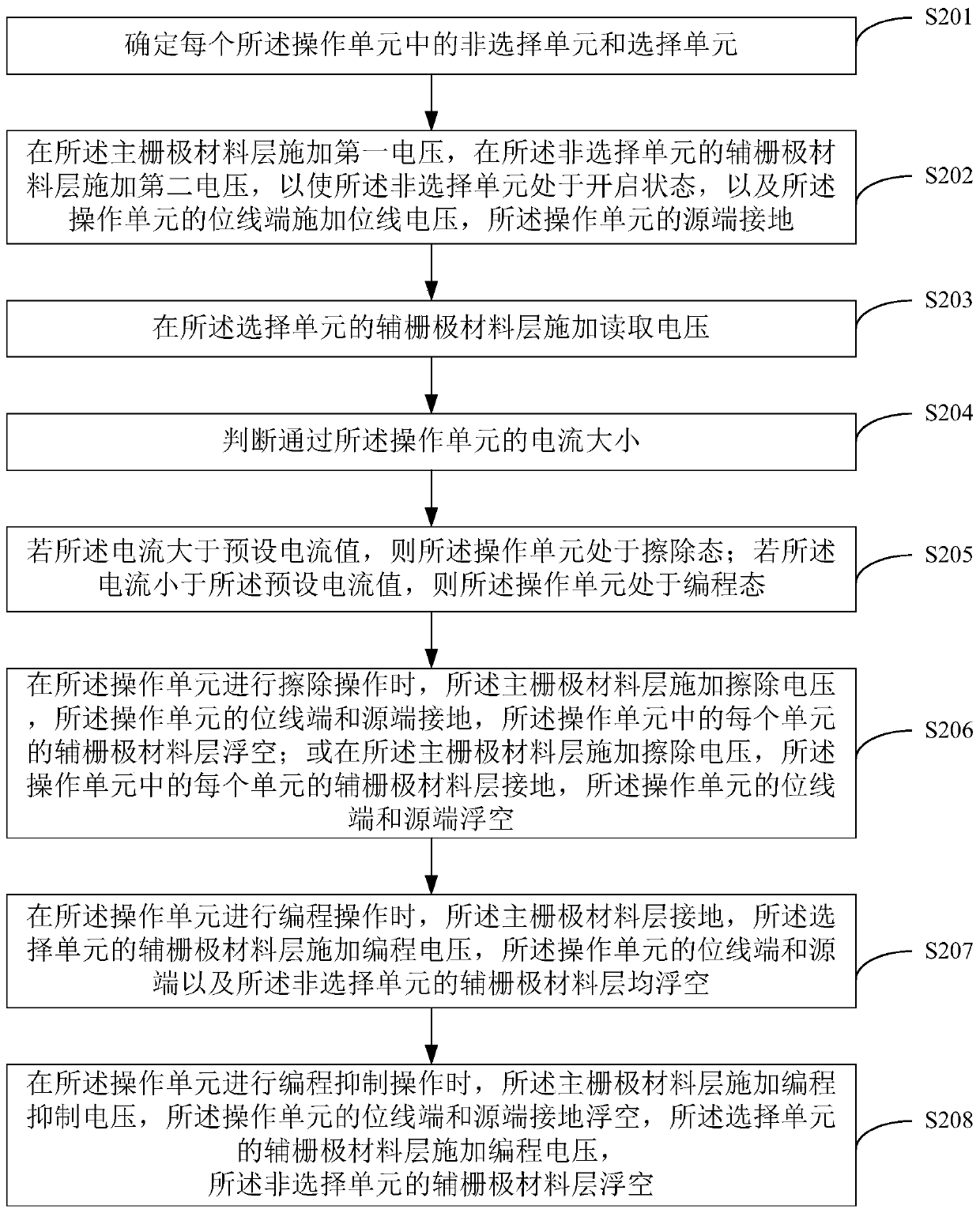

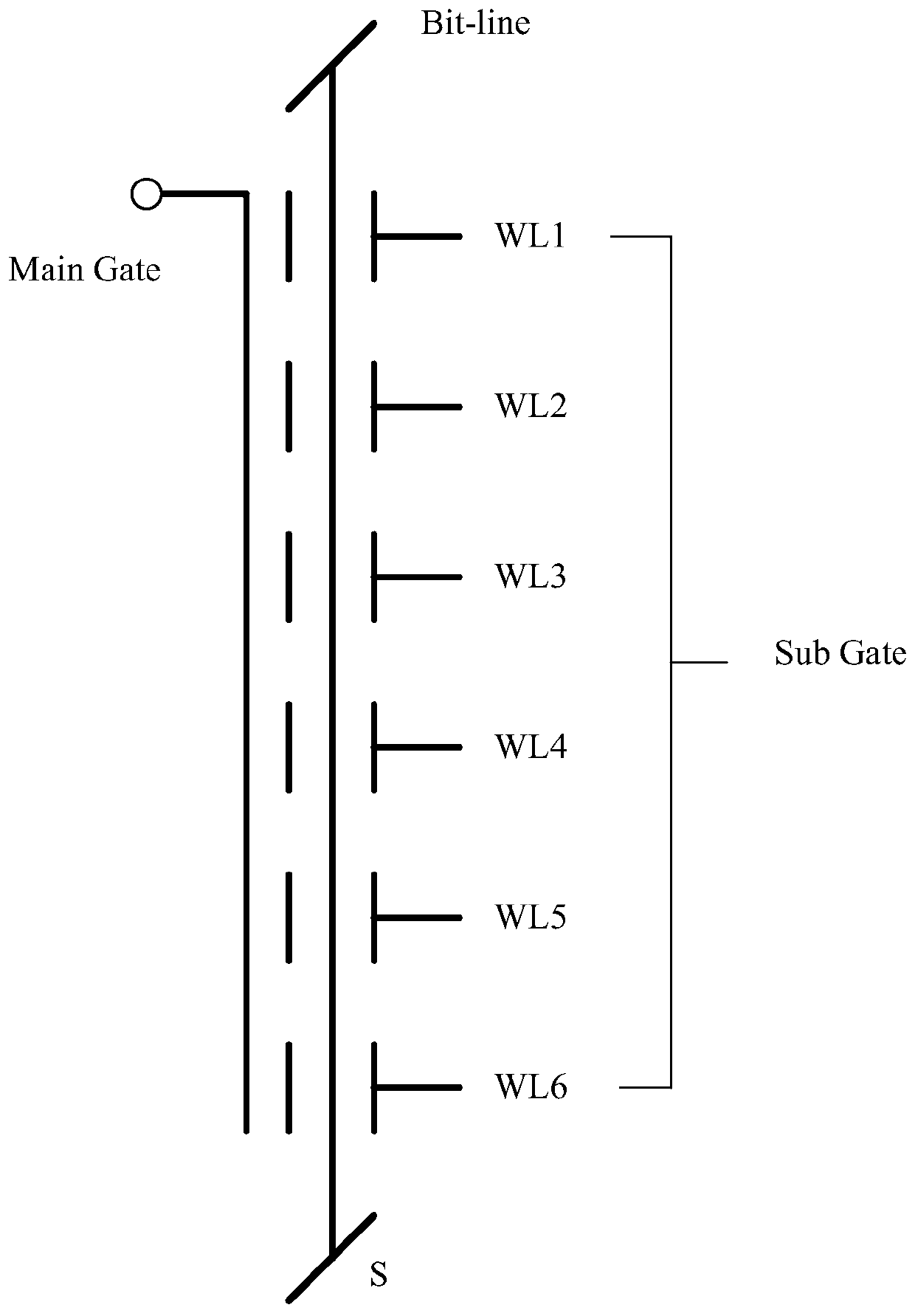

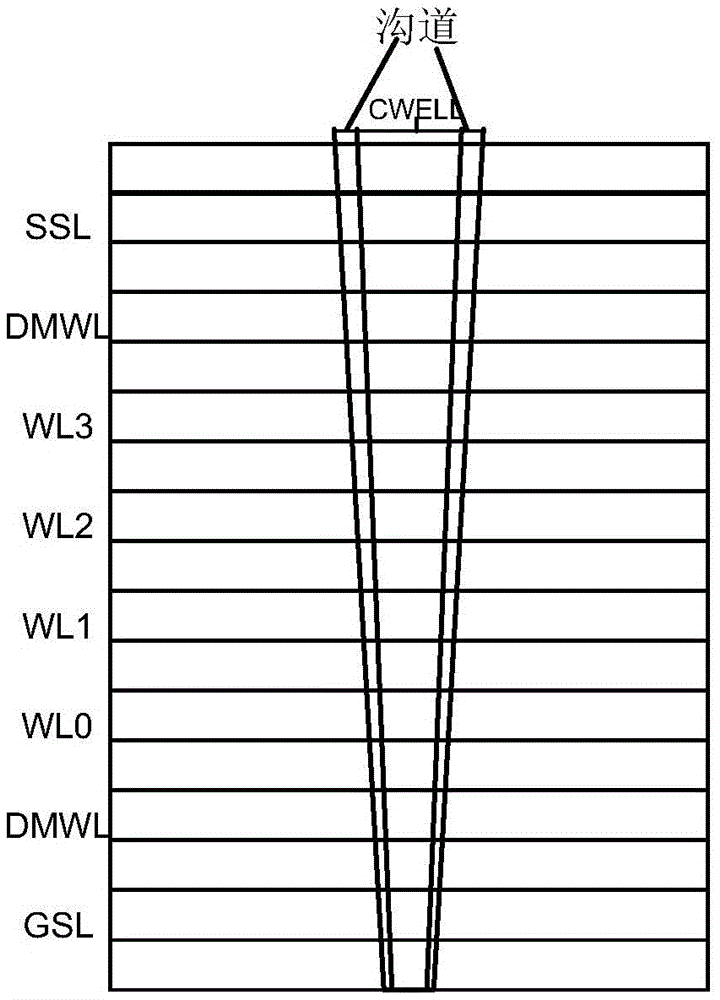

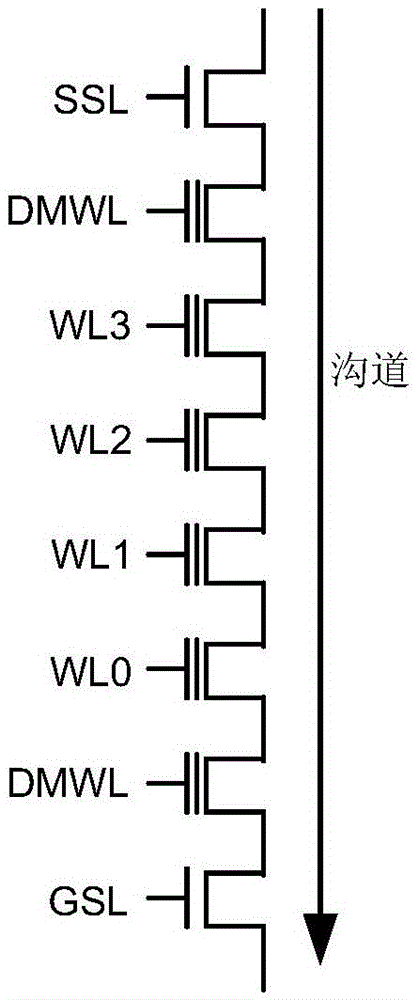

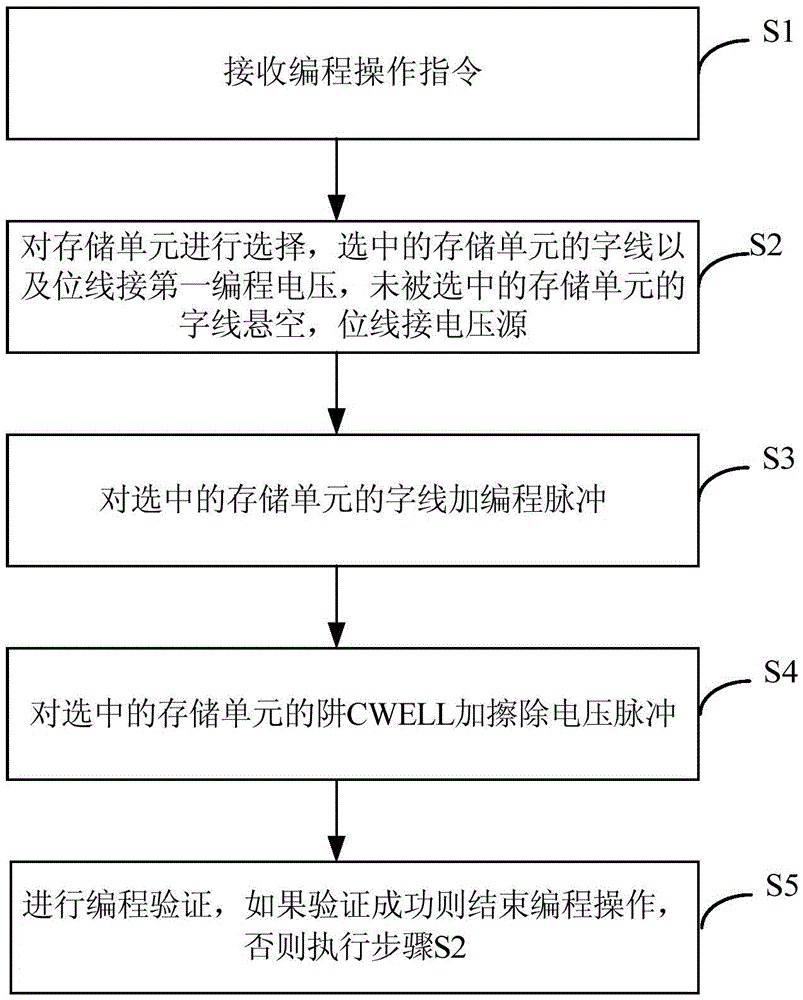

Erasure method for memory unit

The invention discloses an erasure method for a memory unit. The erasure method is characterized by comprising the steps of S1, receiving a programming operation instruction; S2, selecting a memory unit, connecting a word line and a bit line of the selected memory unit to a first programming voltage, suspending a word line of an unselected memory unit, and connecting a bit line of the unselected memory unit to a voltage source; S3, applying a programming pulse to the selected memory unit; S4, applying an erasure voltage pulse to a well CWELL of the selected memory unit; and S5, performing programming verification, and if the verification succeeds, then ending the programming operation, otherwise, performing the step S2. According to the erasure method for the memory unit, provided by an embodiment of the invention, the erasure pulse is applied to the well of the memory unit after the memory unit is programmed each time, so that electrons captured on a surface layer of the memory unit can be erased and the data retention property of the memory unit can be enhanced.

Owner:GIGADEVICE SEMICON (BEIJING) INC

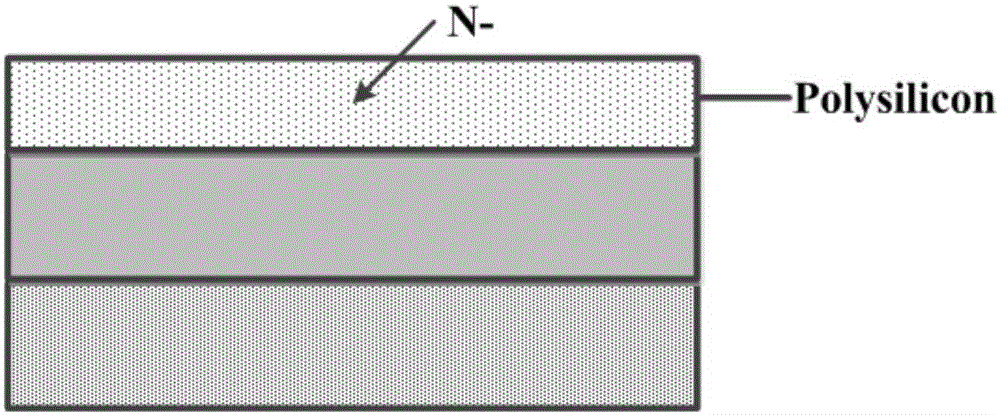

Polysilicon floating gate memorizer based on organic field effect transistor and preparation method therefor.

InactiveCN105006488AReduce manufacturing costAchieve High Density StorageTransistorSolid-state devicesOrganic field-effect transistorOrganic semiconductor

The invention discloses a polysilicon floating gate memorizer based on an organic field effect transistor and a preparation method therefor. A gate electrode employs a heavy-doping low-resistance monocrystalline silicon substrate with a thickness of 100-300nm; a gate insulation dielectric layer is formed on the surface of the silicon substrate of the gate electrode; a polysilicon floating gate is embedded between the gate insulation dielectric layer and a tunneling insulation dielectric layer and employed as a charge storage unit; the tunneling insulation dielectric layer is formed on the surface of the floating gate; an organic semiconductor material is grown on the surface of the tunneling insulation dielectric layer and forms an active layer of a device; vacuum vapor plating of metal through metal masks is carried out on the surface of the active layer, and a source electrode and a drain electrode of the device are formed. The beneficial effects are that a work voltage of a floating gate memorizer based on an organic field effect transistor is decreased, high-density storage of a device is achieved, the device maintaining performance is raised, and the device manufacturing cost is lowered.

Owner:LANZHOU UNIVERSITY

Manufacturing method of three-dimensional memory

ActiveCN111415943AAvoid damageReduce the risk of electric leakageSolid-state devicesSemiconductor devicesEtching rateStructural engineering

The invention provides a manufacturing method of a three-dimensional memory. The method is used in a process of forming sacrificial layers. The top sacrificial layer has a first etching selection ratio A for the bottom sacrificial layer; the top sacrificial layer has a second etching selection ratio B for the middle sacrificial layer; A and B satisfy a relational expression that: A<= B<=1, and A is not equal to 1; and therefore, material components are changed in the deposition stage of the sacrificial layers; the etching rate of the sacrificial layers is changed in the process of removing thesacrificial layers by wet etching; the etching rate of the sacrificial layer on the lower layer is higher than that of the sacrificial layer on the upper layer; the difference of the etching rates can balance the difference of the etching rates of the lower sacrificial layer and the upper sacrificial layer caused by an etching load effect in the process; damage to part of a charge barrier layer in contact with the upper sacrificial layer is reduced; the problem of uneven damage of the charge barrier layer at the upper position and the lower position is effectively solved; and the step coverage capacity of the charge barrier layer at the upper position and the lower position is improved.

Owner:YANGTZE MEMORY TECH CO LTD

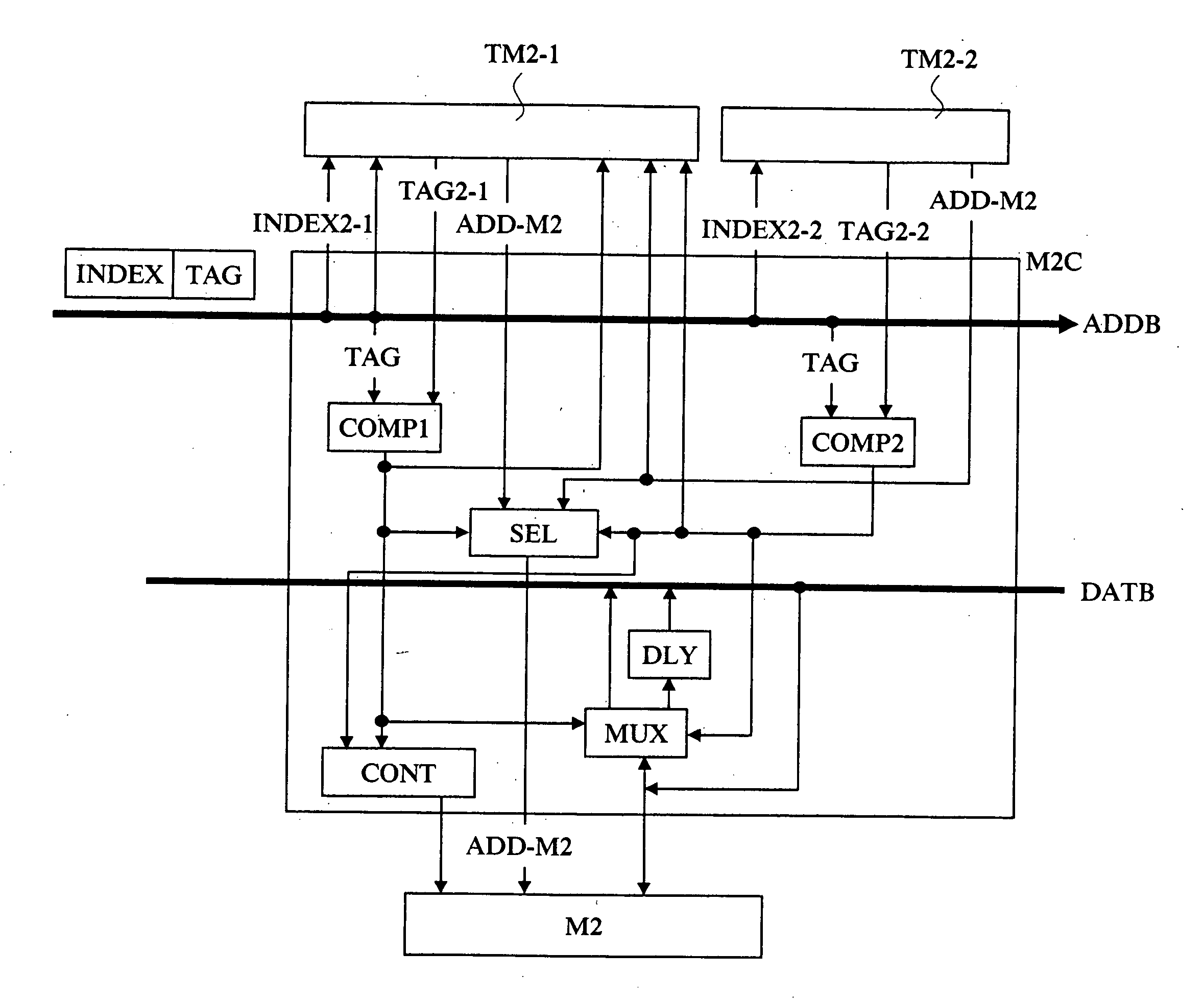

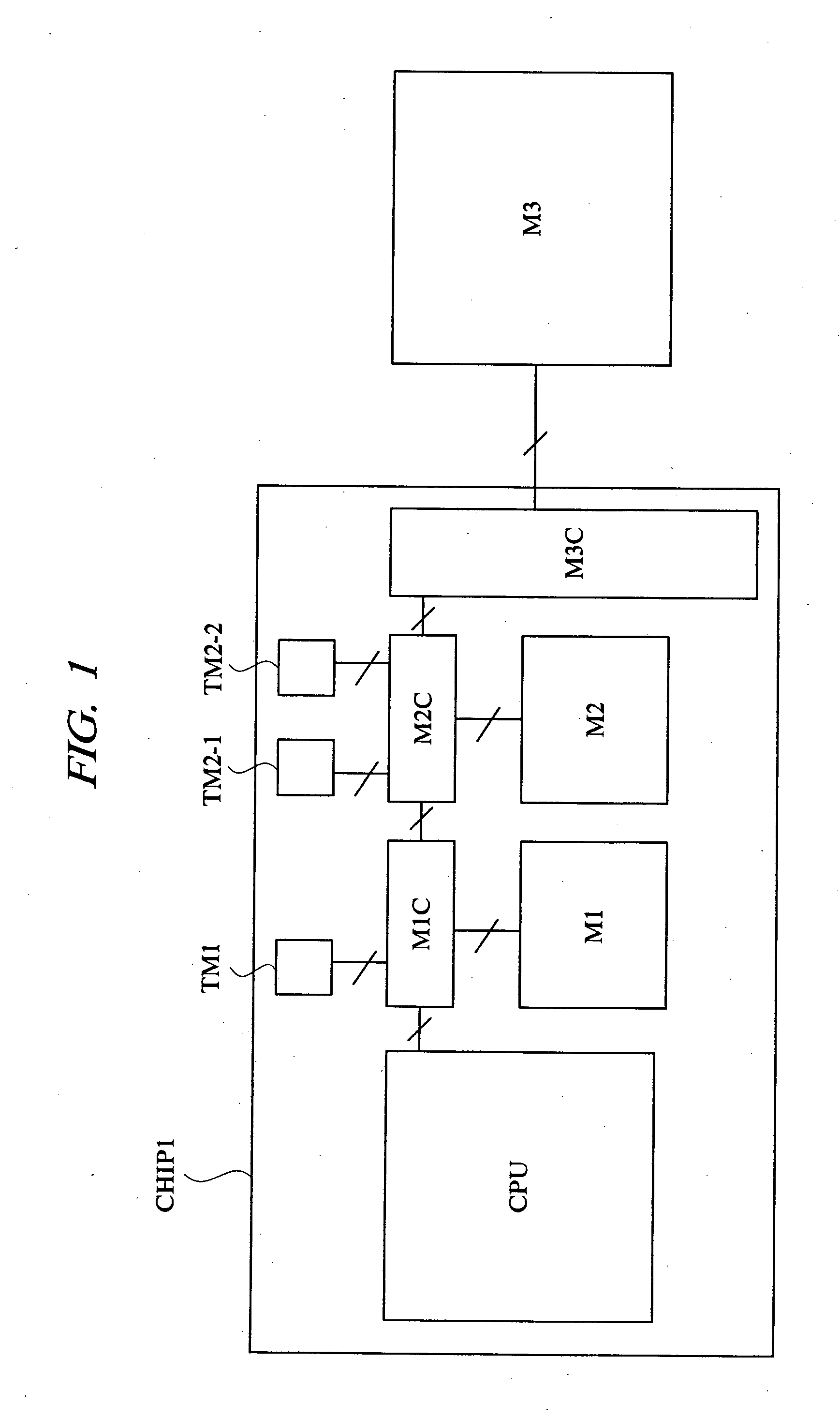

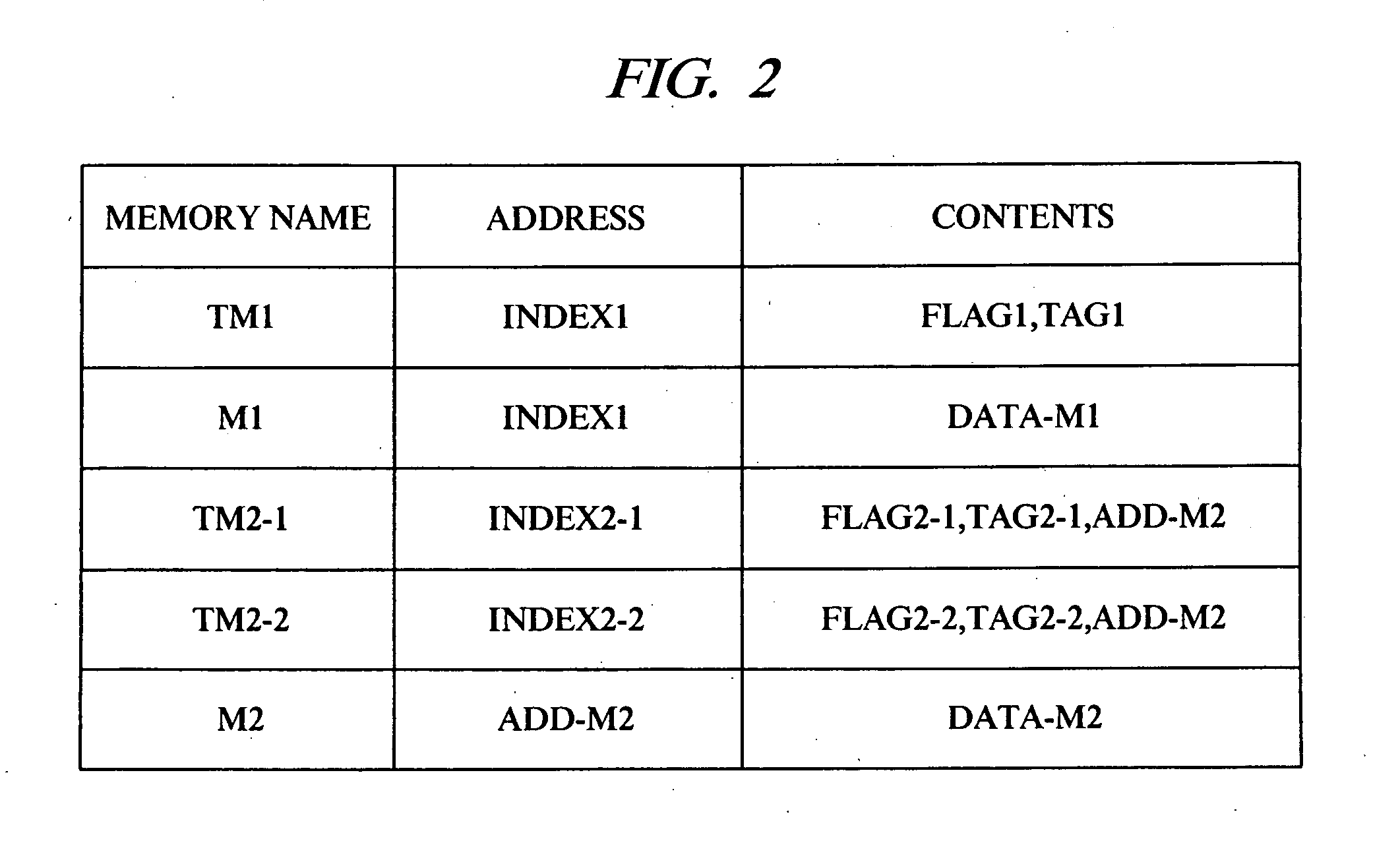

Information processor

InactiveUS20070226405A1Temperature increase is thus suppressedImprove reliabilityMemory architecture accessing/allocationEnergy efficient ICTExternal storageAccess time

In an information processor including memory devices such as DRAMs and others, by reducing the power consumption of memory devices and efficiently repairing defect bits, a highly reliable information processor is realized. In an information processor including an external memory such as a DRAM, a second memory whose power consumption at the access time is smaller than that of the external memory is disposed, and cache data of the external memory and repair data are stored in this second memory. To an input address given from a central processing unit via a primary cache controller, a memory controller determines a hit or a miss with reference to a tag memory for cache and a tag memory for repair, and when one or both of tag memory for cache and a tag memory for repair are hit, it accesses the second memory.

Owner:HITACHI LTD

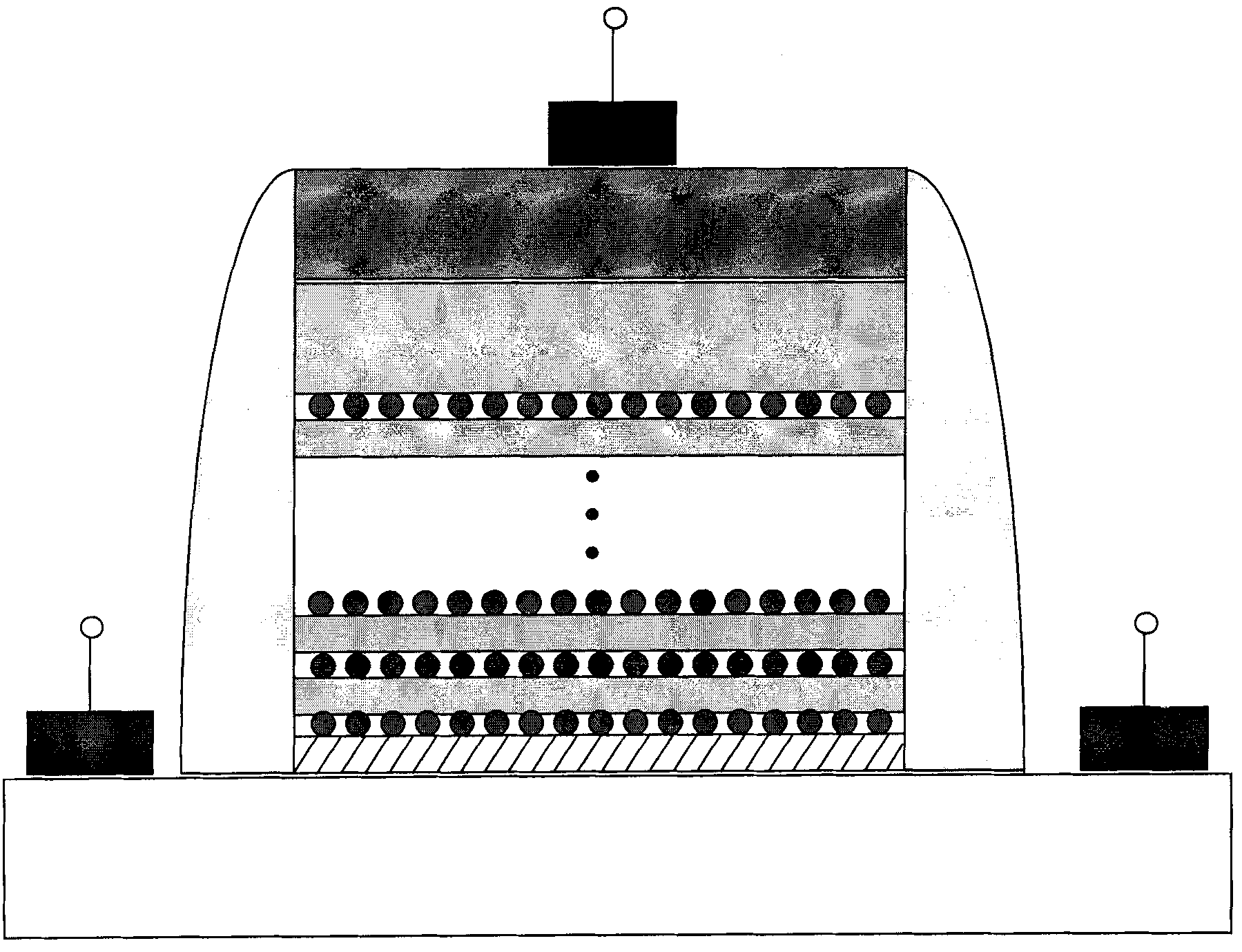

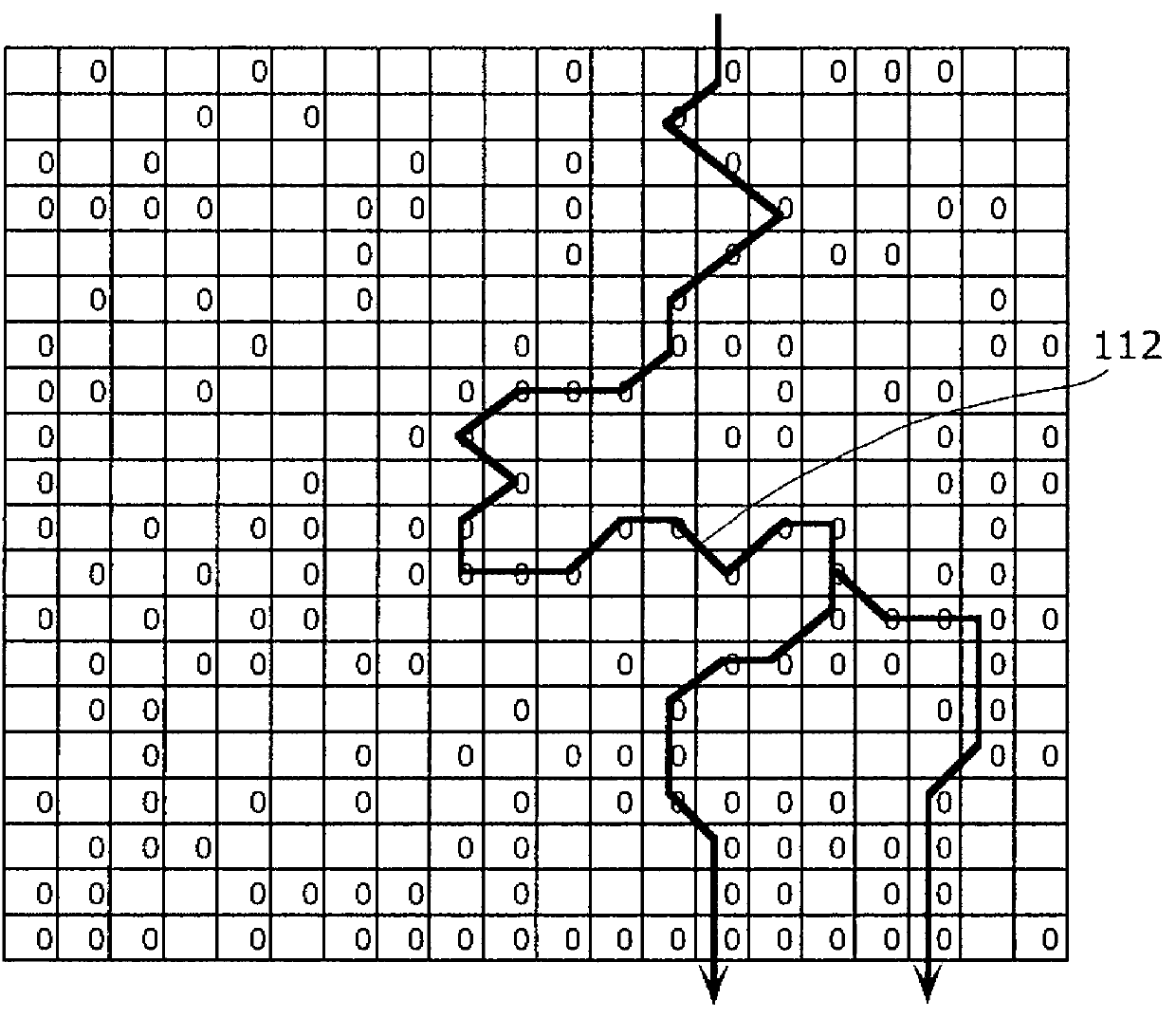

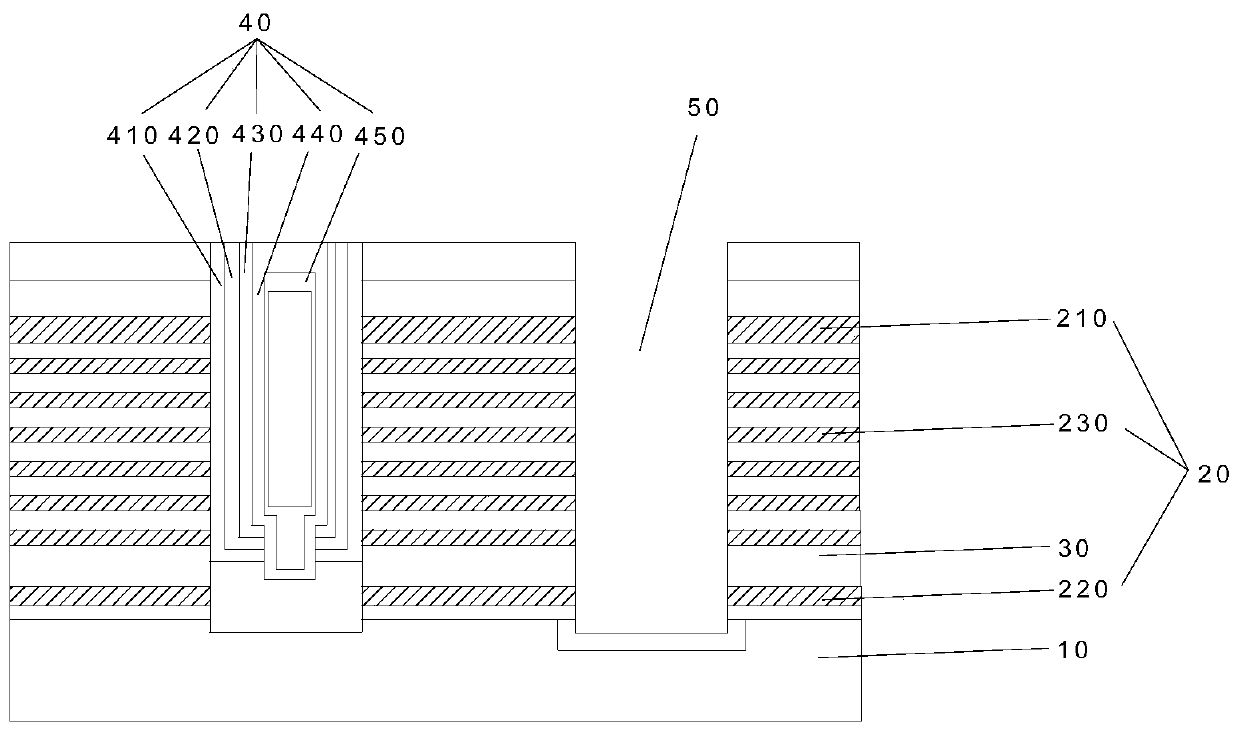

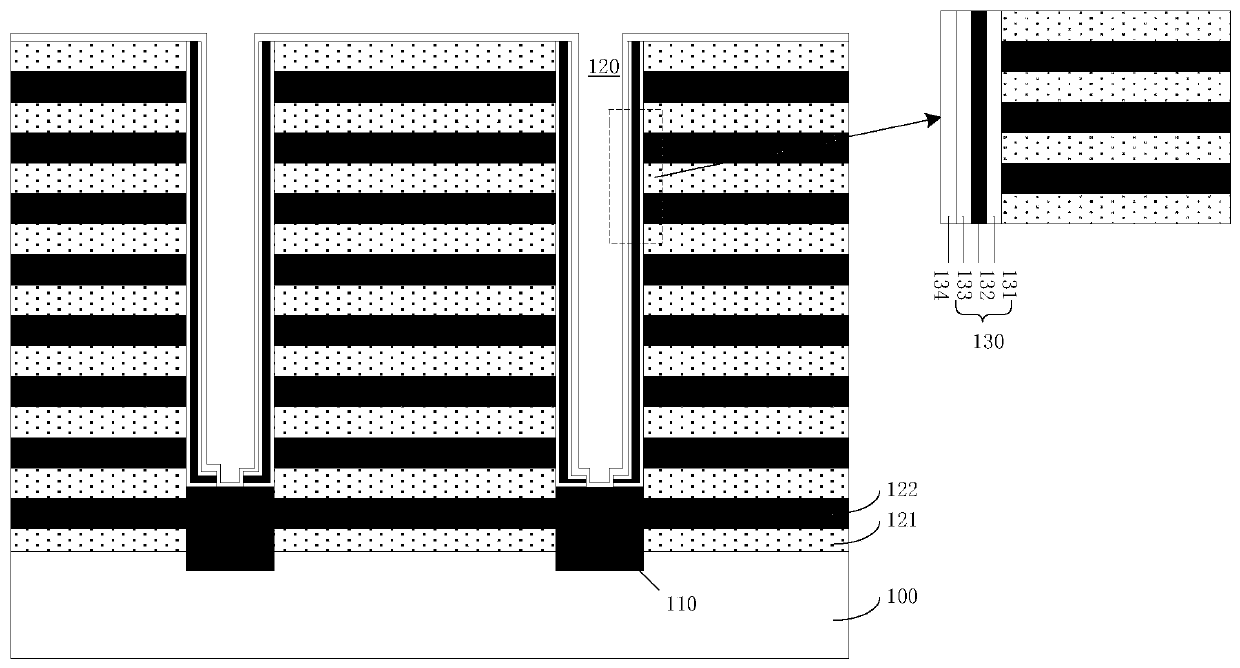

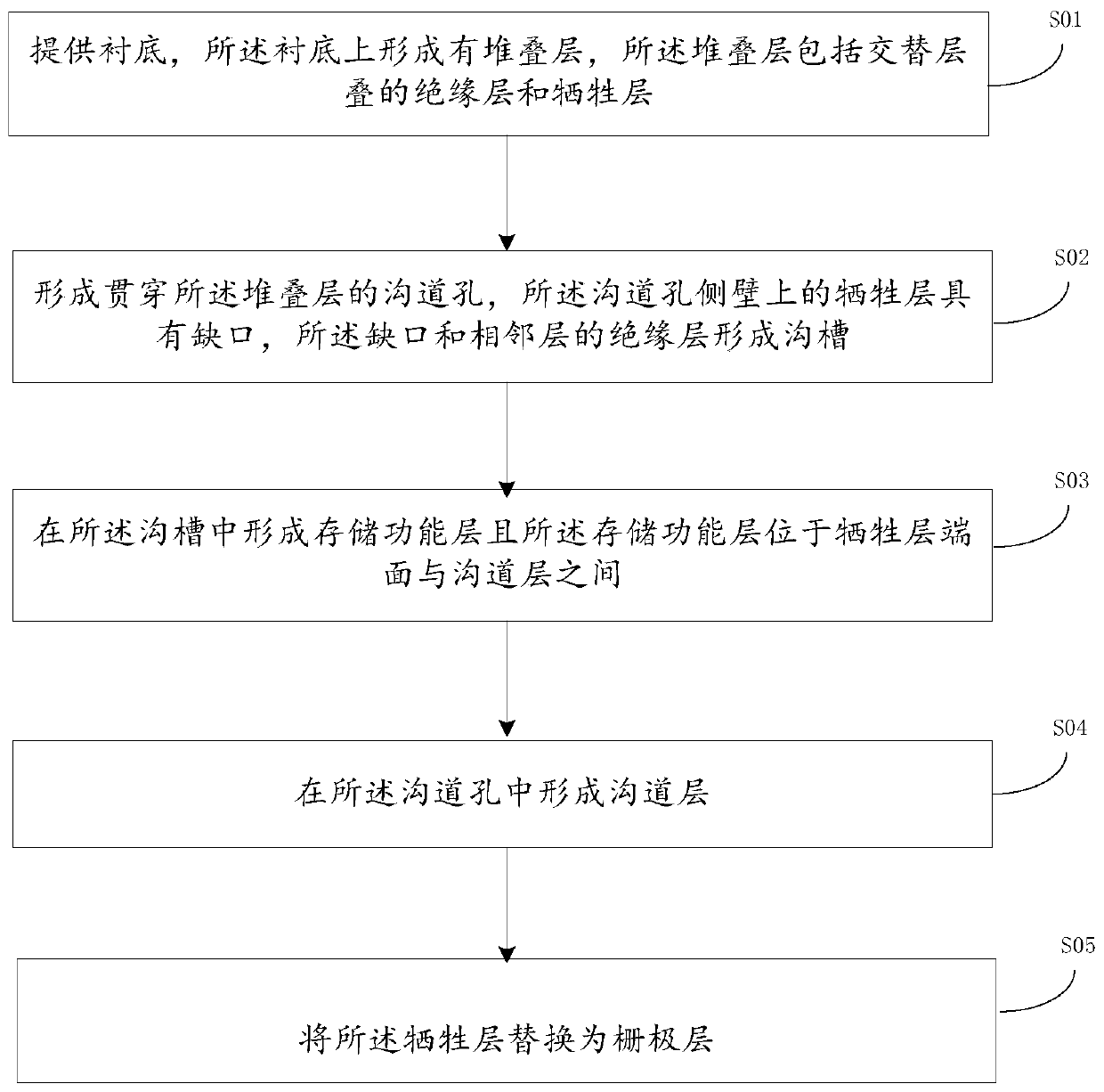

3D NAND memory device and manufacturing method thereof

InactiveCN111463218AImprove retention characteristicsReduce interactionSolid-state devicesSemiconductor devicesMutual influenceStorage cell

The invention provides a 3D NAND memory device. A through channel hole is formed in a stacking layer on a substrate, a gate layer on a side wall of the channel hole is provided with a gap, the gap andan adjacent insulating layer form grooves, a storage function layer is formed in the groove and is positioned between an end surface of the gate layer and the channel layer, thus, storage units are connected through the channel layer, charge storage layers of the storage units are isolated by the insulating layers, so carriers are prevented from migrating along the channel direction, mutual influence among the storage units is reduced, and the retention characteristic of the storage device is improved.

Owner:YANGTZE MEMORY TECH CO LTD

Composite storage medium floating-gate memory structure and manufacture method thereof

InactiveCN101814506AHigh densityIncrease storage windowTransistorIndividual molecule manipulationSilicon nanocrystalsOptoelectronics

The invention discloses a composite storage medium floating-gate memory structure and a manufacture method thereof. The composite storage medium floating-gate memory structure sequentially comprises the following structures from bottom to top: a silicon substrate, a tunneling medium layer, silicon nitride, silicon nanocrystals, high-temperature oxides, a polysilicon layer, a grid and source / drain region and a side wall, wherein the grid and source / drain region is formed on the silicon substrate through etching, and the side wall is etched on the silicon dioxide layer. When being used, the invention solves the problem of reducibility of nodes in the traditional Flash technology, two storage media are adopted for storing electric charges, and a storage window is enlarged, so the reliability of the floating-gate electric charge storage is improved, and the holding feature of a floating-grate device is improved.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

Semiconductor device and method of fabricating the same

InactiveUS20070108550A1Reduce rateImprove retention characteristicsSemiconductor/solid-state device detailsSolid-state devicesDevice materialSemiconductor

The semiconductor device has a semiconductor substrate; an electric fuse provided on the semiconductor substrate, and having a first fuse link and a second fuse link connected in series; and a terminal provided between the first fuse link and the second fuse link, wherein the first fuse link and the second fuse link are configured as being different from each other in current value necessary for blowing.

Owner:RENESAS ELECTRONICS CORP

Liquid crystal display device and associated method for improving holding characteristics of an active element during a vertical blanking interval

InactiveUS8305318B2Improve featuresReduce power consumptionStatic indicating devicesNon-linear opticsElectricityDriver circuit

A liquid crystal display device includes pixels, gate lines and source lines, active elements, a gate driver circuit, a source driver circuit, and a timing controller circuit. The source driver circuit conducts a prescribed operation of supplying the source signals of positive polarity and negative polarity having a prescribed voltage to the source lines during a vertical blanking interval, and electrically cutting the source lines off after the supply of the source signals while establishing a short circuit between adjoining source lines supplied with the source signals of opposite polarities, thereby causing the source lines to hold a prescribed DC voltage value.

Owner:MITSUBISHI ELECTRIC CORP

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com