Gate stack structure suitable for semiconductor flash memory device and manufacturing method of gate stack structure

A flash memory device and gate stack technology, which is used in semiconductor/solid-state device manufacturing, semiconductor devices, electric solid-state devices, etc., can solve the problems of slow operation speed and high operating voltage, and achieve increased electric field strength, storage density, and high density. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

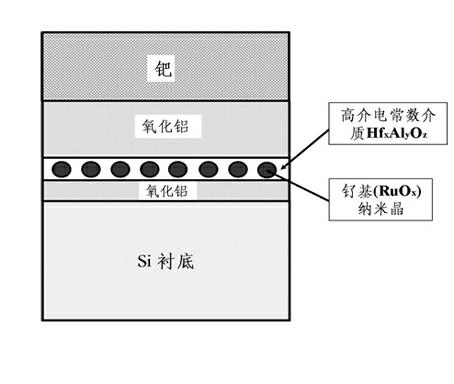

[0044] see figure 1 As shown, the gate stack structure suitable for semiconductor flash memory devices in the present invention, in particular, includes a heterogeneous charge trapping layer based on metal nanocrystals and high dielectric constant films, and in the flash memory capacitor formed by this , set in order from bottom to top:

[0045] 1) A P-type monocrystalline silicon wafer with a crystal orientation of 100 is used as the substrate;

[0046] 2) Al by atomic layer deposition 2 o 3 Thin film, as a charge tunneling layer, with a thickness of 5 to 15 nanometers;

[0047] 3) The heterogeneous charge trapping layer, which further includes:

[0048] As the first charge-trapping layer, metal nanocrystals are composites of ruthenium and ruthenium oxide (denoted as ruthenium-based RuO x Nanocrystalline);

[0049] A high dielectric constant thin film deposited by atomic layer is used as the second charge trapping layer, with a thickness of 3 to 20 nanometers (the prefe...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com