Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

58results about How to "Avoid metastability" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Data buffer of high-speed data exchange interface and data buffer control method thereof

InactiveCN101667451AIncrease flexibilityStorage status detailsDigital storageTransformation unitData link layer

The invention discloses a data buffer of a high-speed data exchange interface and a data buffer control method thereof. The data buffer comprises a data storage unit, a buffer read-write control unit,a state register and a bit width conversion unit, wherein the data storage unit is used for buffering data among asynchronous clock zones; the buffer read-write control unit is used for controlling the read and write operations of the data buffer unit; the state register is used for controlling the exchange with the buffer read-write control unit and the state information; and the bit width conversion unit is used for carrying out bit width conversion when the bit width of the data storage unit and the bit width of a bus are different. The data buffer control process is achieved as follows: transmitting a read-write instruction to the buffer read-write control unit by a pack processing engine in a mode of facing to a unit; saving the storage state of the buffer by a transmitting mark state register; controlling the data transmission by buffer data; and realizing ordered data transmission by a self-increasing pointer. The invention has the advantages of strong control flexibility and high data transmission efficiency, and is used for multiport high-speed data exchange of a network processor and data link layer equipment.

Owner:XIDIAN UNIV

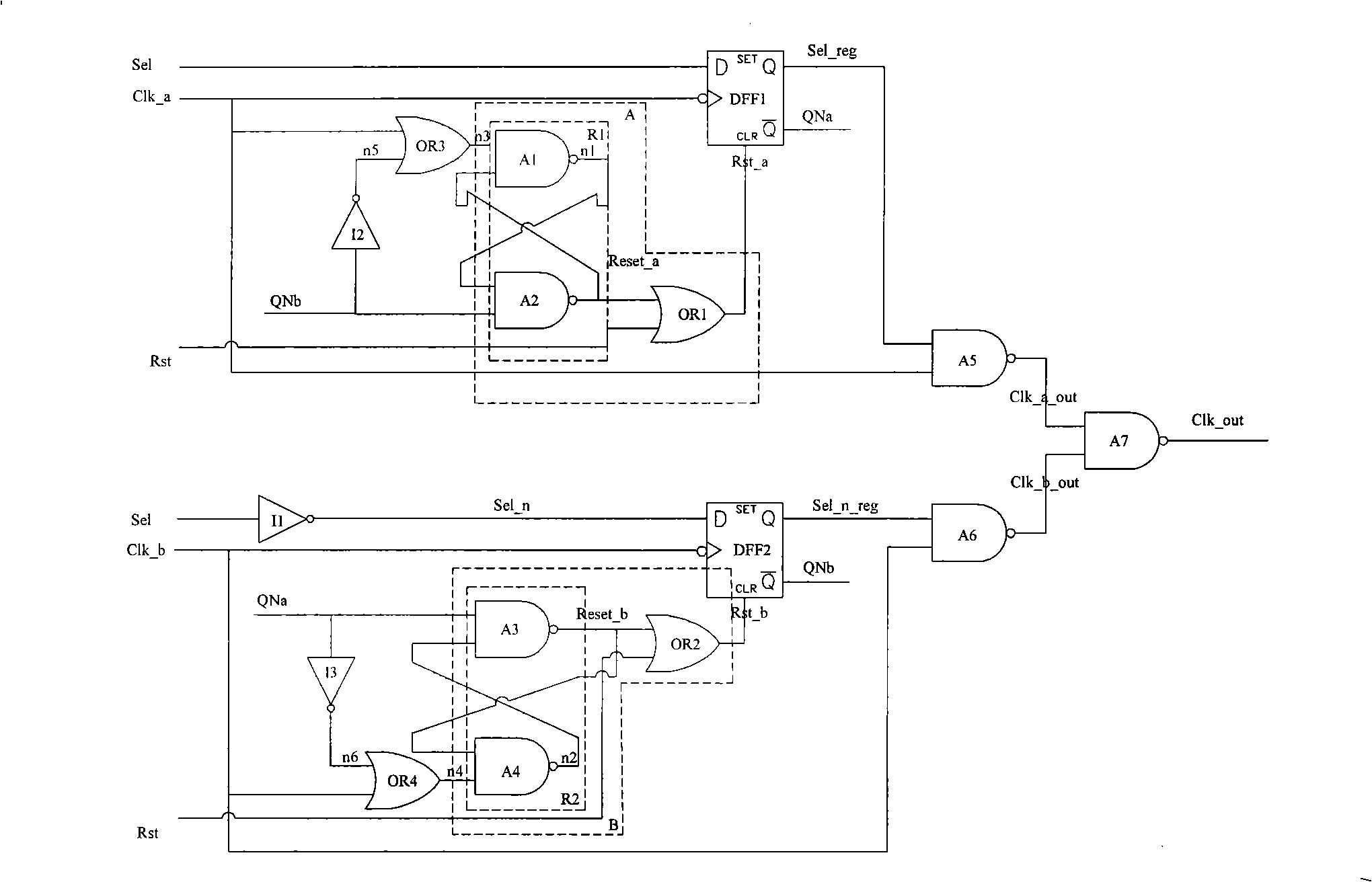

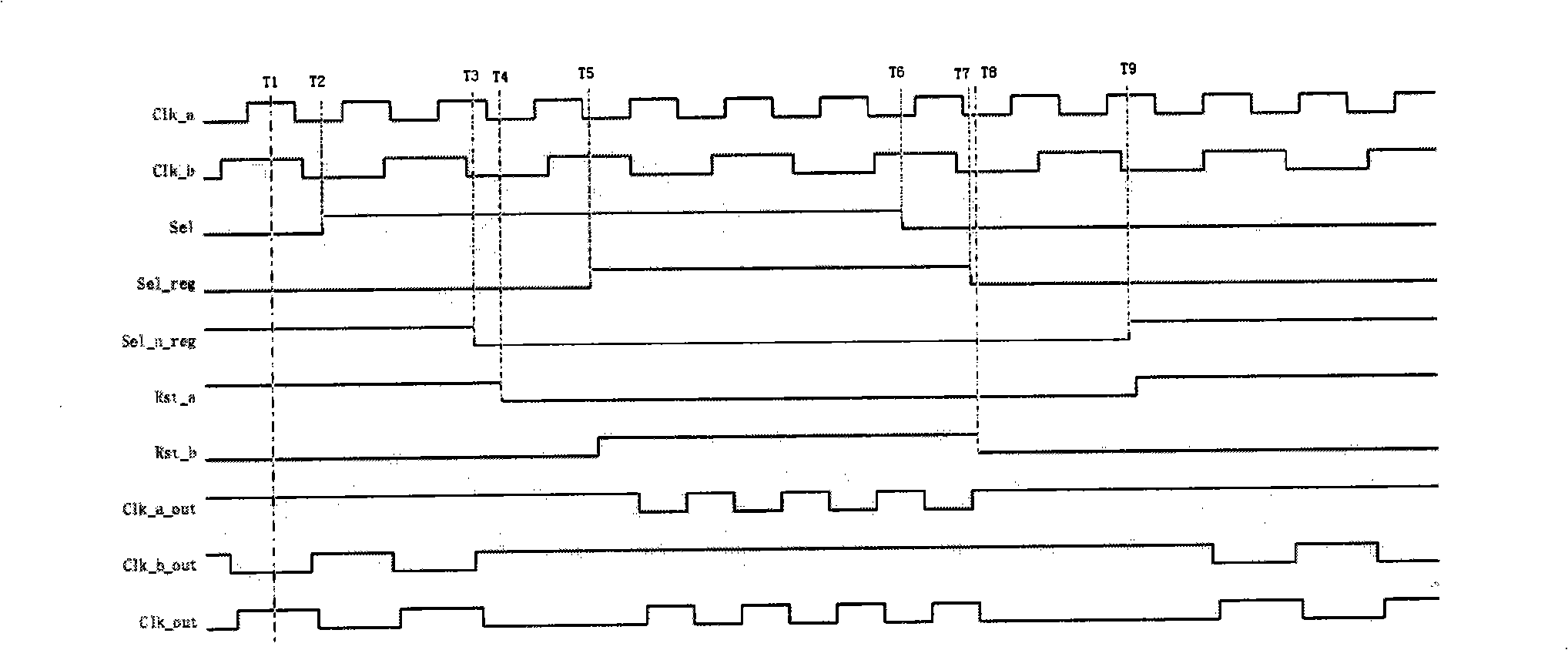

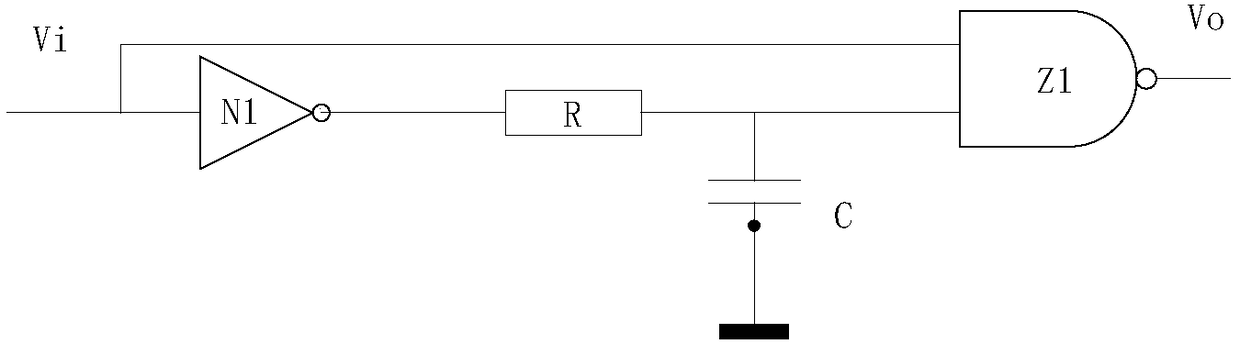

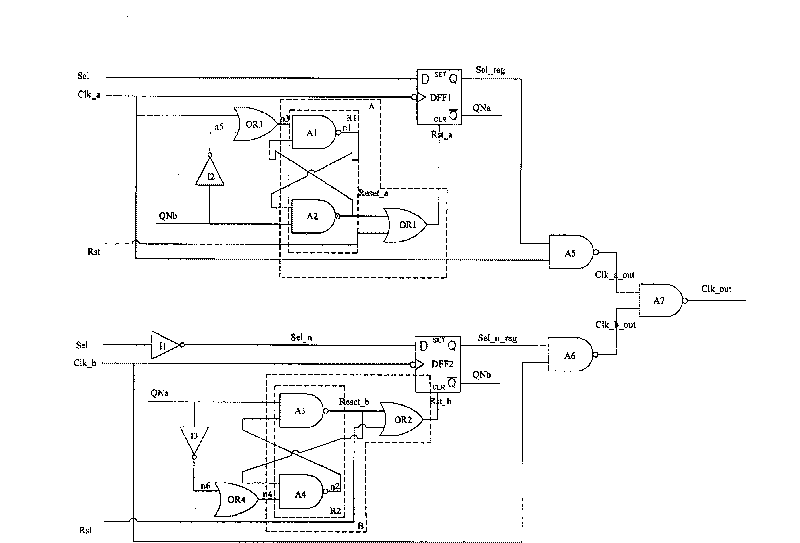

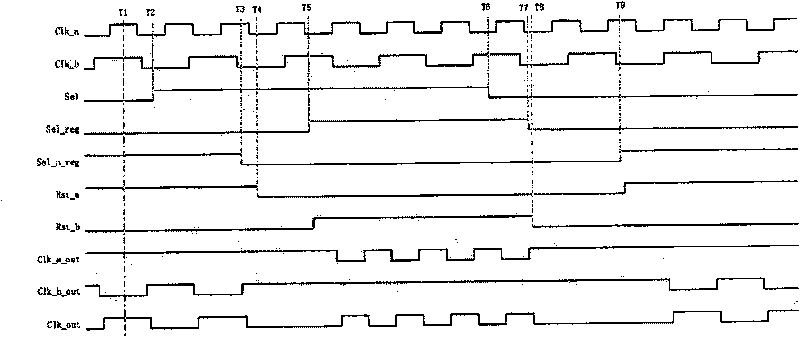

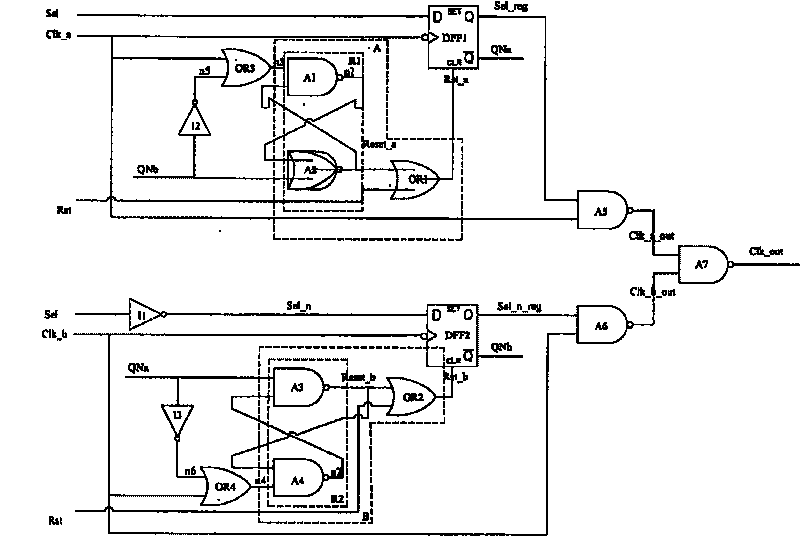

Clock switch circuit

InactiveCN101299159AAvoid metastabilityGenerating/distributing signalsPulse manipulationMetastabilityElectrical and Electronics engineering

The invention discloses a clock commutation circuit, which resolves technical problem of producing bur and metastable state. The clock commutation circuit of the invention is composed of two reset producing circuits, two OR gates, three NOT gates, two D-flip-flops and a clock output circuit, the reset producing circuits and the NOT gates constitutes a RS latch. Compared with the prior technology, when the first clock is switched to the second clock, the gating signal of the first clock is switched off when the first clock is at a low level, meanwhile the reset outputting signal of the second RS latch is released, the gating signal of the second clock is switched-on when the second clock is at a low level, thereby avoiding the bur during the clock switch. The reset producing circuit ensures that the asynchronous reset terminal of the D-flip-flop executes the synchronization operation to the reset signal through the RS latch circuit when the clock is at a low level, thereby avoiding the production of metastable state.

Owner:INVENGO INFORMATION TECH

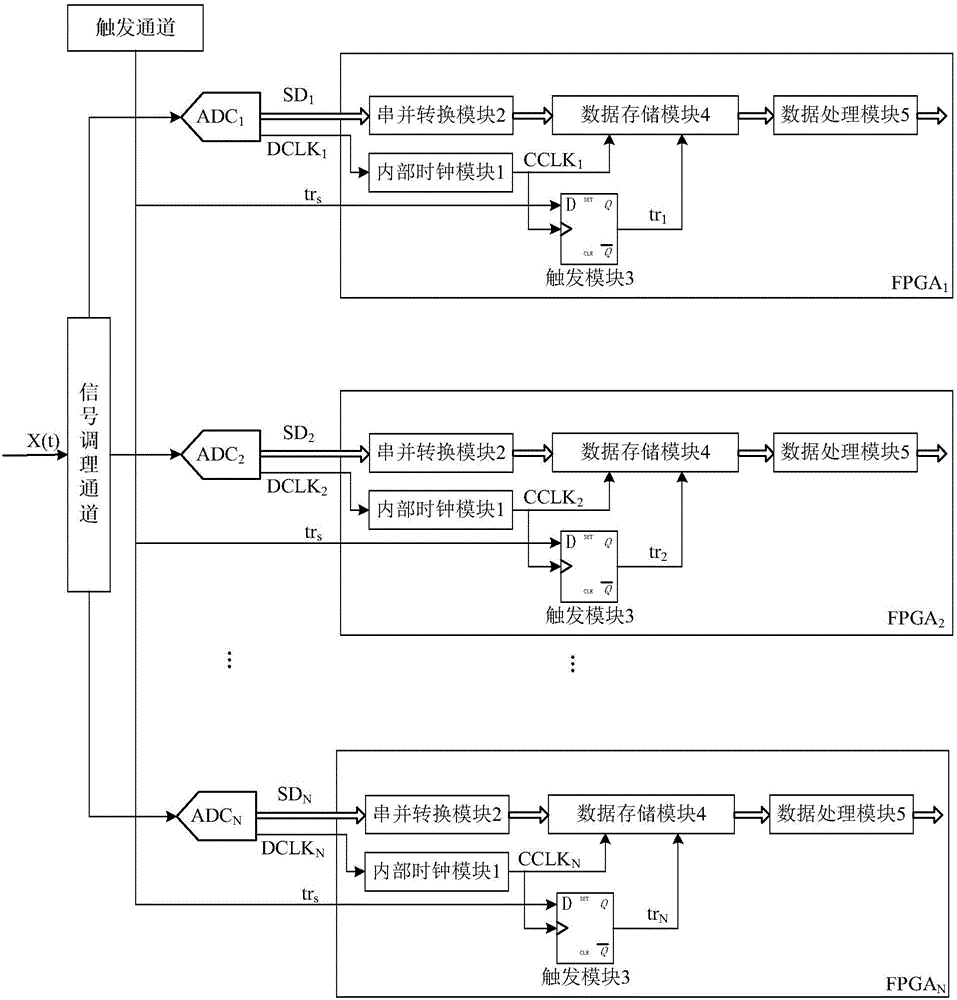

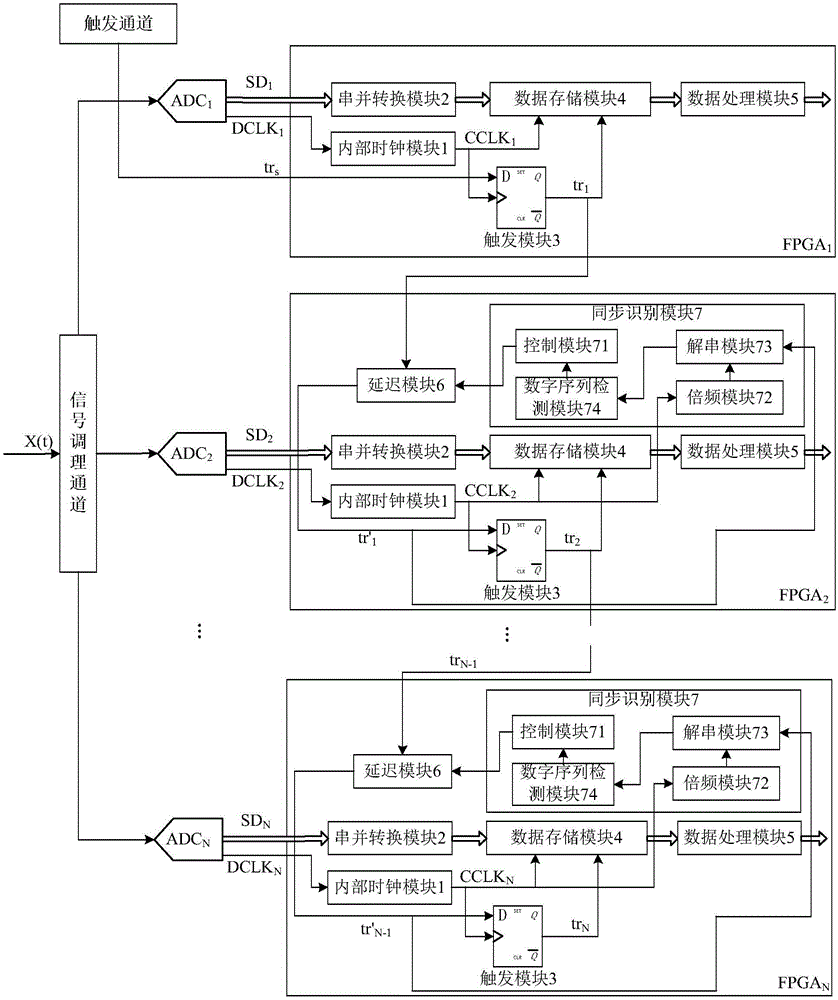

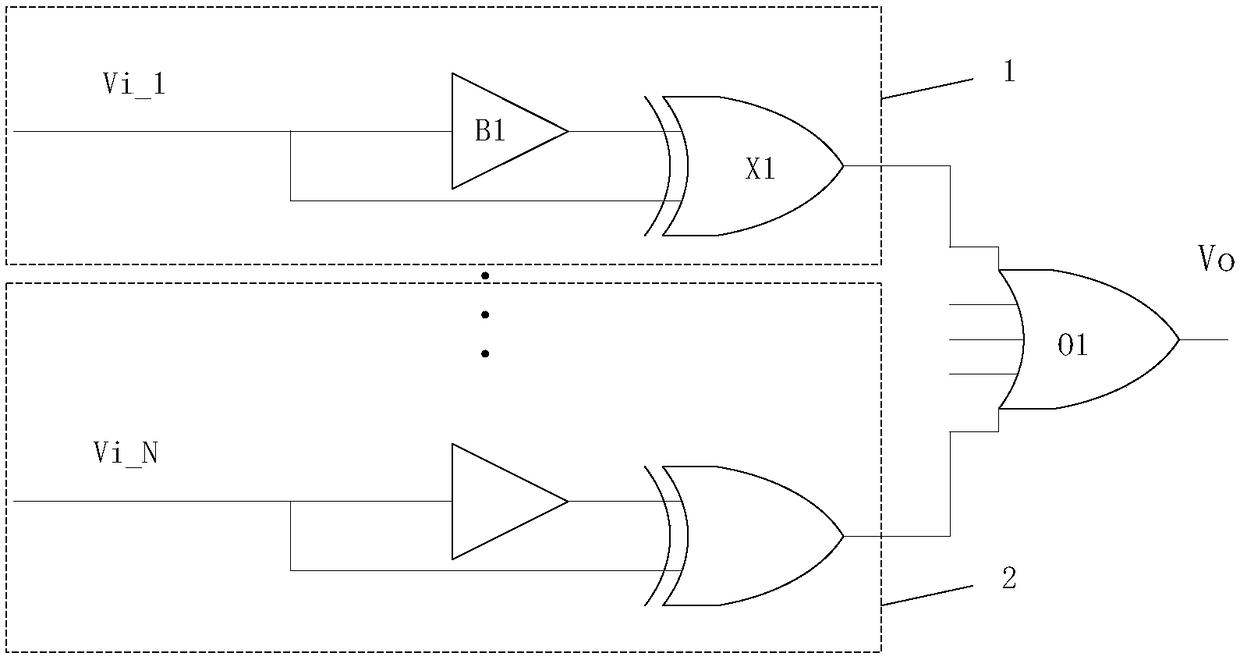

Multi-channel parallel acquisition system with storage function and synchronous recognition function

ActiveCN106385256AGuaranteed correctnessAvoid metastabilityAnalogue/digital conversion calibration/testingComputer moduleComputer science

The invention discloses a multi-channel parallel acquisition system with a storage function and a synchronous recognition function. In the N FPGA modules of the multi-channel parallel acquisition system, the first FPGA module generates valid trigger signals according to the trigger signal of a trigger channel and sends the valid trigger signals to the second FPGA module; and each FPGA module in the second FPGA module to the N-th FPGA module is configured with a delay module and a synchronous recognition module; the synchronous recognition modules are adopted to set the delay values of the delay modules according to the serial numbers of the corresponding FPGA modules in the initialization of the multi-channel parallel acquisition system; and the delay modules receive the valid trigger signals of the previous FPGA modules in the actual operation of the multi-channel parallel acquisition system, and delay the valid trigger signals according to the delay values, and send the delayed valid trigger signals to corresponding trigger modules, so that valid trigger signals can be generated. According to the multi-channel parallel acquisition system of the invention, the valid trigger signals in the FPGA modules in the multi-channel parallel acquisition system are accurately recognized and controlled, so that the correctness of the storage of data sequences of a back-end can be ensured.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

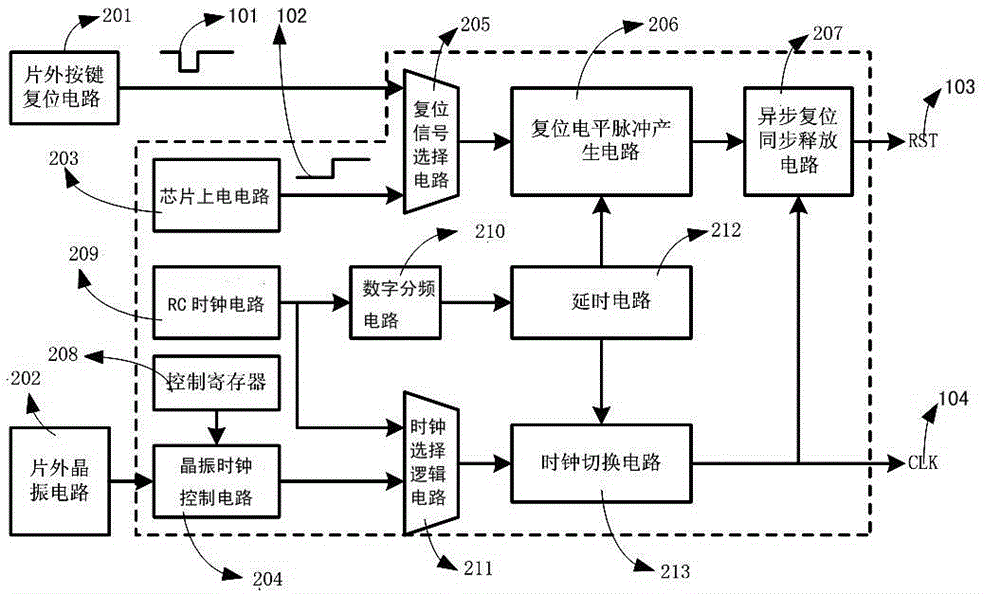

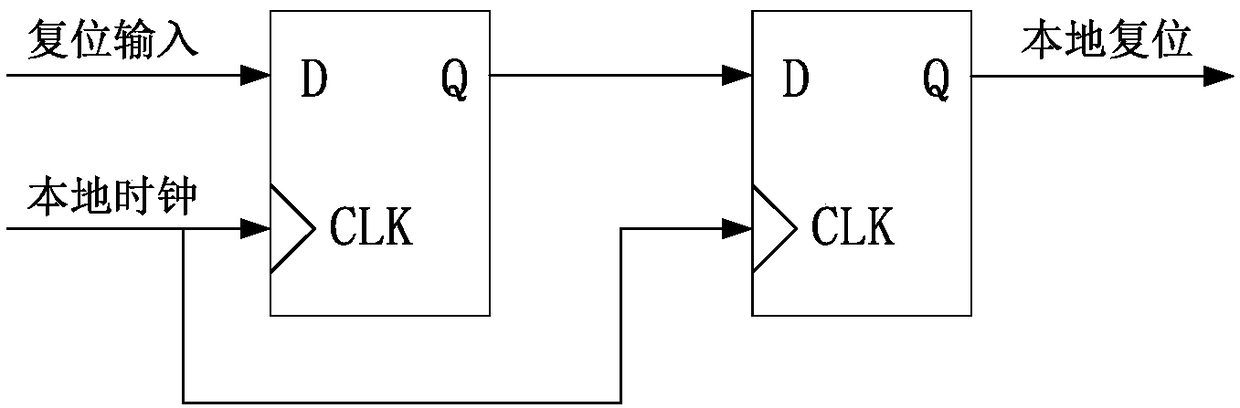

In-chip reset system and reset method for system-on-chip chip

ActiveCN105404374AStabilize the main frequency clockAvoid metastabilityData resettingPower-on resetComputer architecture

The invention proposes an in-chip reset system and reset method for a system-on-chip chip. The system comprises an off-chip key reset circuit, an off-chip crystal oscillation circuit, a chip power-on circuit, a crystal oscillation clock control circuit, a reset signal selection circuit, a reset level pulse generation circuit, an asynchronous reset and synchronous release circuit, a control register, an RC clock circuit, a digital frequency division circuit, a clock selection logic circuit, a delay circuit and a clock switching circuit, wherein except the off-chip key reset circuit and the off-chip crystal oscillation circuit, the rest of circuit modules are all integrated in the system-on-chip (SOC) chip. The in-chip reset system and reset method for the system-on-chip chip have the beneficial technical effects that most circuit modules are integrated in the SOC chip, so that the area is reduced and the cost is lowered; and on the basis of not adding additional circuits, an off-chip key reset mode is effectively combined with an in-chip power-on reset mode, so that the reset system is convenient and easy to use.

Owner:THE 44TH INST OF CHINA ELECTRONICS TECH GROUP CORP

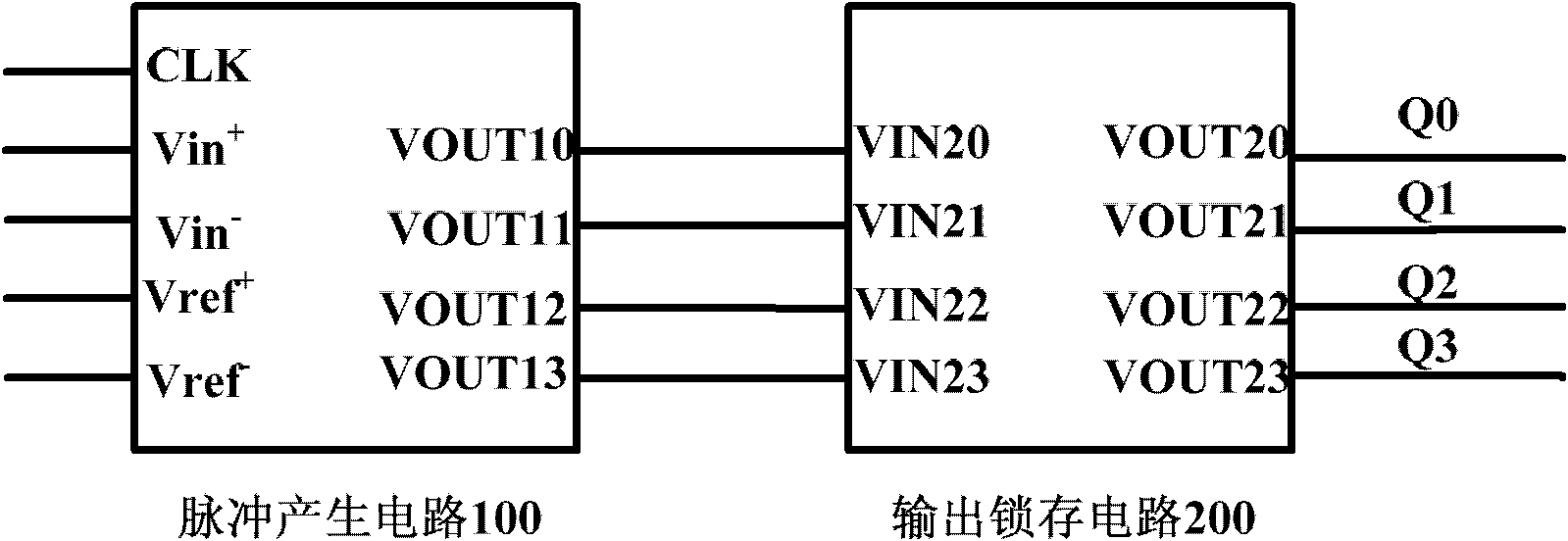

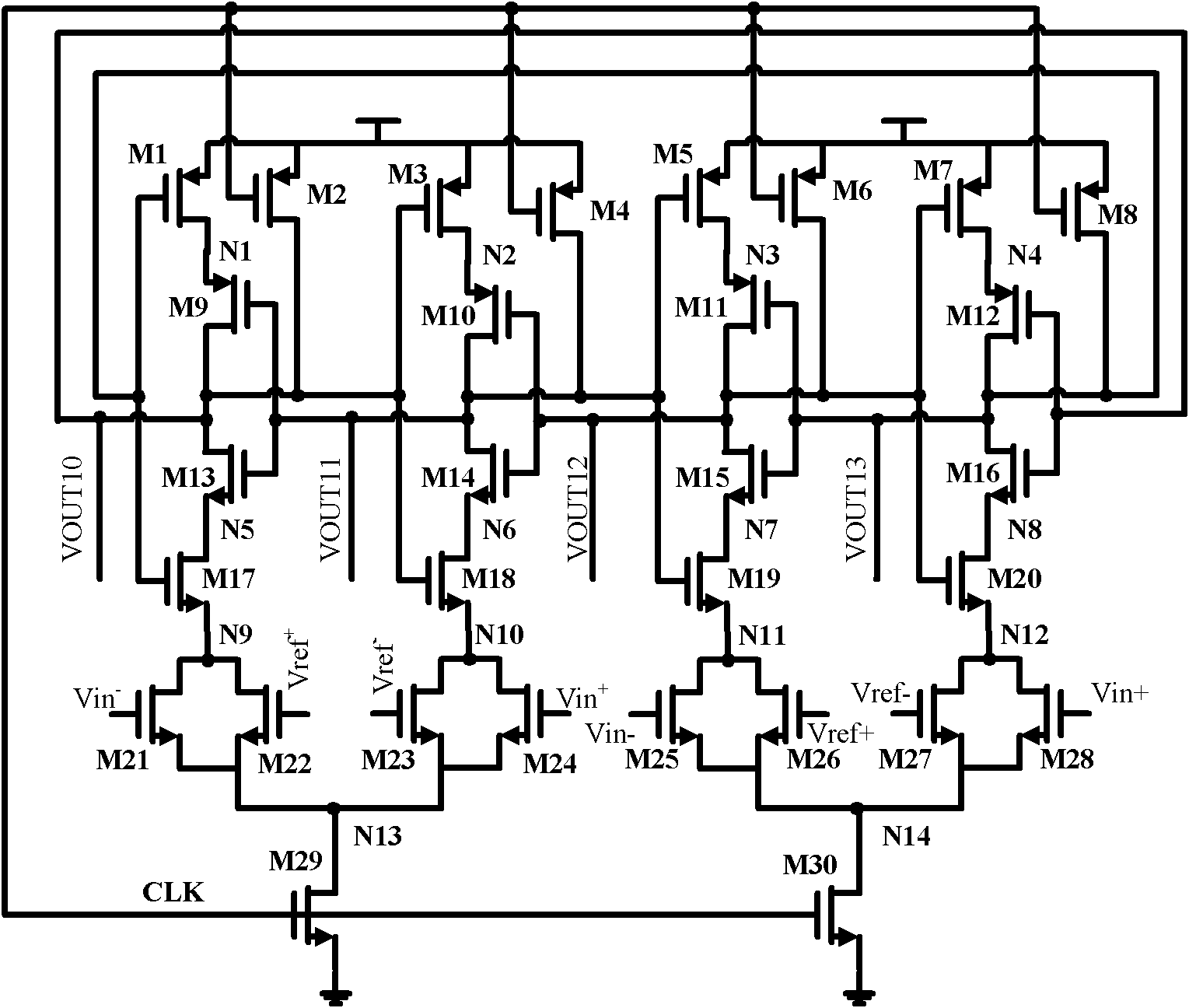

SEU (single event upset)/SET (single event transient)-resistant dynamic comparator

InactiveCN102025351AReduce power consumptionReduced power consumption performance,Multiple input and output pulse circuitsAudio power amplifierClock network

The invention discloses an SEU (single event upset) / SET (single event transient)-resistant dynamic comparator, which comprises a pulse generating circuit based on a sensitive amplifier structure and an output latch circuit; the top of the whole comparator is provided with five input ports and four output ports outwards, the five input ports are respectively connected with clock signals, input signals and reference voltage signals, and the output ports are connected with data output signals; the pulse generating circuit is connected with the clock signals, the input signals, the reference voltage signals and the output latch circuit; and the output latch circuit is connected with the pulse generating circuit and the data output signals. The dynamic comparator has the advantages that the upset threshold LETth is greater than 500MeV / (mg.cm2); the time delay is reduced while the high-speed low power consumption of the SEU / SET-resistant dynamic comparator same as that of a traditional dynamic comparator is achieved; the symmetrical arrangement, equal time delay and same drive capacity of complementary output terminals Q and QB are realized; by adopting the sensitive amplifier structure, the clock network is simple, reliable and small in load; and by adopting the minor clock swing technology, the power consumption is obviously reduced.

Owner:XI AN JIAOTONG UNIV

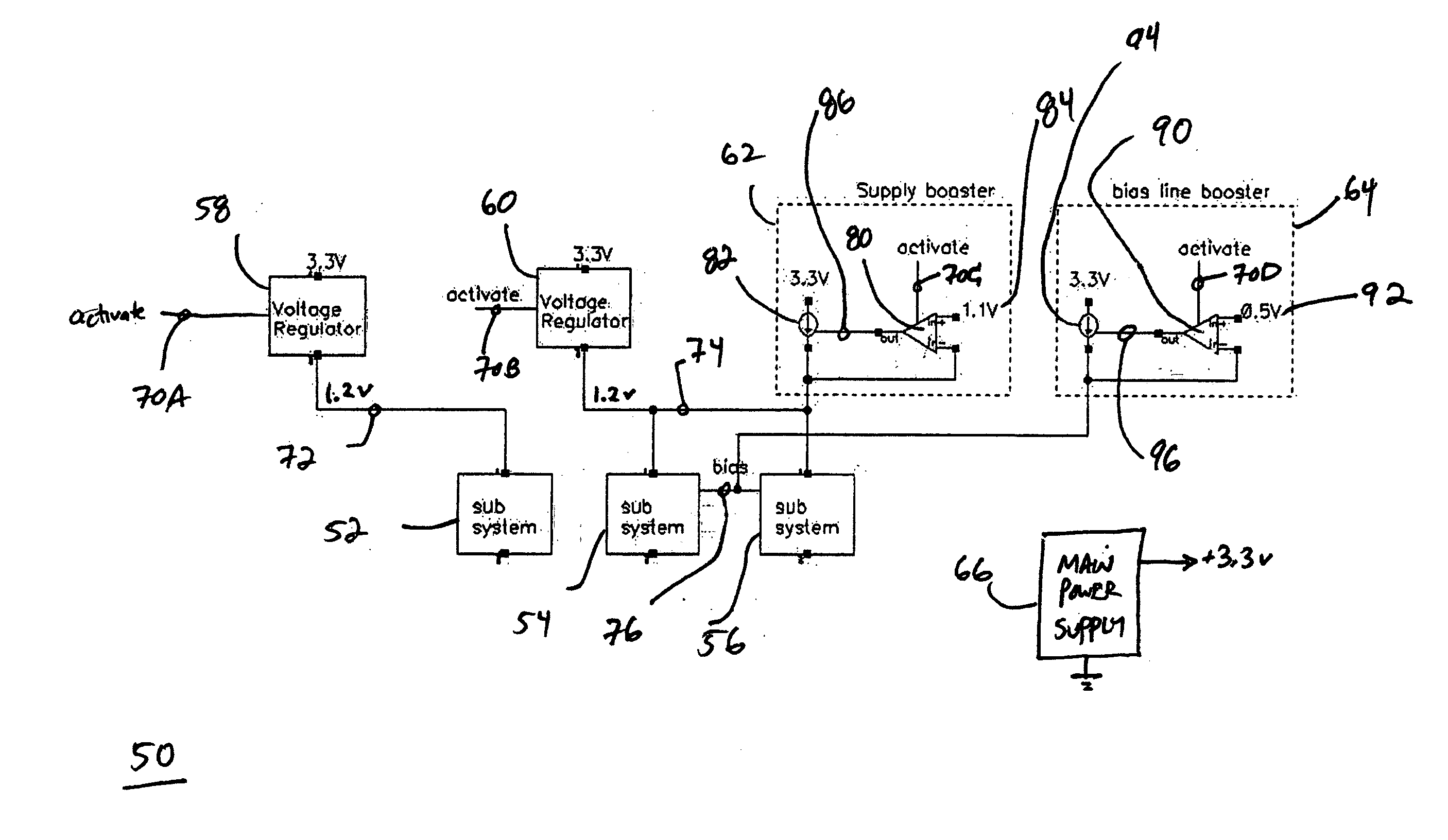

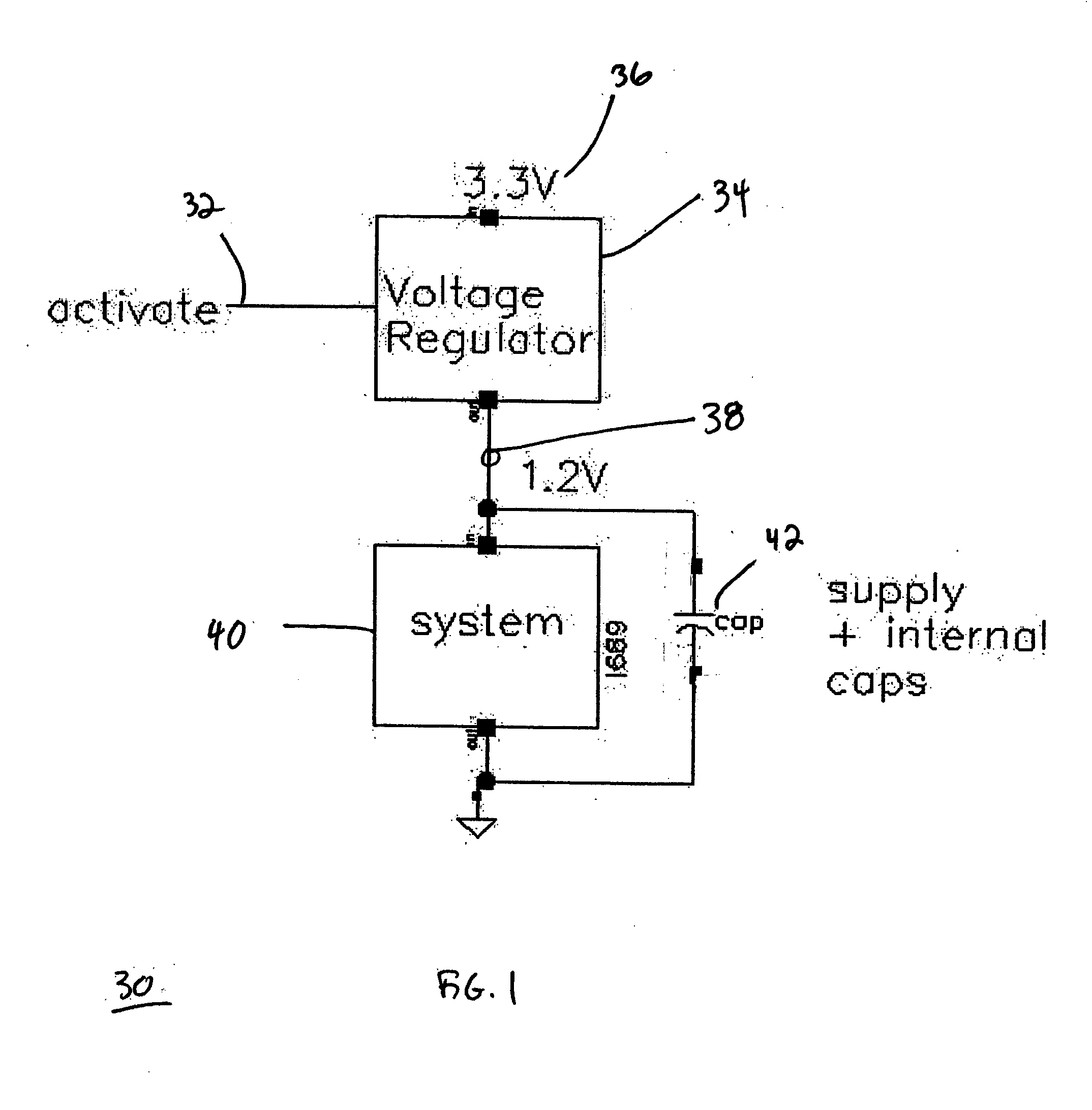

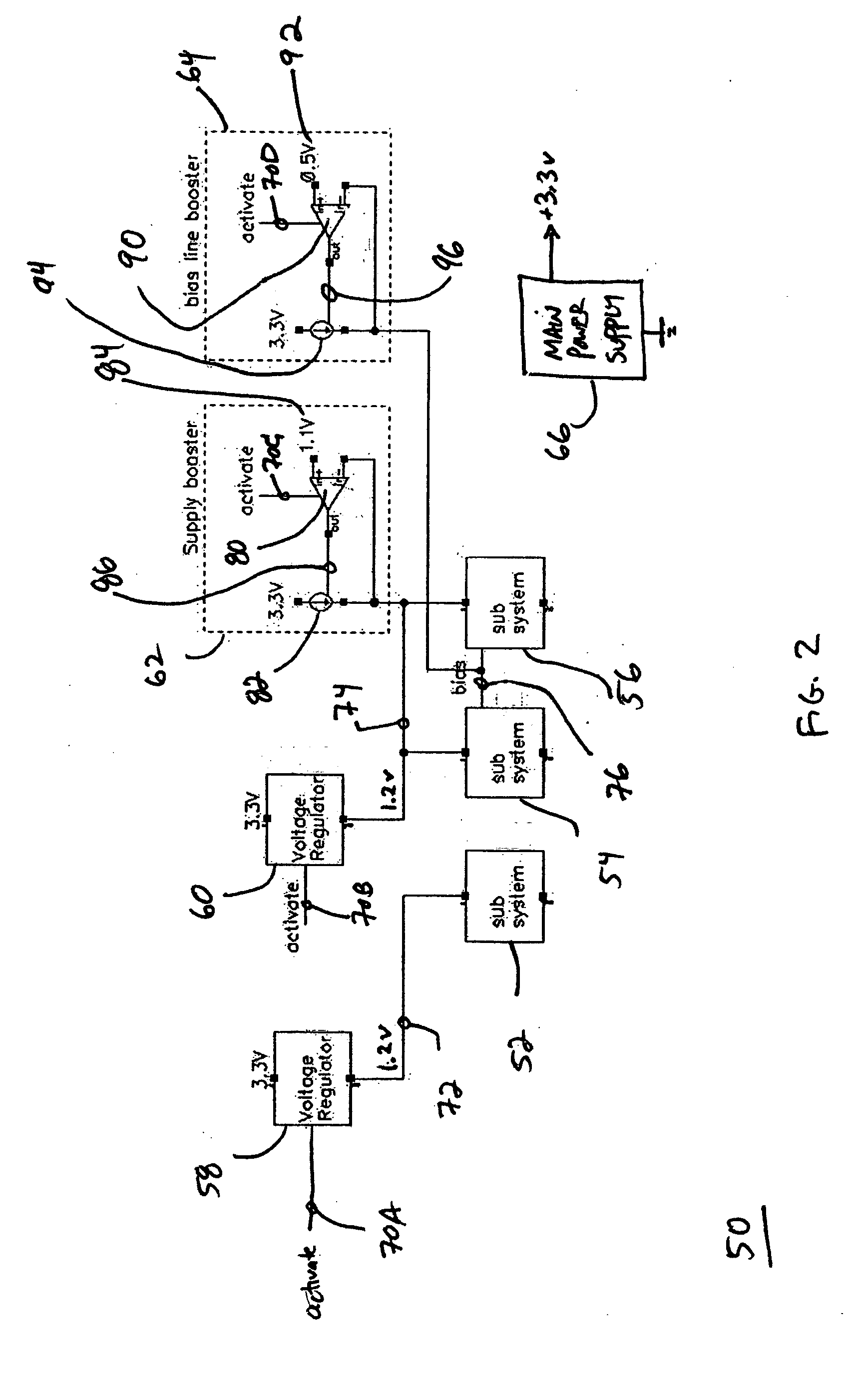

Method and circuit for improving device power up timing and predictability

InactiveUS20050213268A1Avoid metastabilityFaster power-upEmergency protective arrangements for limiting excess voltage/currentElectric variable regulationIntegrated circuitElectricity

Method and system for controllably and sequentially powering up subsystems of an electronic system, device or integrated circuit. In one example, a first supply voltage is selectively applied to a first subsystem, and when the first supply voltage has reached a predetermined value, a second supply voltage is selectively applied to the second subsystem. The first and second supply voltages may also be boosted to provide fast startup timing. In this manner, the first subsystem is powered-up before the second supply voltage is applied to the second subsystem—this provides for controlled, sequential power up of the subsystems of the electronic system, device or integrated circuit.

Owner:CETIN JOSEPH +1

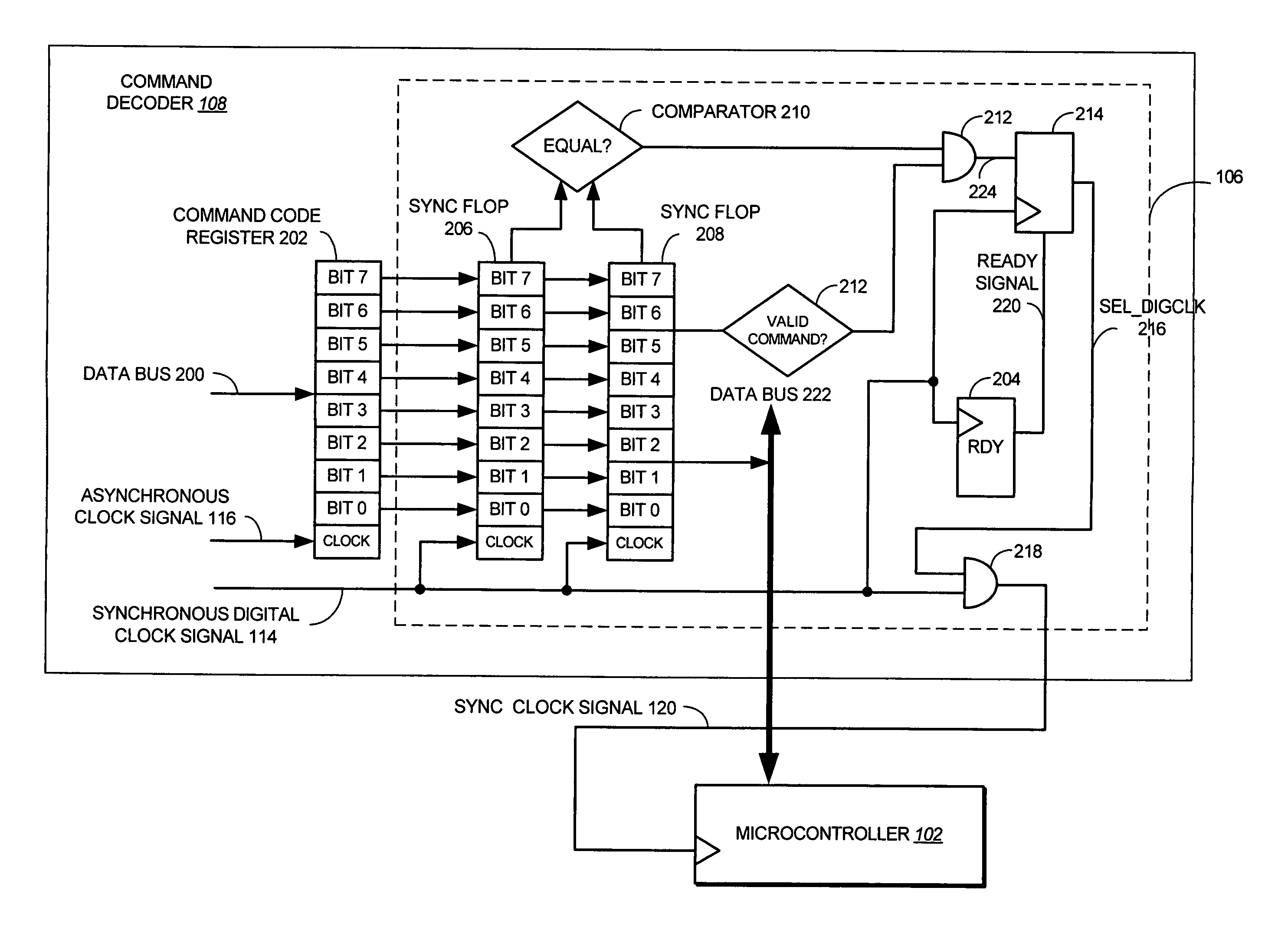

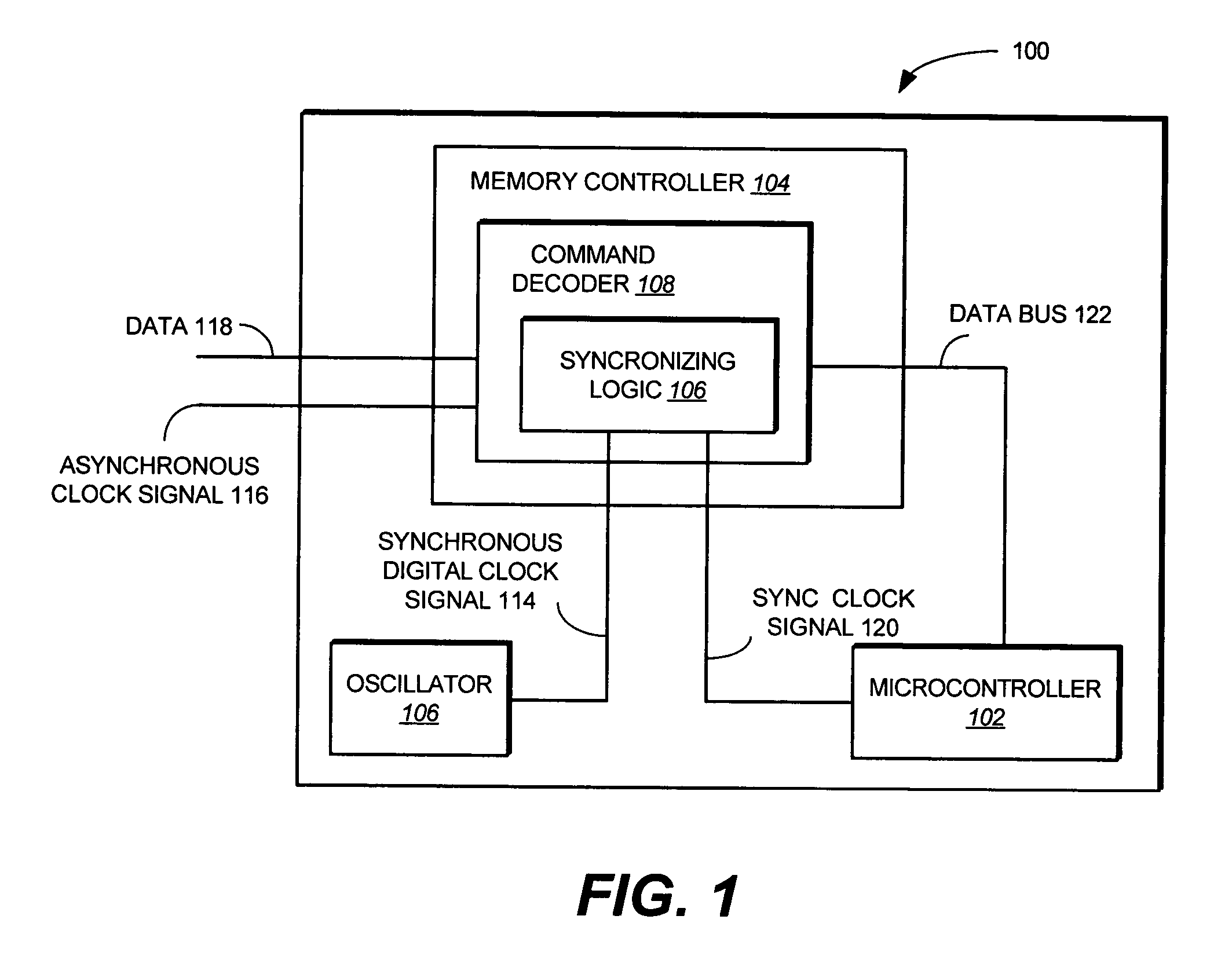

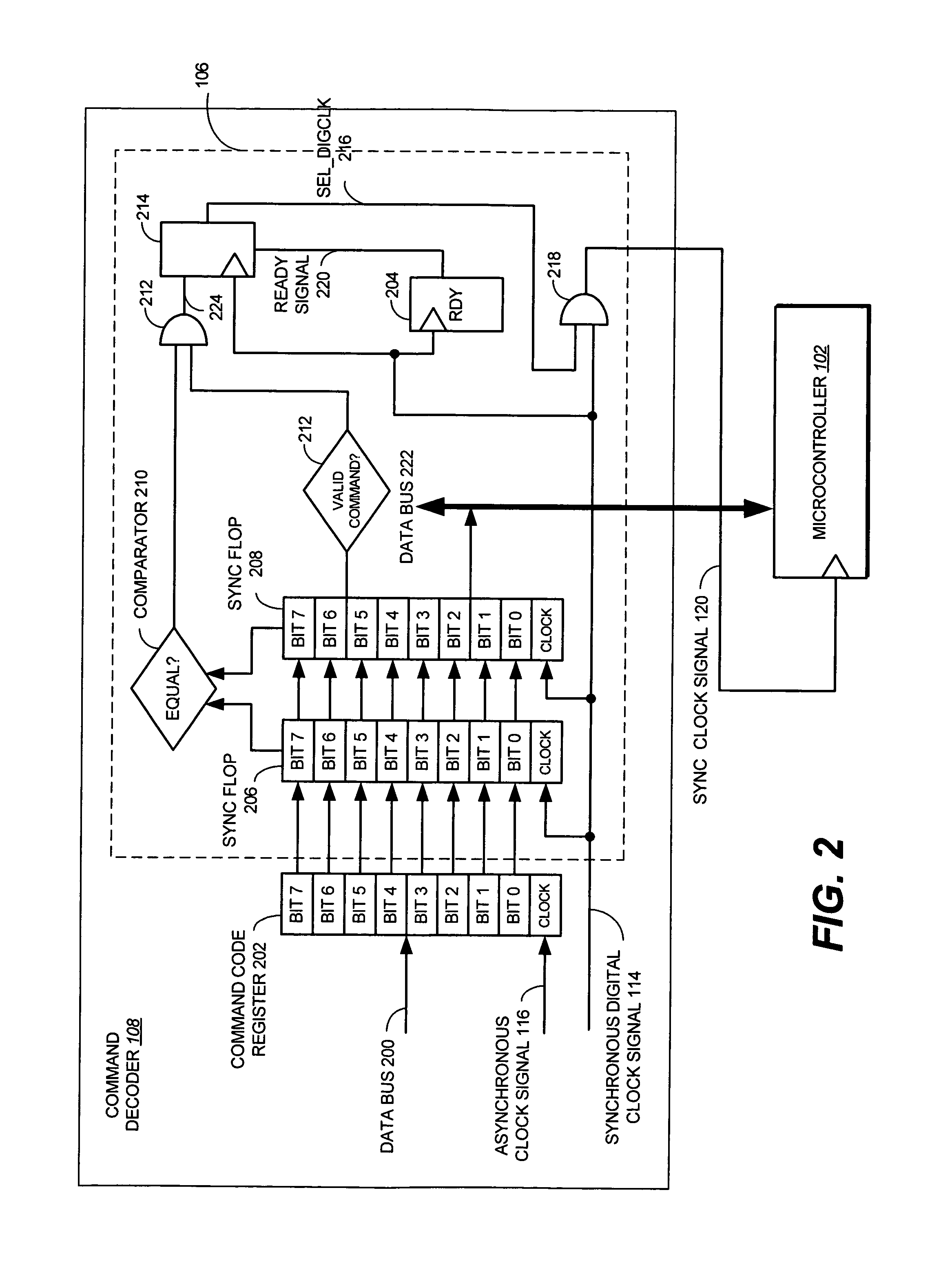

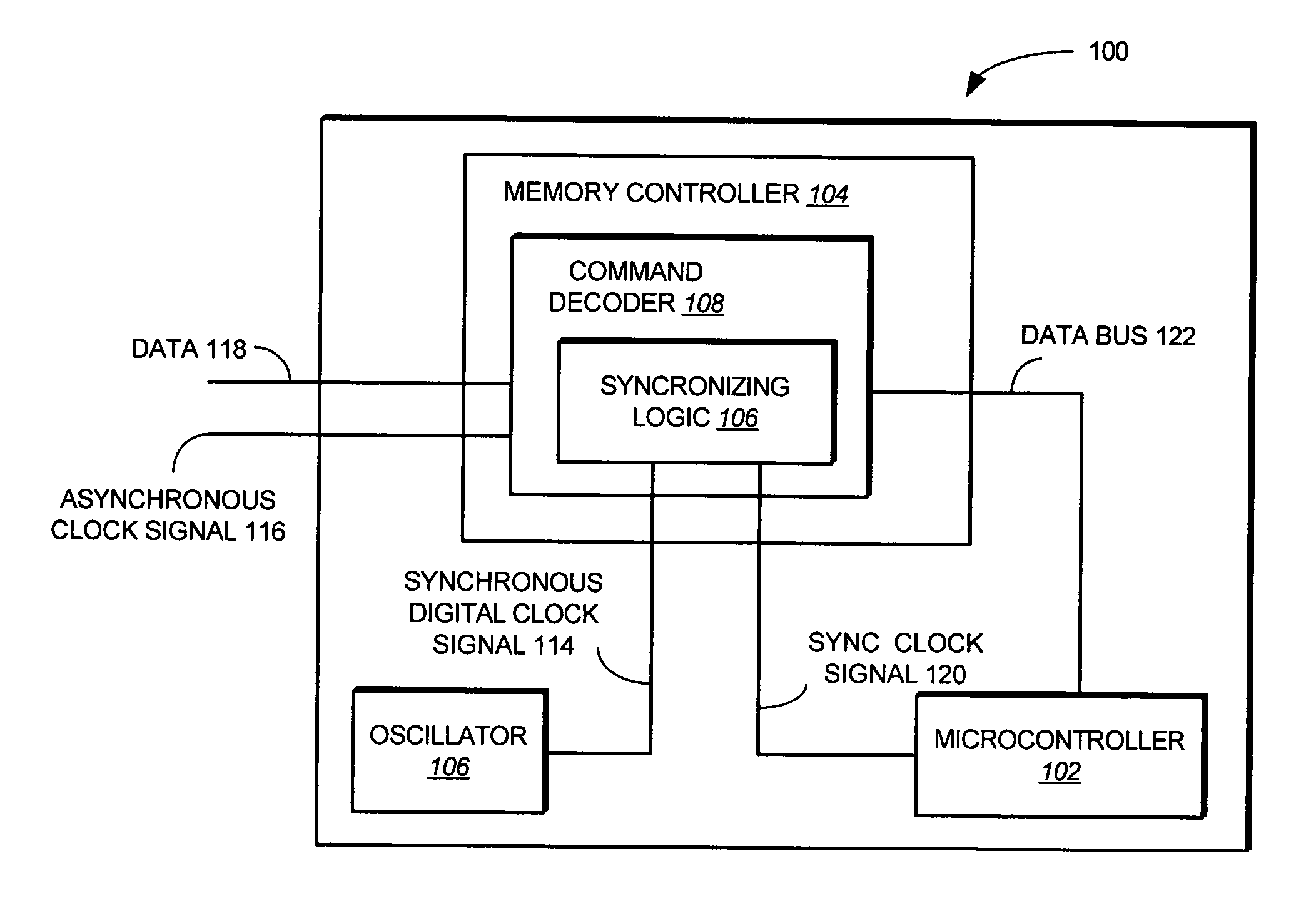

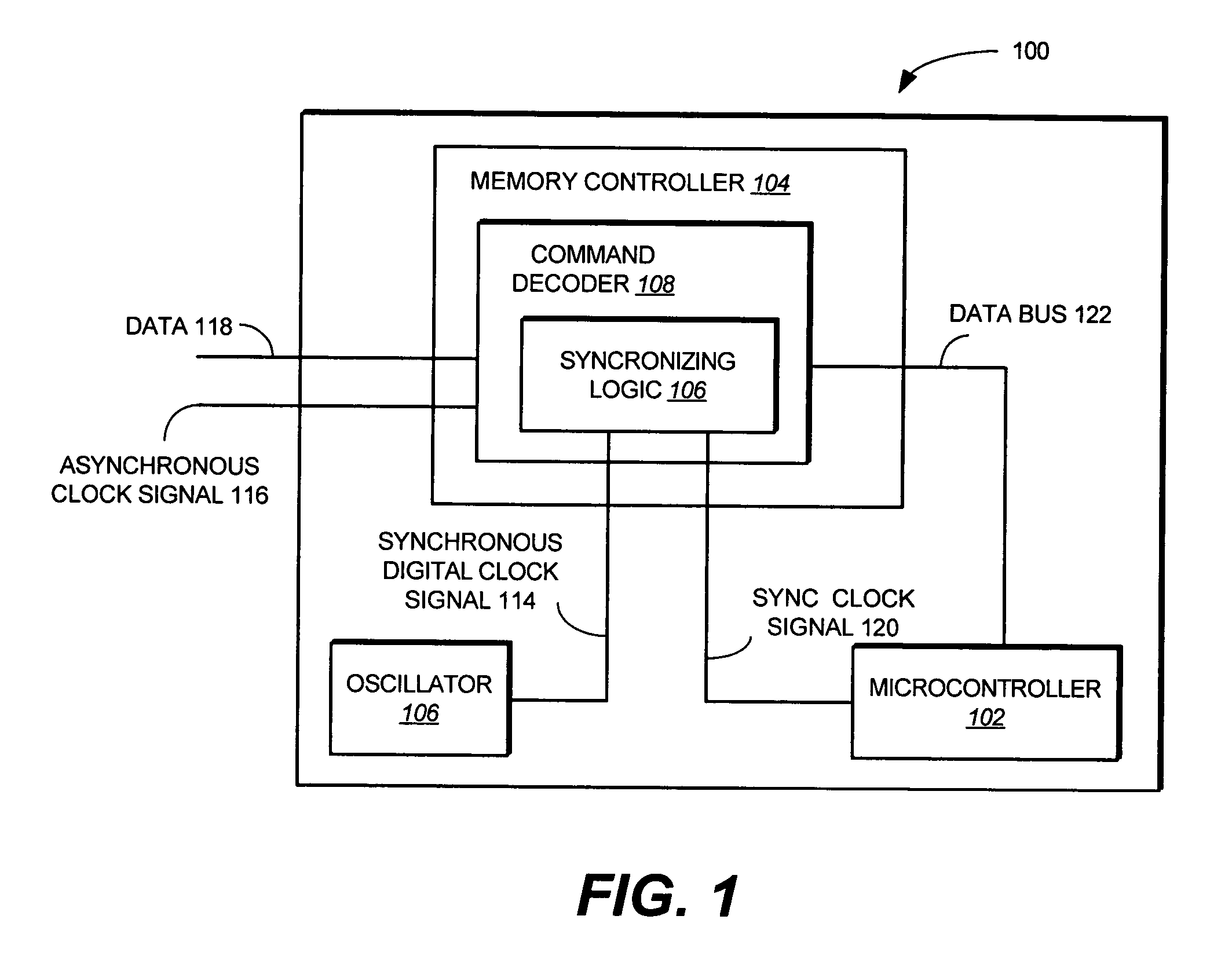

Method and apparatus for synchronizing data between different clock domains in a memory controller

InactiveUS7639764B2Avoid metastabilityEnergy efficient ICTDigital storageComputer hardwareMemory controller

The present invention provides method and apparatus for synchronizing data between different clock domains in a memory controller. In one embodiment, a memory controller is provided that includes a command decoder and synchronizing logic. The command decoder is operable to receive a command in accordance with a first clock domain. The synchronizing logic synchronizes the command to a second clock domain that is different from the first clock domain, and includes a first synchronization flop and a second synchronization flop operable to prevent metastability associated with synchronizing the command to the second clock domain.

Owner:ATMEL CORP

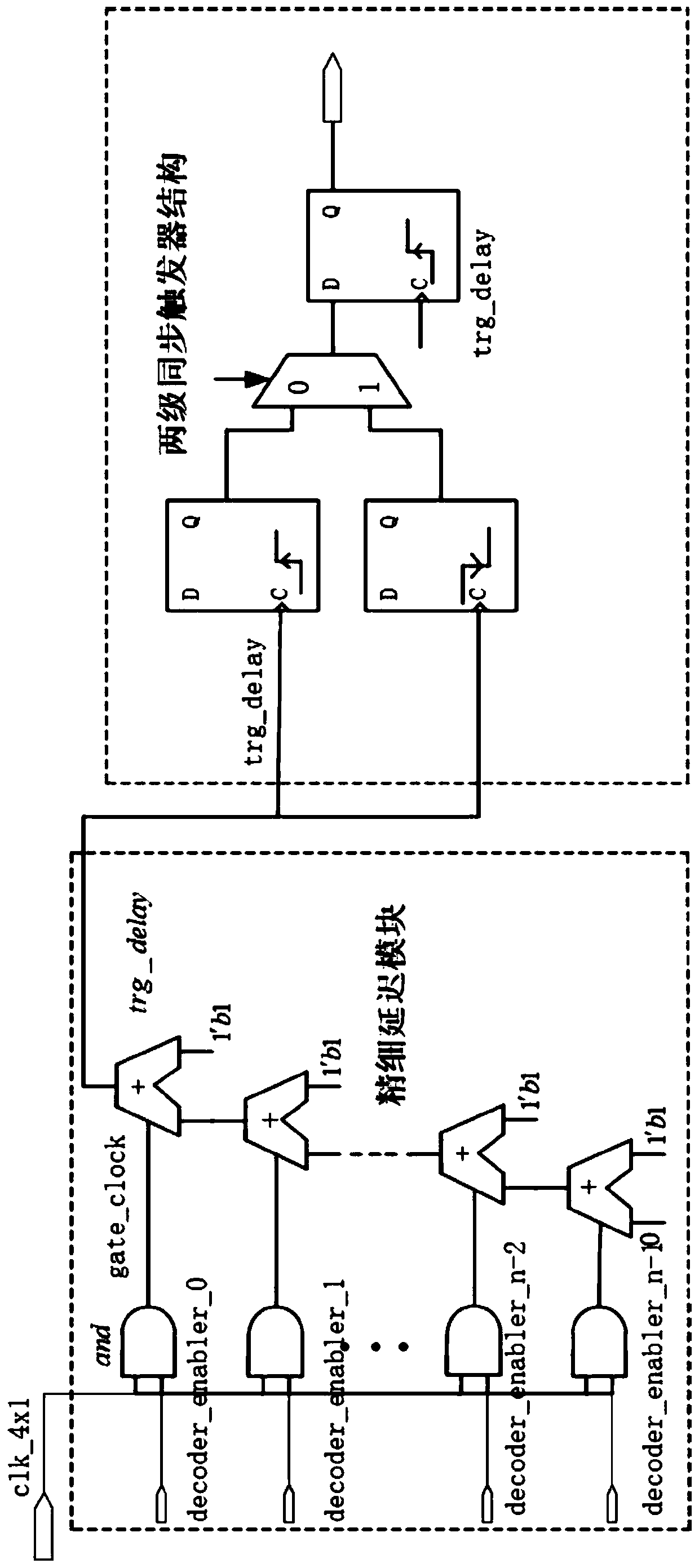

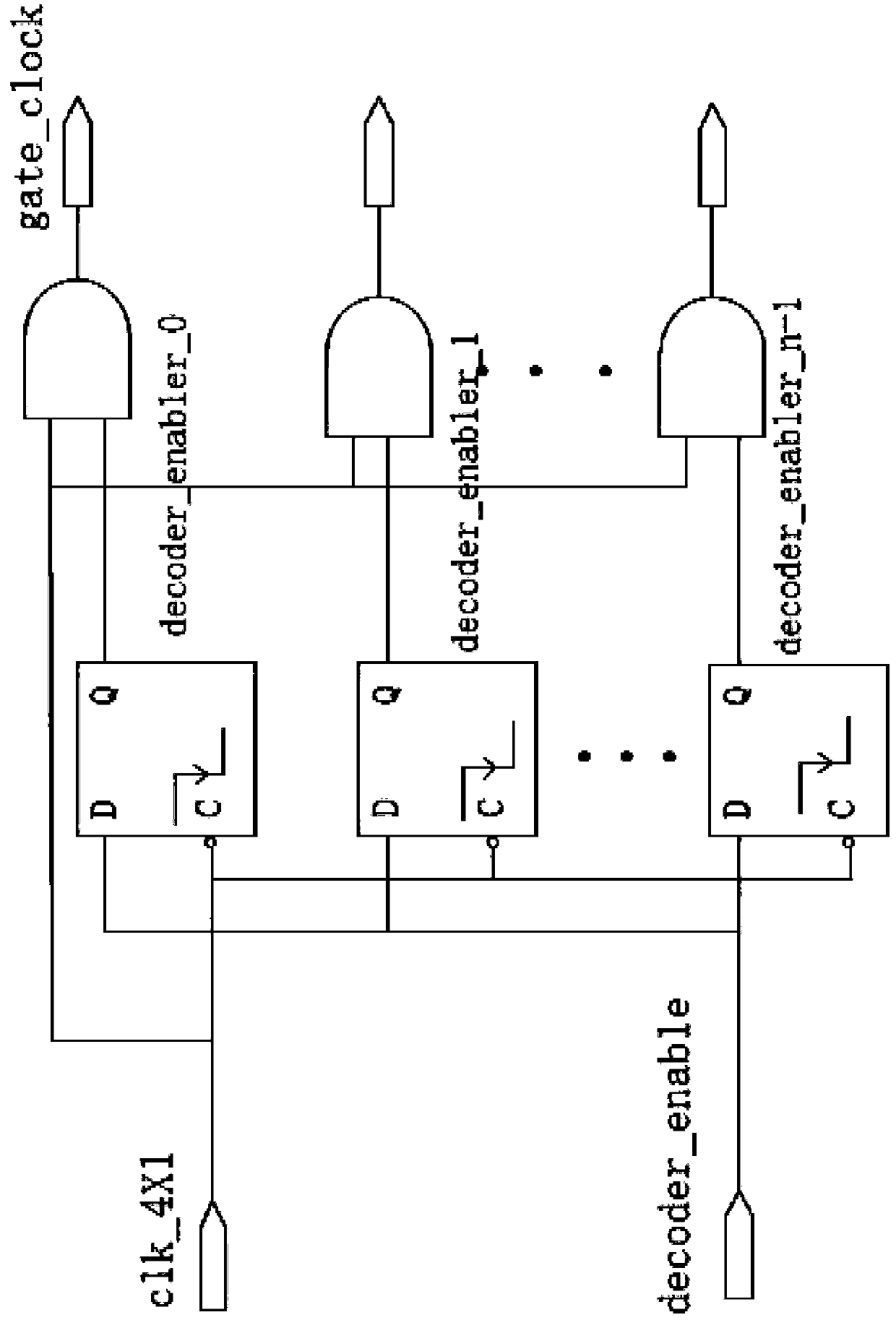

Digital pulse width modulation circuit and working method

ActiveCN110661513AHigh-resolutionReduce usagePulse duration/width modulationPower conversion systemsHemt circuitsFlip-flop

The invention relates to the technical field of power supply management chips, in particular to a digital pulse width modulation circuit, which comprises a coarse delay module based on a counter, a clock management module based on a phase-locked loop, a two-stage synchronous trigger circuit module, a fine delay module based on a carry chain unit, a duty ratio decoding module and a gated clock unit. The invention has the beneficial effects that two-stage synchronous triggers are used on two main paths of high-level output triggering and asynchronous fine phase shift clock signals. Delay of different paths is balanced. Meanwhile, the rising edge of the input clock is prevented from being very close to the rising edge of the fine phase shift clock trigger signal. The clock management module is used for obtaining four paths of signals with the phase difference of 90 degrees, and after the four paths of phase shift clock signals pass through the gating clock unit and the fine delay module,the response speed of digital switch converter voltage regulation and control is increased.

Owner:HEFEI UNIV OF TECH

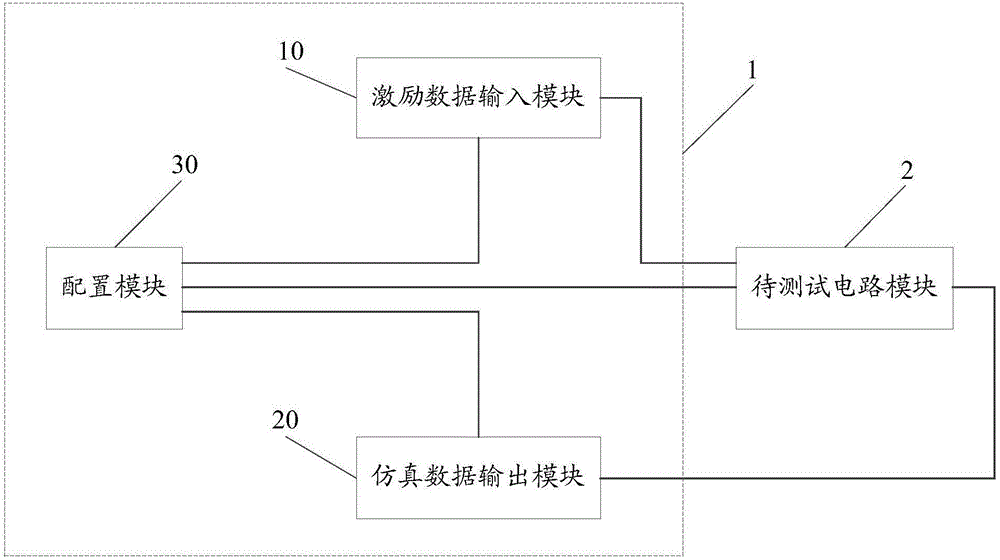

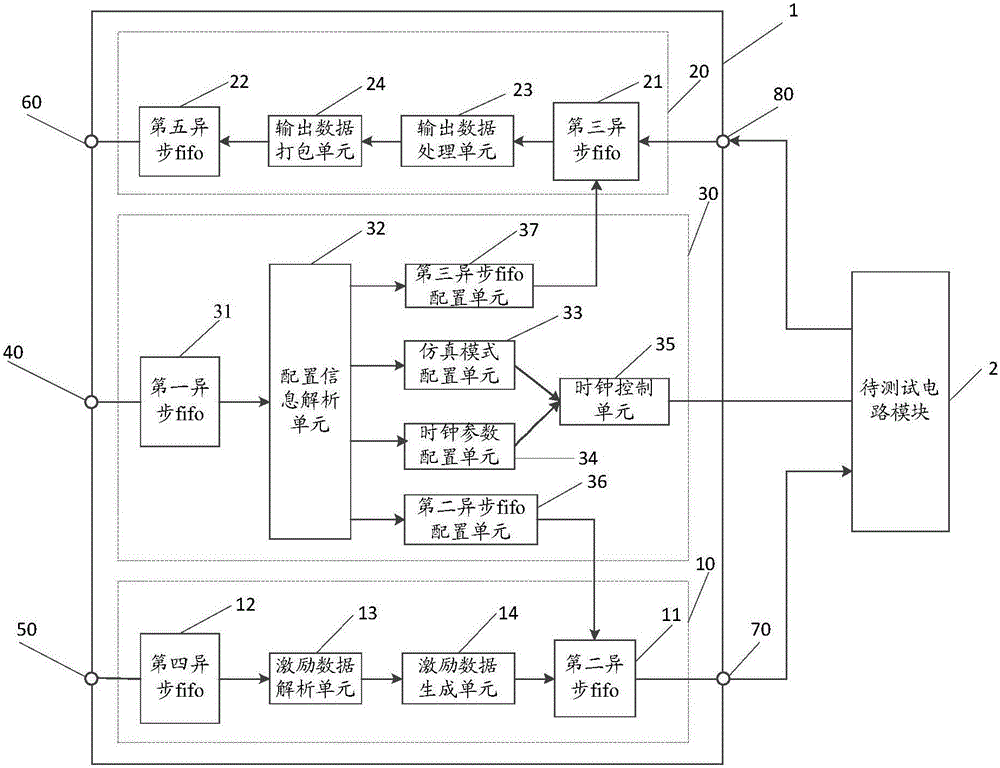

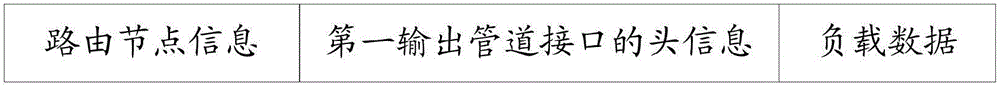

Software-and-hardware collaborative simulation trading device and simulation system

ActiveCN106126854AEasy to expand functionsFlexible useCAD circuit designSpecial data processing applicationsCo-simulationDependability

The invention provides a software-and-hardware collaborative simulation trading device and a simulation system. The trading device comprises an incentive data input module, a simulation data output module and a configuration module, wherein the incentive data input module is connected with a to-be-test circuit module in an FPGA and used for receiving packaged incentive data, obtaining incentive data according to the packaged incentive data and sending the incentive data to the to-be-test circuit module; the simulation data output module is connected with the to-be-test circuit module and used for receiving simulation waveform data generated by the to-be-test circuit module, packaging the simulation waveform data and outputting the packaged simulation waveform data; the configuration module is respectively connected with the incentive data input module, the simulation data output module and the to-be-test circuit module and used for receiving configuration information and configuring the incentive data input module, the simulation data output module and the to-be-test circuit module according to the configuration information. The software-and-hardware collaborative simulation trading device is a module which is independent of a software-and-hardware collaborative simulation system, function expansion is more convenient, and the reliability and the portability are good.

Owner:HEFEI HAIBENLAN TECH

Method and apparatus for synchronizing data between different clock domains in a memory controller

InactiveUS20070041264A1Prevent metastability associateAvoid metastabilityDigital storageSingle machine energy consumption reductionMemory controllerMetastability

The present invention provides method and apparatus for synchronizing data between different clock domains in a memory controller. In one embodiment, a memory controller is provided that includes a command decoder and synchronizing logic. The command decoder is operable to receive a command in accordance with a first clock domain. The synchronizing logic synchronizes the command to a second clock domain that is different from the first clock domain, and includes a first synchronization flop and a second synchronization flop operable to prevent metastability associated with synchronizing the command to the second clock domain.

Owner:ATMEL CORP

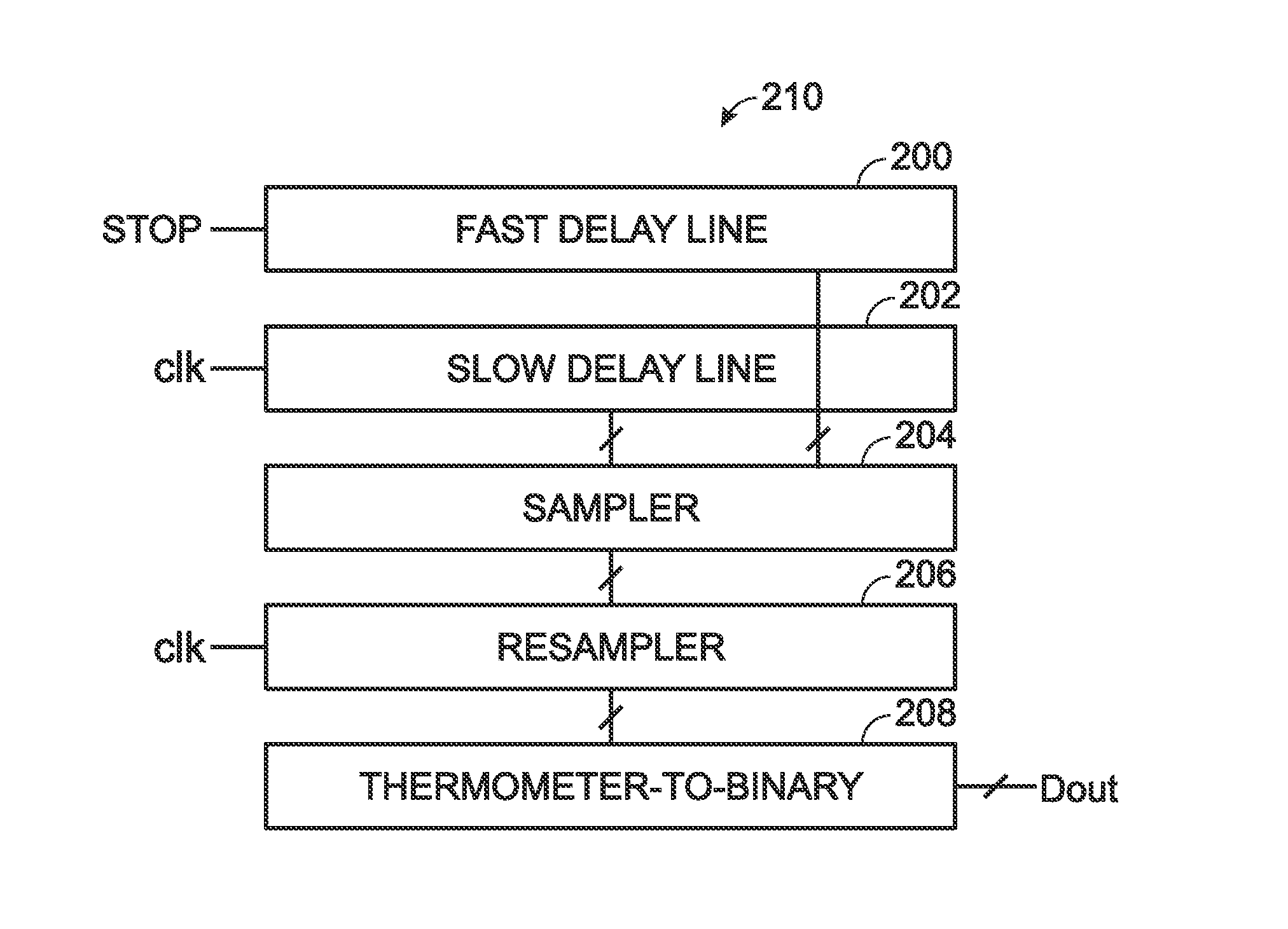

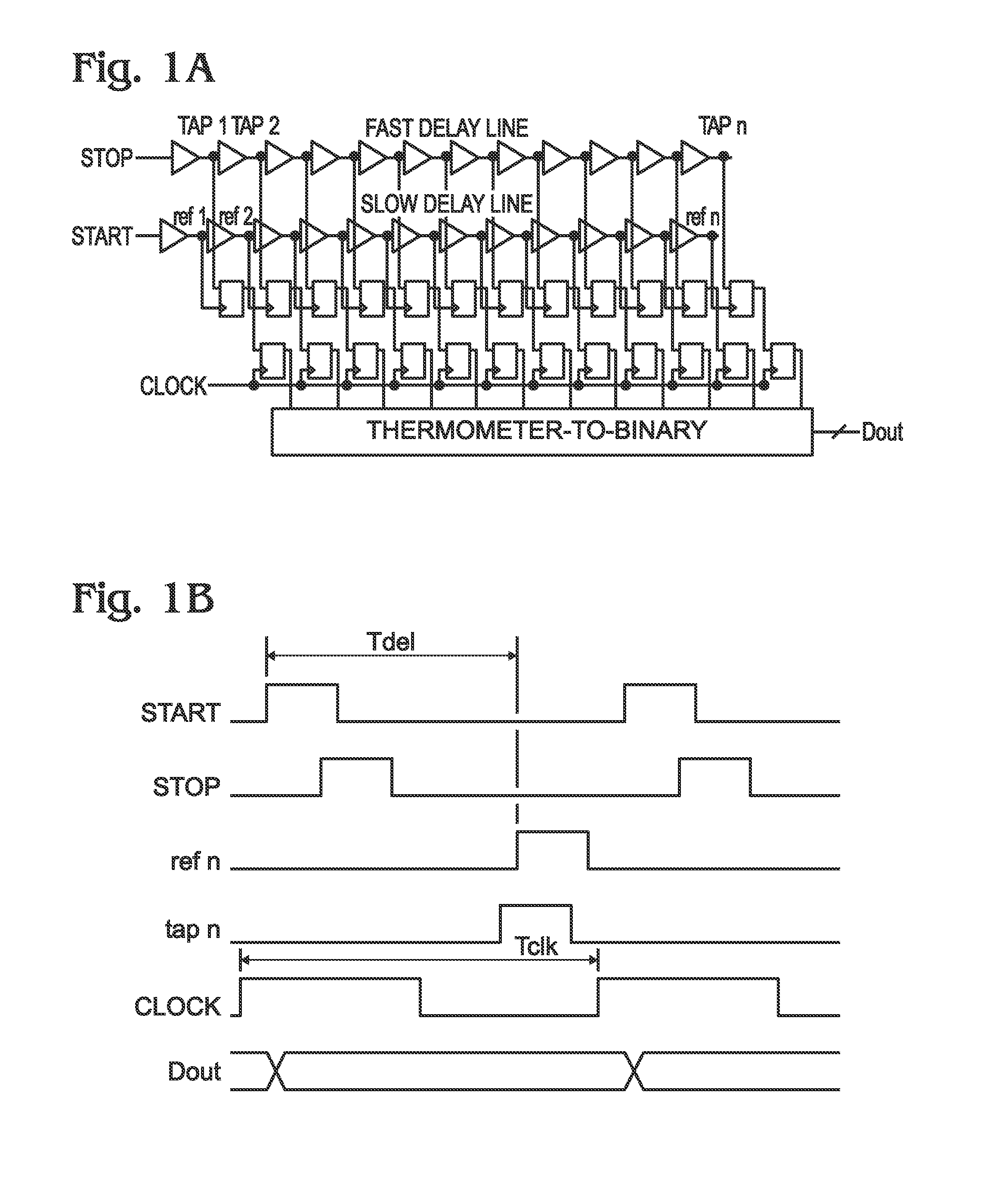

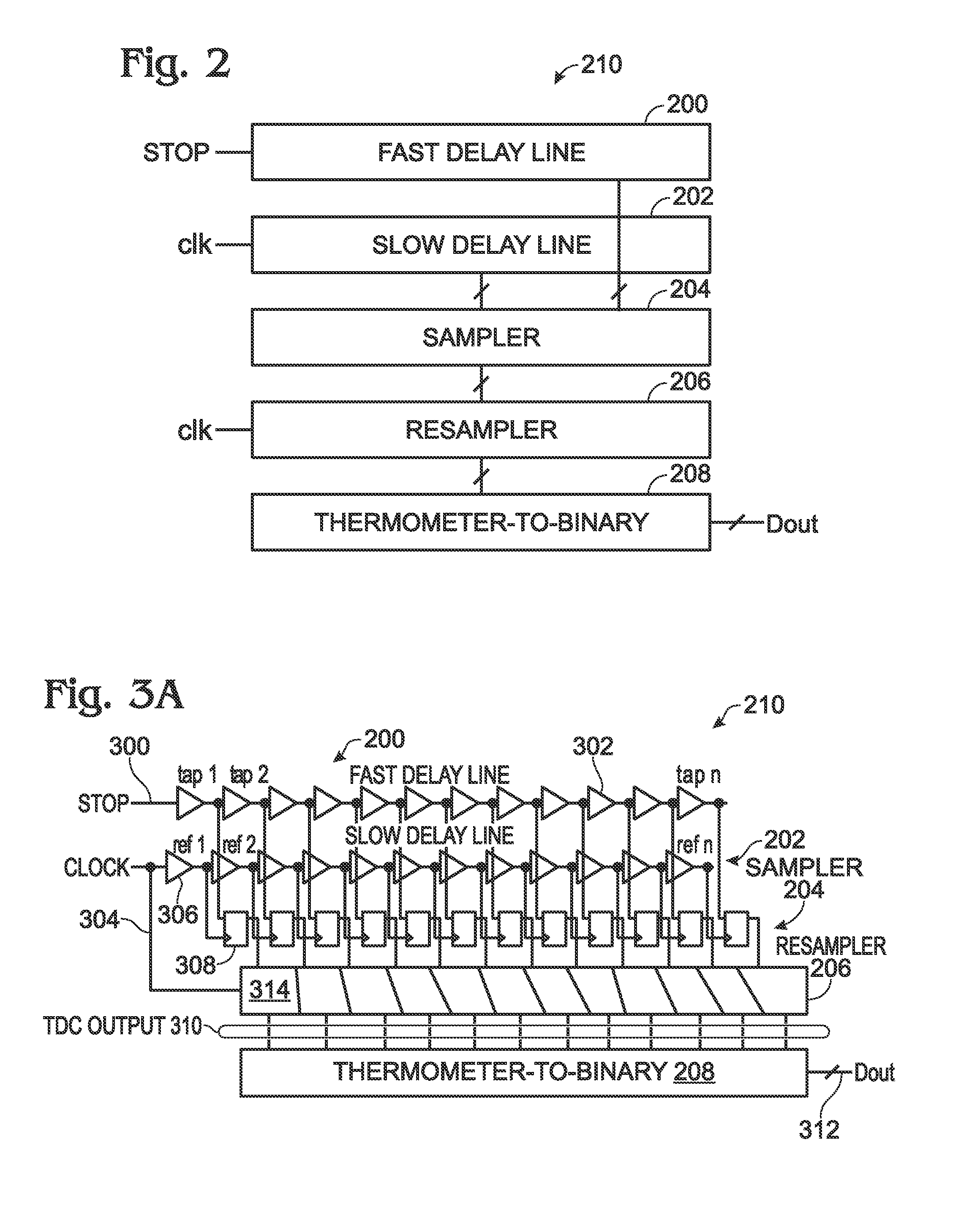

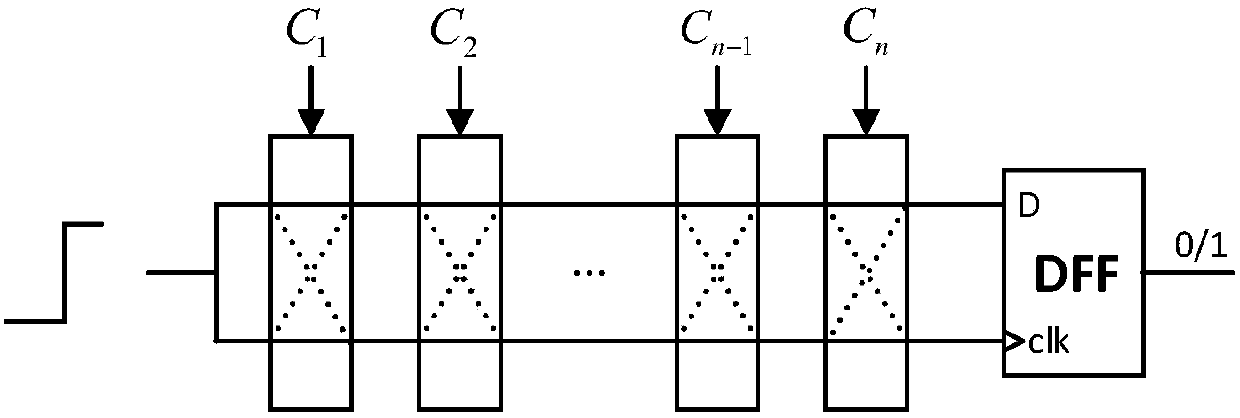

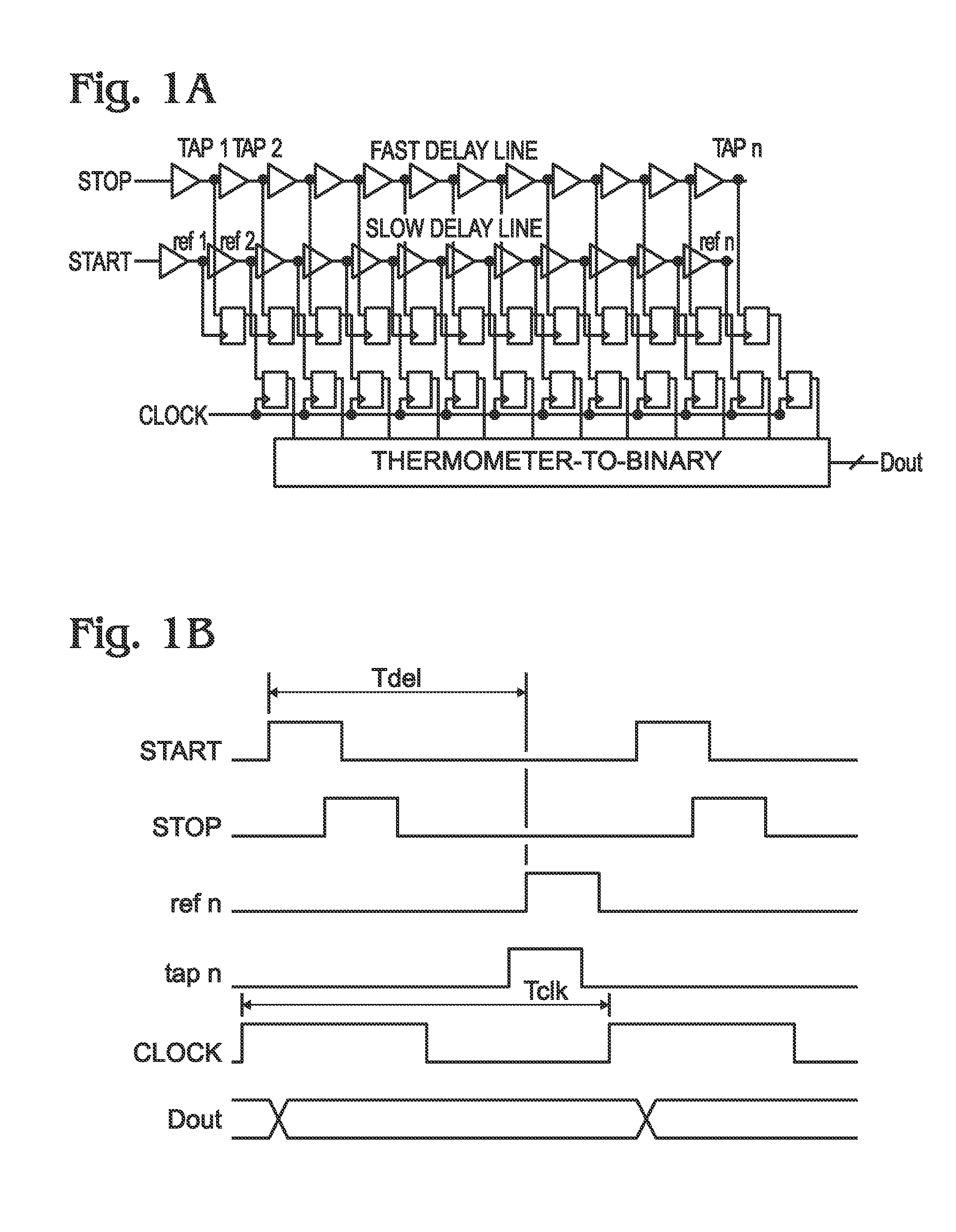

Traveling Pulse Wave Quantizer

ActiveUS20150212494A1Avoid metastabilityElectric signal transmission systemsAnalogue-digital convertersTime delaysEngineering

A Traveling Pulse Wave Quantization method is provided for converting a time sensitive signal to a digital value. A first stop signal is delayed by a first time delay, a first plurality of times, to create a delayed first stop signal. A clock signal is delayed by a second time delay, a first plurality of times, to create a delayed clock signal first period. Each second time delay is associated with a corresponding first time delay, and the second time delay is greater than the first time delay. When the delayed first stop signal occurs before the delayed clock signal first period, a count of the delays is stopped and converted into a digital or thermometer value. An accurate resampled value is provided regardless of the duration in delay between the first stop signal and a second stop signal that is accepted after the first stop signal.

Owner:IQ ANALOG

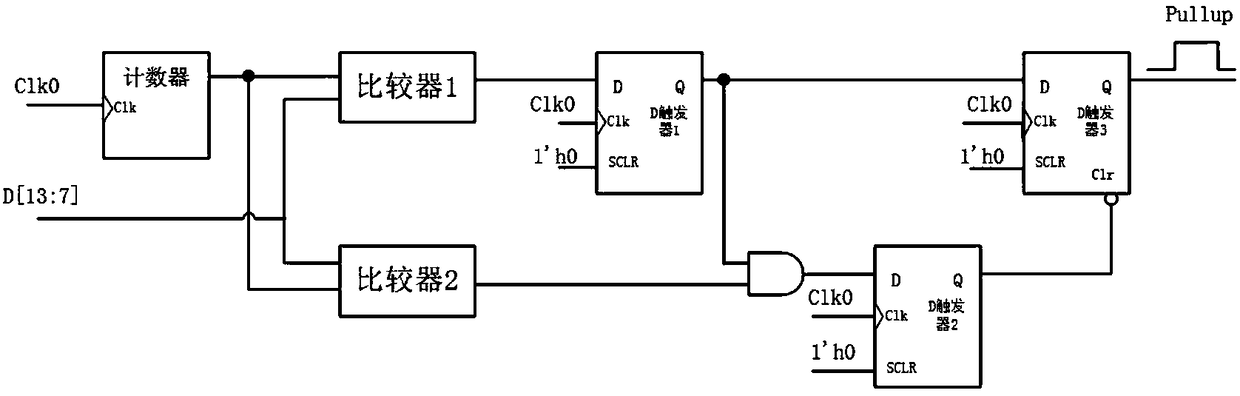

Synchronous hybrid delayed type DPWM module based on FPGA

ActiveCN108155894AImprove time resolutionImprove linearityPulse duration/width modulationDc dc converterFpga implementations

The invention discloses a synchronous hybrid delayed type DPWM structure obtained on the basis of an FPGA. A sub-module of the DPWM structure comprises a rising edge triggering circuit based on a counter, a synchronous clock generation module based on a phased-locked loop (PLL), a falling edge triggering circuit, a pulse width modulating wave output module based on a register, and a duty ratio synchronous encoding module. The linearity and stability of the time resolution ratio and duty ratio of a pulse width modulator can be improved, the ripple waves and stable time of a DC-DC converter arereduced and shortened, and the overshooting and ringing in the modulating process are restrained and weakened; meanwhile, due to the hybrid structure of the counter and a delay chain, the defects thata monotonous structure is limited in frequency and too large in occupied resource can be avoided, the working frequency range of the DPWM is expanded, and the resources occupied by the circuits are educed.

Owner:HEFEI UNIV OF TECH

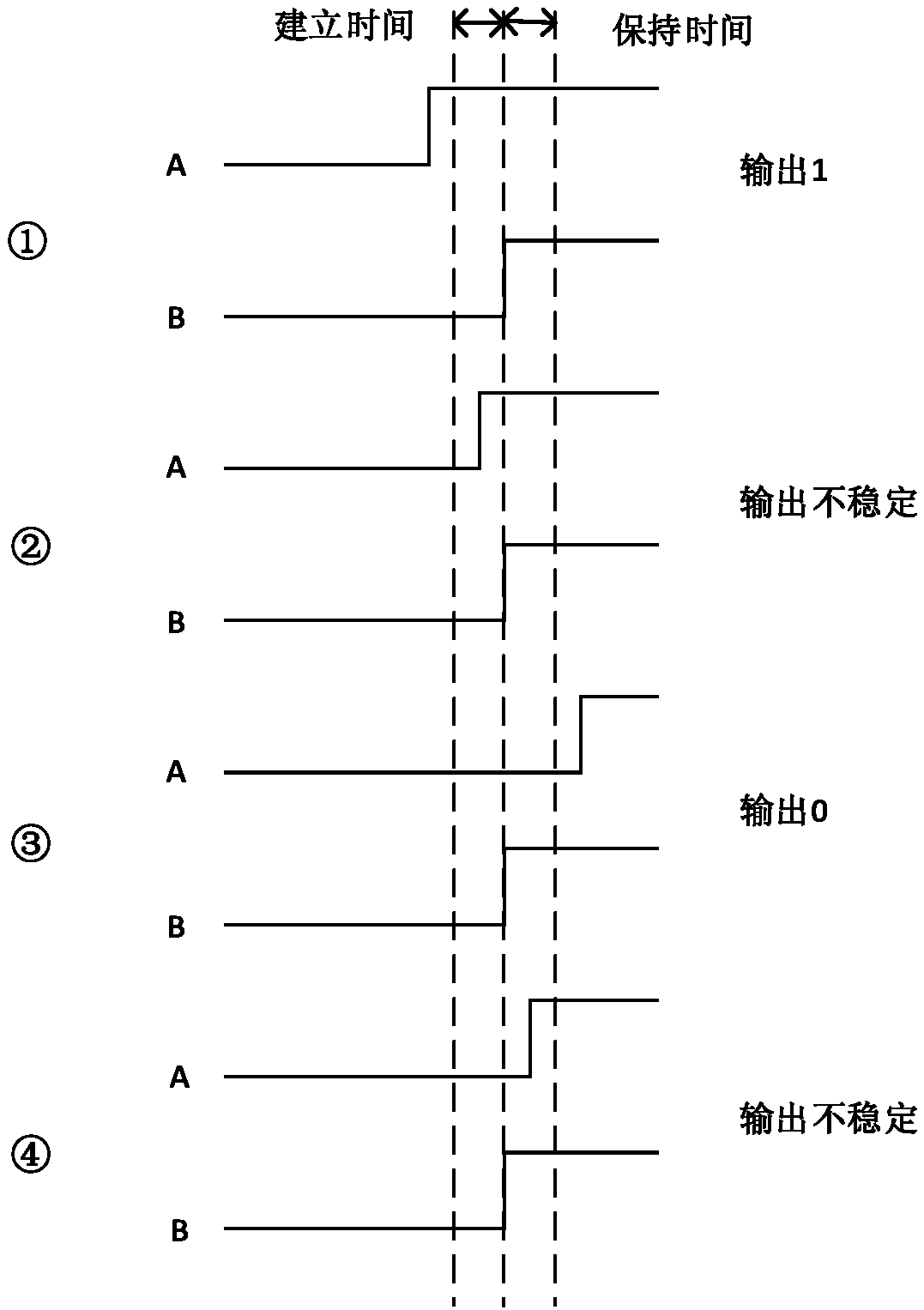

High-stability APUF circuit based on feedback time delay differential adjustment

ActiveCN107729774AImprove stabilityAvoid metastabilityUser identity/authority verificationInternal/peripheral component protectionStable stateResource consumption

The invention discloses a high-stability APUF circuit based on feedback time delay differential adjustment. The circuit comprises a PUF delay chain module, a positive hopping signal loading module, afeedback control module, a timer module and an arbiter. The positive hopping signal output by the PUF delay chain module is fed back to be applied to the PUF delay chain module again, the difference of the time sequence from the positive hopping signals to the arbiter in upper and lower paths is enlarged so as to overcome the semi-stable state of the arbiter, the arbiter stably outputs 0 or 1, andtherefore the APUF stability is improved. The high-stability APUF circuit has the advantages of being high in stability, easy to obtain, low in resource consumption and the like.

Owner:SOUTHEAST UNIV

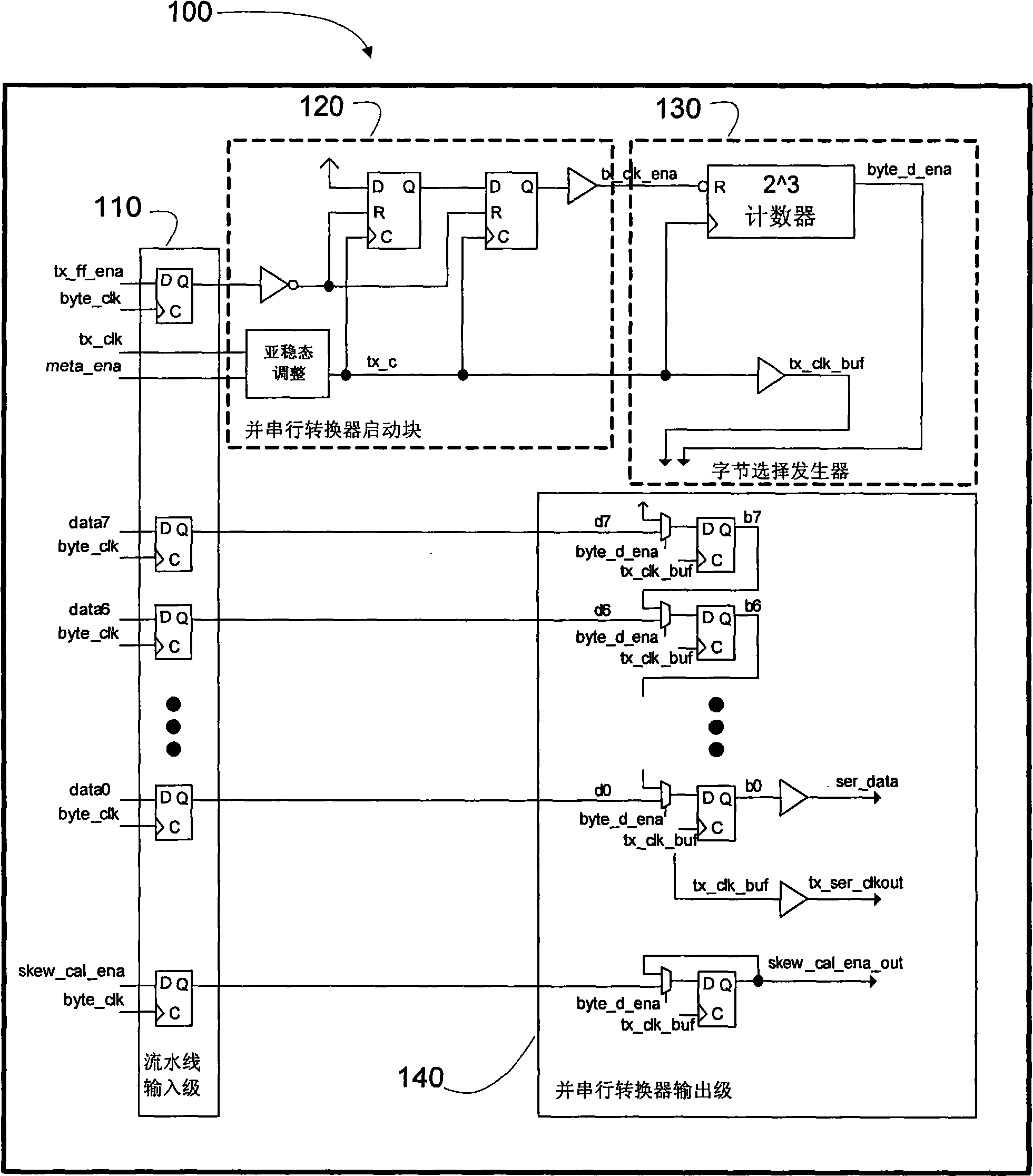

High speed serializer/deserializer transmit architecture

InactiveCN101536318AAvoid metastabilityAvoid control logicParallel/series conversionPulse manipulationNOR gateComputer science

A Serializer / Deserializer (100; 400) apparatus comprises a serializer (100; 400) adapted to take N parallel bits of data and shifts them out serially at N times a clock speed to a transmitter, a transmitter enable block (110, 120, 420) adapted to start the serializer means, and a count block (130; 430). The serializer comprises flip-flops and muxes, and is adapted to N parallel bits of data and shifts them out serially at N times a clock speed to a transmitter. The transmitter enable block (110, 120; 420) comprises an inverter and flip-flops, and is adapted to start the serializer. The count block may comprise a counter or an inverter, f lip-flops,, and a NOR gate, and is adapted to create a divided clock which programs data loading in the serializer.

Owner:QUALCOMM INC

Control circuit for converting asynchronous interface into synchronous interface

ActiveCN108268416AImprove conversion efficiencyAvoid metastabilityElectric digital data processingComputer hardwareControl circuit

The invention discloses a control circuit for converting an asynchronous interface into a synchronous interface and relates to the technical field of integrated circuits. According to the control circuit, through combination of a reading clock detection unit, a writing clock detection unit, a first monostable unit, a second monostable unit and a delay control unit, conversion from the asynchronousinterface into the synchronous interface is realized, synchronous transmission of data is completed, communication between the external asynchronous interface and a local synchronous circuit is realized, conversion is completed in one cycle, signal conversion efficiency is improved, and a metastable state is avoided.

Owner:SHENZHEN STATE MICROELECTRONICS CO LTD

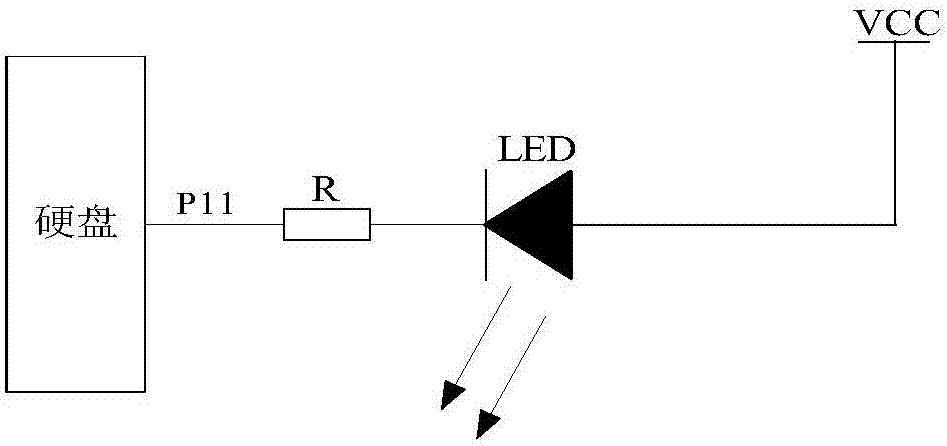

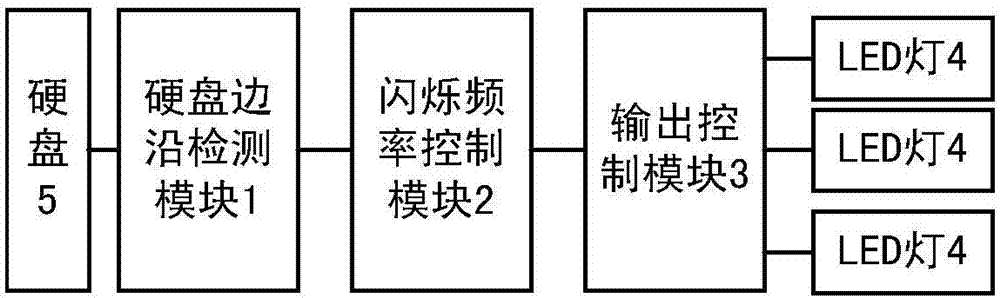

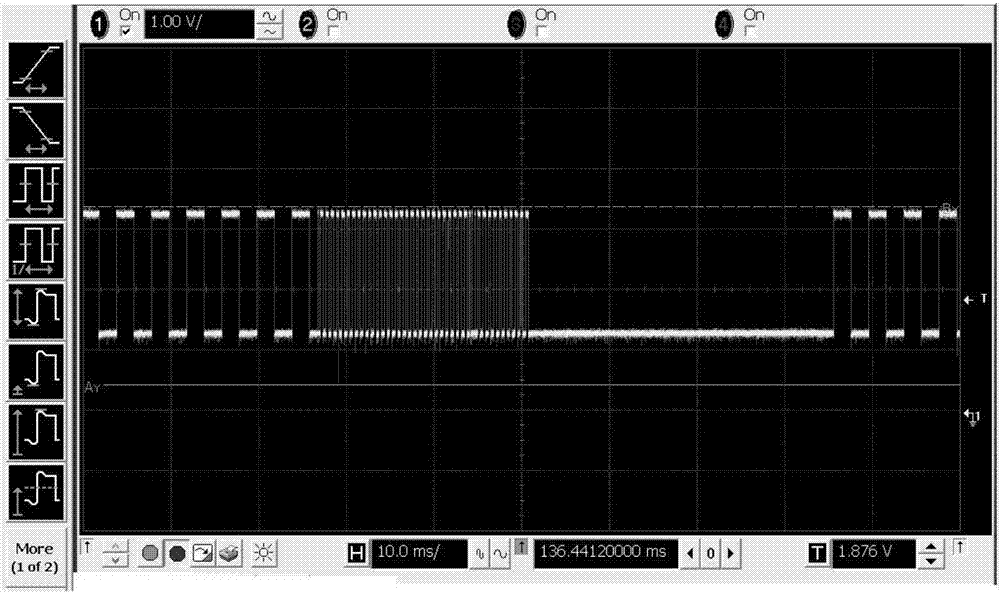

Hard-disc Active-lamp constant-frequency-flickering control system and method

InactiveCN107102933AAvoiding stop misjudgments and metastability problemsAvoid misjudgmentHardware monitoringConstant frequencyElectricity

The invention provides a hard-disc Active-lamp constant-frequency-flickering control system and method. The method includes the steps that reading-and-sporting action information of a hard disc is obtained through a hard-disc edge detection module, and the ACTIVVITY edge information of the hard disc is sent to a flickering frequency control module; the flickering frequency control module receives the ACTIVVITY edges of the hard disc, and all the ACTIVVITY edges of the hard disc are measured through a built-in counter; when the hard disc is located on the ACTIVVITY edges, control signals ACT-OUT are located at the low level, and the hard disc is located at a non-ACTIVITY edge, the control signals ACT-OUT are in the original state; the ACT-OUT level state is detected in real time through an output control module, and when ACT-OUT is located at the low level, LED lamps are controlled to be lighted on; when ACT-OUT is located at the high level, the LED lamps are controlled to be lighted off. Misjudging of users when the flickering frequencies of the LED lamps of all the hard discs are inconsistent is prevented.

Owner:ZHENGZHOU YUNHAI INFORMATION TECH CO LTD

Clock switch circuit

InactiveCN101299159BAvoid metastabilityGenerating/distributing signalsPulse manipulationEngineeringElectrical and Electronics engineering

The invention discloses a clock commutation circuit, which resolves technical problem of producing bur and metastable state. The clock commutation circuit of the invention is composed of two reset producing circuits, two OR gates, three NOT gates, two D-flip-flops and a clock output circuit, the reset producing circuits and the NOT gates constitutes a RS latch. Compared with the prior technology,when the first clock is switched to the second clock, the gating signal of the first clock is switched off when the first clock is at a low level, meanwhile the reset outputting signal of the second RS latch is released, the gating signal of the second clock is switched-on when the second clock is at a low level, thereby avoiding the bur during the clock switch. The reset producing circuit ensuresthat the asynchronous reset terminal of the D-flip-flop executes the synchronization operation to the reset signal through the RS latch circuit when the clock is at a low level, thereby avoiding theproduction of metastable state.

Owner:INVENGO INFORMATION TECH

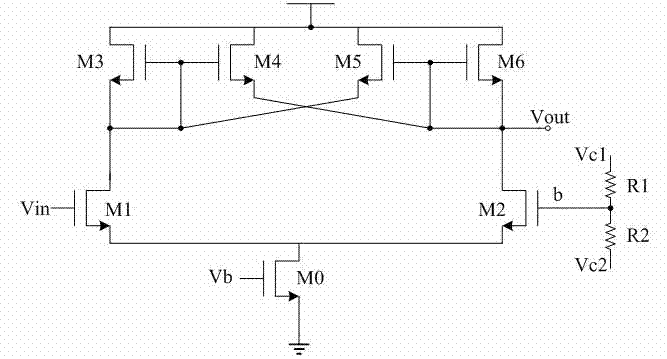

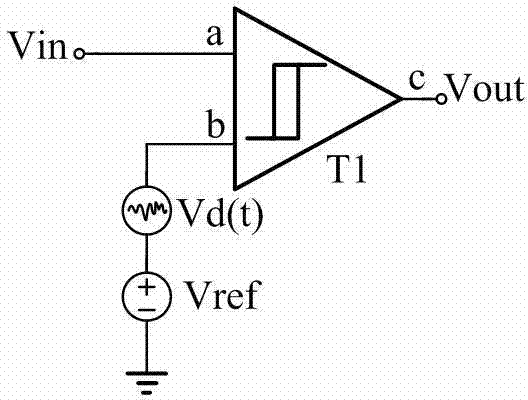

Comparator without metastable state

InactiveCN102355265AAvoid metastabilityAnalogue/digital conversionElectric signal transmission systemsVoltage referenceVoltage source

The invention belongs to the technical field of integrated circuit designing, particularly a comparator without a metastable state. The comparator consists of a reference voltage source Vref, a dithering voltage source Vd(t) and a hysteresis comparator T1. Input voltage Vin is connected with the input end a of the hysteresis comparator T1. The reference voltage source Vref is connected with the input end b of the hysteresis comparator T1 after being connected in series with the dithering voltage source Vd(t) with the direct current level of 0. The output end c of the hysteresis comparator T1 is connected with output voltage Vout. Dithering is added to the reference voltage, thereby avoiding the metastable state of the output of the comparator.

Owner:FUDAN UNIV

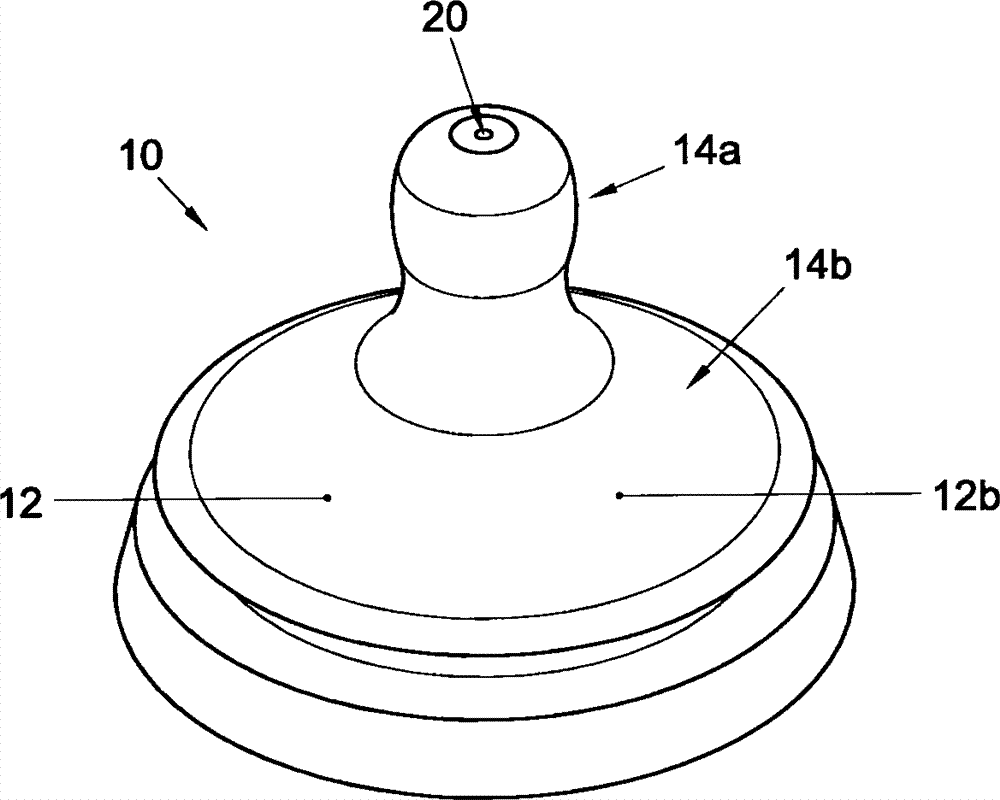

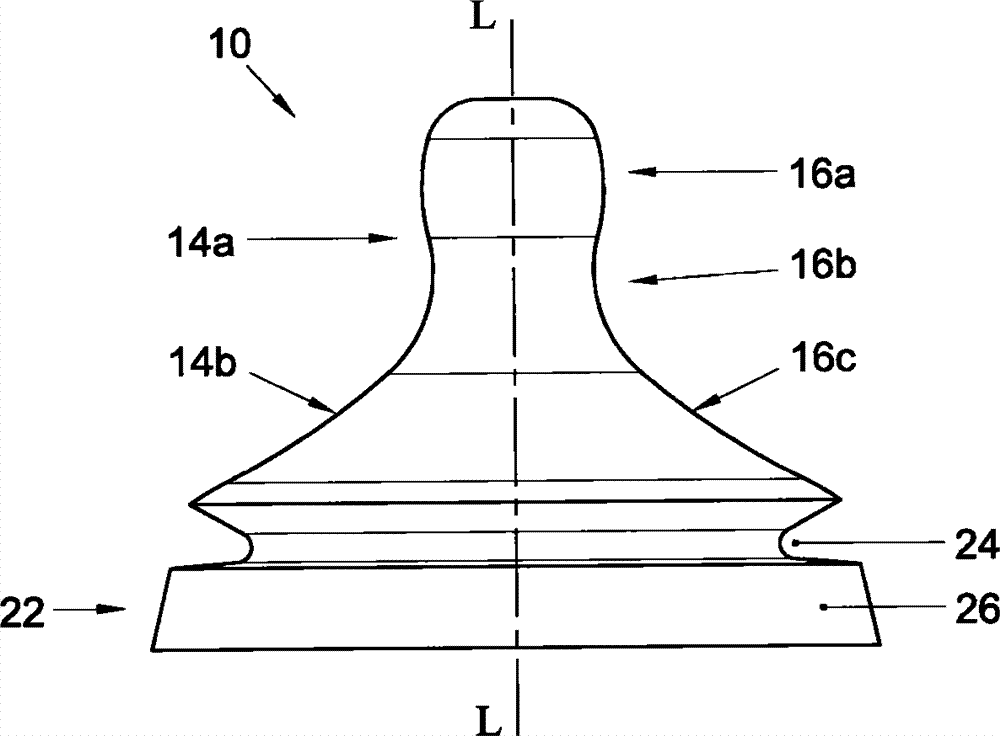

Teat for an infant feeding bottle

A teat (10) for an infant feeding bottle (1), including a resilient wall (12) defining a central nipple (14a) and an areola (14b) that extend around a central axis (L), said teat being elastically transformable between a distended state in which the nipple defines a global maximum (38) and at least one depressed state that is accessible from the distended state by forcing the nipple at least partially into the areola along the central axis, and in which said wall (12) additionally defines an annular double fold (32) that defines an outer local maximum (34) and an inner local minimum (36), both extending circumferentially around the global maximum, wherein the wall defines a circumferential fold region (30) that, in said at least one depressed state, ranges from the local maximum to the local minimum of the double fold, and wherein said fold region has a rotationally asymmetric stiffness distribution.

Owner:KONINKLJIJKE PHILIPS NV

Traveling pulse wave quantizer

ActiveUS9098072B1Avoid metastabilityElectric signal transmission systemsReconfigurable analogue/digital convertersTime delaysPulse wave

A Traveling Pulse Wave Quantization method is provided for converting a time sensitive signal to a digital value. A first stop signal is delayed by a first time delay, a first plurality of times, to create a delayed first stop signal. A clock signal is delayed by a second time delay, a first plurality of times, to create a delayed clock signal first period. Each second time delay is associated with a corresponding first time delay, and the second time delay is greater than the first time delay. When the delayed first stop signal occurs before the delayed clock signal first period, a count of the delays is stopped and converted into a digital or thermometer value. An accurate resampled value is provided regardless of the duration in delay between the first stop signal and a second stop signal that is accepted after the first stop signal.

Owner:AMERICAN RES CAPITAL LLC

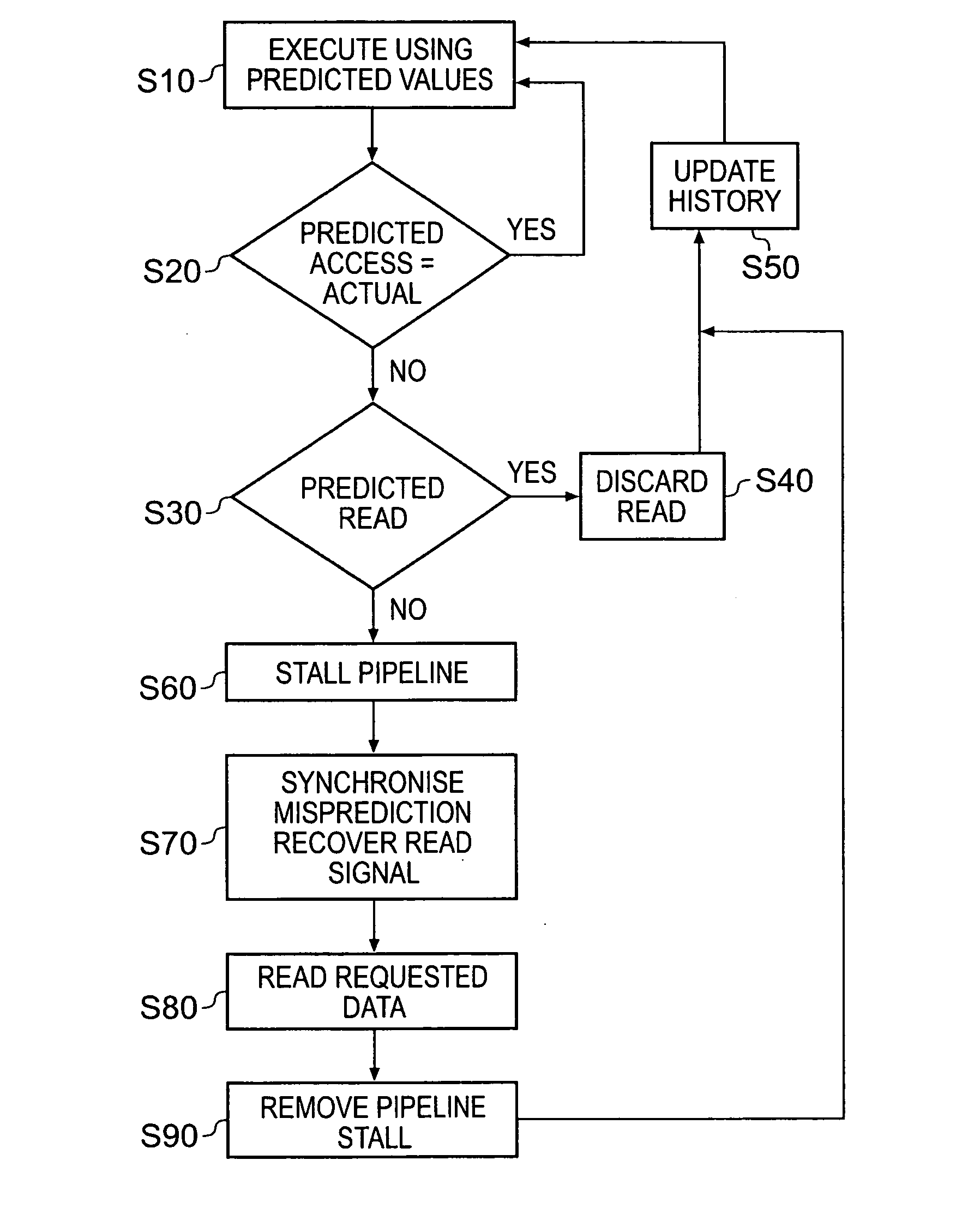

Data access prediction

InactiveUS20060253677A1Reduce throughputAvoid metastabilityDigital storageProgram controlParallel computingData access

A method and integrated circuit for accessing data in a pipelined data processing apparatus in which the operating conditions of the pipelined data processing apparatus are such that metastable signals may occur on at least the boundaries of the pipelined stages is disclosed. The method comprises the steps of: receiving an indication that an instruction is to be processed by the pipelined data processing apparatus; generating a memory access prediction signal, the memory access prediction signal having a value indicative of whether or not the instruction is likely to cause a read access from a memory; generating a predicted memory access control value from the memory access prediction signal, the predicted memory access control value being generated to achieve and maintain a valid logic level for at least a sampling period thereby preventing any metastability in the predicted memory access control value; and in the event that the predicted memory access control value indicates that a read access is likely to occur, causing a read access to be initiated from the memory. Through this approach, an indication that an instruction is to be processed by the pipelined data processing apparatus is received and a memory access prediction signal indicative of whether or not the instruction is likely to cause a read access from a memory is then generated. The predicted memory access control signal is generated in a way which prevents any metastability being present in that signal. Hence, the signals used in a read access are prevented from being metastable which removes the possibility that metastable signals are used directly in the arbitration of data accesses. Also, the metastable signals may be prevented from being propagated from stage to stage.

Owner:ARM LTD

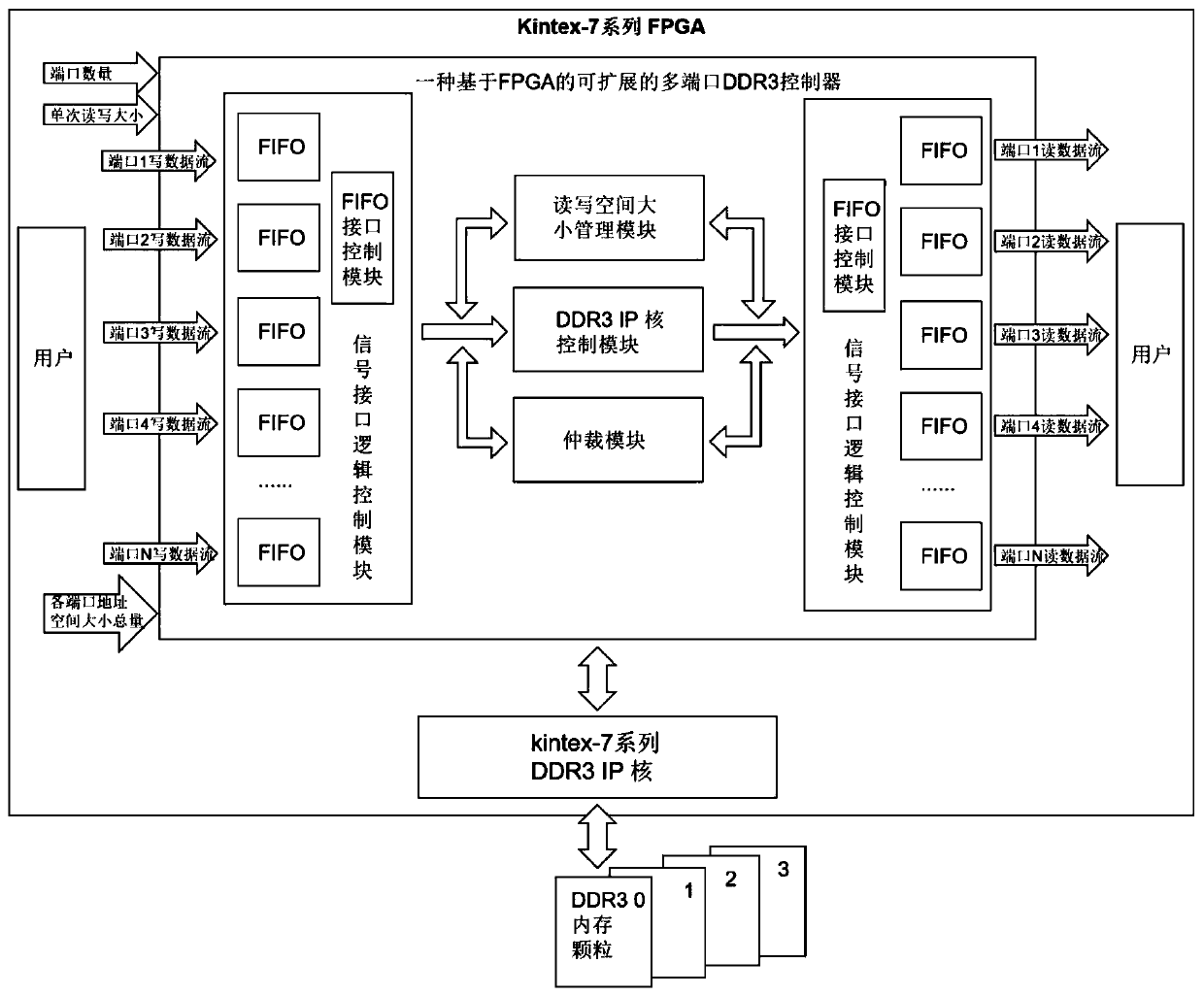

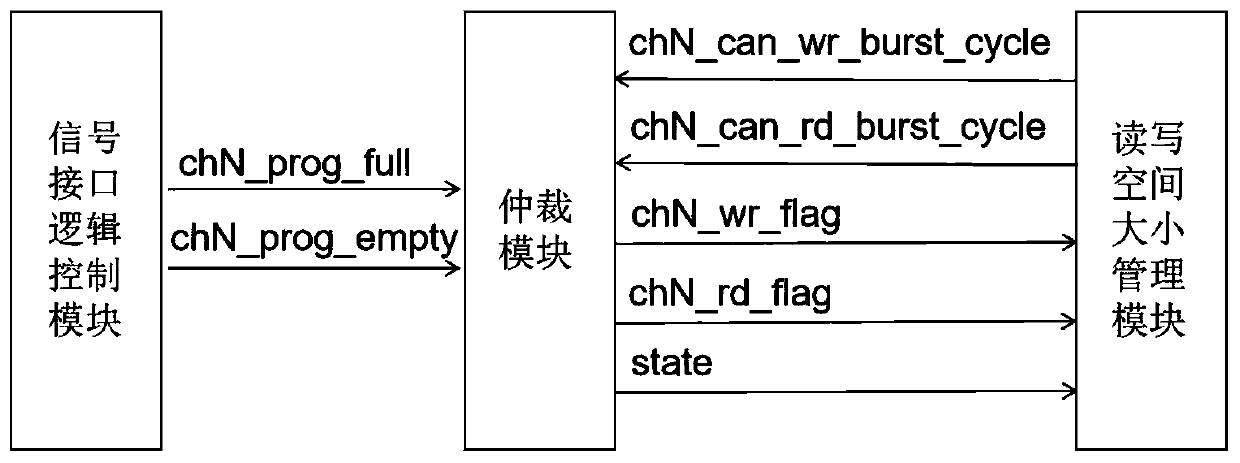

Extensible multi-port DDR3 controller based on FPGA

ActiveCN111581132AEasy to read and writeAvoid metastabilityArchitecture with single central processing unitElectric digital data processingComputer architectureElectrical connection

The invention relates to the technical field of communication, and especially relates to an extensible multi-port DDR3 controller based on an FPGA. The controller comprises an arbitration module, a read-write space size management module, a DDR3 IP core control module and an FIFO interface control module, and the arbitration module, the read-write space size management module, the DDR3 IP core control module and the FIFO interface control module are electrically connected in sequence. The arbitration module is used for comprehensively arbitrating and managing the read-write request of each port according to the size of the read-write residual available address space provided by the read-write space size management module, the FIFO capacity threshold corresponding to each port and the priority information of each port arranged according to the actual demand. The controller has a standard FIFO read-write interface form, the number of ports is configurable, the size of single read-writeis configurable, the total size of the address space of each port is configurable, and the read-write priority arbitration of each port is provided in the controller.

Owner:ウーハン ジョンケ ニウジン マグネティック レゾナンス テクノロジー カンパニー リミテッド

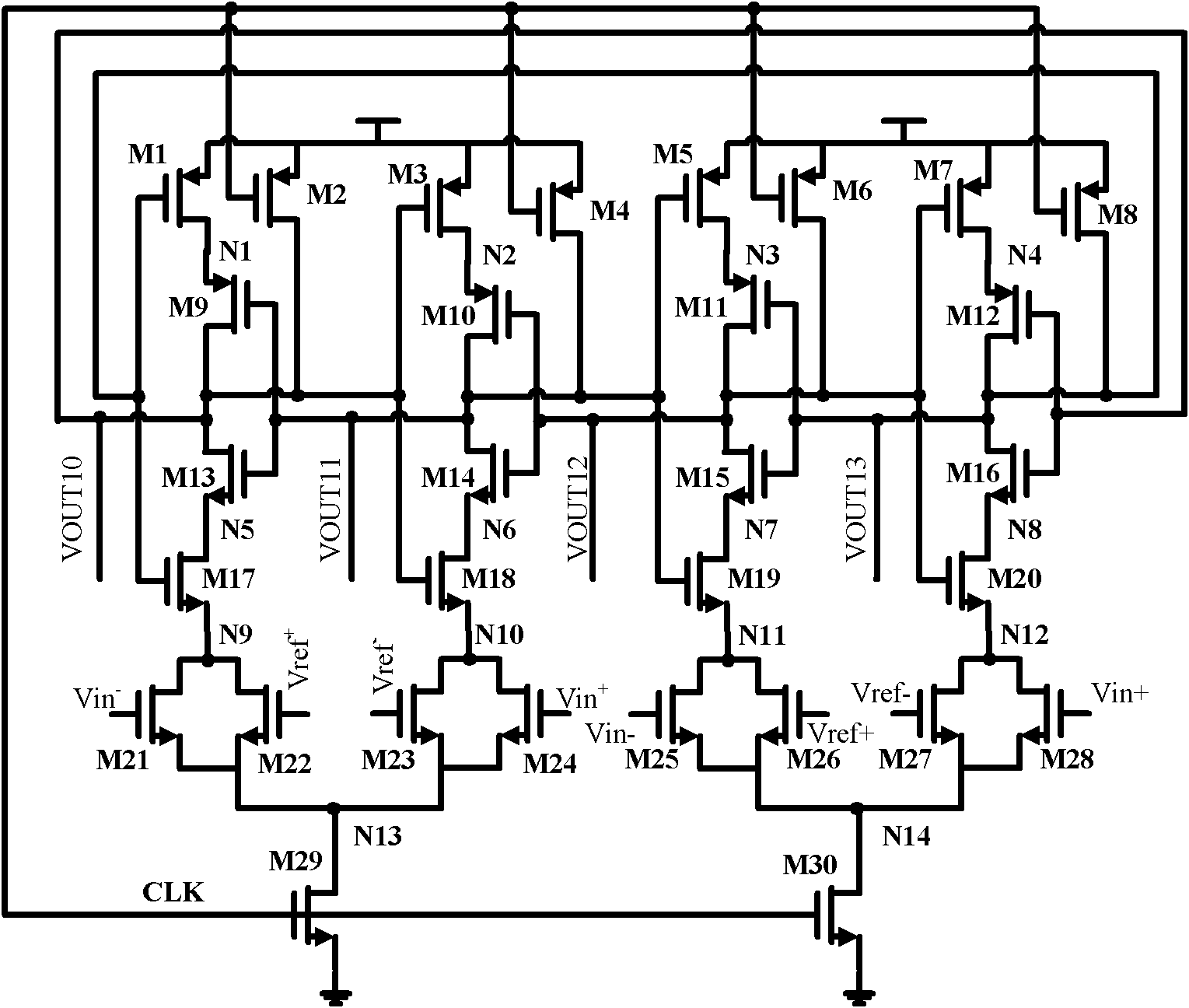

SEU (single event upset)/SET (single event transient)-resistant dynamic comparator

InactiveCN102025351BReduce power consumptionLower latencyMultiple input and output pulse circuitsAudio power amplifierVoltage reference

The invention discloses an SEU (single event upset) / SET (single event transient)-resistant dynamic comparator, which comprises a pulse generating circuit based on a sensitive amplifier structure and an output latch circuit; the top of the whole comparator is provided with five input ports and four output ports outwards, the five input ports are respectively connected with clock signals, input signals and reference voltage signals, and the output ports are connected with data output signals; the pulse generating circuit is connected with the clock signals, the input signals, the reference voltage signals and the output latch circuit; and the output latch circuit is connected with the pulse generating circuit and the data output signals. The dynamic comparator has the advantages that the upset threshold LETth is greater than 500MeV / (mg.cm2); the time delay is reduced while the high-speed low power consumption of the SEU / SET-resistant dynamic comparator same as that of a traditional dynamic comparator is achieved; the symmetrical arrangement, equal time delay and same drive capacity of complementary output terminals Q and QB are realized; by adopting the sensitive amplifier structure, the clock network is simple, reliable and small in load; and by adopting the minor clock swing technology, the power consumption is obviously reduced.

Owner:XI AN JIAOTONG UNIV

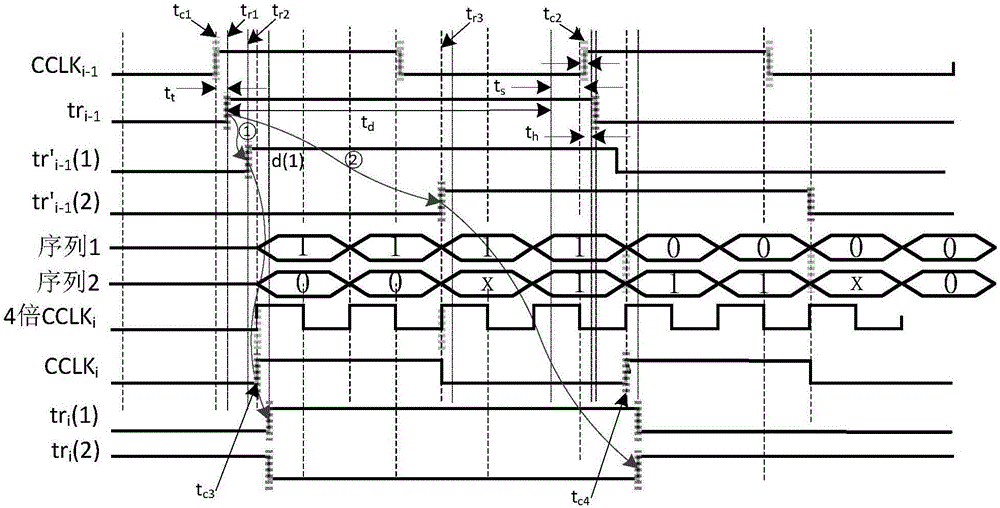

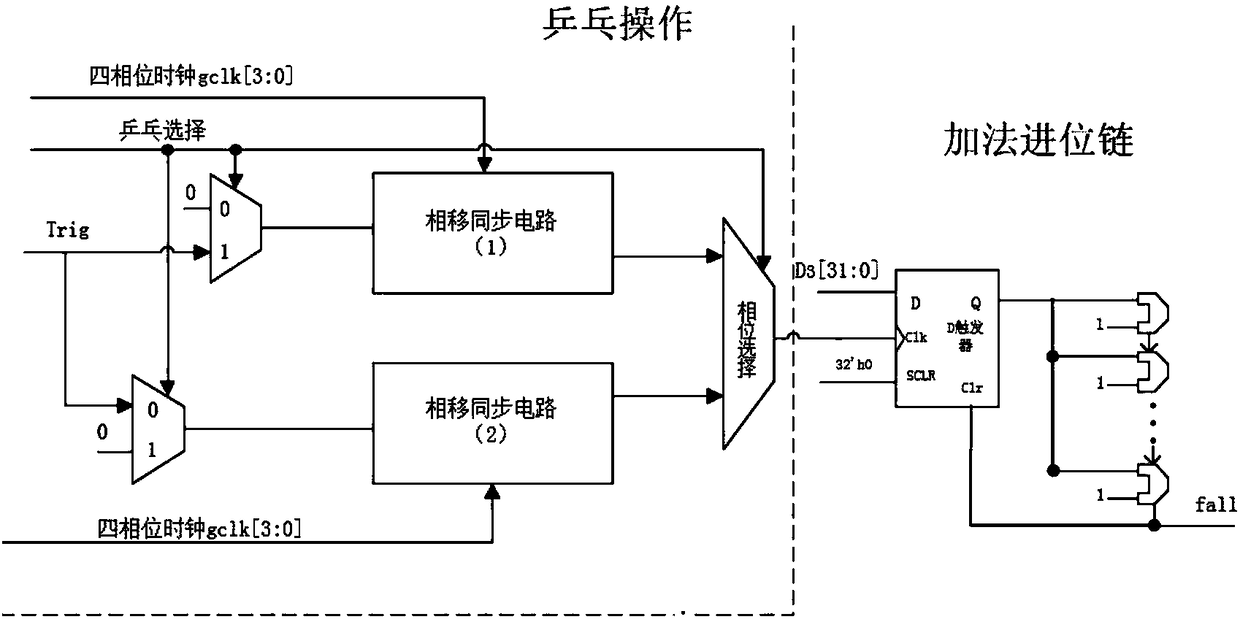

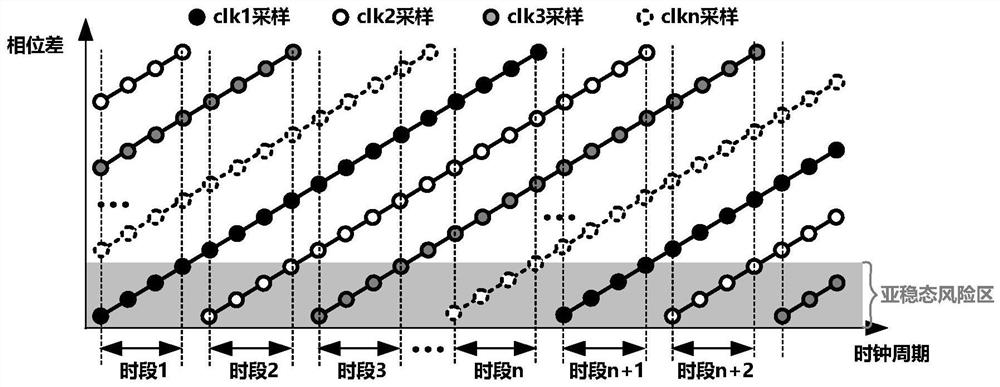

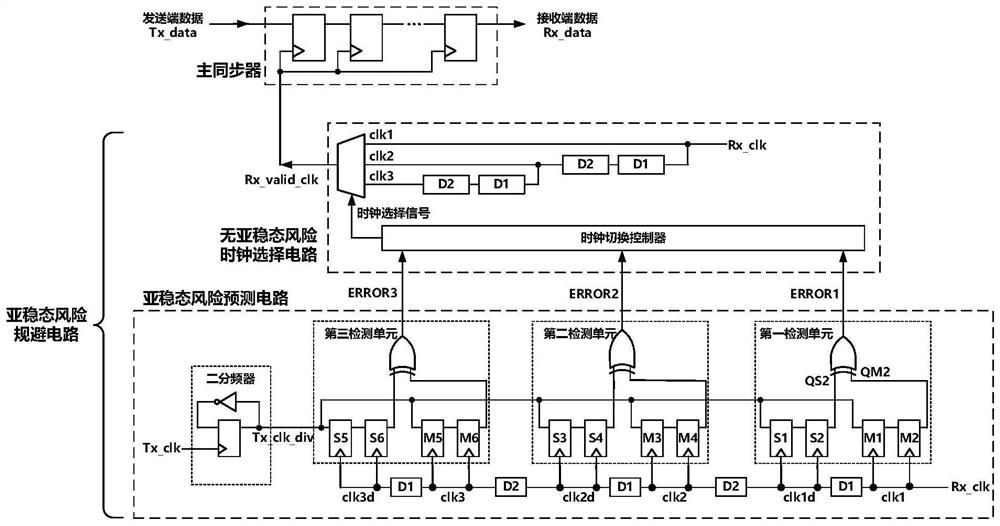

Metastable state risk avoidance method and circuit in cross-clock domain data transmission

PendingCN114356833AImprove reliabilityReliable data transfer across clock domainsDigital computer detailsGenerating/distributing signalsEngineeringData transmission

The invention relates to a metastable-state risk avoidance method and circuit in cross-clock-domain data transmission, and the method comprises the steps: constructing a plurality of receiving end clocks with the same frequency and different phases, sampling transmitting end data in the whole receiving end clock period, and determining the metastable-state risk in the cross-clock-domain data transmission according to the difference of the transmitting end data sampling results of the receiving end clocks with different phases. And judging whether each receiving end clock has a metastable state risk when sampling the data of the sending end in real time, and continuously switching and selecting the receiving end clocks which do not have risks in a future period of time to carry out data communication with the sending end. Compared with the prior art, the method has the advantages that the potential metastable risk can be predicted in advance, and the phase of the effective clock of the receiving end is adaptively adjusted to avoid the imminent metastable risk, so that the reliability of cross-clock domain data transmission is ensured; moreover, the method can be applied to cross-clock domain data transmission of different frequency relationships through simple modeling simulation, does not need to carry out a data test or experiment in advance, and is convenient to use.

Owner:SHANGHAI JIAO TONG UNIV

Control of metastability in the pipelined data processing apparatus

ActiveUS20080209152A1Reduce throughputAvoid metastabilityConcurrent instruction executionDigital storageProcessing InstructionData access

A method and integrated circuit for accessing data in a pipelined data processing apparatus in which the operating conditions of the pipelined data processing apparatus are such that metastable signals may occur on at least the boundaries of the pipelined stages is disclosed. The method comprises the steps of: receiving an indication that an instruction is to be processed by the pipelined data processing apparatus; generating a memory access prediction signal, the memory access prediction signal having a value indicative of whether or not the instruction is likely to cause a read access from a memory; generating a predicted memory access control value from the memory access prediction signal, the predicted memory access control value being generated to achieve and maintain a valid logic level for at least a sampling period thereby preventing any metastability in the predicted memory access control value; and in the event that the predicted memory access control value indicates that a read access is likely to occur, causing a read access to be initiated from the memory. Through this approach, an indication that an instruction is to be processed by the pipelined data processing apparatus is received and a memory access prediction signal indicative of whether or not the instruction is likely to cause a read access from a memory is then generated. The predicted memory access control signal is generated in a way which prevents any metastability being present in that signal. Hence, the signals used in a read access are prevented from being metastable which removes the possibility that metastable signals are used directly in the arbitration of data accesses. Also, the metastable signals may be prevented from being propagated from stage to stage.

Owner:ARM LTD

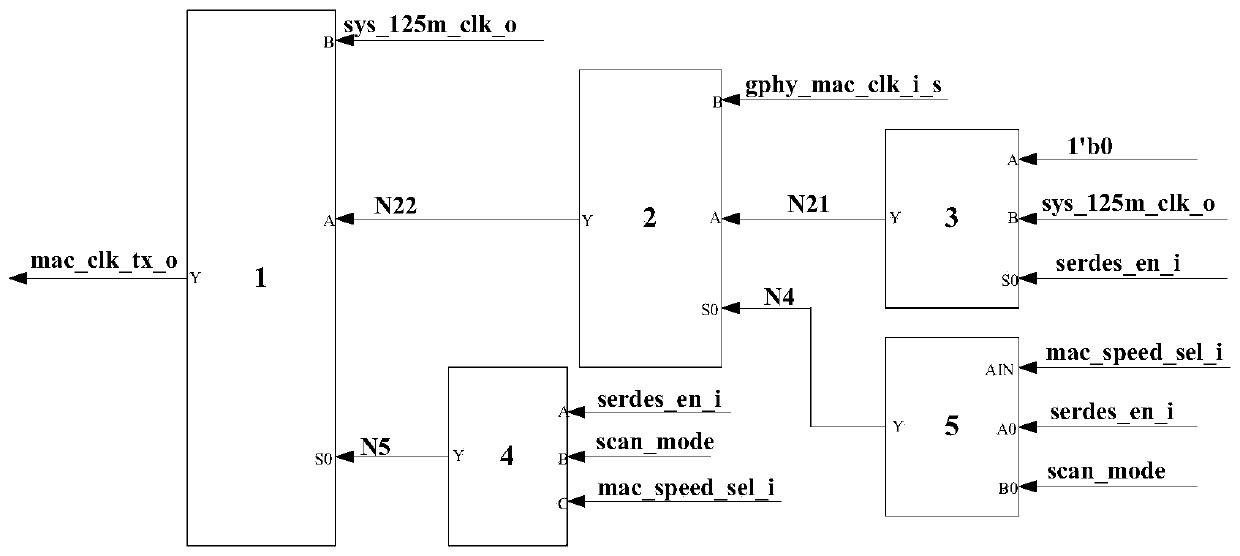

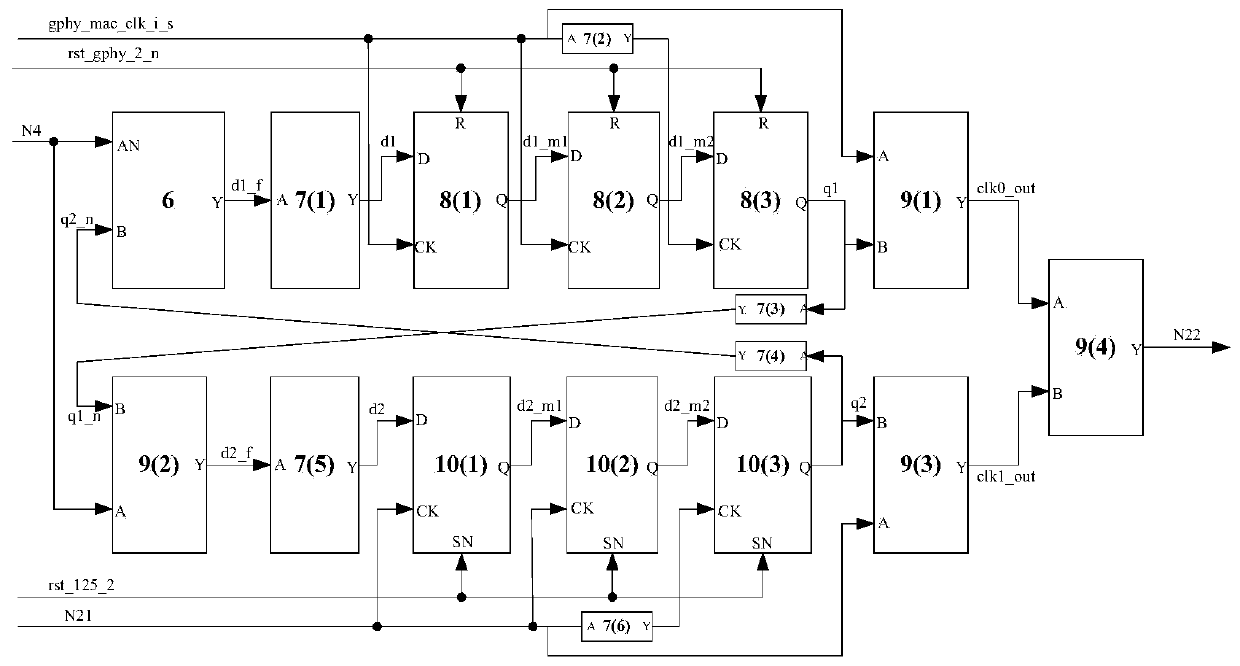

Clock switching circuit of gigabit Ethernet transceiver

ActiveCN111313869ASmooth switchingAvoid the risk of glitches and metastabilityPulse manipulationEmbedded systemTransceiver

The invention provides a clock switching circuit of a gigabit Ethernet transceiver. According to the circuit, smooth switching of different clock domains is achieved through a three-level synchronization and interlocking mechanism, the risk that burrs and metastable states are generated due to clock switching across the clock domains is avoided, the correctness of circuit functions is guaranteed,a correct output clock can be provided during resetting, and the logic function of a chip during resetting is guaranteed.

Owner:XIAN MICROELECTRONICS TECH INST

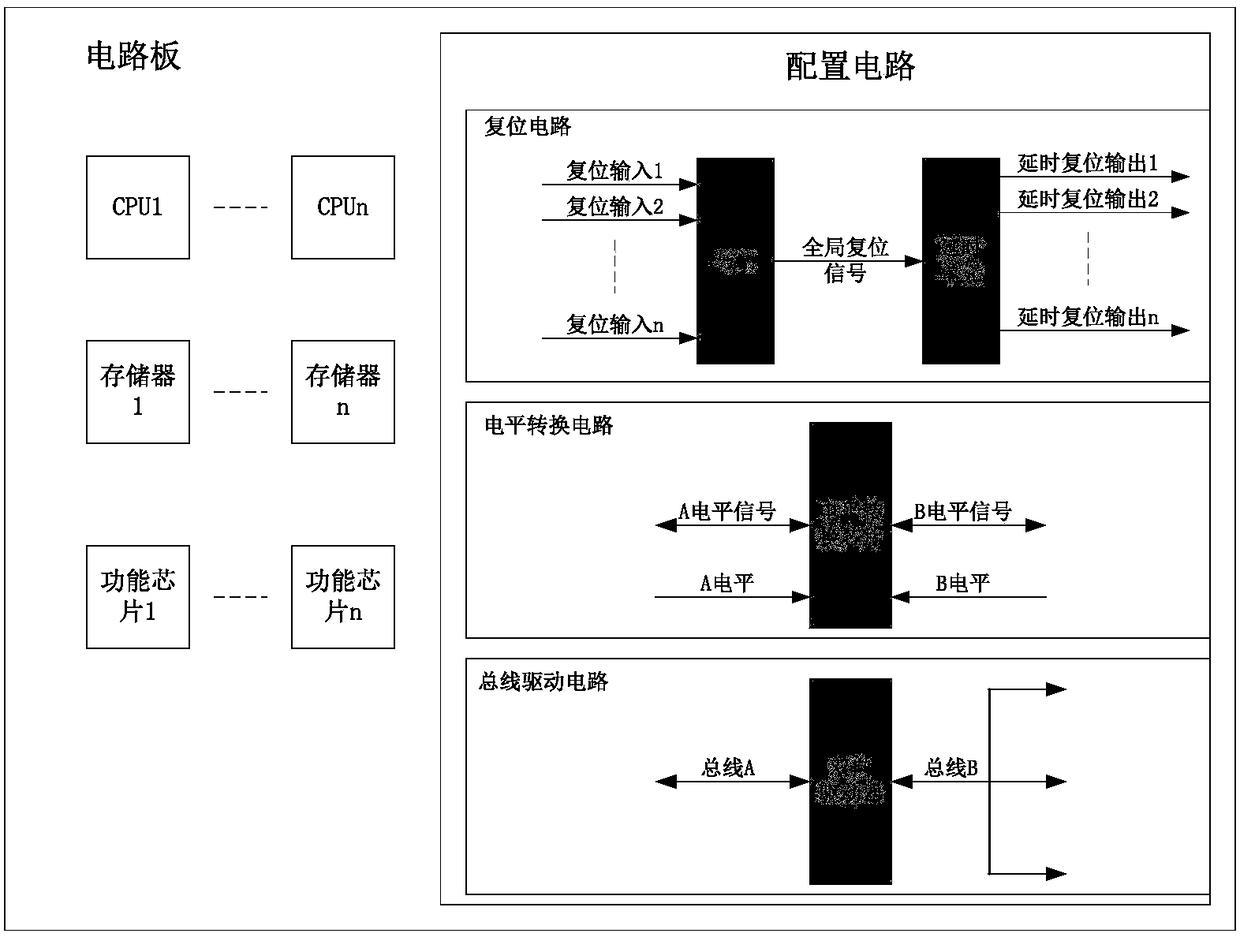

Method for simplifying circuit board configuration circuit

ActiveCN108227607AReduce typesRealize dynamic switchingProgramme control in sequence/logic controllersStable stateProgrammable logic device

The invention belongs to computer hardware technology and relates to an implementation method of a circuit board configuration circuit. According to the invention, a programmable logic device is usedfor implementing functions of resetting, electric level conversion and signal driving and a resetting circuit, an electric level converting circuit and a signal driving circuit using dedicated chips are replaced. According to the invention, no dedicated chips are required, the chip variety is small and the reliability is high. By using the programmable logic device, layout wiring can be simplified. Through a re-programming method, the resetting output and interconnection relation of the configuration circuit can be adjusted. A problem of semi-stable state caused by resetting is solved. Dynamicswitching of a redundancy circuit is realized.

Owner:XIAN AVIATION COMPUTING TECH RES INST OF AVIATION IND CORP OF CHINA

Circuitry for transferring data across reset domains

ActiveUS20210333852A1Reliable indicationAvoid metastabilityData resettingGenerating/distributing signalsComputer hardwarePathPing

An integrated-circuit device comprises a source register in a reset domain, a destination circuit outside the reset domain, and a reset checking circuit. The checking circuit comprises a buffer outside the reset domain for receiving data values output by the source register, a reset detector, and reset checking logic. The checking logic detects a new data value output by the source register, checks whether a reset of the reset domain has been detected, and contingently outputs a control signal for controlling whether the destination circuit receives the new data value from the buffer. The reset detector signals whether a reset has been detected by using a feedback path to hold a predetermined value in a resettable latch until the latch receives a reset signal, and to hold a different value in the latch after receiving a reset signal.

Owner:NORDIC SEMICONDUCTOR

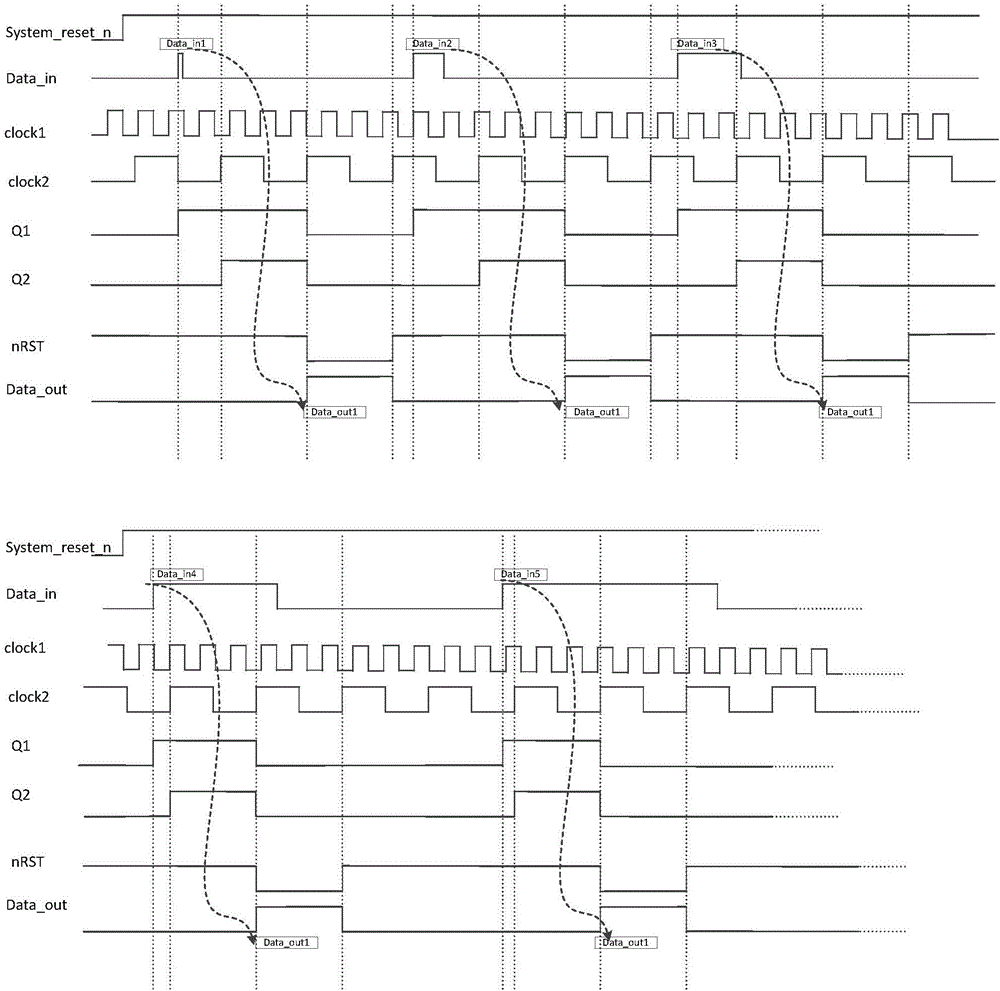

Method for SOC (system on chip) asynchronous clock domain signal interface

ActiveCN106201950ASimple structureGuaranteed not to miss the signalEnergy efficient computingElectric digital data processingStructure of Management InformationComputer science

The invention relates to a method for an SOC (system on chip) asynchronous clock domain signal interface and relates to a design method of the very large scale integration (VLSI) field. The method comprises a clock domain (1), a clock domain (2) and a reset circuit, wherein an input data pulse signal is transmitted to the clock domain (2) from the clock domain (1); the clock domain (1) comprises a first data latch; the clock domain (2) comprises a second data latch and a third data latch; and the reset circuit is mainly composed of one and gate. All the devices in the clock domain (1) realize latching of the input data pulse signal; the devices in the clock domain (2) realize the effects of synchronizing the signal and producing a feedback signal; and the reset circuit eliminates information latched by the first data latch and the second data latch in time according to the feedback signal of the clock domain (2). The method provided by the invention has the advantages that structure is simple, in SOC clock domain crossing design, transmission of two asynchronous clock domain signals can be realized, and metastable state effect is eliminated.

Owner:CENT SOUTH UNIV

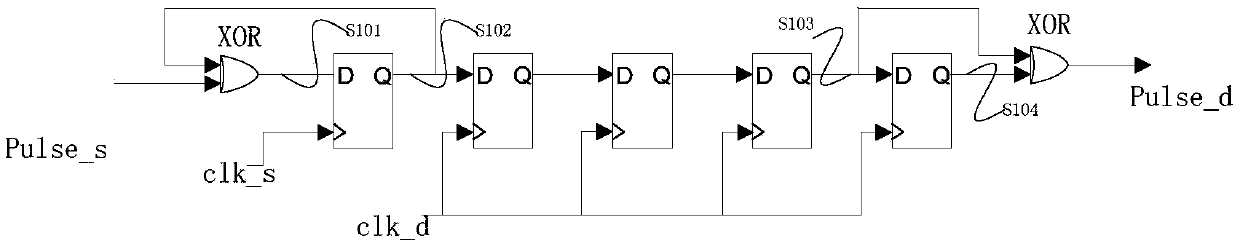

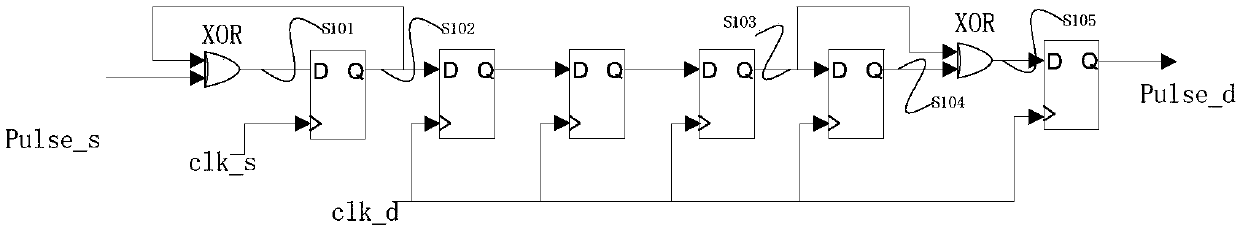

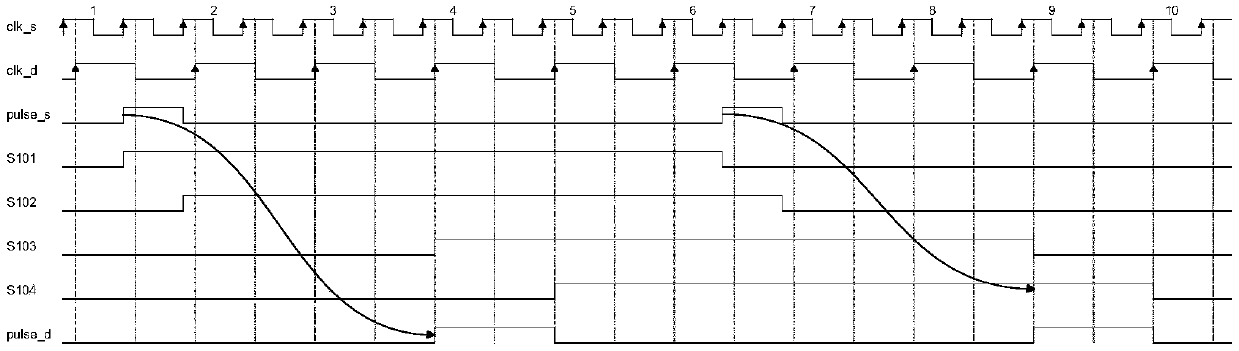

Asynchronous pulse synchronizer

The invention provides an asynchronous pulse synchronizer. The asynchronous pulse synchronizer comprises an input logic unit, a meta-stable elimination unit and an output logic unit; the input logic unit is used for flattening pulse signals of an input clock domain into level signals, wherein an exclusive or gate and a D trigger are included; the meta-stable elimination unit comprises three D triggers; and the output logic unit is used for converting the level signals of an output clock domain into the pulse signals, wherein an exclusive or gate and a D trigger are included. The asynchronous pulse synchronizer provided by the invention can convert the pulse signals of a clock domain into the pulse signals of another asynchronous clock domain in digital circuit cross-clock-domain design; and furthermore, the meta-stable state of the signals in a synchronous process can be prevented.

Owner:天津国芯科技有限公司

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com