Clock switching circuit of gigabit Ethernet transceiver

A Gigabit Ethernet and clock switching technology, which is applied in the field of clock switching circuits, can solve the problems that Gigabit Ethernet circuit functions cannot generate output clocks, do not support skip clock switching, output clock glitches, etc., so as to avoid glitches And the generation of metastable state, smooth switching, and the effect of ensuring correctness

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0050] The present invention will be further described in detail below in conjunction with specific embodiments, which are to explain rather than limit the present invention.

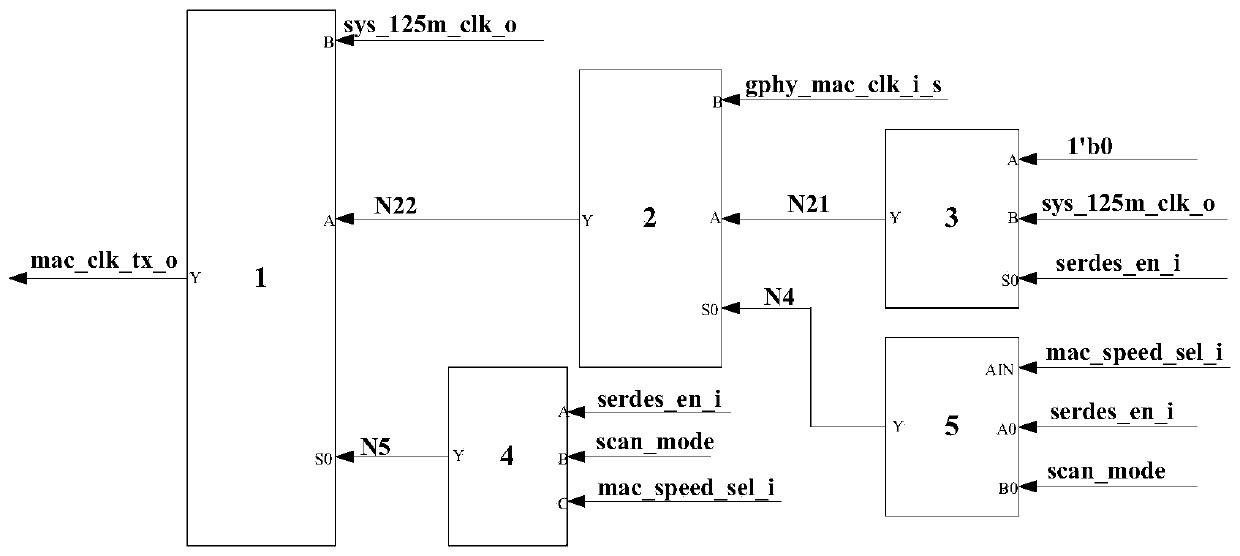

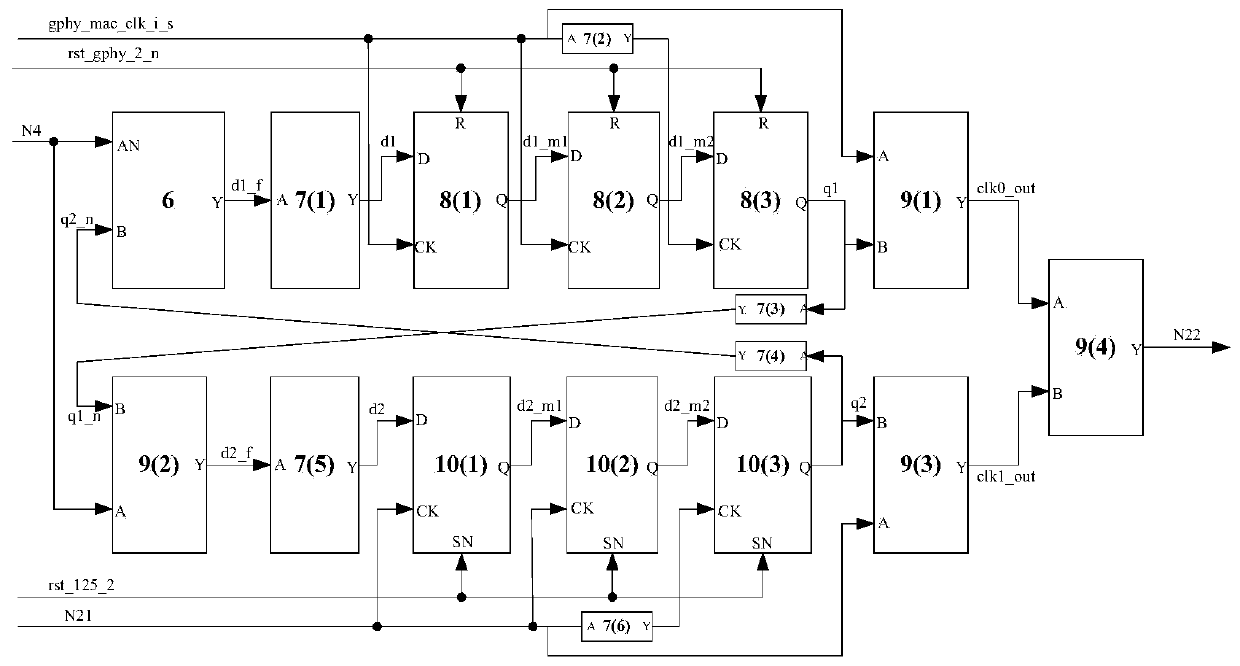

[0051] The clock switching circuit of the Gigabit Ethernet transceiver of the present invention mainly includes MXT2_1-MXT2_3 switching modules, NOR3 three-input or non-modular, OAI2 three-input or NAND module, nandb0 two-input NAND module, inv0-inv5 inversion module, nand0~nand3 two input NAND modules, dffr0~dffr2 reset register module, dffs0~dffs2 set register module.

[0052] Its overall structure diagram is as follows figure 1 shown, the details are as follows:

[0053] 1. The main function of the MXT2_1 switching module (label 1) is to realize the clock switching between the transceiver serdes and gphy working at 1000M, and its logical expression is Y=((~S0)·A+S0·B); in the default mode Output the clock sys_125m_clk_o at the B end, which is the 125MHz working clock of the system. The switching pr...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com