Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

187results about "Reconfigurable analogue/digital converters" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

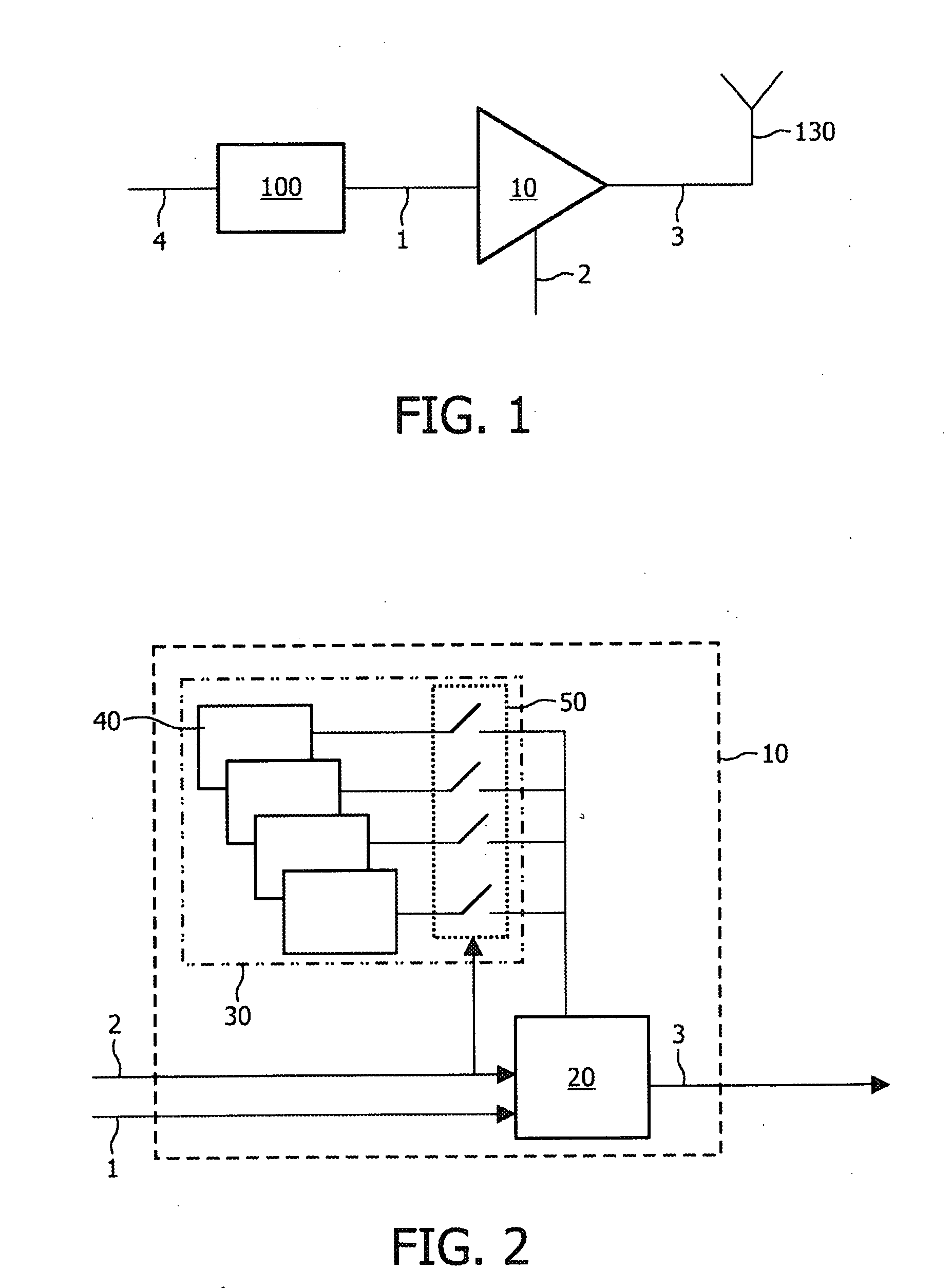

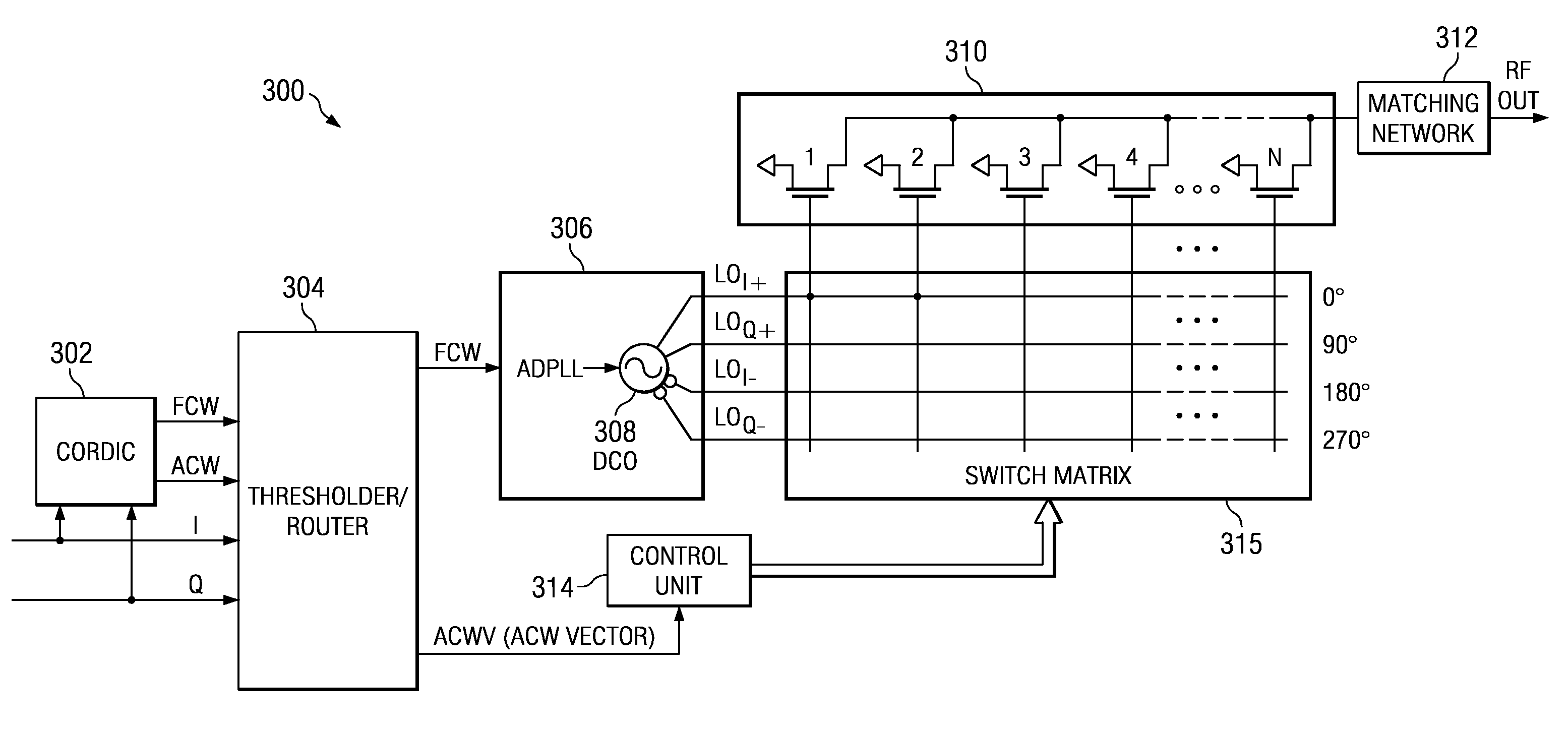

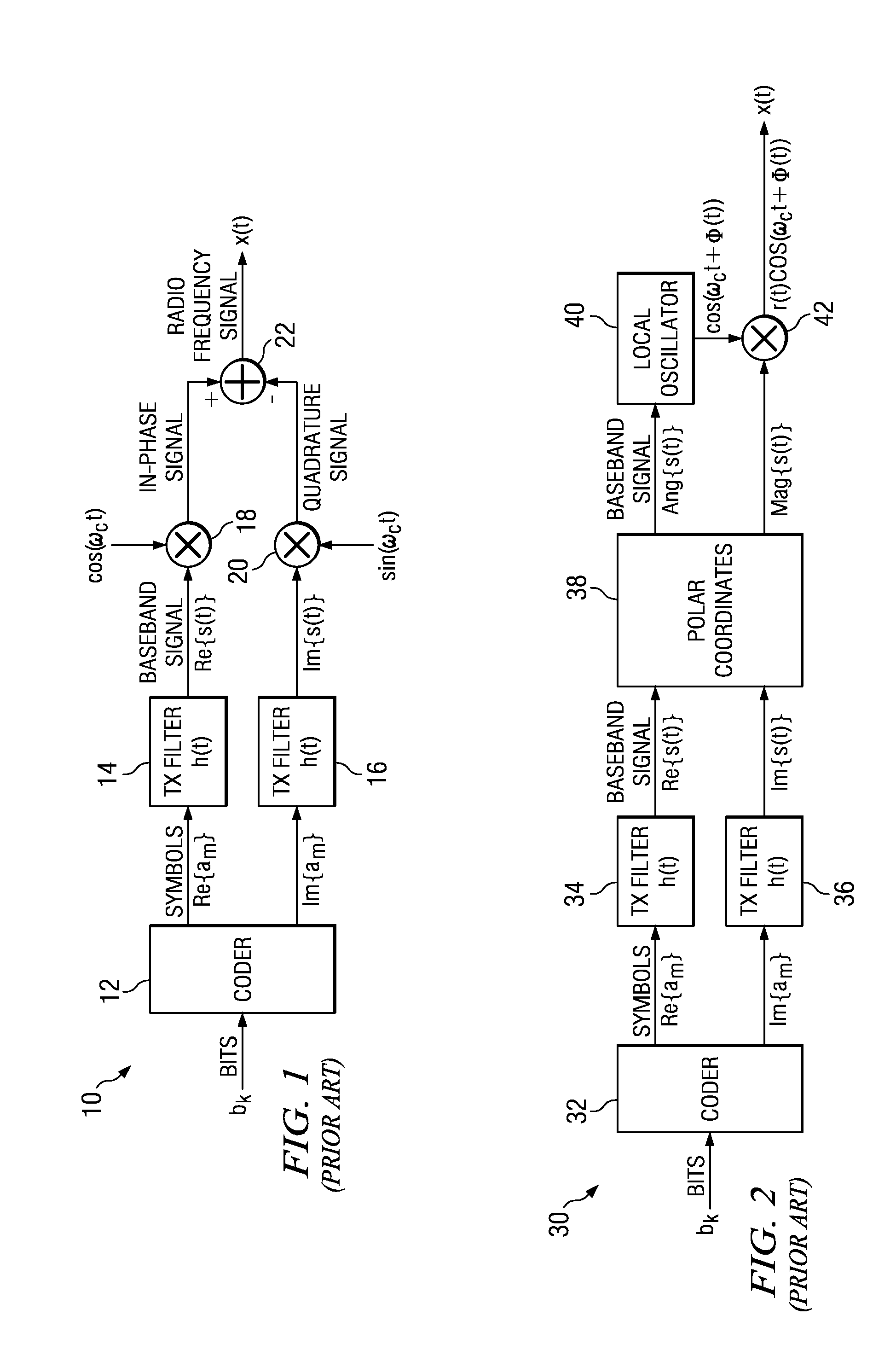

Hybrid polar/cartesian digital modulator

ActiveUS20060038710A1Reconfigurable analogue/digital convertersAnalogue conversionControl powerEngineering

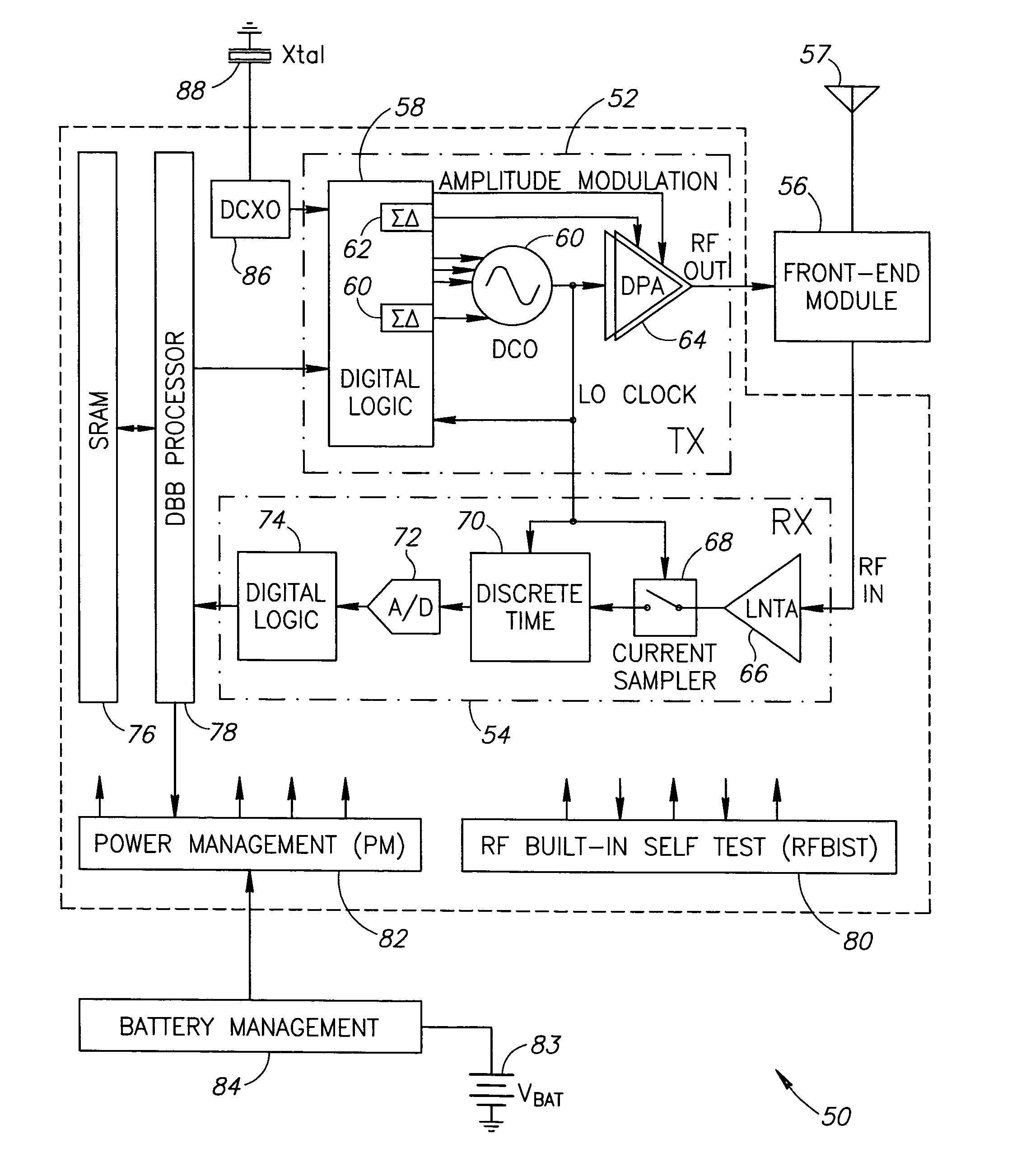

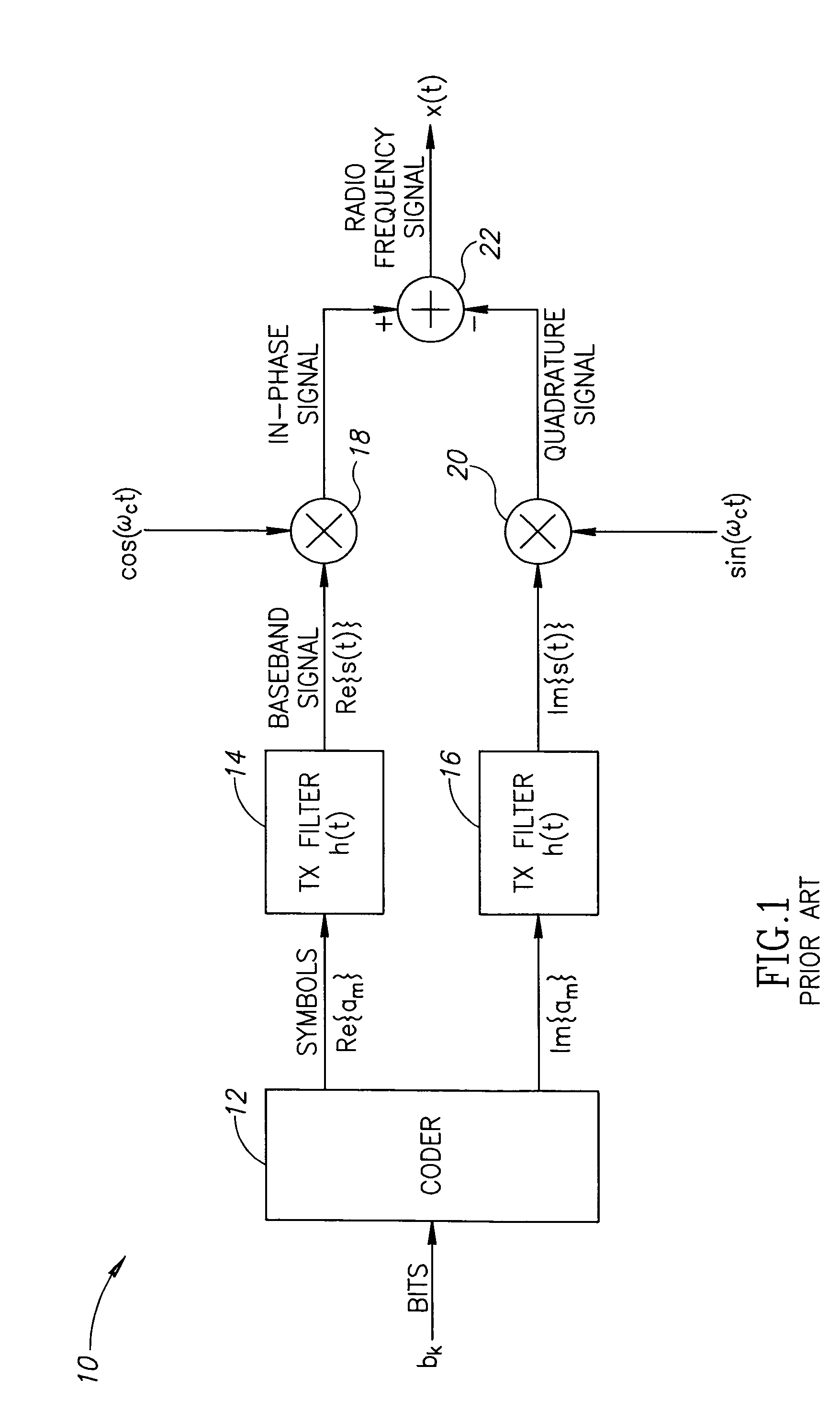

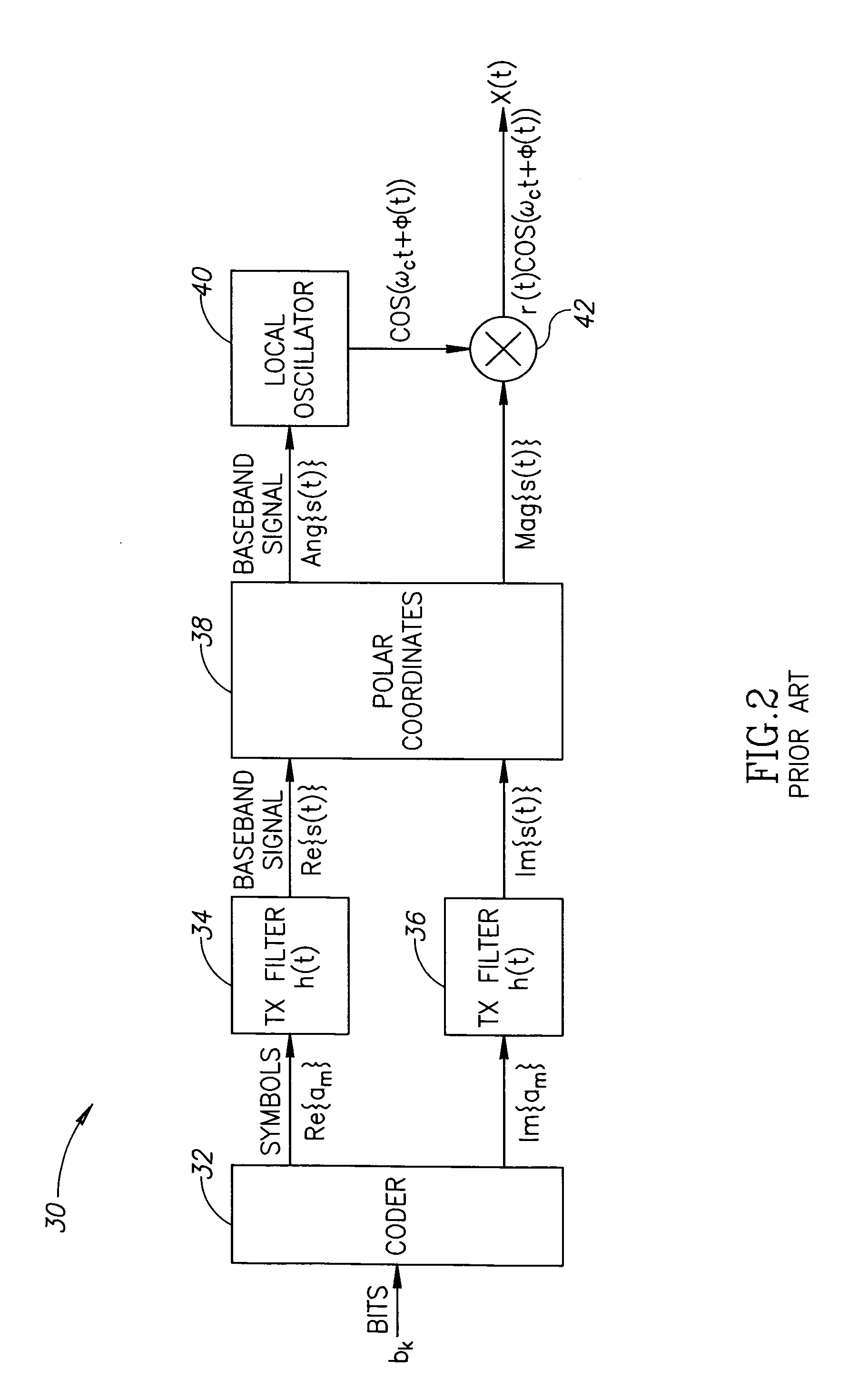

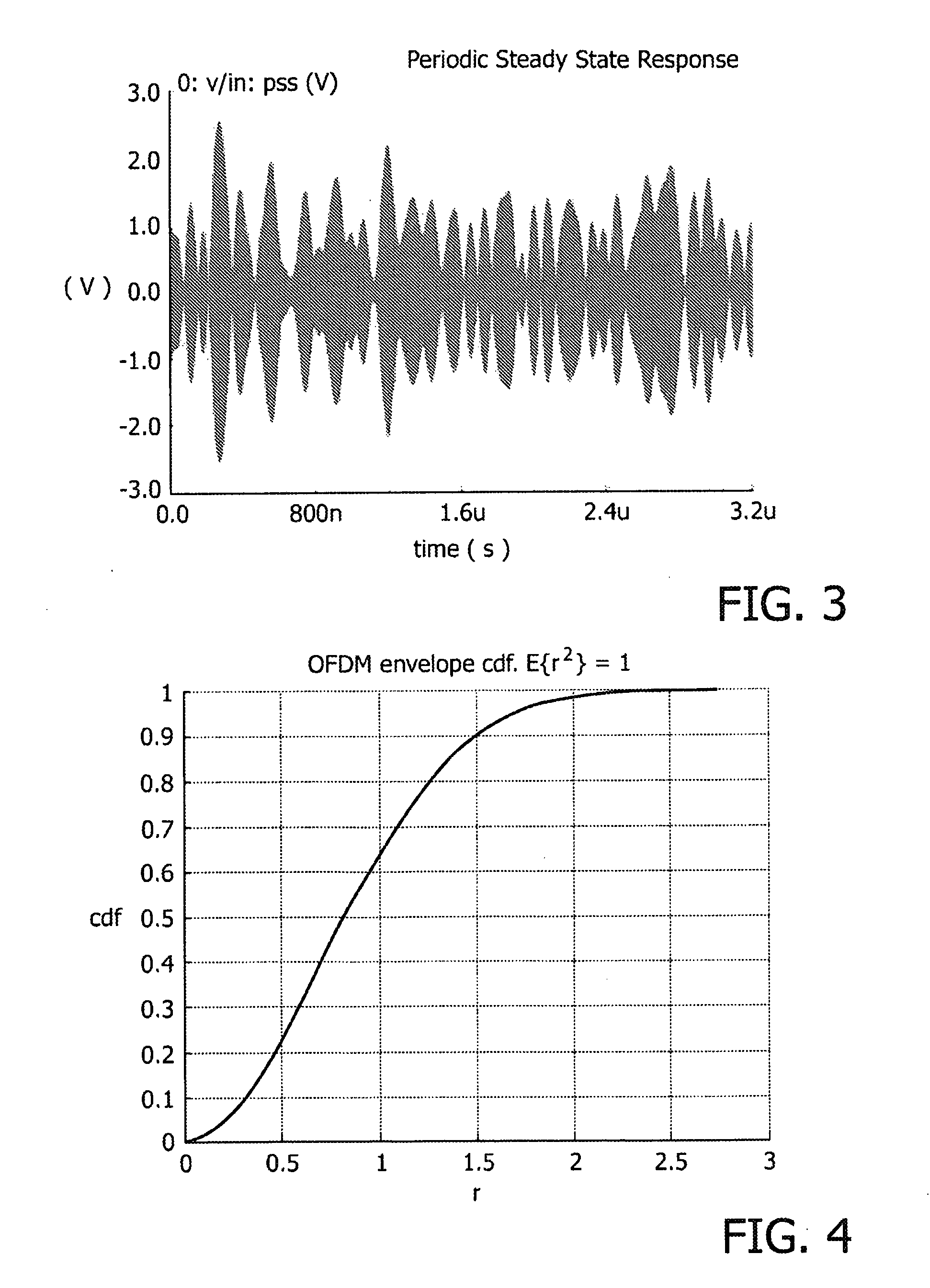

A novel apparatus and method for a hybrid Cartesian / polar digital QAM modulator. The hybrid technique of the present invention utilizes a combination of an all digital phase locked loop (ADPLL) that features a wideband frequency modulation capability and a digitally controlled power amplifier (DPA) that features interpolation between 90 degree spaced quadrature phases. This structure is capable of performing either a polar operation or a Cartesian operation and can dynamically switch between them depending on the instantaneous value of a metric measured by a thresholder / router. In this manner, the disadvantages of each modulation technique are avoided while the benefits of each are exploited.

Owner:TEXAS INSTR INC

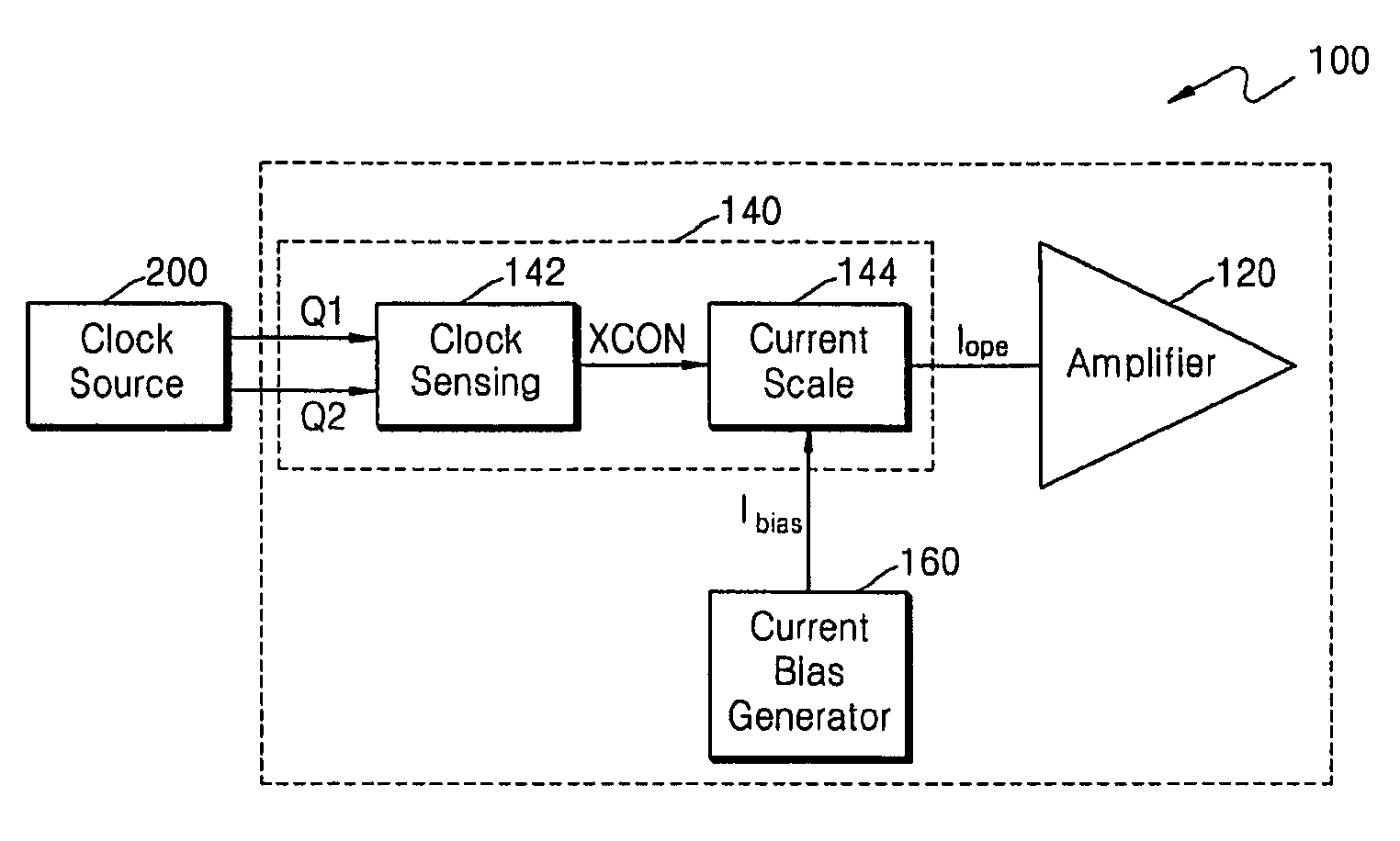

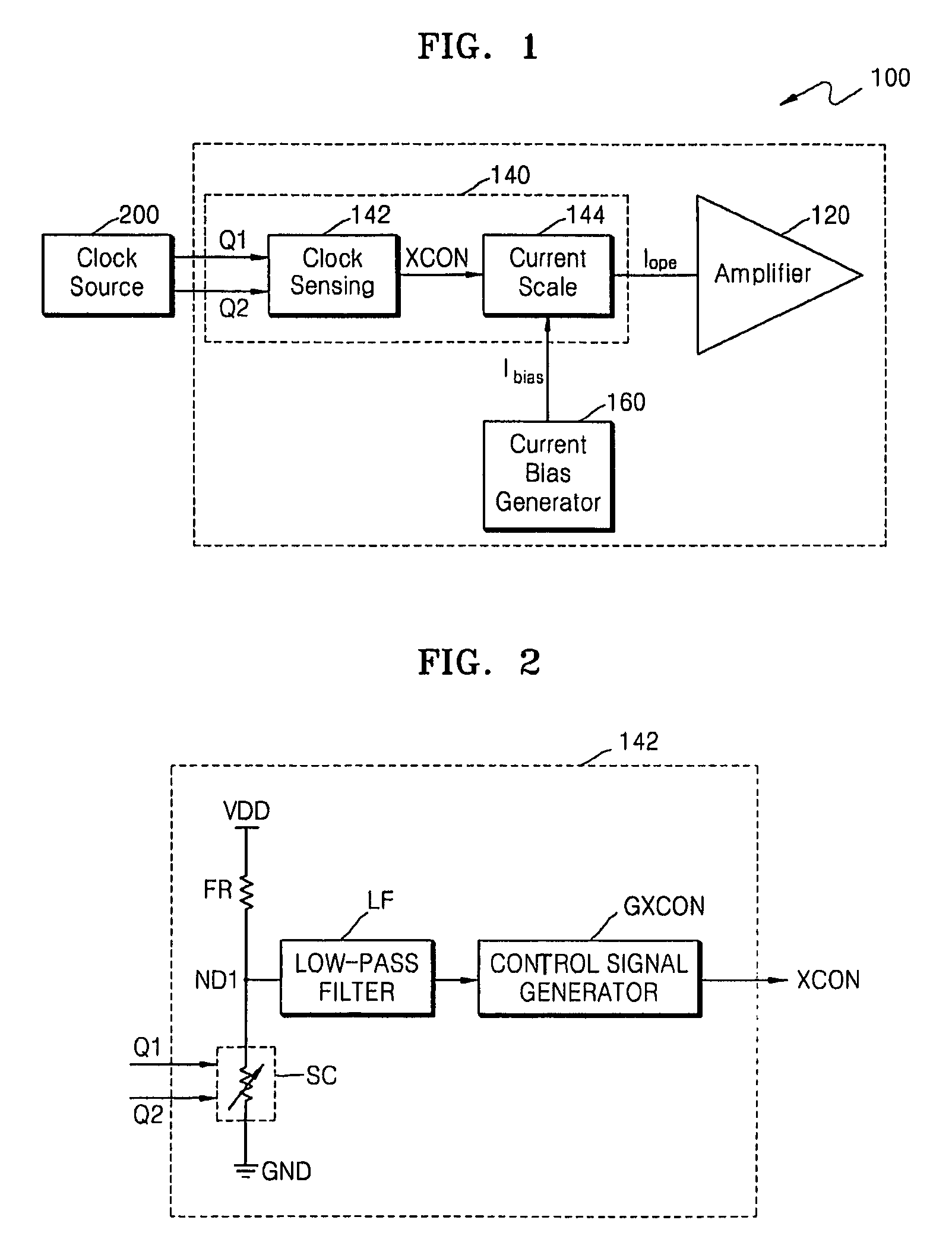

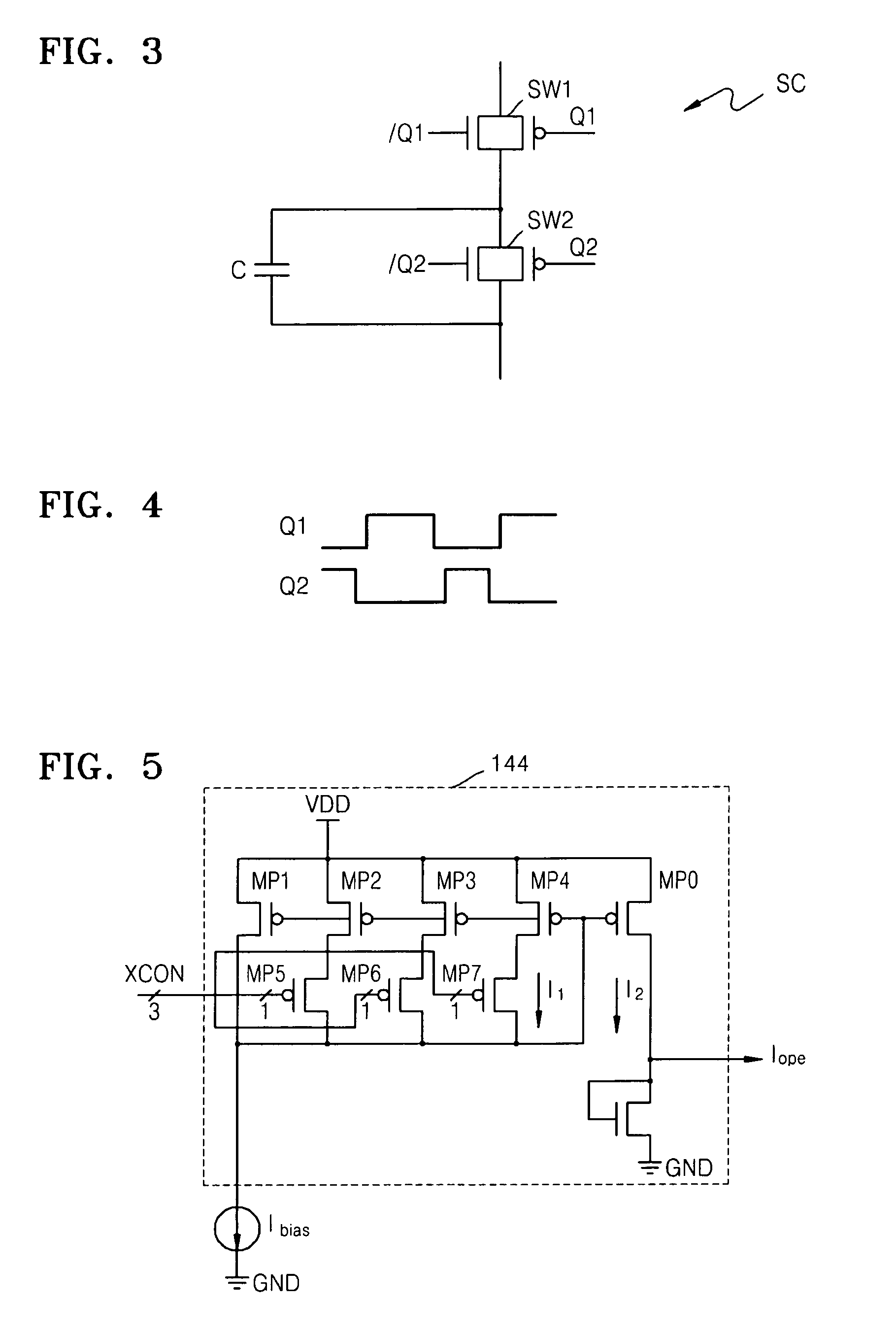

Current control circuit

ActiveUS7808410B2Avoid unnecessary power consumptionPower saving provisionsElectric signal transmission systemsControl signalDevice material

Owner:SAMSUNG ELECTRONICS CO LTD

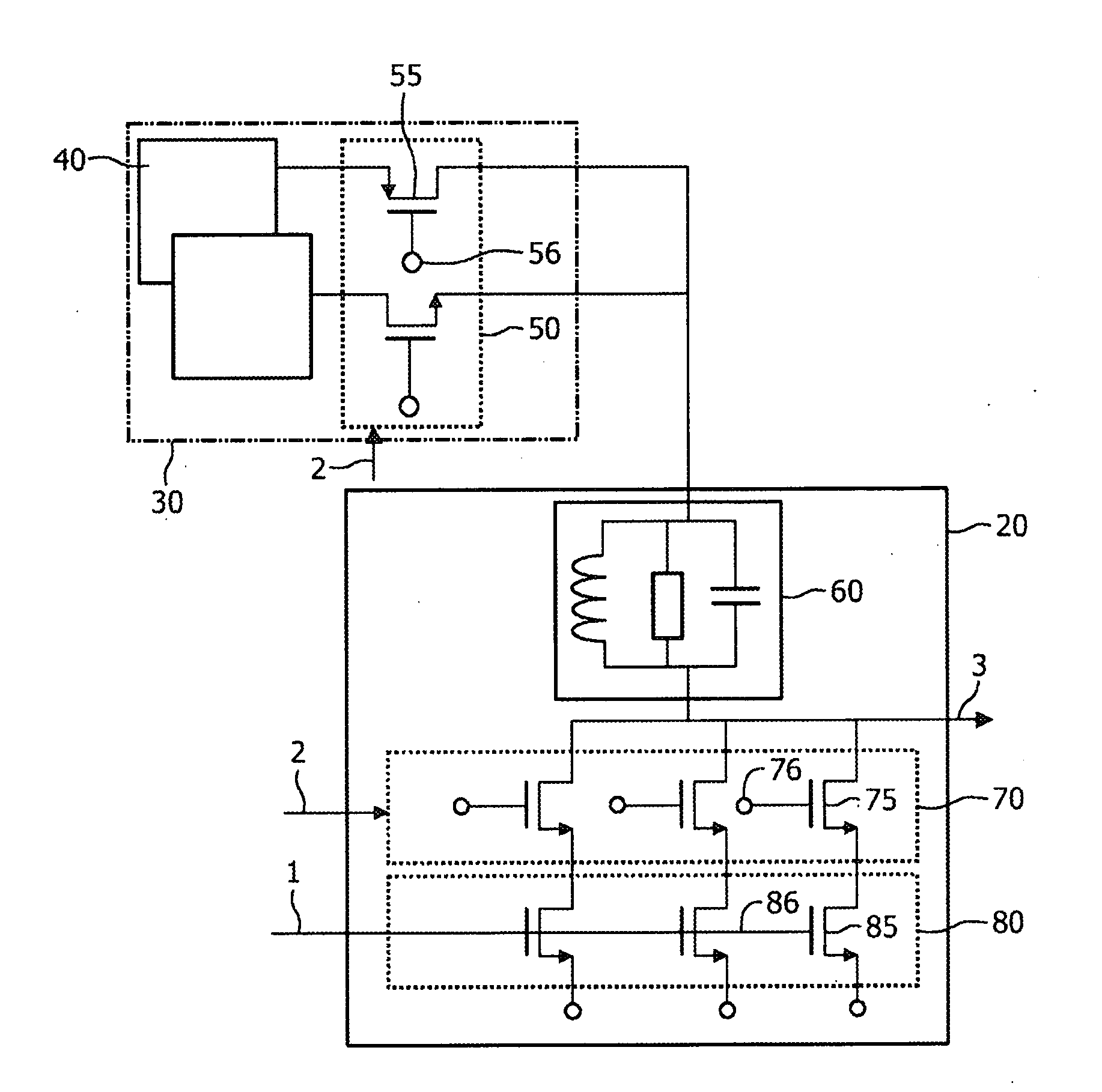

High efficiency modulating RF amplifier

InactiveUS20100001793A1Simple designImprove efficiencyReconfigurable analogue/digital convertersAmplififers with field-effect devicesAudio power amplifierPower switching

A high efficiency modulating RF amplifier (10) for amplitude modulating a signal defined by a phase information signal (1) and an envelope signal (2) comprises a power supply (30) arranged to provide an operating voltage under control of the envelope signal (2). The power supply (30) comprises a plurality of power supply stages (40) and a plurality of supply switches (50) coupled between the plurality of power supply stages (40) and the modulator (20). The power supply (30) is arranged to select one of the power supply stages (40) to provide the operating voltage under control of the envelope signal (2). The high efficiency modulator RF amplifier further comprises a modulator (20) for receiving the phase information signal (1), the envelope signal (2) and the operating voltage. The modulator (20) is arranged to provide an output signal of which an amplitude is modulated under control of the envelope signal (2).

Owner:KONINKLIJKE PHILIPS ELECTRONICS NV

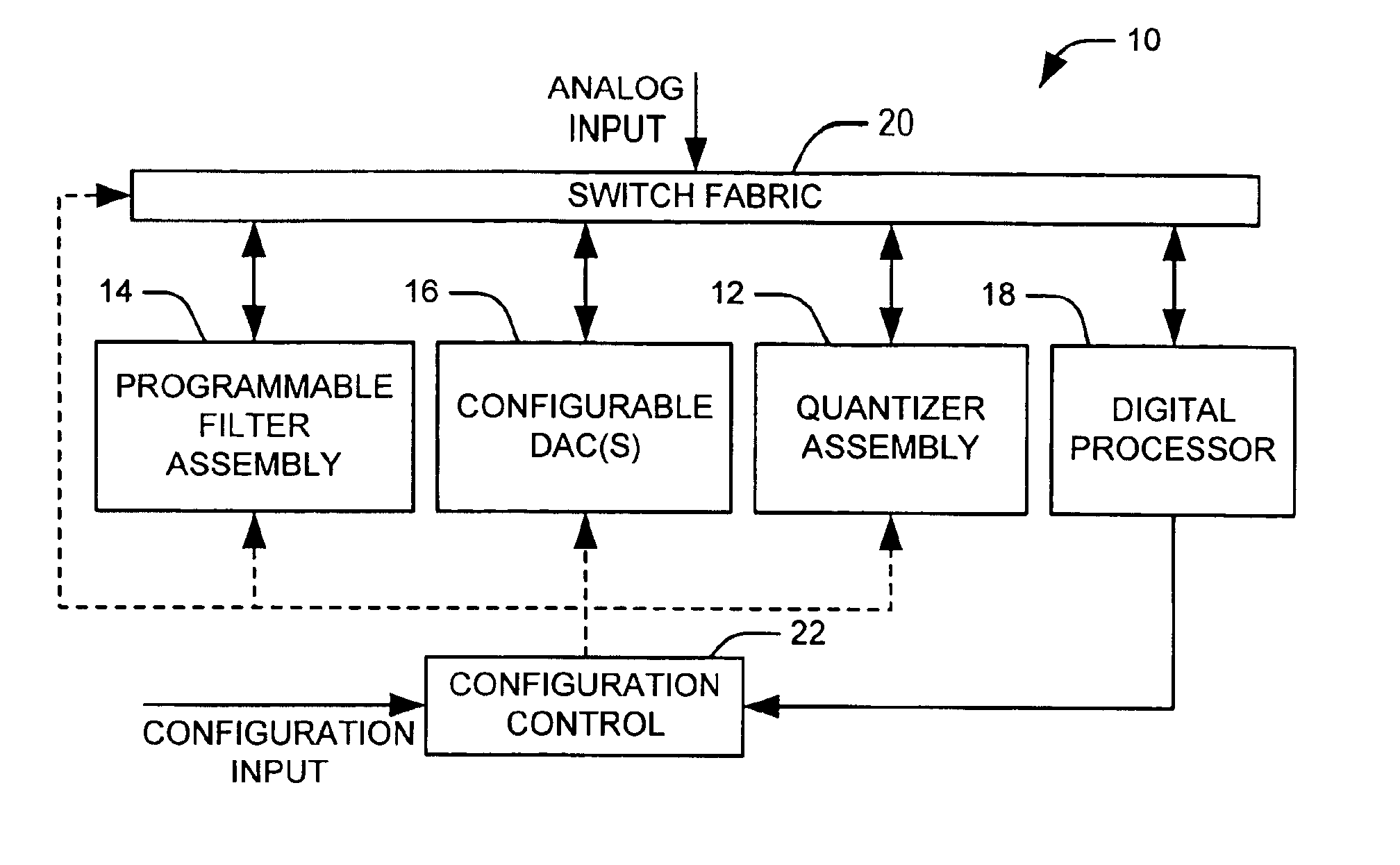

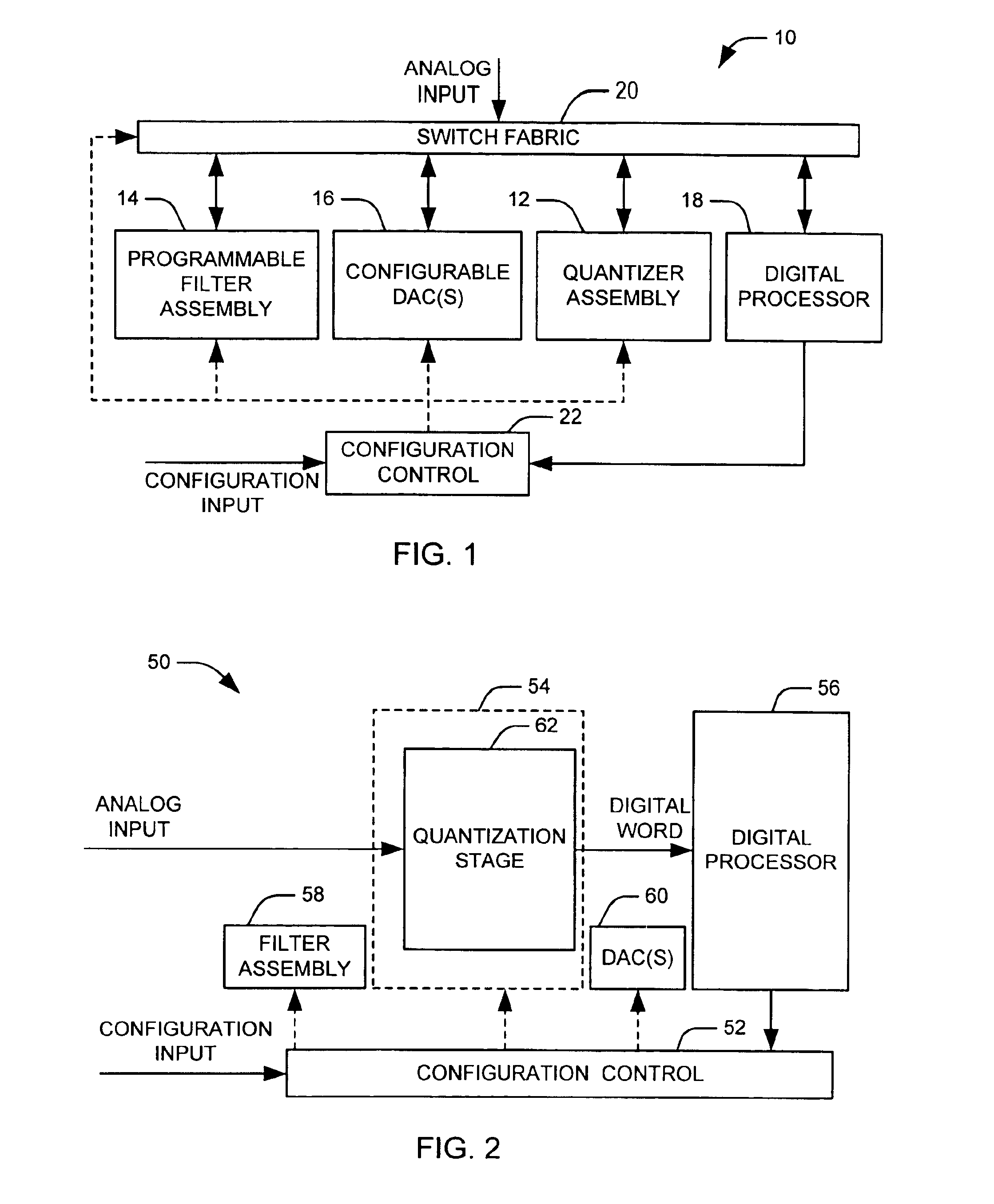

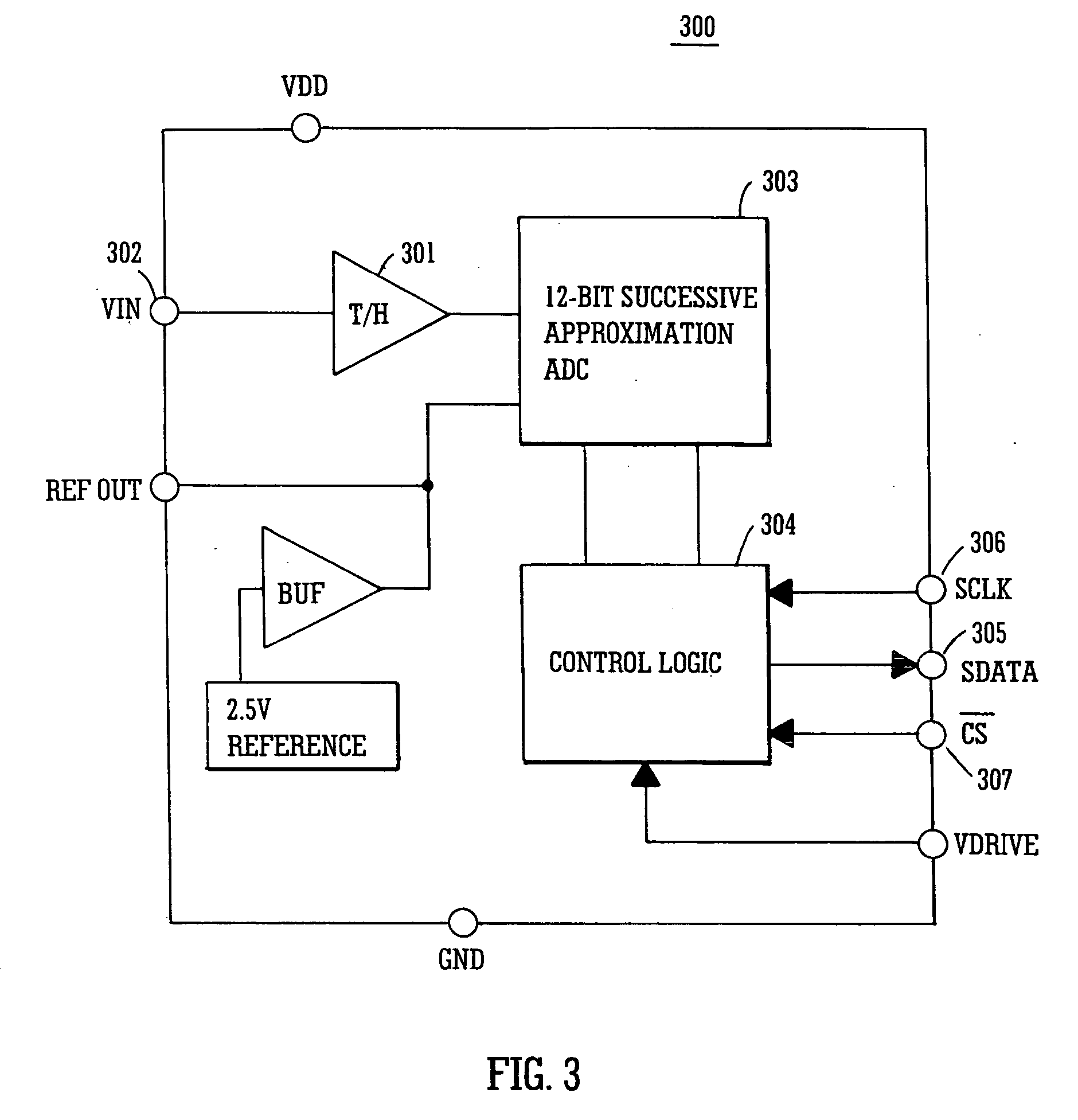

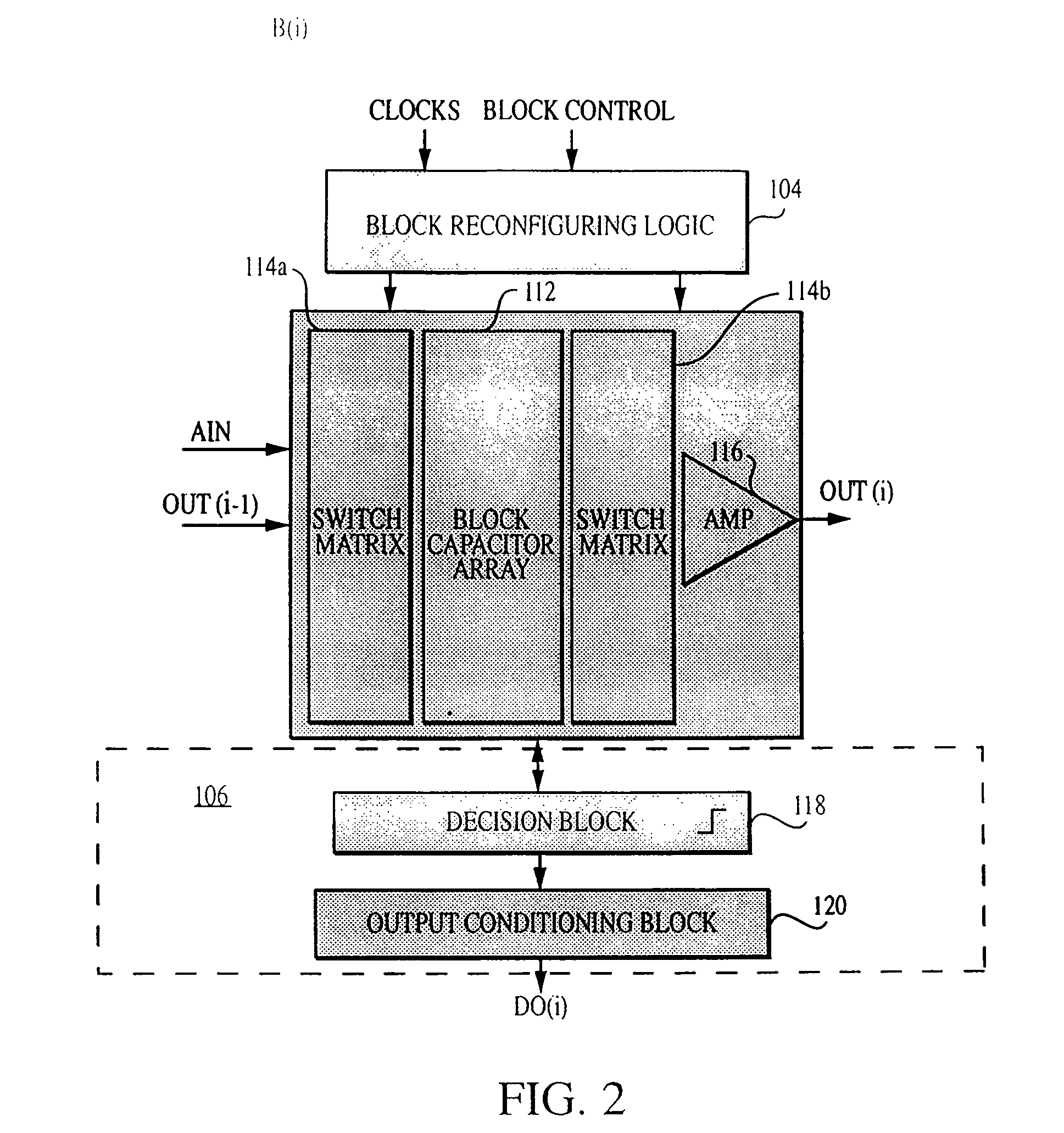

Programmable analog-to-digital converter

ActiveUS6894632B1Electric signal transmission systemsReconfigurable analogue/digital convertersDigital down converterEngineering

Systems and methods are disclosed that employ a programmable analog-to-programmable digital converted system. A programmable analog-to-digital converter system comprises a quantizer assembly and configuration control. The quantizer assembly is configurable to provide at least one quantization stage. A given quantization stage converts an associated analog signal into an associated digital output signal. The configuration control selects among a plurality of configurations and configures the analog-to-digital converter system according to the selected configuration. The quantizer assembly is configurable to provide a plurality of quantization stages arranged in series in a first configuration, or to provide a single quantization stage in a second configuration.

Owner:NORTHROP GRUMMAN SYST CORP

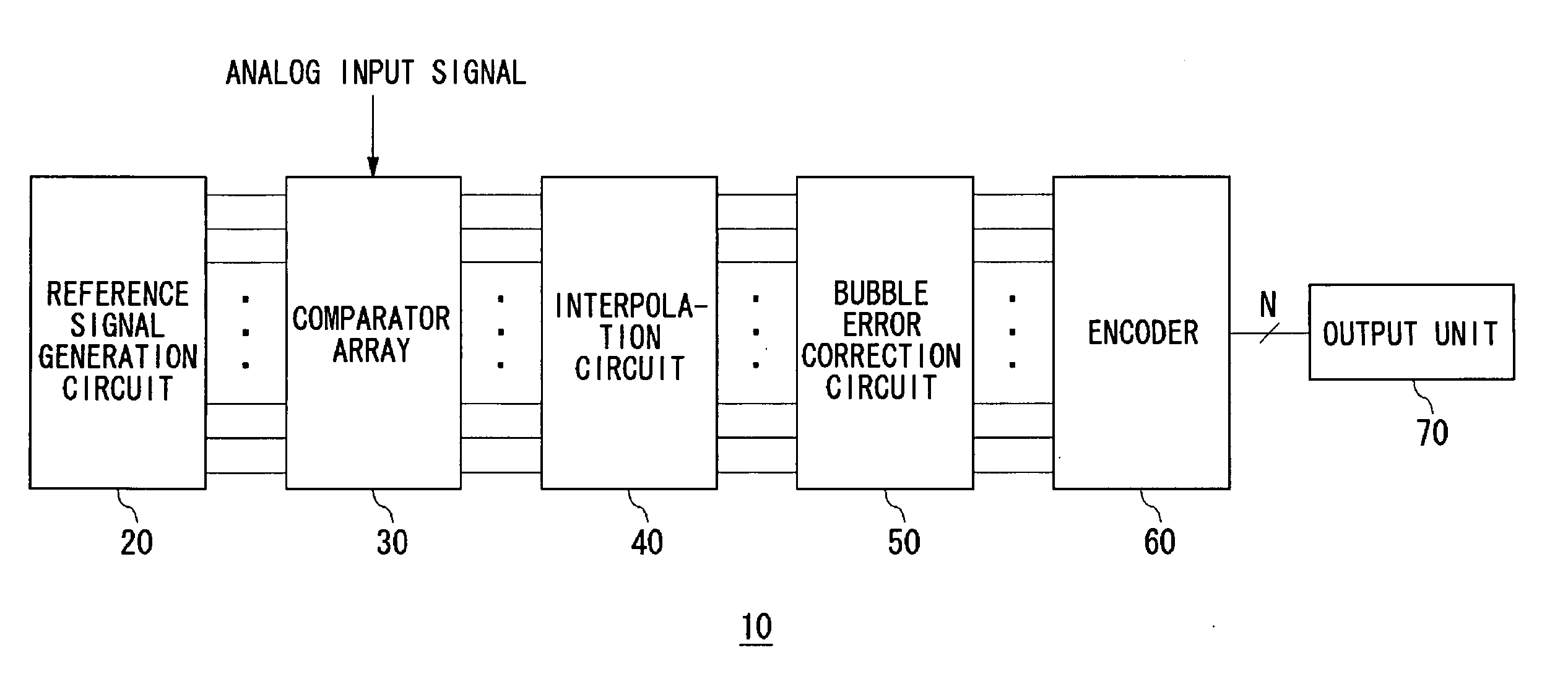

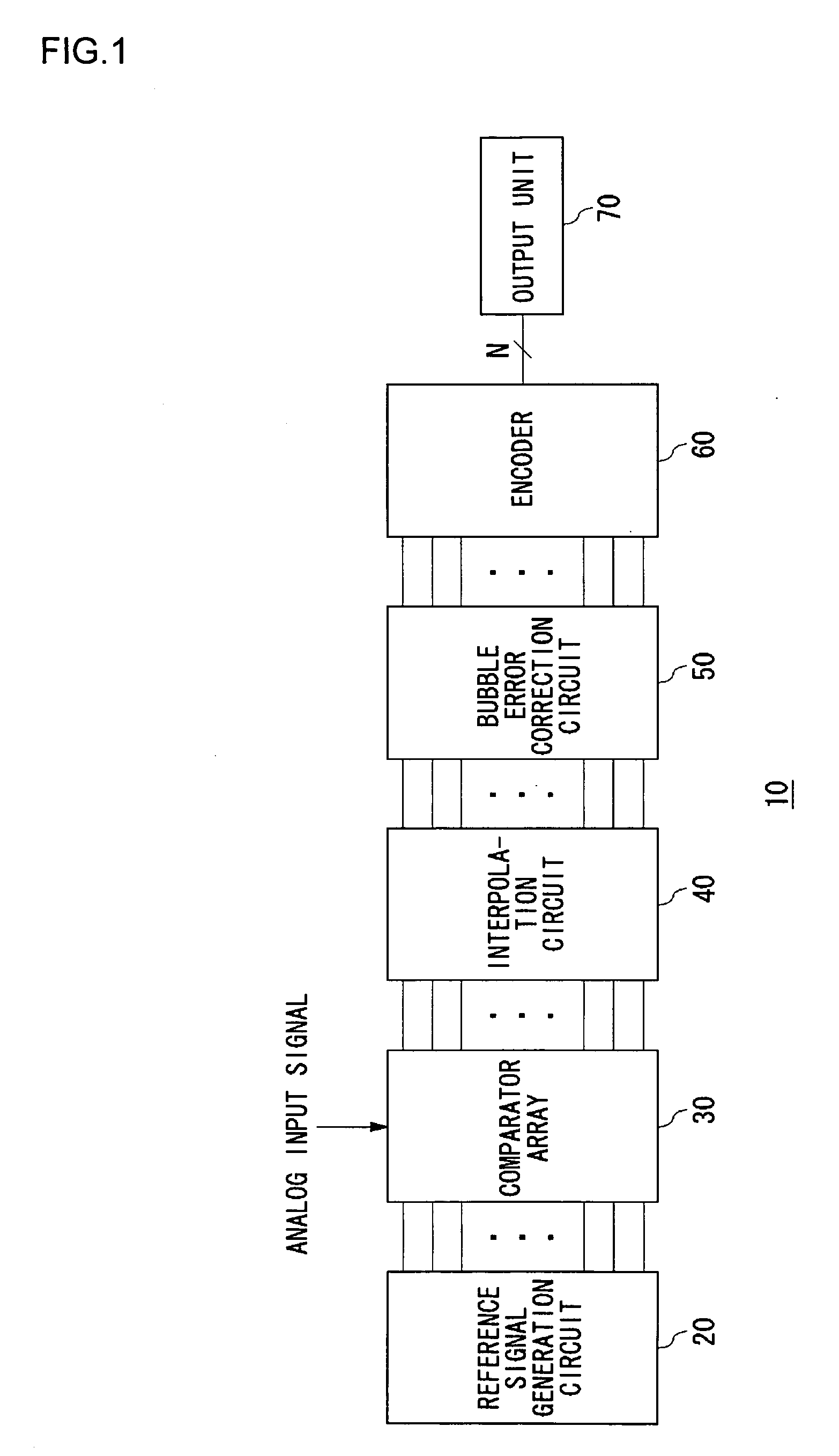

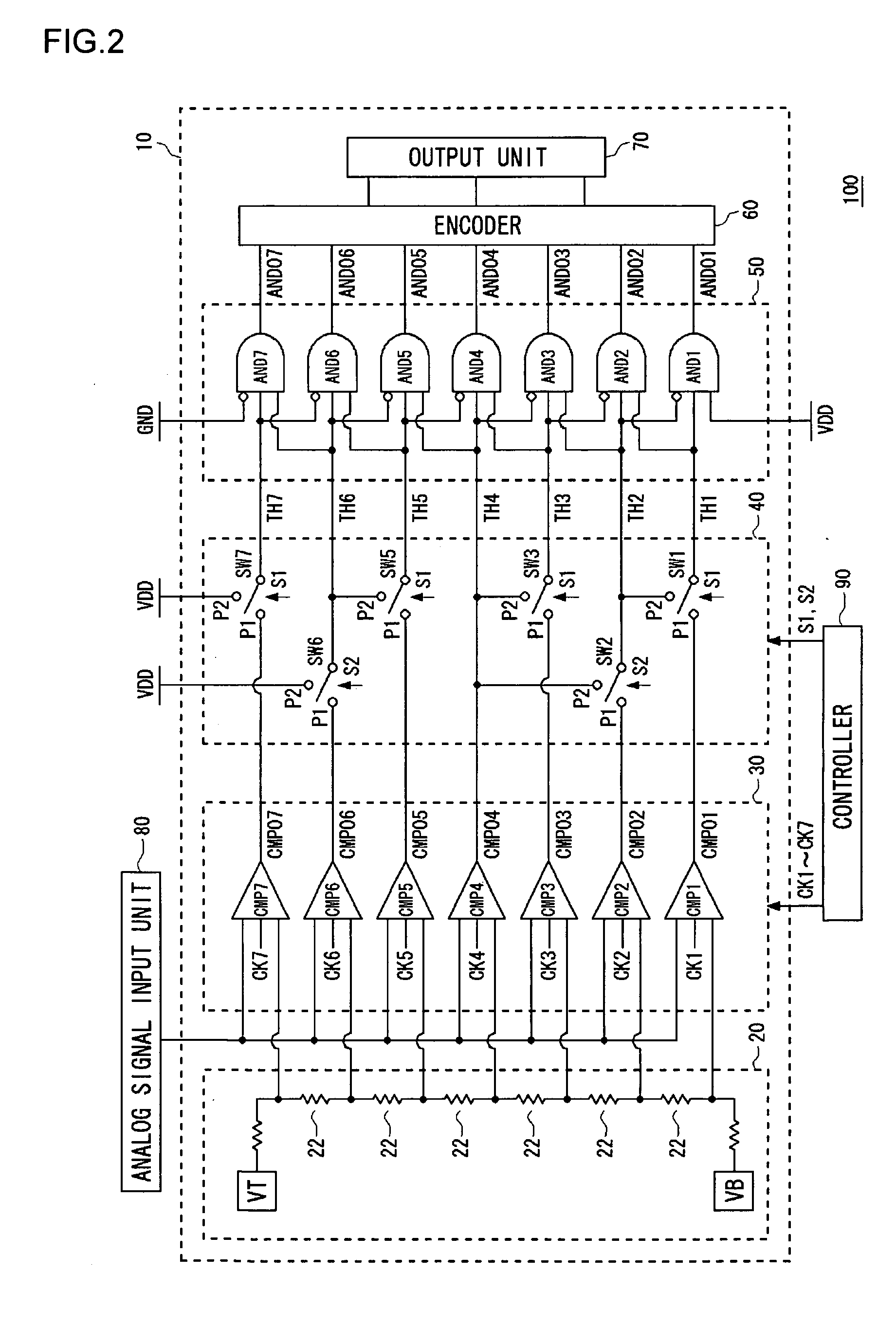

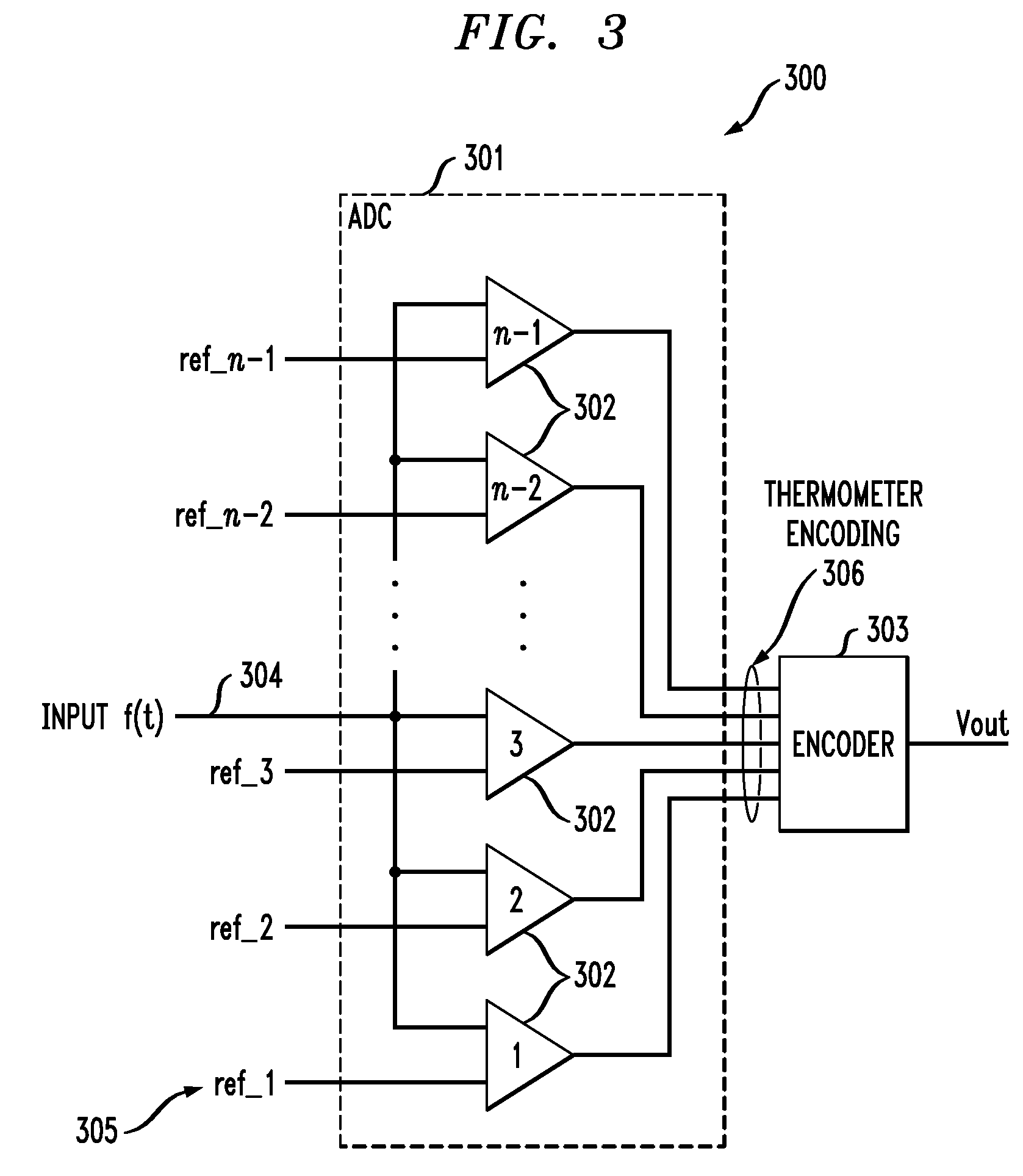

Analog-to digital converter and analog-to digital conversion apparatus

ActiveUS20060187105A1Variable resolutionReduce power consumptionPower saving provisionsElectric signal transmission systemsControl signalImage resolution

An analog-to-digital conversion apparatus which has a variable resolution and allows a reduction in power consumption. This apparatus comprises an analog-to-digital converter (ADC) of parallel type, a controller, and an interpolation circuit. The analog-to-digital converter has a plurality of comparators connected in parallel, each for comparing potentials of an analog input signal and a reference signal. The controller generates a control signal for controlling the resolution of the analog-to-digital converter. Specifically, the controller controls the number of comparators (CMP) to operate by means of the control signal, thereby determining the resolution. The interpolation circuit interpolates the output data of the comparators that are disabled depending on the resolution. The controller avoids simultaneous operation of two adjoining comparators when the analog-to-digital converter is operated at a resolution lower than its maximum resolution.

Owner:SEMICON COMPONENTS IND LLC

Hybrid polar/cartesian digital modulator

ActiveUS7532679B2Reconfigurable analogue/digital convertersAnalogue conversionControl powerQam modulation

A novel apparatus and method for a hybrid Cartesian / polar digital QAM modulator. The hybrid technique of the present invention utilizes a combination of an all digital phase locked loop (ADPLL) that features a wideband frequency modulation capability and a digitally controlled power amplifier (DPA) that features interpolation between 90 degree spaced quadrature phases. This structure is capable of performing either a polar operation or a Cartesian operation and can dynamically switch between them depending on the instantaneous value of a metric measured by a thresholder / router. In this manner, the disadvantages of each modulation technique are avoided while the benefits of each are exploited.

Owner:TEXAS INSTR INC

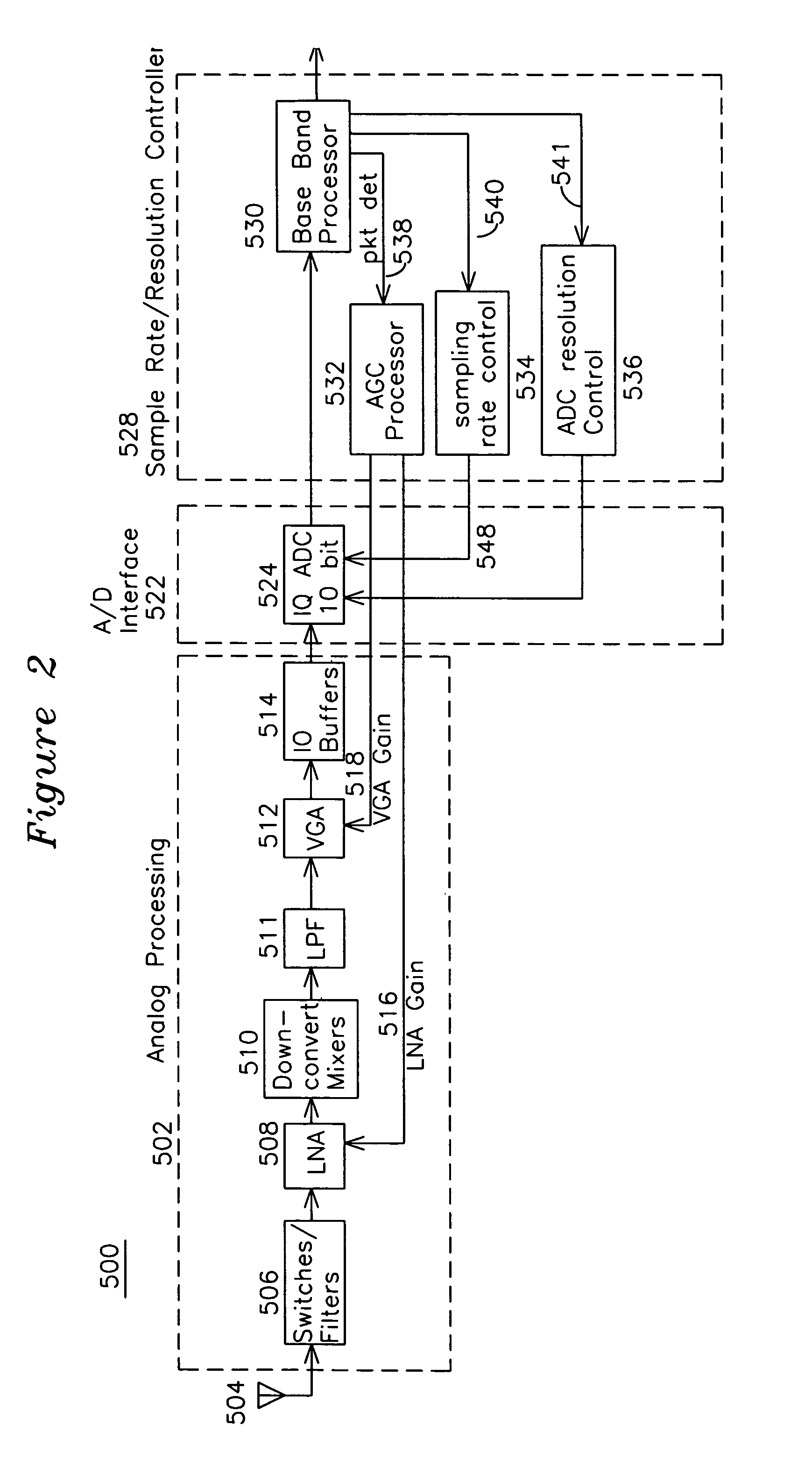

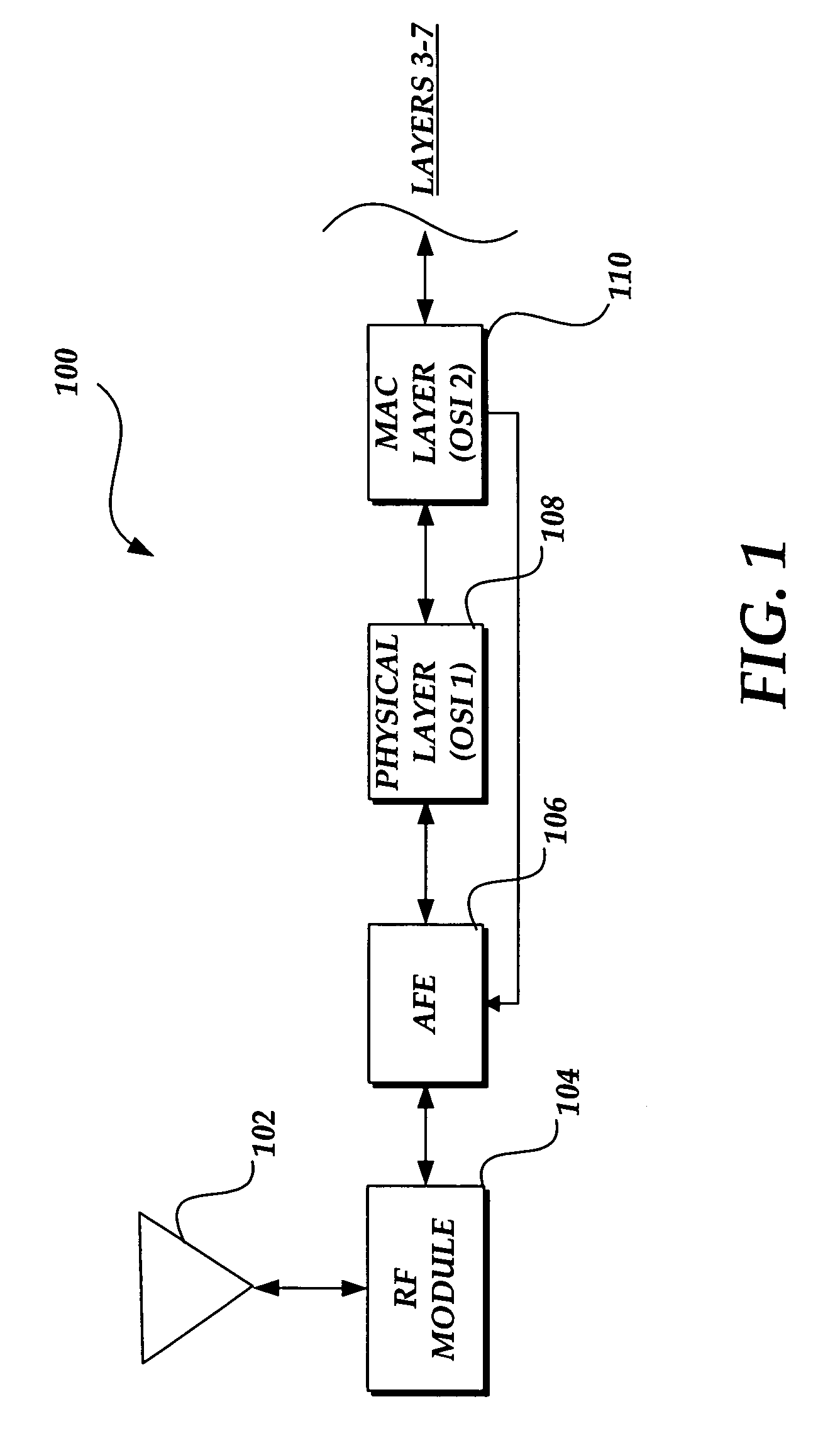

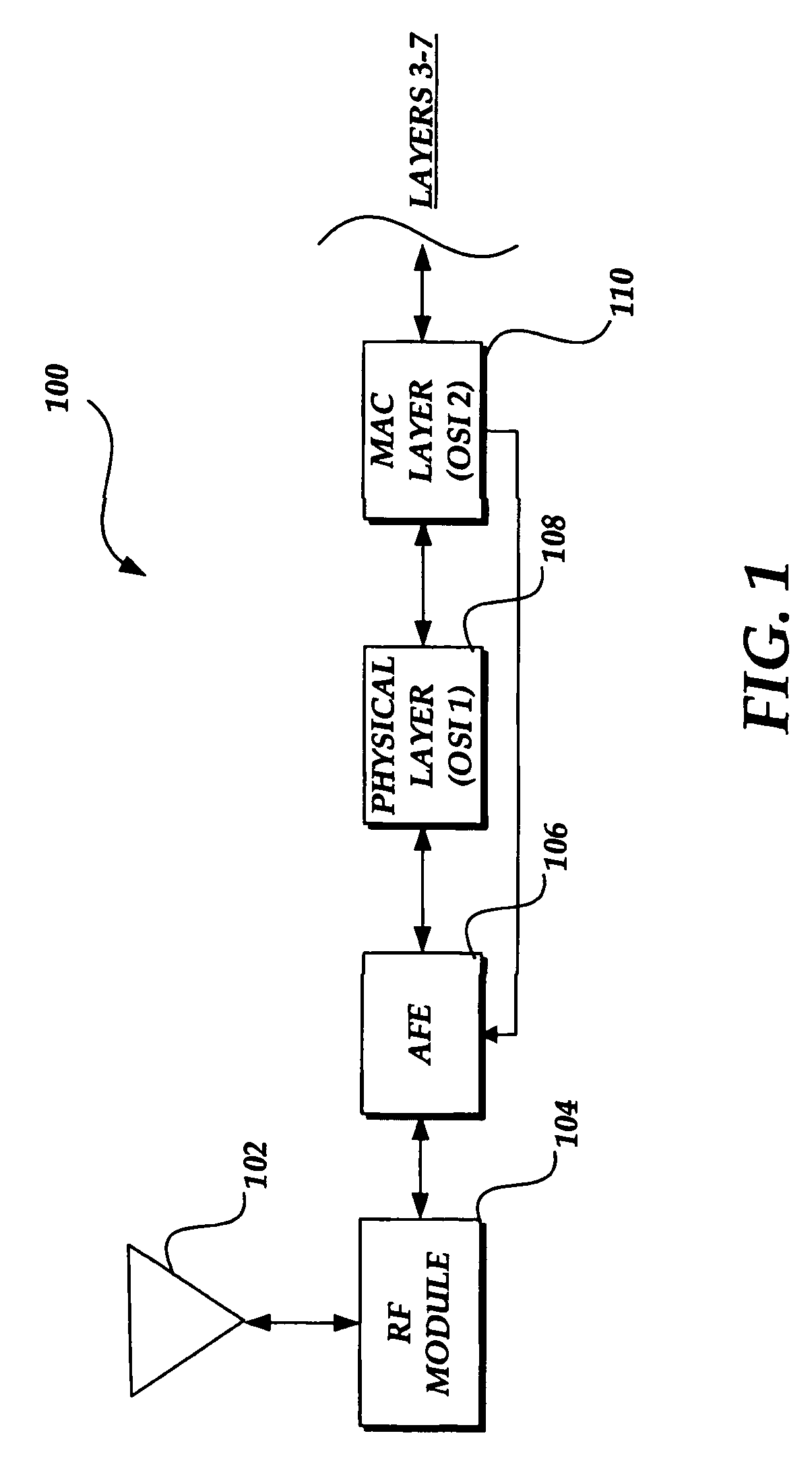

Apparatus for a wireless communications system using signal energy to control sample resolution and rate

ActiveUS7656970B1Save powerReconfigurable analogue/digital convertersModulated-carrier systemsCommunications systemImage resolution

A wireless signal processor includes an analog front end for generating at least one baseband analog signal, at least one analog to digital converter for converting the baseband signal into a digital signal, the analog to digital converter having a resolution width and a sampling rate, and a baseband processor for measuring the signal energy in the analog to digital converter output, and when the incoming signal energy level increases or a baseband processor detects a packet, at least one of the sampling rate or resolution width also increases until the end of the packet, after which the sample rate and resolution are reduced to an interpacket rate and resolution. Additionally, the sampling rate and resolution increase after packet detection at rates and resolutions which are dependent on packet type and data rate.

Owner:SILICON LAB INC

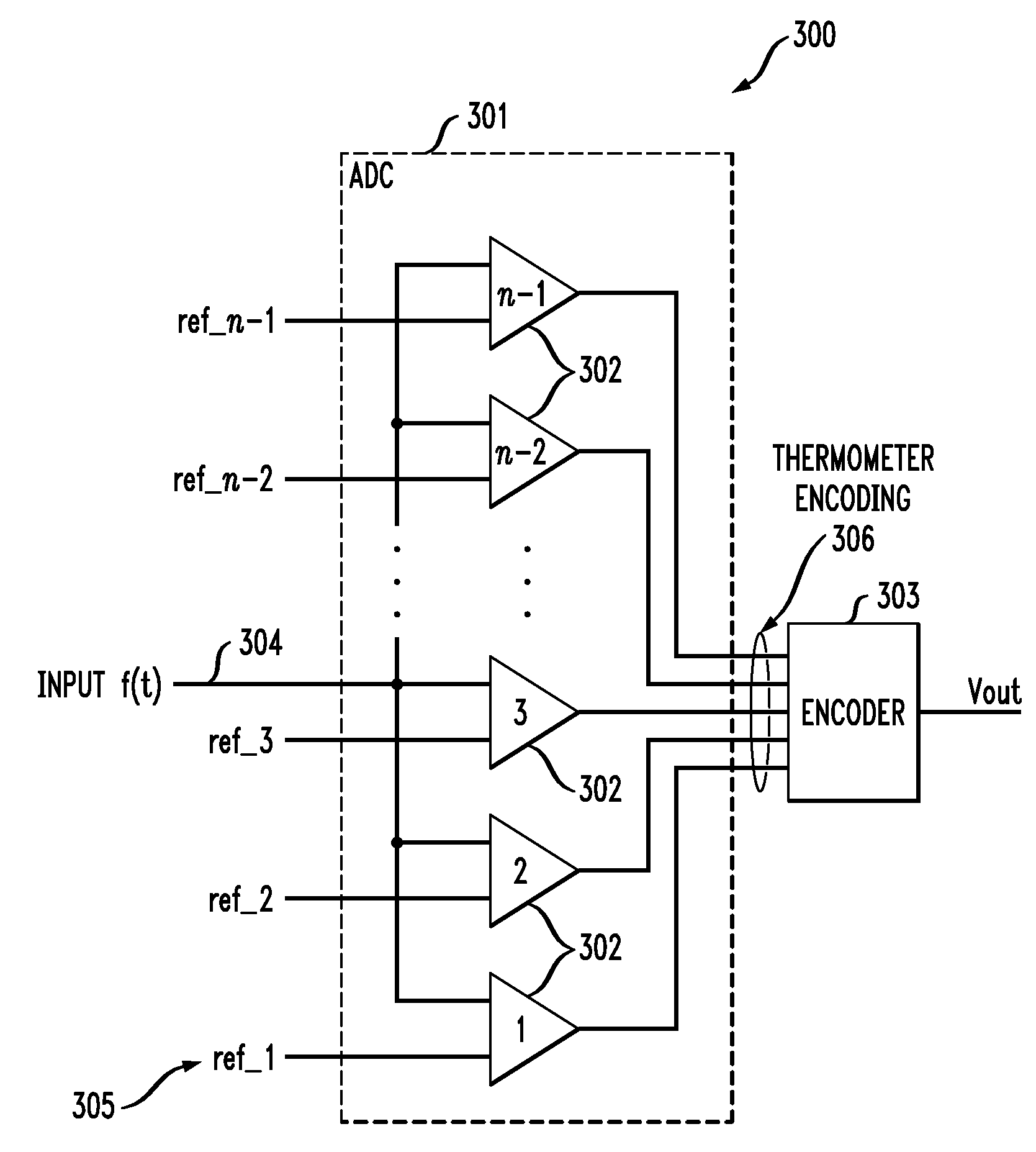

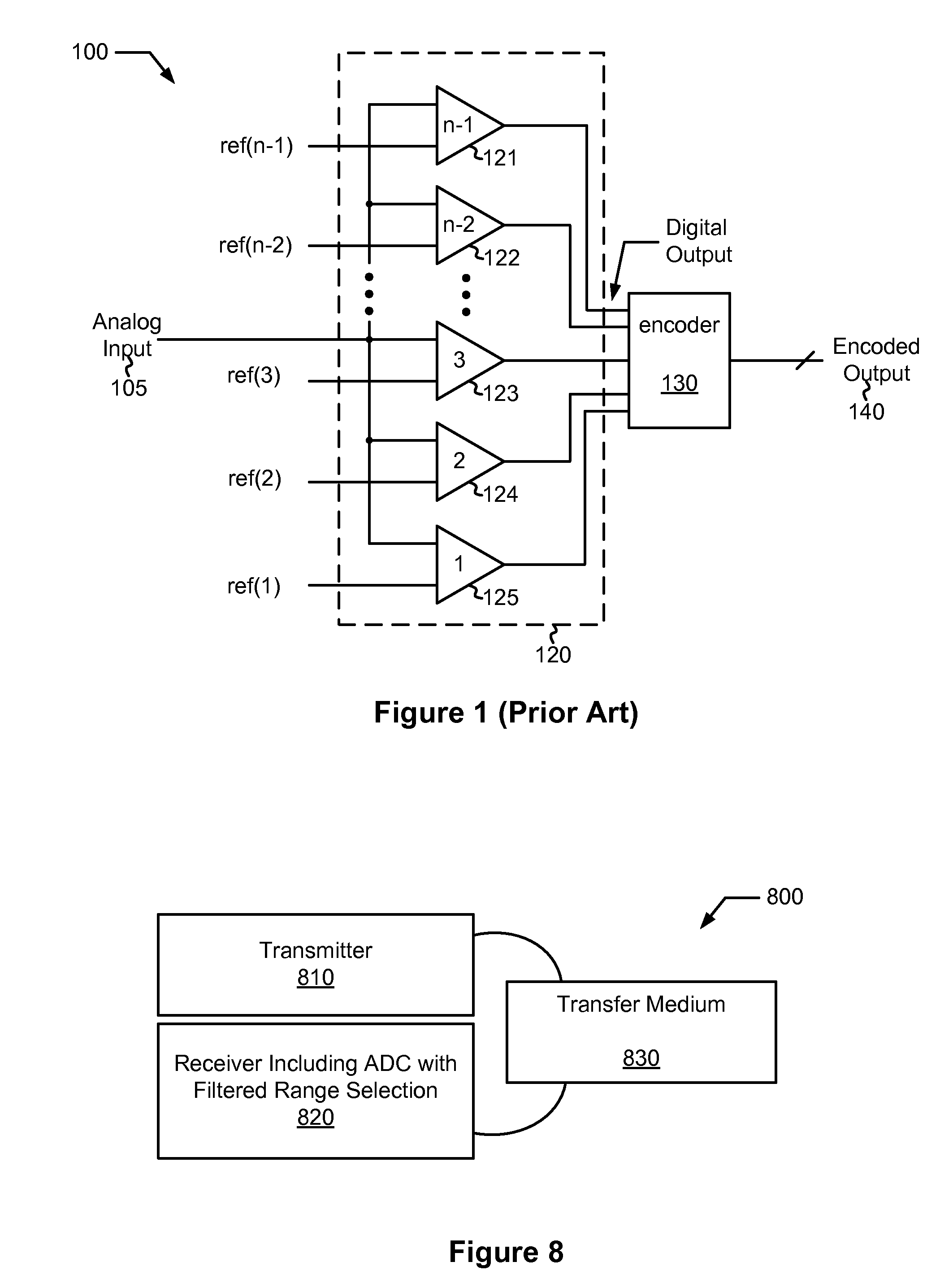

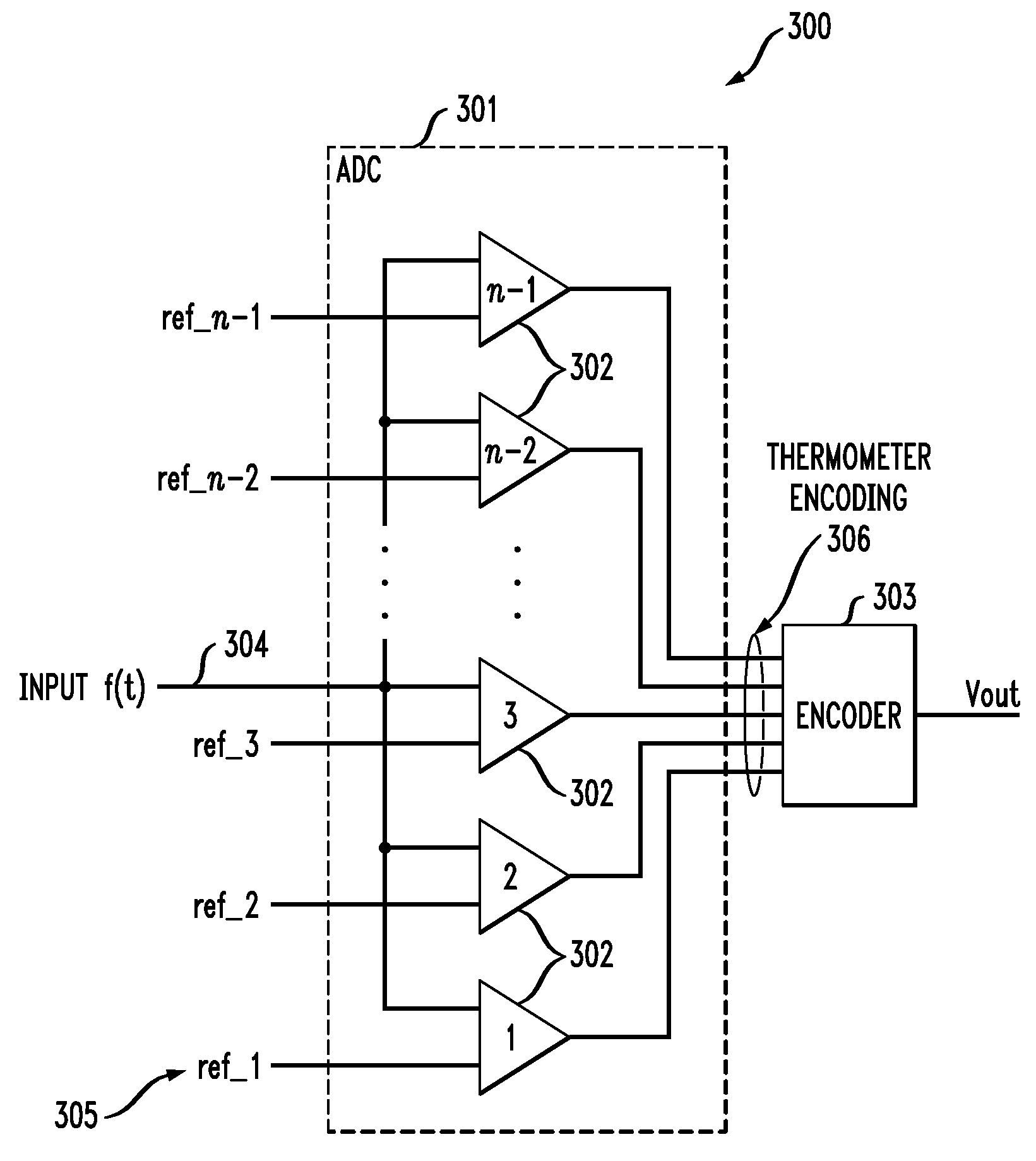

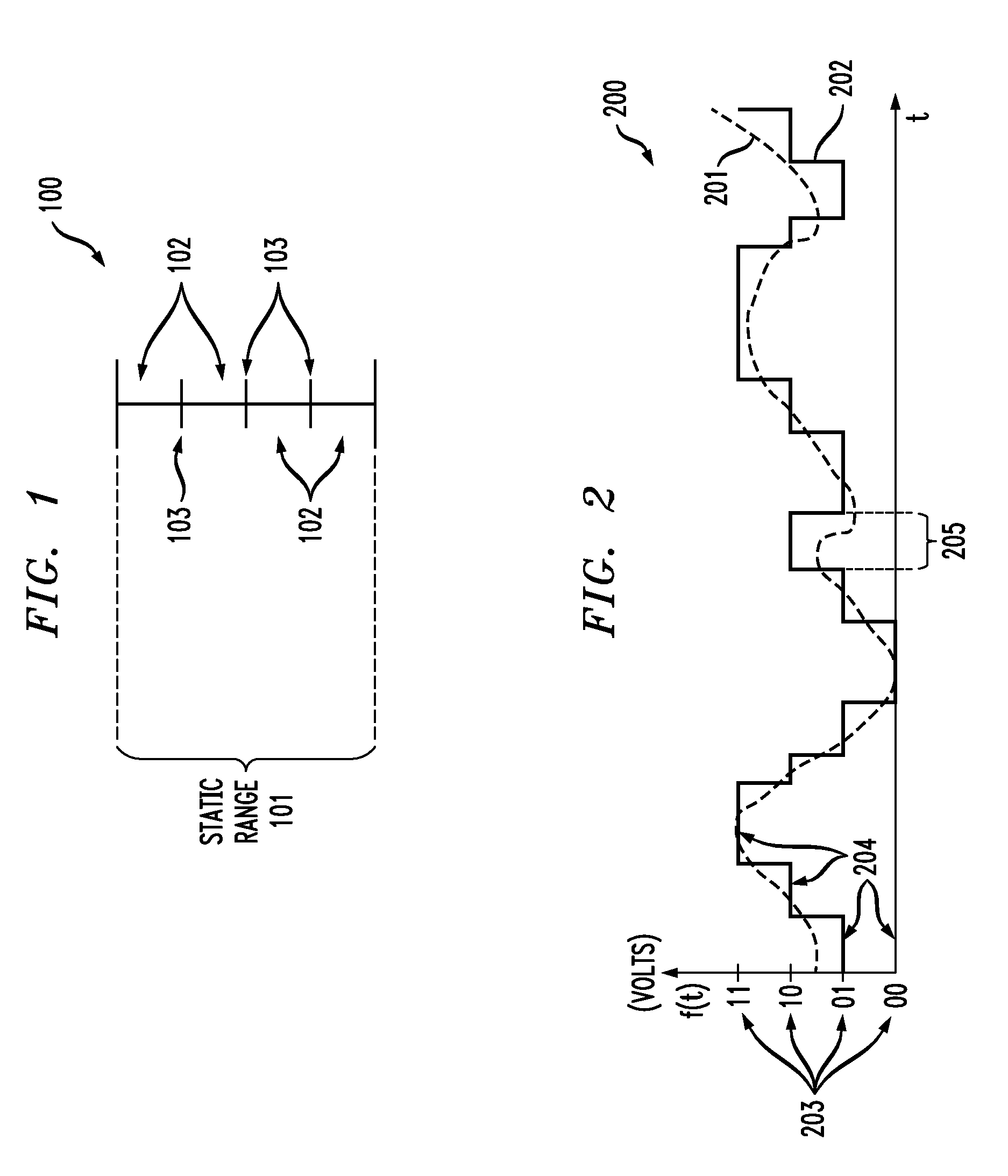

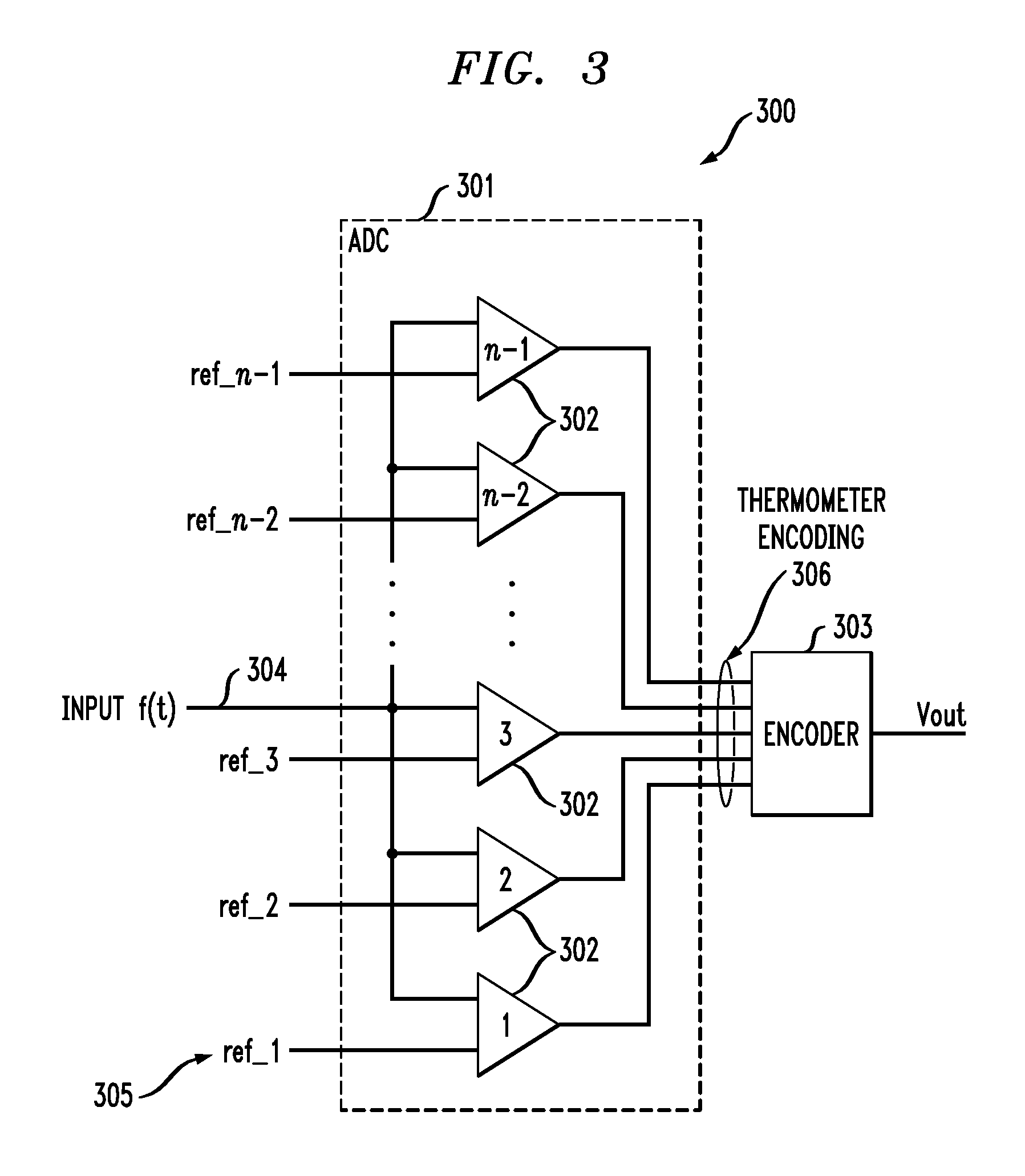

Analog-to-digital converter having reduced number of activated comparators

ActiveUS7696915B2Reduce power consumptionSignificantly degrading performancePower saving provisionsElectric signal transmission systemsControl engineeringA d converter

An ADC circuit includes multiple comparators and a controller coupled to the comparators. Each of the comparators is operative to generate an output indicative of a difference between a first signal representative of an input signal applied to the ADC circuit and a corresponding reference signal. The controller is operative to perform at least one of: (i) activating a subset of the comparators during a given sample period being; and (ii) controlling levels of the corresponding reference signals of the comparators as a function of a level of the input signal. A number of active comparators during the given sample period is no greater than one less than a number of regions into which the input signal is quantized.

Owner:AVAGO TECH INT SALES PTE LTD

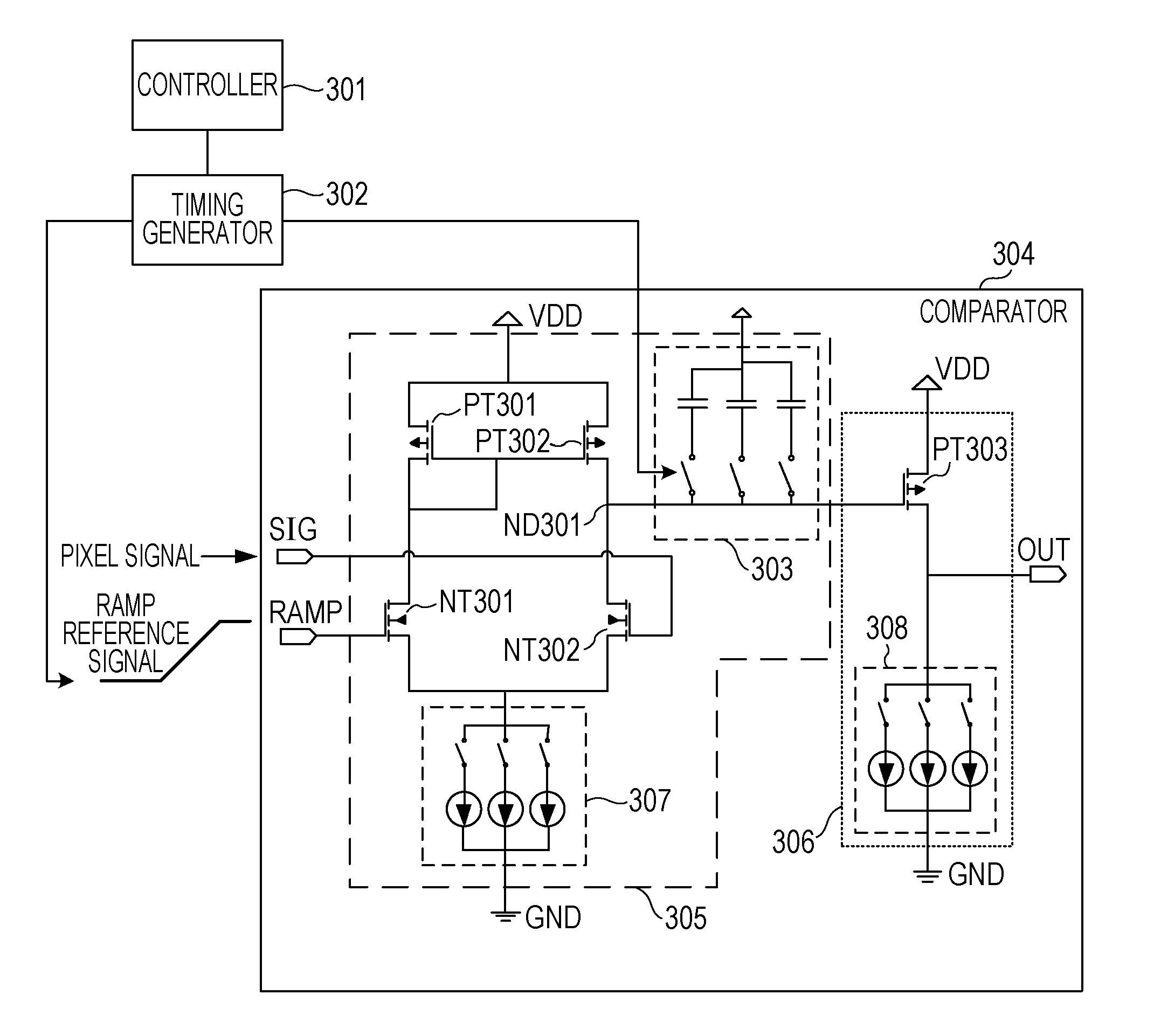

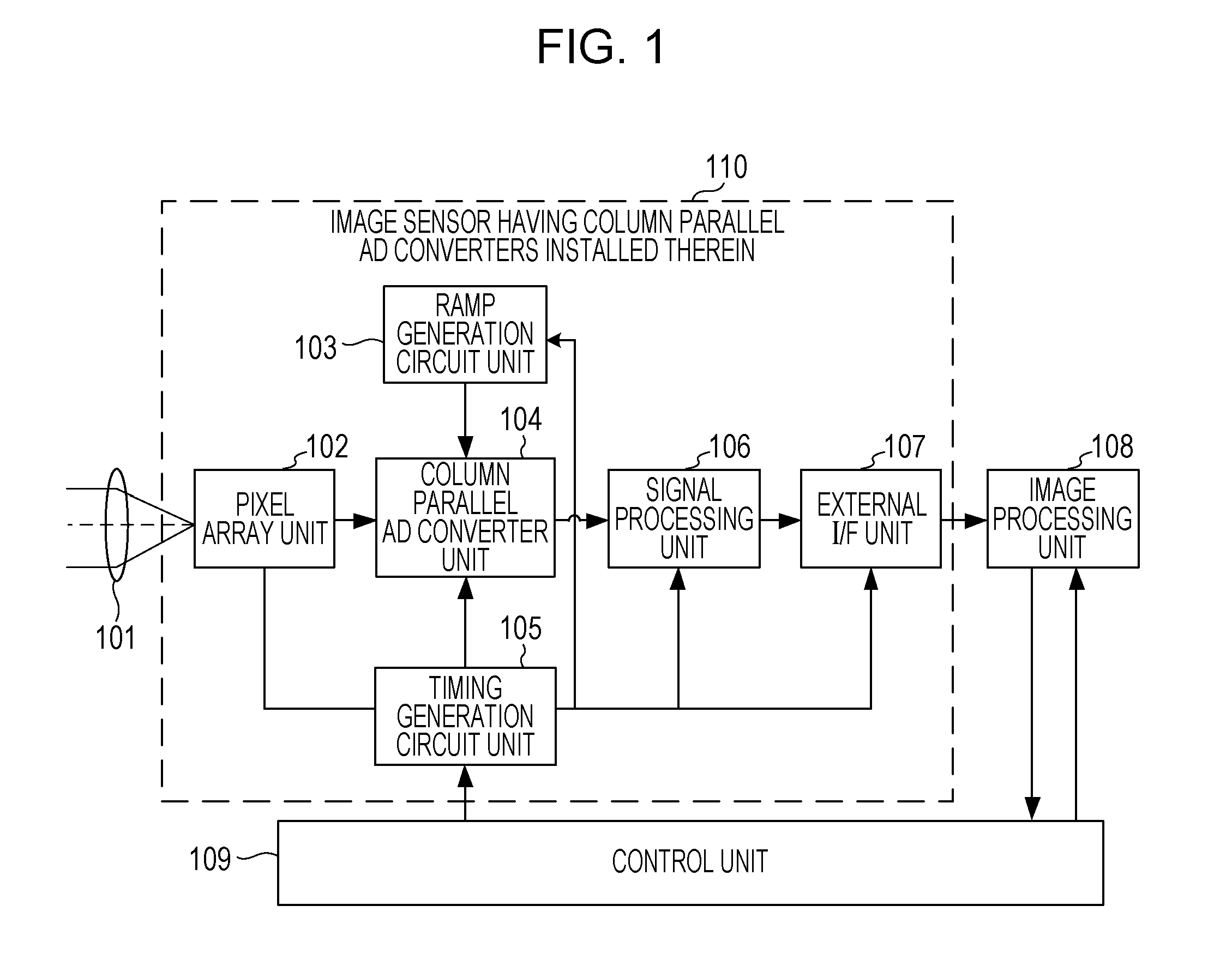

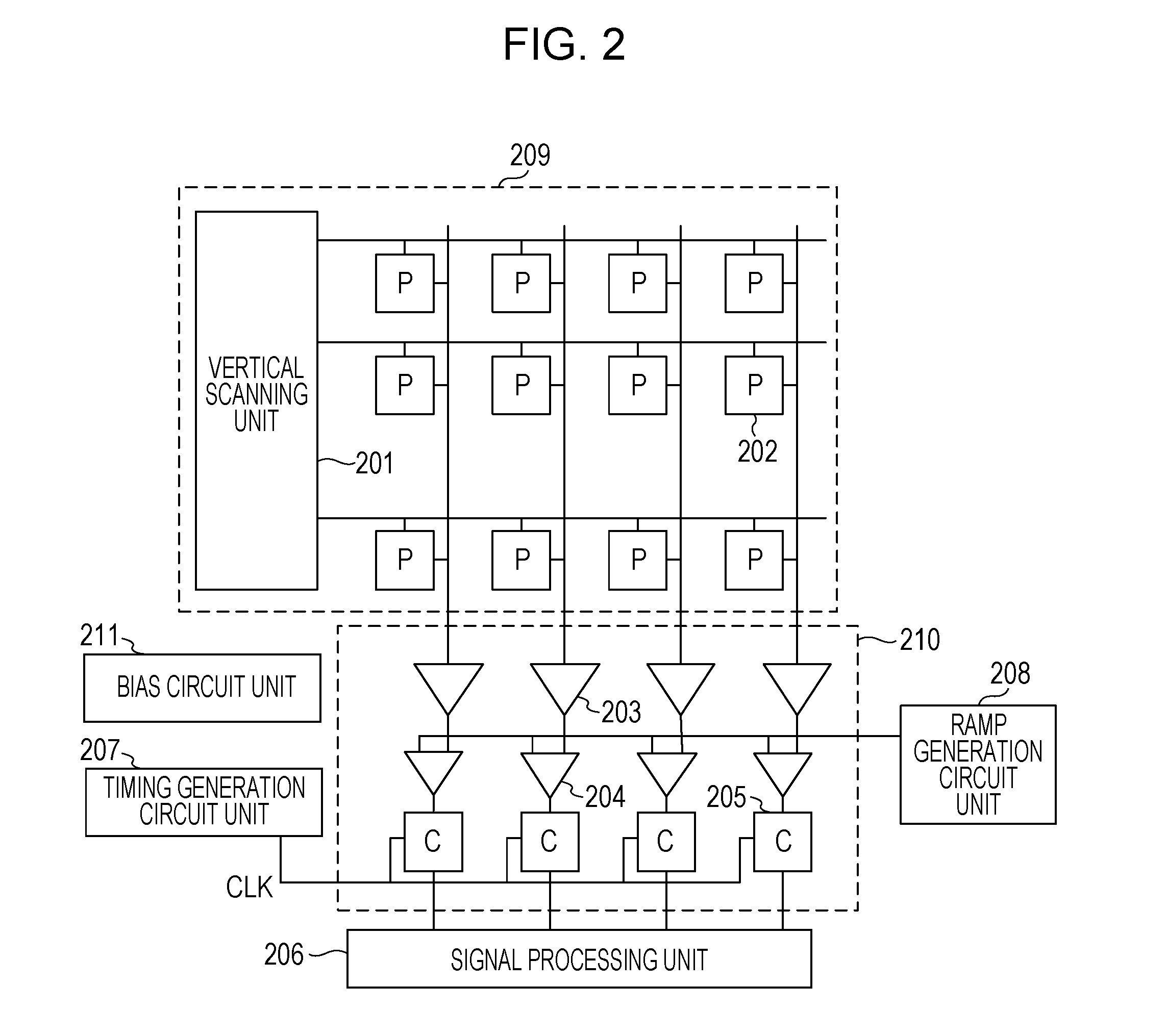

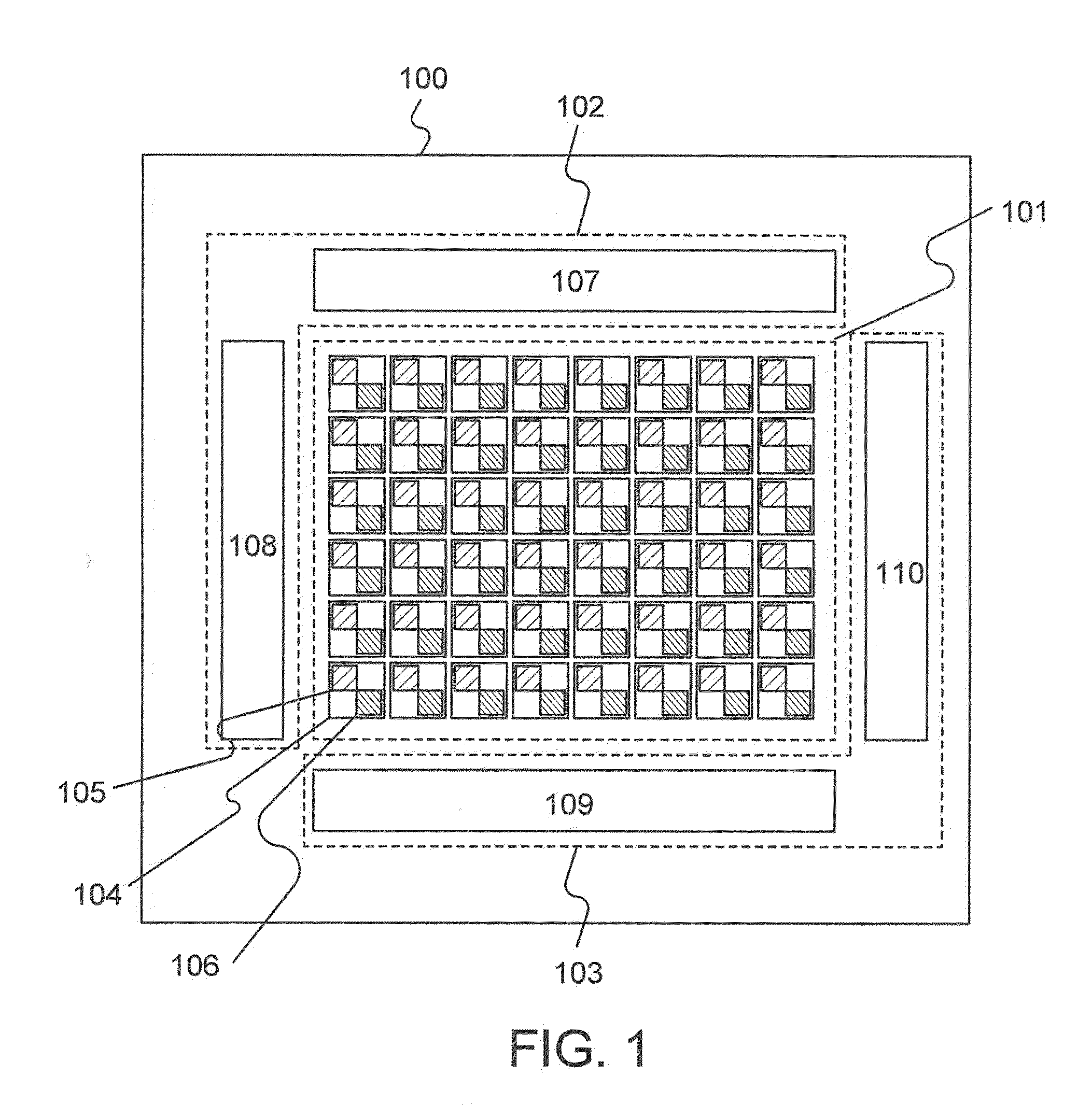

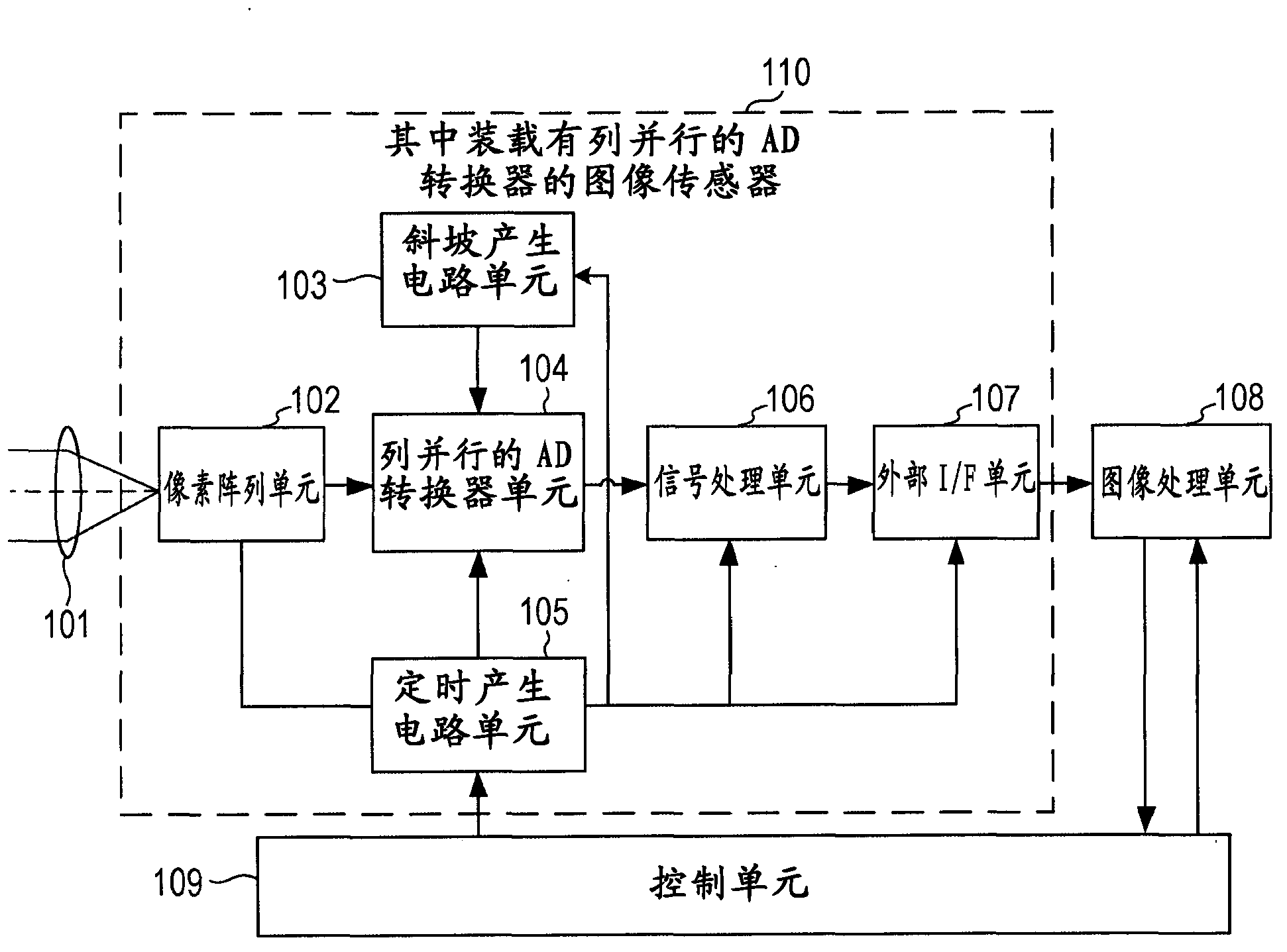

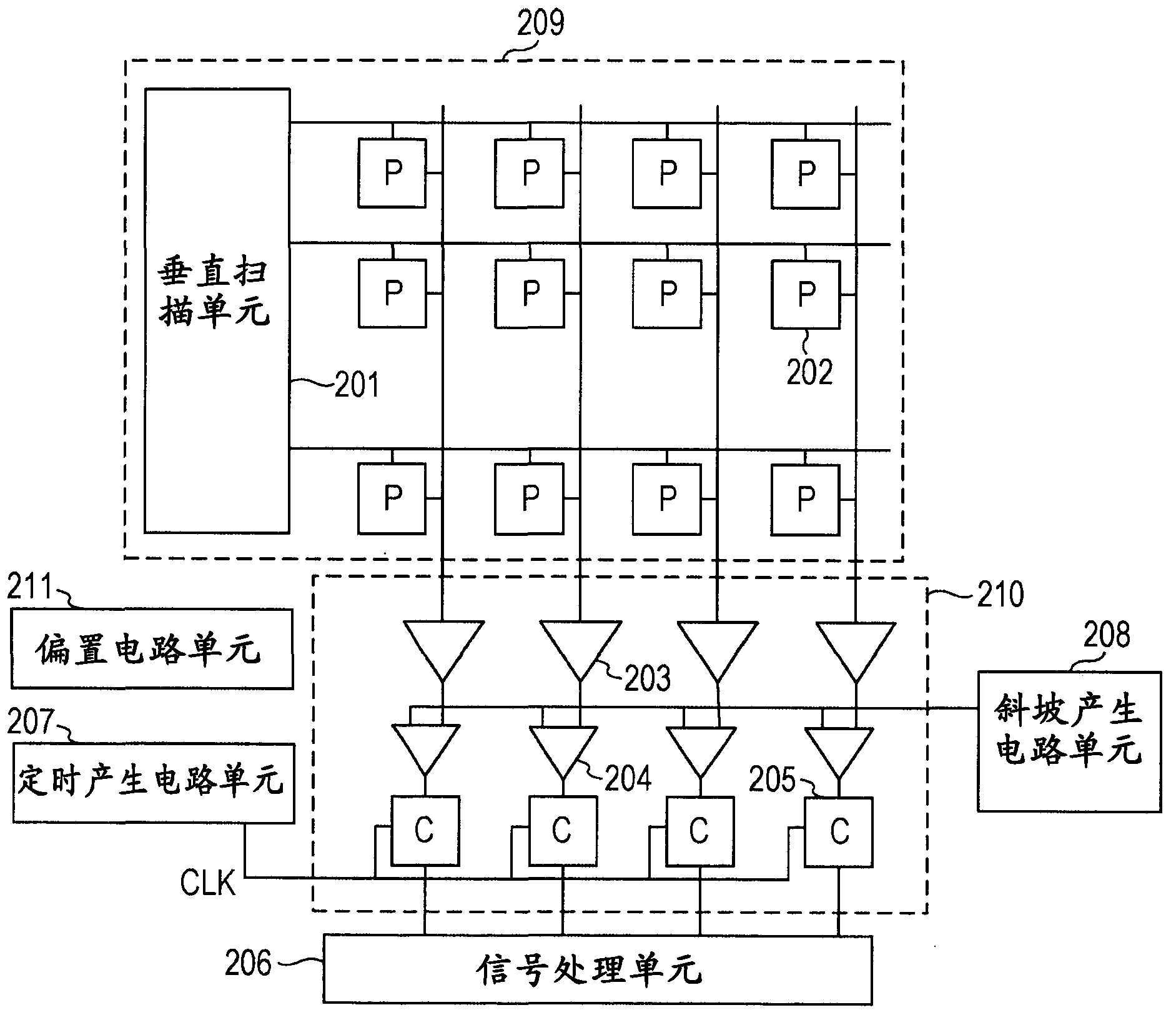

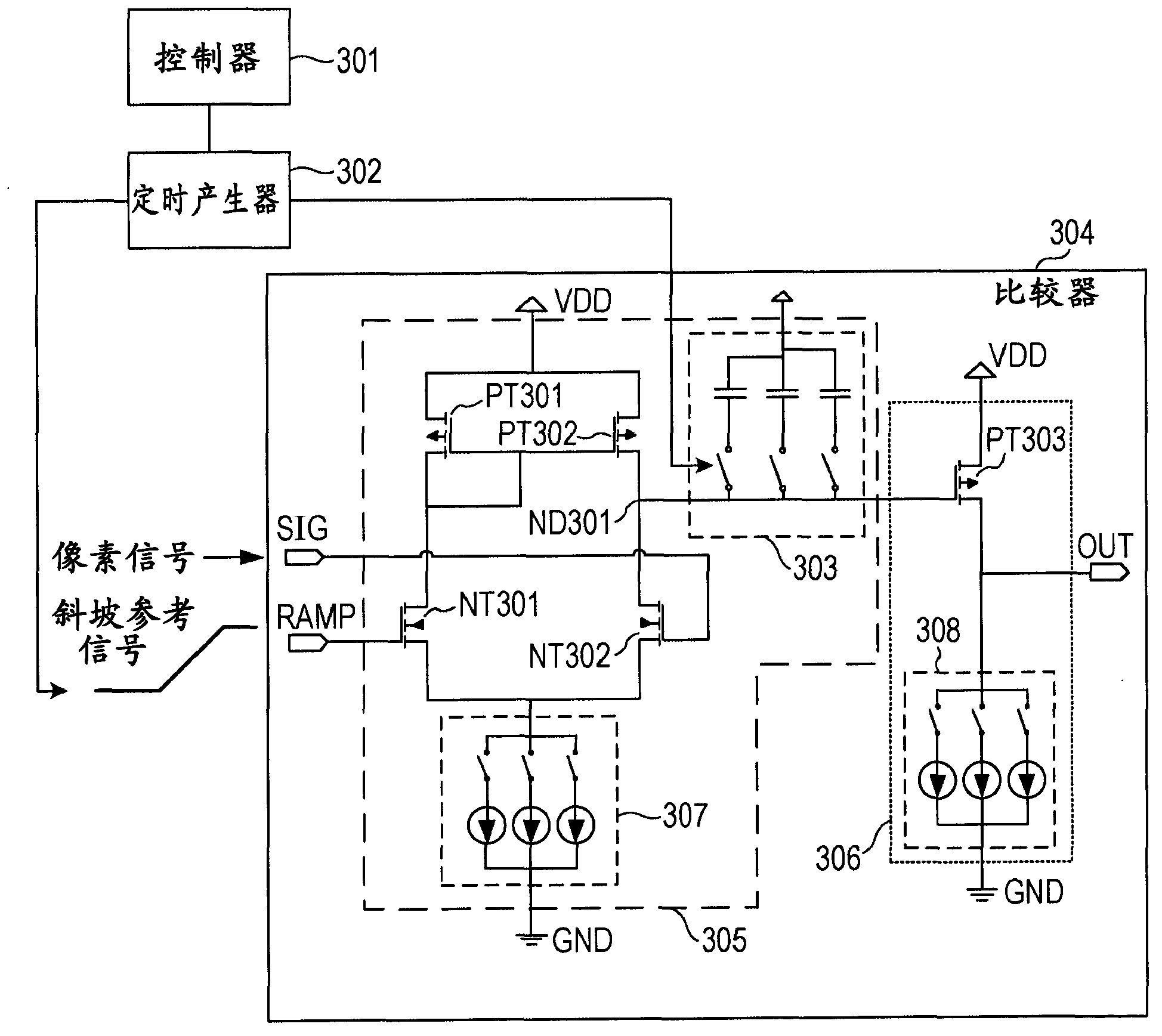

Image pickup apparatus

ActiveUS9094629B2Television system detailsElectric signal transmission systemsAudio power amplifierPhotoelectric conversion

An image pickup apparatus includes a pixel generating a signal by photoelectric conversion, a comparator comparing the signal based on the pixel with a reference signal varied with time, a counter performing counting until the comparator outputs a signal indicating that a relationship in magnitude between the signal based on the pixel and the reference signal is reversed, and a control unit. The comparator includes a first amplifier receiving the reference signal at a first input portion and the signal based on the pixel at a second input portion to compare the signal based on the pixel with the reference signal. The control unit sets a bandwidth of the comparator to a first bandwidth when the reference signal varies at a first rate of change and to a second bandwidth when the reference signal varies at a second rate of change.

Owner:CANON KK

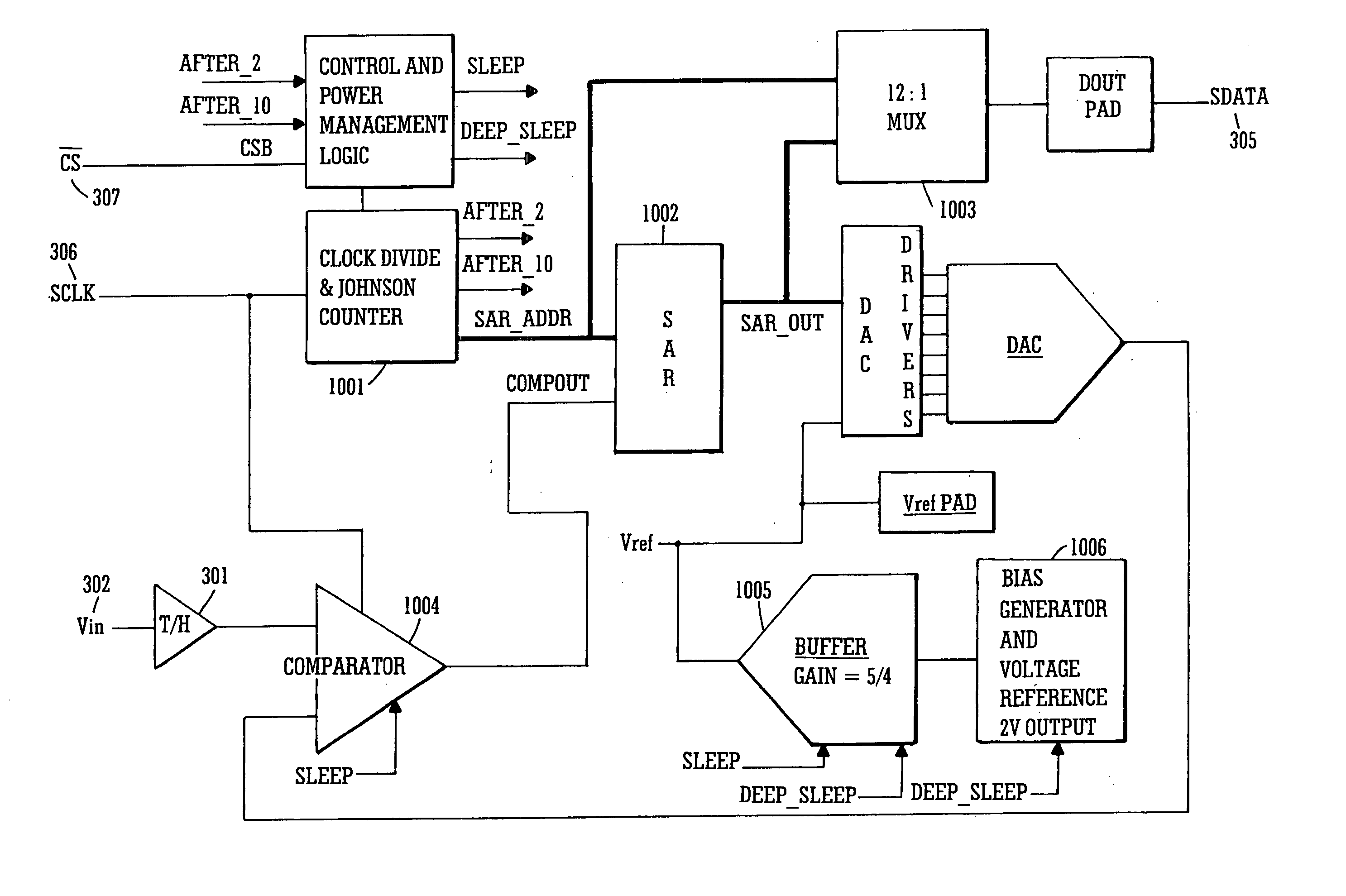

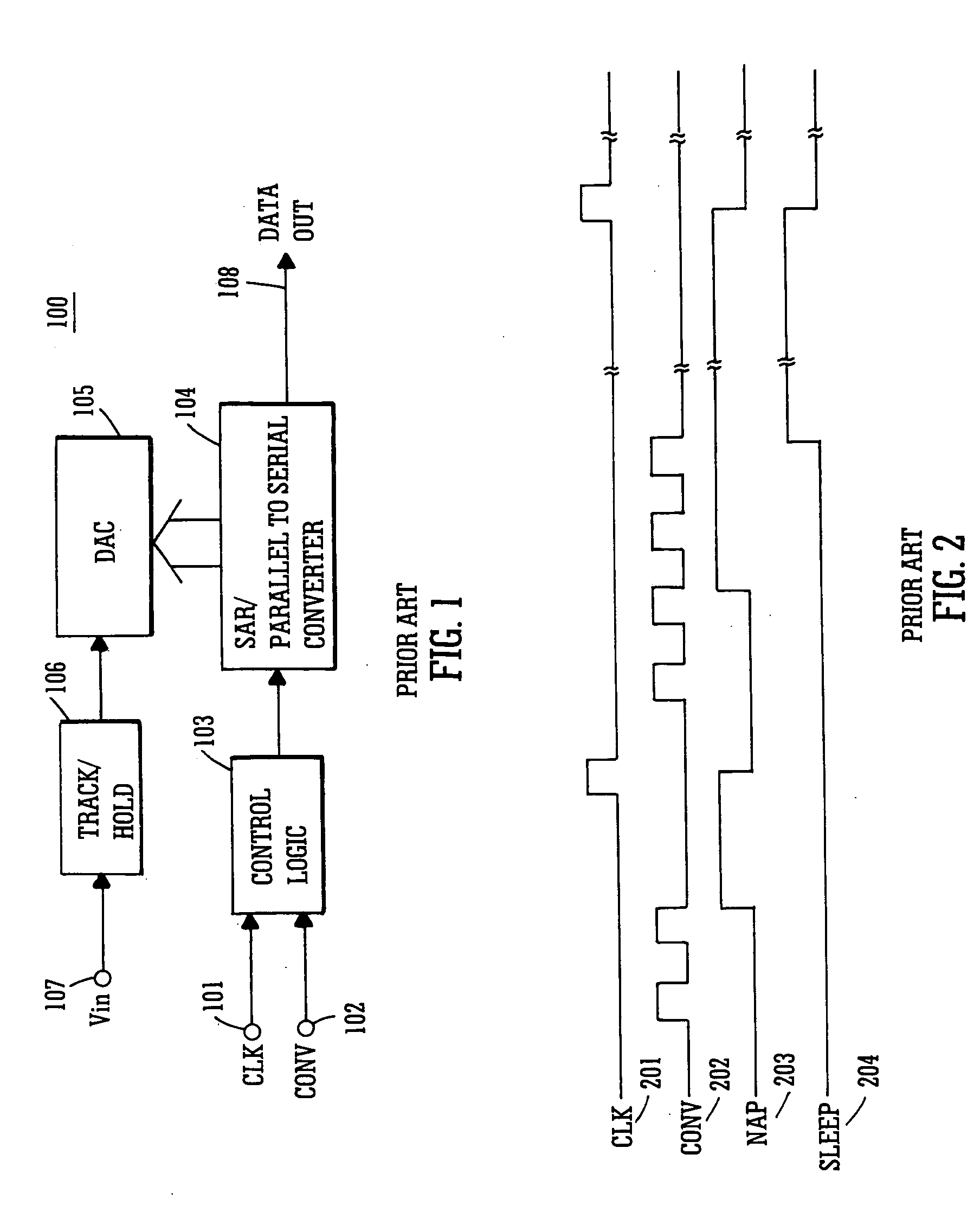

Read-only serial interface with versatile mode programming

InactiveUS20050035895A1Fast device throughputIncreased power consumptionPower managementPower saving provisionsOperation modeLogic state

A method for placing a device in a selected mode of operation. The method comprises the steps of initializing a device select signal into a first logic state, asserting the device select signal in a second logic state, and returning the device select signal to the first logic state within a first user-controlled time window. A device is also described that includes means for detecting logic state transitions at a device select input and a clock input, and means for changing operating mode of the device in response to a predetermined number of logic state transitions at the clock input, occurring between logic state transitions at the device select input. The selected operating mode may be a reduced power consumption mode, for example, or another operating mode of the device, such as a daisy-chain mode of operation, or a mode that accommodates programming of analog input range.

Owner:ANALOG DEVICES INC

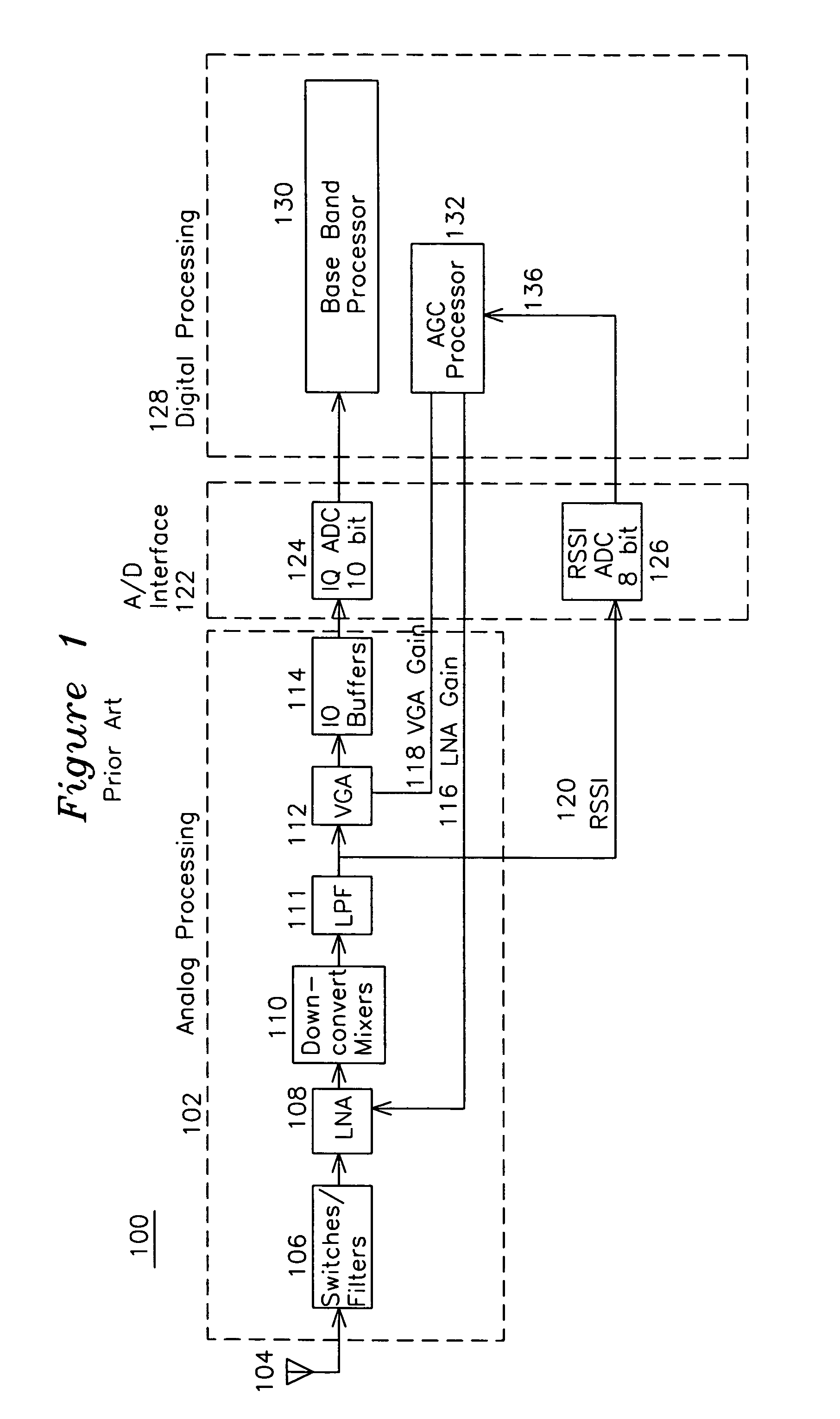

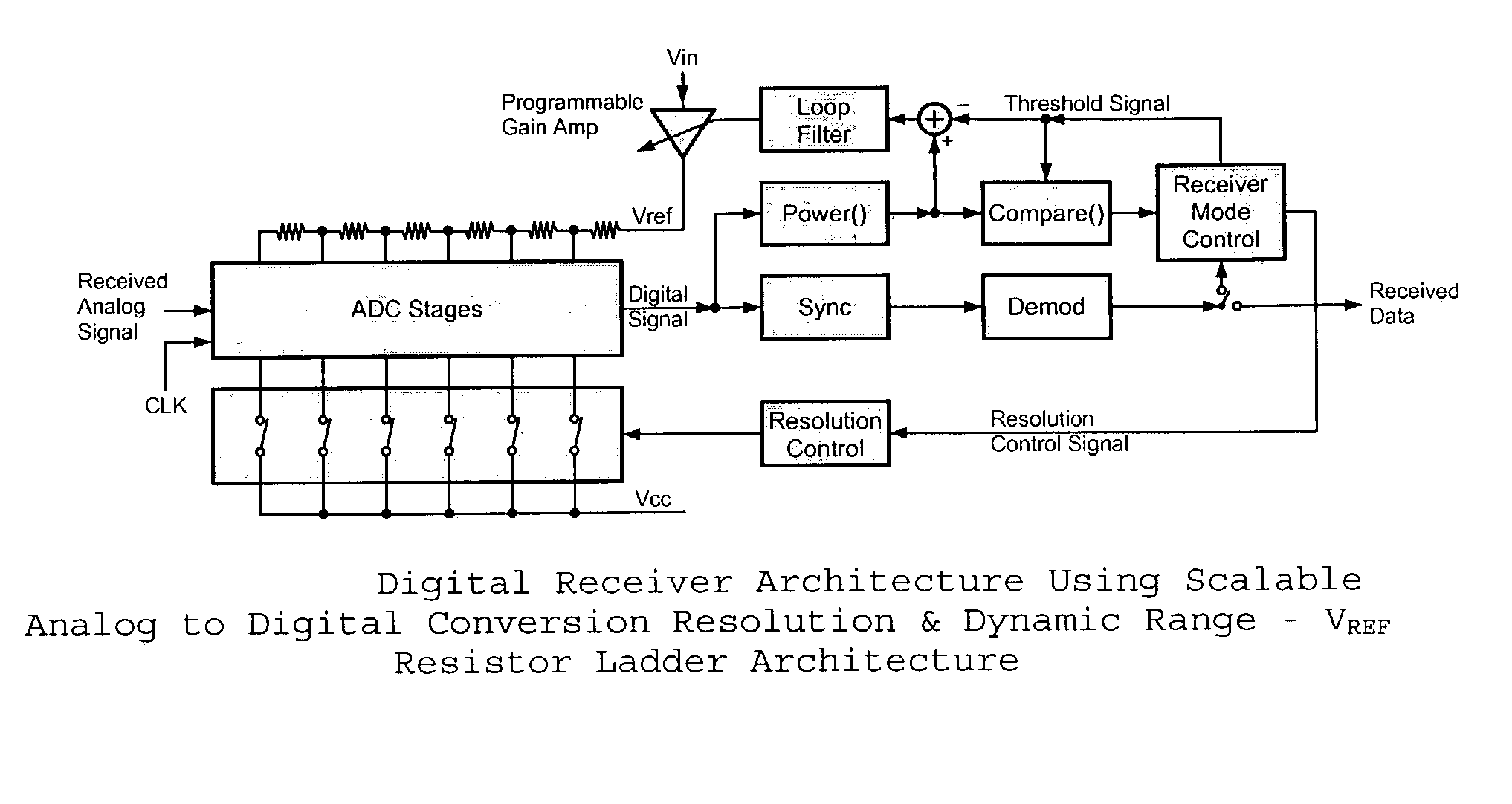

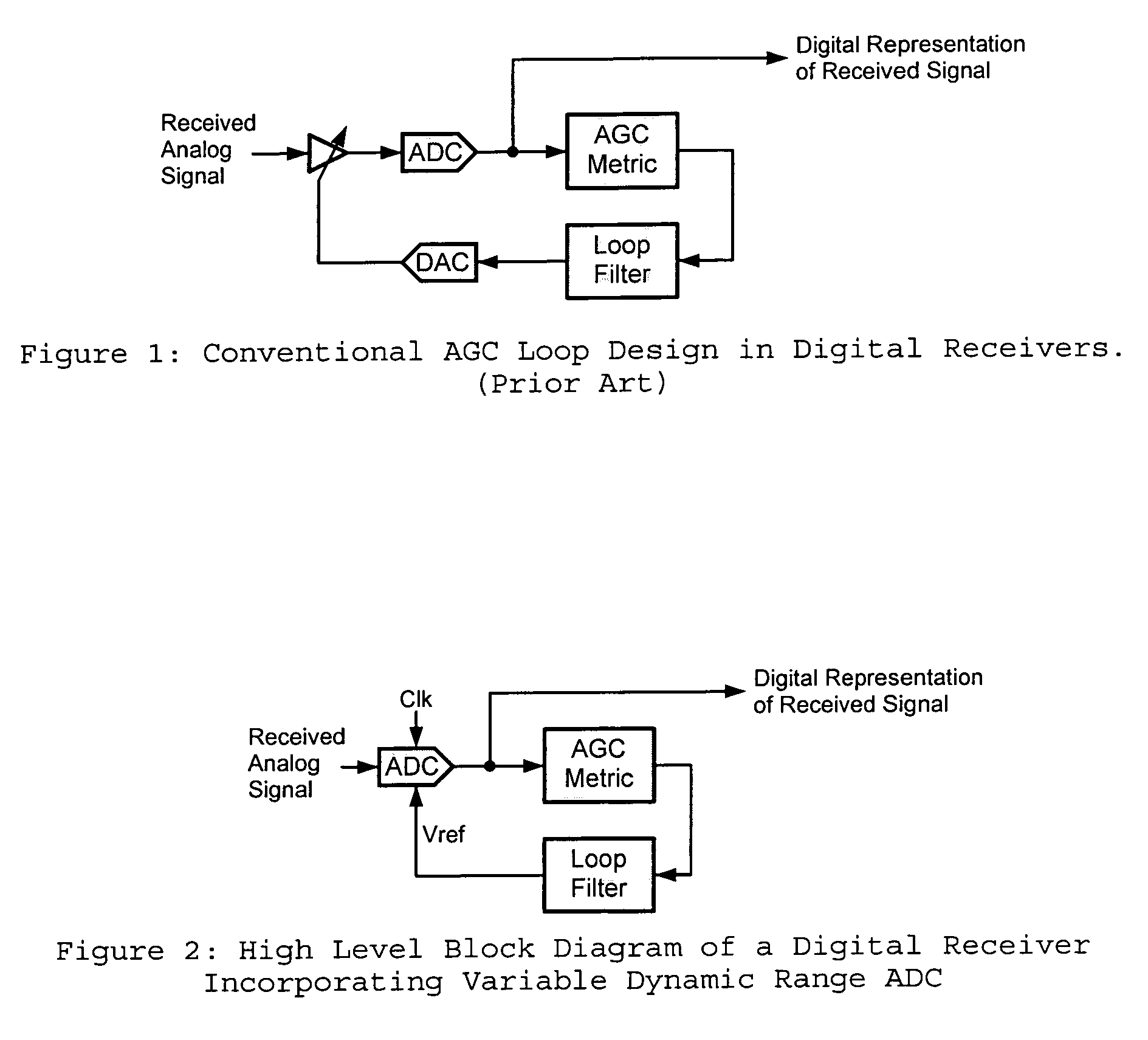

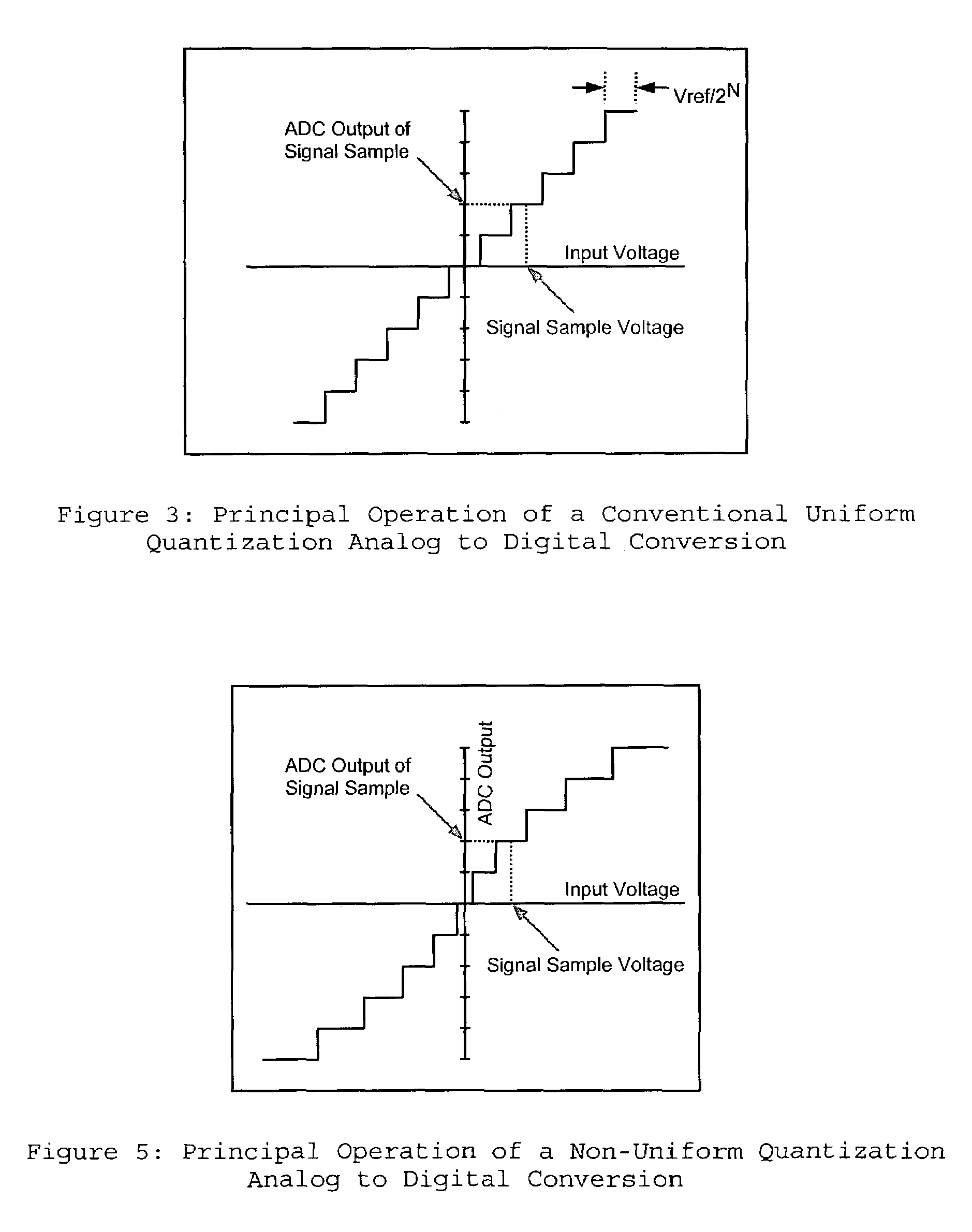

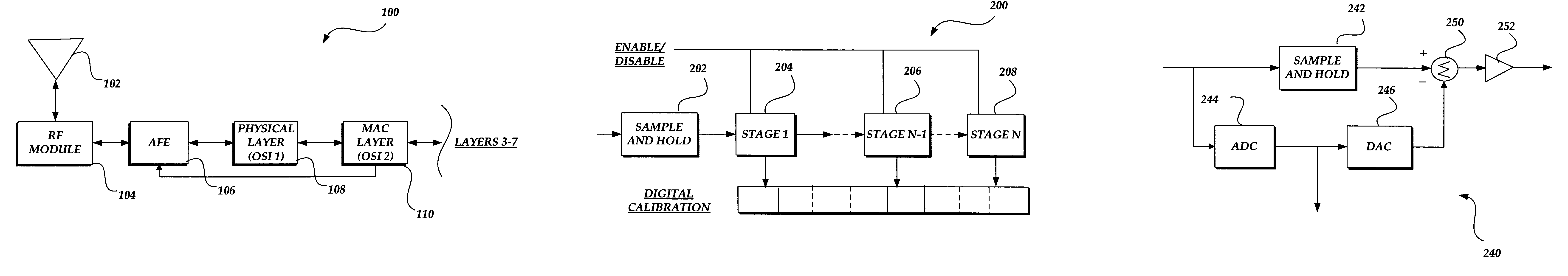

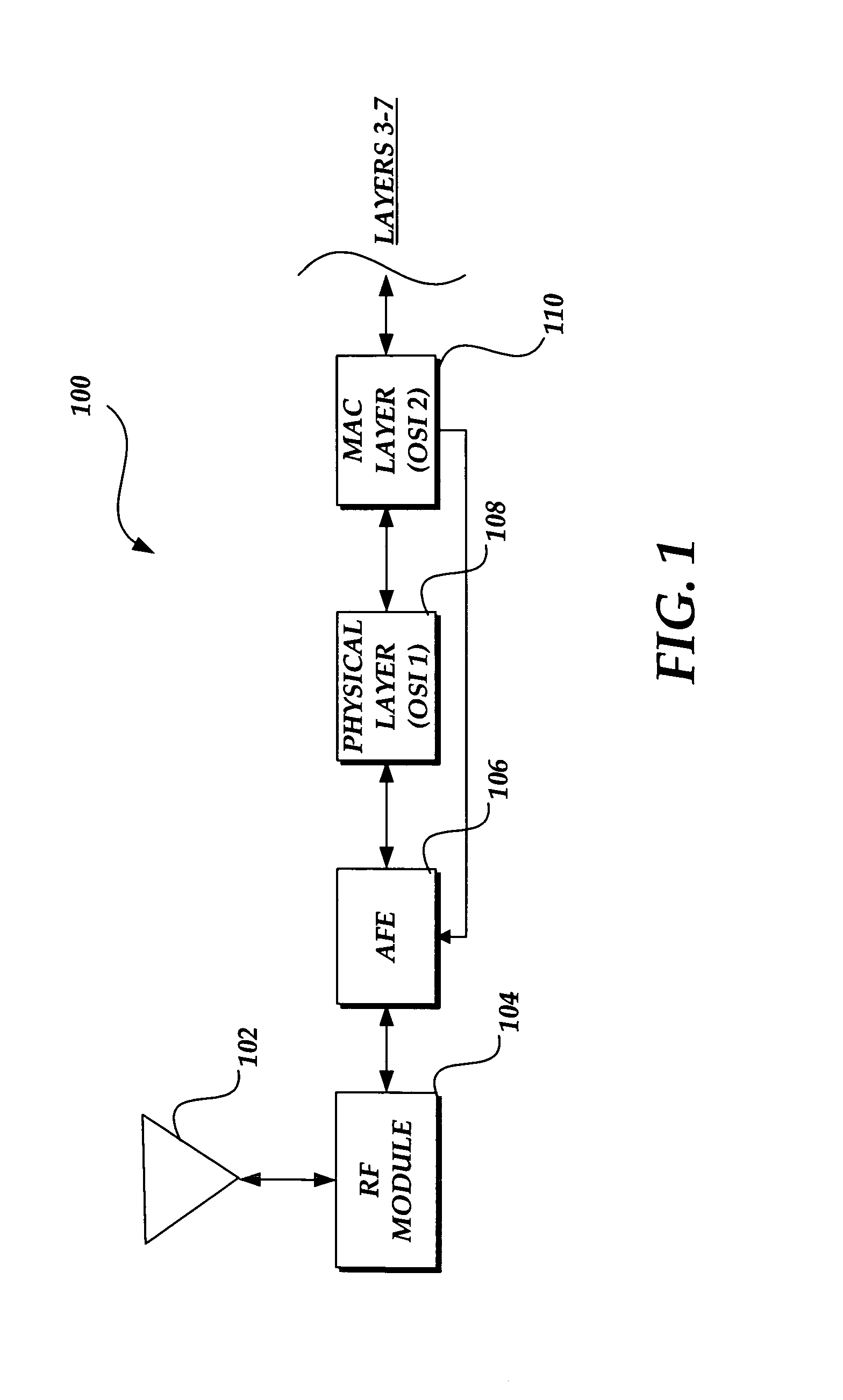

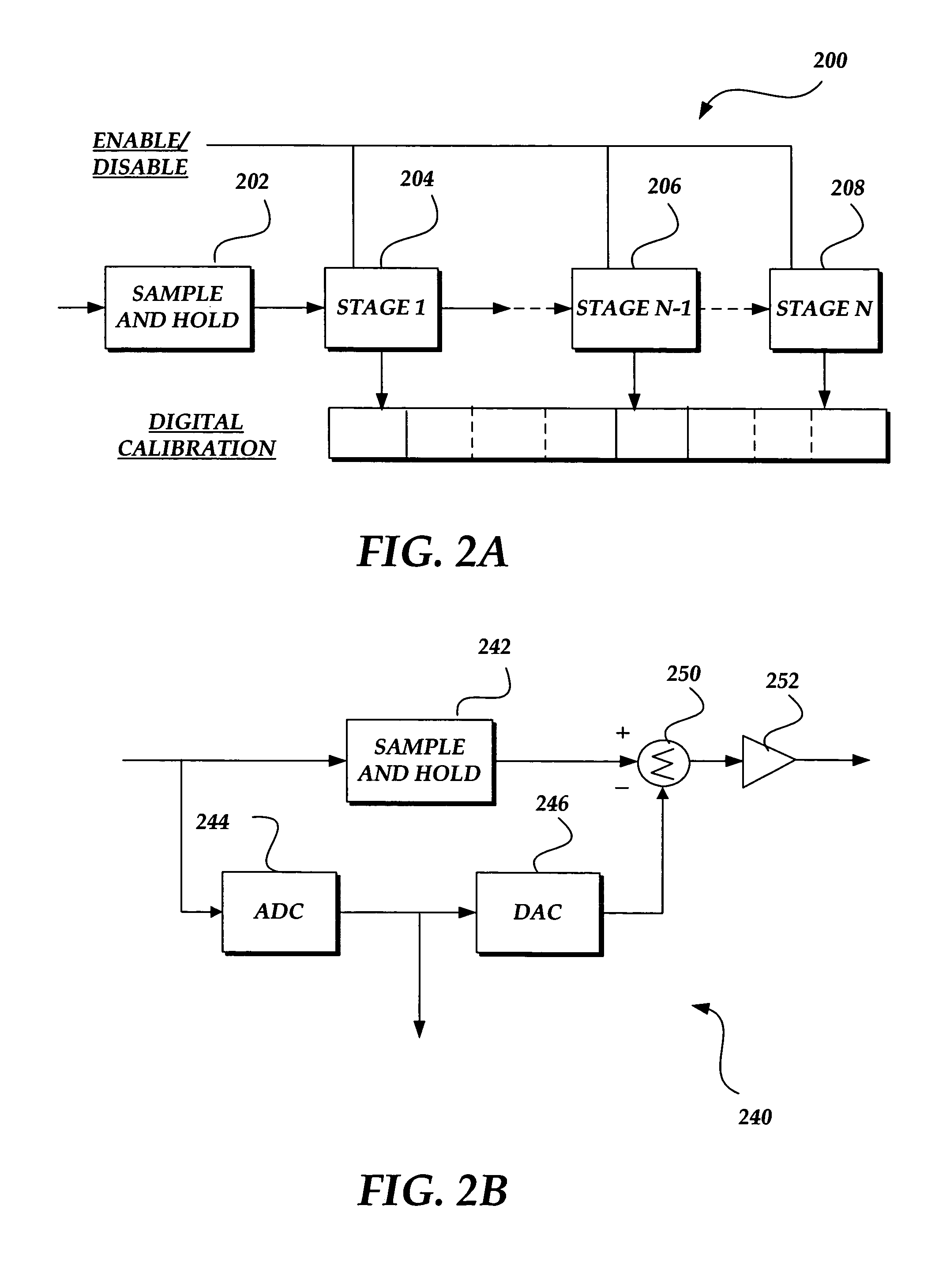

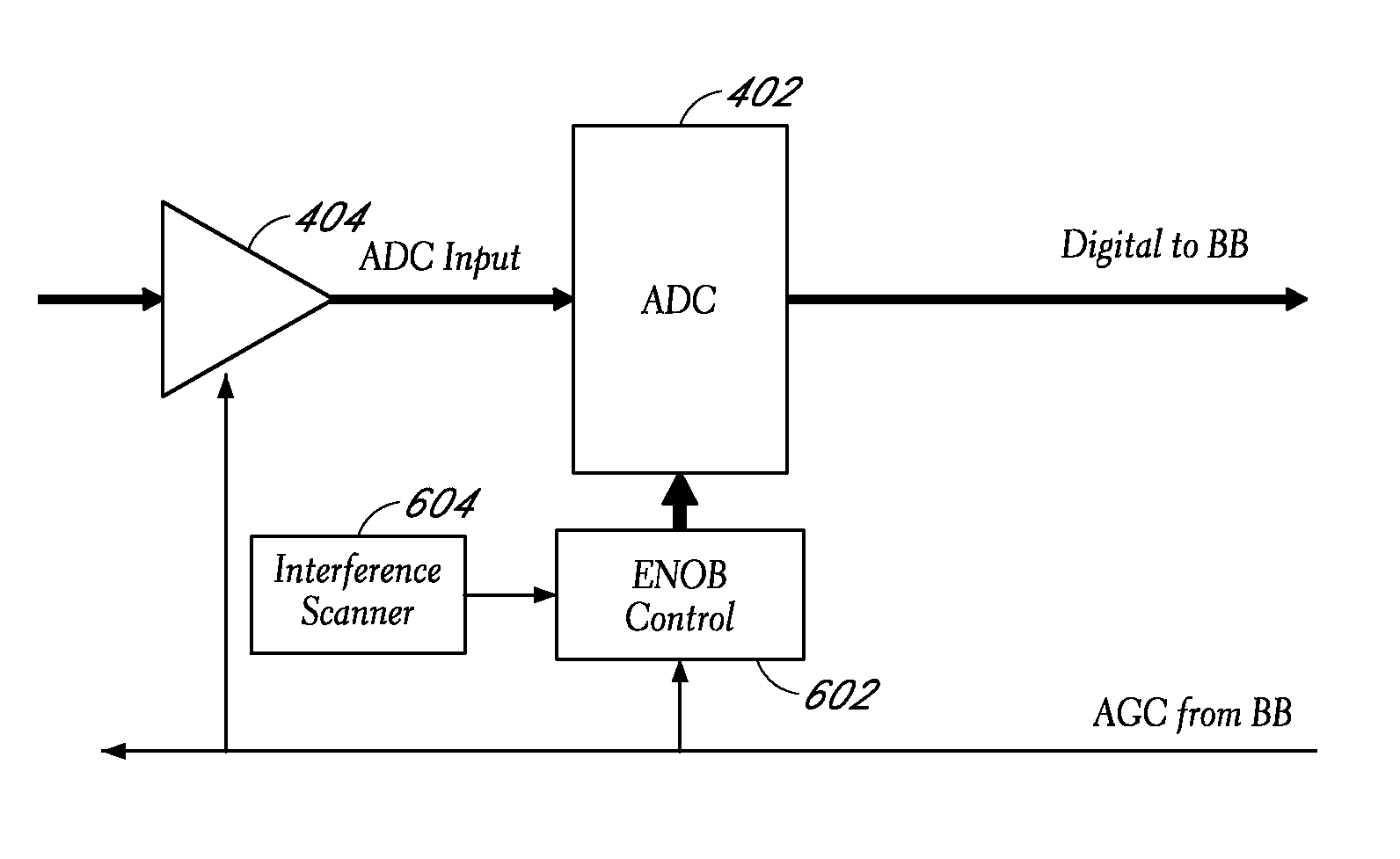

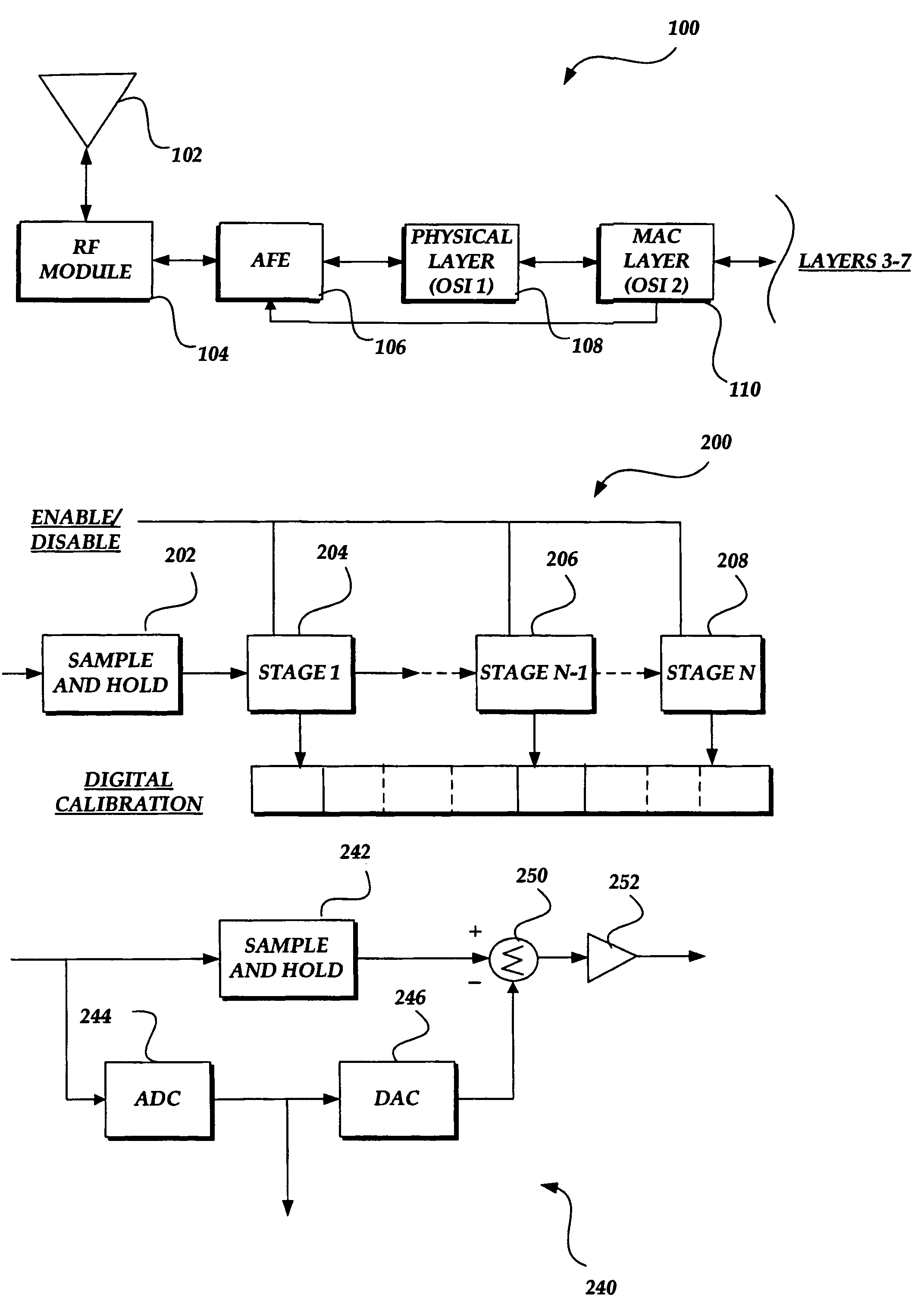

System, method and apparatus to implement low power high performance transceivers with scalable analog to digital conversion resolution and dynamic range

ActiveUS7295645B1Reconfigurable analogue/digital convertersAmplitude-modulated carrier systemsTransceiverImage resolution

The present invention provides for operation of a digital communication receiver having multiple operational modes so that power consumption of the system can be kept at a minimum by using the lowest power operation for the system components performing tasks associated with each of the respective one of the multiple operational modes. An example is the receiver A / D converter operation with the lowest power to provide the desired resolution. Also, the invention provides novel architectures for implementing scalable resolution A / D converters. Furthermore, the invention generally includes a novel architecture for controlling the dynamic range of an A / D converter. In addition, the invention generally involves novel architectures for controlling the dynamic range of an A / D converter to alleviate difficulties associated with AGC control loops. Multiple exemplary embodiments are disclosed.

Owner:OSTENDO TECH INC

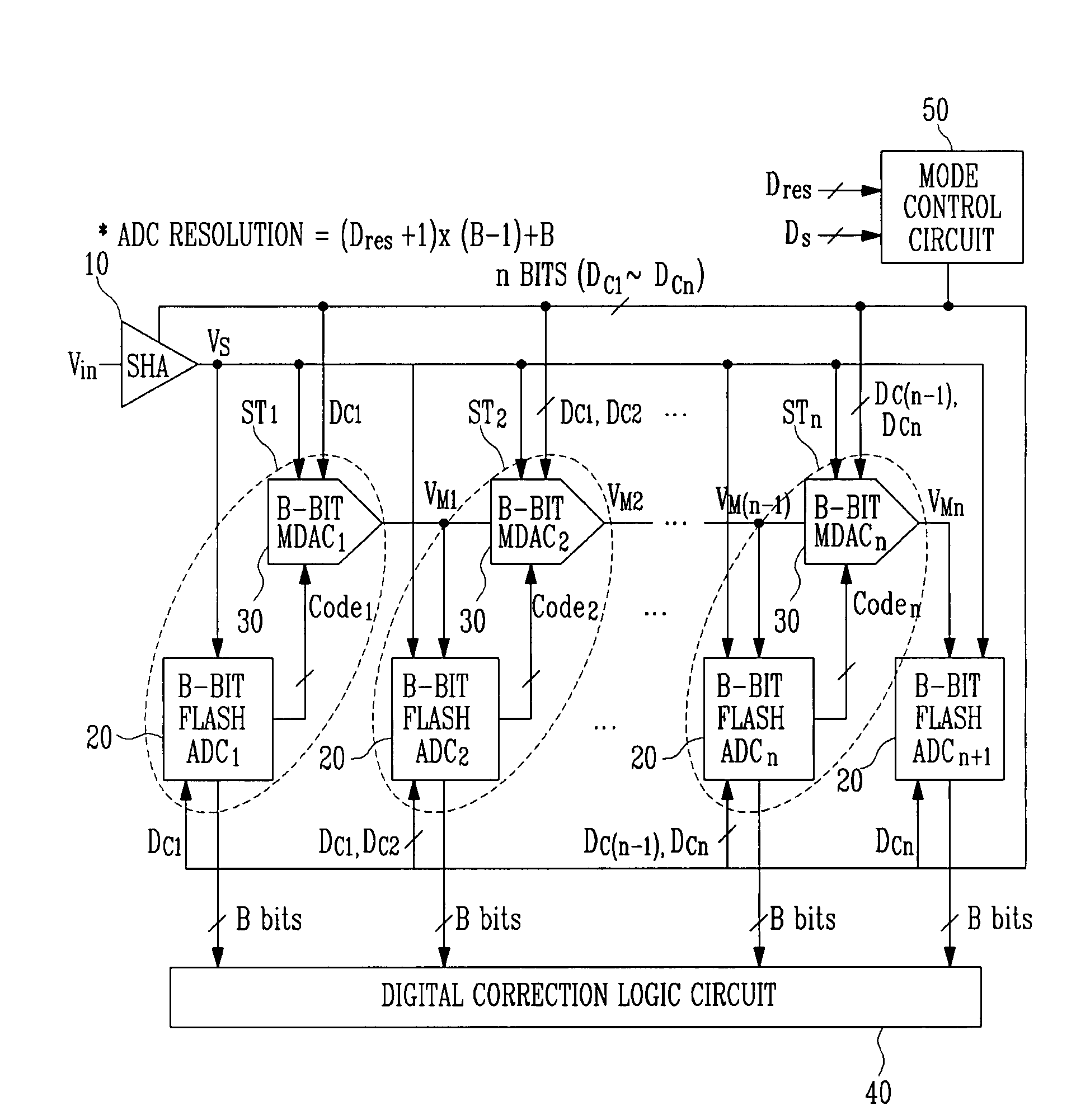

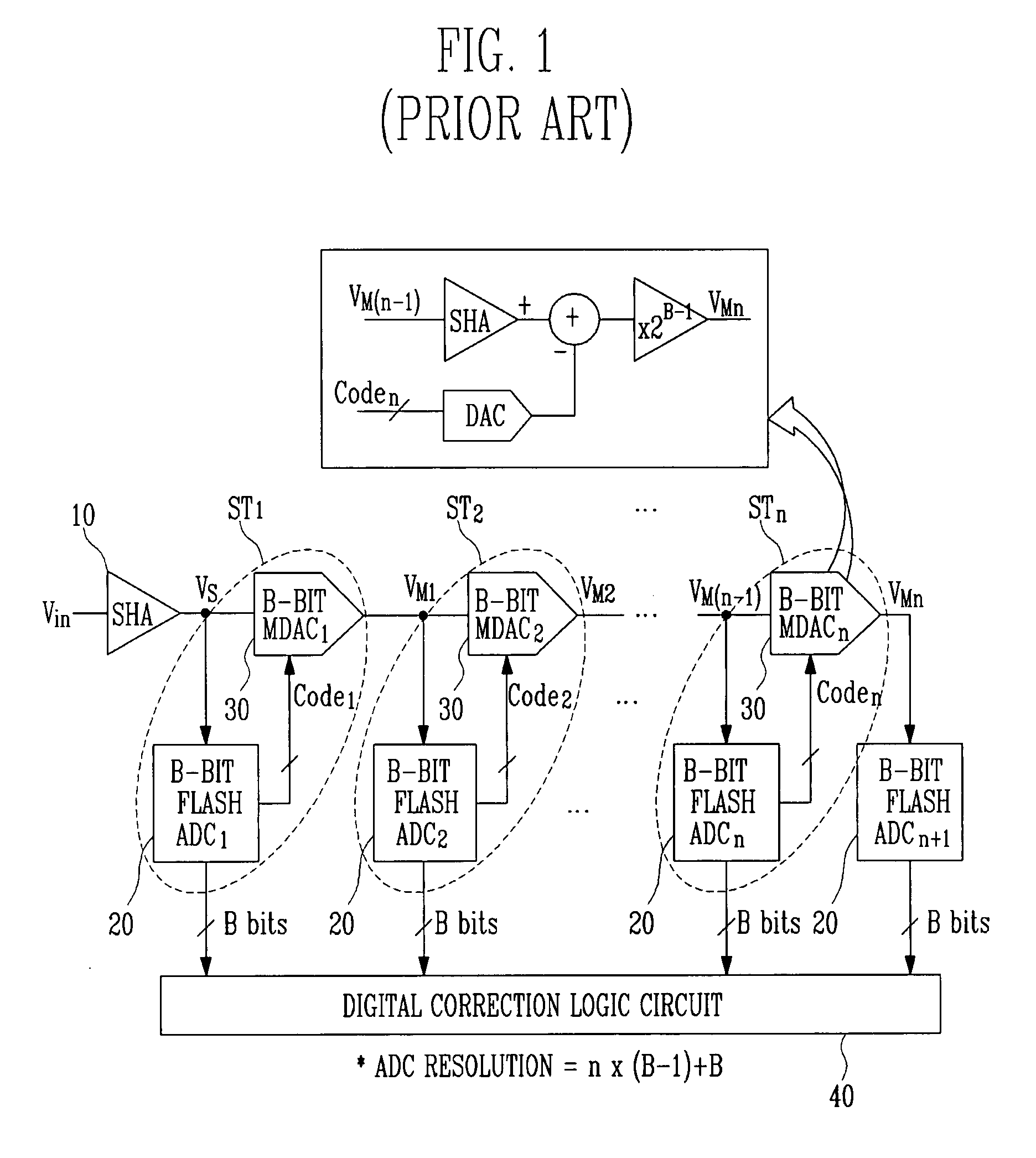

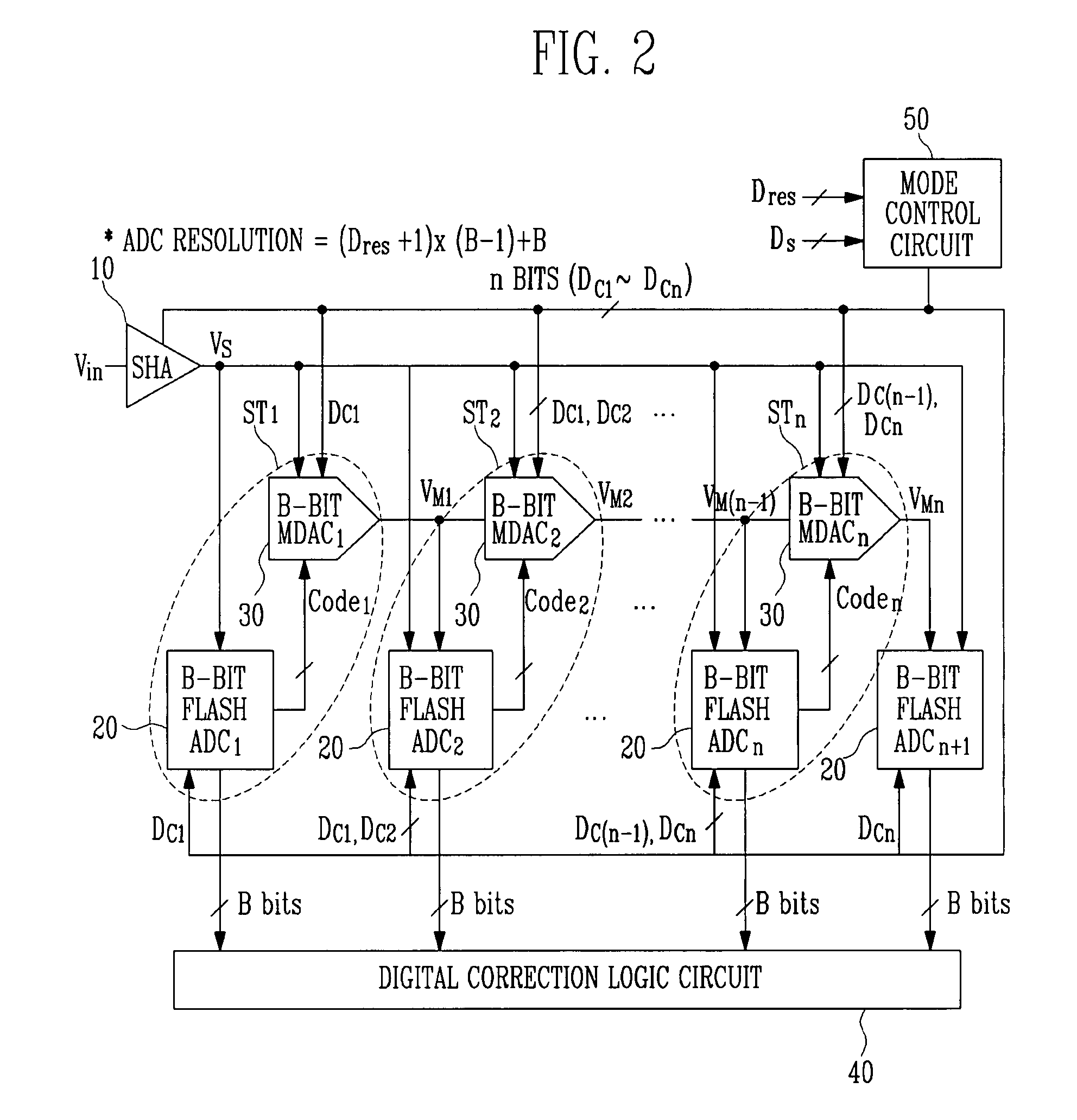

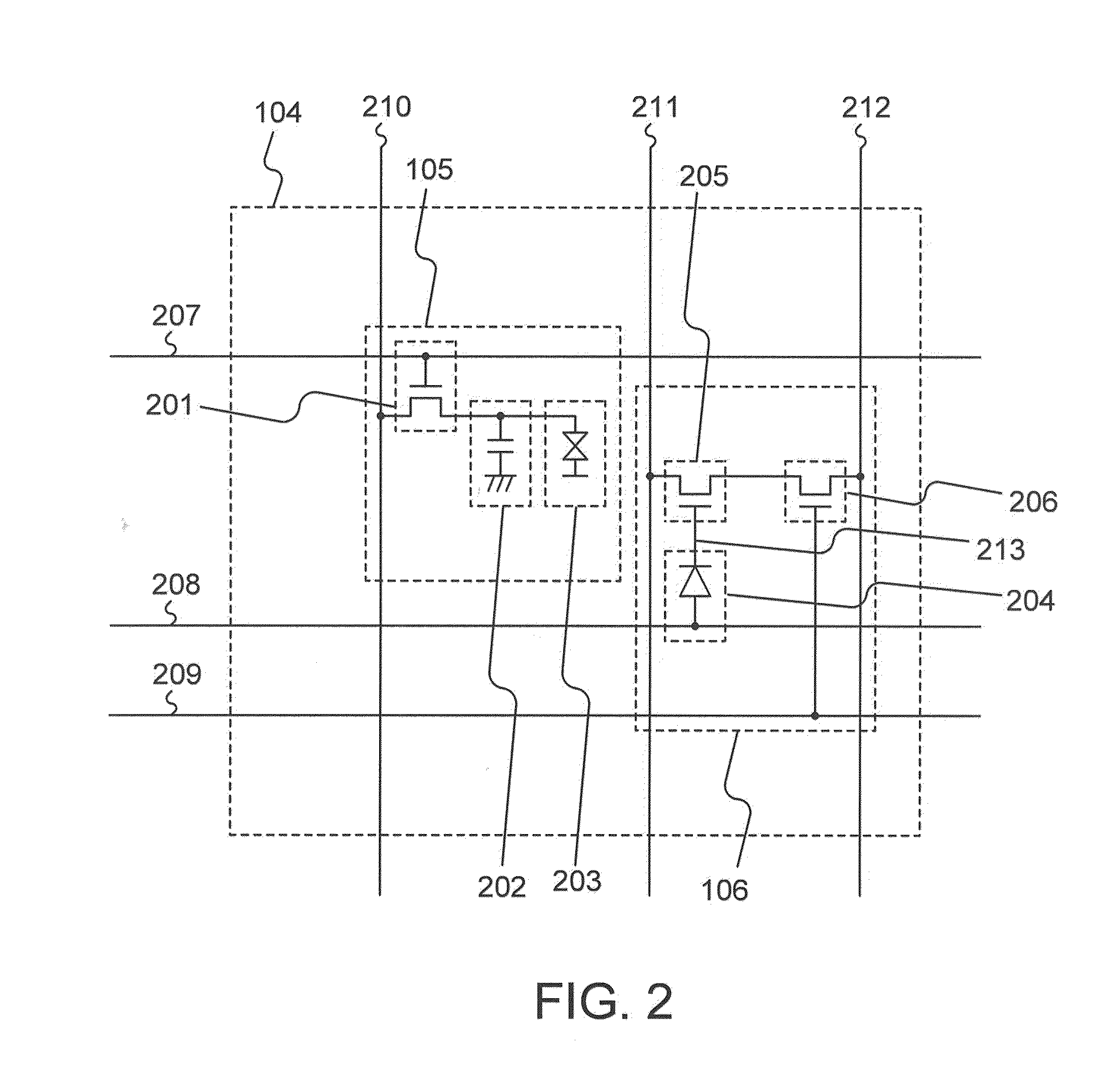

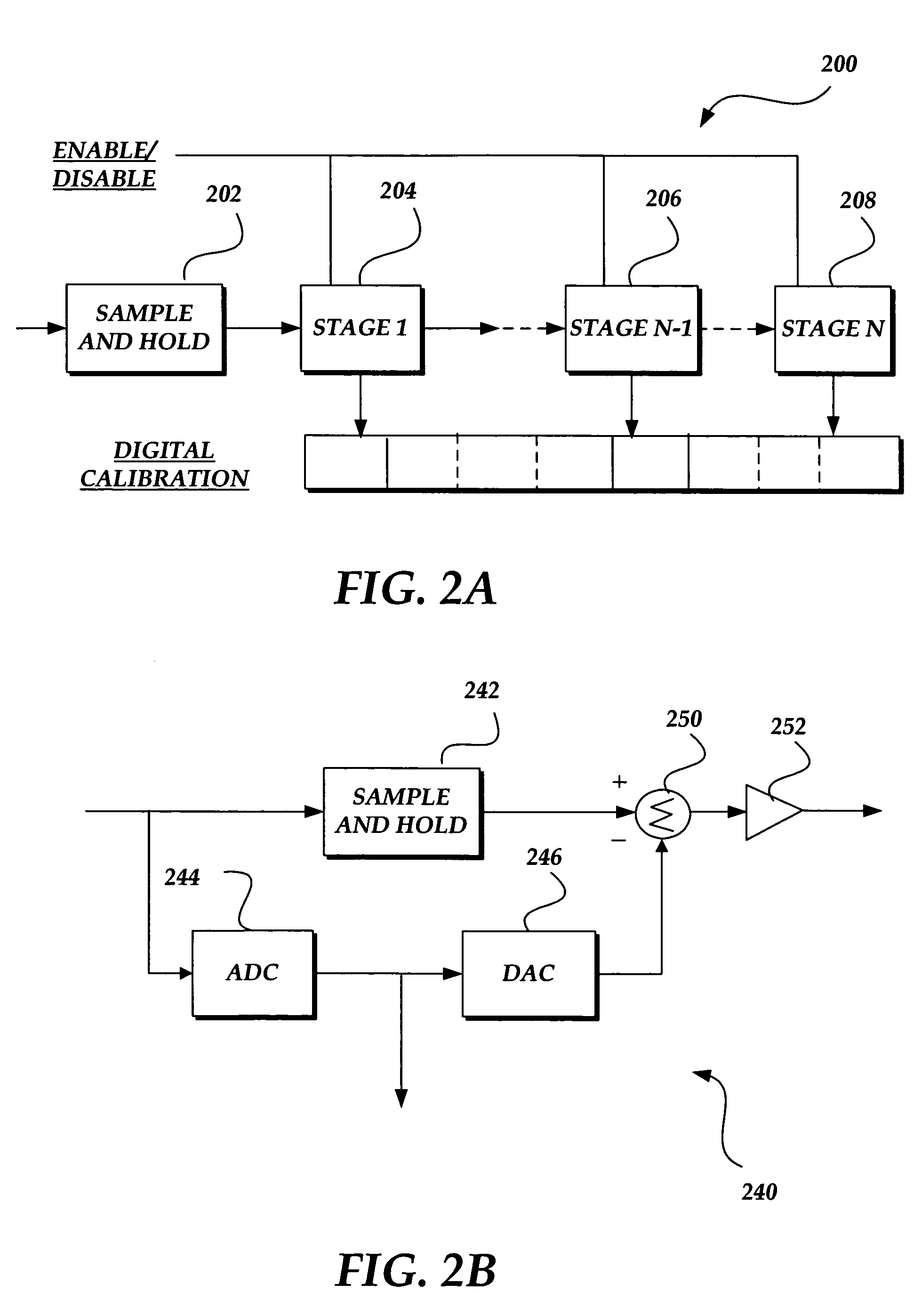

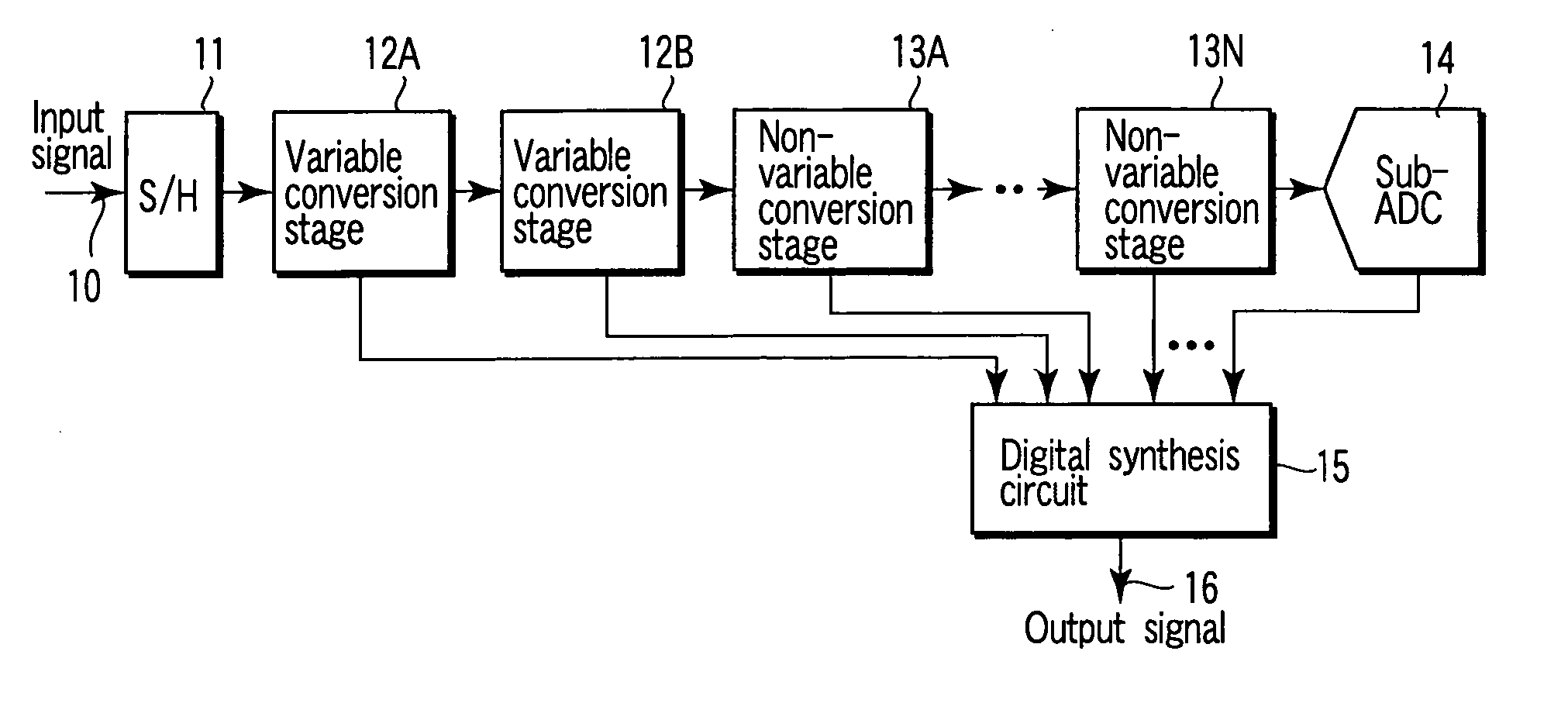

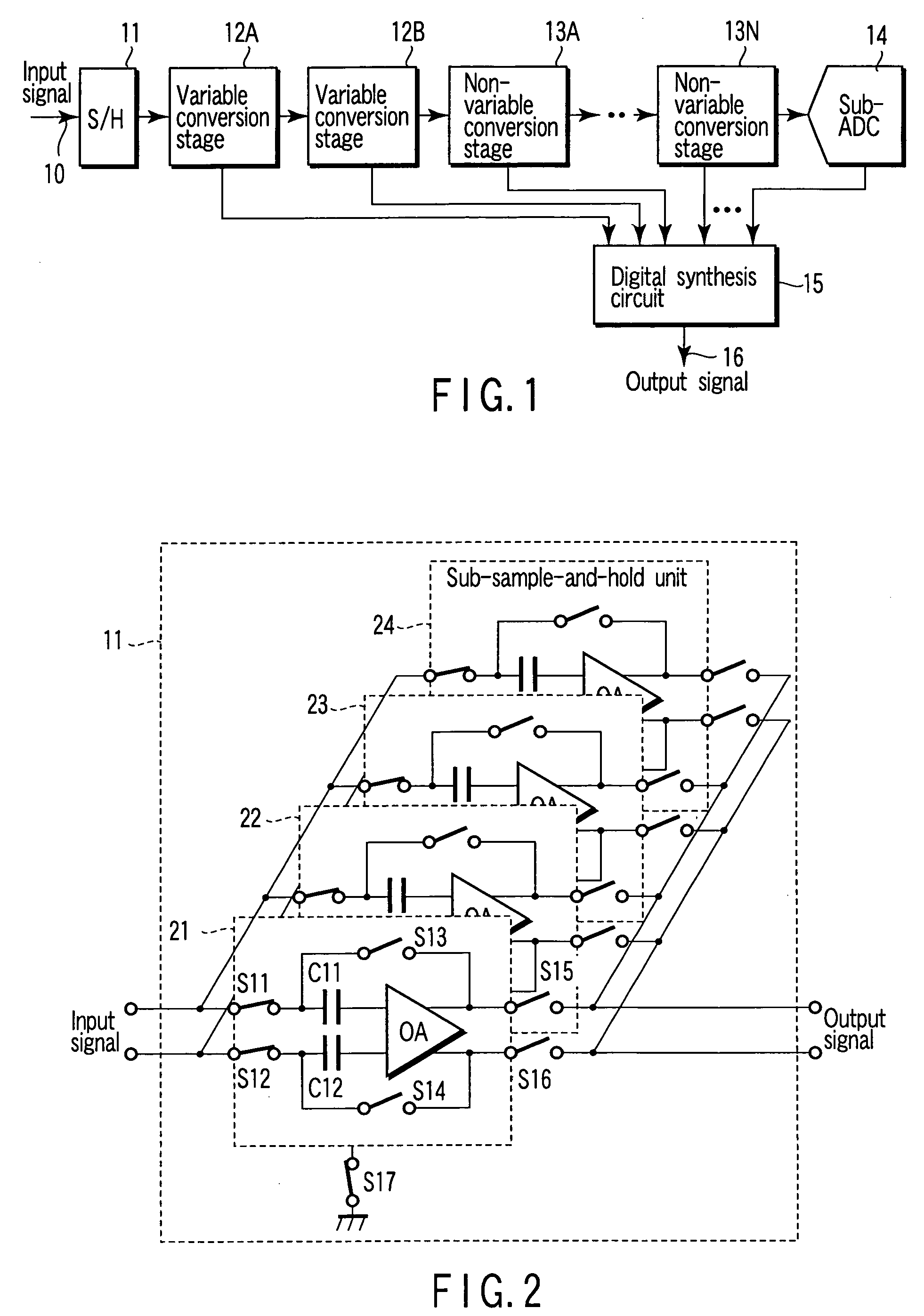

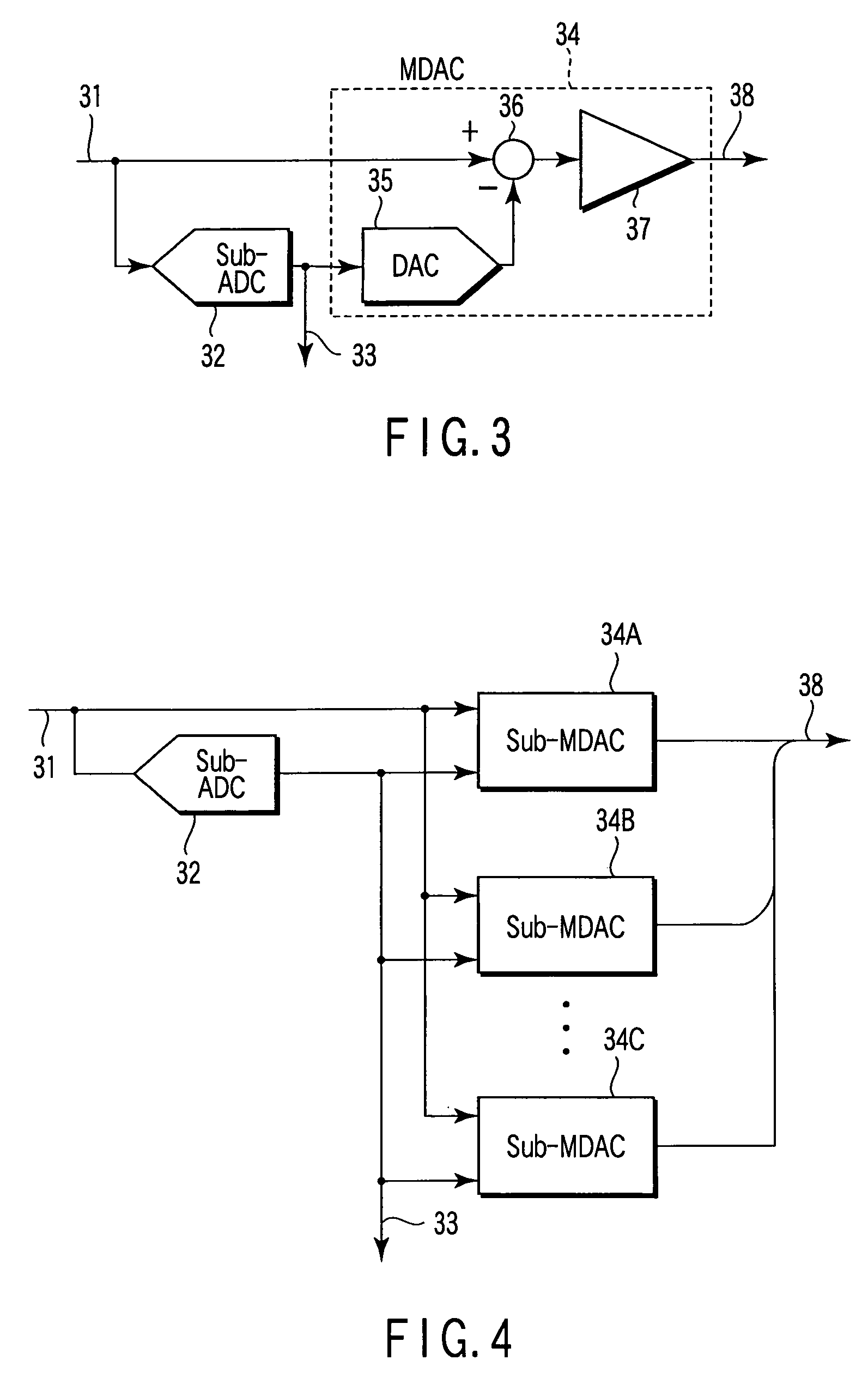

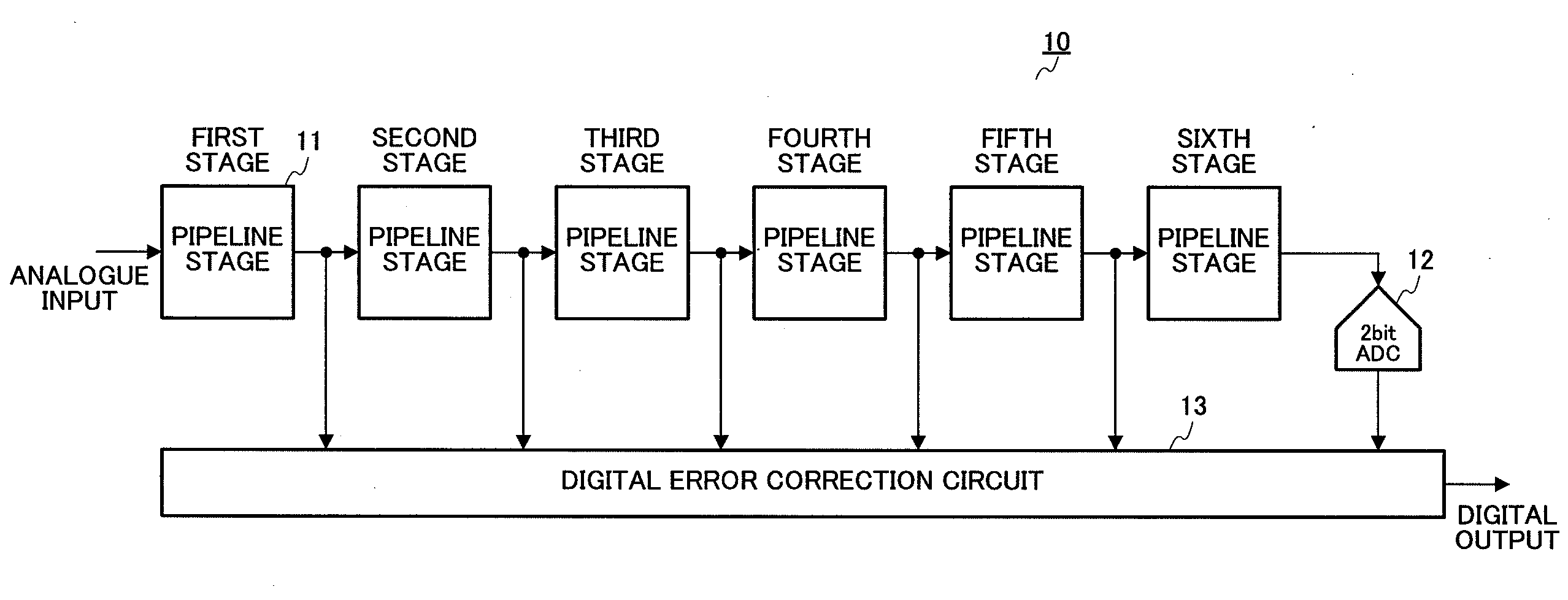

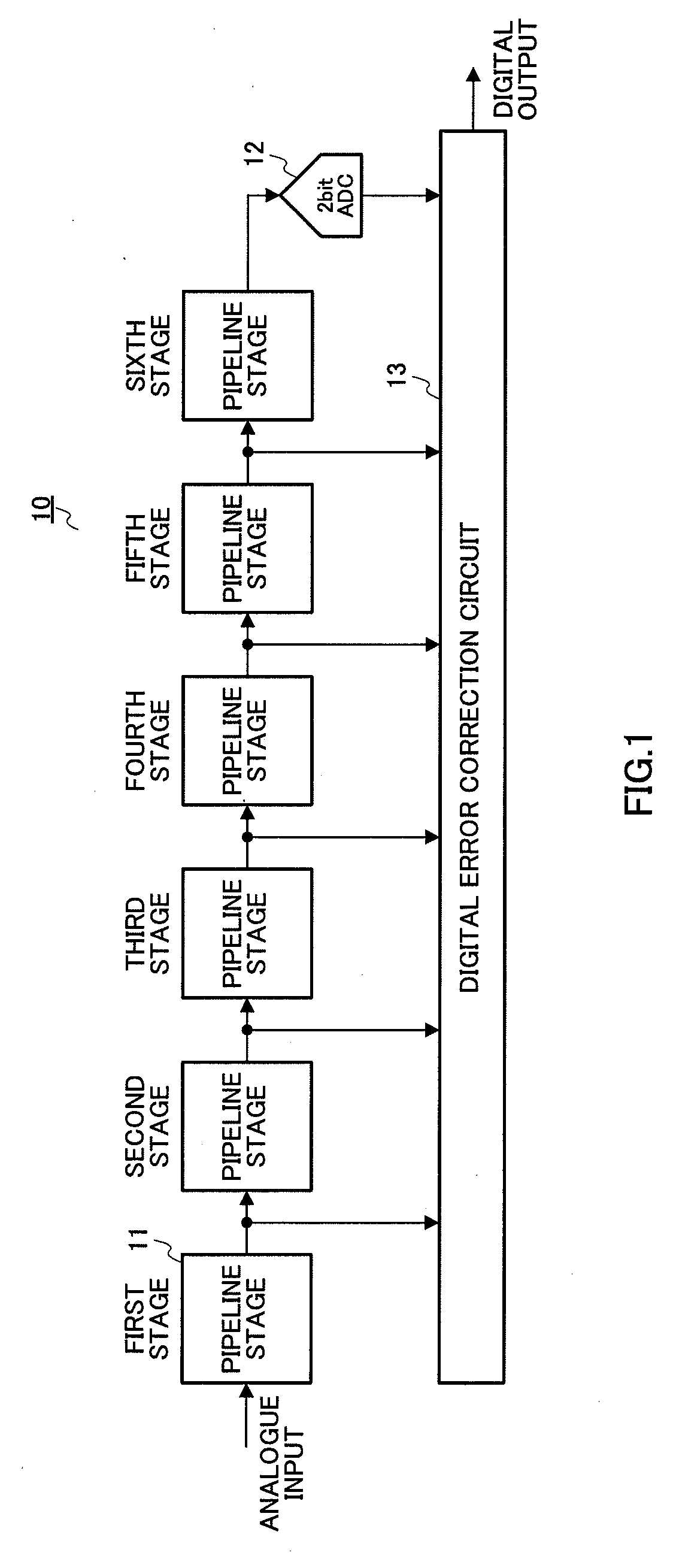

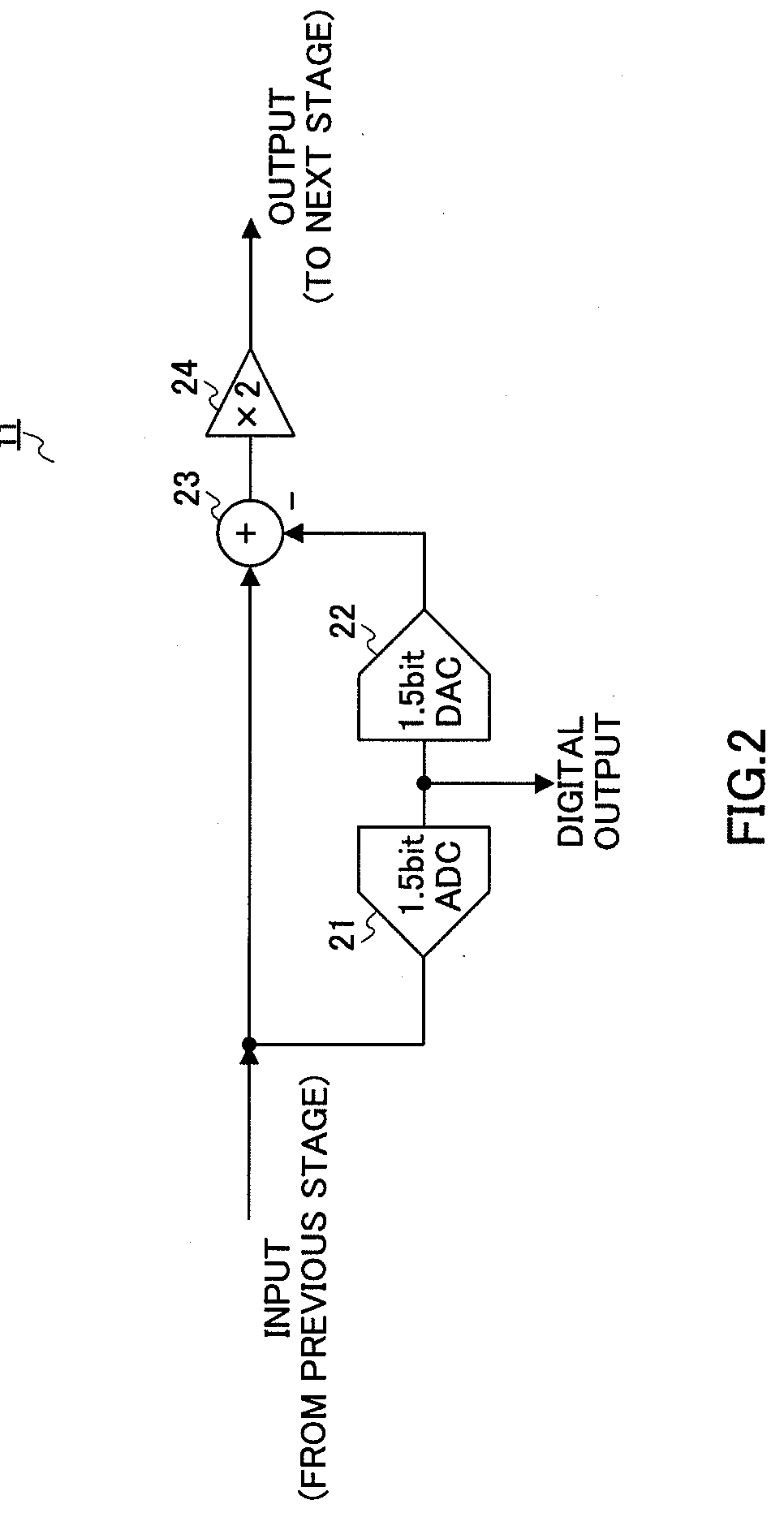

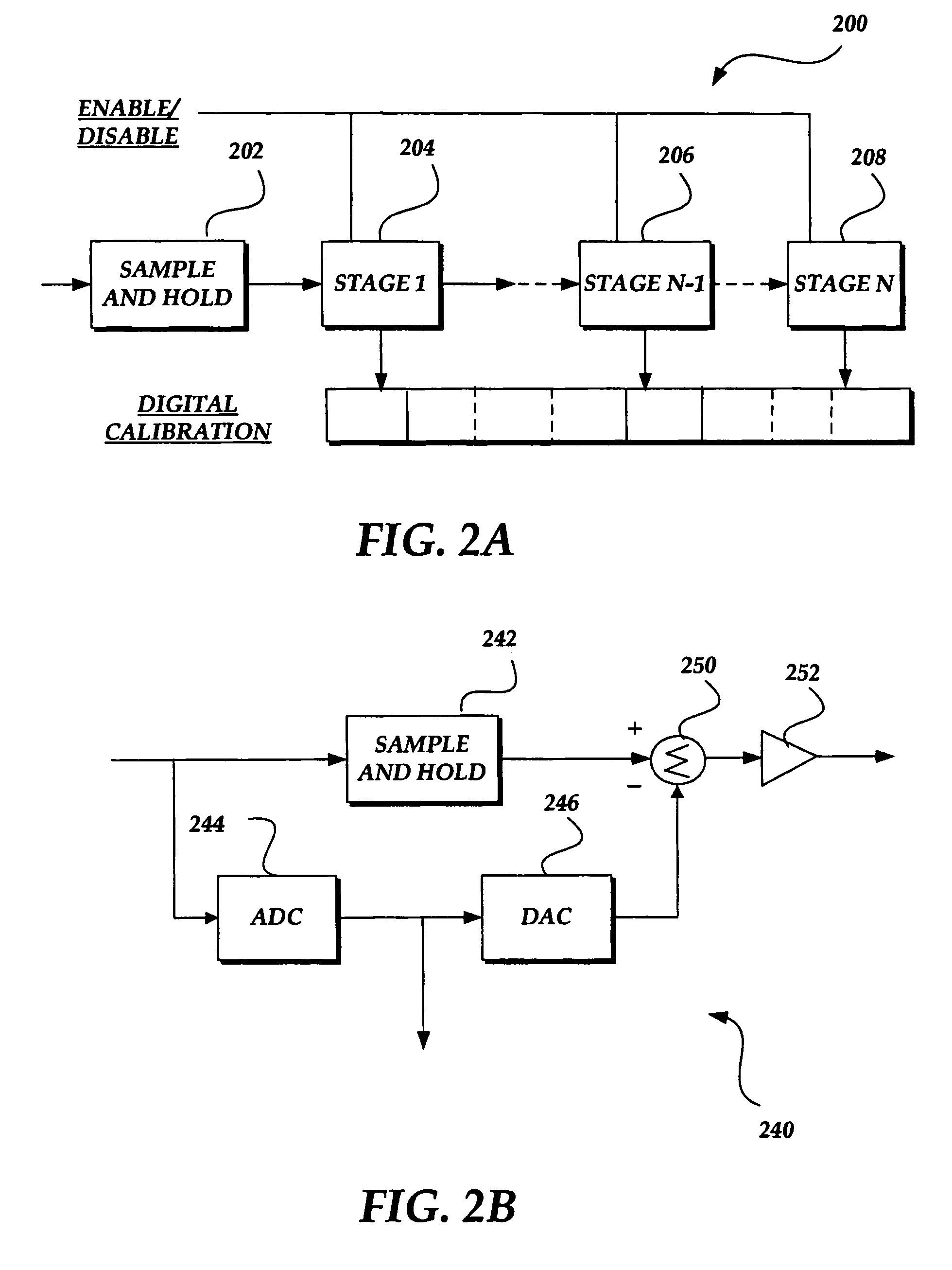

Multi-bit pipeline analog-to-digital converter capable of altering operating mode

InactiveUS20080129567A1Minimize power consumptionPower saving provisionsElectric signal transmission systemsControl signalMode control

Provided is a multi-bit pipeline analog-to-digital converter (ADC) capable of altering an operating mode. The ADC includes: a sample-and-hold amplifier (SHA) for sampling and holding an input analog voltage; an n+1 number of B-bit flash ADCs for receiving an analog signal and converting the analog signal into a digital signal to output the digital signal; an n number of B-bit multiplying digital-to-analog converters (MDACs) for converting a difference between the digital signal output from the B-bit flash ADC and the front-stage output signal into an analog signal to output the analog signal to the next stage; and a mode control circuit for generating n-bit control signals to control the B-bit flash ADC and the B-bit MDAC according to required resolution and operating frequency. In the multi-bit pipeline ADC, an operating mode is altered by controlling the number of stages in a pipeline and a signal path according to required resolution and operating frequency, so that power consumption can be minimized under the corresponding operating condition and signals can be processed in a variety of ways.

Owner:ELECTRONICS & TELECOMM RES INST

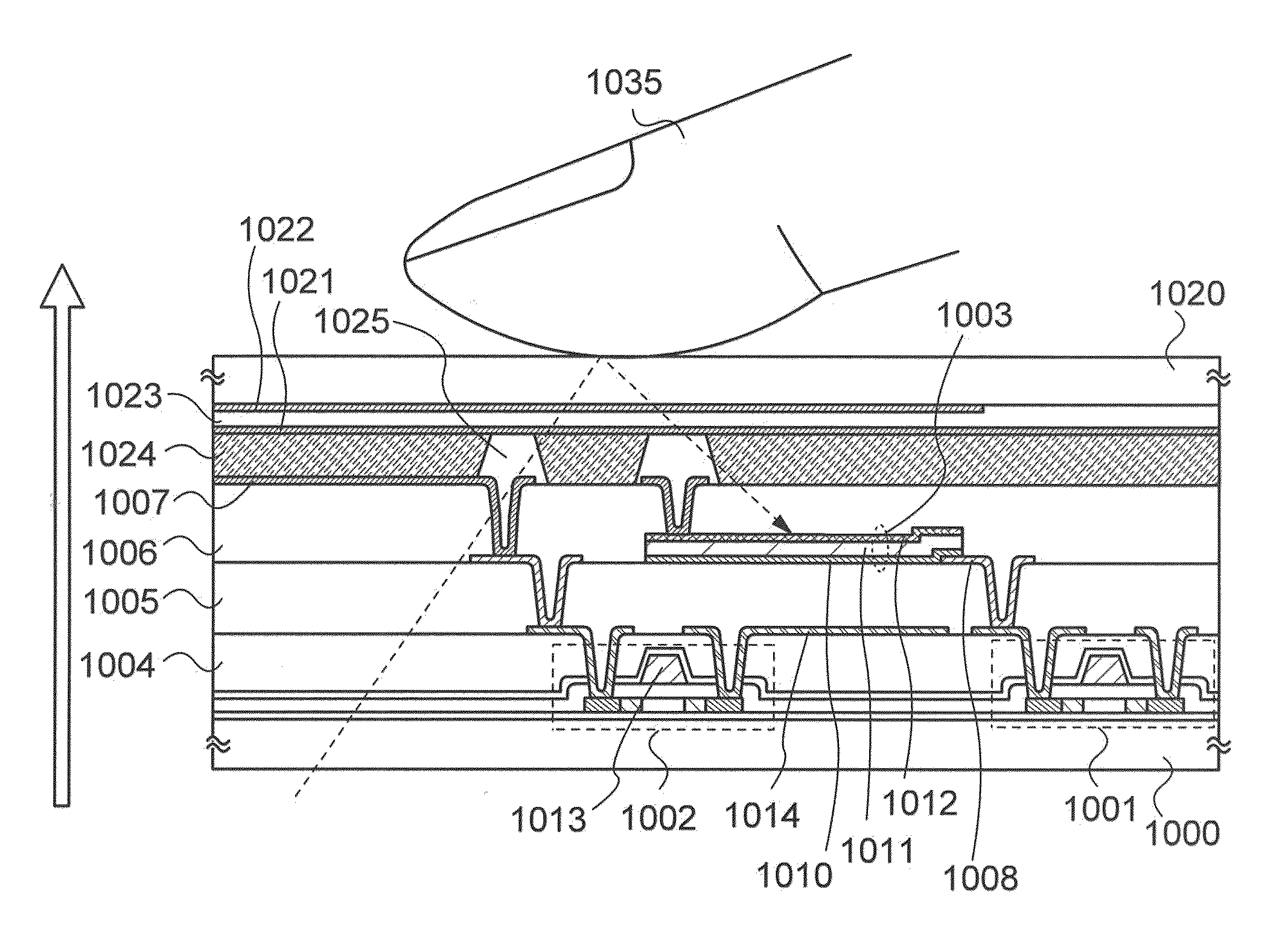

Touch panel

InactiveUS20100225615A1Reconfigurable analogue/digital convertersStatic indicating devicesBuck converterImage resolution

An embodiment of the present invention provides a touch panel that enable data sensing with multi-gray scale and an electronic device. At least a first pixel including a first photosensor portion detecting light with a first color, a second pixel including a second photosensor portion detecting light with a second color, a first A / D converter performing A / D conversion on an output signal of the first photosensor portion, and a second A / D converter performing A / D conversion on an output signal of the second photosensor portion are included. The voltage resolution of the first A / D converter and the voltage resolution of the second A / D converter are different.

Owner:SEMICON ENERGY LAB CO LTD

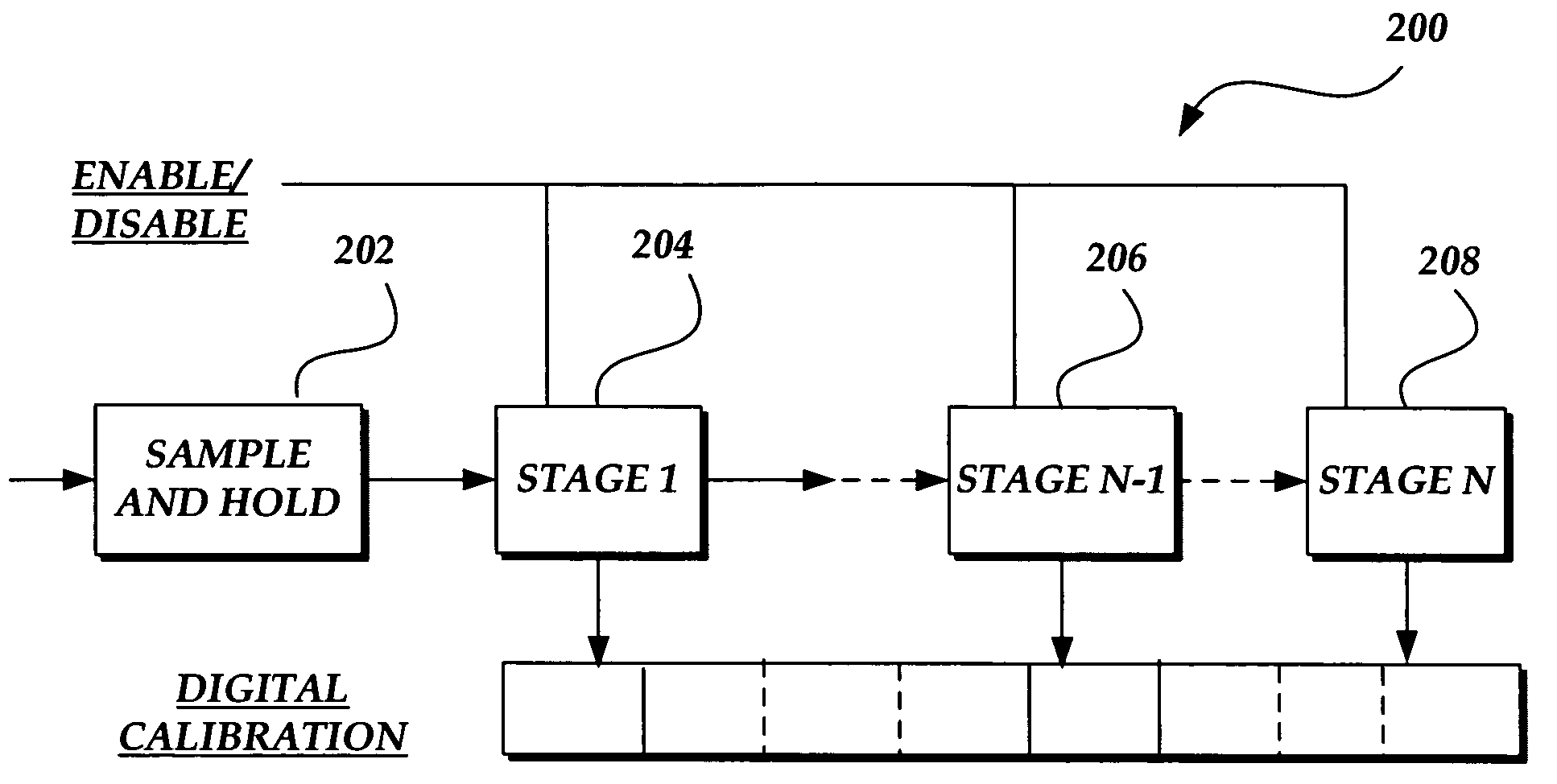

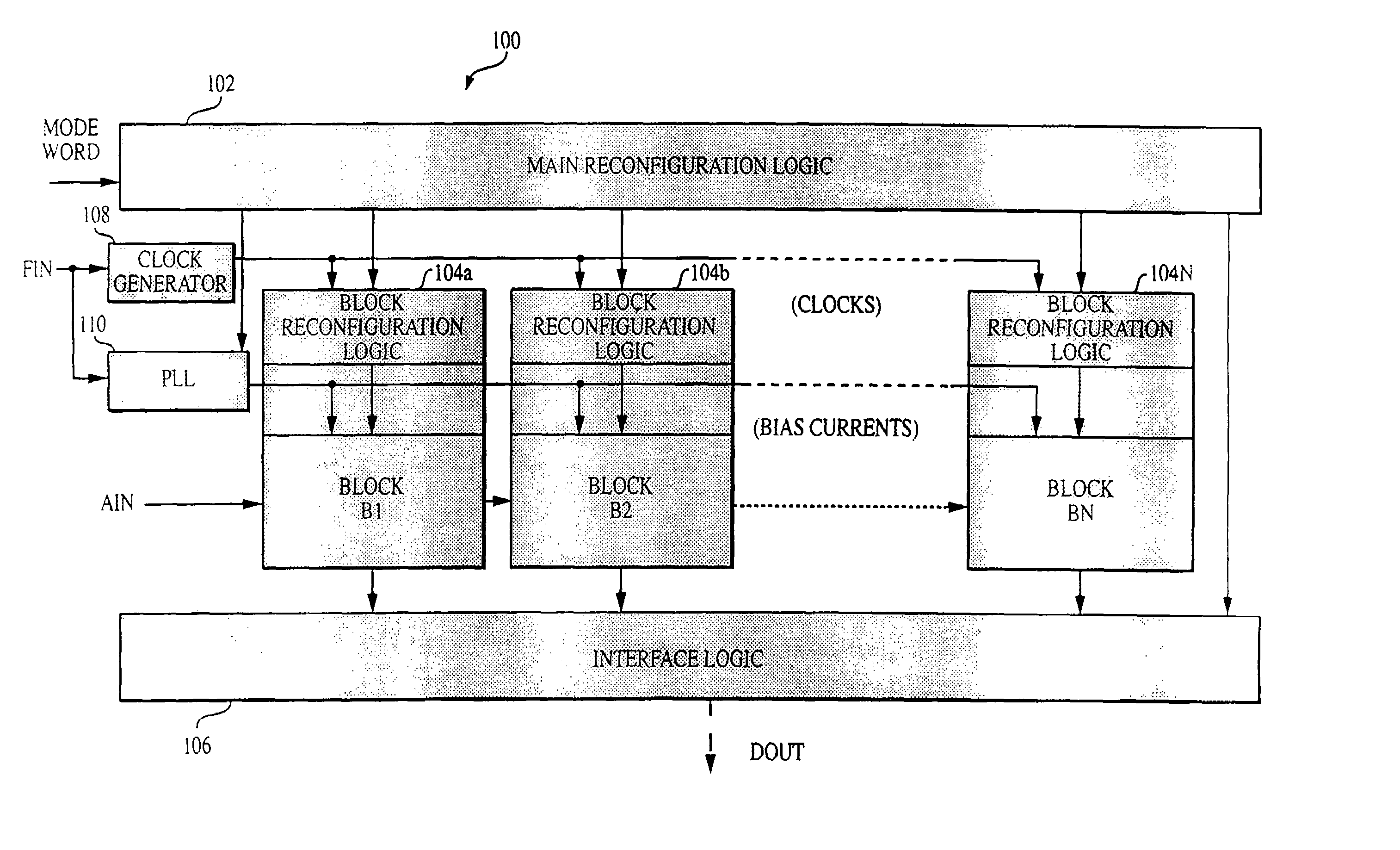

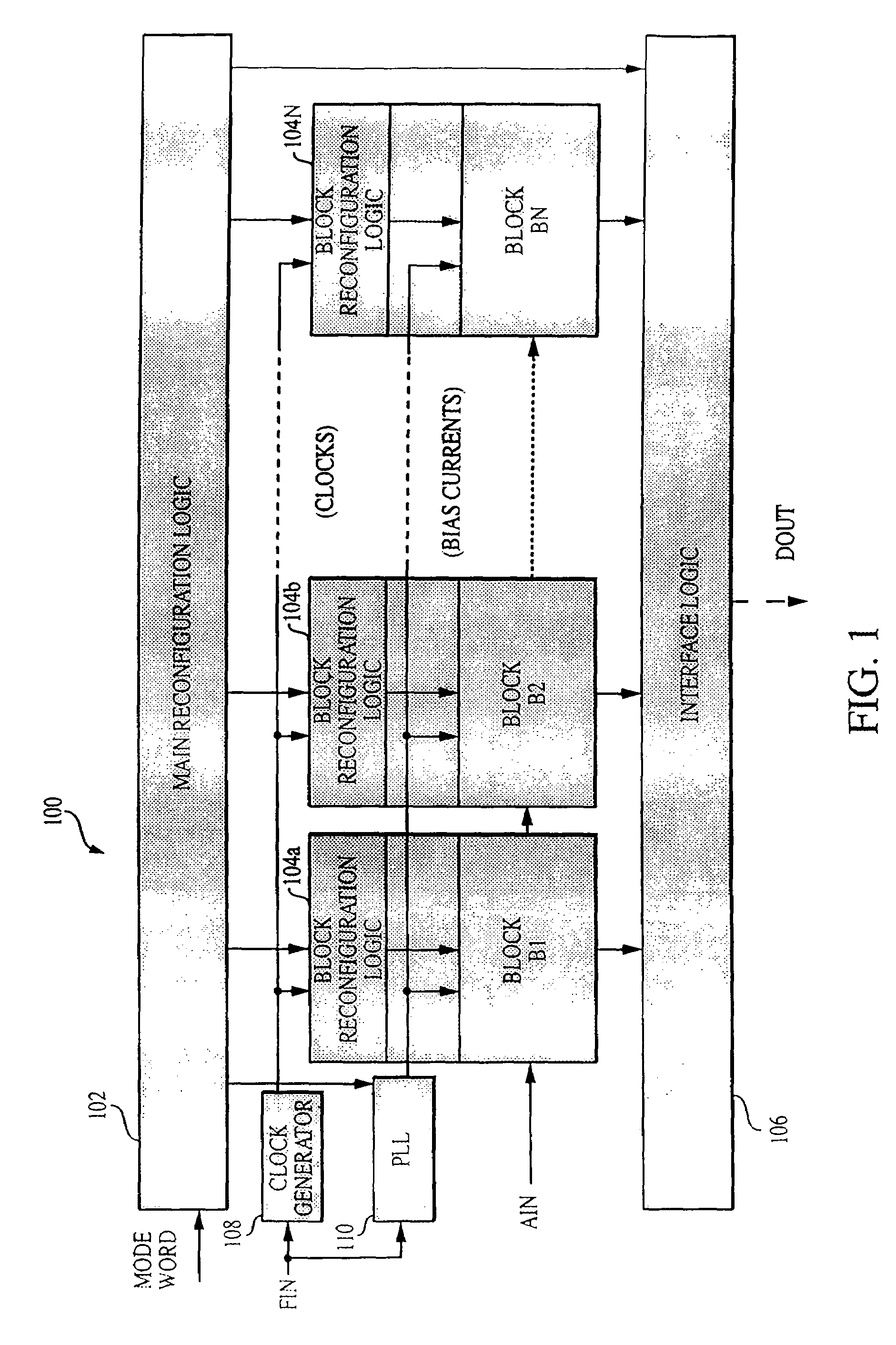

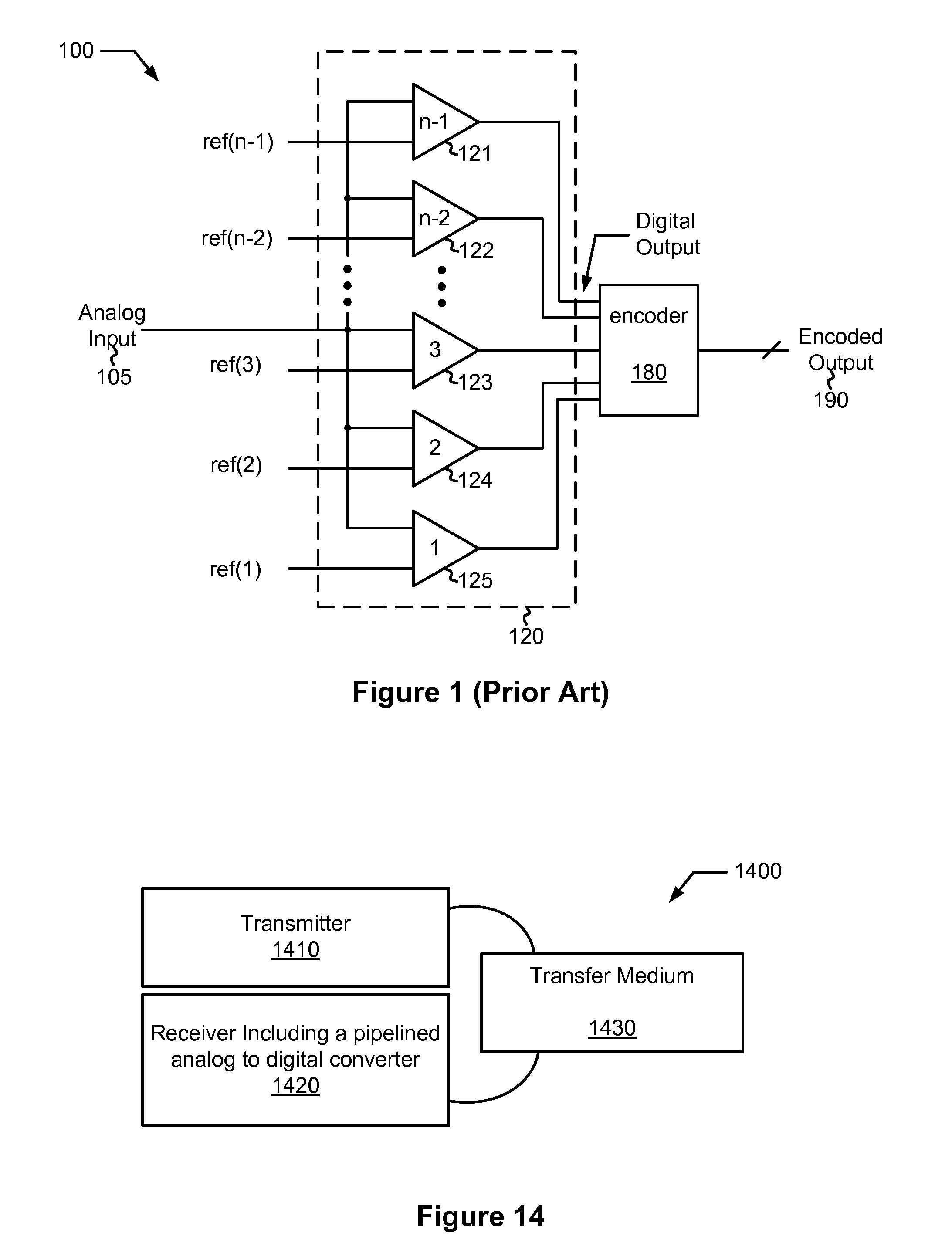

Pipelined analog to digital converter that is configurable based on mode and strength of received signal

ActiveUS7205923B1Electric signal transmission systemsReconfigurable analogue/digital convertersDigital down converterImage resolution

A pipelined analog to digital converter (ADC) that is arranged to dynamically adapt its resolution and sampling frequency based on at least a determined mode of communication and the strength of a received wireless signal. Since standby mode data is typically communicated with a relatively low number of bits (low resolution), the ADC provides for disabling at least a portion of its pipelined stages that provide the higher resolution bits if the standby communication mode is detected. By lowering the ADC's resolution for standby mode communication, it can conserve a considerable amount of power associated with the operation of the higher resolution bits. Similarly, relatively high resolution communication such as receiving and transmitting data and / or voice is process by the ADC by enabling sufficient pipelined stages to provide a higher number of bits.

Owner:NAT SEMICON CORP

Analog-to-digital converter having parametric configurablity

InactiveUS7002501B2High resolutionData rateElectric signal transmission systemsReconfigurable analogue/digital convertersImage resolutionEngineering

Owner:MASSACHUSETTS INST OF TECH

Variable resolution A/D converter

InactiveUS7313380B2Reduce power consumptionVariable resolutionElectric signal transmission systemsReconfigurable analogue/digital convertersBuck converterImage resolution

Owner:KK TOSHIBA

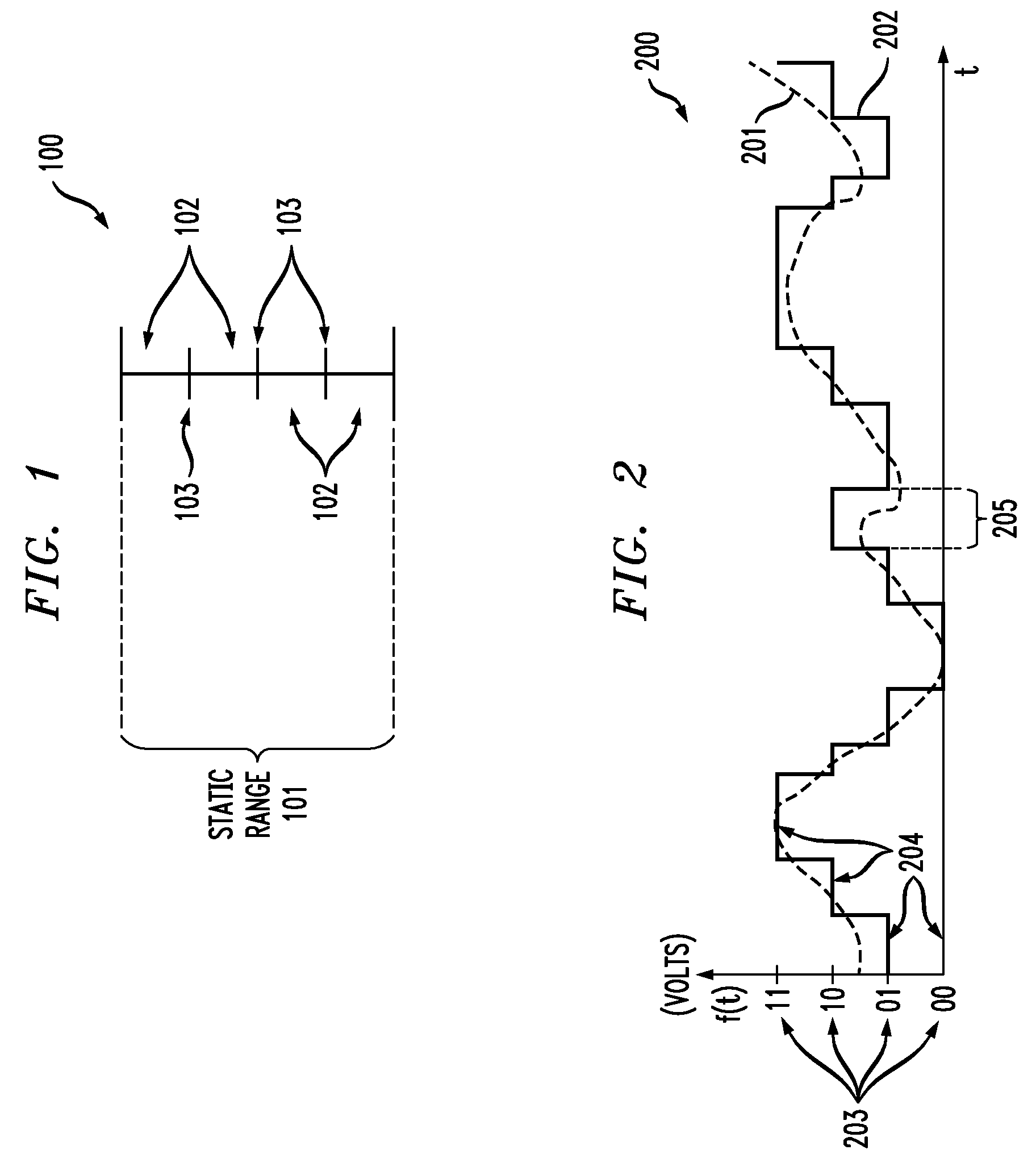

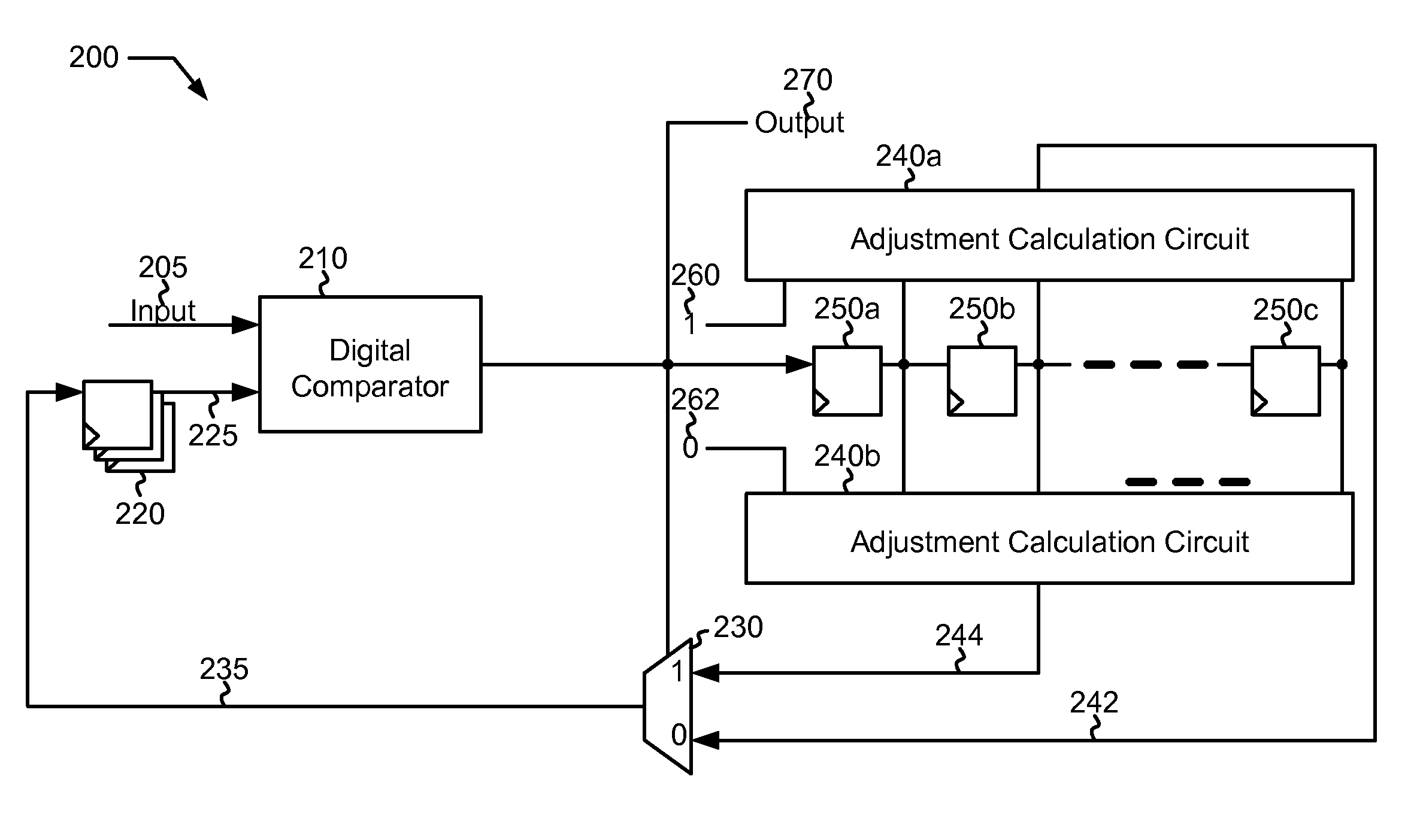

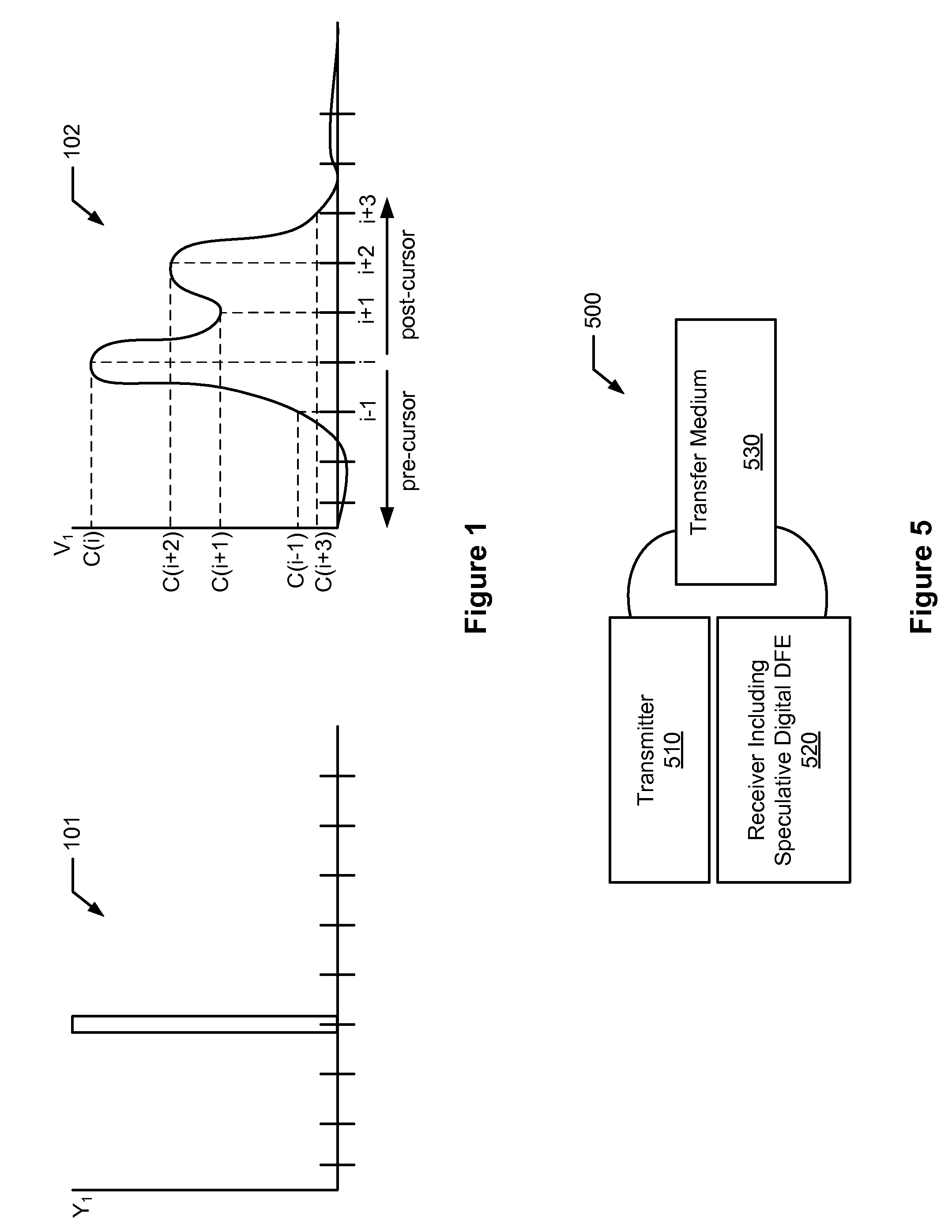

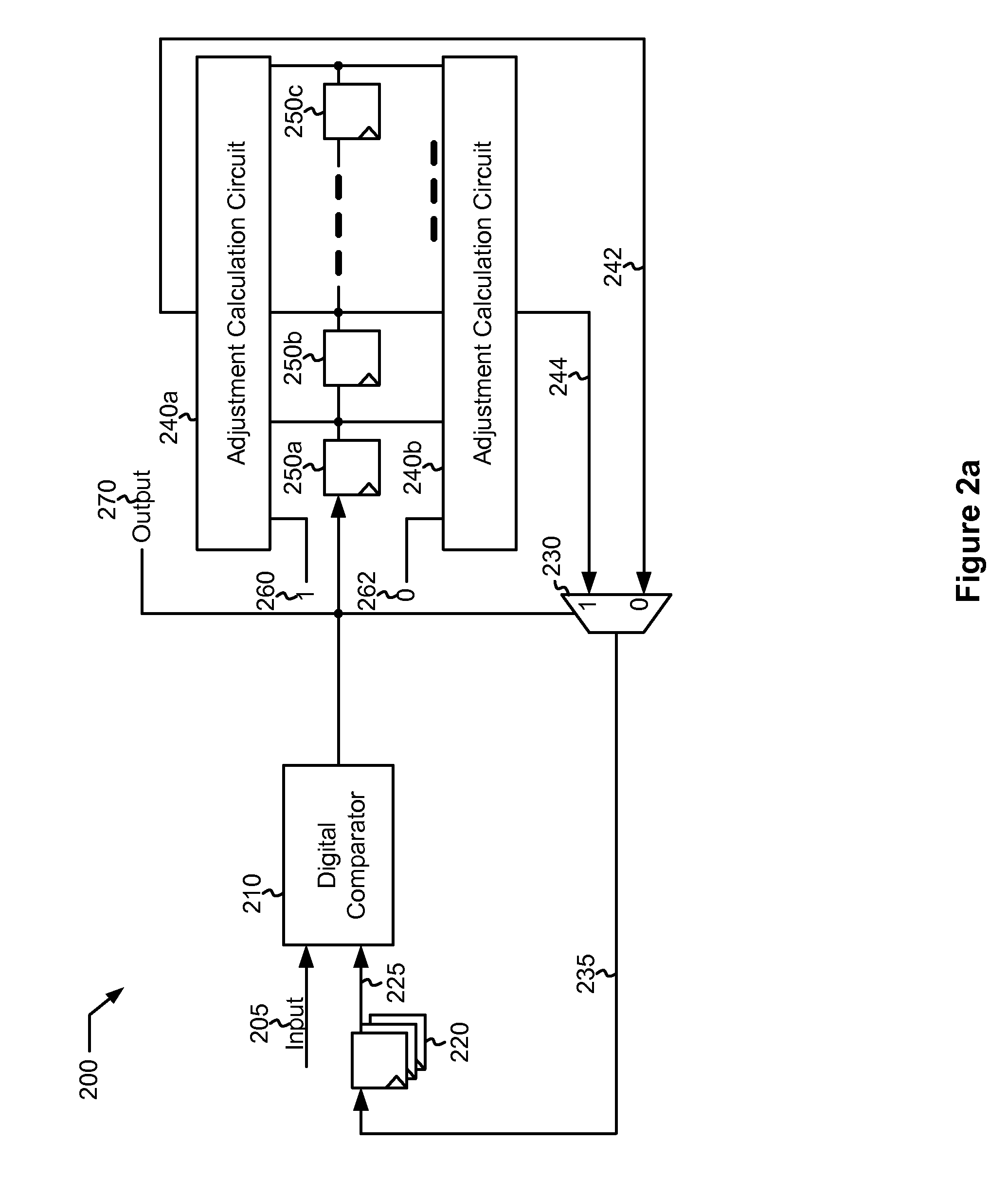

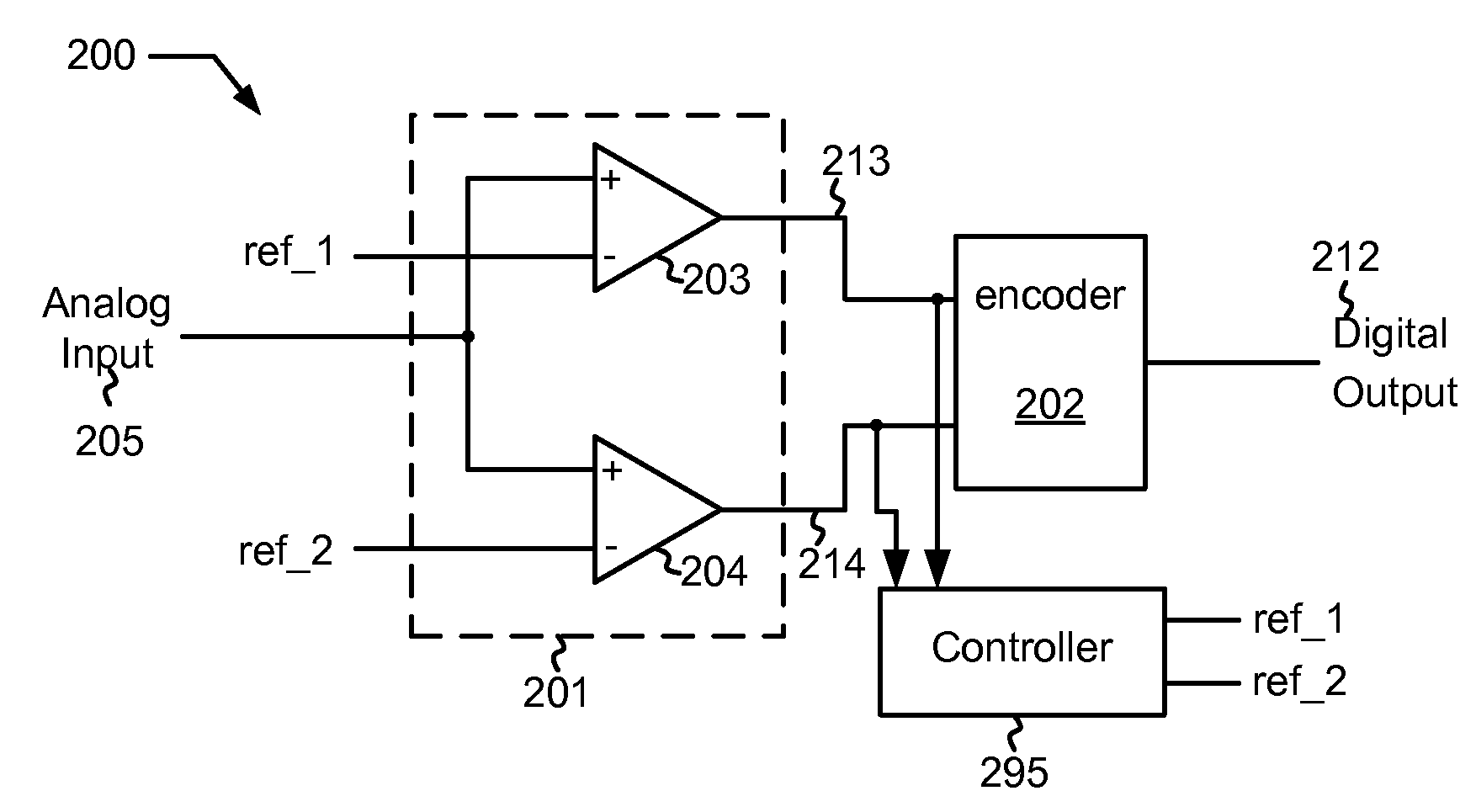

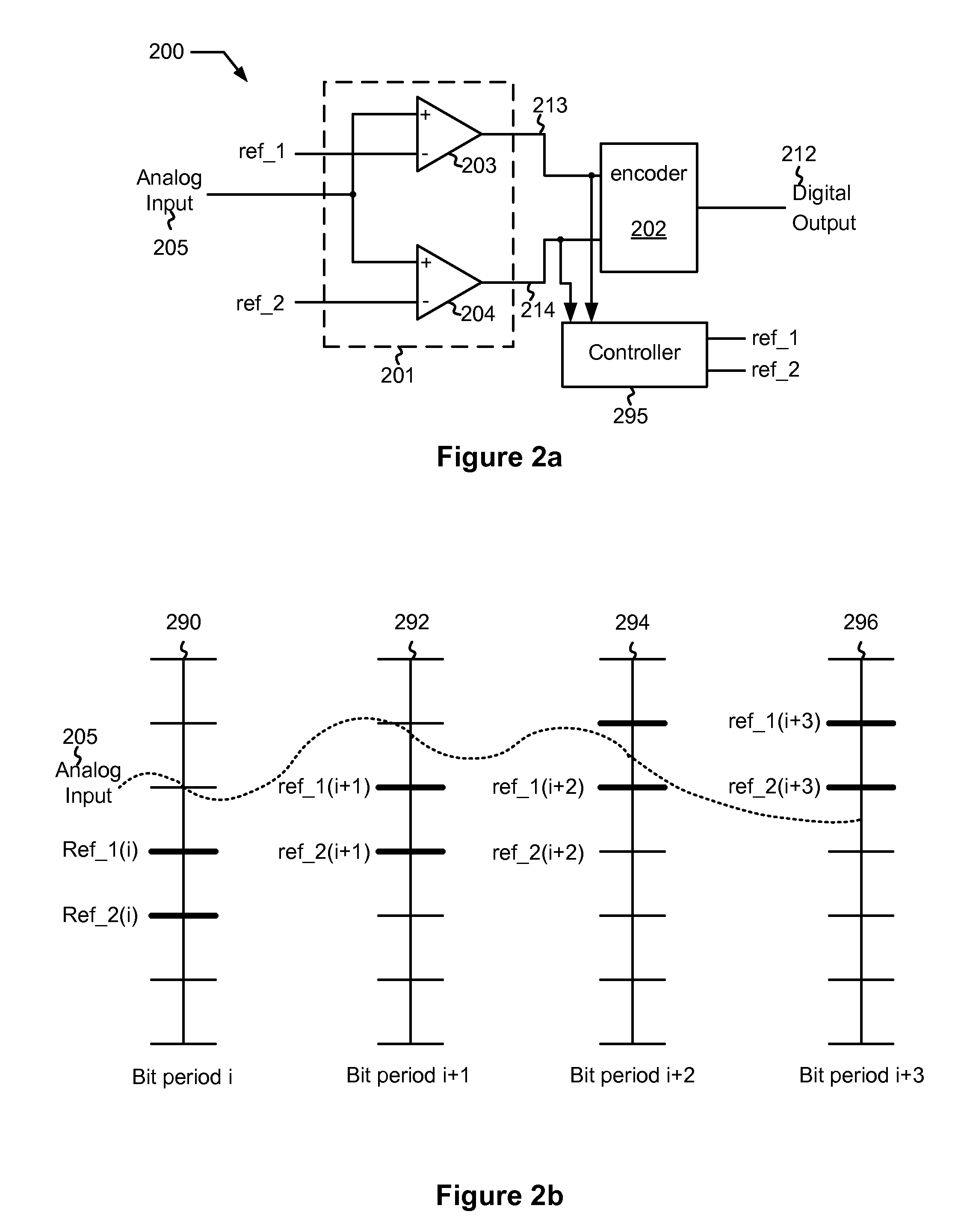

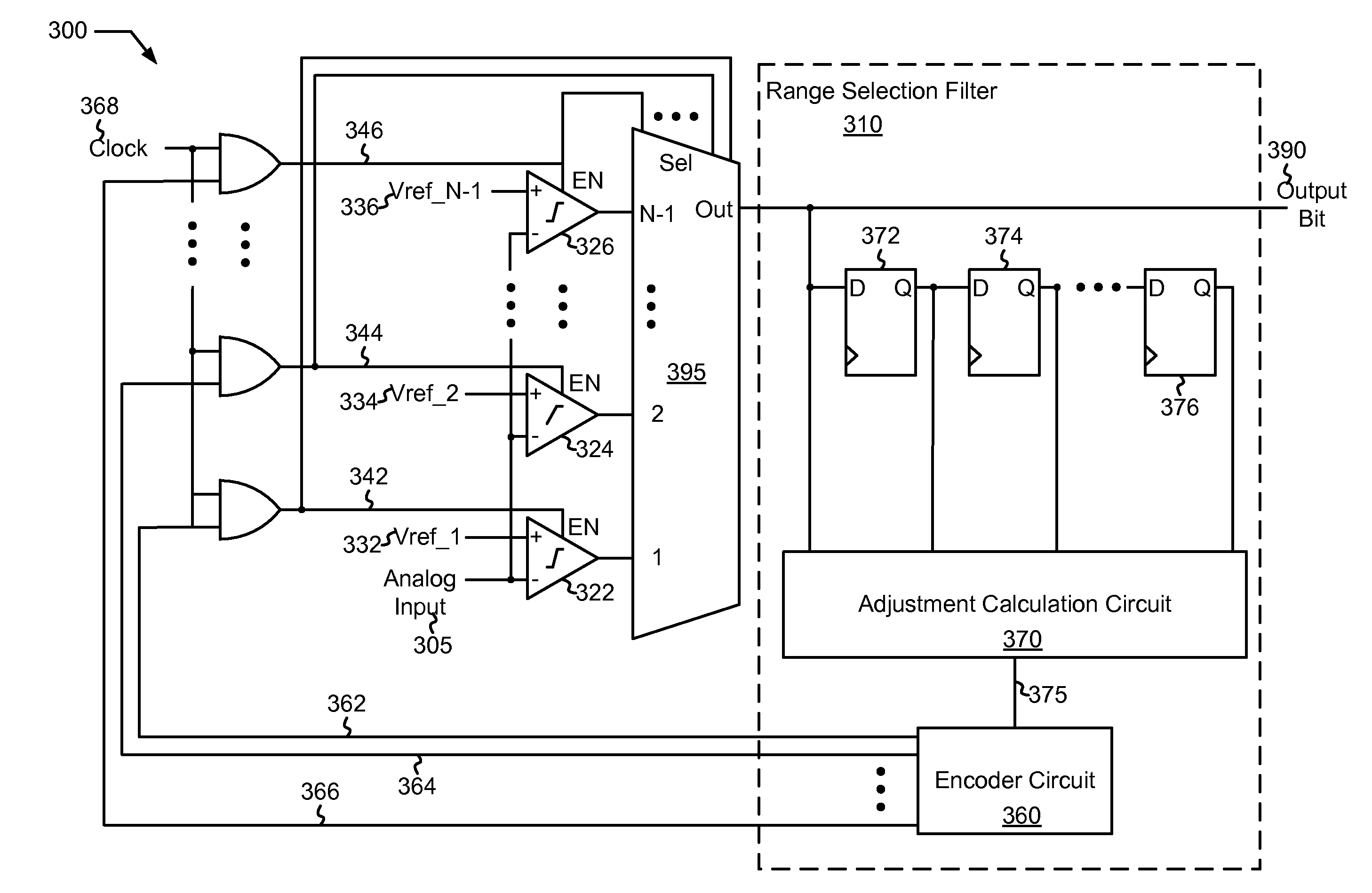

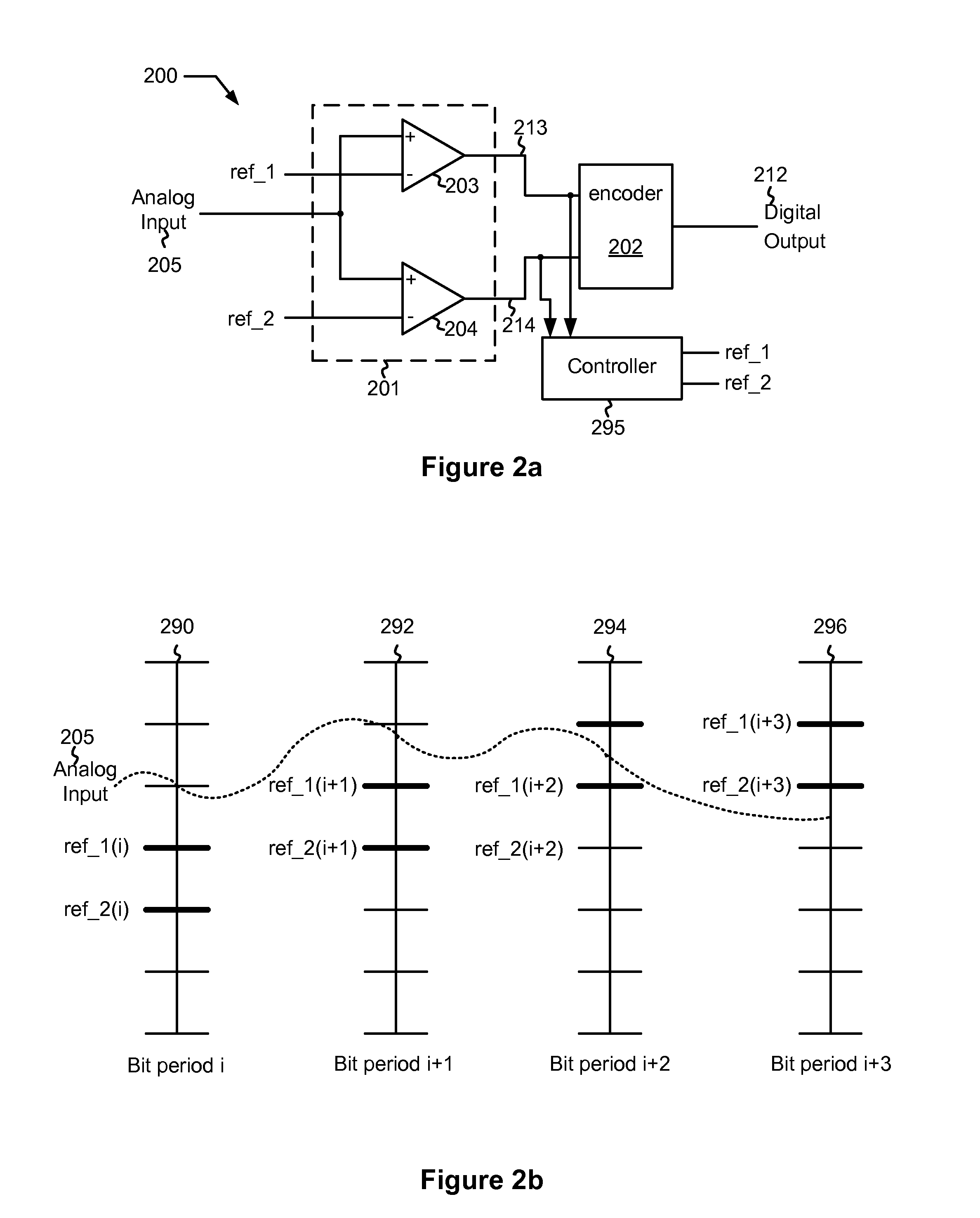

Systems and Methods for Speculative Signal Equalization

Various embodiments of the present invention provide systems and methods for signal equalization, and in some cases analog to digital conversion. For example, an analog to digital converter is disclosed that includes a comparator bank that receives a reference indicator and is operable to provide a decision output based at least in part on a comparison of an analog input with a reference threshold corresponding to the reference indicator. A range selection filter is included that has a first adjustment calculation circuit and a second adjustment calculation circuit. The first adjustment calculation circuit is operable to calculate a first adjustment feedback value based at least in part on a speculation that the decision output is a first logic level, and the second adjustment calculation circuit is operable to calculate a second adjustment feedback value based at least in part on a speculation that the decision output is a second logic level. A selector circuit selects the first adjustment feedback to generate the reference indicator when the decision output is the first logic level, and selects the second adjustment feedback to generate the reference indicator when the decision output is the second logic level.

Owner:AVAGO TECH WIRELESS IP SINGAPORE PTE

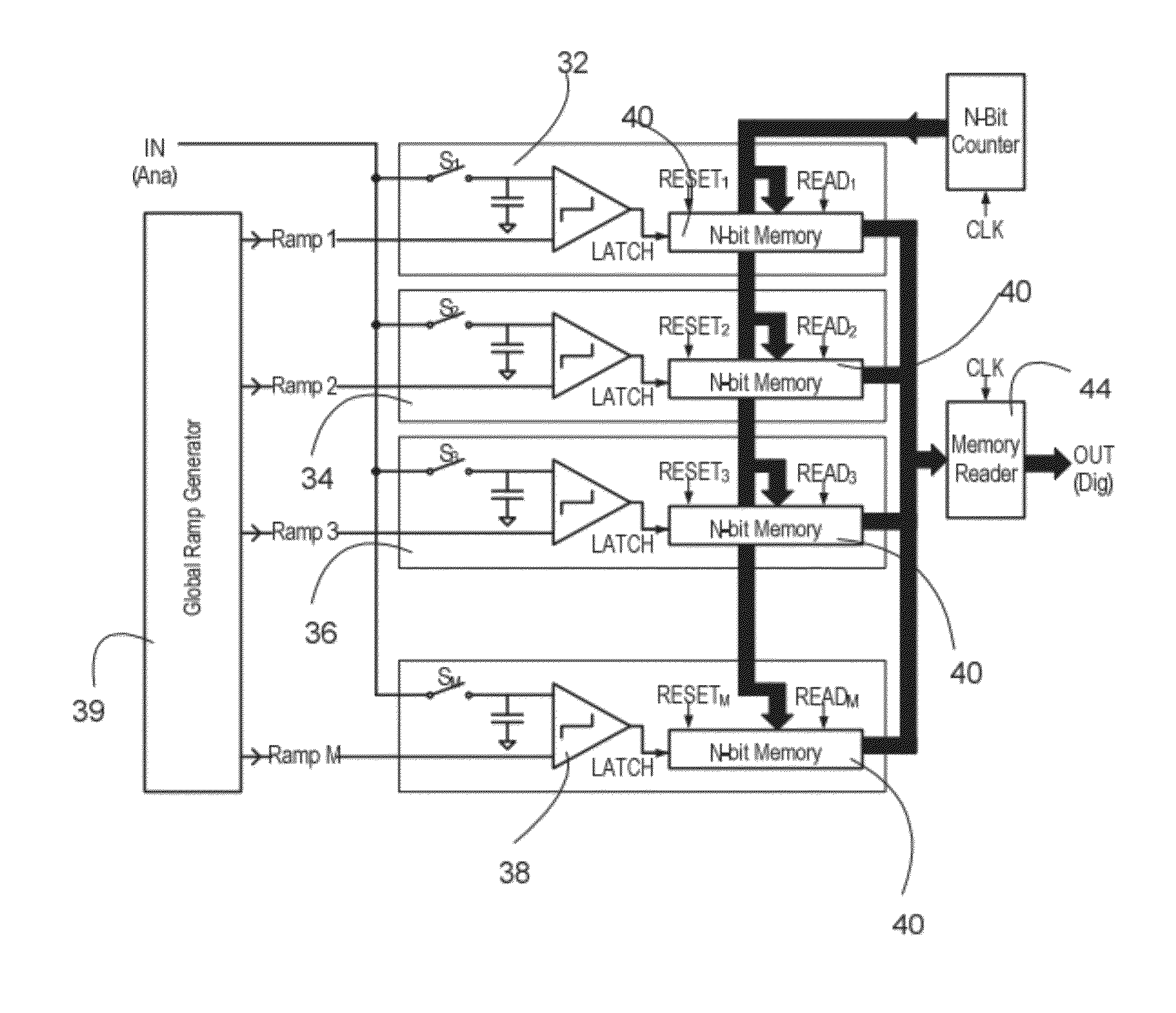

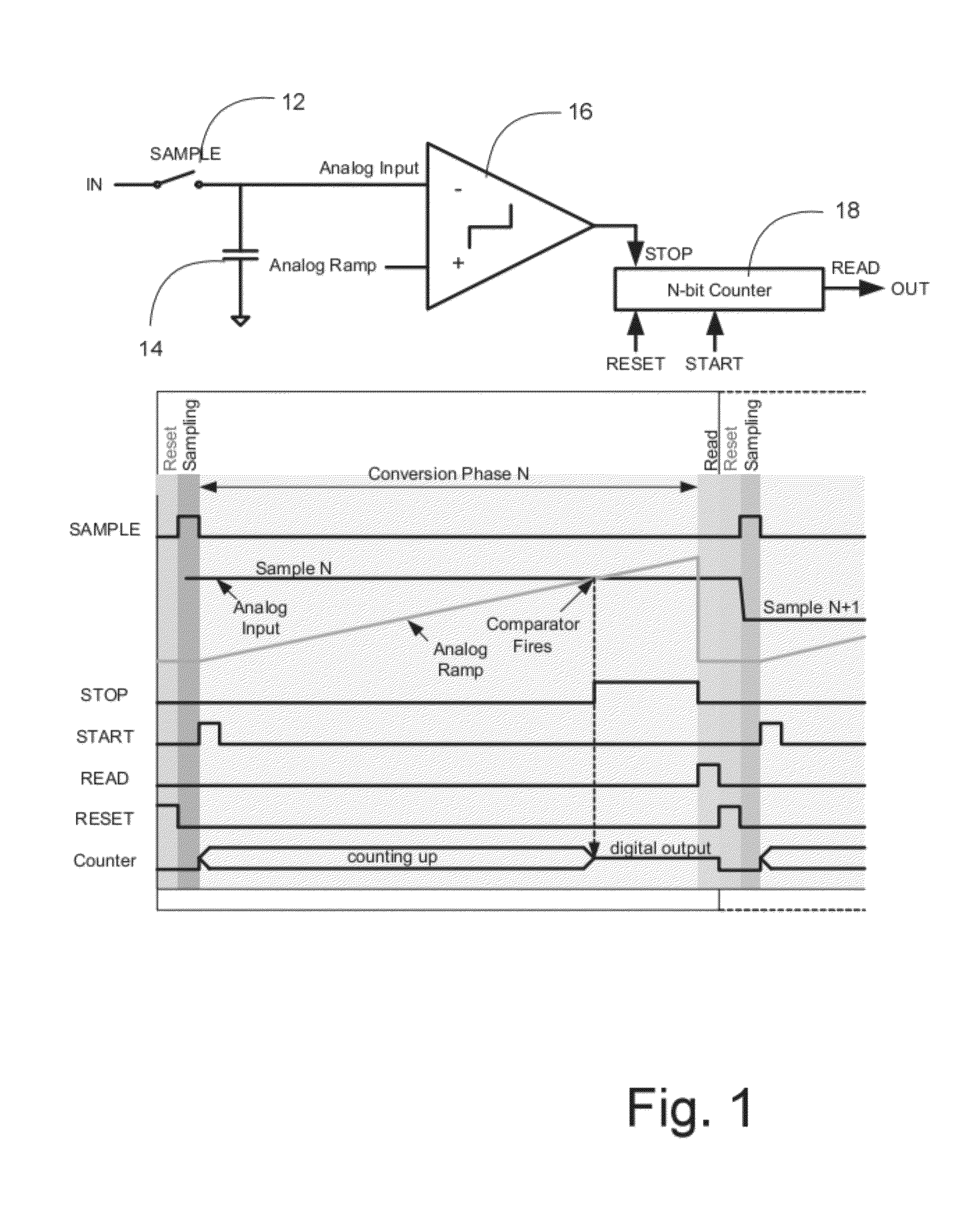

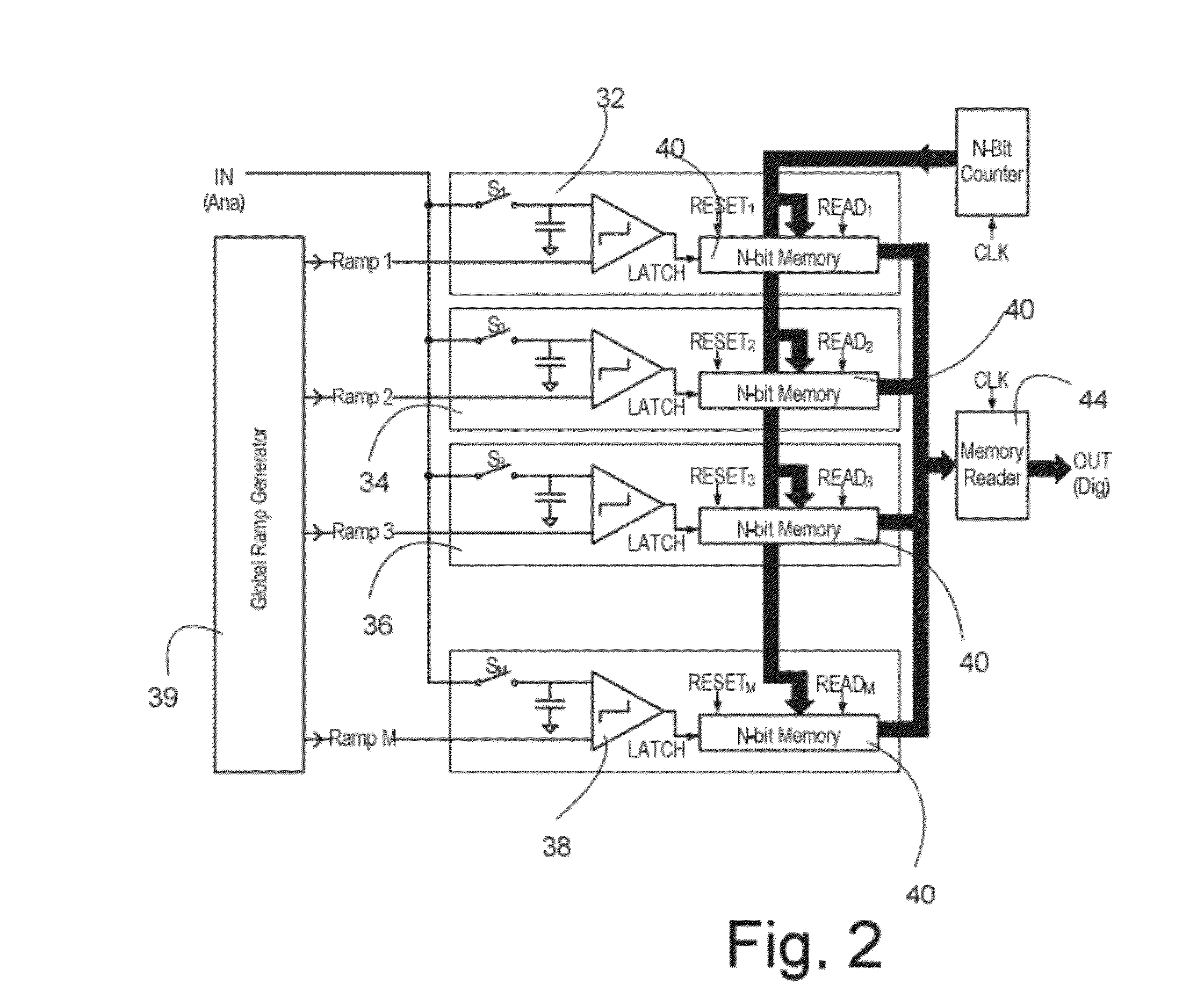

Composite analog-to-digital converter

ActiveUS20120050082A1Electric signal transmission systemsReconfigurable analogue/digital convertersEngineeringAnalog signal

An analog-to-digital converter (ADC) includes a plurality of single slope ADCs, a ramp generator, and digital output circuitry. Each single slope ADC includes an analog input operable to receive an analog input signal, a ramp input operable to receive an analog ramp signal, a comparator operable to compare the analog input signal to the analog ramp signal, and an output operable to produce a digital representation of the analog input signal based upon the comparison, wherein the plurality of single slope ADCs are operable to receive analog ramp signals that are out of phase with each other. The ramp generator that is operable to generate analog ramp signals for each of the plurality of single slope ADCs. The digital output circuitry is operable to receive outputs from each of the plurality of single slope ADCs and to produce a digital representation of the analog input signal based thereupon.

Owner:AVAGO TECH INT SALES PTE LTD

Pipelined analog to digital converter that is configurable based on wireless communication protocol

ActiveUS6980148B1Electric signal transmission systemsReconfigurable analogue/digital convertersWireless communication protocolDigital down converter

A pipelined analog to digital converter (ADC) that is arranged to dynamically adapt its resolution and sampling frequency based on at least one of a determined mode of communication, communication protocol and the strength of a received wireless signal. Since some communication protocols are communicated with a relatively low number of bits (low resolution), the ADC provides for disabling at least a portion of its pipelined stages that provide the higher resolution bits if this type of protocol is detected. By lowering the ADC's resolution and / or frequency for a standby mode communication, a considerable amount of power can be conserved. Similarly, relatively high resolution communication protocol can be processed by the ADC by enabling sufficient pipelined stages to provide a higher resolution (number of bits).

Owner:NAT SEMICON CORP

Systems and methods for analog to digital conversion

ActiveUS20090303096A1Power saving provisionsElectric signal transmission systemsAnalog-to-digital converterComparator

Various embodiments of the present invention provide systems and methods for analog to digital conversion. For example, an analog to digital converter is disclosed that includes an analog input that is provided to a comparator bank. The comparator bank receives a reference indicator, and is operable to provide a current output based at least in part on a comparison of the analog input with a reference threshold corresponding to the reference indicator. The analog to digital converter further includes a range selection filter that is operable to receive the current output and to generate the reference indicator based at least in part on a prior output of the comparator bank.

Owner:AVAGO TECH INT SALES PTE LTD

A/d converter

InactiveUS20070290914A1Circuit scale increaseMinimize power consumptionElectric signal transmission systemsReconfigurable analogue/digital convertersAudio power amplifierIntegrator

An A / D converter that supports multi-mode and that can minimize power consumption is provided. A hybrid A / D converter 100 comprises: hybrid stages 101 to 103 composed of 1.5-bit A / D converter 111, 121 and 131 for pipeline use that convert analogue input signals into digital signals; 1 / 1.5-bit D / A converters 112, 122 and 132 that switch between pipeline use and delta-sigma modulation use according to the mode in use; analogue adders 113, 123 and 133 that subtract output of the 1 / 1.5 D / A converters 112, 122 and 132 from the analogue input signals; and analogue operation circuits 114, 124 and 134 that receive as input the output of the analogue adders 113, 123 and 133 and function as amplifiers in pipeline mode and as integrators in delta-sigma mode.

Owner:PANASONIC CORP

Analog-to-Digital Converter

ActiveUS20090267821A1Reduce power consumptionReduce in quantityPower saving provisionsElectric signal transmission systemsActive ComparatorAnalog-to-digital converter

An ADC circuit includes multiple comparators and a controller coupled to the comparators. Each of the comparators is operative to generate an output indicative of a difference between a first signal representative of an input signal applied to the ADC circuit and a corresponding reference signal. The controller is operative to perform at least one of: (i) activating a subset of the comparators during a given sample period being; and (ii) controlling levels of the corresponding reference signals of the comparators as a function of a level of the input signal. A number of active comparators during the given sample period is no greater than one less than a number of regions into which the input signal is quantized.

Owner:AVAGO TECH INT SALES PTE LTD

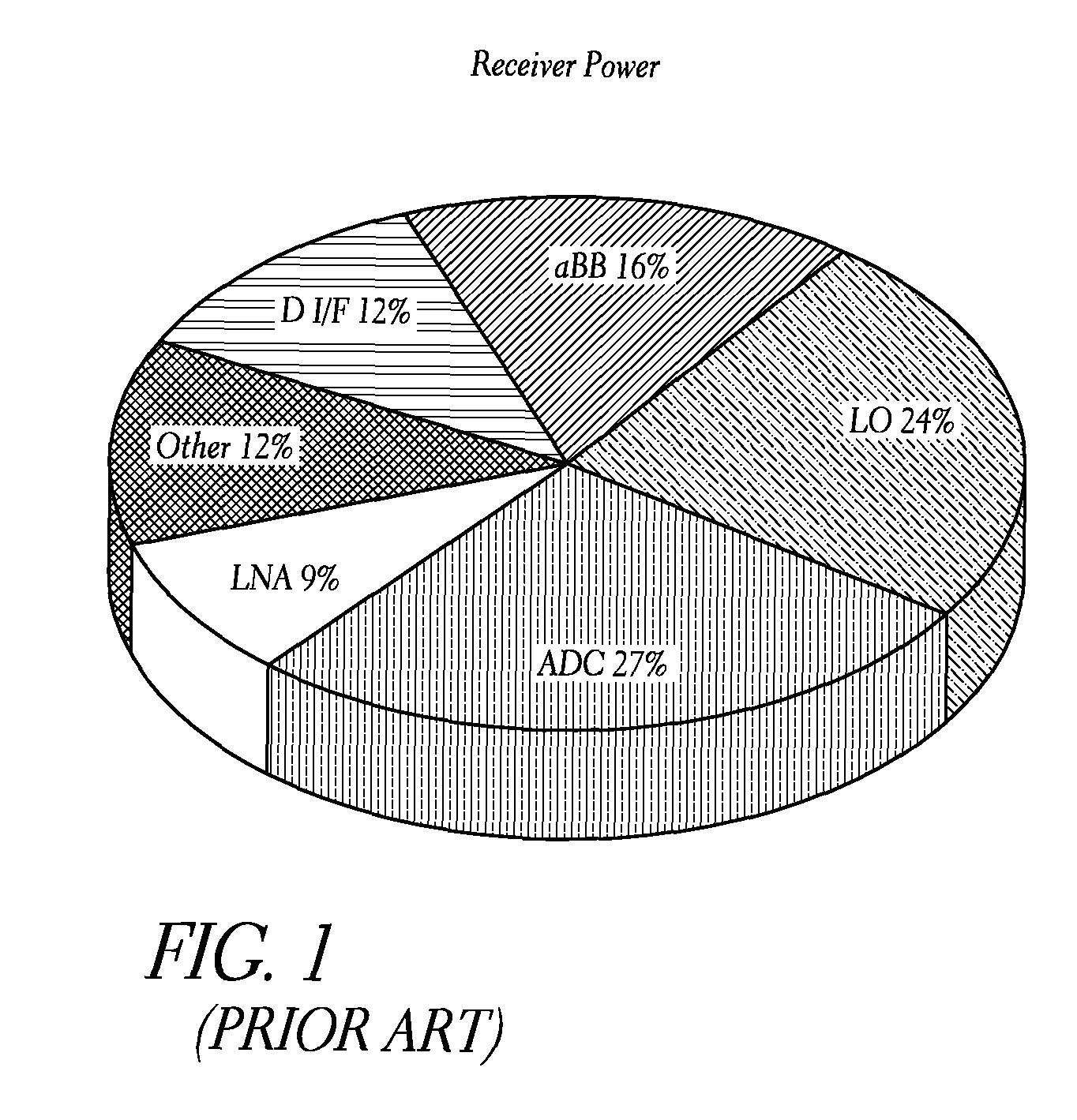

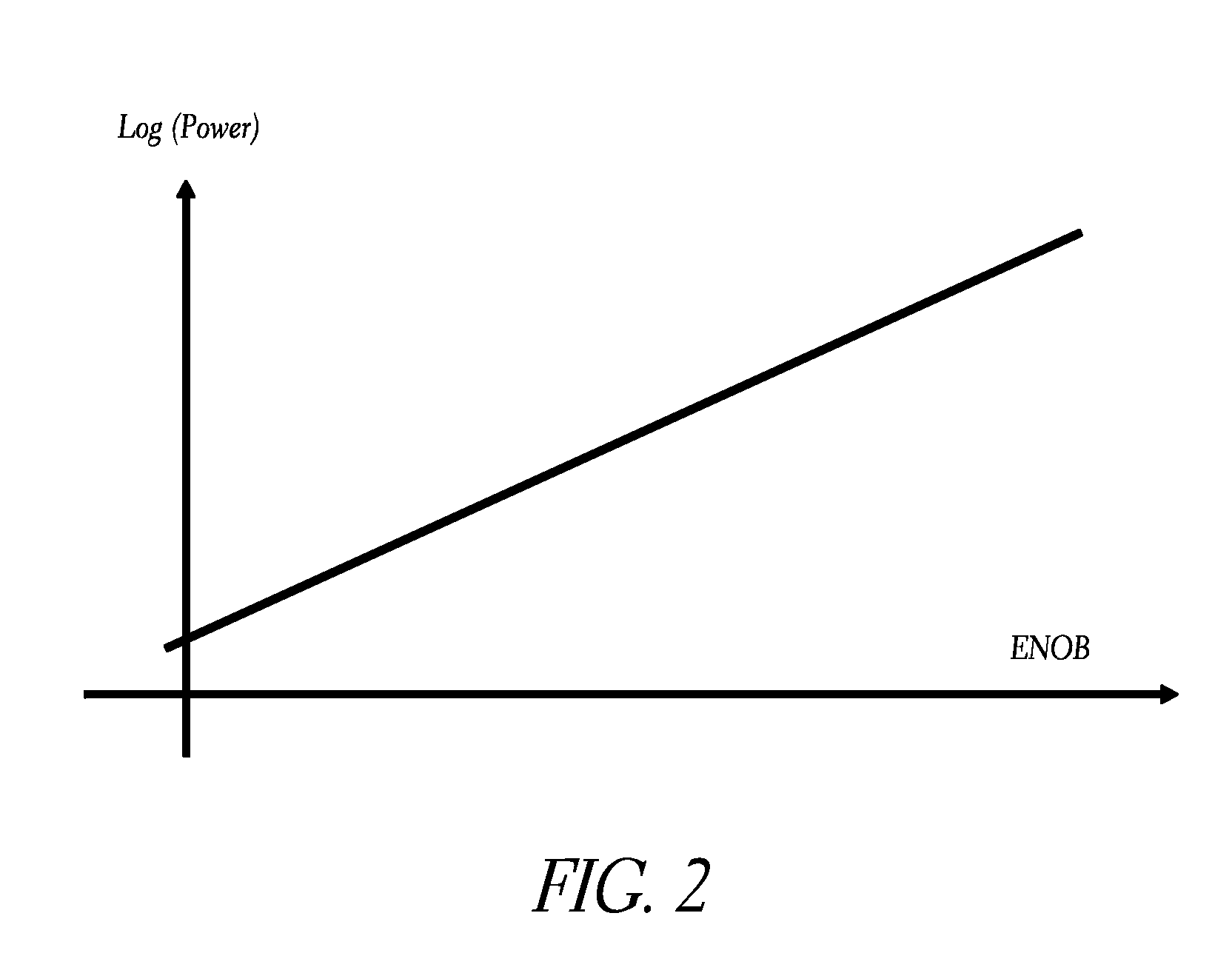

Power optimized ADC for wireless transceivers

ActiveUS7760122B1Reduce power consumptionIncrease powerPower saving provisionsElectric signal transmission systemsWireless transceiverRadio reception

An analog-to-digital converter (ADC) of a radio receiver can consume a relatively large amount of power. It is typically desirable to minimize power consumption, particularly with battery-powered devices, such as in wireless receivers. In certain conditions, the effective number of bits (ENOB) required from an ADC of a receiver can vary. The power consumption of certain ADC topologies, such as pipelined converter topologies, can vary with the number of bits. One embodiment dynamically varies the ENOB of an ADC to more optimally consume power. This can extend battery life.

Owner:MAXLINEAR ASIA SINGAPORE PTE LTD

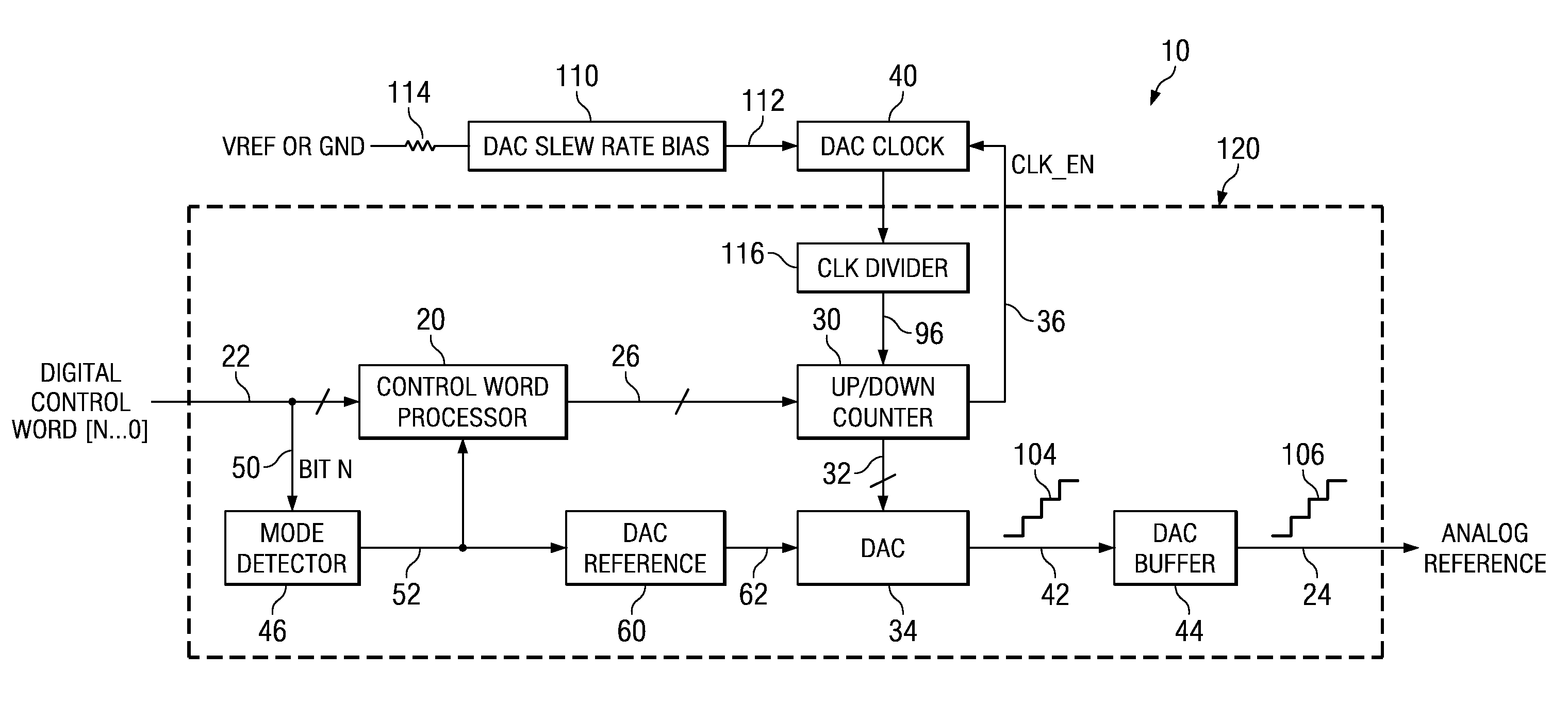

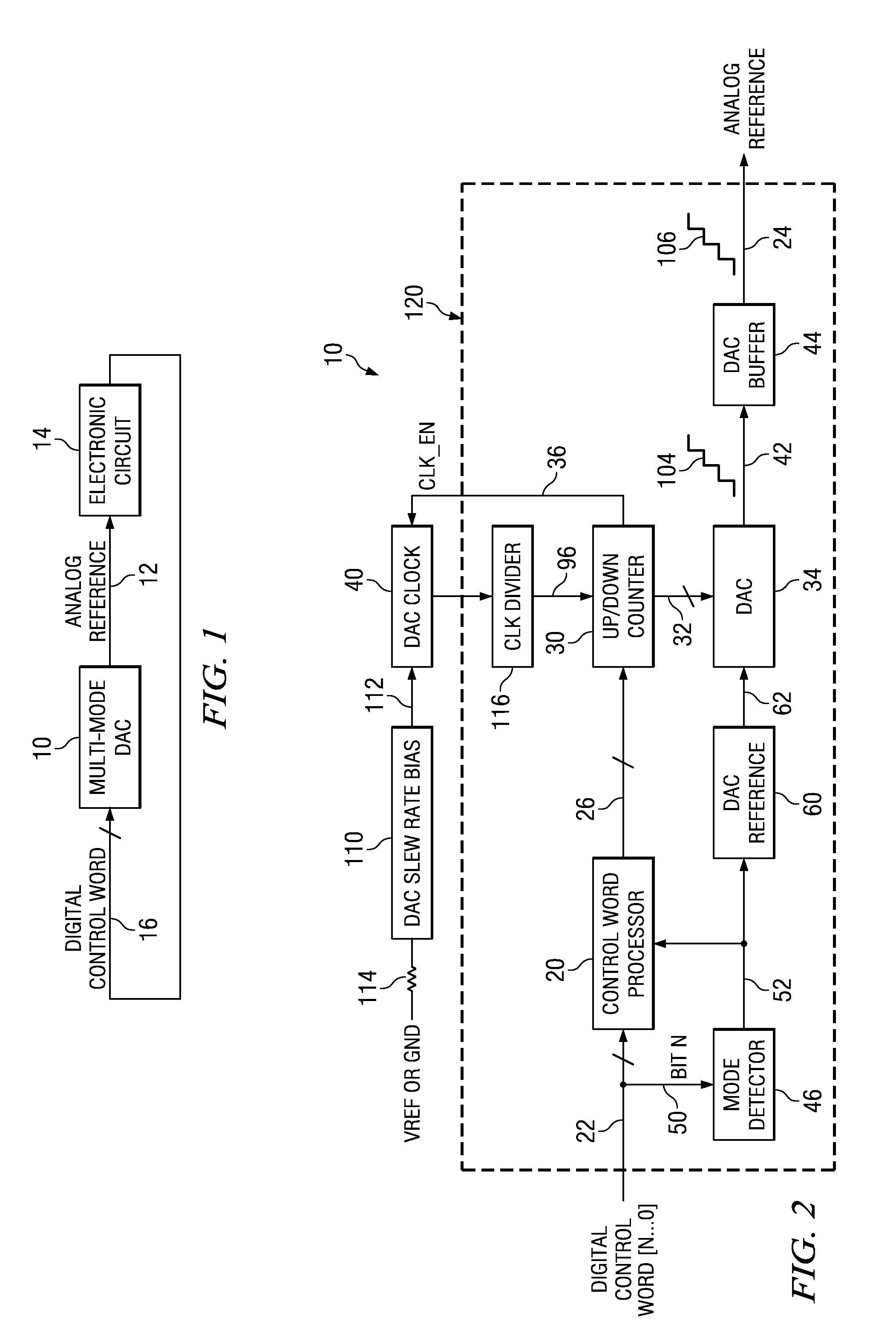

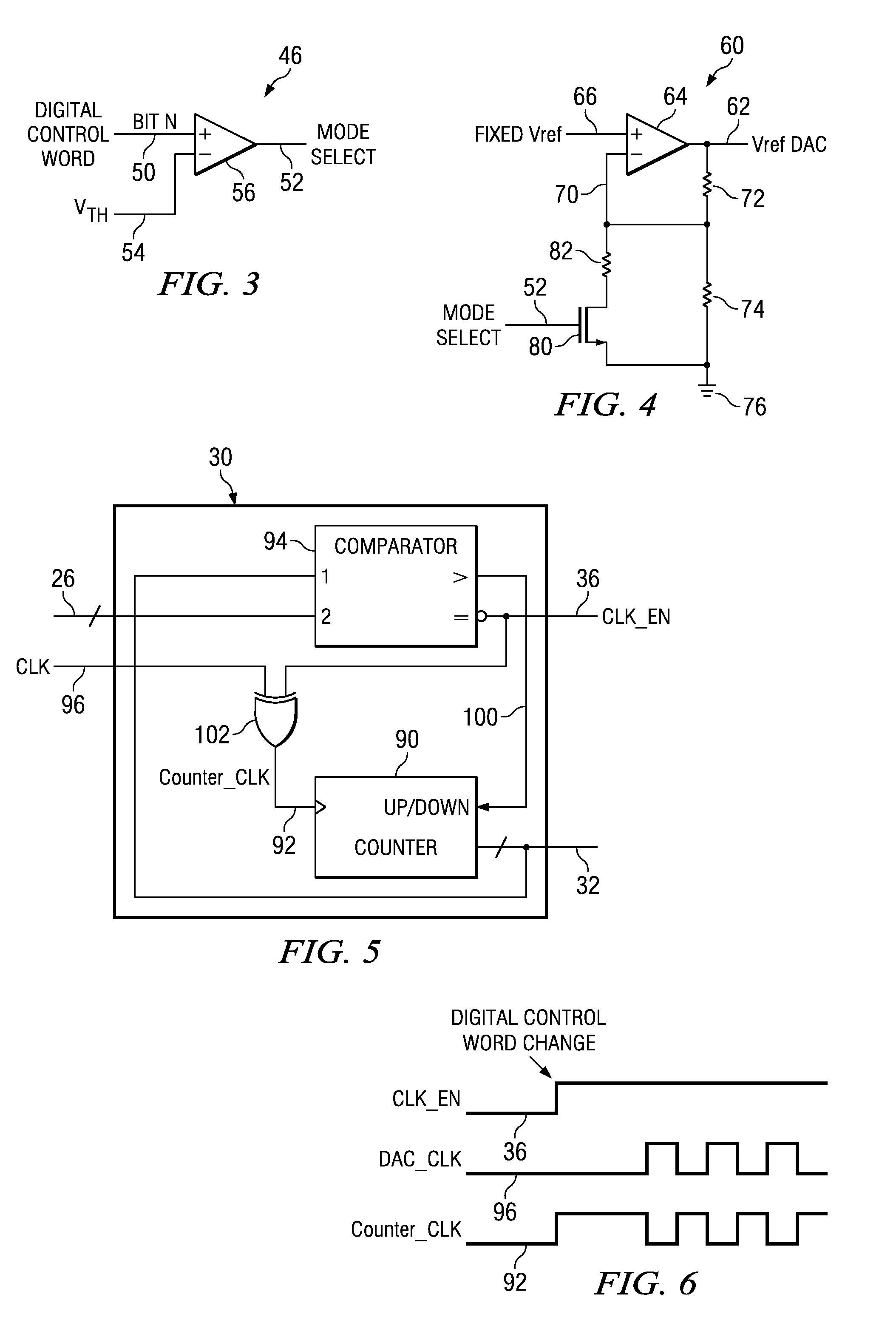

Multi-mode digital-to-analog converter

ActiveUS7728749B2Electric signal transmission systemsReconfigurable analogue/digital convertersGranularityActual count

Various apparatuses, methods and systems for a multi-mode DAC with selectable output range, granularity and offset and controlled slew rate are disclosed herein. For example, some embodiments of the present invention provide an apparatus for supplying a reference signal, including a digital-to-analog converter, a counter and a clock. The digital-to-analog converter has a digital input and an analog output that supplies a reference signal based on the digital input. The counter has a digital control word input, a clock input, a clock enable output and a count output connected to the digital input of the digital-to-analog converter. The counter is adapted to assert the clock enable output when the digital control word input requests an output count that is different from an actual count at the count output of the counter. The clock has an enable input connected to the clock enable output of the counter and a clock output connected to the clock input of the counter. The clock is adapted to produce clock pulses on the clock output while the enable input is asserted.

Owner:TEXAS INSTR INC

Analog to digital converter with power-saving adjustable resolution

ActiveUS7193553B1Power saving provisionsElectric signal transmission systemsDigital down converterImage resolution

A pipelined analog to digital converter (ADC) that is arranged to dynamically adapt its resolution and sampling frequency based on at least one of a determined mode of communication, communication protocol and the strength of a received wireless signal. Since some communication protocols are communicated with a relatively low number of bits (low resolution), the ADC provides for disabling at least a portion of its pipelined stages that provide the higher resolution bits if this type of protocol is detected. By lowering the ADC's resolution and / or frequency for a standby mode communication, a considerable amount of power can be conserved. Similarly, relatively high resolution communication protocol can be processed by the ADC by enabling sufficient pipelined stages to provide a higher resolution (number of bits).

Owner:NAT SEMICON CORP

Image pickup apparatus

ActiveCN102917182ATelevision system detailsReconfigurable analogue/digital convertersAudio power amplifierPhotoelectric conversion

The invention relates to an image pickup apparatus. The image pickup apparatus includes a pixel generating a signal by photoelectric conversion, a comparator comparing the signal based on the pixel with a reference signal varied with time, a counter performing counting until the comparator outputs a signal indicating that the relationship in magnitude between the signal based on the pixel and the reference signal is reversed, and a control unit. The comparator includes a first amplifier receiving the reference signal at a first input portion and the signal based on the pixel at a second input portion to compare the signal based on the pixel with the reference signal. The control unit sets a bandwidth of the comparator to a first bandwidth when the reference signal varies at a first rate of change and to a second bandwidth when the reference signal varies at a second rate of change.

Owner:CANON KK

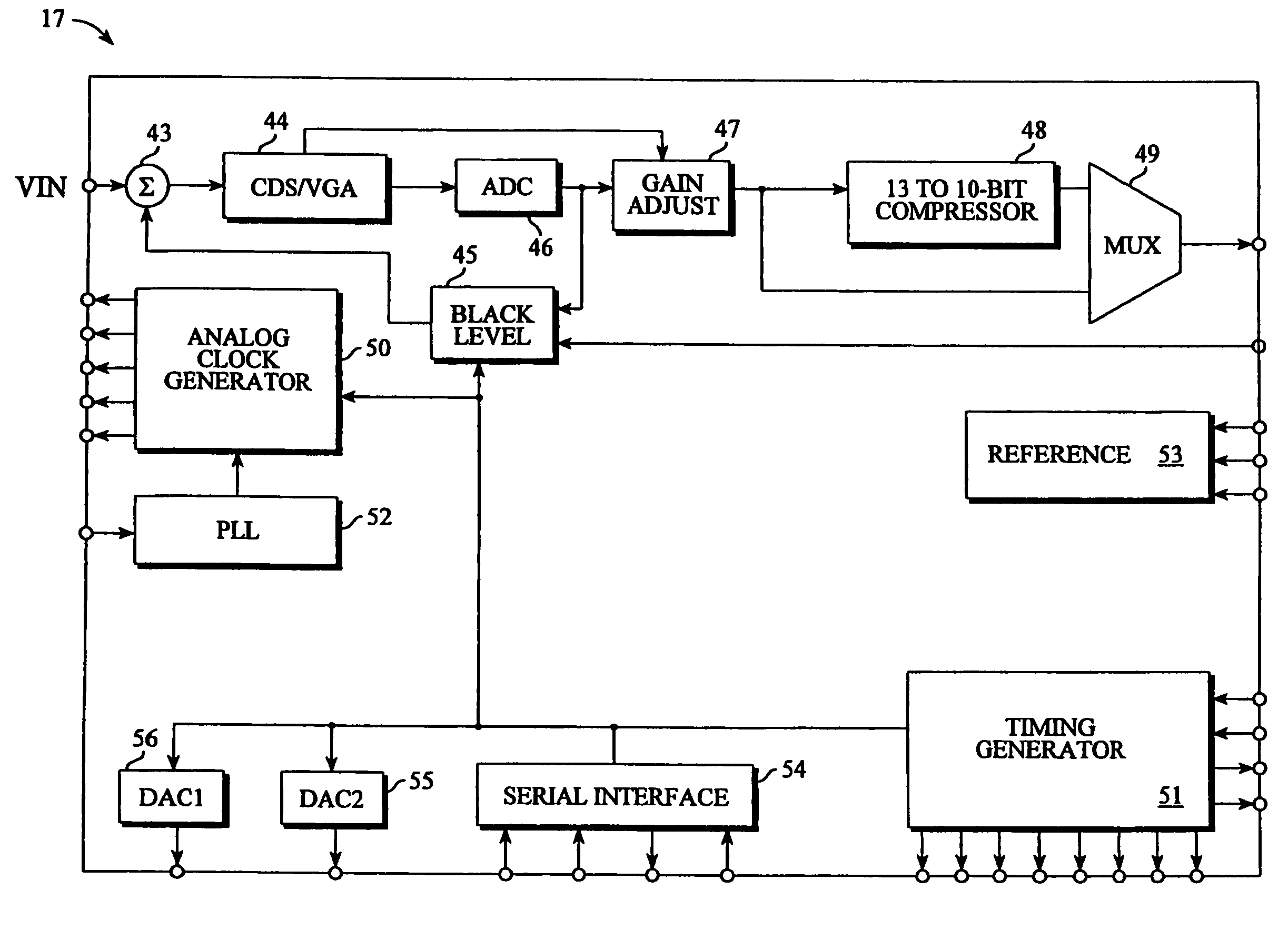

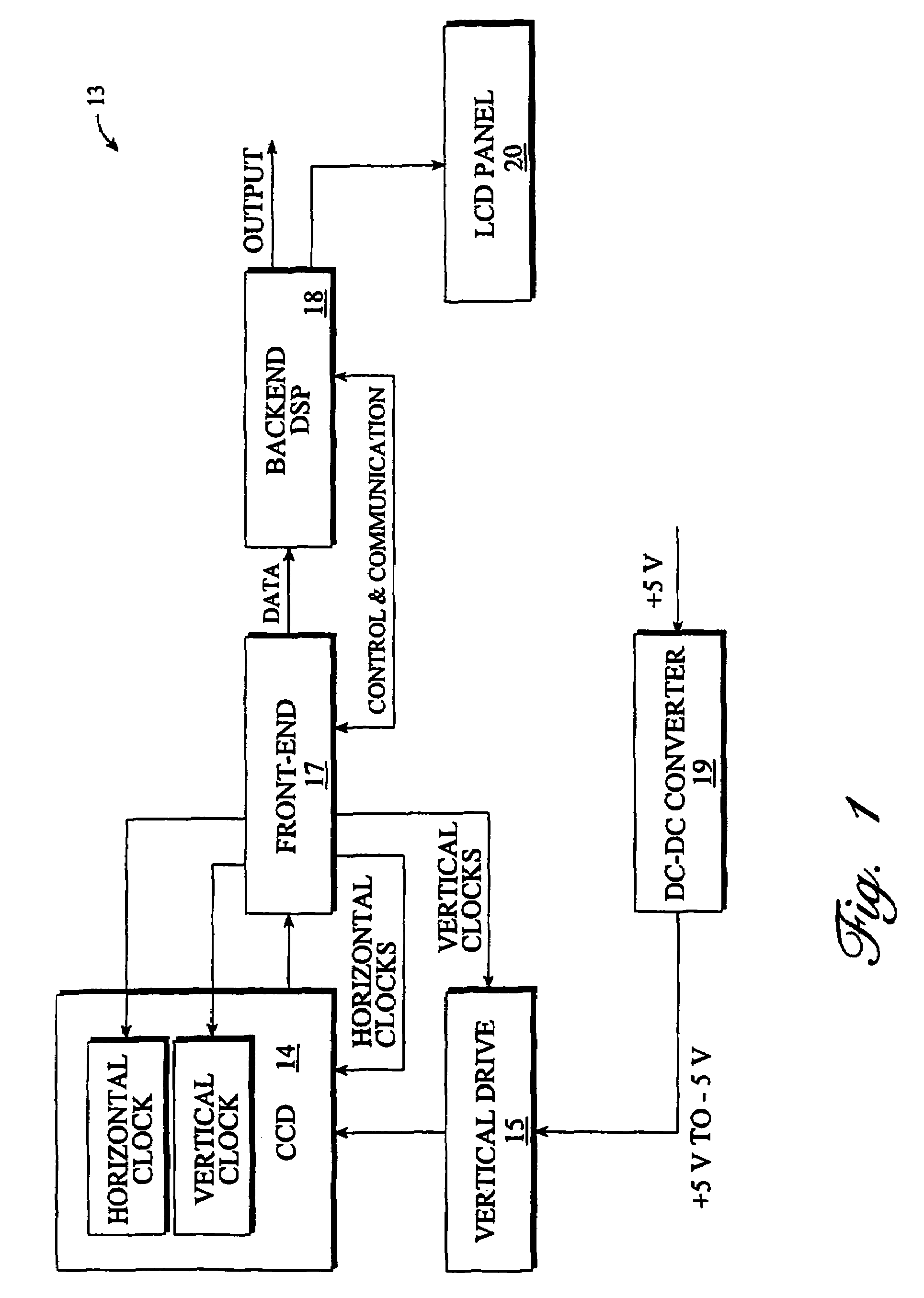

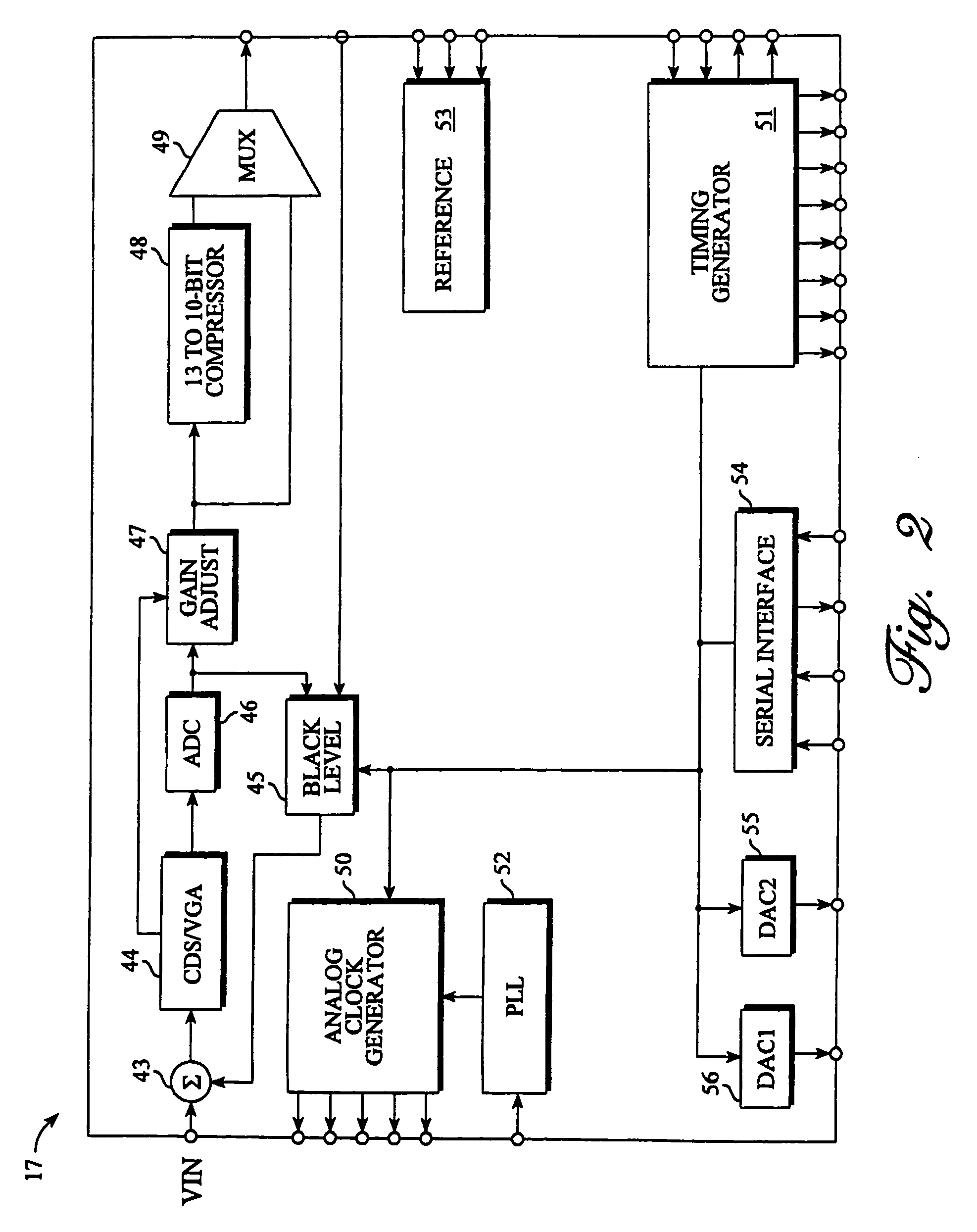

Preview mode low resolution output system and method

InactiveUS7304679B1Reduce total powerReduced preview modeTelevision system detailsPower saving provisionsHandling systemAnalog-to-digital converter

A processing system for a charge coupled device (CCD) or CMOS imaging system includes a correlated double sample (CDS) circuit for receiving data from an imager, a variable gain amplifier (VGA) having amplifiers of selectable current level to enable reduced data resolution in a preview display, a low power mode analog-to-digital converter (ADC) having a selectable narrow bit-width output and coupled to said VGA circuit, and a gain circuit coupled to said ADC. The single chip low-power analog front end produces digitized CCD data in either 13-bit, 12-bit or 10-bit formats at a first current level and 9-bit, 8-bit, or 6-bit formats at a second current level. The VGA amplifier includes symmetrical subcircuits which are independently actuable to enable full or reduced data resolution levels respectively for still image capture operation and video previewing on a separate preview screen.

Owner:CIRRUS LOGIC INC

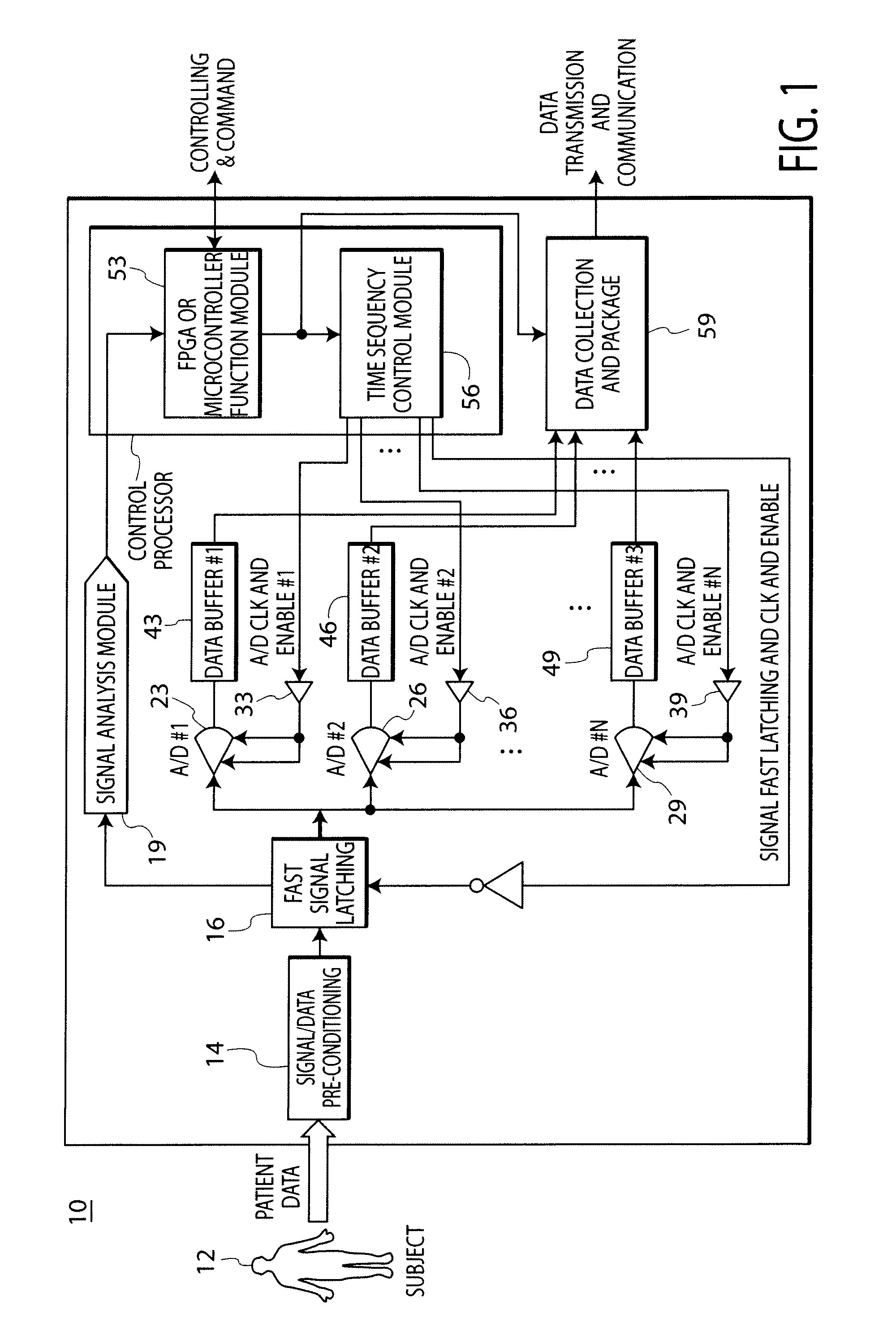

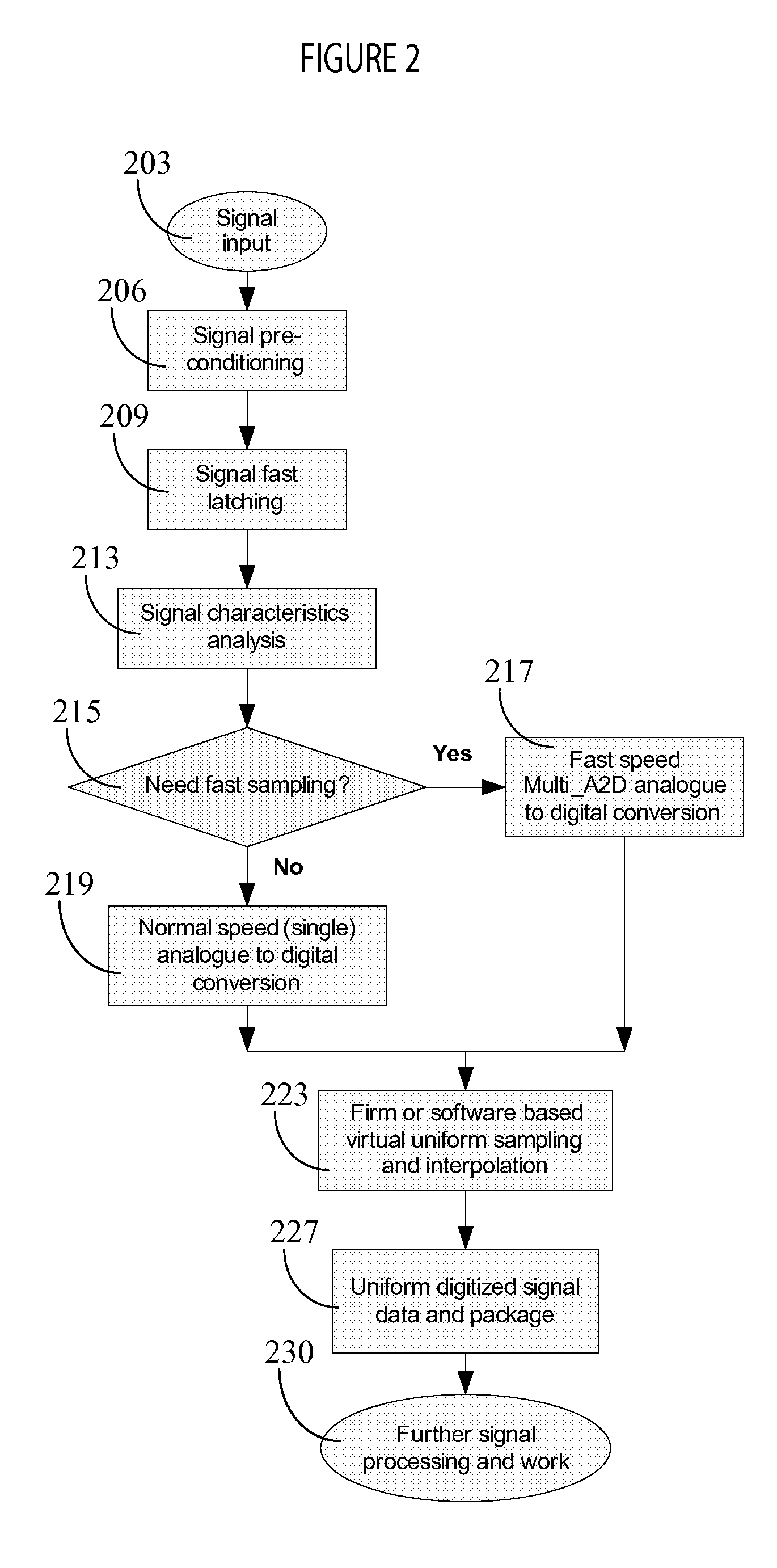

System for processing patient monitoring signals

ActiveUS20100097259A1Improves medical data acquisitionElectric signal transmission systemsElectrocardiographyData rateEngineering

A patient monitoring signal processing system adaptively varies medical signal data rate. The system uses an analog to digital converter for digitizing an analog cyclically varying input signal derived from a patient in response to a sampling clock input. The sampling clock determines frequency of analog to digital sampling of the analog input signal by the analog to digital converter. A detector detects first and second different signal portions within a cycle of the cyclically varying input signal. A control processor coupled to the analog to digital converter and the detector, provides the sampling clock and adaptively determines first and second different frequencies of the sampling clock to be used in sampling within detected corresponding first and second different signal portions of the cyclically varying input signal in response to predetermined information indicating a frequency of a signal component of the cyclically varying input signal in the first signal portion is higher than a frequency of a signal component of the cyclically varying input signal in the second signal portion. Also the first frequency is higher than the second frequency of the first and second different frequencies.

Owner:SIEMENS HEALTHCARE GMBH

Systems and methods for pipelined analog to digital conversion

InactiveUS20090303093A1Power saving provisionsElectric signal transmission systemsMultiplexerVoltage reference

Various embodiments of the present invention provide systems and methods for analog to digital conversion. For example, a pipelined analog to digital converter is disclosed that includes two or more comparators. A first of the comparators is operable to compare an analog input to a first voltage reference upon assertion of the first clock, and a second of the comparators is operable to compare the analog input to a second voltage reference upon assertion of the second clock. The pipelined analog to digital converters further include a multiplexer tree with at least a first tier multiplexer and a second tier multiplexer. The first tier multiplexer receives an output of the first comparator and an output of the second comparator, and the second tier multiplexer receives an output derived from the first tier multiplexer. The second tier multiplexer provides an output bit. A bit enable set is used as a selector input to the first tier multiplexer and the second tier multiplexer, and the bit enable set includes one or more output bits from preceding bit periods.

Owner:AVAGO TECH INT SALES PTE LTD

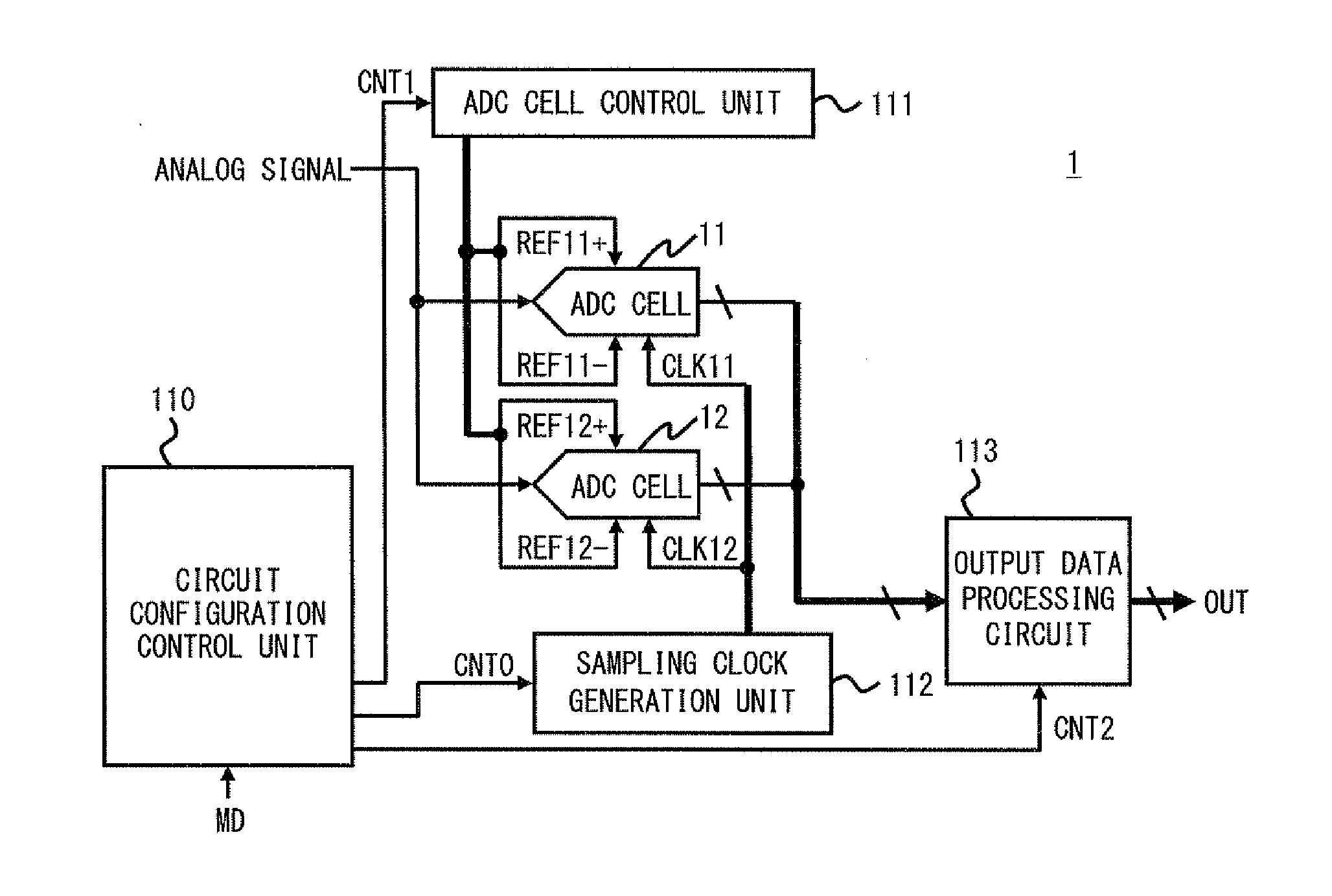

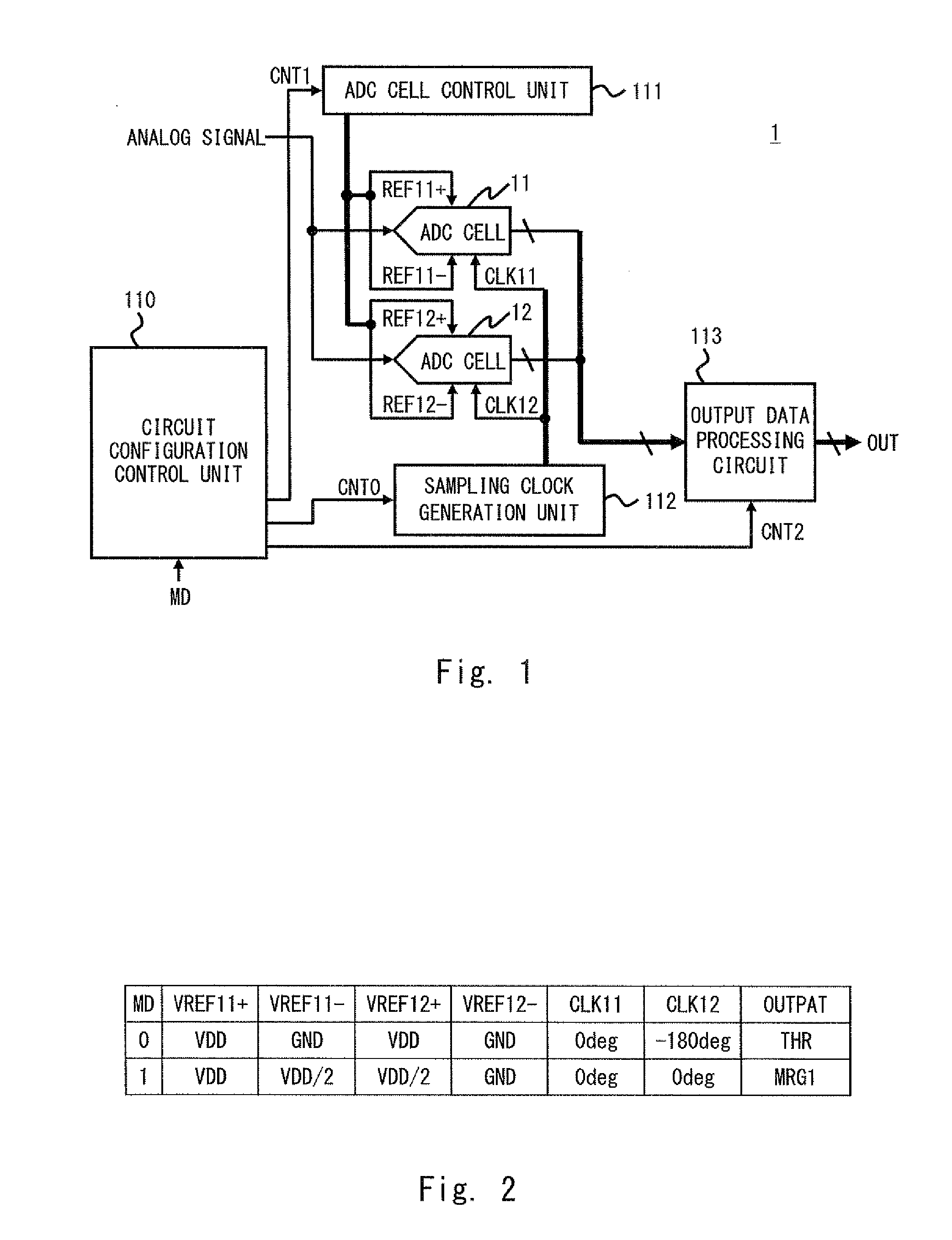

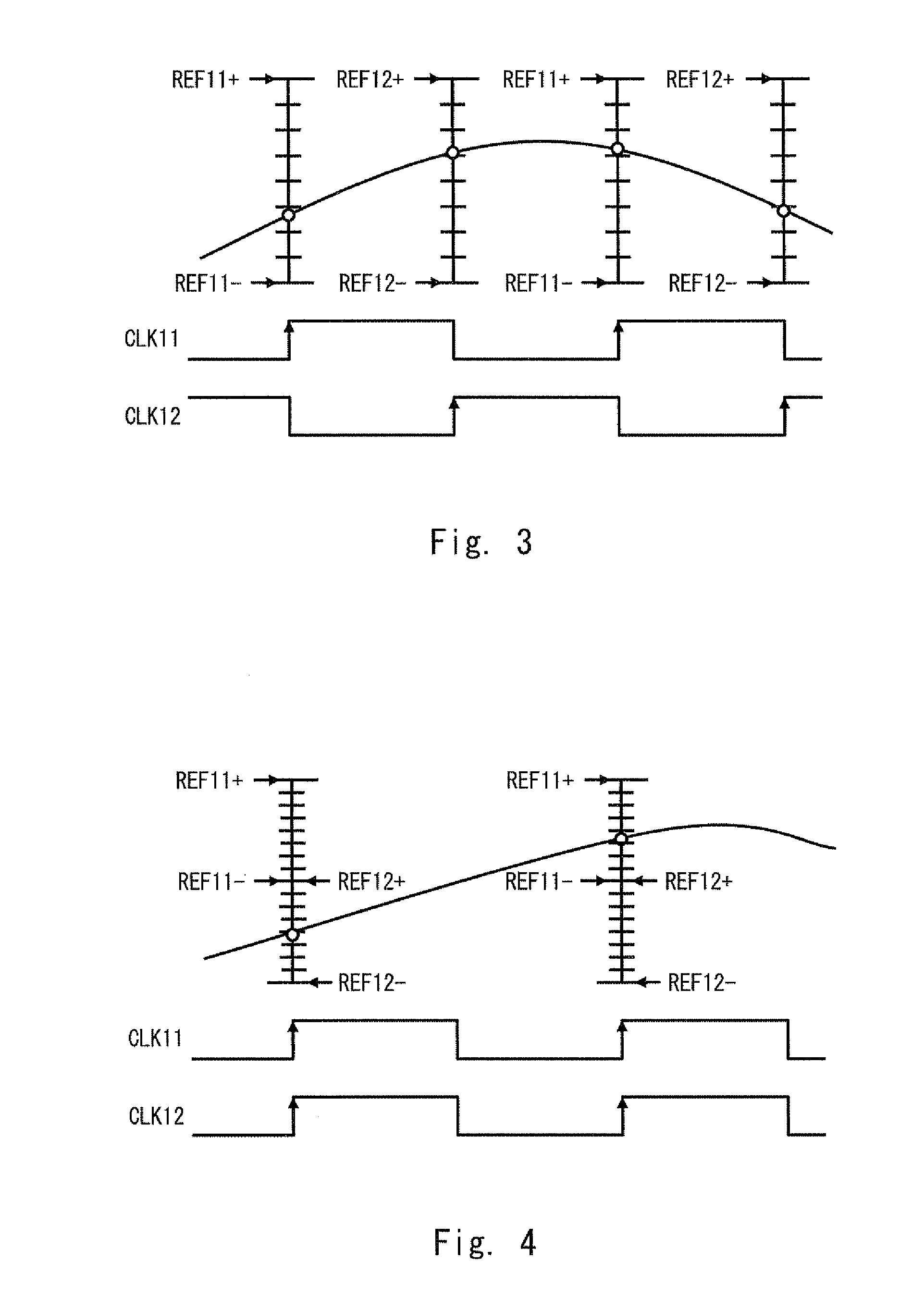

Analog-to-digital converter and analog-to-digital conversion method

ActiveUS20140232577A1Suppress power consumptionPower saving provisionsElectric signal transmission systemsControl signalA d converter

An analog-to-digital converter according to the present invention includes first and second analog-to-digital conversion cells (11, 12), control means (10) for, when a mode specifying signal MD indicates a first mode, generating a control signal that sets first and second input ranges to the same voltage range and sets first and second clocks to different phases, and when the mode specifying signal MD indicates a second mode, generating the control signal that sets the first and second input ranges to one continuous voltage range and sets the first and second clocks to the same phase, ADC cell control means (111) for controlling the voltage ranges of the first and second input ranges according to the control signal, and a sampling clock generation unit (112) that generates the first and second sampling clocks according to the control signal.

Owner:NEC CORP

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com