Asynchronous pulse synchronizer

A pulse synchronous and asynchronous technology, applied in the direction of logic circuit connection/interface layout, logic circuit interface device, etc., can solve the problems of unpredictable and unpredictable unit output level, and achieve the effect of preventing metastable state

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

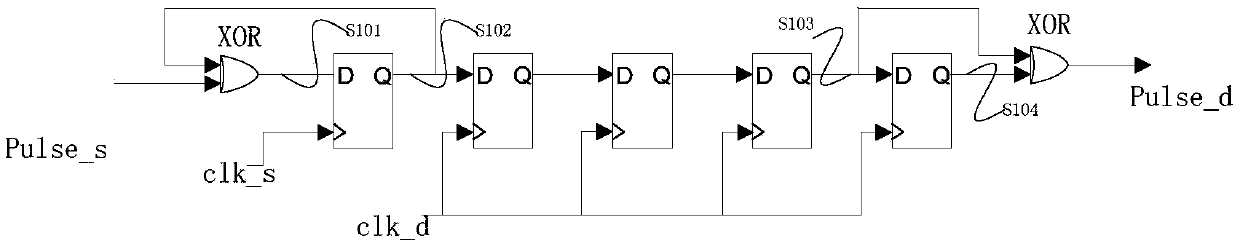

Image

Examples

Embodiment 2

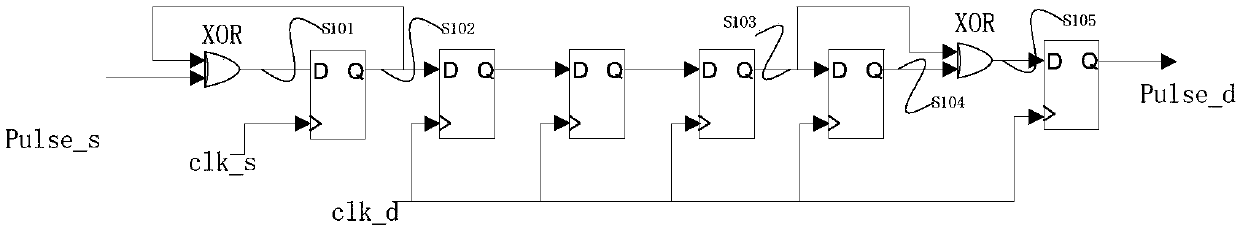

[0028] Embodiment 2, if the timing problem is considered, the output of the output logic unit can be changed to register output, that is, according to the attached figure 2 A circuit is designed to resynchronize the output of the fifth D flip-flop (S104) by one stage before outputting, that is, a sixth D flip-flop is also included, and the input end of the sixth D flip-flop is connected to the output end of the second XOR gate.

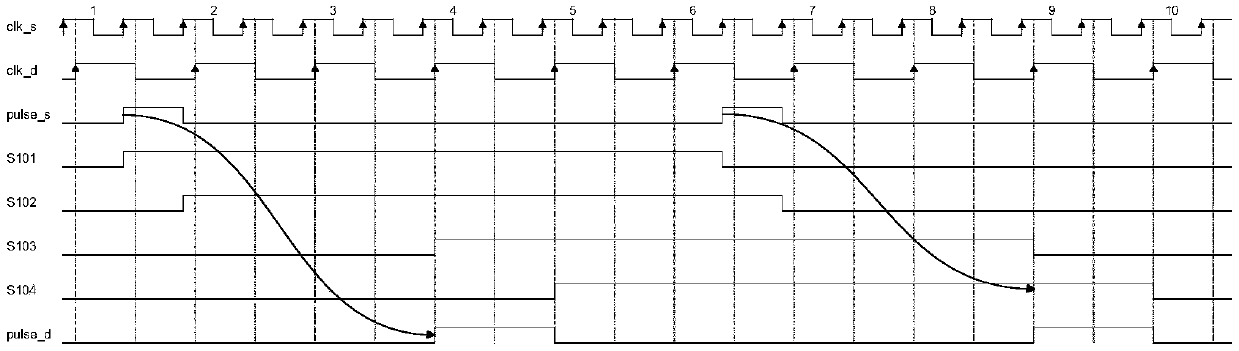

[0029] The waveform diagram of the asynchronous pulse from high frequency to low frequency synchronous process in this embodiment is as follows image 3 As shown, the waveform diagram of the synchronous process of asynchronous pulse from low frequency to high frequency is as follows Figure 4 shown.

[0030] This embodiment supports an input clock clk_s with any frequency phase and an output clock clk_d with any frequency phase.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com