Metastable state risk avoidance method and circuit in cross-clock domain data transmission

A data transmission, cross-clock domain technology, applied in electrical digital data processing, digital computer components, generation/distribution of signals, etc. The effect of metastability risk, reducing data transmission delay, and improving system performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

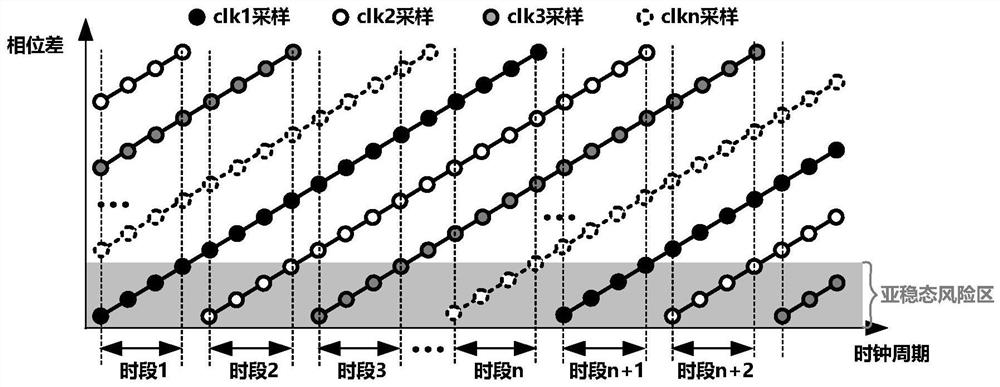

[0040] This embodiment provides a metastable risk avoidance method in cross-clock domain data transmission, which includes constructing multiple receiver clocks with the same frequency and different phases, sampling the data of the transmitter respectively during the entire clock cycle of the receiver, and according to different The difference between the data results of the phase receiving end clock sampling the sending end, judges in real time whether there is a metastable risk when each receiving end clock samples the sending end data, and continuously switches to select the one that does not have the risk of metastable state within the preset first time The receiving end clock is used as the effective clock of the receiving end to transmit data with the sending end.

[0041] As a preferred embodiment, the sampling edges of multiple receiver clocks are distributed sequentially, and when there is a metastable risk between the current receiver clock and the data at the sender,...

Embodiment 2

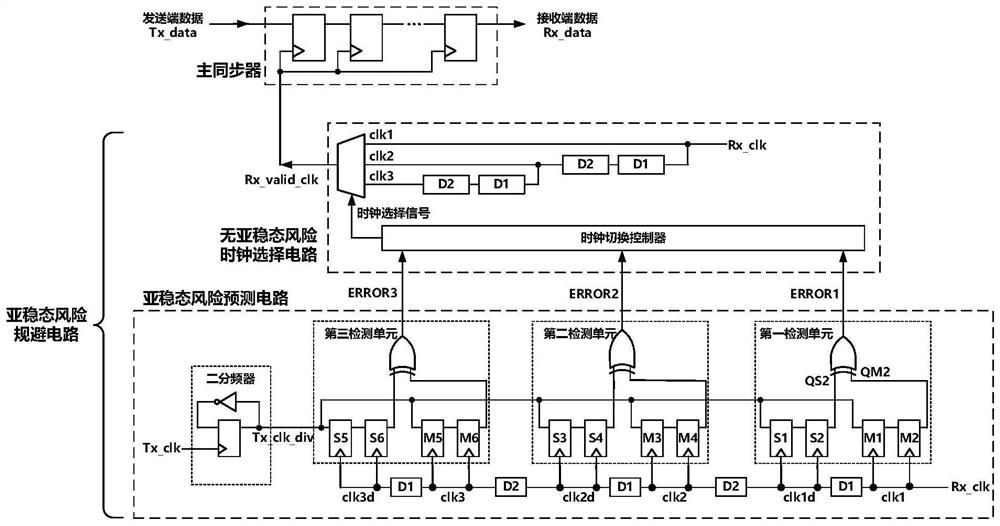

[0048] This embodiment provides a metastable risk avoidance circuit in cross-clock domain data transmission, including a metastable risk prediction circuit and a clock selection circuit without a metastable risk. The metastable risk prediction circuit includes a sending end clock, an original receiving end clock, a plurality of receiver clock test modules and second delay units connected in sequence, the receiver clock test modules include a detection unit and a first delay unit, and the first delay units in each receiver clock test module are connected in sequence, A second delay unit is also connected between two adjacent first delay units, and the two ends of the first delay unit are respectively connected to the detection unit;

[0049] The first delay unit at one end of all receiving-end clock test modules is connected to the original receiving-end clock, and the other end is connected to the sending-end clock through a frequency divider. unit;

[0050] The frequency div...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com