Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

131 results about "Reference counter" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

This method is simply keeping an extra counter along with each object that is created. The counter is the number of references that exist to the object, in the C/C++ case this would how many pointers refer to this object.

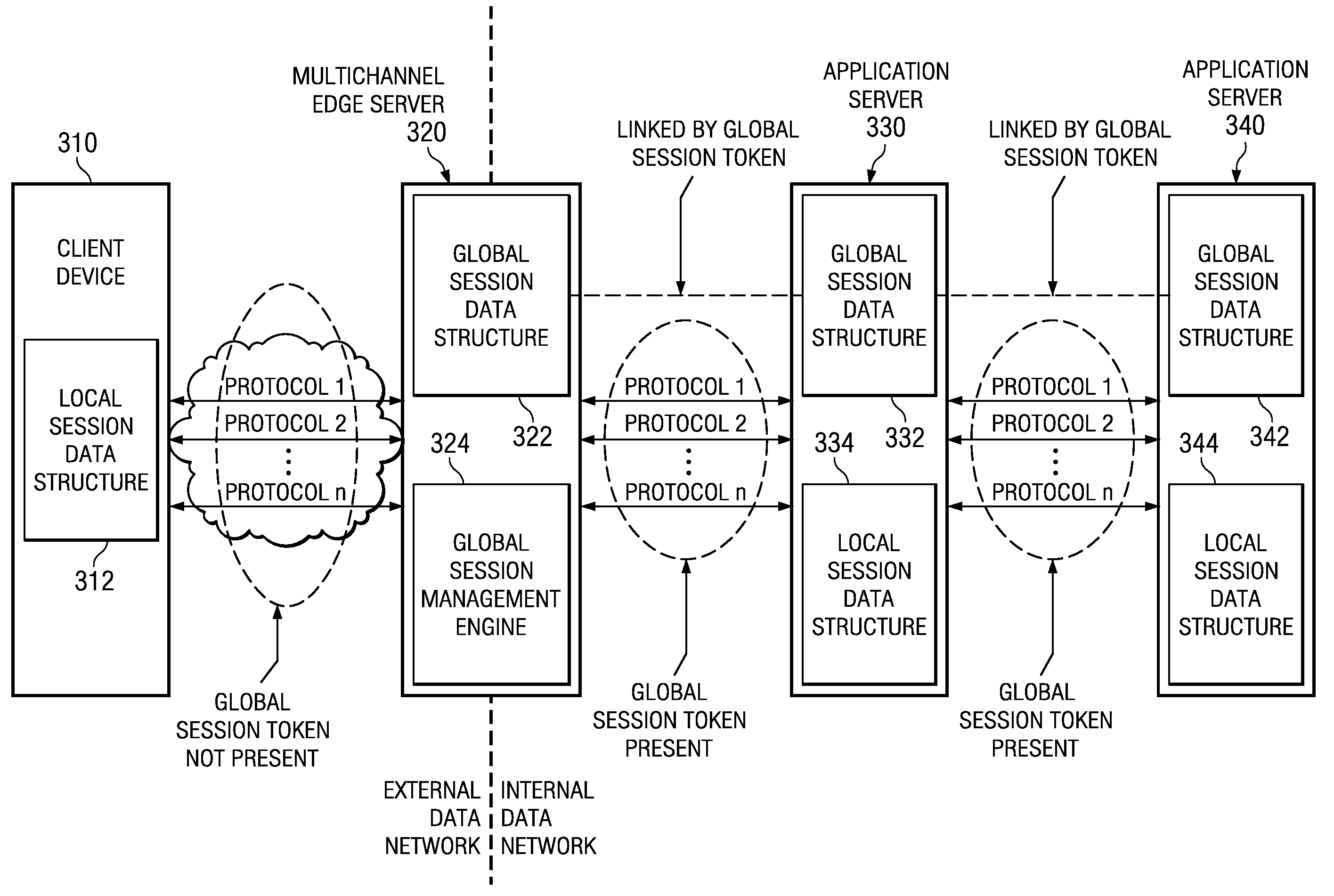

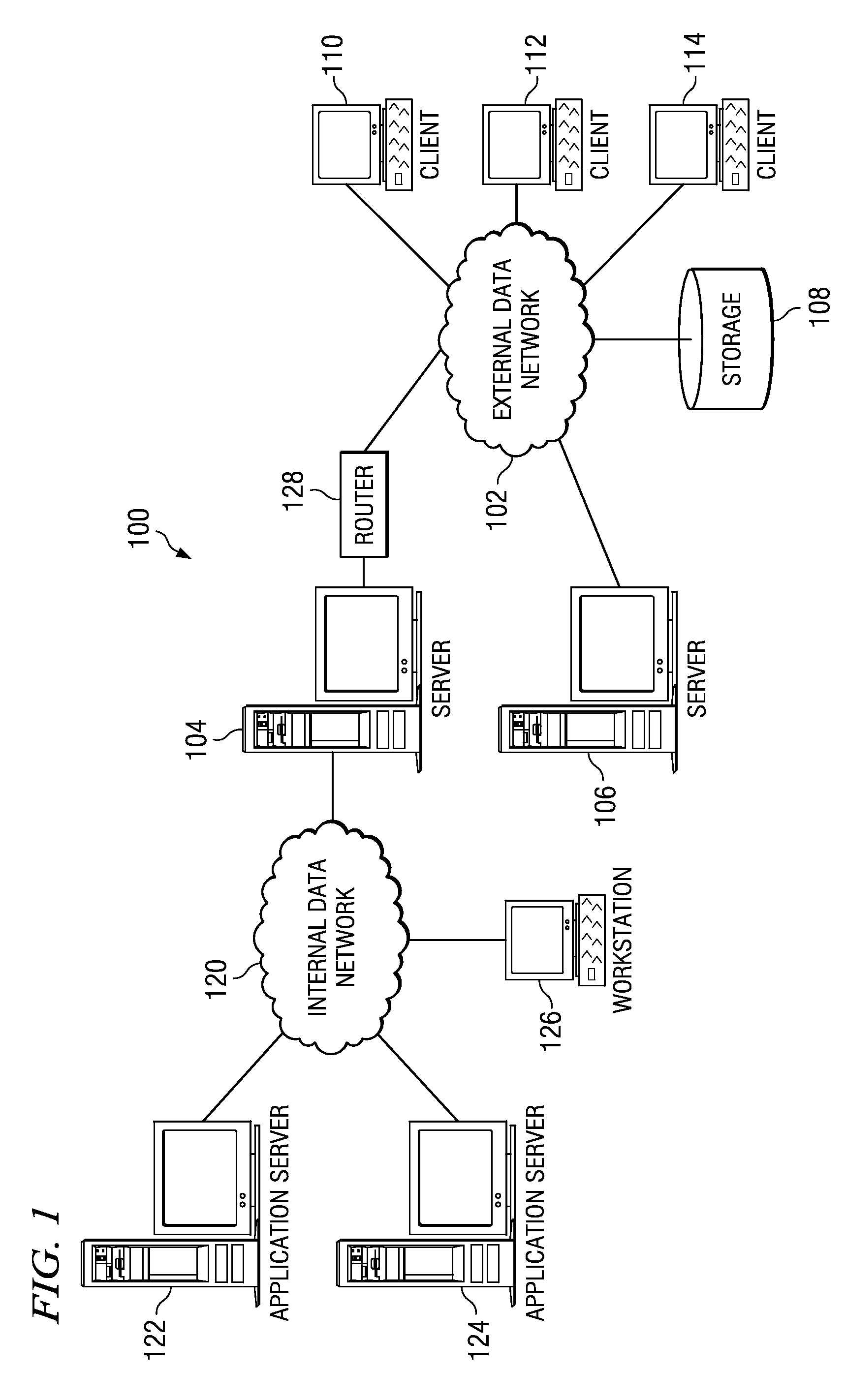

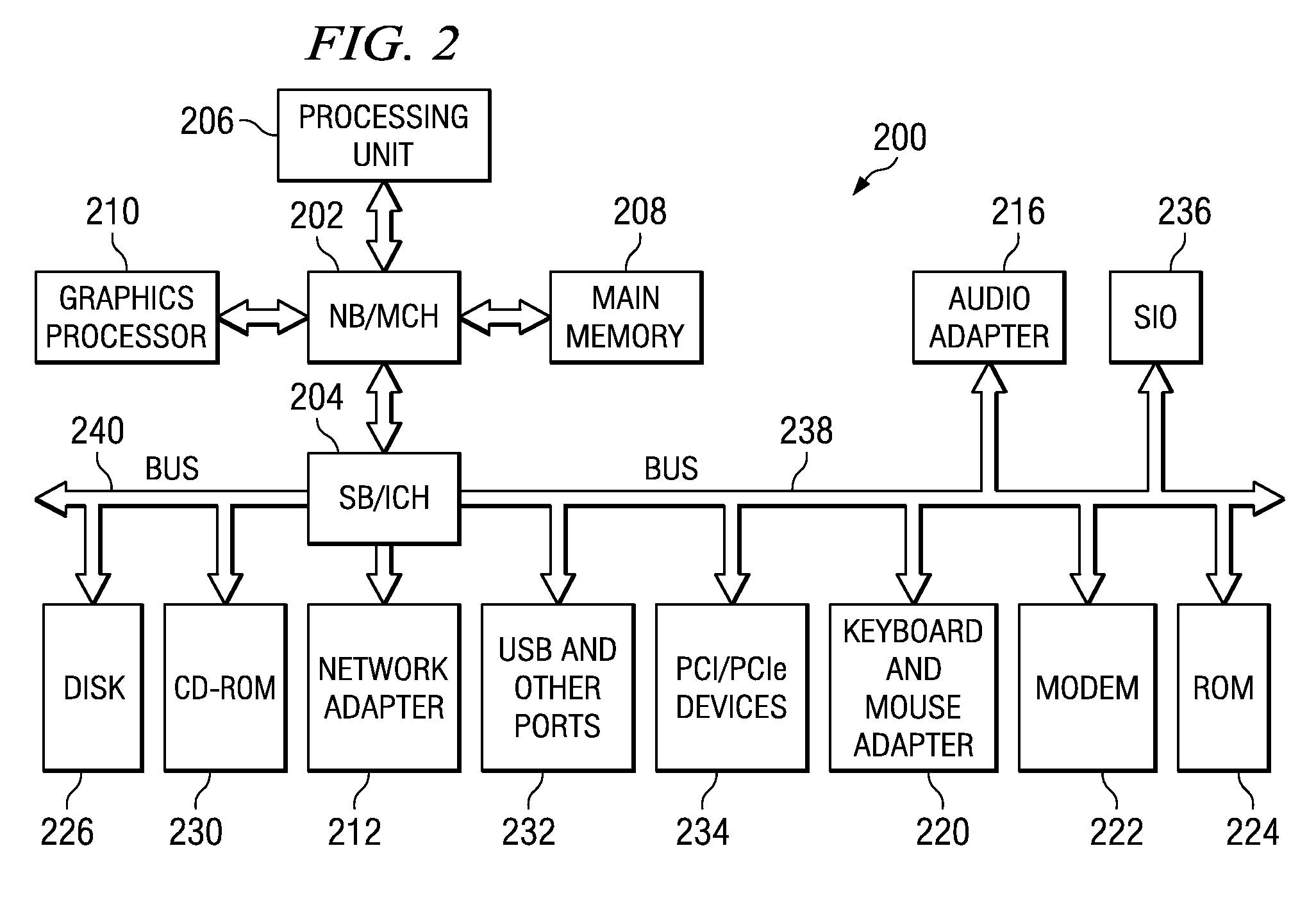

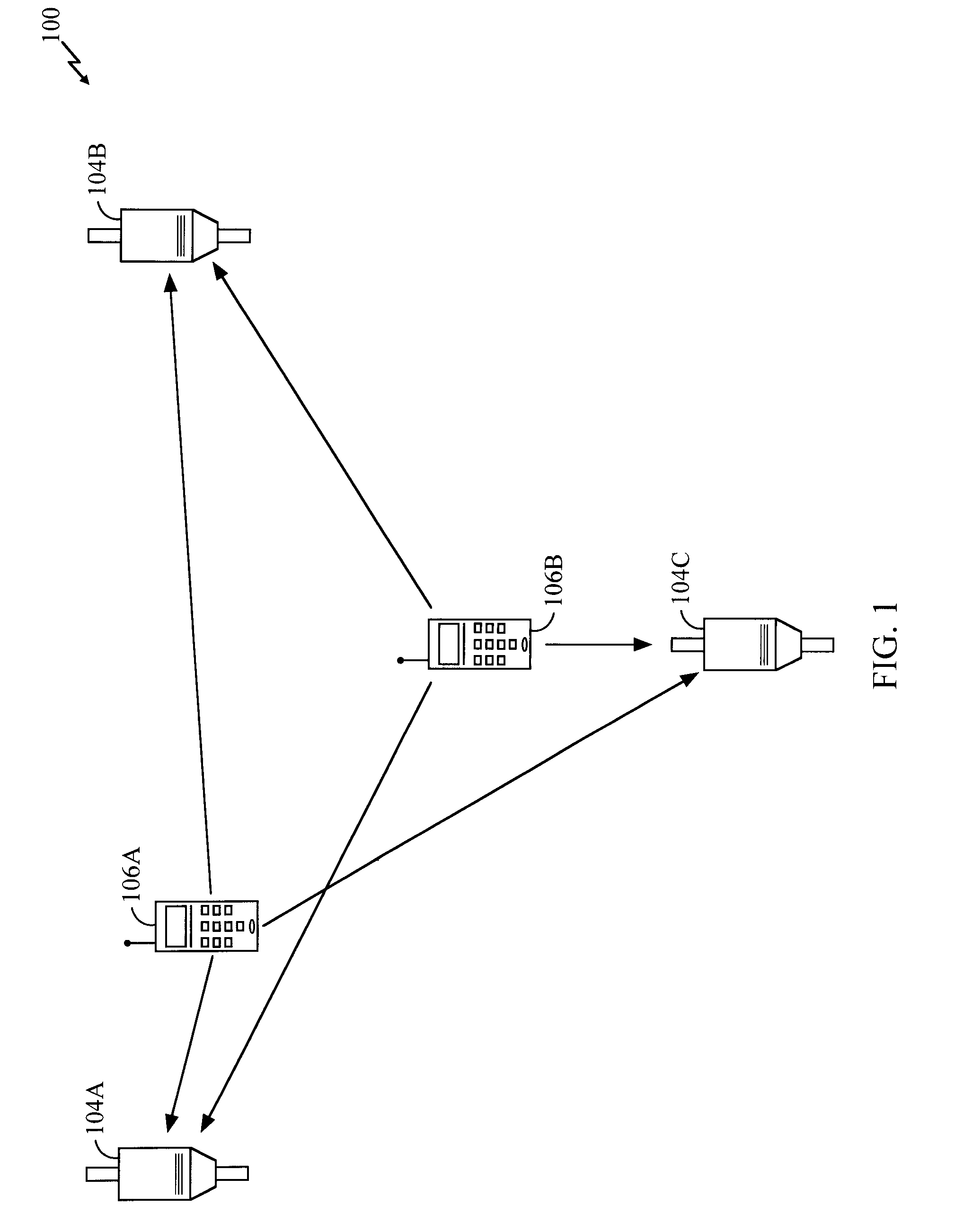

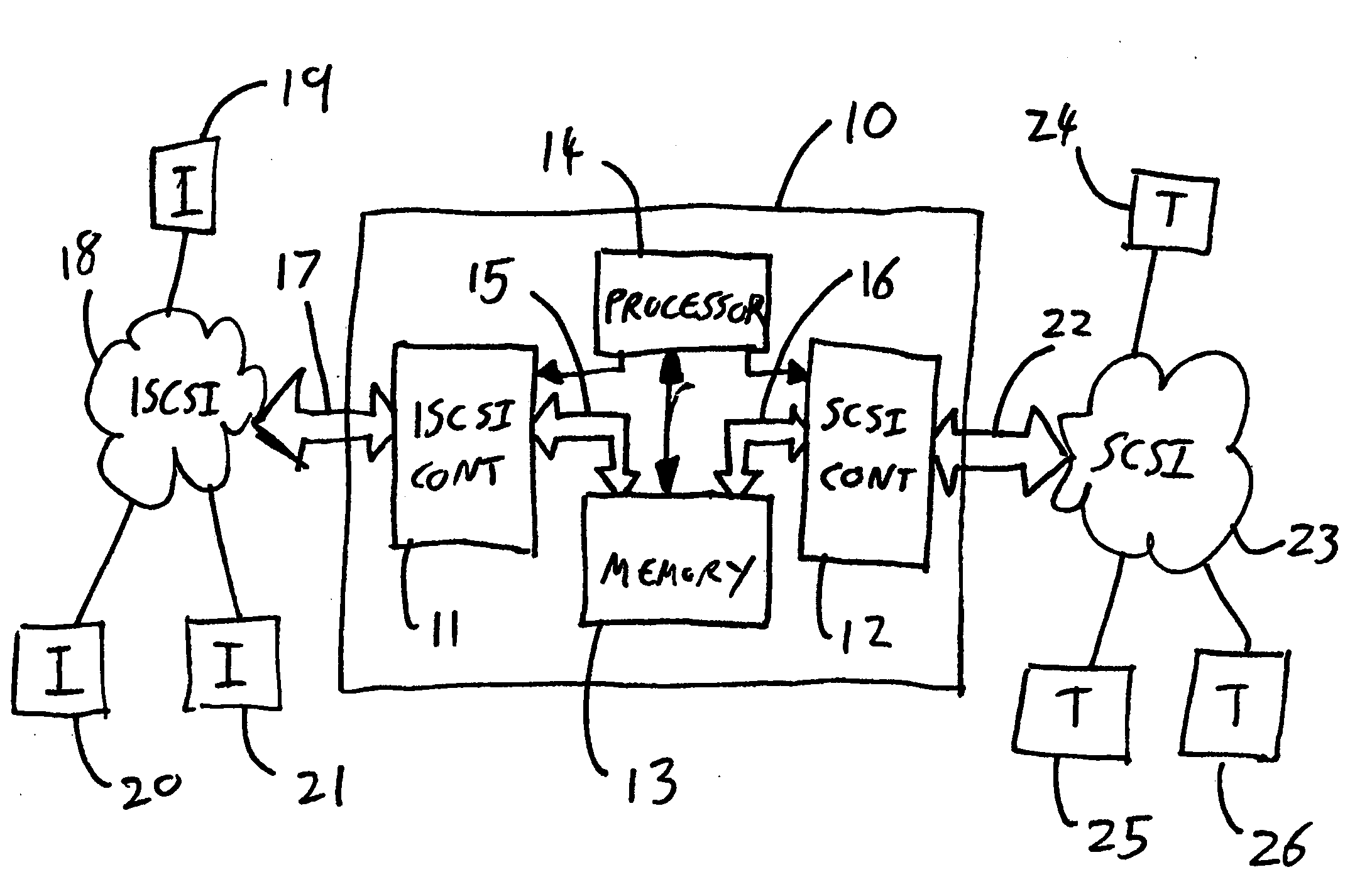

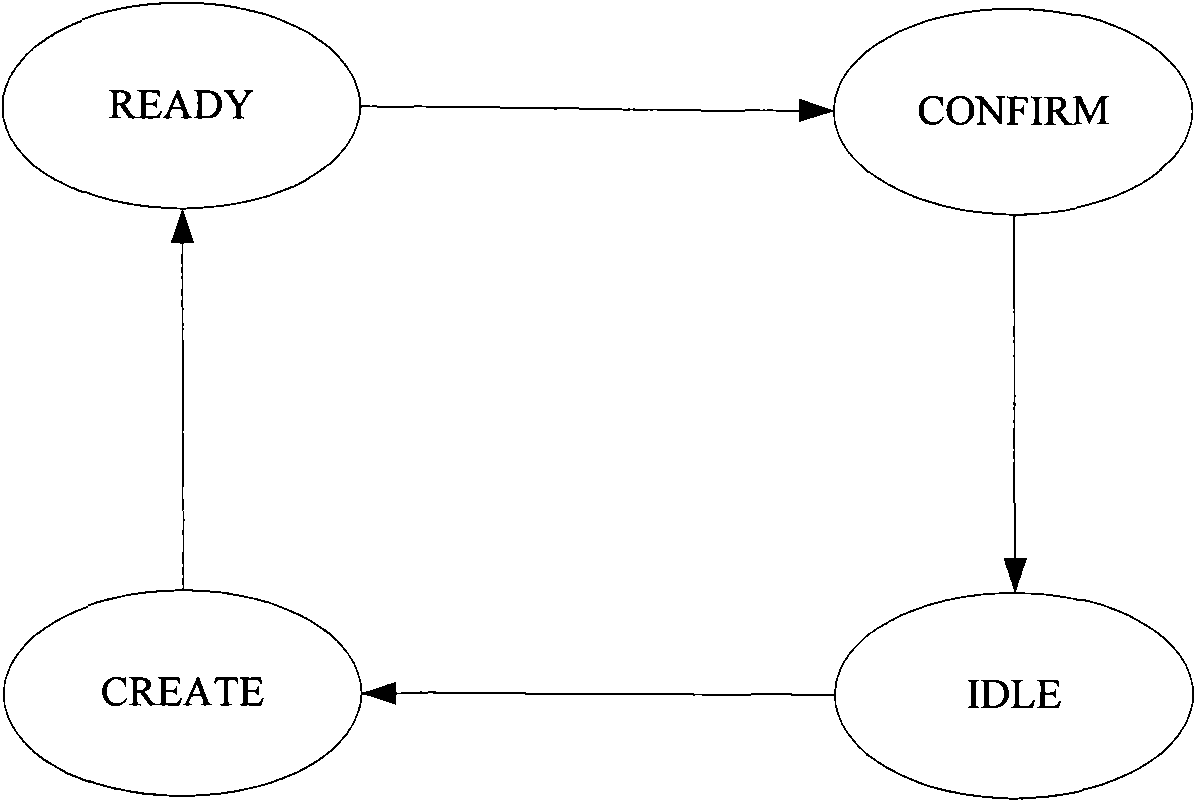

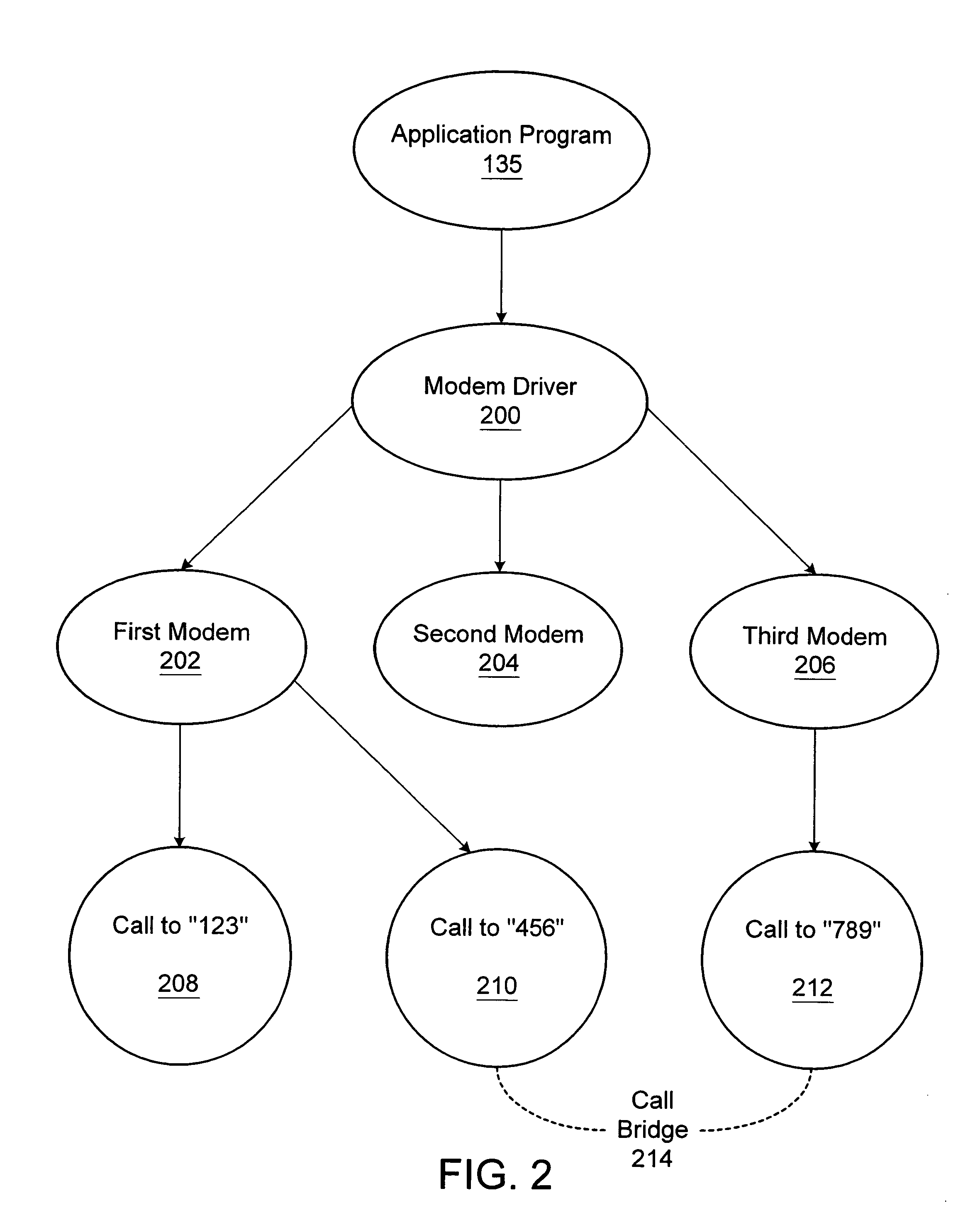

System and Method for Creating Global Sessions Across Converged Protocol Applications

A system and method for creating global sessions across different protocols and multiple converged protocol applications are provided. By creating a global session, state information for each of the individual protocol sessions may be communicated across protocols and utilized in performing operations across converged protocol applications. An edge server is used at the edge of a data network to correlate client interactions over different protocols and to associate them with a global session. The edge server acts as a session reference counter for individual client sessions that are part of a larger global session. The global session is created after the creation of the first protocol session and exists across the creation of future sessions on other protocols and other converged applications. Logical names and global session tokens are utilized to manage the various global sessions handled by the edge server.

Owner:IBM CORP

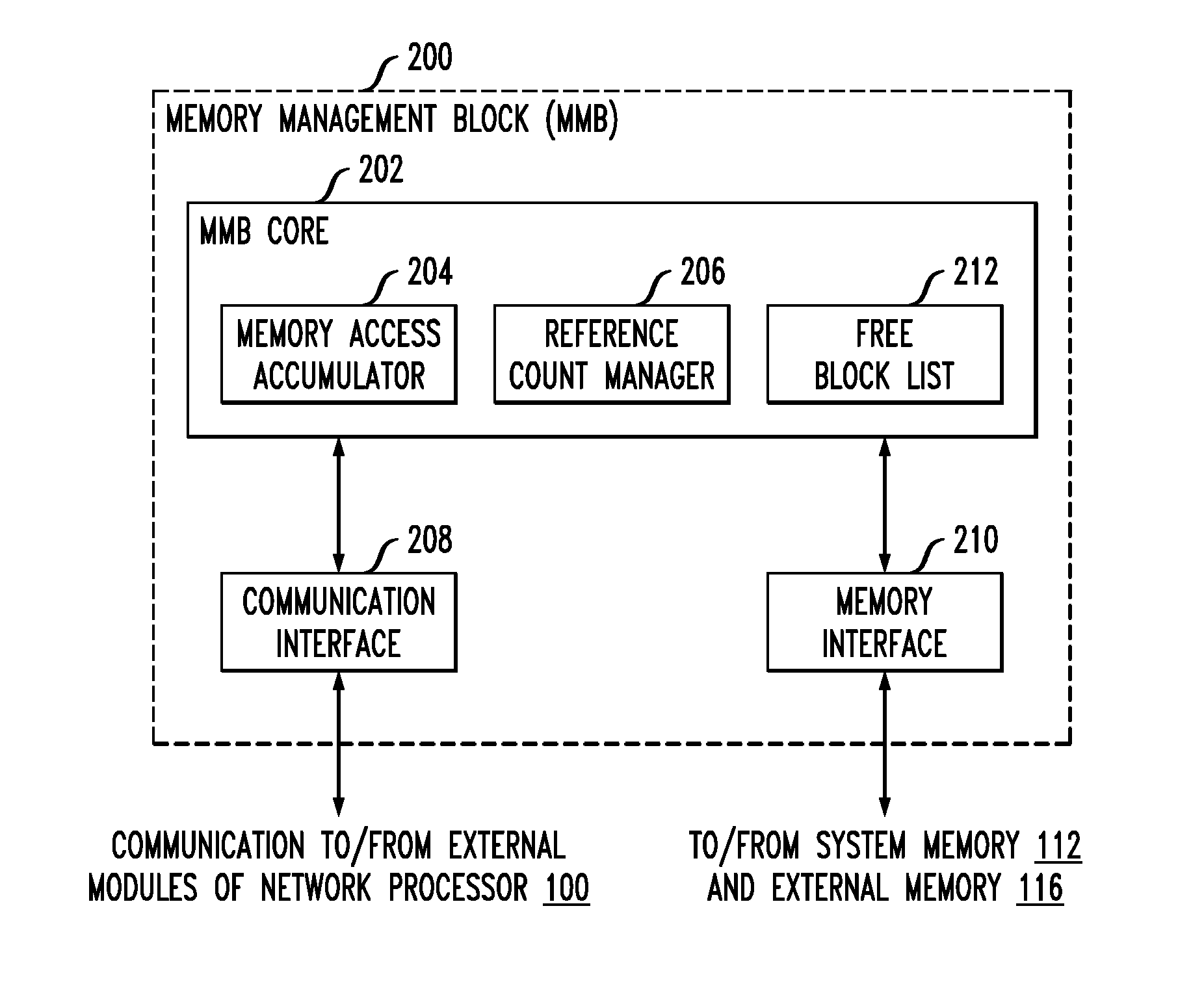

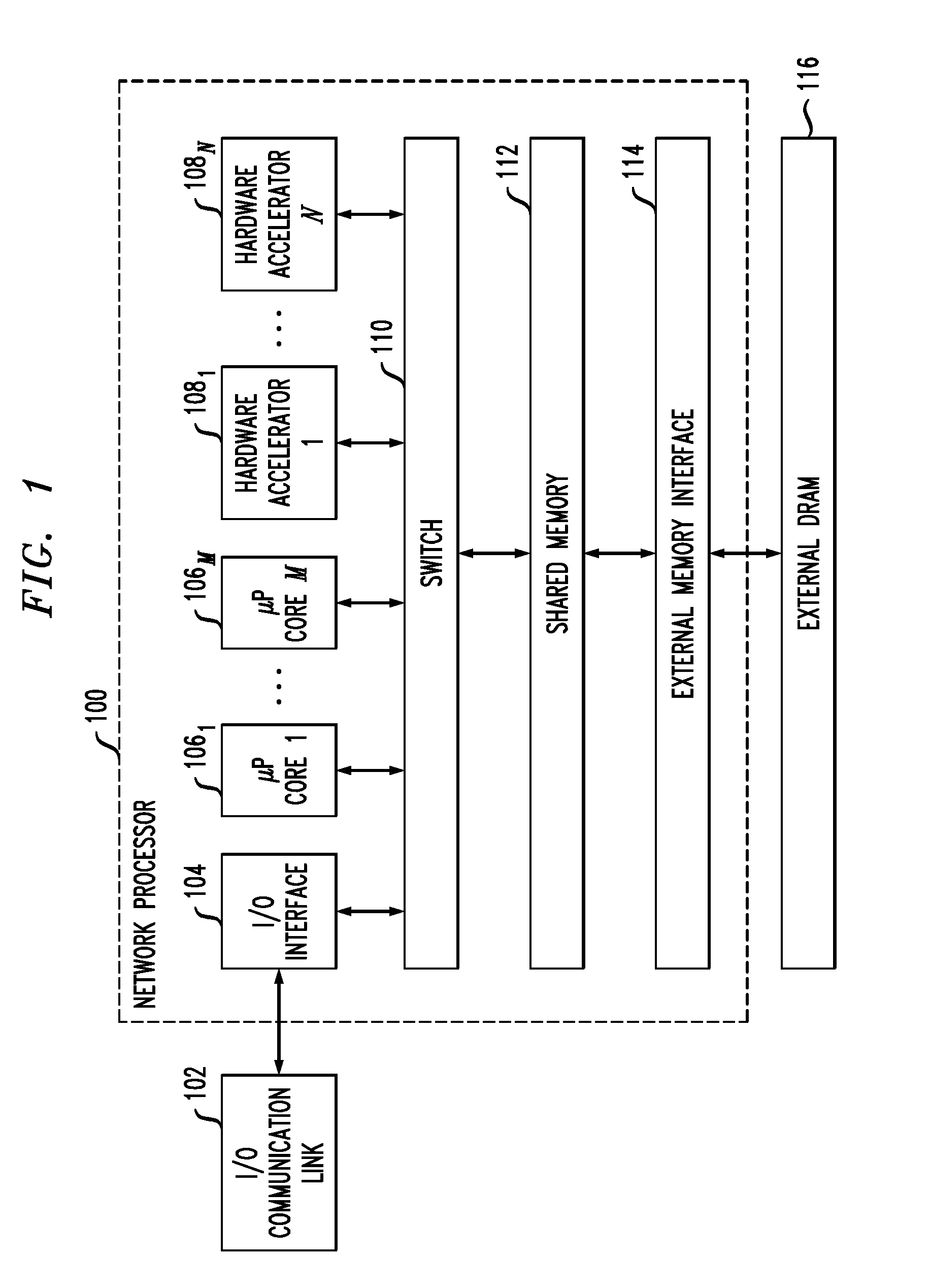

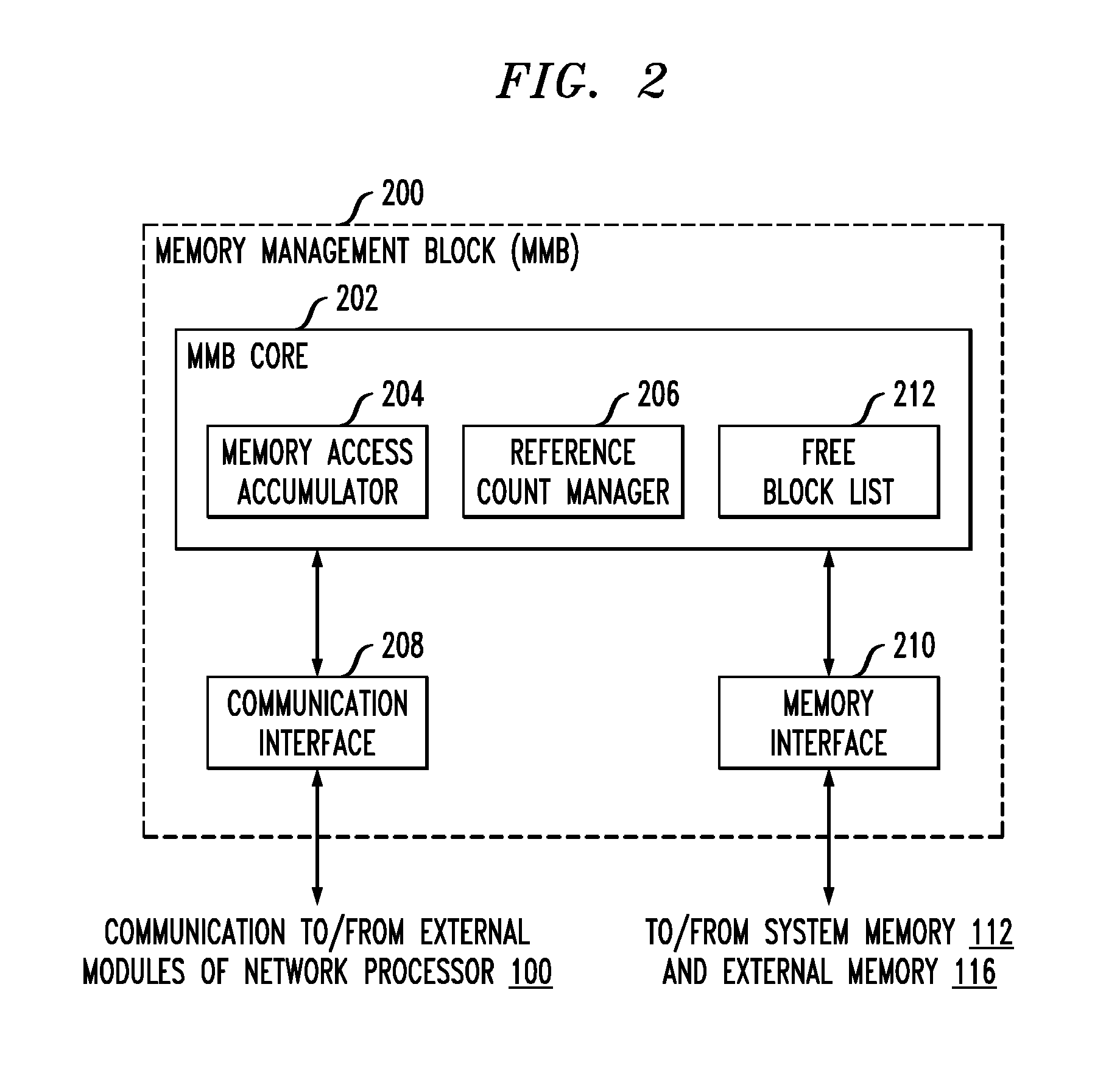

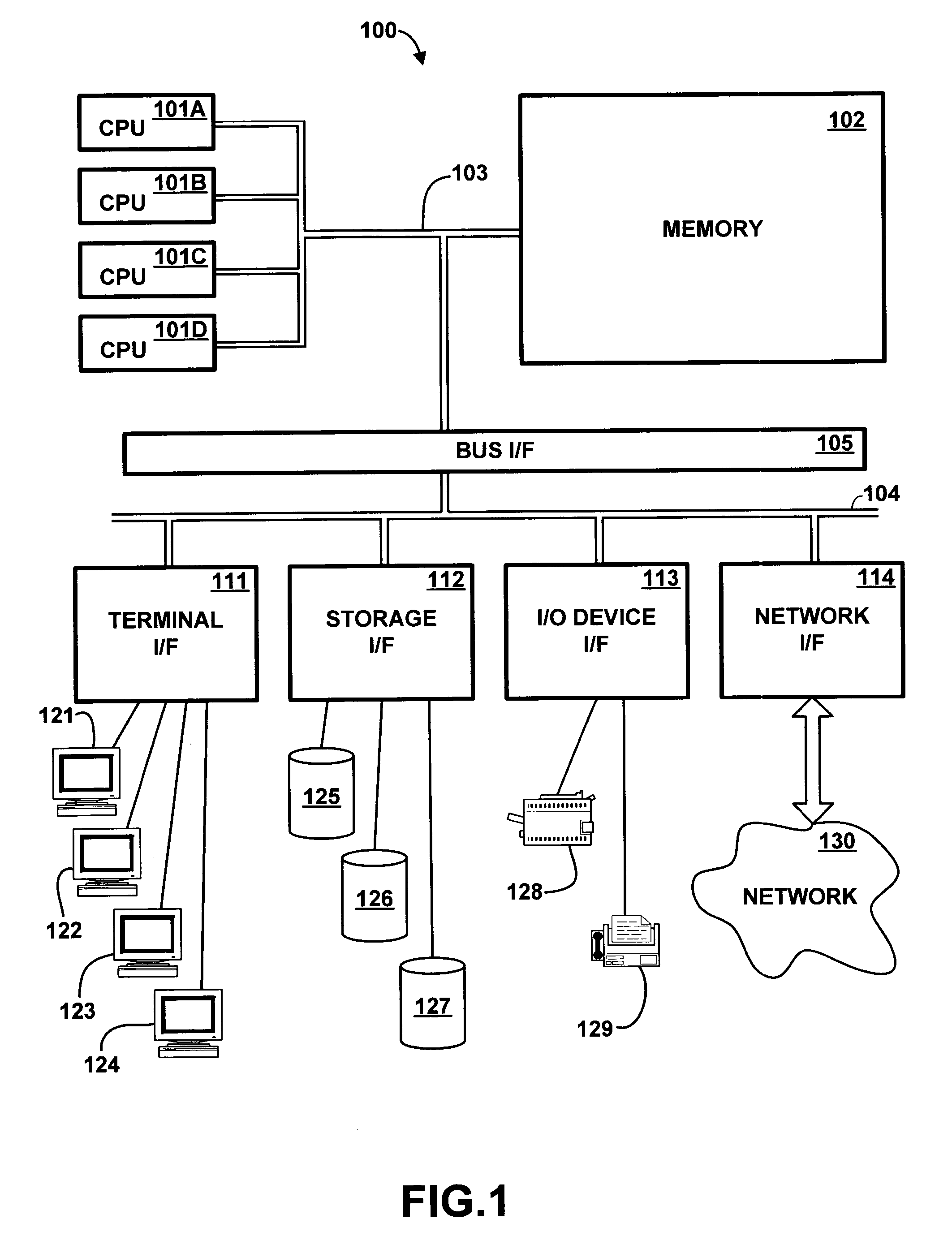

Memory manager for a network communications processor architecture

Described embodiments provide a memory manager for a network processor having a plurality of processing modules and a shared memory. The memory manager allocates blocks of the shared memory to requesting ones of the plurality of processing modules. A free block list tracks availability of memory blocks of the shared memory. A reference counter maintains, for each allocated memory block, a reference count indicating a number of access requests to the memory block by ones of the plurality of processing modules. The reference count is located with data at the allocated memory block. For subsequent access requests to a given memory block concurrent with processing of a prior access request to the memory block, a memory access accumulator (i) accumulates an incremental value corresponding to the subsequent access requests, (ii) updates the reference count associated with the memory block, and (iii) updates the memory block with the accumulated result.

Owner:INTEL CORP

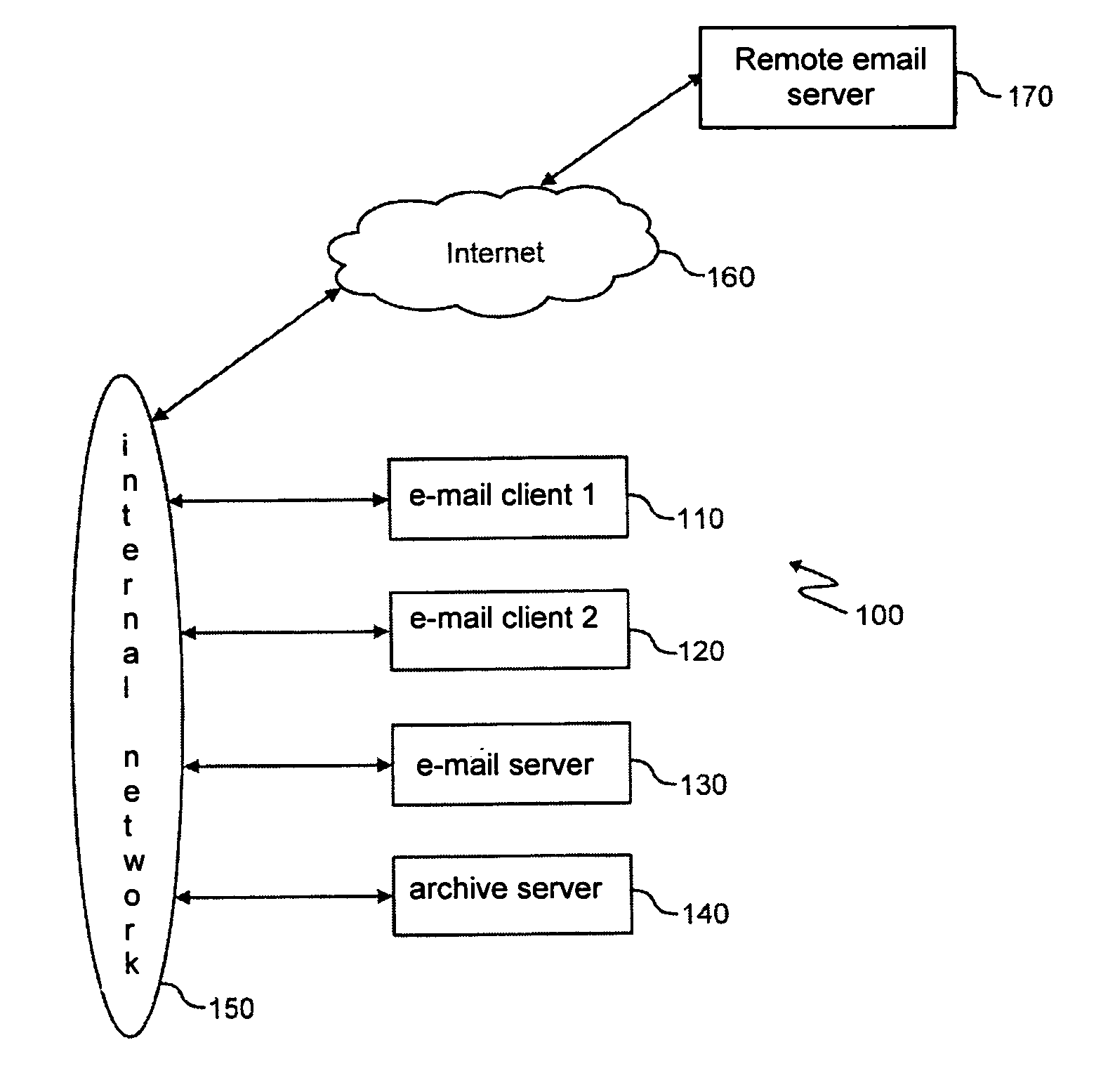

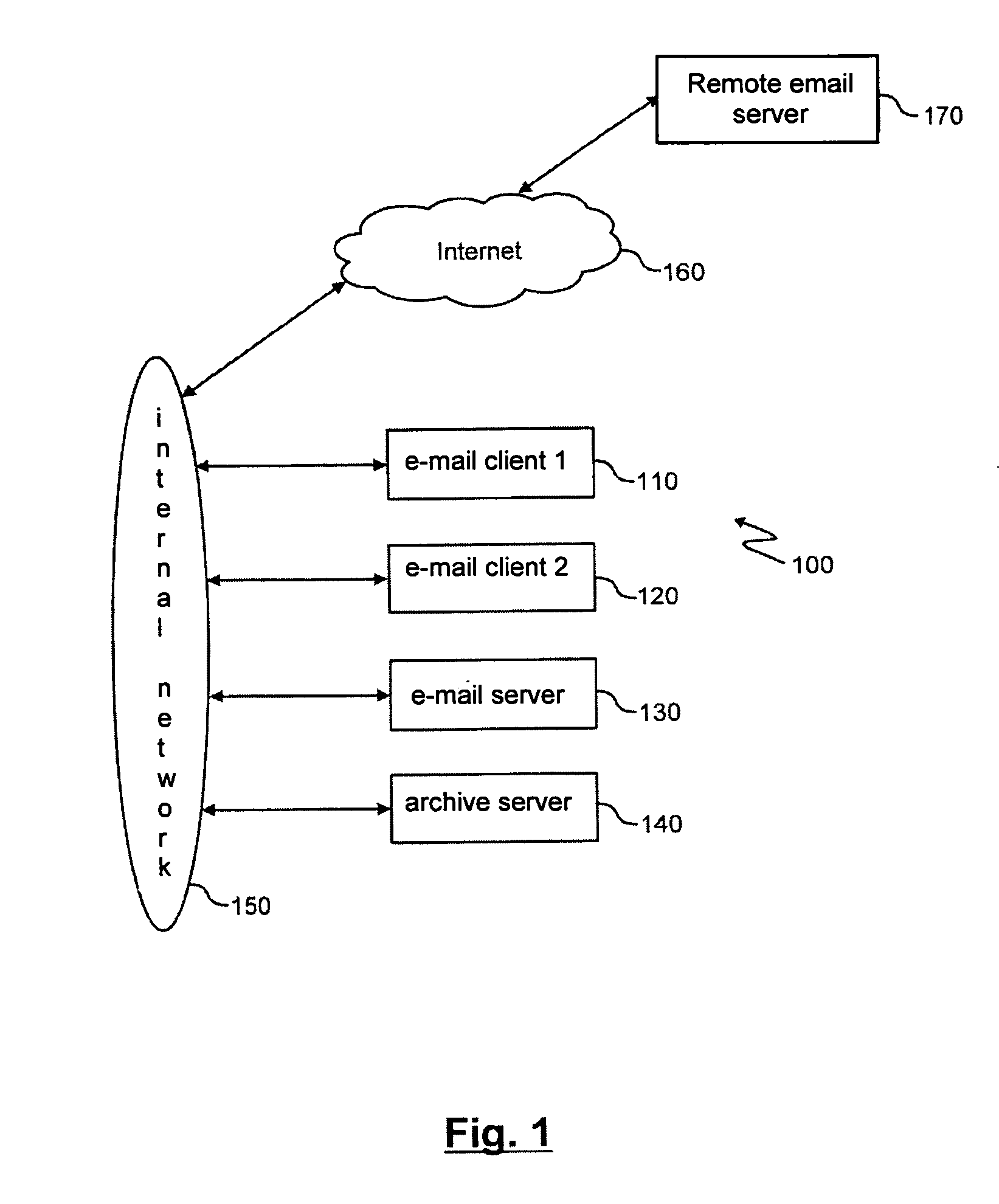

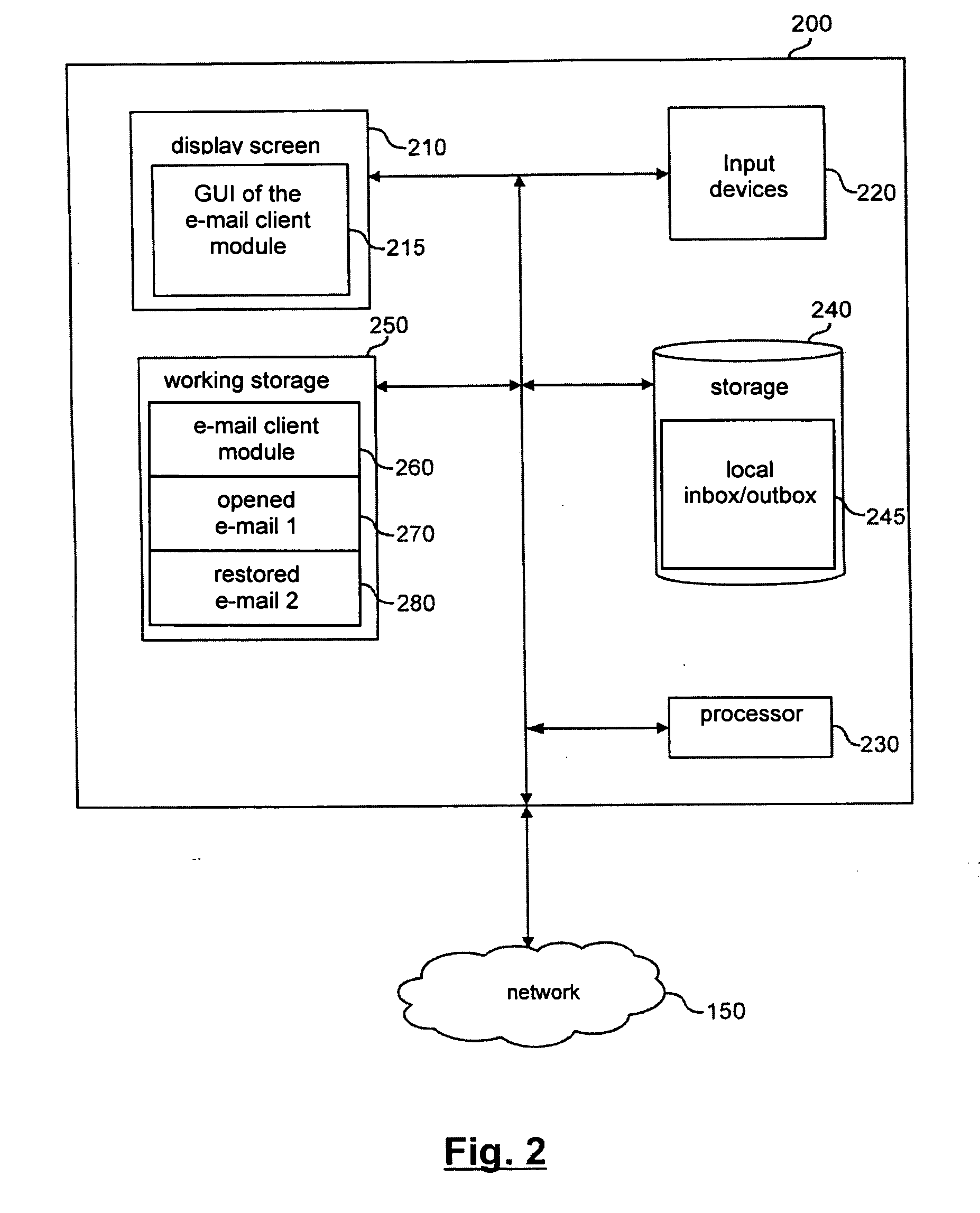

Method and apparatus for managing electronic messages

ActiveUS20050283461A1Reduce redundancyRedundancy to be substantially reducedDigital data processing detailsData switching networksDatabaseReference counter

A method is provided for the storage-efficient management of electronic messages, wherein a message that is to be managed is first received, the message is decomposed into a basic structure and file attachments contained in the message, a unique identification value is calculated for each file attachment, the file attachment is stored as a file with a respective identification value for which no file exists in the storage, or a reference counter of the file attachment for whose identification value a file already exists in the storage, is incremented, and the basic structure with references to the files in the storage, which references correspond to the file attachments originally contained in the message, is stored.

Owner:OPEN TEXT SA ULC

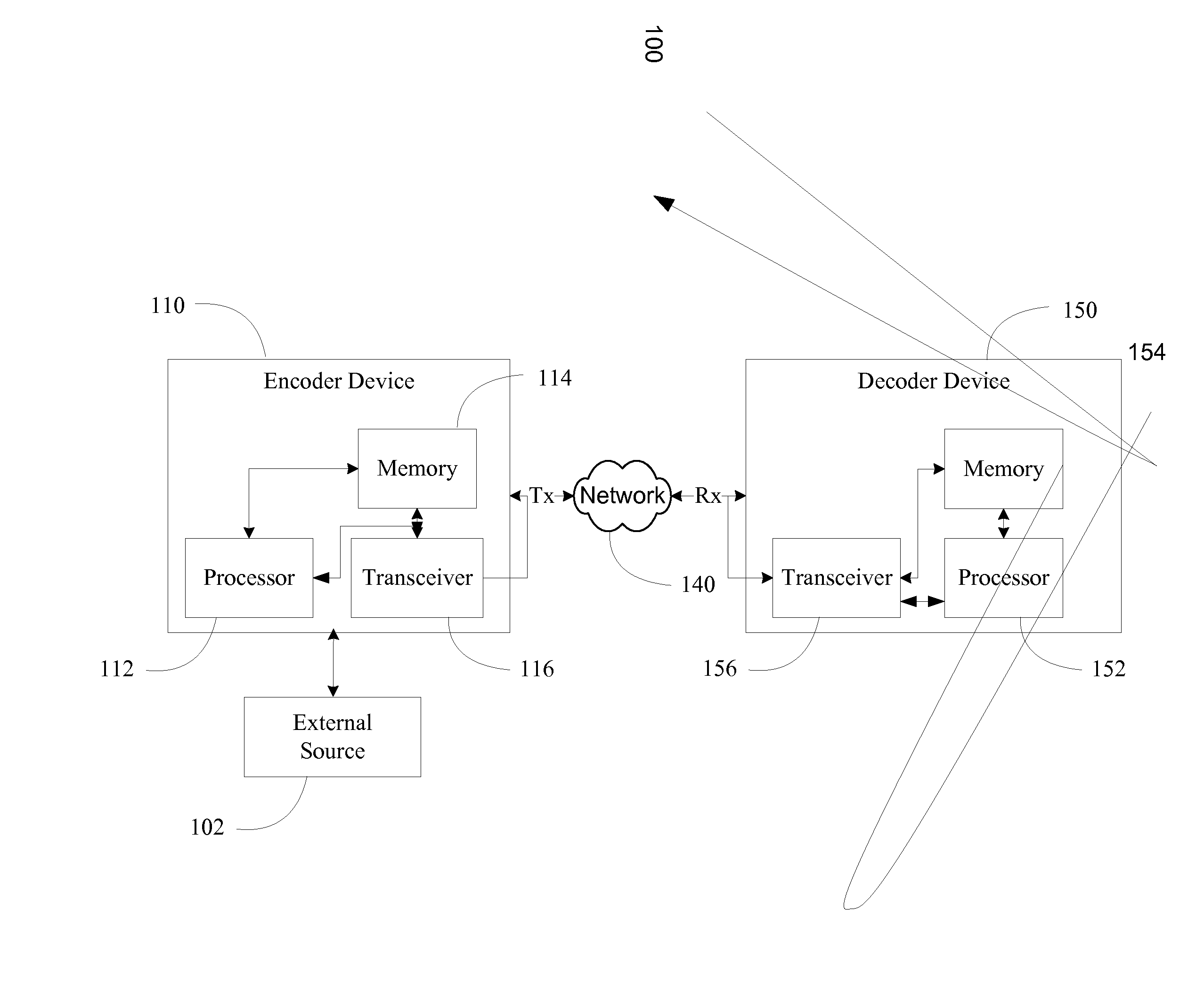

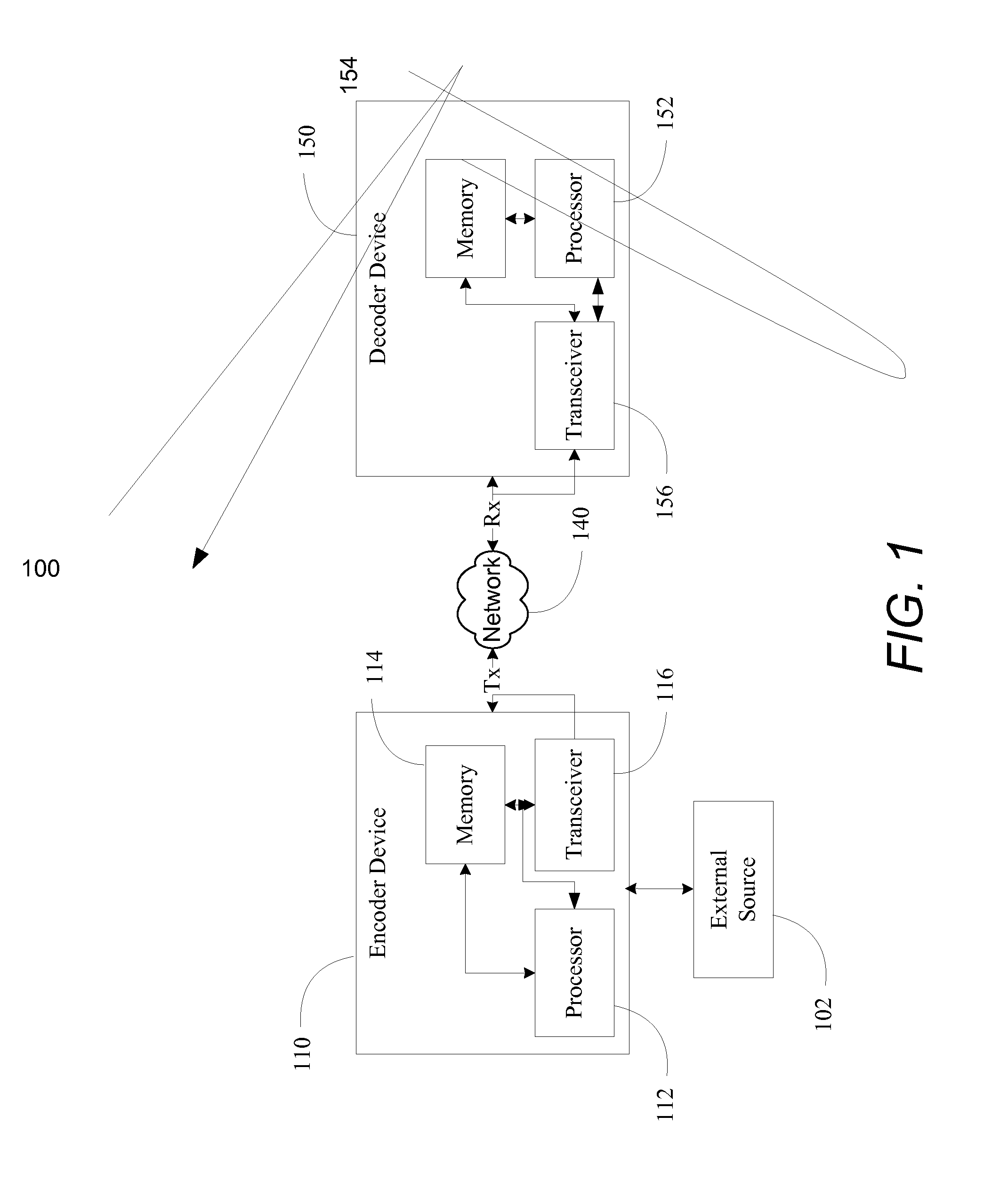

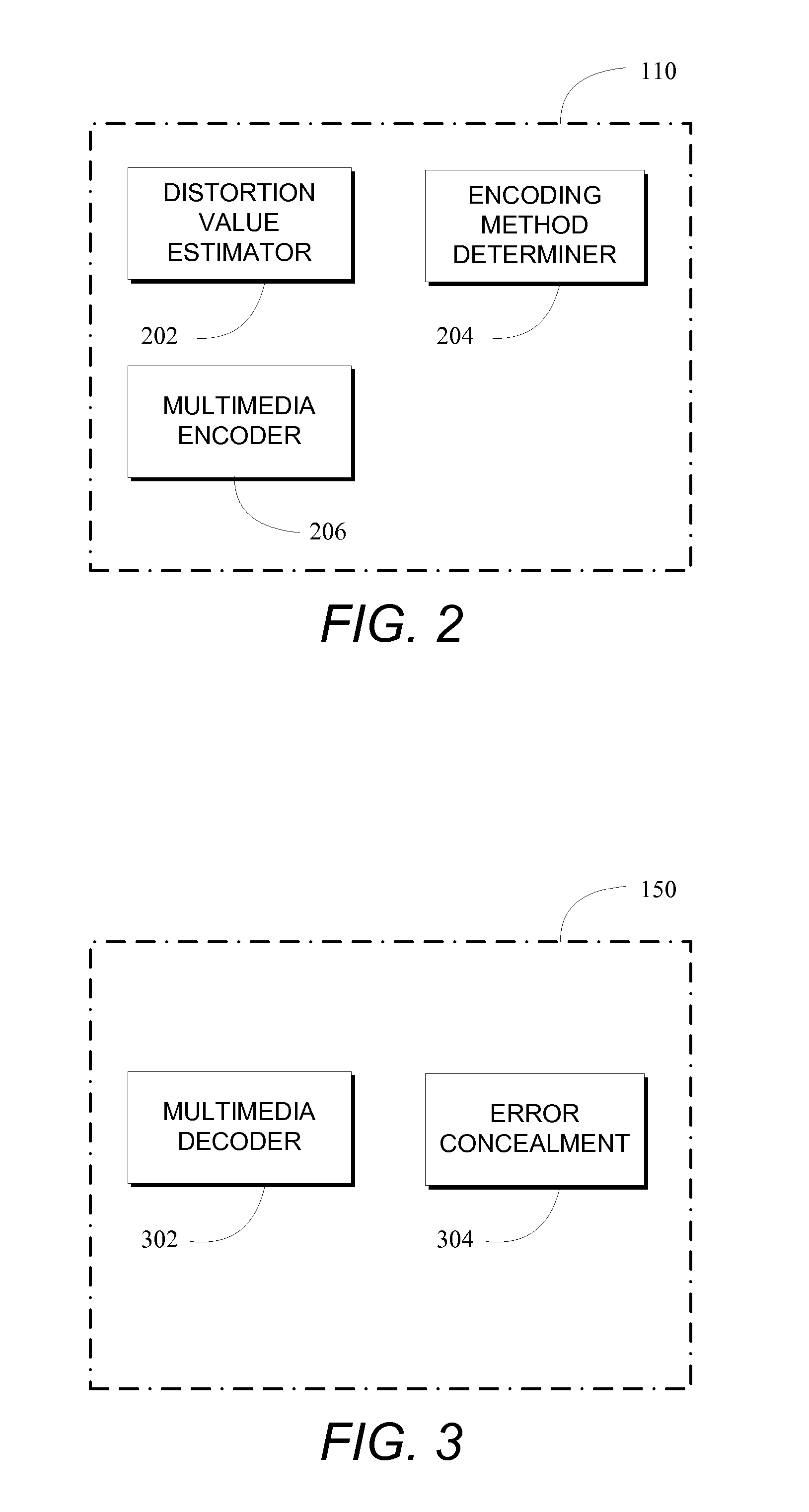

Method and apparatus for error resilience algorithms in wireless video communication

InactiveUS20070177667A1Improve video qualityError recoveryColor television with pulse code modulationColor television with bandwidth reductionFrame basedWireless video

Methods and apparatuses to encode multimedia data enabling, among others, for example, improved decoded video quality, improved error recovery capabilities and / or improved decoding efficiency are described. A method according to the application includes one or more of the following: initializing a pixel-level reference counter for a current frame, performing a prediction of a next frame referring to the current frame, incrementing the pixel-level reference counter for each pixel of the current frame that is referenced during the prediction of the next frame, readjusting a macroblock bandwidth map of the current frame, repeating the steps of initializing, performing and readjusting for each next frame in a plurality of next frames referring to the current frame, and encoding the current frame based at least in part on the readjusted macroblock bandwidth map of the current frame.

Owner:QUALCOMM INC

Method and apparatus for lock-free, non -blocking hash table

InactiveUS20050071335A1Speed up hash list traversalSpeedData processing applicationsDigital data information retrievalTheoretical computer scienceHash table

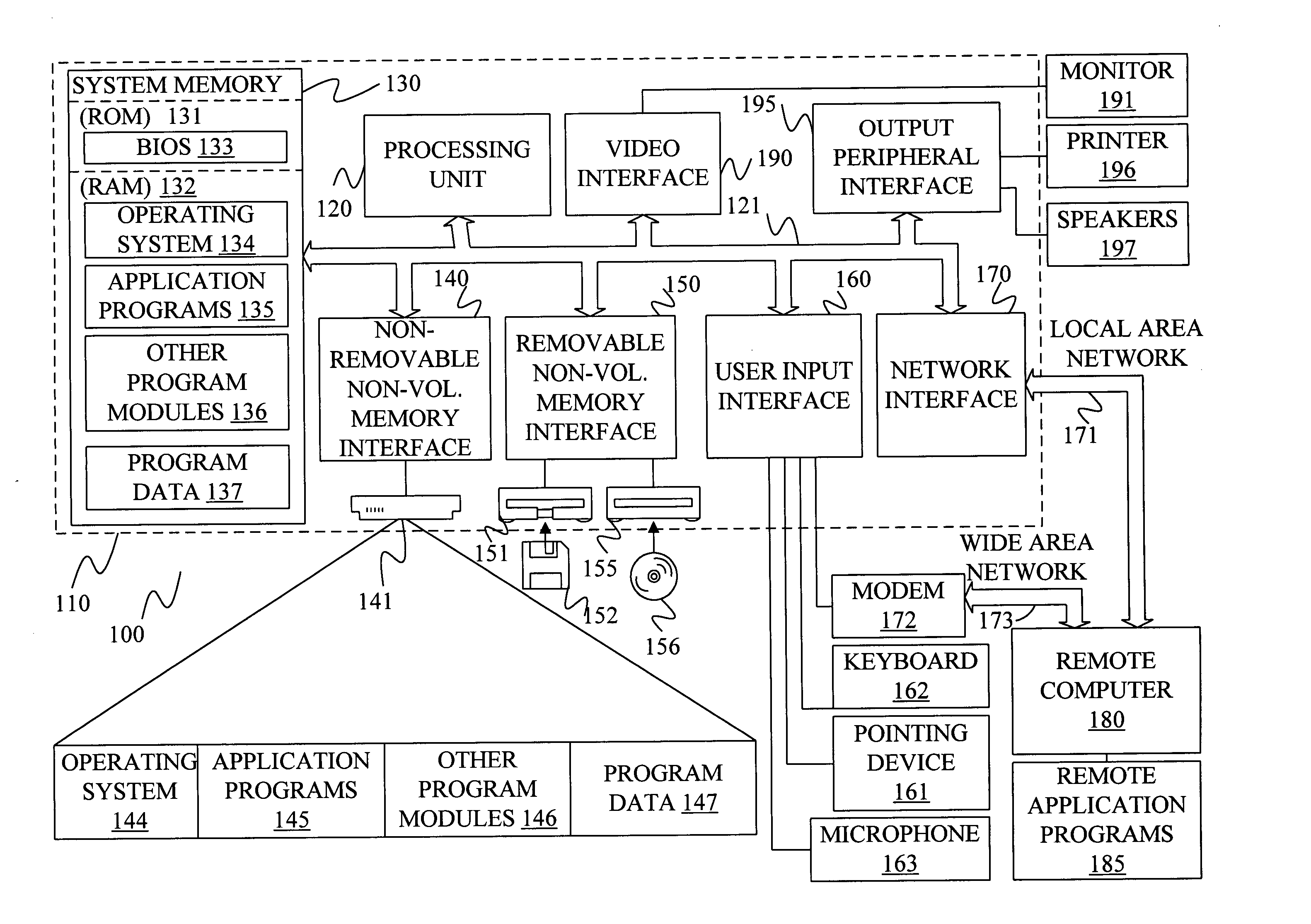

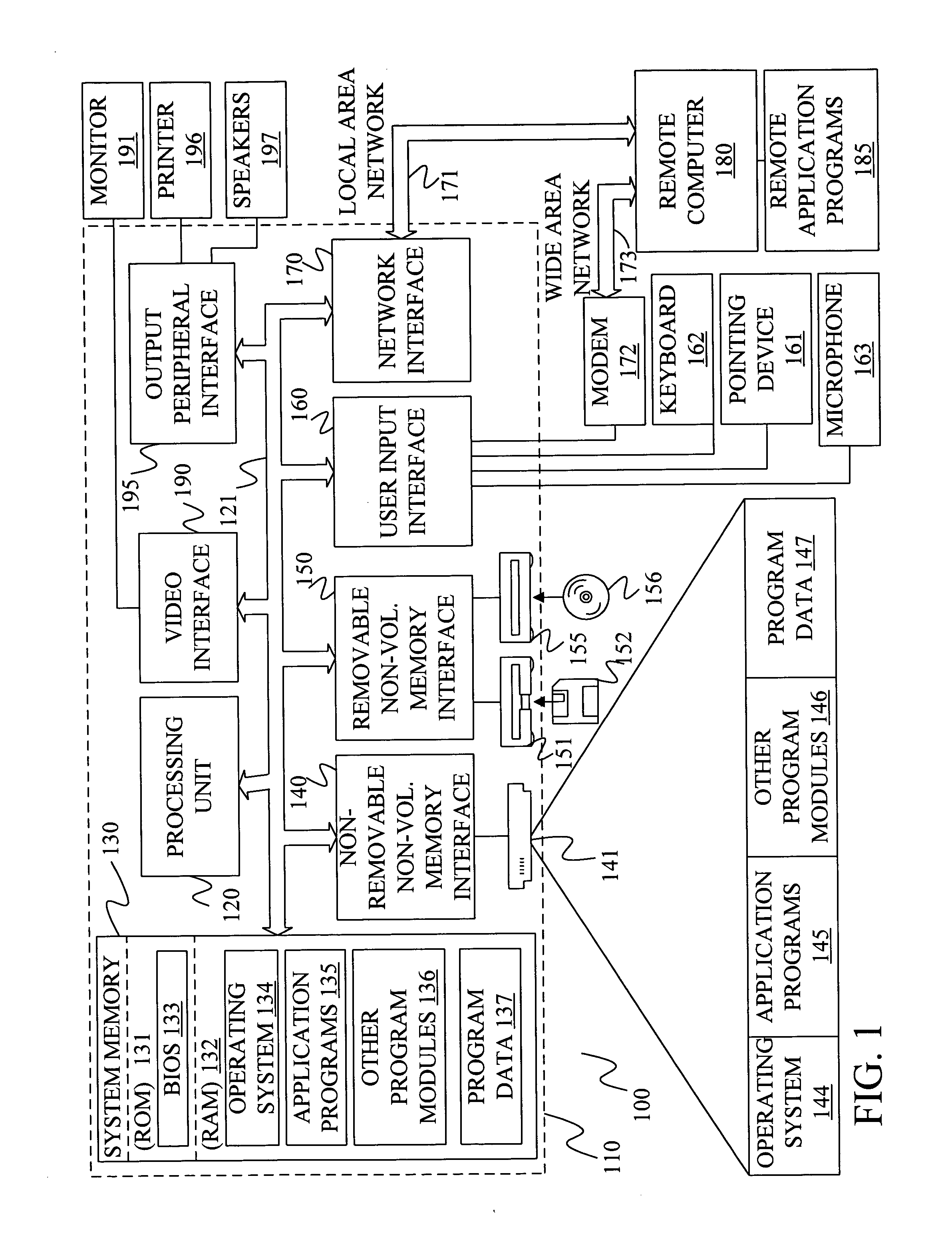

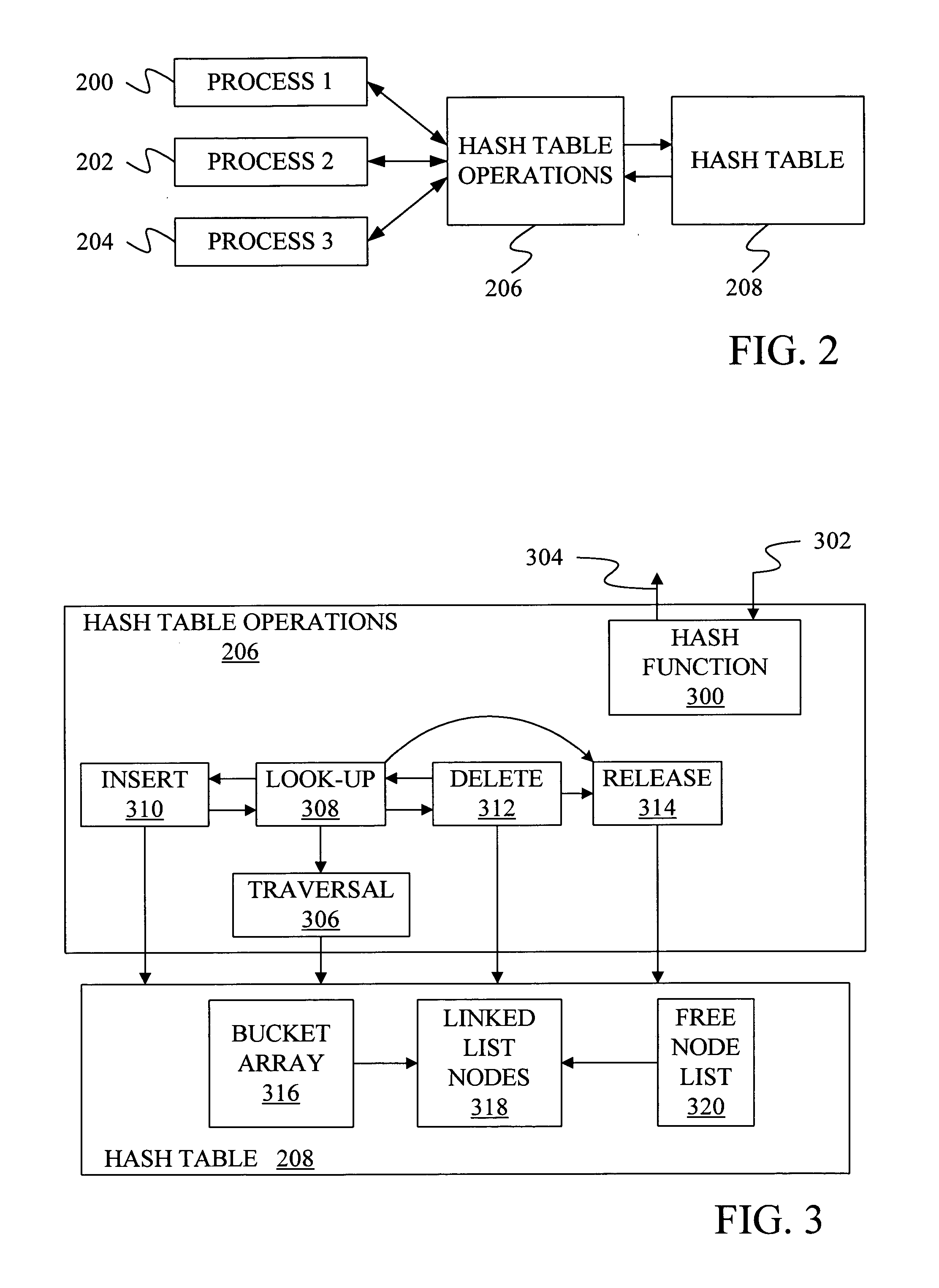

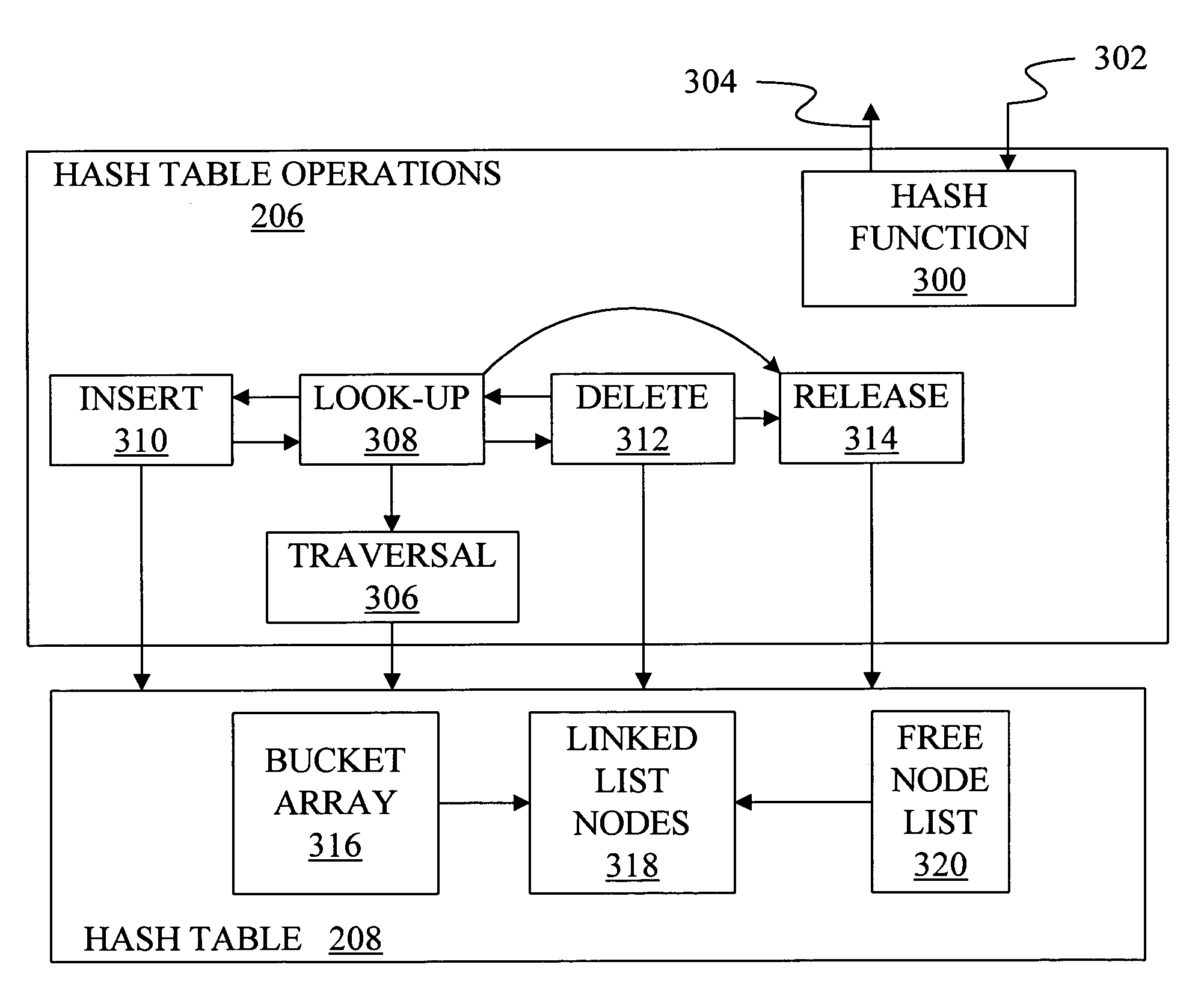

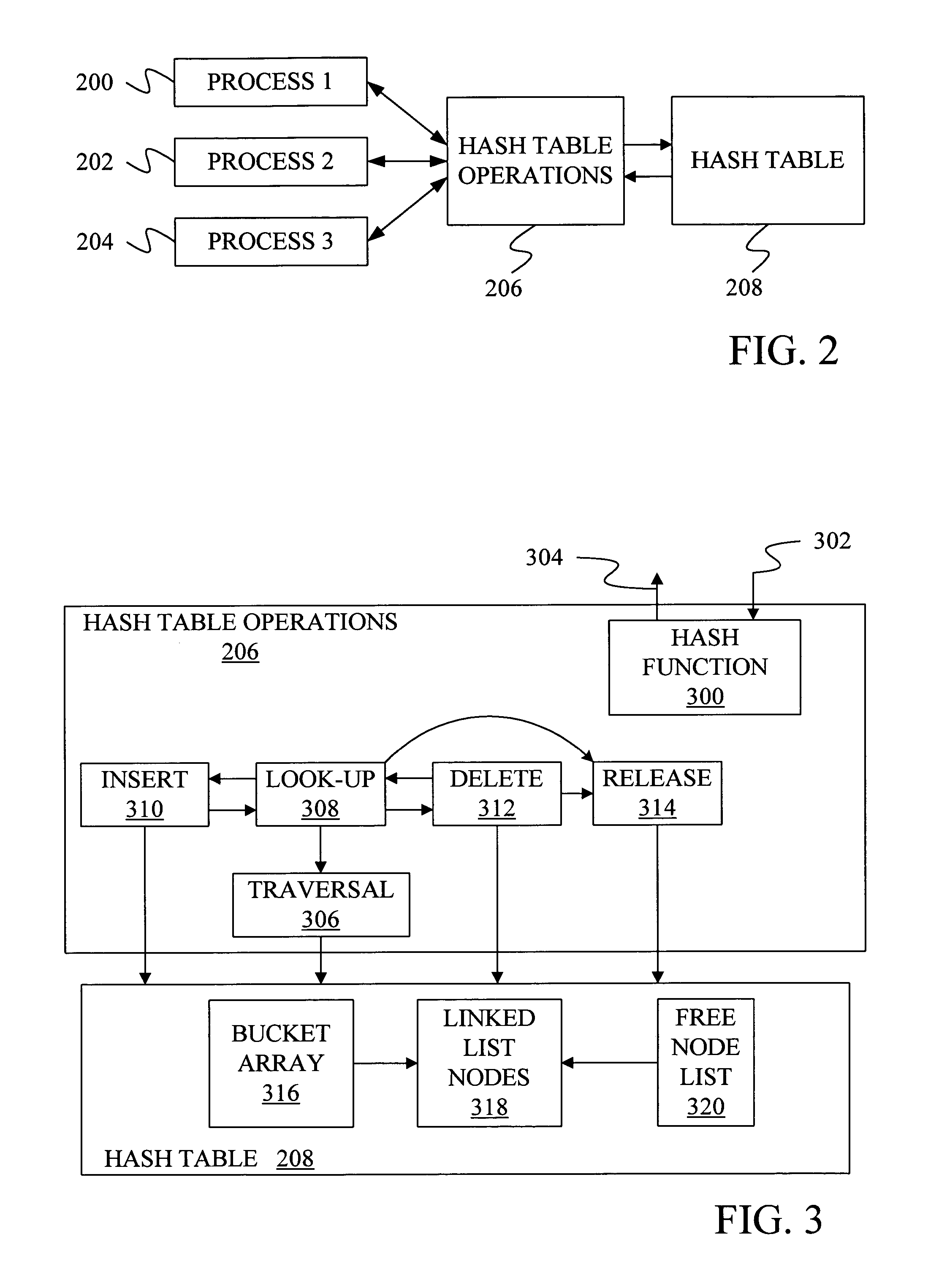

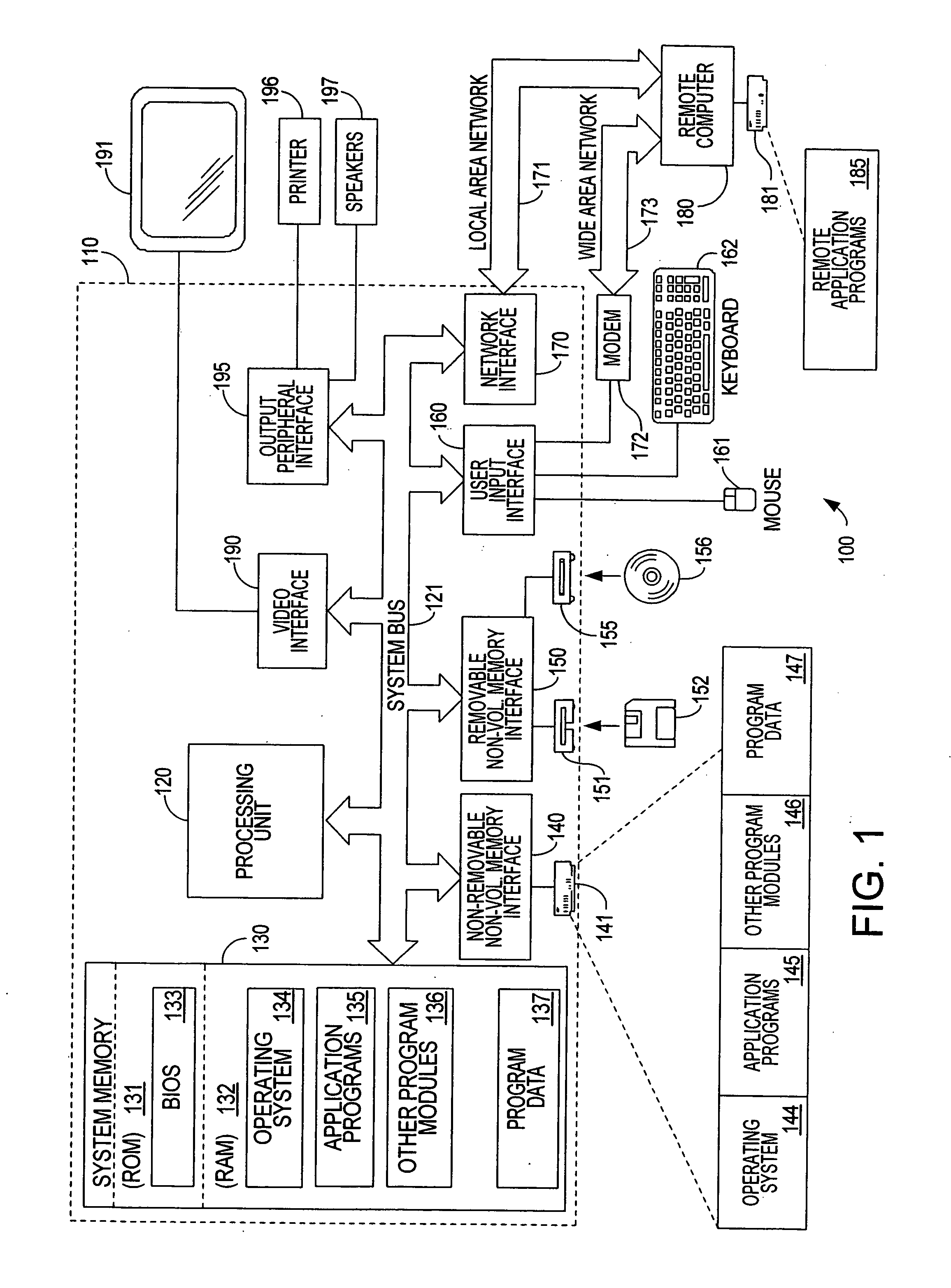

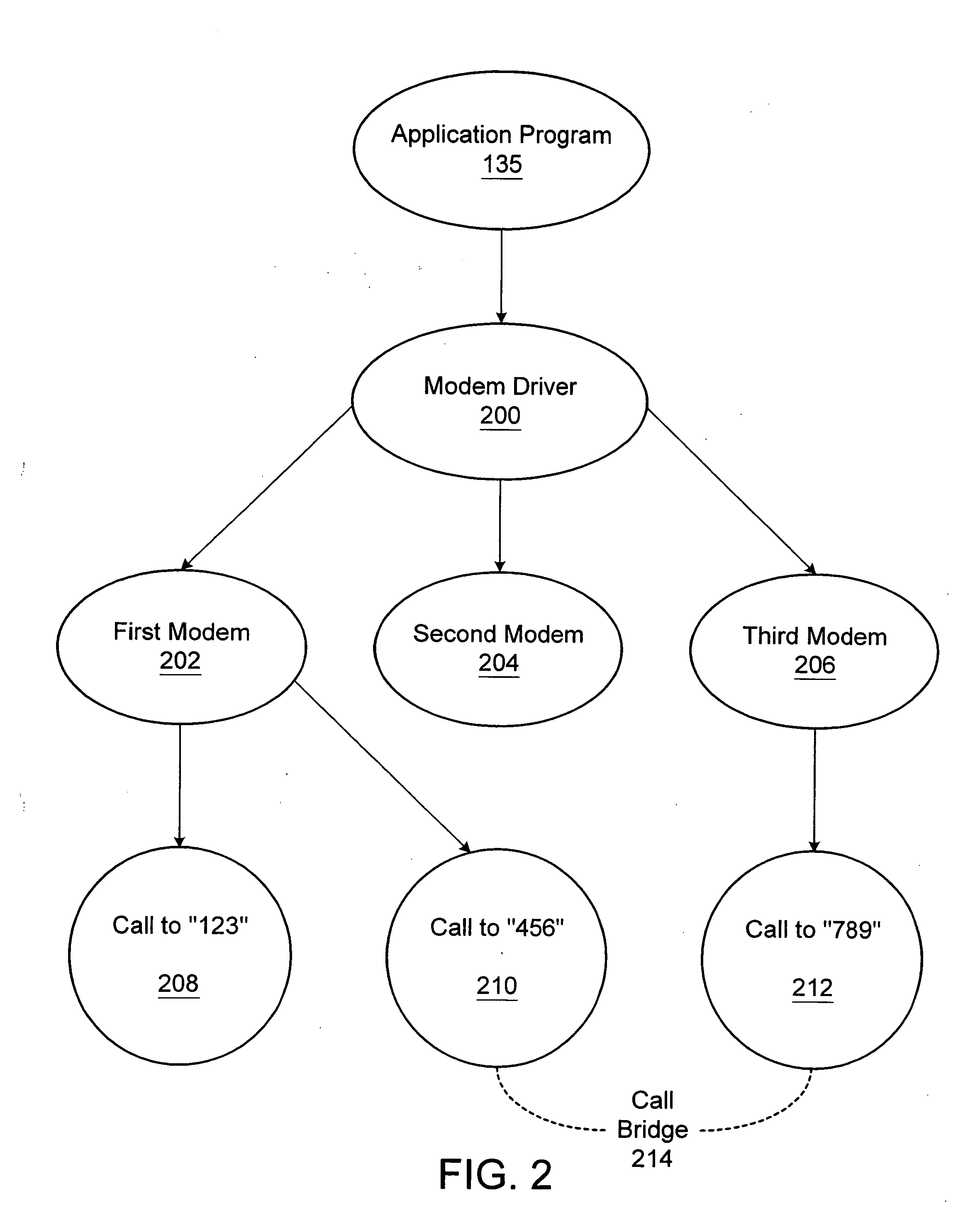

A method and apparatus are provided for an efficient lock-free, non-blocking hash table. Under one aspect, a linked list of nodes is formed in the hash table where each node includes a protected pointer to the next node in the list and a reference counter indicating the number of references currently made to the node. The reference counter of a node must be zero and none of the protected pointers in a linked list can be pointing at the node before the node can be destroyed. In another aspect of the invention, searching for a node in the hash table with a particular key involves examining the hash signatures of nodes along a linked list and only comparing the key of a node to a search key of the node if the hash signature of the node matches a search hash signature.

Owner:MICROSOFT TECH LICENSING LLC

Method and apparatus for lock-free, non-blocking hash table

InactiveUS6988180B2SpeedData processing applicationsDigital data information retrievalTheoretical computer scienceHash table

A method and apparatus are provided for an efficient lock-free, non-blocking hash table. Under one aspect, a linked list of nodes is formed in the hash table where each node includes a protected pointer to the next node in the list and a reference counter indicating the number of references currently made to the node. The reference counter of a node must be zero and none of the protected pointers in a linked list can be pointing at the node before the node can be destroyed. In another aspect of the invention, searching for a node in the hash table with a particular key involves examining the hash signatures of nodes along a linked list and only comparing the key of a node to a search key of the node if the hash signature of the node matches a search hash signature.

Owner:MICROSOFT TECH LICENSING LLC

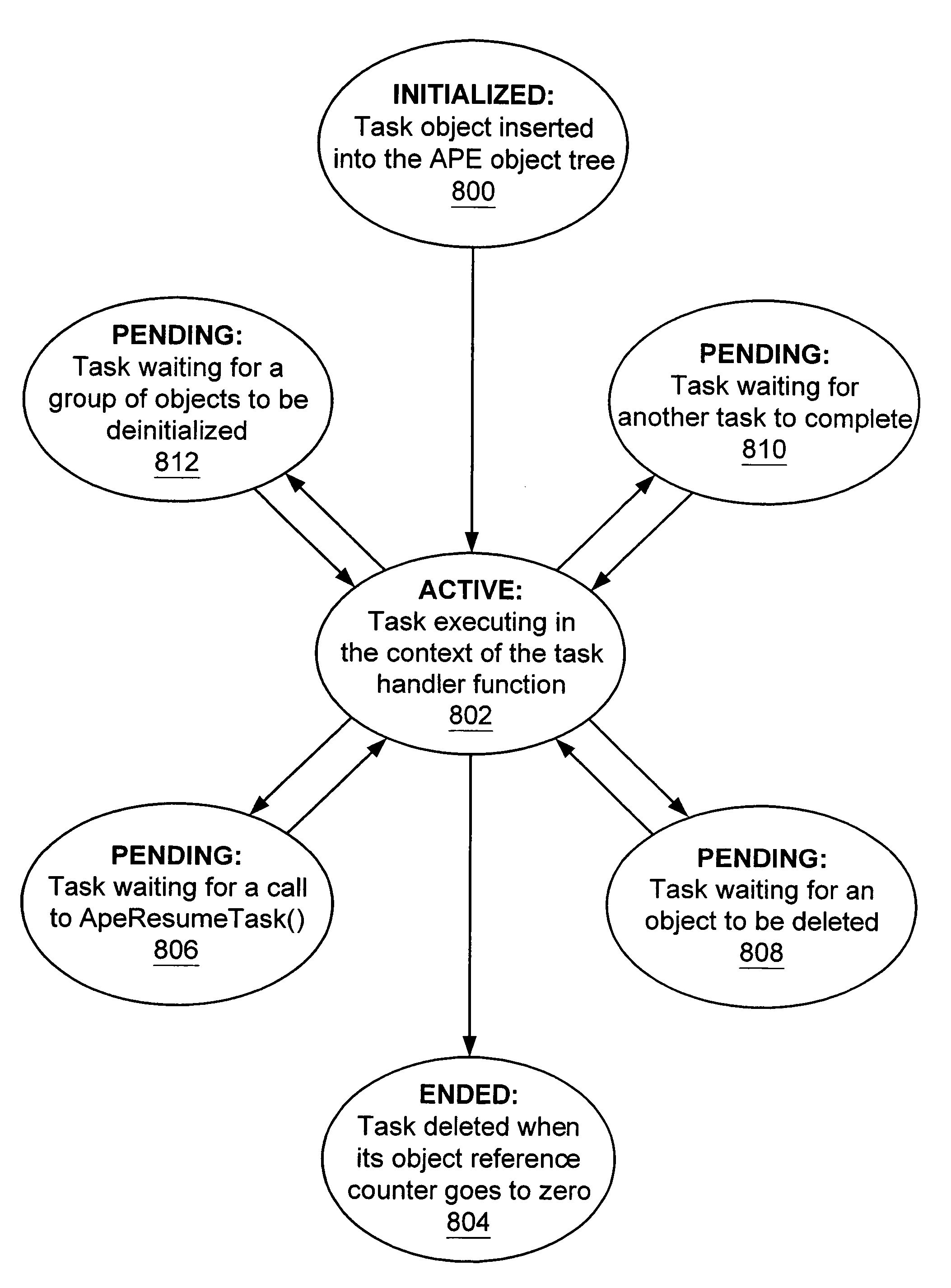

Methods and systems for structuring asynchronous processes

InactiveUS20060059496A1Easy maintenanceReduce chanceError detection/correctionMultiprogramming arrangementsOperating systemDebugger

The invention builds a structure of software objects that captures the historically contingent development of an asynchronous program. The invention builds software objects that represent the resources and subtasks that make up the asynchronous program. The objects are connected into a hierarchy whose structure explicates interactions among the resources and subtasks. When a fault is detected, the structure tells the debugger everything the program was doing at the time of the fault and lays open the developmental history of the program that led to the fault. The debugger uses this information to trace the detected fault back through code and time to its origin. When a new feature is added, the structure tells maintenance personnel how the new feature affects existing functions. Within the structure, the invention provides mechanisms for handling reference counters and software locks. Groups of resources can be handled together, the structure taking care of coordination.

Owner:MICROSOFT TECH LICENSING LLC

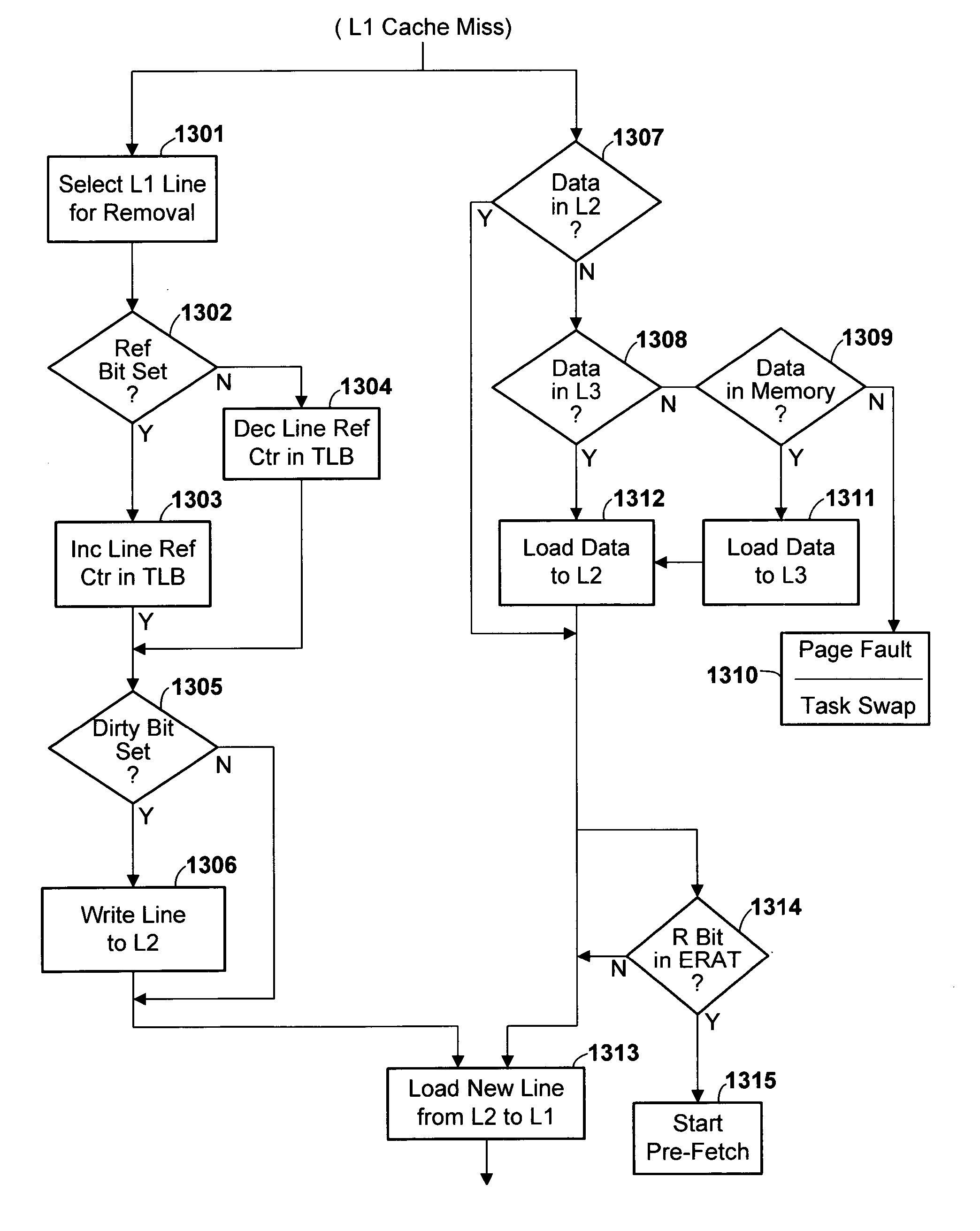

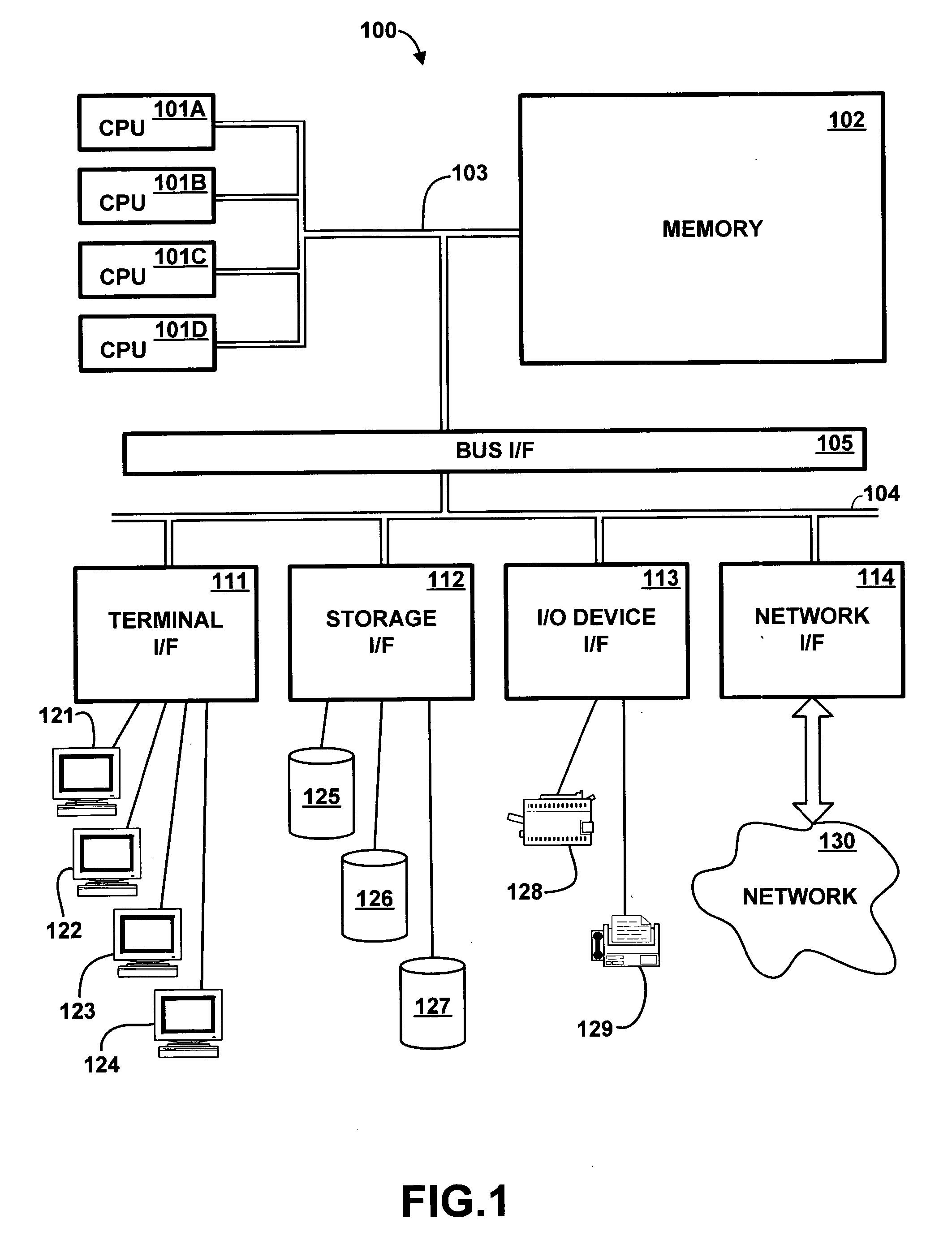

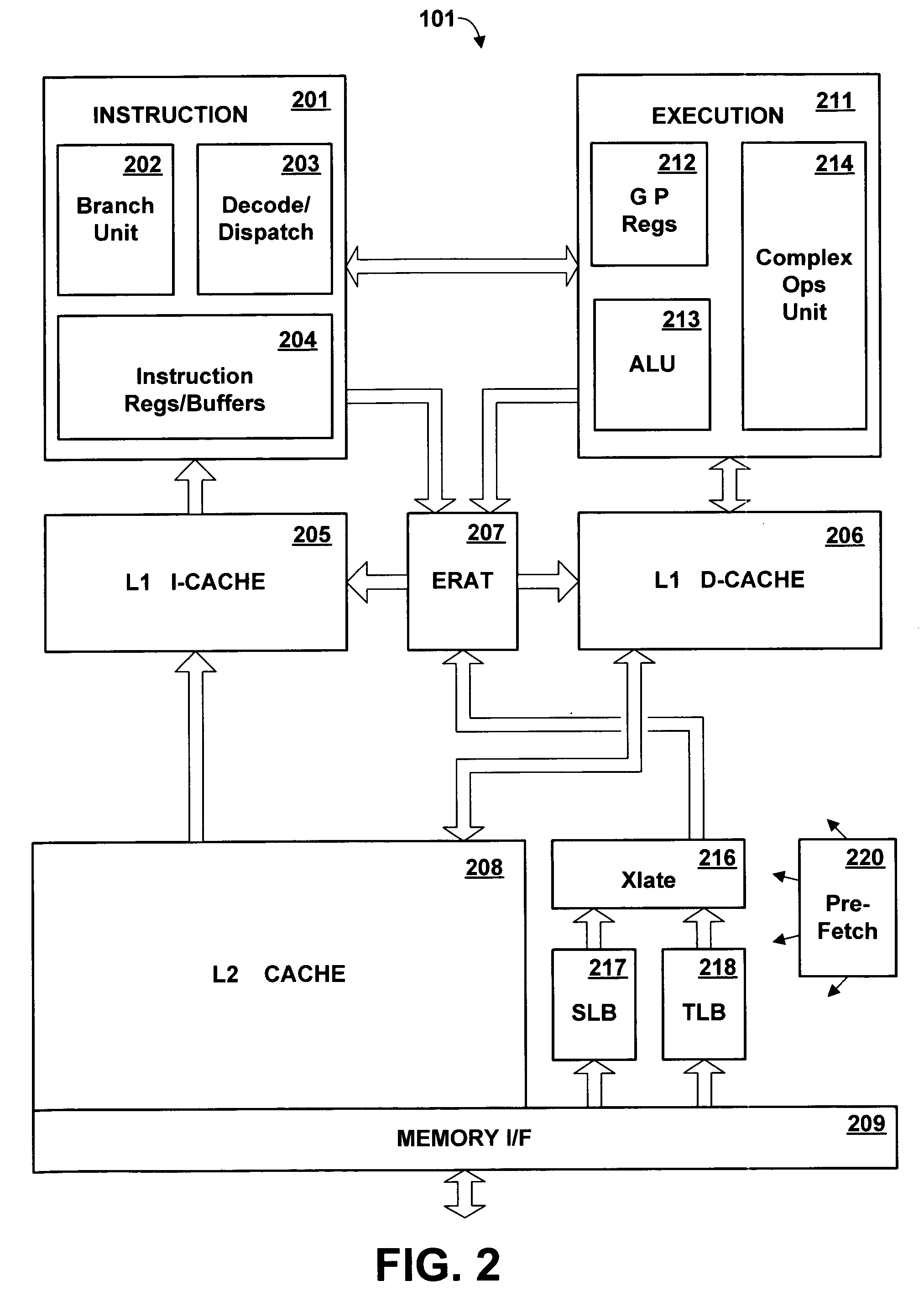

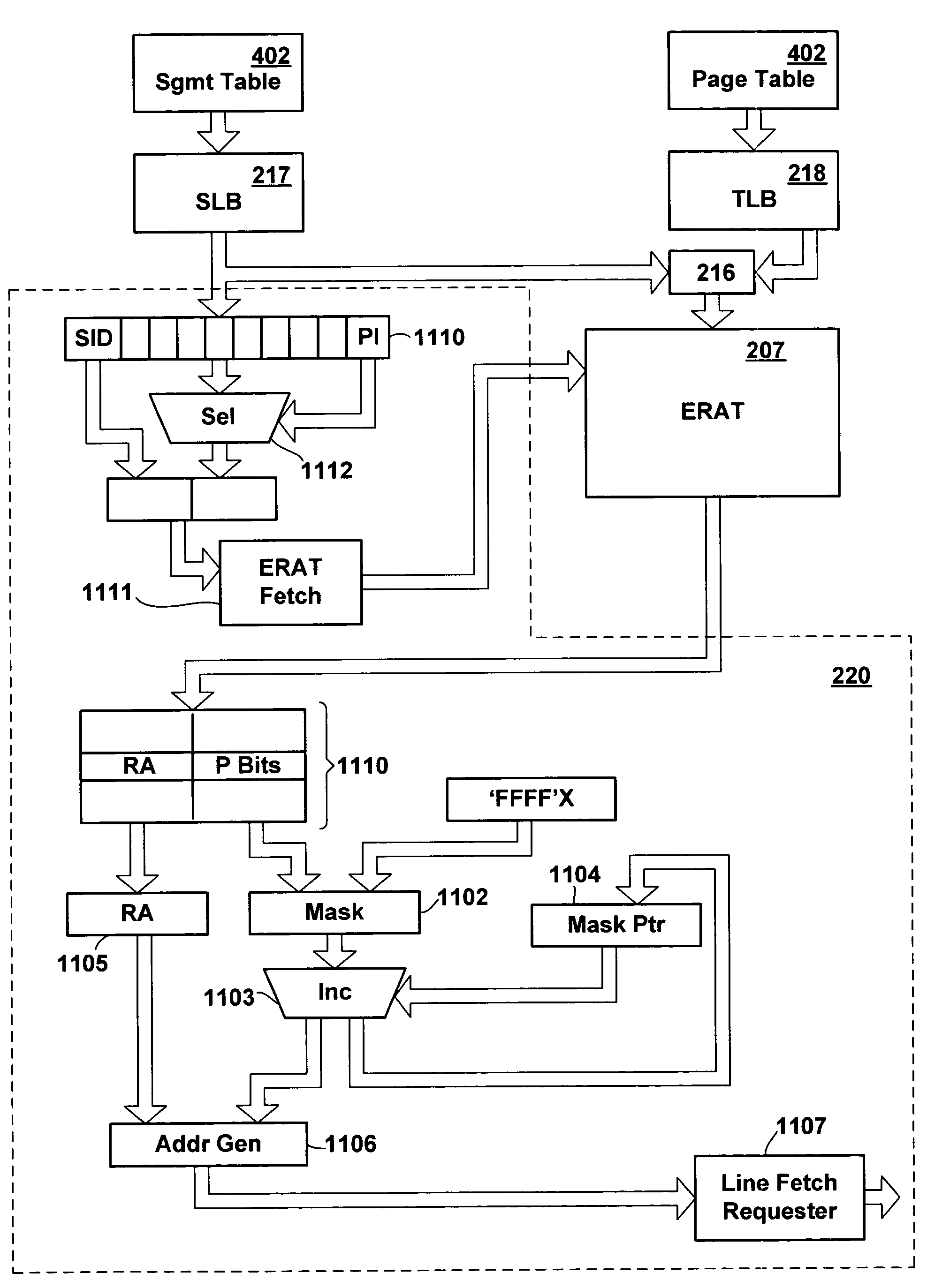

Apparatus and method for pre-fetching data to cached memory using persistent historical page table data

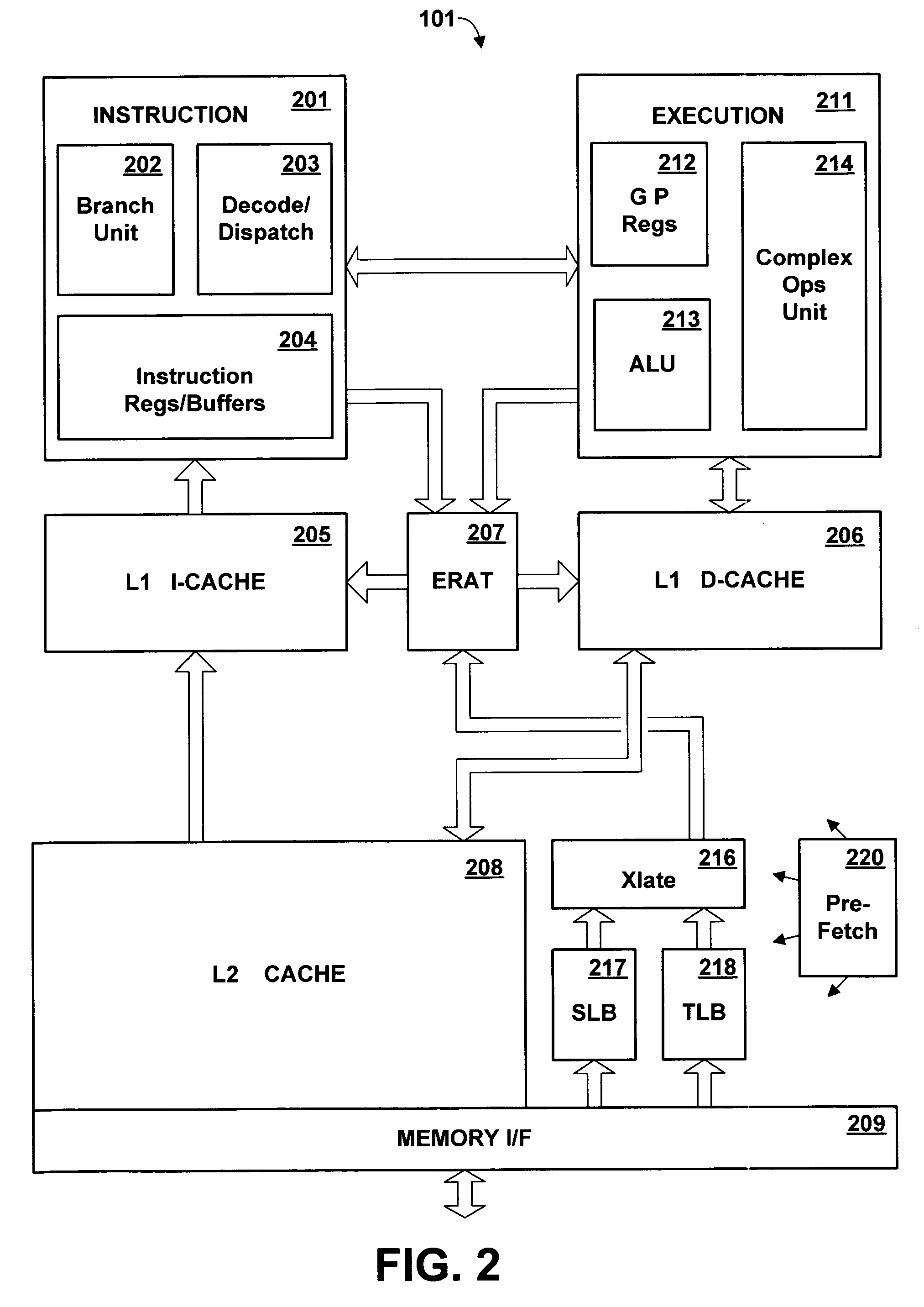

InactiveUS20050071571A1Improve accuracyExpand the scope ofMemory architecture accessing/allocationMemory adressing/allocation/relocationSystem maintenanceComputerized system

A computer system includes a main memory, at least one processor, and at least one level of cache. The system maintains reference history data with respect to each addressable page in memory, preferably in a page table. The reference history data is preferably used to determine which cacheable sub-units of the page should be pre-fetched to the cache. The reference history data is preferably an up or down counter which is incremented if the cacheable sub-unit is loaded into cache and is referenced by the processor, and decremented if the sub-unit is loaded into cache and is not referenced before being cast out. The reference counter thus expresses an approximate likelihood, based on recent history, that the sub-unit will be referenced in the near future.

Owner:IBM CORP

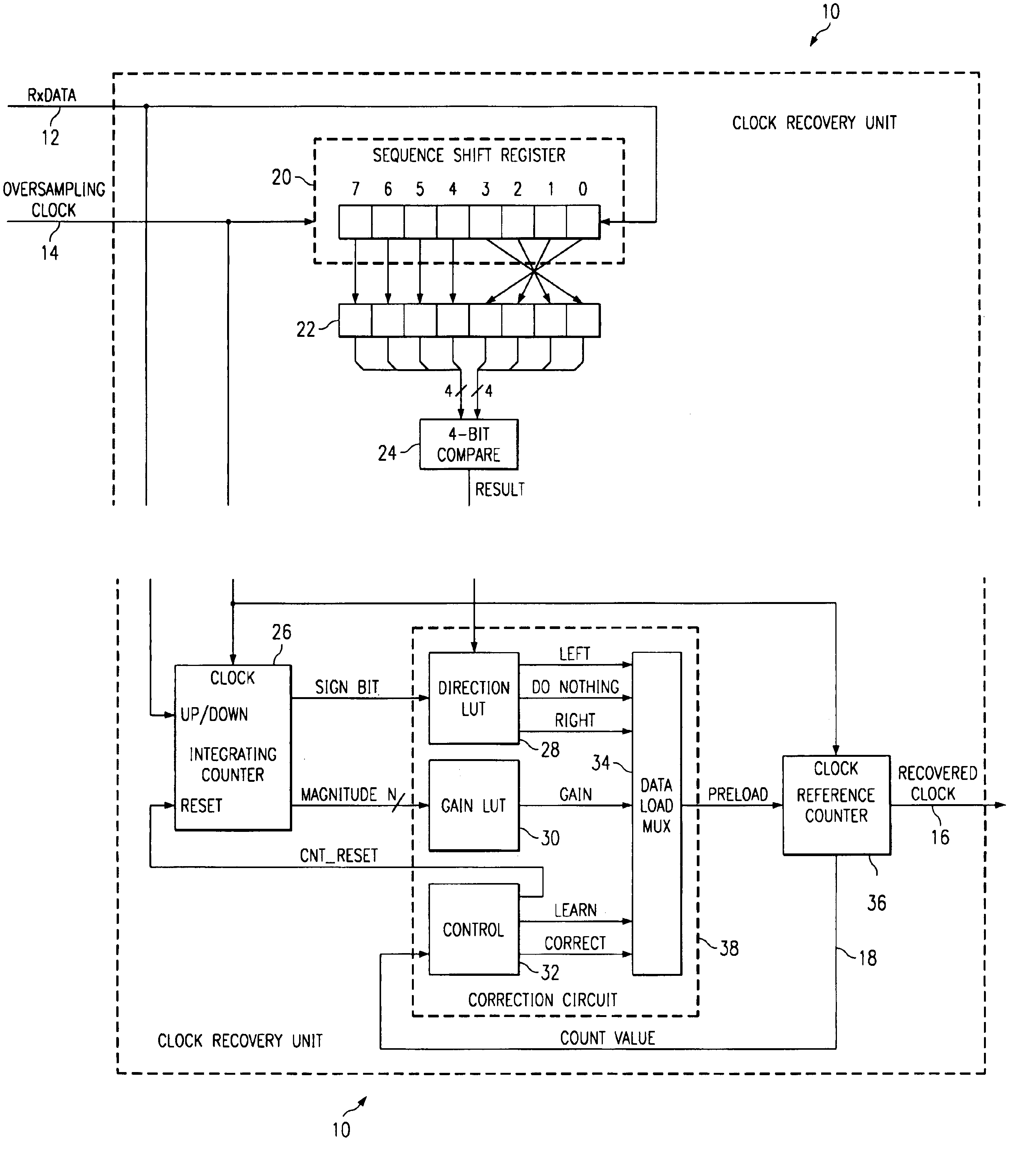

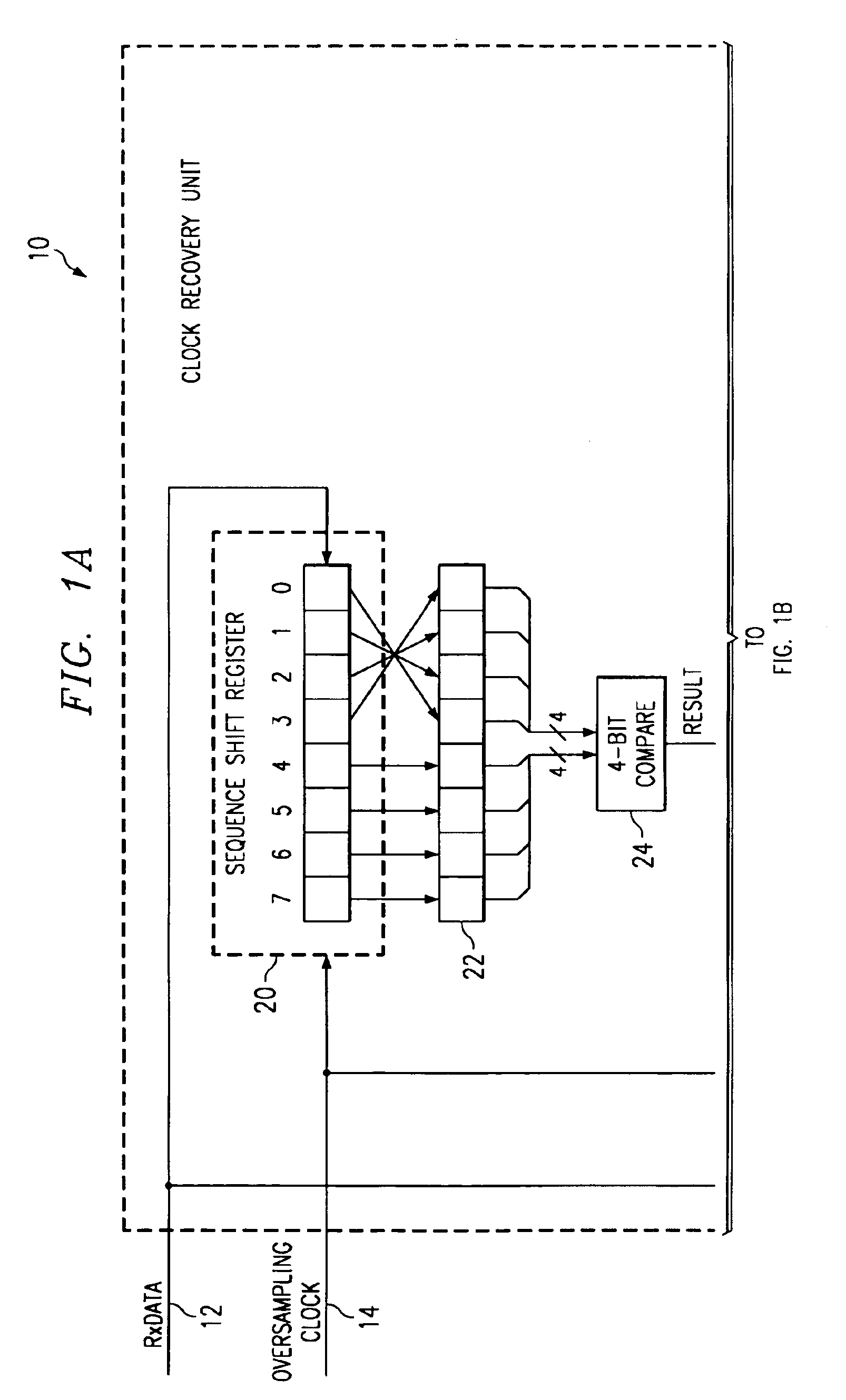

Apparatus for and method of clock recovery from a serial data stream

ActiveUS7016445B2Filter out effect of noiseAccurate and fast recoverySynchronisation signal speed/phase controlSynchronous/start-stop systemsShift registerData stream

A novel and useful apparatus for and method of clock recovery from a serial data stream. The clock recovery mechanism of the present invention provides accurate and fast timing recovery while operative to filter out the effects of noise. The clock recovery mechanism clocks the received serial data into a shift register of N bits, where N is an even number equal to the oversampling factor of the data signal. A timing correction, generated during learning cycles, is applied during the subsequent correction cycle. The timing is adjusted during correction cycles by preloading the reference counter, from which the sampling clock is produced, such that its cycle is either shortened or extended by M clocks, where M corresponds to the required timing correction.

Owner:TEXAS INSTR INC

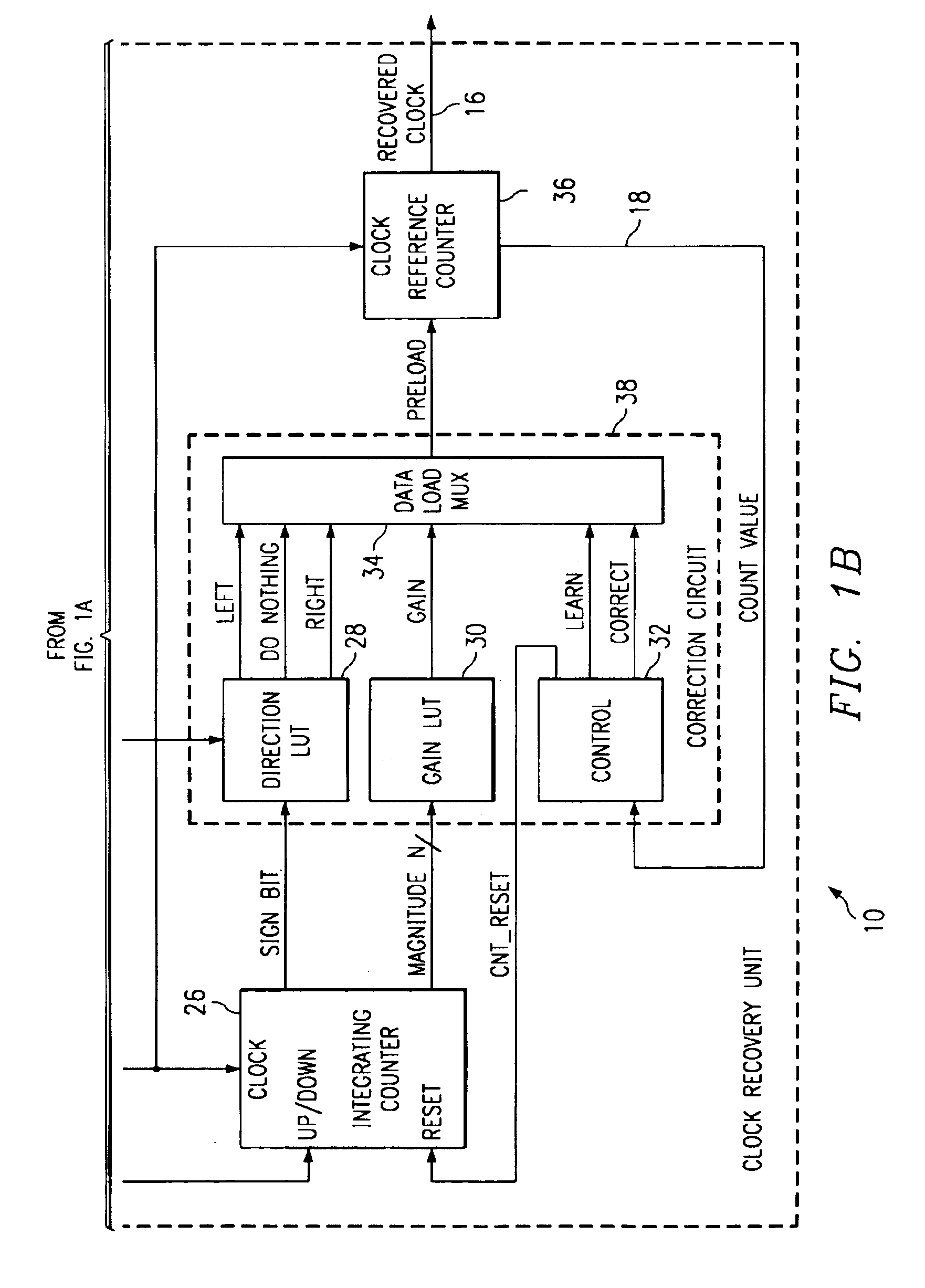

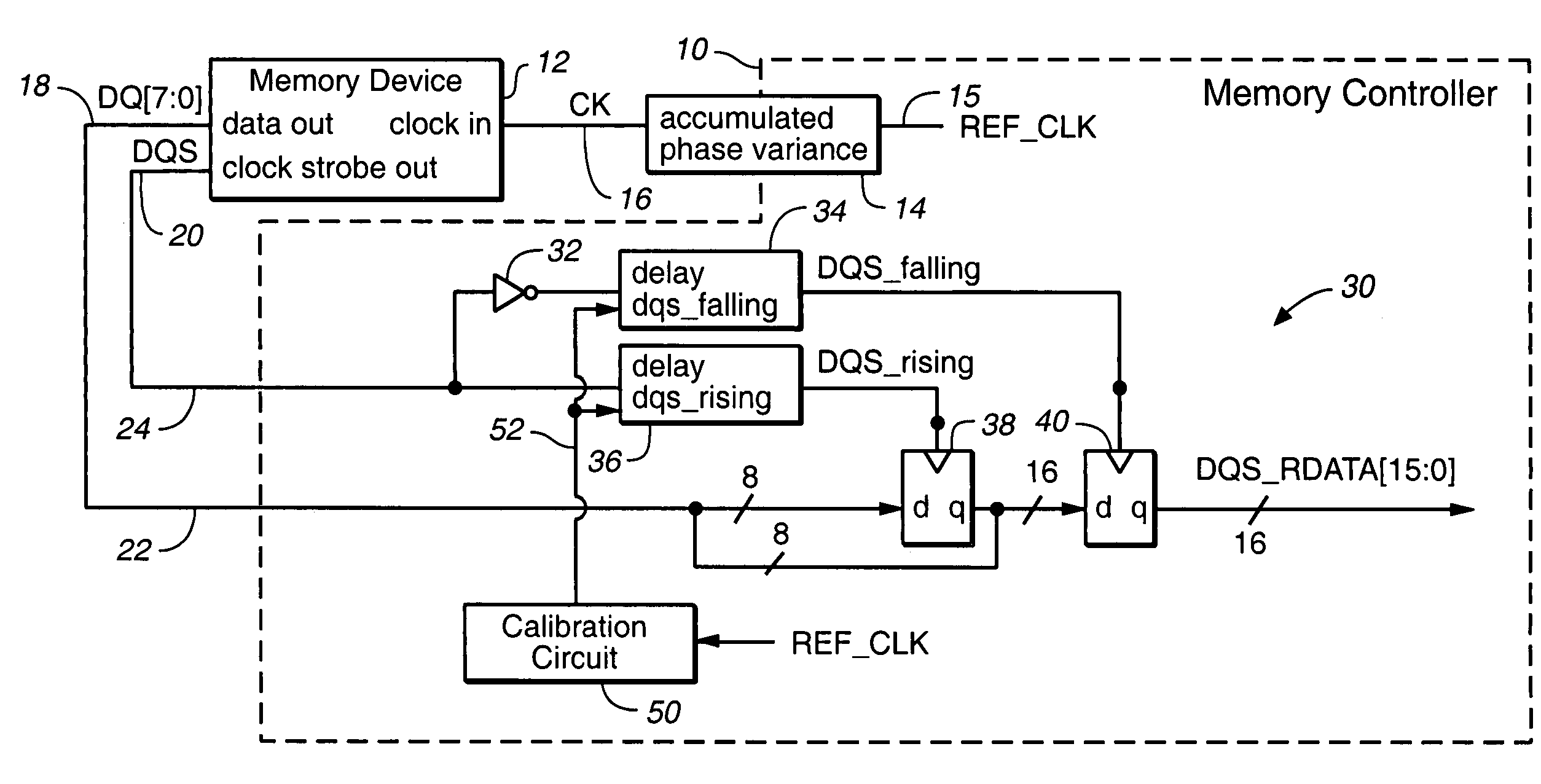

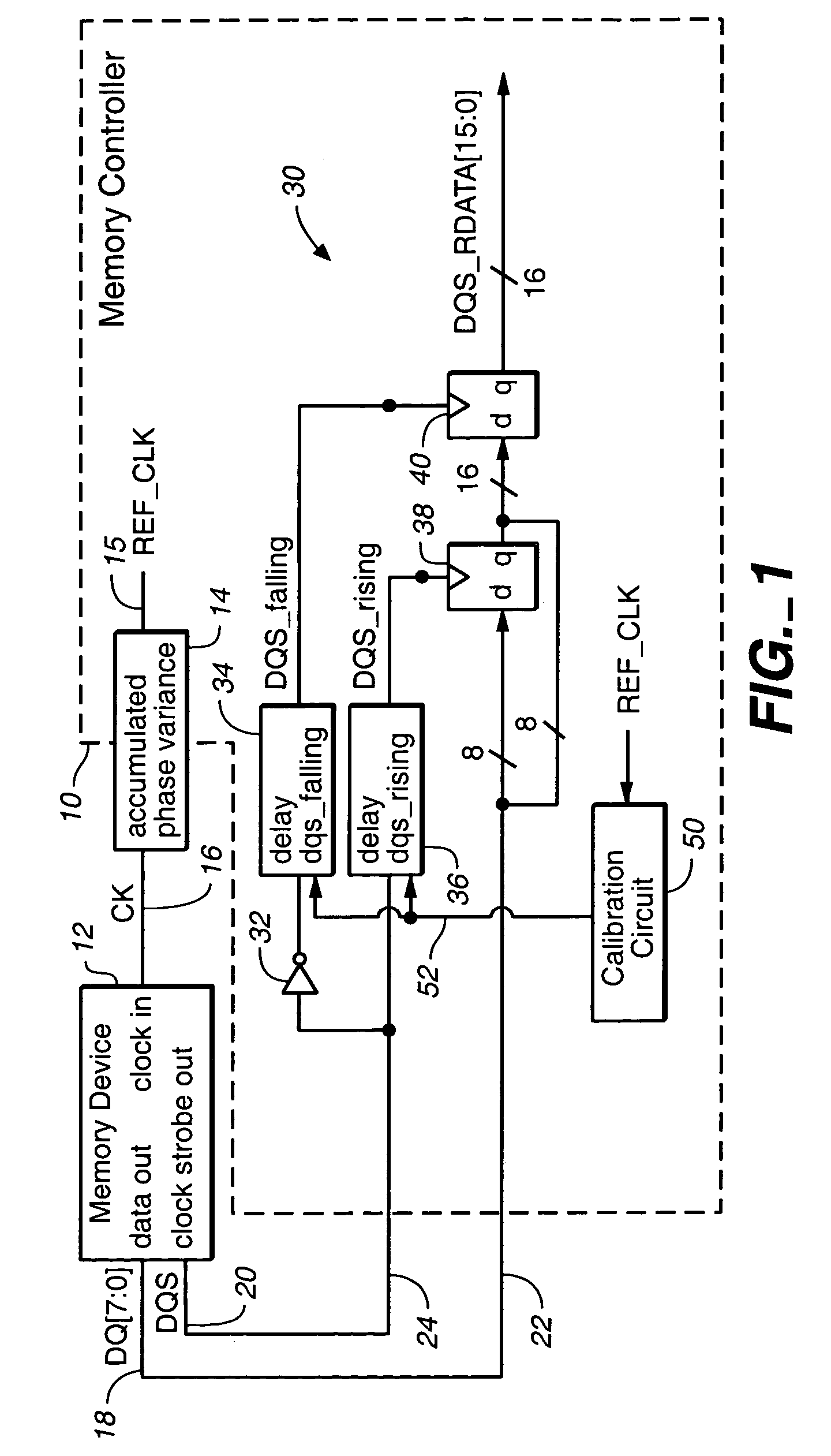

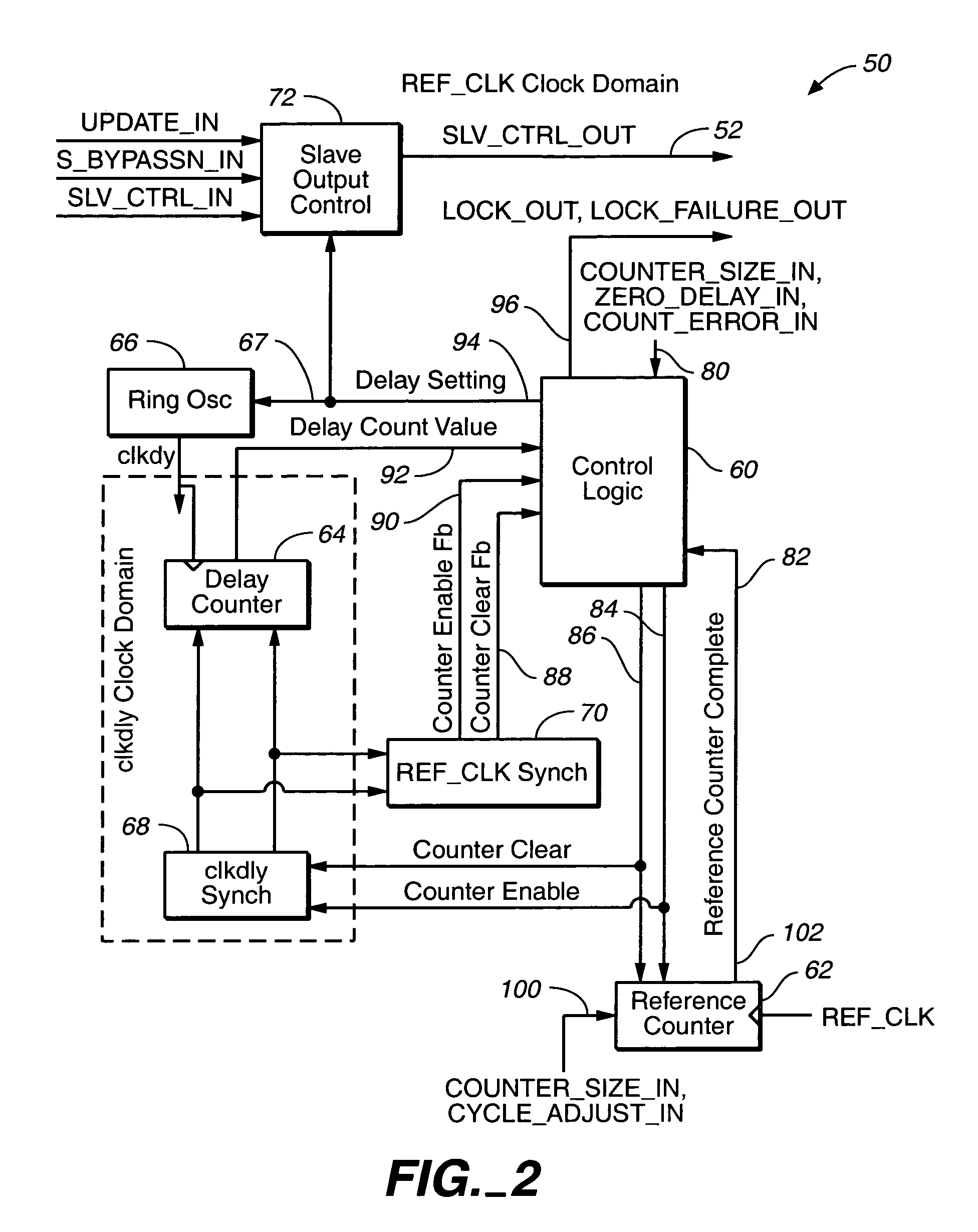

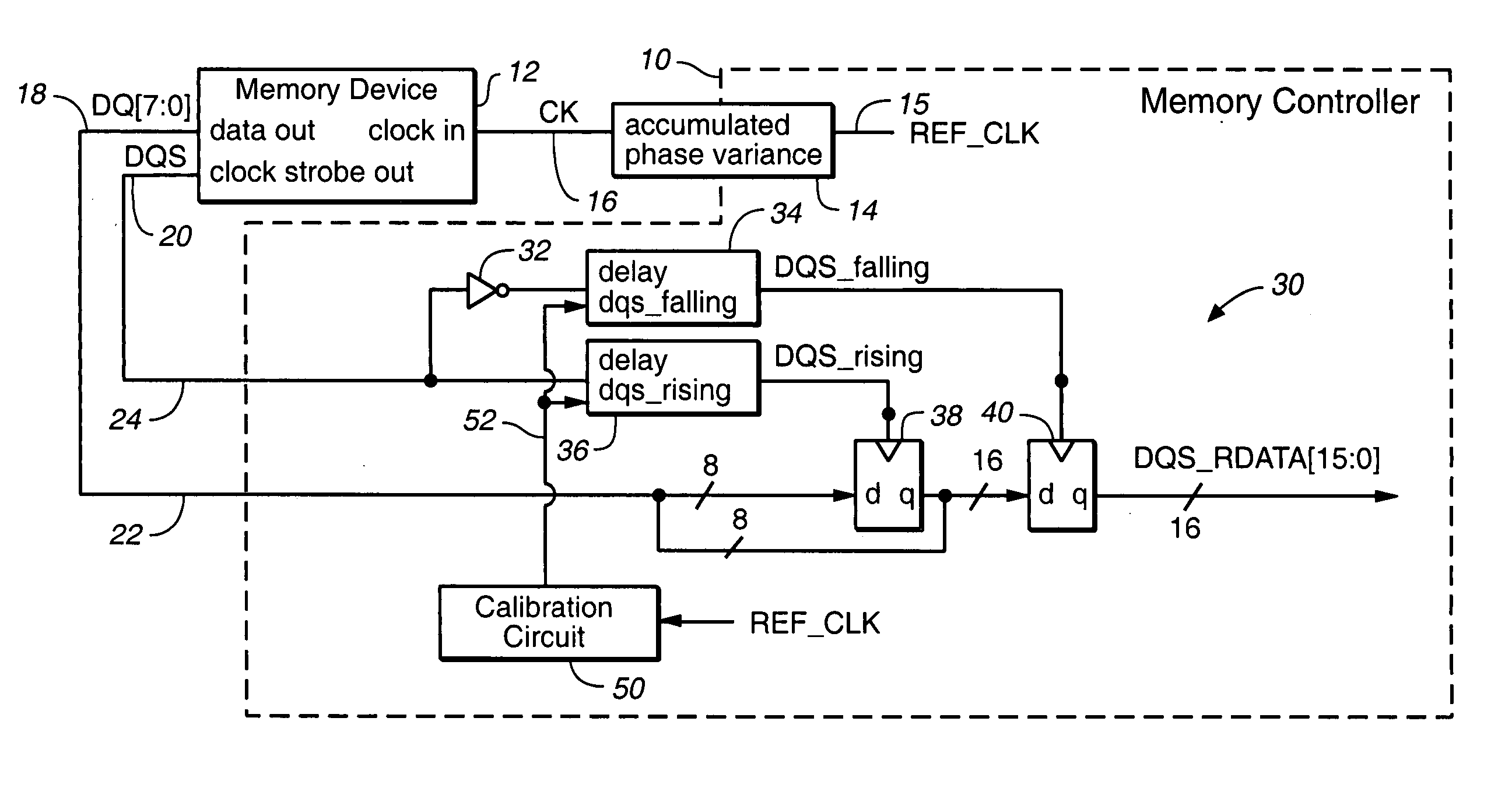

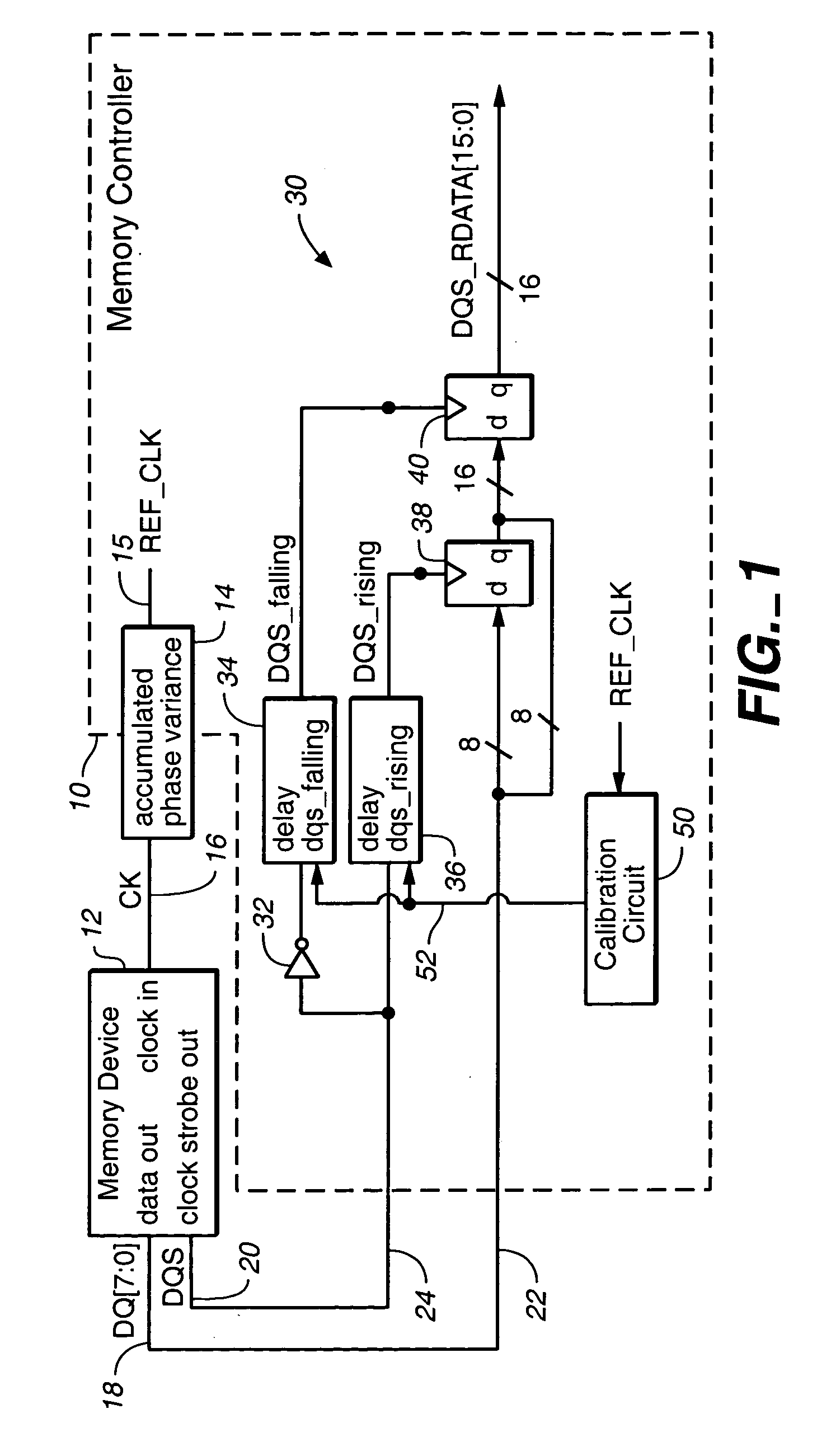

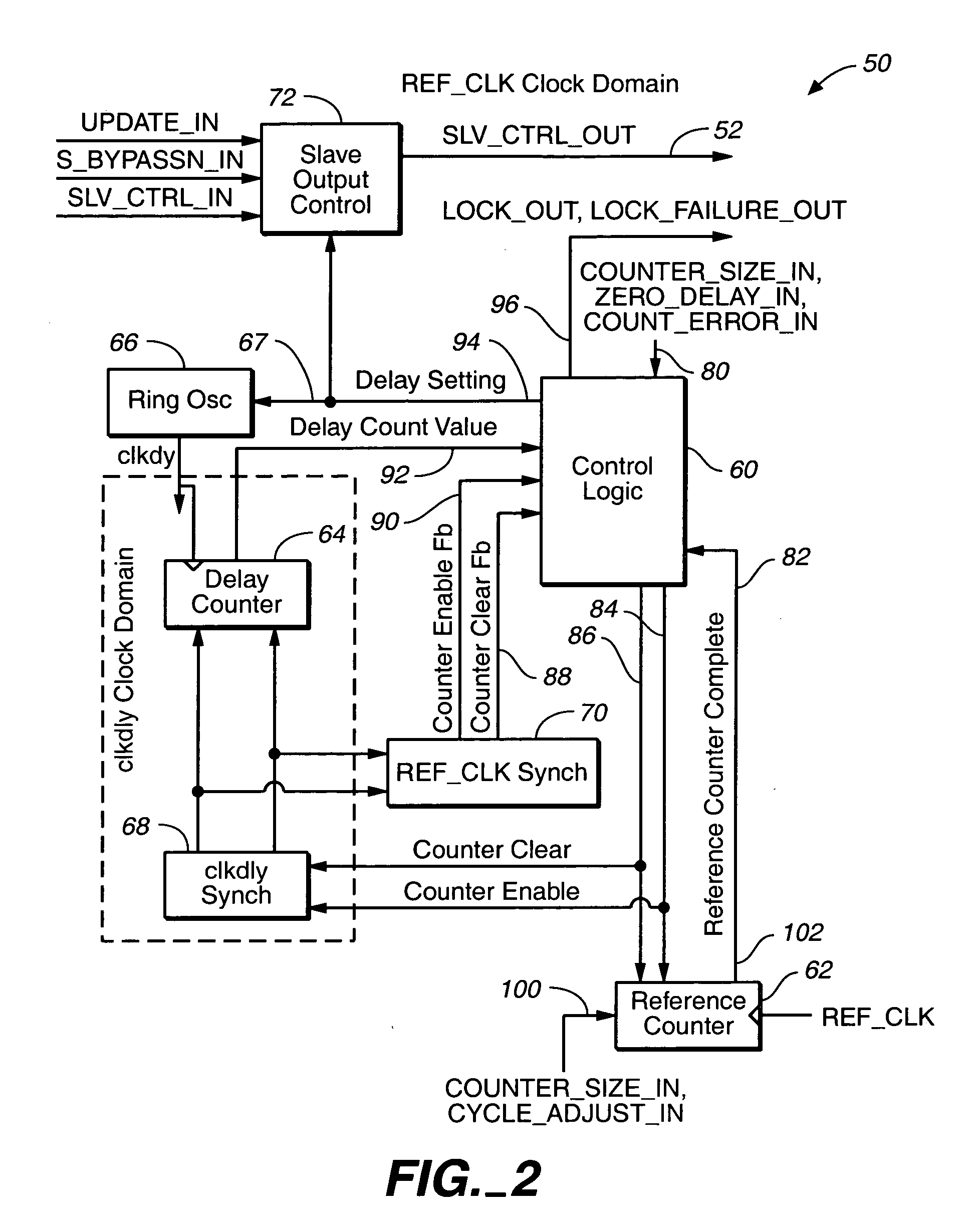

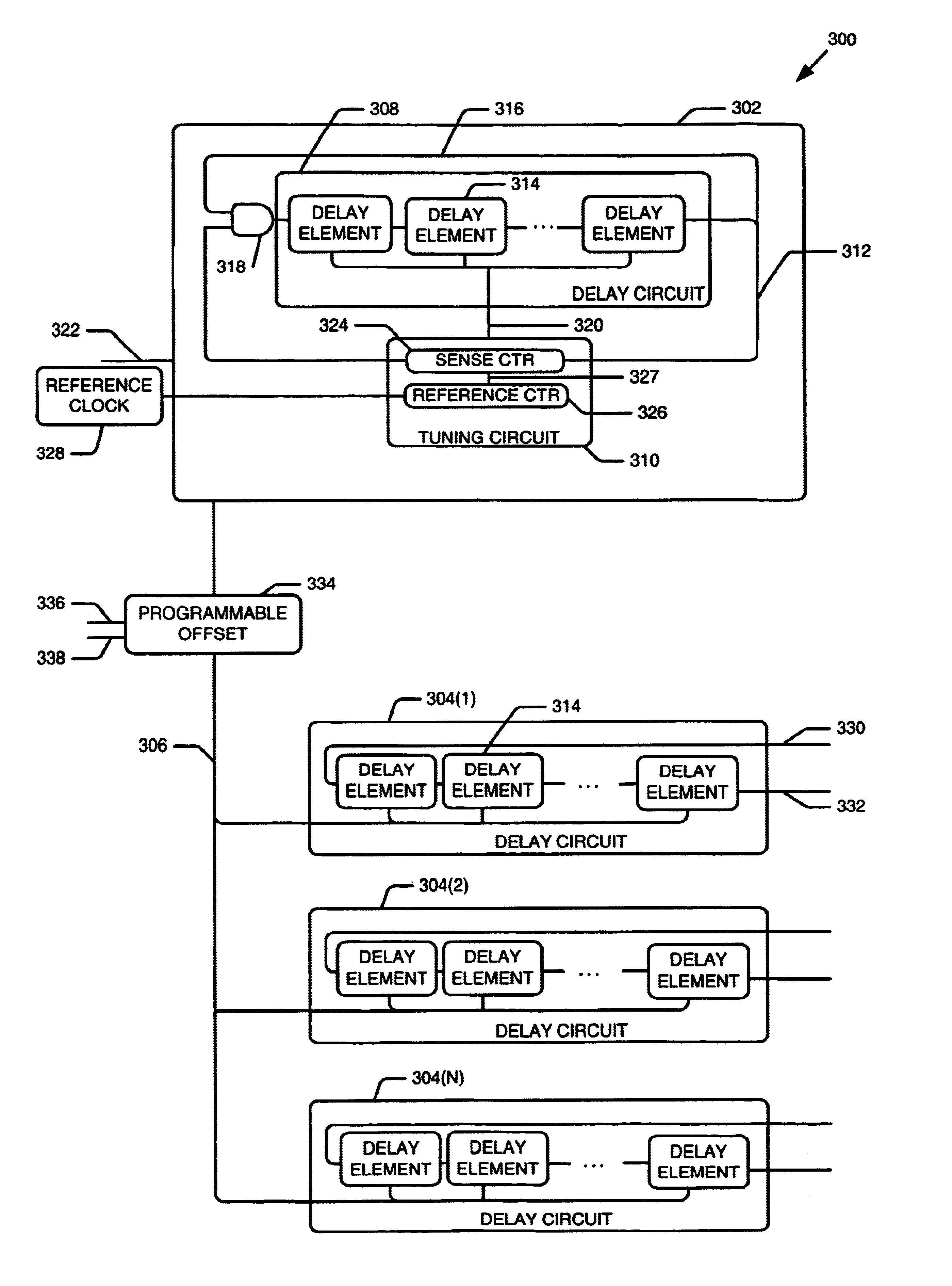

Method and apparatus for calibrating a delay line

InactiveUS7157948B2Reduce the differencePulse automatic controlDigital storagePropagation delayControl circuit

A delay line calibration circuit and method are provided in which a programmable master delay line drives a delay clock and has a propagation delay that is a function of a delay setting. A delay counter is clocked by the delay clock and has a delay count. A reference counter is clocked by a reference clock and has a reference count. A control circuit controls the delay and reference counters, compares a representation of the delay count to a representation of the reference count and responsively generates a modified value for the delay setting to reduce a difference between the representations of delay count and the reference count.

Owner:AVAGO TECH INT SALES PTE LTD

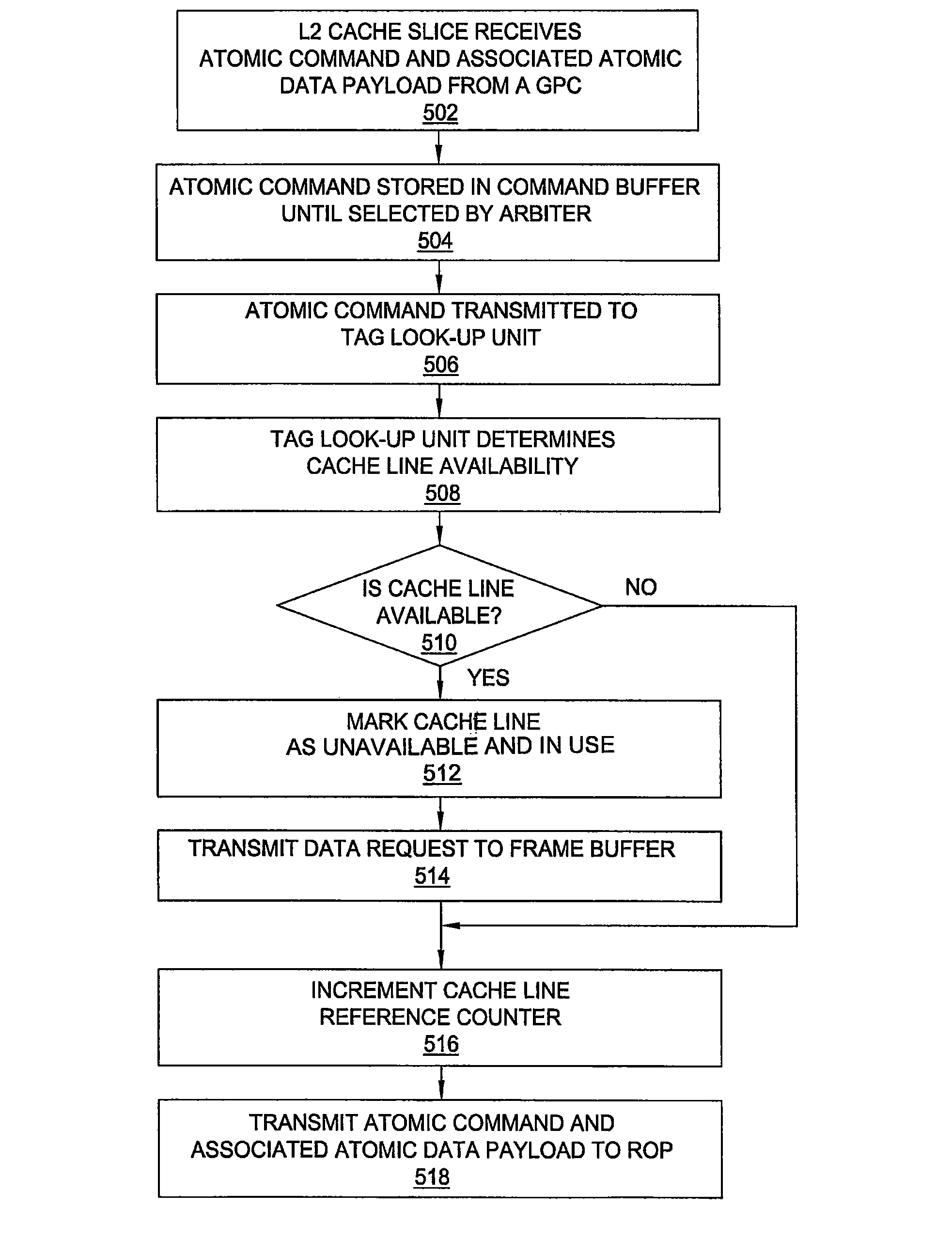

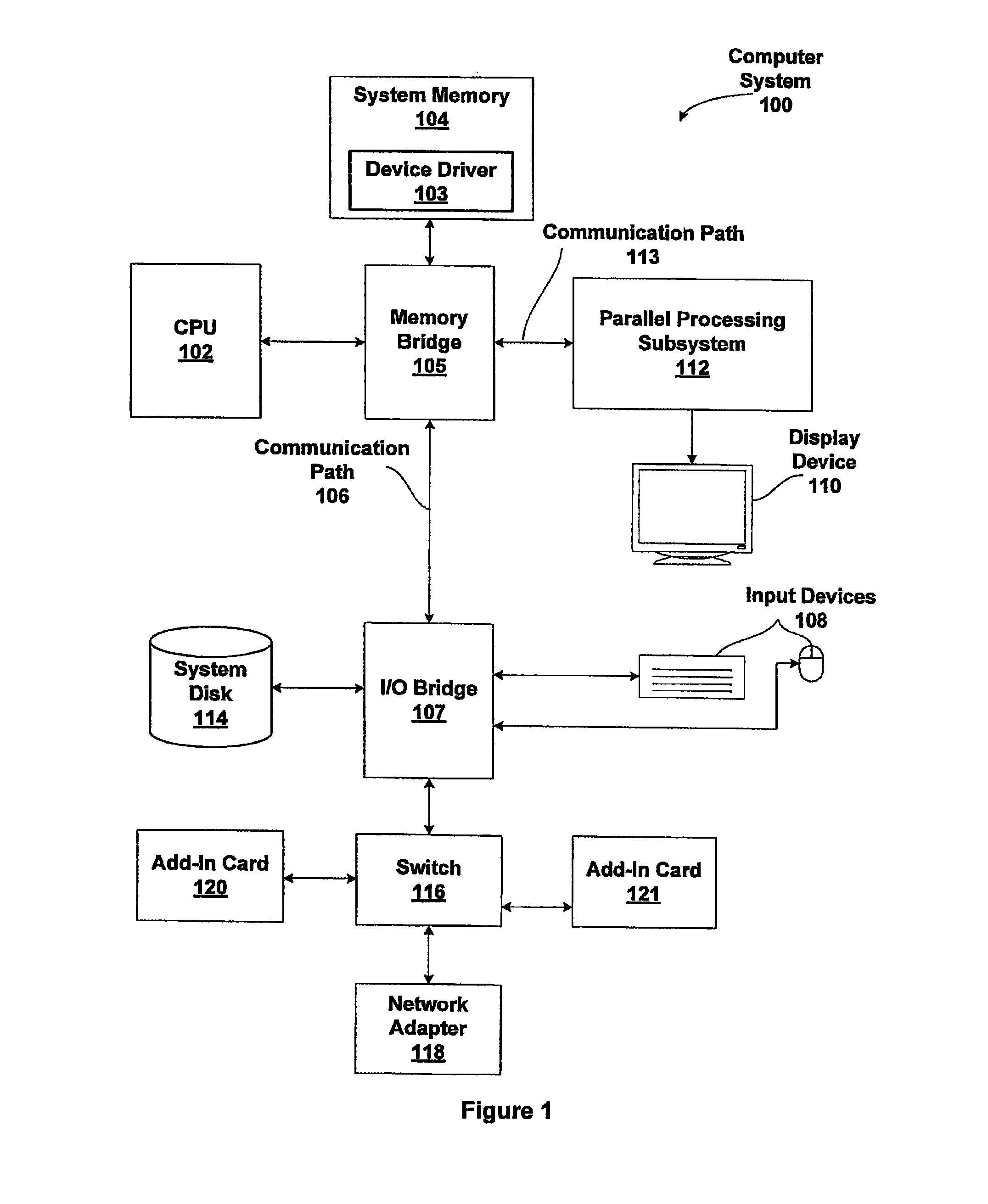

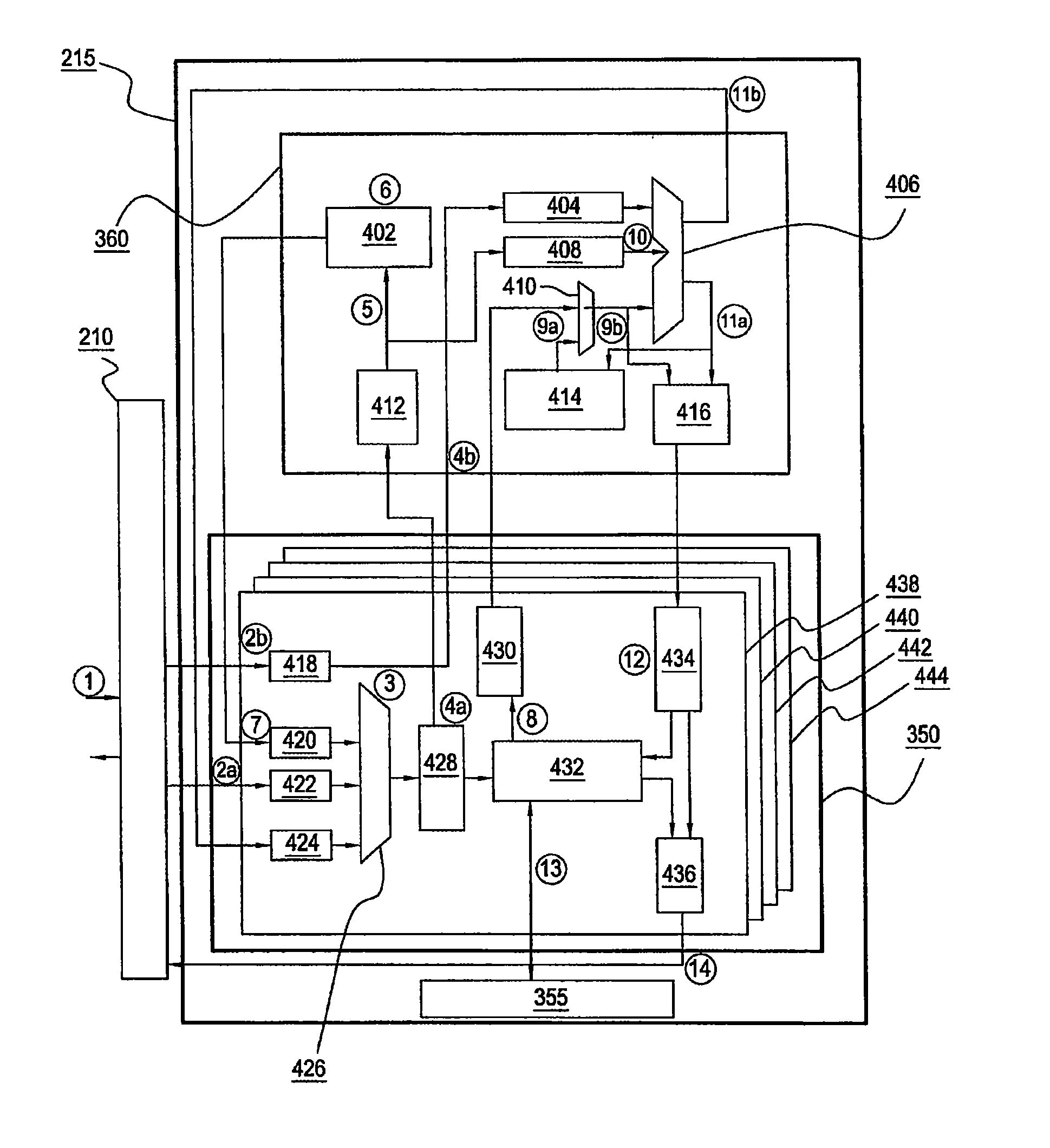

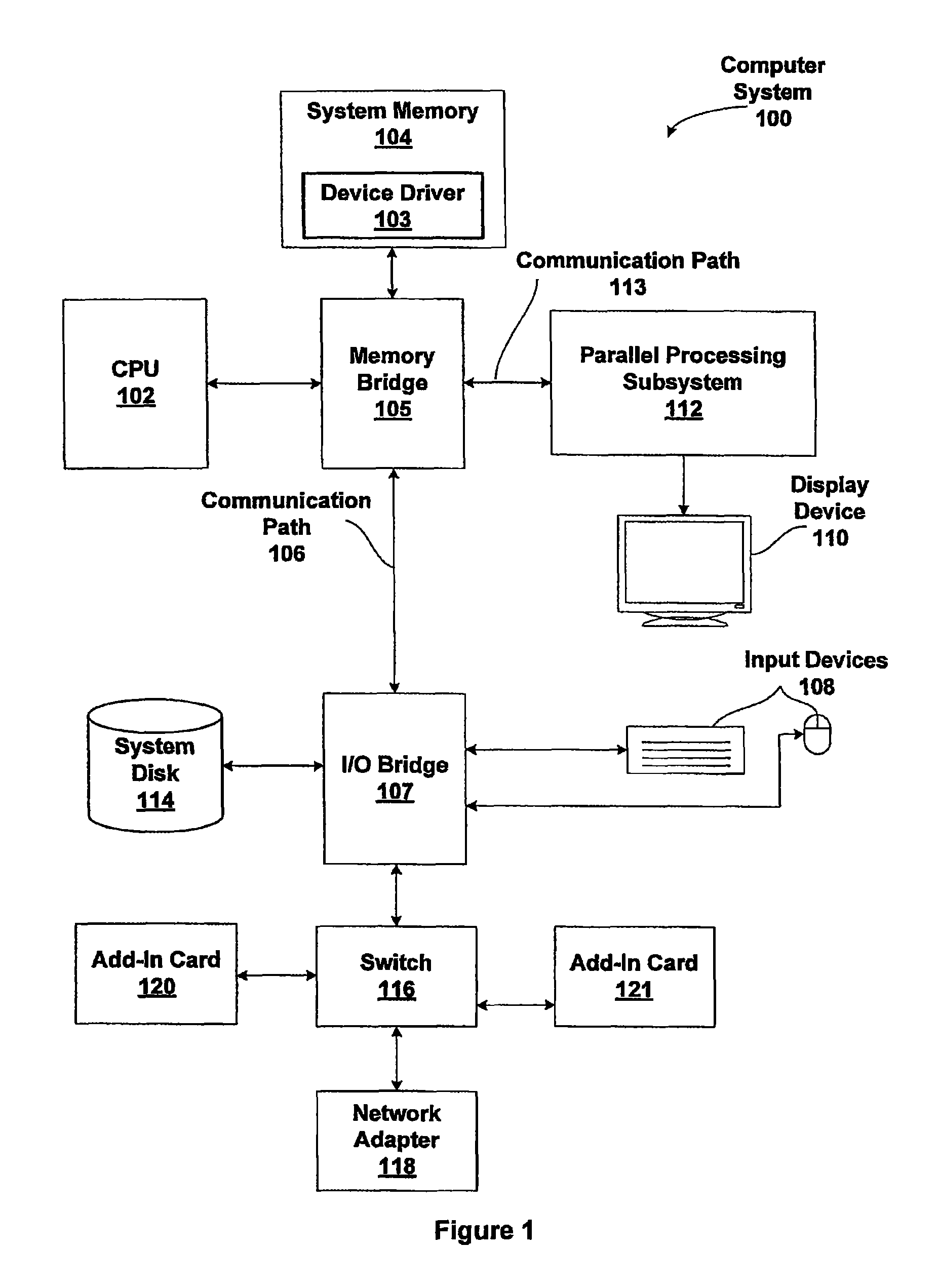

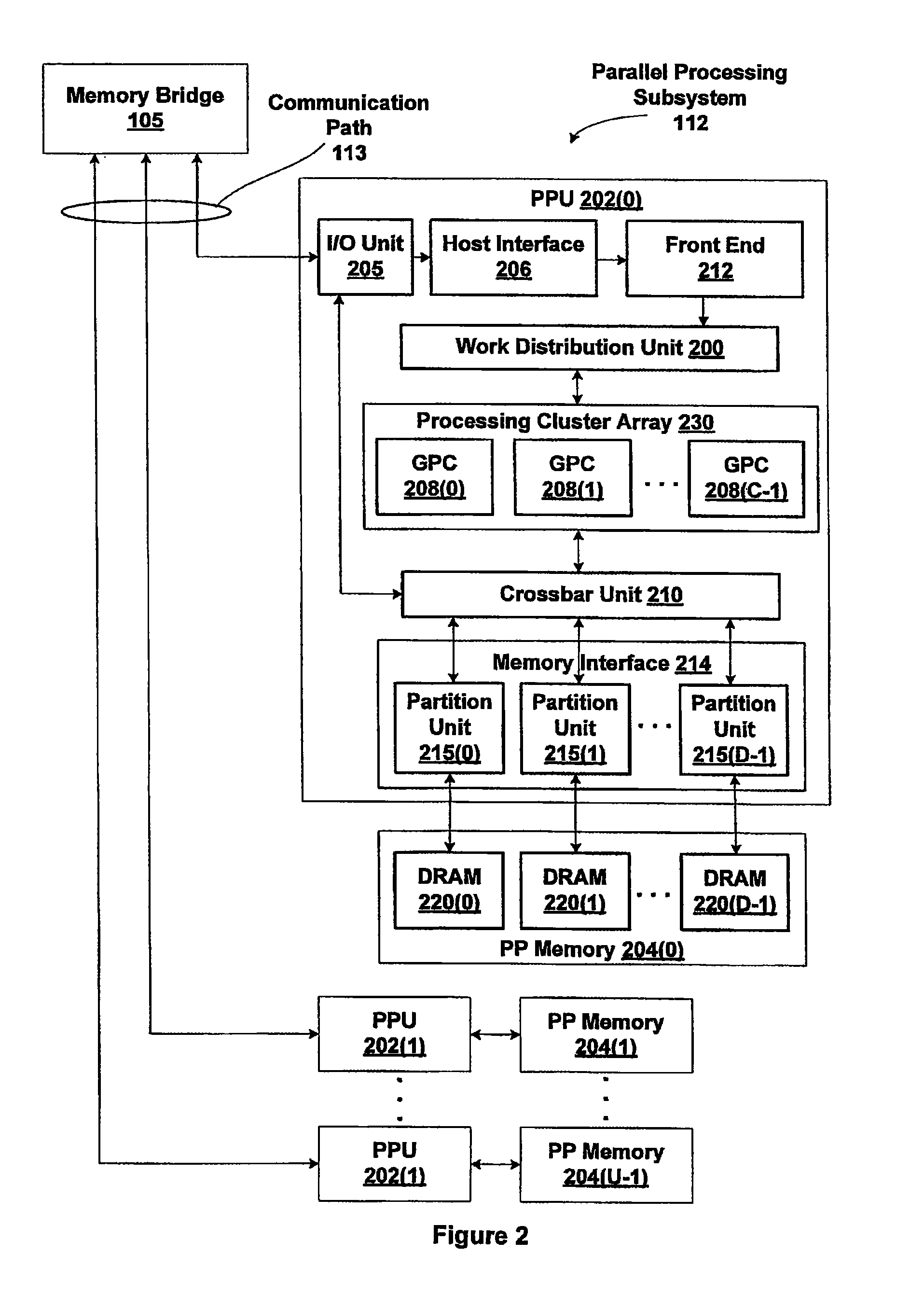

Cache-based control of atomic operations in conjunction with an external ALU block

ActiveUS8108610B1Improve processing efficiencyReduced availabilityMemory architecture accessing/allocationSingle instruction multiple data multiprocessorsAtomic operationsReference counter

One embodiment of the invention sets forth a mechanism for efficiently processing atomic operations transmitted from multiple general processing clusters to an L2 cache. A tag look-up unit tracks the availability of each cache line in the L2 cache, reserves the necessary cache lines for the atomic operations and transmits the atomic operations to an ALU for processing. The tag look-up unit also increments a reference counter associated with a reserved cache line each time an atomic operation associated with that cache line is received. This feature allows multiple atomic operations associated with the same cache line to be pipelined to the ALU. A ROP unit that includes the ALU may request additional data necessary to process an atomic operation from the L2 cache. Result data is stored in the L2 cache and may also be returned to the general processing clusters.

Owner:NVIDIA CORP

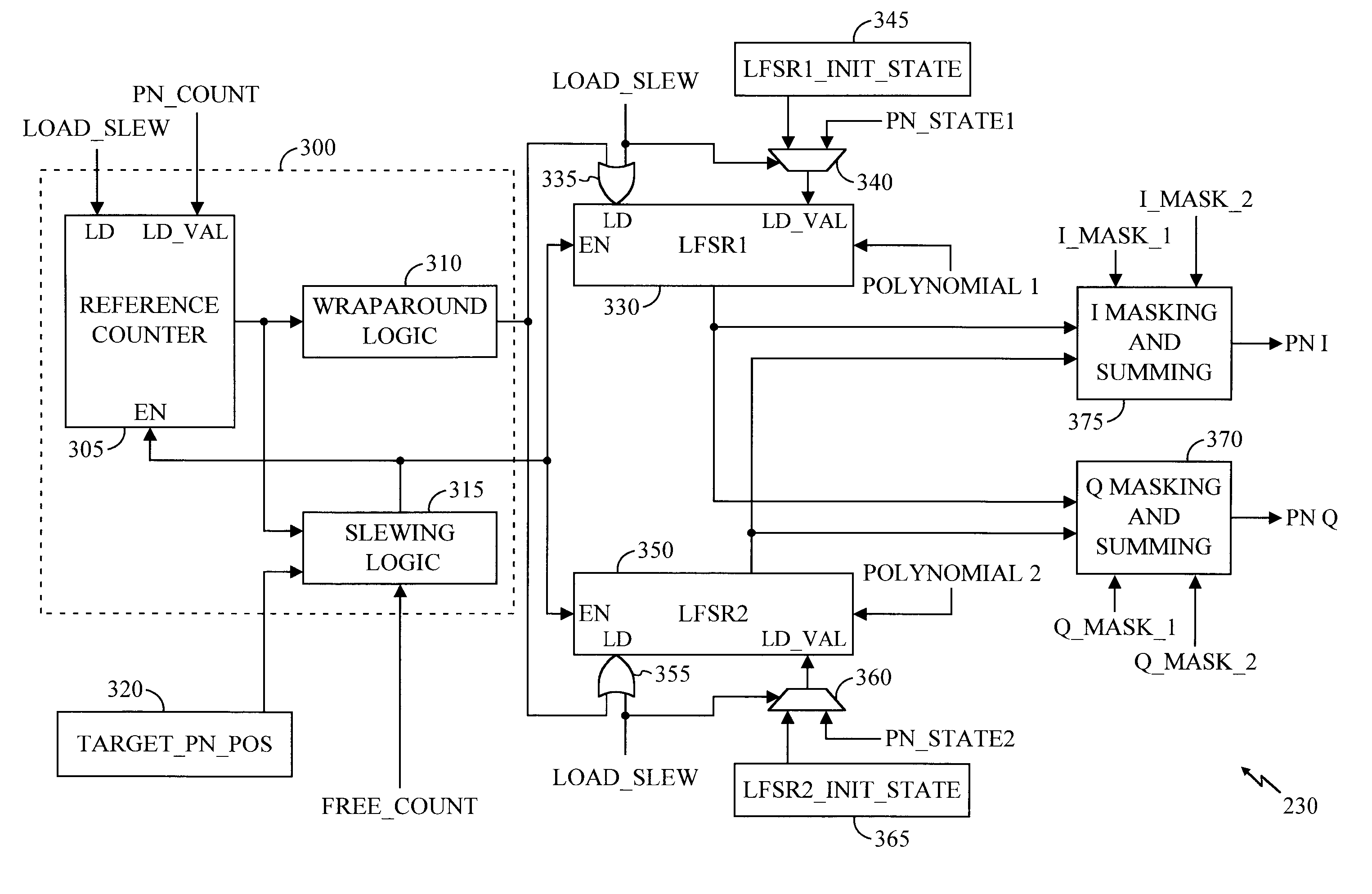

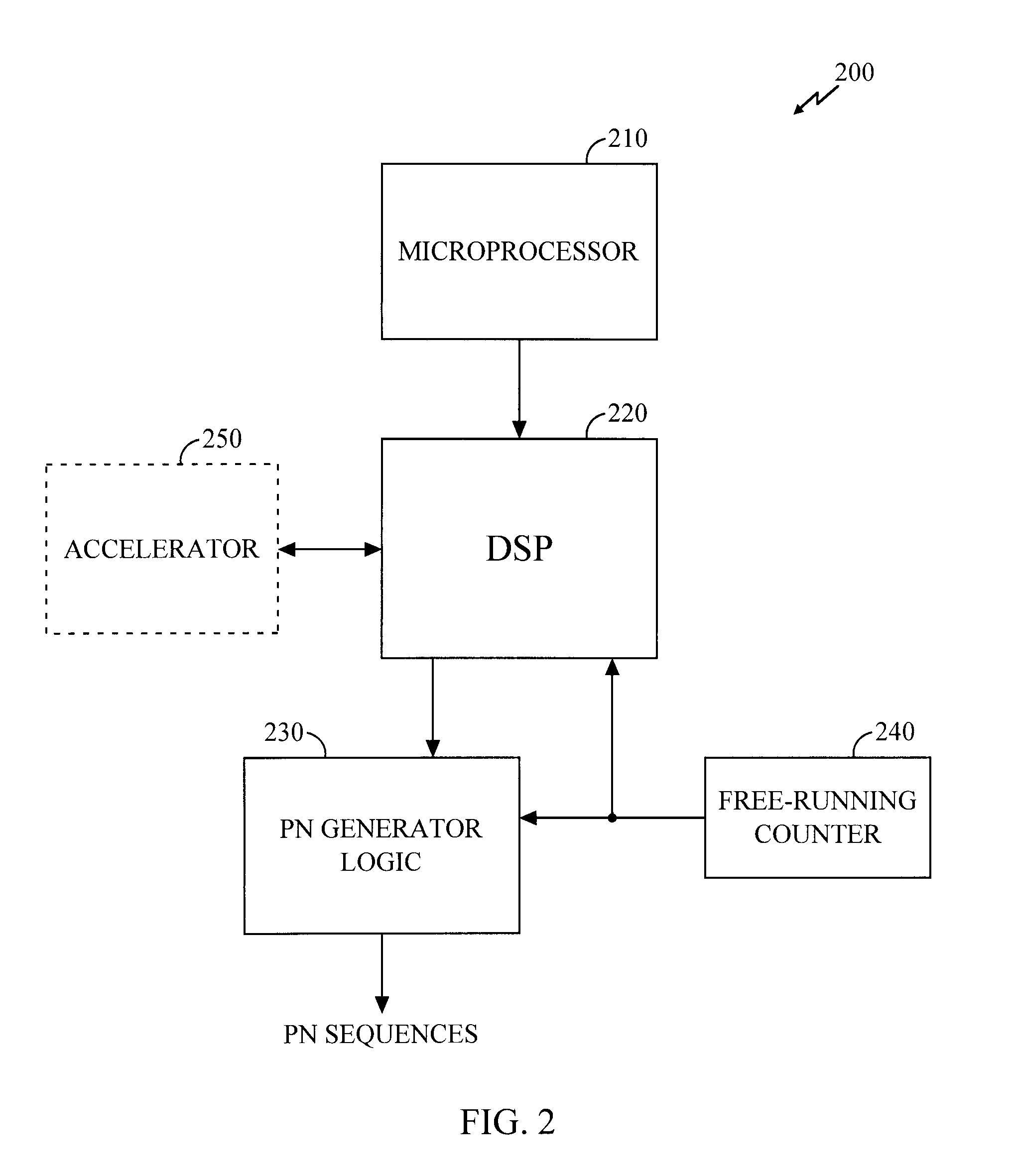

Multi-sequence fast slewing pseudorandom noise generator

InactiveUS6735606B2Reduced conversion timeAcquisition speed is fastRandom number generatorsMultiplex code generationSystem capacityTheoretical computer science

Techniques for fast-slewing of multi-sequence based PN generators are disclosed. In one aspect, LFSR states and reference counter states are loaded into their corresponding components such that consistency among the states is maintained. In another aspect, various methods for determining LFSR states and counter values in response to a desired offset in a unique code are disclosed. Among these methods are matrix-multiplication of LFSR states and generation of advanced LFSR states through masking techniques. Other methods are also presented. These aspects have the benefit of decreasing slew time in an efficient manner, which translates to increased acquisition speed, faster finger lock on multi-path signals, increased data throughput, decreased power, and improved overall system capacity.

Owner:QUALCOMM INC

Double-loop circuit frequency synthesizer and method for tuning gross adjustment loop circuit

The invention discloses a dual-loop frequency synthesizer and a tuning method of rough adjustment loop thereof, belonging to the field of frequency synthesizer in wireless transceiver. The frequency synthesizer consists of a rough adjustment loop and a fine adjustment loop, wherein the rough adjustment loop comprises a crossover frequency counter, a frequency reference counter, a shifter, a comparator and a finite state machine. The input end of the crossover frequency counter is connected with frequency dividing signal Fdiv of a voltage controlled oscillator of the fine adjustment loop, the shifter is connected with the crossover frequency counter or the frequency reference counter for leftwards shifting the counting value of the crossover frequency counter or the frequency reference counter, the counting values of the crossover frequency counter and the frequency reference counter are respectively output to the comparator, the compare result of which is input to the finite state machine. Compared with prior art, the invention reduces the time of rough tuning as well as provides higher tuning precision according to the needs.

Owner:PEKING UNIV

Apparatus and method for pre-fetching data to cached memory using persistent historical page table data

InactiveUS7099999B2Improve accuracyReduce frequencyMemory architecture accessing/allocationMemory adressing/allocation/relocationSystem maintenanceComputerized system

A computer system includes a main memory, at least one processor, and at least one level of cache. The system maintains reference history data with respect to each addressable page in memory, preferably in a page table. The reference history data is preferably used to determine which cacheable sub-units of the page should be pre-fetched to the cache. The reference history data is preferably an up or down counter which is incremented if the cacheable sub-unit is loaded into cache and is referenced by the processor, and decremented if the sub-unit is loaded into cache and is not referenced before being cast out. The reference counter thus expresses an approximate likelihood, based on recent history, that the sub-unit will be referenced in the near future.

Owner:IBM CORP

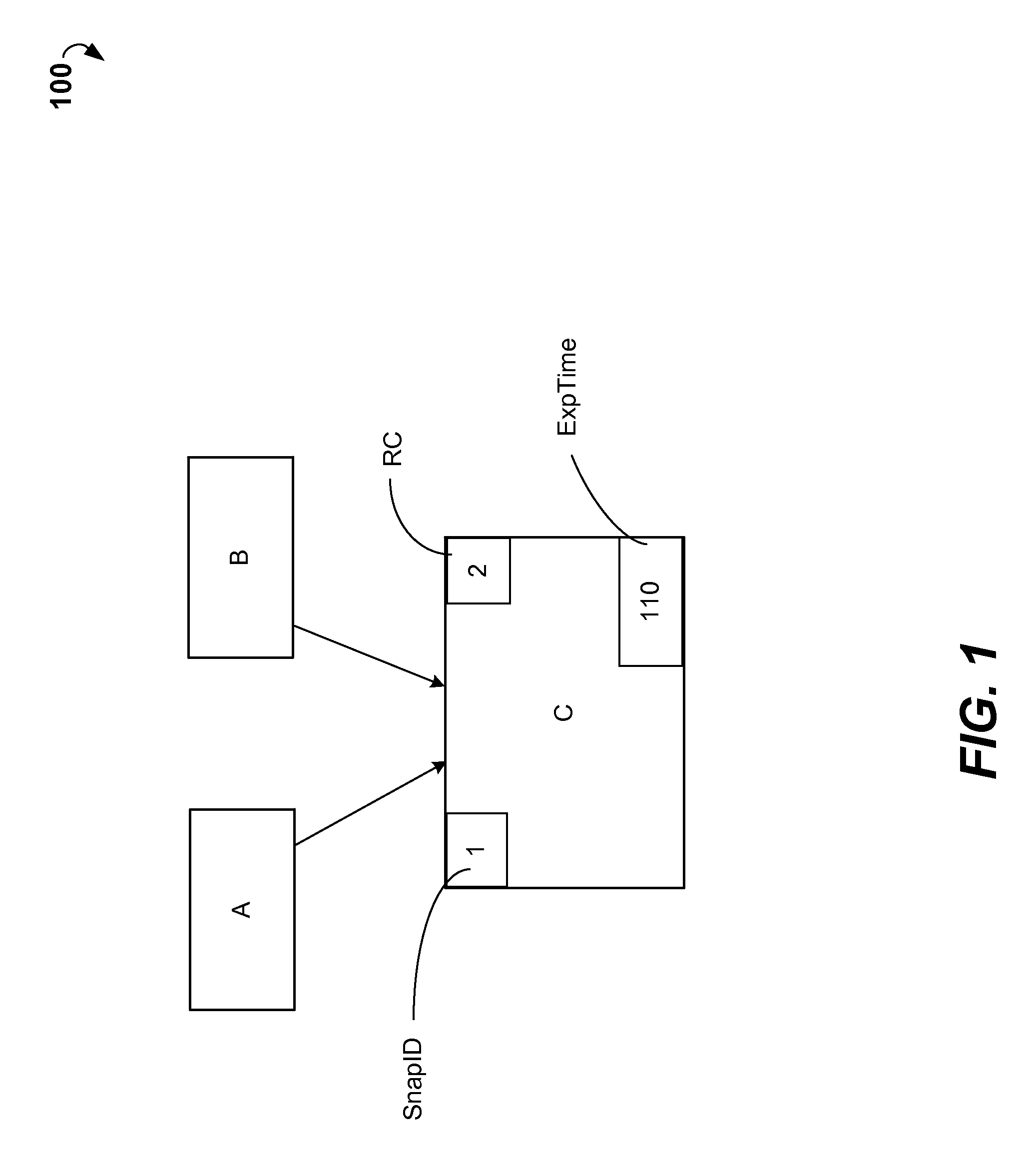

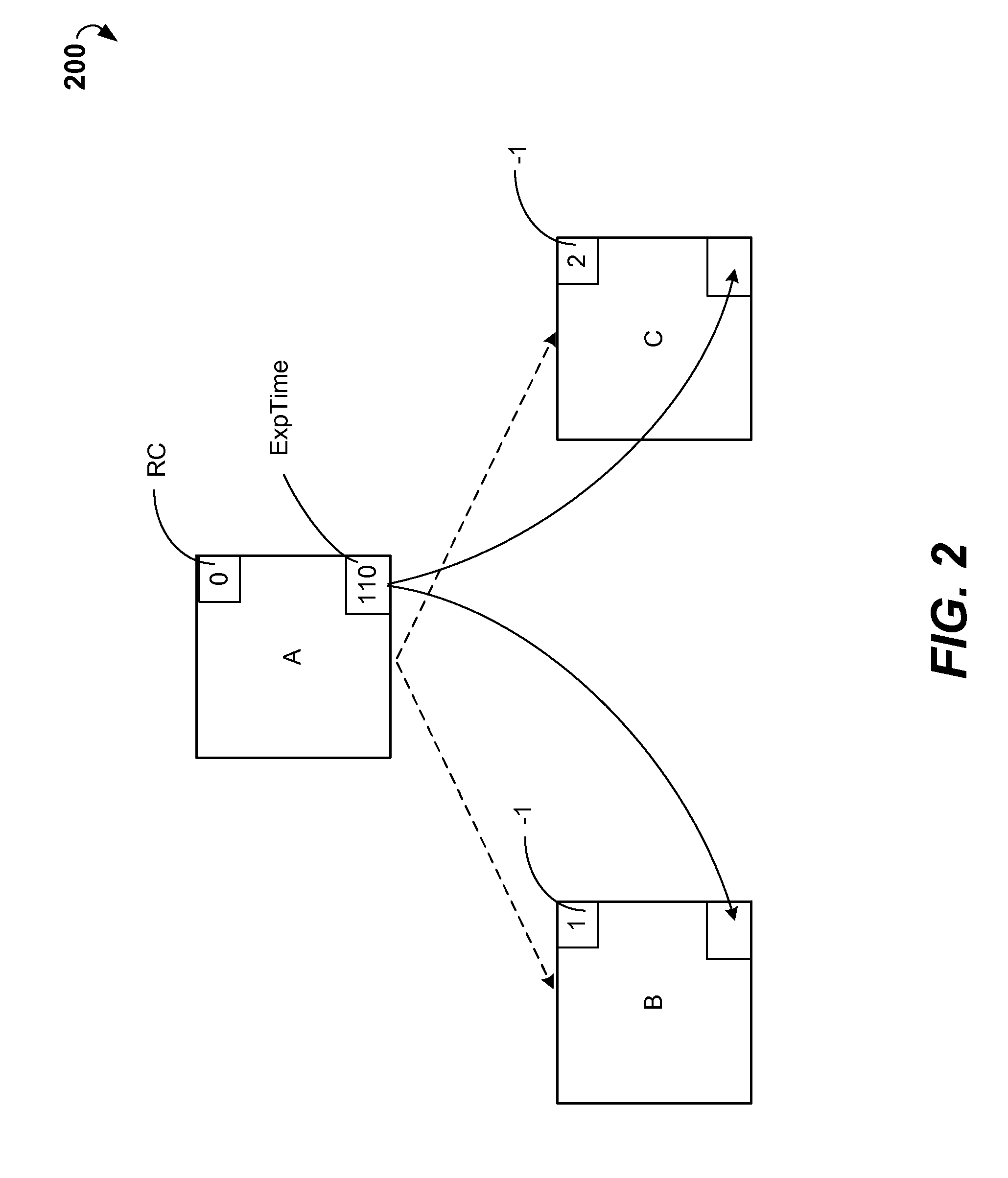

Hybrid garbage collection

ActiveUS20140372490A1Memory adressing/allocation/relocationObject oriented databasesExpiration TimeFile system

Disclosed is a method for hybrid garbage collection of objects in a file system. An example method includes associating, with each object in the file system, a reference counter, an expiration time, and a version identifier. The object is can be kept in the file system while the reference counter of the object is non-zero. After determining that the reference counter of the object is zero, the object can be kept in the file system up to the expiration time associated with the object. When a reference referring to the object is deleted, the expiration time of the object is updated to the latest of the expiration times of the object and the reference. Furthermore, the object can be kept in the file system while the version identifier of the object is larger than a predetermined version number.

Owner:EXABLOX

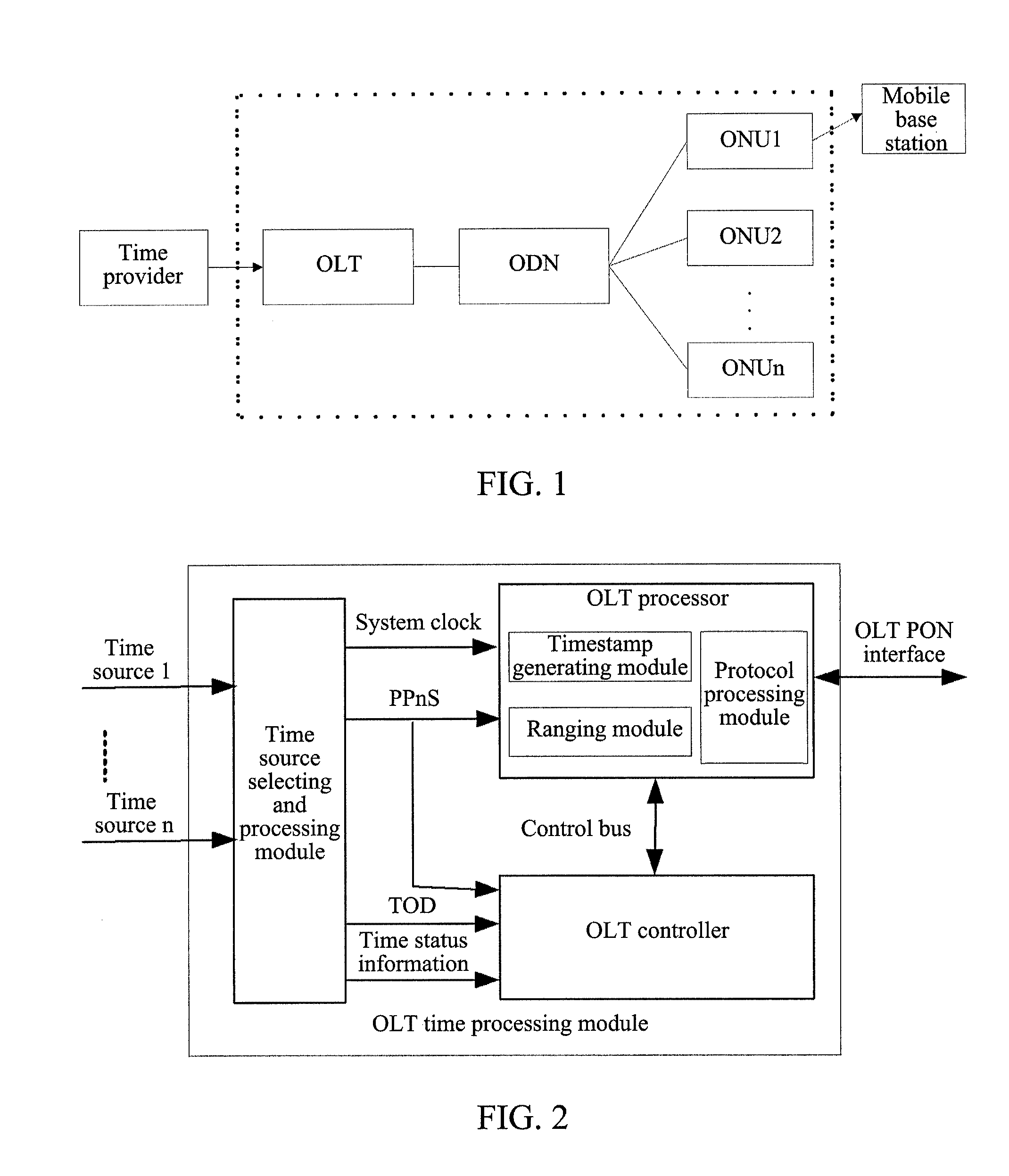

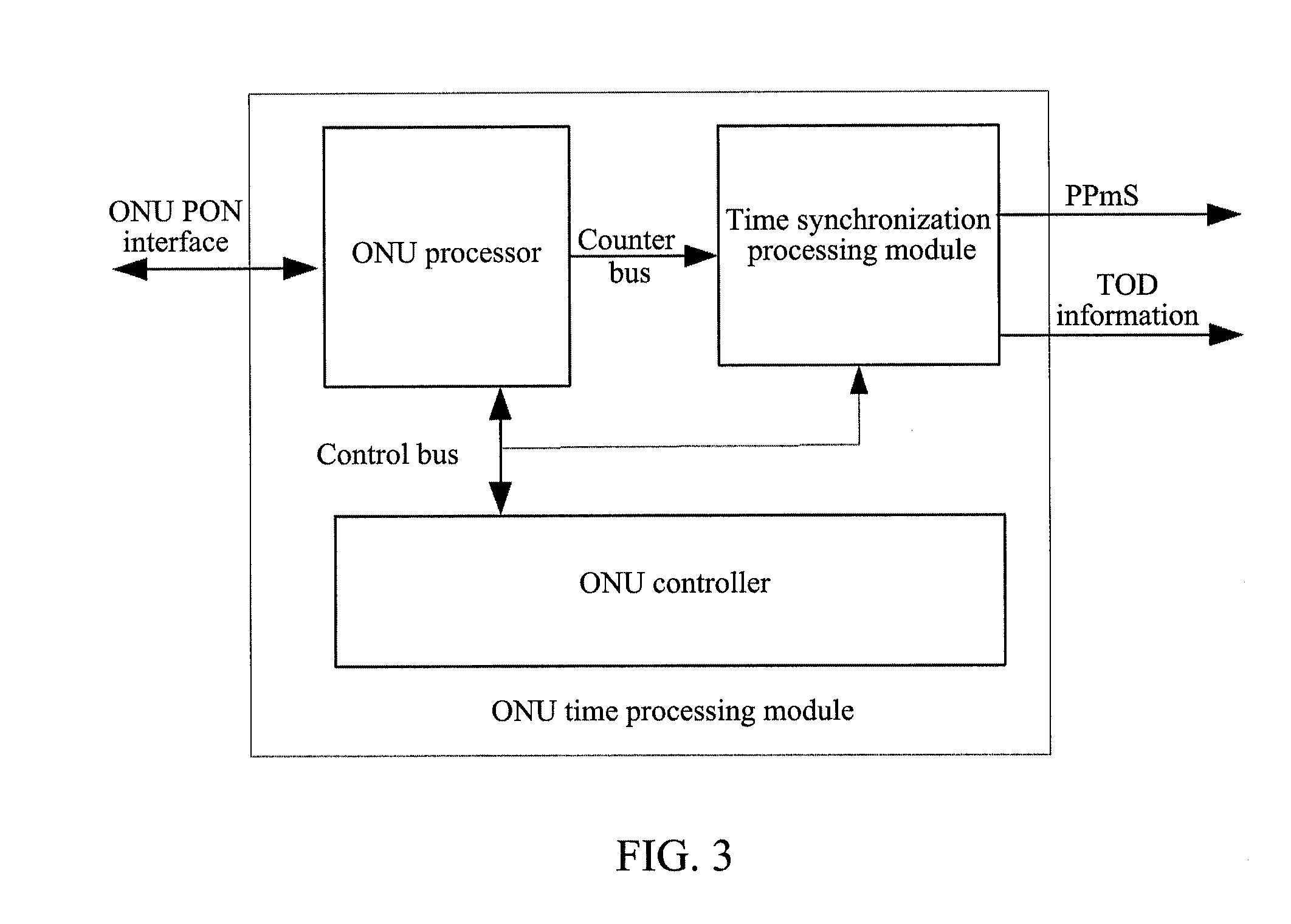

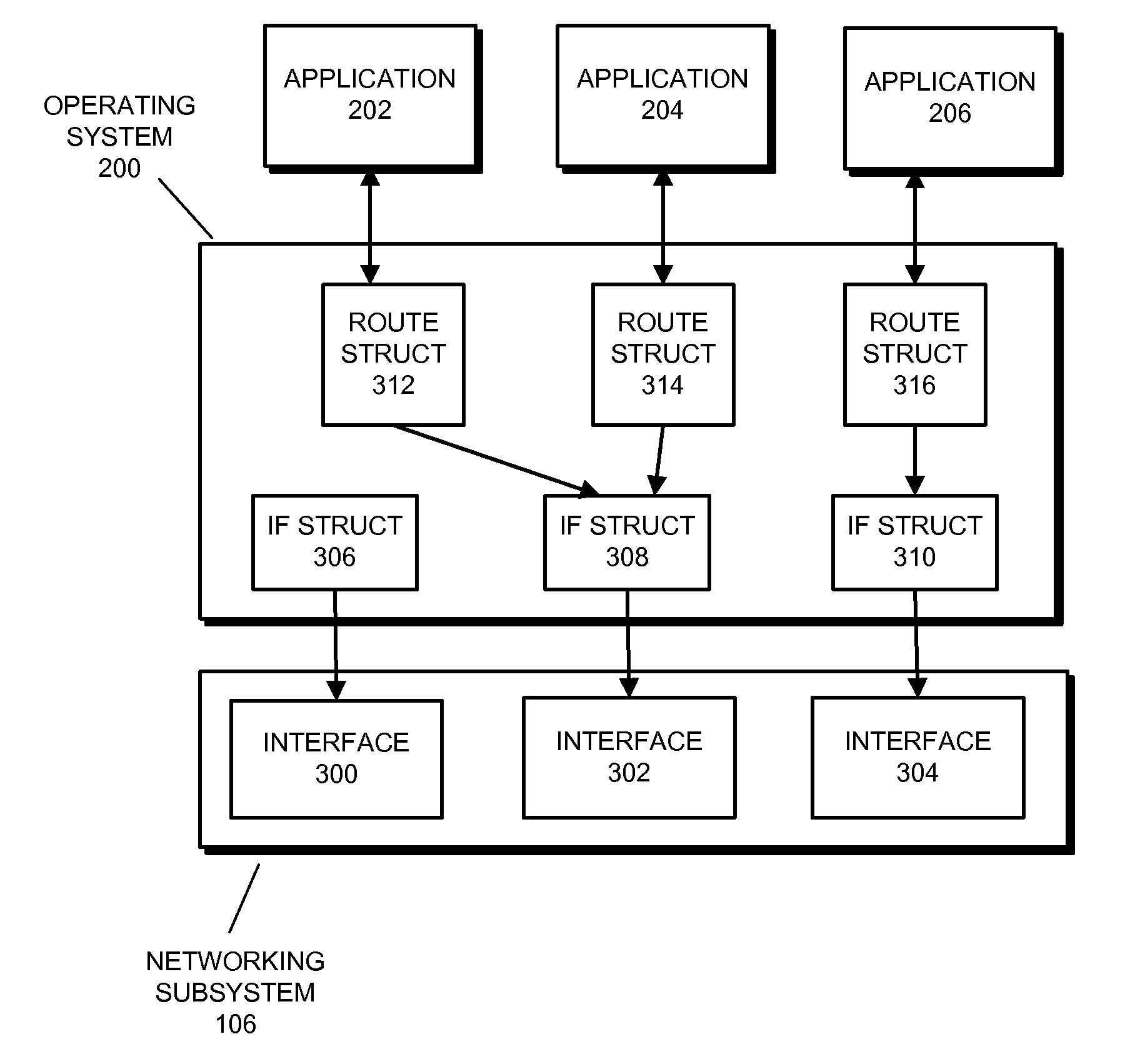

Method and system for transmitting time in passive optical network

ActiveUS20120008953A1Improve accuracyLow hardware costMultiplex system selection arrangementsTime-division multiplexTimestampTime transfer

The present invention discloses a method and system for accurate time transfer in PON. An Optical Line Terminal (OLT) ranges Optical Network Units (ONUs) and obtains ranging information, then, triggered by the periodic Pulse per n Second (PPnS), generates a PPnS timestamp based on the local reference counter and the Time of Day (TOD) above second; OLT transmits the ranging information, the periodic PPnS timestamp and TOD to ONUs; ONUs predicts the time of the next second according to said periodic PPnS timestamp, TOD and ranging information, and outputs the corresponding PPnS. The invention is characterized by the combination of the features of PON point to multi-point and PON ranging into its time transfer method, the high accuracy of time transfer, and the low hardware costs for OLT and ONU, as well as the extremely small bandwidth occupancy.

Owner:IARNACH TECH LTD

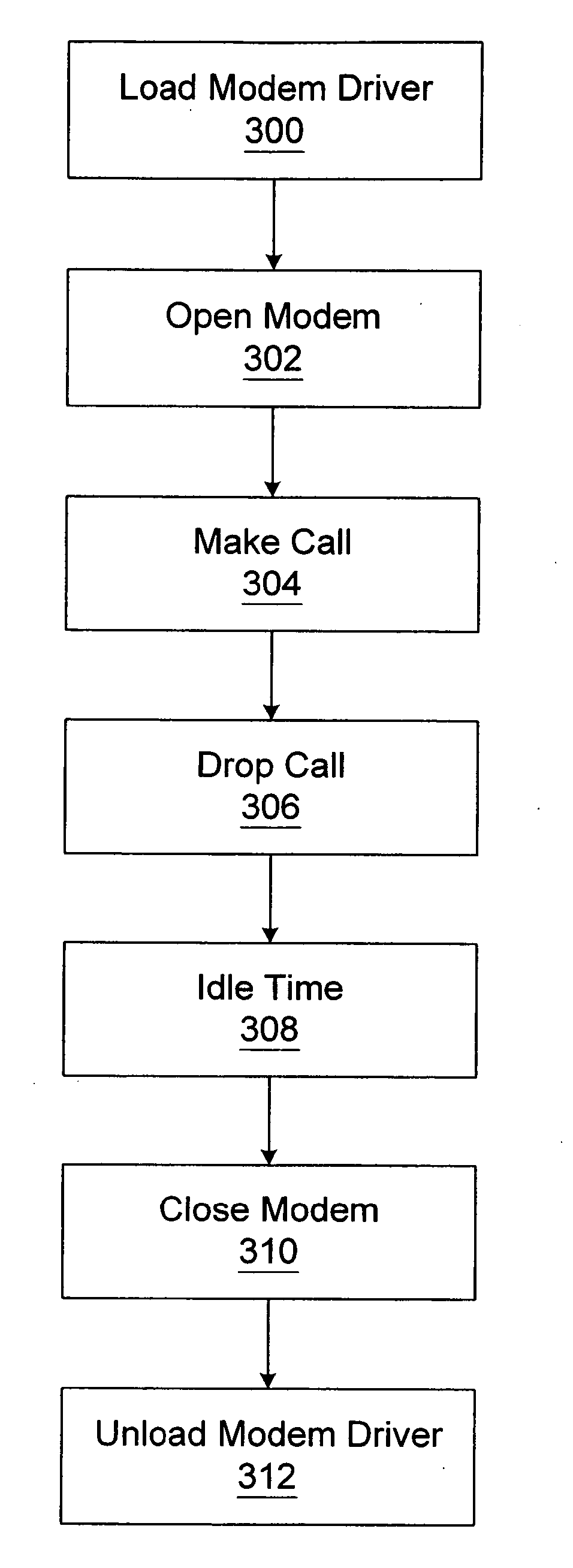

Method and apparatus for idling a network connection

ActiveUS20110179153A1Energy efficient ICTDigital data processing detailsExpiration TimeNetwork connection

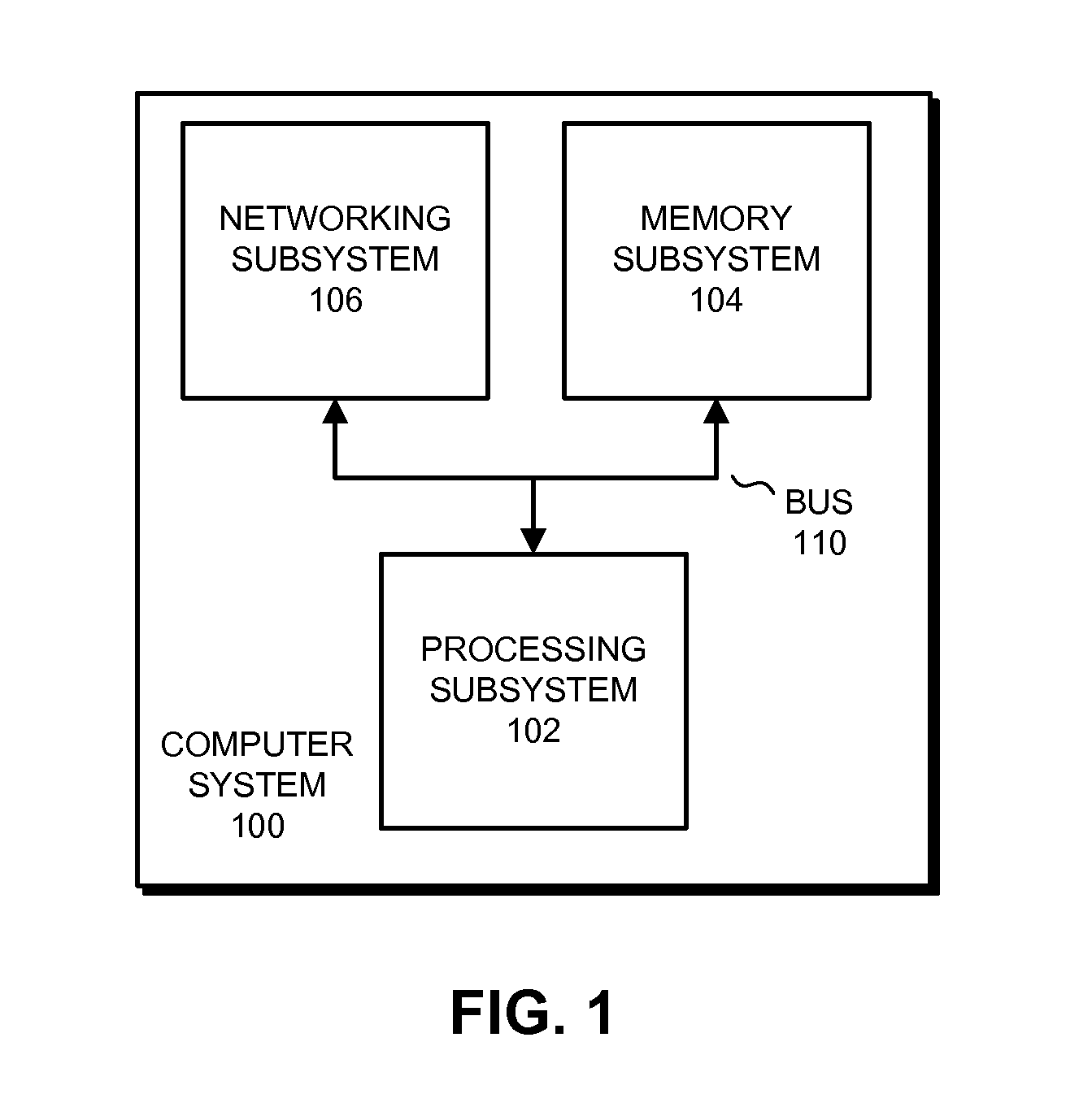

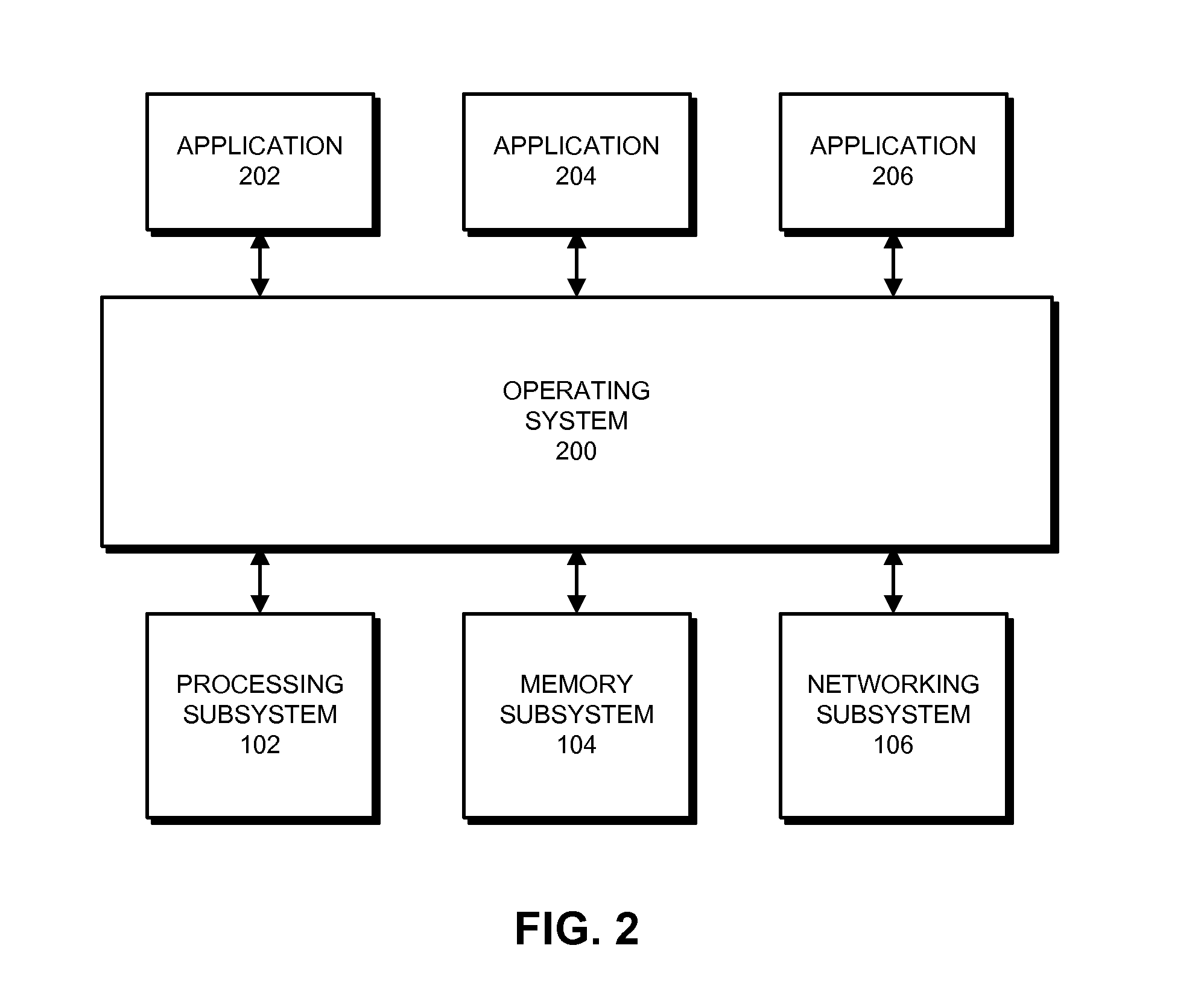

The described embodiments provide a system that controls the operating state of a network interface. During operation, in response to receiving a request from an application to use the network interface for a route, the system creates a route structure for the route and increments a route reference counter in an interface data structure for the network interface. Upon subsequently determining that the application is no longer using the route, the system sets a route expiration timer in the route structure to a predetermined expiration time. When the route expiration timer expires, the system deletes the route structure and decrements the route reference counter in the interface data structure. When decrementing the route reference counter in the interface data structure causes the route reference counter to be equal to zero, the system sends a signal to a configuration application to inform the application that the network interface can be idled.

Owner:APPLE INC

Cache-based control of atomic operations in conjunction with an external ALU block

ActiveUS8135926B1Improve processing efficiencyReduced availabilityMemory adressing/allocation/relocationProgram controlAtomic operationsReference counter

One embodiment of the invention sets forth a mechanism for efficiently processing atomic operations transmitted from multiple general processing clusters to an L2 cache. A tag look-up unit tracks the availability of each cache line in the L2 cache, reserves the necessary cache lines for the atomic operations and transmits the atomic operations to an ALU for processing. The tag look-up unit also increments a reference counter associated with a reserved cache line each time an atomic operation associated with that cache line is received. This feature allows multiple atomic operations associated with the same cache line to be pipelined to the ALU. A ROP unit that includes the ALU may request additional data necessary to process an atomic operation from the L2 cache. Result data is stored in the L2 cache and may also be returned to the general processing clusters.

Owner:NVIDIA CORP

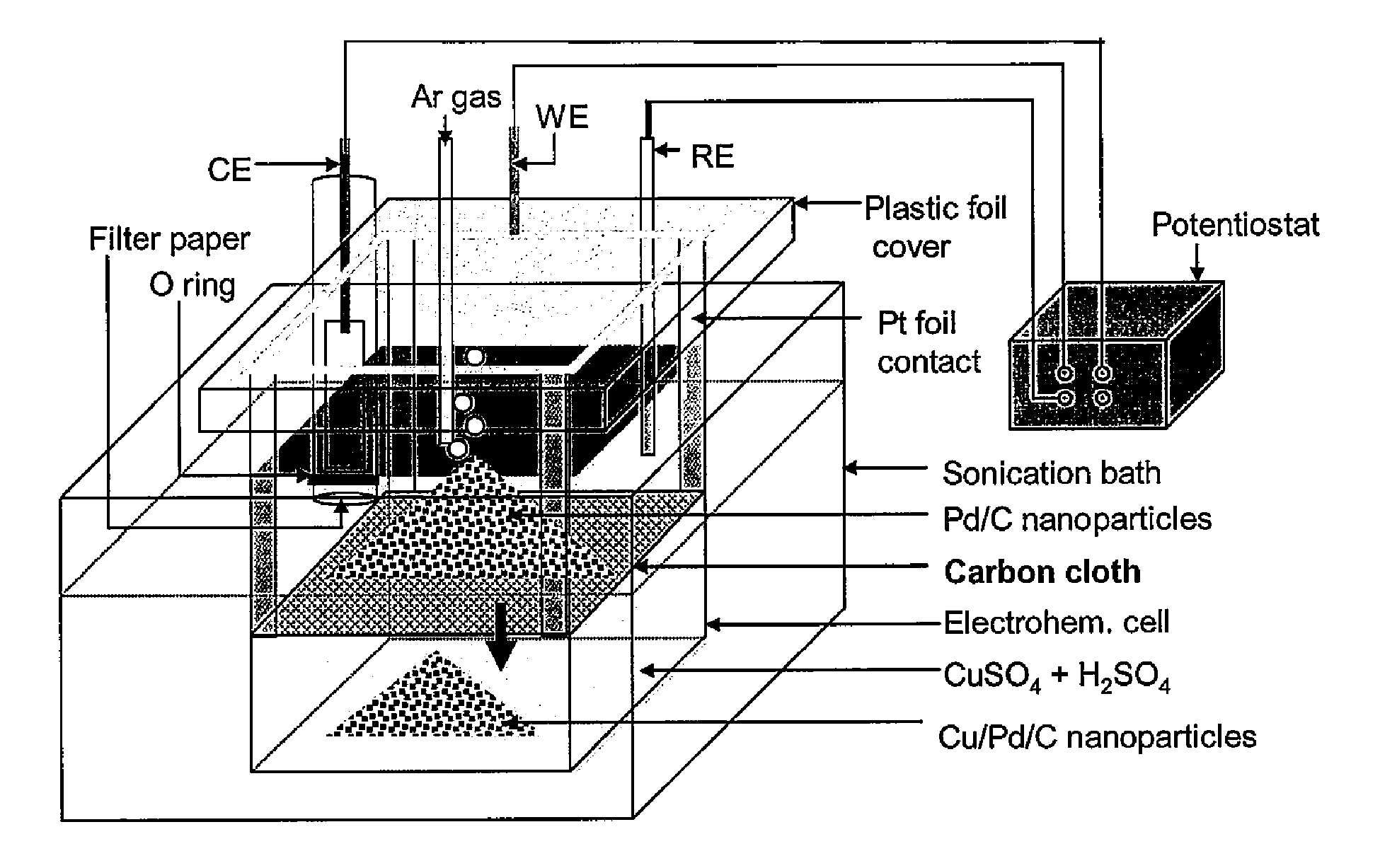

Method and Electrochemical Cell for Synthesis and Treatment of Metal Monolayer Electrocatalysts Metal, Carbon, and Oxide Nanoparticles Ion Batch, or in Continuous Fashion

InactiveUS20120245017A1Suitable for commercial applicationEasy to produceCellsMaterial nanotechnologyMaterials scienceMonolayer

An apparatus and method for synthesis and treatment of electrocatalyst particles in batch or continuous fashion is provided. In one embodiment, the apparatus comprises a sonication bath and a two-compartment chamber submerged in the sonication bath. The upper and lower compartments are separated by a microporous material surface. The upper compartment comprises a cover and a working electrode (WE) connected to a Pt foil contact, with the foil contact connected to the microporous material. The upper chamber further comprises reference counter electrodes. The lower compartment comprises an electrochemical cell containing a solution of metal ions. In one embodiment, the method for synthesis of electrocatalysts comprises introducing a plurality of particles into the apparatus and applying sonication and an electrical potential to the microporous material connected to the WE. After the non-noble metal ions are deposited onto the particles, the non-noble metal ions are displaced by noble-metal ions by galvanic displacement.

Owner:BROOKHAVEN SCI ASSOCS

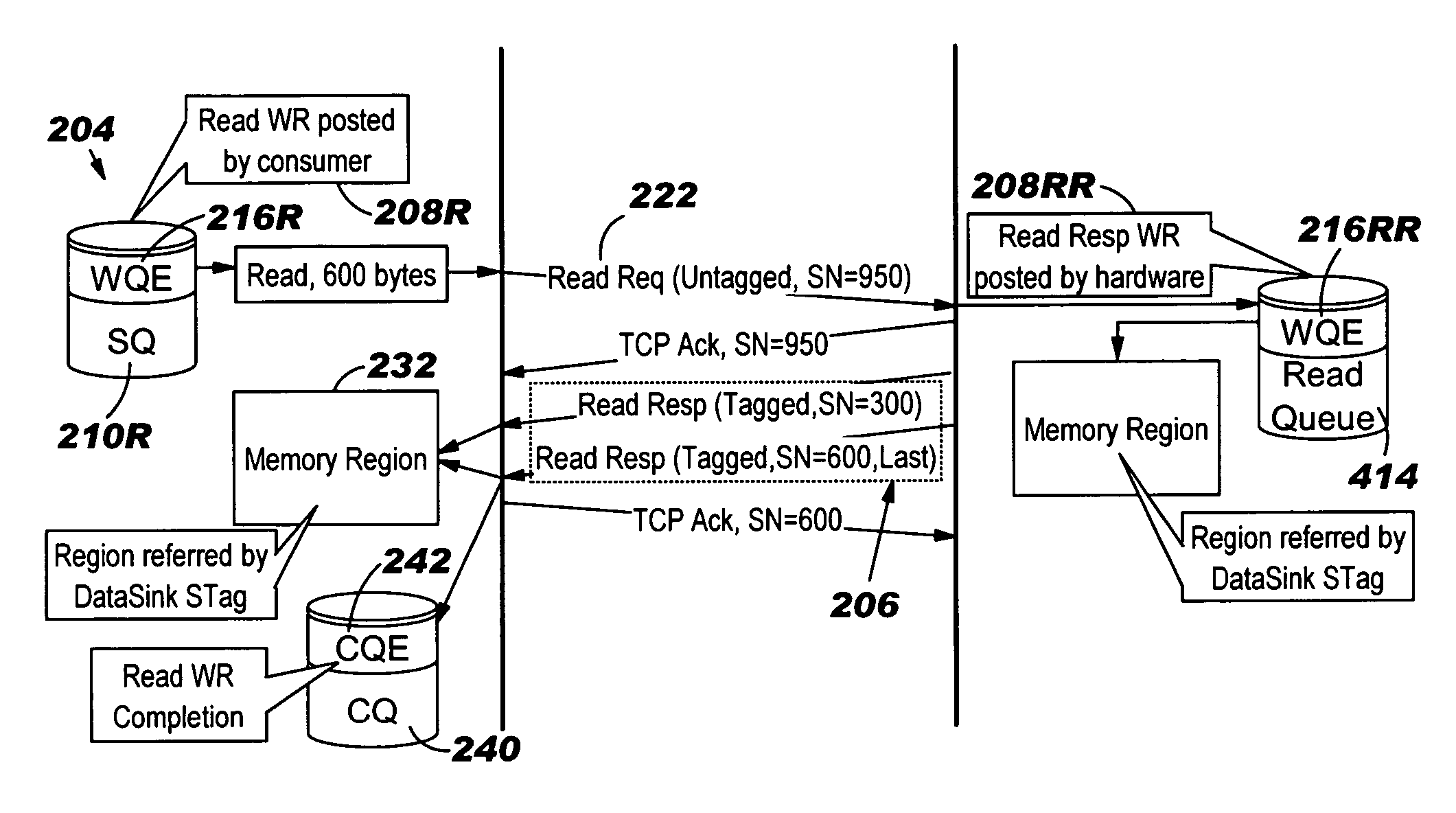

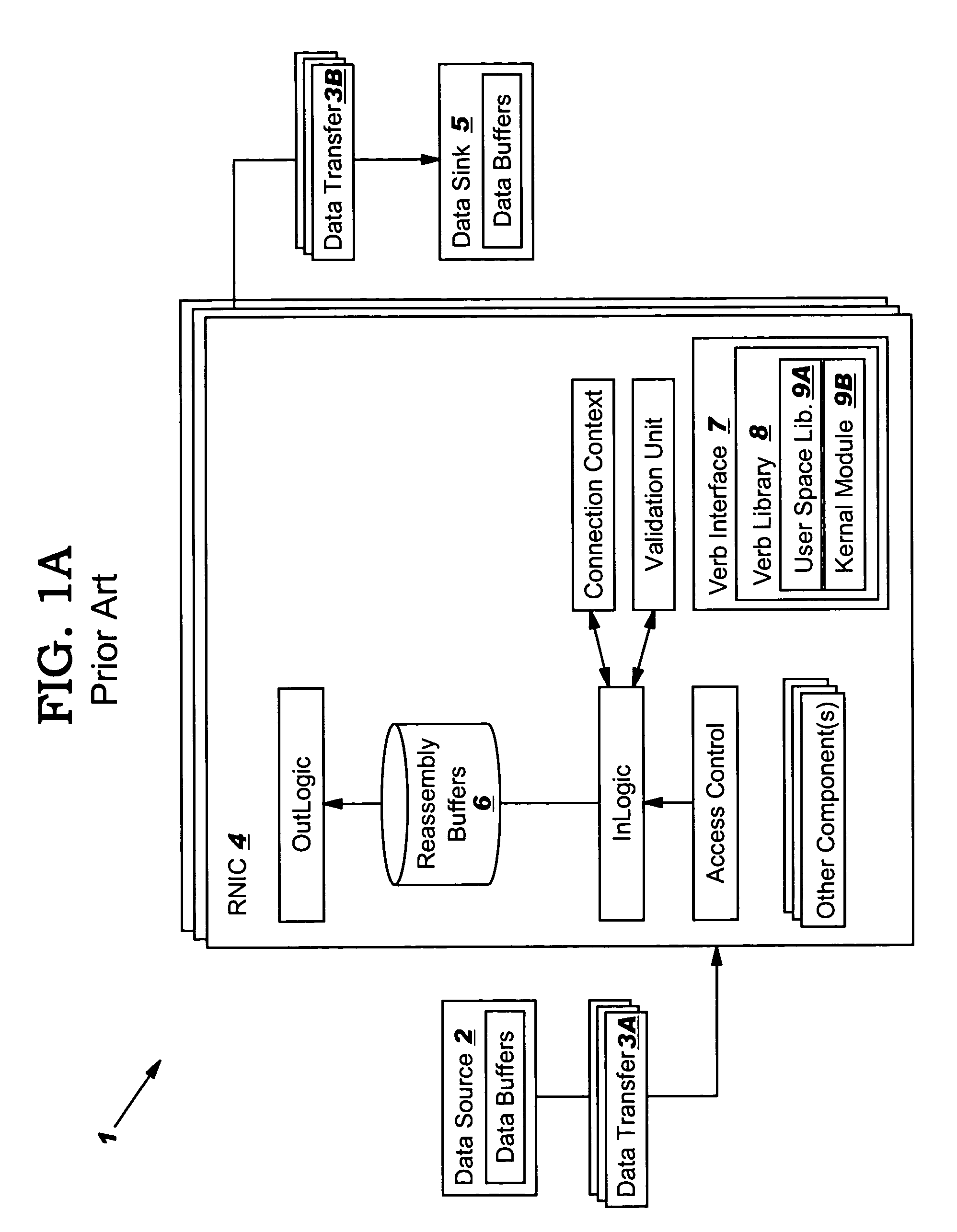

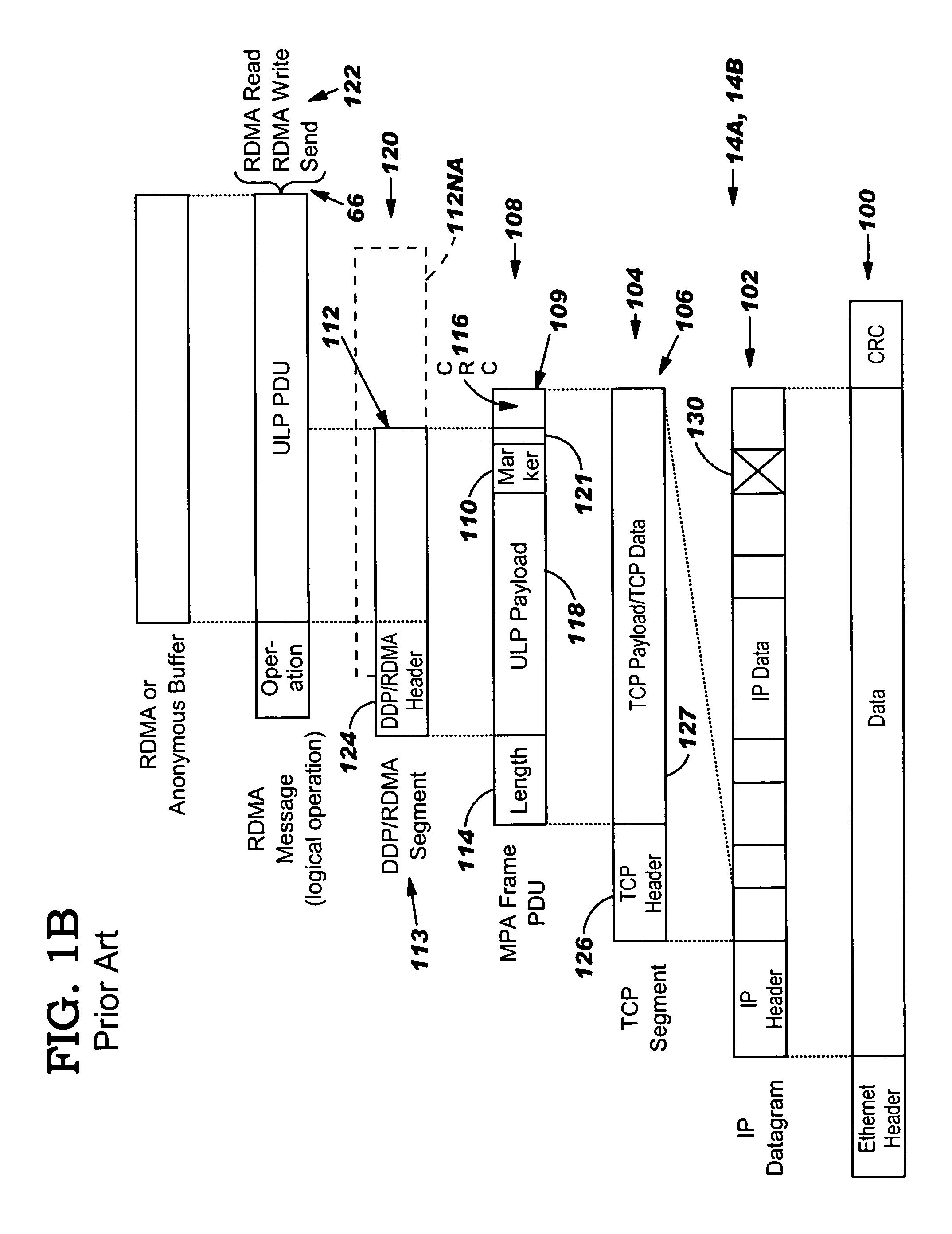

Reducing number of write operations relative to delivery of out-of-order RDMA send messages by managing reference counter

InactiveUS7441006B2Increase probabilityAttenuation bandwidthDigital computer detailsData switching by path configurationConnection typeTerm memory

An RNIC implementation that performs direct data placement to memory where all segments of a particular connection are aligned, or moves data through reassembly buffers where all segments of a particular connection are non-aligned. The type of connection that cuts-through without accessing the reassembly buffers is referred to as a “Fast” connection because it is highly likely to be aligned, while the other type is referred to as a “Slow” connection. When a consumer establishes a connection, it specifies a connection type. The connection type can change from Fast to Slow and back. The invention reduces memory bandwidth, latency, error recovery using TCP retransmit and provides for a “graceful recovery” from an empty receive queue. The implementation also may conduct CRC validation for a majority of inbound DDP segments in the Fast connection before sending a TCP acknowledgement (Ack) confirming segment reception.

Owner:IBM CORP

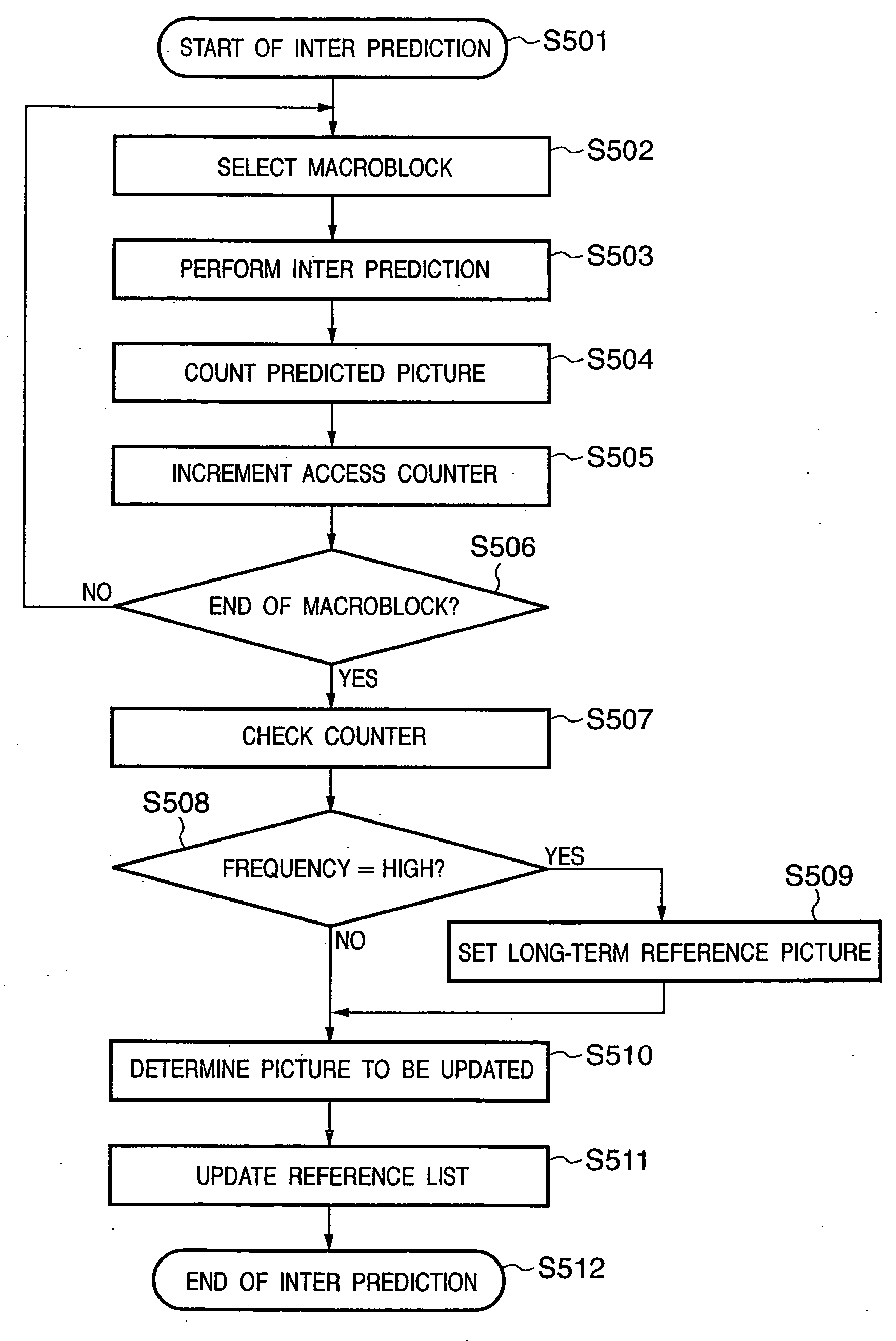

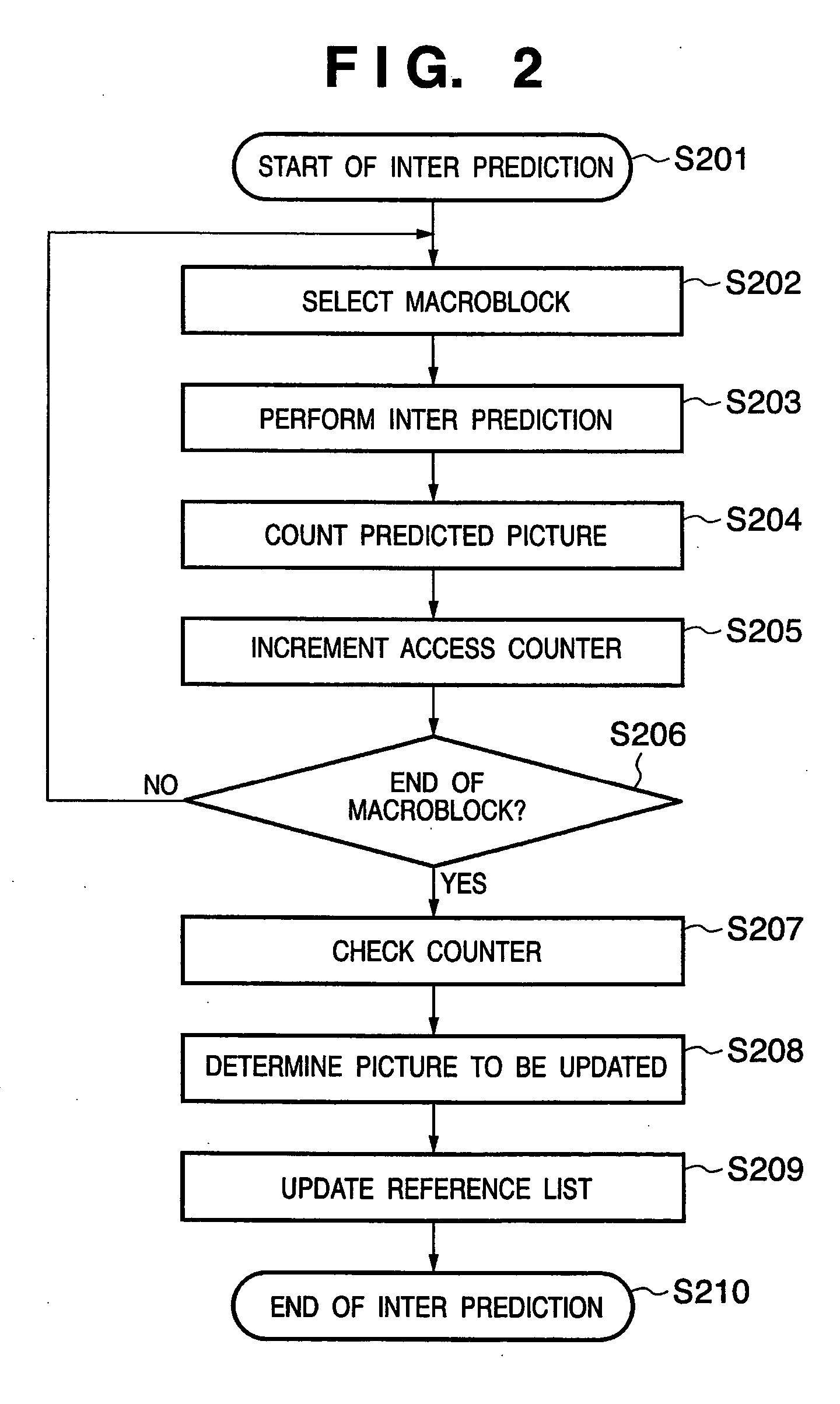

Image processing apparatus and method

InactiveUS20060171680A1Improve coding efficiencyTelevision system detailsColor television with pulse code modulationImaging processingImaging data

This invention provides a coding method and apparatus capable of increasing the coding efficiency. According to this invention, an image processing apparatus which performs predictive coding using image data of a different frame as a reference picture includes a prediction unit which performs motion compensated prediction for each reference picture in at least one reference list formed from a set of reference pictures for prediction, a reference list update unit which updates the reference list by adding or deleting the reference picture, a reference counter unit which measures, for each reference picture, a count at which the reference picture is used for motion compensation predictive coding, and an update picture determination unit which determines a reference picture to be updated in the reference list by using the measurement result of the reference counter unit.

Owner:CANON KK

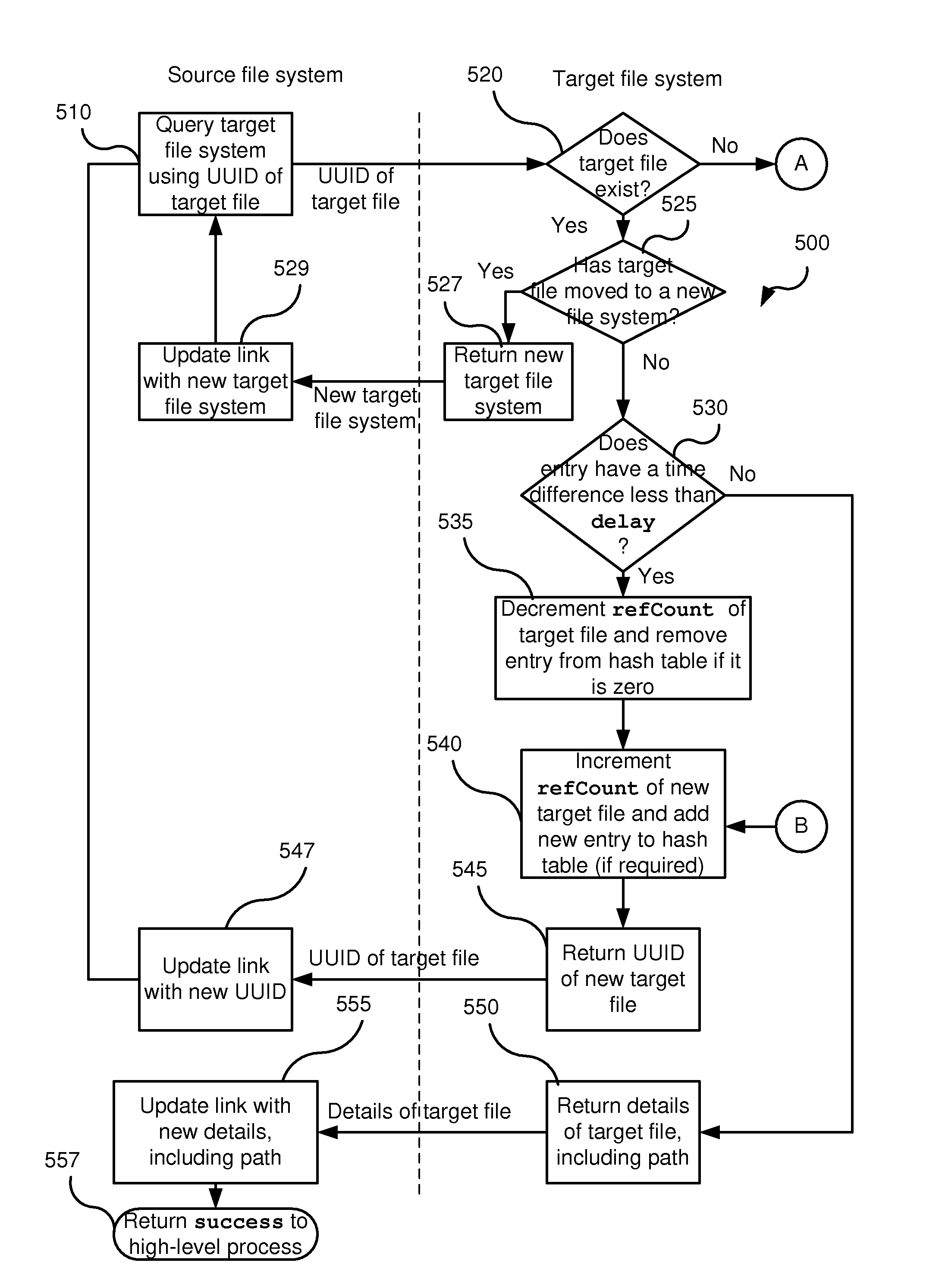

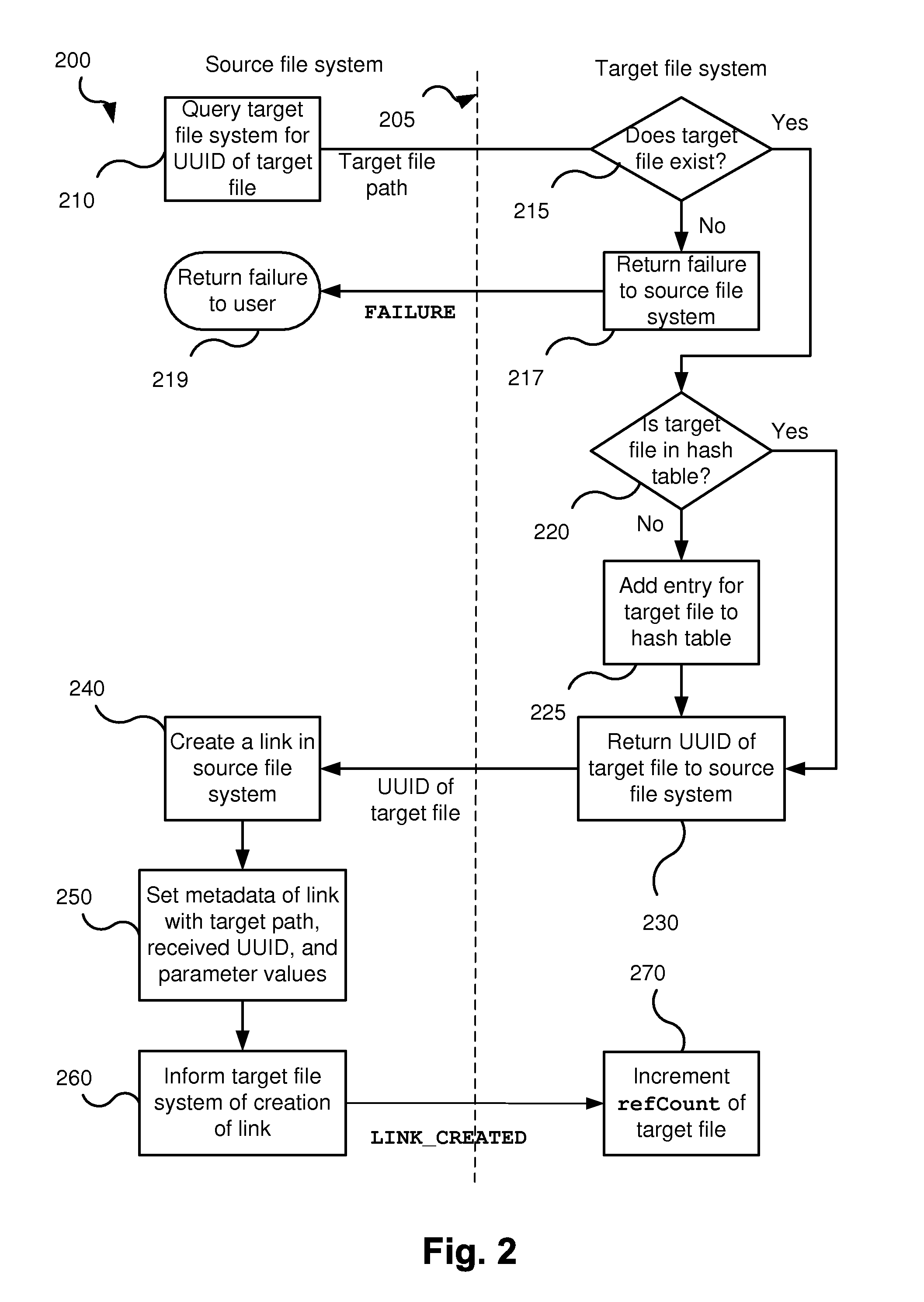

Management of symbolic links

ActiveUS20100030739A1Improve robustnessDigital data processing detailsFile/folder operationsSymbolic linkEngineering

Disclosed is a method of creating a symbolic link in a source file system to a target file in a target file system, the method including querying the target file system for an identifier of the target file; incrementing a reference counter of the target file, the reference counter indicating how many symbolic links the target file is a target of; and creating the symbolic link in the source file system, the symbolic link including the identifier received from the target file system in response to the query.

Owner:IBM CORP

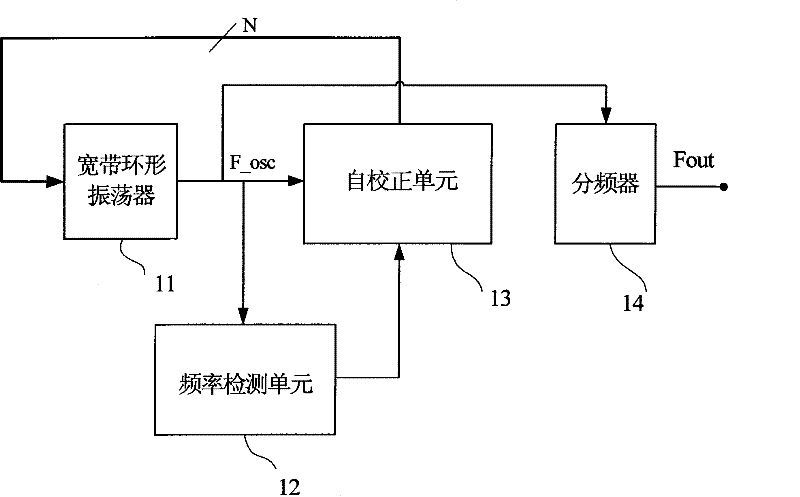

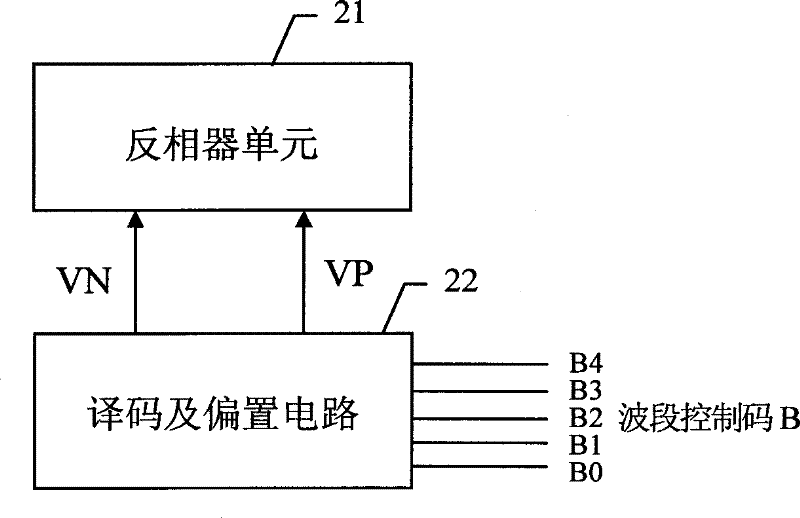

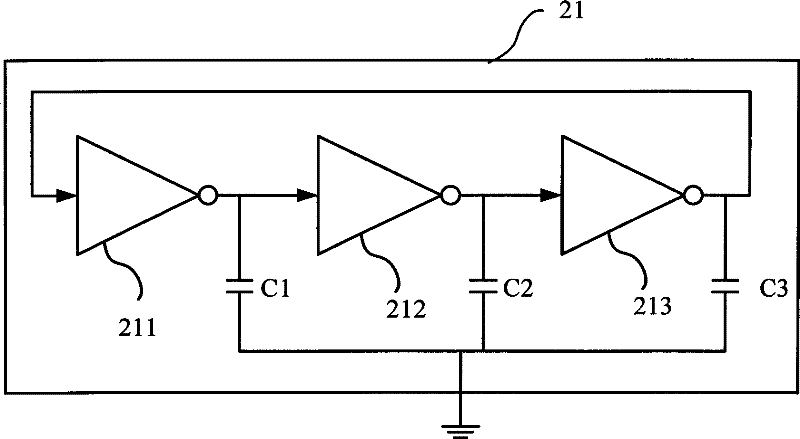

Clock generator with ultralow power consumption

ActiveCN102545838AReduce power consumptionReduced Power RequirementsElectric pulse generatorEngineeringClock generator

The invention discloses a clock generator with ultralow power consumption. The clock generator comprises a broadband annular oscillator, a self-correction unit, a frequency detection unit and a frequency divider, wherein the broadband annular oscillator which consists of a phase inverter unit and a decoding and biasing circuit supplies a linearly changed clock signal with a wide range; the self-correction unit which consists of a rising edge detector, a rising edge counter, a reference frequency divider, a state machine, a reference counter, a comparator and a parameter configuration unit is used for correcting change of an output clock of the broadband annular oscillator, which is caused by a process, temperature and voltage; the frequency detection unit which consists of a frequency detection enabling door, a frequency doubler, a detection counter, a parameter configuration unit and a comparator is used for detecting the output clock; and when the frequency offset of the output clock is greater than a preset value, the self-correction unit is started. The clock generator can adjust the frequency of the output clock according to a requirement, has a simple structure, ultralow power consumption, a small area and high reliability, is easy to integrate, and can be widely applied to communication systems, and the shortcoming of the frequency offset of the clock generator is overcome.

Owner:杭州中科微电子有限公司

Method and apparatus for calibrating a delay line

InactiveUS20060055441A1Reduce the differencePulse automatic controlDigital storagePropagation delayControl circuit

A delay line calibration circuit and method are provided in which a programmable master delay line drives a delay clock and has a propagation delay that is a function of a delay setting. A delay counter is clocked by the delay clock and has a delay count. A reference counter is clocked by a reference clock and has a reference count. A control circuit controls the delay and reference counters, compares a representation of the delay count to a representation of the reference count and responsively generates a modified value for the delay setting to reduce a difference between the representations of delay count and the reference count.

Owner:AVAGO TECH INT SALES PTE LTD

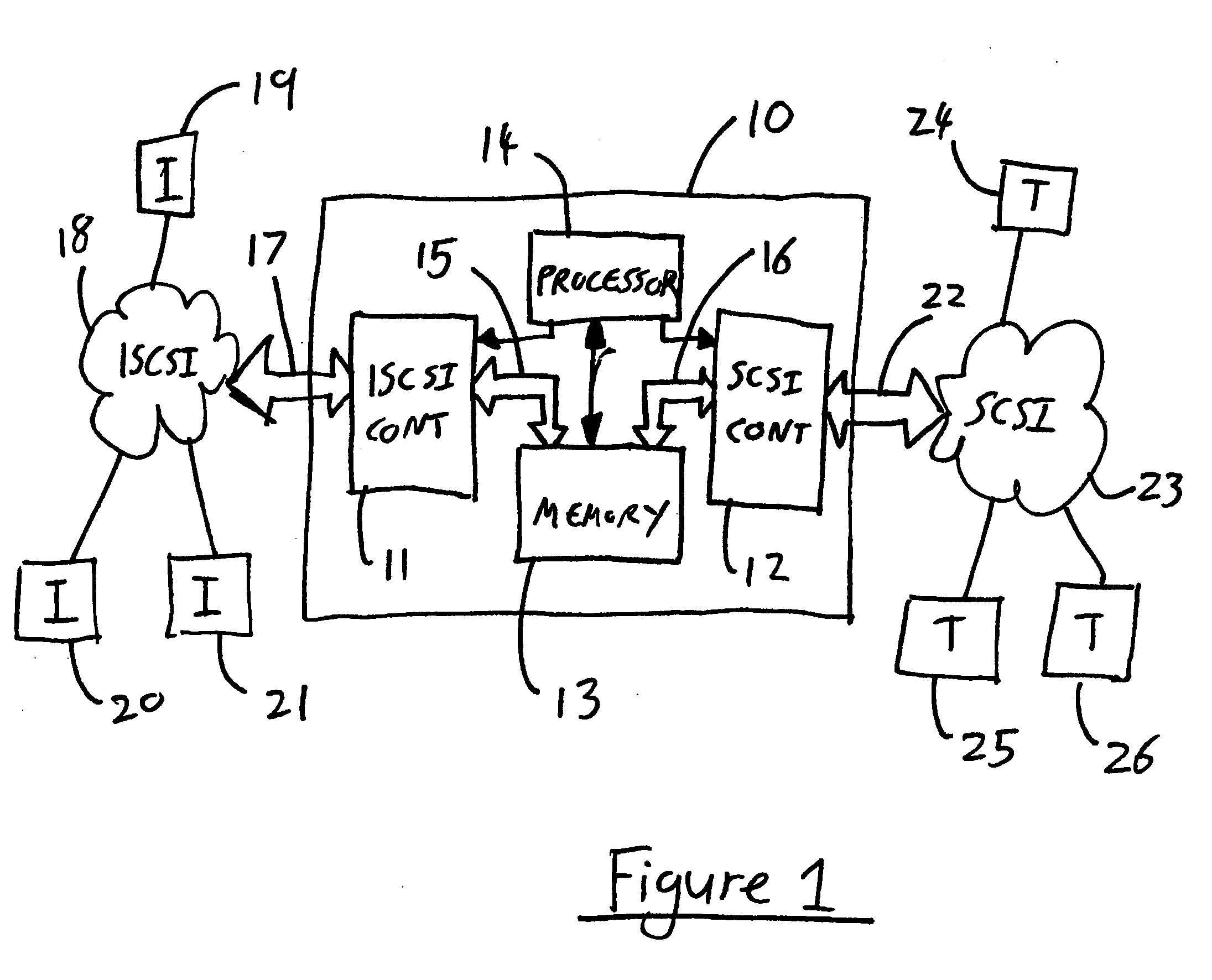

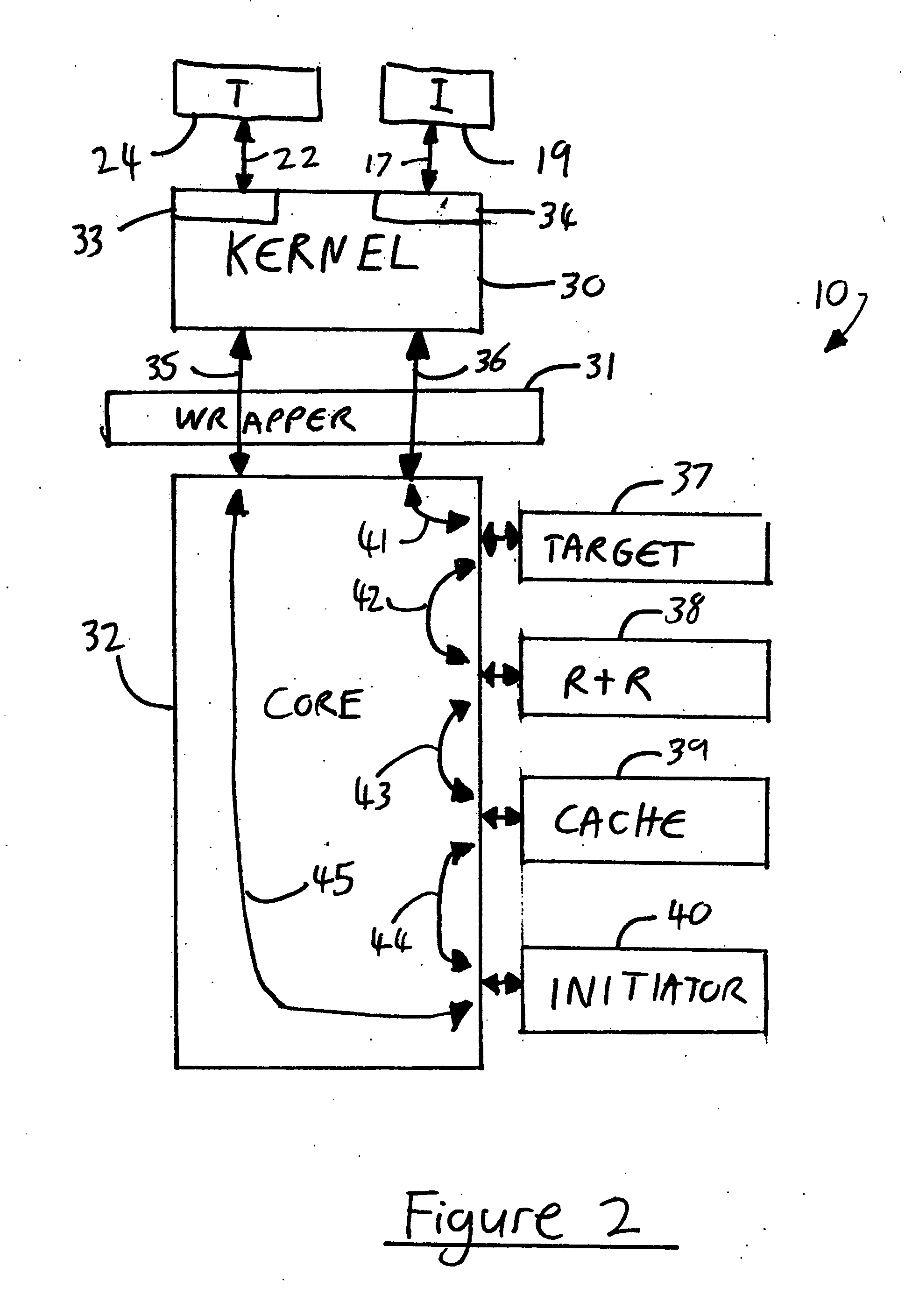

Message handling by a wrapper connected between a kernel and a core

ActiveUS20070288568A1Reduce probabilityProvides portabilityMultiple digital computer combinationsProgram controlMessage handlingSCSI

A wrapper operates to store data relating to messages received from a kernel such that kernel-specific data or information is not passed to a module core. The wrapper on receiving data from the module core uses the data stored in the relevant part of the memory to provide the data or information required by the kernel to handle the message. On receiving a message, the kernel begins to process it. At a certain point the wrapper intercepts the message and creates a SCSI data message and a PLUT element comprising a kernel pointer, a core pointer, and a reference counter. The kernel pointer is provided by the kernel and identifies a memory location where implementation-specific information pertaining to the message, pointers to raw data and a SCSI-formatted command descriptor block resides. The reference counter defines the number of times a message will be processed within the core before the related memory can be reused. The wrapper re-formats data and references the result by the core pointer.

Owner:BRIDGEWORKS LTD

Method for concurrently processing join in multi-core systems

The invention discloses a method for concurrently processing a join in multi-core systems. The method is used for effectively controlling a join life cycle and join state conversion through the comprehensive use of a fine-grained read-write lock, a spin lock, a join reference counter and a memory barrier so that the multi-core systems provide the integrity and consistency of data when sharing thesame join, and the correctness and the performance of the communication and control process of multi-core data are ensured.

Owner:BEIJING TOPSEC NETWORK SECURITY TECH

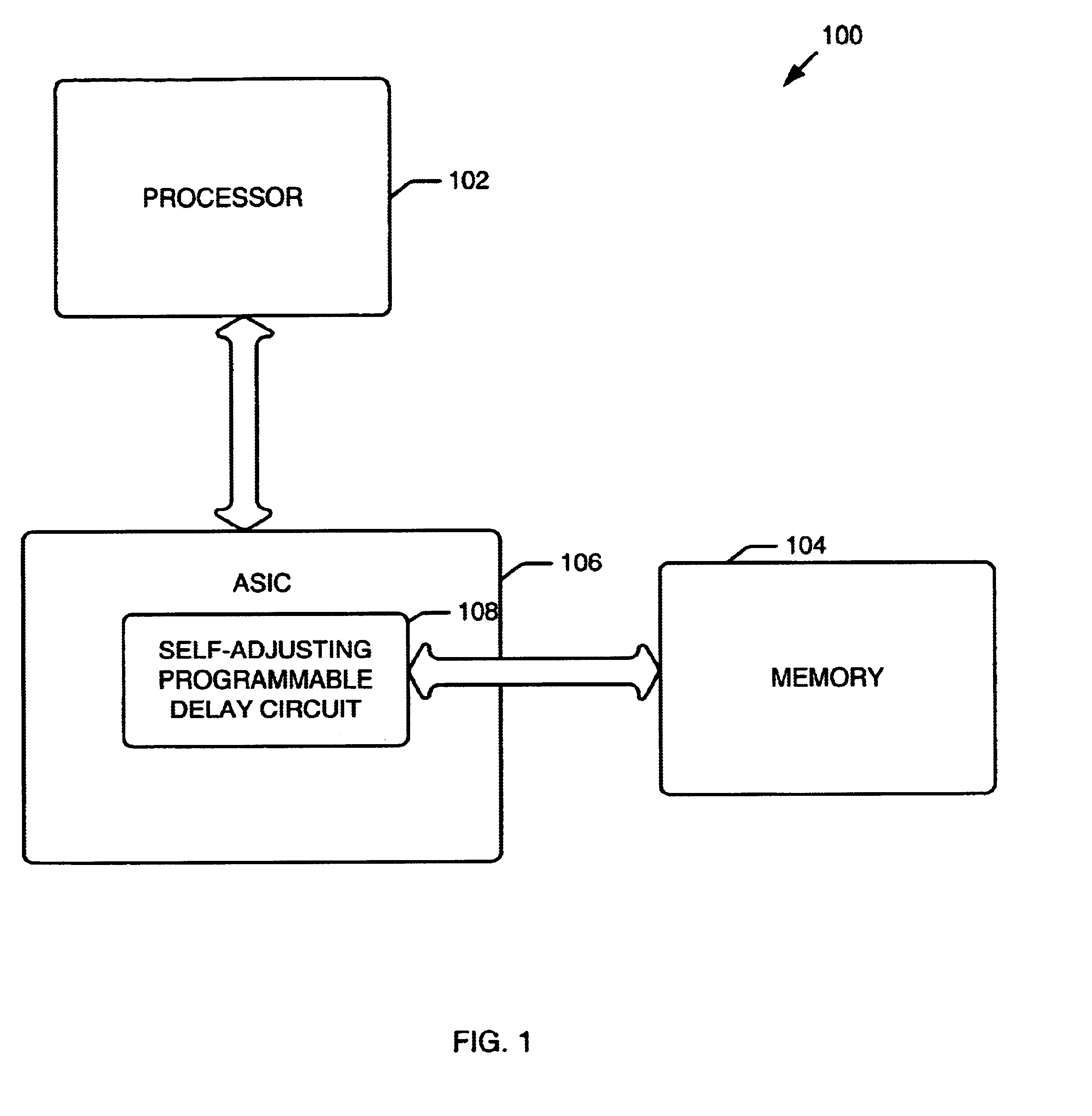

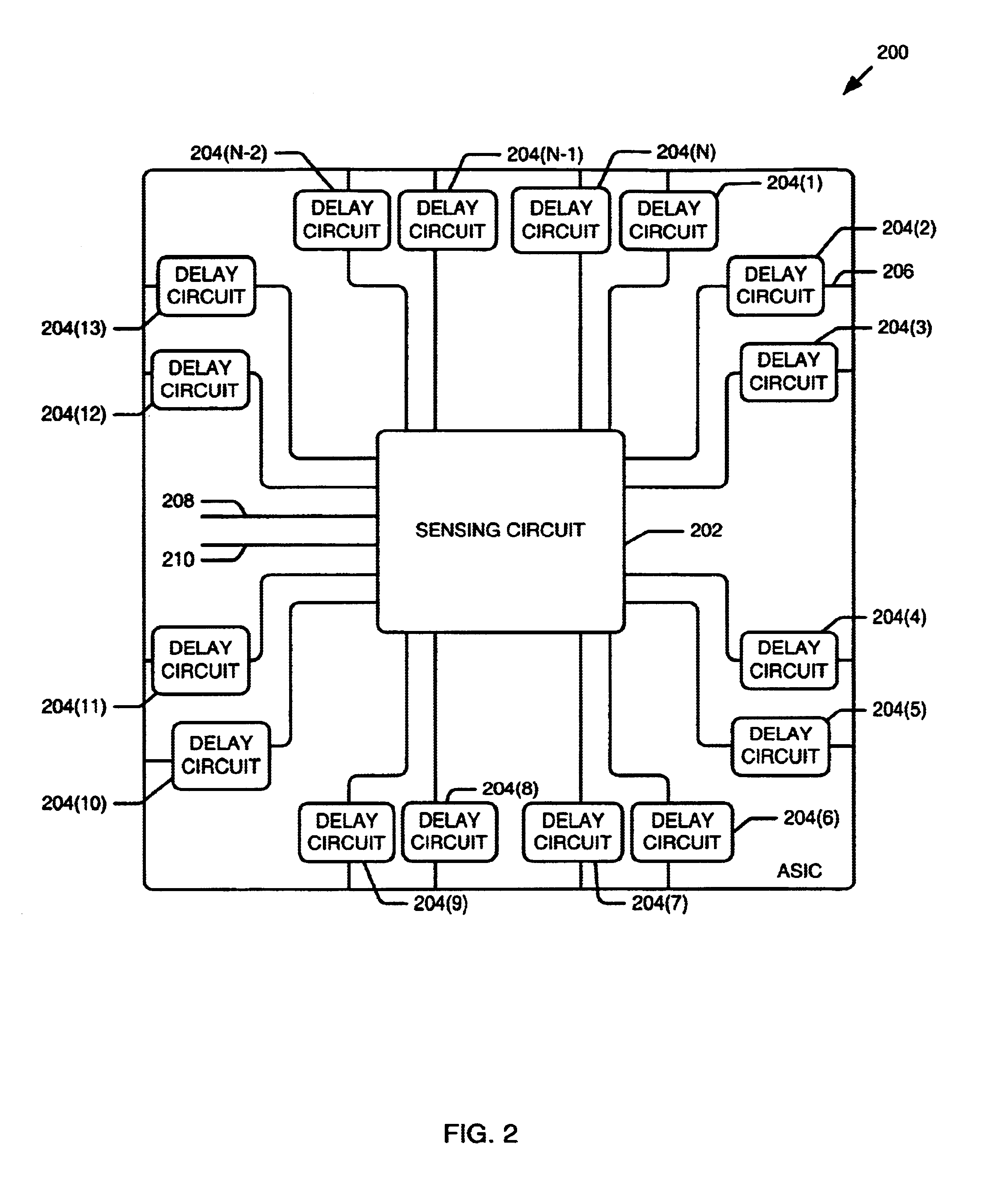

Self-adjusting programmable on-chip clock aligner

A circuit including a sensing circuit, which includes a first delay circuit and a tuning circuit. The tuning circuit includes a sense counter and a reference counter. The sense counter is coupled to the first delay circuit and is configured to count a number of oscillations provided by the first delay circuit and provide a notification to the tuning circuit when the sense counter reaches a threshold value. The reference counter is coupled to the sense counter and a reference clock. The reference counter is configured to store a reference time which represents a time elapsed for the sense counter to reach the threshold value. Also included in the circuit is a second delay circuit coupled to the sensing circuit.

Owner:CISCO TECH INC

Tracking asynchronous execution of program using hierarchical structure of objects

InactiveUS8032886B2Easy maintenanceReduce chanceError detection/correctionMultiprogramming arrangementsDebuggerSoftware

Owner:MICROSOFT TECH LICENSING LLC

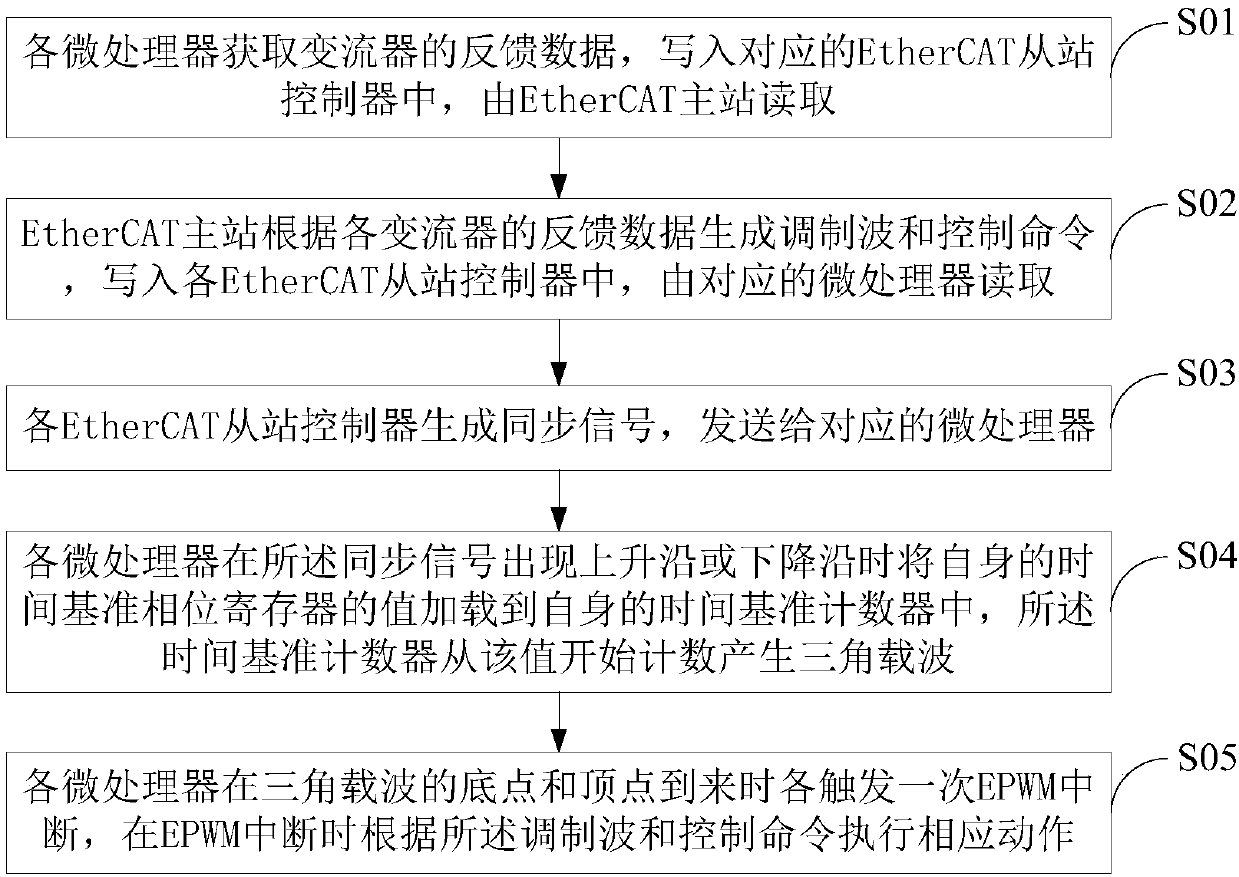

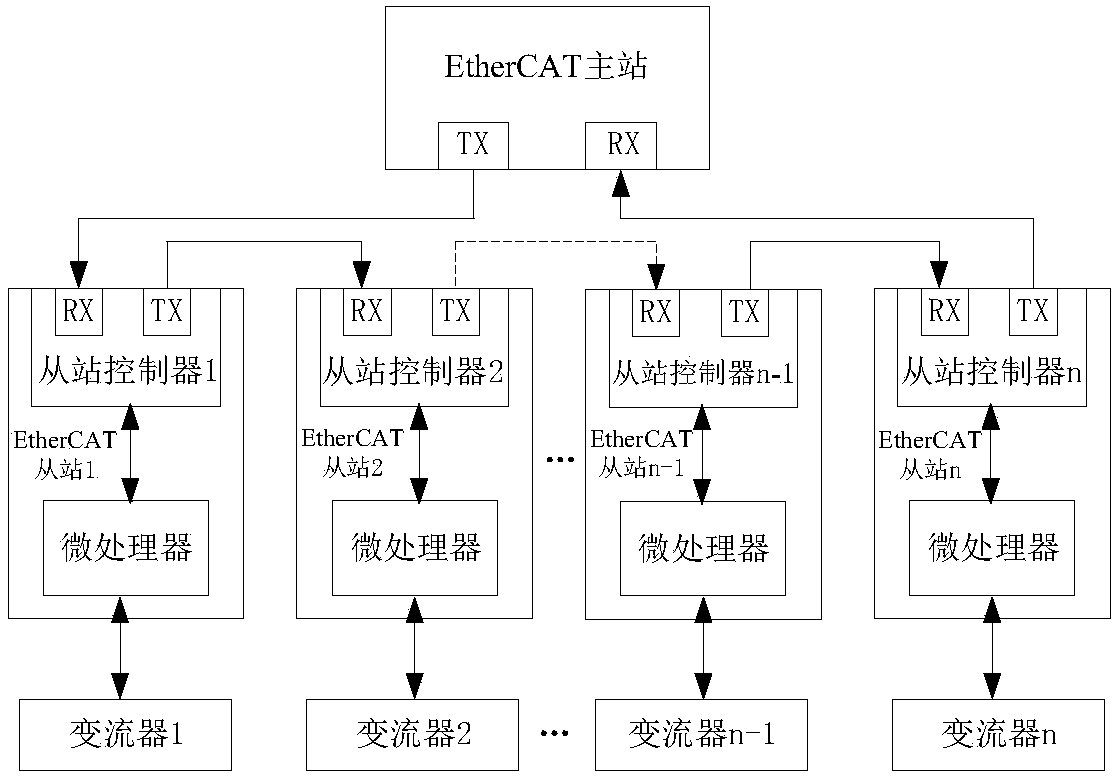

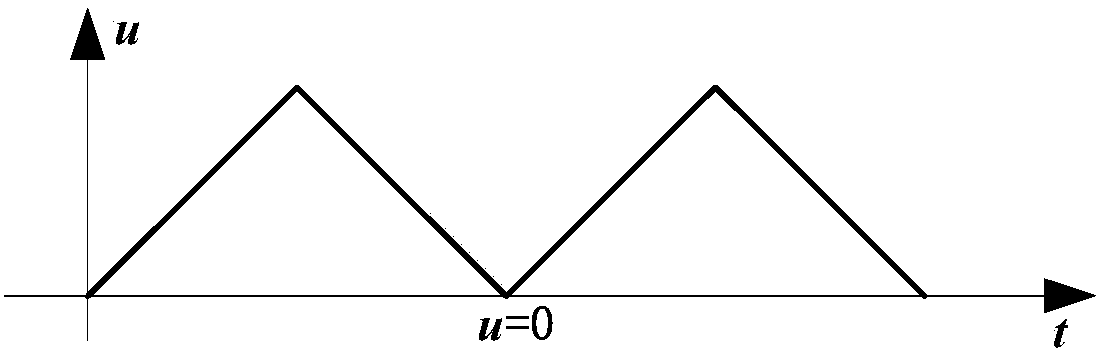

Converter parallel operation control method and converter parallel operation control system

The application discloses a converter parallel operation control method and a converter parallel operation control system. The system comprises an EtherCAT master station and the EtherCAT slave stations which are in one-to-one correspondence arrangement with the converters, each EtherCAT master station comprises a slave station controller and a microprocessor, and the EtherCAT master station and the EtherCAT slave stations are connected into a bus-type network topology structure. The EtherCAT slave station controllers are used to generate the synchronizing signals to send to the correspondingmicroprocessors, and the microprocessors load the values of the time reference phase registers as the counting initial values that the time reference counters count to generate the triangular carrierswhen the rising edges or the falling edges of the synchronizing signals occur, wherein the values of the time reference phase registers and the values of the periodic quantities of the time referencecounters satisfy the situation that the loading moments always occur when or before the nadir points of the triangular carriers arrive. According to the application, the synchronism of the carriers at the converter parallel operation is improved.

Owner:SUNGROW POWER SUPPLY CO LTD

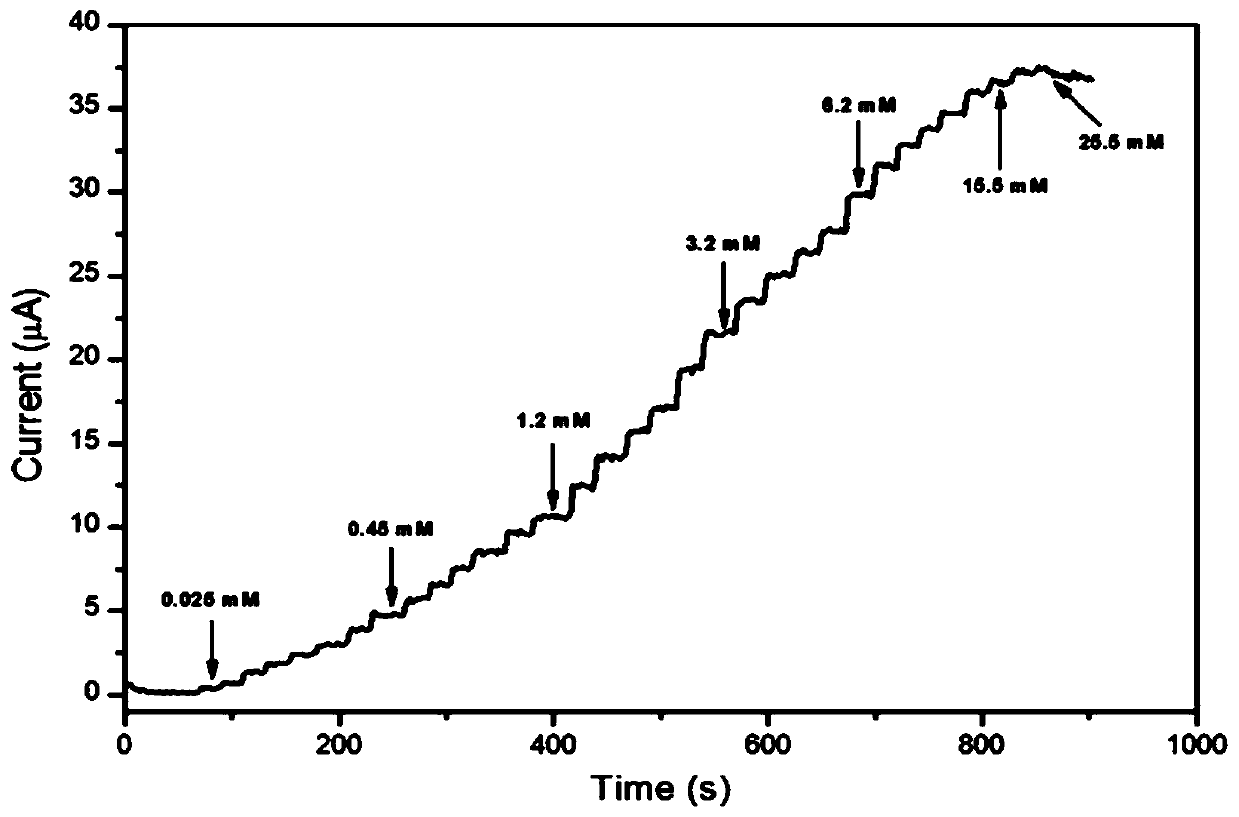

Glucose electrochemical microelectrode sensor based on nano porous metal film

PendingCN110618179AHigh sensitivityLarge linear rangeMaterial electrochemical variablesElectrochemistryPolymer

The invention discloses a preparation method of a nano porous metal film and a microelectrode sensor loaded with glucose oxidase (GOD) on the porous film for blood glucose monitoring, and relates to aprocessing technology of the porous metal film and a sensor technology. Metal and metal oxides of different proportions and thicknesses are subjected to magnetron co-sputtering on a polyimide substrate, treatment is conducted through deionized water or a weak acid solution to remove the metal oxides, metal layers which are each of a three-dimensional porous network structure and are interconnected are left to serves as a support layer and a conductive layer which are loaded with the GOD, the other side of the insulated substrate is coated with Ag / AgCl to serve as a reference-counter electrode, thus an electrochemical two-electrode system is constituted, then the substrate is coated with a high-molecular polymer to serve as a diffusion-limiting layer and an anti-interference hydrophilic layer, and then a glucose sensing microelectrode is constituted. The nano porous metal film is large in specific surface area, the active area of the electrode and the load amount of the GOD are effectively increased, permeability is good, conductivity is high, and physical damage to a microelectrode enzyme film sensing layer can be further prevented to a certain extent. The microelectrode sensor iswide in linear range and good in long-term stability.

Owner:ZHENGREN BEIJING MEDICAL INSTR CO LTD

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com