Clock generator with ultralow power consumption

A clock generator, ultra-low power consumption technology, applied in pulse generation, generation of electrical pulses, electrical components, etc., can solve the problems of inability to meet low power consumption requirements, high power consumption of clock generators, etc., achieve simple structure, ultra-high Low power consumption, small area effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0040] The specific implementation of the present invention will be described in detail below in combination with the embodiments and accompanying drawings, so as to further illustrate the technical solutions and beneficial effects of the present invention.

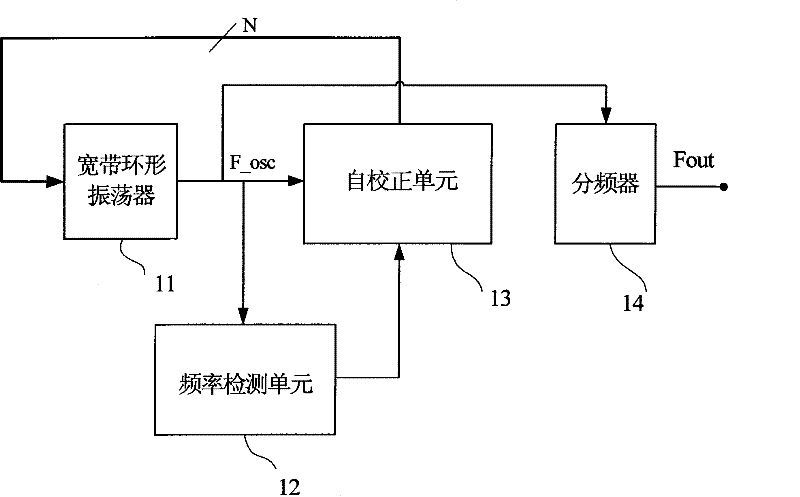

[0041] The compositional block diagram of the ultra-low power clock generator of the embodiment of the present invention, as figure 1 As shown, the clock generator with ultra-low power consumption includes a wideband ring oscillator 11 , a frequency detection unit 12 , a self-calibration unit 13 and a frequency divider 14 . The embodiment of the present invention is integrated on the circuit chip, without the need for a complex structure of the PLL, the output clock frequency is adjustable, and the output clock is kept constant under the conditions of process deviation, power supply voltage fluctuation, and temperature change, and the power consumption of the entire circuit is within 2 microns Ann the following. In this ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com