Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

338 results about "Mask set" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

A mask set or a photomask set is a series of electronic data that define geometry for the photolithography steps of semiconductor fabrication. Each of the physical masks generated from this data is called a photomask.

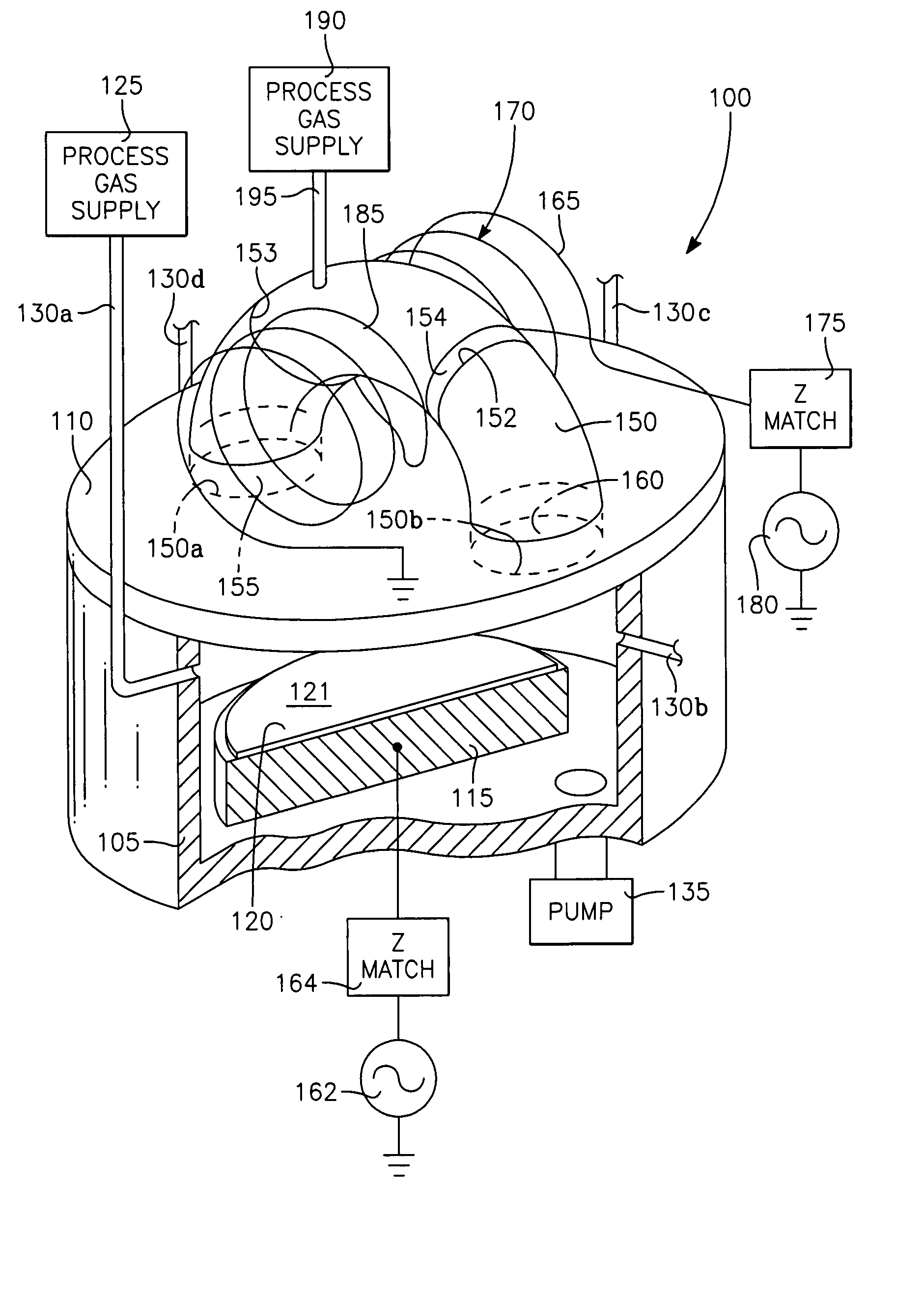

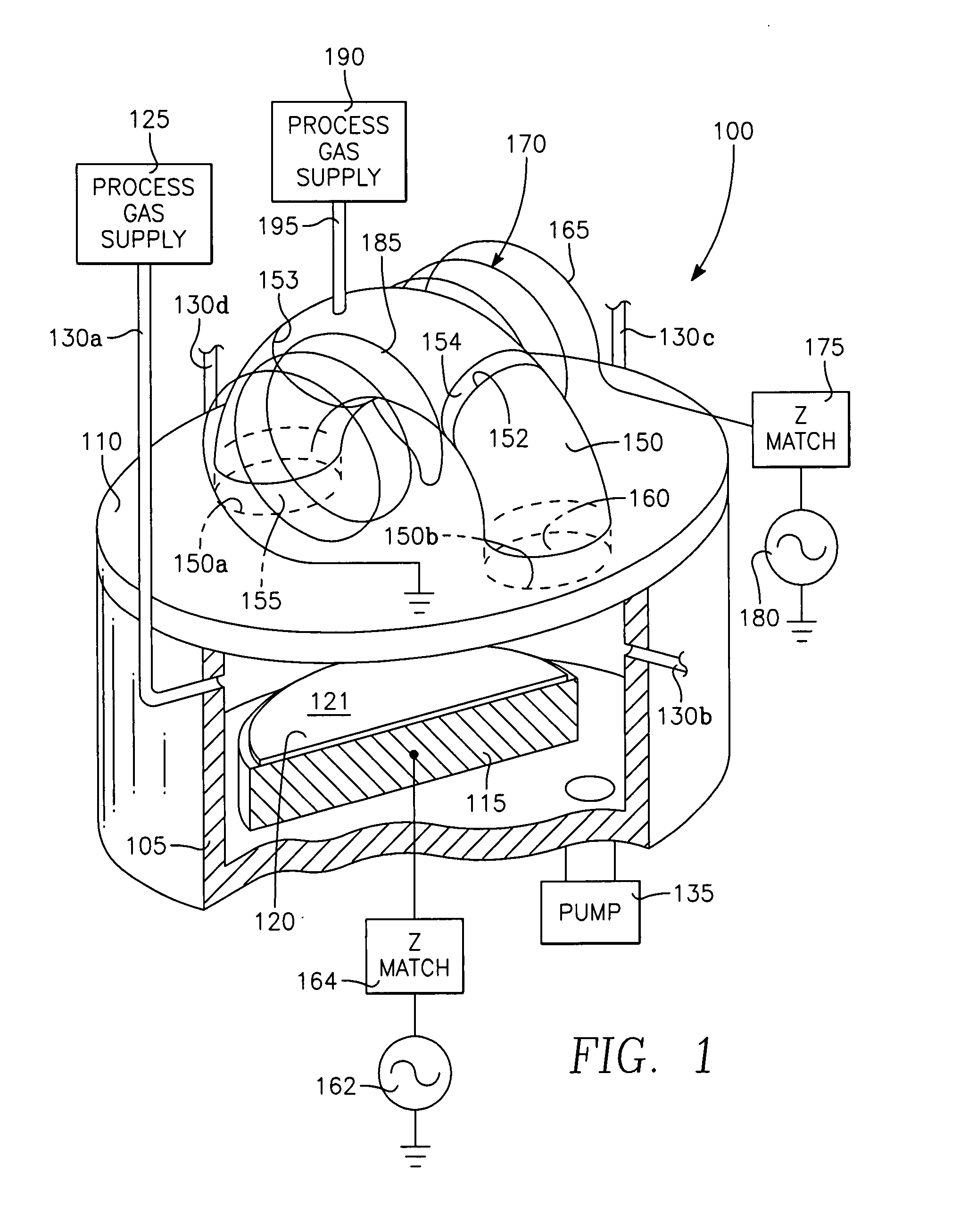

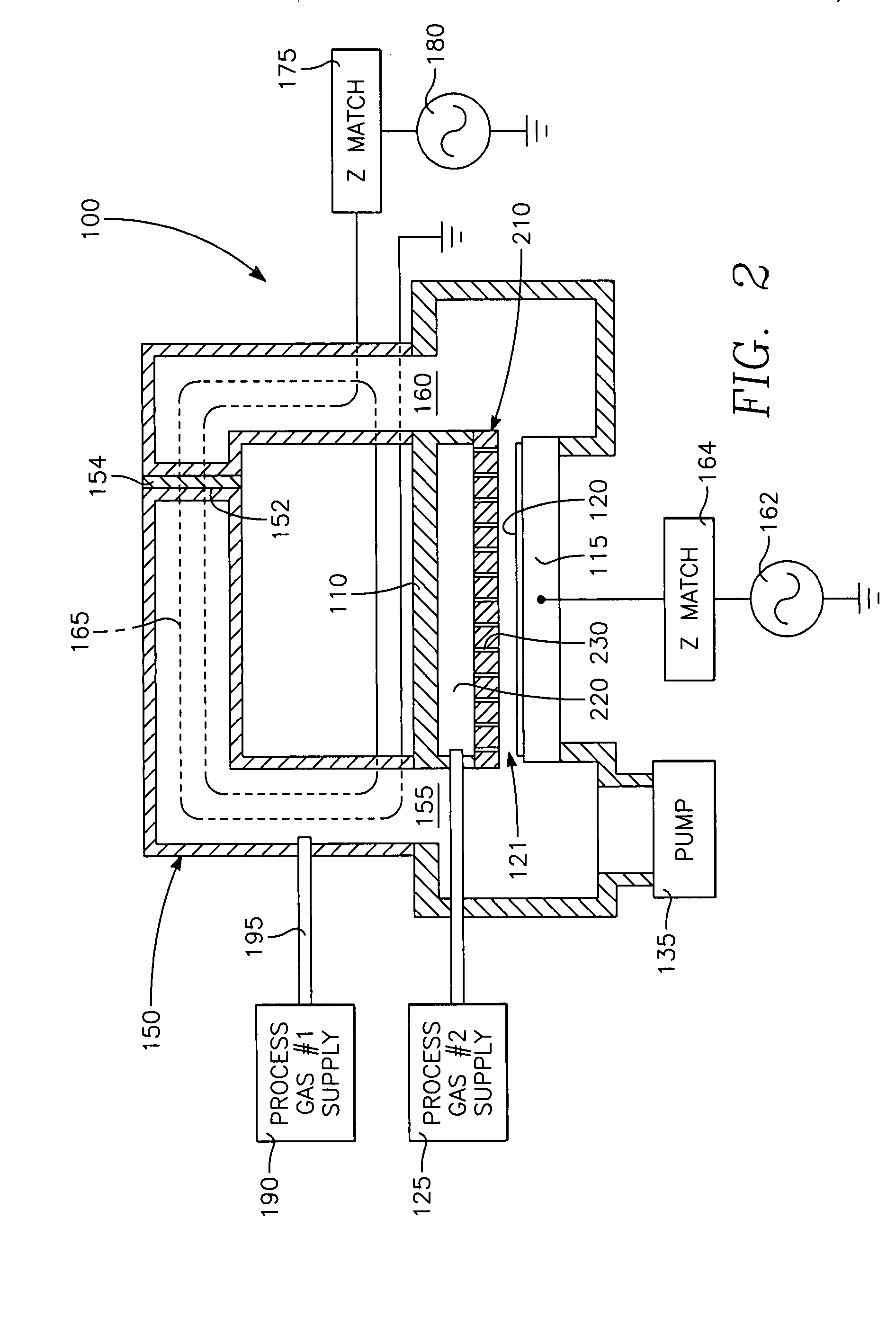

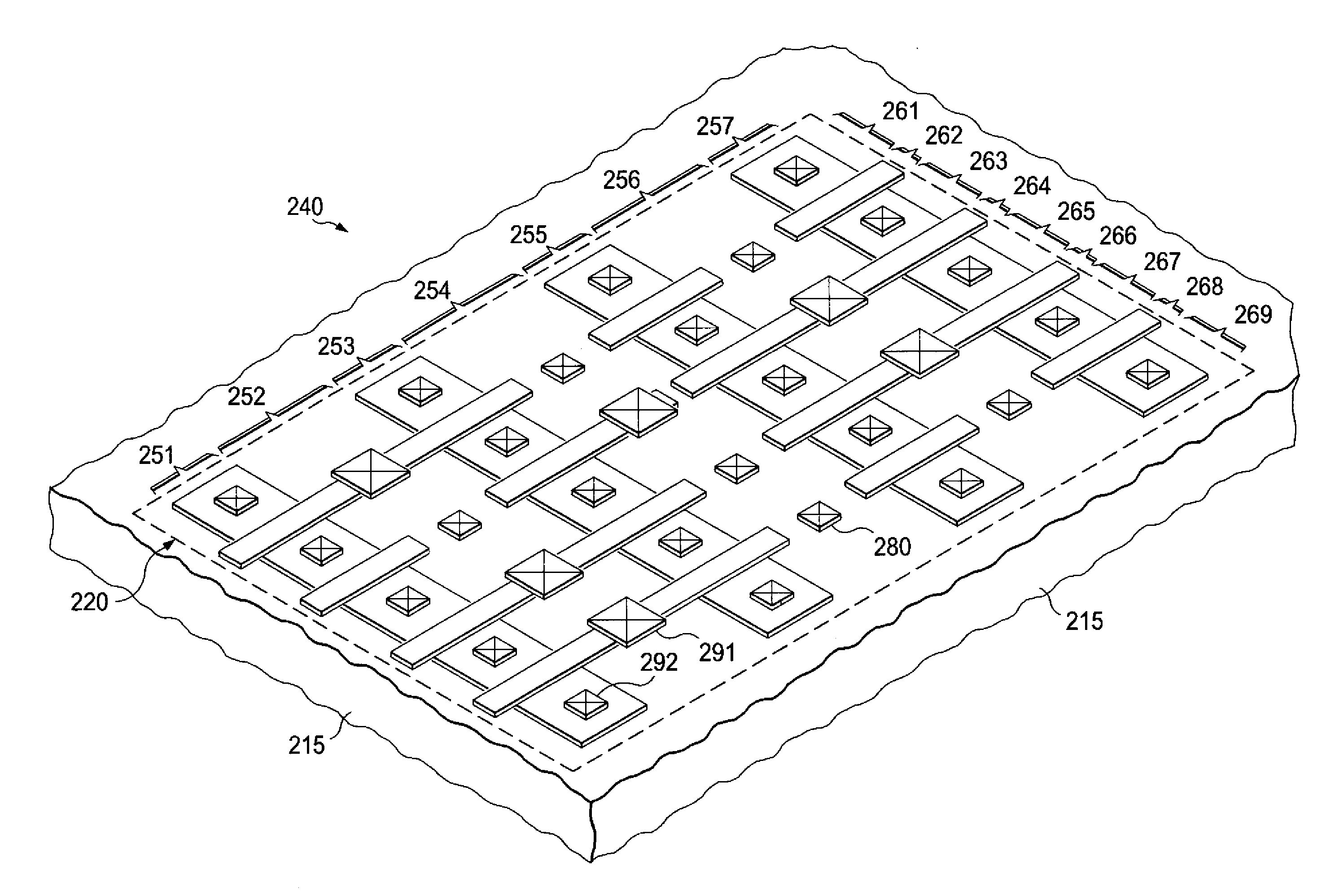

Low temperature CVD process with selected stress of the CVD layer on CMOS devices

Device-enhancing coatings are deposited on CMOS devices by successively masking with photoresist each one of the sets of N-channel and P-channel devices while unmasking or leaving unmasked the other set, and after each step of successively masking one of the sets of devices, carrying out low temperature CVD steps with a toroidal RF plasma current while applying an RF plasma bias voltage. The temperature of the workpiece is held below a threshold photoresist removal temperature. The RF bias voltage is held at a level at which the coating is deposited with a first stress when the unmasked set consists of the P-channel devices and with a second stress when the unmasked set consists of N-channel devices.

Owner:APPLIED MATERIALS INC

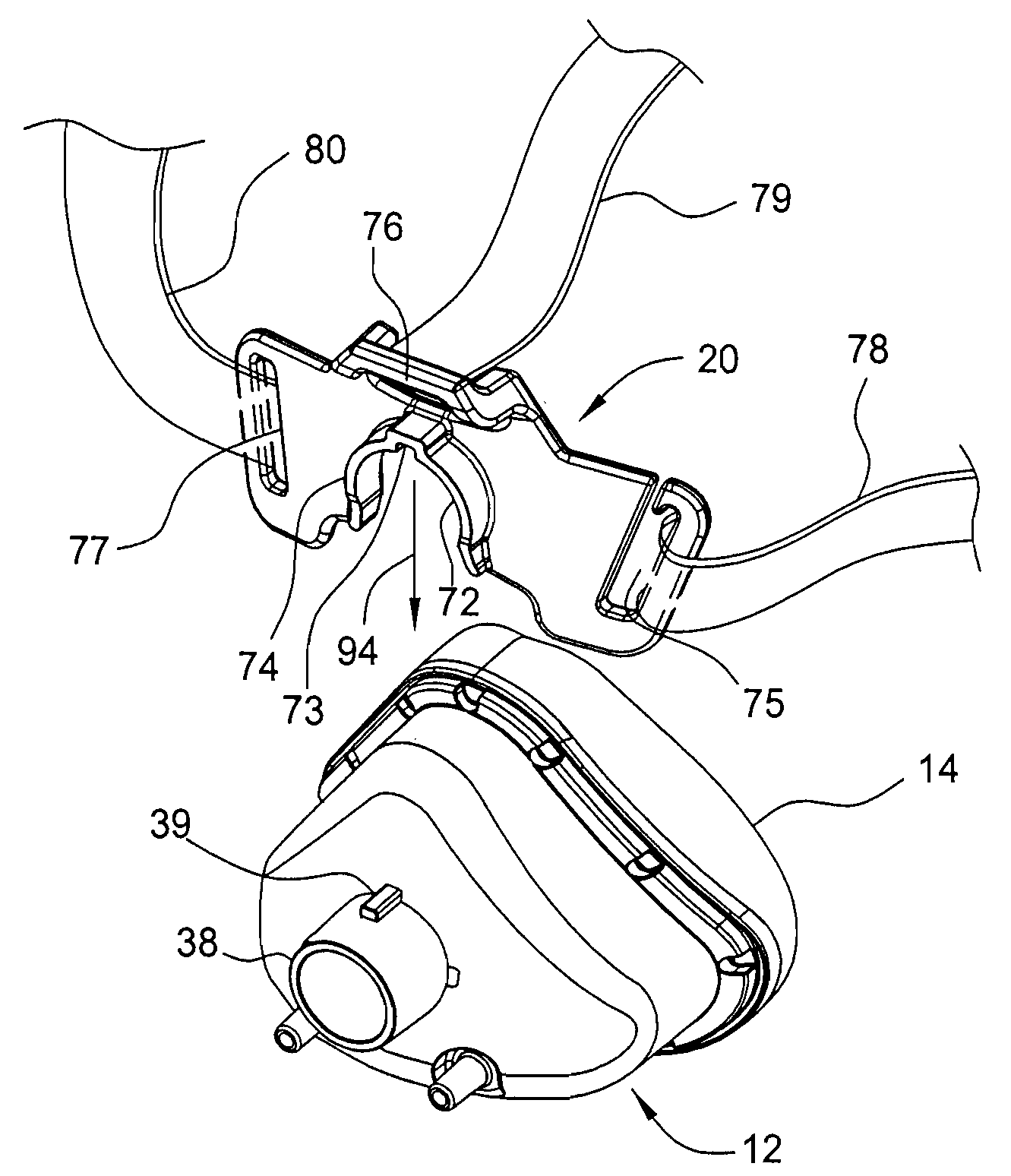

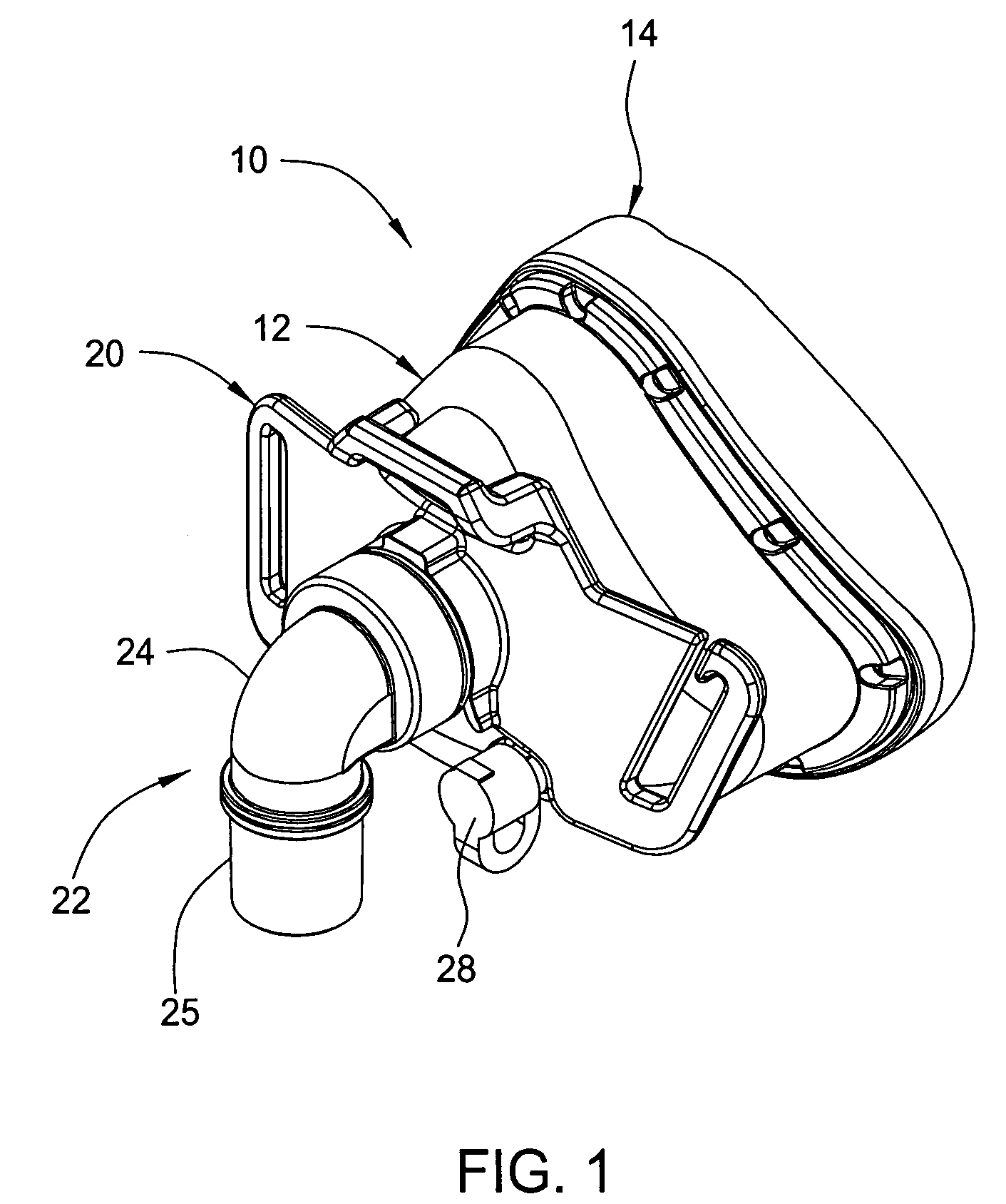

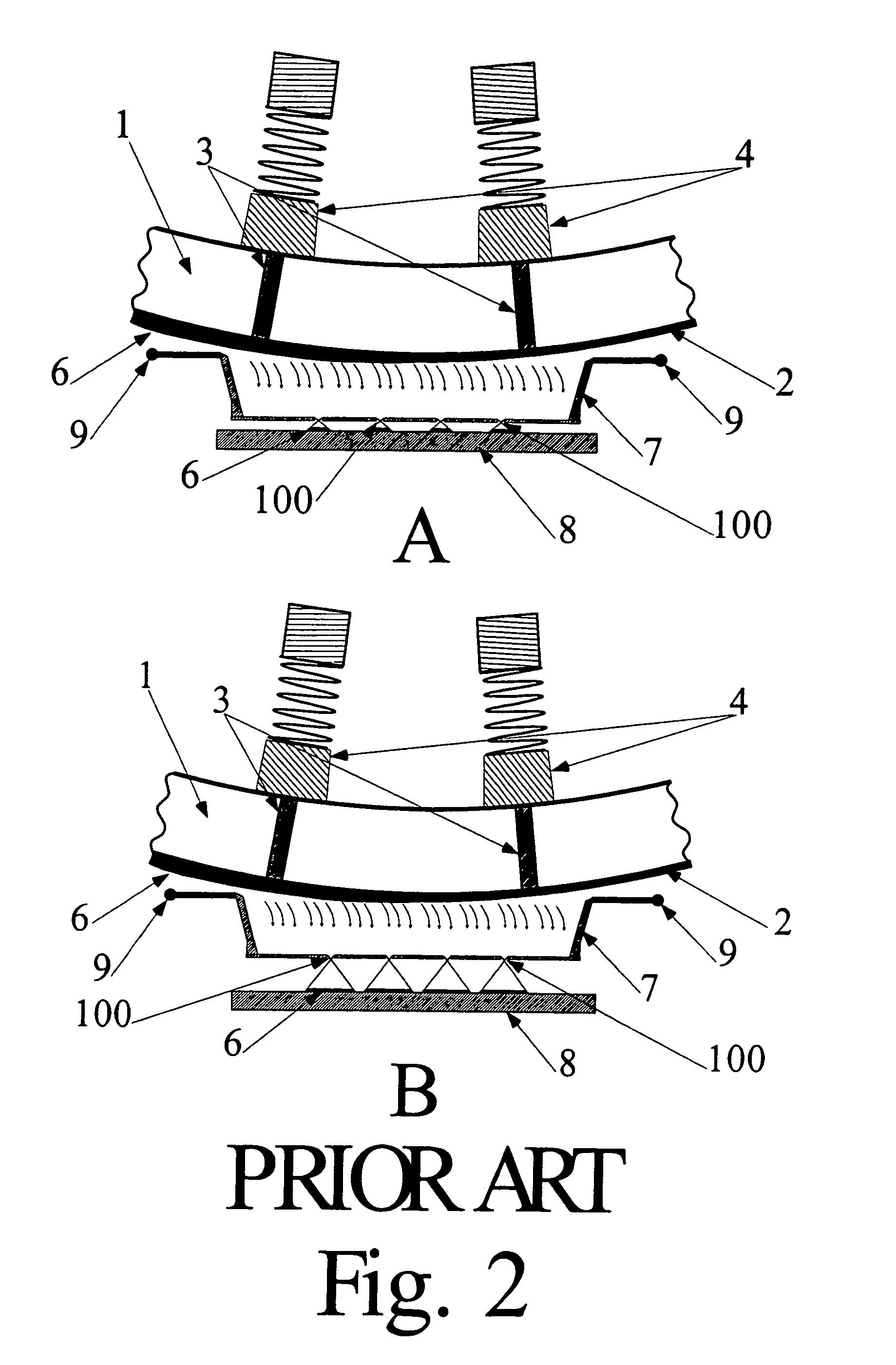

Mask, mask shell and seal with improved mounting, mask seal, method of mask manufacture and mask with reduced exhalation noise

Mask seal having an embedded mounting member for engaging a mounting member on a mask shell to mount the seal and shell together. Headstrap retention bracket having an indentation for wedgedly engaging a mask shell cylinder to removably mount headstraps to the shell, the indentation circumscribed by an outward wall. Triangular mask seal of styrene-ethylene butylene-styrene copolymer modified with mineral oil.

Owner:VITAL SIGNS INC

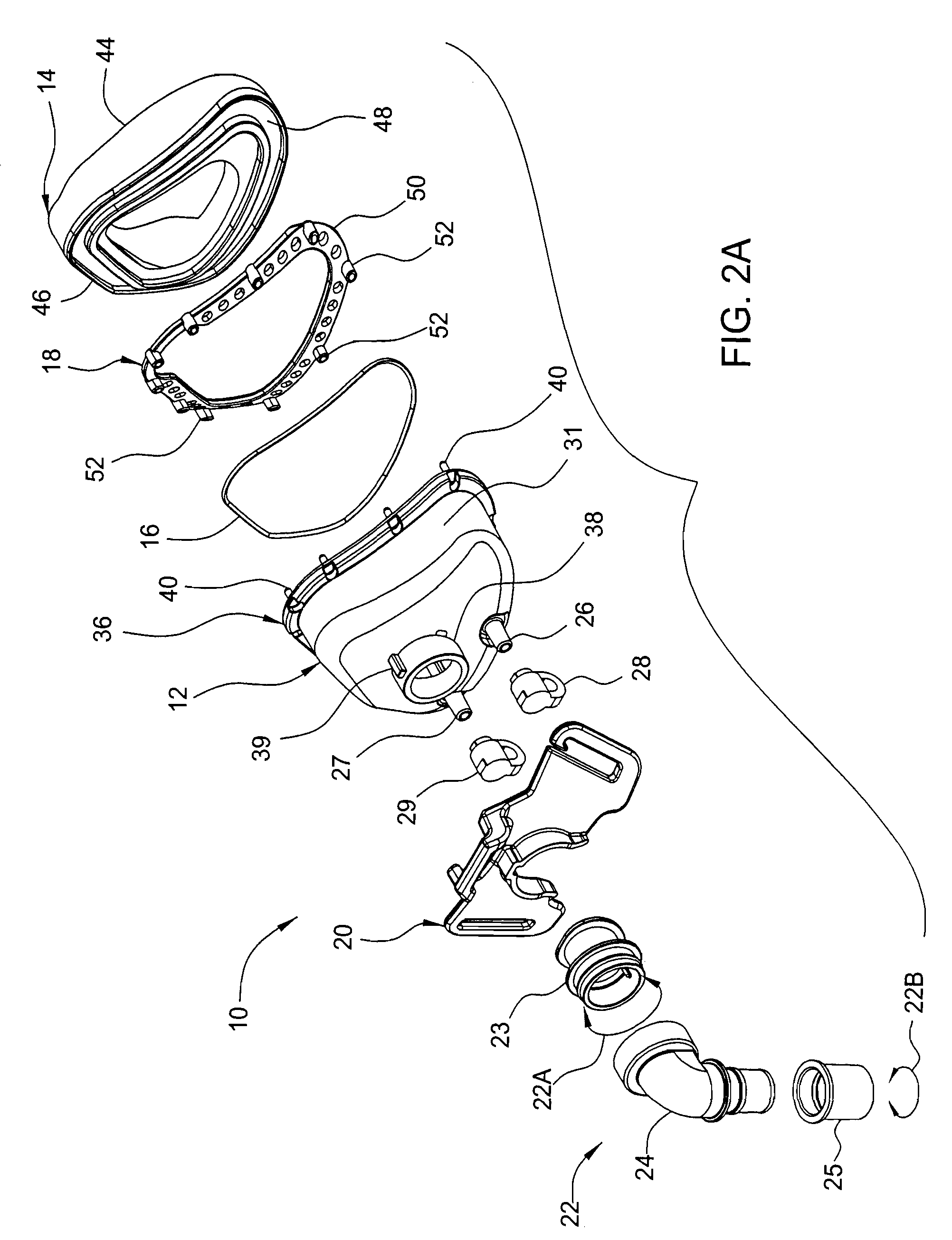

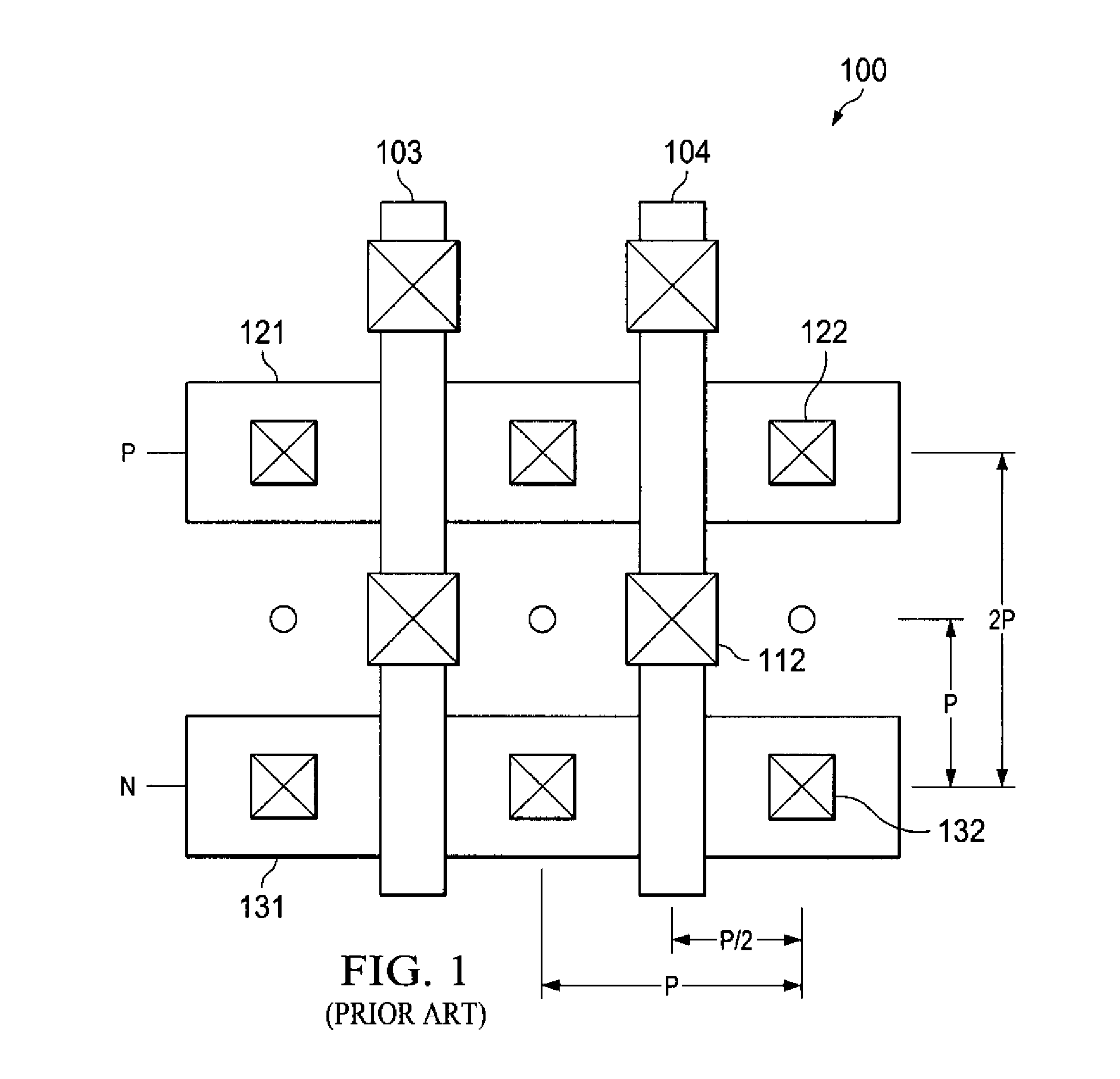

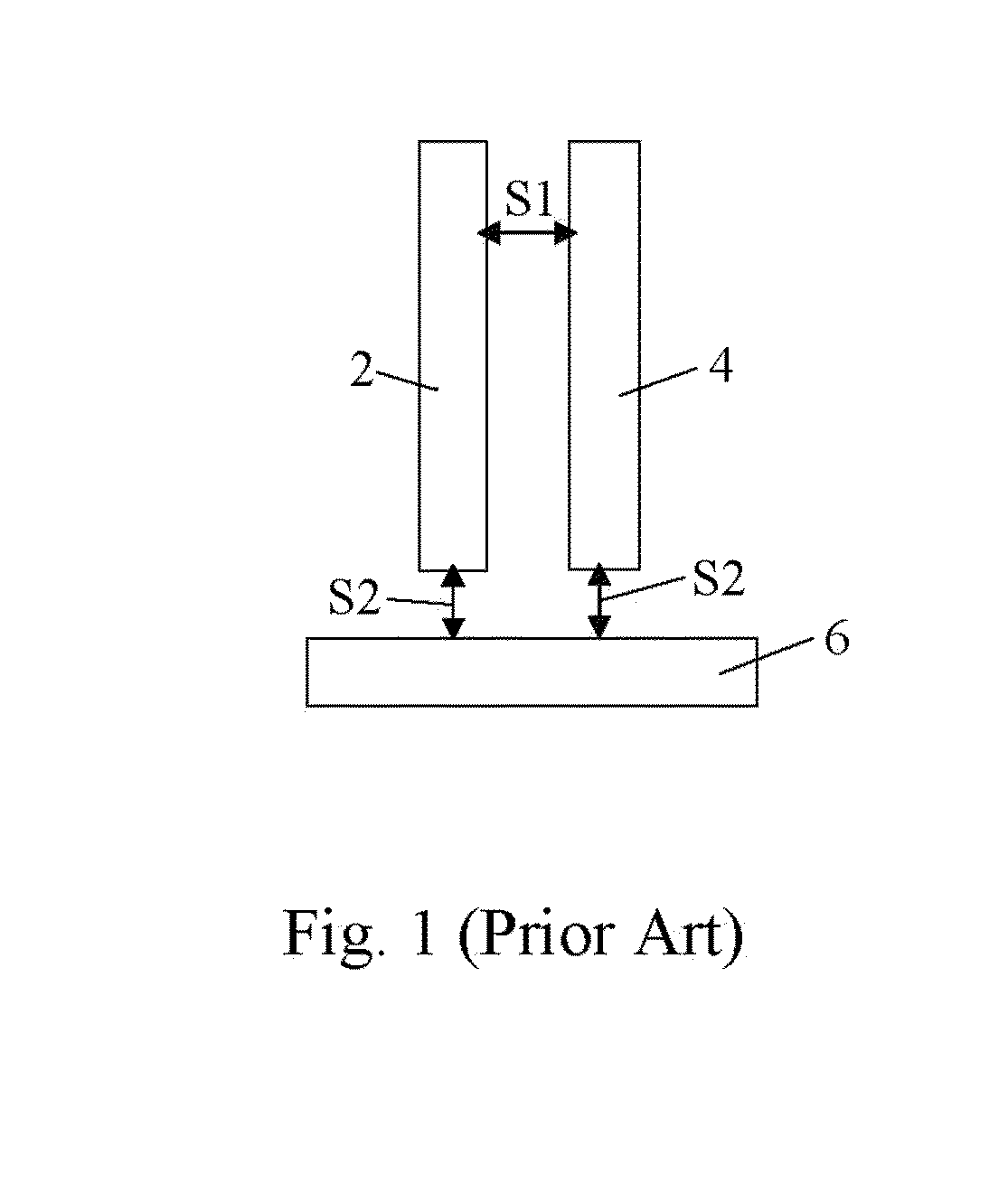

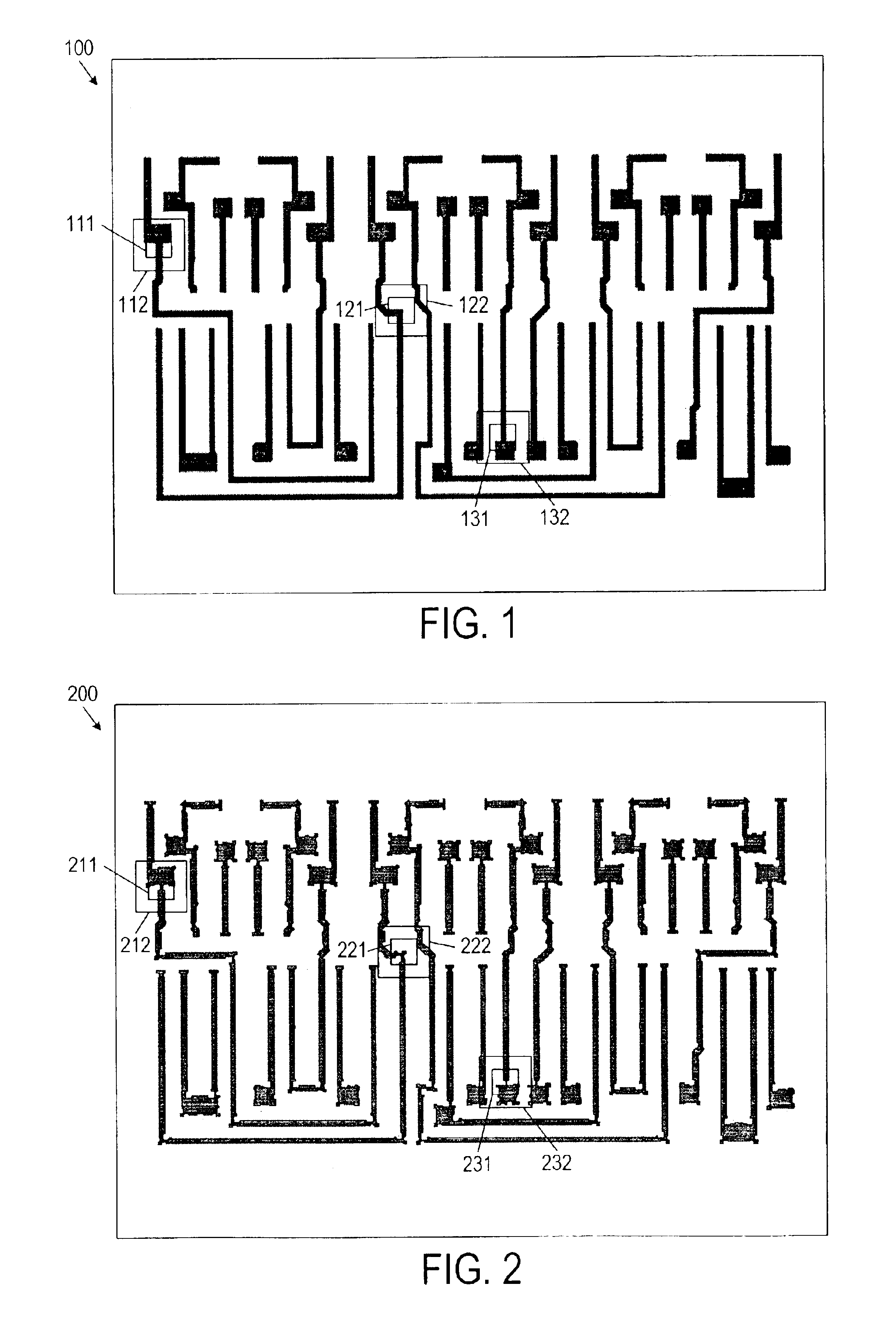

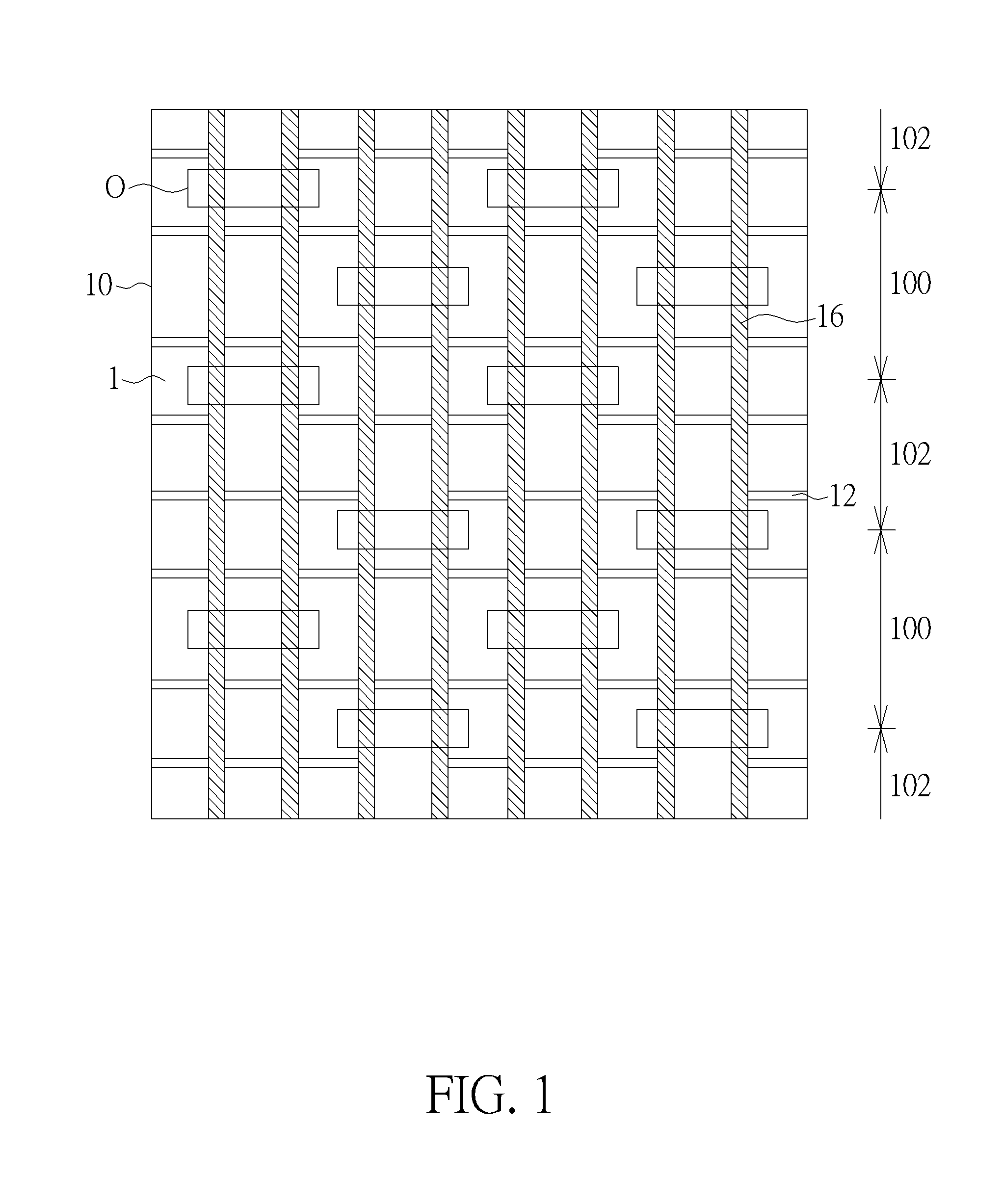

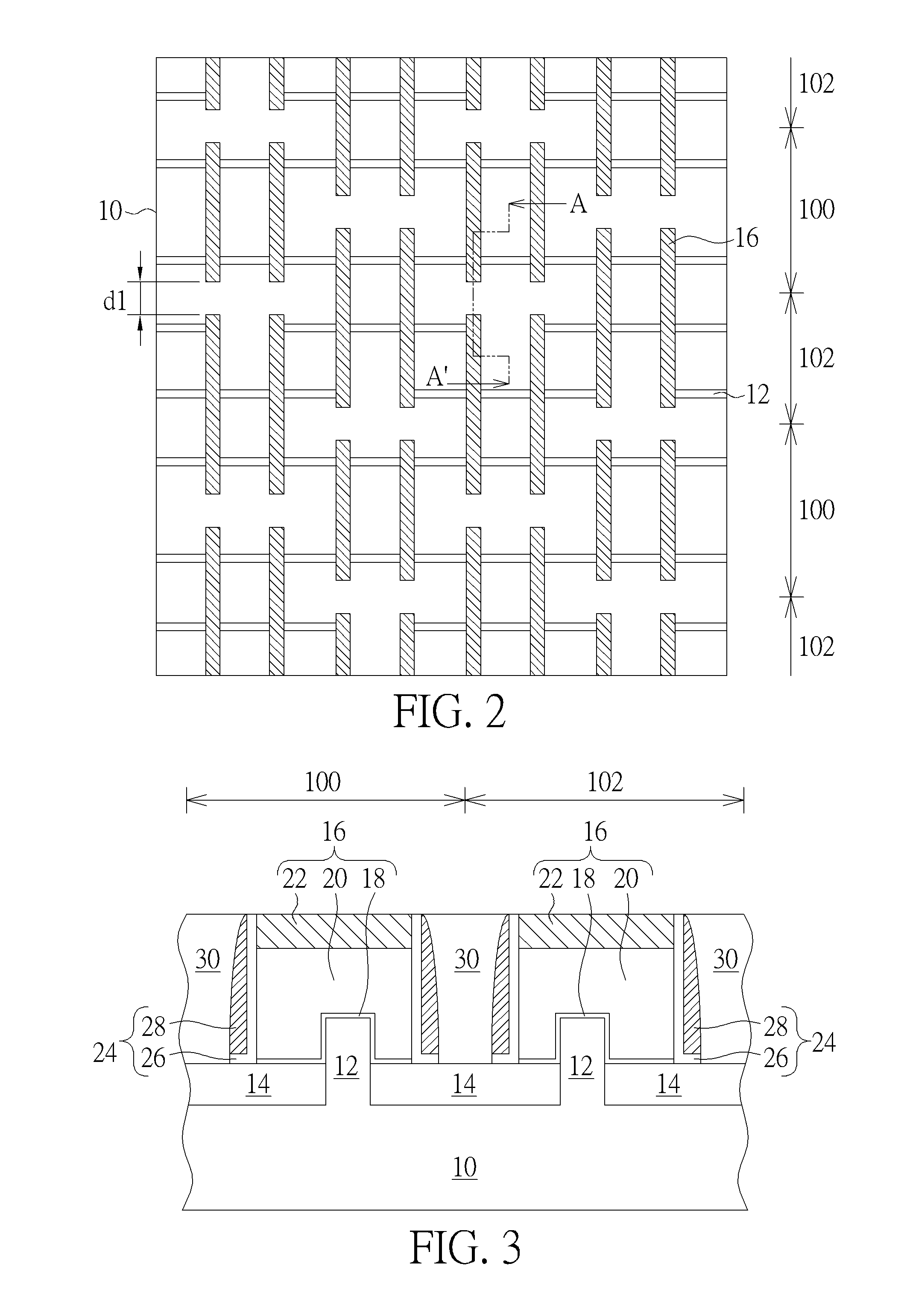

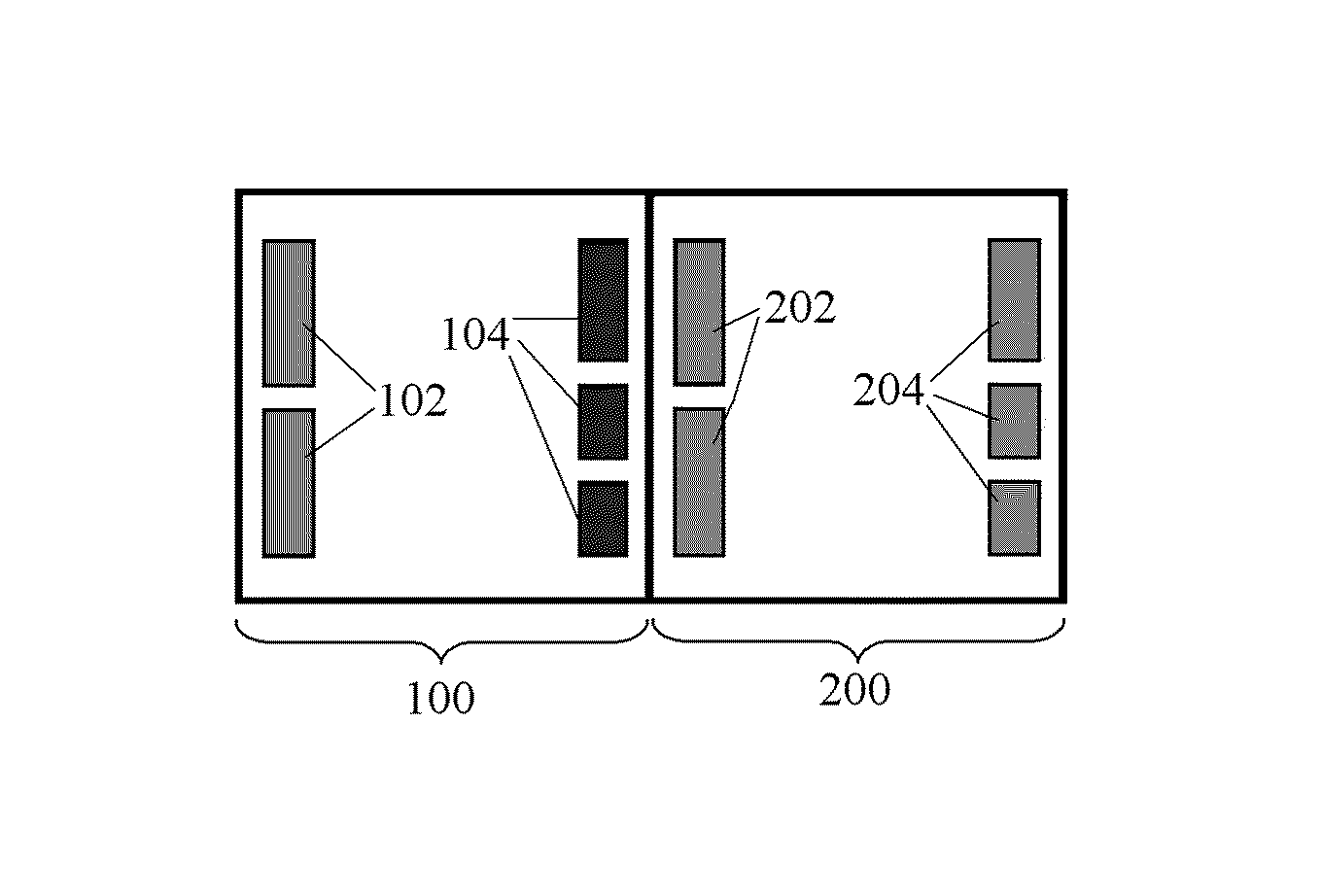

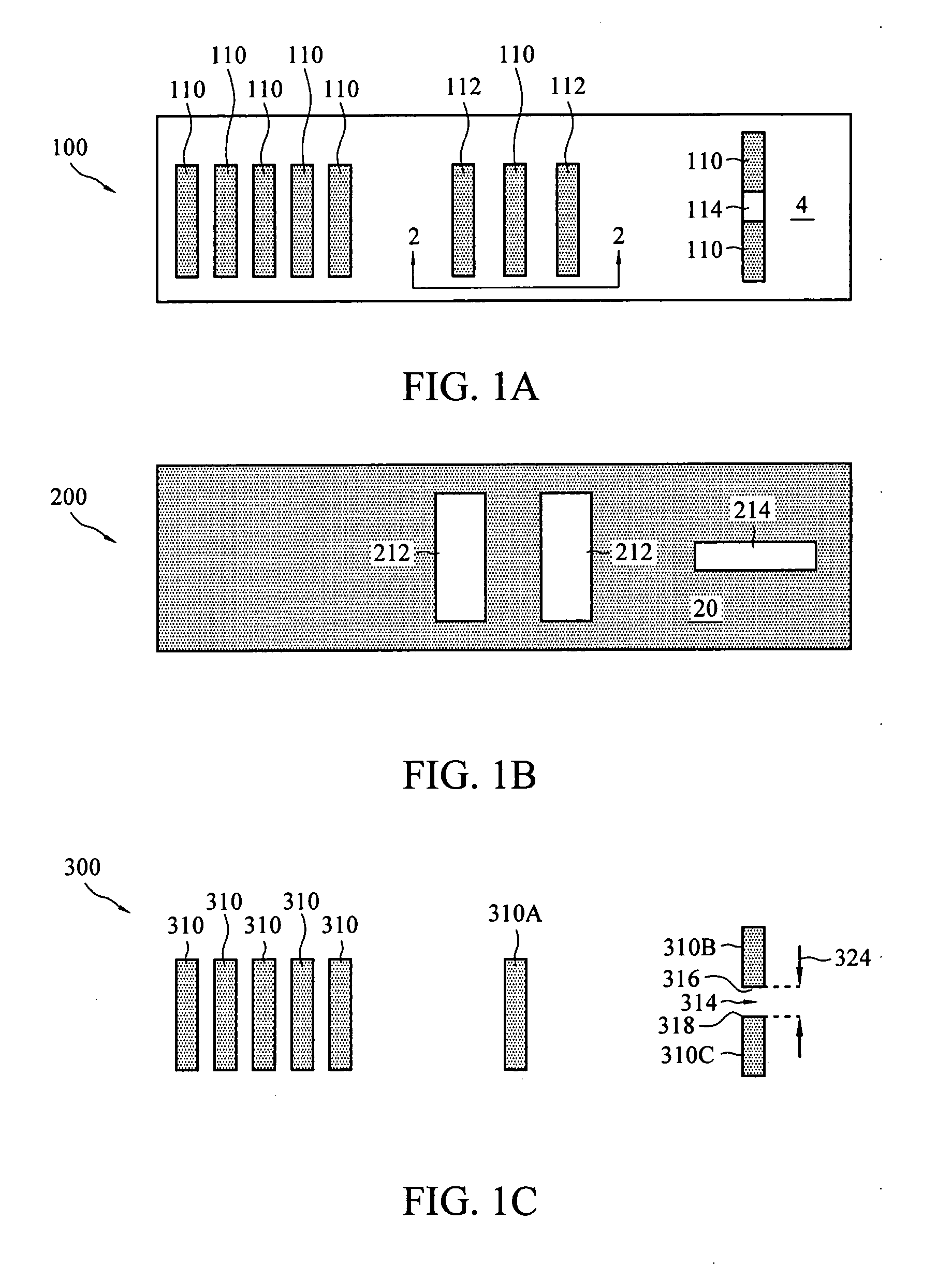

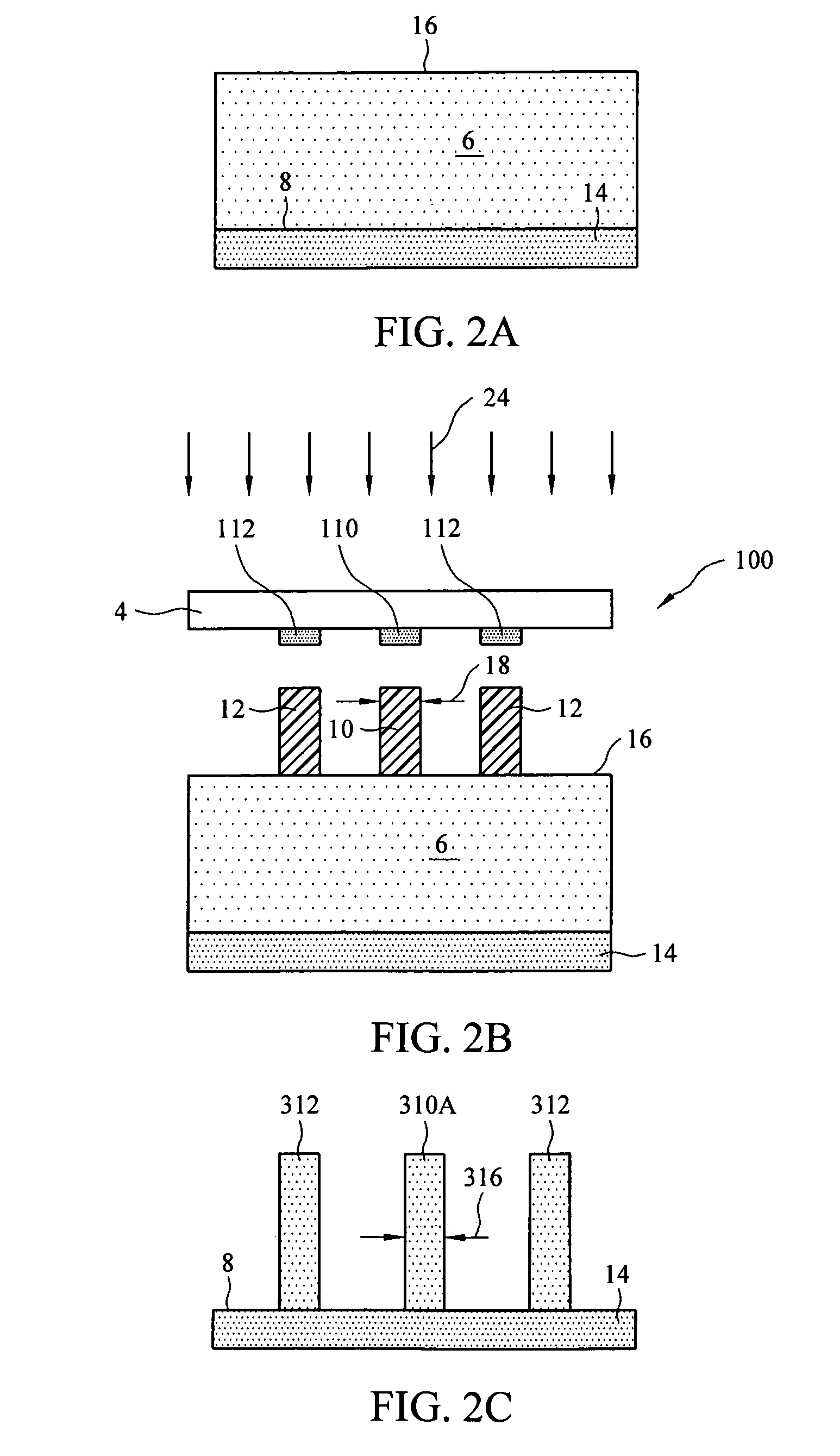

Integrated circuit having interleaved gridded features, mask set and method for printing

ActiveUS20090273100A1Easy interchangeTransistorSemiconductor/solid-state device detailsGrid patternEngineering

A method (300) for fabricating an integrated circuit includes the step of providing a substrate having a semiconductor surface (305). For at least one masking level (e.g. gate electrode, contact or via) of the integrated circuit, a mask pattern for the masking level is partitioned into a first mask and at least a second mask (310). The first mask provides features in a first grid pattern and the second mask provides features in a second grid pattern. The first and second grid pattern have respective features that interleave with one another over at least one area. A first photoresist film is applied onto the surface of the substrate (315). The first grid pattern is printed using the first mask (320). The second grid pattern is printed using the second mask (325). The first and said second grid pattern are then etched into the surface of the substrate (330). Another embodiment of the invention includes an integrated circuit (240) that has vias or contacts in a grid-like feature pattern in at least one multi-transistor area of the circuit including at least 5 transistors, wherein a minimum horizontal or minimum vertical center-to-center spacing distance between neighboring features in the pattern is ≦100 nm.

Owner:TEXAS INSTR INC

Gate critical dimension variation by use of ghost features

ActiveUS7569309B2Photomechanical apparatusSemiconductor/solid-state device manufacturingCritical dimensionComputer science

According to various embodiments, the present teachings include various methods for forming a semiconductor device, computer readable medium for forming a semiconductor device, mask sets for forming a semiconductor device, and a semiconductor device made according to various methods. For example, a method can comprise forming a first feature and a second feature on a substrate by exposing a first mask to a first beam, wherein the second feature is disposed adjacent to the first feature, exposing a second mask to a second beam, and removing the second feature from the substrate.

Owner:TEXAS INSTR INC

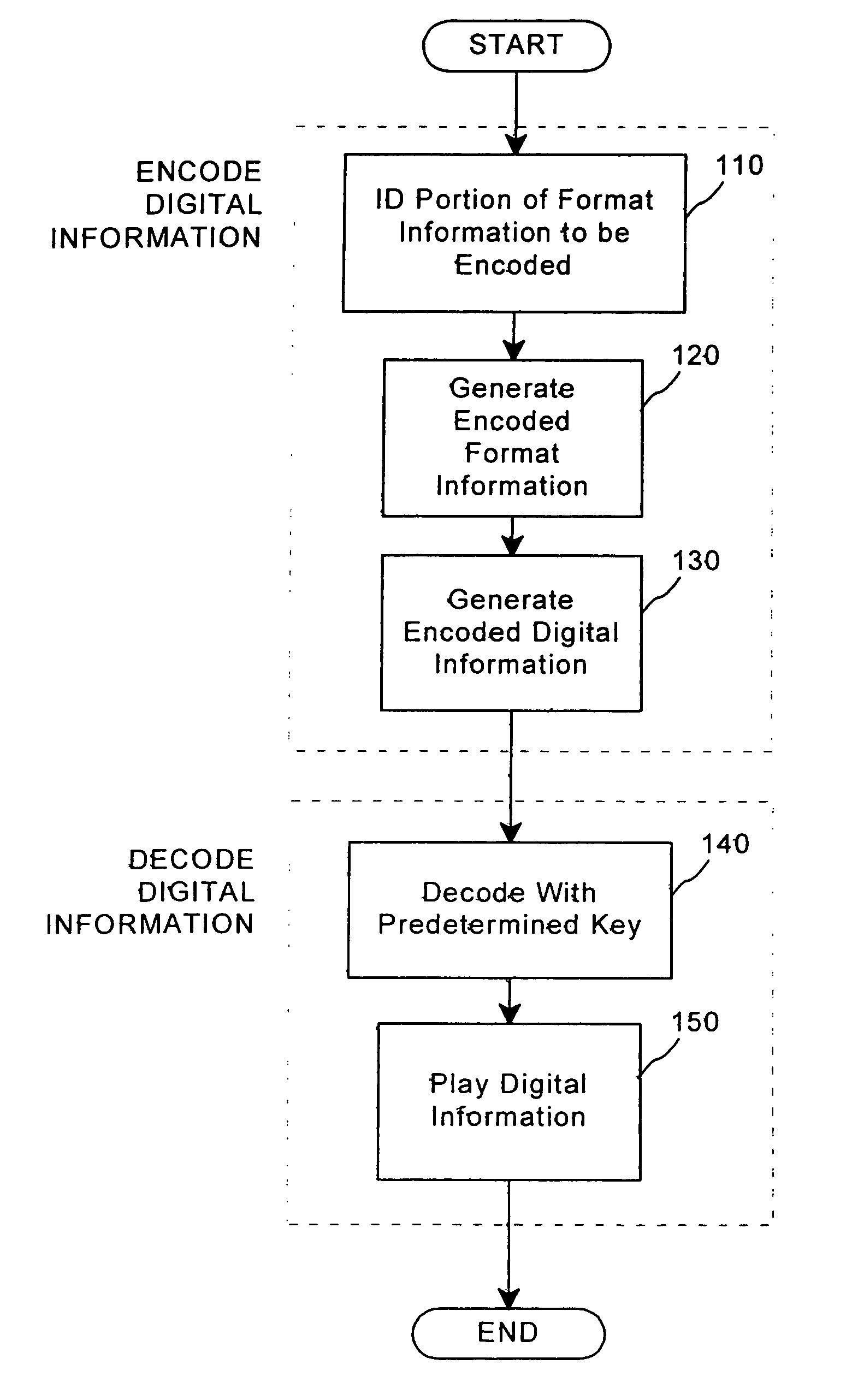

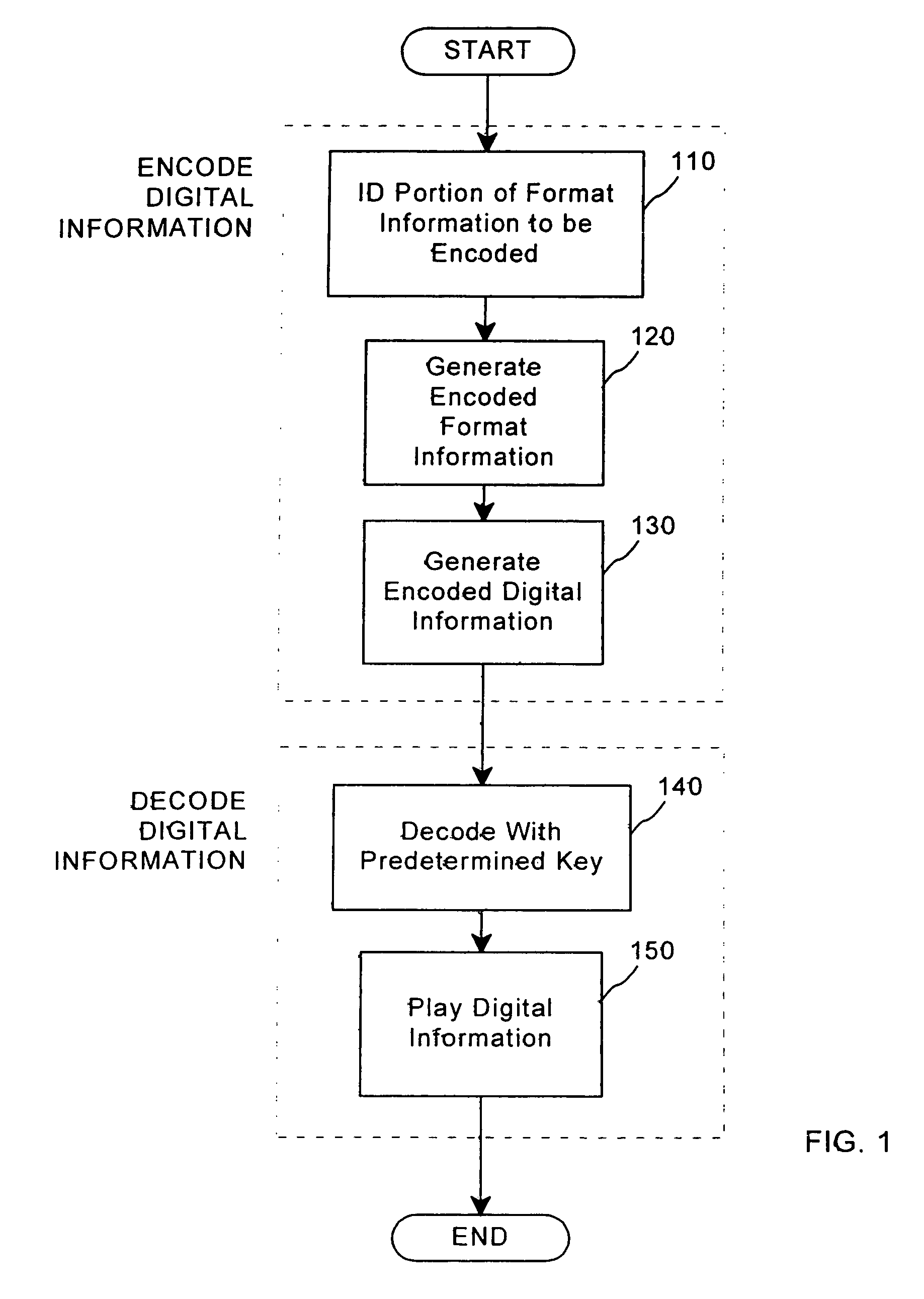

Method for combining transfer functions with predetermined key creation

InactiveUS7664263B2Data stream serial/continuous modificationDigital data processing detailsComputer hardwareGranularity

A method for combining transfer functions with predetermined key creation. In one embodiment, digital information, including a digital sample and format information, is protected by identifying and encoding a portion of the format information. Encoded digital information, including the digital sample and the encoded format information, is generated to protect the original digital information. In another embodiment, a digital signal, including digital samples in a file format having an inherent granularity, is protected by creating a predetermined key. The predetermined key is comprised of a transfer function-based mask set to manipulate data at the inherent granularity of the file format of the underlying digitized samples.

Owner:WISTARIA TRADING INC

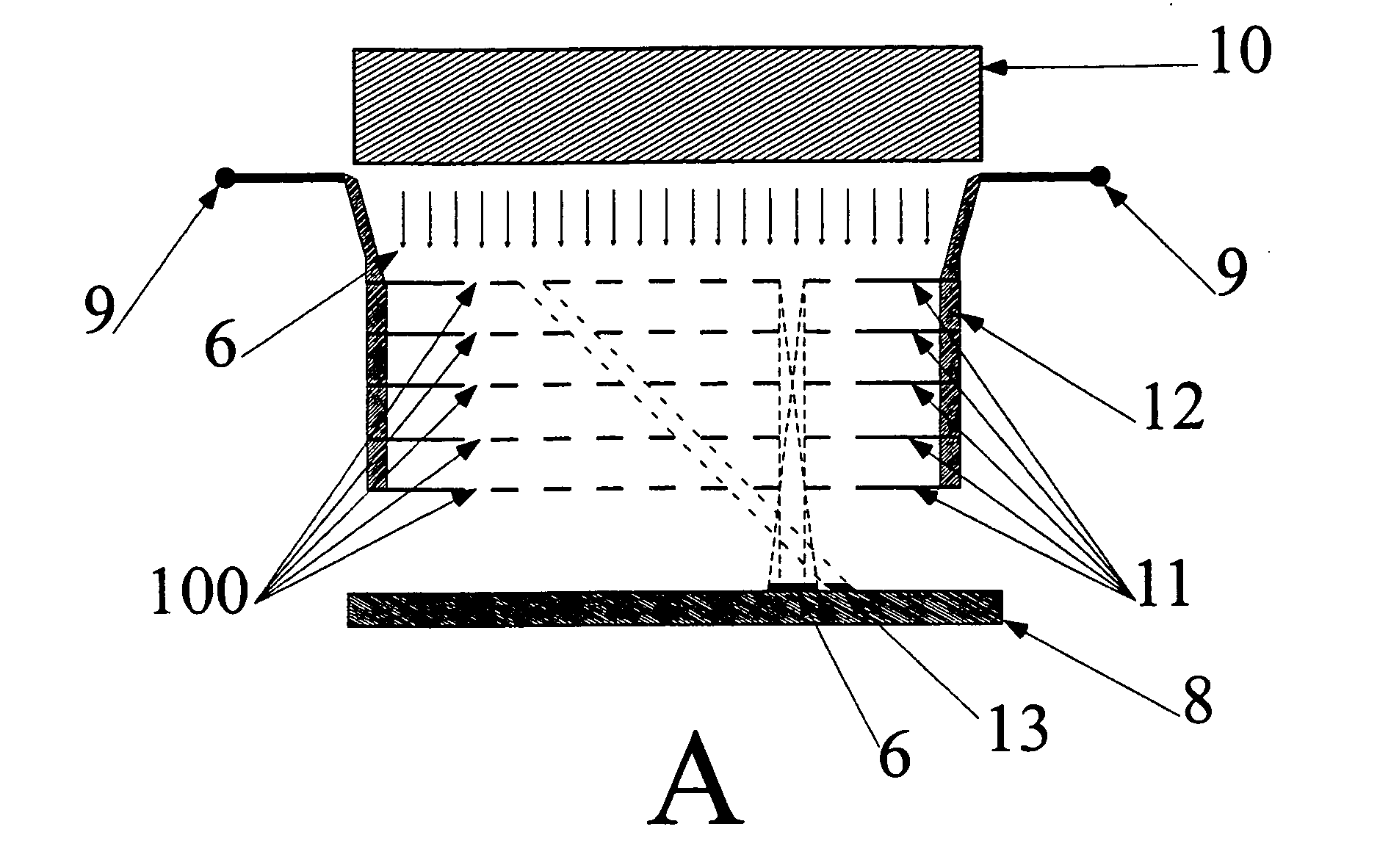

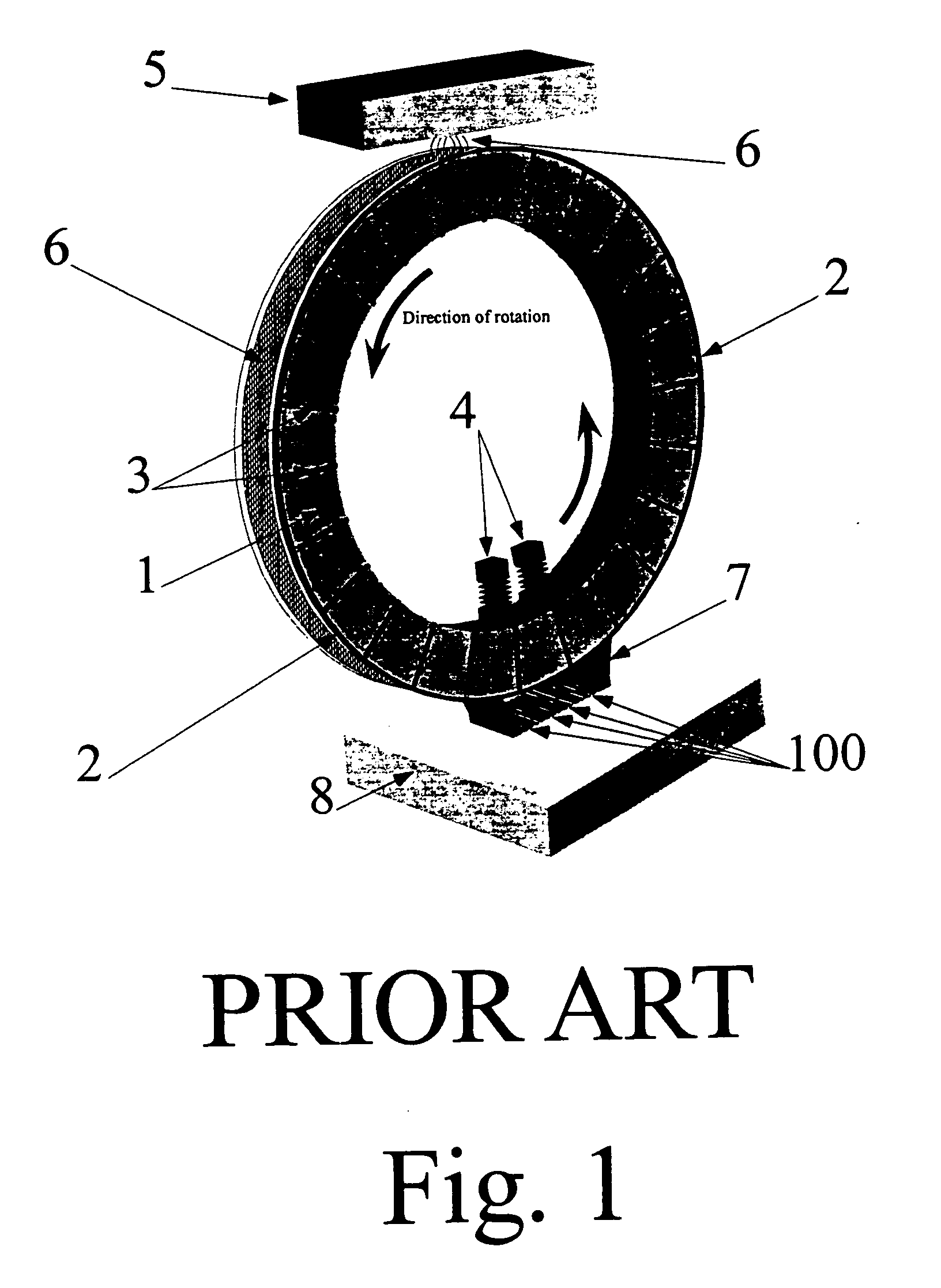

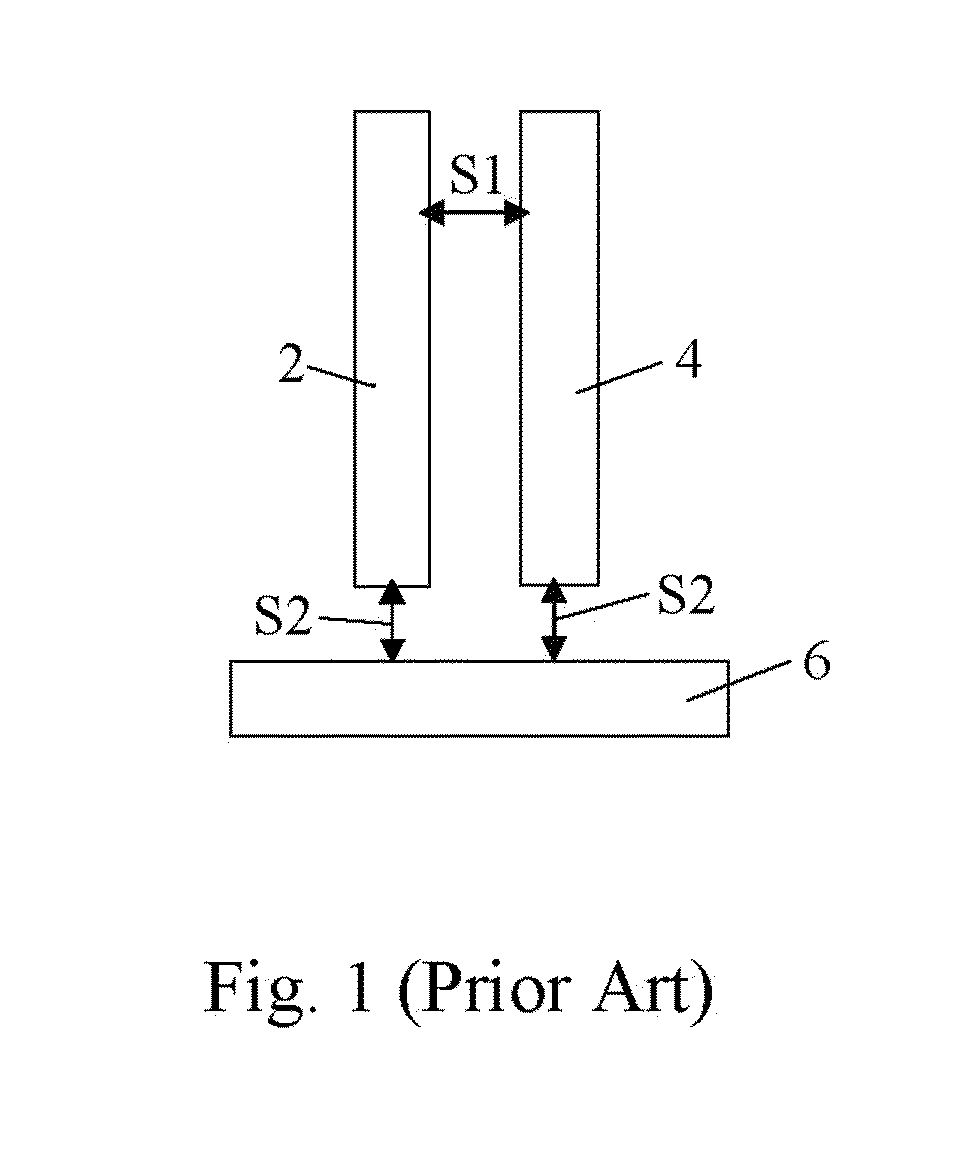

Patterned thin-film deposition using collimating heated masked assembly

InactiveUS20050183670A1Accurate timingUndesired heatingVacuum evaporation coatingSolid-state devicesEvaporationElectrical and Electronics engineering

Scanning localized evaporation and deposition of an evaporant on a substrate utilizes a mask assembly comprised of a series of mask elements with openings thereon and spaced apart in a stack. The openings are aligned so as to direct the evaporant therethrough onto the substrate. The mask elements are heated and the stack may include a movable shutter element to block openings in adjacent mask elements. The evaporant streams are usually vertical but some may be oblique to the substrate, and they may be of different materials.

Owner:OPTOELECTRONICS SYST

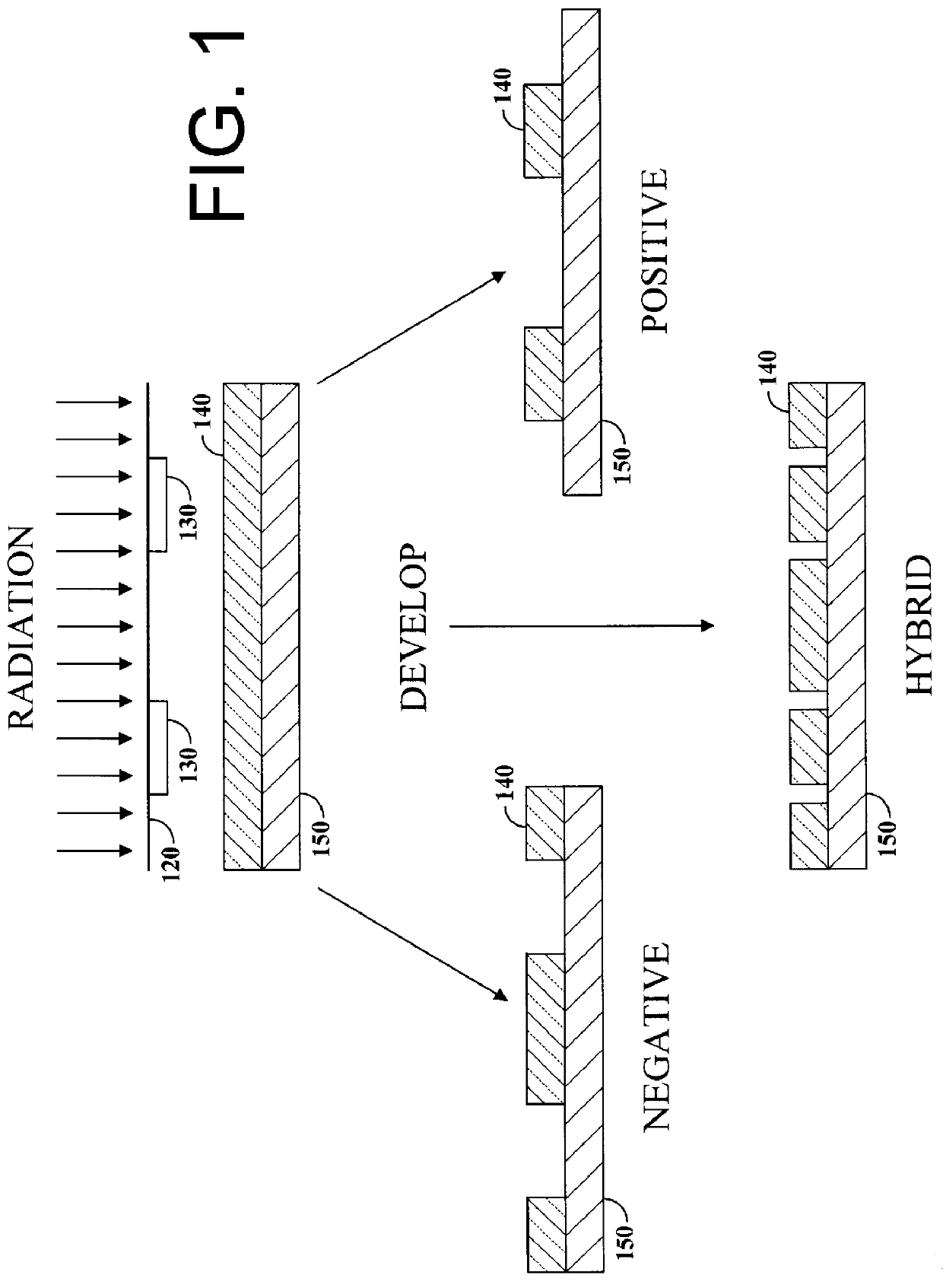

Method of photolithographically defining three regions with one mask step and self aligned isolation structure formed thereby

InactiveUS6147394APositive toneMaintaining focusSemiconductor/solid-state device detailsSolid-state devicesResistCross-link

The preferred embodiment of the present invention provides a method for defining three regions on a semiconductor substrate using a single masking step. The preferred embodiment uses a photoresist material having, simultaneously, both a positive tone and a negative tone response to exposure. This combination of materials can provide a new type of resist, which we call a hybrid resist. The hybrid resist comprises a positive tone component which acts at a first actinic energy level and a negative tone component which acts at a second actinic energy level, with the first and second actinic energy levels being separated by an intermediate range of actinic energy. When hybrid resist is exposed to actinic energy, areas of the resist which are subject to a full exposure cross link to form a negative tone line pattern, areas which are unexposed form remain photoactive and form a positive tone pattern, and areas which are exposed to intermediate amounts of radiation become soluble and wash away during development. This exposes a first region on the mask. By then blanket exposing the hybrid resist, the positive tone patterns become soluble and will wash away during development. This exposes a second region on the mask, with the third region still be covered by the hybrid resist. Thus, the preferred embodiment is able to define three regions using a single masking step, with no chance for overlay errors.

Owner:IBM CORP

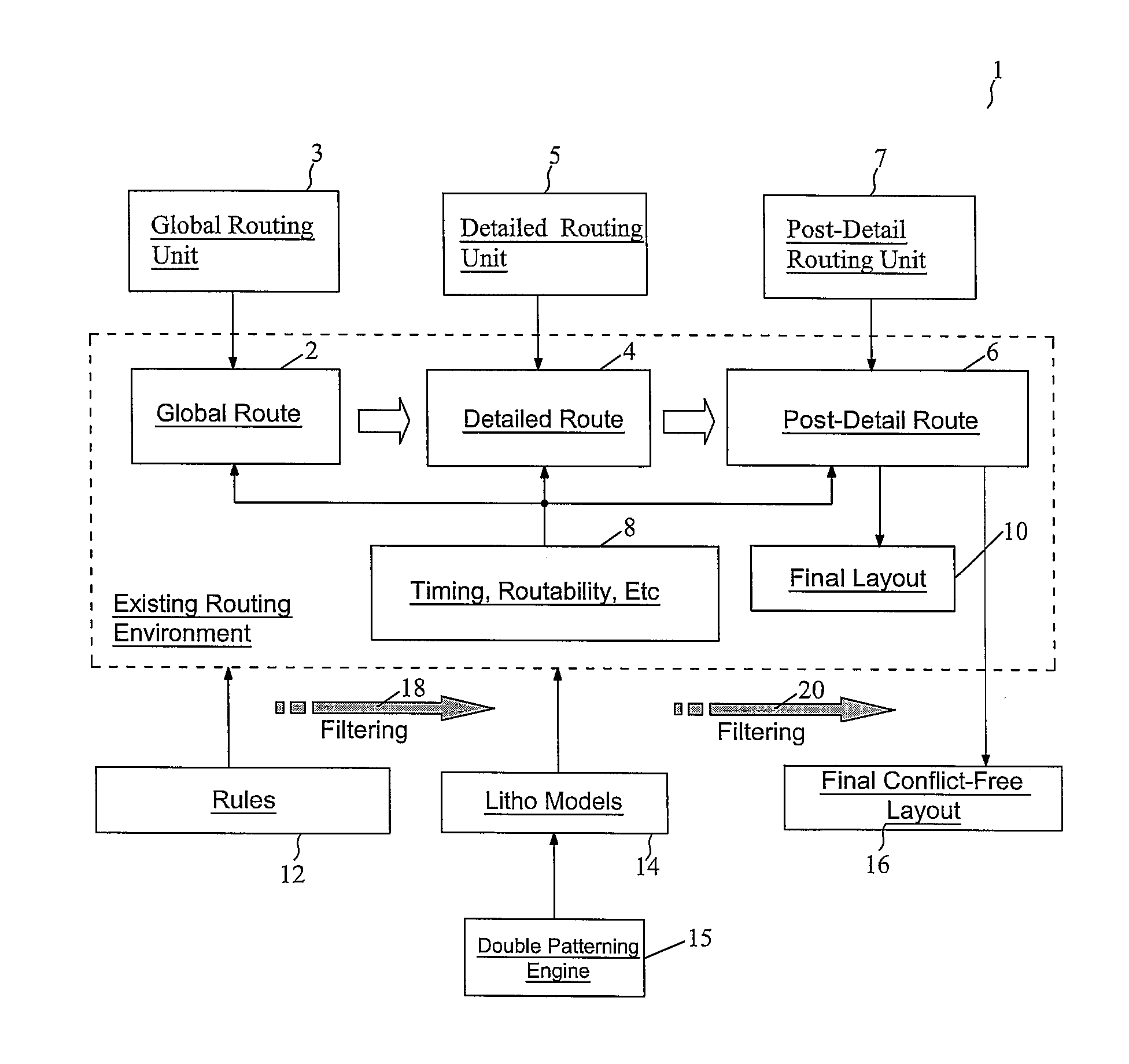

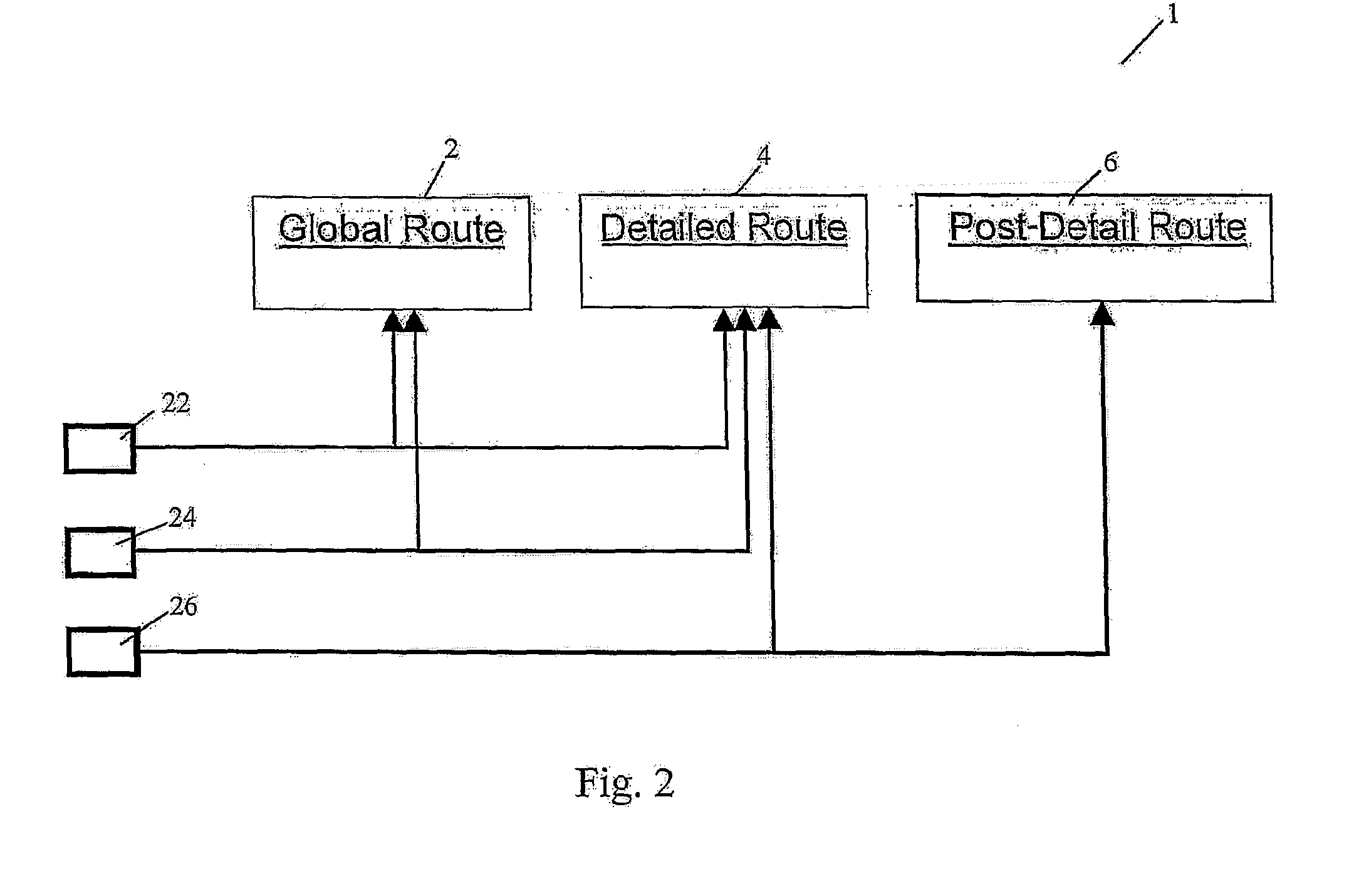

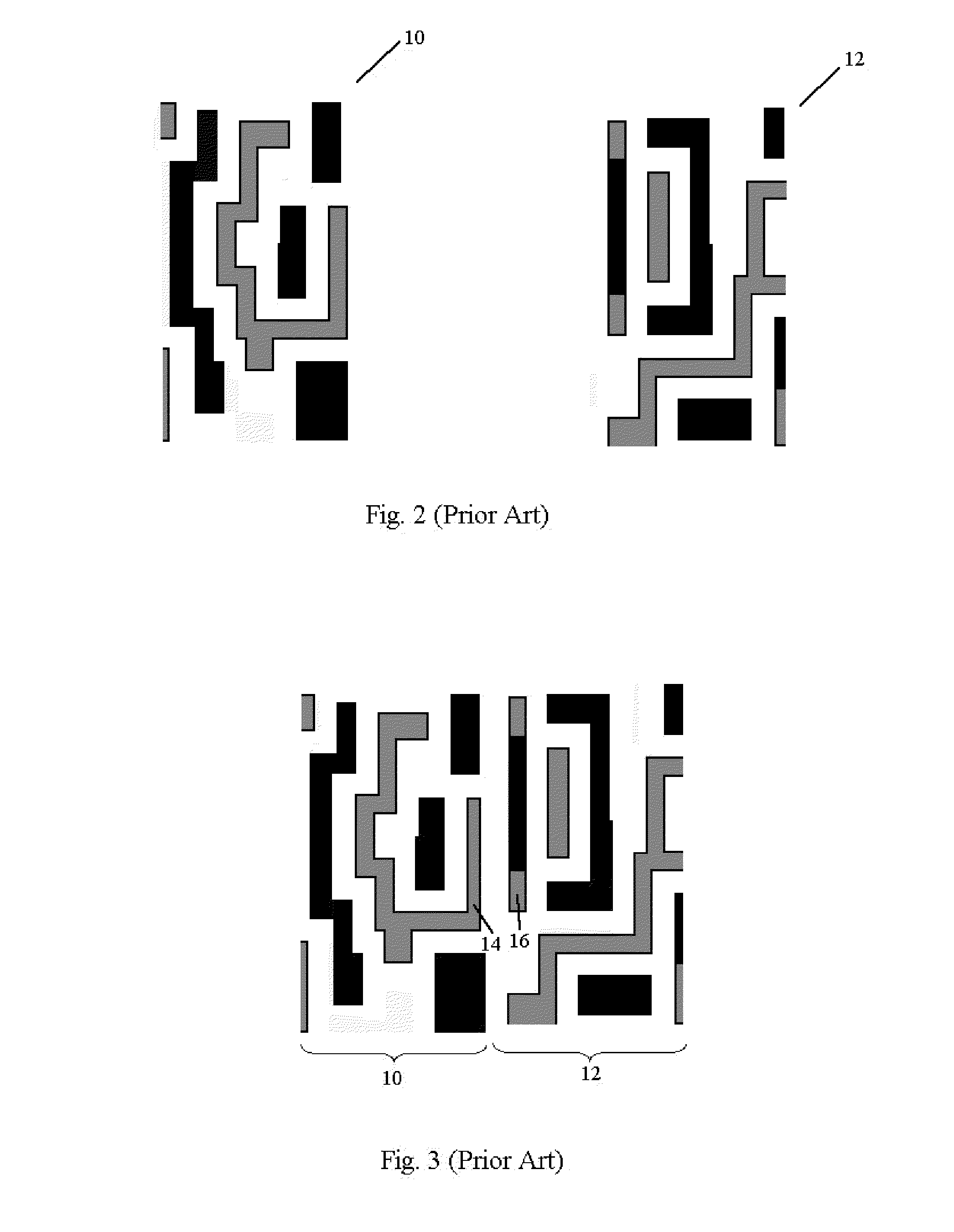

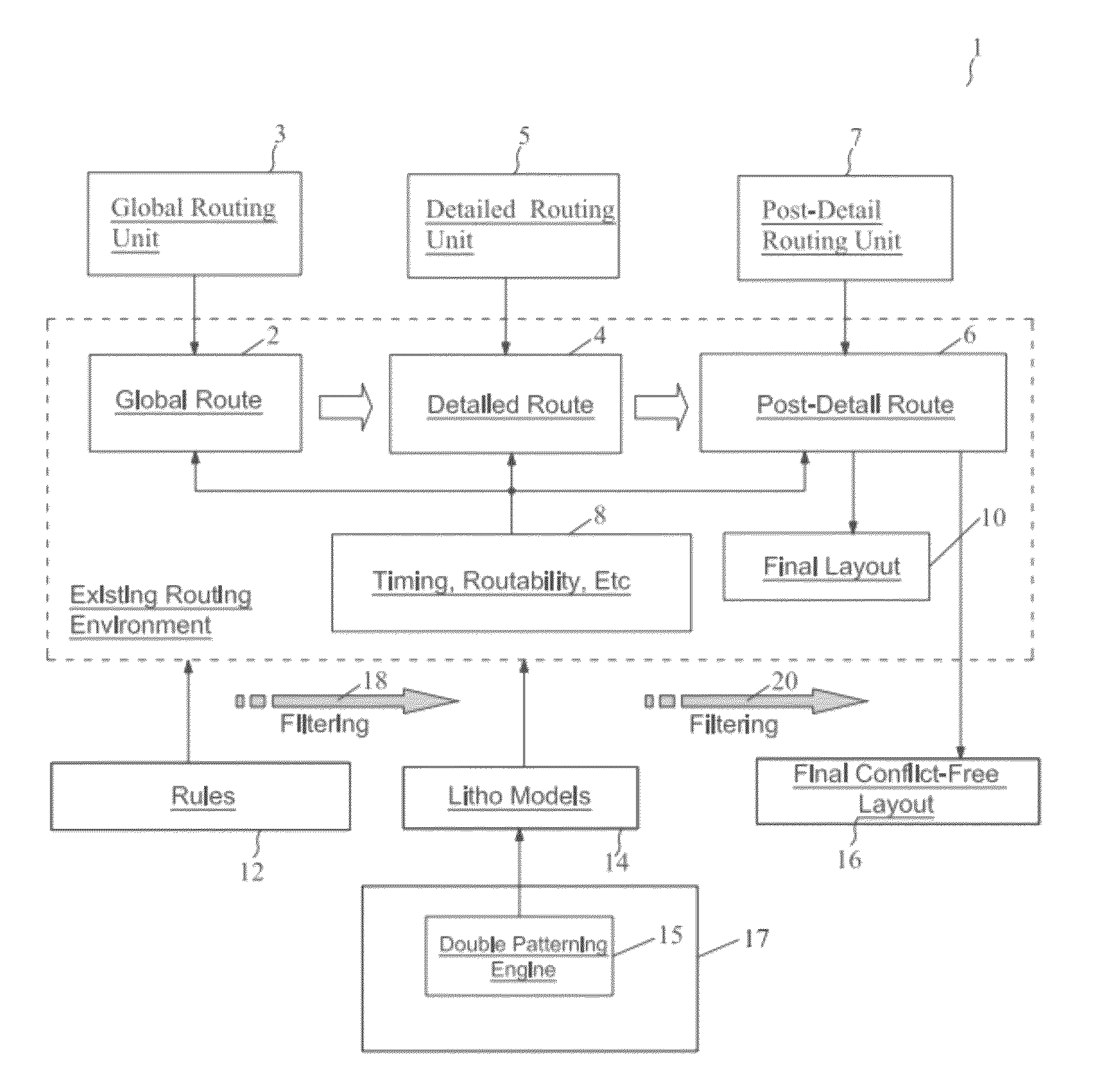

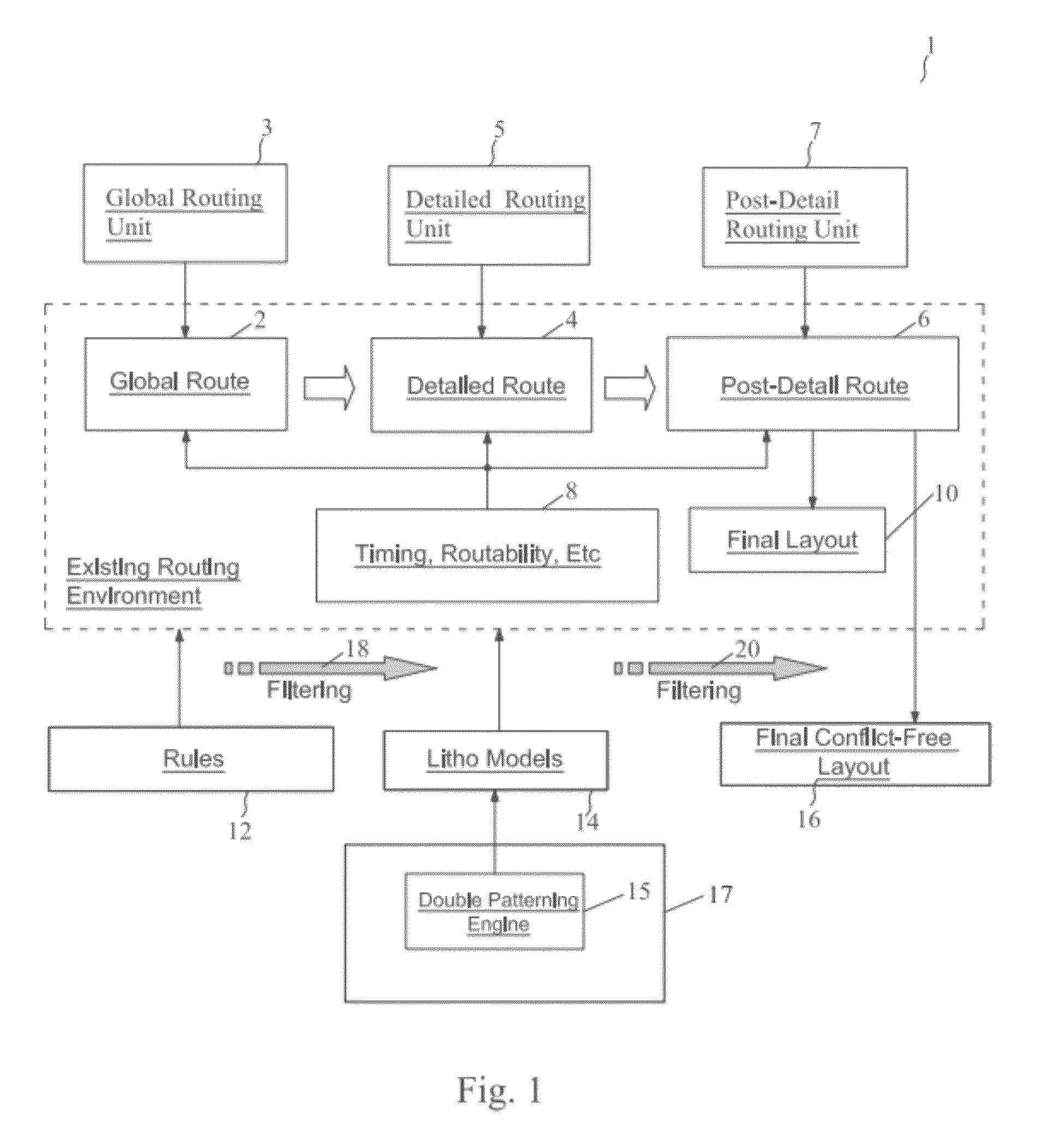

Routing Method for Double Patterning Design

ActiveUS20100199253A1Less Design WorkReduce chip areaPhotomechanical apparatusOriginals for photomechanical treatmentEngineeringGrid cell

A method of designing a double patterning mask set includes dividing a chip into a grid comprising grid cells; and laying out a metal layer of the chip. In substantially each of the grid cells, all left-boundary patterns of the metal layer are assigned with a first one of a first indicator and a second indicator, and all right-boundary patterns of the metal layer are assigned with a second one of the first indicator and the second indicator. Starting from one of the grid cells in a row, indicator changes are propagated throughout the row. All patterns in the grid cells are transferred to the double patterning mask set, with all patterns assigned with the first indicator transferred to a first mask of the double patterning mask set, and all patterns assigned with the second indicator transferred to a second mask of the double patterning mask set.

Owner:TAIWAN SEMICON MFG CO LTD

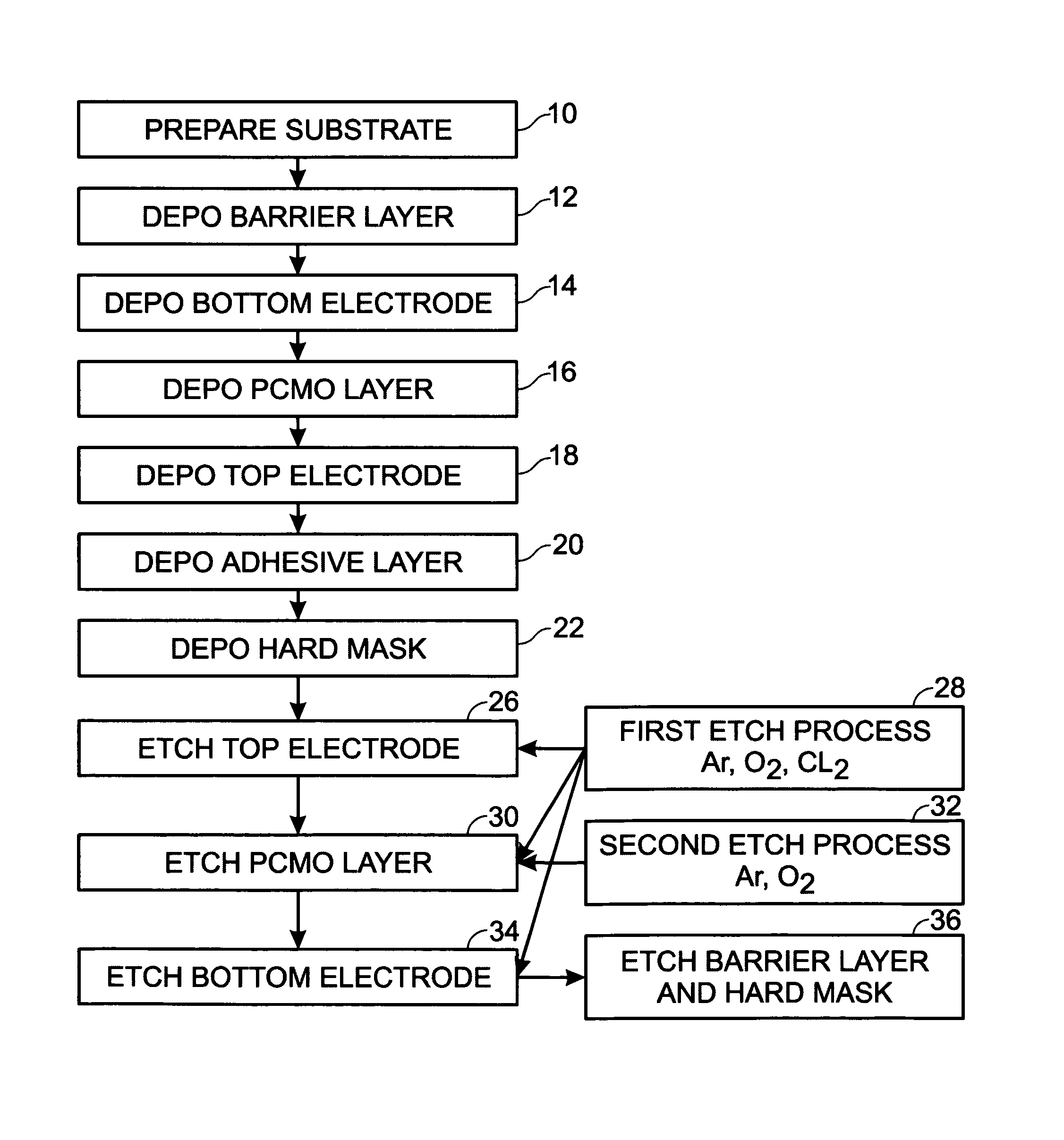

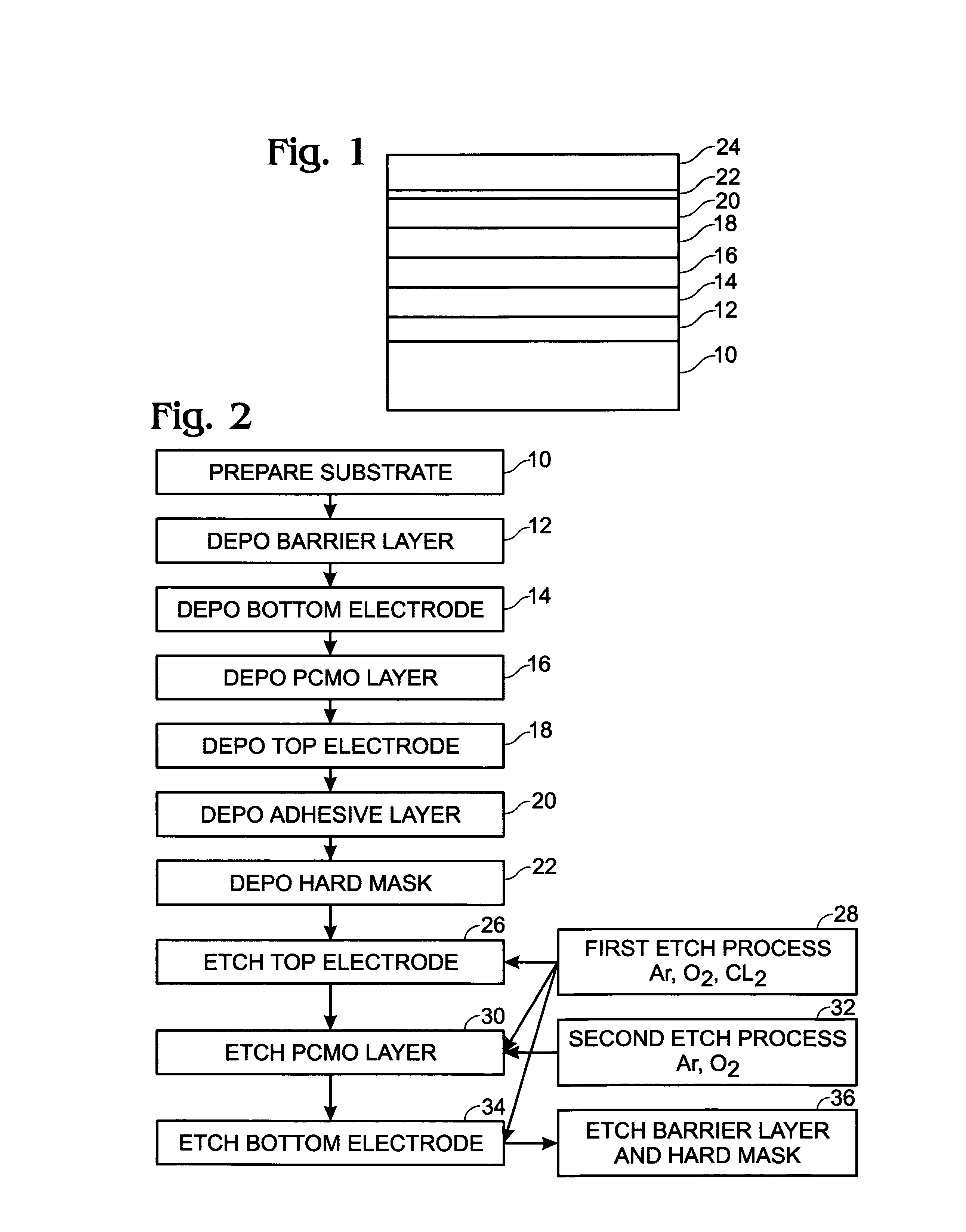

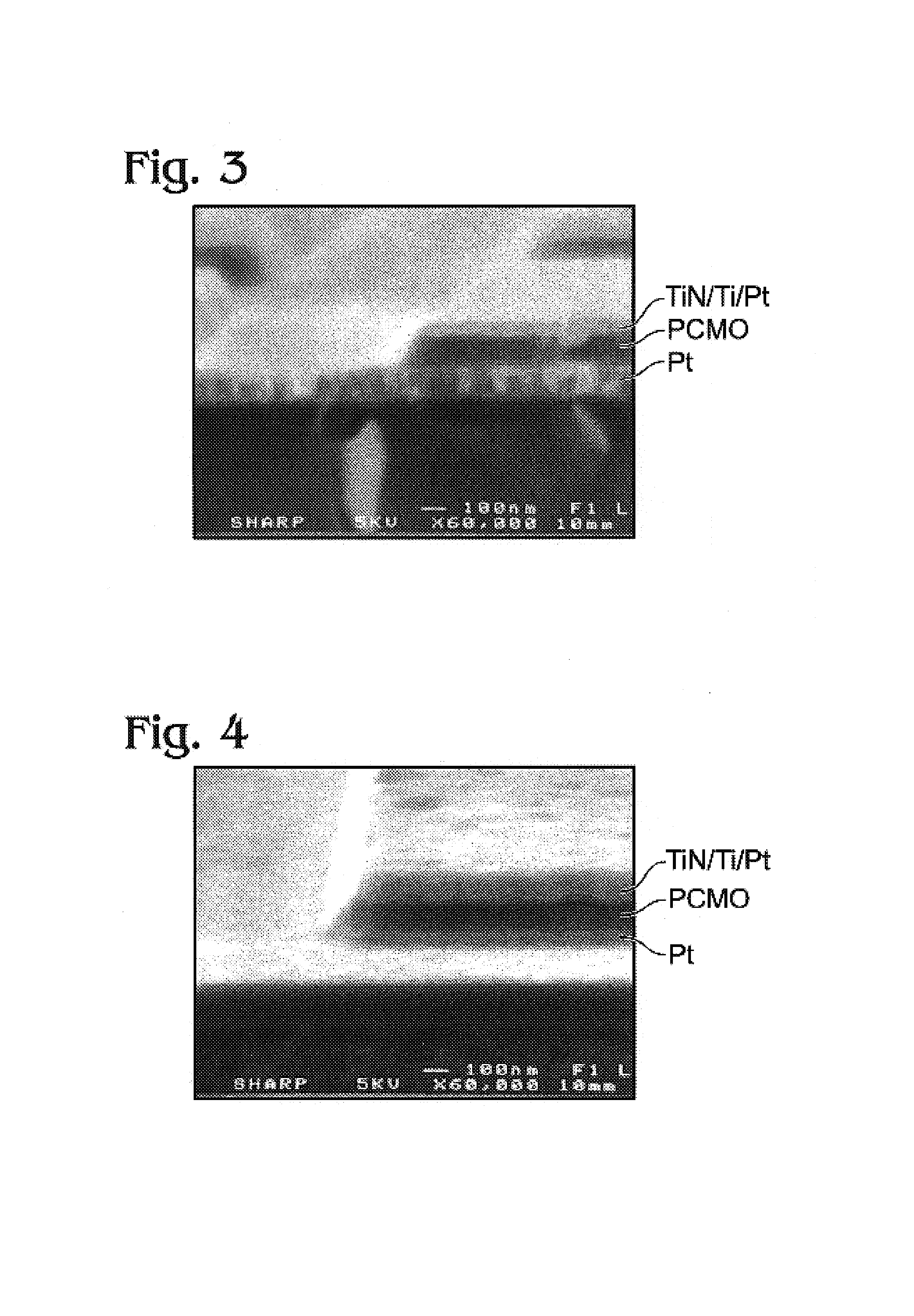

One mask Pt/PCMO/Pt stack etching process for RRAM applications

InactiveUS7169637B2High selectivitySemiconductor/solid-state device manufacturingSilicon dioxideHard mask

A one-mask etching method for use with a PCMO-containing RRAM to reduce stack side-wall residuals, includes preparing a substrate, taken from the group of substrates consisting of silicon, silicon dioxide and polysilicon; depositing a bottom electrode on the substrate; depositing a PCMO layer on the bottom electrode; depositing a top electrode on the PCMO layer; depositing a hard mask on the top electrode; depositing and patterning a photoresist layer on the hard mask; etching the hard mask; etching the top electrode using a first etching process having an etching atmosphere consisting of Ar, O2, and Cl2; etching the PCMO layer using an etching process taken from the group of etching processes consisting of the first etching process and a second etching process having an etching atmosphere consisting of Ar and O2. etching the bottom electrode using the first etching process; and completing the RRAM device.

Owner:XENOGENIC DEV LLC

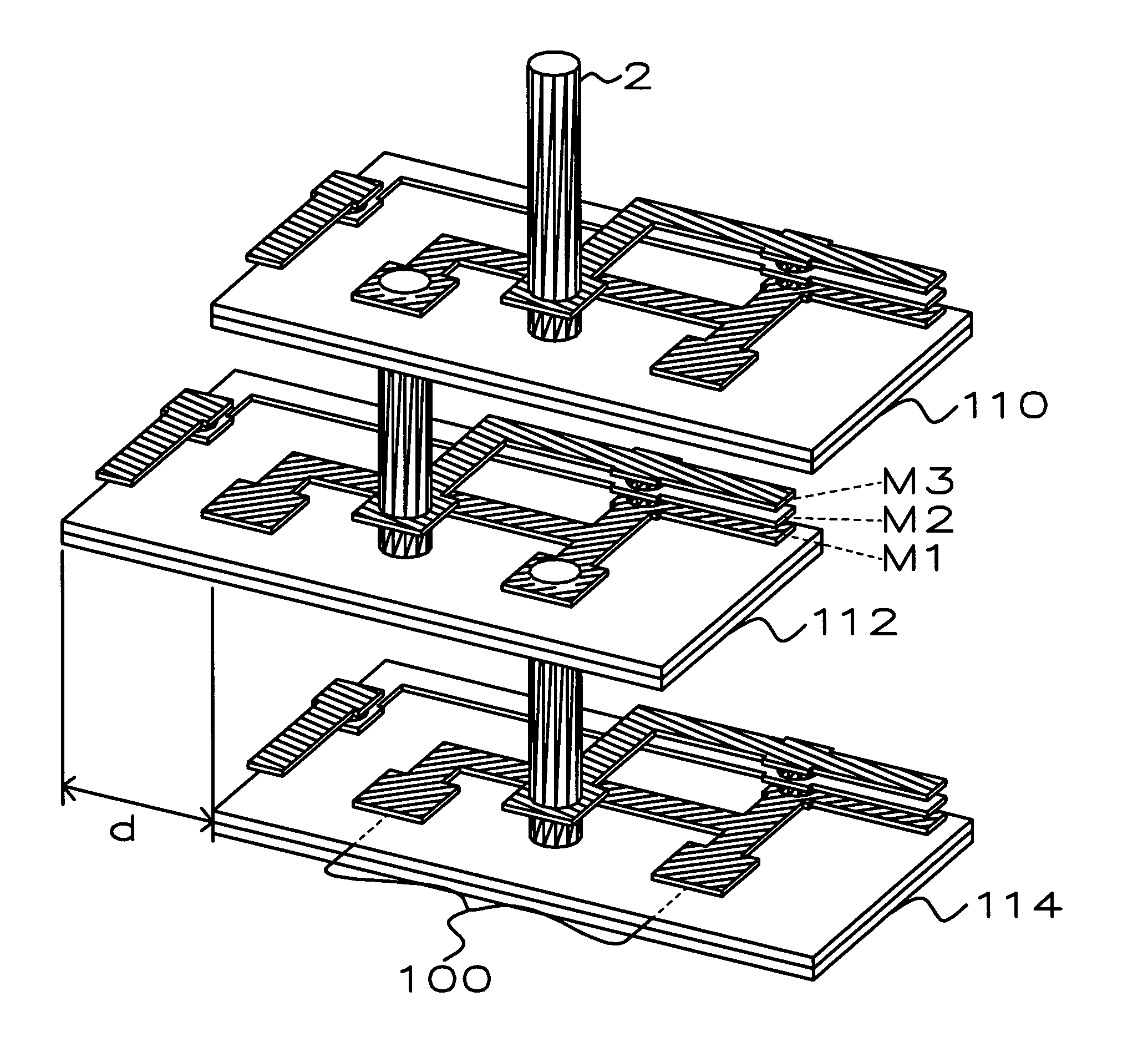

Method for scalable architectures in stackable three-dimensional integrated circuits and electronics

InactiveUS7046522B2Improve the level ofSemiconductor/solid-state device detailsPrinted circuit aspectsEngineeringThree-dimensional integrated circuit

The design methods described enable three-dimensional integrated circuit systems in which all of the dies, in a vertically bonded stack of dies, are identical. Only one mask set and wafer type is required since a single circuit design is produced for one die in the stack and reused for all the dies with little or no modification. The system scales directly as the level of stacking is increased while incurring no extra design effort, beyond that required for the initial design.

Owner:SUNG RAYMOND JIT HUNG +4

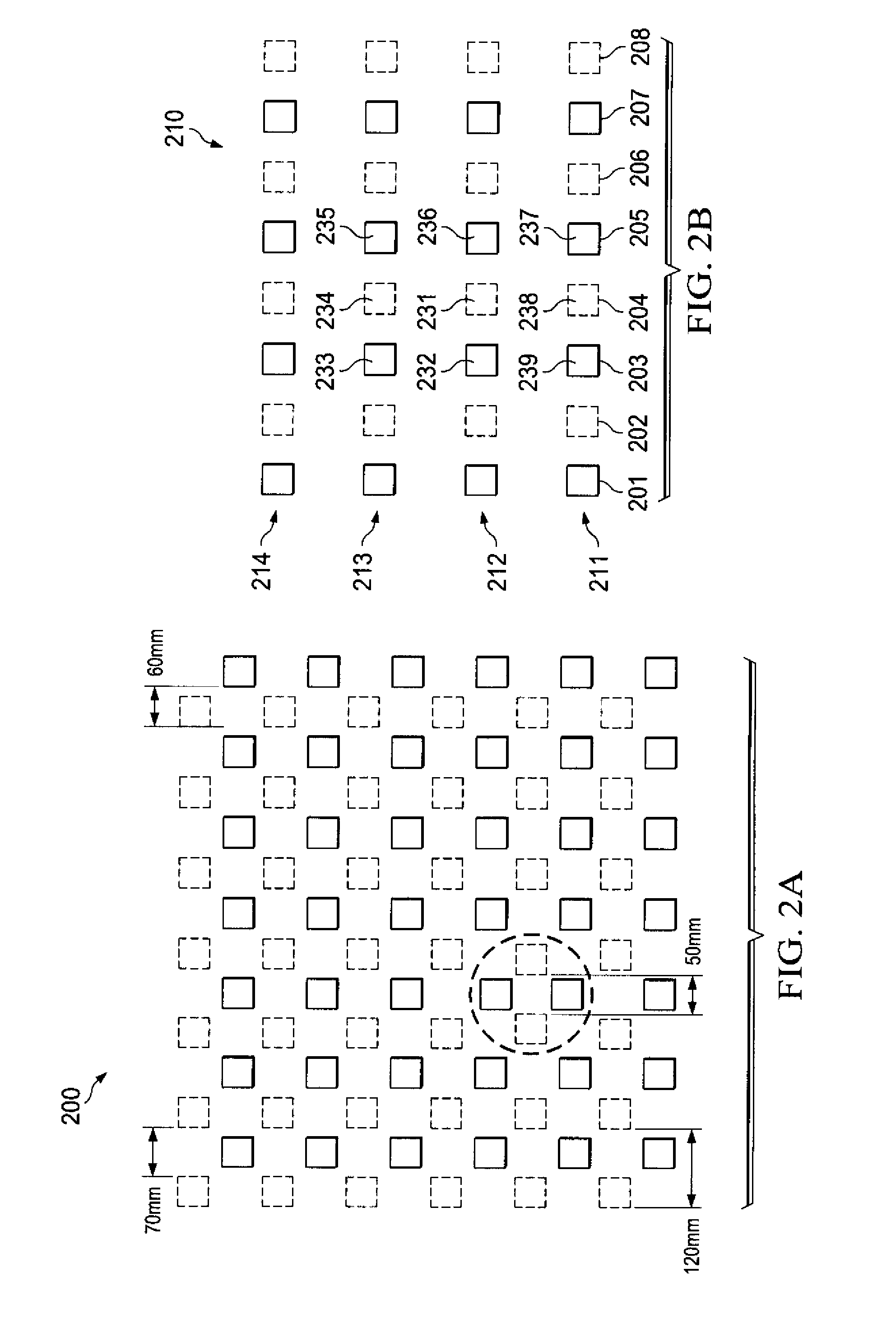

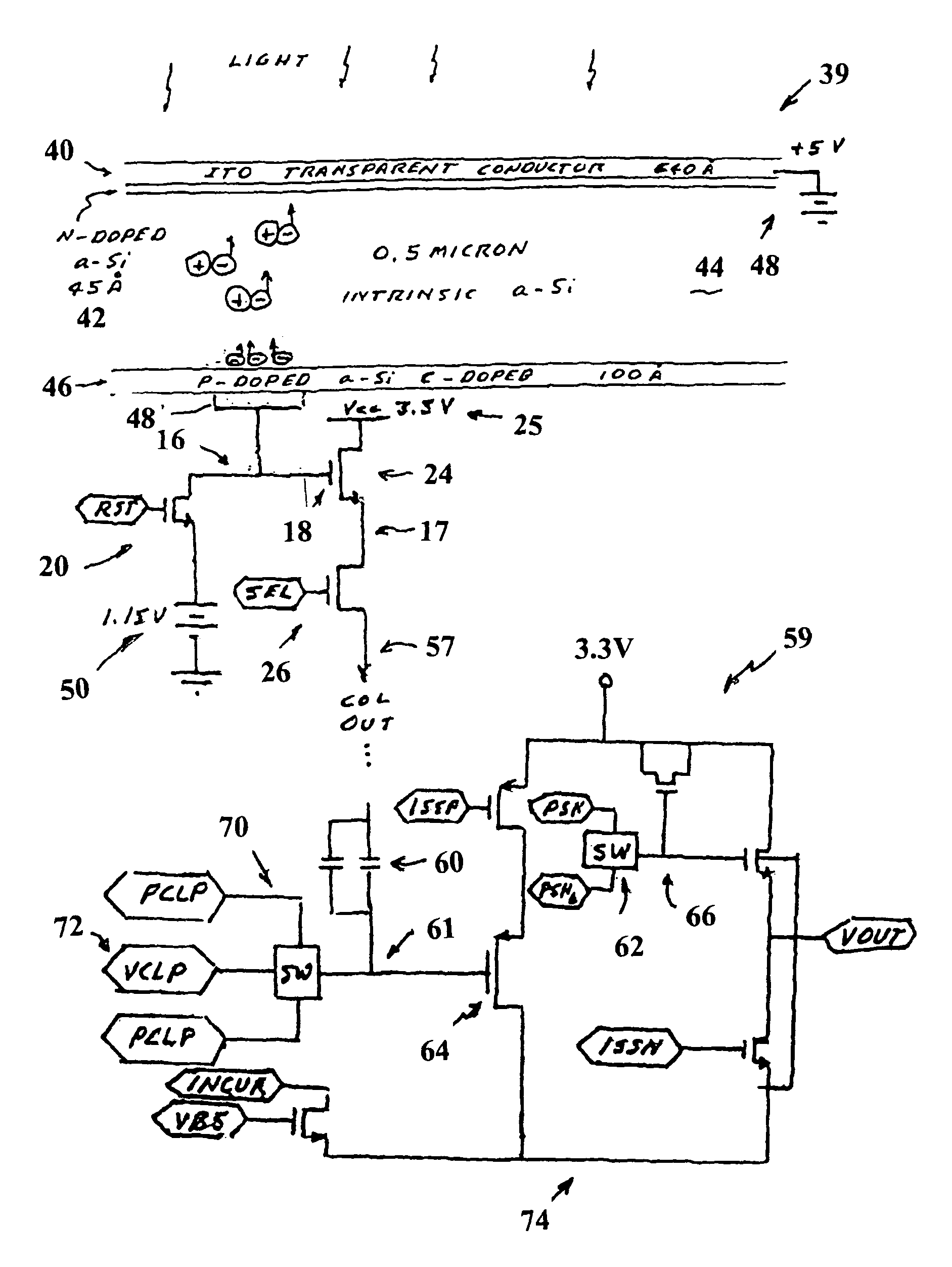

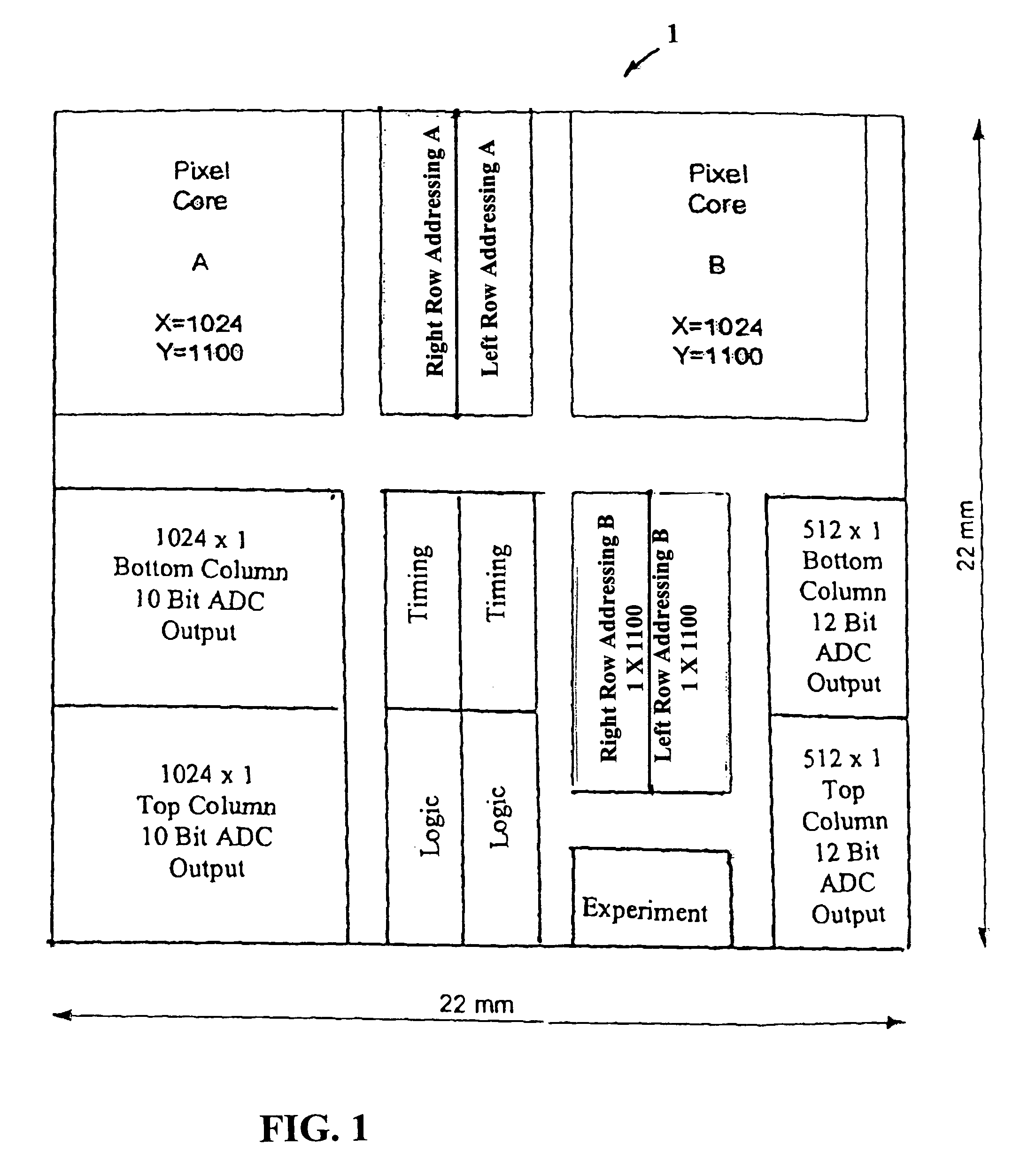

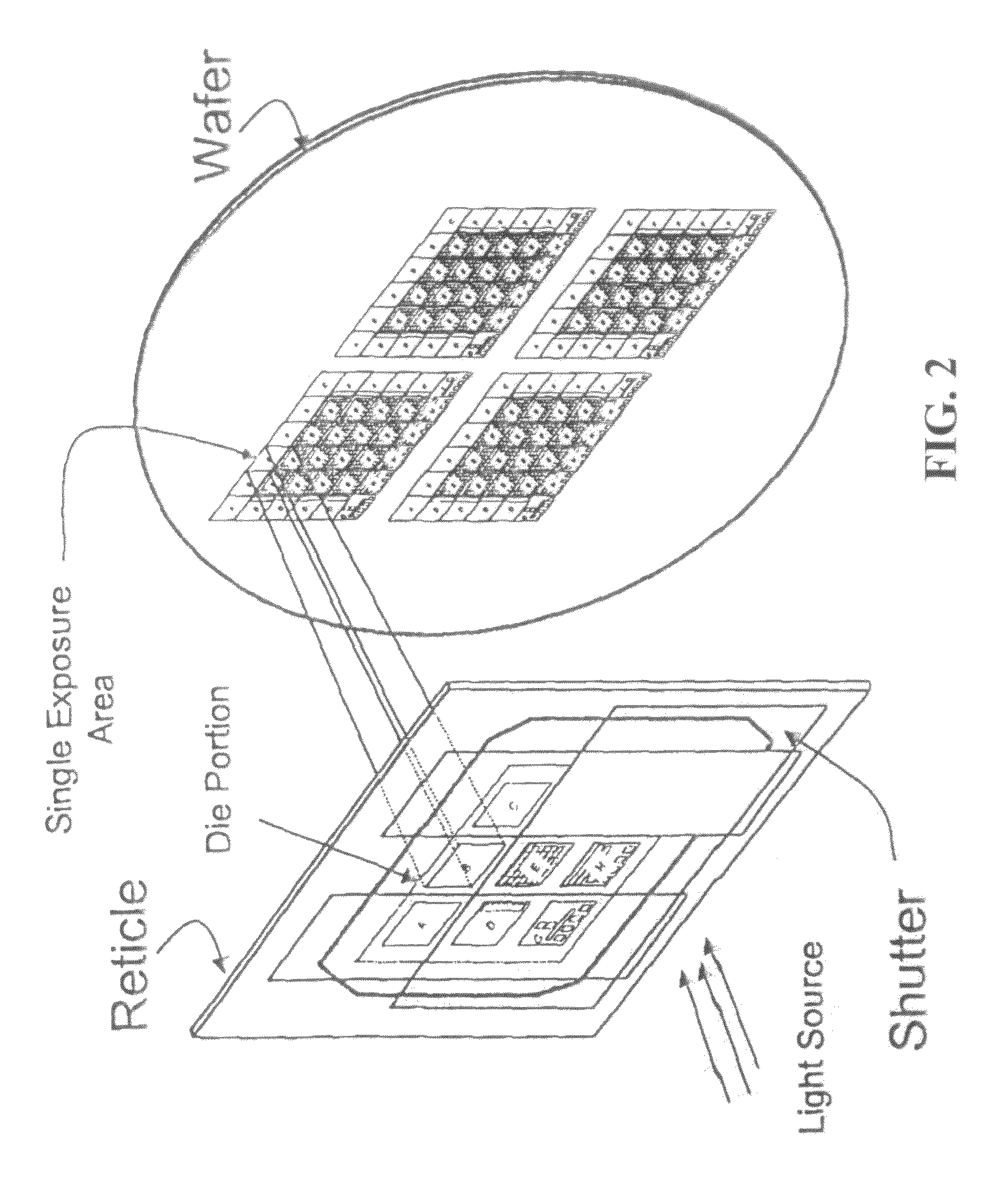

Many million pixel image sensor

A CMOS image sensor with a many million pixel count. Applicants have developed techniques for combining its continuous layer photodiode CMOS sensor technology with CMOS integrated circuit lithography stitching techniques to provide digital cameras with an almost unlimited number of pixels. A preferred CMOS stitching technique exploits the precise alignment accuracy of CMOS stepper processes by using specialized mask sets to repeatedly produce a single pixel array pattern many times on a single silicon wafer with no pixel array discontinuities. The single array patterns are stitched together lithographically to form a pixel array of many million pixels. A continuous multilayer photodiode layer is deposited over the top of the many million pixel array to provide a many million pixel sensor with a fill factor of 100 percent or substantially 100 percent.

Owner:E PHOCUS

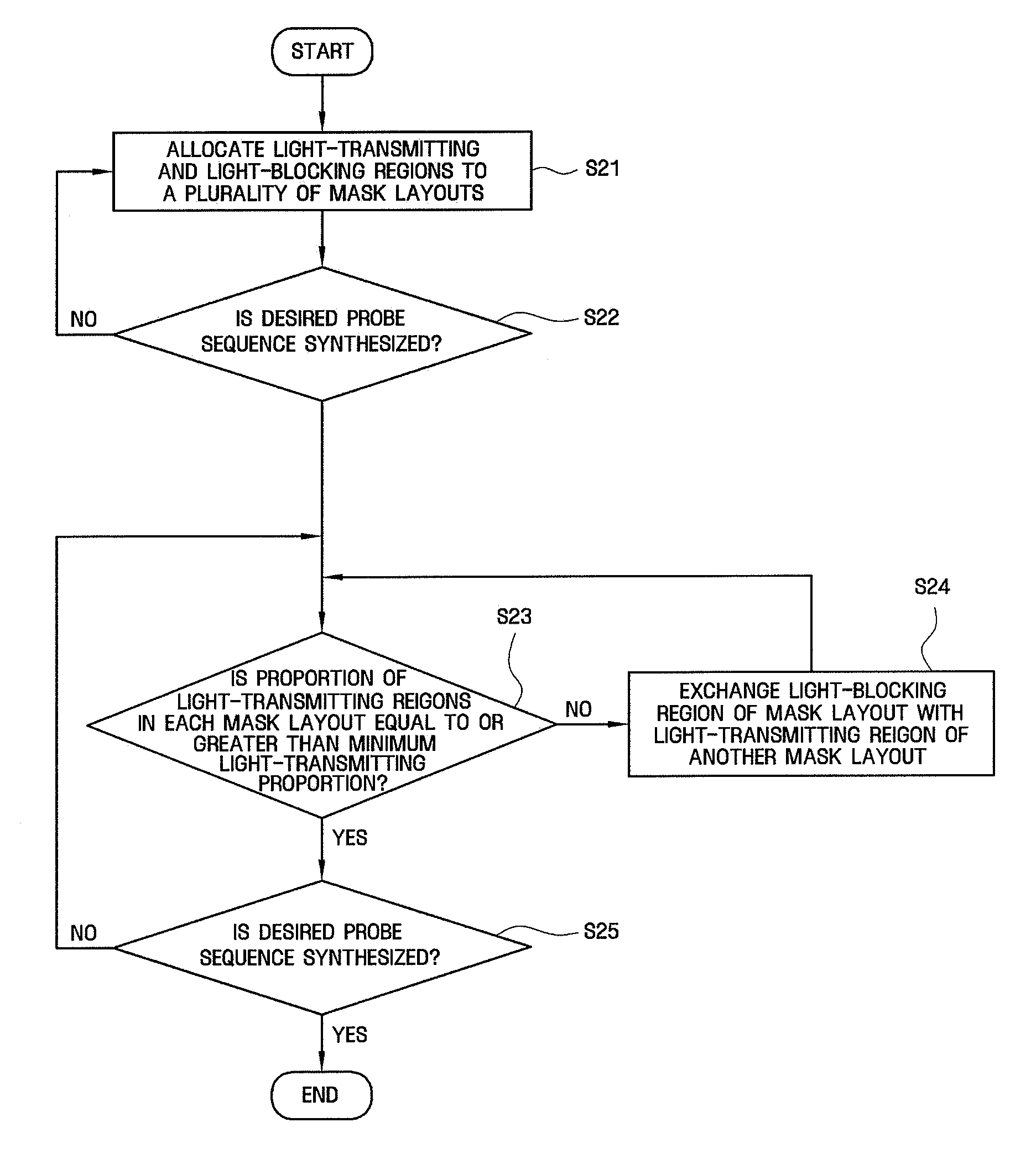

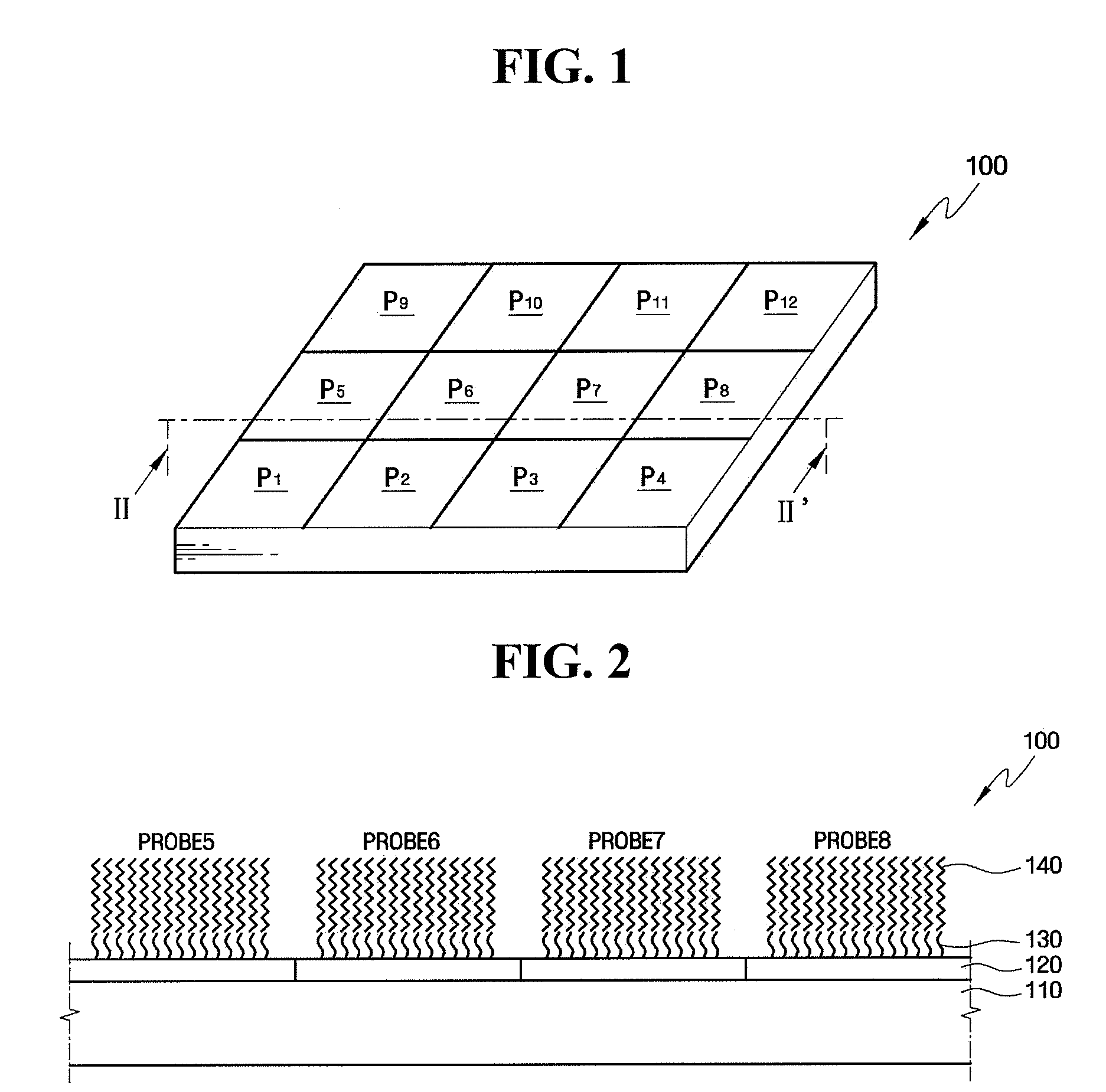

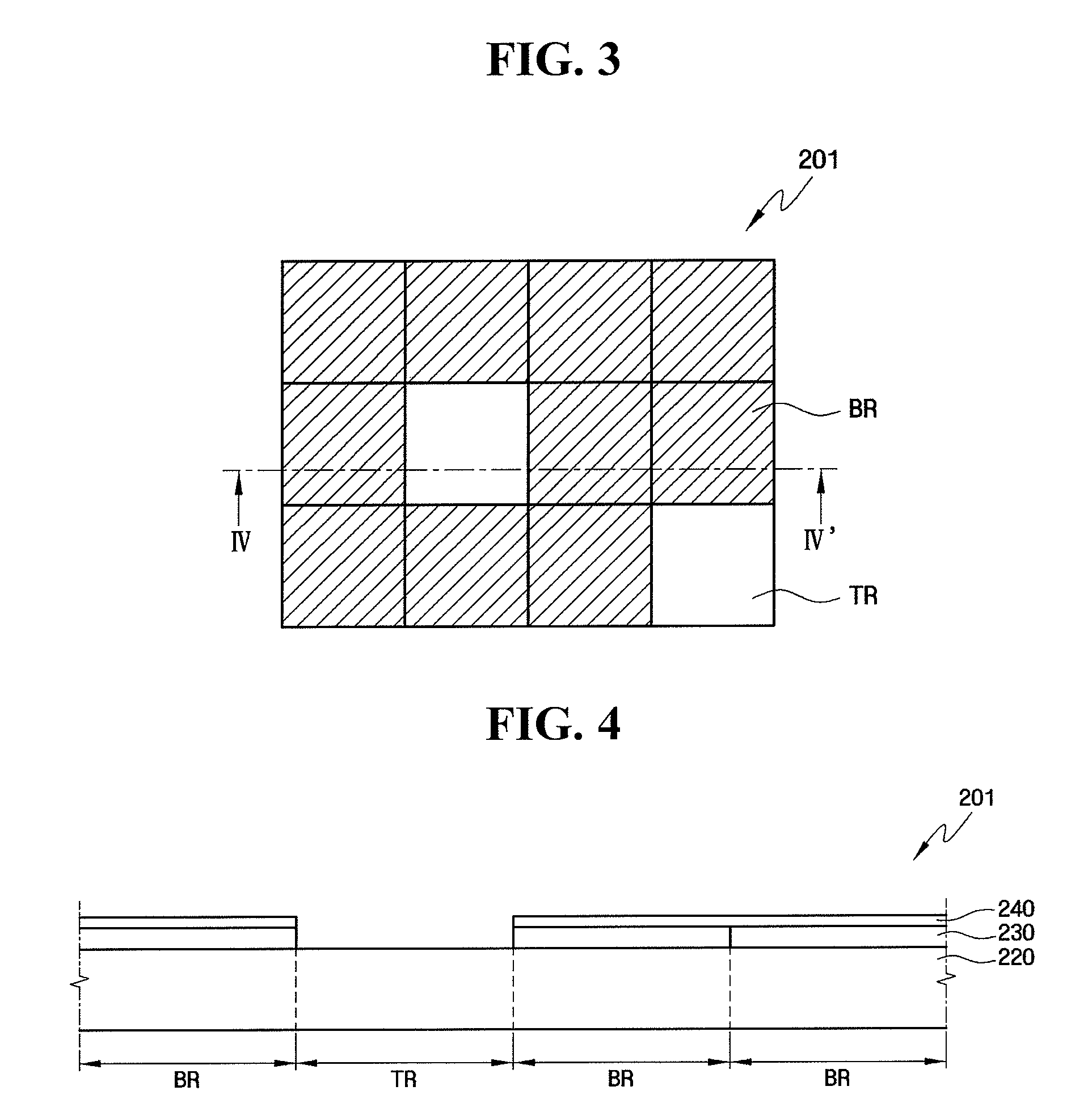

Mask set for microarray, method of fabricating mask set, and method of fabricating microarray using mask set

A mask set with a light-transmitting region of a controlled size includes a plurality of masks for performing in-situ synthesis on probes of a microarray, wherein each mask includes a light-transmitting region and a light-blocking region, and the size of the light-transmitting region is equal to or greater than about 5% of the total size of the light-transmitting and light-blocking regions.

Owner:SAMSUNG ELECTRONICS CO LTD

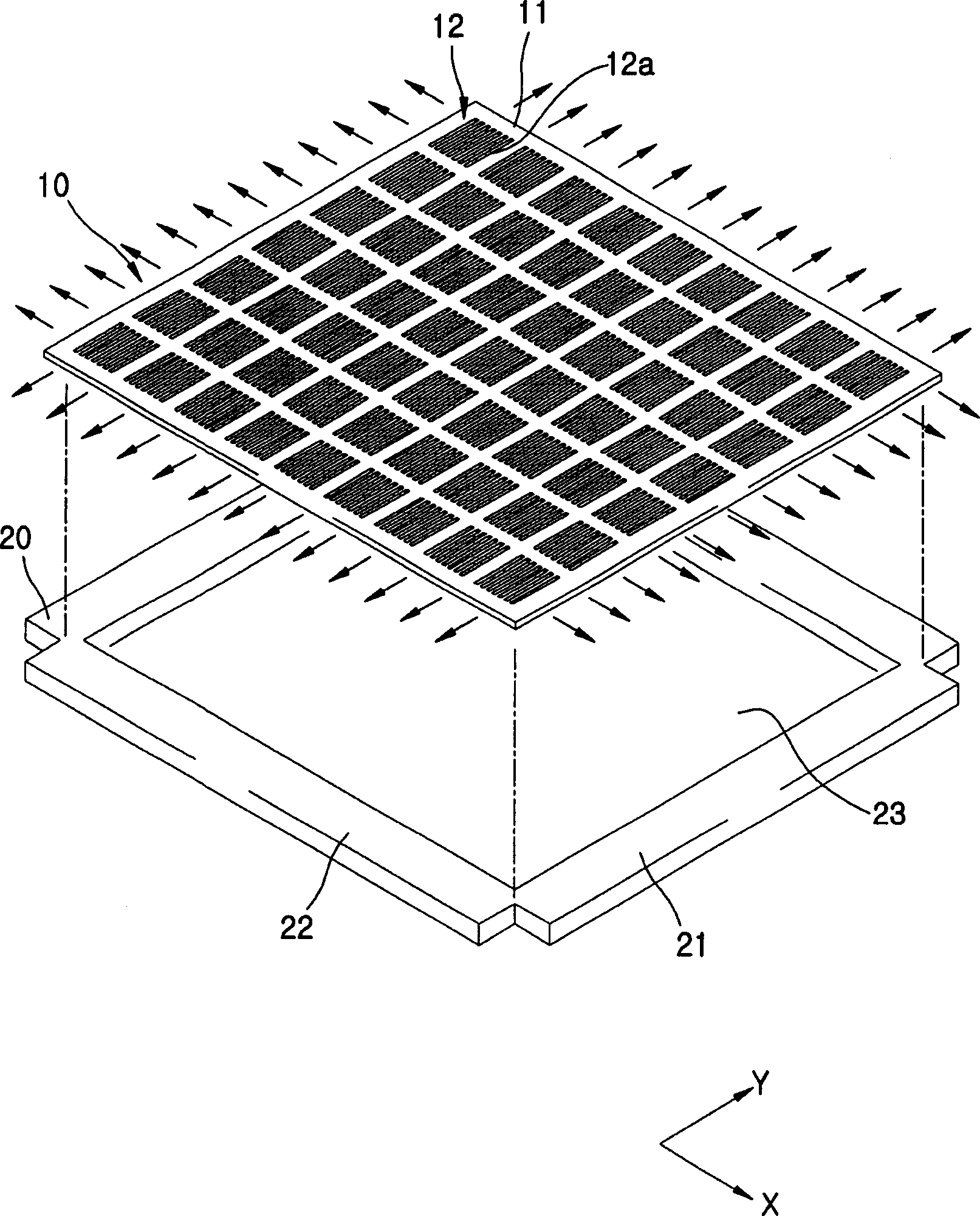

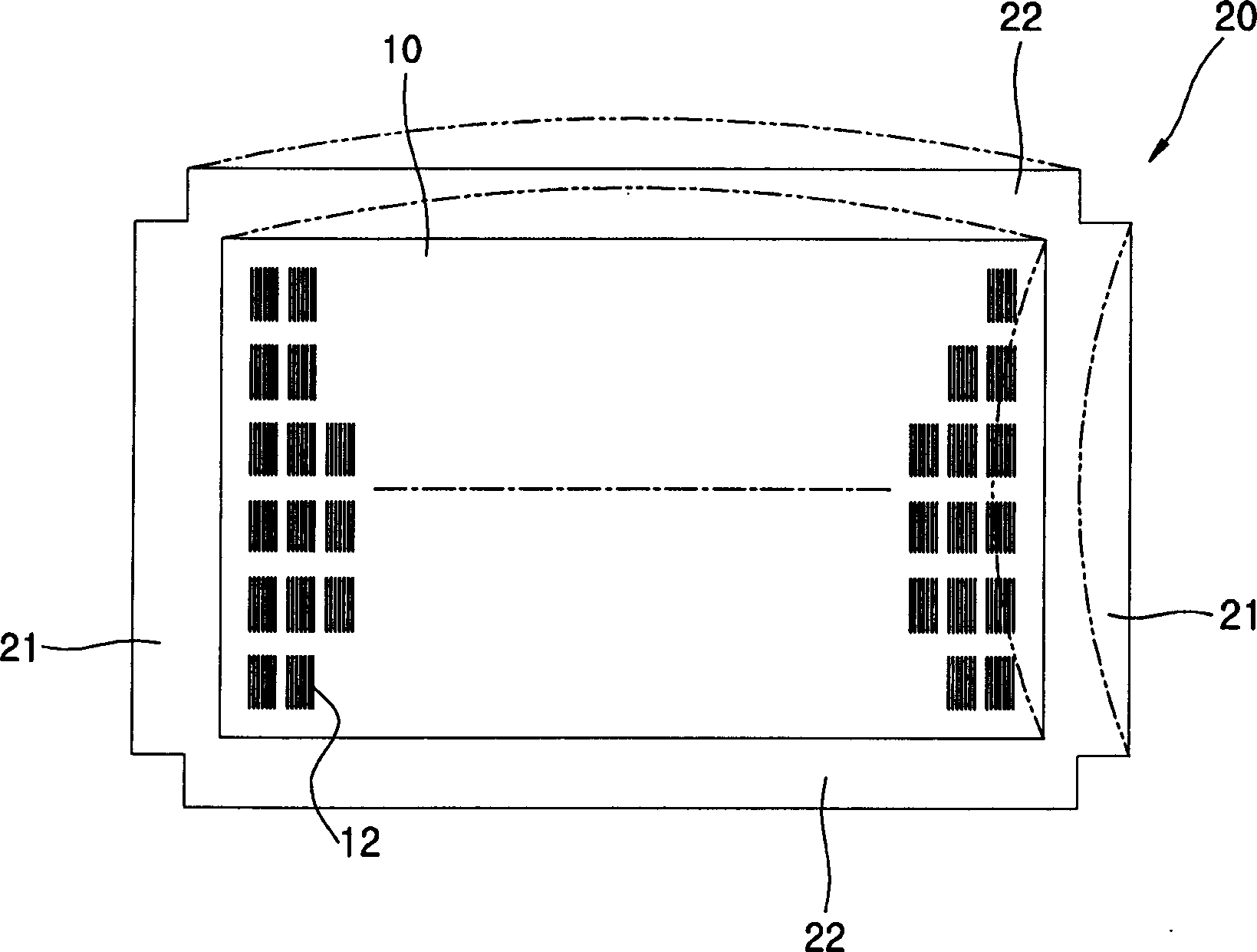

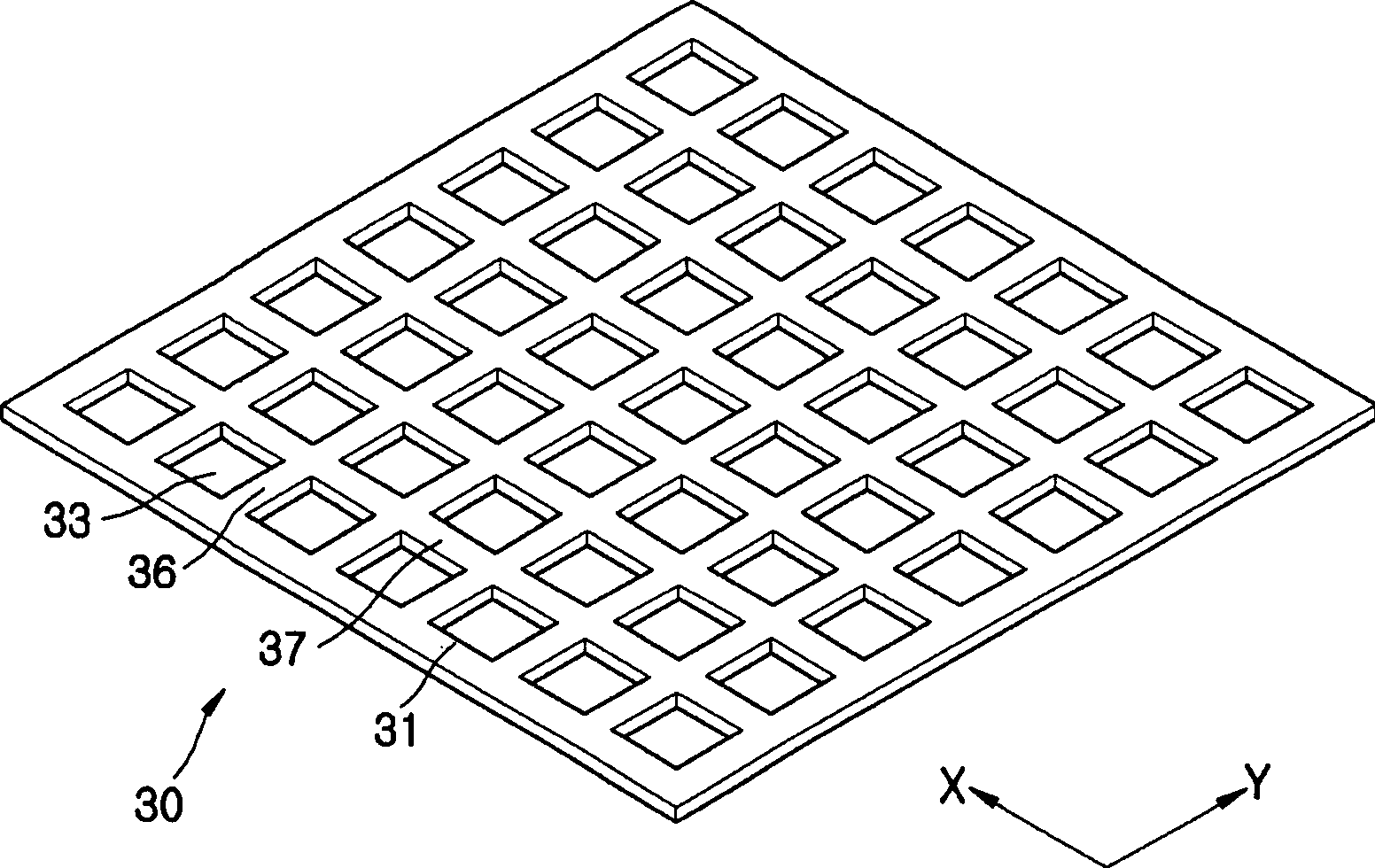

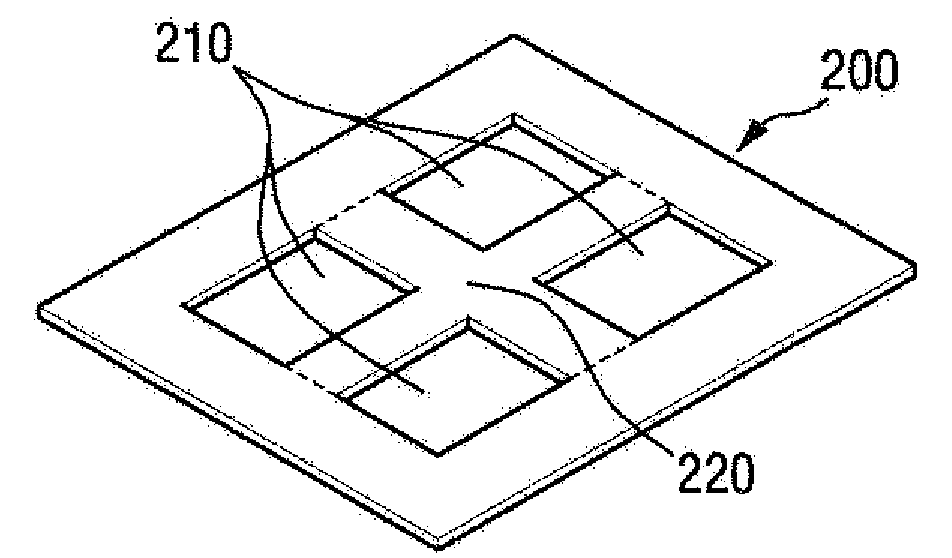

Mask assembly and mask frame assemble using same

The present invention discloses a mask assembly configured to prevent thermal deformation of a mask and maintain a gap between a plurality of divided pattern masks. According to one embodiment, the mask assembly includes: an opening mask having a plurality of first openings arranged in rows or columns; and a pattern mask including a plurality of unit pattern masks. In some embodiments, an end portion of a unit pattern mask including a plurality of mask pattern units configured to be aligned with a plurality of first openings of the open mask may be fixed relative to the open mask. In some embodiments, a pulling force is applied to the unit pattern mask.

Owner:SAMSUNG MOBILE DISPLAY CO LTD

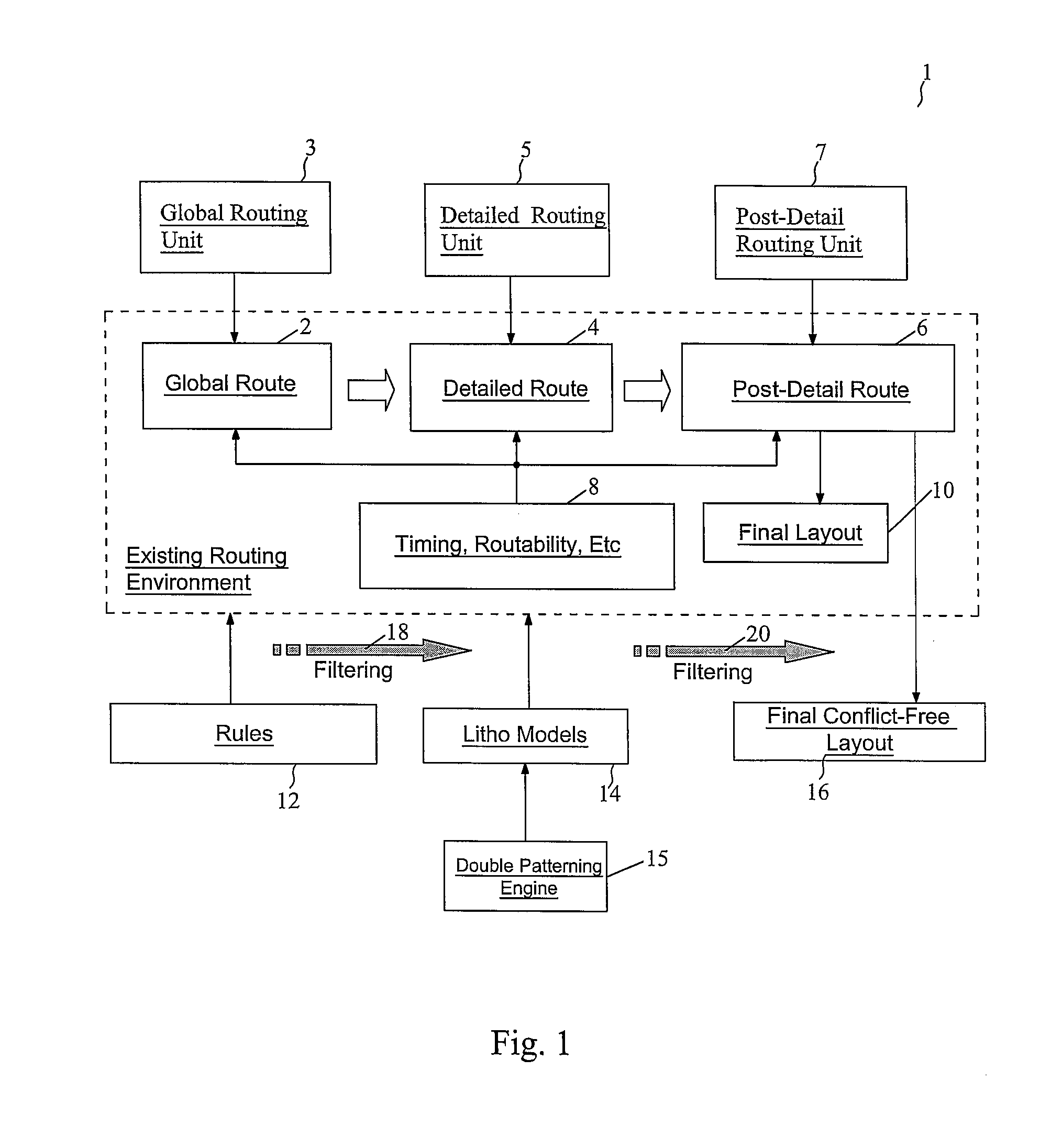

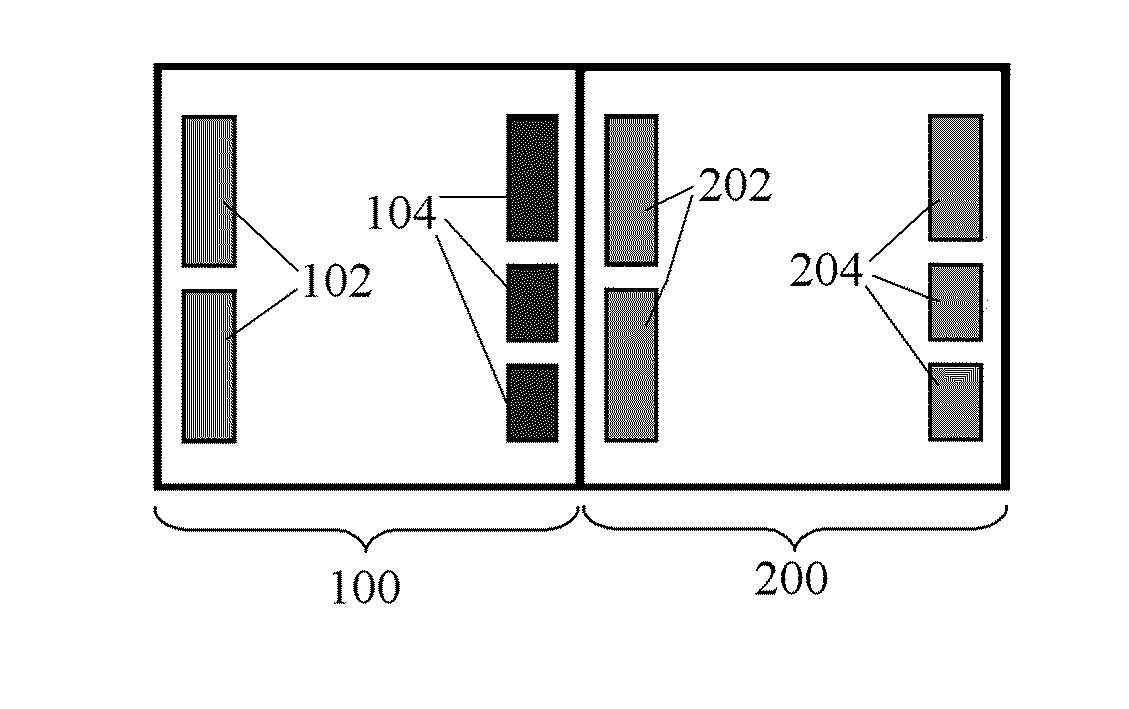

Methods for Cell Boundary Isolation in Double Patterning Design

ActiveUS20100196803A1Less Design WorkReduce chip areaOriginals for photomechanical treatmentSpecial data processing applicationsDesign standardEngineering

A method of designing a double patterning mask set for a layout of a chip includes designing standard cells. In each of the standard cells, all left-boundary patterns are assigned with one of a first indicator and a second indicator, and all right-boundary patterns are assigned with an additional one of the first indicator and the second indicator. The method further includes placing the standard cells in a row of the layout of the chip. Starting from one of the standard cells in the row, indicator changes to the standard cells are propagated throughout the row. All patterns in the standard cells having the first indicator are transferred to a first mask of the double patterning mask set. All patterns in the standard cells having the second indicator are transferred to a second mask of the double patterning mask set.

Owner:TAIWAN SEMICON MFG CO LTD

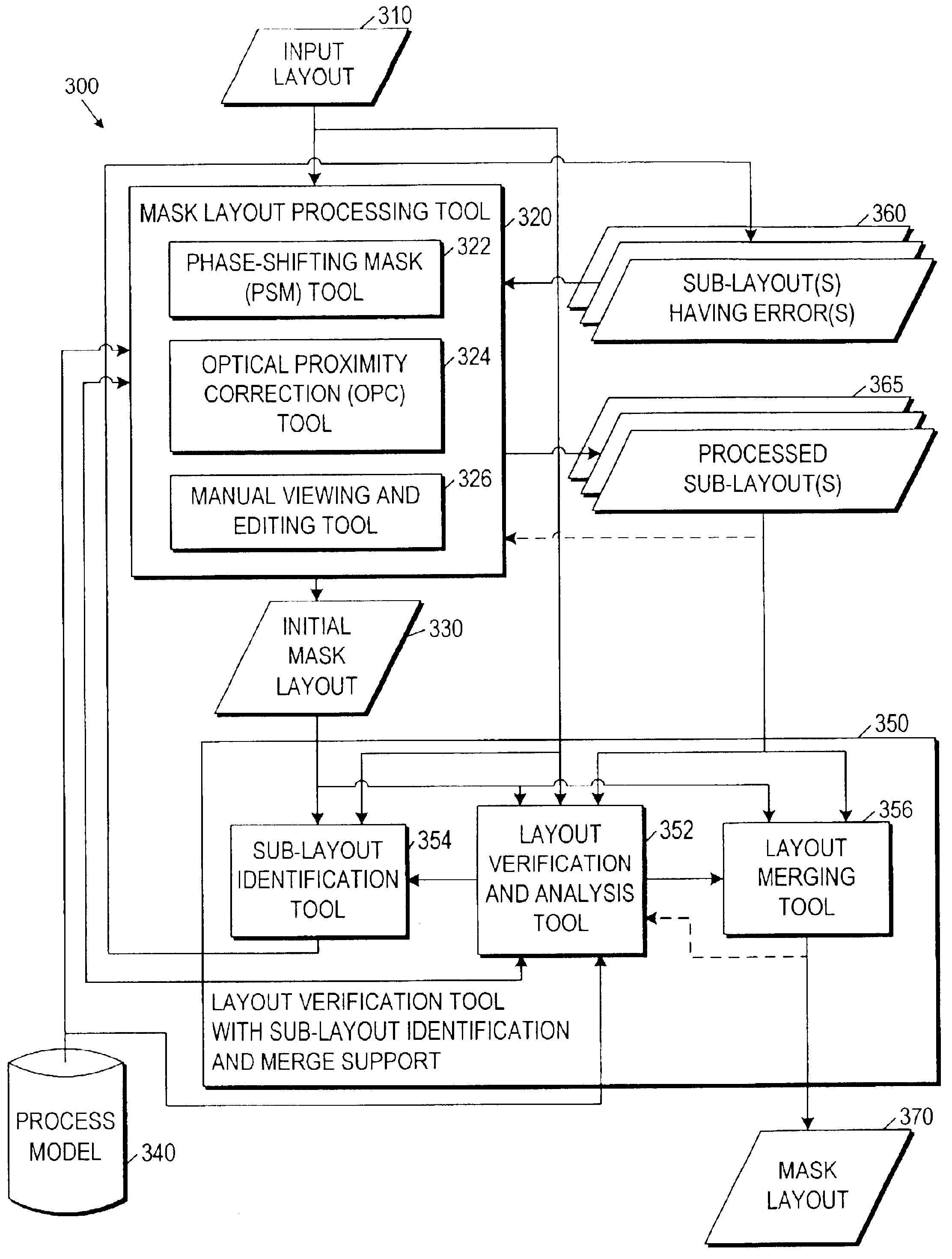

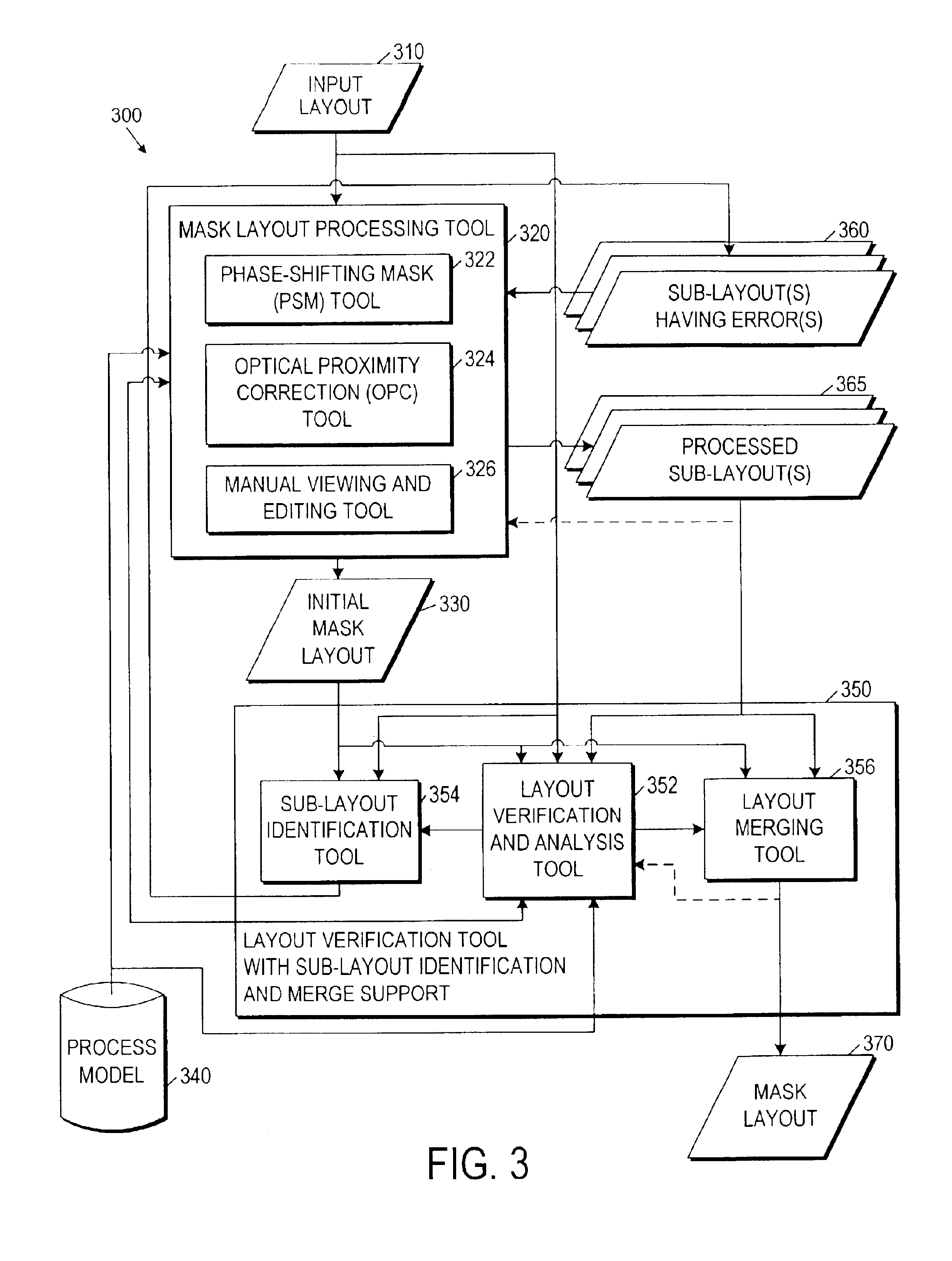

Incremental lithography mask layout design and verification

InactiveUS6904587B2Shorten the timeReduce stepsProgram controlOriginals for photomechanical treatmentLithographic artistIdentification error

A lithography mask layout is designed and verified incrementally to help reduce the amount of time to produce the mask layout. For one embodiment, a layout defining a target pattern may be processed to produce a mask layout, and the mask layout may be verified to identify errors. Rather than processing and verifying the entire mask layout for error correction over one or more subsequent iterations, sub-layouts having errors may be removed or copied from the mask layout for separate processing and verification. Because the amount of data defining a sub-layout is relatively small, the time to design and verify the mask layout is reduced. The resulting mask layout having one or more processed and verified sub-layout(s) may then be used to manufacture a mask set to help print the target pattern in manufacturing integrated circuits (ICs), for example.

Owner:SYNOPSYS INC

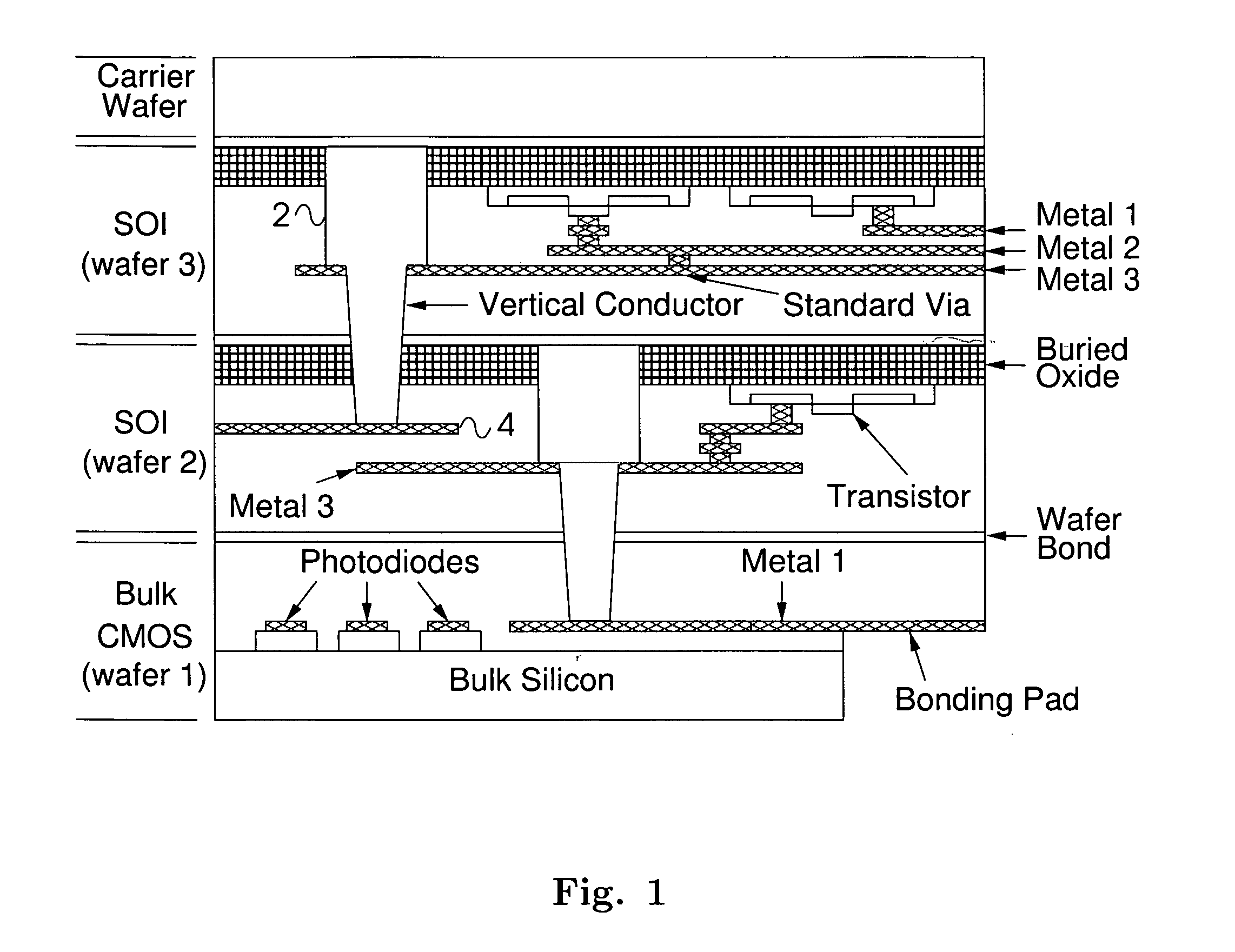

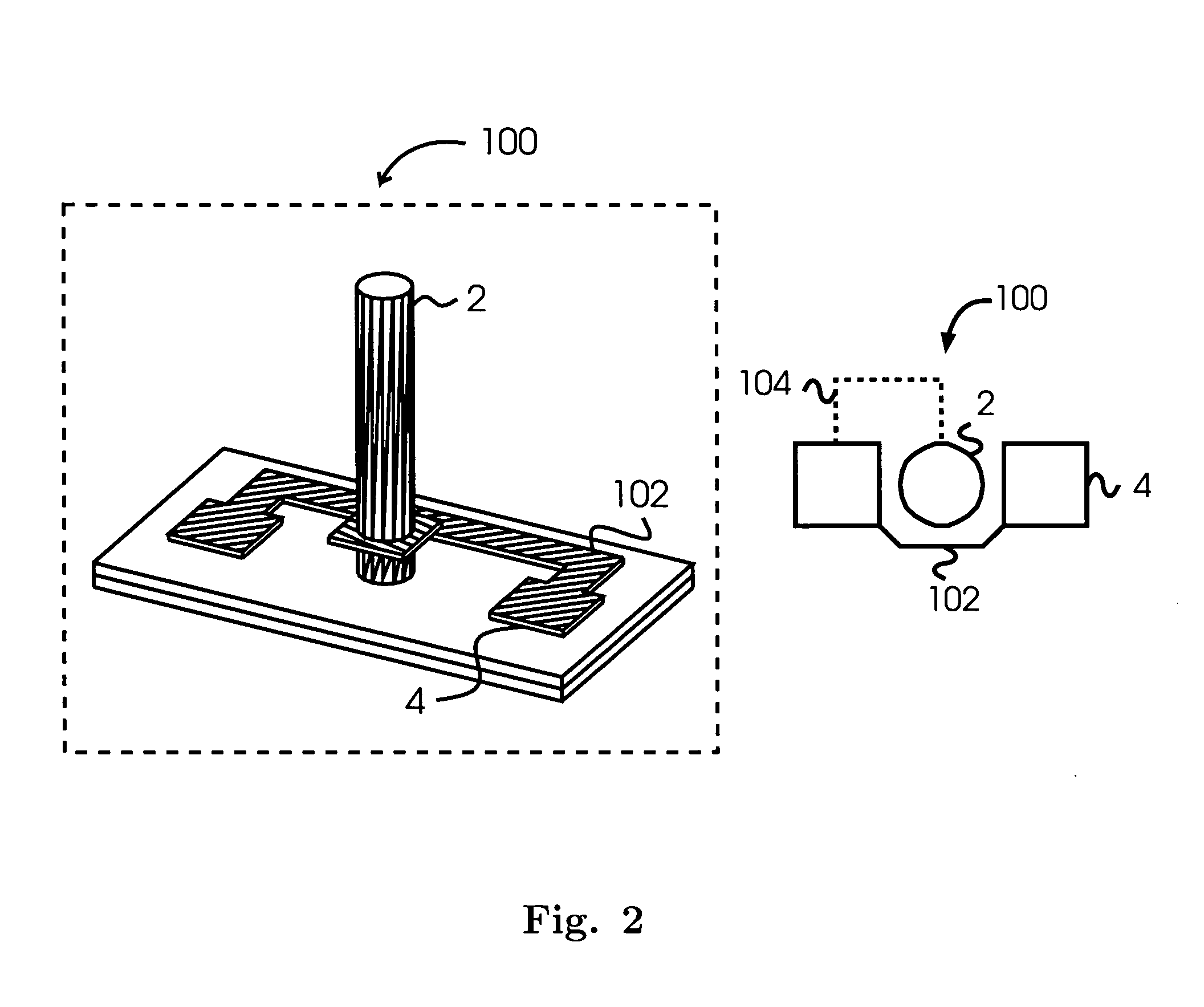

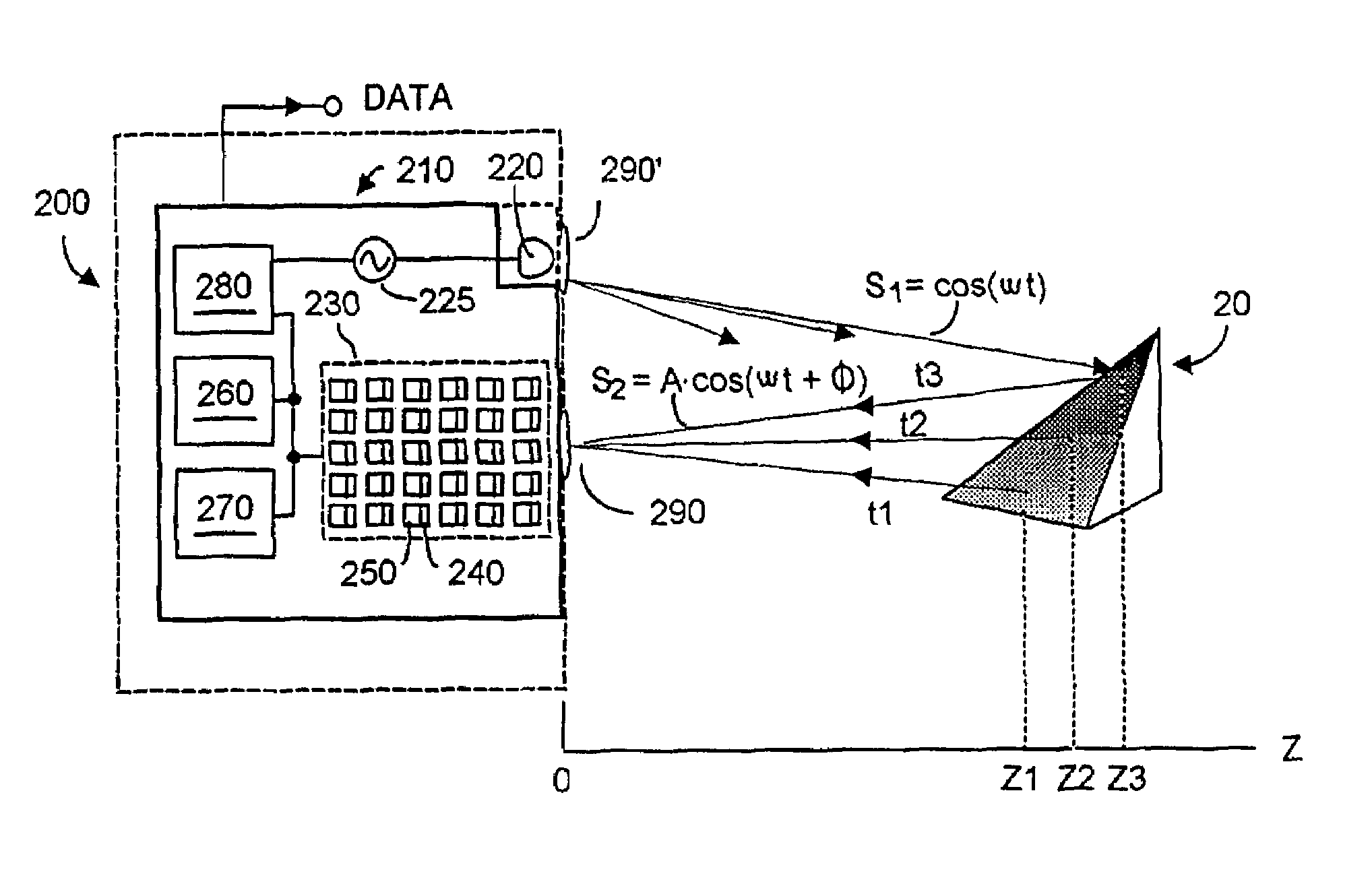

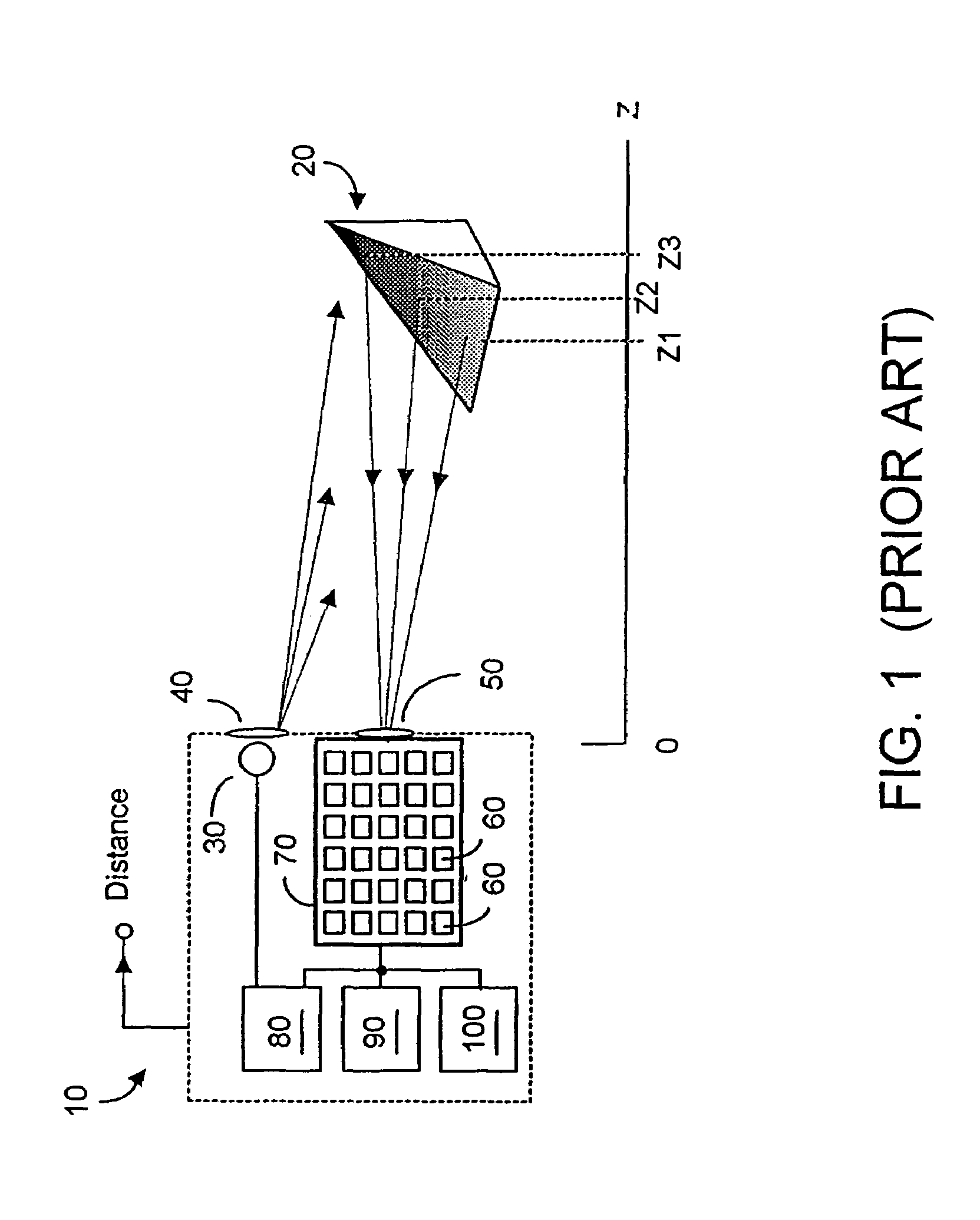

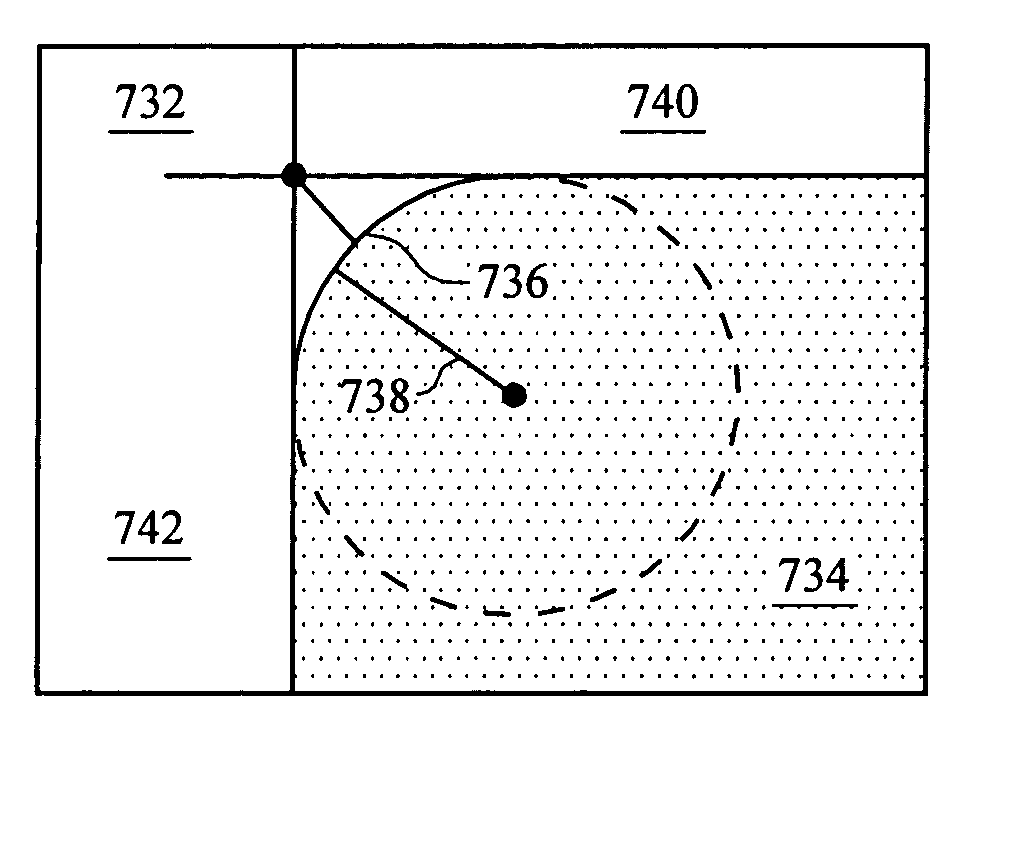

Method enabling a standard CMOS fab to produce an IC to sense three-dimensional information using augmented rules creating mask patterns not otherwise expressible with existing fab rules

InactiveUS7464351B2Reduce peak powerImprove resolution accuracyOptical rangefindersTelevision system scanning detailsCMOSEngineering

CMOS implementable three-dimensional silicon sensors are fabricated using a standard fab but using augmented rules that create mask patterns not expressible with existing fab rules. Standard fab rules are not optimized to produce high quality three-dimensional silicon sensors. Accordingly, the normal set of rules does not permit creating the fab mask patterns necessary for high performance such sensors. However, the present invention can use the fab standard mask set with a rich set of fab instructions to express mask patterns from the mask set that would not otherwise be expressible. The resultant method enables high quality silicon sensors for three-dimensional sensing to be readily mass produced from a standard fab.

Owner:MICROSOFT TECH LICENSING LLC

Deposition Mask and Method of Manufacturing the Same

A deposition mask comprises a mask frame having an open window defined in a center thereof, a first mask sheet placed on the mask frame and including a plurality of open regions and a separation region which separates the open regions, and a second mask sheet placed on the first mask sheet and including a first aperture portion in a region which contacts the separation region of the first mask sheet.

Owner:SAMSUNG DISPLAY CO LTD

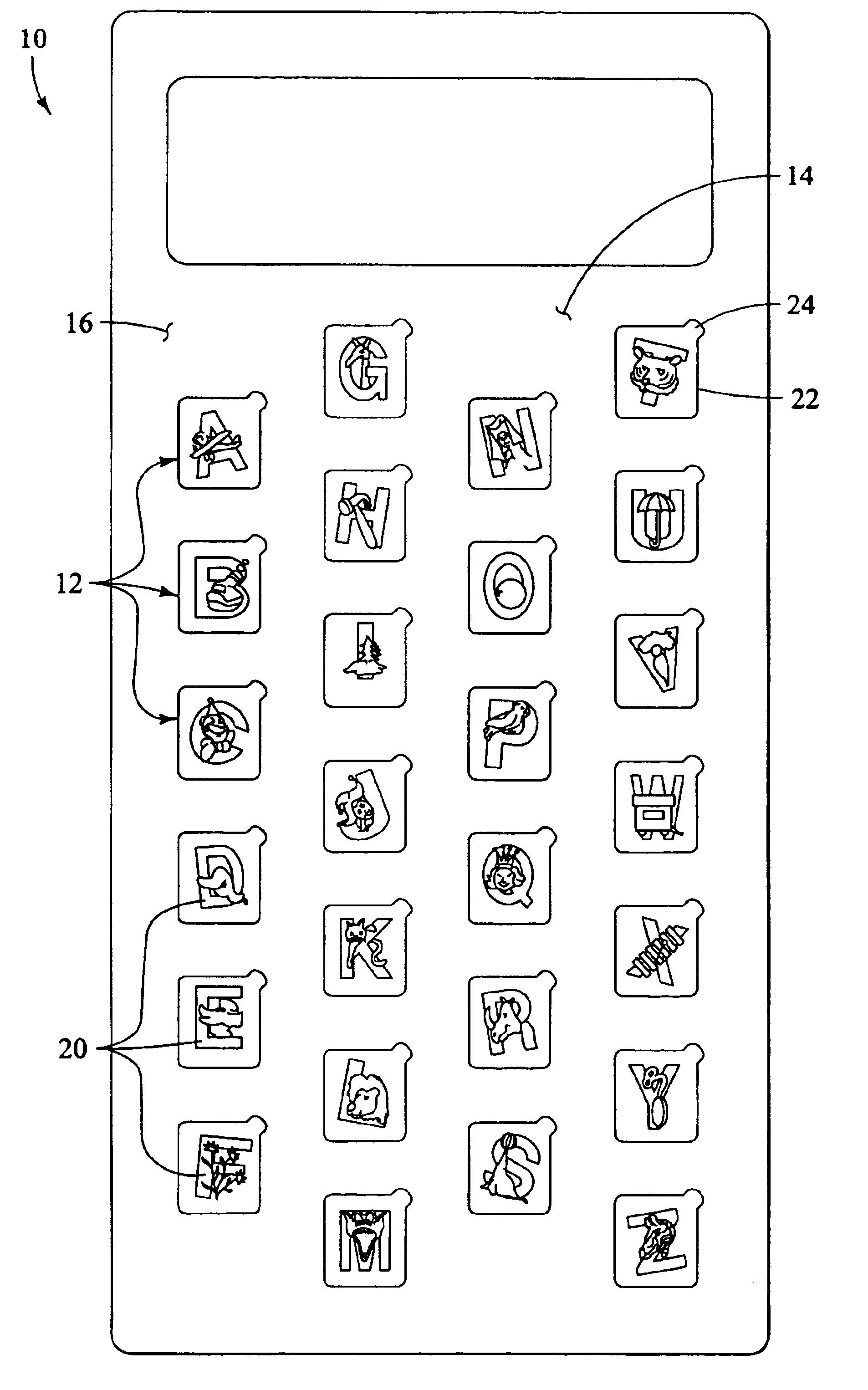

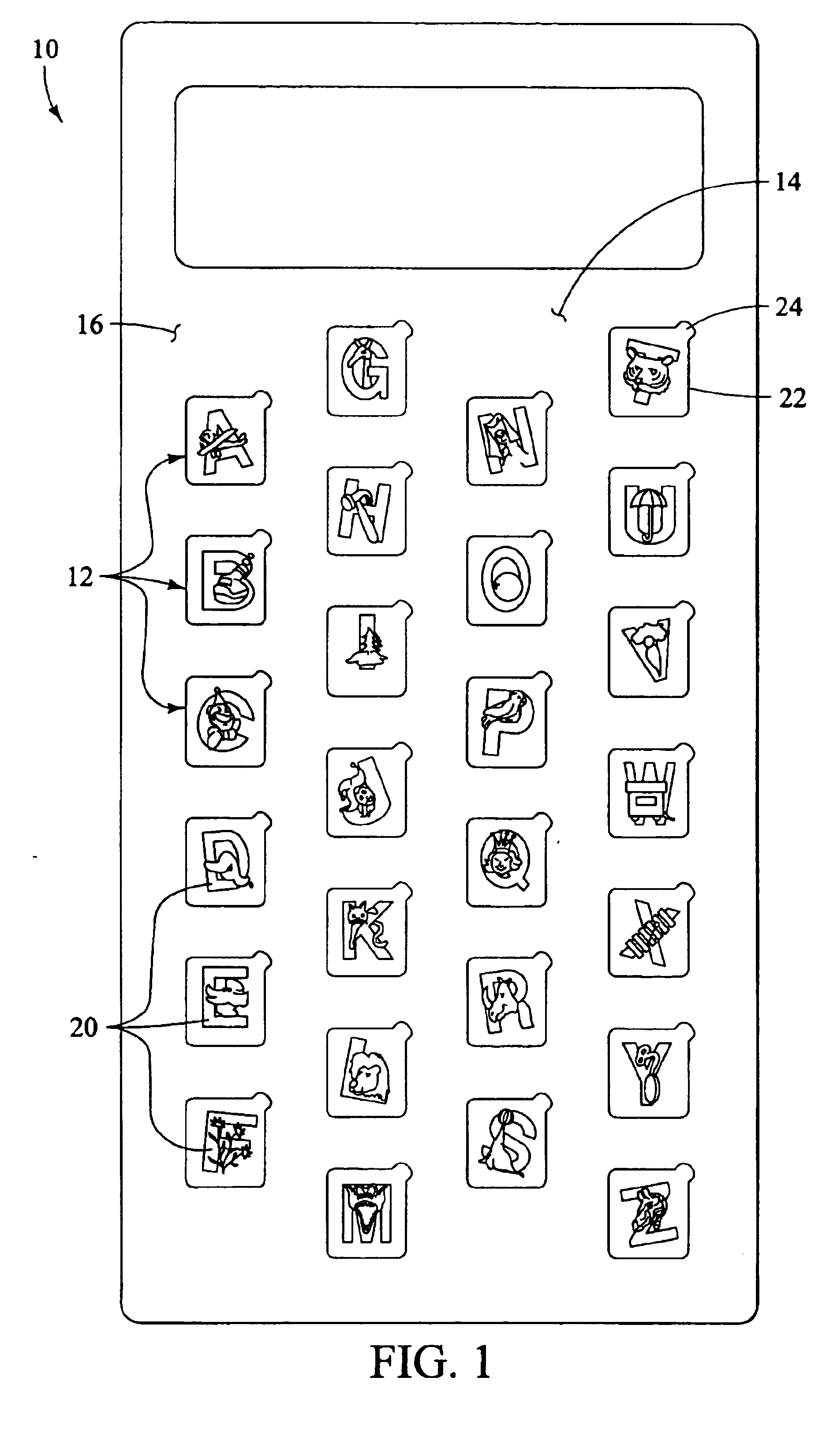

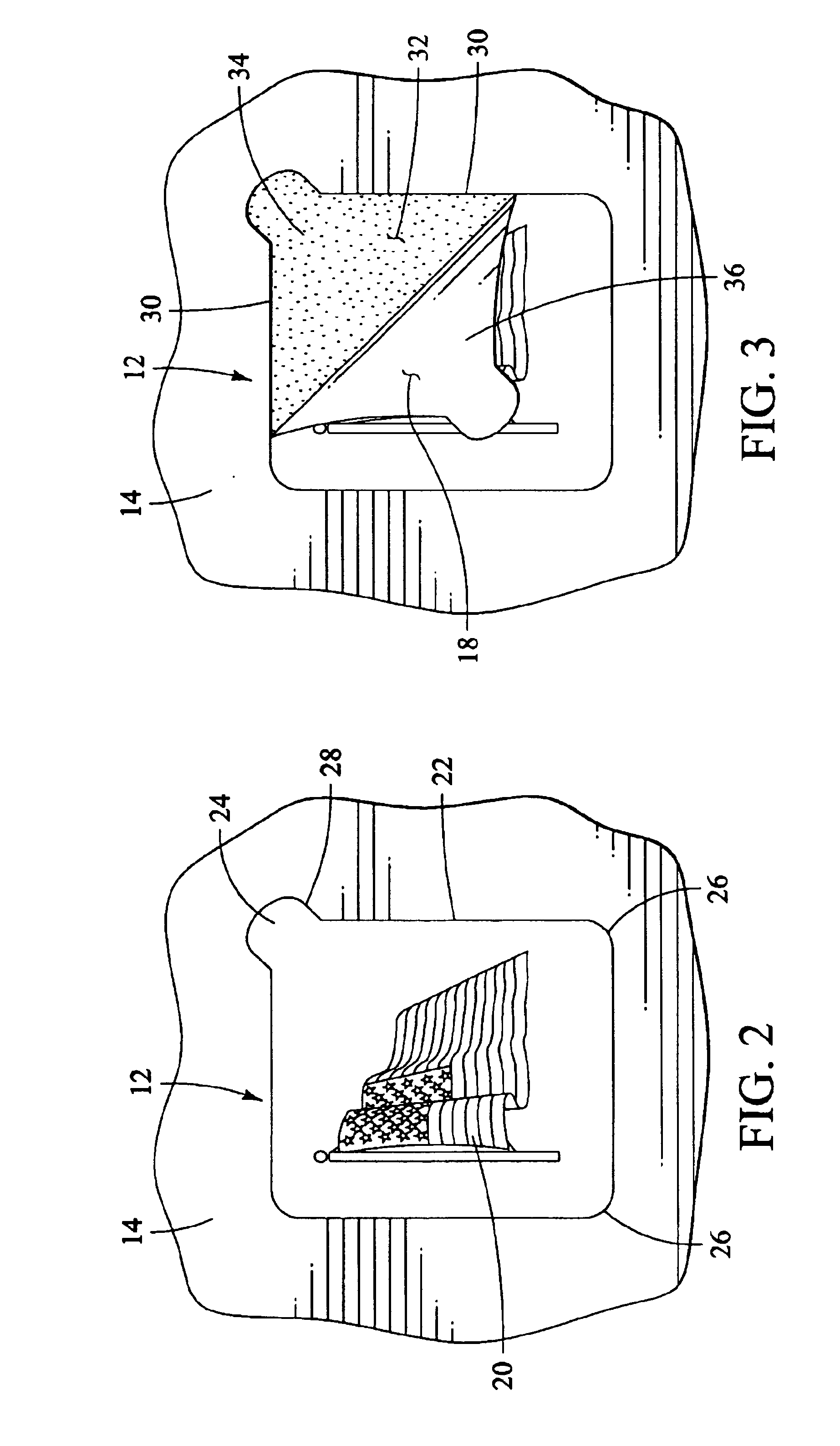

Printable, reusable key masks

InactiveUS6883985B2Avoid spreadingEasy to installInput/output for user-computer interactionStampsPersonalizationGraphics

A functional and decorative key mask is disclosed that is printable and has a uniquely functional geometry for easy and clean removable attachment to the keyfaces of a keyboard or keypad. The materials and design combine to provide a durable and reusable key mask. In the preferred embodiment, the key mask is has a body and a tab extending outward, and a pressure sensitive adhesive adhered to the back surface. It is die-cut from a face stock that is attached by the adhesive to a coated release liner. Mask sets include several key masks having similar or individualized graphic illustrations that enable the user to make unique associations with the keys of the keyboard or keypad, and thus enhance their learning, skill, performance, and enjoyment of a standard keyboard or keypad, or one having specialized key assignments.

Owner:ROBERSON ROBIN CATHERINE

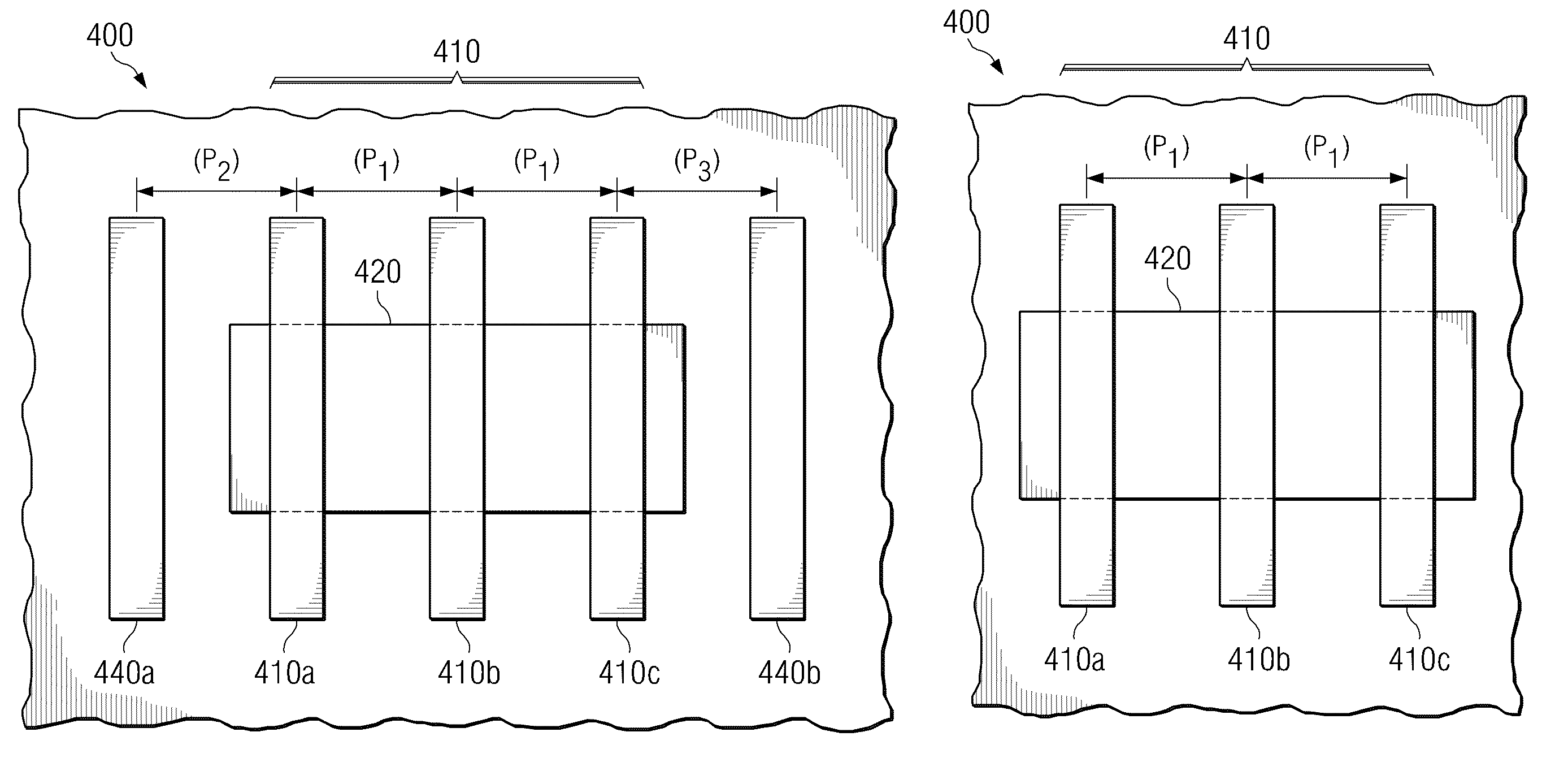

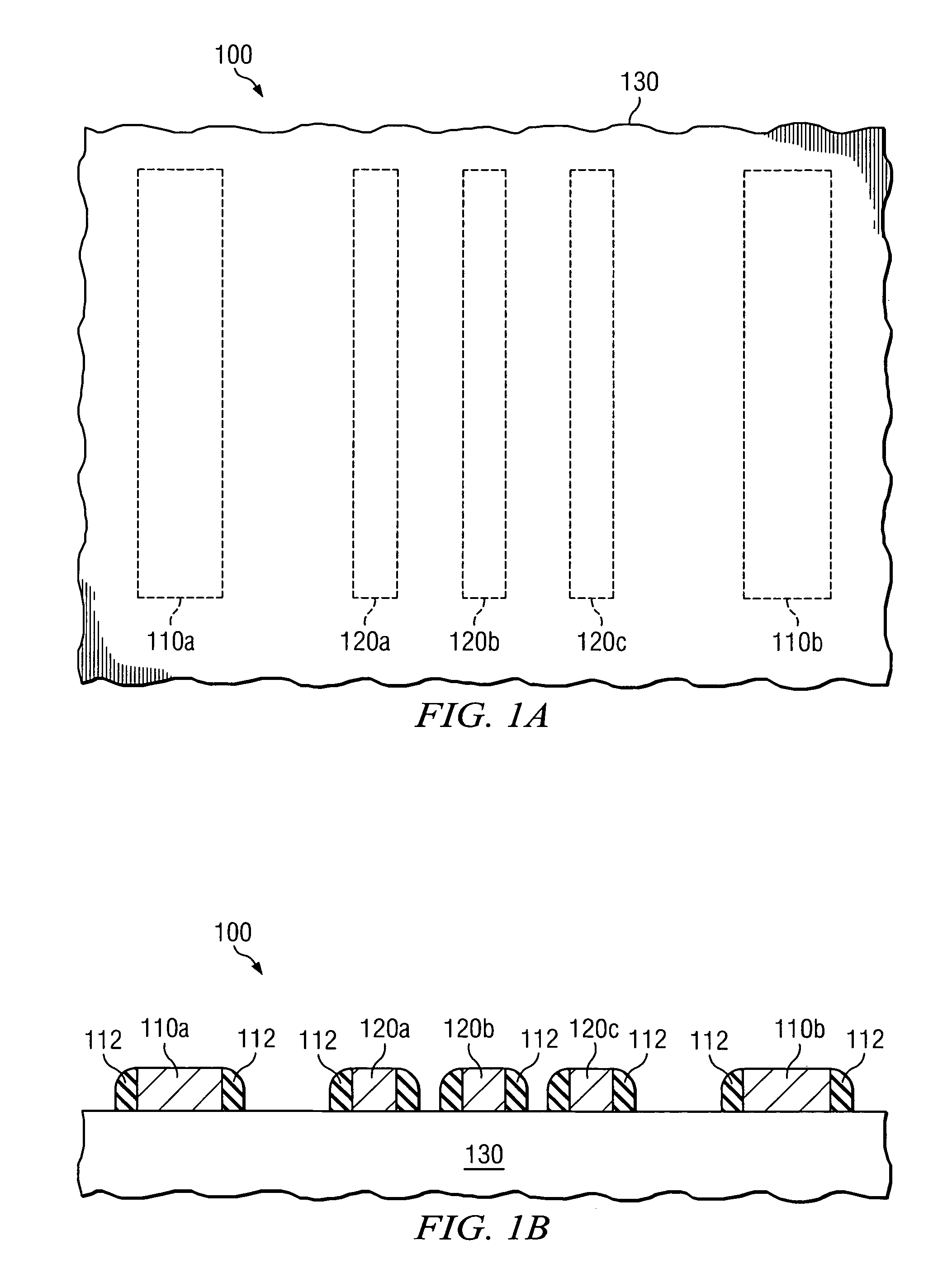

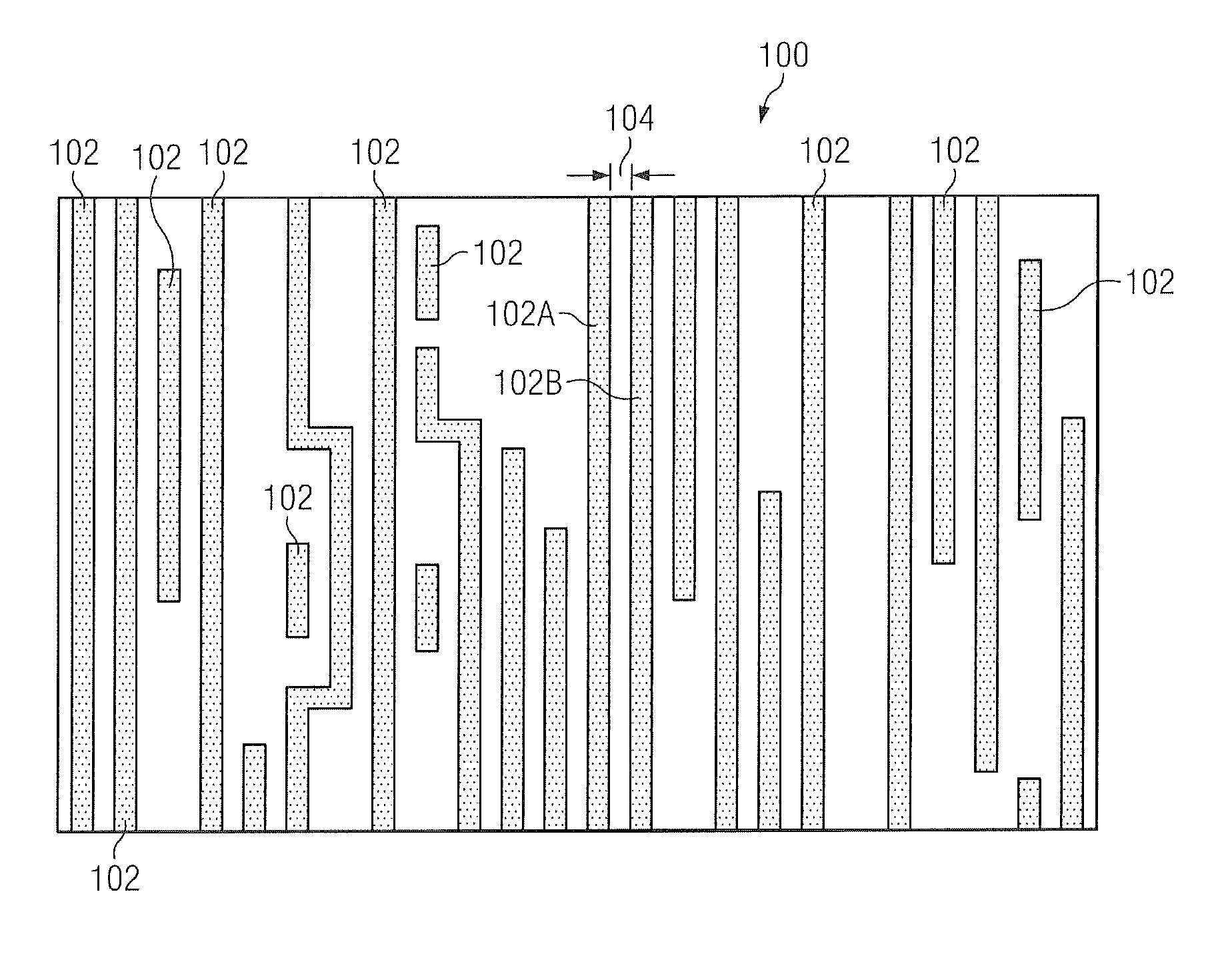

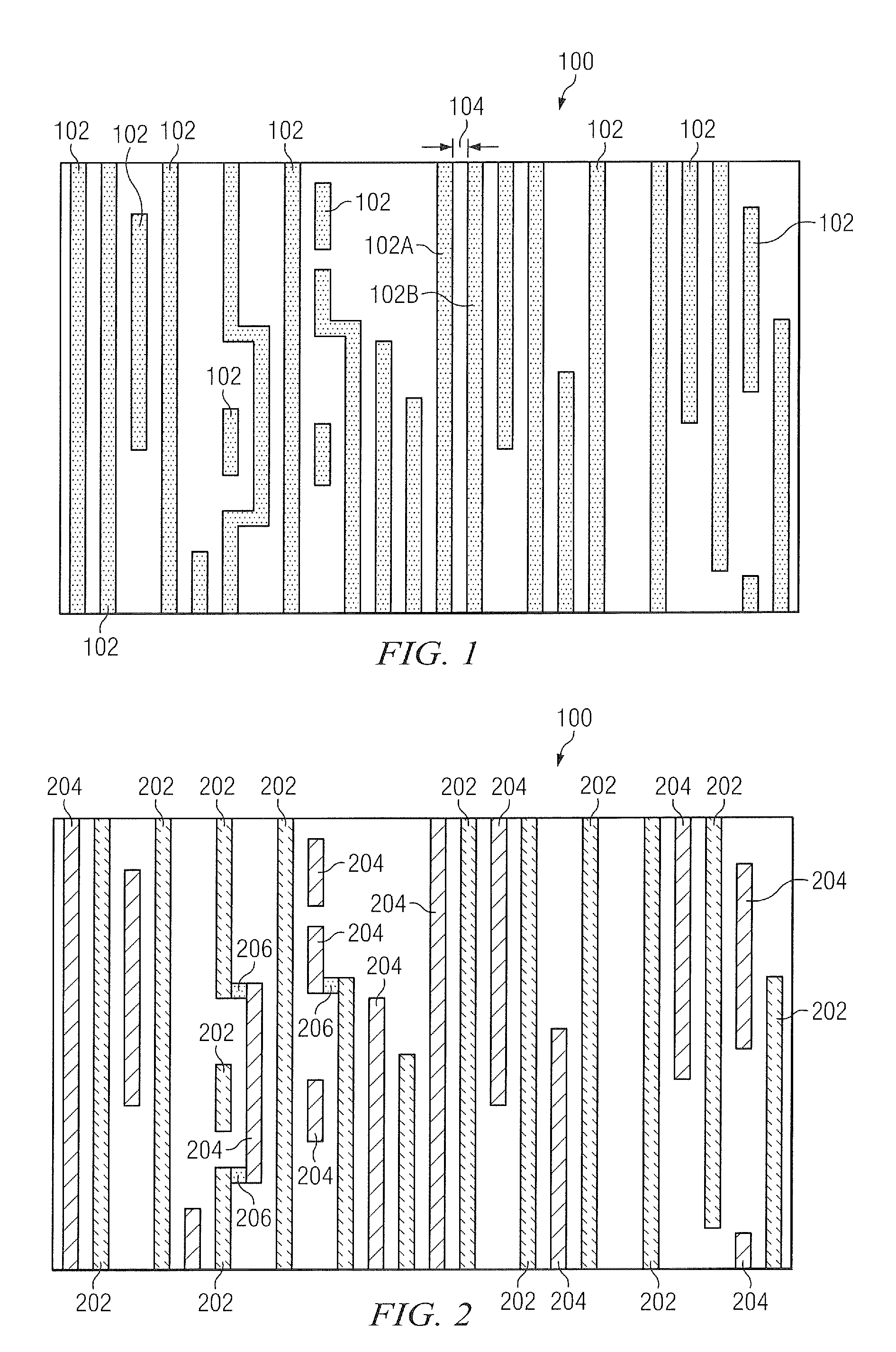

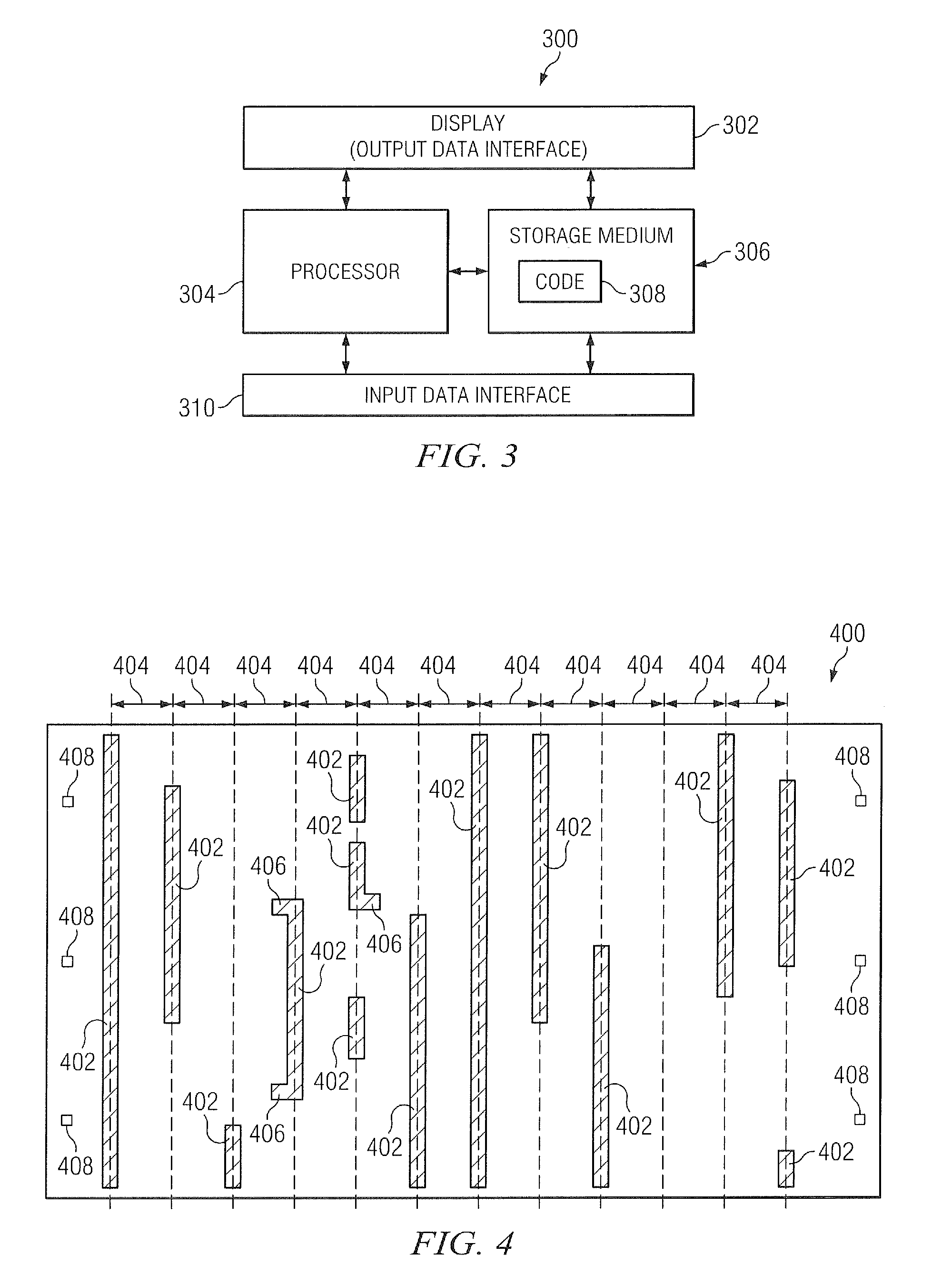

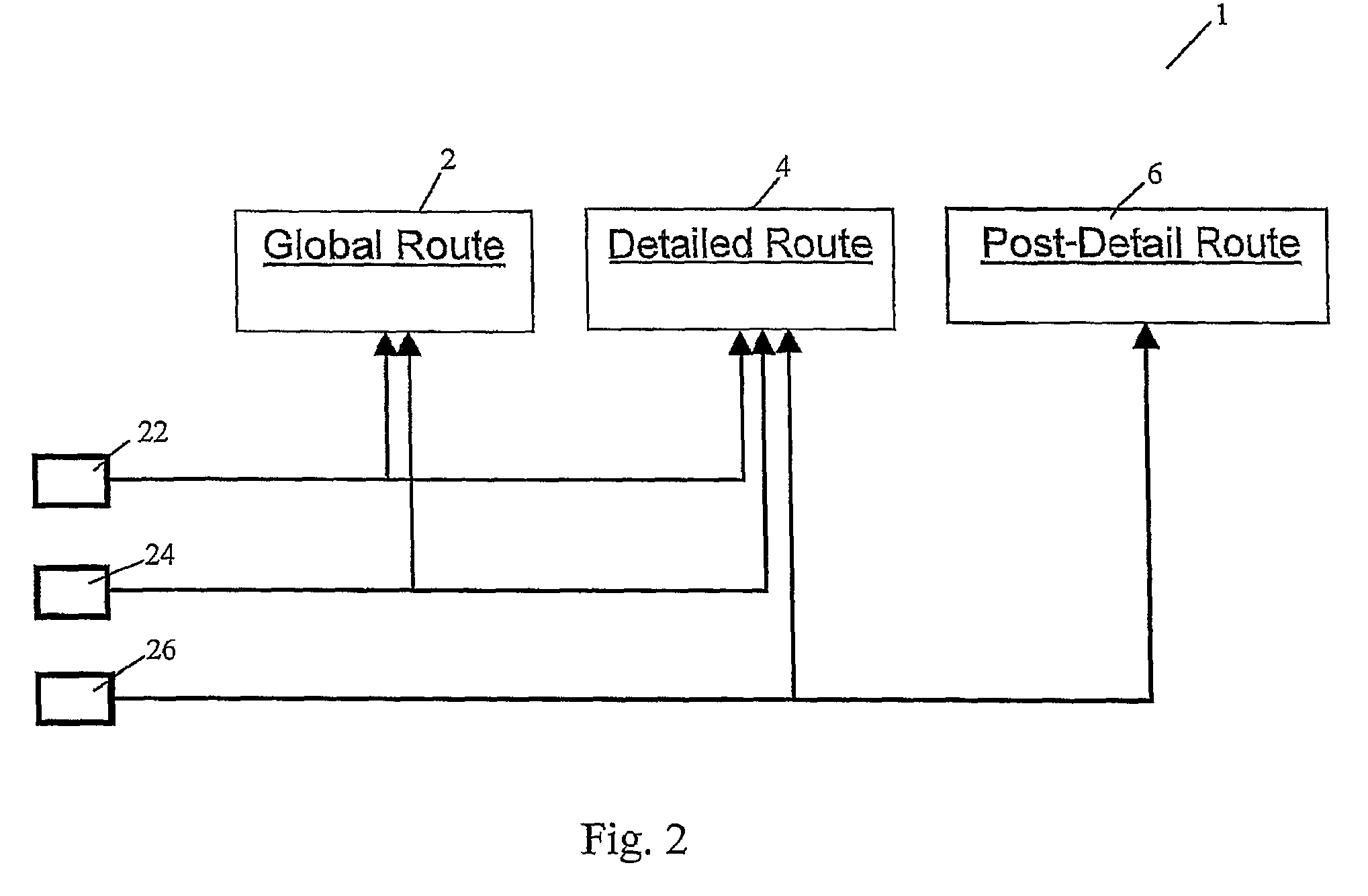

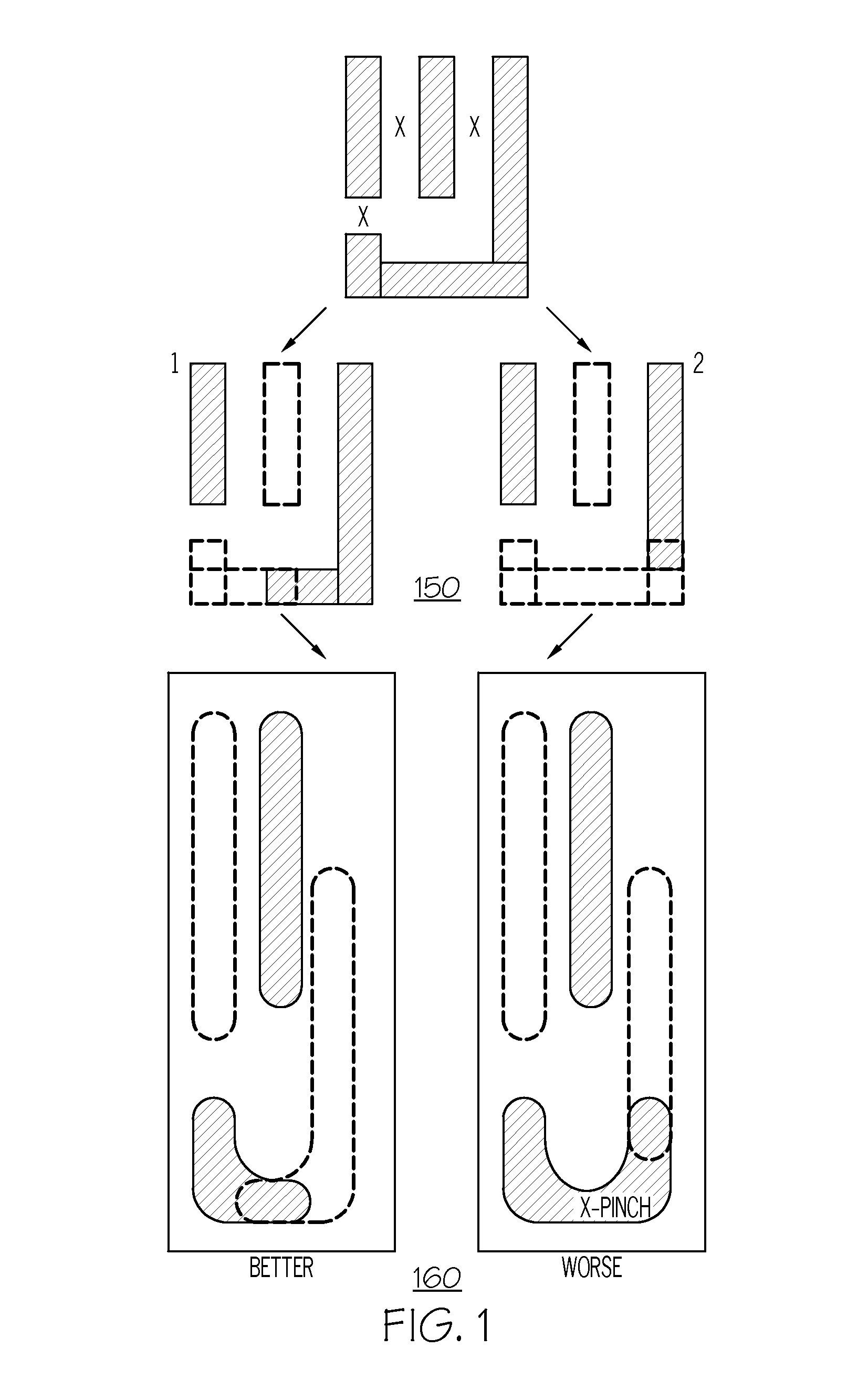

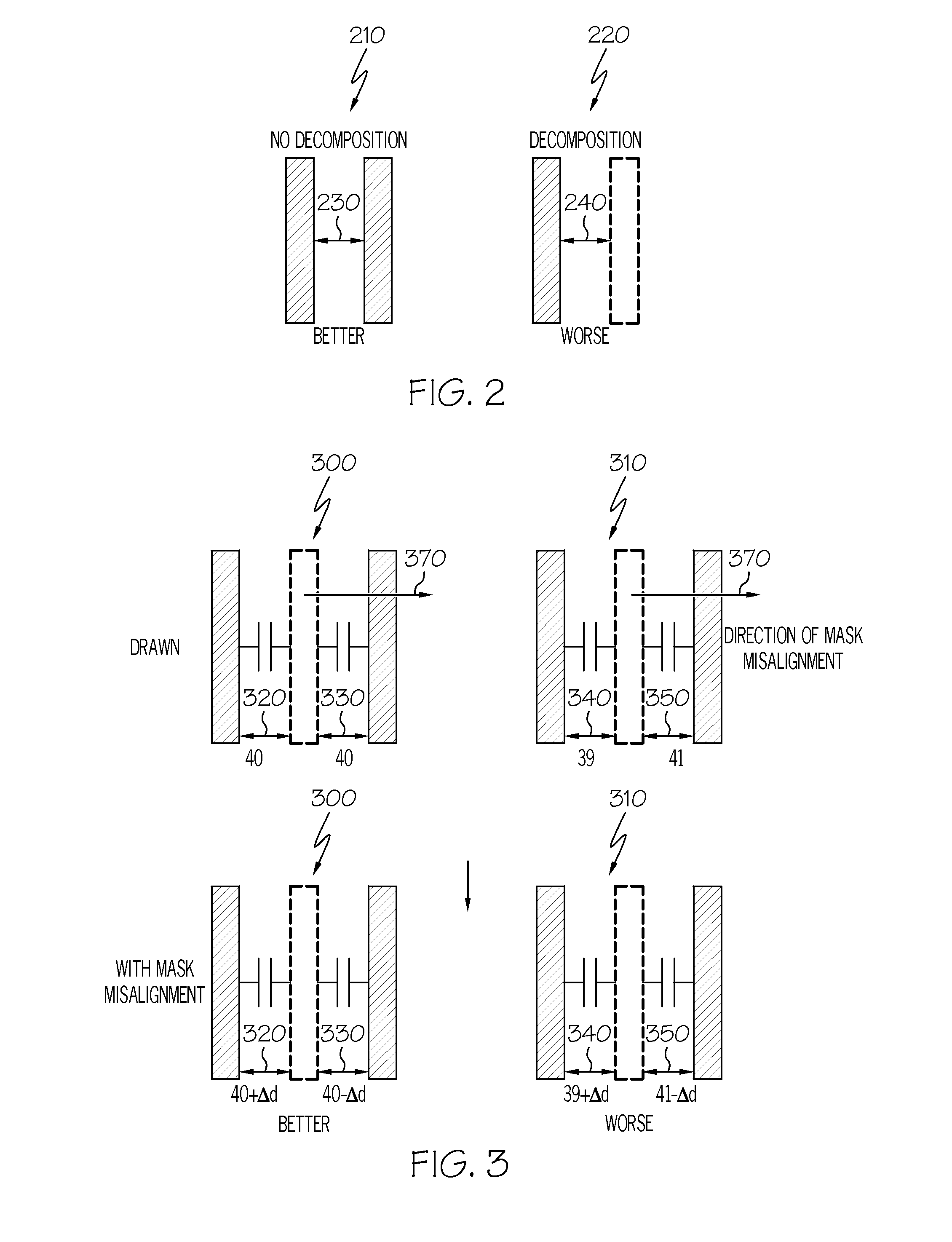

Partitioning features of a single IC layer onto multiple photolithographic masks

ActiveUS20100167537A1Semiconductor/solid-state device manufacturingPhotomechanical exposure apparatusCouplingComputer methods

One embodiment relates to a computer method of providing an electronic mask set for an integrated circuit (IC) layer. In the method, a first electronic mask is generated for the IC layer. The first electronic mask includes a first series of longitudinal segments from the IC layer, where the first series has fewer than all of the longitudinal segments in the IC layer. A second electronic mask is also generated for the IC layer. The second electronic mask includes a second series of longitudinal segments from the IC layer, where the second series has fewer than all of the longitudinal segments in the IC layer and differs from the first series. The first and second masks are generated so a coupling segment extends traverse to the first direction and couples one longitudinal segment on the IC layer to another longitudinal segment on the IC layer.

Owner:TEXAS INSTR INC

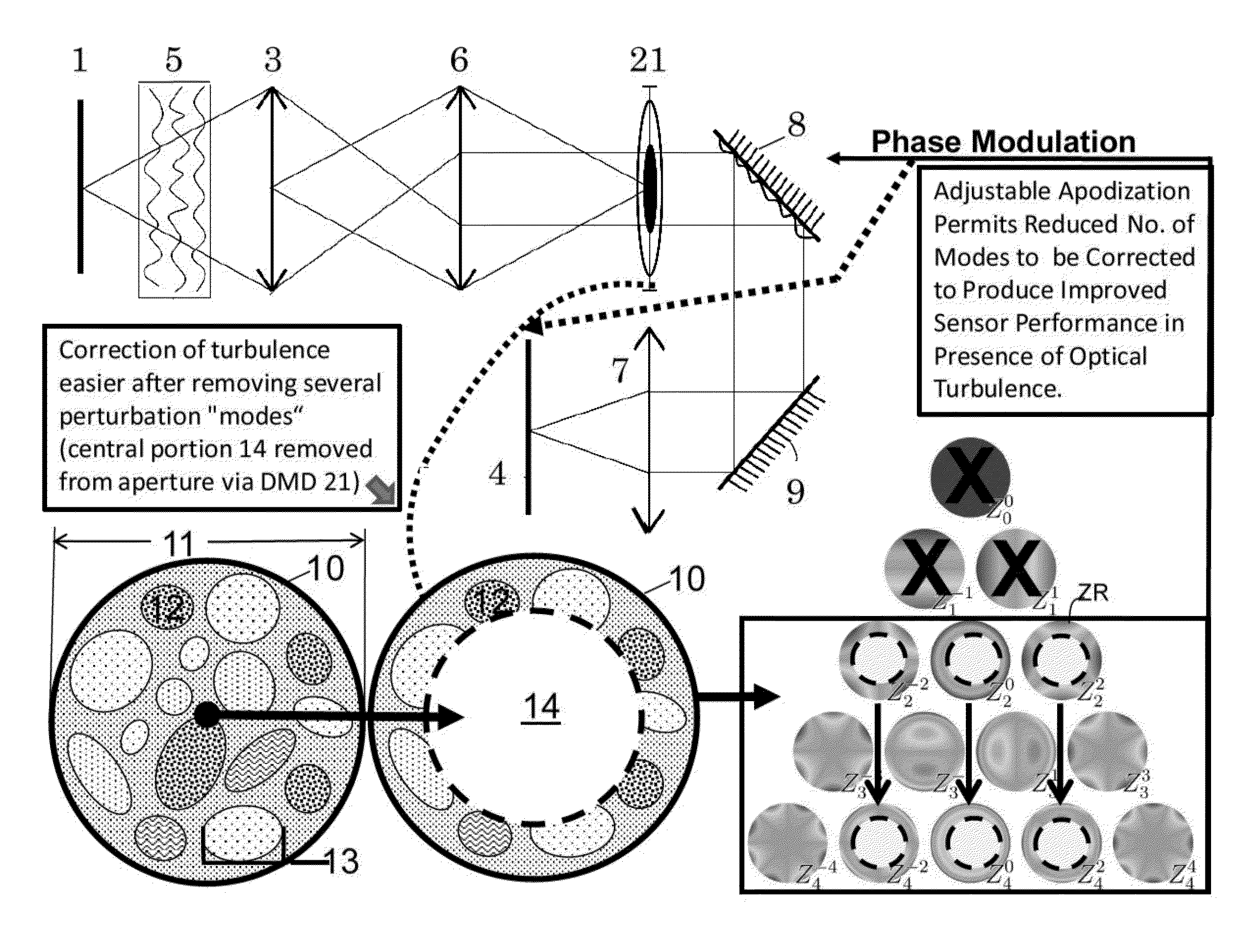

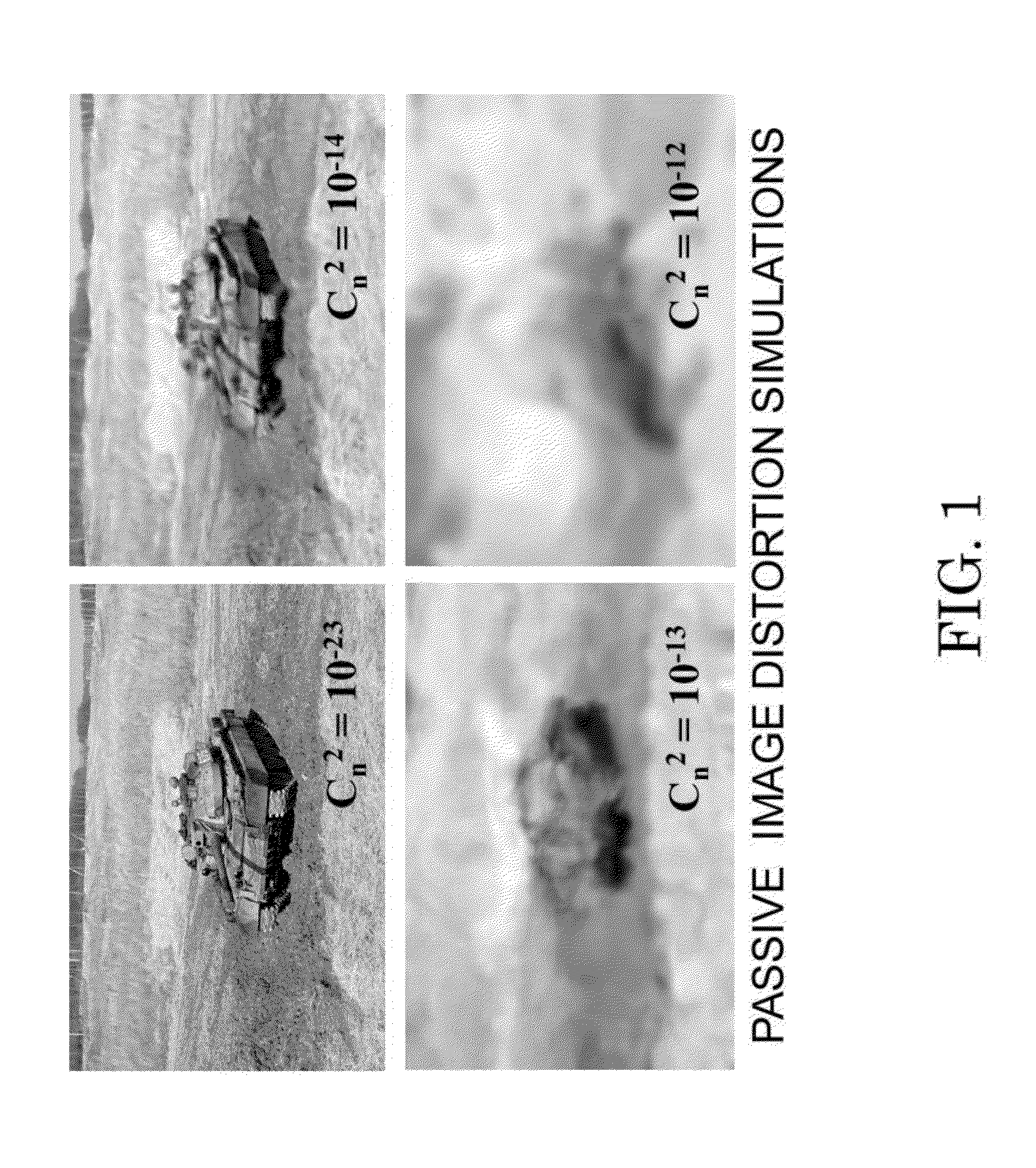

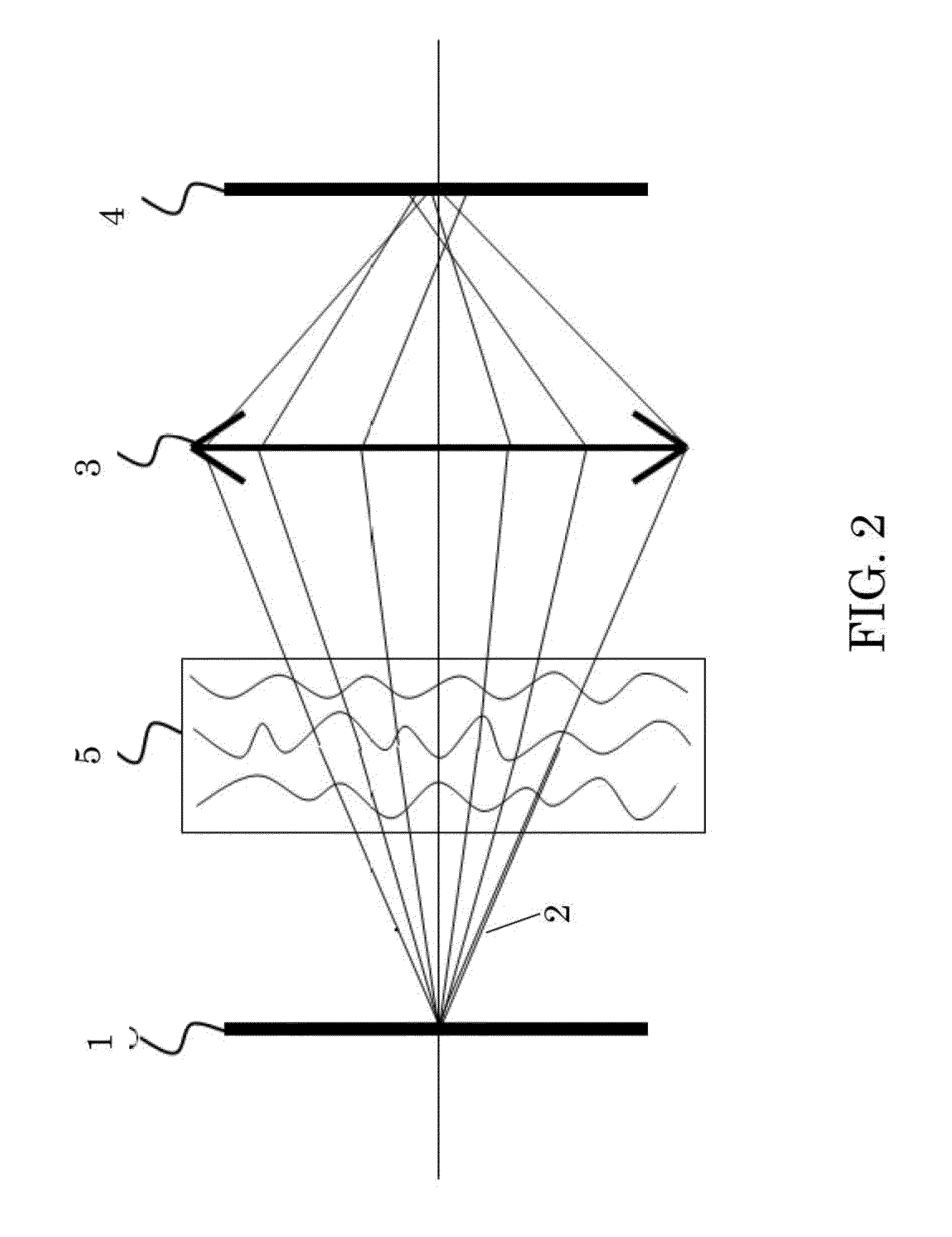

Passive Imaging Correction System Using Feedback and Method Thereof

InactiveUS20140125860A1Effective quantityEffective aperture diameterImage enhancementTelevision system detailsImaging processingImage correction

A method and system for image processing comprising an opening for entrance of light for forming an image by the system; at least one optical element through which the light passes; a variable aperture operatively associated with the at least one optical element placed in the optical train at an image plane and comprising a plurality of settings comprising first mask settings for shielding portions of the light and second mask settings for selectively masking portions of the light that pass through the first mask settings; an imager, the at least one processor being operatively connected to the variable aperture and imager for controlling the passage of the light through the variable aperture by selecting one of plurality of first mask settings and associated second mask settings, obtaining image results using the settings, comparing image results obtained by the respective mask settings, and determining the optimal first mask setting.

Owner:UNITED STATES GOVERNMENT AS REPRESENTATIVES BY THE SEC OF THE ARMY THE

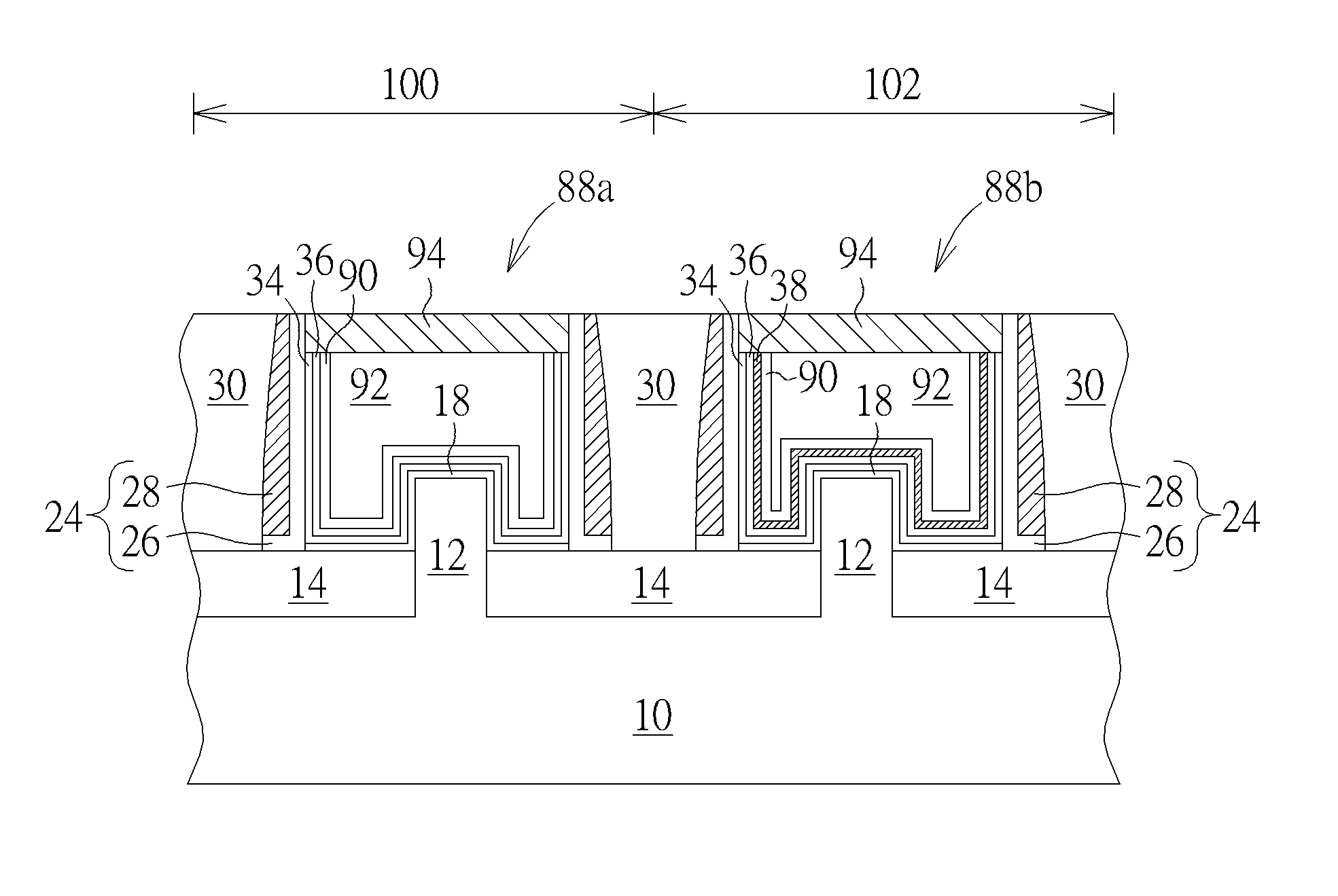

Mask set and method for fabricating semiconductor device by using the same

ActiveUS20150348850A1Reduce impactSemiconductor/solid-state device manufacturingOriginals for photomechanical treatmentLong axisComputer science

A mask set includes a first mask and a second mask. The first mask includes geometric patterns. The second mask includes at least a strip-shaped pattern with a first edge and a second edge opposite to the first edge. The strip-shaped pattern has a centerline along a long axis of the strip-shaped pattern. The first edge includes inwardly displaced segments shifting towards the centerline and each of the inwardly displaced segments overlaps each of the geometric patterns.

Owner:UNITED MICROELECTRONICS CORP

Routing method for double patterning design

ActiveUS8327301B2Reduce effortReduce chip areaPhotomechanical apparatusOriginals for photomechanical treatmentEngineeringGrid cell

In a method of designing a double patterning mask set, a chip is first divided into a grid that includes grid cells. A metal layer of the chip is laid out. In substantially each of the grid cells, all left-boundary patterns of the metal layer are assigned with a first indicator, and all right-boundary patterns of the metal layer are assigned with a second indicator. Starting from one of the grid cells in a row, indicator changes are propagated throughout the row. All patterns in the grid cells are transferred to the double patterning mask set. All patterns assigned with the first indicator are transferred to a first mask of the double patterning mask set, and all patterns assigned with the second indicator transferred to a second mask of the double patterning mask set.

Owner:TAIWAN SEMICON MFG CO LTD

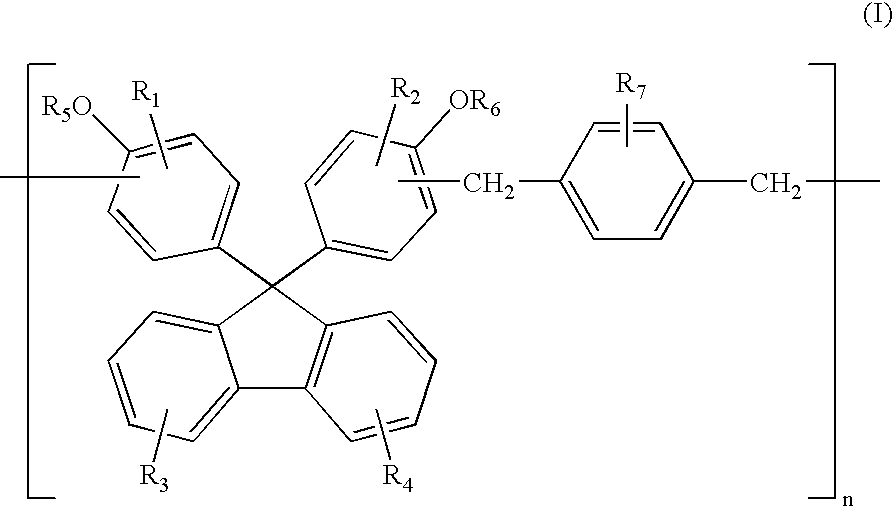

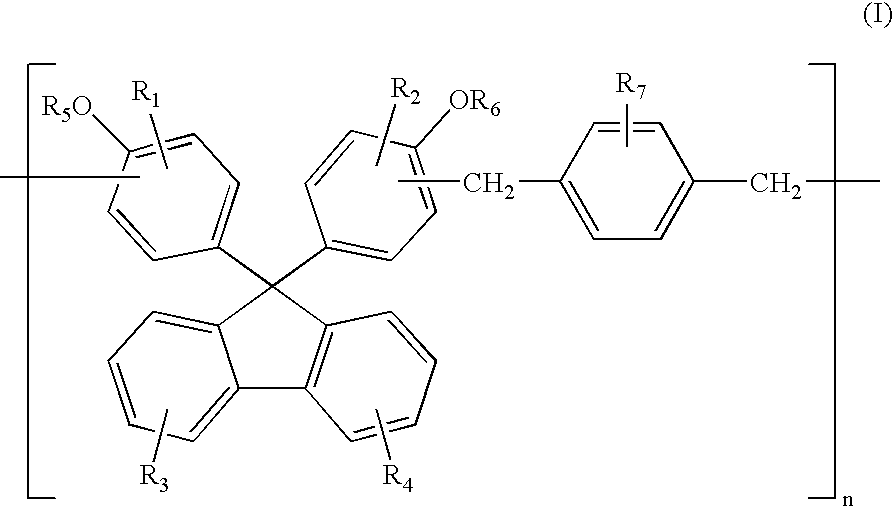

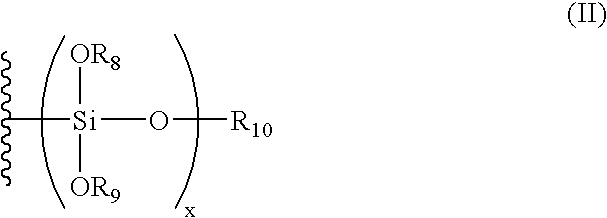

Antireflective hardmask composition and methods for using same

Hardmask compositions having antireflective properties useful in lithographic processes, methods of using the same, and semiconductor devices fabricated by such methods, are provided. Antireflective hardmask compositions of the invention include: (a) a polymer component including at least one polymer having a monomeric unit of Formula (I) wherein R1 and R2 may each independently be hydrogen, hydroxyl, alkyl, aryl, allyl, halo, or any combination thereof; R3 and R4 may each independently be hydrogen, a crosslinking functionality, a chromophore, or any combination thereof; R5 and R6 may each independently be hydrogen or an alkoxysilane group; R7 may each independently be hydrogen, alkyl, aryl, allyl, or any combination thereof; and n may be a positive integer; (b) a crosslinking component; and (c) an acid catalyst.

Owner:CHEIL IND INC

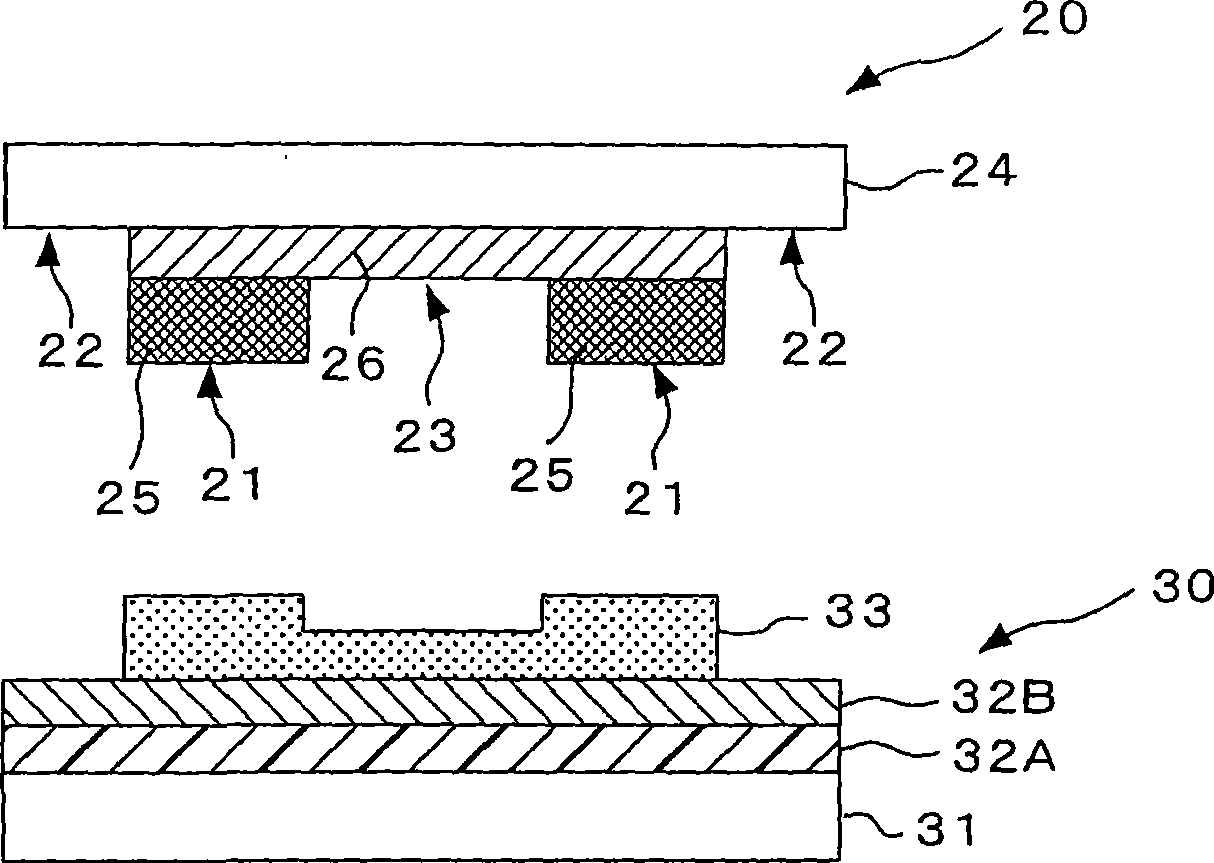

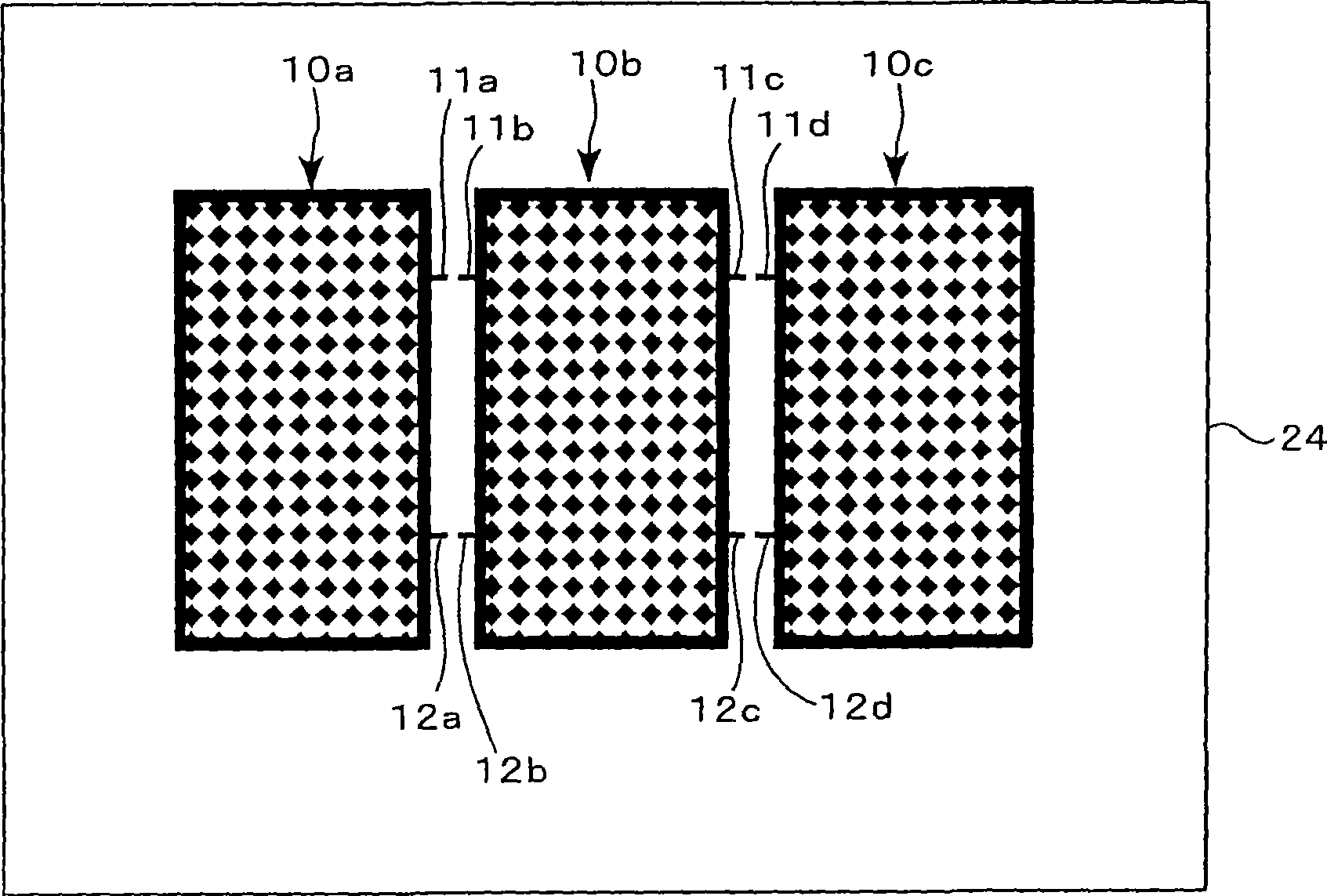

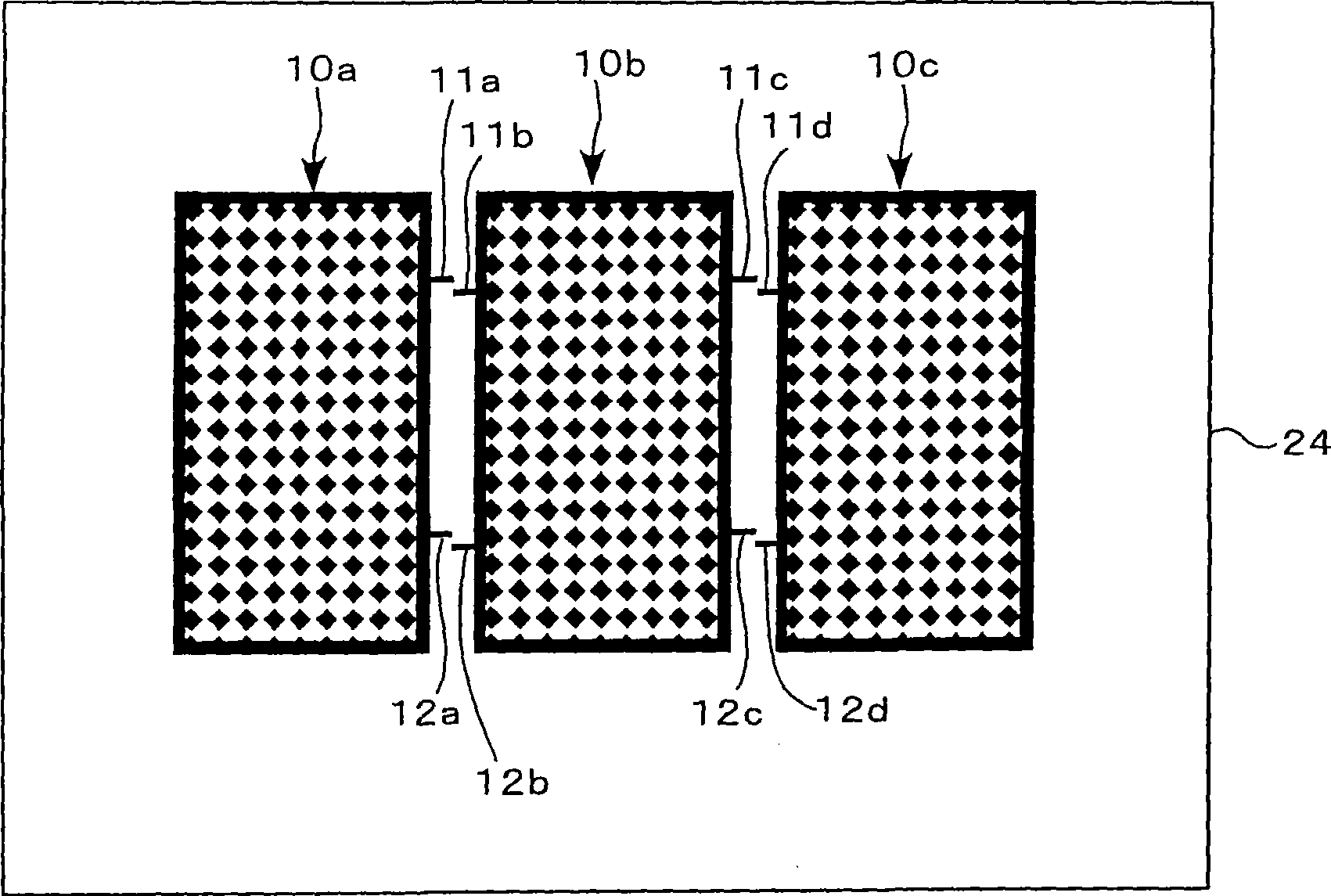

Photomask, manufacturing method thereof, and pattern transfer print method

InactiveCN101441408AAvoid electrostatic damageHigh precisionPhotomechanical apparatusSemiconductor/solid-state device manufacturingEngineeringMask set

The invention provides a photomask, a method for manufacturing the photomask, and a pattern transfer method. An object of the invention is to provide a photomask such as a gray mask, which can restrain electrostatic destruction of pattern caused in treatment in mask use, even if electrostatic destruction is generated, mask design formed by an apparatus may not be affected in use. According to the invention, a photomask is provided on a transparent substrate (24) for forming desired mask patterns of the transfer patterns (such as gray masks), and conductive patterns separately guided from separated a plurality of mask designs (11a and 11b, 11c and 11d, 12a and 12b, 12c and 12d) are provided. The conductive patterns have non-contact parts nearer each other in comparison with each space between each mask pattern, which is formed by such as semitranslucent film or translucent film.

Owner:HOYA CORP

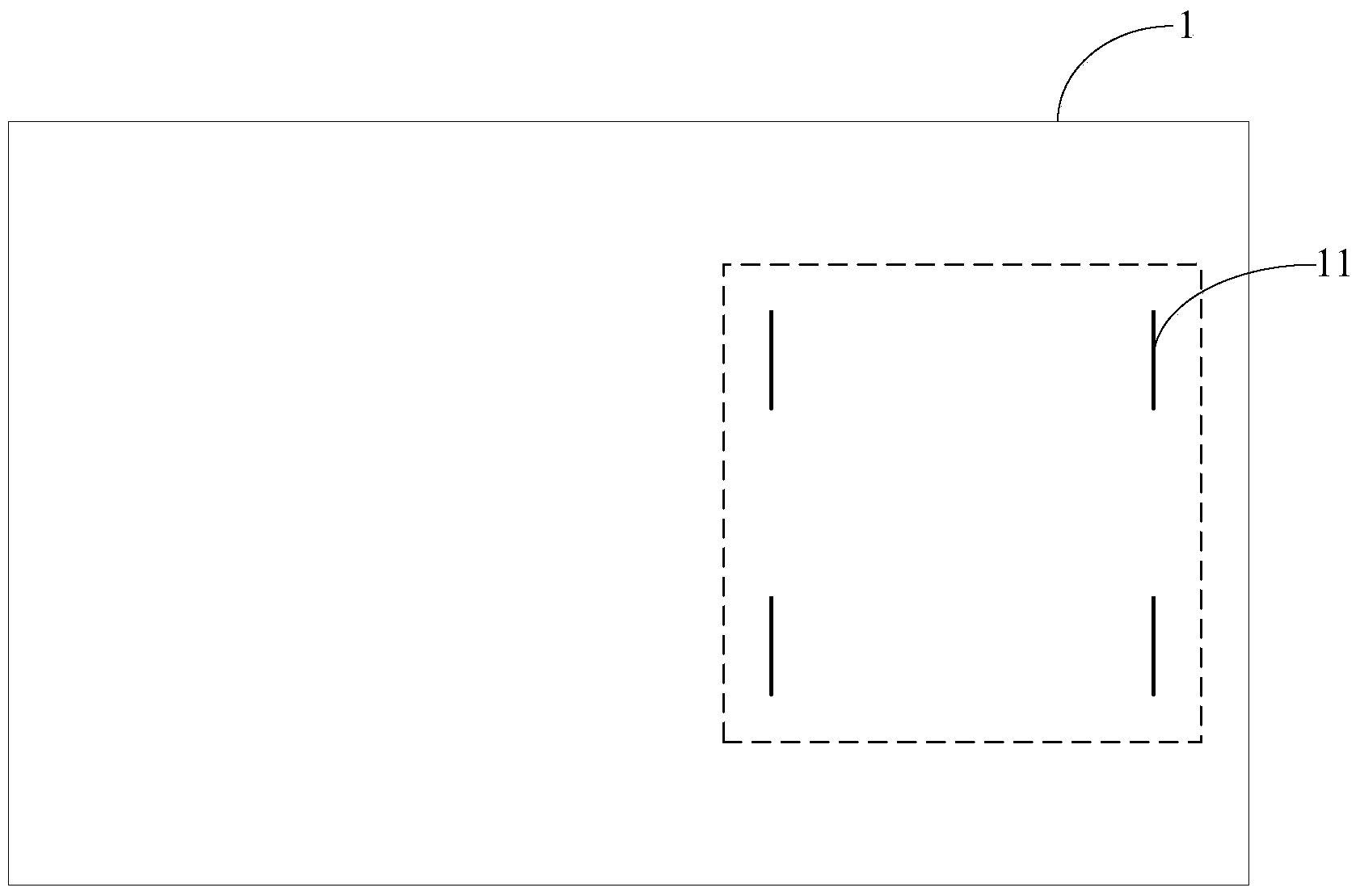

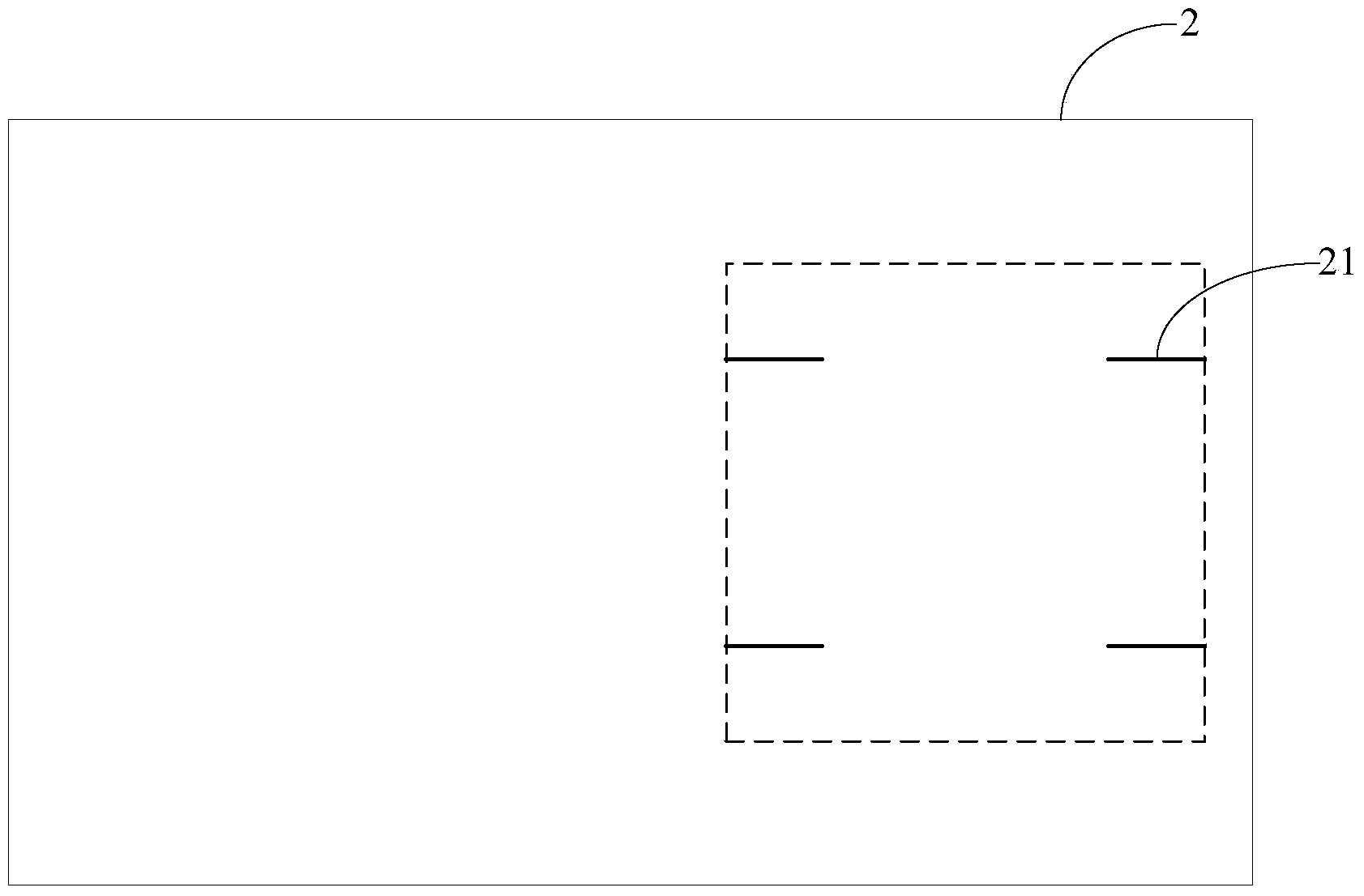

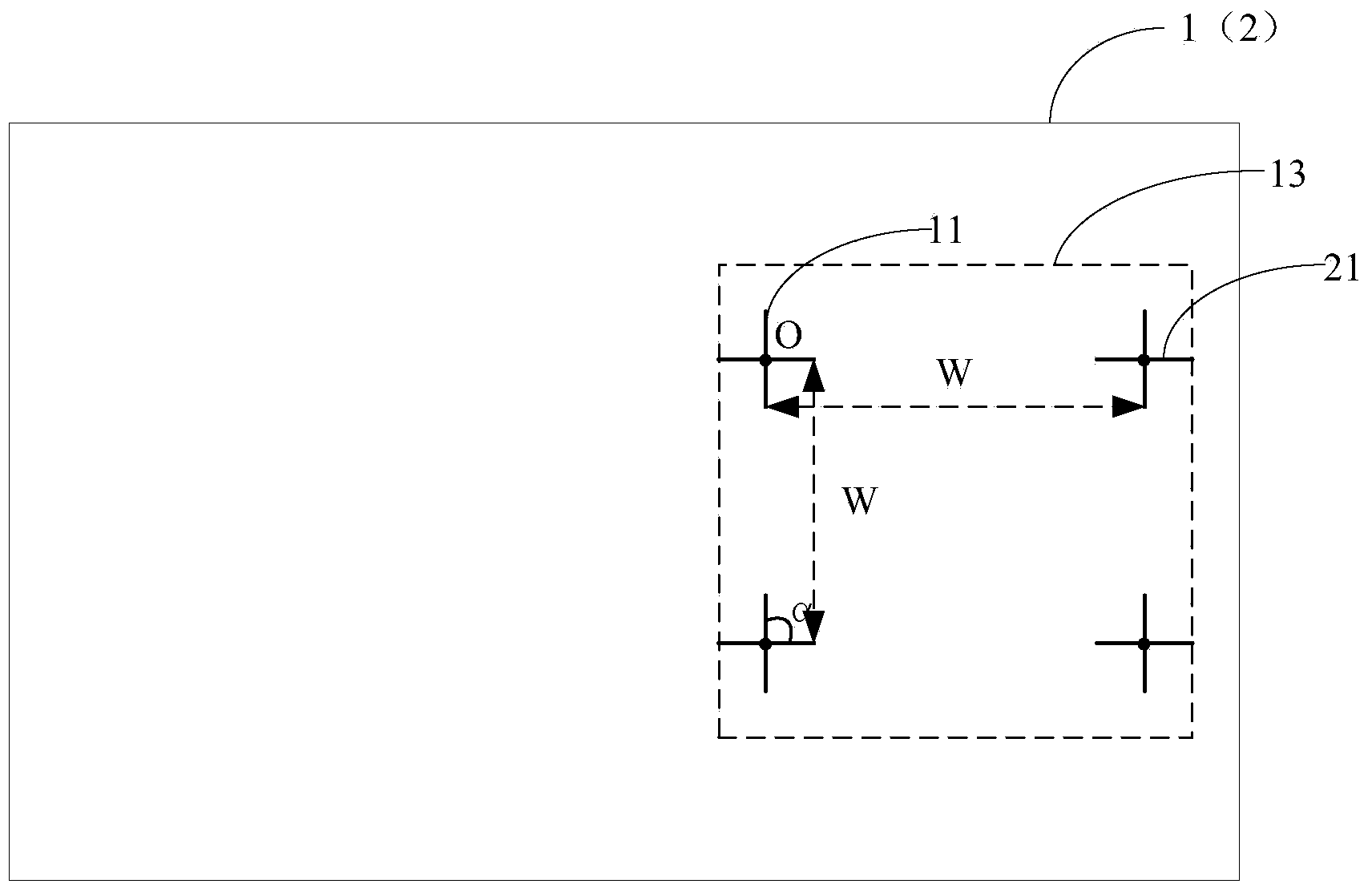

Mask set and method for detecting alignment precision by utilizing mask set

ActiveCN103713467APhotomechanical exposure apparatusMicrolithography exposure apparatusComputer scienceLine segment

The invention discloses a mask set and a method for detecting the alignment precision by utilizing the mask set, and provides a novel mask set and a method for detecting the alignment precision by utilizing the mask set. The mask set comprises a first mask and at least one second mask; each second mask comprises one or more point positions for detecting the alignment precision; the area, corresponding to the point position, of the first mask is provided with at least one first alignment mark, and the first alignment mark is a line segment with a set length; the area, corresponding to the point positions, of the second mask is provided with second alignment marks corresponding to the first alignment marks one by one, and each second alignment mark is a line segment with a set length; the projection of the first alignment marks on the first mask is intersected with that of the second alignment marks on the first mask, and the projection of the first alignment mark and the projection of the second alignment mark form a set angle.

Owner:HEFEI BOE OPTOELECTRONICS TECH +1

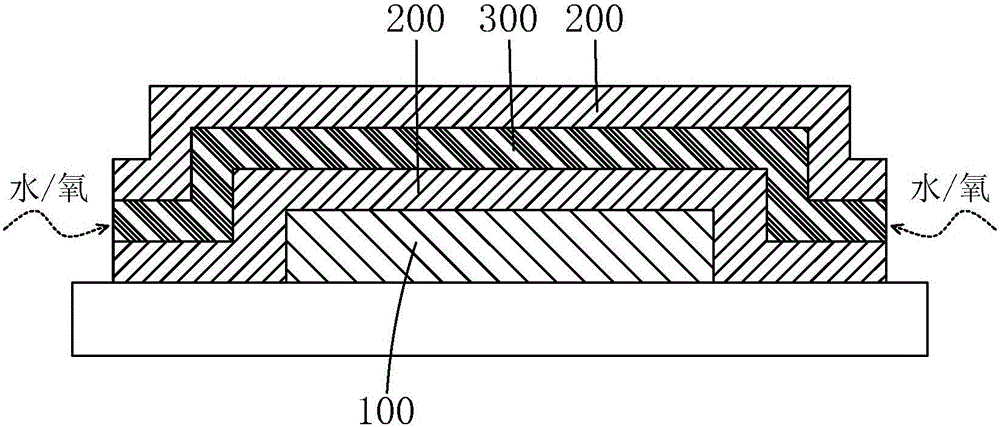

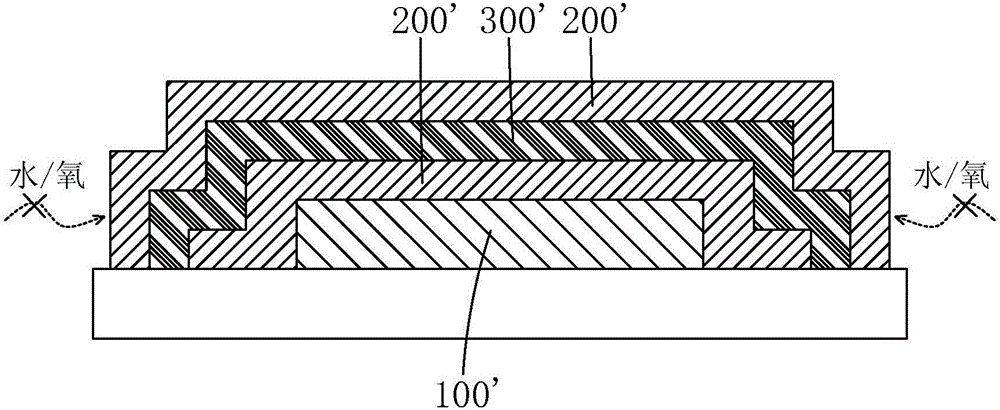

OLED (organic light emitting display) packaging method and OLED packaging structure

ActiveCN106684259AReduce usageImprove packaging effectSolid-state devicesSemiconductor/solid-state device manufacturingOrganic layerOLED

Owner:TCL CHINA STAR OPTOELECTRONICS TECH CO LTD

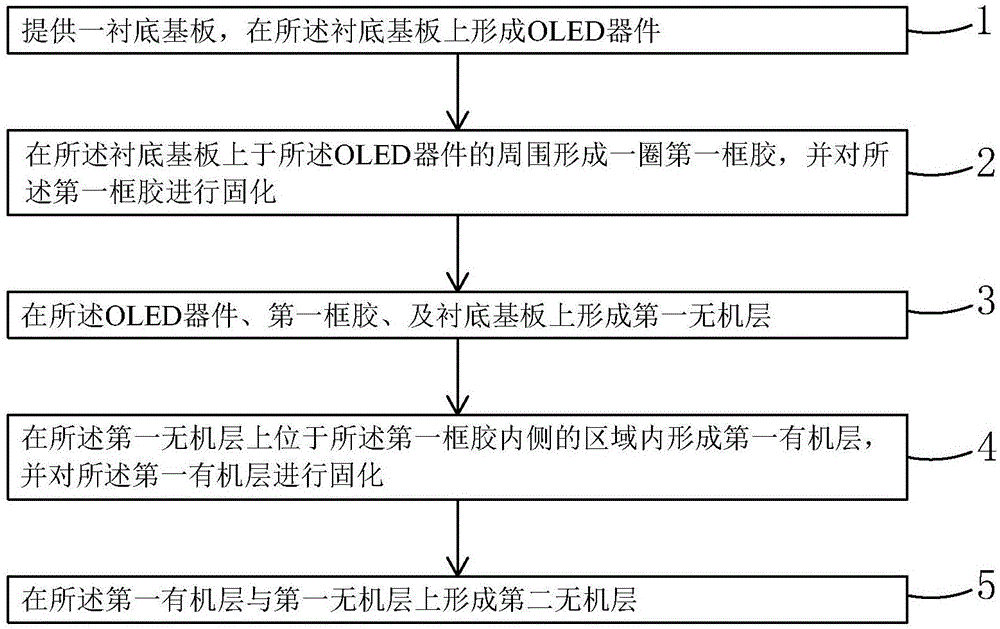

Methods for quantitatively evaluating the quality of double patterning technology-compliant layouts

ActiveUS20130198696A1Improve scoreComputer programmed simultaneously with data introductionOriginals for photomechanical treatmentEngineeringSemiconductor

A method for fabricating an integrated circuit is disclosed that includes, in accordance with an embodiment, providing a double patterning technology-compliant logical design for the integrated circuit, the logical design including a plurality of elements; scoring the design of one or more of the plurality of elements to produce a design score; modifying the design based at least in part on the design score; generating a mask set implementing the modified logical design; and employing the mask set to implement the logical design in and on a semiconductor substrate.

Owner:GLOBALFOUNDRIES US INC

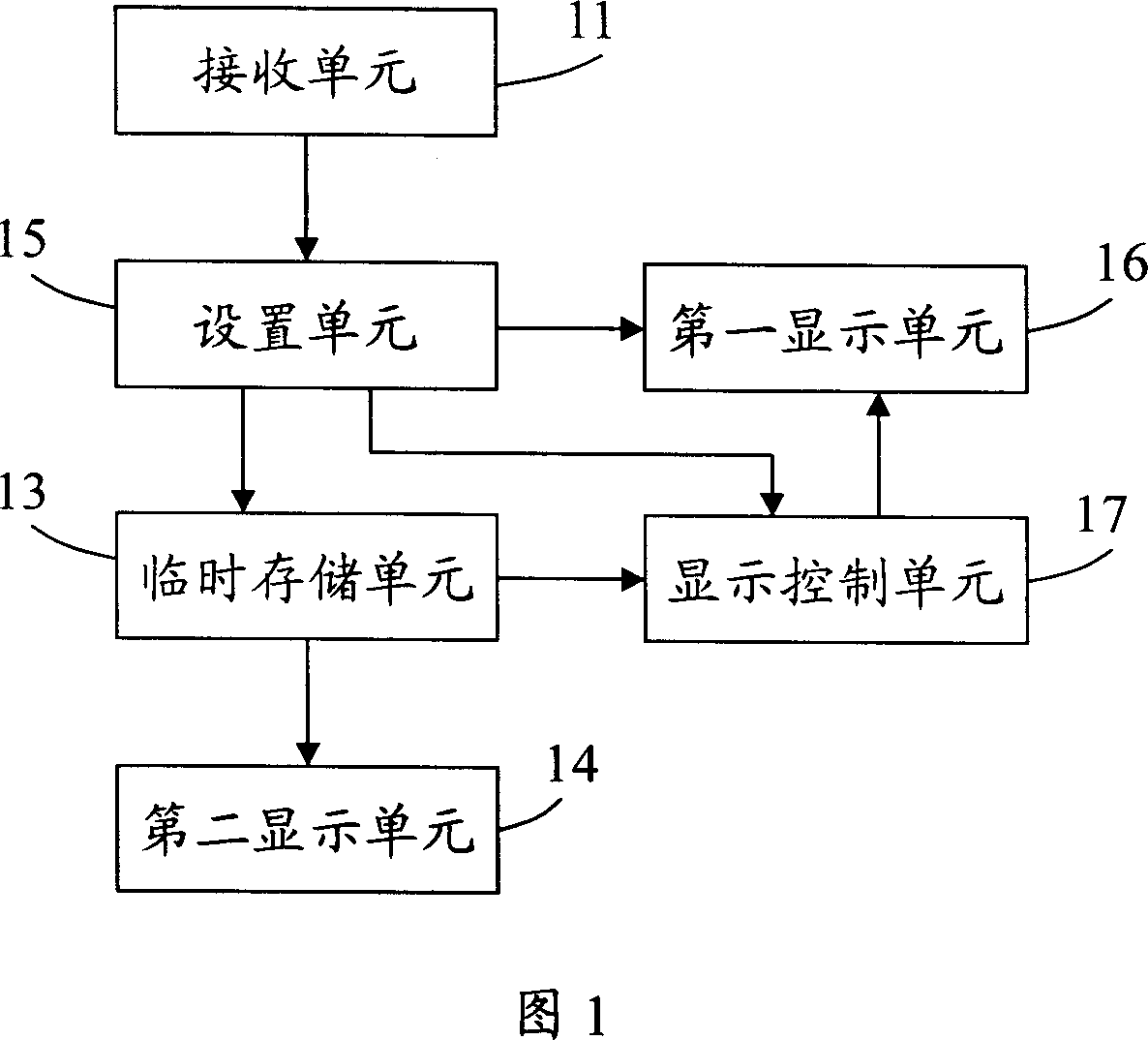

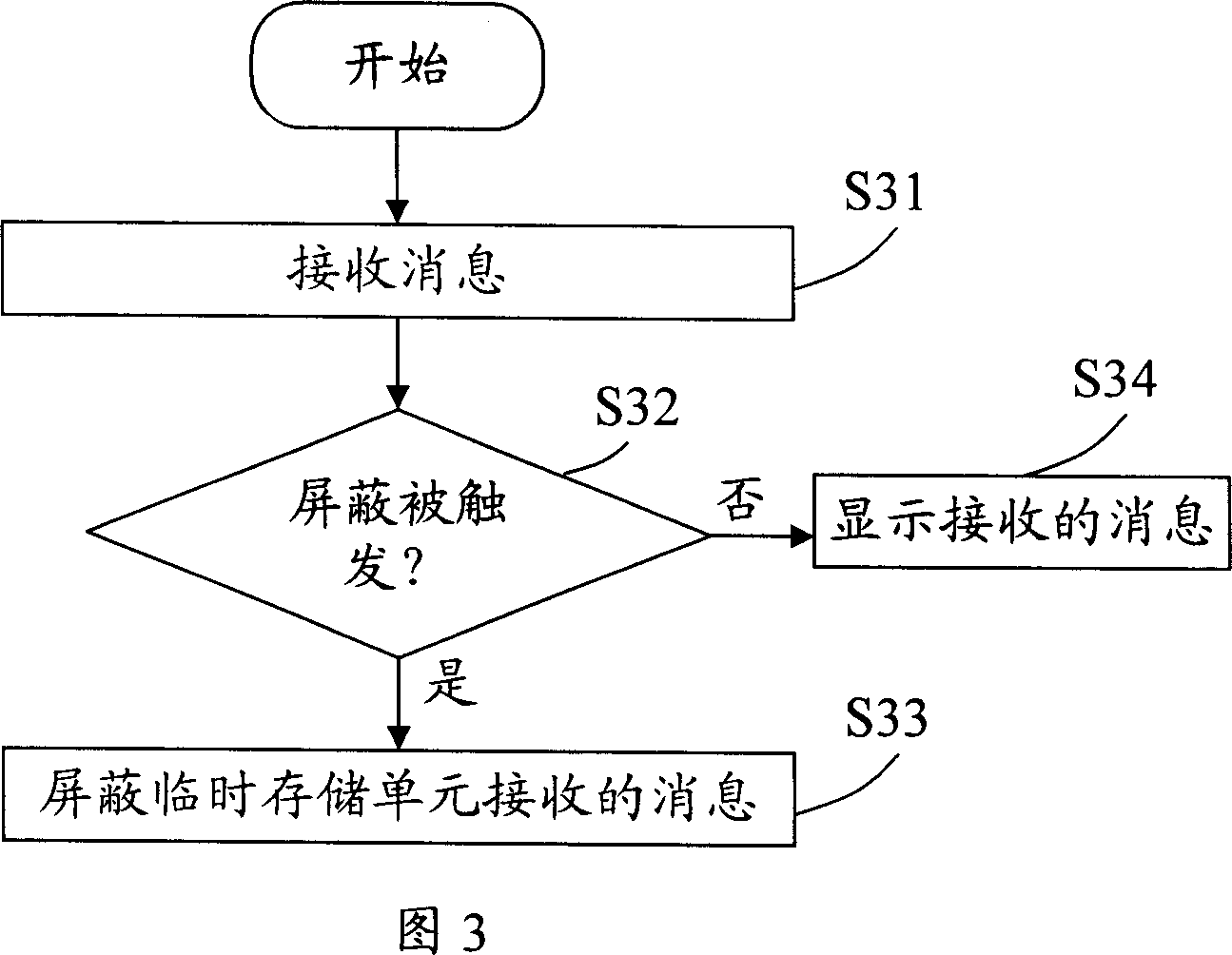

A system and method for shielding instant message

InactiveCN101079833AAchieve shieldingReduce cumbersome operationsData switching networksComputer scienceInstant messaging

The invention discloses a masking system and method of timely communication information, which comprises the following parts: receiving unit, which receives the timely communication information, first display unit, which displays the timely communication information of linker and group in the non-masking condition to modify the condition of all linkers and group of user into non-masking condition during triggering demasking operation; temporary storage unit, which reserves the timely communication information of linker and group in the masking condition. The invention reduces the complex operation of mask setting for each link and group separately, which realizes the mask of all linker and group information through one-time masking operation.

Owner:TENCENT TECH (SHENZHEN) CO LTD

Methods for cell boundary isolation in double patterning design

ActiveUS8255837B2Reduce effortReduce chip areaOriginals for photomechanical treatmentSpecial data processing applicationsDesign standardEngineering

A method of designing a double patterning mask set for a layout of a chip includes designing standard cells. In each of the standard cells, all left-boundary patterns are assigned with one of a first indicator and a second indicator, and all right-boundary patterns are assigned with an additional one of the first indicator and the second indicator. The method further includes placing the standard cells in a row of the layout of the chip. Starting from one of the standard cells in the row, indicator changes to the standard cells are propagated throughout the row. All patterns in the standard cells having the first indicator are transferred to a first mask of the double patterning mask set. All patterns in the standard cells having the second indicator are transferred to a second mask of the double patterning mask set.

Owner:TAIWAN SEMICON MFG CO LTD

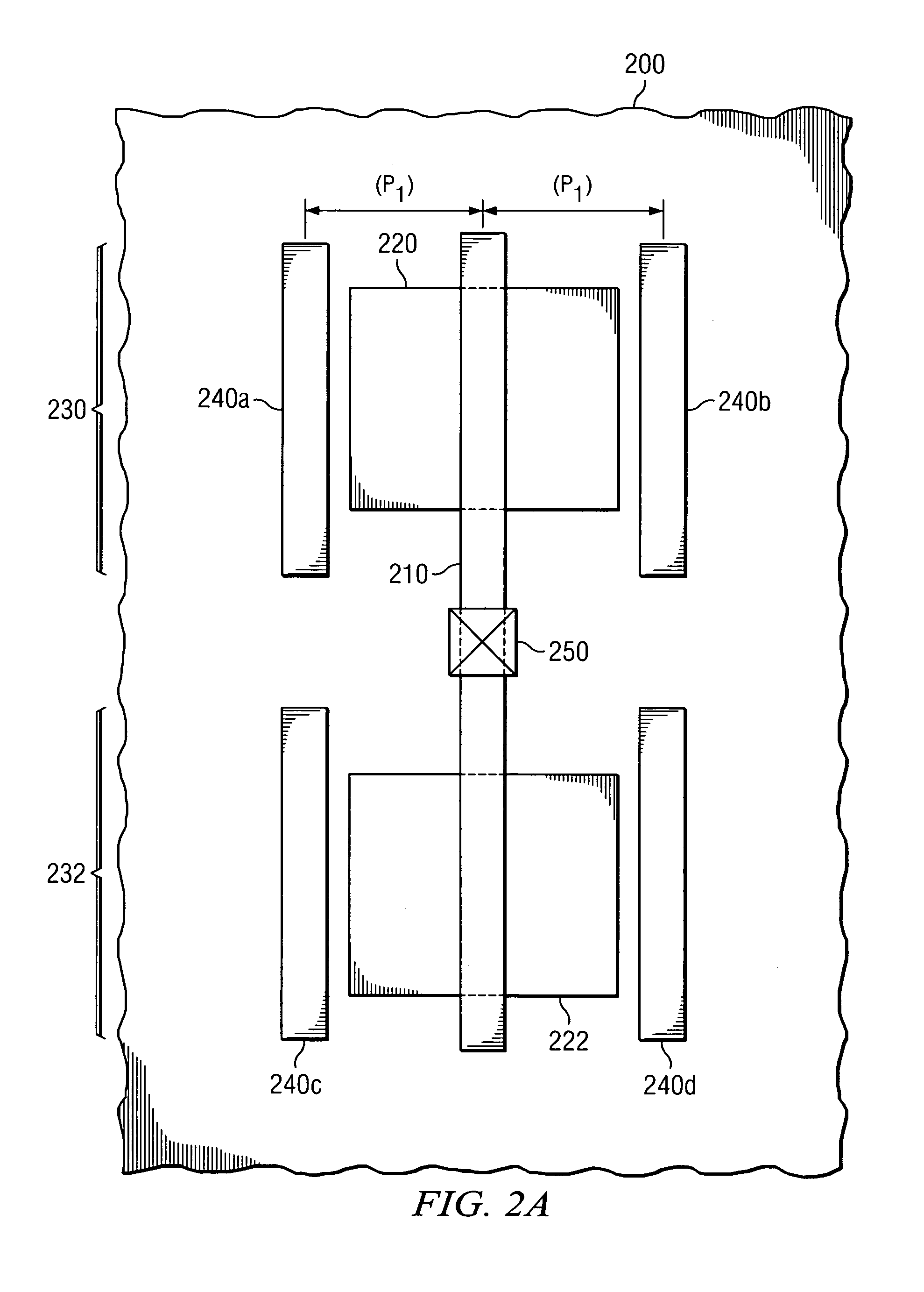

Utilizing compensation features in photolithography for semiconductor device fabrication

ActiveUS20050250021A1Semiconductor/solid-state device detailsSolid-state devicesDevice materialEngineering

A photomask set includes at least two masks that combine to form a device pattern in a semiconductor device. Orthogonal corners may be produced in a semiconductor device pattern to include one edge defined by a first mask and an orthogonal edge defined by a second mask. The mask set may include a first mask with compensation features and a second mask with void areas overlaying the compensation features when the first and second masks are aligned with one another, such that the compensation features are removed when patterns are successfully formed from the first and second masks. The compensation features alleviate proximity effects during the formation of device features.

Owner:TAIWAN SEMICON MFG CO LTD

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com