Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

855 results about "Low-temperature polycrystalline silicon" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Low-temperature polycrystalline silicon (LTPS) is polycrystalline silicon that has been synthesized at relatively low temperatures (~650 °C and lower) compared to in traditional methods (above 900 °C). LTPS is important for display industries, since the use of large glass panels prohibits exposure to deformative high temperatures. More specifically, the use of polycrystalline silicon in thin-film transistors (LTPS-TFT) has high potential for large-scale production of electronic devices like flat panel LCD displays or image sensors.

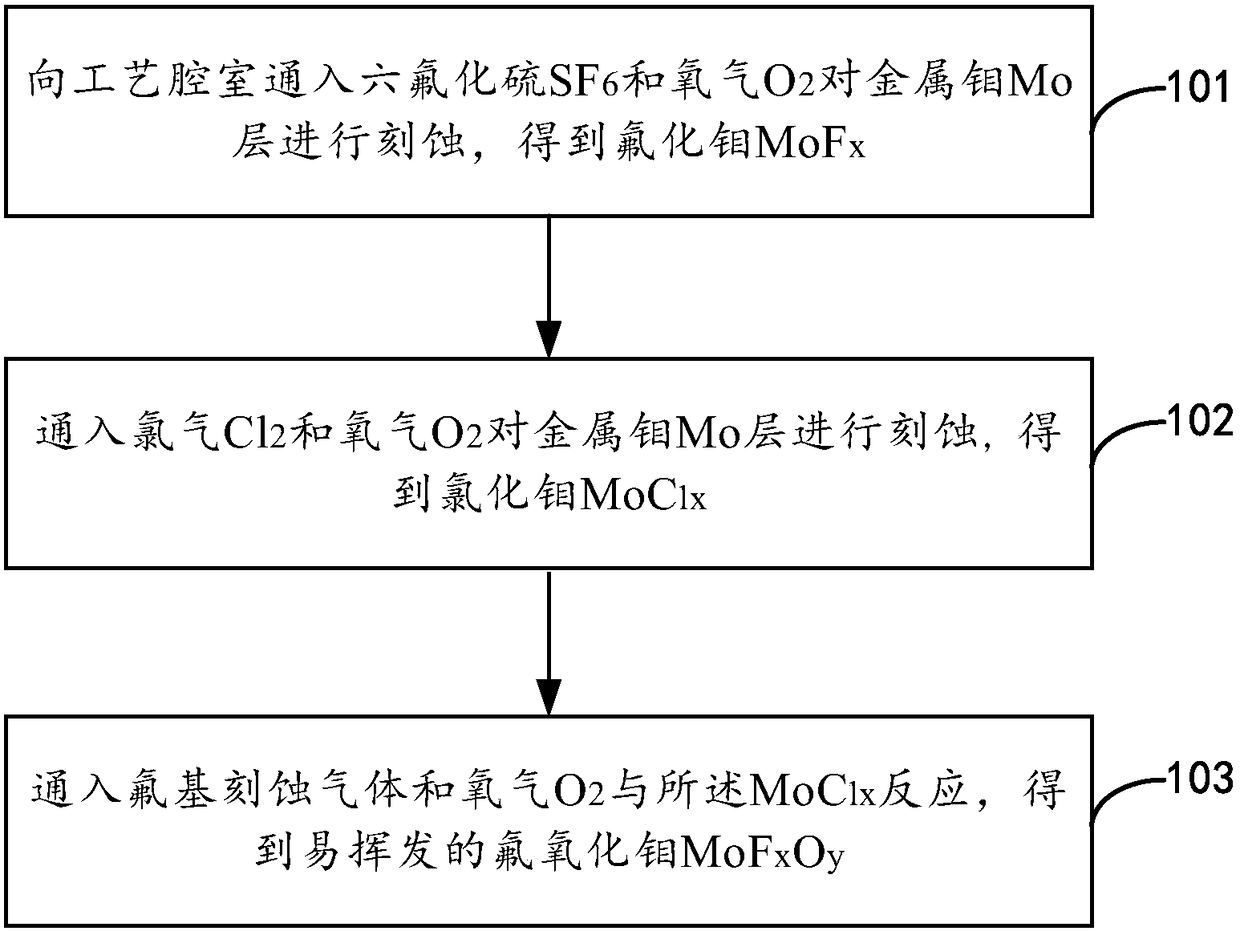

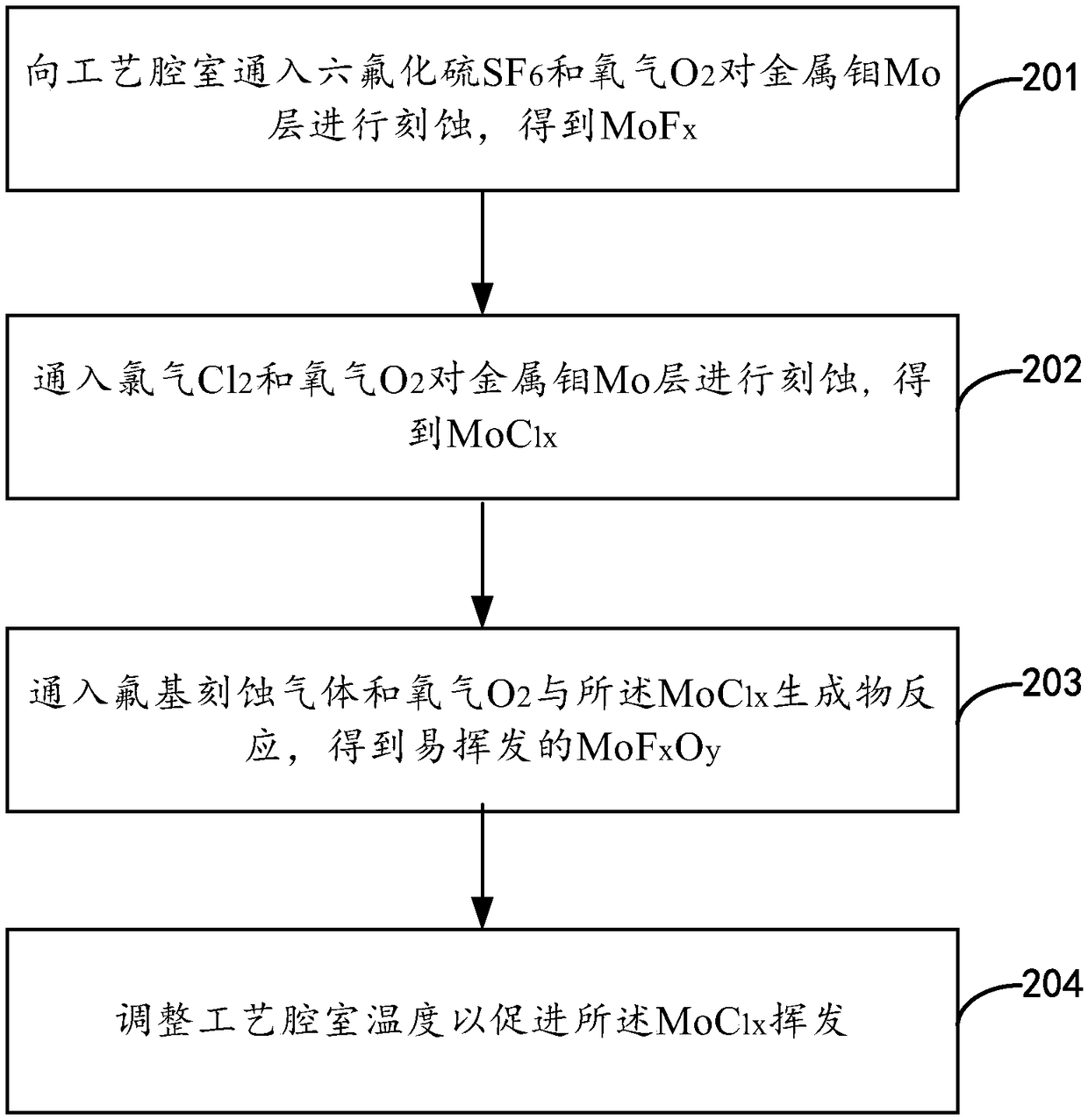

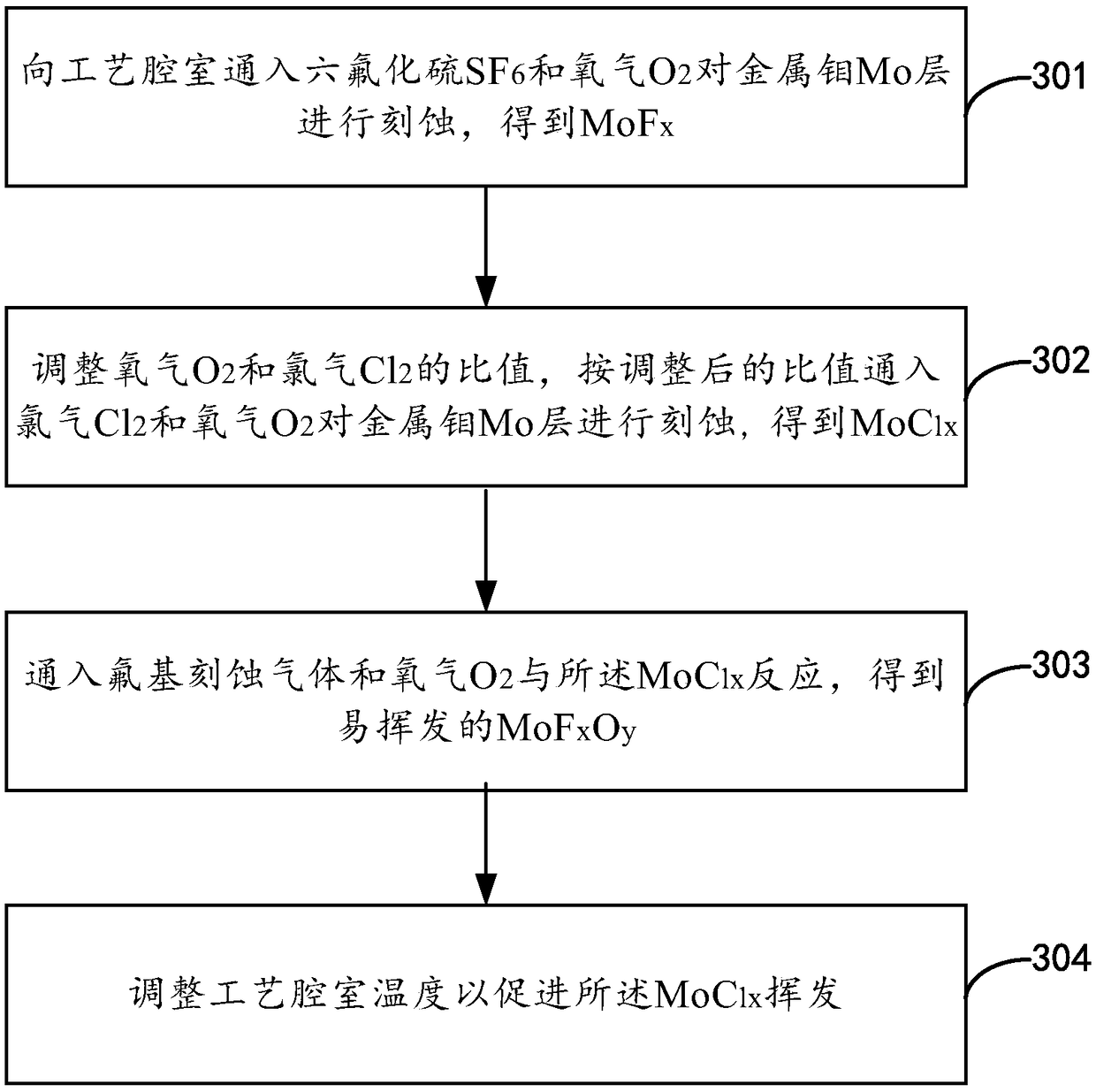

Etching method, low-temperature polysilicon thin film transistor and AMOLED panel

ActiveCN108389798AEasy to handlePrevent dark spotsTransistorSolid-state devicesSulfur hexafluorideOxygen

Owner:TRULY HUIZHOU SMART DISPLAY

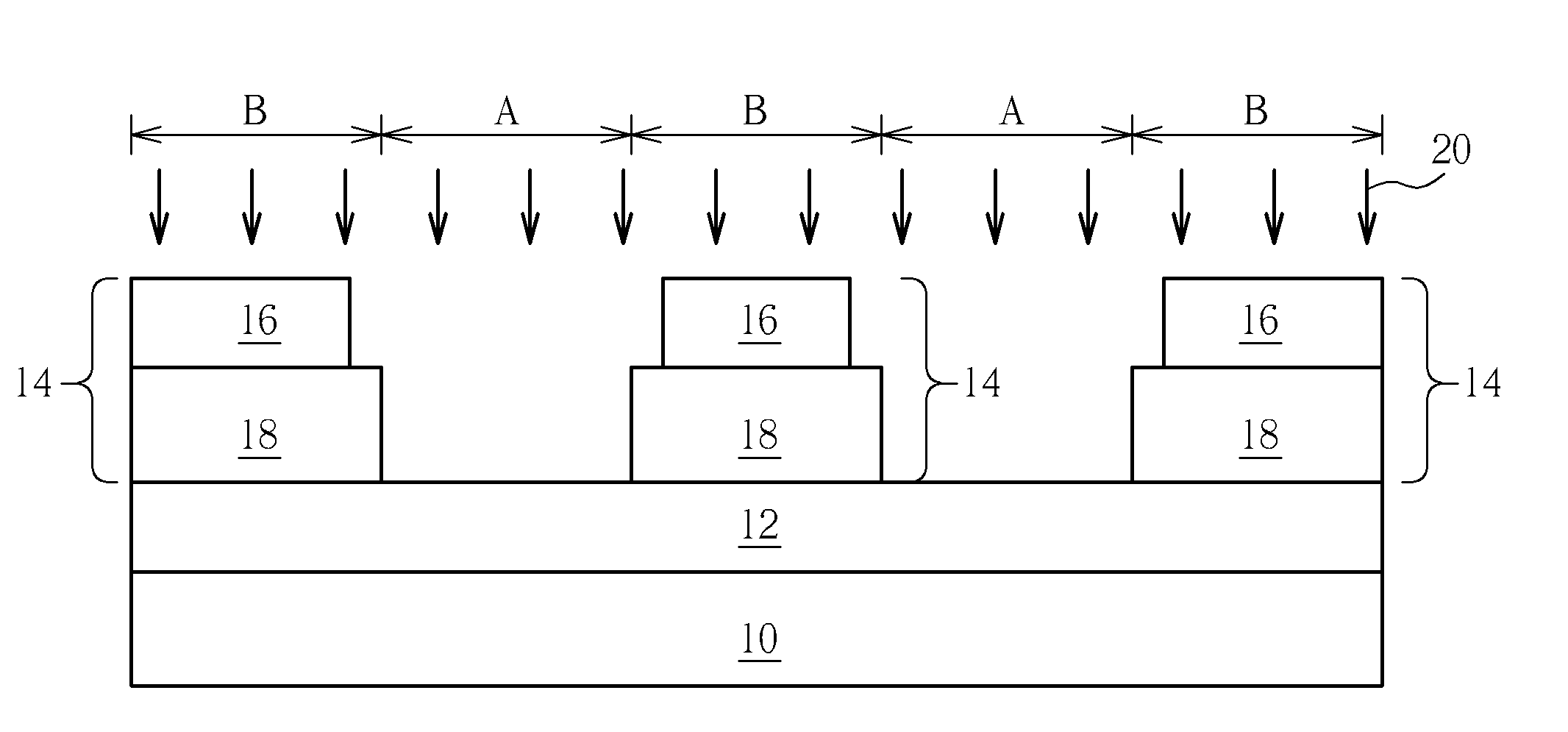

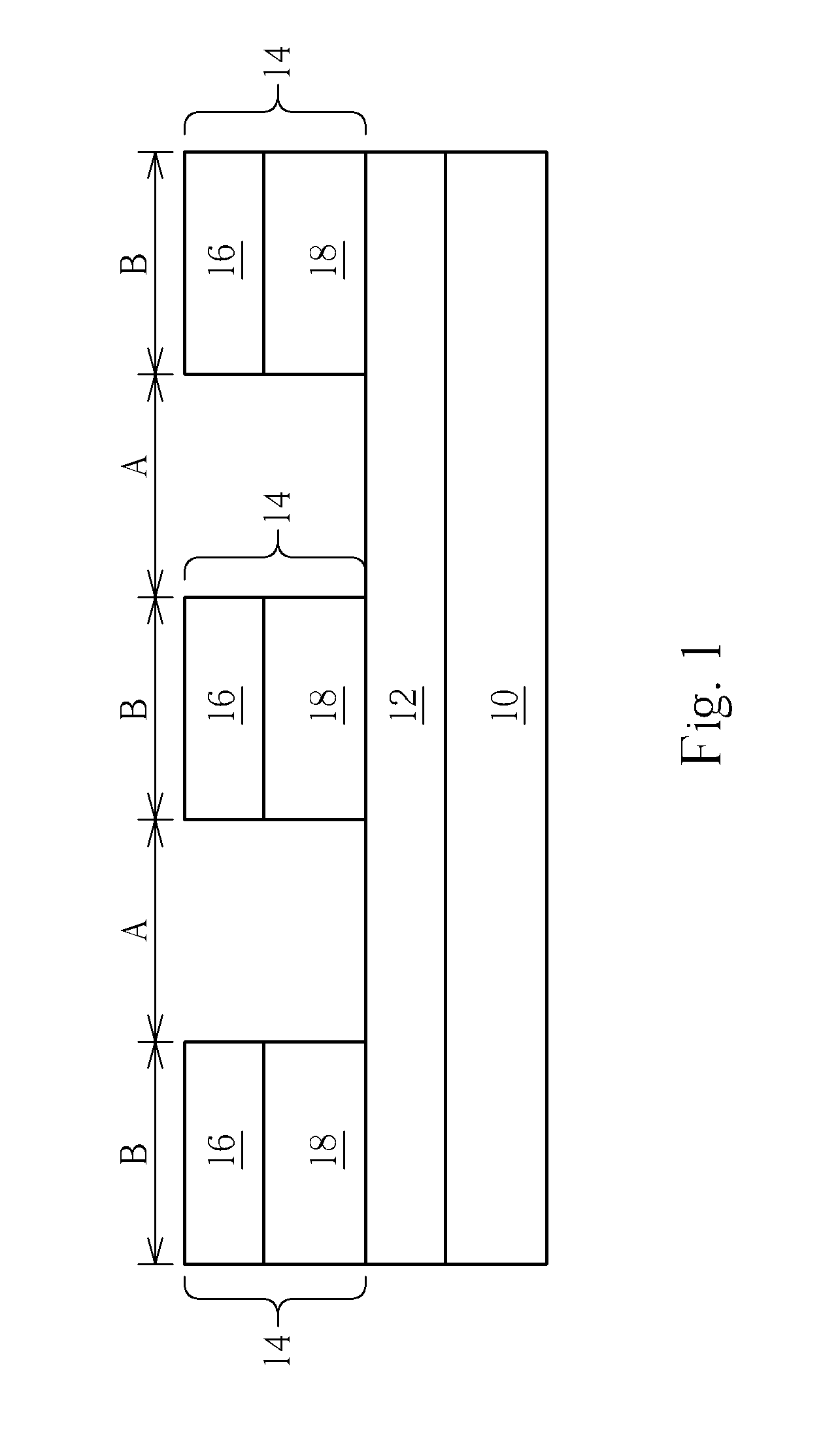

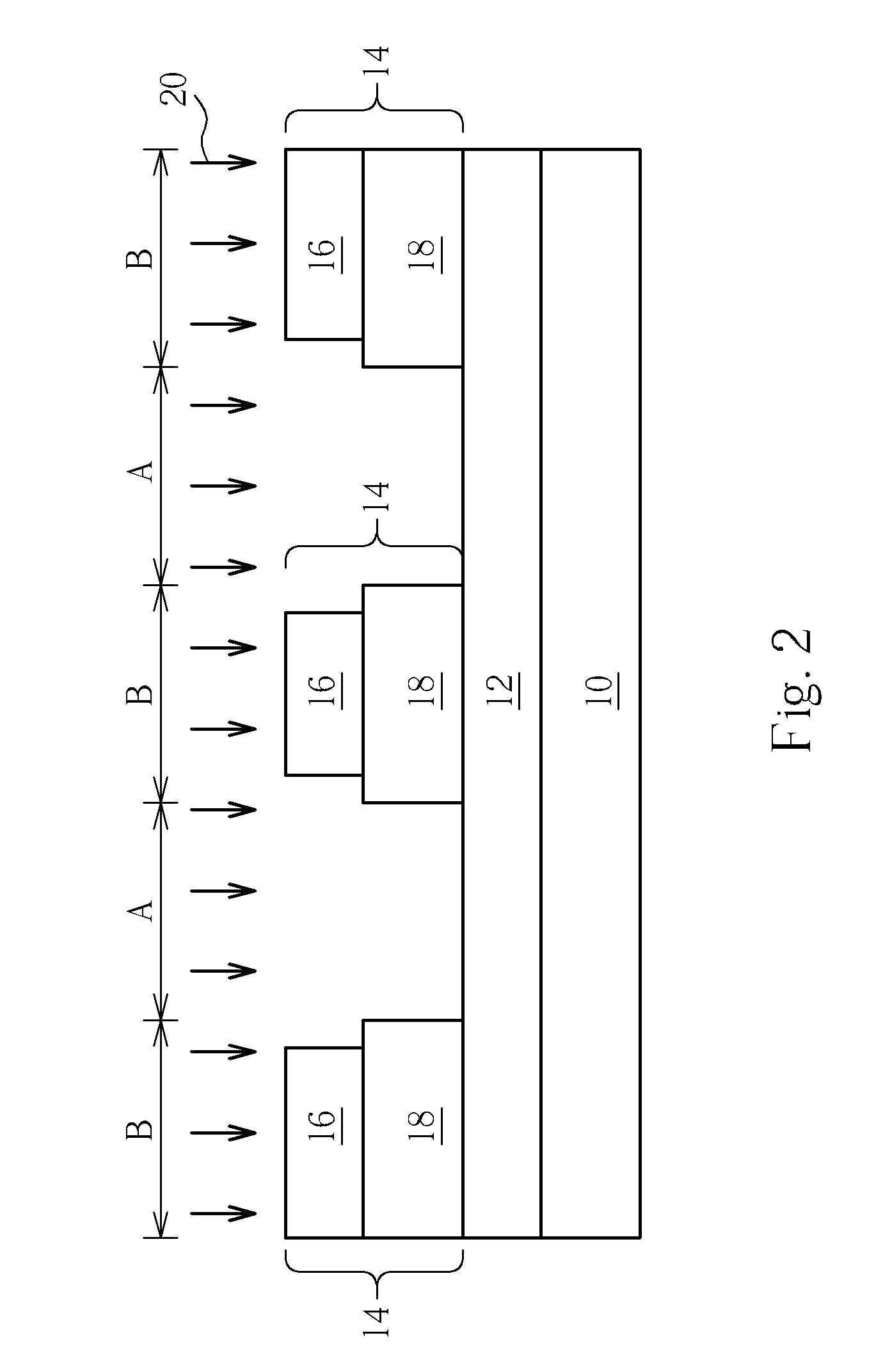

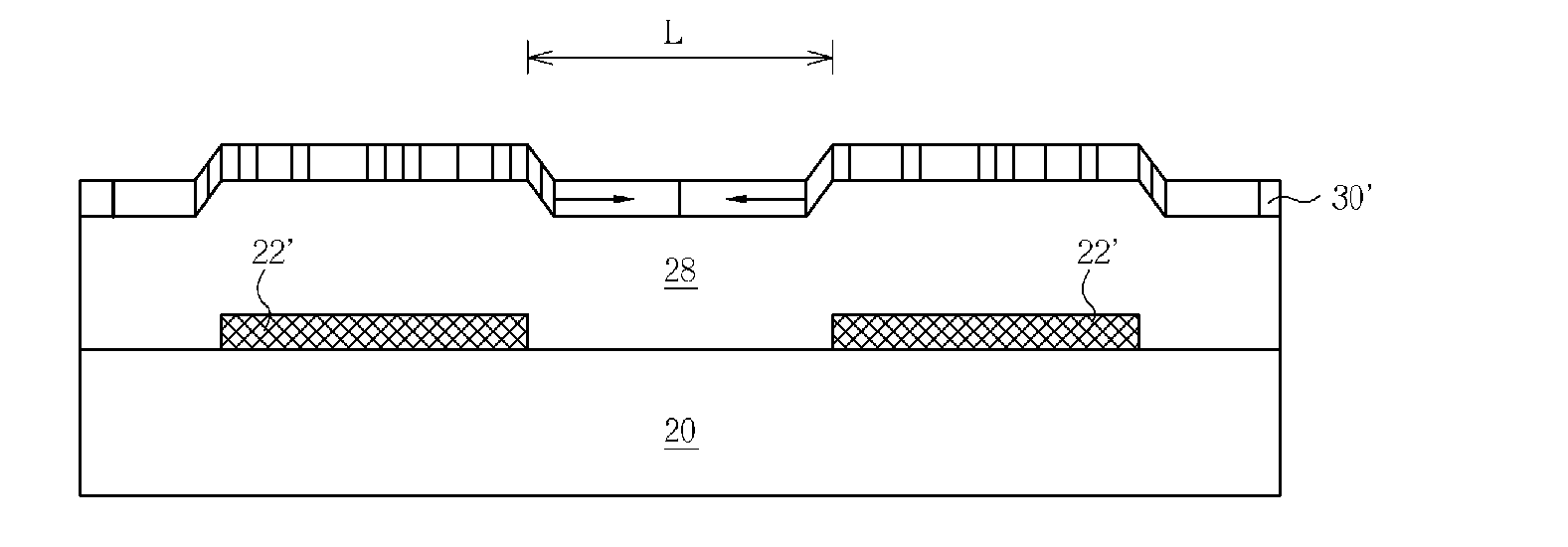

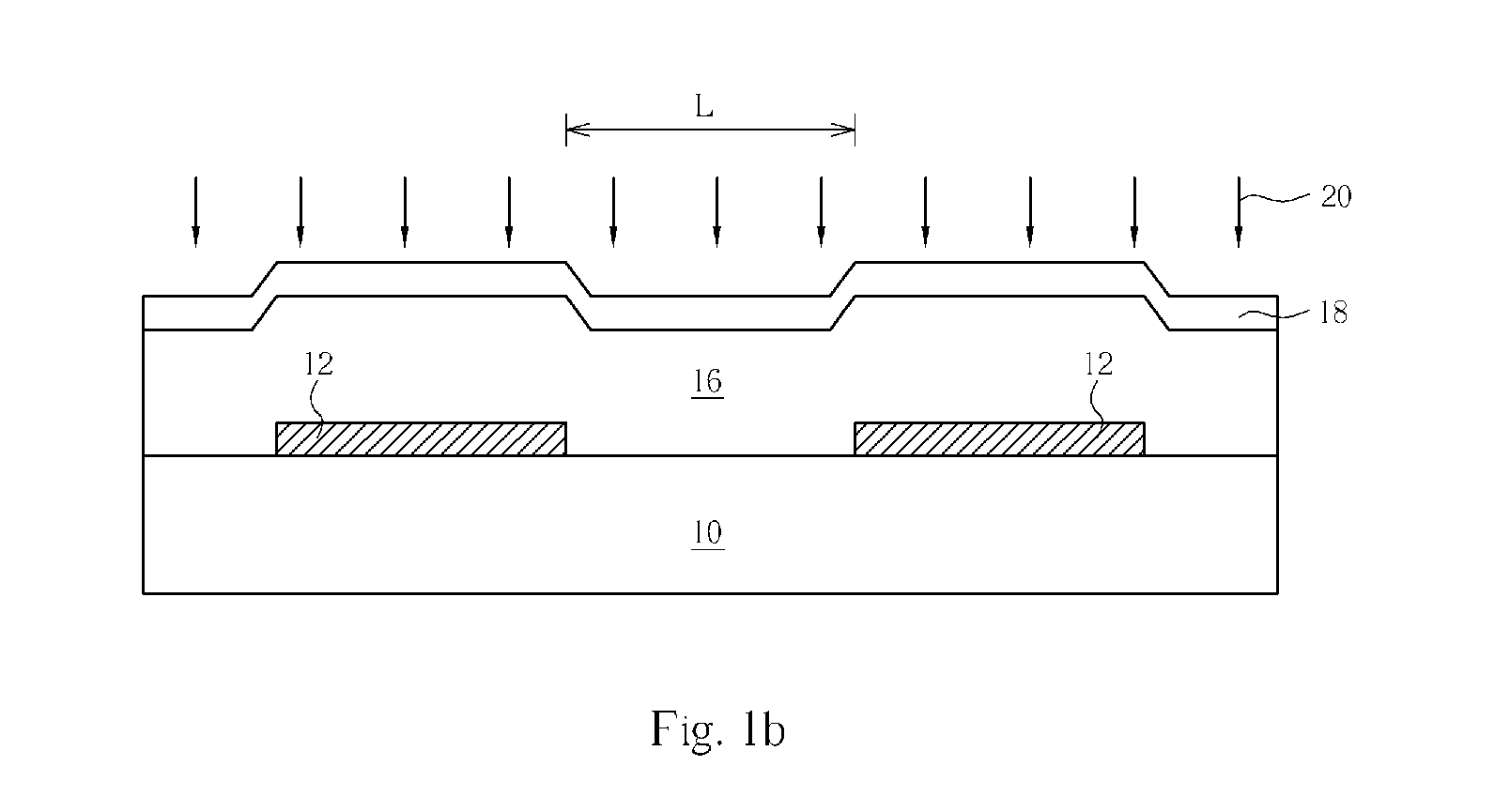

Semiconductor device and method of fabricating a low temperature poly-silicon layer

InactiveUS20060043367A1Promotes lateral growthHighly practicalTransistorSemiconductor/solid-state device detailsDevice materialAmorphous silicon

A method of fabricating a low temperature poly-silicon (LTPS). A plurality of semiconductor heat sinks are formed over a substrate. A buffer layer and an amorphous silicon layer are formed over the substrate and the semiconductor heat sinks. Following that, a laser crystallization process is performed to transform the amorphous silicon layer into a poly-silicon layer.

Owner:AU OPTRONICS CORP

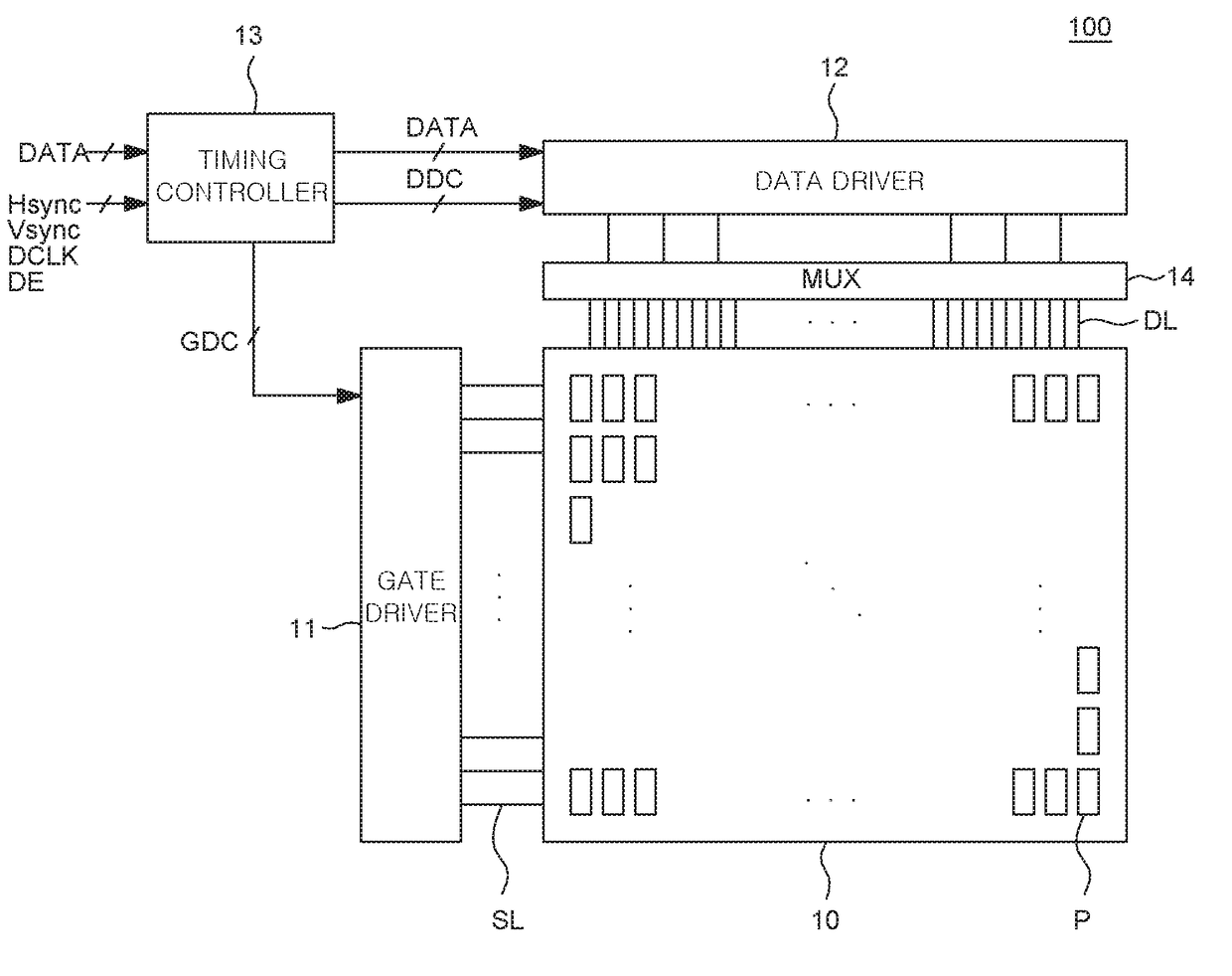

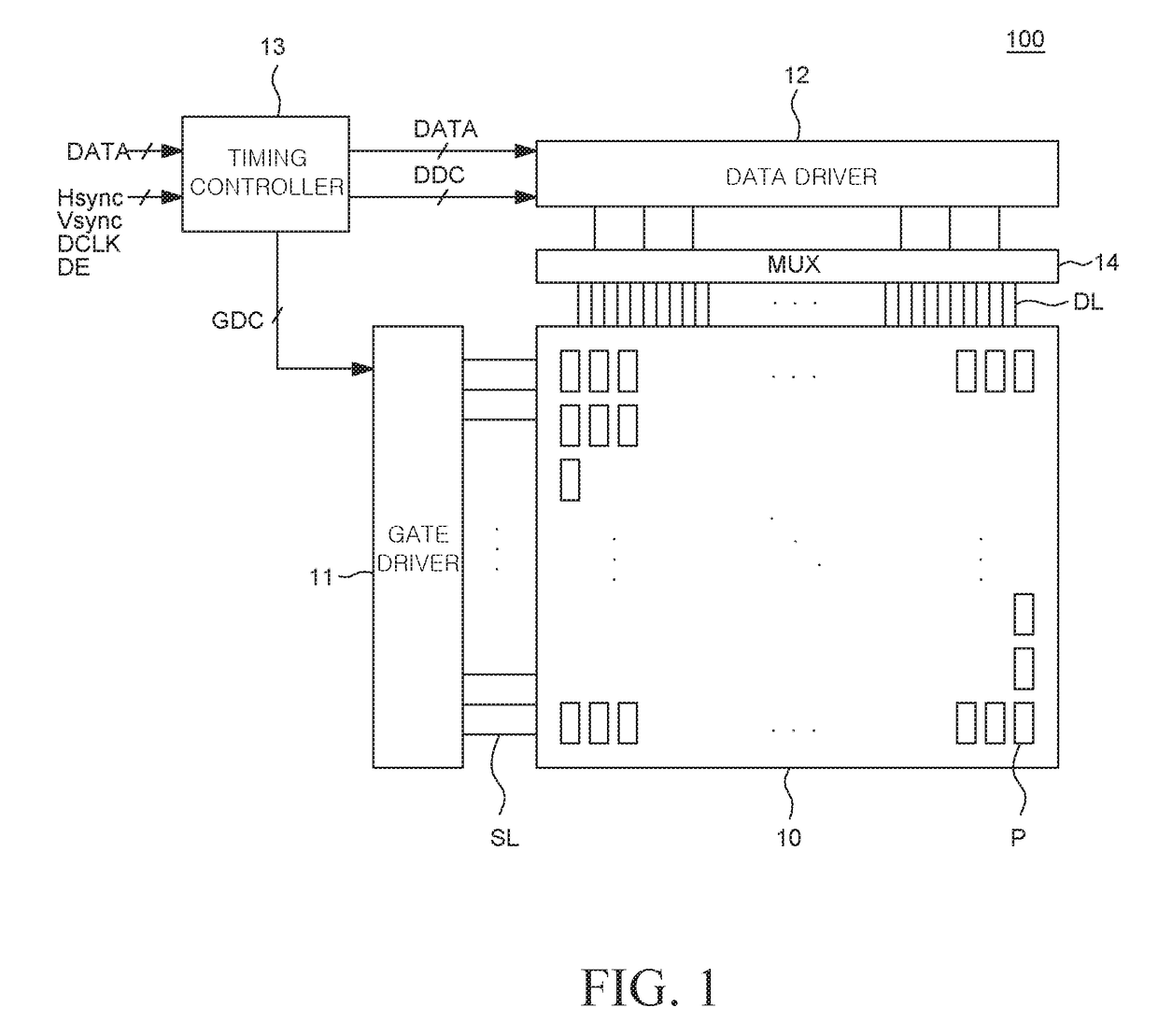

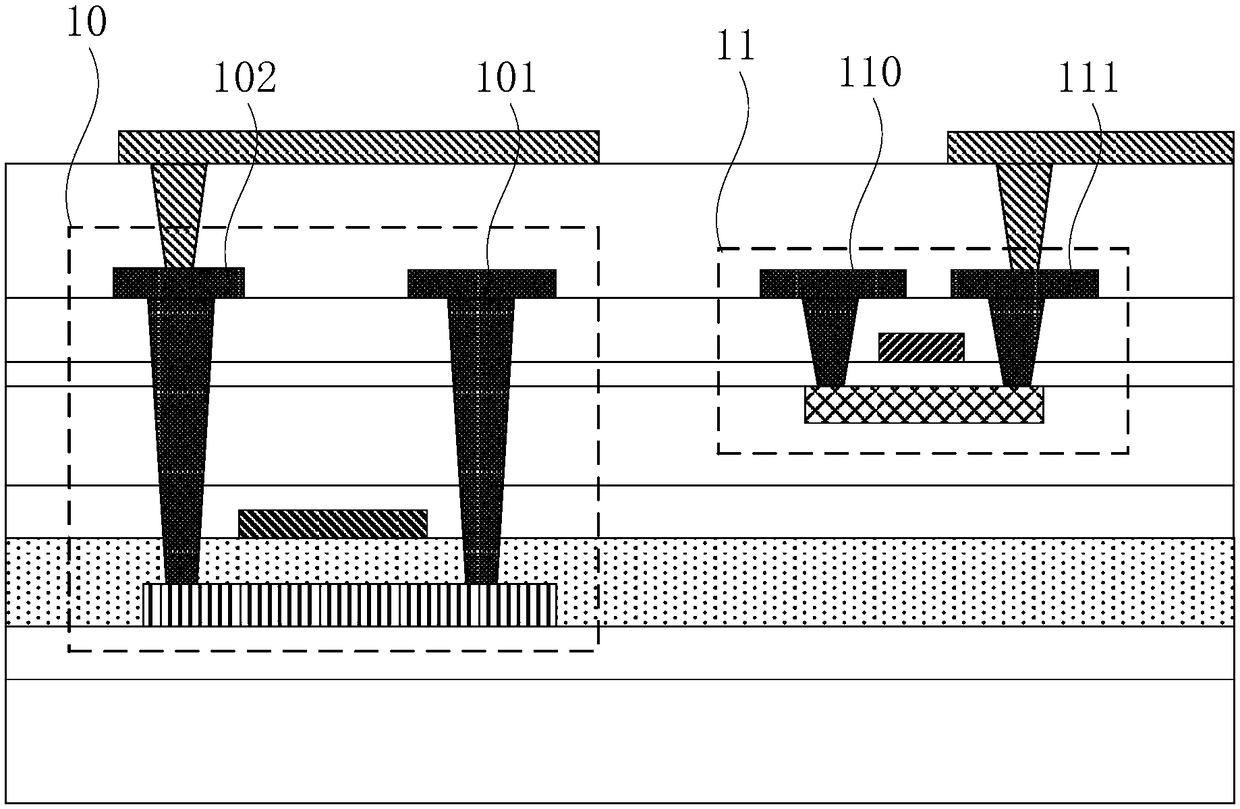

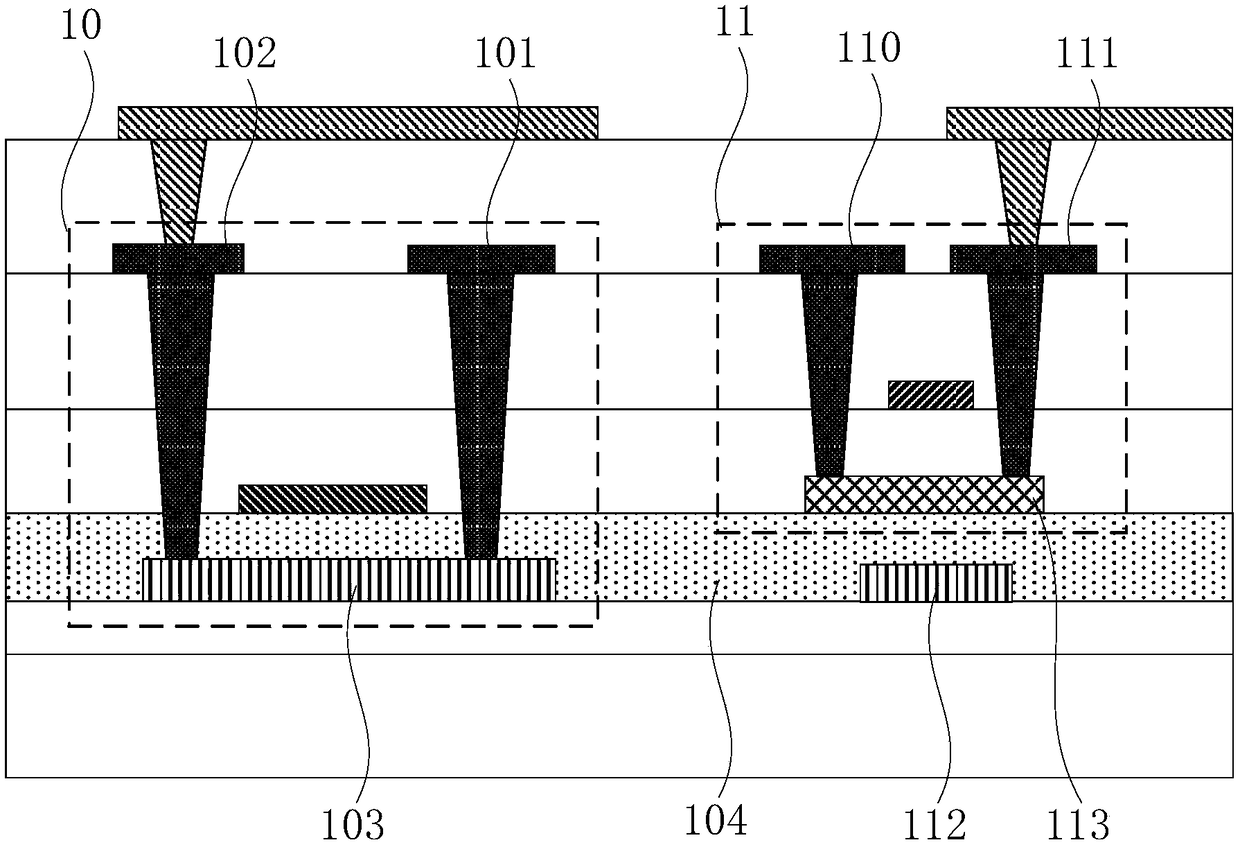

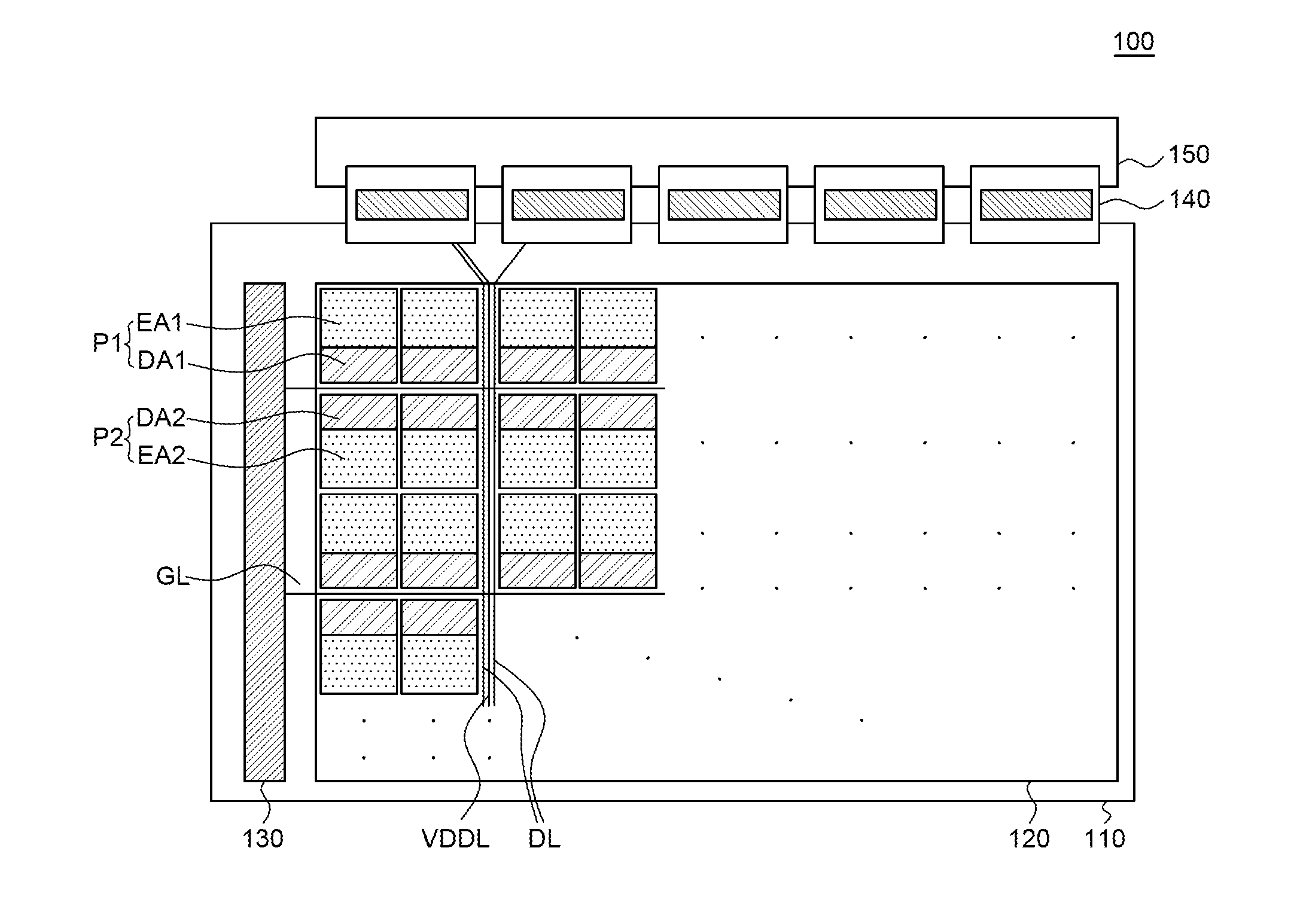

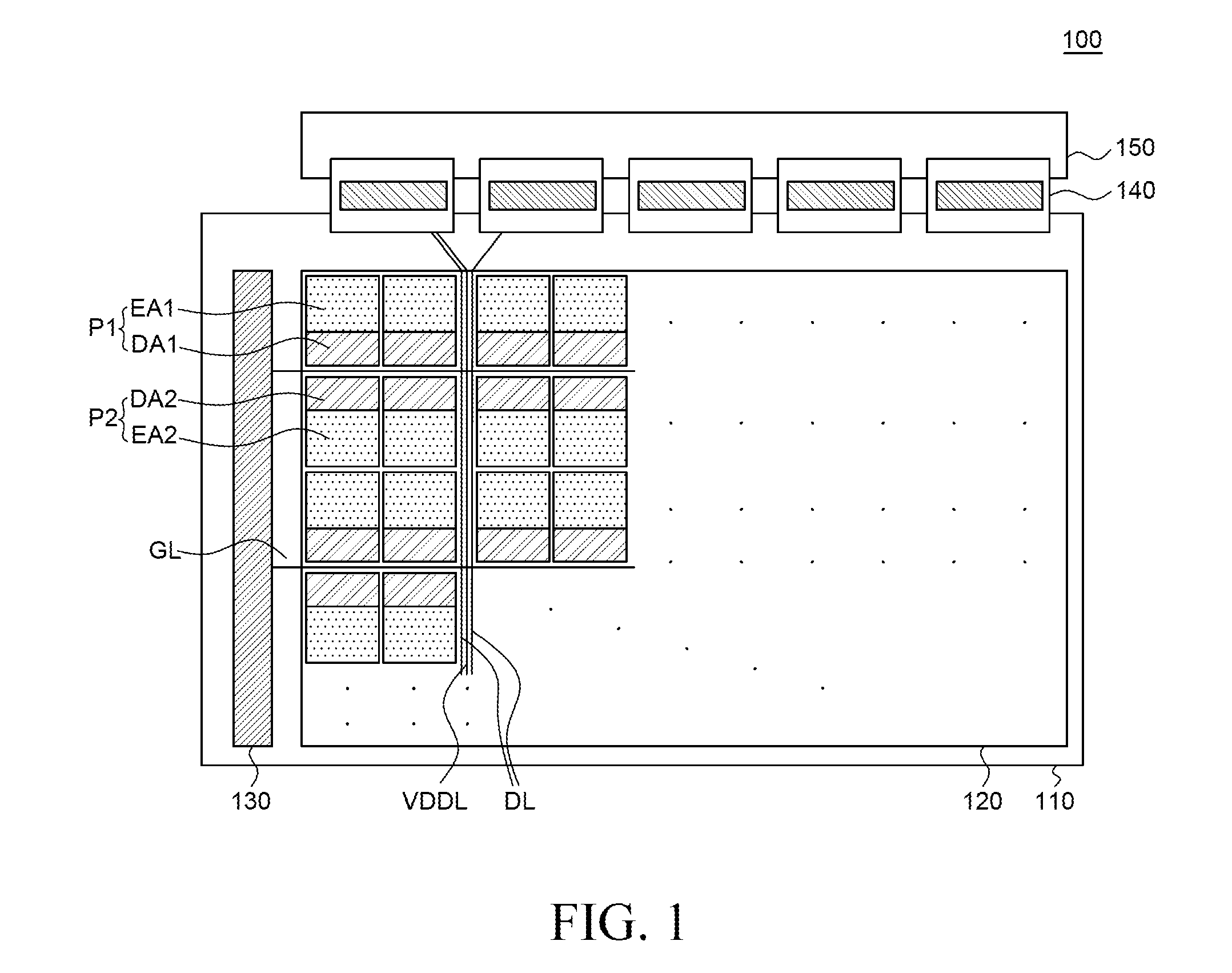

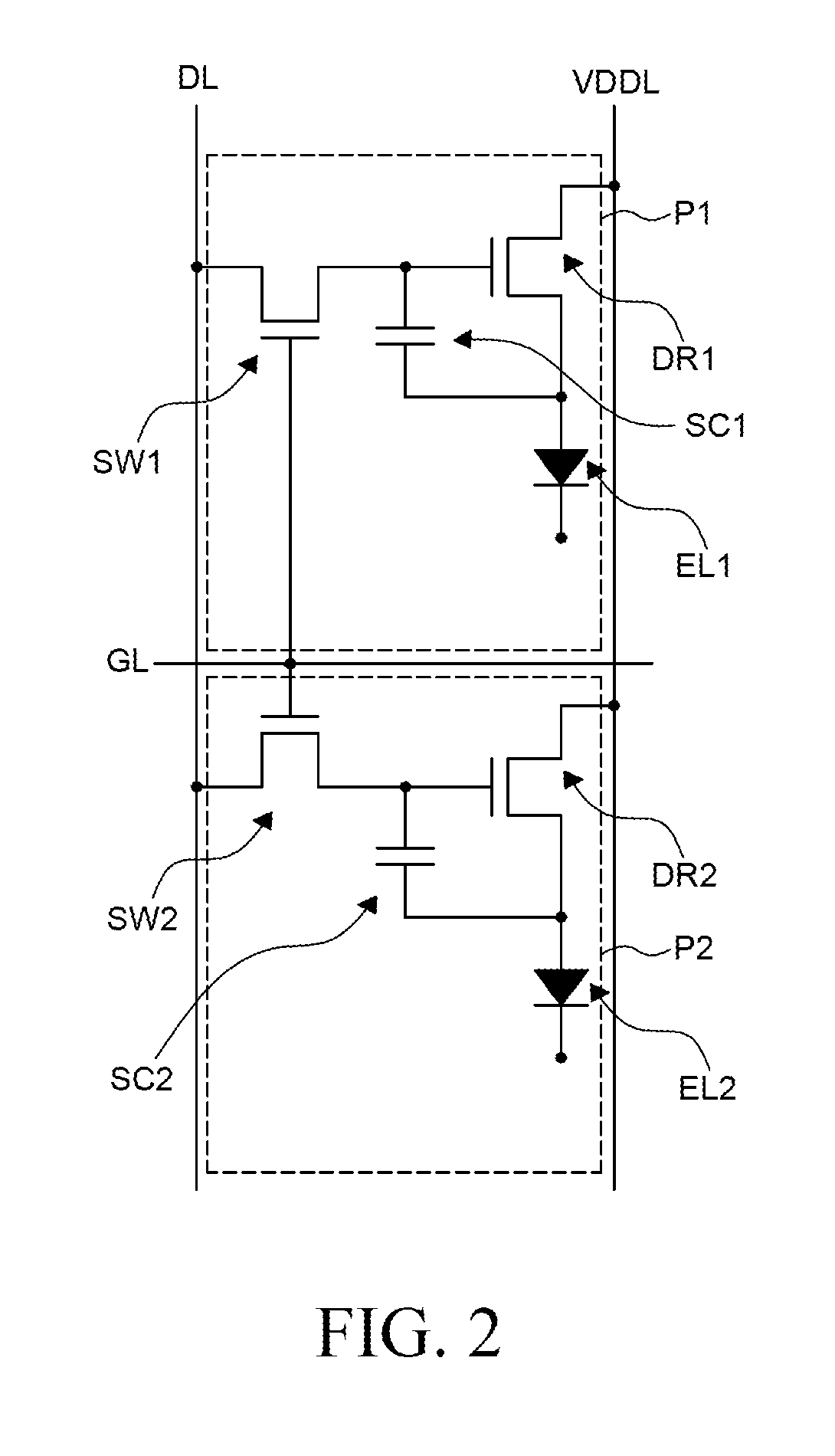

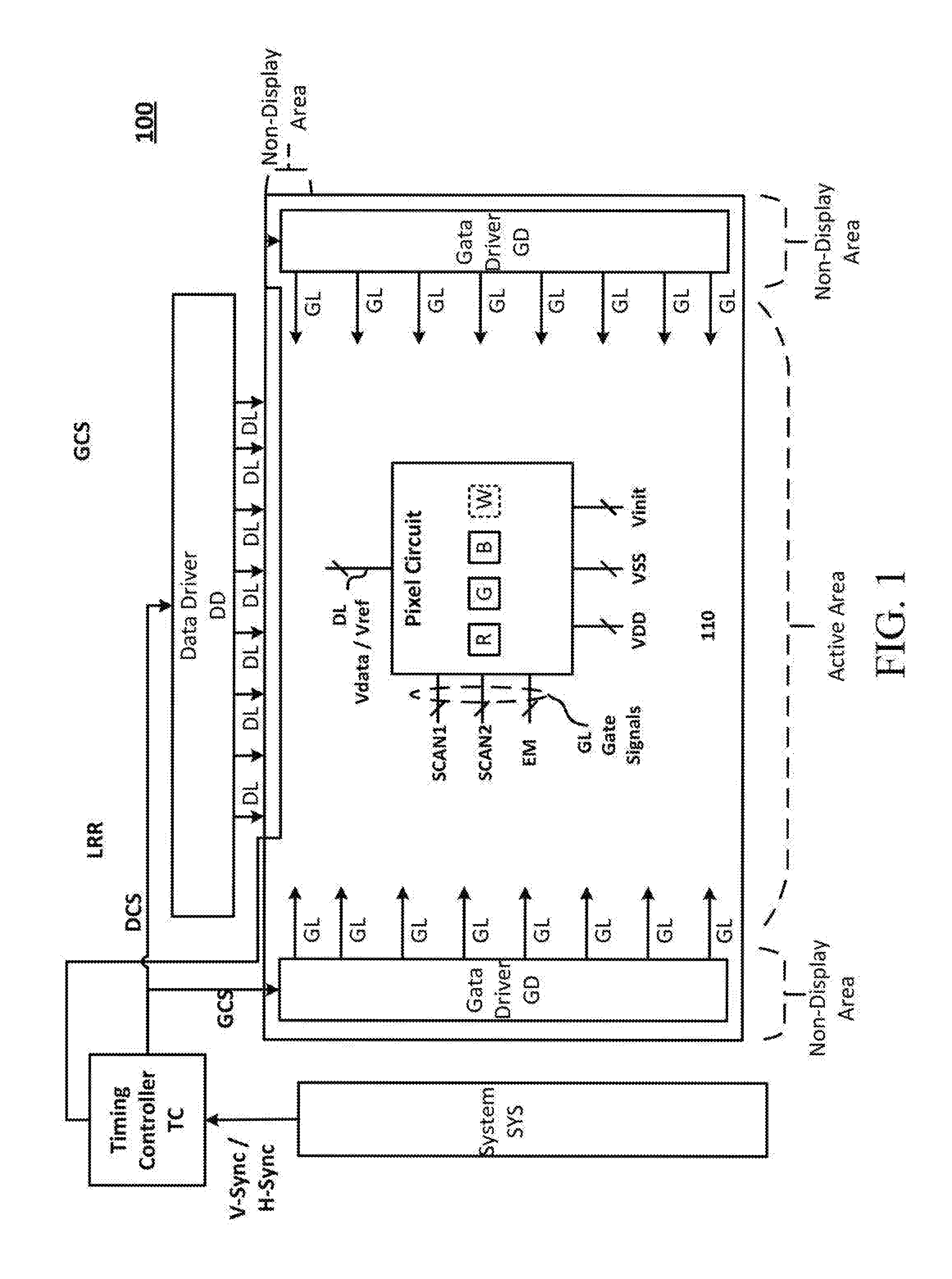

Organic light emitting display device

ActiveUS20150243722A1Increase opening ratioHigh resolutionSolid-state devicesSemiconductor/solid-state device manufacturingDisplay deviceSemiconductor

Disclosed herein is an OLED (Organic Light Emitting Display) device. A switching thin-film transistor configured to be an oxide semiconductor thin-film transistor is disposed in a first pixel. A second pixel is adjacent to the first pixel in the direction in which data lines are extended. A switching thin-film transistor configured to be an LTPS (Low Temperature Poly-Silicon) thin-film transistor is disposed in the second pixel. The switching thin-film transistor of the first pixel and the switching thin-film transistor of the second pixel are connected to the same gate line. A pixel and another pixel adjacent to the pixel connected to a gate line in common, so that it is possible to provide an OLED device with high aperture ratio and high resolution.

Owner:LG DISPLAY CO LTD

Apparatus of ion sensitive thin film transistor and method of manufacturing of the same

InactiveUS20060035400A1Reduce weightLow costFinal product manufactureSemiconductor/solid-state device detailsDriver circuitSignal processing circuits

The present invention discloses an apparatus of ion sensitive thin film transistor and method of manufacturing of the same. The apparatus of the invention, formed on a glass substrate, comprises an ion detector, formed on said glass substrate, including a plurality of ion sensitive transistors and a signal processor with display, also formed on said glass substrate, being coupled with said ion detector. The signal processor with display further comprises a circuit of signal processing, a driver circuit, and a display, wherein by means of the method of Low Temperature PolySilicon, i.e. LTPS technology, the invention integrates said ion detector and said signal processor with display on said glass substrate to become an tiny, light and thin apparatus with portable and disposable characteristics.

Owner:IND TECH RES INST

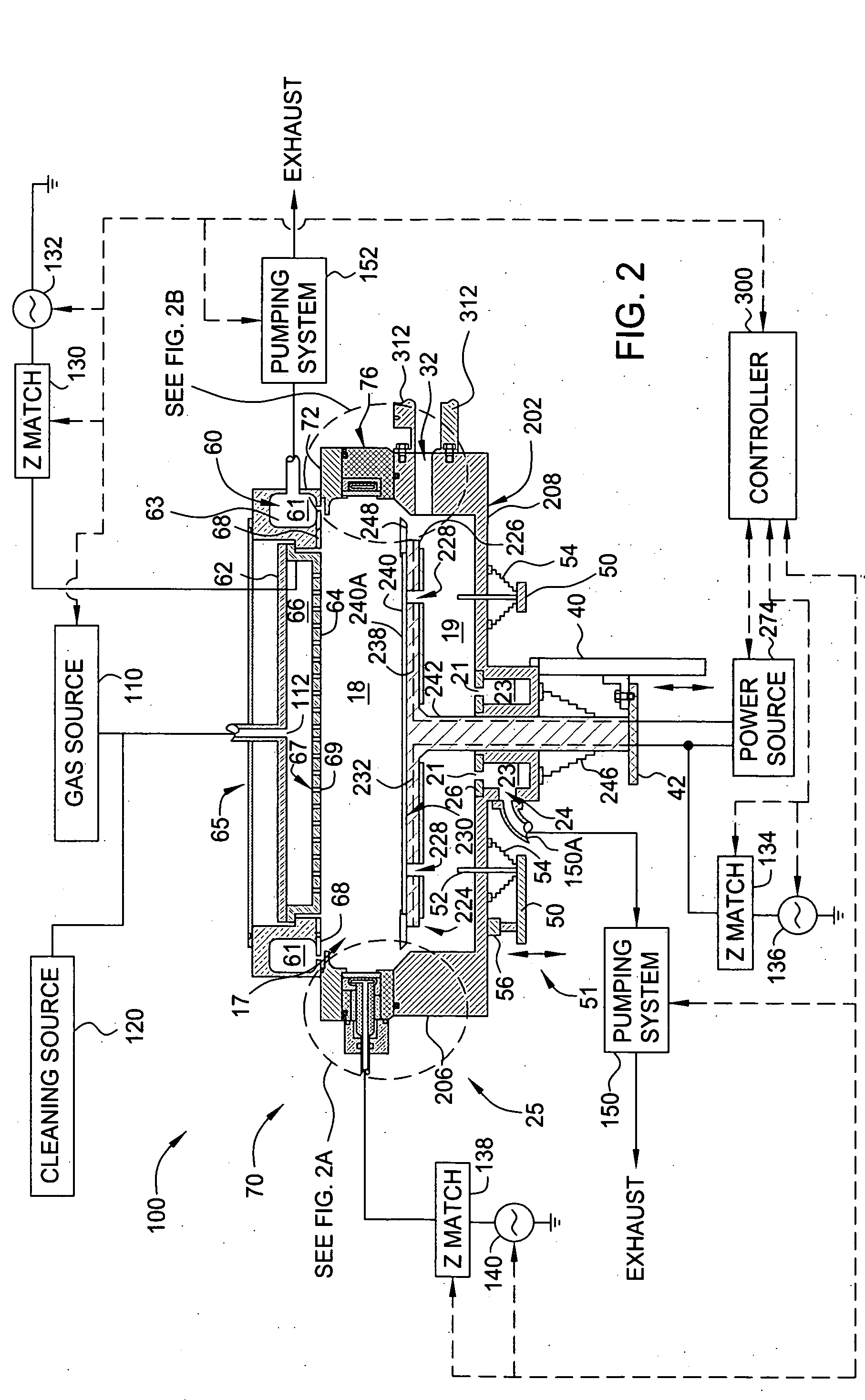

Multi-layer high quality gate dielectric for low-temperature poly-silicon TFTs

InactiveUS20060105114A1Quality improvementSolid state diffusion coatingChemical vapor deposition coatingCapacitanceEngineering

A method and apparatus that is useful for forming a high quality gate dielectric layer in MOS TFT devices using a high density plasma oxidation (HDPO) process. The HDPO process forms a good interface and then a second layer, which has good bulk electrical properties, is deposited at a higher deposition rate over the HDPO layer. In one embodiment a thin HDPO process layer is formed over the channel, source and drain regions to form a high quality dielectric interface and then one or more dielectric layers are deposited on the HDPO layer to form a high quality gate dielectric layer. The HDPO process generally entails using an inductively and / or capacitively coupled RF energy transmitting device to generate and control the plasma generated over the surface of the substrate and injecting a gas containing an oxidizing source to grow the interfacial layer. A second dielectric layer may then be deposited on the surface of the substrate using a CVD or plasma enhanced CVD deposition process. Aspects of the present invention also provide a cluster tool that contains at least one specialized plasma processing chamber that is capable of depositing a high quality gate dielectric layer. The cluster tool is advantageous because it supports both the pre-processing steps, such as, preheating the substrate, pre-cleaning the surface of the substrate prior to processing, and cool down after processing, all in a single controlled environment.

Owner:APPLIED MATERIALS INC

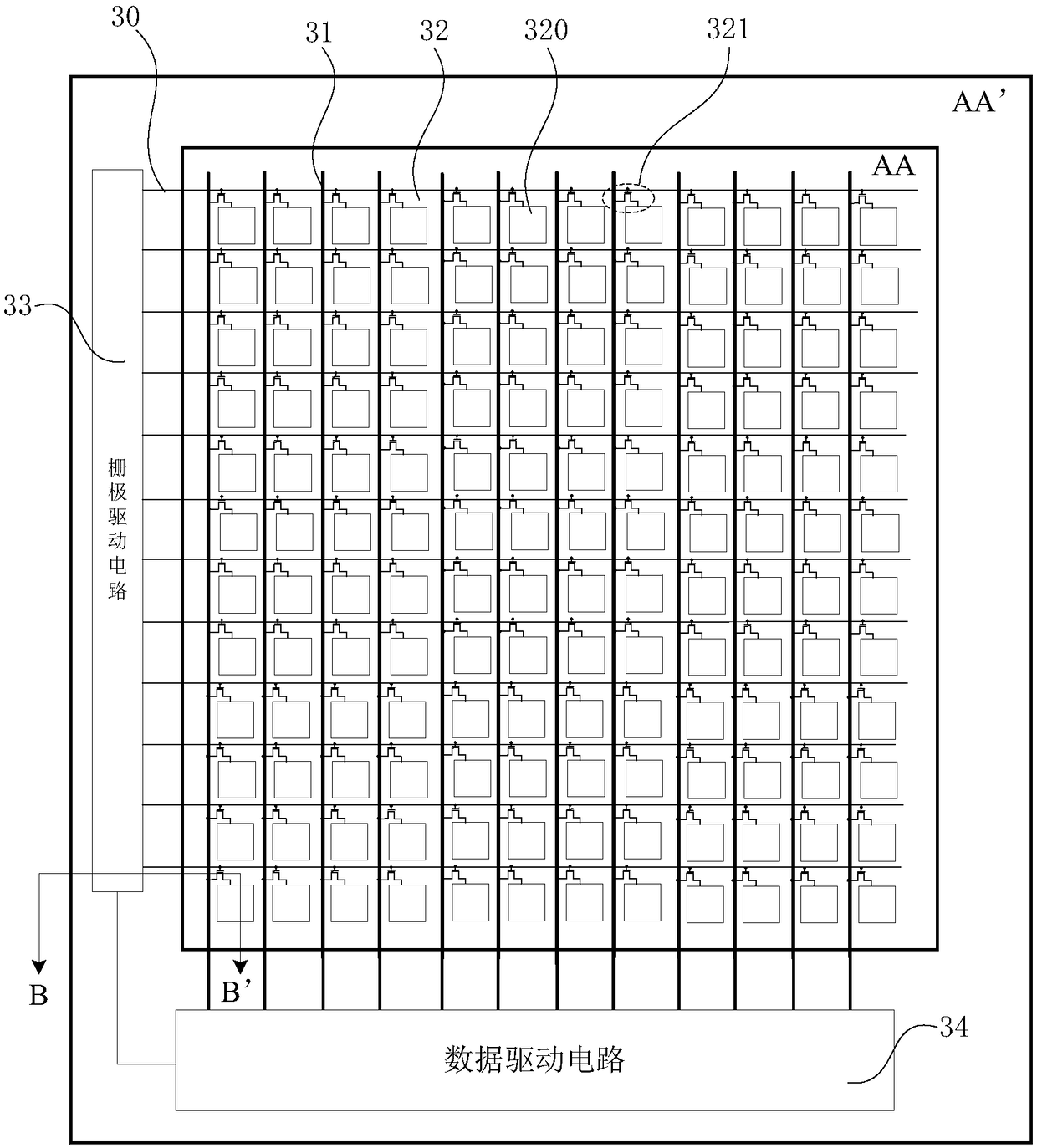

Array substrate and manufacturing method therefor

InactiveCN106876412AImprove electrical performanceImprove stabilitySolid-state devicesSemiconductor/solid-state device manufacturingOxide thin-film transistorElectrical performance

Embodiments of the invention disclose an array substrate and a manufacturing method therefor. The array substrate comprises a plurality of first thin film transistors and a plurality of second thin film transistors; the first thin film transistors and the second thin film transistors are formed above a substrate; the active layer of each first thin film transistor is low-temperature polysilicon; the active layer of each second thin film transistor is an oxide semiconductor; the first thin film transistors are positioned in a peripheral circuit region of the array substrate; the second thin film transistors are positioned in a display region of the array substrate; the grid electrodes of the first thin film transistors and the second thin film transistors are positioned on different layers; and the source and drain electrodes of the first thin film transistors and the source and drain electrodes of the second thin film transistors are positioned on the same layer. By adoption of the array substrate and the manufacturing method therefor, the problem of incompatibility of two film layers of two types of thin film transistors when the metal oxide thin film transistors and the low-temperature polysilicon thin film transistors are formed in a display panel at the same time is solved, so that the electrical performance and the stability of the display panel are improved.

Owner:XIAMEN TIANMA MICRO ELECTRONICS

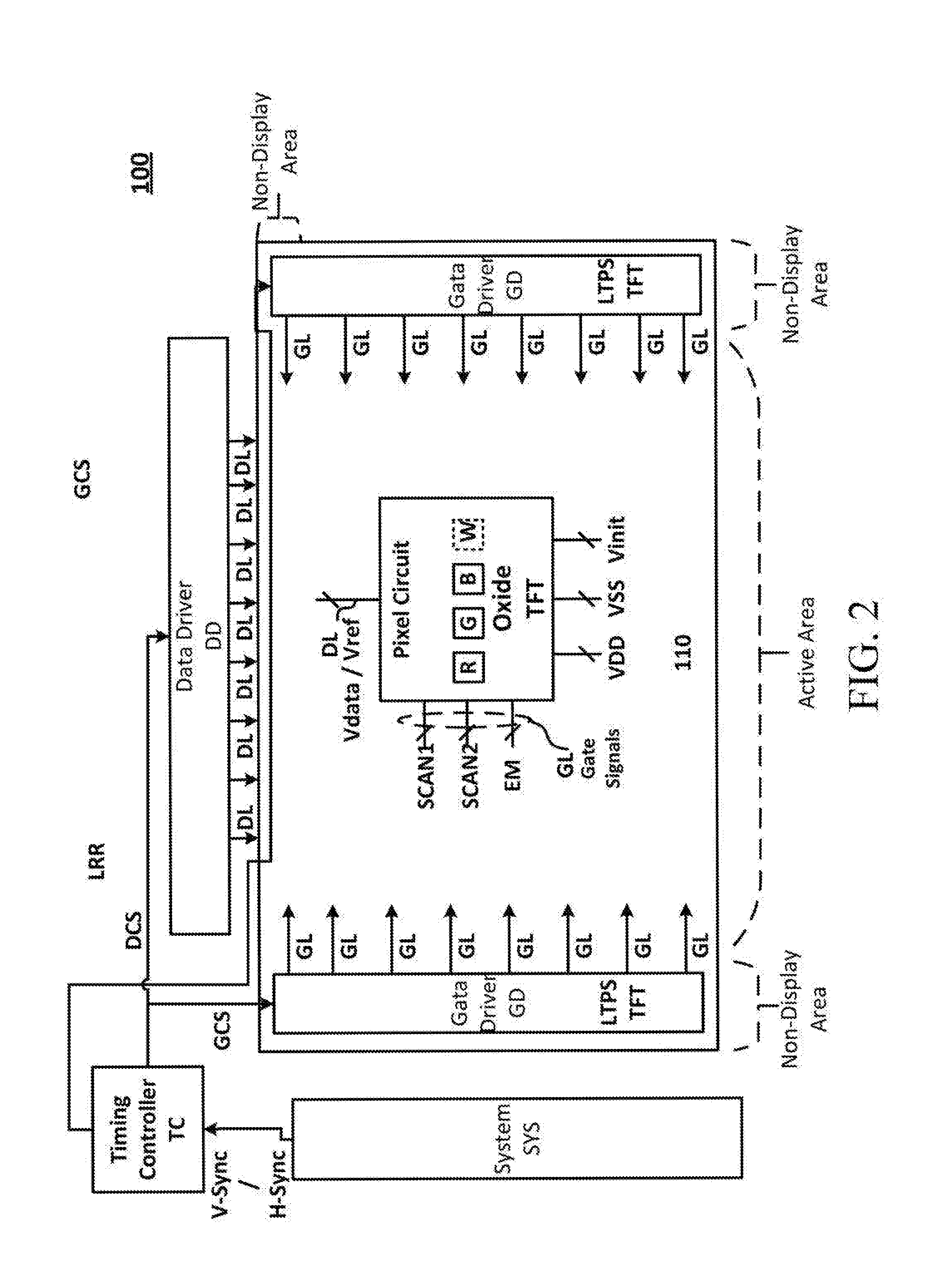

Display backplane and method of fabricating the same

ActiveUS20160240565A1High resolutionReduce power consumptionTransistorStatic indicating devicesLight-emitting diodeSilicon

An organic light emitting display is provided. The organic light emitting display comprises a multi-type thin-film transistor (TFT) and an organic light emitting diode. The multi-type TFT has a low-temperature-poly-silicon (LTPS) TFT and an oxide semiconductor TFT (oxide TFT) disposed on the LTPS TFT. The organic light emitting diode is electrically connected to the multi-type TFT. The LTPS TFT and the oxide TFT are connected to the same gate line.

Owner:LG DISPLAY CO LTD

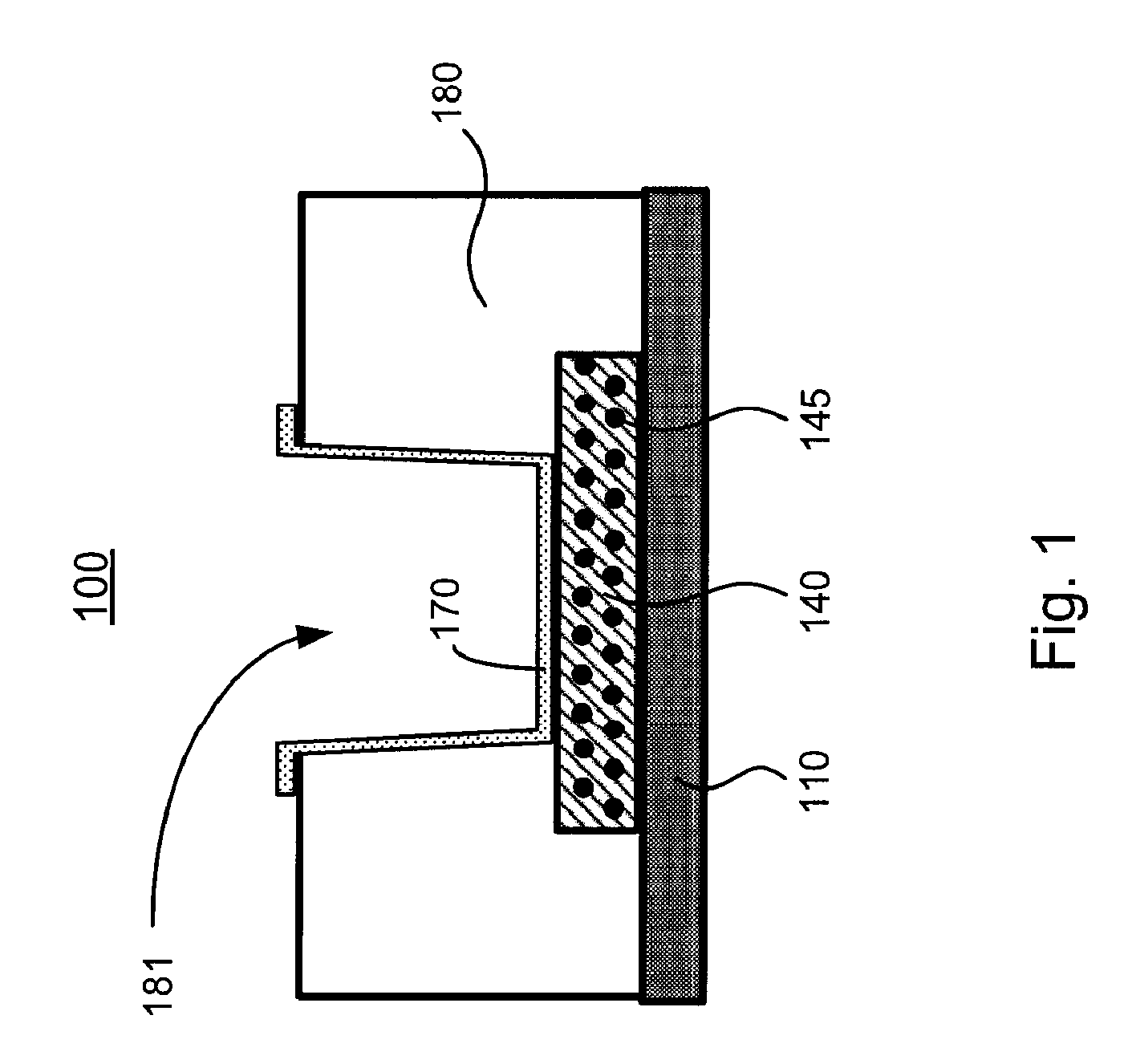

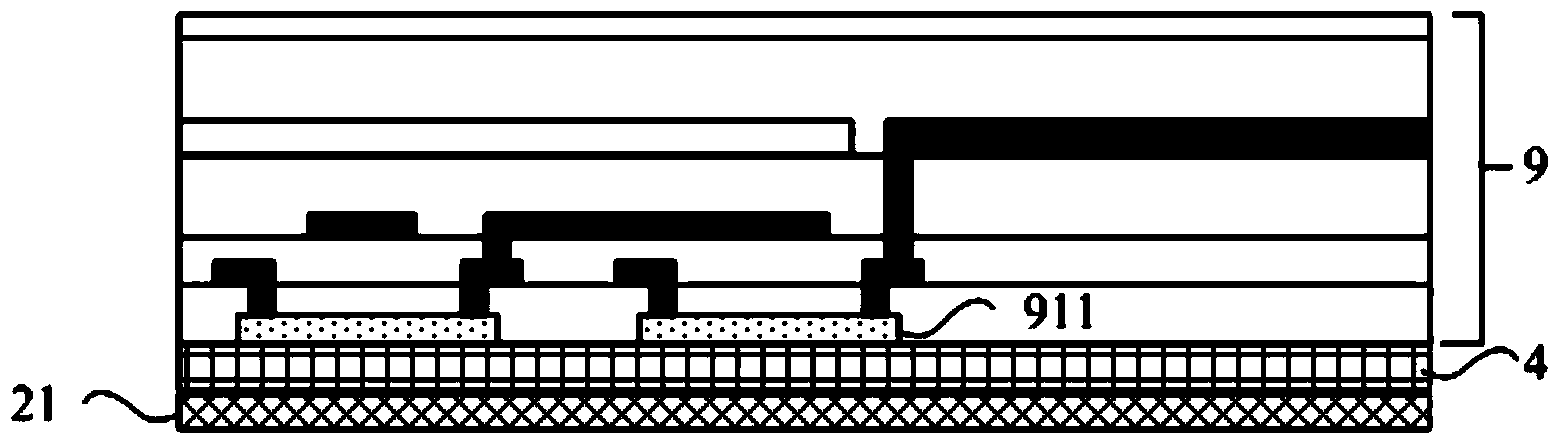

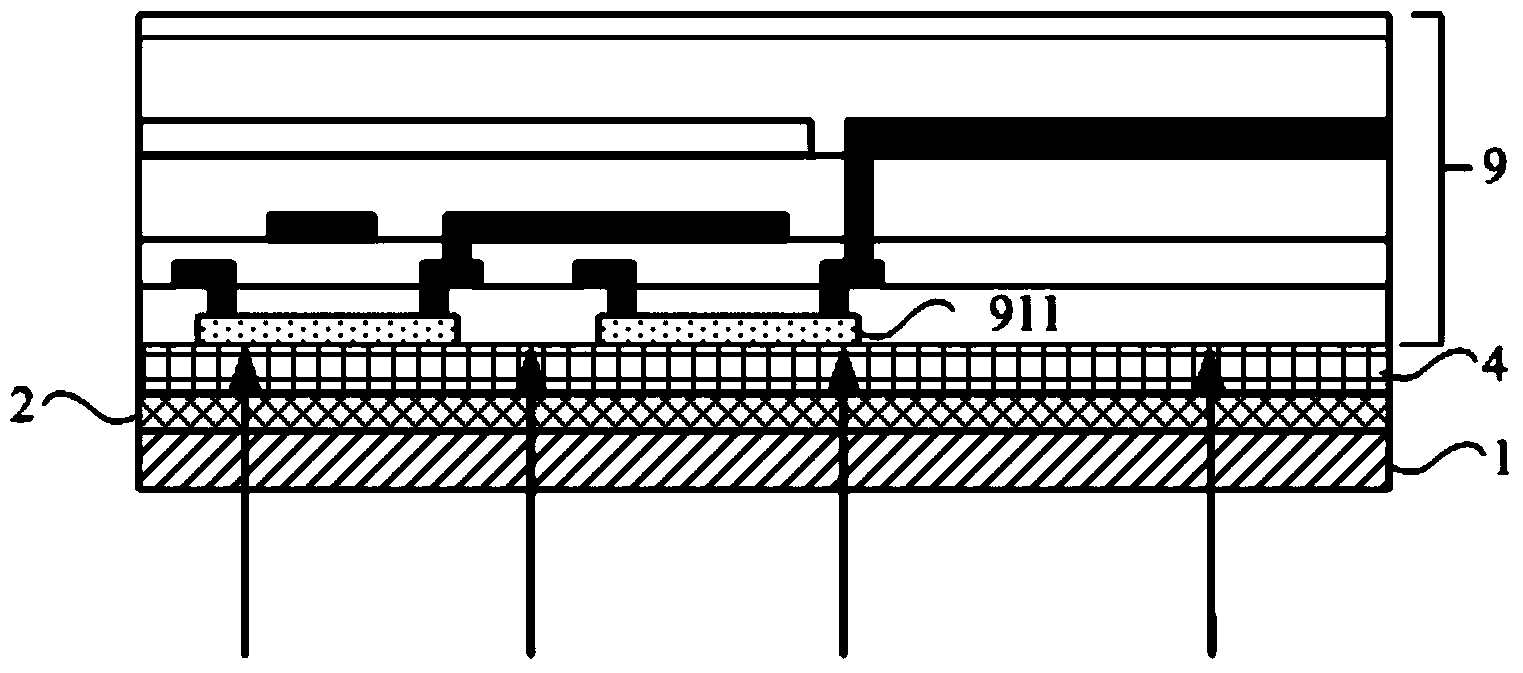

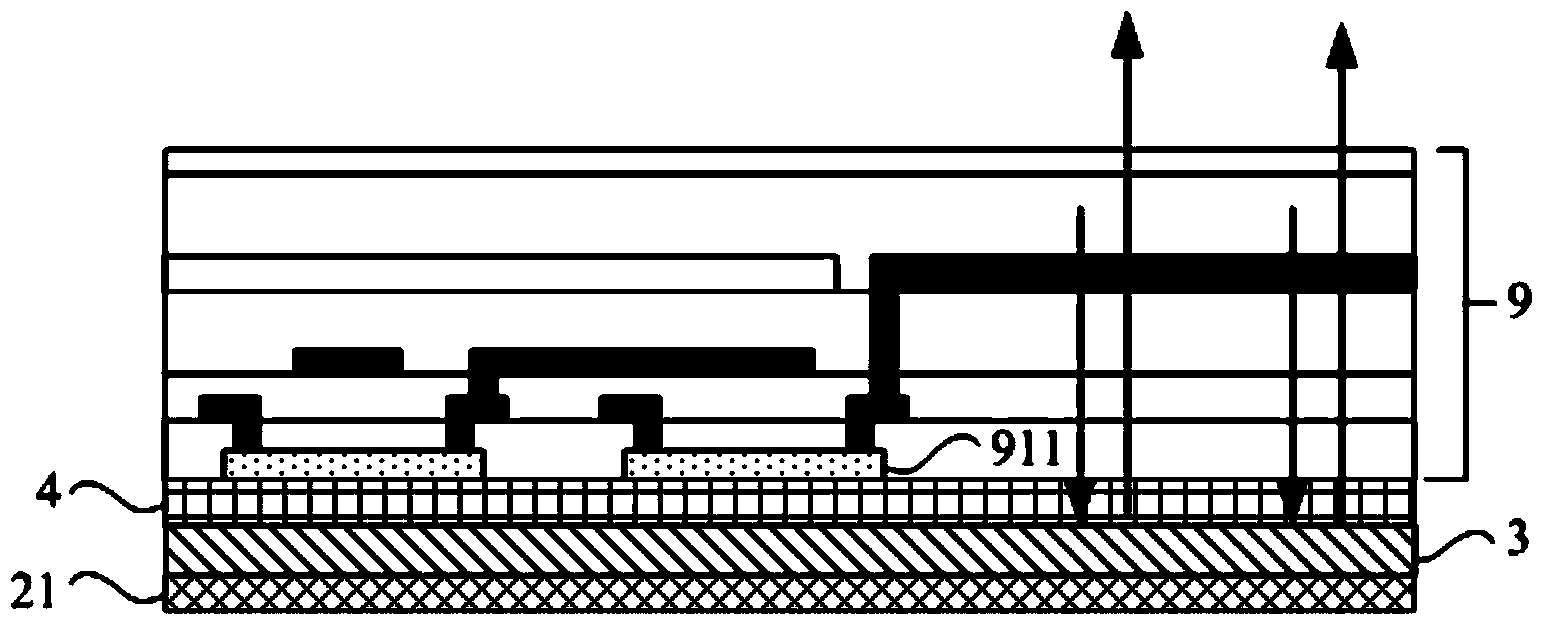

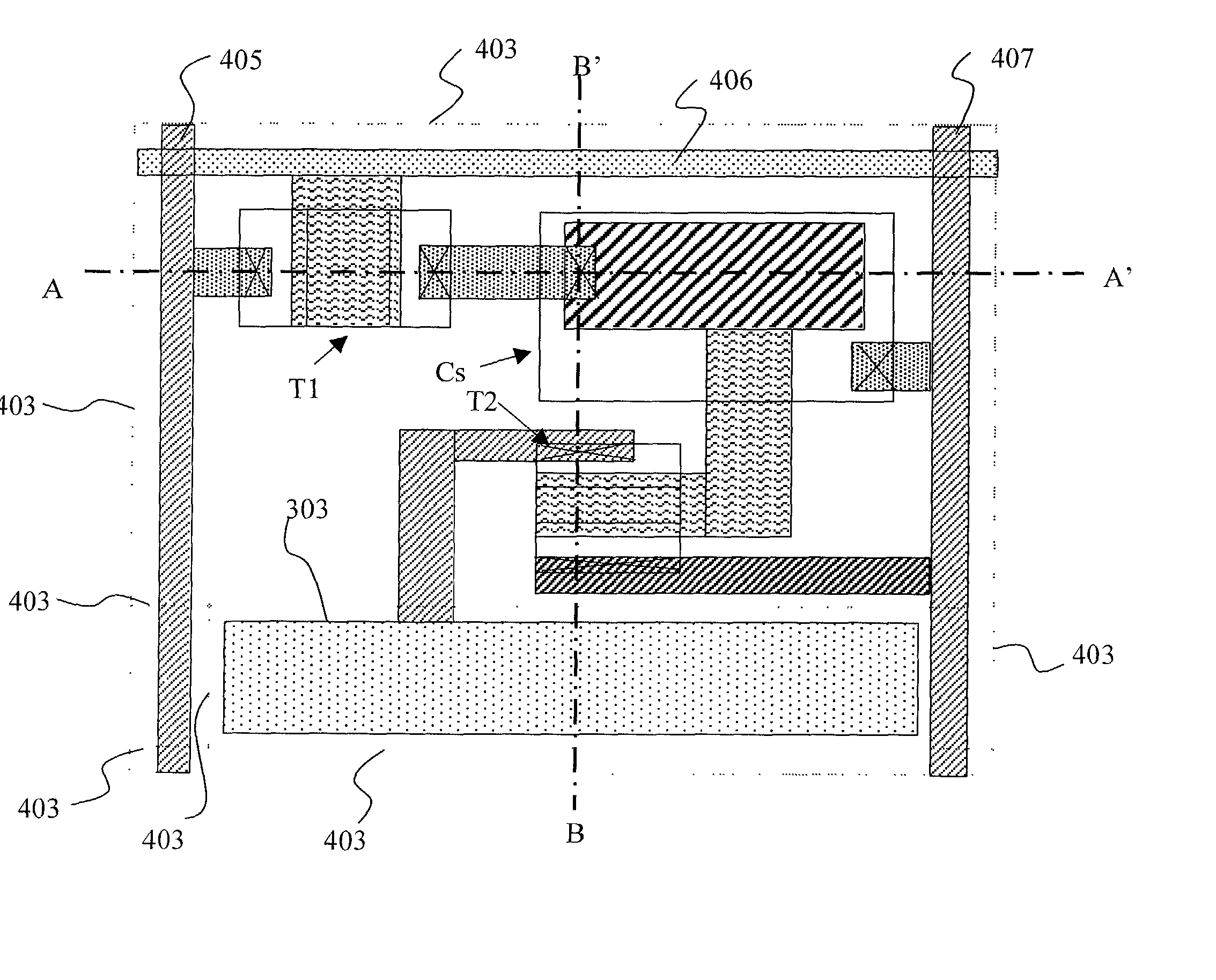

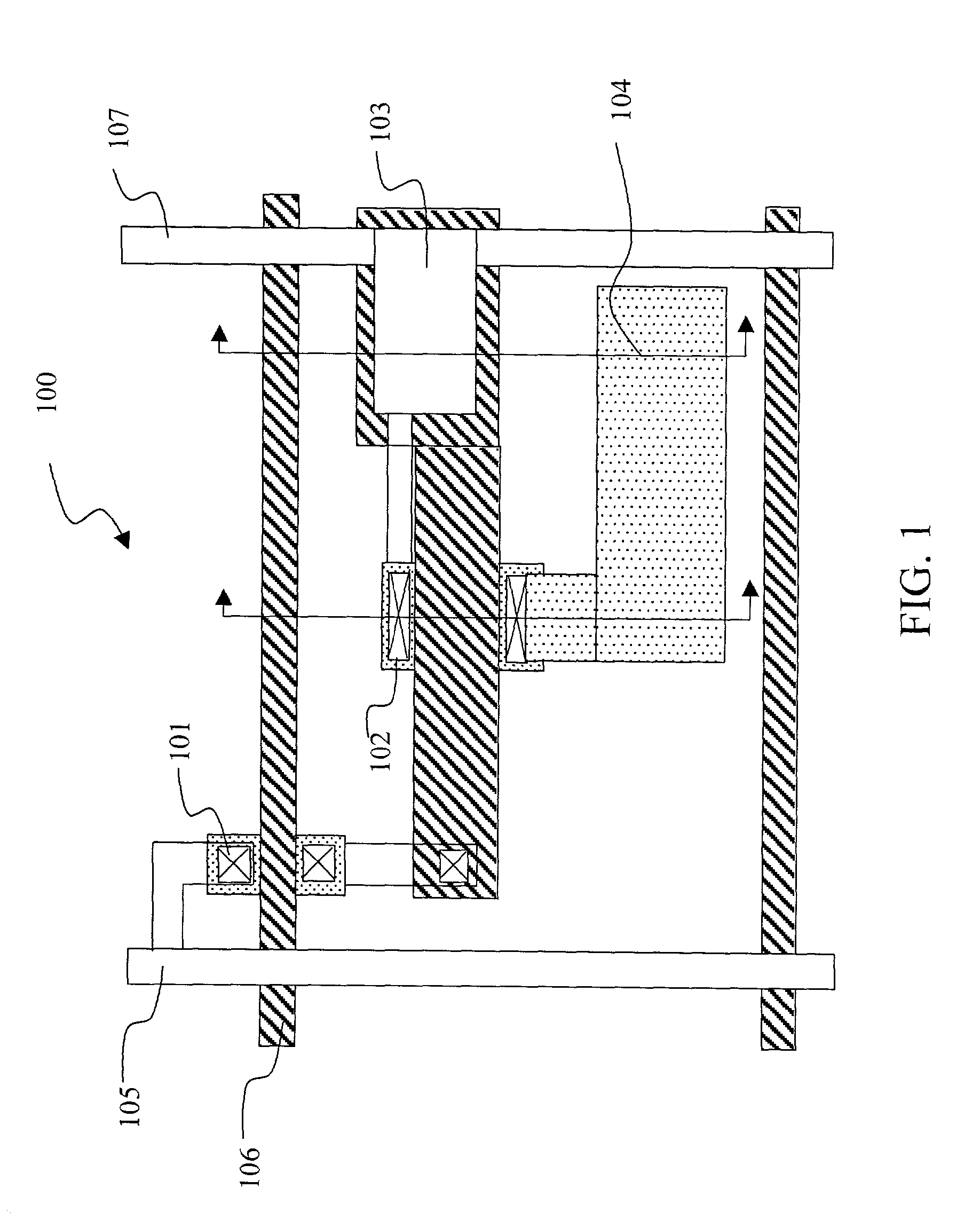

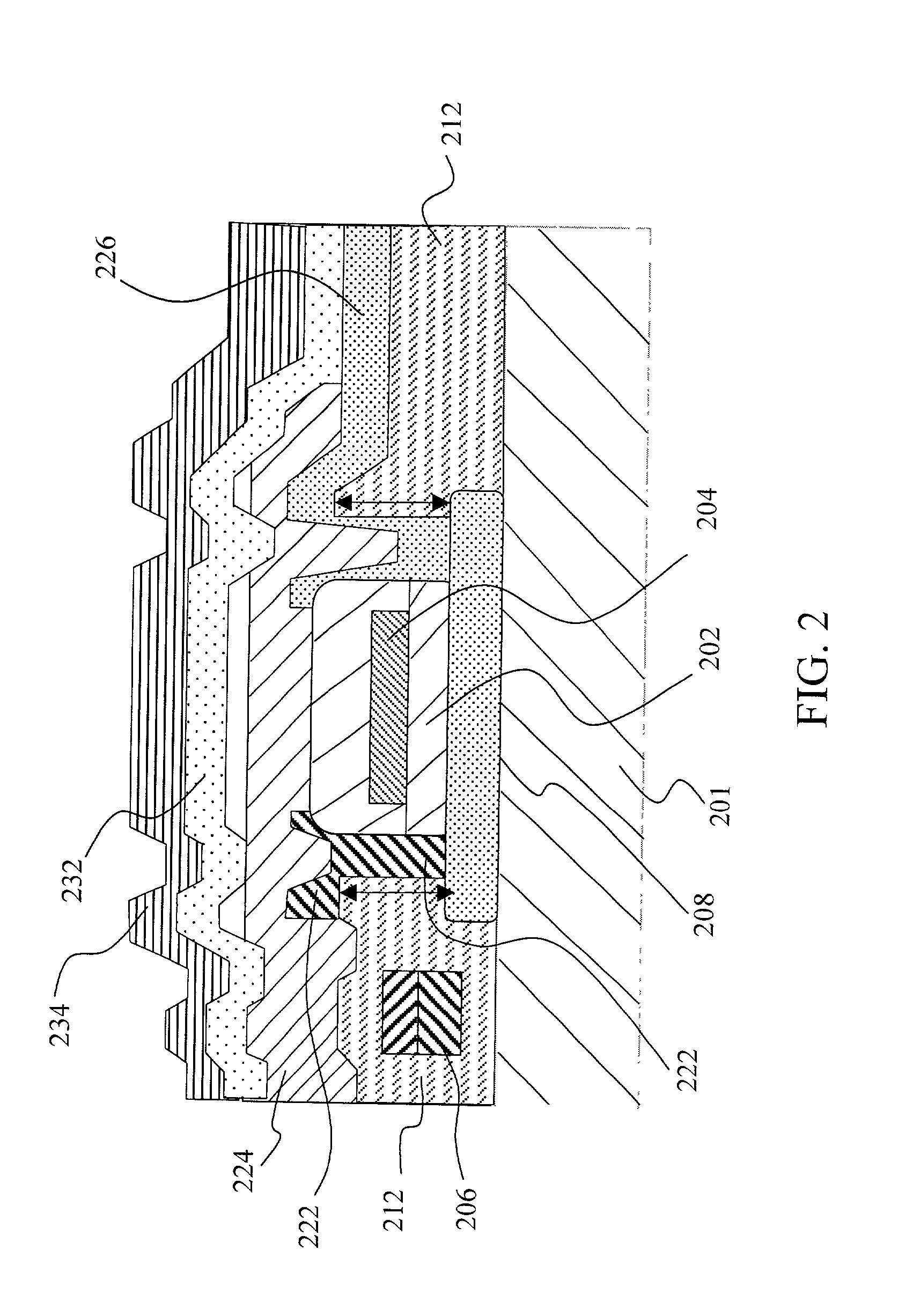

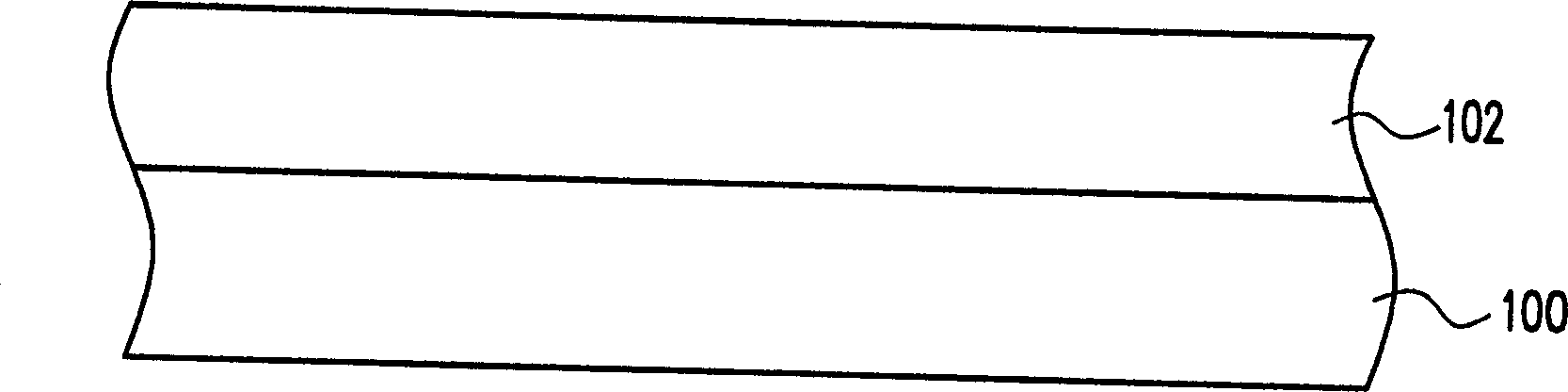

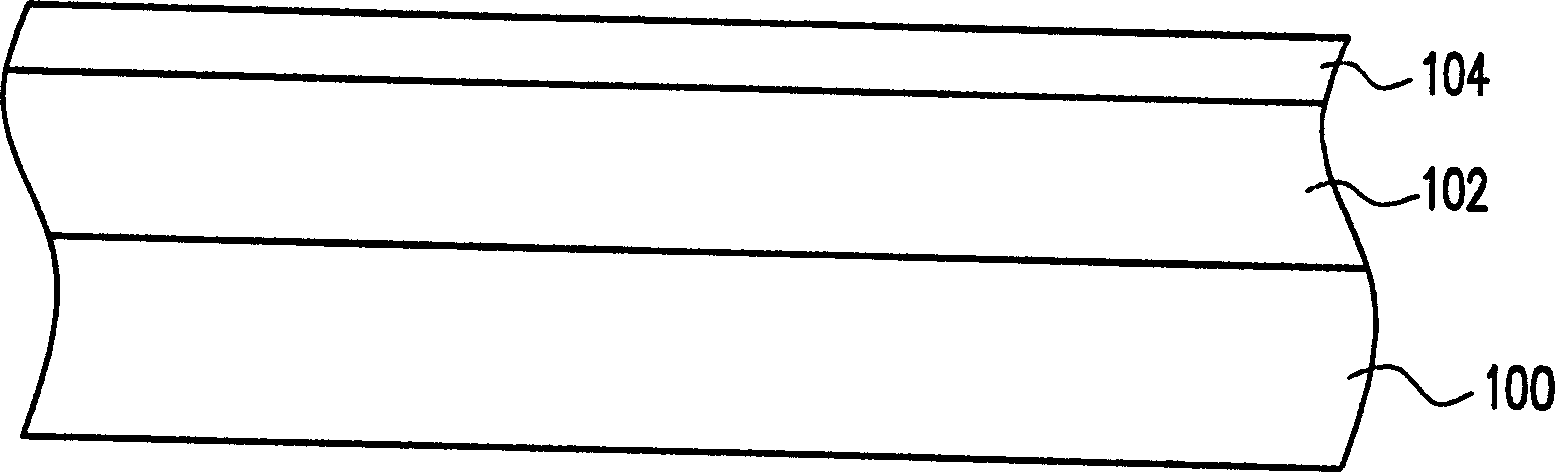

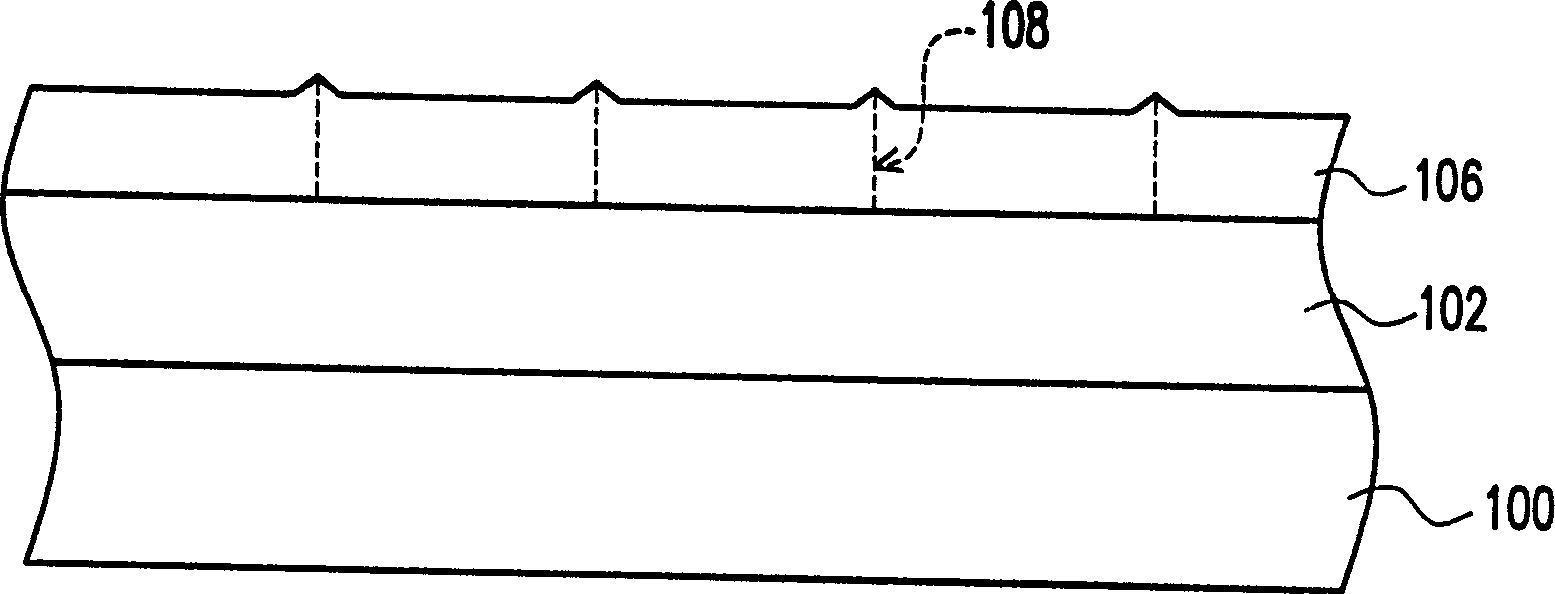

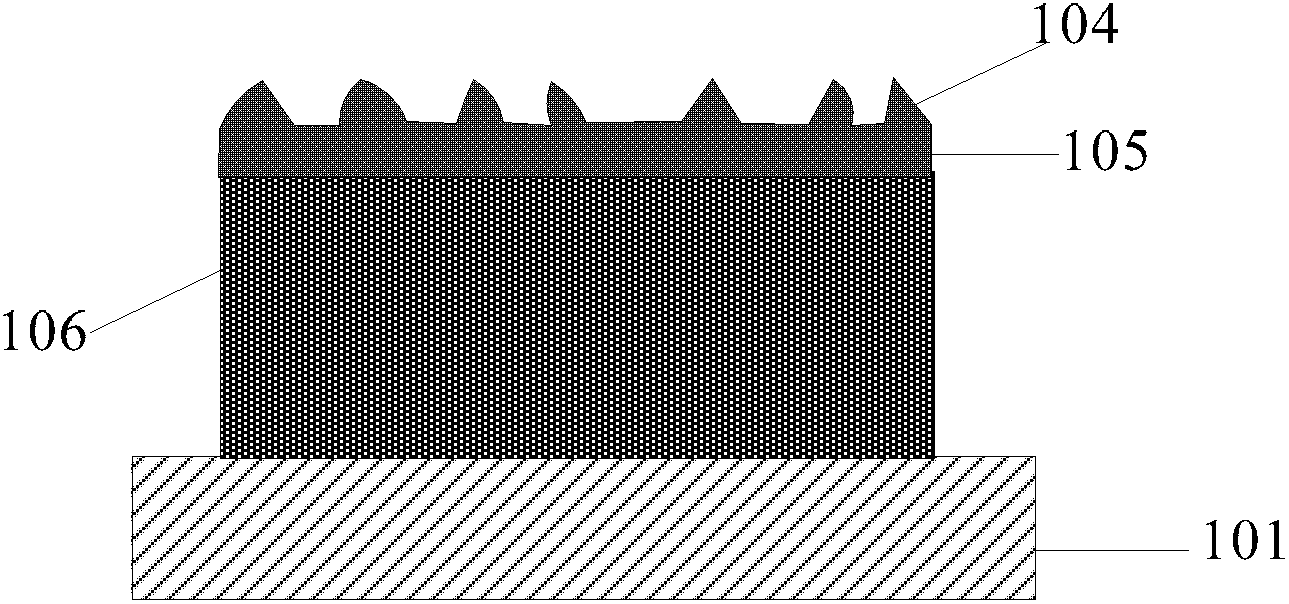

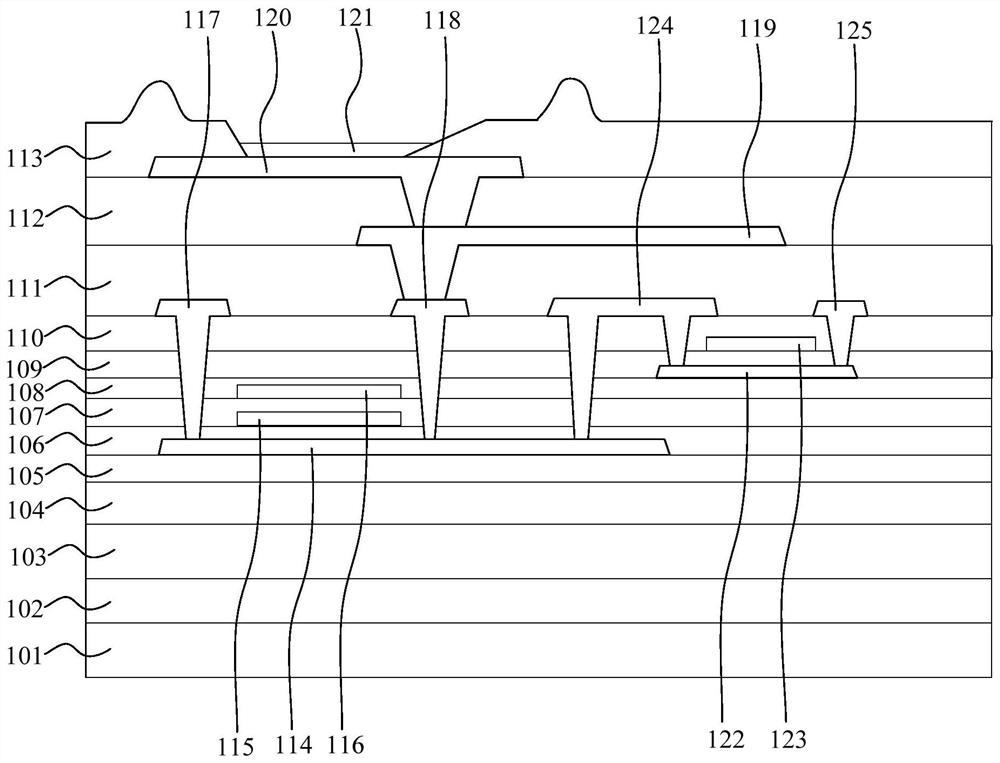

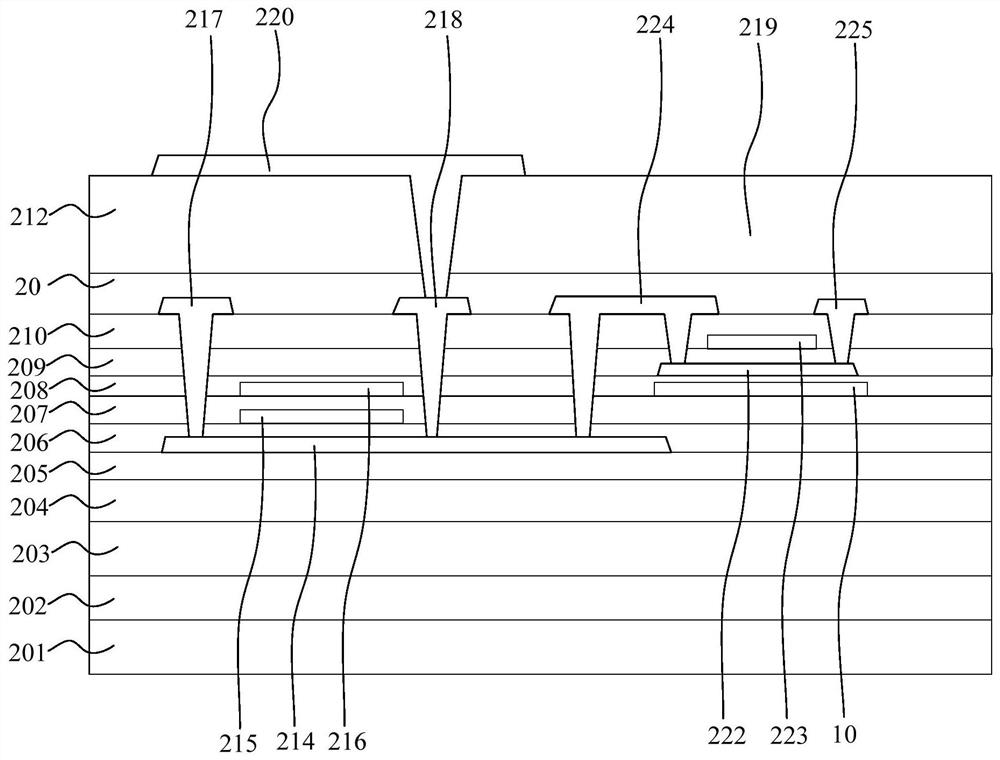

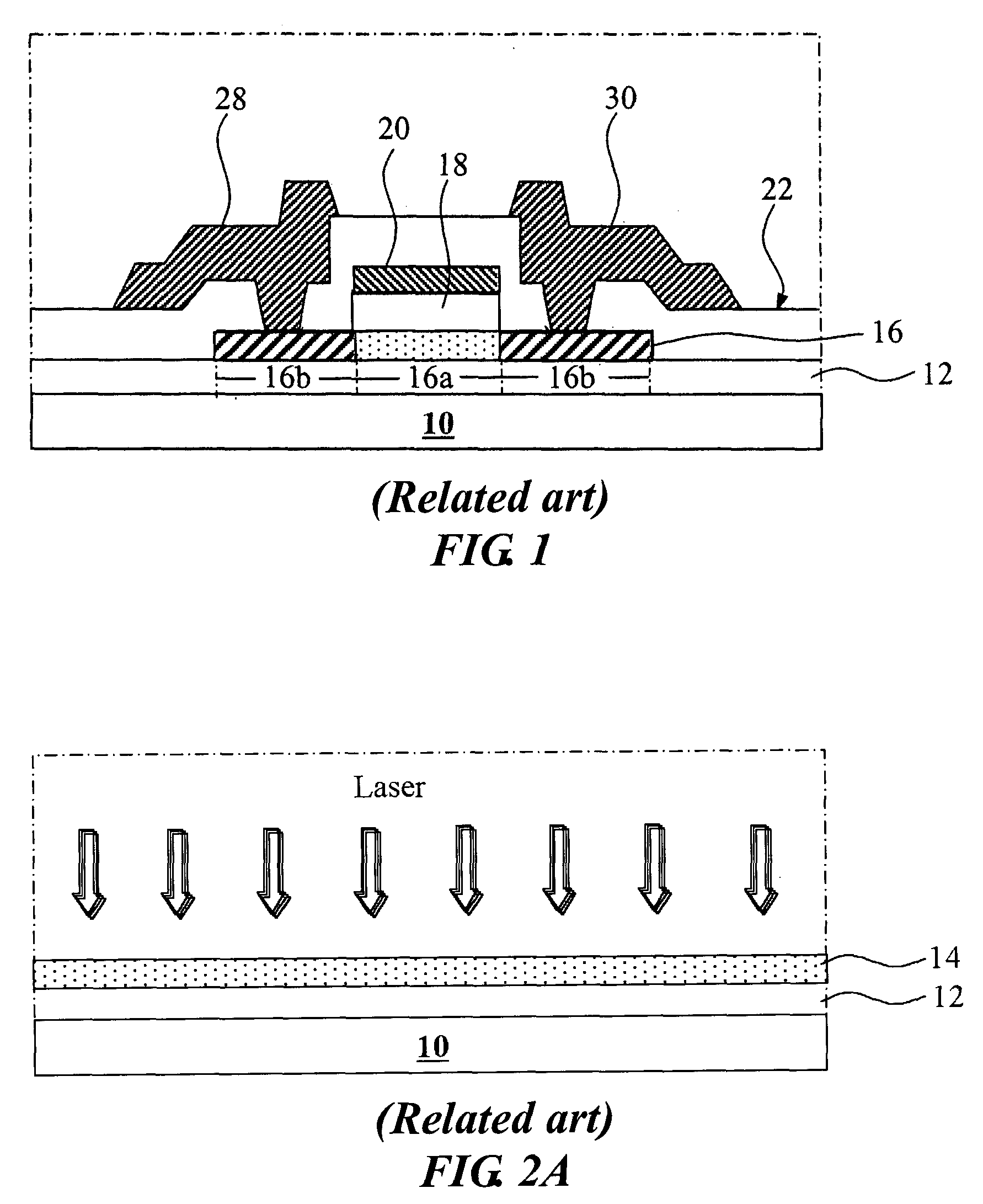

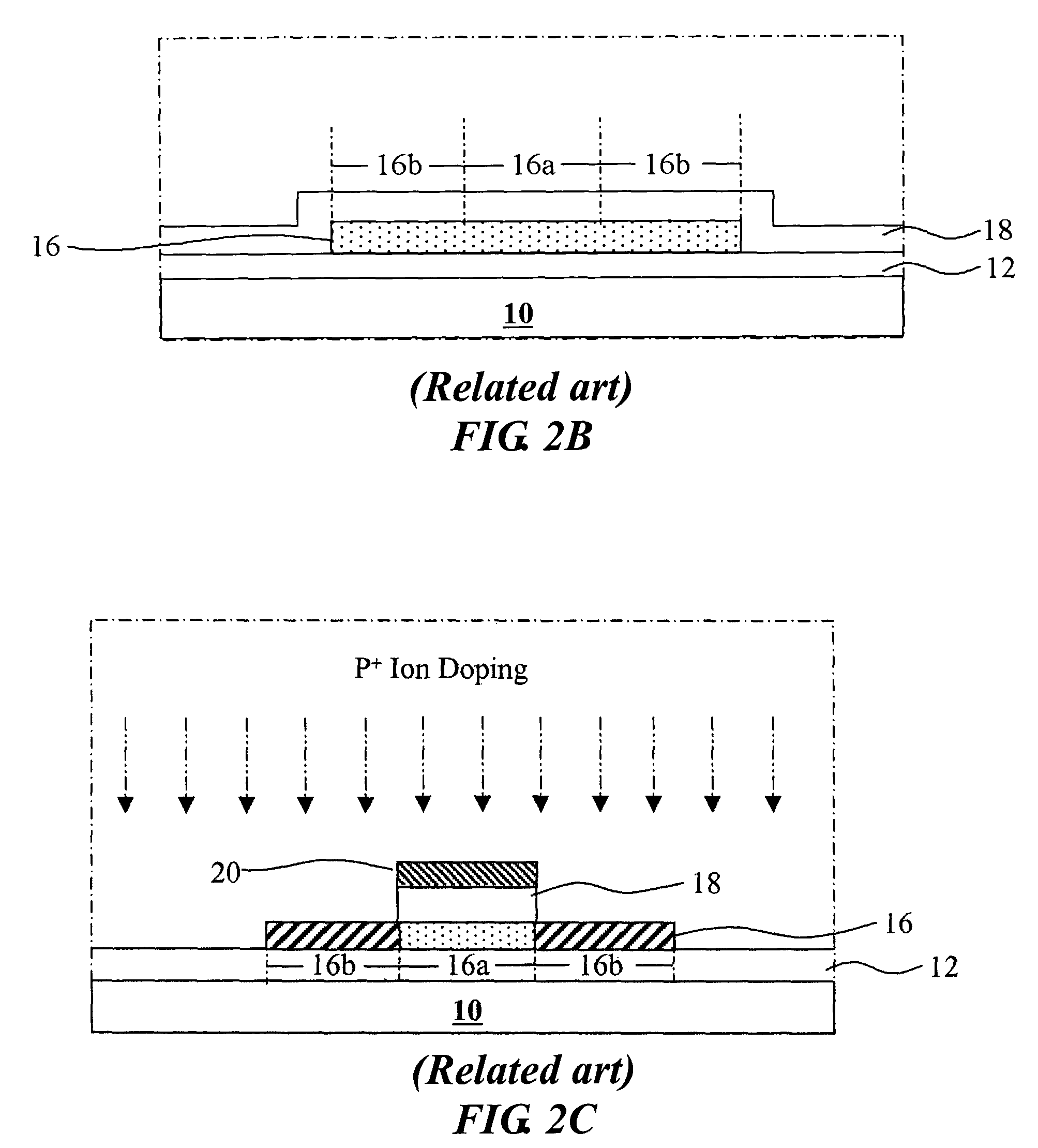

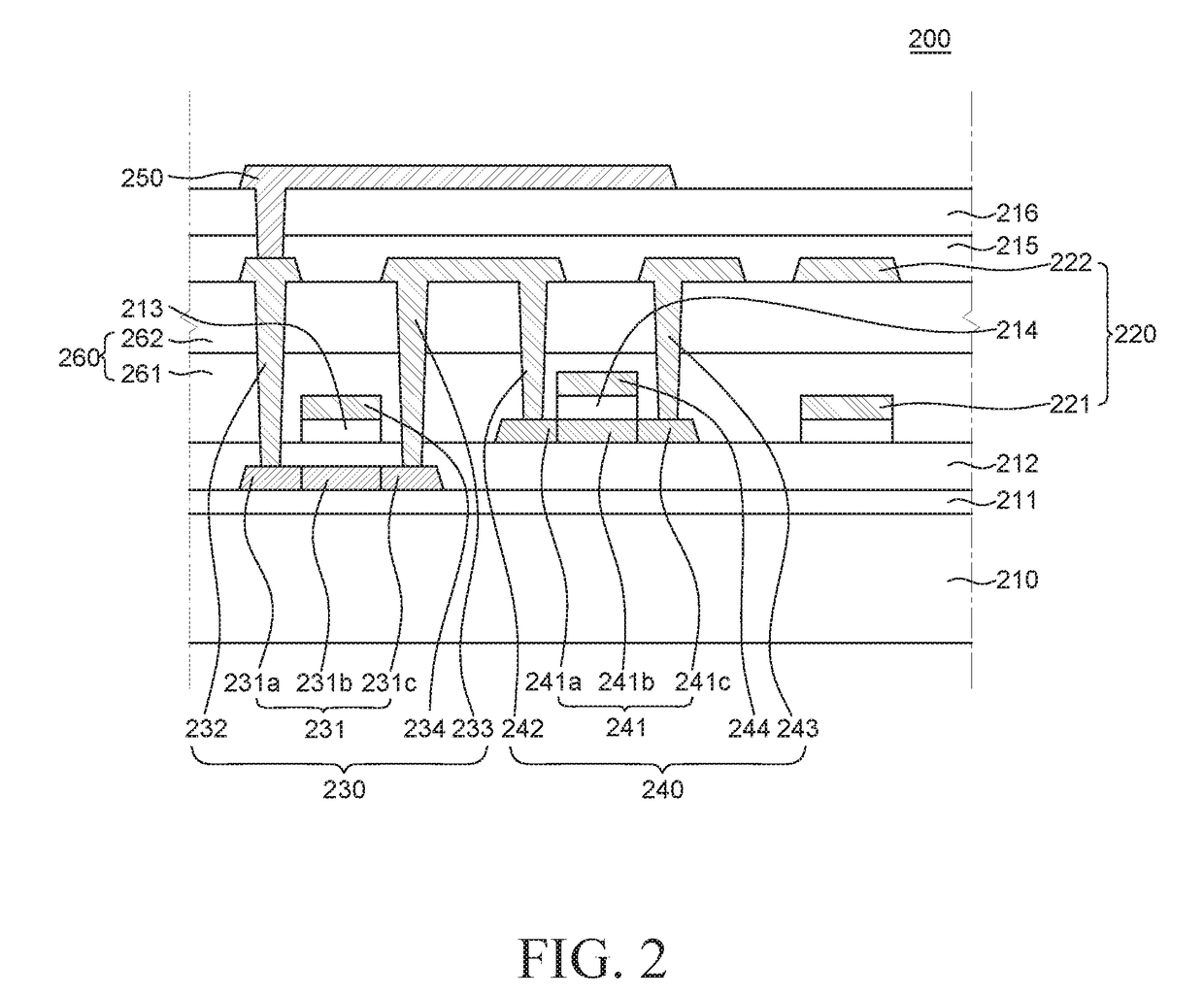

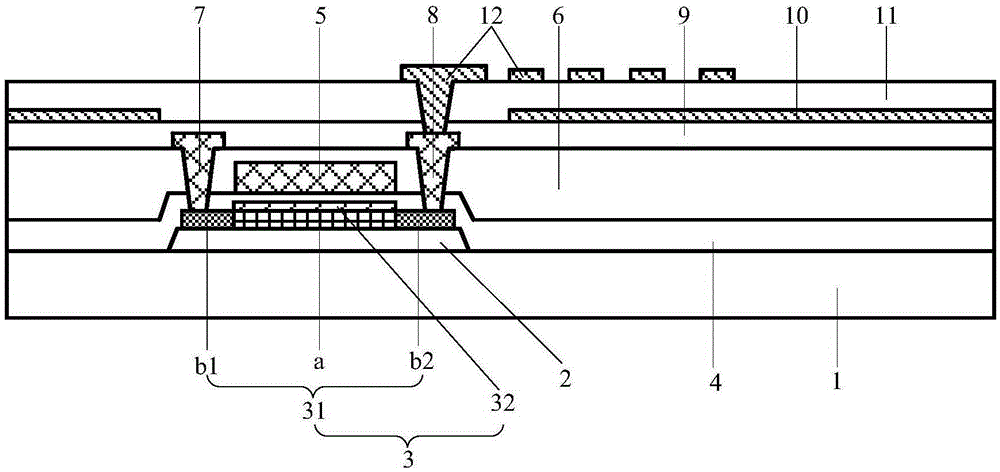

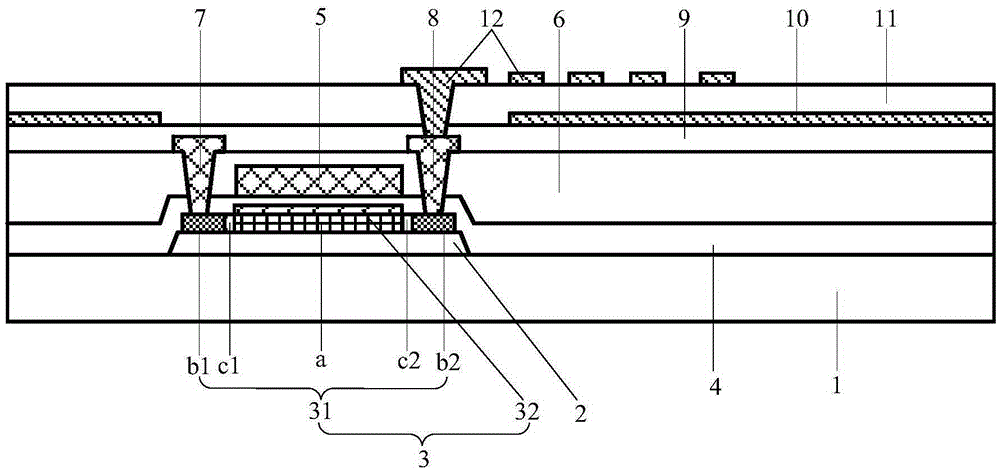

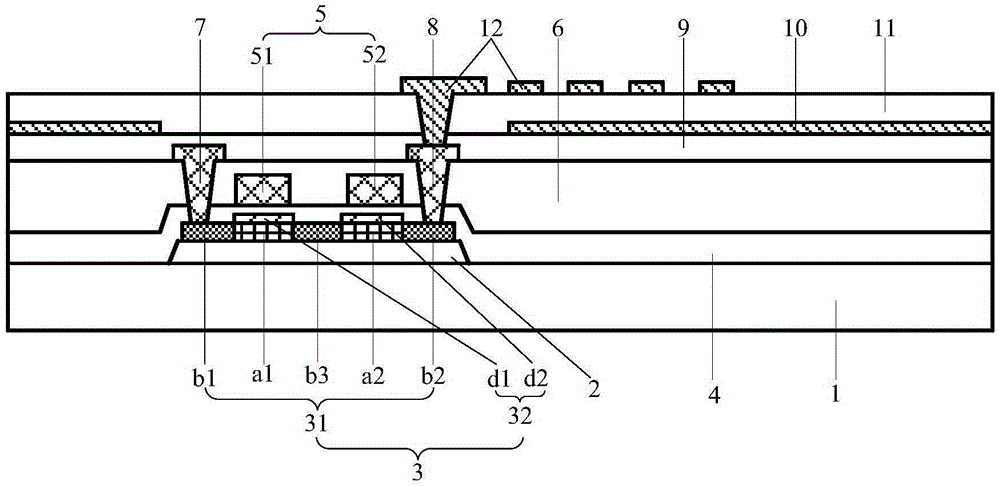

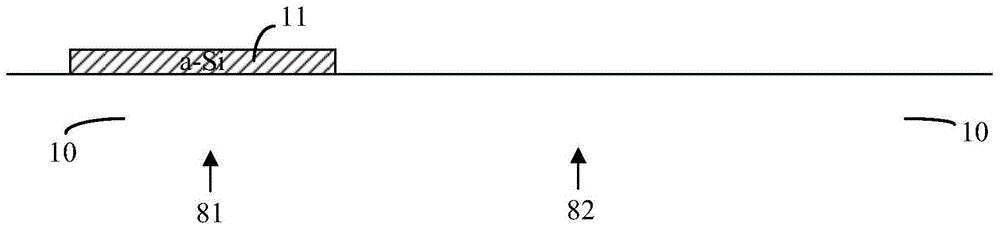

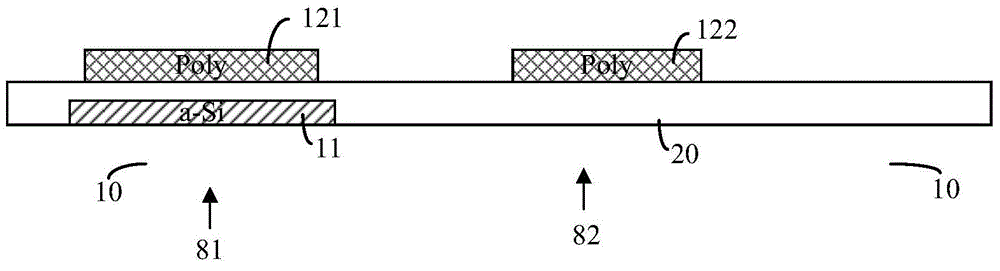

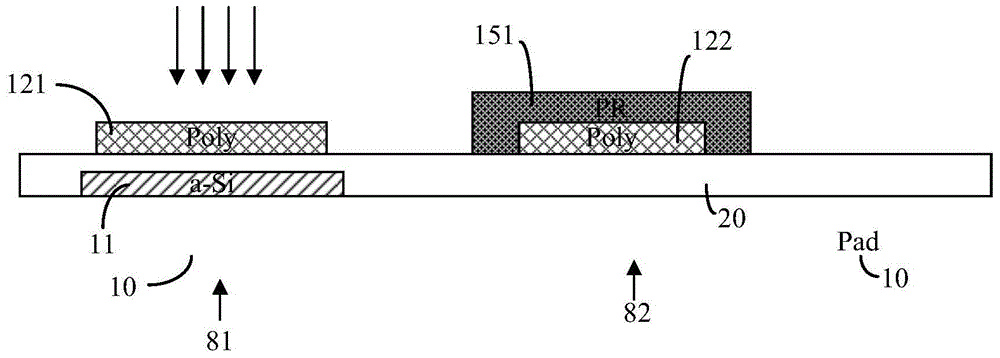

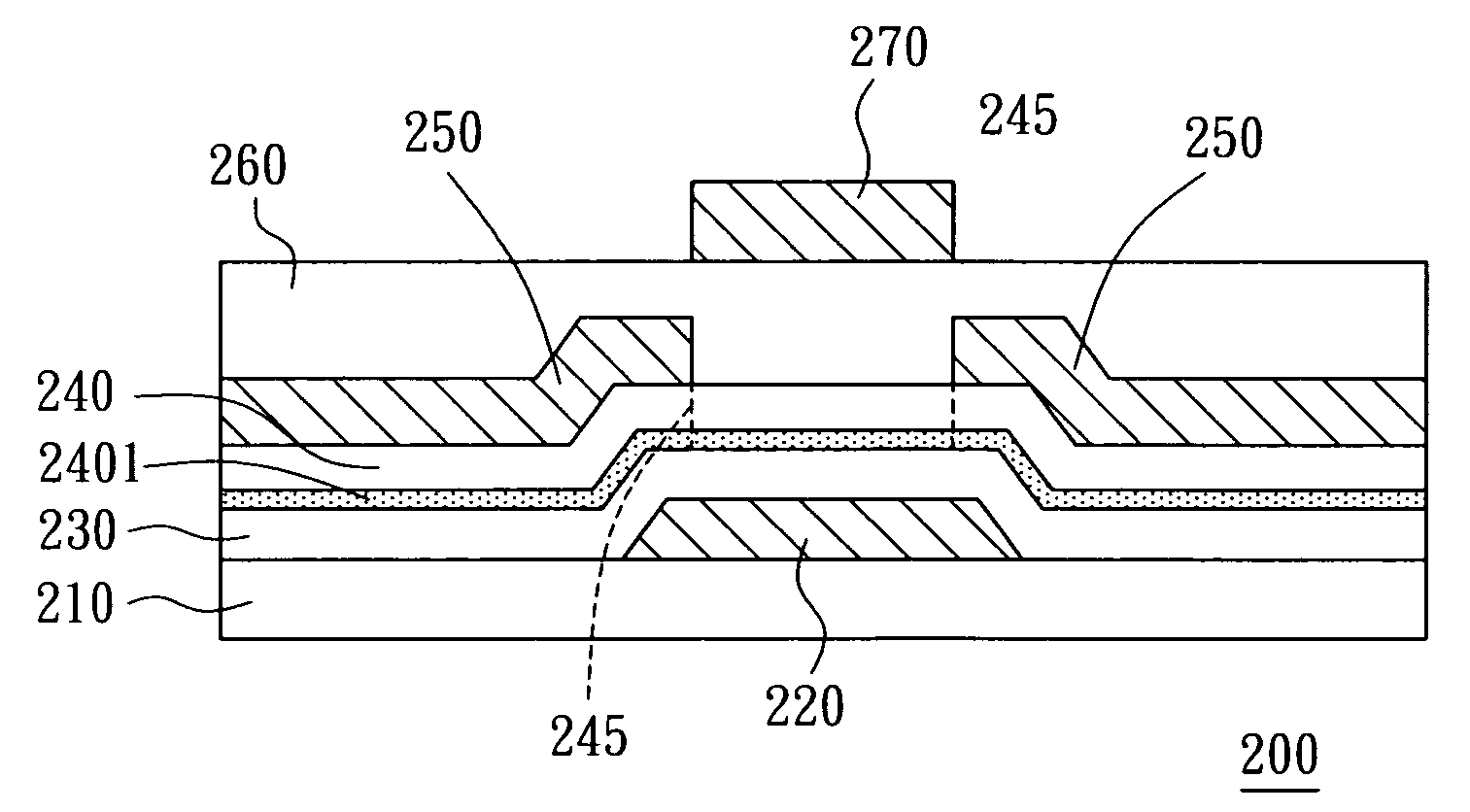

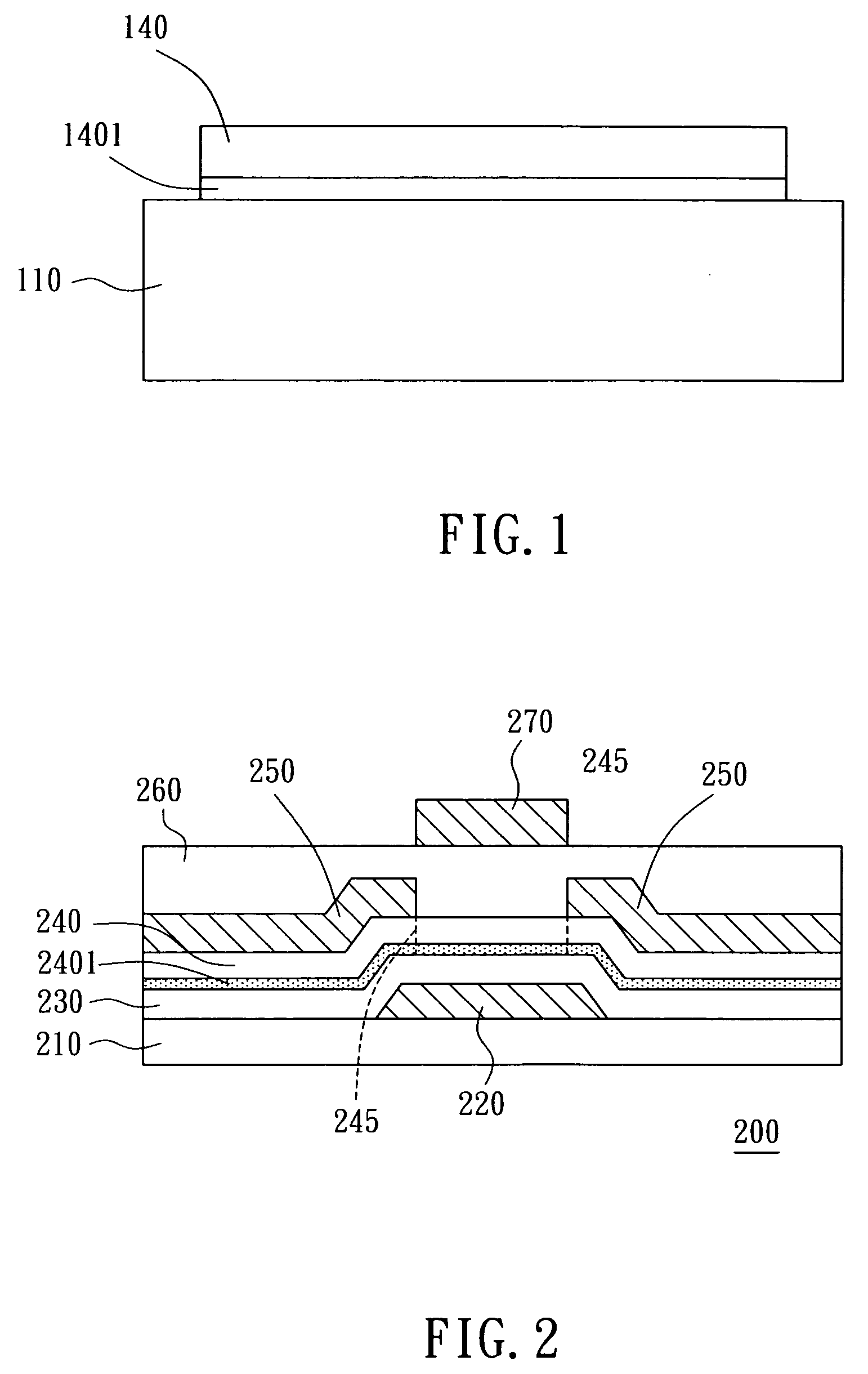

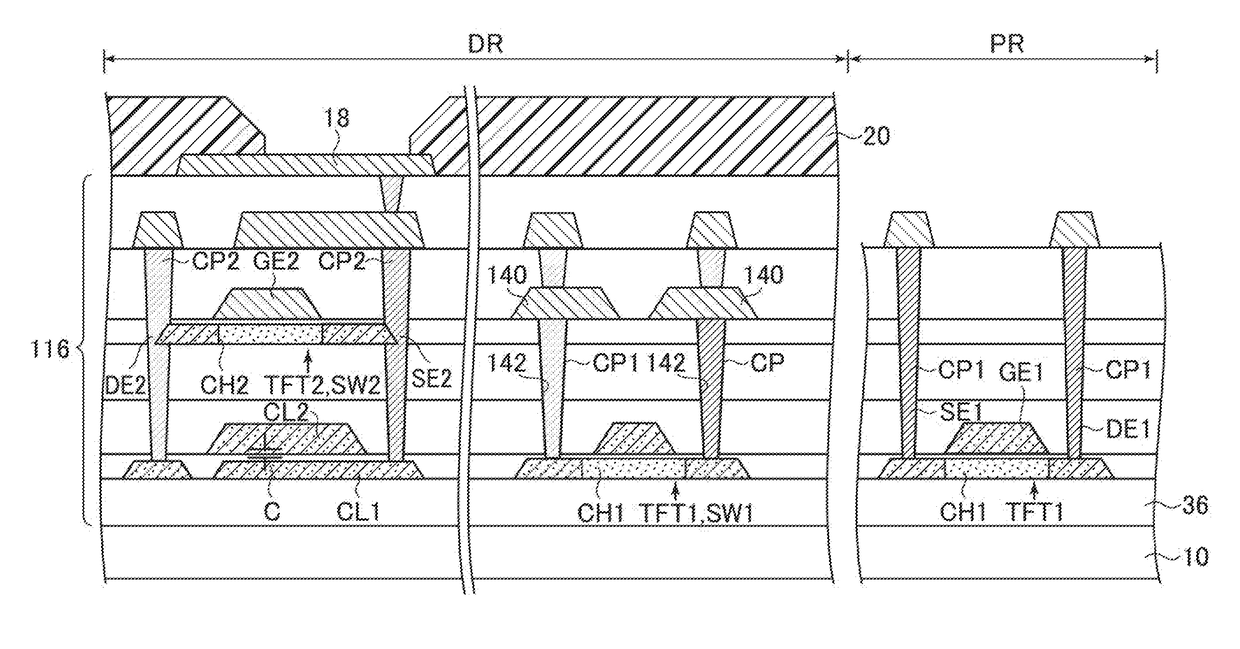

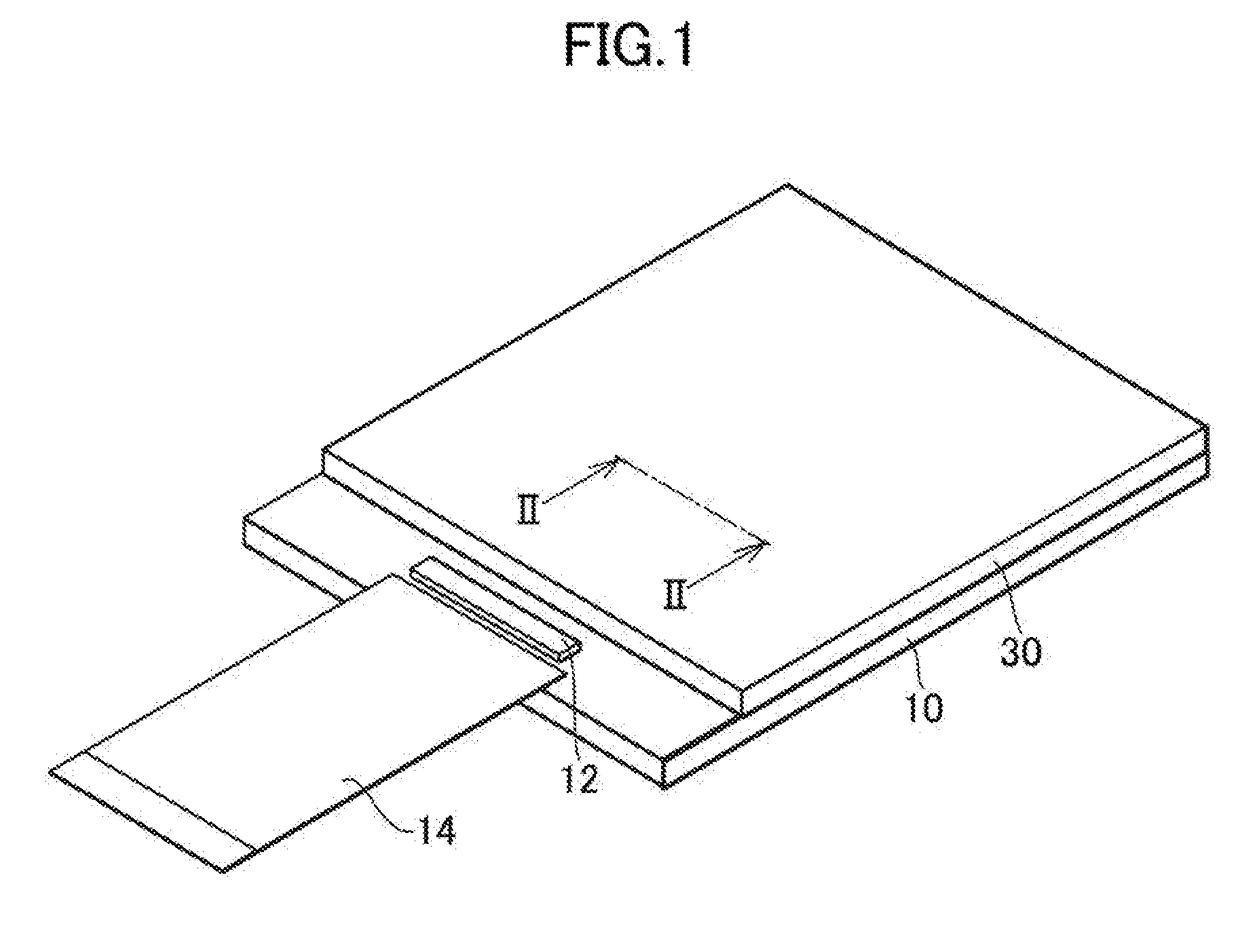

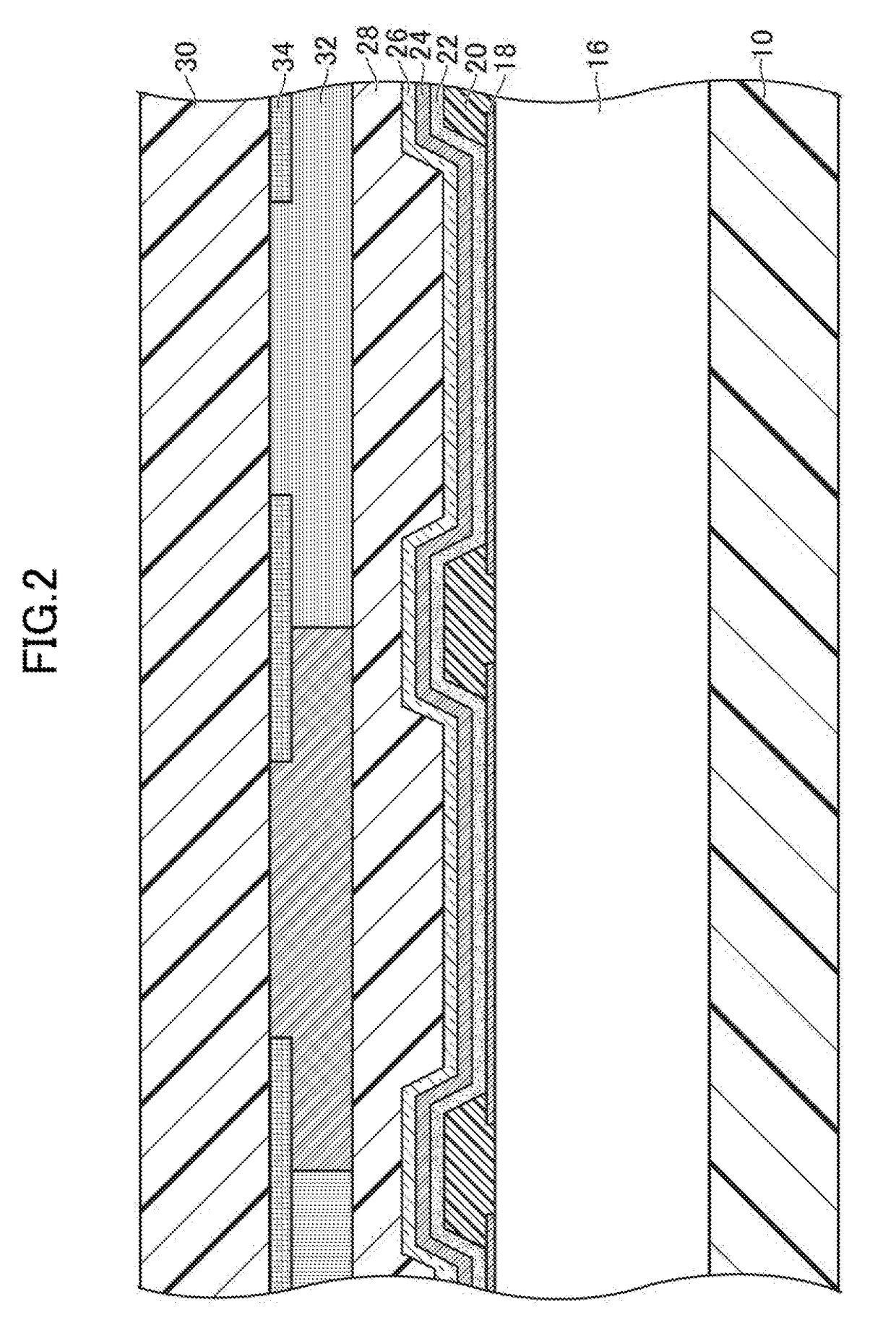

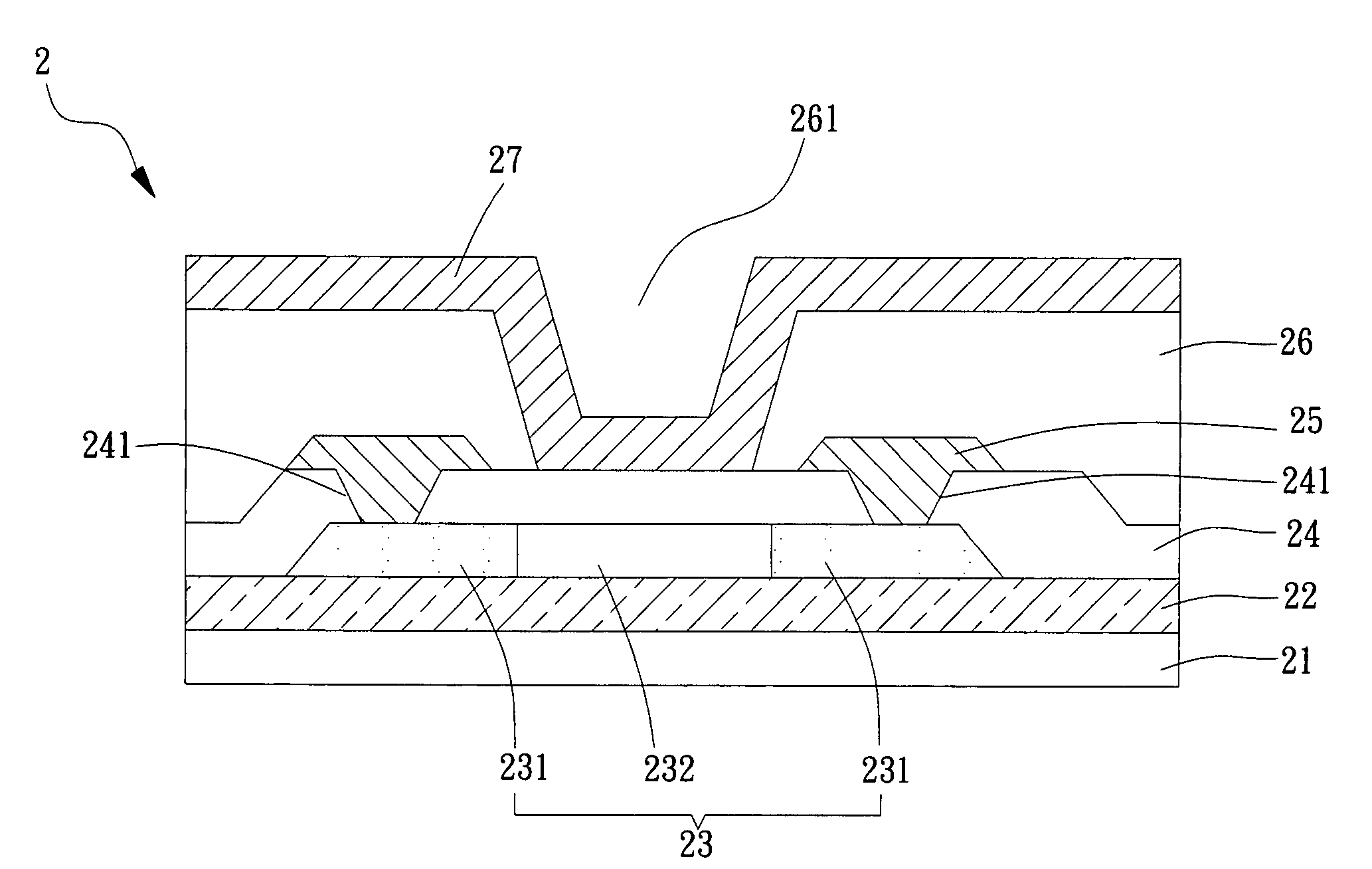

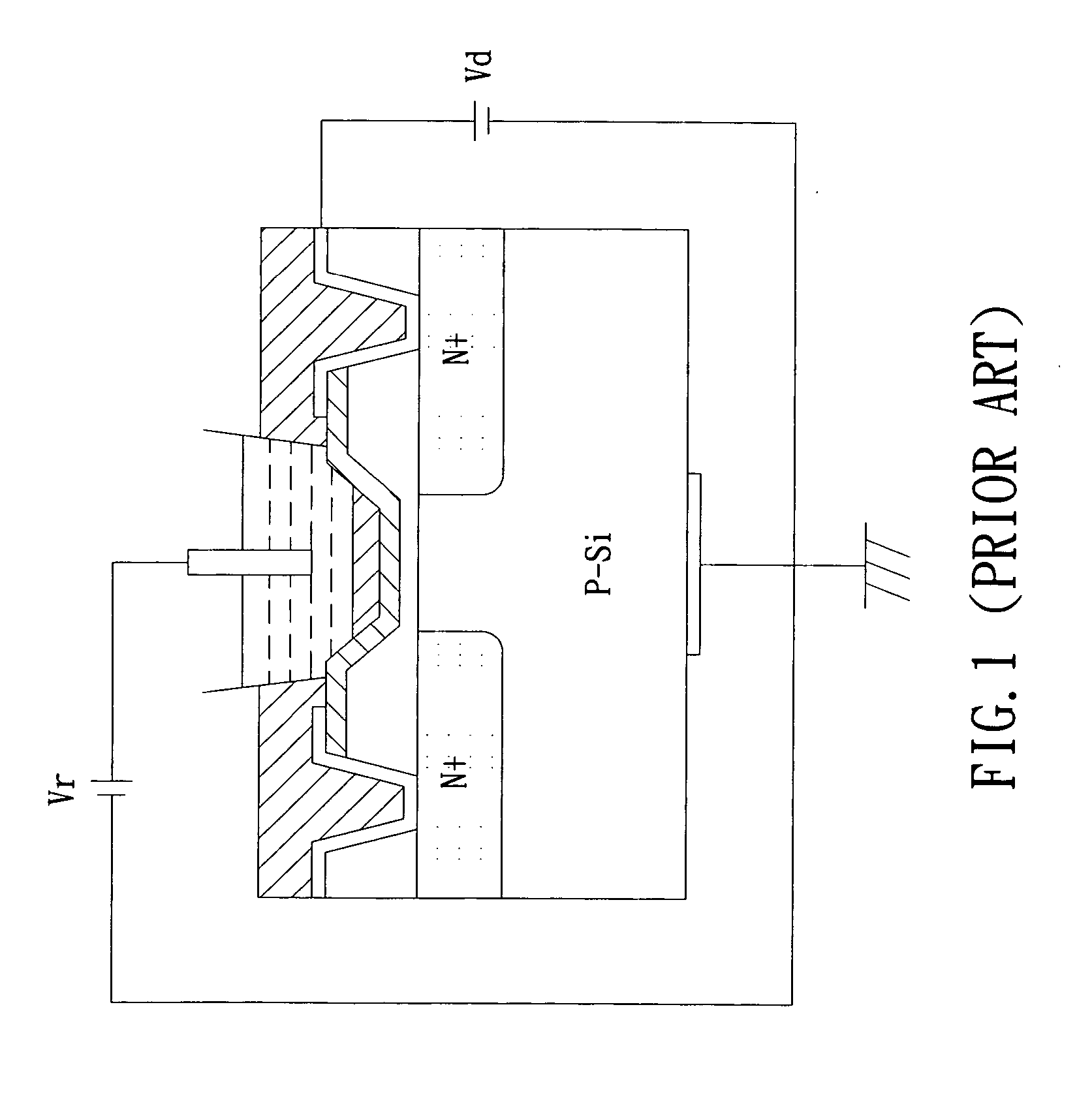

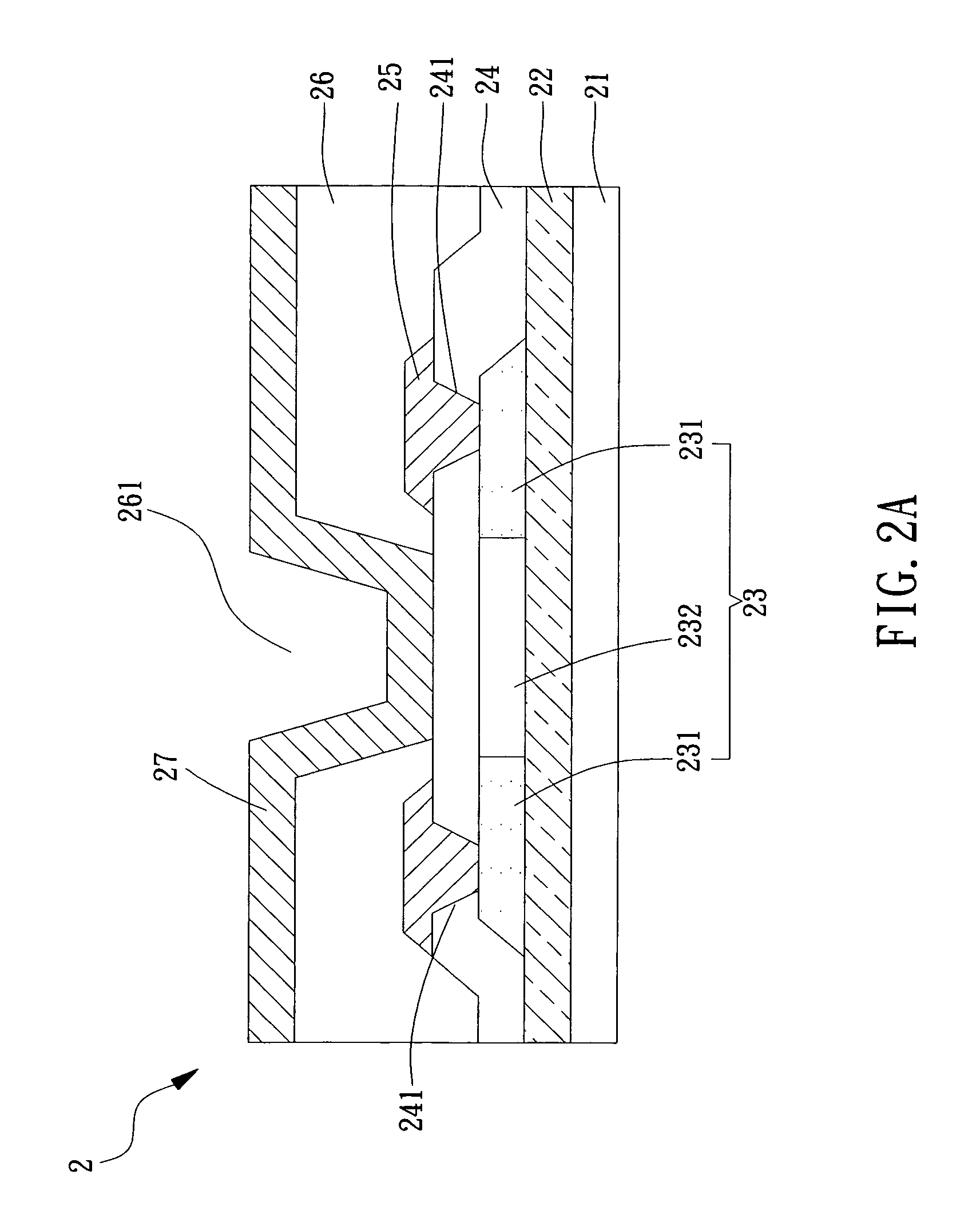

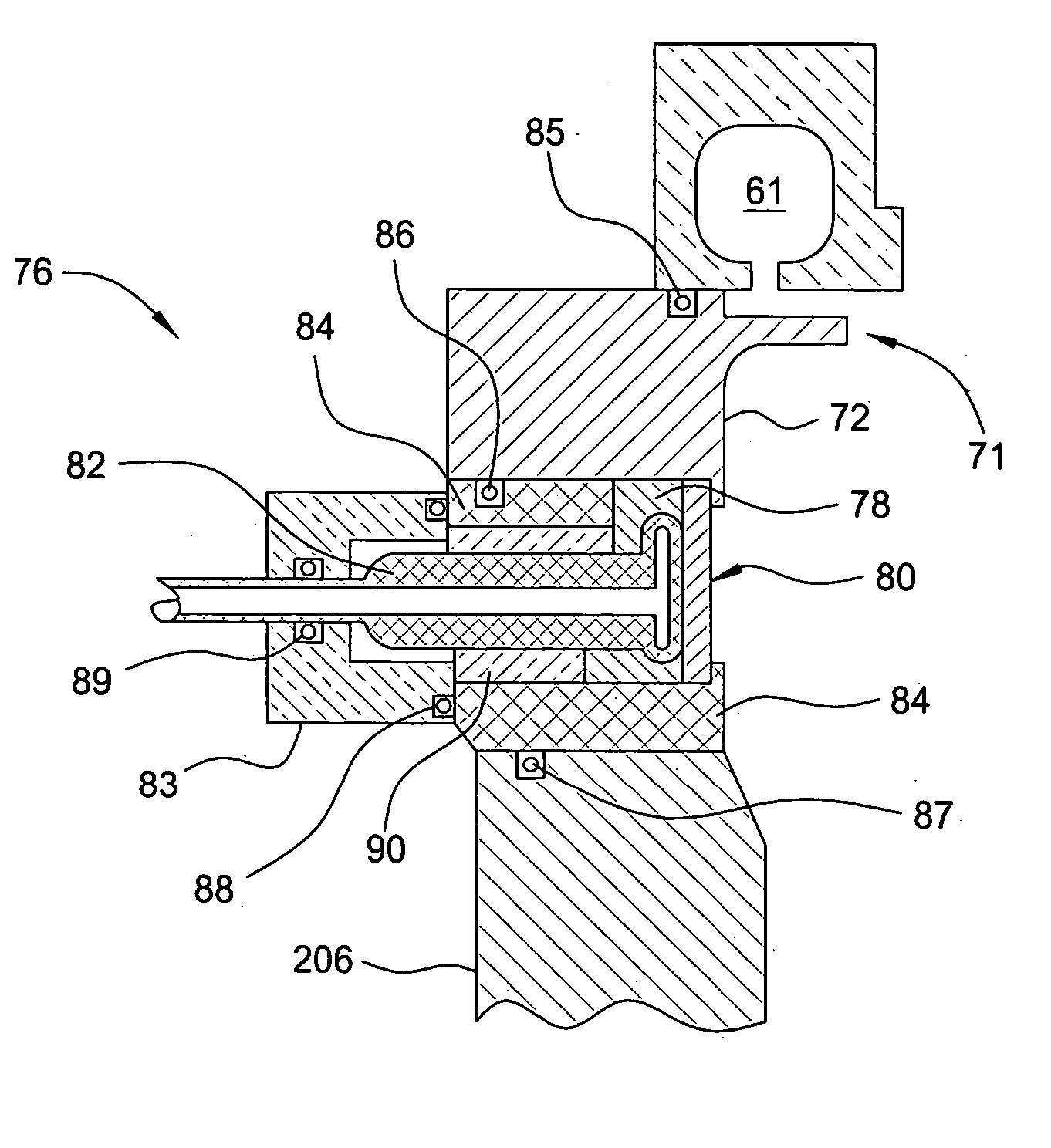

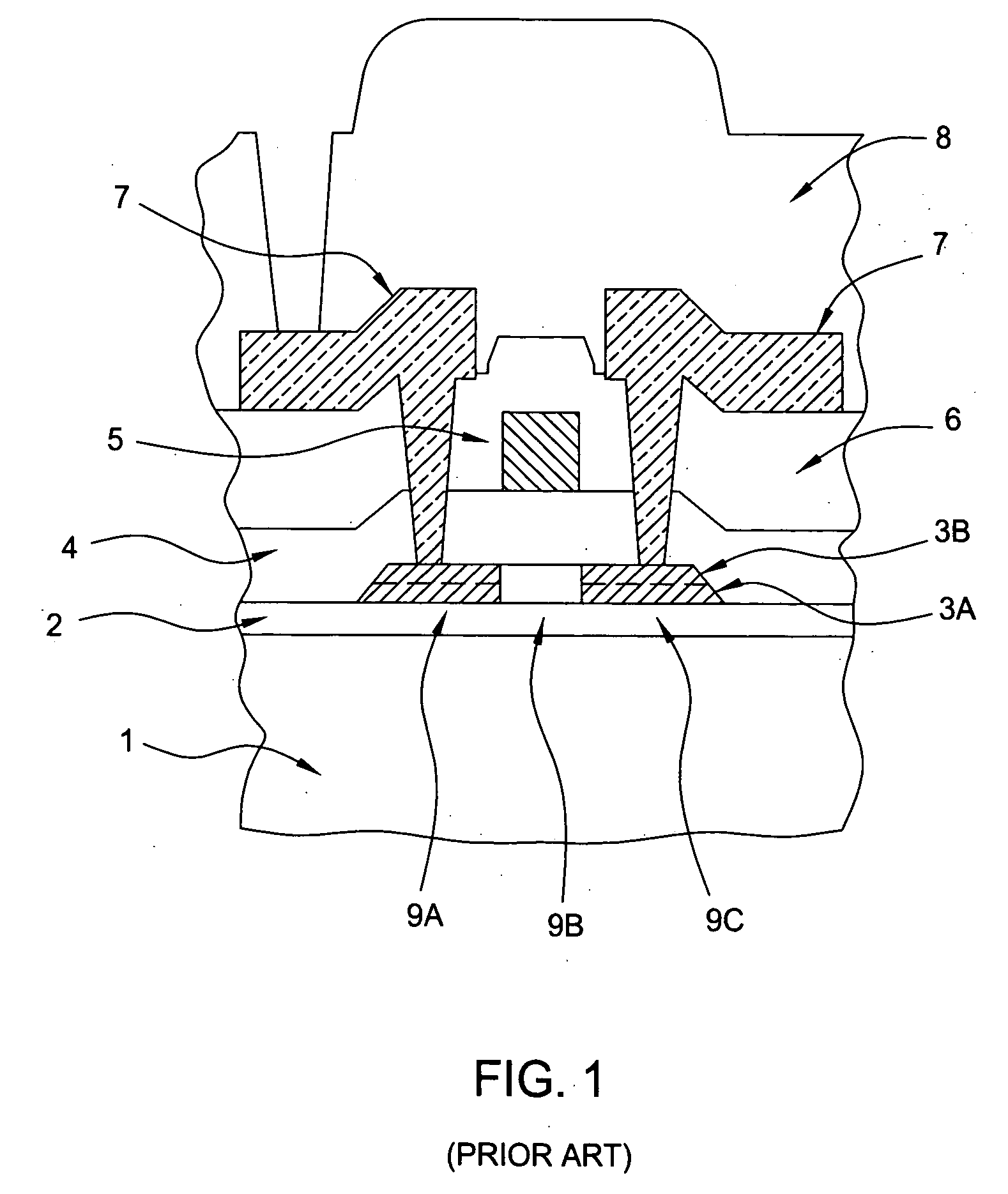

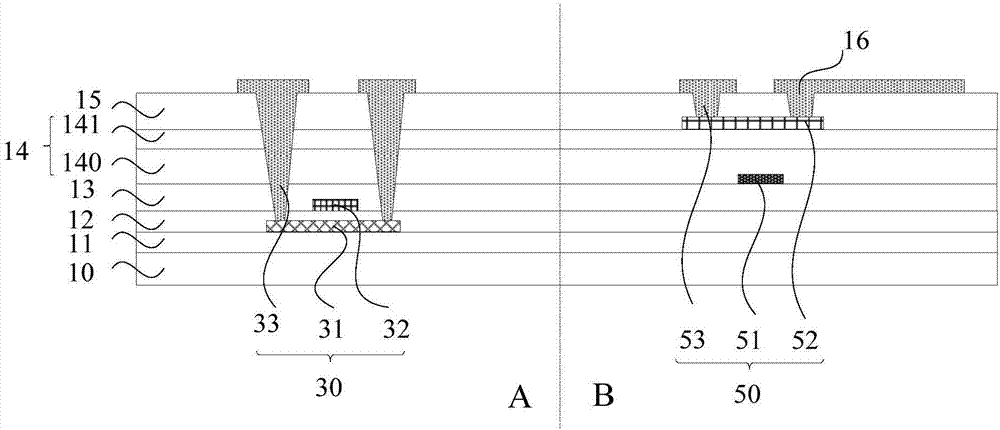

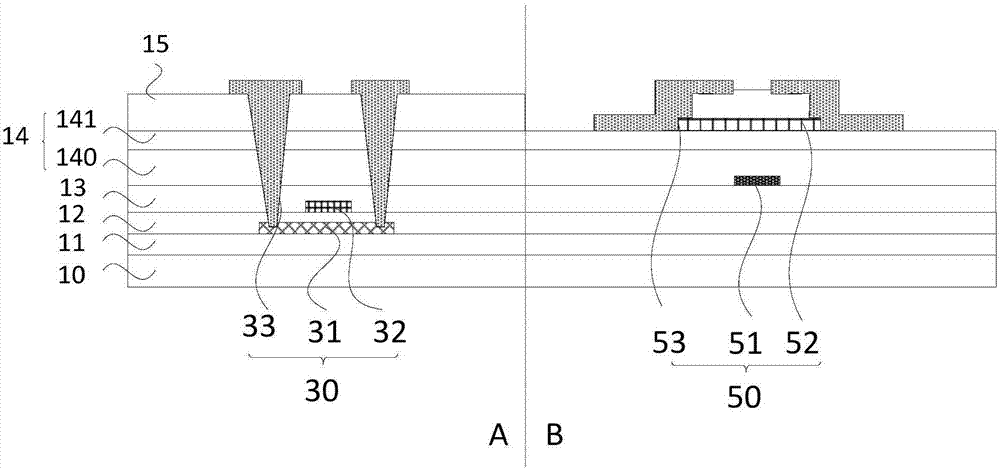

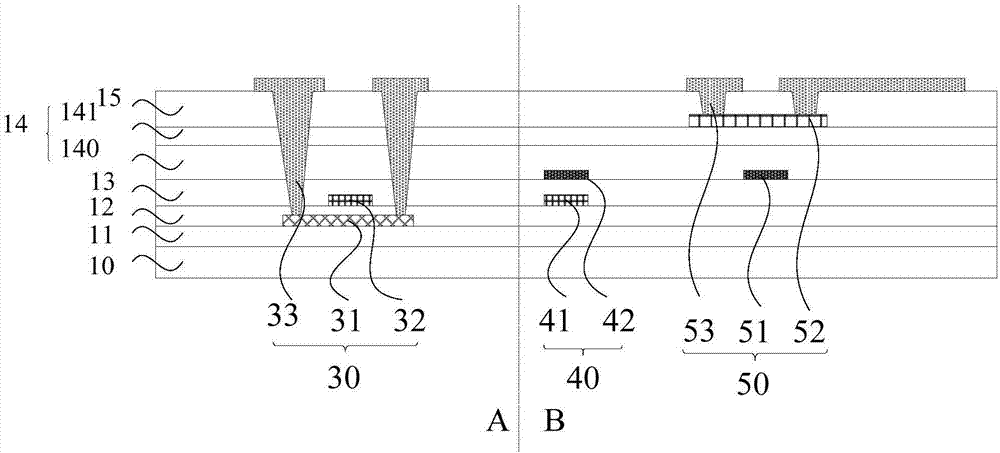

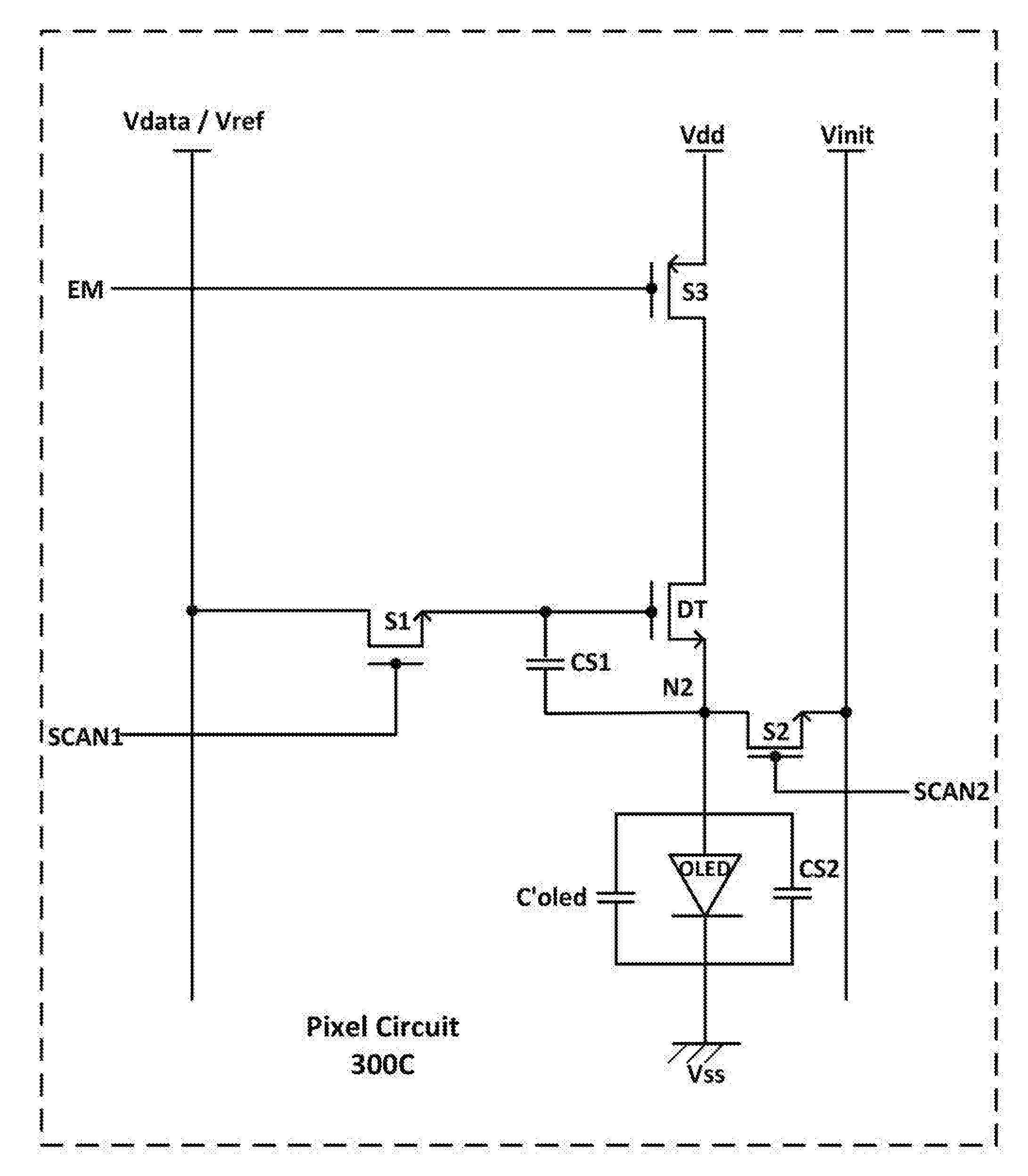

[low-temperature polysilicon thin film transistor and fabrication method thereof]

InactiveUS20050218403A1Improve device performanceReduce manufacturing costTransistorSolid-state devicesGate dielectricOhmic contact

An LTPS-TFT structure comprises a gate, a gate dielectric layer, a patterned silicon layer, a patterned insulating layer, an ohmic contact layer and a source / drain layer. The gate and the gate dielectric layer are disposed on the substrate. The patterned silicon layer and the patterned insulating layer are disposed on the gate dielectric layer over the gate. The patterned silicon layer comprises a polysilicon channel region and an amorphous silicon hot carrier restrain region. The ohmic contact layer is disposed on a portion of the patterned silicon layer other than the polysilicon channel region and the amorphous silicon hot carrier restrain region and a portion of the patterned insulating layer over the amorphous silicon hot carrier restrain region. The source / drain layer is disposed on the ohmic contact layer and the gate dielectric layer.

Owner:AU OPTRONICS CORP

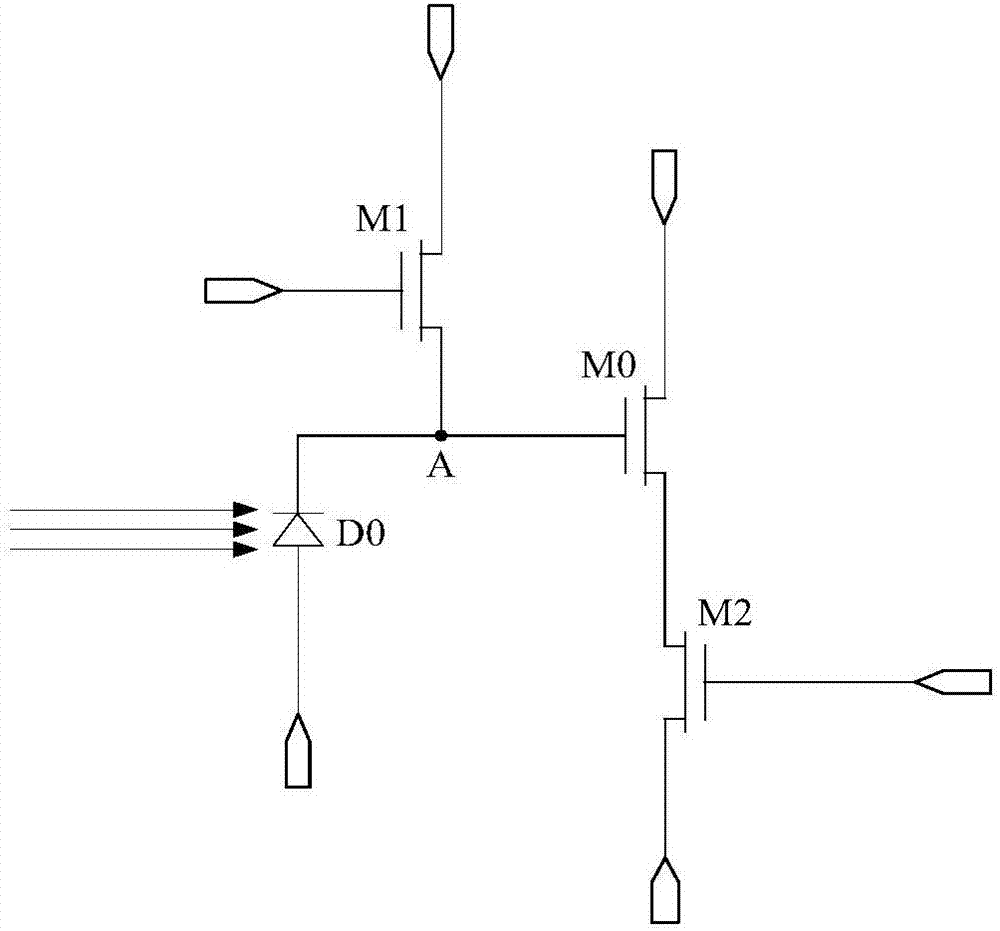

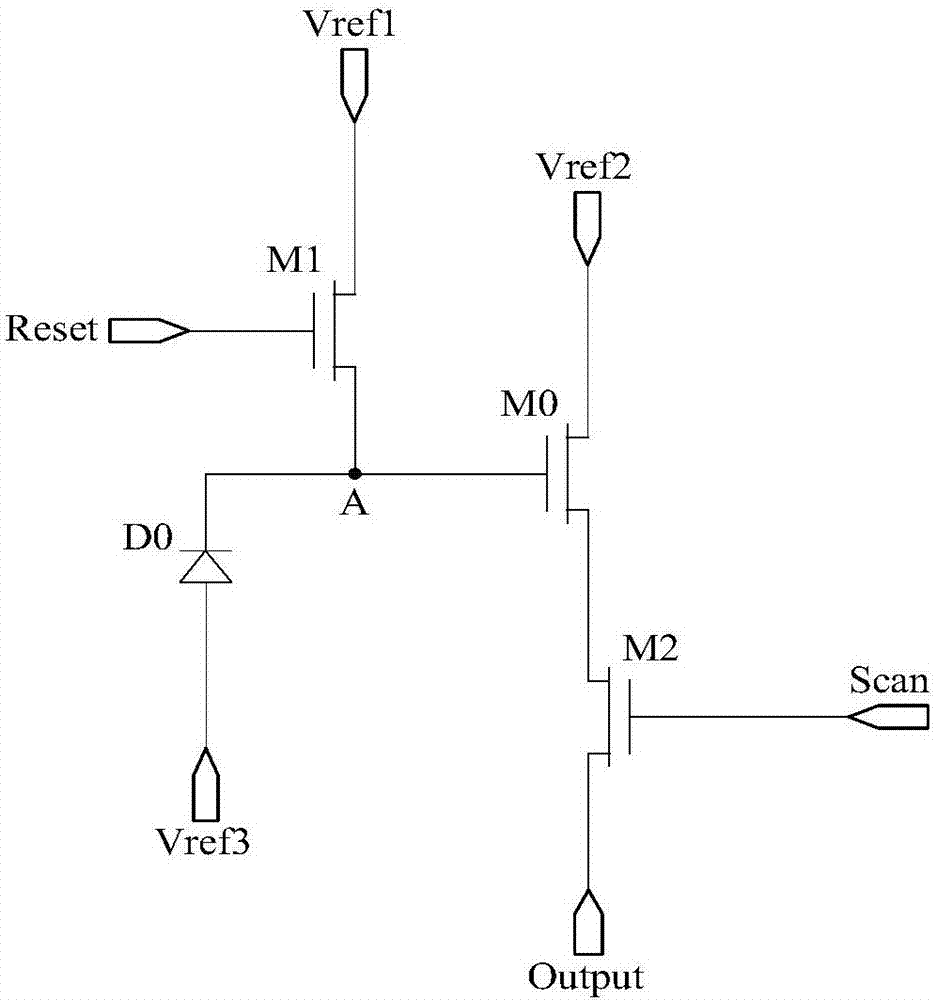

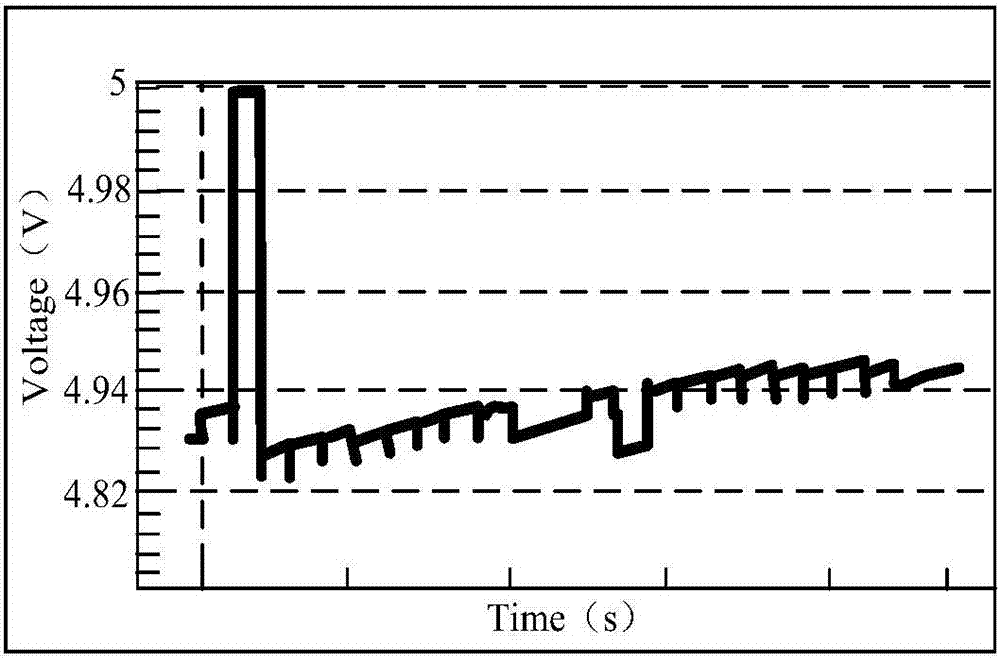

Fingerprint identification detection circuit, touch screen and display device

ActiveCN106971172AImprove detection accuracyReduce leakage currentPrint image acquisitionInput/output processes for data processingDisplay deviceEngineering

The invention discloses a fingerprint identification detection circuit, a touch screen and a display device. The fingerprint identification detection circuit comprises a photosensitive diode, a first switch transistor, a second switch transistor and a voltage following transistor. The first switch transistor is a metallic oxide transistor. The second switch transistor and the voltage following transistor are low-temperature polycrystalline silicone transistors. According to the invention, by using the first switch transistor as the metallic oxide transistor, the leaked current of the first switch transistor is quite small and even if the light is quite weak, light current can be also detected, so detection precision of the fingerprint identification detection circuit is improved.

Owner:BOE TECH GRP CO LTD

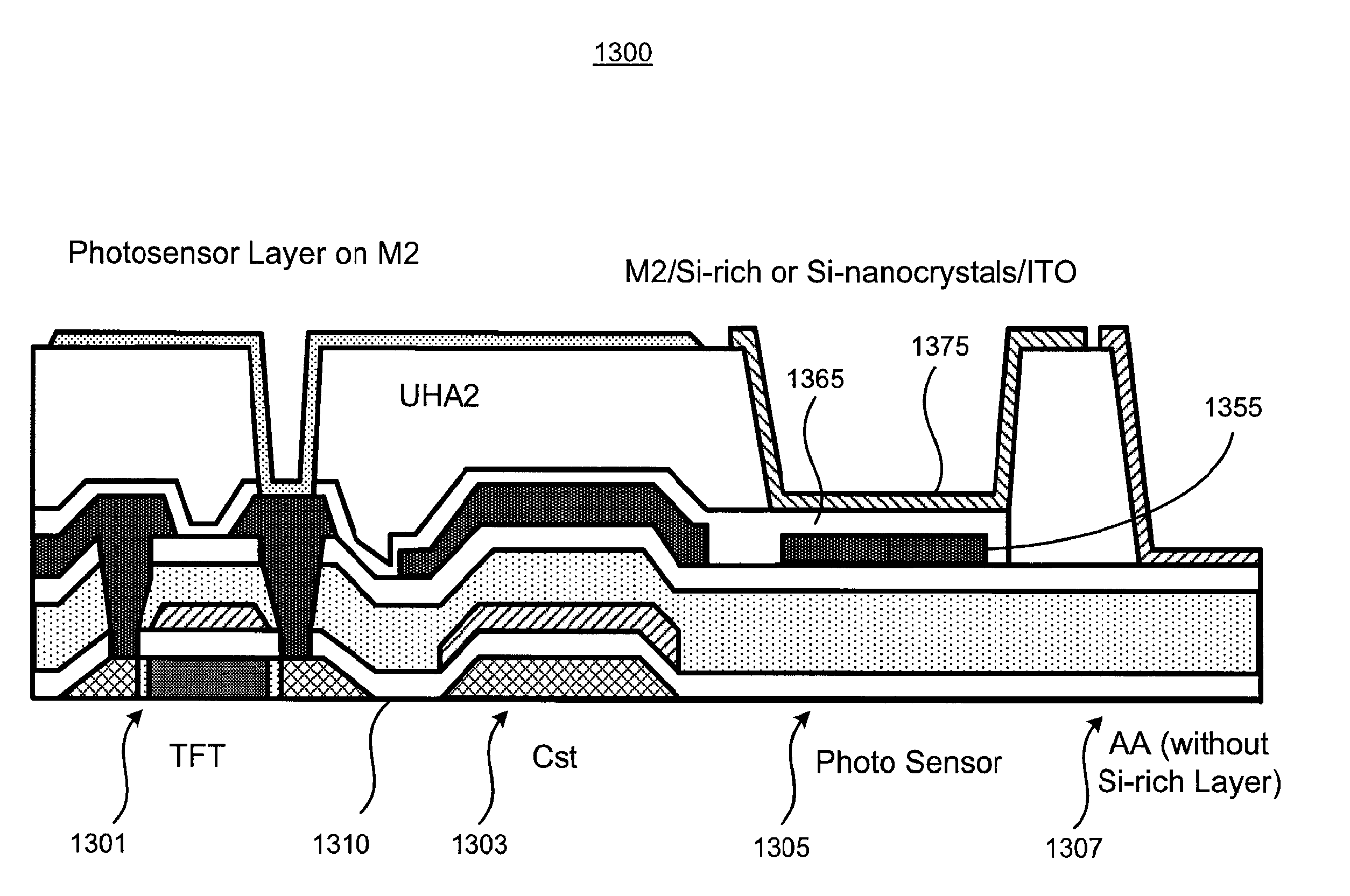

Photovoltaic Cells of Si-Nanocrystals with Multi-Band Gap and Applications in a Low Temperature Polycrystalline Silicon Thin Film Transistor Panel

ActiveUS20090009675A1High photovoltaic efficiencyWavelength tuneabilityFinal product manufacturePhotometryMulti bandNanocrystalline silicon

One aspect of the present invention relates to a photovoltaic cell. In one embodiment, the photovoltaic cell includes a first conductive layer, an N-doped semiconductor layer formed on the first conductive layer, a first silicon layer formed on the N-doped semiconductor layer, a nanocrystalline silicon (nc-Si) layer formed on a first silicon layer, a second silicon layer formed on the nc-Si layer, a P-doped semiconductor layer on the second silicon layer, and a second conductive layer formed on the P-doped semiconductor layer, where one of the first silicon layer and the second silicon layer is formed of amorphous silicon, and the other of the first silicon layer and the second silicon layer formed of polycrystalline silicon.

Owner:AU OPTRONICS CORP

Flexible display substrate, manufacturing method thereof and flexible display device

InactiveCN103474583AAvoid damageFinal product manufactureSolid-state devicesDisplay deviceEngineering

The invention provides a flexible display substrate, a manufacturing method of the flexible display substrate and a flexible display device, and belongs to the technical field of flexible display. The problem that a display structure in an existing flexible display substrate is probe to being damaged in the laser lift-off process can be solved. The flexible display substrate comprises a flexible base, a display structure and a reflective layer arranged between the flexible base and the display structure. The manufacturing method of the flexible substrate comprises the steps of forming a flexible material layer on the base, forming the reflective layer on the flexible material layer, forming the display structure and separating the flexible material layer from the base through the laser lift-off mode to obtain the flexible display substrate. The flexible display substrate and the manufacturing method of the flexible display substrate are suitable for the flexible display device, especially a flexible top transmission type organic light emitting diode display device, and a flexible array substrate with a low-temperature polycrystalline silicon thin film transistor.

Owner:BOE TECH GRP CO LTD

Pixel structure of an organic light-emitting diode display device and its fabrication method

InactiveUS20020125820A1High resolutionWide viewing angleTransistorDischarge tube luminescnet screensDisplay deviceGreen-light

A pixel structure of a full-color organic light-emitting diode (OLED) display device comprises a black matrix, a color changing medium, two thin film transistors, a storage capacitor, and an OLED device arranged on a substrate. The pixel structure of the display device uses blue organic light-emitting diodes or polymer light-emitting diodes as electroluminescent media. The low-temperature poly Si (LTPS) thin film transistors provide a current to the OLED device and serve as an active driving device. The color changing medium changes blue light into red or green light to form full-color OLED. The processing steps include the black matrix process, the island process, the gate process, the interlayer process, the color changing medium process, and the OLED deposition process. Because a color changing medium is integrated on the LTPS thin film transistors, this invention can make display devices of high resolution, high luminous efficiency and wide viewing angle.

Owner:IND TECH RES INST

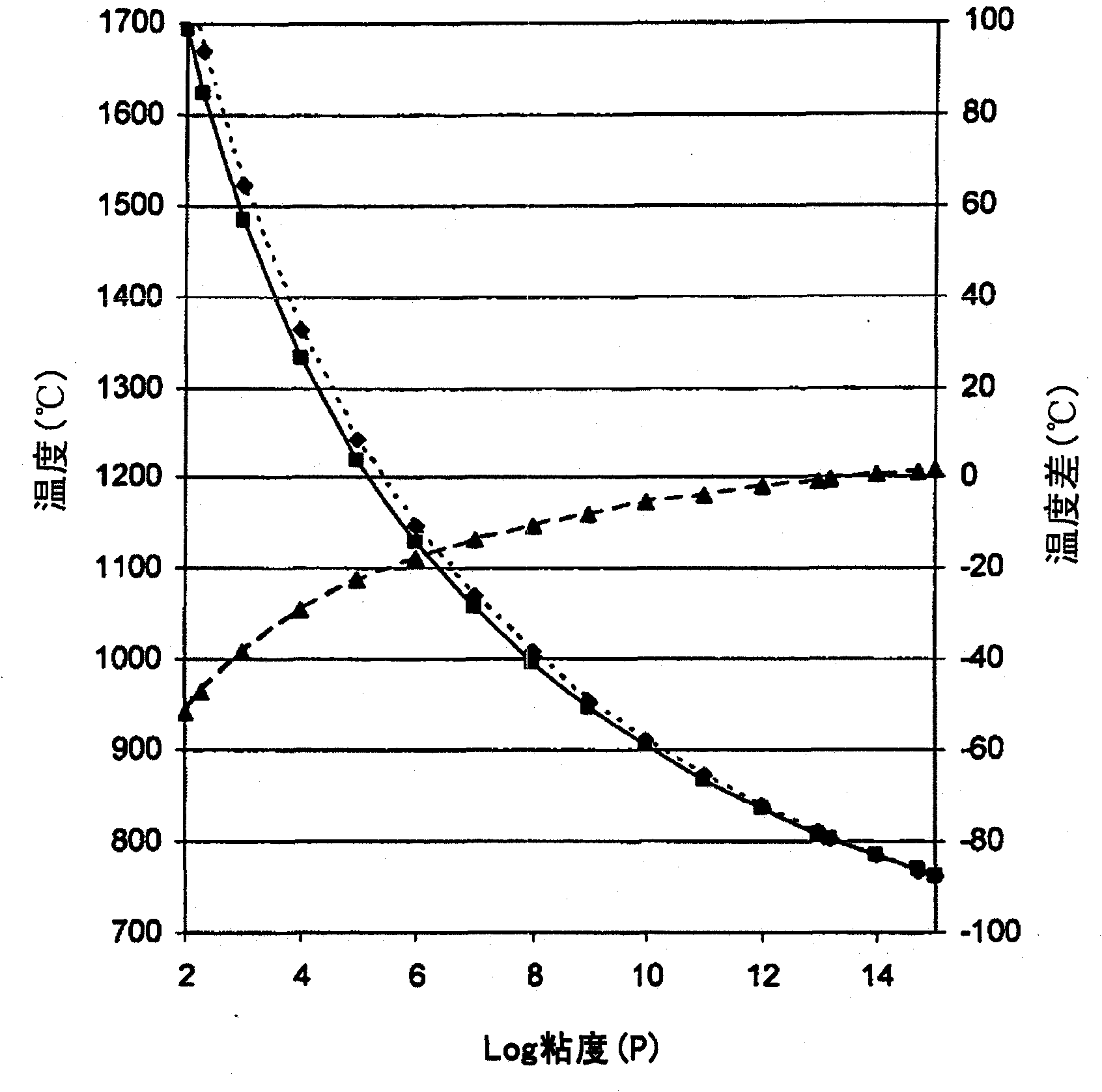

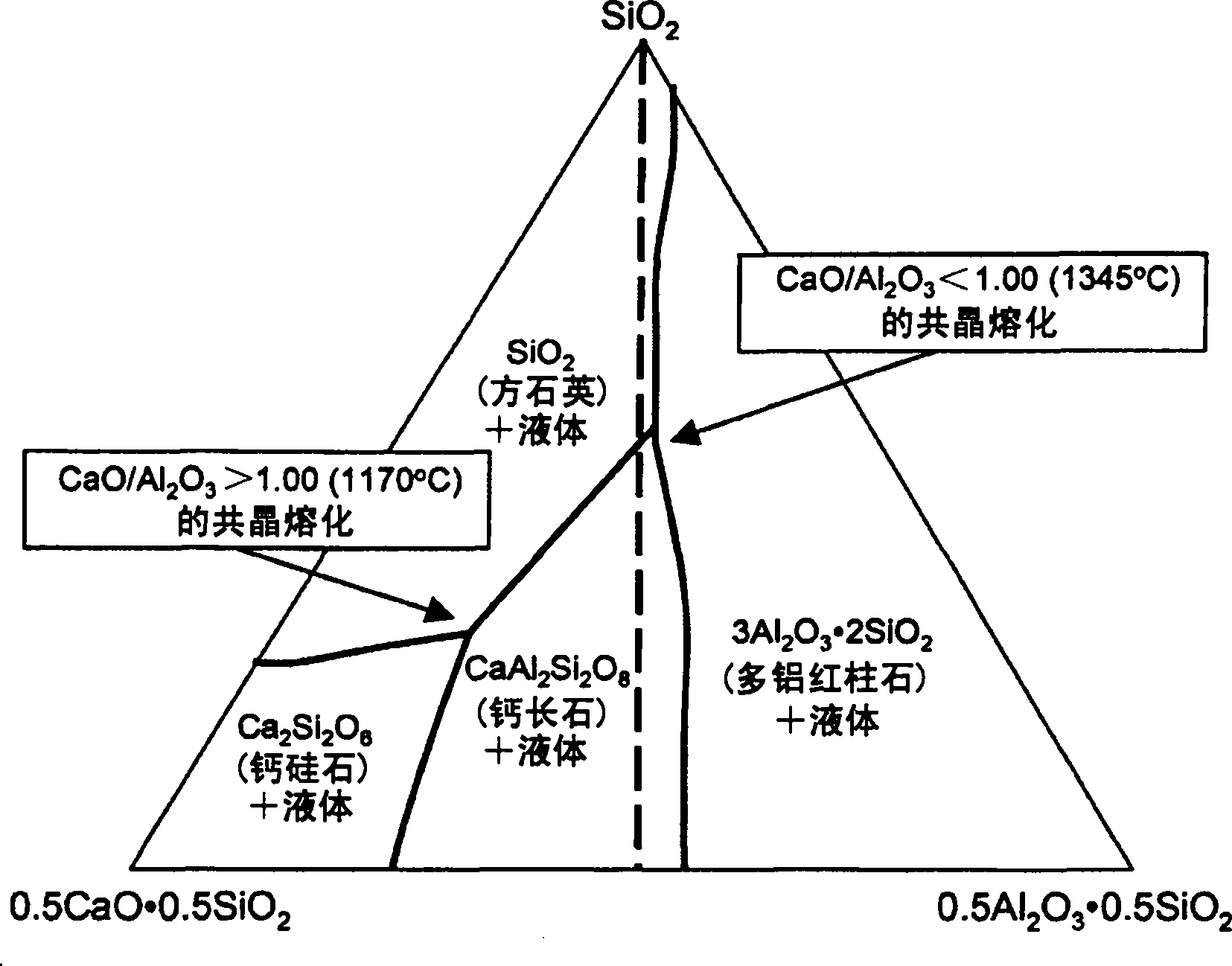

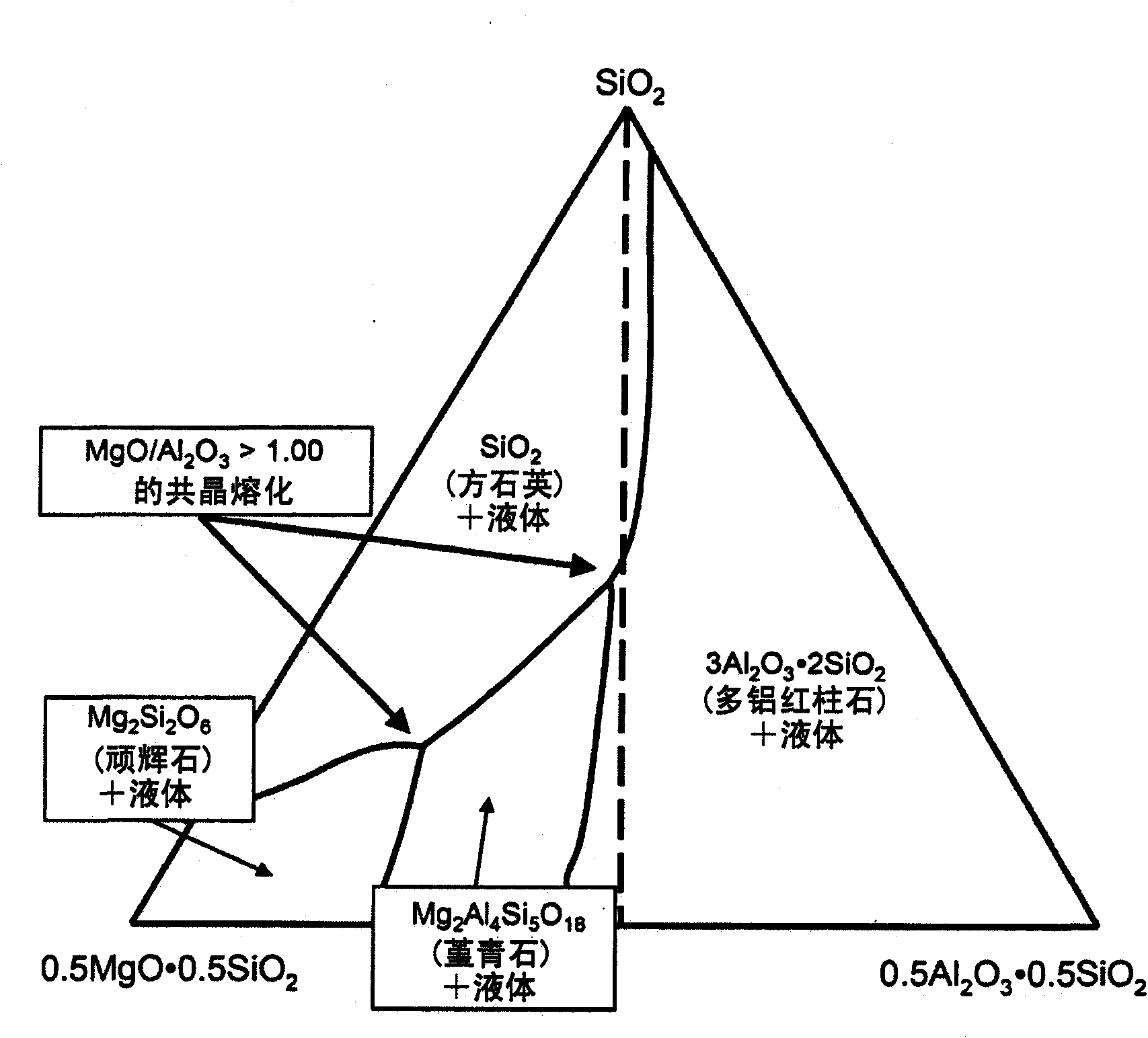

Rare-earth-containing glass material and substrate and device comprising such substrate

A rare-earth-containing glass material has a composition, expressed in mole percentages on an oxide basis, comprising: SiO2 : 66-75 Al2O3 : 11-17 B2O3 : 0-4 MgO : 1-6.5 CaO : 2-7 SrO : 0-4 BaO : 0-4 Y2O3 : 0-4 La2O3 : 0-4 Y2O3+La2O3 : 0.1-4. The inclusion Of Y2O3 and / or La2O3 in the composition reduces the T2.3 of the glass thereby allowing higher annealing-point glasses to be produced. The glass is particularly useful for low-temperature polycrystalline silicon-based semiconductor devices.

Owner:CORNING INC

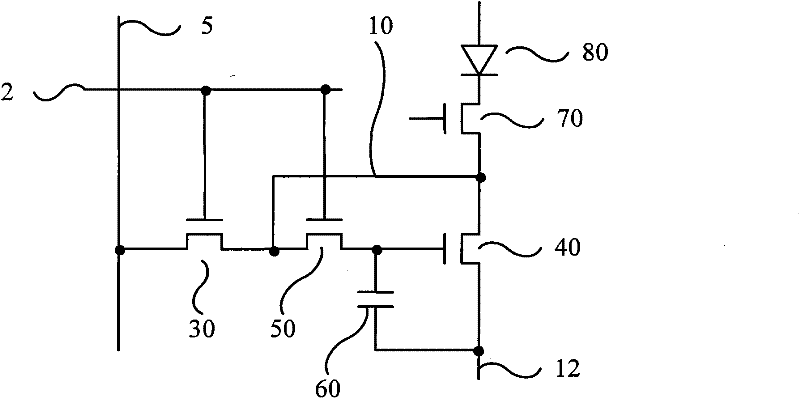

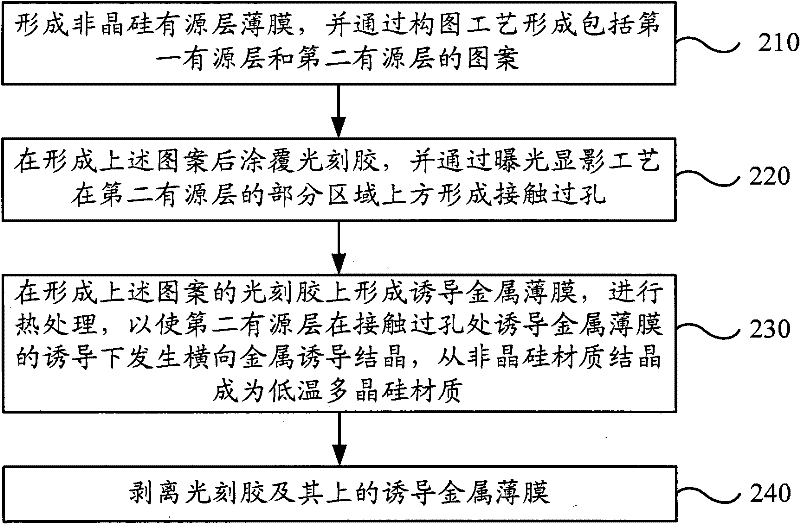

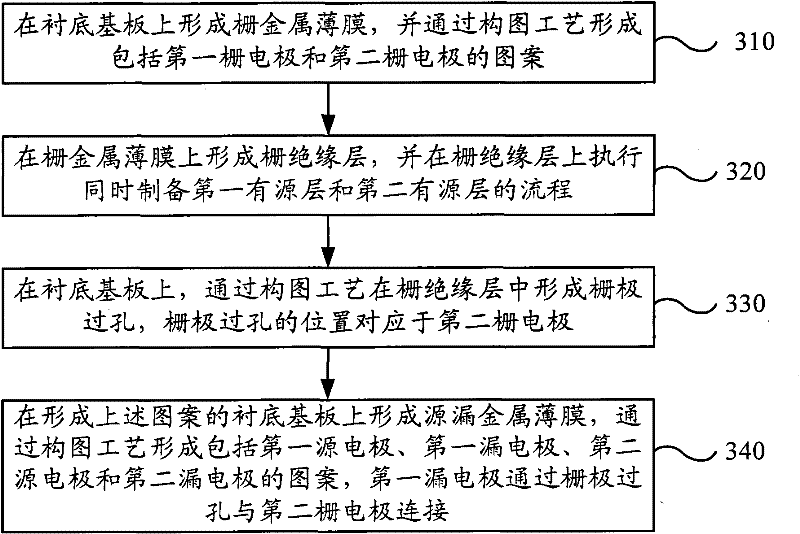

Thin film transistor and active matrix rear panel as well as manufacturing methods thereof and display

The invention discloses a thin film transistor and an active matrix rear panel as well as manufacturing methods thereof and a display. The manufacturing method of the thin film transistor comprises a flow of preparing a first thin film transistor and a second thin film transistor, wherein the flow of simultaneously preparing a first active layer and a second active layer comprises the following steps of: forming an amorphous silicon active layer thin film and forming patterns including the first active layer and the second active layer through a pattern forming process; coating photoresist and forming a contact through hole above a partial region of the second active layer through an exposure and development process; forming an inductive metal thin film on the photoresist for forming the pattern and carrying out heat treatment; and then inducing the second active layer by the inductive metal thin film at the contact through hole to be subjected to transverse metal inductive crystallization, so as to crystallize an amorphous silicon material to a low-temperature polycrystalline silicon material; and stripping the photoresist and the inductive metal thin film on the photoresist. According to the invention, through a transverse metal inductive crystallization process, the active layers of the amorphous silicon TFT (Thin Film Transistor) and the low-temperature polycrystalline silicon TFT can be prepared on the same layer at the same time.

Owner:BOE TECH GRP CO LTD

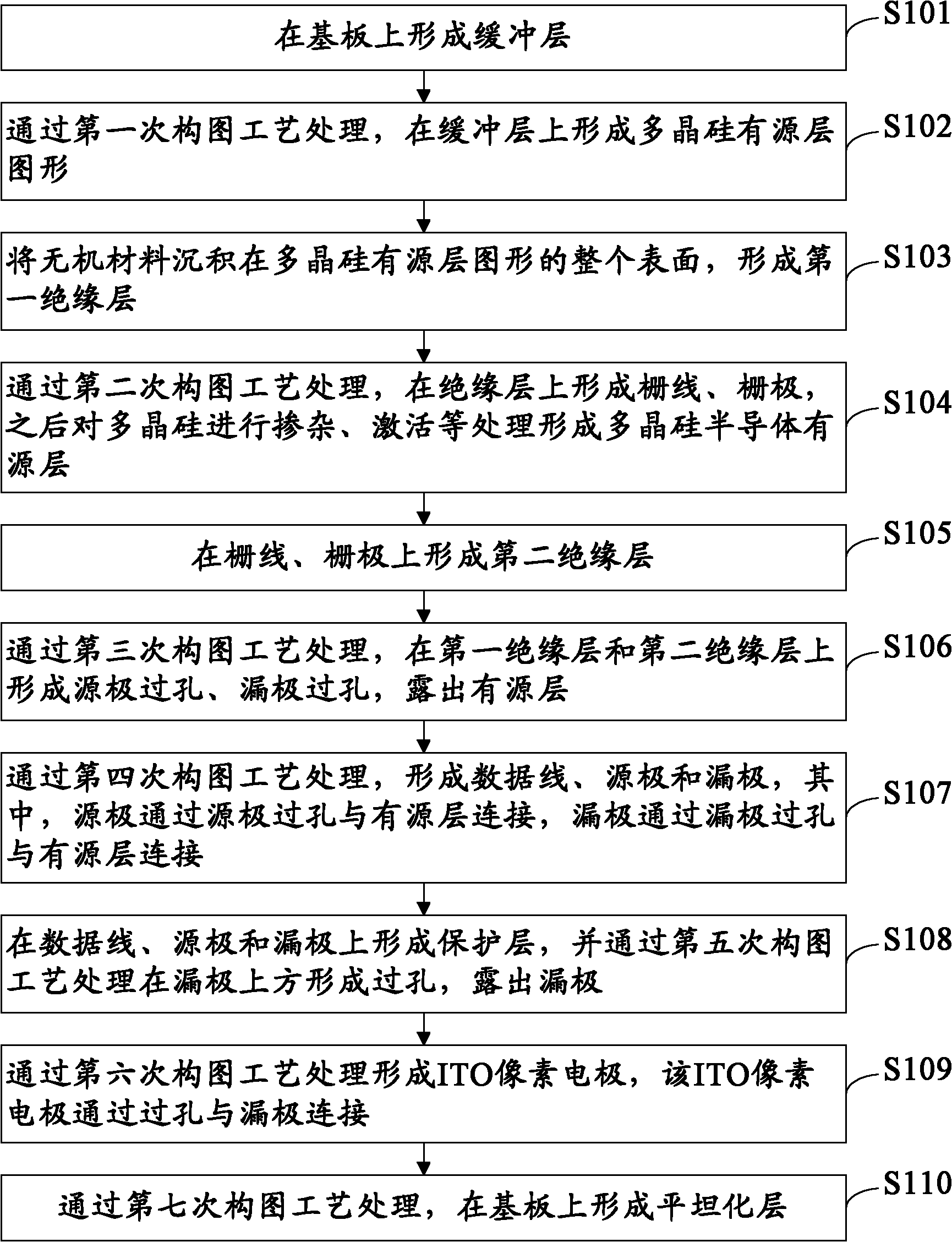

Low-temperature polycrystalline silicon TFT (Thin Film Transistor) array substrate and manufacturing method thereof

ActiveCN102683338AReduce operational processingReduce process complexitySolid-state devicesSemiconductor/solid-state device manufacturingLiquid-crystal displayActive matrix

The embodiment of the invention provides a low-temperature polycrystalline silicon TFT (Thin Film Transistor) array substrate and a manufacturing method thereof, and relates to the field of manufacturing of liquid crystal displays and AMOLED (Active Matrix / Organic Light Emitting Diode) displays. The treatment frequency of a composition technology is reduced, so that the manufacturing flow is simplified and the manufacturing cost is reduced. The method provided by the invention comprises the following steps of: forming a buffer layer on a substrate; forming a polycrystalline silicon layer on the buffer layer; forming a first metal layer on the polycrystalline silicon layer; performing composition process treatment on the first metal layer and the polycrystalline silicon layer by using a gray tone mask plate or semitransparent mask plate; and obtaining patterns of a data line, a source electrode, a drain electrode and a polycrystalline silicon semiconductor part through one-time composition process. The embodiment of the invention is used for manufacturing the low-temperature polycrystalline silicon TFT array substrate.

Owner:BOE TECH GRP CO LTD

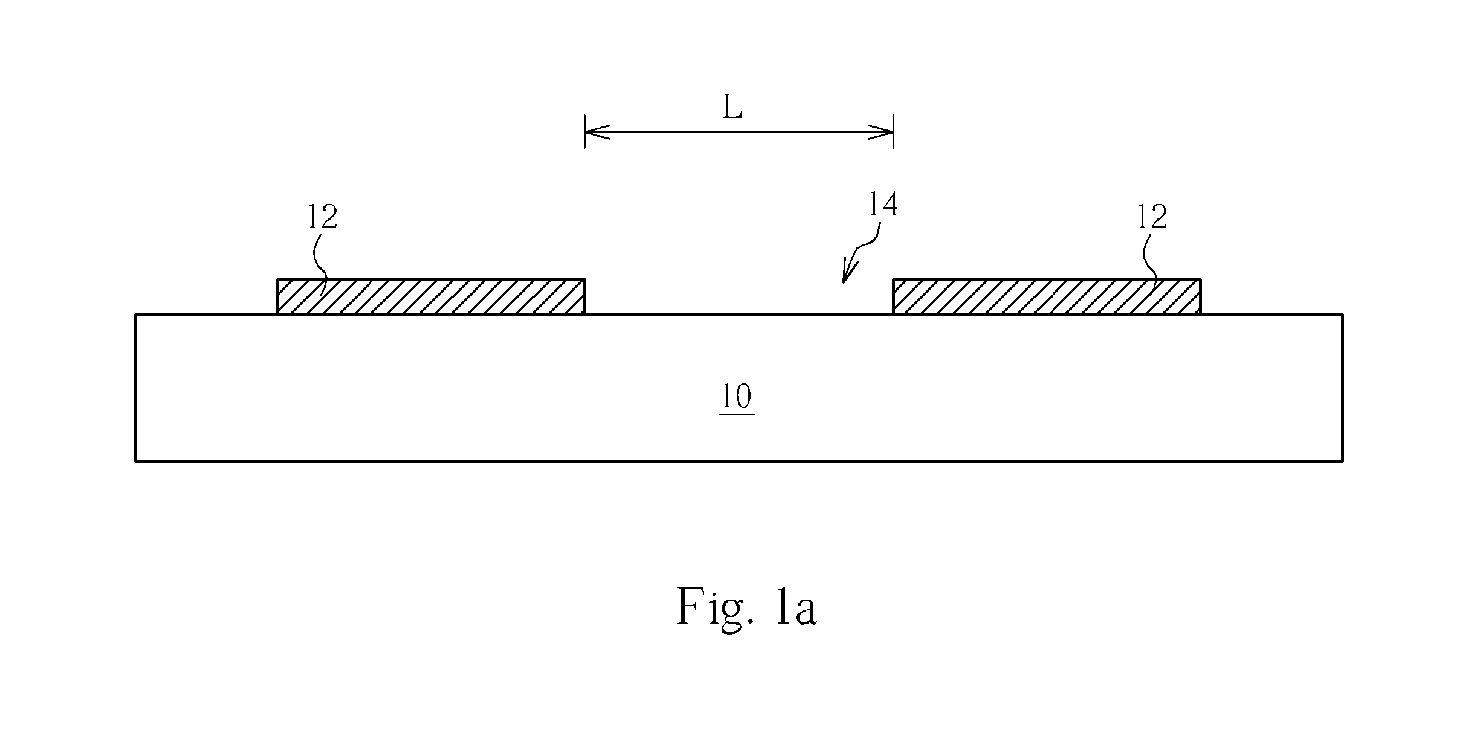

Method for making polysilicon layer

InactiveCN1501449ALarge crystal sizeImprove uniformityPolycrystalline material growthSemiconductor/solid-state device manufacturingLiquid-crystal displayCrystalline silicon

The present invention discloses a method for making polycrystalline silicon layer which comprises, providing a substrate, forming a breaker having a plurality of ditches on the substrate, forming a non-crystalline silicon layer on the breaker, proceeding a laser annealing process to form a polycrystalline silicon. The invention can be applied into the production of low-temperature polycrystalline silicon thin film transistor LCDs.

Owner:AU OPTRONICS CORP

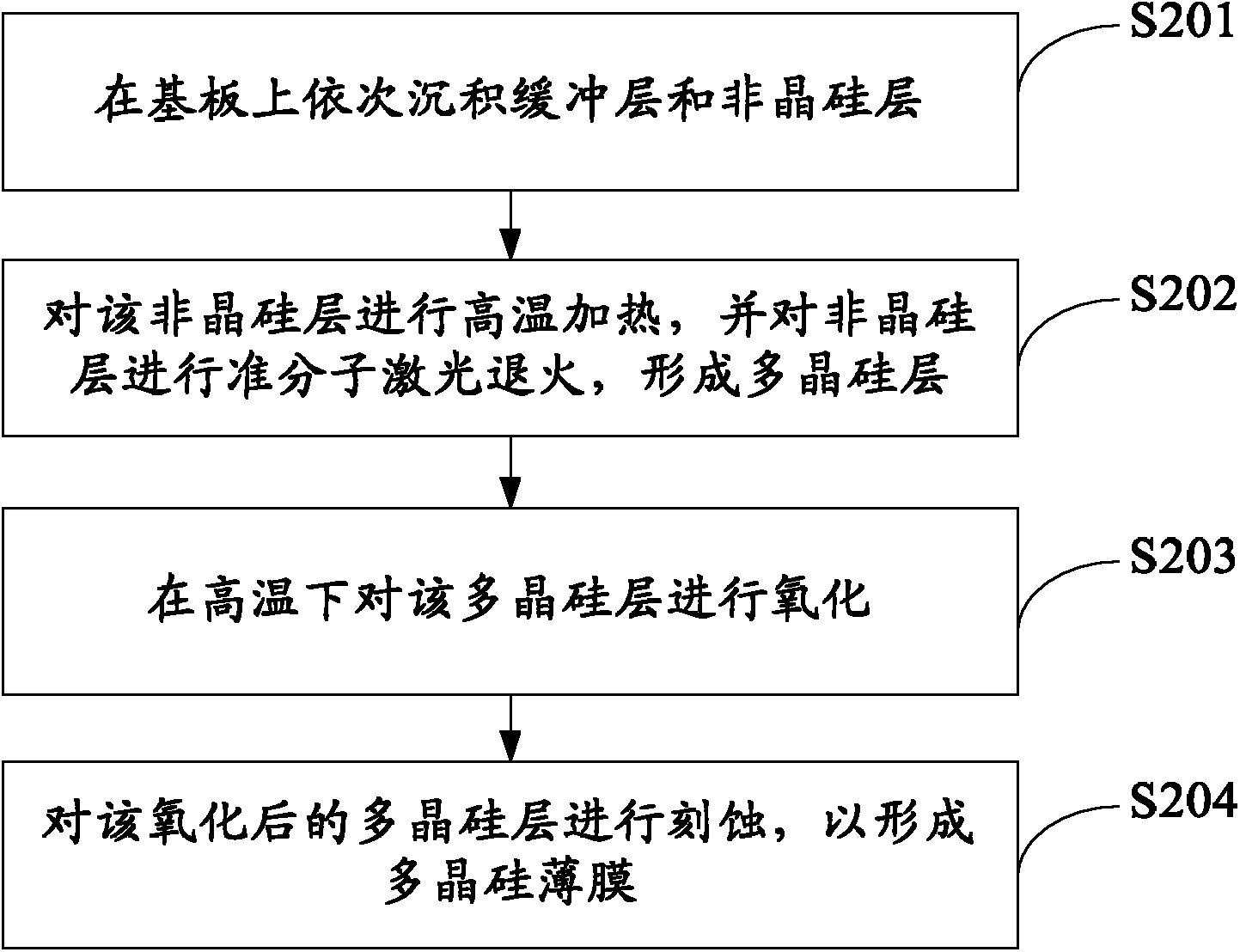

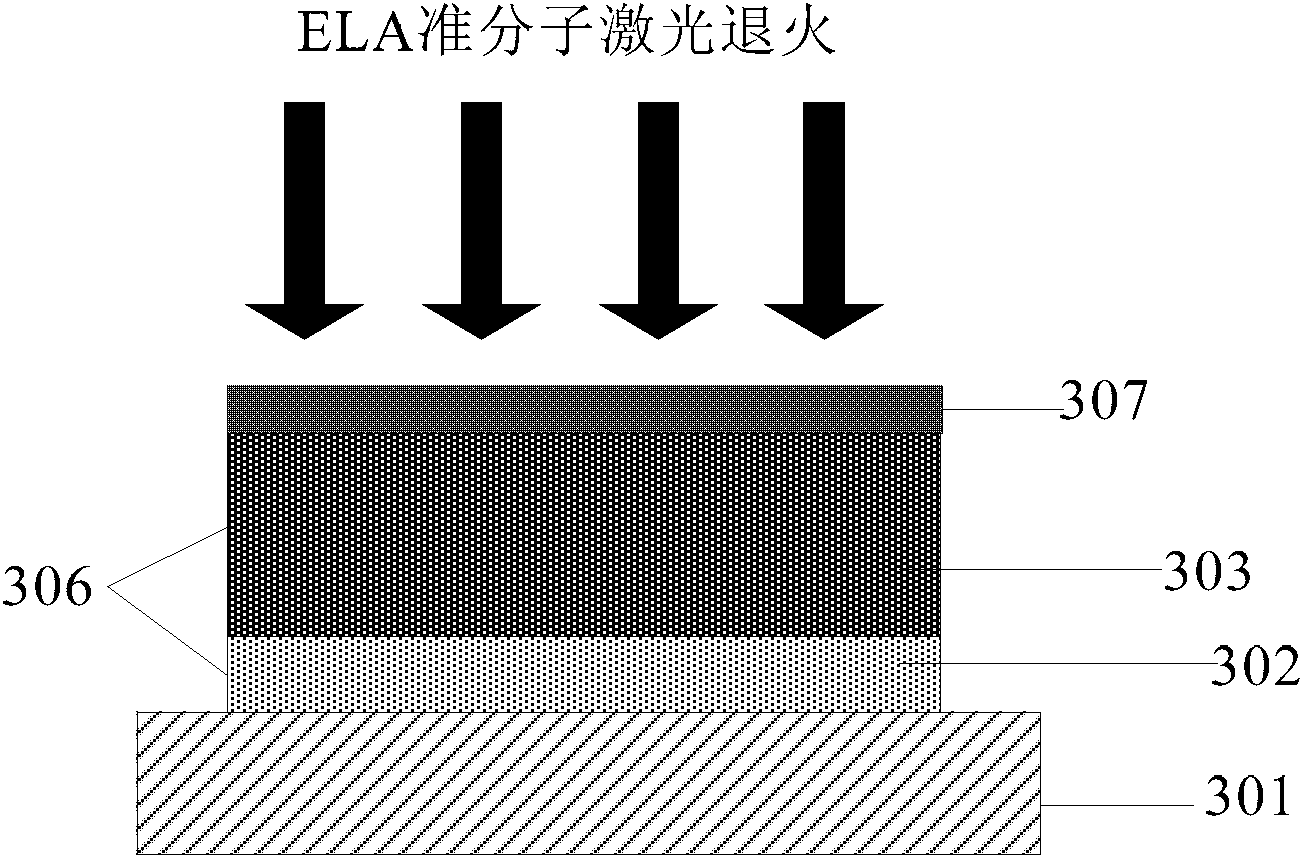

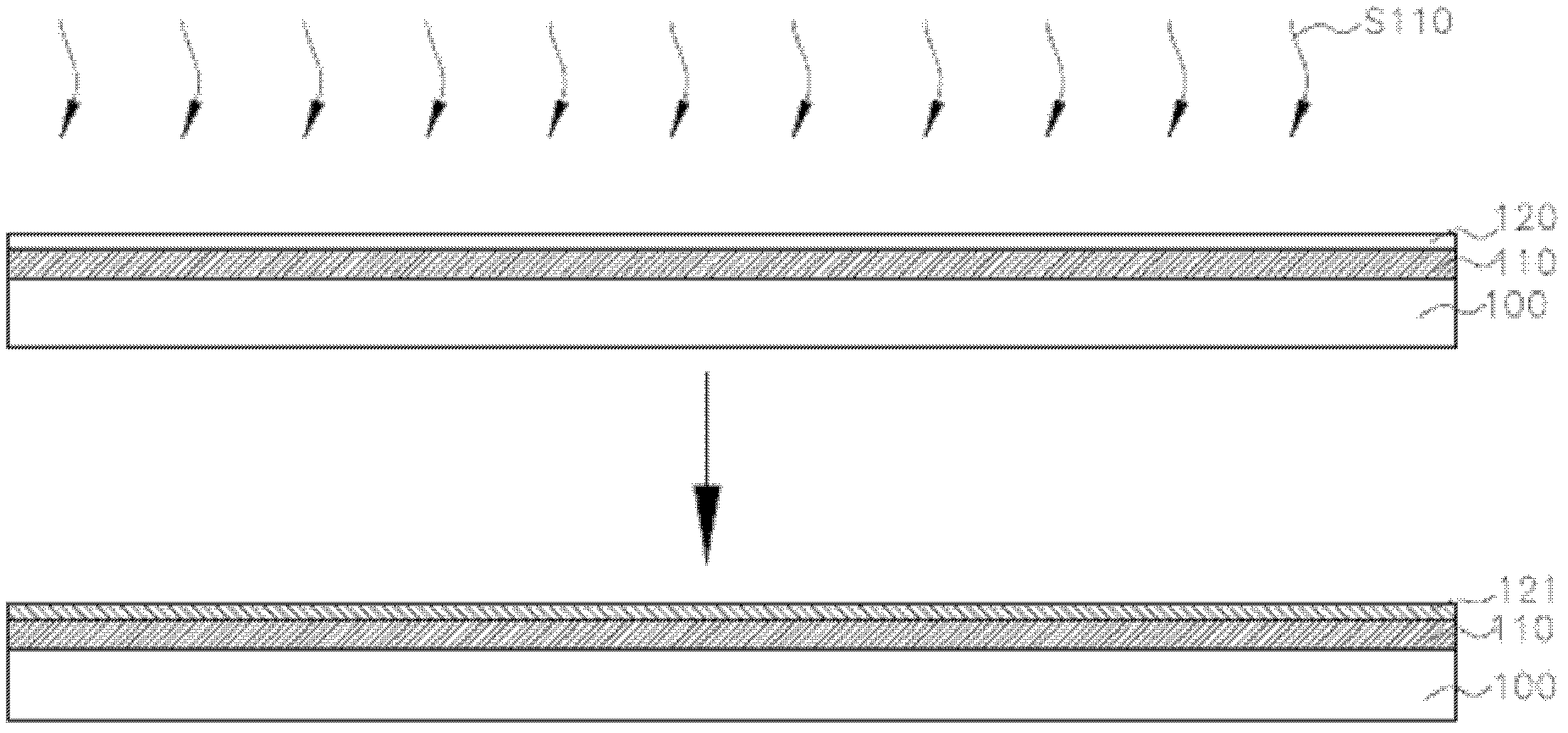

Production method for low-temperature polycrystalline silicon thin film

InactiveCN102655089AReduce leakage currentImprove product qualitySolid-state devicesSemiconductor/solid-state device manufacturingMetallurgyExcimer laser annealing

The embodiment of the invention provides a production method for a low-temperature polycrystalline silicon thin film, relating to the field of manufacturing for a liquid crystal panel, and used for reducing the leakage current generated by the polycrystalline silicon thin film during a use process, and thus improving product quality. The production method for a low-temperature polycrystalline silicon thin film comprises the following steps of: sequentially depositing a buffering layer and an amorphous silicon layer on a substrate; performing high-temperature heating on the amorphous silicon layer, and performing excimer laser annealing on the amorphous silicon layer to form a polycrystalline silicon layer; oxidizing the polycrystalline silicon layer at a high temperature; and etching the oxidized polycrystalline silicon layer to form the polycrystalline silicon thin film. The production method provided by the embodiment of the invention is used for manufacturing a thin-film transistor.

Owner:BOE TECH GRP CO LTD

Array substrate and display panel

ActiveCN111863837APrevent feature driftImprove stabilitySolid-state devicesSemiconductor devicesOxide thin-film transistorHemt circuits

The invention provides an array substrate and a display panel. A driving circuit layer in the array substrate is formed on one side of a substrate, and the driving circuit layer comprises a low-temperature polycrystalline silicon thin film transistor and a low-temperature polycrystalline oxide thin film transistor which are electrically connected. The low-temperature polycrystalline silicon thin film transistor sequentially comprises a polycrystalline silicon active layer, a first grid electrode, a first source electrode and a first drain electrode in the direction away from the low-temperature polycrystalline silicon thin film transistor, and the low-temperature polycrystalline oxide thin film transistor sequentially comprises an oxide active layer, a second grid electrode, a second source electrode and a second drain electrode; a hydrogen barrier layer is formed on at least one side of the upper side or the lower side of the oxide active layer; a pixel electrode layer is formed on the side, away from the substrate, of the drive circuit layer, a pixel electrode is formed through patterning, and the pixel electrode is connected with the first source electrode or the first drain electrode. The hydrogen barrier layer can prevent hydrogen ions in other film layers from invading the oxide active layer to cause device characteristic drift, so that the performance of the transistorsis improved.

Owner:WUHAN CHINA STAR OPTOELECTRONICS SEMICON DISPLAY TECH CO LTD

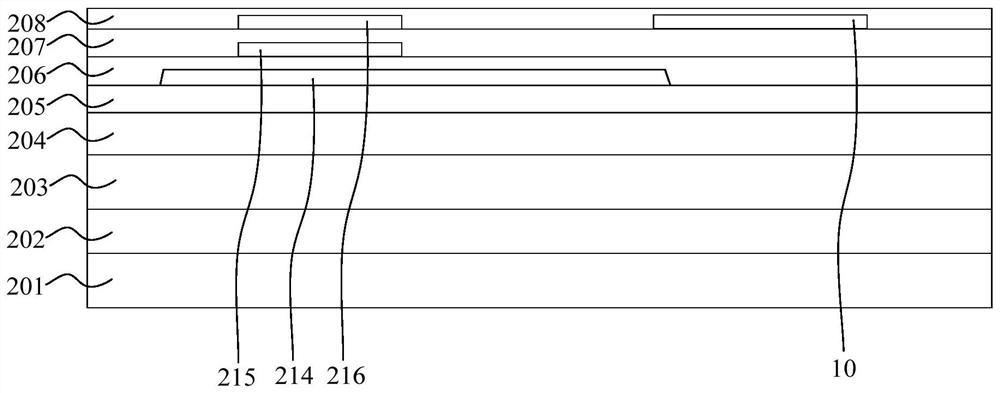

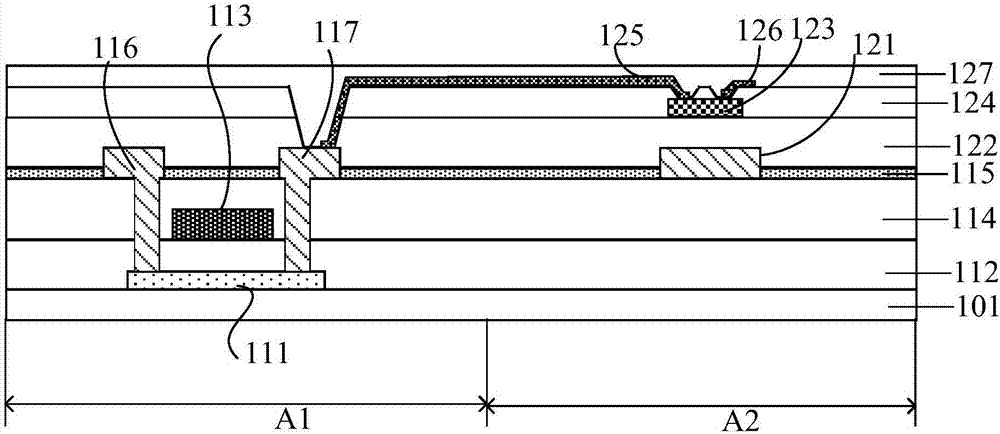

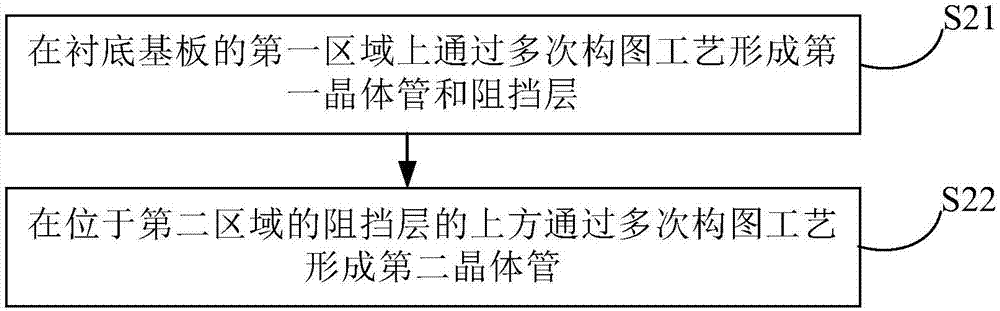

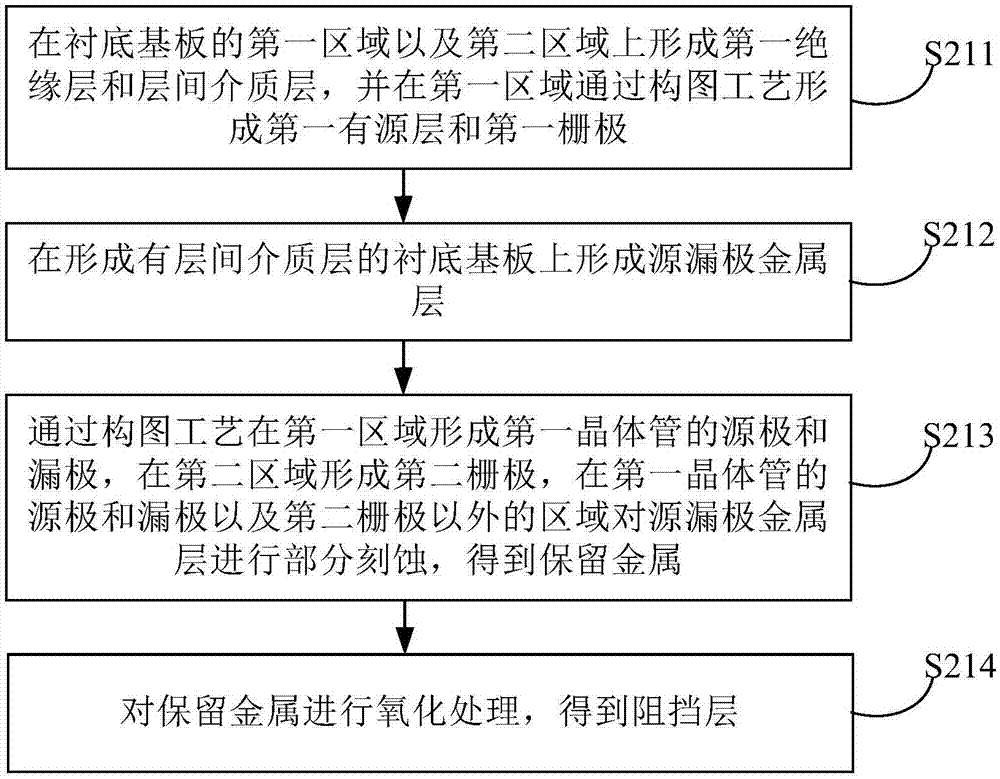

Array substrate and manufacturing method thereof, and display device

ActiveCN107275350ACharacteristic impactPrevent hydrogen permeationTransistorSolid-state devicesHydrogenOxide thin-film transistor

The invention discloses an array substrate and a manufacturing method thereof, and a display device. The array substrate comprises a substrate, wherein a first region and a second region of the substrate are respectively provided with a first transistor and a second transistor, the first transistor has a first active layer, the first active layer is low temperature polysilicon, the second transistor has a second active layer, the second active layer is metal-oxide semiconductor, the first active layer, an interlayer dielectric layer and the second active layer are sequentially arranged on the substrate, and a blocking layer is arranged between the interlayer dielectric layer and the second active layer. The array substrate is advantaged in that through arranging the blocking layer, the insulation and hydrogen blocking effect between the interlayer dielectric layer of the low temperature polysilicon film transistor and the active layer of the oxide film transistor is realized, hydrogen penetration in the subsequent heat treatment technology between the low temperature polysilicon film transistor and the oxide film transistor can be prevented, and bad influence of transistor characteristics of the low temperature polycrystalline silicon film transistor and the oxide film transistor can be prevented.

Owner:BOE TECH GRP CO LTD

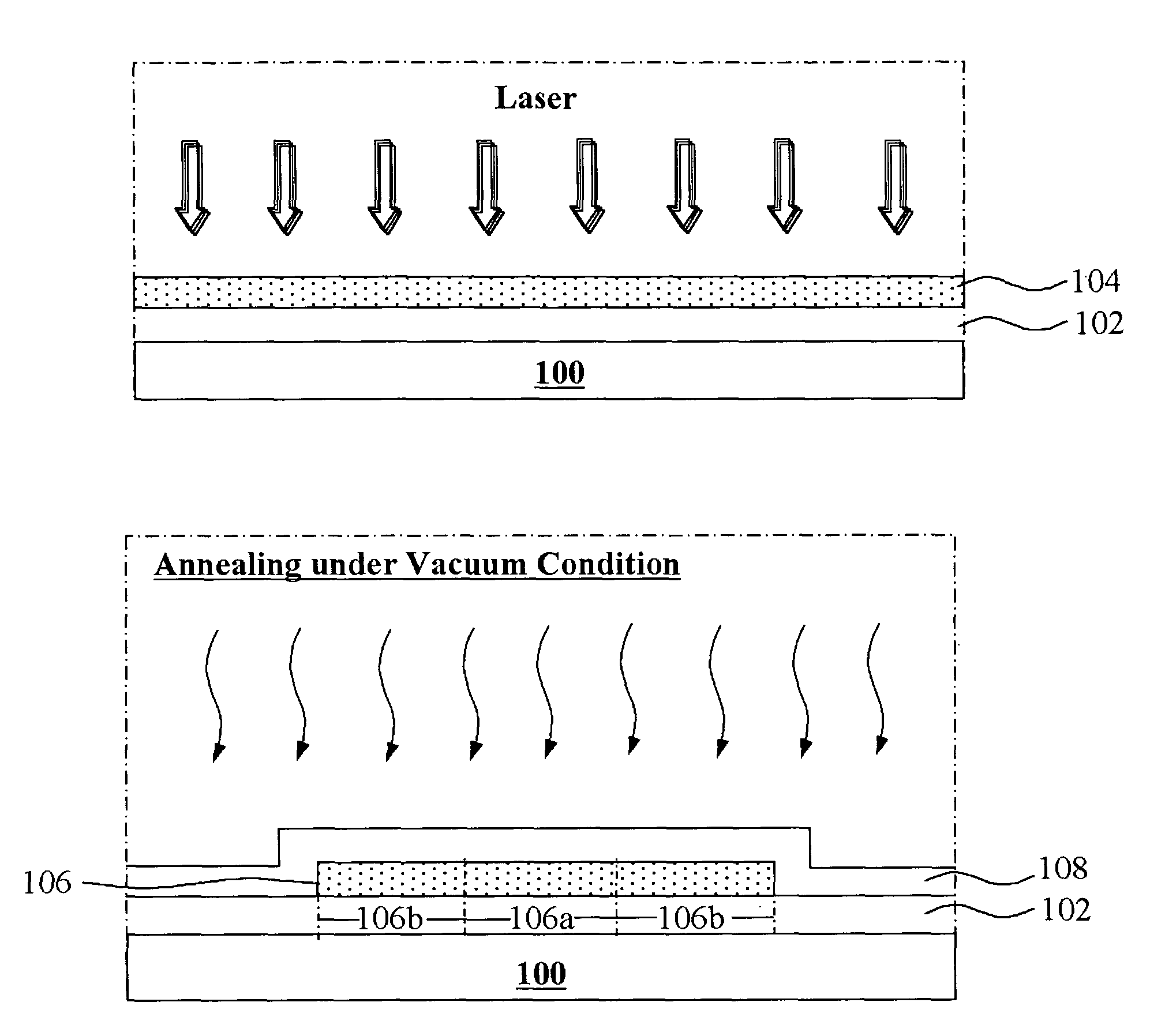

Method of fabricating top gate type thin film transistor having low temperature polysilicon

InactiveUS7052940B2Easy to optimizeImprove reliabilityTransistorSemiconductor/solid-state device manufacturingInsulation layerAmorphous silicon

A method of forming a polysilicon thin film transistor that includes depositing an amorphous silicon layer over a substrate, crystallizing the amorphous silicon layer into a polycrystalline silicon layer, patterning the polycrystalline silicon layer to form a polysilicon active layer for a thin film transistor, depositing silicon oxide over the polysilicon active layer to form a gate insulation layer under a vacuum condition, applying heat to anneal the gate insulation layer under a vacuum condition and forming a gate electrode on the annealed gate insulation layer.

Owner:LG DISPLAY CO LTD

Manufacturing method of low-temperature polycrystalline silicon (poly-Si) thin film transistor (TFT)

ActiveCN102629558ALarge grainImprove mobilitySemiconductor/solid-state device manufacturingHydrogenOptoelectronics

The invention discloses a manufacturing method of a low-temperature polycrystalline silicon (poly-Si) thin film transistor (TFT). The method is characterized by: forming an amorphous silicon (a-Si) layer on a substrate; carrying out hydrogen relief treatment on the a-Si layer so that the a-Si layer becomes a microgranular; then, forming the a-Si layer which does not be performed with grain refining on the a-Si layer of the microgranular; and then carrying out the hydrogen relief treatment on the a-Si layer so that the a-Si layer becomes the microgranular; and continuously repeating so as to form the a-Si layer and carrying out the hydrogen relief treatment so as to form the a-Si layer with multilayer micromeritics; finally, carrying out excimer laser annealing (ELA) so that the a-Si layer with the multilayer micromeritics crystallizes into a poly-Si layer. After the poly-Si layer becomes the a-Si layer of the multilayer micromeritic through pretreatment, the ELA is performed so that the crystalline grain of the poly-Si layer becomes larger and a carrier mobility is high.

Owner:CENTURY DISPLAY (SHENZHEN) CO LTD

Organic light-emitting display device comprising multiple types of thin-film transistors and method of fabricating the same

An OLED device includes a low-temperature poly-silicon (LTPS) thin-film transistor having a first channel layer, a first gate electrode, a first source electrode and a first drain electrode; an oxide semiconductor thin-film transistor having a second channel layer, a second gate electrode, a second source electrode and a second drain electrode; and a functional layer between the first channel layer and the first gate electrode. The second channel layer is in contact with an upper surface of the functional layer.

Owner:LG DISPLAY CO LTD

Thin film transistor, manufacturing method thereof, array substrate, and display device

ActiveCN105390551ATransistorSemiconductor/solid-state device manufacturingElectrical conductorOxide thin-film transistor

The present invention provides a manufacturing method of a thin film transistor, an array substrate and a display device, relating to the technical field of display. The invention is used for solving the problems of large current, high power consumption of a low-temperature polysilicon thin film transistor. The thin film transistor comprises semiconductor layers comprising a first semiconductor layer and a second semiconductor layer, and the first semiconductor layer and the second semiconductor layer are laminated. The material of the first semiconductor layer is low-temperature polysilicon, and the carrier mobility of the second semiconductor layer is smaller than the carrier mobility of the first semiconductor layer. The above thin film transistor is used in the array substrate, and pixels are driven.

Owner:BOE TECH GRP CO LTD

Low-temperature polycrystalline silicon thin-film transistor based on dual-gate structure and preparation method thereof

InactiveCN104409512AReduce volumeImprove reliabilityTransistorSolid-state devicesBottom gateP channel

The invention discloses a low-temperature polycrystalline silicon thin-film transistor based on a dual-gate structure and a preparation method of the low-temperature polycrystalline silicon thin-film transistor with the dual-gate structure. The low-temperature polycrystalline silicon thin-film transistor comprises a substrate; at least one patterning amorphous silicon layer which is arranged in the barrier layer of the substrate and forms a bottom-gate; an N-channel metal oxide semiconductor which is arranged on the barrier layer; and a P-channel metal oxide semiconductor which is located on the barrier layer, wherein the patterning gate electrode layer formed by the N-channel metal oxide semiconductor and the bottom-gate formed by at least one patterning amorphous silicon layer are combined to form dual-gate structure, so that the current-voltage characteristic is more stable and the breakover current is improved obviously; the driving capacity is increased, the power consumption is reduced and the yield rate of products is improved.

Owner:SHENZHEN CHINA STAR OPTOELECTRONICS TECH CO LTD

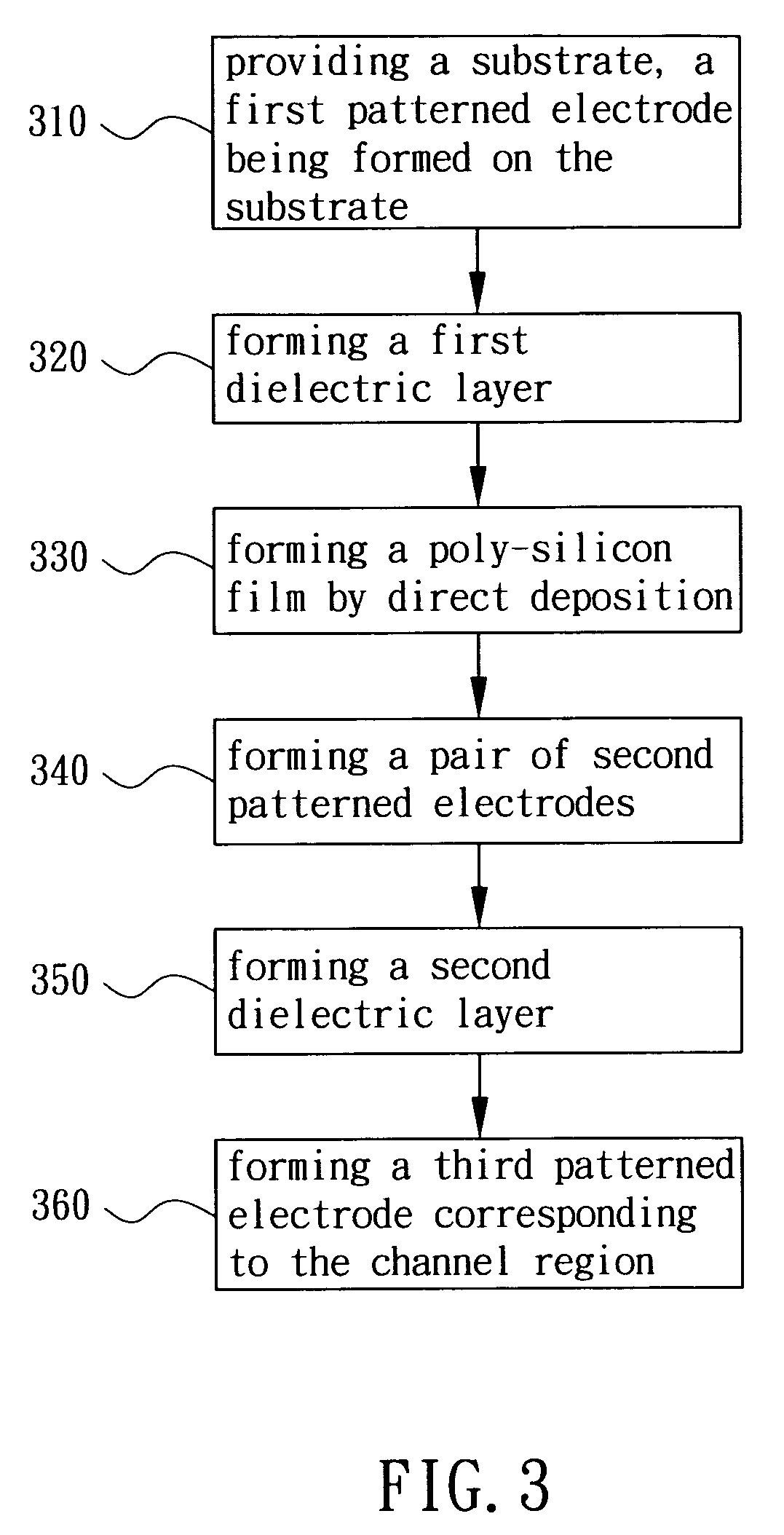

Double gate thin-film transistor and method for forming the same

InactiveUS20070207574A1Excellent electrical propertiesImprove featuresSemiconductor/solid-state device manufacturingSemiconductor devicesAmorphous siliconDielectric layer

A double-gate thin-film transistor and a method for forming the same, using low-temperature poly-silicon formed by direct deposition on a substrate so as to simplify the manufacturing process and improve the electrical characteristics. The double-gate thin-film transistor comprises: a first patterned electrode formed on a substrate; a first dielectric layer; a poly-silicon film, formed by direct deposition on the first dielectric layer so as to form between the poly-silicon film and the first dielectric layer an incubation layer comprising amorphous silicon; a pair of second patterned electrodes, formed on the poly-silicon film so as to define in the poly-silicon film and the incubation layer between the second patterned electrodes a channel region corresponding to the first patterned electrode; a second dielectric layer; and a third patterned electrode corresponding to the channel region. The method comprises steps of: providing a substrate, a first patterned electrode being formed on the substrate; forming a first dielectric layer; forming a poly-silicon film by direct deposition on the first dielectric layer so as to form between the poly-silicon film and the first dielectric layer an incubation layer comprising amorphous silicon; forming a pair of second patterned electrodes on the poly-silicon film so as to define in the poly-silicon film and the incubation layer between the second patterned electrodes a channel region corresponding to the first patterned electrode; forming a second dielectric layer; and forming a third patterned electrode corresponding to the channel region.

Owner:IND TECH RES INST

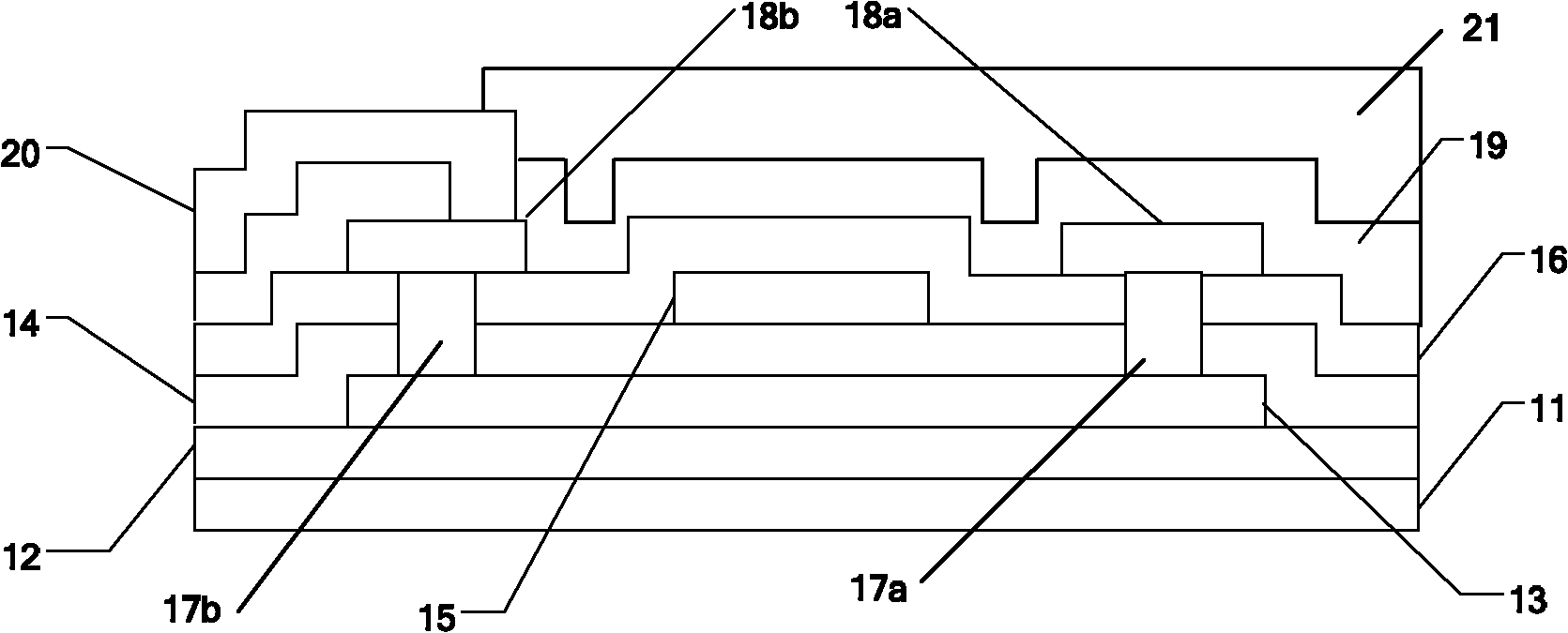

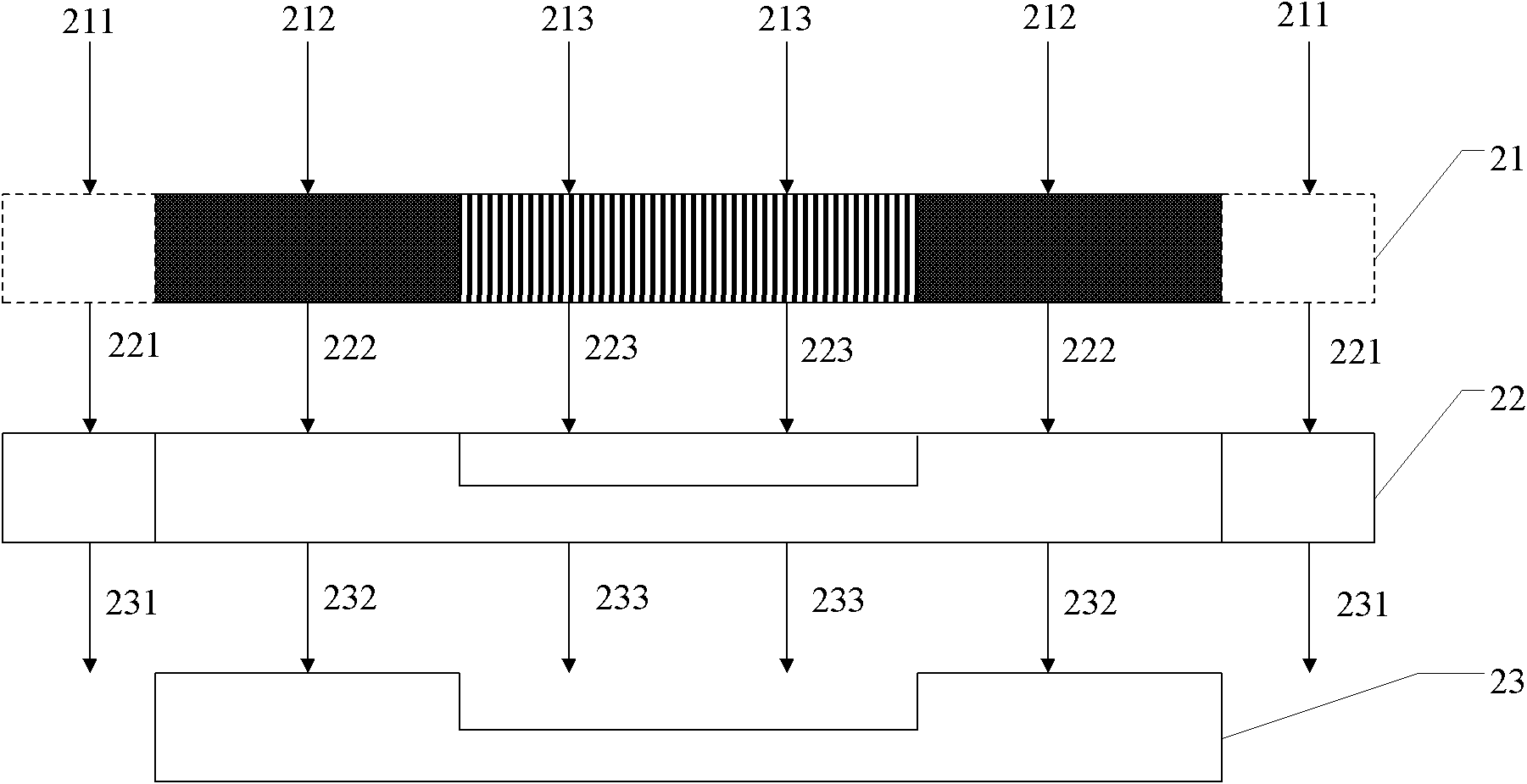

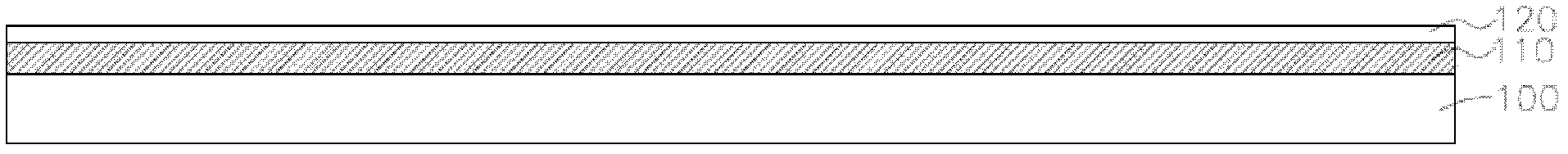

Low-temperature poly-silicon manufacturing method, method for manufacturing TFT substrate by utilization of low-temperature poly-silicon manufacturing method, and TFT substrate structure

InactiveCN104064451AImprove insulation effectReduce the number of grain boundariesTransistorSolid-state devicesEngineeringPre treatment

The invention provides a low-temperature poly-silicon manufacturing method, a method for manufacturing a TFT substrate by utilization of the low-temperature poly-silicon manufacturing method, and a TFT substrate structure. The low-temperature poly-silicon manufacturing method comprises the following steps that 1, the substrate (1) is provided; 2, a buffer layer (2) is formed on the substrate (1) in a deposition mode; 3, pattern processing is carried out on the buffer layer (2), and a convex portion (21) and a concave portion (23) which are different in thickness are formed; 4, an amorphous silicon layer (3) is formed on the buffer layer (2) provided with the convex portion (21) and the concave portion (23) in a deposition mode; 5, excimer laser annealing pretreatment is carried out on the amorphous silicon layer (3); 6, excimer laser annealing is carried out on the amorphous silicon layer (3), the whole surface of the amorphous silicon layer (3) is scanned through laser beams, and the amorphous silicon layer (3) is made to melt and is recrystallized to form a poly-silicon layer (4). The method can effectively control the crystallization position and crystallization direction when the amorphous silicon layer is recrystallized.

Owner:TCL CHINA STAR OPTOELECTRONICS TECH CO LTD

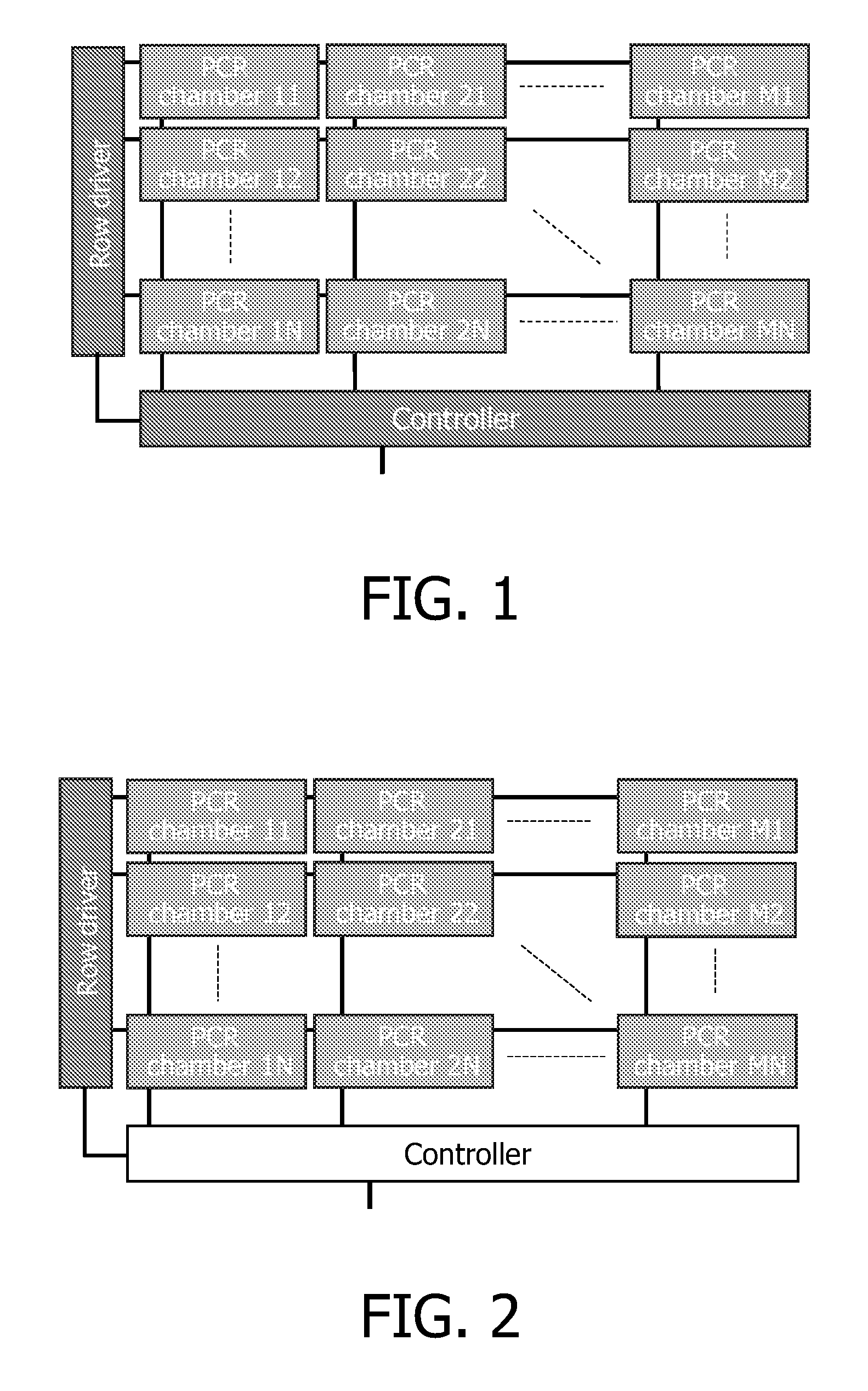

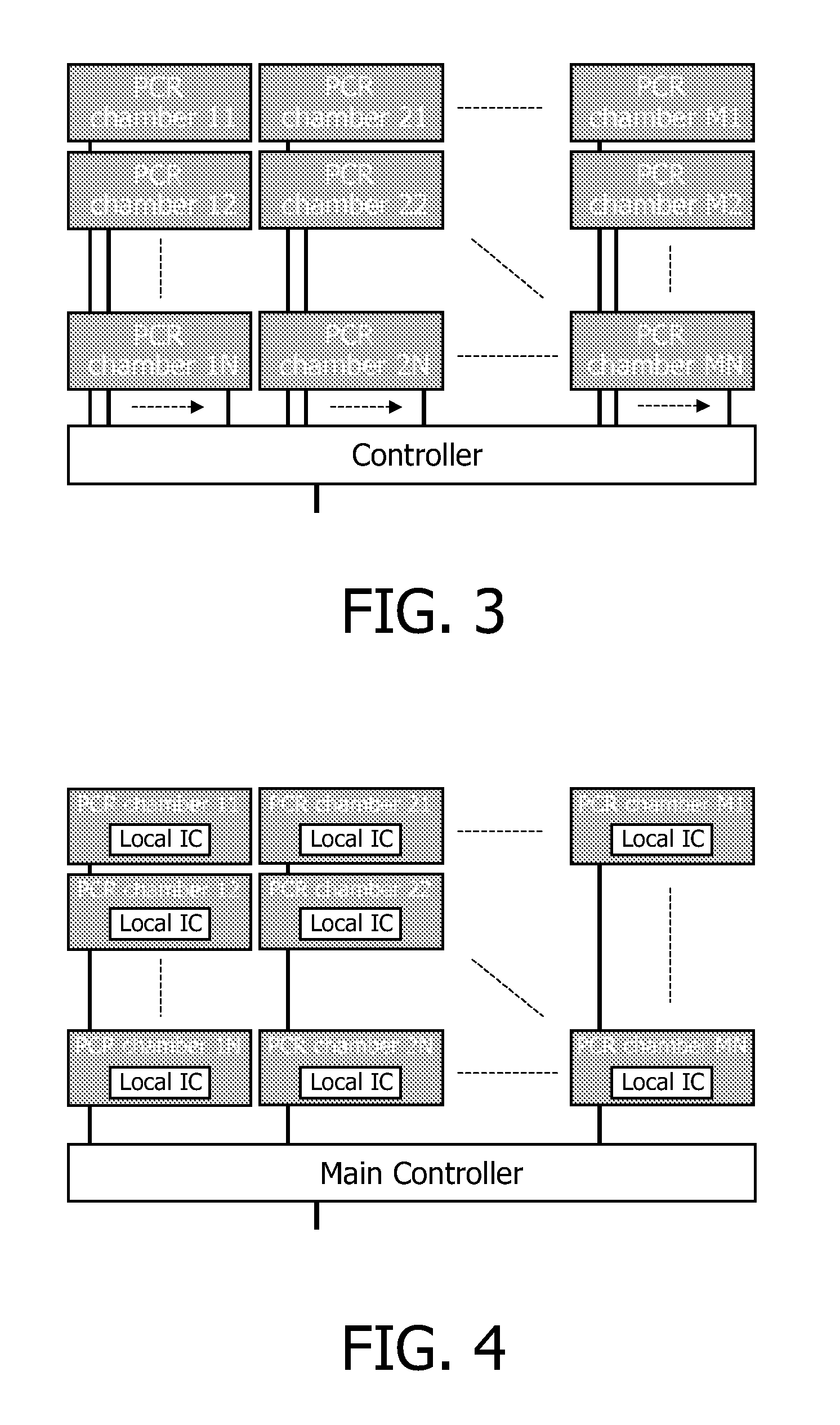

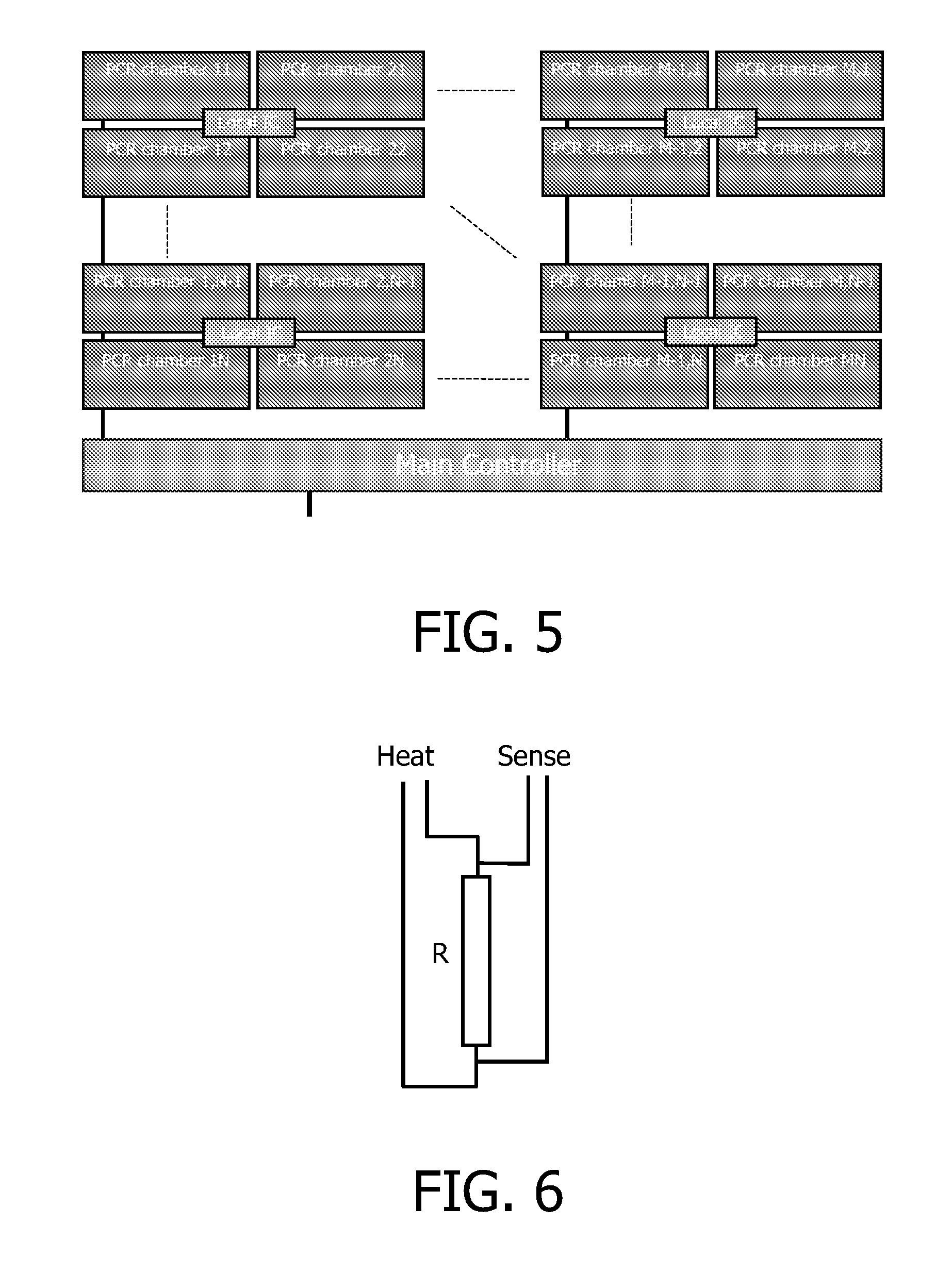

Integrated microfluidic device with reduced peak power consumption

InactiveUS20100086991A1Reduce peak power consumptionLoss of precisionBioreactor/fermenter combinationsHeating or cooling apparatusActive matrixControl line

An integrated microfluidic device having a number of chambers (11-MN) for heating a fluid, a number of electrical heating elements (R) for heating different ones of the chambers, a controller for controlling the heating elements to vary a temperature of the fluid in the chambers repeatedly through a cycle of different temperatures, the controller being arranged to time the temperature cycle for a given one of the chambers to be out of phase with temperature cycles of others of the chambers. This can help reduce peak power consumption, and thus reduce unwanted voltage drops on supply lines. These can cause loss of precision in heating and sensing circuits. The device can comprise a low temperature polysilicon on a glass substrate. The controller can be coupled to the heating elements using an active matrix of control lines and switches (T2).

Owner:KONINKLIJKE PHILIPS ELECTRONICS NV

Semiconductor device and method of fabricating a ltps film

InactiveUS20060060848A1Improve electrical performanceImprove mobilityTransistorSemiconductor/solid-state device manufacturingDevice materialLaser crystallization

A semiconductor device and a method of fabricating a low-temperature polysilicon film are provided. An amorphous silicon film is formed over a substrate. An insulating layer and a laser absorption layer are formed over the amorphous silicon film. A photolithographic and etching process is performed to remove portions of the laser absorption layer and the insulating layer to expose portions of the amorphous silicon film. A laser crystallization process is utilized to convert the amorphous silicon film into a polysilicon film.

Owner:AU OPTRONICS CORP

Display device and method for manufacturing the same

ActiveUS20170278916A1Decrease current variationSmall parasitic capacitanceSolid-state devicesSemiconductor devicesDisplay deviceEngineering

A plurality of thin film transistors provided in a peripheral region are first staggered thin film transistors where a first channel layer configured of low-temperature polysilicon is included, and the first channel layer is not interposed between a first source electrode and a first gate electrode, and between a first drain electrode and the first gate electrode. A plurality of thin film transistors provided in a display region are second staggered thin film transistors where a second channel layer configured of an oxide semiconductor is included, and the second channel layer is not interposed between a second source electrode and a second gate electrode, and between a second drain electrode and the second gate electrode. The first thin film transistor is located below the second thin film transistor.

Owner:JAPAN DISPLAY INC

Array substrate, display panel and display device

ActiveCN109300915AEfficient use ofAffect performanceSolid-state devicesSemiconductor/solid-state device manufacturingDisplay deviceEngineering

The invention provides an array substrate, a display panel and a display device. The array substrate comprises a substrate body and first and second thin film transistors (TFT) thereon, and the activelayer material of the first TFT is different from that of the second TFT; the first TFT comprises the first active layer, a first gate, a first source and a first drain, and the first active layer isa low-temperature polycrystalline silicon layer; the second TFT comprises a second active layer, a second gate, a second source and a second drain; the first source, the first drain, the second source and the second drain are positioned in the same layer; and there is a first gate insulating layer between the first active layer and the first gate, and the second active layer is positioned in theslide, close to or far from the substrate, of the first gate insulating layer and does not make direct contact with the first gate insulating layer. Thus, the film layer on the array substrate can bereduced, and the first gate in the first TFT is avoided from influencing influence of the second TFT.

Owner:XIAMEN TIANMA MICRO ELECTRONICS

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com

![[low-temperature polysilicon thin film transistor and fabrication method thereof] [low-temperature polysilicon thin film transistor and fabrication method thereof]](https://images-eureka-patsnap-com.libproxy1.nus.edu.sg/patent_img/4dc3a9dc-5b5e-4d88-9831-cc022abd9f60/US20050218403A1-20051006-D00000.png)

![[low-temperature polysilicon thin film transistor and fabrication method thereof] [low-temperature polysilicon thin film transistor and fabrication method thereof]](https://images-eureka-patsnap-com.libproxy1.nus.edu.sg/patent_img/4dc3a9dc-5b5e-4d88-9831-cc022abd9f60/US20050218403A1-20051006-D00001.png)

![[low-temperature polysilicon thin film transistor and fabrication method thereof] [low-temperature polysilicon thin film transistor and fabrication method thereof]](https://images-eureka-patsnap-com.libproxy1.nus.edu.sg/patent_img/4dc3a9dc-5b5e-4d88-9831-cc022abd9f60/US20050218403A1-20051006-D00002.png)