Thin film transistor, manufacturing method thereof, array substrate, and display device

A thin film transistor and array substrate technology, applied in the display field, can solve the problems of large leakage current, short display time and high refresh frequency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

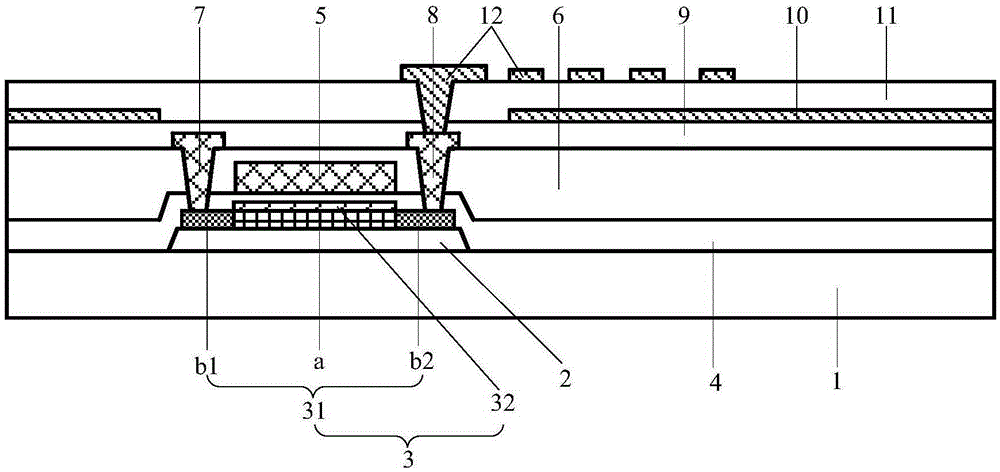

[0037] see figure 1 , this embodiment provides a thin film transistor, the thin film transistor includes a semiconductor layer 3, the semiconductor layer 3 includes a first semiconductor layer 31 and a second semiconductor layer 32, the first semiconductor layer 31 and the second semiconductor layer 32 are stacked, The material of the first semiconductor layer 31 is low temperature polysilicon, and the carrier mobility of the second semiconductor layer 32 is lower than that of the first semiconductor layer 31 .

[0038] The semiconductor layer of the low-temperature polysilicon thin film transistor in the prior art is only formed of low-temperature polysilicon, which causes electrons to pass through the low-temperature polysilicon regardless of whether the thin film transistor is in an on state or an off state. High, thus resulting in high carrier mobility and high concentration of the current in the off state, that is, a large leakage current. Compared with the prior art, th...

Embodiment 2

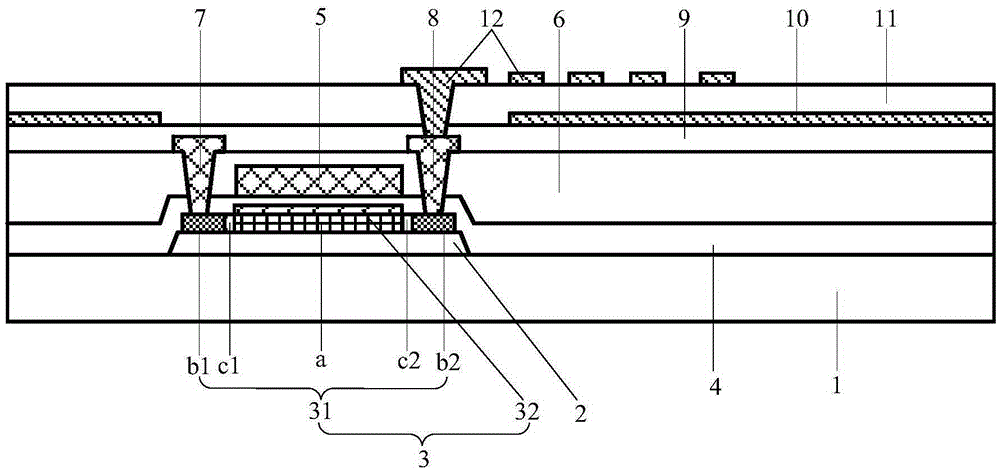

[0046] Based on Example 1, such as figure 2 As shown, in the thin film transistor provided in this embodiment, the first lightly doped region c1 is set between the first heavily doped region b1 and the channel region a of the first semiconductor layer 31, and the second heavily doped A second lightly doped region c2 is provided between the region b2 and the channel region a.

[0047] Since the concentration of metal ions doped in the lightly doped region is less than the concentration of metal ions doped in the heavily doped region, the resistance of the lightly doped region is smaller than that of the heavily doped region, so that in the first semiconductor On the premise that the size of the layer 31 remains unchanged, it is equivalent to increasing the resistance of the first semiconductor layer 31, that is, increasing the resistance on the electron conduction path, and further reducing the leakage current of the thin film transistor in the off state.

Embodiment 3

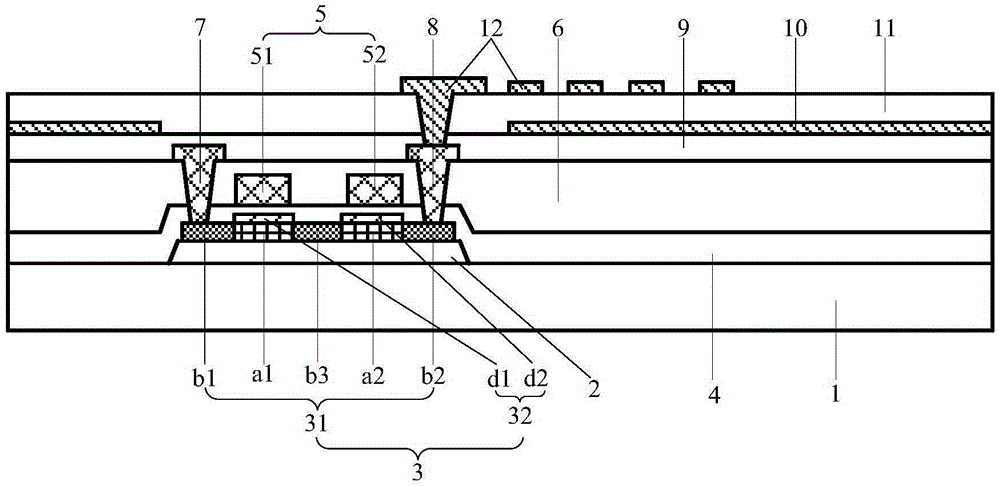

[0049] Based on Example 1, such as image 3 As shown, in the thin film transistor provided in this embodiment, the channel region a of the first semiconductor layer 31 includes a first channel region a1 and a second channel region a2; the first semiconductor layer 31 also includes a third heavily doped region b3, the third heavily doped region b3 is located between the first channel region a1 and the second channel region a2. The second semiconductor layer 32 includes a third channel region d1 and a fourth channel region d2, the orthographic projection of the third channel region d1 on the first channel region a1 is located in the first channel region a1, the first channel region a1 Orthographic projections of the four channel regions d2 on the second channel region a2 are located in the second channel region a2. The gate 5 in the thin film transistor includes a first gate 51 and a second gate 52, the first gate 51 is set corresponding to the first channel region a1, and the ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com