Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

73 results about "Double heterostructure" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

A double heterostructure is formed when two semiconductor materials are grown into a "sandwich". One material (such as AlGaAs) is used for the outer layers (or cladding), and another of smaller band gap (such as GaAs) is used for the inner layer. In this example, there are two AlGaAs-GaAs junctions (or boundaries), one at each side of the inner layer. There must be two boundaries for the device to be a double heterostructure. If there was only one side of cladding material, the device would be a simple heterostructure.

Low bandgap, monolithic, multi-bandgap, optoelectronic devices

InactiveUS20060162768A1Semiconductor/solid-state device manufacturingPhotovoltaic energy generationPhotovoltaic detectorsPhotodetector

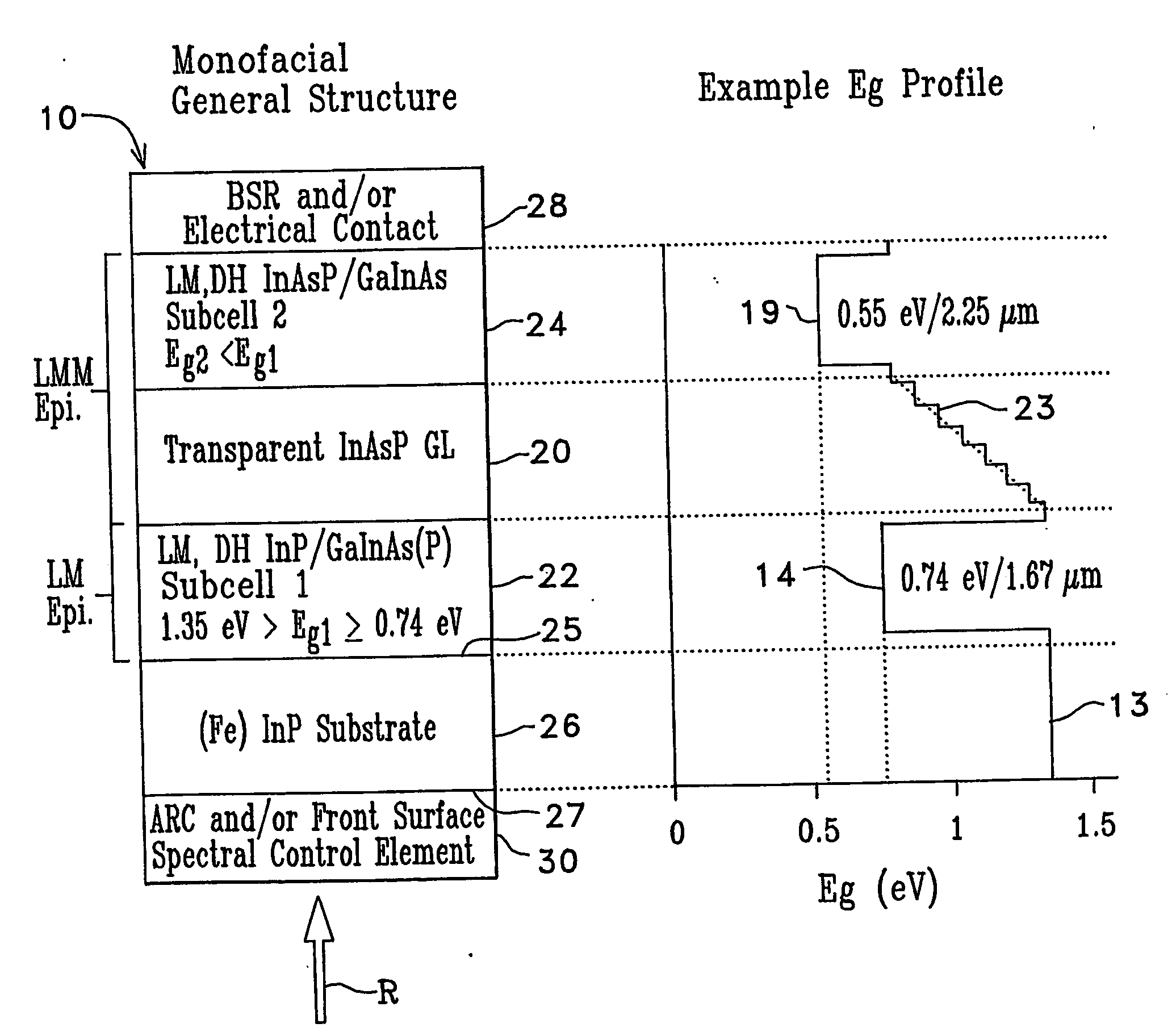

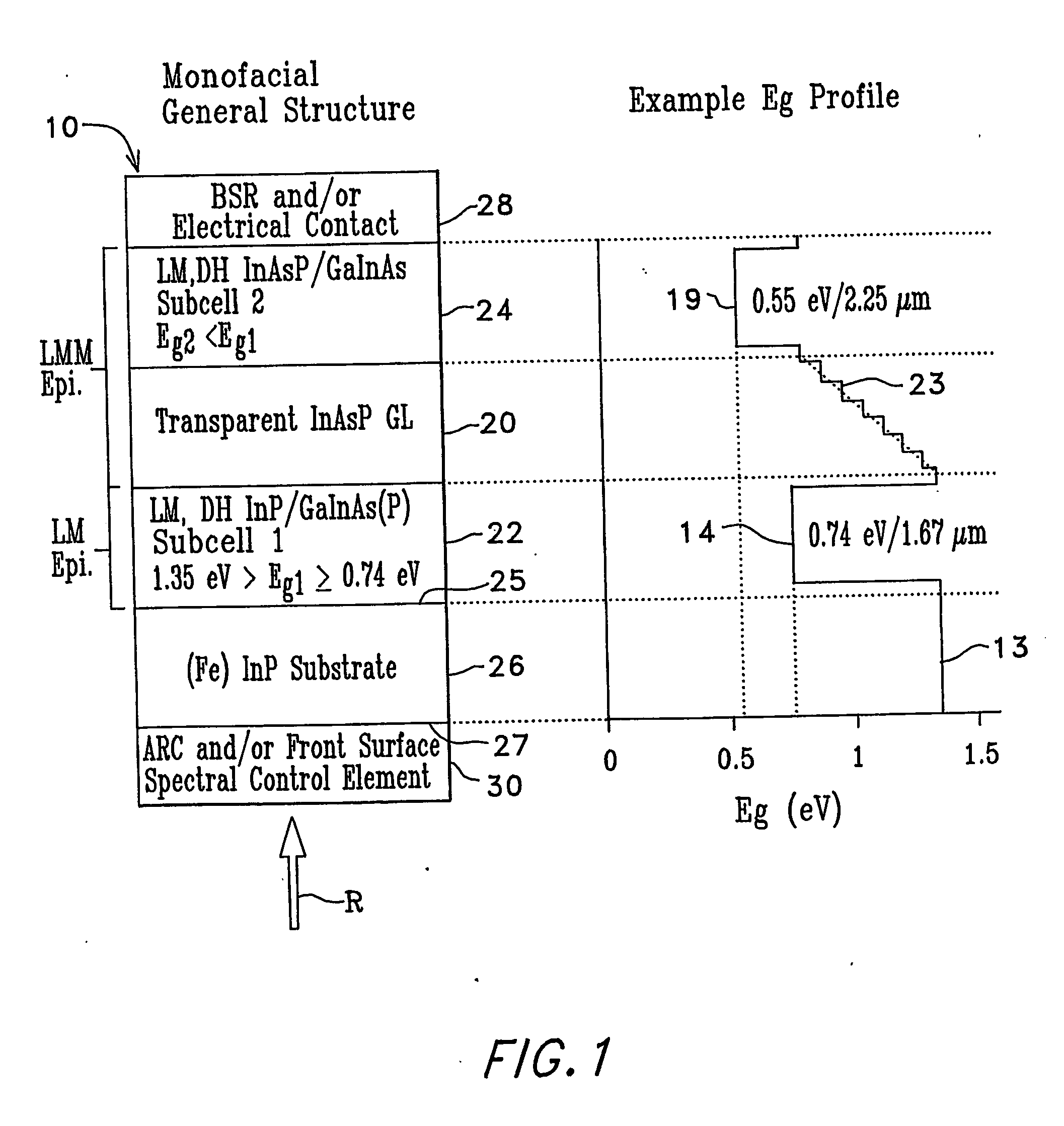

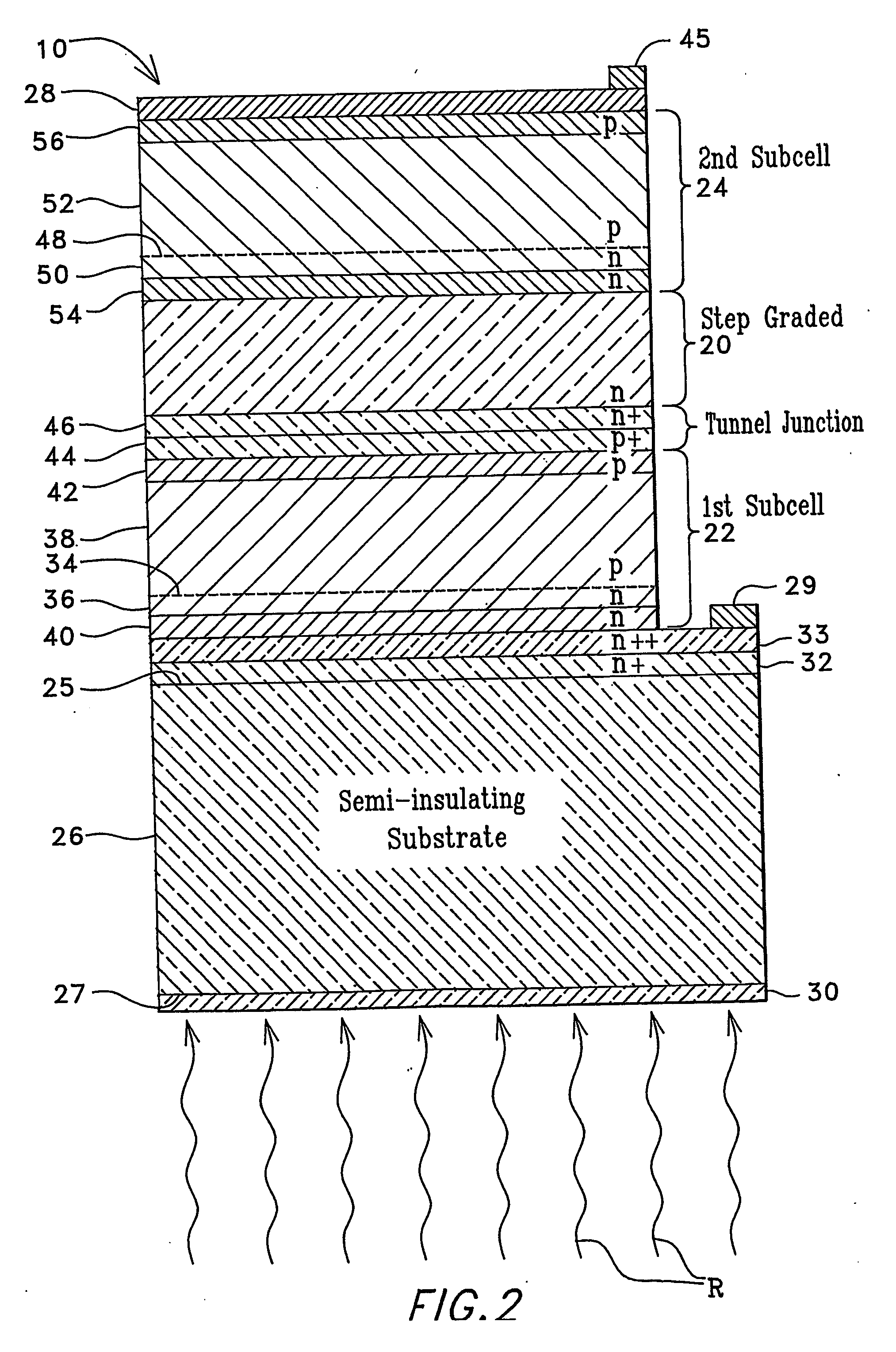

Low-bandgap, monolithic, multi-bandgap, optoelectronic devices (10), including PV converters, photodetectors, and LED's, have lattice-matched (LM), double-heterostructure (DH), low-bandgap GaInAs(P) subcells (22, 24) including those that are lattice-mismatched (LMM) to InP, grown on an InP substrate (26) by use of at least one graded lattice constant transition layer (20) of InAsP positioned somewhere between the InP substrate (26) and the LMM subcell(s) (22, 24). These devices are monofacial (10) or bifacial (80) and include monolithic, integrated, modules (MIMs) (190) with a plurality of voltage-matched subcell circuits (262, 264, 266, 270, 272) as well as other variations and embodiments.

Owner:ALLIANCE FOR SUSTAINABLE ENERGY

Transparent contacts for organic devices

InactiveUS20070132369A1Low production costSubstantially transparentStatic indicating devicesSolid-state devicesHead-up displayEngineering

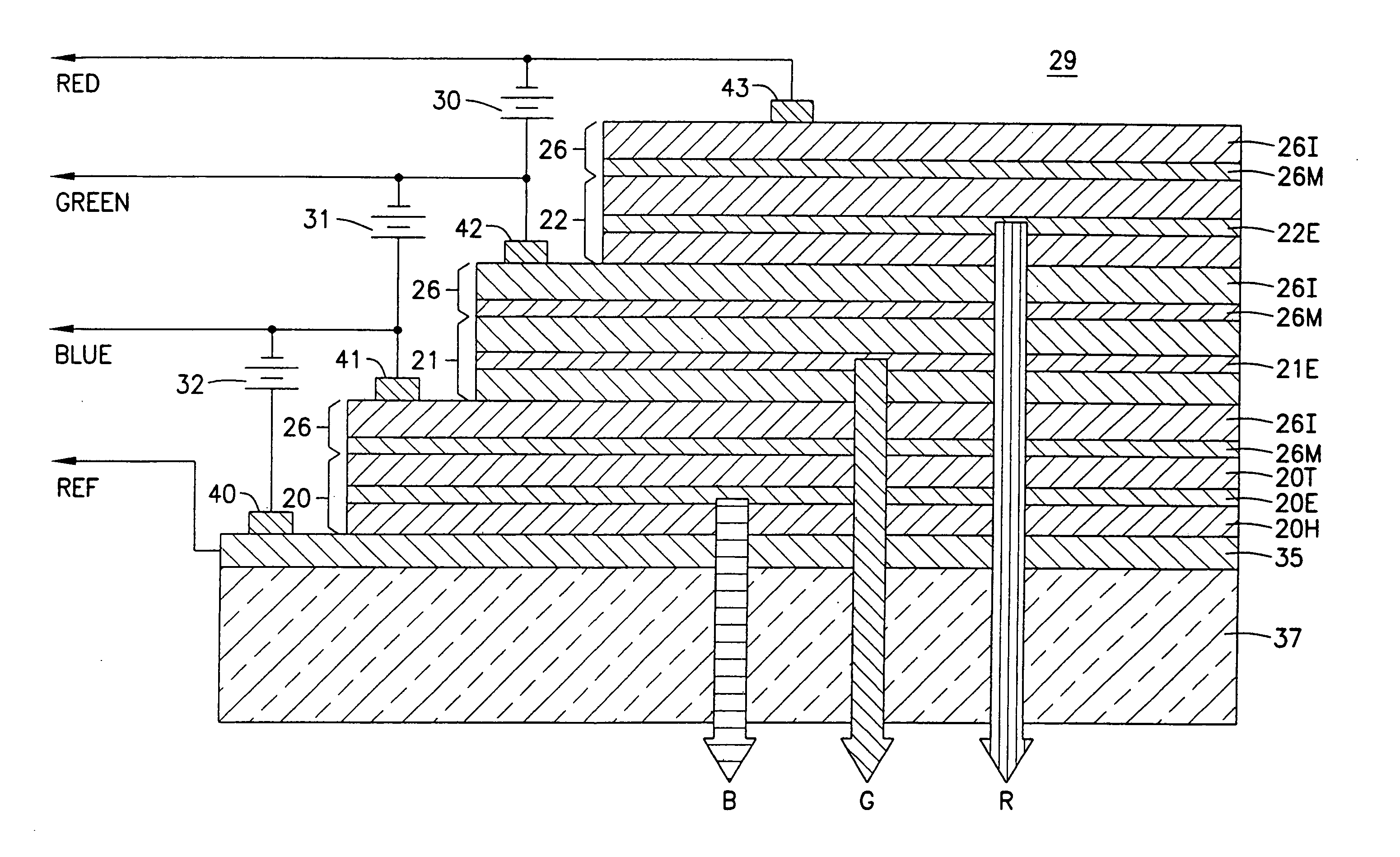

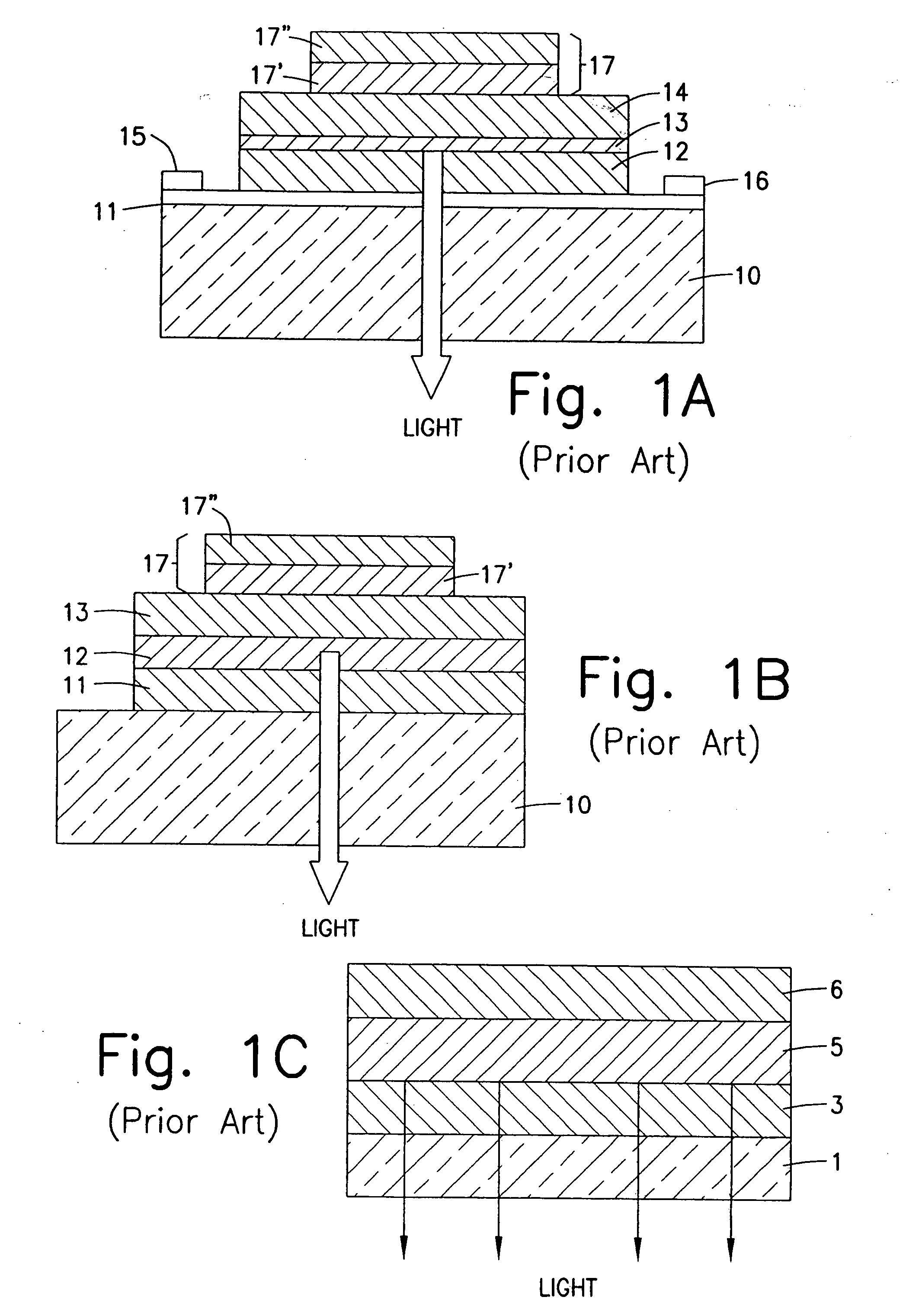

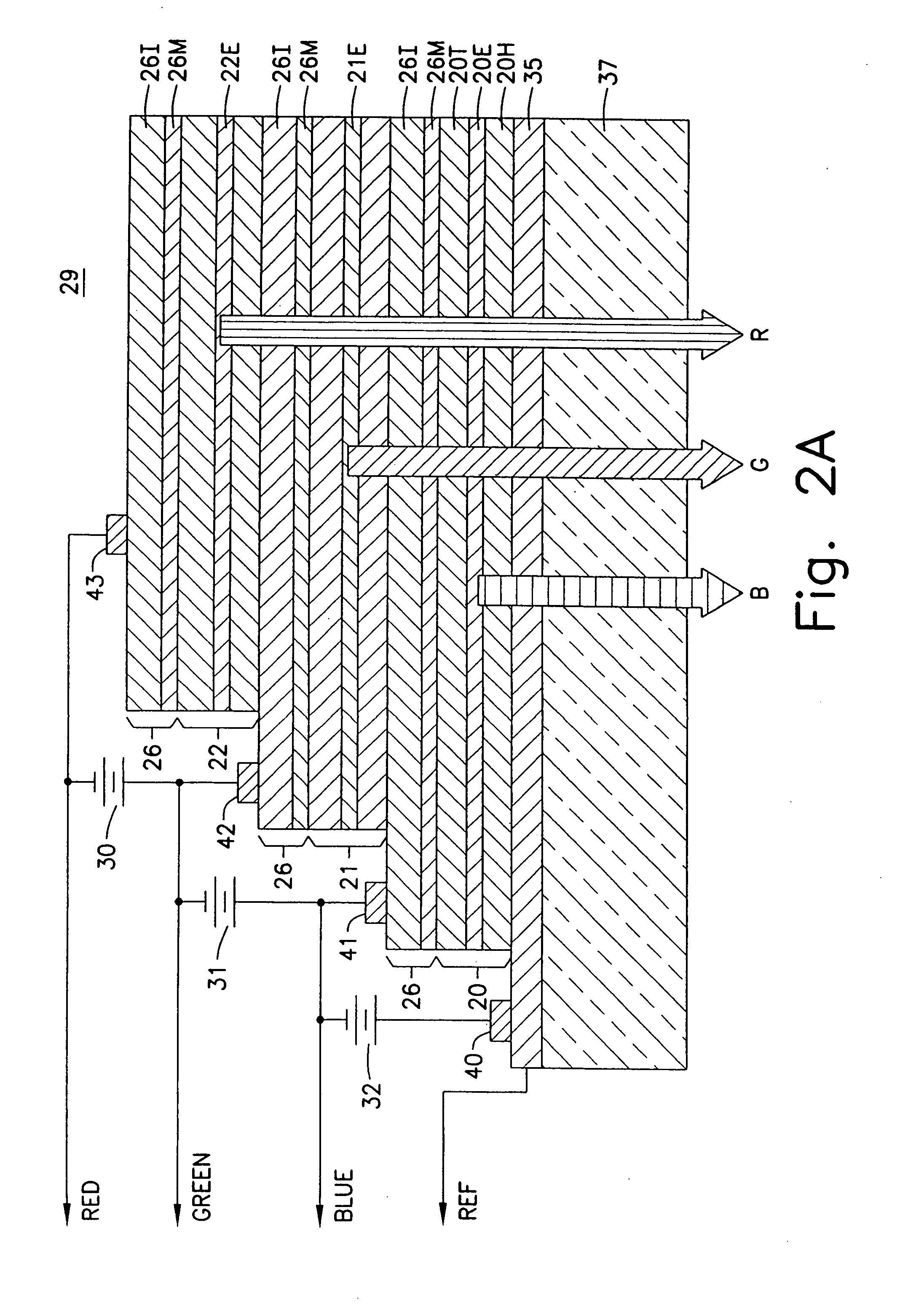

A multicolor organic light emitting device employs vertically stacked layers of double heterostructure devices which are fabricated from organic compounds. The vertical stacked structure is formed on a glass base having a transparent coating of ITO or similar metal to provide a substrate. Deposited on the substrate is the vertical stacked arrangement of three double heterostructure devices, each fabricated from a suitable organic material. Stacking is implemented such that the double heterostructure with the longest wavelength is on the top of the stack. This constitutes the device emitting red light on the top with the device having the shortest wavelength, namely, the device emitting blue light, on the bottom of the stack. Located between the red and blue device structures is the green device structure. The devices are configured as stacked to provide a staircase profile whereby each device is separated from the other by a thin transparent conductive contact layer to enable light emanating from each of the devices to pass through the semitransparent contacts and through the lower device structures while further enabling each of the devices to receive a selective bias. The devices are substantially transparent when de-energized, making them useful for heads-up display applications.

Owner:THE TRUSTEES FOR PRINCETON UNIV

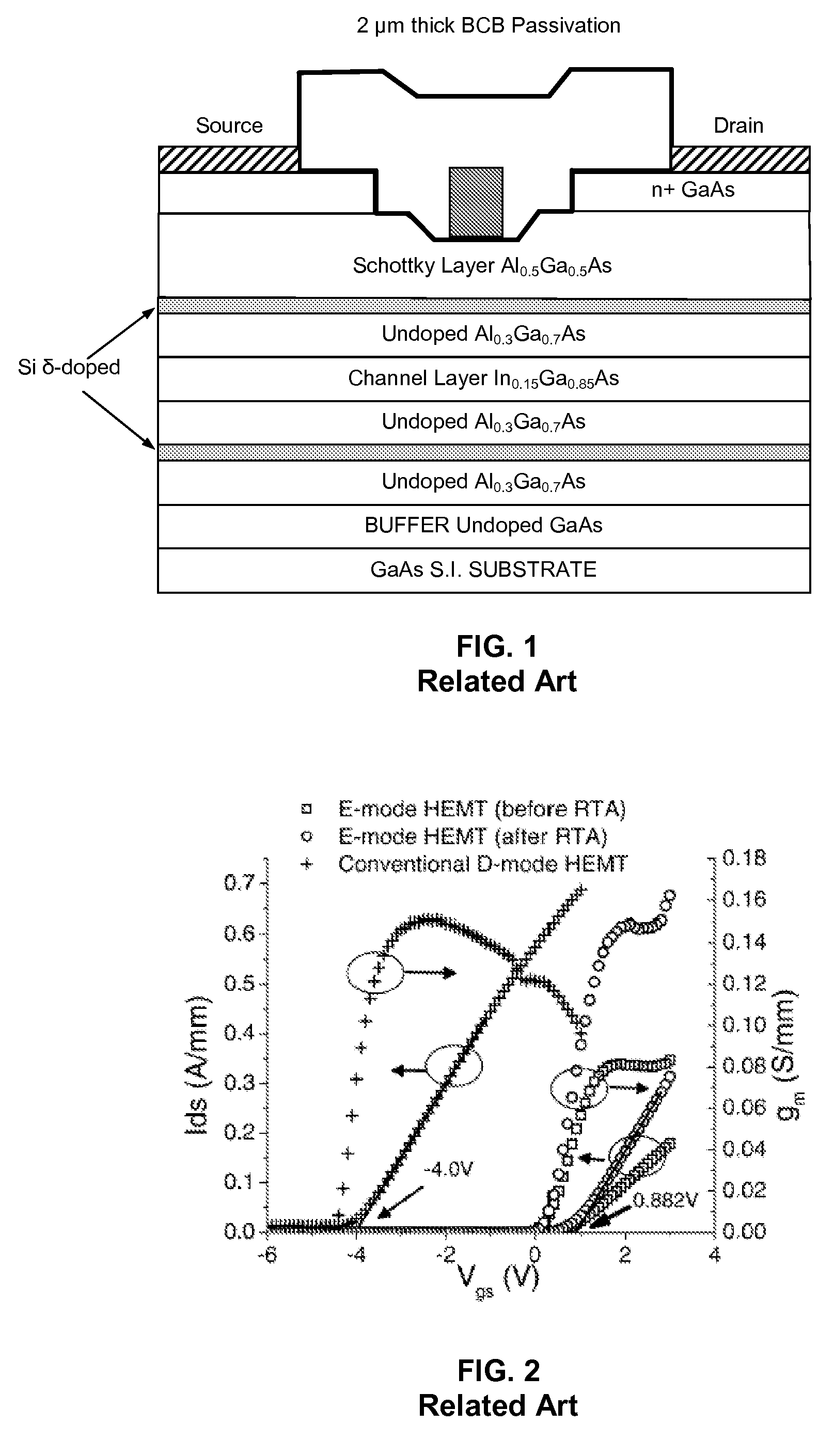

Enhancement mode insulated gate heterostructure field-effect transistor

ActiveUS20080203430A1Enhancement mode operationAccurate control of threshold voltageSemiconductor devicesCharge carrierGate current

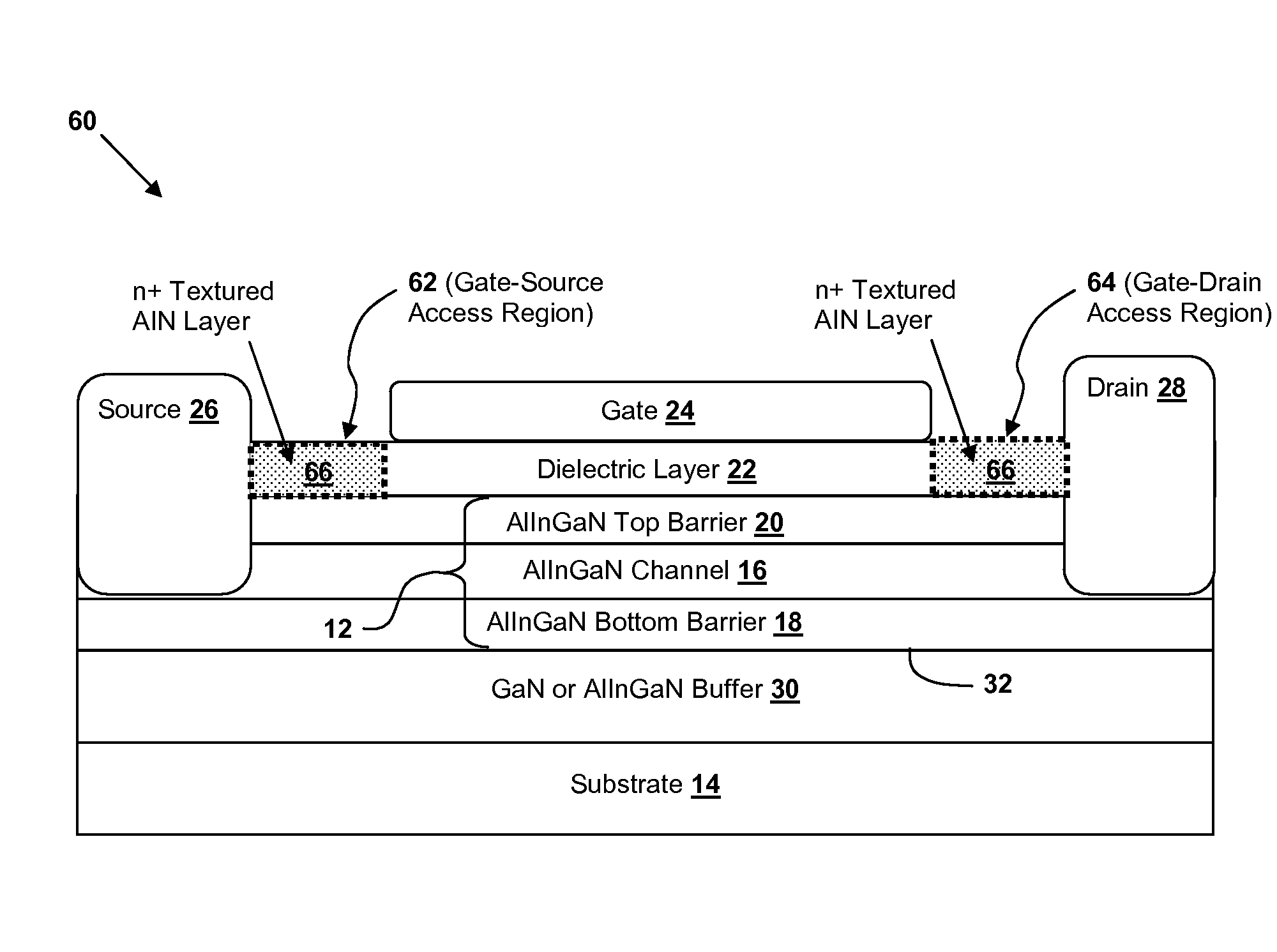

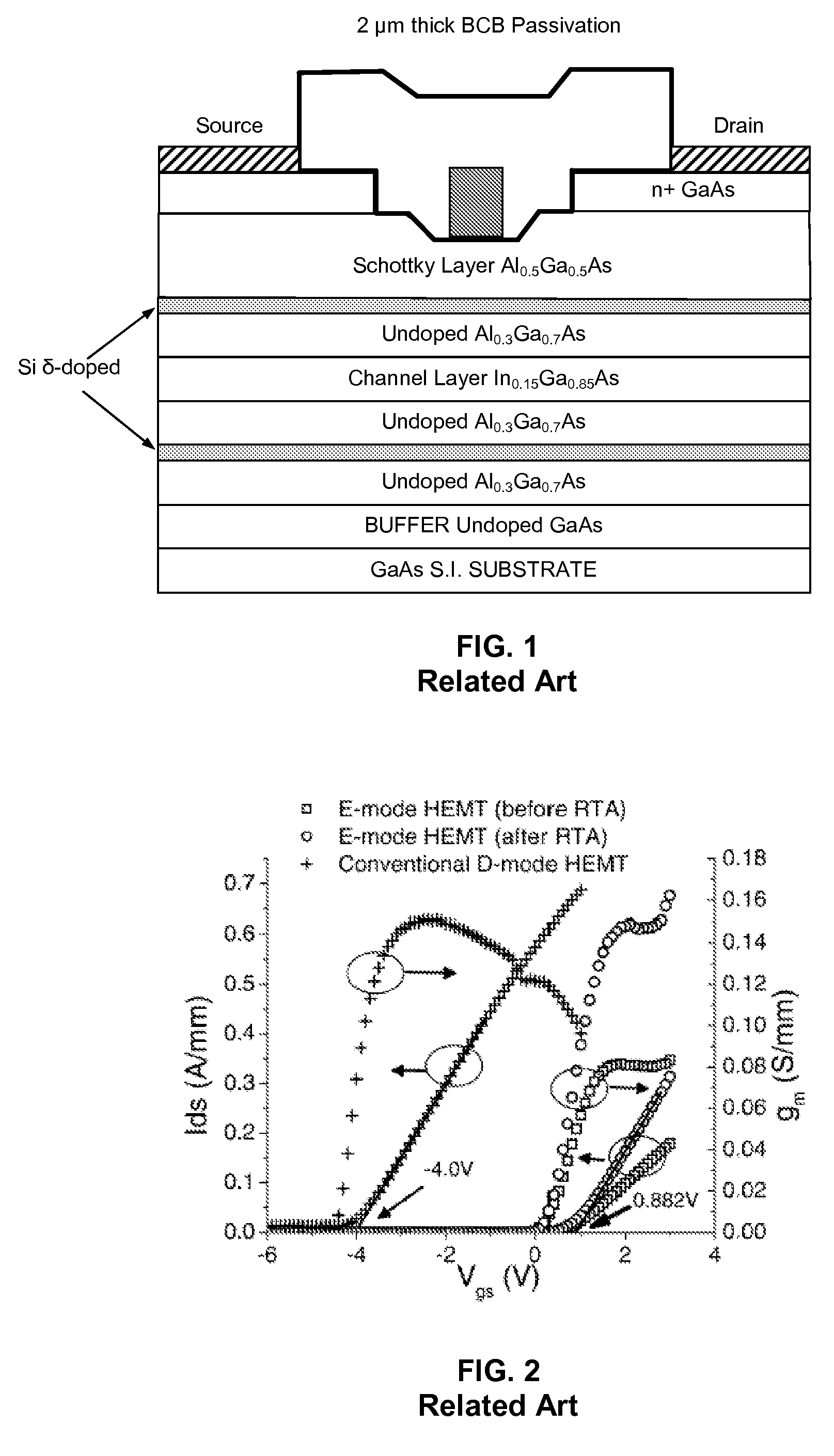

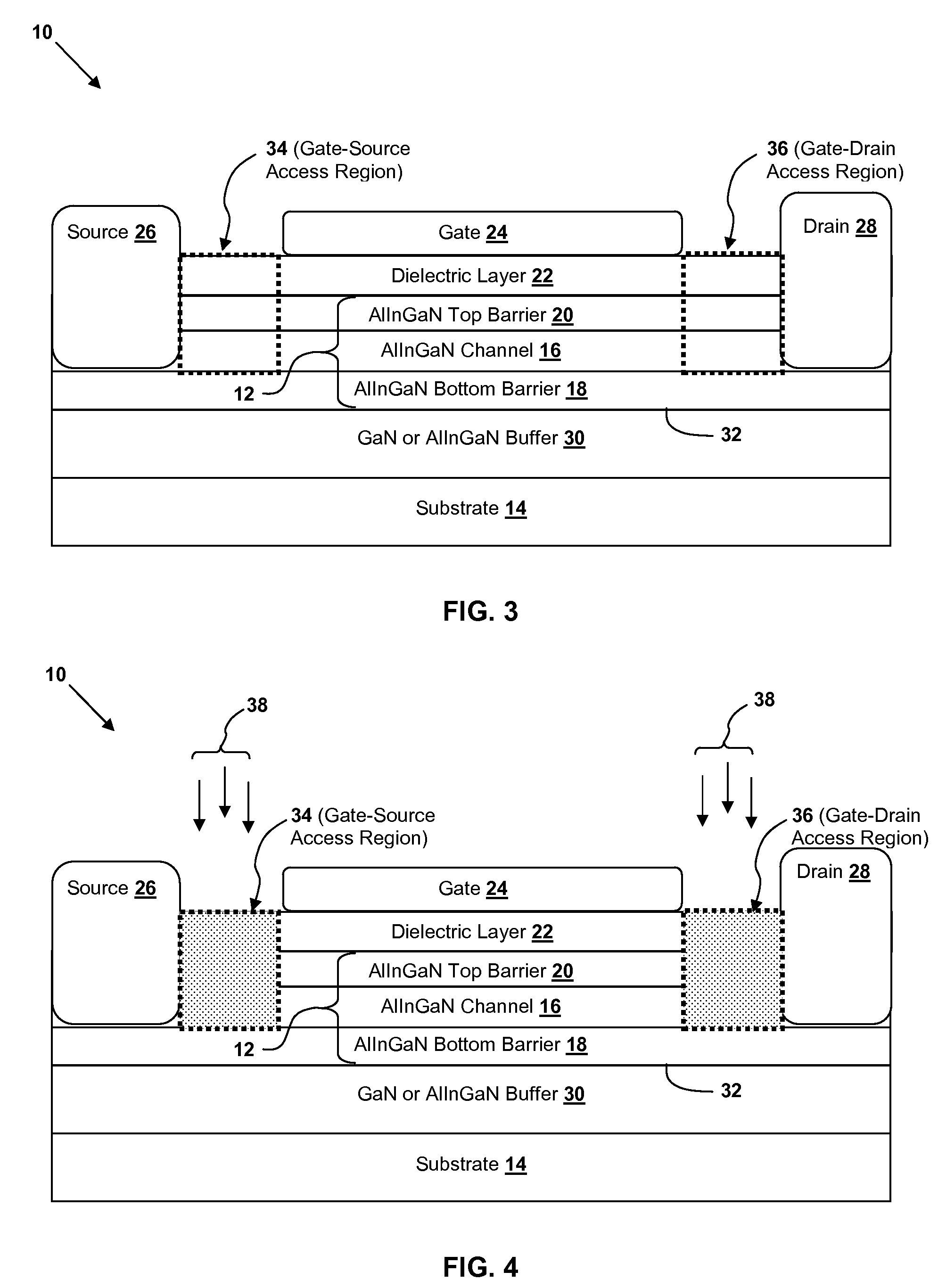

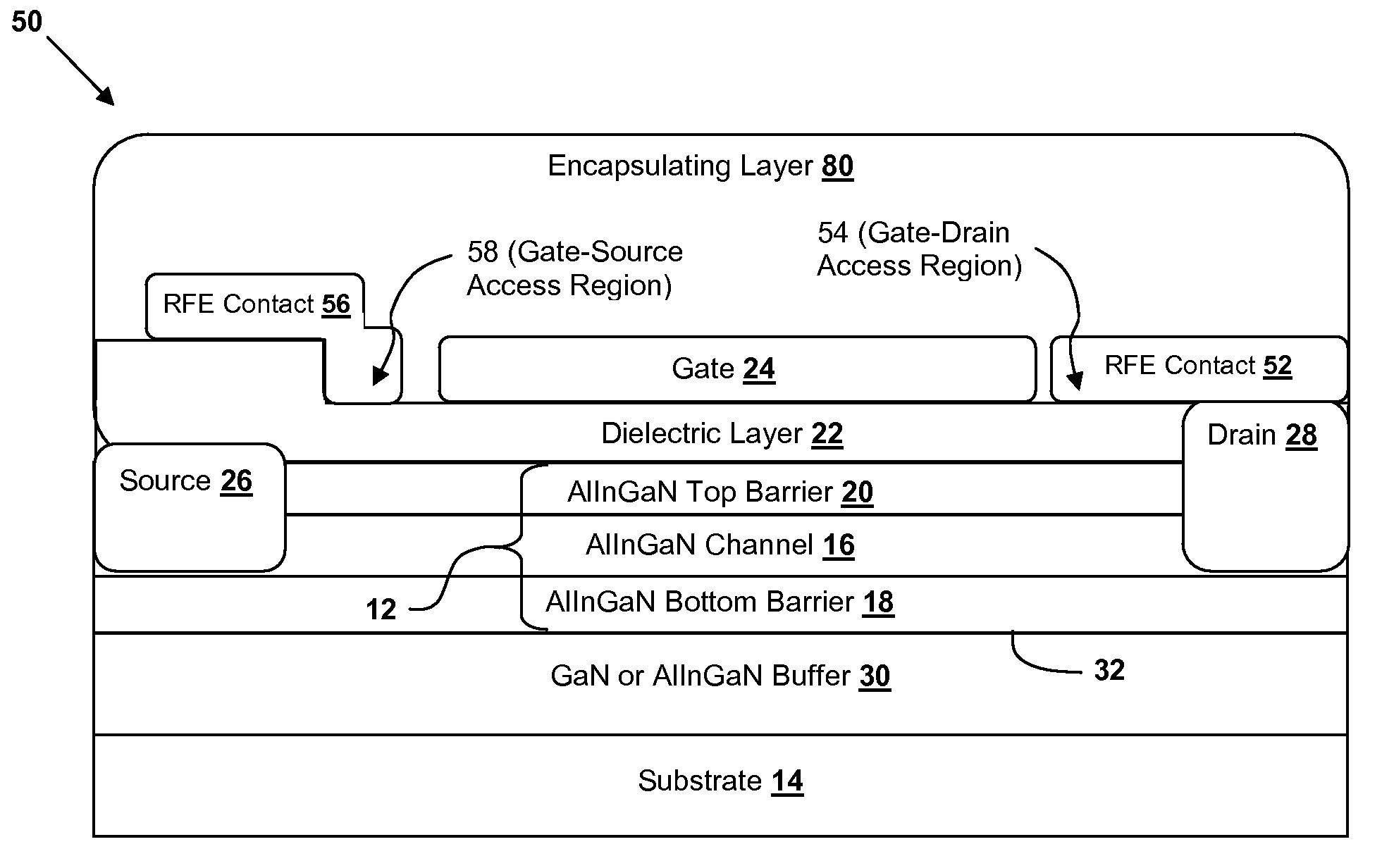

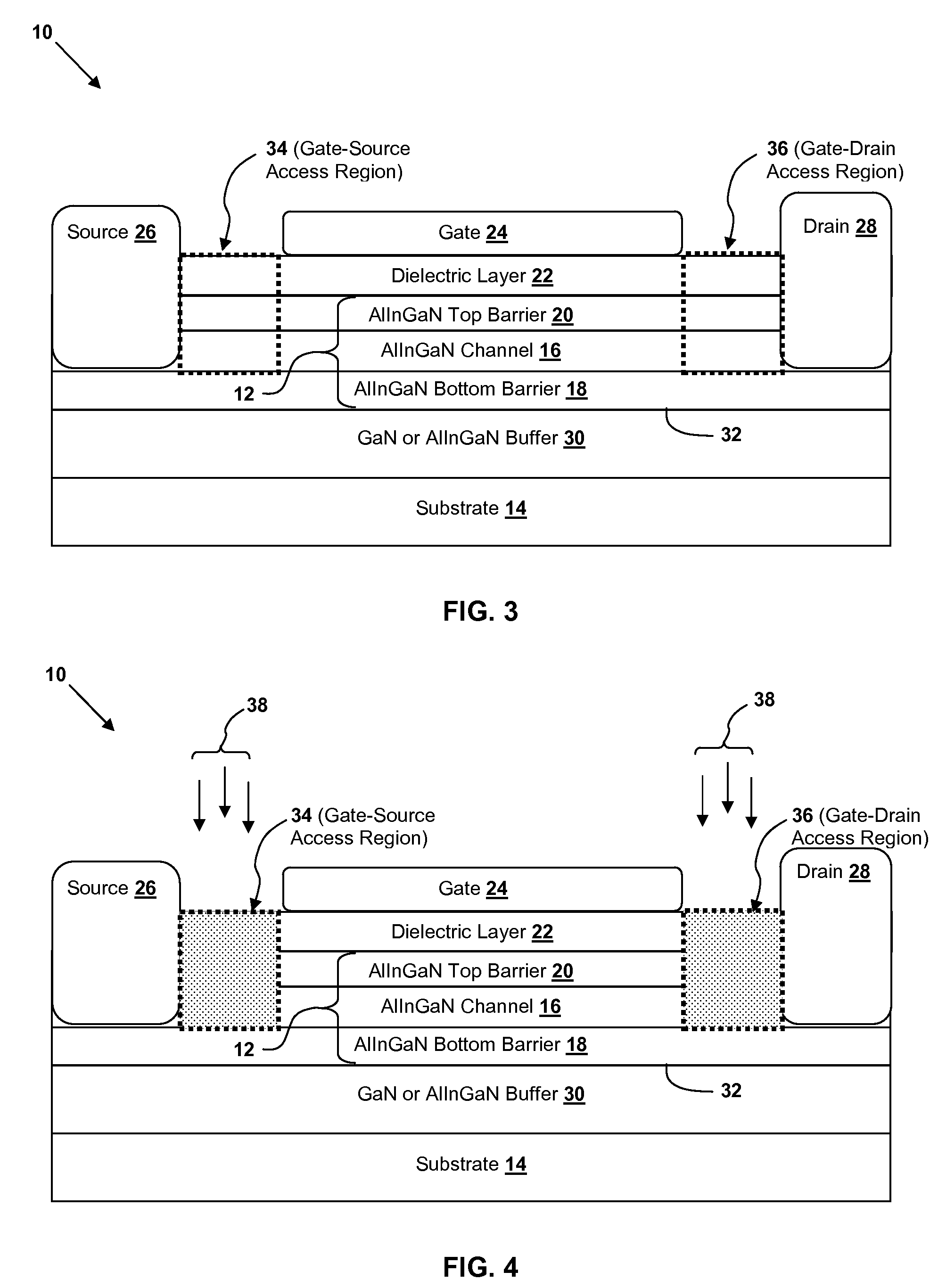

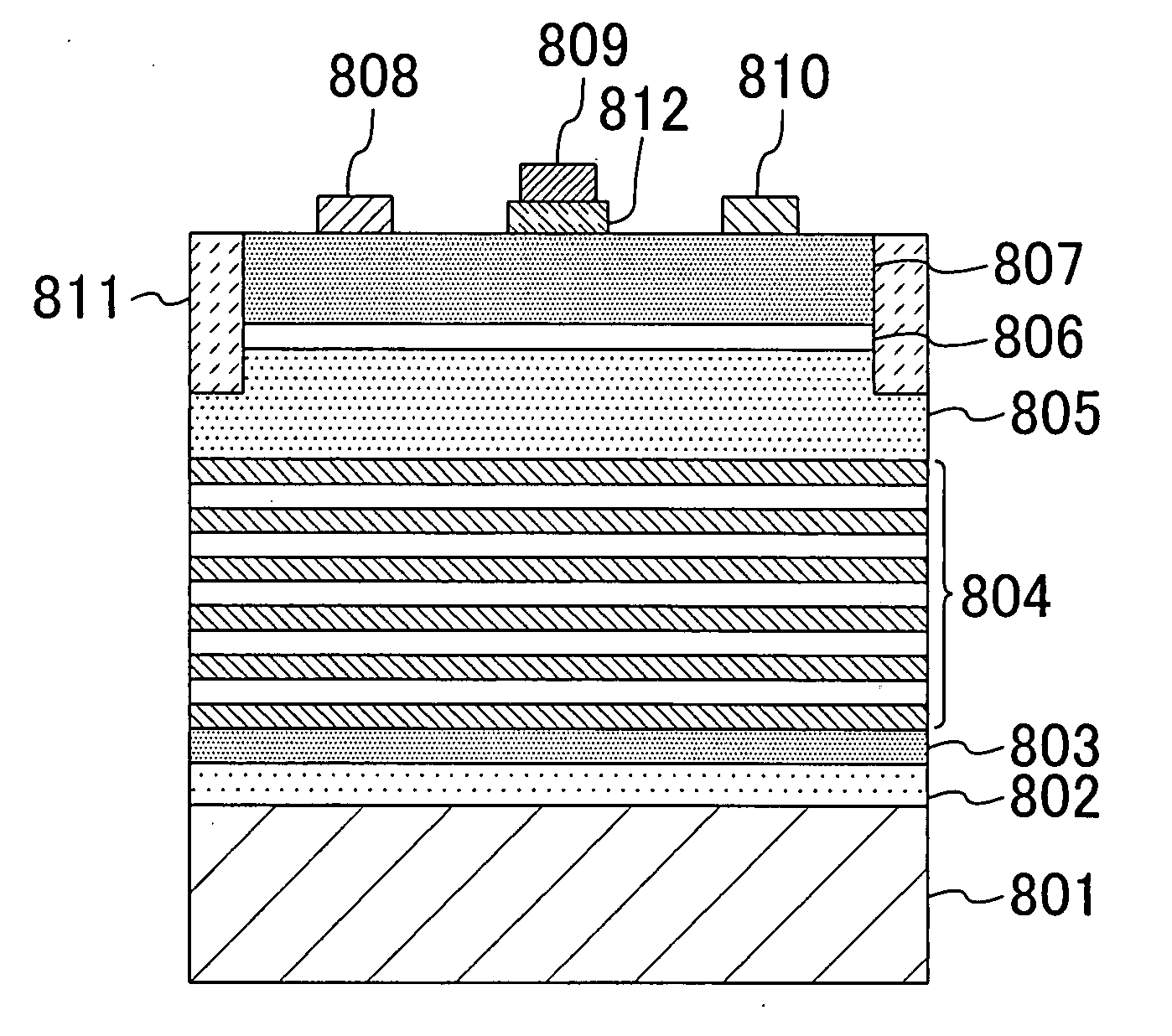

Aspects of the present invention provide an enhancement mode (E-mode) insulated gate (IG) double heterostructure field-effect transistor (DHFET) having low power consumption at zero gate bias, low gate currents, and / or high reliability. An E-mode HFET in accordance with an embodiment of the invention includes: top and bottom barrier layers; and a channel layer sandwiched between the bottom and the top barrier layers, wherein the bottom and top barrier layers have a larger bandgap than the channel layer, and wherein polarization charges of the bottom barrier layer deplete the channel layer and polarization charges of the top barrier layer induce carriers in the channel layer; and wherein a total polarization charge in the bottom barrier layer is larger than a total polarization charge in the top barrier layer such that the channel layer is substantially depleted at zero gate bias.

Owner:SENSOR ELECTRONICS TECH

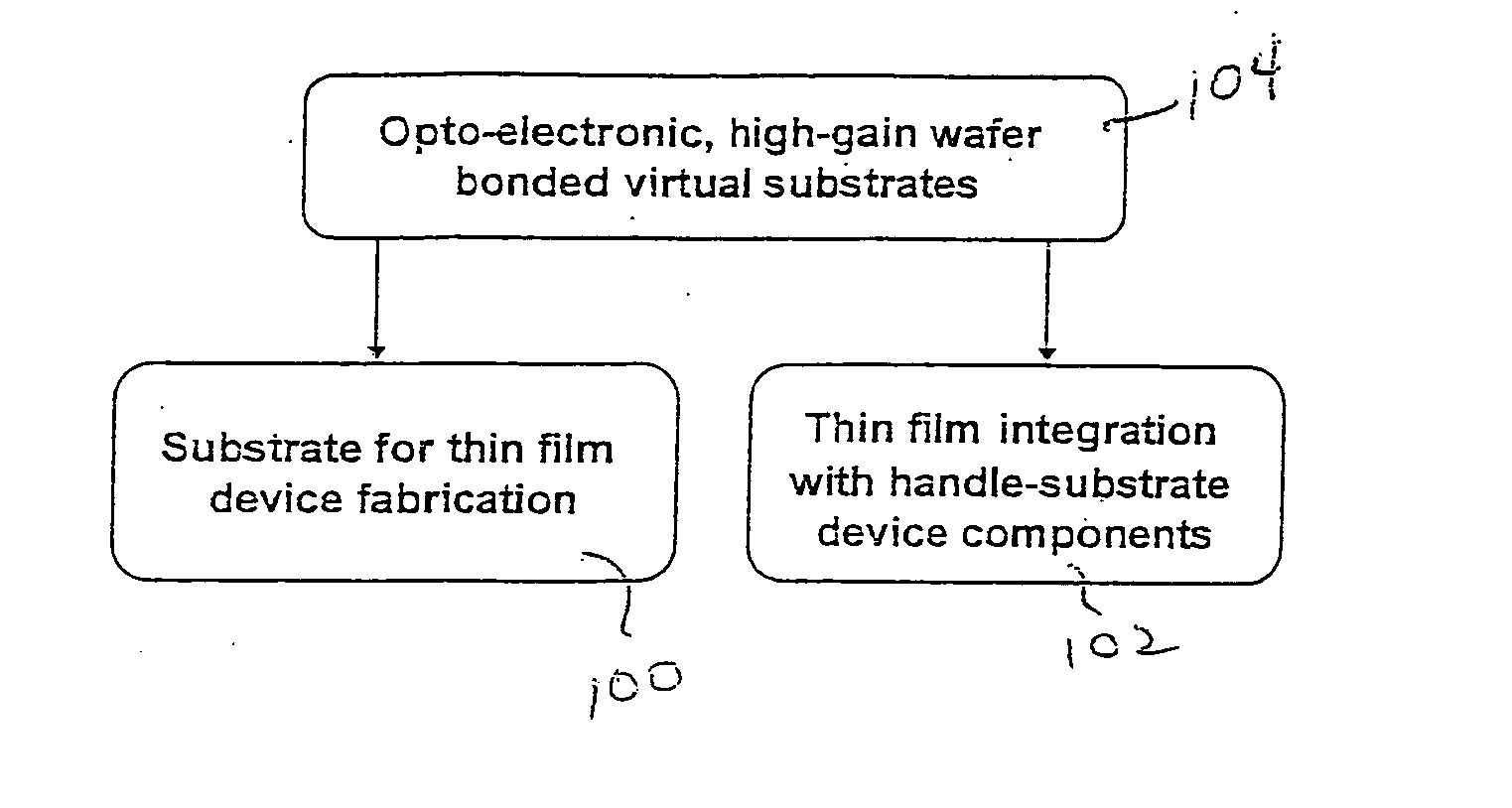

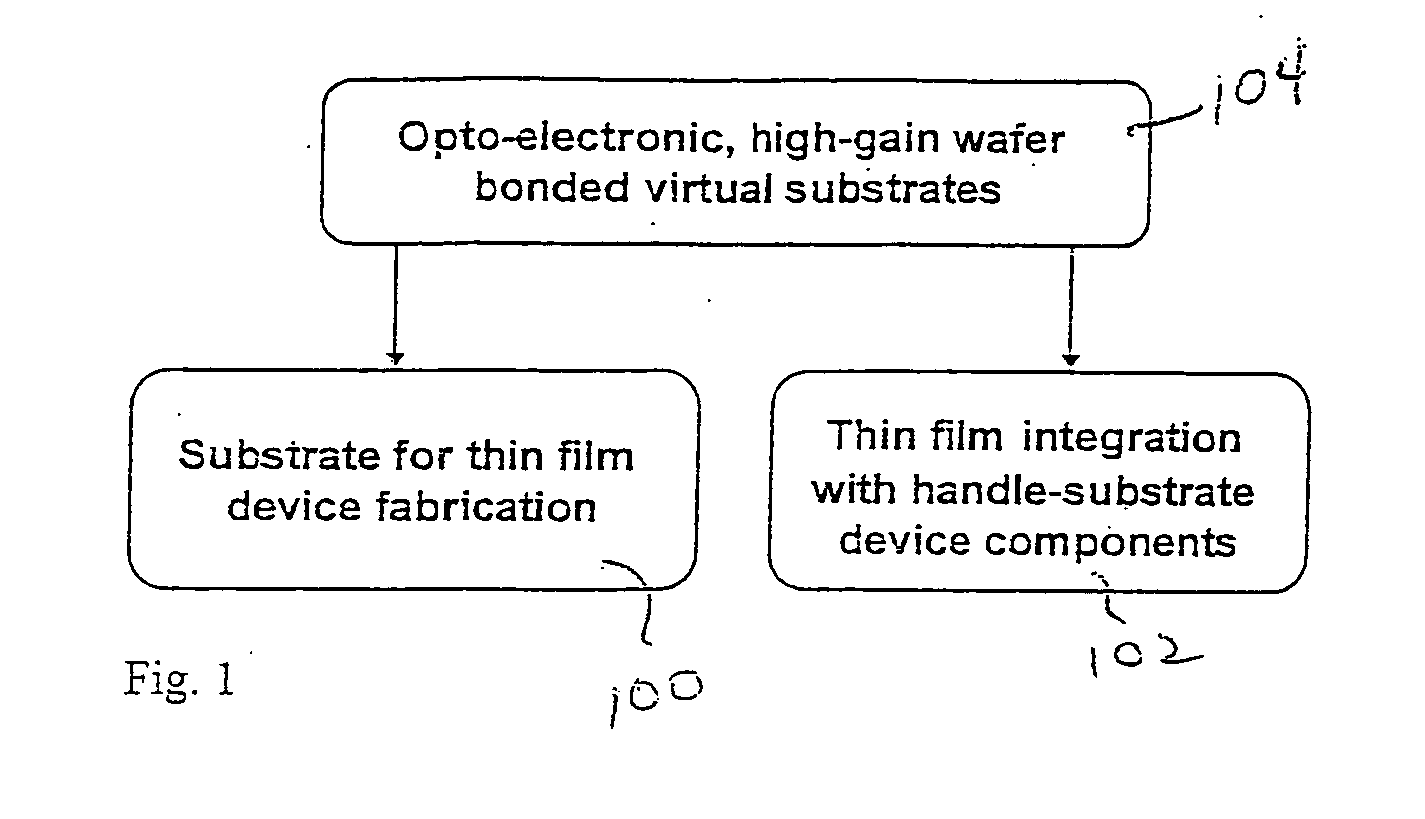

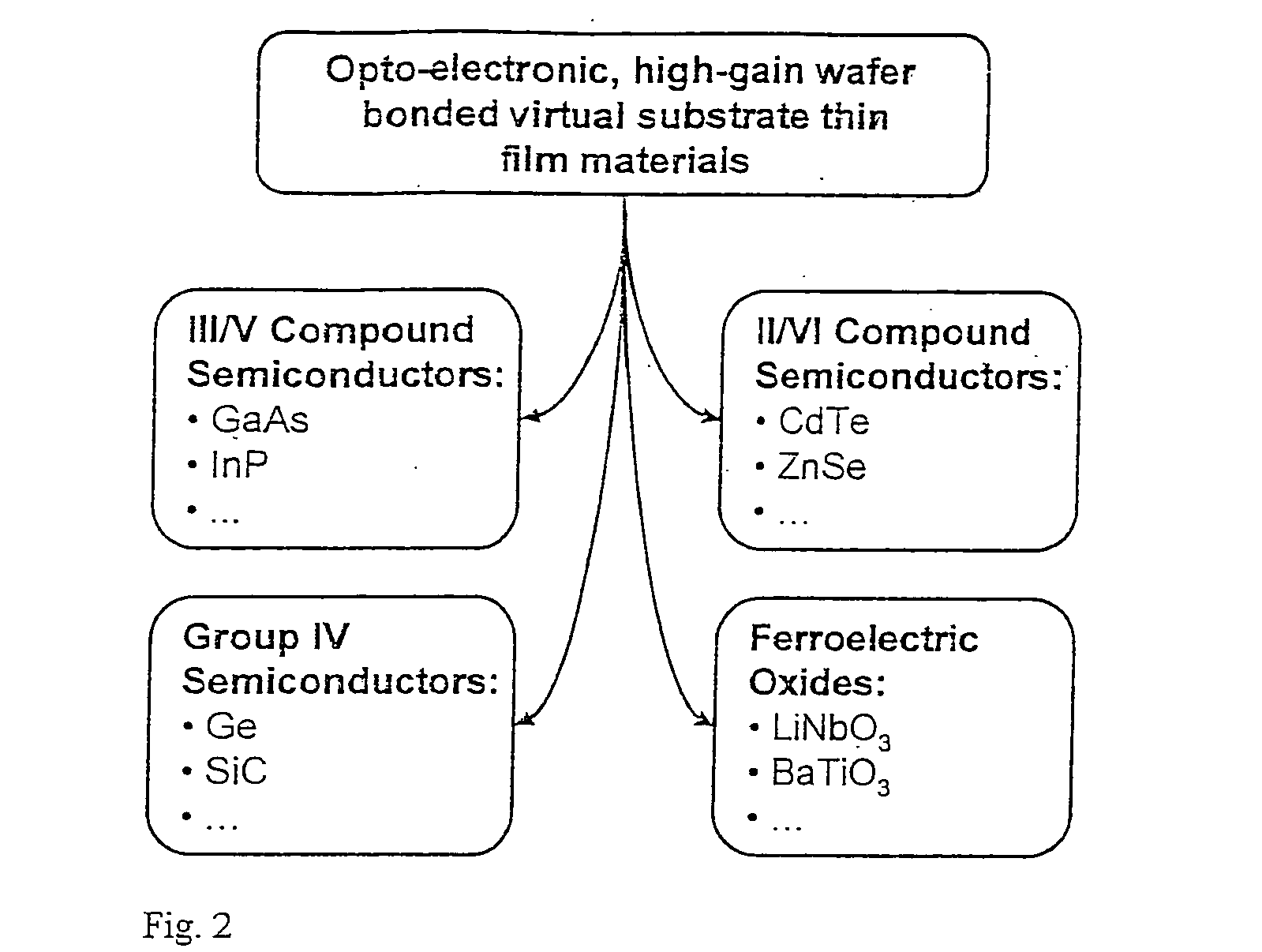

Wafer bonded epitaxial templates for silicon heterostructures

InactiveUS20050026432A1High mechanical strengthSimple methodSemiconductor/solid-state device manufacturingPhotovoltaic energy generationSingle crystalWafer bonding

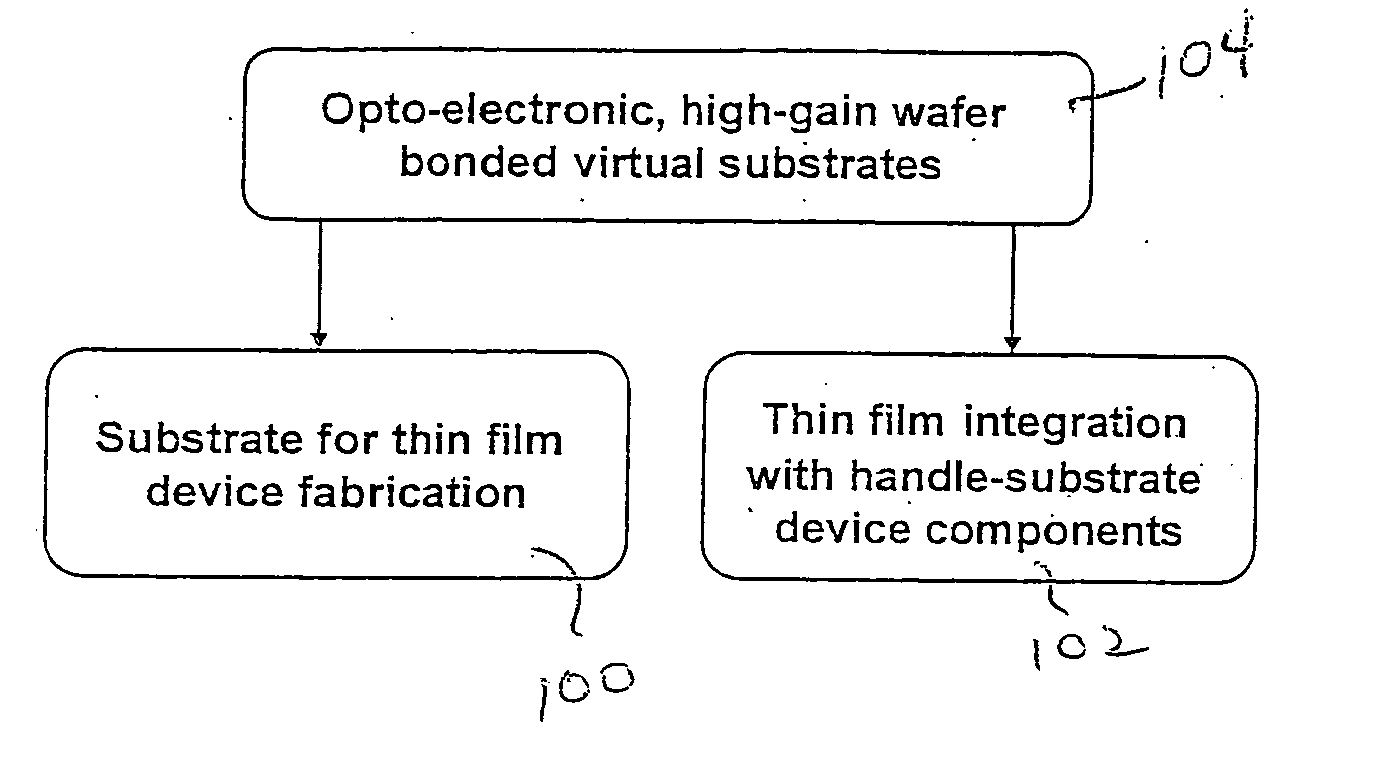

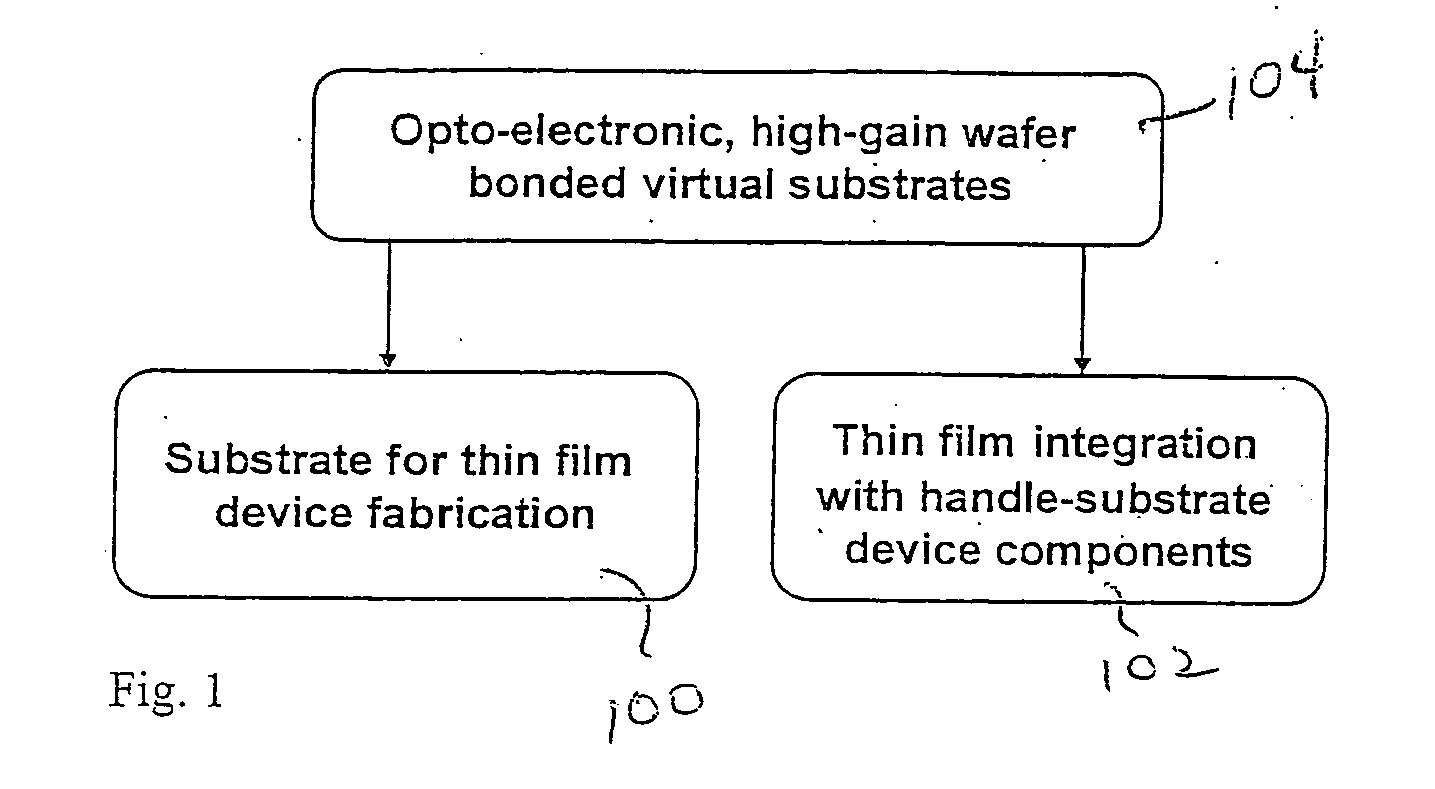

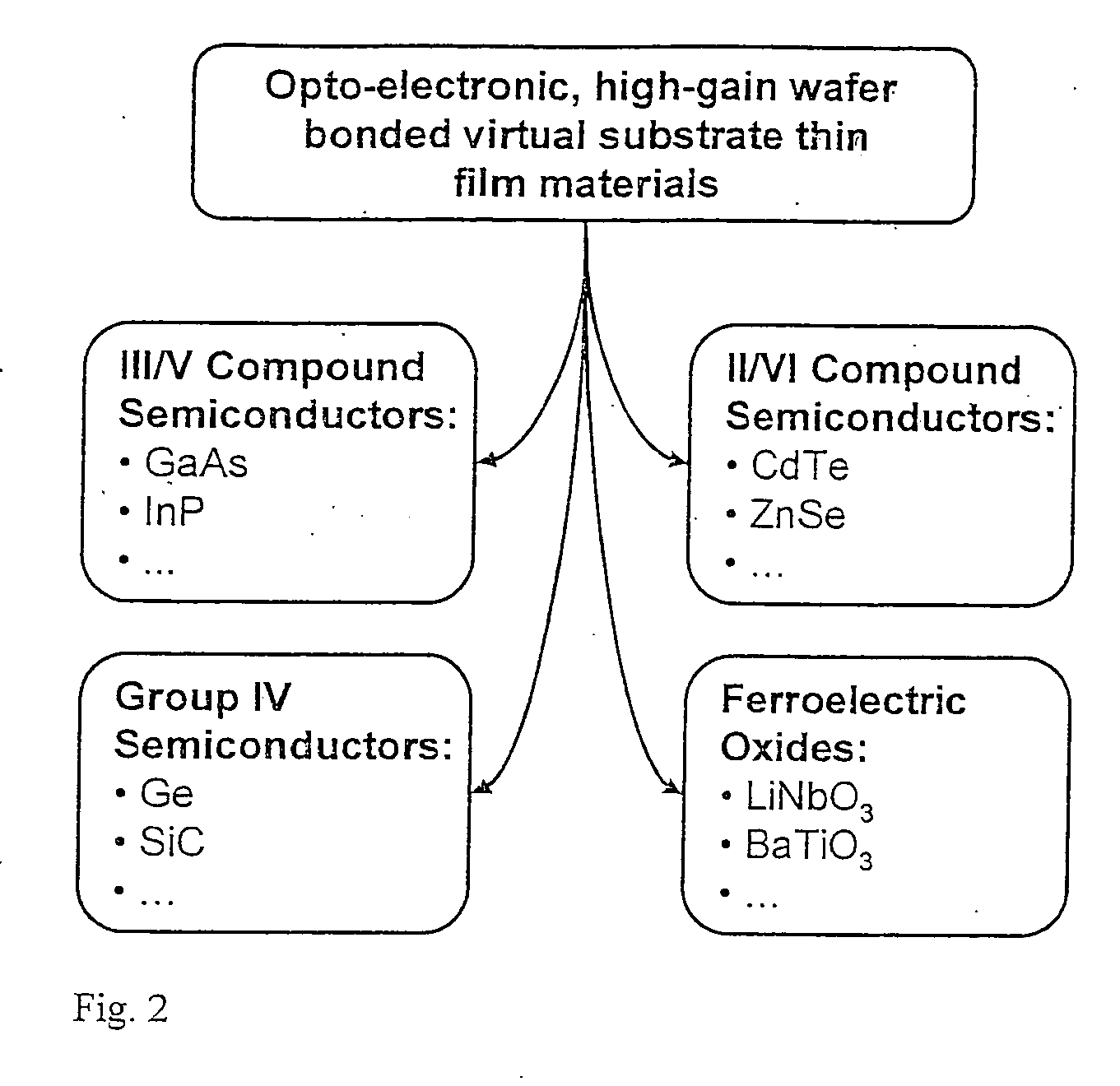

A heterostructure device layer is epitaxially grown on a virtual substrate, such as an InP / InGaAs / InP double heterostructure. A device substrate and a handle substrate form the virtual substrate. The device substrate is bonded to the handle substrate and is composed of a material suitable for fabrication of optoelectronic devices. The handle substrate is composed of a material suitable for providing mechanical support. The mechanical strength of the device and handle substrates is improved and the device substrate is thinned to leave a single-crystal film on the virtual substrate such as by exfoliation of a device film from the device substrate. An upper portion of the device film exfoliated from the device substrate is removed to provide a smoother and less defect prone surface for an optoelectronic device. A heterostructure is epitaxially grown on the smoothed surface in which an optoelectronic device may be fabricated.

Owner:CALIFORNIA INST OF TECH

Metal oxide semiconductor film structures and methods

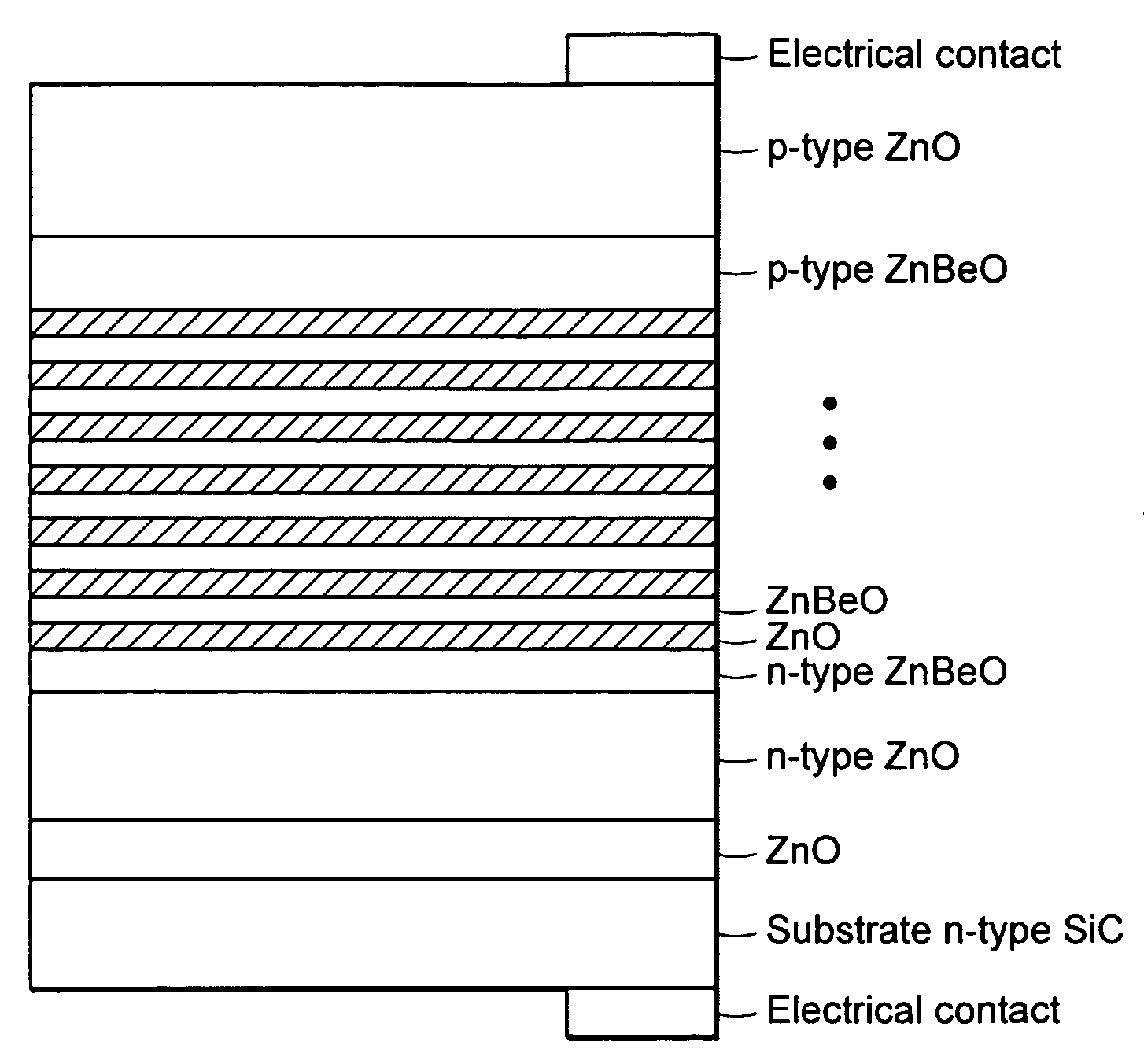

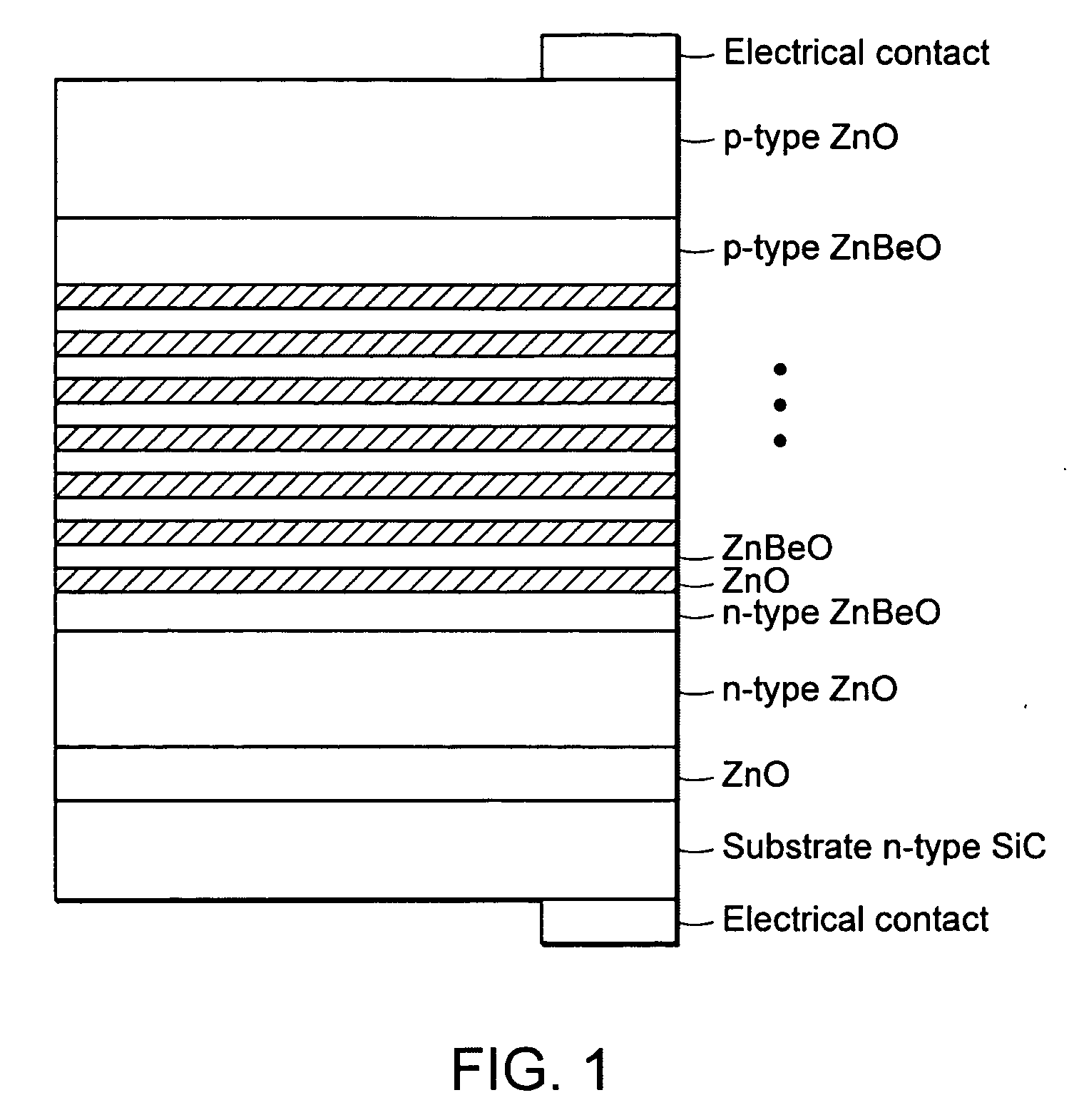

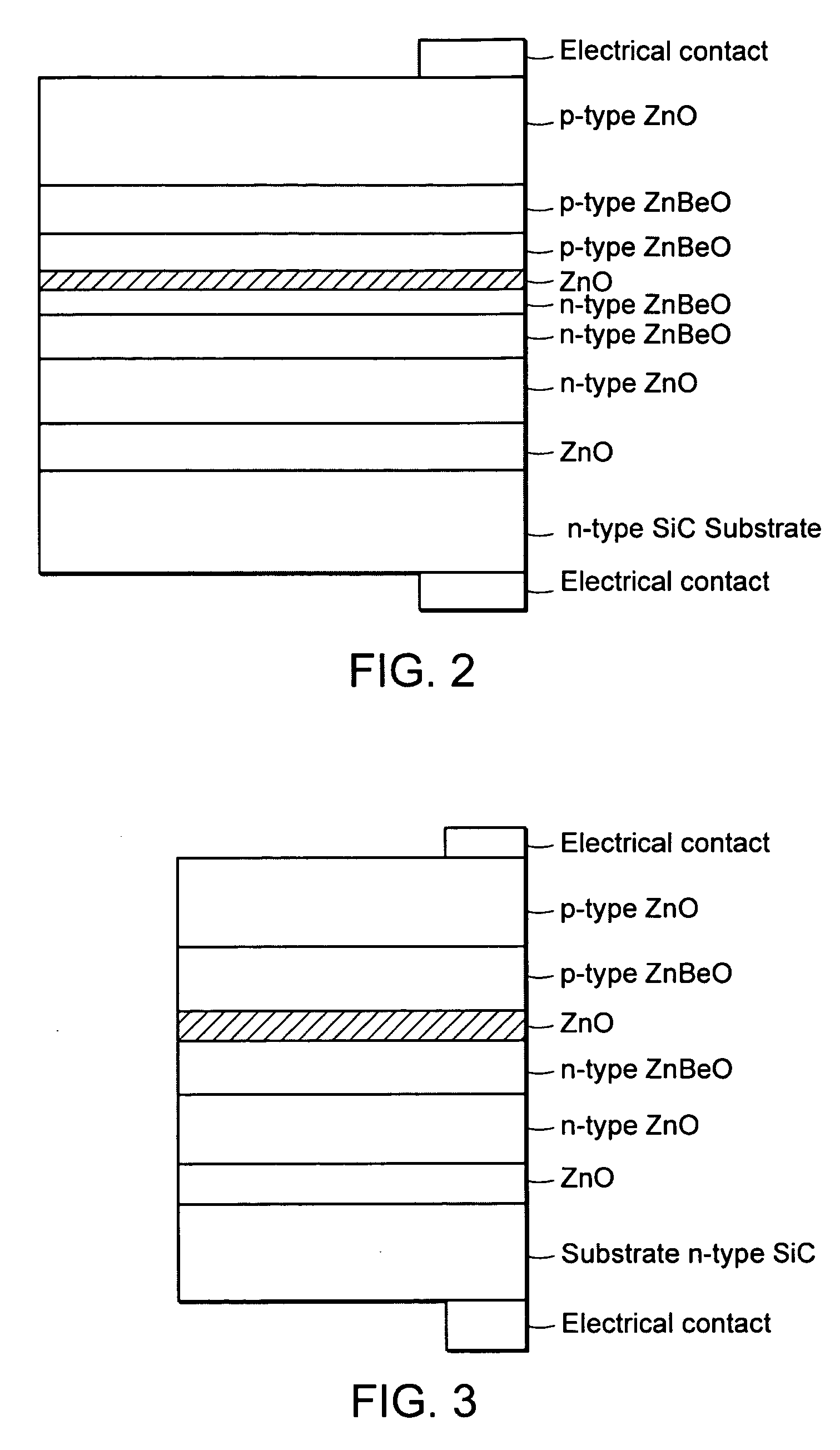

InactiveUS20070126021A1Lower bandgapLaser active region structureNanoopticsDevice materialSemiconductor

Layered and film structures for improving the performance of semiconductor devices include single and multiple quantum wells and double heterostructures and superlattice structures.

Owner:MOXTRONICS

Wafer bonded epitaxial templates for silicon heterostructures

InactiveUS20050142879A1High mechanical strengthSmoother and less defect proneSemiconductor/solid-state device manufacturingPhotovoltaic energy generationEngineeringSingle crystal

A heterostructure device layer is epitaxially grown on a virtual substrate, such as an InP / InGaAs / InP double heterostructure. A device substrate and a handle substrate form the virtual substrate. The device substrate is bonded to the handle substrate and is composed of a material suitable for fabrication of optoelectronic devices. The handle substrate is composed of a material suitable for providing mechanical support. The mechanical strength of the device and handle substrates is improved and the device substrate is thinned to leave a single-crystal film on the virtual substrate such as by exfoliation of a device film from the device substrate. An upper portion of the device film exfoliated from the device substrate is removed to provide a smoother and less defect prone surface for an optoelectronic device. A heterostructure is epitaxially grown on the smoothed surface in which an optoelectronic device may be fabricated.

Owner:CALIFORNIA INST OF TECH

Enhancement mode insulated gate heterostructure field-effect transistor with electrically isolated RF-enhanced source contact

Aspects of the present invention provide an enhancement mode (E-mode) insulated gate (IG) double heterostructure field-effect transistor (DHFET) having low power consumption at zero gate bias, low gate currents, and / or high reliability. An E-mode HFET in accordance with an embodiment of the invention includes: top and bottom barrier layers; and a channel layer sandwiched between the bottom and the top barrier layers, wherein the bottom and top barrier layers have a larger bandgap than the channel layer, and wherein polarization charges of the bottom barrier layer deplete the channel layer and polarization charges of the top barrier layer induce carriers in the channel layer; and wherein a total polarization charge in the bottom barrier layer is larger than a total polarization charge in the top barrier layer such that the channel layer is substantially depleted at zero gate bias.

Owner:SENSOR ELECTRONICS TECH

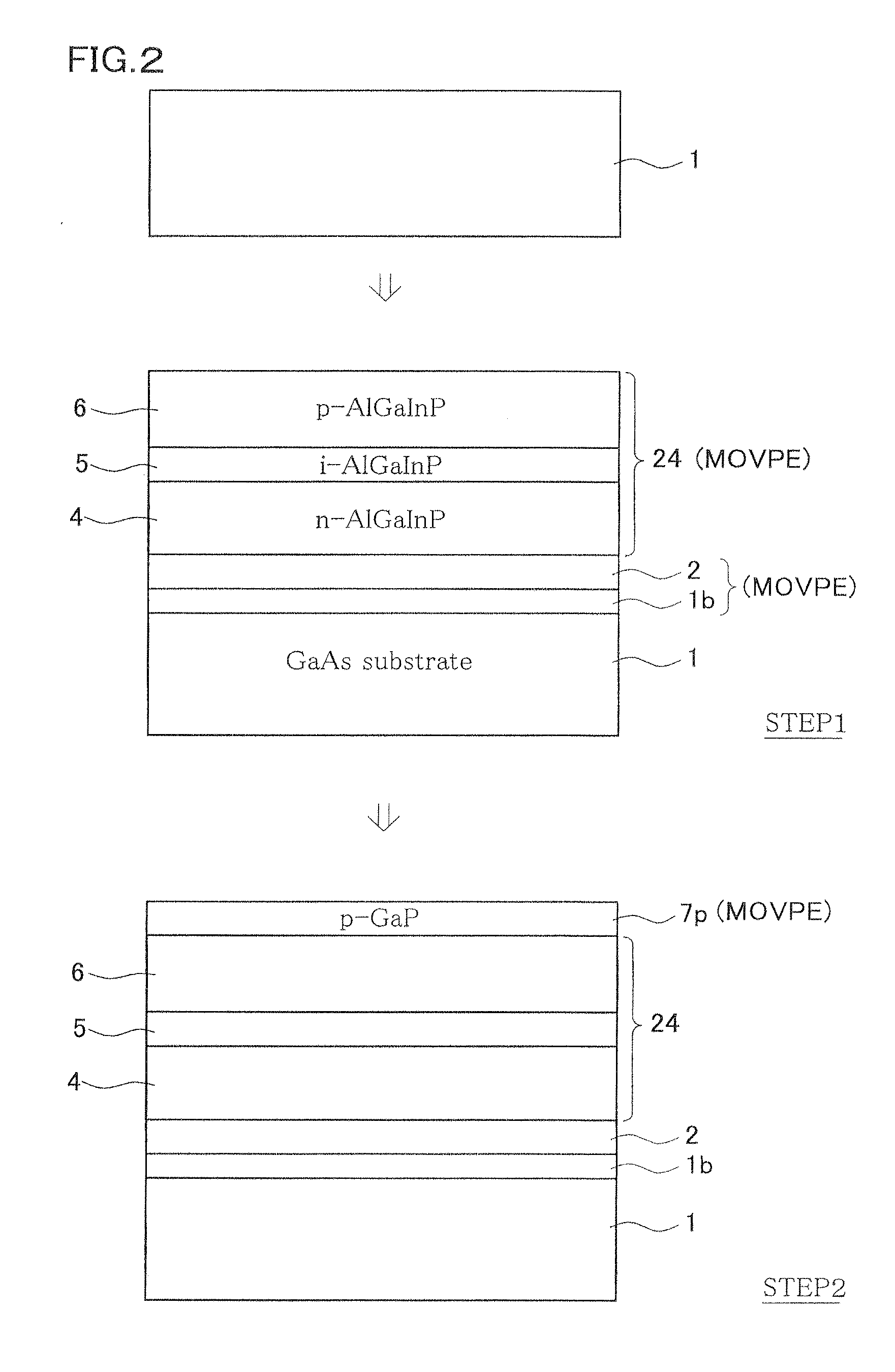

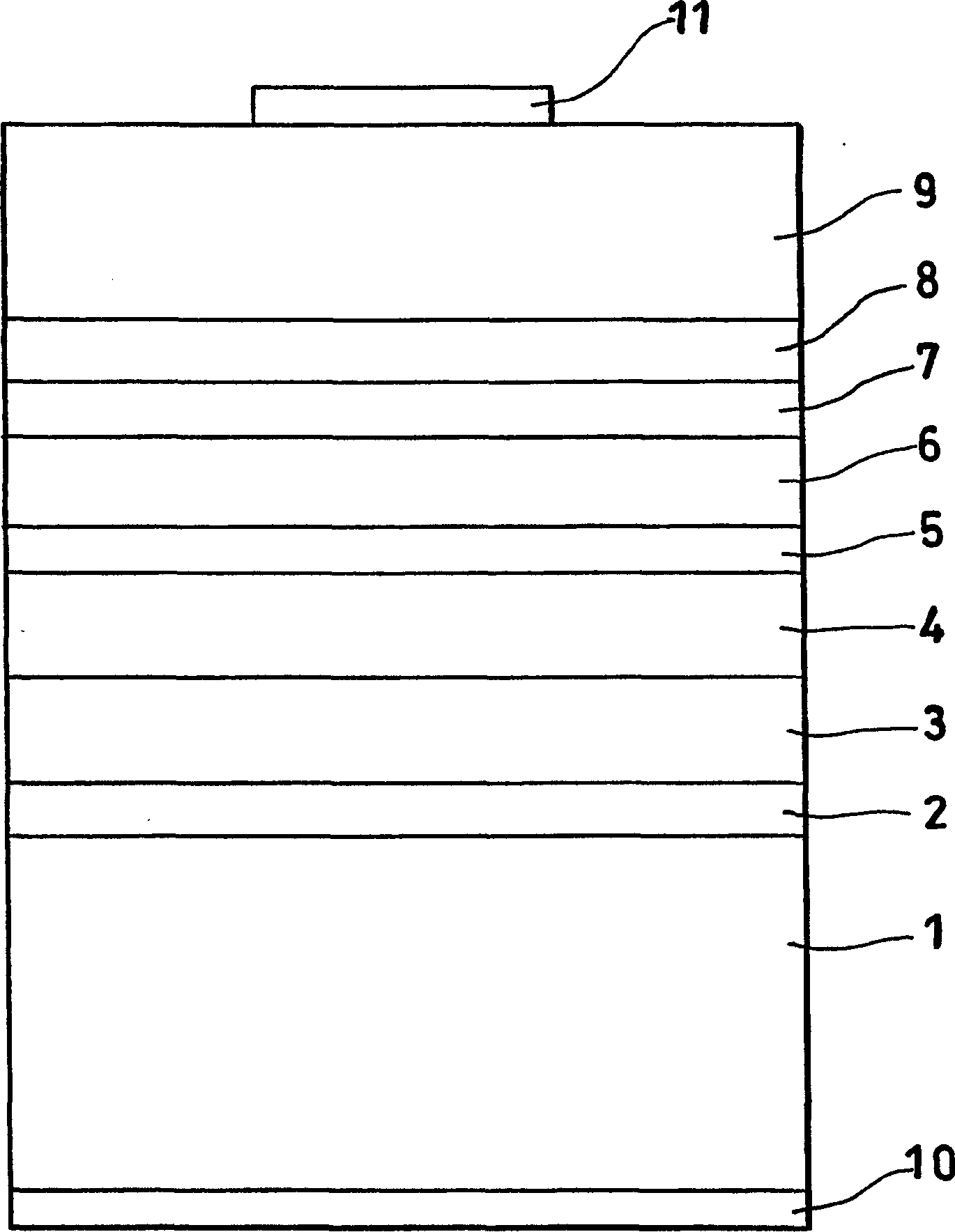

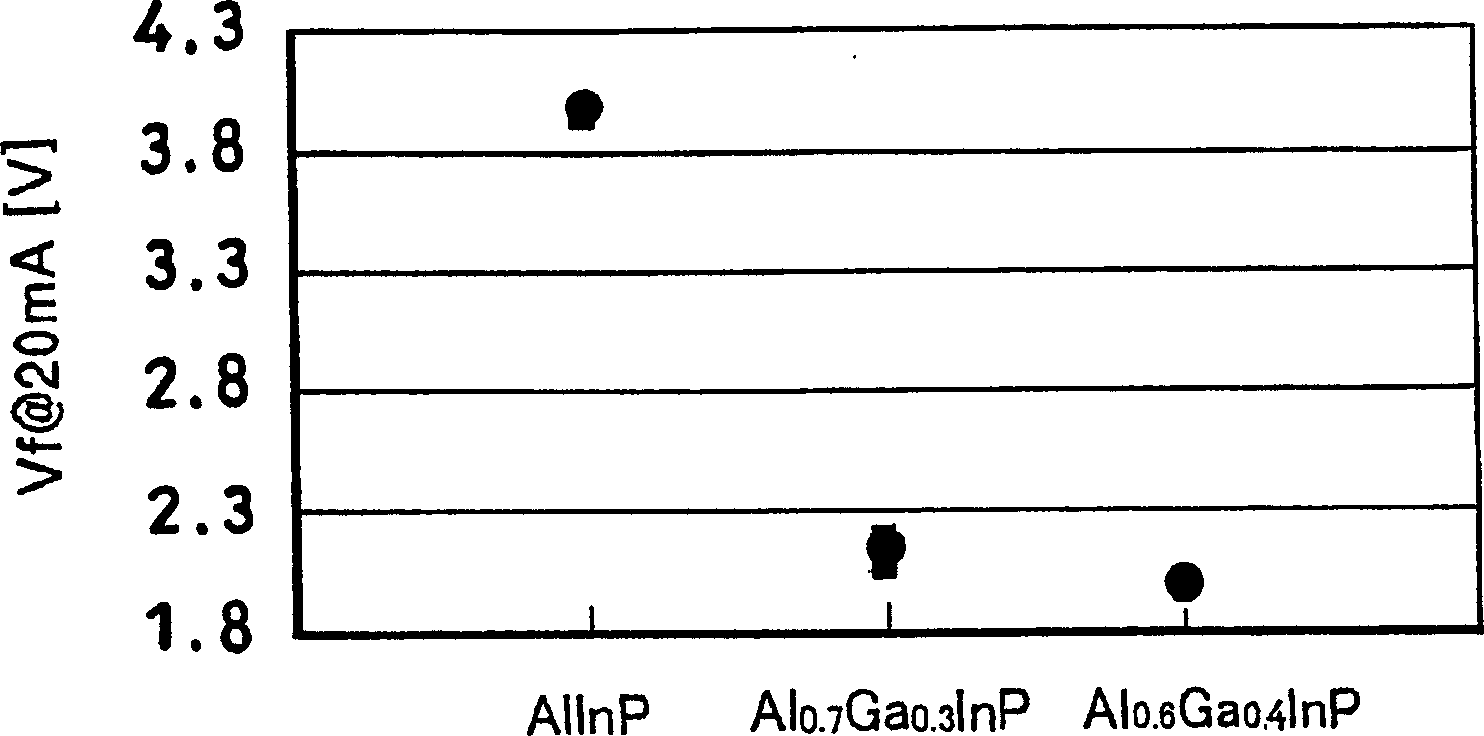

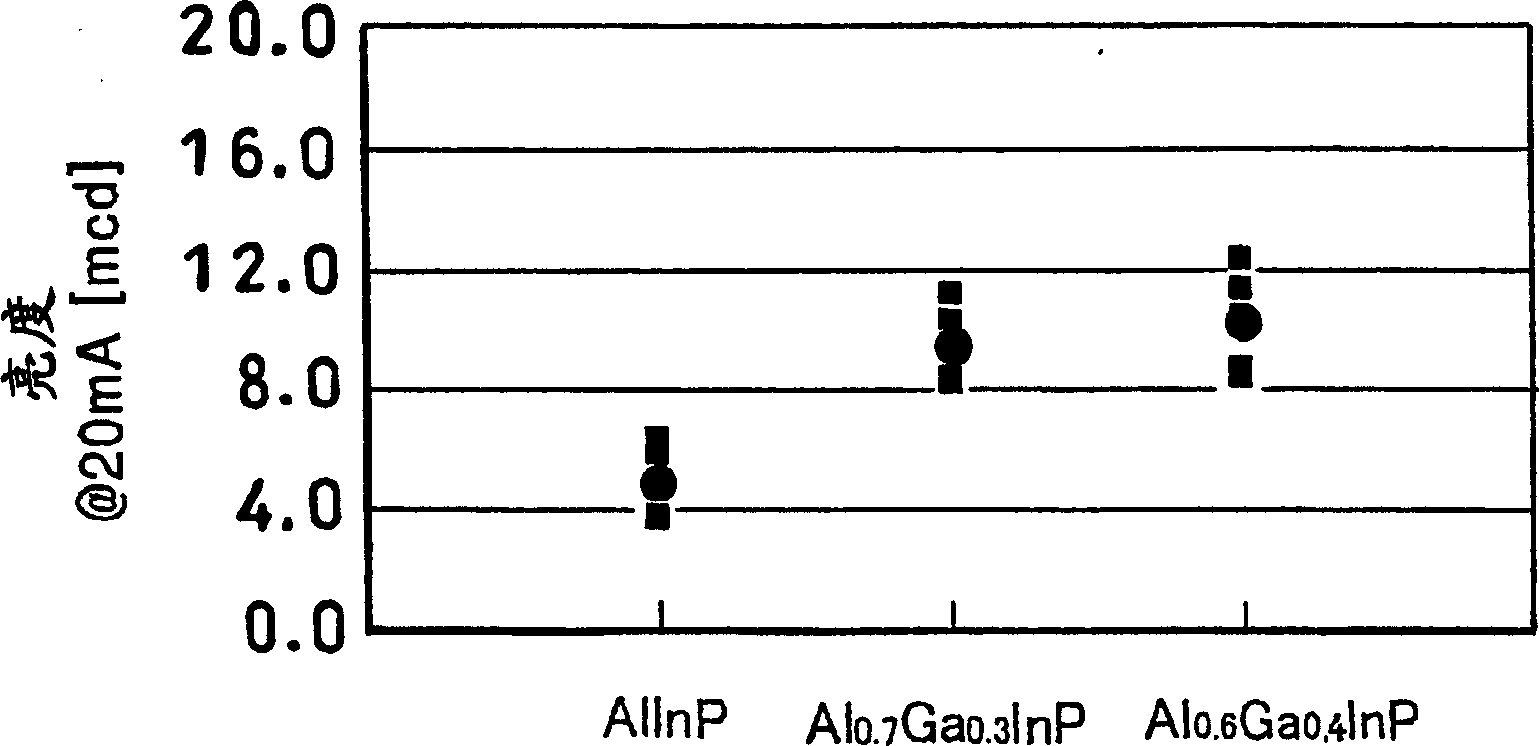

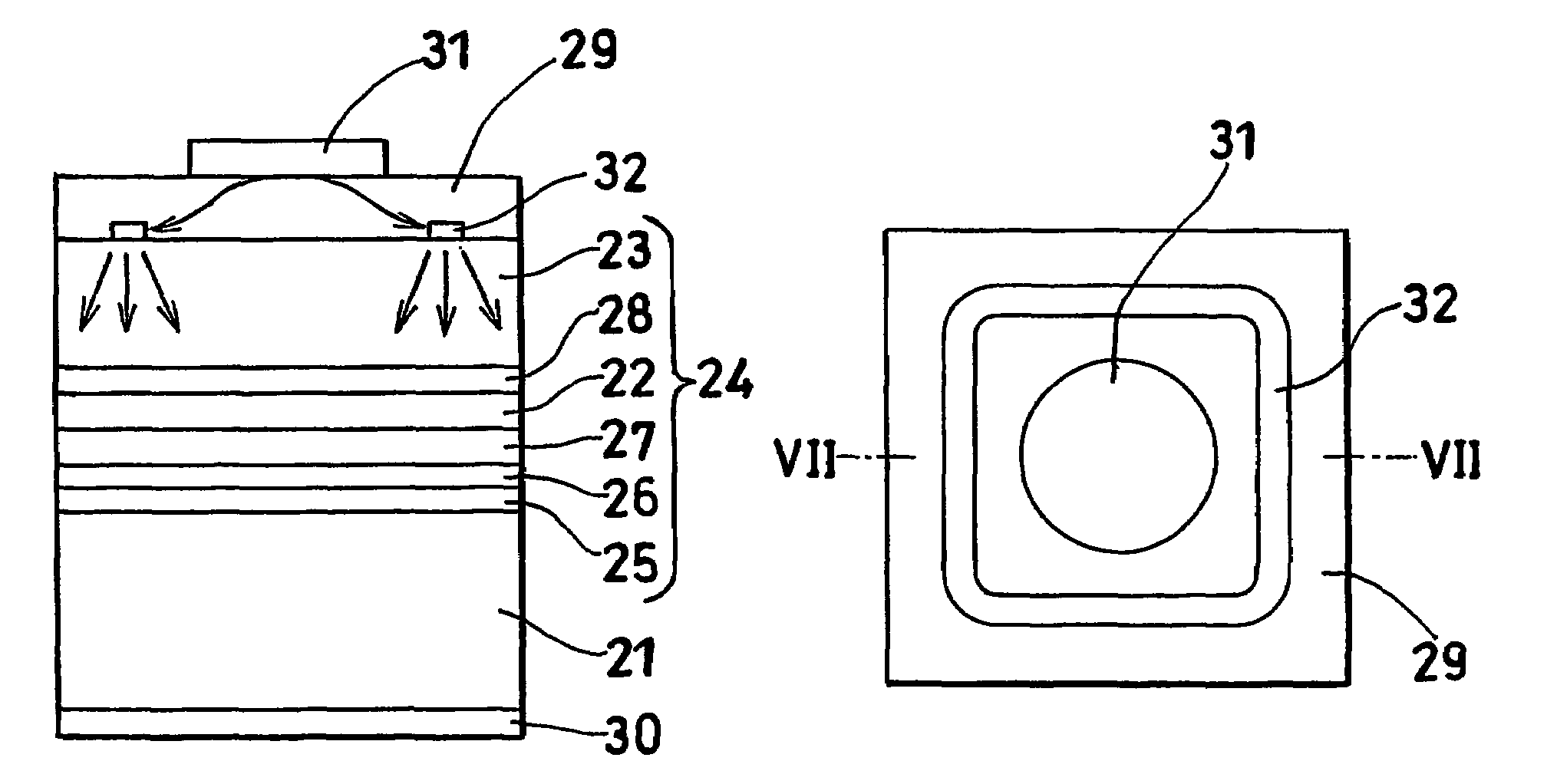

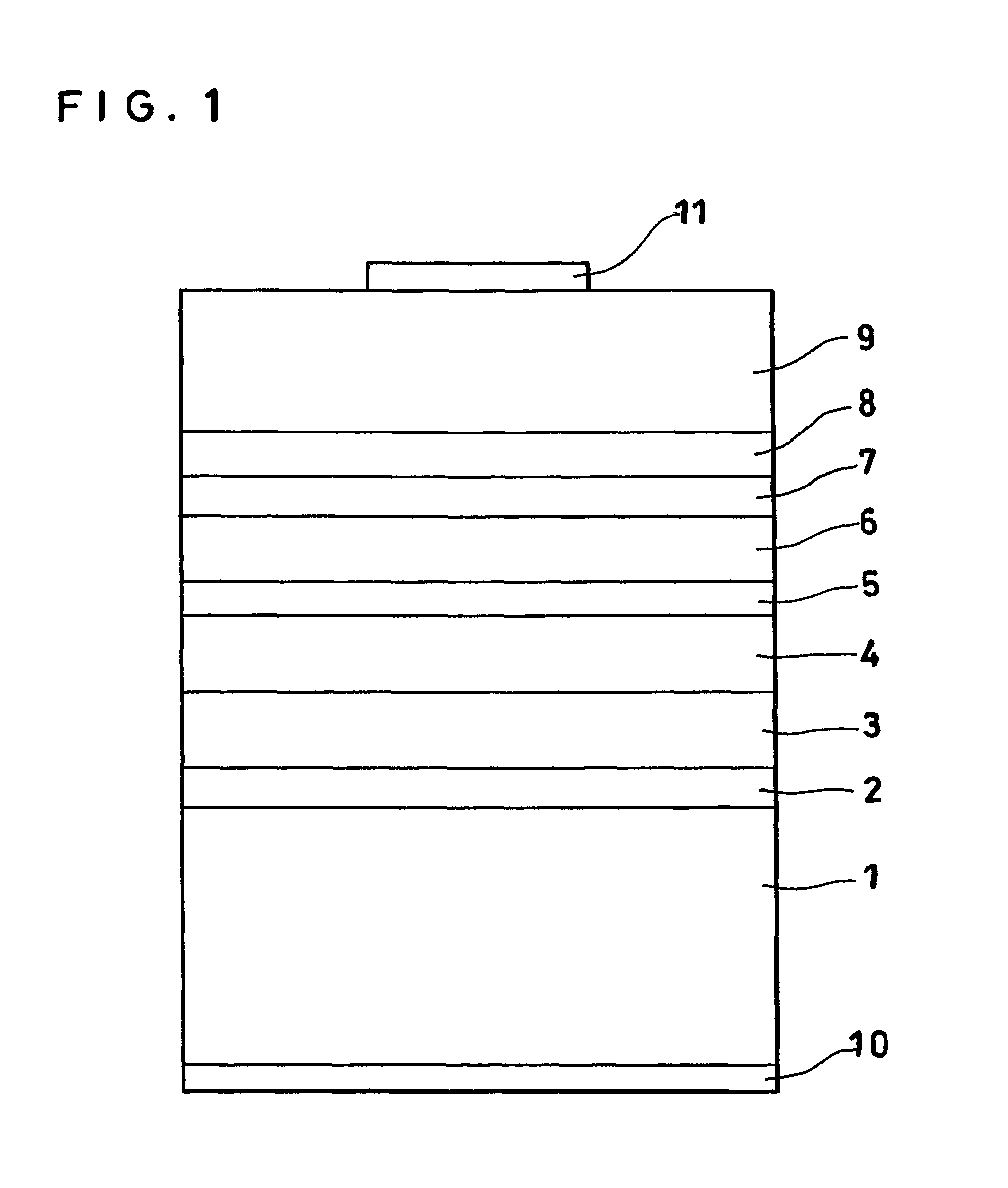

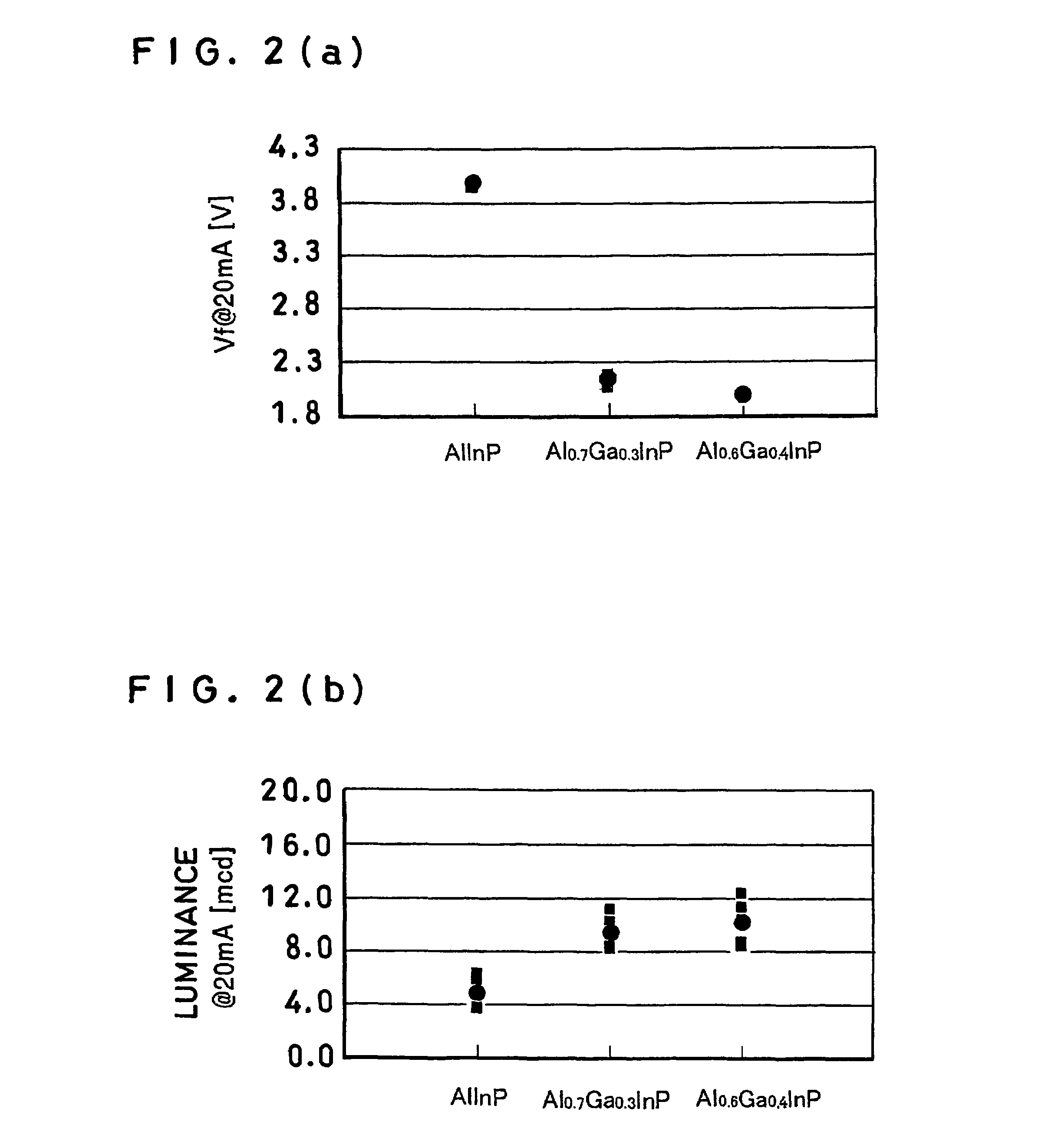

Light-emitting diode device and production method thereof

InactiveUS20060163603A1High precisionHigh crystallinitySemiconductor/solid-state device manufacturingSemiconductor devicesCrystallinityLight-emitting diode

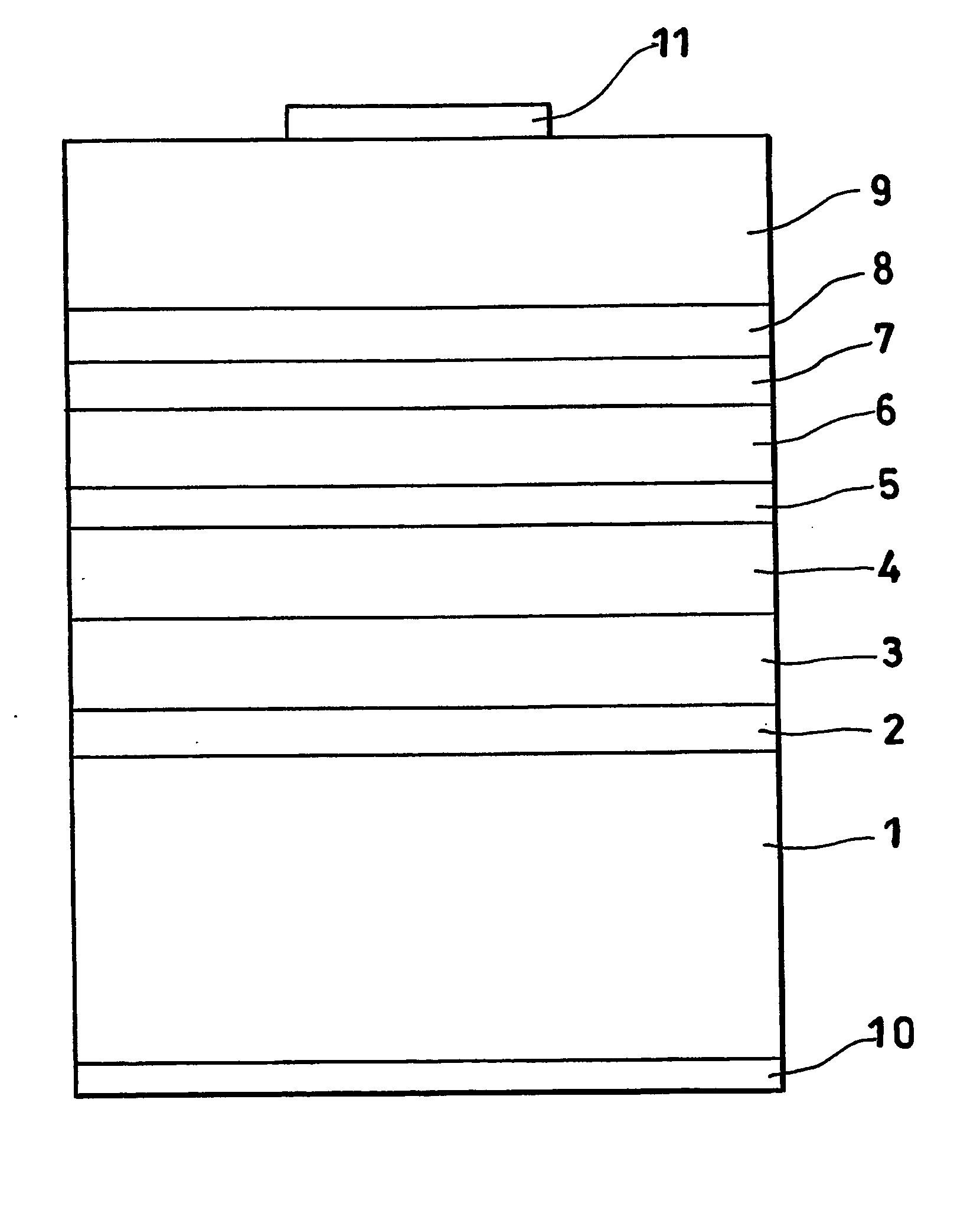

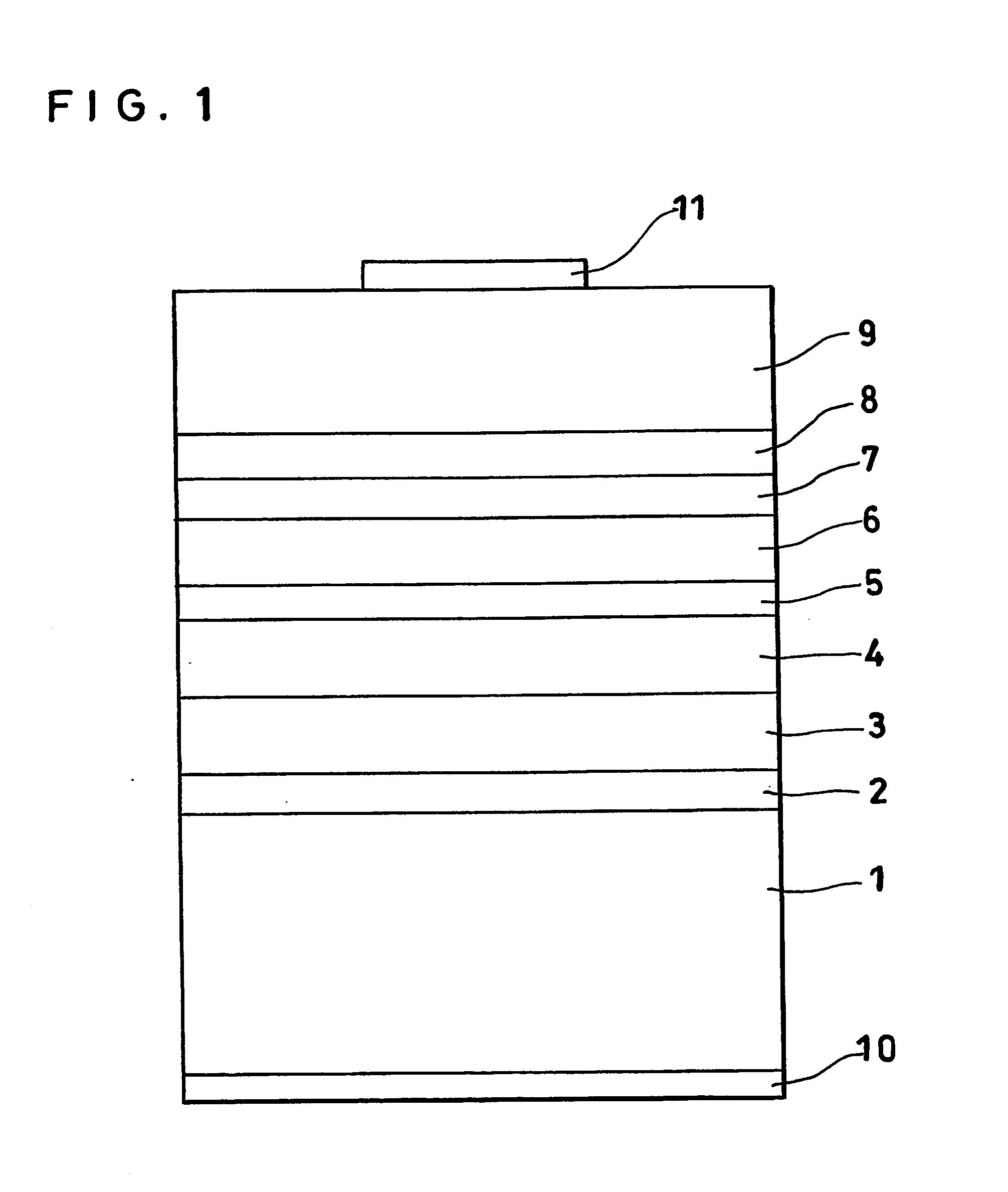

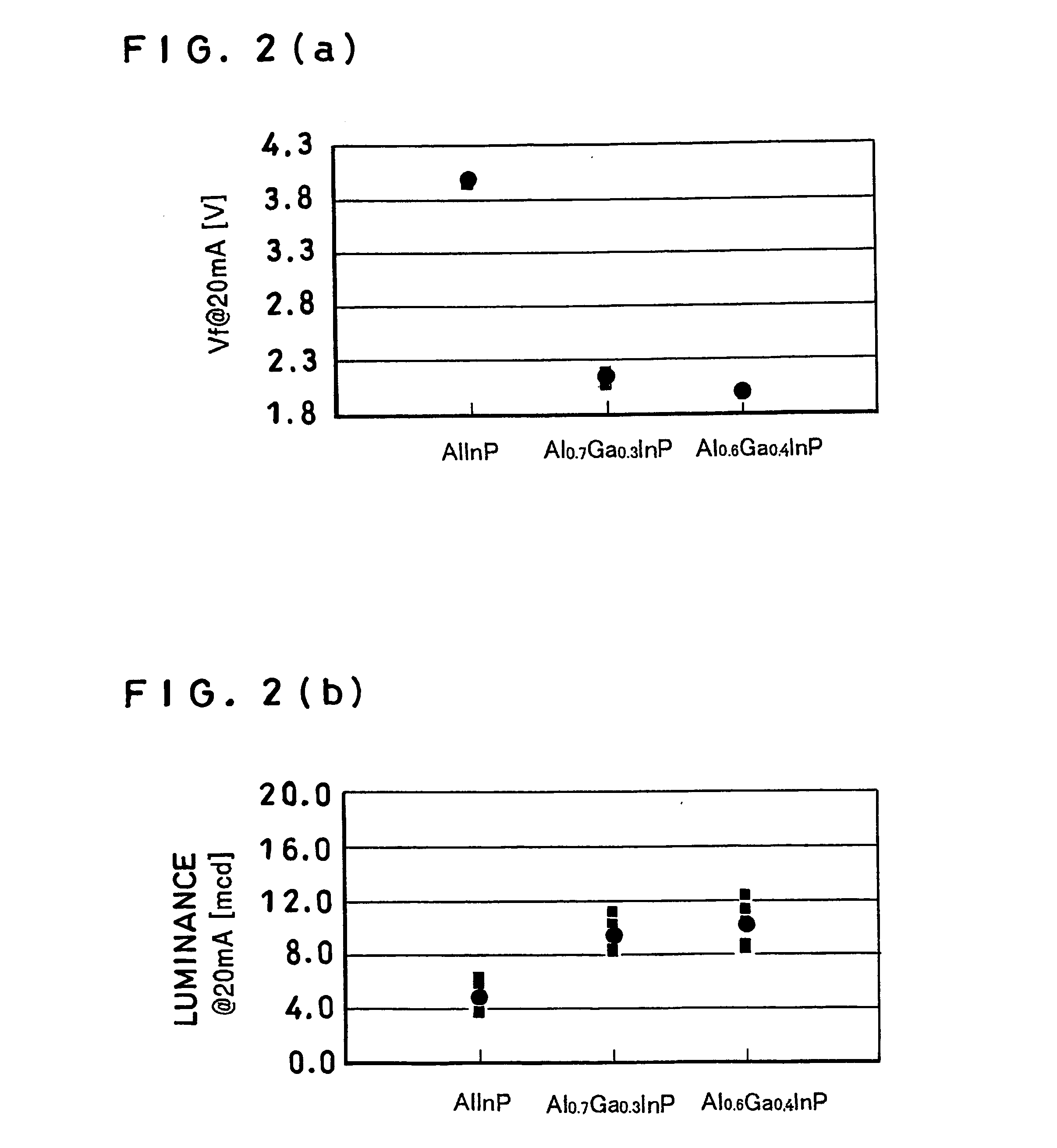

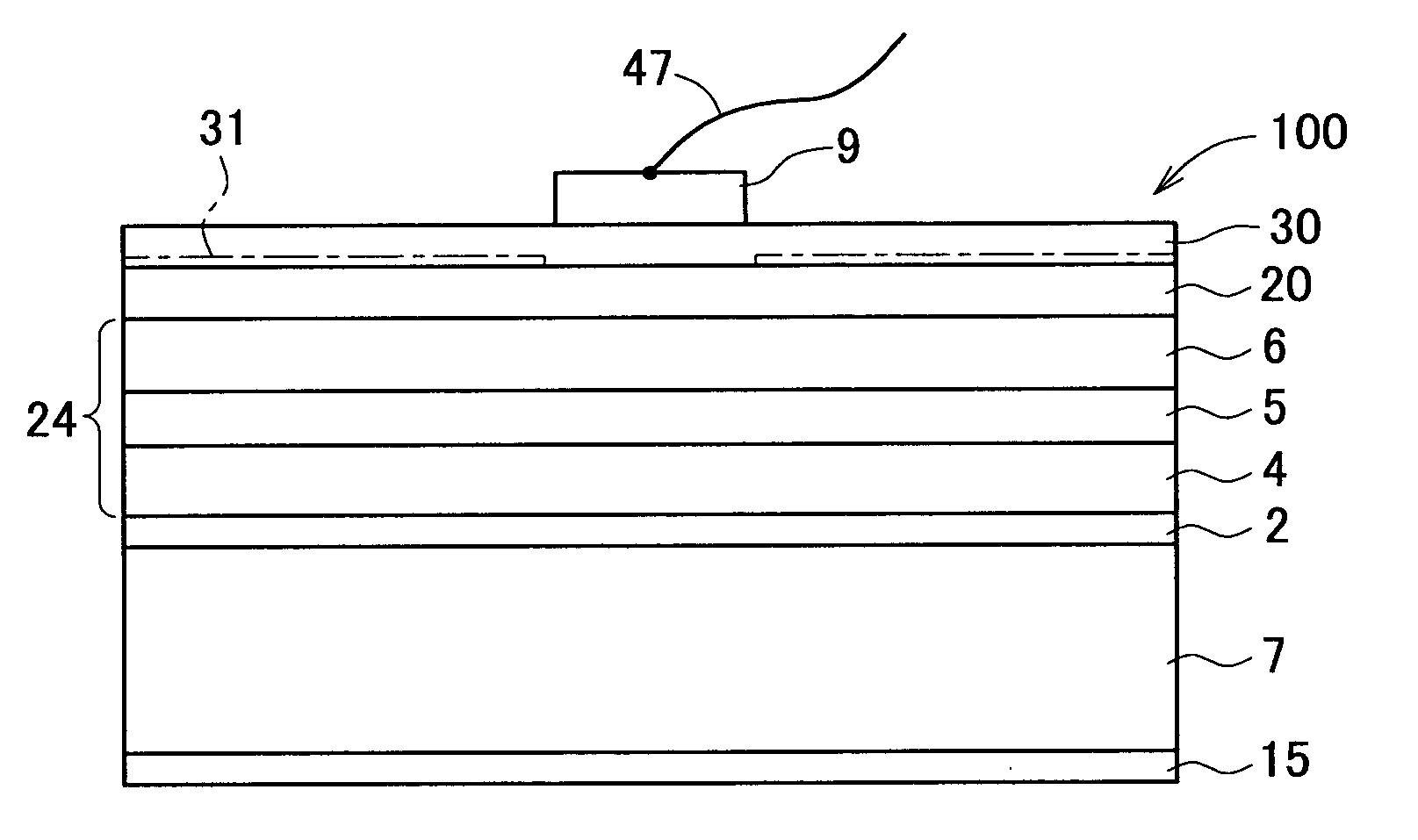

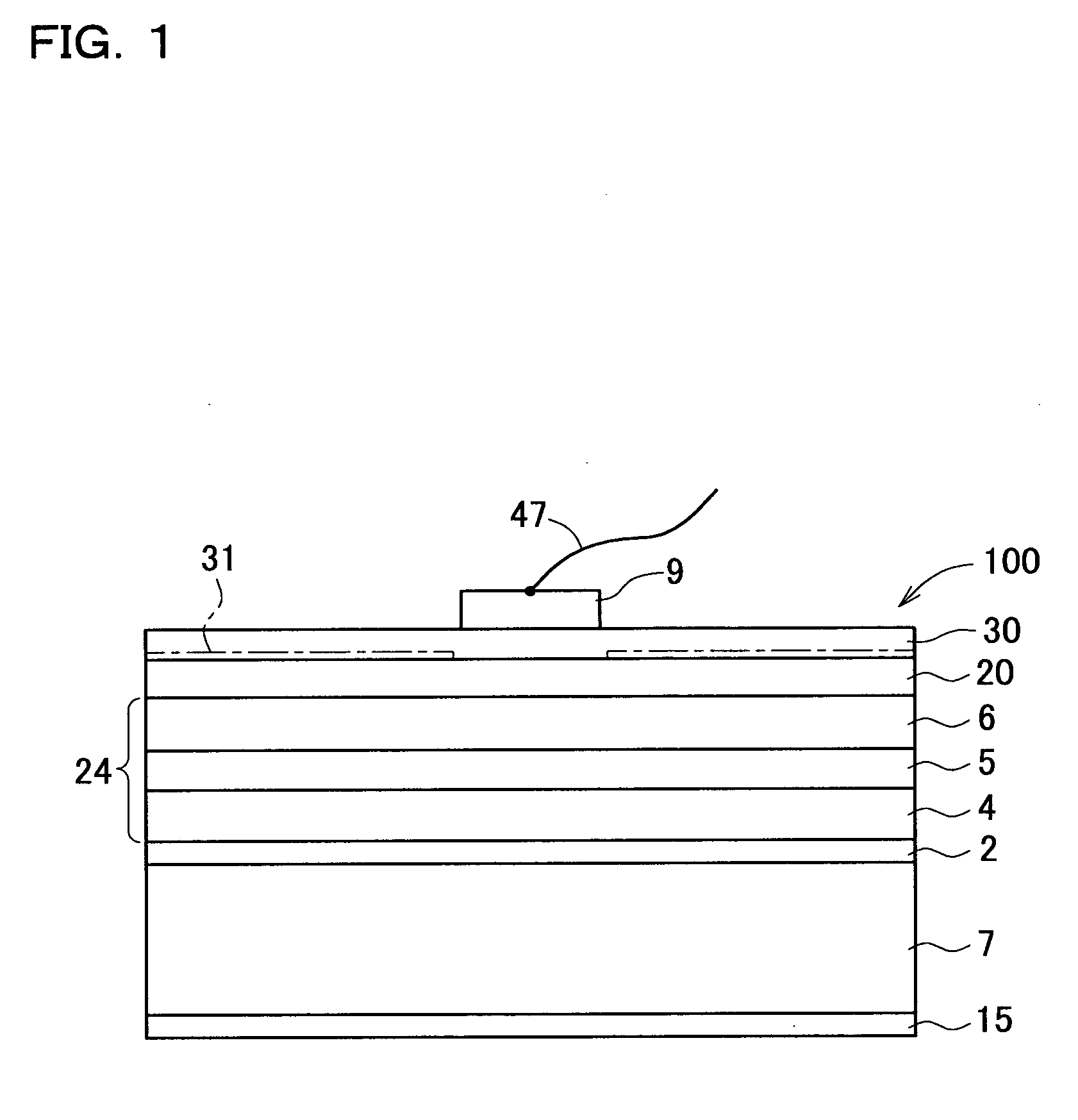

A double hetero structure light-emitting diode device includes an active layer (6), a positive-electrode-side cladding layer, a negative-electrode-side cladding layer (4), a window layer (9) and an undoped AlInP layer. The positive-electrode-side cladding layer includes an undoped AlInP layer (7) grown to have a thickness of 0.5 μm and an intermediate layer (8) doped to assume p-type conductivity and having an intermediate energy band gap value between that of the undoped AlInP layer and that of the window layer. The window layer on the intermediate layer is a GaP layer grown at 730° C. or higher and at a growth rate of 7.8 μm / hour or more in the presence of Ze serving as a dopant. The negative-electrode-side cladding layer is provided with an undoped AlInP layer (5) having a thickness of 0.1 μm or more. With this configuration, there is provided a light-emitting diode device that enhances the crystallinity of a window layer, prevents generation of faults caused by a high-temperature process and attains high luminance at a wavelength falling within a yellow-green band.

Owner:SHOWA DENKO KK

Method And System For Germanium-On-Silicon Photodetectors Without Germanium Layer Contacts

ActiveUS20160155884A1Microbiological testing/measurementMaterial analysis by optical meansPhotovoltaic detectorsPhotodetector

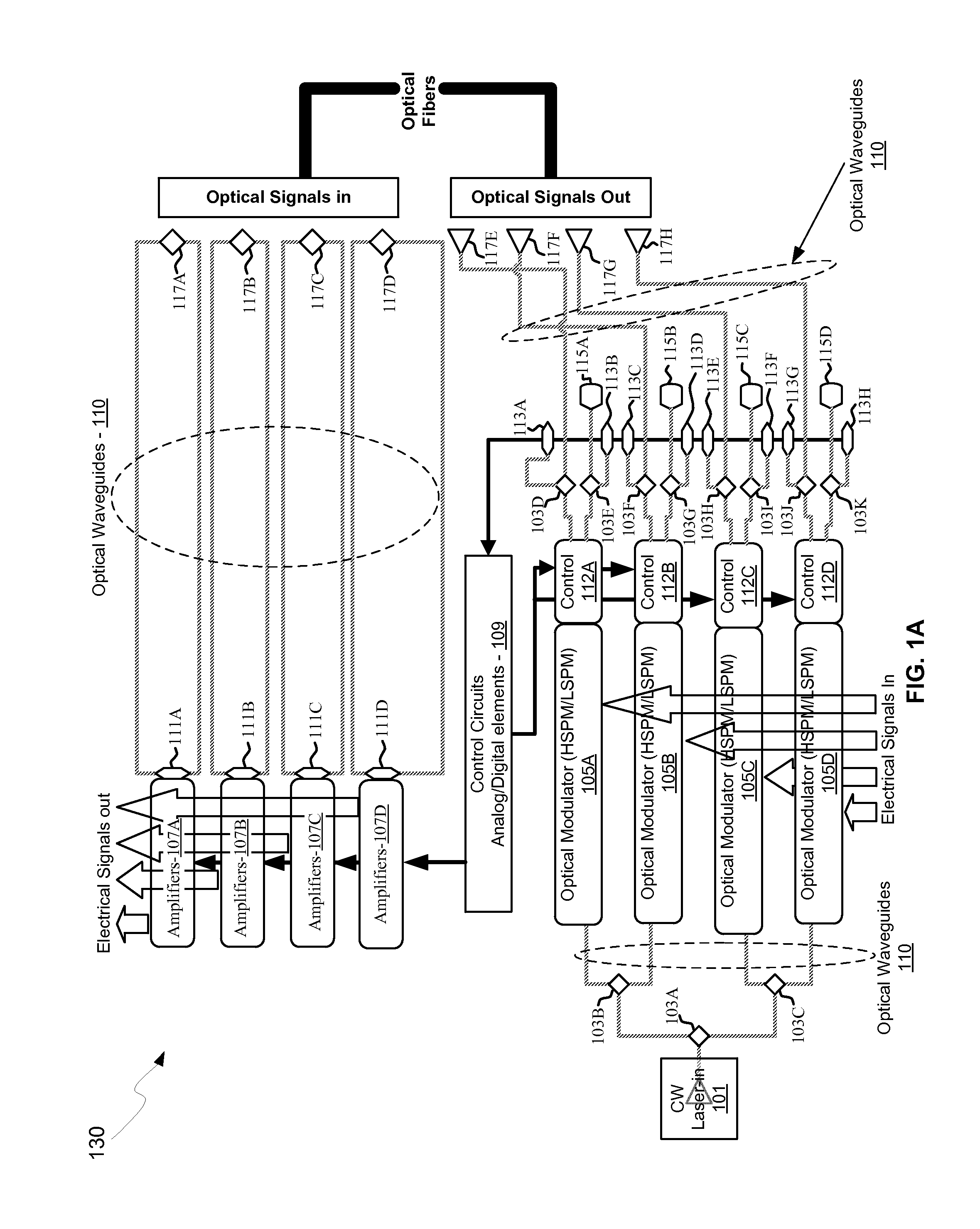

Methods and systems for germanium-on-silicon photodetectors without germanium layer contacts are disclosed and may include, in a semiconductor die having a photodetector, where the photodetector includes an n-type silicon layer, a germanium layer, a p-type silicon layer, and a metal contact on each of the n-type silicon layer and the p-type silicon layer: receiving an optical signal, absorbing the optical signal in the germanium layer, generating an electrical signal from the absorbed optical signal, and communicating the electrical signal out of the photodetector via the n-type silicon layer and the p-type silicon layer. The photodetector may include a horizontal or vertical junction double heterostructure where the germanium layer is above the n-type and p-type silicon layers. An intrinsically-doped silicon layer may be below the germanium layer between the n-type silicon layer and the p-type silicon layer. A top portion of the germanium layer may be p-doped.

Owner:CISCO TECH INC

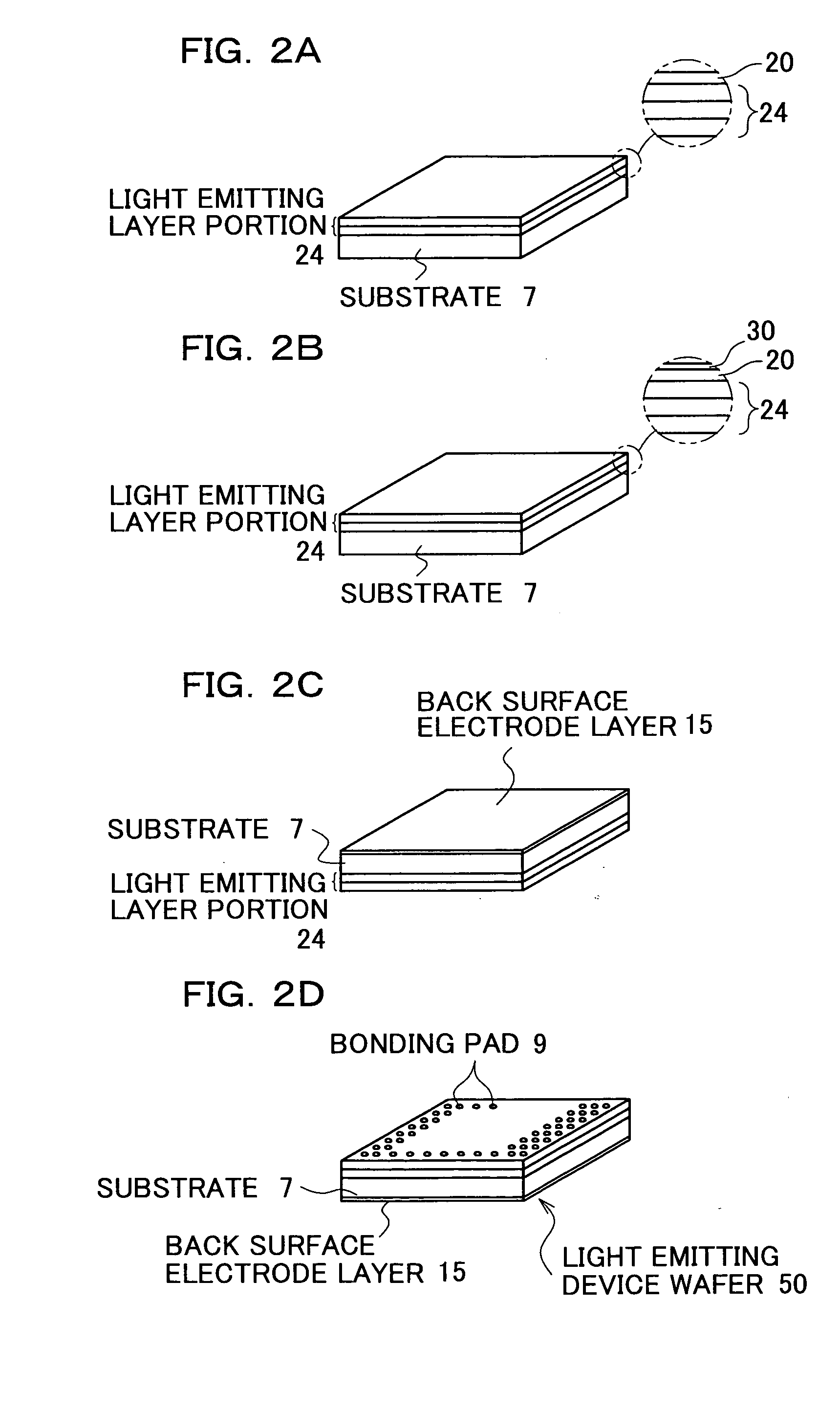

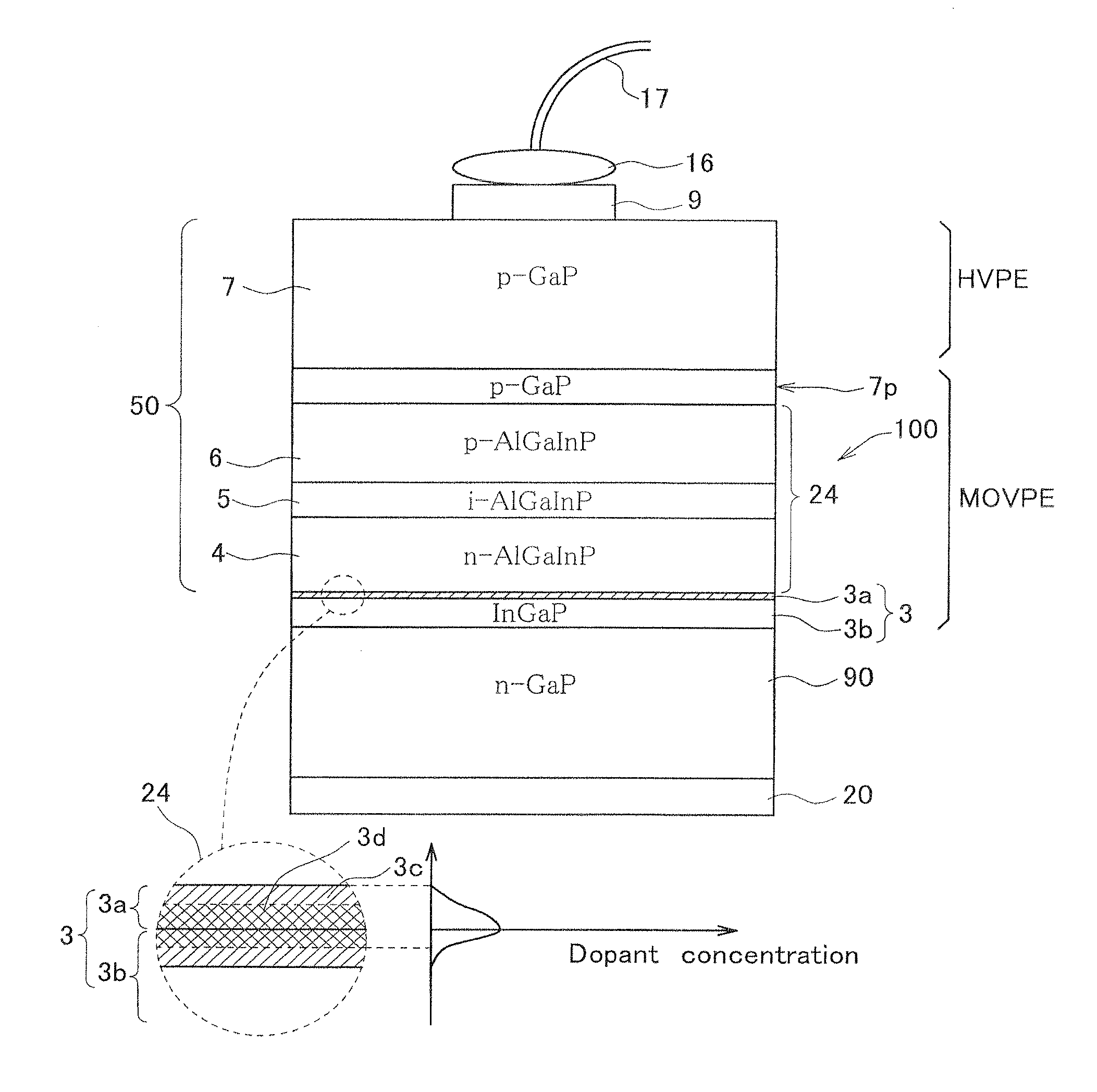

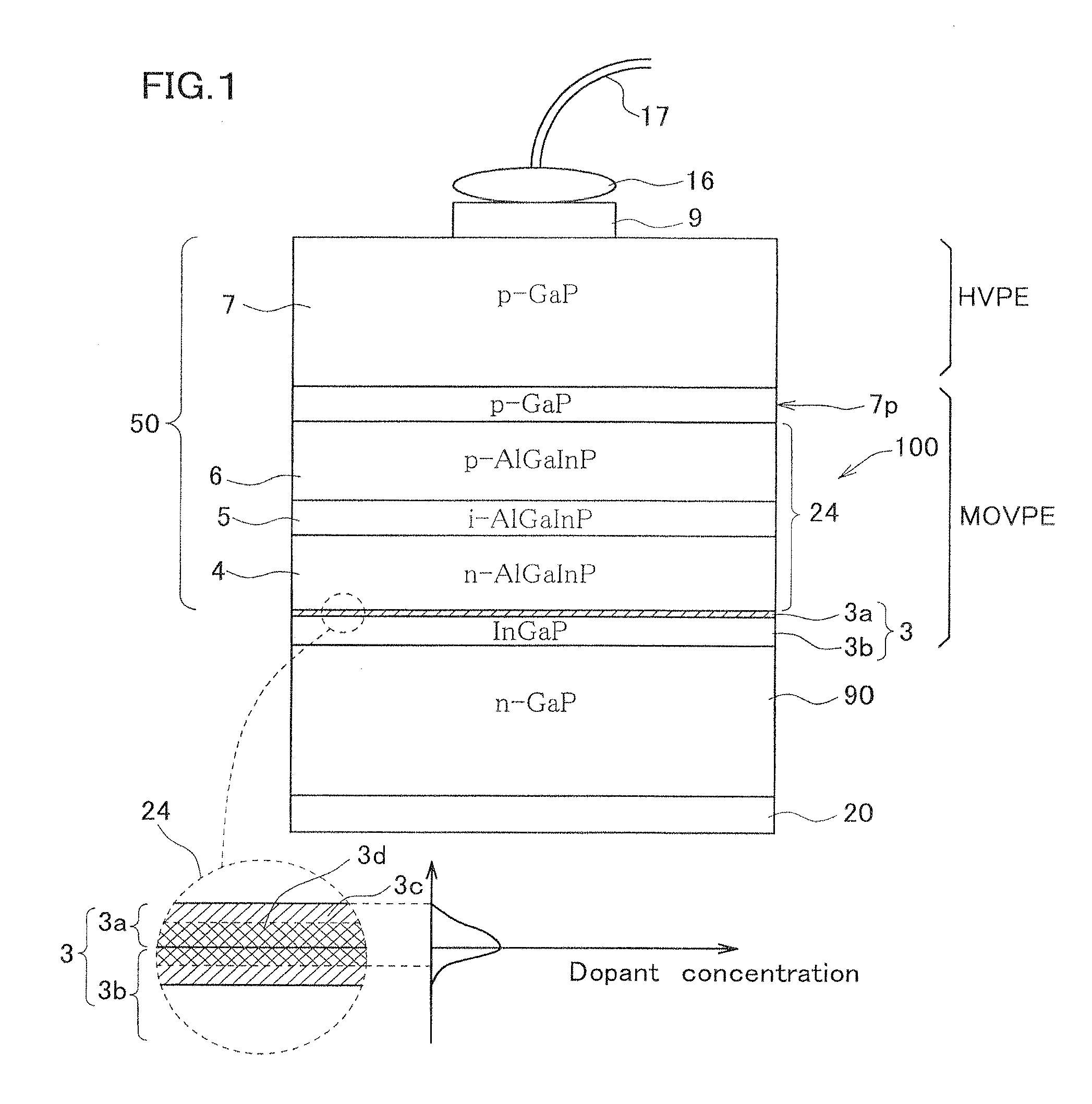

Light emitting device and method of fabricating the same

A light emitting device having an oxide transparent electrode layer as an emission drive electrode, and designed so that damage possibly occurs during bonding of electrode wires to the bonding pads is less influential to a light emitting layer portion is disclosed. The light emitting device has the light emitting layer portion composed of a compound semiconductor and has a double heterostructure in which a first-conductivity-type cladding layer, an active layer and a second-conductivity-type cladding layer are stacked in this order; and the light emitting layer portion is applied with emission drive voltage through an oxide transparent electrode layer formed so as to cover the main surface of the second-conductivity-type cladding layer. A bonding pad composed of a metal is disposed on the oxide transparent electrode layer, and to the bonding pad an electrode wire for current supply is bonded. Between the second-conductivity cladding layer and the oxide transparent electrode layer, a cushion layer composed of a compound semiconductor having a dopant concentration lower than that of the second-conductivity-type cladding layer is disposed.

Owner:SHIN-ETSU HANDOTAI CO LTD +1

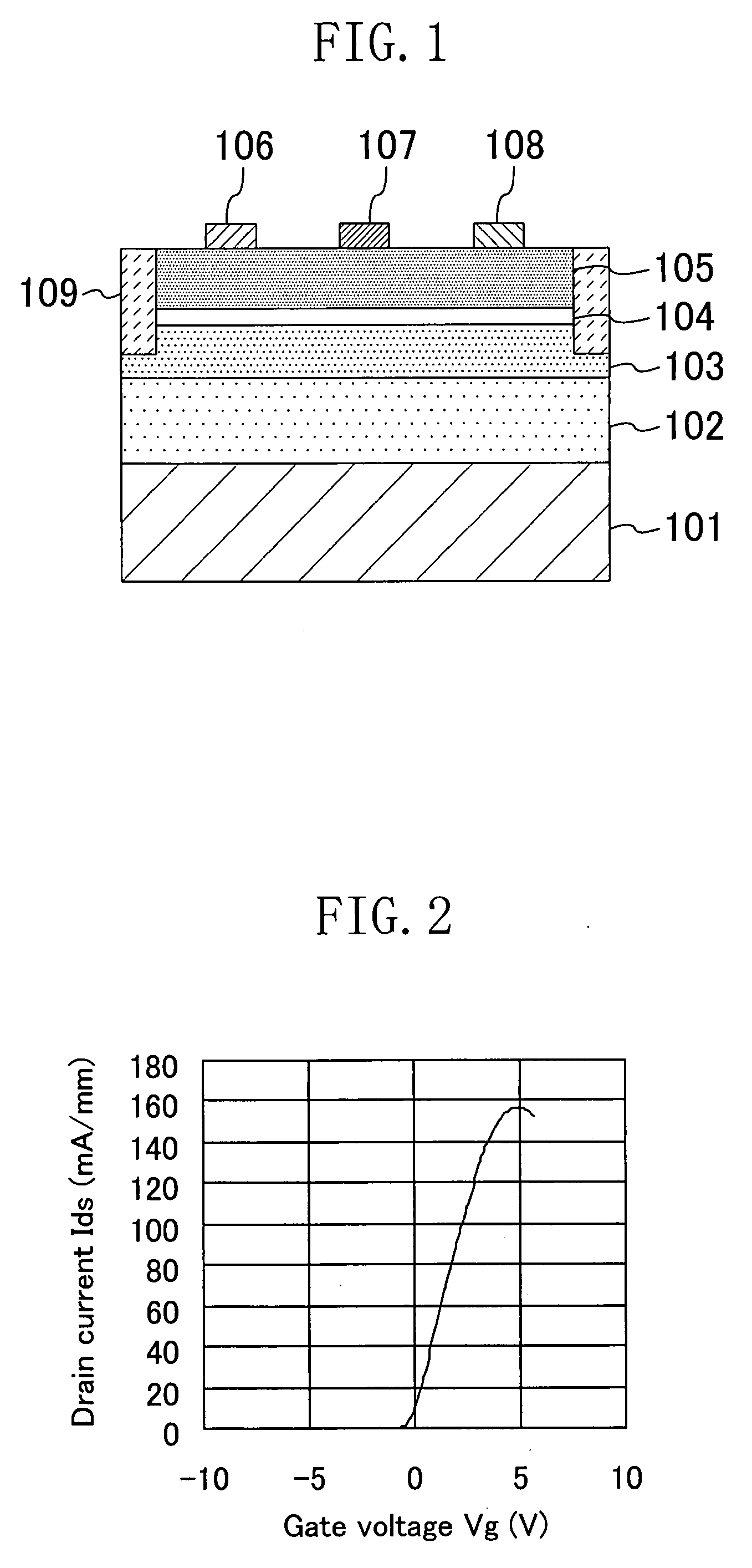

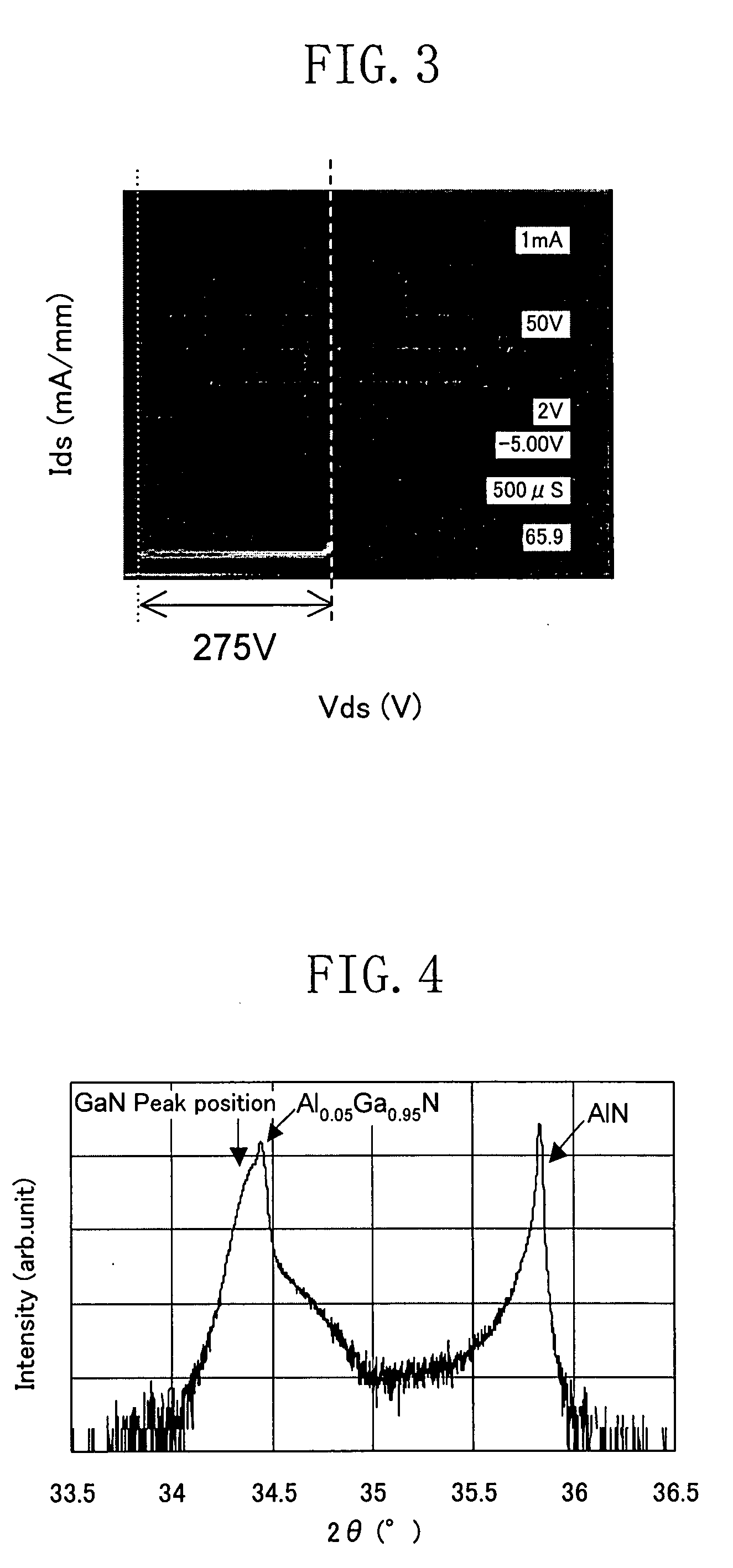

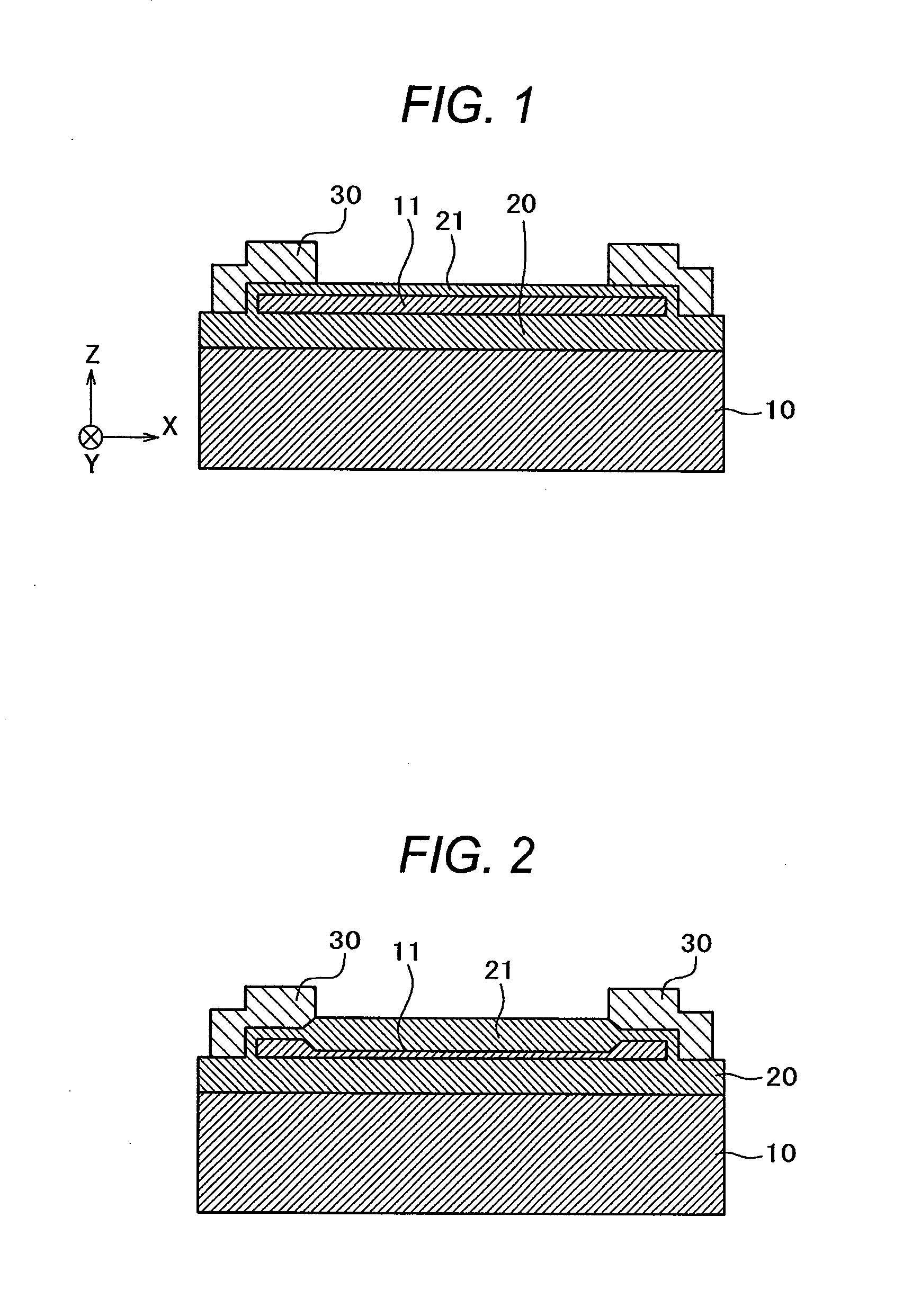

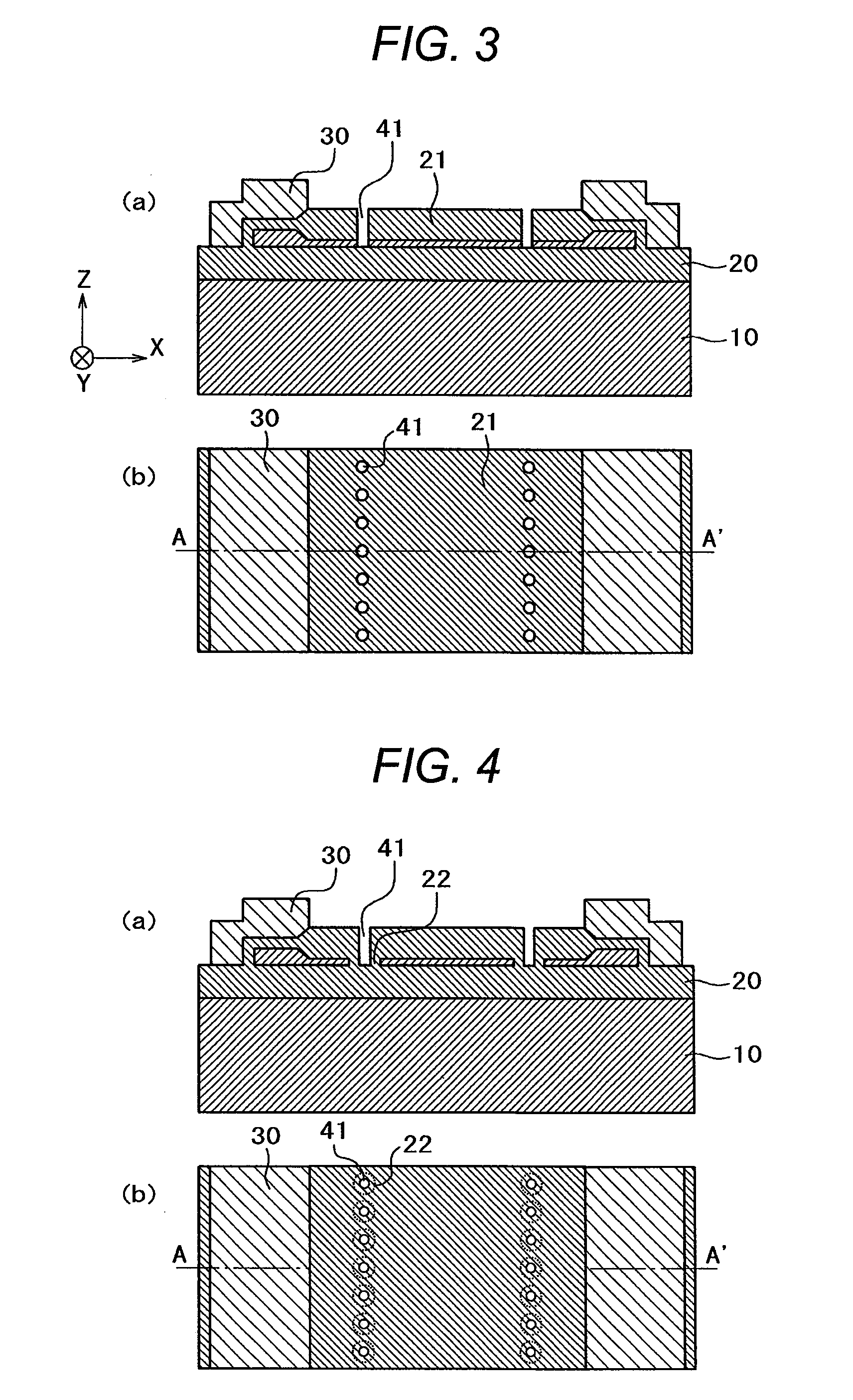

Field-effect transistor

ActiveUS20070272945A1Semiconductor/solid-state device manufacturingSemiconductor devicesField-effect transistorElectron

A field-effect transistor has a so-called double heterostructure which is formed such that a channel layer through which electrons travel is provided between an electron supply layer and a liner layer, wherein a forbidden band width of the liner layer and a forbidden band width of the electron supply layer are broader than a forbidden bandwidth of the channel layer.

Owner:PANASONIC CORP

Production method for light emitting element

InactiveUS20050224825A1Improve stabilityGood reproducibilityPolycrystalline material growthSemiconductor/solid-state device manufacturingChemical reactionSemiconductor materials

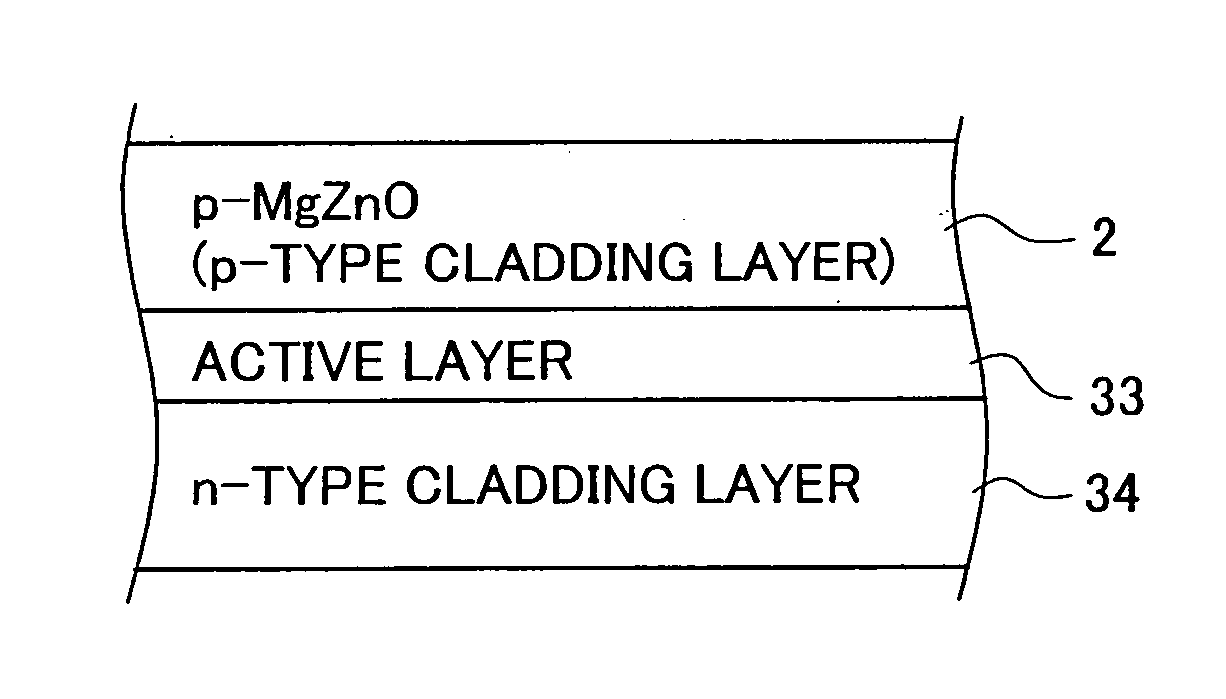

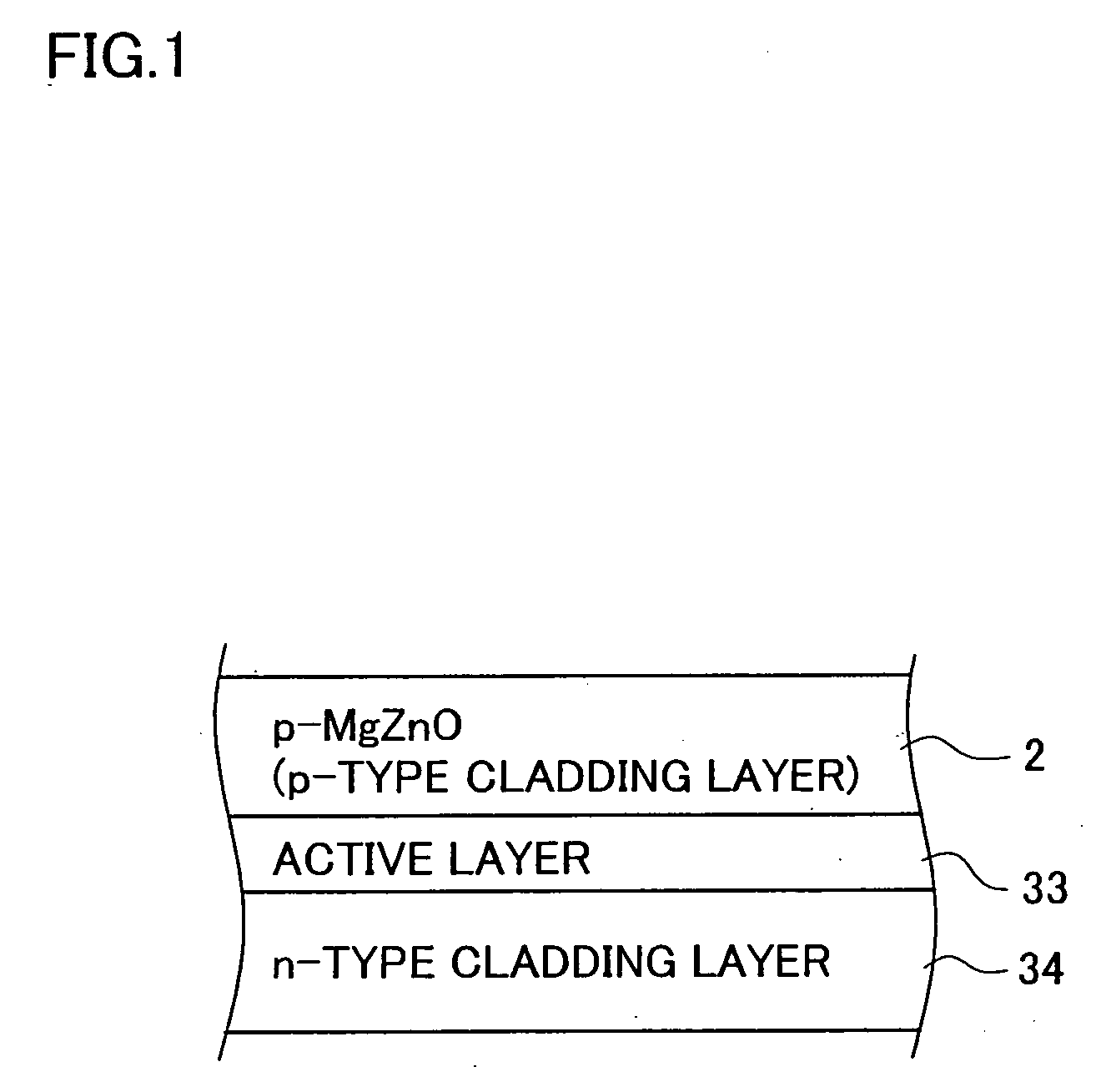

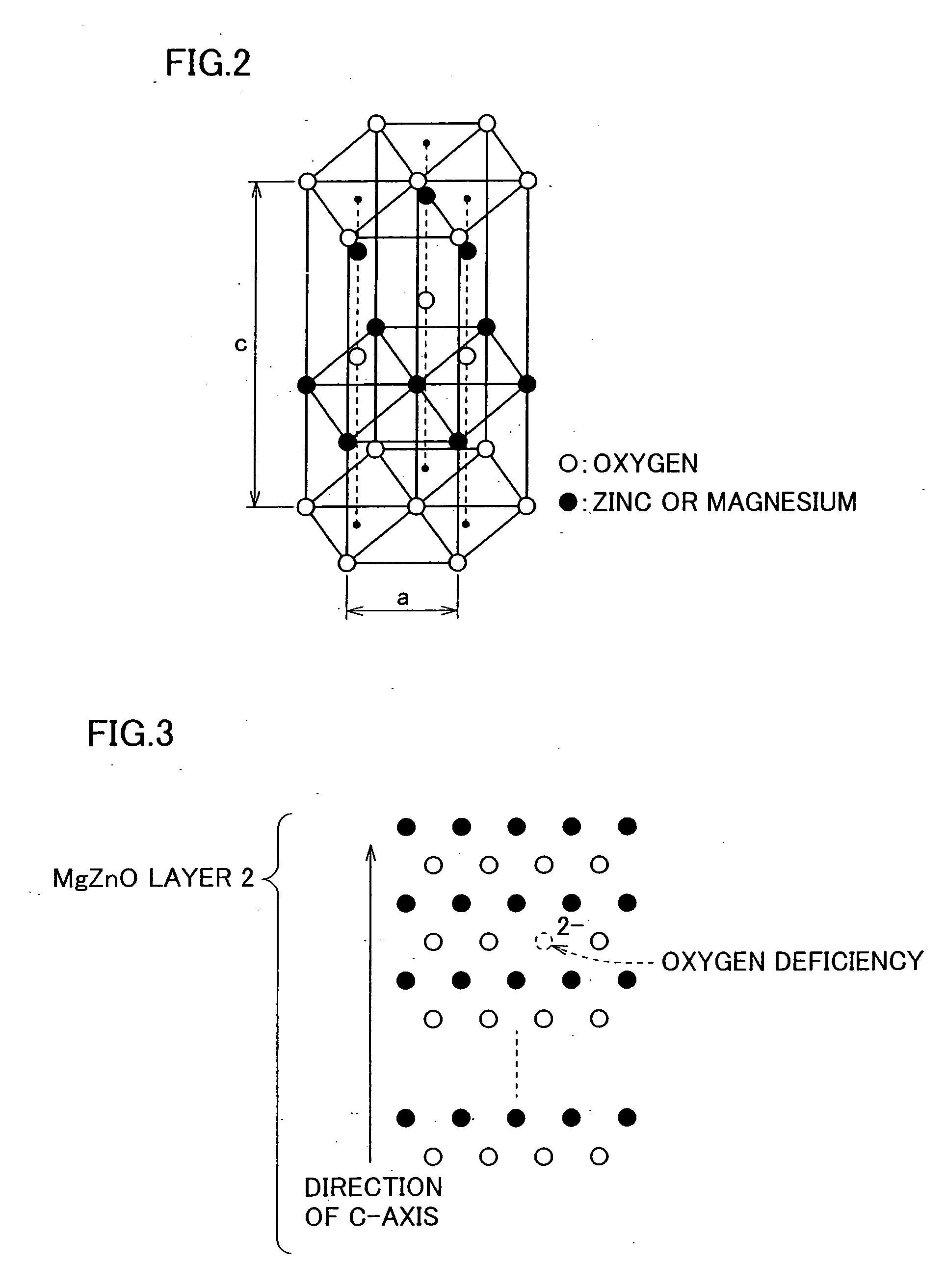

In a first invention, a p-type MgxZn1-xO-type layer is grown based on a metal organic vapor-phase epitaxy process by supplying organometallic gases which serves as a metal source, an oxygen component source gas and a p-type dopant gas into a reaction vessel. During and / or after completion of the growth of the p-type MgxZn1-xO-type layer, the MgxZn1-xO-type thereof is annealed in an oxygen-containing atmosphere. This is successful in forming the layer of p-type oxide in a highly reproducible and stable manner for use in light emitting device having the layer of p-type oxide of Zn and Mg. In a second invention, a semiconductor layer which composes the light emitting layer portion is grown by introducing source gases in a reaction vessel having the substrate housed therein, and by depositing a semiconductor material produced by chemical reactions of the source gas on the main surface of the substrate. A vapor-phase epitaxy process of the semiconductor layer is proceed while irradiating ultraviolet light to the main surface of the substrate and the source gases. This is successful in sharply enhancing reaction efficiency of the source gases when the semiconductor layer for composing the light emitting layer portion is formed by a vapor-phase epitaxy process, and in readily obtaining the semiconductor layer having only a less amount of crystal defects. In a third invention, a buffer layer having at least an MgaZn1-aO-type oxide layer on the contact side with the light emitting layer portion is grown on the substrate, and the light emitting layer portion is grown on the buffer layer. The buffer layer is oriented so as to align the c-axis thereof to the thickness-wise direction, and is obtained by forming a metal monoatomic layer on the substrate based on the atomic layer epitaxy, and then by growing residual oxygen atom layers and the metal atom layers. This is successful in obtaining the light emitting portion with an excellent quality. In a fourth invention, a ZnO-base semiconductor active layer included in a double heterostructured, light emitting layer portion is formed using a ZnO-base semiconductor mainly composed of ZnO containing Se or Te, so as to introduce Se or Te, the elements in the same Group with oxygen, into oxygen deficiency sites in the ZnO crystal possibly produced during the formation process of the active layer, to thereby improve crystallinity of the active layer. Introduction of Se or Te shifts the emission wavelength obtainable from the active layer towards longer wavelength regions as compared with the active layer composed of ZnO having a band gap energy causative of shorter wavelength light than blue light. This is contributive to realization of blue-light emitting devices.

Owner:SHIN-ETSU HANDOTAI CO LTD

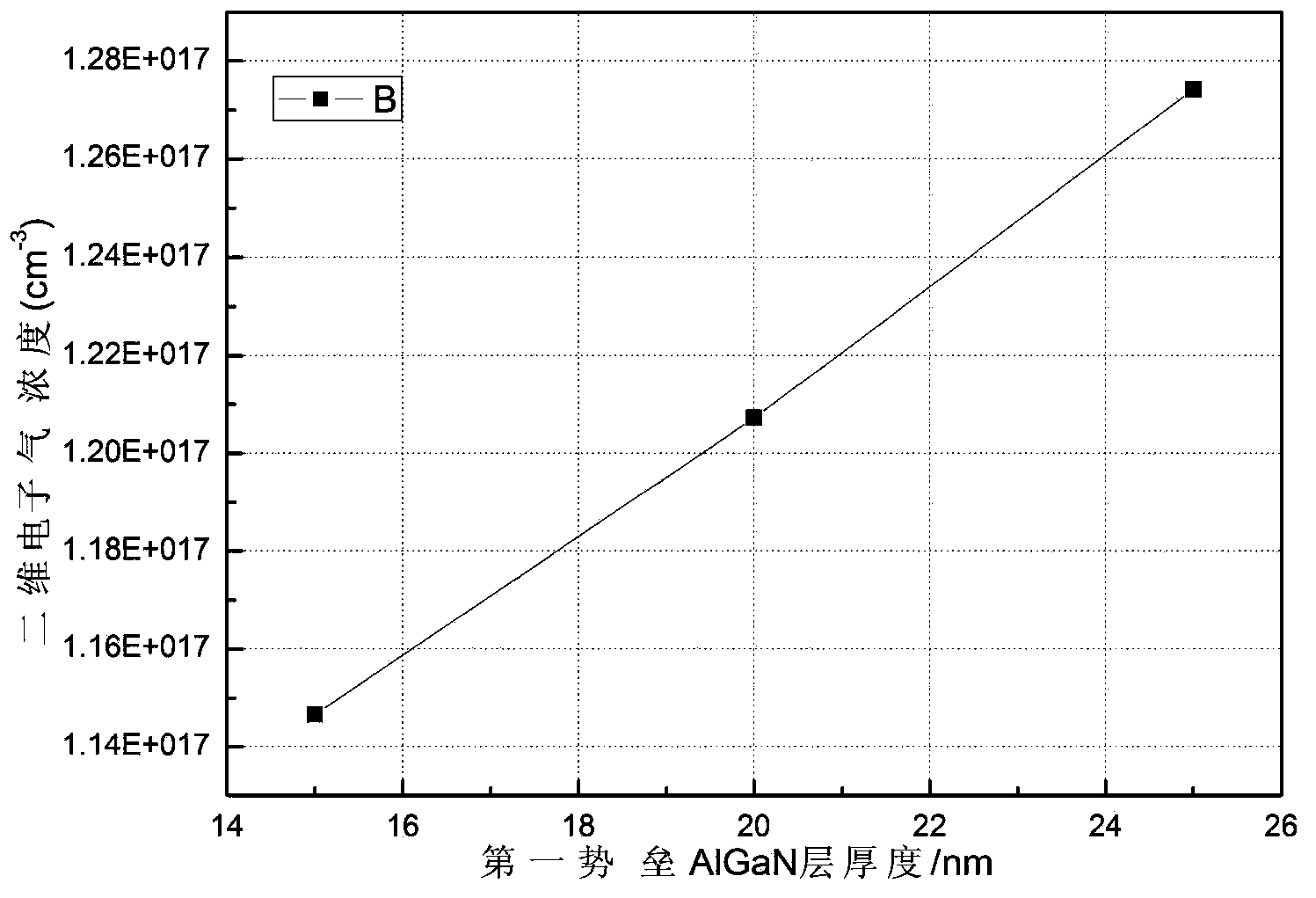

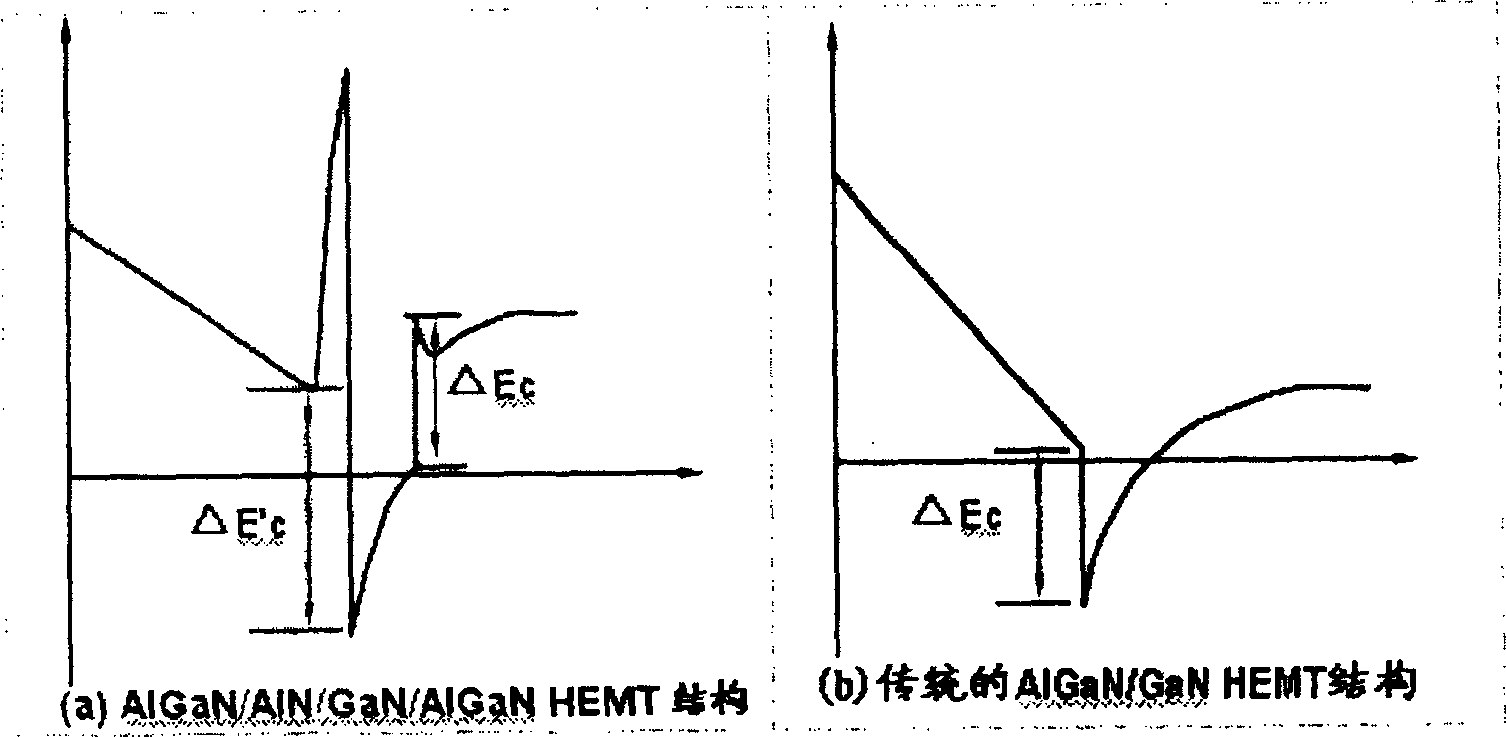

Double-channel transistor and preparation method for double-channel transistor

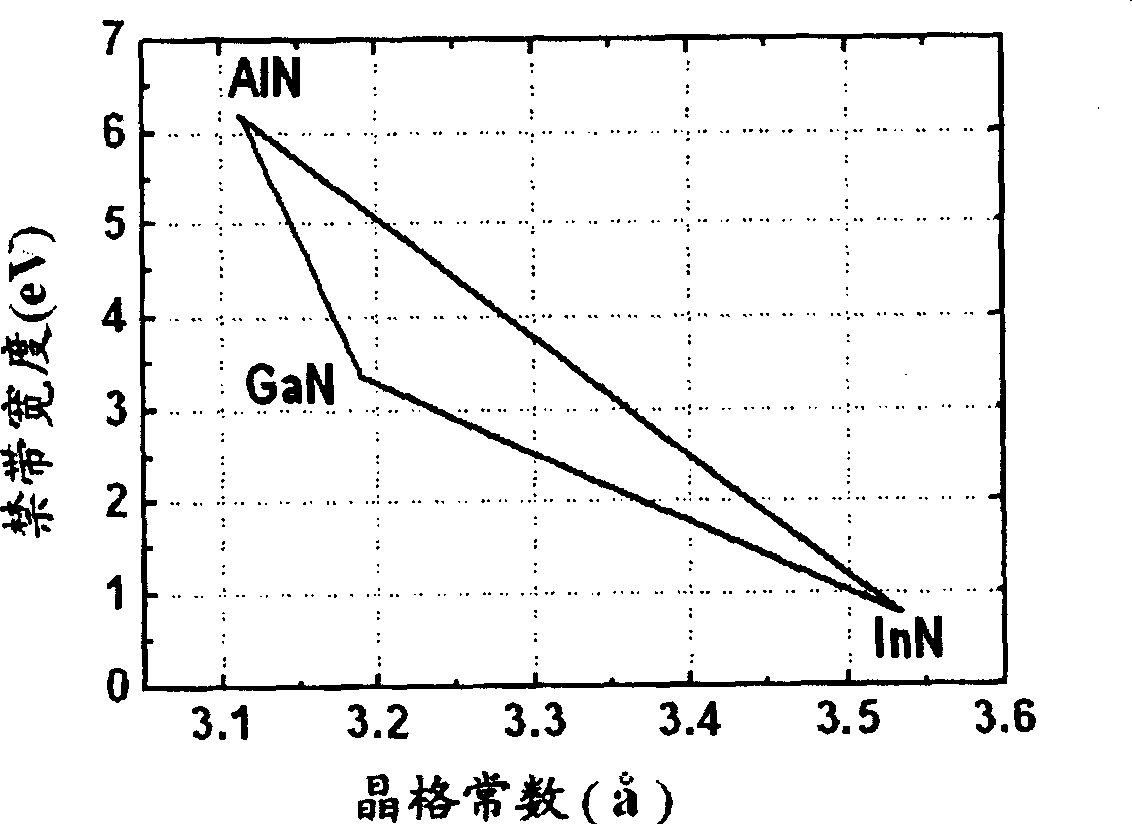

ActiveCN103681830AEnhanced 2DEG localizationImprove reliabilityTransistorSemiconductor/solid-state device manufacturingNitrogenGallium

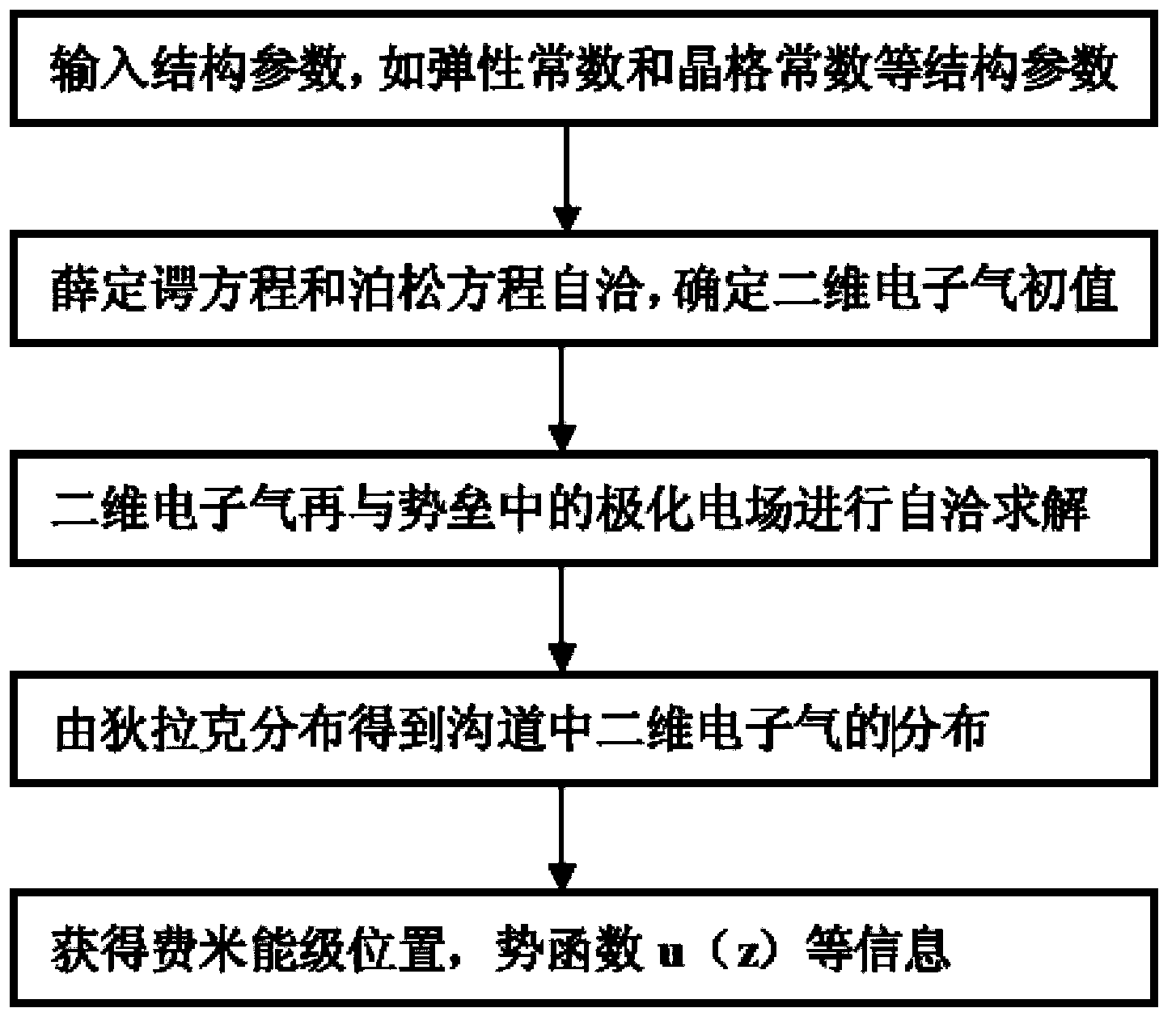

The invention discloses a double-channel transistor. The double-channel transistor is made of GaN (gallium nitride), and includes two channels, i.e. a first channel and a second channel, wherein the first channel serves as an interface of a barrier layer and a GaN channel layer, the second channel serves as an interface of a back barrier layer and the GaN channel layer, and the barrier layer and the back barrier layer are both made of AlGaN (aluminum gallium nitride); the thickness of the AlGaN back barrier layer is 20 nm, and the aluminum content is 30 percent; the thickness of the AlGaN barrier layer is 20 nm, and the aluminum content is 30 percent; a substrate of the transistor is a silicon carbide substrate. The double-channel transistor and a preparation method for the double-channel transistor have the advantages that AlGaN with a certain aluminum content and a certain thickness serves as the back barrier layer, so as to form an AlGaN / GaN / AlGaN double heterostructure; a two-dimensional electron gas (2DEG) in the channels is confined in two extremely high barriers through a strong polarization electric field to form the two channels, which improves the 2DEG carrier confinement in the channels and the device reliability.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

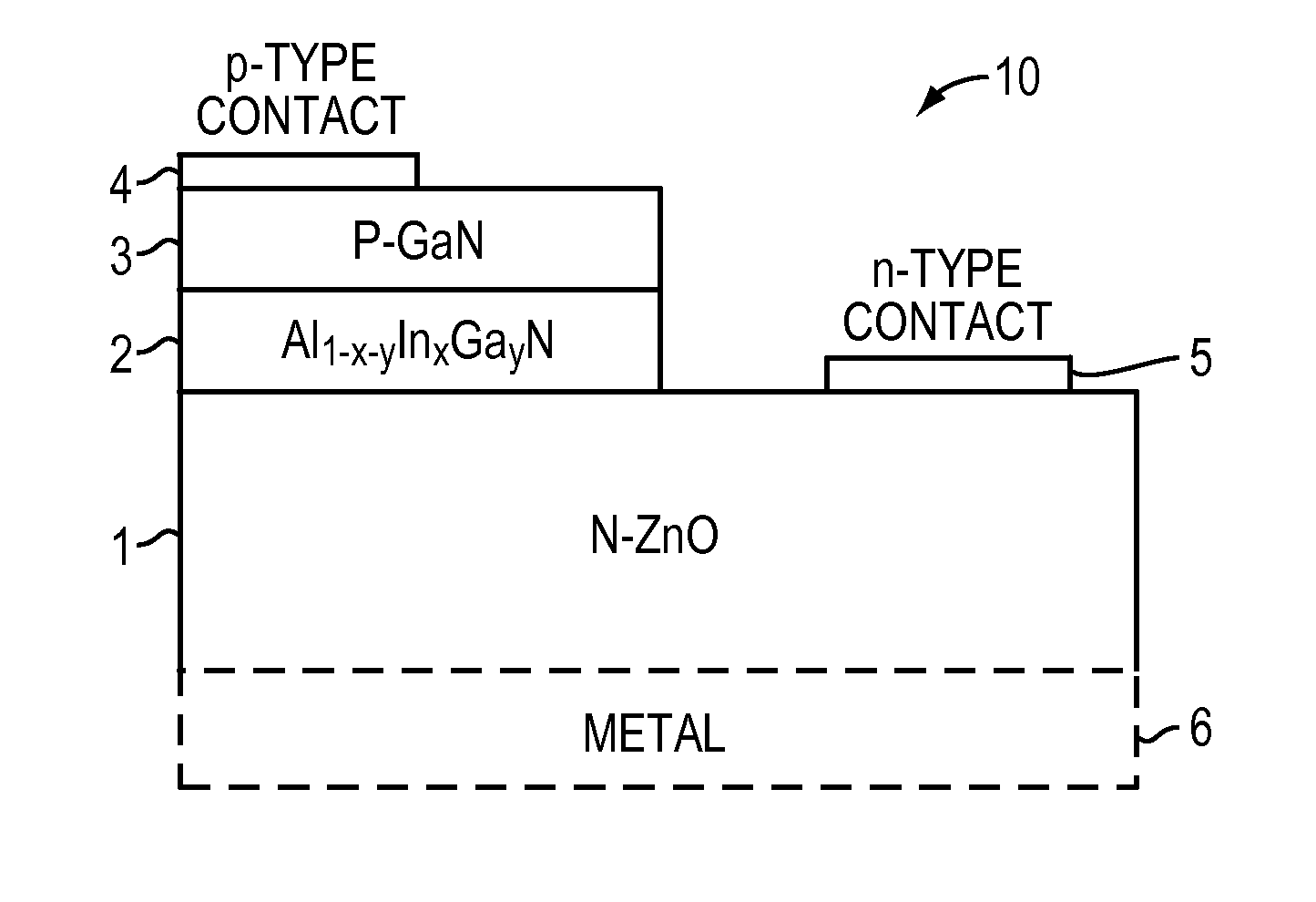

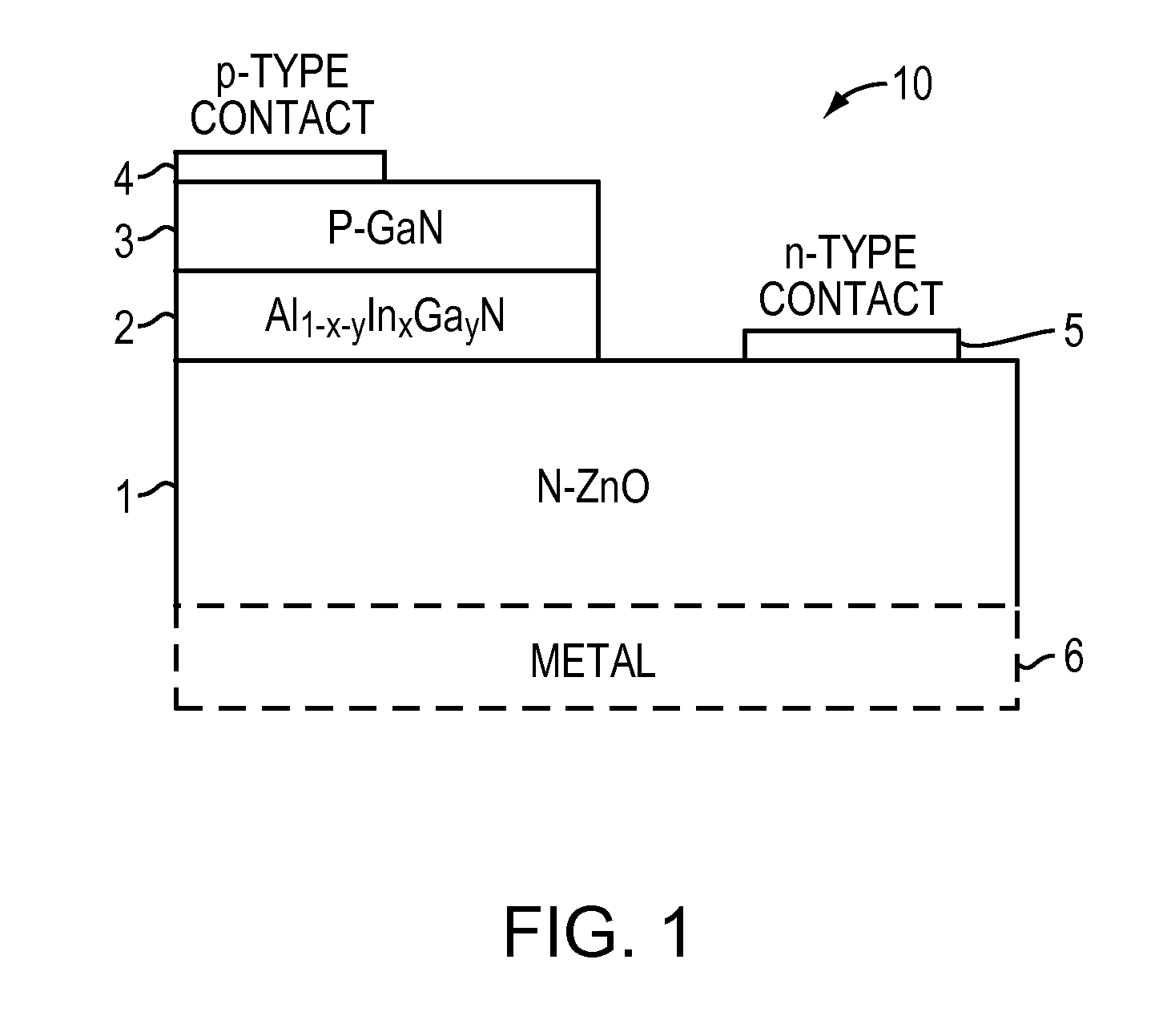

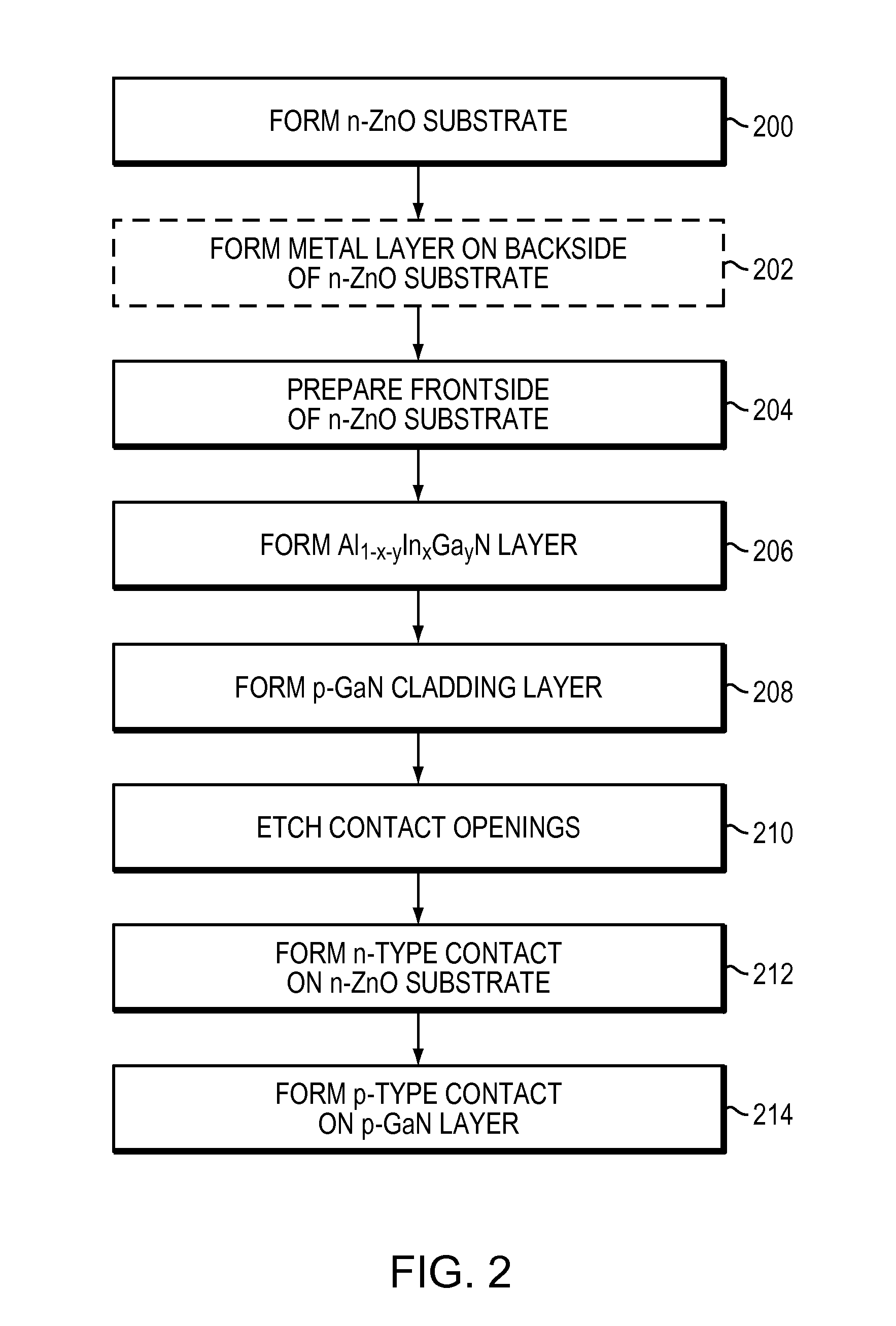

Nitride/zinc oxide based light-emitting diodes

A light-emitting nitride / zinc oxide based compound semiconductor device of double heterostructure. The double-heterostructure includes a light-emitting layer formed of an Al1-x-yInxGayN; 0≦x<1, 0<y≦1, and x+y=0.1 to 1 compound semiconductor doped an impurity. Single or multi quantum well light-emitting active layers Al1-x-yInxGayN / GaN; 0≦x<1, 0<y≦1, and x+y=0.1 to 1 are positioned between p-type GaN and n-type ZnO substrates.

Owner:GEORGIA TECH RES CORP

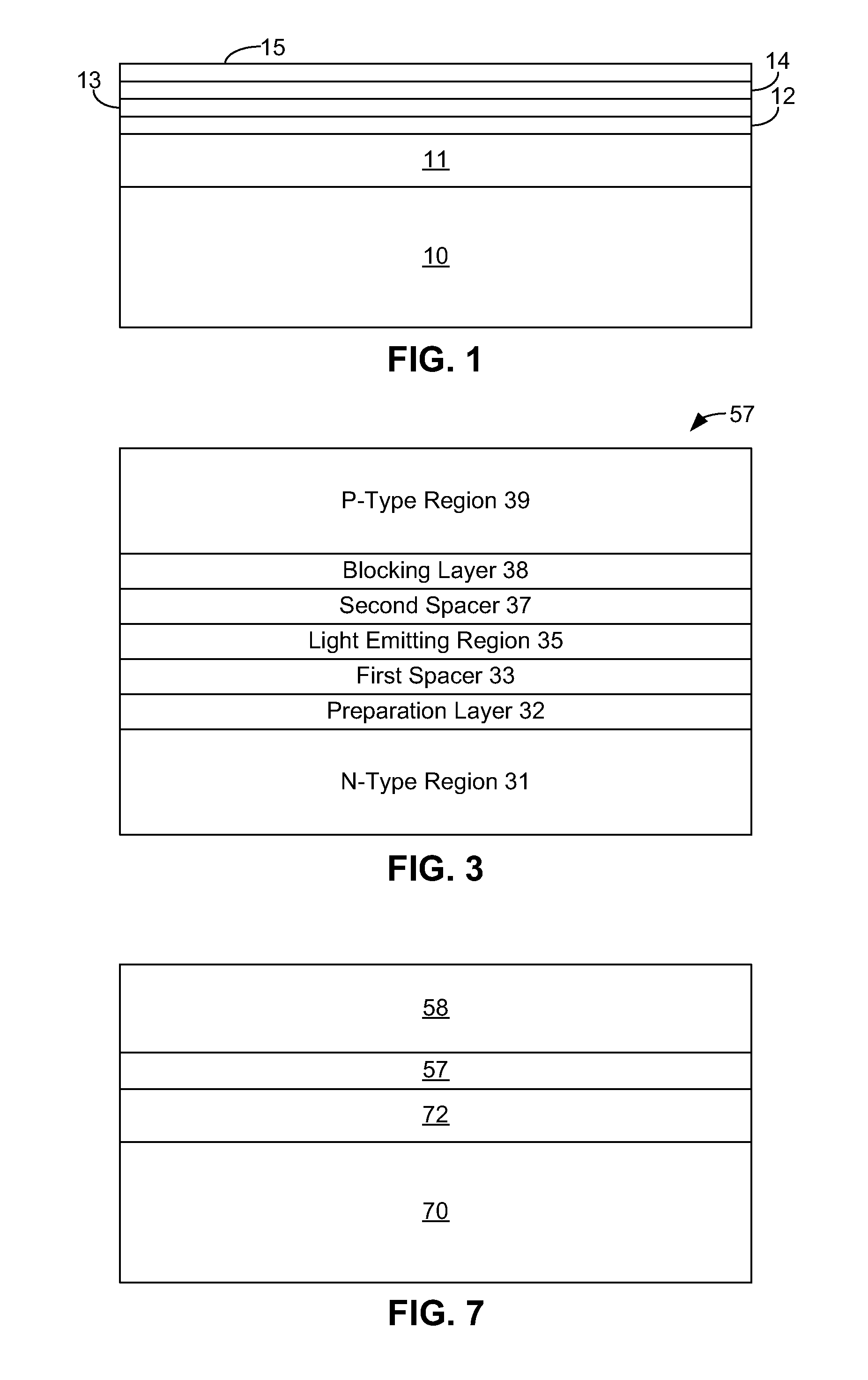

Nitride Semiconductor Light Emitting Element

ActiveUS20100224892A1Improve light extraction efficiencyWider irradiation angleSolid-state devicesSemiconductor devicesContact layerReflective layer

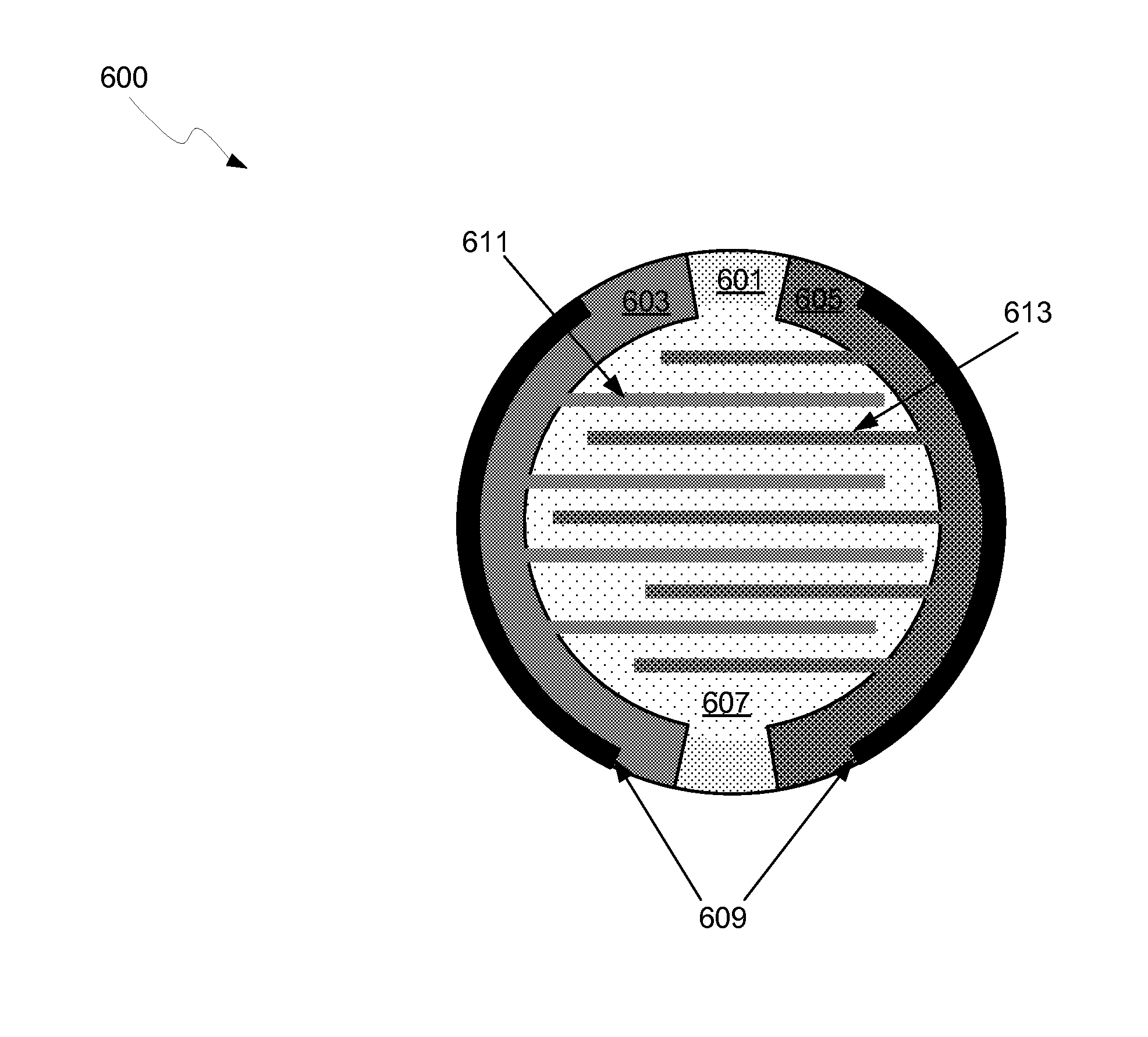

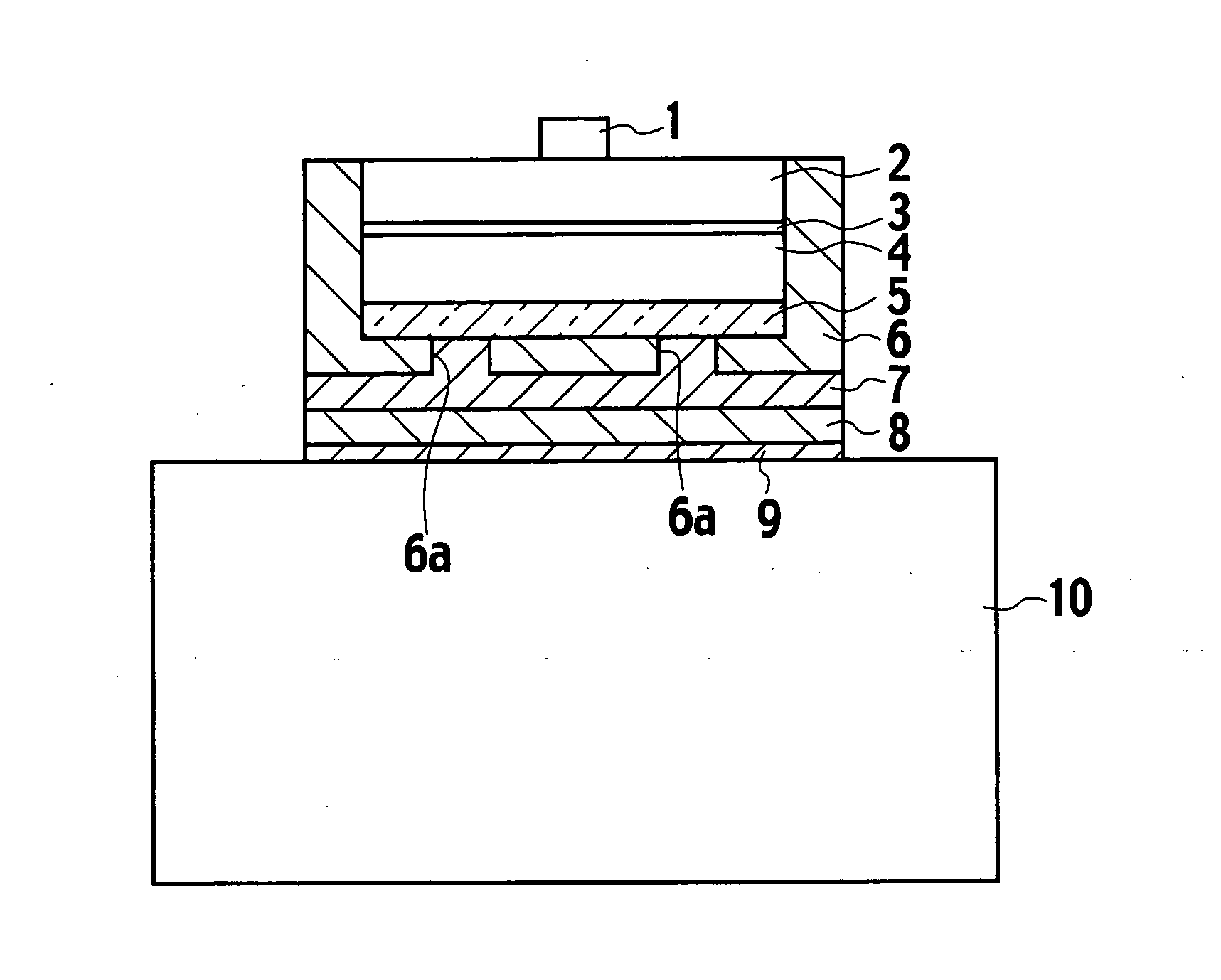

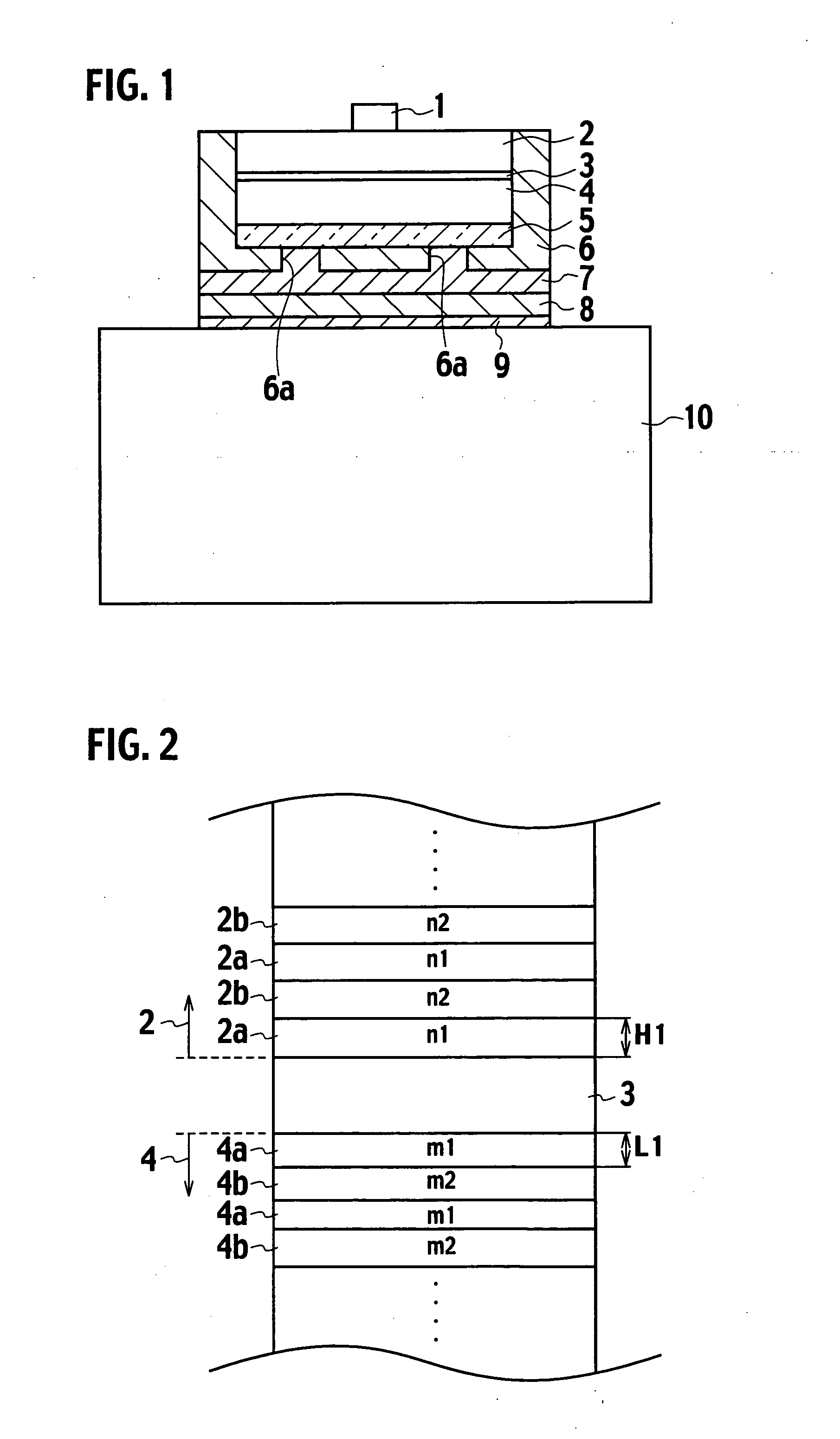

Provided is a nitride semiconductor light emitting element that has improved light extraction efficiency and a wide irradiation angle of outgoing light irrespective of the reflectance of a metal used for an electrode. An n side anti-reflection layer 2 and a p side Bragg reflection layer 4 are formed so as to sandwich an MQW active layer 3 that serves as a light emitting region, and the nitride semiconductor light emitting element has a double hetero structure. On top of the n side anti-reflection layer 2, an n electrode 1 is formed. Meanwhile, at the lower side of the p side Bragg reflection layer 4, a p electrode 5, a reflection film 7, and a pad electrode 8 are formed, and the pad electrode is bonded to a support substrate 10 with a conductive bonding layer 9 interposed in between. Both the n side anti-reflection layer 2 and the p side Bragg reflection layer 4 also serve as contact layers. The n side anti-reflection layer 2 is disposed on the light-extracting-direction side while the p side Bragg reflection layer 4 is disposed on the opposite side to the light-extracting-direction side. Consequently, the light extraction efficiency is improved.

Owner:ROHM CO LTD

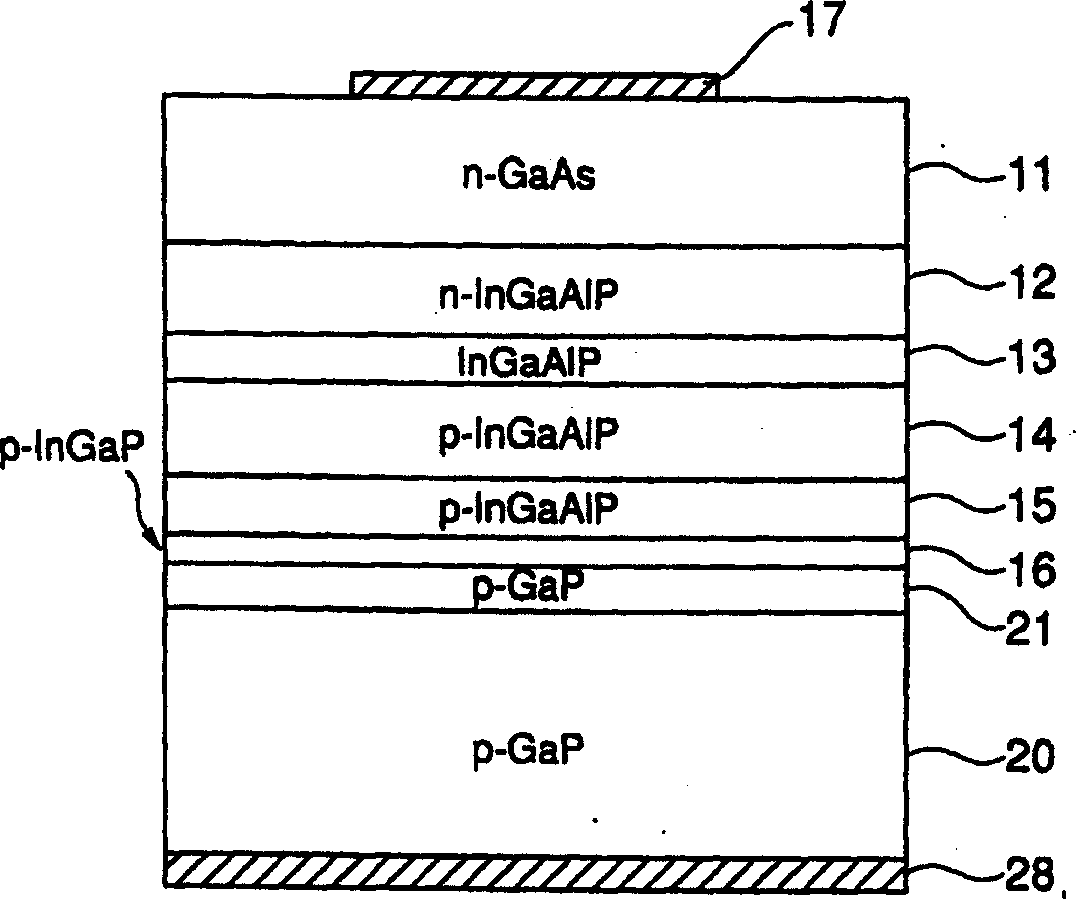

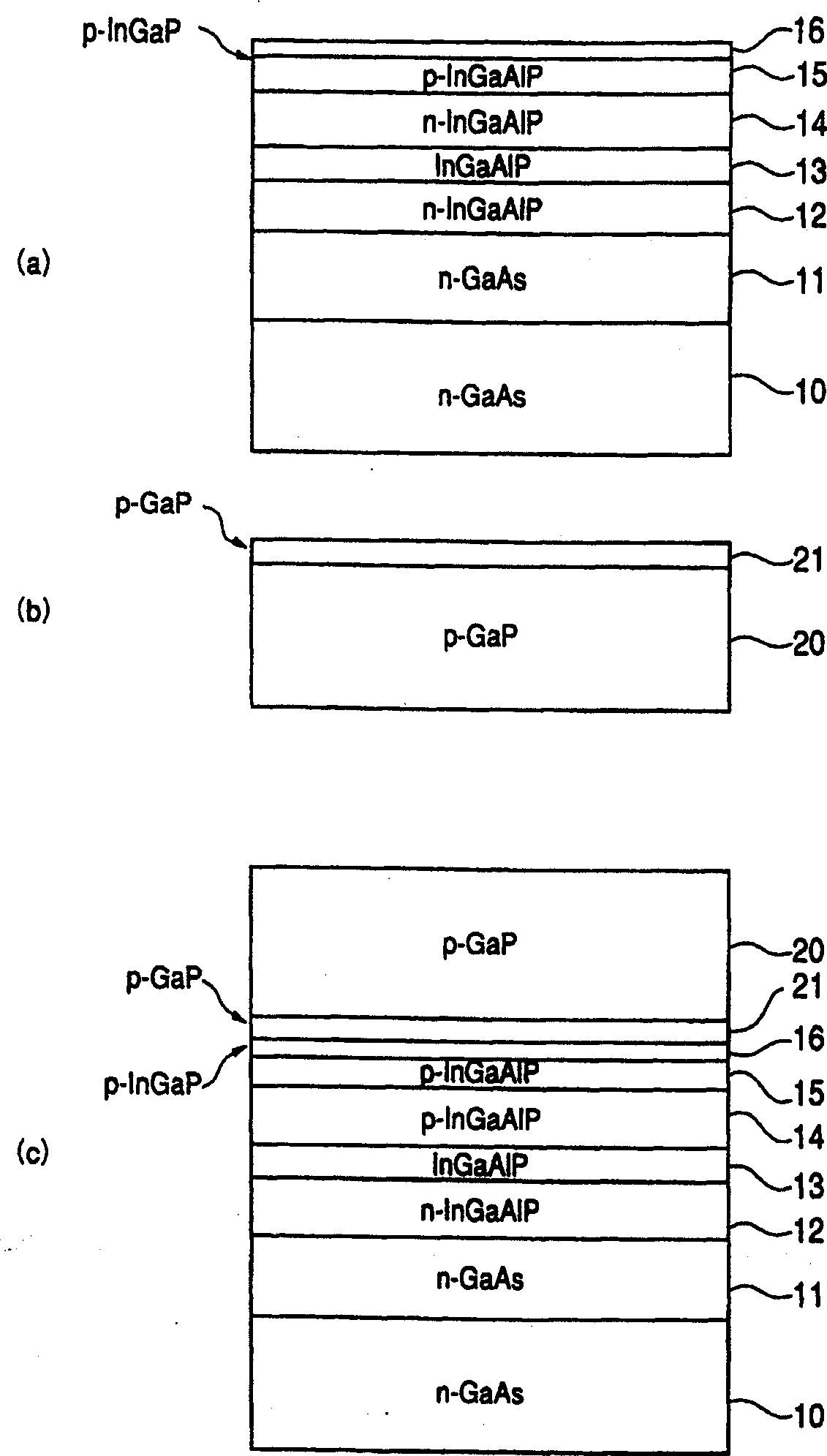

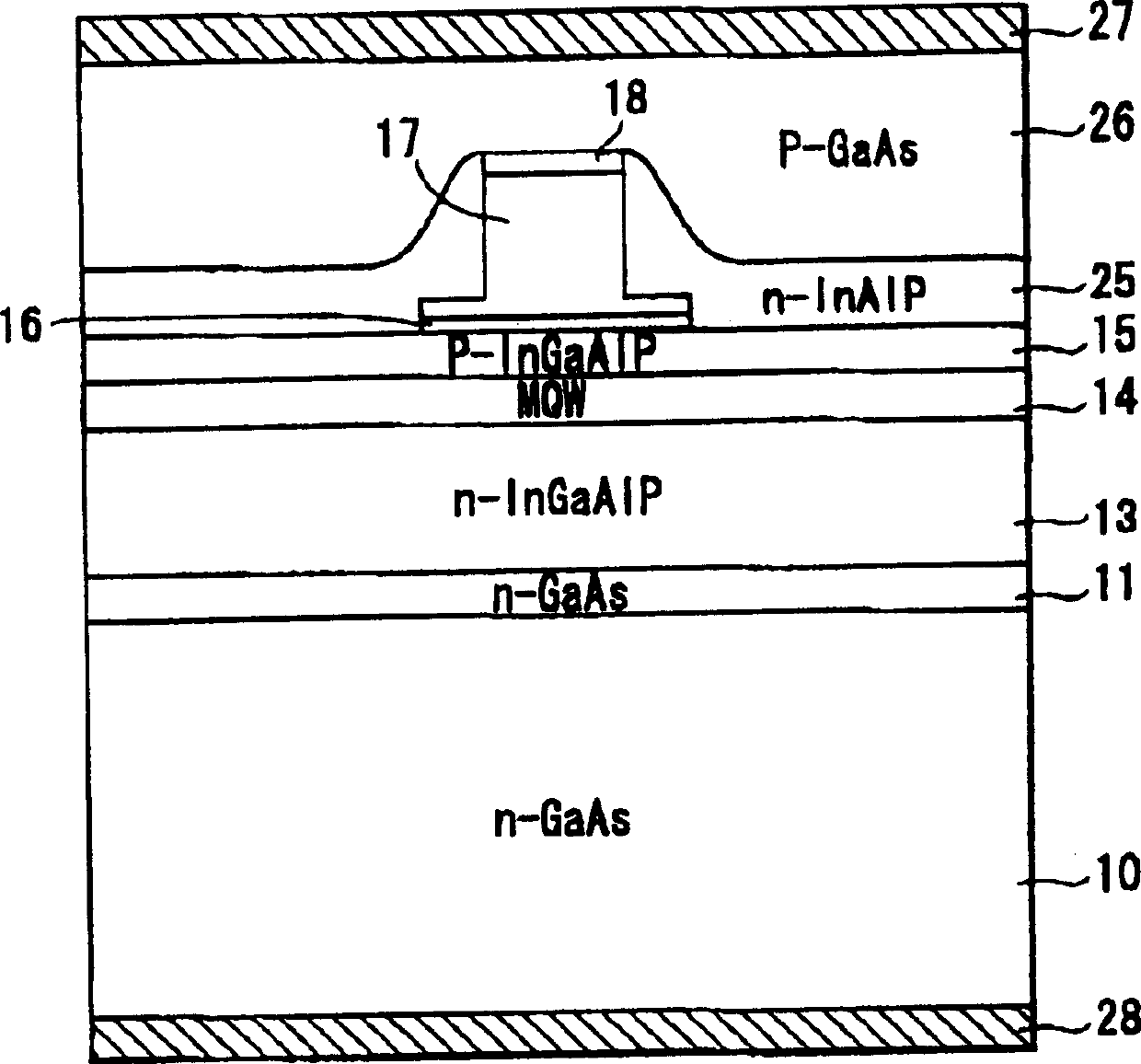

Illuminant semiconductor element and method for mfg. same

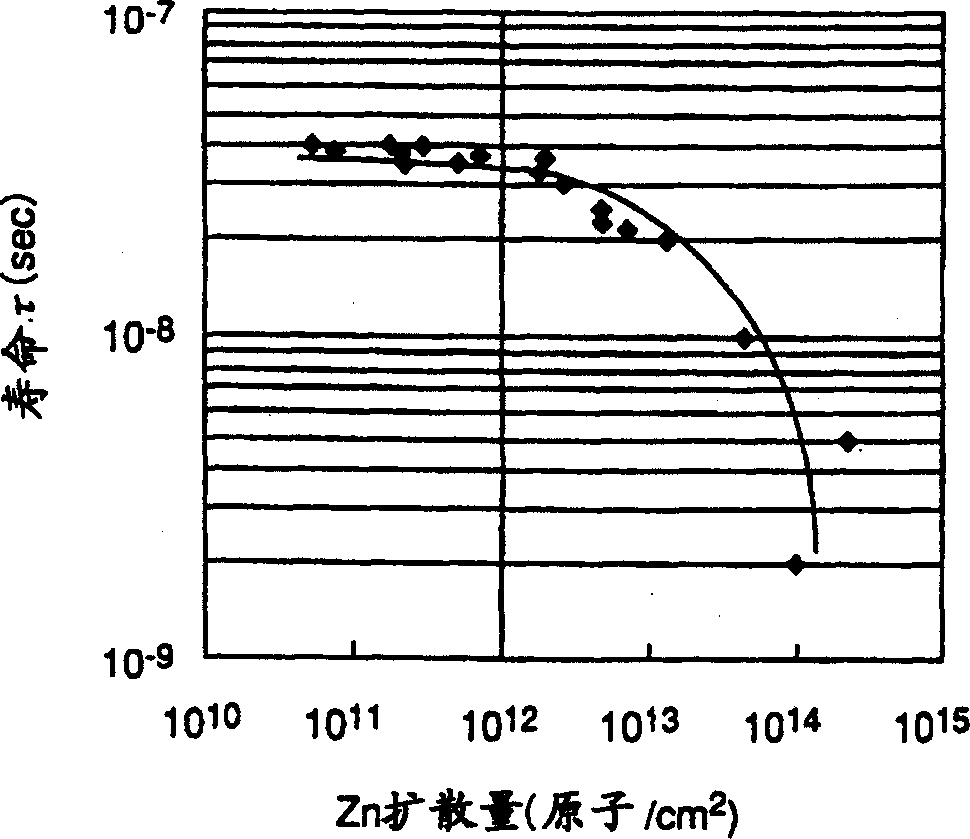

InactiveCN1347160APrevent proliferationInhibition formationLaser detailsSemiconductor lasersDopantActive layer

The subject of the present invention is to provide a method to prevent the diffusion of P-type dopants from the substrate to the active layer, inhibit the formation of non-light-emitting centers, so as to obtain higher brightness and stability. The semiconductor light-emitting element utilizing the chip bonding technology comprises: a double hetero structure formed of InGaAlP material layers including an active layer 13 acting as a light emitting layer and an n-type, p-type cladding layer 12, 14 having the active layer sandwiched in between, and a p-type GaP substrate 20 directly bonded to the p-type cladding layer 14 of the double hetero structure, and a Zn diffusion preventing layer formed of InGaAlP, which is interposed between the p-type cladding layer 14 and p-type GaP substrate 20. The Zn diffusion preventing layer 15 is formed by doping p-type dopant Zn and Si with n-type dopants simultaneously. When the impurity concentration of Zn, Si is Na, Nd respectively, they satisfy the condition: Na > Nd, and Nd > 2x10<17> cm-3.

Owner:KK TOSHIBA

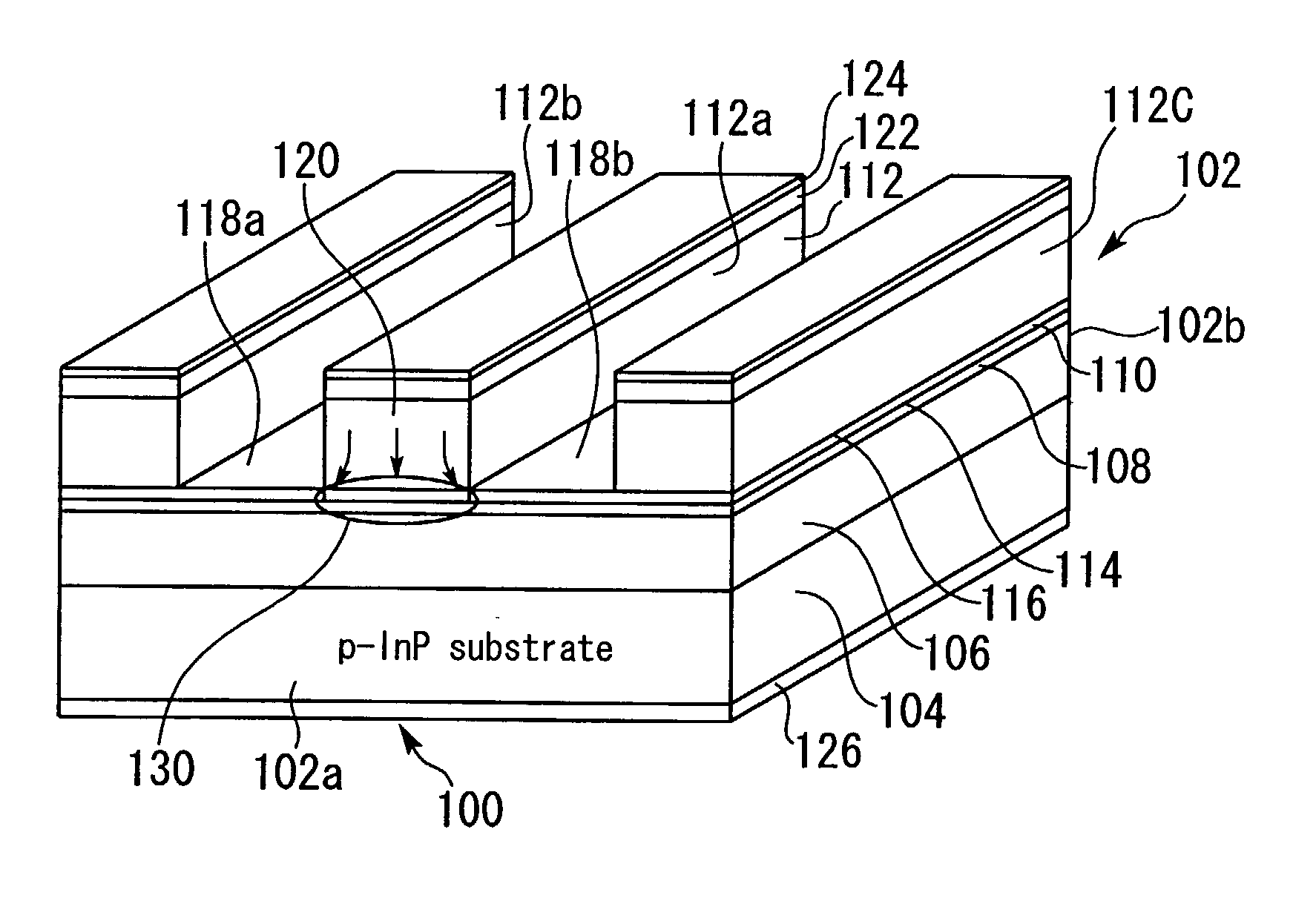

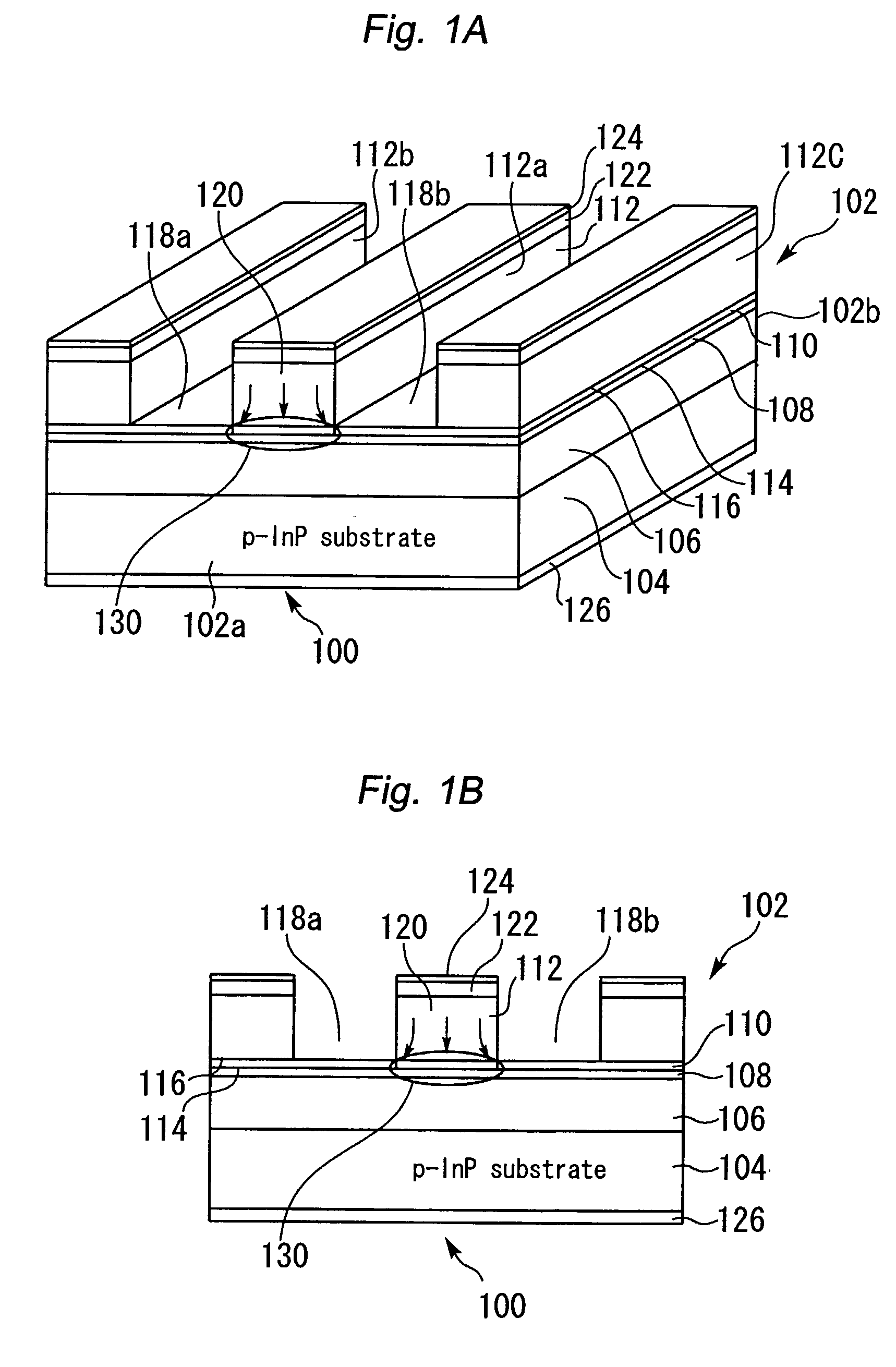

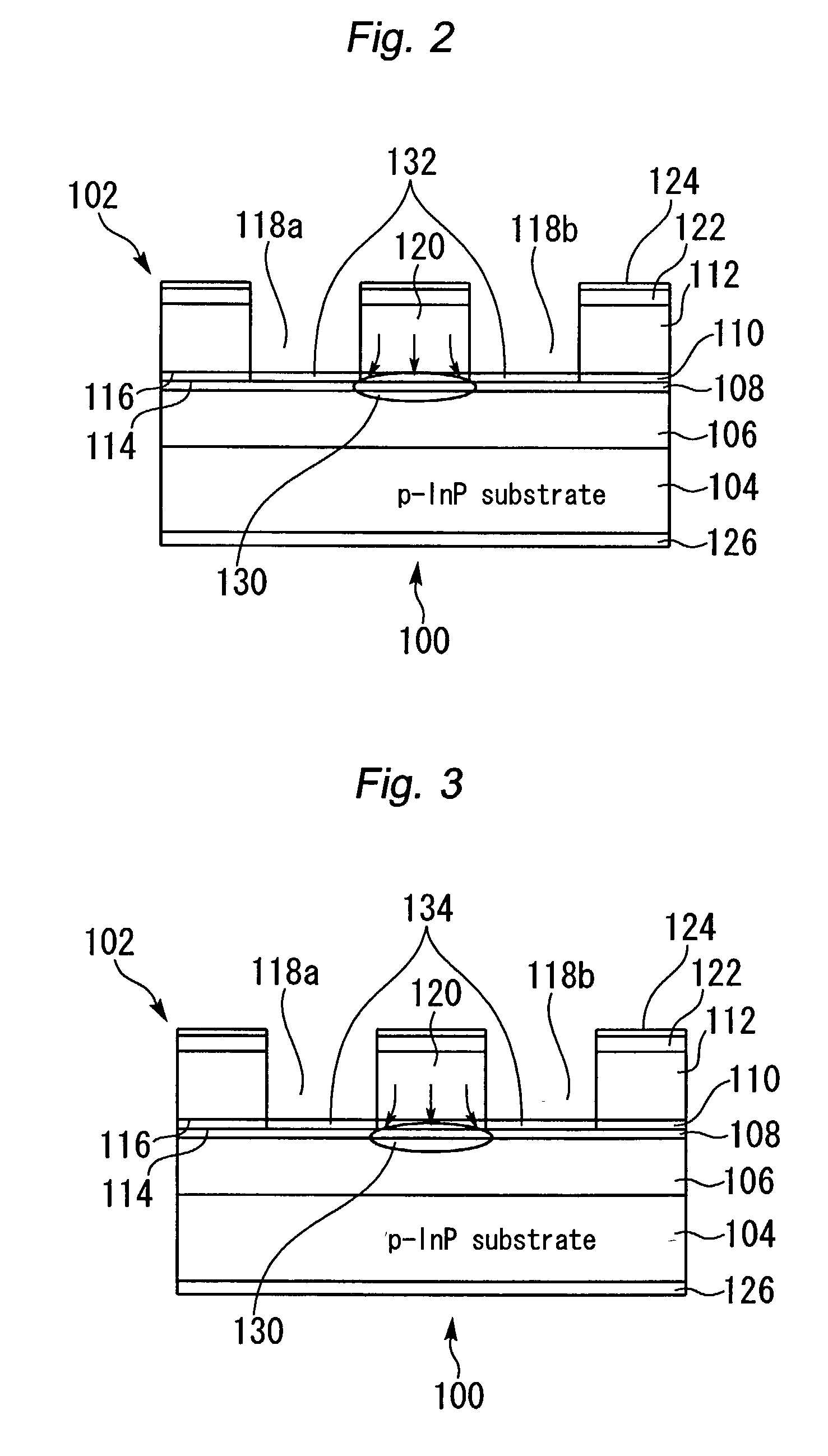

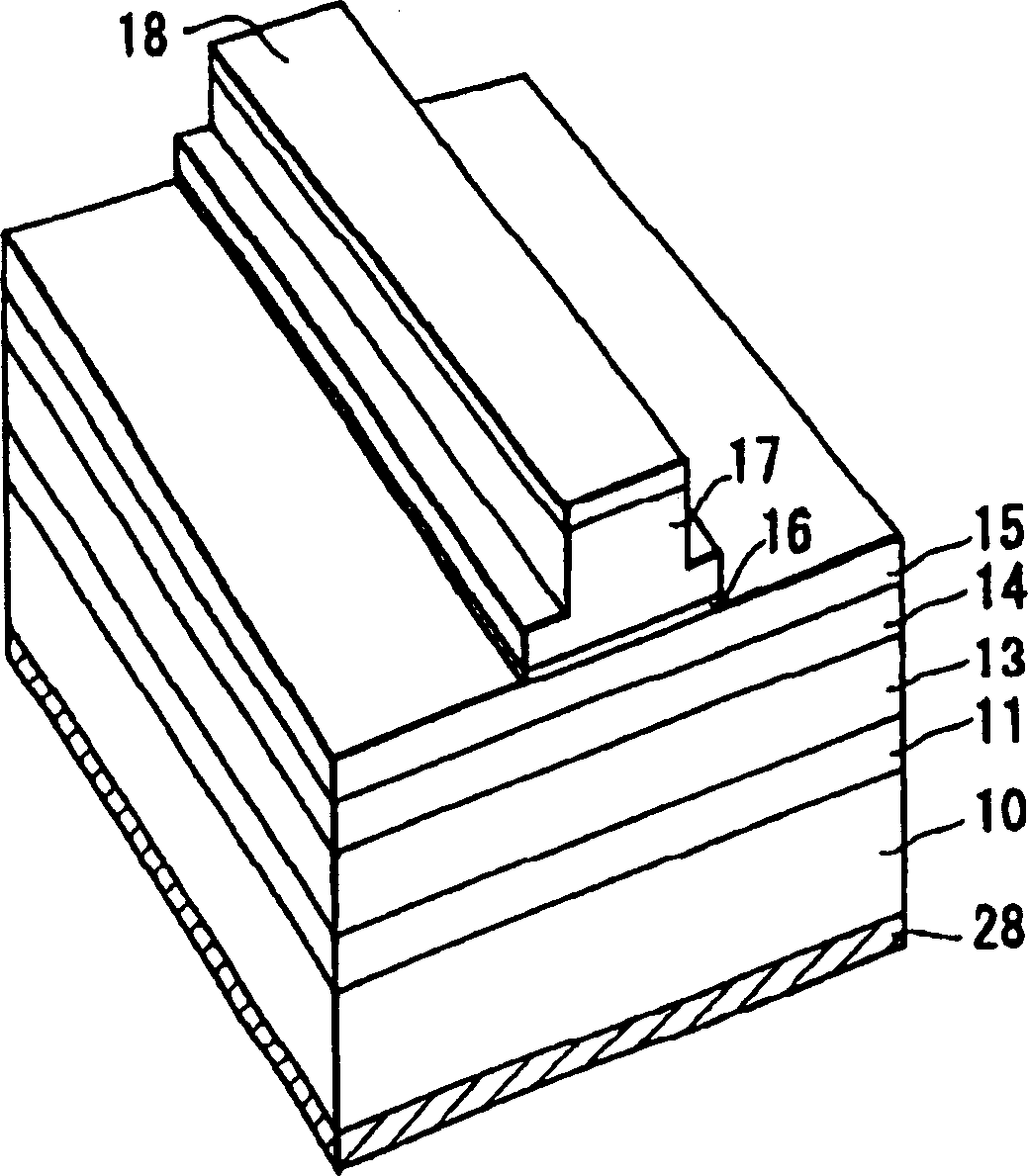

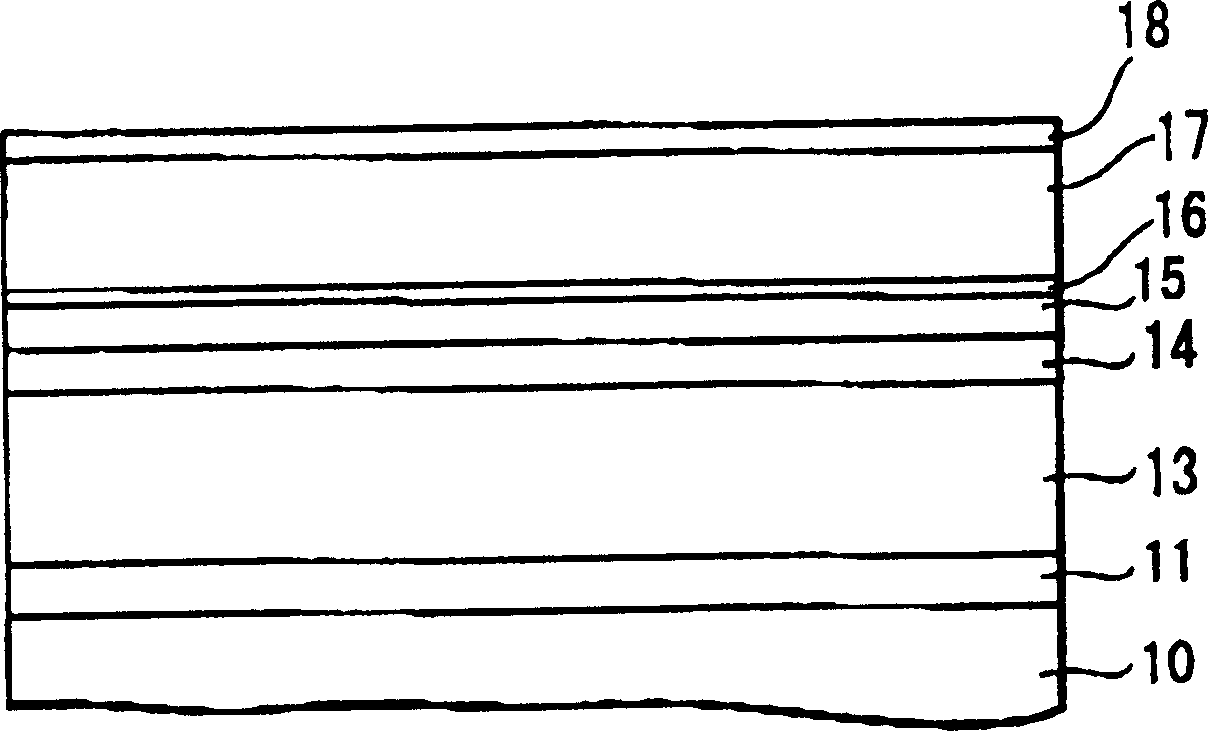

Ridge-waveguide semiconductor laser device

InactiveUS20030179794A1Improve temperature characteristic and high speed operating characteristicContainment leakOptical wave guidanceLaser detailsHigh resistanceQuantum well

A laser device includes a double hetero-structure element constructed by depositing a p-type cladding layer, a quantum well active layer, an n-type thin first cladding layer and an n-type thick second cladding layer sequentially. A ridge-waveguide is shaped between two trenches formed in the second cladding layer. The first cladding layer serves as an etching stopper while etching the second cladding layer to form the two trenches. The trenches reach to or reach in vicinity to the surface of the first cladding layer. High-resistance regions may be formed in portions of the first cladding layer directly underneath the trenches. The thin first cladding layer, suppresses leakage current and improves the temperature characteristics and the operating speed characteristics of the laser device.

Owner:MITSUBISHI ELECTRIC CORP

Monolithic semiconductor laser and method of manufacturing the same

InactiveUS20050069005A1Optical wave guidanceSemiconductor laser arrangementsSemiconductor materialsLength wave

A monolithic semiconductor laser having plural semiconductor lasers having different emission wavelengths from each other, including: a semiconductor substrate; a first double hetero-structure formed within a first area on the semiconductor substrate and having first clad layers disposed above and below a first active layer; and a second double hetero-structure formed within a second area on the semiconductor substrate and having second clad layers disposed above and below a second active layer. The first and second active layers are made of different semiconductor materials from each other. The first clad layers above and below the first active layer are of approximately the same semiconductor materials and the second clad layers above and below the second active layer are of approximately the same semiconductor materials.

Owner:MITSUBISHI ELECTRIC CORP

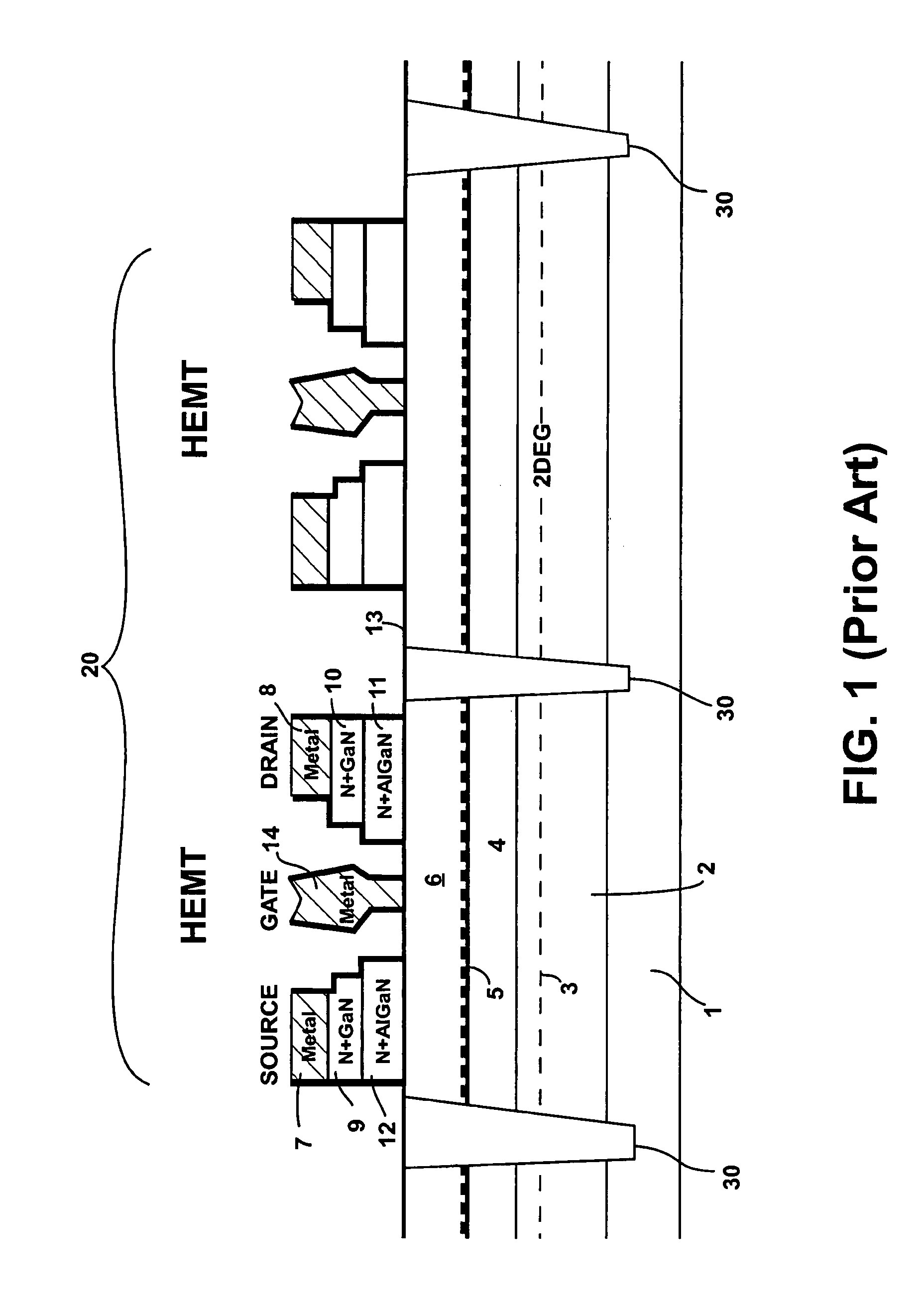

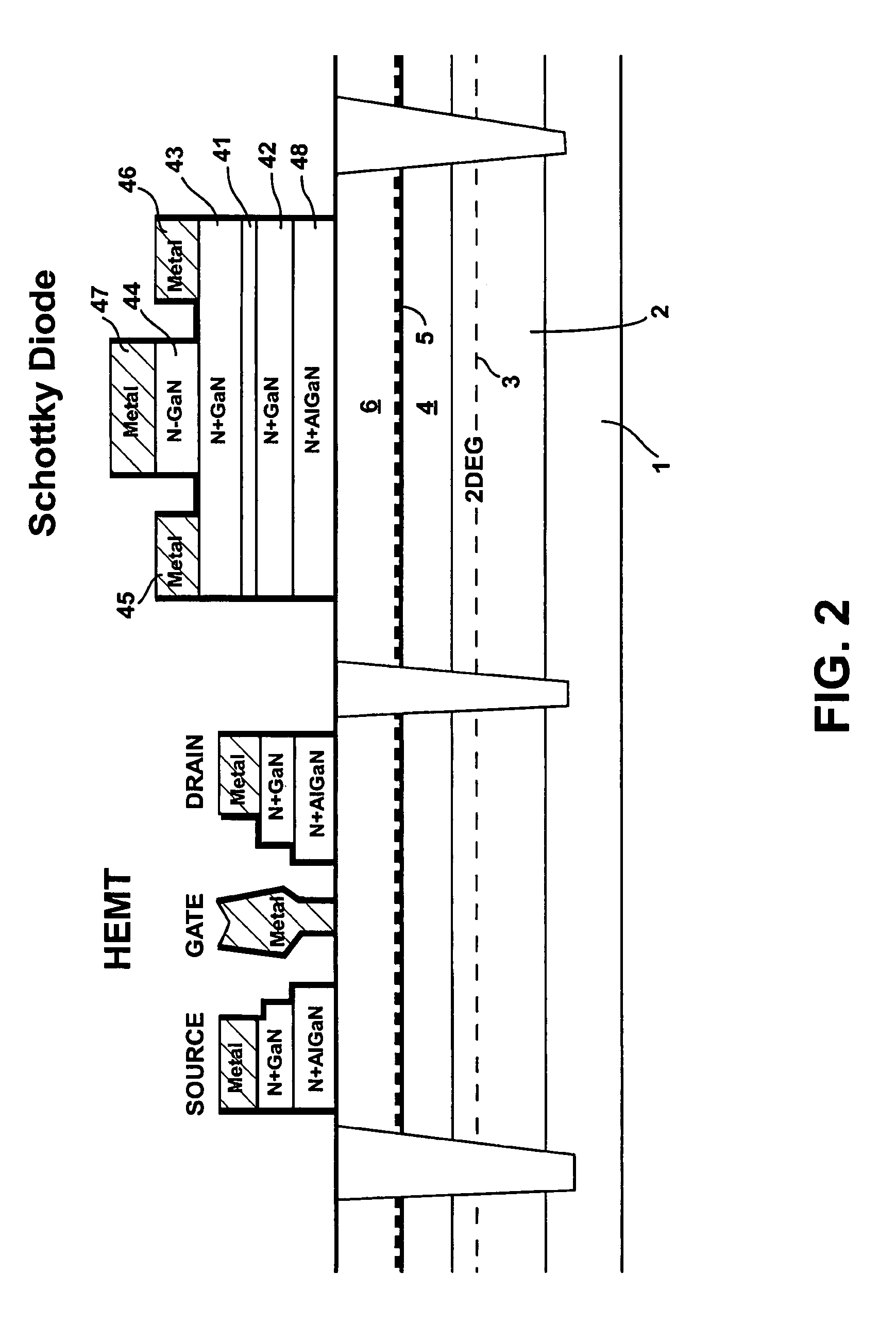

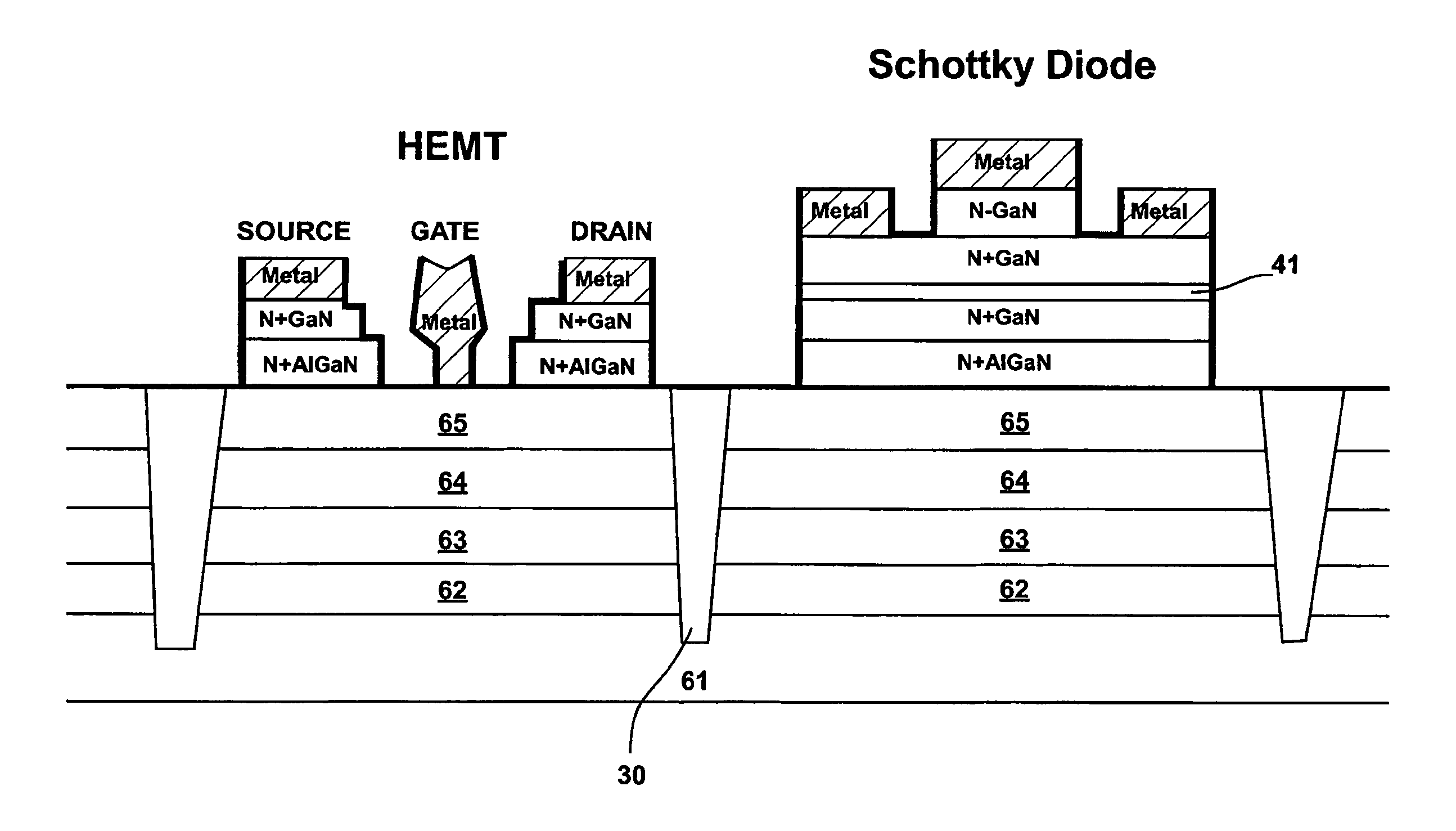

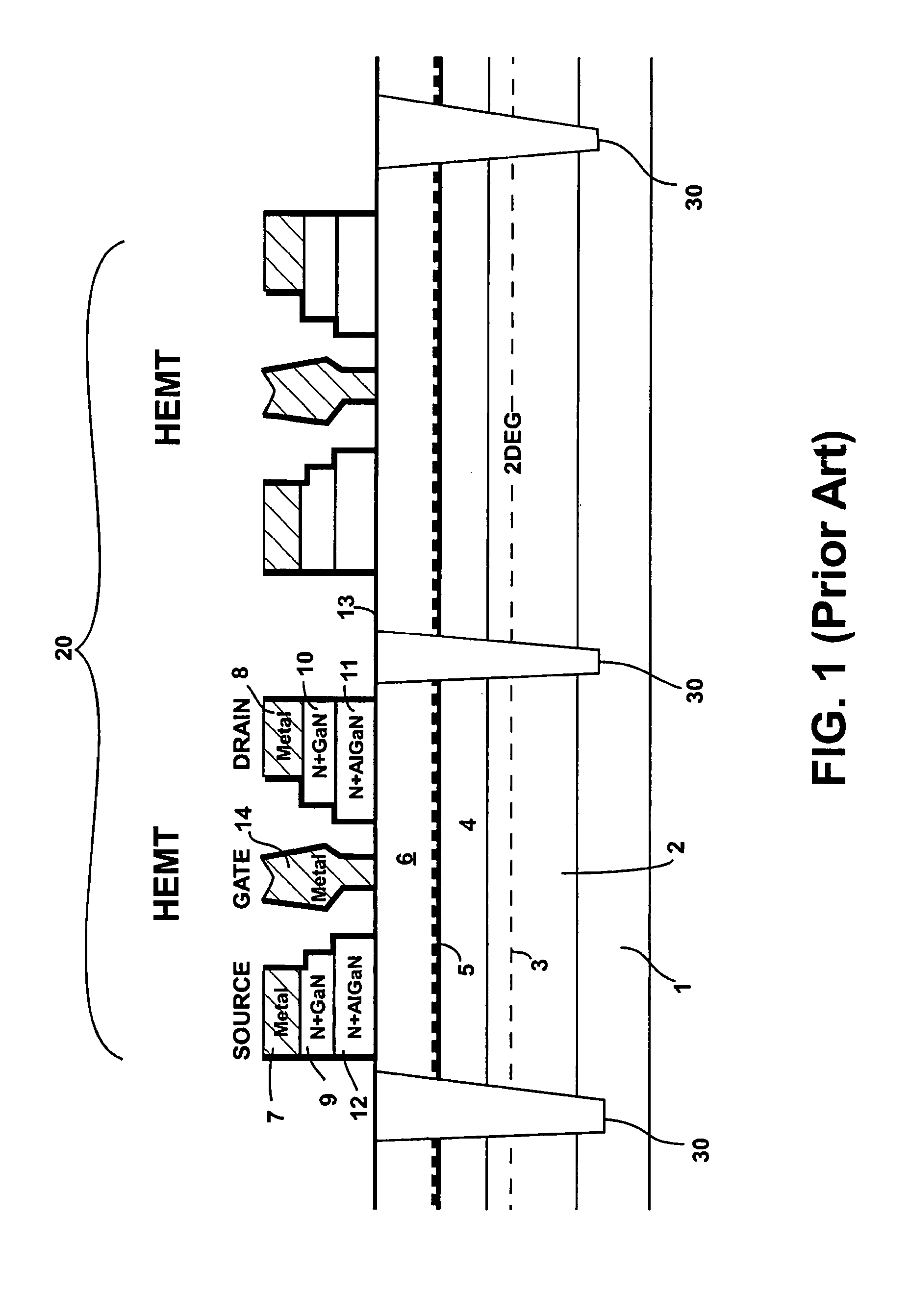

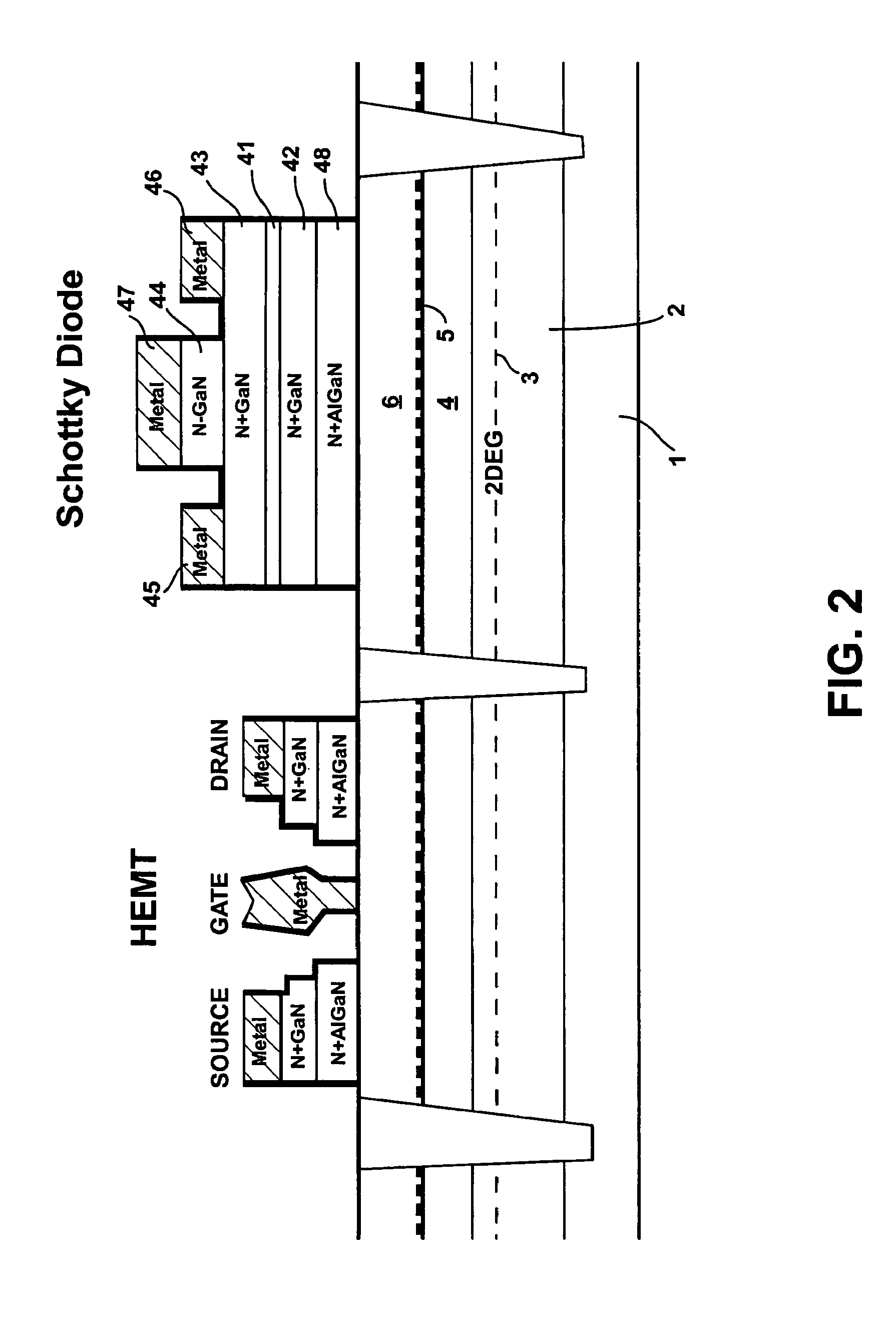

Integrated structure with transistors and Schottky diodes and process for fabricating the same

ActiveUS7989277B1Minimize parasitic capacitancePhysical size minimizedTransistorSolid-state devicesParasitic capacitanceEngineering

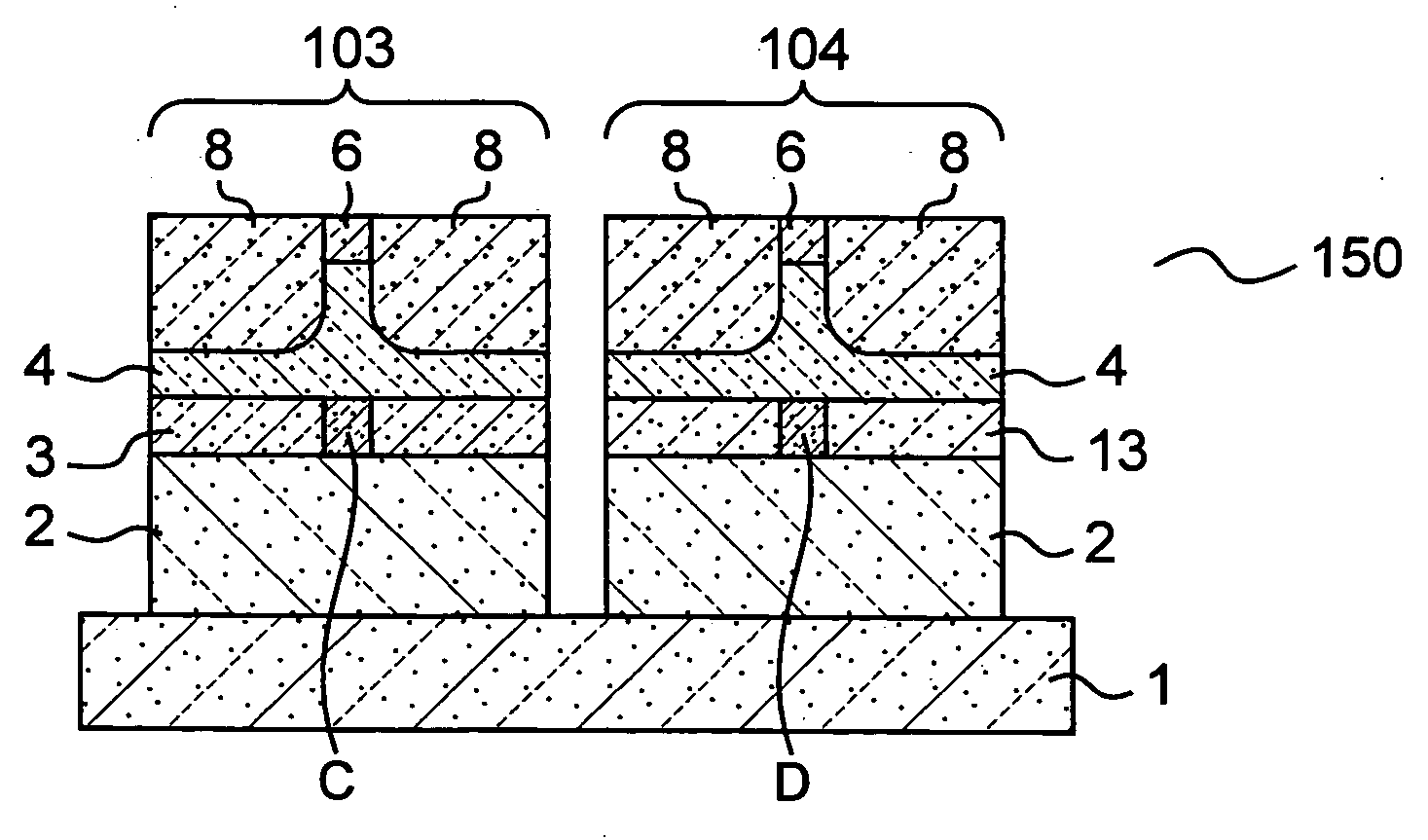

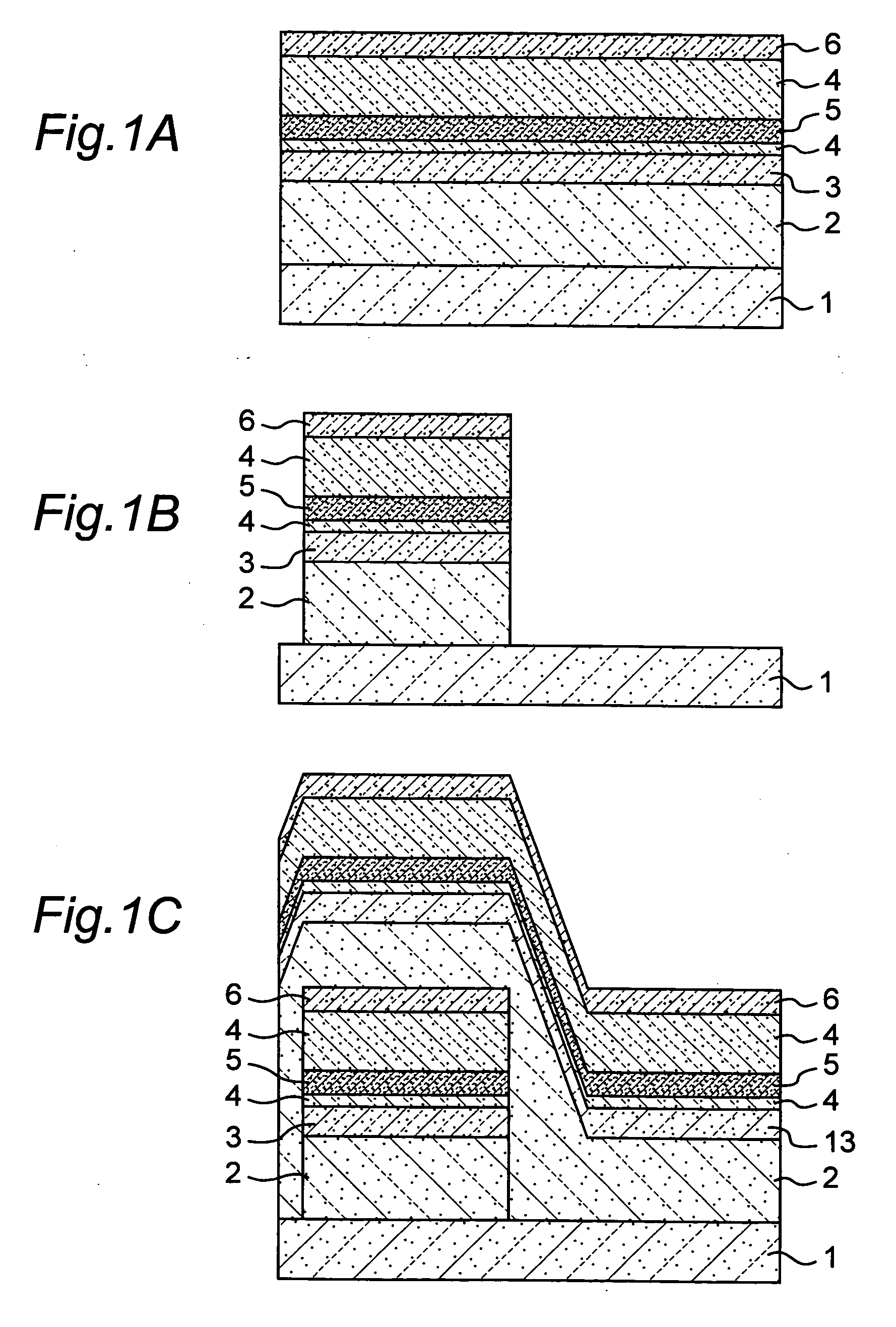

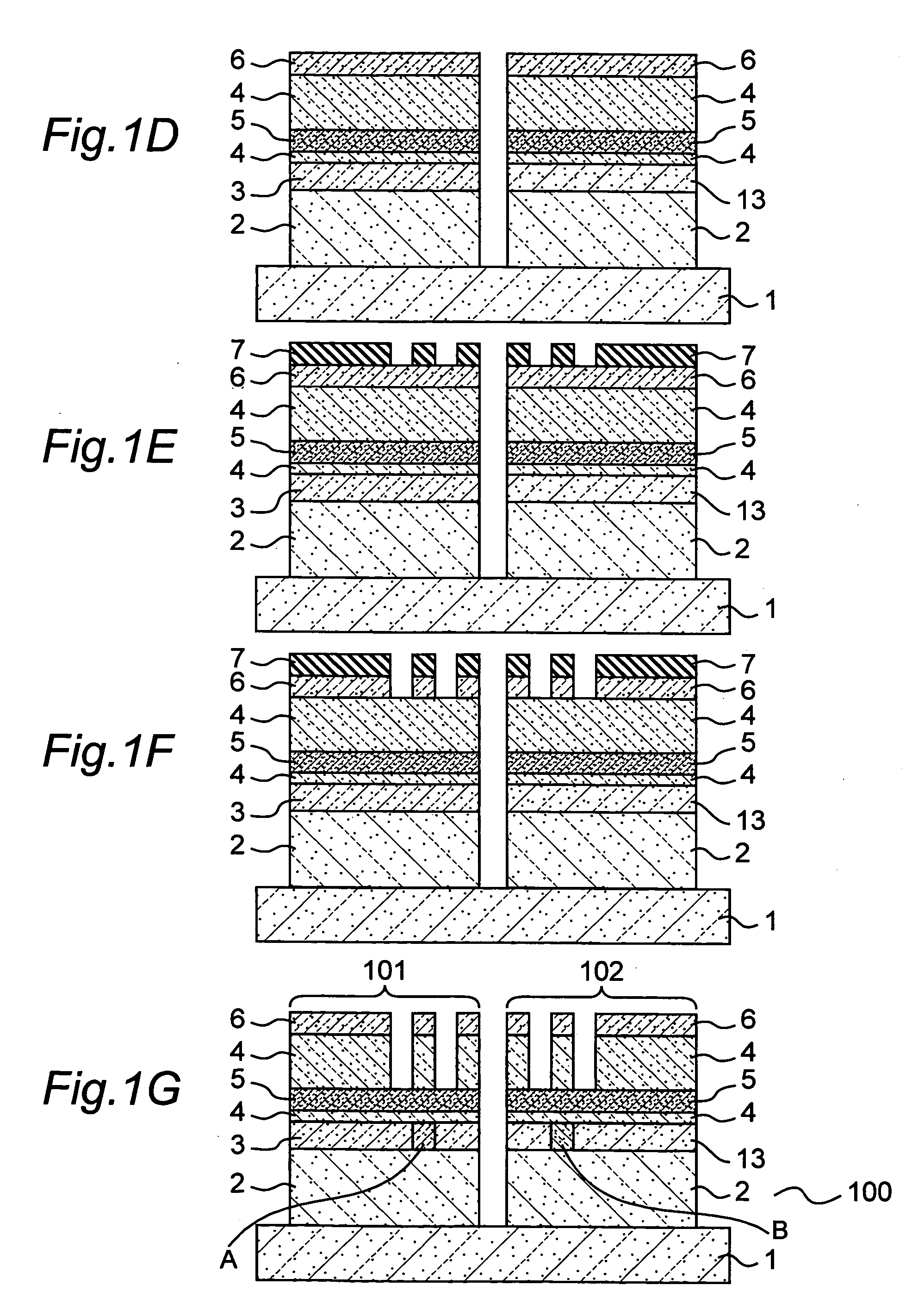

A process for fabricating an integrated group III nitride structure comprising high electron mobility transistors (HEMTs) and Schottky diodes, and the resulting structure, are disclosed. Integration of vertical junction Schottky diodes is enabled, and the parasitic capacitance and resistance as well as the physical size of the diode are minimized. A process for fabricating an integrated group III nitride structure comprising double-heterostructure field effect transistors (DHFETs) and Schottky diodes and the resulting structure are also disclosed.

Owner:HRL LAB

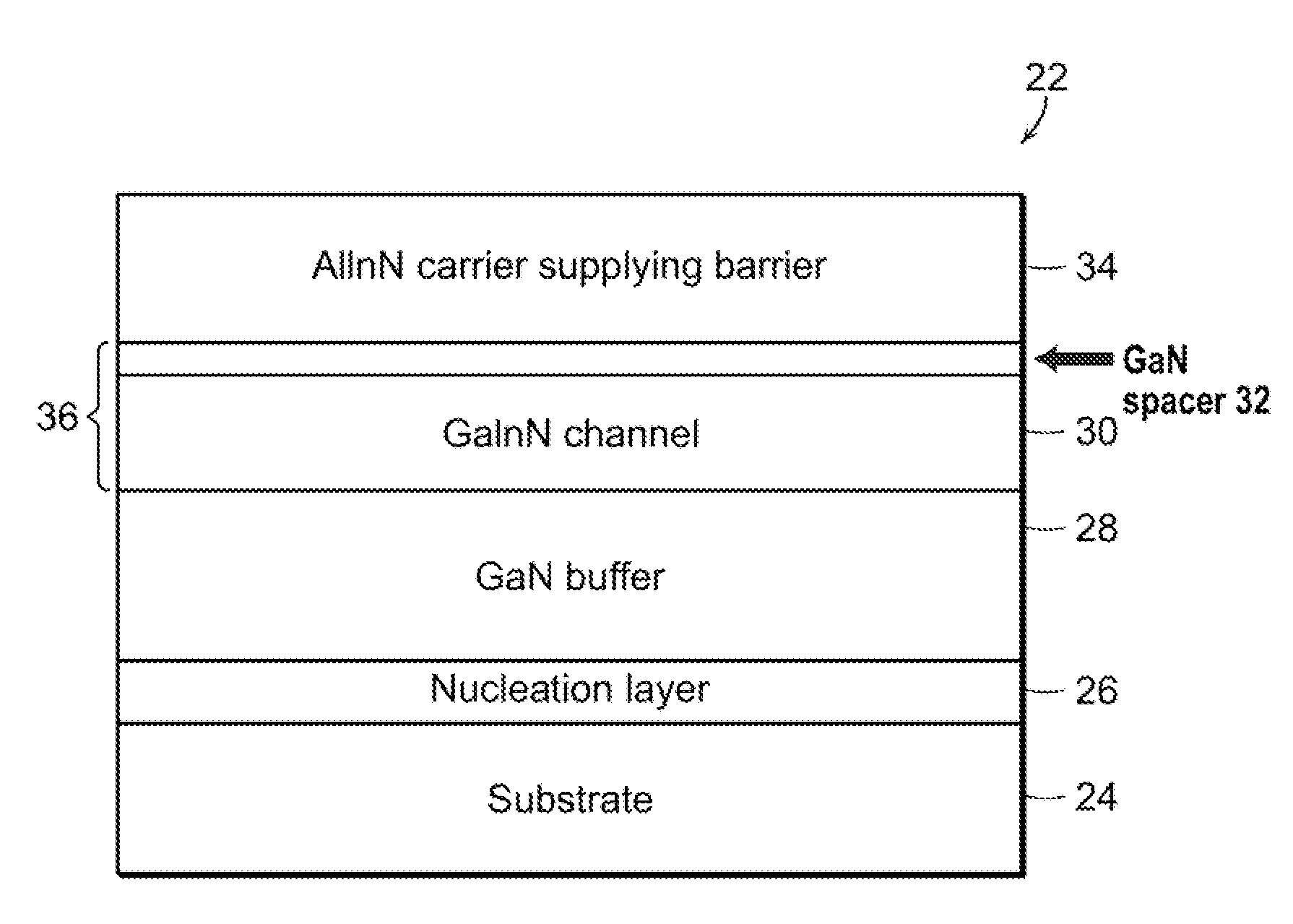

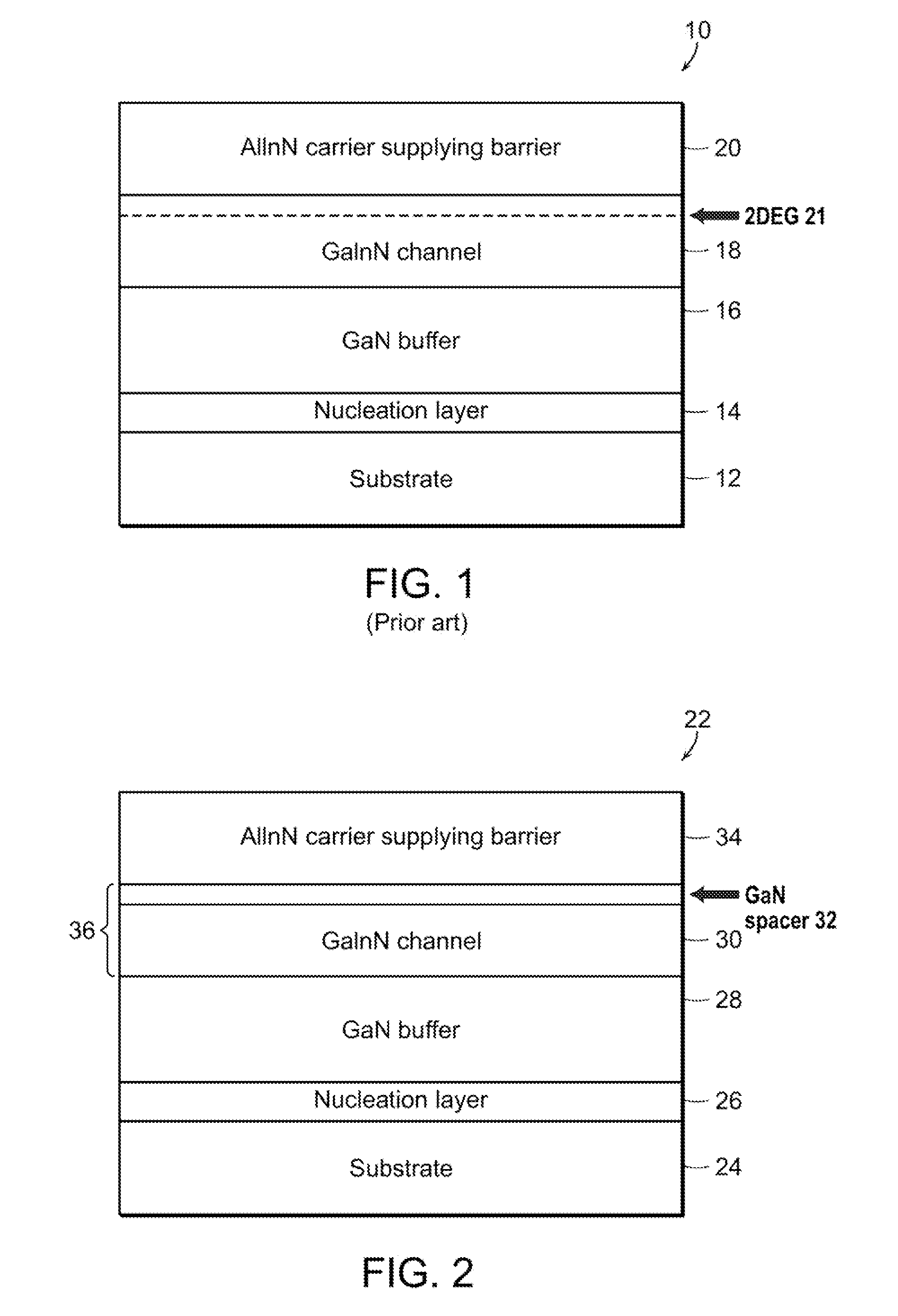

InGaN-Based Double Heterostructure Field Effect Transistor and Method of Forming the Same

InactiveUS20130207078A1Improved DEG mobilityReduce leakage currentSemiconductor/solid-state device manufacturingSemiconductor devicesTernary alloyDouble heterostructure

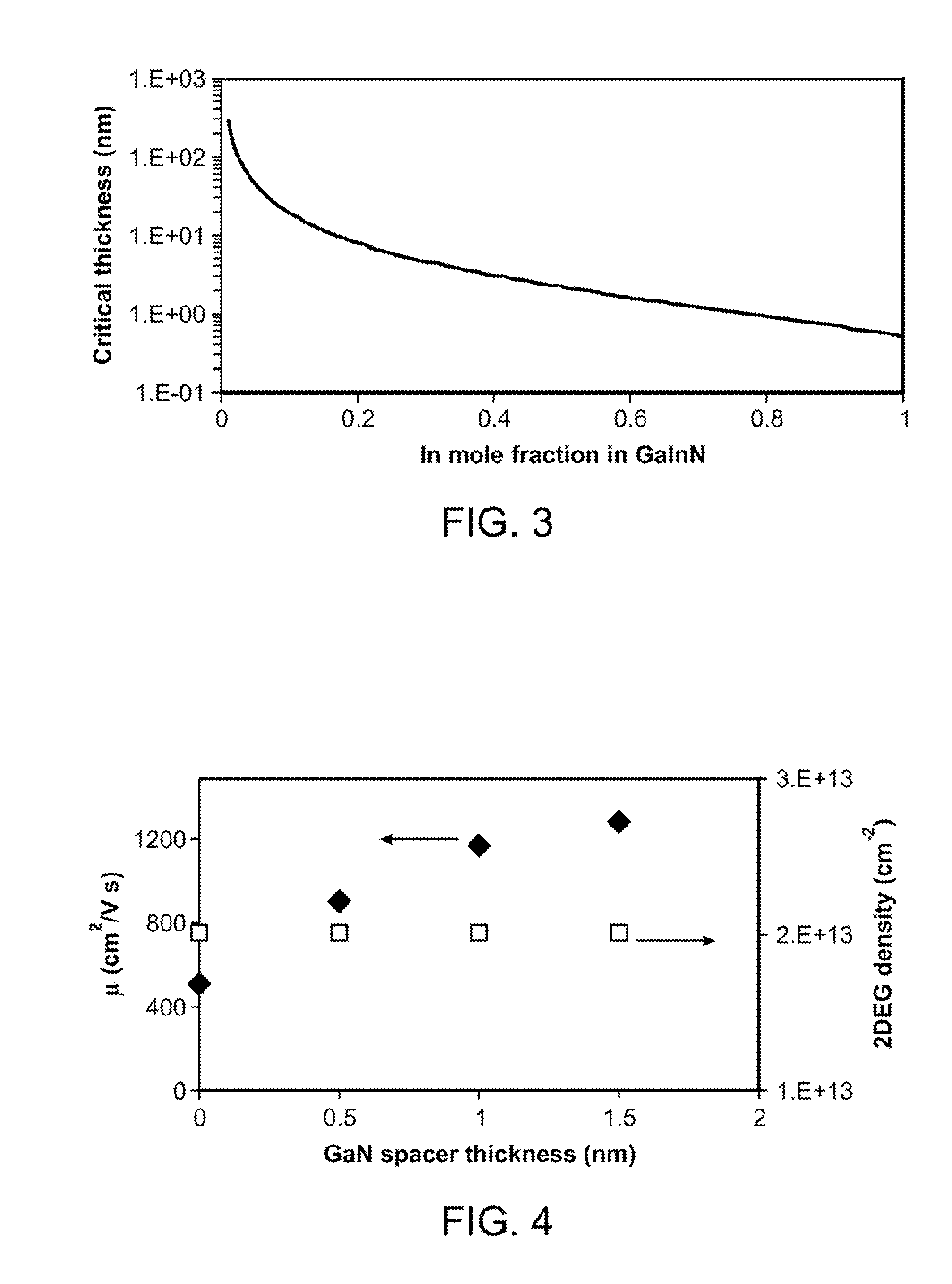

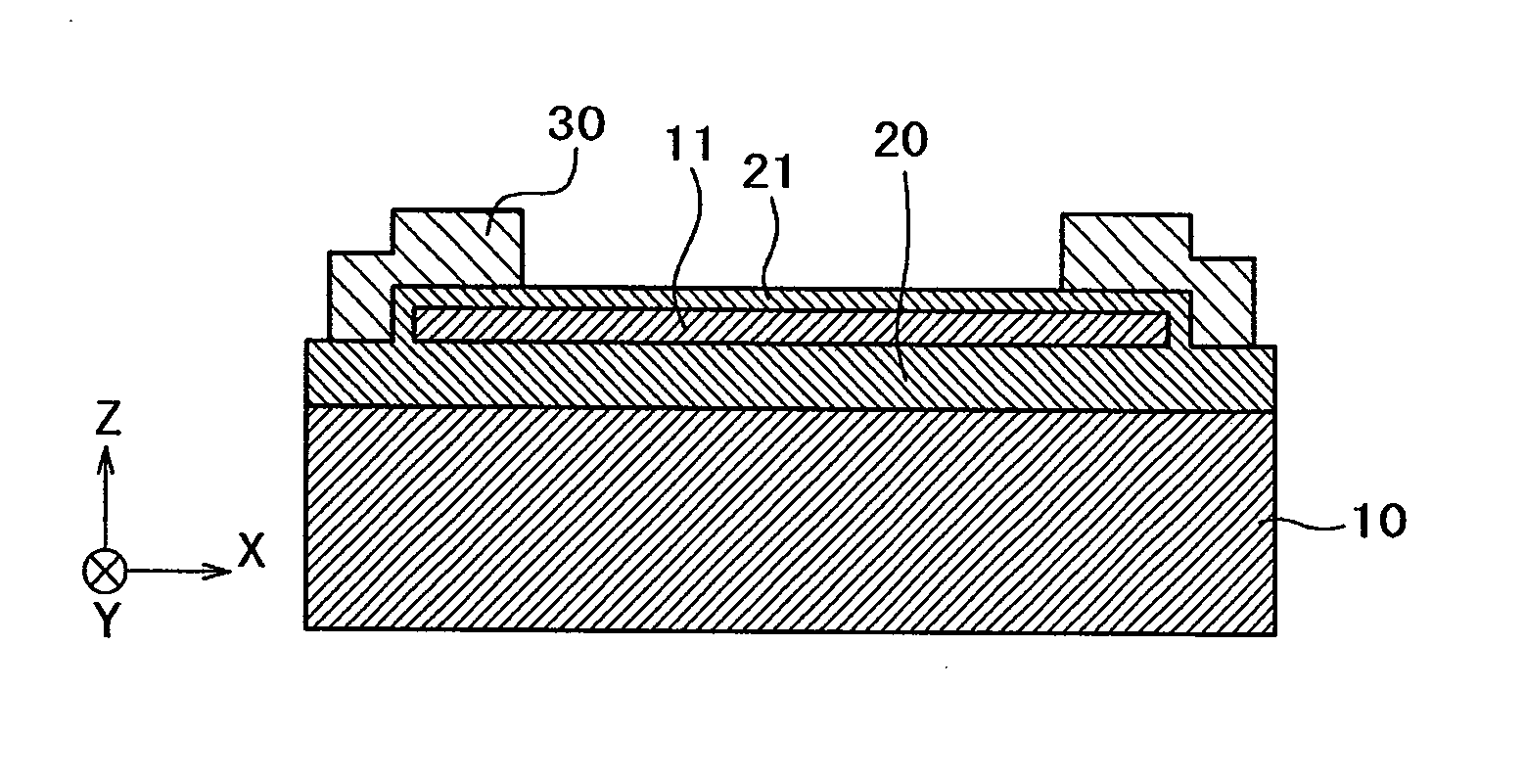

A double heterojunction field effect transistor (DHFET) includes a substrate, a buffer layer consisting of GaN back-barrier buffer layer formed on the substrate, a channel layer consisting of an InxGa1-xN ternary alloy in one embodiment, and in another embodiment, InGaN / GaN superlattice (SL) formed on the GaN back-barrier buffer layer opposite to the substrate. A GaN spacer layer is formed on the InxGa1-xN or InGaN / GaN superlattice channel layer opposite to the GaN buffer layer and a carrier-supplying layer consisting of an Al1-yInyN ternary alloy is formed on the GaN spacer layer opposite to the channel layer. A preferred thickness of the GaN spacer layer is less than about 1.5 nm. The InGaN / GaN SL preferably includes 1 to 5 InGaN—GaN pairs and a preferred thickness of the InGaN layer in the InGaN / GaN SL is equal to or less than about 0.5 nm. A two-dimensional electron gas is formed at the interface between the InxGa1-xN or InGaN / GaN SL channel and GaN spacer layers.

Owner:IQE KC

Silicon-germanium light-emitting element

InactiveUS20140175490A1Solve low luminous efficiencyWell formedSemiconductor lasersSemiconductor devicesElectron holeErbium lasers

Provided is an element structure whereby it is possible to produce a silicon-germanium light-emitting element enclosing an injected carrier within a light-emitting region. Also provided is a method of manufacturing the structure. Between the light-emitting region and an electrode there is produced a narrow passage for the carrier, specifically, a one-dimensional or two-dimensional quantum confinement region. A band gap opens up in this section due to the quantum confinement, thereby forming an energy barrier for both electrons and positive holes, and affording an effect analogous to a double hetero structure in an ordinary Group III-V semiconductor laser. Because no chemical elements other than those used in ordinary silicon processes are employed, the element can be manufactured inexpensively, simply by controlling the shape of the element.

Owner:HITACHI LTD

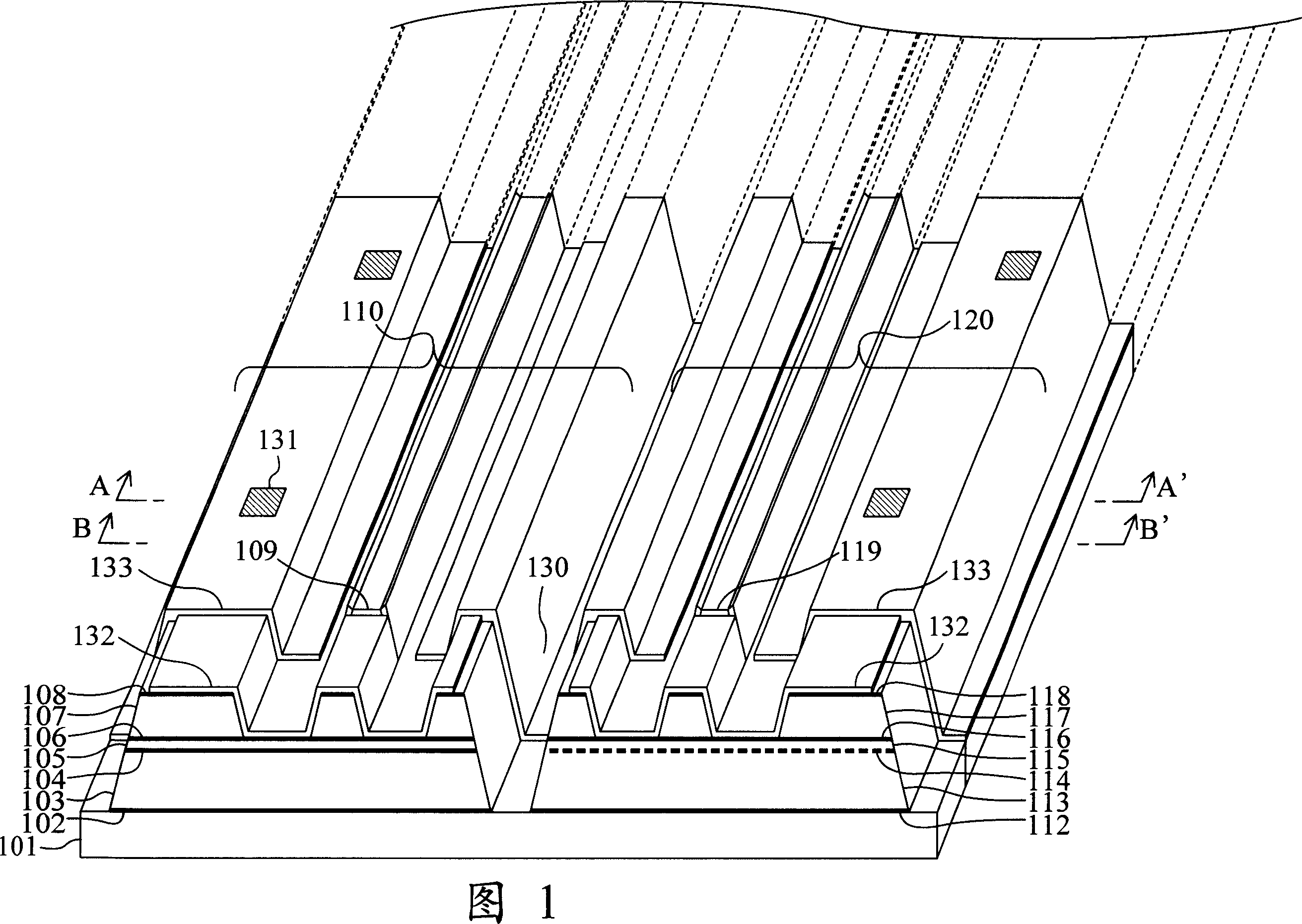

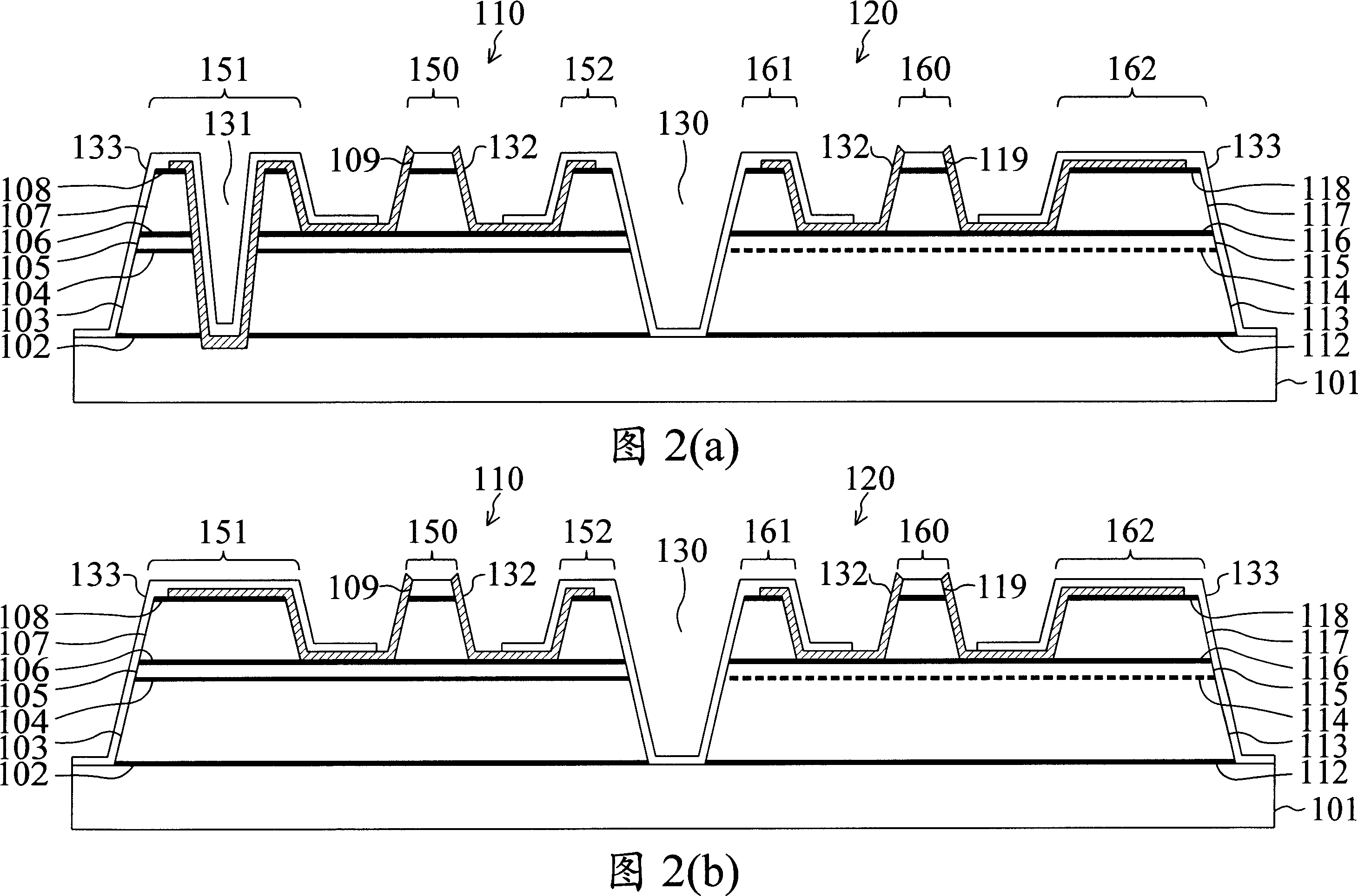

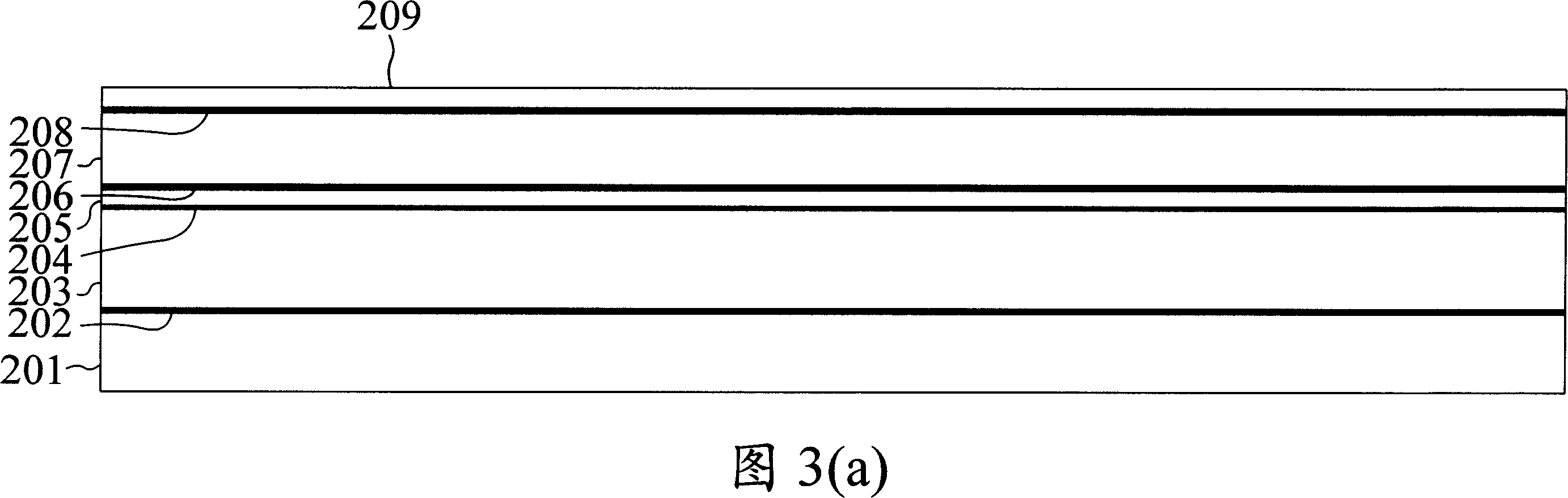

Semiconductor laser device and method for fabricating the same

InactiveCN101064412AImprove yieldPrevent short circuit defectsOptical wave guidanceLaser optical resonator constructionRed laserContact layer

The present invention provides a monolithic multiple-wavelength semiconductor laser device capable of achieving a high yield, and provides a method of manufacturing the same. An infrared laser device 110 and red laser device 120 are formed on the same substrate 101. Each of the laser elements 110, 120 is provided with a double heterostructure composed by laminating an n-type cladding layer 103 or 113, an active layer 104 or 114, and a p-type first cladding layer 105 or 115 in that order; and a ridge-shaped waveguide 150 or 160 including a p-type second cladding layer 107 or 117, and a p-type contact layer 109 or 209 provided on the p-type second cladding layer. A current blocking layer 132 is formed on both side-walls of each ridge-shaped waveguide 150, 160 and around them. A leakage preventing layer 133 is formed on the current blocking layer 132.

Owner:PANASONIC CORP

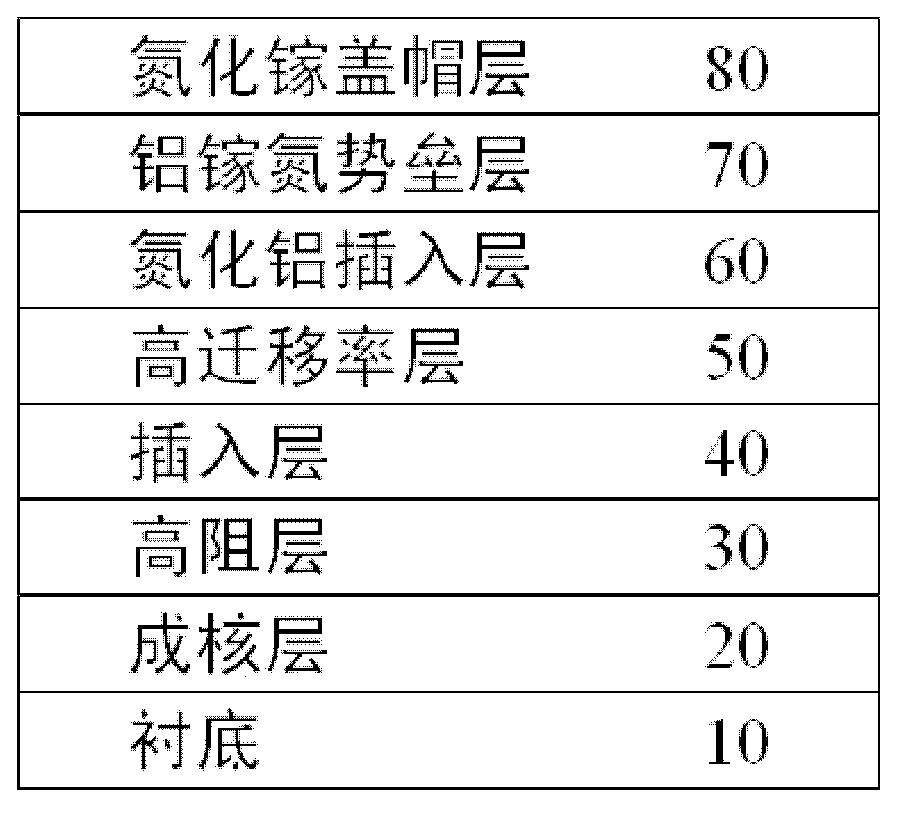

Crystal tube structure with high electronic shifting ratio of gallium nitrate base of double heterogenous structure and mfg. method thereof

InactiveCN1787229AControl leakageIncrease concentrationSemiconductor/solid-state device manufacturingSemiconductor devicesHigh resistanceGallium nitride

The invention is a double-heterostructured GaN-base high-electron migration rate transistor structure, characterized in comprising: a sapphire, silicon carbide or silicon substrate; a high resistance GaN buffer layer made on the substrate; a thin unpurposed doped GaN insert layer made on the buffer layer; a high-migration rate GaN channel layer made on the thin unpurposed doped GaN insert layer; a thin AlN insert layer made on the channel layer; a n-type doped or unpurposed doped Al-Ga-N barrier layer made on the thin AlN insert layer.

Owner:INST OF SEMICONDUCTORS - CHINESE ACAD OF SCI

Light Emitting Device and Method of Fabricating the Same

ActiveUS20100270568A1Reduced series resistanceImprove responseSolid-state devicesSemiconductor/solid-state device manufacturingHigh concentrationInter layer

A light emitting device comprises a light emitting layer section having a double heterostructure of an n-type cladding layer, an active layer and a p-type cladding layer, each composed of AlGaInP stacked in this order. Supposing a bonding object layer having a first main surface side as p type and a second main surface side as n type, a light extraction side electrode is formed to cover the first main surface partially. An n-type transparent device substrate composed of Group III-V compound semiconductor having greater band gap energy than the active layer is bonded to the second main surface of the bonding object layer. On one sides of the transparent device substrate and the bonding object layer, a bonding surface to the other is formed, and an InGaP intermediate layer is formed to have a high concentration Si doping layer formed on the bonding surface side.

Owner:SHIN-ETSU HANDOTAI CO LTD

Light-emitting diode device and production method thereof

InactiveCN1759490AHigh crystallinityDouble the brightnessSemiconductor devicesWavelengthCrystallinity

A double hetero structure light-emitting diode device includes an active layer ( 6 ), a positive-electrode-side cladding layer, a negative-electrode-side cladding layer ( 4 ), a window layer ( 9 ) and an undoped AlInP layer. The positive-electrode-side cladding layer includes an undoped AlInP layer ( 7 ) grown to have a thickness of 0.5 mum and an intermediate layer ( 8 ) doped to assume p-type conductivity and having an intermediate energy band gap value between that of the undoped AlInP layer and that of the window layer. The window layer on the intermediate layer is a GaP layer grown at 730 DEG C. or higher and at a growth rate of 7.8 mum / hour or more in the presence of Ze serving as a dopant. The negative-electrode-side cladding layer is provided with an undoped AlInP layer ( 5 ) having a thickness of 0.1 mum or more. With this configuration, there is provided a light-emitting diode device that enhances the crystallinity of a window layer, prevents generation of faults caused by a high-temperature process and attains high luminance at a wavelength falling within a yellow-green band.

Owner:SHOWA DENKO KK

Light-emitting diode device and production method thereof

InactiveUS7528417B2High precisionHigh crystallinitySemiconductor/solid-state device manufacturingSemiconductor devicesCrystallinityLight-emitting diode

A double hetero structure light-emitting diode device includes an active layer (6), a positive-electrode-side cladding layer, a negative-electrode-side cladding layer (4), a window layer (9) and an undoped AlInP layer. The positive-electrode-side cladding layer includes an undoped AlInP layer (7) grown to have a thickness of 0.5 μm and an intermediate layer (8) doped to assume p-type conductivity and having an intermediate energy band gap value between that of the undoped AlInP layer and that of the window layer. The window layer on the intermediate layer is a GaP layer grown at 730° C. or higher and at a growth rate of 7.8 μm / hour or more in the presence of Ze serving as a dopant. The negative-electrode-side cladding layer is provided with an undoped AlInP layer (5) having a thickness of 0.1 μm or more. With this configuration, there is provided a light-emitting diode device that enhances the crystallinity of a window layer, prevents generation of faults caused by a high-temperature process and attains high luminance at a wavelength falling within a yellow-green band.

Owner:RESONAC HOLDINGS CORPORATION

Integrated structure with transistors and schottky diodes and process for fabricating the same

ActiveUS8368119B1Minimizing capacitanceMinimizing resistanceTransistorSolid-state devicesParasitic capacitanceEngineering

A process for fabricating an integrated group III nitride structure comprising high electron mobility transistors (HEMTs) and Schottky diodes, and the resulting structure, are disclosed. Integration of vertical junction Schottky diodes is enabled, and the parasitic capacitance and resistance as well as the physical size of the diode are minimized. A process for fabricating an integrated group III nitride structure comprising double-heterostructure field effect transistors (DHFETs) and Schottky diodes and the resulting structure are also disclosed.

Owner:HRL LAB

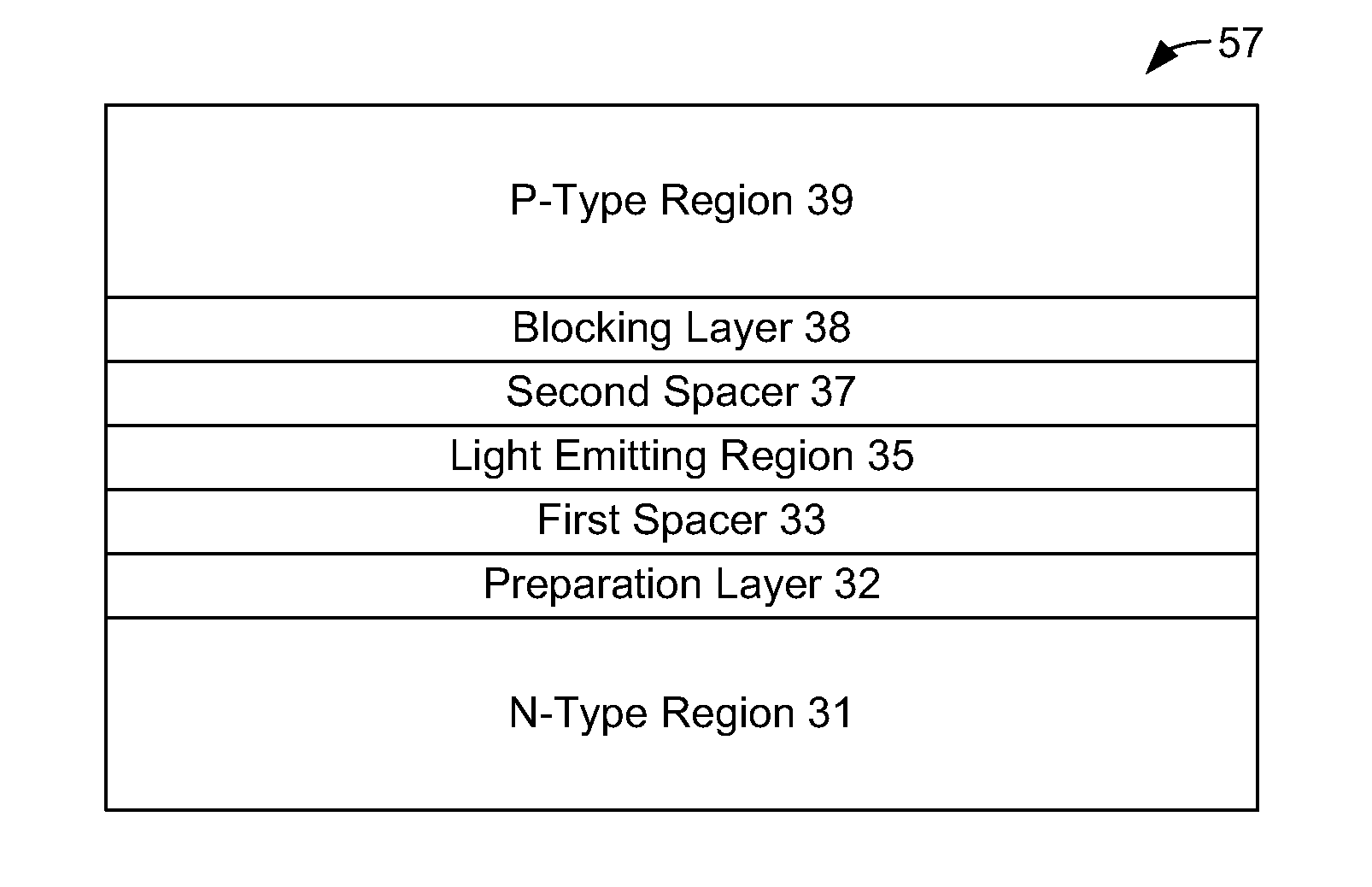

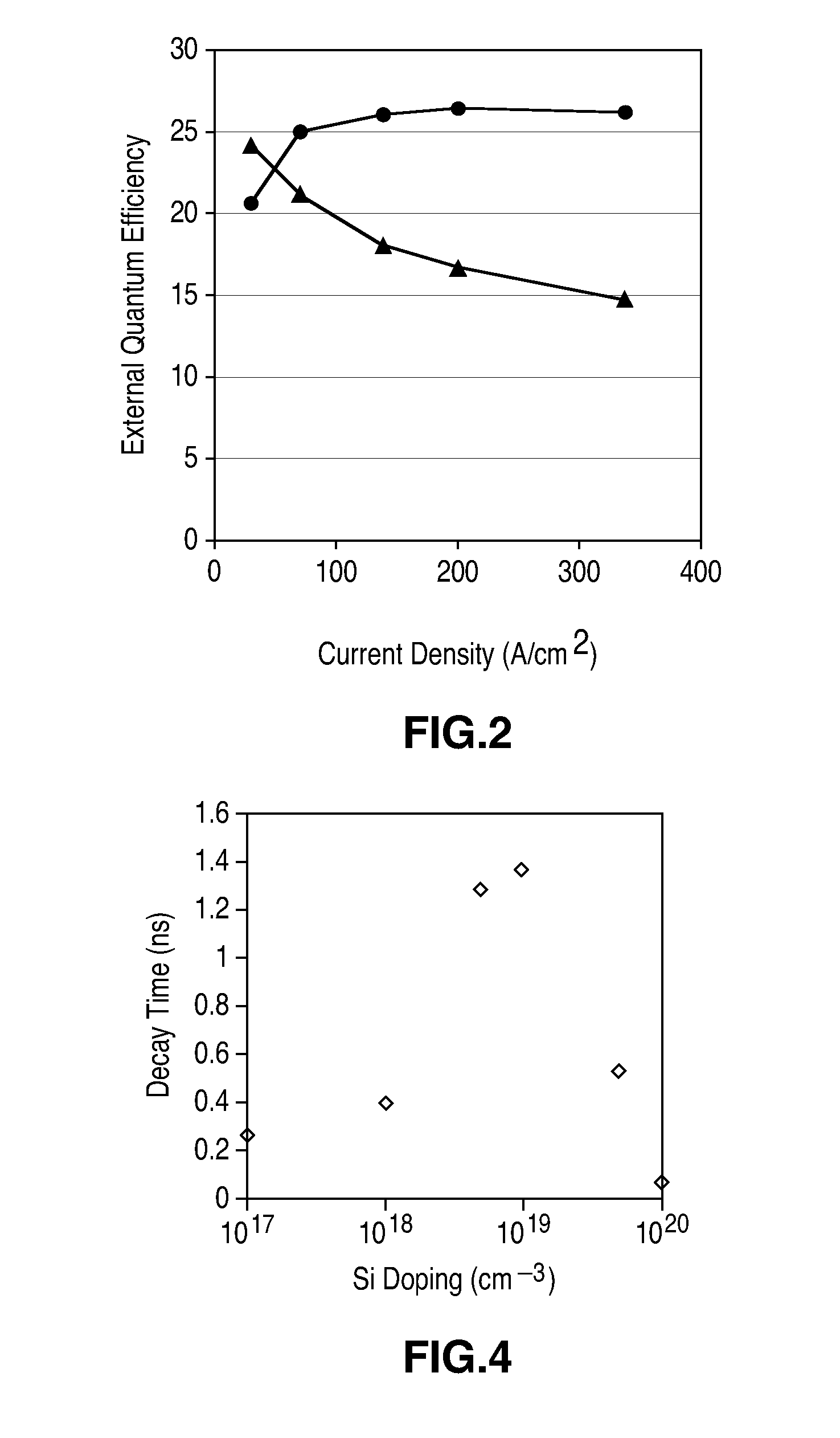

III-Nitride Light Emitting Device with Double Heterostructure Light Emitting Region

In a device, a III-nitride light emitting layer is disposed between an n-type region and a p-type region. A first spacer layer, which is disposed between the n-type region and the light emitting layer, is doped to a dopant concentration between 6×1018 cm3 and 5×1019 cm−3. A second spacer layer, which is disposed between the p-type region and the light emitting layer, is not intentionally doped or doped to a dopant concentration less than 6×1018 cm−3.

Owner:LUMILEDS

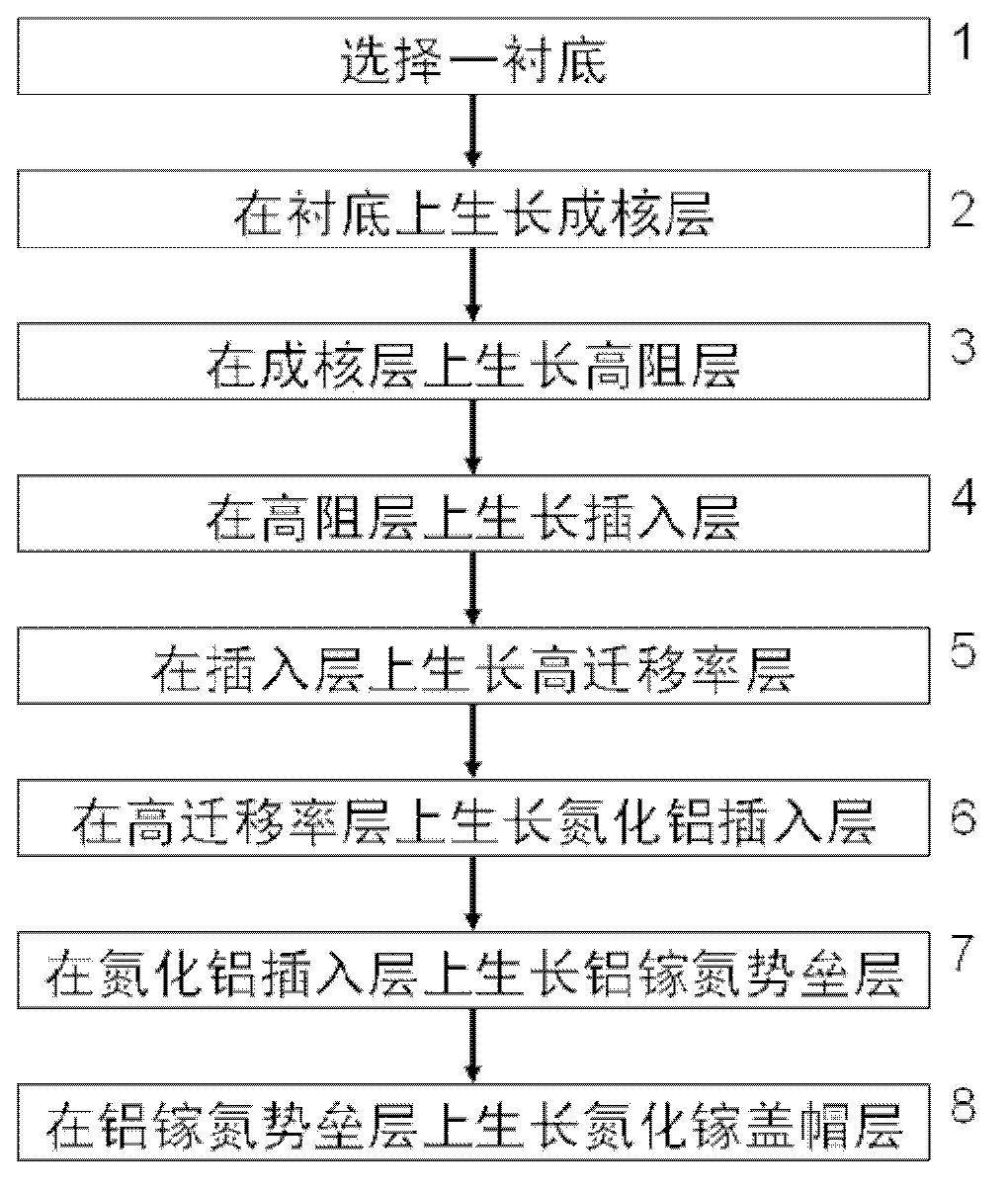

Double-heterostructure GaN-based high-electron mobility transistor structure and preparation method

ActiveCN102842613AHigh two-dimensional electron gas mobilityReduce leakageSemiconductor/solid-state device manufacturingSemiconductor devicesHigh resistanceGallium nitride

A double-heterostructure GaN-based high-electron mobility transistor structure comprises: a substrate; a nucleating layer prepared on the substrate; an unpurposed doped high resistance layer prepared on the nucleating layer; an unpurposed doped inserting layer prepared on the unpurposed doped high resistance layer; an unpurposed doped high mobility layer prepared on the unpurposed doped inserting layer; an unpurposed doped aluminum nitride inserting layer prepared on the high mobility layer; an unpurposed doped ALGaN barrier layer prepared on the unpurposed doped aluminum nitride inserting layer; and an unpurposed doped GaN capping layer prepared on the unpurposed doped ALGaN barrier layer.

Owner:INST OF SEMICONDUCTORS - CHINESE ACAD OF SCI

Semiconductor laser and method for manufacturing same

InactiveCN1467891ASuppression of distortionHigh outputOptical wave guidanceLaser detailsLine widthSemiconductor package

A semiconductor laser includes a substrate, a double hetero structure portion formed on the substrate, the double hetero structure including a first clad layer formed on the substrate, an active layer formed on the first clad layer and a second clad layer formed on the active layer, the second clad layer having a stripe-form projection on an upper surface thereof, the projection having an upper portion whose sidewalls are substantially vertically formed on the surface of the substrate and a step-shaped lower portion whose line width is larger than that of the upper portion, and a current blocking layer formed extending from side surfaces of the projection to the upper surface of the second clad layer except an upper surface of the projection.

Owner:KK TOSHIBA

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com