Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

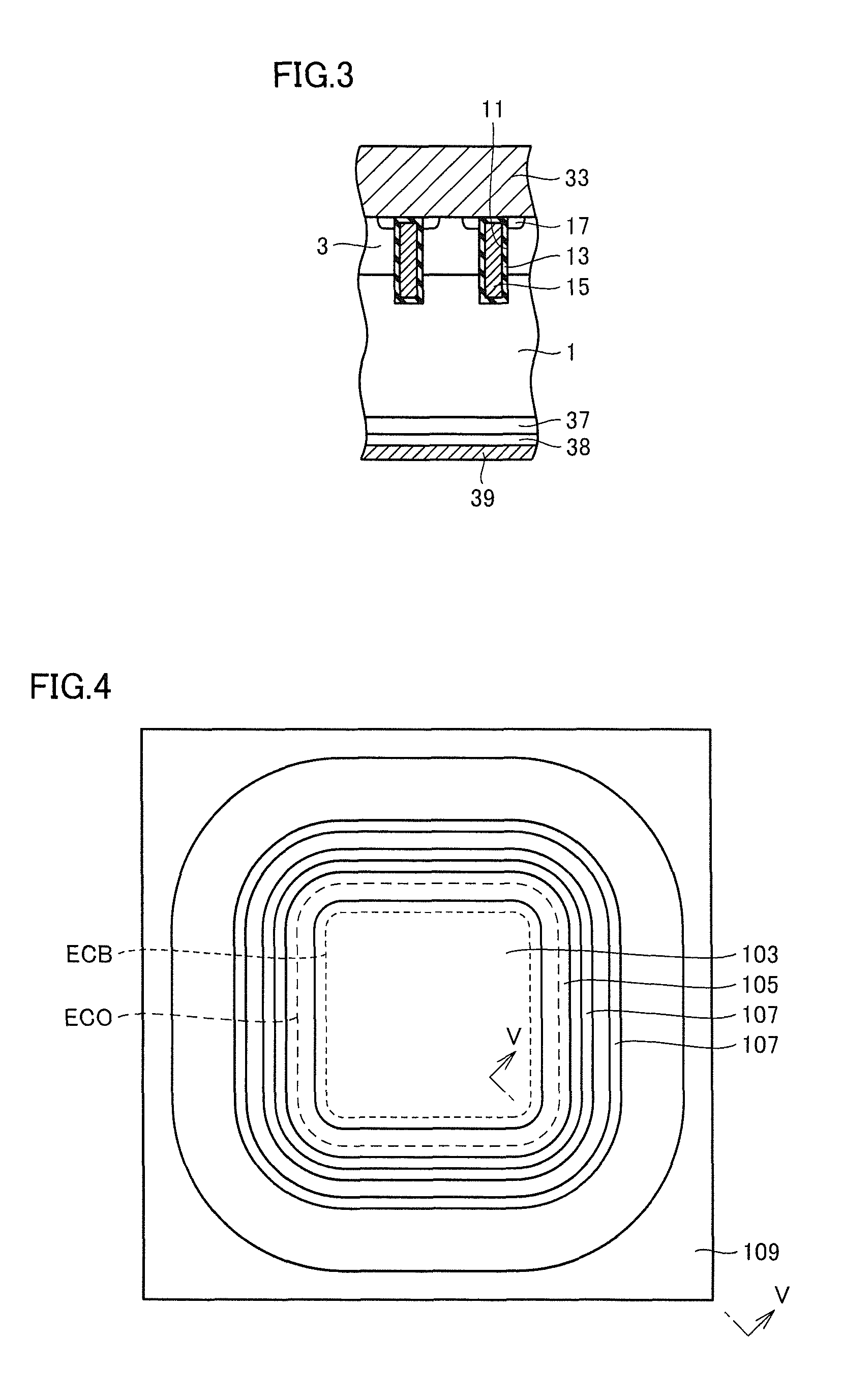

62 results about "Channel-stopper" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

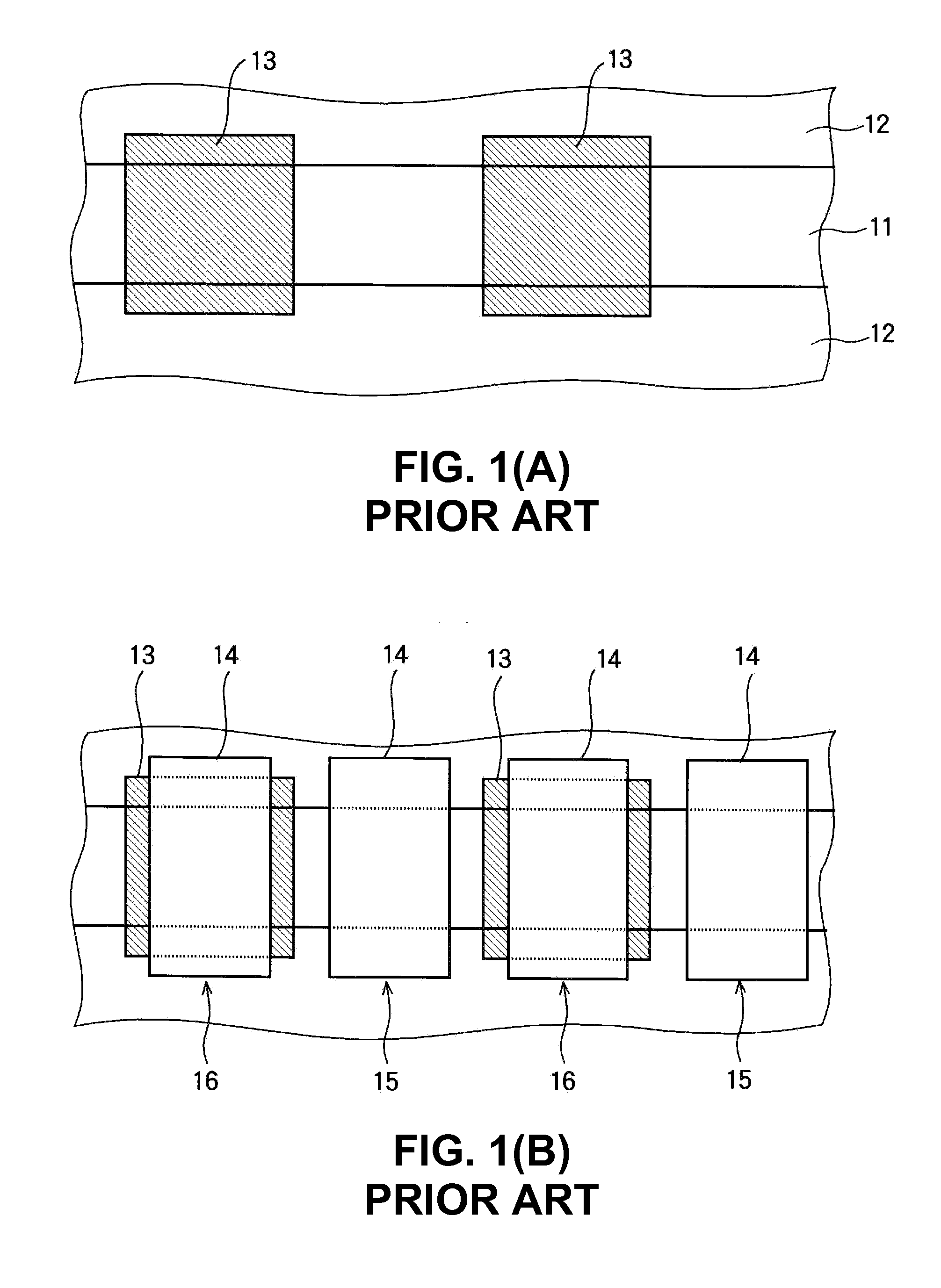

In semiconductor device fabrication, channel-stopper or channel-stop is an area in semiconductor devices produced by implantation or diffusion of ions, by growing or patterning the silicon oxide, or other isolation methods in semiconductor material with the primary function to limit the spread of the channel area or to prevent the formation of parasitic channels (inversion layers).

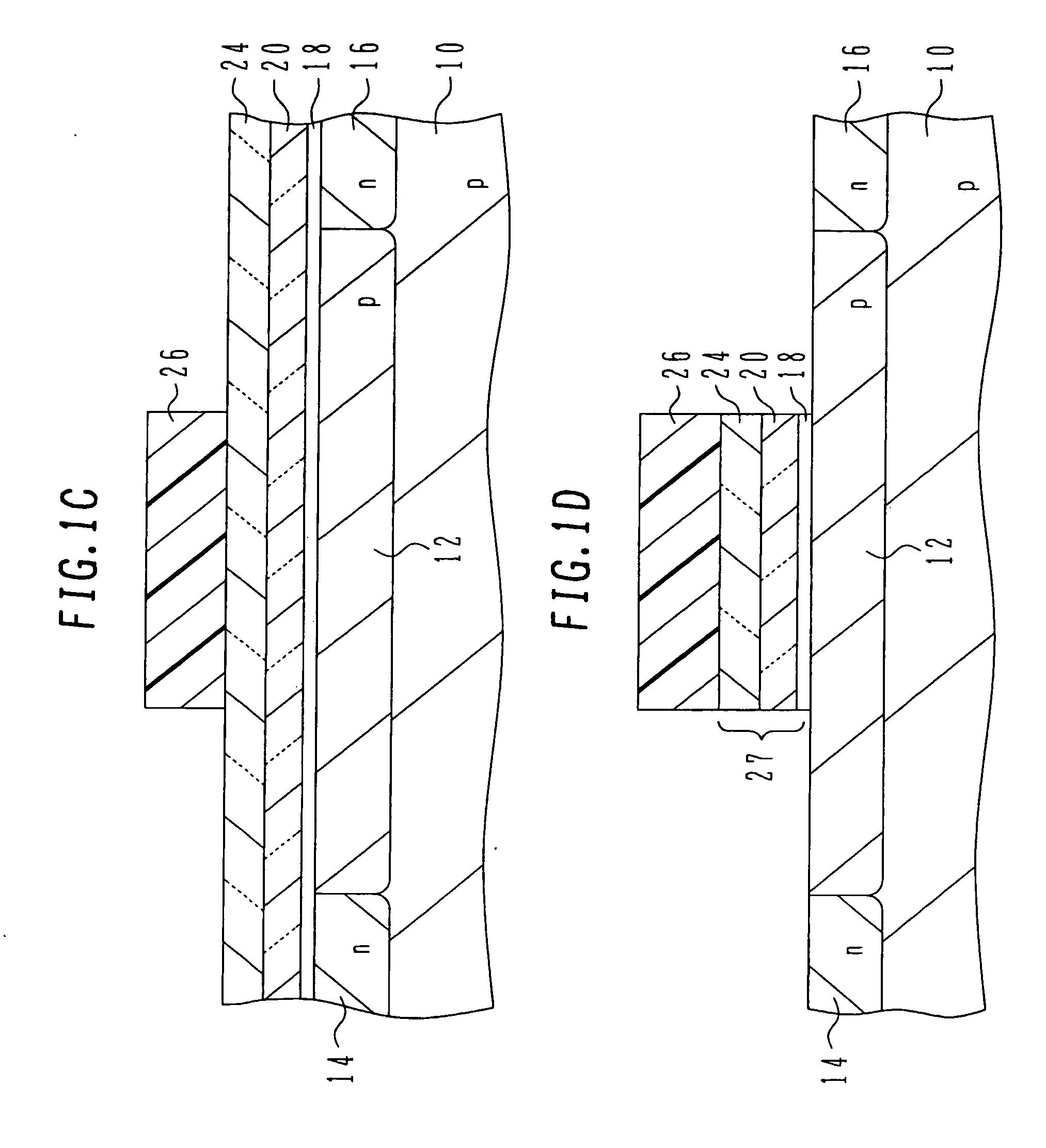

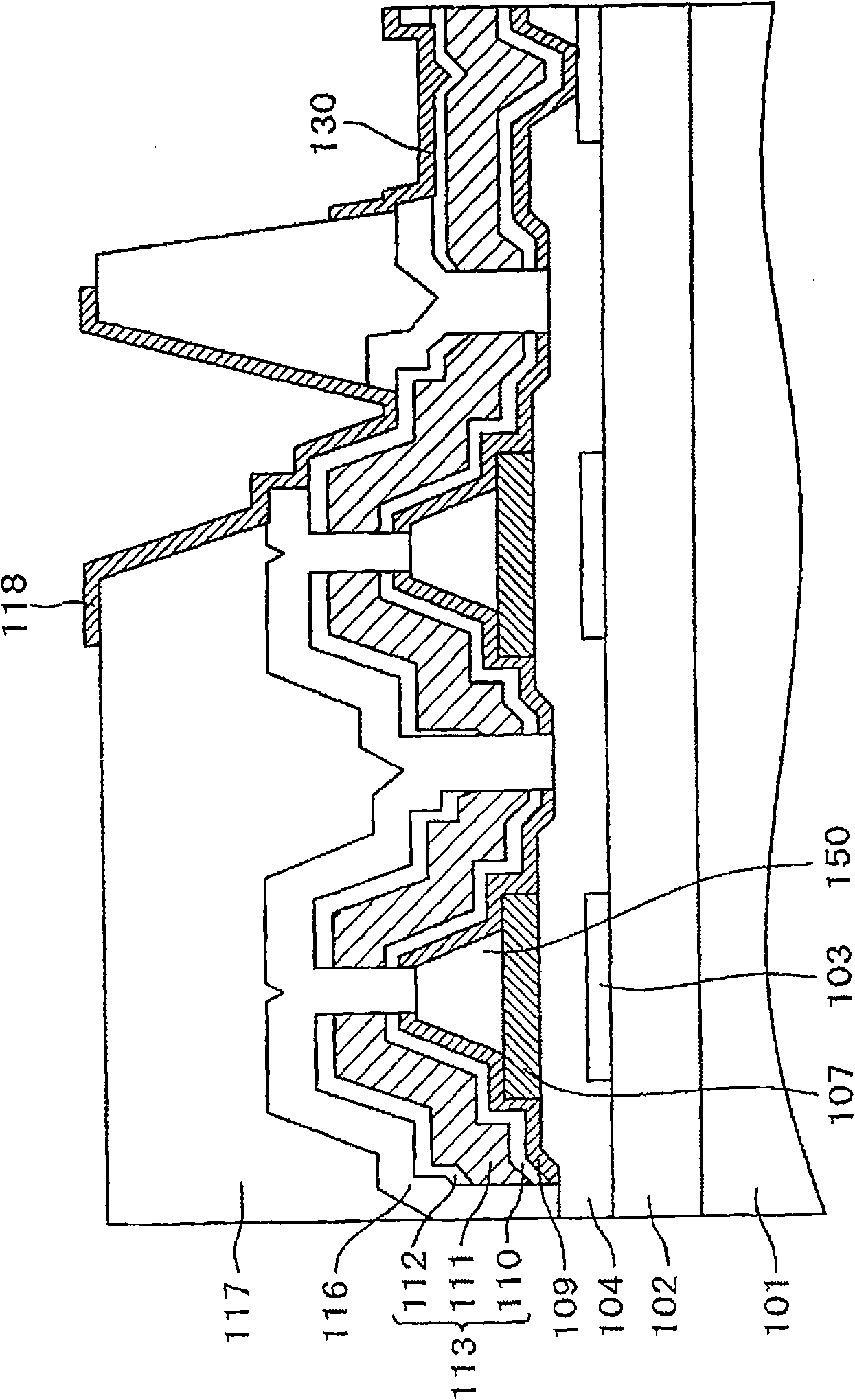

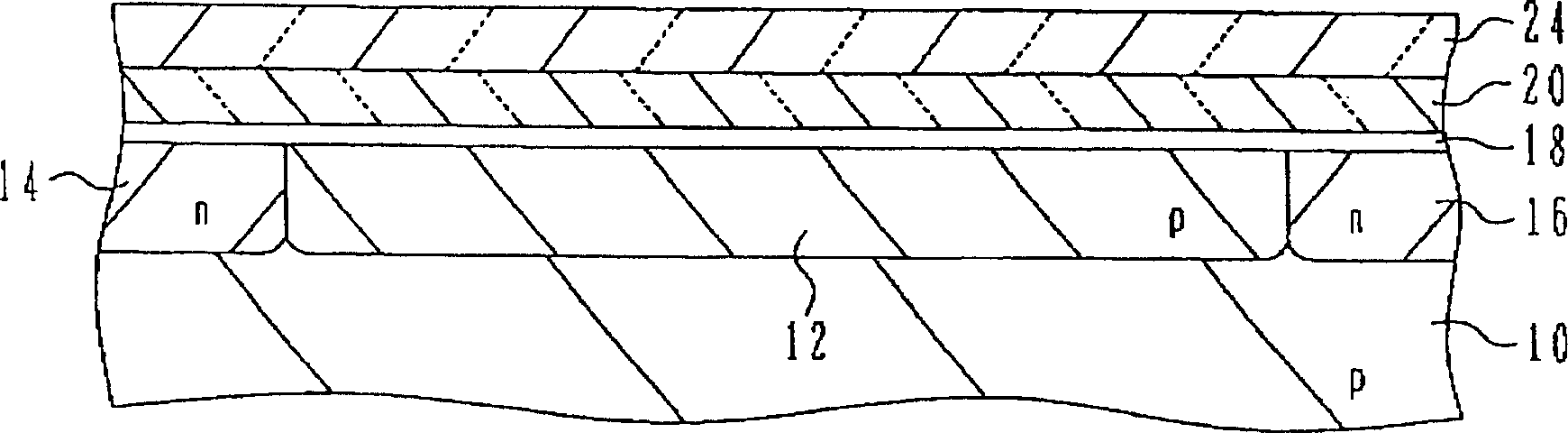

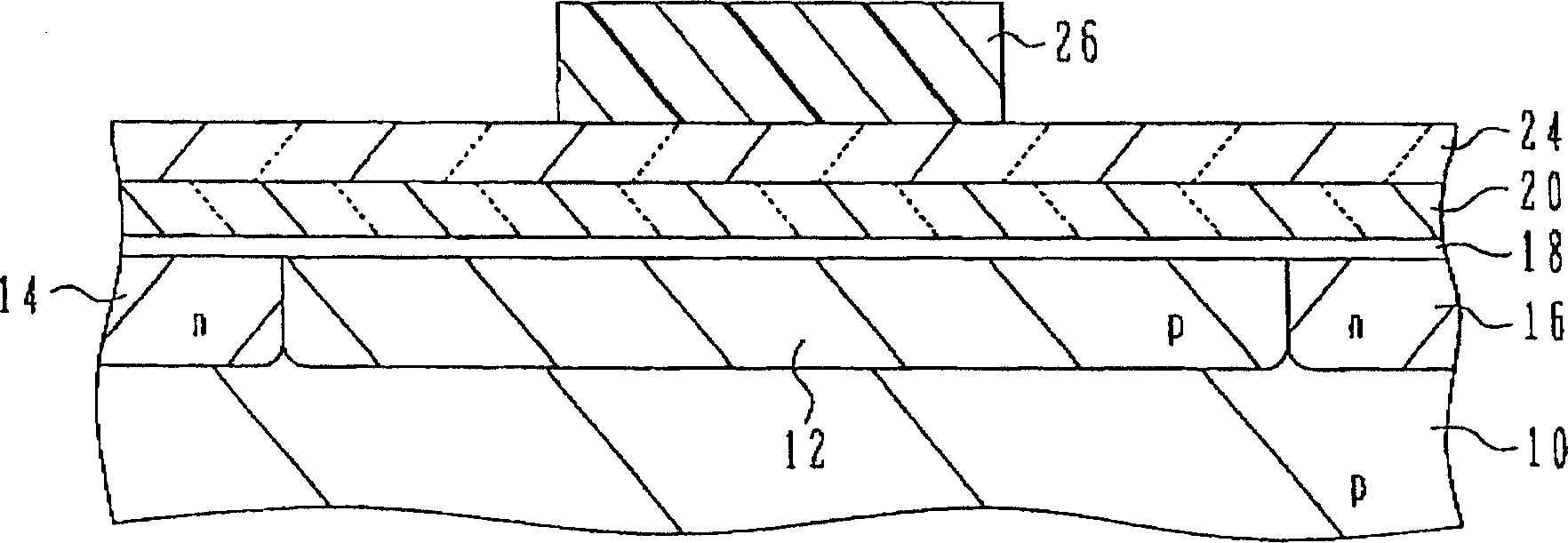

Liquid Crystal Display Device

InactiveUS20090225251A1High currentSuppressing increaseTransistorSolid-state devicesLiquid-crystal displayChannel-stopper

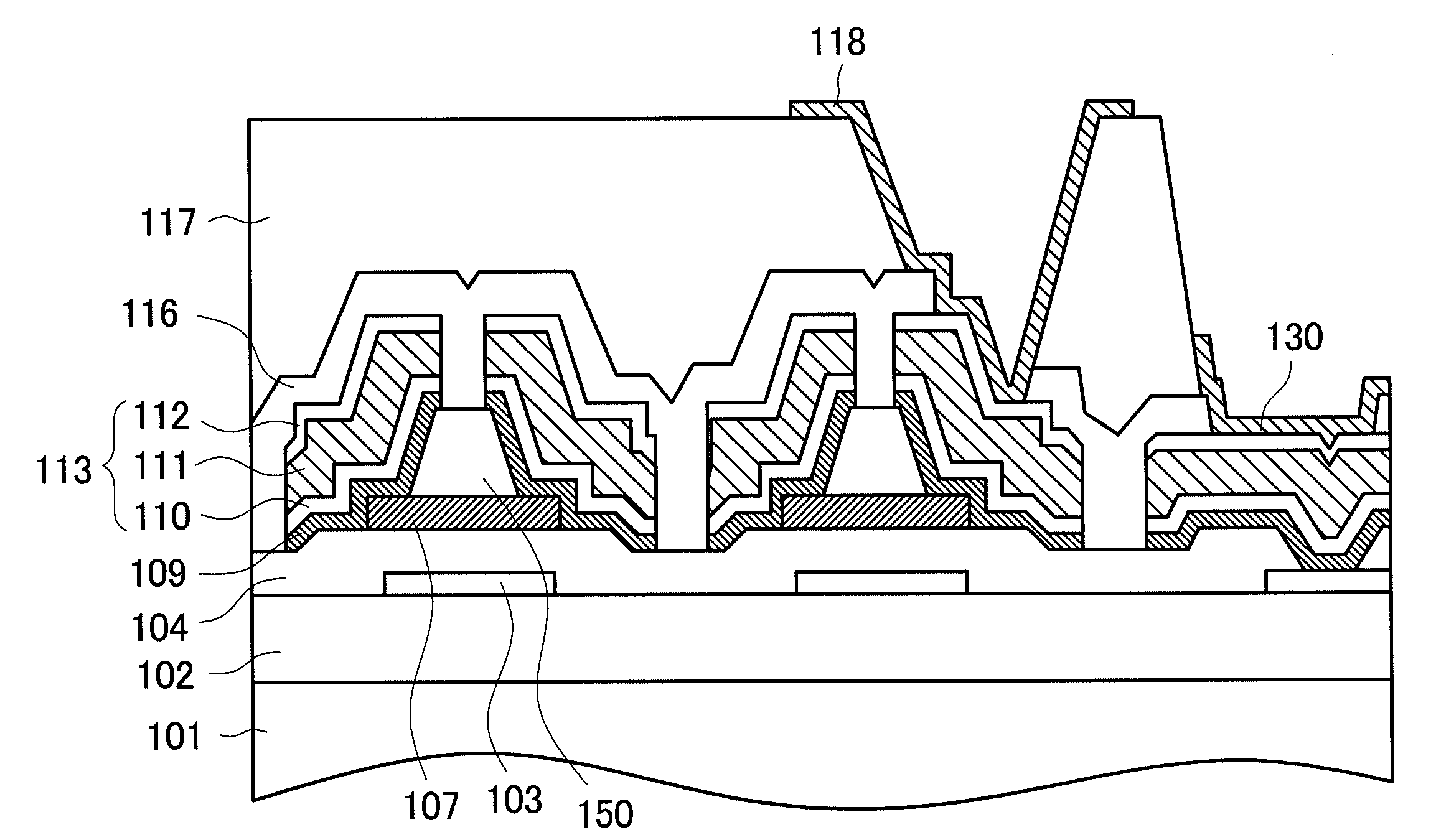

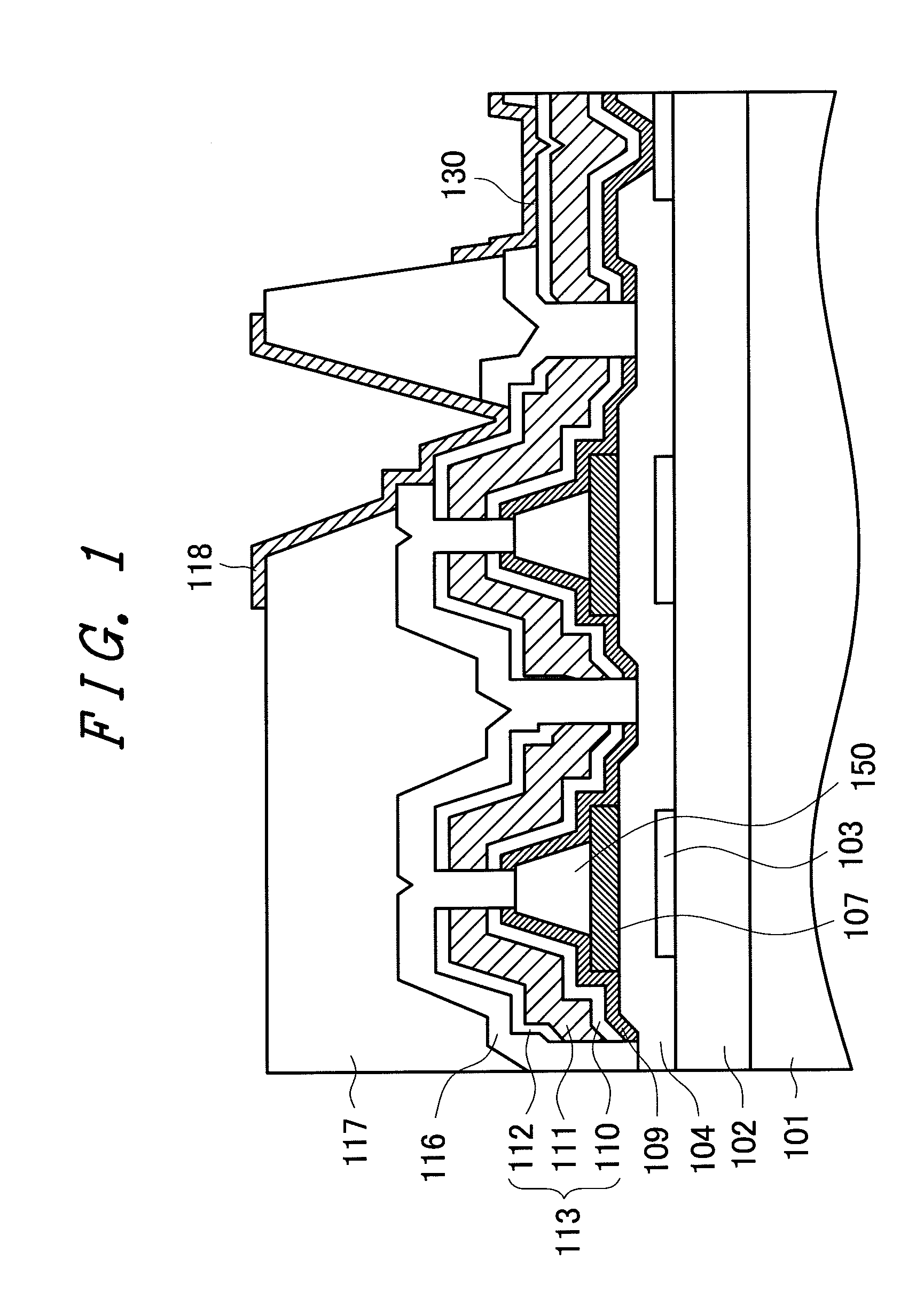

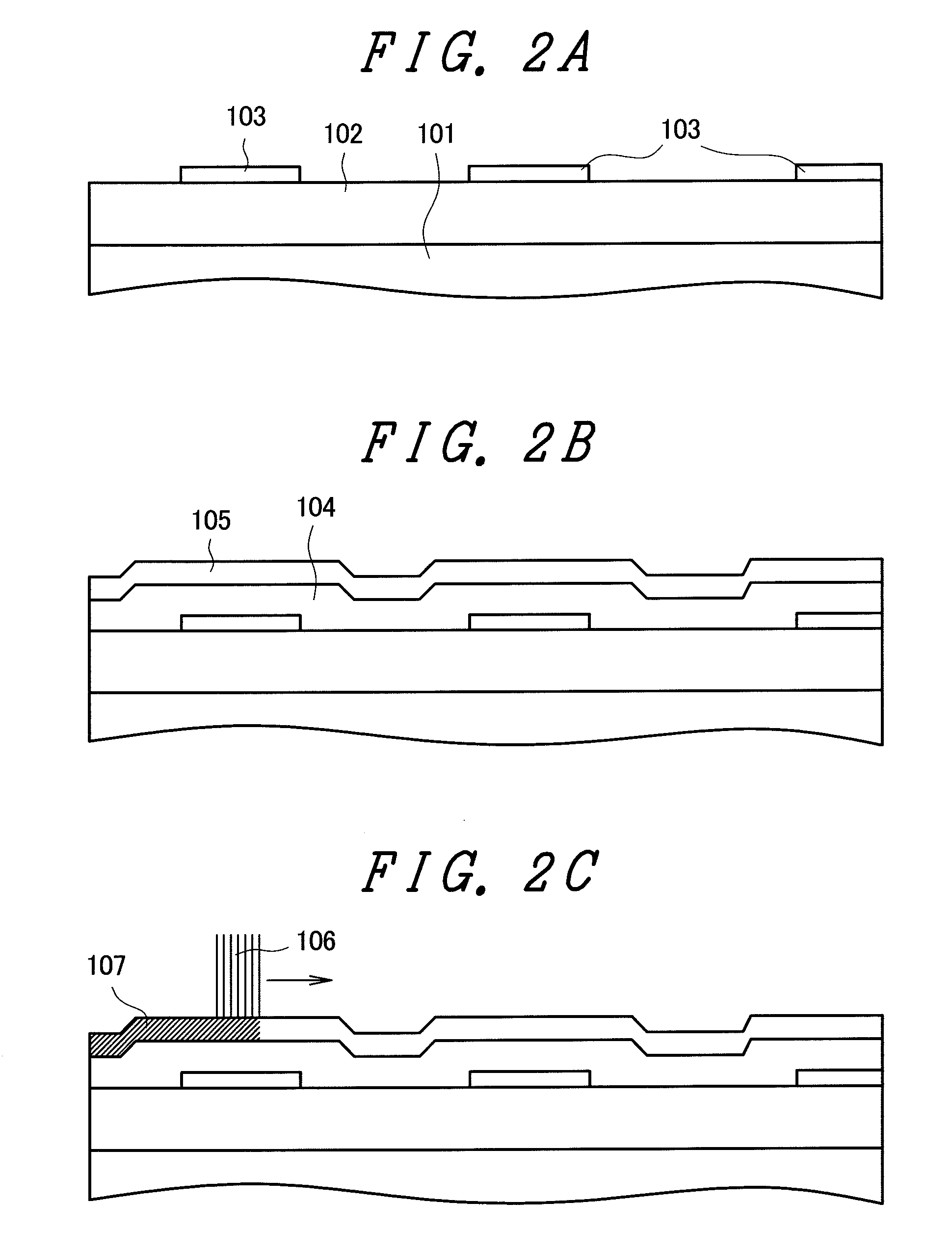

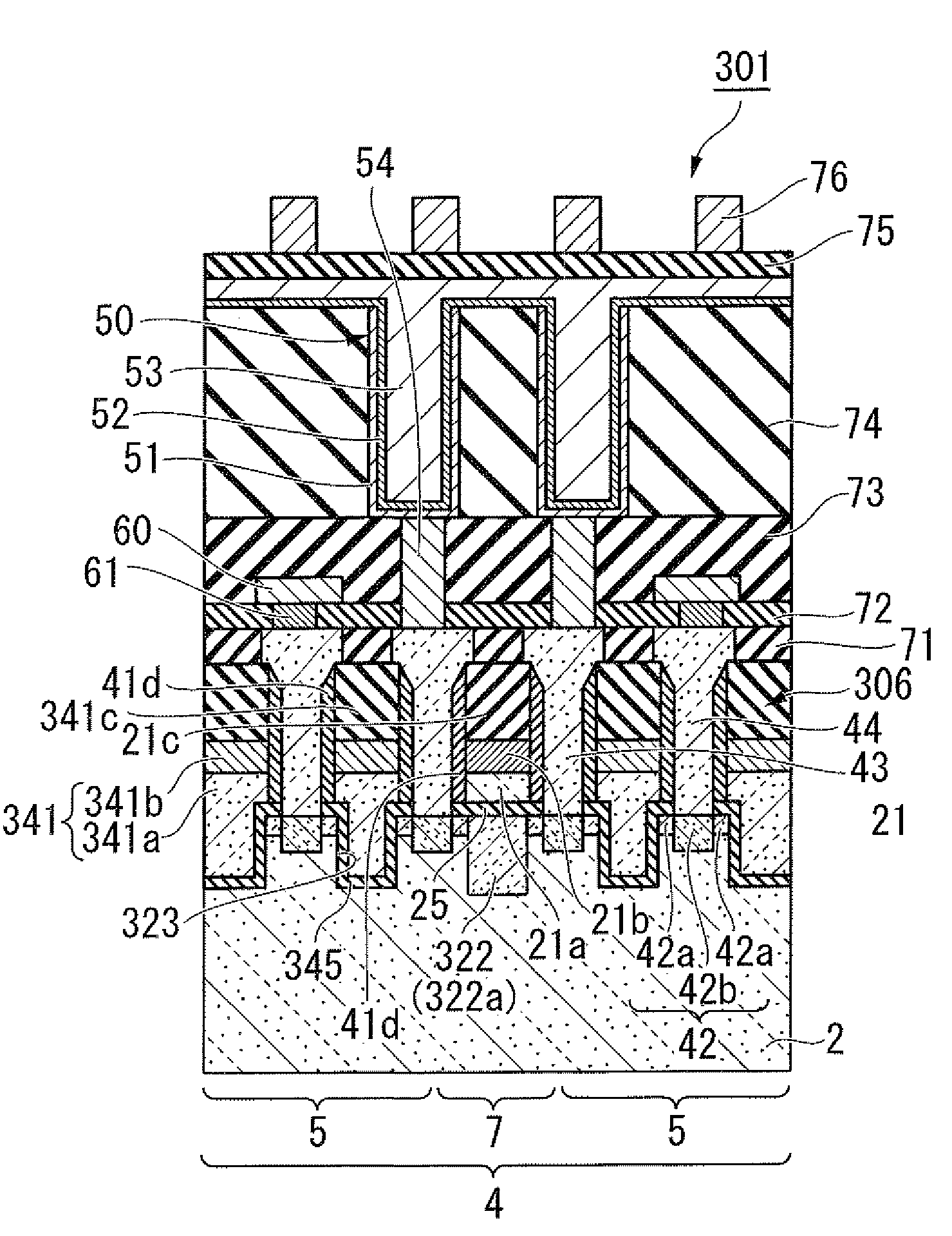

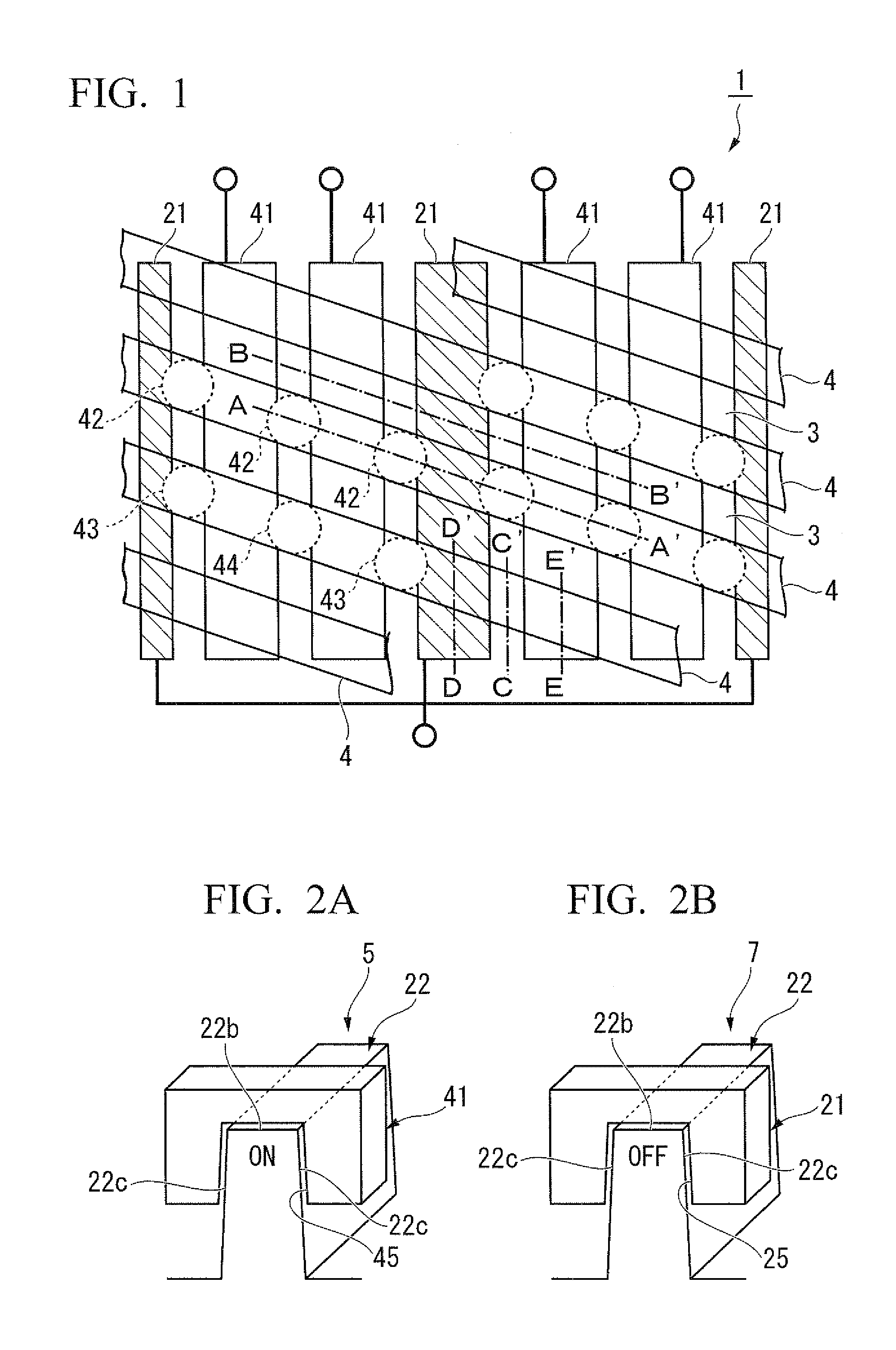

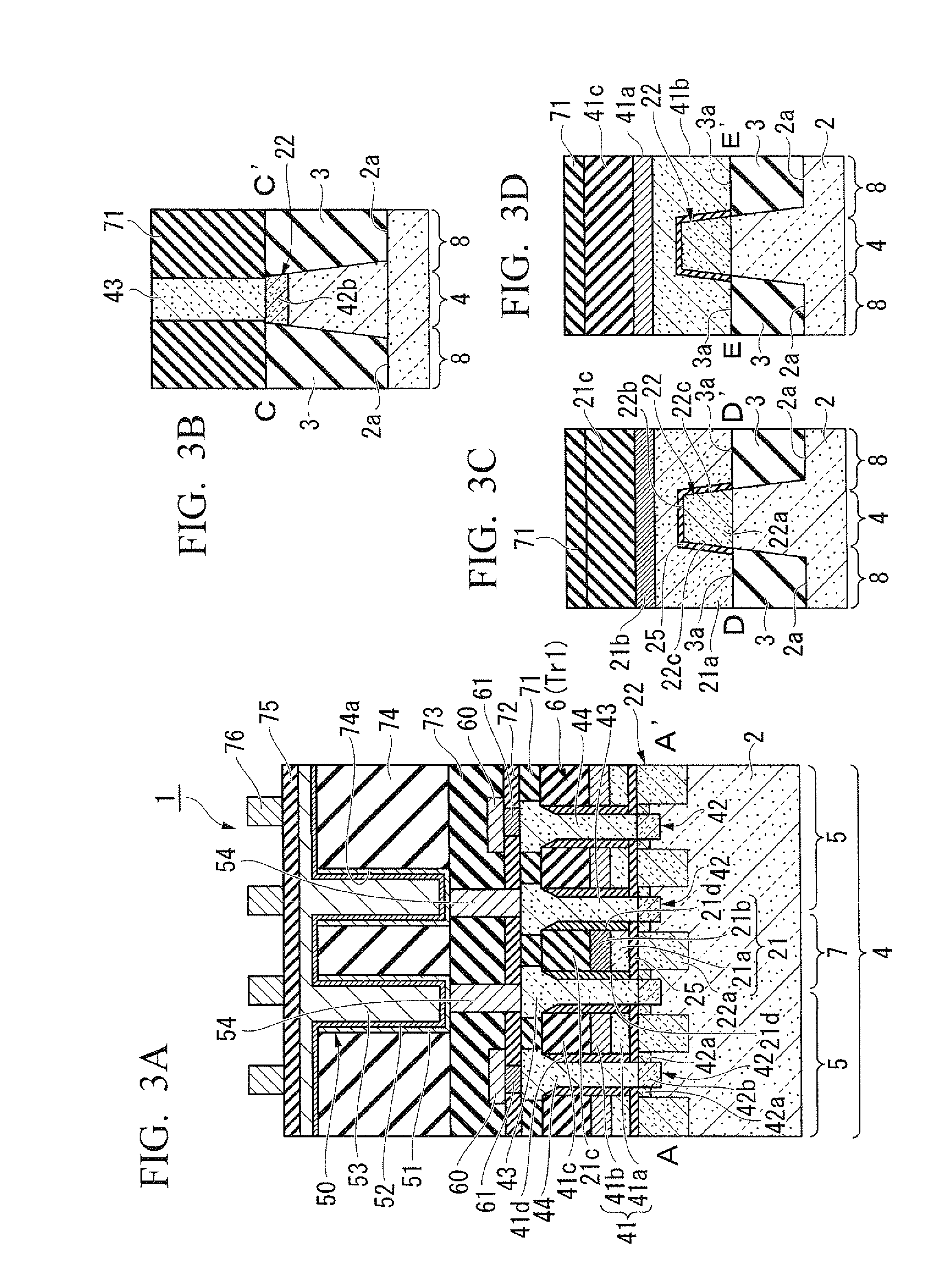

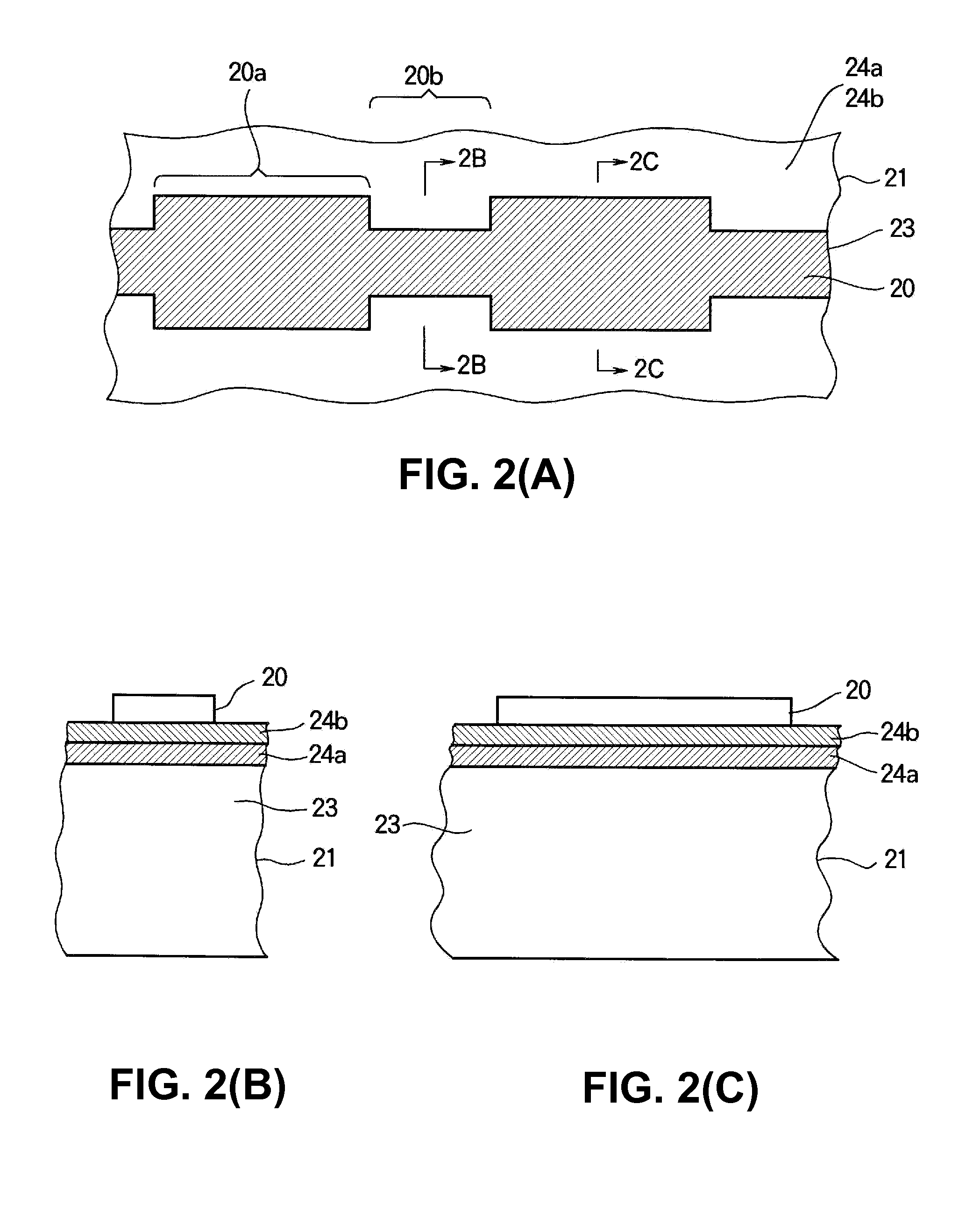

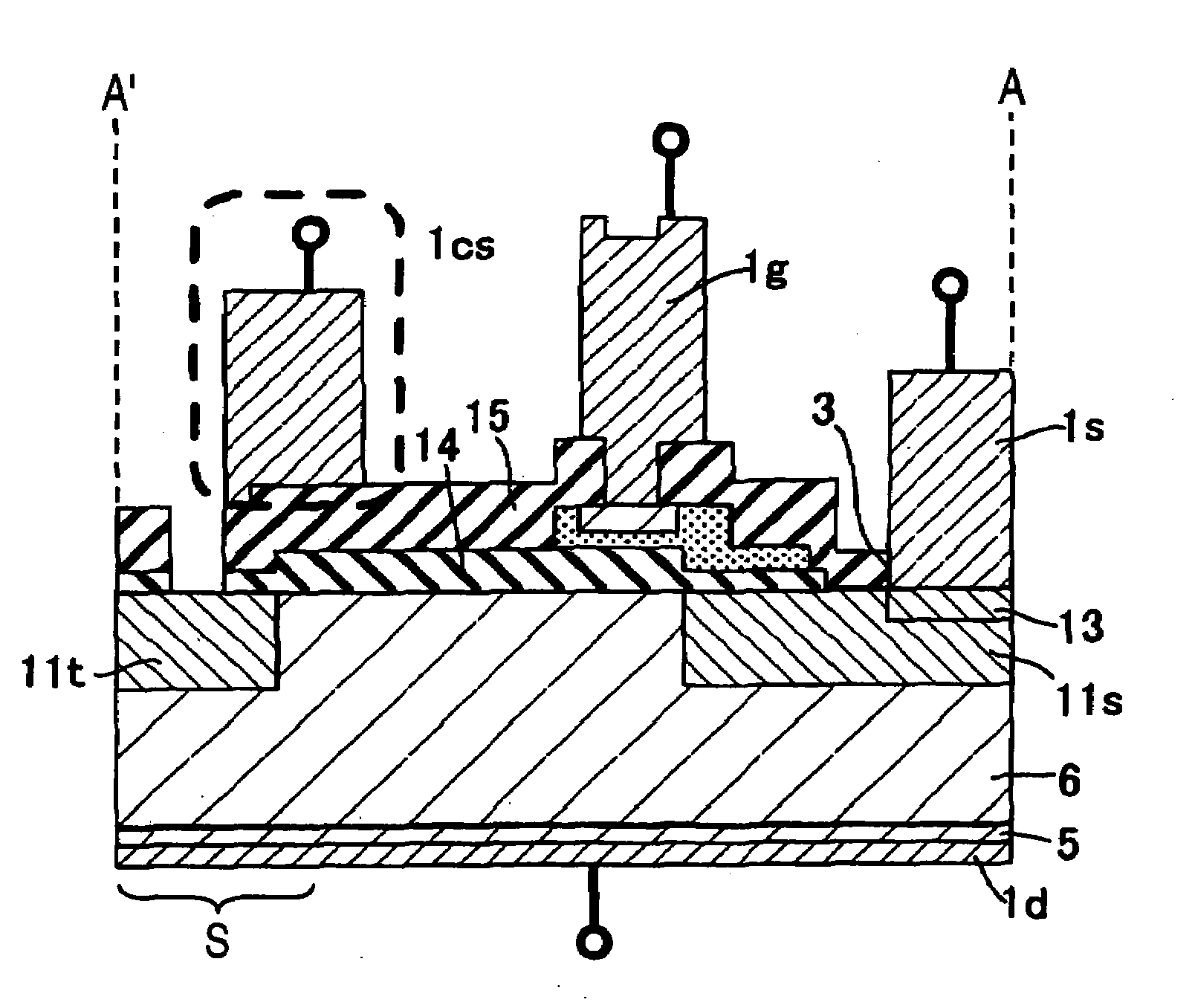

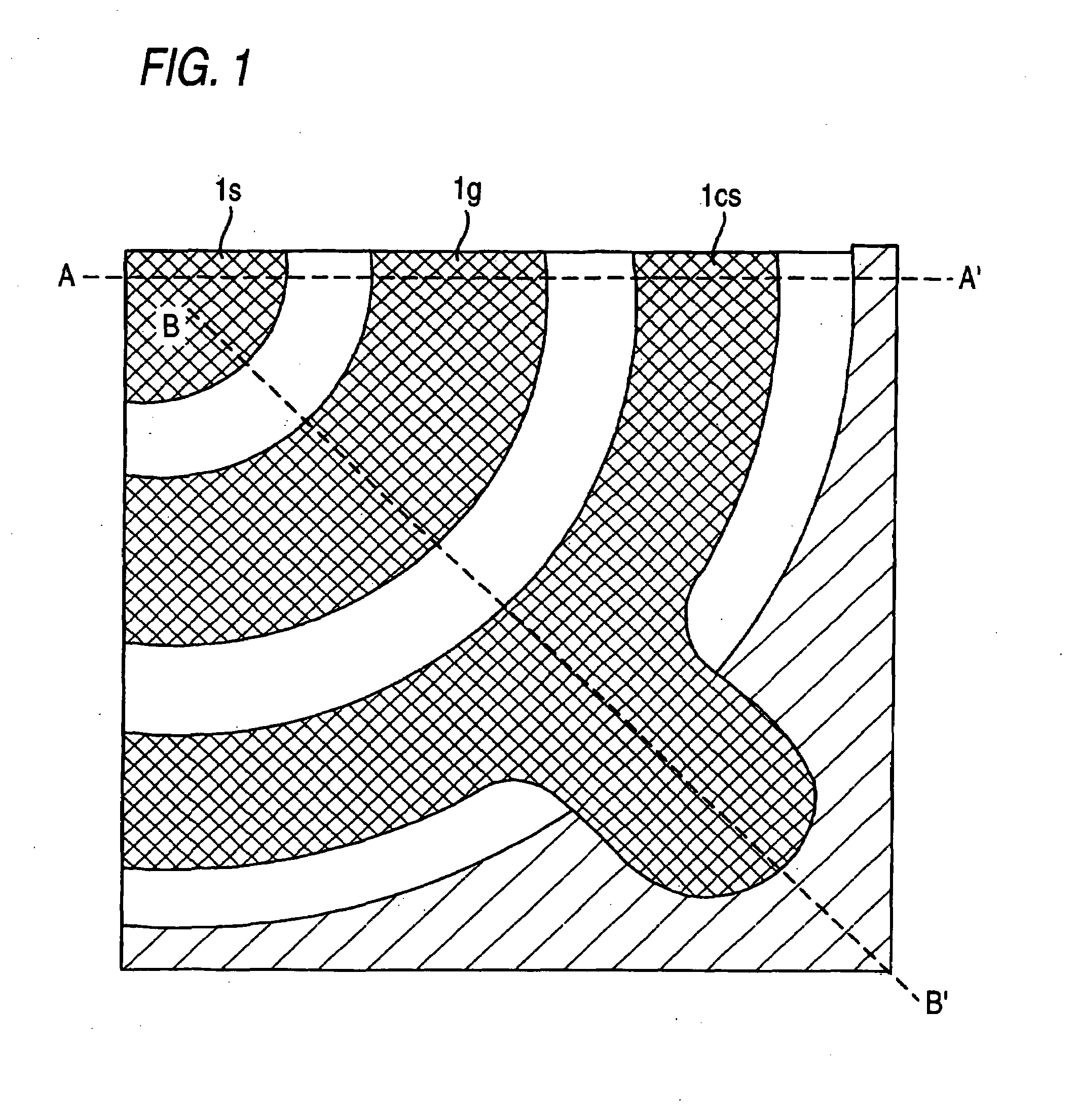

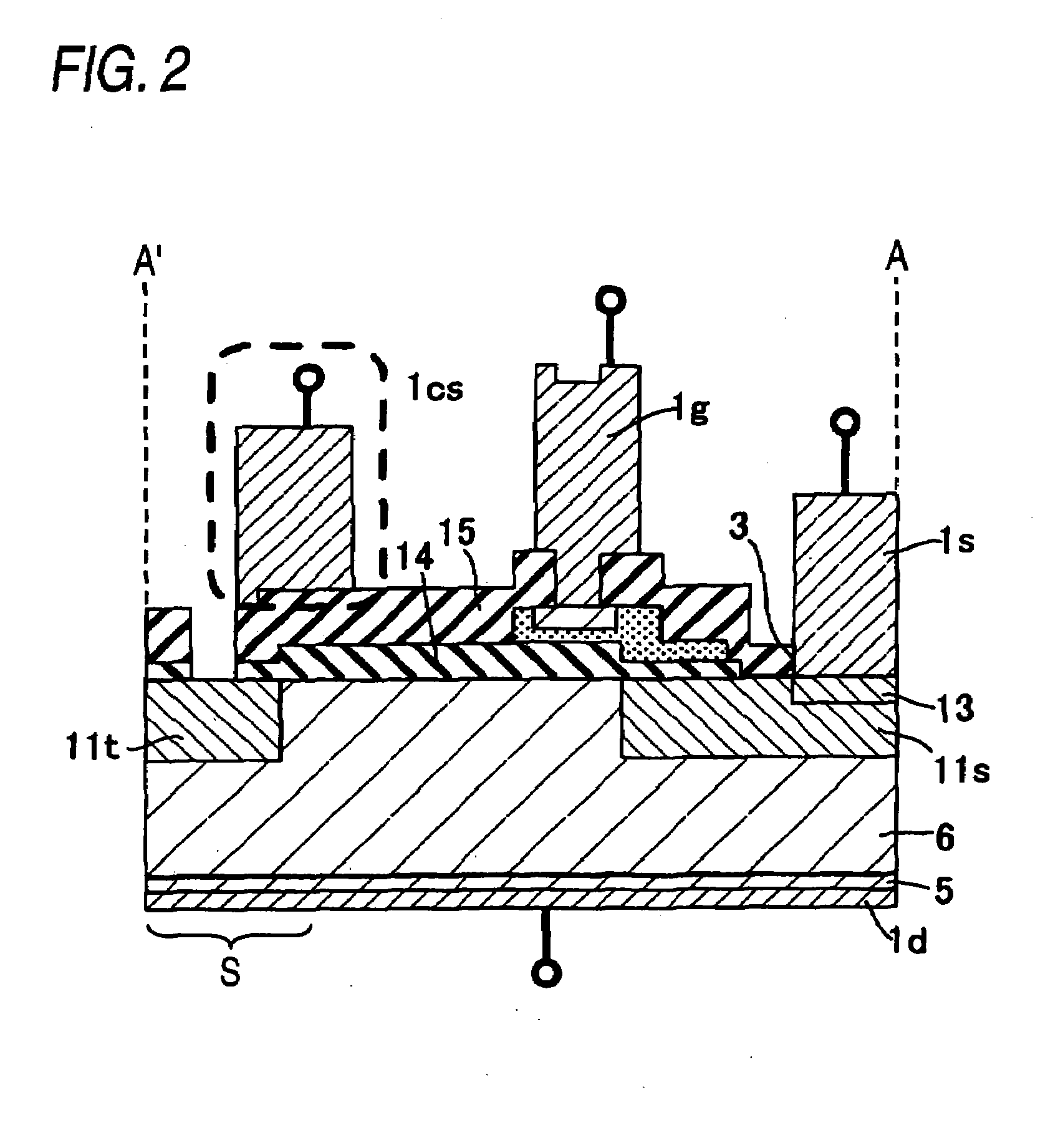

In bottom-gate-type thin film transistors used in a liquid crystal display device, a channel stopper layer is formed on a poly-Si layer thus stabilizing a characteristic of the thin film transistor. The channel stopper layer is formed into a desired shape by wet etching, and the poly-Si layer is formed into a desired shape by dry etching. By applying side etching to the channel stopper layer, a peripheral portion of the poly-Si layer is exposed from the channel stopper layer, and this region is brought into contact with an n+Si layer. Due to such constitution, ON resistance of the thin film transistor can be decreased thus increasing an ON current which flows in the thin film transistor.

Owner:PANASONIC LIQUID CRYSTAL DISPLAY CO LTD +1

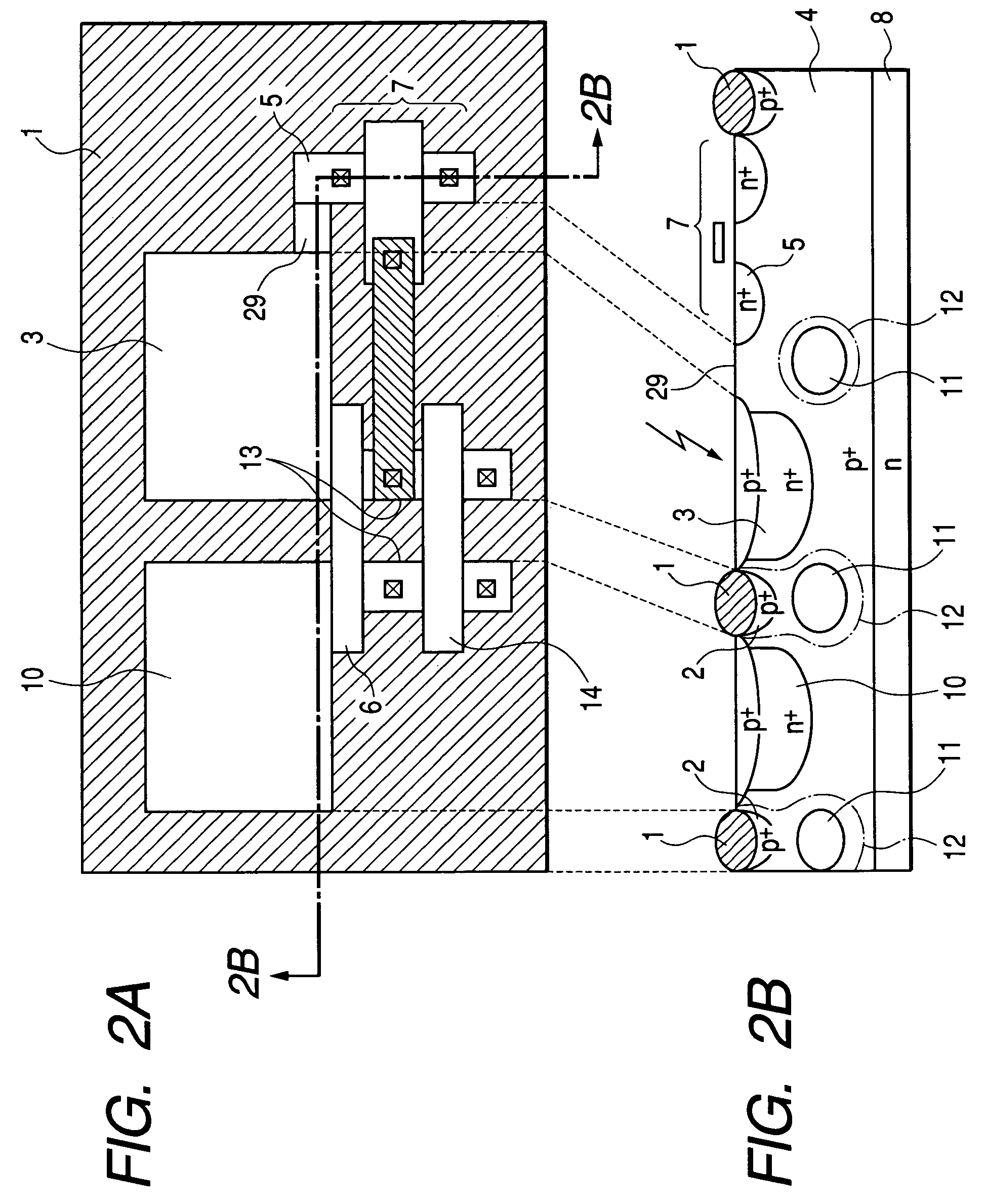

Semiconductor apparatus

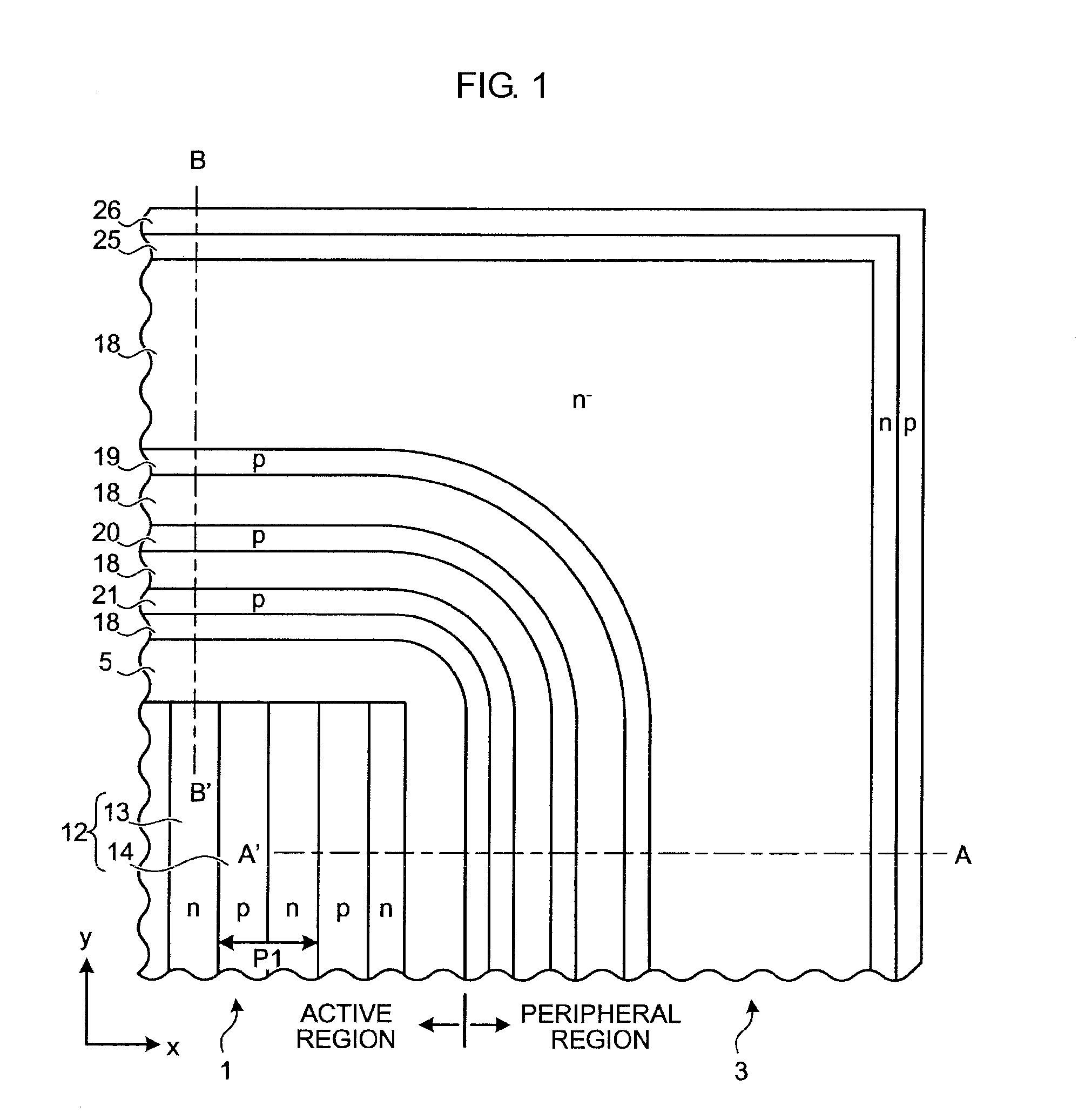

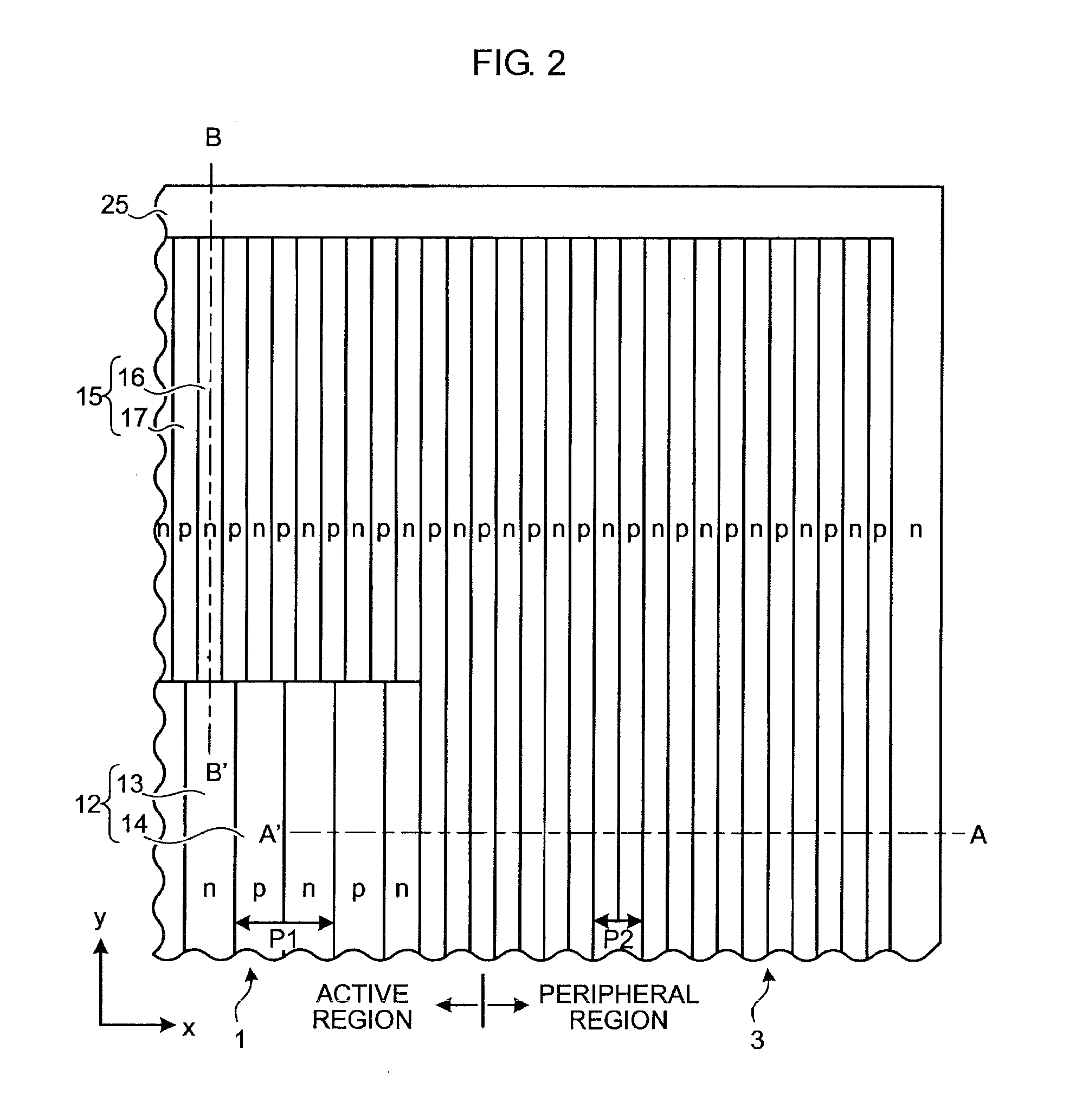

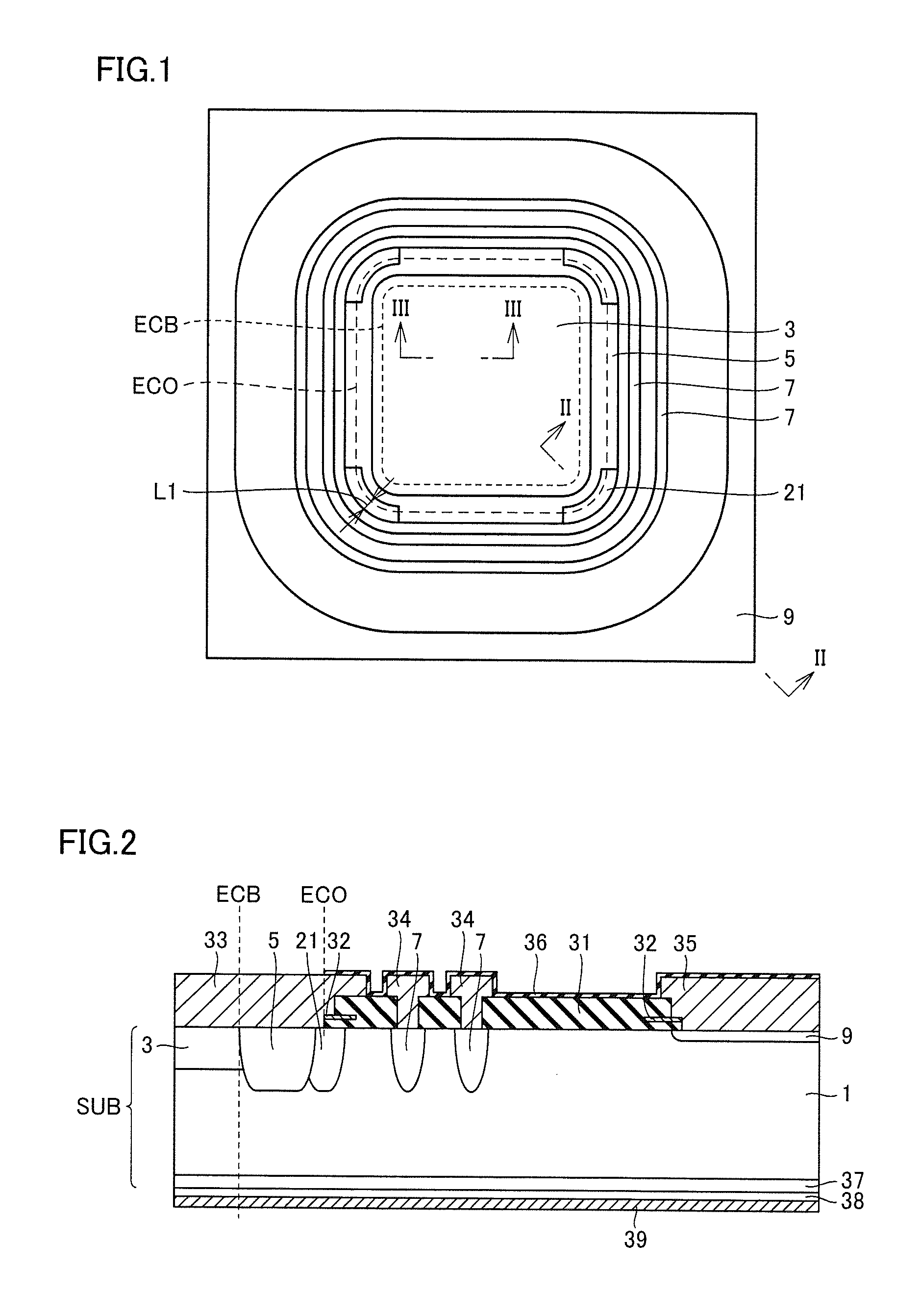

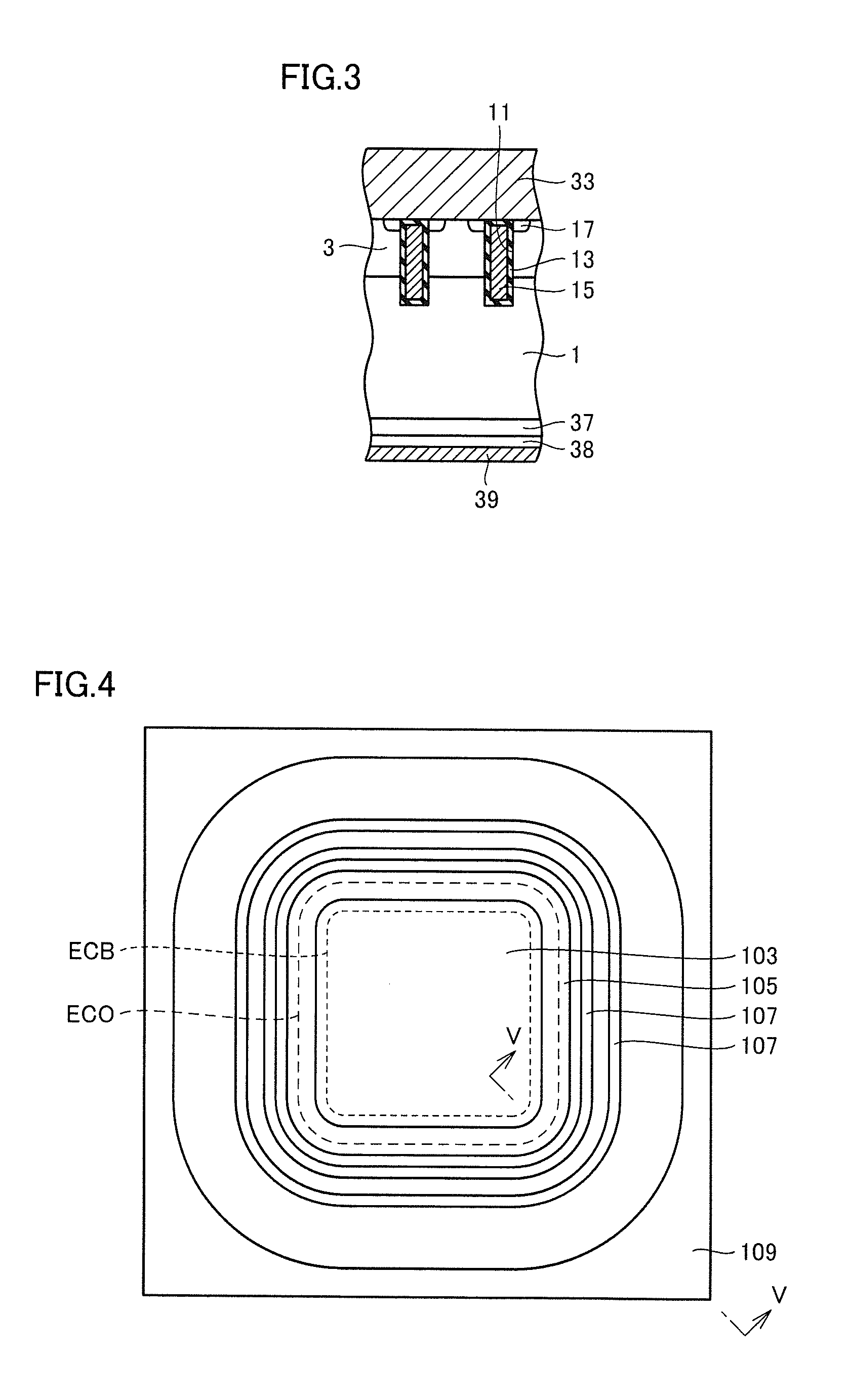

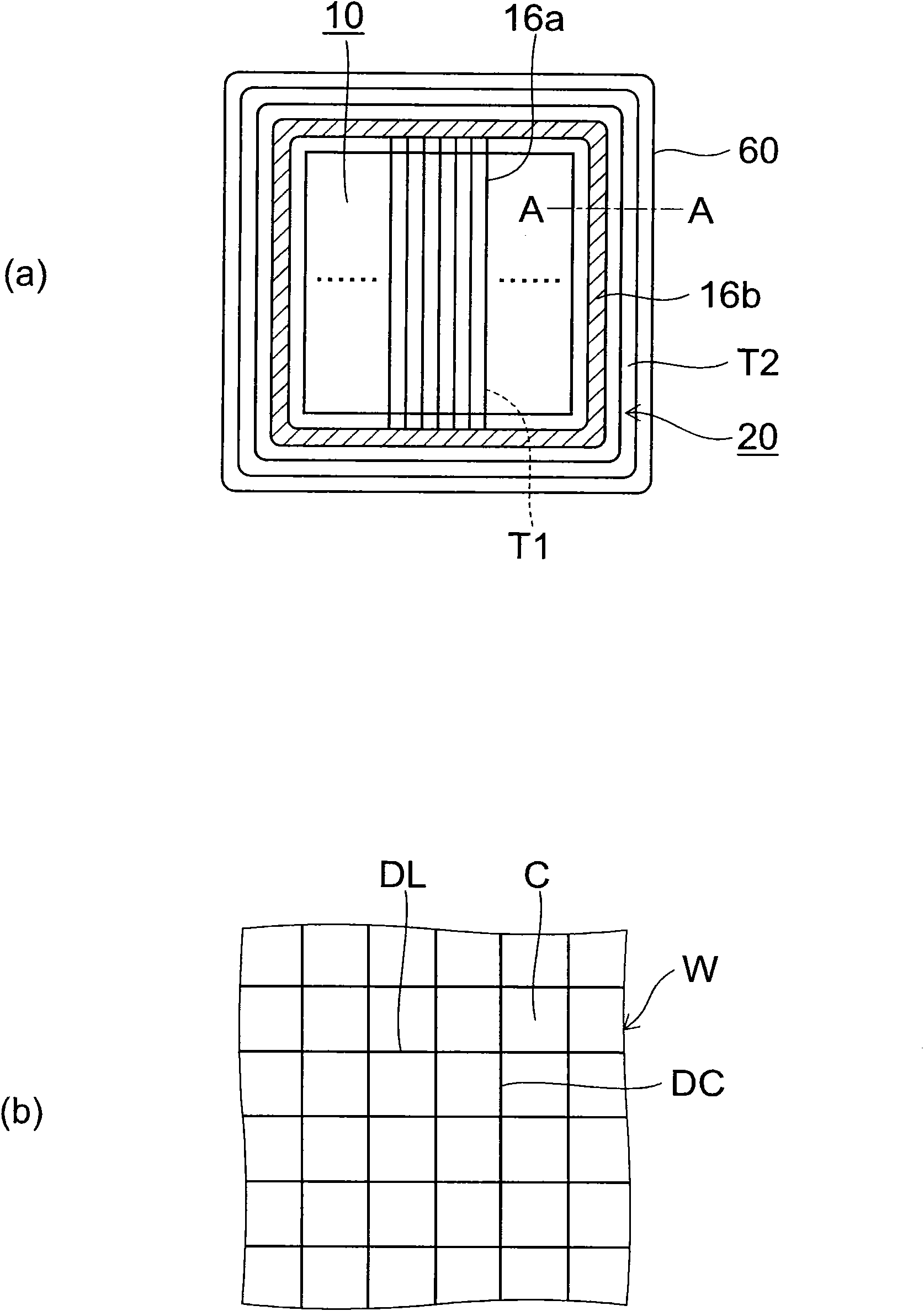

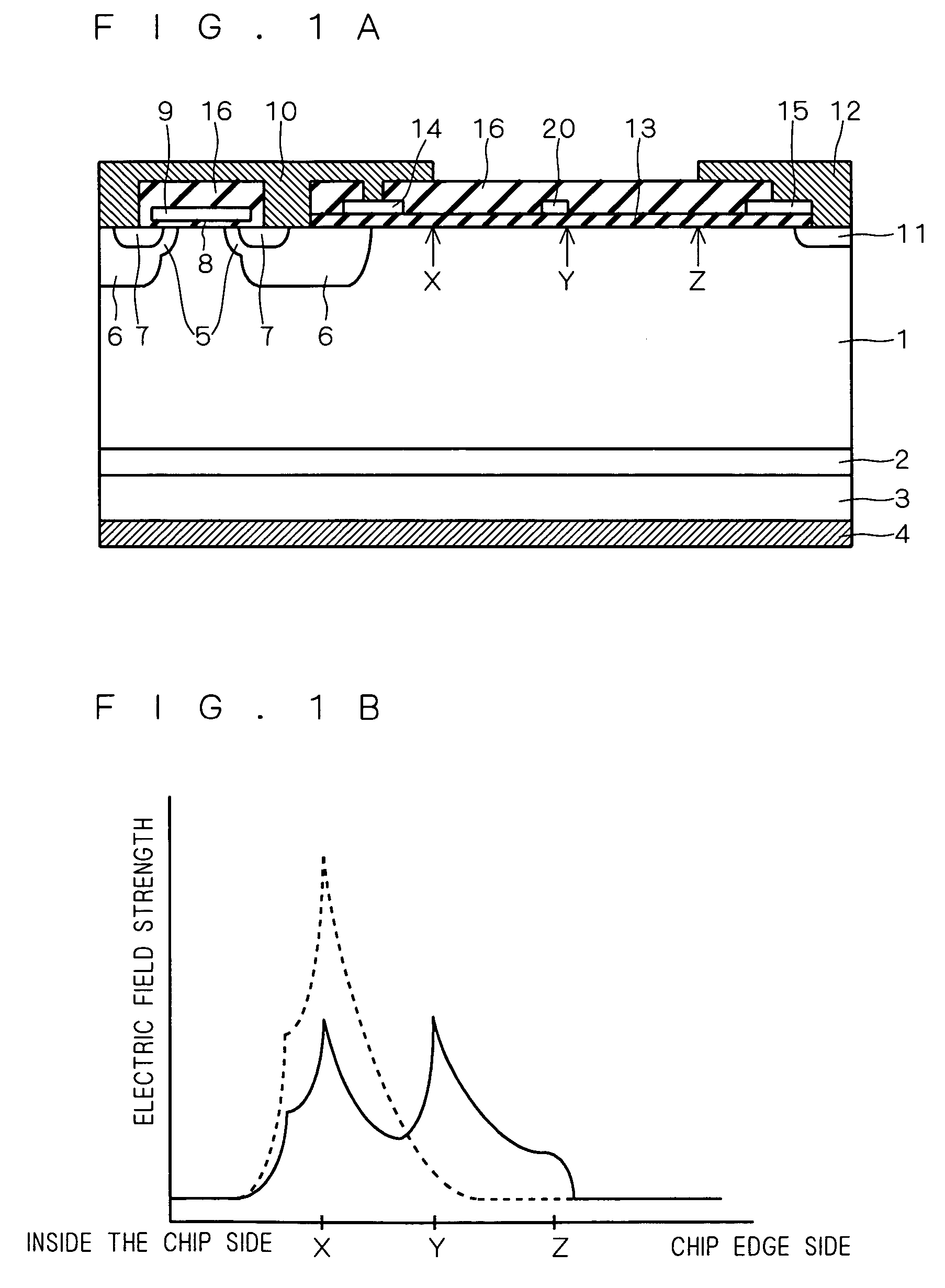

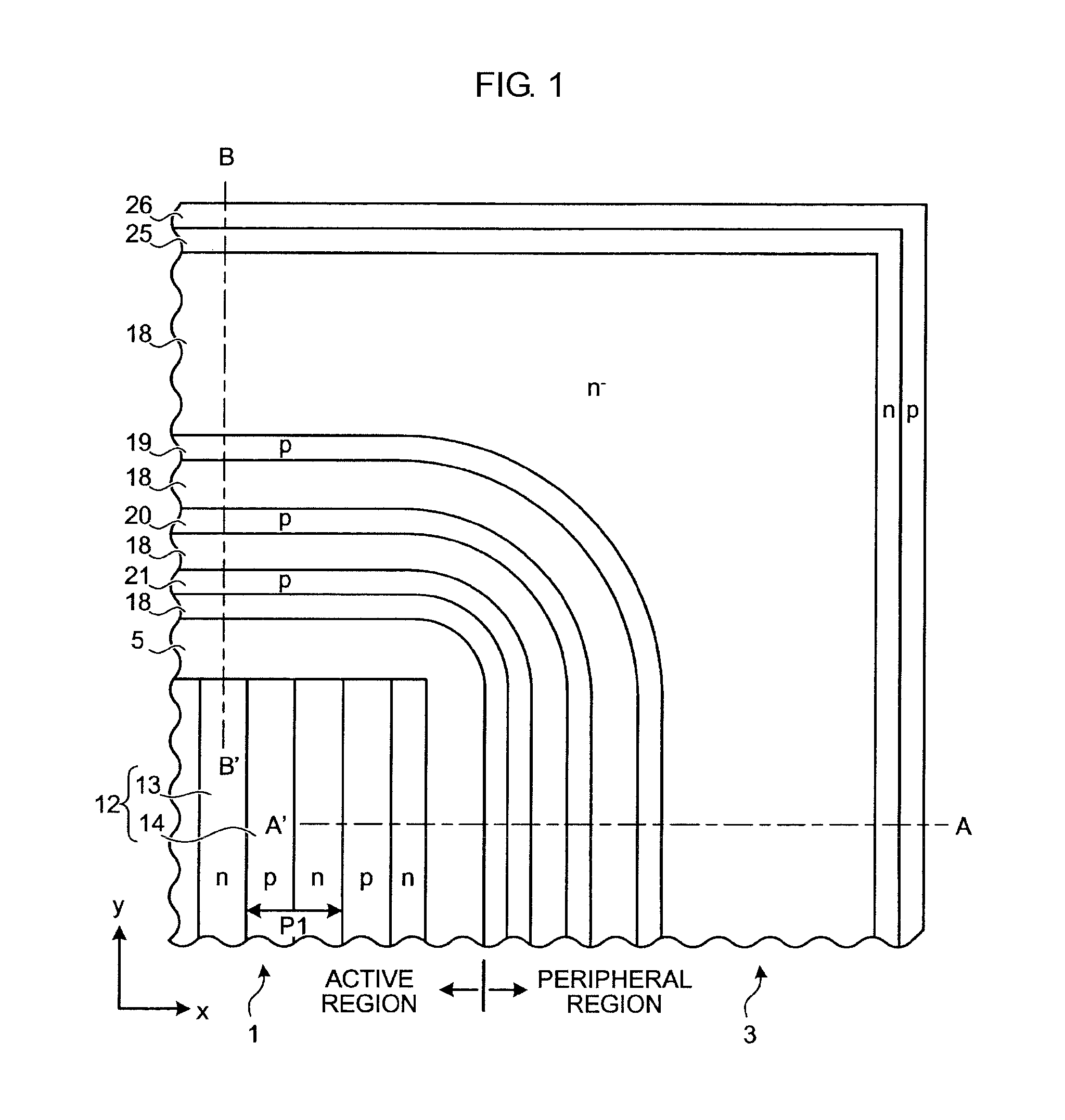

ActiveUS20120126315A1Suppresses fluctuation of breakdown voltageSuppresses drop in breakdown voltageSemiconductor devicesChannel-stopperSemiconductor

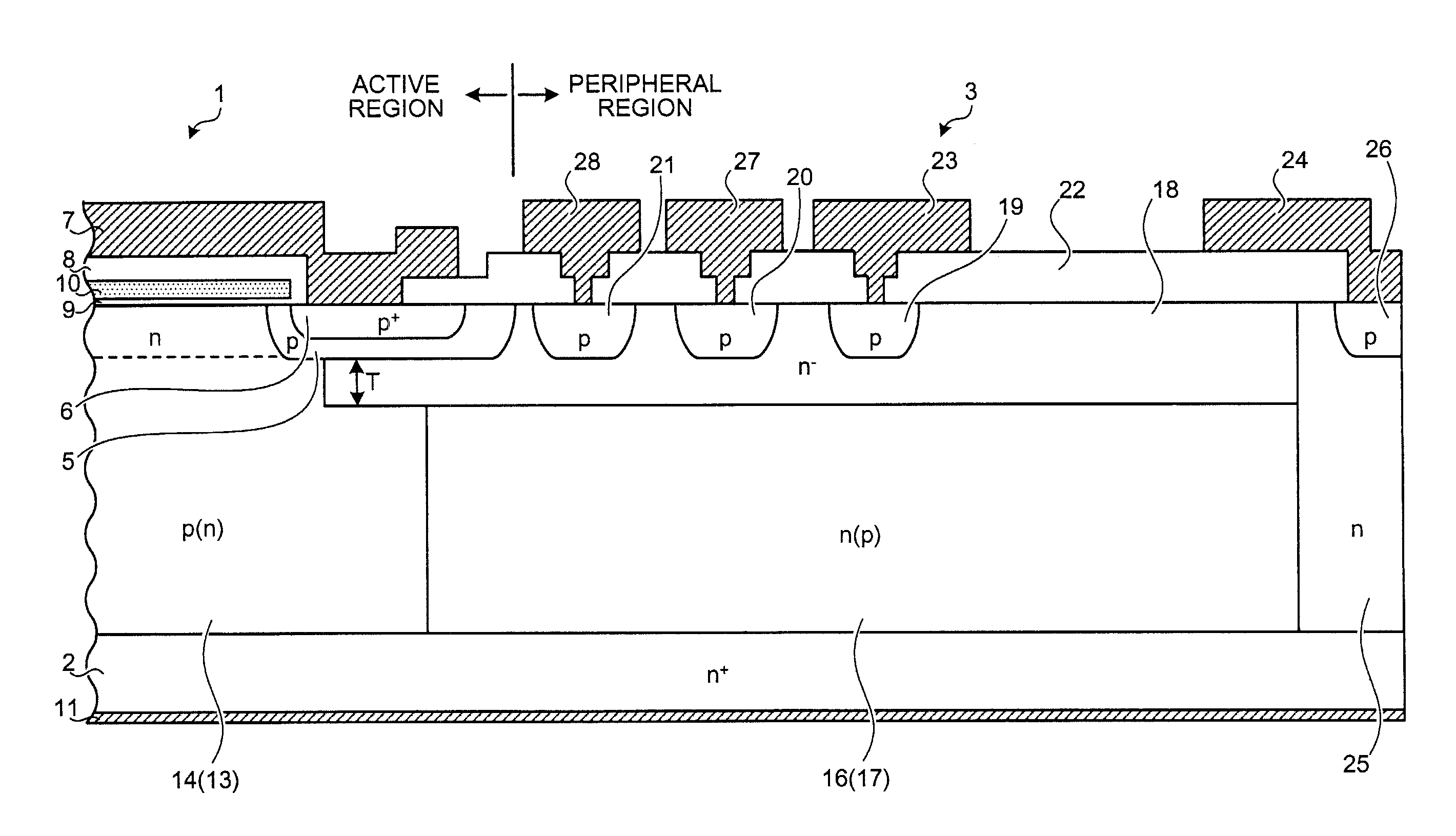

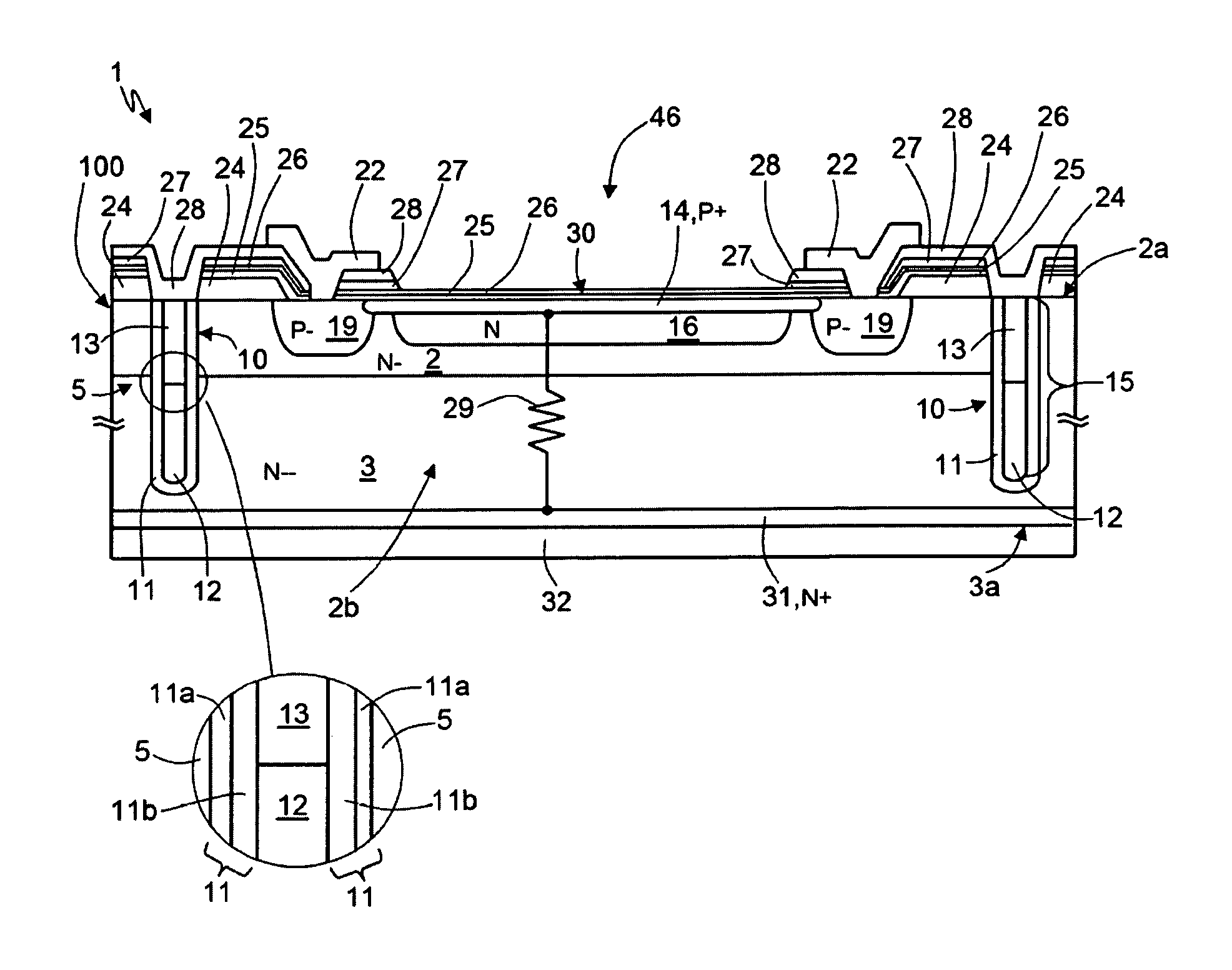

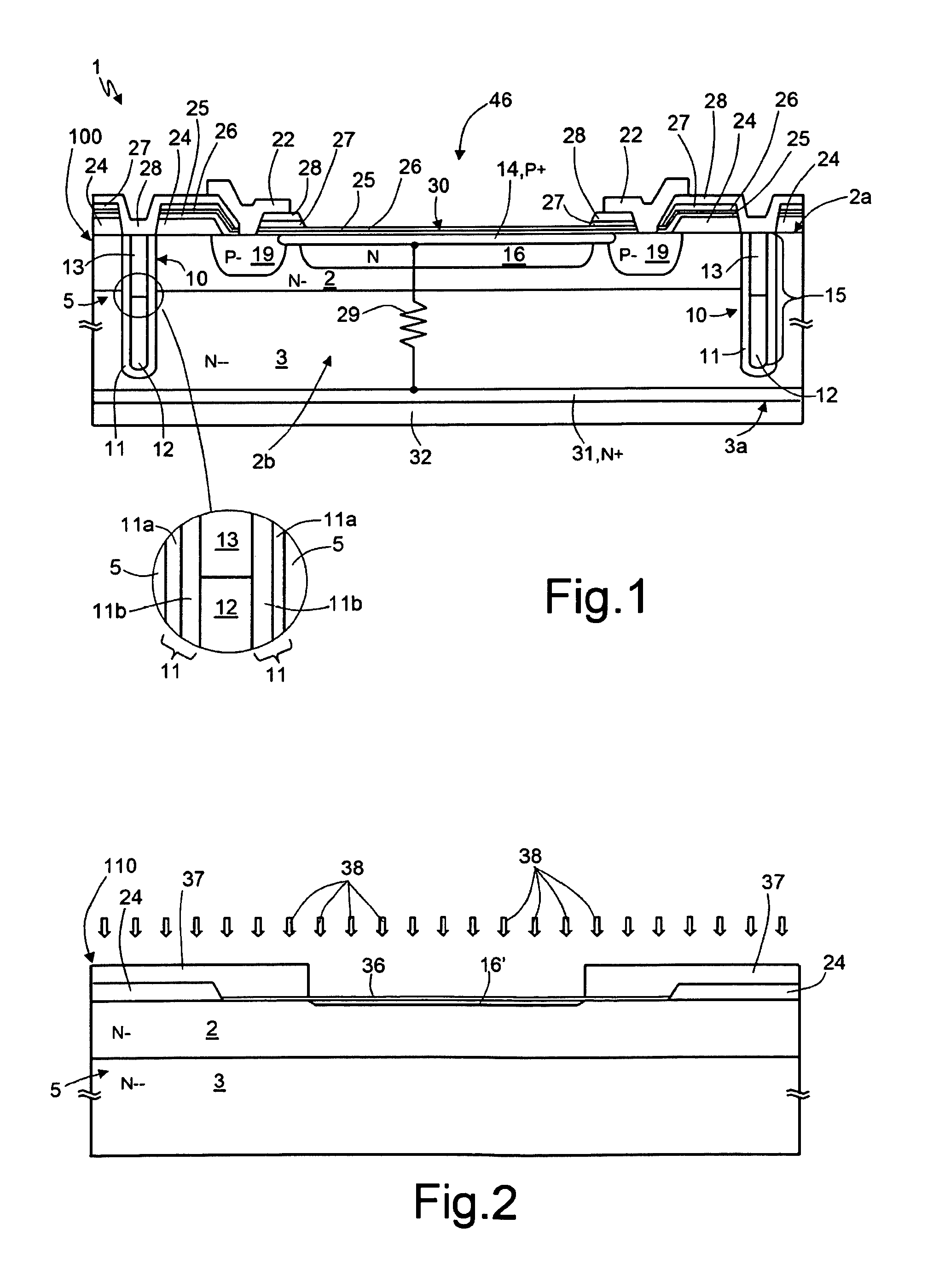

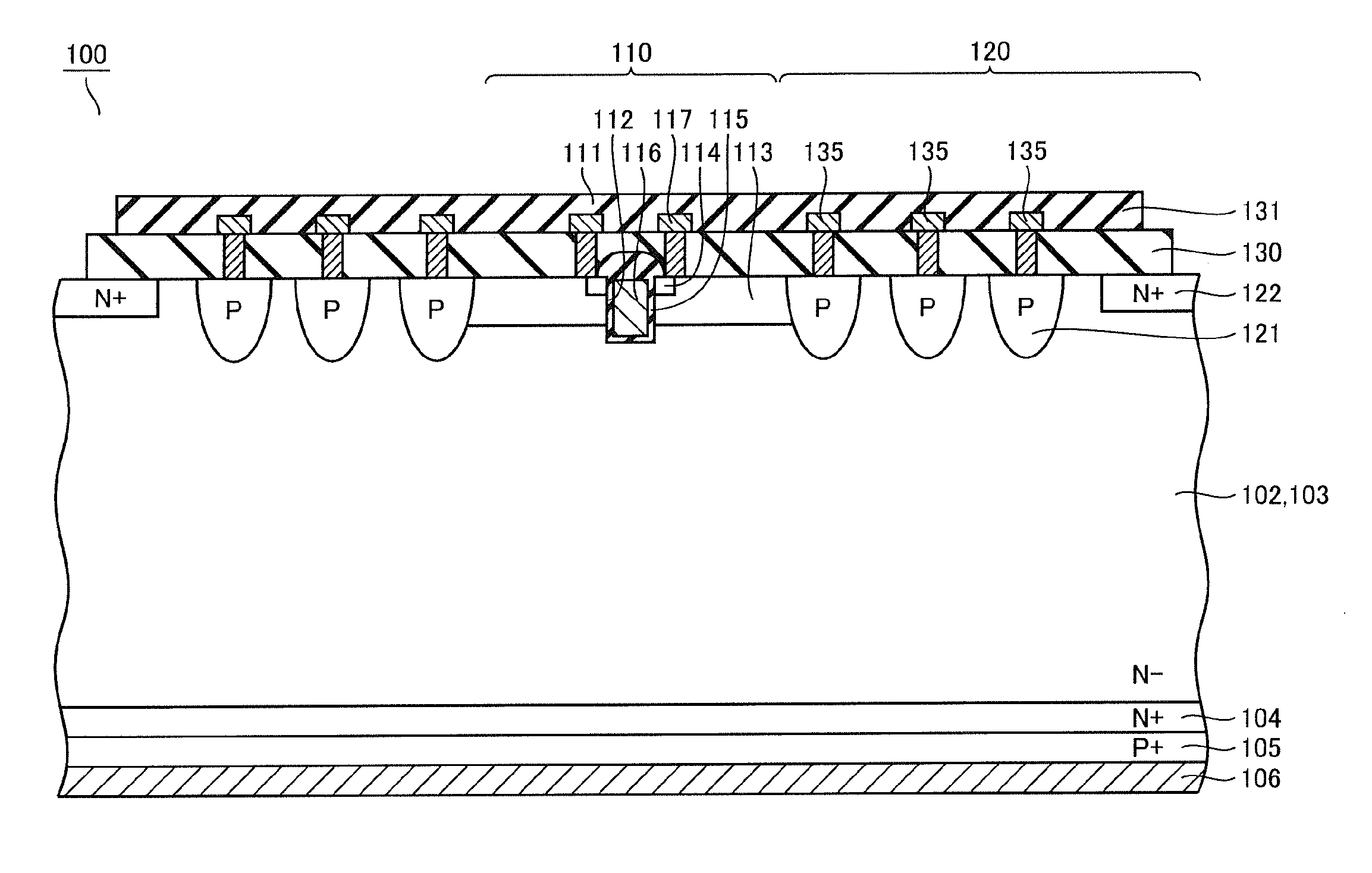

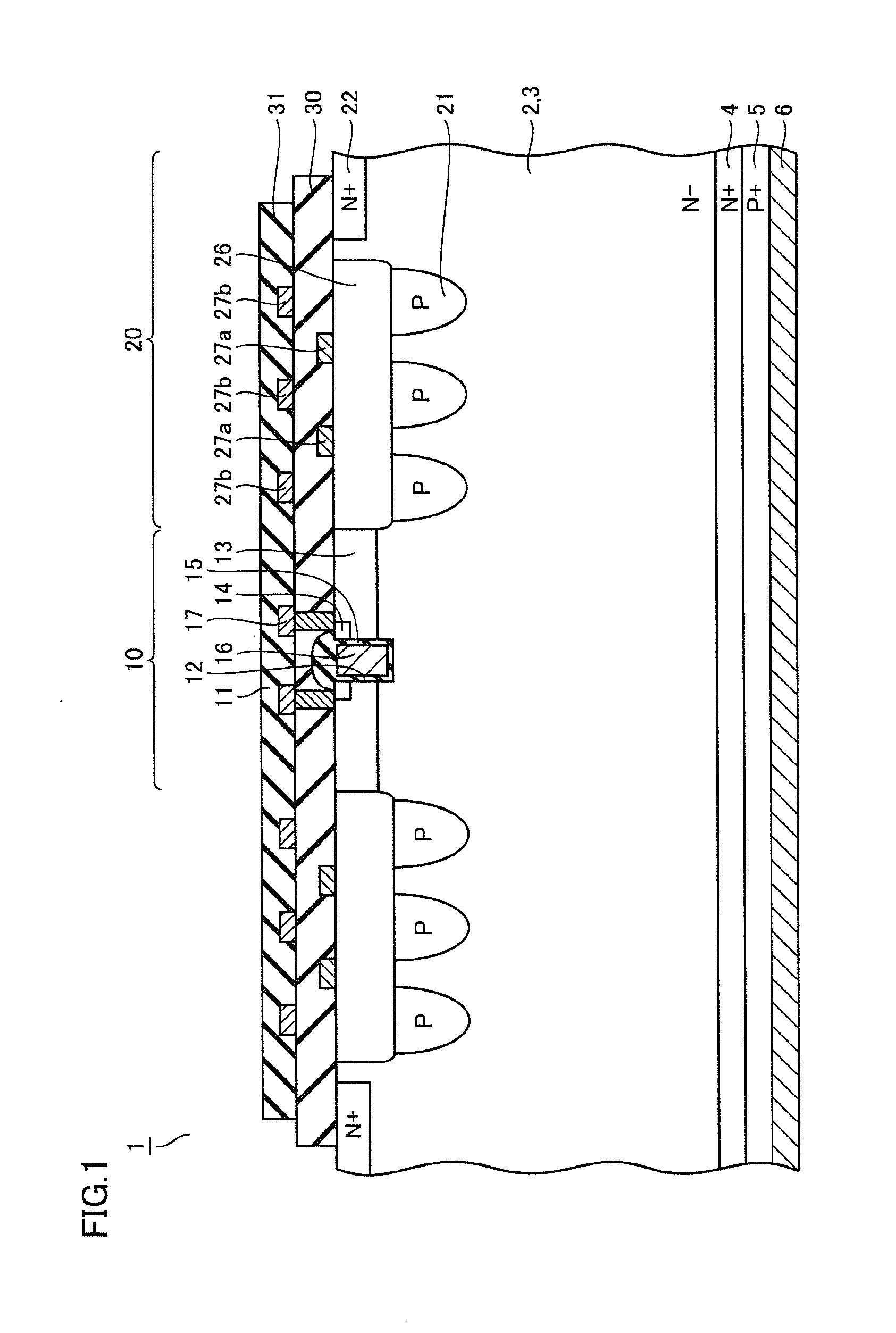

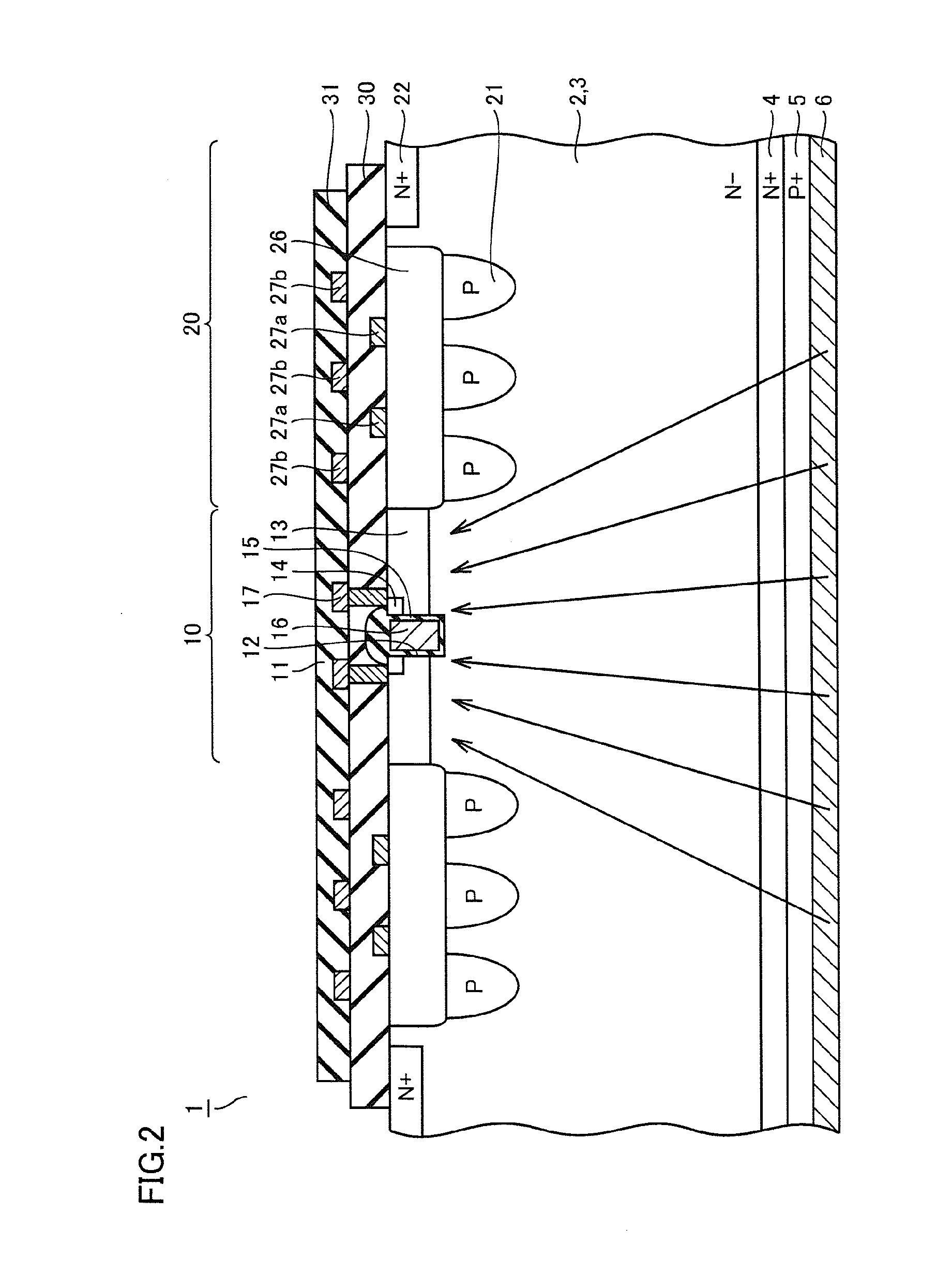

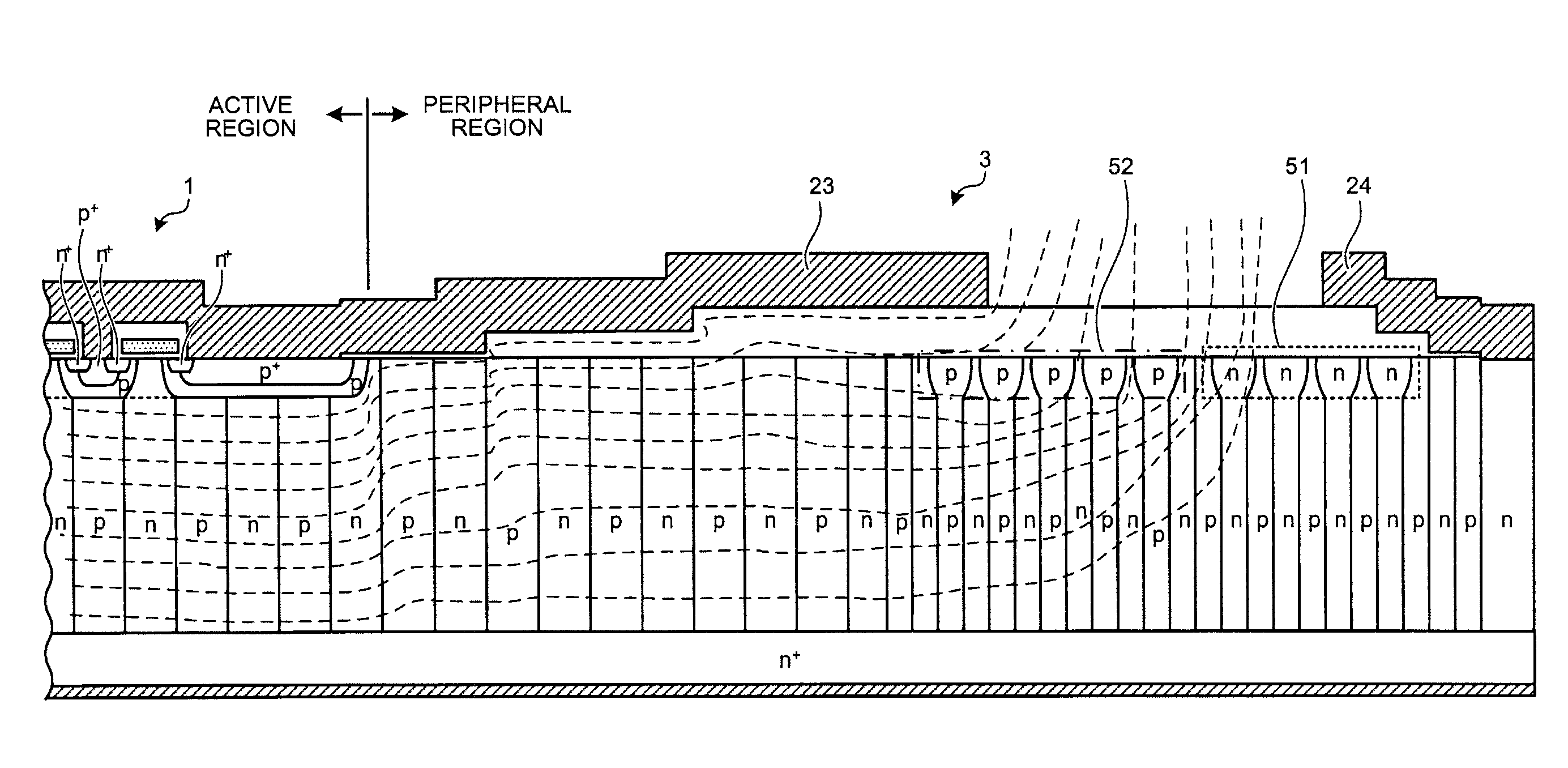

A semiconductor apparatus that has a first parallel pn-layer formed between an active region and an n+-drain region. A peripheral region is provided with a second parallel pn-layer, which has a repetition pitch narrower than the repetition pitch of the first parallel pn-layer. An n−-surface region is formed between the second parallel pn-layer and a first main surface. On the first main surface side of the n−-surface region, a plurality of p-guard ring regions are formed to be separated from each other. A field plate electrode is connected electrically to the outermost p-guard ring region among the p-guard ring regions. A channel stopper electrode is connected electrically to an outermost peripheral p-region of the peripheral region.

Owner:FUJI ELECTRIC CO LTD

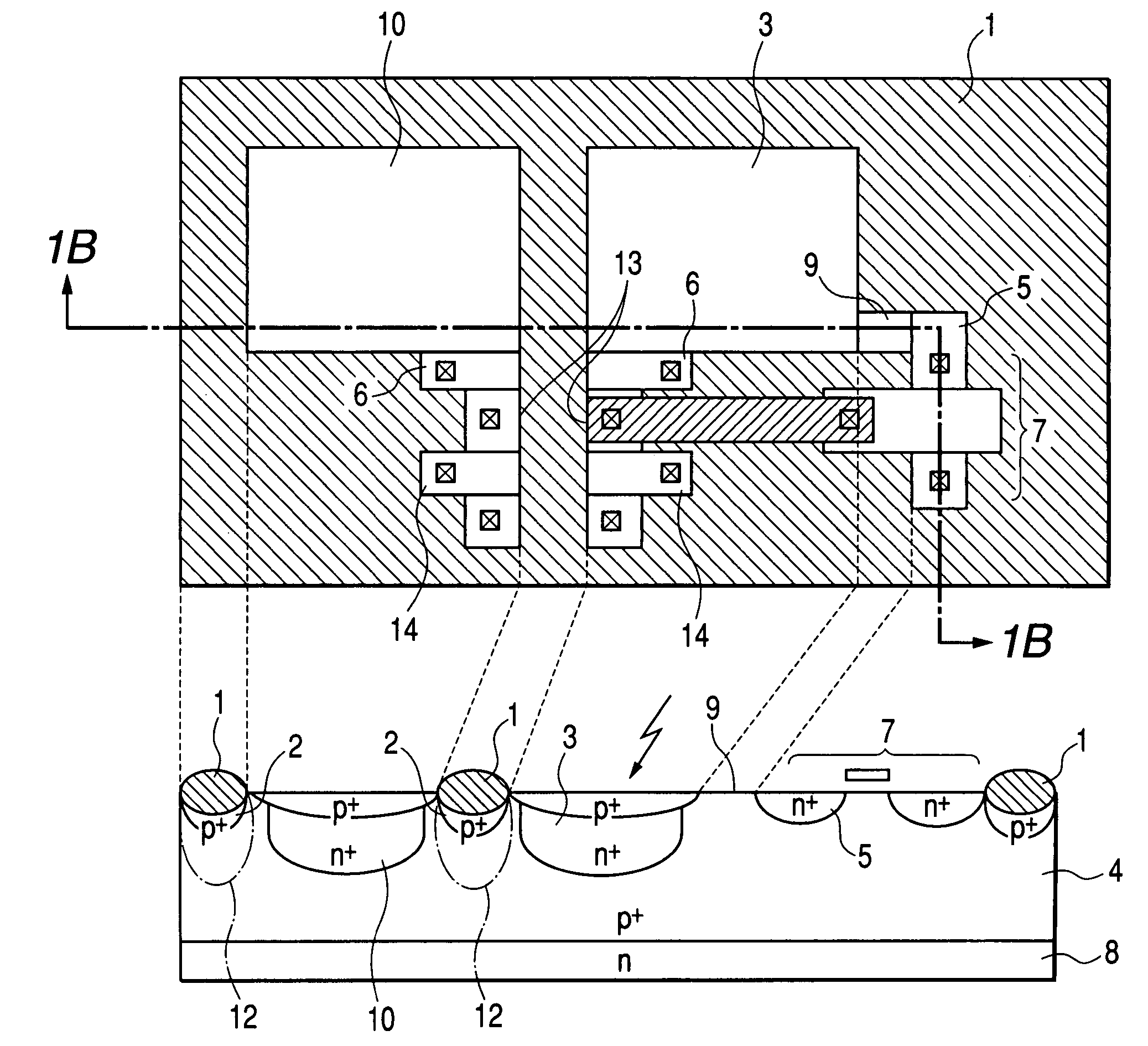

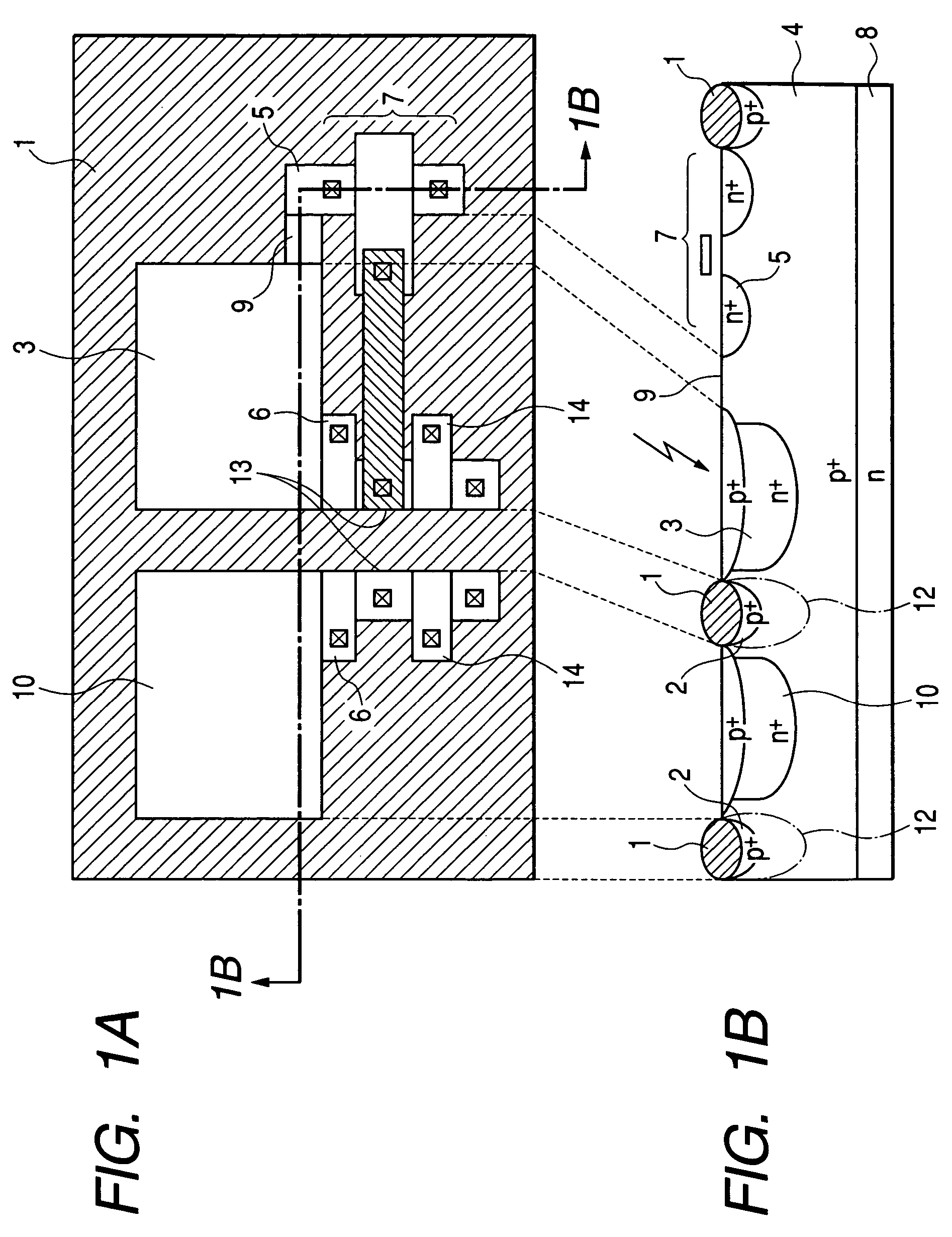

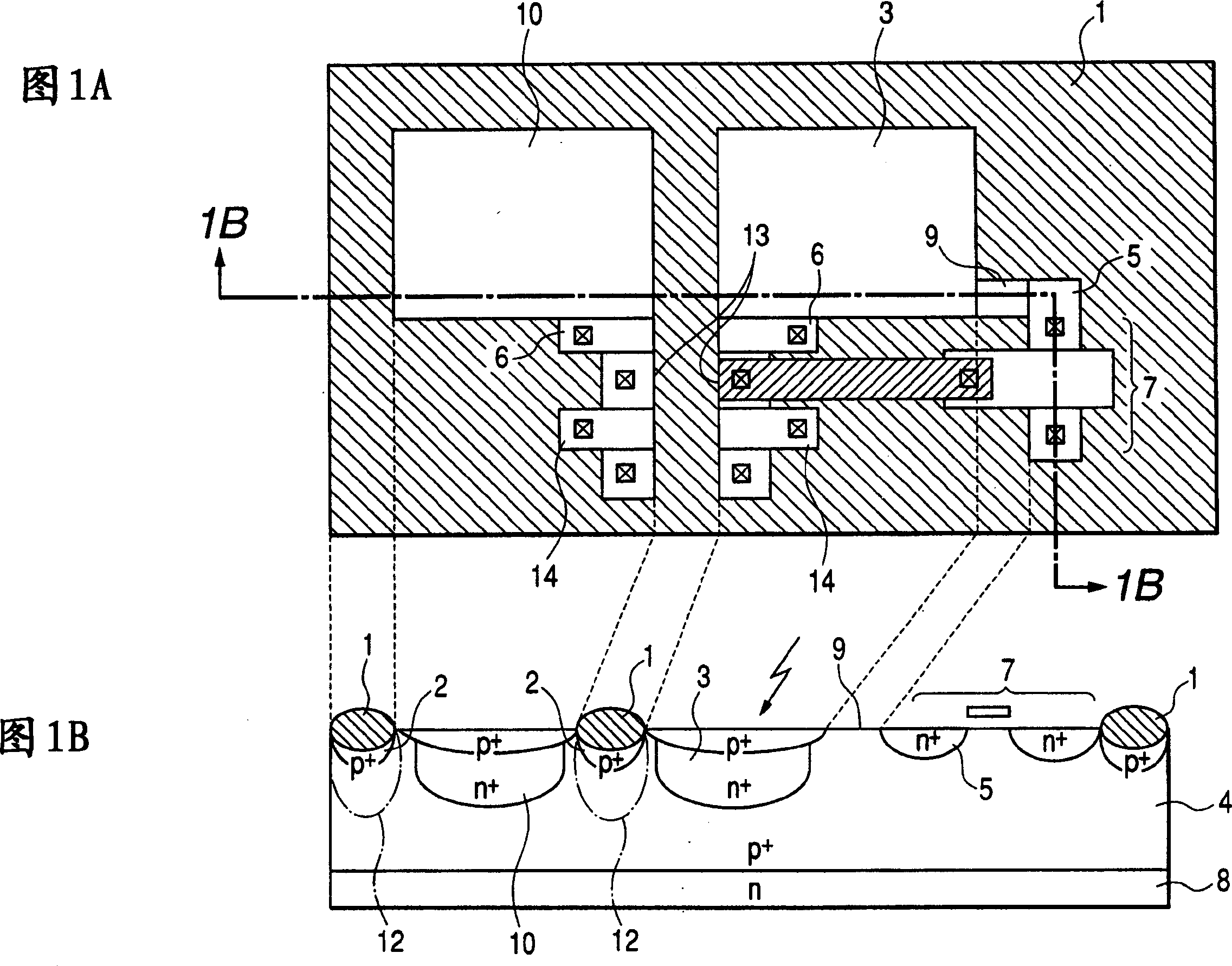

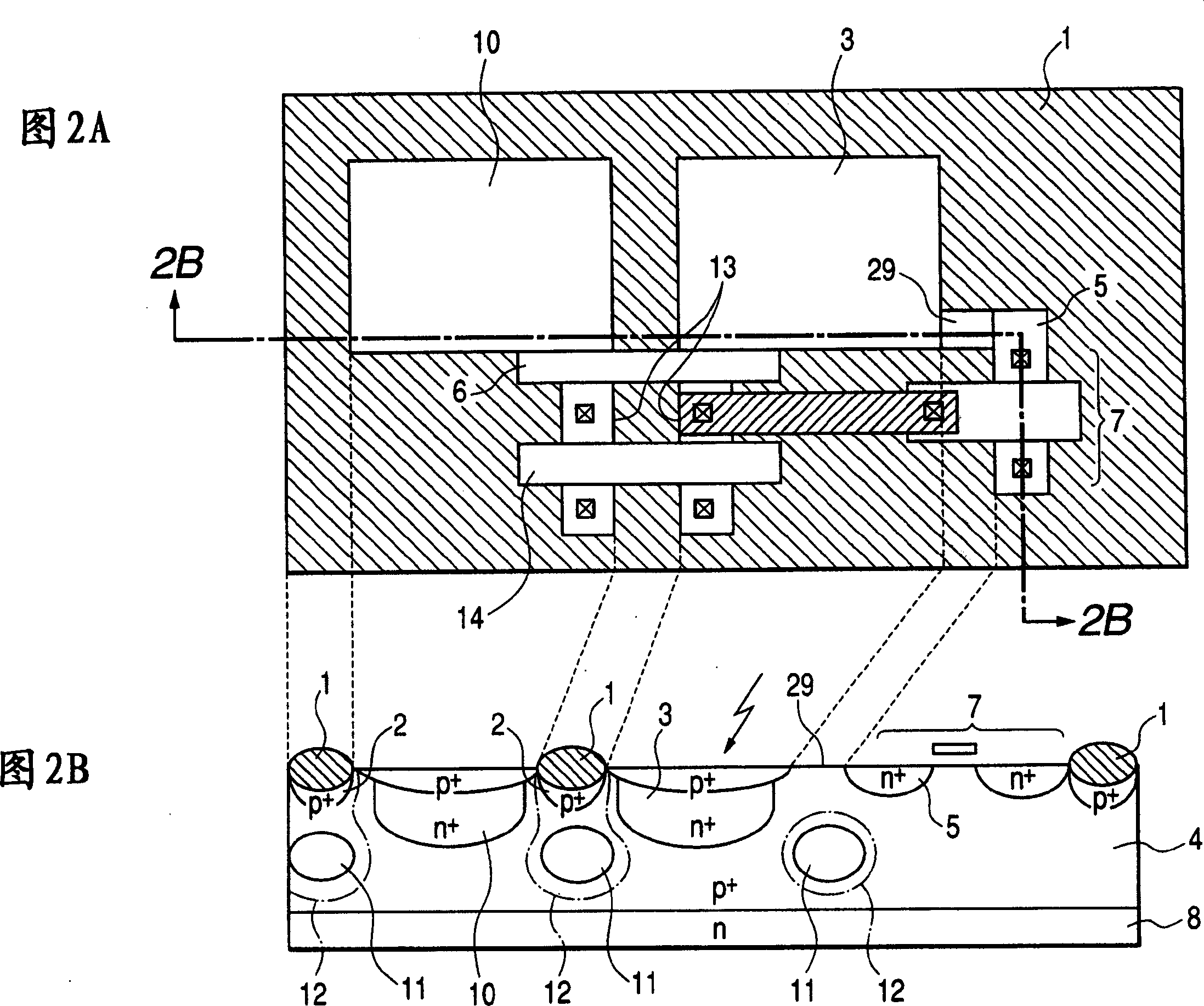

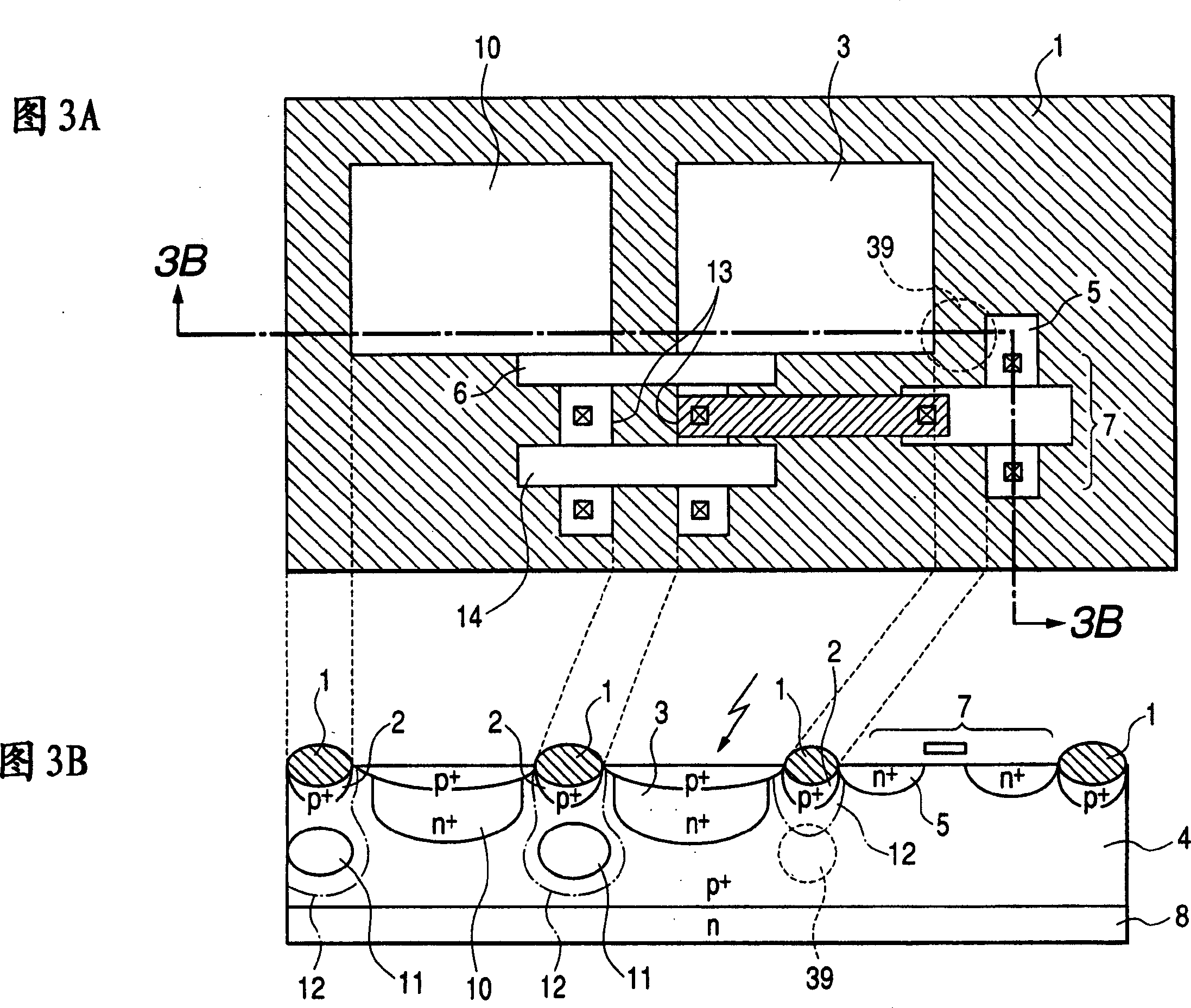

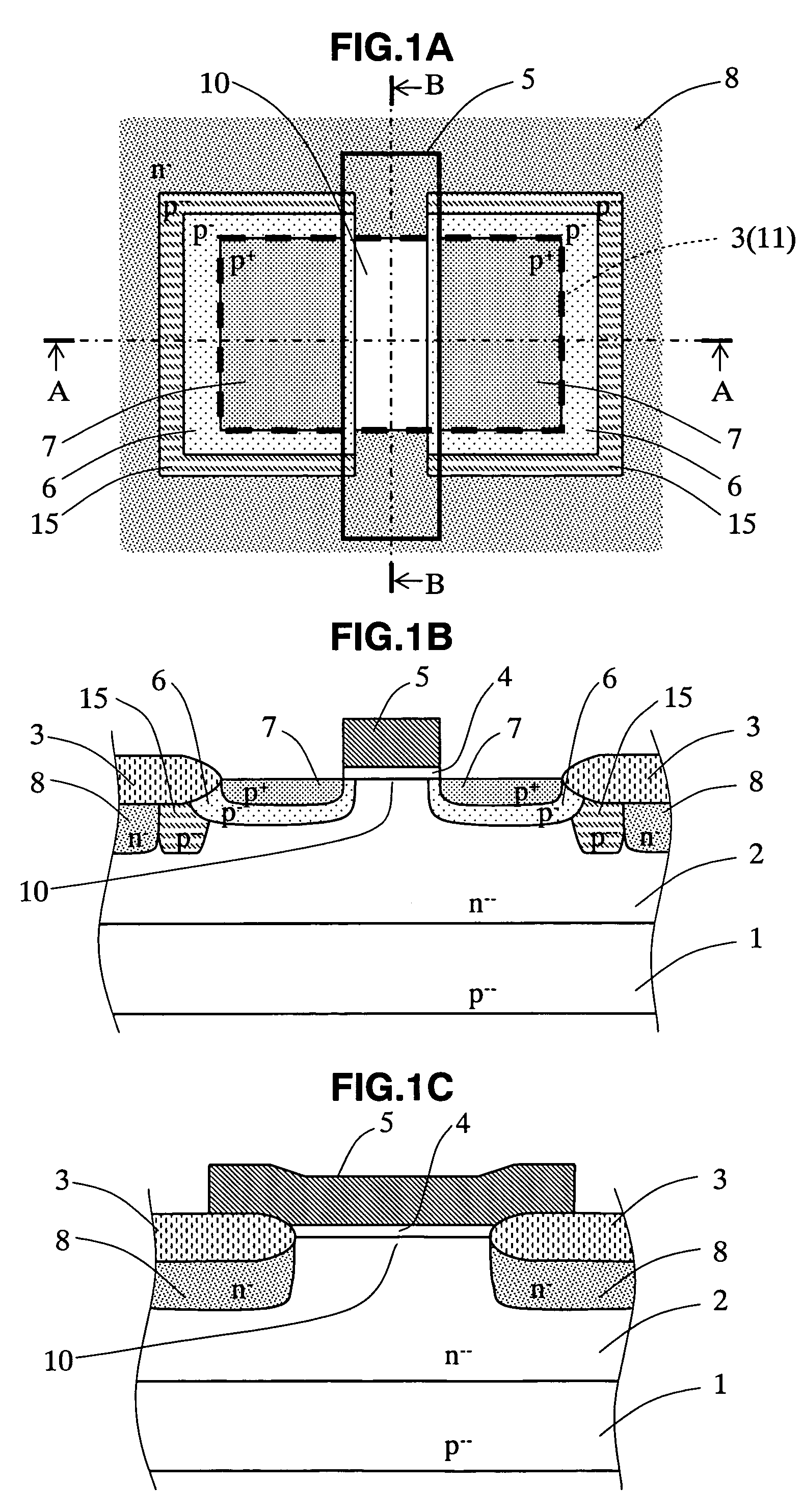

Photoelectric conversion device and image pick-up system using the photoelectric conversion device

InactiveUS7456888B2Improve efficiencyControl the height of the barrierTelevision system detailsTelevision system scanning detailsChannel-stopperCharge carrier

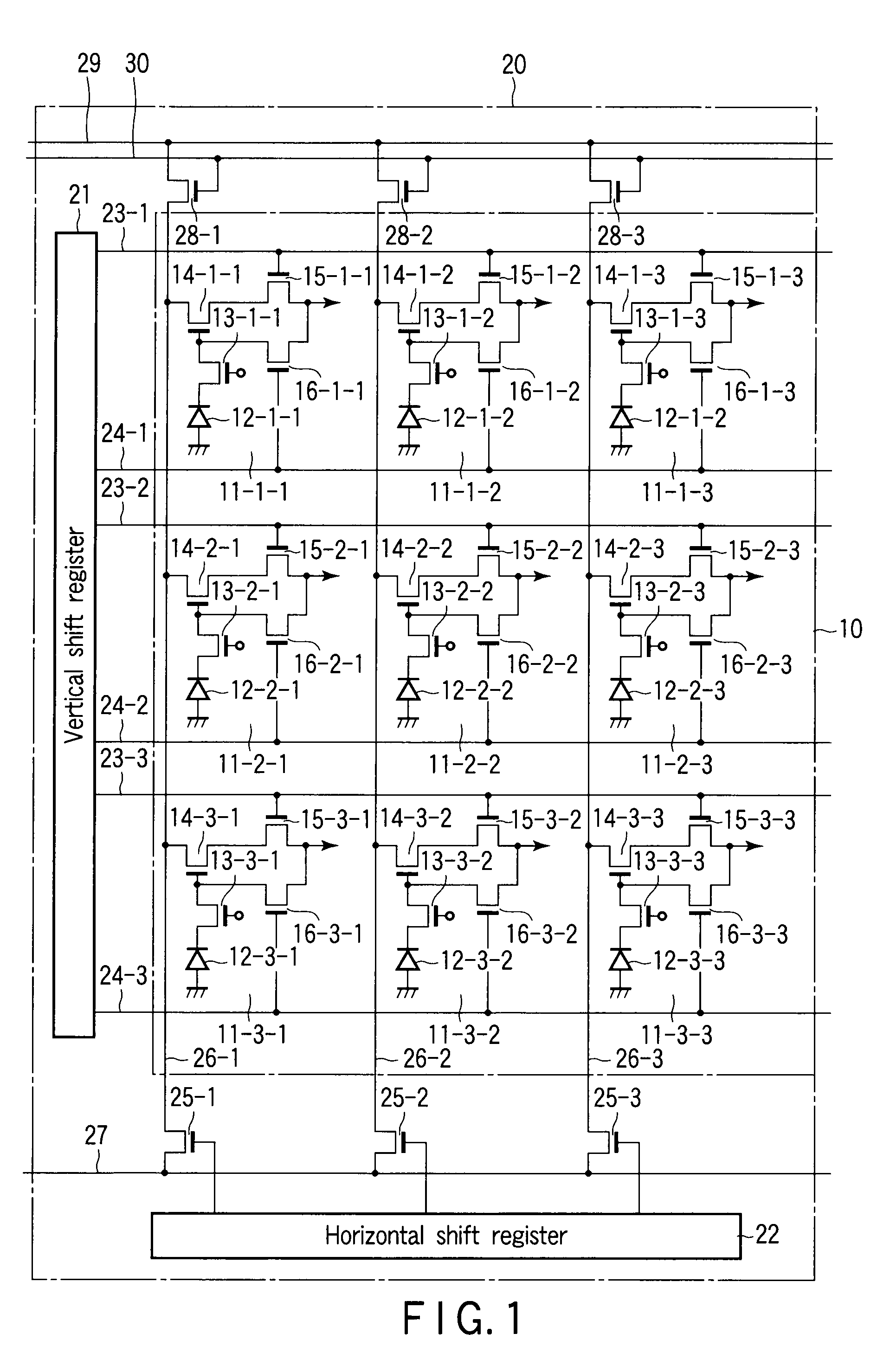

In a photoelectric conversion device with a photoelectric conversion region for accumulating electric charges that correspond to incident light and an amplifying filed effect transistor into which a signal charge from the photoelectric conversion region is inputted, the photoelectric conversion region is surrounded by a potential barrier region (a selectively oxidized film and a channel stopper), a nick region (overflow channel) is formed in a part of the potential barrier region, and a drain region of the field effect transistor that has the same conductivity type as the photoelectric conversion region is placed next to the nick region. Thus excess carriers are prevented from flowing into adjacent pixels or other floating regions.

Owner:CANON KK

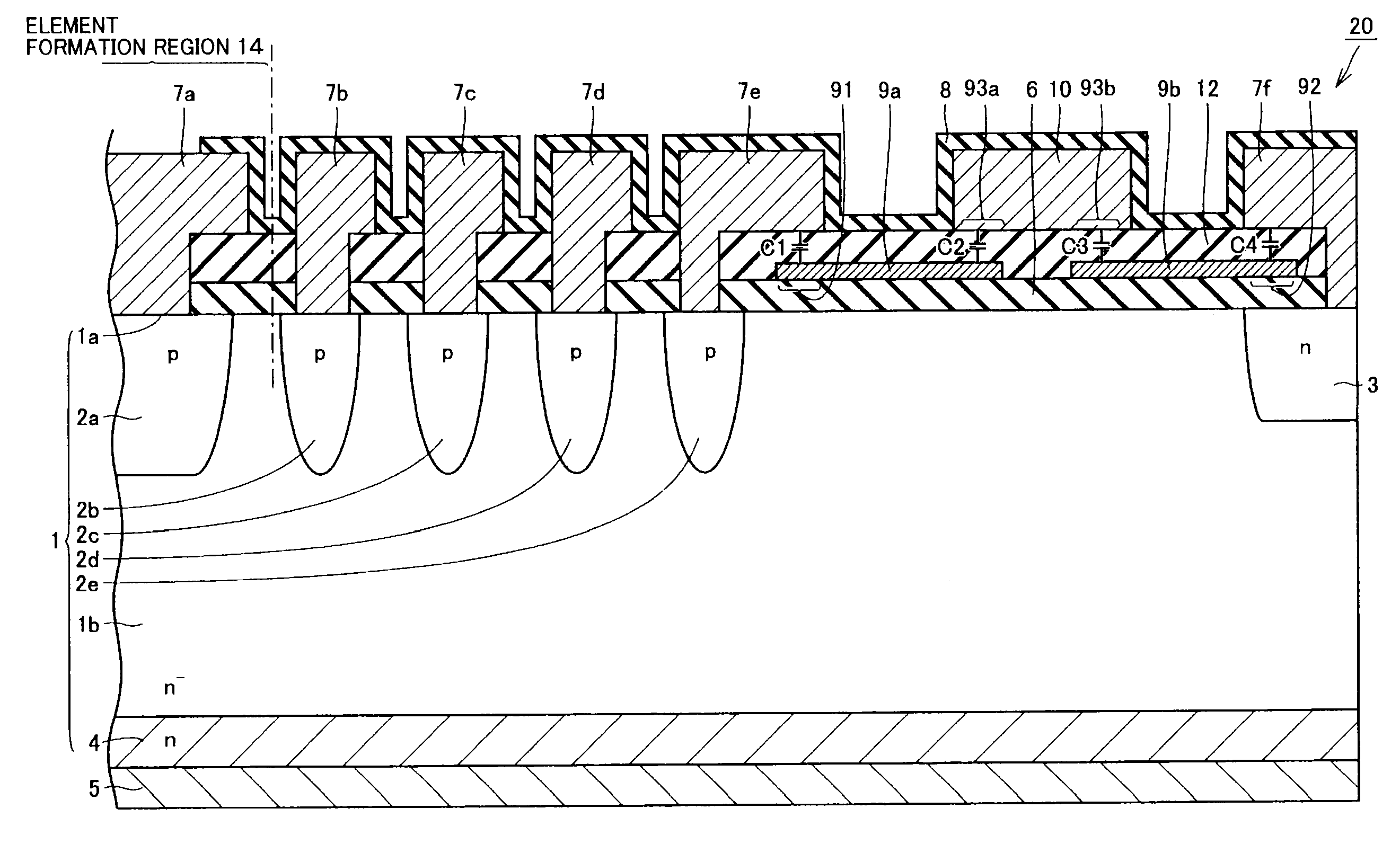

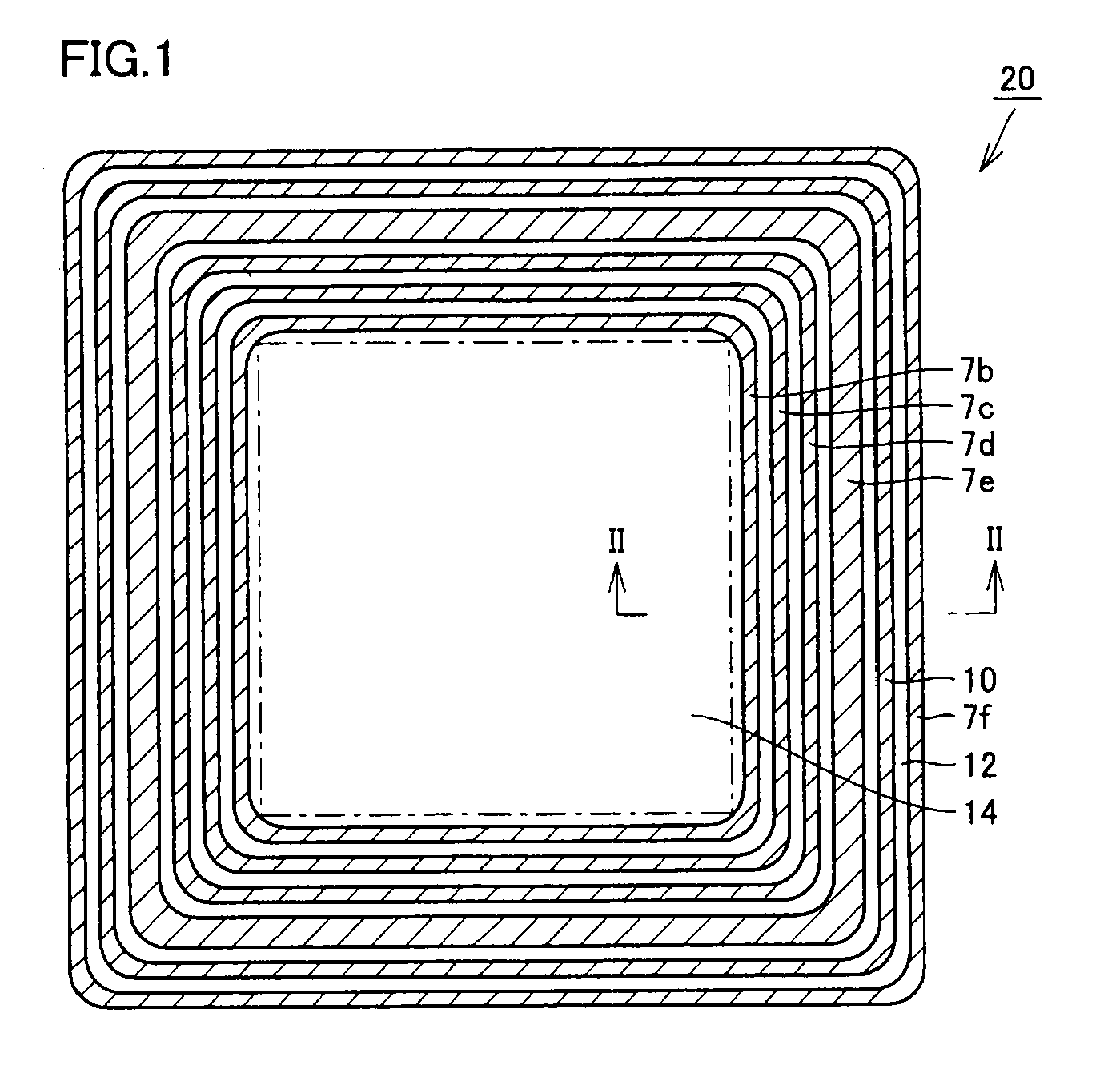

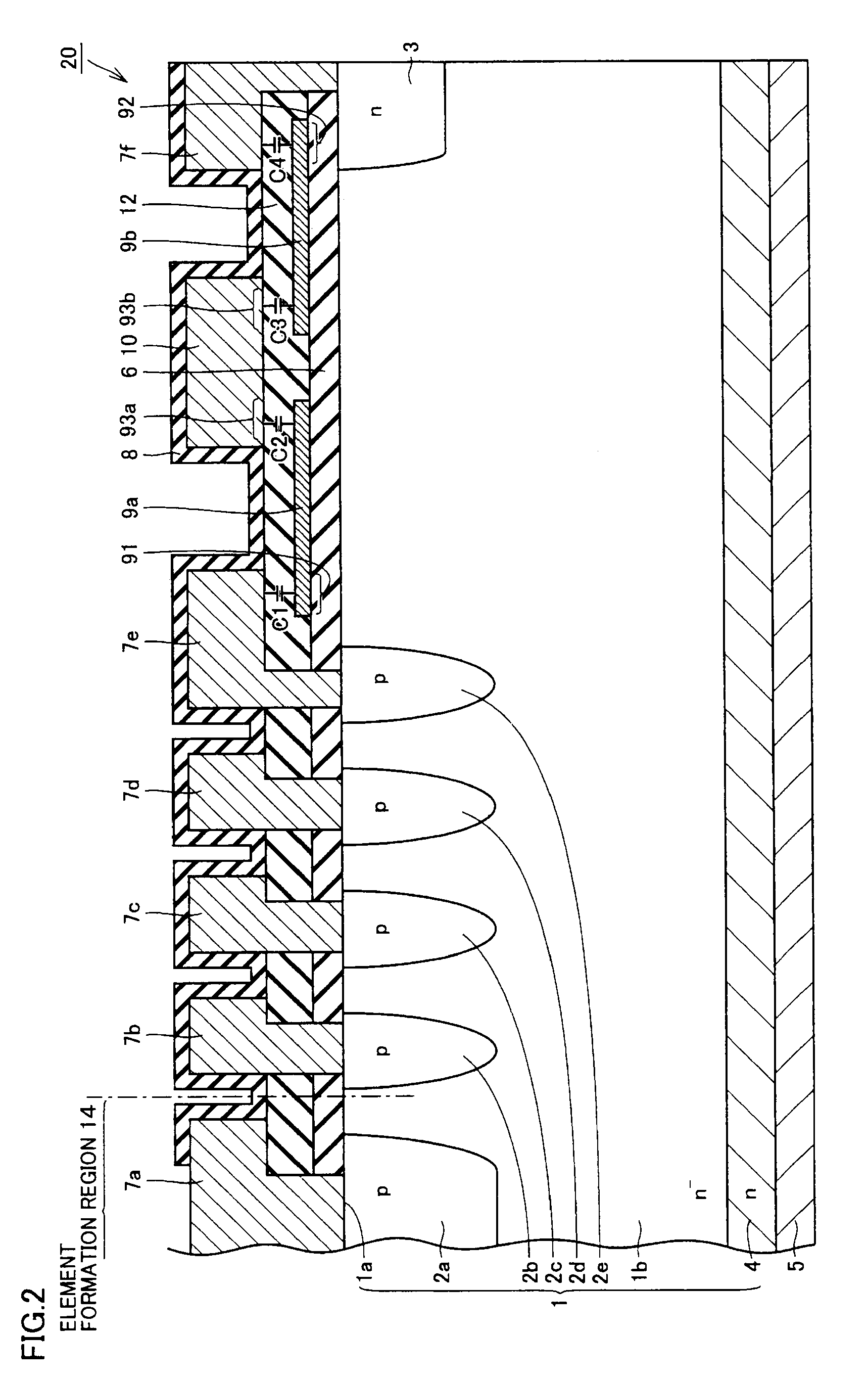

Semiconductor device

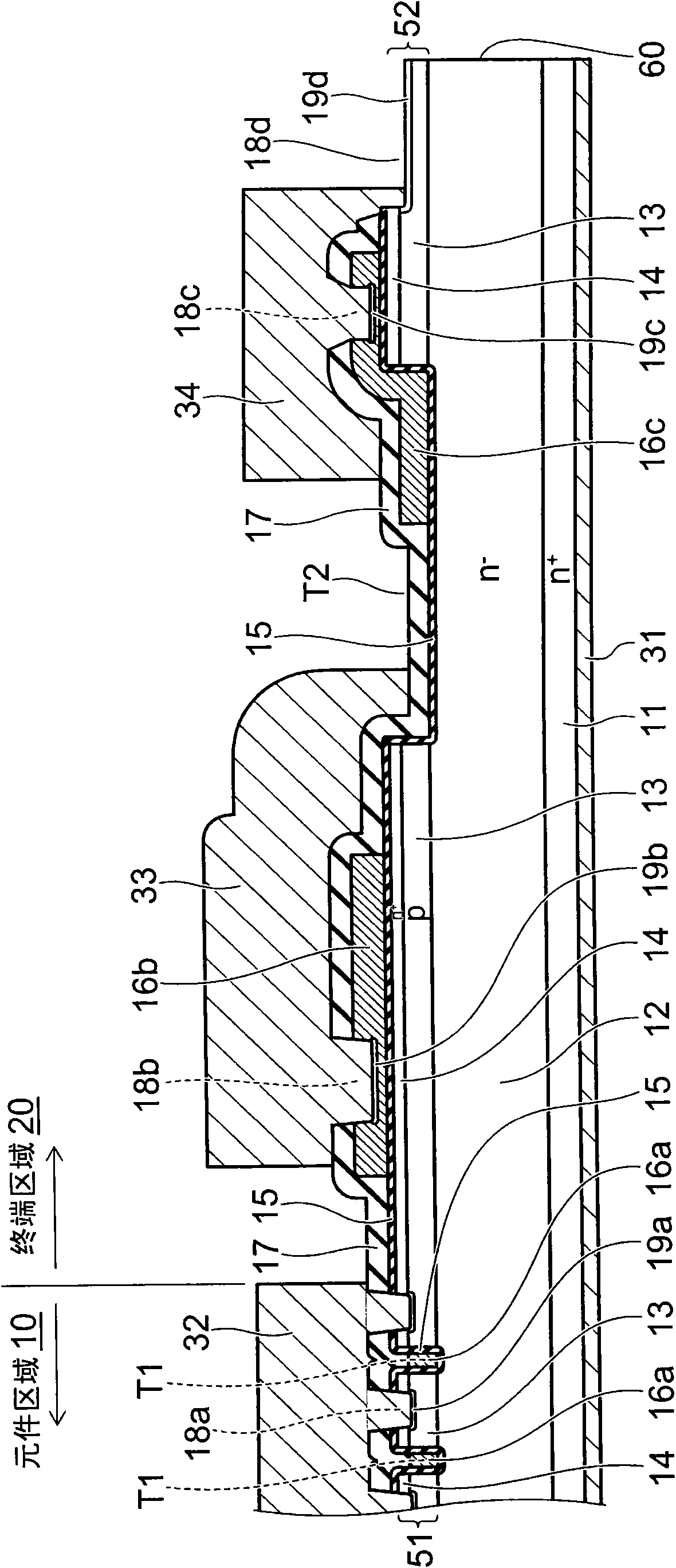

ActiveUS20100264507A1Stable breakdown voltageAvoid concentrationSemiconductor/solid-state device detailsSolid-state devicesChannel-stopperDevice material

A semiconductor device includes: a semiconductor substrate having a main surface having an element formation region, a guard ring, a guard ring electrode, a channel stopper region, a channel stopper electrode, and a field plate disposed over and insulated from the semiconductor substrate. The field plate includes a first portion located between the main surface of the semiconductor substrate and the guard ring electrode, and a second portion located between the main surface of the semiconductor substrate and the channel stopper electrode. The first portion has a portion overlapping with the guard ring electrode when viewed in a plan view. The second portion has a portion overlapping with the channel stopper electrode when viewed in the plan view. In this way, a semiconductor device allowing for stabilized breakdown voltage can be obtained.

Owner:ARIGNA TECH LTD

Semiconductor device

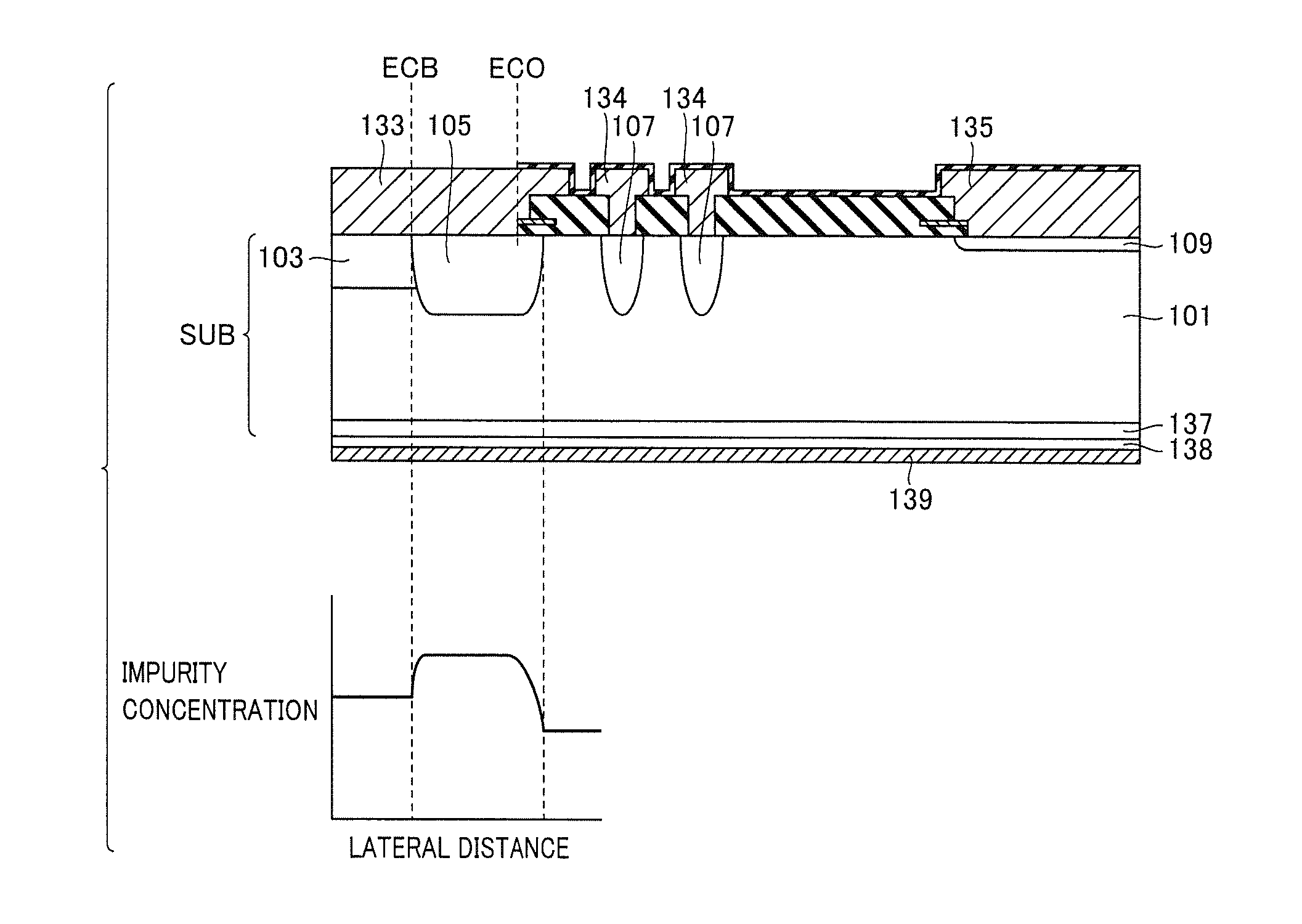

ActiveUS20130153954A1Suppress failureIncrease production costSemiconductor devicesPower semiconductor deviceChannel-stopper

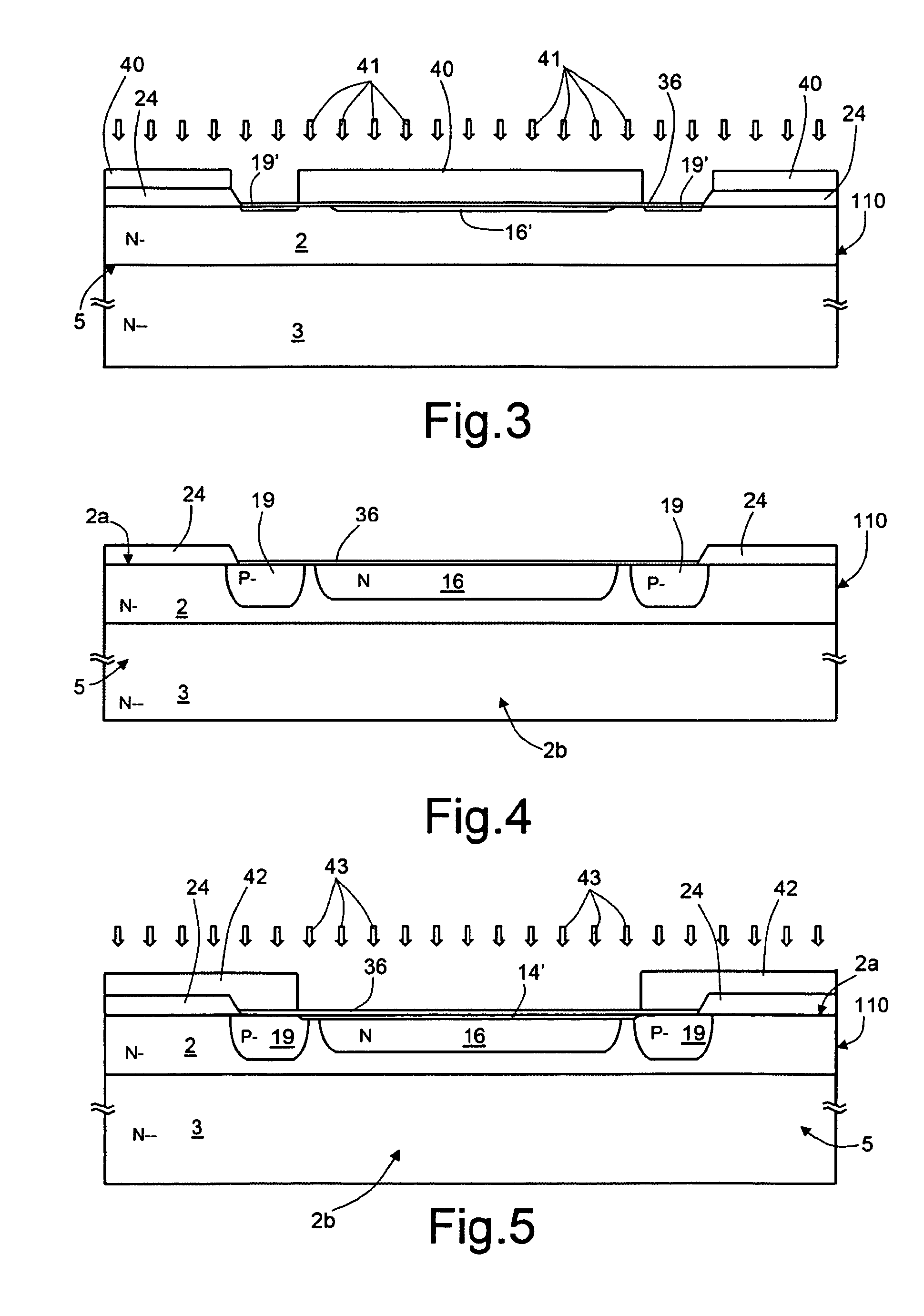

In one surface of a semiconductor substrate, an n− layer, a p base layer, a p well layer, another p well layer, a channel stopper layer, an emitter electrode, a guard ring electrode, and a channel stopper electrode for example are formed. In the other surface of the semiconductor substrate, an n+ buffer layer, a p+ collector layer, and a collector electrode are formed. In a curved corner of the p well layer, a p low-concentration layer having a lower impurity concentration than the impurity concentration of the p well layer is formed from the surface to a predetermined depth.

Owner:MITSUBISHI ELECTRIC CORP

Semiconductor device and manufacturing method thereof

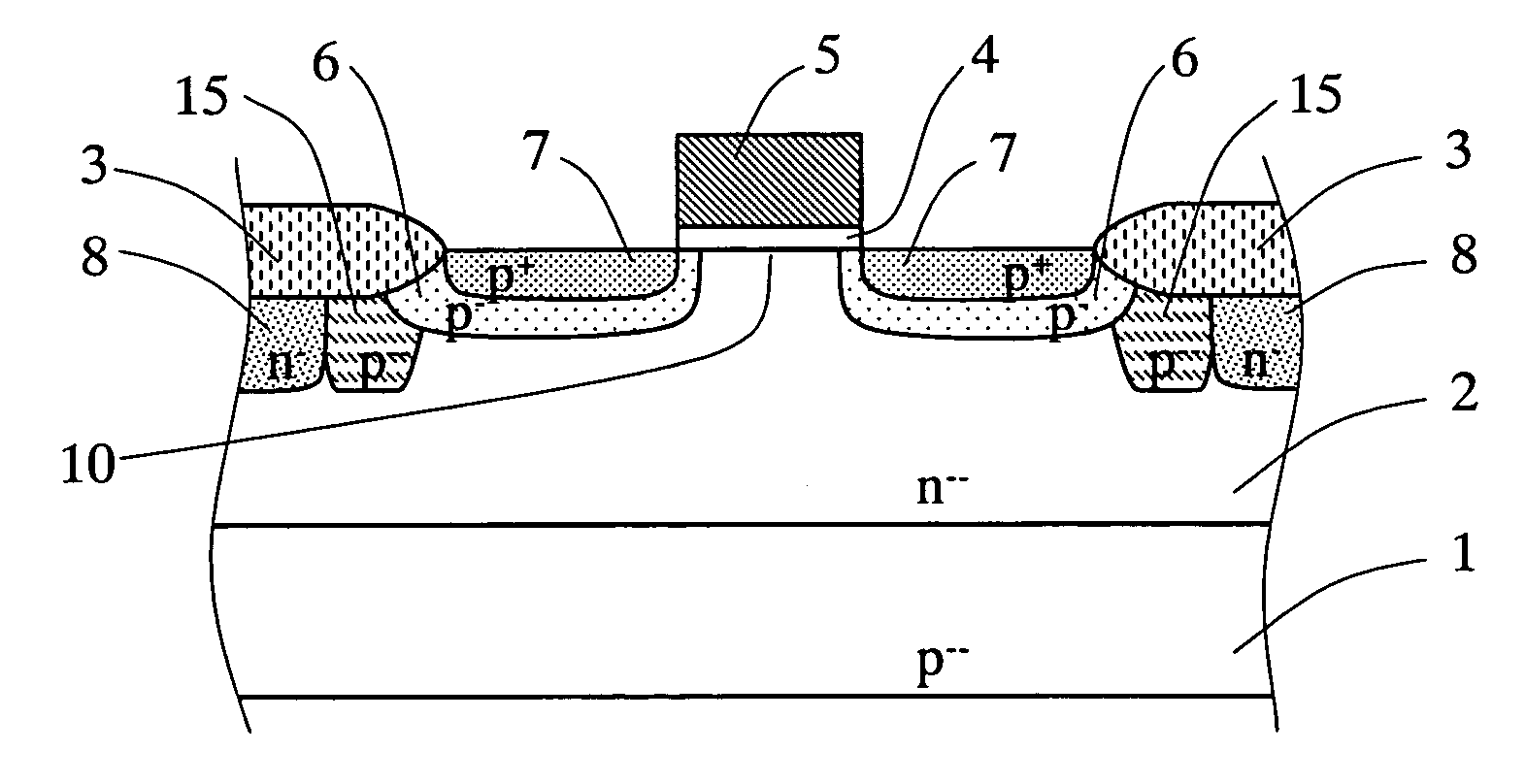

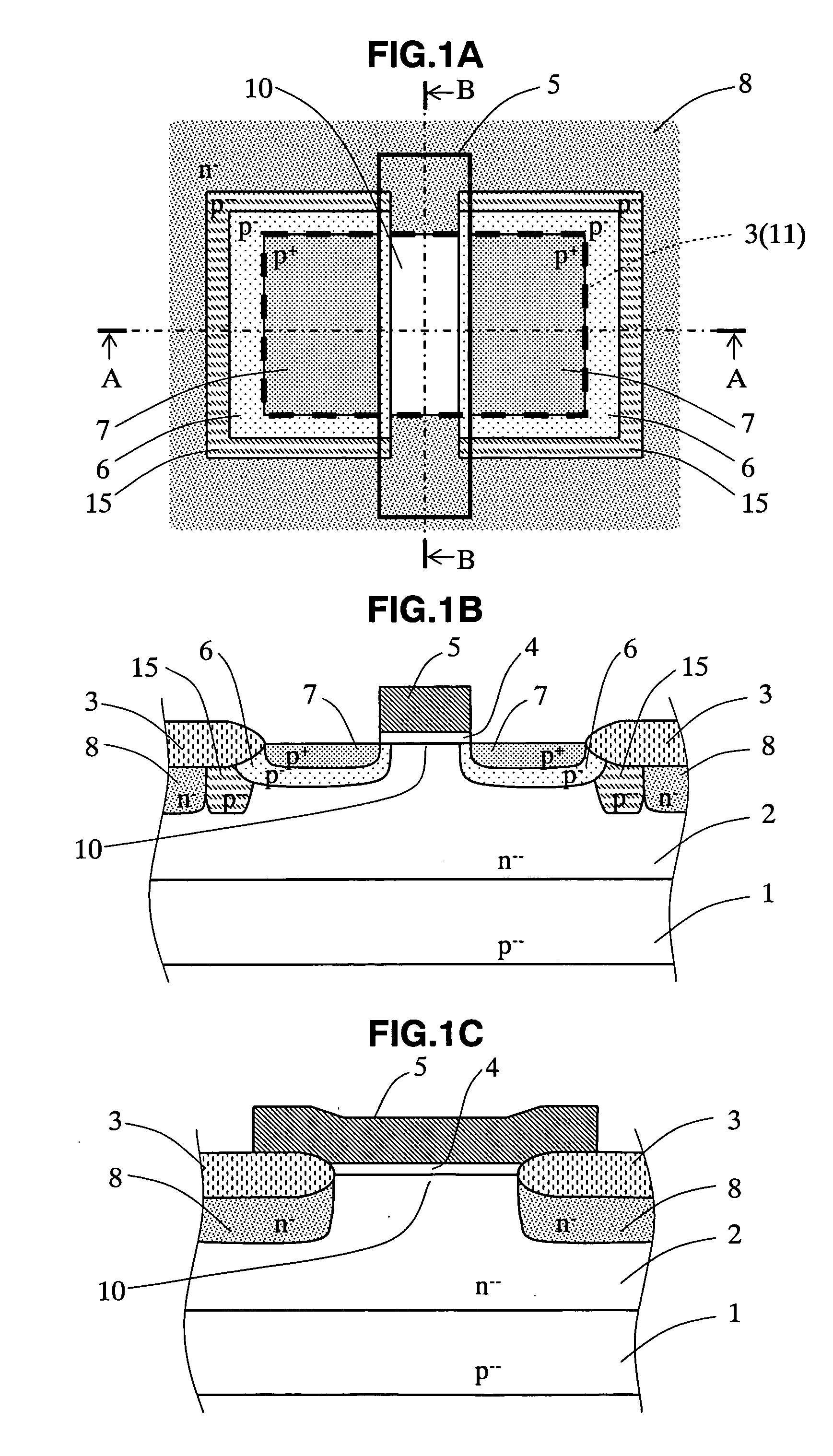

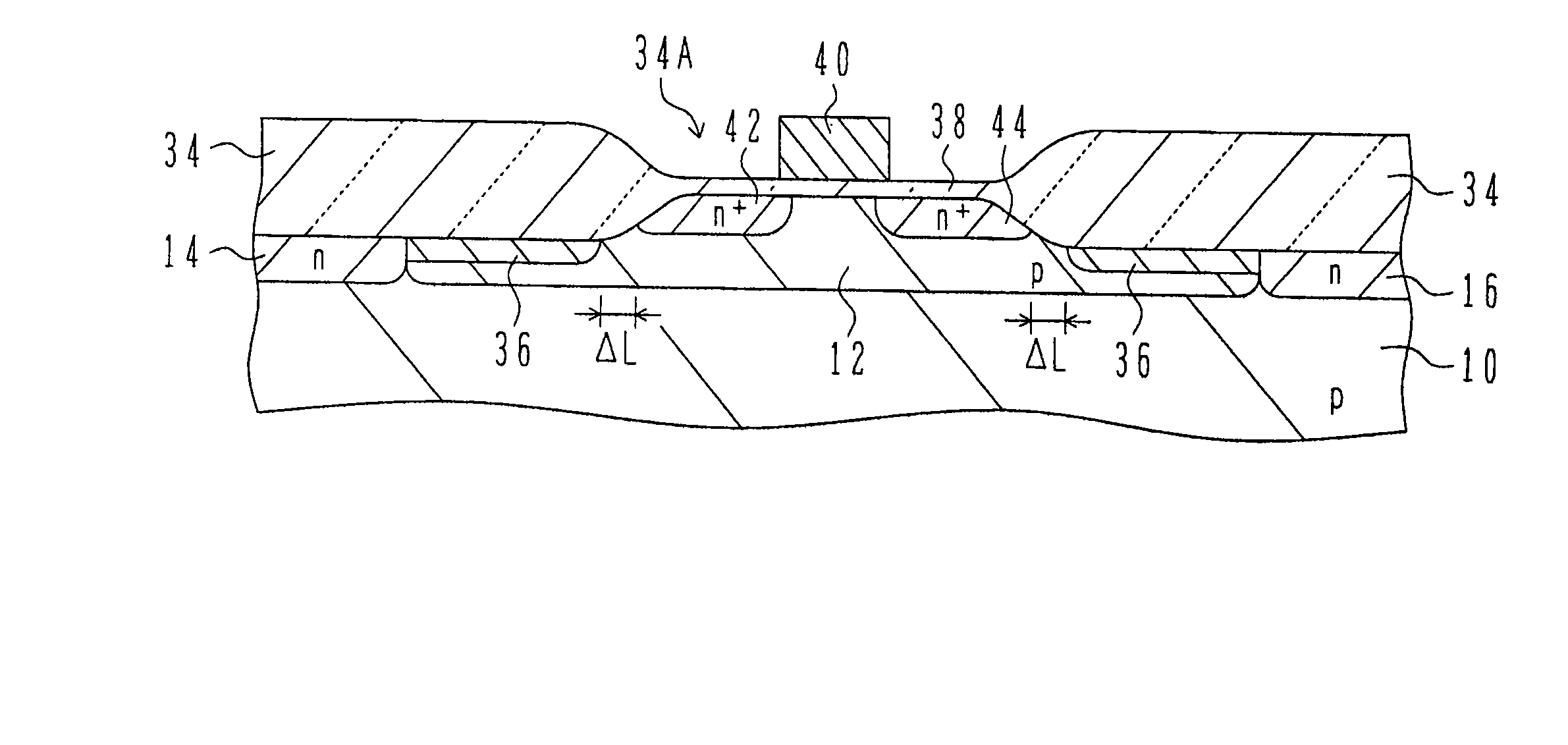

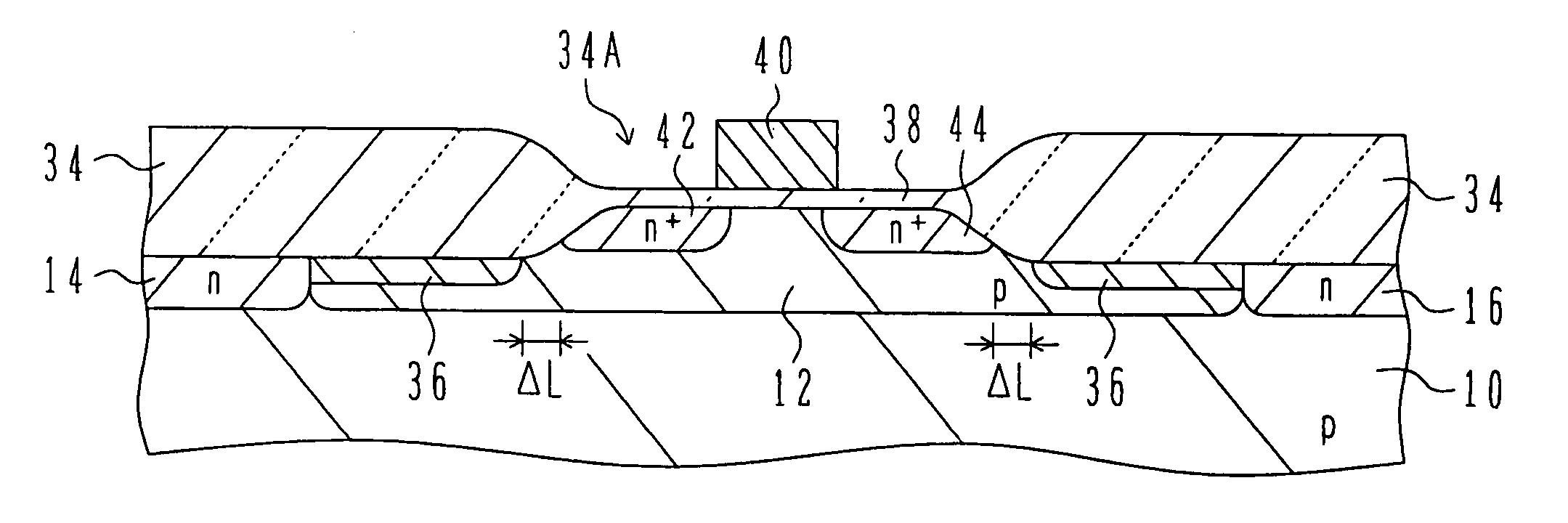

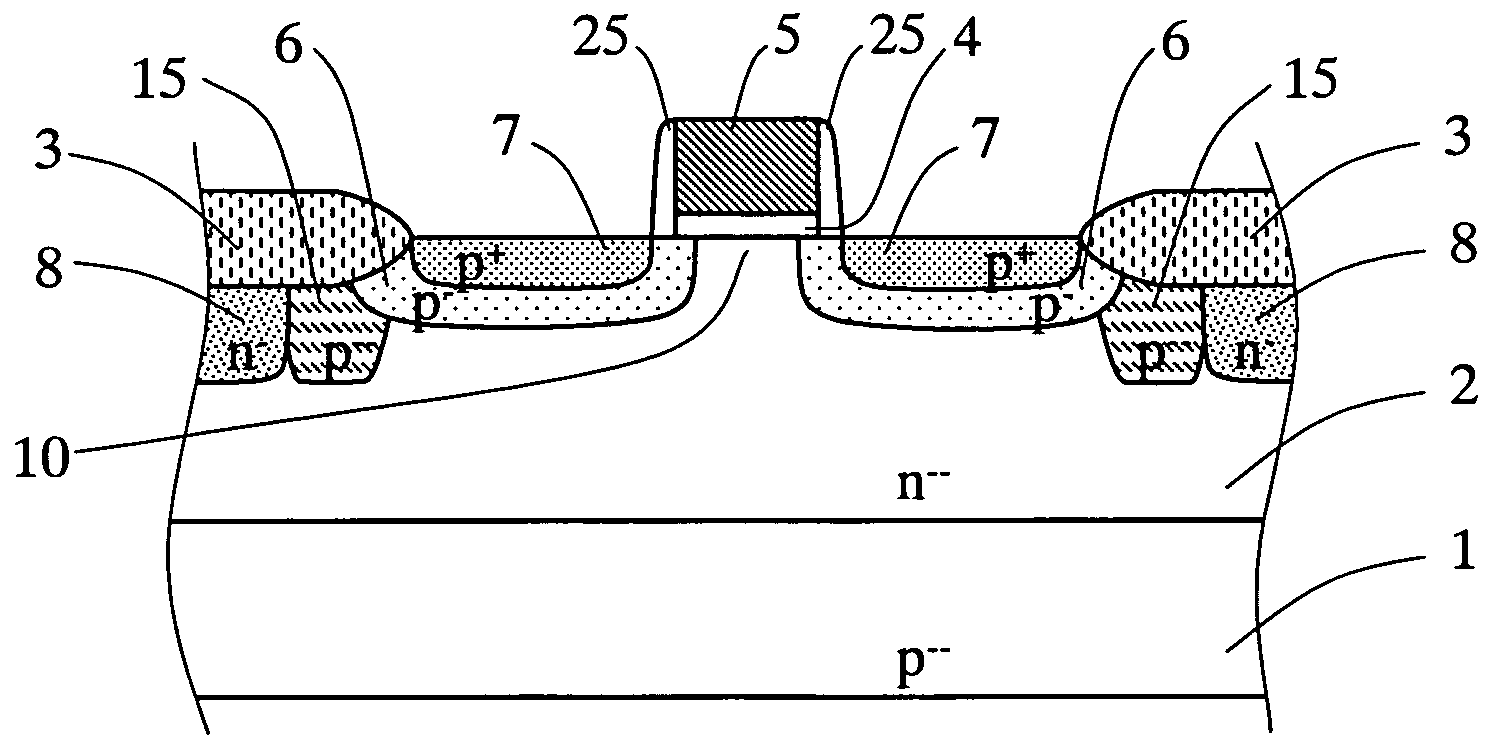

ActiveUS20060231916A1Avoid it happening againImprove featuresTransistorSolid-state devicesHigh concentrationChannel-stopper

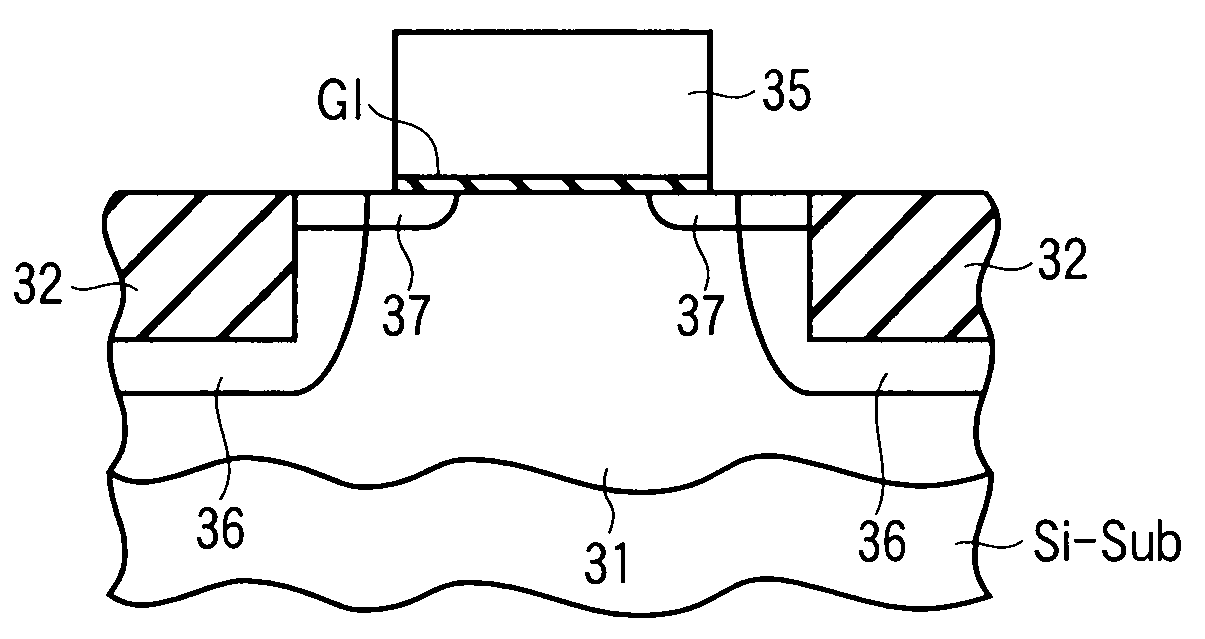

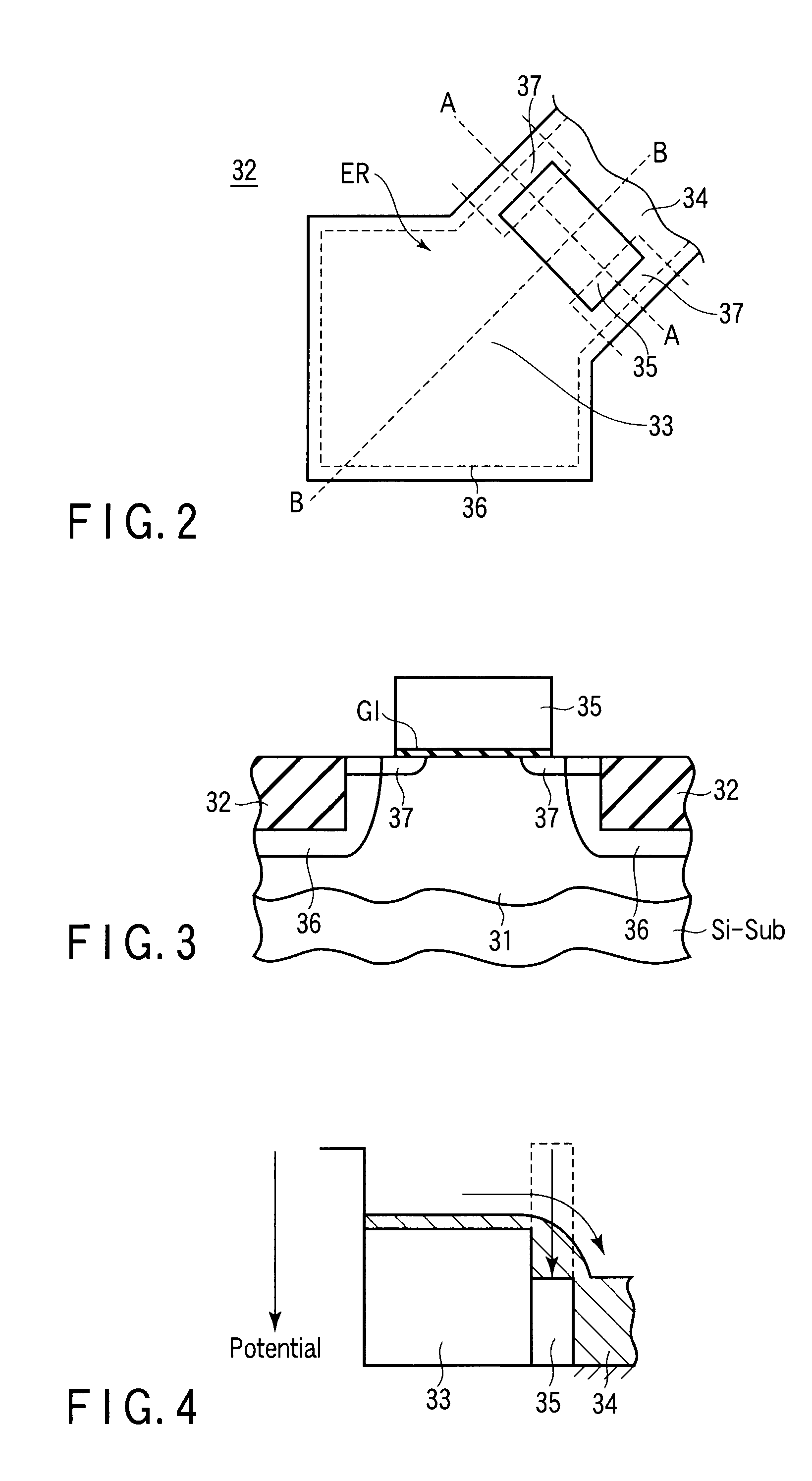

In this invention, the semiconductor device is provided with a gate electrode formed on a gate insulating film in a region sectioned by an element isolation formed on a semiconductor layer of the first conduction type, and a source region and a drain region of the second conduction type. At least one of the source region and the drain region has a first low concentration region and a high concentration region. Also, the semiconductor device of the present invention is provided with a second low concentration region of the second conduction type between a channel stopper region formed below the element isolation and the source region, and between the channel stopper region and the drain region. The semiconductor layer immediately below the gate electrode projects to the channel stopper region side along the gate electrode, and the semiconductor layer and the channel stopper region make contact with each other.

Owner:PANNOVA SEMIC

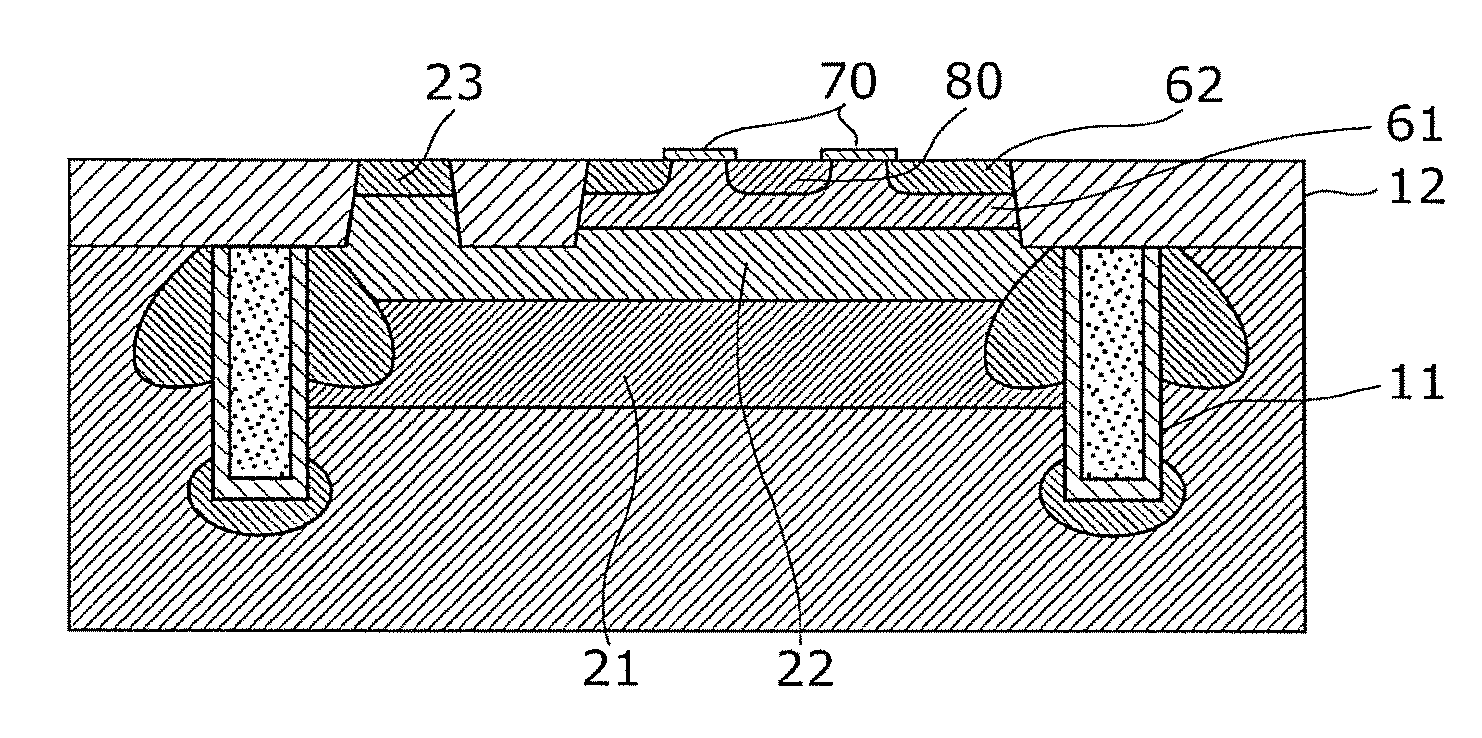

Semiconductor device and method for manufacturing the same

InactiveCN102097470ALow costSemiconductor/solid-state device manufacturingSemiconductor devicesChannel-stopperElectrical conductor

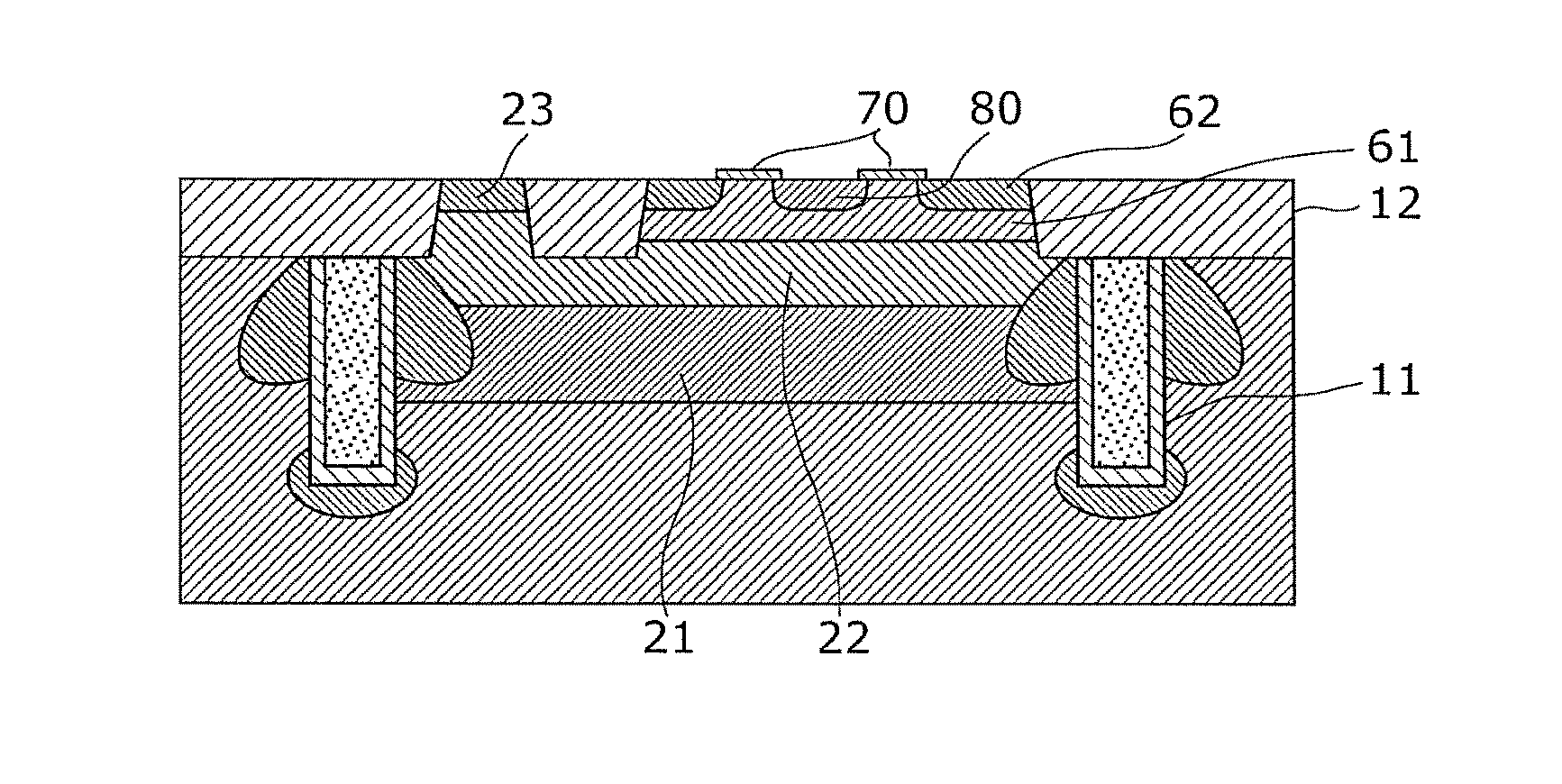

The invention provides a semiconductor device and a method for manufacturing the same. The semiconductor device comprises: a first semiconductor layer of a first conductivity type; a second semiconductor layer of the first conductivity type; a third semiconductor layer of a second conductivity type; a fourth semiconductor layer of the first conductivity type; first trenches which penetrate the fourth semiconductor layer and the third semiconductor layer to reach the second semiconductor layer; a second trench which penetrates the fourth semiconductor layer and the third semiconductor layer, on a side closer to a termination than the first trenches, to reach the second semiconductor layer, the second trench dividing the fourth semiconductor layer and the third semiconductor layer into a element part including a region wherein the first trenches are formed and a termination part; an insulating film; a gate electrode; a first main electrode; a second main electrode; a channel stopper layer provided in the second trench via the insulating film; and a channel stopper electrode provided on the termination part of the third semiconductor layer and the termination part of the fourth semiconductor layer and connecting the channel stopper layer and the termination part.

Owner:KK TOSHIBA

Manufacture Method for Semiconductor Device Having Field Oxide Film

InactiveUS20080003776A1Improve accuracyFormed with easeSemiconductor/solid-state device manufacturingSemiconductor devicesResistChannel-stopper

Owner:YAMAHA CORP

Semiconductor device and method of manufacturing the same

A semiconductor device includes: an active region insulated by an element-isolation insulating film embedded on a semiconductor substrate; multiple element forming sections that are provided in the active region; a semiconductor element that is formed in each of the element forming sections; and a channel stopper that is provided in the active region to insulate the element forming sections from each other. The channel stopper comprises: a fin that protrudes between grooves provided in the element-isolation insulating film and on both sides of the active region; a dummy-gate insulating film that covers the fin; and a dummy gate electrode that straddles the fin.

Owner:ELPIDA MEMORY INC

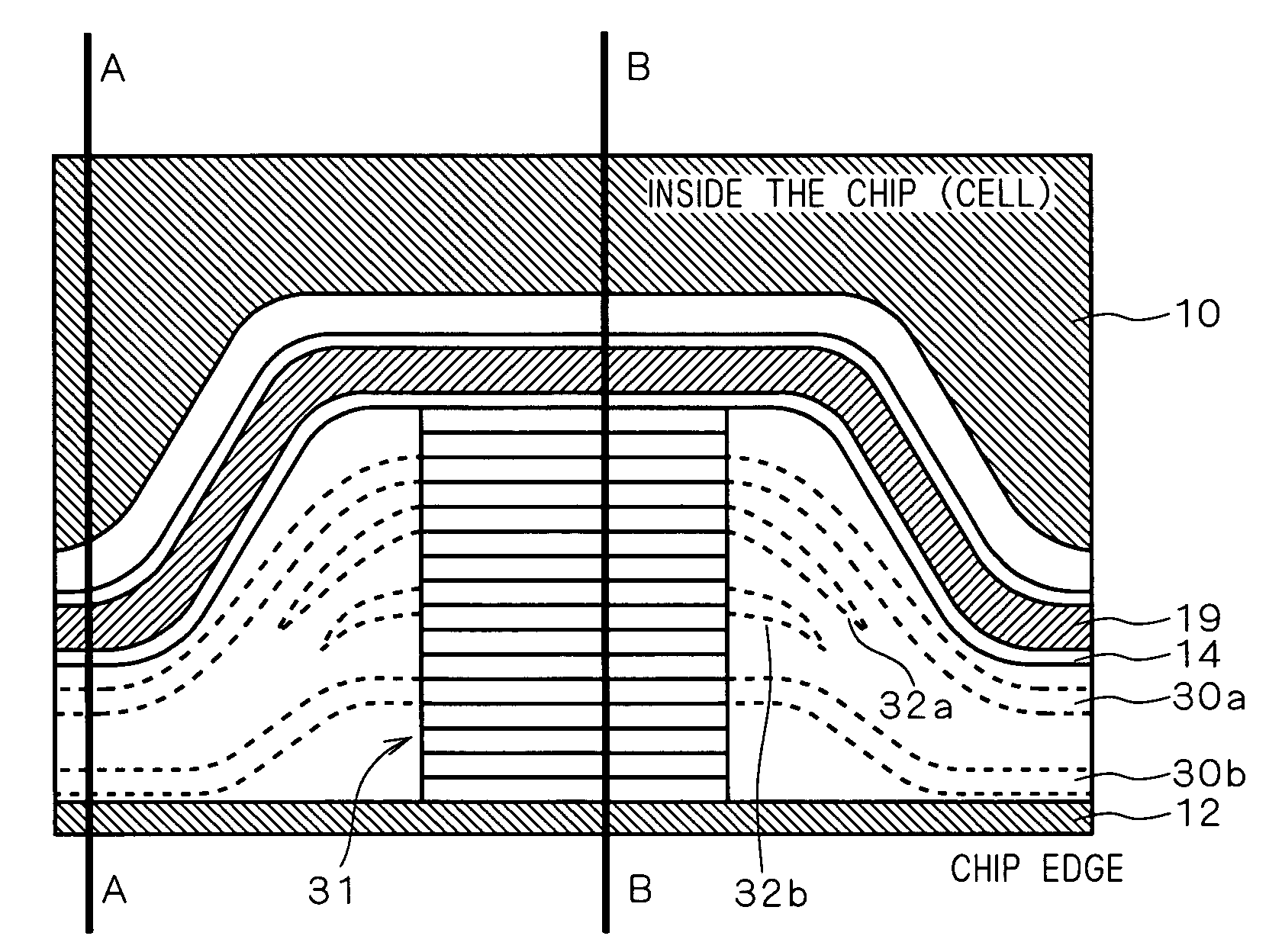

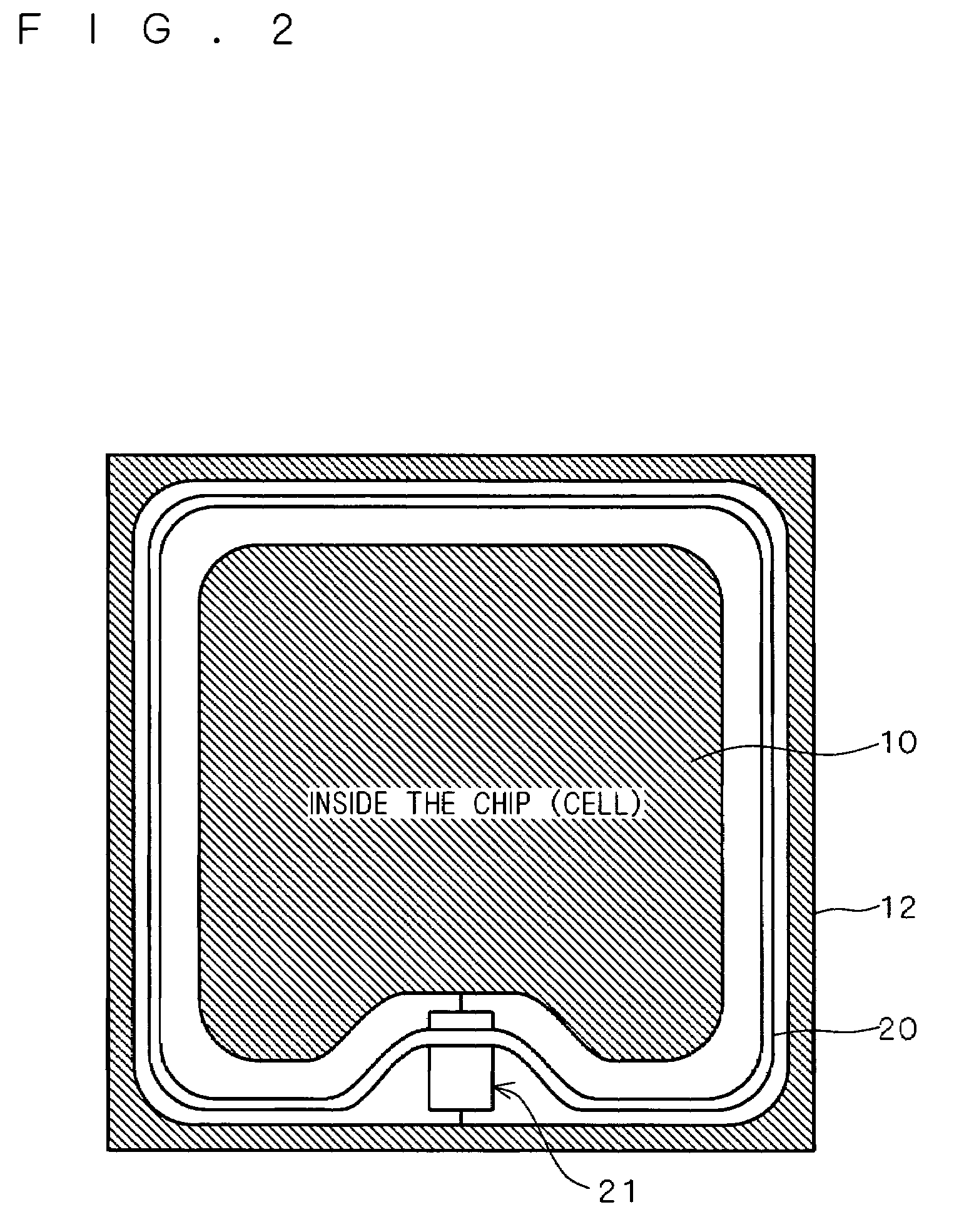

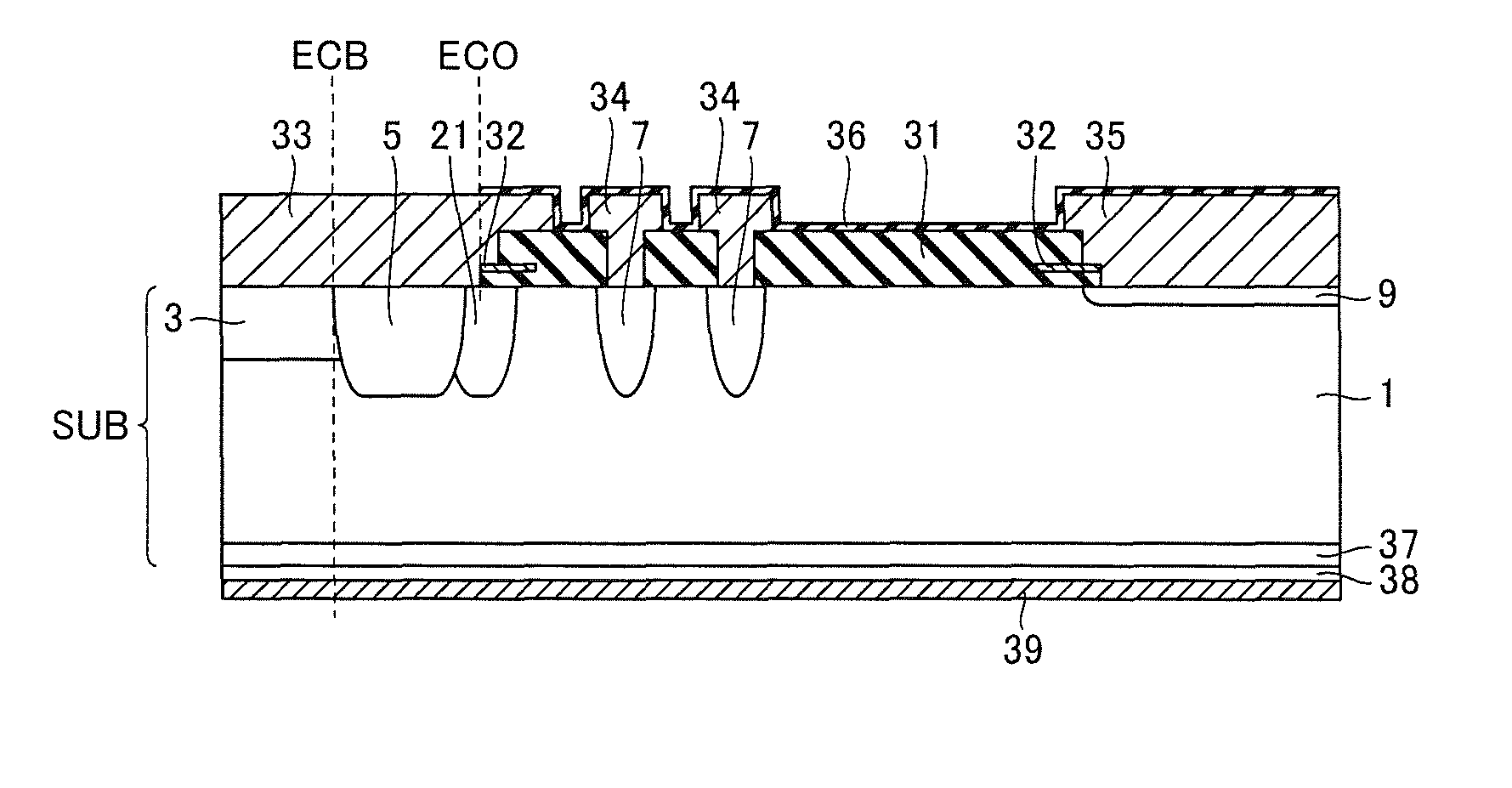

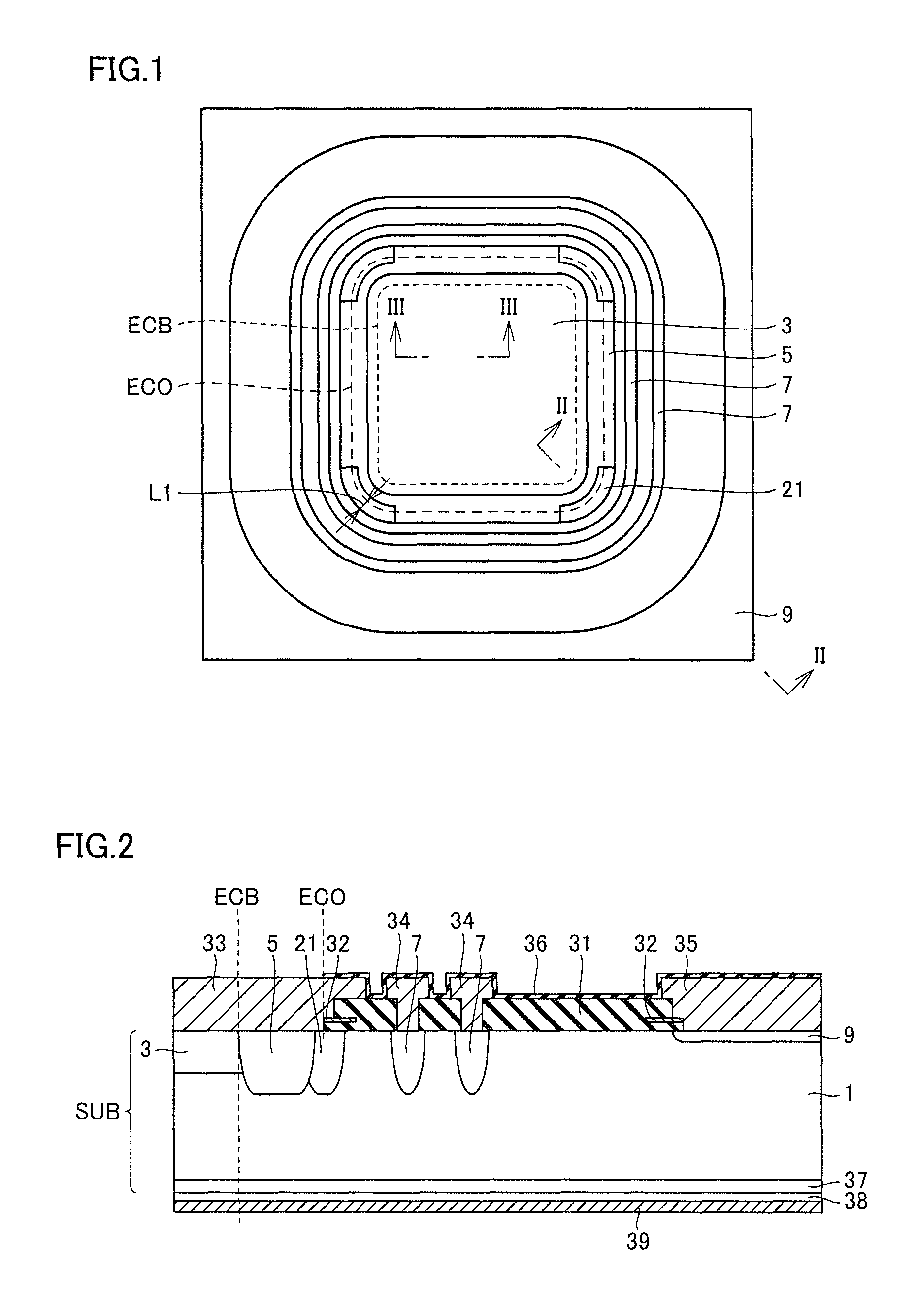

Semiconductor device with enhanced breakdown voltage

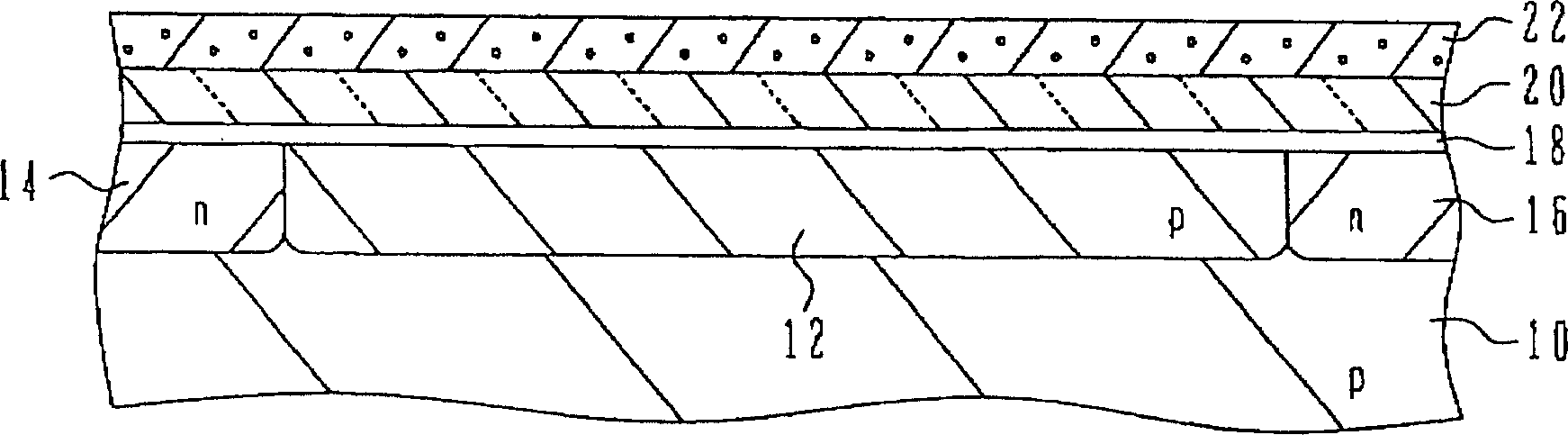

In a peripheral portion of an IGBT chip, an intermediate potential electrode (20) is provided between a field plate (14) and a field plate (15) on a field oxide film (13), to surround an IGBT cell. The intermediate potential electrode (20) is supplied with a prescribed intermediate potential between the potentials at an emitter electrode (10) and a channel stopper electrode (12) from intermediate potential applying means that is formed locally in a partial region on the chip peripheral portion.

Owner:MITSUBISHI ELECTRIC CORP

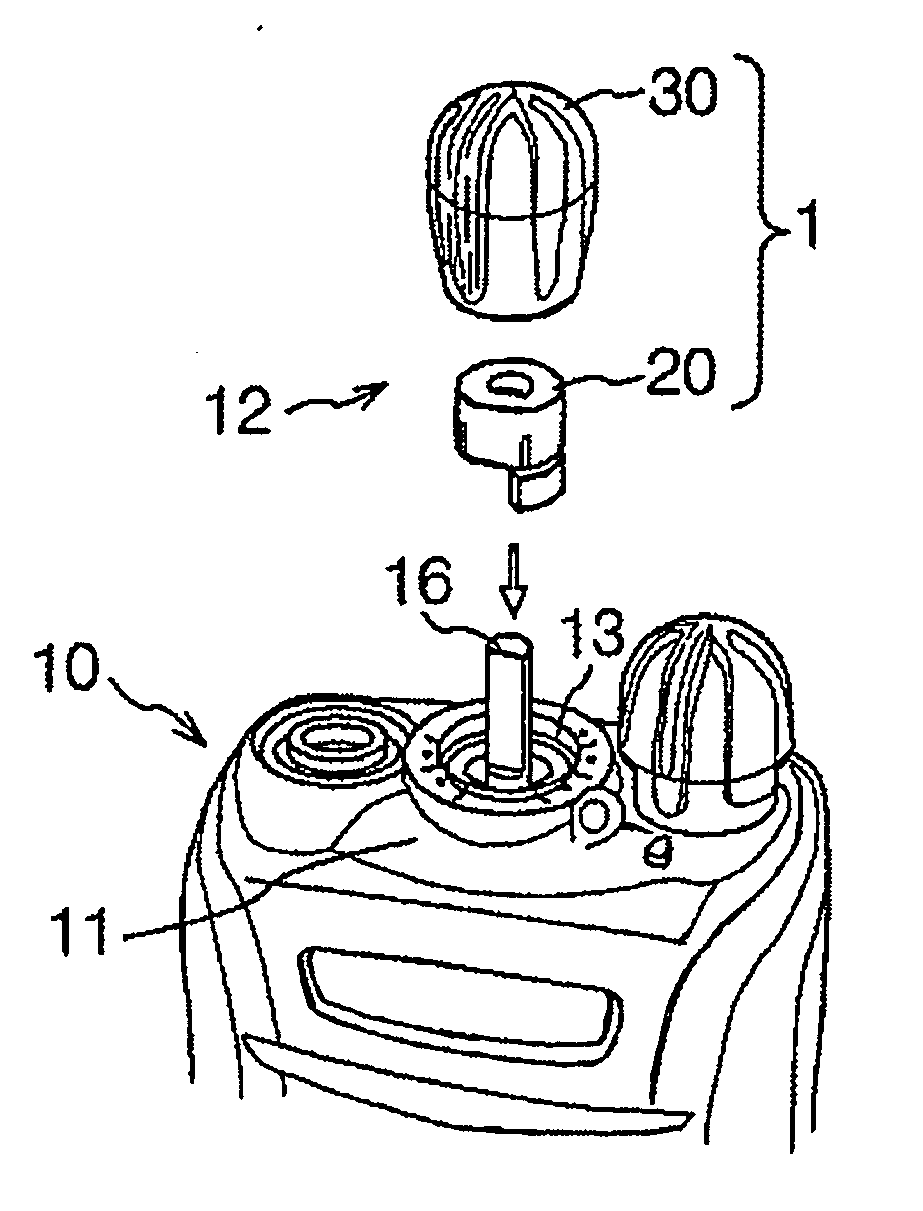

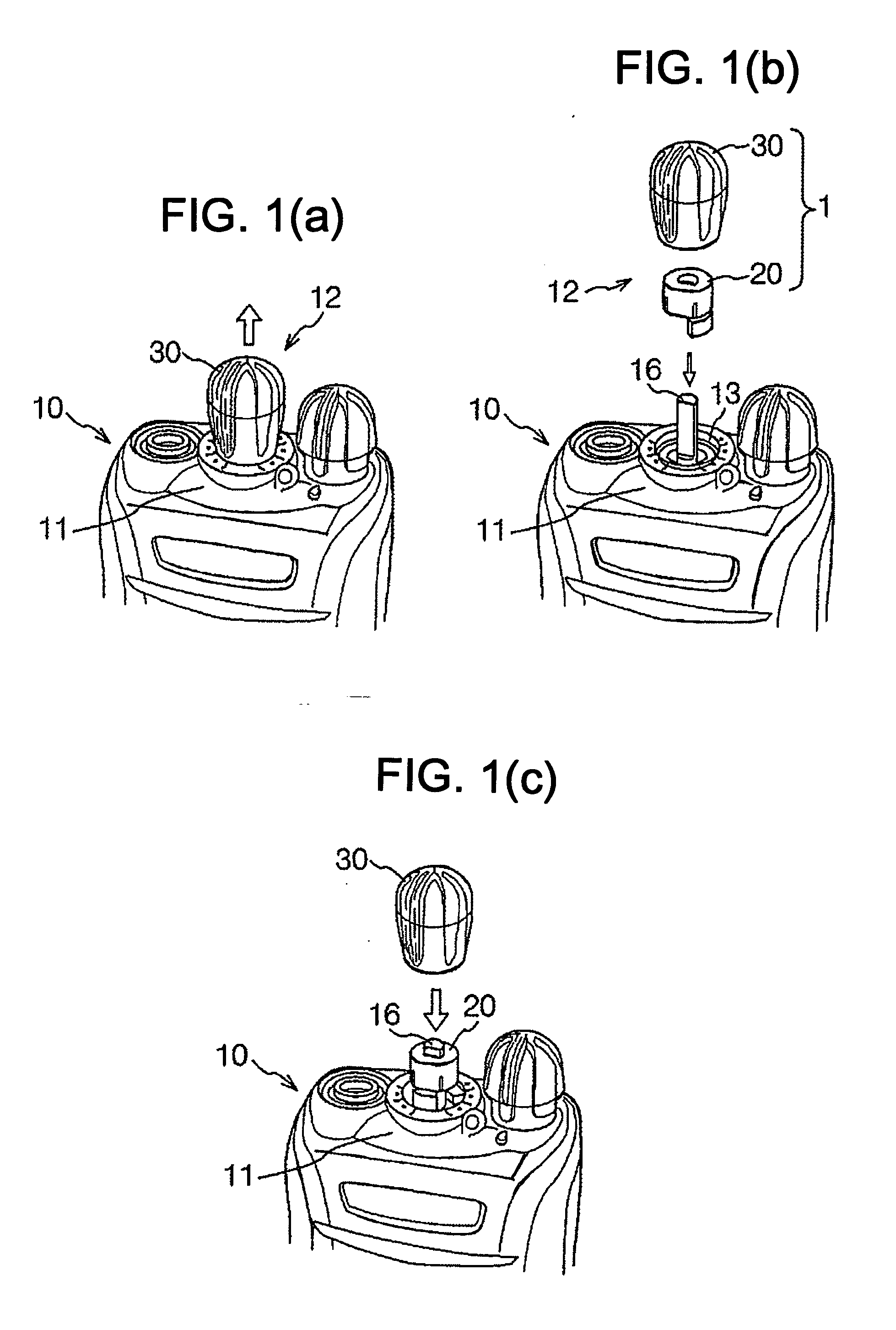

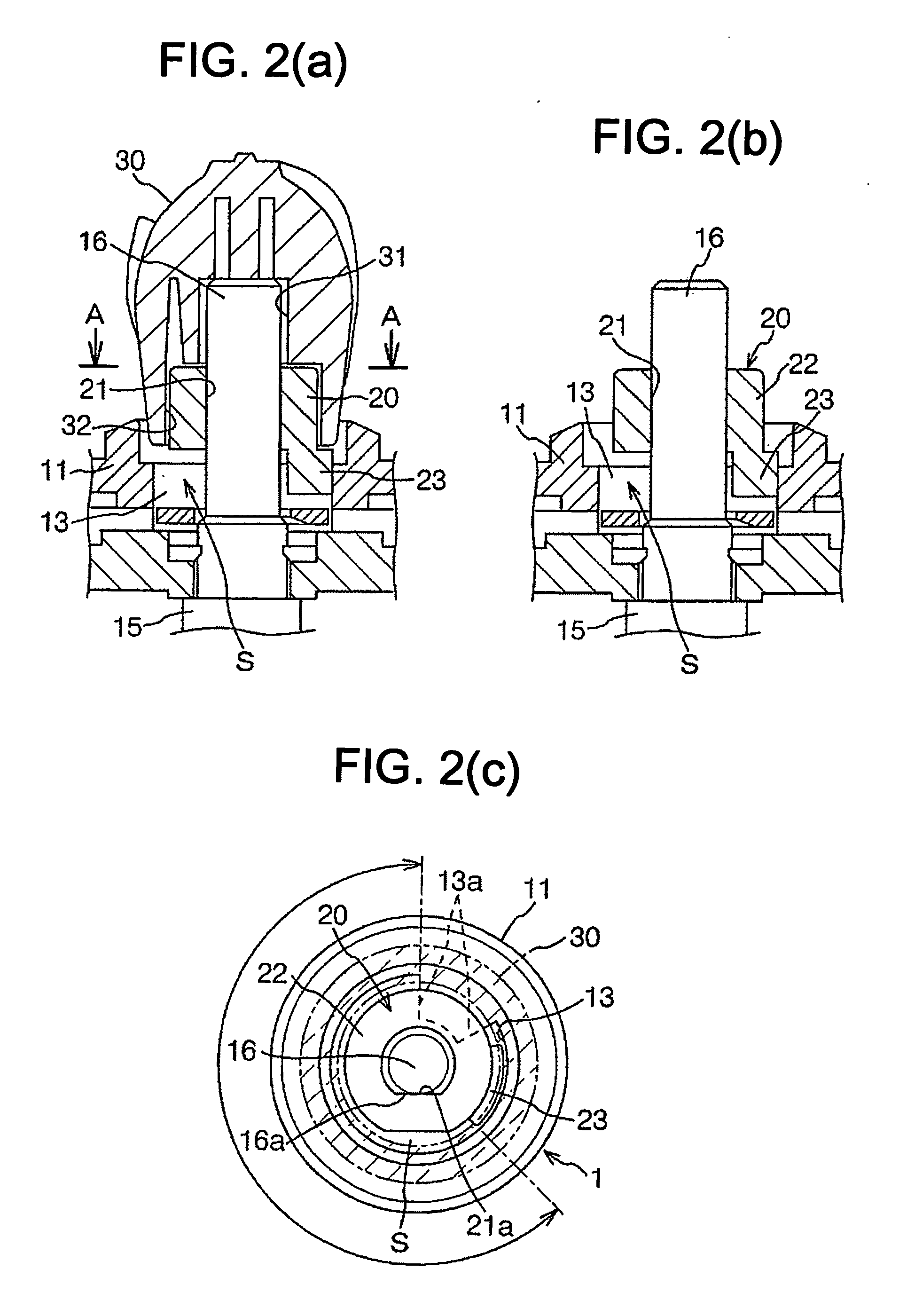

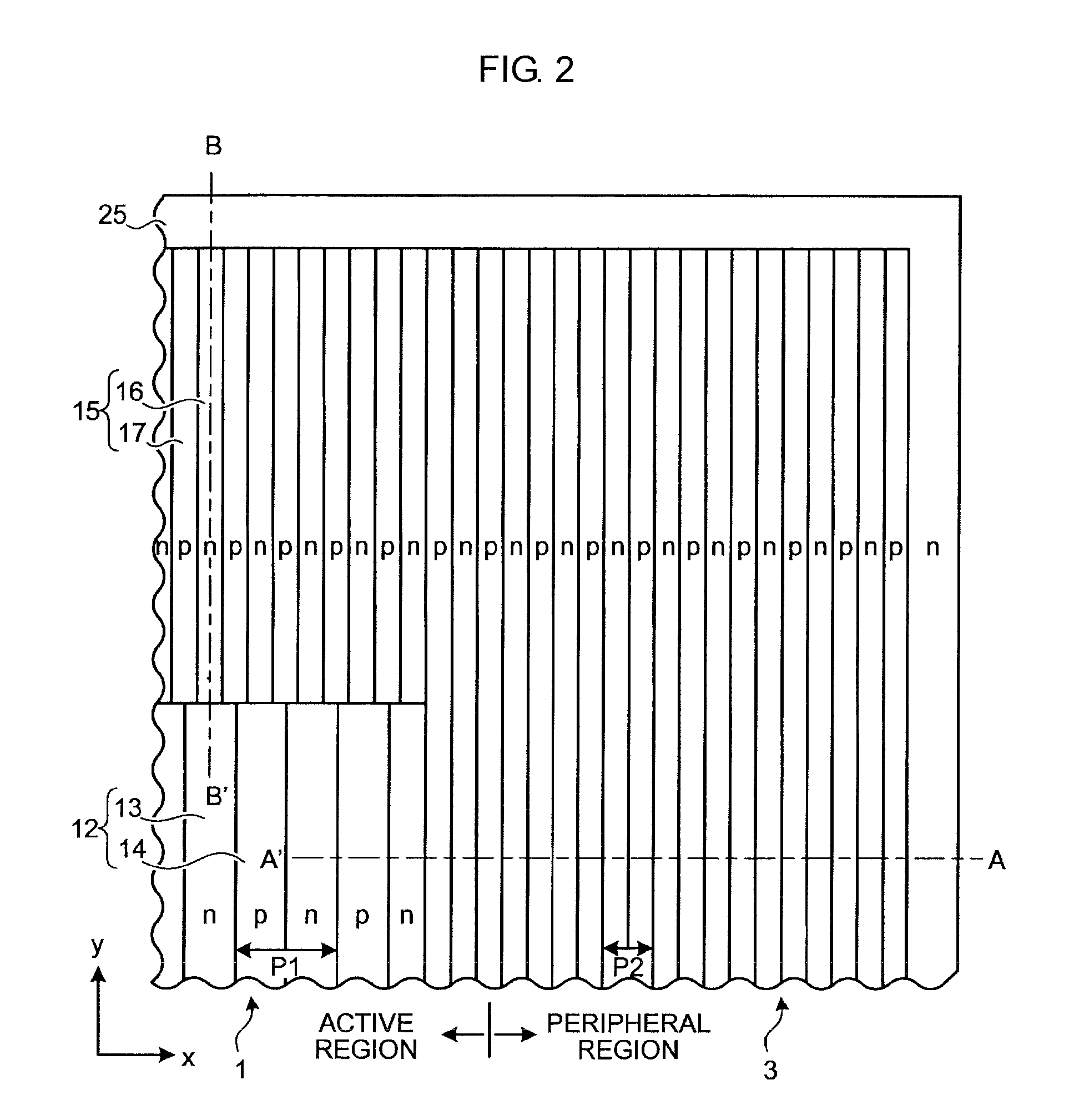

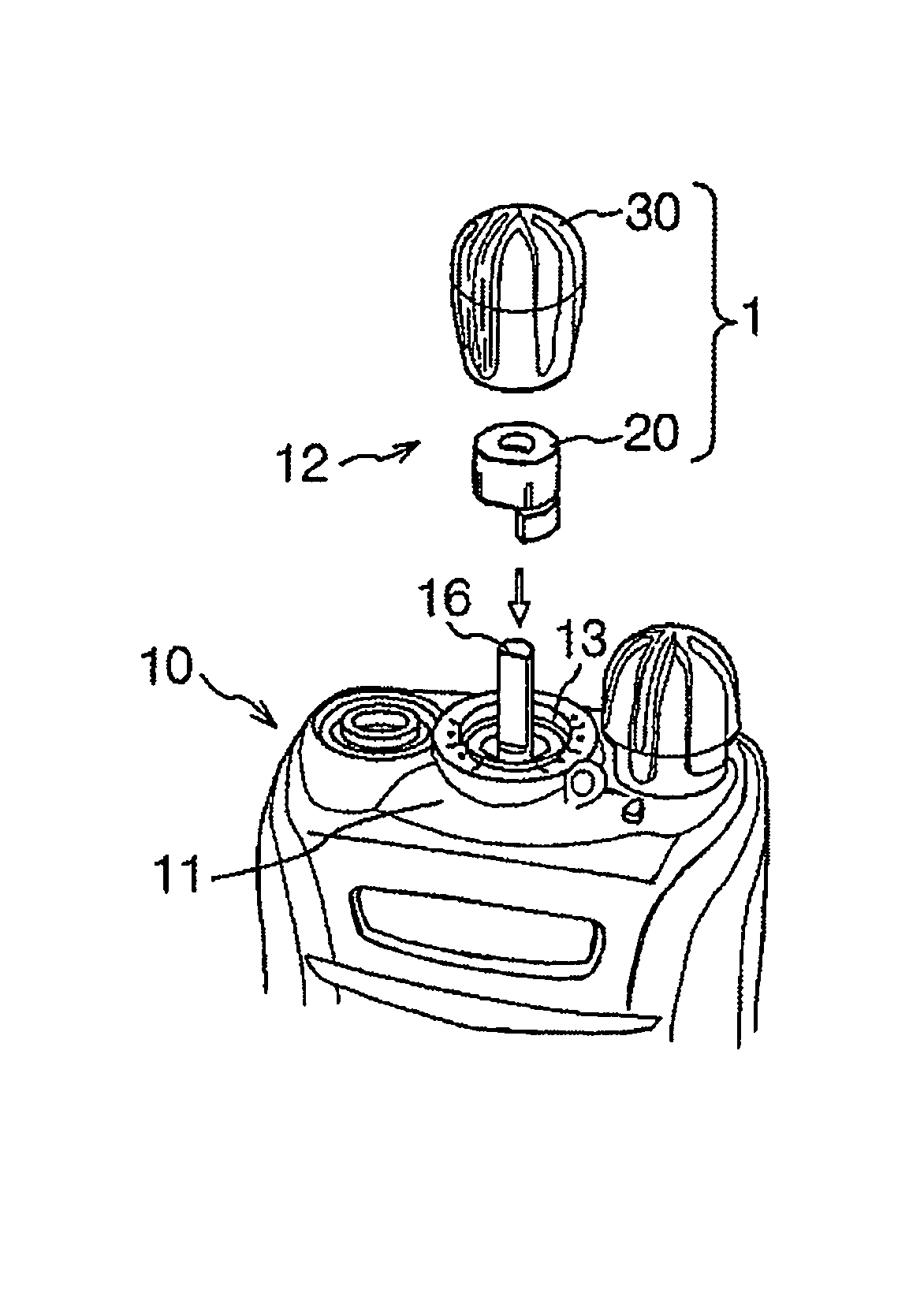

Stopper structure for rotary operation member, electronic device, and channel stopper

ActiveUS20110181378A1Avoid bitesAvoid insufficient lengthResonant circuit detailsElectric switchesChannel-stopperEngineering

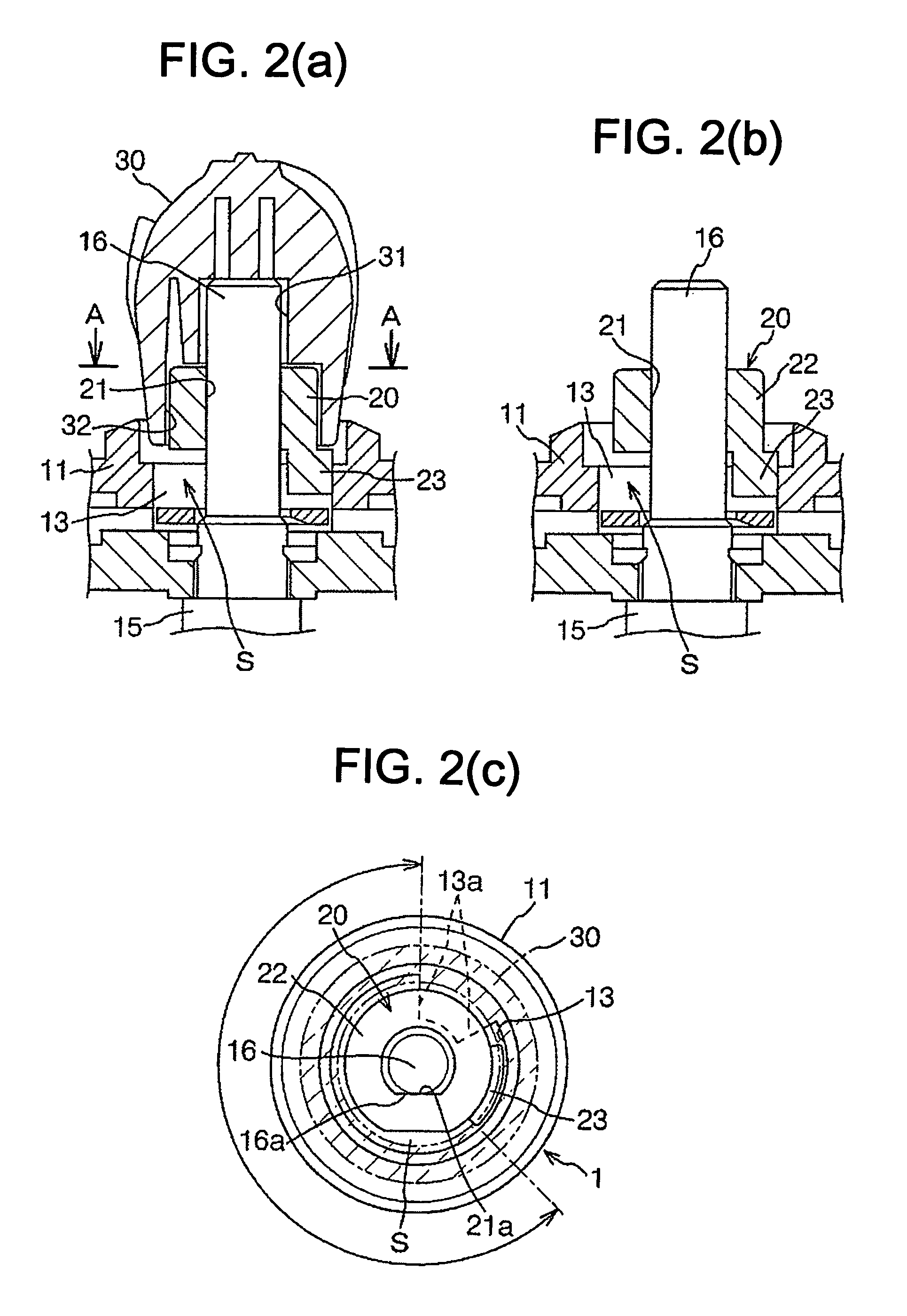

A stopper structure includes a wall defining an opening. A rotary electronic component has a rotational shaft extending through the opening. A channel stopper has a tubular body and an engagement projection. The tubular body is detachably mounted on the rotational shaft and is inhibited from rotating relative thereto. The engagement projection extends from an end of the tubular body in an axial direction and a radial direction with respect to the rotational shaft. A rotary operation member is detachably mounted on the rotational shaft and the tubular body and is inhibited from rotating relative thereto. The rotary operation member has an axial hole in which at least portions of the rotational shaft and the tubular body fit. A limiting portion provided on the wall is engageable with the engagement projection for liming a range of rotation of the rotational shaft.

Owner:JVC KENWOOD CORP A CORP OF JAPAN

Semiconductor device and method of manufacturing the same

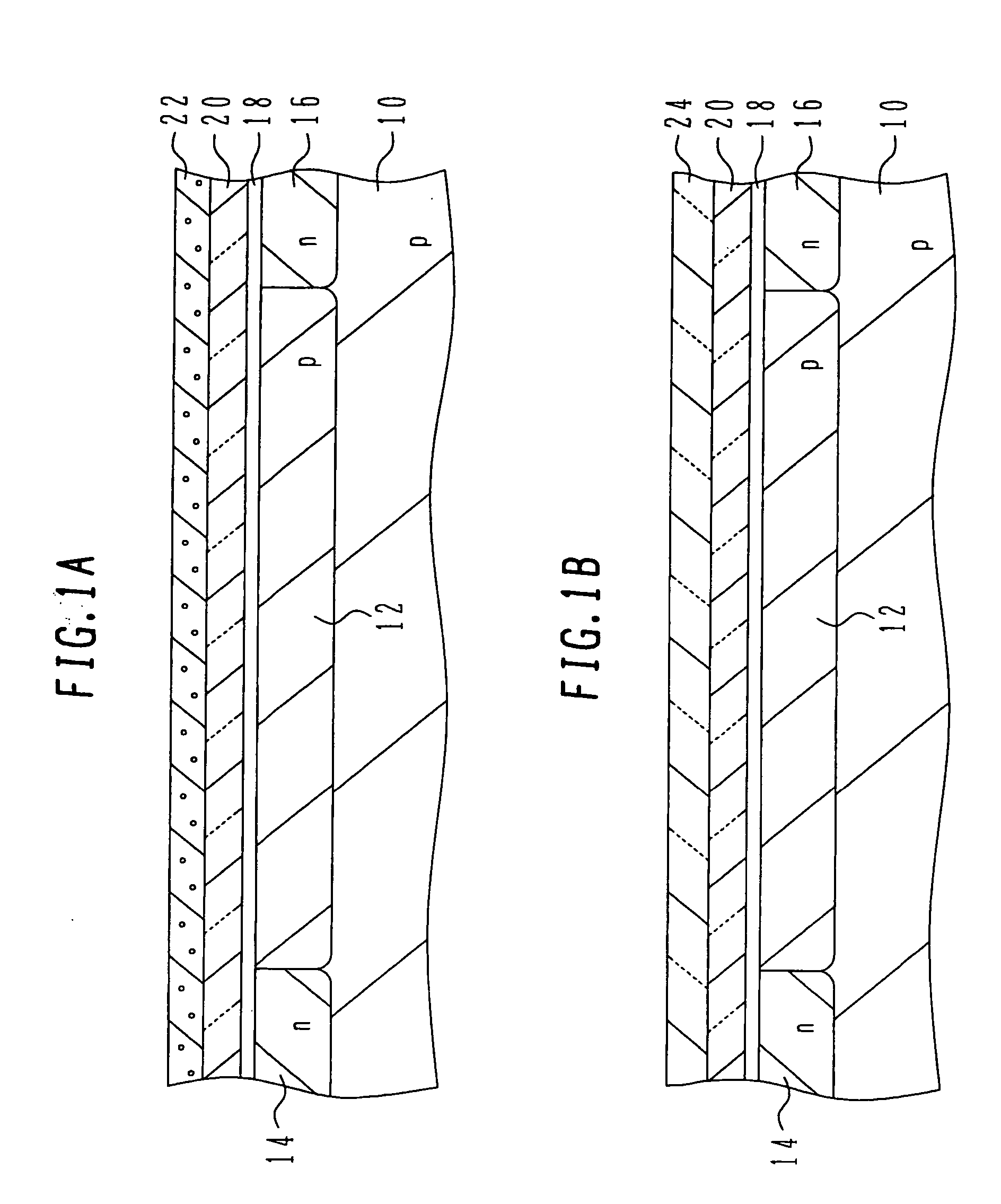

InactiveUS20130134550A1Improve featuresReduce leakage currentSemiconductor/solid-state device manufacturingSemiconductor devicesChannel-stopperDiffusion layer

A semiconductor device according to the present invention includes a p-type semiconductor substrate, a first n-type collector diffusion layer formed in the p-type semiconductor substrate, a deep trench formed in the p-type semiconductor substrate so as to surround the first n-type collector diffusion layer, a p-type channel stopper layer formed beneath the deep trench, and an n-type diffusion layer formed between a sidewall of the deep trench and the first n-type collector diffusion layer.

Owner:PANASONIC CORP

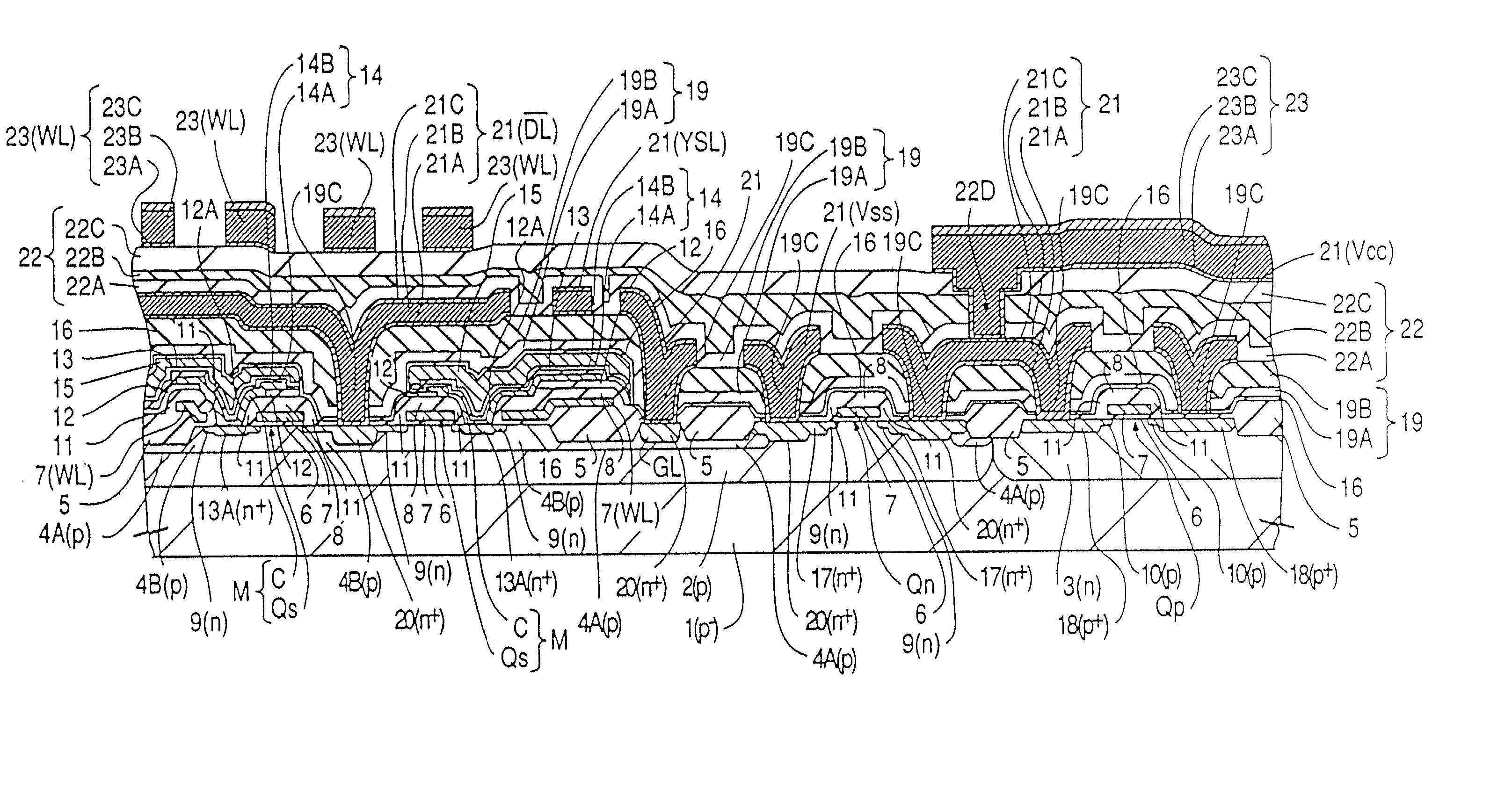

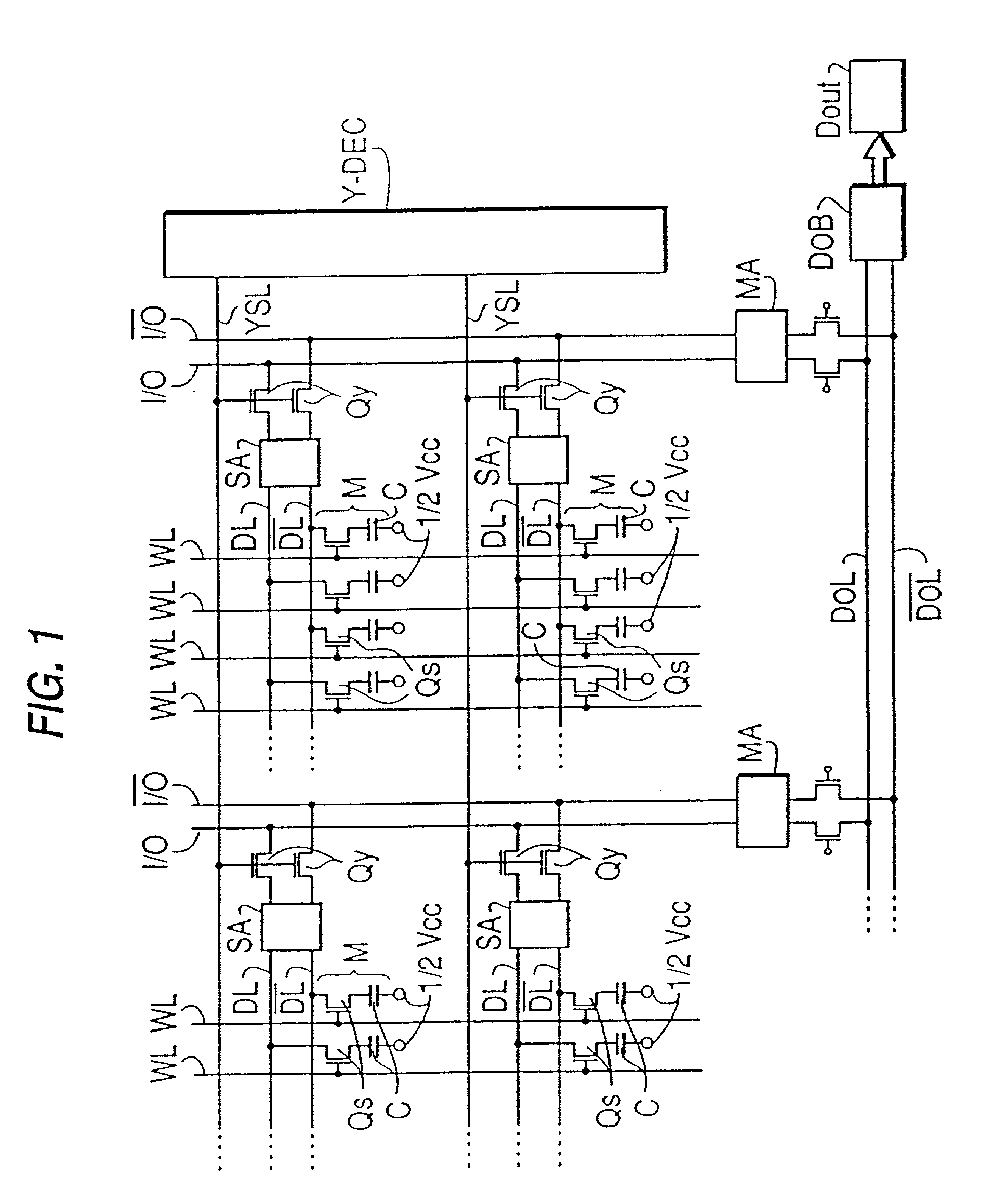

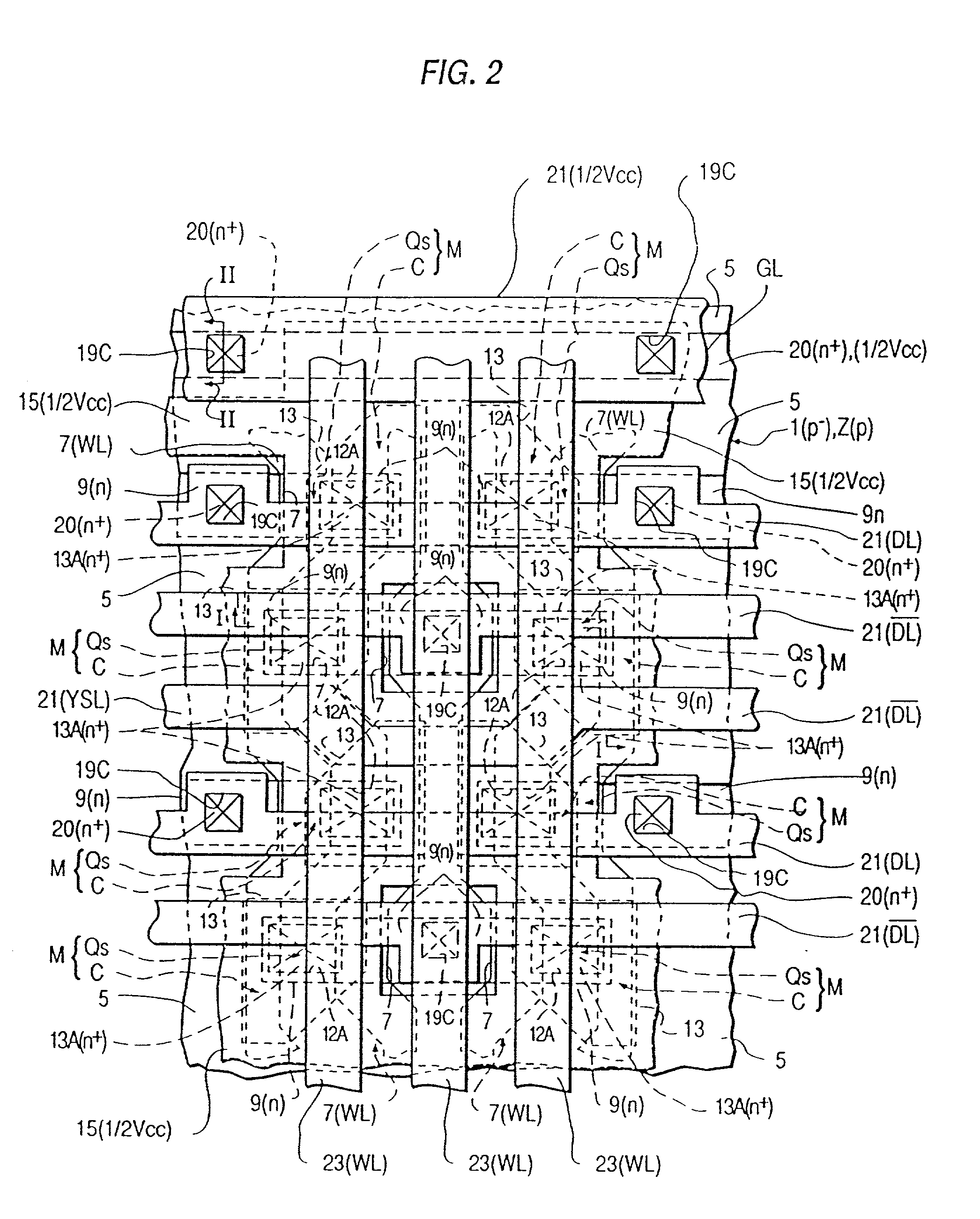

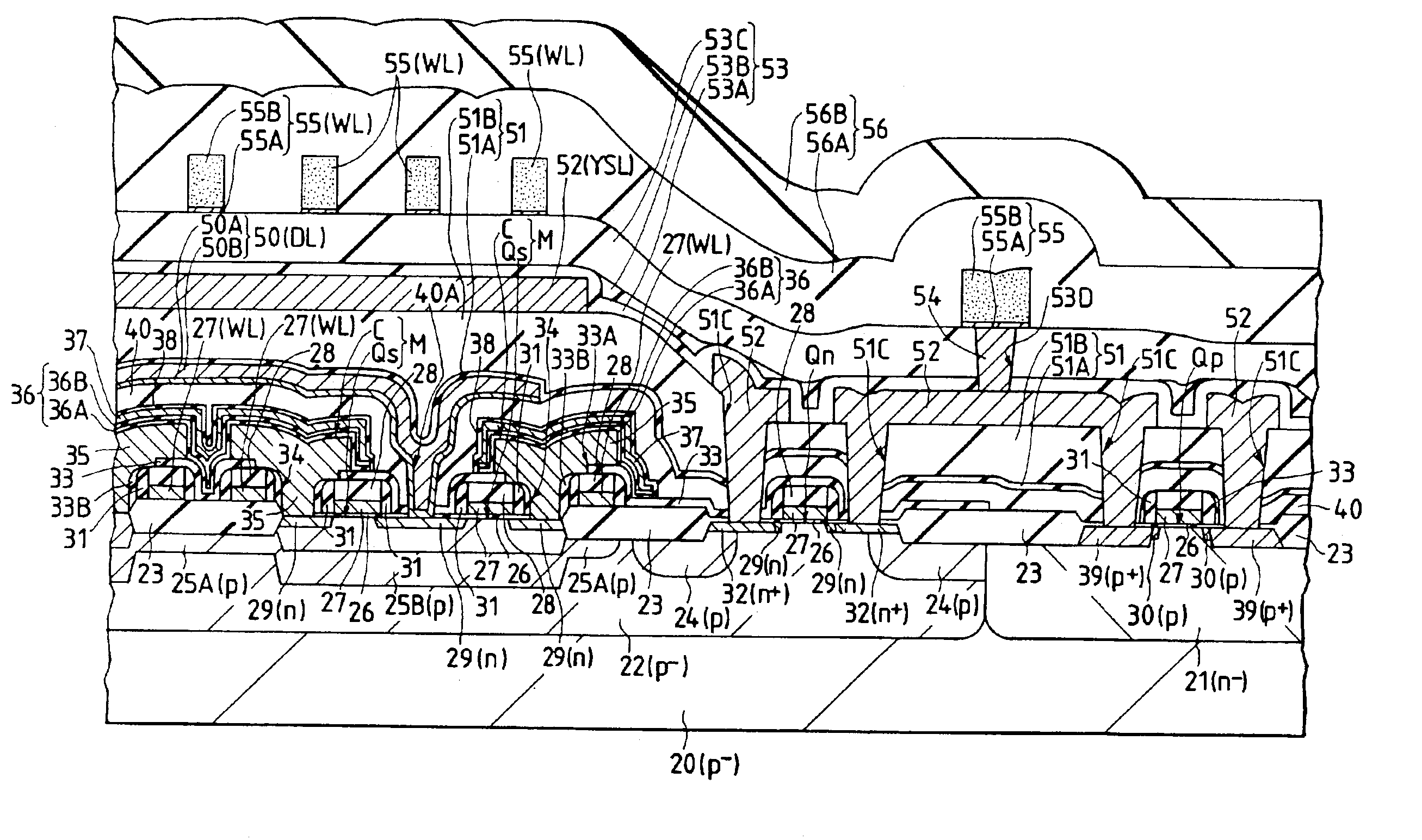

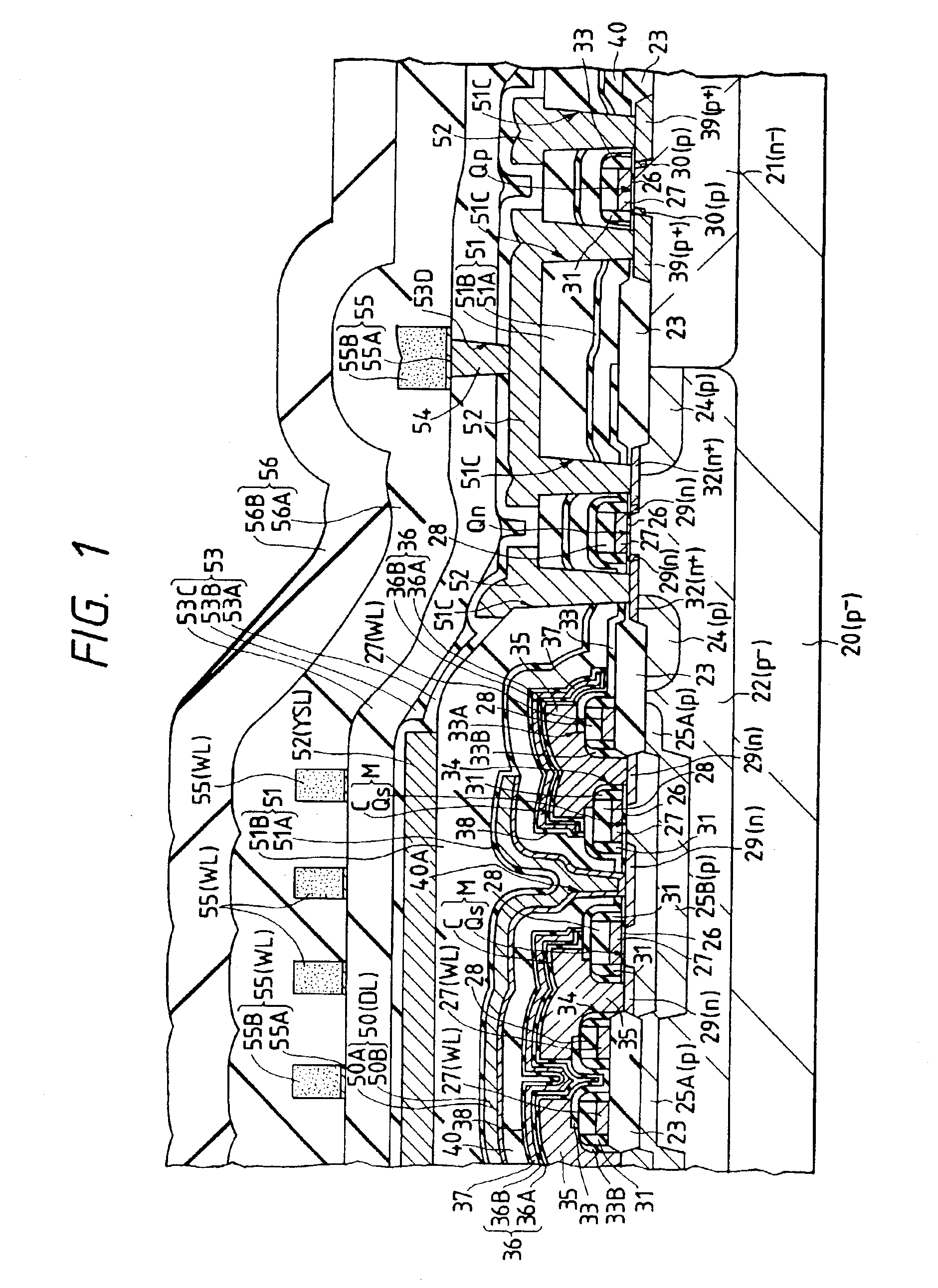

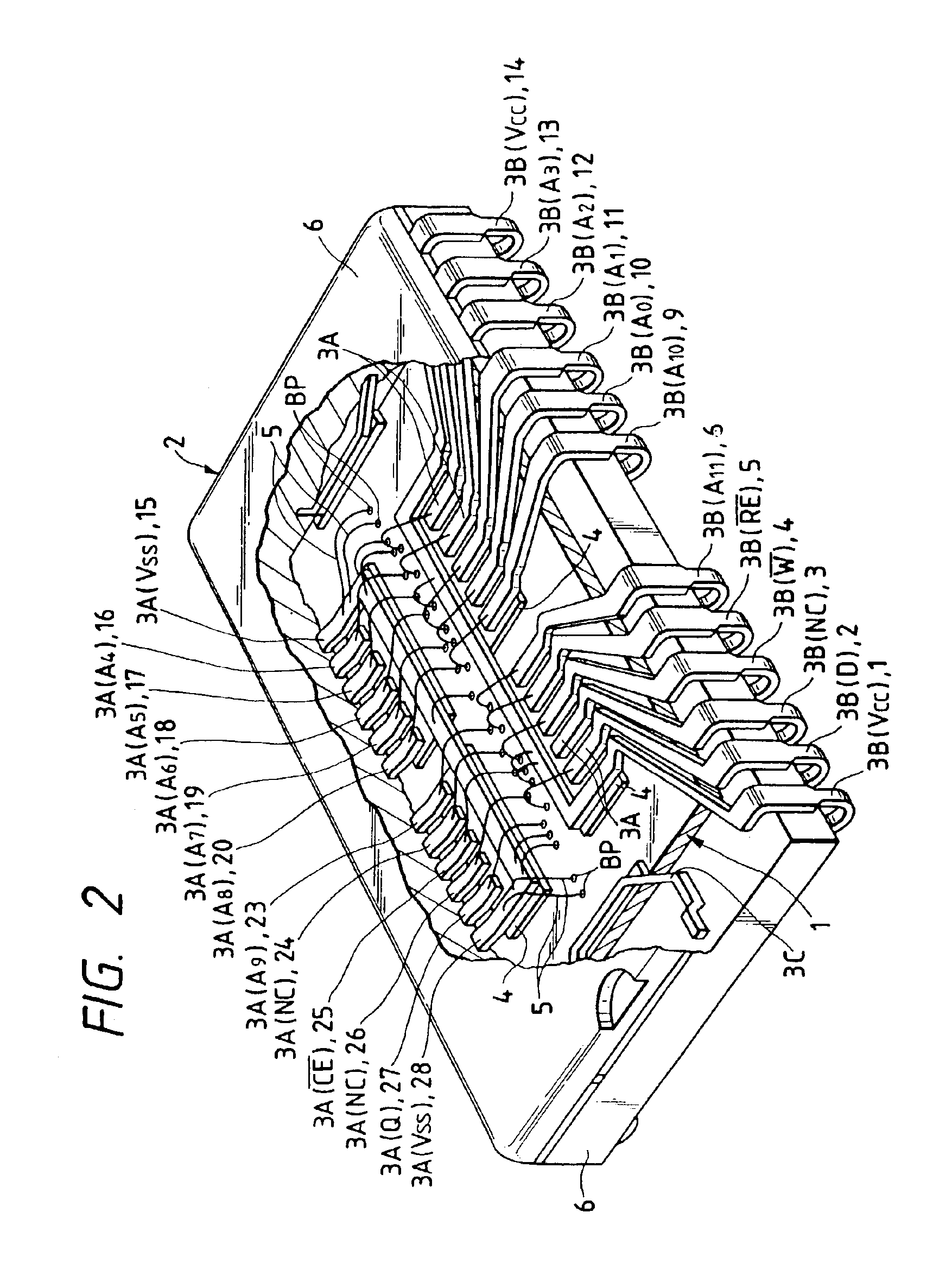

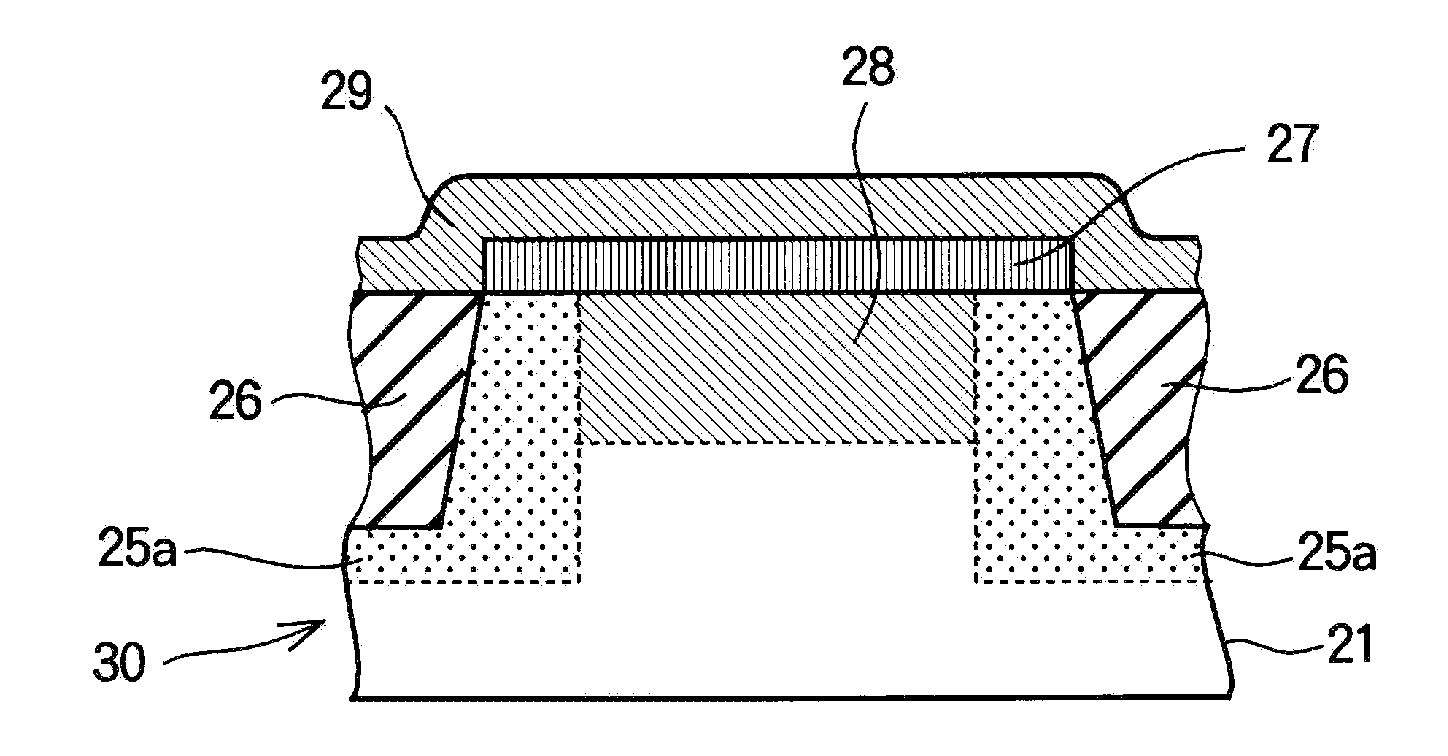

Semiconductor integrated circuit device having switching misfet and capacitor element and method of producing the same, including wiring therefor and method of producing such wiring

InactiveUS20020127793A1Reduce contact resistanceElectrical connectionTransistorSolid-state devicesDielectricSilicon oxide

A semiconductor integrated circuit device having a switching MISFET, and a capacitor element formed over the semiconductor substrate, such as a DRAM, is disclosed. In a first aspect of the present invention, the impurity concentration of the semiconductor region of the switching MISFET to which the capacitor element is connected is less than the impurity concentration of semiconductor regions of MISFETs of peripheral circuitry. In a second aspect, the Y-select signal line overlaps the lower electrode layer of the capacitor element. In a third aspect, a potential barrier layer, provided at least under the semiconductor region of the switching MISFET to which the capacitor element is connected, is formed by diffusion of an impurity for a channel stopper region. In a fourth aspect, the dielectric film of the capacitor element is co-extensive with the capacitor electrode layer over it. In a fifth aspect, the capacitor dielectric film is a silicon nitride film having a silicon oxide layer thereon, the silicon oxide layer being formed by oxidizing a surface layer of the silicon nitride under high pressure. In sixth and seventh aspects, wiring is provided. In the sixth aspect, an aluminum wiring layer and a protective (and / or barrier) layer are formed by sputtering in the same vacuum sputtering chamber without breaking the vacuum between forming the layers; in the seventh aspect, a refractory metal, or a refractory metal suicide QSi.sub.x, where Q is a refractory metal and 0<x<2, is used as a protective layer, for an aluminum wiring containing an added element (e.g., Cu) to prevent migration.

Owner:HITACHI LTD

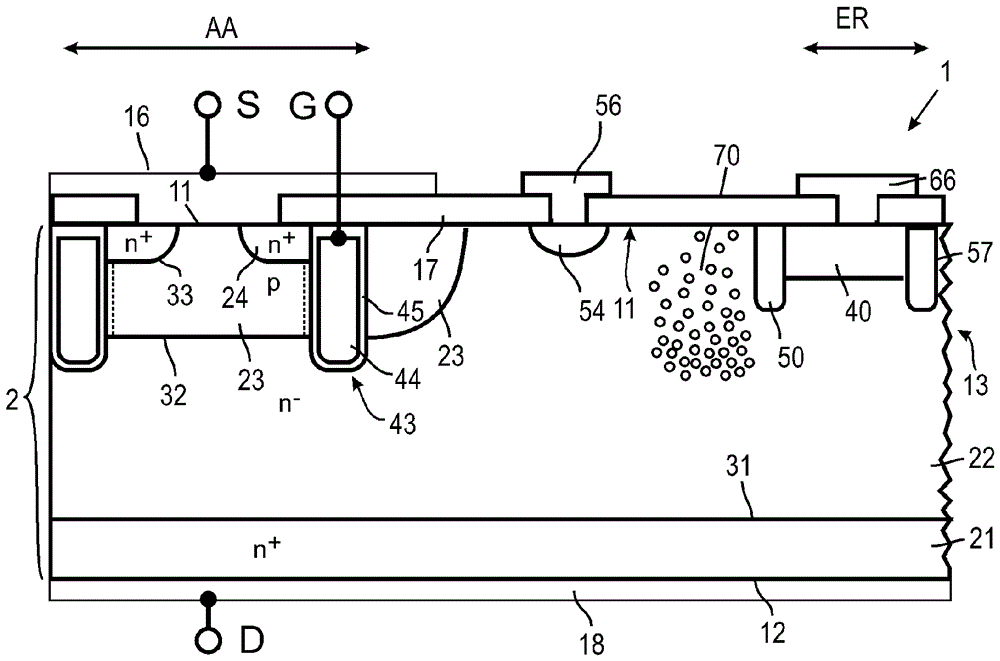

Semiconductor device with channel stopper and method for producing the same

ActiveCN106024857ASemiconductor/solid-state device detailsSolid-state devicesPower semiconductor deviceChannel-stopper

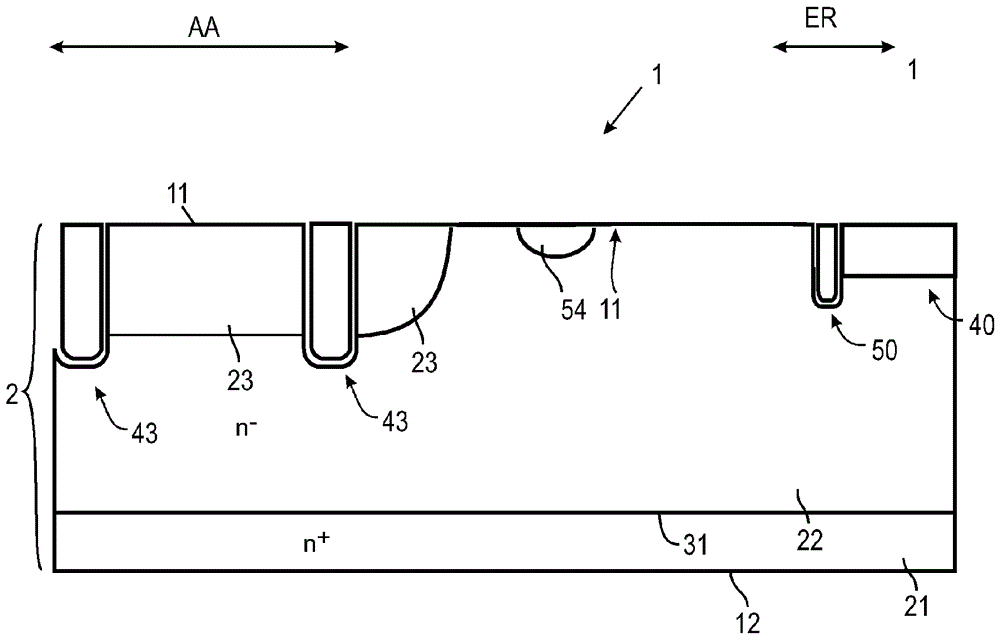

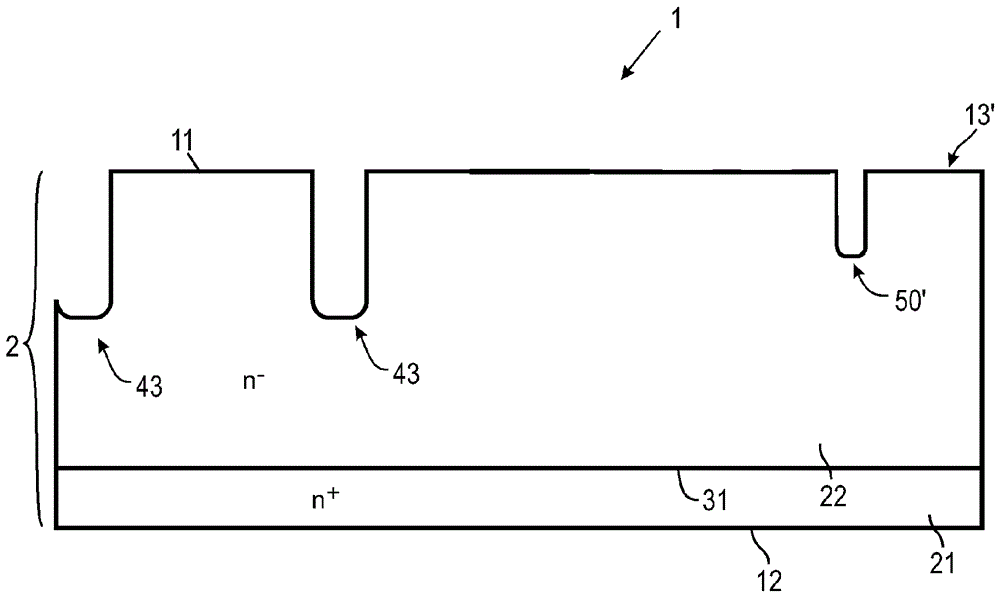

The invention relates to a semiconductor device with a channel stopper and a method for producing the same. A vertical semiconductor device (1) comprises a substrate (2) having a front surface (11) and a back surface (12), an active area (AA) located in the substrate (2), having a drift region (22) doped with a first dopant type, an edge termination region (ER) laterally surrounding the active area (AA), a channel stopper terminal (40) provided at the front surface and located in the edge termination region (ER), and a first suppression trench (50) located on a side of the channel stopper terminal (40) towards the active region (AA), and provided adjacent to the channel stopper terminal (40). Further, a production method for such a semiconductor device is provided.

Owner:INFINEON TECH AG

Solid-state imaging device with improved charge transfer efficiency

A transfer gate is formed such that both end portions thereof in a second direction, which crosses a first direction in which a photodiode and a floating diffusion layer that is formed with a distance from the photodiode are arranged, are located inside boundaries with element isolation regions. Channel stopper layers are formed on surface portions of a device region in the vicinity of lower parts of both end portions of the transfer gate in the second direction in such a manner to extend to the boundaries with the element isolation regions.

Owner:KK TOSHIBA

Array of mutually isolated, geiger-mode, avalanche photodiodes and manufacturing method thereof

ActiveUS8778721B2Reduction of opticalReduction of electrical cross-talkSolid-state devicesSemiconductor/solid-state device manufacturingSemiconductor materialsChannel-stopper

An embodiment of array of Geiger-mode avalanche photodiodes, wherein each photodiode is formed by a body of semiconductor material, having a first conductivity type and housing an anode region, of a second conductivity type, facing a top surface of the body, a cathode-contact region, having the first conductivity type and a higher doping level than the body, facing a bottom surface of the body, an insulation region extending through the body and insulating an active area from the rest of the body, the active area housing the anode region and the cathode-contact region. The insulation region is formed by a first mirror region of polycrystalline silicon, a second mirror region of metal material, and a channel-stopper region of dielectric material, surrounding the first and second mirror regions.

Owner:STMICROELECTRONICS SRL

Semiconductor integrated circuit device, process for fabricating the same, and apparatus for fabricating the same

InactiveUS6894334B2Reduce narrow channel effectReduce the amount of diffusionTransistorSemiconductor/solid-state device detailsChannel-stopperEngineering

Herein disclosed is a semiconductor integrated circuit device fabricating process for forming MISFETs over the principal surface in those active regions of a substrate, which are surrounded by inactive regions formed of an element separating insulating film and channel stopper regions, comprising: the step of for forming a first mask by a non-oxidizable mask and an etching mask sequentially over the principal surface of the active regions of the substrate; the step of forming a second mask on and in self-alignment with the side walls of the first mask by a non-oxidizable mask thinner than the non-oxidizable mask of the first mask and an etching mask respectively; the step of etching the principal surface of the inactive regions of the substrate by using the first mask and the second mask; the step of forming the element separating insulating film over the principal surface of the inactive regions of the substrate by an oxidization using the first mask and the second mask; and the step of forming the channel stopper regions over the principal surface portions below the element separating insulating film of the substrate by introducing an impurity into all the surface portions including the active regions and the inactive regions of the substrate after the first mask and the second mask have been removed.

Owner:RISING SILICON

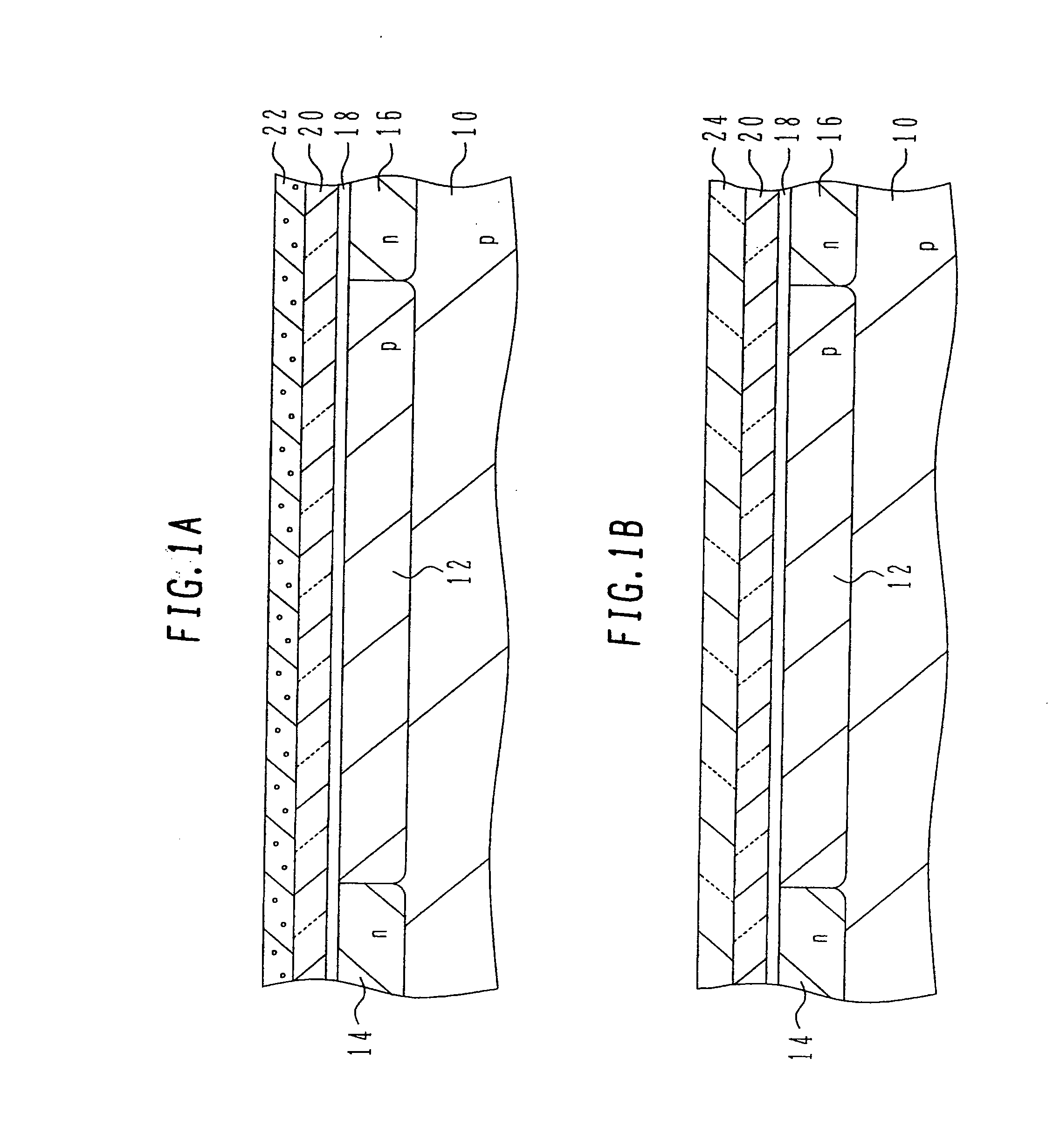

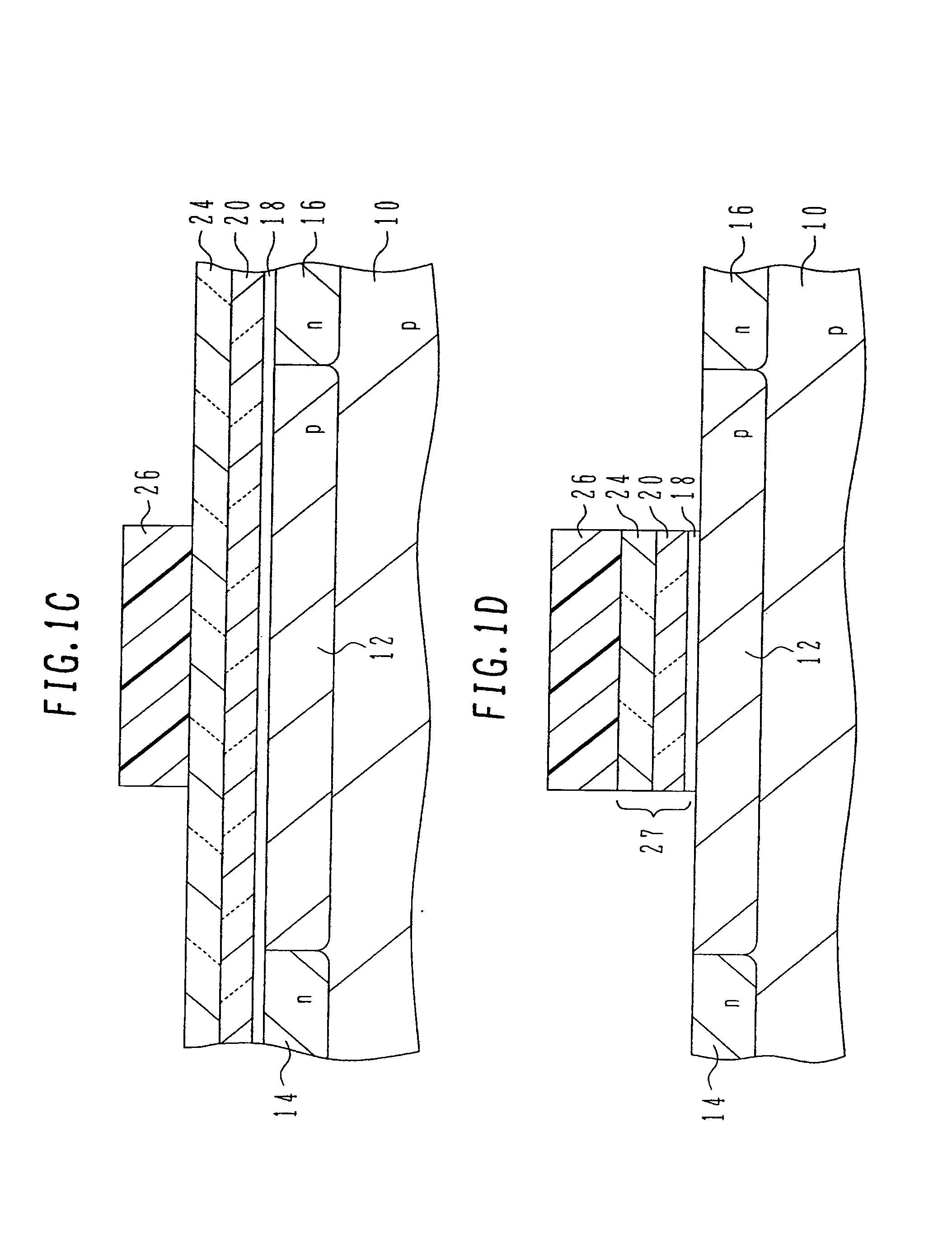

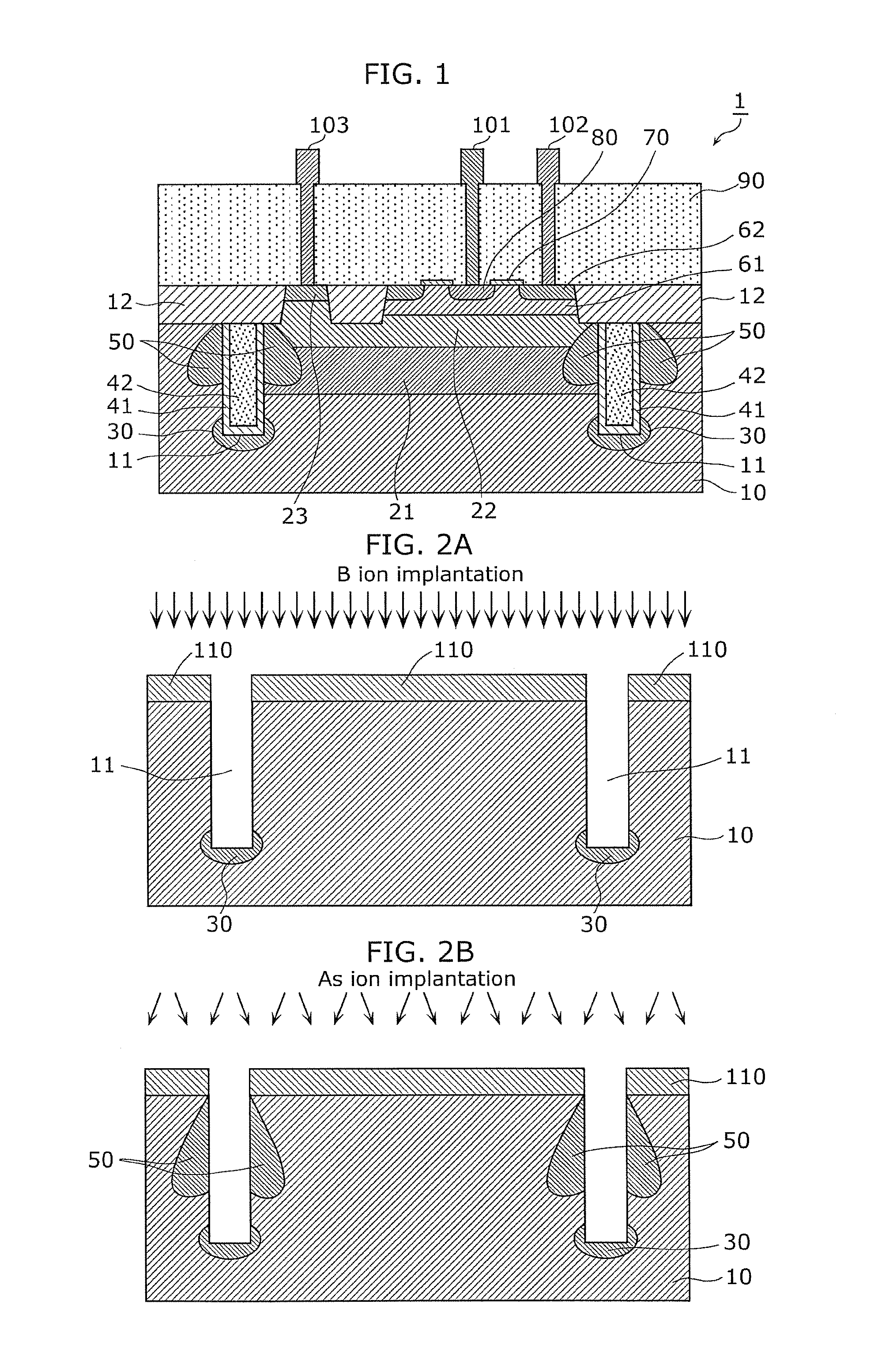

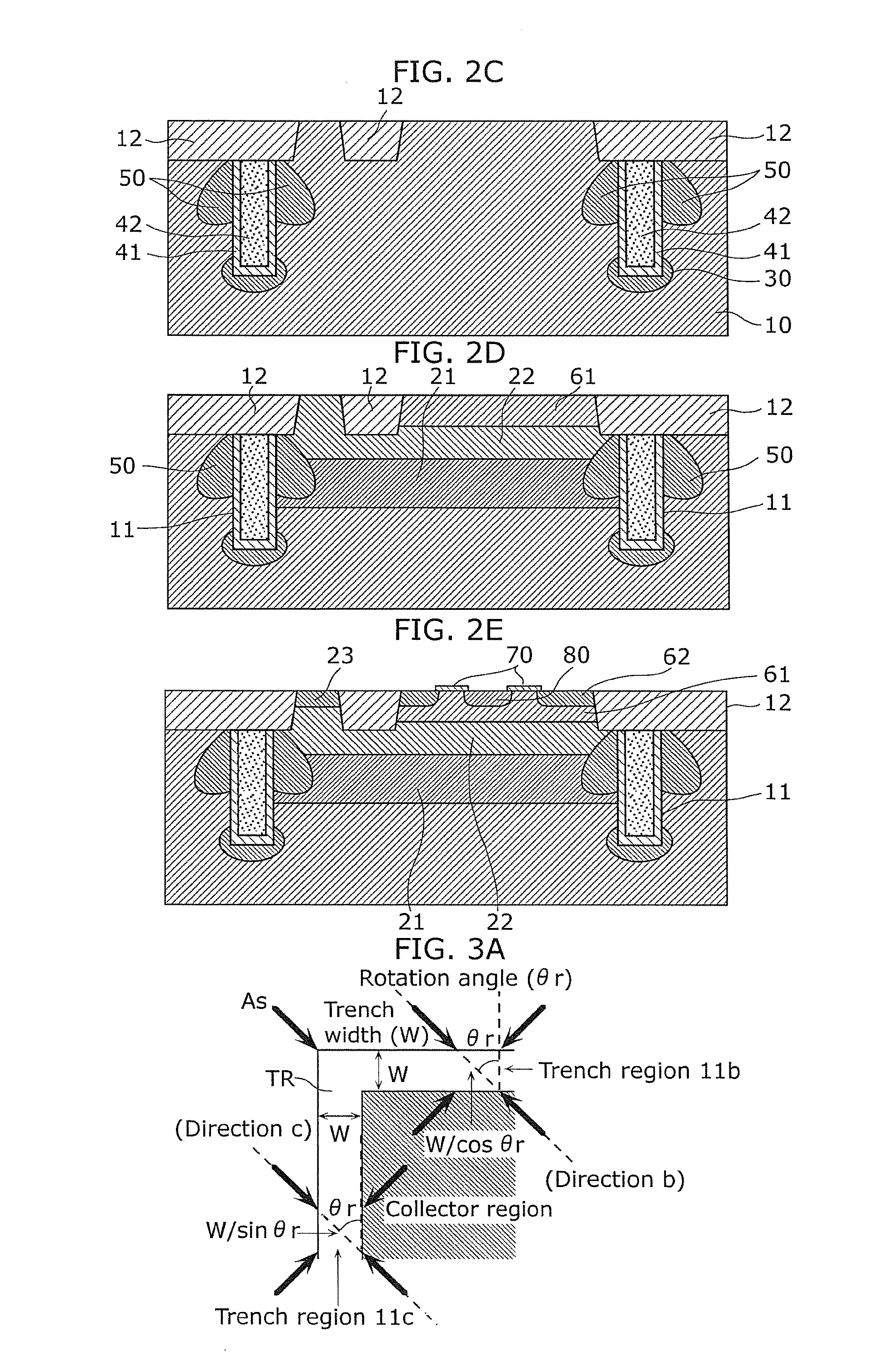

Semiconductor device and method of producing semiconductor device

InactiveUS20110207281A1Lower device costReduce manufacturing costSolid-state devicesSemiconductor/solid-state device manufacturingPower semiconductor deviceInsulation layer

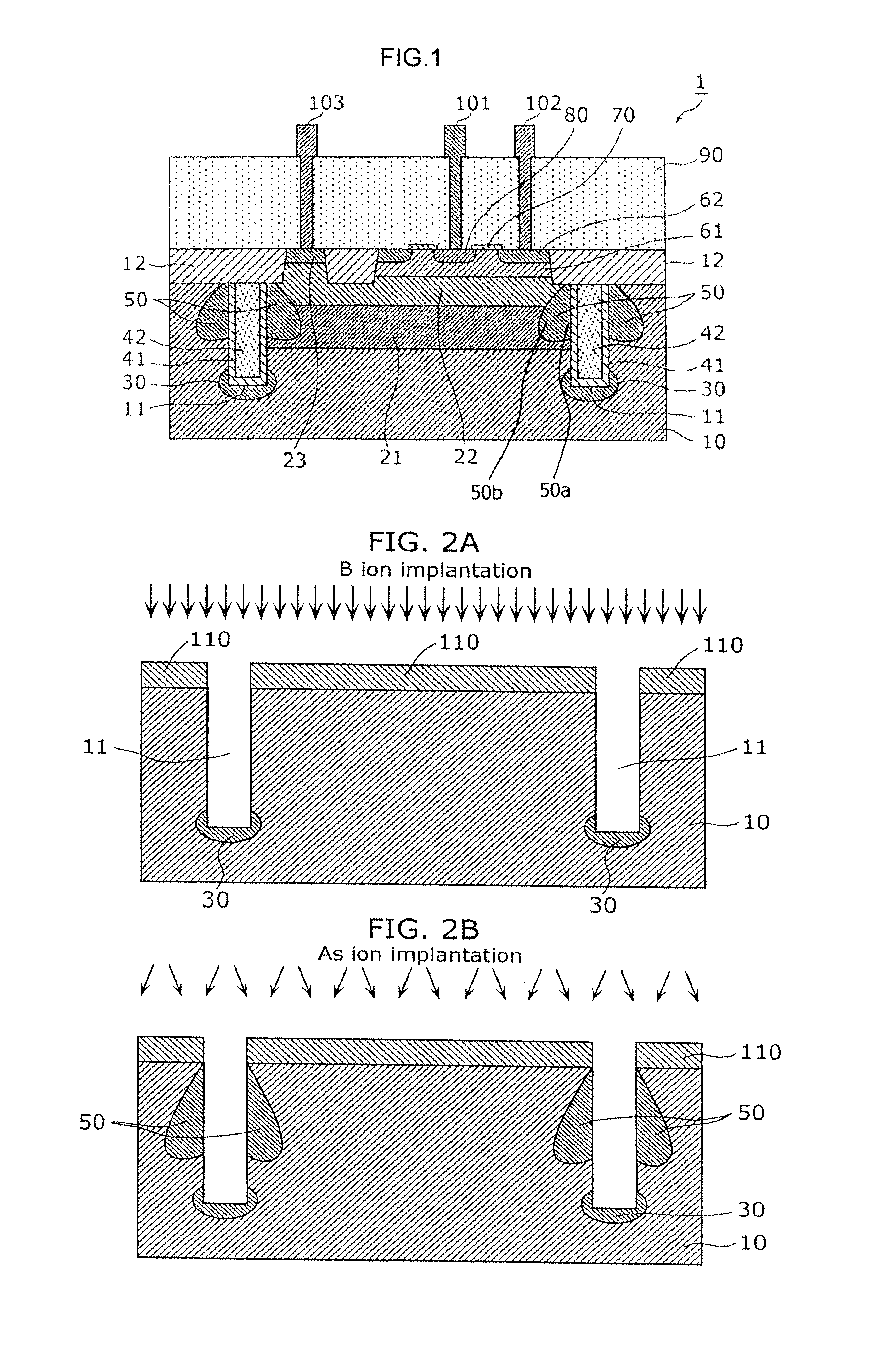

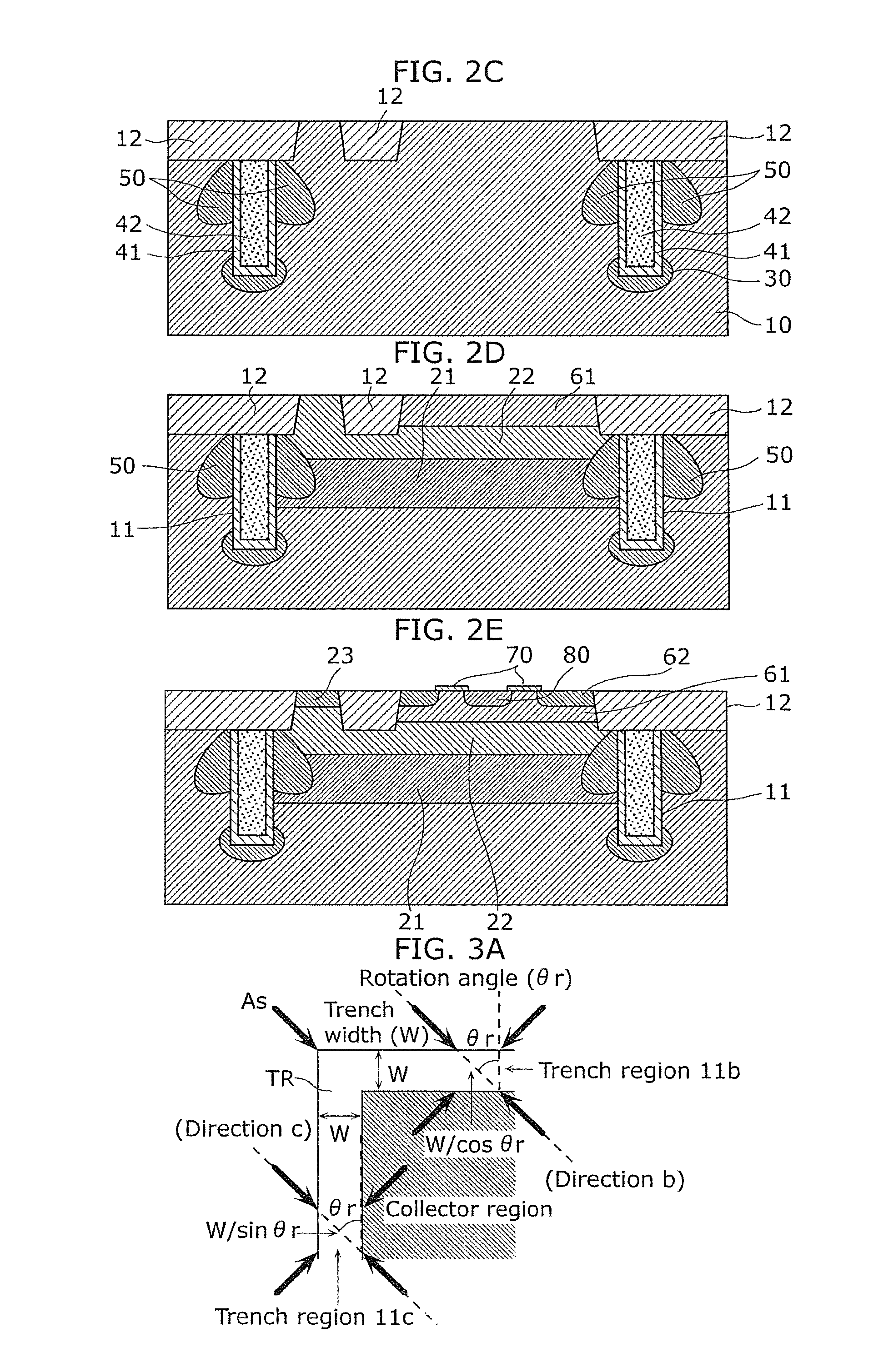

A method of producing a semiconductor device includes the steps of forming a trench in a semiconductor substrate of a first conductive type so that an active region having a first portion and a second region is formed; implanting a first impurity of the first conductive type at an implantation angle between 30 degrees and 45 degrees relative to a normal line in an implantation direction rotating relative to the normal line so that a first channel diffusion region and a channel stopper region of the first conductive type are formed; filling the trench with an insulation layer; implanting a second impurity of a second conductive type so that a second channel diffusion region of the second conductive type is formed; forming a gate insulation film on the first portion and the second portion; and forming a gate electrode on the gate insulation film.

Owner:LAPIS SEMICON CO LTD

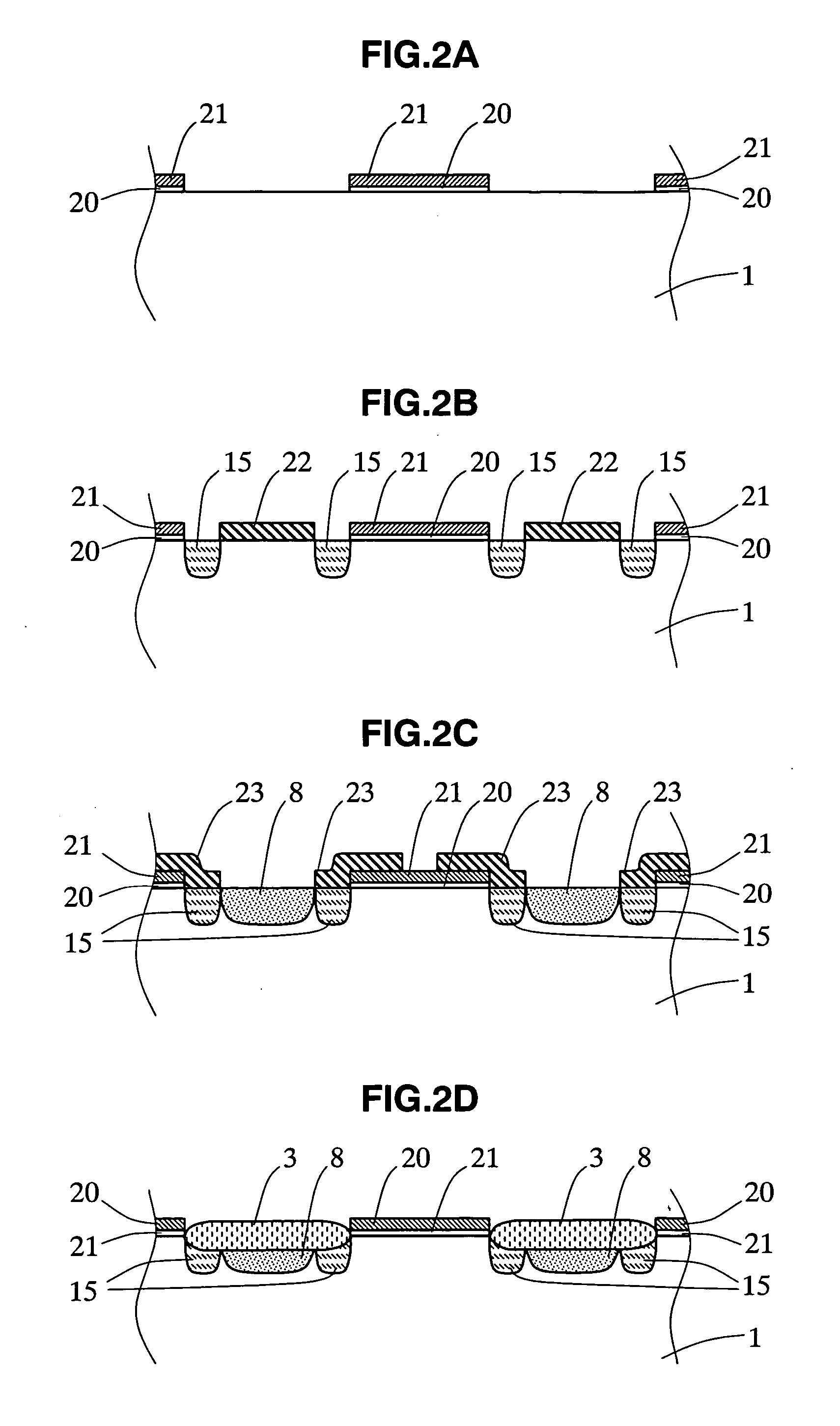

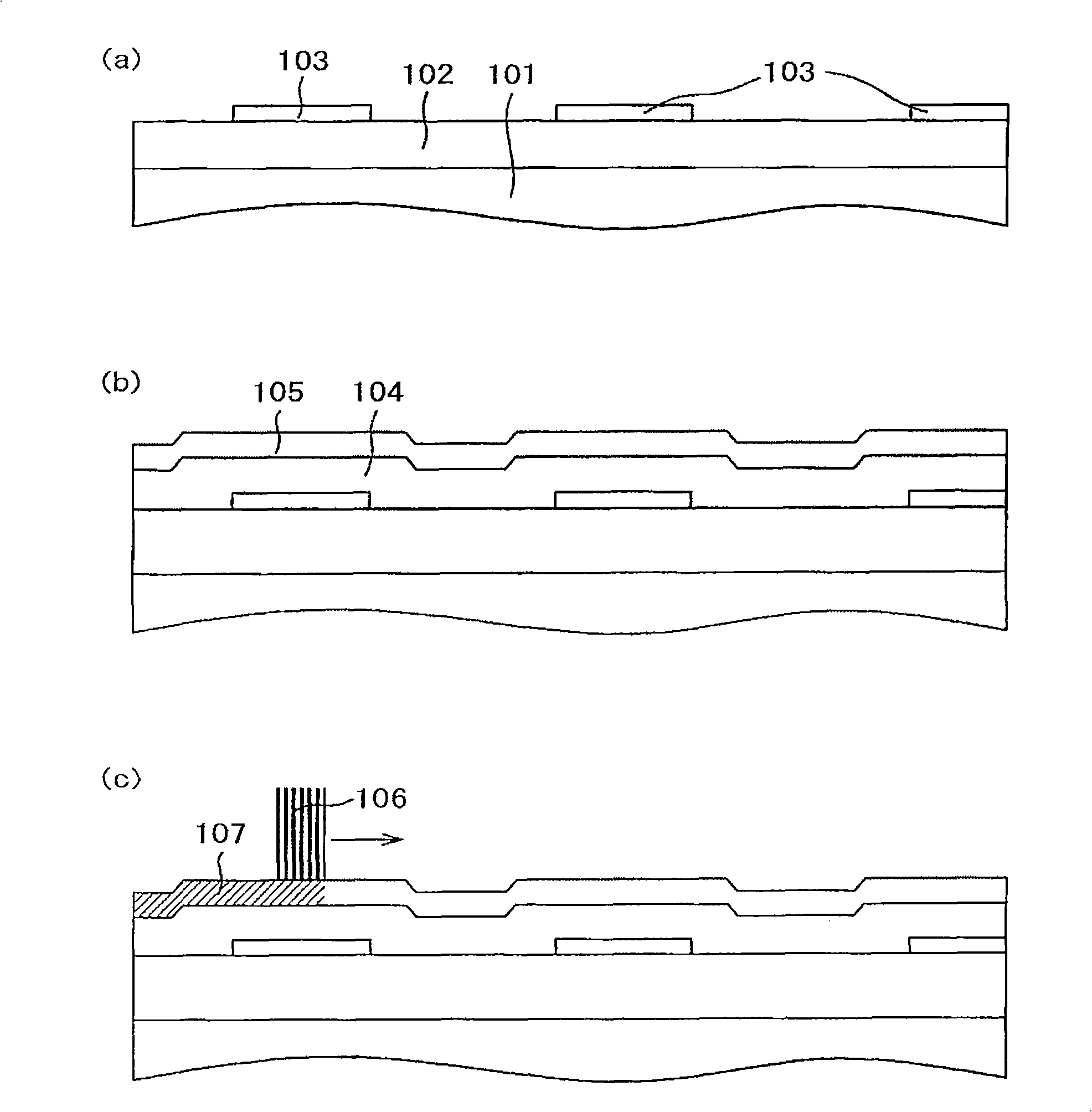

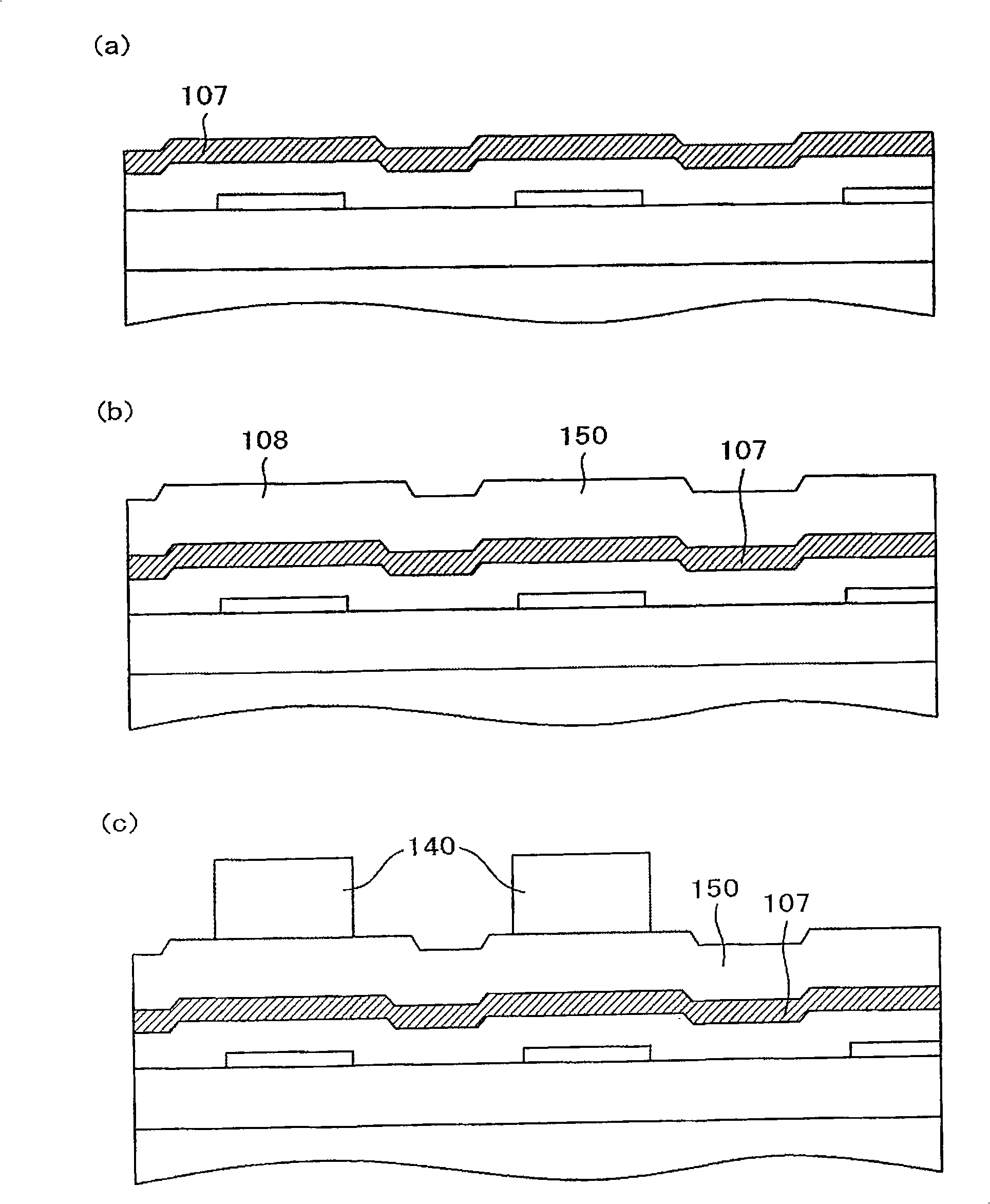

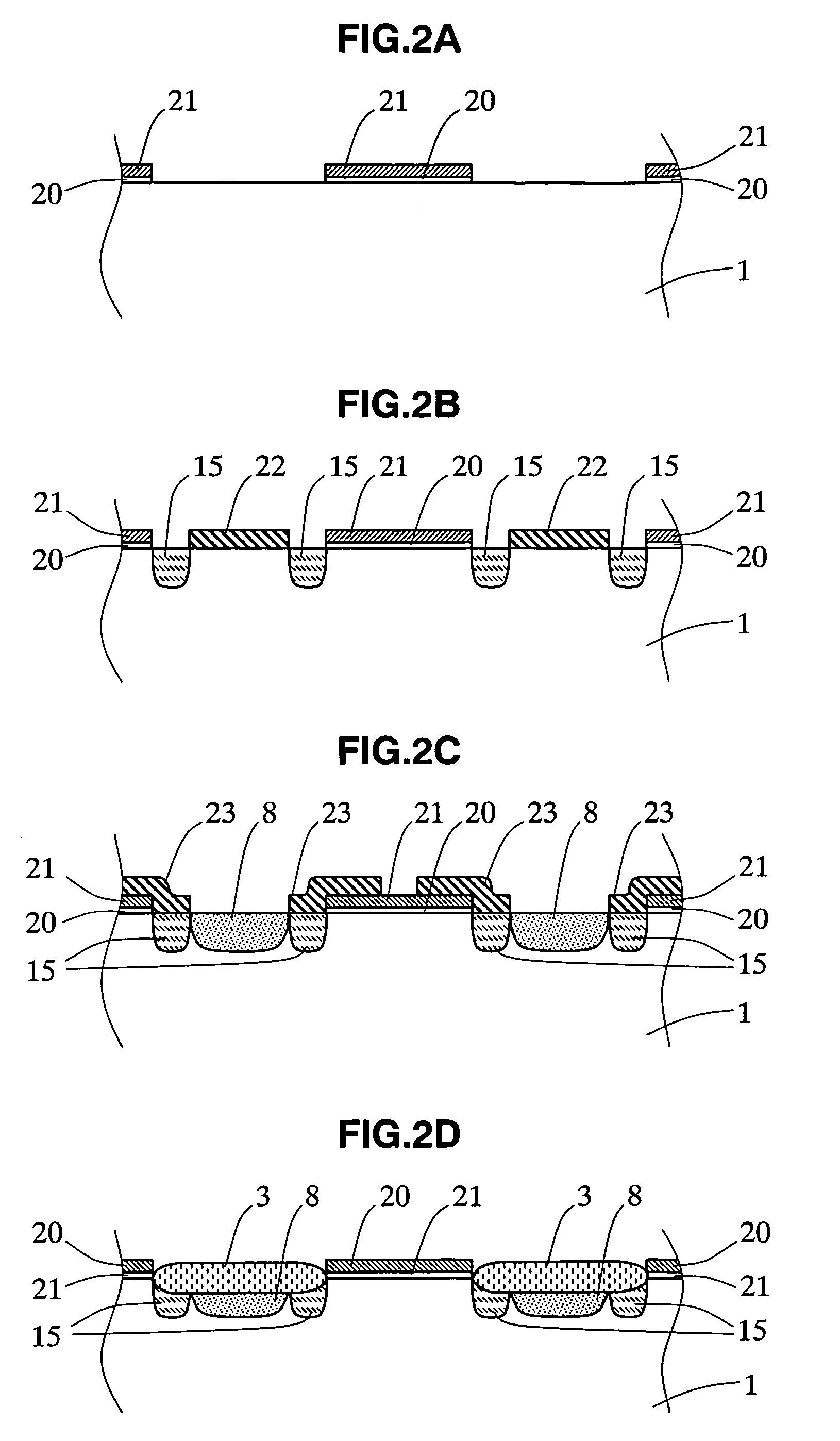

Manufacture method for semiconductor device having field oxide film

InactiveUS20060189106A1Well formedImprove accuracySemiconductor/solid-state device manufacturingSemiconductor devicesResistChannel-stopper

On the principal surface of a silicon substrate, a side spacer made of silicon nitride is formed on the side wall of a lamination including a silicon oxide film, a silicon nitride film and a silicon oxide film. Thereafter, a channel stopper ion doped region is formed by implanting impurity ions by using as a mask the lamination, side spacer and resist layer. After the resist layer and side spacer are removed, a field oxide film is formed through selective oxidation using the lamination as a mask, and a channel stopper region corresponding to the ion doped region is formed. After the lamination is removed, a circuit device such as a MOS type transistor is formed in each device opening of the field oxide film.

Owner:YAMAHA CORP

Photoelectric conversion device and image pick-up system using the photoelectric conversion device

InactiveCN1505162AReduce crosstalkHigh sensitivityTelevision system detailsSolid-state devicesChannel-stopperCharge carrier

In a photoelectric conversion device with a photoelectric conversion region for accumulating electric charges that correspond to incident light and an amplifying filed effect transistor into which a signal charge from the photoelectric conversion region is inputted, the photoelectric conversion region is surrounded by a potential barrier region (a selectively oxidized film and a channel stopper), a nick region (overflow channel) is formed in a part of the potential barrier region, and a drain region of the field effect transistor that has the same conductivity type as the photoelectric conversion region is placed next to the nick region. Thus excess carriers are prevented from flowing into adjacent pixels or other floating regions.

Owner:CANON KK

Liquid crystal display divice

ActiveCN101526709ASuppression of manufacturing cost increaseReduce manufacturing costTransistorStatic indicating devicesChannel-stopperLiquid-crystal display

The invention provides a liquid crystal display device. In bottom-gate-type thin film transistors used in a liquid crystal display device, a channel stopper layer is formed on a poly-Si layer thus stabilizing a characteristic of the thin film transistor. The channel stopper layer is formed into a desired shape by wet etching, and the poly-Si layer is formed into a desired shape by dry etching. By applying side etching to the channel stopper layer, a peripheral portion of the poly-Si layer is exposed from the channel stopper layer, and this region is brought into contact with an n+Si layer. Due to such constitution, ON resistance of the thin film transistor can be decreased thus increasing an ON current which flows in the thin film transistor.

Owner:JAPAN DISPLAY INC +1

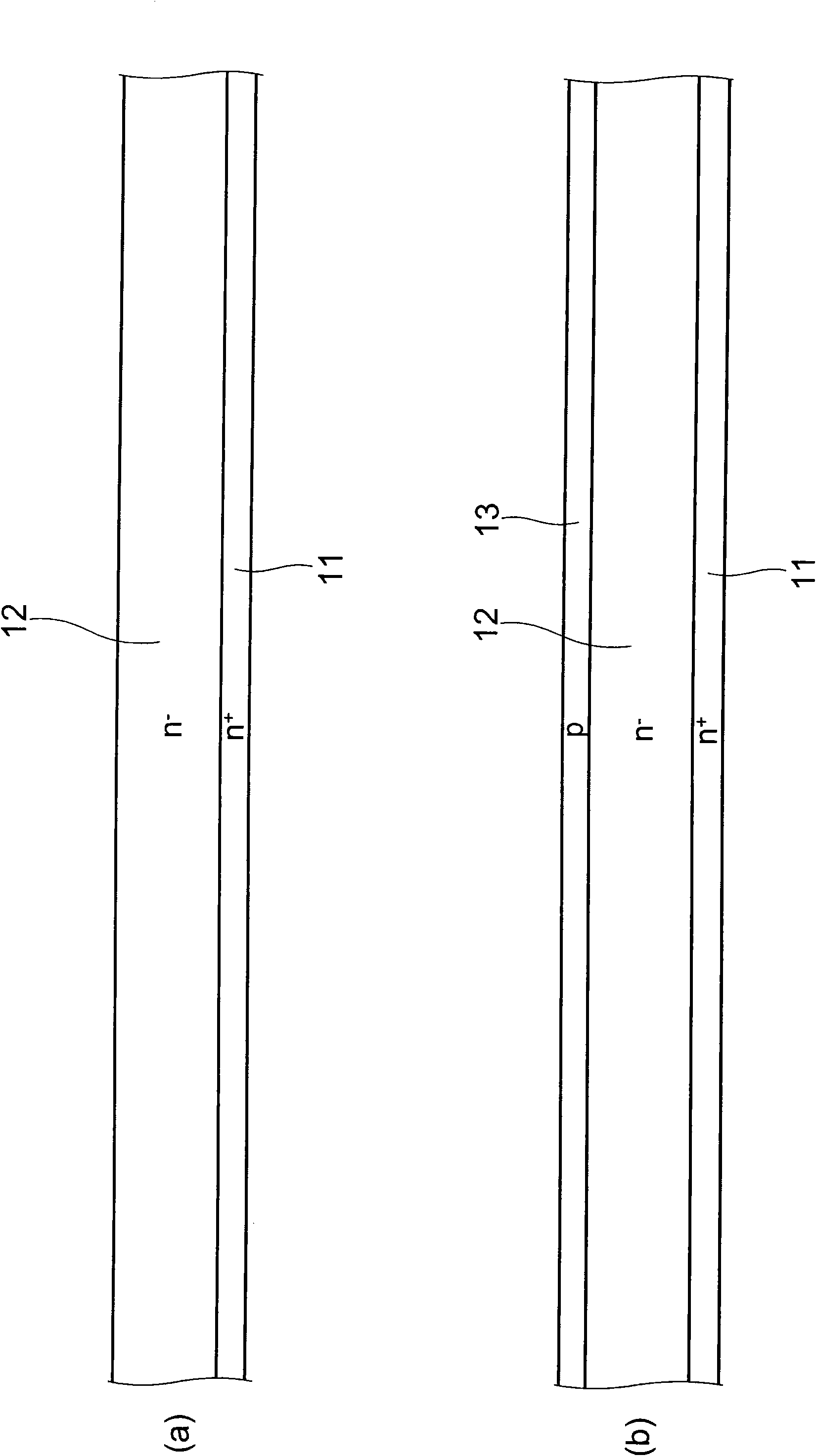

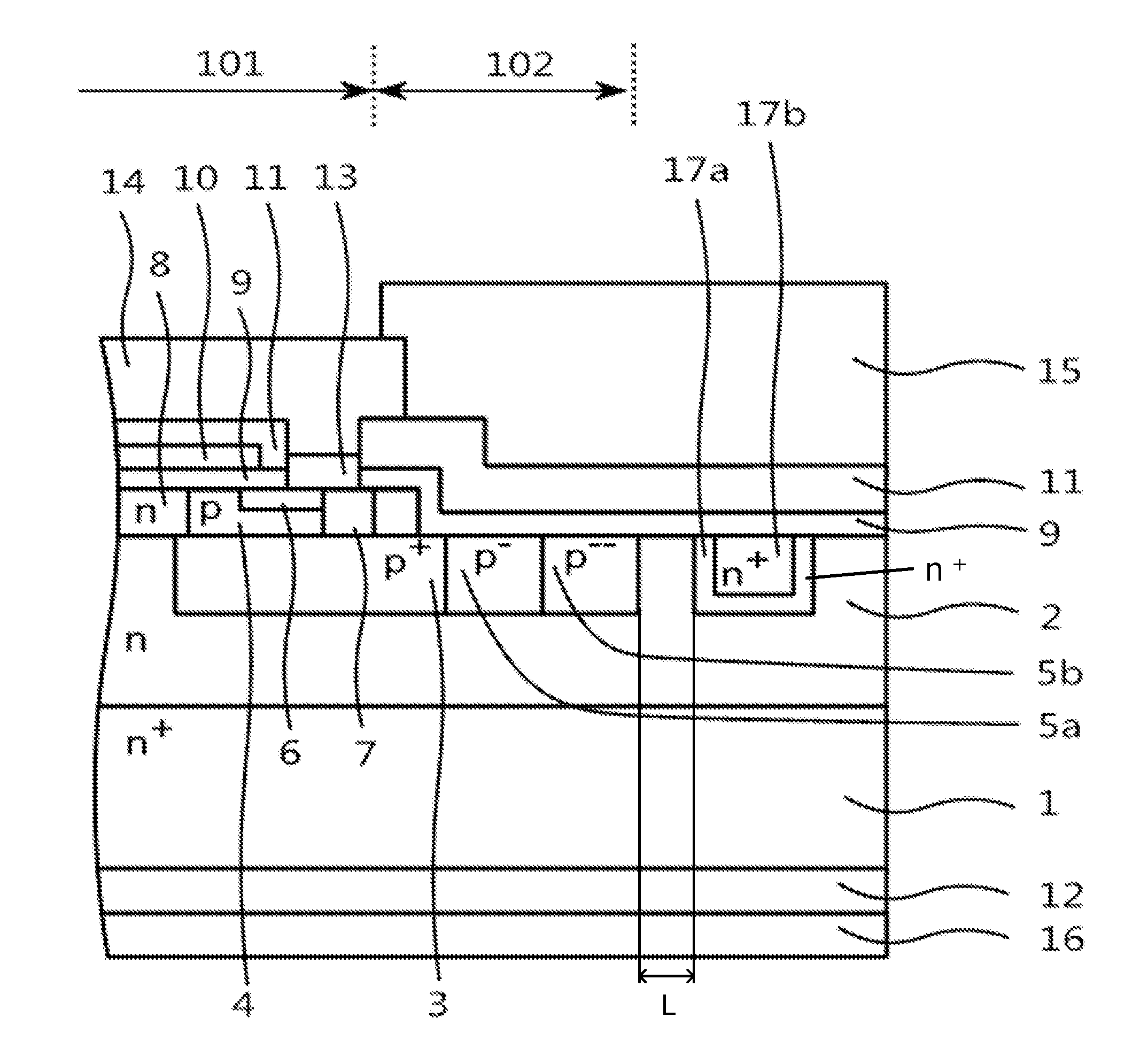

Semiconductor device and method of manufacturing semiconductor device

ActiveUS20160315187A1Improve breakdown voltageLower average currentSemiconductor/solid-state device manufacturingSemiconductor devicesPower semiconductor deviceChannel-stopper

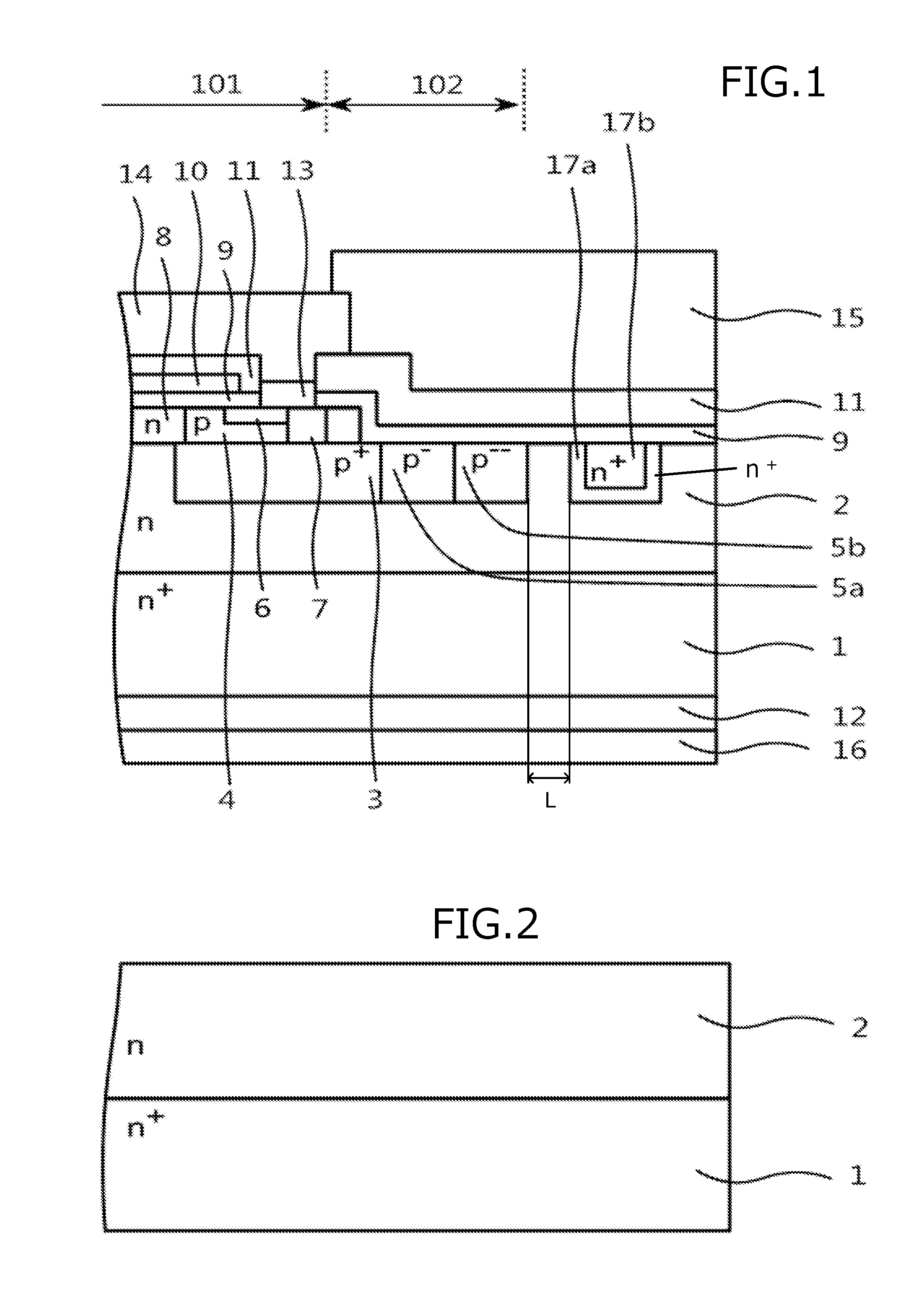

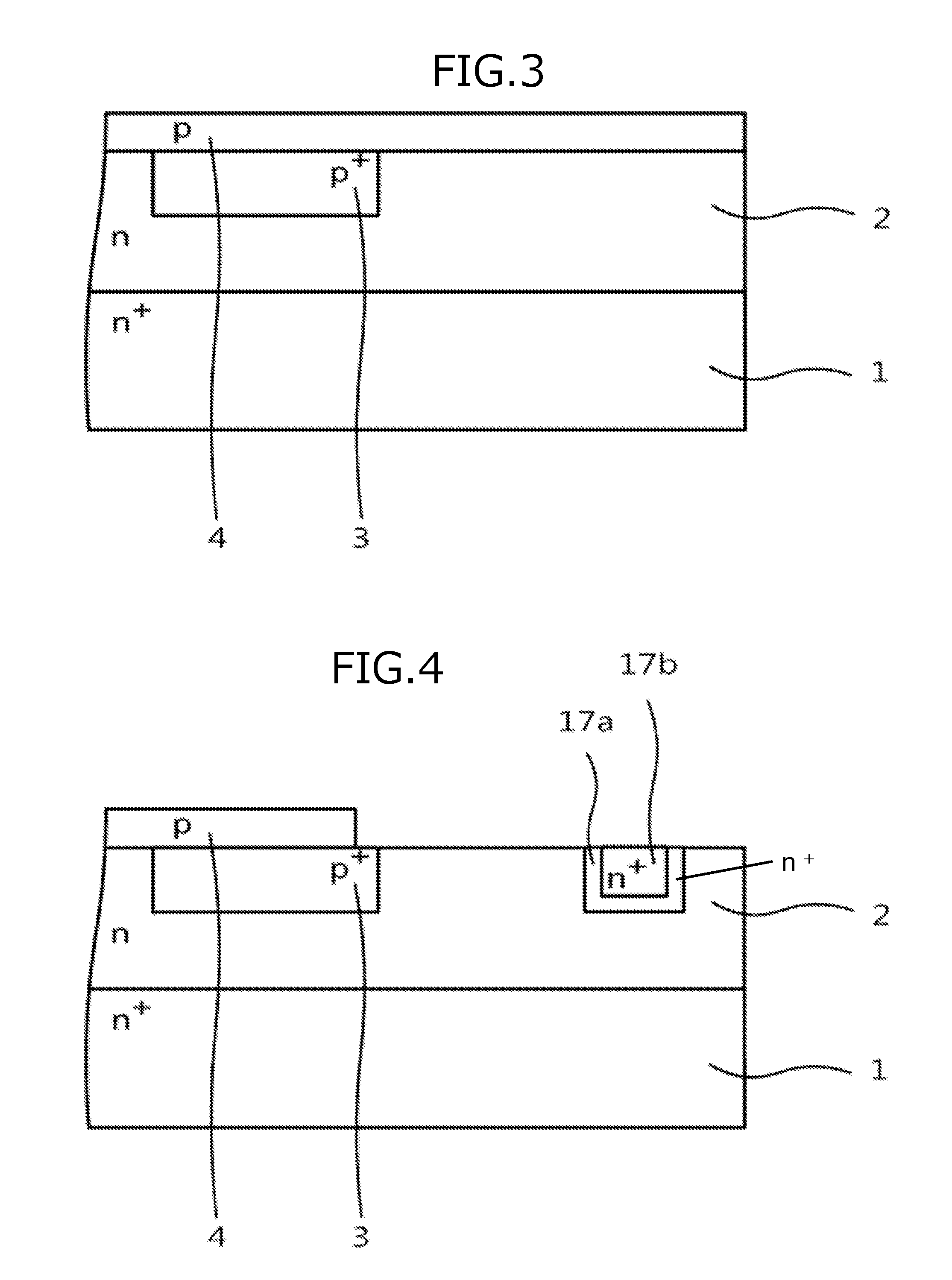

A semiconductor device of an embodiment includes a p+-type region selectively disposed in a surface of an n-type silicon carbide epitaxial layer disposed on an n+-type silicon carbide substrate, an element structure that includes a source electrode and a p+-type region that form a metal-semiconductor junction on the n-type silicon carbide epitaxial layer, a p−-type region and another p−-type region that surround the periphery of the element structure, and an n+-type channel stopper region that surrounds the periphery of the p−-type regions so that the n-type silicon carbide epitaxial layer is therebetween. The n+-type channel stopper region has a second n+-type channel stopper region whose impurity concentration is high, and a first n+-type channel stopper region that encompasses the second n+-type channel stopper region and whose impurity concentration is lower than that of the second n+-type channel stopper region.

Owner:FUJI ELECTRIC CO LTD

Semiconductor device

ActiveUS8963198B2Increase production costBreakdown is effectively preventedSemiconductor devicesChannel-stopperImpurity

In one surface of a semiconductor substrate, an n− layer, a p base layer, a p well layer, another p well layer, a channel stopper layer, an emitter electrode, a guard ring electrode, and a channel stopper electrode for example are formed. In the other surface of the semiconductor substrate, an n+ buffer layer, a p+ collector layer, and a collector electrode are formed. In a curved corner of the p well layer, a p low-concentration layer having a lower impurity concentration than the impurity concentration of the p well layer is formed from the surface to a predetermined depth.

Owner:MITSUBISHI ELECTRIC CORP

Semiconductor device

In one surface of a semiconductor substrate, an active region in which main current flows and an IGBT is disposed is formed. A termination structure portion serving as an electric-field reduction region is formed laterally with respect to the active region. In the termination structure portion, a porous-oxide-film region, a p-type guard ring region, and an n+-type channel stopper region are formed. A plurality of floating electrodes are formed to contact the surface of the porous-oxide-film region. Another plurality of floating electrodes are formed to contact a first insulating film.

Owner:MITSUBISHI ELECTRIC CORP

Bipolar transistor with diffused layer between deep trench sidewall and collector diffused layer

InactiveUS8710621B2Improve featuresReduce leakage currentSemiconductor/solid-state device manufacturingSemiconductor devicesChannel-stopperDiffusion layer

A semiconductor device according to the present invention includes a p-type semiconductor substrate, a first n-type collector diffusion layer formed in the p-type semiconductor substrate, a deep trench formed in the p-type semiconductor substrate so as to surround the first n-type collector diffusion layer, a p-type channel stopper layer formed beneath the deep trench, and an n-type diffusion layer formed between a sidewall of the deep trench and the first n-type collector diffusion layer.

Owner:PANASONIC CORP

Semiconductor apparatus

ActiveUS9577087B2Suppresses fluctuation of breakdown voltageSuppresses drop in breakdown voltageSemiconductor devicesChannel-stopperSemiconductor

A semiconductor apparatus that has a first parallel pn-layer formed between an active region and an n+-drain region. A peripheral region is provided with a second parallel pn-layer, which has a repetition pitch narrower than the repetition pitch of the first parallel pn-layer. An n−-surface region is formed between the second parallel pn-layer and a first main surface. On the first main surface side of the n−-surface region, a plurality of p-guard ring regions are formed to be separated from each other. A field plate electrode is connected electrically to the outermost p-guard ring region among the p-guard ring regions. A channel stopper electrode is connected electrically to an outermost peripheral p-region of the peripheral region.

Owner:FUJI ELECTRIC CO LTD

Stopper structure for rotary operation member, electronic device, and channel stopper

ActiveUS8717126B2Avoid bitesEasy to installResonant circuit driving/adjusting meansElectric switchesChannel-stopperEngineering

A stopper structure includes a wall defining an opening. A rotary electronic component has a rotational shaft extending through the opening. A channel stopper has a tubular body and an engagement projection. The tubular body is detachably mounted onto the rotational shaft and is inhibited from rotating relative thereto. The engagement projection extends from an end of the tubular body in an axial direction and a radial direction with respect to the rotational shaft. A rotary operation member is detachably mounted onto the rotational shaft and the tubular body and is inhibited from rotating relative thereto. The rotary operation member has an axial hole in which at least portions of the rotational shaft and the tubular body fit. A limiting portion provided on the wall is engageable with the engagement projection for limiting a range of rotation of the rotational shaft.

Owner:JVC KENWOOD CORP A CORP OF JAPAN

Semiconductor device and manufacturing method thereof

ActiveUS7528442B2Avoid it happening againImprove featuresTransistorSolid-state devicesHigh concentrationChannel-stopper

In this invention, the semiconductor device is provided with a gate electrode formed on a gate insulating film in a region sectioned by an element isolation formed on a semiconductor layer of the first conduction type, and a source region and a drain region of the second conduction type. At least one of the source region and the drain region has a first low concentration region and a high concentration region. Also, the semiconductor device of the present invention is provided with a second low concentration region of the second conduction type between a channel stopper region formed below the element isolation and the source region, and between the channel stopper region and the drain region. The semiconductor layer immediately below the gate electrode projects to the channel stopper region side along the gate electrode, and the semiconductor layer and the channel stopper region make contact with each other.

Owner:PANNOVA SEMIC

Semiconductor device

InactiveUS20100078719A1Avoid it happening againInhibition formationTransistorSemiconductor/solid-state device detailsChannel-stopperEngineering

A semiconductor device in which a desired device is formed, comprising a semiconductor substrate having a first impurity region of a first conductivity type provided around an edge of a region in which the desired device is formed, and a second impurity region of the first conductivity type provided in a scribe region of the semiconductor substrate; wherein a channel stopper is formed between the first impurity region and the second impurity region.

Owner:PANASONIC CORP

Manufacture method for semiconductor device having field oxide film

InactiveCN1819137AImprove manufacturing yieldLow costSemiconductor/solid-state device manufacturingResistChannel-stopper

To provide a method of forming a field oxide film capable of simply and accurately forming a channel stopper region separately from an element hole immediately under the field oxide film. On the principal surface of a silicon substrate, a side spacer made of silicon nitride is formed on the side wall of a lamination including a silicon oxide film, a silicon nitride film and a silicon oxide film. Thereafter, a channel stopper ion doped region is formed by implanting impurity ions by using as a mask the lamination, side spacer and resist layer. After the resist layer and side spacer are removed, a field oxide film is formed through selective oxidation using the lamination as a mask, and a channel stopper region corresponding to the ion doped region is formed. After the lamination is removed, a circuit device such as a MOS type transistor is formed in each device opening of the field oxide film.

Owner:YAMAHA CORP

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com