Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

92results about How to "Electrical connection" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

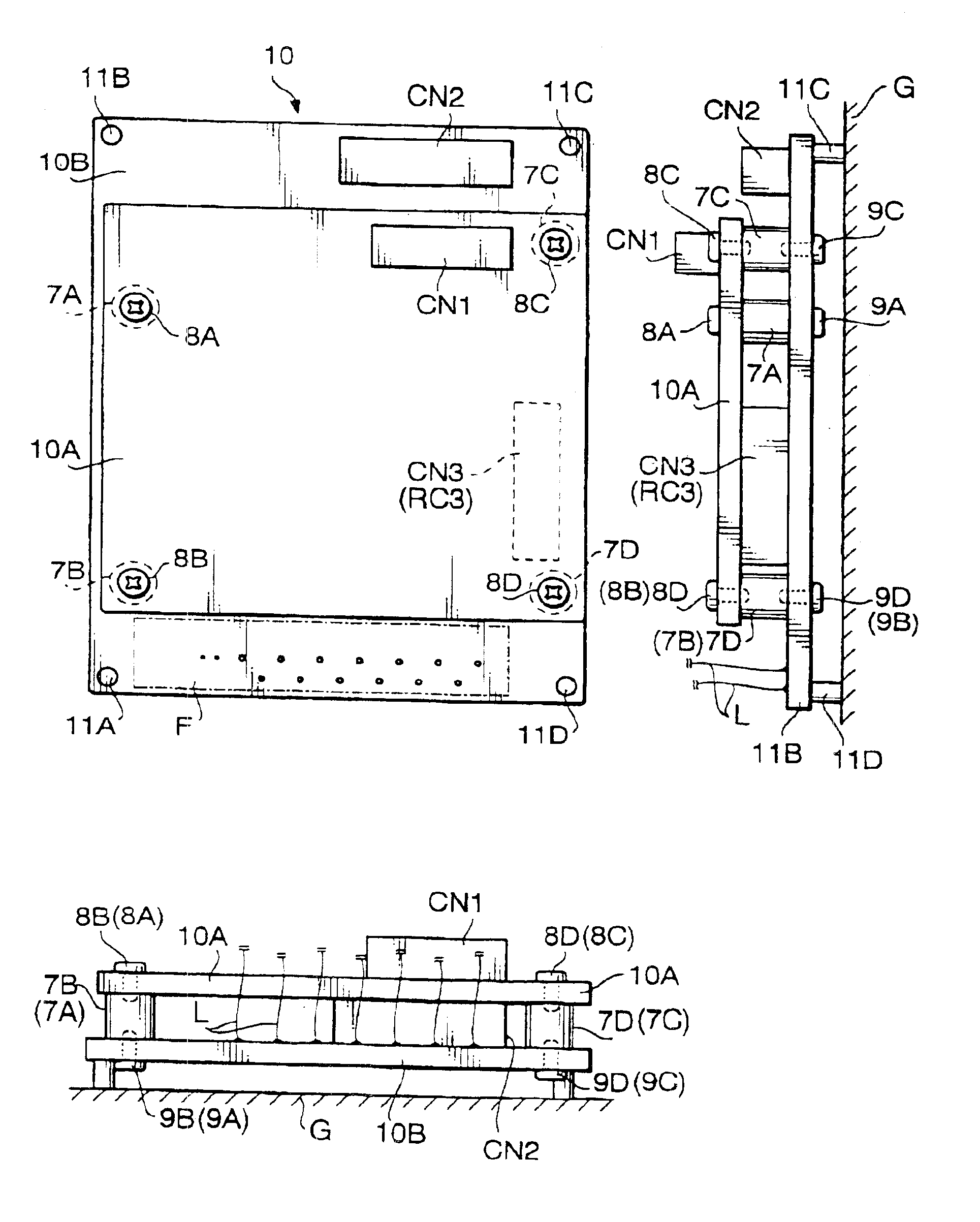

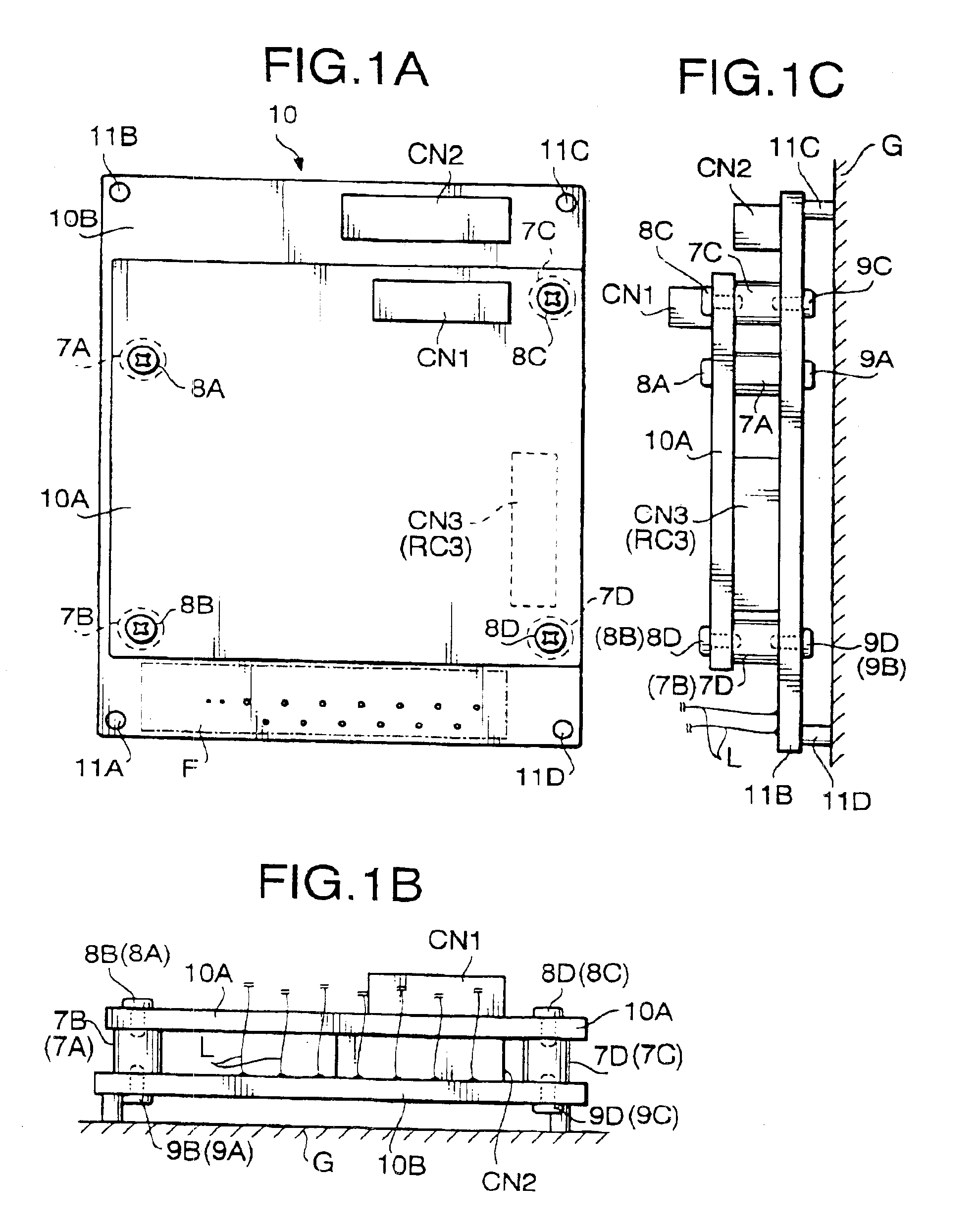

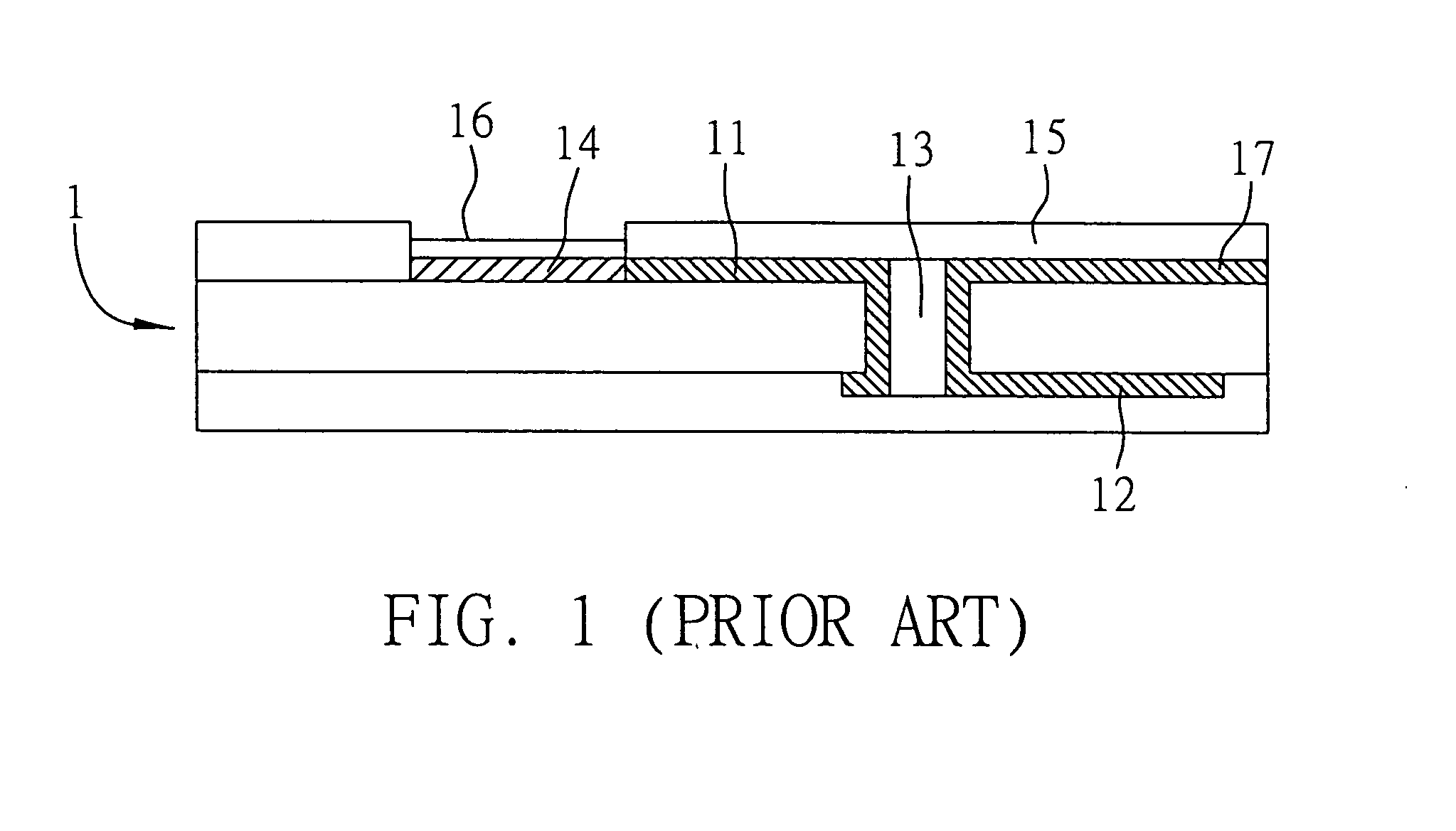

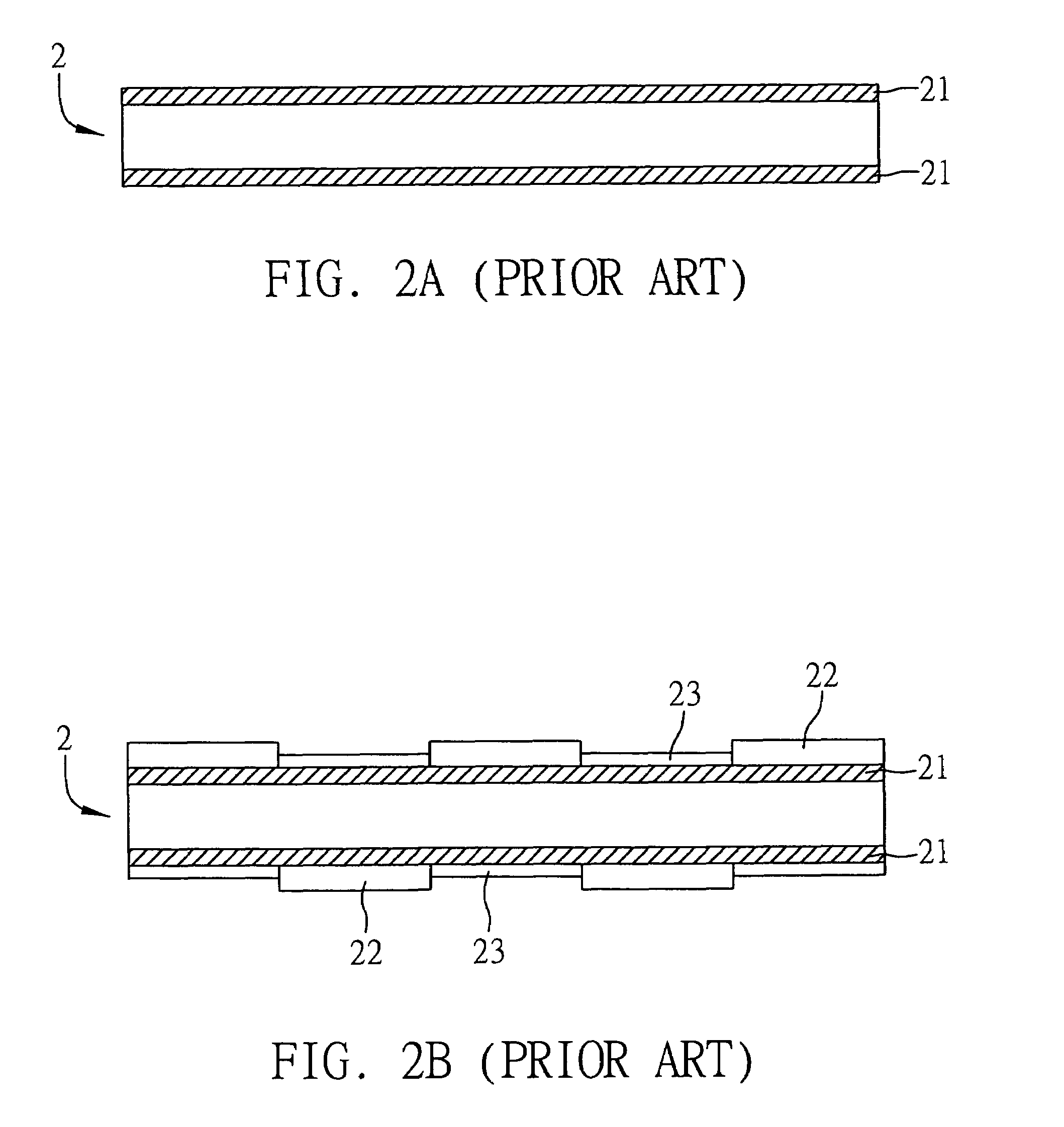

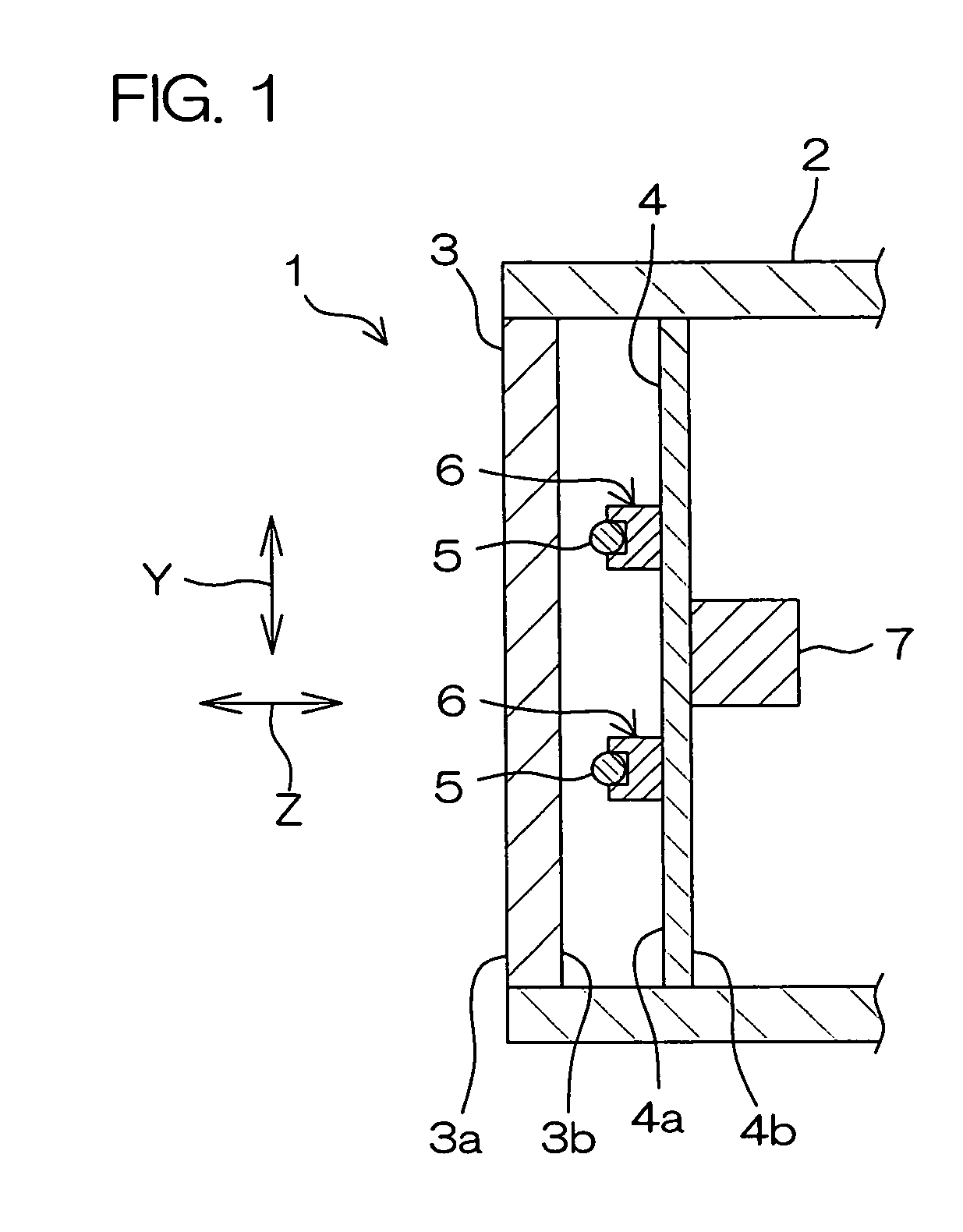

PCB structure for scope unit of electronic endoscope

InactiveUS6898086B2Simple structureElectrical connectionTelevision system detailsEndoscopesEngineeringBoard structure

A printed circuit board structure for a scope unit of an electronic endoscope system, which is provided with a first printed circuit board formed with a first circuit section, and a second printed circuit board formed with a second circuit section. The first printed circuit board is piled on the second printed circuit board. The second printed circuit board having an area covered with the first printed circuit board and at least one area which is not covered with the first circuit board. The at least one area is used for electrically connecting the second circuit section with an electrical unit other than the second circuit section.

Owner:ASAHI KOGAKU KOGYO KK

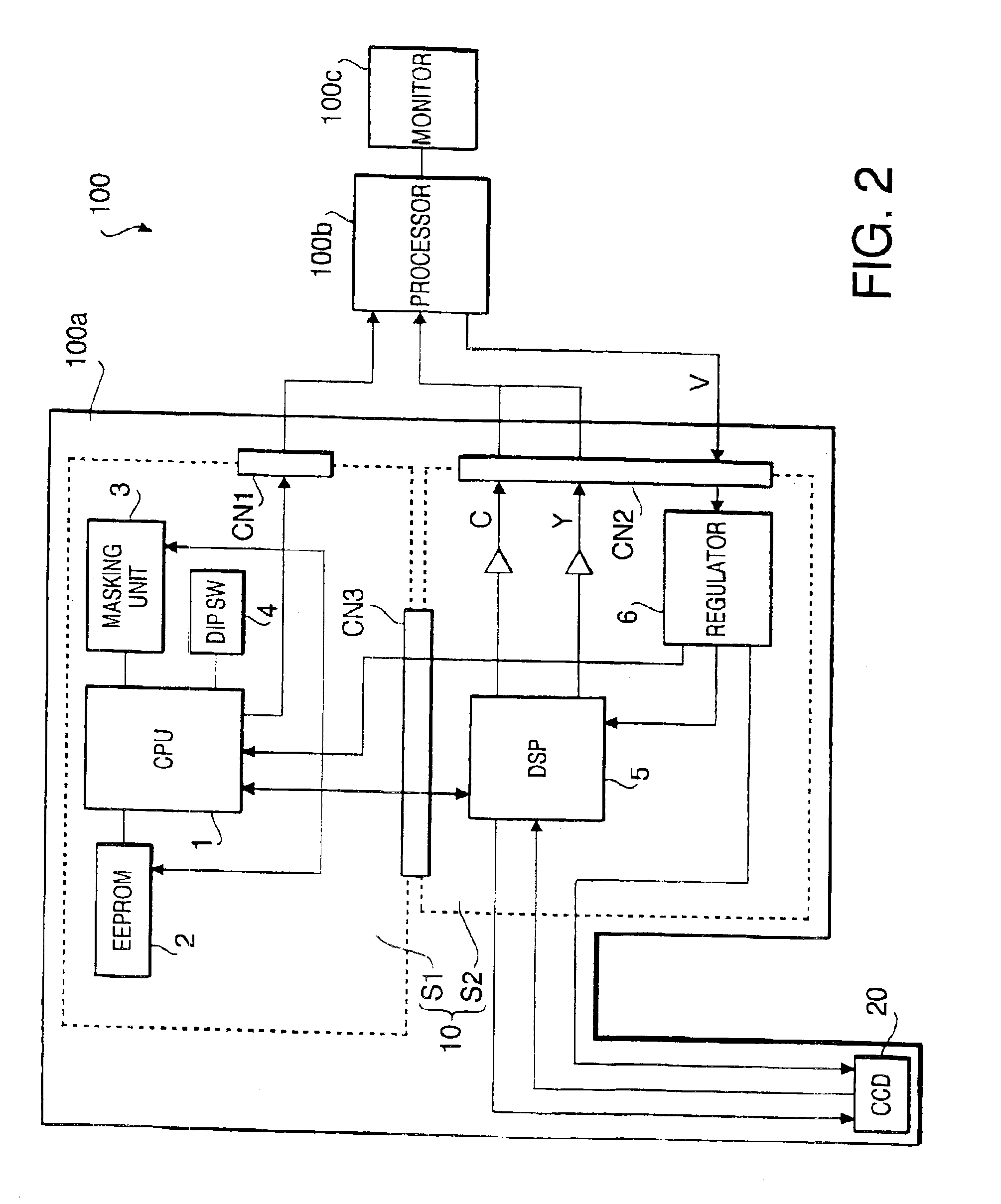

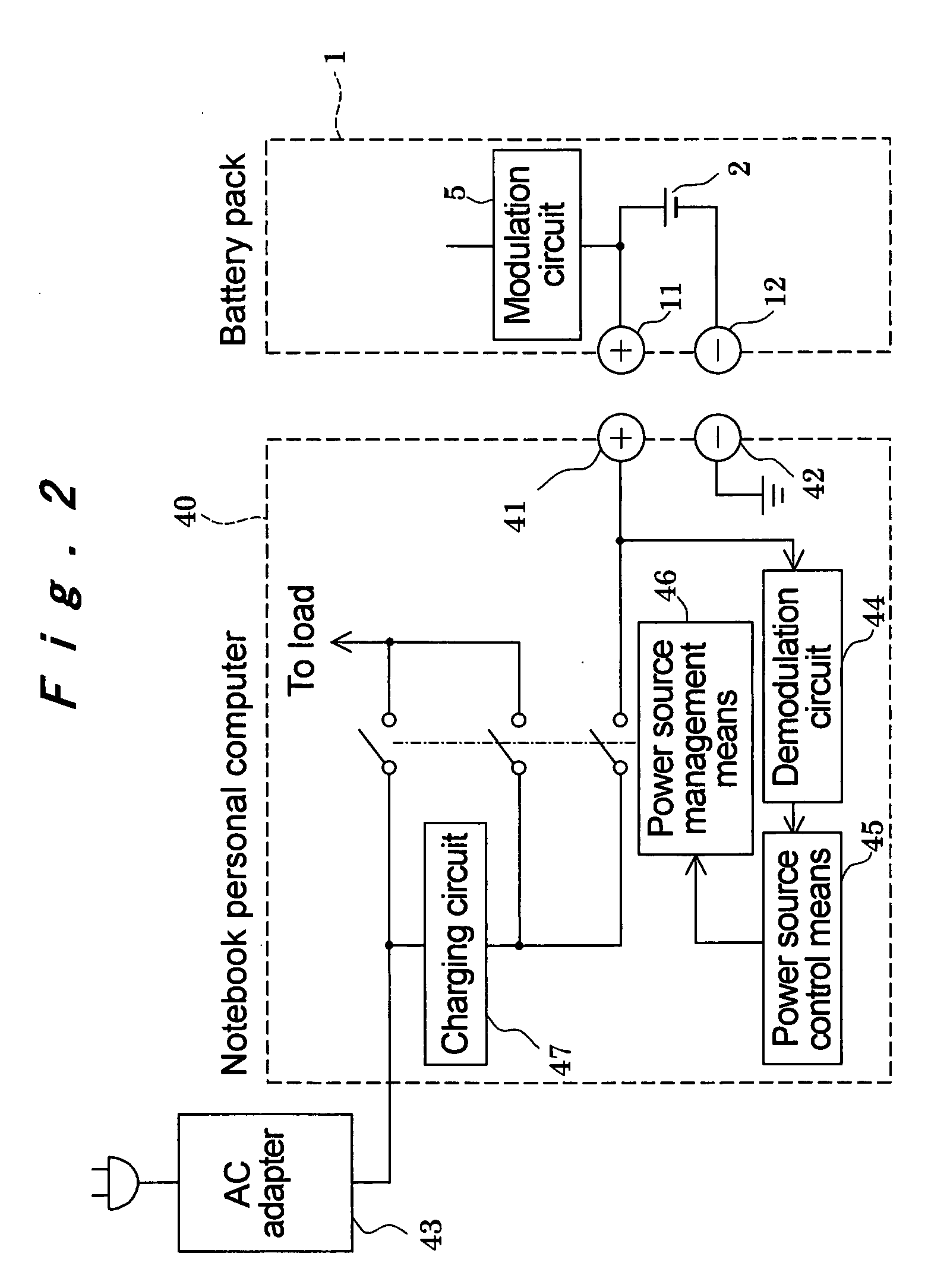

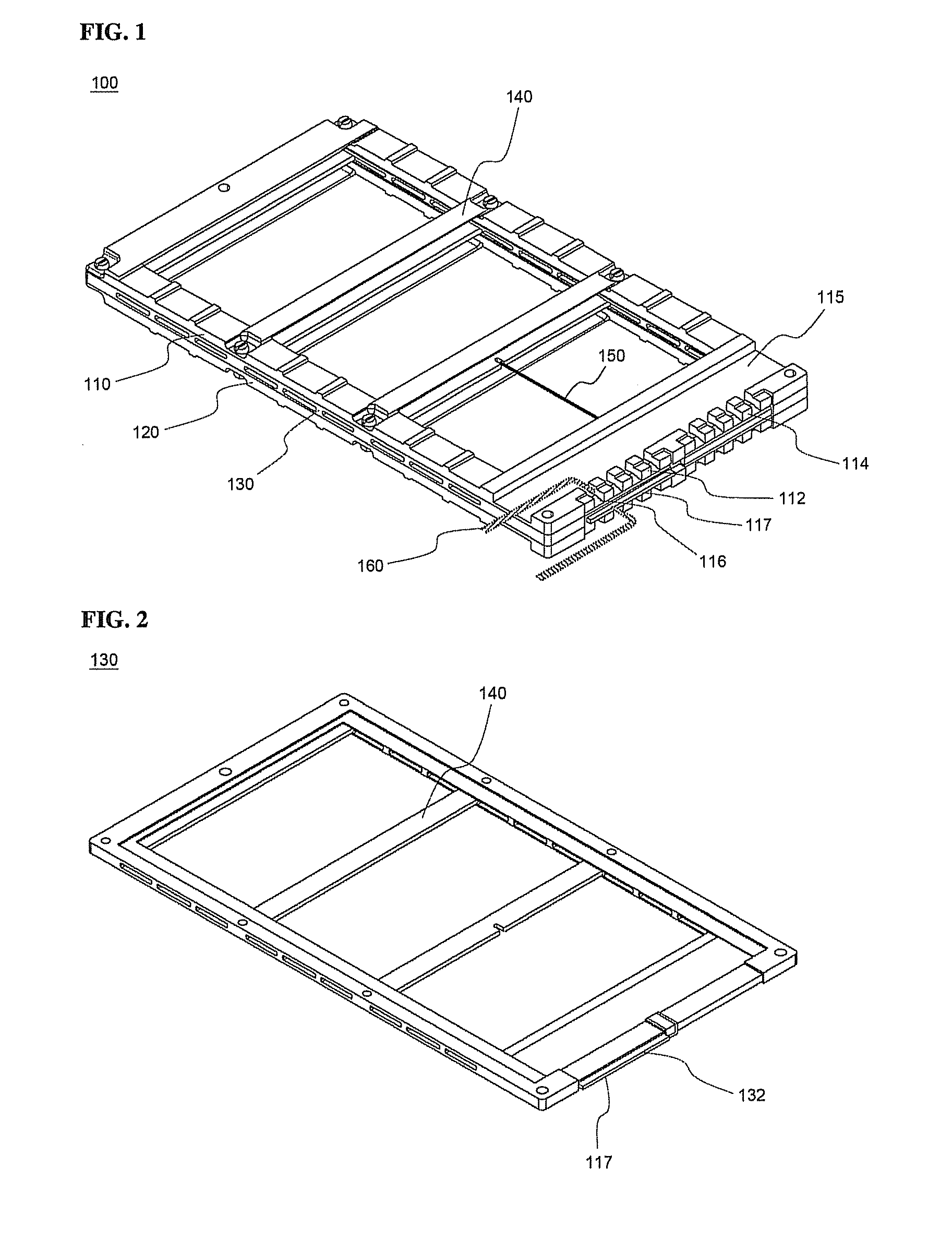

Battery pack and connection system thereof

InactiveUS20090039833A1Avoid it happening againQuick responseCircuit authenticationTransmission/receiving by adding signal to waveEngineeringElectric power

In a battery pack (1), control means (3) reads identification information or operating state detection information out of identification information memory means (4) or battery operating state detection means (10) and inputs it to a modulation circuit (5). The modulation circuit (5) modulates the information into an information signal which can be superimposed on a direct-current power transmission line and sends it to a charging device (20) or a loading device (30) through a positive charge and discharge terminal (11). The charging device (20) or the loading device (30) demodulates the sent information signal to take out the identification information or the operating state detection information and allows power source control means (25, 35) to control the output of charging energy from a charging power source (23) or the output of discharging energy to a load (33). Thus, in addition to the transmission of direct-current power, information can be transmitted only by the connection of two positive and negative terminals.

Owner:PANASONIC CORP

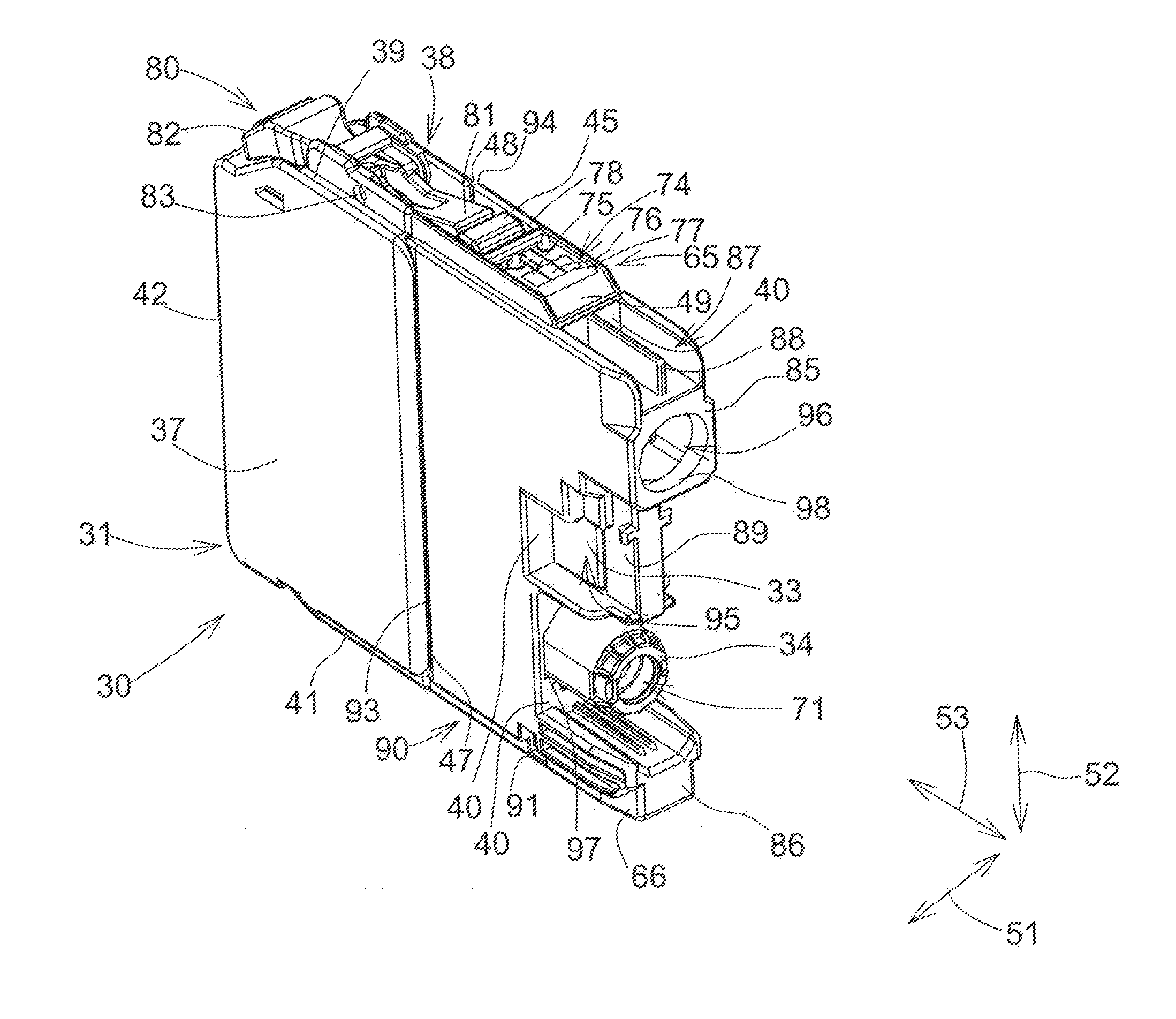

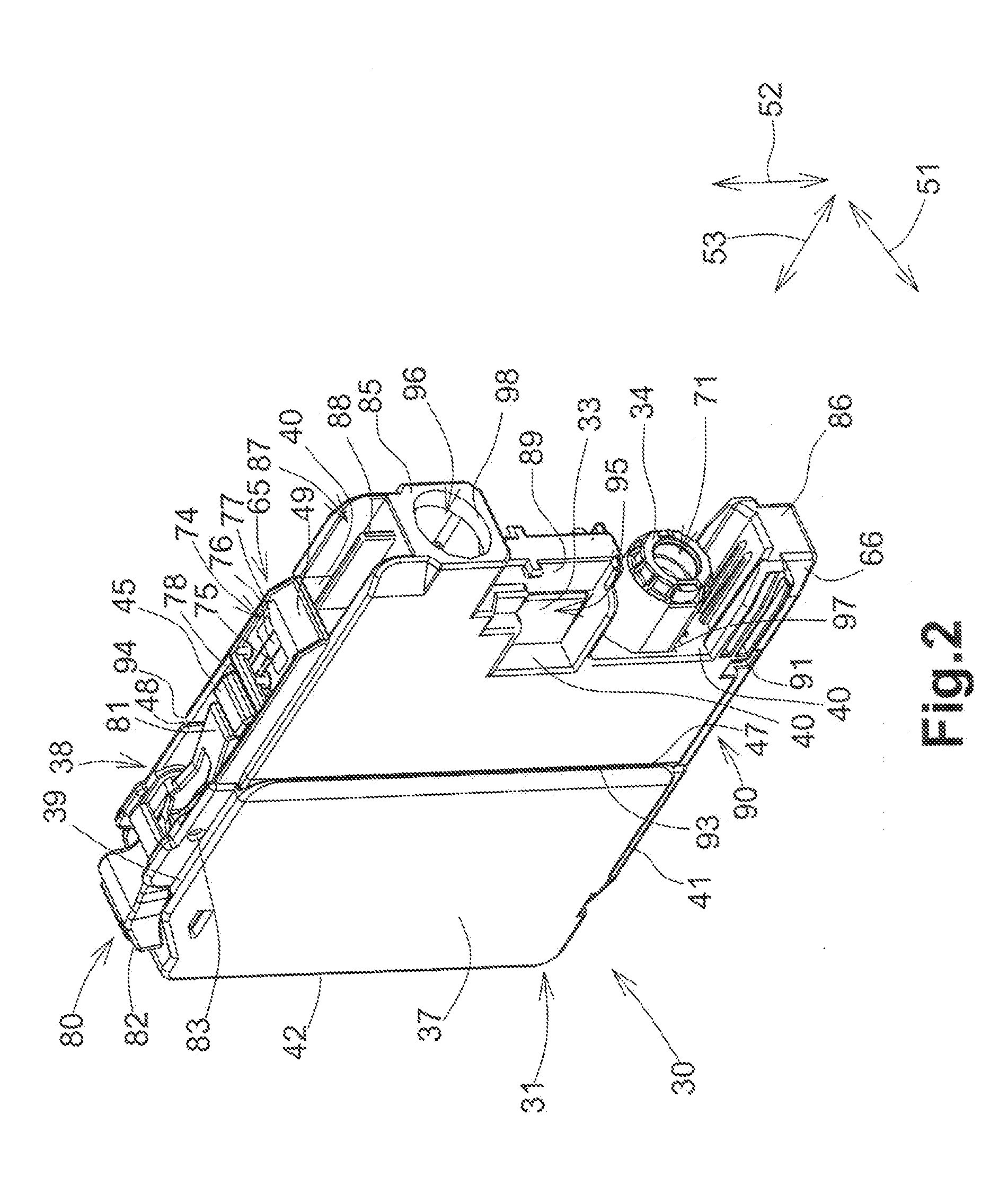

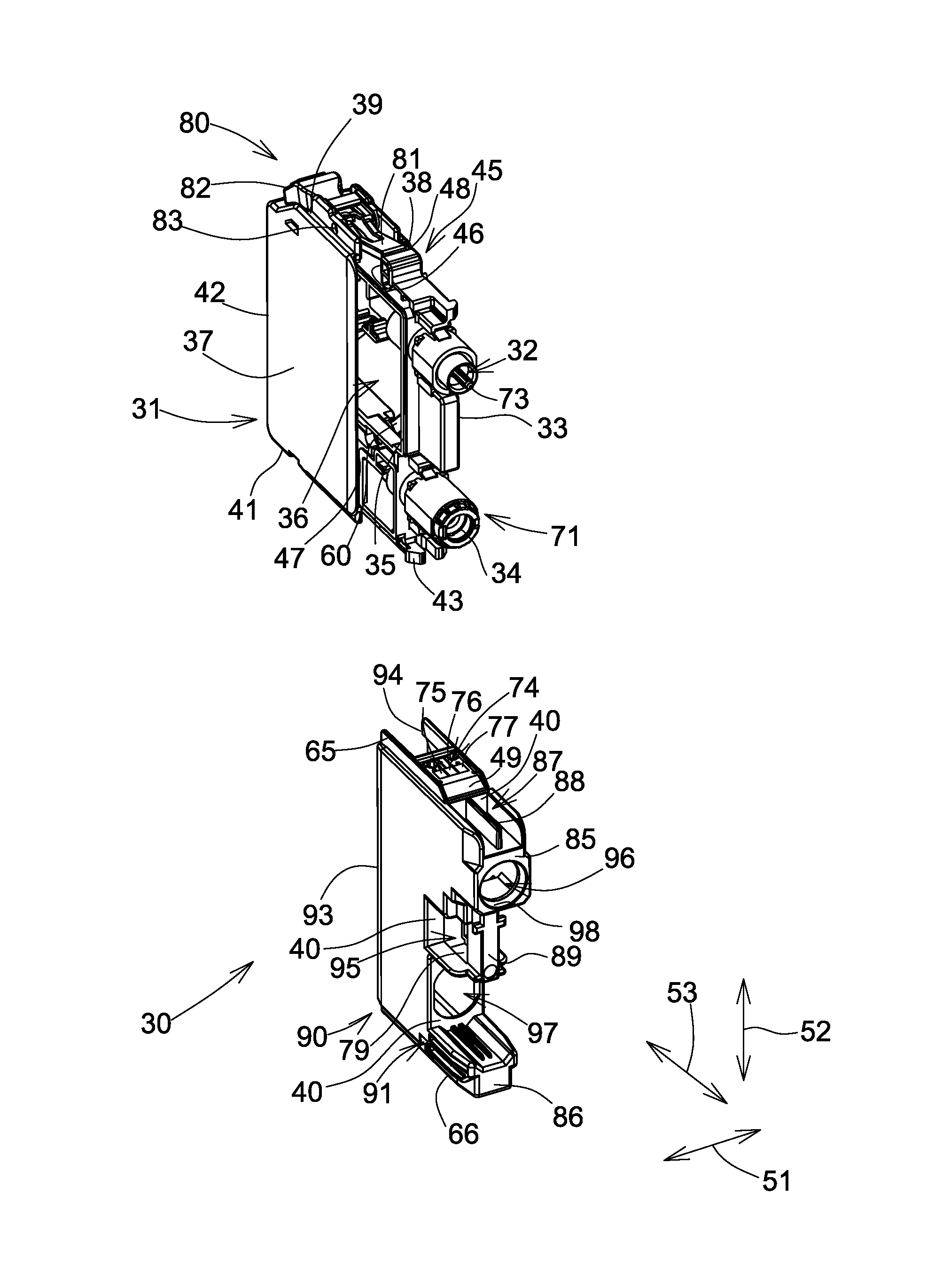

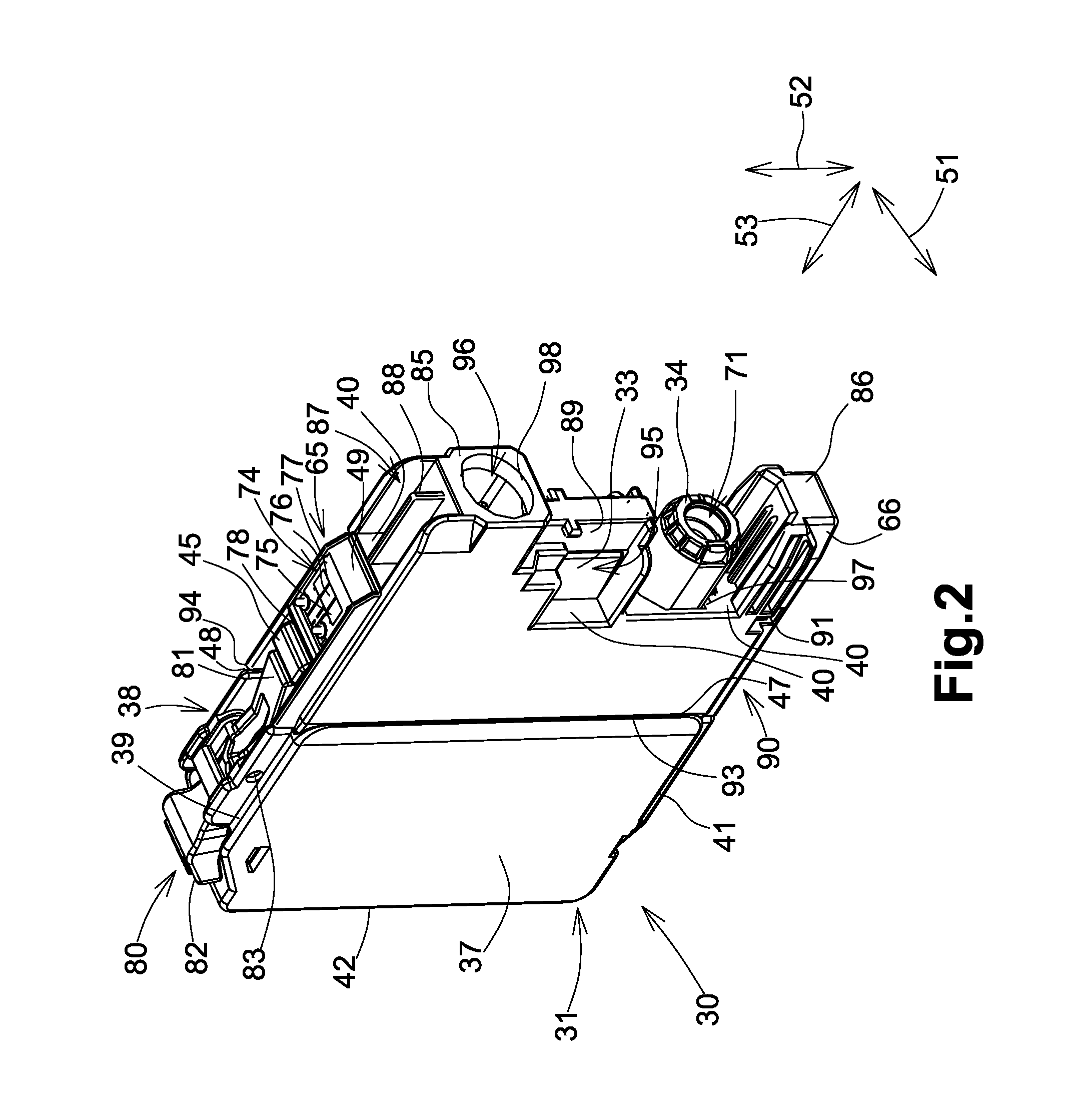

Printing fluid cartridge, printing apparatus, and use of printing fluid cartridge

A printing fluid cartridge includes a front face oriented toward a first direction, a printing fluid supply portion positioned at the front face, a rear face positioned opposite the front face and oriented toward a second direction opposite the first direction, at least one electrical interface positioned between the front face and the rear face, and an engagement surface facing in the second direction. The at least one electrical interface is offset from the printing supply portion with respect to a third direction perpendicular to the first direction and the second direction. The at least one electrical interface is positioned closer to the front face than the engagement surface is, and the at least one electrical interface and the engagement surface intersect a plane which is parallel with the first direction, the second direction, and the third direction.

Owner:BROTHER KOGYO KK

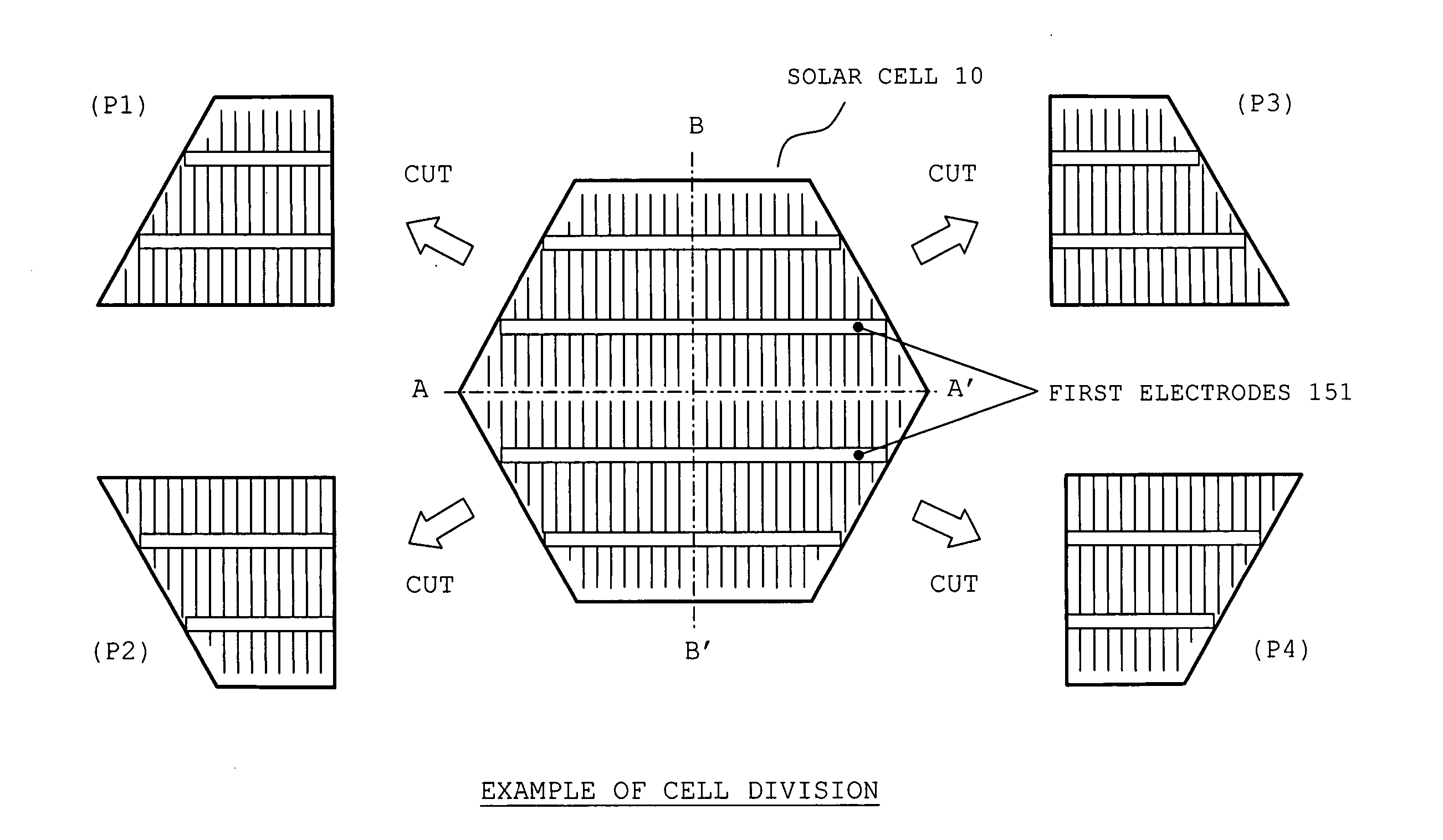

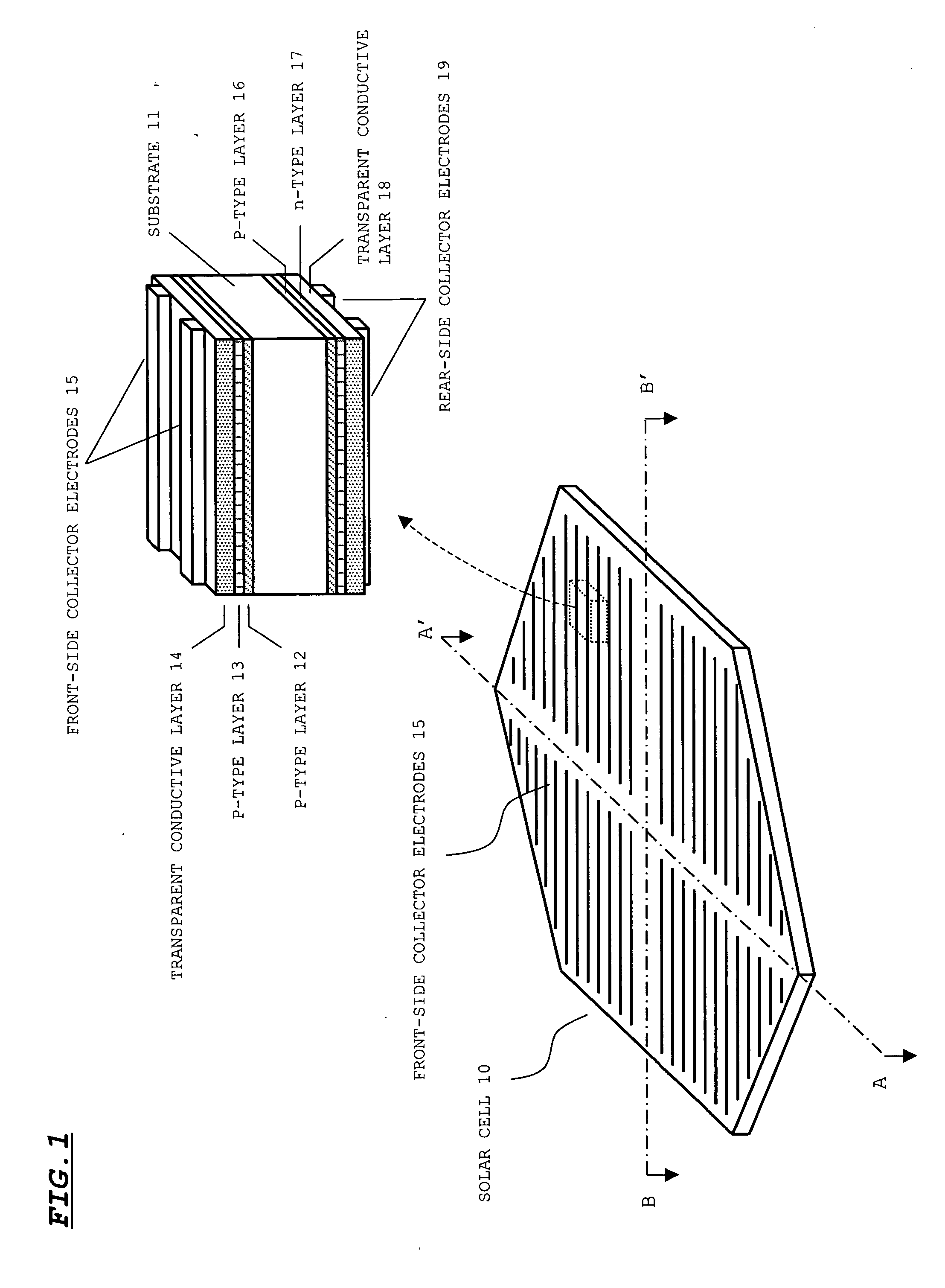

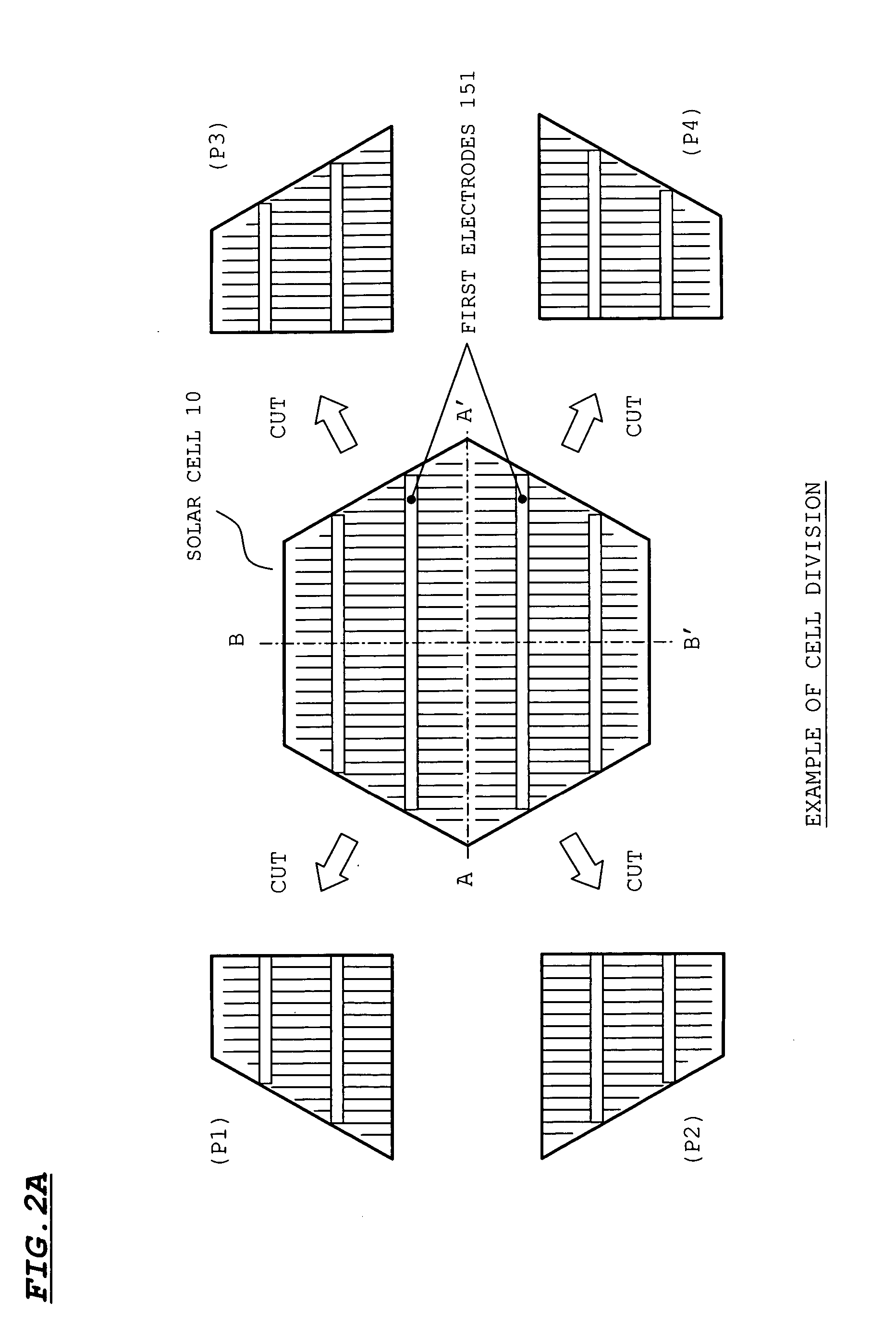

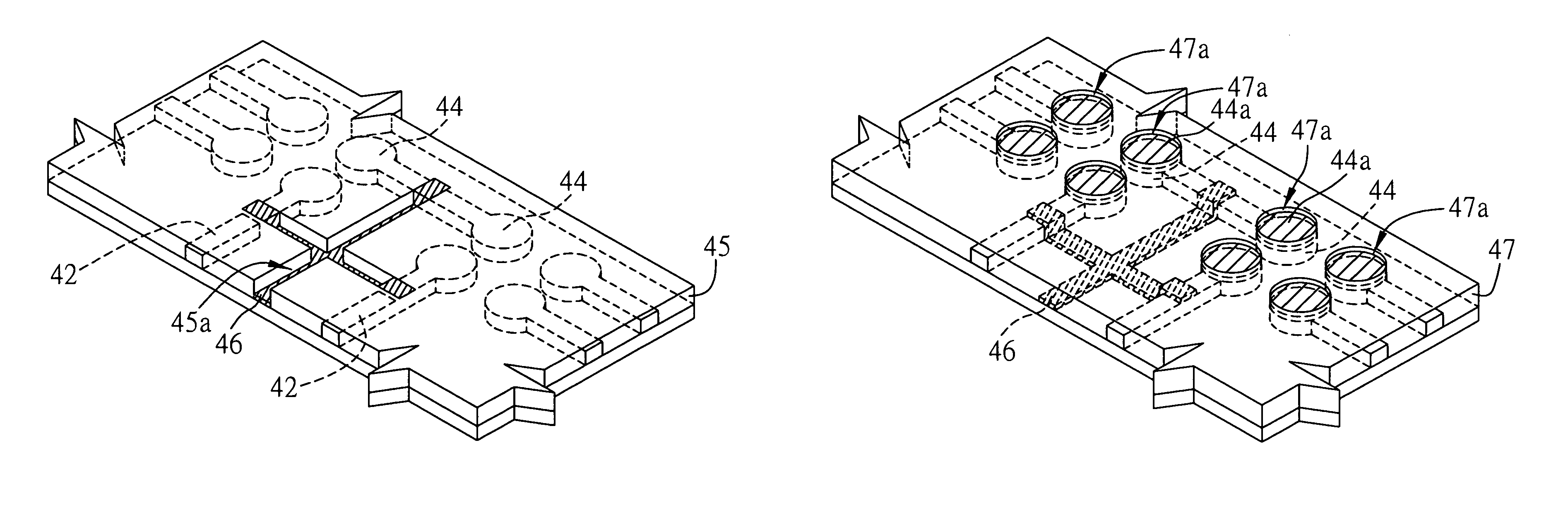

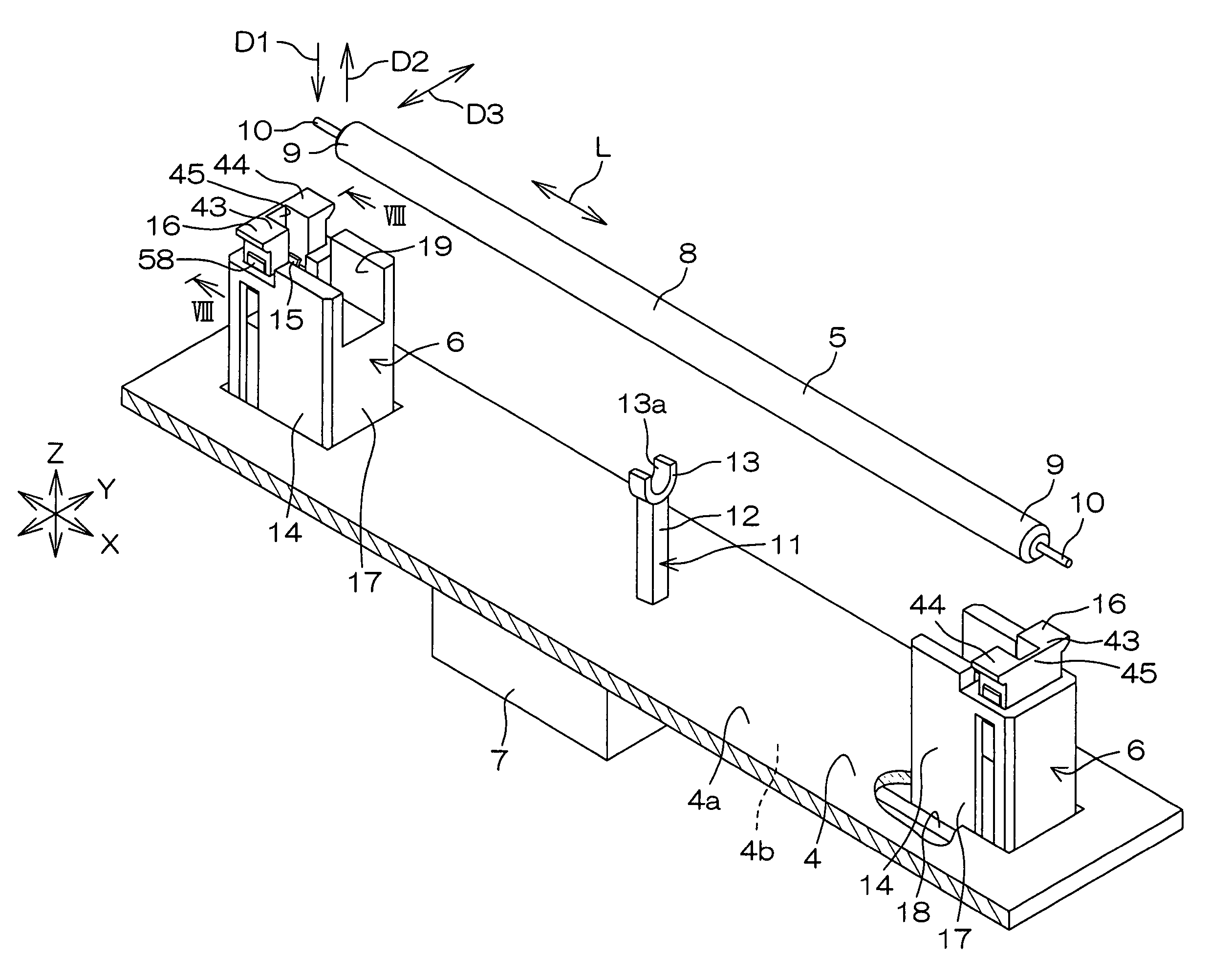

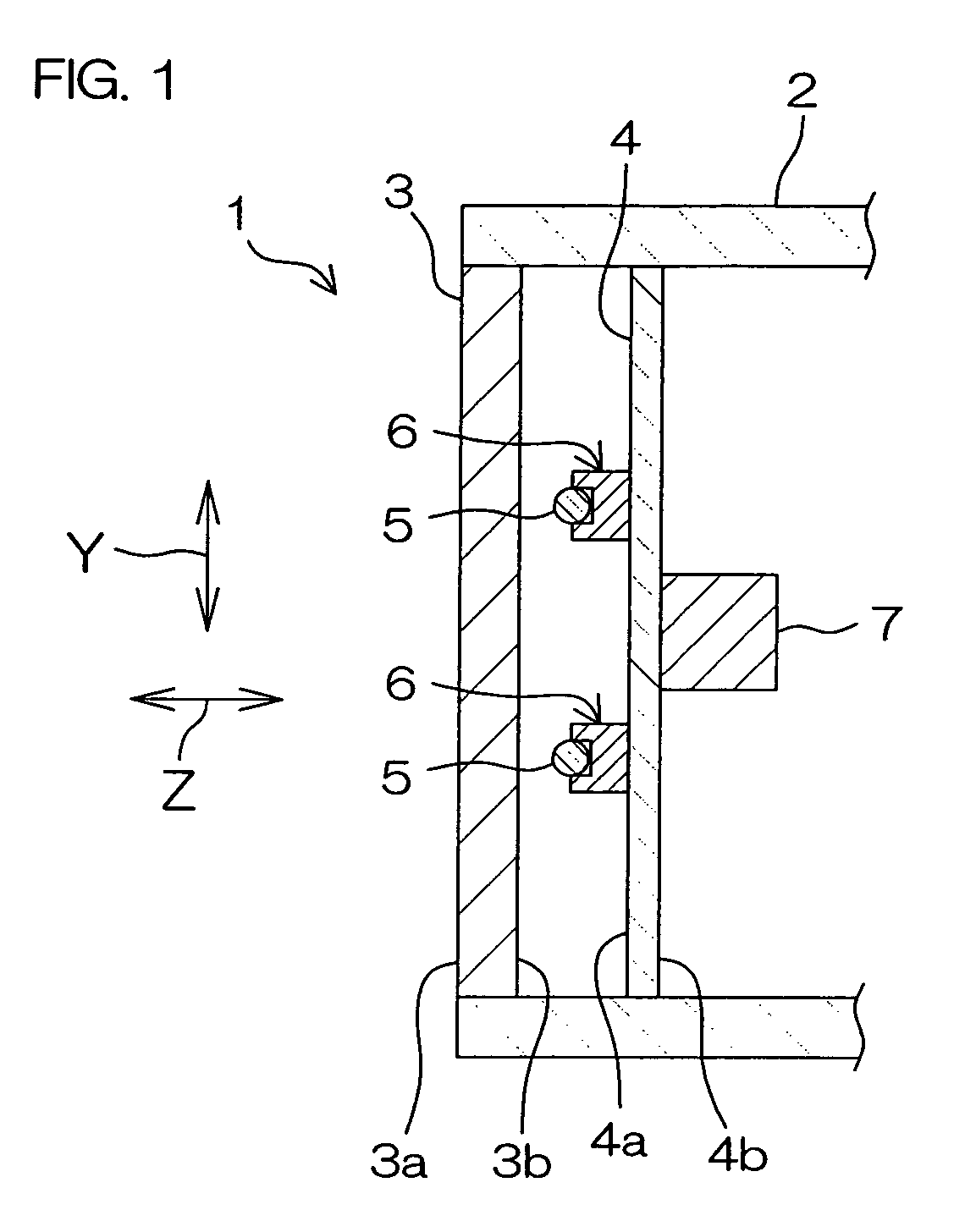

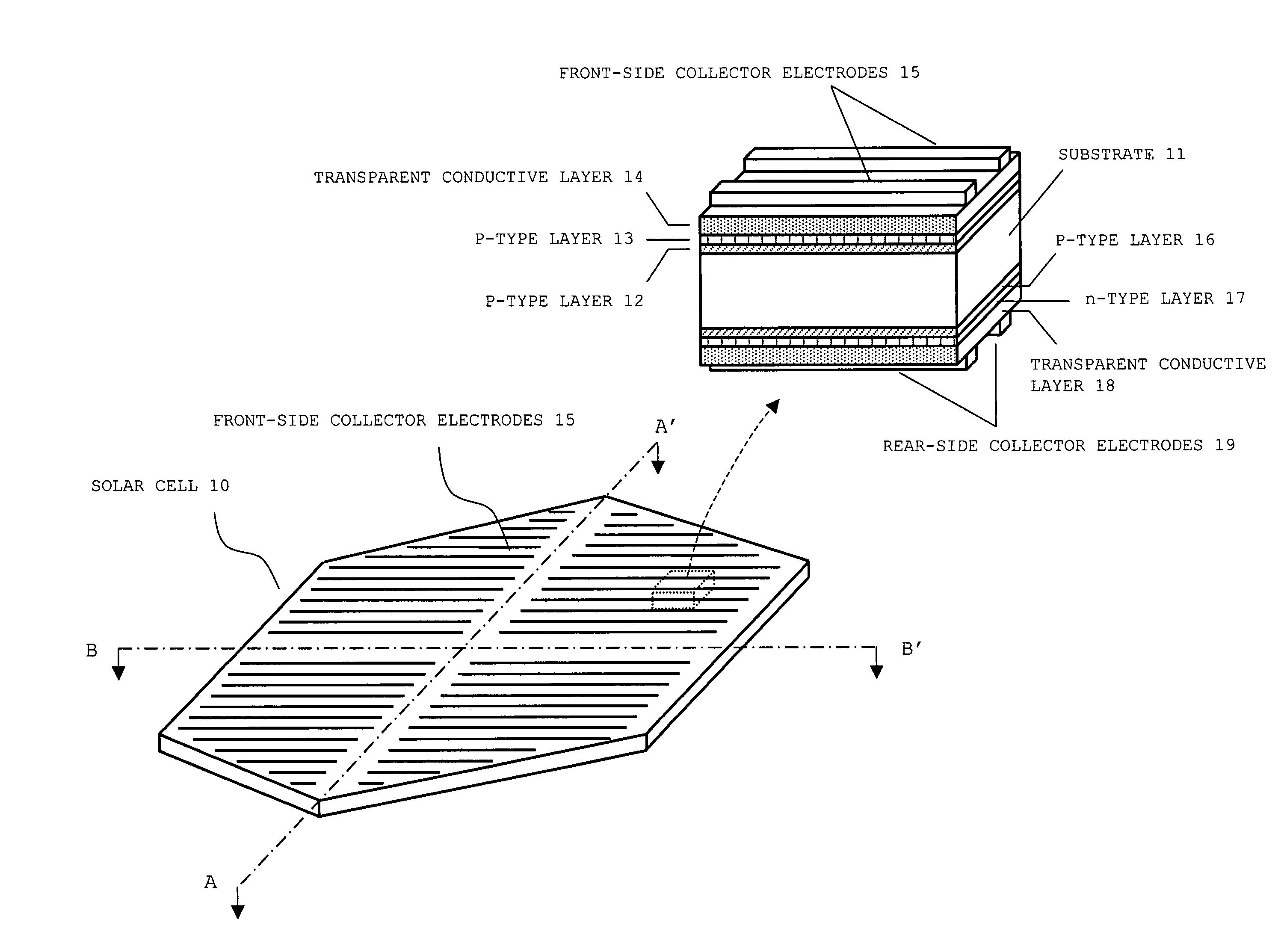

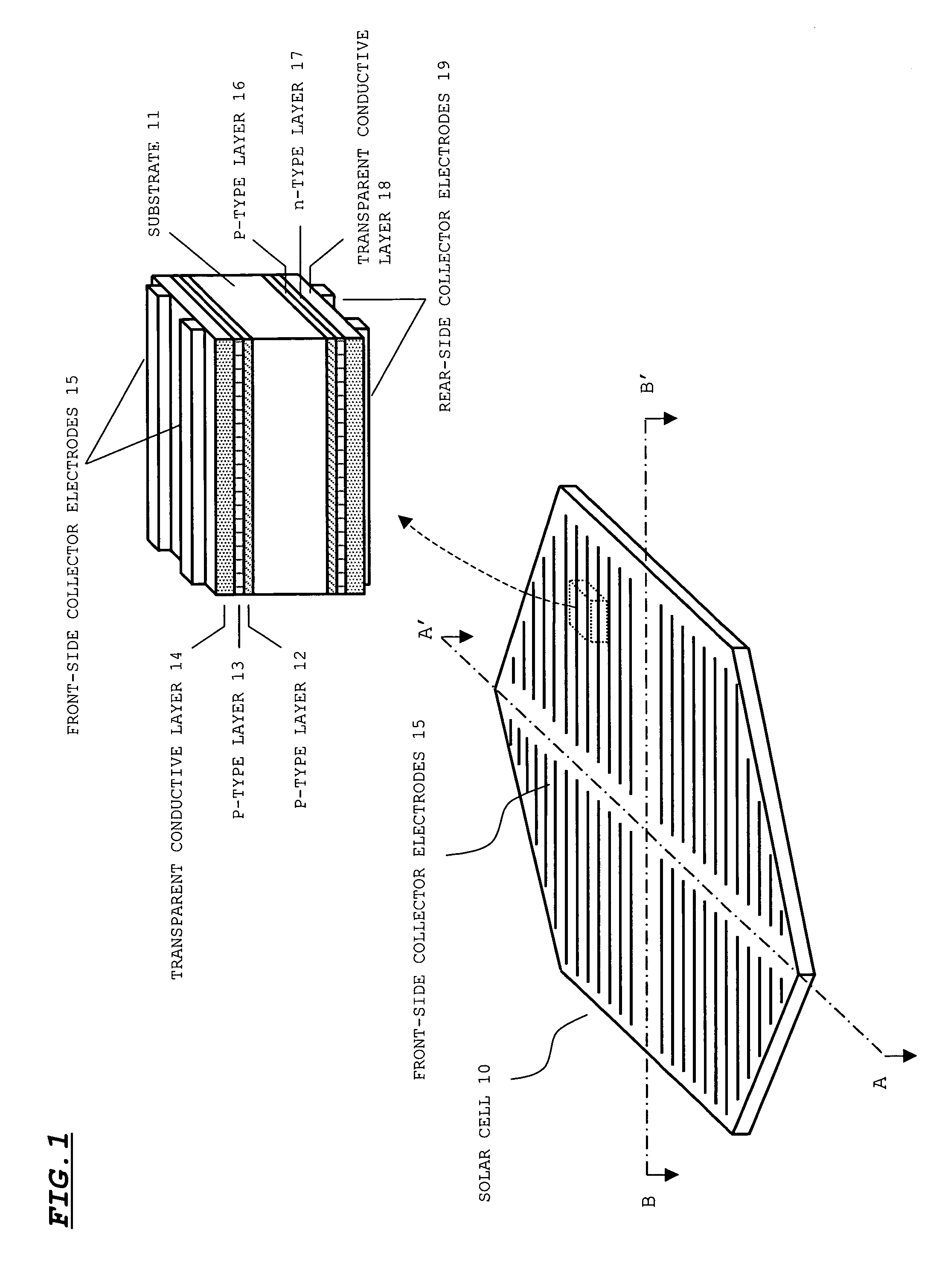

Manufacturing method of solar cell module, and solar cell and solar cell module

ActiveUS20070074756A1Electrical connectionConvenient ArrangementPV power plantsPhotovoltaic energy generationElectricityEngineering

A double-side light receiving solar cell in a planer regular hexagon shape and having first electrodes on both surfaces are divided into four pieces by a line A-A′ connecting two opposing apexes and by a line B-B′ perpendicular to the line A-A′ and connecting center points on two opposing sides. By matching oblique lines of two divided pieces without misalignment and with respective surfaces in an inversed state, the first electrodes on the same side of the two divided pieces align along the same single straight line. Then, the first electrodes that are on the same side are connected with a first inter connecter, thereby constructing a unit having a rectangular outline. Units thus constructed are arranged so that relevant sides match without misalignment. By handling on a unit basis as described above, it is possible to facilitate an arrangement of the cells and an electricity connection work.

Owner:SANYO ELECTRIC CO LTD

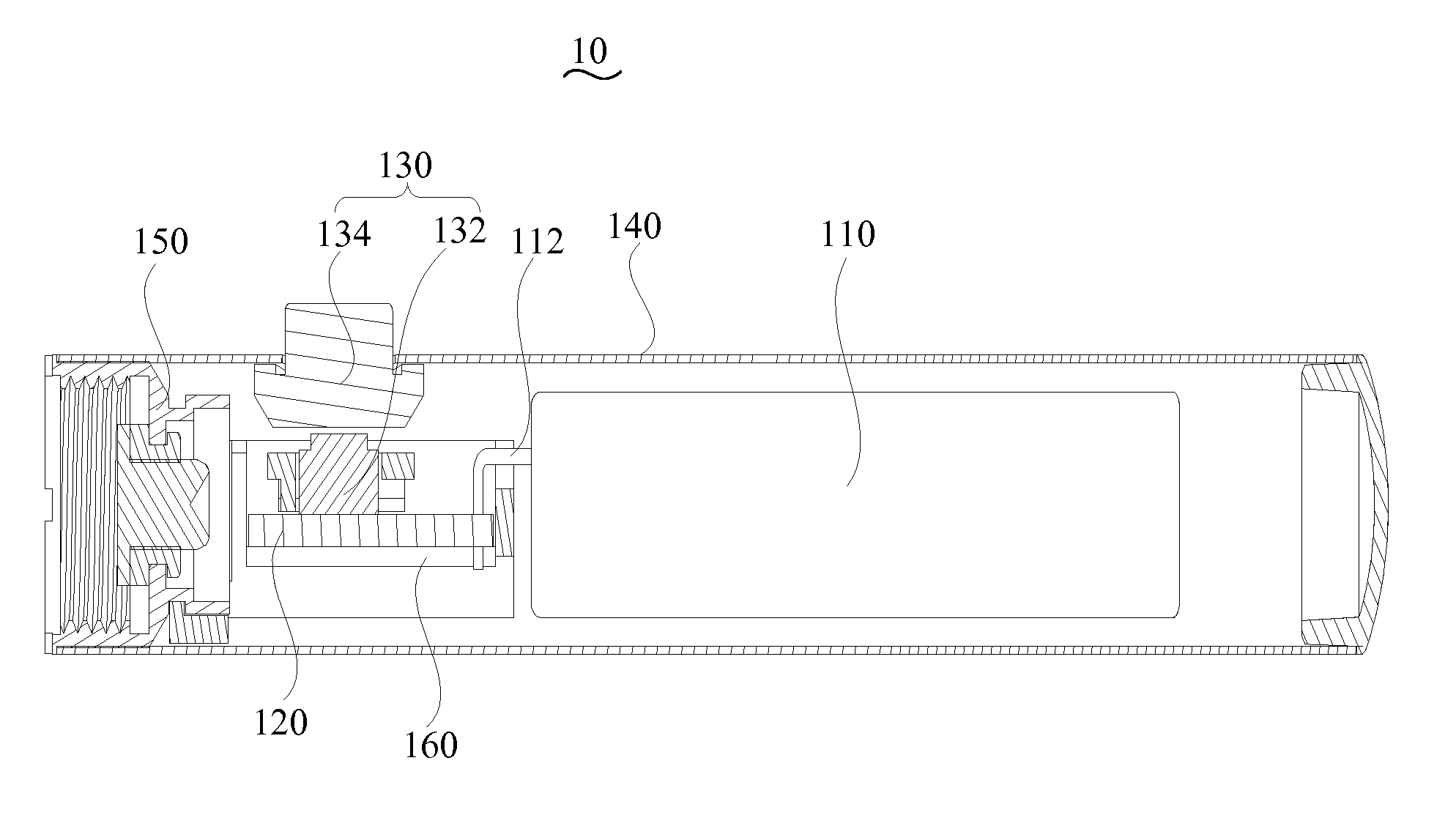

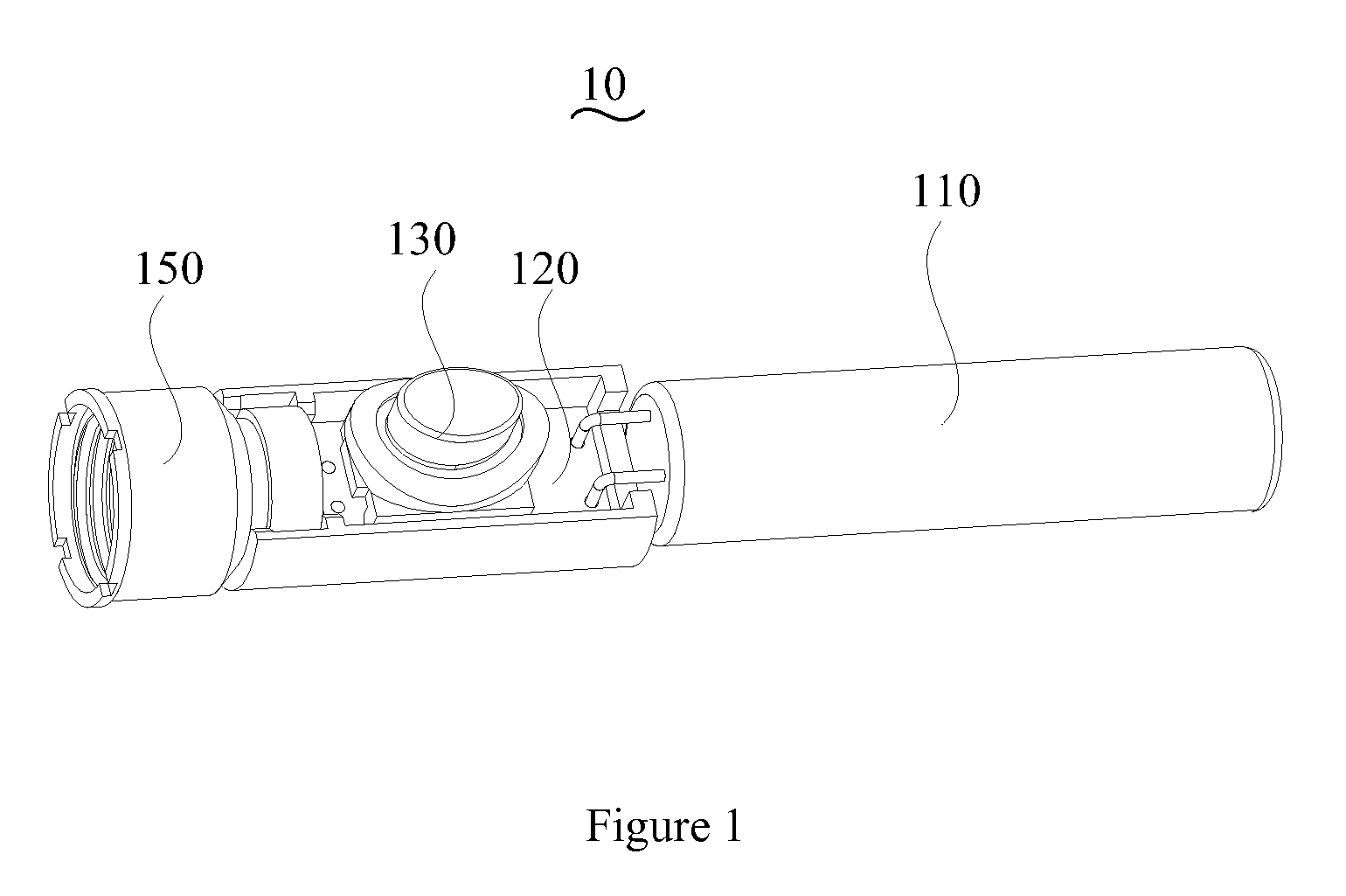

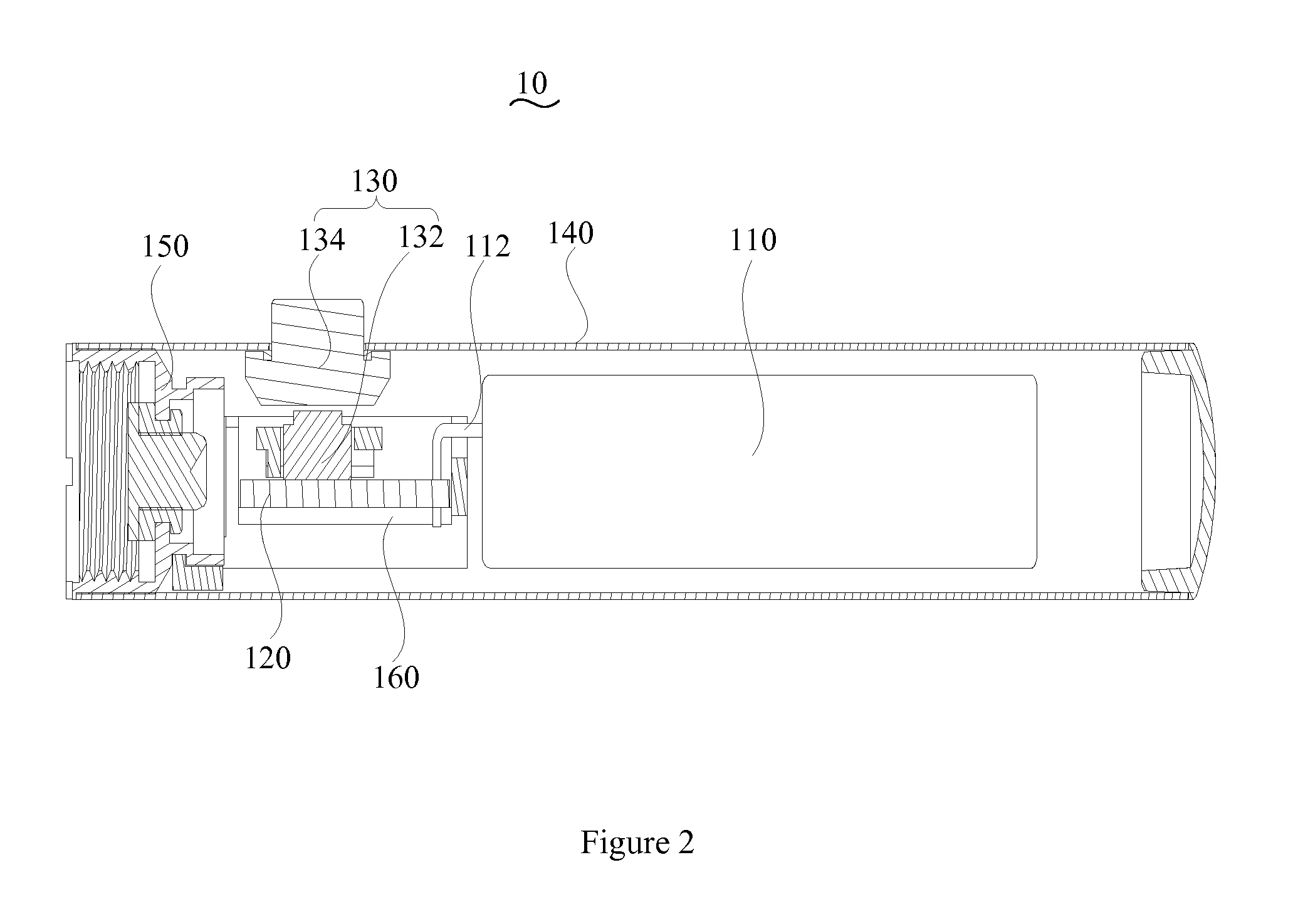

Electronic cigarette

InactiveUS9414628B2Simplify the assembly processImprove efficiencyTobacco devicesElectronic cigaretteEngineering

An electronic cigarette is provided, which comprises a battery component. A battery, a PCB board and a press-key switch are provided in the battery component, and the press-key switch is set on the PCB board. An end face of the battery is located opposite one end face of the PCB board. A first electrode pin and a second electrode pin are provided on one end face of the battery, wherein the end face of the battery is adjacent to the PCB board. A first socket and a second socket are provided at one side of the PCB board, wherein the side of the PCB board is adjacent to the battery. The first electrode pin is inserted and soldered in the first socket, and the second electrode pin is inserted and soldered in the second socket.

Owner:HUIZHOU KIMREE TECH

Method for fabricating semiconductor package substrate with plated metal layer over conductive pad

ActiveUS7041591B1Easy to oxidizeElectrical connectionElectrolysisSemiconductor/solid-state device detailsResistSolder mask

A method for fabricating a semiconductor package substrate having a plated metal layer on a conductive pad is proposed. First of all, a first resist layer is formed on a semiconductor package substrate having a plurality of traces and conductive pads on a surface thereof. The first resist layer is provided with at least an opening, such that the opening is able to contact the adjacent trace. Subsequently, a conductive film is formed in the opening, such that the conductive film can electrically connect the adjacent trace and conductive pad. After removing the first resist layer, a second resist layer having a plurality of openings is formed on the surface of the substrate to expose the conductive pad. Afterwards, an electroplating process is performed on the substrate, so that a metal layer is formed on an exposed surface of the conductive pad. The second resist layer and the conductive film are then removed from the substrate. A solder mask layer having a plurality of openings is also formed on the surface of the substrate to expose the conductive pad which has been covered by the metal layer using the electroplating process.

Owner:PHOENIX PRECISION TECH CORP

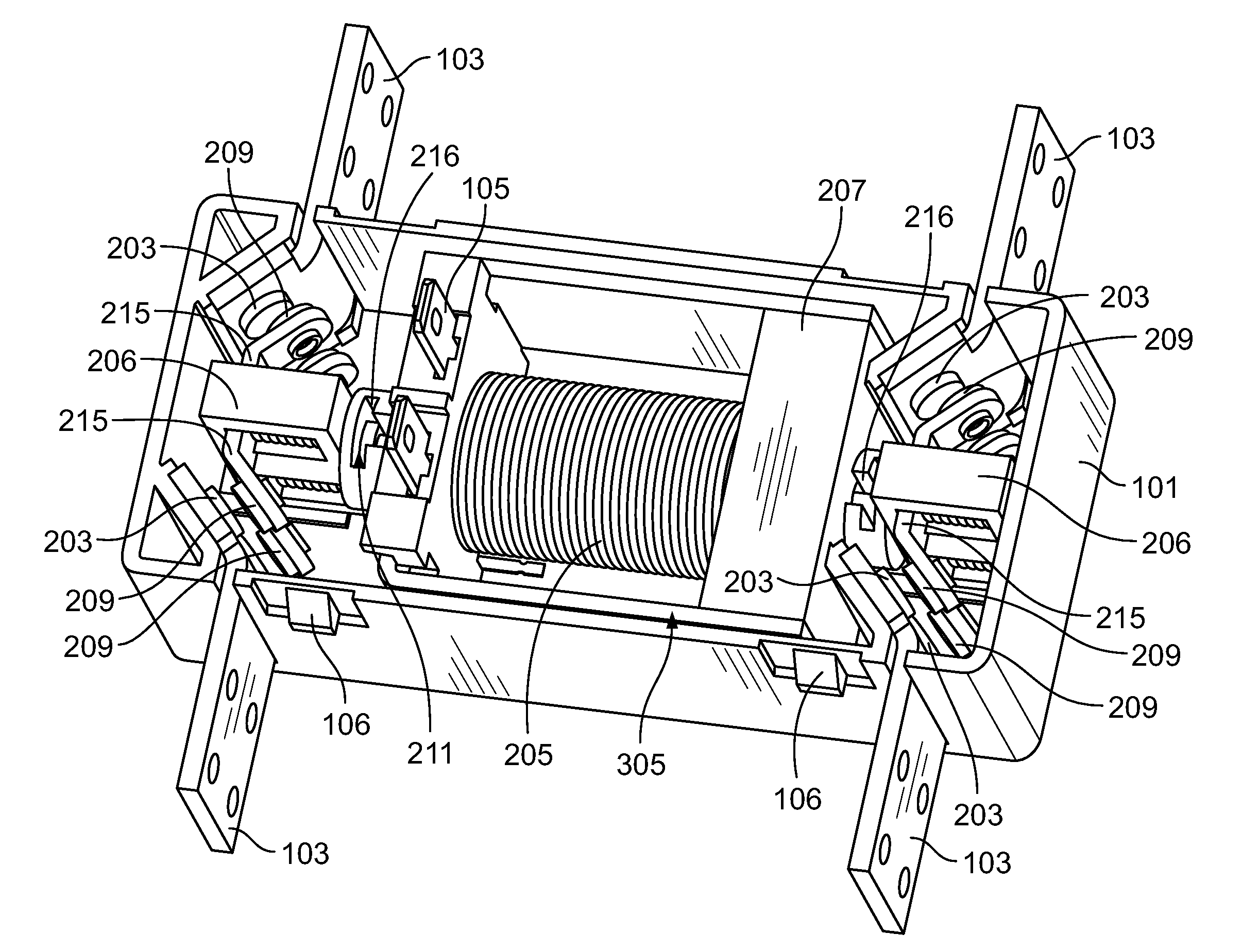

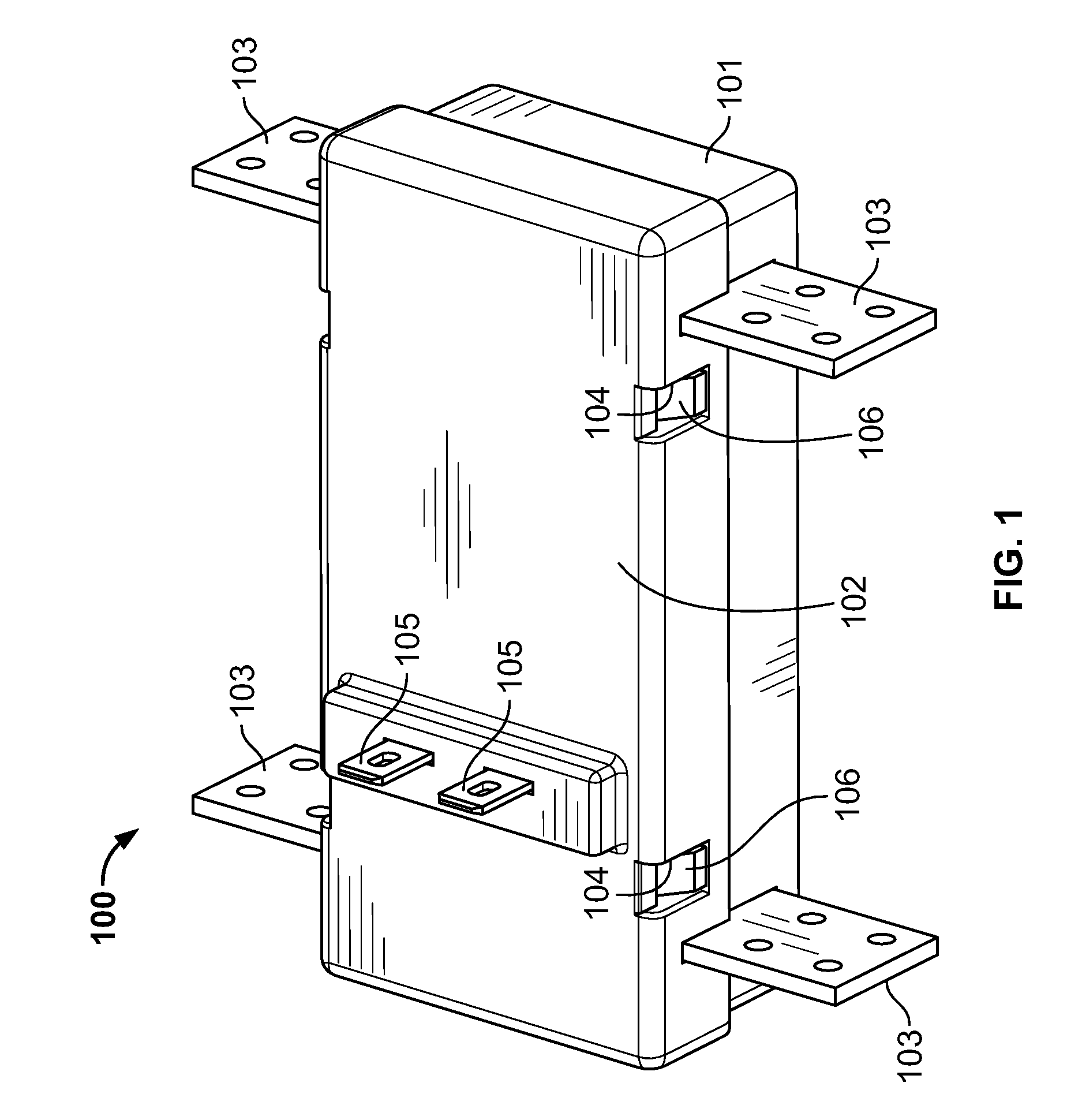

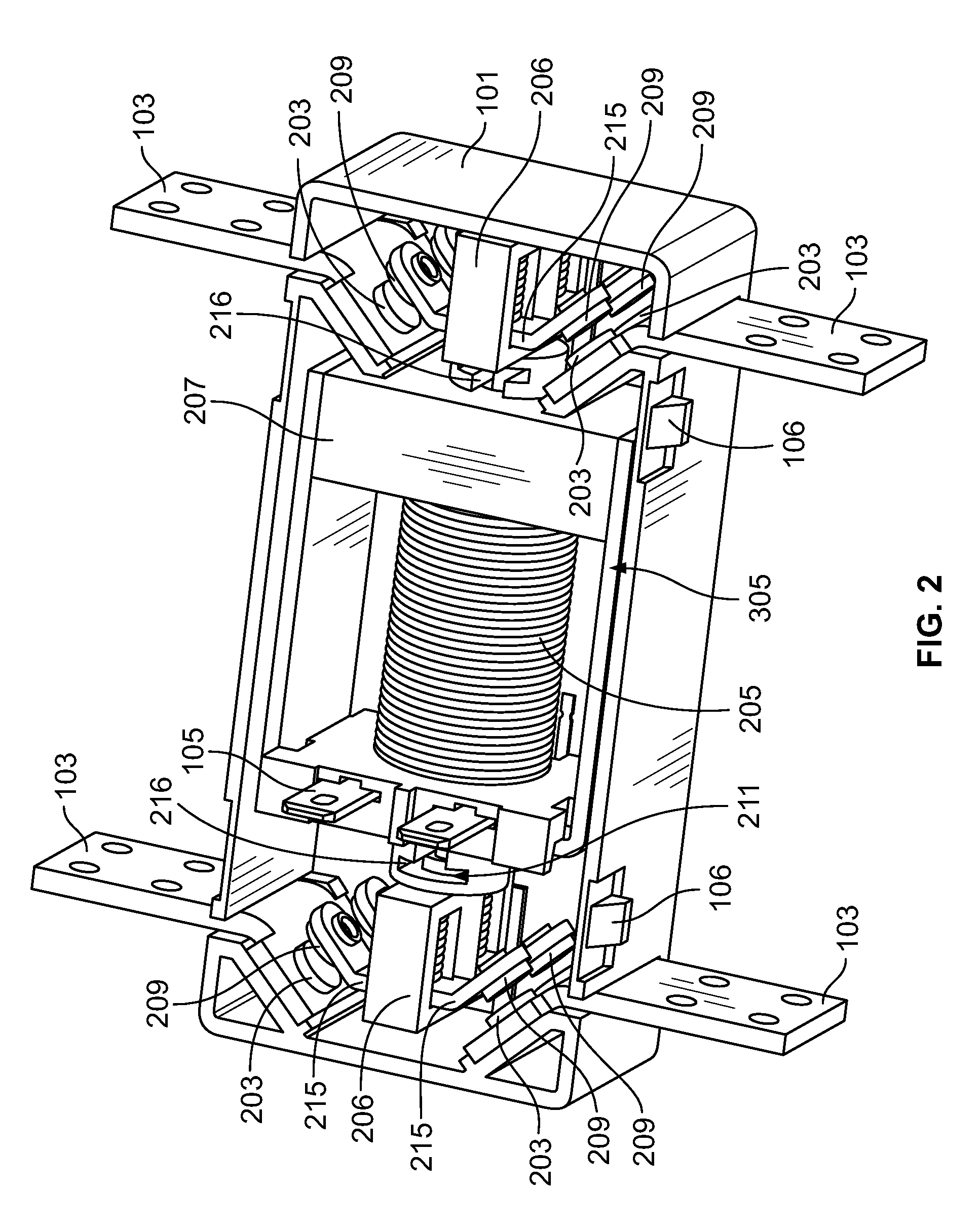

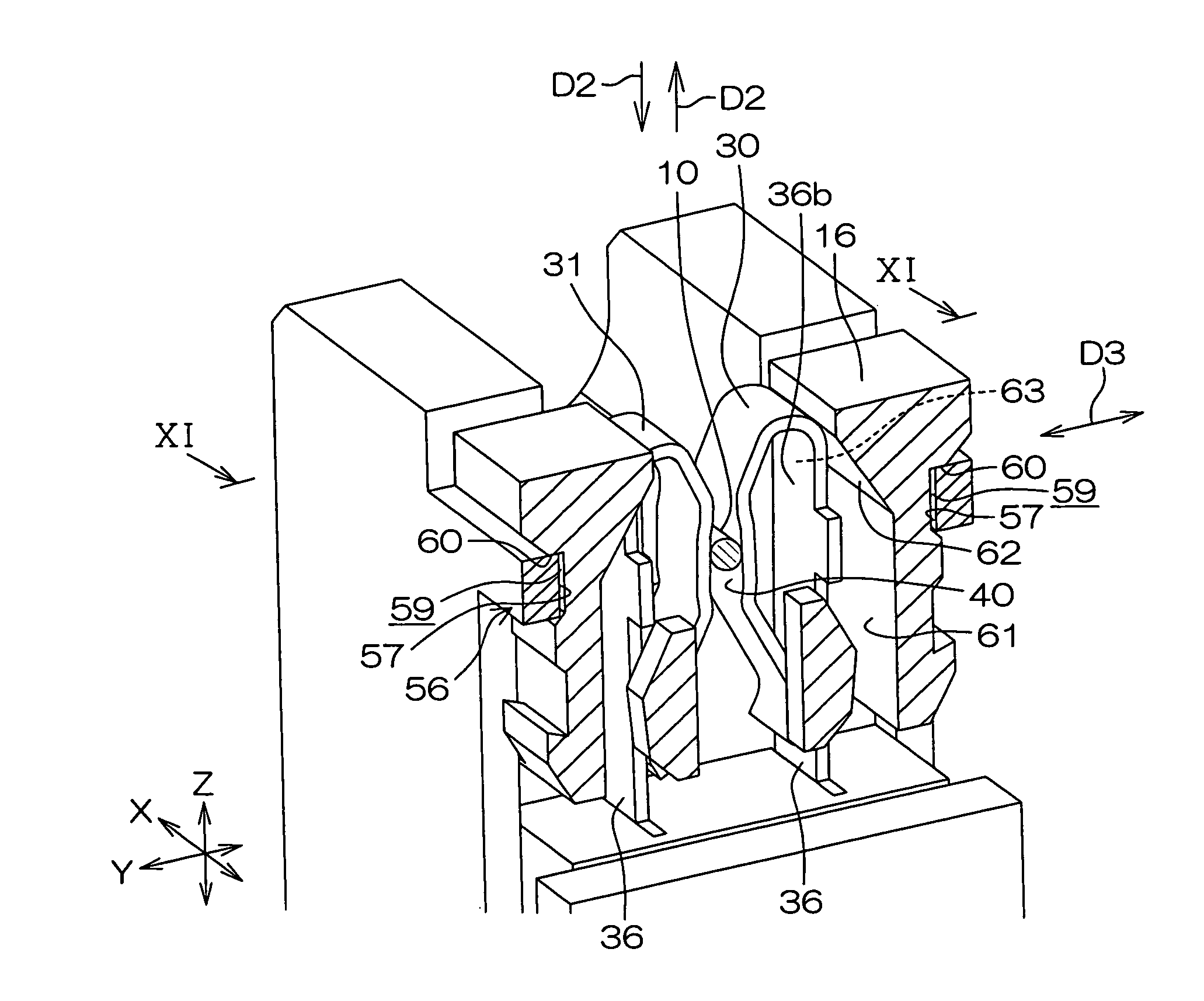

Switching device

ActiveUS20100026427A1Low costEasy to produceContact mechanismsElectromagnetic relay detailsLinear motionMotor drive

The invention is directed to a switch assembly which can be used in situation in which the switch accommodates the flow of high voltage current. An actuator assembly with moveable contacts is moved by a motor driven armature. The moveable contacts are in electrical engagement with the stationary contacts when the armature is in the first position, and the moveable contacts are spaced from the stationary contacts when the armature is in the second position. By angling the stationary contacts and moveable contacts, the linear motion of the armature causes the moveable contacts to move across the surface of the stationary contacts as the armature approaches the first position. As all of the movements of the assembly are in a direction parallel to the axis of the armature, the assembly can be manufactured and operated reliably in a relatively small space. In addition, the linear movement on the angled contact provides for a positive electrical connection even in adverse environments.

Owner:TYCO ELECTRONICS LOGISTICS AG (CH)

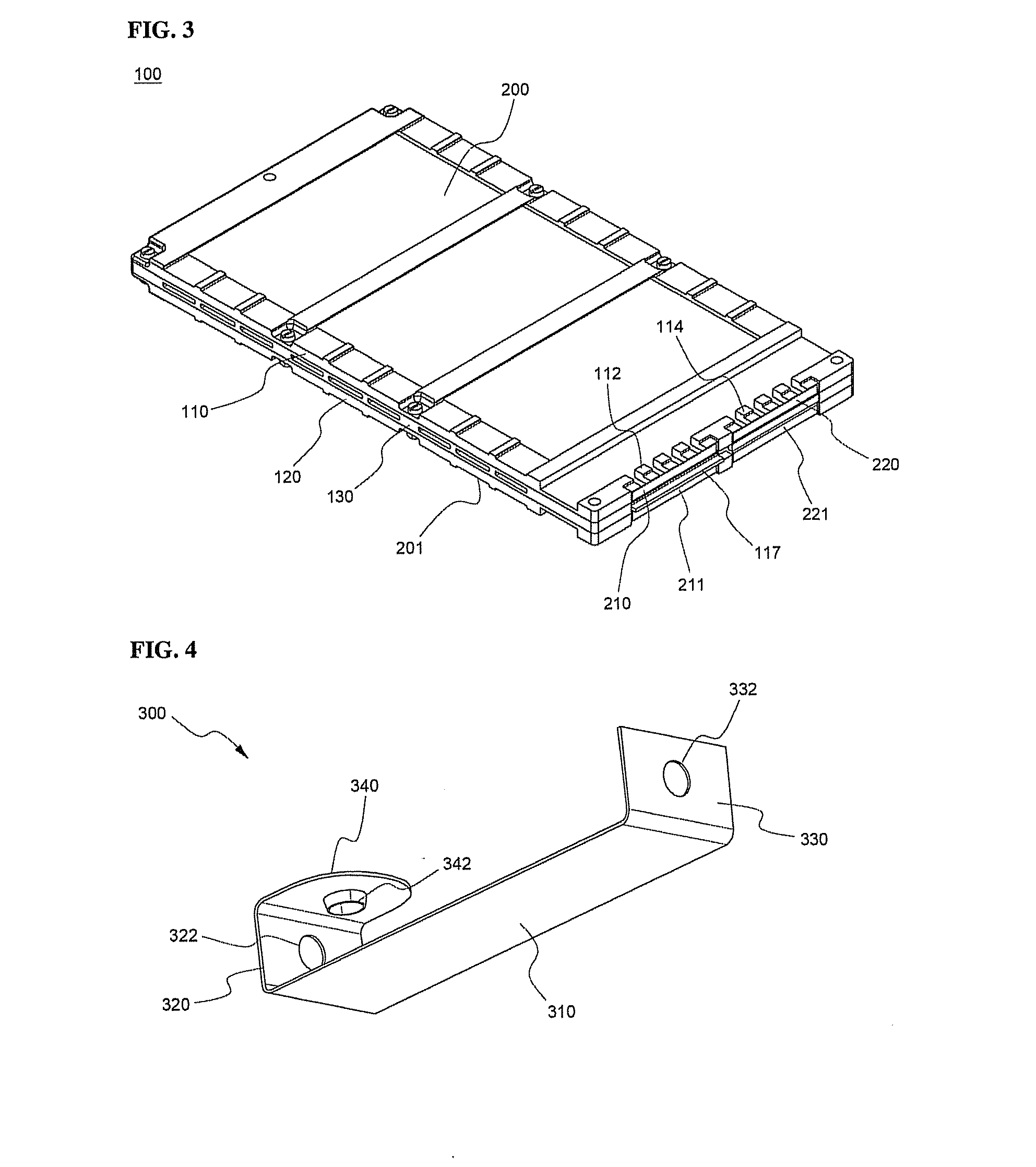

Novel bus bar for electric connection and middle and battery module comprising the same

ActiveUS20080199765A1Simplifies electrical connectionsImprove featuresSingle bars/rods/wires/strips conductorsCells structural combinationElectrical resistance and conductanceElectricity

Disclosed herein are a bus bar that simultaneously performs the electrical connection between a plurality of unit cells and the detection of voltage of the unit cells in a battery module having the unit cells mounted therein, wherein the bus bar includes: vertical bent parts formed by bending opposite ends of a strip-shaped bar body in the same direction, respectively, the vertical bent parts being provided with coupling grooves or protrusions; and a horizontal bent part formed by bending one of the vertical bent parts such that the horizontal bent part is parallel with the bar body, and a medium- or large-sized battery module including a plurality of unit cells, wherein the electrical connection between the unit cells and the detection of voltage of the unit cells are simultaneously performed using the bus bar. It is not necessary to use additional connecting members for detecting the voltage of unit cells when the bus bar according to the present invention is used in a battery module or a battery pack. Consequently, the battery module or the battery pack can be manufactured in a compact structure. Also, the electrical connection and the mechanical coupling are easily accomplished in spite of the compact structure. Furthermore, the electrical characteristics, such as electrical resistance at connected regions after the electrical connection, and the mechanical strength against external impacts or vibrations are excellent. In addition, it is possible to prevent occurrence of short circuits, which may be caused by a user or an operator, during a manufacturing process of the battery module or the battery pack or during a maintenance process of the battery module or the battery pack.

Owner:LG ENERGY SOLUTION LTD

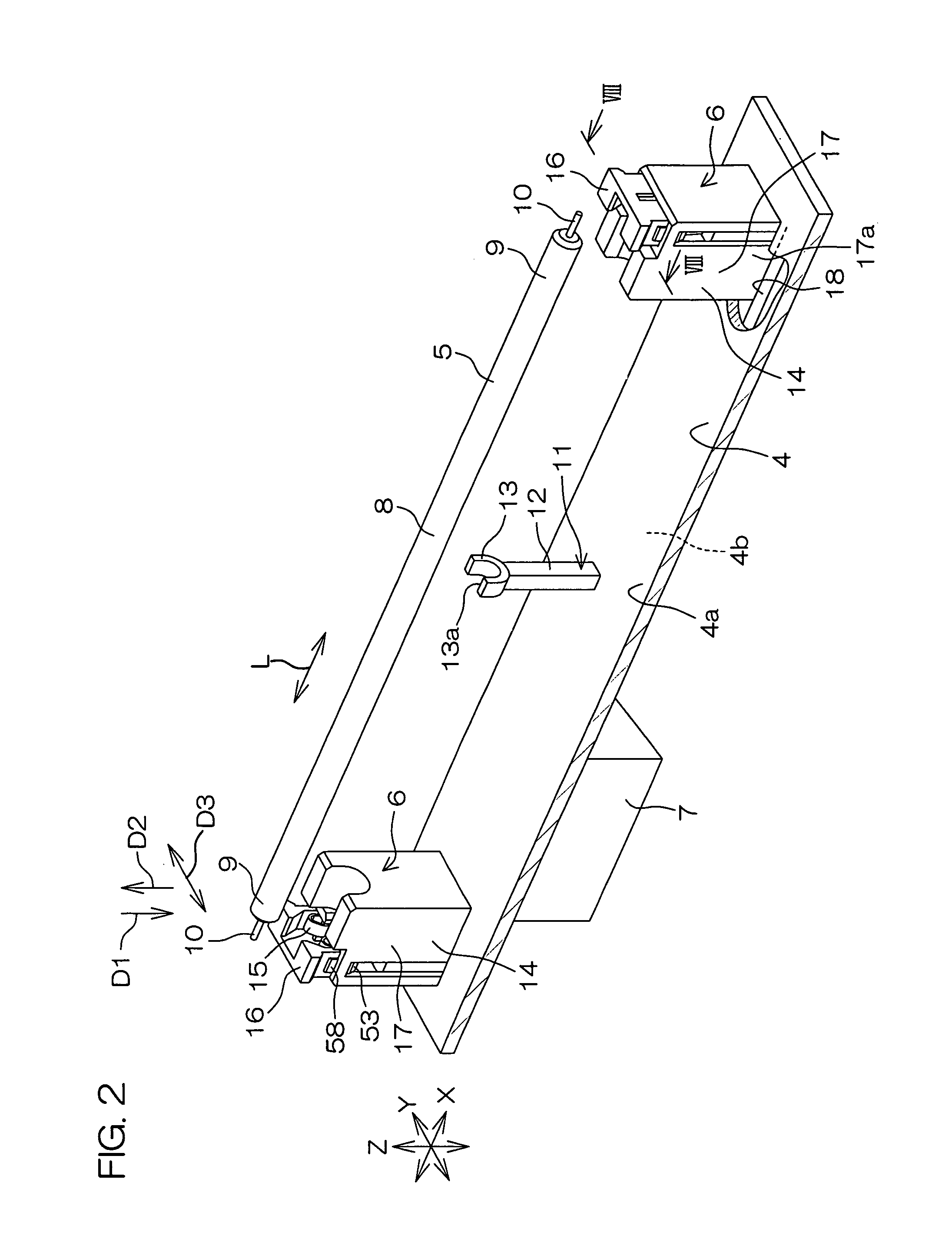

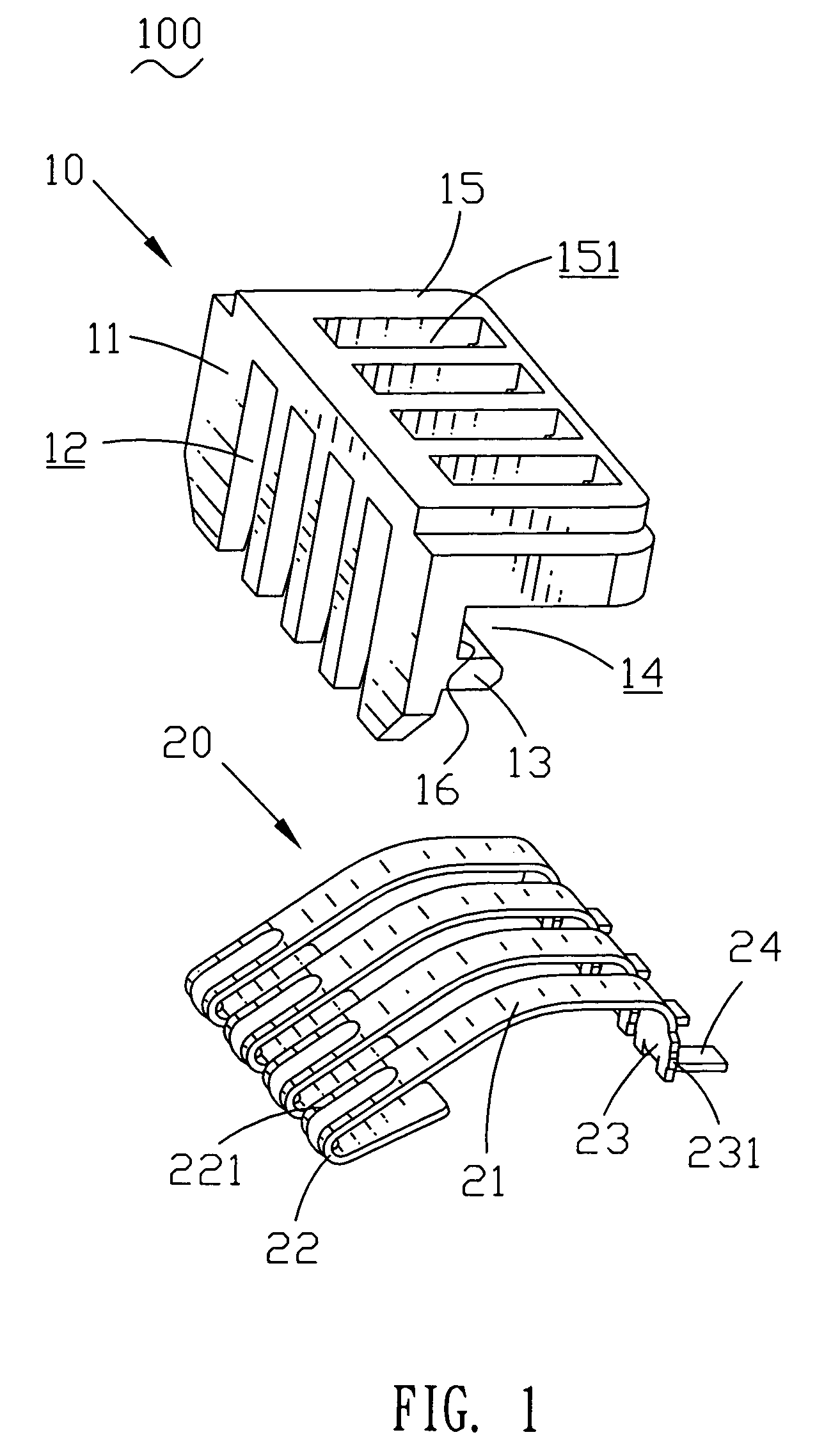

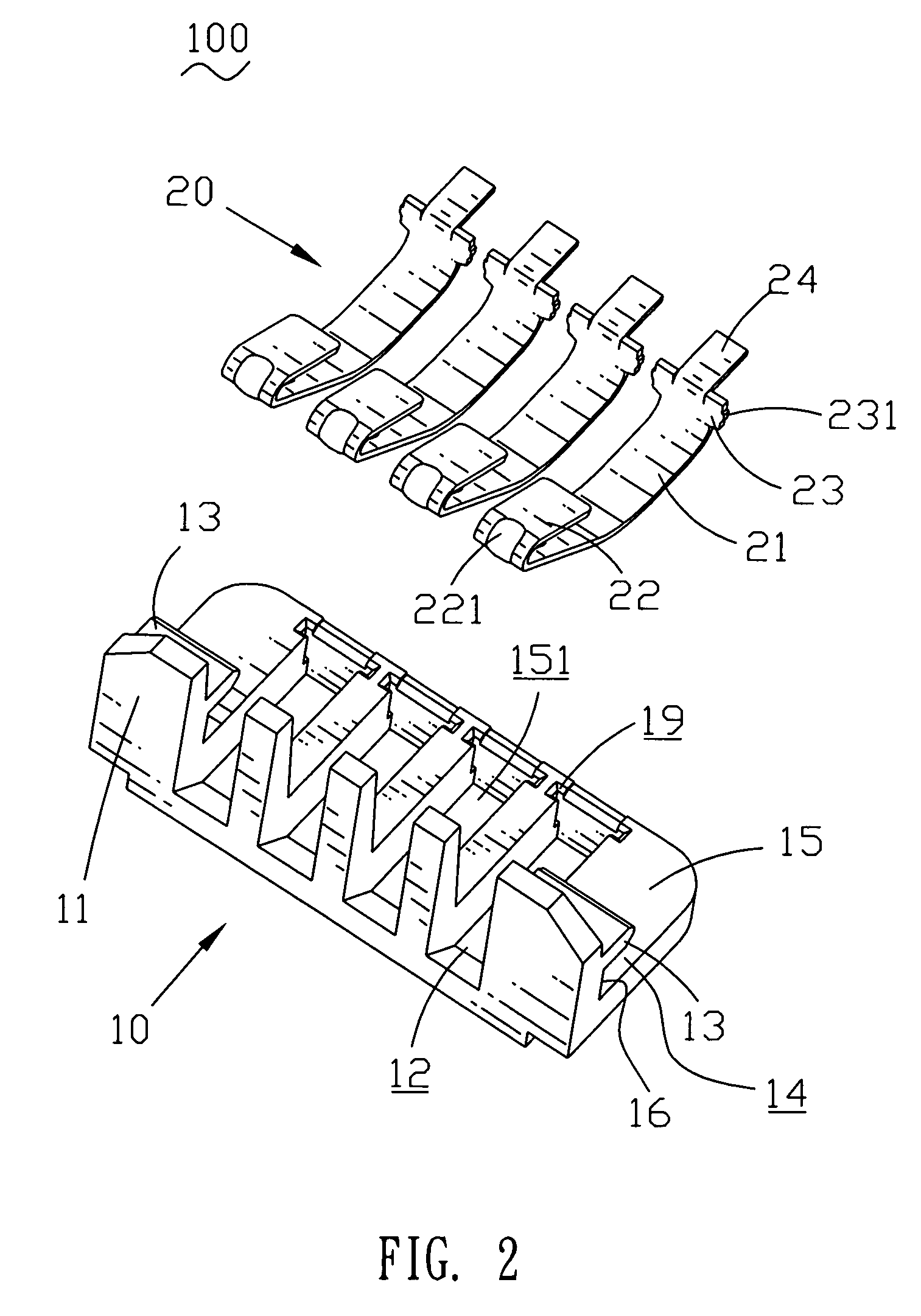

Electrical connector and liquid crystal display device

InactiveUS7344397B2Electrical connectionEasy to insertElectric discharge tubesCoupling contact membersLiquid-crystal displayEngineering

An electrical connector has a contact held by a housing and an operating member for operating the contact. The housing includes an insertion recess into which a shaft-like terminal is inserted along a first direction. A pair of elastic pieces of the contact respectively include clamp portions for clipping the terminal in predetermined clamping directions orthogonal to the first direction. The first direction is along a radial direction of the terminal. The operating member includes a widening operating portion for widening the distance between the clamp portions of the pair of elastic pieces.

Owner:JST MFG CO LTD

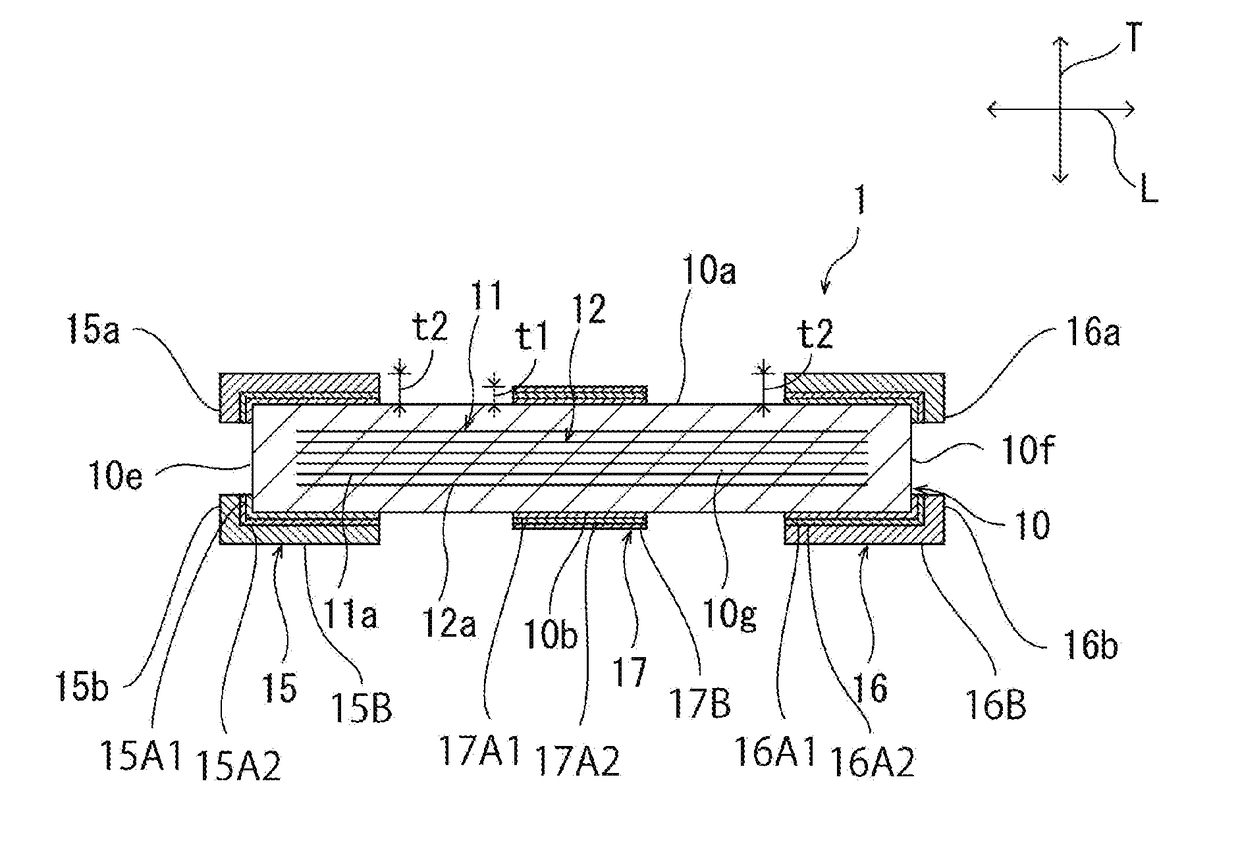

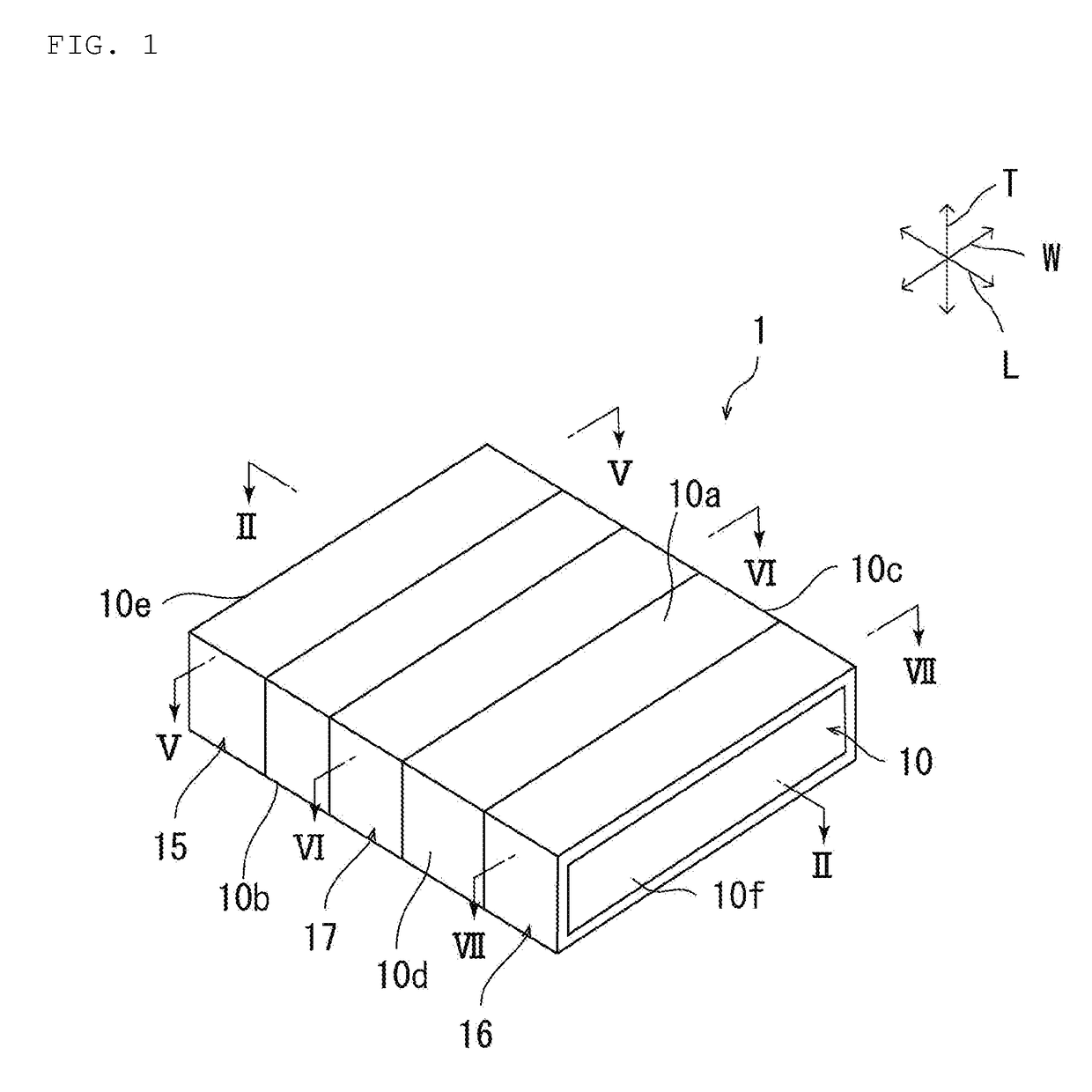

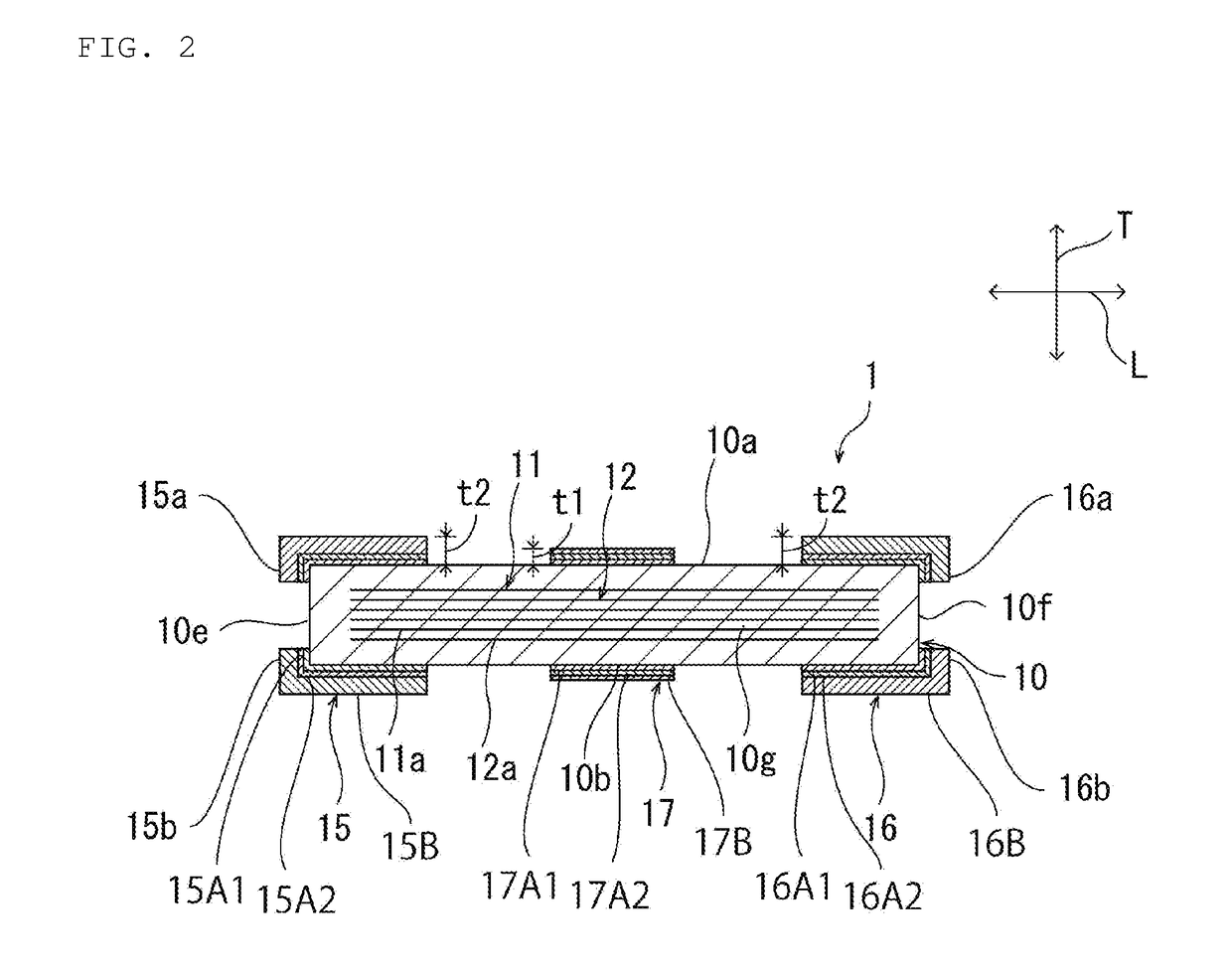

Ceramic capacitor

ActiveUS20170345566A1Low ESLReduce thicknessFixed capacitor electrodesFixed capacitor dielectricCeramic capacitorOptoelectronics

A ceramic capacitor which is low in ESL and suitable for being built into a substrate includes a first external electrode, a second external electrode and a third external electrode. Each of the first, second and third external electrodes include a sputtering electrode film. Each of the outermost layers of the first, second and third external electrodes contains Cu.

Owner:MURATA MFG CO LTD

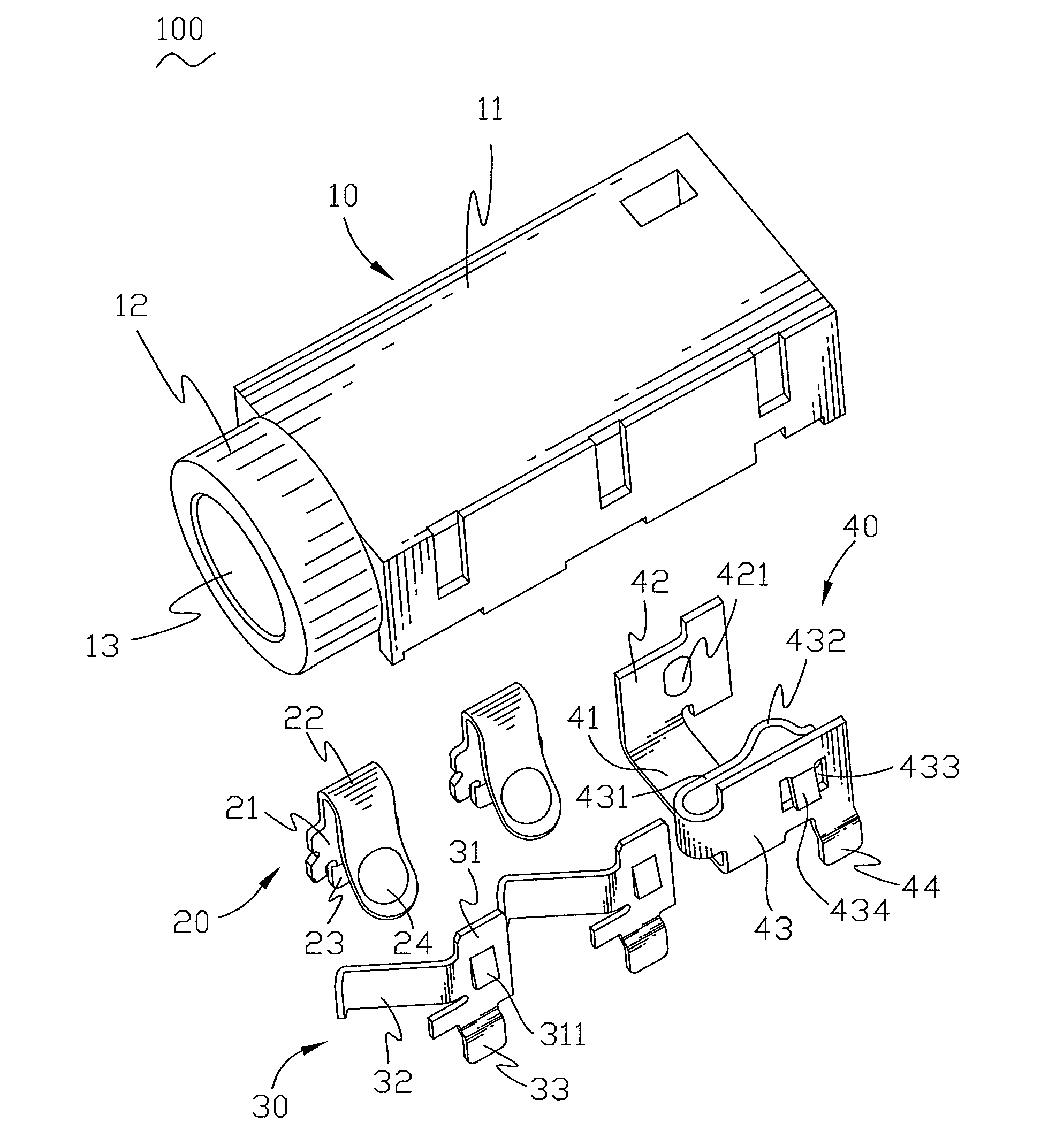

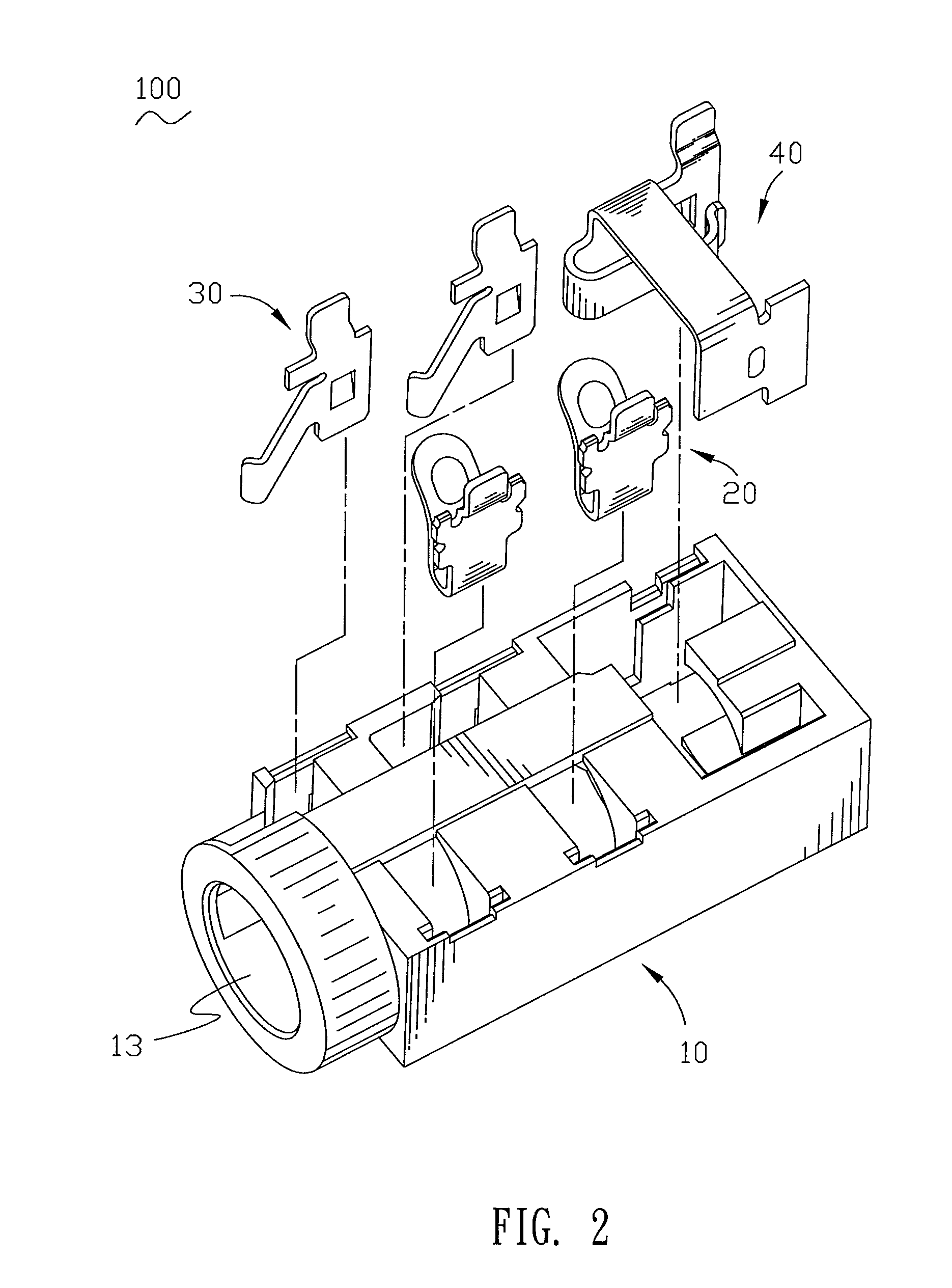

Audio jack connector

InactiveUS7789712B1Electrical connectionCoupling device detailsTwo-part coupling devicesDielectricEngineering

An audio jack connector includes a dielectric housing and a plurality of contacts received in the dielectric housing. The dielectric housing defines an insertion hole therein for an audio plug inserted into. One of the contacts is located at a rear of the dielectric housing and includes a bottom plate, a first fixed plate and a second fixed plate respectively extended upward from two opposite ends of the bottom plate. A contact protuberance is protruded towards the second fixed plate from a portion of the first fixed plate. A flexible plate is extended from the second fixed plate to be located between the first and second fixed plates. The flexible plate defines a contact convex protruded towards the first fixed plate at a free end thereof. The contact protuberance and the contact convex are both projected into the insertion hole for contacting with the audio plug.

Owner:CHENG UEI PRECISION IND CO LTD

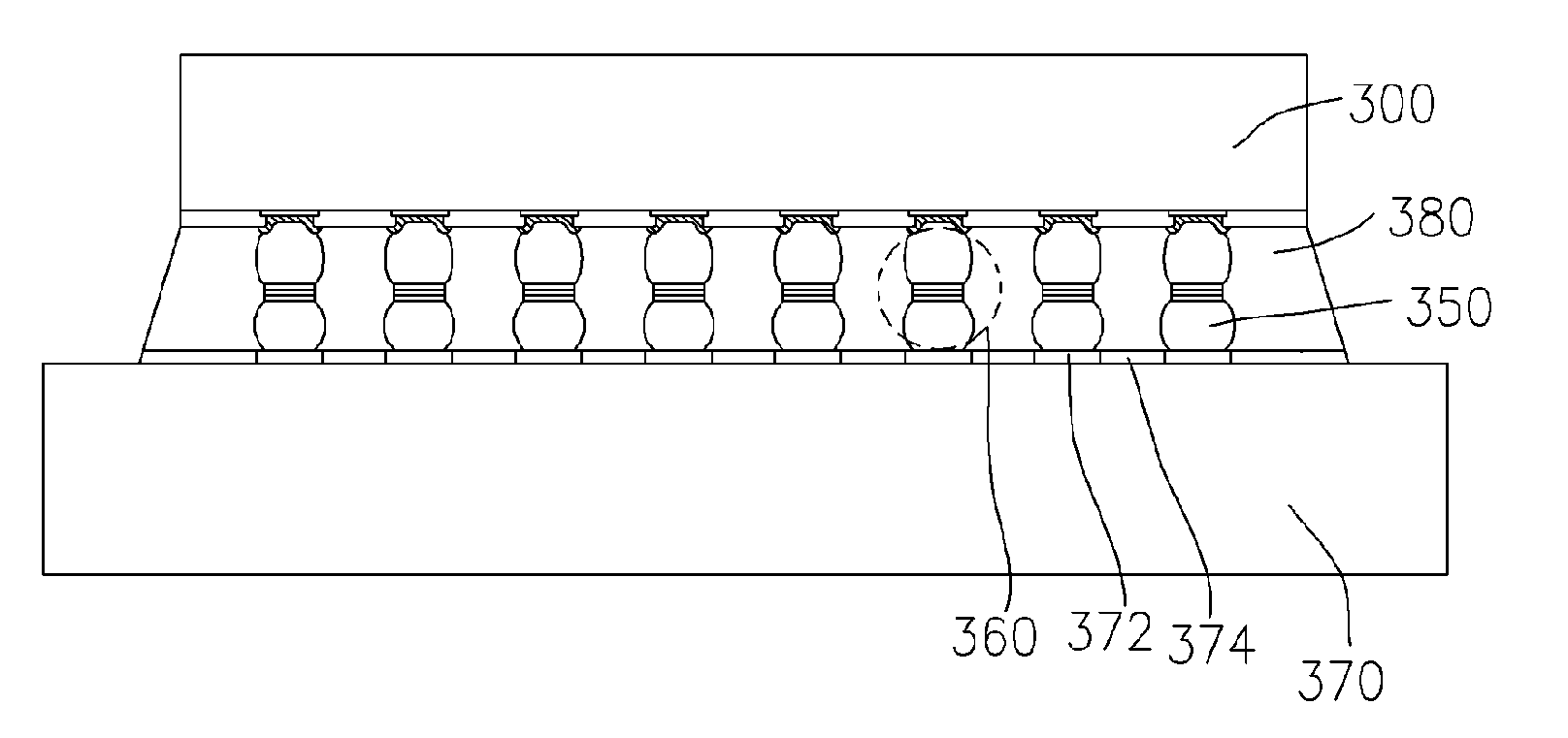

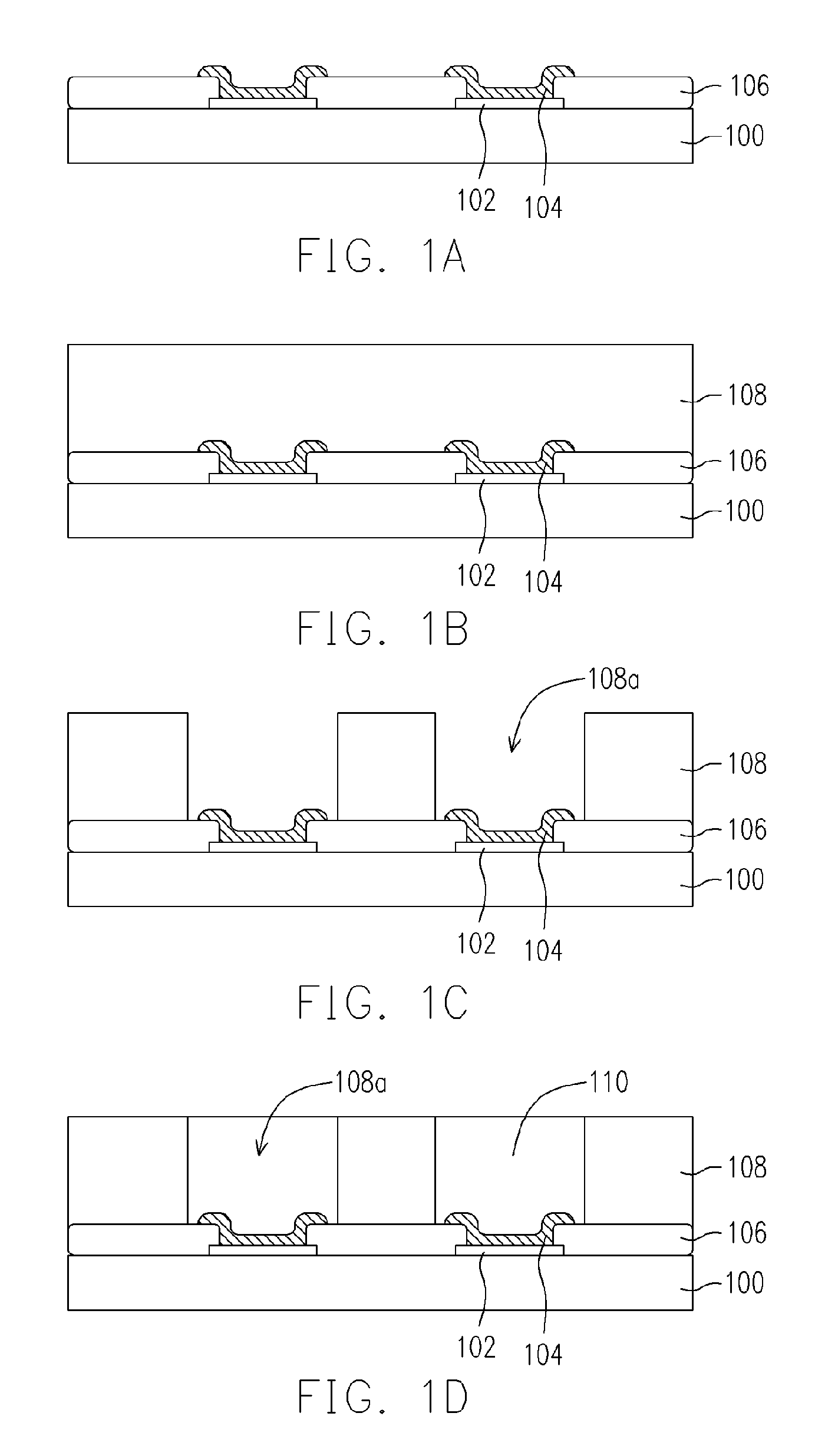

Bumping process, bump structure, packaging process and package structure

InactiveUS20050214971A1Electrical connection reliableIncrease heightPrinted circuit assemblingFinal product manufactureEngineering

A bumping process, a bump structure, a packaging process and a package structure are described. The bump structure comprises a first solder portion, a second solder portion and a conductive layer. The second solder portion is disposed on the first solder portion and the conductive layer is disposed between the first solder portion and the second solder portion. The bumping process produces a bump structure having a greater height. The bumping process can also be applied in a package process to form a package structure having a highly reliable connection between a chip and a packaging substrate.

Owner:ADVANCED SEMICON ENG INC

Bus bar for electric connection and middle and battery module comprising the same

ActiveUS7611798B2Simplifies electrical connectionsImprove featuresBus-bar/wiring layoutsSingle bars/rods/wires/strips conductorsPotential differenceElectrical connection

Owner:LG ENERGY SOLUTION LTD

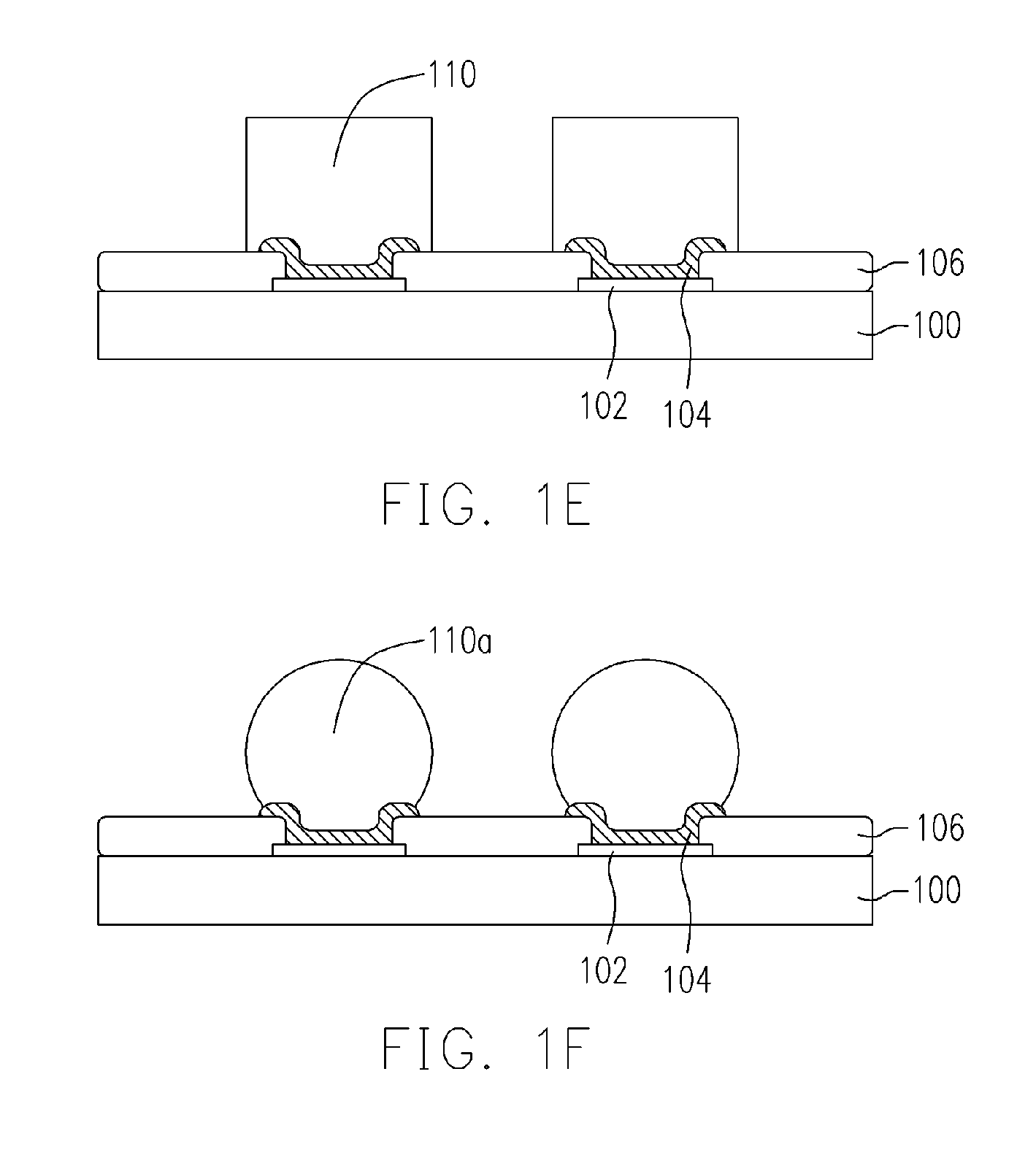

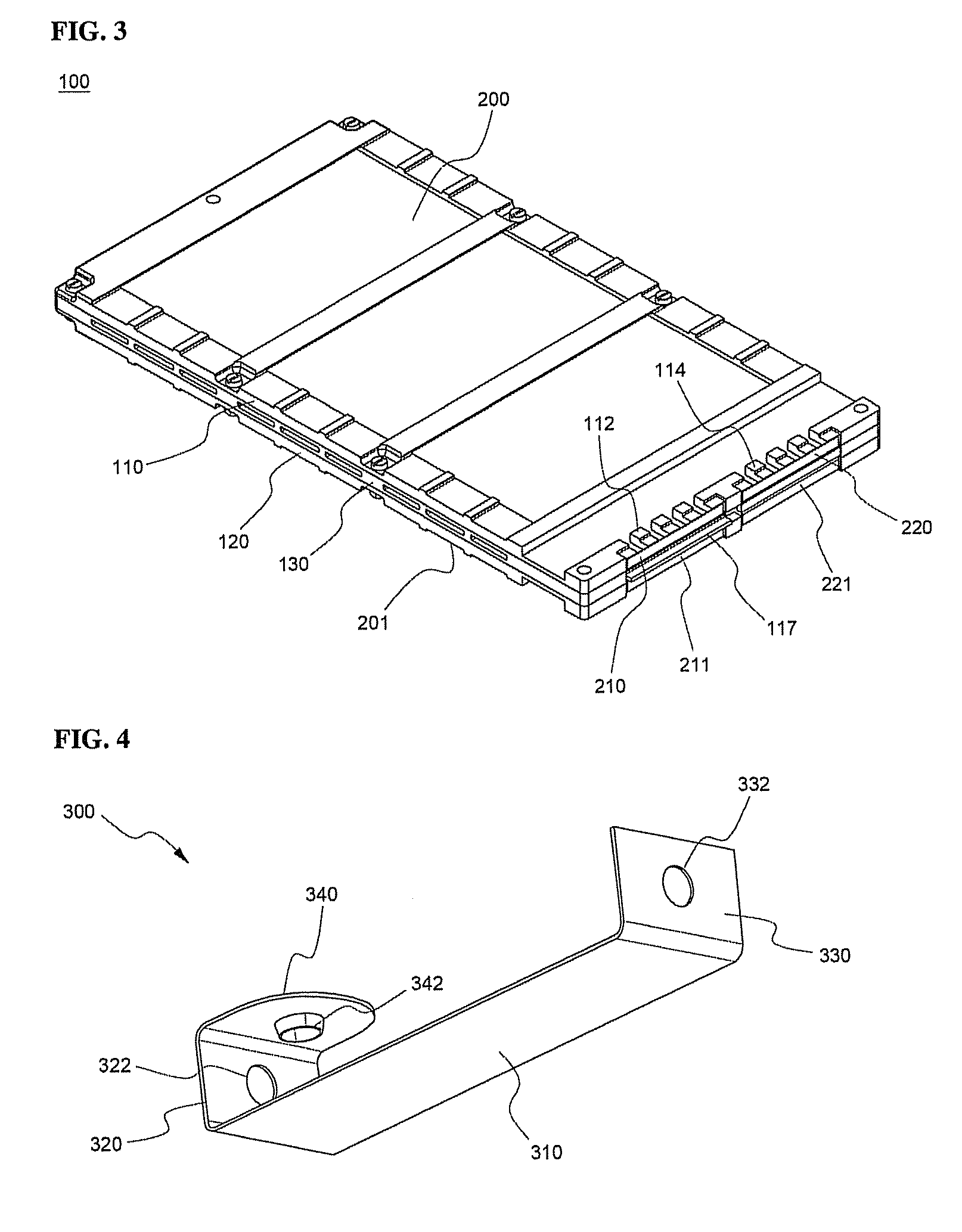

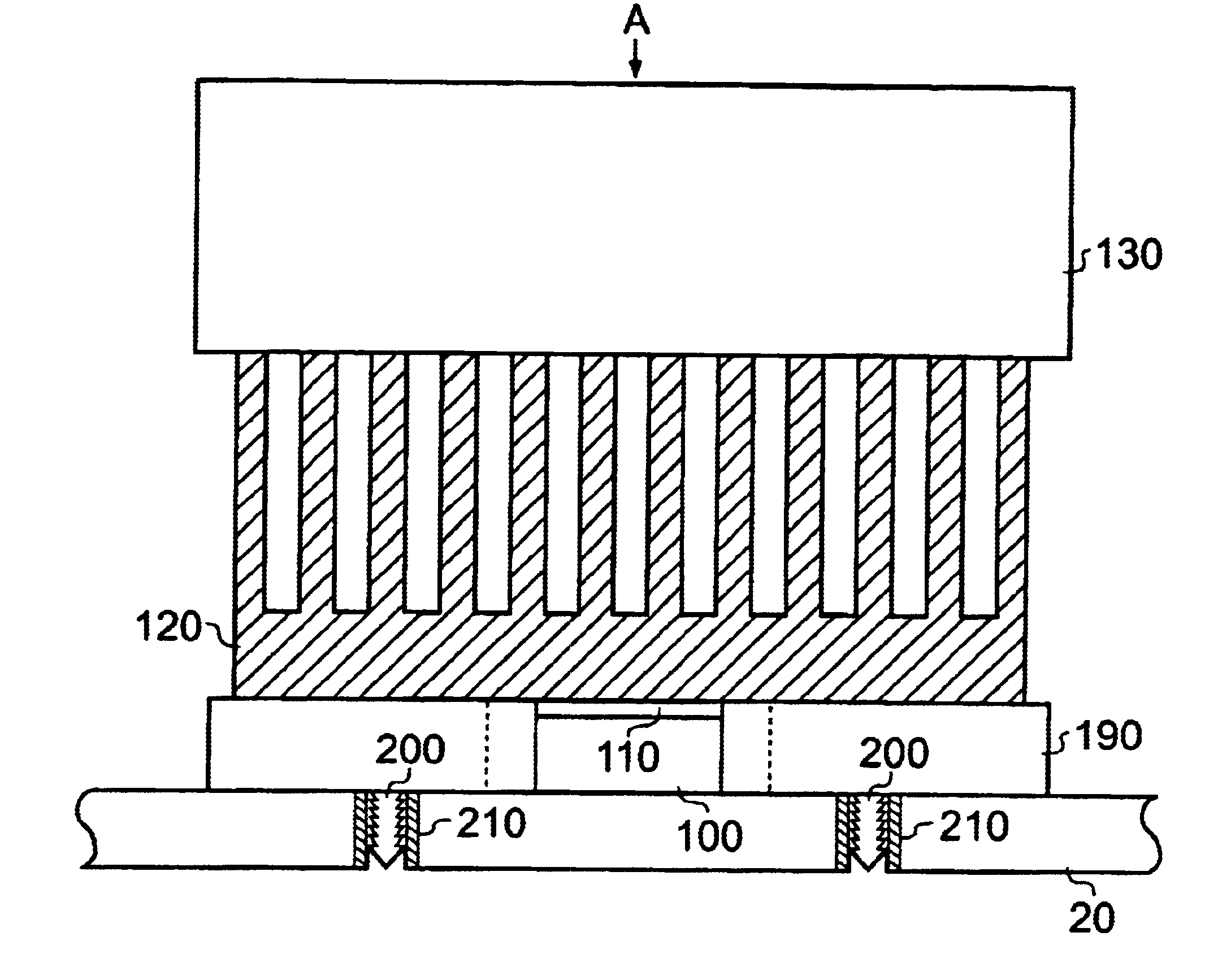

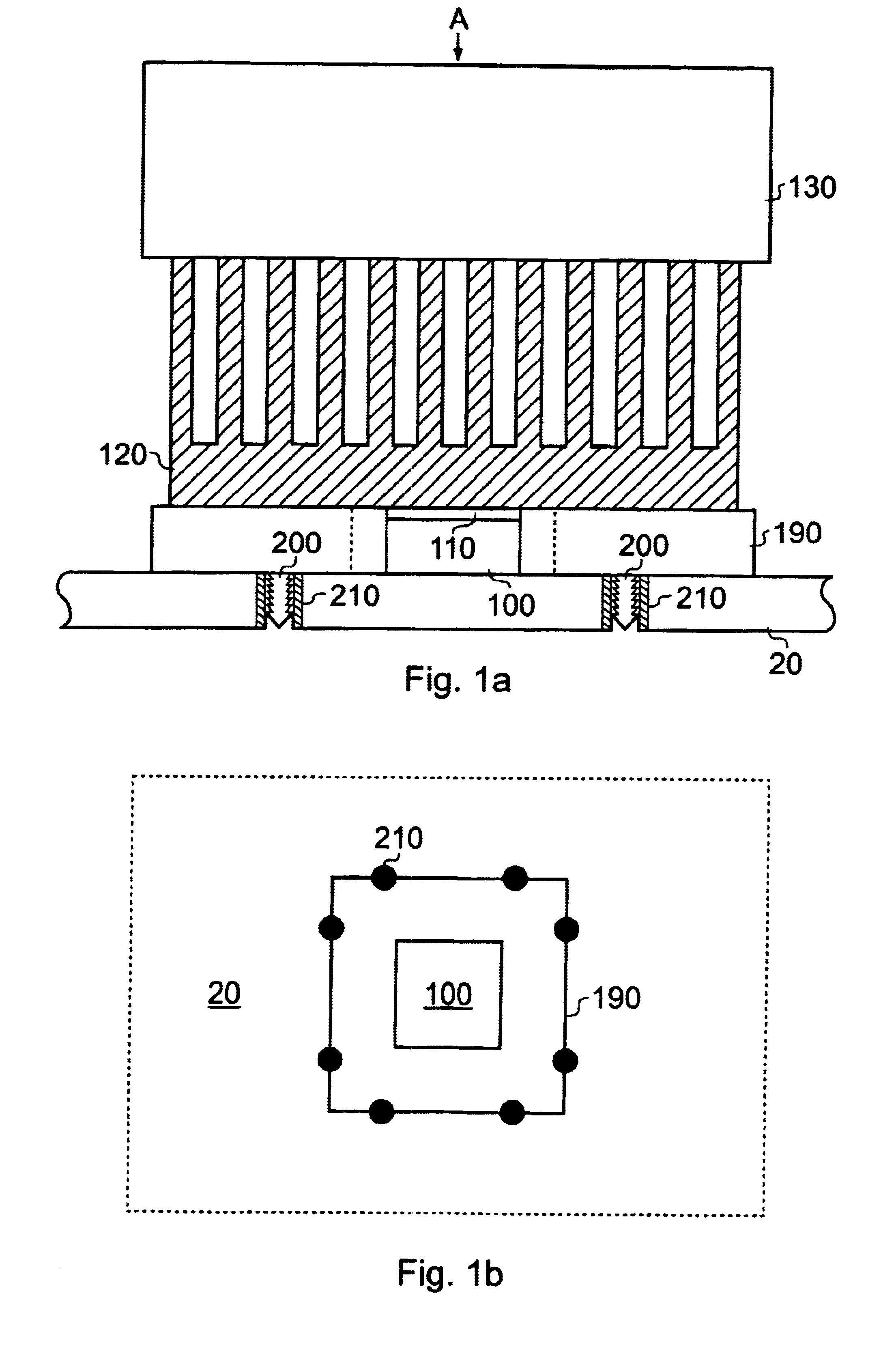

Grounding mechanism retention feature

ActiveUS6858796B1Easy to installElectrical connectionPrinted circuit assemblingMagnetic/electric field screeningElectrical connectionComputerized system

An electromagnetic (EM) shielding assembly includes an electrically conductive shielding portion and one or more electrically conductive protrusions for engaging with respective conductive apertures in a circuit board. The electrically conductive protrusions can be in electrical communication with the EM shielding portion. The protrusions can enable the EM shielding assembly to be attached to a circuit board in a computer system while also providing an electrical connection to logical ground. Further components, for example a heat sink that may be in electrical communication with the EM shielding portion, may thereby also be connected to logical ground.

Owner:ORACLE INT CORP

Printing fluid cartridge, printing apparatus, and use of printing fluid cartridge

Owner:BROTHER KOGYO KK

Electrical connector and liquid crystal display device

InactiveUS7530828B2Narrow distanceElectrical connectionAircraft componentsEngagement/disengagement of coupling partsLiquid-crystal displayElectrical connector

An electrical connector has a contact held by a housing and an operating member for operating the contact. The housing includes an insertion recess into which a shaft-like terminal is inserted in a first direction. A pair of elastic pieces of the contact respectively includes clamp portions for clamping the terminal in predetermined clamping directions orthogonal to the first direction. The first direction is in a radial direction of the terminal. The operating member includes widening operating portions for widening the distance between the clamp portions of the pair of elastic pieces.

Owner:JST MFG CO LTD

Electronic pressure-sensitive device for detecting the magnitude of load as electrical resistance

InactiveUS20020056918A1No deterioration in performanceBig burden to solveWeighing apparatus using elastically-deformable membersPedestrian/occupant safety arrangementElectrical resistance and conductanceElectrical contacts

Disclosed is an electronic pressure-sensitive device which has a long service life and which is capable of detecting with high accuracy loads of various magnitudes including values in proximity to zero. In the electronic pressure-sensitive device, first and second resistive element layers 2b and 6b are formed on the outermost surfaces of first and second contact portions 2 and 6, and the first and second resistive element layers 2b and 6b are constantly maintained in an electrical contact state, the force bringing the first and second resistive element layers 2b and 6b into press contact with each other being detected as the electrical resistance between the first and second contact portions 2 and 6.

Owner:ALPS ALPINE CO LTD

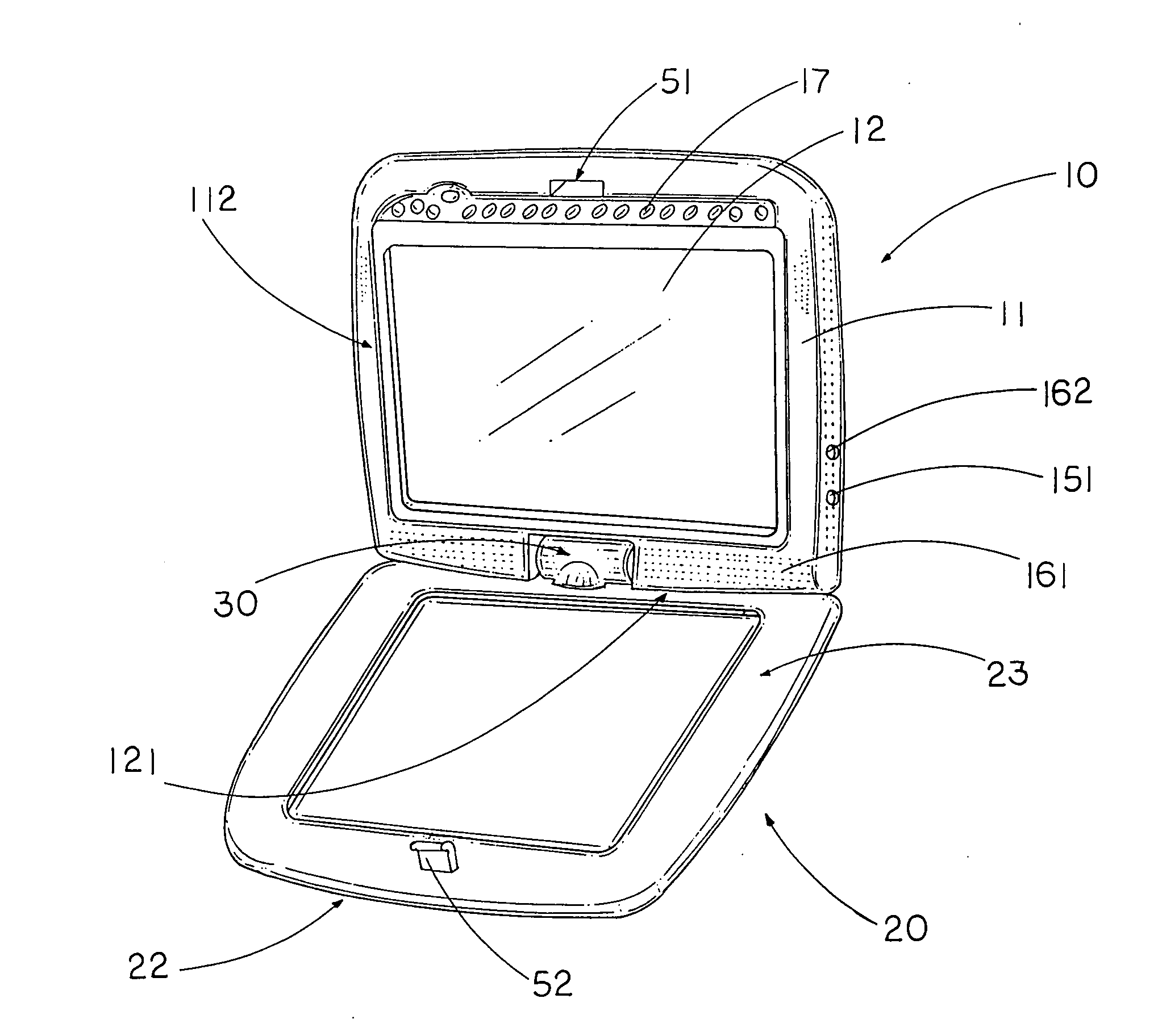

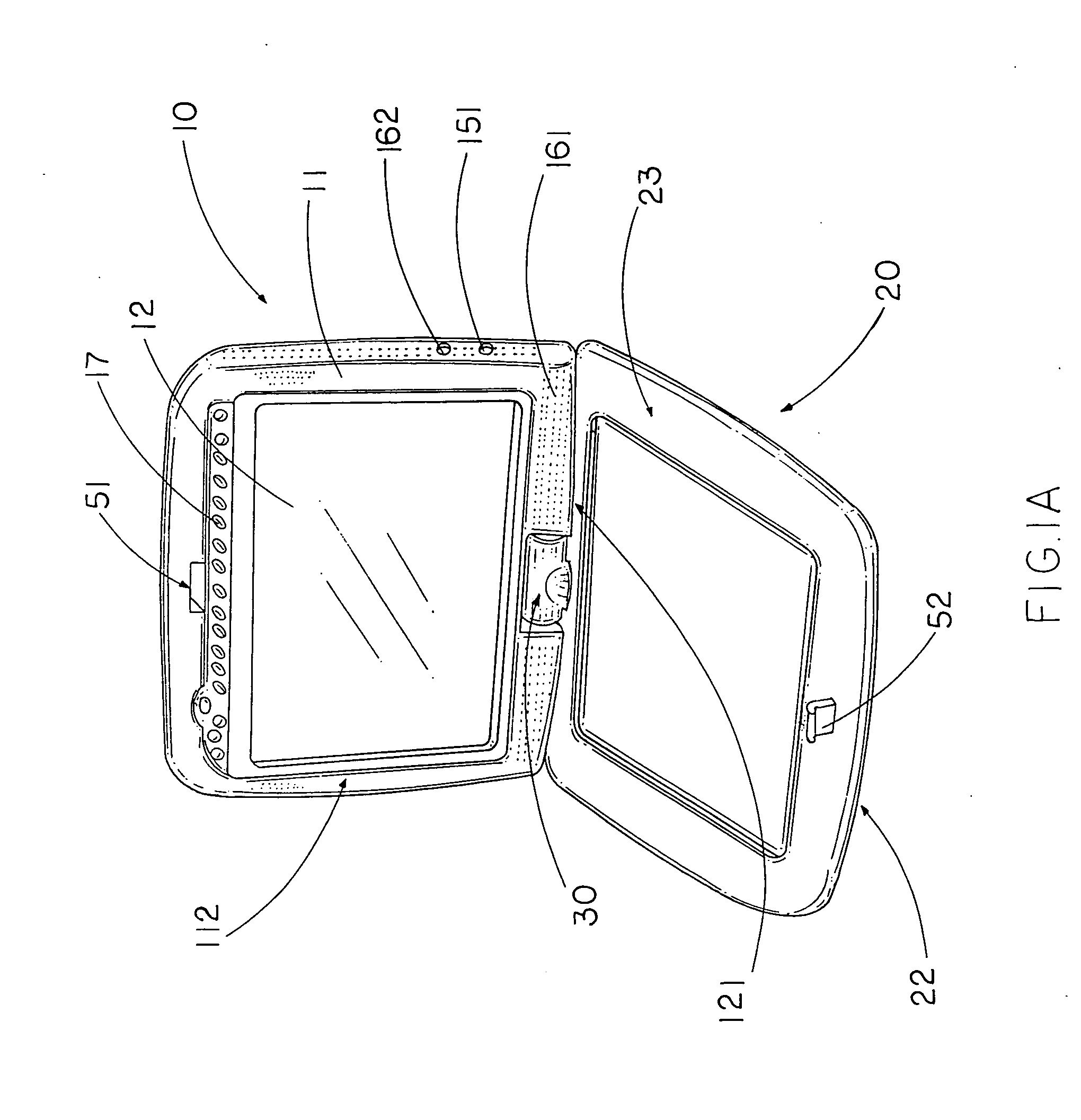

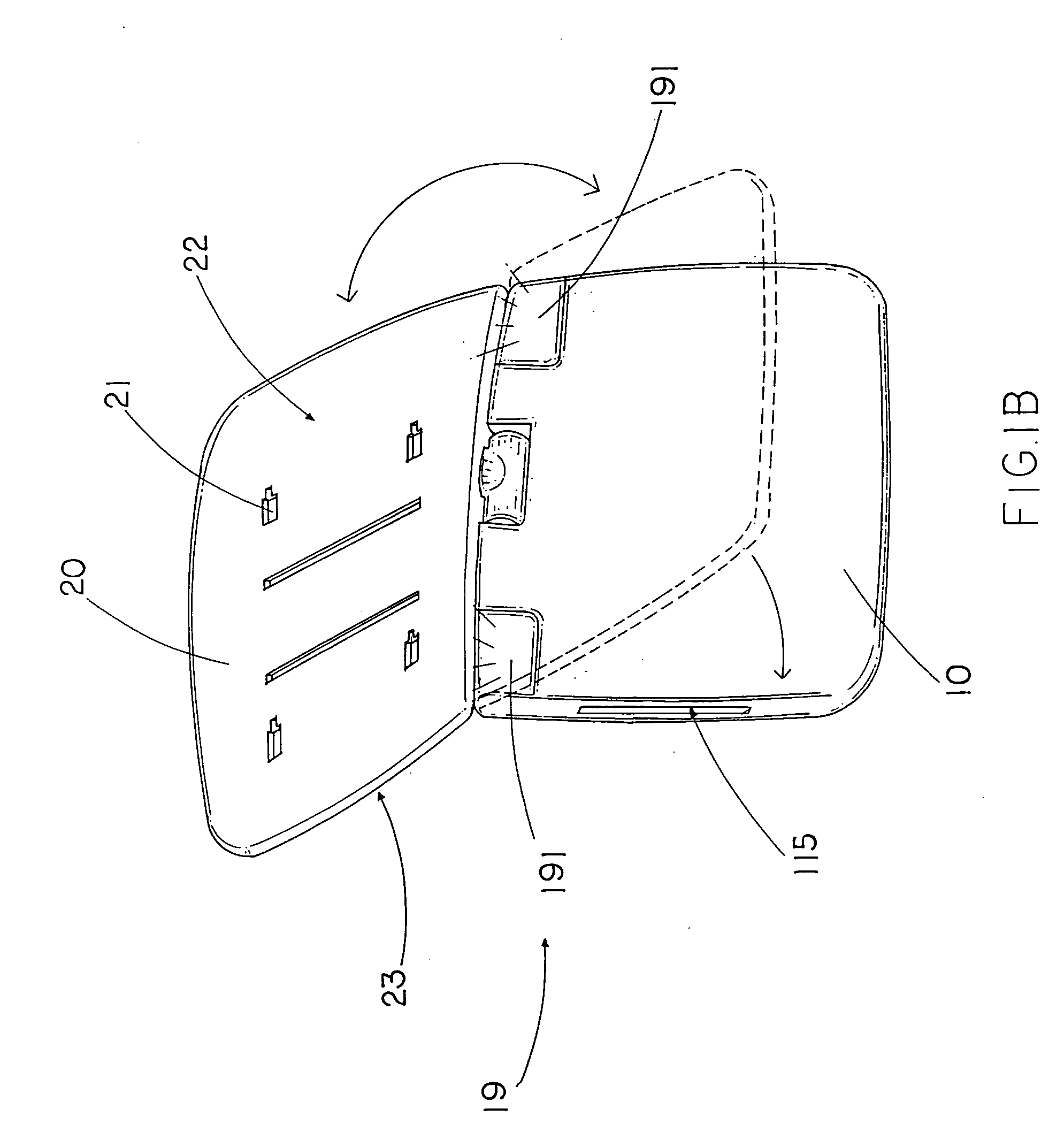

Universal entertainment system

InactiveUS20050047069A1Optimal display orientationImprove the display effectFurniture partsCabinetsDigital dataBiomedical engineering

A universal entertainment system includes an entertainment unit, a universal mounting stand, and a folding joint. The entertainment unit includes an entertainment housing having a multimedia compartment, a display screen provided on a screen side, and a multi-functional multimedia circuitry disposed in the multimedia compartment for reading digital data of a multimedia. The universal mounting stand is adapted for supporting at a fixture surface. The folding joint pivotally connects the entertainment unit with the universal mounting stand in a rotatably movable manner, wherein the entertainment unit is adapted to pivotally fold with respect to the universal mounting stand to selectively adjust a tilt angle of the display screen with respect to the fixture surface and is adapted to rotatably fold with respect to the universal mounting stand to selectively adjust a revolving angle with respect to the universal mounting stand.

Owner:INT SYST TECH

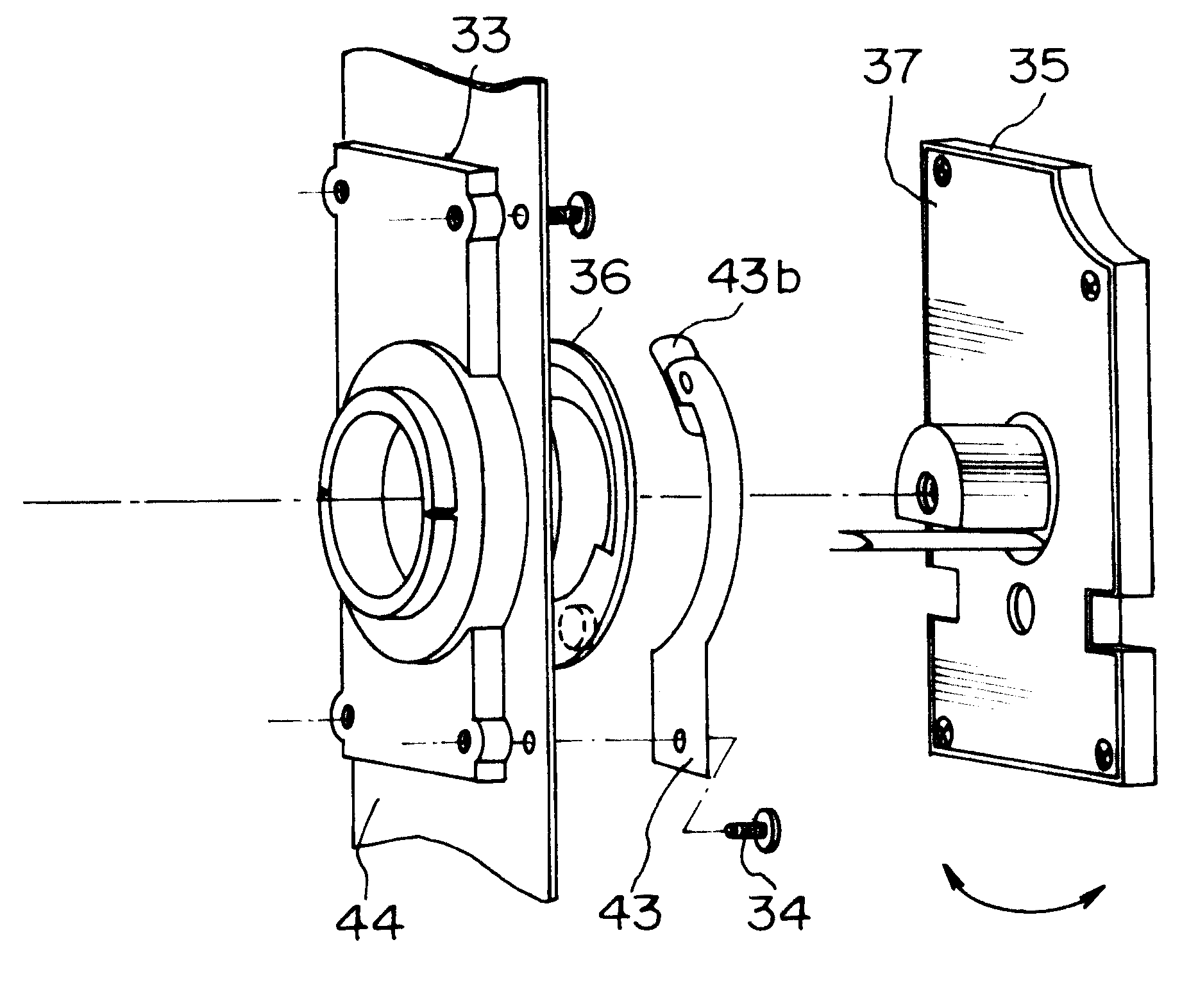

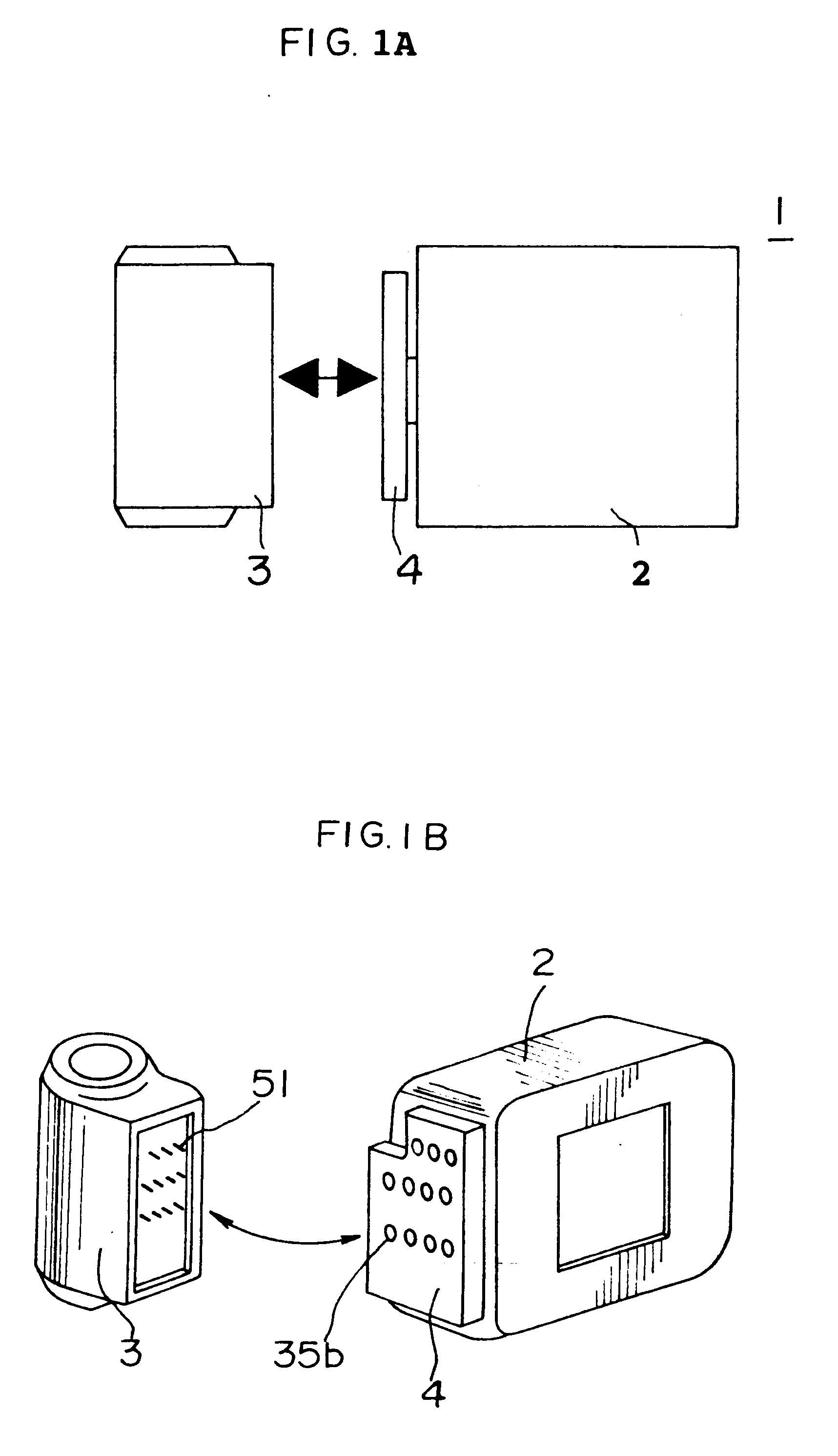

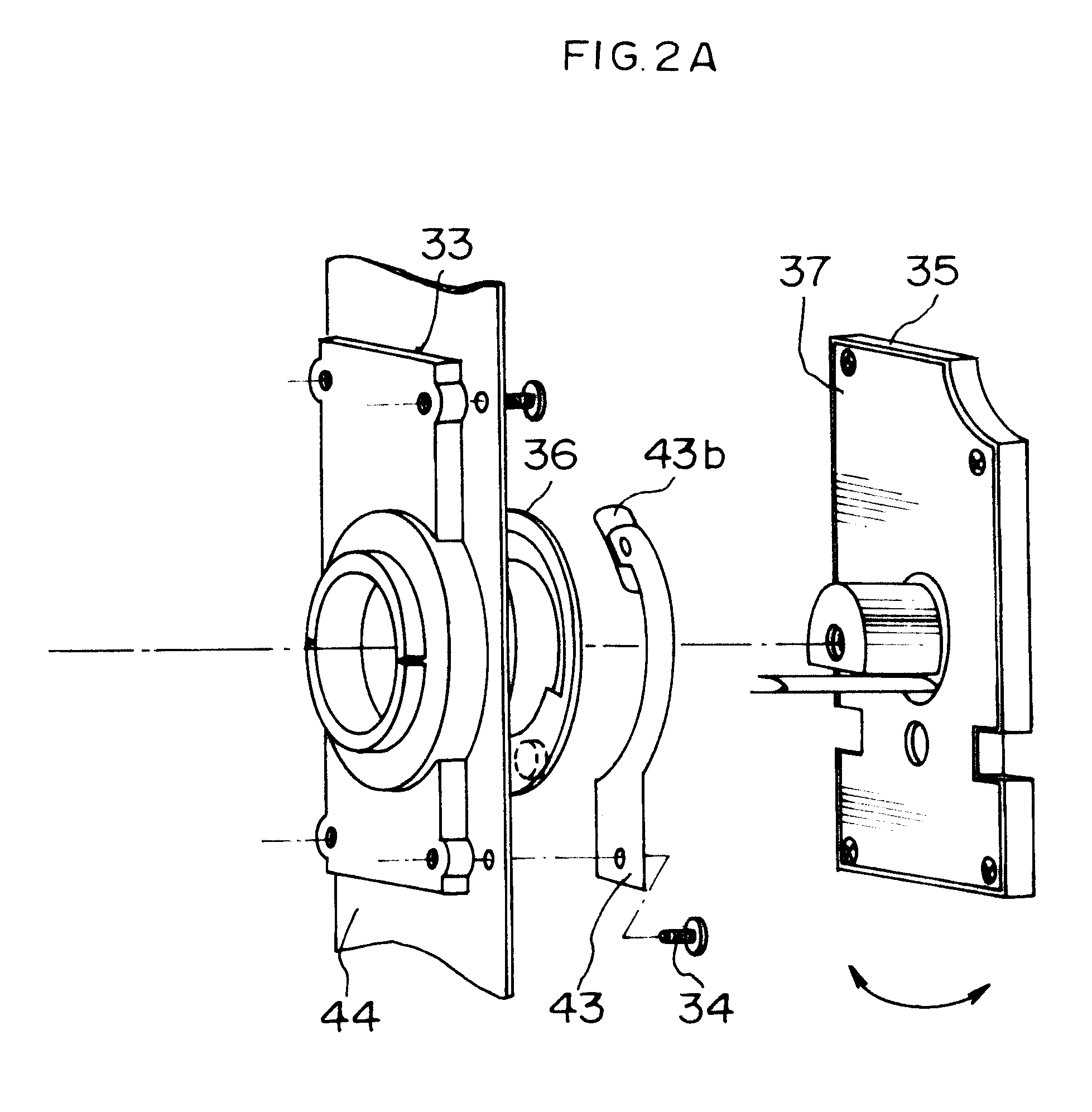

Image recording device having a ground connector

InactiveUS6249653B1Increases size of deviceReduce generationTelevision system detailsColor television detailsCamera lensElectricity

Camera body and taking lens unit are constructed such that they may rotate relative to each other, and circuit board of connector to which taking lens unit is mounted and the electrical circuitry inside the camera body are connected by means of flexible circuit board. Further, the grounding line is strengthened by having reinforcing plate that is in electrical contact with detachable circuit board comprise a metal plate and by having metal plate connected with the grounding line of the camera body to move against reinforcing plate.

Owner:MINOLTA CO LTD

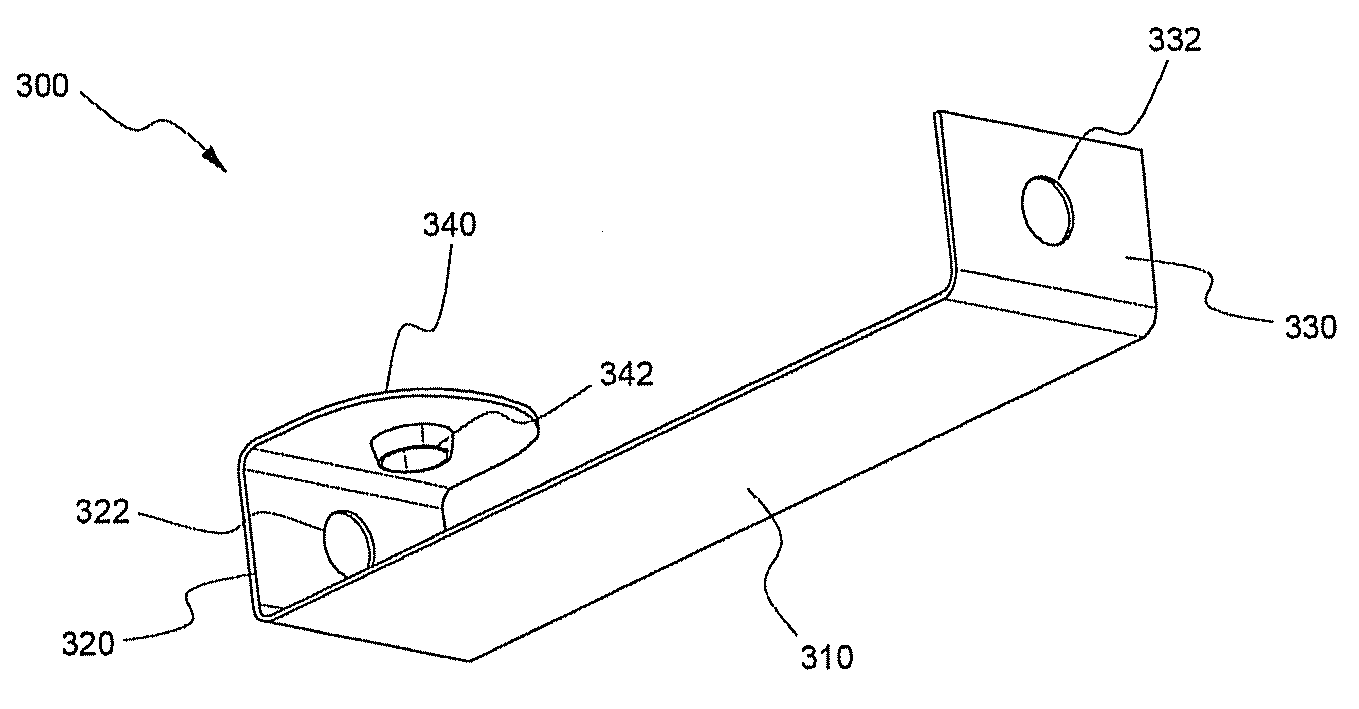

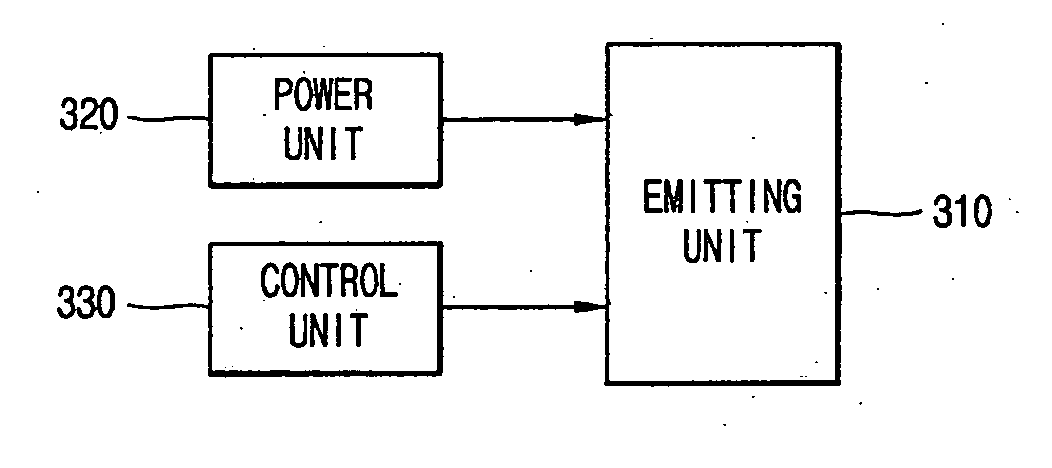

Back-light apparatus for liquid crystal display device

ActiveUS20050151889A1Improve productivitySuitable for useElectrical apparatusStatic indicating devicesPower unitLiquid-crystal display

A back-light apparatus for a display includes: a plurality of light emitting diodes attached on a substrate; a first common line mounted on the substrate to commonly connect first electrodes of the light emitting diodes; a second common line mounted on the substrate to commonly connect second electrodes of the light emitting diodes; a plurality of third lines connected to preceding second electrodes of the light emitting diodes and succeeding first electrodes of the light emitting diodes; first and second selection switches disconnecting the first common line and the second common line so that the light emitting diodes are connected in parallel; third selection switches for disconnecting the third lines so that the light emitting diodes are connected in series; a power unit to supply power to the light emitting diodes; and a control unit to control the first, second and third selection switches for the light emitting diodes.

Owner:LG DISPLAY CO LTD

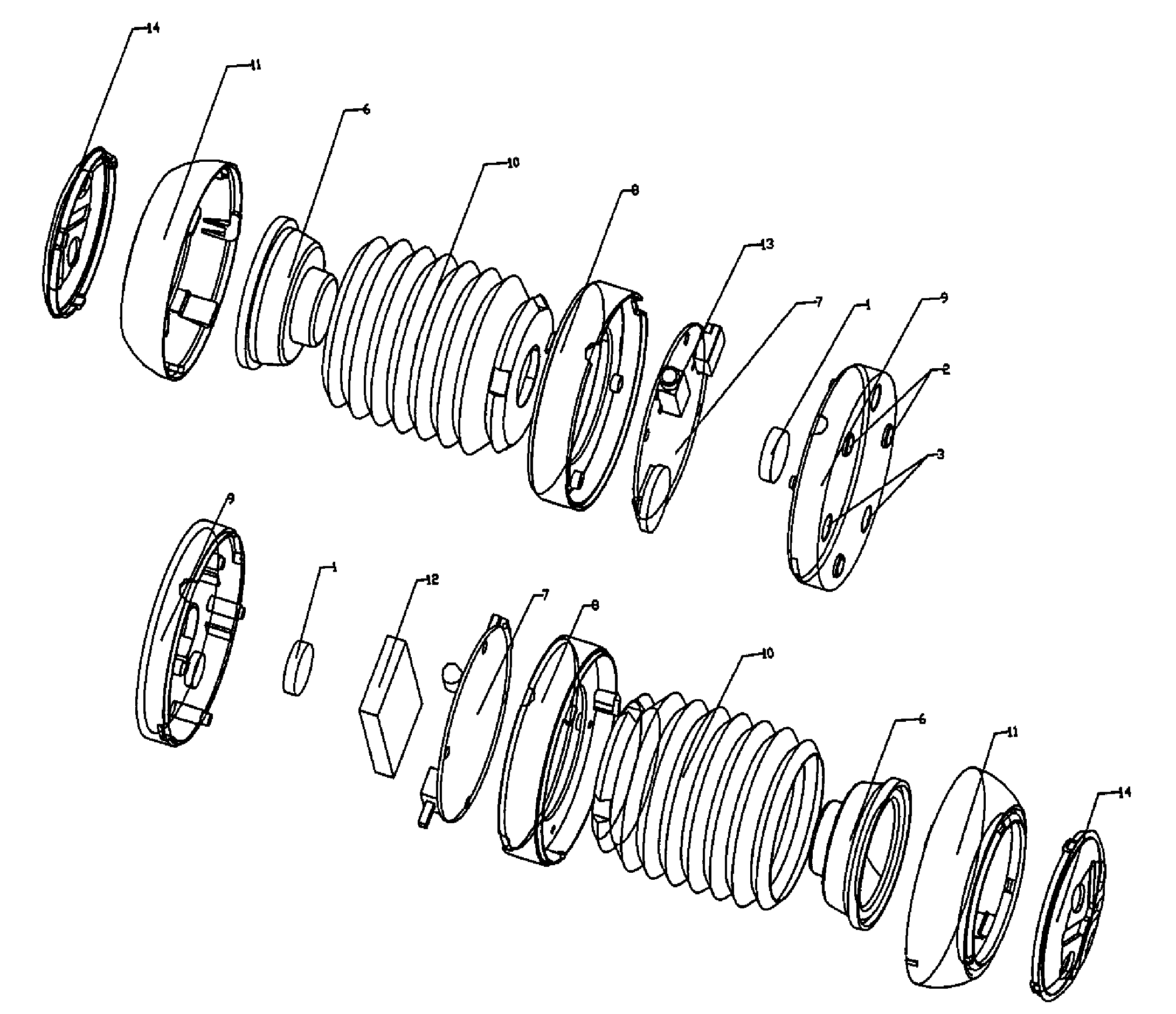

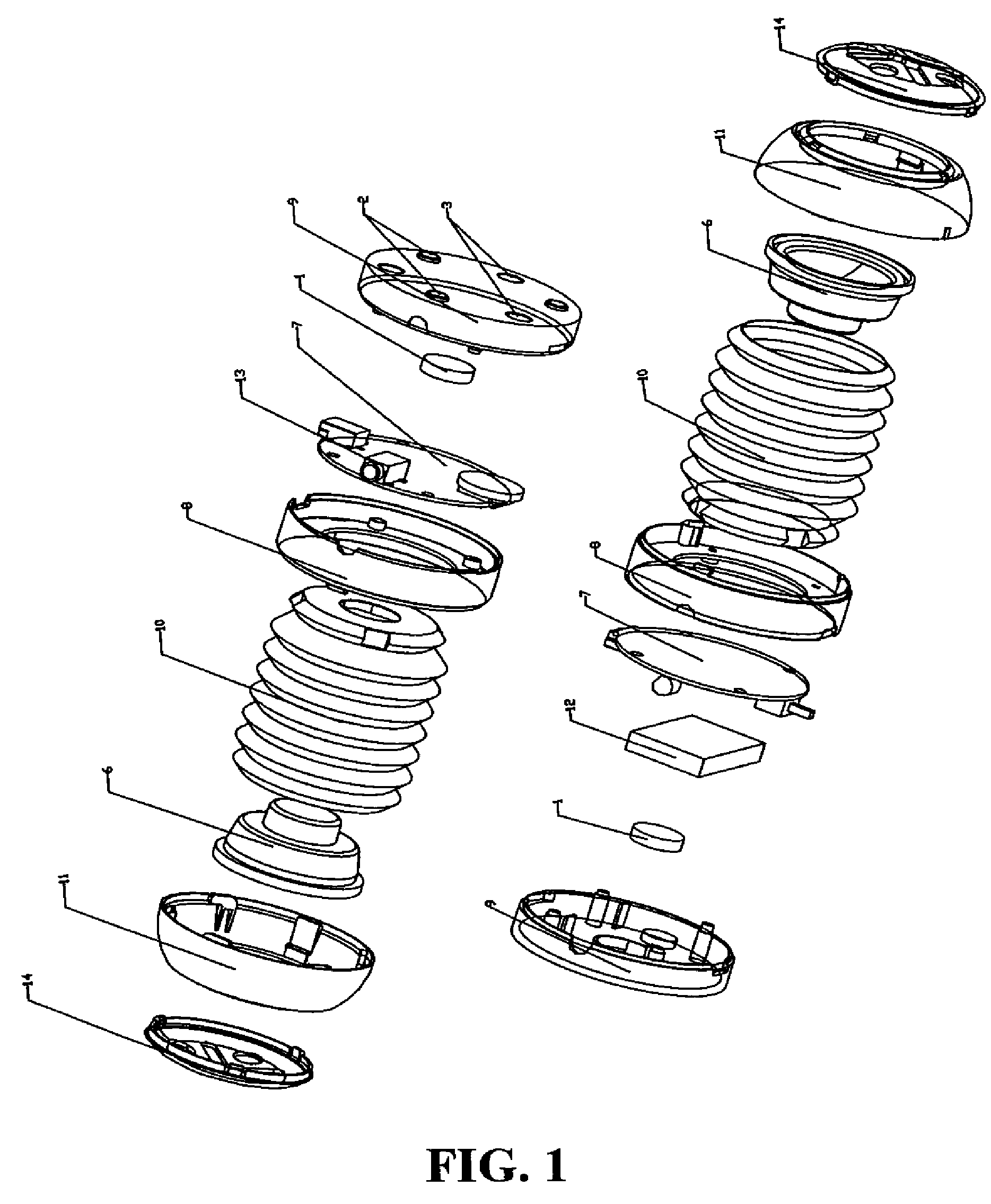

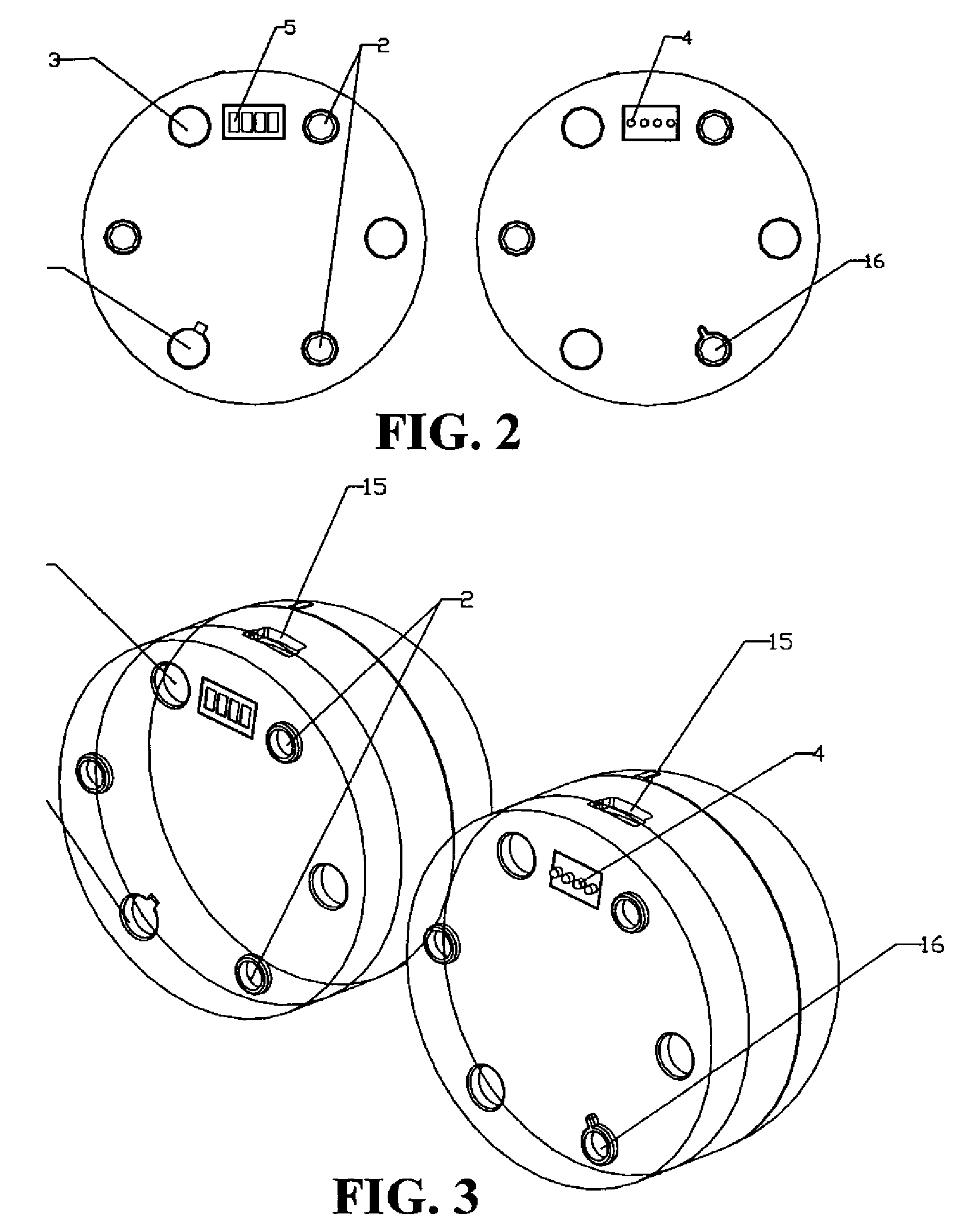

Portable sound box assembly

InactiveUS8094860B2Superior stereo soundEasy to separateLoudspeaker casing supportsCabinetsElectrical polarityEngineering

Owner:SHENZHEN YAGUAN ELECTRONICS CO LTD

Manufacturing method of solar cell module, and solar cell and solar cell module

ActiveUS8067295B2Electrical connectionConvenient ArrangementPV power plantsSemiconductor/solid-state device manufacturingElectricityComputer module

A double-side light receiving solar cell in a planer regular hexagon shape and having first electrodes on both surfaces are divided into four pieces by a line A-A′ connecting two opposing apexes and by a line B-B′ perpendicular to the line A-A′ and connecting center points on two opposing sides. By matching oblique lines of two divided pieces without misalignment and with respective surfaces in an inversed state, the first electrodes on the same side of the two divided pieces align along the same single straight line. Then, the first electrodes that are on the same side are connected with a first inter connecter, thereby constructing a unit having a rectangular outline. Units thus constructed are arranged so that relevant sides match without misalignment. By handling on a unit basis as described above, it is possible to facilitate an arrangement of the cells and an electricity connection work.

Owner:SANYO ELECTRIC CO LTD

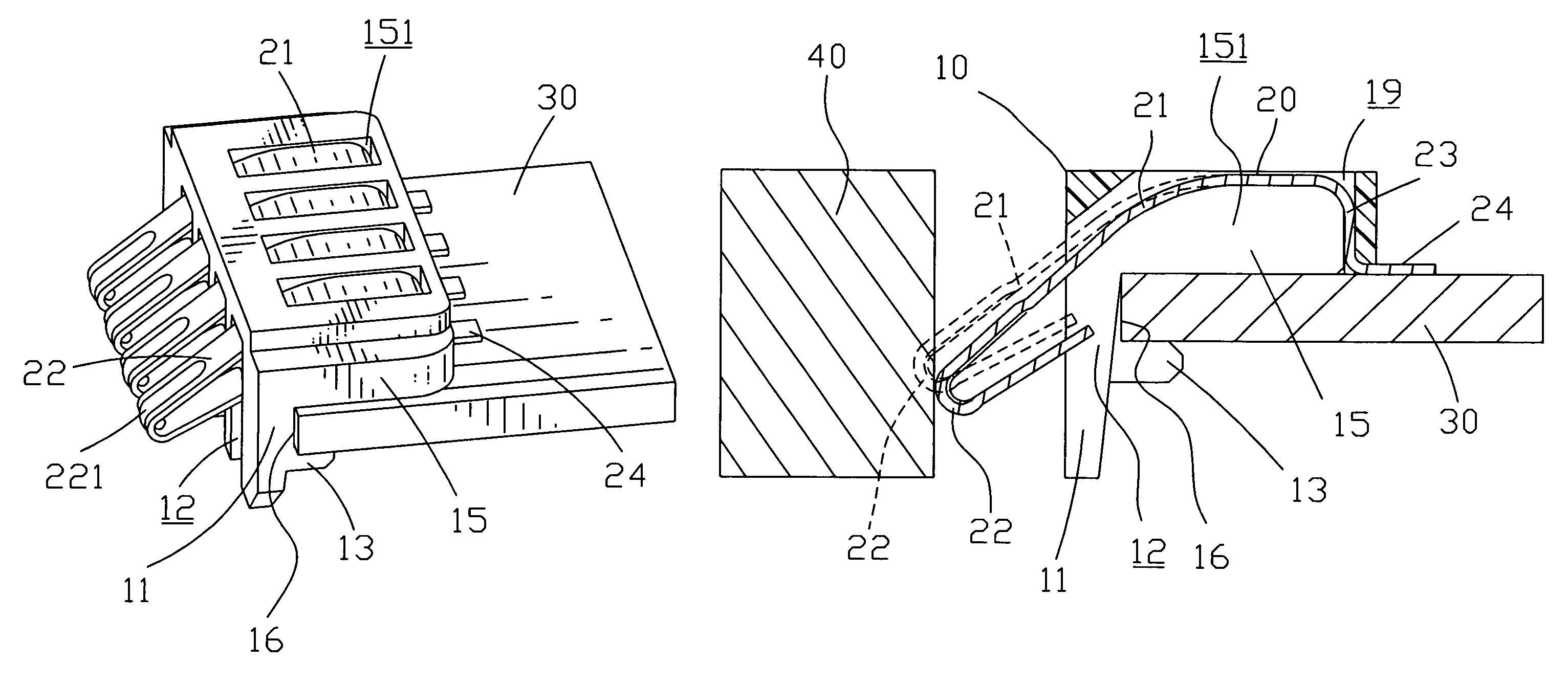

Battery connector with retaining board

InactiveUS7258571B1Electrical connectionAvoid horizontal displacementCoupling contact membersElectric connection structural associationsElectrical connectionEngineering

A battery connector with retaining board includes an insulating housing and a plurality of terminals received in the insulating housing. Each terminal includes a connecting portion, a contacting portion and a soldering portion. The insulating housing has a vertical cooperating wall. A top wall and a retaining board backward extend from the backside of the vertical cooperating wall, thereby a retaining space is formed therebetween. The backside of the cooperating wall defines a contacting side formed between the top wall and the retaining board. A printed circuit board is retained in the retaining space and one end of the printed circuit board is depressed against the contacting side of the insulating housing whereby a firmly engagement is between the printed circuit board and the battery connector. Therefore, an electrical connection therebetween is stable.

Owner:CHENG UEI PRECISION IND CO LTD

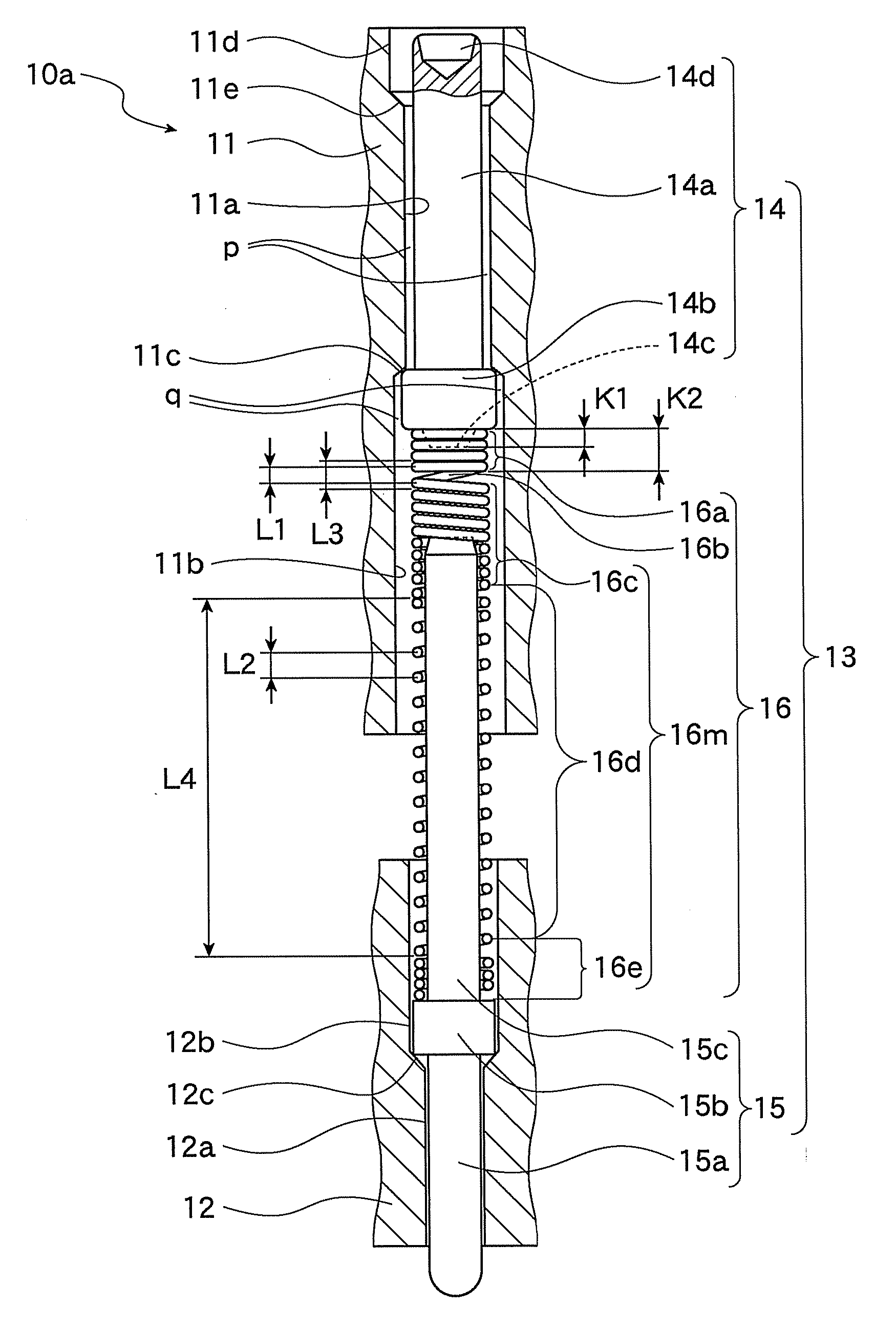

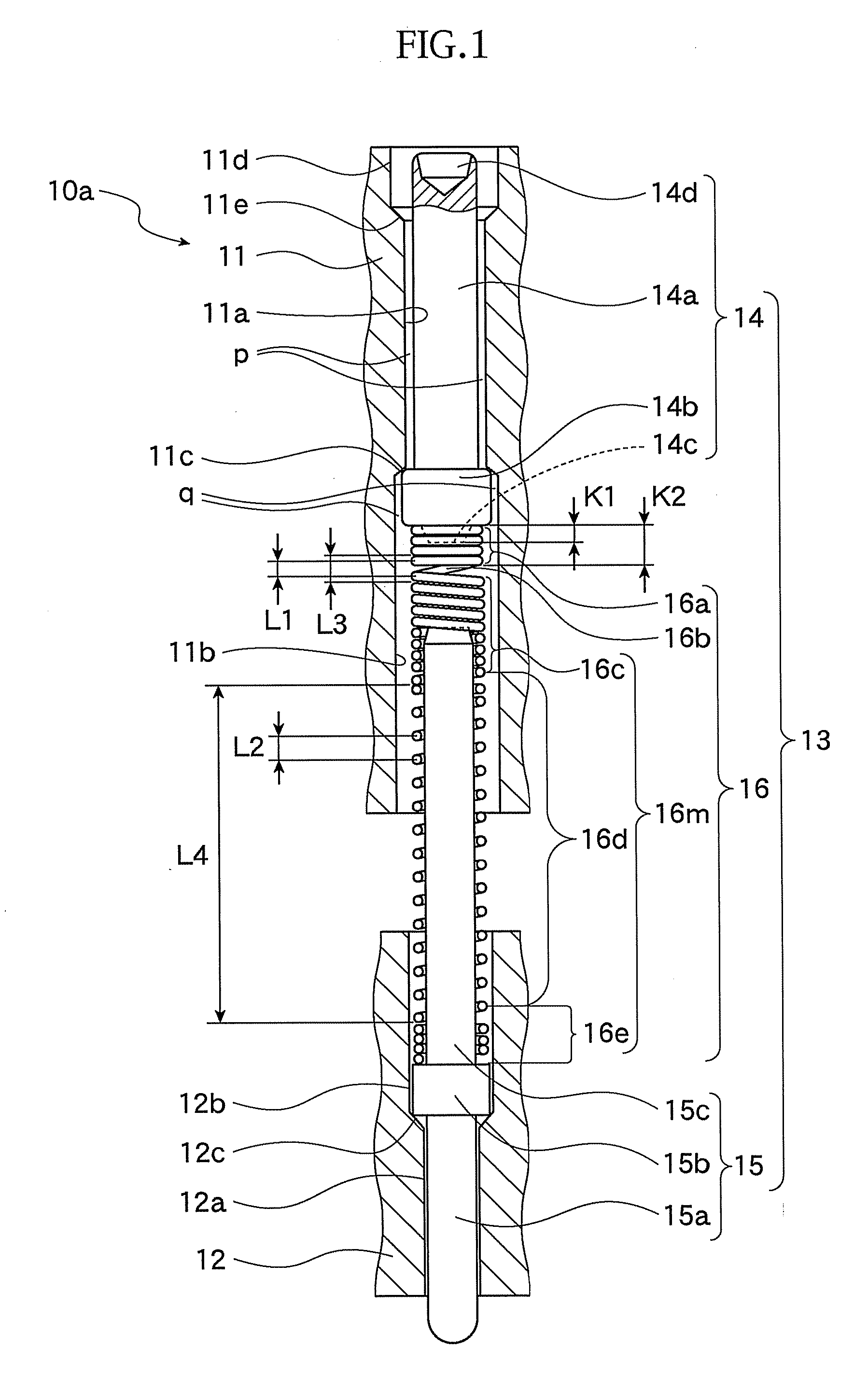

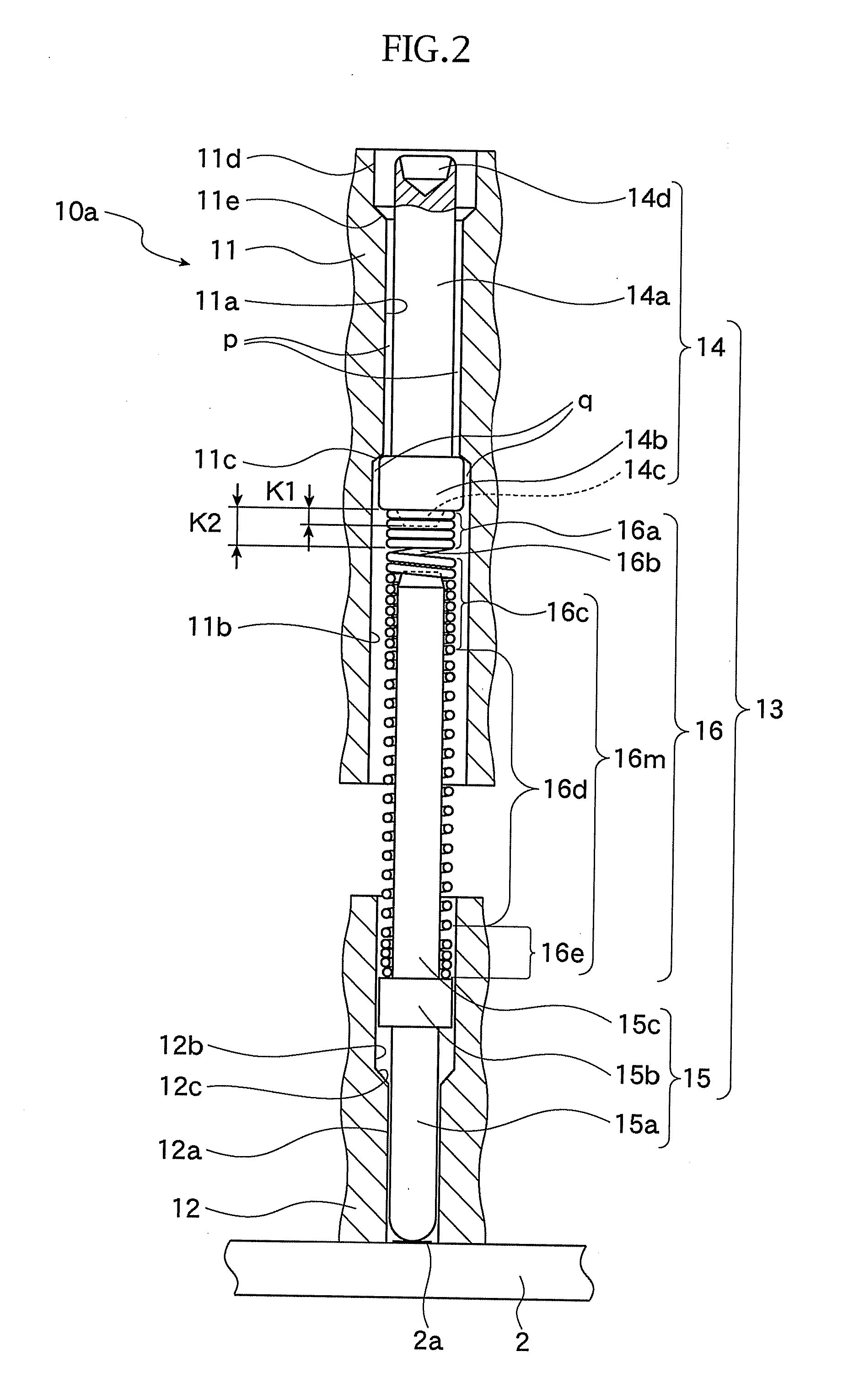

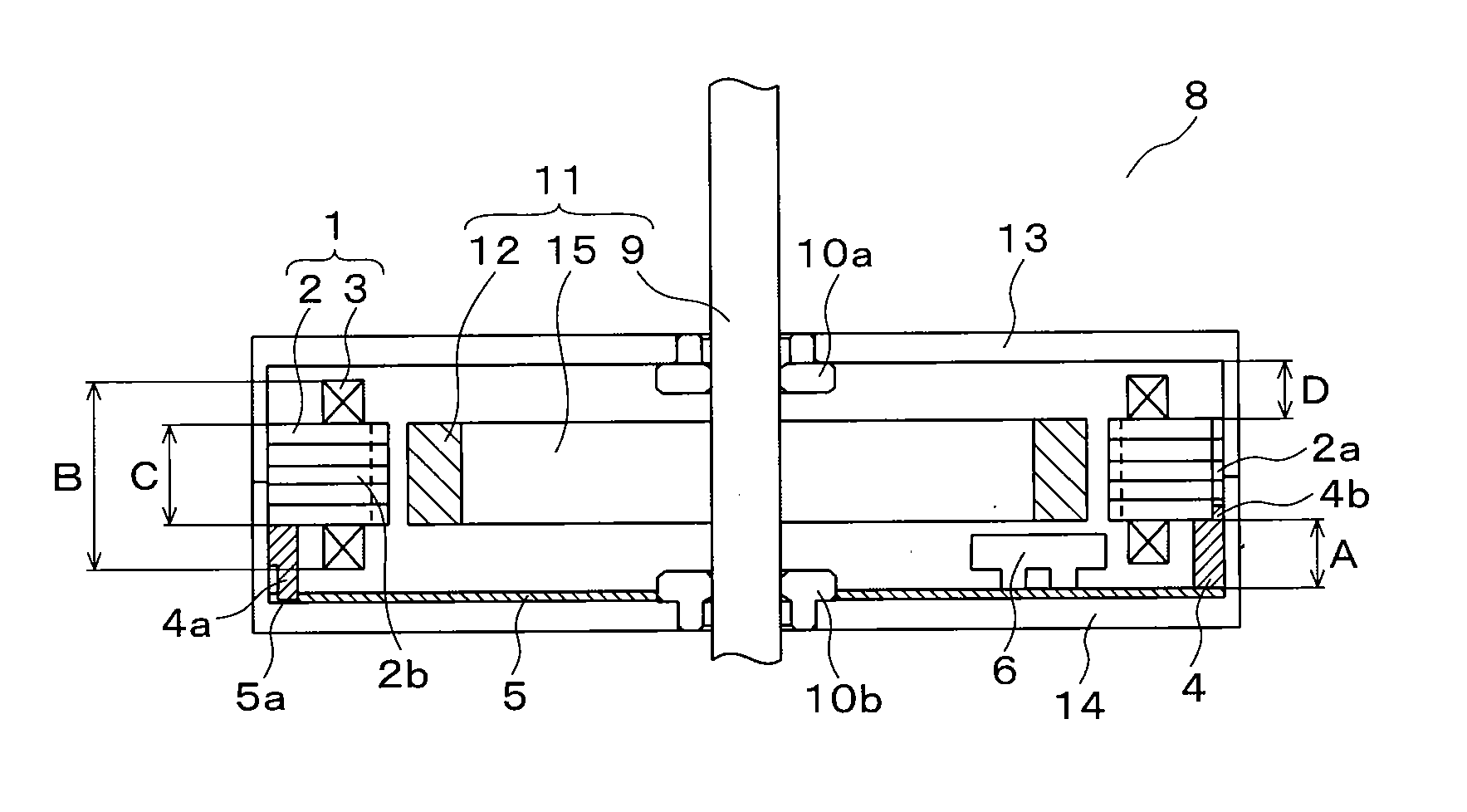

Electric contact and socket for electrical part

InactiveUS20080064270A1Electrical connectionReduce resistanceCoupling contact membersCoil springElectric contact

An electric contact of a socket for an electrical part is disposed between a first electrical part and a second electrical part so as to electrically connect the first and second electrical parts, and includes: a first electrical part side contact member contacting the first electrical part; a second electrical part side contact member contacting the second electrical part, the coil spring including a first spring portion abutting against the first electrical part side contact member and a second spring portion abutting against the second electrical part side contact member. When the first electrical part contacts the first electrical part side contact member, an axis of the first spring portion inclines with respect to an axis of the second spring portion, and then, a portion of the first electrical part side contact member on a side contacting the first electrical part is transversely moved.

Owner:ENPLAS CORP

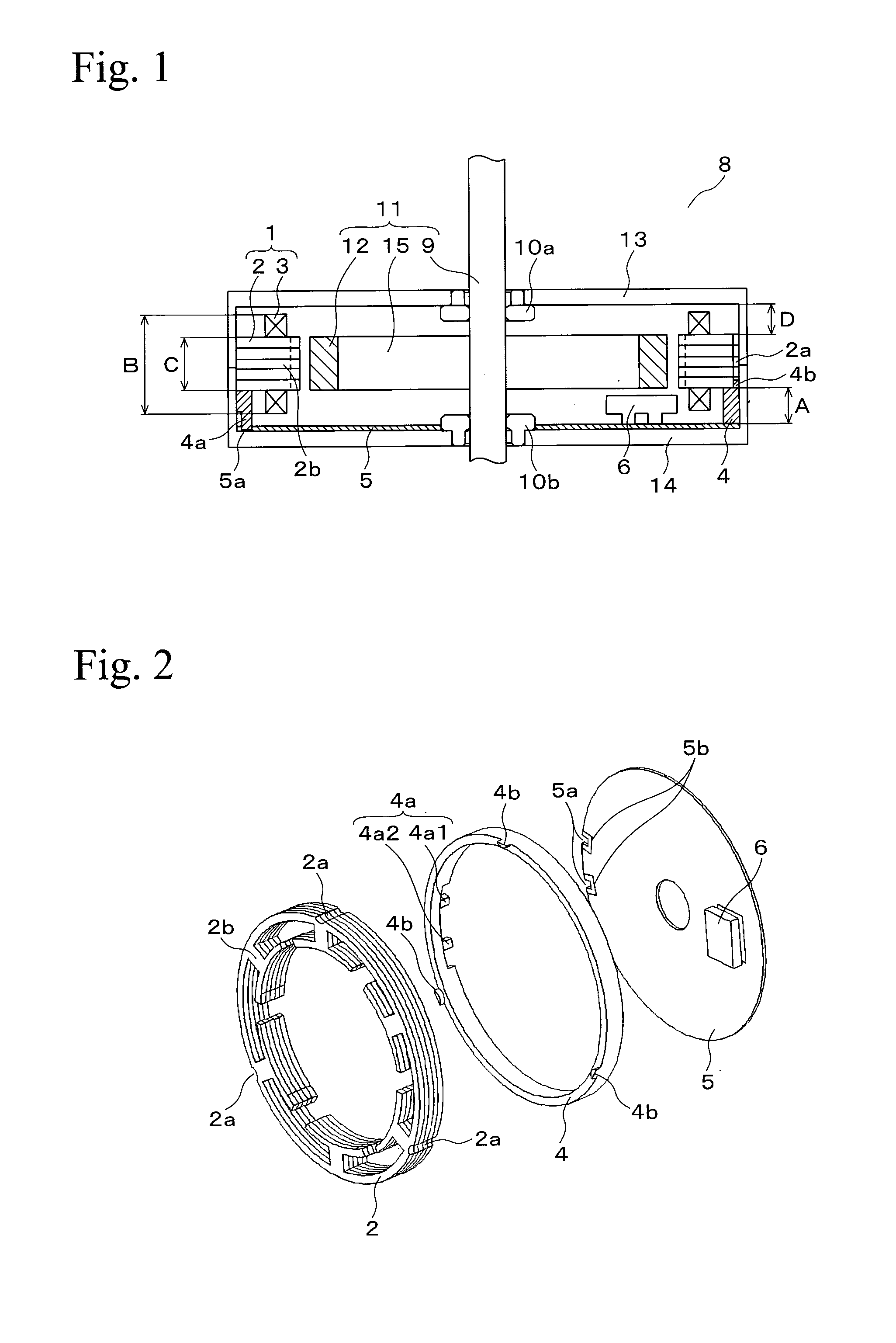

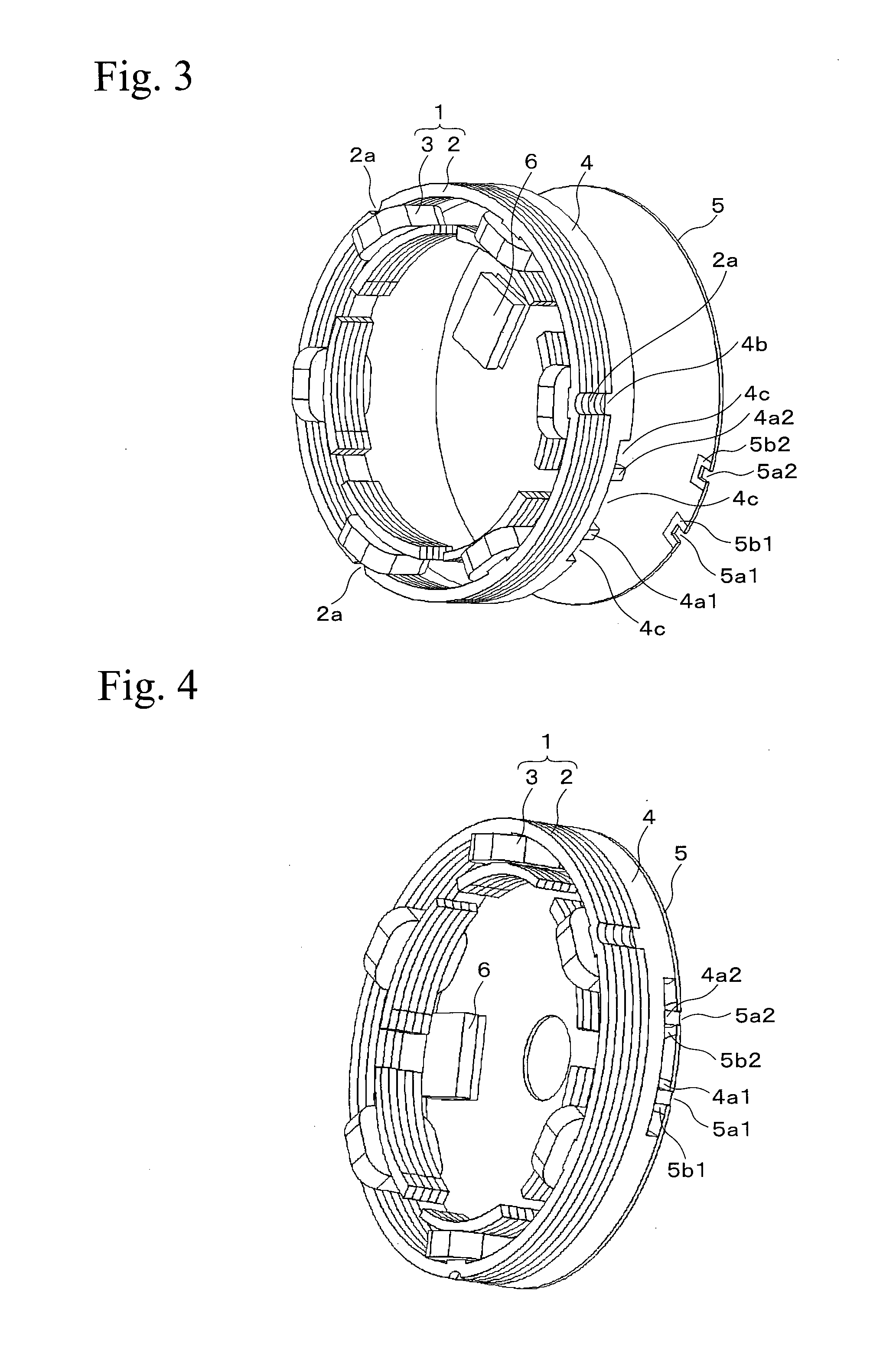

Brushless DC motor

InactiveUS20110198952A1Accurate and reliableElectrical connectionWindingsSupports/enclosures/casingsEngineeringDC motor

A brushless DC motor includes a housing having an upper and a lower housings, a stator including a stator core and a coil wound around the stator core, a rotor rotatably disposed in the stator, an annular terminal block disposed at an axial side of the stator and having an axially protruding terminal connected to an end of the coil, a disc-shaped substrate holding the annular terminal block with the stator and having a sensor IC and a driving circuit, the substrate provided with a fitting portion closely fitted by the terminal, wherein the terminal of the terminal block is closely fitted into the fitting portion of the substrate and the end of the coil is electronically connected to the substrate via a portion in which the end of the coil is connected to the terminal.

Owner:MINEBEA CO LTD

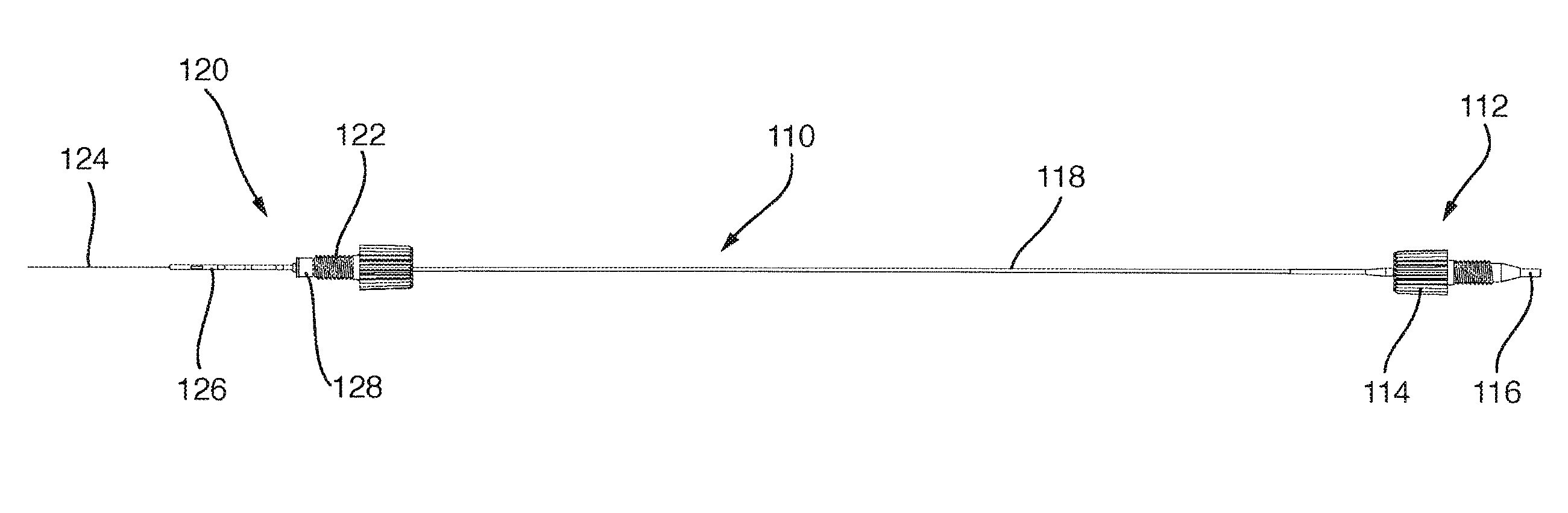

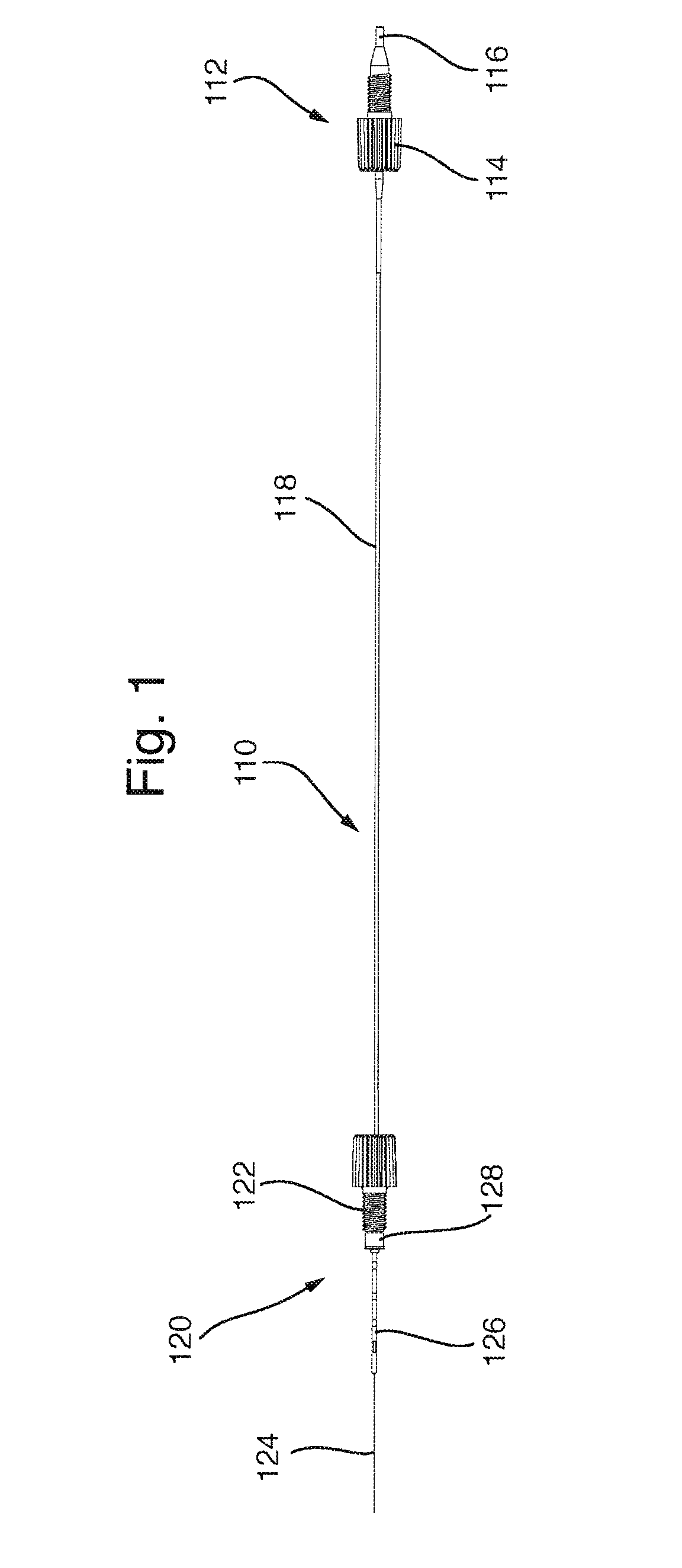

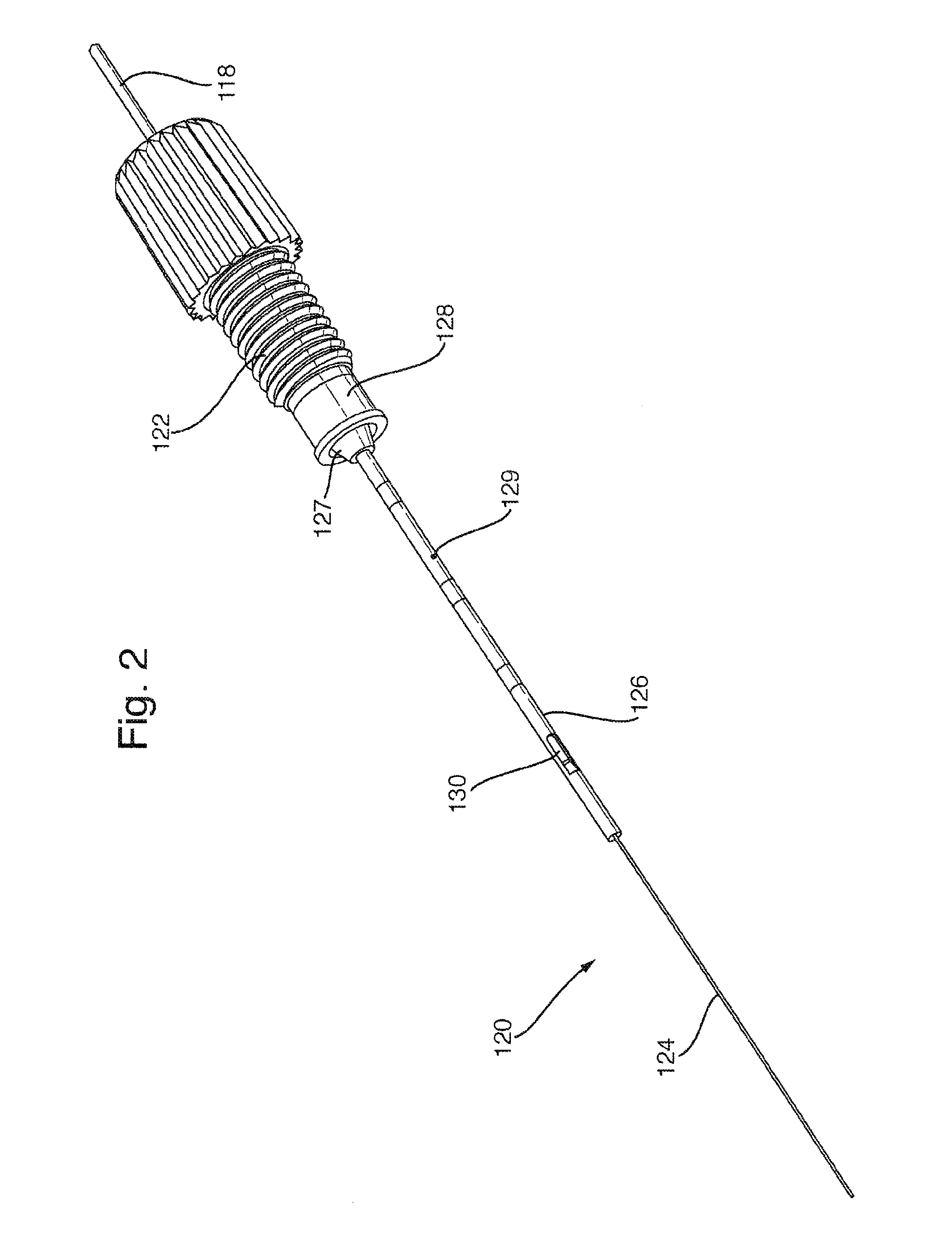

Probe Assembly for Attaching a Chromatography Device to a Mass Spectrometer

ActiveUS20160217992A1Prevent leakageAvoid dangerComponent separationSamples introduction/extractionConductive polymerElectrical connection

A probe assembly is disclosed comprising an inlet for receiving an eluent from a chromatography device; an outlet (120) for delivering the eluent to an ion source of a mass spectrometer; and an attachment device (122) for attaching the outlet to the mass spectrometer. The outlet comprises an electrically conductive capillary (124) and an electrically conductive member (129) surrounding at least part of the electrically conductive capillary (124). The electrically conductive member (129) is arranged to receive a voltage upon connection of the attachment device (122) to the mass spectrometer and the electrically conductive member (129) is arranged to provide an electrical connection from the electrically conductive member (129) to the electrically conductive capillary (124).

Owner:MICROMASS UK LTD

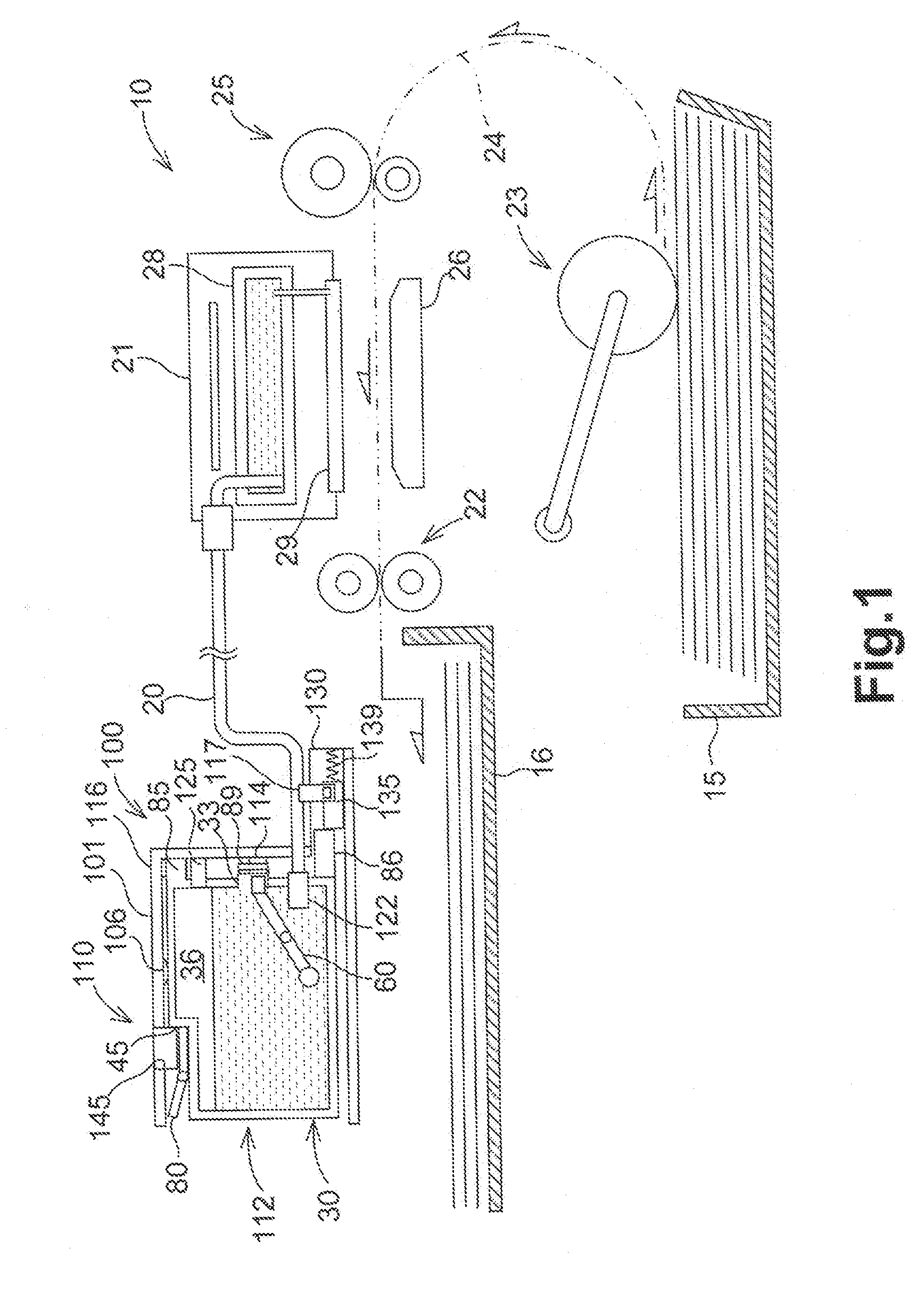

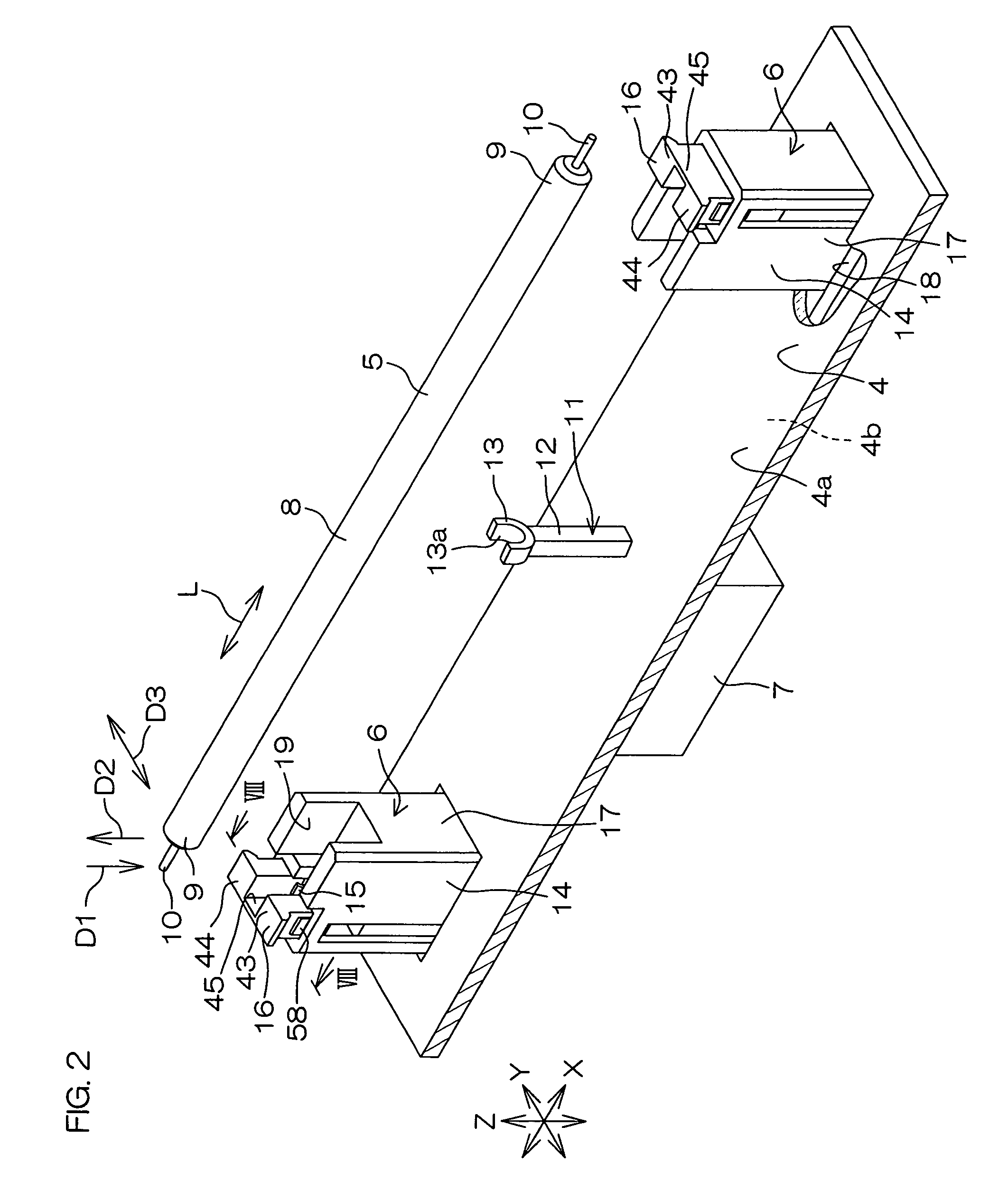

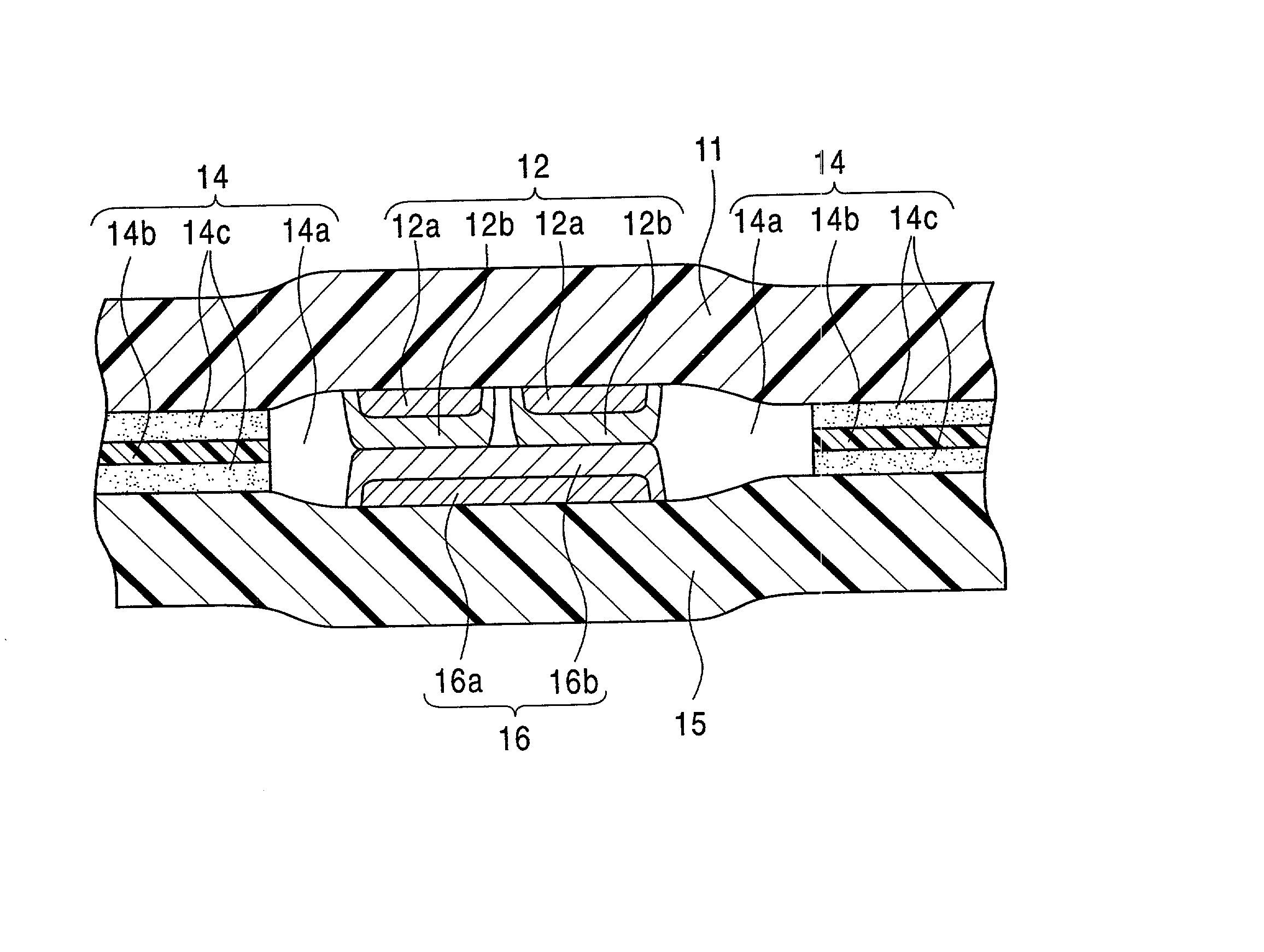

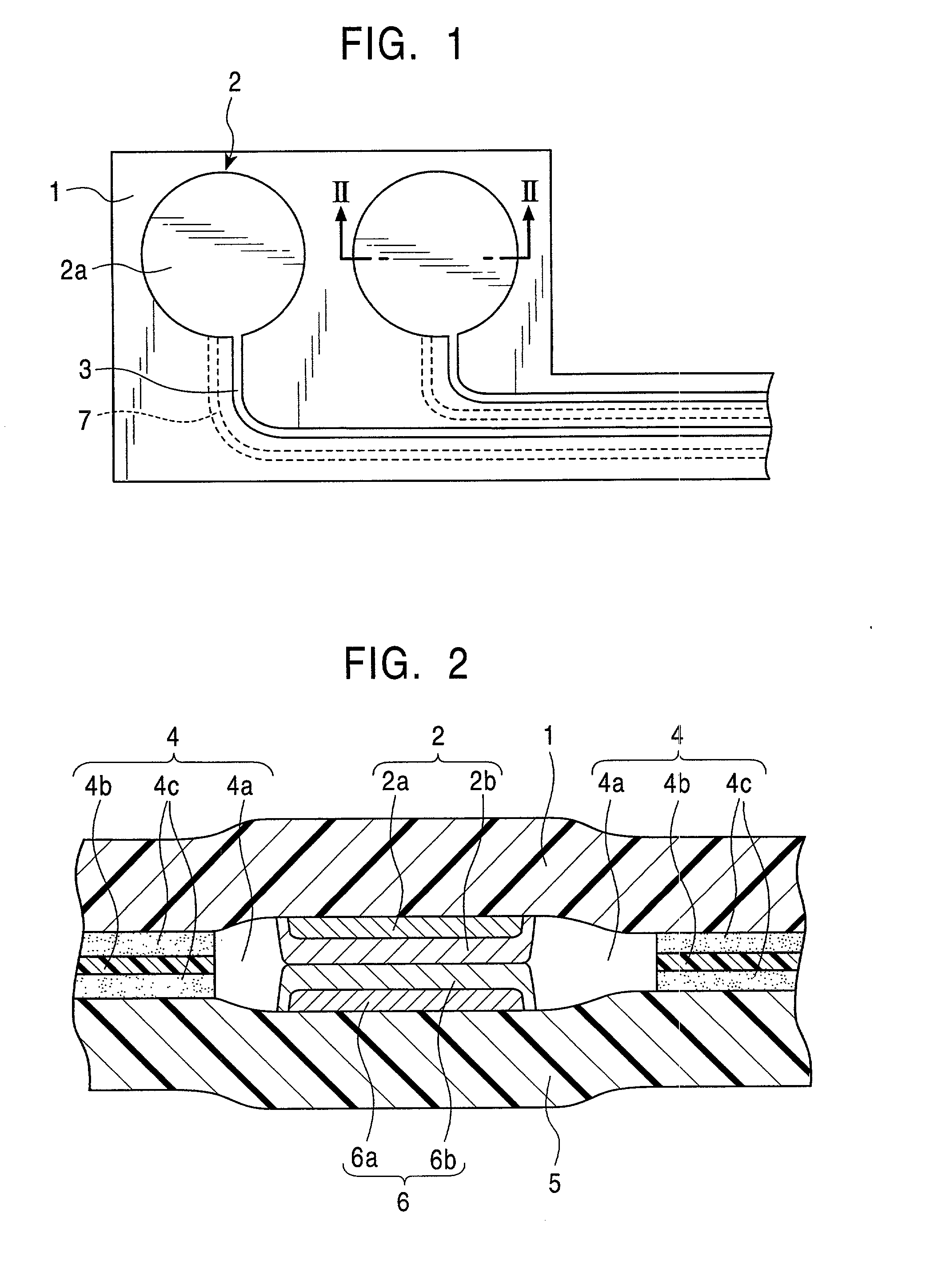

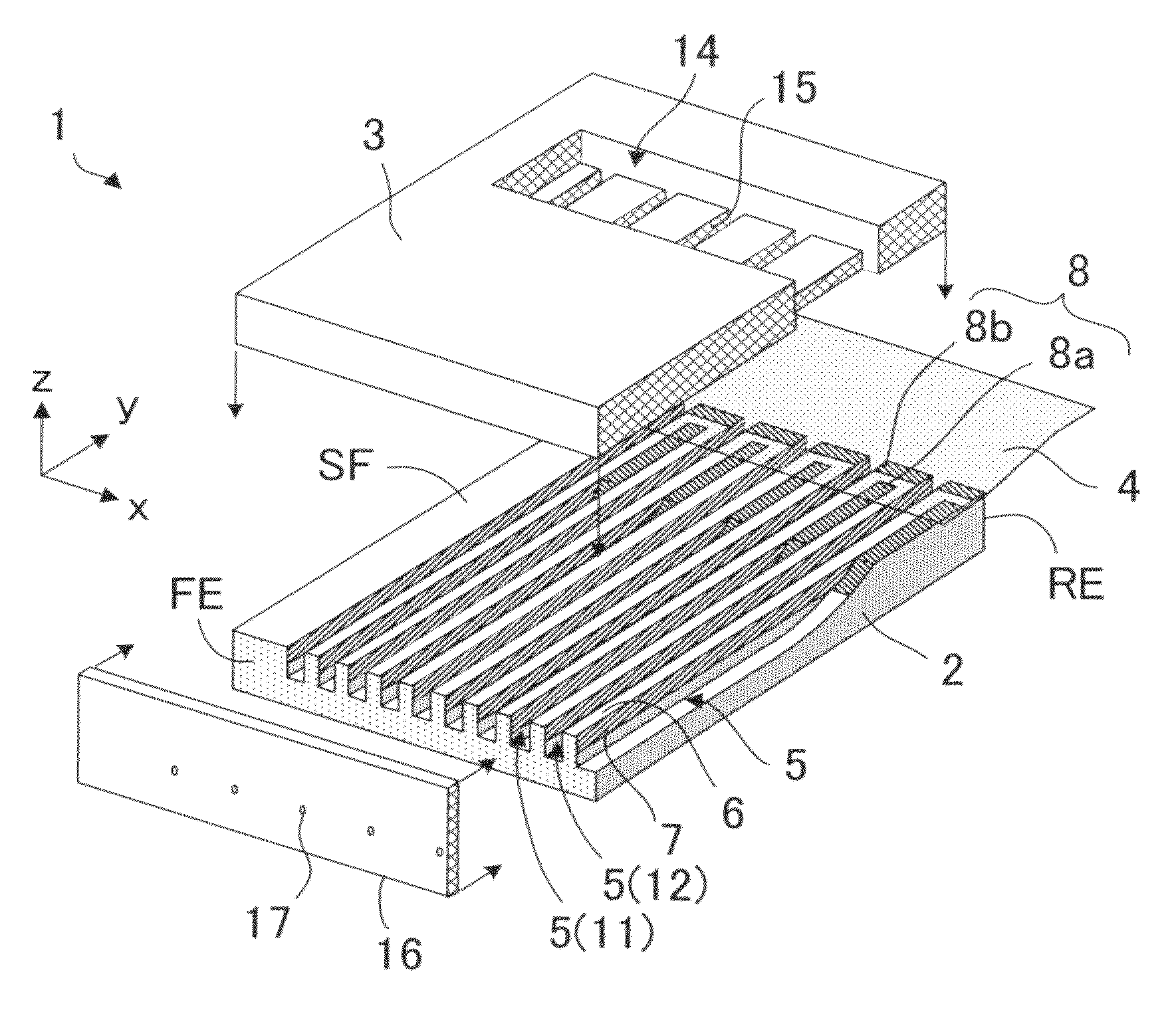

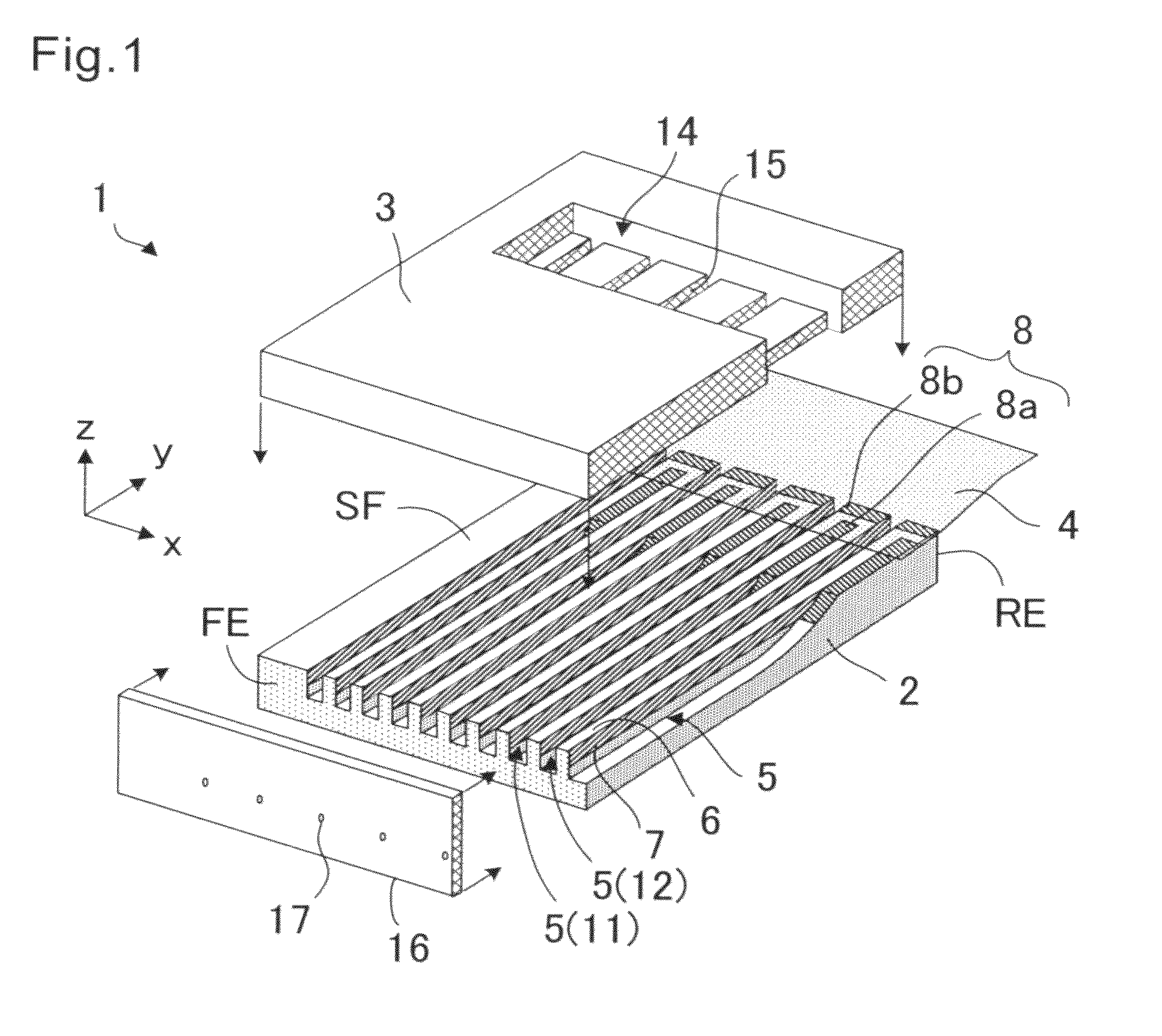

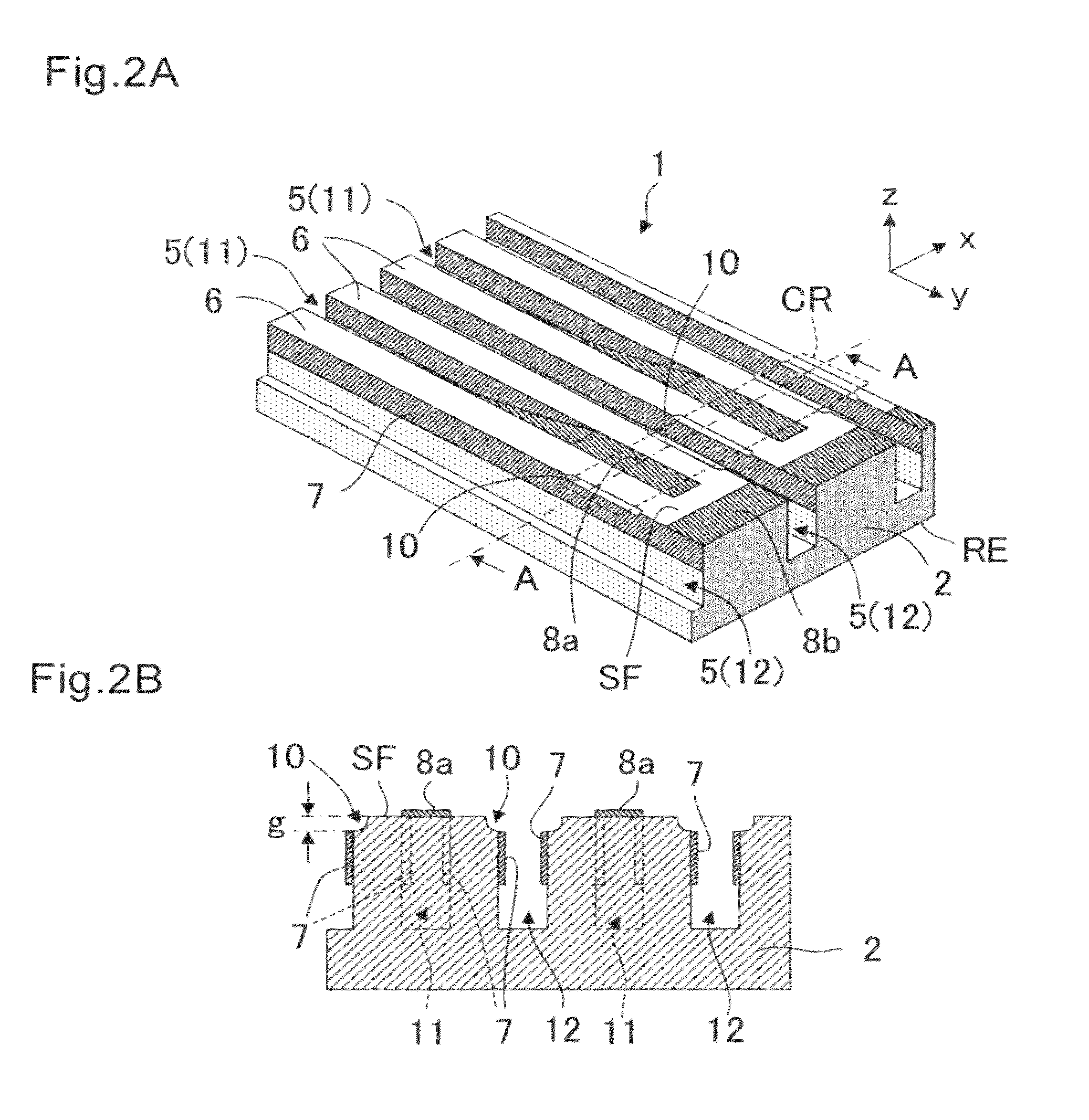

Liquid jet head and liquid jet apparatus incorporating same

A liquid jet head includes an actuator substrate having grooves, and a flexible substrate for supplying a drive signal to the actuator substrate. On a surface of the actuator substrate, in the vicinity of a rear end thereof, are formed a common extension electrode and an individual extension electrode connected to drive electrodes of a discharge channel and dummy channels, respectively. The common extension electrode and the individual extension electrode are connected to a common wiring electrode and an individual wiring electrode of the flexible substrate, respectively. In a common wiring intersection region in which the common wiring electrode of the flexible substrate intersects the drive electrodes of the actuator substrate, upper end portions of the drive electrodes on side surfaces of the dummy channels are formed deeper than the substrate surface.

Owner:SII PRINTEK

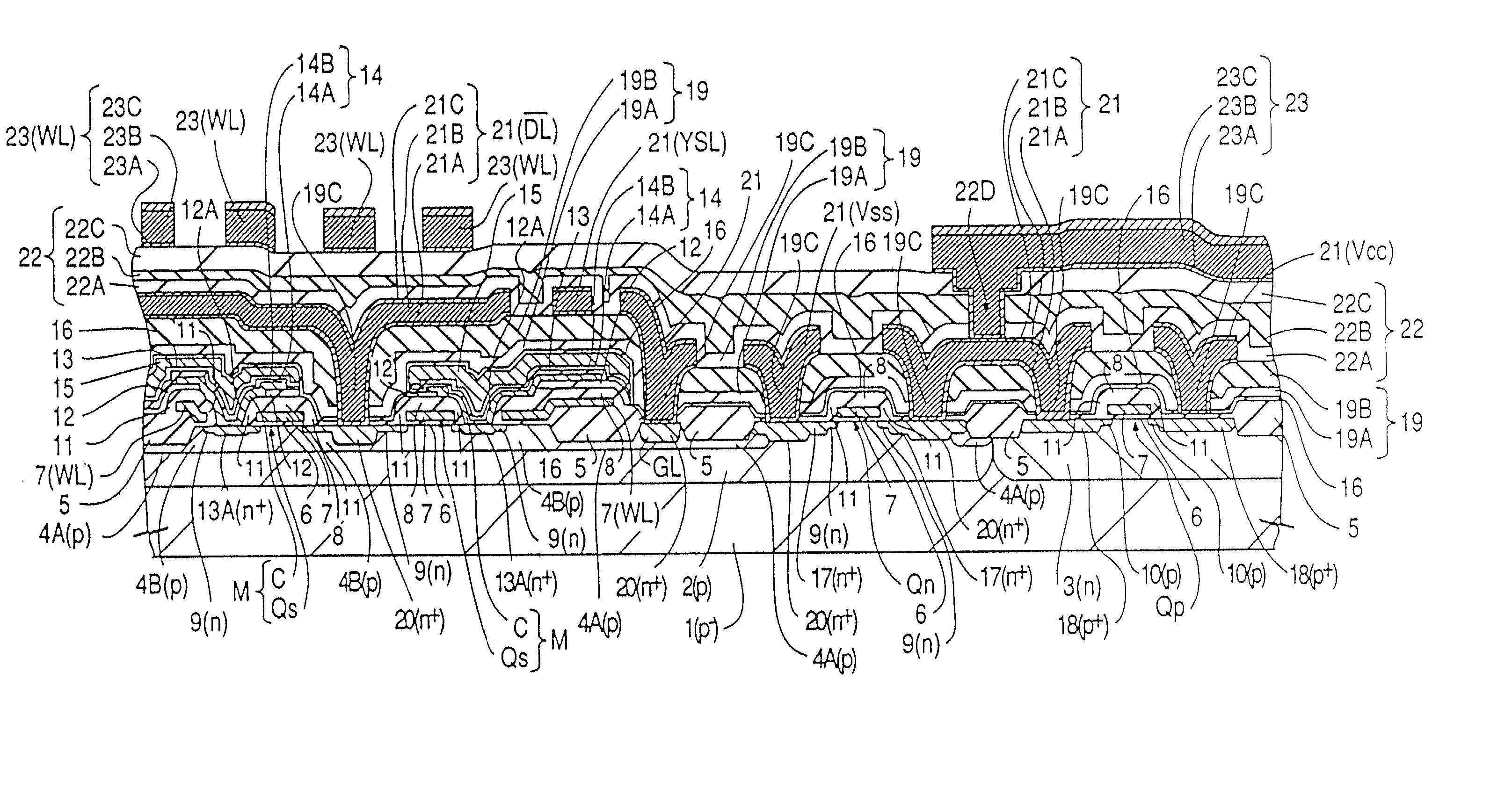

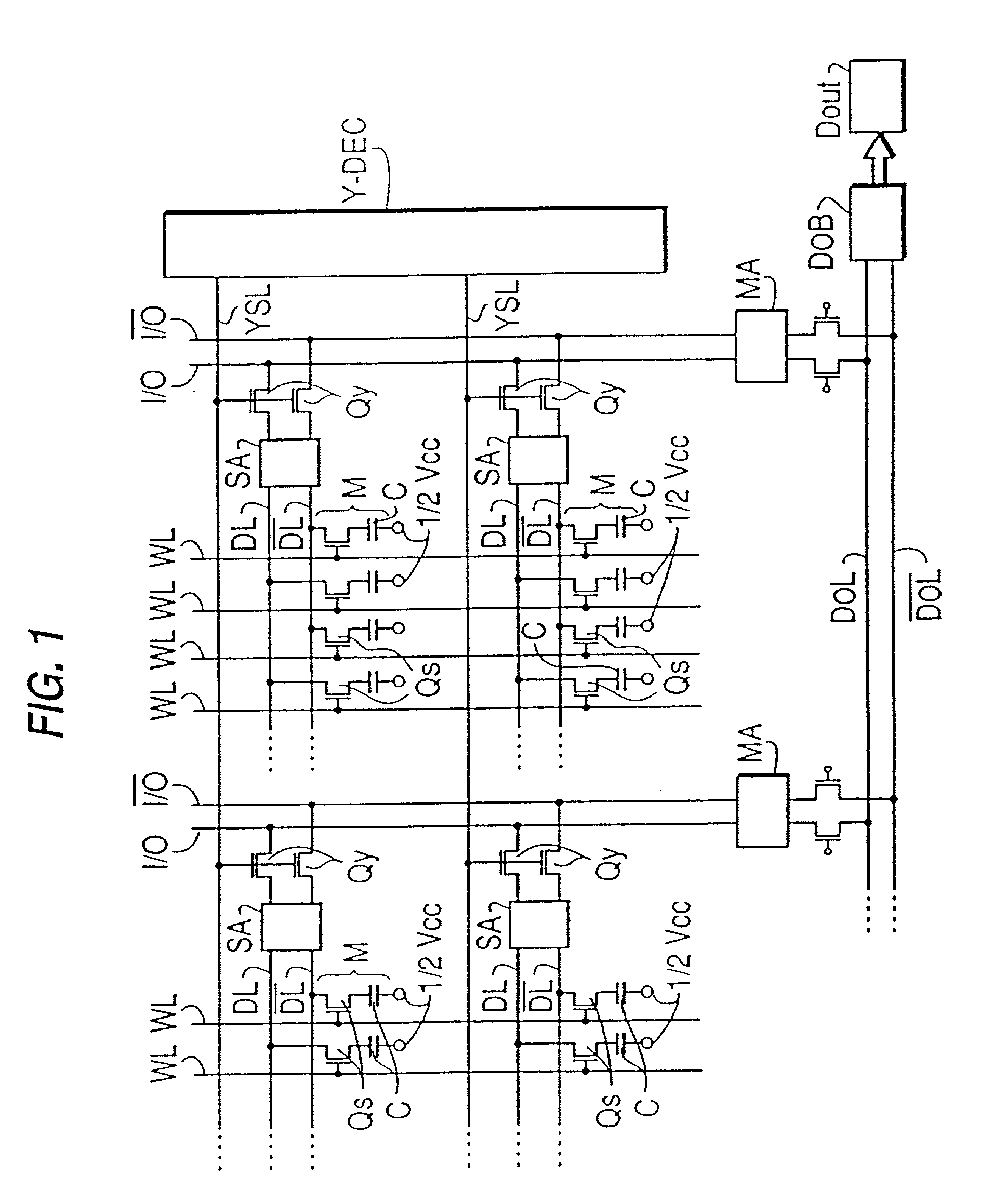

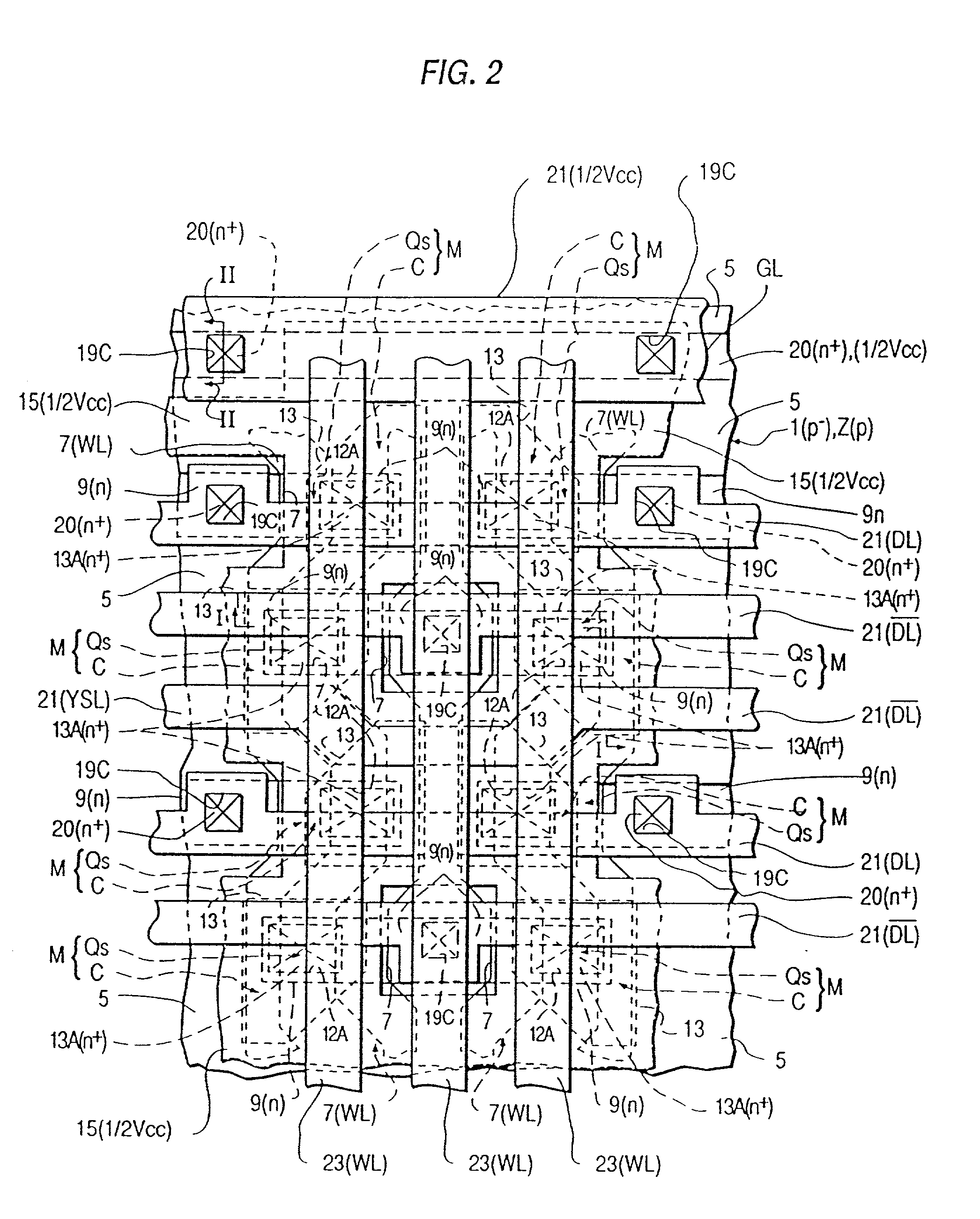

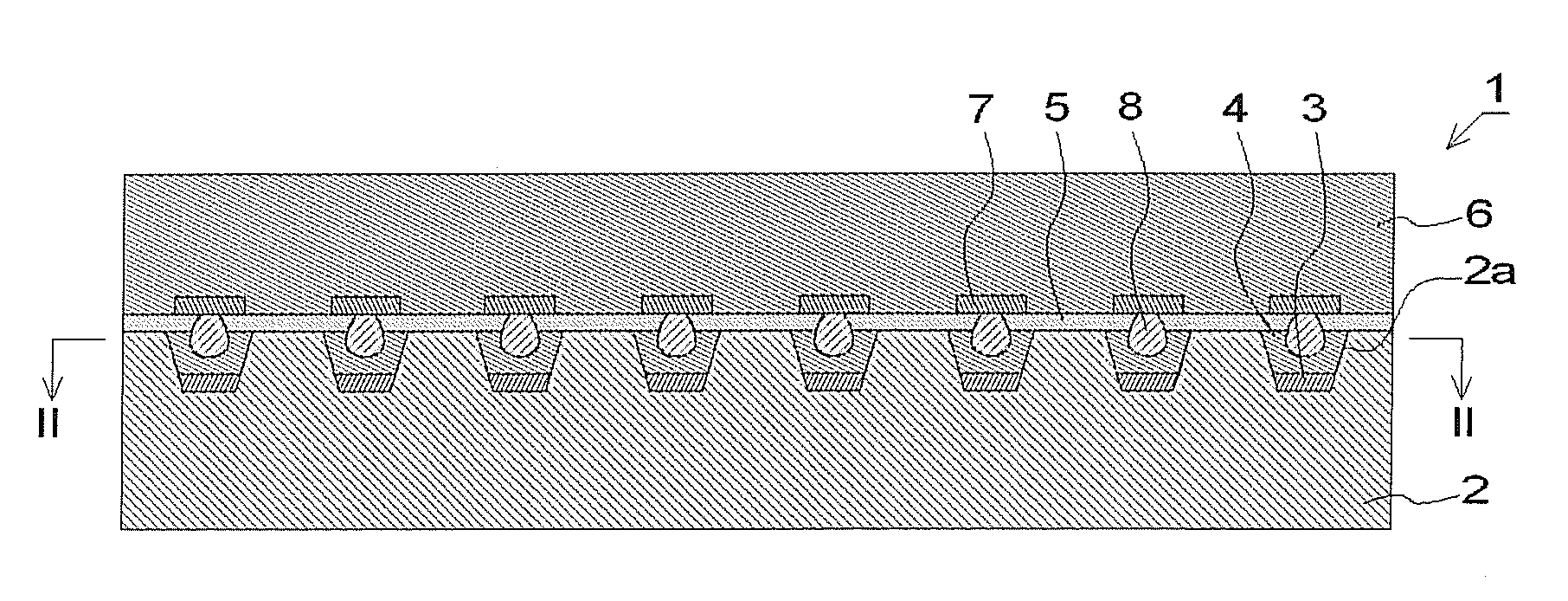

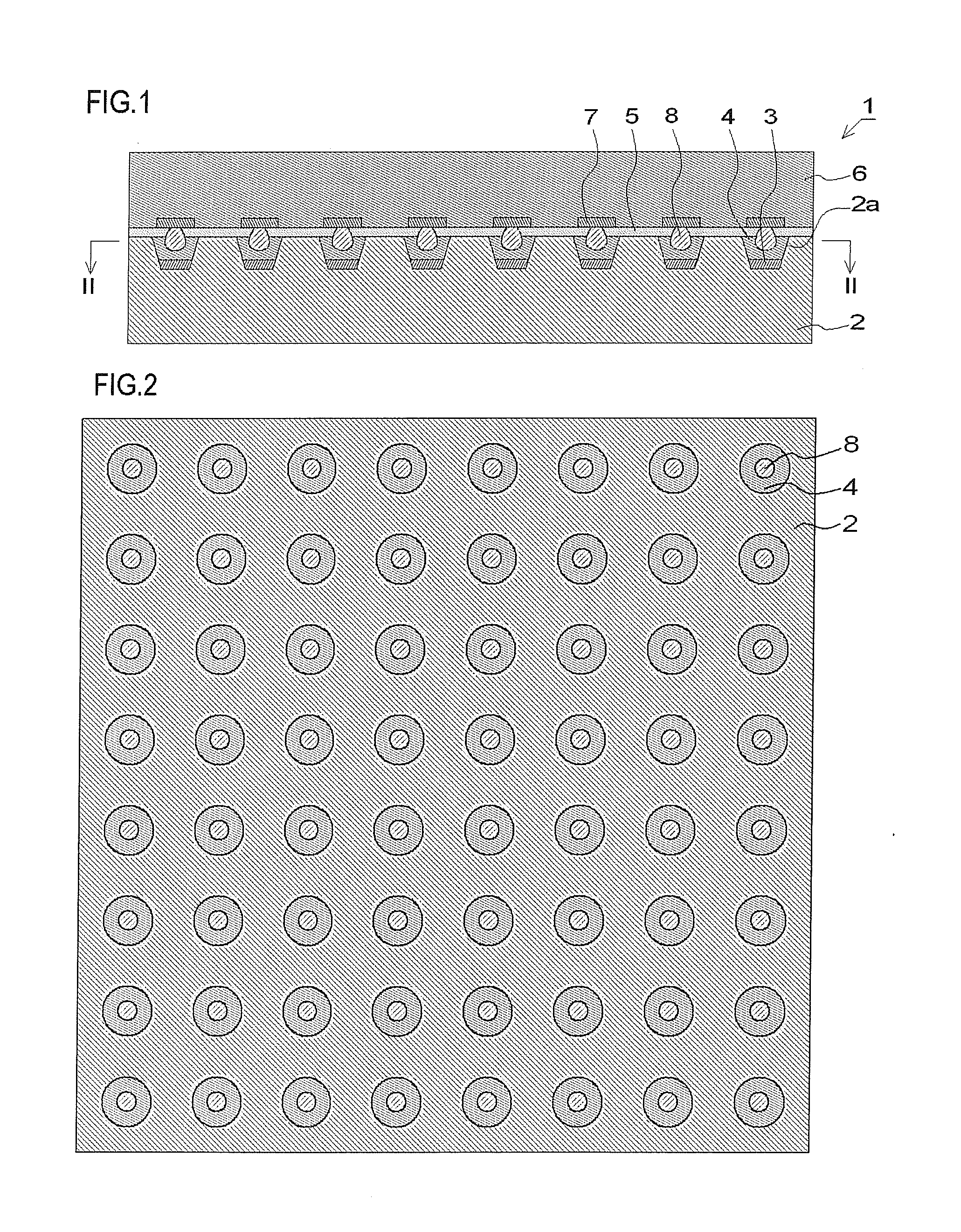

Semiconductor integrated circuit device having switching misfet and capacitor element and method of producing the same, including wiring therefor and method of producing such wiring

InactiveUS20020127793A1Reduce contact resistanceElectrical connectionTransistorSolid-state devicesDielectricSilicon oxide

A semiconductor integrated circuit device having a switching MISFET, and a capacitor element formed over the semiconductor substrate, such as a DRAM, is disclosed. In a first aspect of the present invention, the impurity concentration of the semiconductor region of the switching MISFET to which the capacitor element is connected is less than the impurity concentration of semiconductor regions of MISFETs of peripheral circuitry. In a second aspect, the Y-select signal line overlaps the lower electrode layer of the capacitor element. In a third aspect, a potential barrier layer, provided at least under the semiconductor region of the switching MISFET to which the capacitor element is connected, is formed by diffusion of an impurity for a channel stopper region. In a fourth aspect, the dielectric film of the capacitor element is co-extensive with the capacitor electrode layer over it. In a fifth aspect, the capacitor dielectric film is a silicon nitride film having a silicon oxide layer thereon, the silicon oxide layer being formed by oxidizing a surface layer of the silicon nitride under high pressure. In sixth and seventh aspects, wiring is provided. In the sixth aspect, an aluminum wiring layer and a protective (and / or barrier) layer are formed by sputtering in the same vacuum sputtering chamber without breaking the vacuum between forming the layers; in the seventh aspect, a refractory metal, or a refractory metal suicide QSi.sub.x, where Q is a refractory metal and 0<x<2, is used as a protective layer, for an aluminum wiring containing an added element (e.g., Cu) to prevent migration.

Owner:HITACHI LTD

Electronic device and manufacturing method thereof

InactiveUS20090102048A1Short circuitRelieve pressureSemiconductor/solid-state device detailsPrinted circuit aspectsElectronic componentElectronic equipment

Electronic device has substrate having at least one pad, electronic component having bump connected with pad of substrate electrically and mounting on substrate by flip chip bonding, conductive resin electrically connecting pad with bump, and insulation sheet disposed between substrate and electronic component. Substrate has recess on surface opposite to electronic component. Pad is formed on recess bottom. Conductive resin is provided on pad and in recess. Sheet has through hole corresponding to each bump. Opening area of through hole is smaller than that of recess. Bump is inserted into through hole, in contact with inner wall of through hole, electrically connected with pad via conductive resin, without direct contact with pad.

Owner:NEC CORP

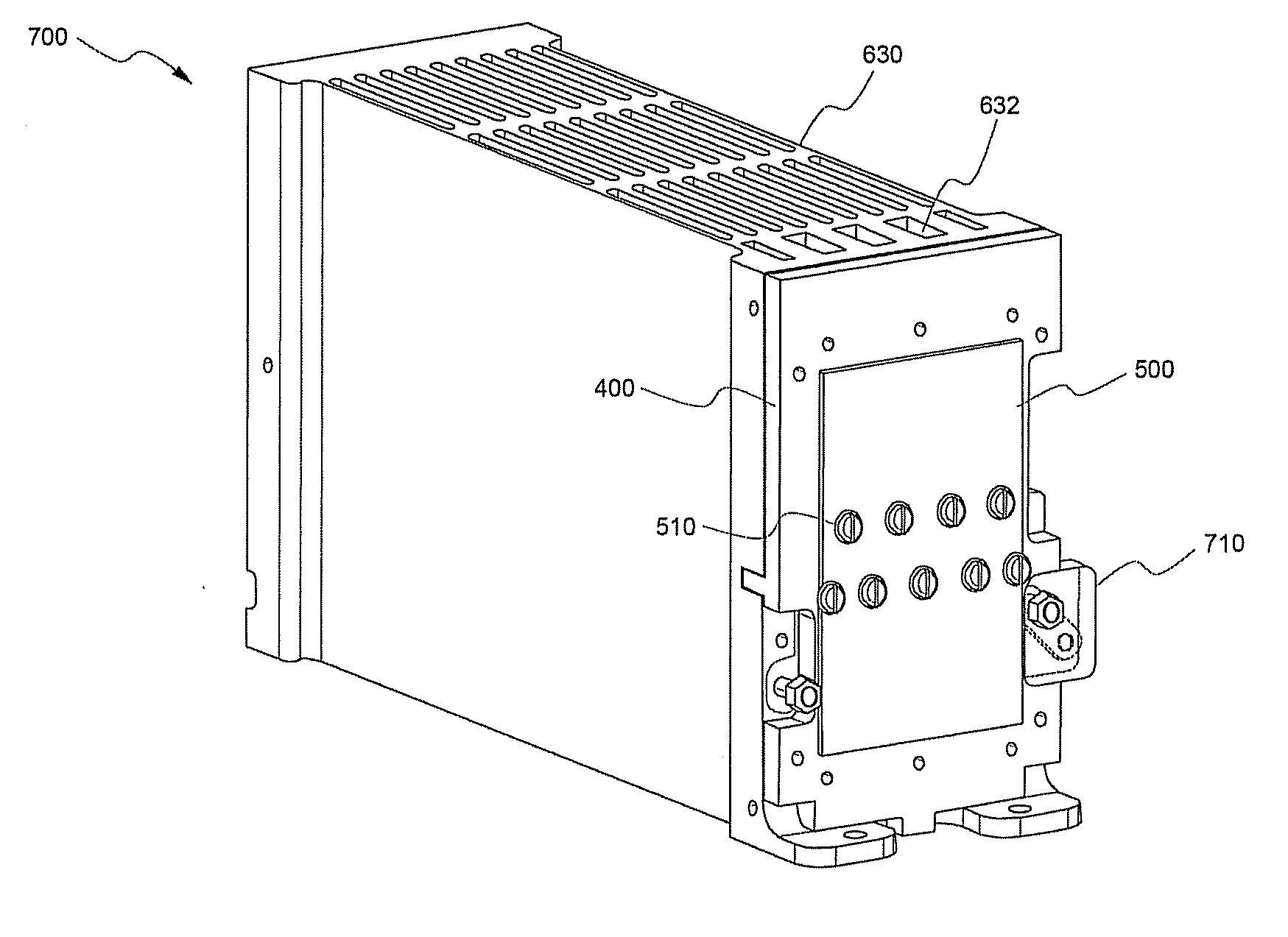

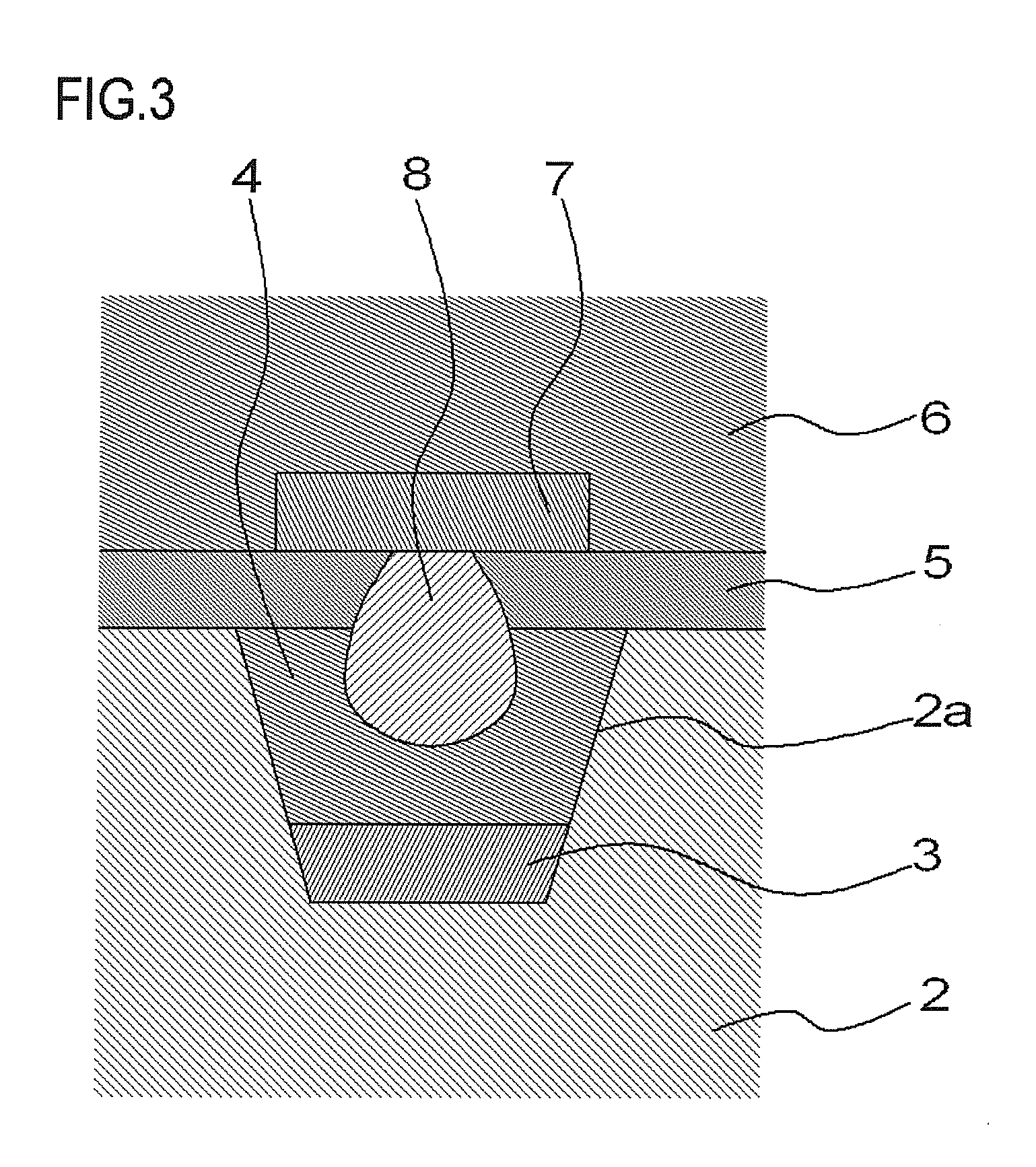

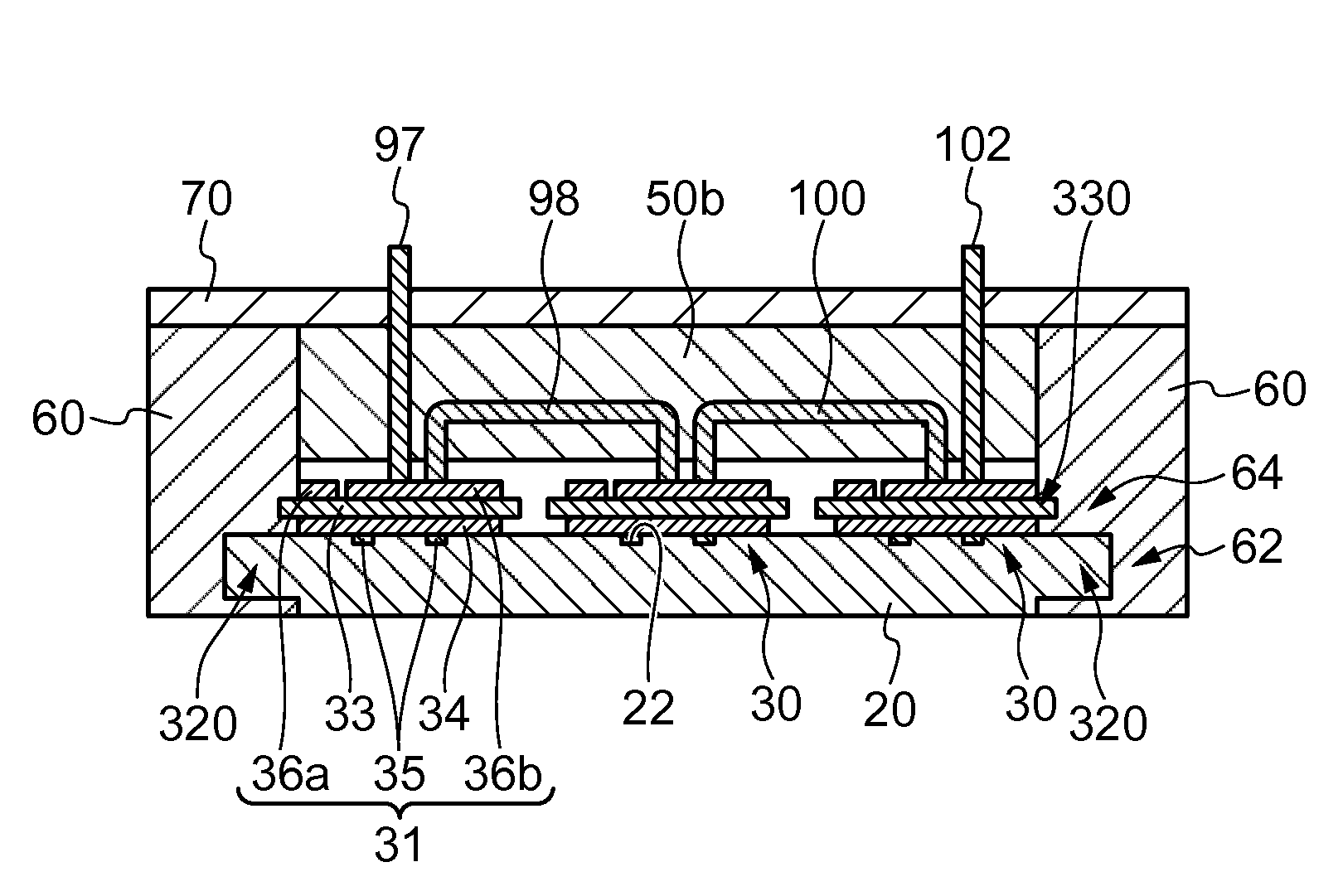

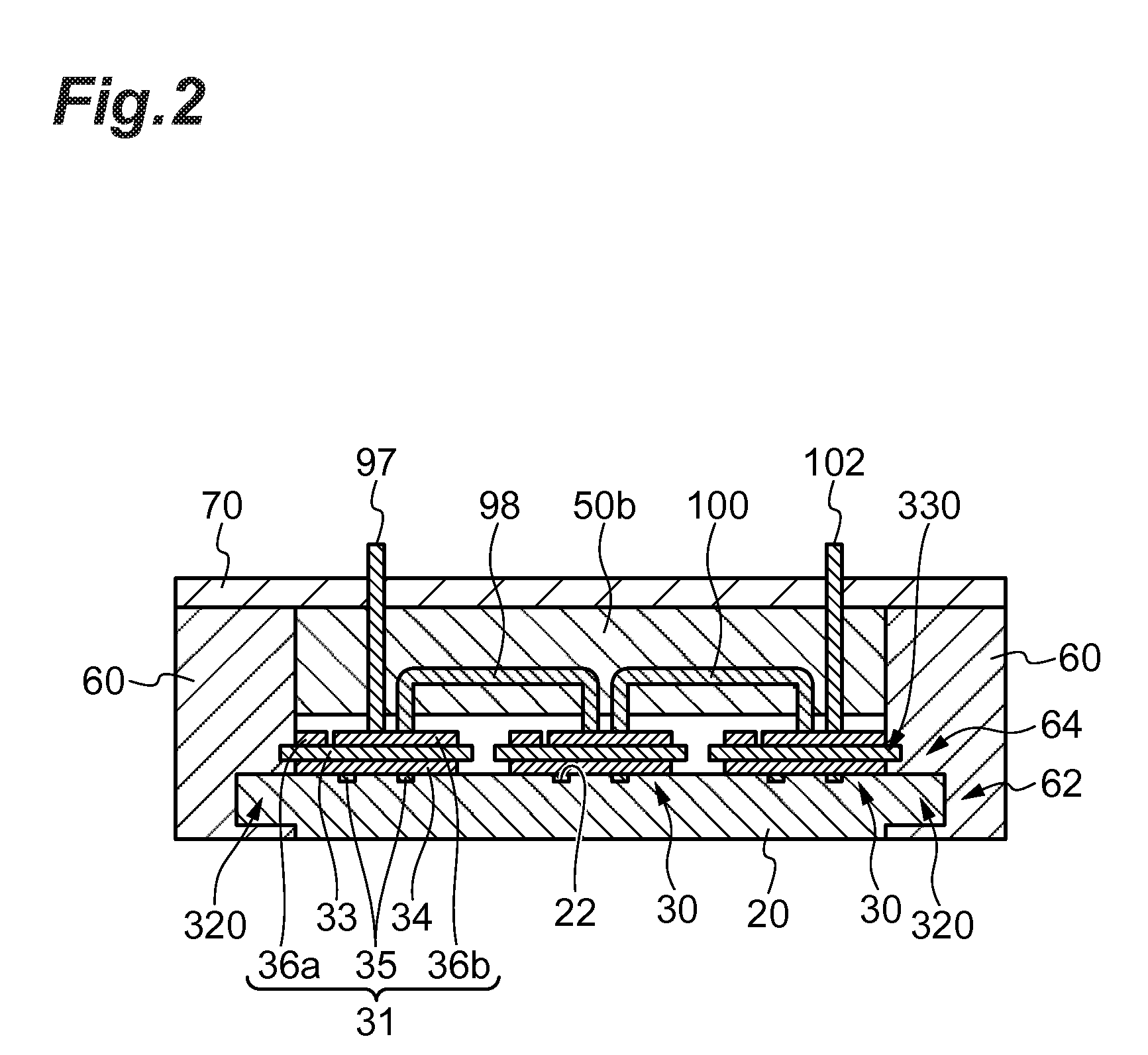

Semiconductor module and method for manufacturing semiconductor module

ActiveUS20130112994A1High positioning accuracyEasy to assembleSemiconductor/solid-state device detailsSolid-state devicesEngineeringSemiconductor components

The semiconductor module includes a base and at least one circuit substrate. The at least one circuit substrate has a supporting substrate and a semiconductor element supported by the supporting substrate. The base and / or the supporting substrate has a structure for fitting the at least one circuit substrate with the base.

Owner:SUMITOMO ELECTRIC IND LTD

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com