Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

43results about How to "Lower effective dielectric constant" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Semiconductor device and method for manufacturing the same

ActiveUS20050029669A1Lower effective dielectric constantEasy to manufactureSemiconductor/solid-state device detailsSolid-state devicesDevice materialEngineering

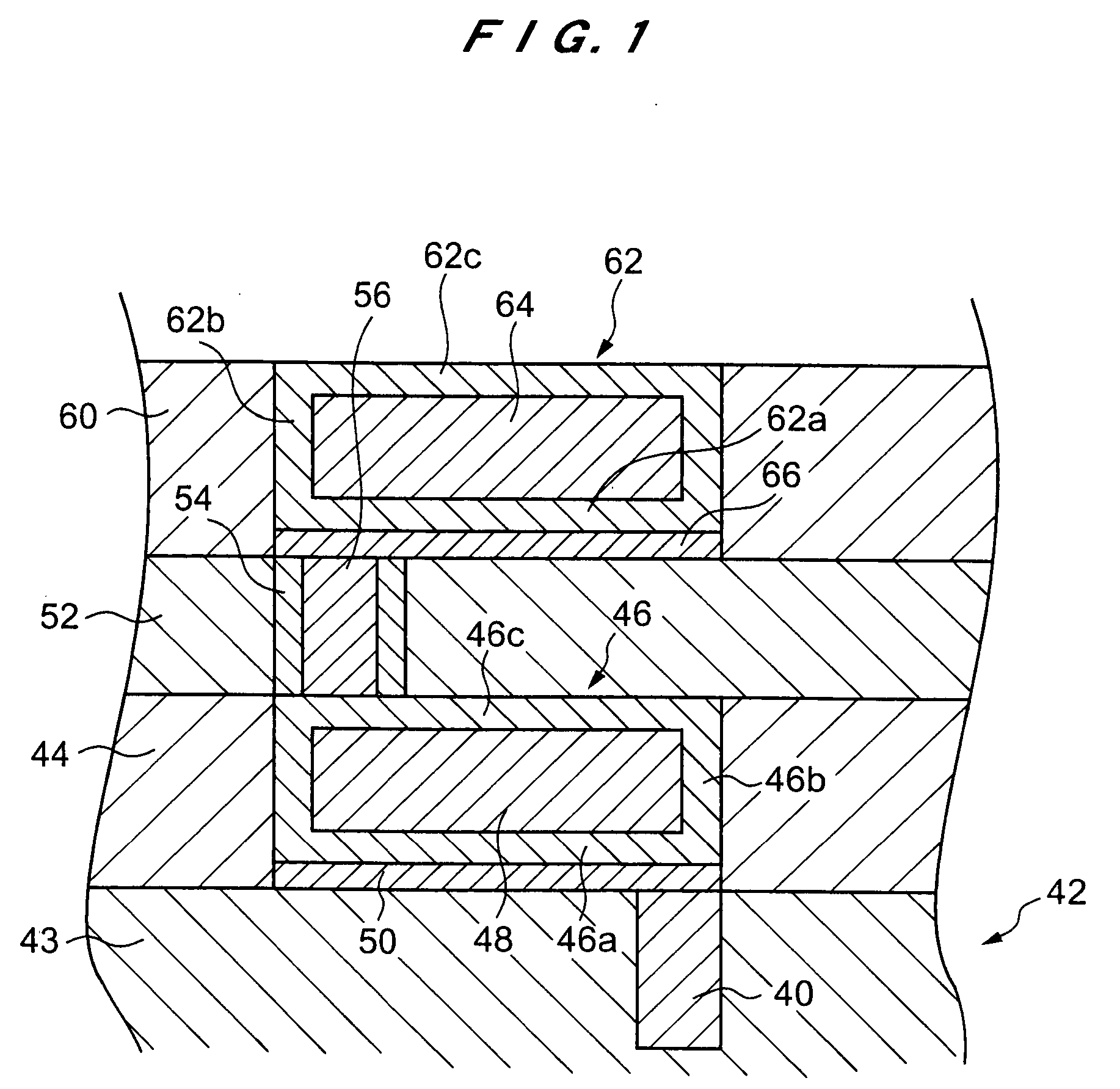

A semiconductor device including a highly reliable multi-level interconnect structure having a low effective dielectric constant and which can be easily manufactured with a relatively inexpensive process, and a method for manufacturing the semiconductor device. The semiconductor device includes a lower-level interconnect and an upper-level interconnect, each surrounded by a barrier layer, and a via plug surrounded by a barrier layer and electrically connecting the lower-level interconnect and the upper-level interconnect.

Owner:EBARA CORP

Wideband single layer microstrip patch antenna

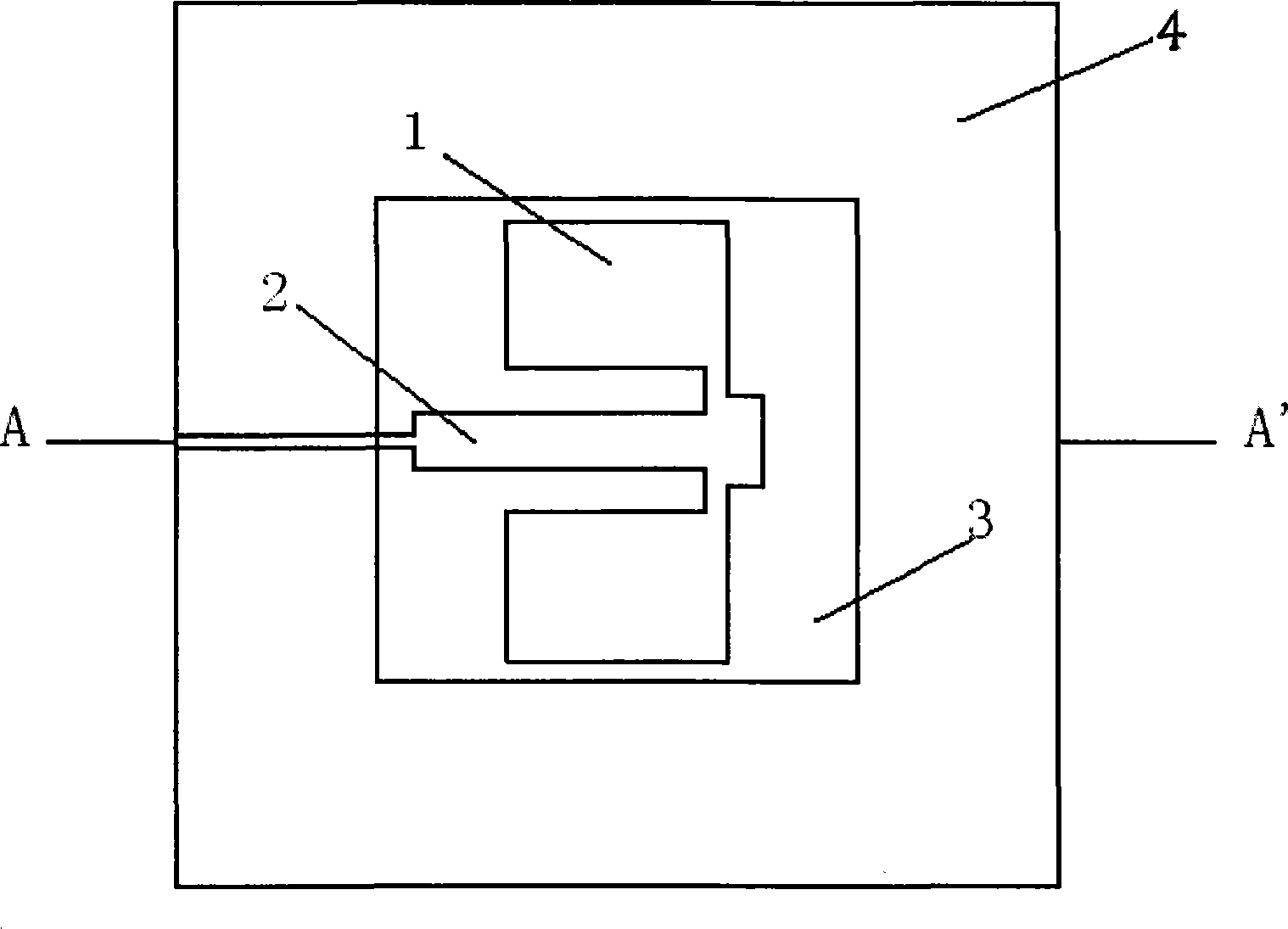

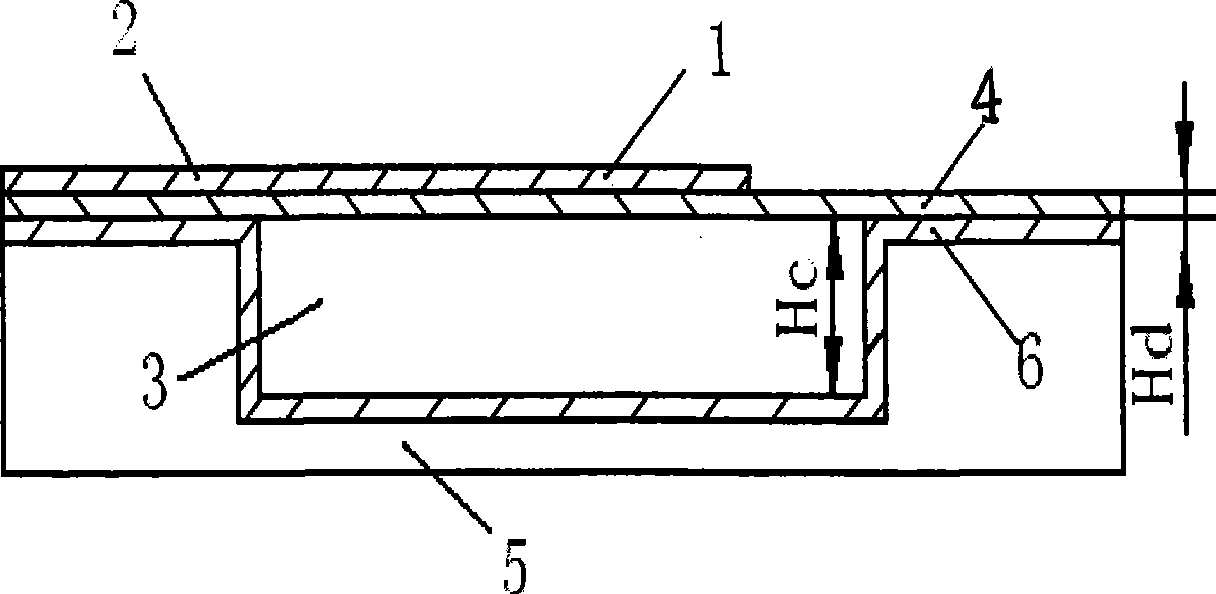

ActiveCN101420066ASimple structureCompact structureRadiating elements structural formsMicrostrip patch antennaAntenna bandwidth

The invention relates to a wide band one-layer microstrip patch antenna, which solves the problem of narrow impedance width in the currently common microstrip antenna. The microstrip patch of the antenna is a one-layer microstrip patch; one end of a stair-stepping coplane microstrip line with two widths is inserted in the patch antenna by the open slot on a convex microstrip patch, and the other end of a feeding microstrip line is positioned at the edge of a microstrip dielectric-slab; a concave metal carinal cavity is arranged at the back surface of the microstrip dielectric-slab excluding the position corresponding to the microstrip patch and in the middle of structural mounting plate. The wide band one-layer microstrip patch antenna can form a large microstrip patch antenna array easily, which is in favor of impedance matching of the antenna, the subnetwork design for microstrip work, the weight reduction of the antenna and the bandwidth widening of the antenna; the wide band one-layer microstrip patch antenna of the invention has the advantages of simple and compact structure and small cross section, which improves the telecommunication performance and reduces the whole weightof the antenna array.

Owner:CHINA ELECTRONIC TECH GRP CORP NO 38 RES INST

Composition containing a cross-linkable matrix precursor and a poragen, and a porous matrix prepared therefrom

InactiveUS20050014855A1Lower effective dielectric constantLow dielectric constantFoundry mouldsSemiconductor/solid-state device manufacturingCross-linkFlat panel display

A suitable cross-linkable matrix precursor and a poragen can be treated to form a porous cross-linked matrix having a Tg of greater than 300° C. The porous matrix material has a lower dielectric constant than the corresponding non-porous matrix material, making the porous matrix material particularly attractive for a variety of electronic applications including integrated circuits, multichip modules, and flat panel display devices.

Owner:DOW GLOBAL TECH LLC

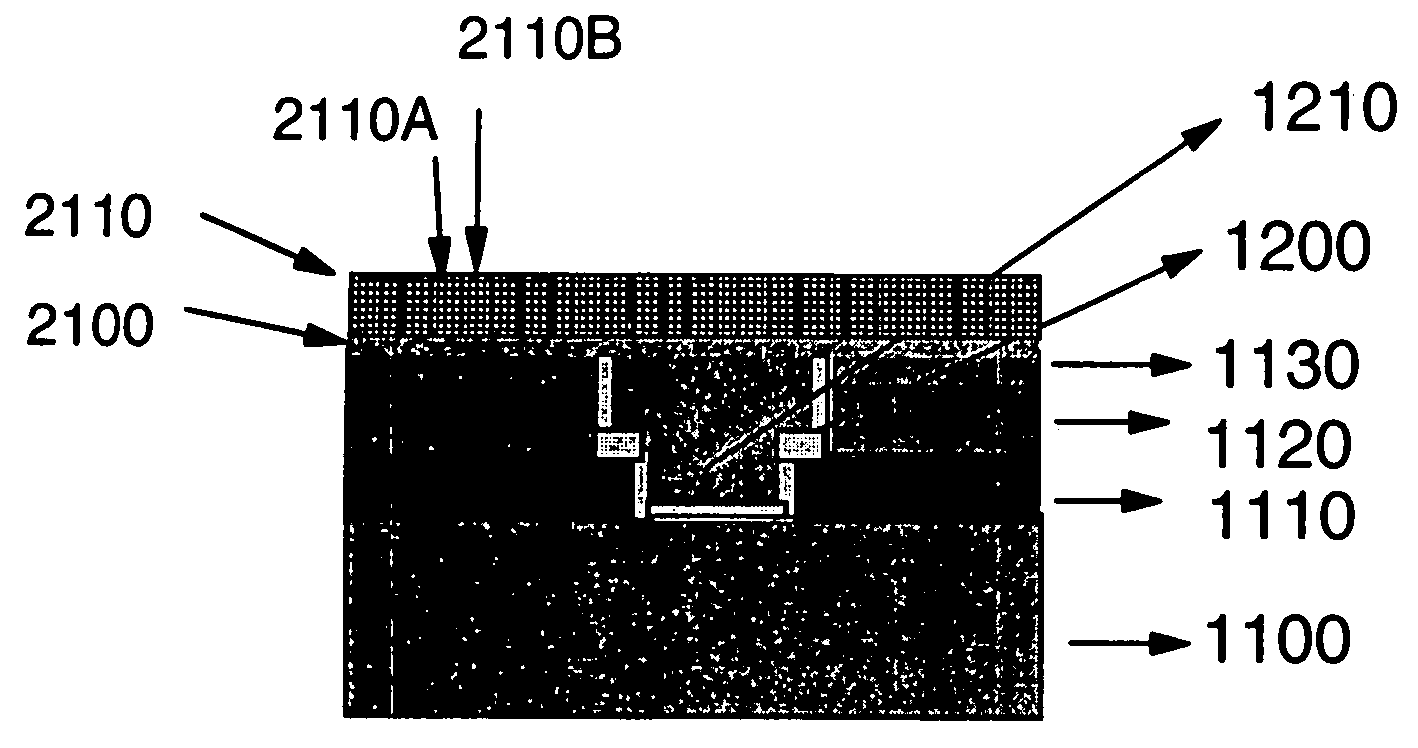

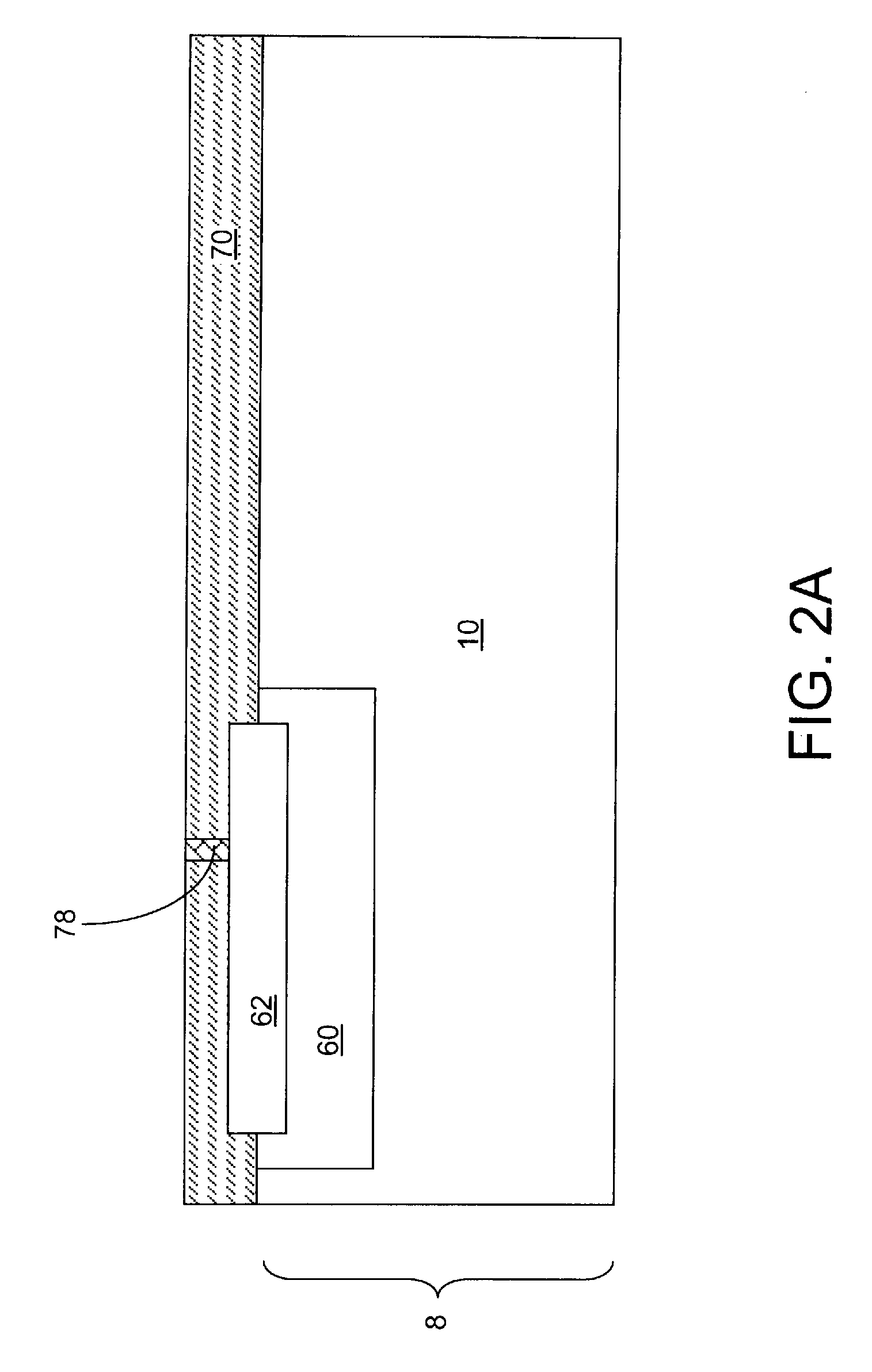

Integrated millimeter wave antenna and transceiver on a substrate

ActiveUS20100035370A1Improve radiation efficiencyReduce effective dielectric constantSemiconductor/solid-state device manufacturingProtective material radiating elementsPhysicsTransceiver

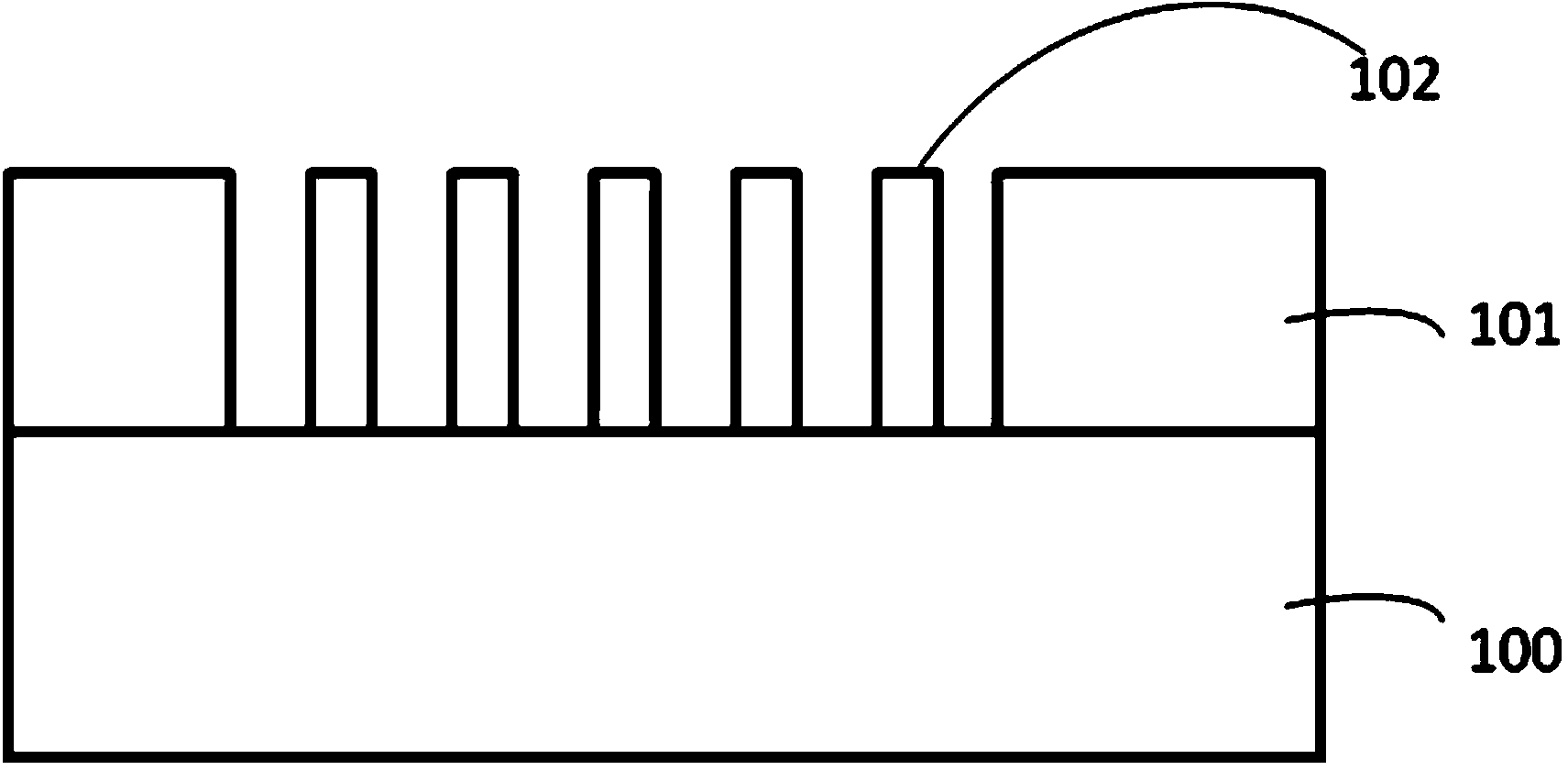

A semiconductor chip integrating a transceiver, an antenna, and a receiver is provided. The transceiver is formed on a front side of a semiconductor substrate. At least one through substrate via provides electrical connection between the transceiver and the backside of the semiconductor substrate. The antenna, which is connected to the transceiver, is formed in a dielectric layer on the front side. The reflector plate is connected to the through substrate via, and is formed on the backside. The separation between the reflector plate and the antenna is about the quarter wavelength of millimeter waves, which enhances radiation efficiency of the antenna. An array of through substrate trenches may be formed and filled with a dielectric material to reduce the effective dielectric constant of the material between the antenna and the reflector plate, thereby reducing the wavelength of the millimeter wave and enhance the radiation efficiency.

Owner:GLOBALFOUNDRIES US INC

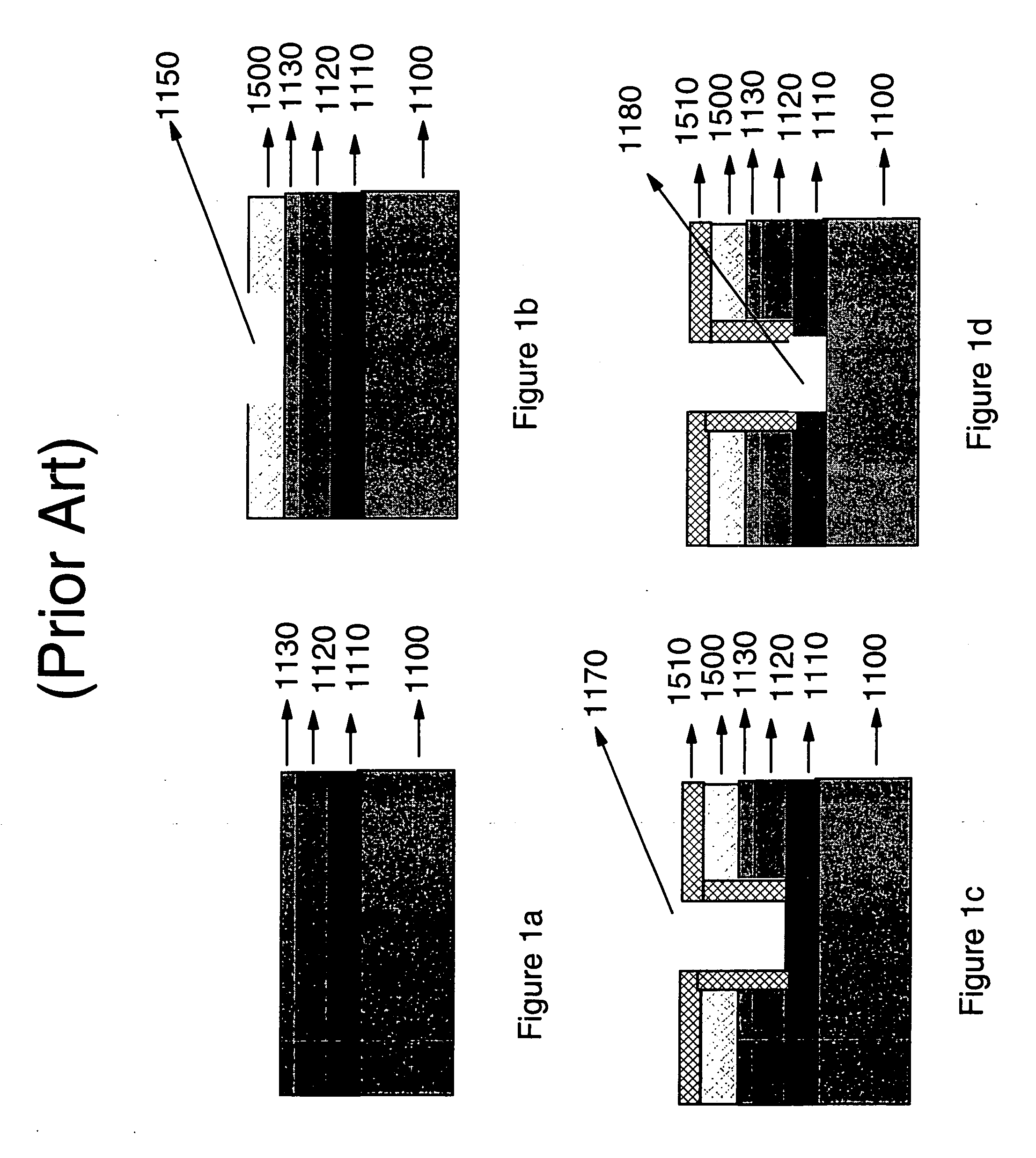

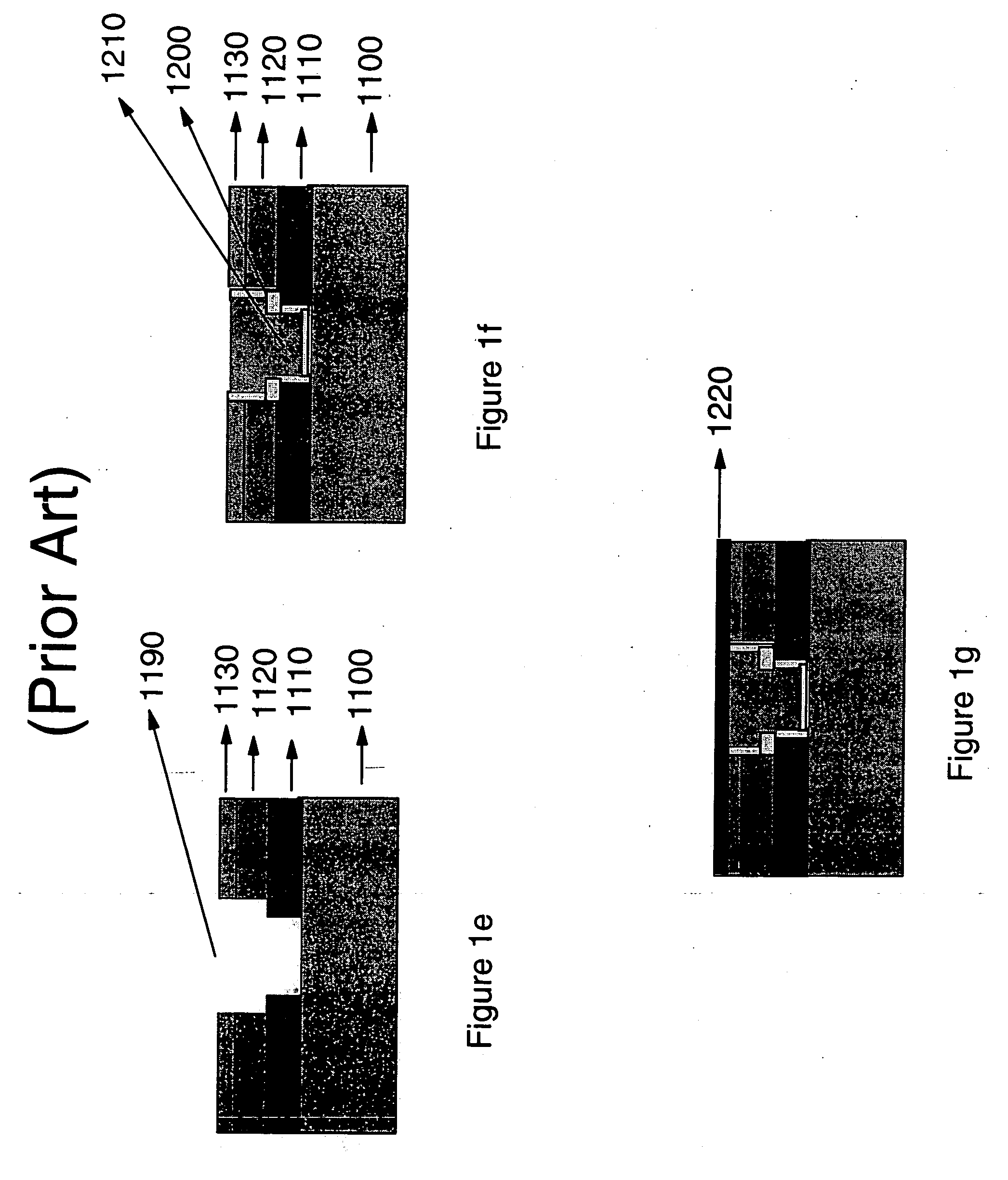

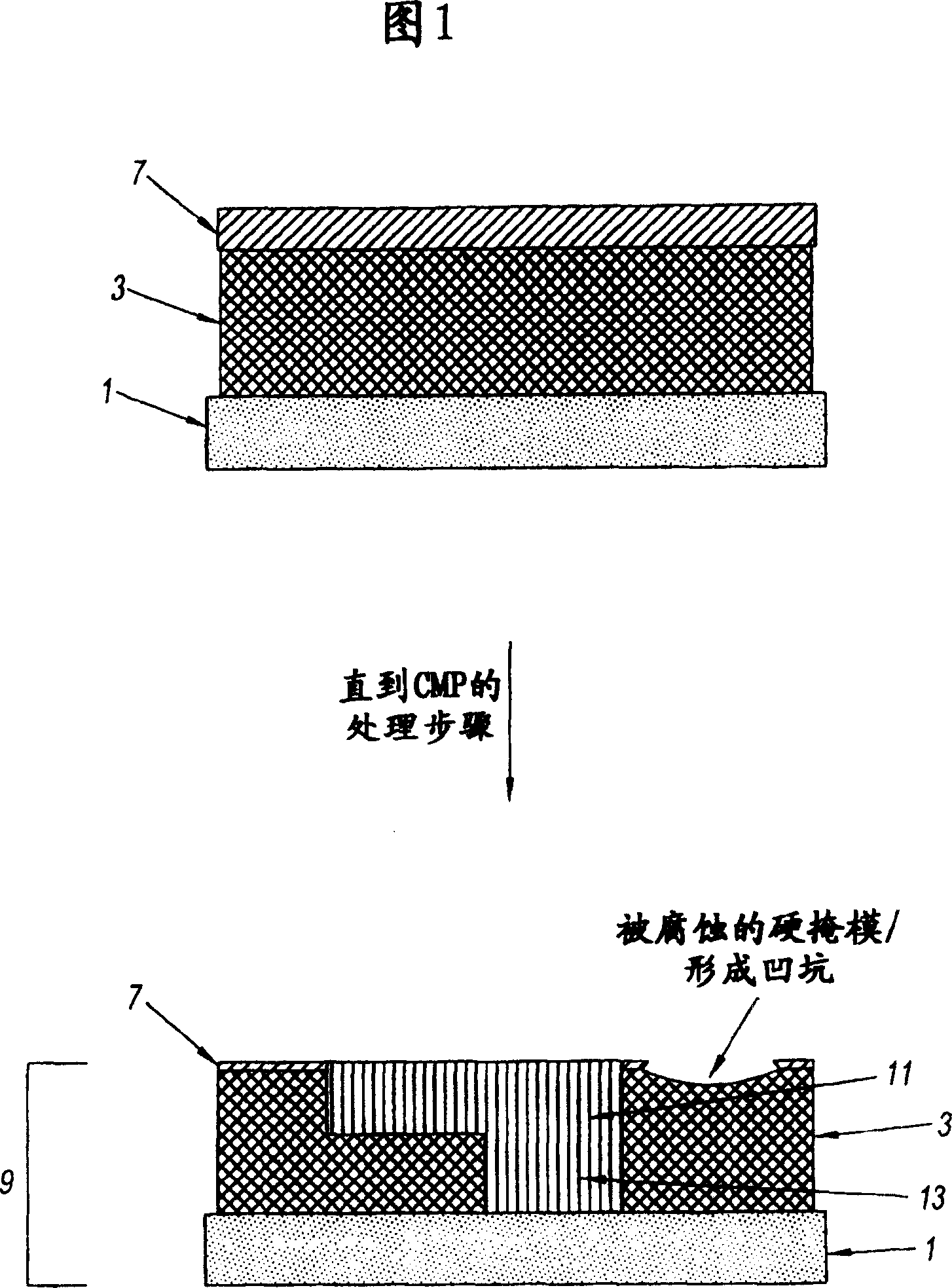

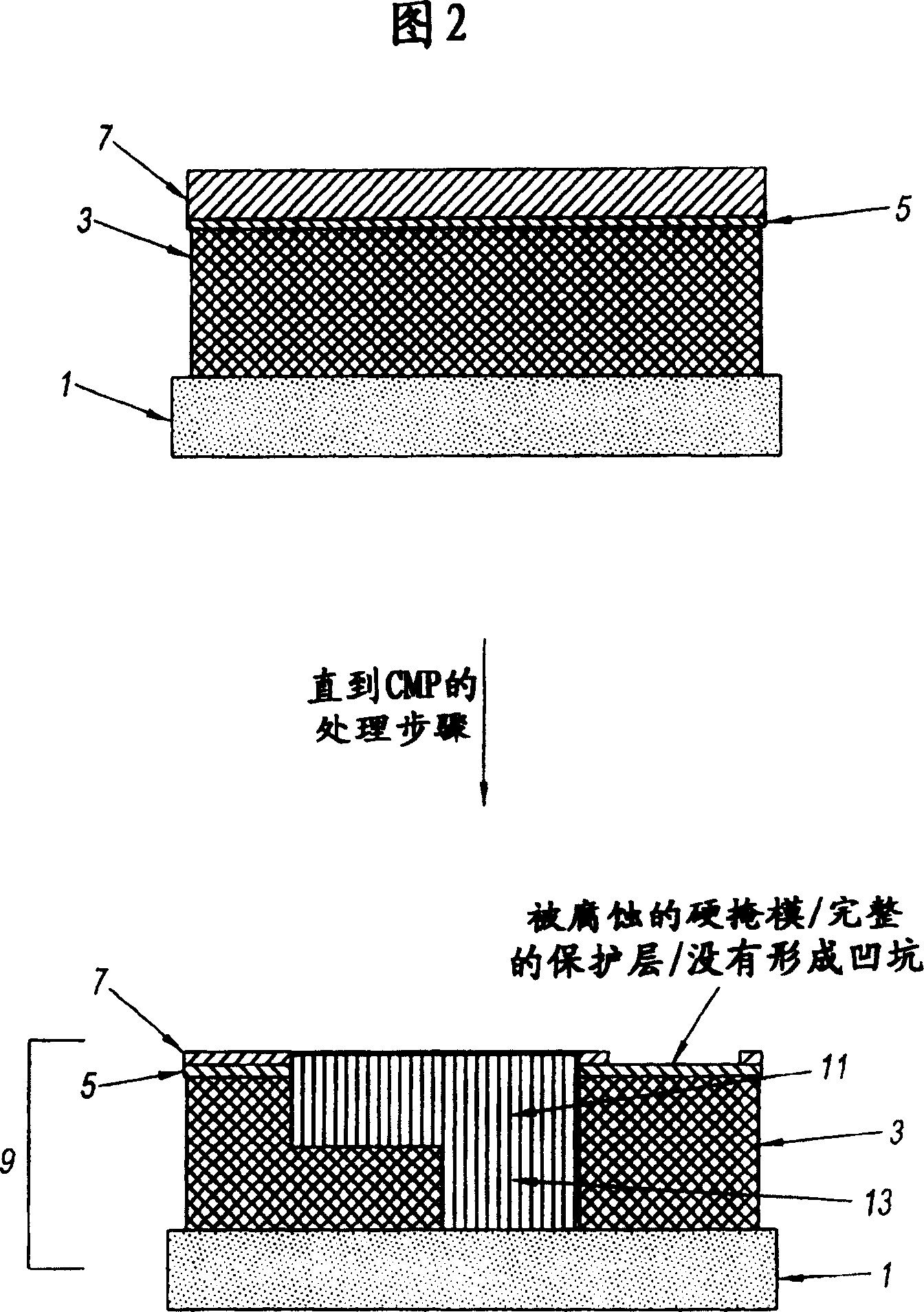

Method of manufacturing a semiconductor device

InactiveUS6333258B1Effective permittivity can be made lowLower effective dielectric constantSemiconductor/solid-state device detailsSolid-state devicesInter layerPermittivity

A manufacturing method for forming a dual damascene structure in which the effective permittivity of an inter-layer insulating film is lowered without an etching mask for forming a contact hole, which is otherwise formed in the inter-layer insulating film. The manufacturing method comprises the step of forming an inorganic film to serve as an etching mask, on the inter-layer insulating film; the step of forming a first opening pattern for forming a wiring groove, in an upper part of the inorganic film; and the step of forming a second opening pattern for forming a contact hole, so as to coincide with the first opening pattern at least partially. Further, the contact hole is formed in the inter-layer insulating film by employing an etching mask made of the inorganic film, the inorganic film is etched into a state where only a third opening pattern obtained by transferring the first opening pattern is formed, and a wiring groove is formed in the inter-layer insulating film by employing the resulting inorganic film as the etching mask.

Owner:SONY CORP

Interconnect structures with engineered dielectrics with nanocolumnar porosity

ActiveUS20050079719A1Lower effective dielectric constantImprove performanceSemiconductor/solid-state device detailsSolid-state devicesPorosityDielectric

A method for forming an interconnect structure with nanocolumnar intermetal dielectric is described involving the construction of an interconnect structure using a solid dielectric, and introducing a regular array of vertically aligned nanoscale pores through stencil formation and etching to form a hole array and subsequently pinching off the tops of the hole array with a cap dielectric. Variations of the method and means to construct a multilevel nanocolumnar interconnect structure are also described.

Owner:GLOBALFOUNDRIES US INC

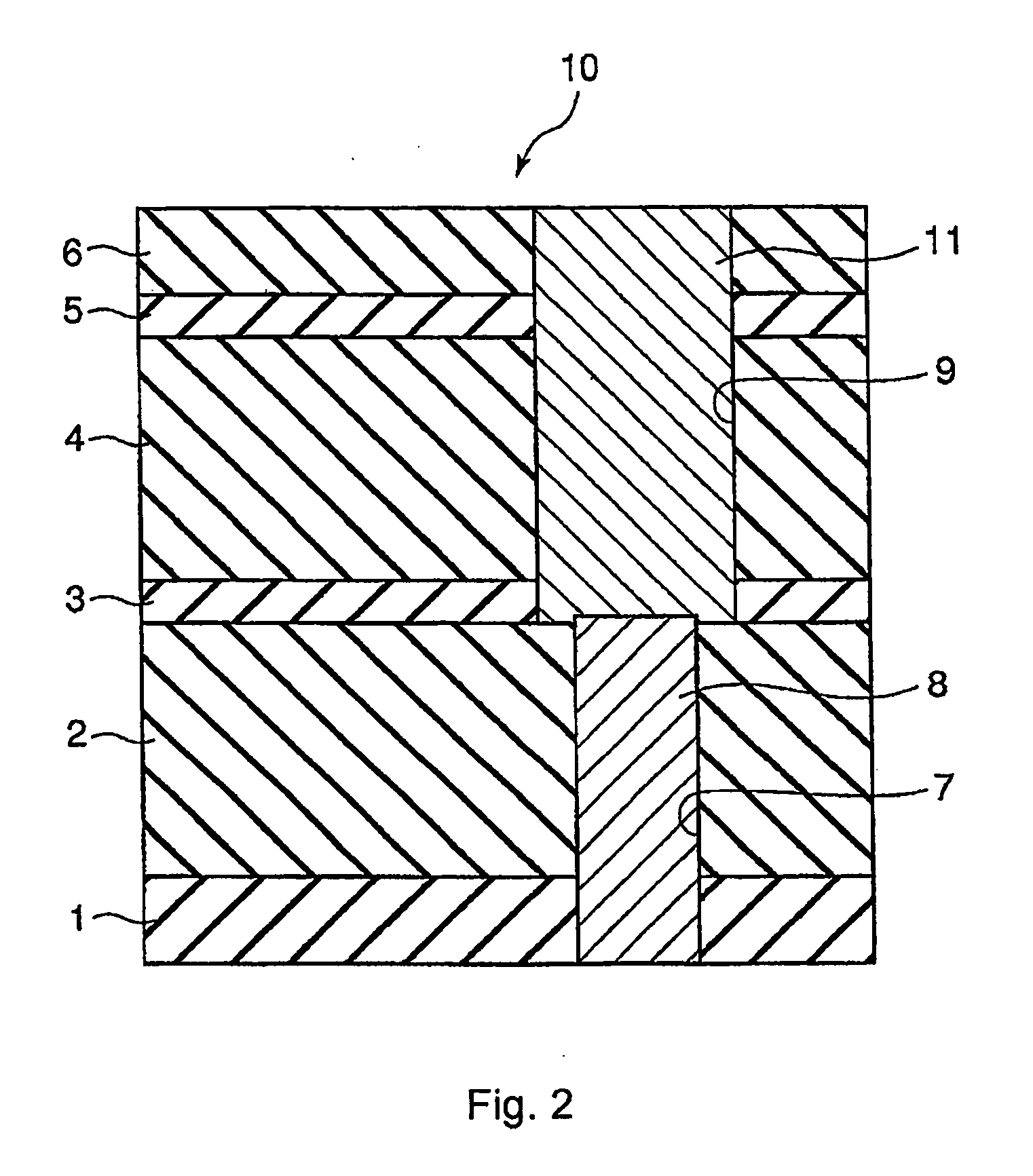

Low-dielectric constant structure with a multilayer stack of thin films with pores

InactiveUS7034380B2Lower effective dielectric constantReduce power consumptionSemiconductor/solid-state device detailsSolid-state devicesOptoelectronicsLow-k dielectric

The present invention describes a structure having a multilayer stack of thin films, the thin films being a low-dielectric constant material, the thin films having pores, and a method of forming such a structure.

Owner:INTEL CORP

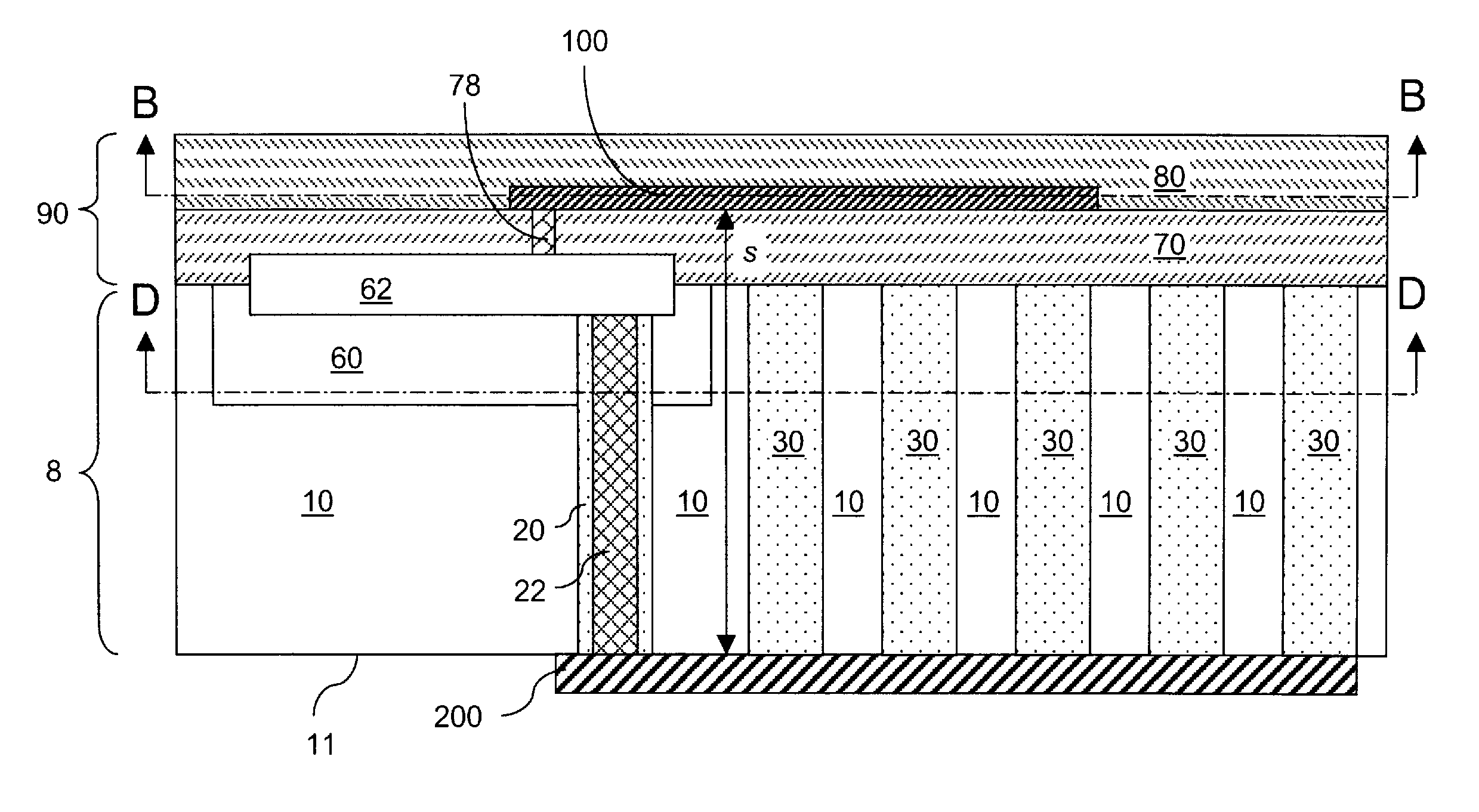

Integrated millimeter wave antenna and transceiver on a substrate

ActiveUS7943404B2Improve radiation efficiencyLower effective dielectric constantSemiconductor/solid-state device manufacturingProtective material radiating elementsTransceiverElectrical connection

A semiconductor chip integrating a transceiver, an antenna, and a receiver is provided. The transceiver is formed on a front side of a semiconductor substrate. At least one through substrate via provides electrical connection between the transceiver and the backside of the semiconductor substrate. The antenna, which is connected to the transceiver, is formed in a dielectric layer on the front side. The reflector plate is connected to the through substrate via, and is formed on the backside. The separation between the reflector plate and the antenna is about the quarter wavelength of millimeter waves, which enhances radiation efficiency of the antenna. An array of through substrate trenches may be formed and filled with a dielectric material to reduce the effective dielectric constant of the material between the antenna and the reflector plate, thereby reducing the wavelength of the millimeter wave and enhance the radiation efficiency.

Owner:GLOBALFOUNDRIES US INC

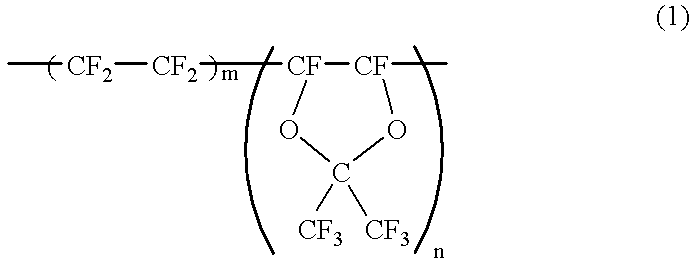

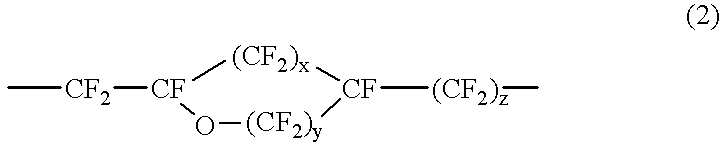

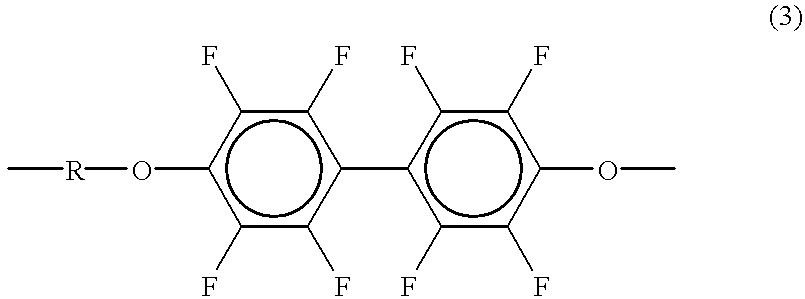

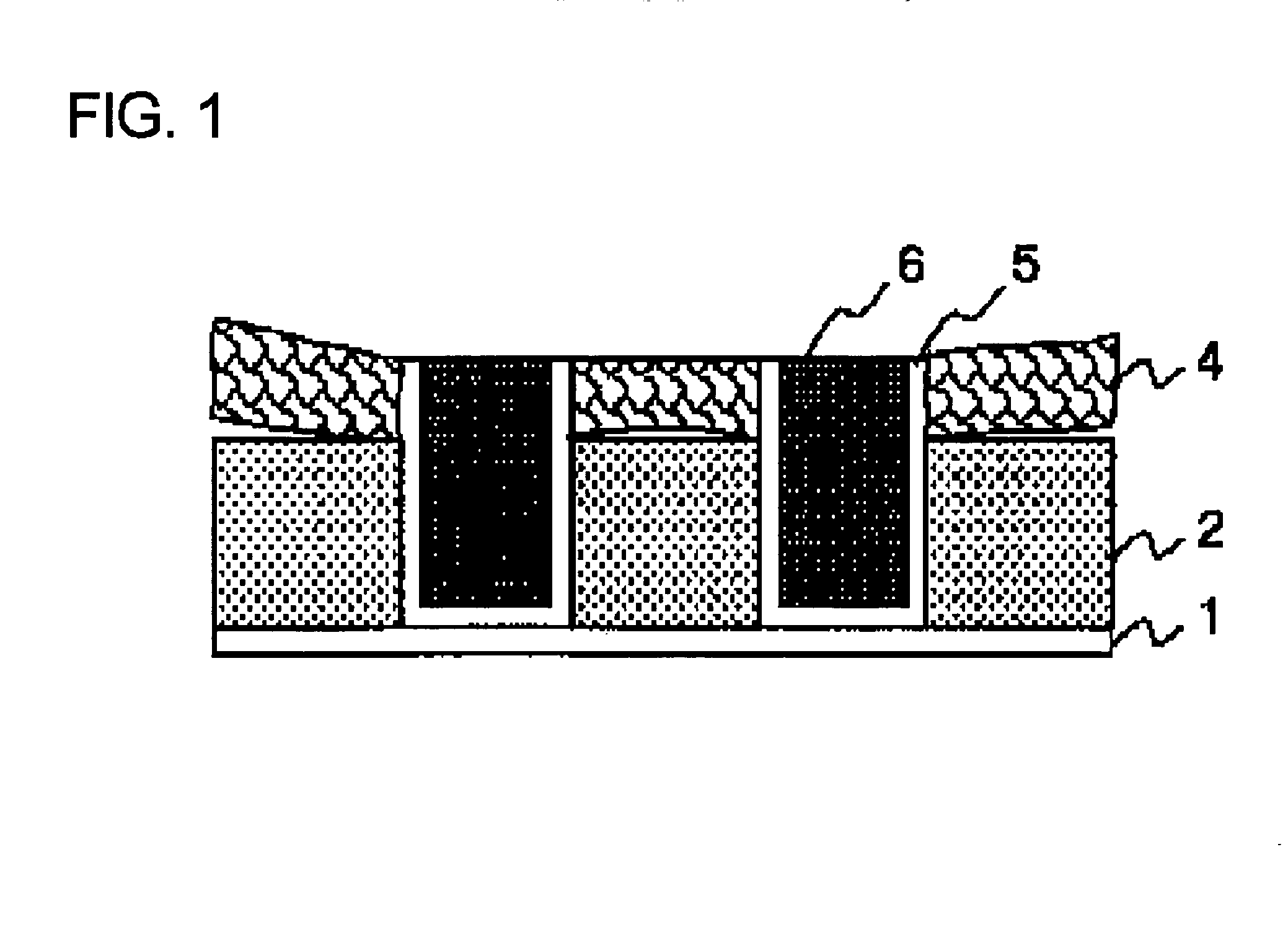

Interlayer Insulating Film, Interconnection Structure, and Methods of Manufacturing the Same

InactiveUS20090108413A1Low dielectric constantReduce outgassingSemiconductor/solid-state device detailsSolid-state devicesPermittivityInterconnection

This invention provides an interlayer insulating film for a semiconductor device, which has low permittivity, is free from the evolution of gas such as CFx and SiF4 and is stable, and a wiring structure comprising the same. In an interlayer insulating film comprising an insulating film provided on a substrate layer, the interlayer insulating film has an effective permittivity of not more than 3. The wiring structure comprises an interlayer insulating film, a contact hole provided in the interlayer insulating film, and a metal filled into the contact hole. The insulating film comprises a first fluorocarbon film provided on the substrate layer and a second fluorocarbon film provided on the first fluorocarbon film.

Owner:TOHOKU UNIV +1

Integrated millimeter wave antenna and transceiver on a substrate

ActiveUS8232920B2Improve radiation efficiencyLower effective dielectric constantSimultaneous aerial operationsRadiating elements structural formsTransceiverElectrical connection

A semiconductor chip integrating a transceiver, an antenna, and a receiver is provided. The transceiver is located on a front side of a semiconductor substrate. A through substrate via provides electrical connection between the transceiver and the receiver located on a backside of the semiconductor substrate. The antenna connected to the transceiver is located in a dielectric layer located on the front side of the substrate. The separation between the reflector plate and the antenna is about the quarter wavelength of millimeter waves, which enhances radiation efficiency of the antenna. An array of through substrate dielectric vias may be employed to reduce the effective dielectric constant of the material between the antenna and the reflector plate, thereby reducing the wavelength of the millimeter wave and enhance the radiation efficiency. A design structure for designing, manufacturing, or testing a design for such a semiconductor chip is also provided.

Owner:GLOBALFOUNDRIES U S INC

Insulator with air dielectric cavities for electrical connector

ActiveUS8597047B2Lower effective dielectric constantPreserving signal fidelityElectric discharge tubesSecuring/insulating coupling contact membersDielectricElectricity

Owner:AIRBORN

Semiconductor structure having an air-gap region and a method of manufacturing the same

ActiveCN102163592AIncrease coverageLower effective dielectric constantSemiconductor/solid-state device detailsSolid-state devicesSemiconductor structureMaterials science

The invention provides a semiconductor structure, a method for manufacturing the semiconductor structure and a method for manufacturing a light cover with an air-gap region. The semiconductor structure includes a first metal-containing layer, a dielectric capping layer, a second metal-containing layer, and a conductive pad. The first metal-containing layer includes a set of metal structures, a dielectric filler disposed to occupy a portion of the first metal-containing layer, and an air-gap region defined by at least the set of metal structures and the dielectric filler and abutting at least a portion of the set of metal structures. The second metal-containing layer includes at least a via plug electrically connected to a portion of the set of metal structures. The conductive pad and the via plug do not overlap the air-gap region.

Owner:TAIWAN SEMICON MFG CO LTD

Semiconductor device including ladder-shaped siloxane hydride and method for manufacturing same

ActiveUS7230337B2Lower effective dielectric constantImprove reliabilitySemiconductor/solid-state device detailsSolid-state devicesCopper interconnectMoisture absorption

Owner:RENESAS ELECTRONICS CORP

Insulator with Air Dielectric Cavities for Electrical Connector

ActiveUS20130122743A1Lower effective dielectric constantPreserving signal fidelityElectric discharge tubesSecuring/insulating coupling contact membersDielectricEngineering

An insulator for an electrical connector that comprises a back shell, metal shell, EMI band, and the insulator. The insulator features alternating contact cavities and air dielectric cavities. The air dielectric cavities reduce the effective dielectric constant of the connector, which allows high-speed data to be transmitted while maintaining impedance, thereby preserving signal fidelity.

Owner:AIRBORN

Composition containing a cross-linkable matrix precursor and a poragen, and a porous matrix prepared therefrom

InactiveUS6887910B2Lower effective dielectric constantFoundry mouldsSemiconductor/solid-state device manufacturingFlat panel displayOrganic chemistry

A suitable cross-linkable matrix precursor and a poragen can be treated to form a porous cross-linked matrix having a Tg of greater than 300° C. The porous matrix material has a lower dielectric constant than the corresponding non-porous matrix material, making the porous matrix material particularly attractive for a variety of electronic applications including integrated circuits, multichip modules, and flat panel display devices.

Owner:DOW GLOBAL TECH LLC

Semiconductor device and method for manufacturing the same

ActiveUS7157370B2Lower effective dielectric constantEasy to manufactureSemiconductor/solid-state device detailsSolid-state devicesEngineeringSemiconductor

A semiconductor device includes a highly reliable multi-level interconnect structure having a low effective dielectric constant and which can be easily manufactured with a relatively inexpensive process, and a method for manufacturing the semiconductor device. The semiconductor device includes a lower-level interconnect and an upper-level interconnect, each surrounded by a barrier layer, and a via plug surrounded by a barrier layer and electrically connecting the lower-level interconnect and the upper-level interconnect.

Owner:EBARA CORP

Antenna module and method for manufacturing the same

InactiveUS20140203994A1Reduce effectEasily adjustAntenna supports/mountingsRadiating elements structural formsEngineeringSemiconductor

An antenna module includes a support body and an antenna body. The support body has a flat support surface and a support surface that extends obliquely upward from one side of the support surface. The antenna body is attached to the support surface while being bent along the support surface of the support body. The antenna body is constituted by a dielectric film, a pair of electrodes and a semiconductor device. The pair of electrodes is formed on a main surface of the dielectric film, and the semiconductor device is mounted on the end of the electrode.

Owner:NITTO DENKO CORP

Semiconductor device and method of manufacturing the same

ActiveUS7795133B2Suppressing increase in permittivityReduce signal delaySemiconductor/solid-state device detailsSolid-state devicesEngineeringRelative permittivity

By covering inner surfaces of a wiring groove 26c and a via hole 27a with a fourth insulation film 25 containing porogen during a manufacturing process of a semiconductor device, an increase in the relative permittivity of the fourth insulation film 25 that is a low-permittivity film on the inner surfaces of the wiring groove 26c and the via hole 27a can be suppressed in a manufacturing process of a semiconductor device such as a barrier metal sputtering process.

Owner:PANNOVA SEMIC

Semiconductor device and method for manufacturing same

InactiveUS20060276029A1Avoid introducingImprove reliabilitySemiconductor/solid-state device detailsSolid-state devicesCopper interconnectDevice material

The present invention reduces the effective dielectric constant of the interlayer insulating film while inhibiting the decrease of the reliability of the semiconductor device, which otherwise is caused by a moisture absorption. A copper interconnect comprising a Cu film 209 is formed in multilayer films comprising a L-Ox™ film 203 and a SiO2 film 204. Since the L-Ox™ film 203 comprises ladder-shaped siloxane hydride structure, the film thickness and the film characteristics are stable, and thus changes in the film quality is scarcely occurred during the manufacturing process.

Owner:NEC ELECTRONICS CORP

Dual damascene circuit with upper wiring and interconnect line positioned in regions formed as two layers including organic polymer layer and low-permittivity layer

InactiveUS6977438B2Good body shapeWell reduced effective permittivitySemiconductor/solid-state device detailsSolid-state devicesVolumetric Mass DensityOragene

A dual damascene circuit has lower wiring and upper wiring positioned in regions formed as two layers including a CH-based organic polymer layer and a low-permittivity layer made of porous MSQ or the like. The organic polymer layer and the low-permittivity layer have high etching selectively with respect to each other to form an upper groove and a via hole to a good shape, allowing upper wiring and the interconnect line to have good electric characteristics. The organic polymer layer and the low-permittivity layer are low in density and permittivity, thus reducing the effective permittivity of the dual damascene circuit in its entirety.

Owner:RENESAS ELECTRONICS CORP

Semiconductor device and method of manufacturing the same

ActiveUS20090152732A1Low dielectric constantReduce signal delaySemiconductor/solid-state device detailsSolid-state devicesManufacturing technologyDevice material

By covering inner surfaces of a wiring groove 26c and a via hole 27a with a fourth insulation film 25 containing porogen during a manufacturing process of a semiconductor device, an increase in the relative permittivity of the fourth insulation film 25 that is a low-permittivity film on the inner surfaces of the wiring groove 26c and the via hole 27a can be suppressed in a manufacturing process of a semiconductor device such as a barrier metal sputtering process.

Owner:PANNOVA SEMIC

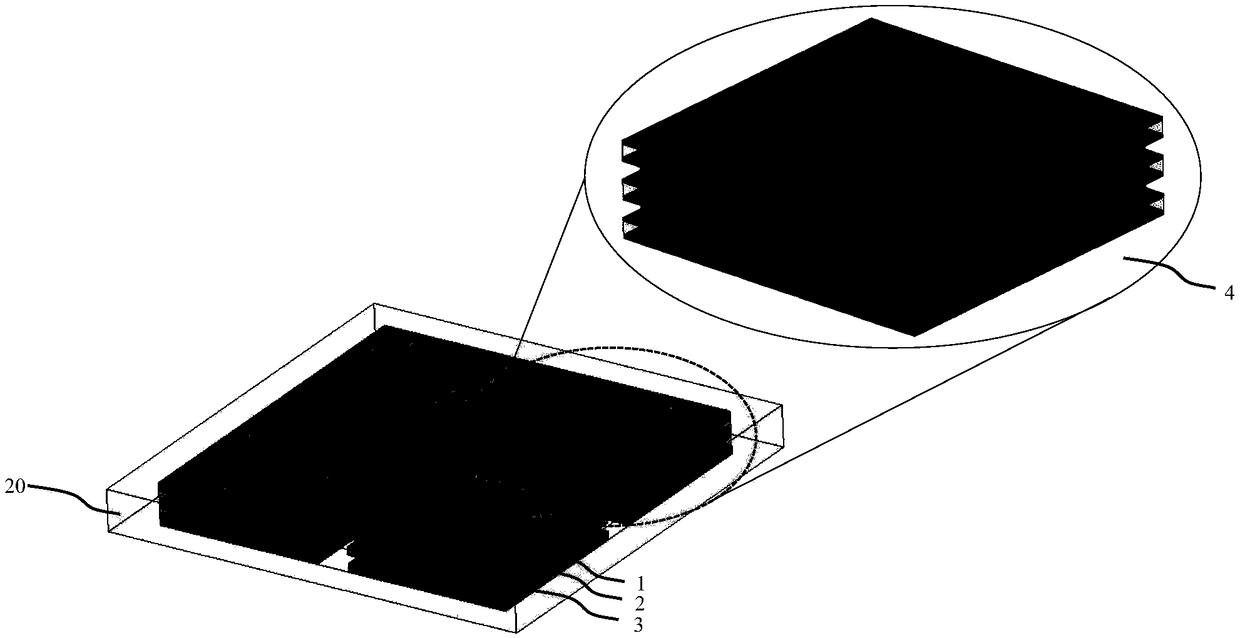

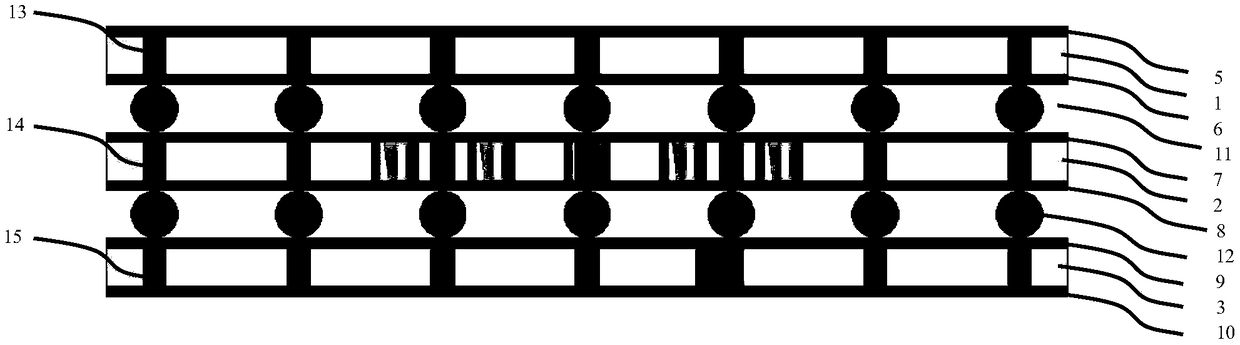

Radio frequency micro-electromechanical microstrip antenna

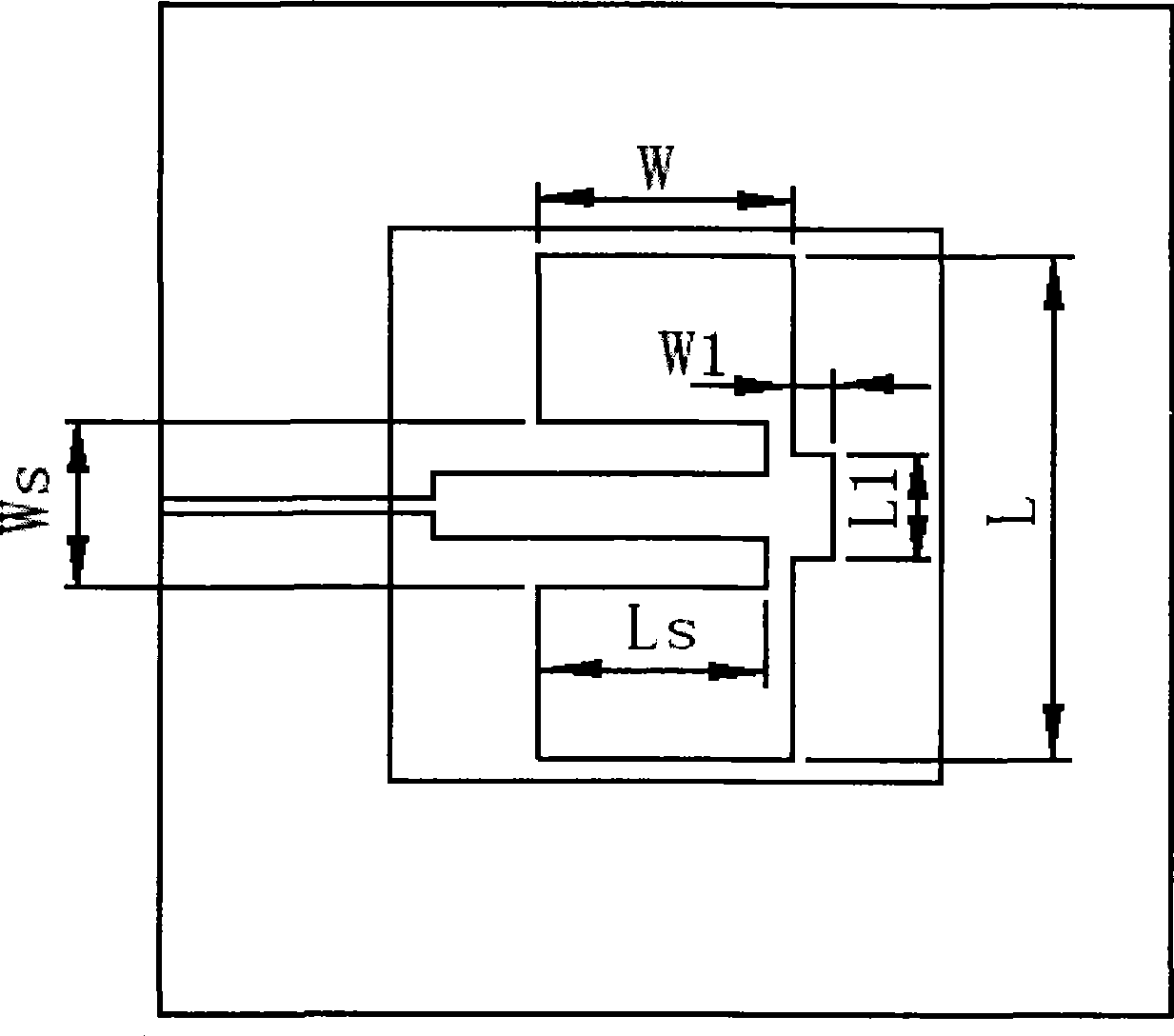

ActiveCN109462028AHigh bandwidthHigh gainRadiating elements structural formsIndividually energised antenna arraysHigh bandwidthAntenna bandwidth

The invention discloses a radio frequency micro-electromechanical microstrip antenna, and belongs to the technical field of wireless communication. The radio frequency micro-electromechanical microstrip antenna comprises a metal frame and a microstrip antenna unit, wherein the microstrip antenna unit comprises a first adapter plate, a second adapter plate and a third adapter plate; metal shieldingstructures surrounding the central areas of the respective adapter plates are arranged on the three adapter plates, and the vertical interconnection of the metal shielding structures among the threeadapter plates is achieved by BGA interconnection structures; a first radiation patch is arranged on the front face of the first adapter plate; an air hole and a parasitic patch are arranged on the second adapter plate; a second radiation patch is arranged on the front face of the third adapter plate, and a reflecting surface s arranged on the back surface of the third adapter plate; and a feedinghole and a grounding hole are formed in the central area of the third adapter plate. The radio frequency micro-electromechanical microstrip antenna disclosed by the invention has the characteristicsof low profile, high gain and high bandwidth, and can solve the problems of narrow bandwidth and low gain of a low-profile microstrip antenna of a semiconductor substrate with a high dielectric constant.

Owner:NO 54 INST OF CHINA ELECTRONICS SCI & TECH GRP

Method of improved high K dielectric-polysilicon interface for CMOS devices

InactiveUS7129128B2Lower effective dielectric constantReduce leakageSolid-state devicesSemiconductor/solid-state device manufacturingMaterials sciencePolycrystalline silicon

Methods for forming dielectric layers over polysilicon substrates, useful in the construction of capacitors and other semiconductor circuit components are provided. A self-limiting nitric oxide (NO) anneal of a polysilicon layer such as an HSG polysilicon capacitor electrode, at less than 800° C., is utilized to grow a thin oxide (oxynitride) layer of about 40 angstroms or less over the polysilicon layer. The NO anneal provides a nitrogen layer at the polysilicon-oxide interface that limits further oxidation of the polysilicon layer and growth of the oxide layer. The oxide layer is exposed to a nitrogen-containing gas to nitridize the surface of the oxide layer and reduce the effective dielectric constant of the oxide layer. The process is particularly useful in forming high K dielectric insulating layers such as tantalum pentoxide over polysilicon. The nitridized oxynitride layer inhibits oxidation of the underlying polysilicon layer in a post-treatment oxidizing anneal of the high K dielectric, thus maintaining the oxide layer as a thin layer over the polysilicon layer.

Owner:MICRON TECH INC

Method for preparing FeSiAl-series alloy micro powder electromagnetic absorbent

ActiveCN106521312AMicrowave permeability does not decreaseReduced microwave permeabilityMagnetic/electric field screeningTransportation and packagingDielectricMicrowave

The invention belongs to the technical field of electronic materials, and particularly relates to a method for preparing FeSiAl-series alloy micro powder electromagnetic absorbent. The method includes the steps that FeSiAl-series alloy micro powder is put into a tube furnace, and a protective atmosphere is connected in; and then heat treatment is carried out, and accordingly the electromagnetic absorbent prepared through the method can be obtained. When the electromagnetic absorbent and an auxiliary material are compounded according to the volume ratio of the absorbent to the auxiliary material being 28.5%-35% to be prepared into an electromagnetic wave absorbing material, and the effect that the microwave magnetic conductivity of the material is not lowered can be guaranteed. Meanwhile, the effective dielectric constant of the material is lowered obviously, impedance matching can be better achieved, and the microwave absorbing property is improved. Moreover, the operating method is convenient and easy to implement. Compared with the prior art, cost is reduced, and the method is suitable for large-scale production.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

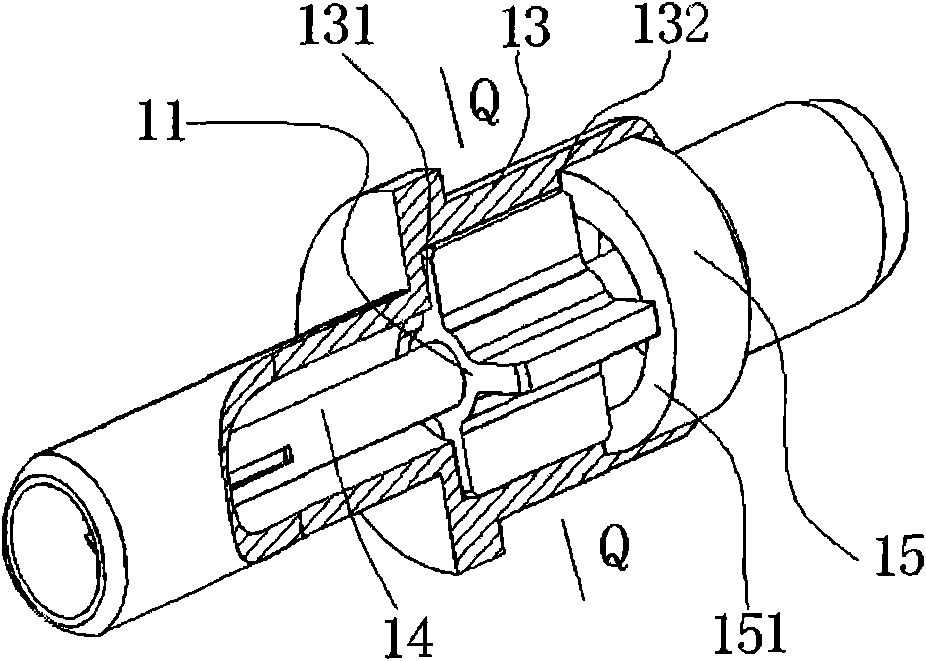

Medium supporting structure applied to radio-frequency coaxial connector

InactiveCN102097698AIncrease the volume ratioLower effective dielectric constantSecuring/insulating coupling contact membersTwo-part coupling devicesElectrical conductorEngineering

The invention discloses a medium supporting structure applied to a radio-frequency coaxial connector, comprising an insulation supporting piece, a first positioning structural piece and a second positioning structural piece. The first positioning structural piece is arranged outside the insulation supporting piece to limit the radial freedom degree of the insulation supporting piece, the first positioning structural piece and the second positioning structural piece are matched and fixed from both ends of the insulation supporting piece to limit the axial freedom degree of the insulation support piece, the insulation supporting piece comprises a plurality of thin-walled insulation supporting ribs, an inner hole for inserting an inner conductor of the coaxial connector is arranged in the center of the insulation supporting piece, a circle is formed on the outer margin of the plurality of thin-walled insulation supporting ribs of the insulation supporting piece and is structurally coaxial with the inner hole, and the internal diameter of the inner hole of the insulation supporting piece is consistent with the diameter of the part which the inner conductor is inserted into the inner hole. The invention can greatly increase the volume ratio between air and the insulation medium in the medium supporting segment and remarkably decrease the effective SIC (Specific Inductive Capacity) of the medium supporting segment on the premise that the mechanical strength is ensured.

Owner:SUZHOU HUAZHAN SPACE APPLIANCE

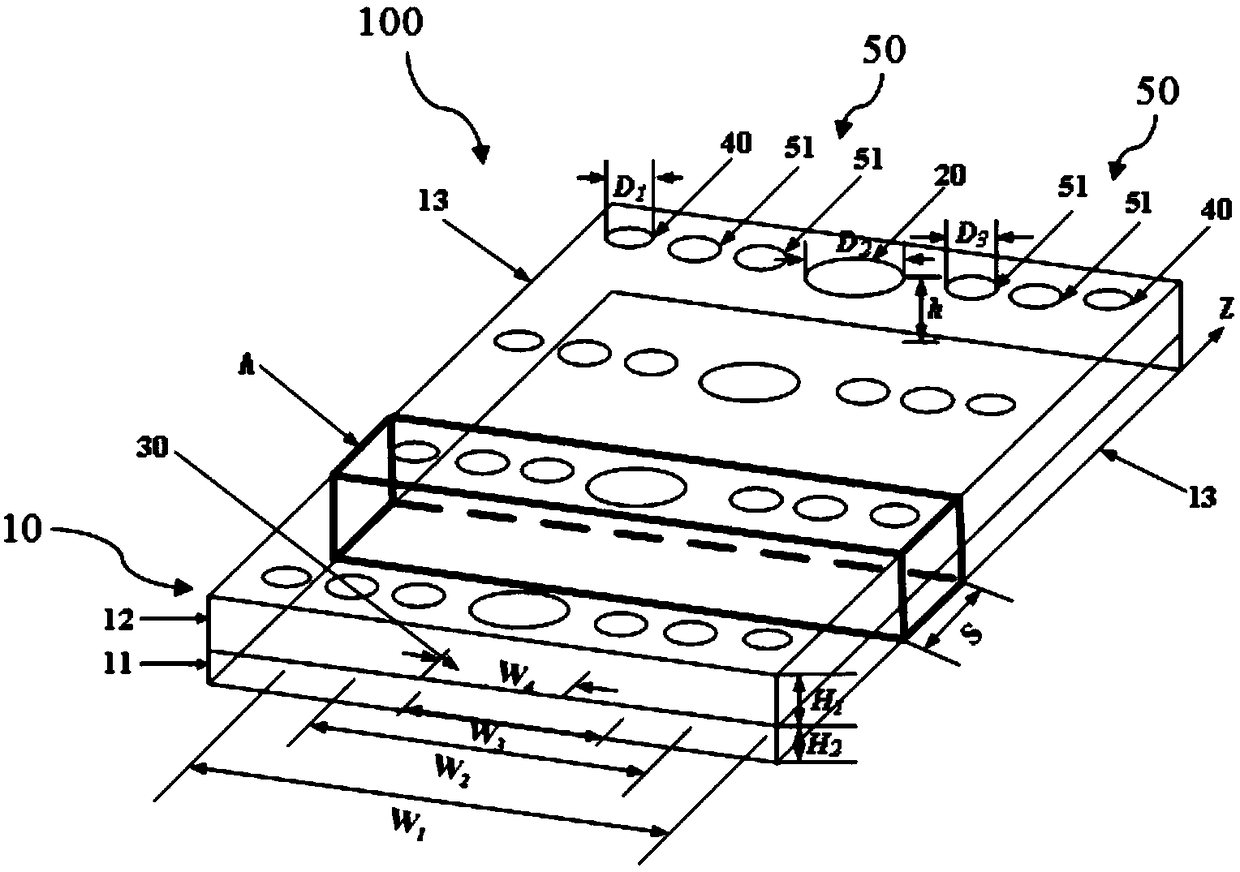

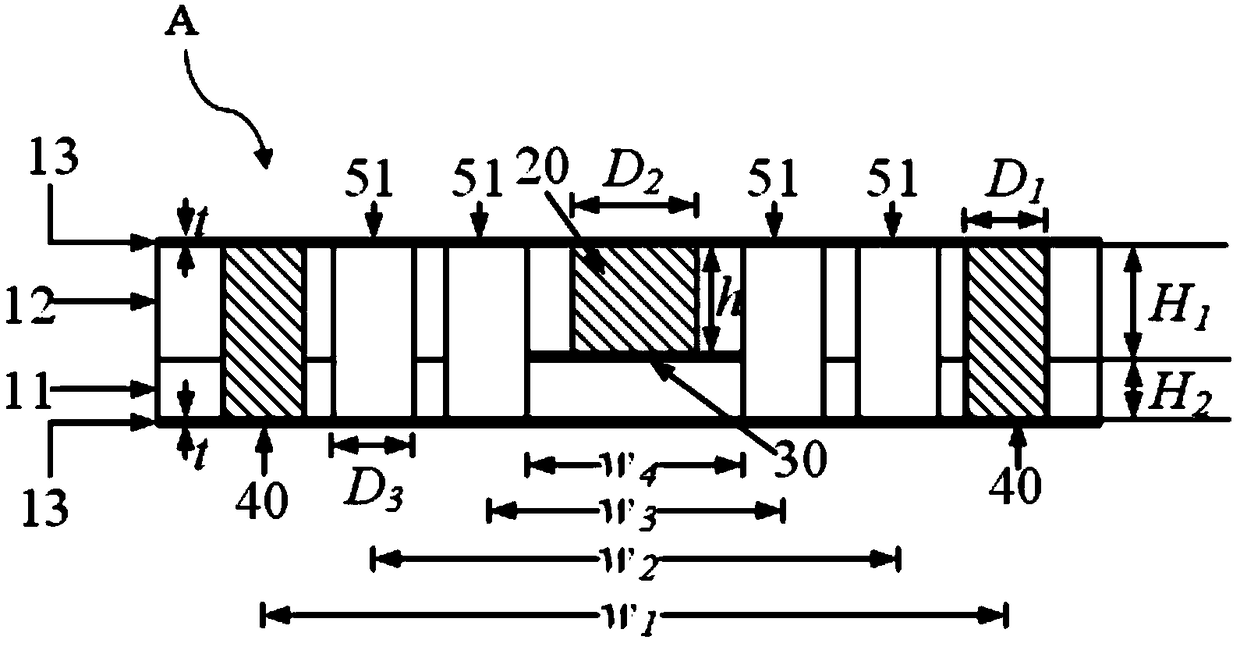

A novel substrate integrated ridge waveguide structure

The invention provides a novel substrate integrated ridge waveguide structure, comprising: a dielectric substrate unit, comprising a lower dielectric substrate and an upper dielectric substrate arranged on the lower dielectric substrate, wherein the dielectric constant of the upper dielectric substrate is different from that of the lower dielectric substrate. A suspended metal column embedded in the upper dielectric substrate along a direction perpendicular to the dielectric substrate unit and periodically arranged on a centerline in the longitudinal direction of the upper dielectric substrate; And a metal strip arranged at the bottom of the suspended metal column. The novel substrate integrated ridge waveguide is composed of two dielectric substrates with different dielectric constants. The gap between the lower surface of the suspended metal column embedded in the structure and the lower surface of the dielectric substrate unit forms the ridge capacitance, which reduces the cutoff frequency of the main mode. In addition, the area between the electrode plates is increased by the metal strips arranged at the bottom of the suspended metal column, so that the ridge capacitance valueis increased, the cutoff frequency of the main mode is further reduced, and the working bandwidth of the obtained main mode is greatly improved.

Owner:UNIV OF SHANGHAI FOR SCI & TECH

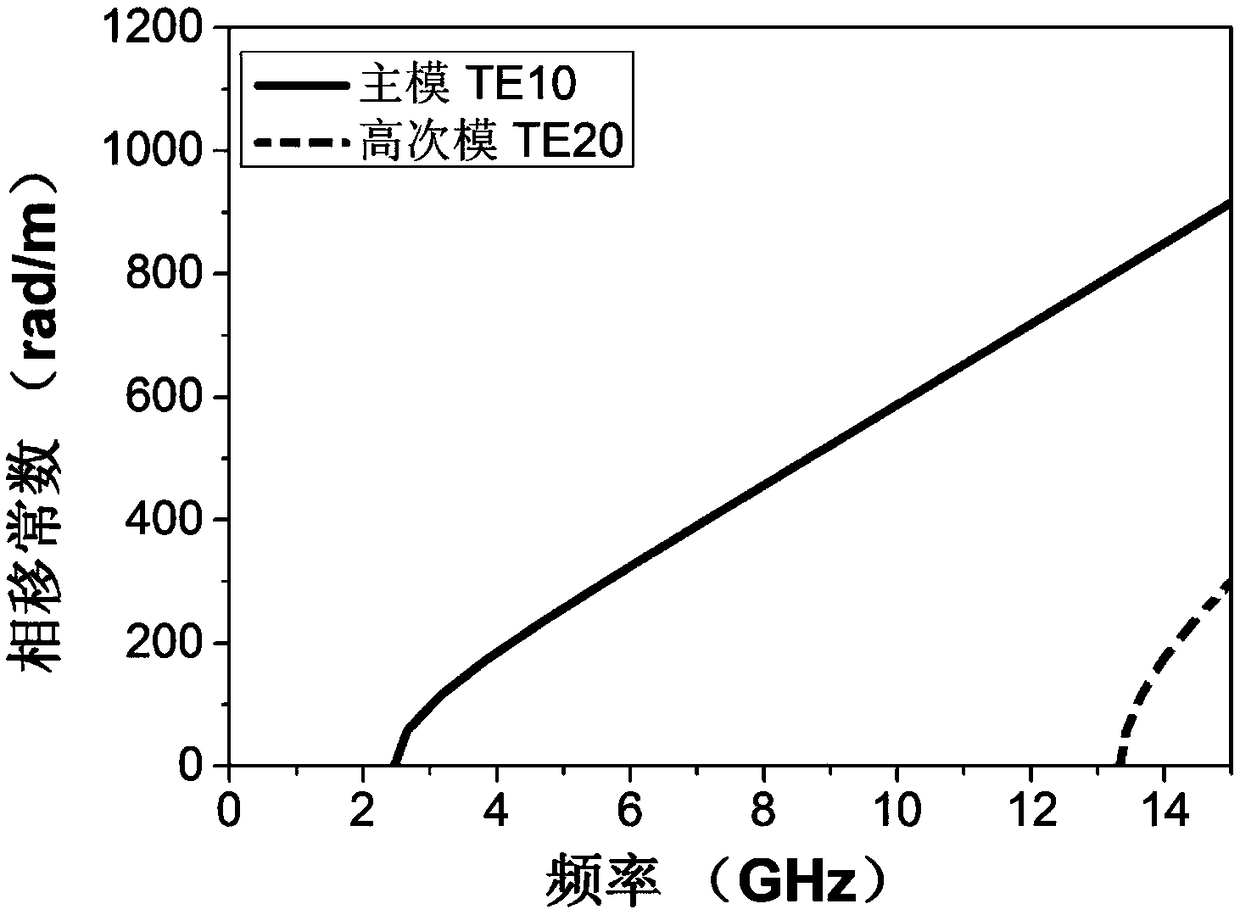

Manufacturing method for thin film with ultralow dielectric constant

ActiveCN104319259AReduce porosityRecovery apertureSemiconductor/solid-state device manufacturingPorosityHigh stress

The invention discloses a manufacturing method for a thin film with an ultralow dielectric constant. A thin film with a low dielectric constant is etched, wherein the thin film is formed by deposition. A required pattern structure is formed (the porosity of a dielectric film is low at the moment, and the dielectric film has enough mechanical strength to support the high stress introduced by a hard mask), carbon injection and ultraviolet radiation are carried out to recover the aperture and the porosity of the dielectric film, the thin film with the ultralow dielectric constant is further formed, the phenomenon that the dielectric film collapses is avoided, and the effective dielectric constant (K value) of the dielectric film can be kept to be the smallest, and the method can be compatible with the existing industrial process.

Owner:SHANGHAI INTEGRATED CIRCUIT RES & DEV CENT

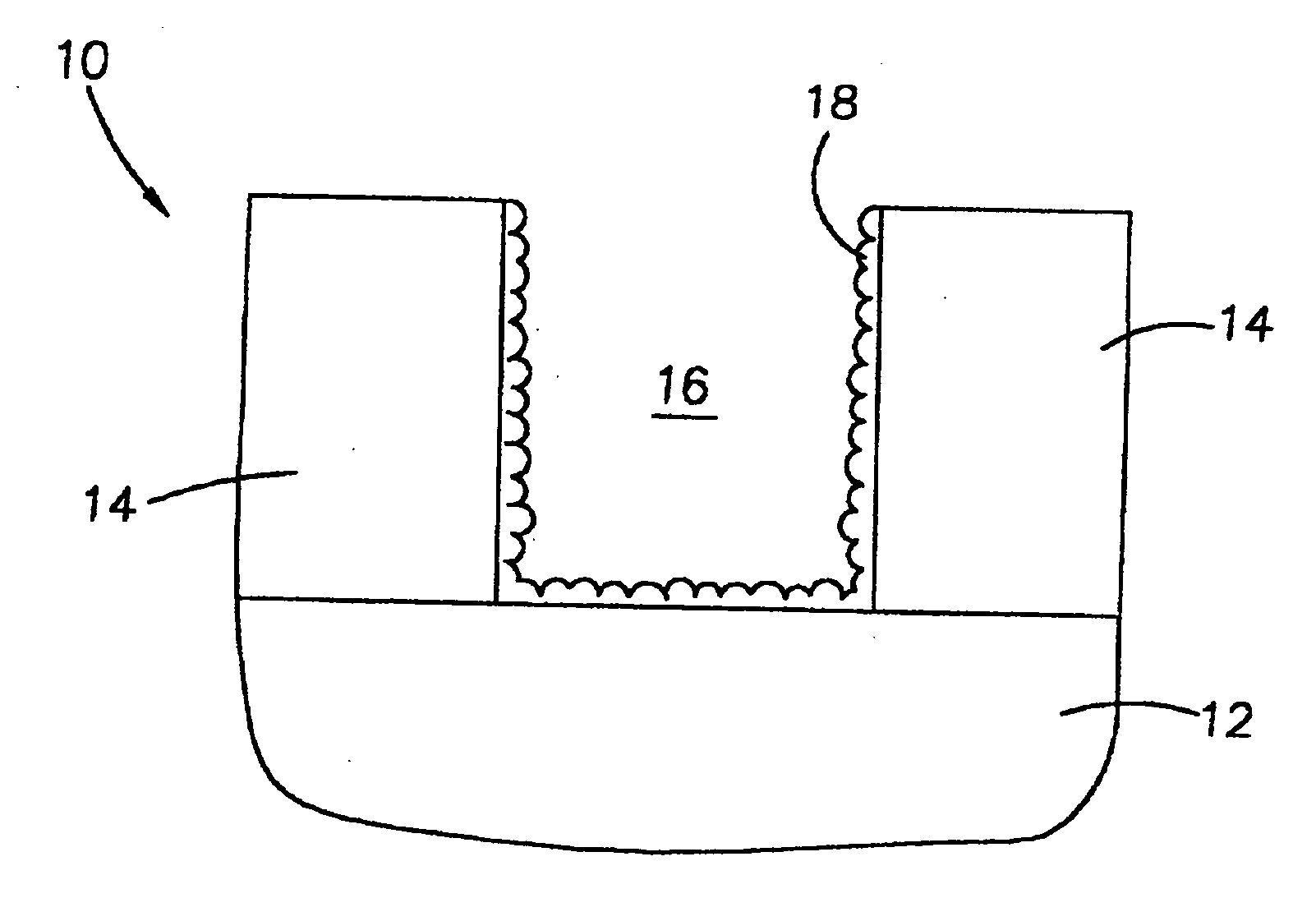

Electric interconnecting structure on substrate and producing method thereof

InactiveCN1309074CPrecise and Uniform ControlLower effective dielectric constantSemiconductor/solid-state device detailsSolid-state devicesEngineeringProtection layer

An electrical interconnect structure on a substrate, which includes: a first low-k dielectric layer; a spin-on low k CMP protective layer that is covalently bonded to the first low-k dielectric layer; and a CVD deposited hardmask / CMP polish stop layer is provided. Electrical vias and lines can be formed in the first low k dielectric layer. The spin-on low k CMP protective layer prevents damage to the low k dielectric which can be created due to non-uniformity in the CMP process from center to edge or in areas of varying metal density. The thickness of the low-k CMP protective layer can be adjusted to accommodate larger variations in the CMP process without significantly impacting the effective dielectric constant of the structure.

Owner:GLOBALFOUNDRIES INC

Method of improved high K dielectric - polysilicon interface for CMOS devices

InactiveUS20060141698A1Electrical lead thickness is decreasedMore capacitanceSolid-state devicesSemiconductor/solid-state device manufacturingCMOSSelf limiting

Methods for forming dielectric layers over polysilicon substrates, useful in the construction of capacitors and other semiconductor circuit components are provided. A self-limiting nitric oxide (NO) anneal of a polysilicon layer such as an HSG polysilicon capacitor electrode, at less than 800° C., is utilized to grow a thin oxide (oxynitride) layer of about 40 angstroms or less over the polysilicon layer. The NO anneal provides a nitrogen layer at the polysilicon-oxide interface that limits further oxidation of the polysilicon layer and growth of the oxide layer. The oxide layer is exposed to a nitrogen-containing gas to nitridize the surface of the oxide layer and reduce the effective dielectric constant of the oxide layer. The process is particularly useful in forming high K dielectric insulating layers such as tantalum pentoxide over polysilicon. The nitridized oxynitride layer inhibits oxidation of the underlying polysilicon layer in a post-treatment oxidizing anneal of the high K dielectric, thus maintaining the oxide layer as a thin layer over the polysilicon layer.

Owner:MICRON TECH INC

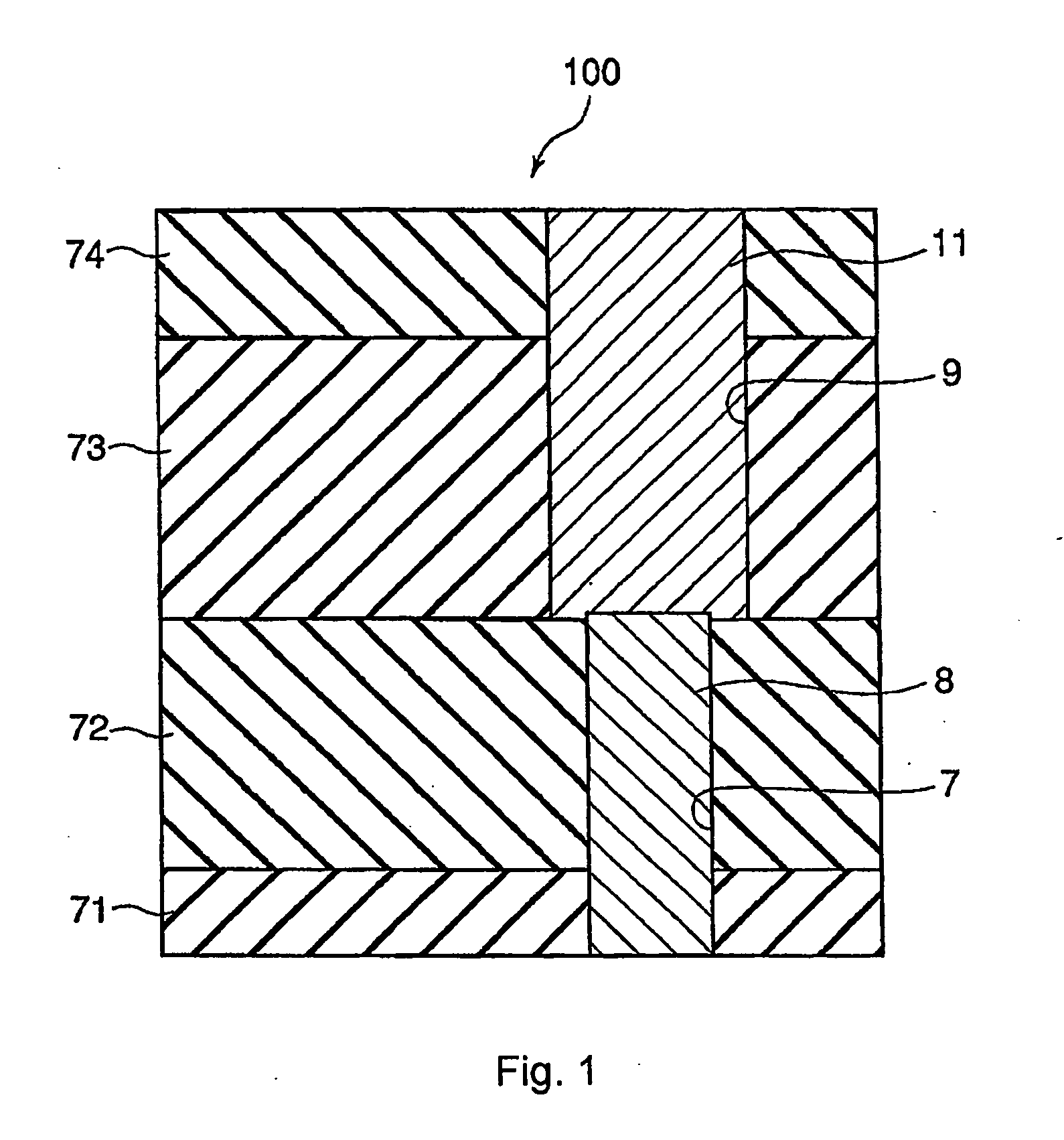

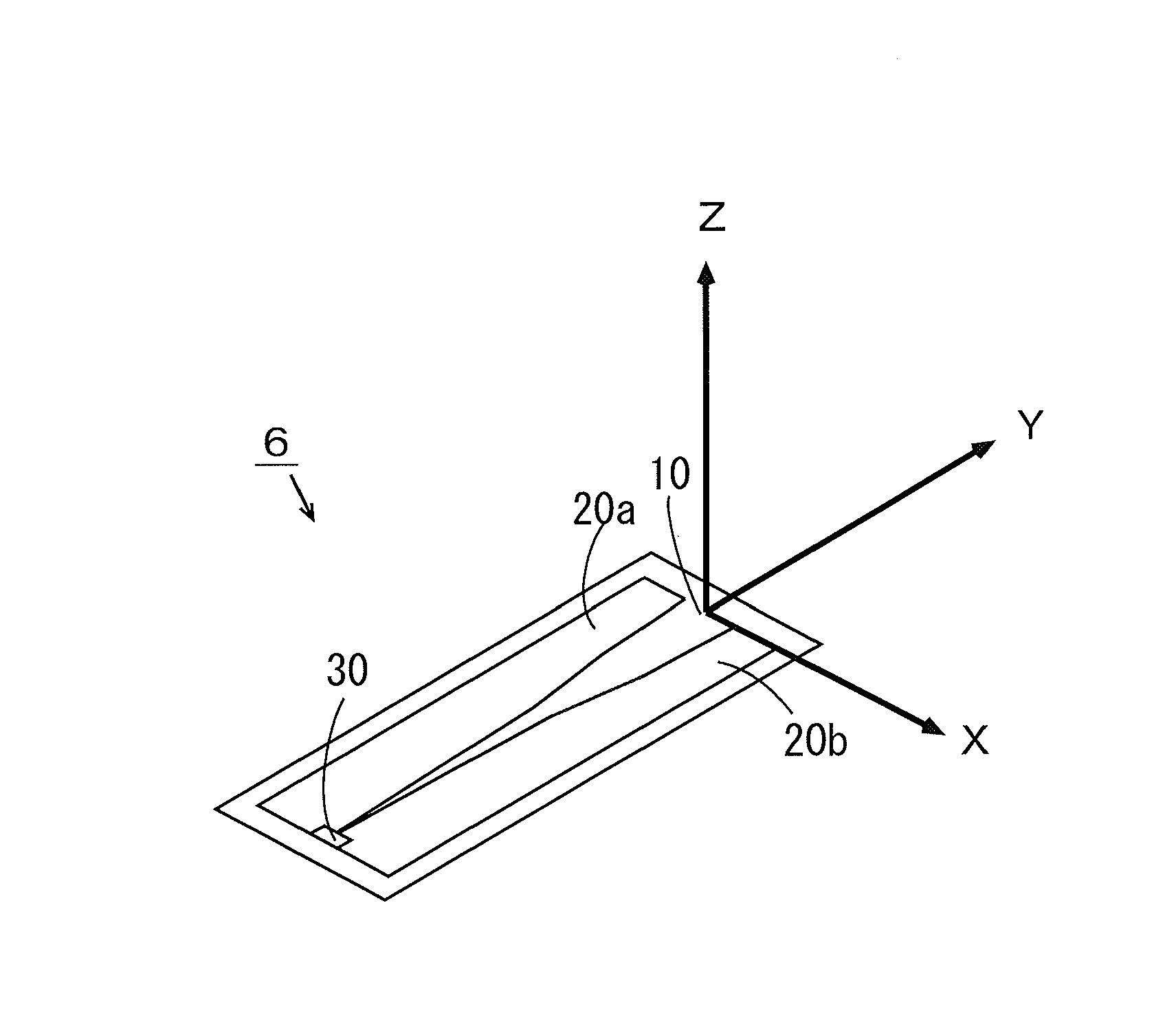

Antenna module, communication device, and array antenna

PendingUS20210184344A1Small sizeEffective permittivityAntenna supports/mountingsRadiating elements structural formsDielectric substrateCommunication device

An antenna module (100) includes a dielectric substrate (160) having a multilayer structure, a first radiation electrode (122), a second radiation electrode (121), and a ground electrode (GND). The second radiation electrode (121) is arranged between the first radiation electrode (122) and the ground electrode (GND) in a lamination direction of the dielectric substrate (160). In the dielectric substrate (160), a hollow portion (150) is disposed in at least a portion between the first radiation electrode (122) and the second radiation electrode (121).

Owner:MURATA MFG CO LTD

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com